Patents

Literature

90 results about "Polycide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

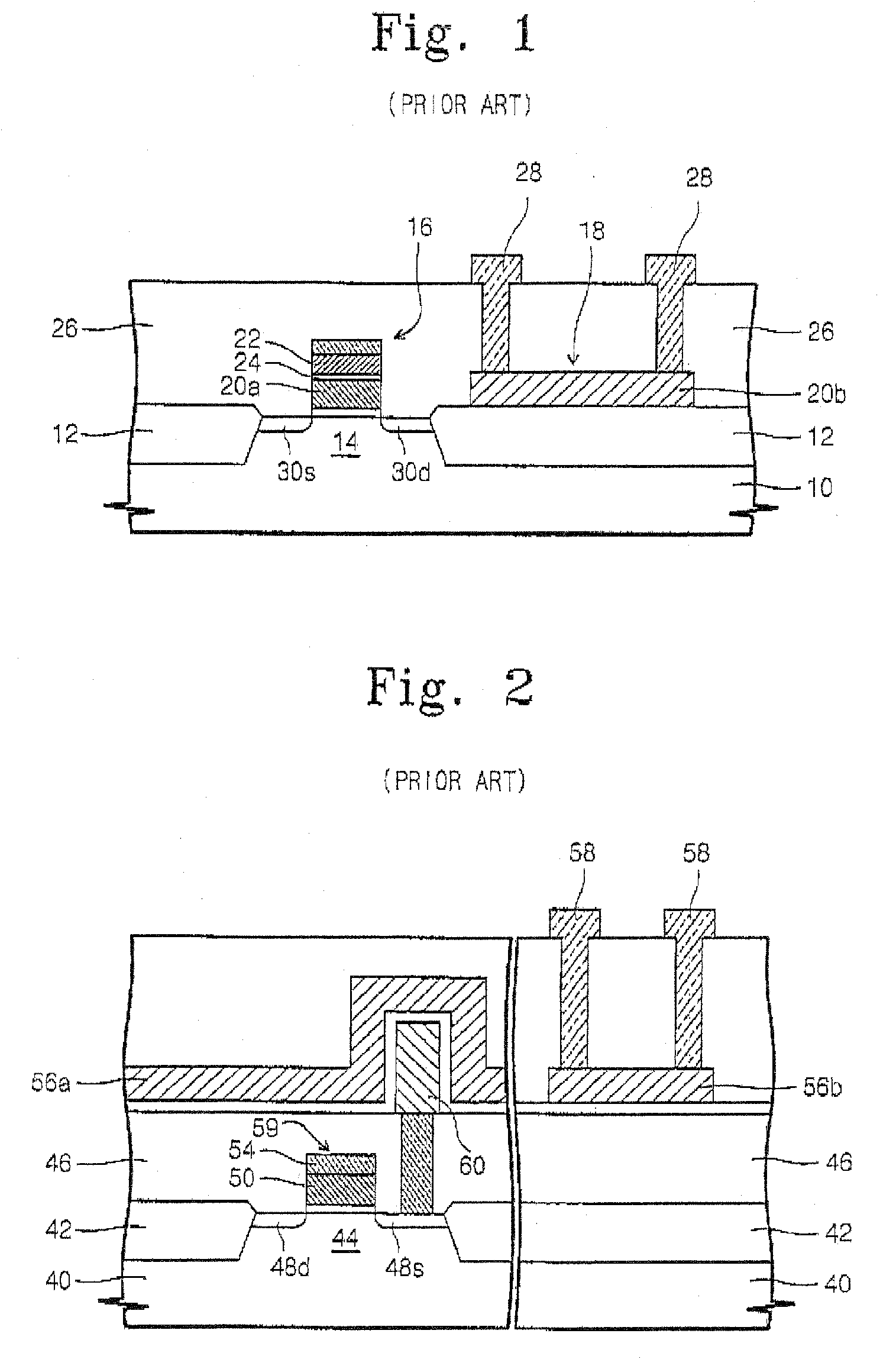

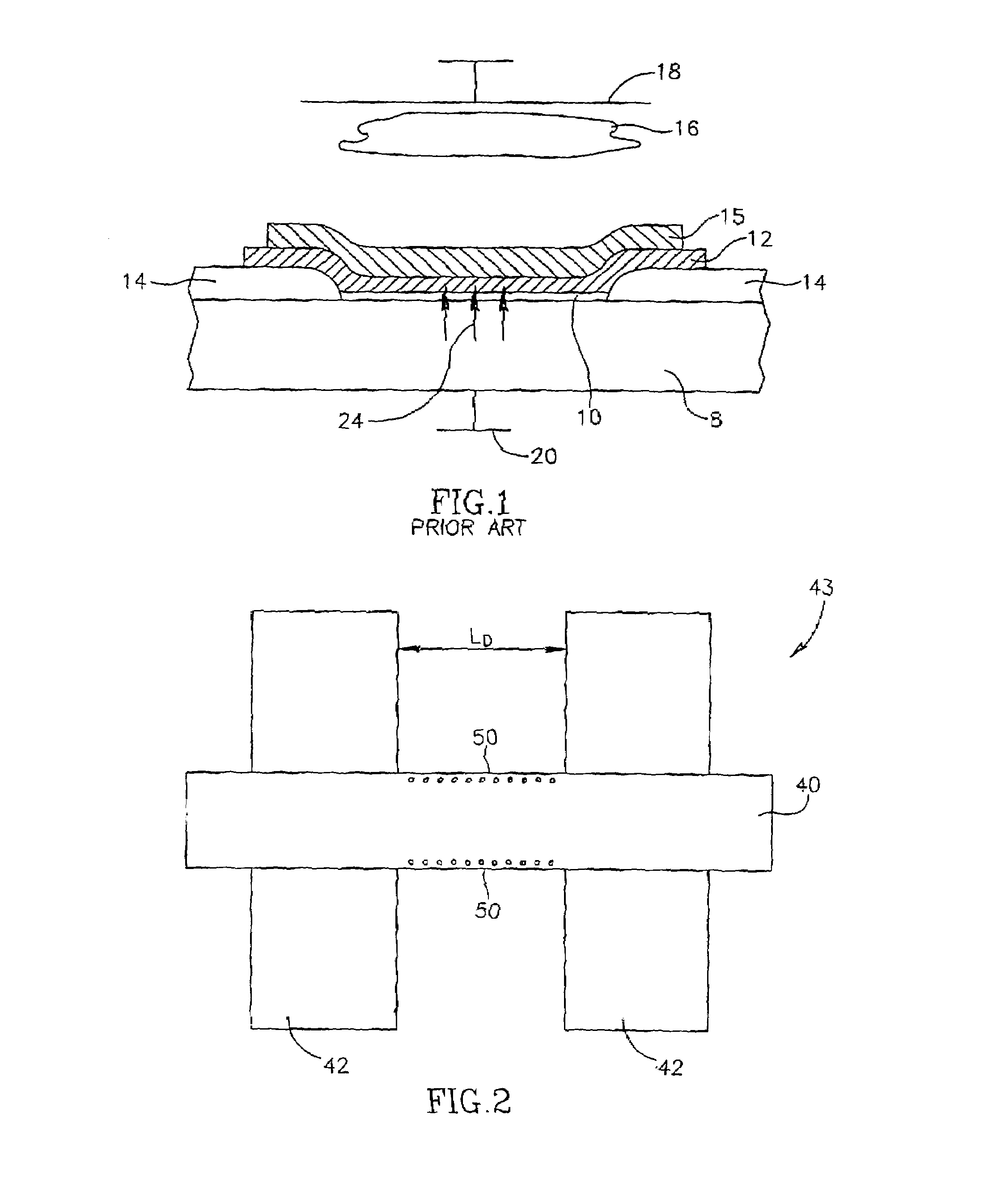

Polycide is a silicide formed over polysilicon. Widely used in DRAMs. In a polycide MOSFET transistor process, the silicide is formed only over the polysilicon film as formation occurs prior to any polysilicon etch. Polycide processes contrast with salicide processes in which silicide is formed after the polysilicon etch. Thus, with a salicide process, silicide is formed over both the polysilicon gate and the exposed monocrystalline terminal regions of the transistor in a self-aligned fashion.

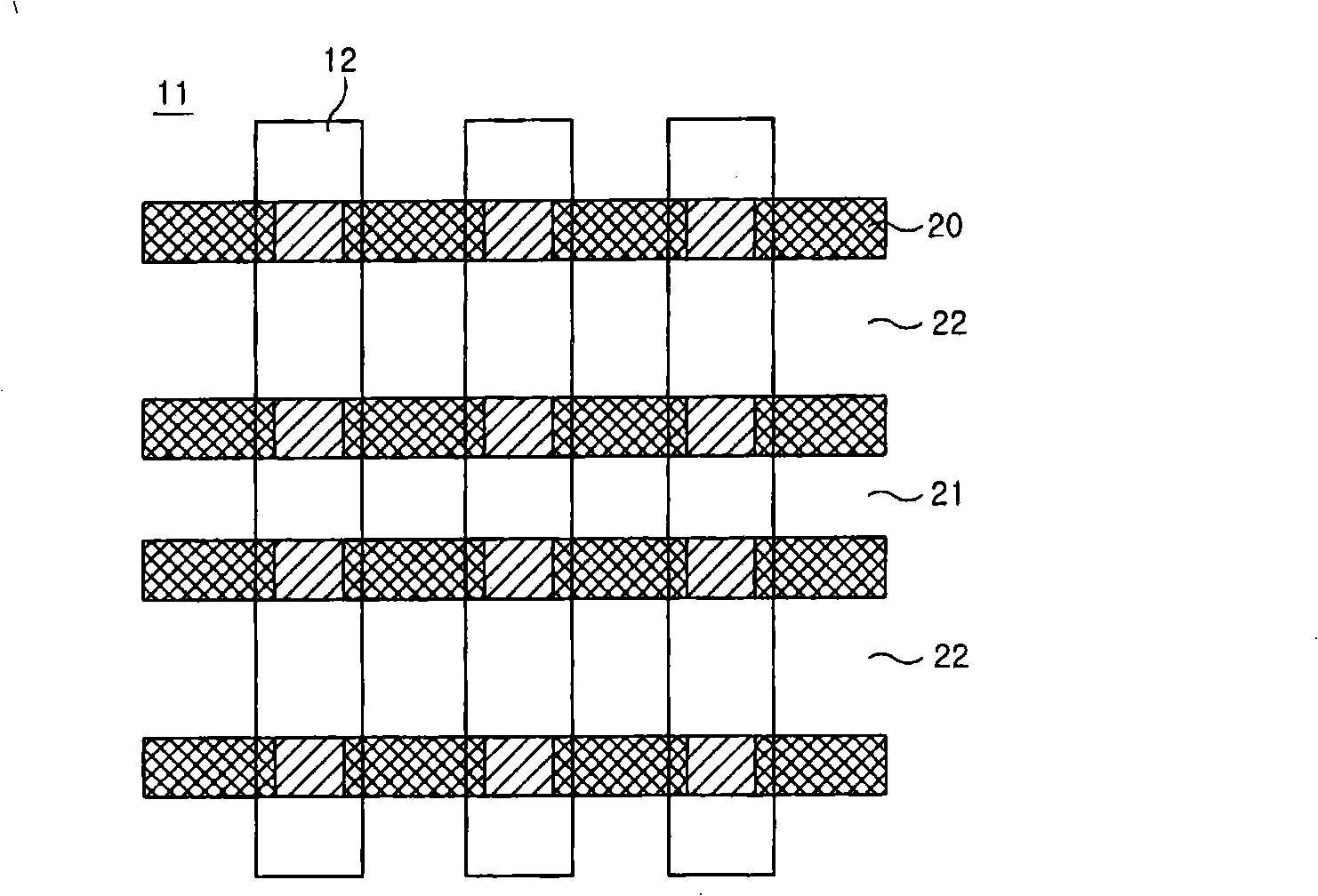

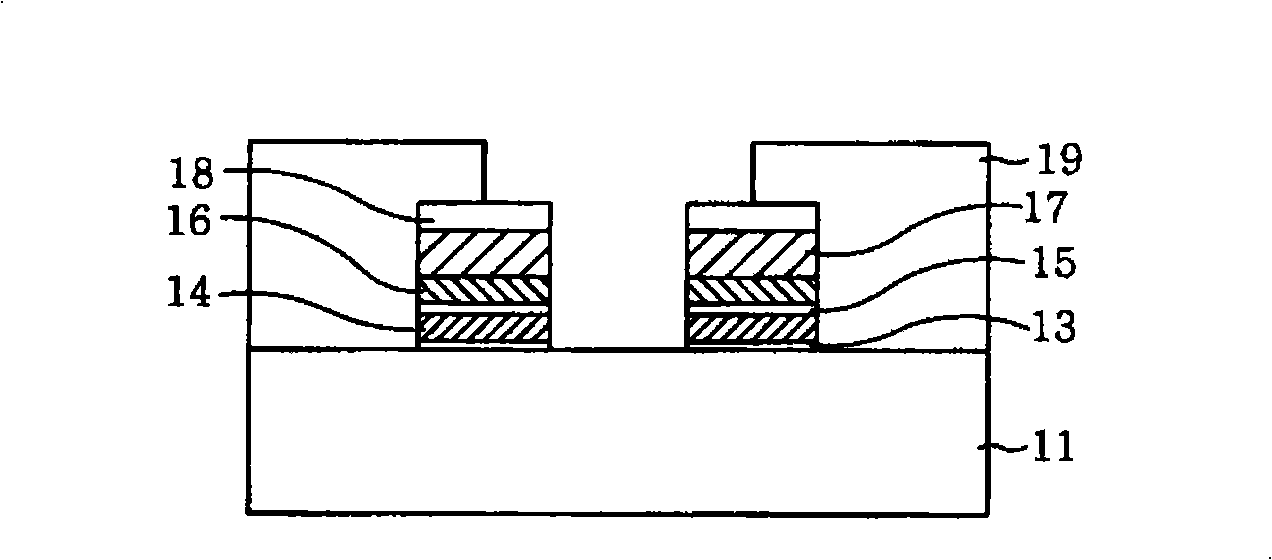

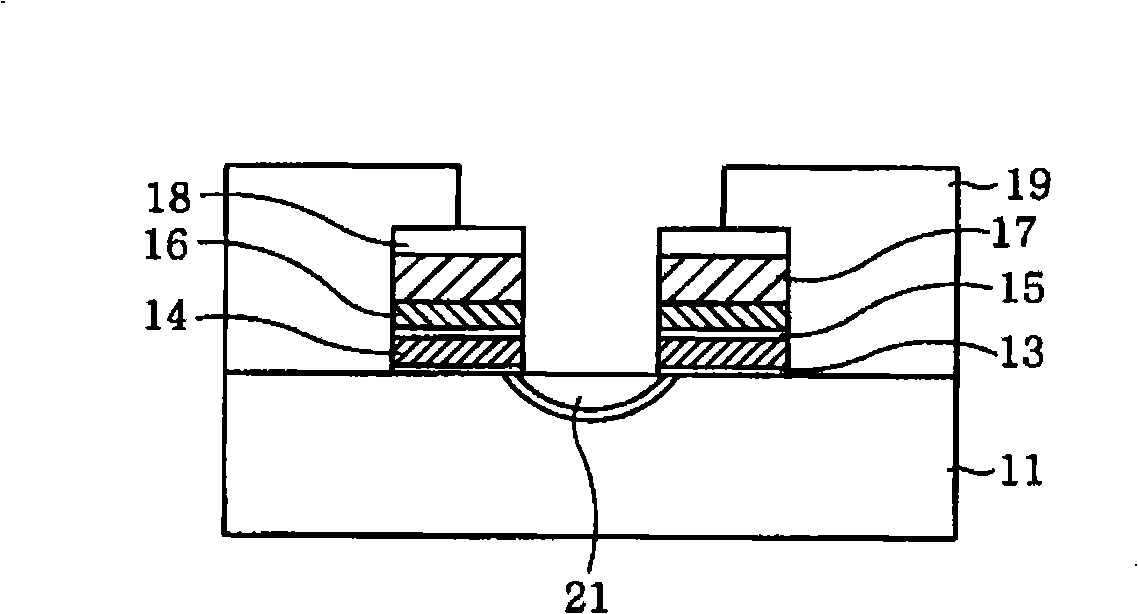

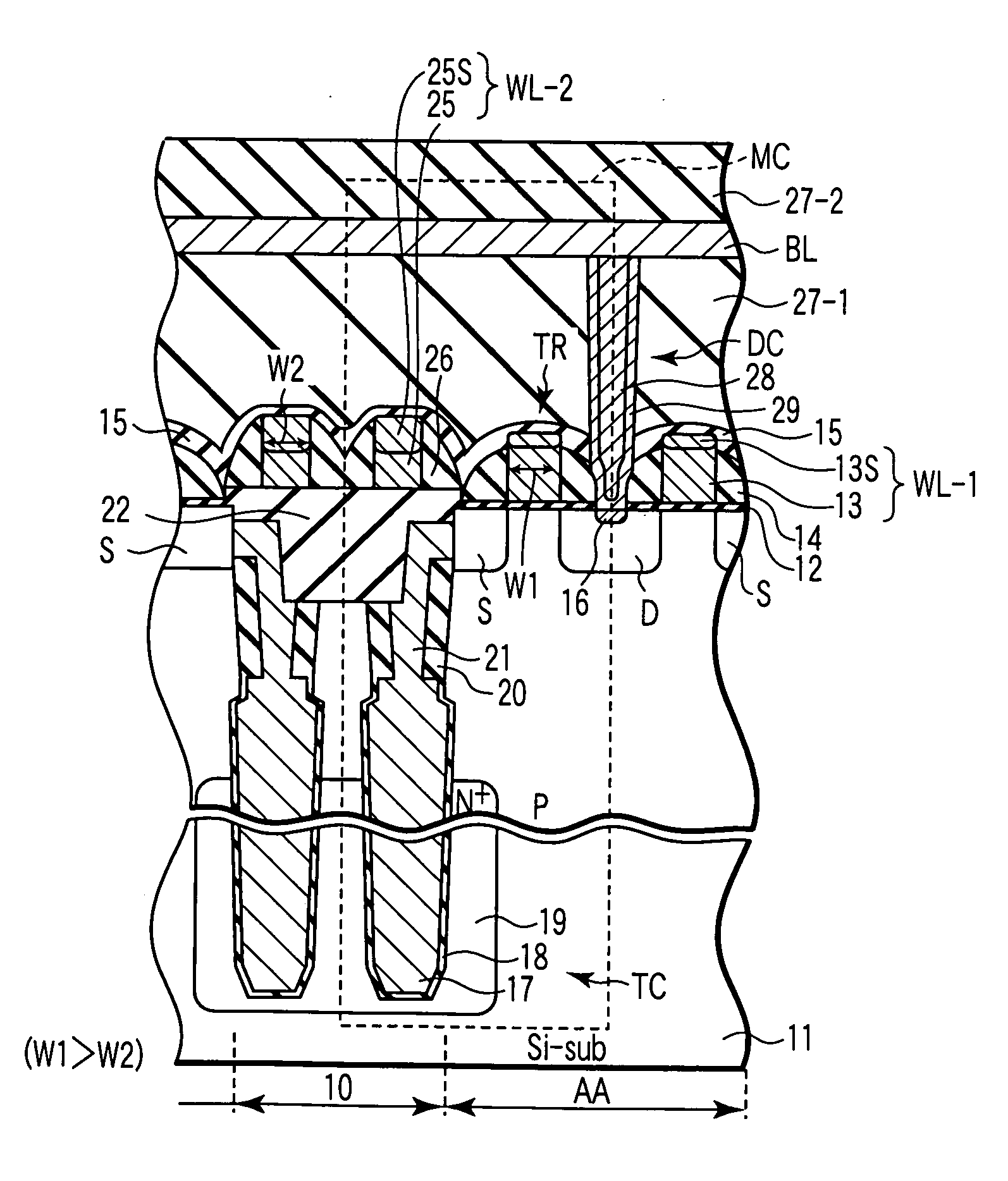

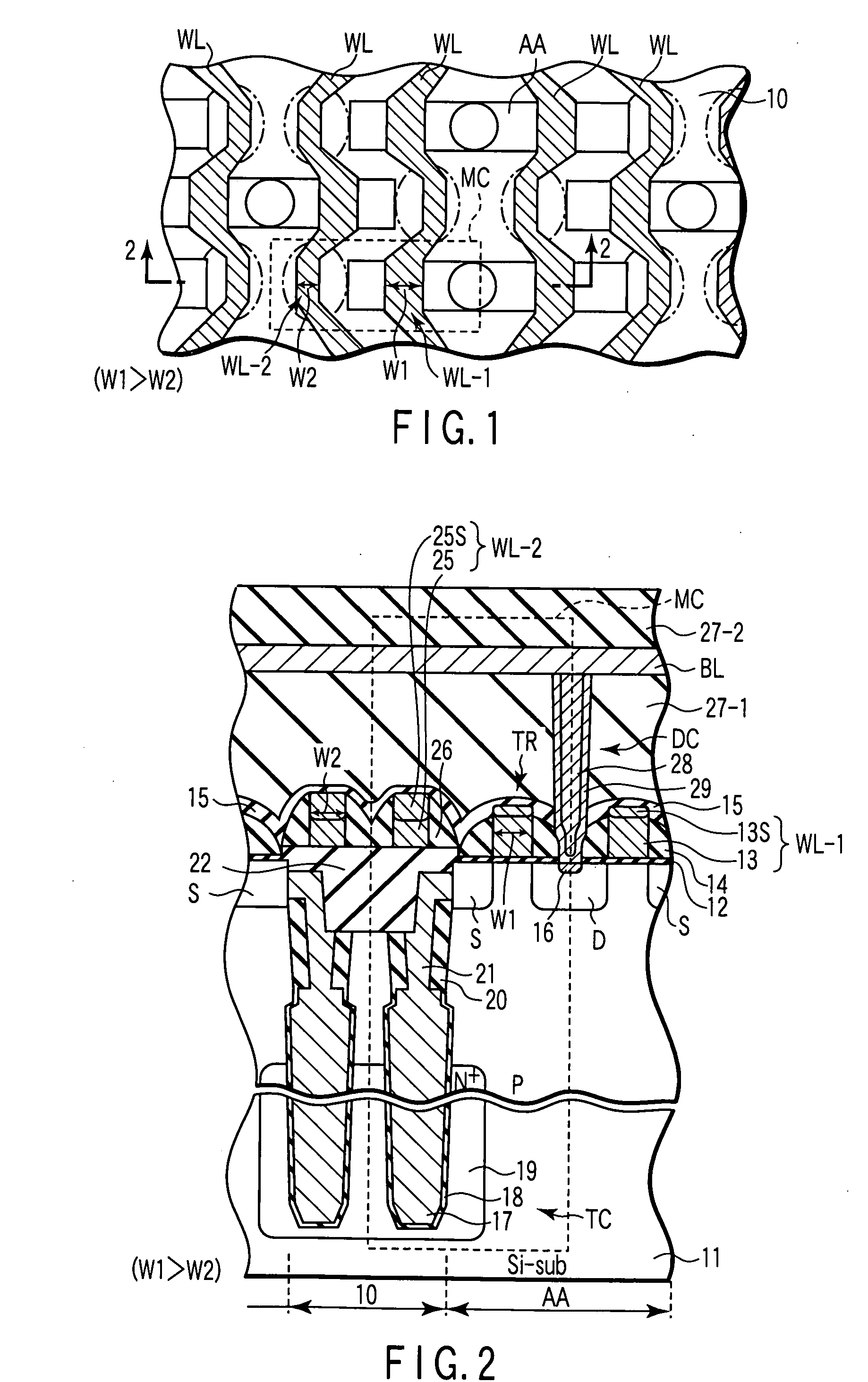

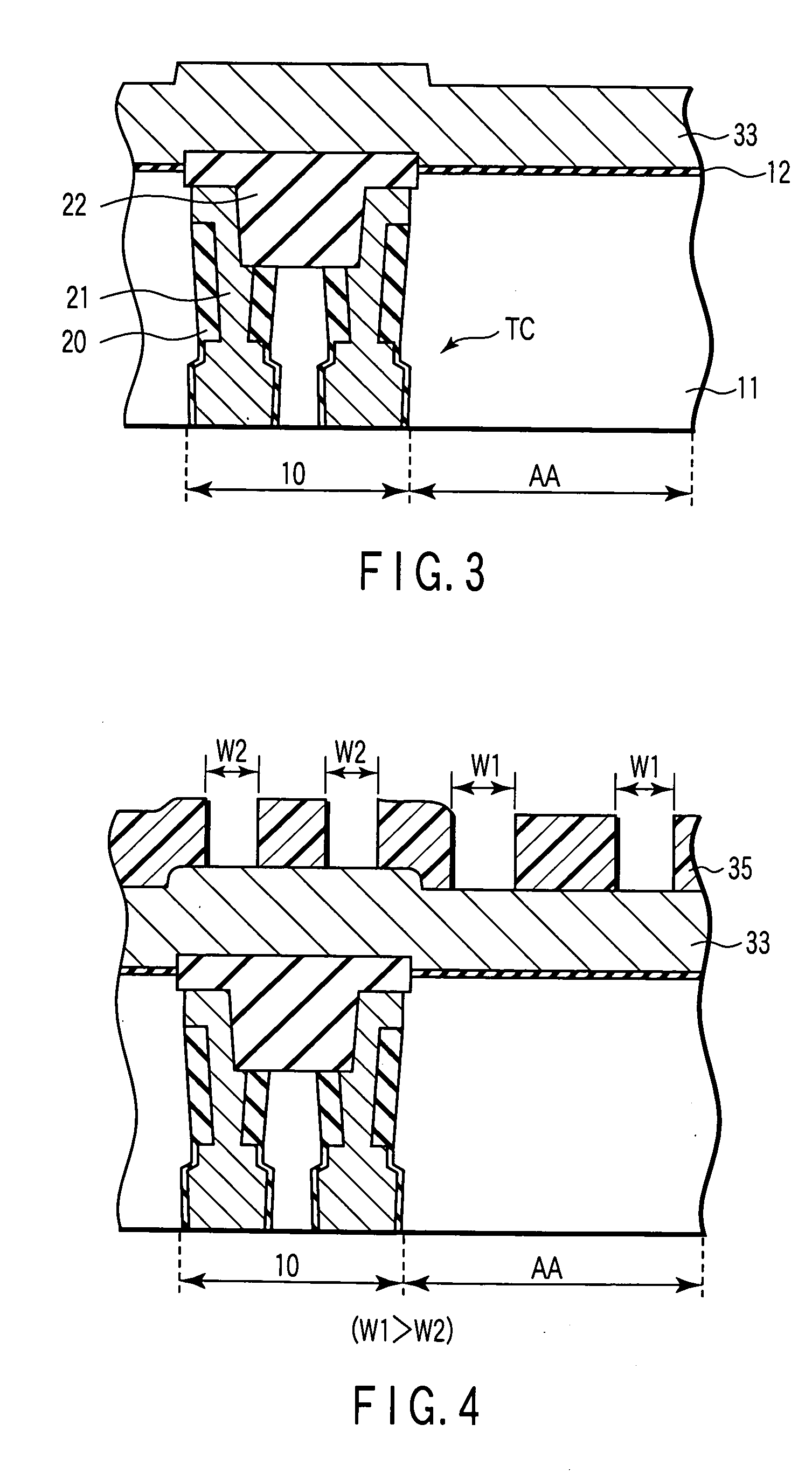

Non-volatile memory array having vertical transistors and manufacturing method thereof

InactiveUS20050148173A1Superior charge storingReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingDopantBit line

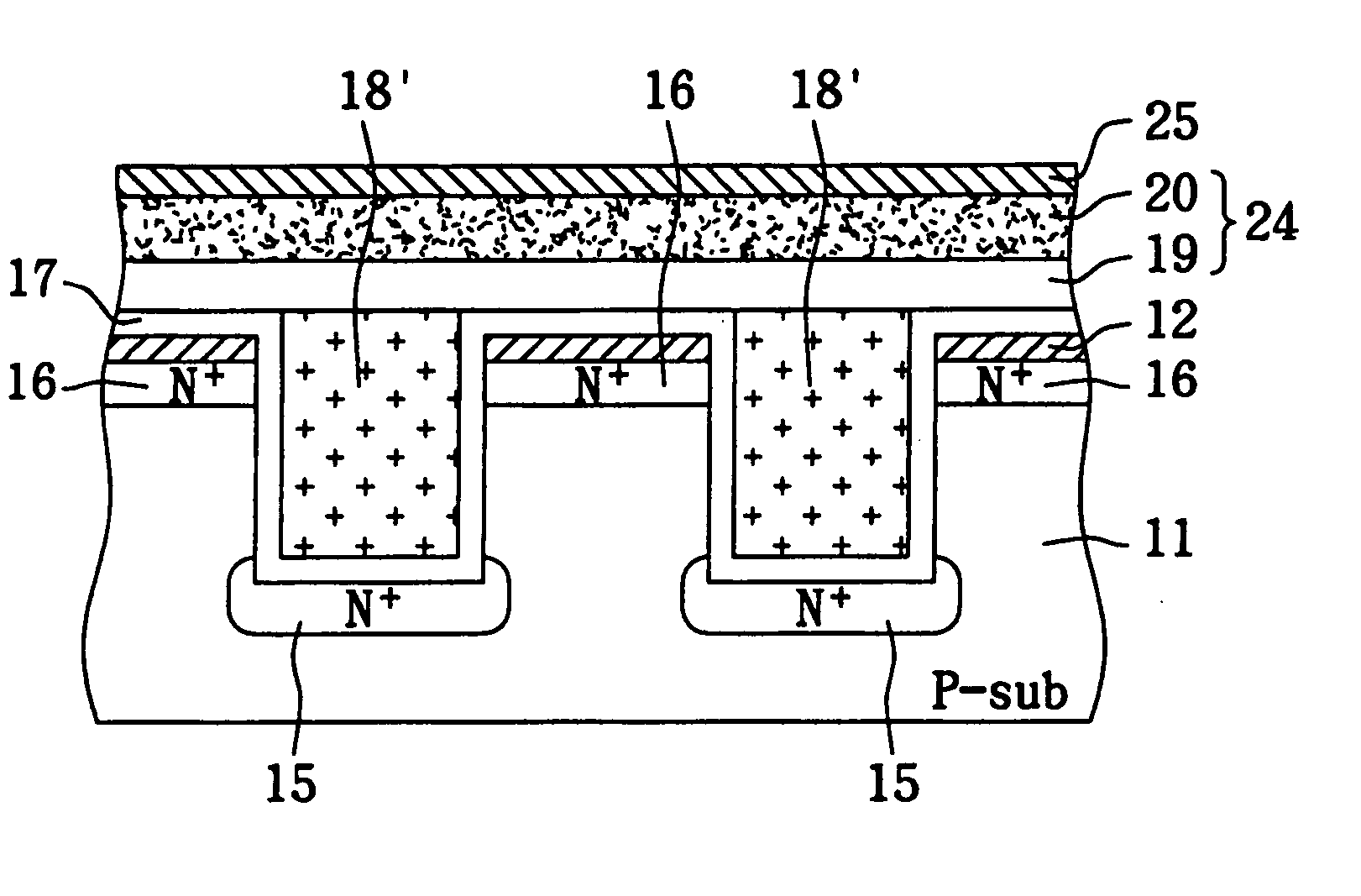

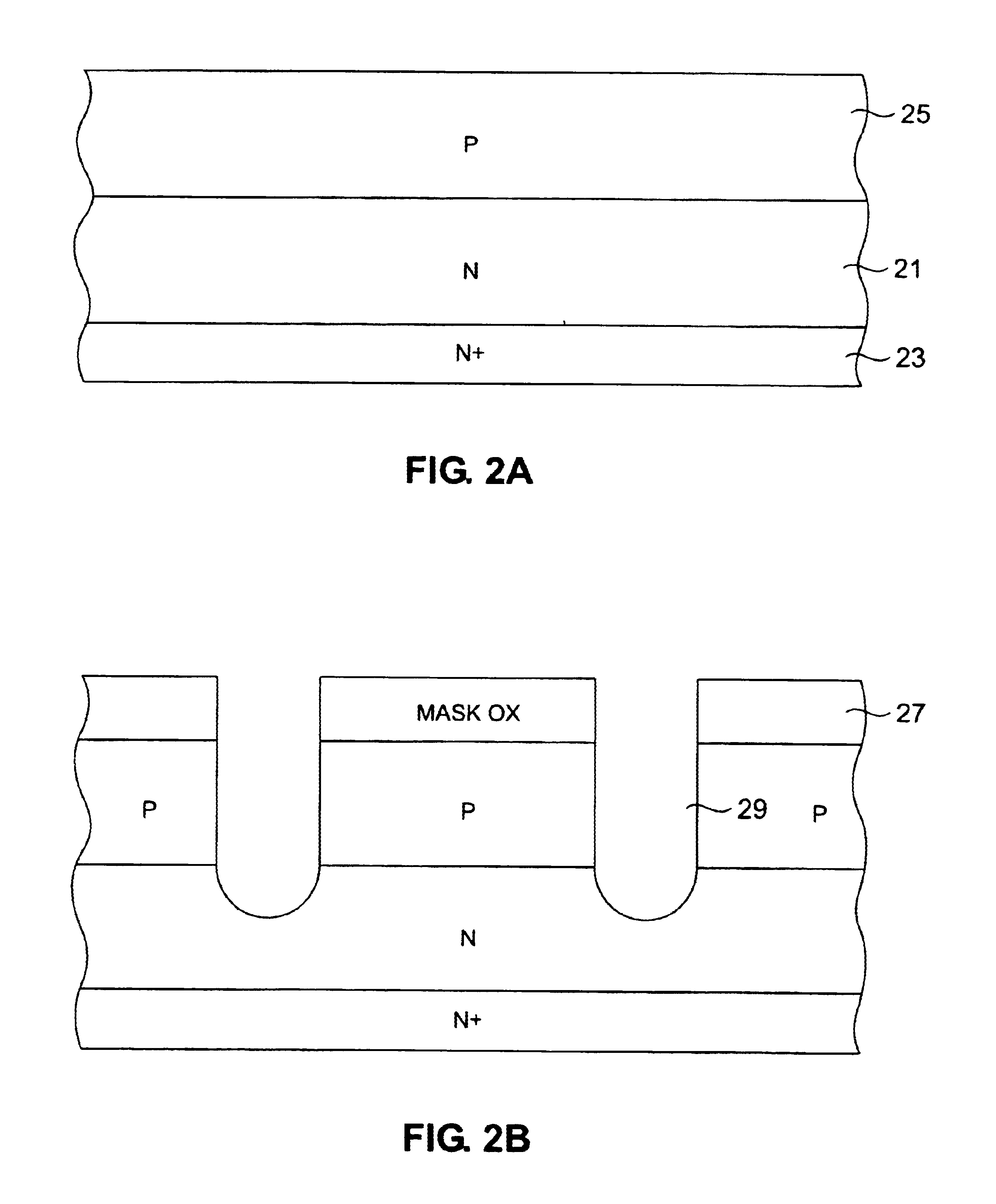

A method of manufacturing a non-volatile memory array having vertical field effect transistors is revealed. First, a semiconductor substrate having multiple trenches is provided, and then dopants are implanted into the semiconductor substrate to form first doping regions and second doping regions respectively serving as source and drain bit lines at different heights. Secondly, a gate dielectric including at least one nitride film, e.g., an oxide / nitride / oxide (ONO) layer, is formed onto the surface of the semiconductor substrate, and polysilicon plugs serving as gate electrodes are filled up the multiple trenches afterward. After that, a polysilicon layer and a tungsten silicide (WiSix) layer are sequentially deposited followed by masking and etching processes to form parallel polycide lines serving as word lines, and then an oxide layer is deposited therebetween and planarized for isolation.

Owner:SKYMEDI CORPORATION

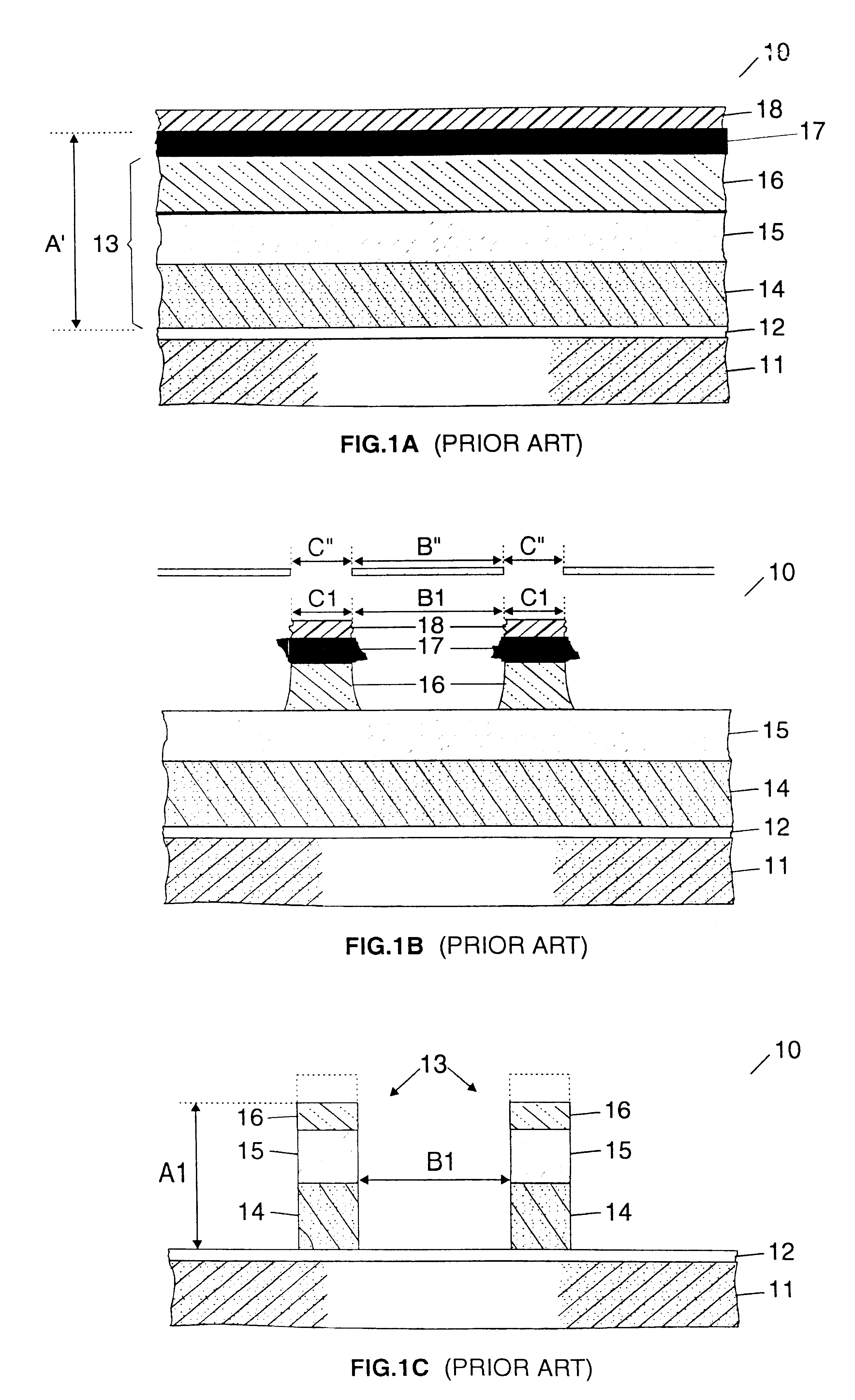

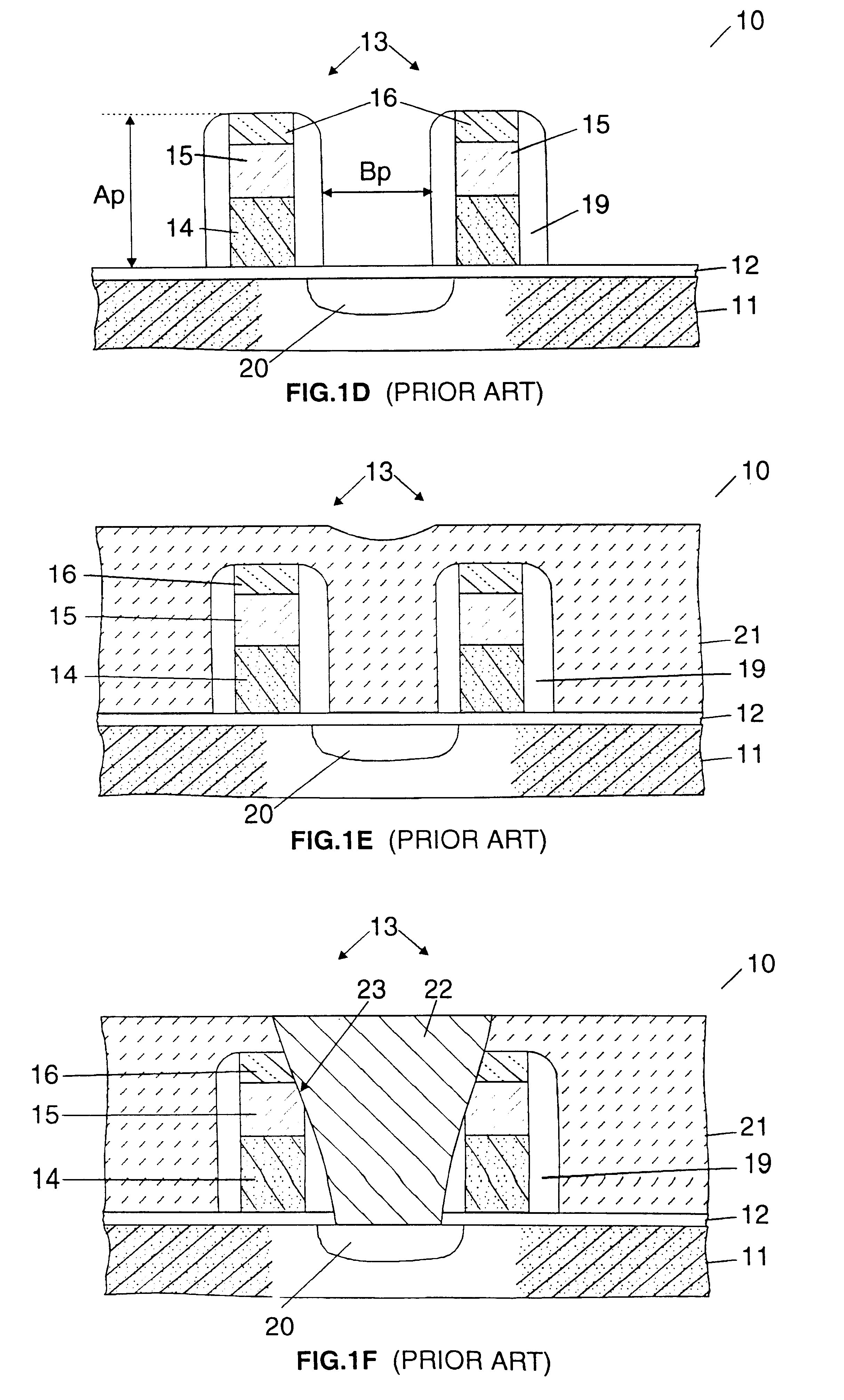

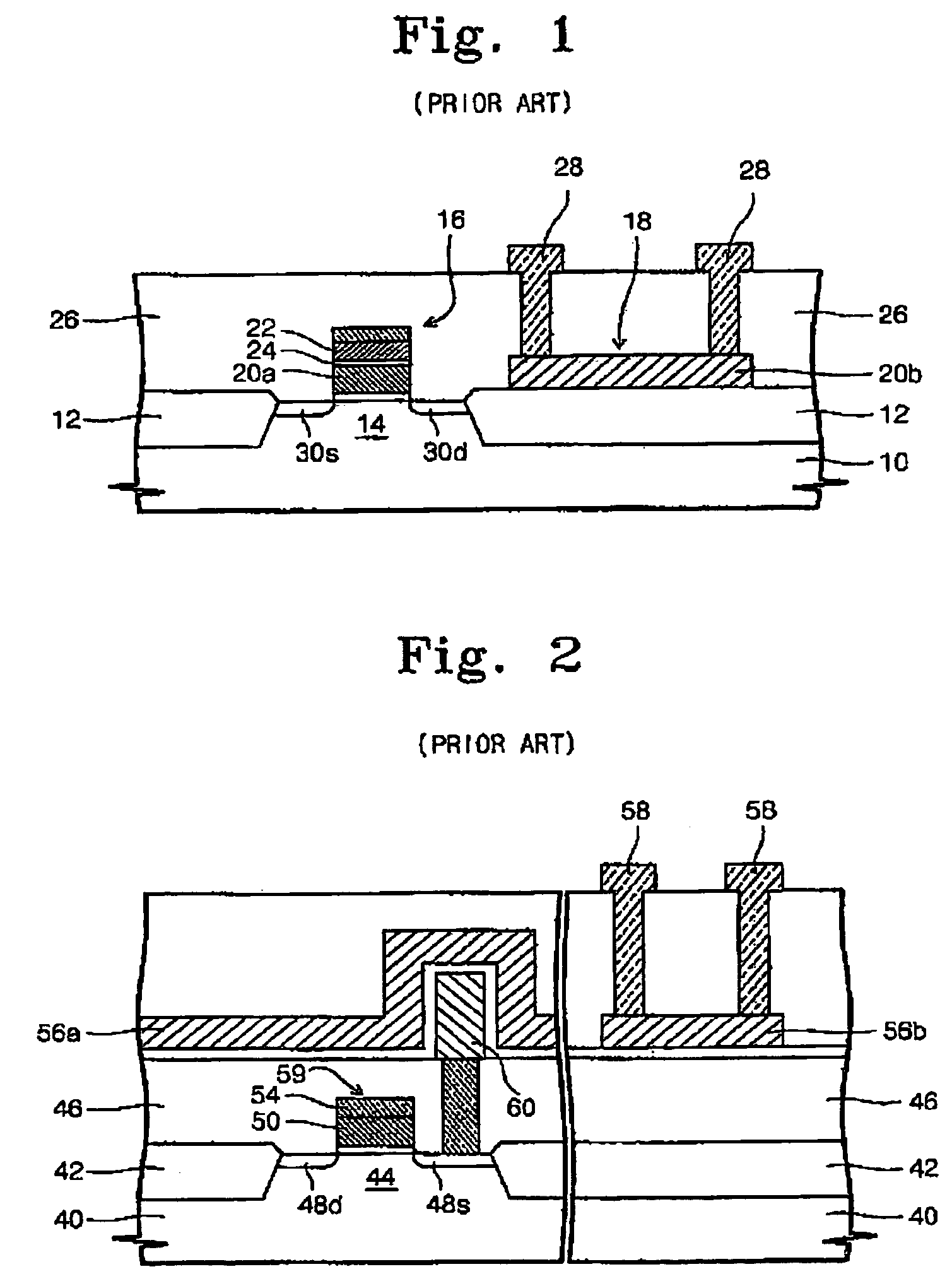

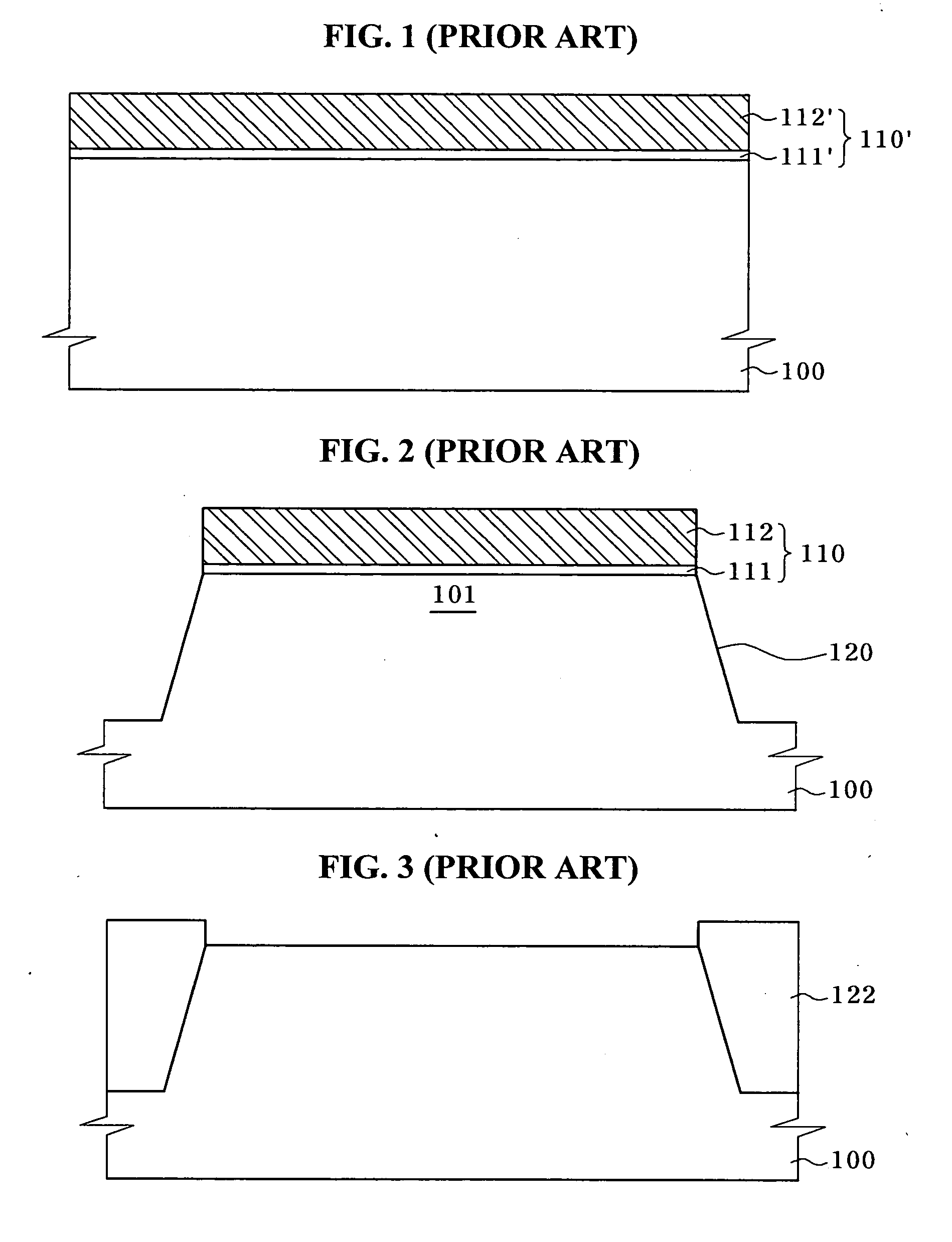

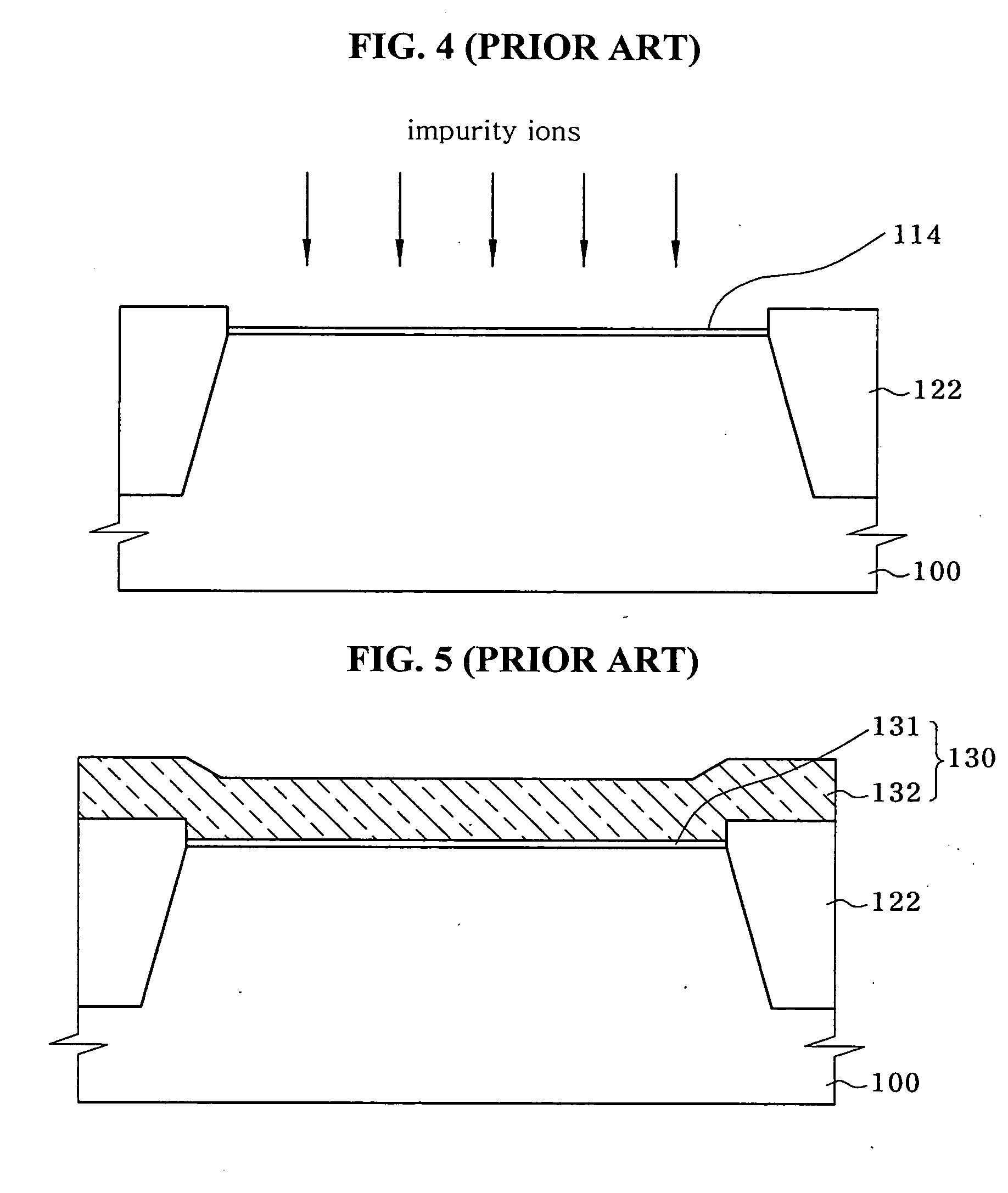

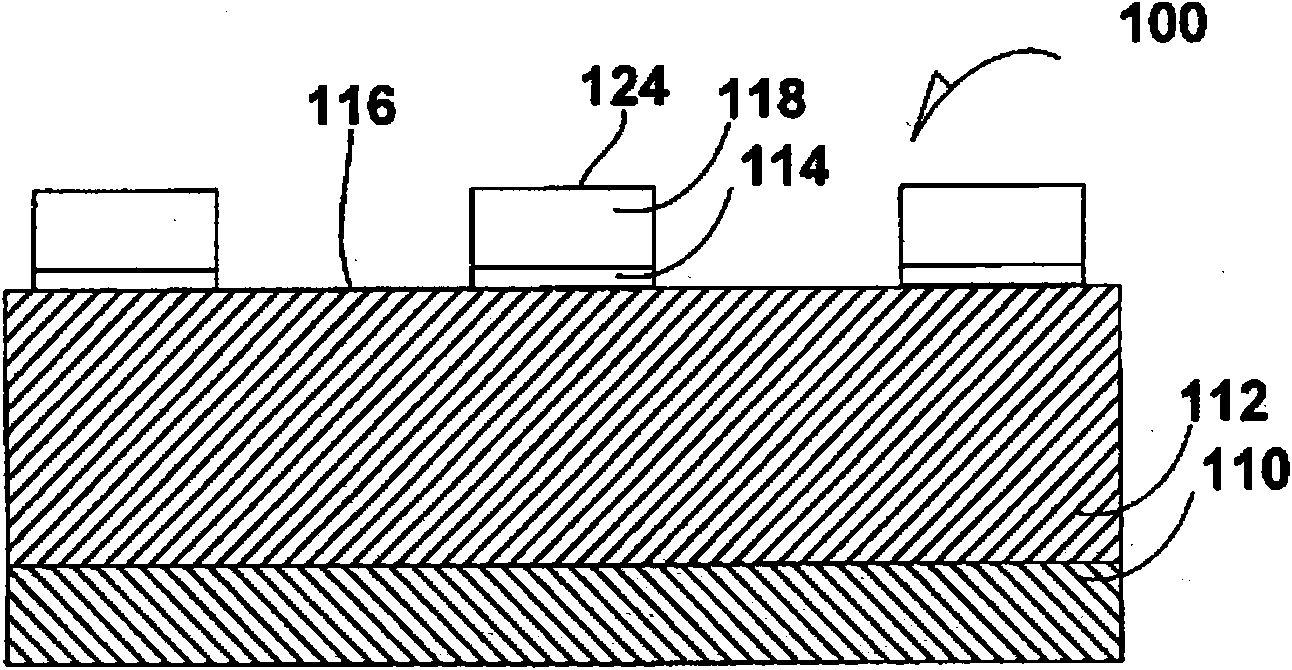

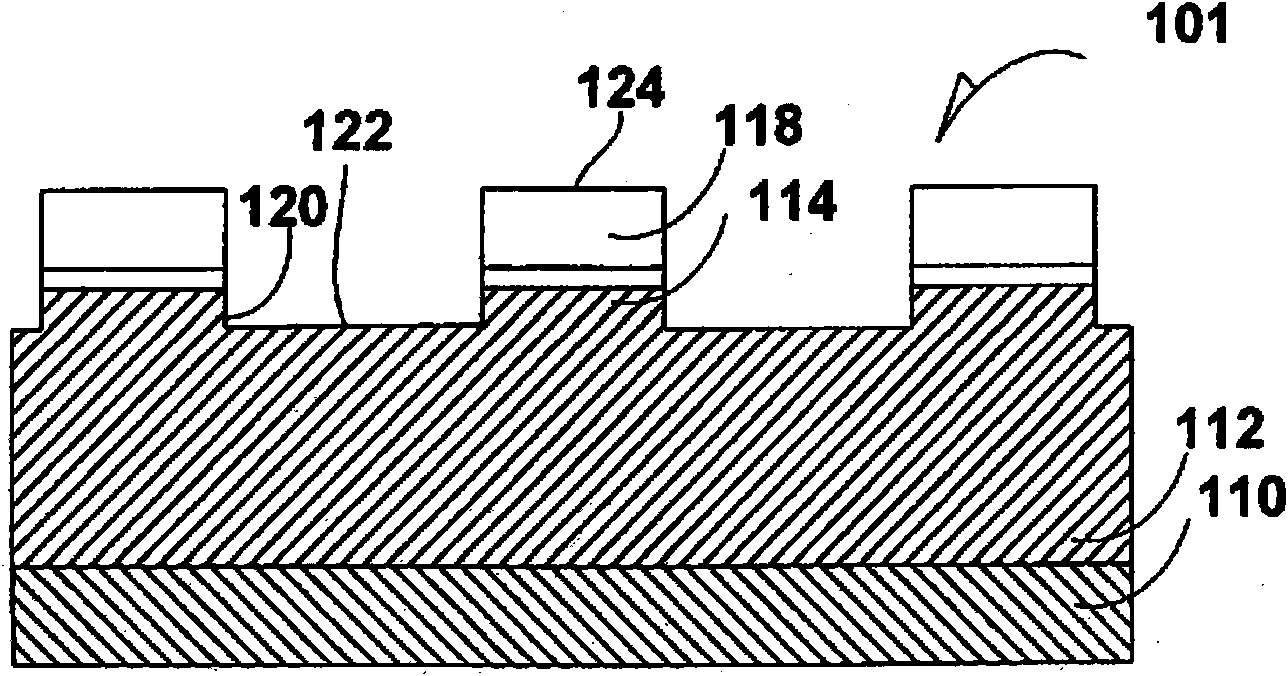

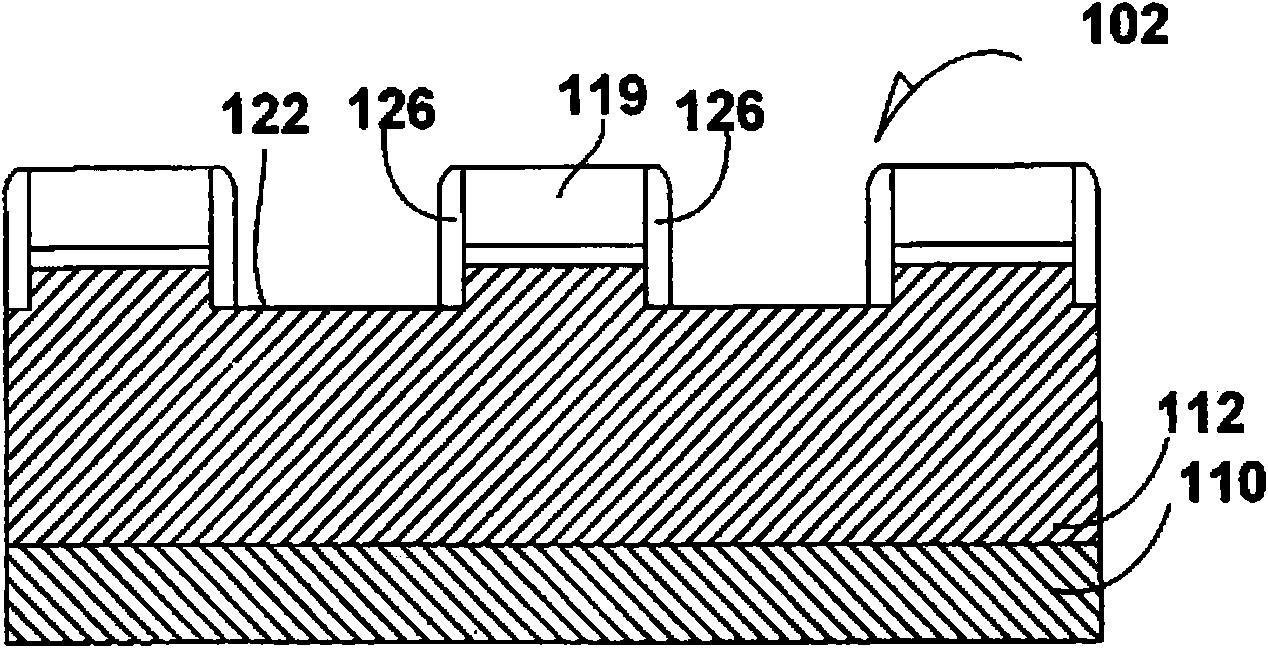

Method of fabricating a Si3N4/polycide structure using a dielectric sacrificial layer as a mask

InactiveUS6342452B1Added fabricationReduce the height of the structureSemiconductor/solid-state device manufacturingResistPhotoresist

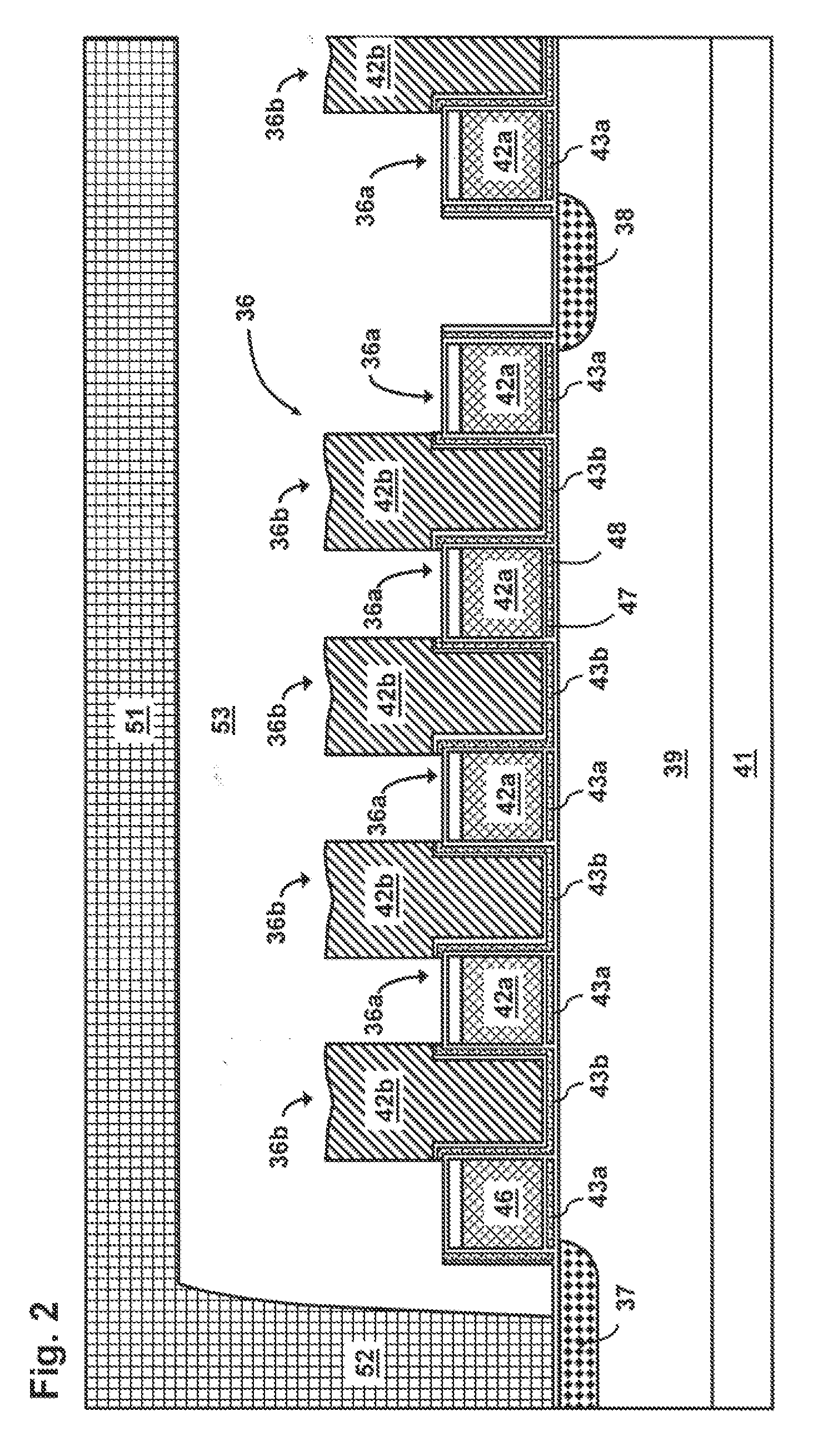

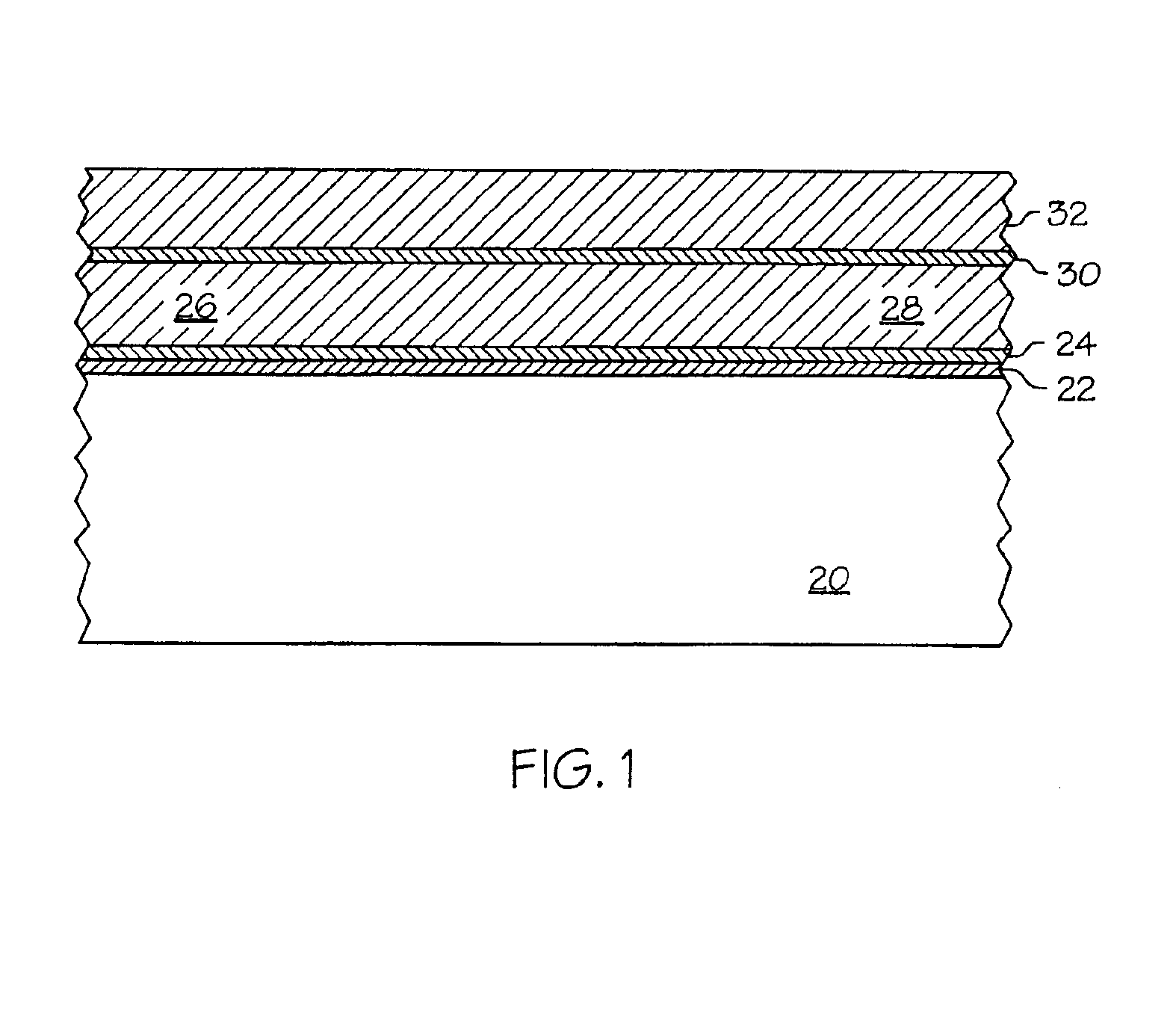

According to the disclosed method, there is provided a structure consisting of a silicon substrate coated with a bottom thin SiO2 layer, a doped polysilicon layer, a refractory metal layer and a top Si3N4 capping layer. Said refractory metal and doped polysilicon layers will form a polycide layer under subsequent thermal treatments. First, a sacrificial layer of a dielectric material such as oxynitride is deposited onto the structure. Oxynitride is impervious to UV radiation and has excellent conformal properties. Then, a layer of a photoresist material is deposited onto the structure and patterned to form a mask. Now the dielectric and top Si3N4 layers are anisotropically etched using the photoresist mask. The mask is stripped and the refractory metal and doped polysilicon layers are anisotropically dry etched down to the SiO2 layer using the patterned dielectric layer as an in-situ hard mask. A conformal layer of Si3N4 is deposited onto the structure, then anisotropically dry etched until the thin SiO2 layer is exposed to form the Si3N4 spacers. Diffusion regions are formed in the substrate by ion implantation. A layer of BPSG is deposited onto the structure and planarized. Contact holes are formed to expose said diffusion regions and filled with a metal to create borderless metal contacts therewith.

Owner:IBM CORP

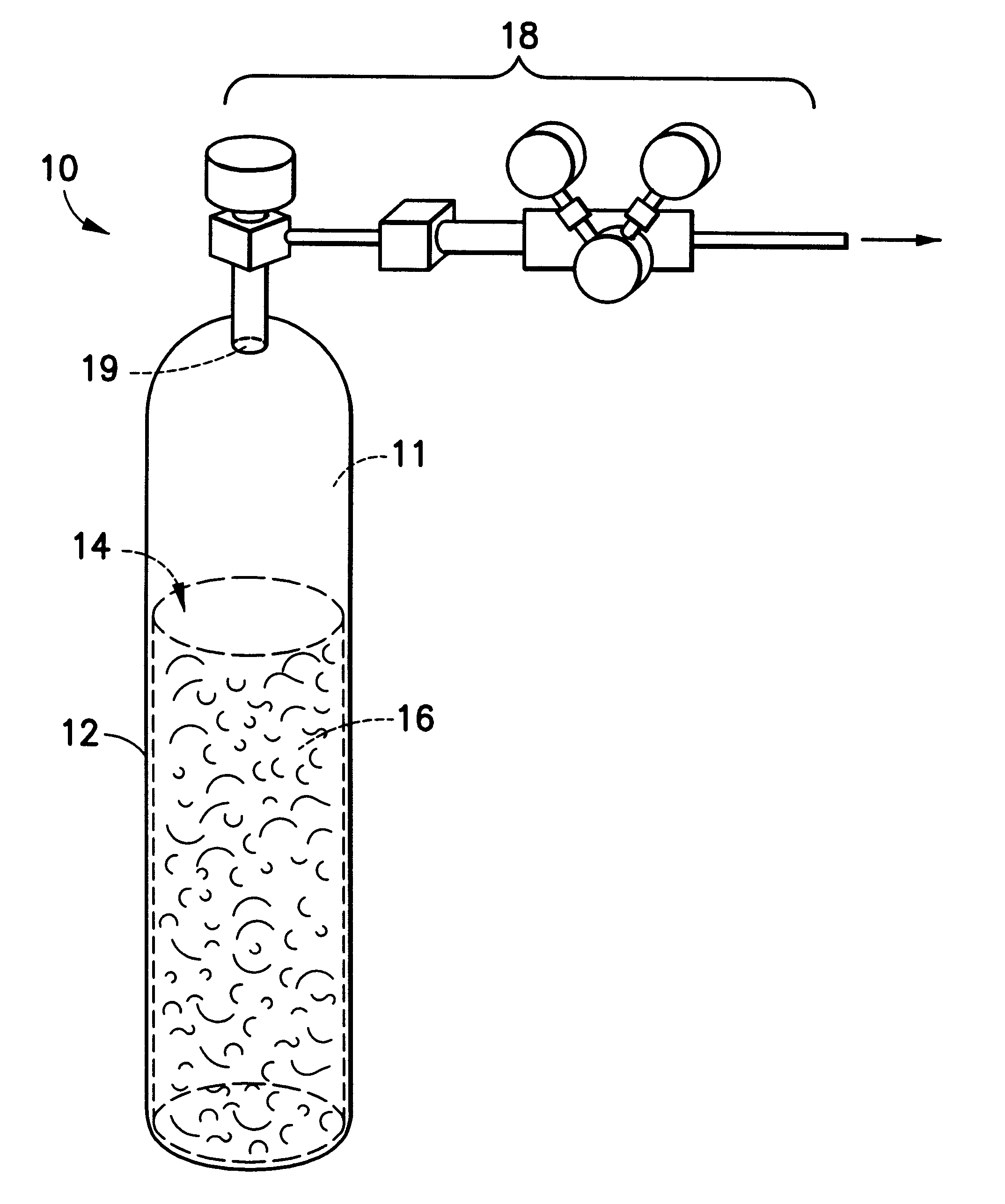

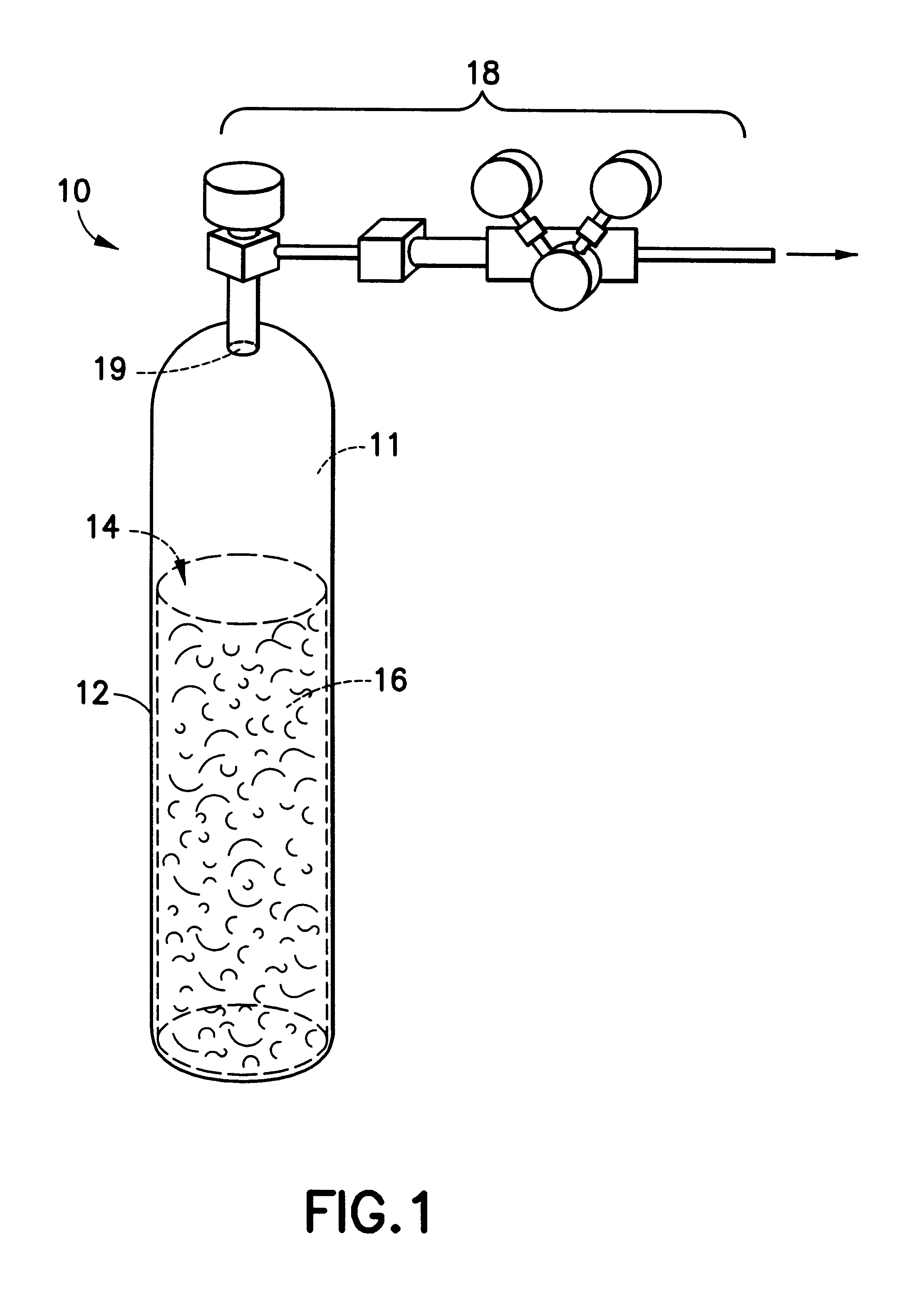

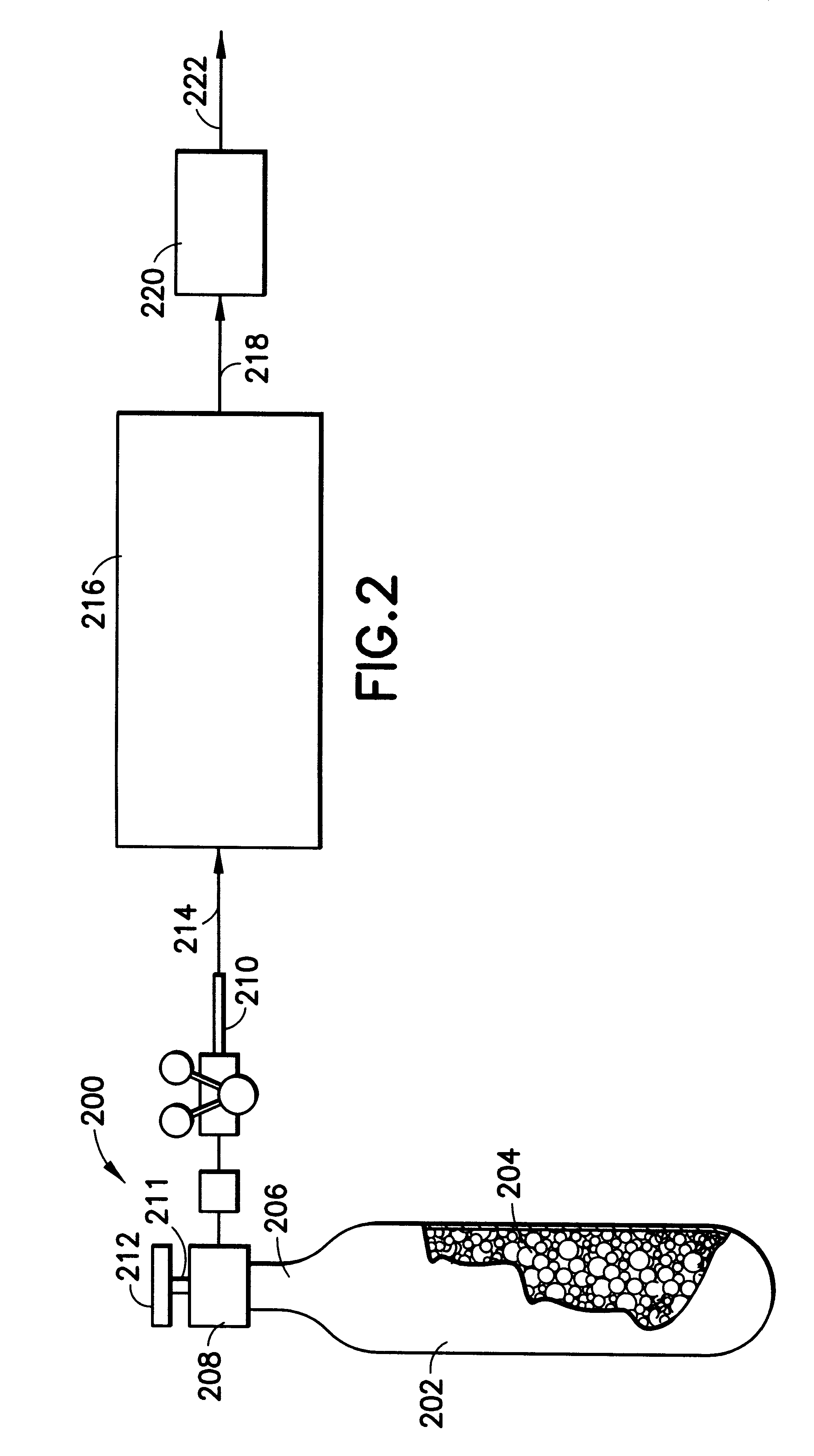

Apparatus and process for manufacturing semiconductor devices, products and precursor structures utilizing sorbent-based fluid storage and dispensing system for reagent delivery

InactiveUS6204180B1Vessel mounting detailsSemiconductor/solid-state device manufacturingGas phaseSorbent

A process for fabricating an electronic device structure on or in a substrate. A storage and dispensing vessel is provided, containing a solid-phase physical sorbent medium having physically adsorbed thereon a fluid for fabrication of the electronic device structure, e.g., a source fluid for a material constituent of the electronic device structure, or a reagent such as an etchant or mask material which is utilized in the fabrication of the electronic device structure but does not compose or form a material constituent of the electronic device structure. In the process, the source fluid is desorbed from the physical sorbent medium and dispensing source fluid from the storage and dispensing vessel, and contacted with the substrate, under conditions effective to utilize the material constituent on or in the substrate. The contacting step of the process may include process steps such as ion implantation; epitaxial growth; plasma etching; reactive ion etching; metallization; physical vapor deposition; chemical vapor deposition; cleaning; doping; etc. The process of the invention may be employed to fabricate electronic device structures such as transistors; capacitors; resistors; memory cells; dielectric material; buried doped substrate regions; metallization layers; channel stop layers; source layers; gate layers; drain layers; oxide layers; field emitter elements; passivation layers; interconnects; polycides; electrodes; trench structures; ion implanted material layers; via plugs; precursor structures for the foregoing electronic device structures; and device assemblies comprising more than one of the foregoing electronic device structures. The electronic device structure fabricated by such process may in turn may be employed as a component of an electronic product such as a telecommunications device or electronic appliance.

Owner:ENTEGRIS INC

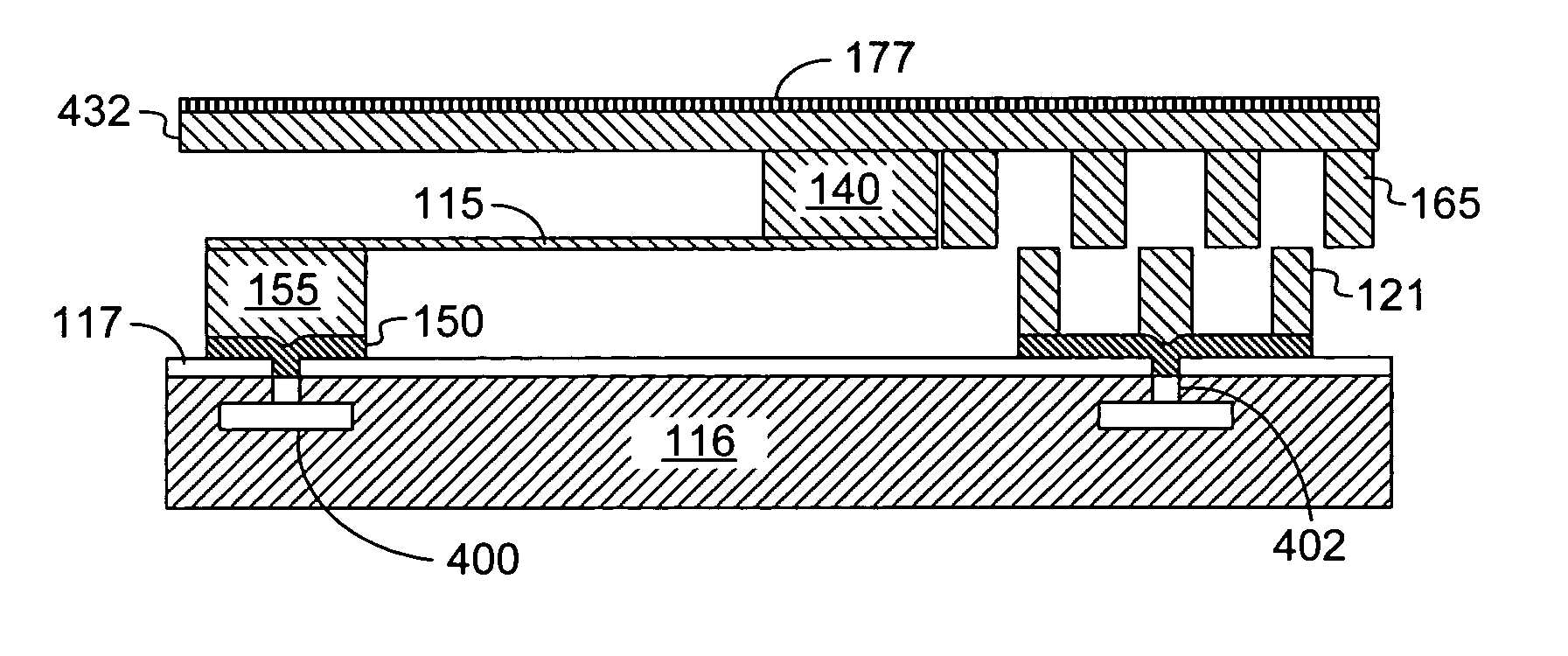

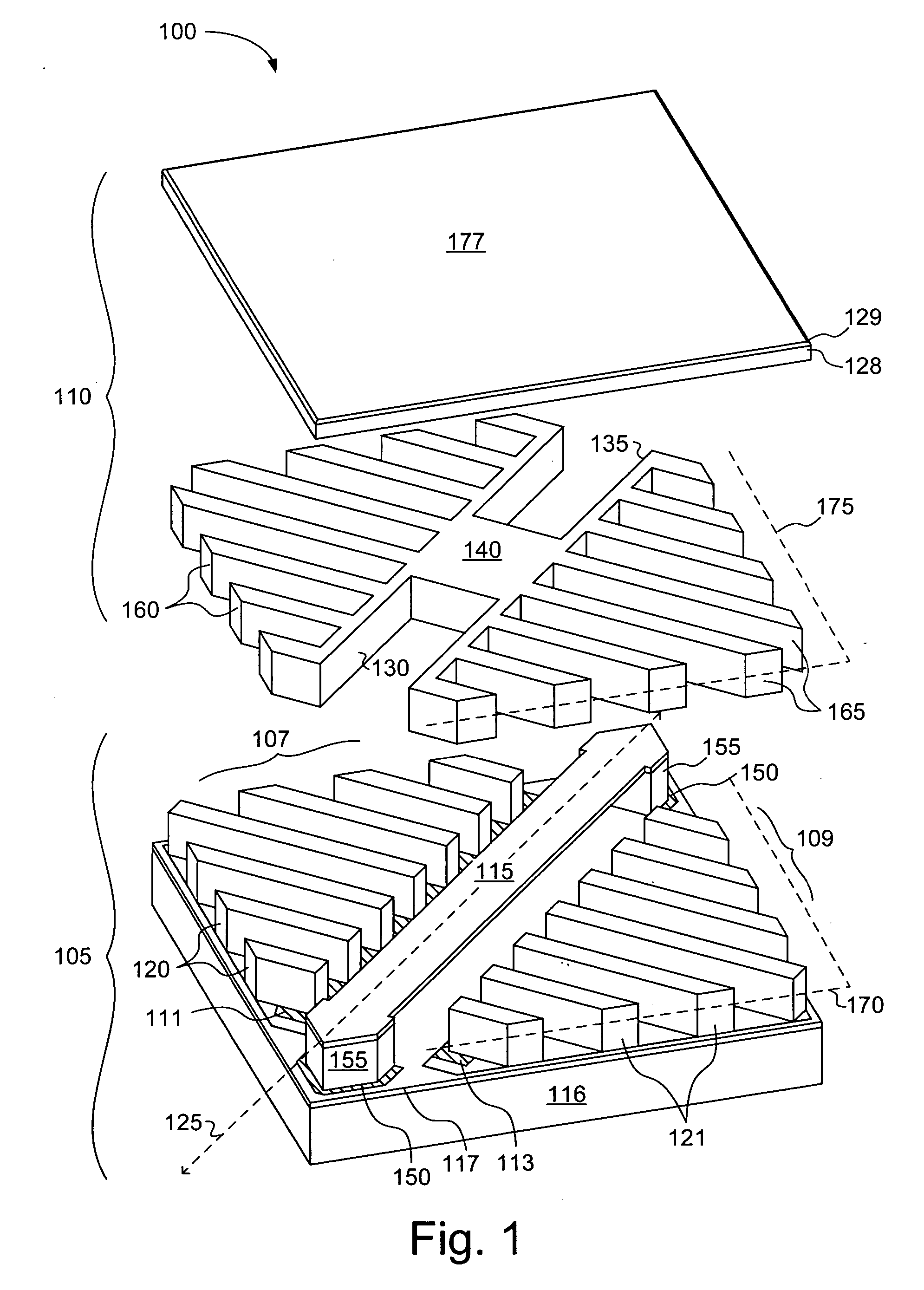

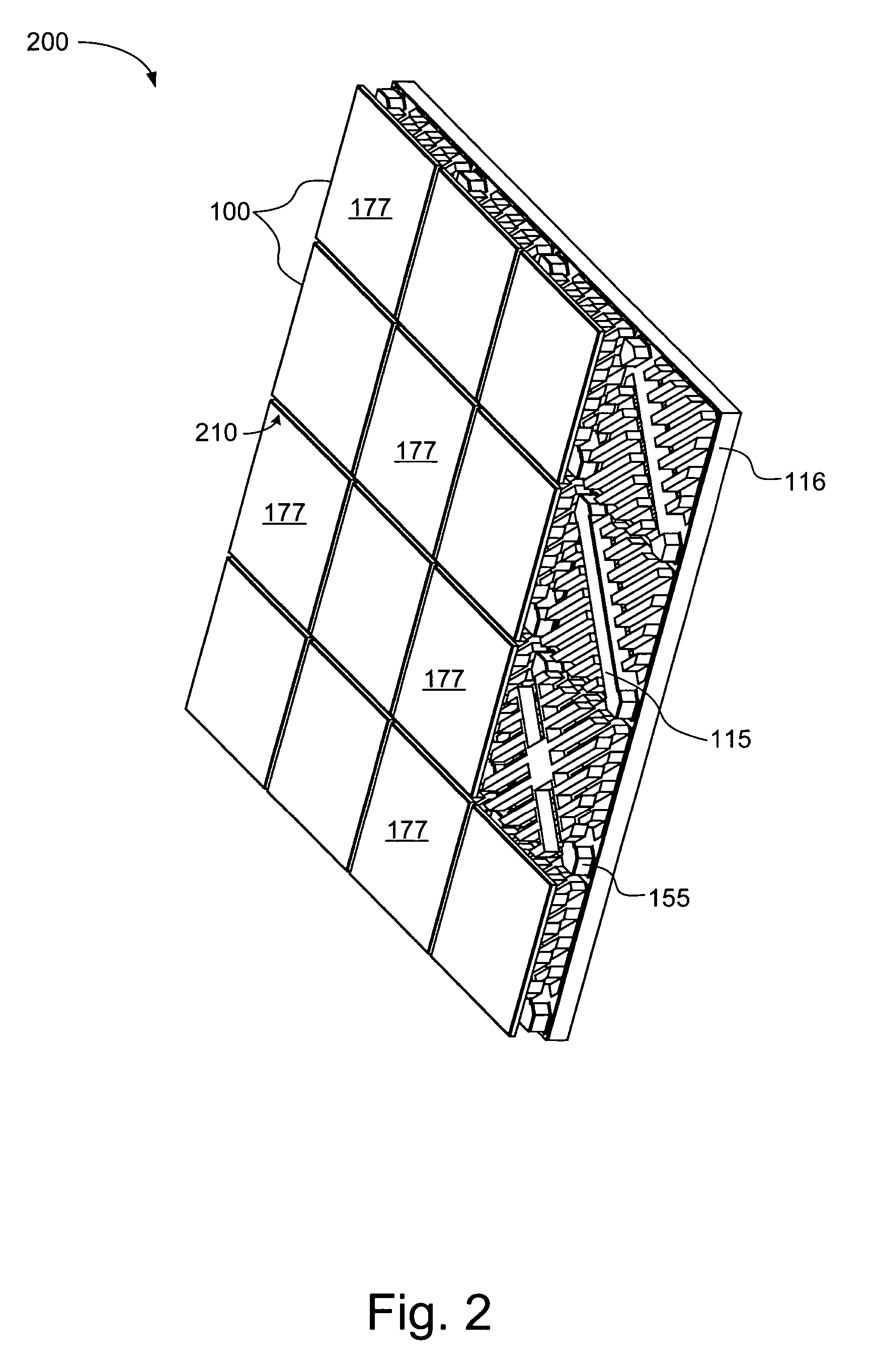

MEMS devices monolithically integrated with drive and control circuitry

InactiveUS20050002079A1Semiconductor/solid-state device manufacturingCathode-ray tube indicatorsCMOSControl electronics

Described are MEMS mirror arrays monolithically integrated with CMOS control electronics. The MEMS arrays include polysilicon or polysilicon-germanium components that are mechanically superior to metals used in other MEMS applications, but that require process temperatures not compatible with conventional CMOS technologies. CMOS circuits used with the polysilicon or polysilicon-germanium MEMS structures use interconnect materials that can withstand the high temperatures used during MEMS fabrication. These interconnect materials include doped polysilicon, polycides, and tungsten metal.

Owner:II VI DELAWARE INC

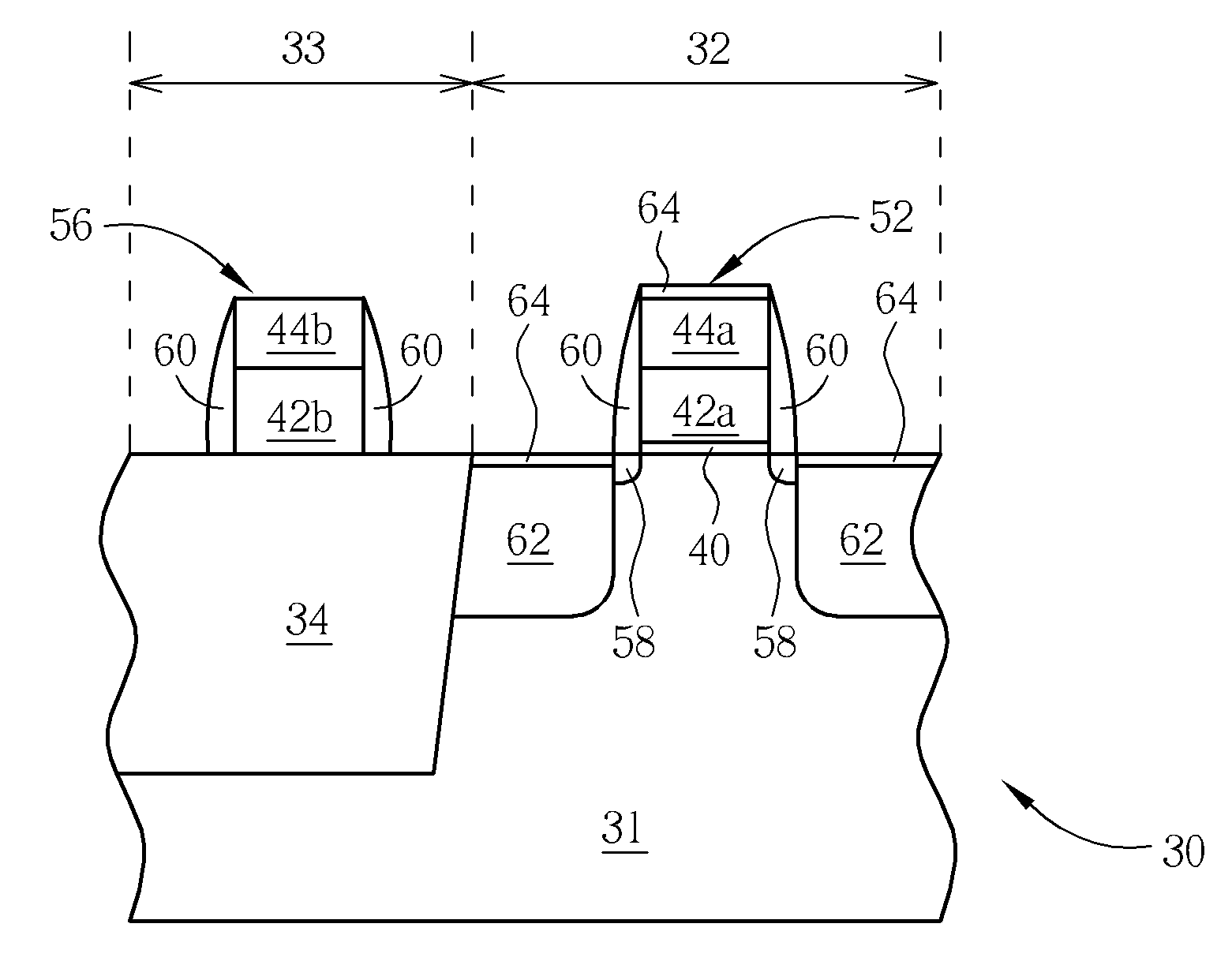

NAND Flash Memory with Densely Packed Memory Gates and Fabrication Process

NAND flash memory cell array and fabrication process in which cells having memory gates and charge storage layers are densely packed, with the memory gates in adjacent cells either overlapping or self-aligned with each other. The memory cells are arranged in rows between bit line diffusions and a common source diffusion, with the charge storage layers positioned beneath the memory gates in the cells. The memory gates are either polysilicon or polycide, and the charge storage gates are either a nitride or the combination of nitride and oxide. Programming is done either by hot electron injection from silicon substrate to the charge storage gates to build up a negative charge in the charge storage gates or by hot hole injection from the silicon substrate to the charge storage gates to build up a positive charge in the charge storage gates. Erasure is done by channel tunneling from the charge storage gates to the silicon substrate or vice versa, depending on the programming method. The array is biased so that all of the memory cells can be erased simultaneously, while programming is bit selectable.

Owner:SILICON STORAGE TECHNOLOGY

Semiconductor device with resistor pattern and method of fabricating the same

InactiveUS20060246654A1Improve sheet resistanceTransistorSolid-state devicesDevice materialLine width

Owner:SAMSUNG ELECTRONICS CO LTD

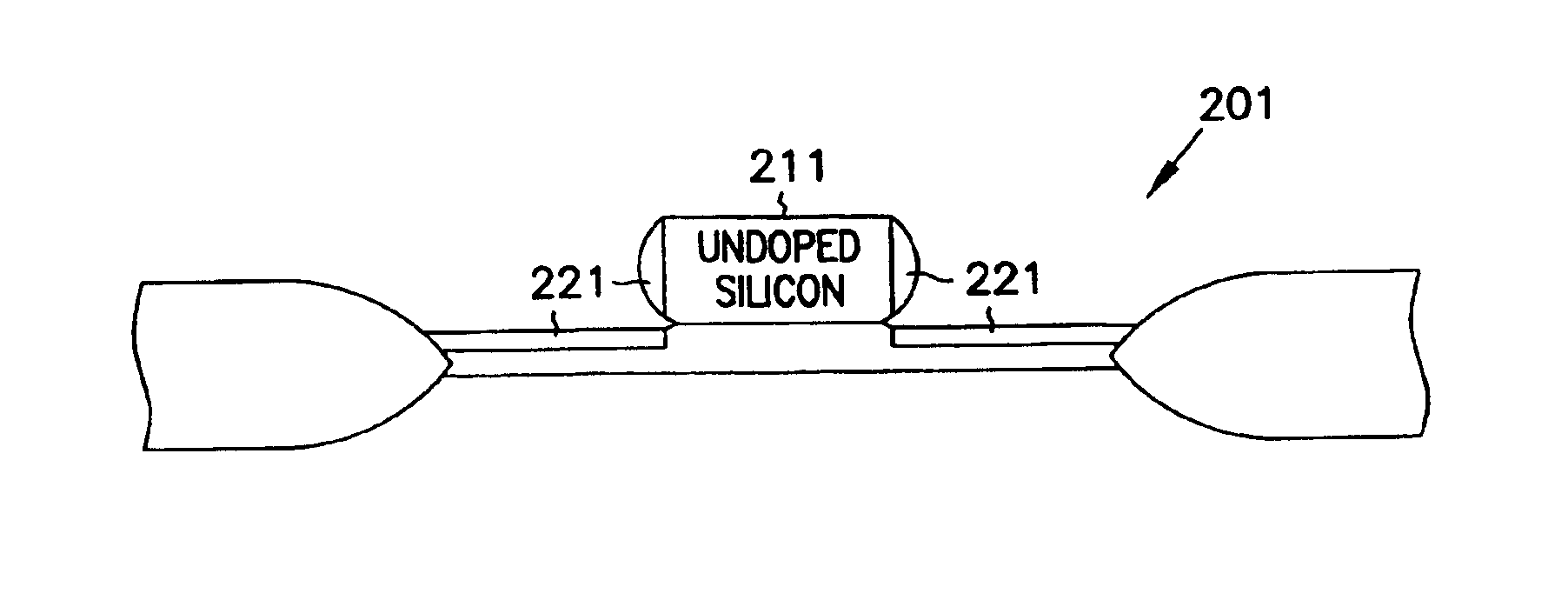

Efuse structure

InactiveUS20060157819A1Improve maintenance yieldEasy to blowSemiconductor/solid-state device detailsSolid-state devicesElectrical conductionSemiconductor

A surface of a semiconductor substrate comprises at least one electrical conduction structure and at least one eFuse. The electrical conduction structure comprises a first poly silicon layer and a first poly silicide layer formed in the first poly silicon layer. The eFuse comprises a second poly silicon layer and a second poly silicide layer formed on the second poly silicon layer. The area of the second poly silicide layer is smaller than the area of the first poly silicide layer.

Owner:UNITED MICROELECTRONICS CORP

High speed trench DMOS

InactiveUS6849899B2Lower gate resistanceReduce gate capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePropagation delay

A method for making trench DMOS is provided that utilizes polycide and refractory techniques to make trench DMOS which exhibit low gate resistance, low gate capacitance, reduced distributed RC gate propagation delay, and improved switching speeds for high frequency applications.

Owner:GEN SEMICON

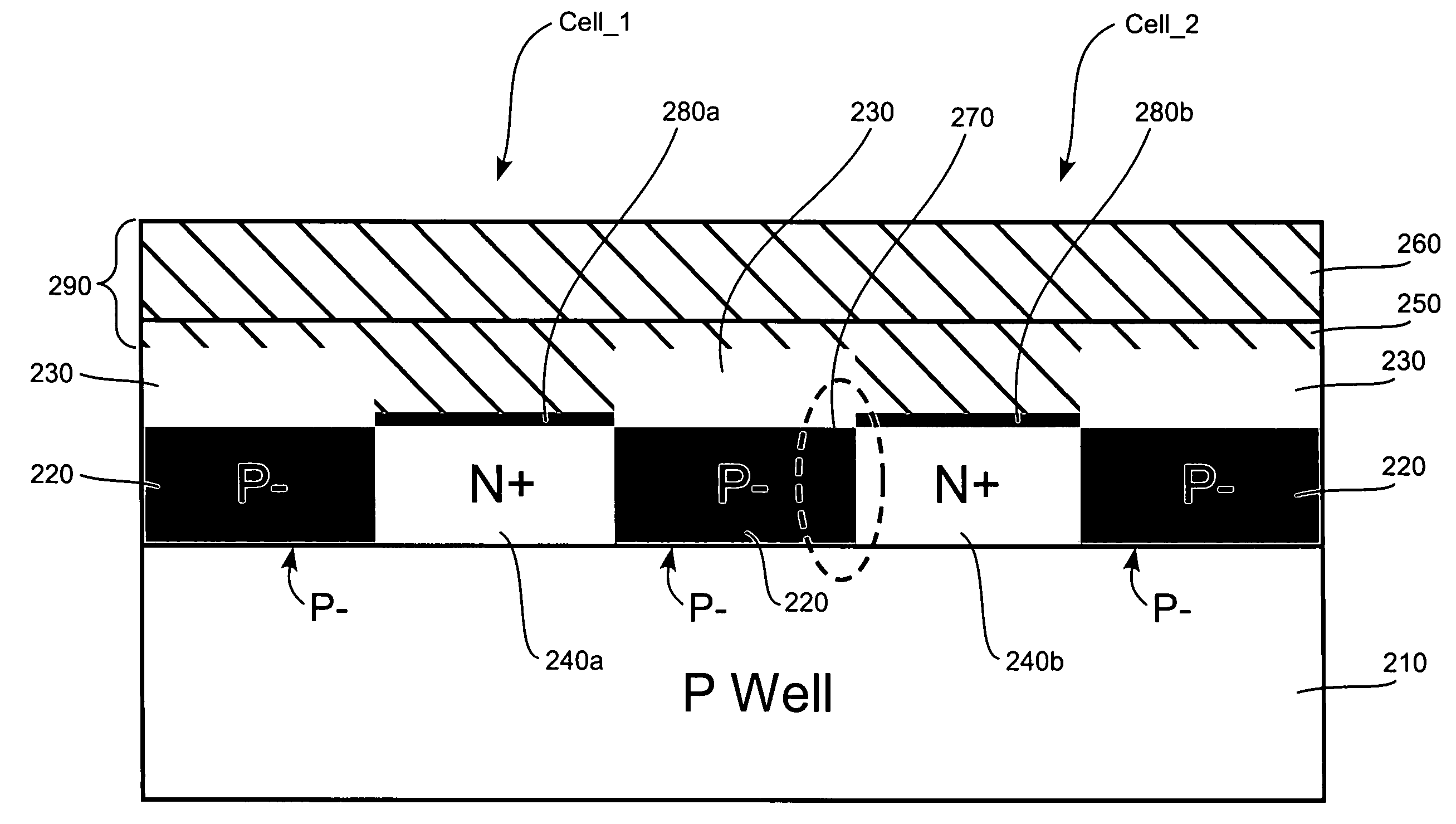

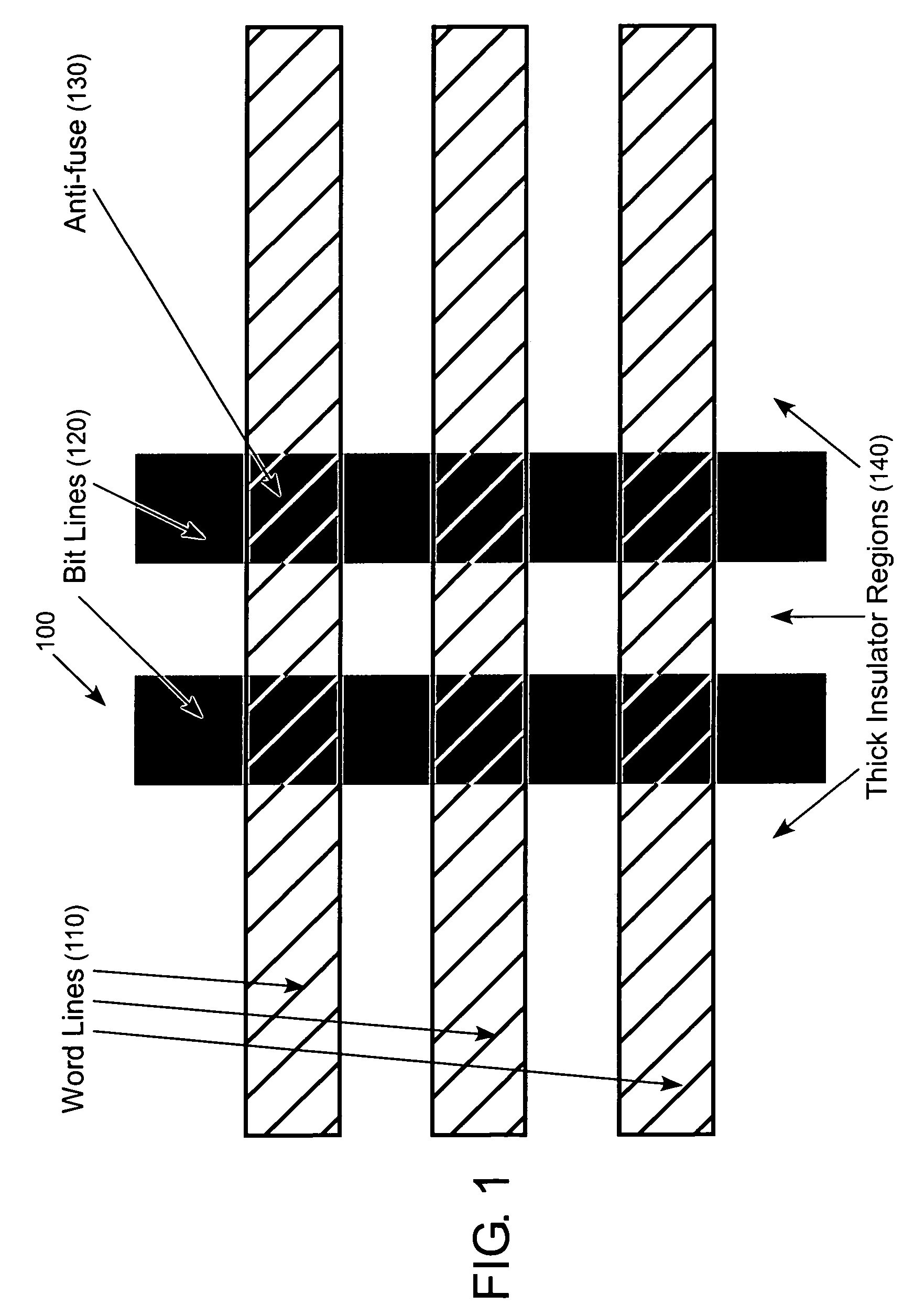

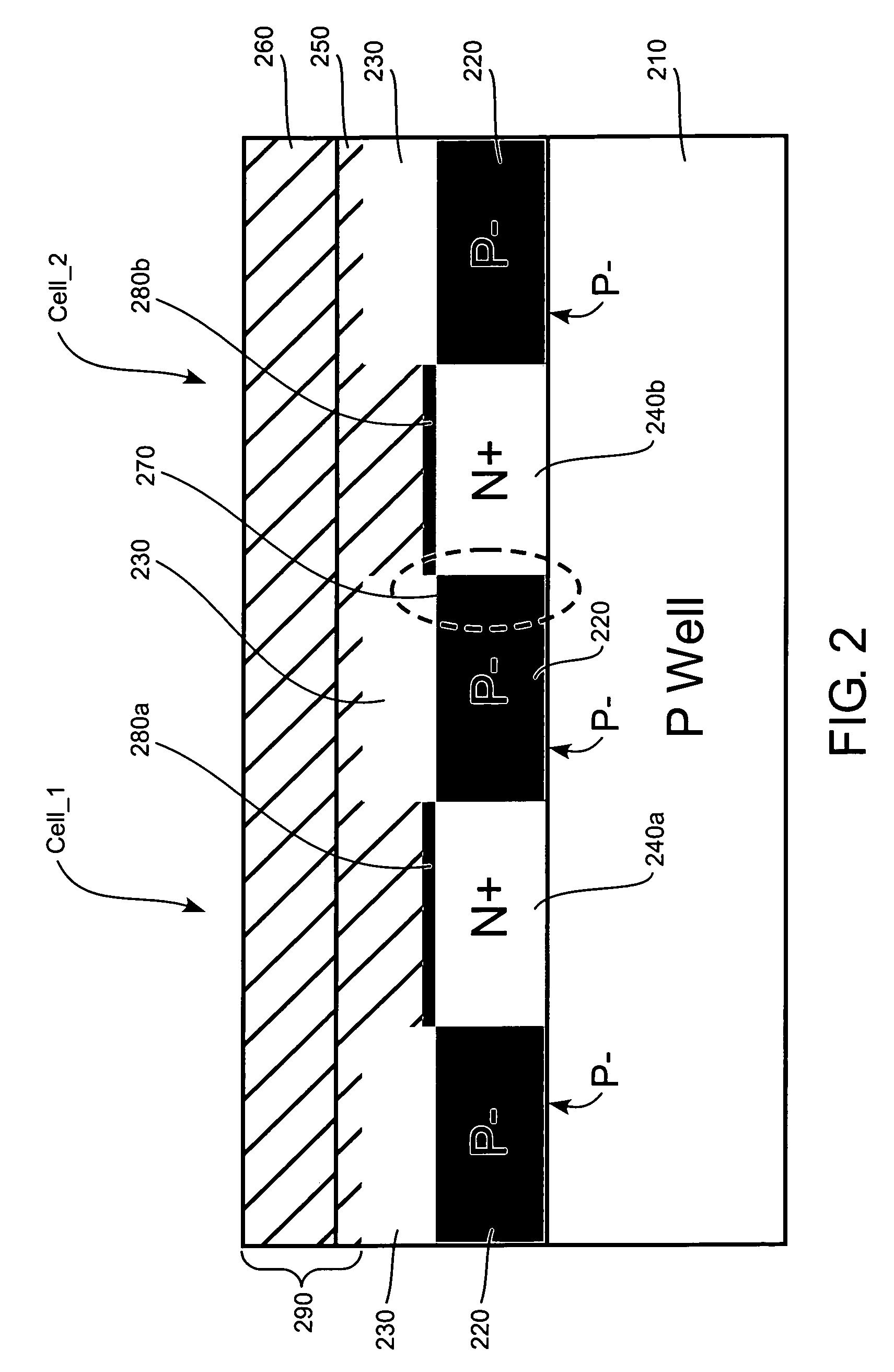

Anti-fuse one-time-programmable nonvolatile memory

InactiveUS7638855B2Low costSimple structureSemiconductor/solid-state device detailsSolid-state devicesBit lineAntifuse

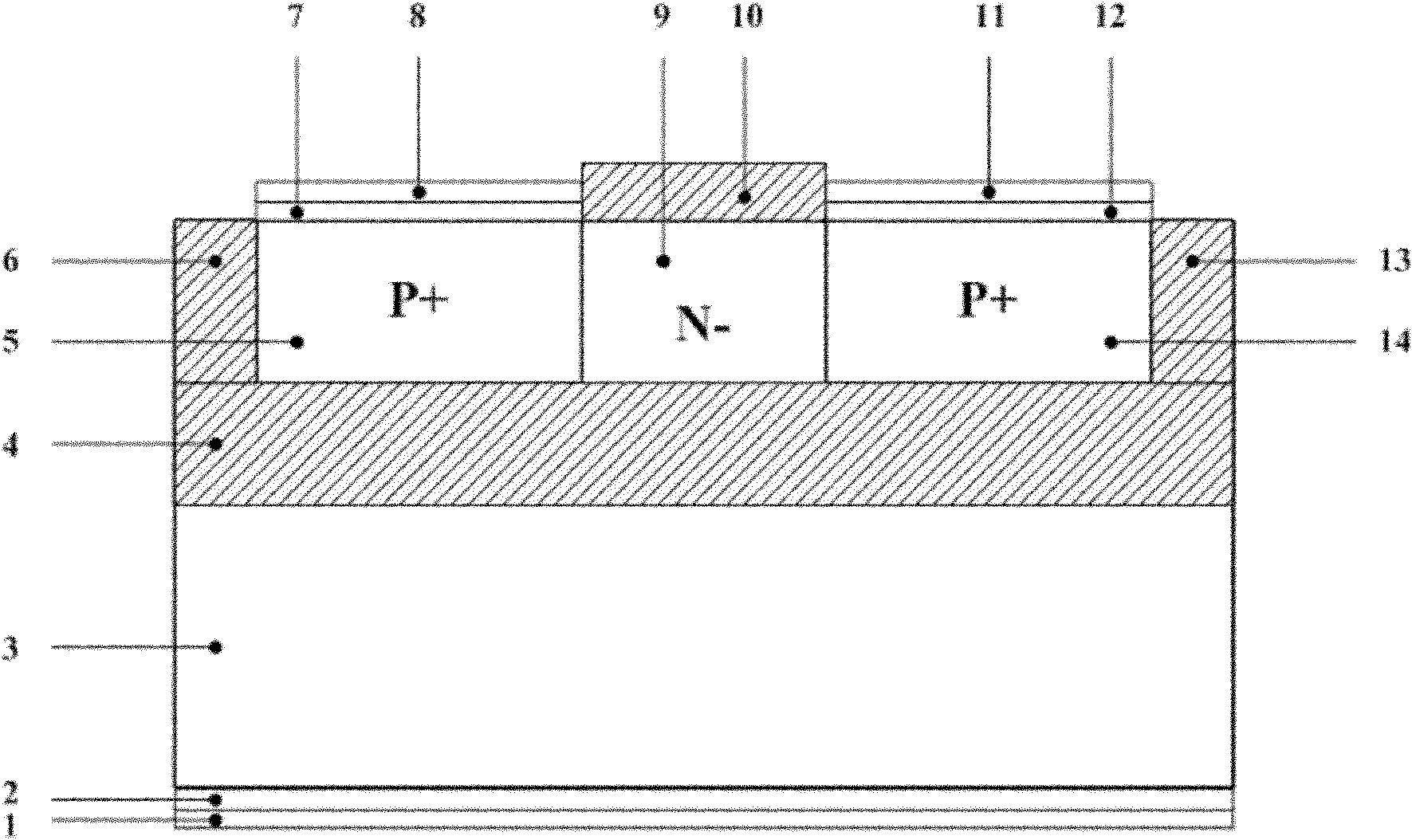

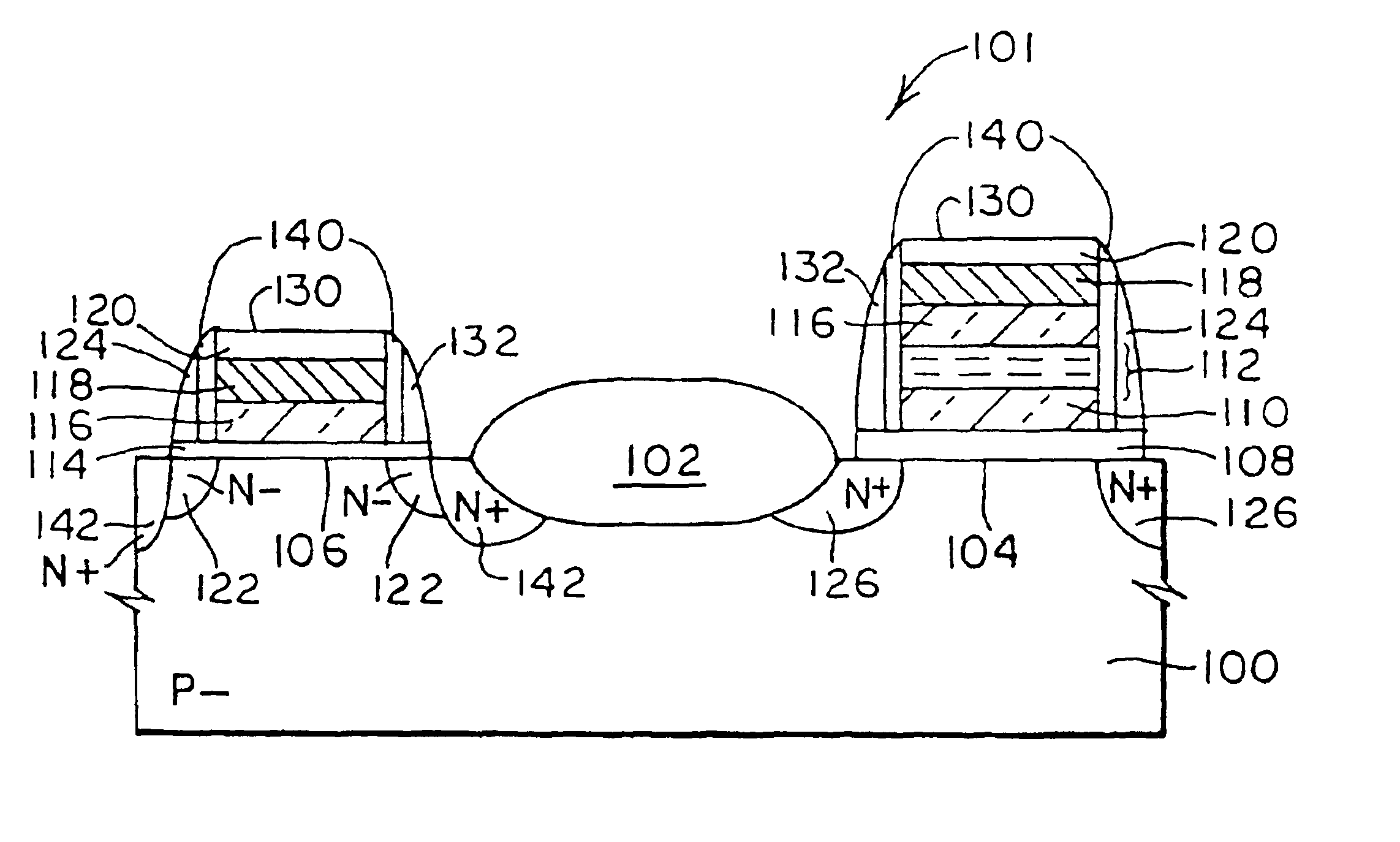

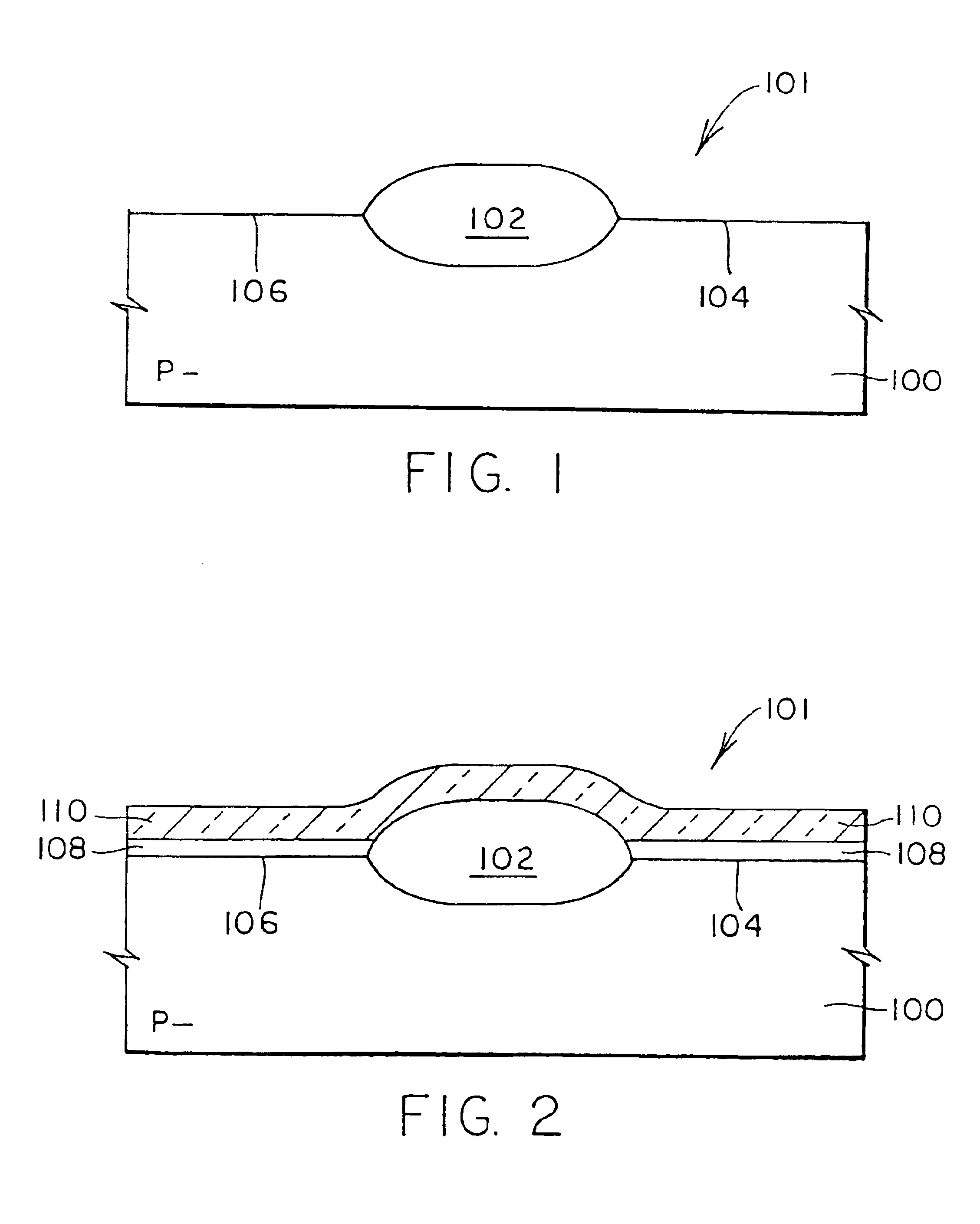

An anti-fuse one-time-programmable (OTP) nonvolatile memory cell has a P well substrate with two P− doped regions. Another N+ doped region, functioning as a bit line, is positioned adjacent and between the two P− doped regions on the substrate. An anti-fuse is defined over the N+ doped region. Two insulator regions are deposited over the two P− doped regions. An impurity doped polysilicon layer is defined over the two insulator regions and the anti-fuse. A polycide layer is defined over the impurity doped polysilicon layer. The polycide layer and the polysilicon layer function as a word line. A programmed region, i.e., a link, functioning as a diode, is formed on the anti-fuse after the anti-fuse OTP nonvolatile memory cell is programmed. The array structure of anti-fuse OTP nonvolatile memory cells and methods for programming, reading, and fabricating such a cell are also disclosed.

Owner:MACRONIX INT CO LTD

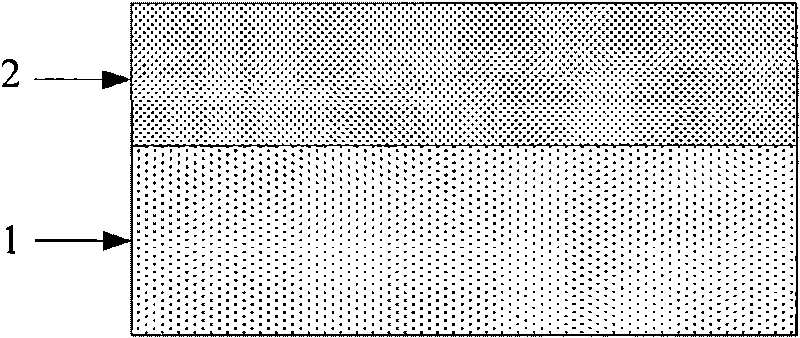

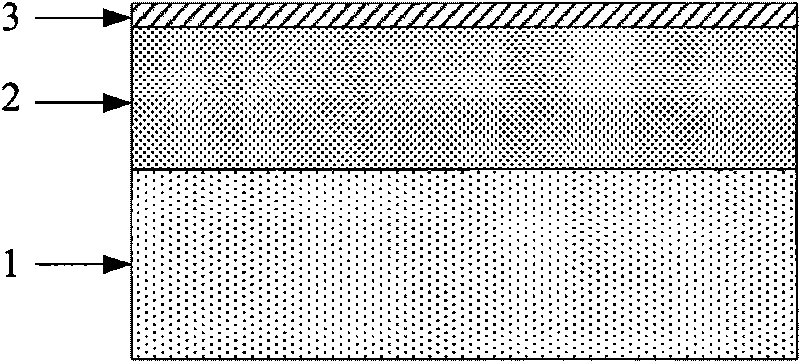

Silicon rich barrier layers for integrated circuit devices

InactiveUS6903425B2Inhibited DiffusionPrevent penetrationSolid-state devicesSemiconductor/solid-state device manufacturingDopantSubject matter

Semiconductor devices and memory cells are formed using silicon rich barrier layers to prevent diffusion of dopants from differently doped polysilicon films to overlying conductive layers or to substrates. A polycilicide gate electrode structure may be formed using the silicon rich barrier layers. Methods of forming the semiconductor devices and memory cells are also provided. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that is will not be used to interpret or limit the scope or meaning of the claims. 37 CFR 1.72(b).

Owner:MICRON TECH INC

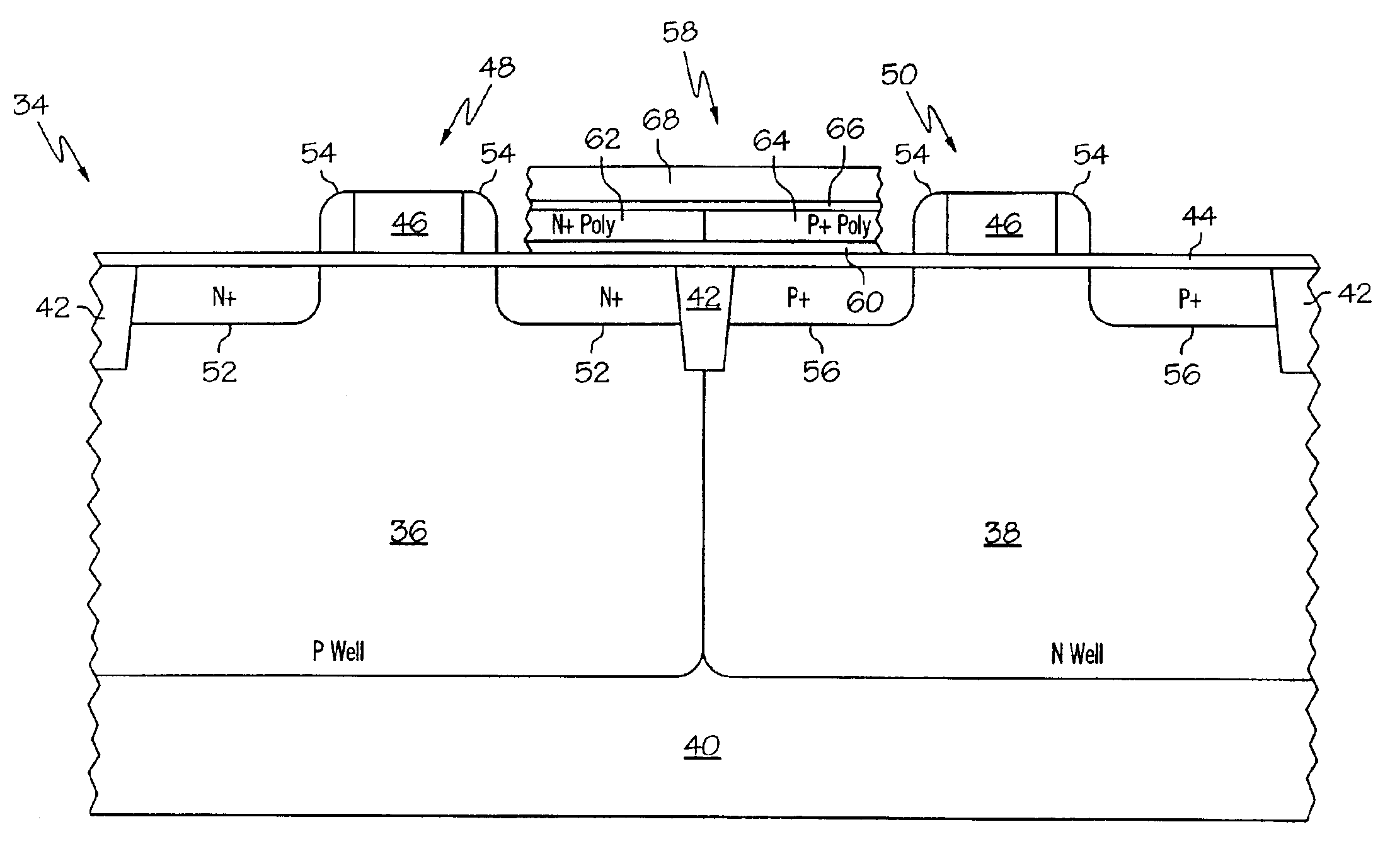

CMOS device with dual polycide gates and method of manufacturing the same

ActiveUS20070004119A1Prevent a dopant inter-diffusionStabilize gate characteristicTransistorSolid-state devicesCMOSBit line

A CMOS device having dual polycide gates is formed by first providing a silicon substrate, which is divided into a cell area and a peripheral circuit area and has a device isolation layer, a P-well, and a N-well in the peripheral circuit area. The n+ polycide gate at the P-well and the p+ polycide gate at the N-well are formed. An interlayer dielectric layer is formed on the resultant of the silicon substrate having the n+ polycide gate and the p+ polycide gate. A first bit-line contact hole for exposing the n+ polycide gate is formed, and a second bit-line contact hole for exposing the p+ polycide gate is formed. Bit-lines with a bridge structure on the interlayer dielectric layer is formed. The bit-lines simultaneously contact the n+ polycide gate and the p+ polycide gate through the first and second bit-line contact holes.

Owner:SK HYNIX INC

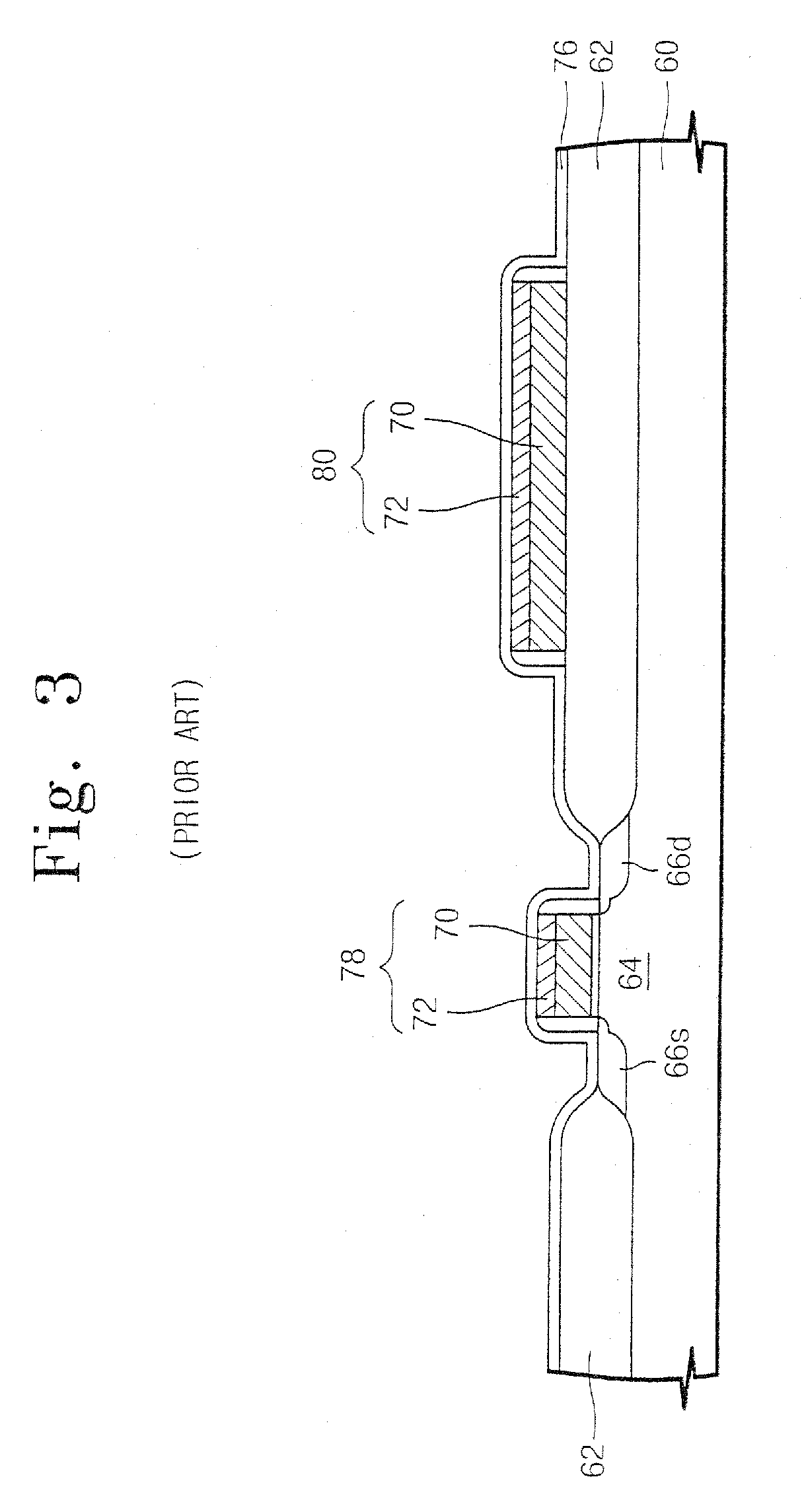

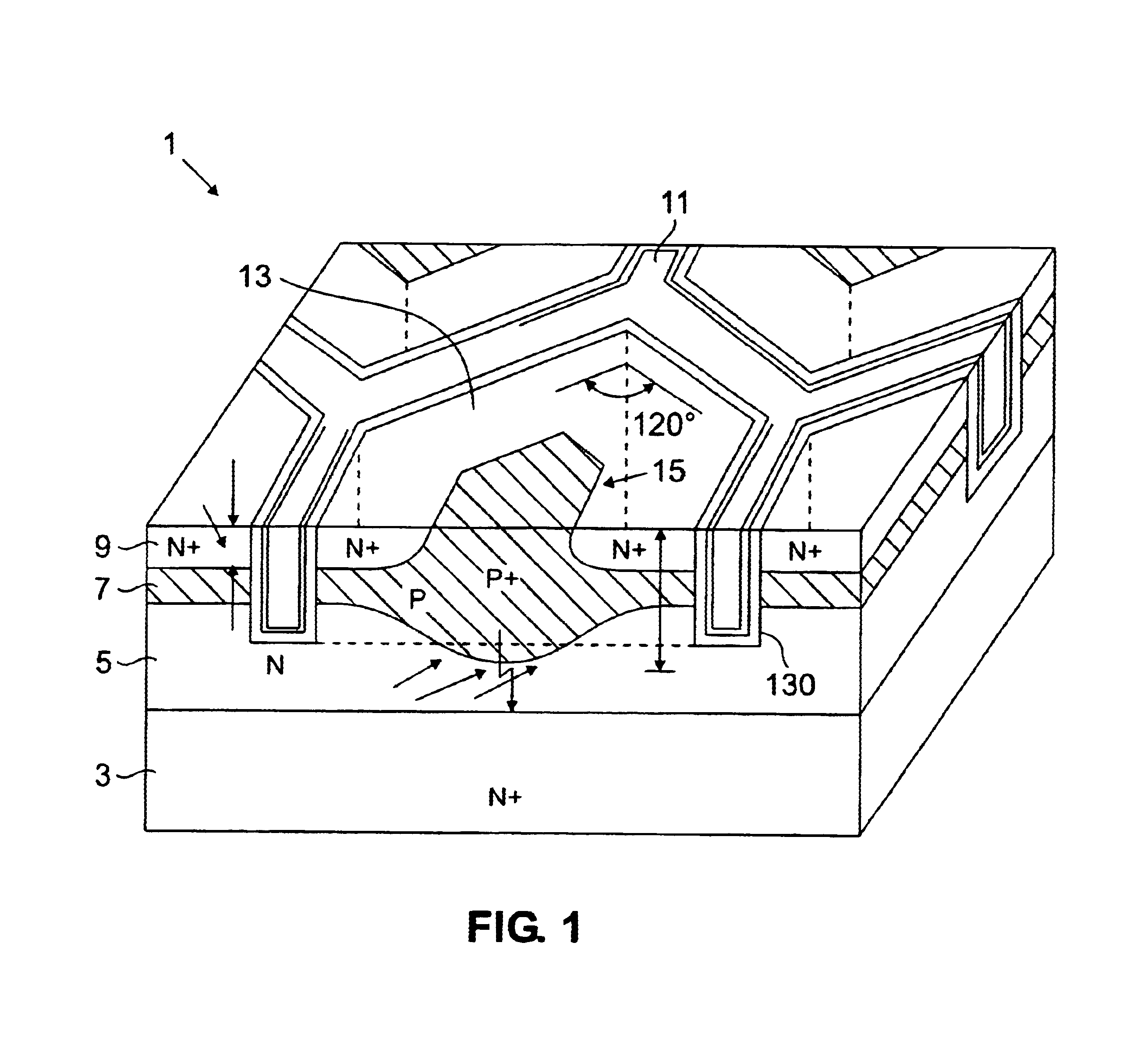

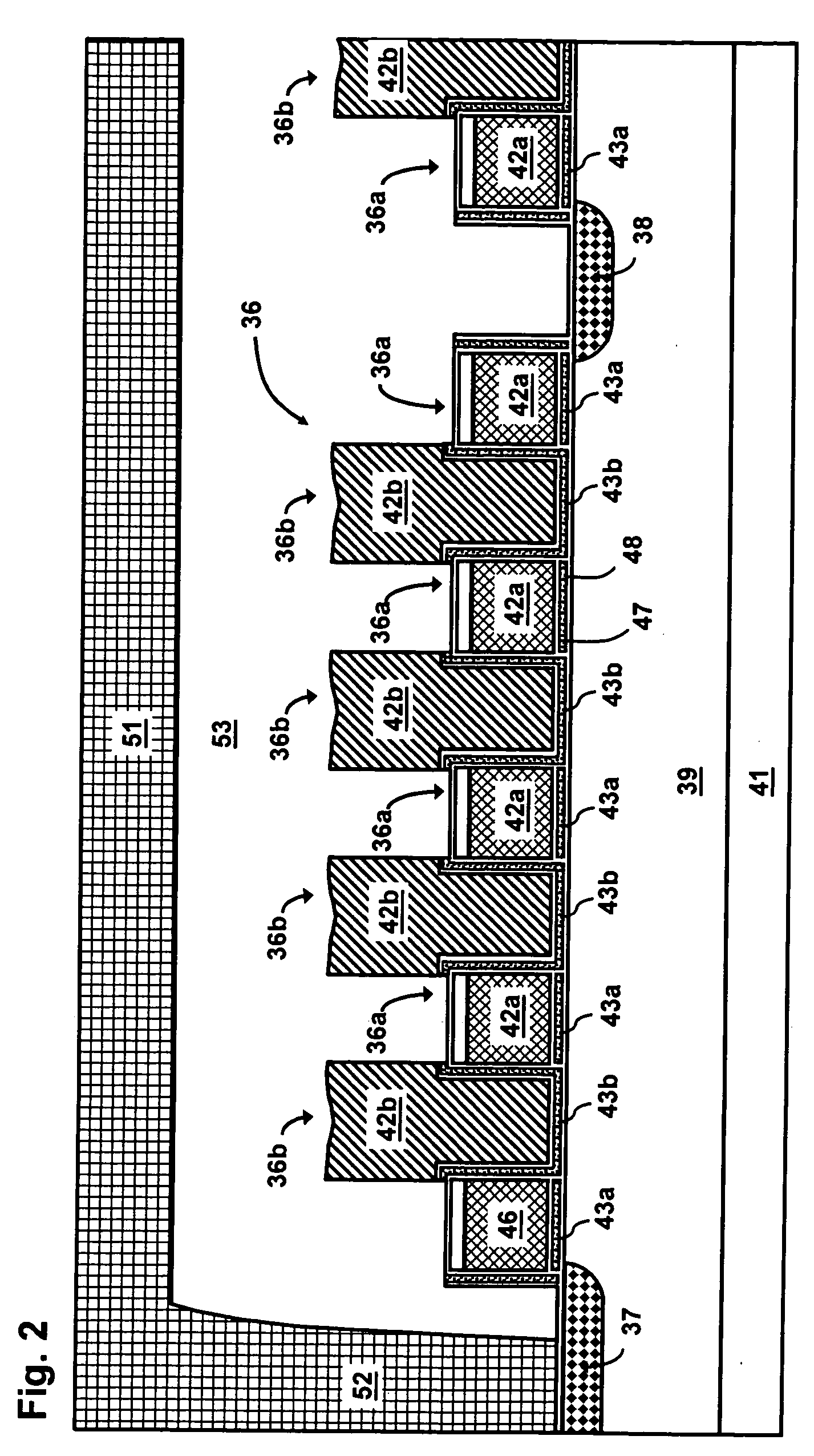

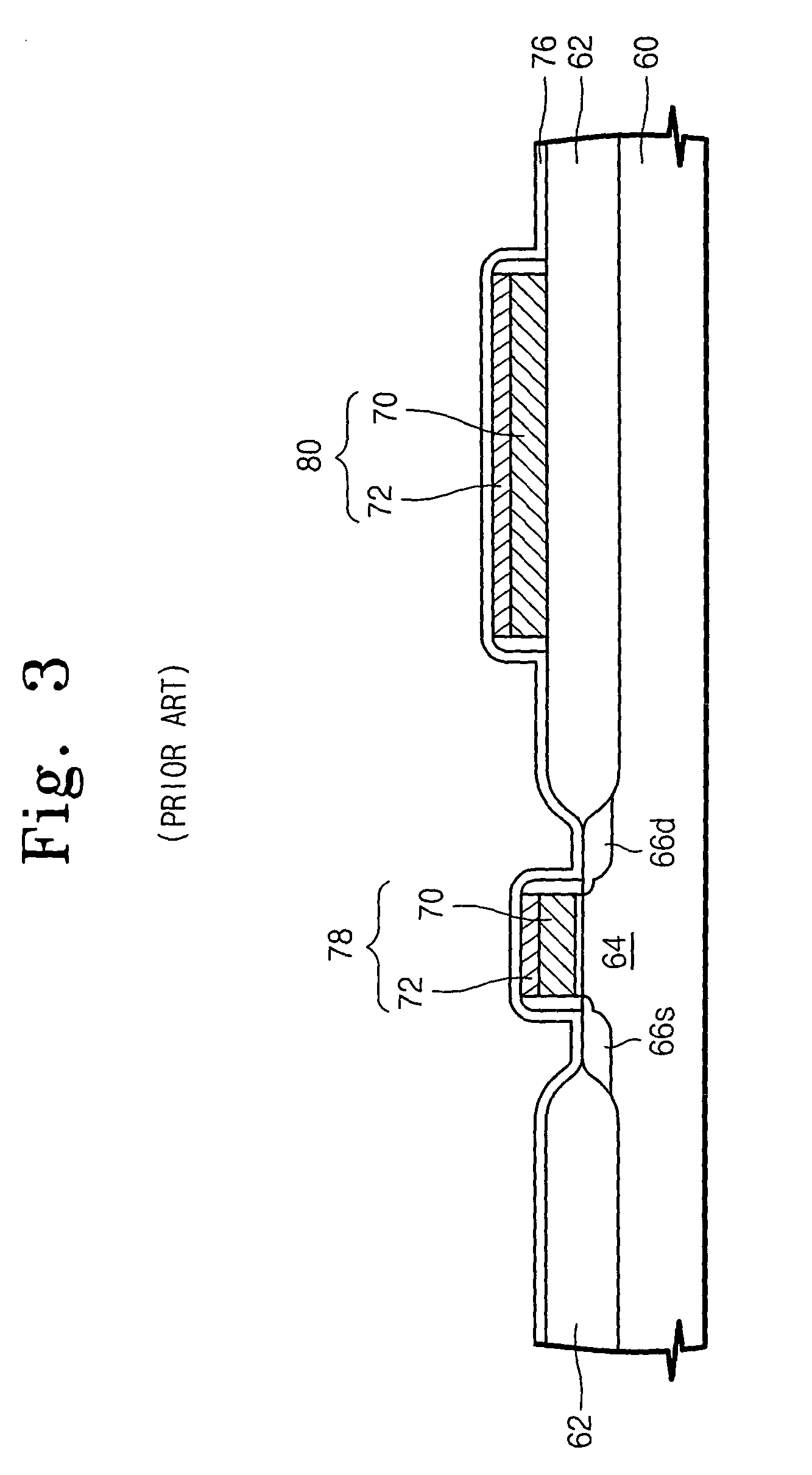

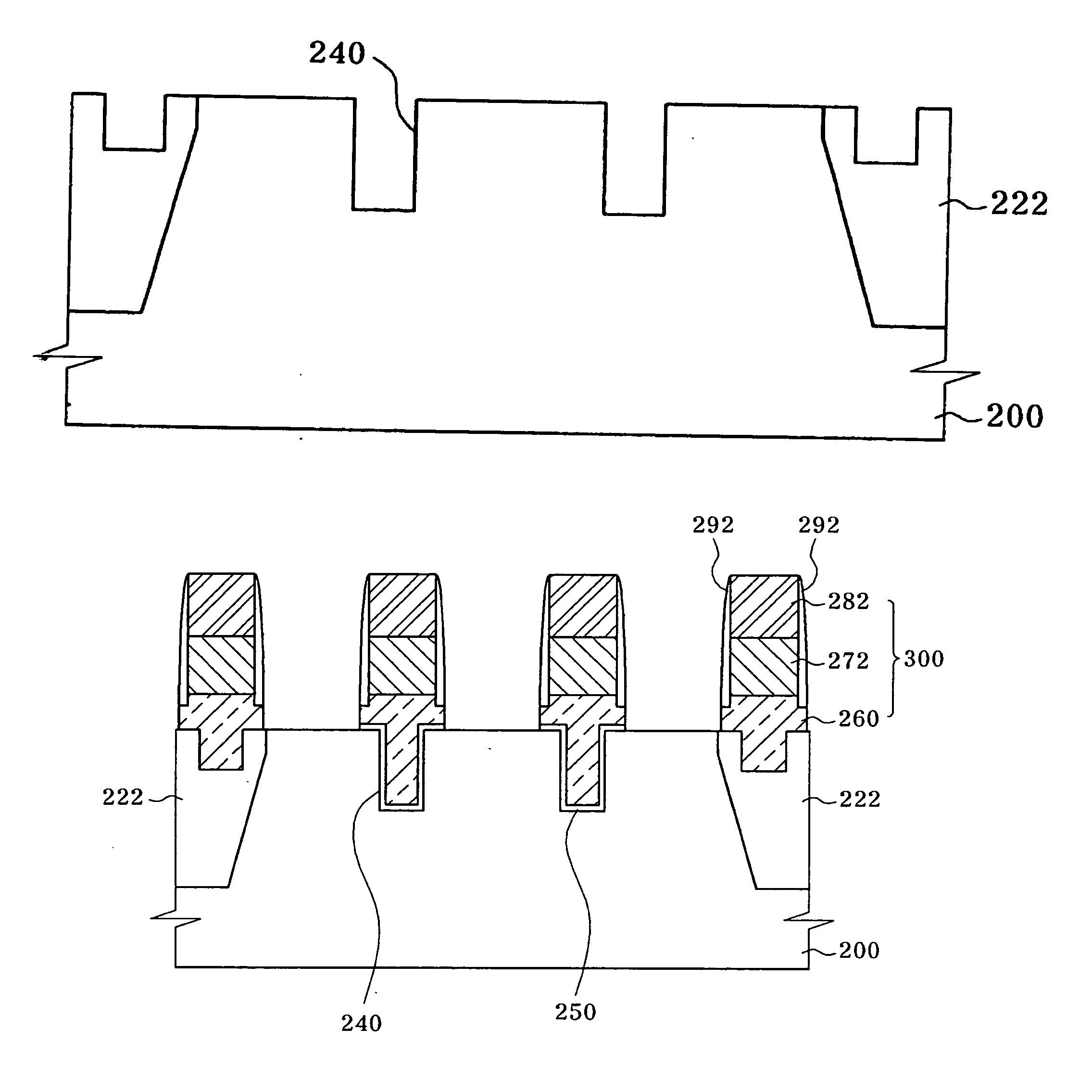

Method for making y-shaped multi-fin stacked capacitors for dynamic random access memory cells

InactiveUS6083790ACost-effective manufacturing processTransistorSolid-state devicesCapacitanceBit line

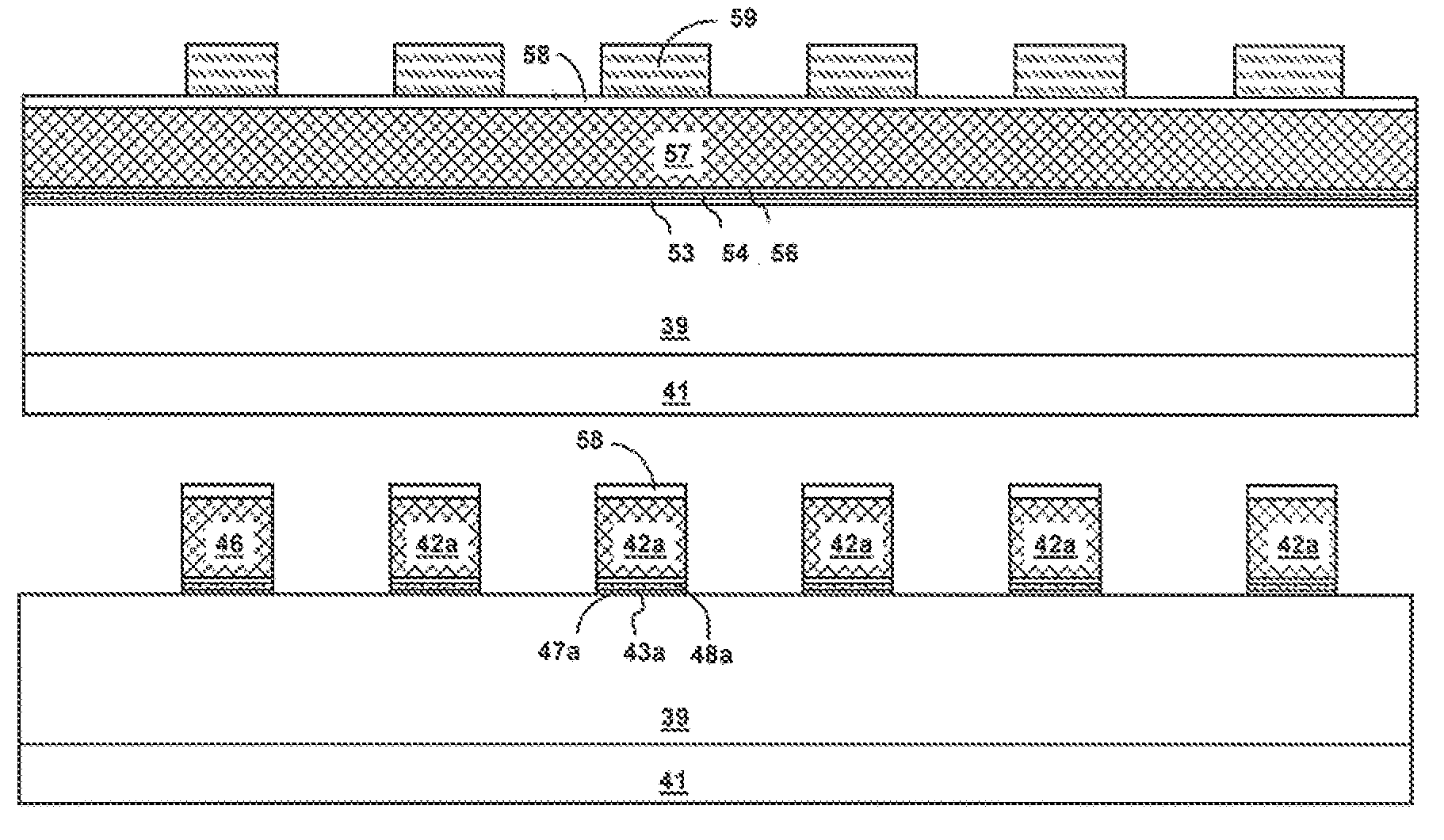

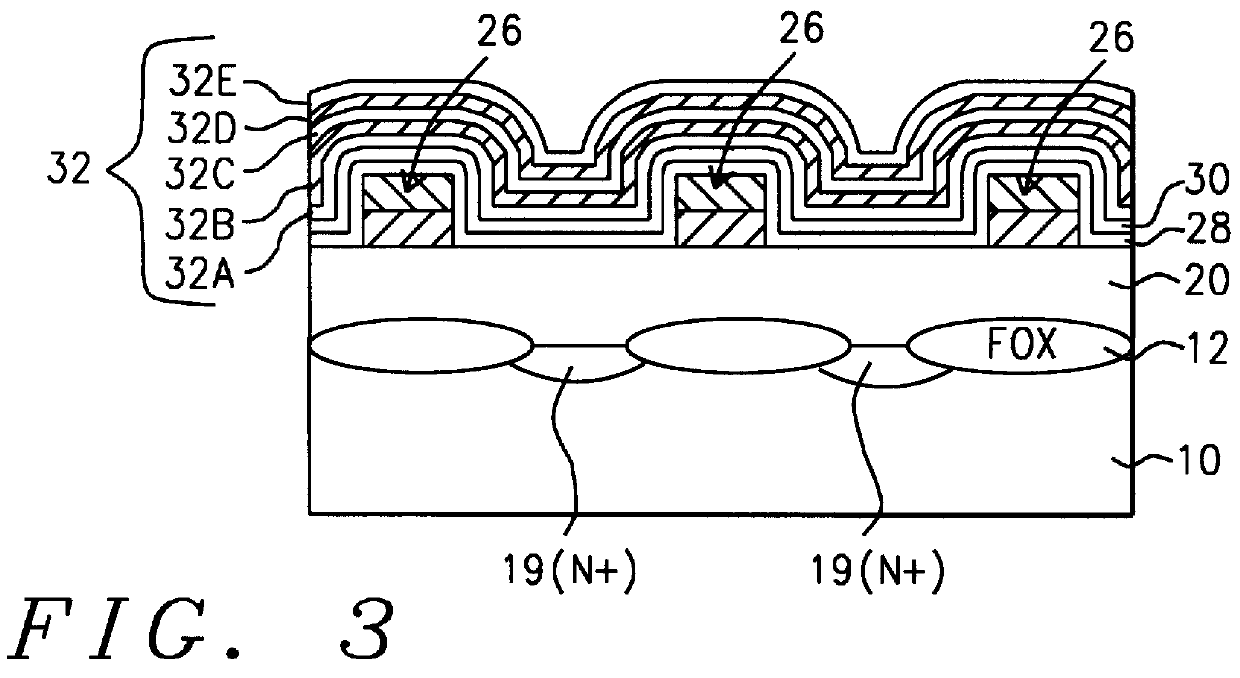

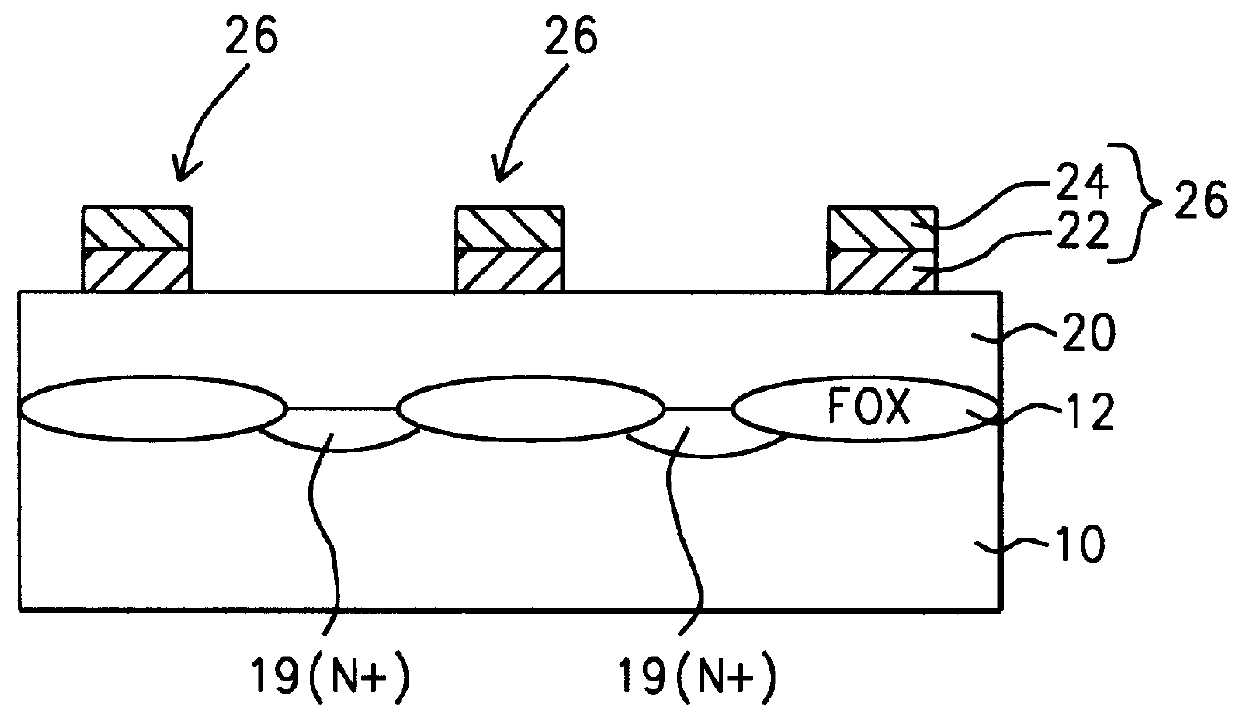

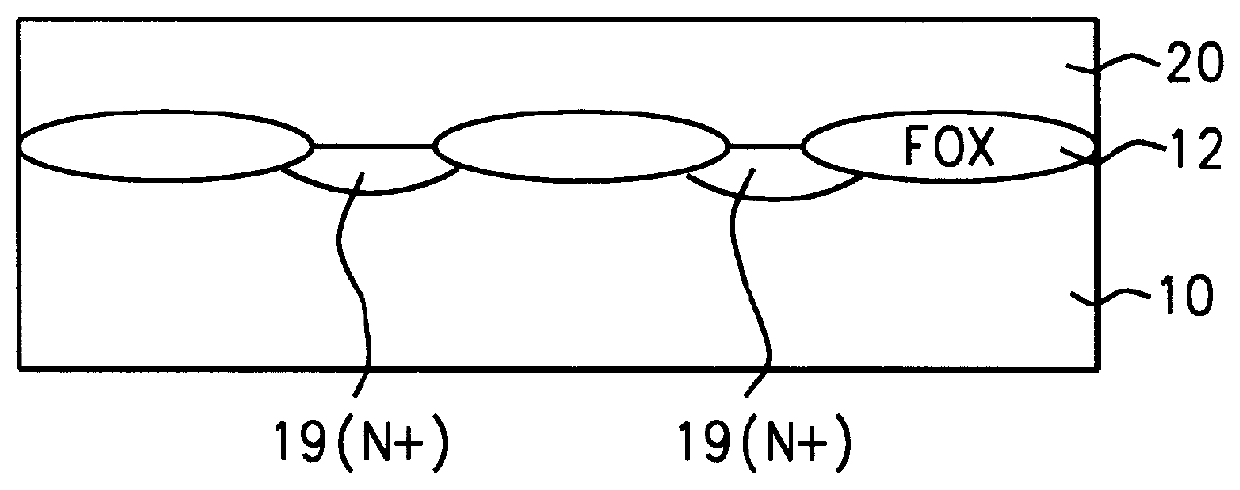

An array of DRAM cells having Y-shaped multi-fin stacked capacitors with increased capacitance is achieved. A planar first insulating layer is formed over the semi-conductor devices on the substrate. Polycide bit lines are formed on the first insulating layer, and a second insulating layer and a silicon nitride (Si3N4) etch-stop layer are conformally deposited. A multilayer, composed of a alternating insulating and polysilicon layers, is conformally deposited over the bit lines. Capacitor node contact openings are etched in the multilayer and in the underlying layers to the substrate. A fourth polysilicon layer is deposited sufficiently thick to fill the node contact openings and to form the node contacts. The multilayer is then patterned to leave portions over the node contacts, and an isotropic etch is used to remove the insulating layers exposed in the sidewalls of the patterned multilayer to provide Y-shaped multi-fin capacitor bottom electrodes over the bit lines. These Y-shaped multi-fin capacitors increase the capacitance by 37% over T-shaped multi-fin capacitors. The DRAM capacitors are then completed by forming an interelectrode dielectric layer on the bottom electrodes and by depositing a fifth polysilicon layer to form the capacitor top electrodes.

Owner:TAIWAN SEMICON MFG CO LTD

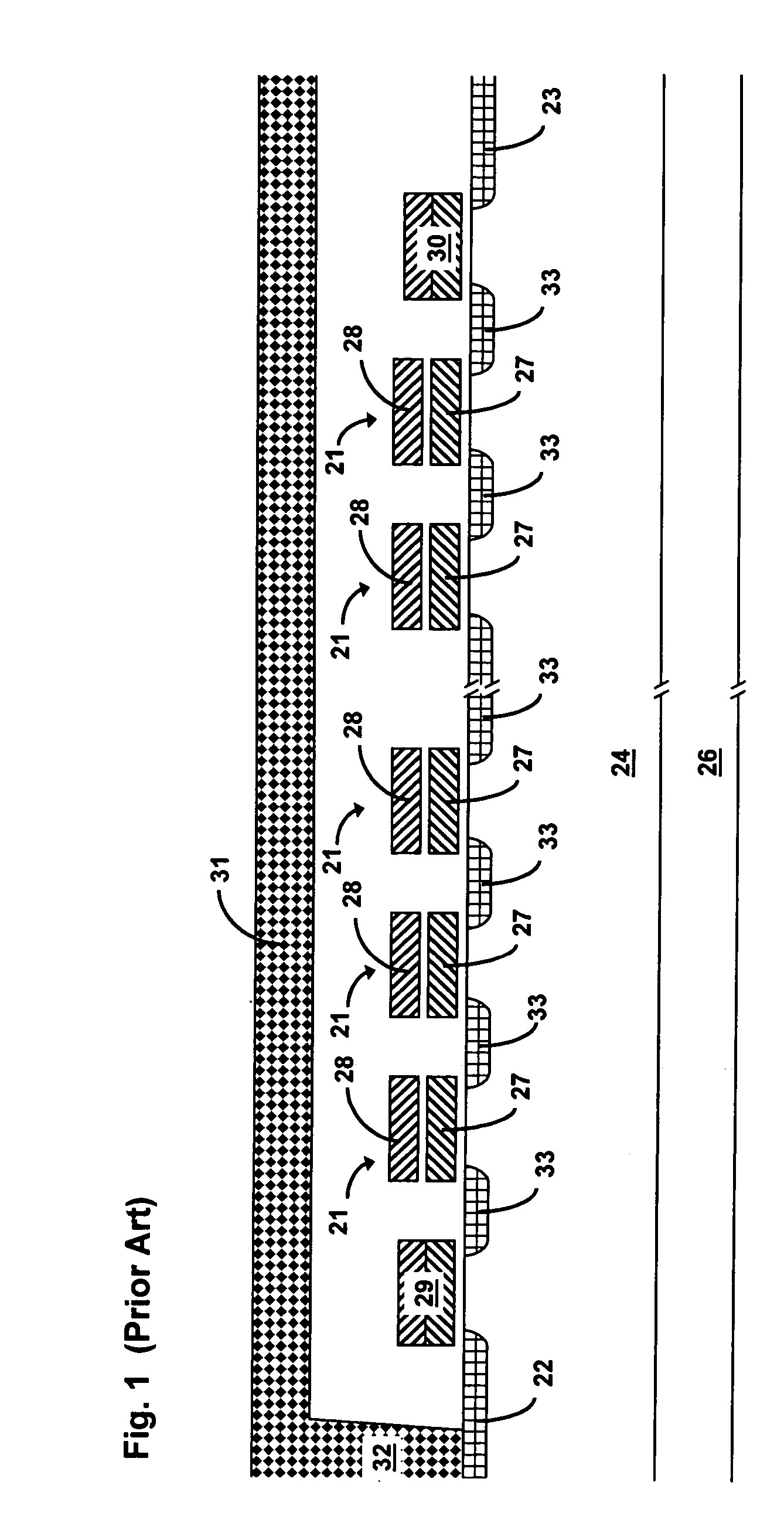

Integrated stacked capacitor and method of fabricating same

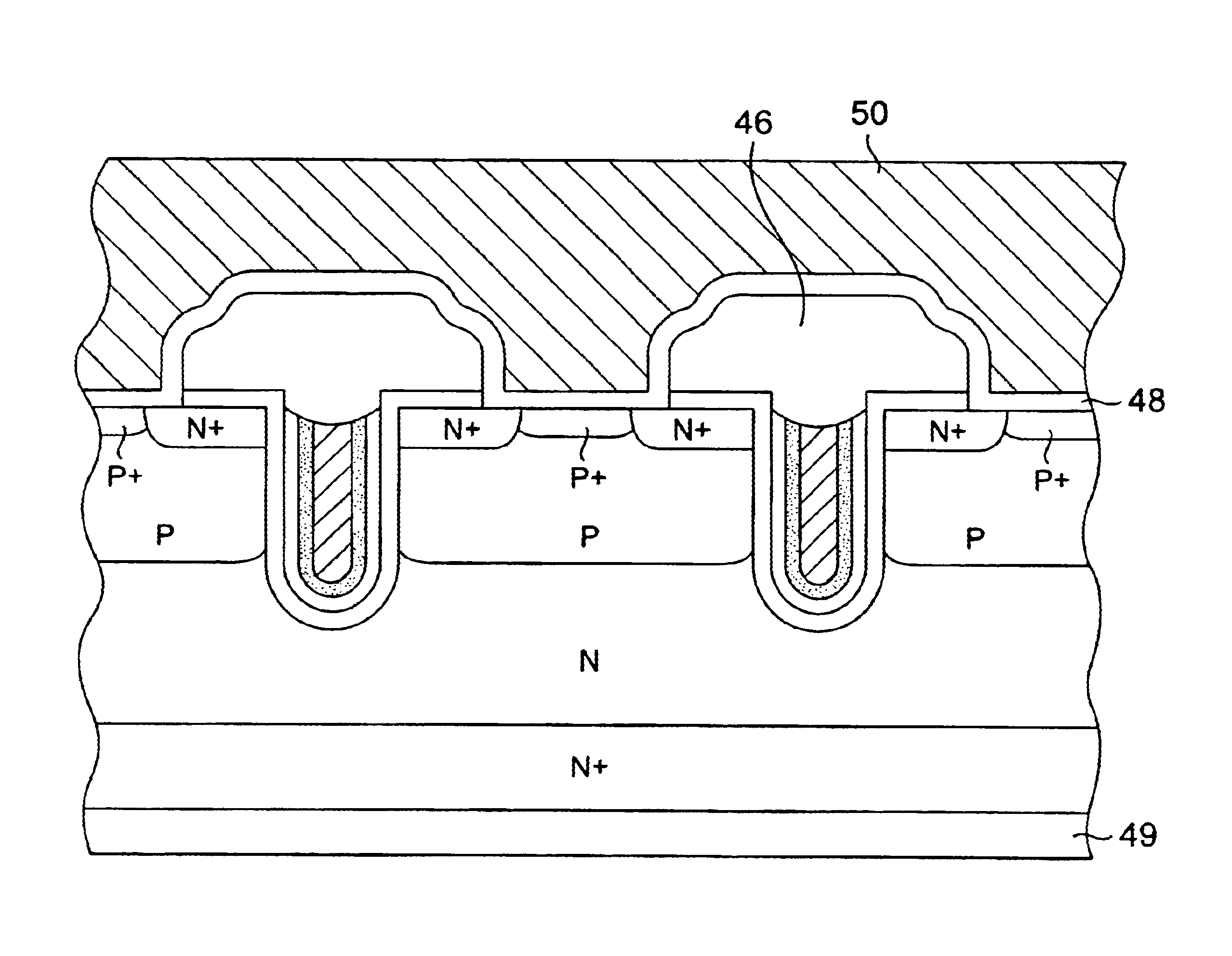

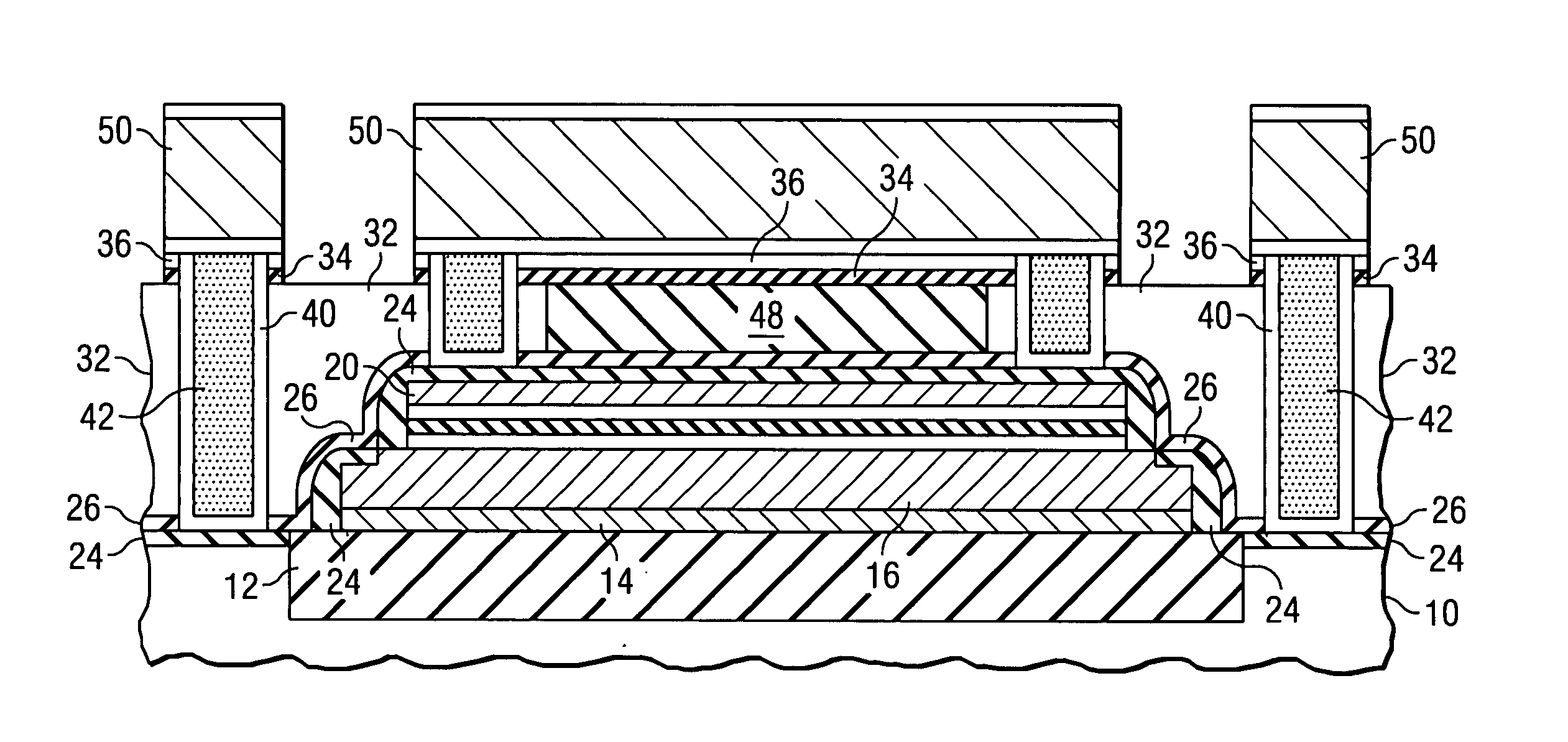

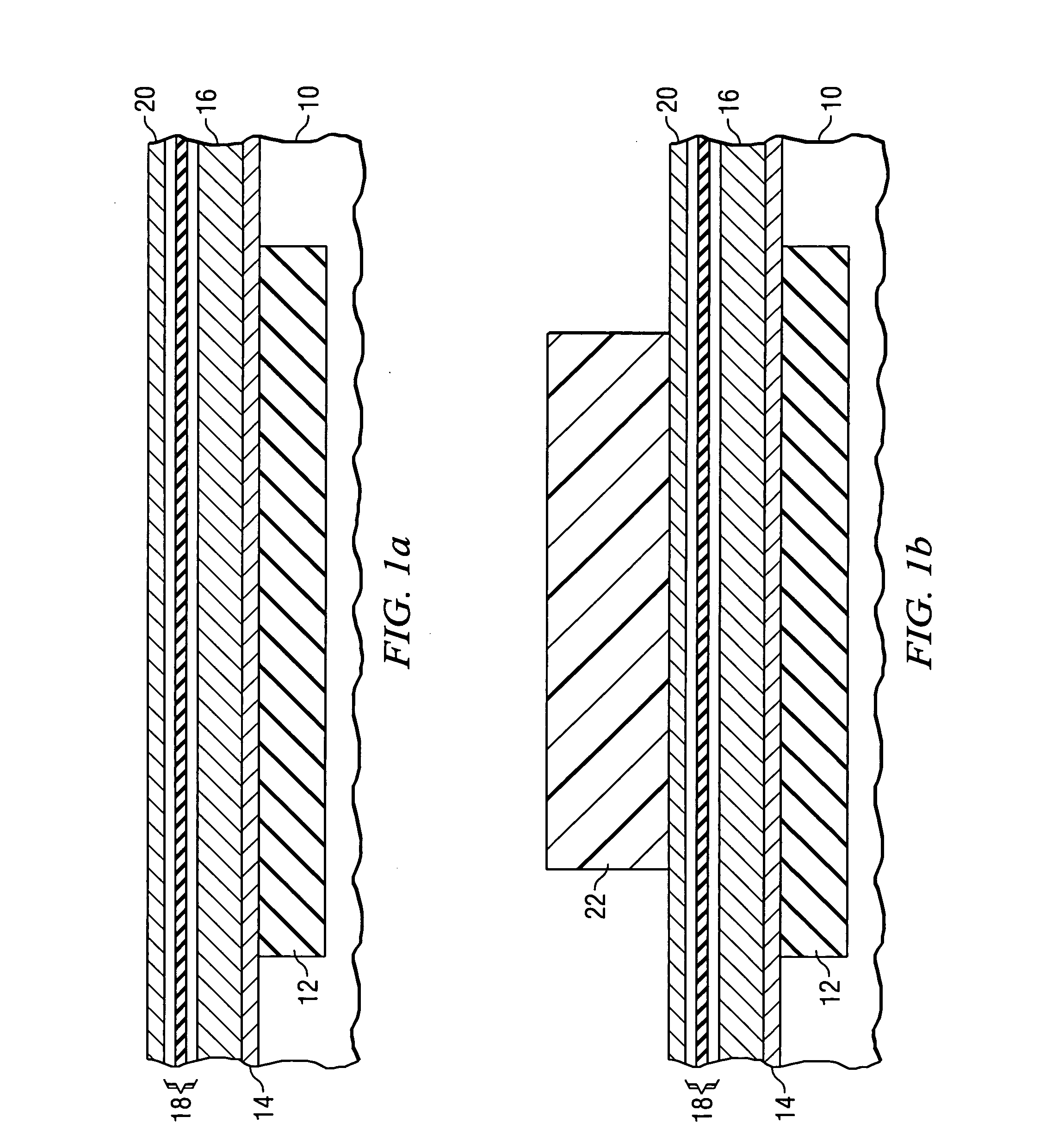

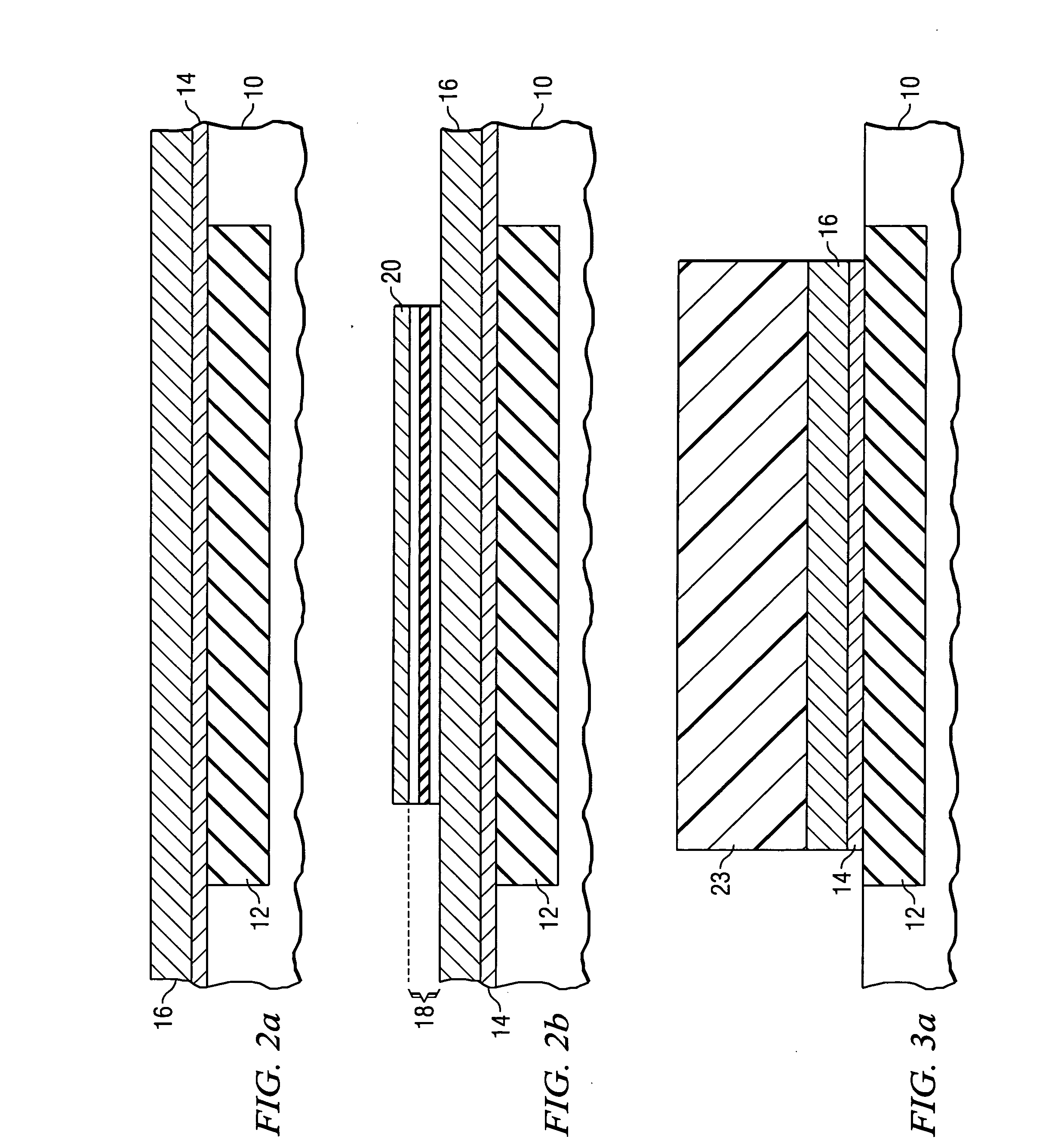

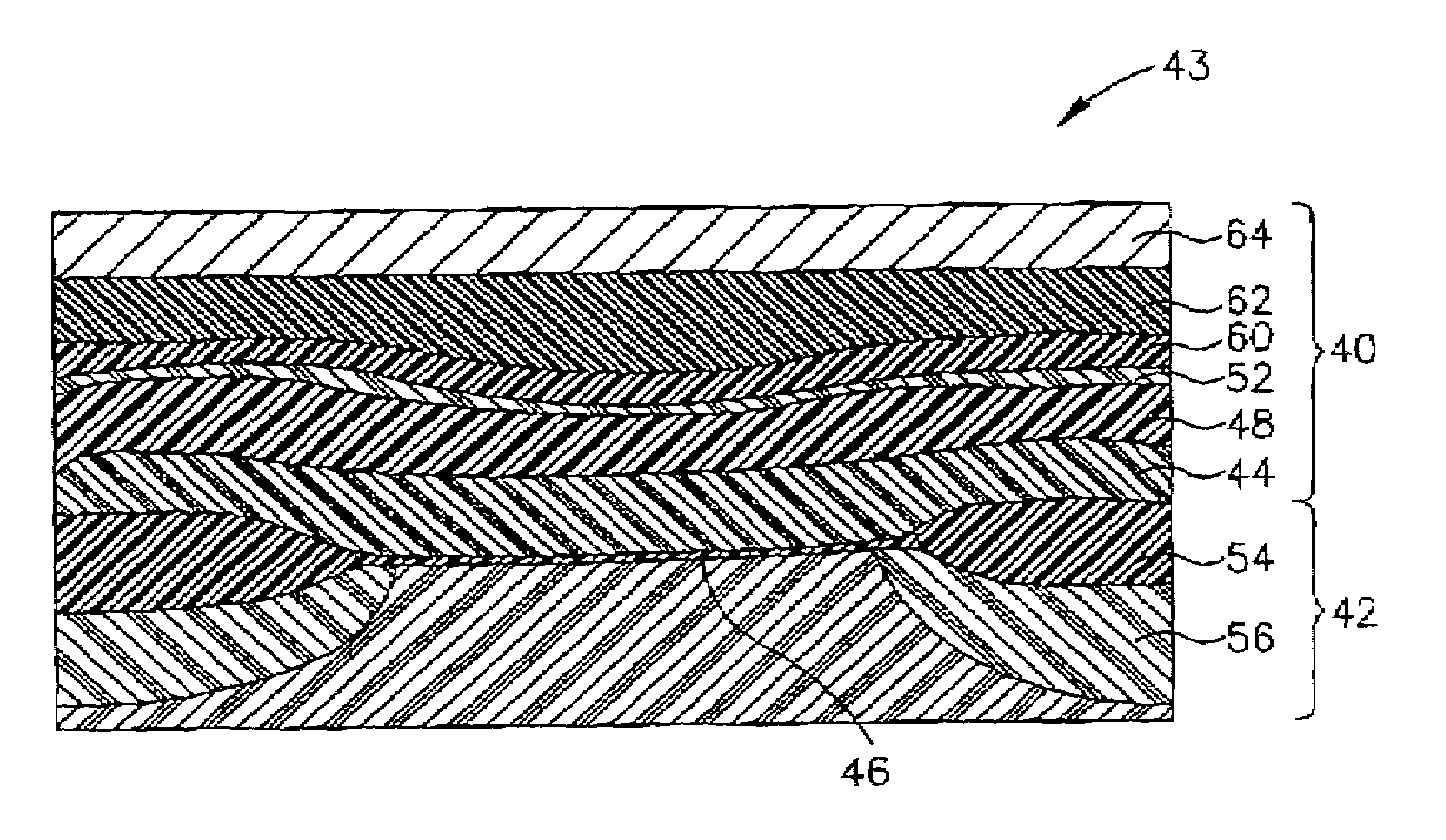

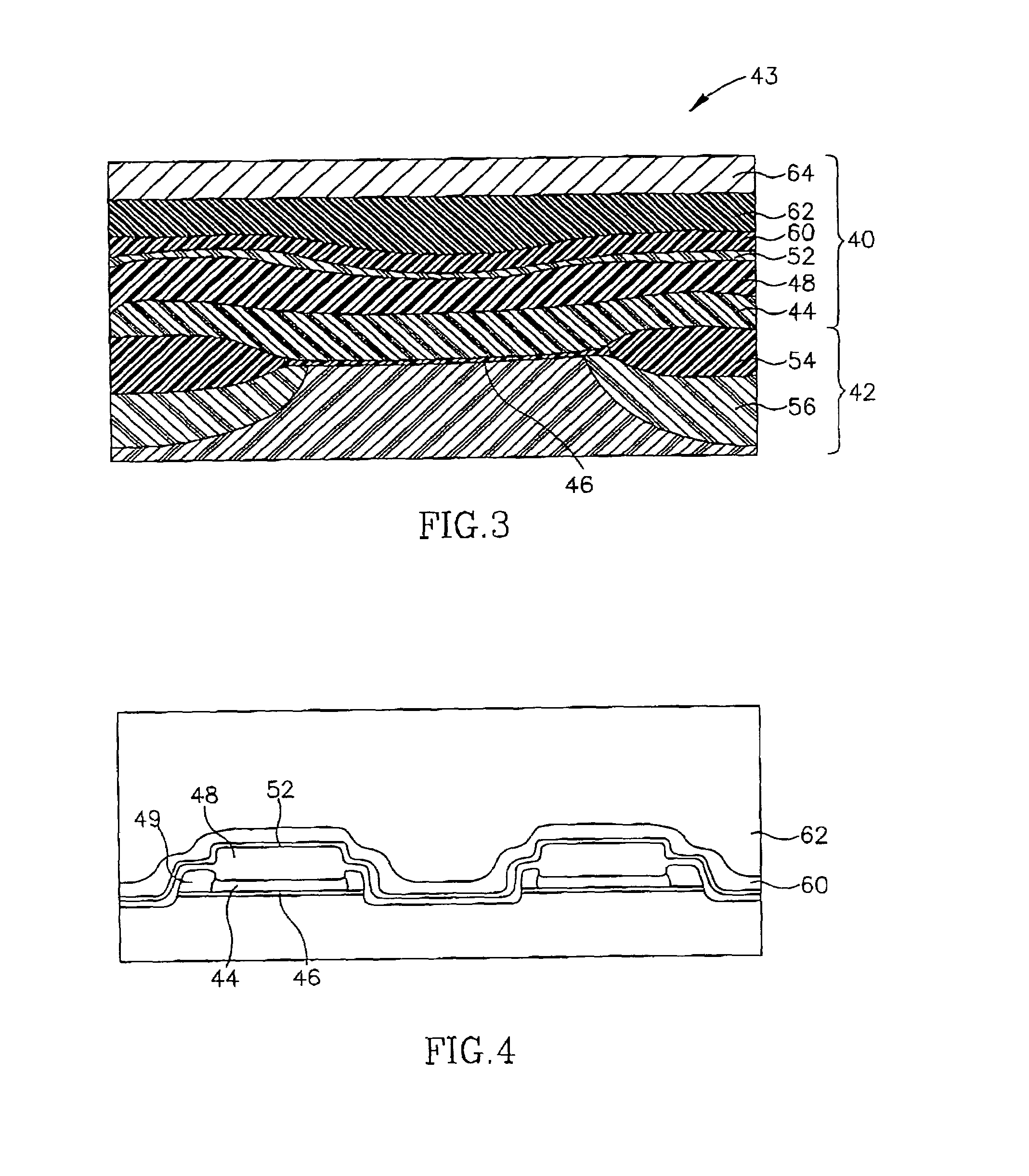

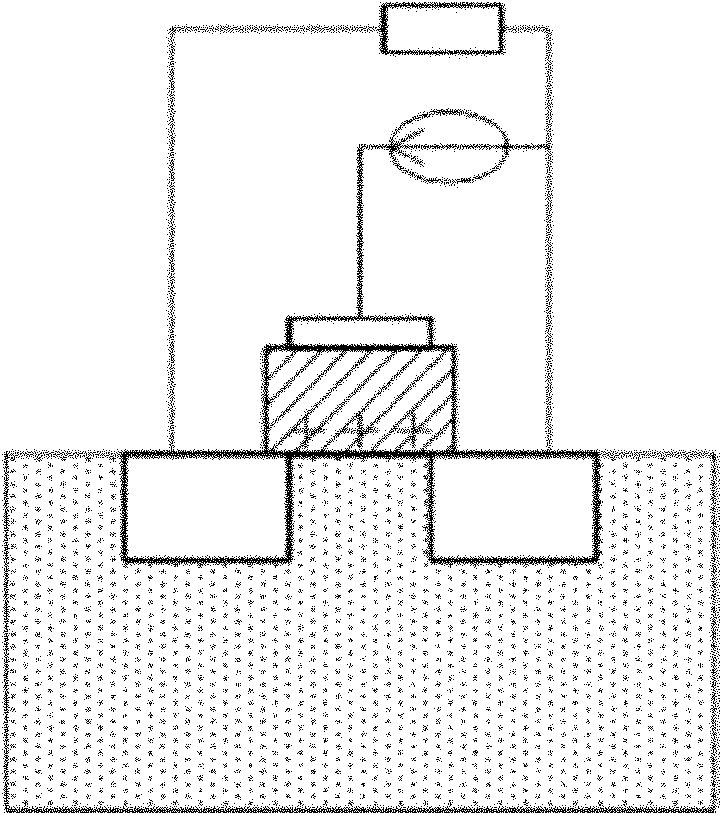

An integrated stacked capacitor comprises a first capacitor film (46) of polycrystalline silicide (poly), a second capacitor film (48) and a first dielectric (26) sandwiched between the first capacitor film (46) and second capacitor film (48). A second dielectric (34) and a third capacitor film (50) are provided. The second dielectric (34) is sandwiched between the second capacitor film (48) and third capacitor film (50). A method for fabrication of an integrated stacked capacitor comprises the following sequence of steps: applying a polysilicide layer (20) to form the first capacitor film (46); applying a first dielectric (26); applying a first metallization layer (28) to form the second capacitor film (48); applying a second dielectric (34); and applying a second metallization layer (34) to form the third capacitor film (50).

Owner:TEXAS INSTR INC

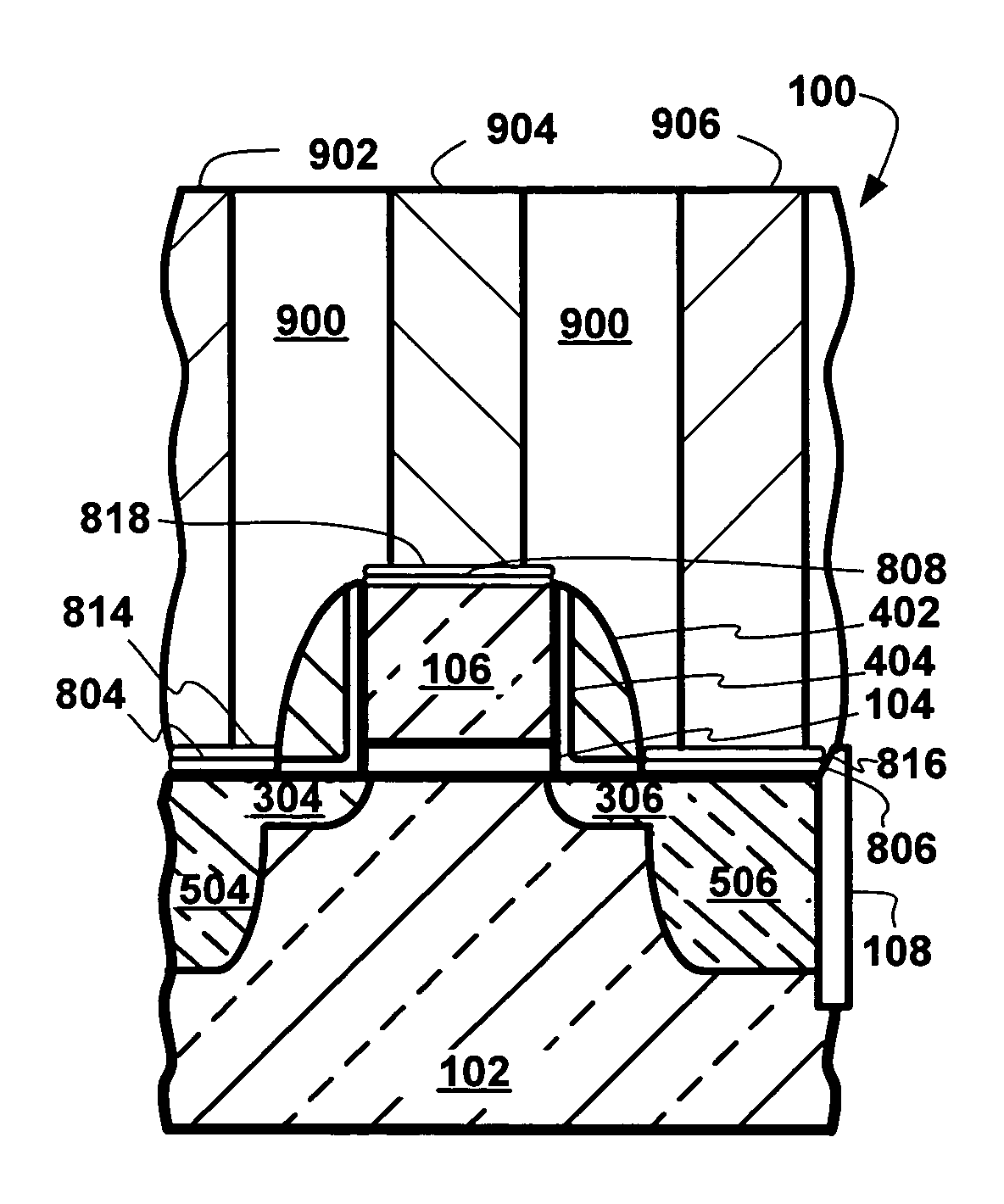

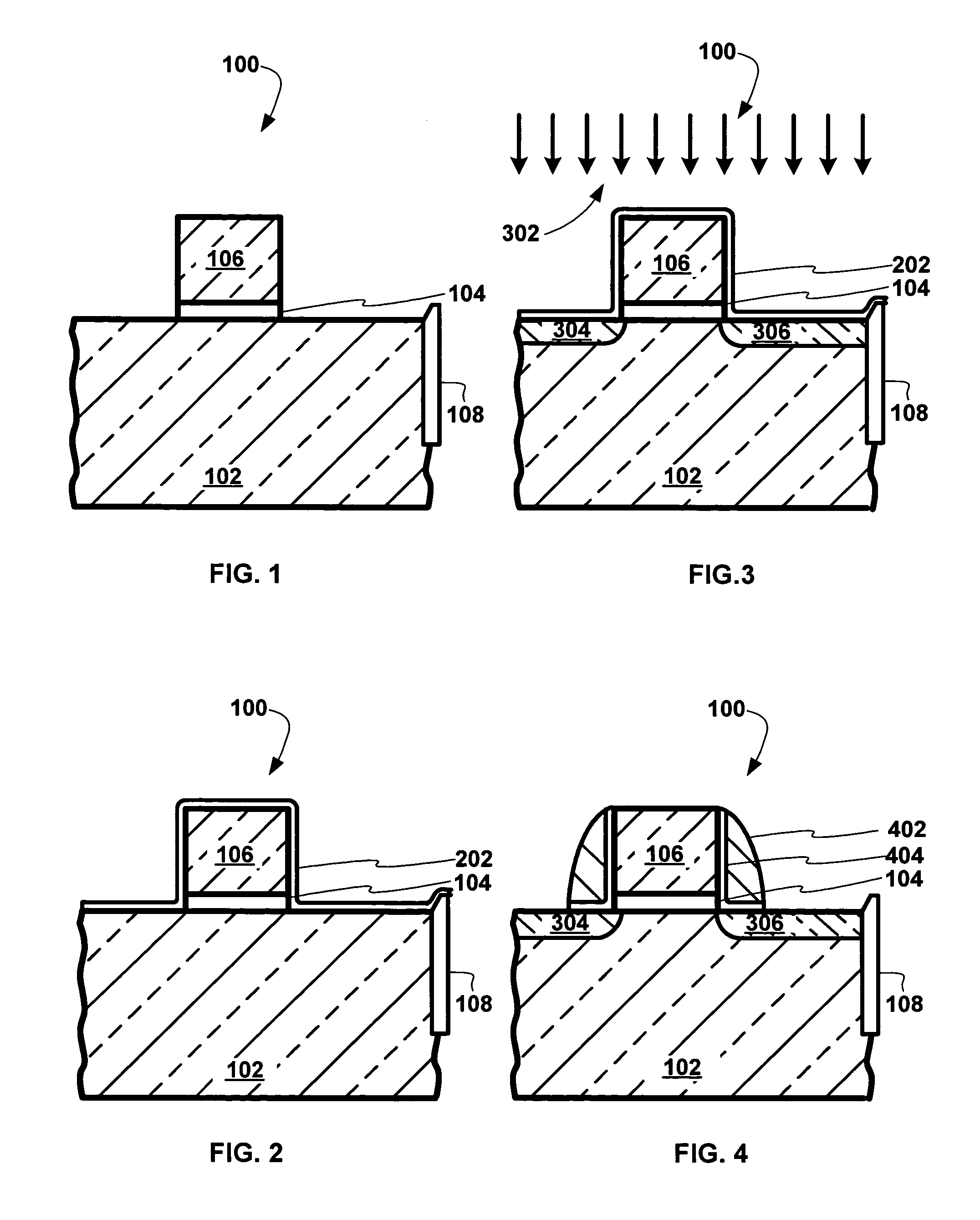

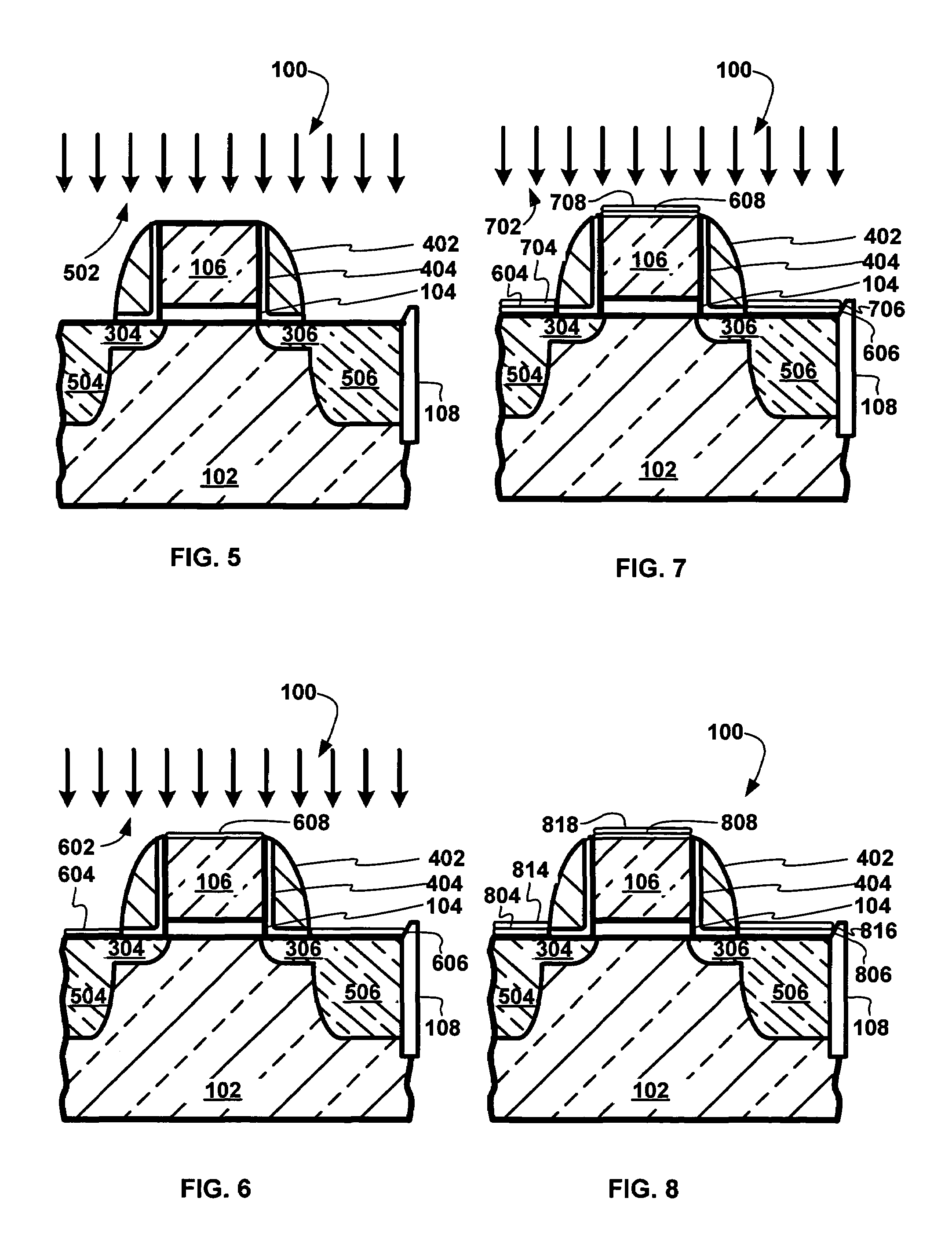

Protective layer in memory device and method therefor

A method for protecting a non-volatile memory device, the method including forming a non-volatile memory device including a polycide structure formed over a non-conducting charge trapping layer, and forming a protective layer over at least a portion of the polycide structure, the protective layer being adapted to absorb electromagnetic wave energy having a wavelength shorter than visible light. A device constructed in accordance with the method is also disclosed.

Owner:SAIFUN SEMICON

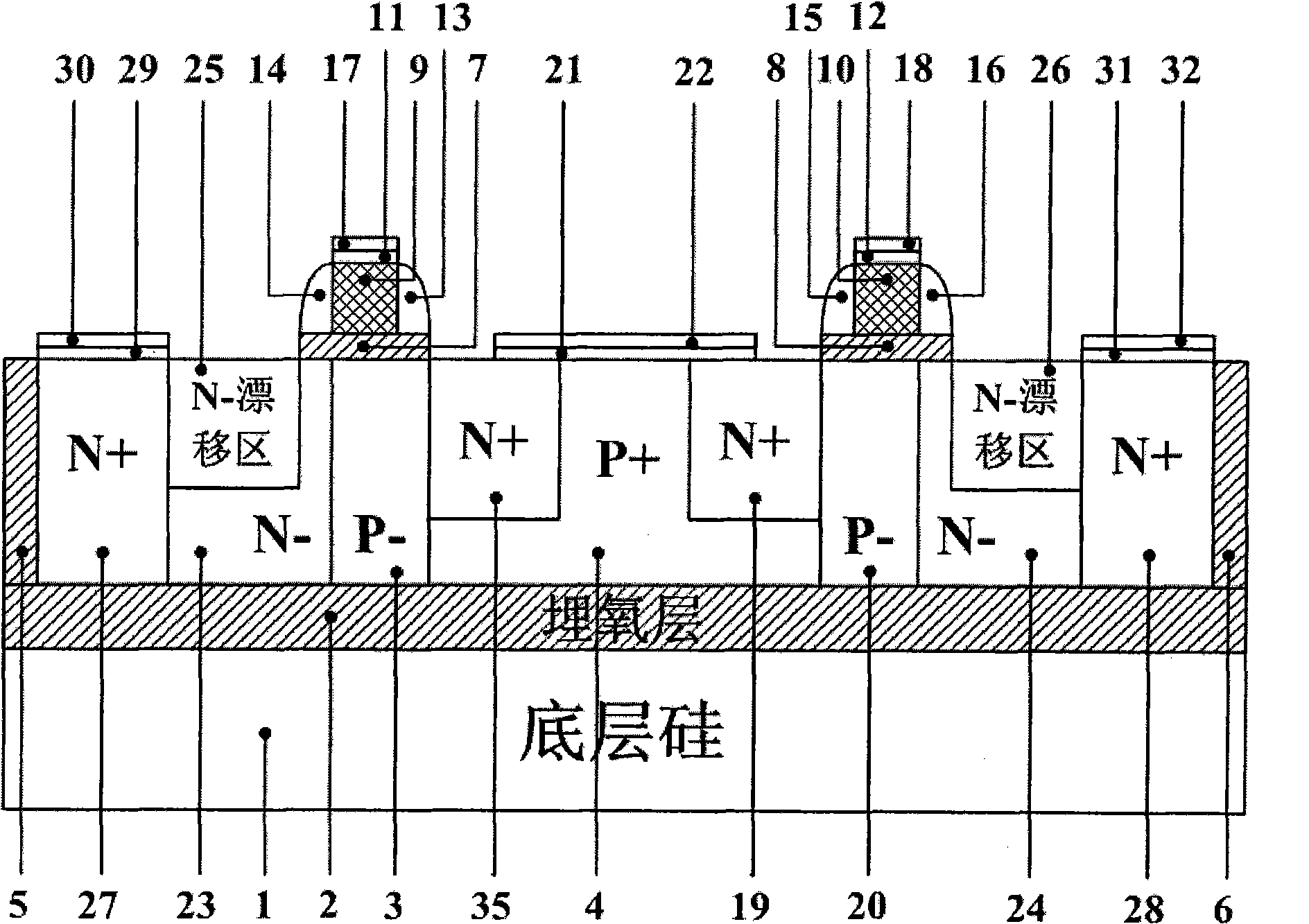

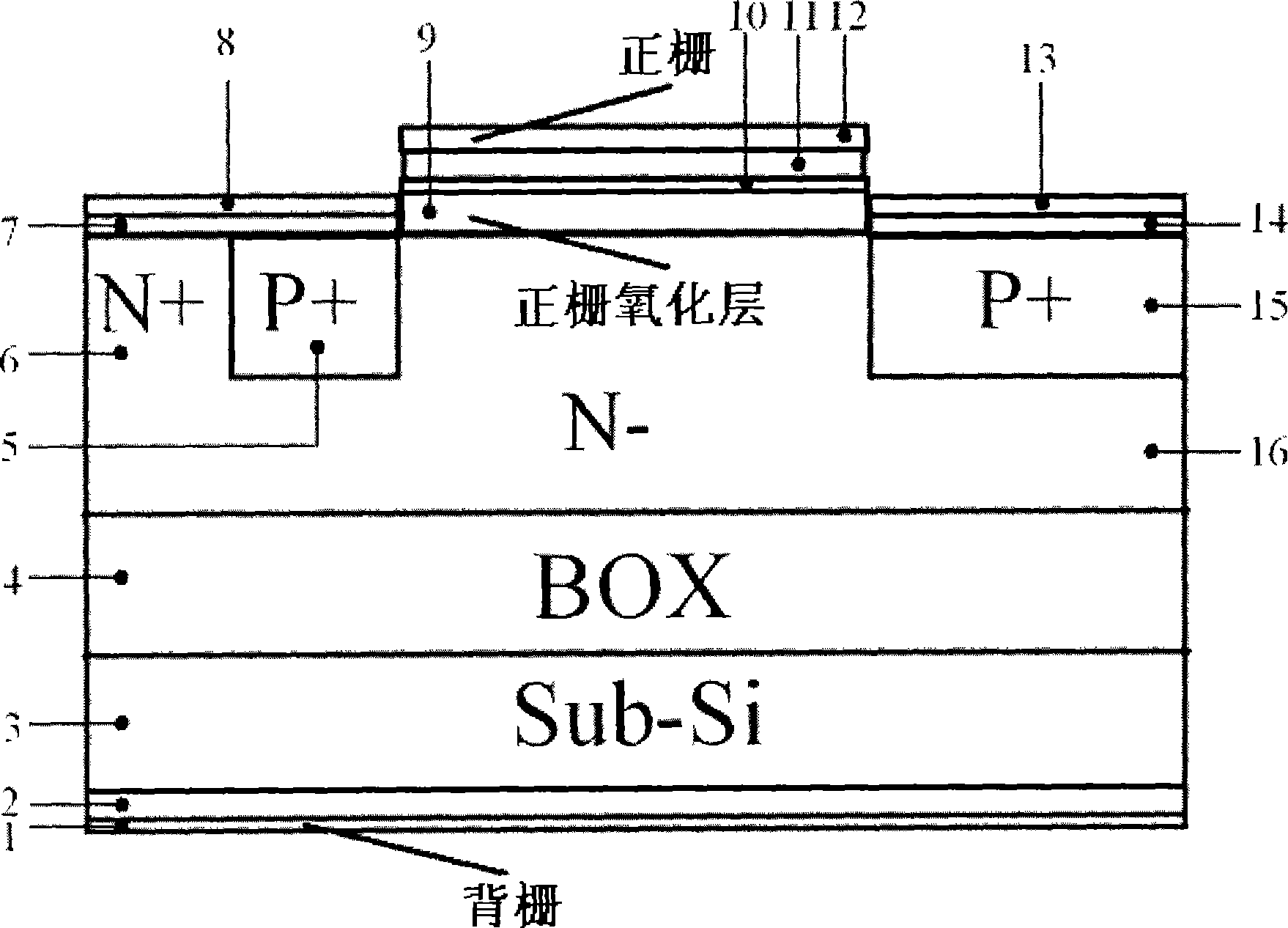

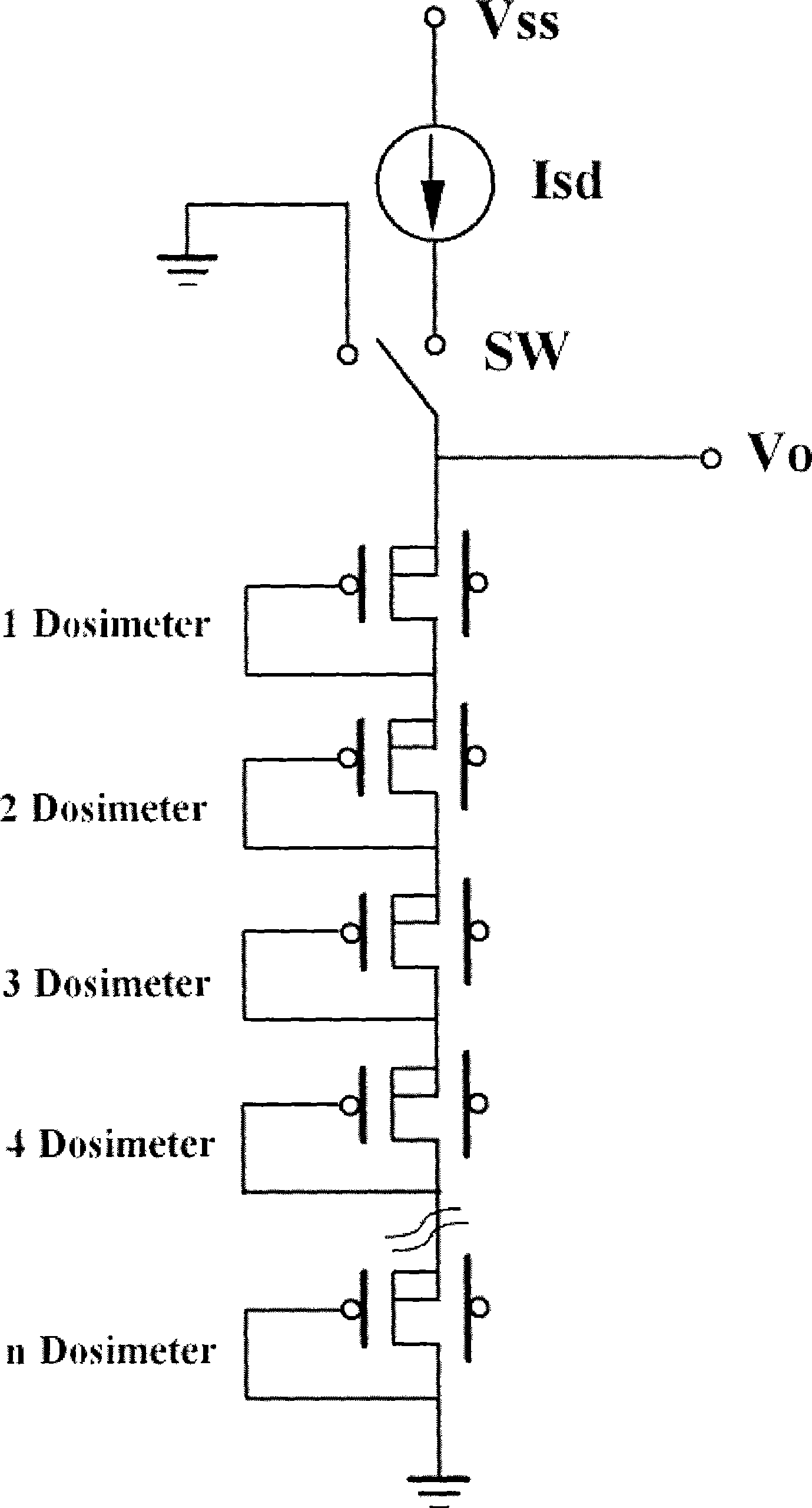

PMOS radiation dosimeter based on silicon on insulator

InactiveCN102466806AHigh sensitivitySimple structureDosimetersSemiconductor devicesDosimeterSoi cmos technology

The invention relates to a PMOS radiation dosimeter based on a silicon on insulator. The PMOS radiation dosimeter comprises a silicon on insulator that successively includes top silicon, a buried oxide layer, and bottom silicon. Besides, the PMOS radiation dosimeter also comprises: a positive gate oxide layer, which is arranged on the upper surface of the top silicon; a source region, which is arranged at one side of the top silicon; a drain region, which is arranged at the other side of the top silicon; a source region polycrystalline silicide layer, which is arranged on the upper surface of the source region, and a source electrode, which is arranged on the upper surface of the source region polycrystalline silicide layer; a first isolation oxide region, which is arranged at one side of the source region; a drain region polycrystalline silicide layer, which is arranged on the upper surface of the drain region, and a drain electrode, which is arranged on the upper surface of the drain region polycrystalline silicide layer; a second isolation oxide layer, which is arranged at one side of the drain region; and a back gate metal layer, which is arranged on the lower surface of the bottom silicon, and a back gate electrode, which is arranged on the lower surface of the back gate metal layer. According to the invention, a PMOS radiation dosimeter with high sensitivity is provided; the manufacturing process of the dosimeter is compatible with an SOI CMOS technology; and an integrated level can be effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

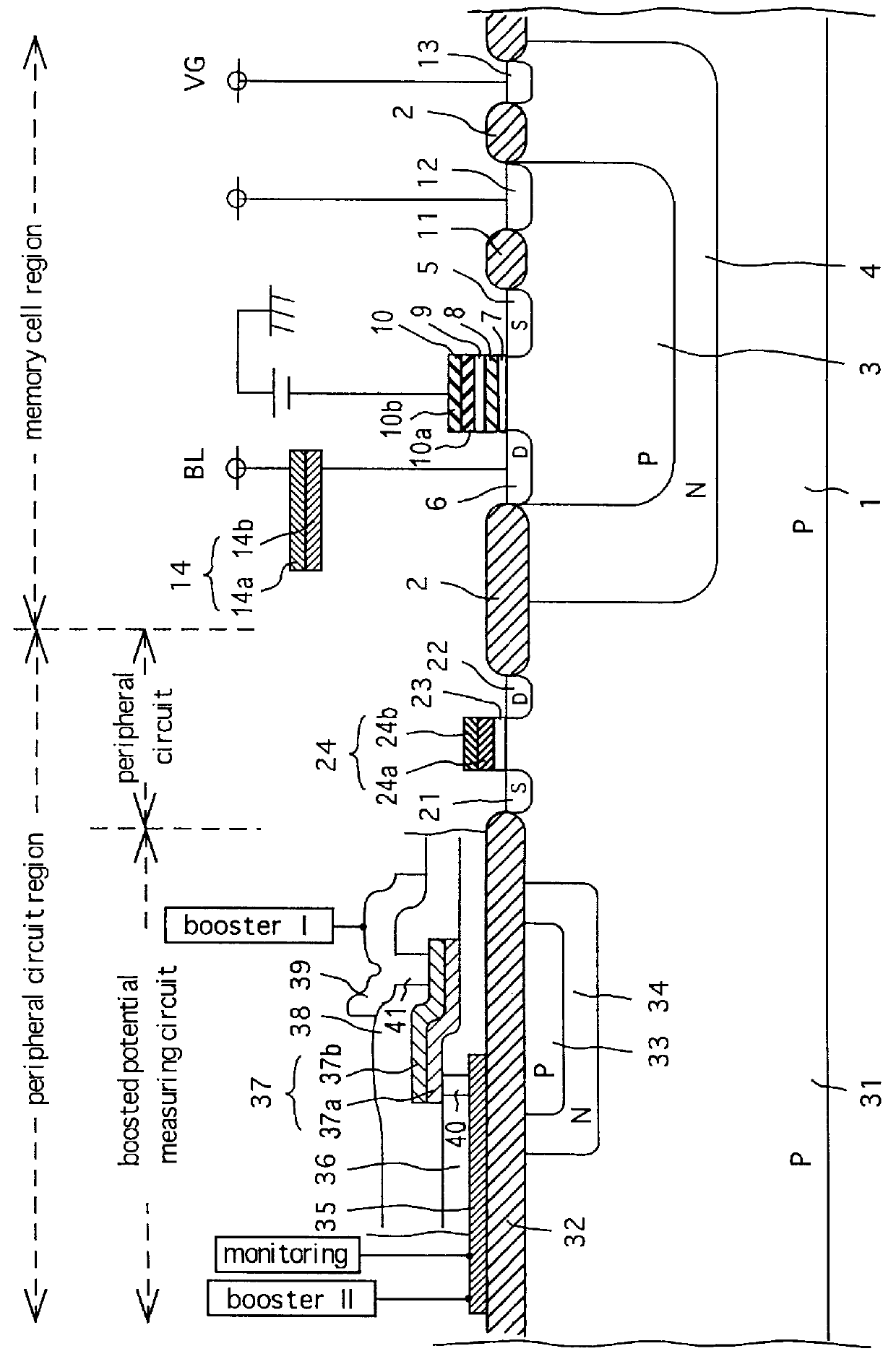

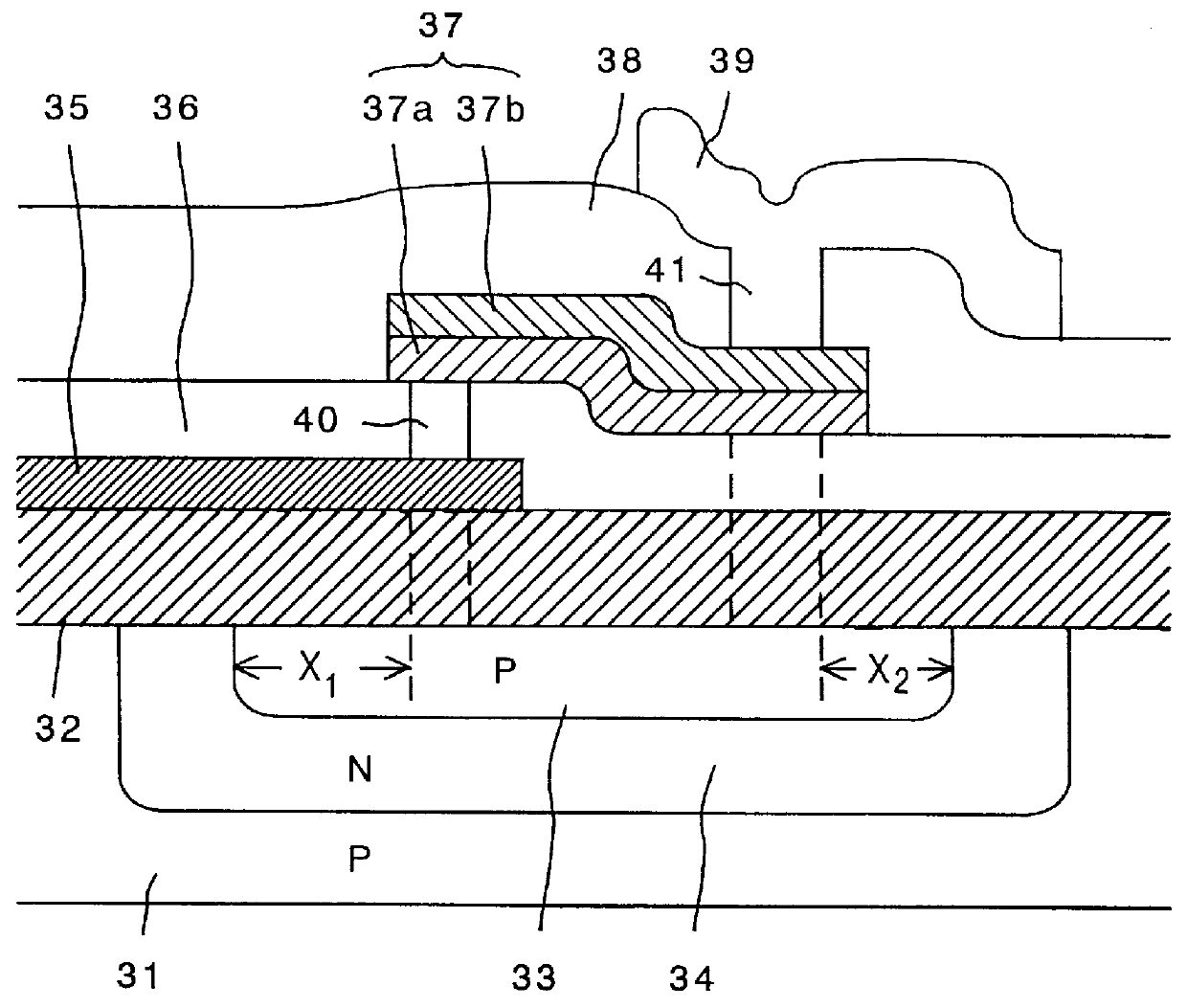

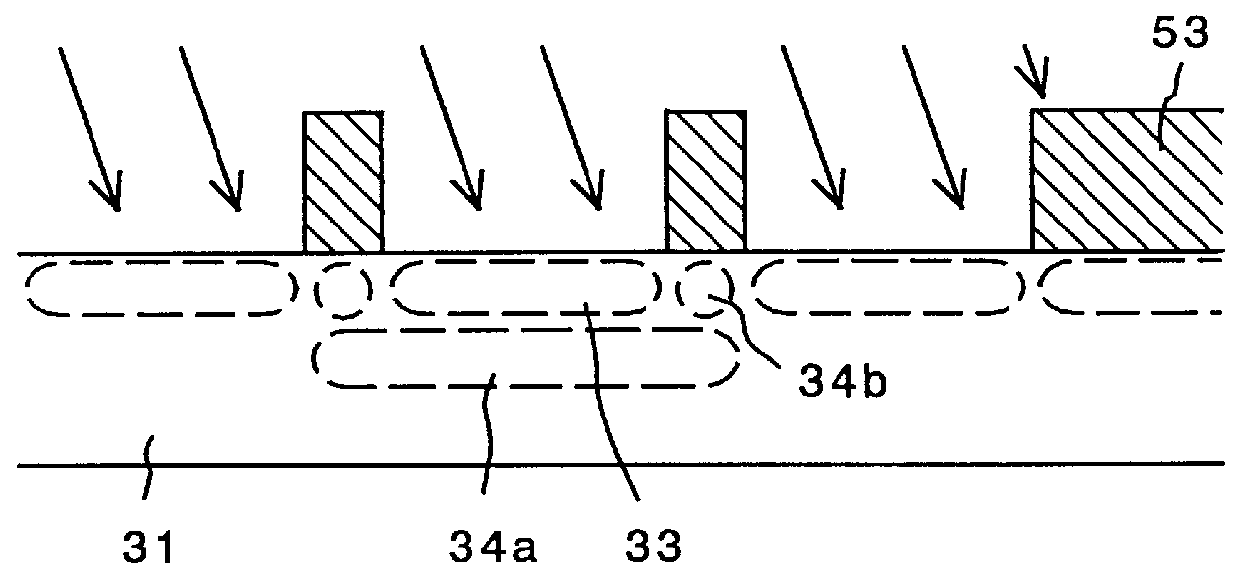

Semiconductor device having a structure for detecting a boosted potential

A p-type well and an n-type well surrounding the p-type well are formed in a p-type semiconductor substrate under a field insulating film. A polysilicon resistance film is formed on the field insulating film simultaneously with a floating gate formed in a memory cell region. A polycide conductive film is formed on a interlayer insulating film simultaneously with an auxiliary bit line formed in the memory cell region, and the polycide conductive film is connected to the resistance film by a contact formed in a via hole. A wiring line formed on an interlayer insulating film is connected to the polycide conductive film by a contact formed in a via hole penetrating the interlayer insulating film. The two via holes are formed at positions corresponding to regions in the p-type well. A negative voltage is applied to the wiring line, and the potential of a predetermined point on the resistance film is measured.

Owner:RENESAS ELECTRONICS CORP

Self-aligned bipolar semiconductor device and fabrication method thereof

InactiveUS20060148187A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialNitride

A self-aligned bipolar semiconductor device and a fabrication method thereof are provided. After a silicon layer and a collector contact are formed on a buried collector layer, an oxide dummy pattern is formed on the silicon layer to define both an extrinsic base and an intrinsic base. A polycide layer used as the extrinsic base is formed thereon and selectively removed to expose the dummy pattern. After the exposed dummy pattern is removed, an epitaxial layer used as the intrinsic base is grown on both the silicon layer and the polycide layer, and selectively removed from the top of the polycide layer. An oxide layer and a nitride layer are deposited in sequence thereon, and the nitride layer is blanket-etched to form spacers defining an emitter. After a photoresist pattern is formed to mostly cover the oxide layer and partly expose the oxide layer between the spacers over the intrinsic base, the oxide layer is etched by using the photoresist pattern and the spacers as an etch mask.

Owner:DONGBU ELECTRONICS CO LTD

Non-oxidizing spacer densification method for manufacturing semiconductor devices

InactiveUS6849510B2Low costHigh yieldSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETSalicide

Non-oxidizing spacer densification method for producing semiconductor devices, such as MOSFET devices, and that may be implemented during semiconductor fabrication with little or substantially no polycide adhesion loss experienced during spacer densification. The method may be implemented to provide good polycide adhesion characteristics with reduced process complexity over conventional methods by eliminating the need for additional process steps such as metal silicide encapsulation or polysilicon surface treatments.

Owner:MAXIM INTEGRATED PROD INC

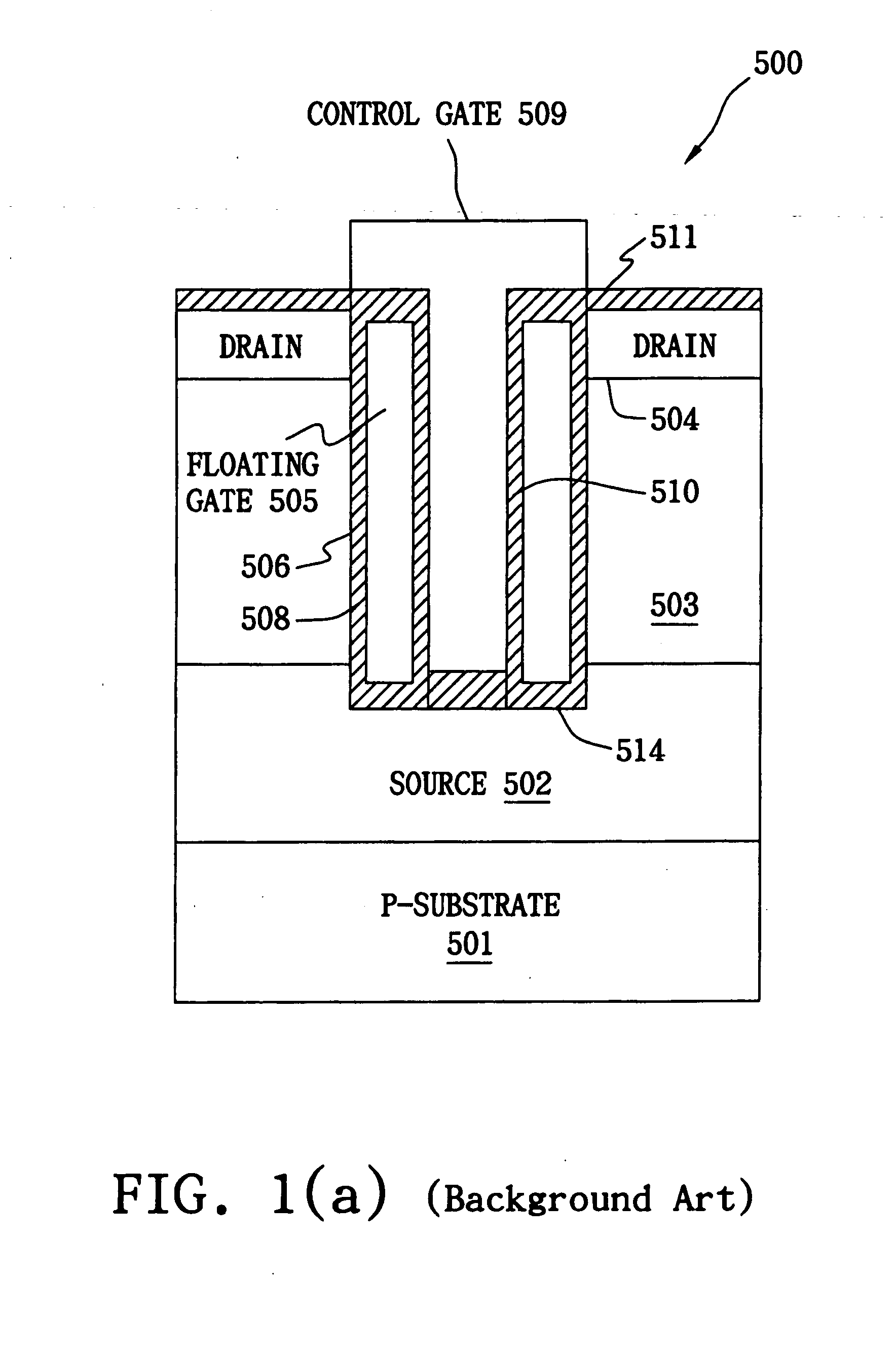

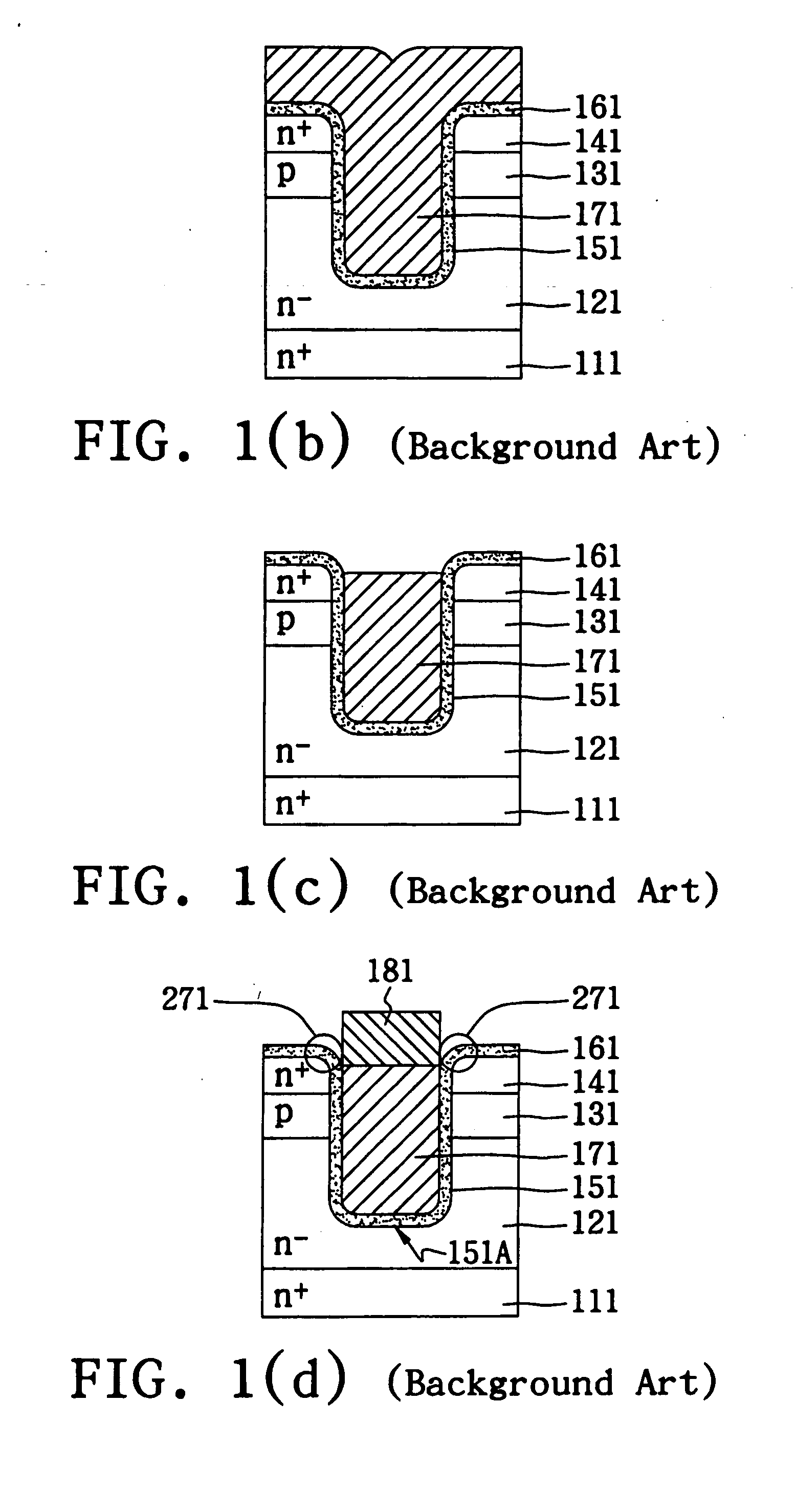

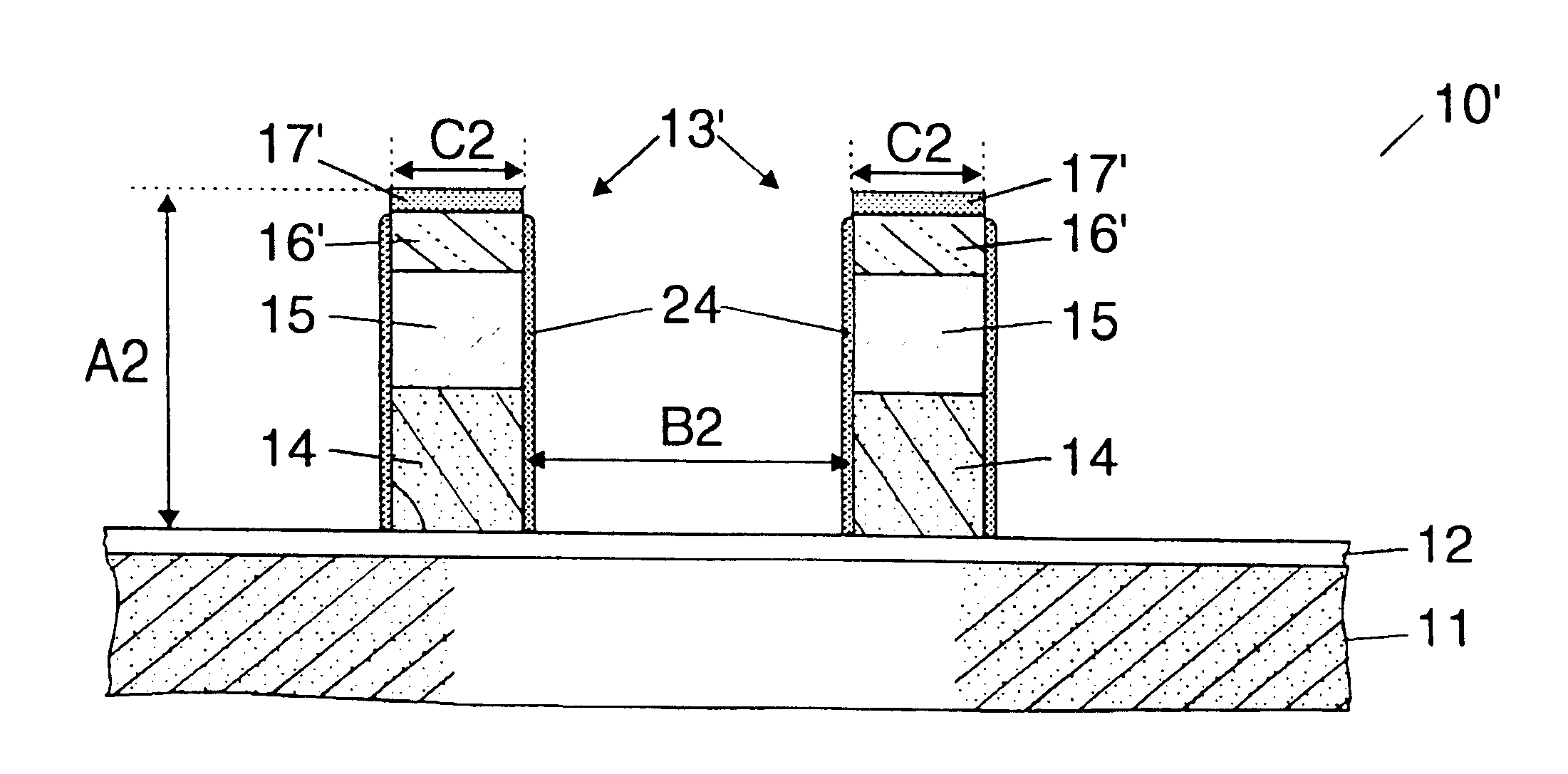

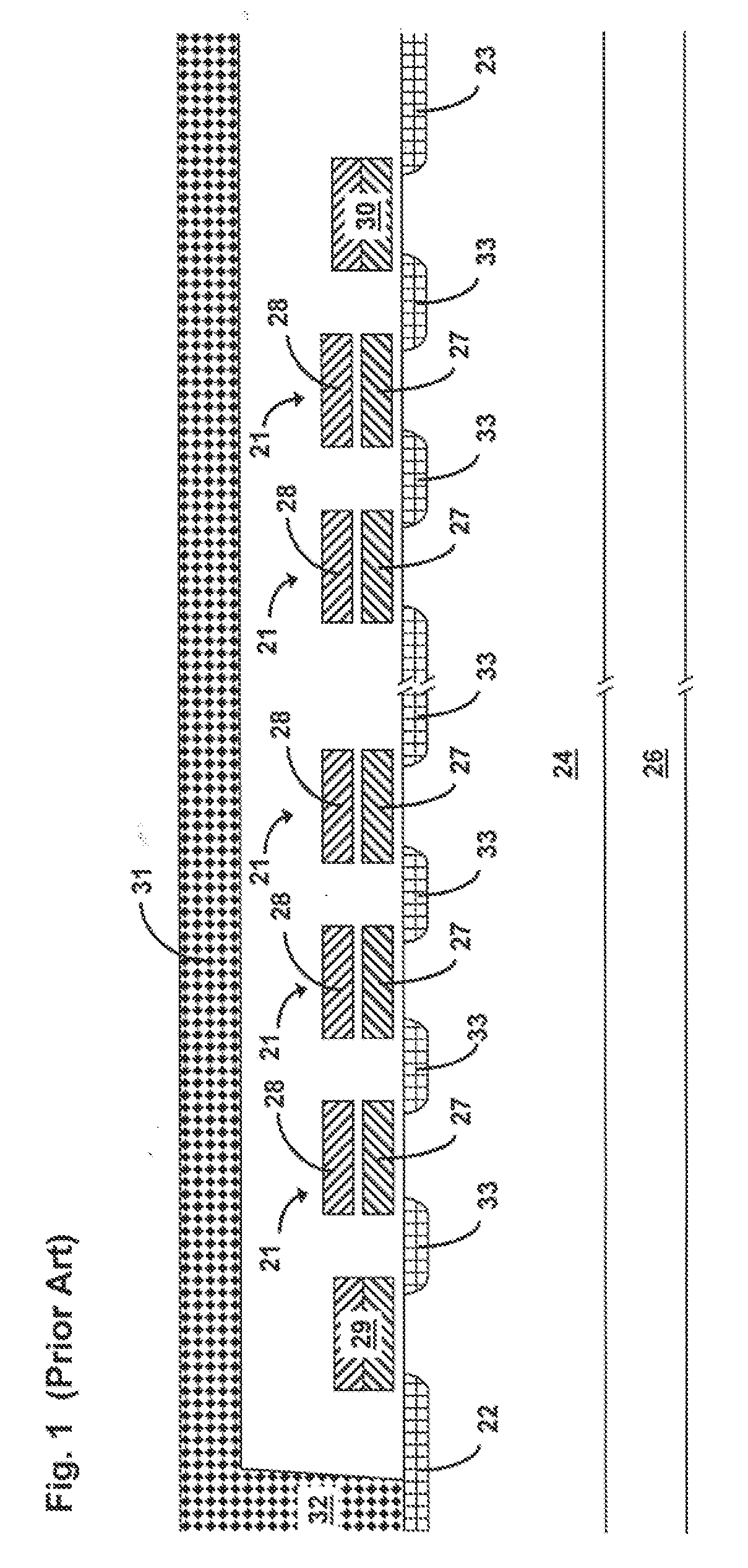

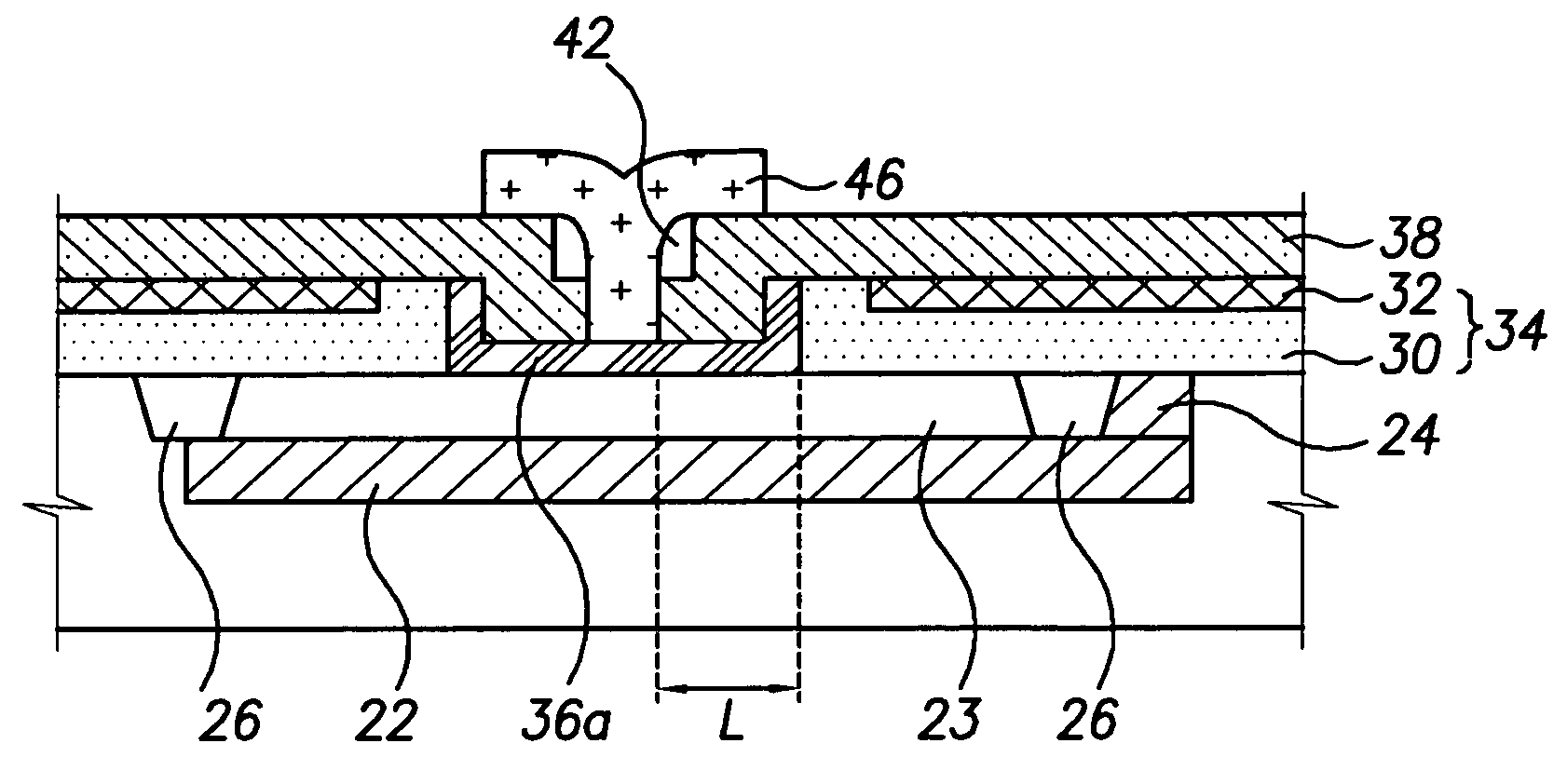

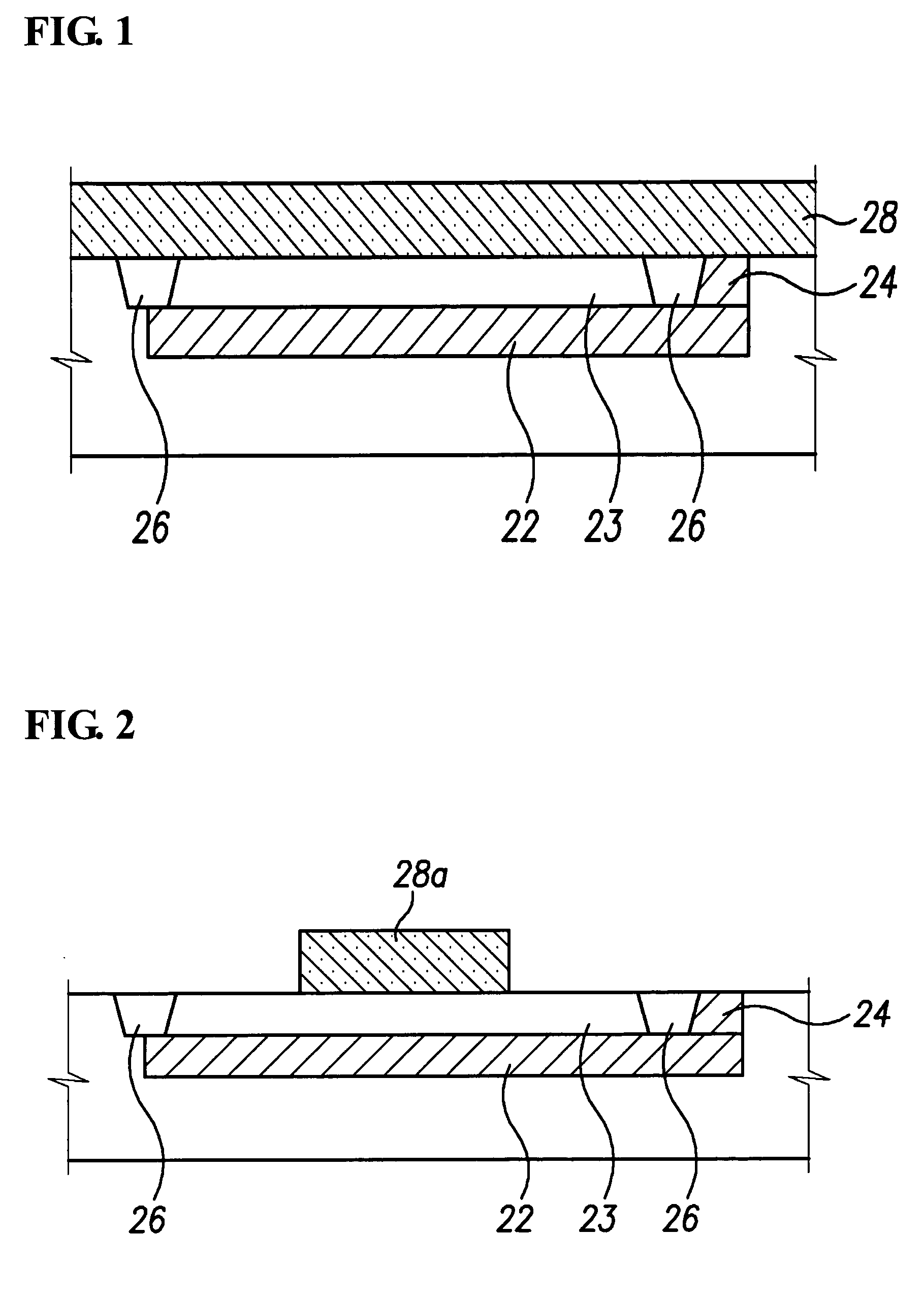

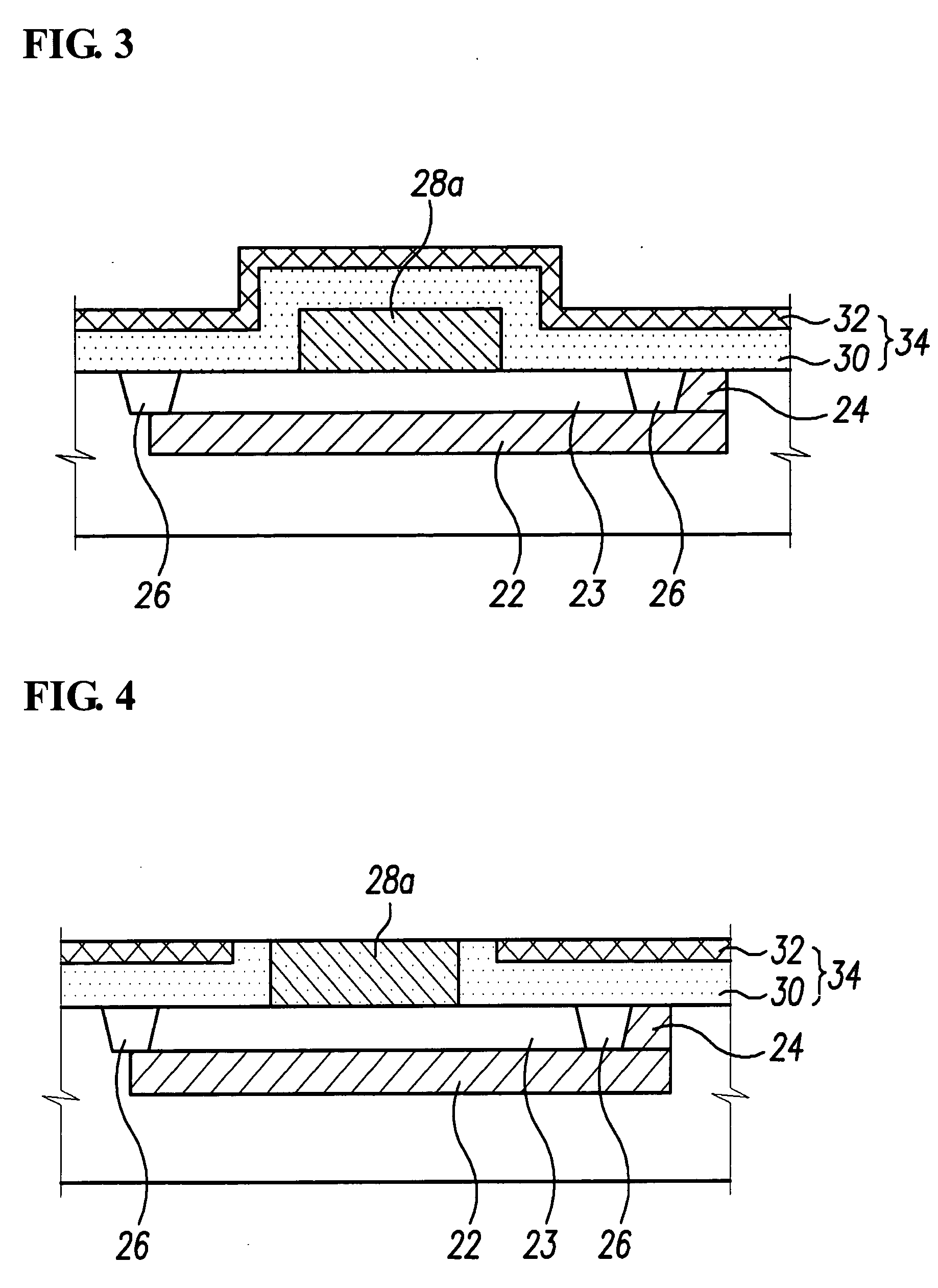

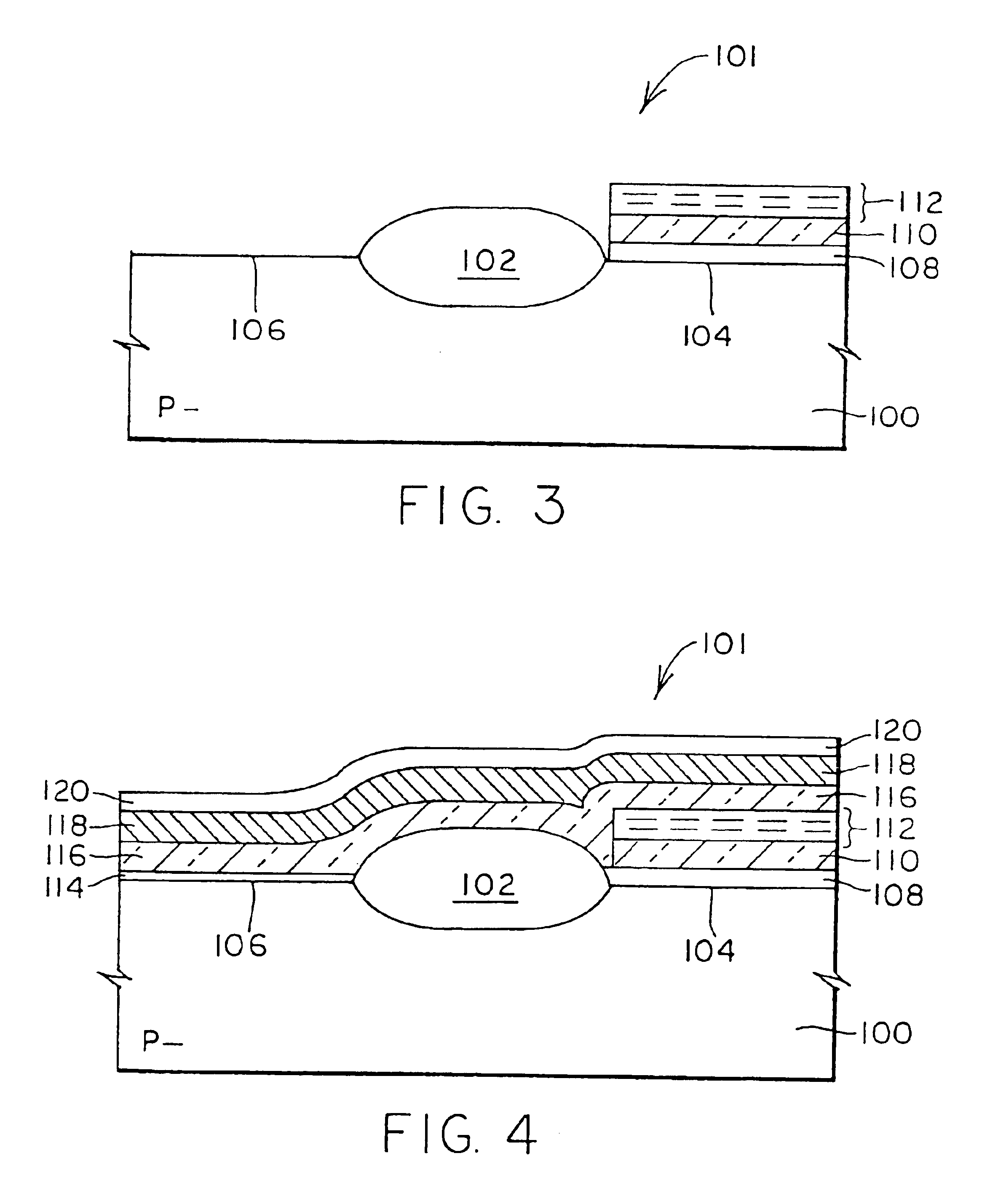

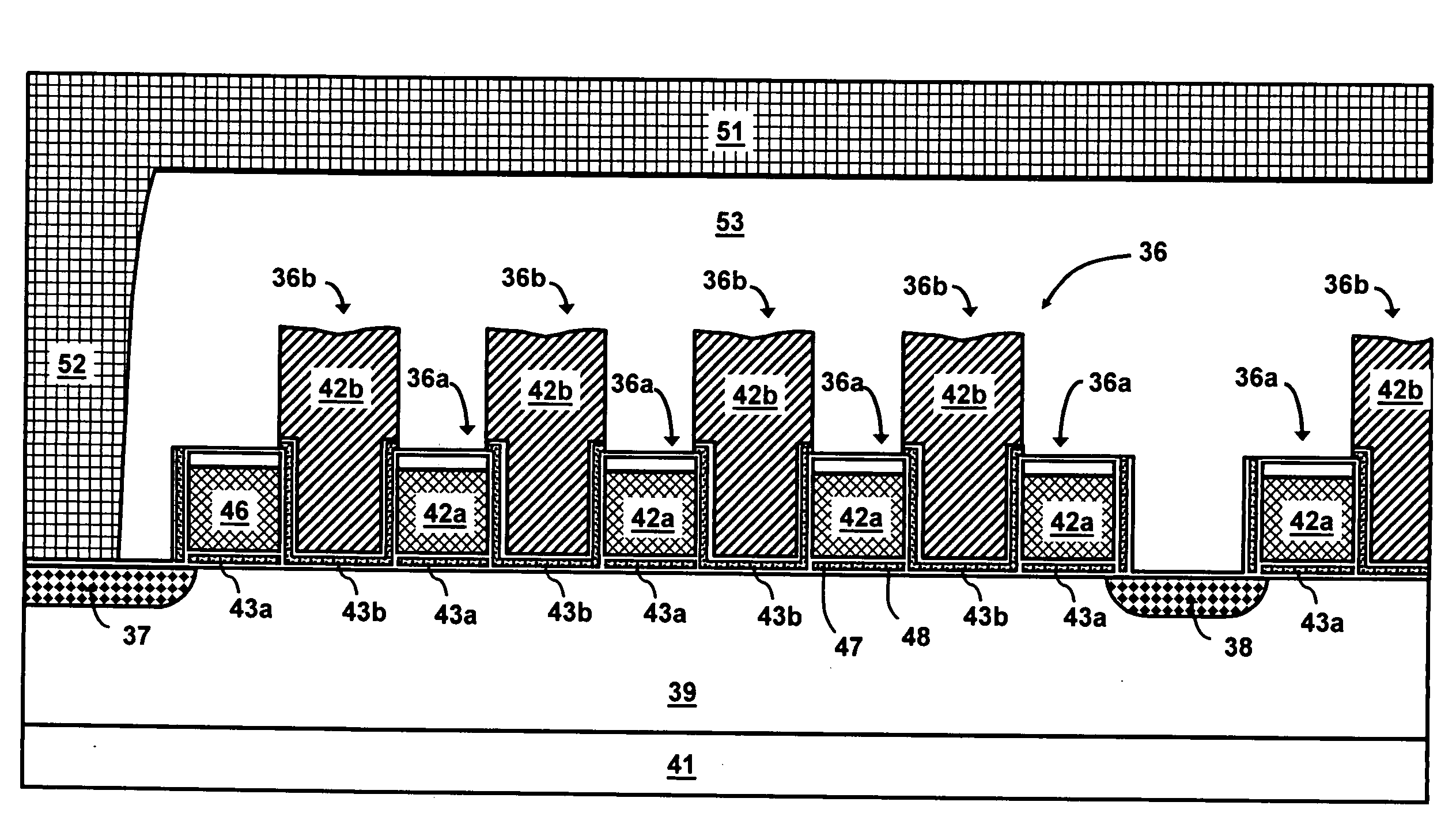

NAND flash memory with densely packed memory gates and fabrication process

NAND flash memory cell array and fabrication process in which cells having memory gates and charge storage layers are densely packed, with the memory gates in adjacent cells either overlapping or self-aligned with each other. The memory cells are arranged in rows between bit line diffusions and a common source diffusion, with the charge storage layers positioned beneath the memory gates in the cells. The memory gates are either polysilicon or polycide, and the charge storage gates are either a nitride or the combination of nitride and oxide. Programming is done either by hot electron injection from silicon substrate to the charge storage gates to build up a negative charge in the charge storage gates or by hot hole injection from the silicon substrate to the charge storage gates to build up a positive charge in the charge storage gates. Erasure is done by channel tunneling from the charge storage gates to the silicon substrate or vice versa, depending on the programming method. The array is biased so that all of the memory cells can be erased simultaneously, while programming is bit selectable.

Owner:SILICON STORAGE TECHNOLOGY

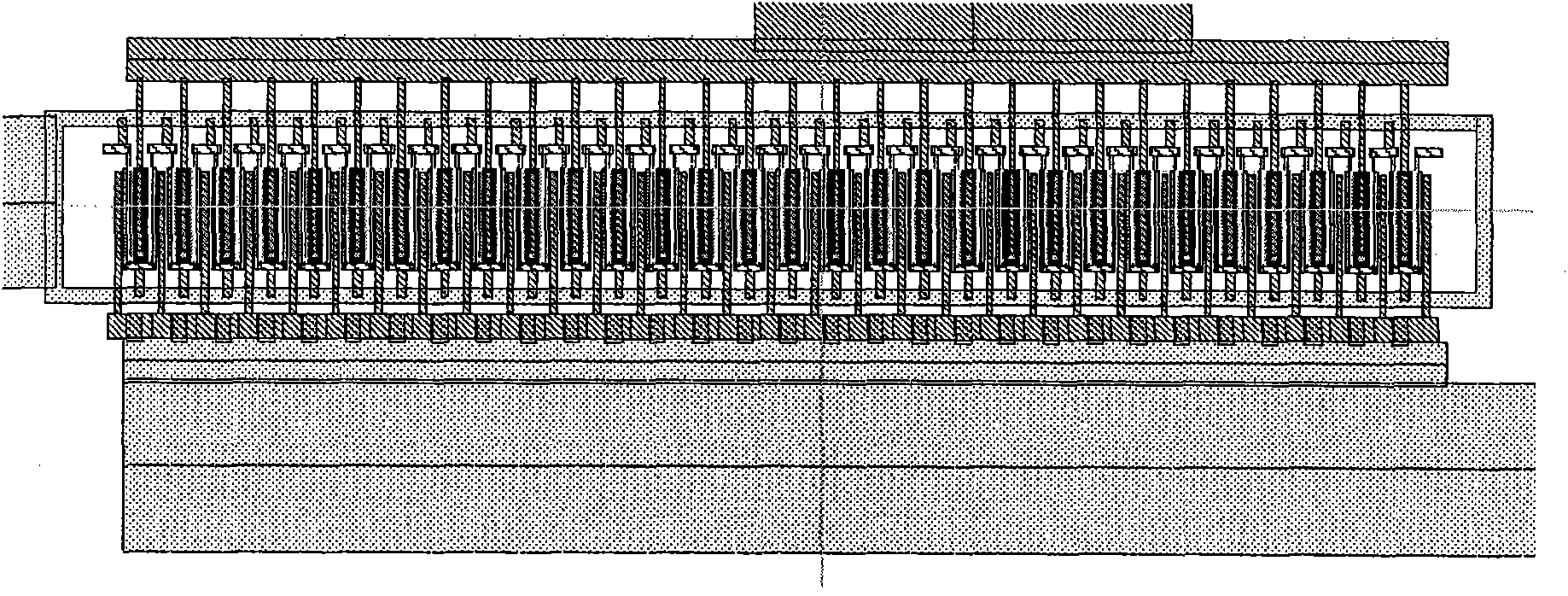

Radio frequency laterally diffused metal oxide semiconductor (LDMOS) device based on silicon on insulator (SOI) and method for injecting device

ActiveCN102054845AIncrease working frequencyImprove breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesRadio frequencyPolycrystalline silicon carbide

The invention discloses a radio frequency silicon on insulator(SOI) laterally diffused metal oxide semiconductor (LDMOS) device provided with a low potential barrier body lead-out, which comprises a bottom layer silicon, a concealed oxide layer, a top layer silicon, a P-region, a N-region, a gate oxide layer, a polysilicon gate layer, a gate polycrystalline silicon carbide layer, a gate electrode, a side wall, a N-drift region, a drain region, a drain region silicate layer, a leakage electrode, a source region, a low potential barrier body lead-out region, a body region, a source region silicide layer, and a source electrode. In the invention, the radio frequency LDMOS device is manufactured on an SOI substrate, and a low potential barrier body lead-out is in a short circuit with the source region is formed by utilizing a heavily doped region homotypic with the P- region; the source / body, leakage / body as well as a gate is interconnected with each electrode by utilizing a silicide; a plurality of grate bars are in interdigital type parallel connection so as to enlarge the driving power of the device; and the invention provides a method for rectifying, back gate injection, N-region injection as well as N-drift region injection compatible with a complementary metal-oxide-semiconductor (CMOS) technology, as well as a N-drift region silicide conceal method compatible with the CMOS technology.

Owner:BEIJING ZHONGKE XINWEITE SCI & TECH DEV

Semiconductor memory device and its manufacture method

InactiveCN101312160ATransistorSemiconductor/solid-state device detailsElectrical resistance and conductanceEngineering

Self-aligned polysilicon process is implemented on a common source polar line to reduce the surface resistance and the contact resistance, thereby improving the unit current characteristics. Therefore, the size of the chip is reduced and the chip of each wafer is increased, thereby obtaining high yield. In addition, the structure limit of a flash unit is overcome when a semiconductor storing device is integrated highly and reduced.

Owner:DONGBU HITEK CO LTD

Semiconductor device with resistor pattern and method of fabricating the same

ActiveUS7109566B2Improve sheet resistanceTransistorSolid-state devicesElectrical resistance and conductanceDevice material

Disclosed is a semiconductor device with a resistor pattern and methods of fabricating the same. Embodiments of the present invention provide a method of fabricating a resistor pattern having high sheet resistance by using a polycide layer for a gate electrode in a semiconductor device with the resistor pattern. Embodiments of the invention also provide a semiconductor device with a resistor pattern that is formed narrower than the minimum line width that can be defined in a photolithographic process so that sheet resistance thereof increases, and a method of fabricating the same.

Owner:SAMSUNG ELECTRONICS CO LTD

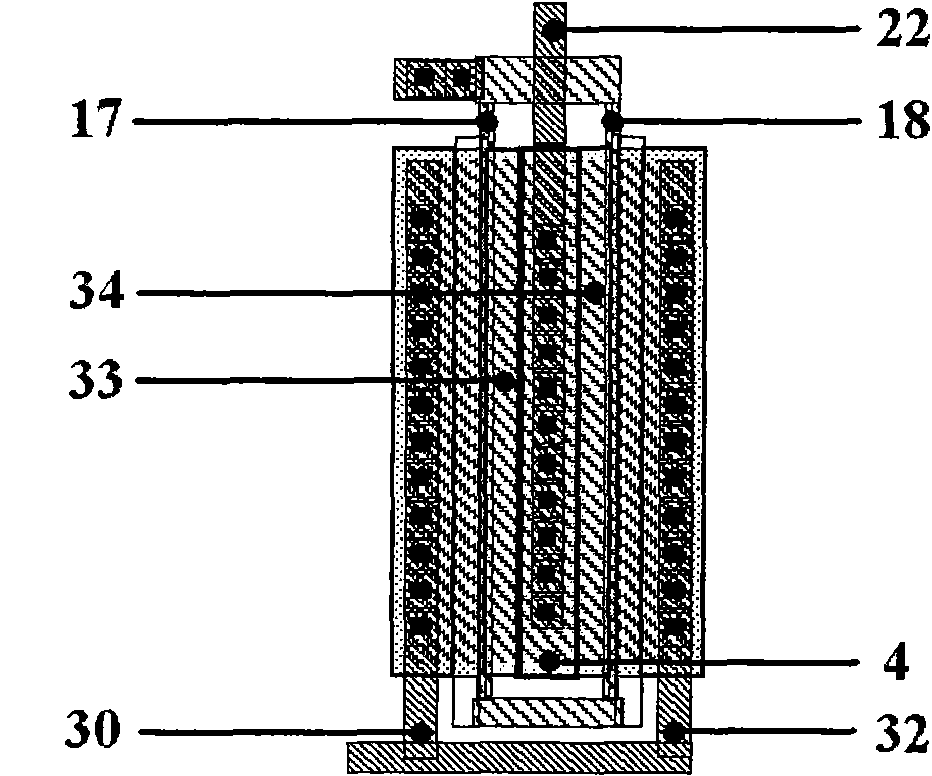

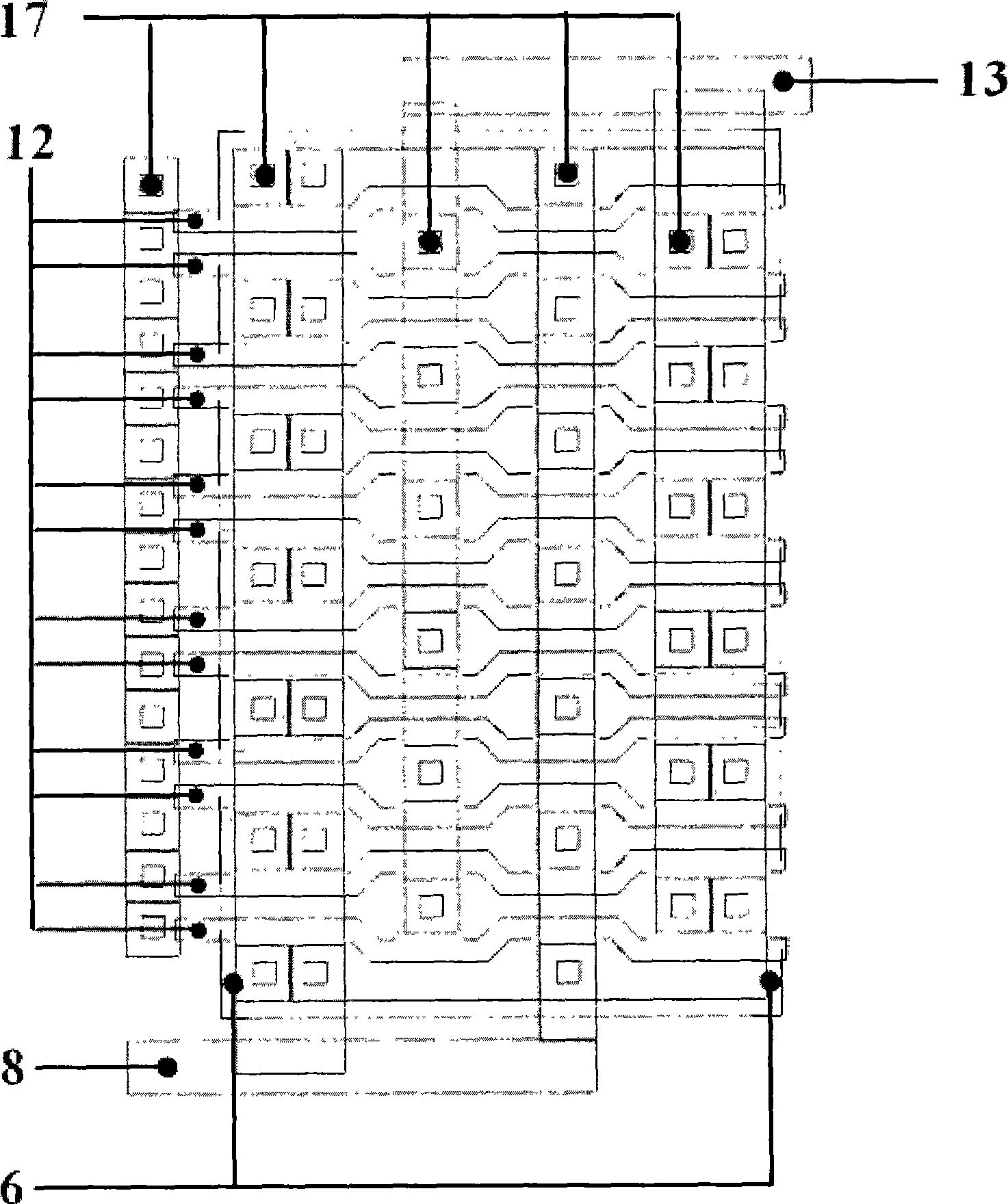

Silicic double probe PMOS radiation dose meter based on insulator

The invention relates to the field of ionizing radiation dose measurement and discloses a PMOS radiation dosimeter which is based on SOI technology and can be recycled. The radiation dosimeter comprises a back-gate electrode, a multicrystalline silicide layer, a semiconductor substrate, a buried oxide layer, a toplevel silicon film, a body contact zone, a source zone, a drain region, a source electrode, a drain electrode, a front gate oxide, a front gate polycrystalline silicon layer and a front gate electrode. In the invention, the dosimeter is manufactured on an SOI substrate and is provided with two electrode probes to measure different dose rates; tuned-grid injections of a front gate and a back gate with different modes are adopted to adjust the measurement range of the probe; a high doping region which has the same shape as the toplevel silicon film is utilized to form the body contact which is short connected with the source zone; source / body, drain / body, the front gate and the back gate are connected with the respective electrode by the multicrystalline silicide; the front gate adopts a plurality of grid bars which are connected in parallel in an interdigital mode to enlarge the sensitive zone of the probe; the invention also provides annealing process control, bias condition, annealing temperature and time control and a circuit measuring method and a structure of a stacking dosimeter capable of adjusting the measuring range.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device having polycide wiring layer, and manufacturing method of the same

InactiveUS20060076603A1TransistorSemiconductor/solid-state device detailsDevice materialSemiconductor

A semiconductor device is provided with a semiconductor substrate comprising element isolation regions and an element region surrounded by the element isolation regions, a first polysilicon layer formed in the element region of the semiconductor substrate, an element-isolating insulation film formed in the element isolation region of the semiconductor substrate, a second polysilicon layer formed on the element-isolating insulation film, a first silicide layer formed on the first polysilicon layer. And the device further comprising a second silicide layer formed on the second polysilicon layer and being thicker than the first silicide layer.

Owner:KK TOSHIBA

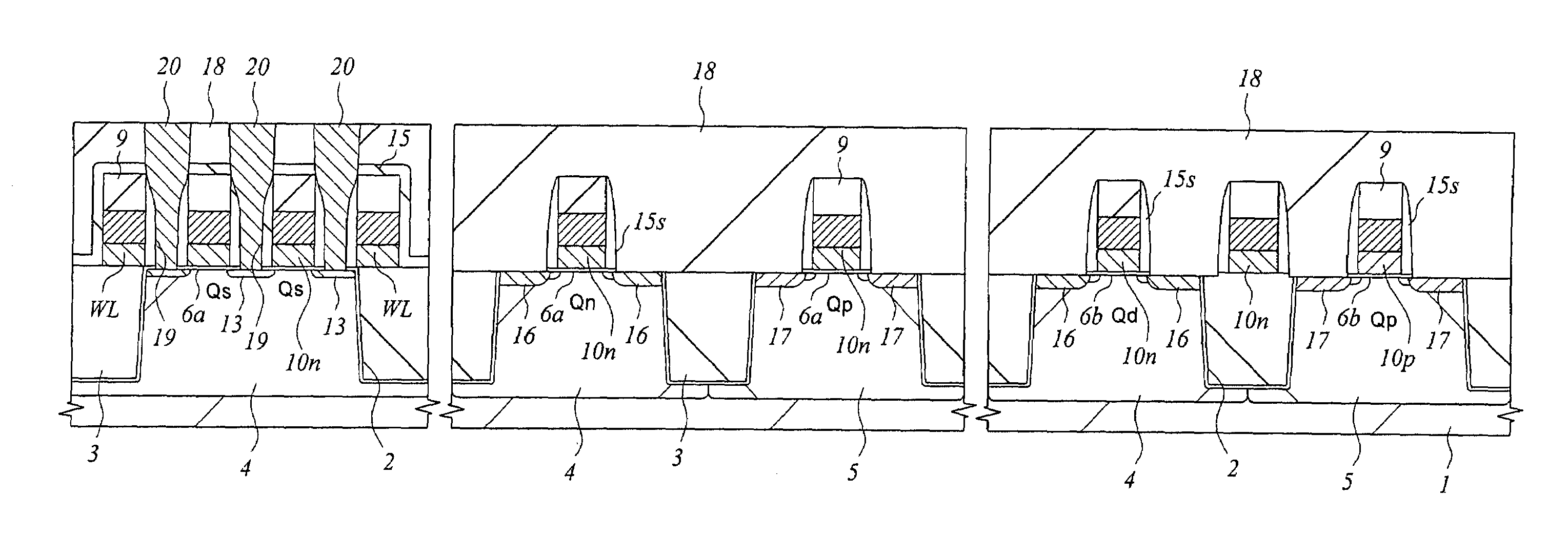

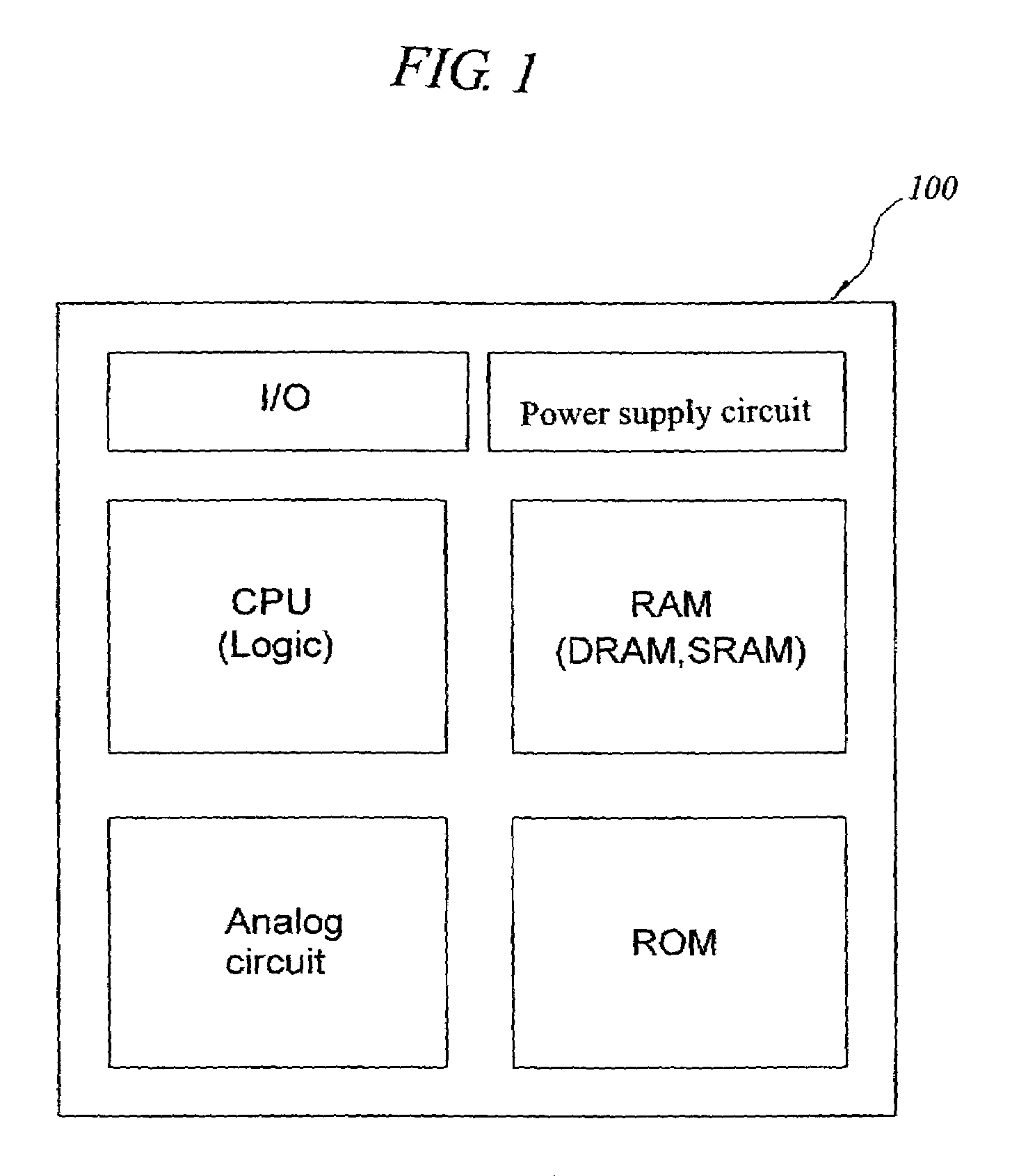

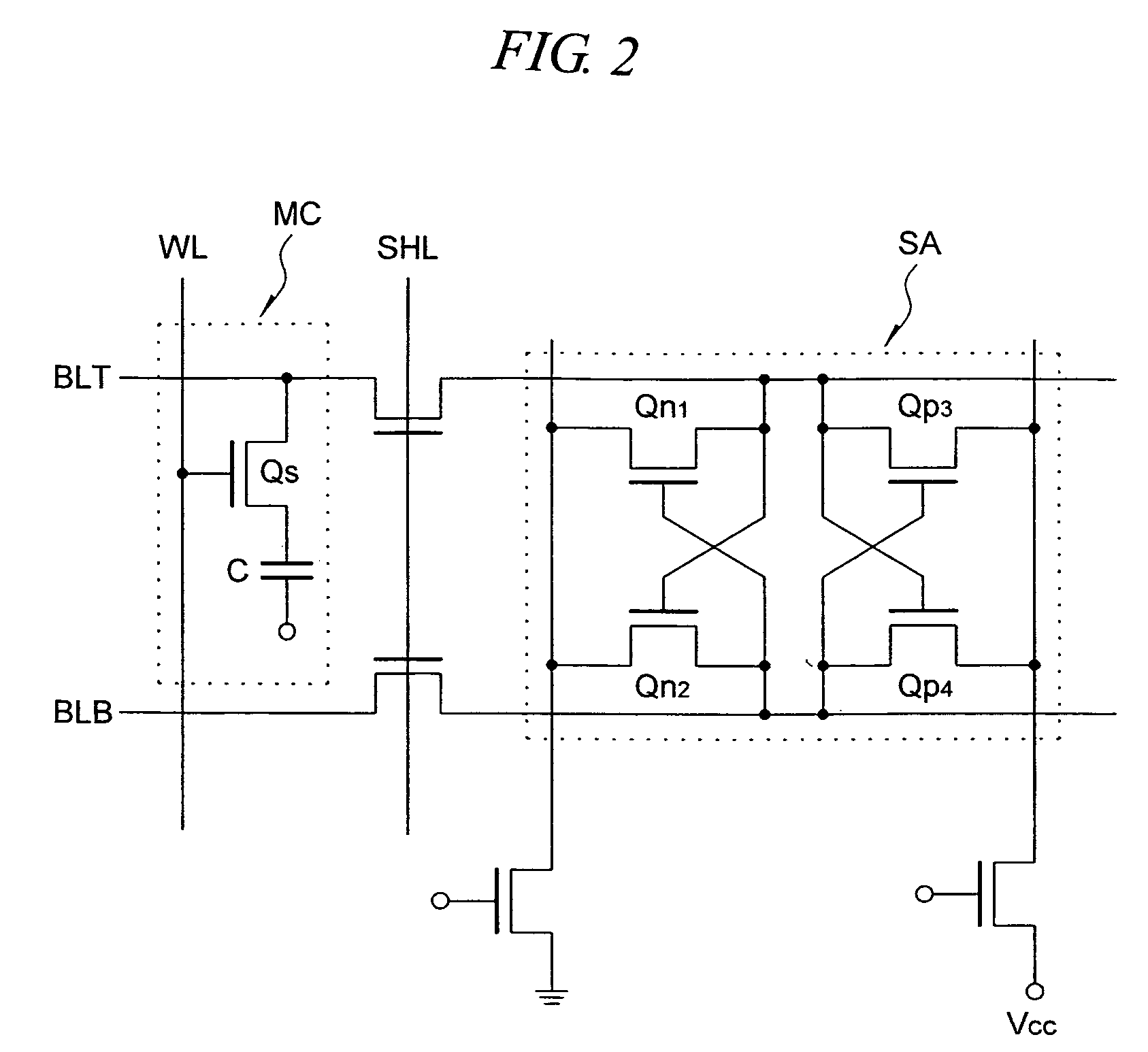

Method of manufacturing semiconductor integrated circuit device, and semiconductor integrated circuit device made by its method

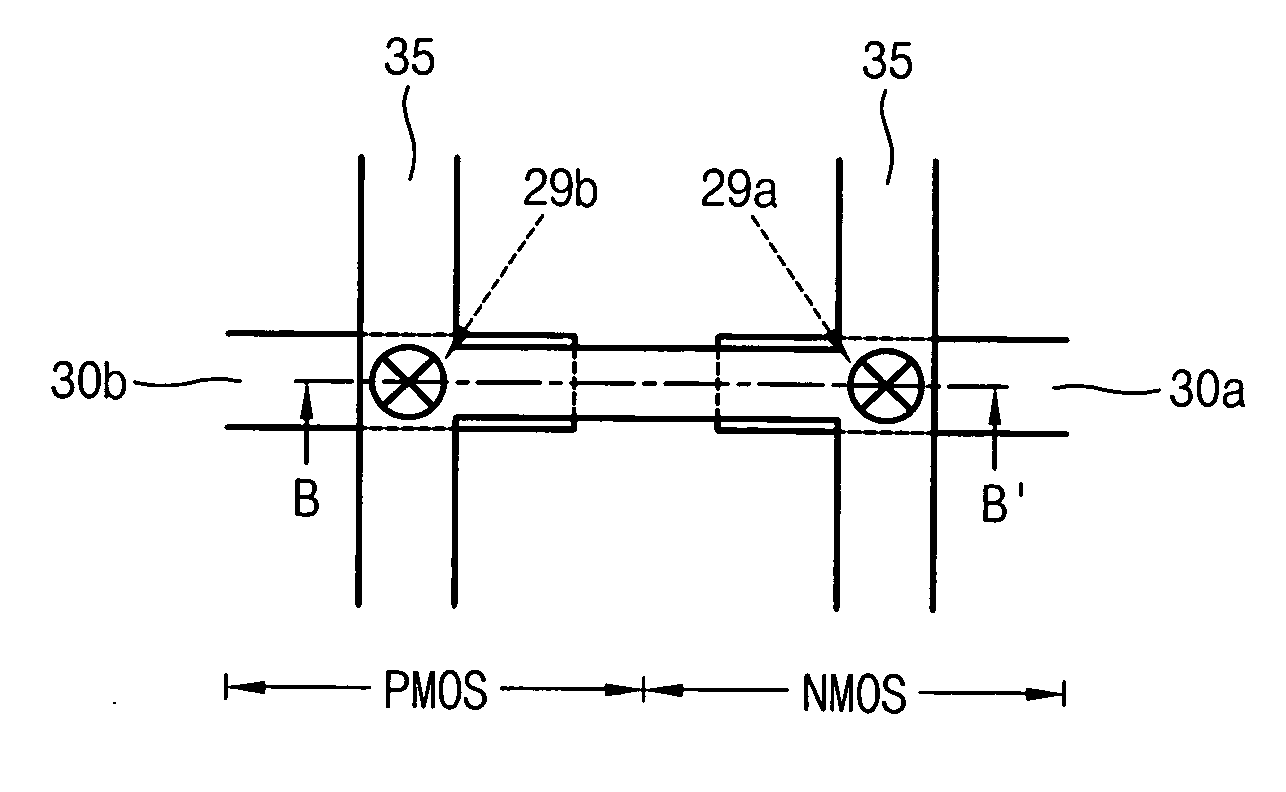

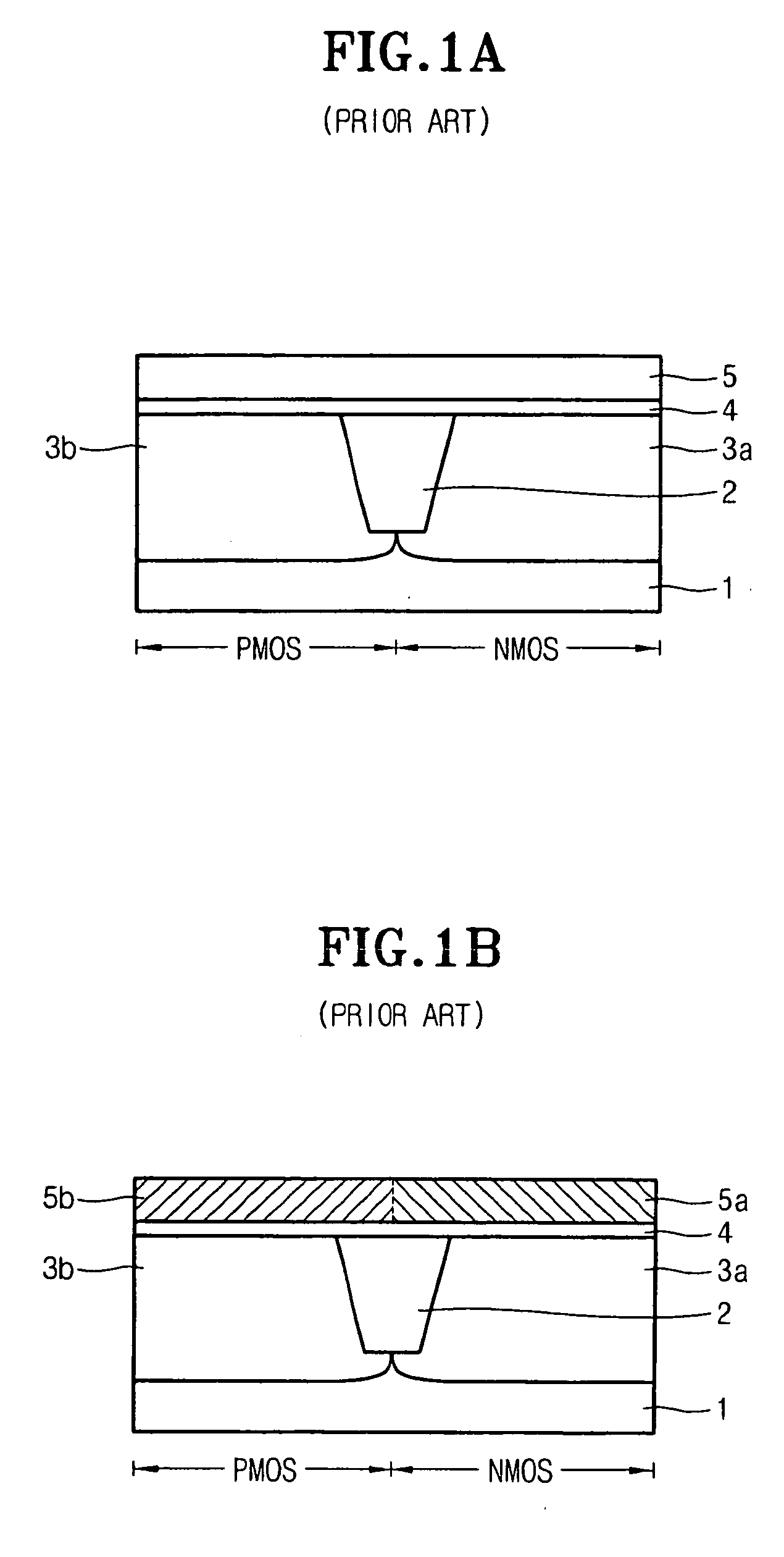

InactiveUS7109076B2Suppressing mutual diffusion of impurityMinimized increaseTransistorSolid-state devicesEngineeringP channel

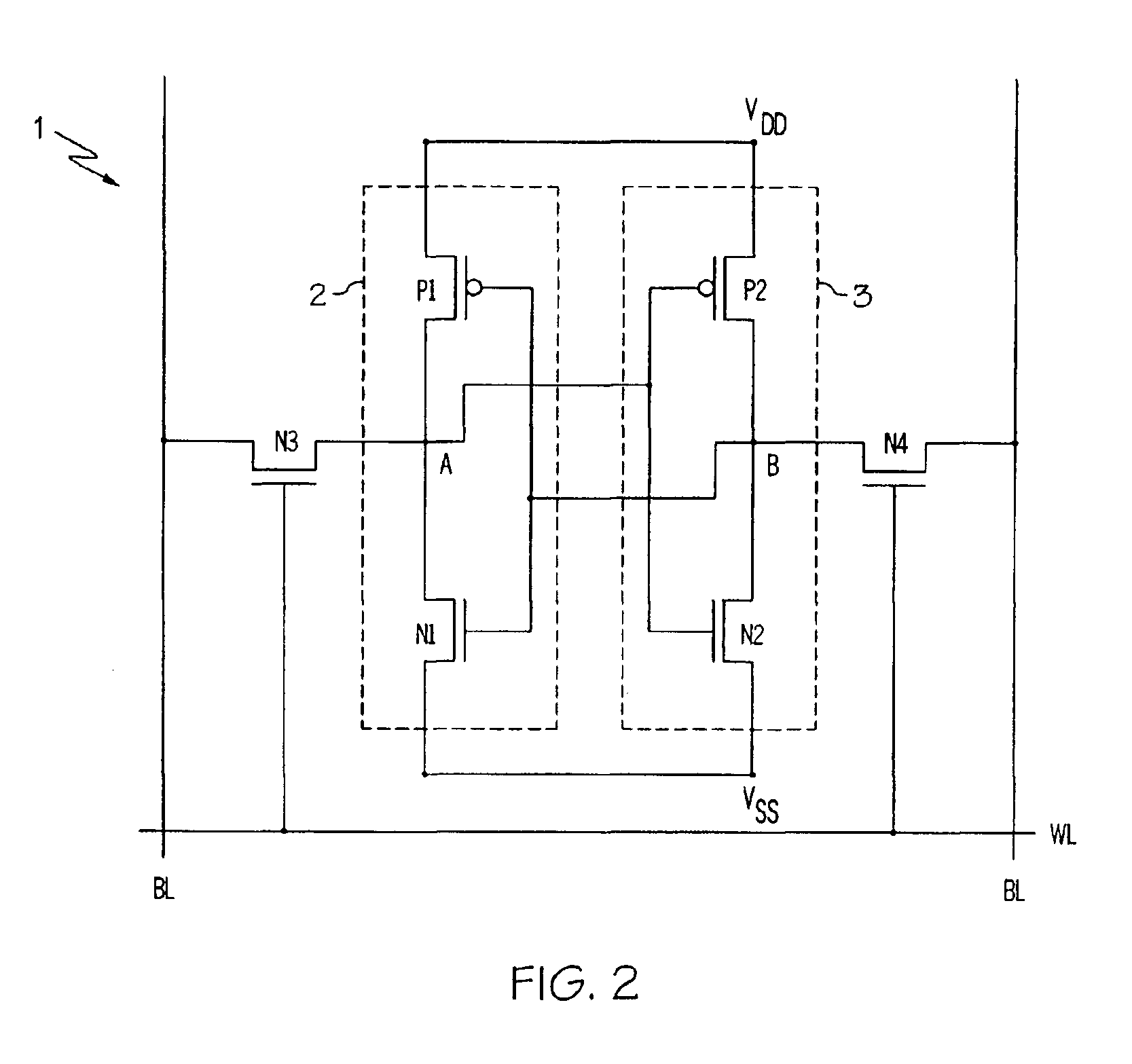

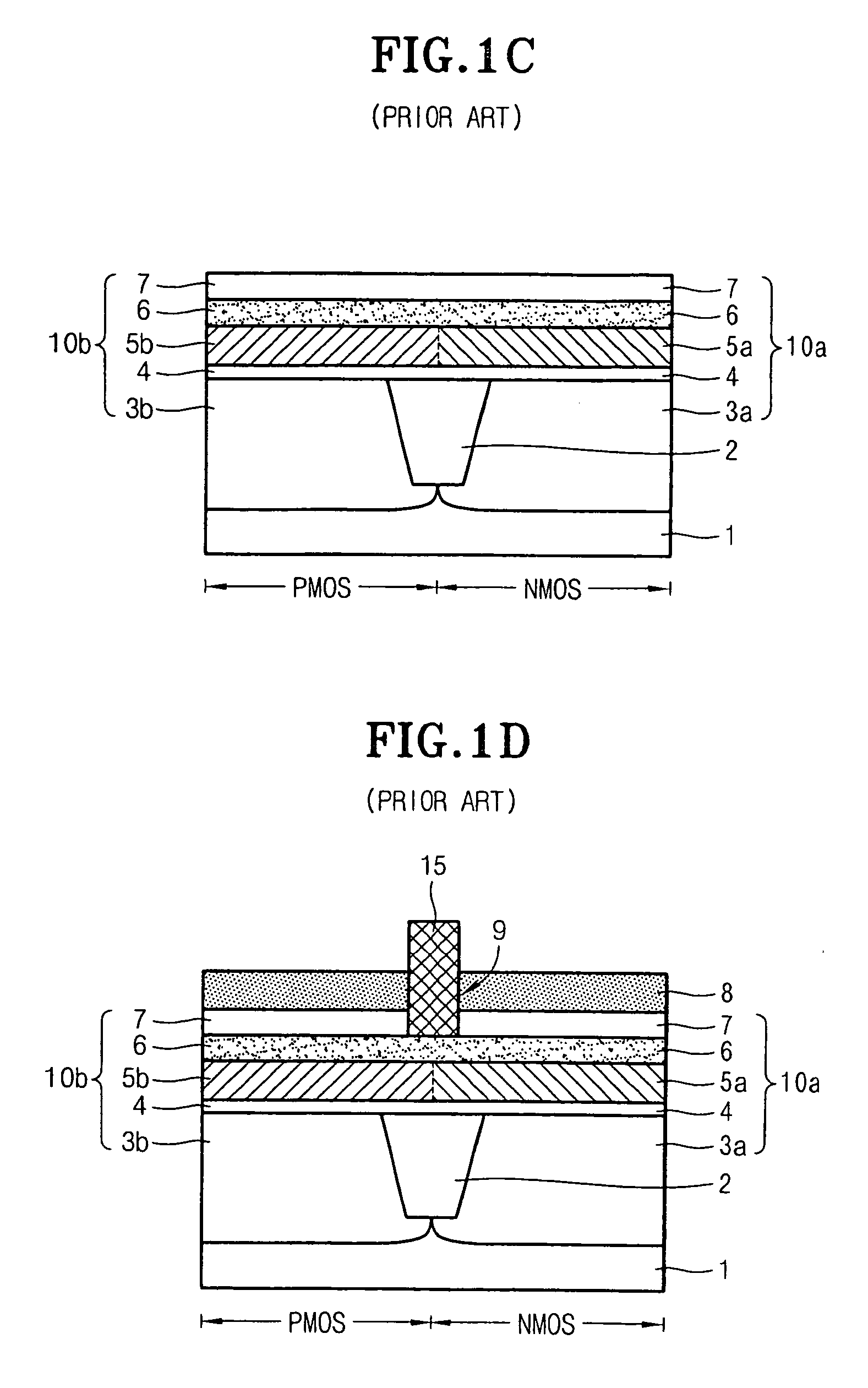

Mutual diffusion of impurities in a gate electrode is suppressed near a boundary between an n-channel type MISFET and a p-channel type MISFET, which adopt a polycide's dual-gate structure. Since a gate electrode of an n-channel type MISFET and a gate electrode of a p-channel type MISFET are of mutually different conductivity types, they are separated to prevent the mutual diffusion of the impurities and are electrically connected to each other via a metallic wiring formed in the following steps. In a step before a gate electrode material is patterned to separate the gate electrodes, the mutual diffusion of the impurities before forming the gate electrodes is prevented by performing no heat treatment at a temperature of 700° C. or higher.

Owner:RENESAS TECH CORP

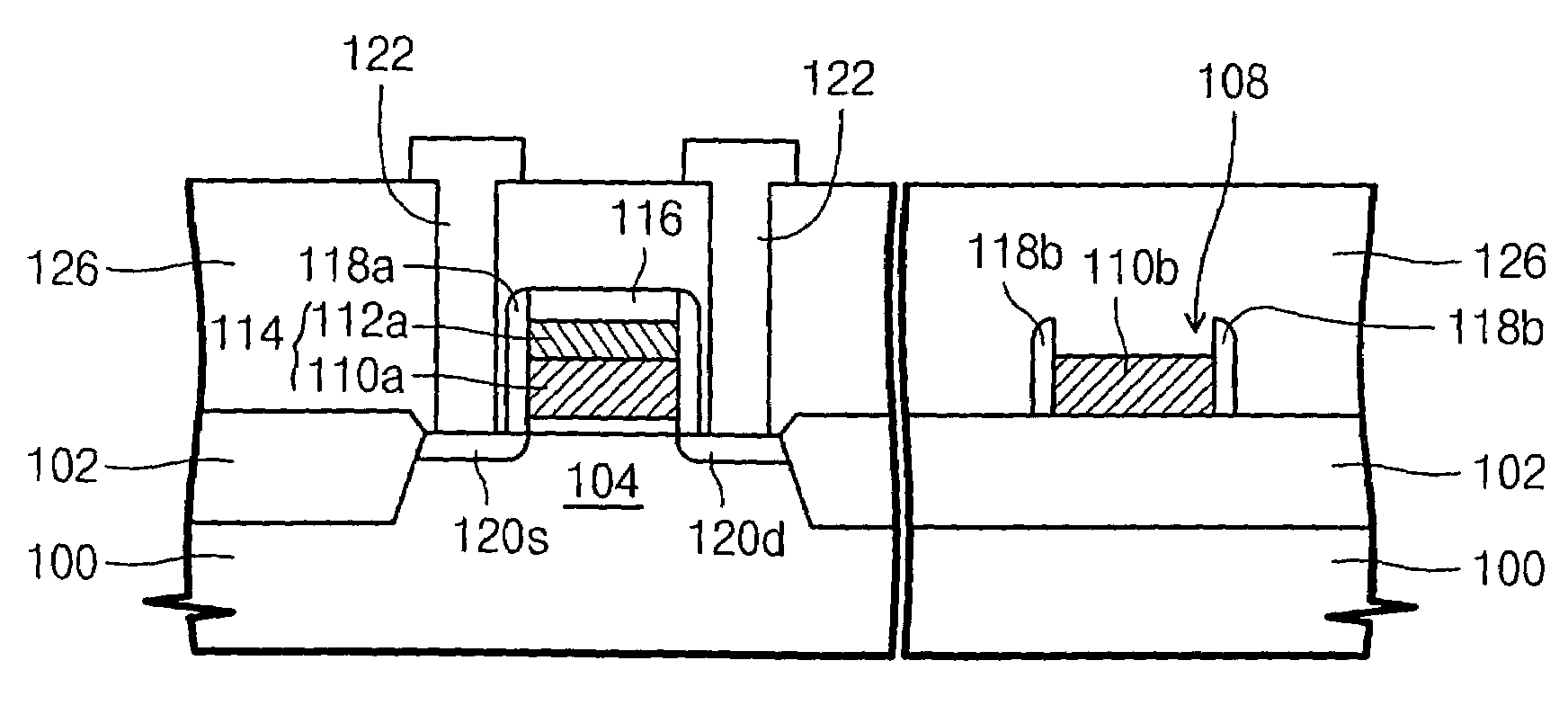

Method for fabricating semiconductor device with metal-polycide gate and recessed channel

InactiveUS20070117294A1Semiconductor/solid-state device manufacturingSemiconductor devicesEtchingDevice material

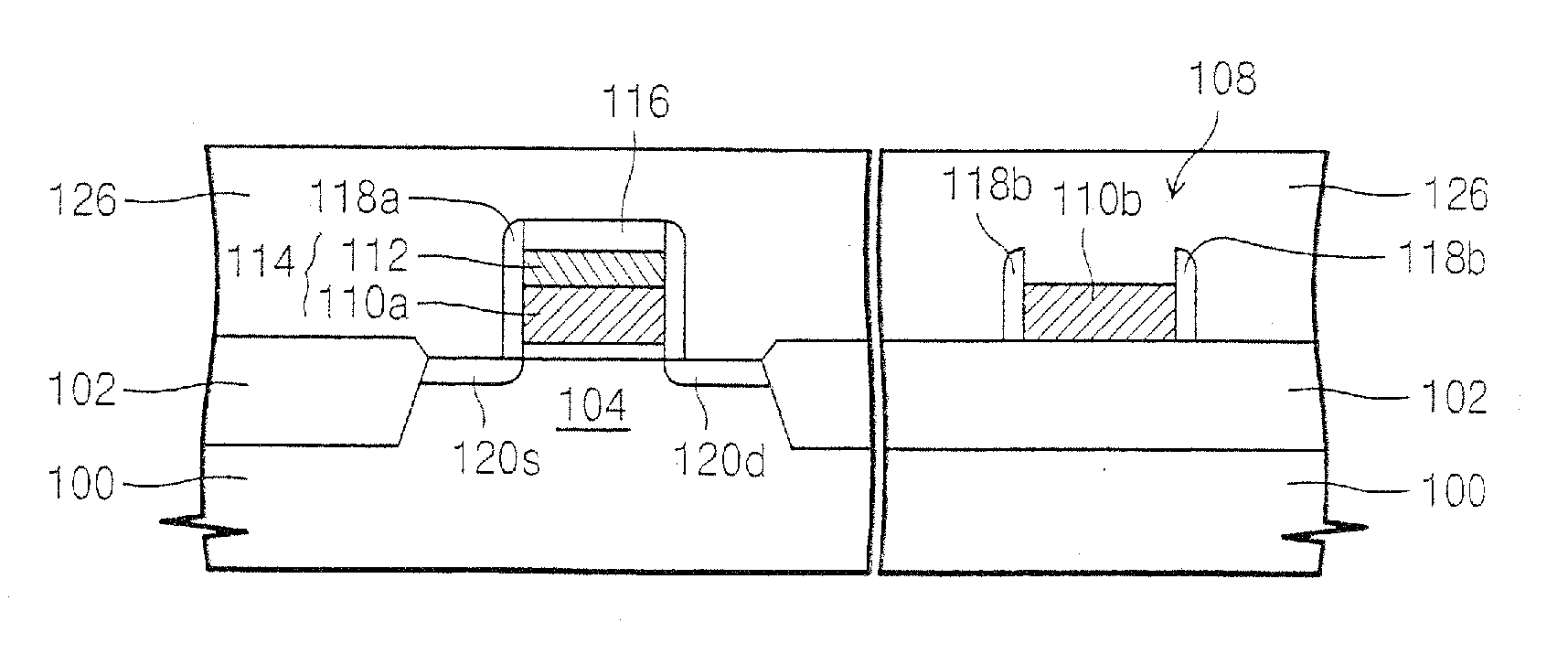

A method for fabricating a semiconductor device with a metal-polycide gate and a recessed channel, including the steps of: forming trenches for a recessed channel in an active area of a semiconductor substrate; forming a gate insulating layer on the semiconductor substrate having the trenches; forming a gate conductive layer on the entire surface of the resulting structure so that the trenches are buried; forming a silicon-rich amorphous metal silicide layer and a gate hard mask on the gate conductive layer; etching the resulting structure until upper portions of the gate conductive layer are removed by a predetermined thickness, upon first patterning for gate stacks, and forming a metal layer on the entire surface of the resulting structure; forming lateral metal capping layers on sides of the silicon-rich amorphous metal silicide layer by blanket etching, completing formation of gate stacks; and thermally processing the silicon-rich amorphous metal silicide layer to form a crystallized metal silicide layer.

Owner:SK HYNIX INC

Process for manufacturing surface channel PMOS device with polycide

ActiveCN101740387AImprove short channel effectSmall sizeSemiconductor/solid-state device manufacturingLow leakageP type silicon

The invention discloses a process for manufacturing a surface channel PMOS device with polycide, which comprises the following steps of: 1, doping an N-type impurity on a P-type silicon substrate to form an N-type channel; 2, depositing a layer of oxidized silicon nitride on the surface of a silicon wafer; 3, depositing a layer of polysilicon on the surface of the silicon wafer and doping a P-type impurity in a gate region of the layer of polysilicon to form P-type polysilicon; 4, forming the polycide on the surface of the silicon wafer; 5, etching the polycide, the P-type polysilicon and the oxidized silicon nitride except for the polycide, the P-type polysilicon and the oxidized silicon nitride outside the gate region until the N-type channel is exposed; 6, depositing a layer of silicon nitride on the surface of the silicon wafer and etching the layer of silicon nitride until the N-type channel is exposed and part of silicon nitride side wall is reserved on the side wall of the P-type polysilicon; and 7, performing ion implantation of the P-type impurity on the silicon wafer to form a source region and a drain region of the PMOS device. The surface channel PMOS device manufactured by the invention can realize low leakage of electricity under a lower threshold voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Multi-silicide in integrated circuit technology

A method of forming an integrated circuit, and an integrated circuit, are provided. A gate dielectric is formed on a semiconductor substrate, and a gate is formed over the gate dielectric. A sidewall spacer is formed around the gate and a source / drain junction is formed in the semiconductor substrate using the sidewall spacer. A bottom silicide metal is deposited on the source / drain junction and then a top silicide metal is deposited on the bottom silicide metal. The bottom and top silicide metals are formed into their silicides. A dielectric layer is deposited above the semiconductor substrate and a contact is formed in the dielectric layer to the top silicide.

Owner:GLOBALFOUNDRIES INC

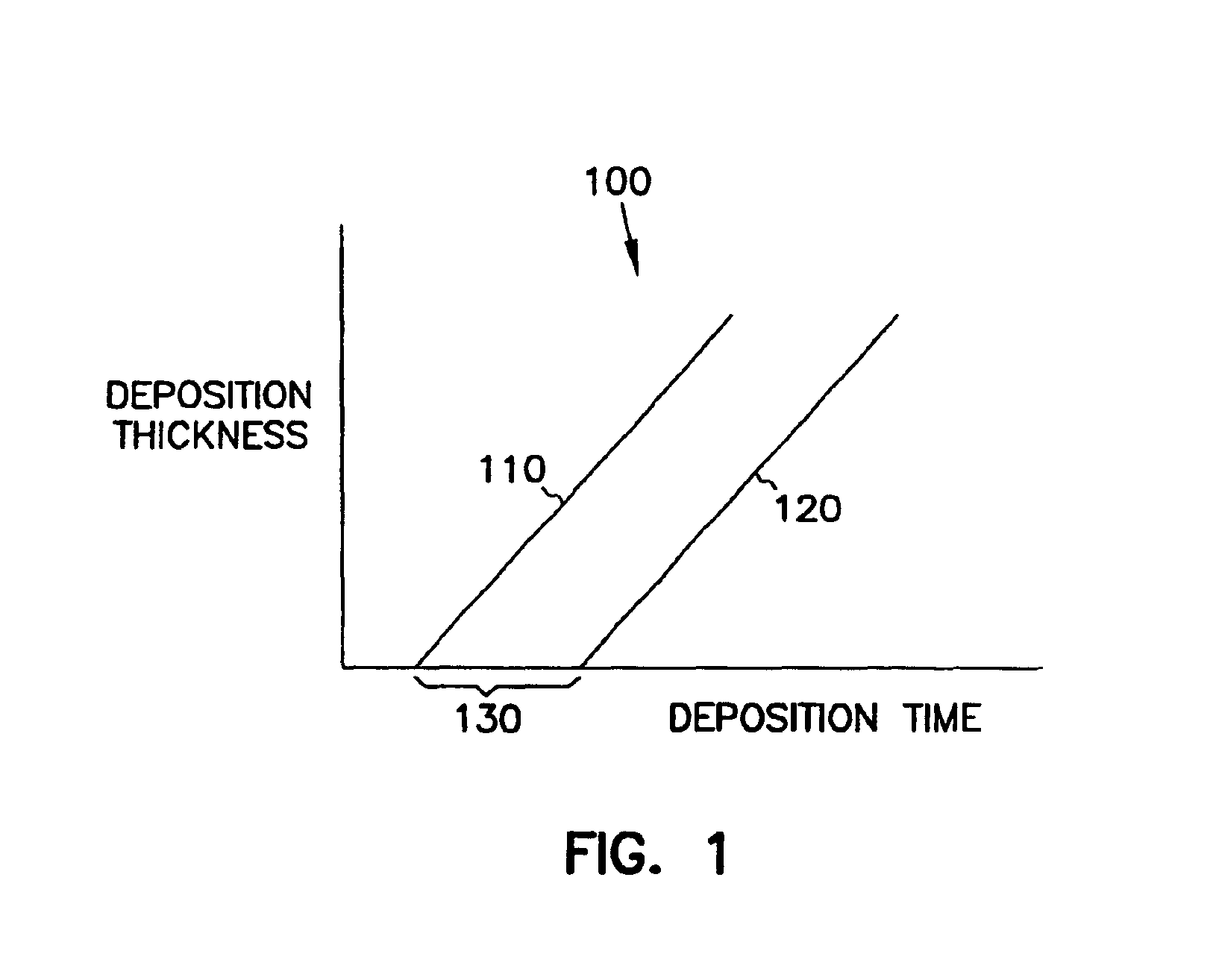

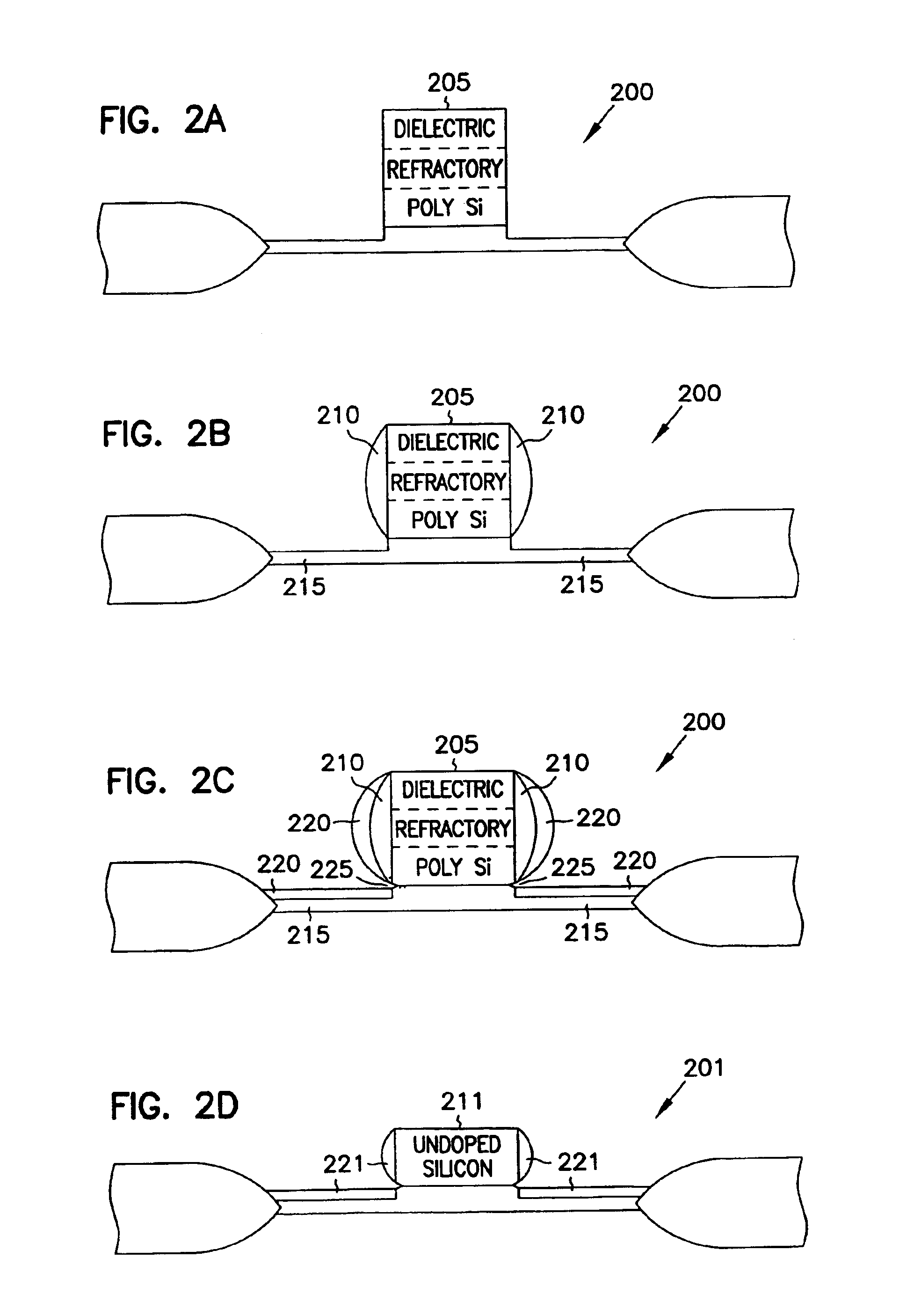

Selective spacer to prevent metal oxide formation during polycide reoxidation

InactiveUS7009264B1Avoid undesirable formationInhibits oxide formationSolid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconSilicon dioxide

A selective spacer to prevent metal oxide formation during polycide reoxidation of a feature such as an electrode and a method for forming the selective spacer are disclosed. A material such as a thin silicon nitride or an amorphous silicon film is selectively deposited on the electrode by limiting deposition time to a period less than an incubation time for the material on silicon dioxide near the electrode. The spacer is deposited only on the electrode and not on surrounding silicon dioxide. The spacer serves as a barrier for the electrode during subsequent oxidation to prevent metal oxide formation while allowing oxidation to take place over the silicon dioxide.

Owner:MICRON TECH INC

Buried low-resistance metal word lines for cross-point variable-resistance material memories

ActiveCN101803025ASolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceSalicide

Variable-resistance material memories include a buried salicide word line disposed below a diode. Variable-resistance material memories include a metal spacer spaced apart and next to the diode. Processes include the formation of one of the buried salicide word line and the metal spacer. Devices include the variable-resistance material memories and one of the buried salicided word line and the spacer word line.

Owner:MICRON TECH INC