Semiconductor memory device and its manufacture method

A storage device and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as cell current degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

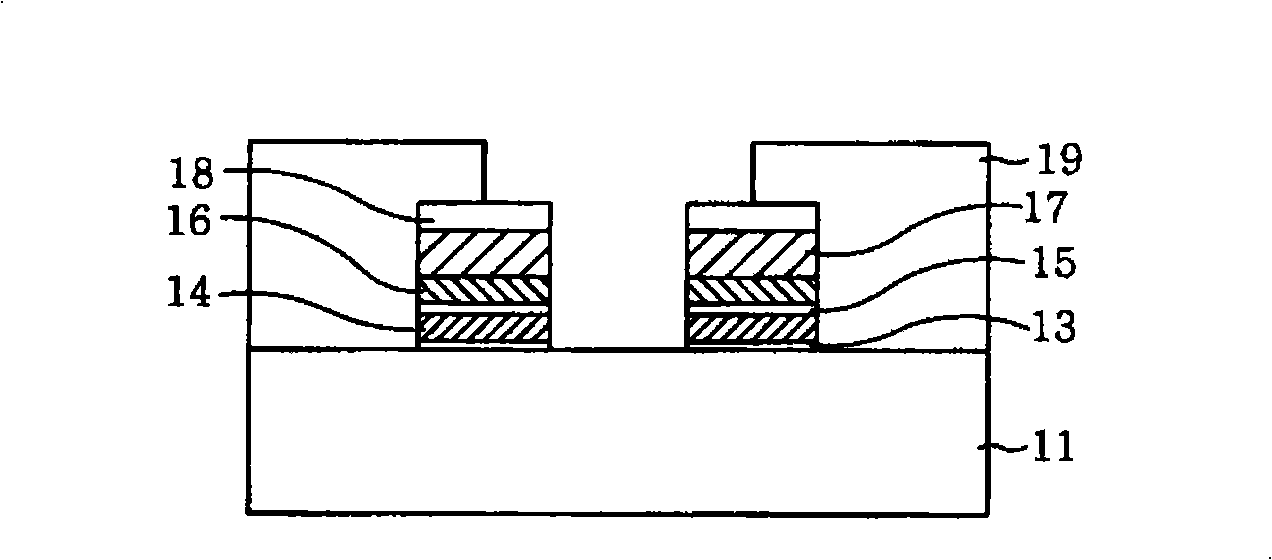

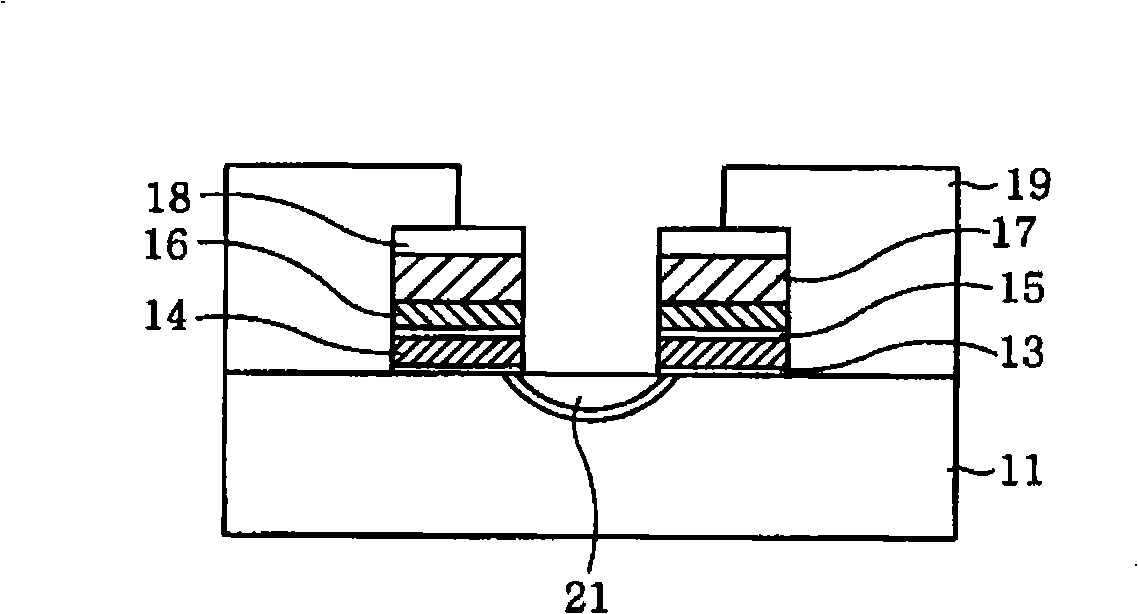

[0017] as in the exemplary Figure 3A As illustrated in , the device isolation film may be formed in the device isolation region of the semiconductor substrate 101 . A trench oxide film 103 and a first polysilicon film 104 may then be sequentially formed on and / or over the entire structure, followed by patterning by a photolithography process and an etching process using a floating gate mask, thereby forming a floating gate pole. A dielectric film 105, a second polysilicon film 106, a tungsten silicide film 107, and an oxide film 108 may then be sequentially formed on and / or over the entire structure, followed by patterning by a photolithography process and an etching process using a control gate mask , thereby forming a control gate. In this way, a stacked gate structure including a floating gate and a control gate stacked can be formed. A photosensitive film 109 may then be formed on and / or over the entire structure, followed by patterning through an exposure process and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More