Patents

Literature

72results about How to "Reduce metal pollution" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

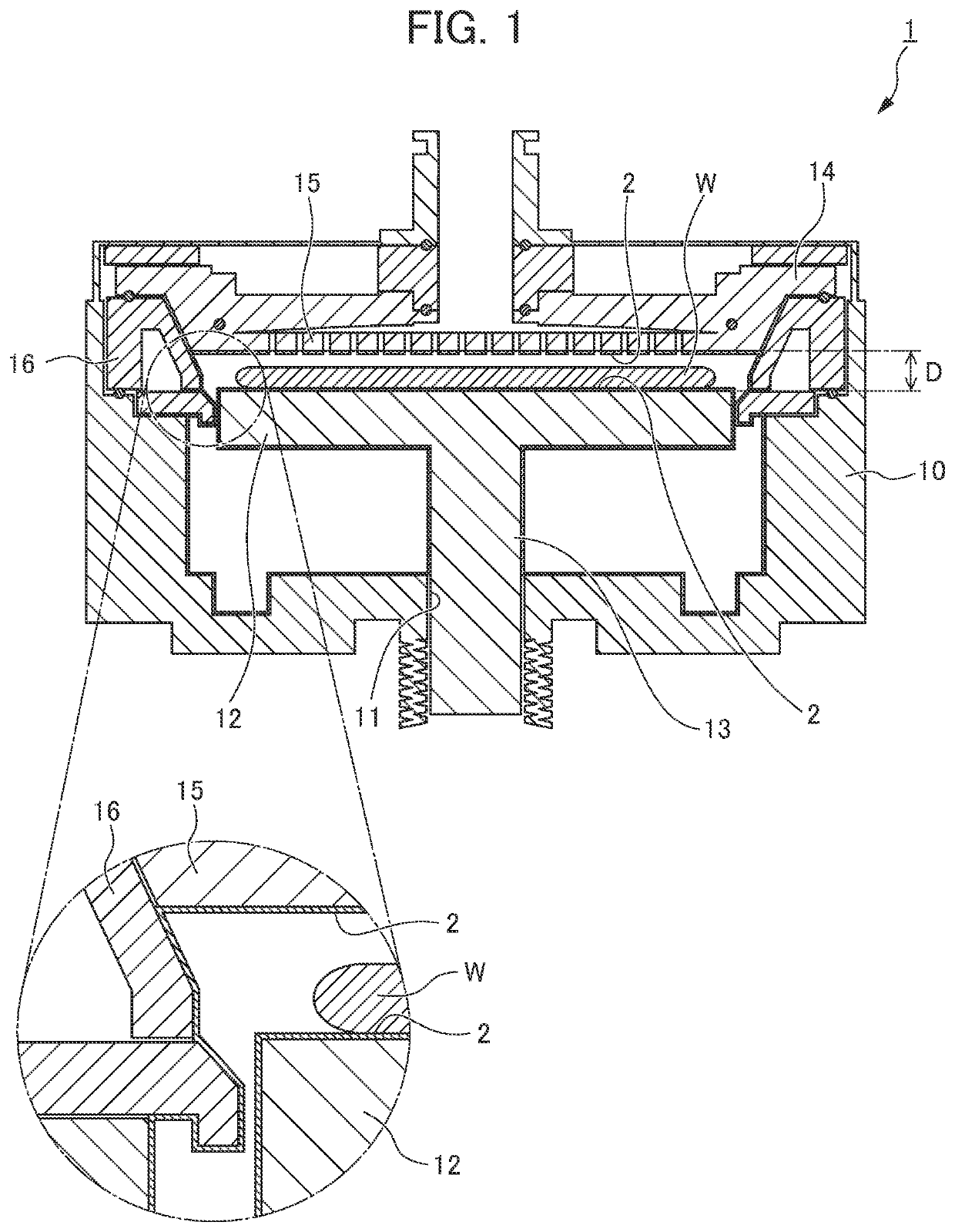

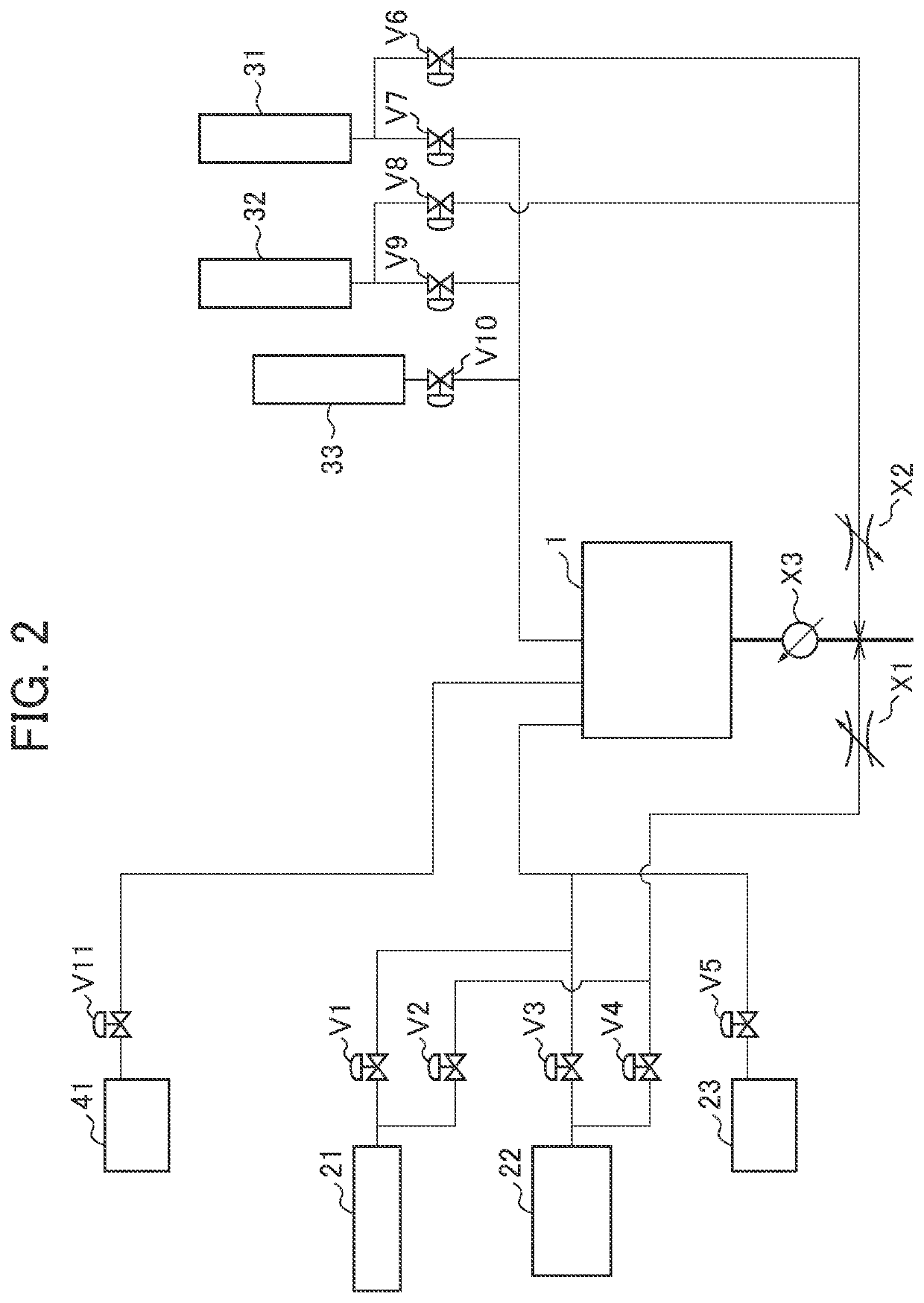

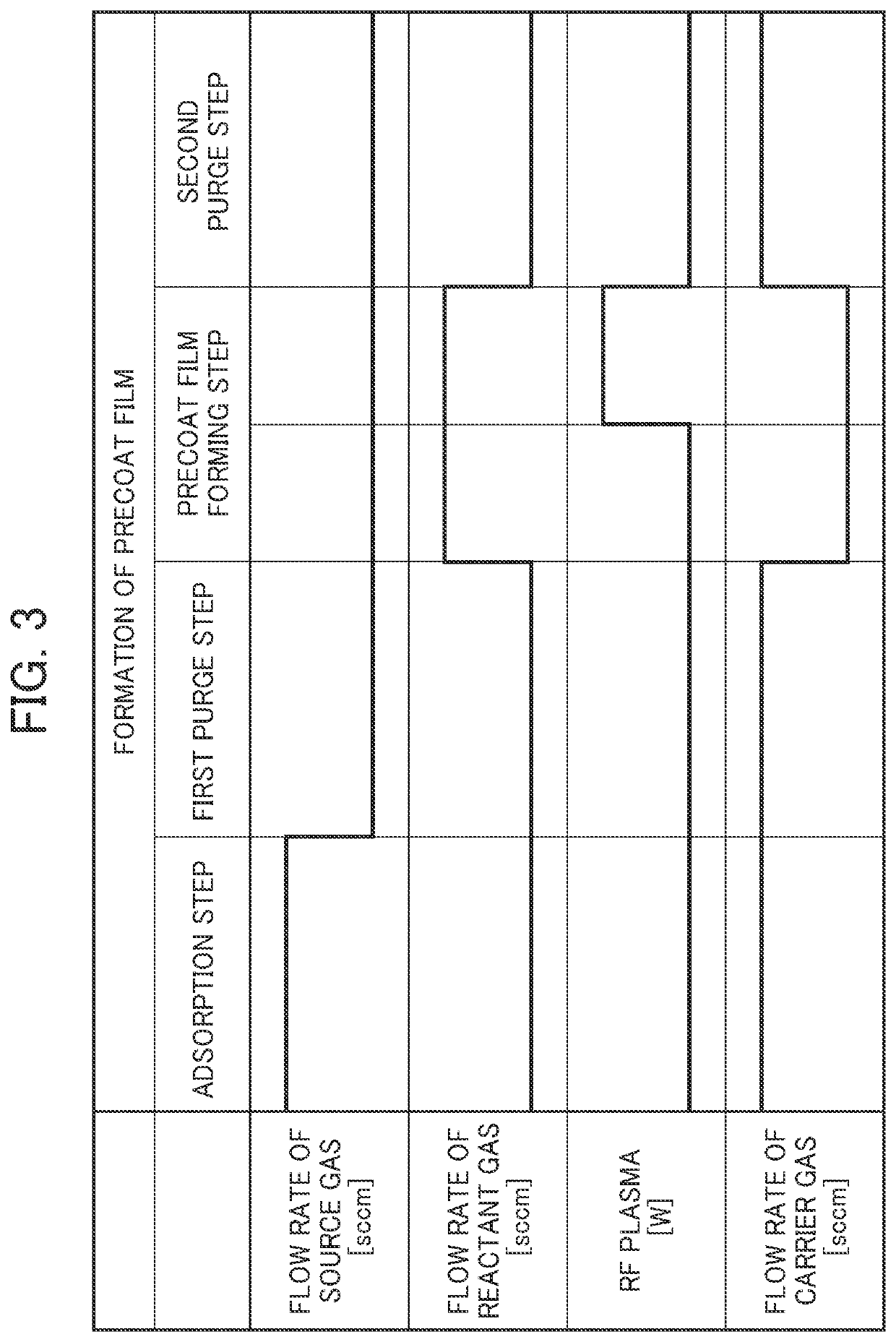

Method for forming precoat film and method for forming silicon-containing film

PendingUS20210324510A1Quality improvementReduce metal pollutionElectric discharge tubesSemiconductor/solid-state device manufacturingHigh frequency powerPhysical chemistry

A method for forming a precoat film on a metal surface in a chamber before forming a silicon-containing film having an identical composition system with that of the precoat film on a substrate in the chamber using a PECVD method, wherein the precoat film is formed using a PEALD method in which a first gas and a second gas are supplied into the chamber by shifting timing of supply, the PEALD method comprises an adsorption step comprising supplying the first gas into the chamber so that the source gas component adsorbs on the metal surface, a first purge step comprising discharging an excessive source gas component not adsorbed on the metal surface, and a precoat film forming step comprising supplying the second gas into the chamber and applying high-frequency power to generate plasma in the reactant gas component in the second gas.

Owner:ASM IP HLDG BV

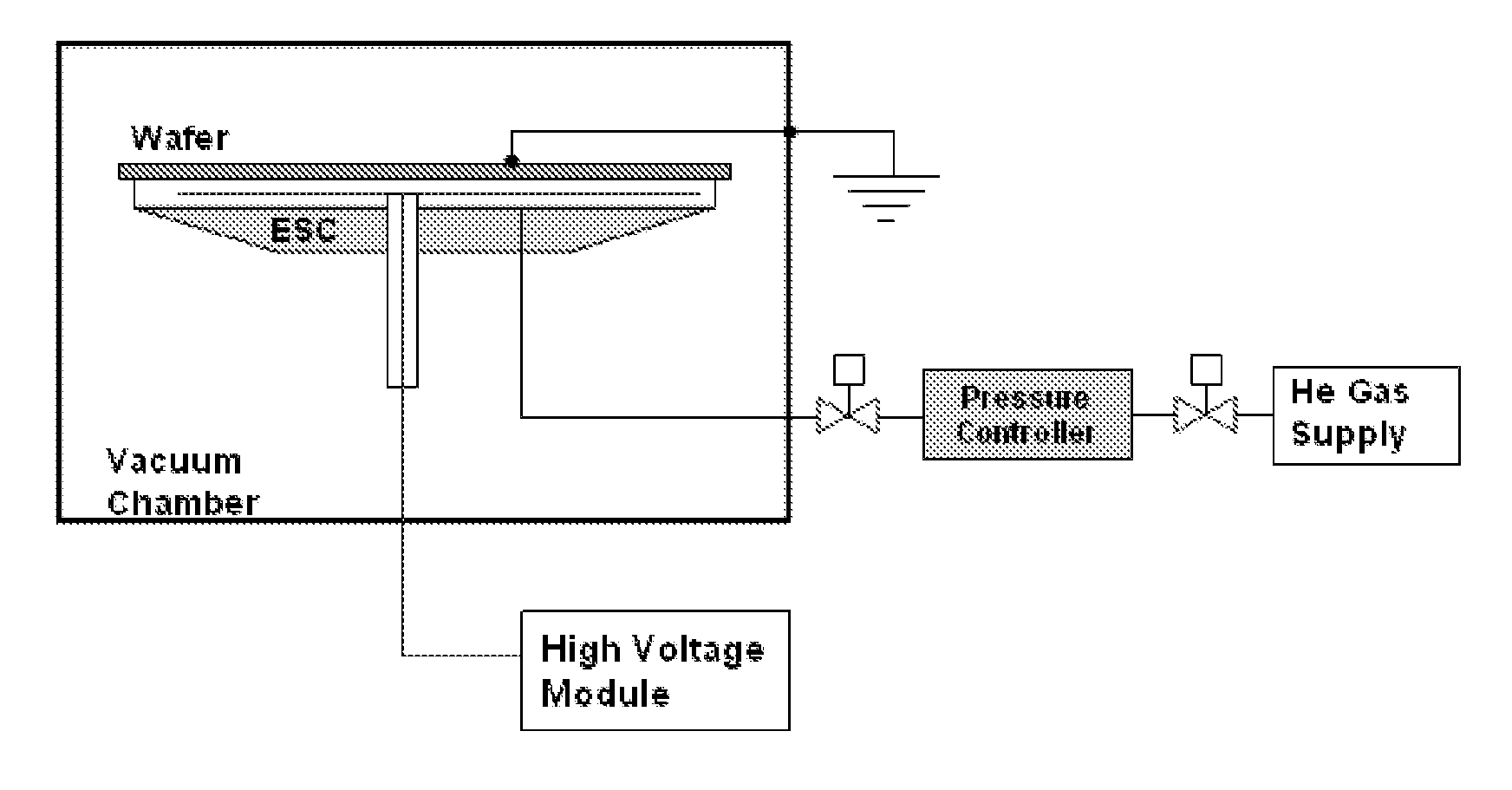

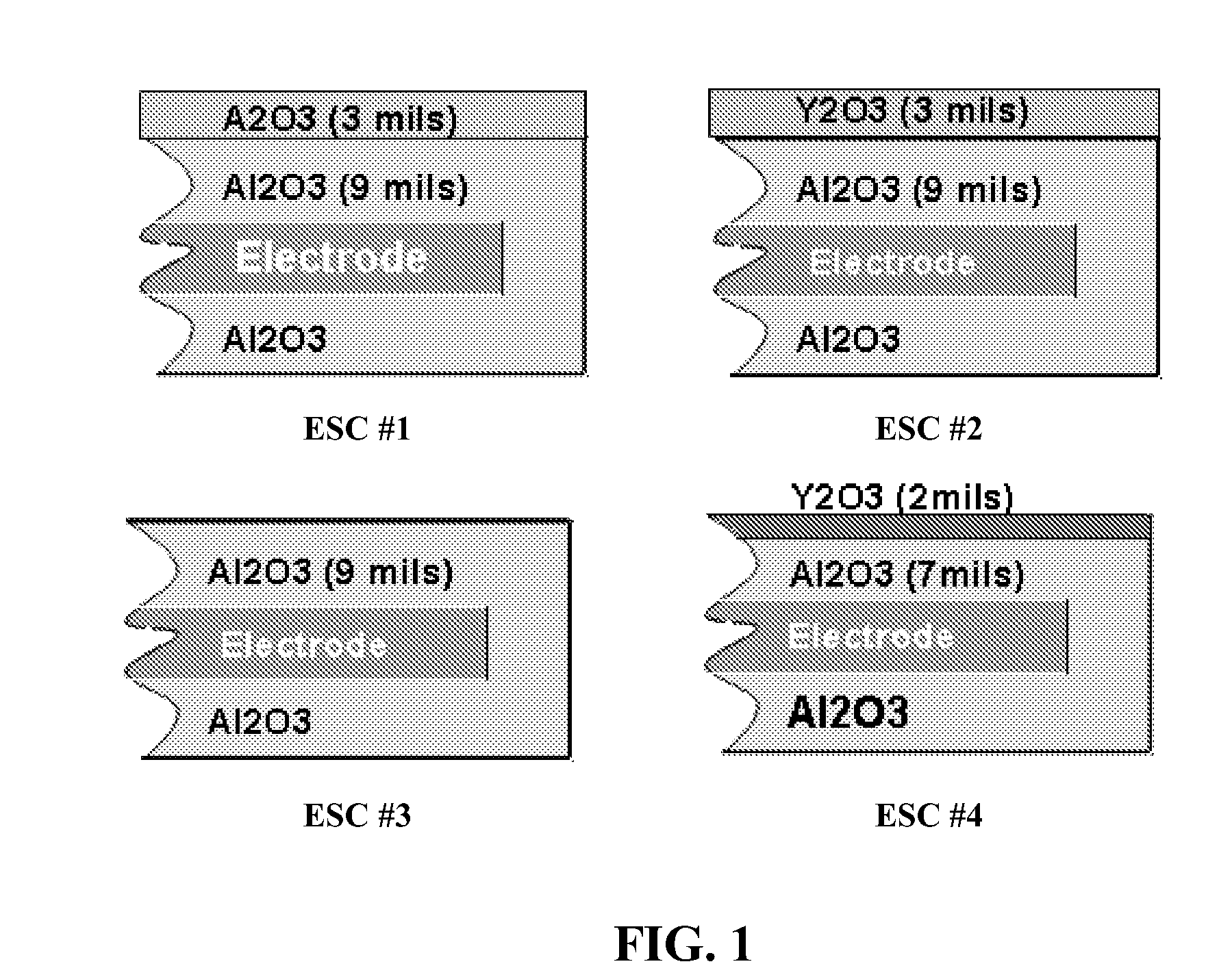

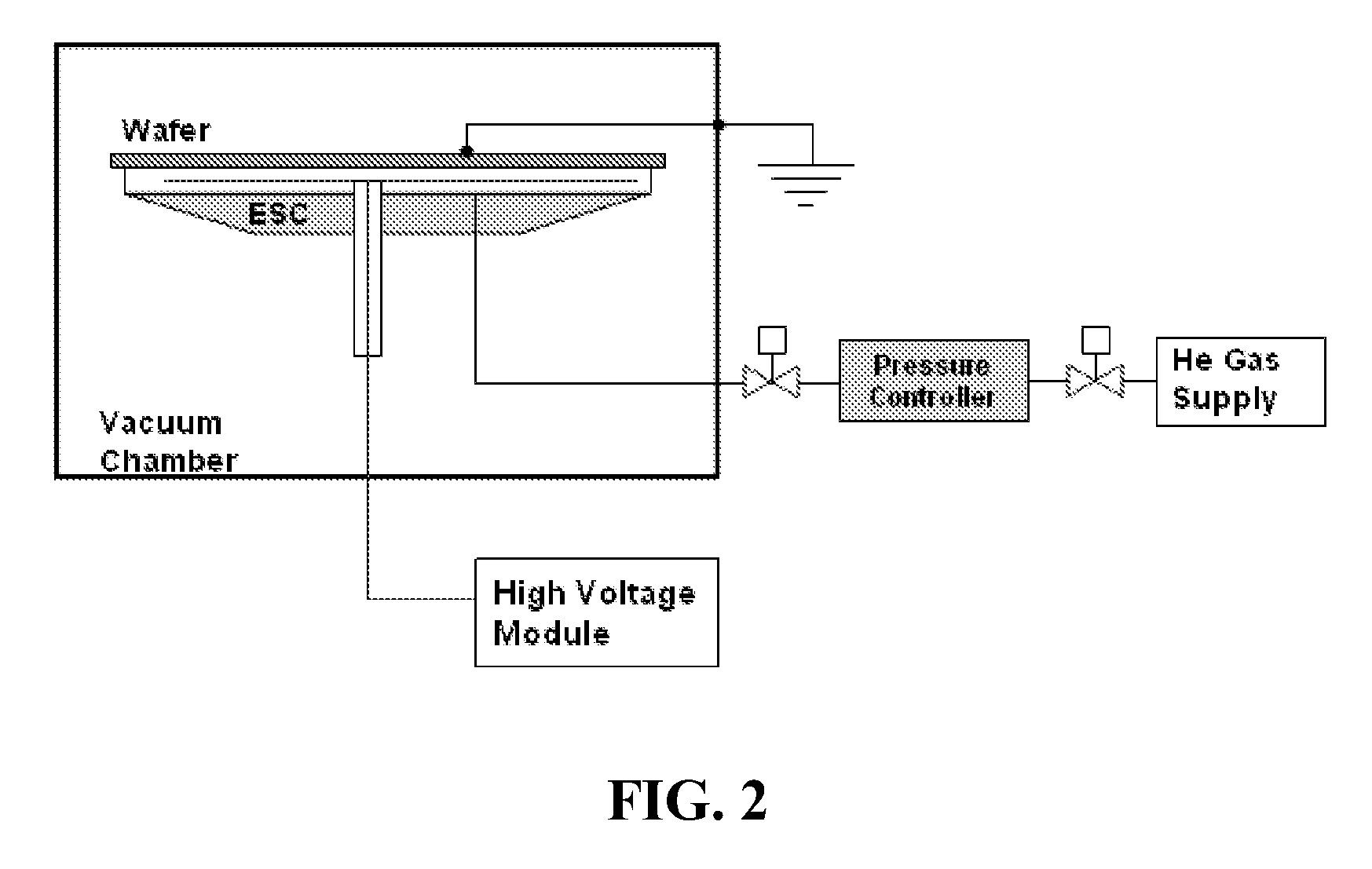

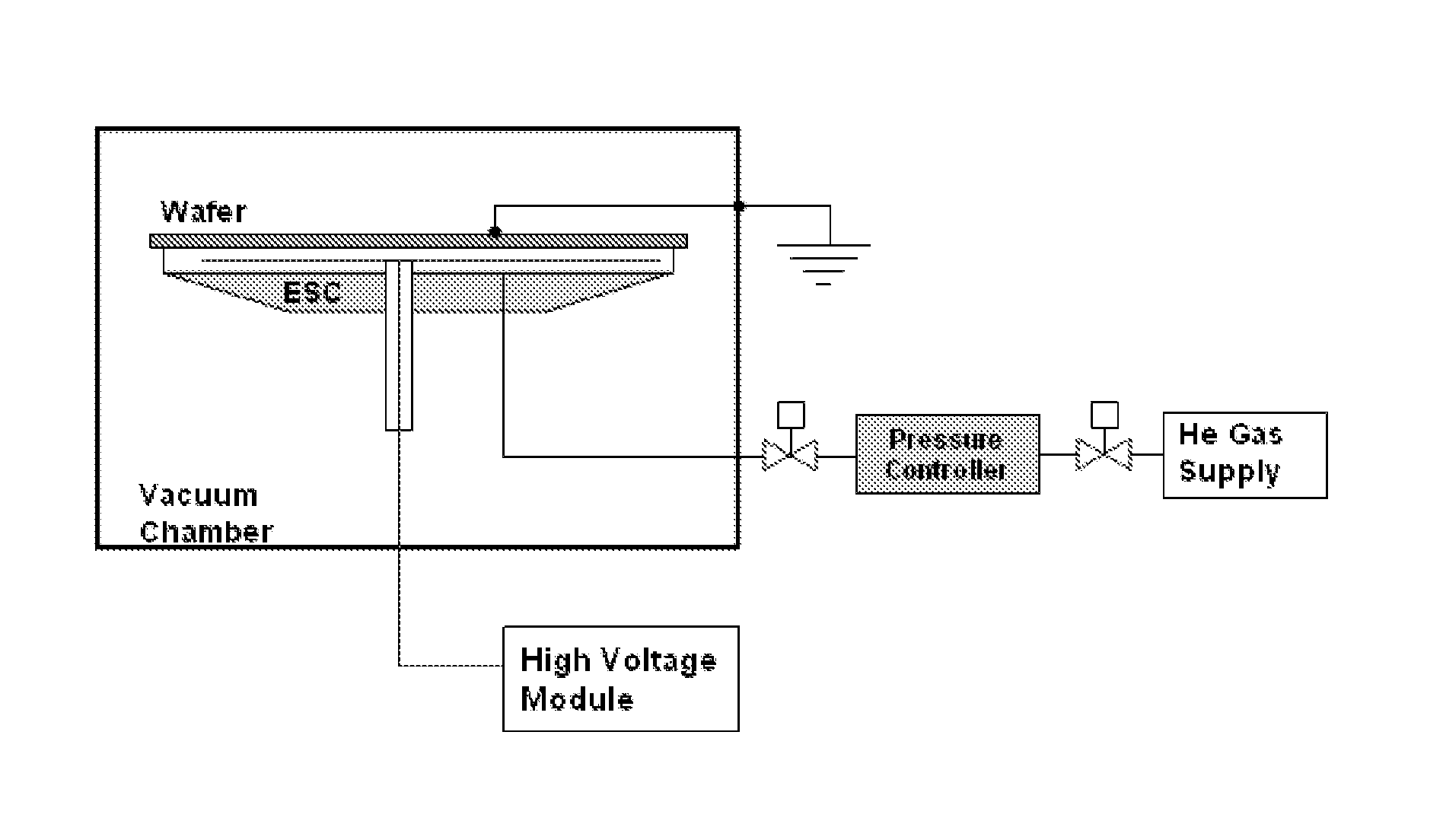

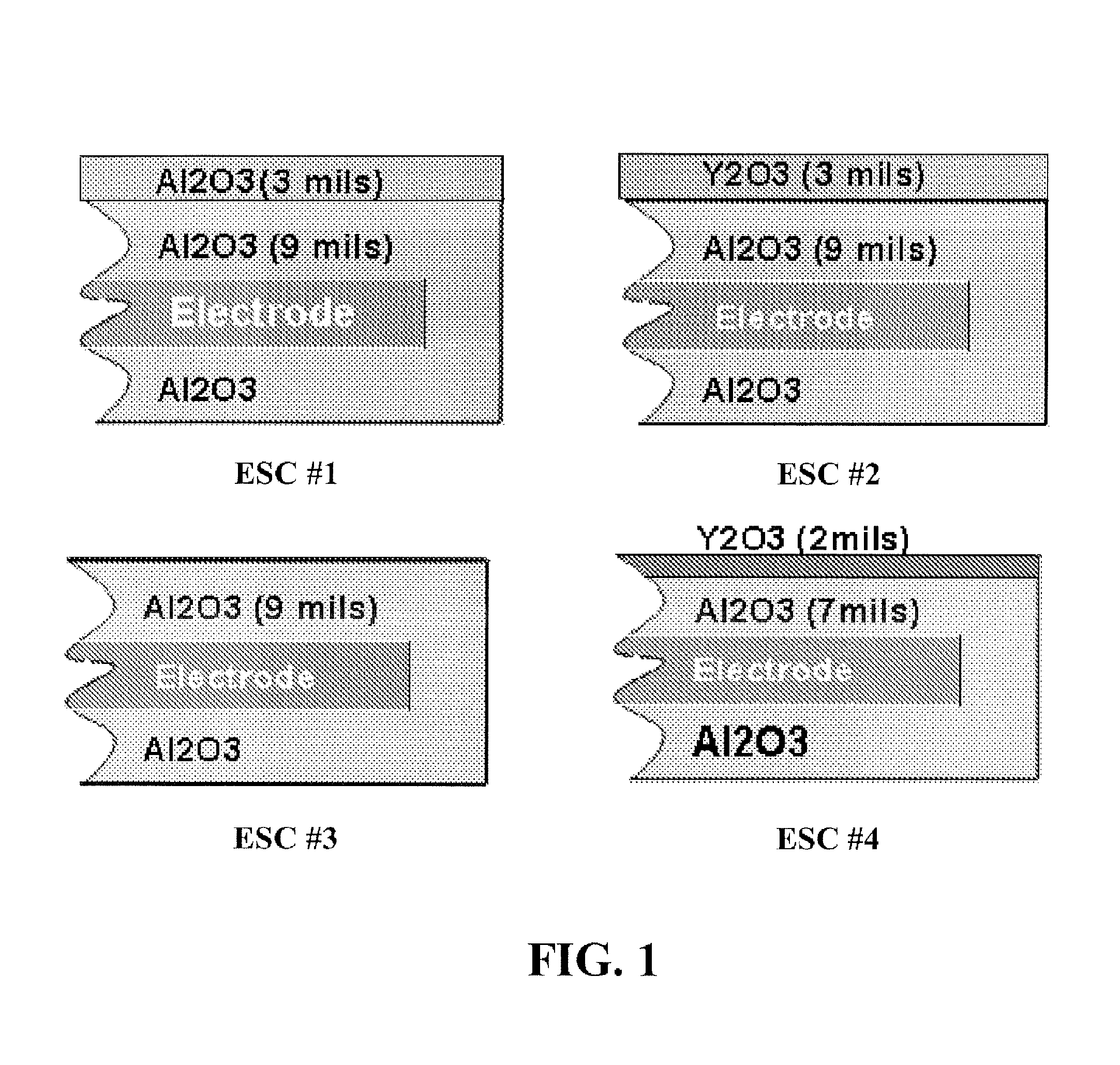

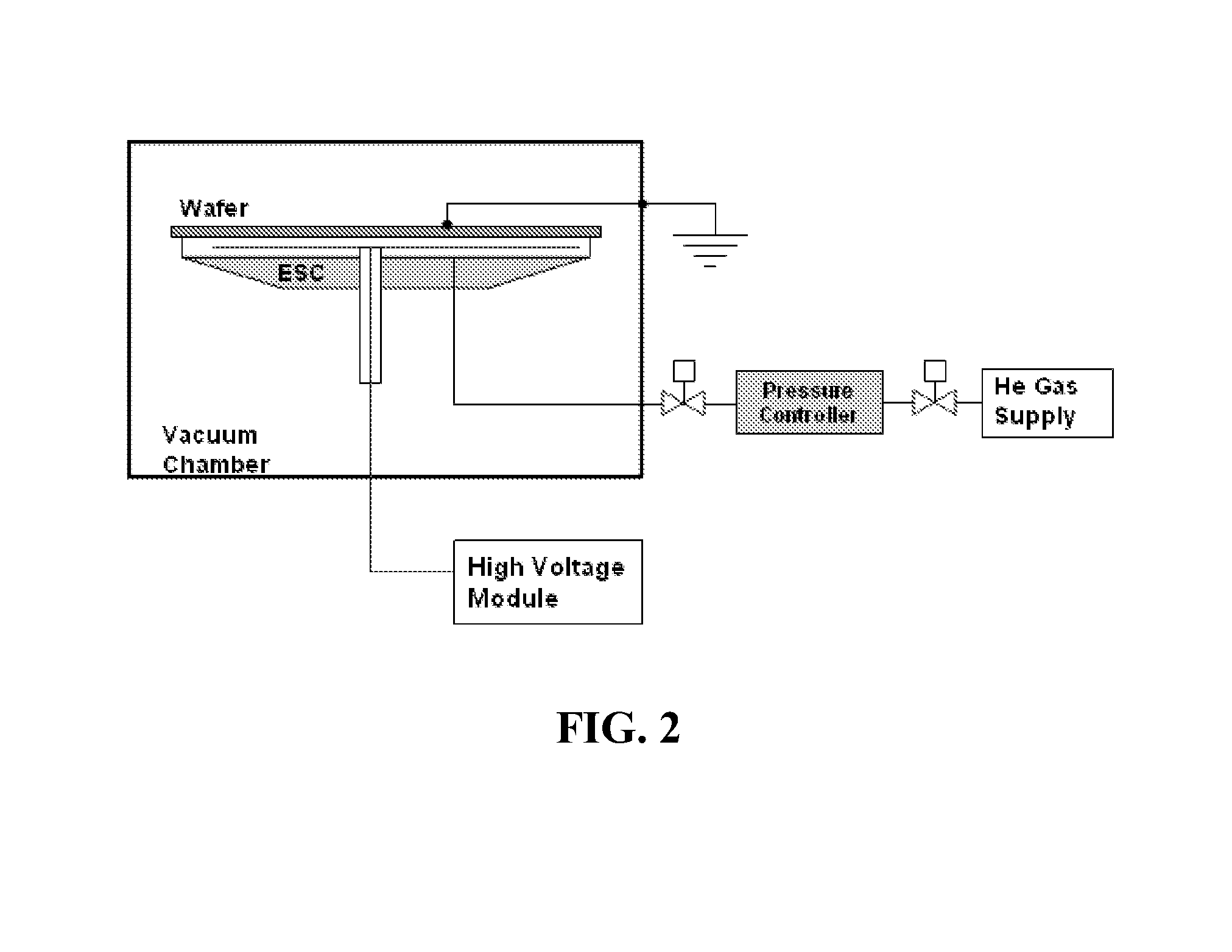

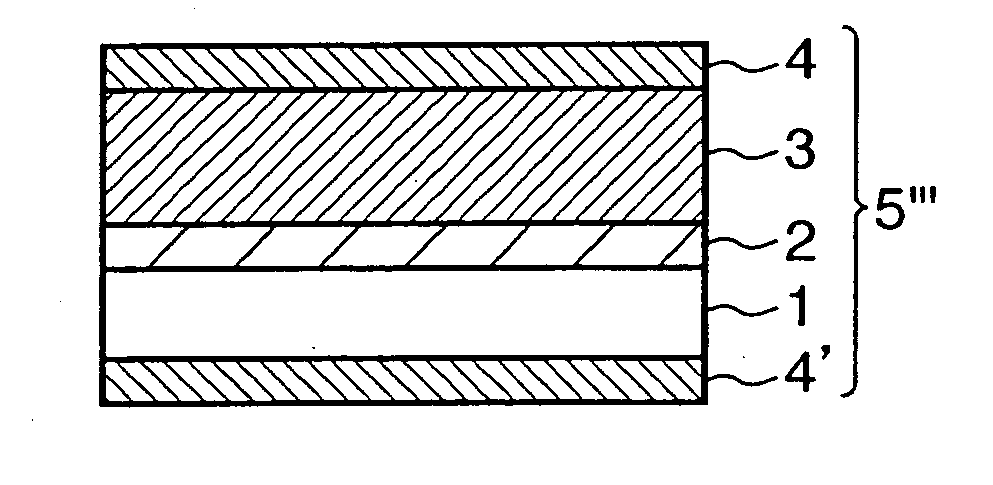

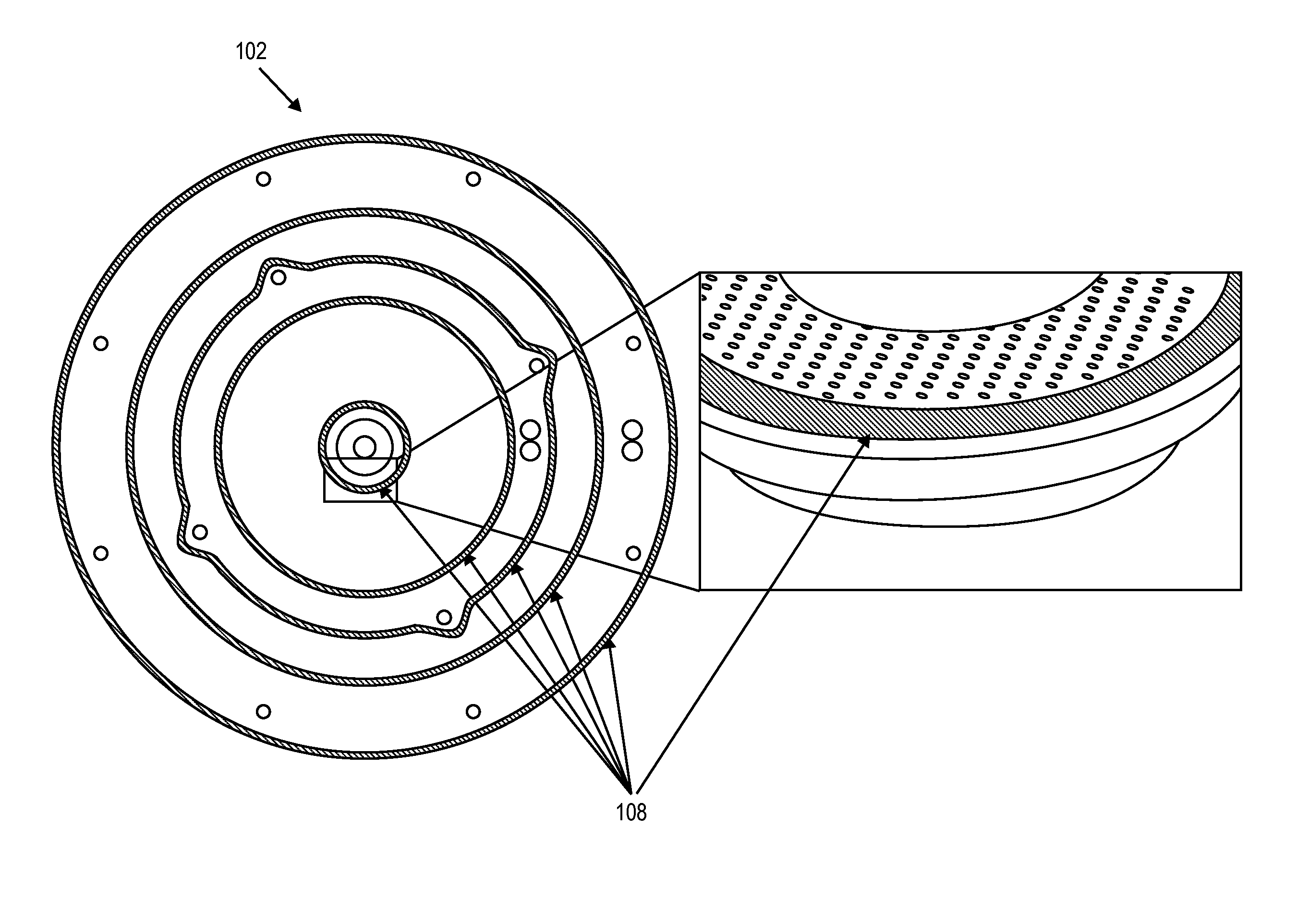

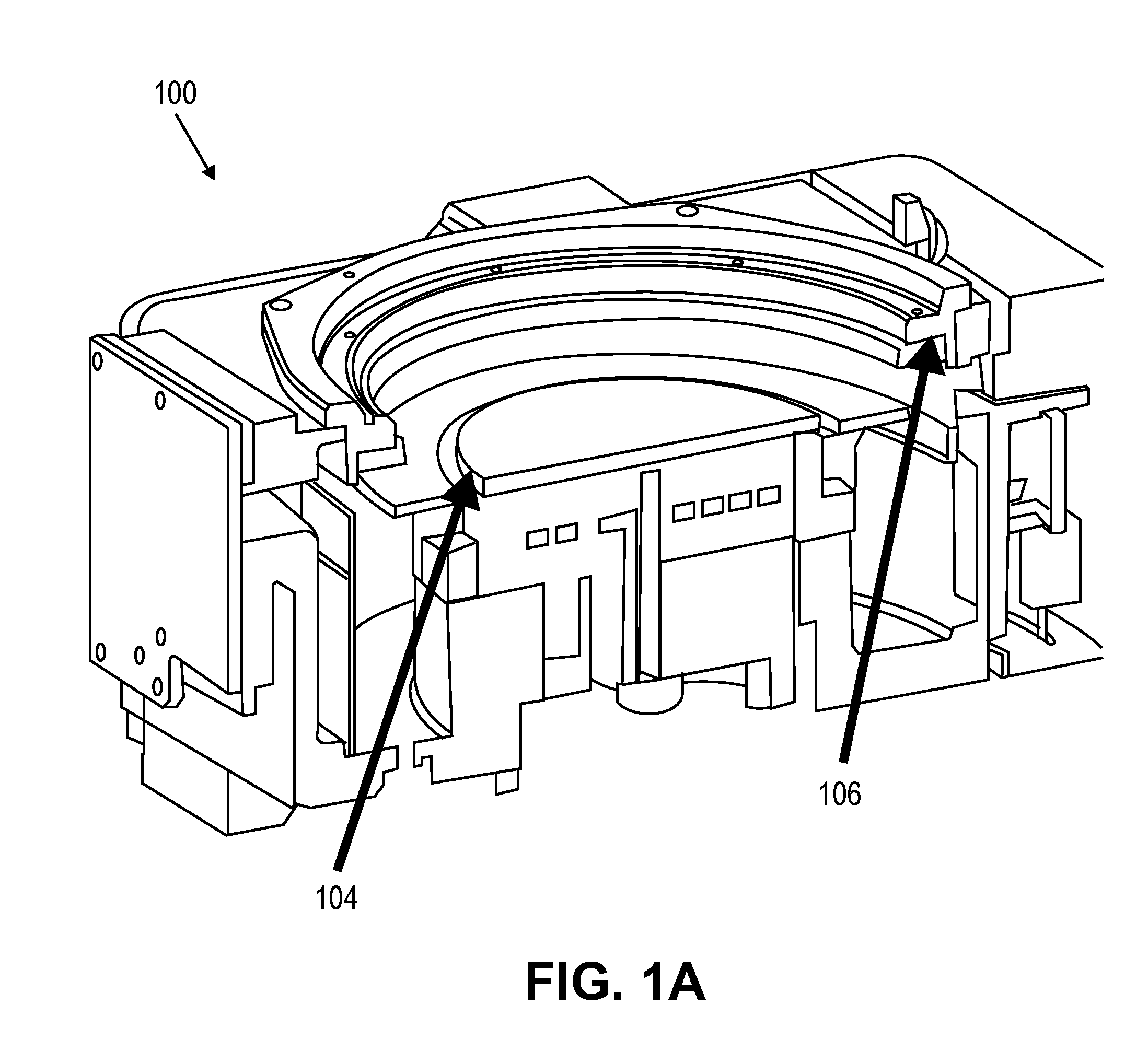

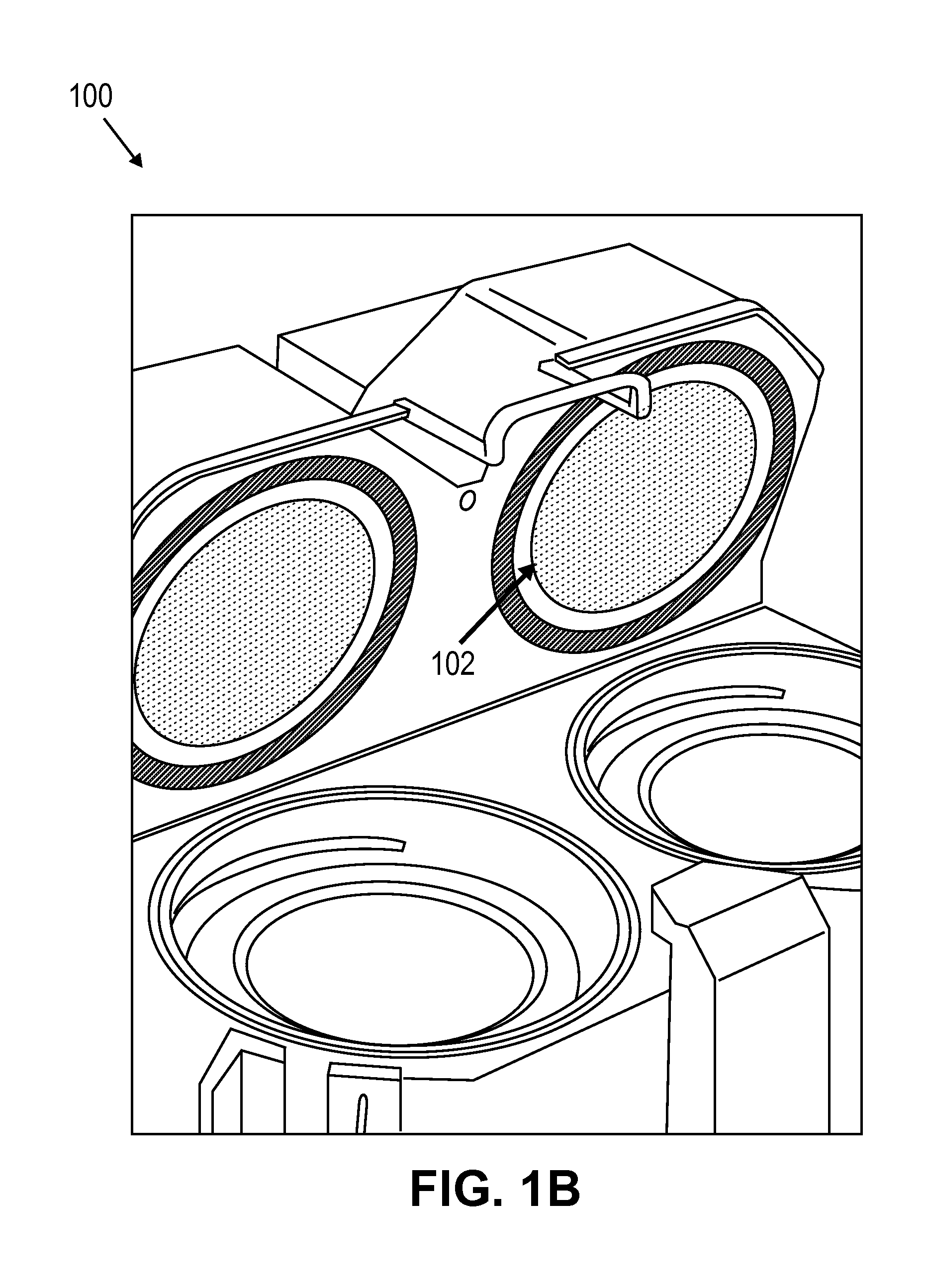

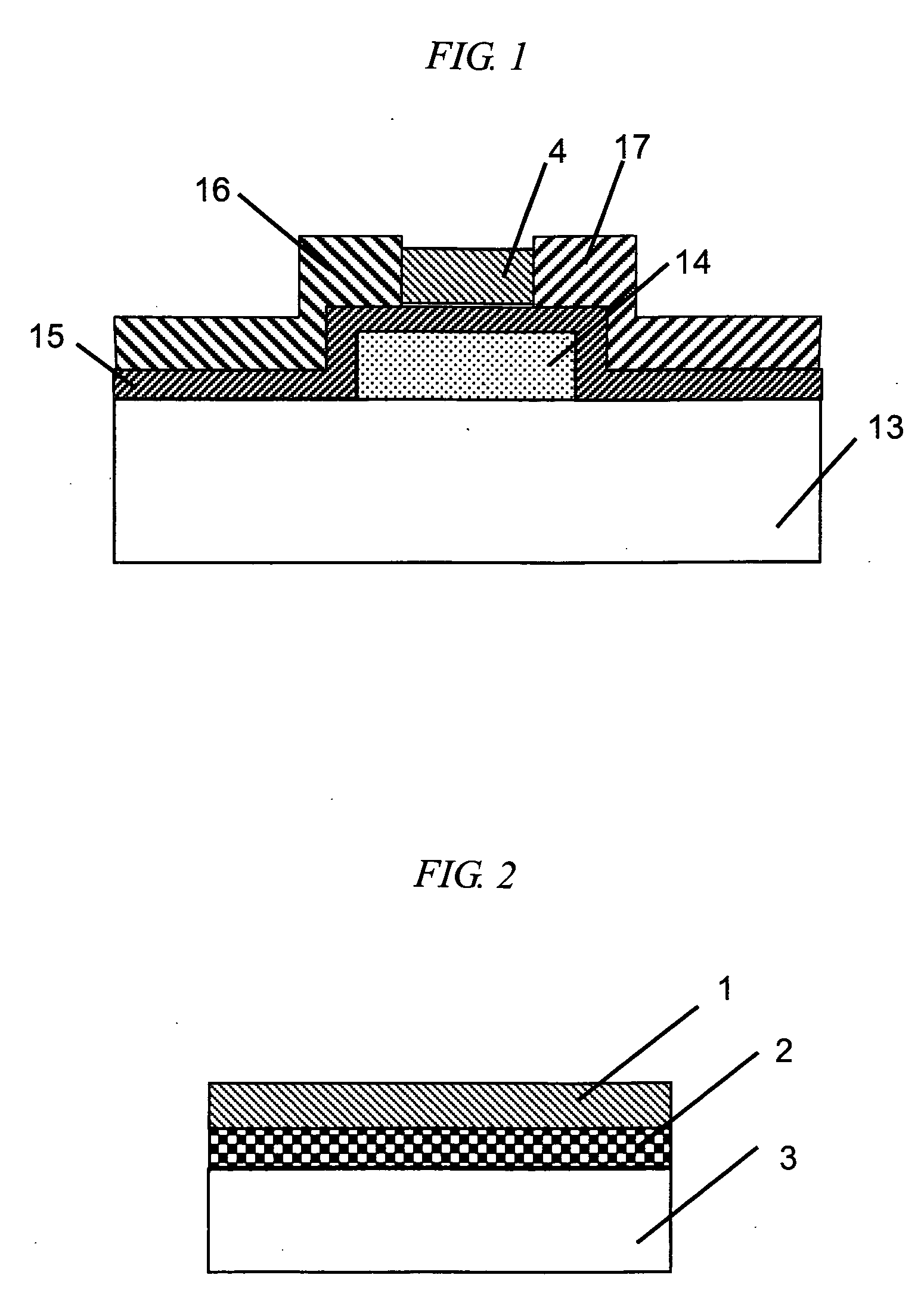

Substrate supports for semiconductor applications

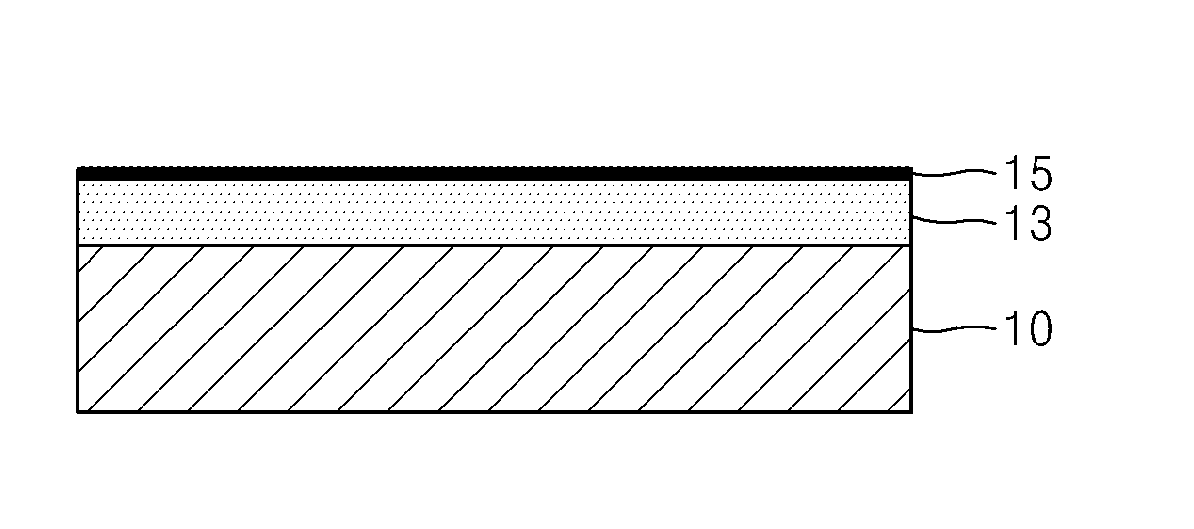

ActiveUS20120141661A1Enhance attractive and chuck forceMinimize currentSemiconductor/solid-state device manufacturingCoatingsCorrosionOxide

This invention relates to substrate supports, e.g., coated electrostatic chucks, having a dielectric multilayer formed thereon; dielectric multilayers that provide erosive and corrosive barrier protection in harsh environments such as plasma treating vessels used in semiconductor device manufacture; process chambers, e.g., deposition chambers, for processing substrates; methods for protecting substrate supports; and methods for producing substrate supports and electronic devices. The dielectric multilayer comprises (a) an undercoat dielectric layer comprising a metal oxide or metal nitride formed on a surface; and (b) a topcoat dielectric layer comprising a metal oxide formed on the undercoat dielectric layer. The topcoat dielectric layer has an aluminum oxide content of less than about 1 weight percent. The topcoat dielectric layer has a corrosion resistance and / or plasma erosion resistance greater than the corrosion resistance and / or plasma erosion resistance of the undercoat dielectric layer. The undercoat dielectric layer can have a resistivity greater than the resistivity of the topcoat dielectric layer. The topcoat dielectric layer can have a dielectric constant greater than the dielectric constant of the undercoat dielectric layer. The undercoat dielectric layer can have a porosity greater than the porosity of the topcoat dielectric layer. The invention is useful, for example, in the manufacture and protection of electrostatic chucks used in semiconductor device manufacture.

Owner:FM INDS

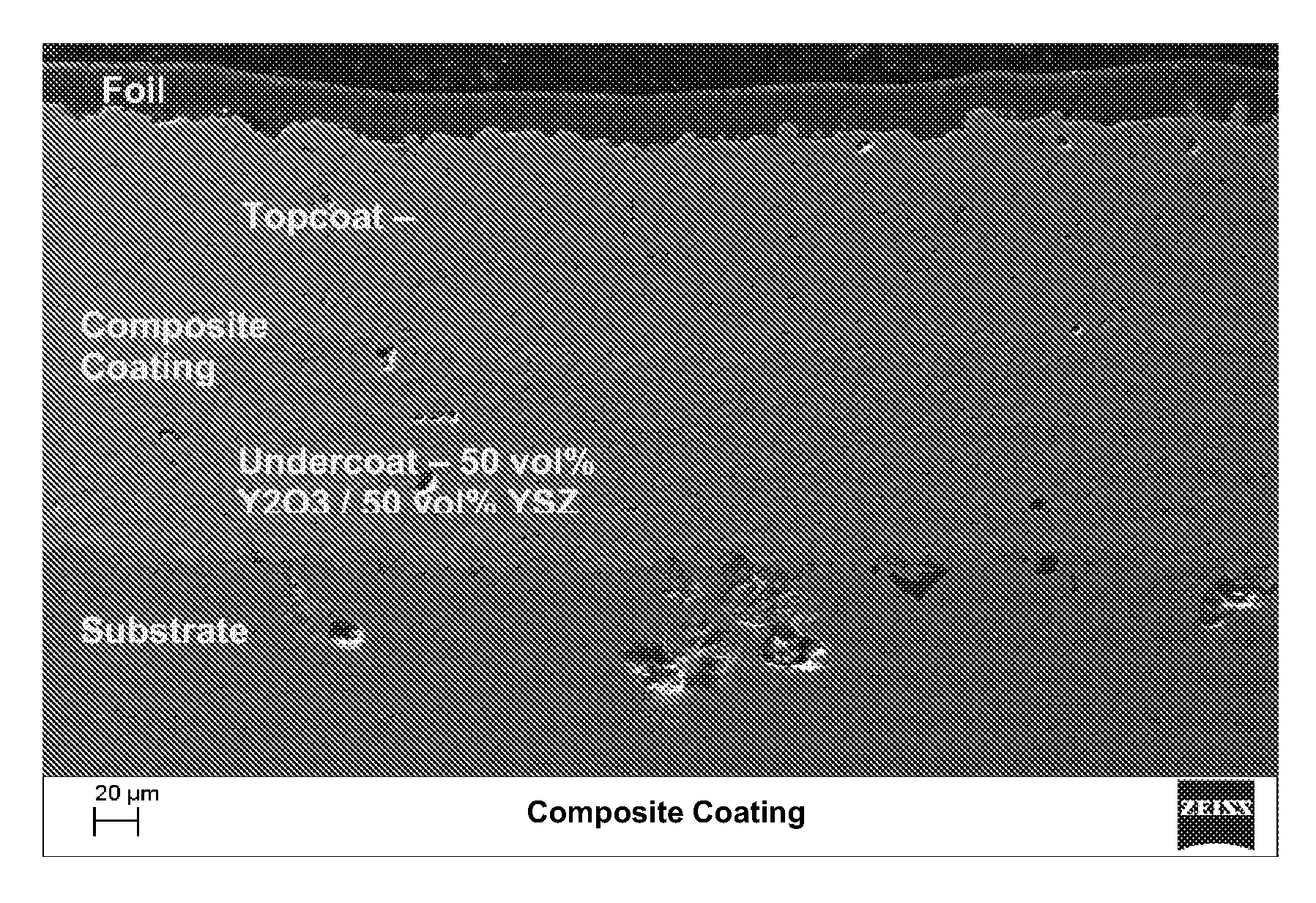

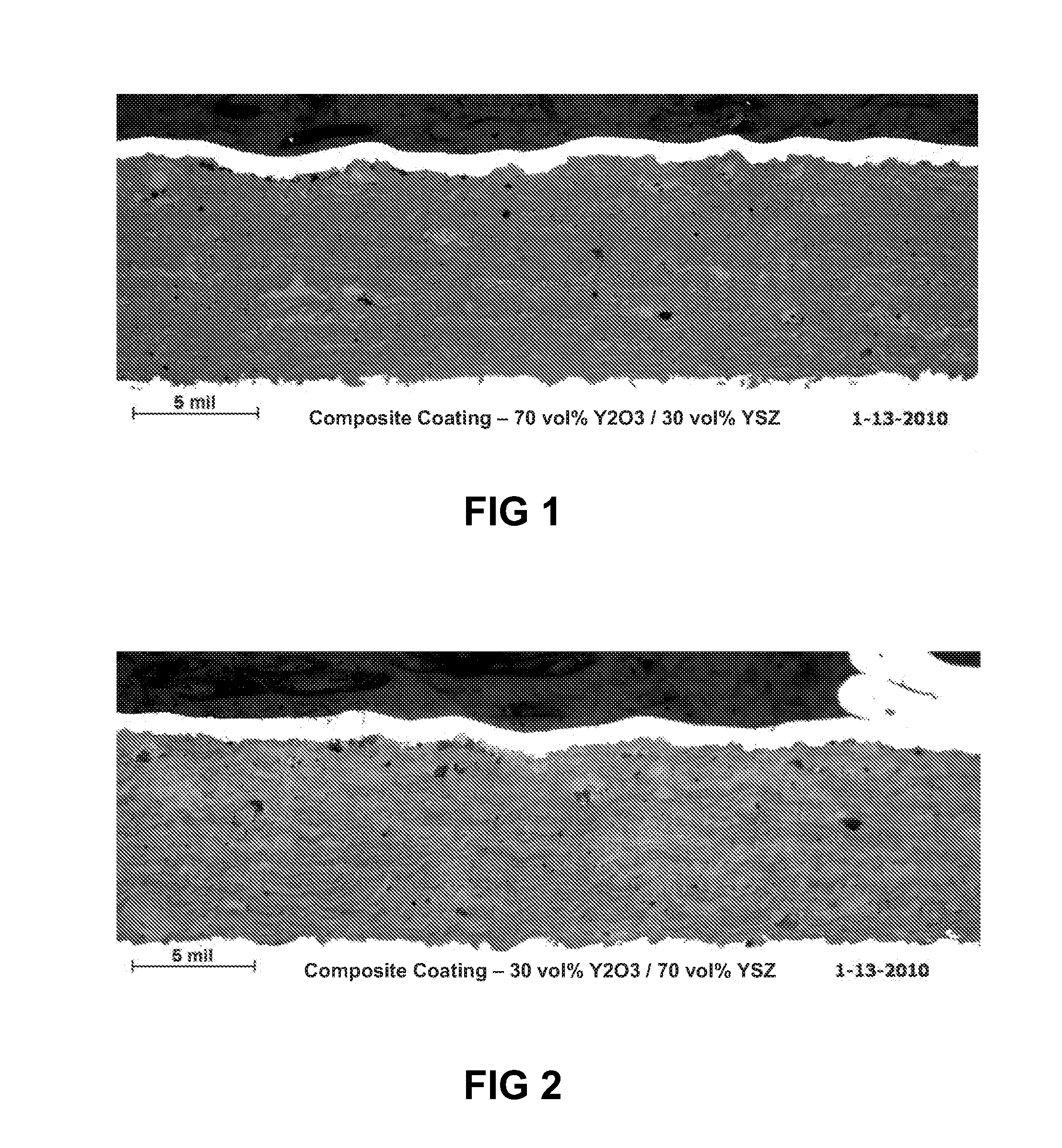

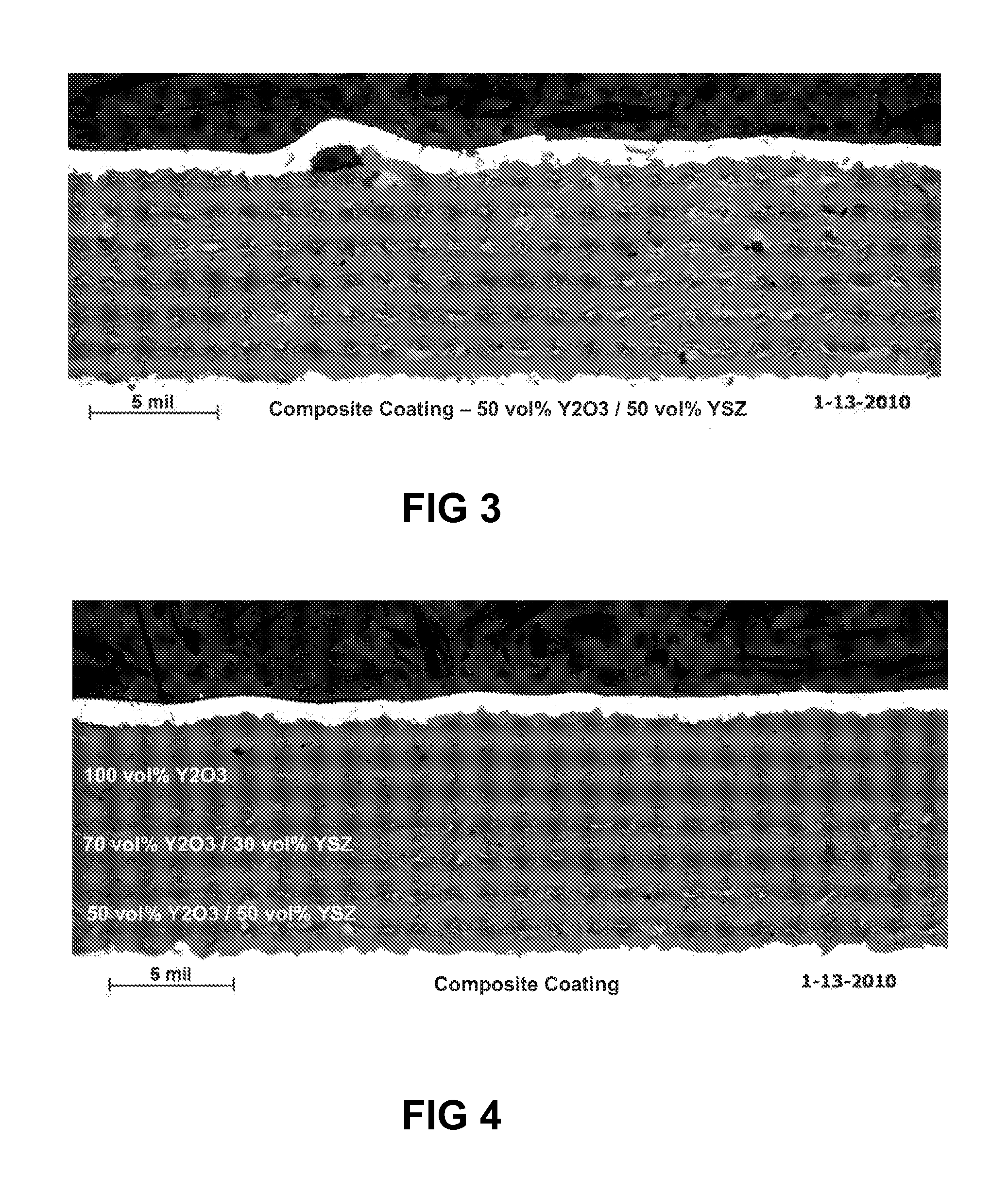

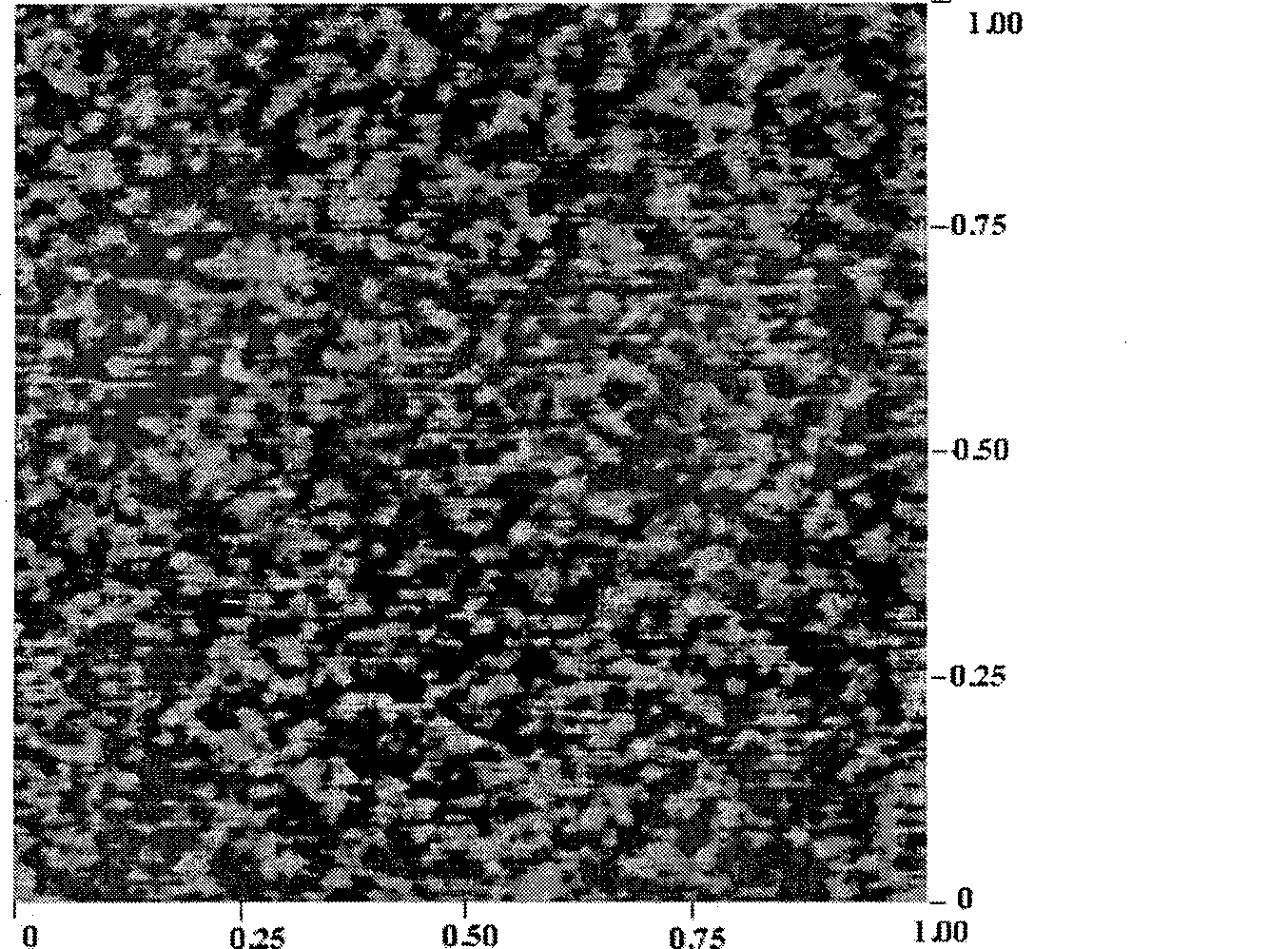

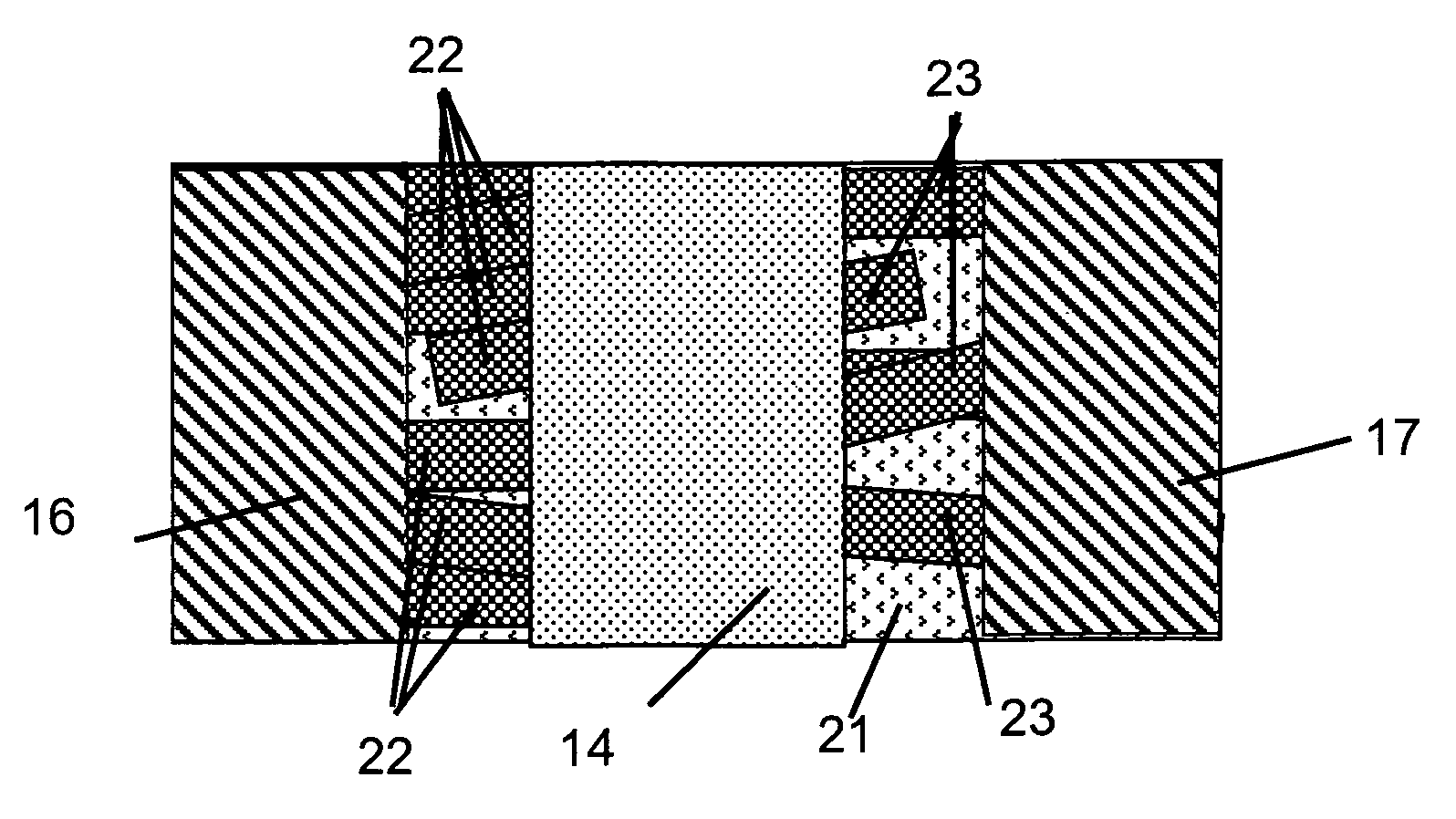

Thermal spray composite coatings for semiconductor applications

InactiveUS20120196139A1Improved erosion and corrosion resistantLower Level RequirementsLiquid surface applicatorsMolten spray coatingThermal sprayingCeramic composite

This invention relates to thermal spray composite coatings on a metal or non-metal substrate. The thermal spray composite coatings comprise (i) a ceramic composite coating undercoat layer having at least two ceramic material phases randomly and uniformly dispersed and / or spatially oriented throughout the ceramic composite coating, and (ii) a ceramic coating topcoat layer applied to the undercoat layer. At least a first ceramic material phase is present in the undercoat layer in an amount sufficient to provide corrosion resistance to the ceramic composite coating, and at least a second ceramic material phase is present in the undercoat layer in an amount sufficient to provide plasma erosion resistance to the ceramic composite coating. This invention also relates to methods of protecting metal and non-metal substrates by applying the thermal spray coatings. The composite coatings provide erosion and corrosion resistance at processing temperatures higher than conventional processing temperatures used in the semiconductor etch industry, e.g., greater than 100° C. The coatings are useful, for example, in the protection of semiconductor manufacturing equipment, e.g., integrated circuit, light emitting diode, display, and photovoltaic, internal chamber components, and electrostatic chuck manufacture.

Owner:PRAXAIR ST TECH INC

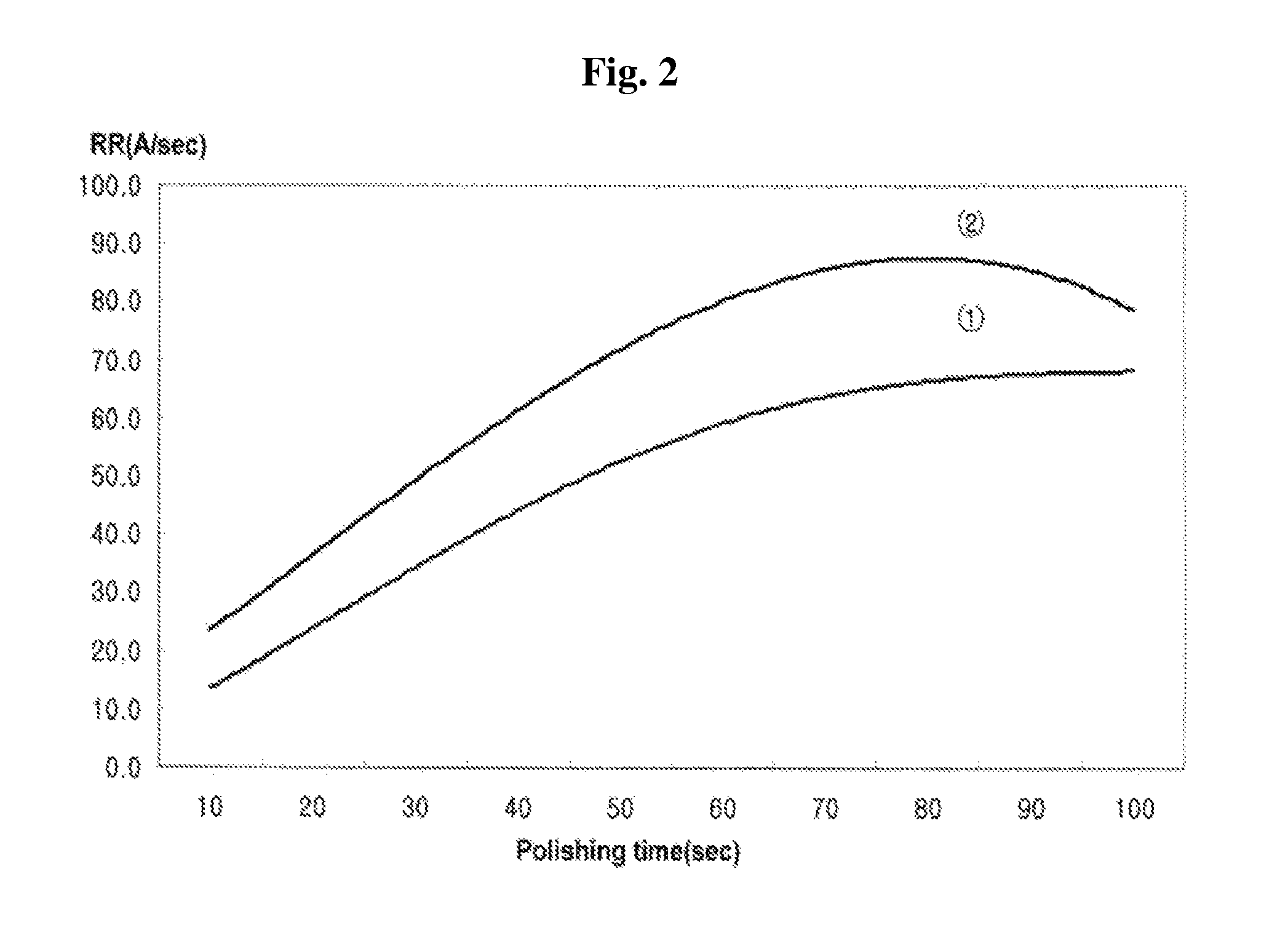

Polishing composite for silicon wafer polishing

InactiveCN101451046AFast polishing rateReduce surface defectsSemiconductor/solid-state device manufacturingPolishing compositions with abrasivesIonEther

The invention discloses a silicon wafer polishing composition in the field of chemical mechanical polishing (CMP). The polishing composition comprises silica, a polishing interface control agent, a surfactant, a chelating agent, an alkaline compound and water, wherein the particle diameter of the silica in the polishing composition is between 1 and 200 nm; the content of the silica is between 0.05 and 50 weight percent; the polishing interface control agent is polyhydroxy cellulose ether; the content of the polishing interface control agent is between 0.001 and 10 weight percent; the content of the surfactant is between 0.001 and 1 weight percent; the content of the chelating agent is between 0.001 and 1 weight percent; the content of the alkaline compound is between 0.001 and 10 weight percent; the balance being water; and the PH value is between 8.5 and 12. The polishing interface control agent can control a polishing interface between abrasive particles and a polishing object in the chemical mechanical polishing process in order that the surface of the polished silicon wafer is more perfect. The polishing composition is in particular suitable for polishing the silicon wafer and has the advantages of rapid polishing speed, little surface defect and high planeness; and the polished silicon wafer has few metal ion contaminants and is easy to clean.

Owner:TSINGHUA UNIV +1

Substrate supports for semiconductor applications

ActiveUS8619406B2Minimize current leakageEliminate concernsSemiconductor/solid-state device manufacturingSpecial surfacesPorosityElectron

Owner:FM INDS

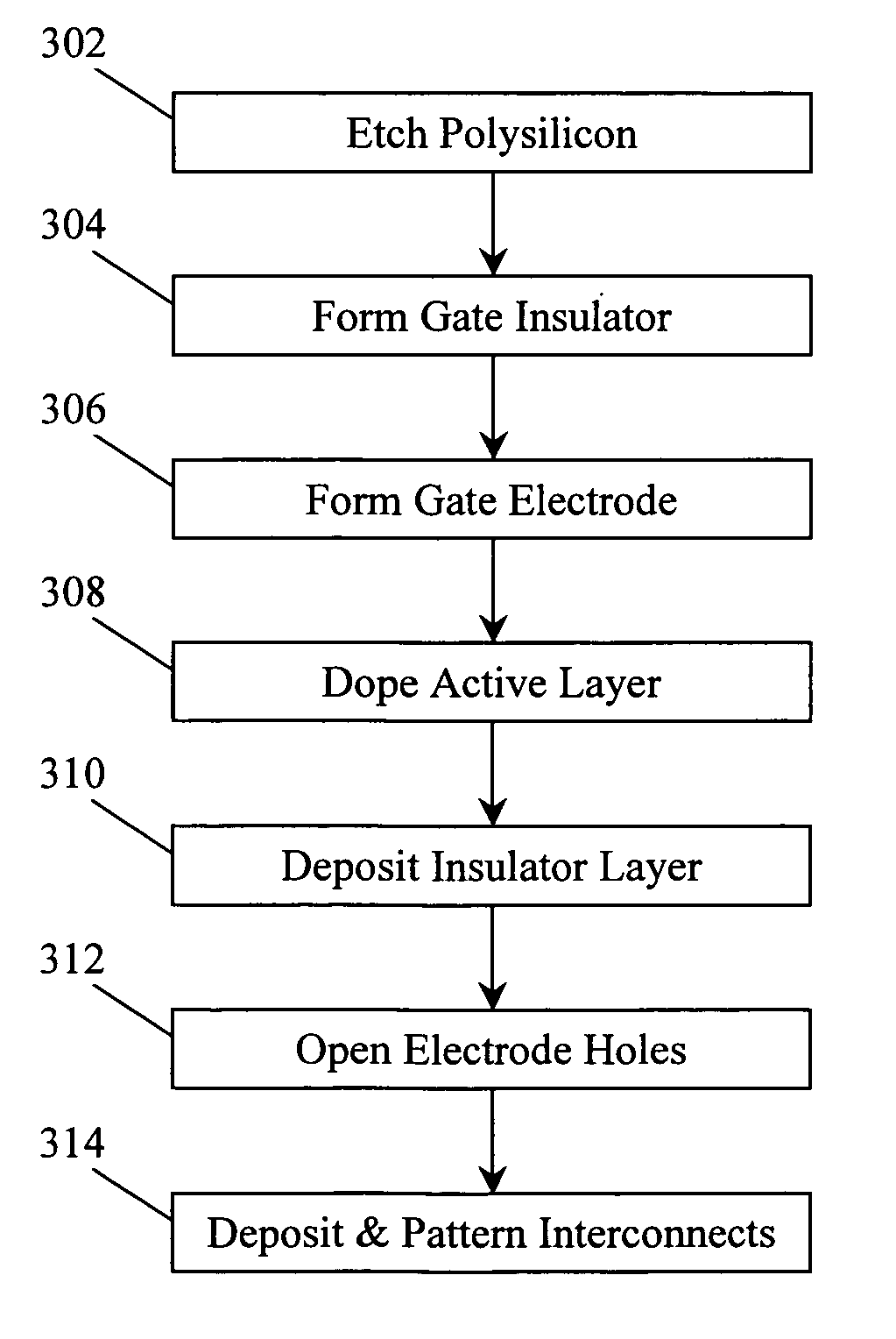

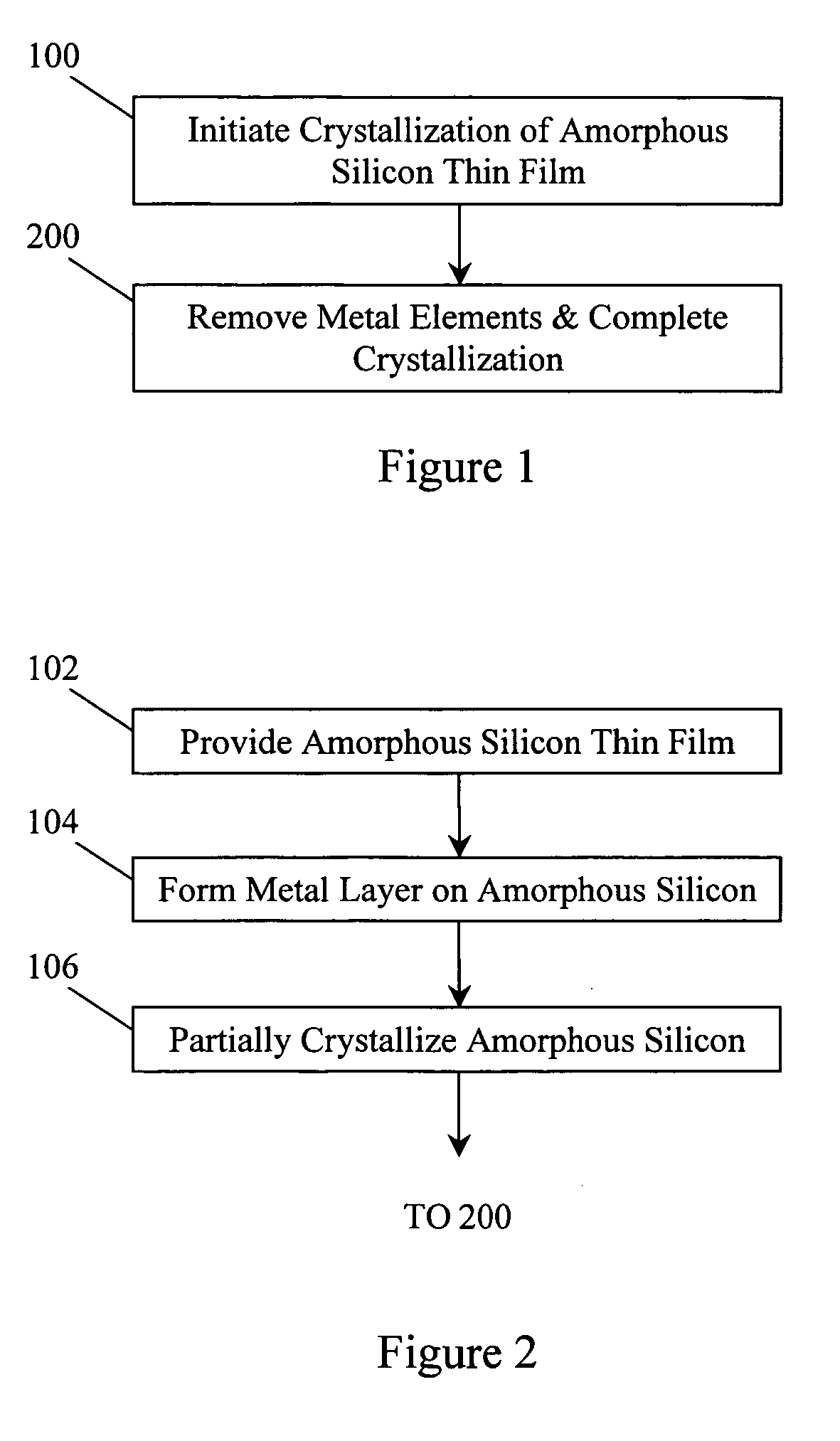

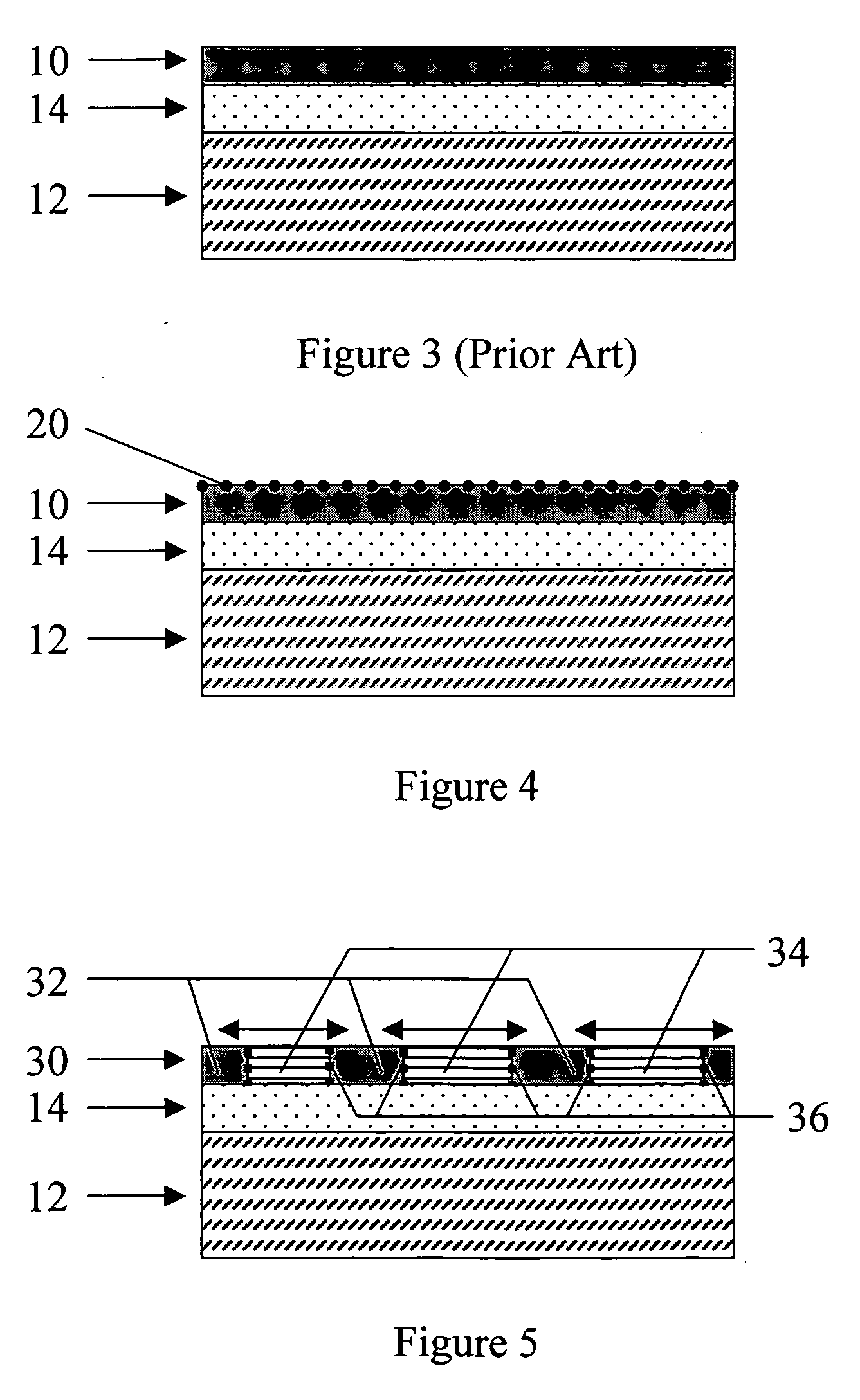

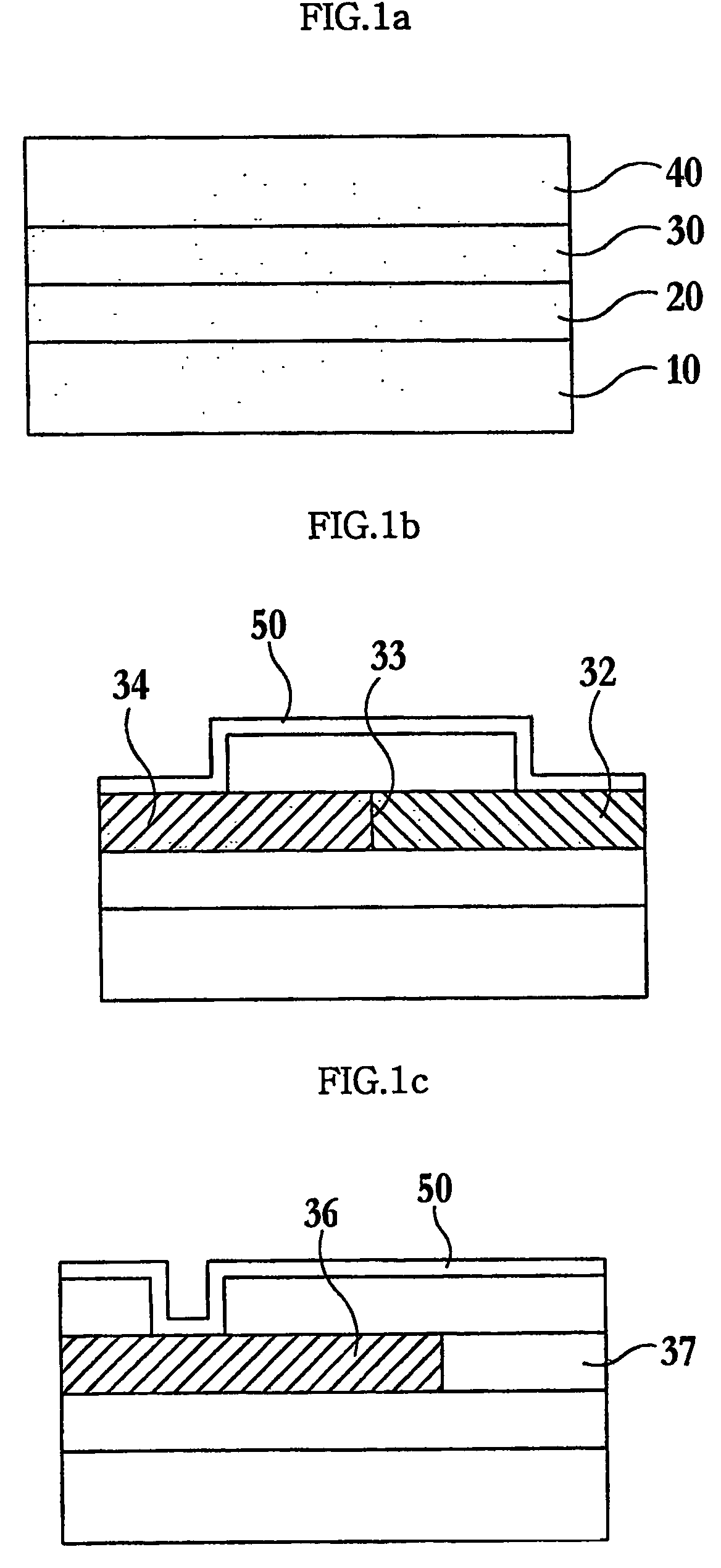

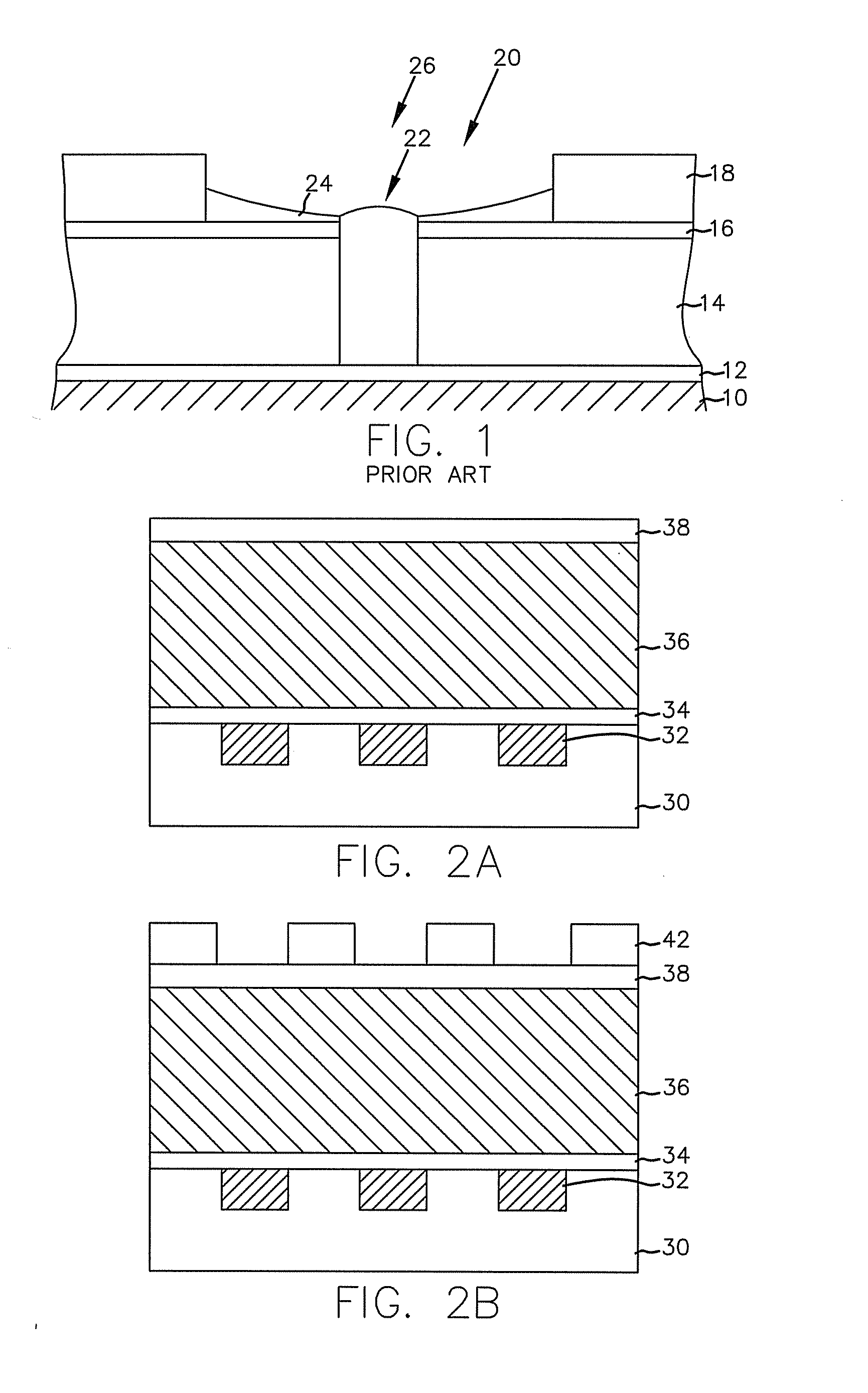

Metal-induced crystallization of amorphous silicon, polycrystalline silicon thin films produced thereby and thin film transistors produced therefrom

ActiveUS20060263957A1Quality improvementResidue reductionSolid-state devicesSemiconductor/solid-state device manufacturingTreatment completedNucleation

Crystallization-inducing metal elements are introduced onto an amorphous silicon thin film. A first, low-temperature, heat-treatment induces nucleation of metal-induced crystallization (MIC), resulting in the formation of small polycrystalline silicon “islands”. A metal-gettering layer is formed on the resulting partially crystallized thin film. A second, low-temperature, heat-treatment completes the MIC process, whilst gettering metal elements from the partially crystallized thin film. The process results in the desired polycrystalline silicon thin film.

Owner:THE HONG KONG UNIV OF SCI & TECH

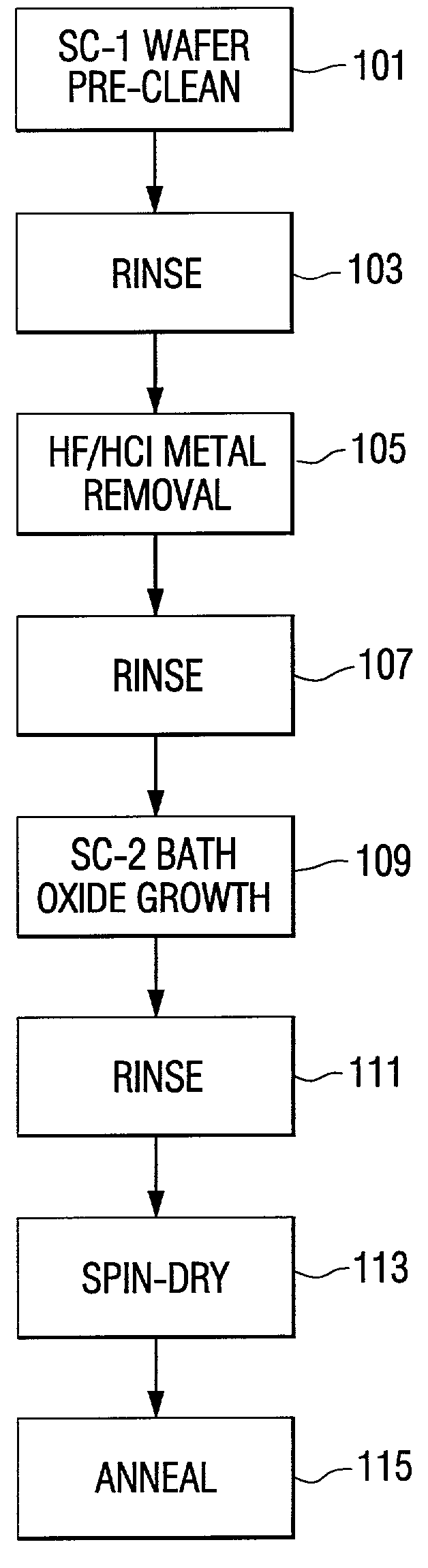

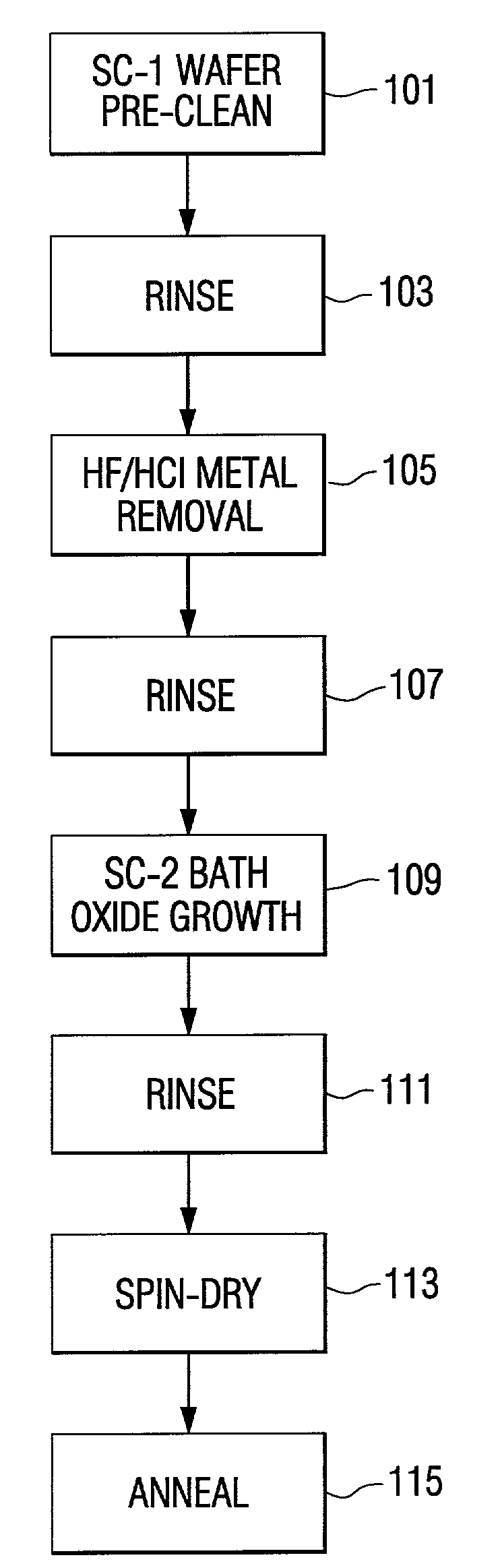

Sc-2 based pre-thermal treatment wafer cleaning process

InactiveUS20020189640A1Reduce metal pollutionImprovement in P-type siliconSemiconductor/solid-state device manufacturingIonChemistry

Pre heat-treatment processing of a silicon wafer to grow a hydrophilic oxide layer includes an initial step of contacting the wafer with a pre-clean SC-1 bath, thereby producing a silicon wafer surface that is highly particle free. After a deionized water rinse, the wafer is scoured with an aqueous solution containing hydrofluoric acid and hydrochloric acid to remove metallic-containing oxide from the wafer surface. In order to grow a hydrophilic oxide layer, an SC-2 bath (containing hydrogen peroxide and a dilute concentration of metal-scouring HCl) is used. The resulting hydrophilic silicon oxide layer grown on the surface of the silicon wafer using the combined SC-1->AF / HCL->SC-2 wafer cleaning process has a metal concentration no greater than 1x109. The diffusion length of minority carriers is increased from a range on the order of 500-600 microns to a range on the order of 800-900 microns.

Owner:INTERSIL CORP

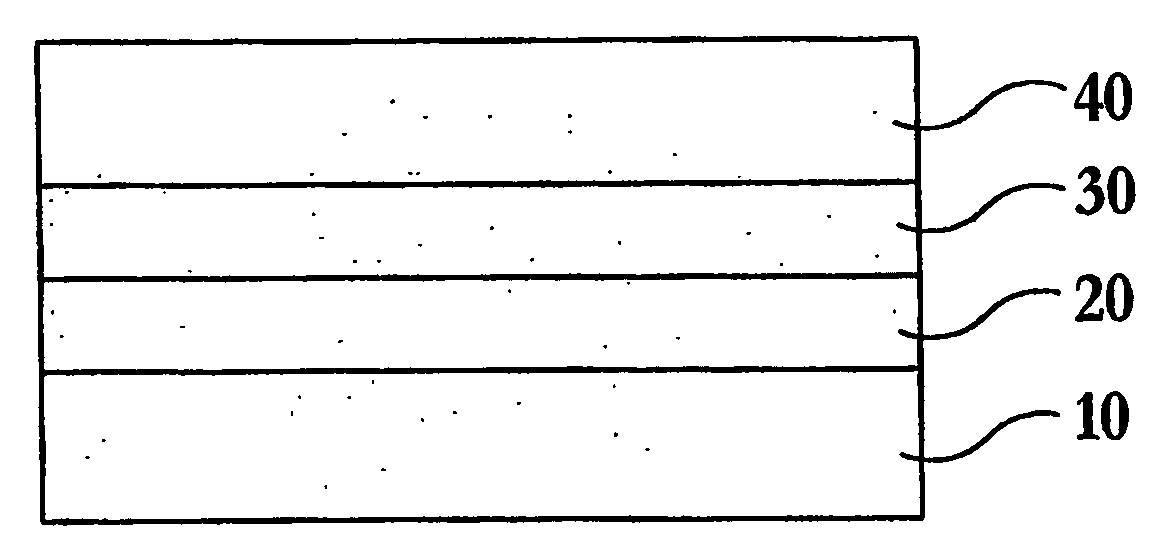

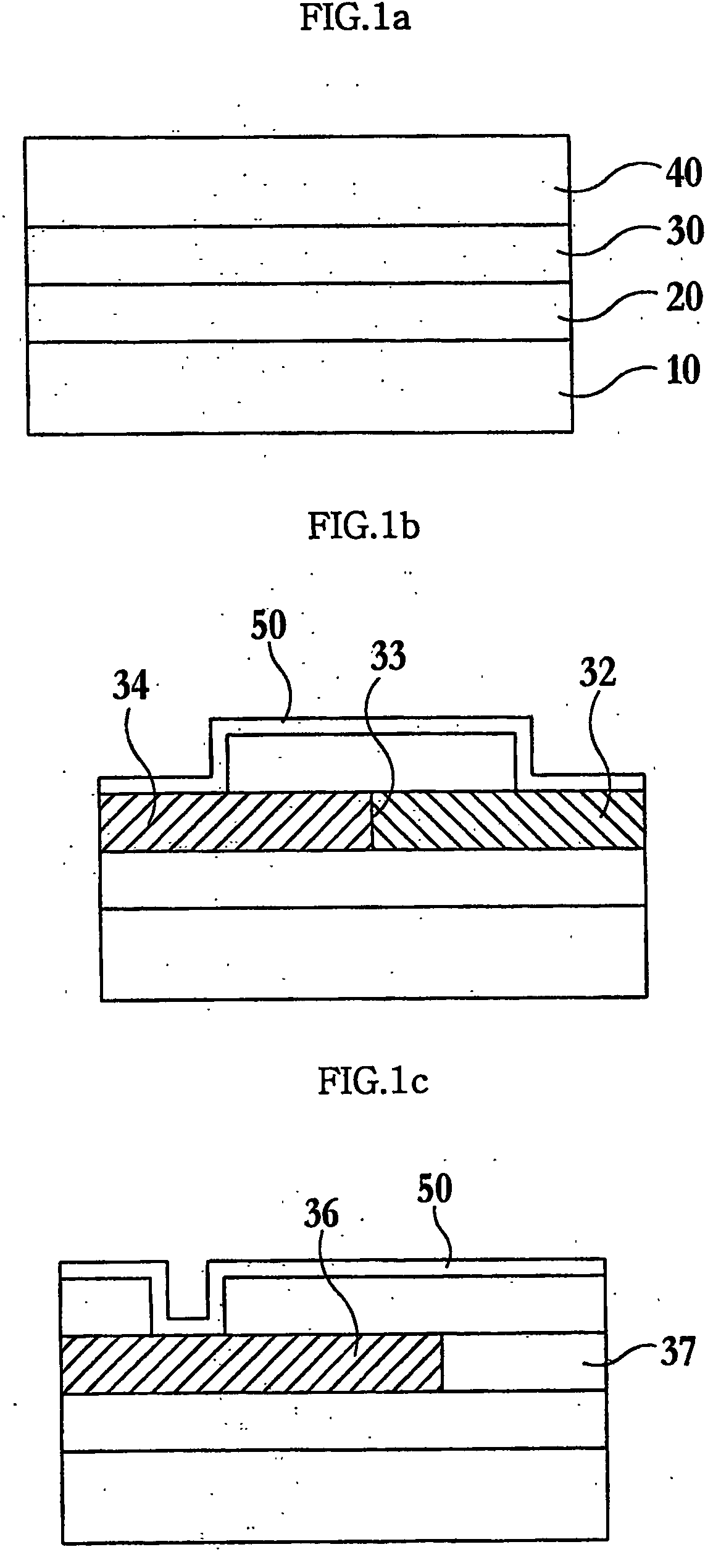

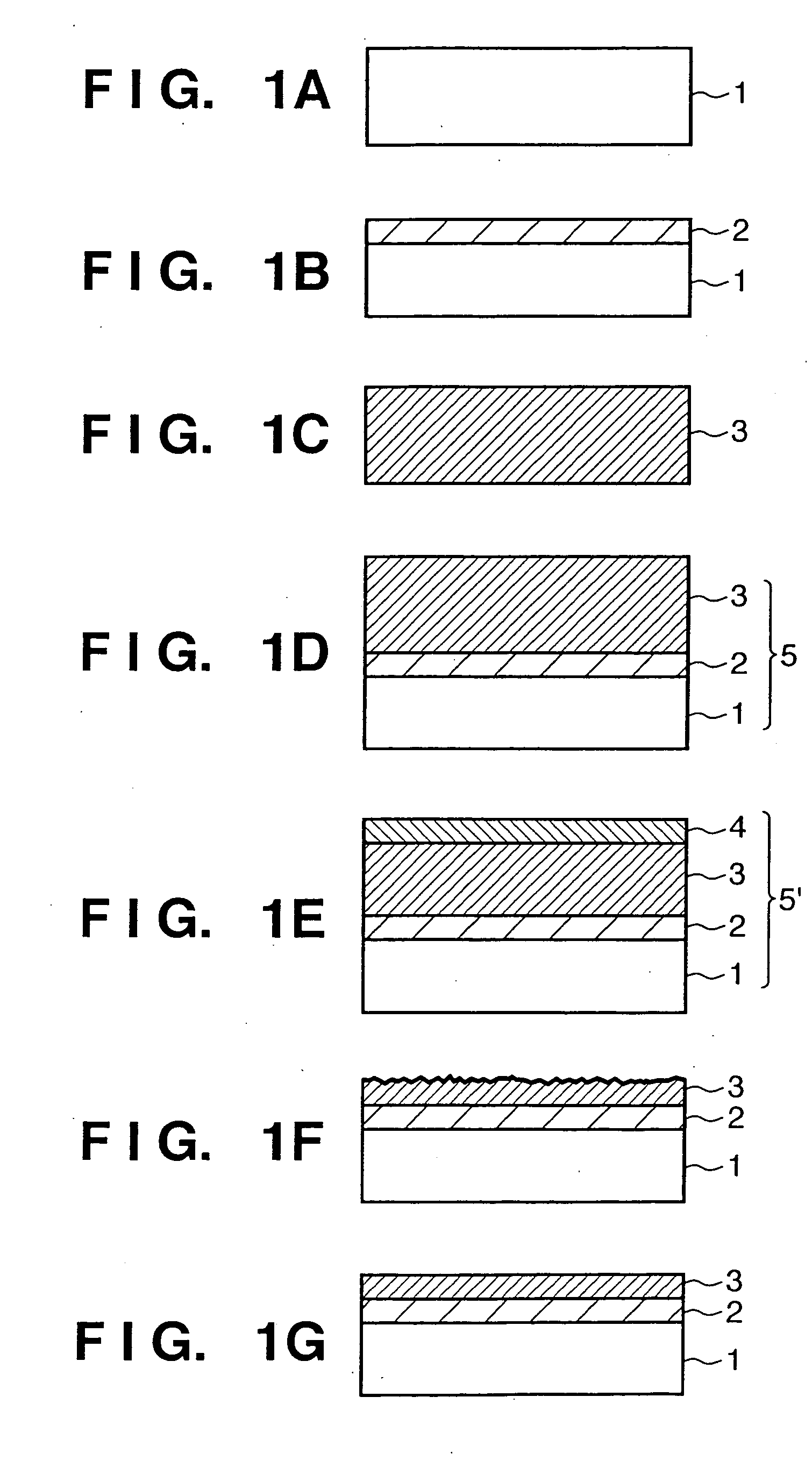

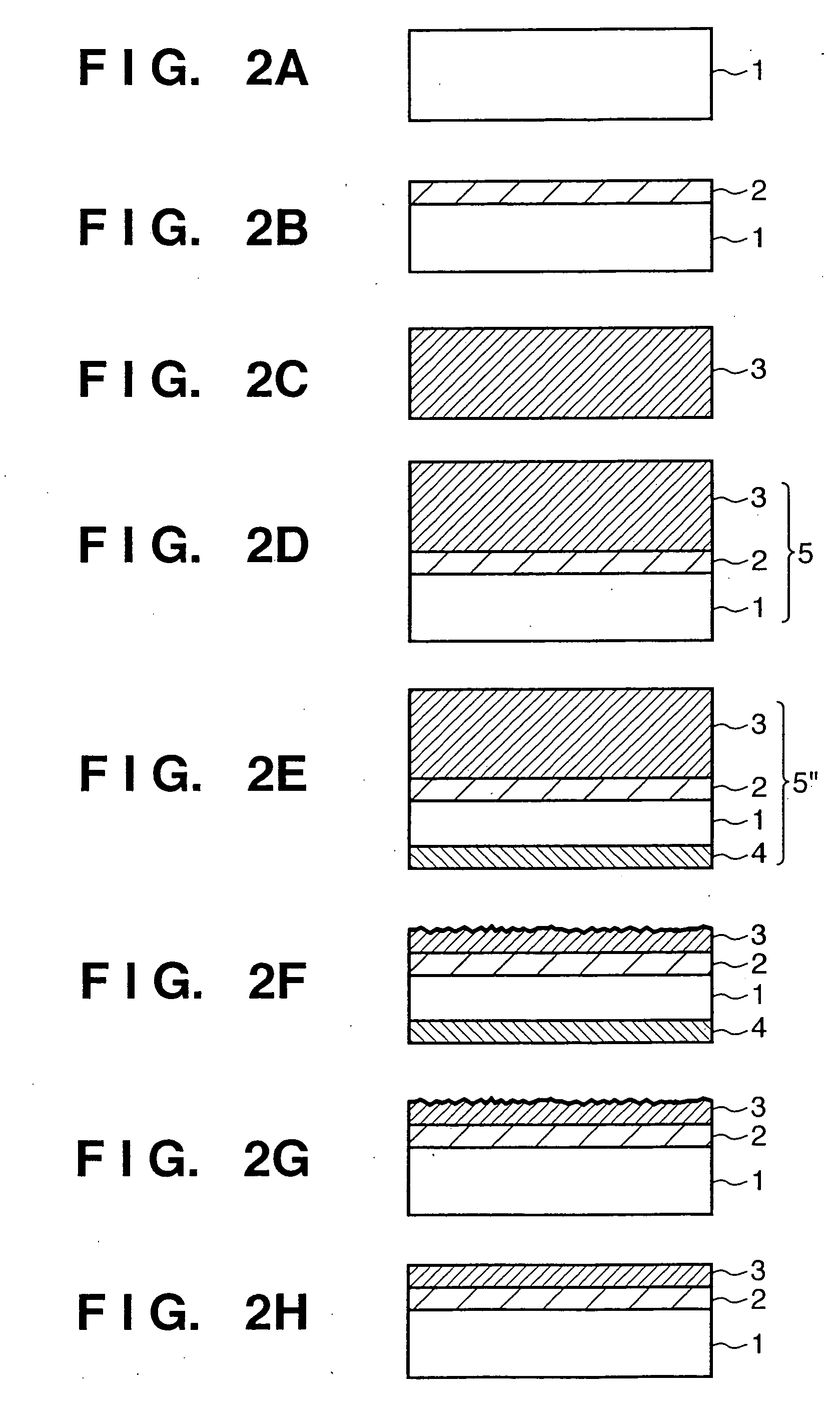

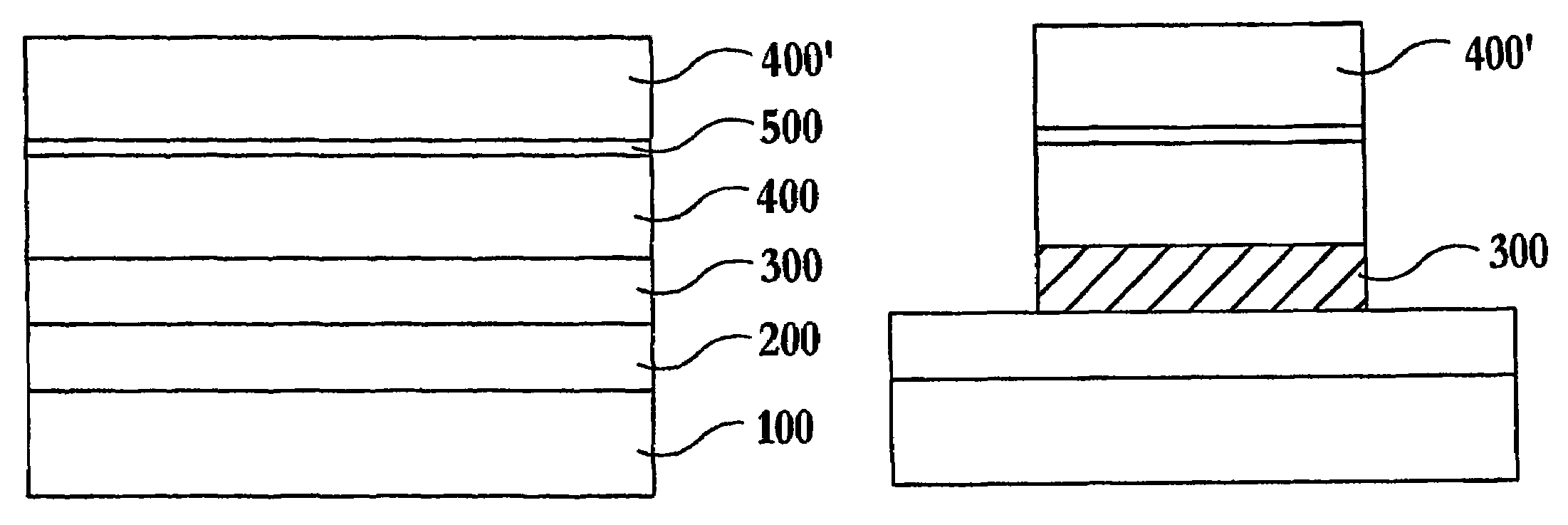

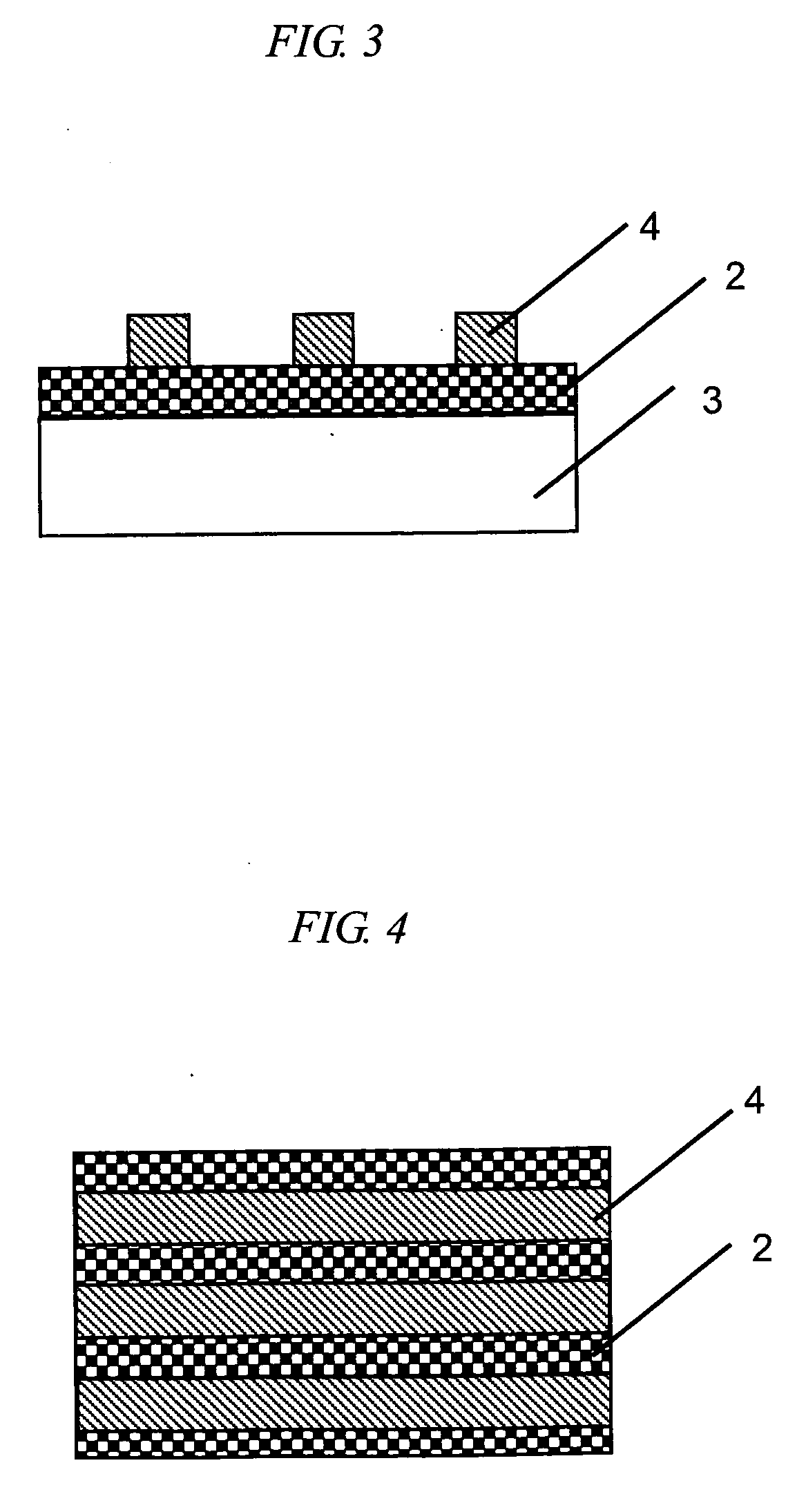

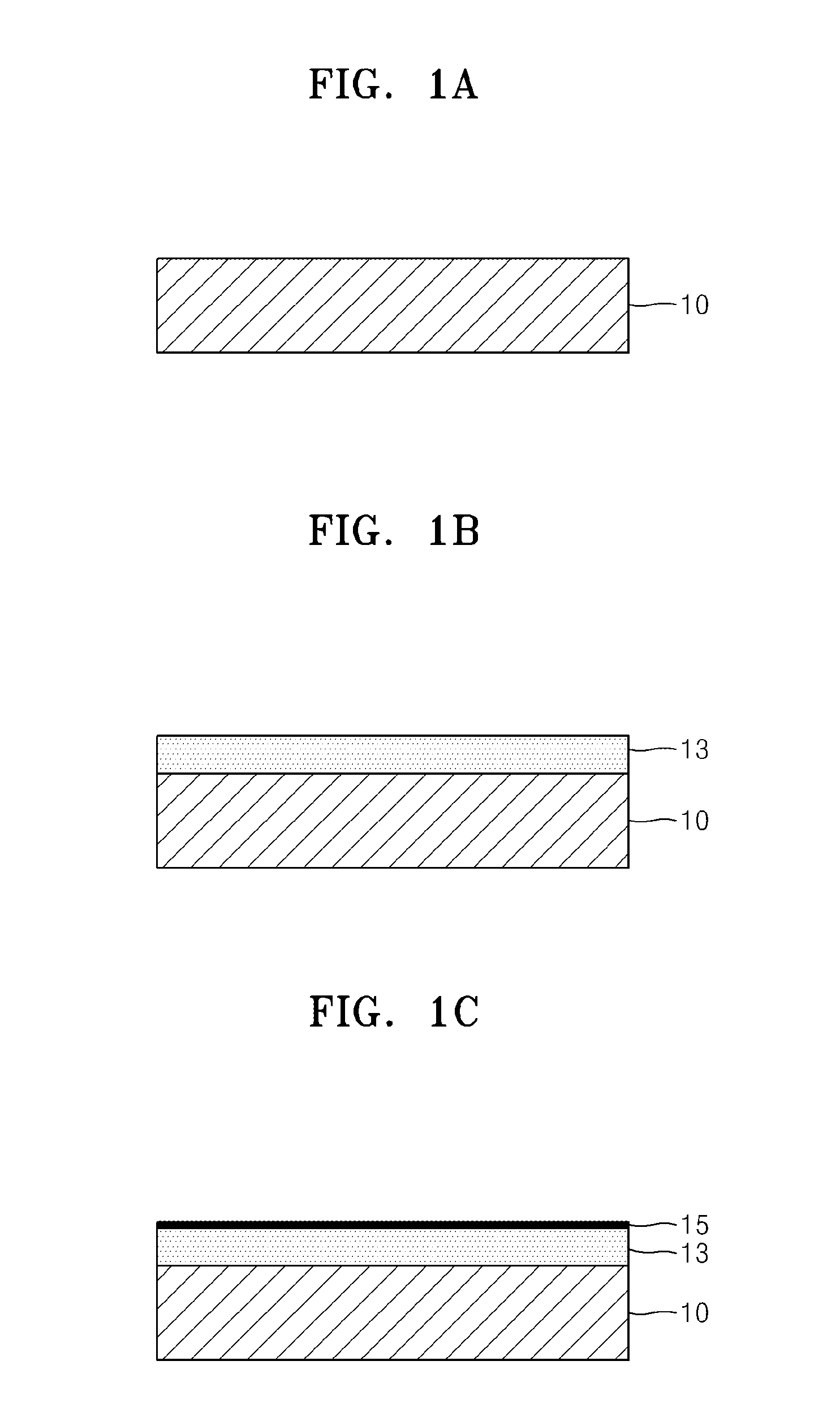

Phase transition method of amorphous material using cap layer

ActiveUS20060130939A1Reduce metal pollutionImprove productivitySemiconductor/solid-state device manufacturingMetal layered productsDielectric substrateMetal contamination

The present invention provides a phase transition method of an amorphous material, comprising steps of: depositing the amorphous material on a dielectric substrate; forming a cap layer on the amorphous material; depositing a metal on the cap layer; and crystallizing the amorphous material. According to the present invention, the surface of the amorphous material is protected by the cap layer, so that clean surface can be obtained and the roughness of the surface can be remarkably reduced during thermal process and sample handling. In addition, the cap layer is disposed between the amorphous material and the metal to diffuse the metal, so that the metal contamination due to the direct contact of the metal and the amorphous material in the conventional method can be remarkably reduced.

Owner:SILICON DISPLAY TECH CO LTD

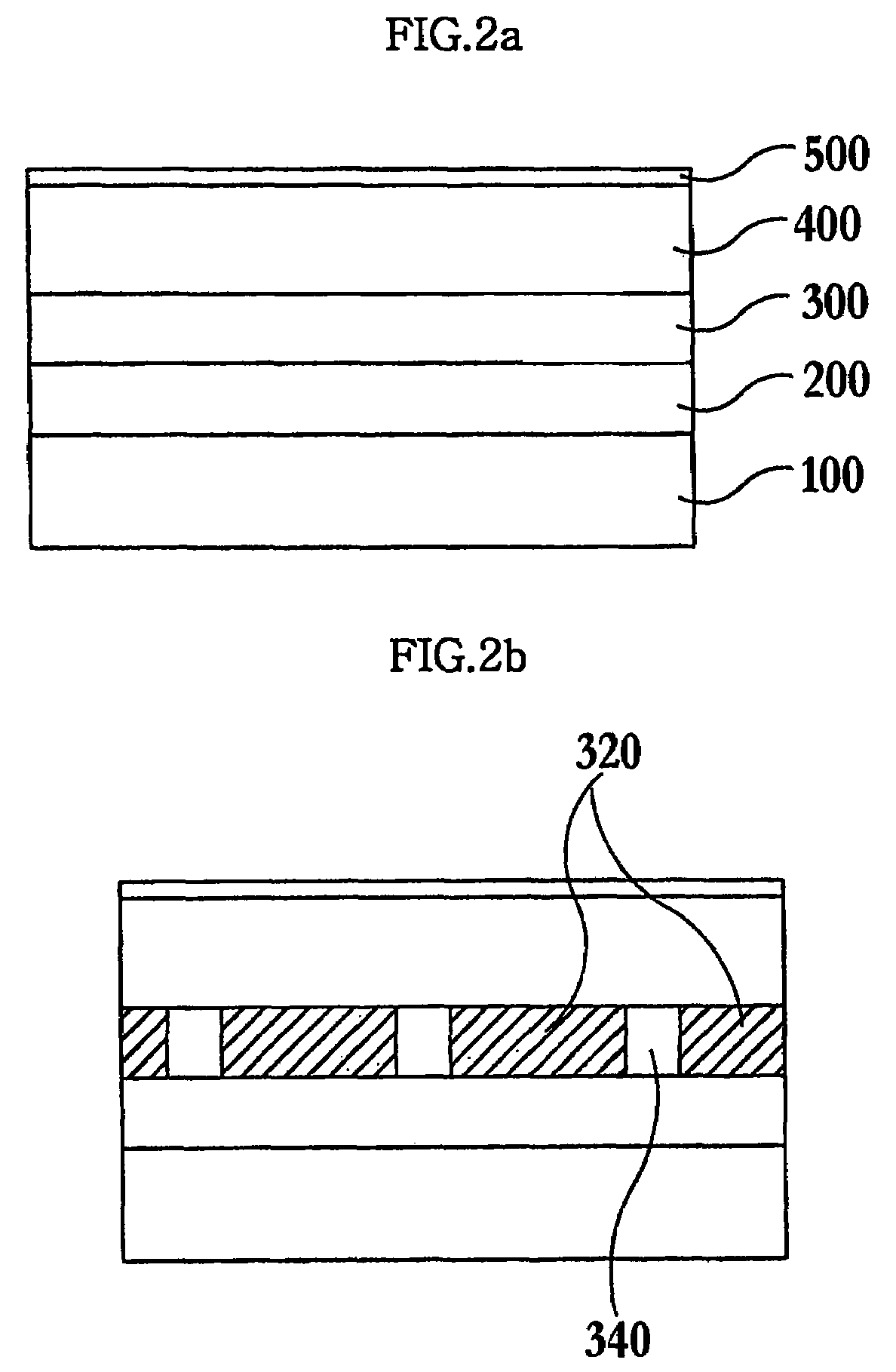

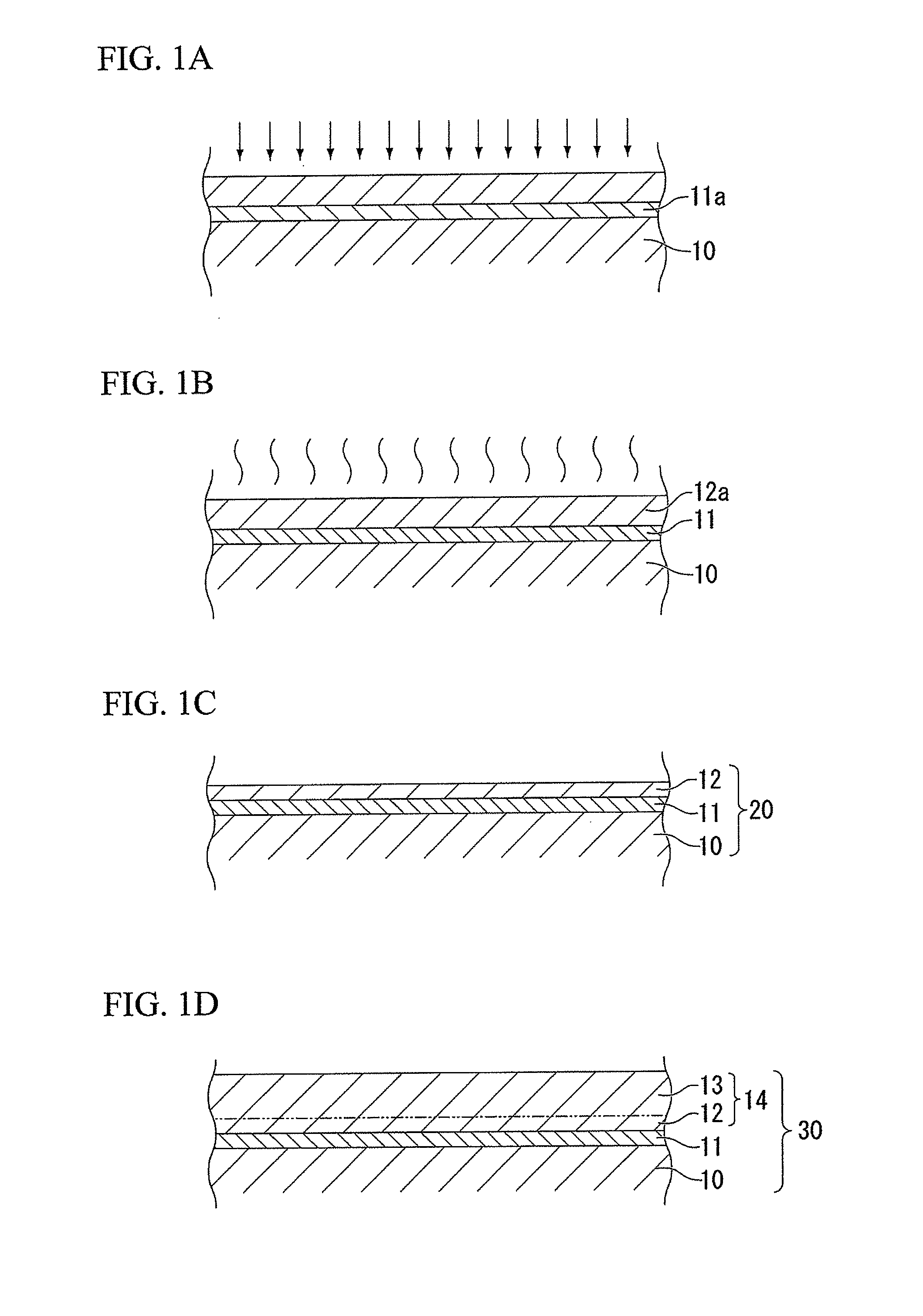

Substrate manufacturing method

InactiveUS20050239267A1Reduce decreaseReduce metal pollutionSolid-state devicesSemiconductor/solid-state device manufacturingComposite substrateOptoelectronics

A substrate manufacturing method includes steps of preparing a bonded substrate stack formed by bonding a second substrate to a first substrate having an insulator at least on a surface, forming a gettering layer to capture a metal contamination on the surface of the bonded substrate stack to form a composite substrate stack, annealing the composite substrate stack, and removing the gettering layer from the composite substrate stack.

Owner:CANON KK

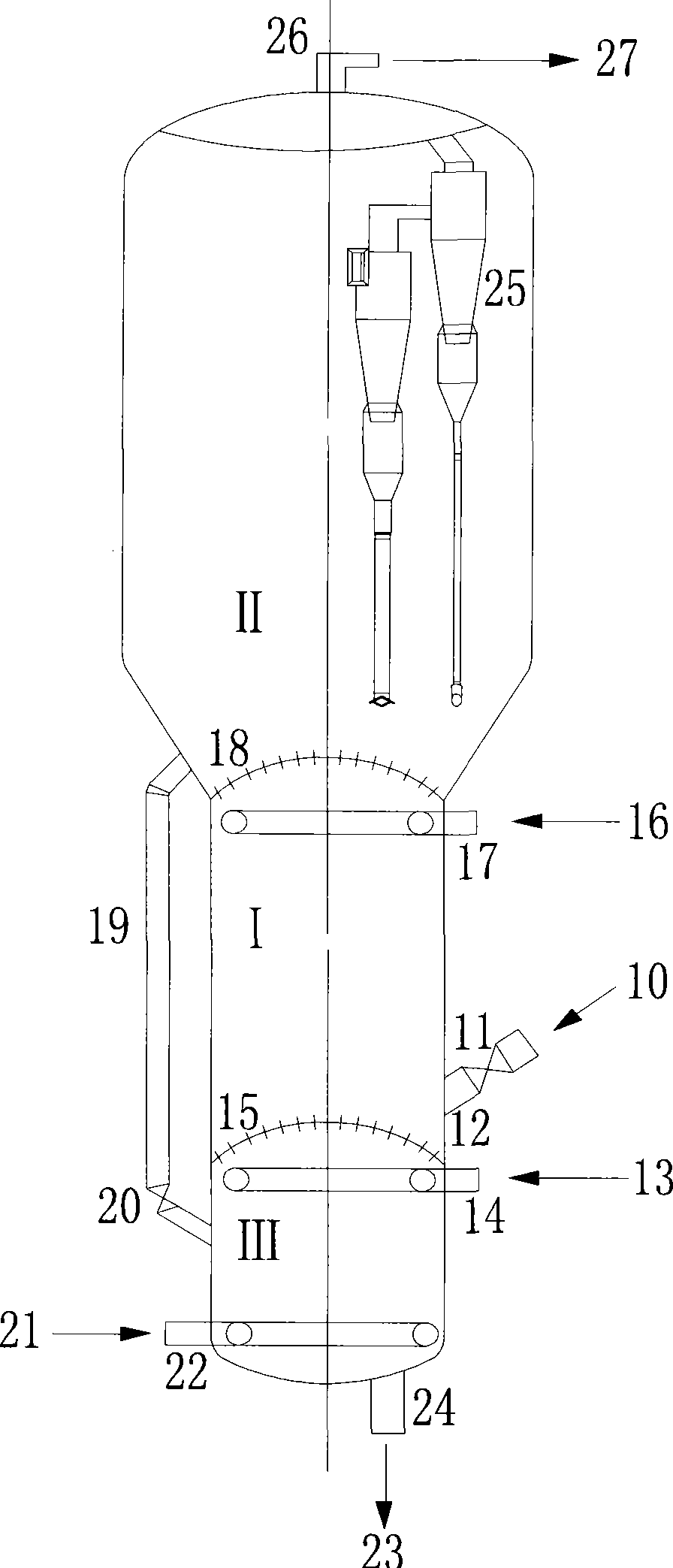

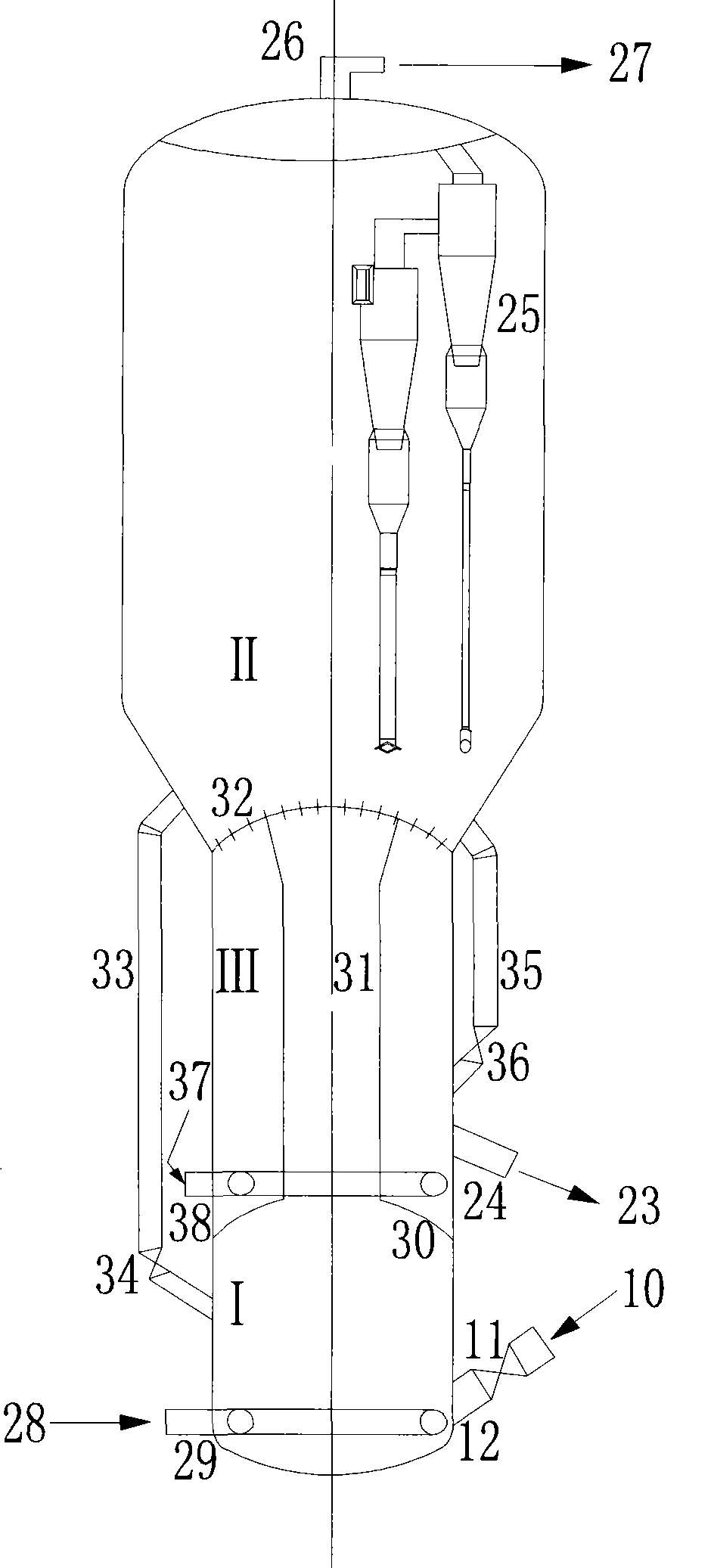

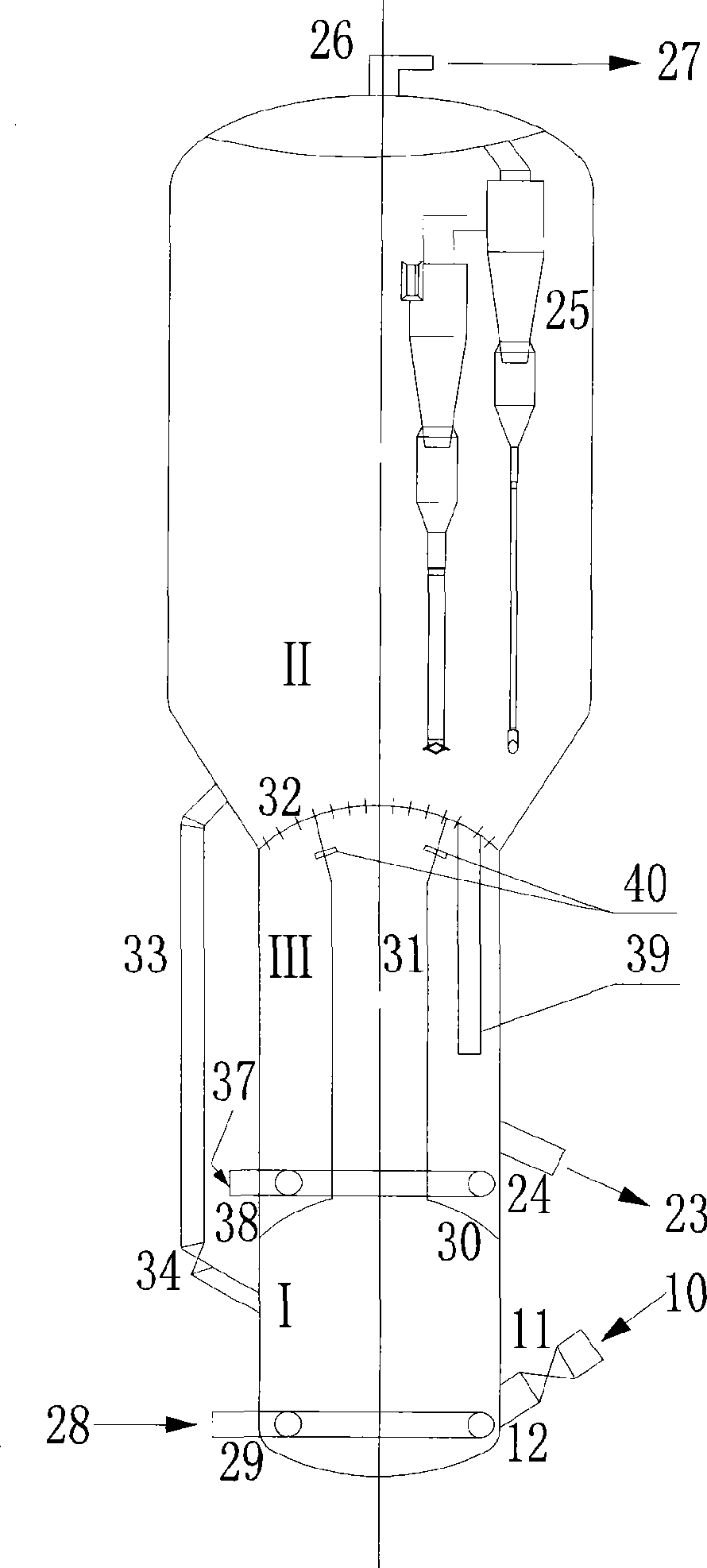

Catalyst multistage regeneration method and device

InactiveCN101391234AIncreased average chemical kinetic speedPromote regenerationCatalyst regeneration/reactivationRegenerative processLine tubing

The invention introduces a catalyst multi-section regeneration method and an apparatus, firstly, a spent catalyst enters a first section regenerator, and is in contact reaction with oxygen-containing gases in the first section regenerator, a second section regenerator and a third section regenerator sequentially, oxygen-containing regeneration flue gas of the first section enters the second section for continuous utilization, and the fresh compressed air is input to the third section for regeneration reaction, so as to complete the whole regenerative process. The fresh compressed air can also be supplemented to the first section regeneration reaction or the second section regeneration reaction, and the catalyst can also reflux to other sections for regeneration. The regeneration apparatus is composed of a first section turbulent bed regenerator, a second section turbulent bed regenerator and a third section turbulent bed regenerator in series connection, a distribution plate or a baffle and a catalyst standpipe are arranged, and all the regenerators are in coaxial arrangement. The invention adopts the multi-section counter-current regeneration, increases the average chemical kinetics speed, strengthens the regenerative process, saves the oxygen-containing gas usage, and reduces the production expense; and realizes the feeding of the spent catalyst from the bottom part or the middle part of each regenerator, lowers the height of the corresponding catalytic conversion device, shortens the oil-gas pipe-line, and reduces the construction investment.

Owner:QINGDAO JINGRUN PETROCHEM ENG

Filled polymer composition for etch chamber component

InactiveUS20100140222A1Extended service lifeIncrease temperatureNon-macromolecular adhesive additivesOther chemical processesAdhesiveRare earth

A filled polymer composition having improved plasma resistance is disclosed. The composition includes a particle filler dispersed in a polymer matrix. The particle filler can be Nb2O5, YF3, AlN, SiC or Si3N4 and rare earth oxides. In an embodiment, the composition is utilized as a bonding adhesive for electrostatic chuck, bonding adhesive for shower head, bonding adhesive for liner, sealing material, O-ring, or plastic component.

Owner:APPLIED MATERIALS INC

Phase transition method of amorphous material using cap layer

ActiveUS7618852B2Reduce metal pollutionImprove productivitySemiconductor/solid-state device manufacturingMetal layered productsDielectric substrateMetal contamination

The present invention provides a phase transition method of an amorphous material, comprising steps of: depositing the amorphous material on a dielectric substrate; forming a cap layer on the amorphous material; depositing a metal on the cap layer; and crystallizing the amorphous material. According to the present invention, the surface of the amorphous material is protected by the cap layer, so that clean surface can be obtained and the roughness of the surface can be remarkably reduced during thermal process and sample handling. In addition, the cap layer is disposed between the amorphous material and the metal to diffuse the metal, so that the metal contamination due to the direct contact of the metal and the amorphous material in the conventional method can be remarkably reduced.

Owner:SILICON DISPLAY TECH CO LTD

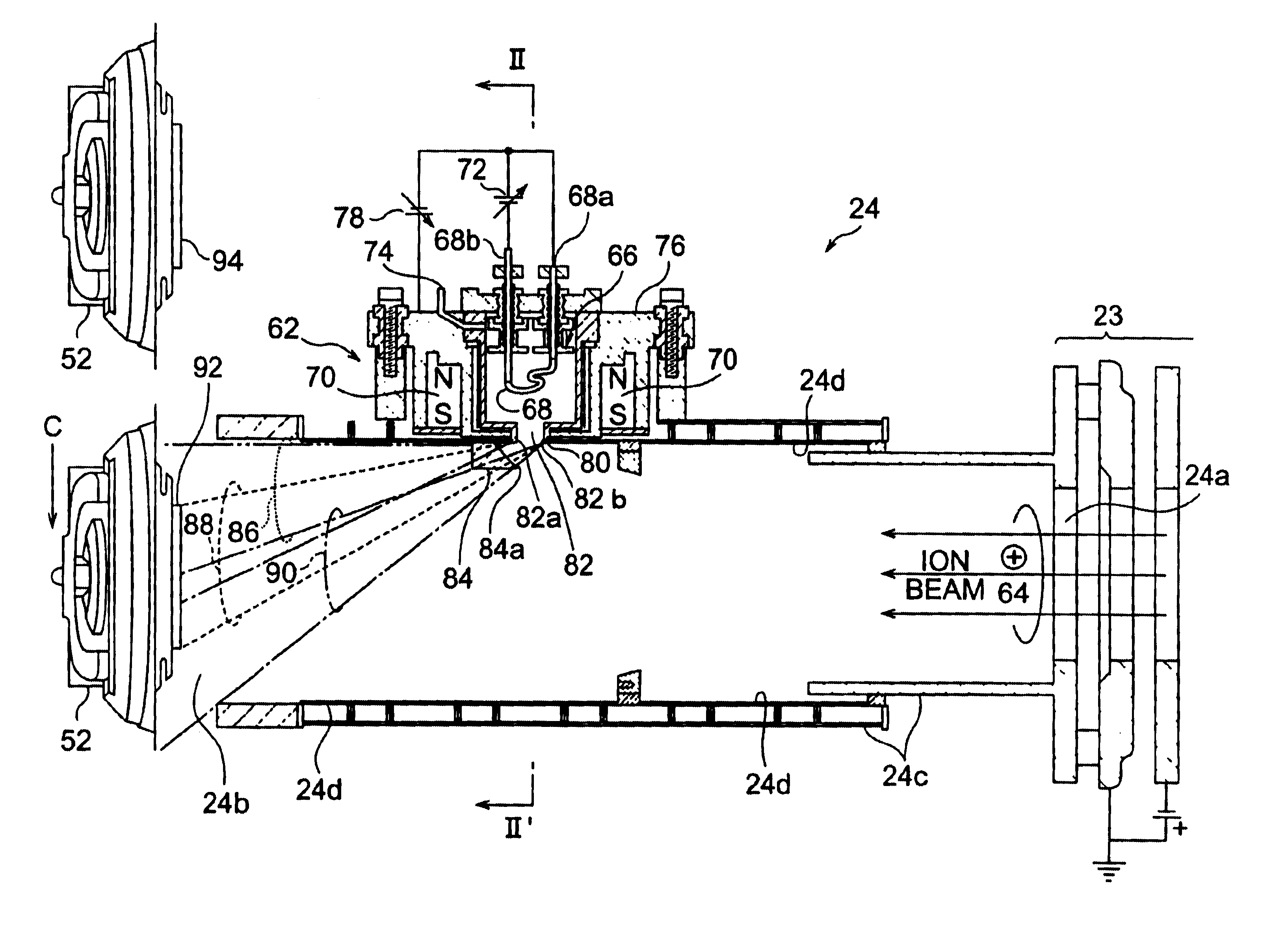

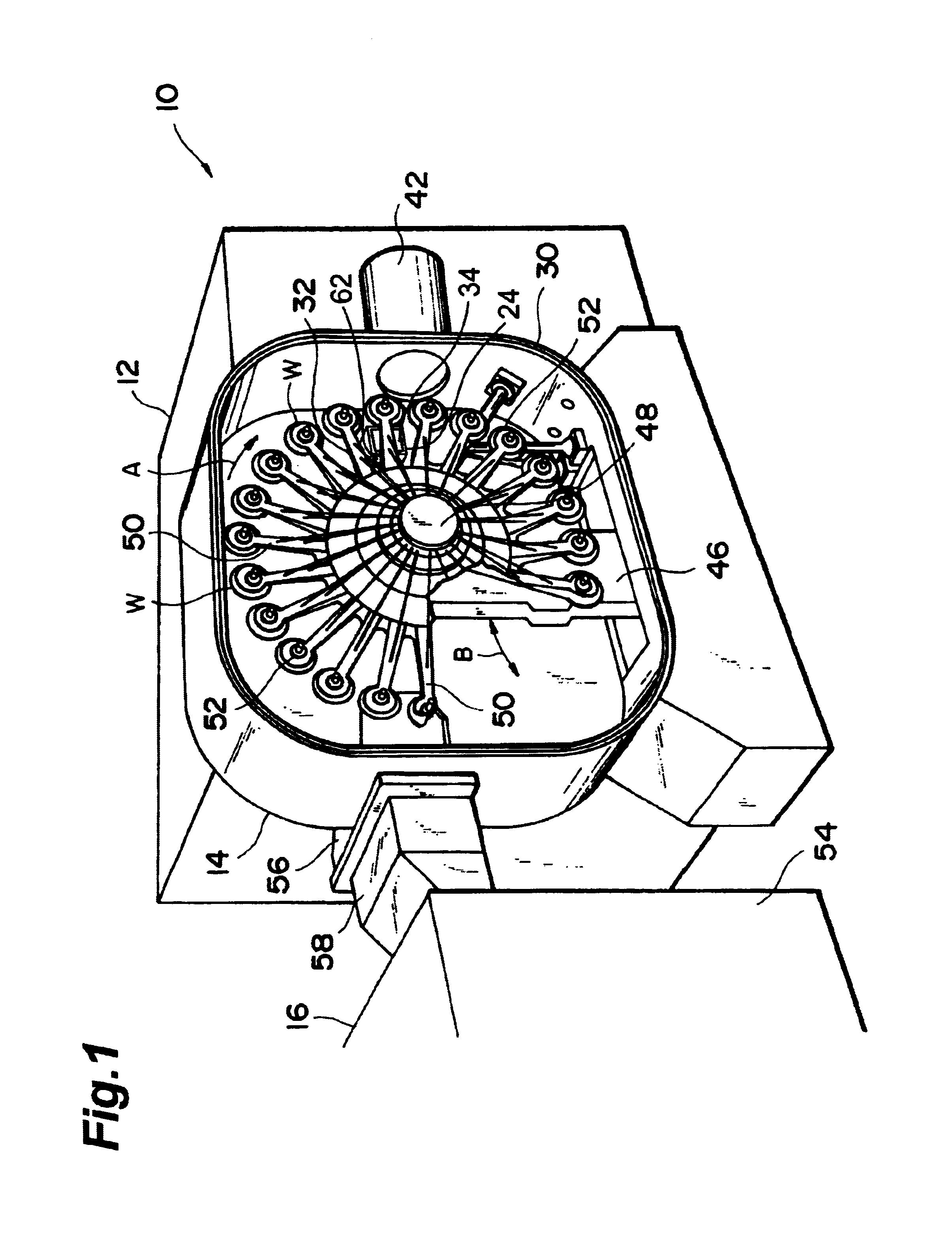

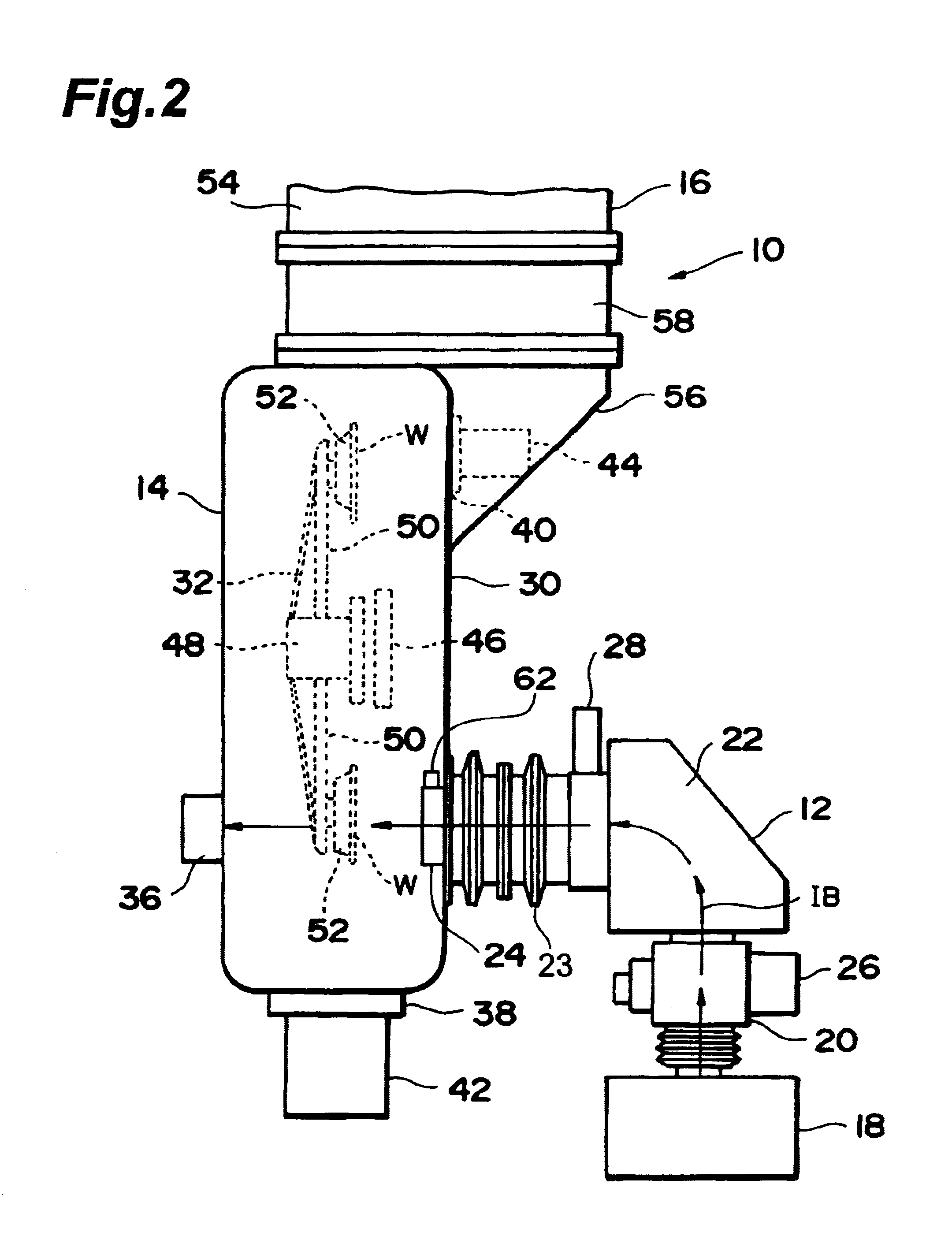

Apparatus for ion implantation

InactiveUS6867422B1Reduce metal pollutionLaser detailsElectric discharge tubesIon sourceCharged particle

An ion implantation apparatus comprises an ion source section (18) for generating ions; an ion implantation section (14) for implanting the ions generated in the ion source section (18), in a substrate (92); a charged particle generator (62) for generating charged particles having a charge opposite to that of the ions; a beam guide section (24) having an inlet aperture (24a) for accepting the ions from the ion source section (18), an outlet aperture (24b) for delivering the ions into the ion implantation section (18), a guide tube (24c) extending from the inlet aperture (24a) to the outlet aperture (24b), and an introducing section (80) having an opening (82) thereof in an internal surface (24d) of the guide tube (24c), for introducing the charged particles from the charged particle generator (62) into the guide tube (24c); and a shield section (84) located between the opening (82) of the introducing section (80) and the outlet aperture (24b) inside the guide tube (24c). A shield surface (84a) of the shield section (84) blocks the charged particles' reaching the wafer.

Owner:APPLIED MATERIALS INC

Semiconductor material, field effect transistor and manufacturing method thereof

InactiveUS20060088960A1Forming accuratelySolve the real problemNanoinformaticsSolid-state devicesResistEtching

The silicon wires formed around metal particles by crystal growth have the problem of metal pollution. For its solution, in the present invention, a silicon bridge is formed through standard silicon processes such as the lithography and the wet etching using hydrofluoric acid performed to an SOI substrate. Thereafter, a thermal oxide film is desirably formed at a high temperature to form a high-quality gate insulating film. It is also desirable to form a coaxial gate electrode. Then, after burying the bridge sections of the silicon bridge in a resist film, the silicon on the bridge girders is removed, and thereafter, the silicon wires buried in the resist film are collected. In this manner, the silicon wires can be collected without dispersing into the hydrofluoric acid solution. Then, a transistor using the silicon wires as a channel is formed.

Owner:HITACHI LTD

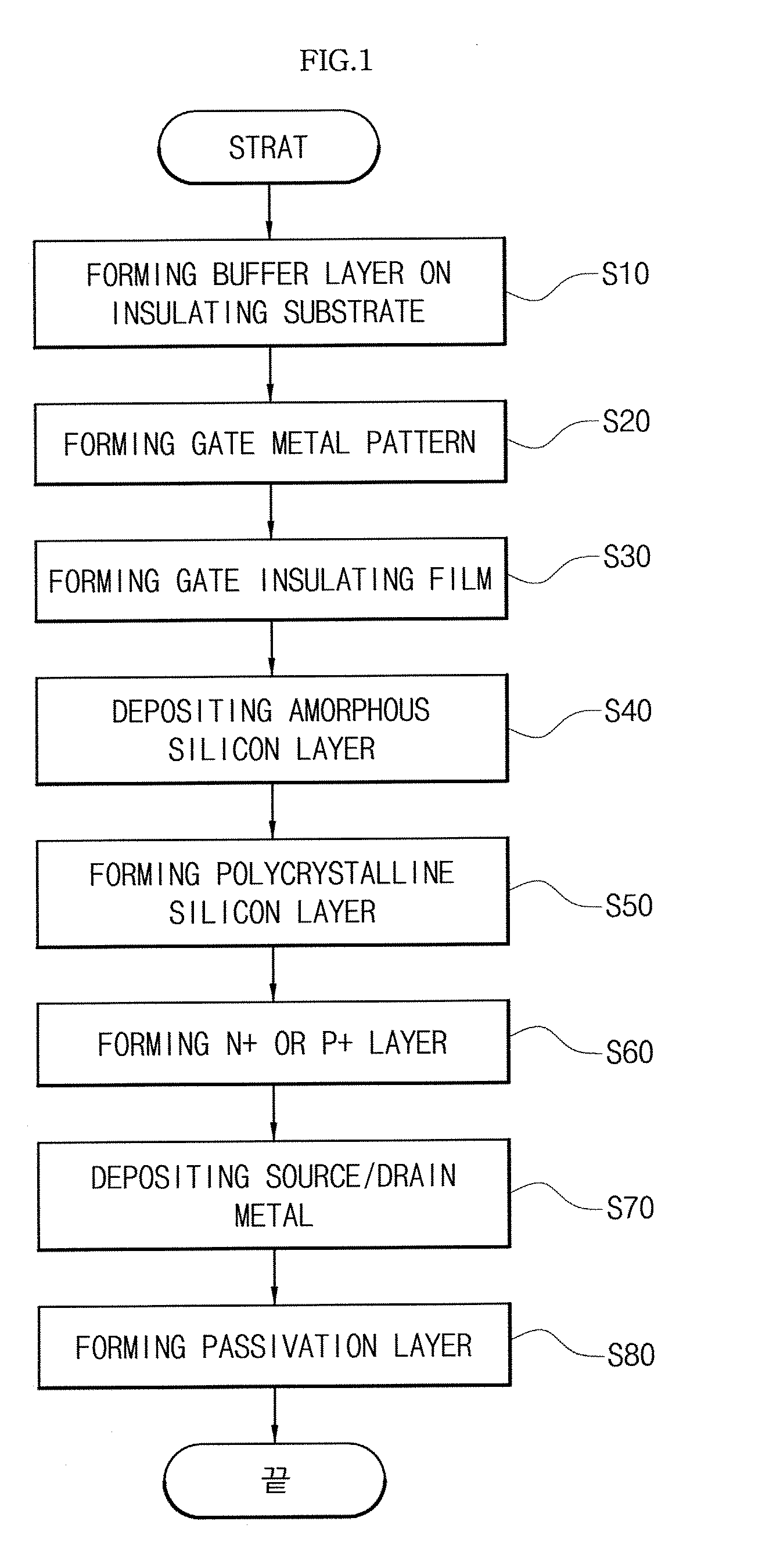

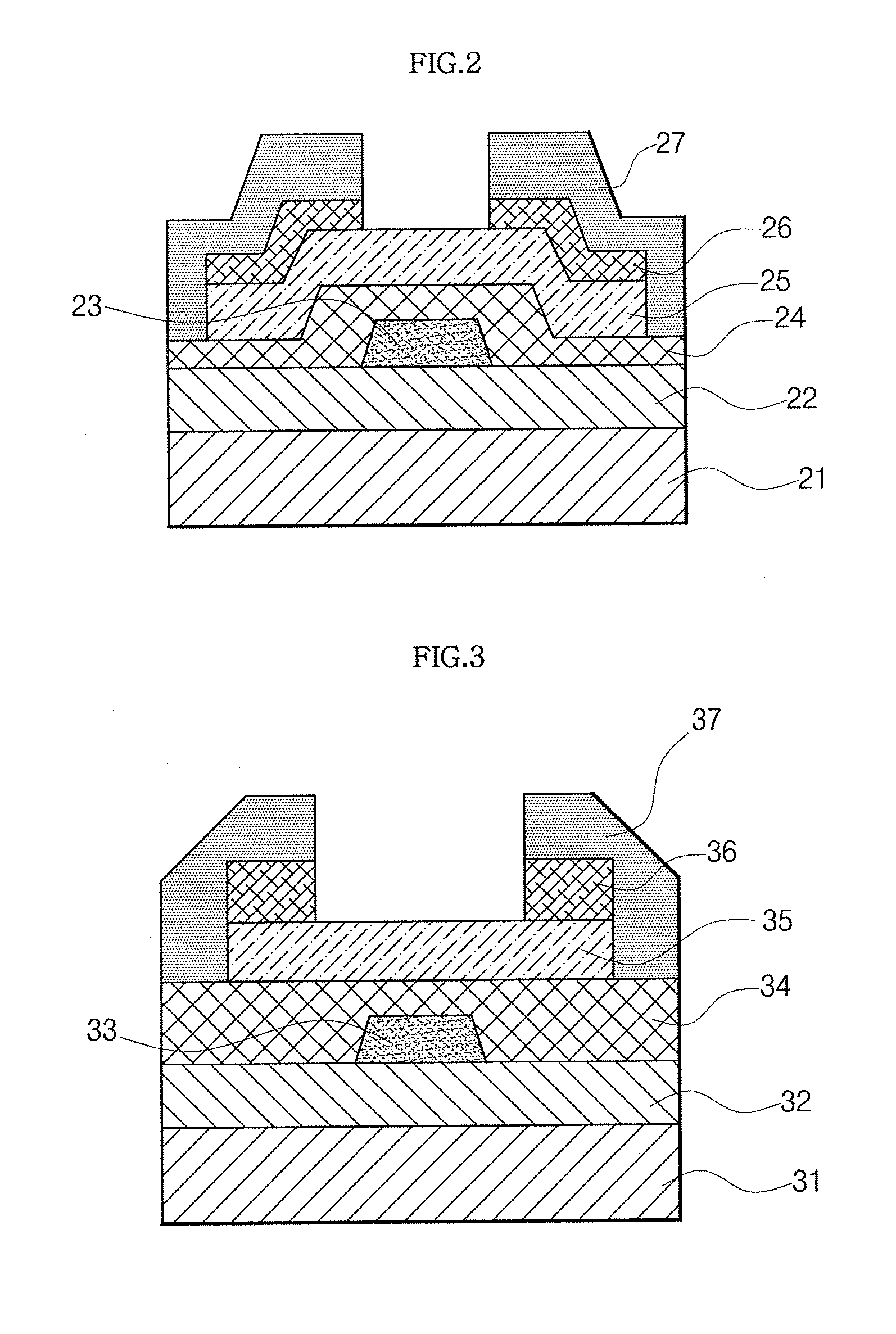

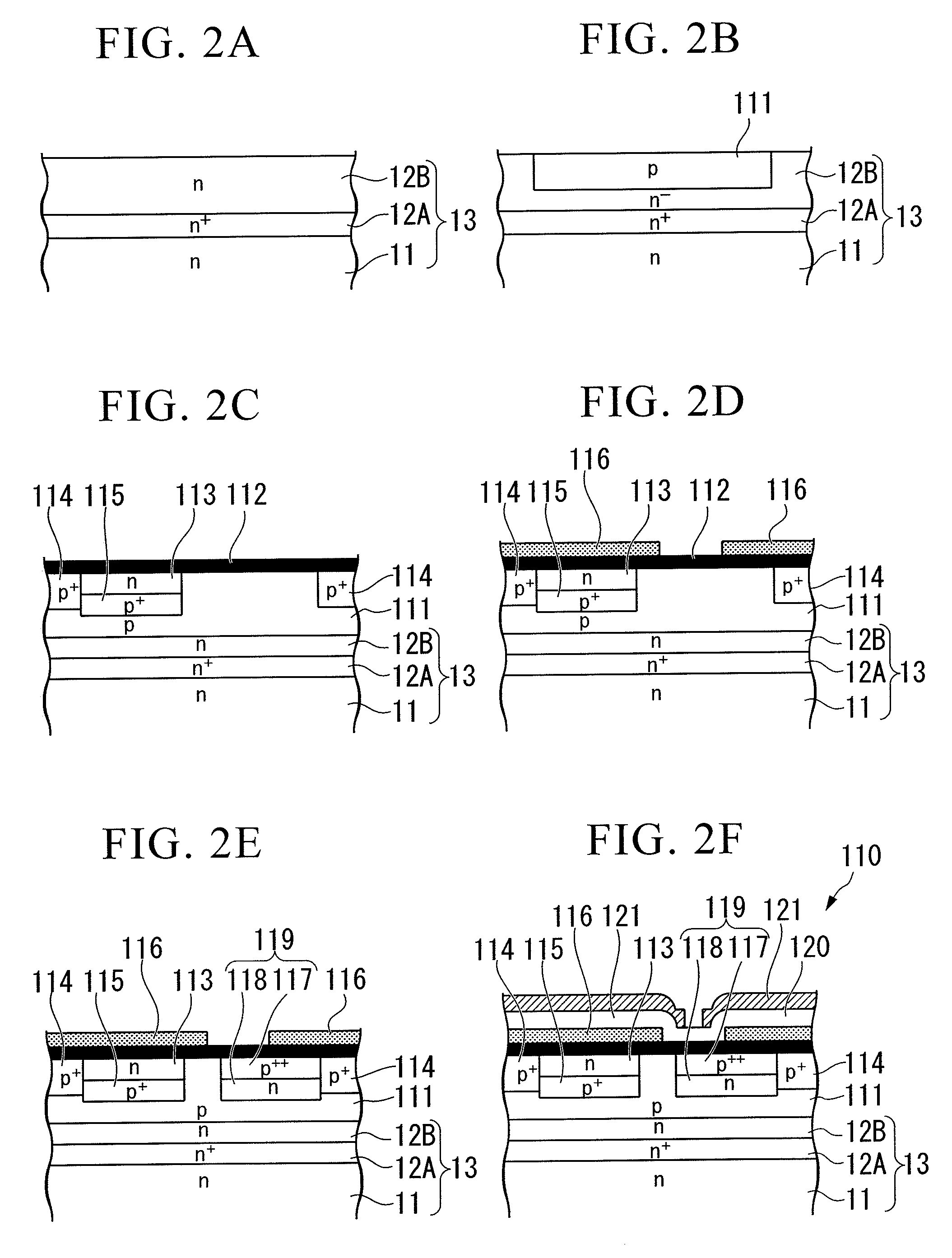

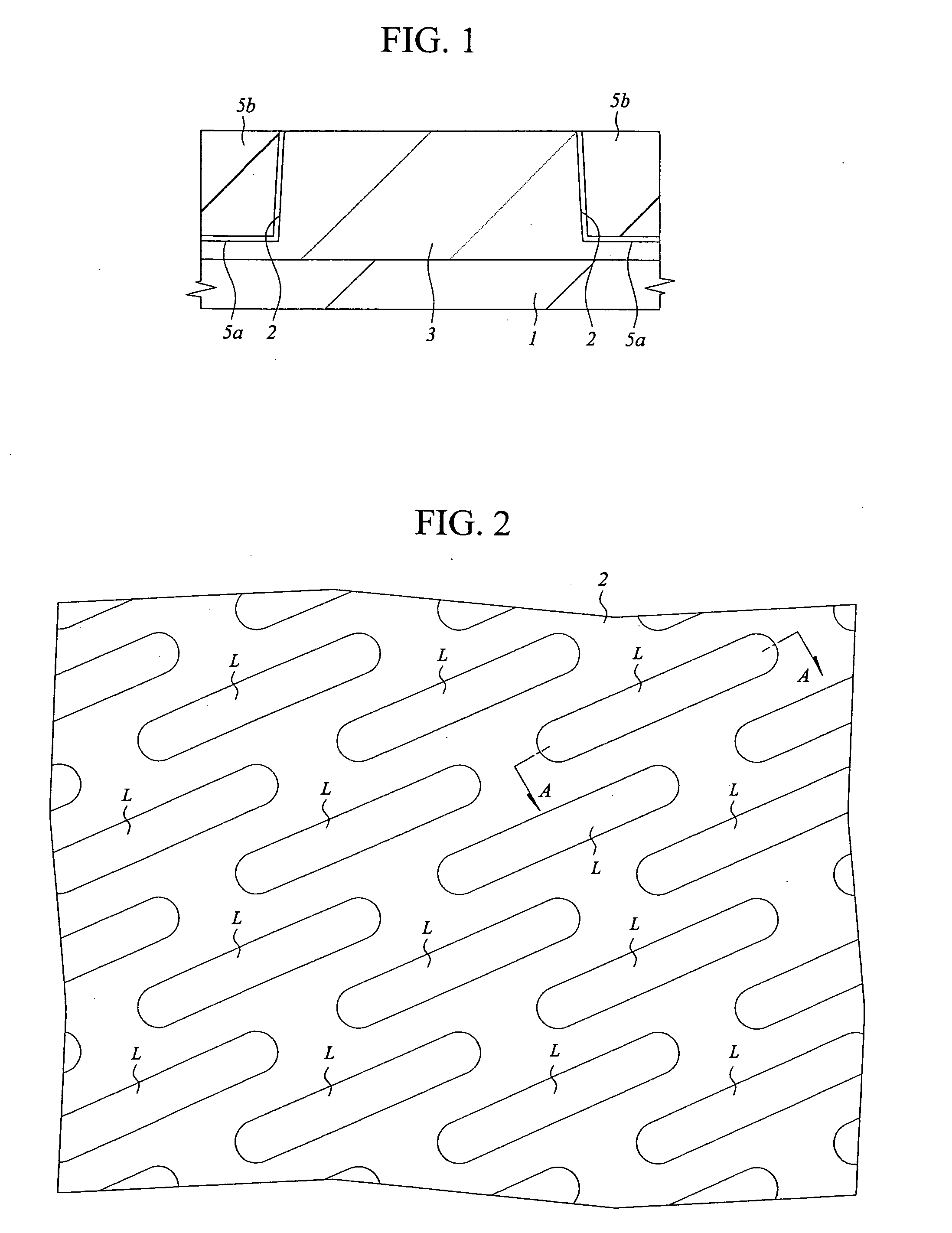

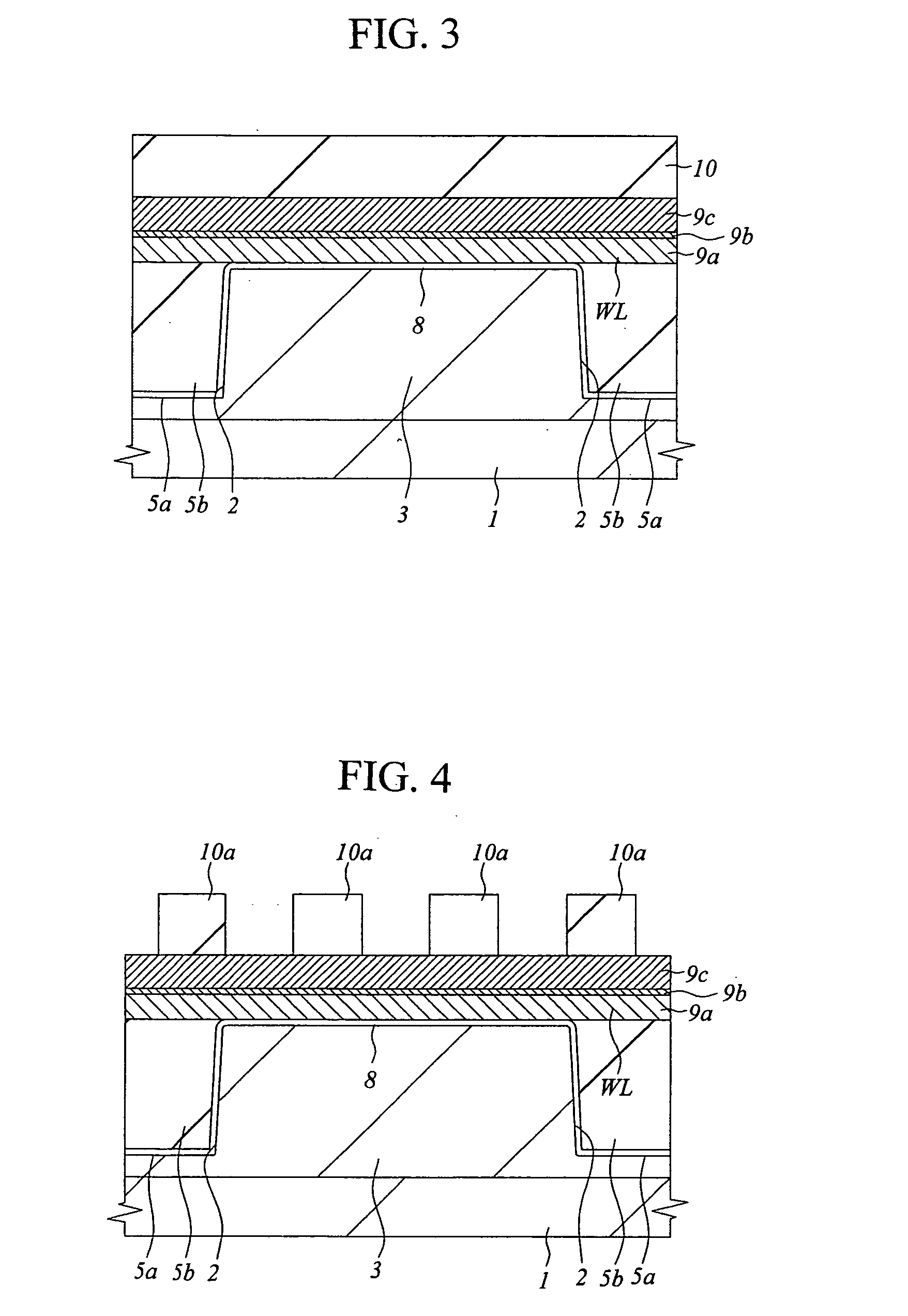

Method for fabricating reverse-staggered thin film transistor

InactiveUS20070134856A1Reduce metal pollutionUniform particle sizeSolid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconOptoelectronics

Disclosed herein is a method for fabricating a reverse-staggered polycrystalline silicon thin film transistor, and more specifically a method for fabricating a reverse-staggered polycrystalline silicon thin film transistor wherein a phosphosilicate-spin-on-glass (P-SOG) is used for a gate insulating film. The method comprises the steps of: forming a buffer layer on an insulating substrate; forming a gate metal pattern on the buffer layer; forming a planarized gate insulating film on the gate metal pattern; depositing an amorphous silicon layer on the gate insulating film; crystallizing the amorphous silicon layer into a polycrystalline silicon layer; forming a n+ or p+ layer on the polycrystalline silicon layer; forming a source / drain metal layer on the n+ or p+ layer; and forming a passivation layer on the source / drain metal layer.

Owner:UNIV IND COOP GRP OF KYUNG HEE UNIV

Etchant, etching method and semiconductor silicon waffer

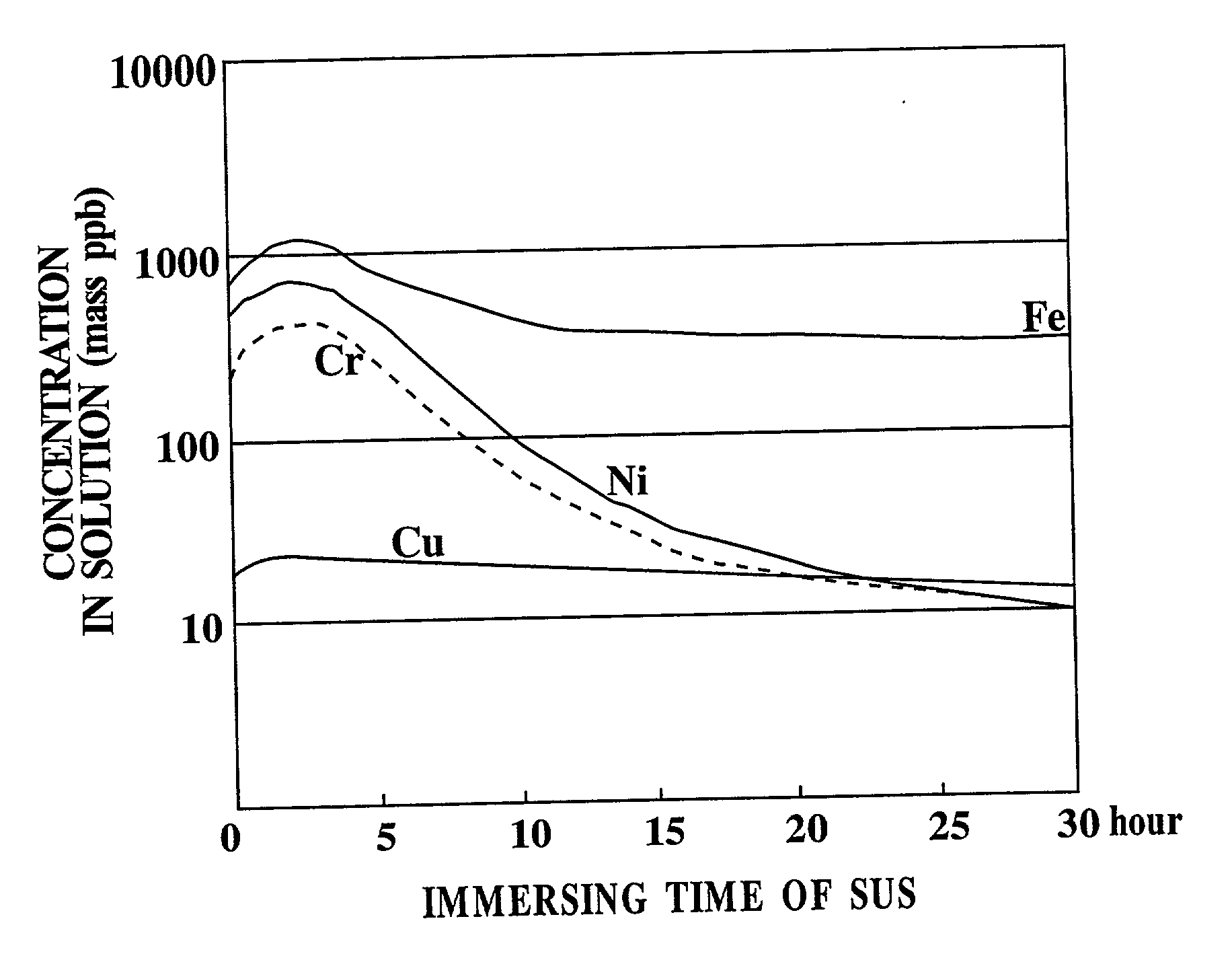

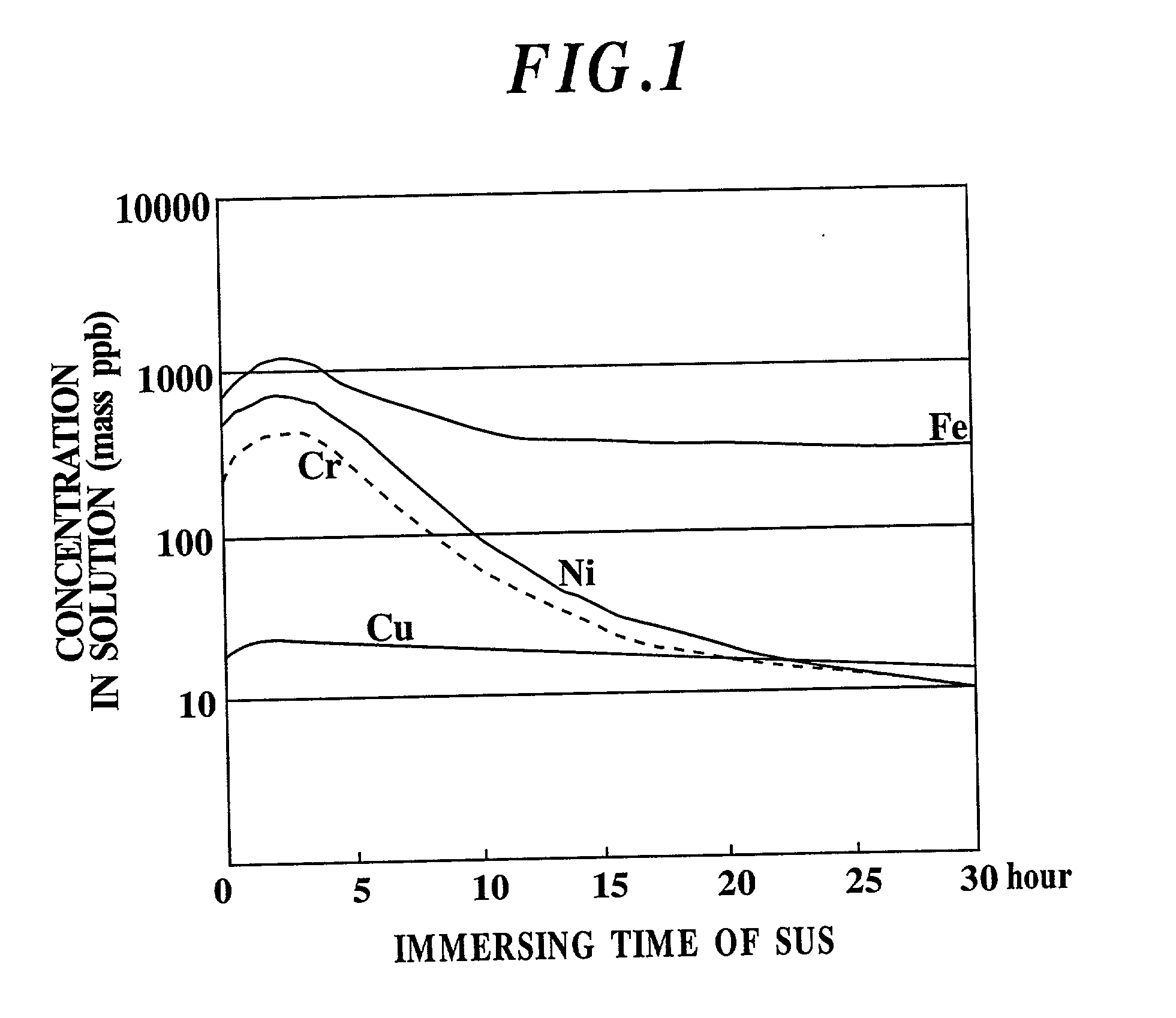

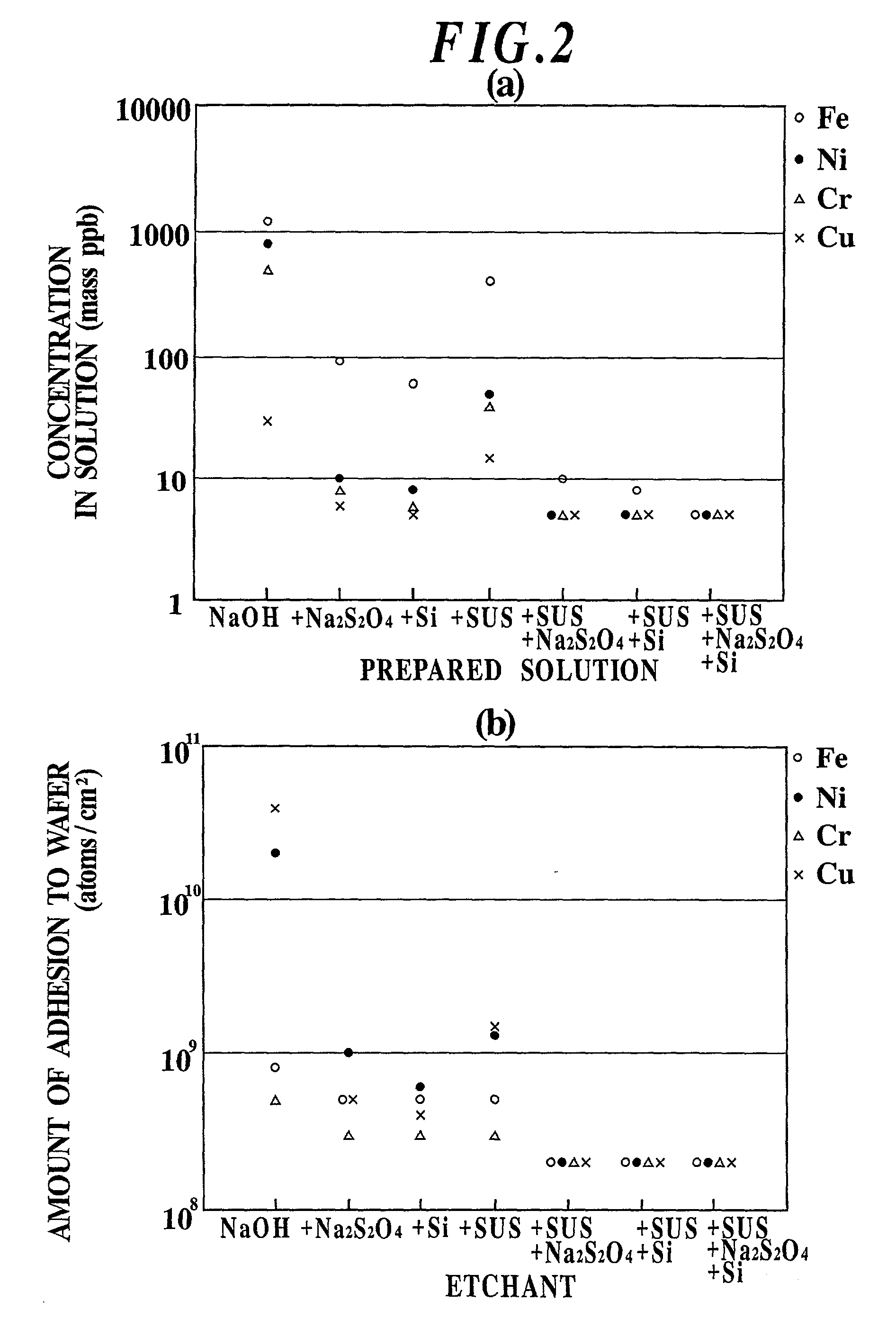

InactiveUS20030008504A1Reduce metal pollutionReduce concentrationPolycrystalline material growthAfter-treatment detailsMetal contaminationAqueous solution

An etchant and an etching method that contribute to prevention of metal contamination of a semiconductor silicon wafer, and a semiconductor silicon wafer in which metal contamination is extremely reduced, are provided. The etchant according to the present invention is prepared by immersing stainless steel in an alkali aqueous solution for not less than 10 hours. In the etching method according to the present invention, a semiconductor silicon wafer is etched by using the etchant. Thereby, the semiconductor silicon wafer according to the present invention, in which metal contamination is extremely reduced, is obtained.

Owner:SHIN-ETSU HANDOTAI CO LTD

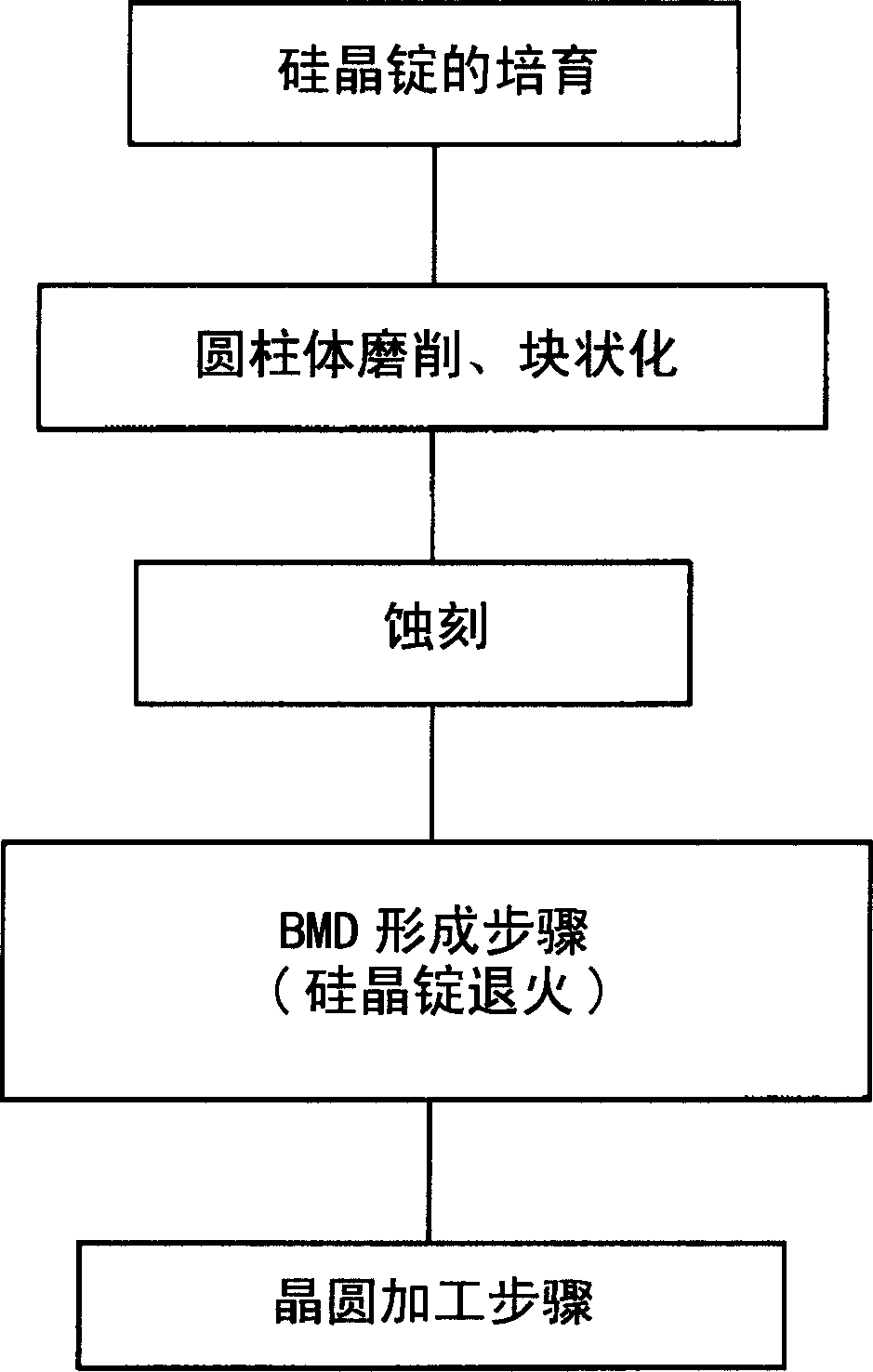

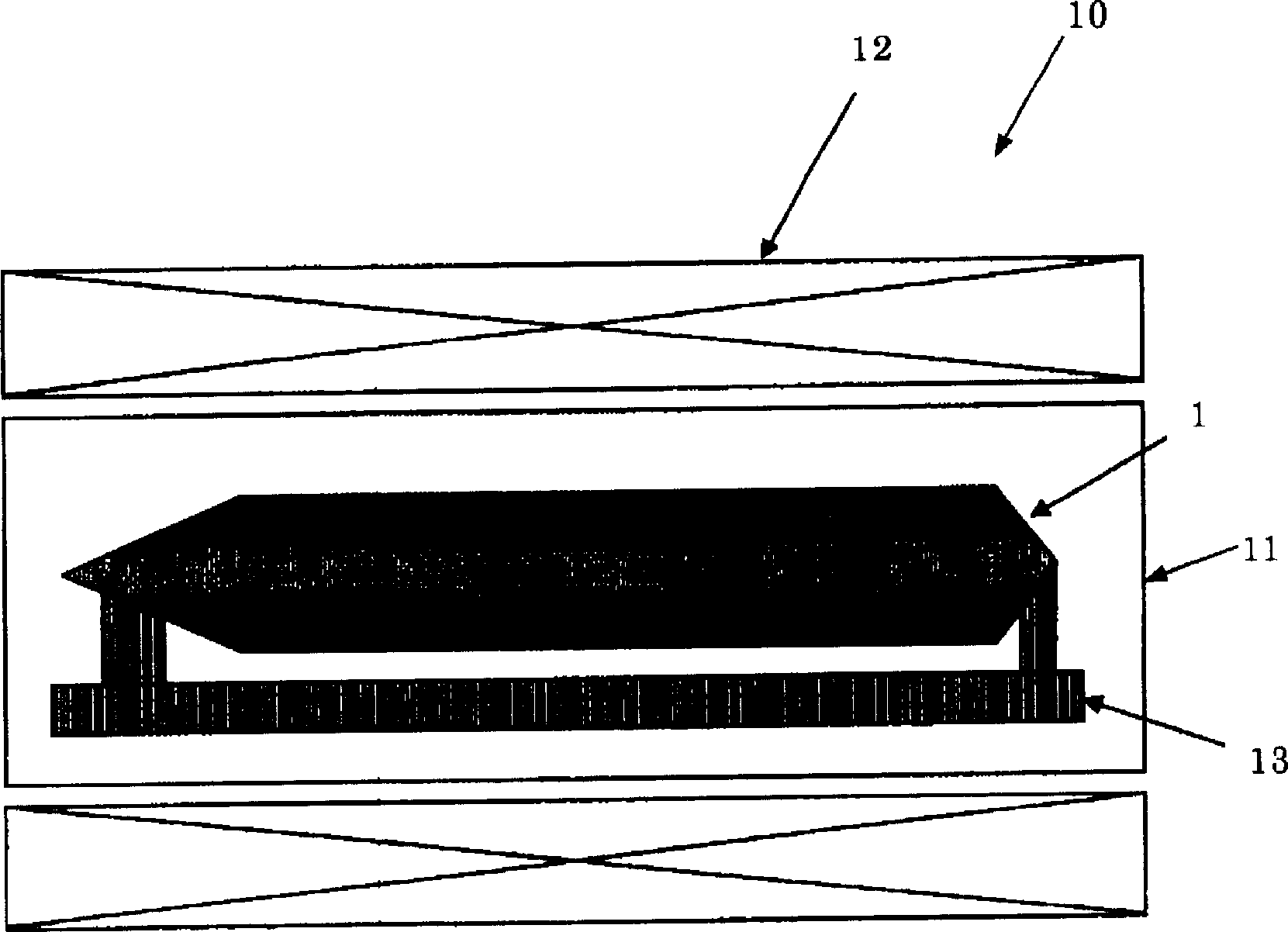

Process for producing wafer

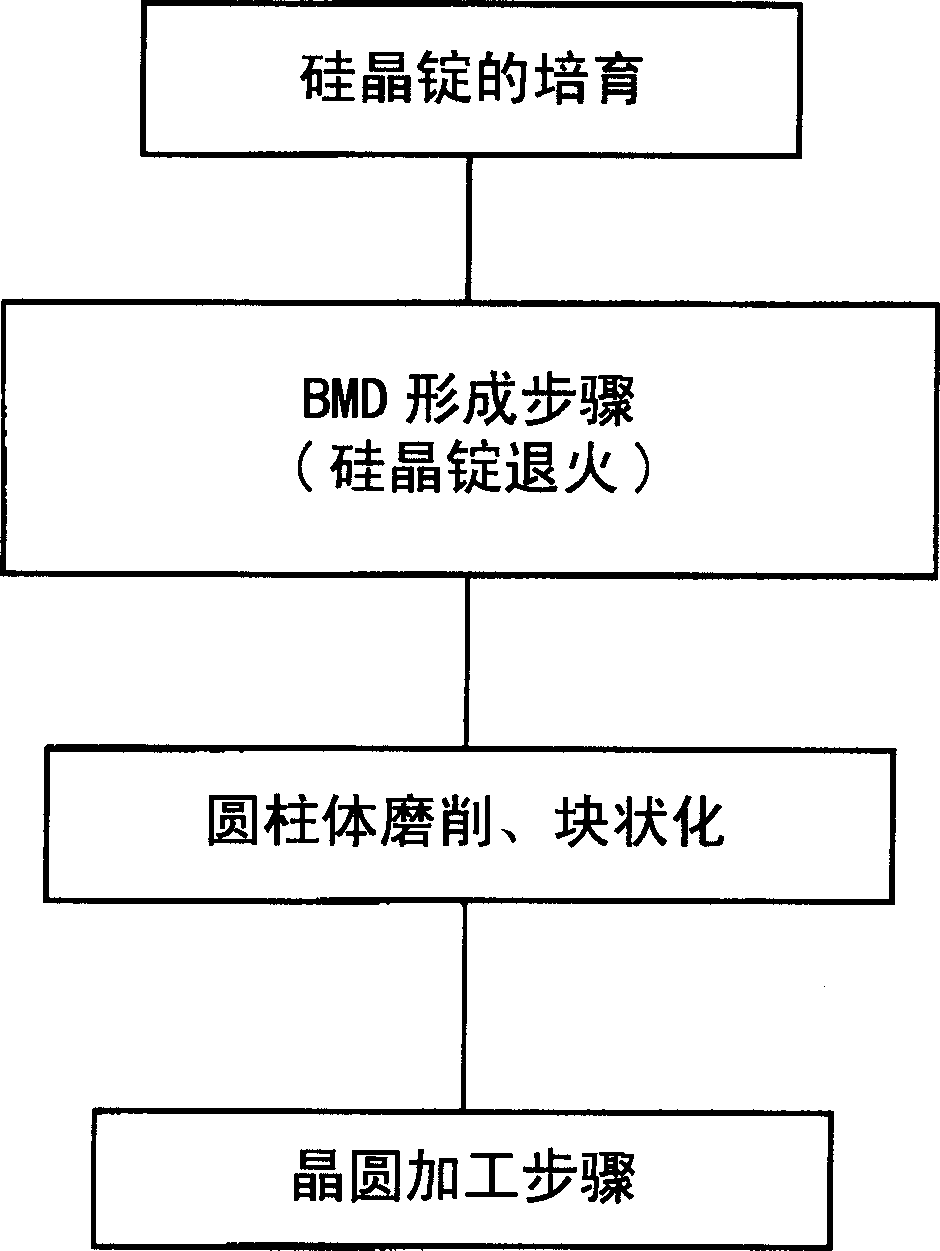

InactiveCN1836062AHigh IG capabilityIncrease production capacityPolycrystalline material growthSemiconductor/solid-state device manufacturingIngotSingle crystal

A process for producing a wafer, comprising at least the BMD formation step of subjecting a silicon single crystal having the form of an ingot to heat treatment to thereby form bulk microdefects (BMD) in the interior thereof, and the wafer machining step of machining the ingot furnished with the bulk microdefects (BMD) into a wafer. In this process for producing a wafer, the heat treatment for imparting IG capability in the wafer production can be shortened to thereby enable mass production of wafers of high IG capability. The process can further comprise the wafer heat treatment step of performing heat treatment of wafers after machining and the epitaxial growth step of forming an epitaxial layer on each of the wafers with the result that the productivity of, excelling in gettering effect, anneal wafers and epitaxial wafers can be enhanced.

Owner:SHIN-ETSU HANDOTAI CO LTD

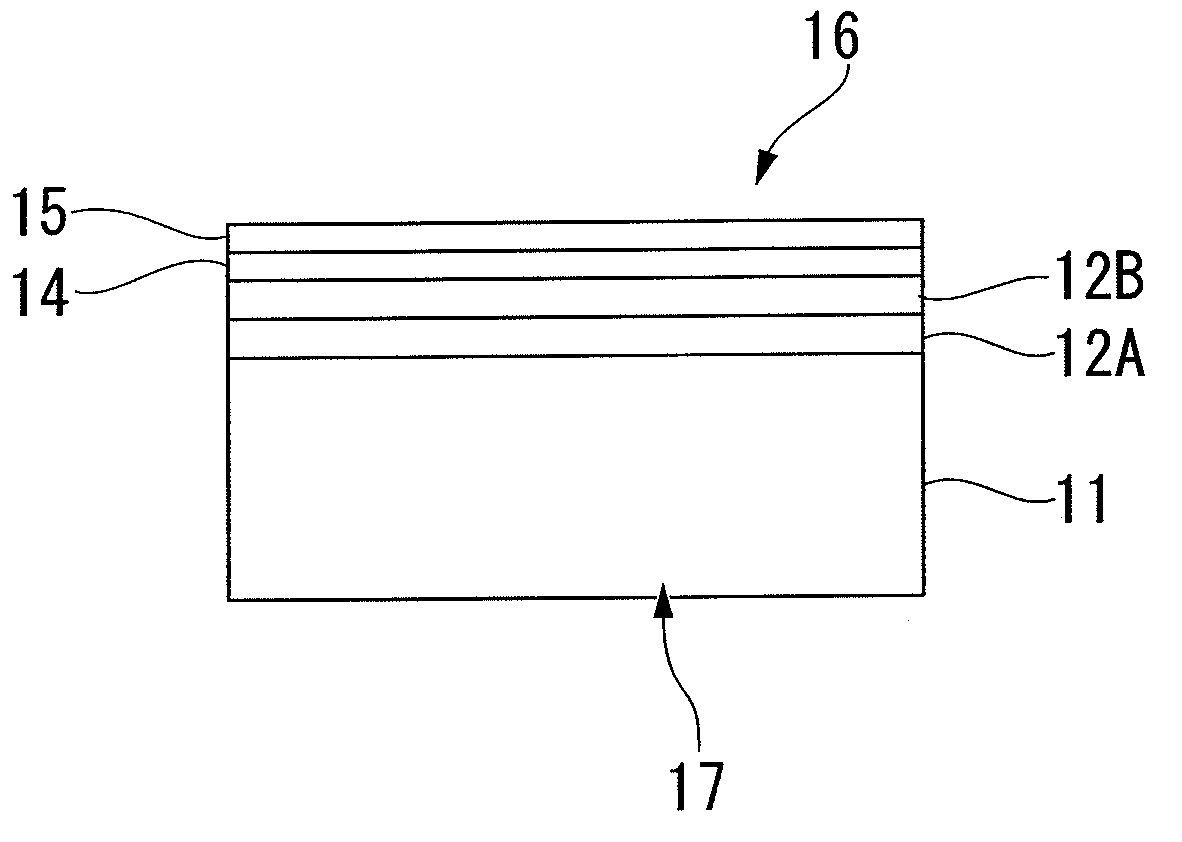

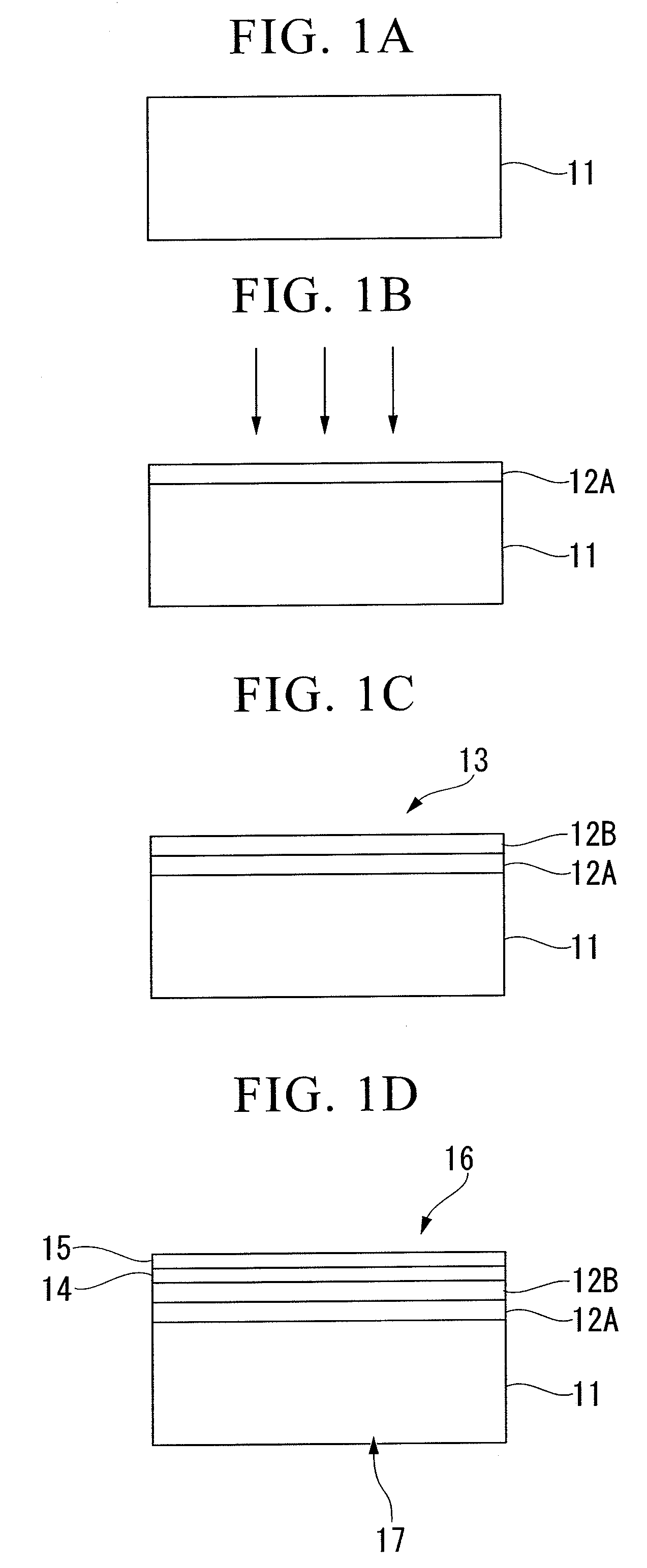

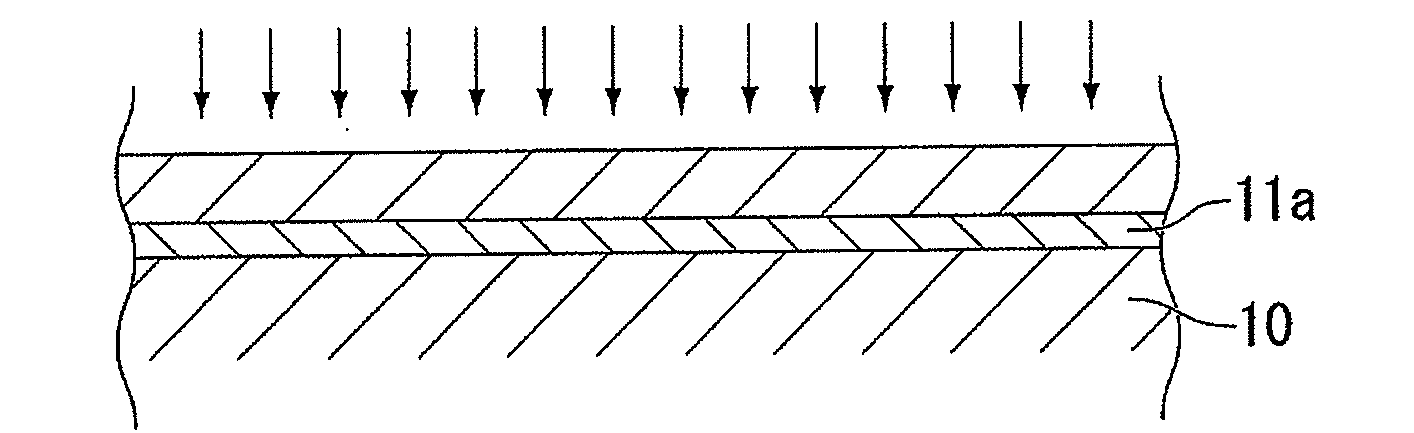

Silicon substrate and manufacturing method thereof

ActiveUS20090224367A1Prevent reduction in gettering capabilityIncrease productionPolycrystalline material growthSemiconductor/solid-state device manufacturingOxygenMaterials science

A silicon substrate is manufactured from a single crystal silicon that is doped with phosphorus (P) and is grown by a CZ method to have a predetermined carbon concentration and a predetermined initial oxygen concentration. An n+ epitaxial layer or an n+ implantation layer that is doped with phosphorus (P) at a predetermined concentration or more is formed on the silicon substrate. An n epitaxial layer that is doped with phosphorus (P) at a predetermined concentration is formed on the n+ layer.

Owner:SUMCO CORP

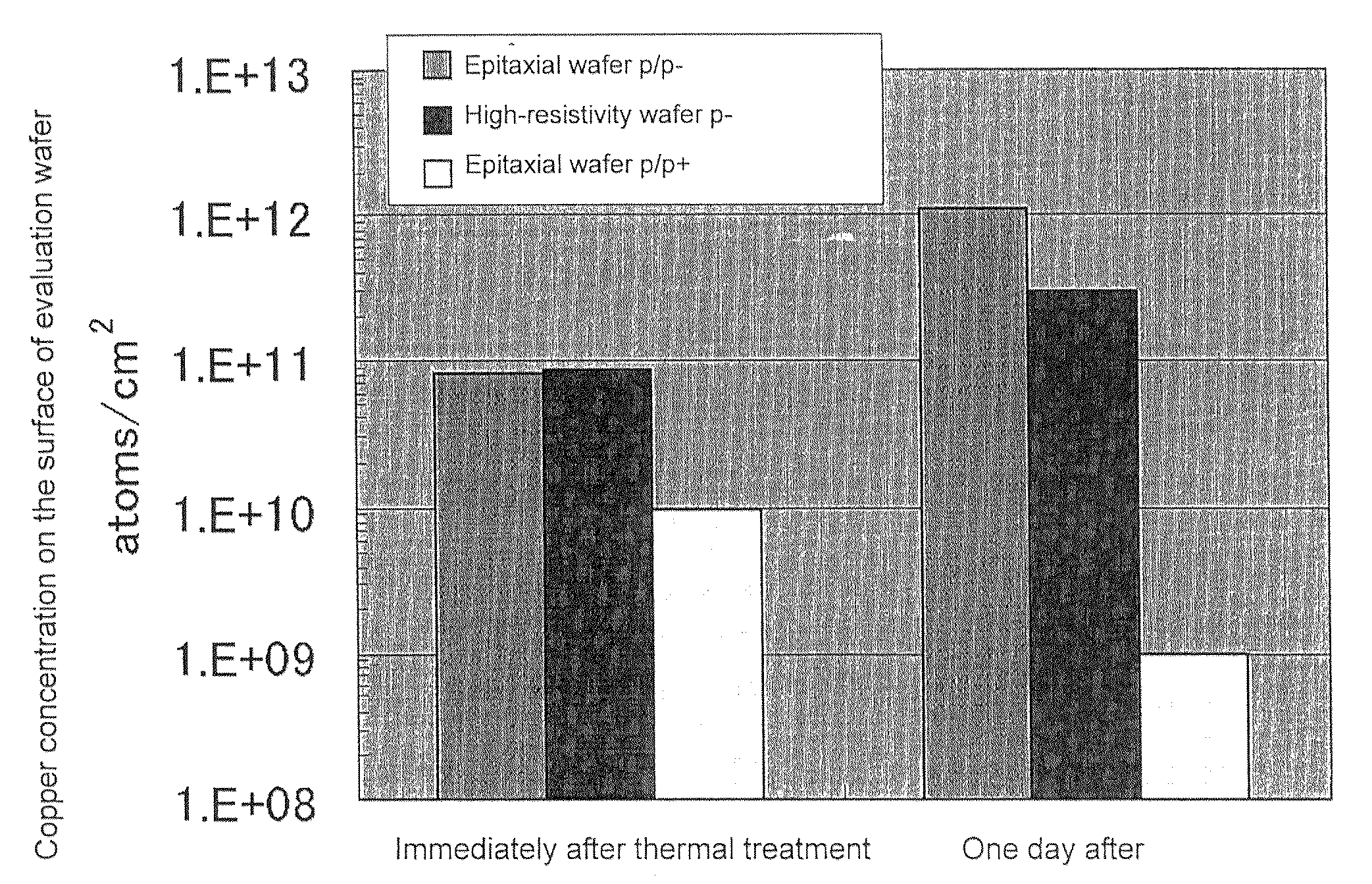

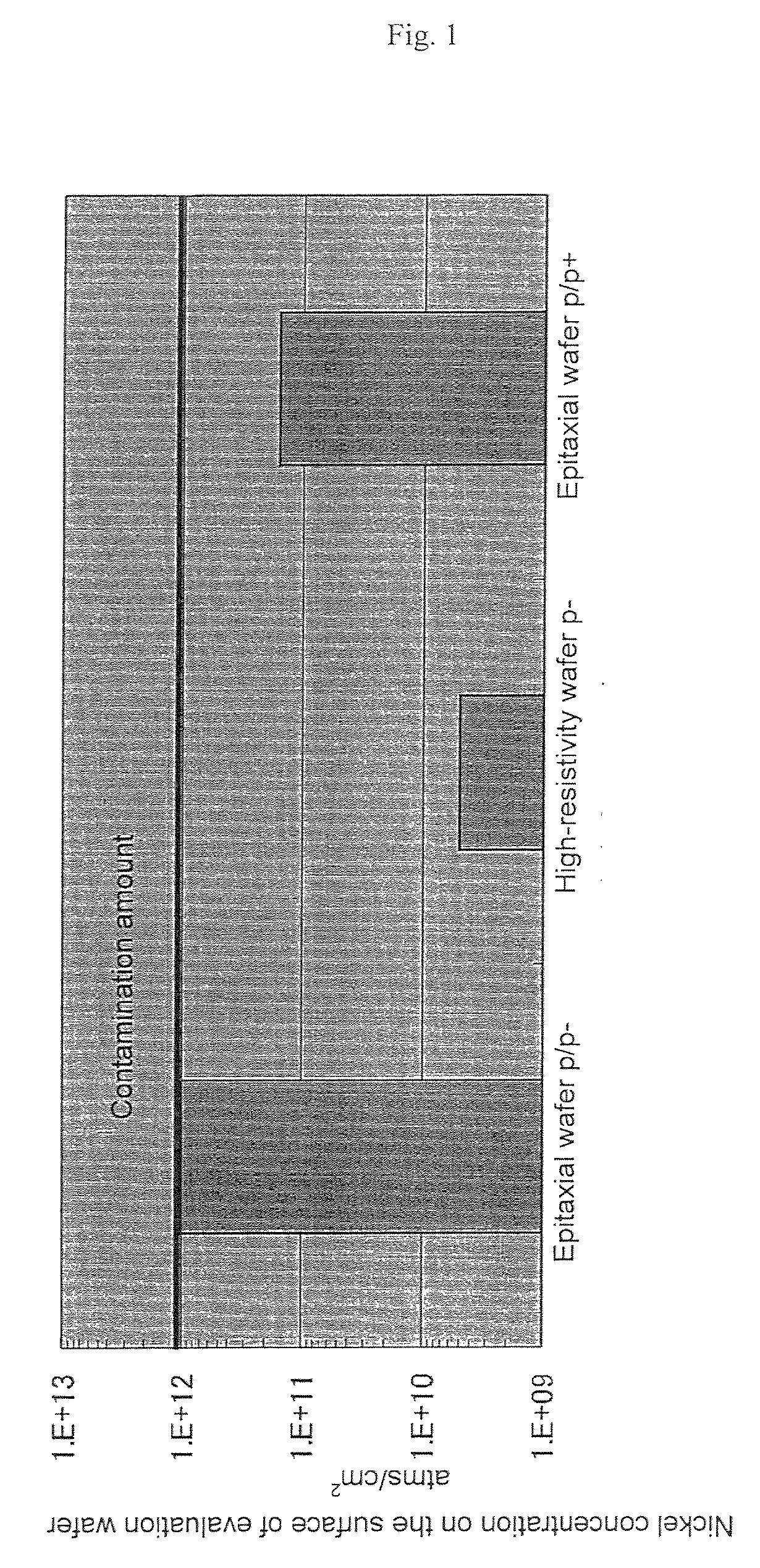

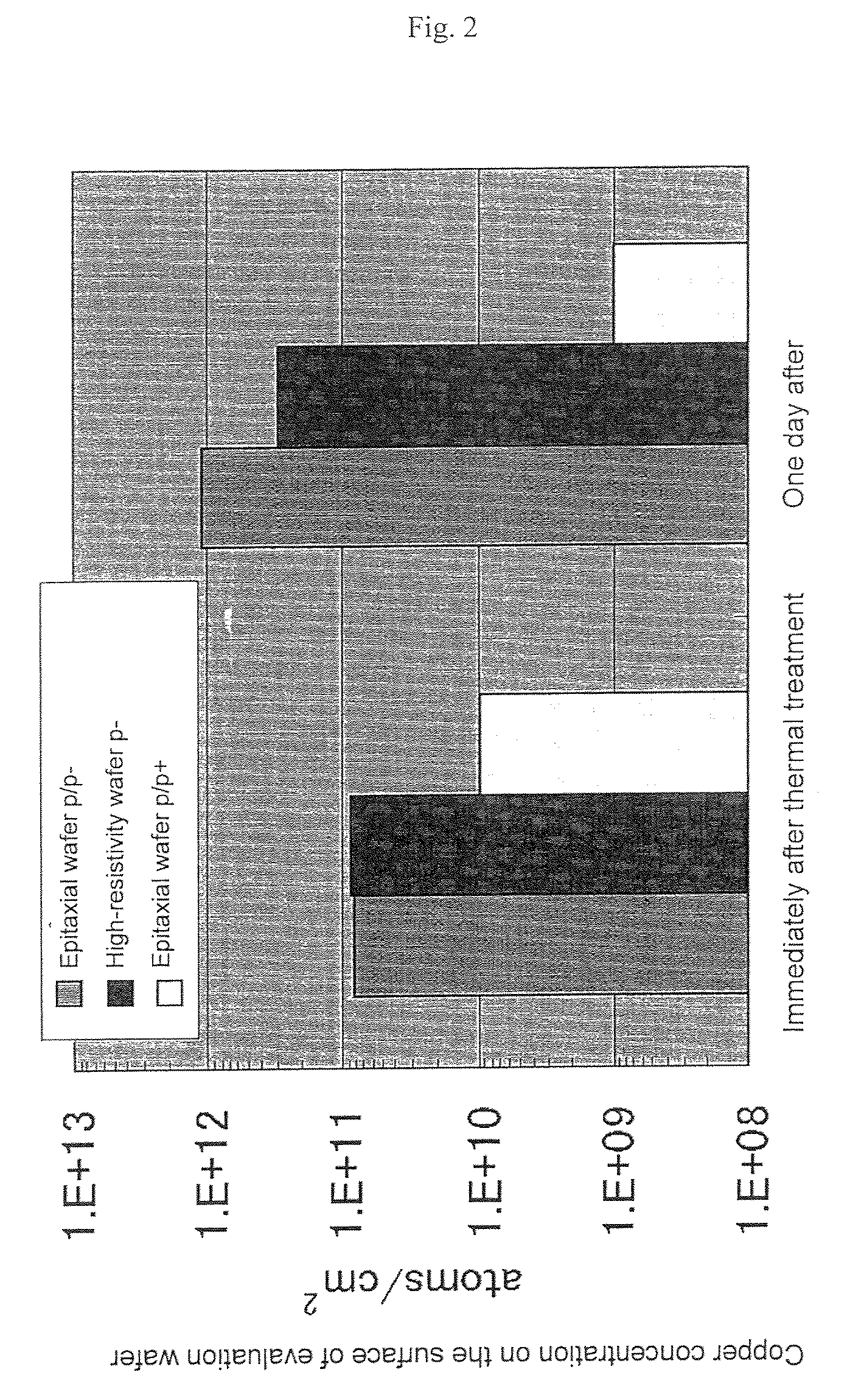

Method of evaluating thermal treatment and method of manufacturing semiconductor wafer

ActiveUS20080020496A1Conveniently evaluating contaminationHigh sensitivitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingOxygenThermal treatment

Provided are the methods of evaluating thermal treatment. In the methods, a wafer comprising a silicon substrate having an oxygen concentration of approximately equal to or less than 1.0×1018 atoms / cm3 and a silicon epitaxial layer on at least one surface of the substrate is employed.

Owner:SUMCO CORP

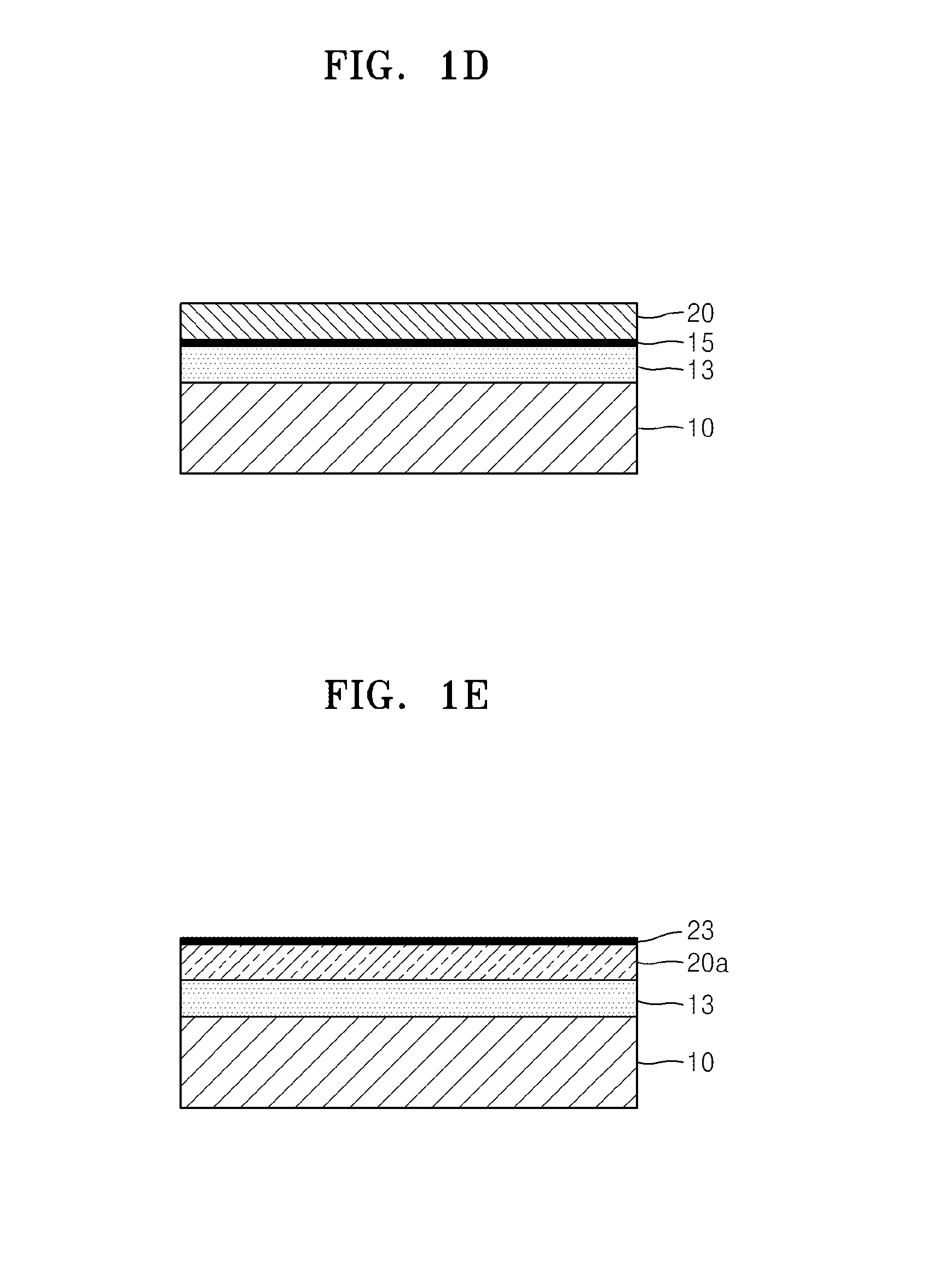

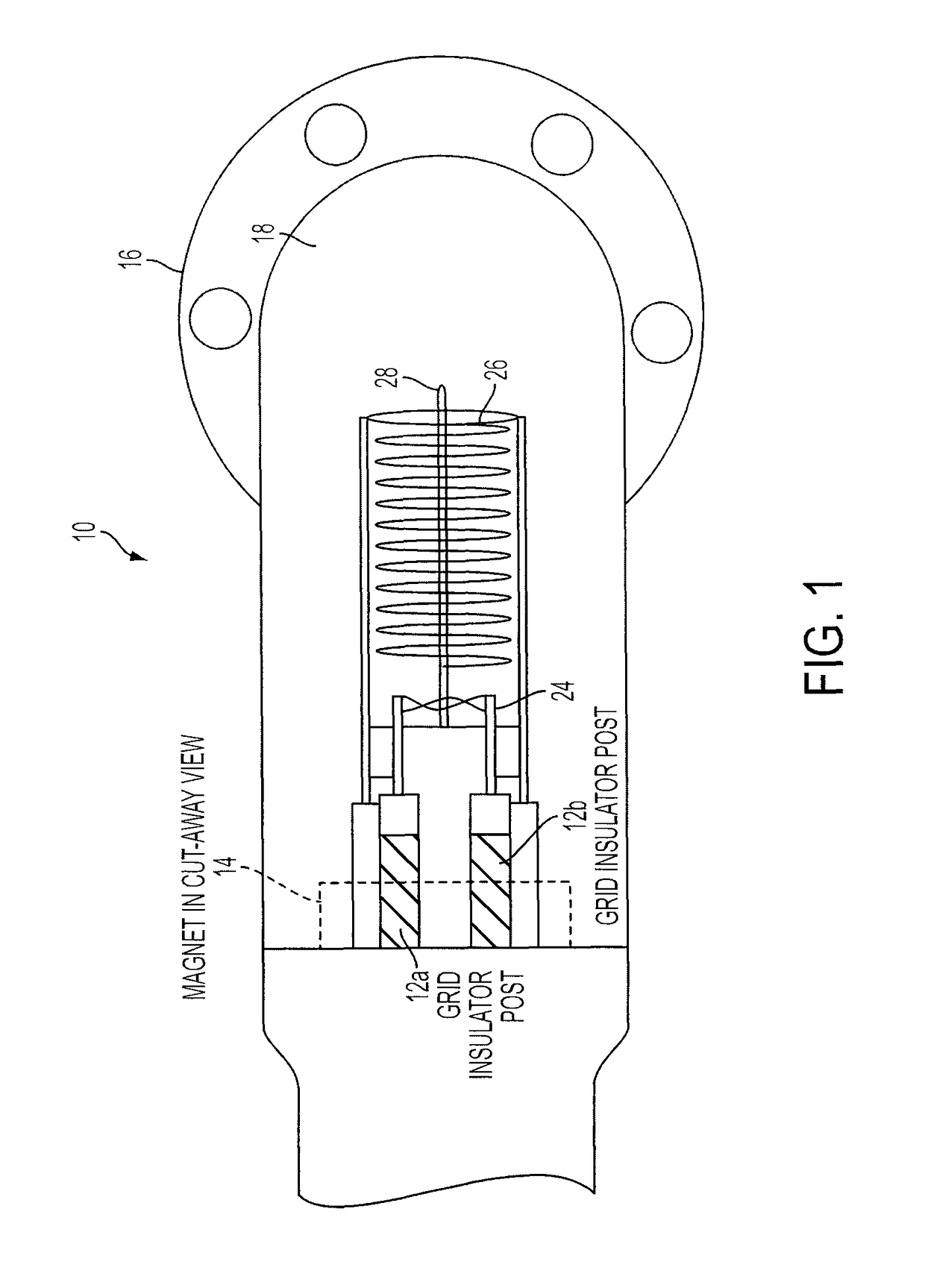

Molecular shield for an ionizaton vacuum gauge

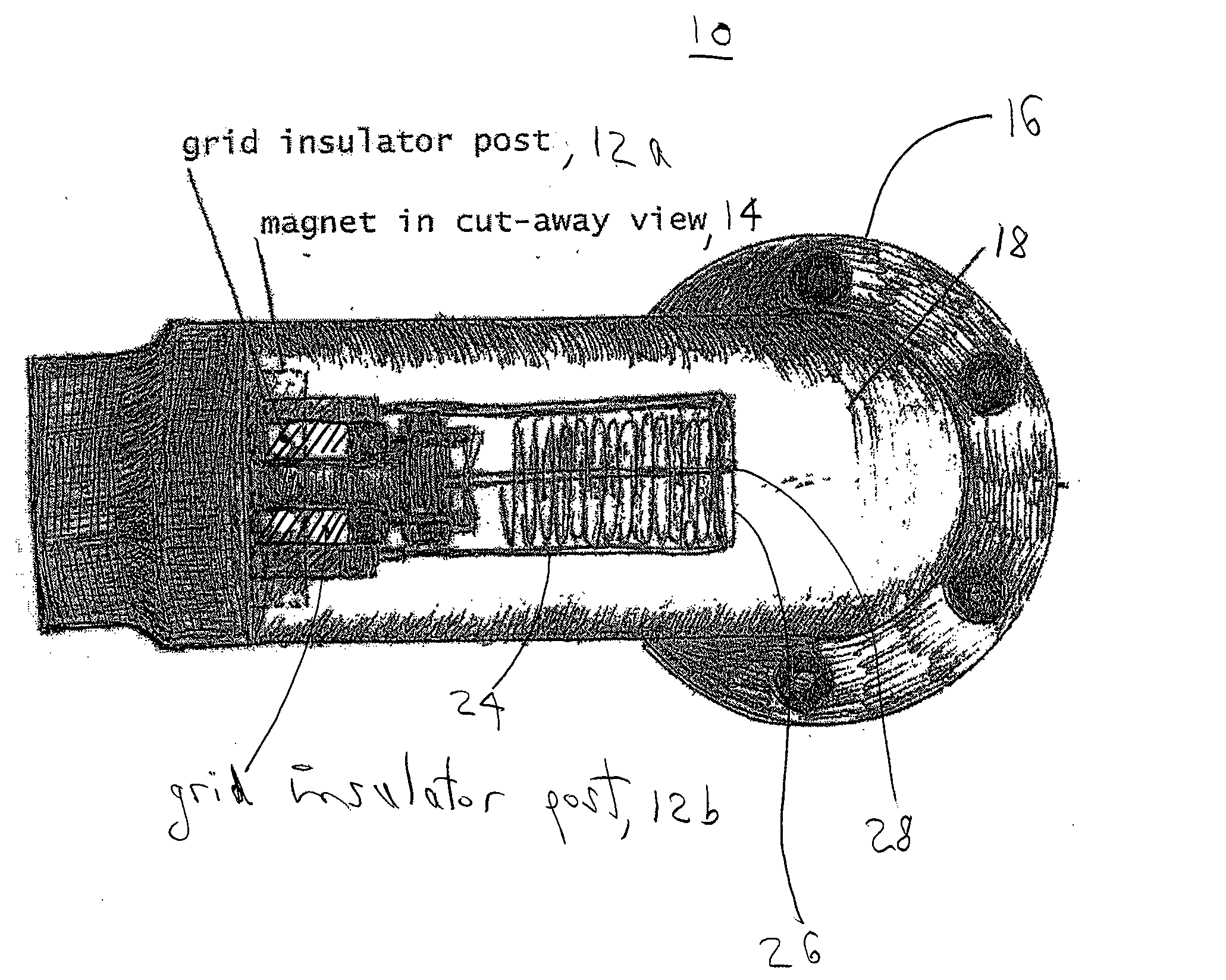

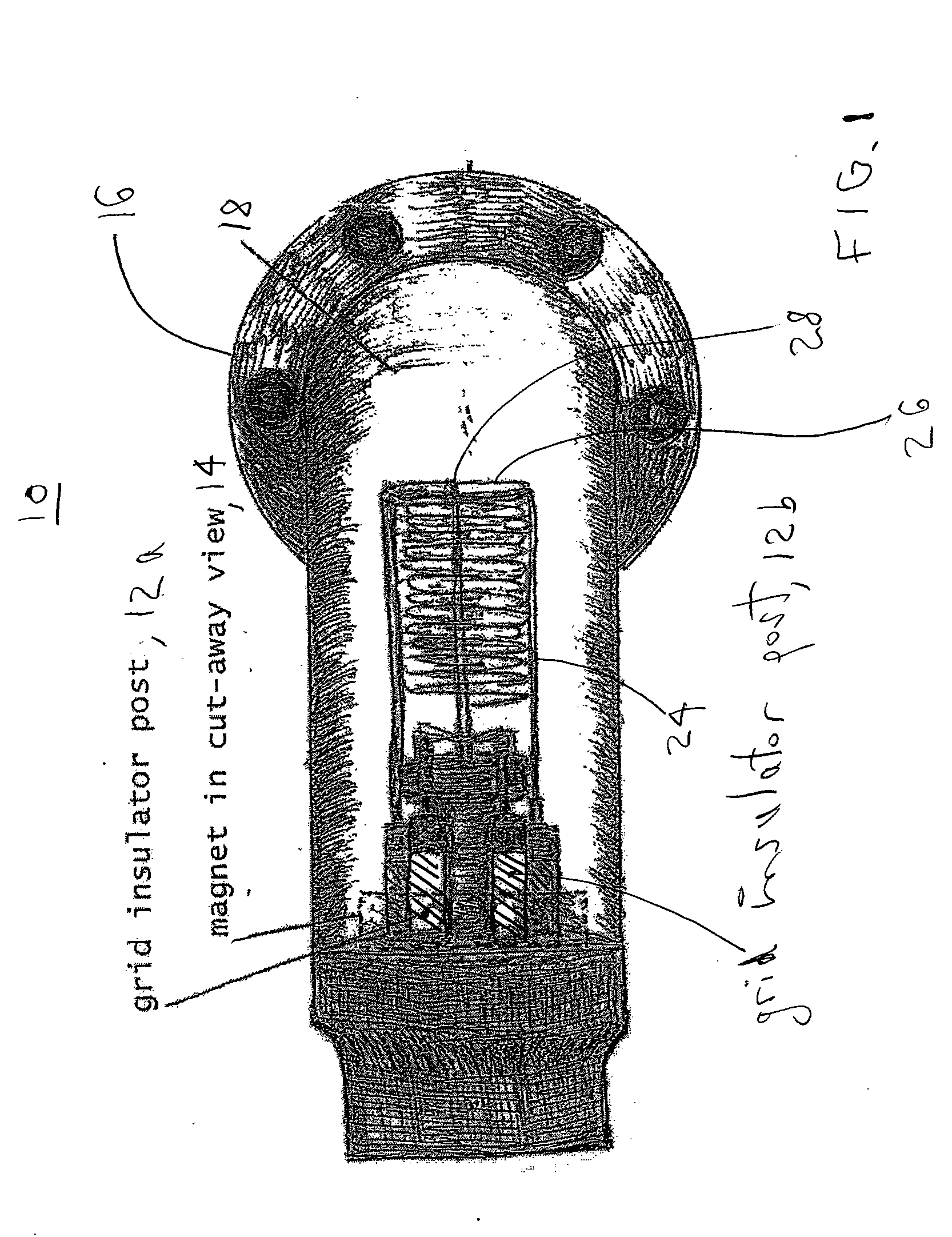

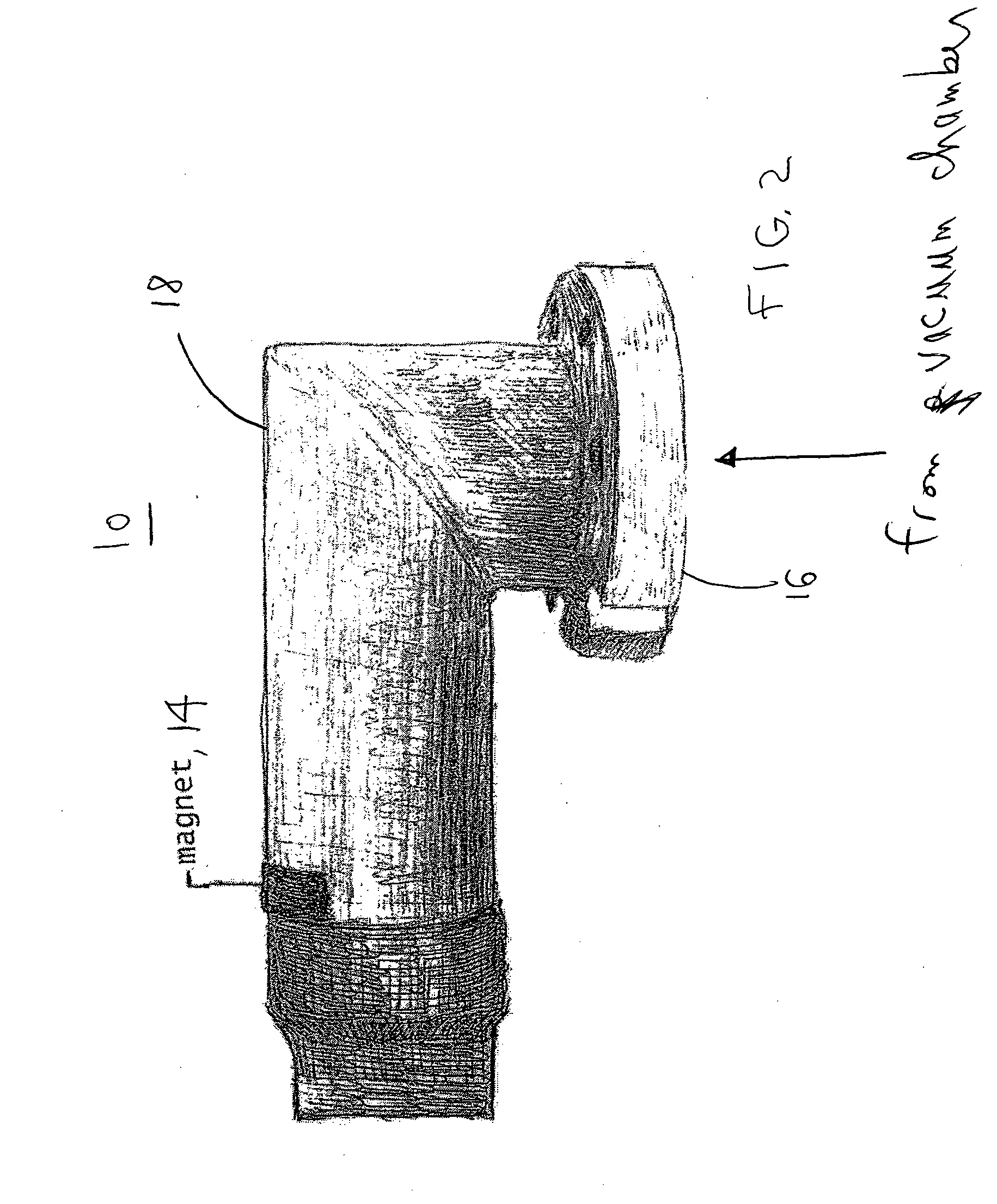

InactiveUS20100090703A1Reduce metal pollutionEfficient reductionVacuum gauge using ionisation effectsMaterial analysis by electric/magnetic meansEngineeringMagnet

A system for measuring gas density in a vacuum includes a gauge, a housing for containing the gauge, and a magnet secured to an exterior surface of the housing. The magnet is a flexible magnetic strips, and positioned around the exterior surface of the housing. The gauge includes grid insulator posts extending longitudinally along a tubular section of the housing, and the magnet is secured to the exterior surface of the housing adjacent to the grid insulator posts, and oriented transversely to the grid insulator posts. The magnet is a flexible magnetic strip, and a clamp secures the magnet to the exterior surface of the housing.

Owner:EXCELIS INC

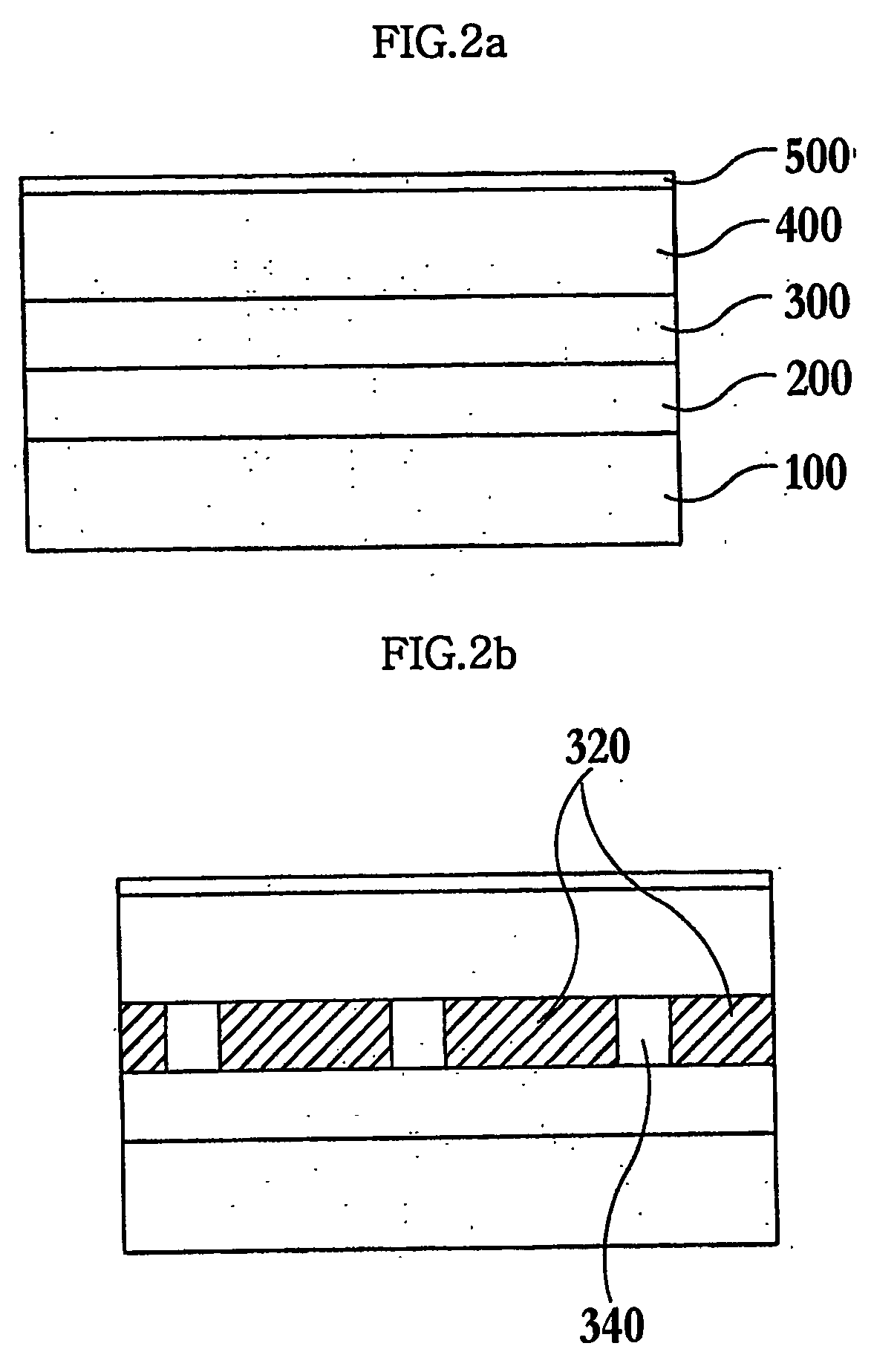

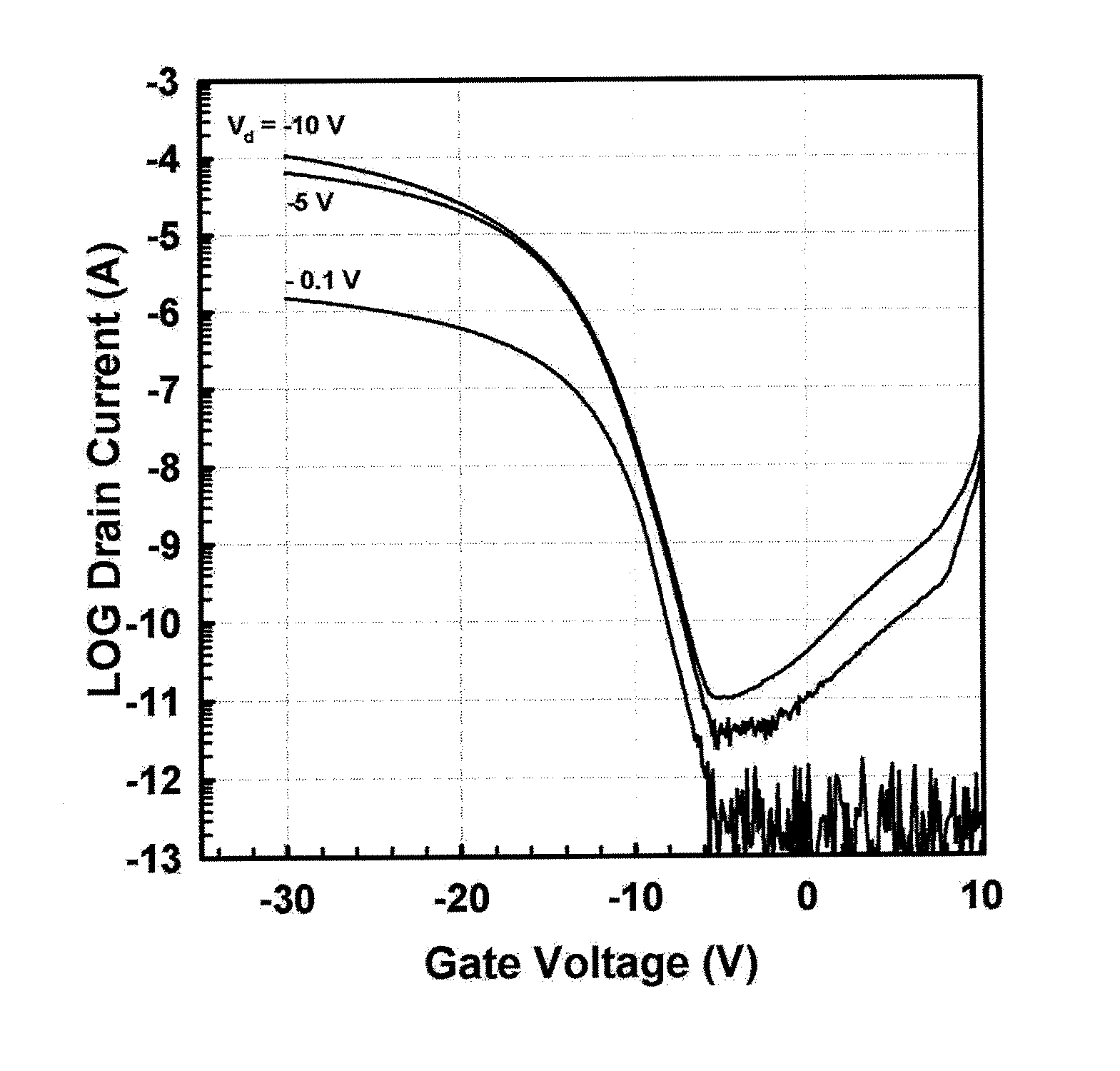

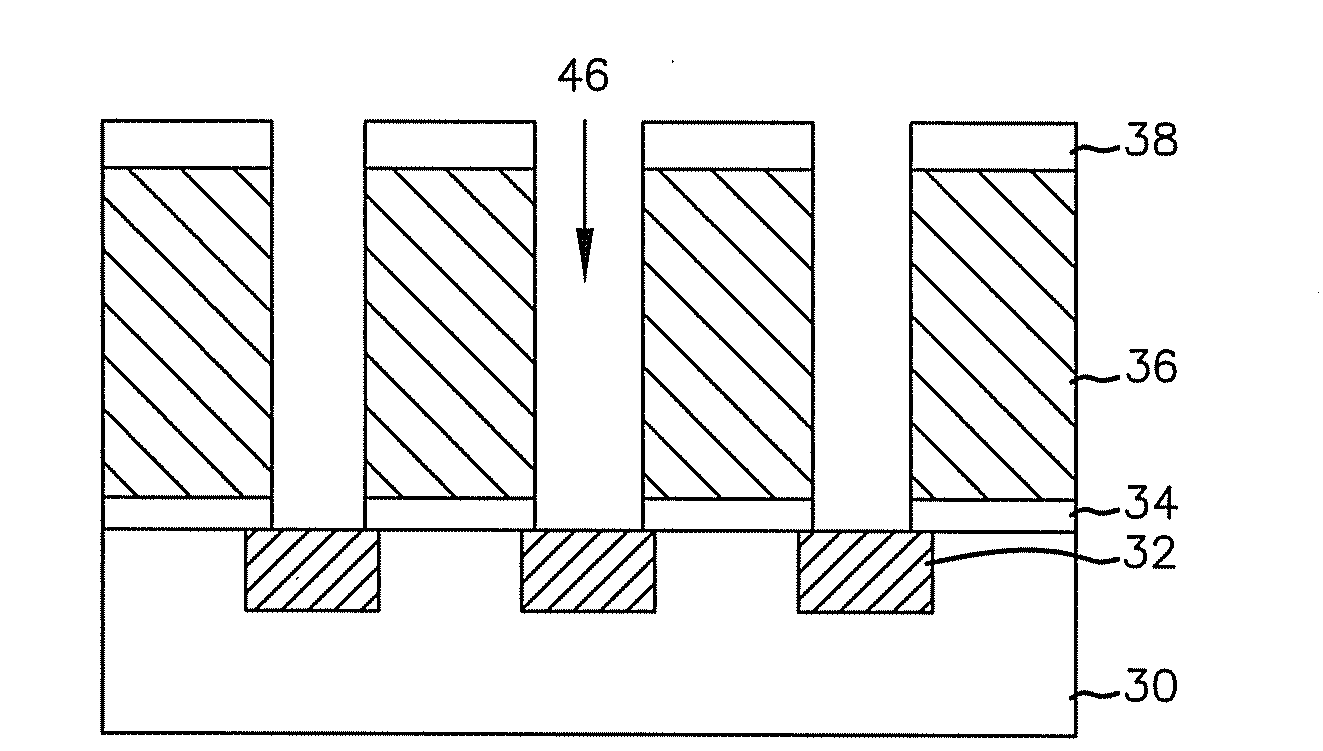

Semiconductor device and manufacturing method of semiconductor device using metal oxide

ActiveUS20140117349A1Reduce metal pollutionSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialPhysical chemistry

A method of manufacturing a semiconductor device using a metal oxide includes forming a metal oxide layer on a substrate, forming an amorphous semiconductor layer on the metal oxide layer, and forming a polycrystalline semiconductor layer by crystallizing the amorphous semiconductor layer using the metal oxide layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Molecular shield for an ionizaton vacuum gauge

InactiveUS7906971B2Reduce metal pollutionReducing metallic depositsVacuum gauge using ionisation effectsMaterial analysis by electric/magnetic meansEngineeringMagnet

A system for measuring gas density in a vacuum includes a gauge, a housing for containing the gauge, and a magnet secured to an exterior surface of the housing. The magnet is a flexible magnetic strips, and positioned around the exterior surface of the housing. The gauge includes grid insulator posts extending longitudinally along a tubular section of the housing, and the magnet is secured to the exterior surface of the housing adjacent to the grid insulator posts, and oriented transversely to the grid insulator posts. The magnet is a flexible magnetic strip, and a clamp secures the magnet to the exterior surface of the housing.

Owner:EXCELIS INC

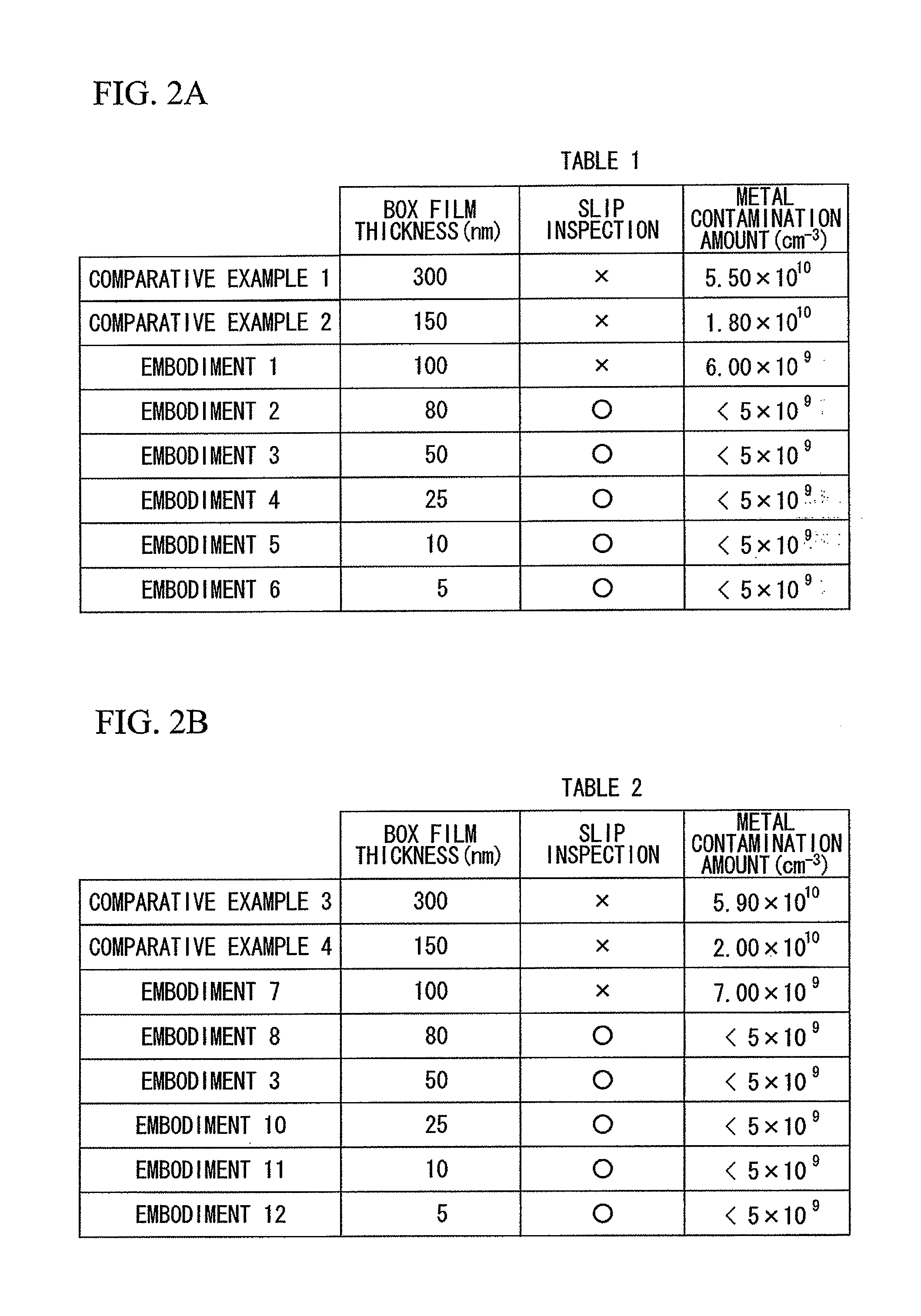

Method of manufacturing semiconductor substrate and method of evaluating quality of semiconductor substrate

ActiveUS20070193686A1Reduce metal pollutionSemiconductor/solid-state device testing/measurementPreparing sample for investigationForeign matterSlurry

The method of manufacturing a semiconductor substrate including mirror polishing a silicon wafer surface, wherein the mirror polishing is conducted using a slurry having a Cu content of approximately equal to or less than 10 ppb, a Ni content of approximately equal to or less than 10 ppb, and an Fe content of approximately equal to or less than 1,000 ppb. The method of evaluating a quality of a semiconductor substrate including etching the surface of the semiconductor substrate by SC-1 cleaning and / or a HF cleaning, detecting bright points on the surface of the etched substrate with a foreign matter inspection device, and evaluating the quality of the semiconductor substrate based on the bright points detected on the surface of the substrate.

Owner:SUMCO CORP

Method for manufacturing SIMOX wafer

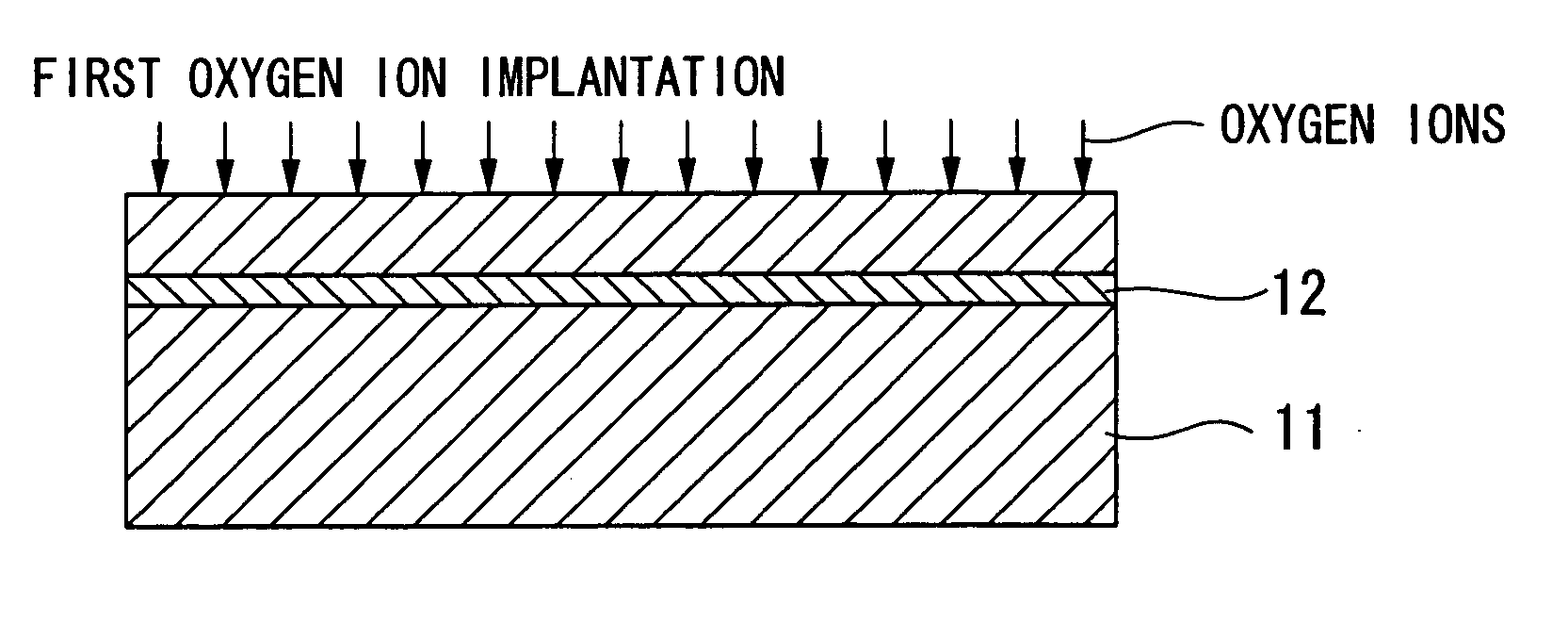

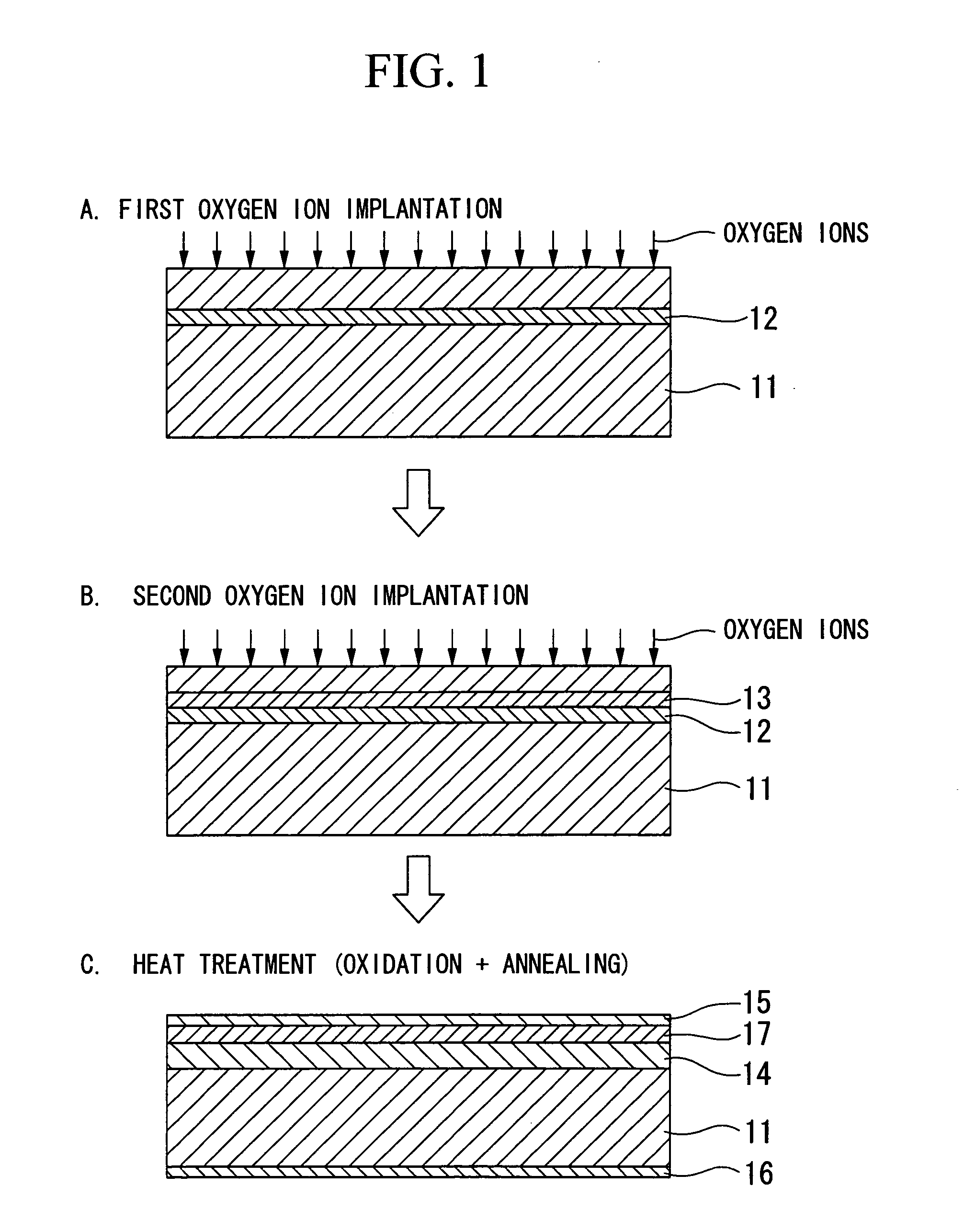

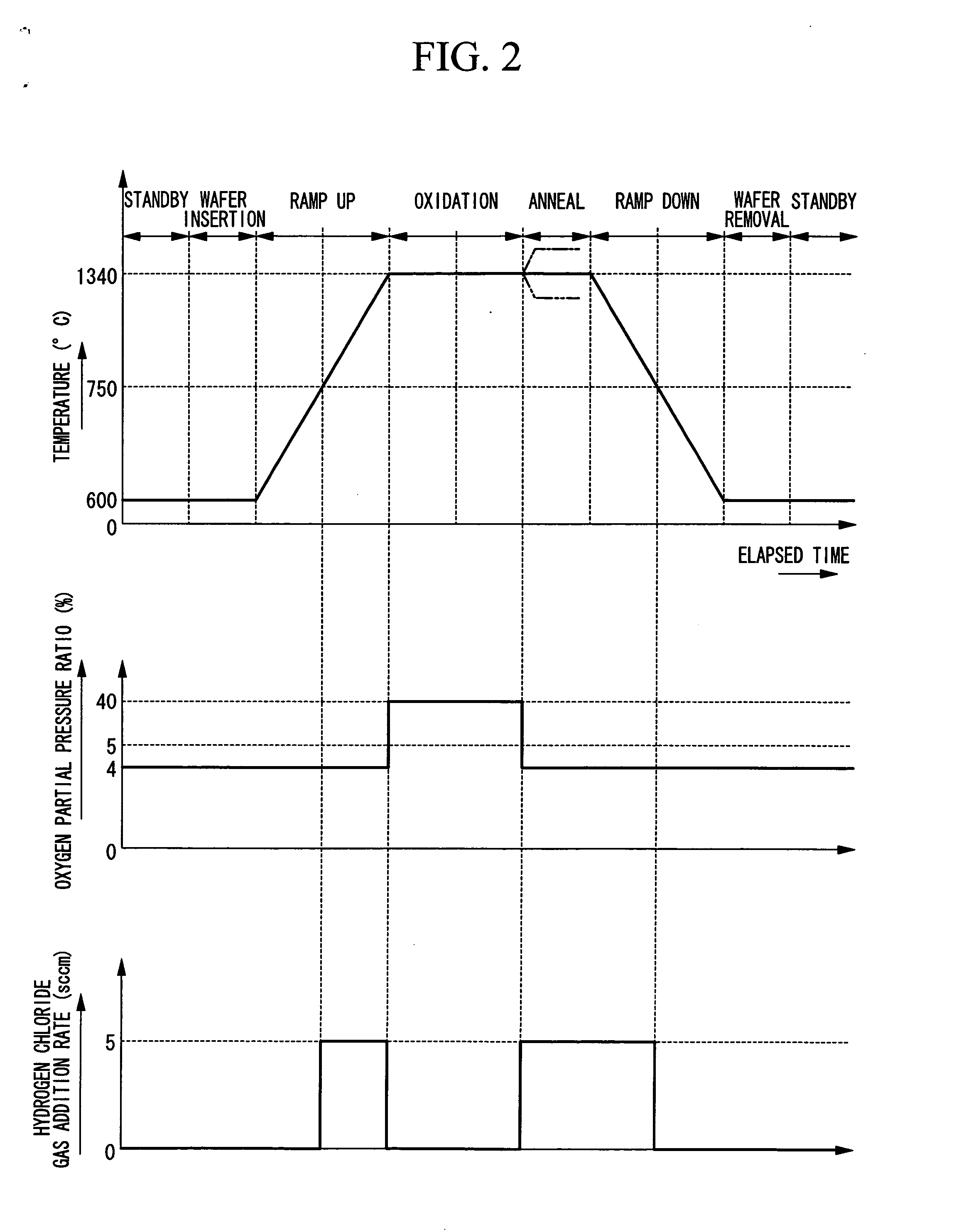

InactiveUS20060228492A1Reduce metal contaminationEnhance dielectric withstand voltagePolycrystalline material growthAfter-treatment detailsBuried oxideHigh oxygen

In the method for manufacturing a SIMOX wafer, oxygen ions are implanted into a silicon wafer, then the silicon wafer is subjected to a prescribed heat treatment so as to form a buried oxide layer in the silicon wafer. The prescribed heat treatment includes: a step of ramping up a temperature of the silicon wafer in a low oxygen partial pressure gas atmosphere having an oxygen partial pressure ratio of less than 5%; either or both of a step of oxidizing the silicon wafer in a high oxygen partial pressure gas atmosphere having an oxygen partial pressure ratio of 5% or more and a step of annealing the silicon wafer in a low oxygen partial pressure gas atmosphere having an oxygen partial pressure ratio of less than 5%; and a step of ramping down the temperature of the silicon wafer in a low oxygen partial pressure gas atmosphere having an oxygen partial pressure ratio of less than 5%. A hydrogen chloride gas is mixed with the low oxygen partial pressure gas having an oxygen partial pressure ratio of less than 5% in at least one step from among the ramp-up step, the anneal step and the ramp-down step.

Owner:SUMCO CORP

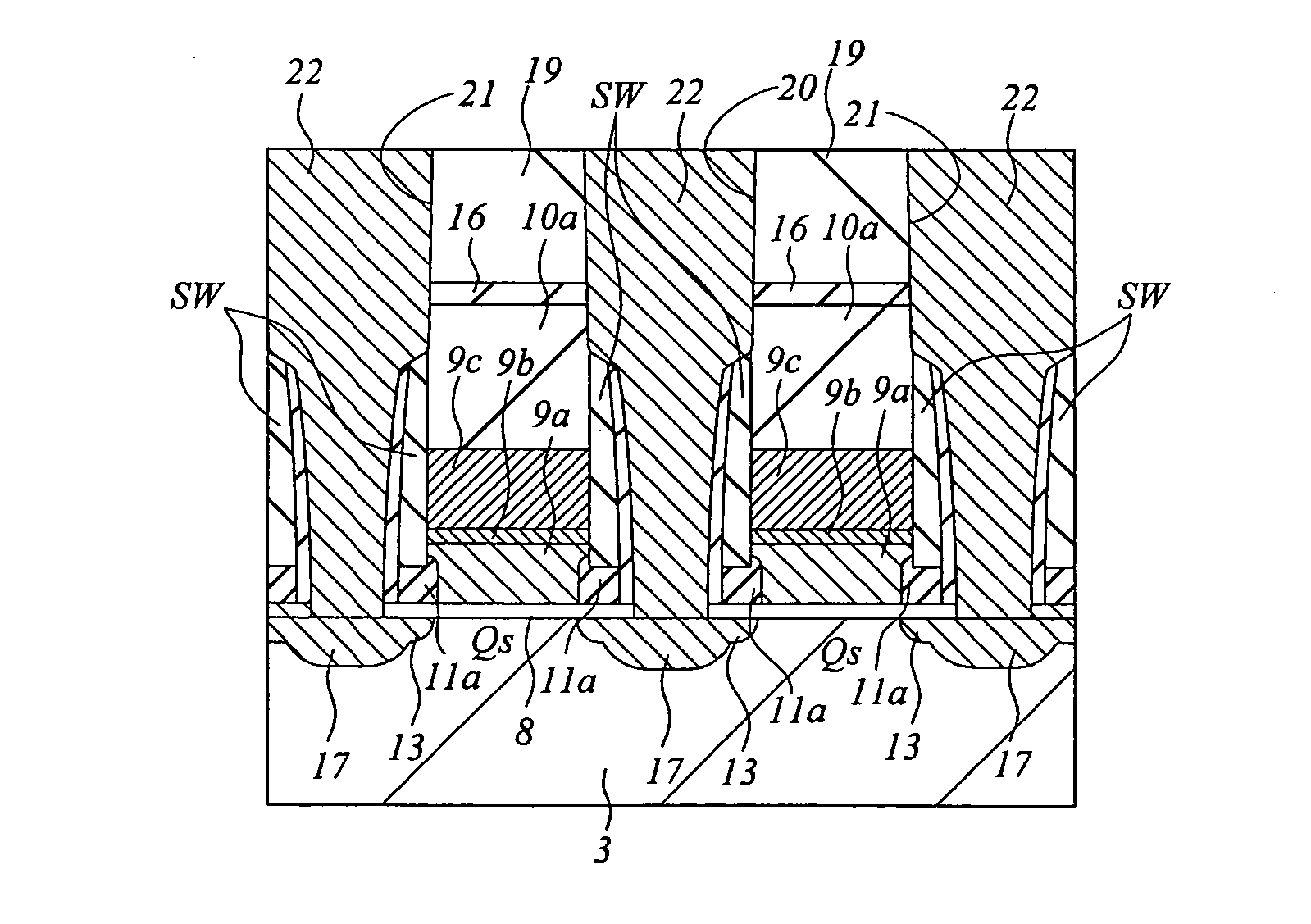

Method for manufacturing semiconductor integrated circuit device

InactiveUS20050087880A1Reduce leakage currentReduce metal pollutionTransistorSemiconductor/solid-state device detailsEtchingEngineering

Disclosed is a technique for reducing the leak current by reducing contamination of metal composing a polymetal gate of a MISFET: Of a polycrystalline silicon film, a WN film, a W film, and a cap insulating film formed on a gate insulating film on a p-type well (semiconductor substrate), the cap insulating film, the W film, and the WN film are etched and the over-etching of the polycrystalline silicon film below them is performed. Then, a sidewall film is formed on sidewalls of these films. Thereafter, after etching the polycrystalline silicon film with using the sidewall film as a mask, a thermal treatment is performed in an oxidation atmosphere, by which a light oxide film is formed on the sidewall of the polycrystalline silicon film. As a result, the contamination on the gate insulating film due to the W and the W oxide can be reduced, and also, the diffusion of these materials into the semiconductor substrate (p-type well) and the resultant increase of the leak current can be prevented.

Owner:SEMICON PATENT

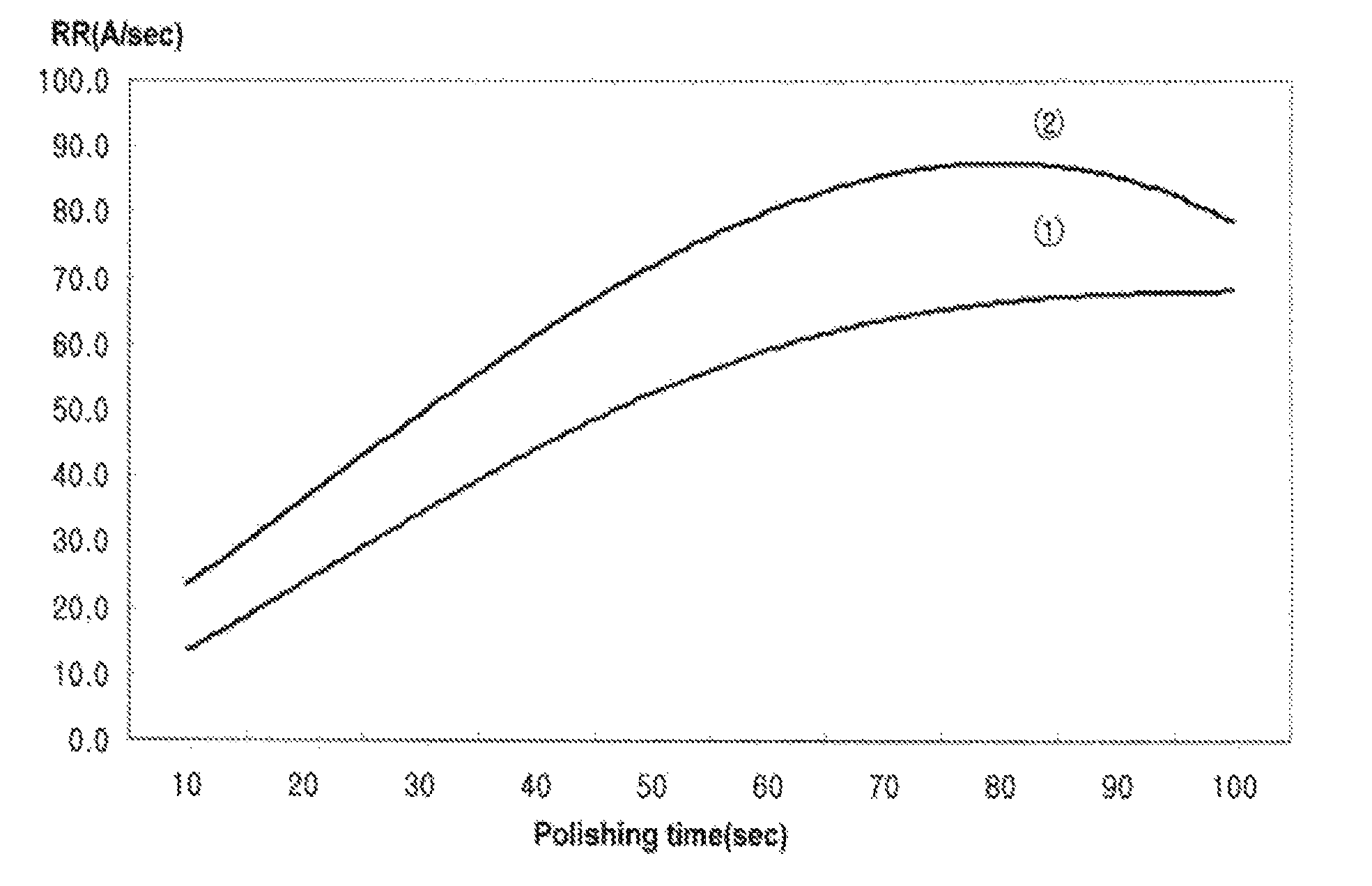

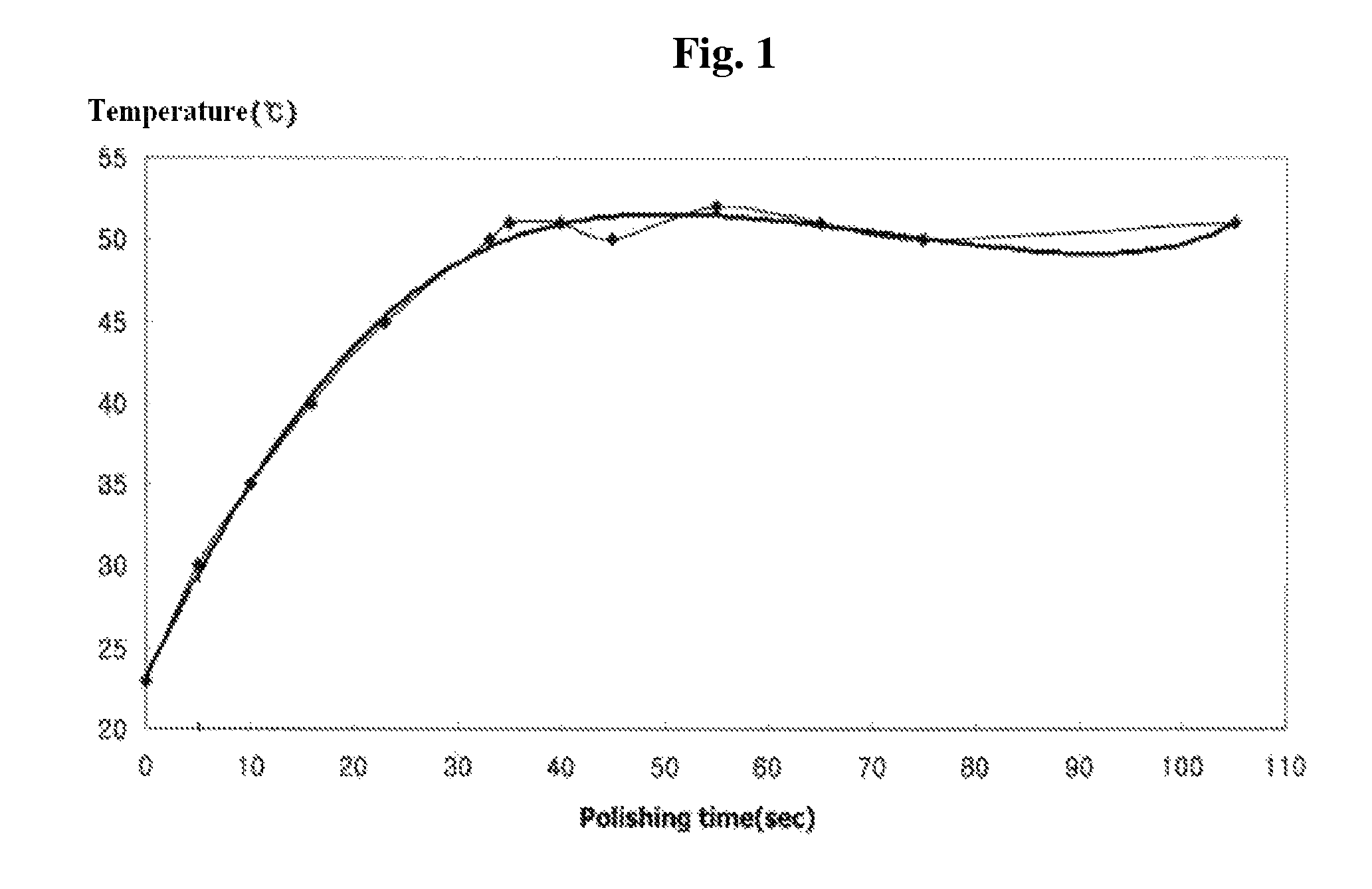

Chemical mechanical polishing slurry composition including non-ionized, heat activated nano-catalyst and polishing method using the same

ActiveUS7887715B1Reduce contamination levelLow metal contaminationNanostructure manufactureOther chemical processesNano catalystChemical-mechanical planarization

Disclosed herein are a chemical mechanical polishing slurry composition for chemical mechanical planarization of metal layers, which comprises a non-ionized, heat-activated nano-catalyst, and a polishing method using the same. The polishing slurry composition comprises: a non-ionized, heat-activated nano-catalyst which releases electrons and holes by energy generated in a chemical mechanical polishing process; an abrasive; and an oxidizing agent. The non-ionized heat-activated nano-catalyst and the abrasive are different from each other, and the non-ionized, heat-activated nano-catalyst is preferably a semiconductor material which releases electrons and holes at a temperature of 10 to 100° C. in an aqueous solution state, more preferably a transition metal silicide selected from the group consisting of CrSi, MnSi, CoSi, ferrosilicon (FeSi), mixtures thereof, and most preferably, a semiconductor material such as nano ferrosilicon. The content of the content of the non-ionized, heat-activated nano-catalyst is 0.00001 to 0.1 wt % based on the total weight of the slurry composition.

Owner:DONGJIN SEMICHEM CO LTD

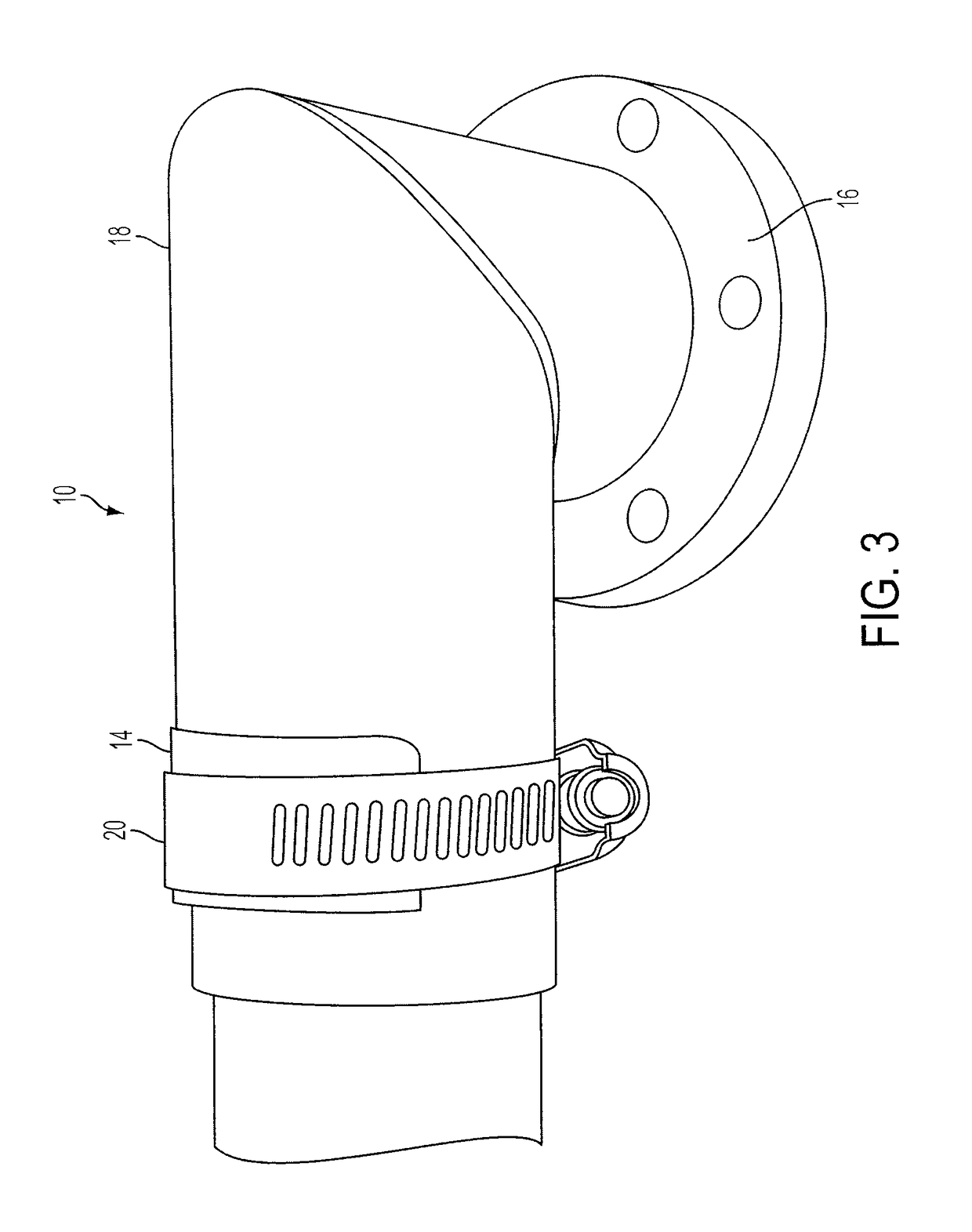

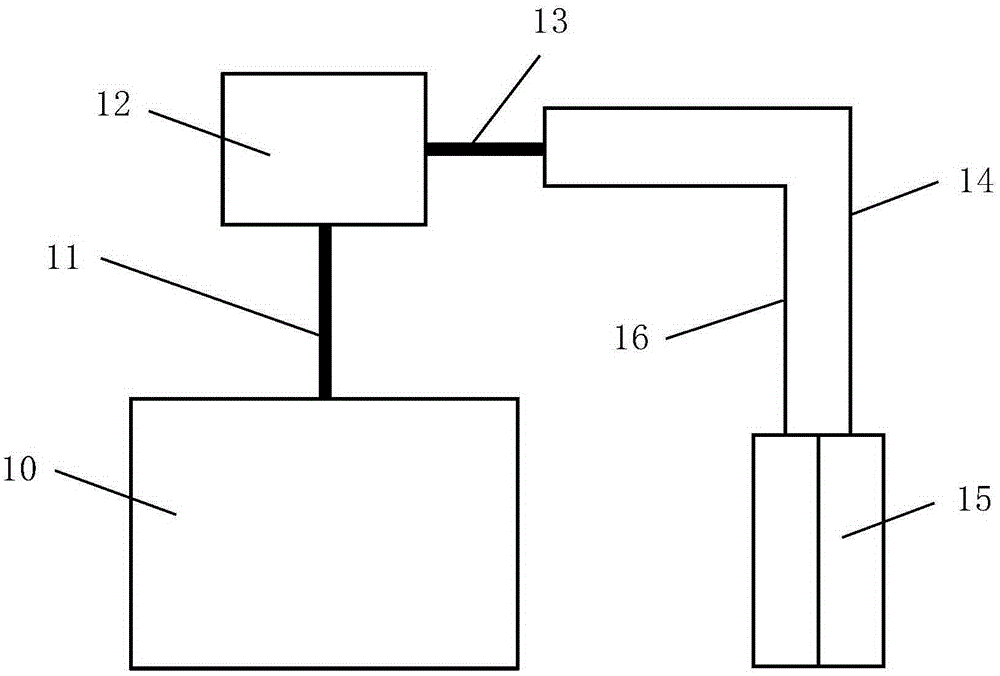

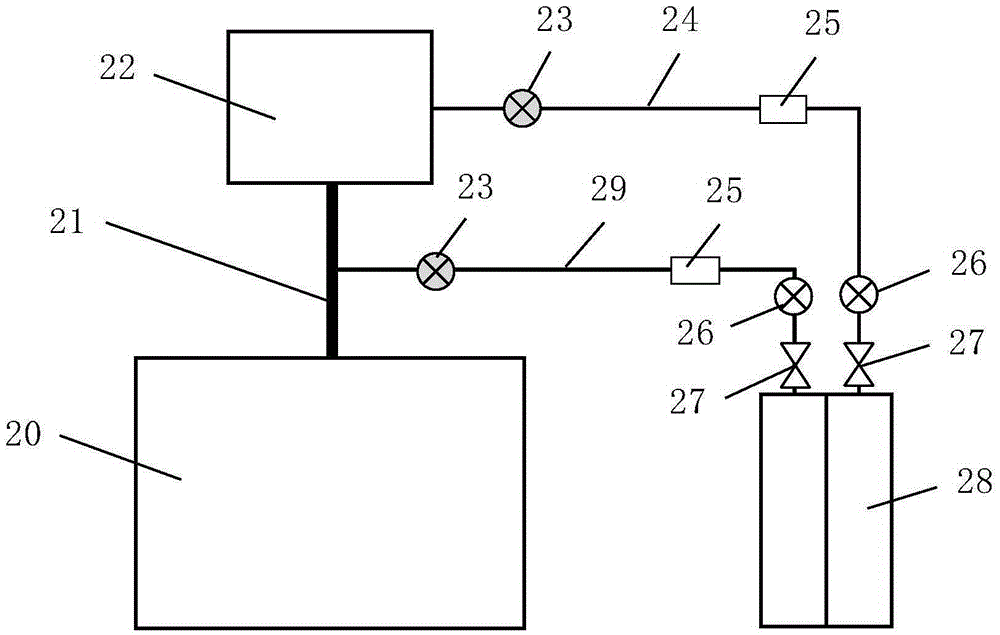

Pipeline device for high-density plasma stock

InactiveCN105390363AReduce metal pollution problemsAvoid legacyElectric discharge tubesMetal pollutionCorrosion

The invention discloses a pipeline device for a high-density plasma stock. An NF3 gas for cleaning a cavity and an NF3 gas for participating in an etching process respectively adopt an independent first branch pipe and a second branch pipe to enter the cavity, the NF3 gas for participating in the etching process can directly enter the stock cavity without through a remote plasma system, and thus, the fact that during an STI etching process, due to corrosion of the NF3 gas for participating in the etching process, metal elements are left in the inner cavity of the remote plasma system can be avoided, and metal pollution problems caused by metal element over specification during the STI etching process can be reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method of manufacturing semiconductor substrate

InactiveUS20100062588A1Reduce metal pollutionHigh crystallinitySemiconductor/solid-state device manufacturingBuried oxideOxide

A method of manufacturing a semiconductor substrate, in which a silicon layer is provided on a buried oxide film, includes preparing a base substrate having a seed layer of the silicon layer on the buried oxide film with a film thickness equal to or more than 1 nm and equal to or less than 100 nm, and epitaxially growing the seed layer at a temperature equal to or more than 1000° C. and equal to or less than 1300° C. so as to form the silicon layer with a film thickness equal to or more than 1 μm and equal to or less than 20 μm.

Owner:SUMCO CORP

Poly silicon hard mask

InactiveUS20080122107A1Reduce metal pollutionSemiconductor/solid-state device detailsSolid-state devicesEtchingGas plasma

A method of forming an opening on a low-k dielectric layer using a polysilicon hard mask rather than a metal hard mask as used in prior art. A polysilicon hard mask is formed over a low-k dielectric layer and a photoresist layer is formed over the polysilicon hard mask. The photoresist layer is patterned and the polysilicon hard mask is etched with a gas plasma to create exposed portions of the low-k dielectric layer. The photoresist layer in stripped prior to the etching of the exposed portions of the low-k dielectric layer to avoid damage to the low-k dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

Method for manufacturing semiconductor integrated circuit device

InactiveUS20070187783A1Reduce leakage currentReduce metal pollutionTransistorSolid-state devicesEtchingEngineering

Owner:SEMICON PATENT