Field-effect tranisistor realizing memory function and method of producing the same

A field-effect transistor and memory technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as limiting integration density and affecting reliability, and achieve the effect of great flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

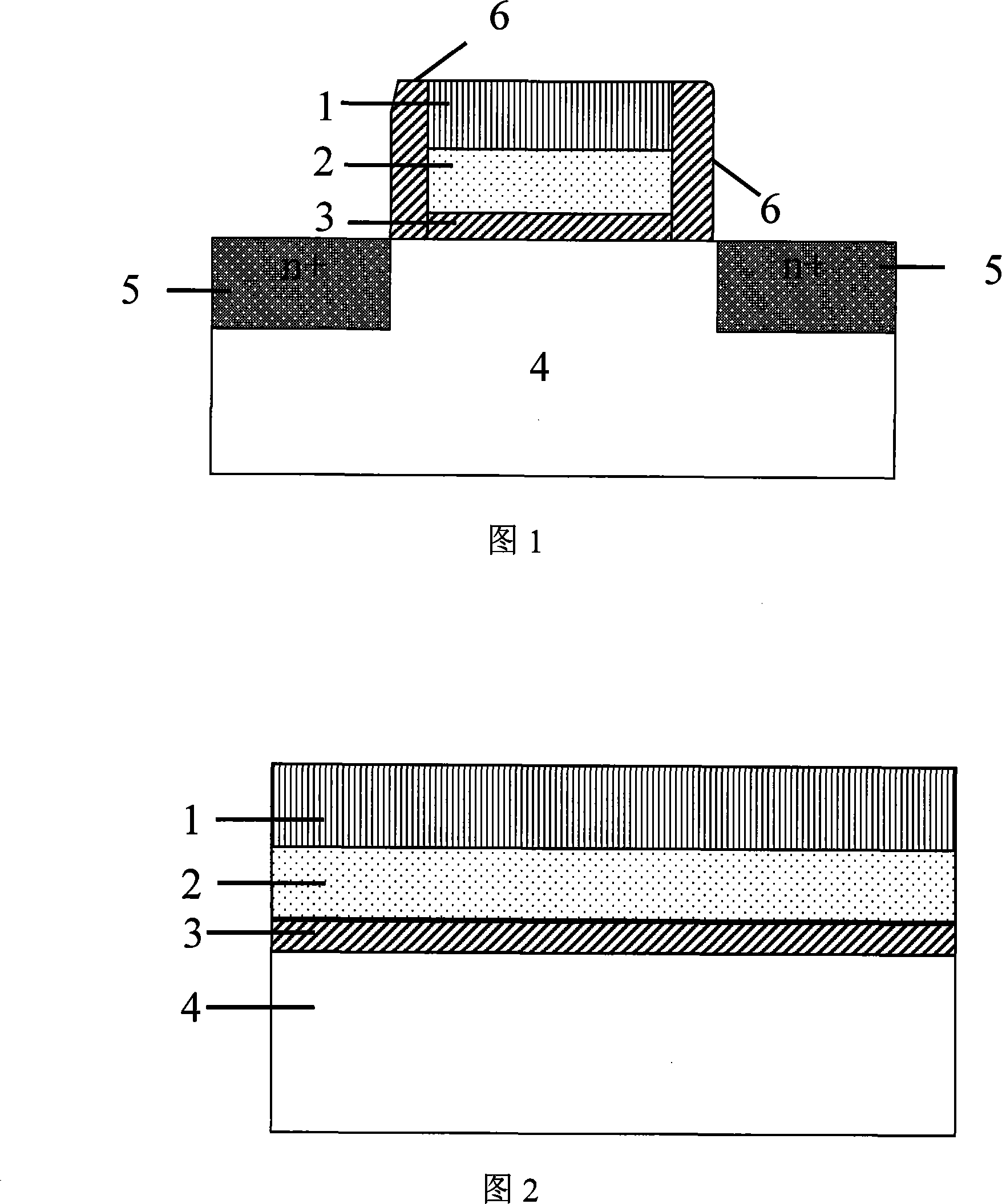

[0036] A cross-sectional view of a field effect transistor (RFET) device proposed by the present invention is shown in FIG. 1 . It includes: a conductive electrode layer 1; a resistive variable dielectric layer 2; a tunnel oxide layer 3; a substrate layer 4; a source region and a drain region 5;

[0037] The specific steps of the resistive field effect transistor preparation process in the present invention are as follows:

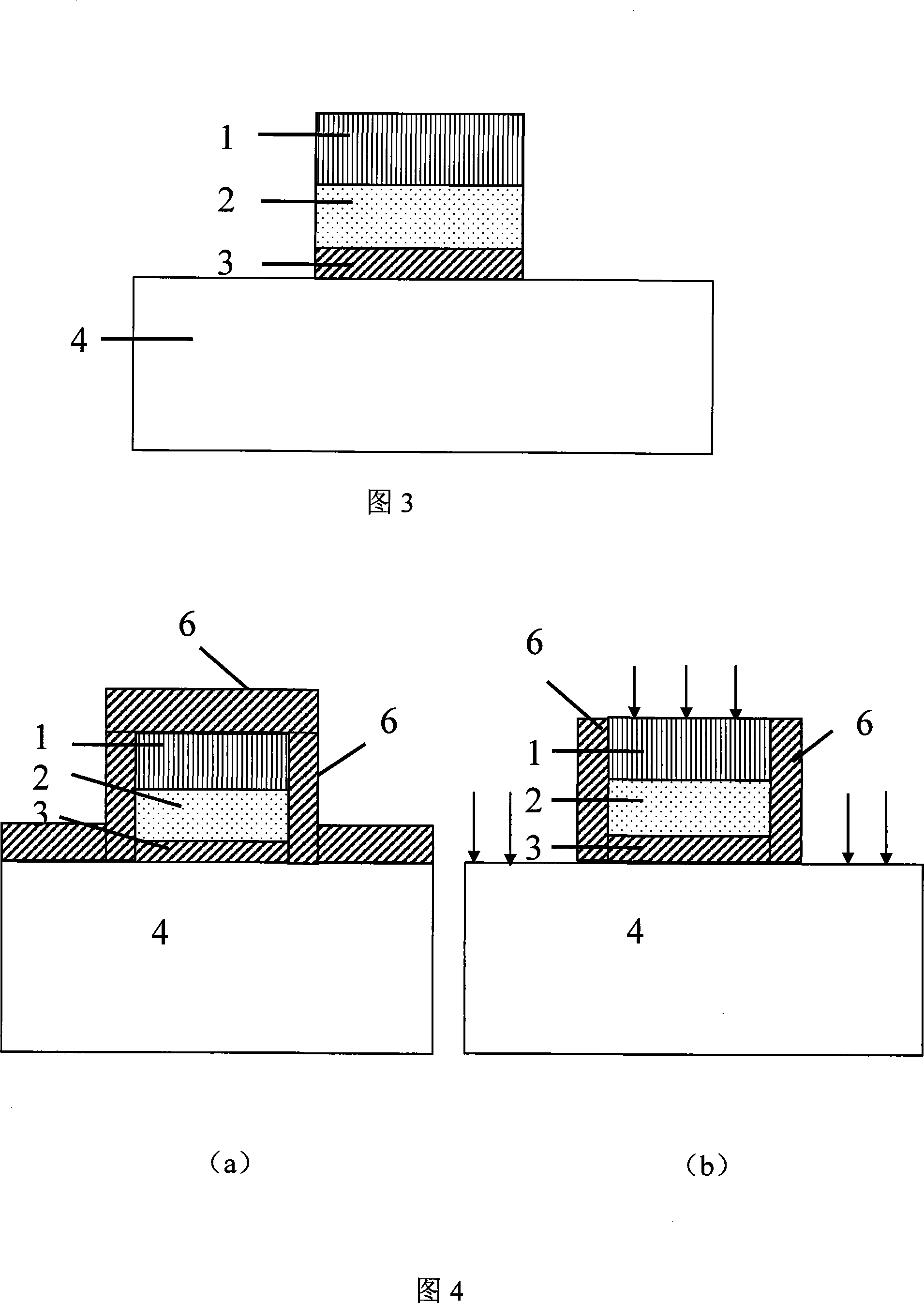

[0038] As shown in FIG. 2 : the thin film deposition process for preparing a resistive field effect transistor. On the cleaned P-type silicon substrate, a thin gate oxide preparation process is used to form a tunneling layer by means of thermal oxidation and rapid thermal annealing (RTP). The thickness of the tunneling layer is 1.5-5nm, and the composition can be silicon dioxide (SiO 2 ), silicon nitride (Si 3 N 4 ) or high-K gate dielectric layer (Al 2 o 3 , HfO 2 Wait). Afterwards, the deposition of the resistive material layer can be performed b...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More