Patents

Literature

133results about How to "Reduced package area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

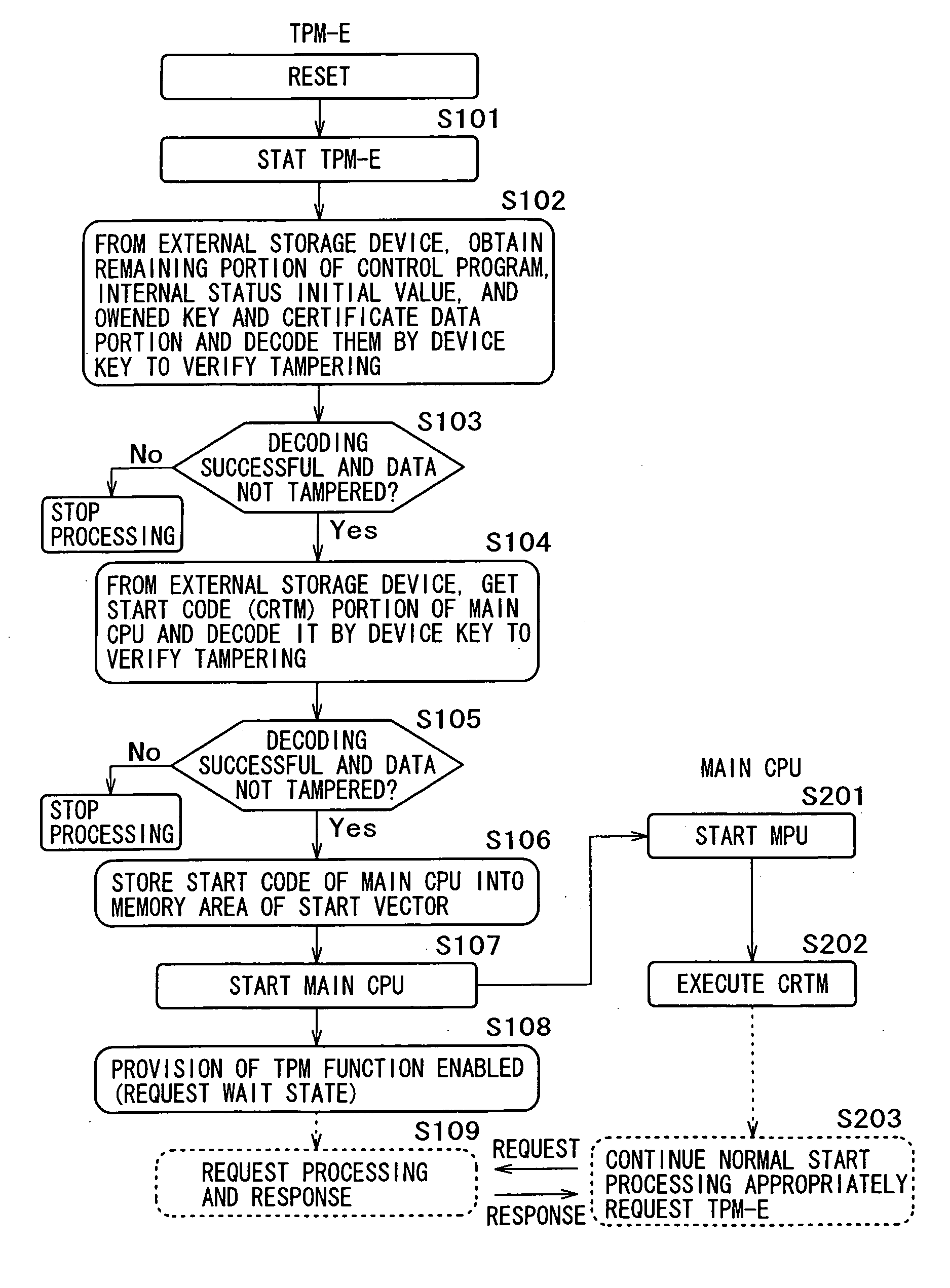

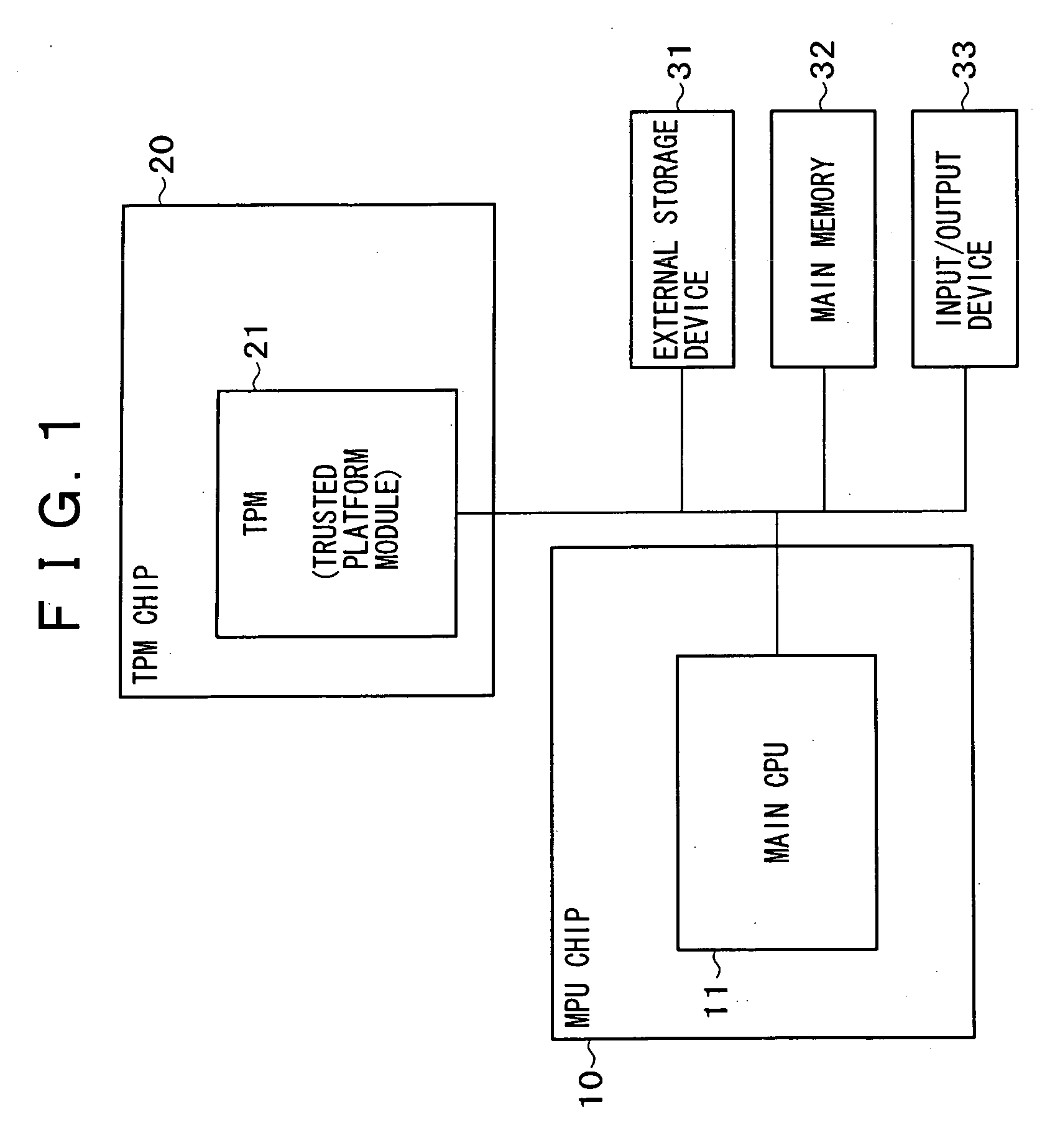

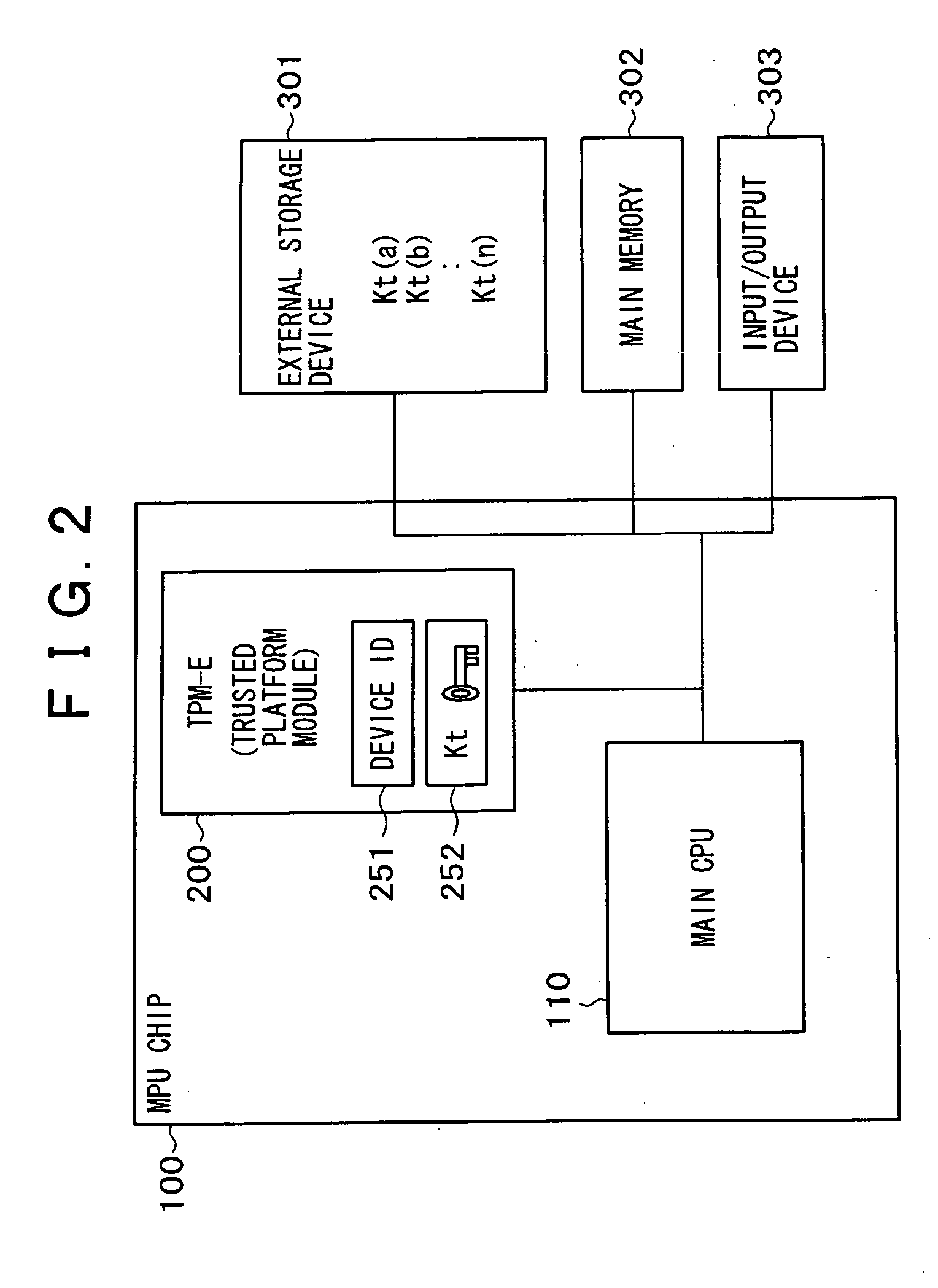

Information processing apparatus and method and computer program

InactiveUS20050182952A1Reduced package areaReduce the amount requiredUnauthorized memory use protectionHardware monitoringInformation processingExternal storage

The present invention provides an information processing apparatus of space-saved type that can execute the processing corresponding to a security function module. A security function module storing a device key is integrally arranged in an MPU chip, the secret data including programs and data to be applied to the data processing to be executed in the security function module are encrypted with the device key or attached with a falsification verification value and the resultant programs and data are stored in an external storage section. This novel configuration can significantly reduce the amount of data to be stored in the security function module and therefore eliminate the necessity for a large-capacity flash memory. Consequently, the security function module can be integrally arranged in the MPU chip having the main CPU, thereby significantly reducing the packaging area and the production cost.

Owner:SONY CORP

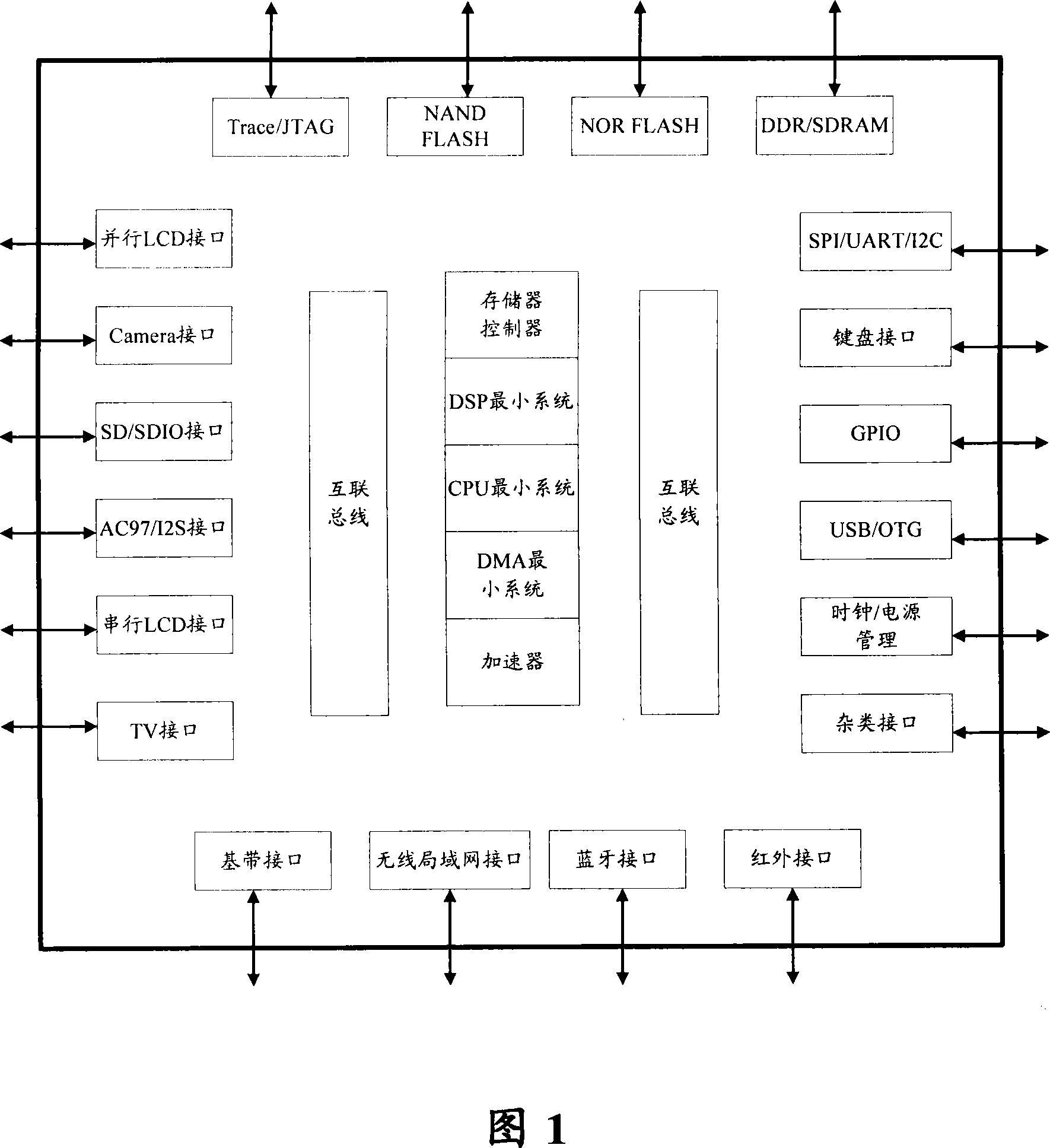

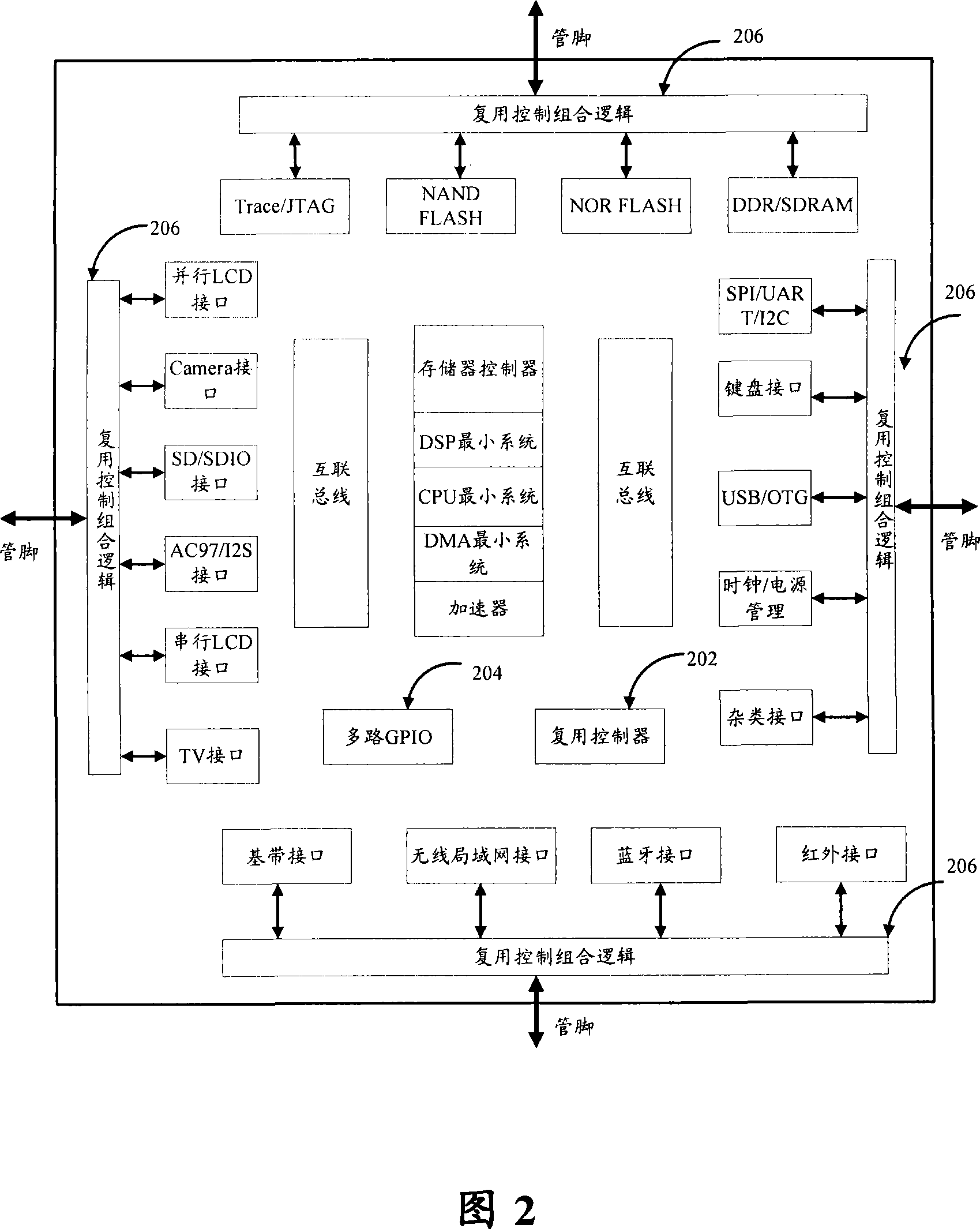

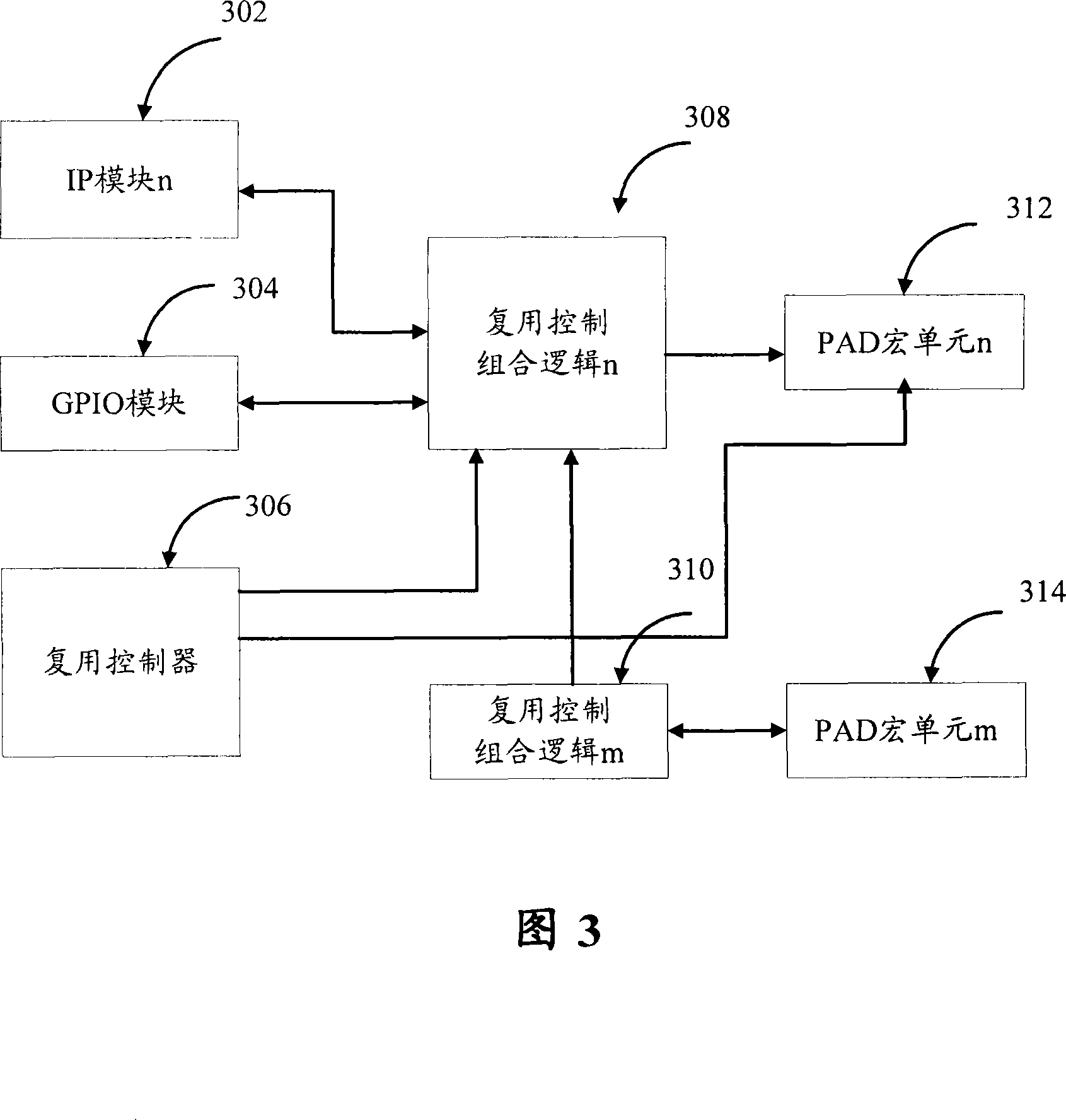

Terminal chip pin multiplexing device

InactiveCN101136005AReduce in quantityReduced package areaElectric digital data processingMultiplexingSystems design

The method comprises: a multiplexing control module used for controlling the switching between the functional module and general I / O interface module, and controlling the signal direction of the functional module and general I / O interface module; and a general I / O interface module used for controlling the signal direction of the I / O interface module and outputting CPU configuration level to multiplex pins, and reading the signal of the multiplex pin. Wherein, each multiplexing control combination logic module corresponds to a multiplexing pin.

Owner:ZTE CORP

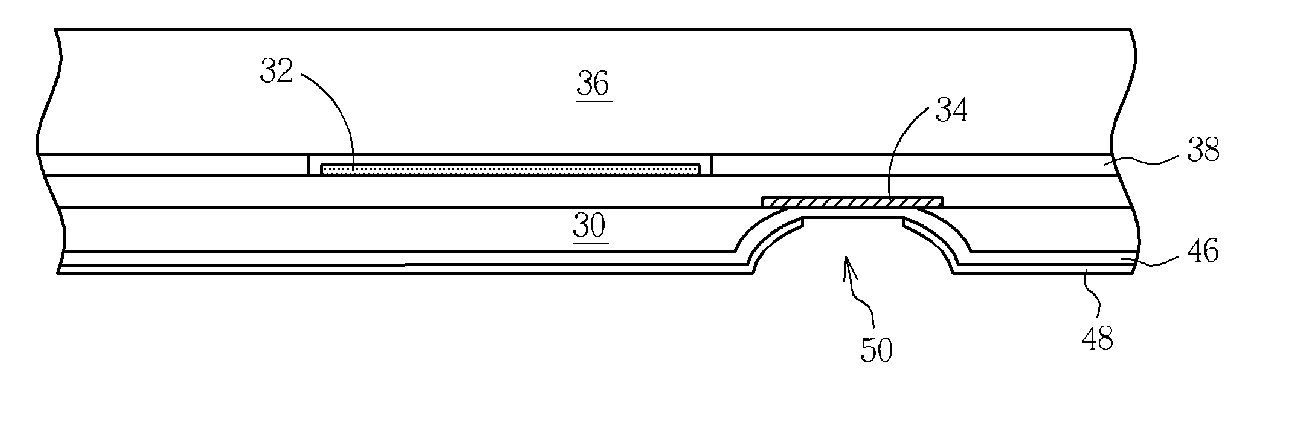

Method of forming a wafer backside interconnecting wire

ActiveUS20060057775A1Reduced package areaLow costSemiconductor/solid-state device detailsSolid-state devicesEngineeringMask layer

A method of forming a wafer backside interconnecting wire includes forming a mask layer on the back surface, the mask layer including at least an opening corresponding to the bonding pad, performing a first etching process from the back surface to remove the wafer unprotected by the mask layer to form a recess, removing the mask layer, and forming an interconnecting wire on the back surface.

Owner:TESSERA ADVANCED TECH

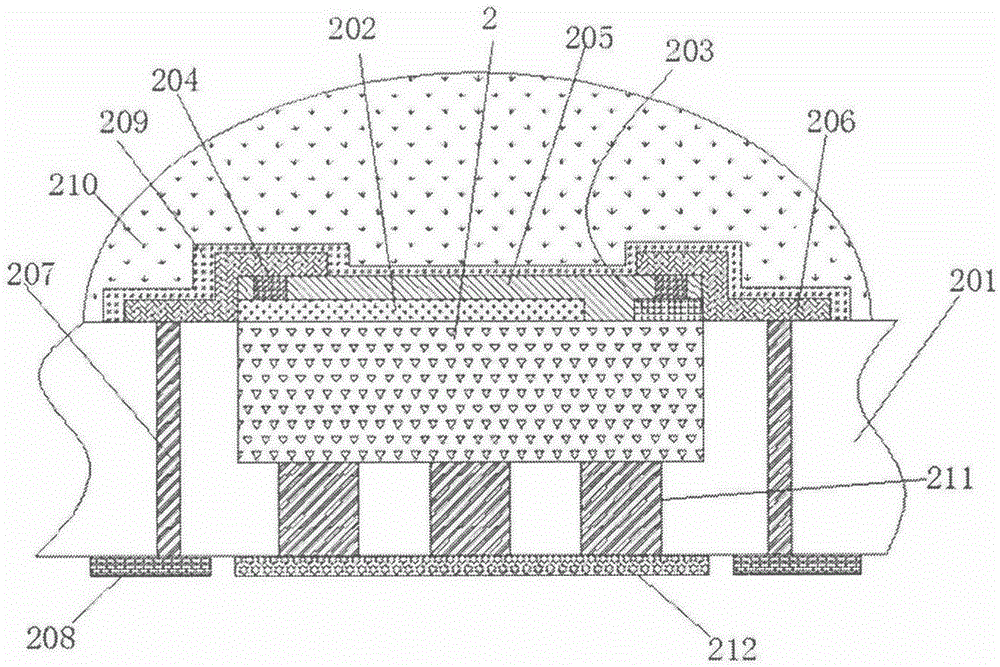

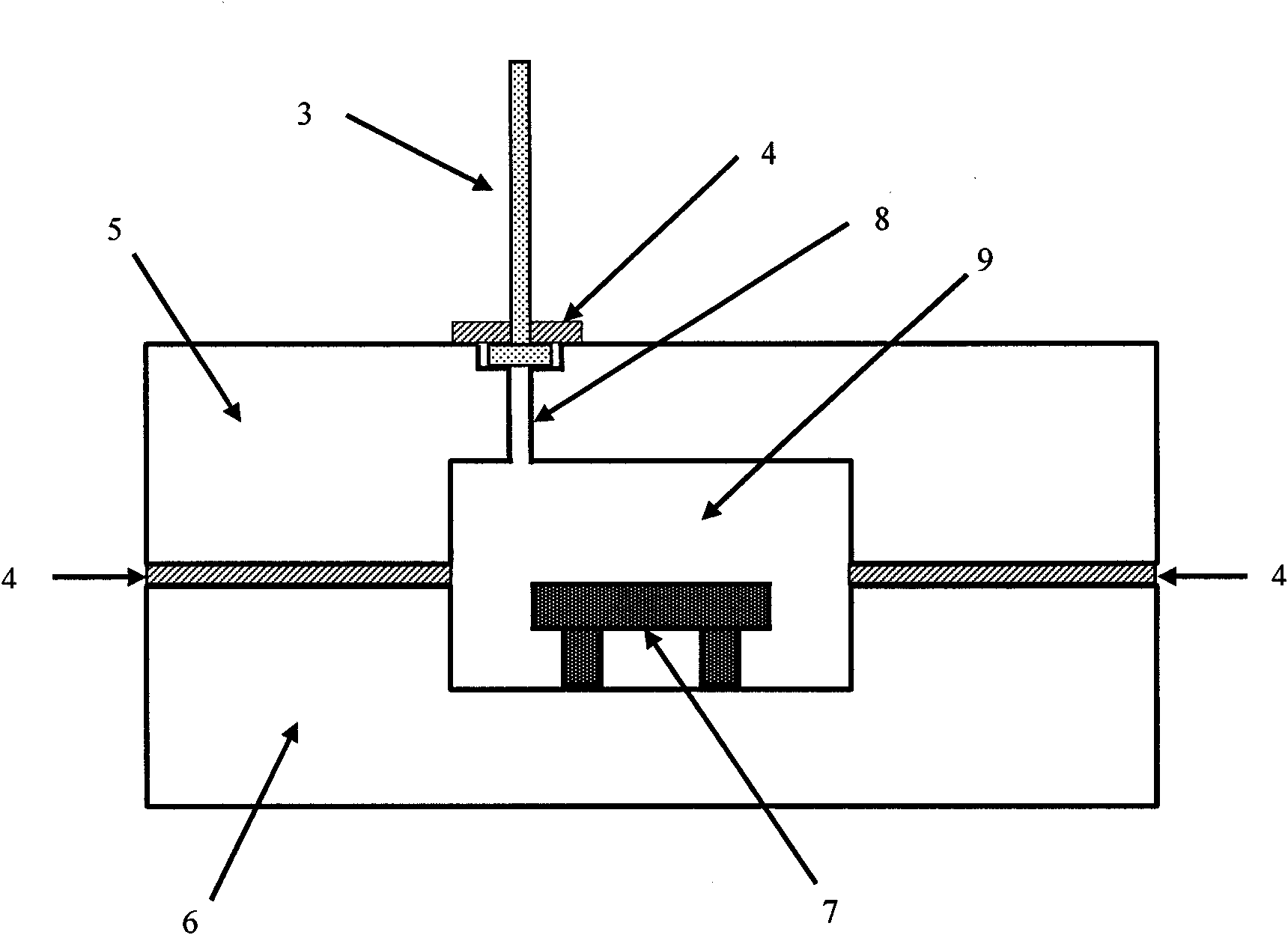

MEMS (Micro-Electromechanical System) sensor encapsulation structure and encapsulation method thereof

ActiveCN103950886ACompact structureReduce electrical connectionsDecorative surface effectsSolid-state devicesHigh densityThermal expansion

The invention relates to an MEMS sensor encapsulation structure and an encapsulation method thereof, which are used for encapsulating an MEMS sensor. The MEMS sensor encapsulation structure is characterized by comprising a ceramic base, a side wall and a top cap, wherein a plurality of metal bonding pads are respectively arranged on a top layer and a bottom layer of the ceramic base; the metal bonding pads on the top layer of the ceramic base are connected with leads of the MEMS sensor; the MEMS sensor is arranged on the ceramic base; the metal bonding pads on the bottom layer of the ceramic base are connected with an external circuit; the ceramic base adopts one-layer or multi-layer perpendicularly interconnected structure; the side wall and the top cap are both made of kovar alloy. According to the invention, the ceramic base of which coefficient of thermal expansion is approximate to that of the MEMS sensor material is selected as the encapsulation material, in order to reduce influence of the base expansion stress to the MEMS sensor; meanwhile, the ceramic base can be utilized to realize one-layer perpendicular interconnection or multi-layer perpendicular interconnection; the system-level integration between the MEMS sensor and the peripheral circuit can be realized within a small area; high-density system-level encapsulation can be realized; the encapsulation flexibility and the expansibility of the MEMS sensor can be realized.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

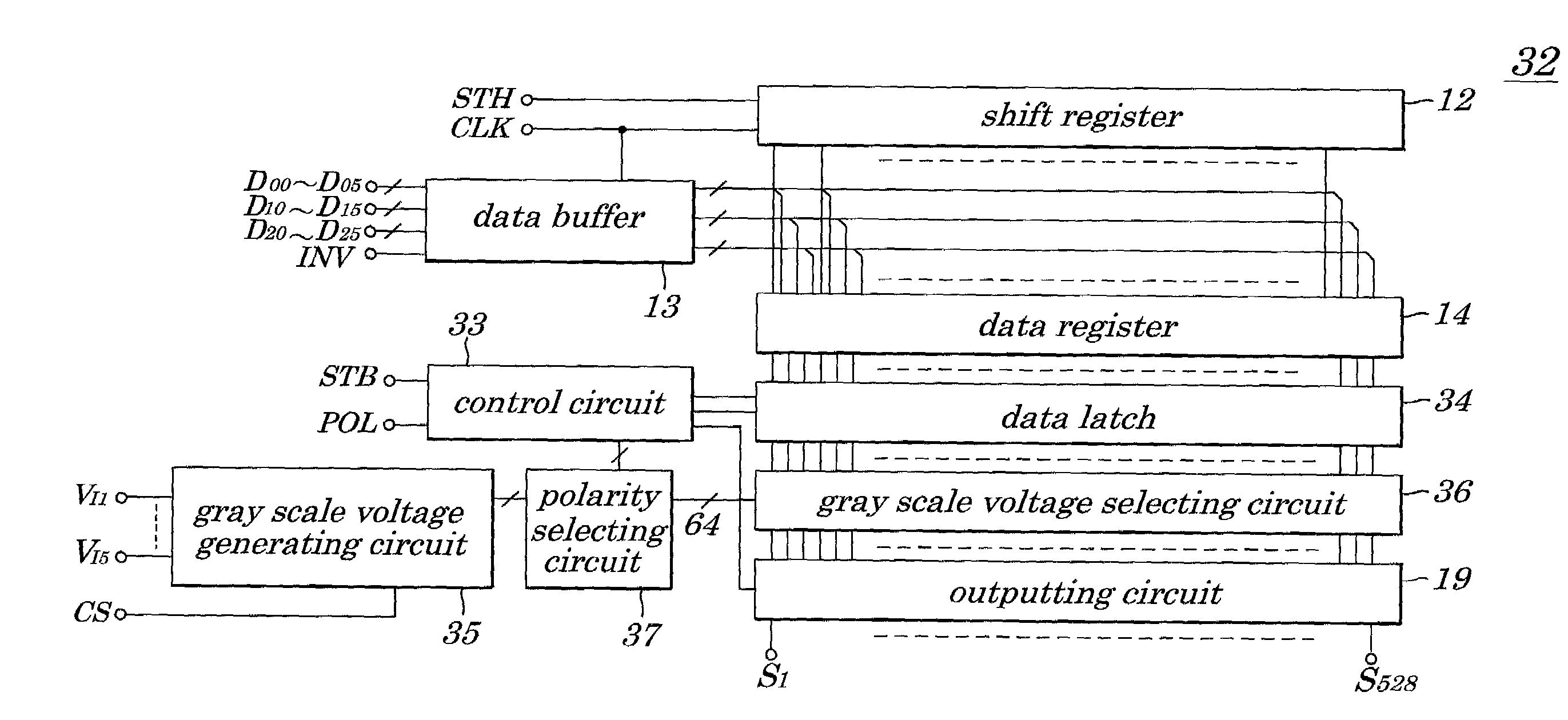

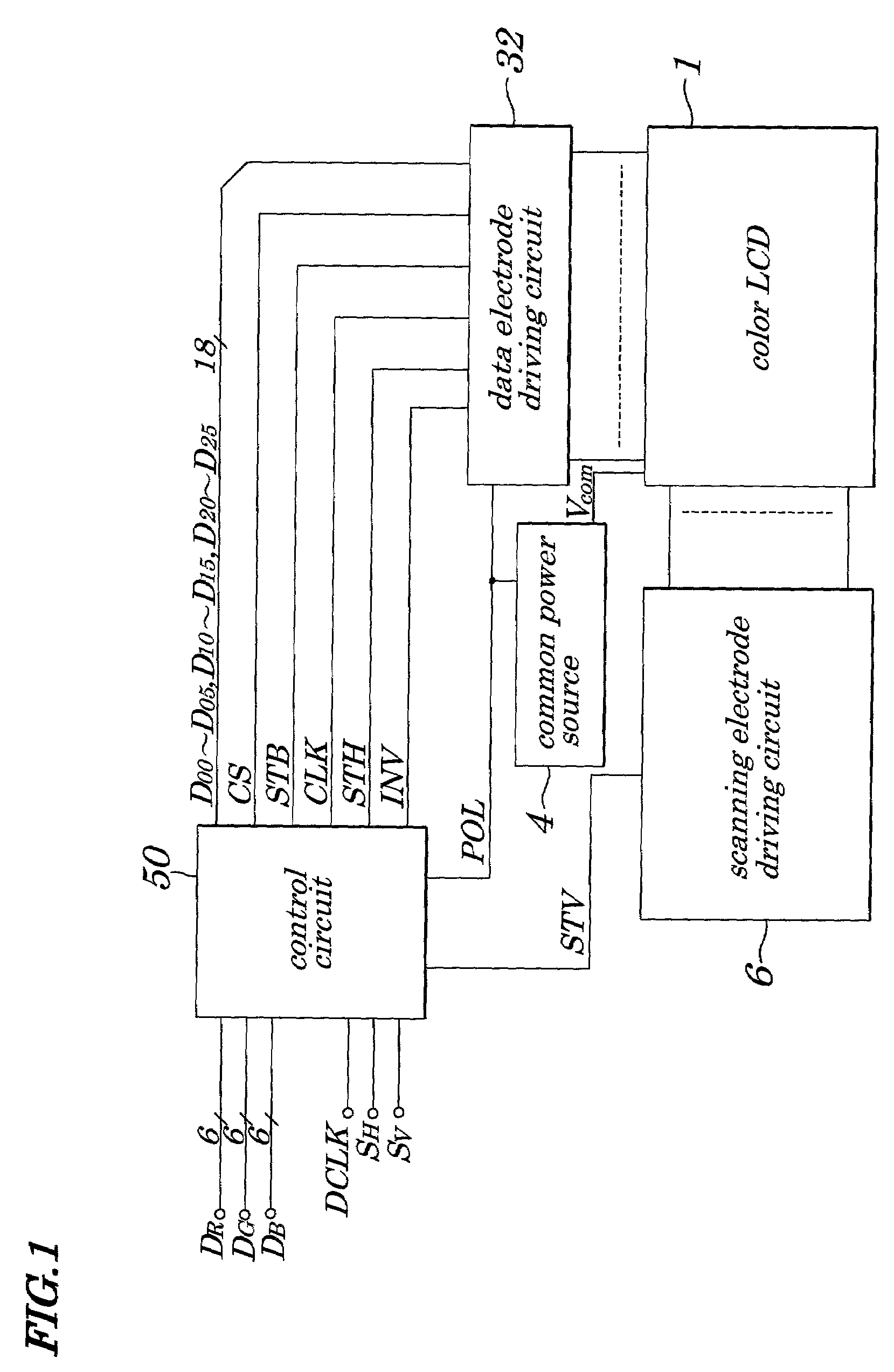

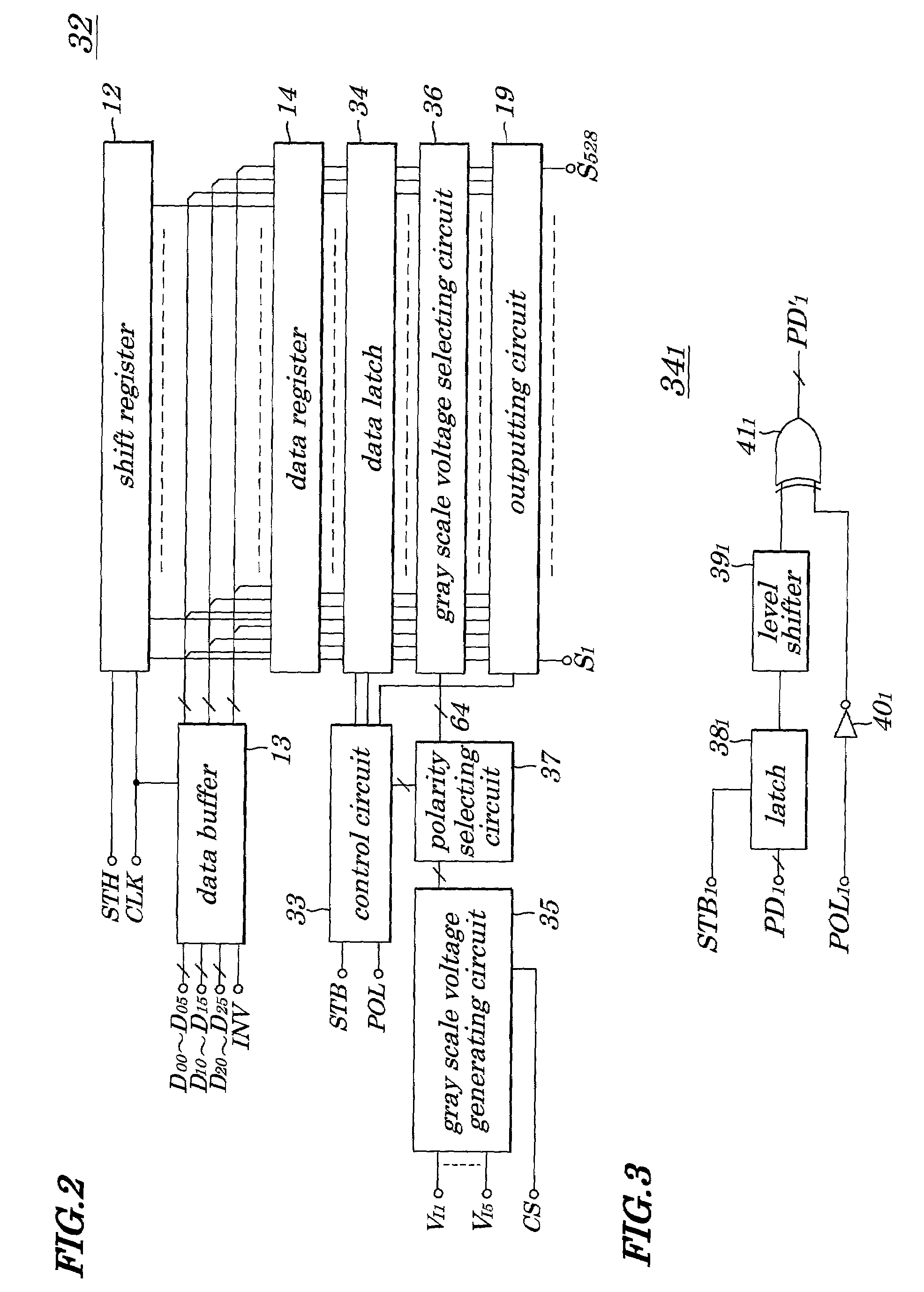

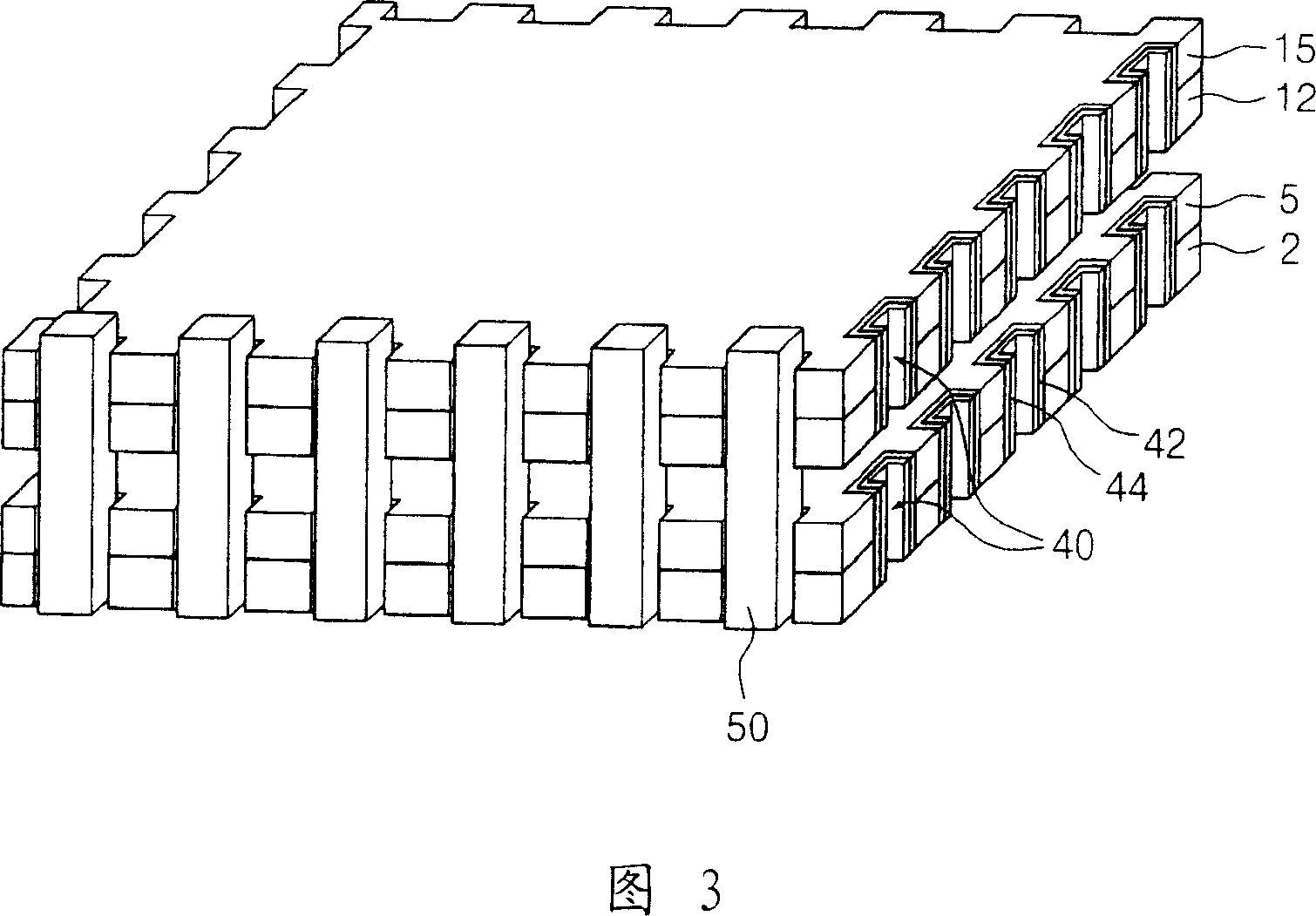

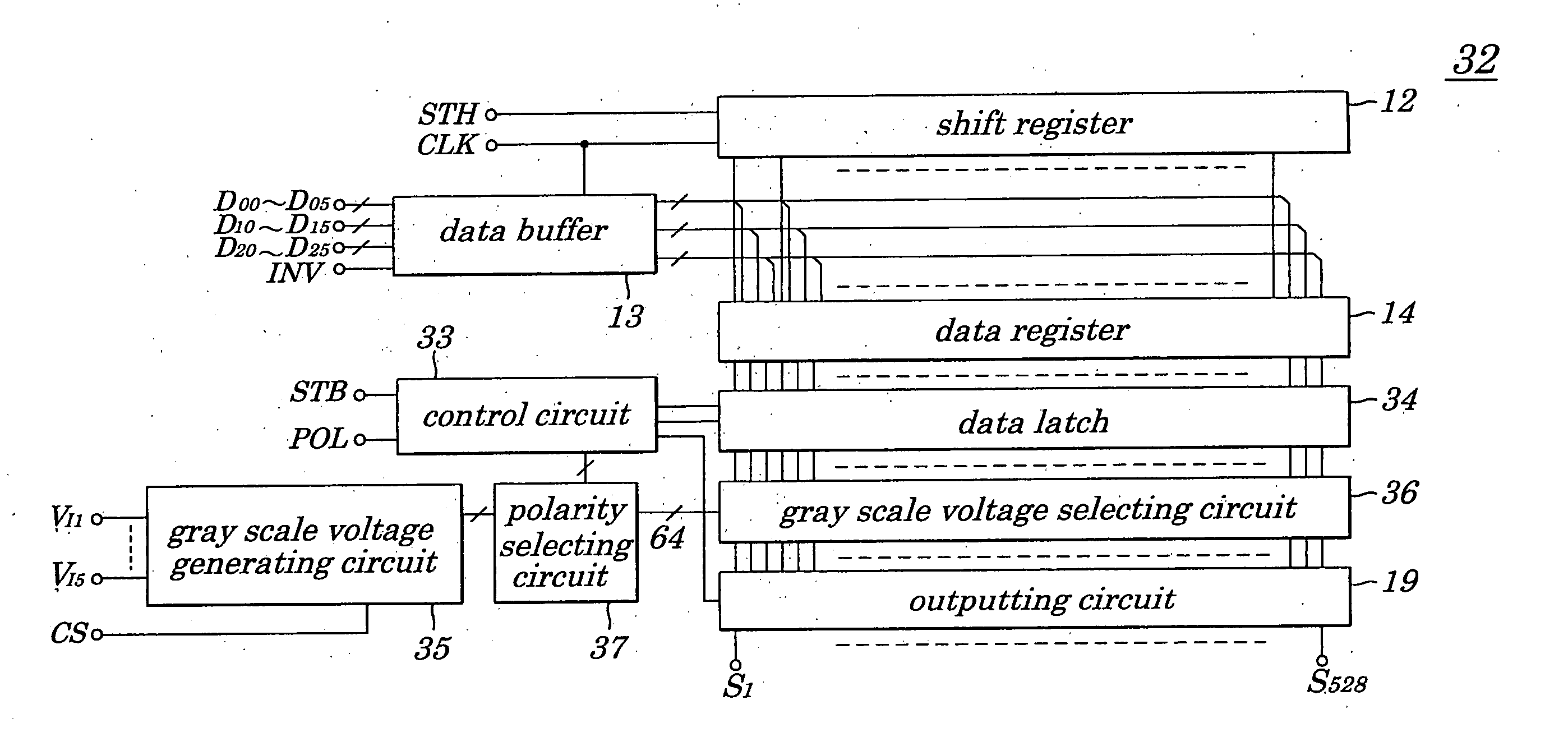

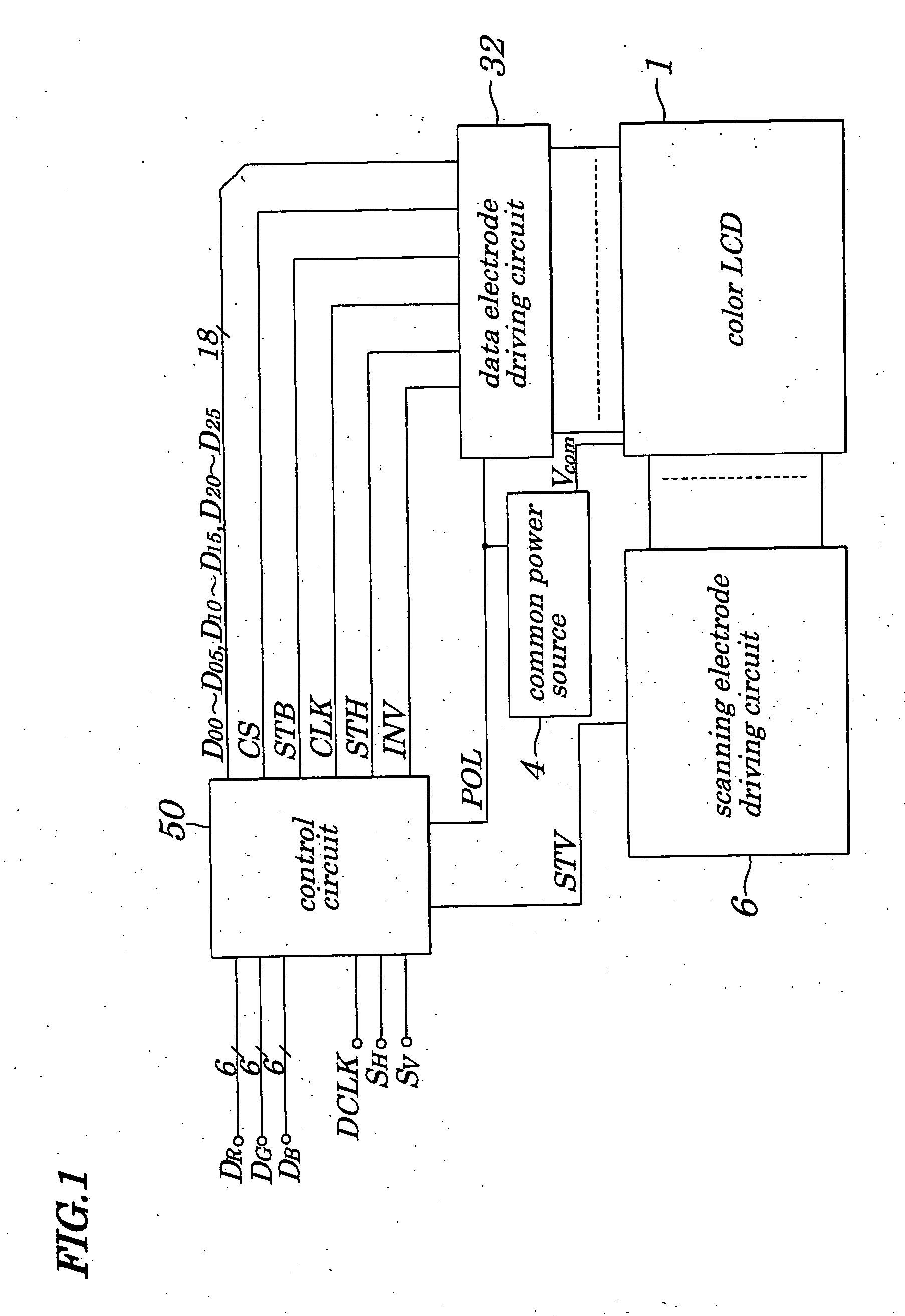

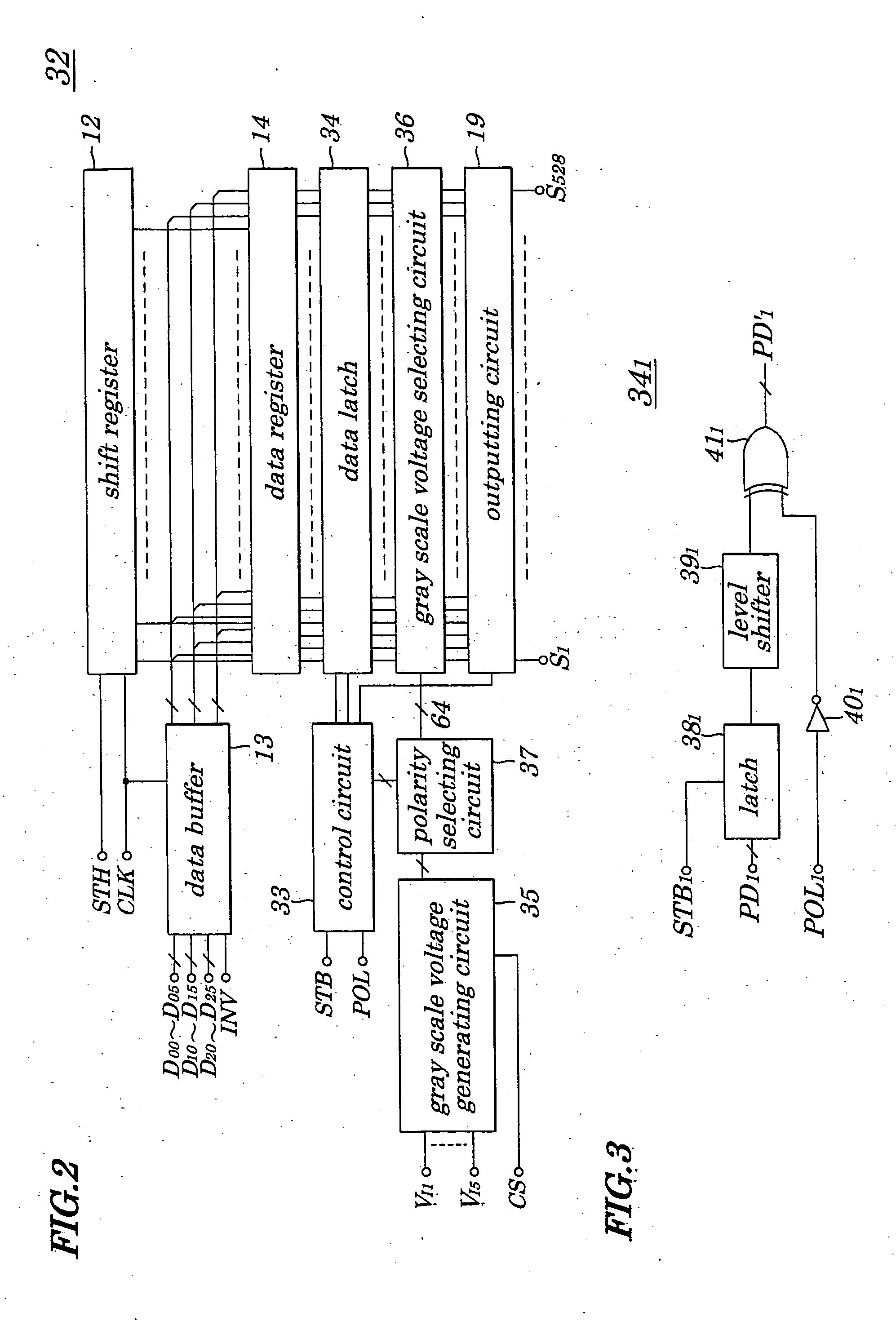

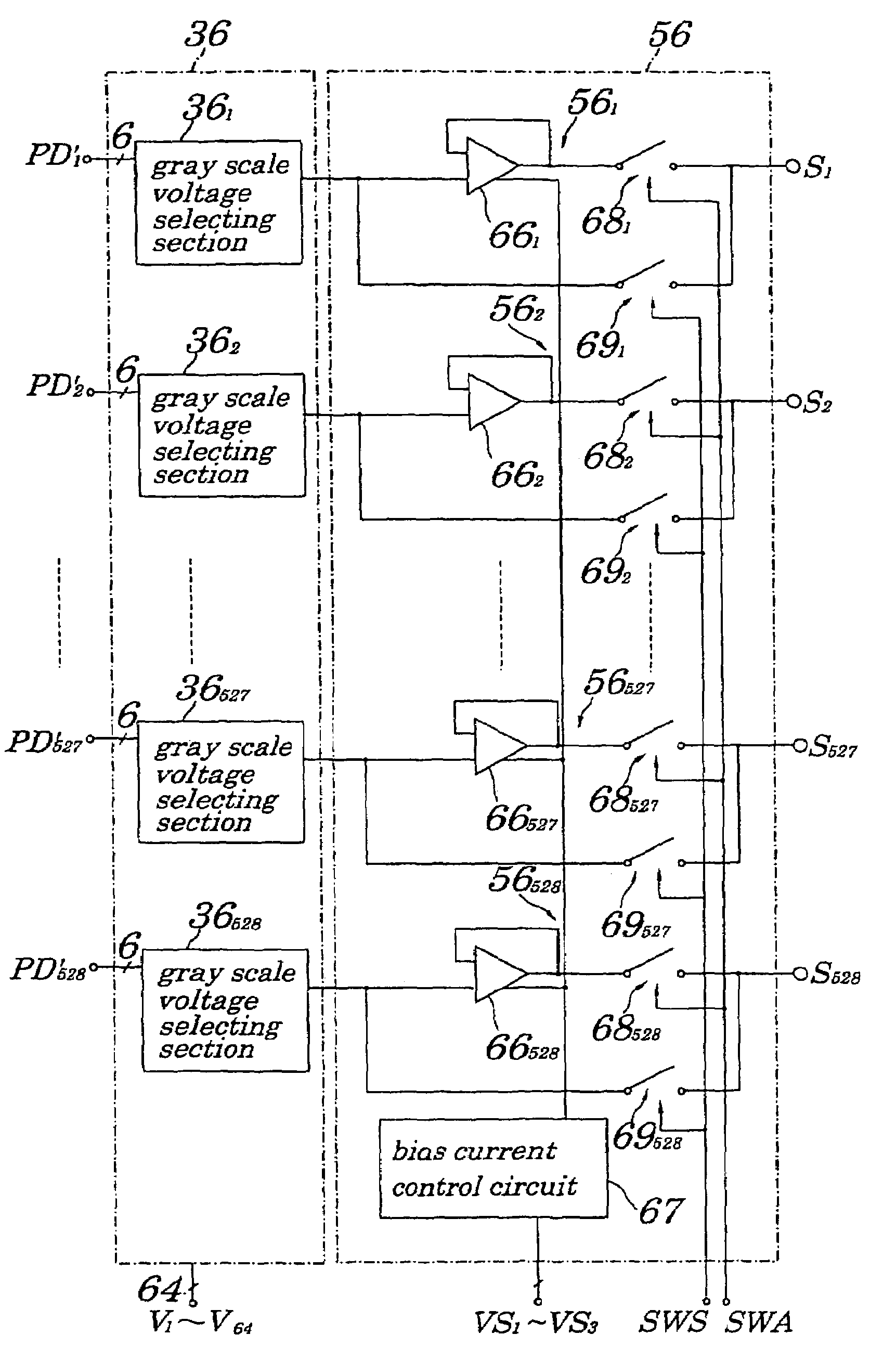

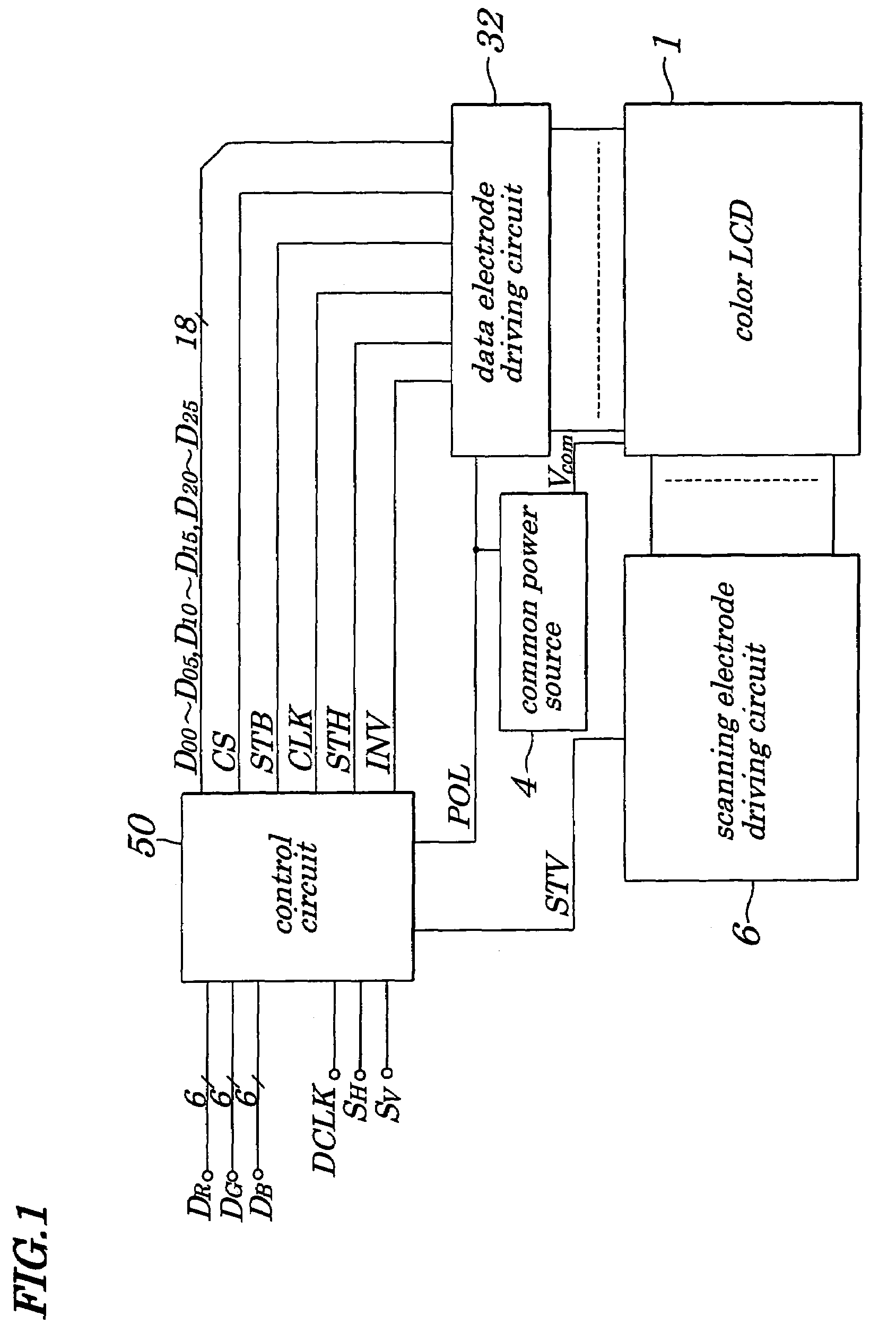

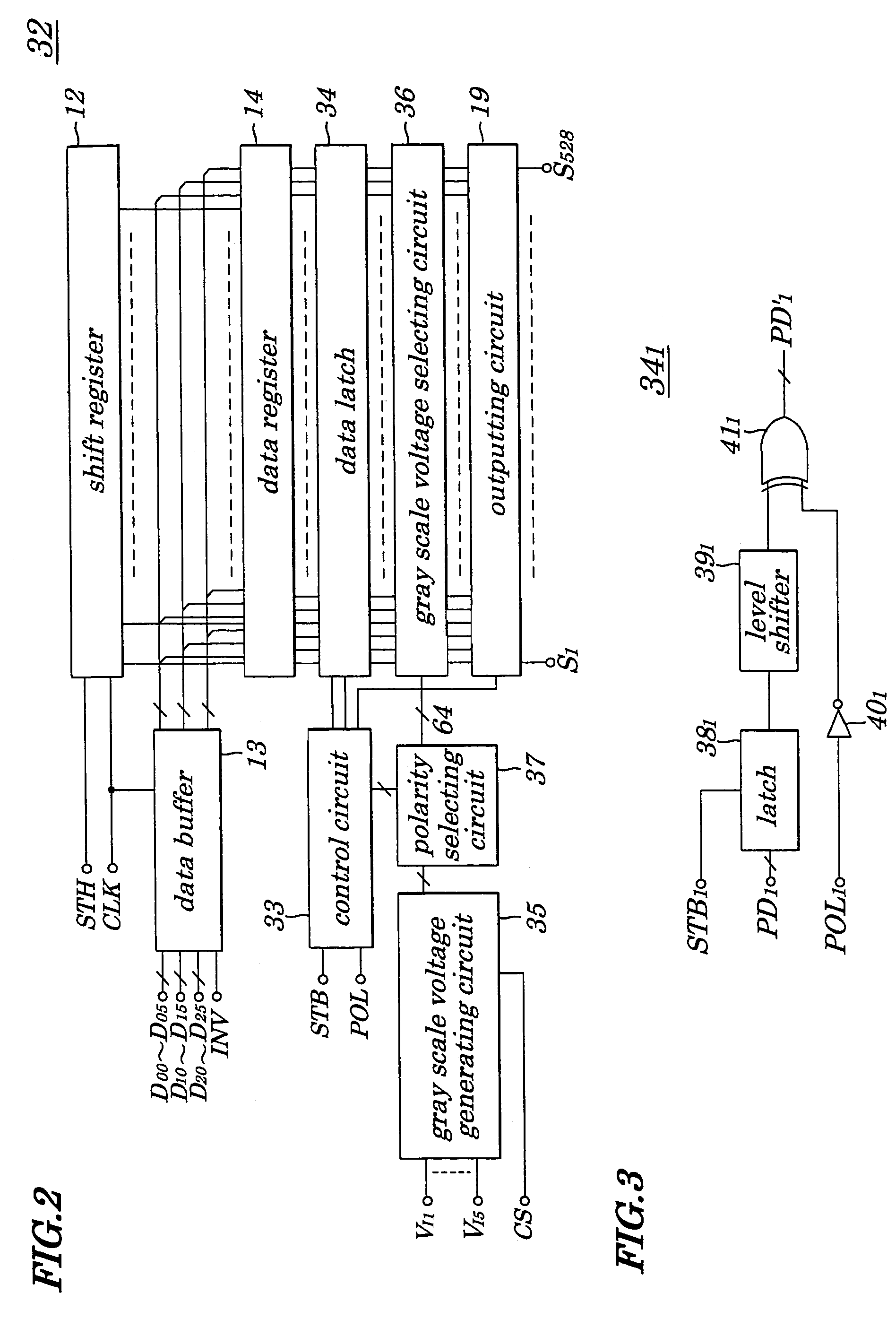

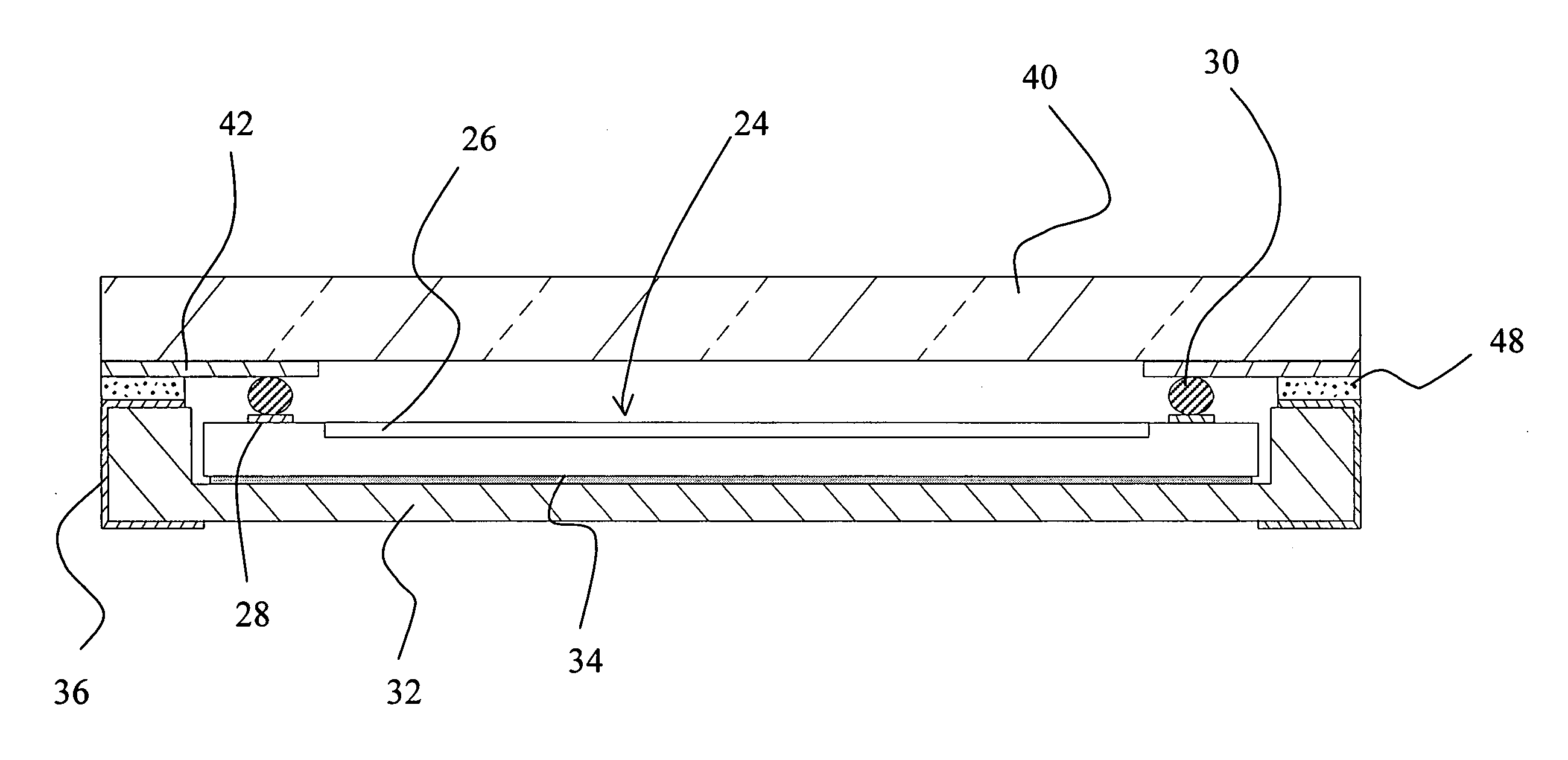

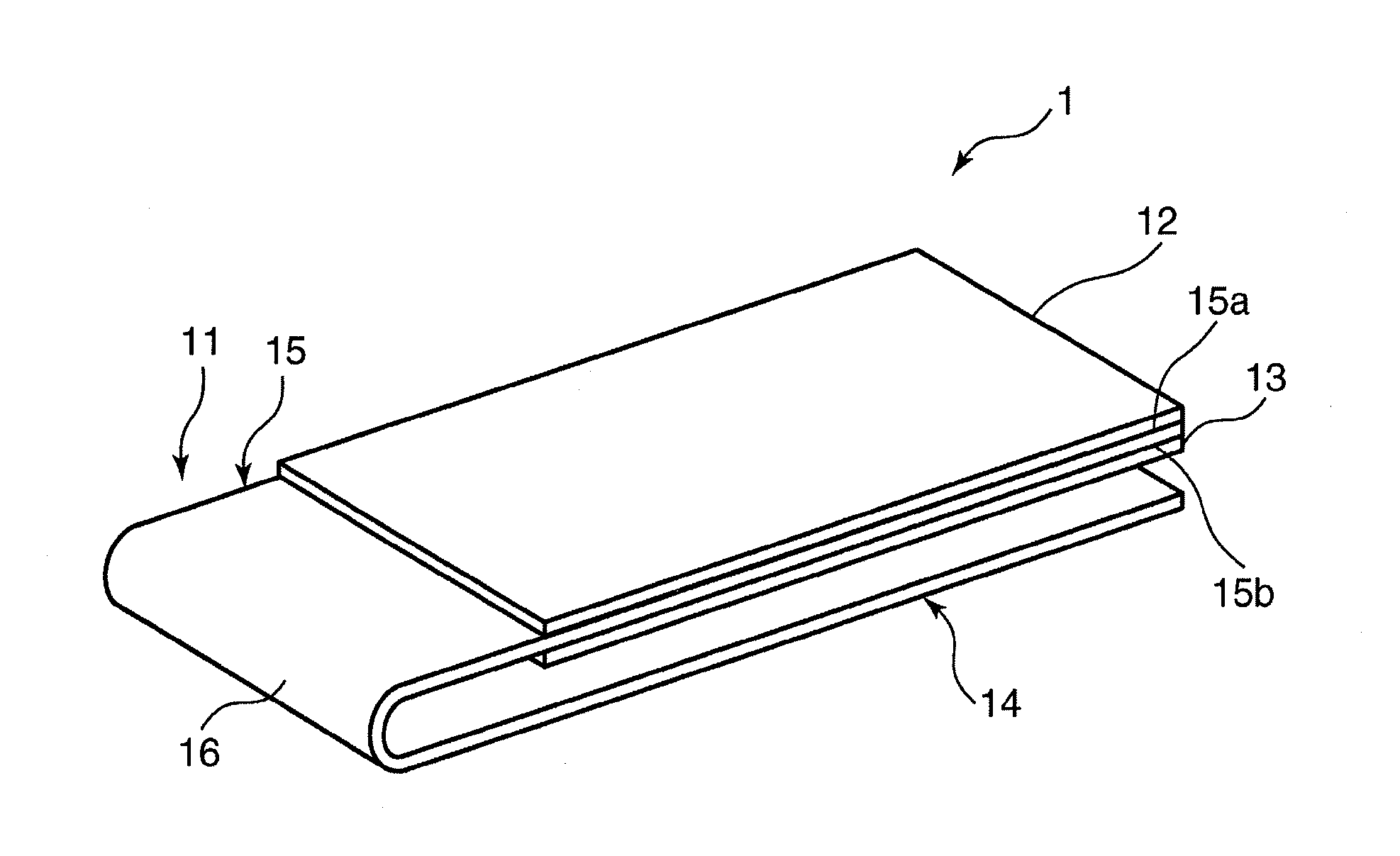

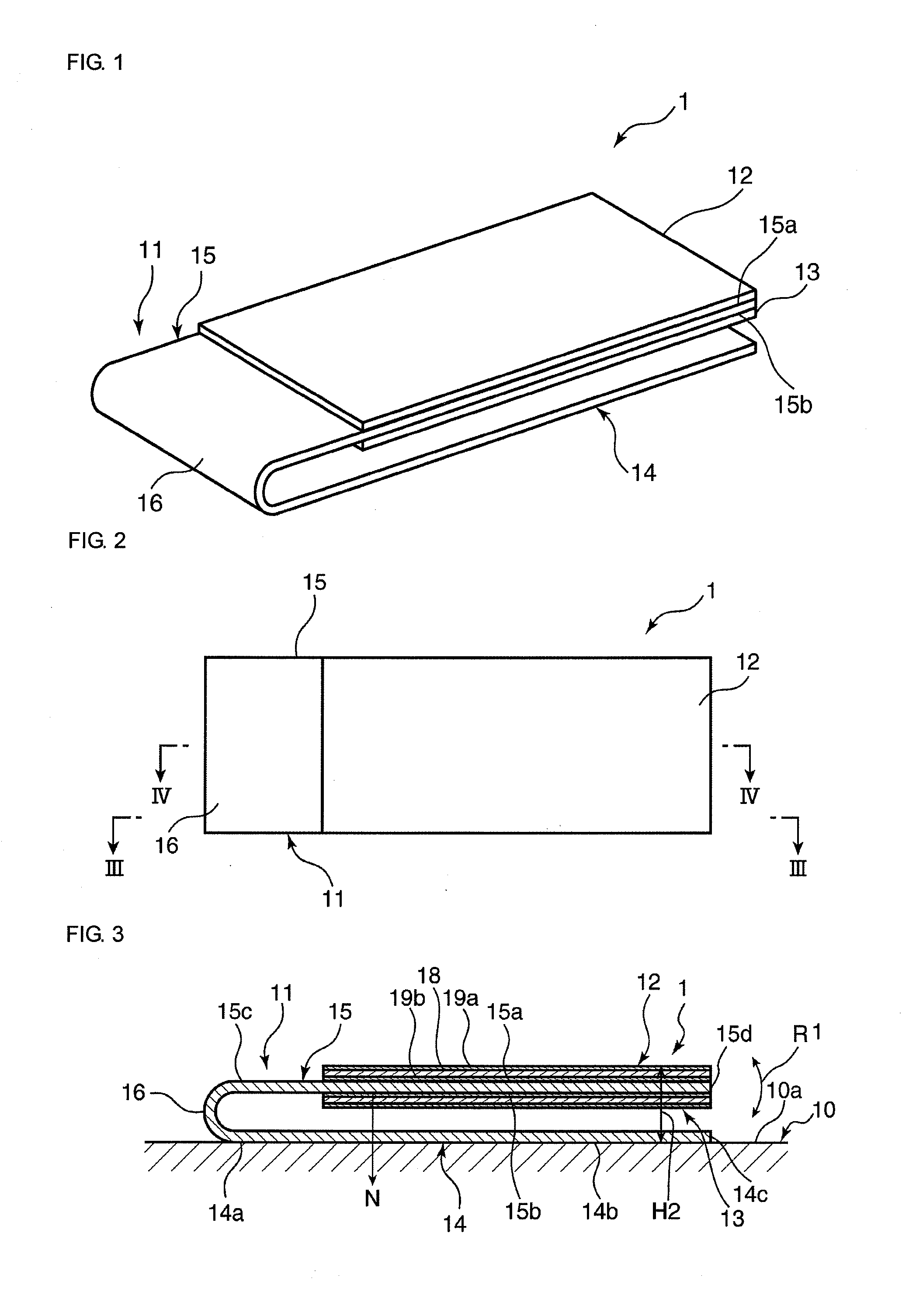

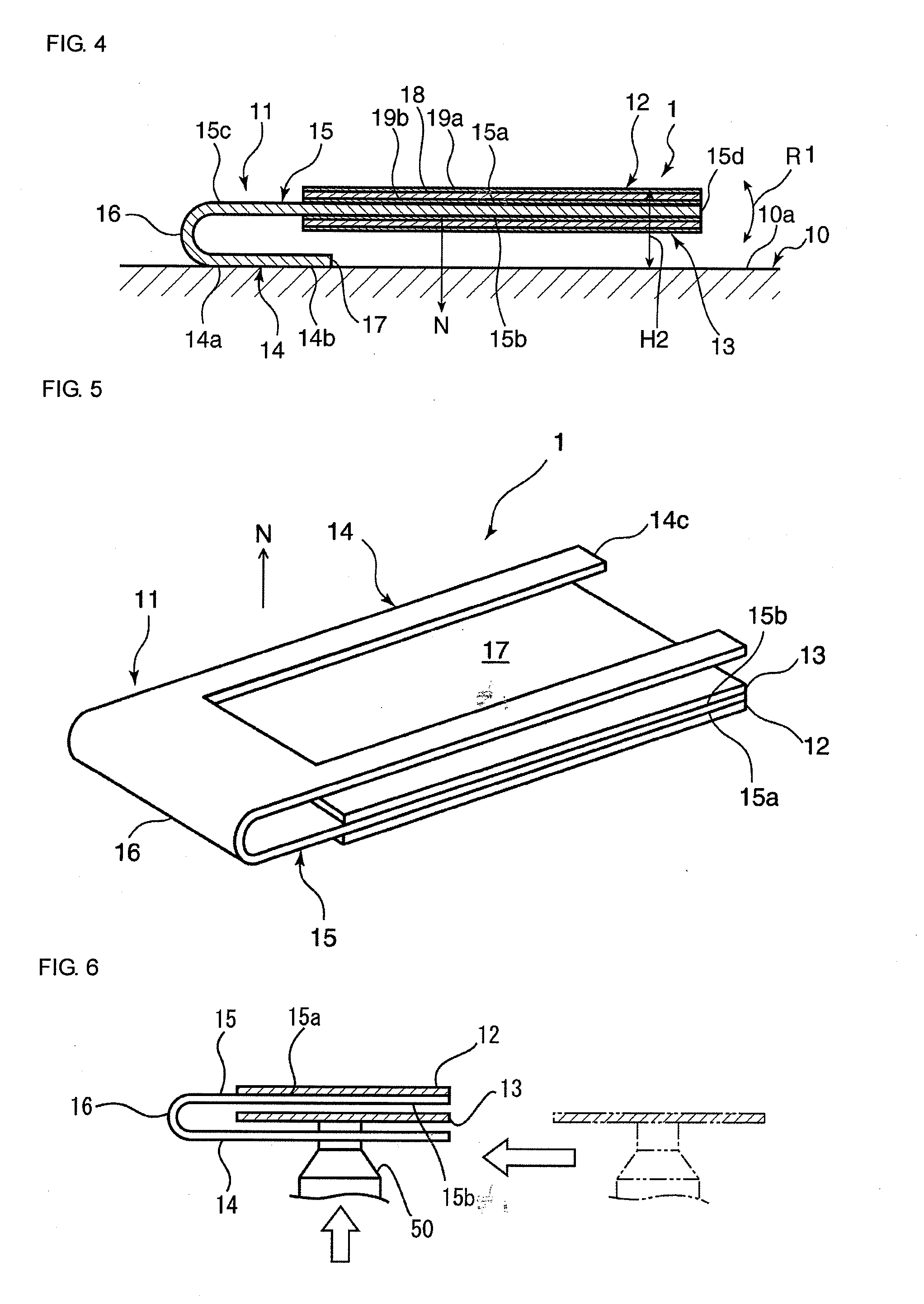

Method and circuit for driving liquid crystal display, and portable electronic device

InactiveUS7046223B2Reduce power consumptionReduced package areaCathode-ray tube indicatorsInput/output processes for data processingDigital videoLiquid-crystal display

A method for driving a liquid crystal display capable of reducing power consumption, decreasing a packaging area or a number of packaged parts, and providing an image of high quality when the liquid crystal display having a comparatively small display screen is driven by a line inverting driving method or by a frame inverting driving method.Digital video data is output, with or without data being inverted, based on a polarity signal being inverted in every one horizontal sync period or in every one vertical sync period. A plurality of gray scale voltages is selected, being provided so as to have either of a voltage of positive or negative to match an applied voltage of positive polarity or negative polarity transmittance characteristic. Any one of the gray scale voltage out of the plurality of gray scale voltages having a selected polarity is selected based on digital video data, with or without inversion of a polarity of gray scale voltages. The selected one gray scale voltage is applied as a data signal to a corresponding data electrode.

Owner:RENESAS ELECTRONICS CORP

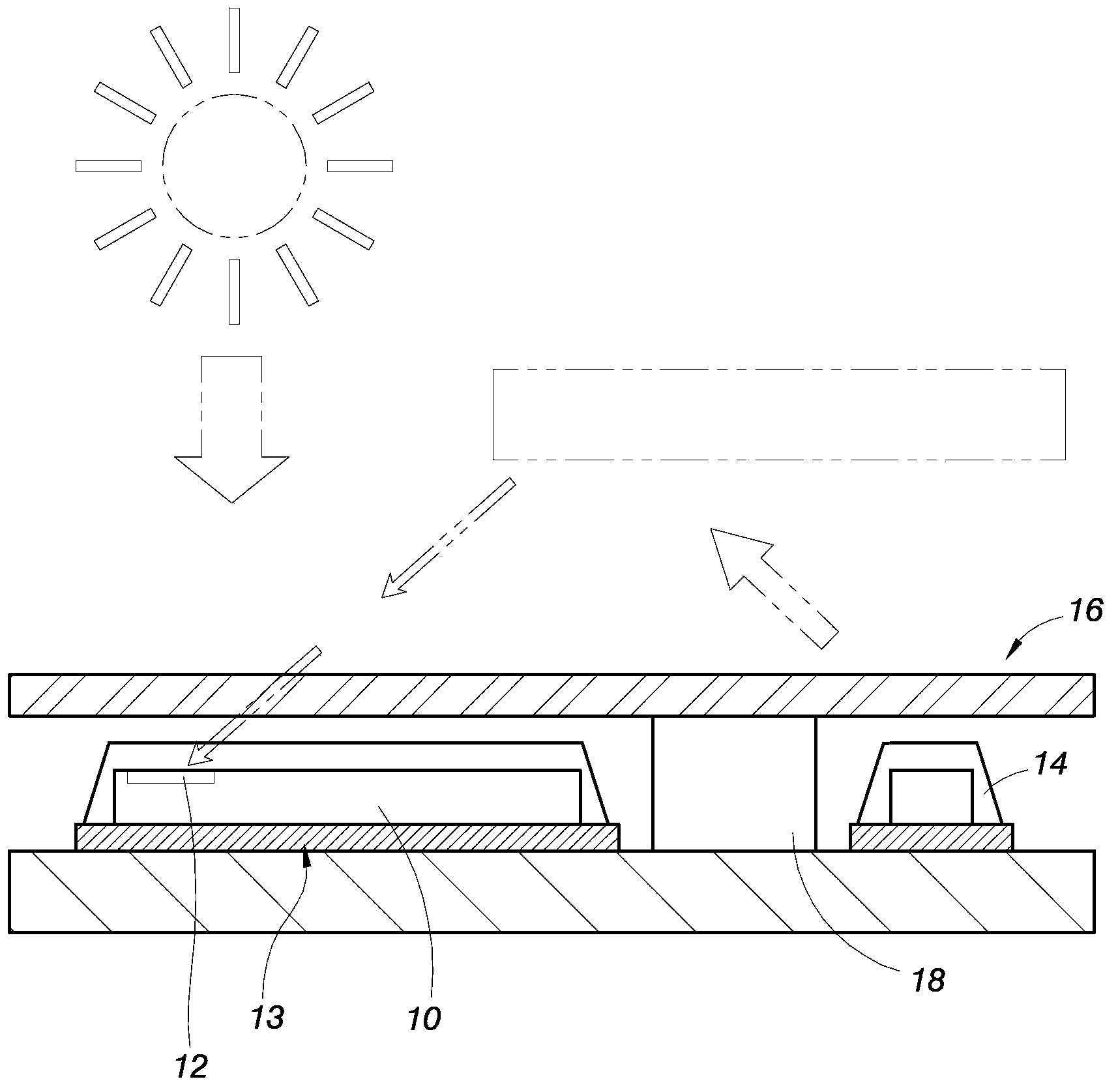

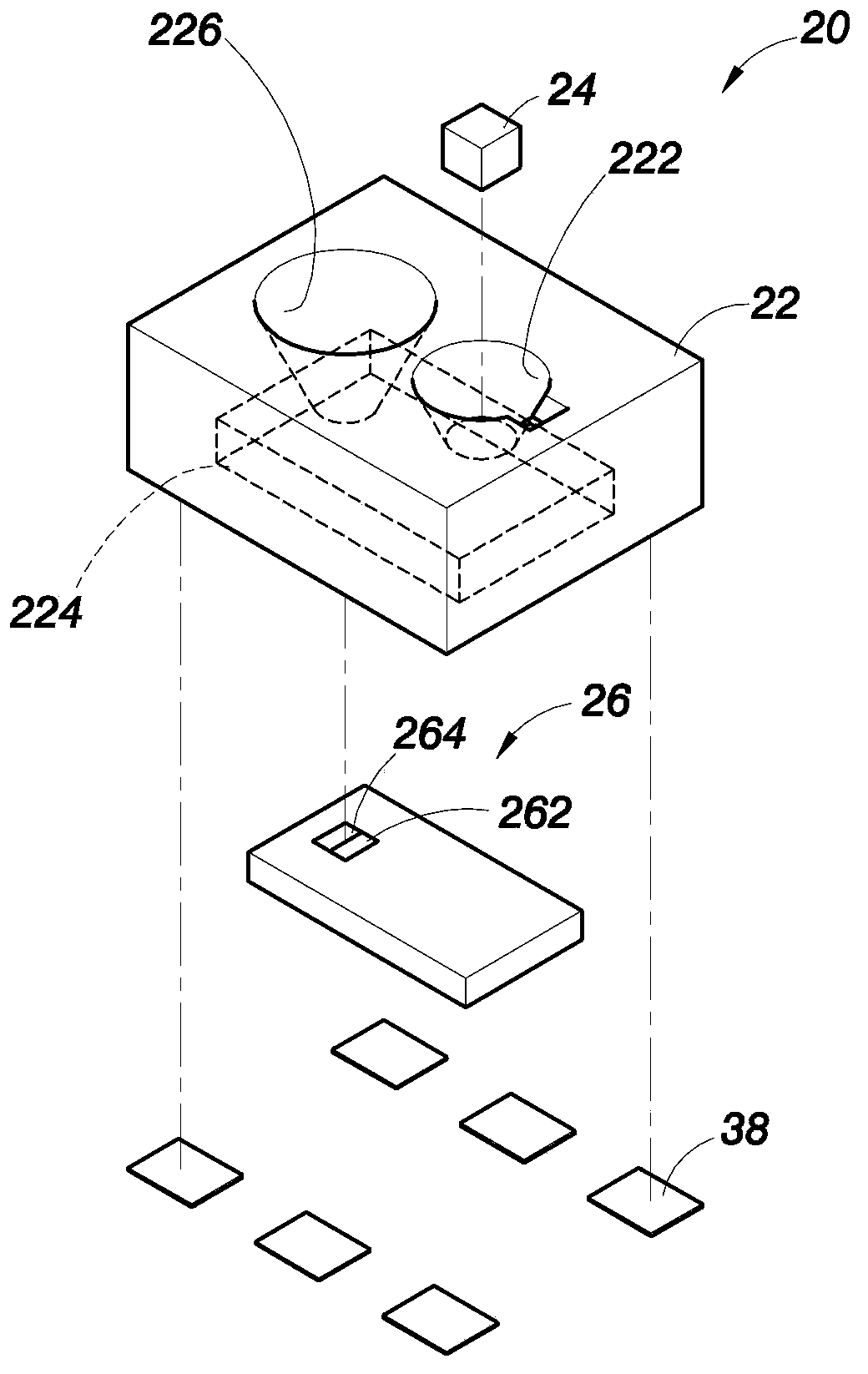

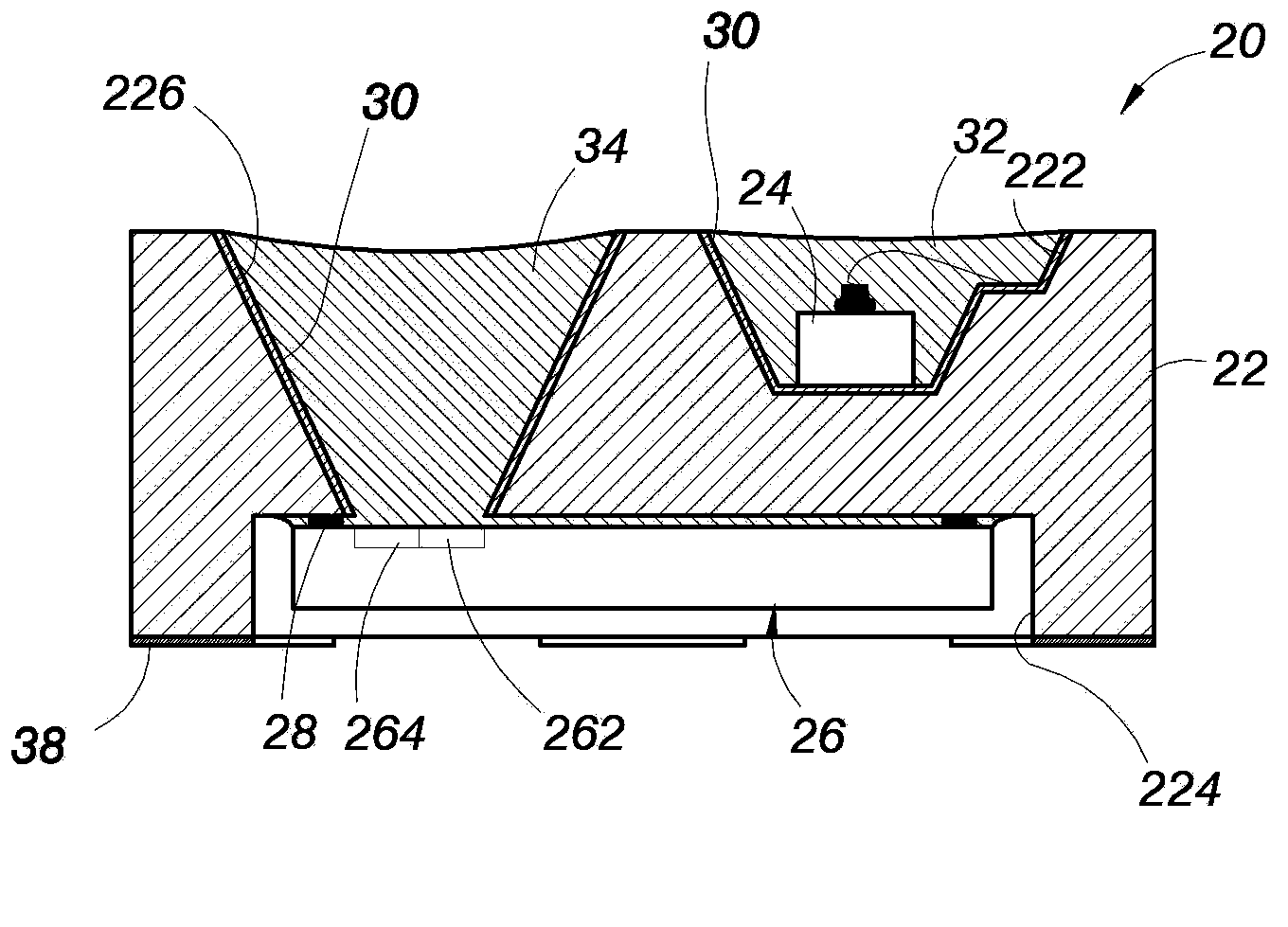

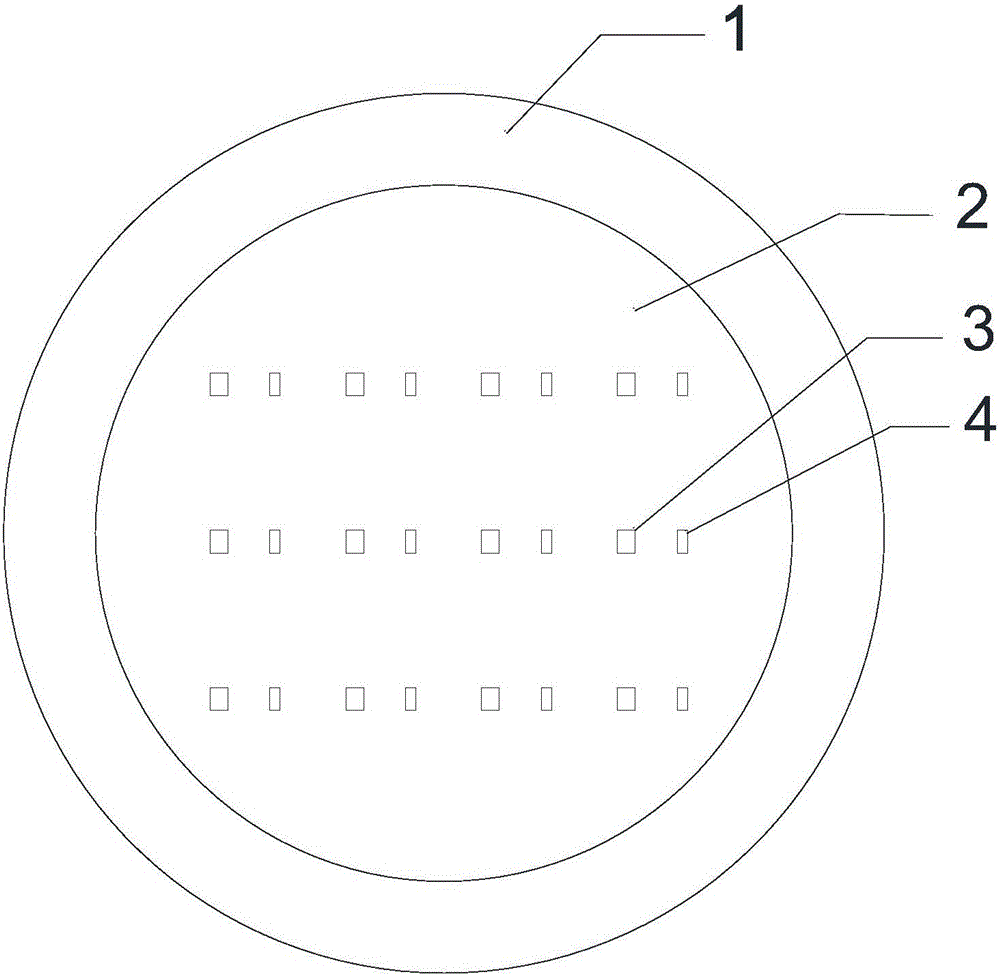

Photosensor chip package structure

ActiveCN103515372AReduced package areaSimple structureSemiconductor/solid-state device detailsSolid-state devicesLight sensingLight guide

A photosensor chip package structure comprises a substrate, a light-emitting chip and a photosensor chip including an ambient light sensing unit and a proximity sensing unit. The substrate has a first basin, a second basin and a light-guiding channel. The openings of the first and second basins respectively face different directions. One opening of the light-guiding channel and the opening of the first basin face the same direction. The other opening of the light-guiding channel interconnects with the second basin. The light-emitting chip is arranged in the first basin. The photosensor chip is arranged in the second basin. The light-guiding channel conducts the light generated by the light-emitting chip and the ambient light to the photosensor chip, so as to make the photosensor chip act.

Owner:TXC CORP

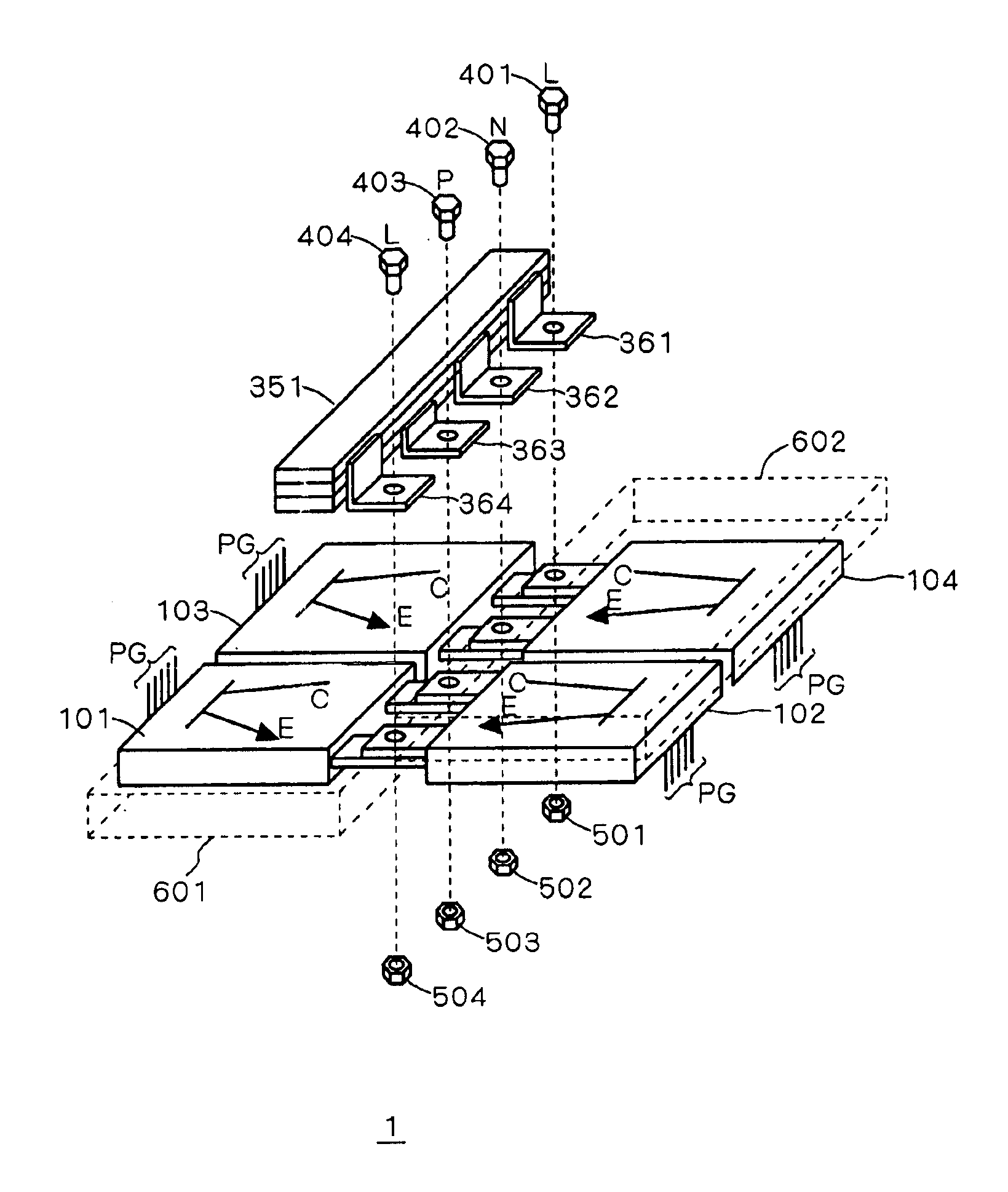

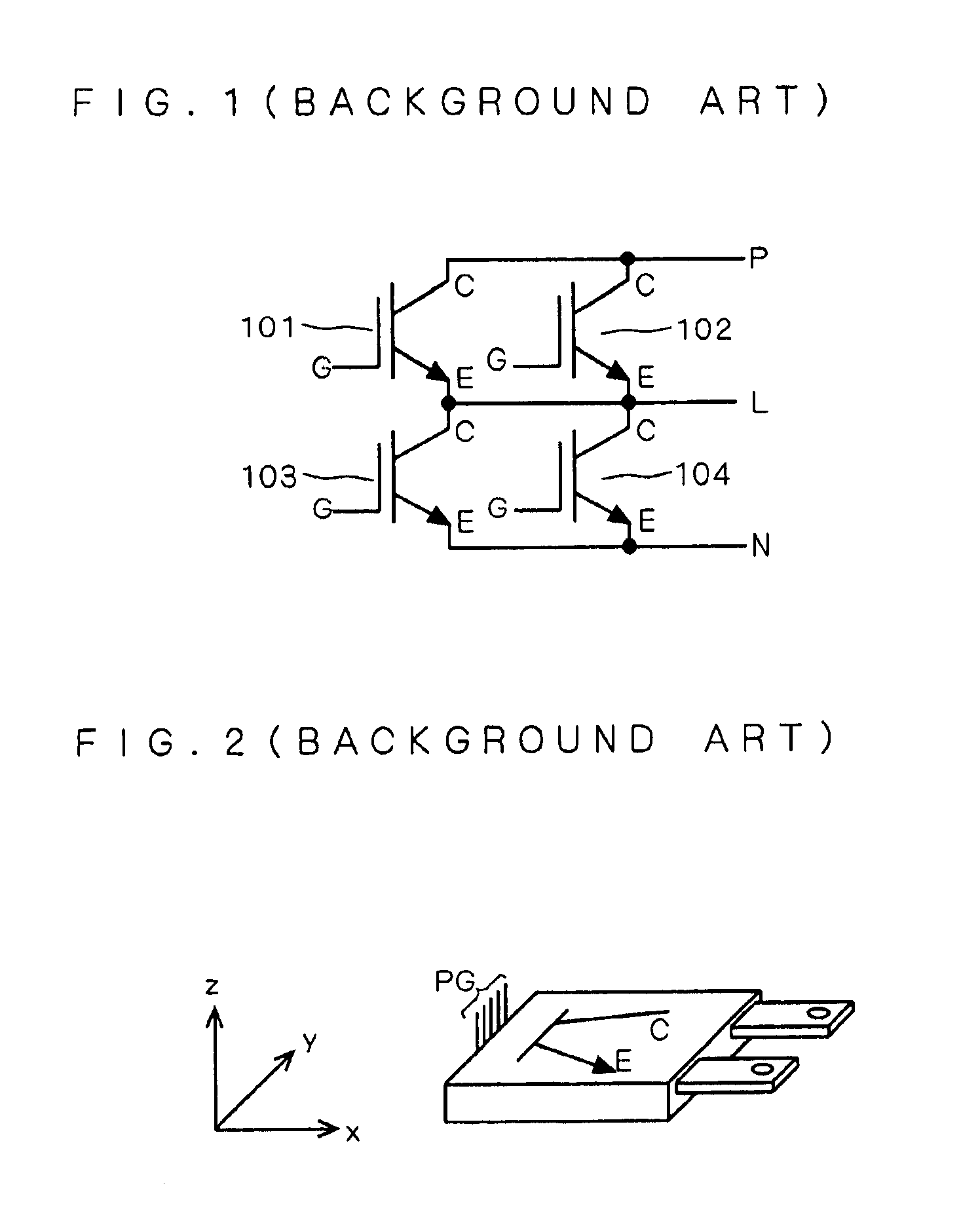

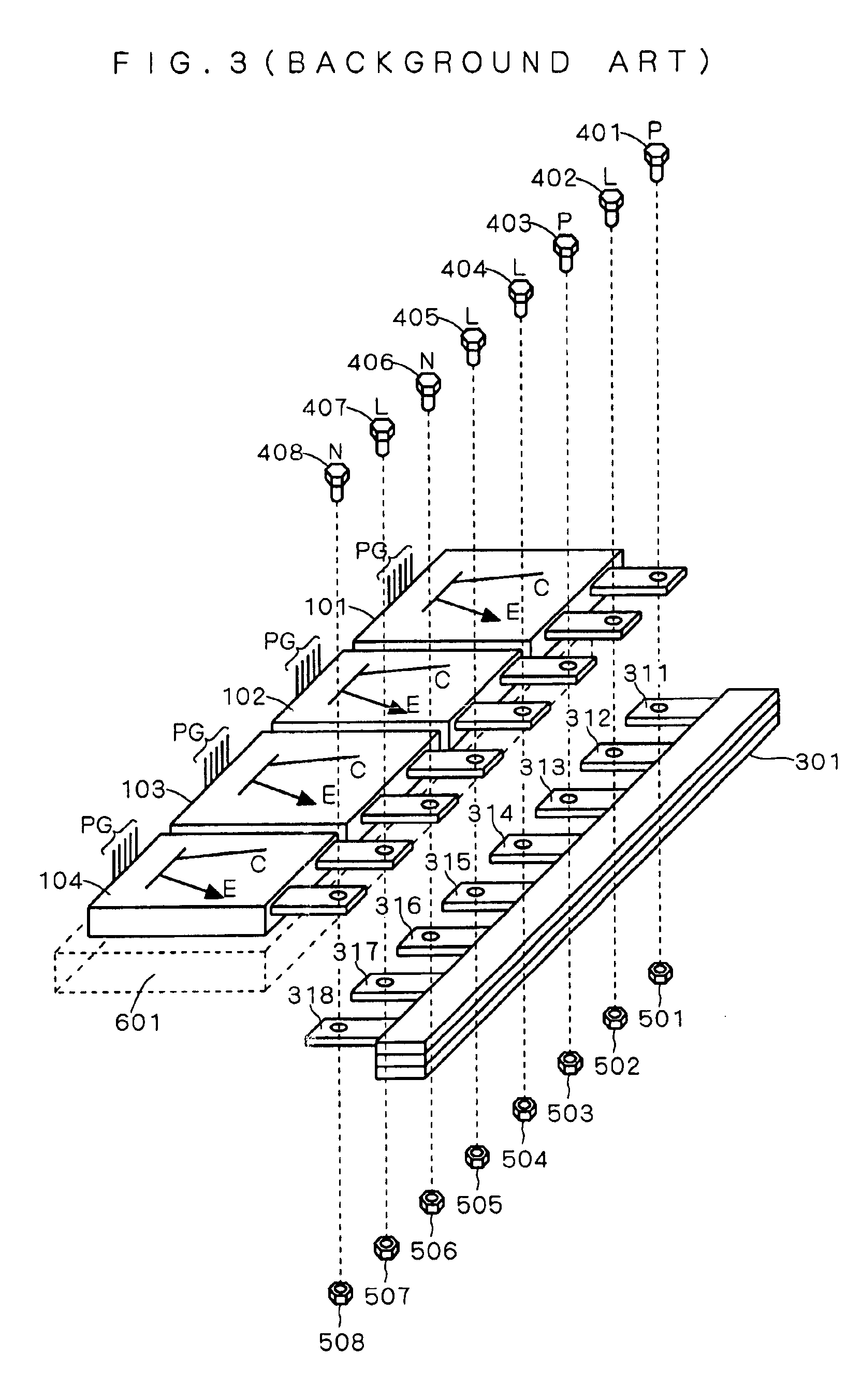

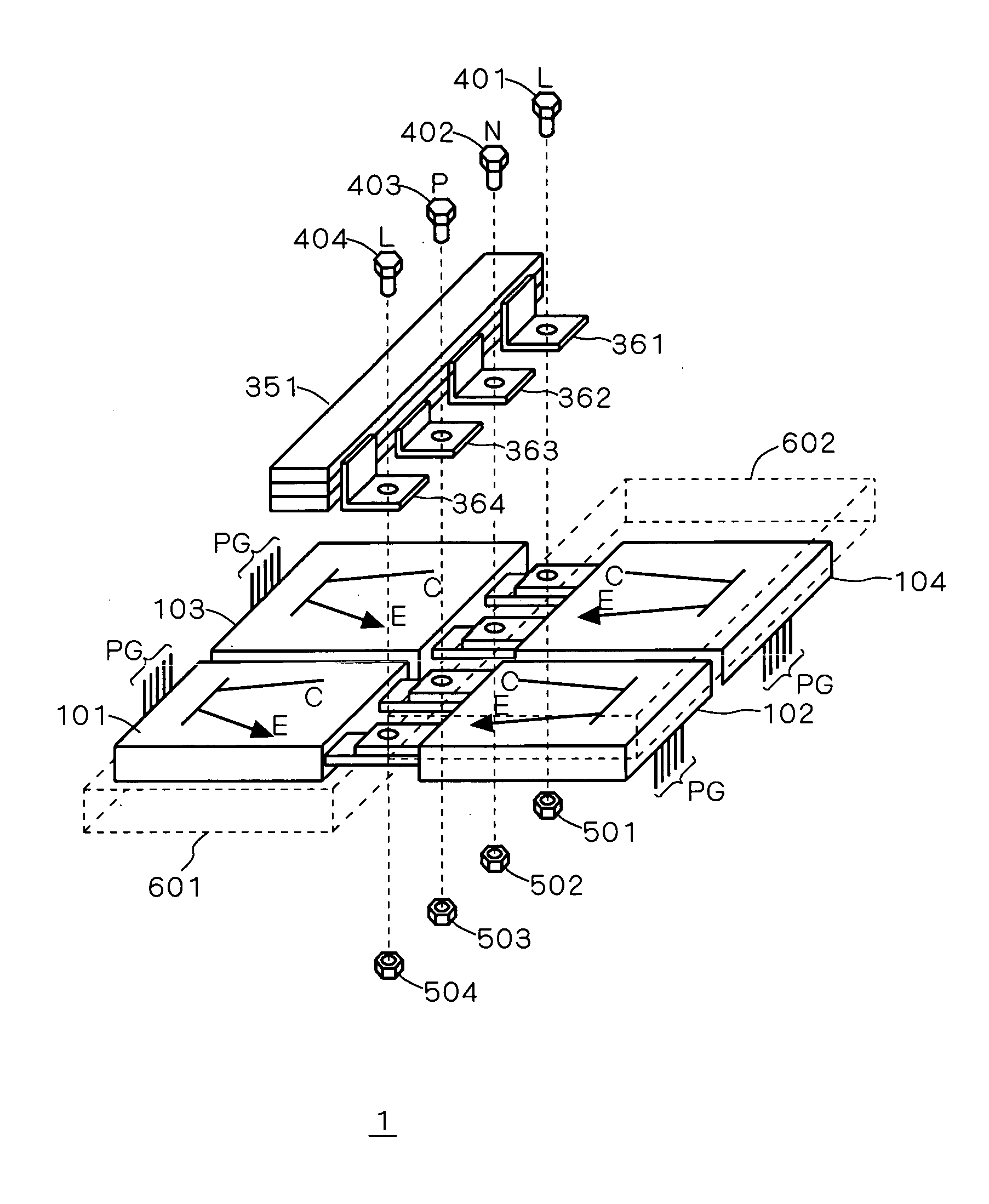

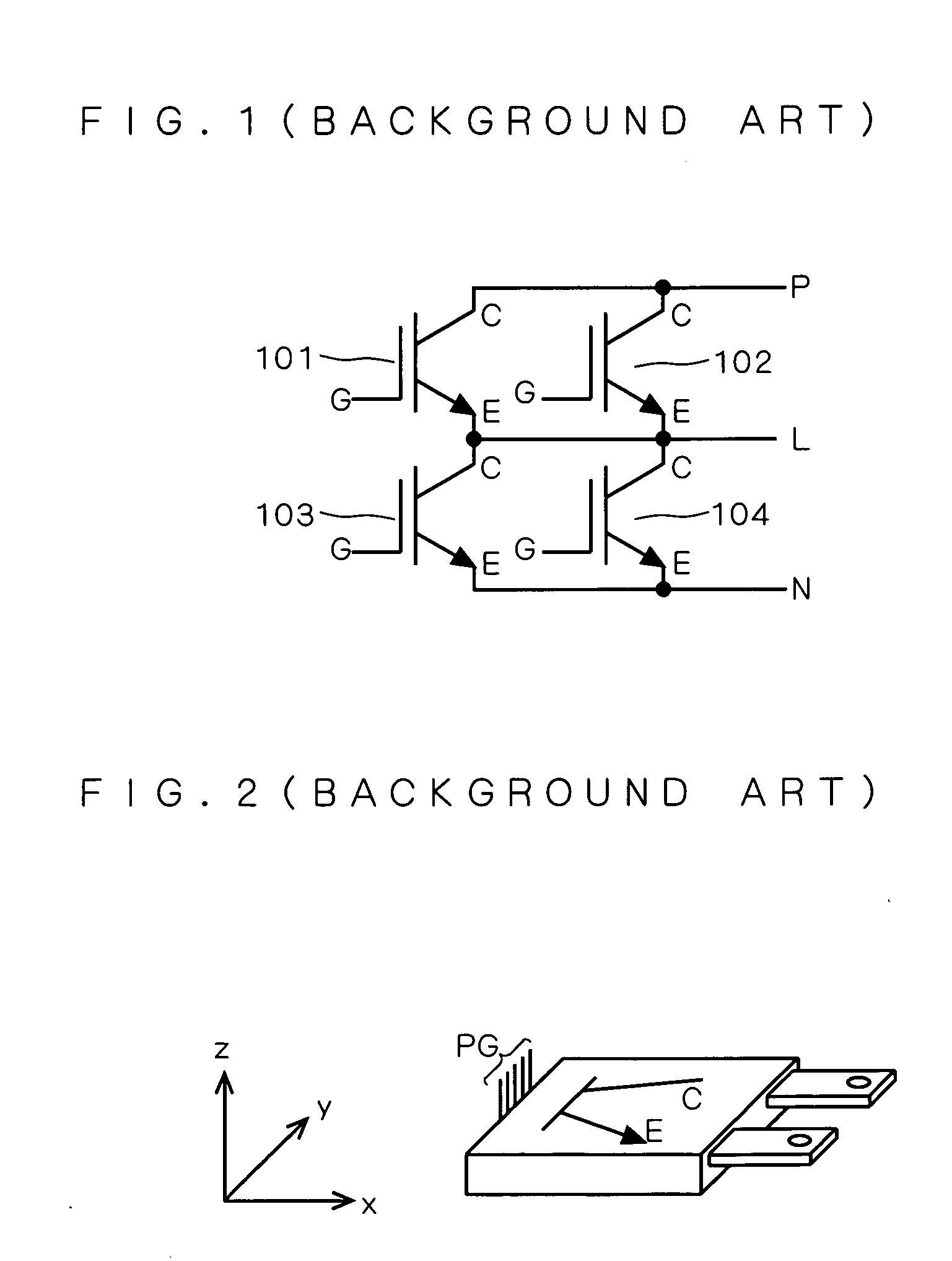

Power semiconductor device

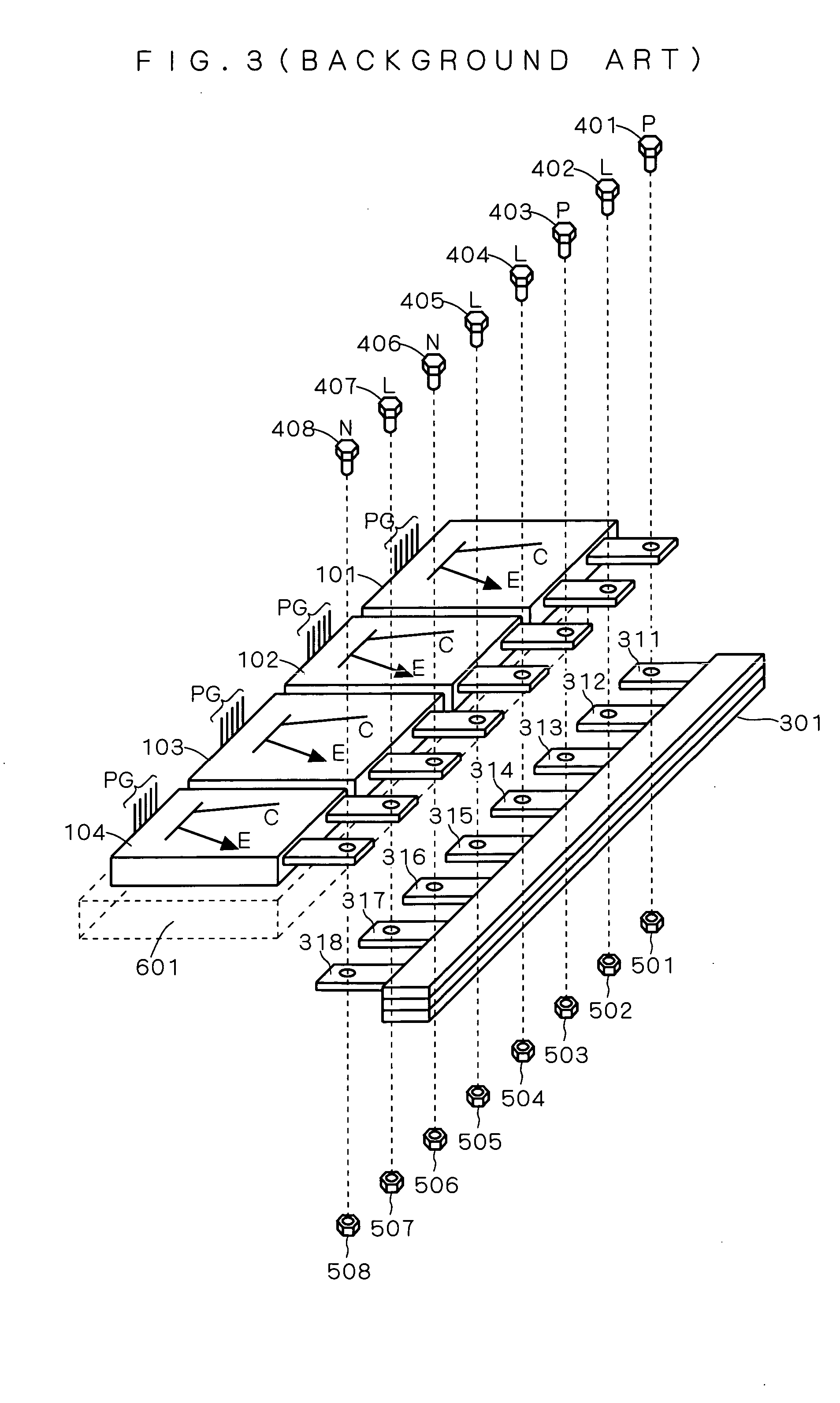

ActiveUS6870253B1Shorten the line lengthReduction of the wiring inductanceBus-bar/wiring layoutsSemiconductor/solid-state device detailsPower semiconductor deviceSemiconductor

Emitter electrodes (Es) and collector electrodes (Cs) of elements (101 to 104) are connected to bus electrodes (361 to 364) of a bus bar (351), respectively. The bus bar (351) contains seven layers including four insulating layers (not shown) and three conductive layers (shown) interposed between the insulating layers. Namely, each of the bus electrodes (361 to 364) is connected to one of the conductive layers corresponding to one of a positive electrode (P), a negative electrode (N) and an intermediate electrode (L). The collector electrodes (Cs) of the elements (103 and 104) are connected one over the other to the bus electrode (361). The emitter electrodes (Es) of the elements (103 and 104) are connected one over the other to the bus electrode (362). The collector electrodes (Cs) of the elements (101 and 102) are connected one over the other to the bus electrode (363). The emitter electrodes (Es) of the elements (101 and 102) are connected one over the other to the bus electrode (364).

Owner:MITSUBISHI ELECTRIC CORP

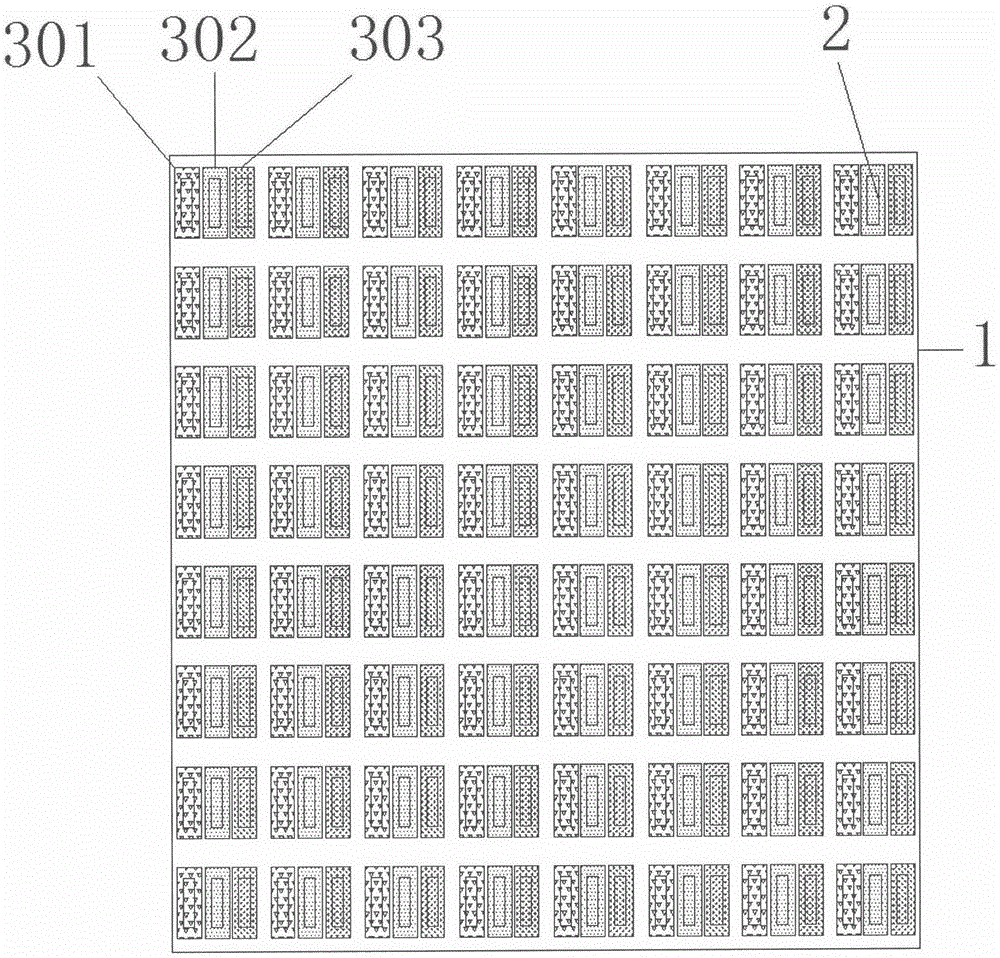

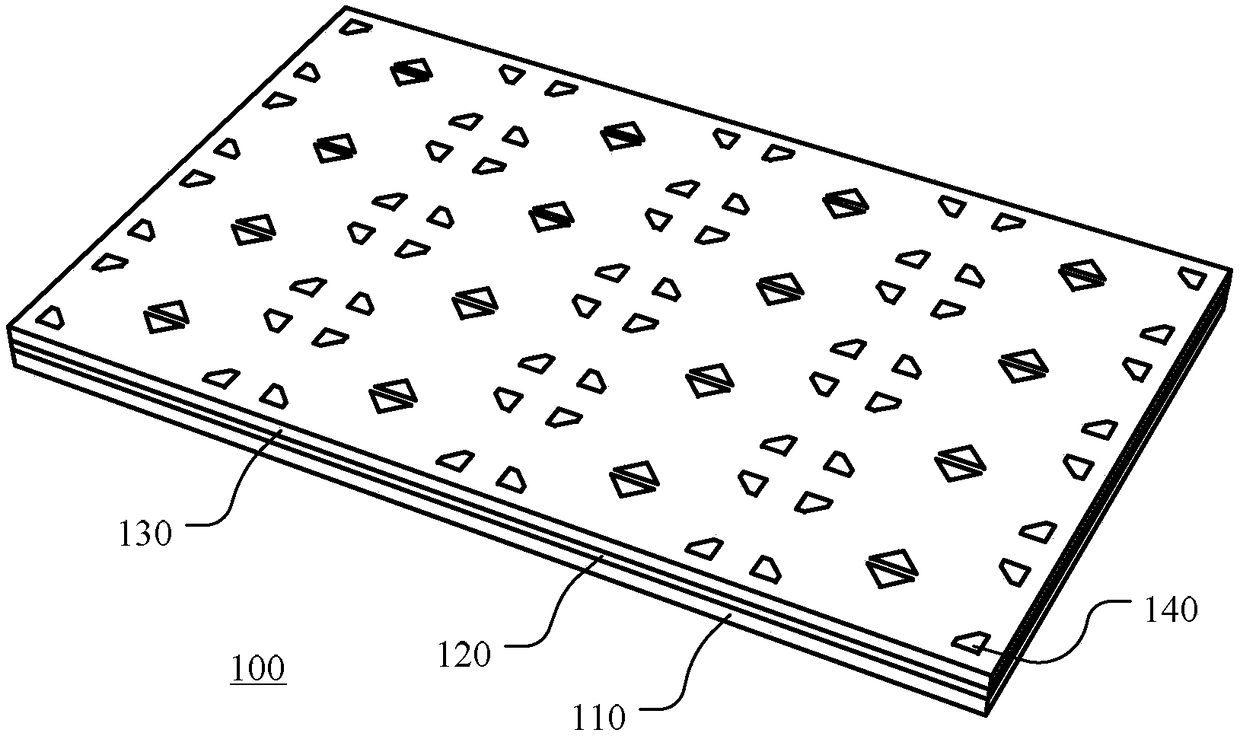

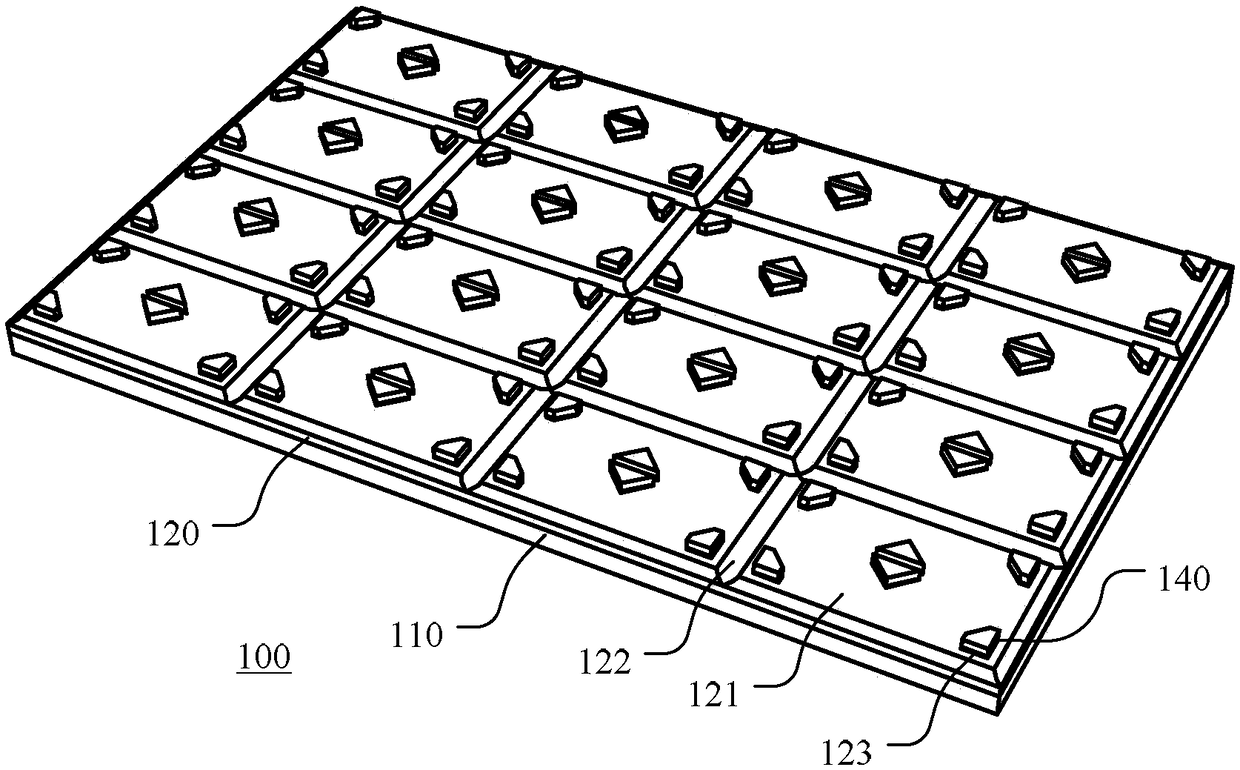

Super-high-density LED display device and manufacturing method thereof

PendingCN105206642APrevent light diffusionHigh resolutionSolid-state devicesIdentification meansHigh densityLED display

The invention discloses a super-high-density LED display device which comprises a substrate and an LED chip array packaged on the substrate. The chip array comprises a plurality of LED chips distributed evenly at intervals. By means of the Fan-Out Wafer-Level Package (FOWLP) process, the packaging area is narrowed, and the resolution ratio of an LED display screen is increased; all the LED chips are the same in structure, light-emitting wave band and type, the LED chips emit red light, green light and blue light after being coated with red light fluorescent powder, green light fluorescent powder and blue light fluorescent powder in a chip light-emitting curing mode respectively, and therefore it is ensured that the LED chips are consistent in light attenuation in the use process, and the development performance of the display screen is improved; pixel point distances can be smaller than 1 mm and even smaller than 0.1 mm, better performance such as high integrity, high resolution and consistent light color of the LED display device is achieved, and the super-high-density LED display device is importantly applied to indoor high-density display screens, projection devices and wearable display devices.

Owner:NANJING UNIV

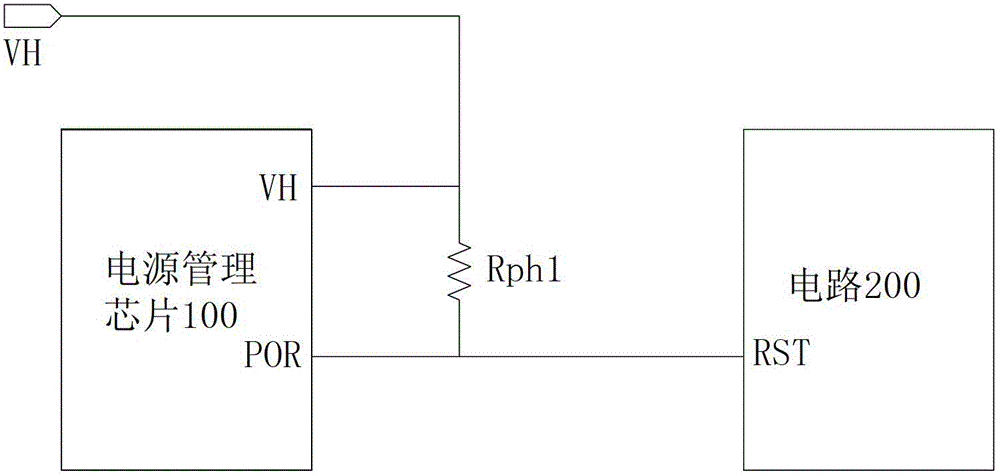

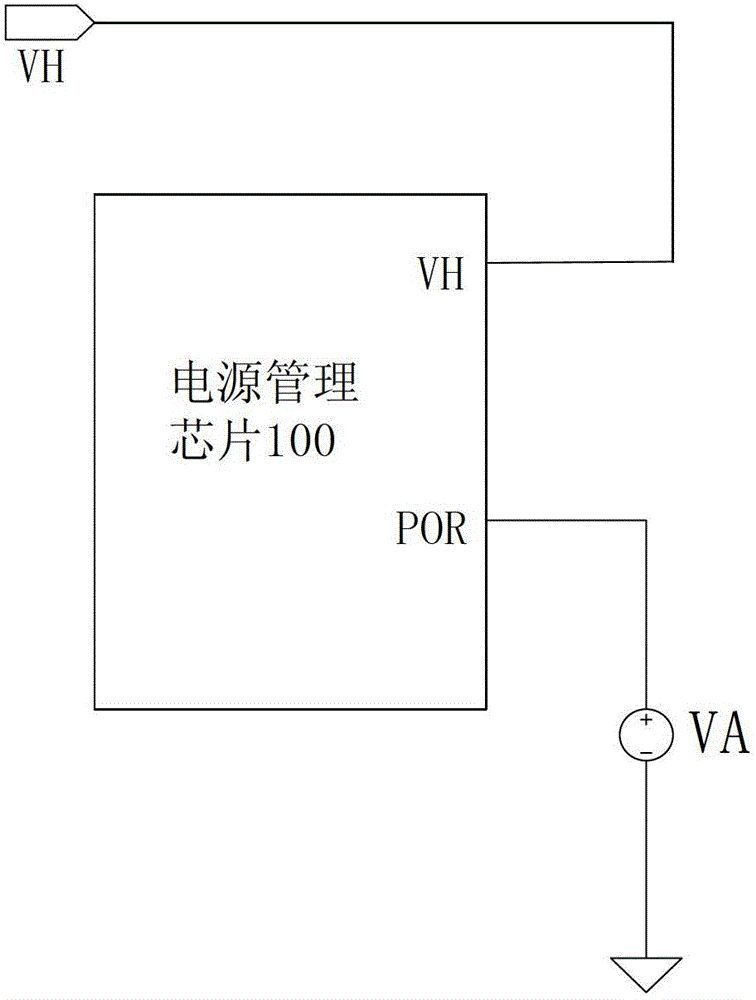

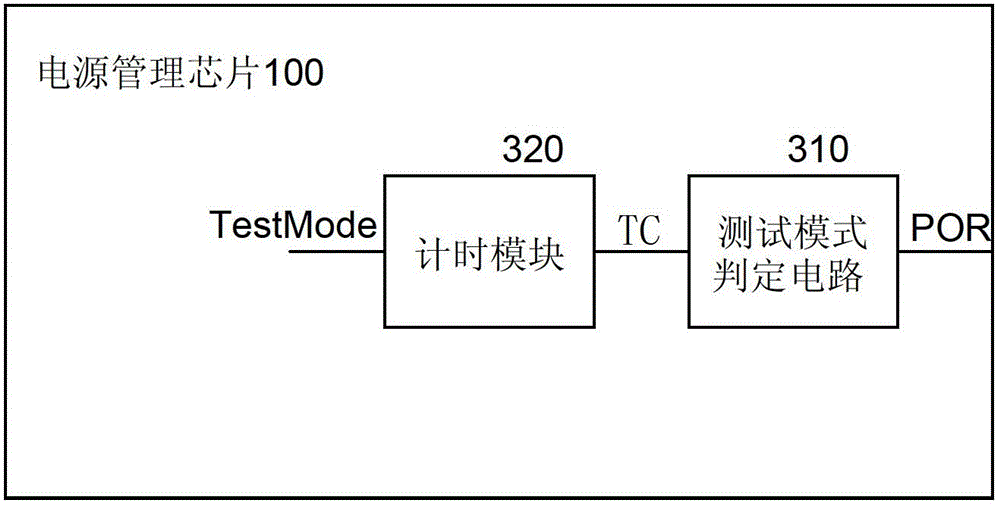

Chip provided with multiplex pin

ActiveCN103066985ASave pinsReduced package areaLogic circuit coupling/interface arrangementsVoltageEngineering

The invention provides a chip provided with a multiplex pin. The chip comprises the multiplex pin. When the multiplex pin is applied to another pin besides a test pin, voltage of the multiplex pin is larger than first threshold voltage or smaller than second threshold voltage. When the voltage of the multiplex pin is smaller than the first threshold voltage and larger than the second threshold voltage, the chip is in a test mode, and at the moment, the multiplex pin serves as the test pin and the first threshold voltage is larger than the second threshold voltage. Compared with the prior art, the chip is provided with the multiplex pin, whether the multiplex pin serves as the test pin is confirmed through testing of the voltage of the multiplex pin. The multiplex pin can serve as other pins, so the number of pins of the chip is reduced and a packaging area is reduced.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

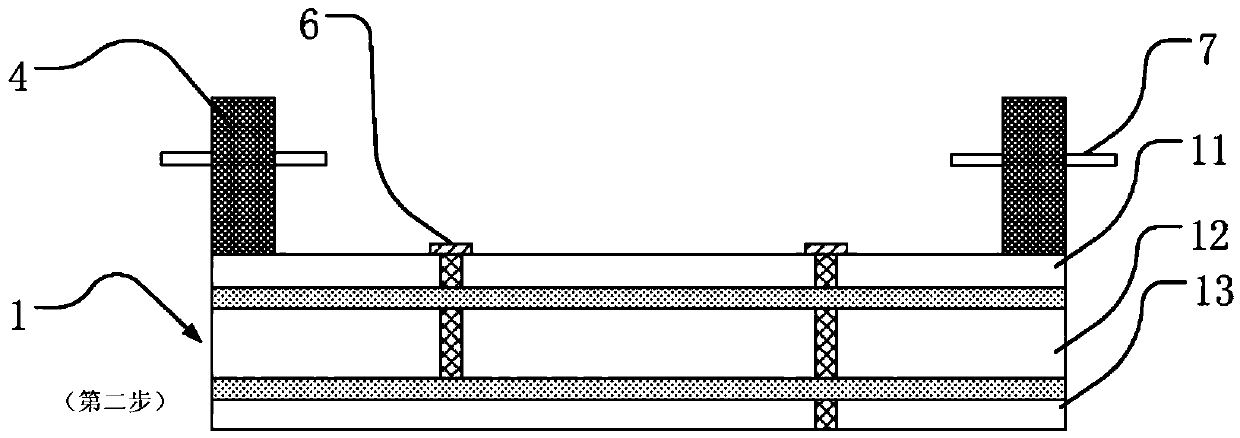

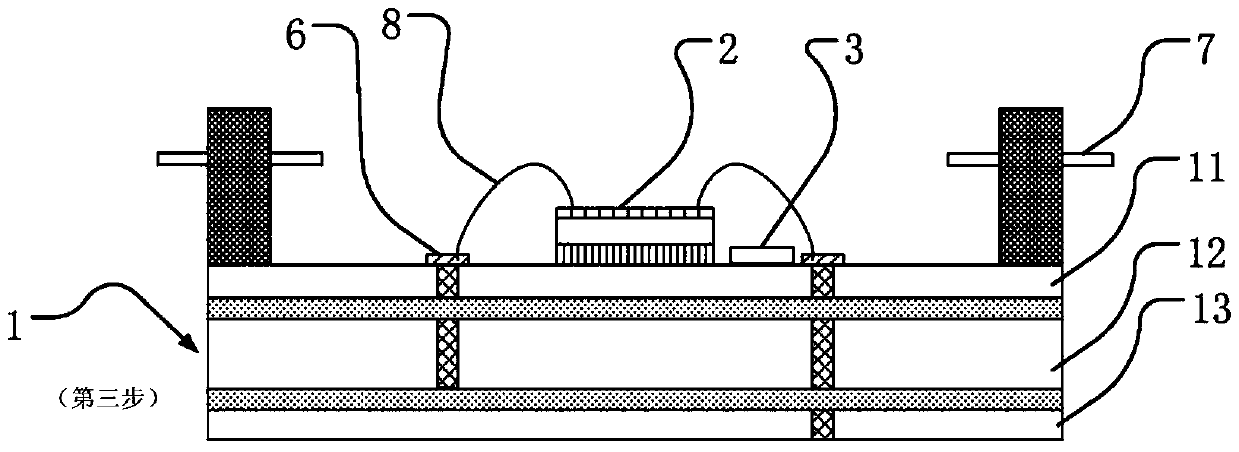

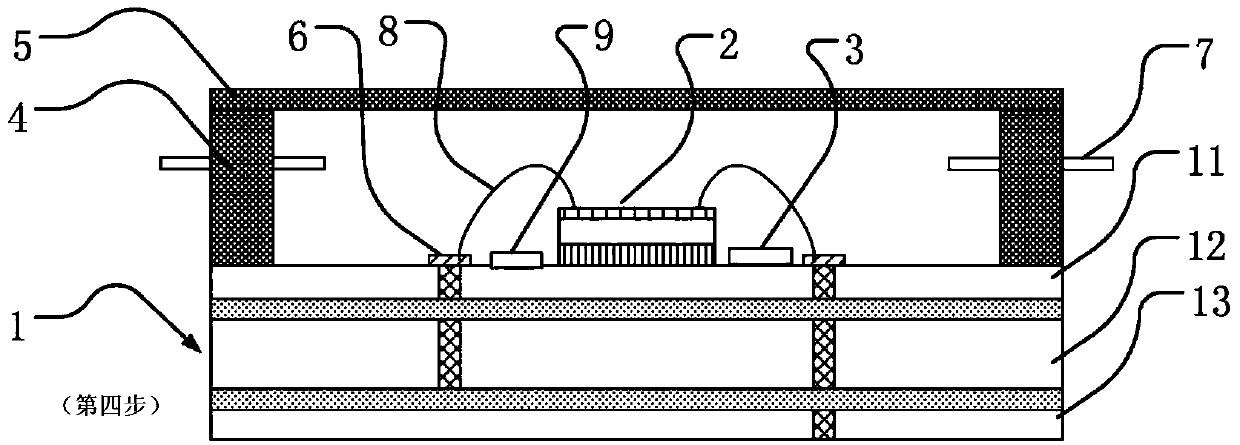

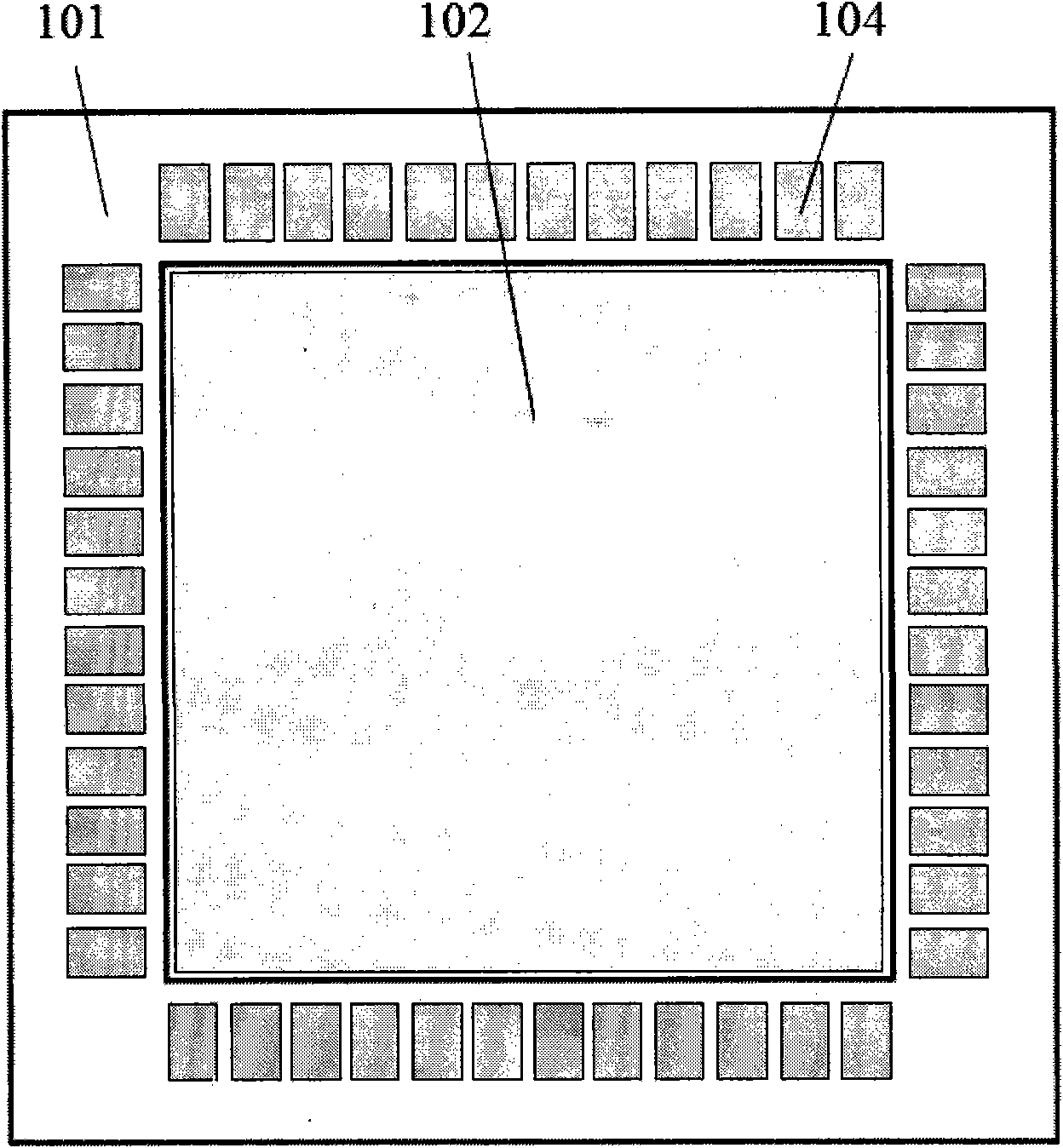

Three-dimensional multi-chip encapsulation module based on buried substrate and method

InactiveCN102163590AProne to warpingAvoid warpingSemiconductor/solid-state device detailsSolid-state devicesHigh densityLead bonding

The invention provides a buried substrate based multi-chip module structure for realizing three-dimensional high-density encapsulation (3D-MCM). The upper surface and the lower surface of the substrate have concave cavity structures; different chips having larger size difference are placed and wires are arranged in the cavity structures having different sizes so as to form a buried three-dimensional encapsulation structure; a plurality of chips are interconnected by using a conventional wire bonding method; a chip protection mode adopts two packing processes, namely sealing glue dropping and surrounding dam packing; a pin output form adopts a peripheral ball grid array mode; and by the concave cavity structures, the encapsulation area is reduced, the encapsulation density is enhanced, the bonded wire is shortened effectively, and the signal delay is decreased. The whole process and the surface assembling process are compatible with each other and have characteristics of simpleness and low cost. By the concave cavity structures on the upper surface and the lower surface of the substrate, the warping of the substrate is decreased and the reliability of the three-dimensional encapsulation structure is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

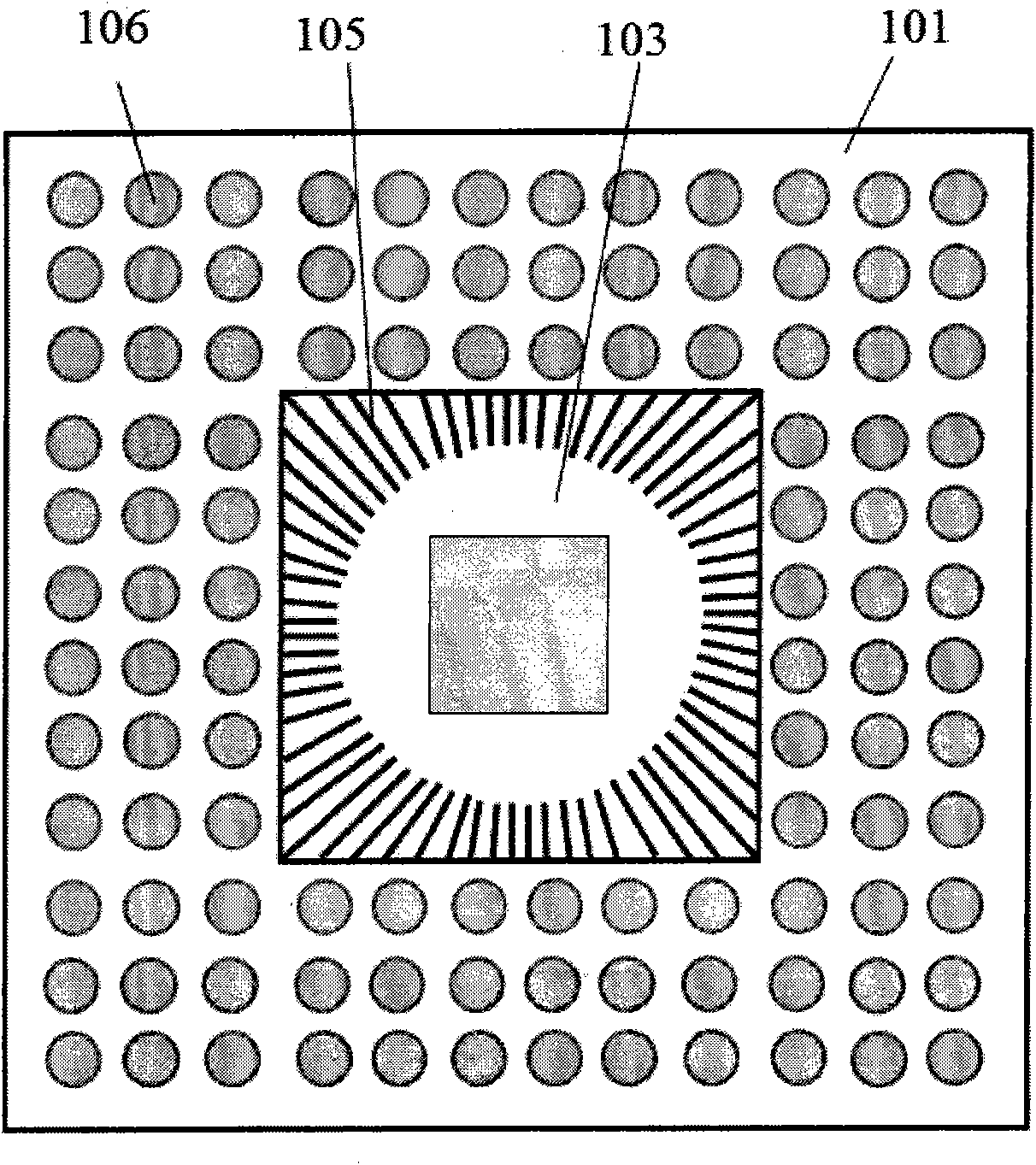

Semiconductor package stack with through-via connection

InactiveCN101047167AReduce manufacturing costReduce defective rateSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

A package stack includes at least two packages stacked on each other. Each package has a substrate, a circuit pattern positioned on the substrate, a semiconductor chip attached to the substrate, and a number of through-vias formed on a lateral surface. A number of electrical connection members are attached to the through-vias so as to electrically connect the packages to each other. The through-vias are vertically positioned on the lateral or side surface of the packages. And a solder ball is attached to the lower surface of the substrate of the lowest package.

Owner:SK HYNIX INC

Method and driving circuit for driving liquid crystal display, and portable electronic device

InactiveUS20060061532A1Reduce power consumptionReduce areaCathode-ray tube indicatorsInput/output processes for data processingDigital videoLiquid-crystal display

A method for driving a liquid crystal display capable of reducing power consumption, decreasing a packaging area or a number of packaged parts, and providing an image of high quality. Digital video data is output, with or without data being inverted, based on a polarity signal being inverted in every one horizontal sync period or in every one vertical sync period. A plurality of gray scale voltages is selected having either a positive or negative voltage. Any one of the plural gray scale voltages is selected based on digital video data, with or without inversion of a polarity of gray scale voltages. The selected one gray scale voltage is applied as a data signal to a corresponding data electrode.

Owner:RENESAS ELECTRONICS CORP

Method and driving circuit for driving liquid crystal display, and portable electronic device

InactiveUS7477227B2Reduce power consumptionReduced package areaCathode-ray tube indicatorsInput/output processes for data processingDigital videoLiquid-crystal display

A method for driving a liquid crystal display capable of reducing power consumption, decreasing a packaging area or a number of packaged parts, and providing an image of high quality. Digital video data is output, with or without data being inverted, based on a polarity signal being inverted in every one horizontal sync period or in every one vertical sync period. A plurality of gray scale voltages is selected having either a positive or negative voltage. Any one of the plural gray scale voltages is selected based on digital video data, with or without inversion of a polarity of gray scale voltages. The selected one gray scale voltage is applied as a data signal to a corresponding data electrode.

Owner:RENESAS ELECTRONICS CORP

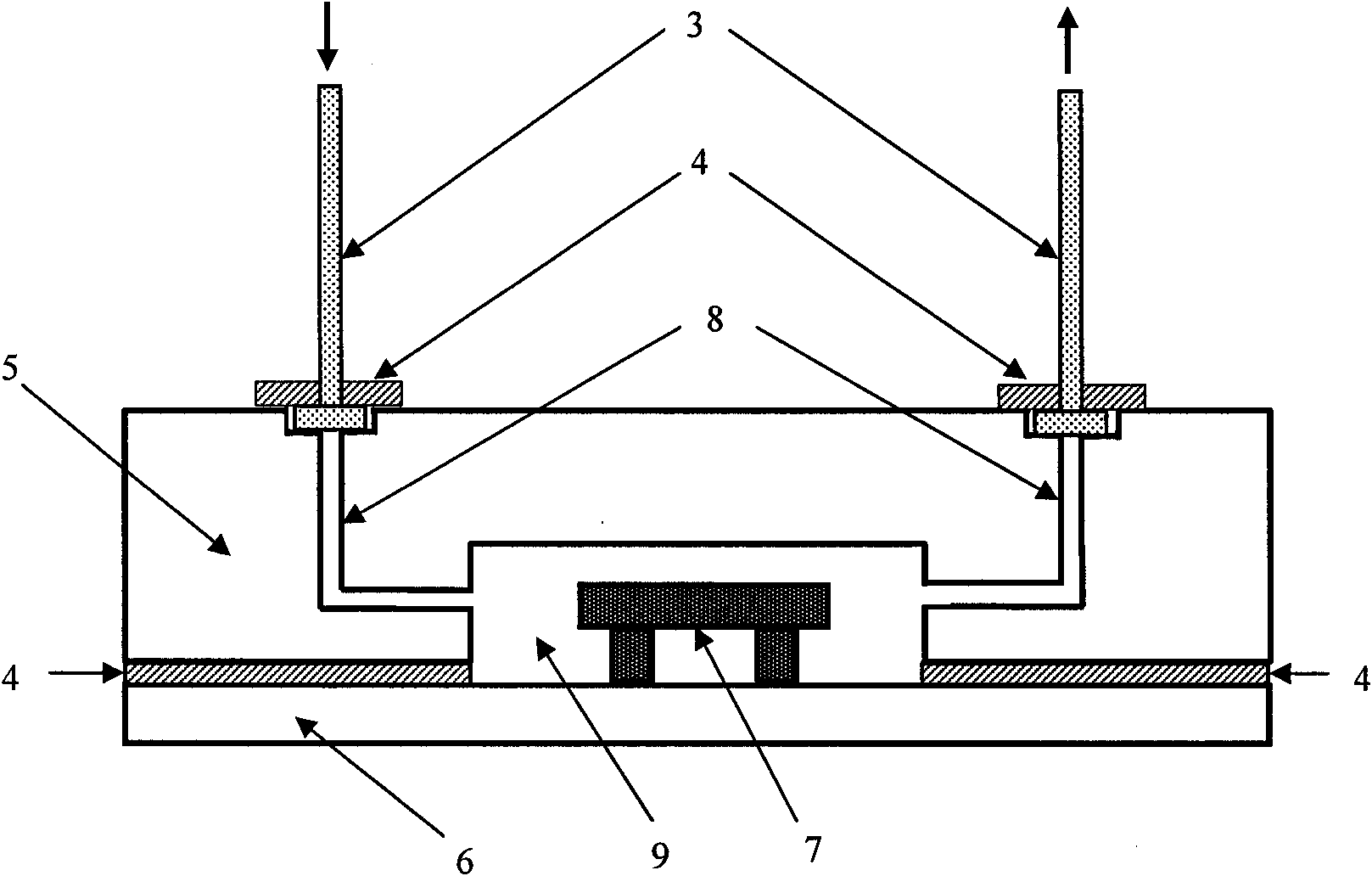

Low temperature co-fired ceramic-based micro-electromechanical system (MEMS) packaging method

InactiveCN101875481ARealize transportationExchangeDecorative surface effectsChemical vapor deposition coatingCo-fired ceramicOpen cavity

The invention discloses a low temperature co-fired ceramic-based micro-electromechanical system (MEMS) packaging method. The method comprises the following steps of: preparing an upper low temperature co-fired ceramic substrate and a lower low temperature co-fired ceramic substrate respectively and forming a three-dimensional electrically-interconnected network, an embedded micro-channel and an open cavity in the upper substrate and / or the lower substrate; aligning the upper substrate with the lower substrate for packaging, packaging components and parts in the cavity and communicating the micro-channel with the cavity and the outside of a packaged body; and connecting an external micro-tube to the outlet of the micro-channel, which leads to the outside of the package body, and realizing gas or liquid flow between the cavity and the outside through the external micro-tube. The method has the advantages of improving the integration level, the stability and the flexibility of MEMS packaging, realizing vacuum packaging and heat dissipation of the components and parts in the cavity by conveying a circulating radiating medium through the micro-channel and conveying detection samples and the like to medical, biological or chemical MEMS components and parts in the packaging cavity through the micro-channel.

Owner:PEKING UNIV

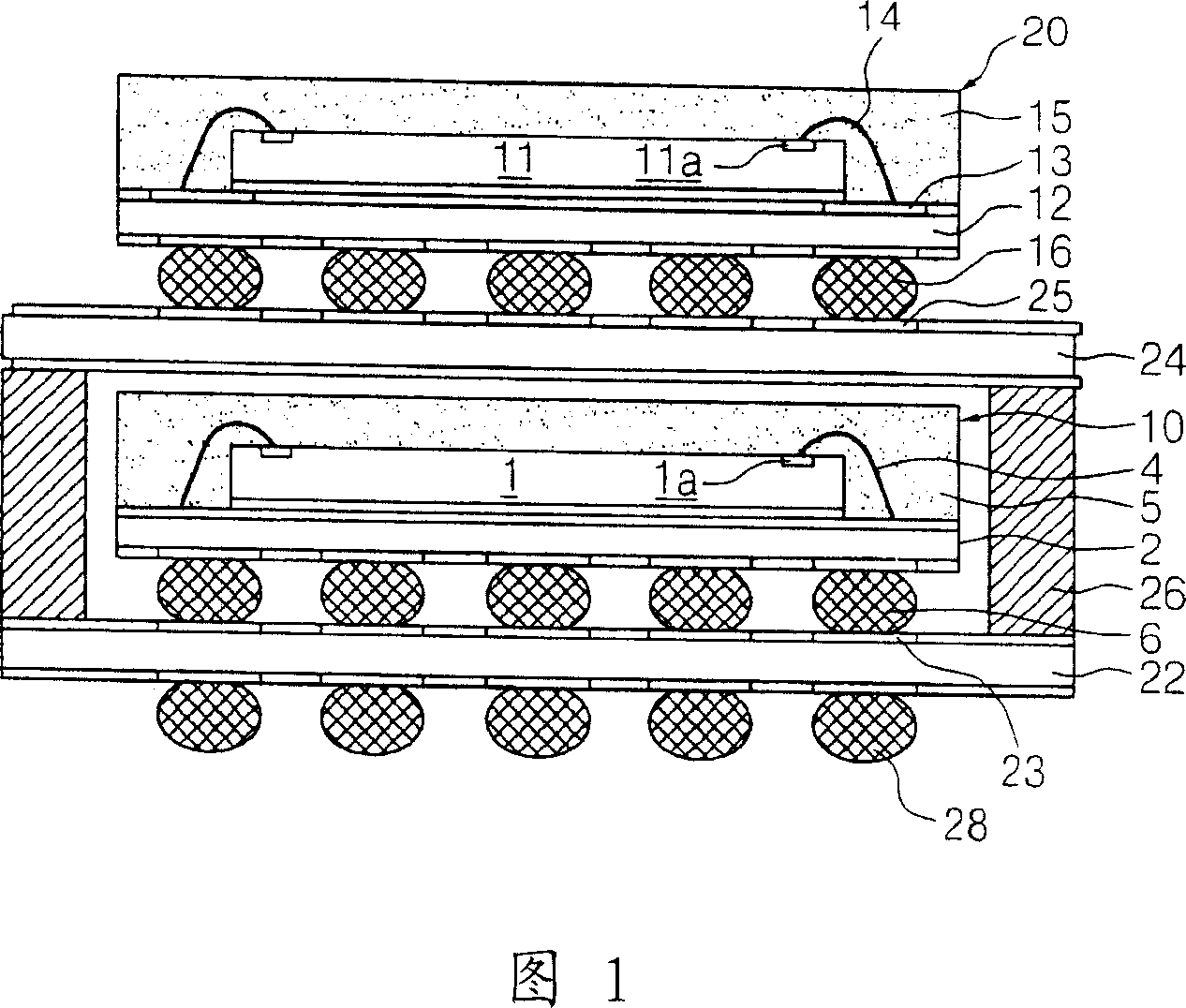

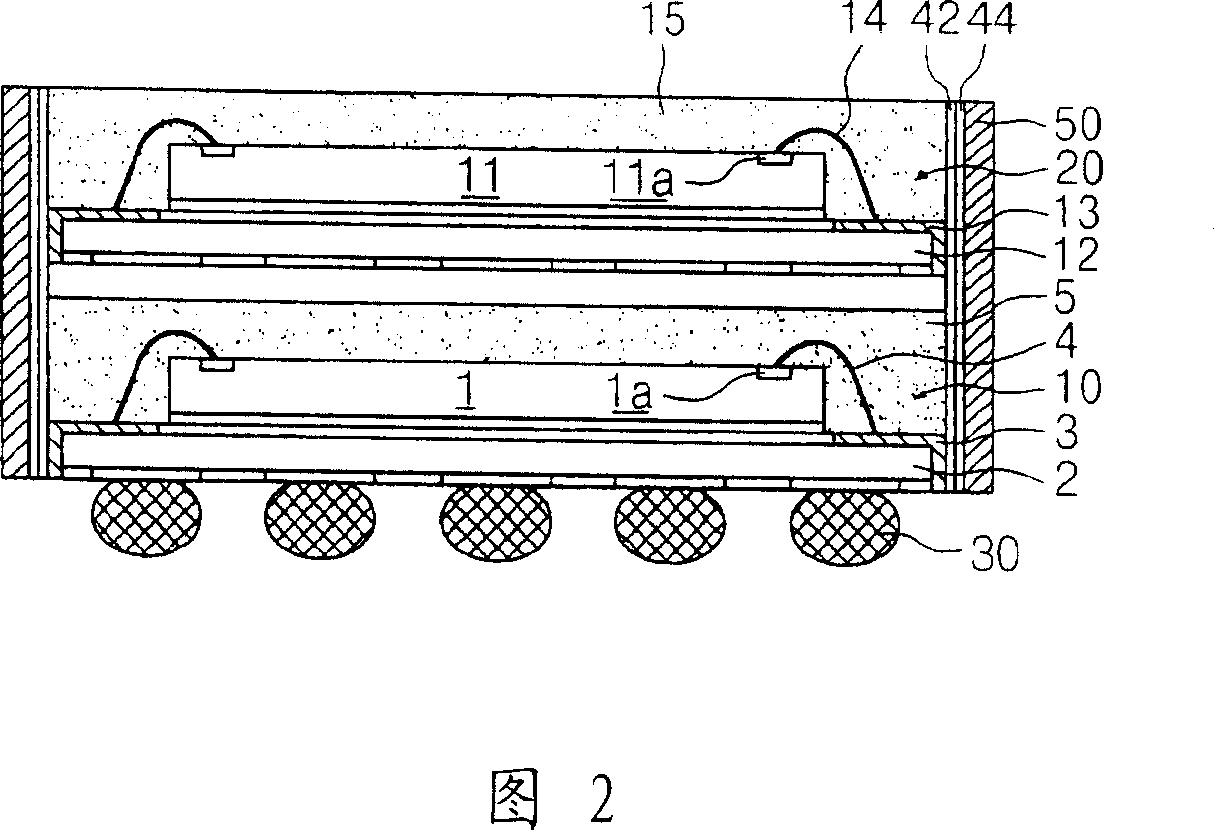

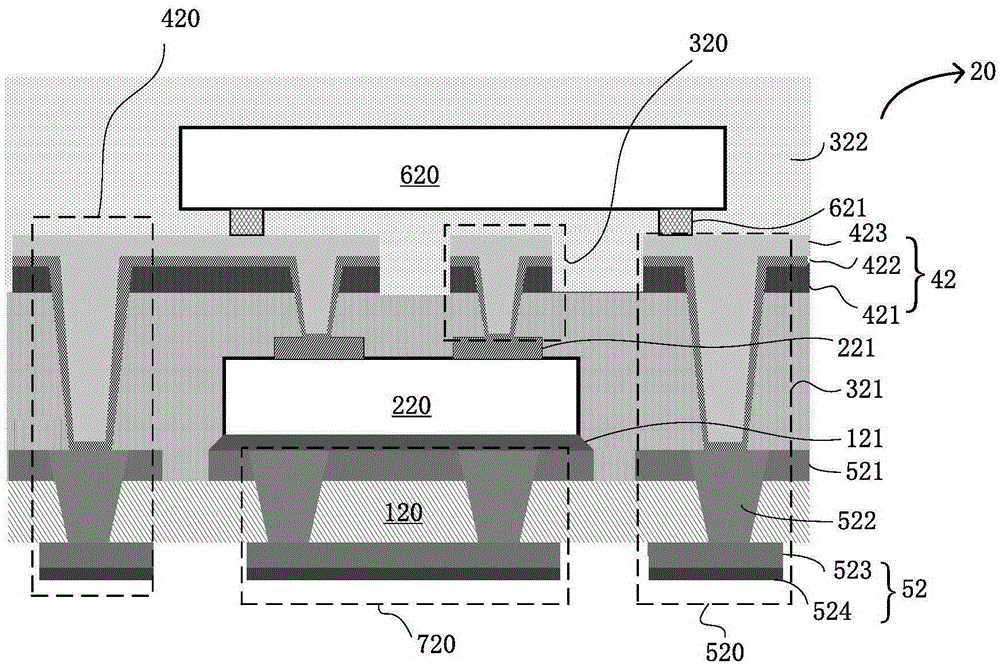

Package-on-package structure of chip and package-on-package method

ActiveCN105261611AReduced package areaReduce package resistanceSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitEngineering

The invention provides a package-on-package structure of a chip and a package-on-package method. In the package-on-package structure, an electrode is leaded out through an interconnector and a first rewiring member in packaging a first layer of pipe cores. The package-on-package structure and the package-on-package method are suitable for packaging the chip with relatively high pad spacing. Furthermore no bonding lead is required and a packaging resistance is reduced. Furthermore a penetrating member which penetrates a first packaging member and a substrate is used for leading the electrode on a second layer of the chip out, thereby realizing chip packaging in a package-on-package manner, effectively reducing the packaging area of an integrated circuit and number of pins.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

Color-temperature-adjustable COB packaging structure and packaging method thereof

InactiveCN105977245ARealize color temperature adjustmentSimple production processSolid-state devicesSemiconductor devicesDriving currentFluorescence

The invention discloses a color-temperature-adjustable COB packaging structure and a packaging method thereof. The color-temperature-adjustable COB packaging structure comprises a packaging substrate, CSP chip scale packaging devices, LED chips and a florescent glue sealing layer. The CSP chip scale packaging devices and the LED chips are fixed on the packaging substrate and wrapped by the florescent glue sealing layer. The florescent glue sealing layer is internally provided with at least one CSP chip scale packaging device and the LED chip, wherein the CSP chip scale packaging devices comprise chips and florescent glue wrapping the chips. The florescent glue and the florescent glue sealing layer are different in phosphor concentration. Light emitted by the CSP chip scale packaging devices and the LED chips passes through different numbers of phosphor powder particles and then color of different color temperature is obtained. The effect of color temperature adjustment can be achieved by controlling driving current in the CSP chip scale packaging devices and the LED chips.

Owner:ZHONGSHAN LITI LIGHTING TECH

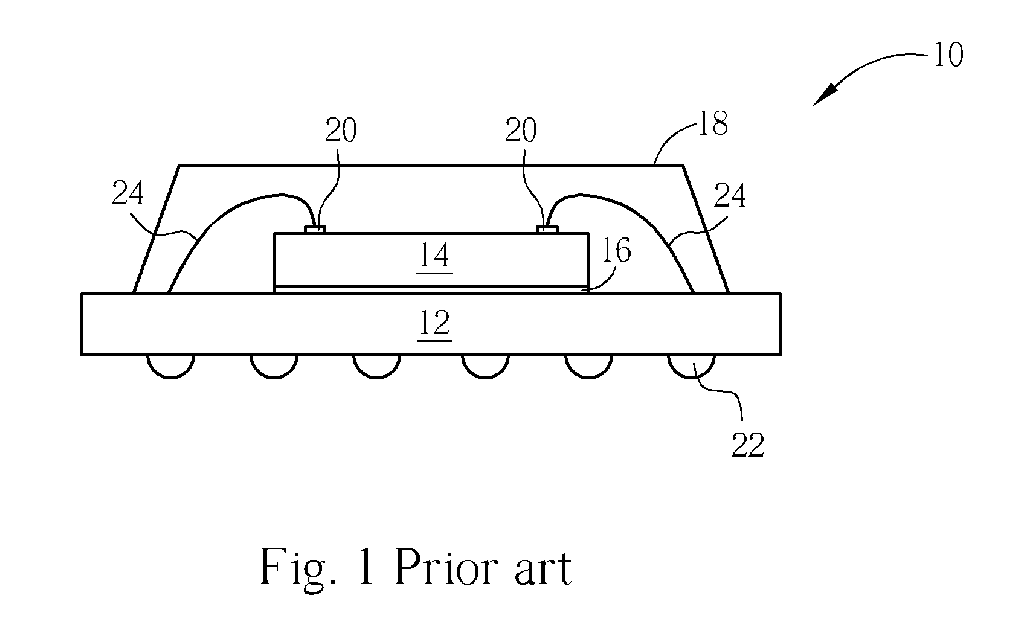

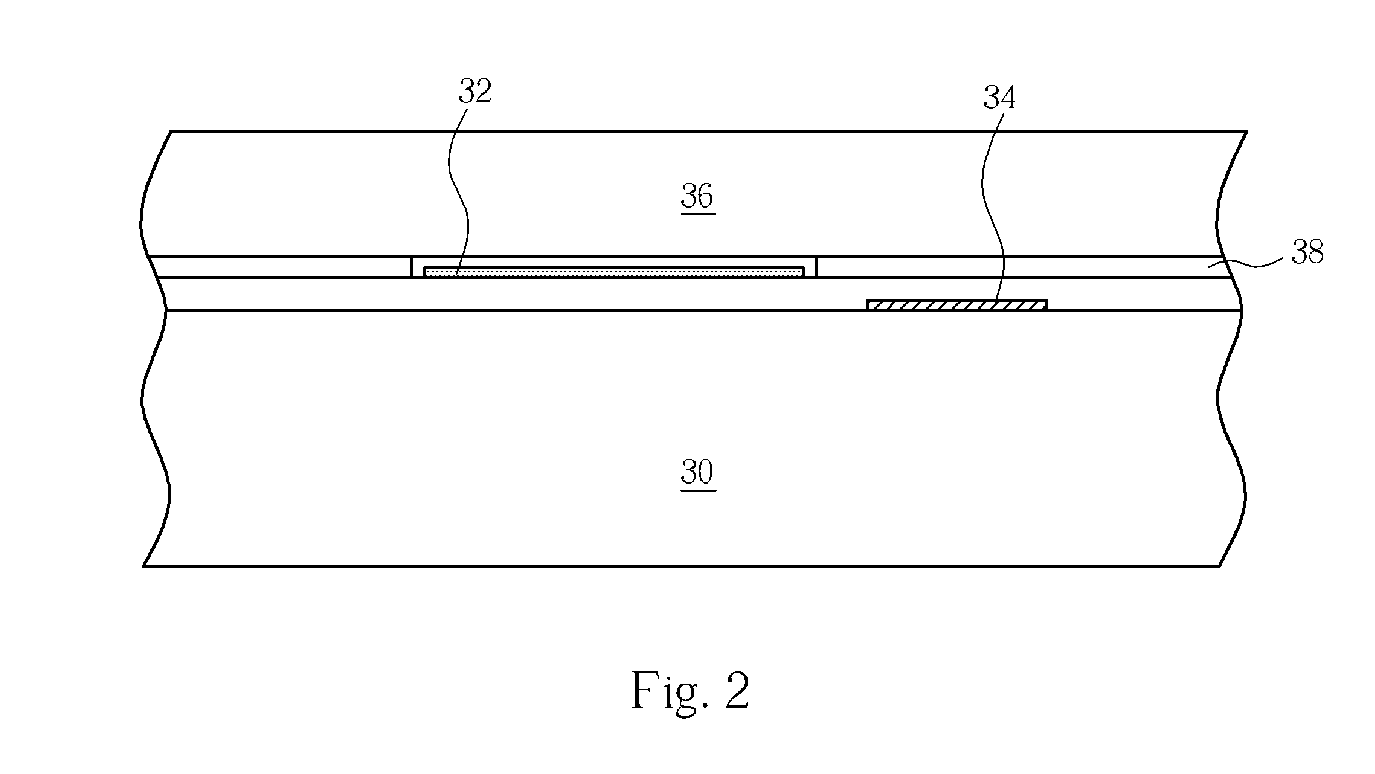

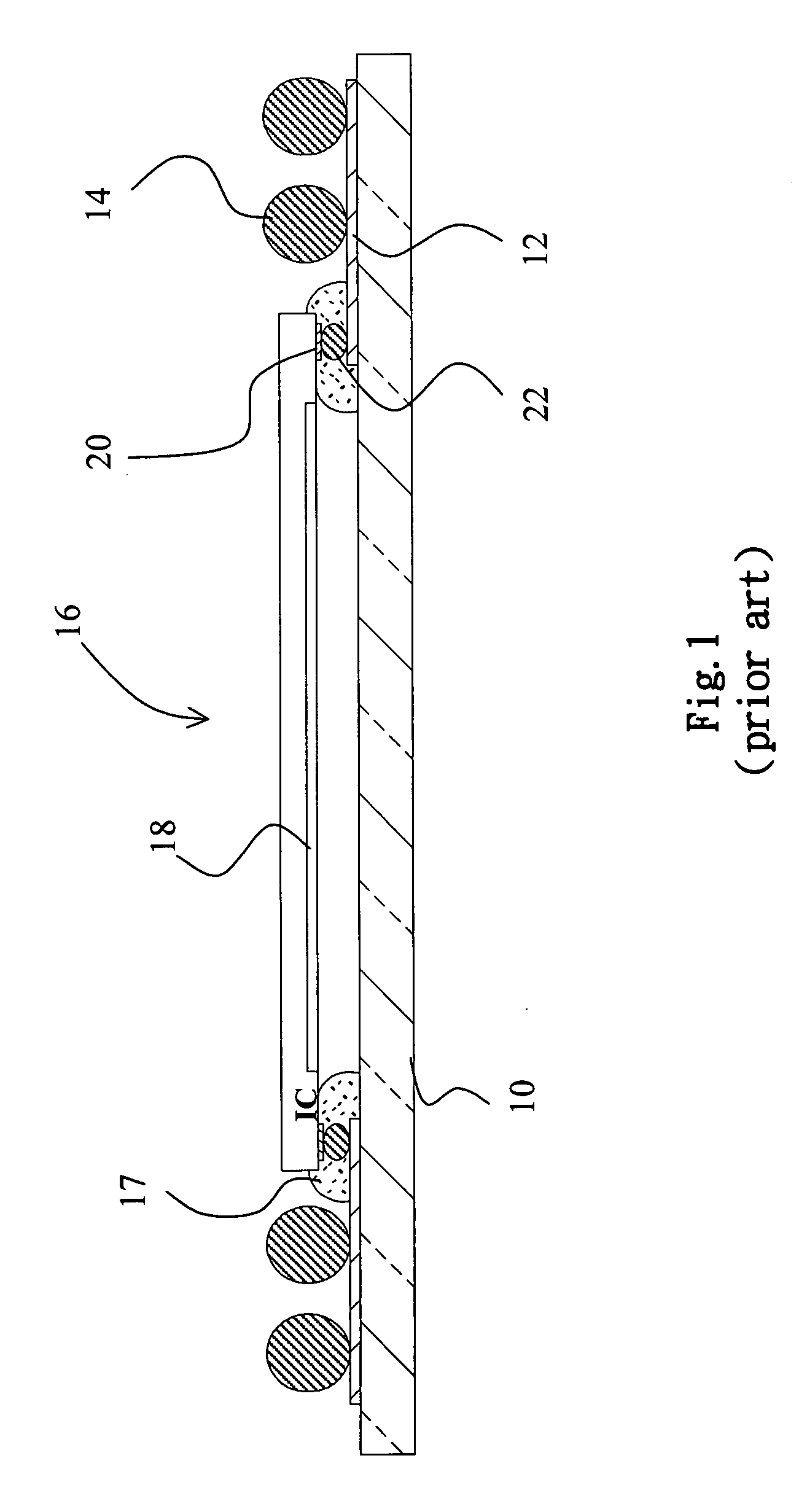

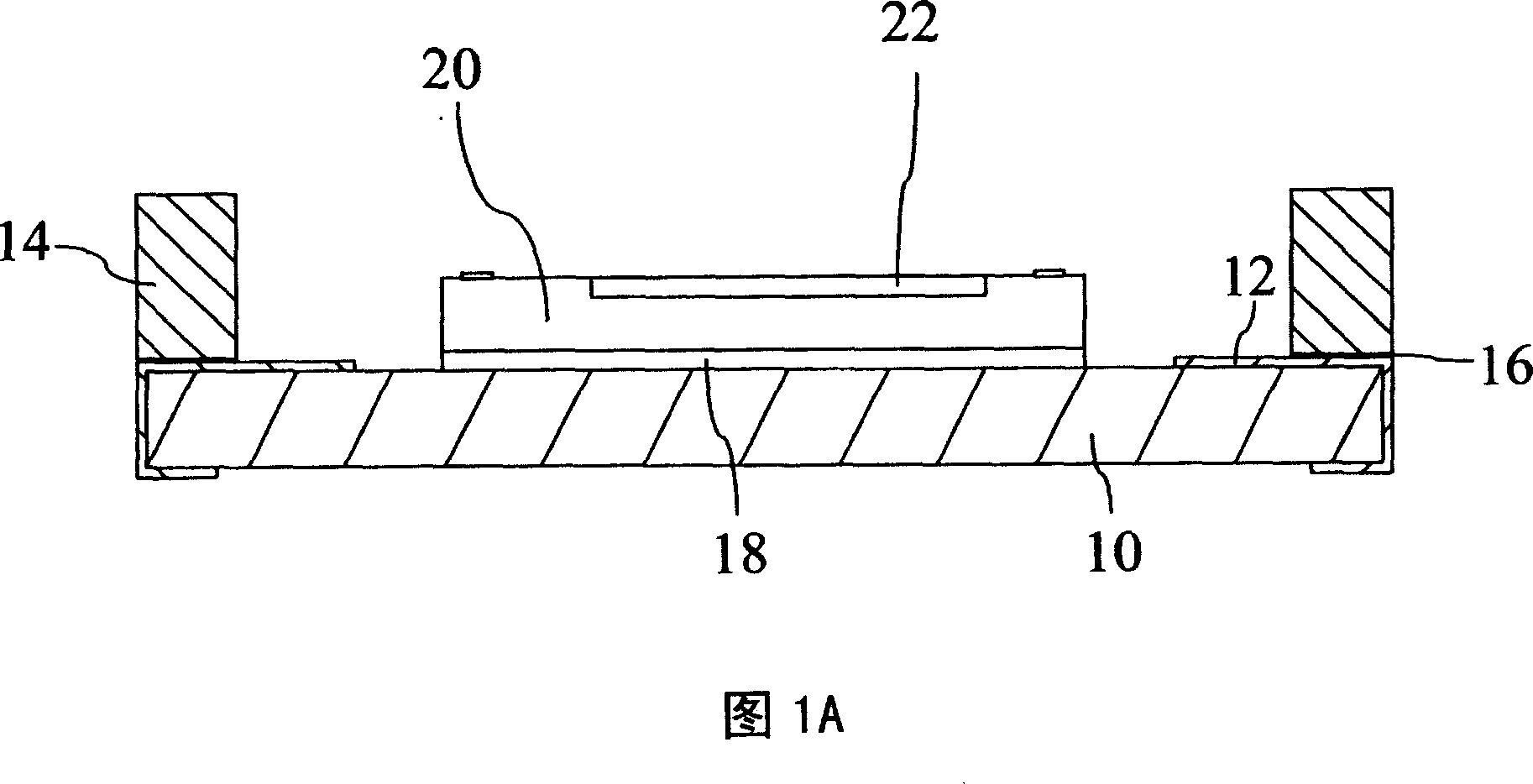

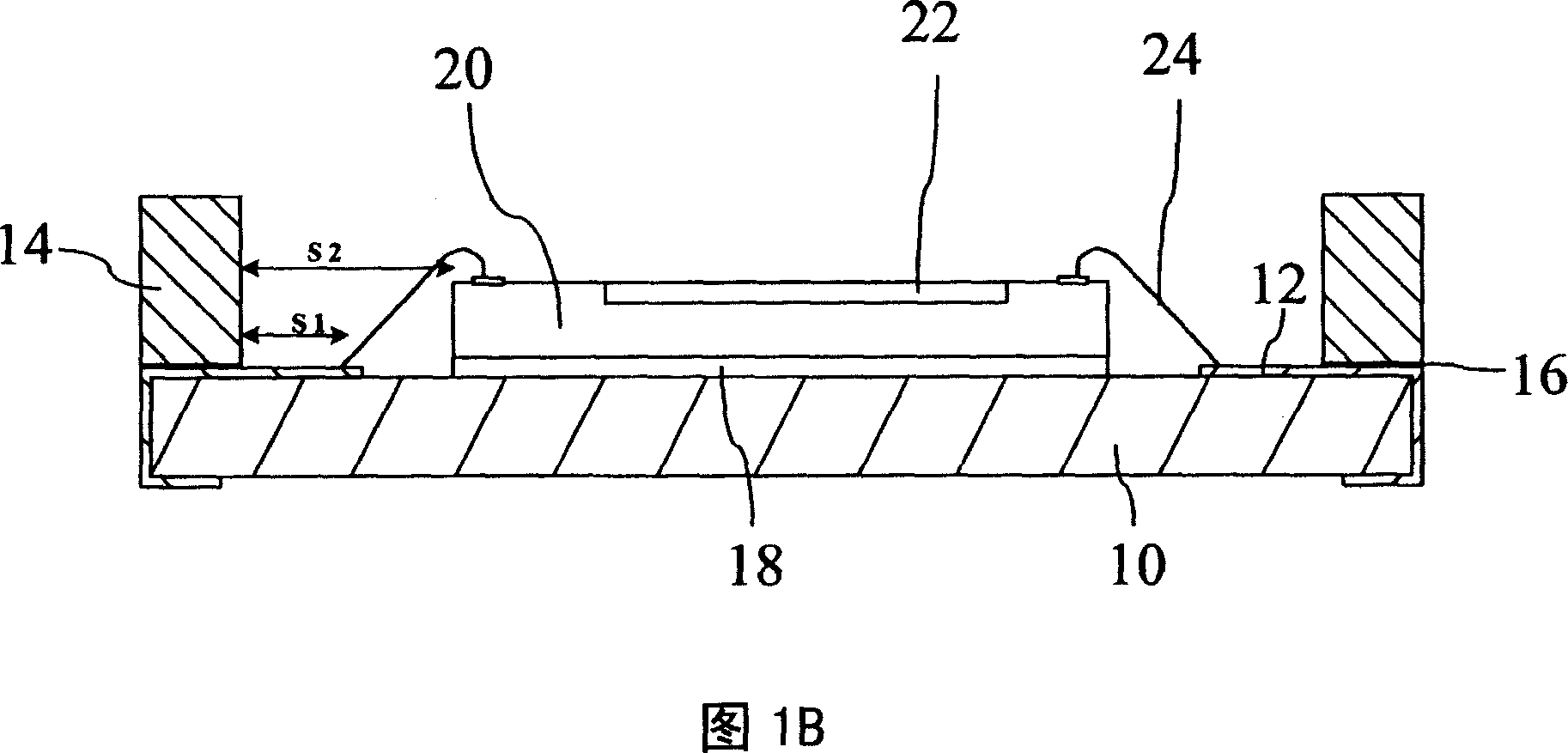

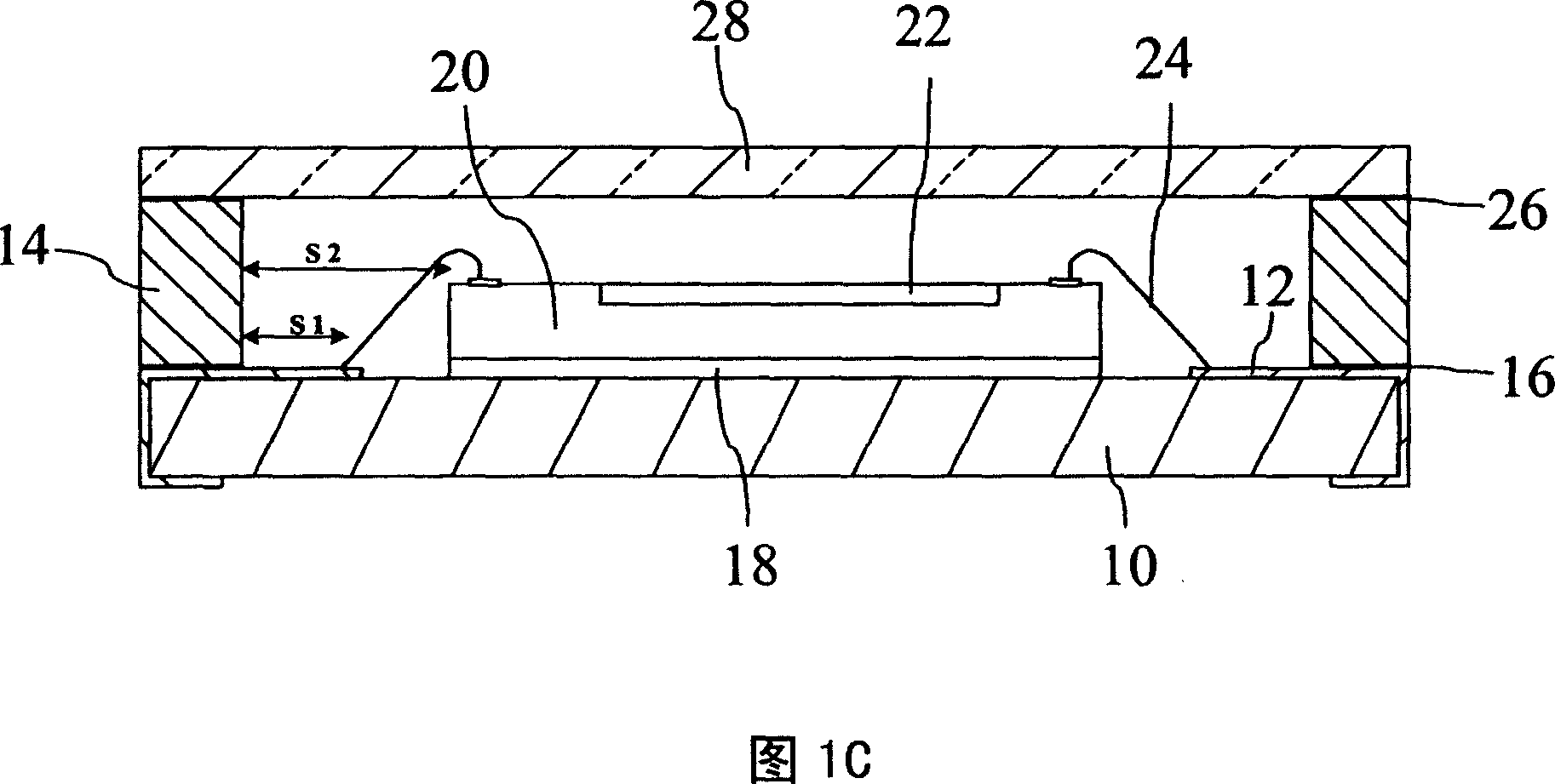

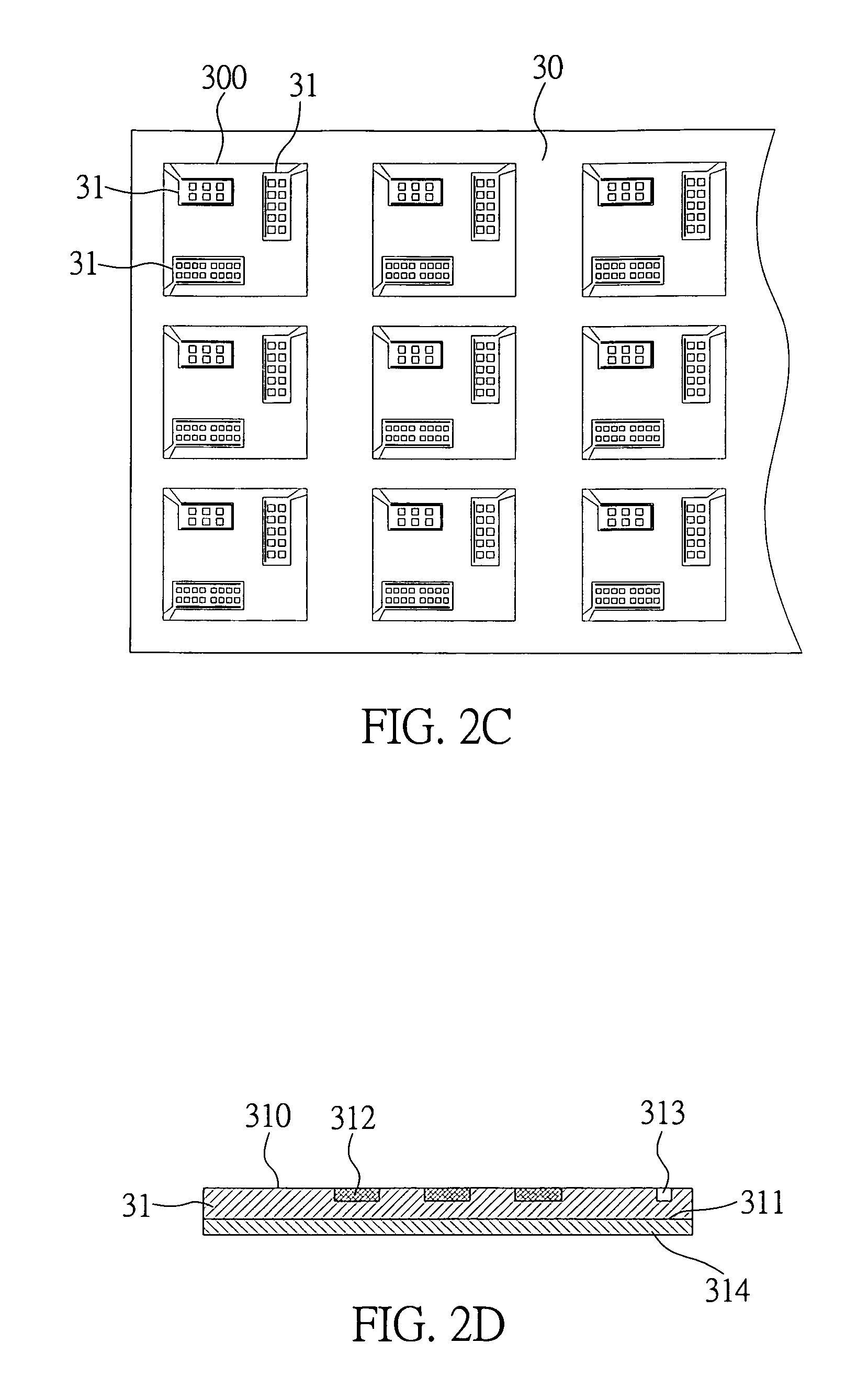

Image sensor package structure

InactiveUS20070090478A1Improve package yieldAvoid pollutionSolid-state devicesSemiconductor devicesCMOSSolder ball

An image sensor package structure is proposed, in which an image sensor is fixed on a substrate having metallization traces and an adhesion layer. Electric paths of the package structure are changed from the COG (chip on glass) process to the CIS (CMOS image sensor) process to improve electric characteristics. Moreover, spacers are formed at appropriate positions to prevent glue overflow from contaminating the sensing regions and solder balls. The proposed package structure can also shrink the package area to greatly enhance the yield and quality.

Owner:SIGURD MICROELECTRONICS CORP

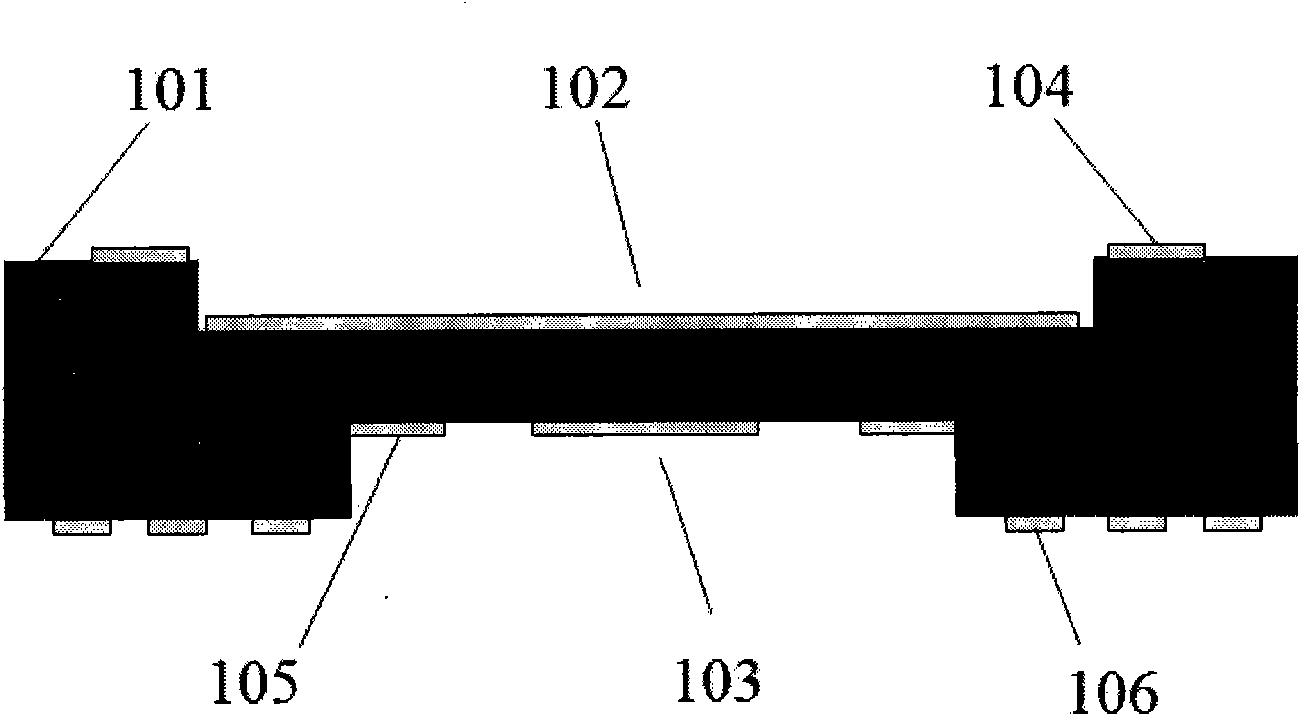

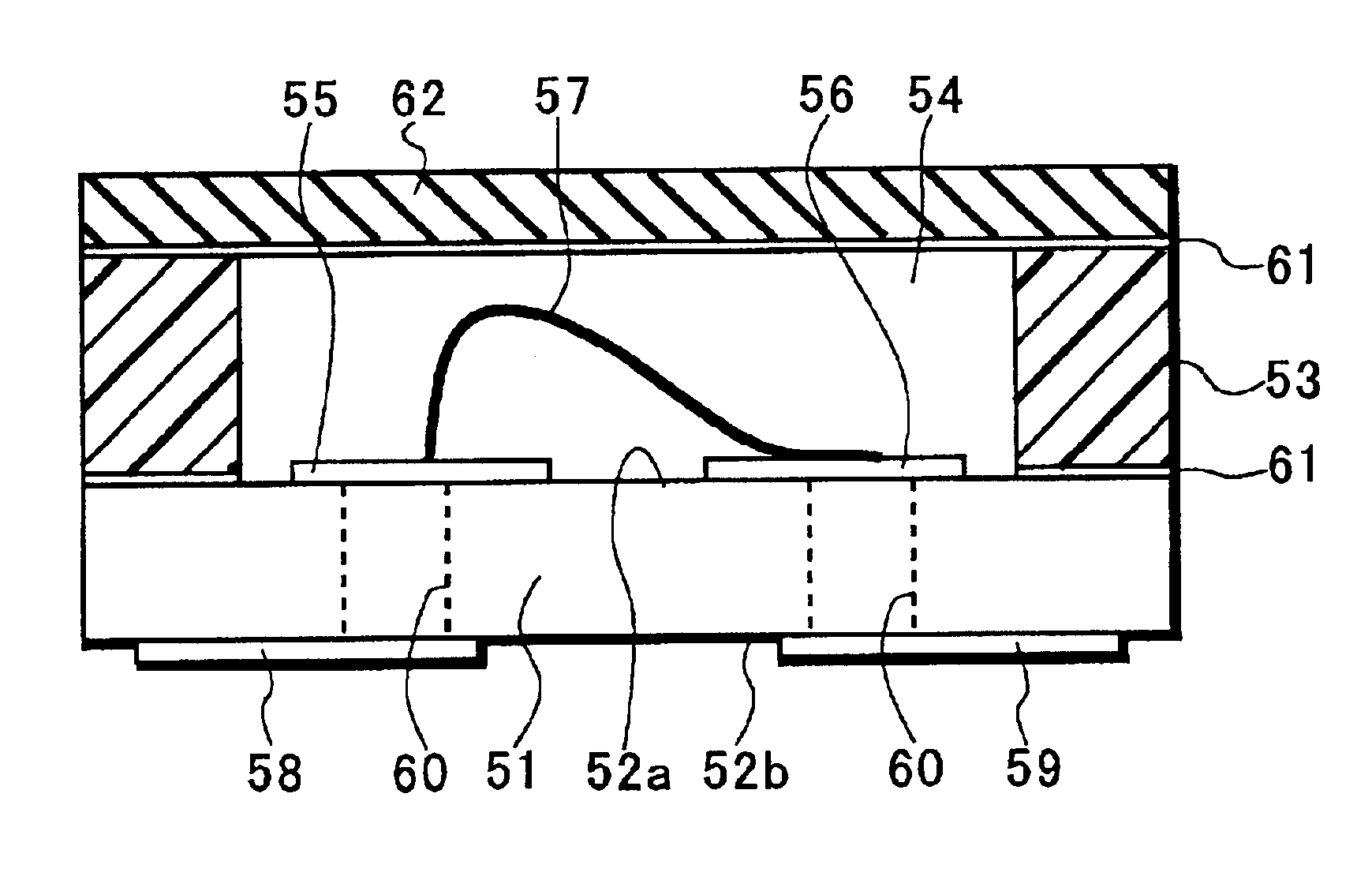

Power semiconductor device

ActiveUS20050051874A1Shorten the line lengthReduction of the wiring inductanceTransistorBus-bar/wiring layoutsPower semiconductor deviceEngineering

Emitter electrodes (Es) and collector electrodes (Cs) of elements (101 to 104) are connected to bus electrodes (361 to 364) of a bus bar (351), respectively. The bus bar (351) contains seven layers including four insulating layers (not shown) and three conductive layers (shown) interposed between the insulating layers. Namely, each of the bus electrodes (361 to 364) is connected to one of the conductive layers corresponding to one of a positive electrode (P), a negative electrode (N) and an intermediate electrode (L). The collector electrodes (Cs) of the elements (103 and 104) are connected one over the other to the bus electrode (361). The emitter electrodes (Es) of the elements (103 and 104) are connected one over the other to the bus electrode (362). The collector electrodes (Cs) of the elements (101 and 102) are connected one over the other to the bus electrode (363). The emitter electrodes (Es) of the elements (101 and 102) are connected one over the other to the bus electrode (364).

Owner:MITSUBISHI ELECTRIC CORP

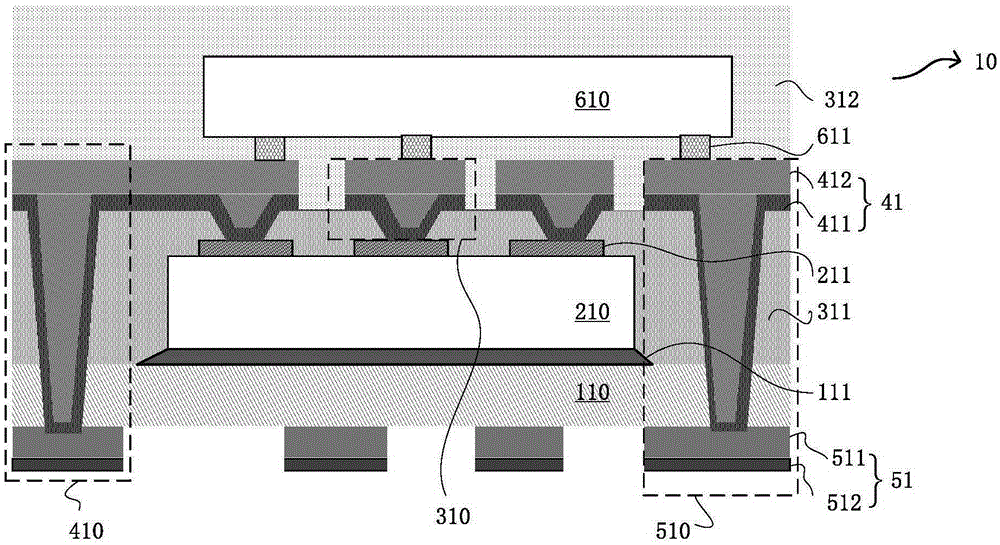

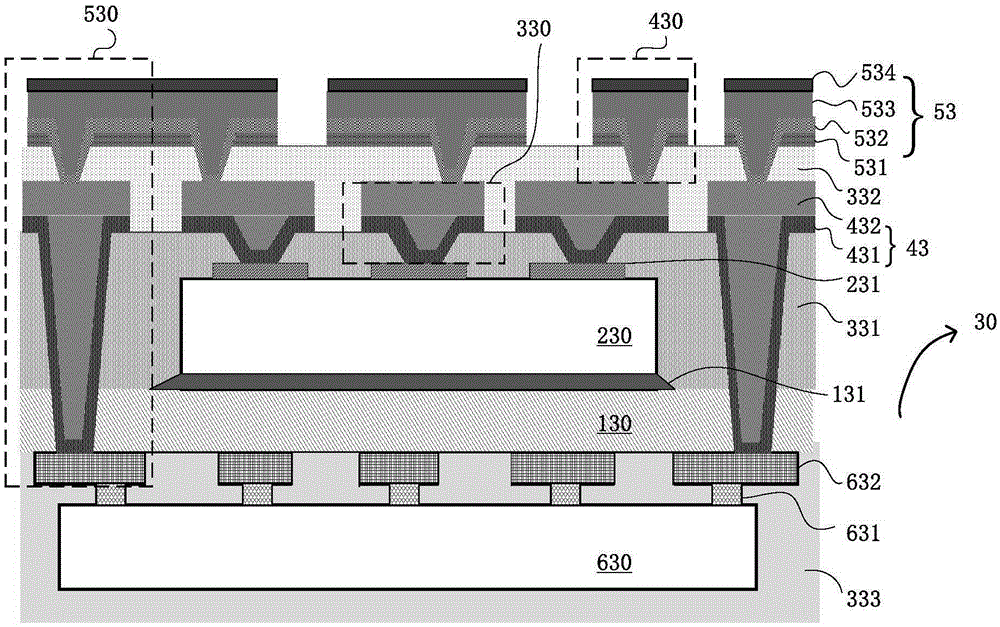

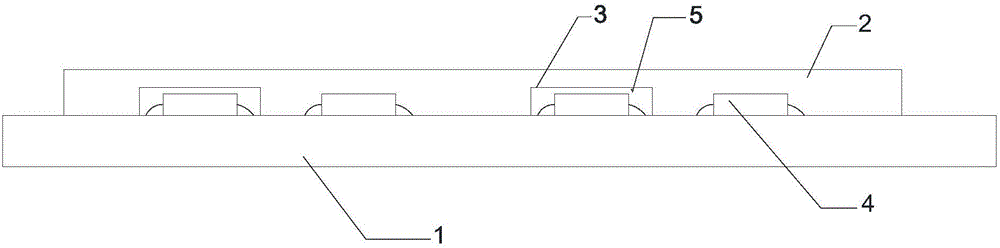

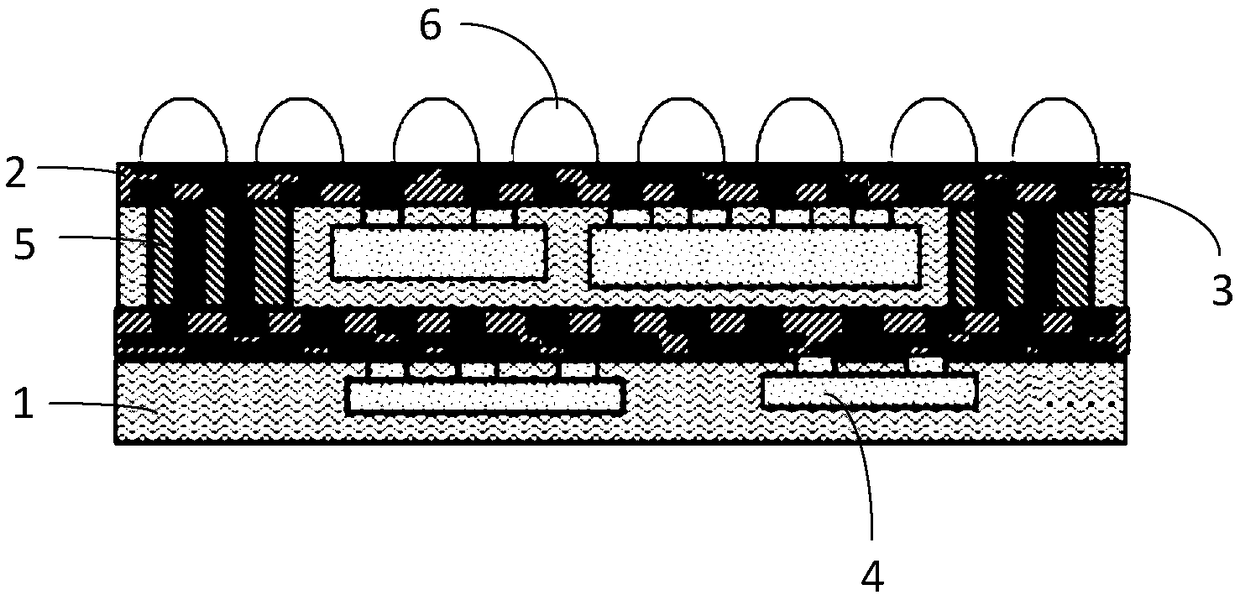

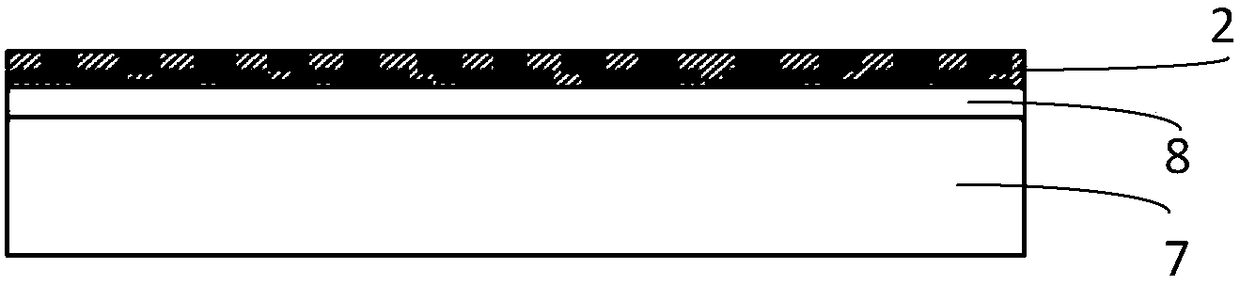

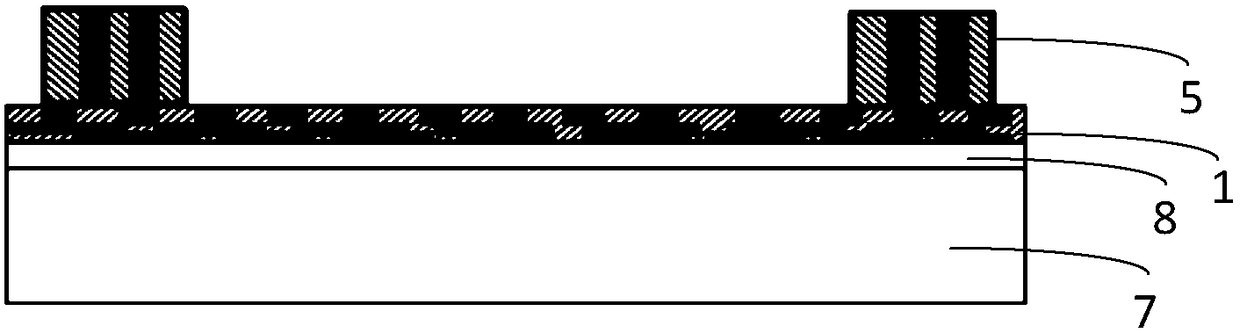

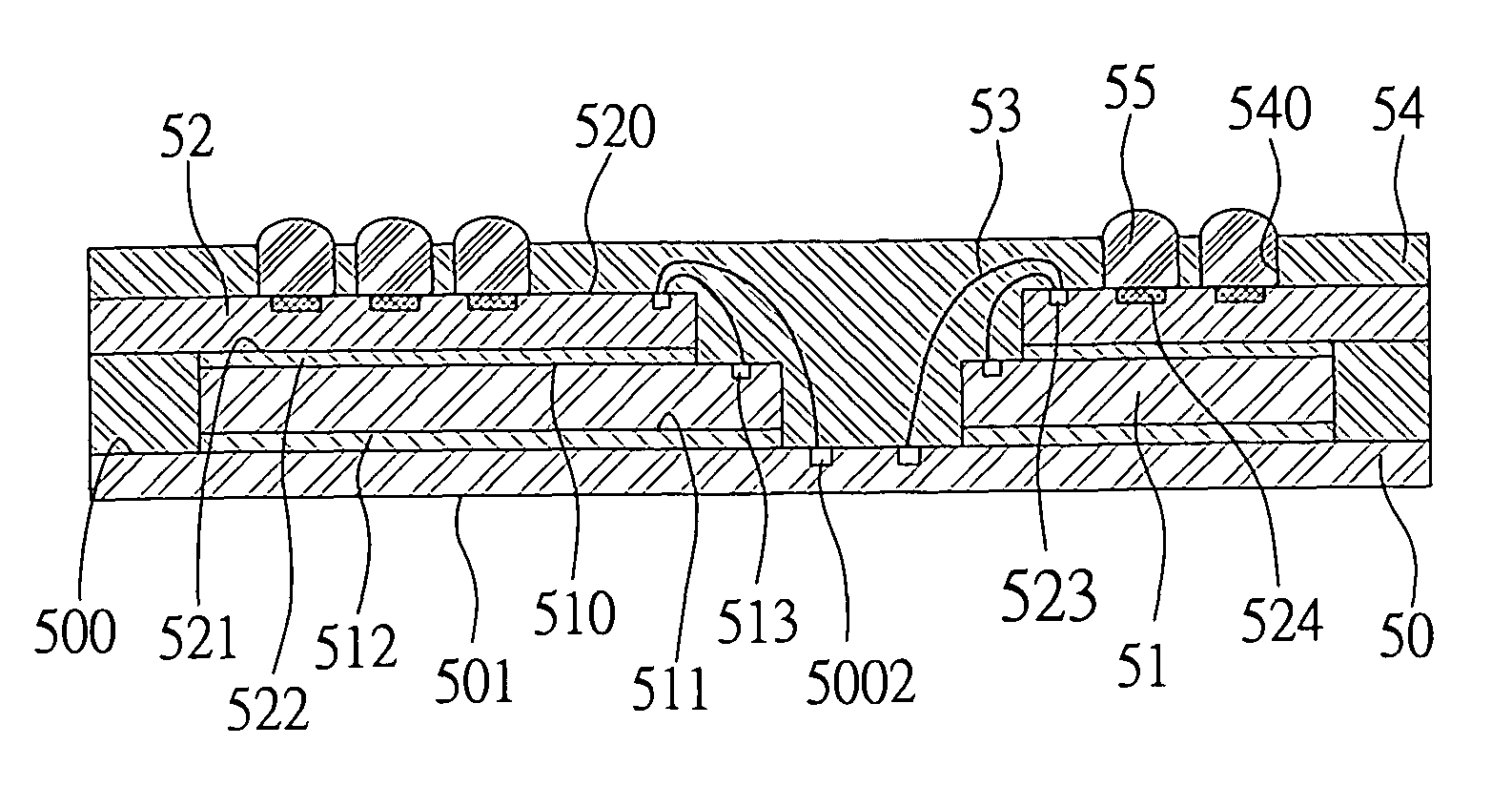

Multi-chip wafer level fan-out type three-dimensional package structure and packaging process thereof

PendingCN108389823AHighly integratedReduced package areaSemiconductor/solid-state device detailsSolid-state devicesEngineeringFan-out

The invention relates to a multi-chip wafer level fan-out type three-dimensional package structure, comprising at least two rewiring layers, wherein the rewiring layers are dielectric layers, metal connecting structures connected with two sides to match each other and form interconnecting structures are provided on two sides of the dielectric layers, the metal connecting structures expose the dielectric layers to form metal contacts, a plastic sealing layer is arranged on one side of the rewiring layers, chips or passive elements are packaged in the plastic sealing layer, and the adjacent rewiring layers are connected by micro silicon blocks. The invention also discloses a packaging process for the multi-chip wafer level fan-out type three-dimensional package structure. By adopting the design scheme, passive devices of different sizes can be simultaneously integrated and packaged with bare chips, so that the degree of integration is greatly improved, the packaging process is particularly suitable for application of wifi, PA, PMU and the like using a large number of passive devices, and at the same time, the three-dimensional stacking method greatly reduces the packaging area.

Owner:王新

Packaging structure for optical sensing assembly and method of manufacture

InactiveCN1921125ANot pollutedImprove processing yieldSolid-state devicesSemiconductor/solid-state device manufacturingAdhesiveColloid

The invention relates to a package of light-sensitive element and relative production. Wherein, it comprises: mounting light-sensitive chip on the base plate; clearing the contaminant; then using adhesive to mount a transparent sealing cover with chamber above the base plate, to cover the chip; therefore, it can clear the contaminant, improve the yield and reduce the packing area; in addition, the invention can arrange connecting part above the base plate and sealing cover to support connection.

Owner:SIGURD MICROELECTRONICS CORP

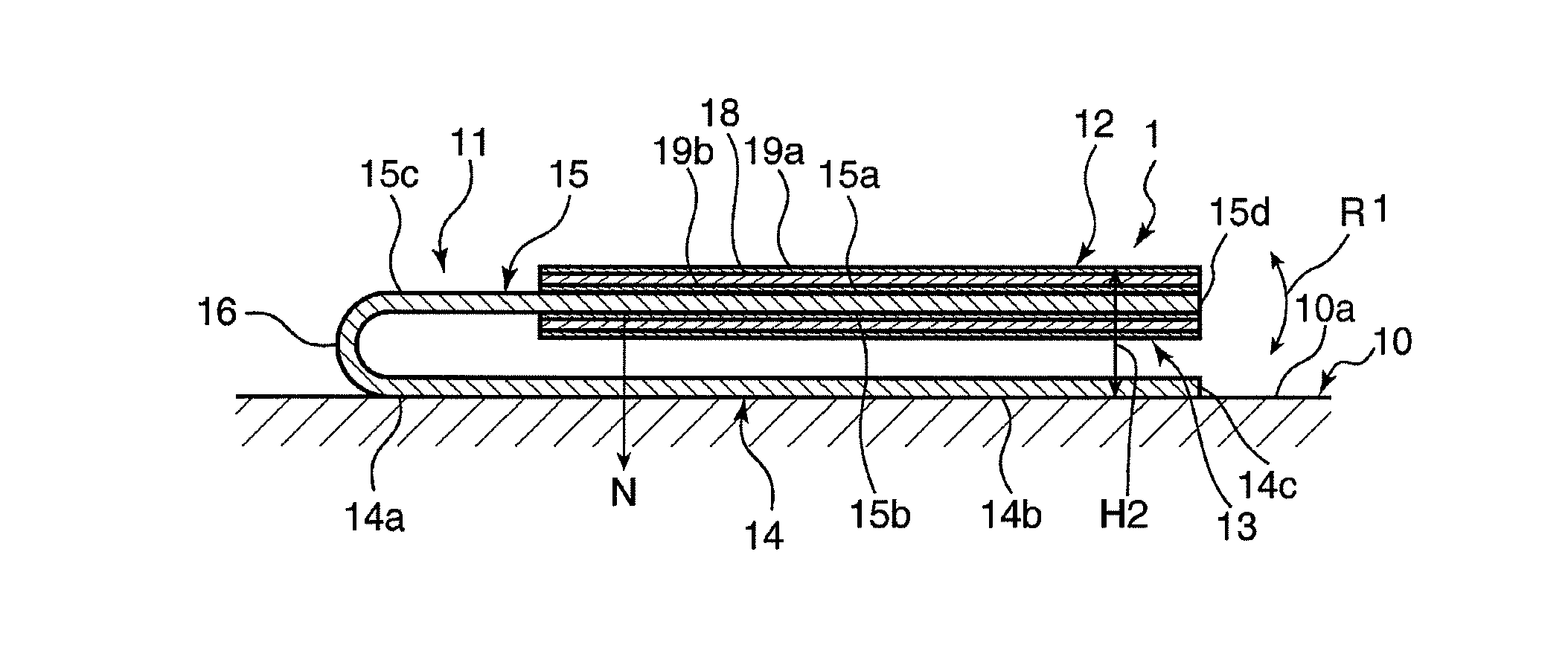

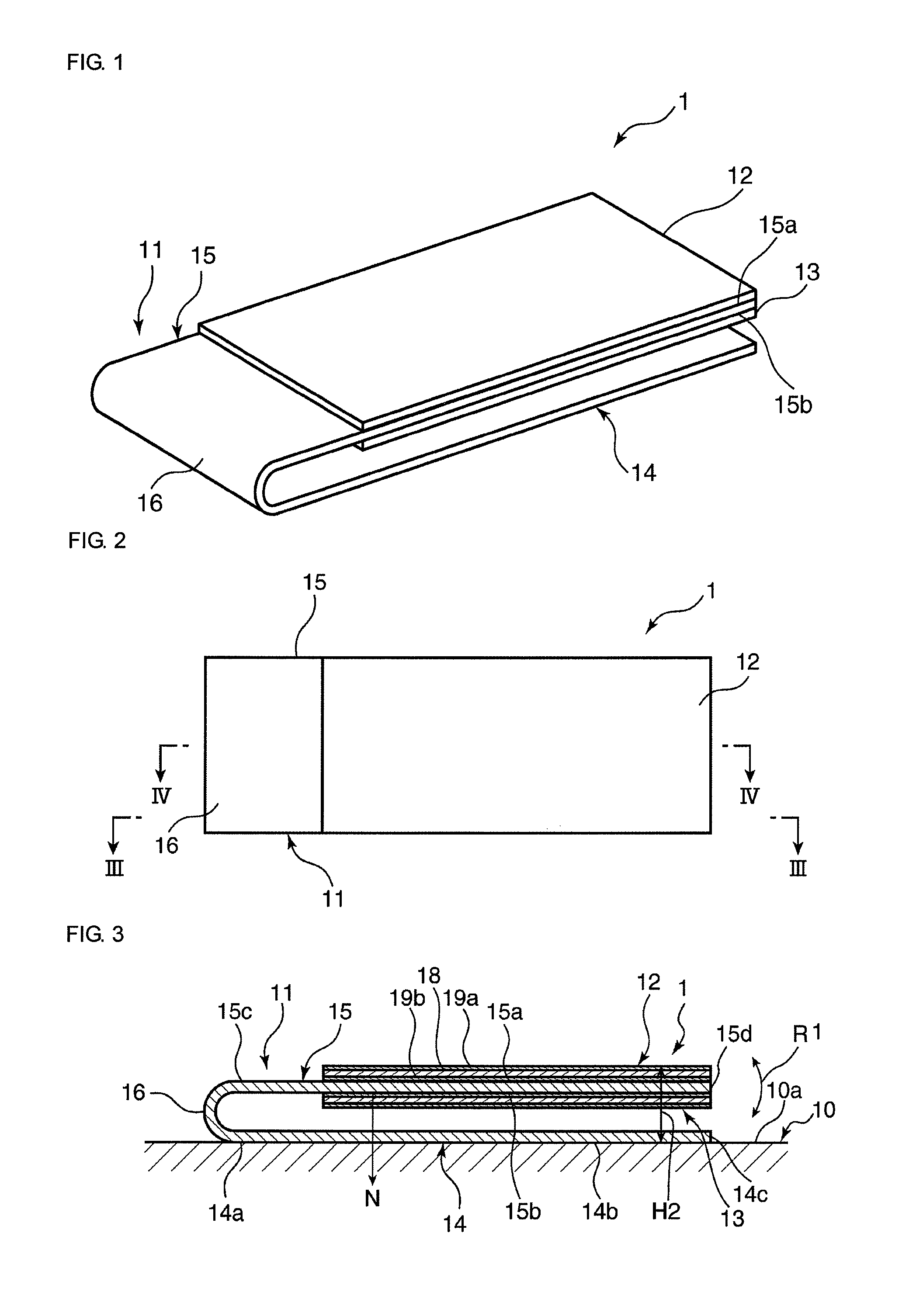

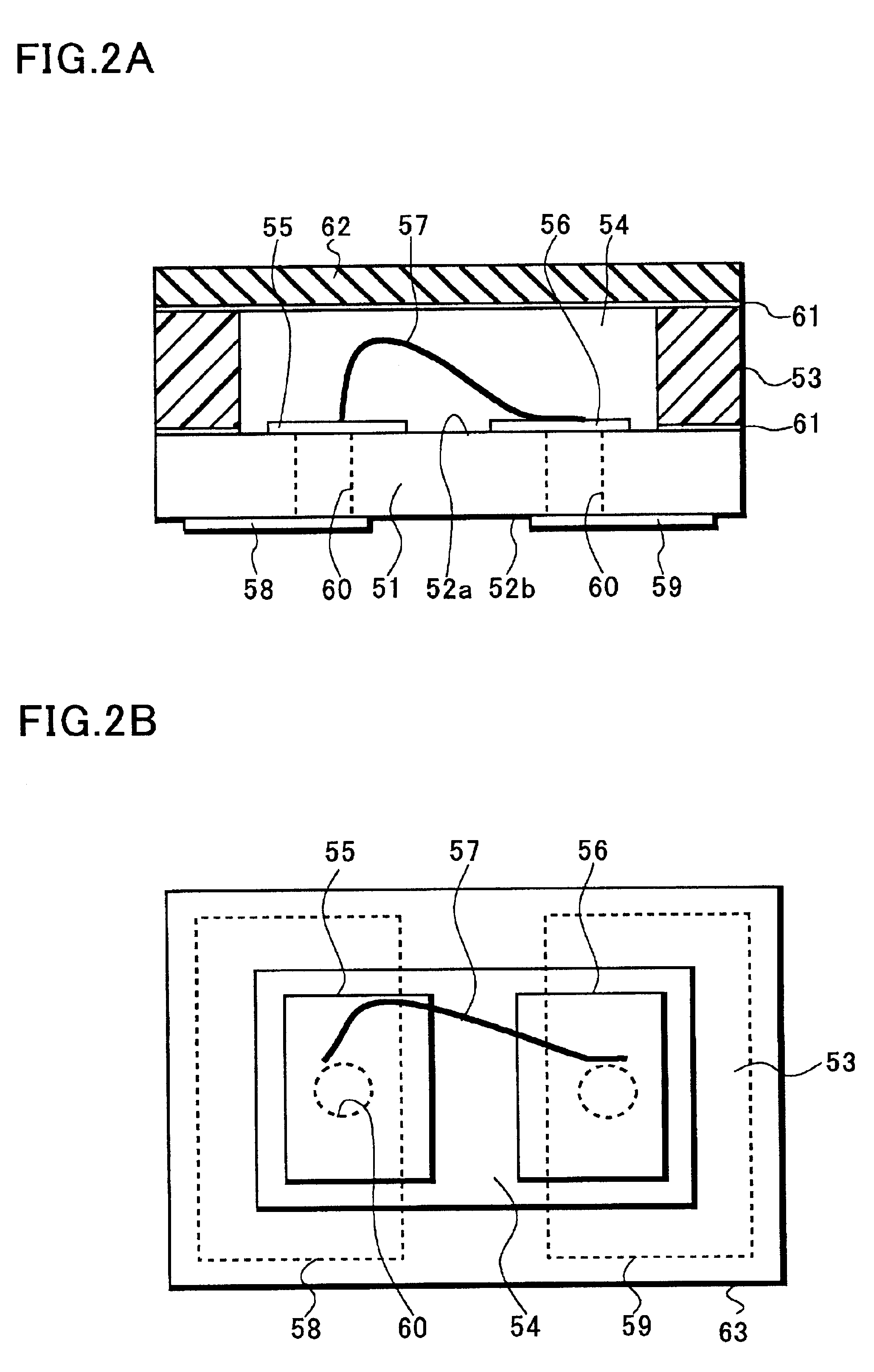

Electronic component device and method for manufacturing the same

ActiveUS8247954B2Low part-countHigh vibration transmission efficiencyPiezoelectric/electrostriction/magnetostriction machinesMechanical vibrations separationElectronic component

Owner:MURATA MFG CO LTD

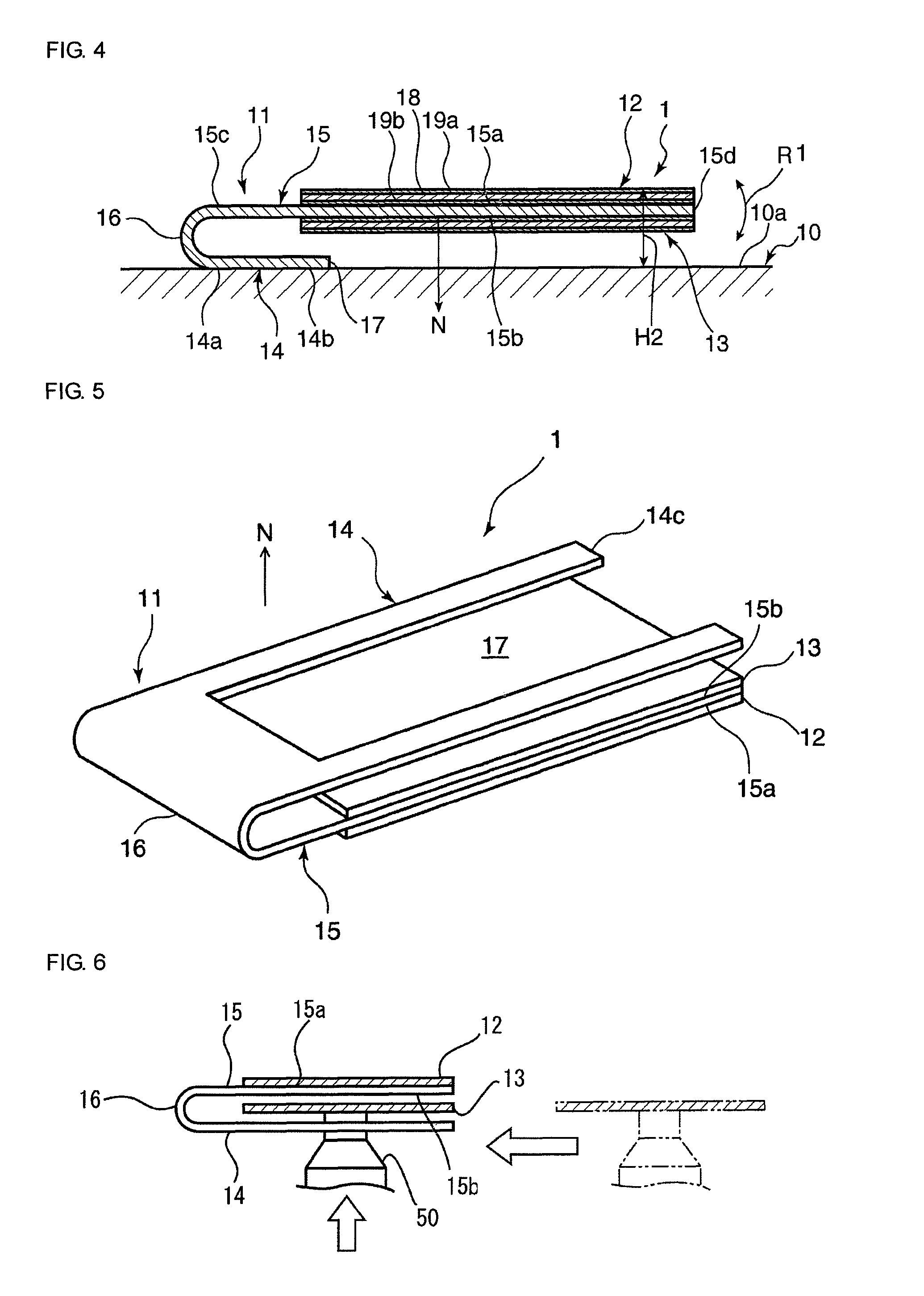

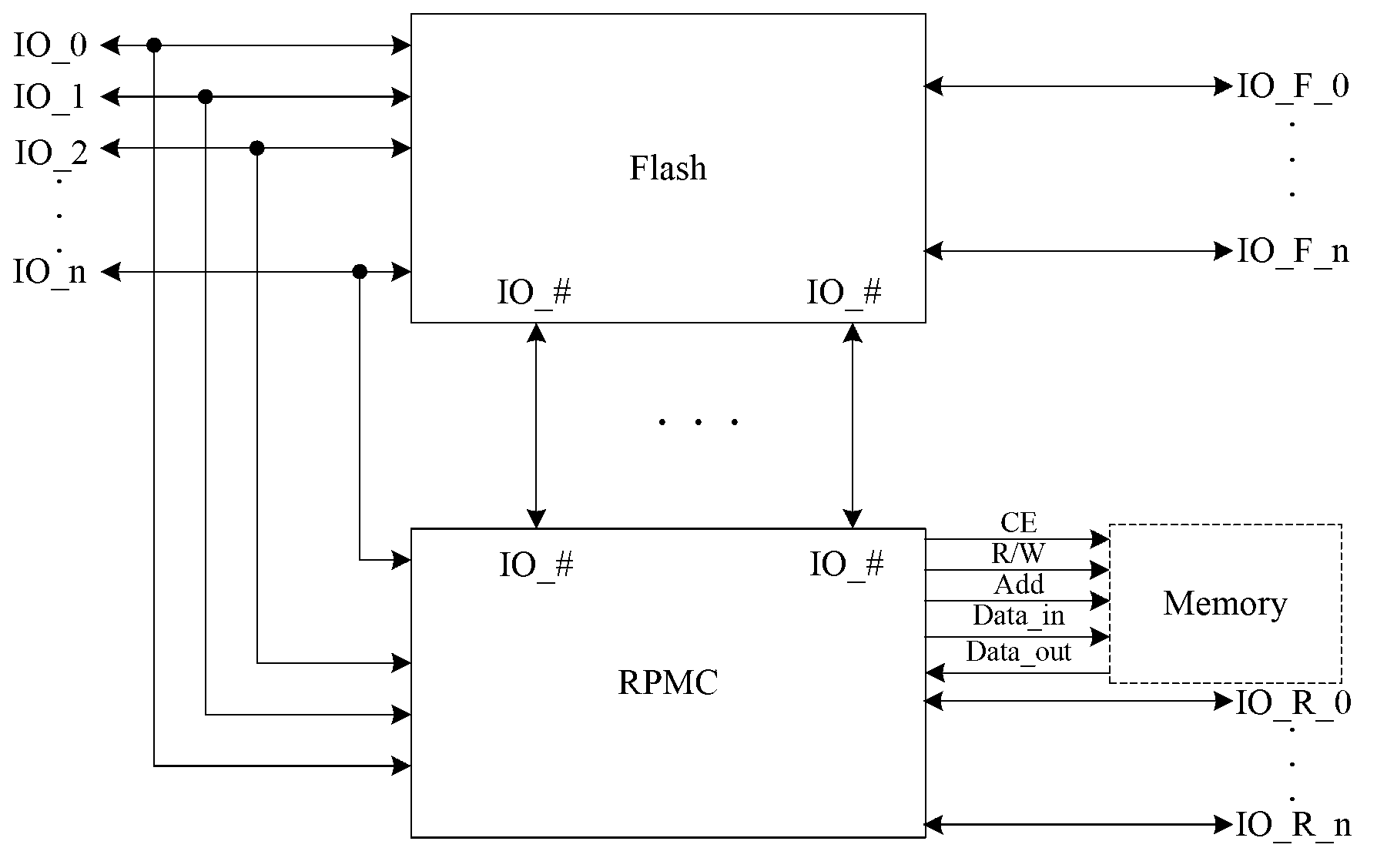

RPMC-comprising (replay protection monotonic counter-comprising) enhanced flash chip and packaging method thereof

ActiveCN103236428AGuaranteed synchronizationImprove performanceSemiconductor/solid-state device detailsSolid-state devicesEmbedded systemHigh complexity

The invention provides an RPMC-comprising (replay protection monotonic counter-comprising) enhanced flash chip and a packaging method thereof. The RPMC-comprising enhanced flash chip comprises a flash, an RPMC, and a memory chip, wherein the flash and the RPMC are packaged together and the memory chip is connected with the RPMC. Both the flash and the RPMC comprise respectively independent controllers. Same IO (input and output) pins in the flash and the RPMC are interconnected and are connected to a same external shared pin of the chip. Both the flash and the RPMC further comprise internal IO pins. The RPMC and the memory chip further comprise signal transmission IO pins. By the RPMC-comprising enhanced flash chip, the problems of high complexity, long cycle, high cost and large chip area in chip design are solved.

Owner:GIGADEVICE SEMICON (BEIJING) INC

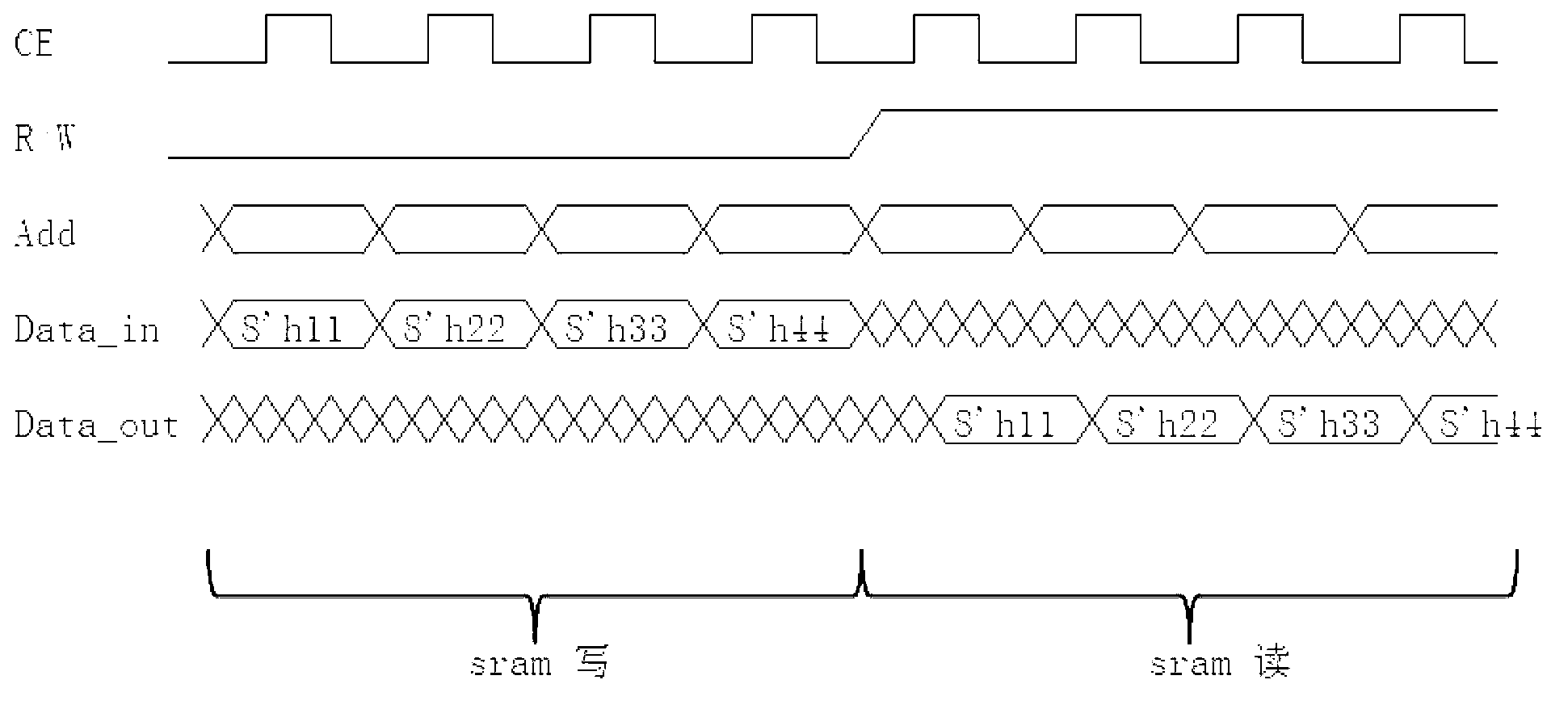

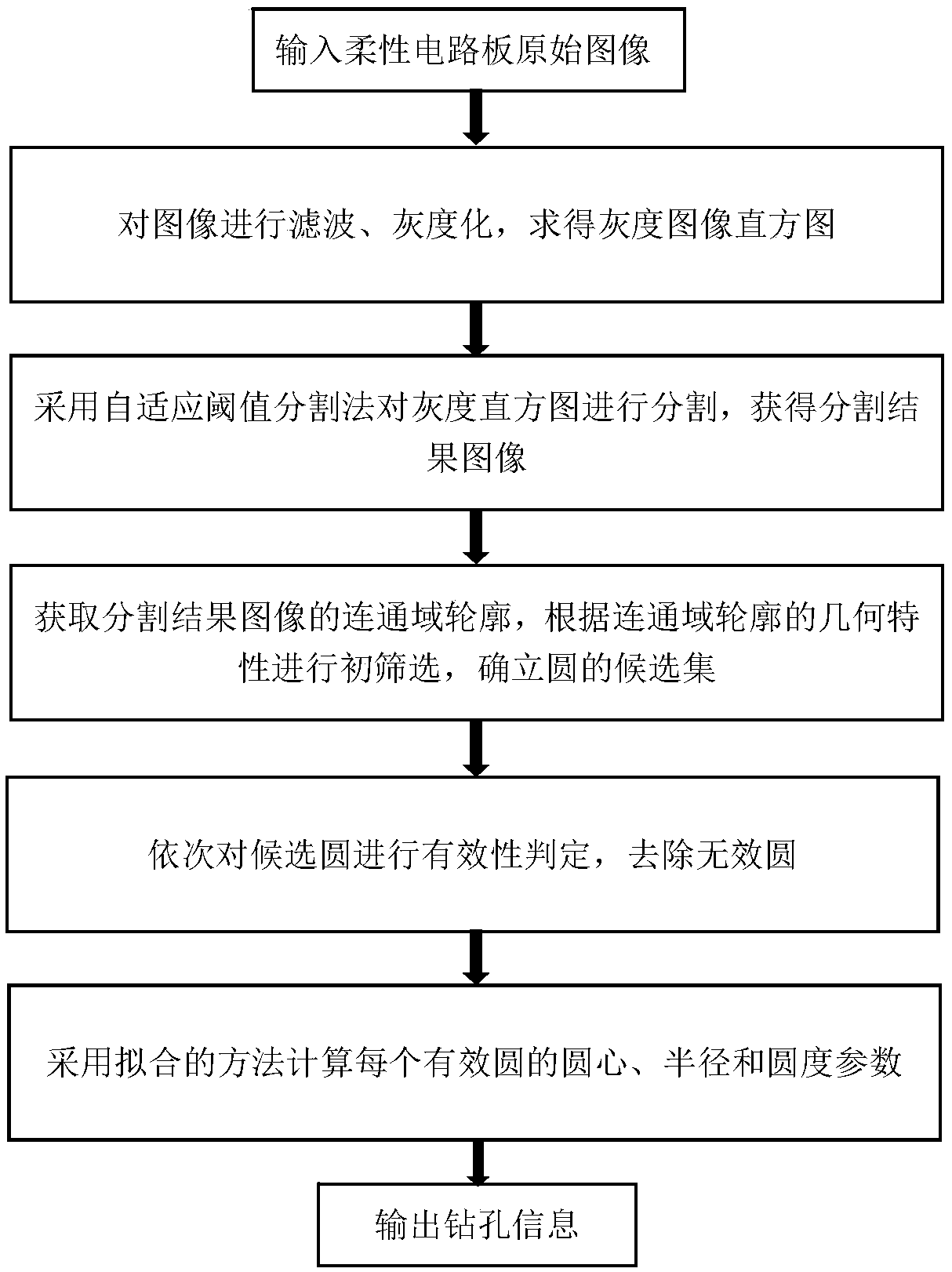

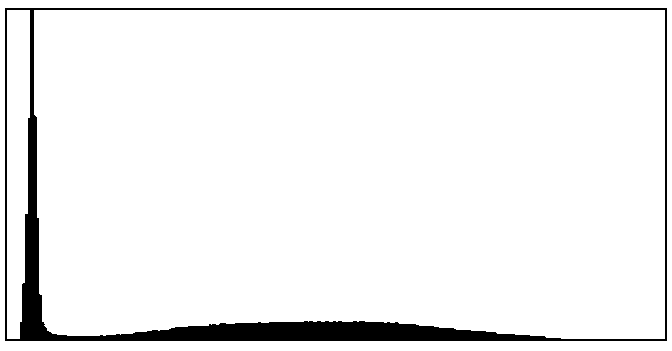

Method of threshold segmentation detection for circular holes in flexible circuit board

ActiveCN107705297AQuick checkEfficient and accurate detectionImage enhancementImage analysisGeometric propertyFlexible circuits

The invention discloses a method of threshold segmentation detection for circular holes in a flexible circuit board. The method comprises the steps of obtaining a gray scale image of a flexible circuit board according to an original image of the flexible circuit board; segmenting the gray scale image of the flexible circuit board by using an adaptive threshold segmentation method based on a gray scale histogram and obtaining a segmentation result image of the flexible circuit board; obtaining a connected domain contour image of the segmentation result image of the flexible circuit board, performing initial screening based on geometric properties of the connected domain contour, and establishing a candidate set of circles; judging the validity of candidate circles in the candidate set in sequence, determining the valid candidate circles and the invalid candidate circles in the candidate set, and removing the invalid candidate circles in the candidate set; and calculating the circle center, radius and roundness parameters of the valid circles by using a fitting method. The method of the invention can detect the circular holes in the flexible circuit board more quickly and accurately,and realizes the real-time detection of the circular holes; and for flexible substrates, the method of the invention has higher detection precision of the circular holes therein.

Owner:SOUTH CHINA UNIV OF TECH

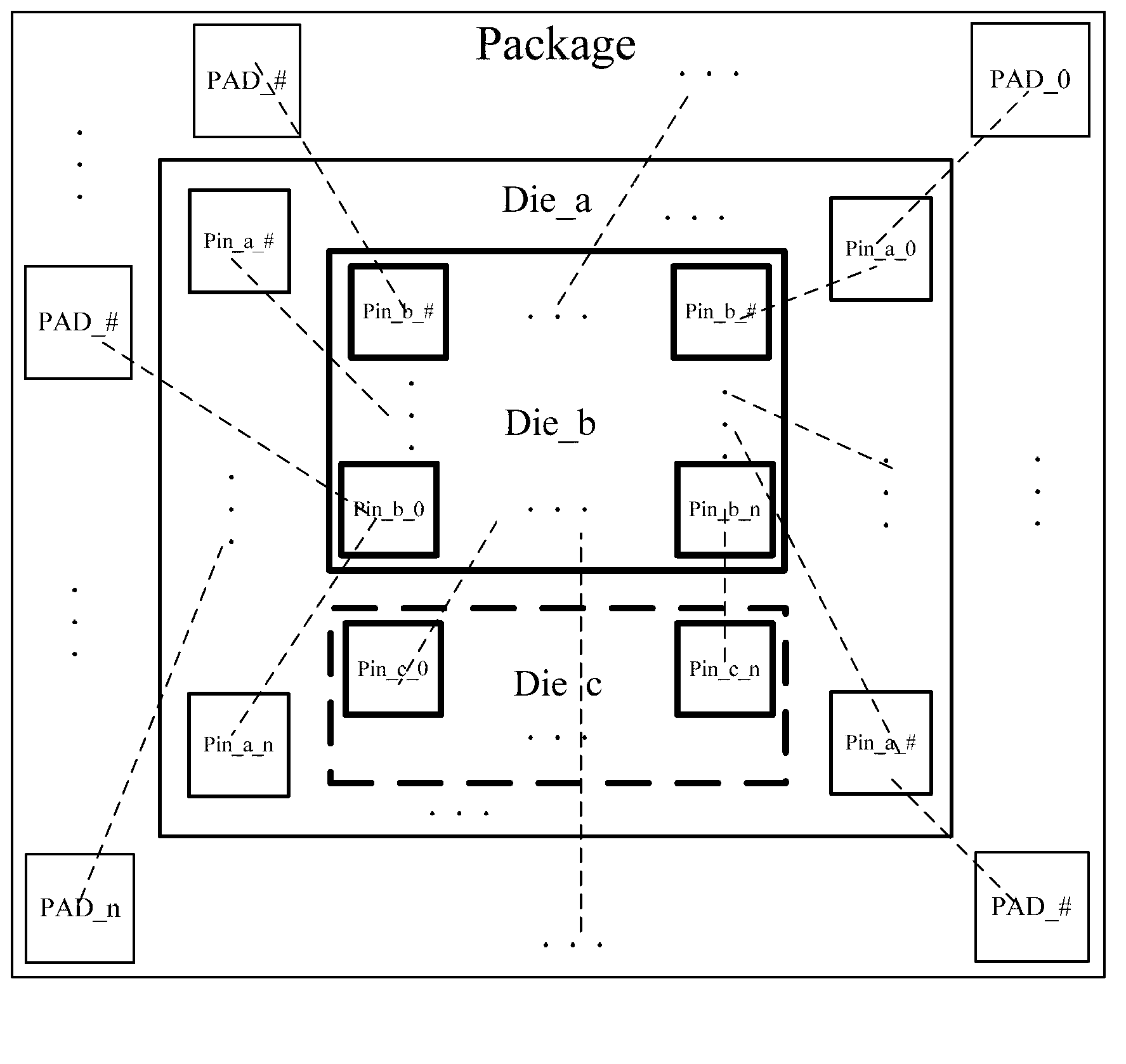

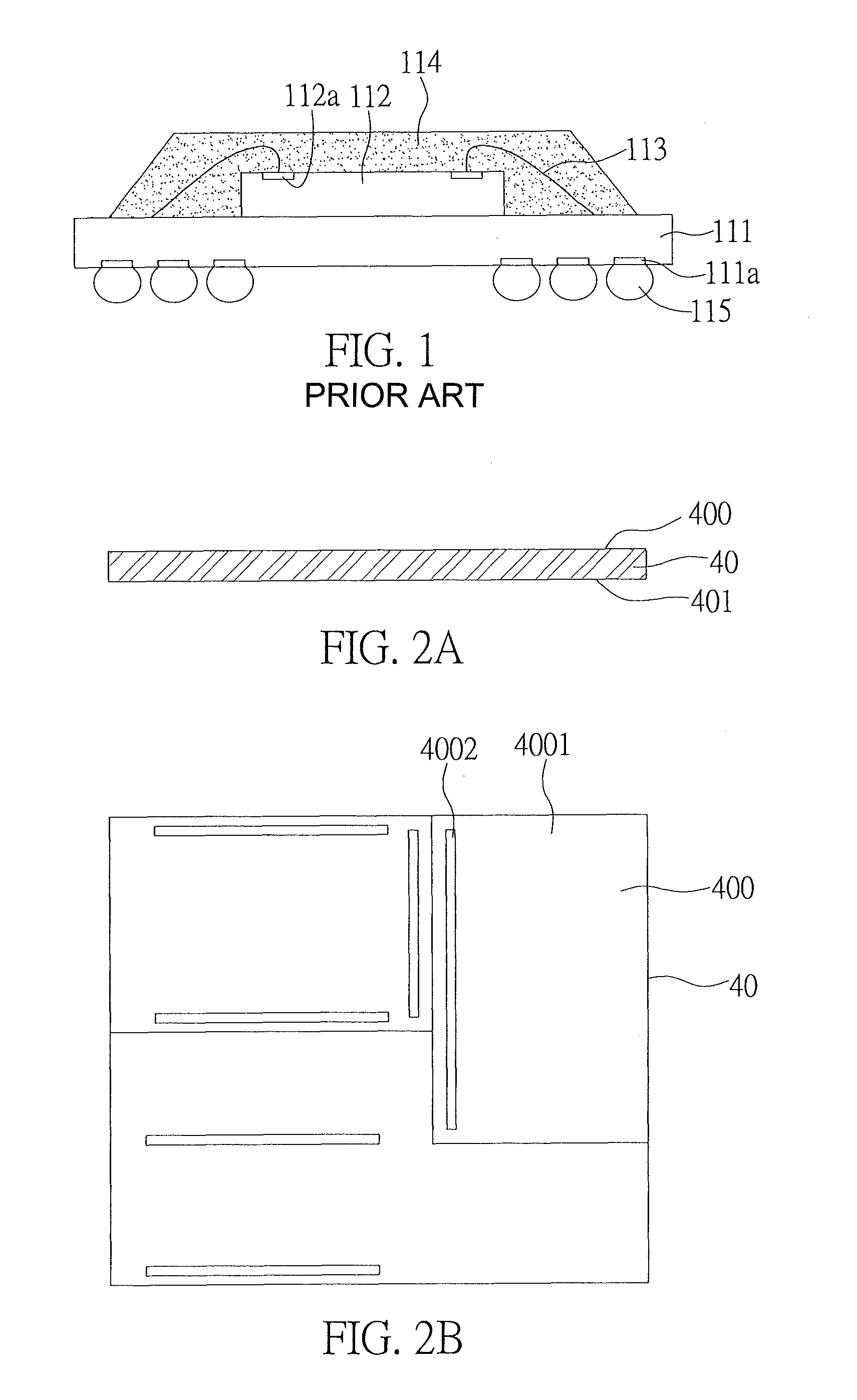

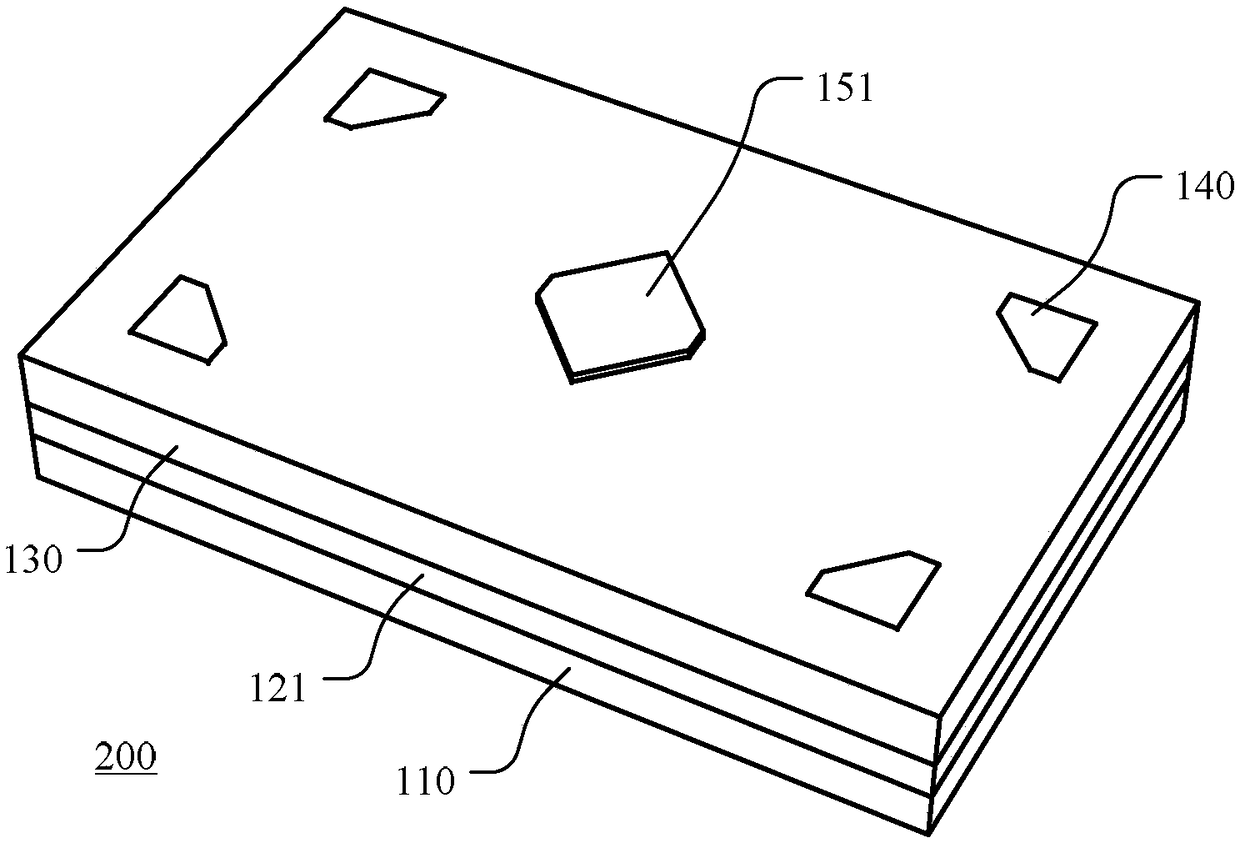

Multi-substrate region-based package and method for fabricating the same

ActiveUS7859118B2Cost-effectiveIncrease productionSemiconductor/solid-state device detailsSolid-state devicesEngineeringActive surface

A multi-substrate region-based package and a method for fabricating the same are provided. An active surface of a chip is divided into a plurality of functional regions, and each of the functional regions is electrically connected to a corresponding substrate via bonding wires. Each of the functional regions has a separate system, and the circuit layout thereof is not limited by the substrate or other systems but can be flexibly and independently designed, thereby allowing the package to be made smaller and thinner. Each set of the functional region and its corresponding substrate functions as an independent unit, such that the substrates are not affected by each other, thereby providing good compatibility, improved reliability and reduced packaging area.

Owner:UTAC HEADQUARTERS PTE LTD

Circuit module and manufacturing method thereof

PendingCN108447841AImprove performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical connectionPrinted circuit board

The invention discloses a circuit module and a manufacturing method thereof. The circuit module comprises a printed circuit board, a package chip and a switch tube, wherein the package chip and the switch tube are arranged on the printed circuit board, the package chip comprises a chip, a first plastic package layer and a plurality of metal posts, the first plastic package layer covers the chip, each metal post comprises a first end and a second which are opposite to each other, the first end is in contact with the chip, and the second end is exposed out of the first plastic package layer. Thepackage chip in the circuit module employs the metal posts to external electrical connection, so that the package area is reduced, and the reliability is improved.

Owner:HANGZHOU SILAN MICROELECTRONICS

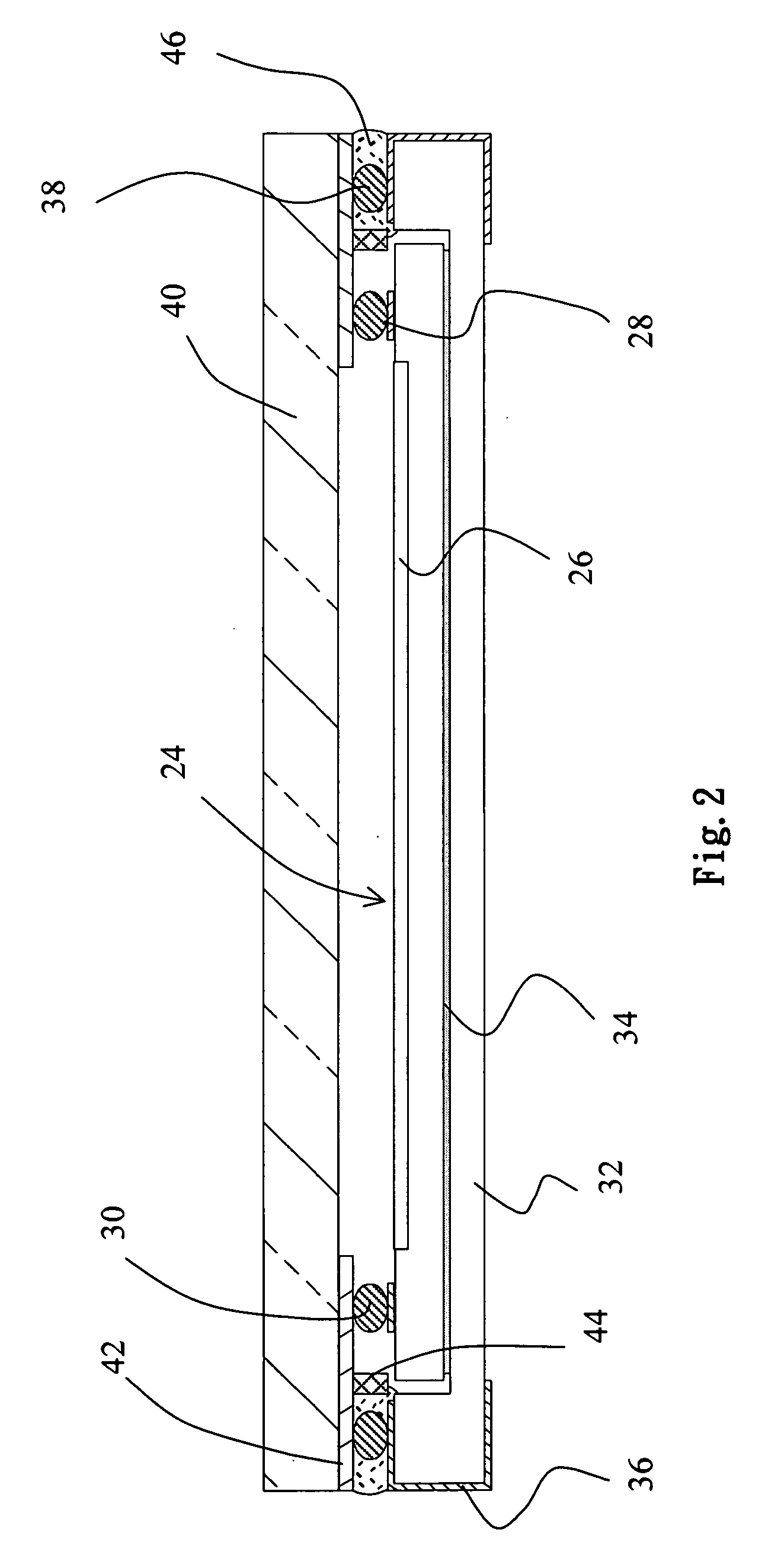

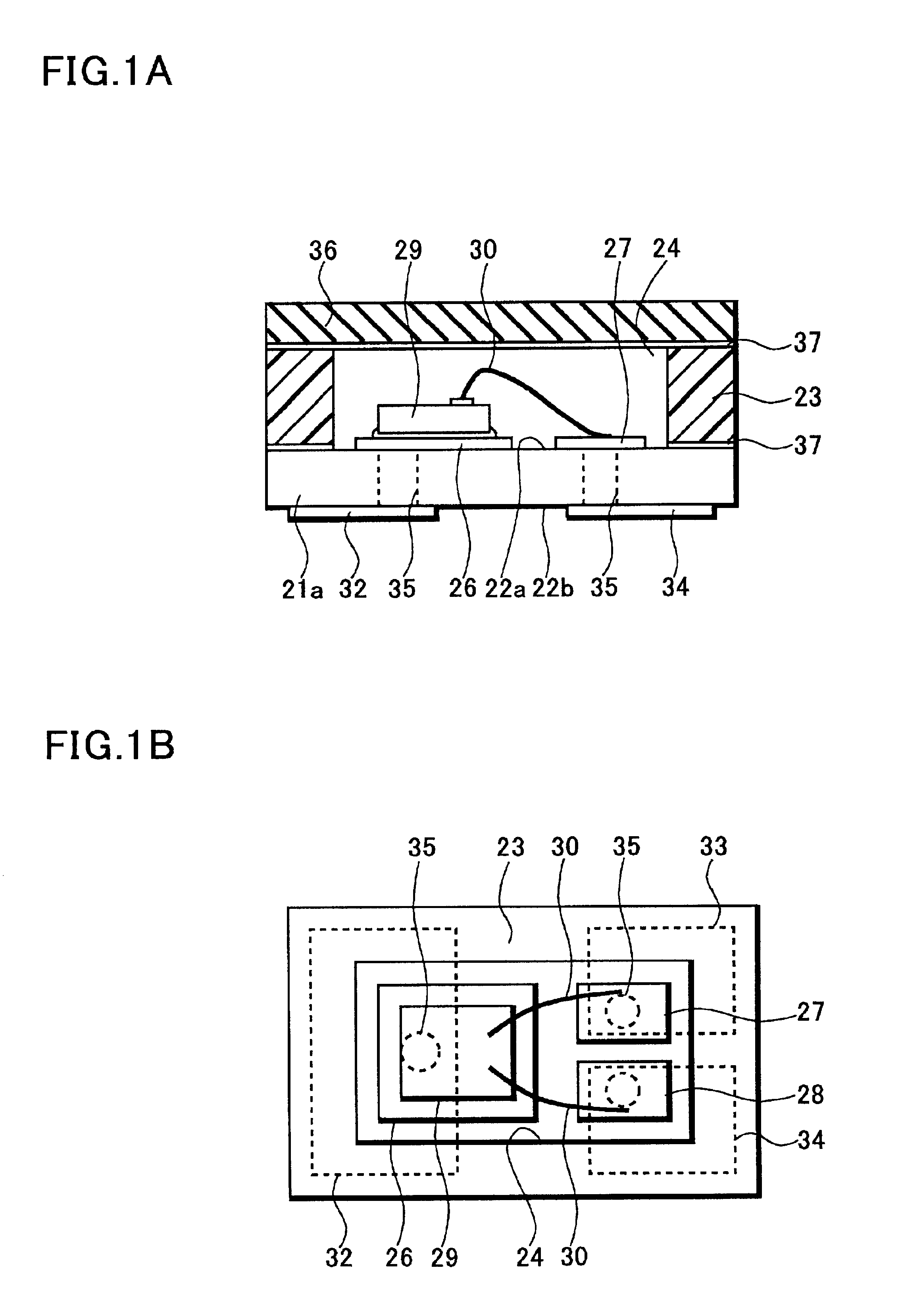

Semiconductor device and manufacturing method thereof

InactiveUS6838765B2Reduced package areaSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

The present invention comprises a first main face (22a) on a surface side of a substrate (21a). An island portion (26) is formed on the first main face (22a) and a semiconductor chip (29), etc. are adhered thereto. The semiconductor chip (29), etc. are sealed in the hollow portion that is constructed by a column portion (23) and a transparent glass plate (36). Then, the column portion (23) and the transparent glass plate (36) are adhered by epoxy resin, or the like.

Owner:SEMICON COMPONENTS IND LLC

Electronic Component Device and Method for Manufacturing the Same

ActiveUS20110140574A1Improve productivityShorten the counting processPiezoelectric/electrostriction/magnetostriction machinesMechanical vibrations separationEngineeringElectronic component

Owner:MURATA MFG CO LTD

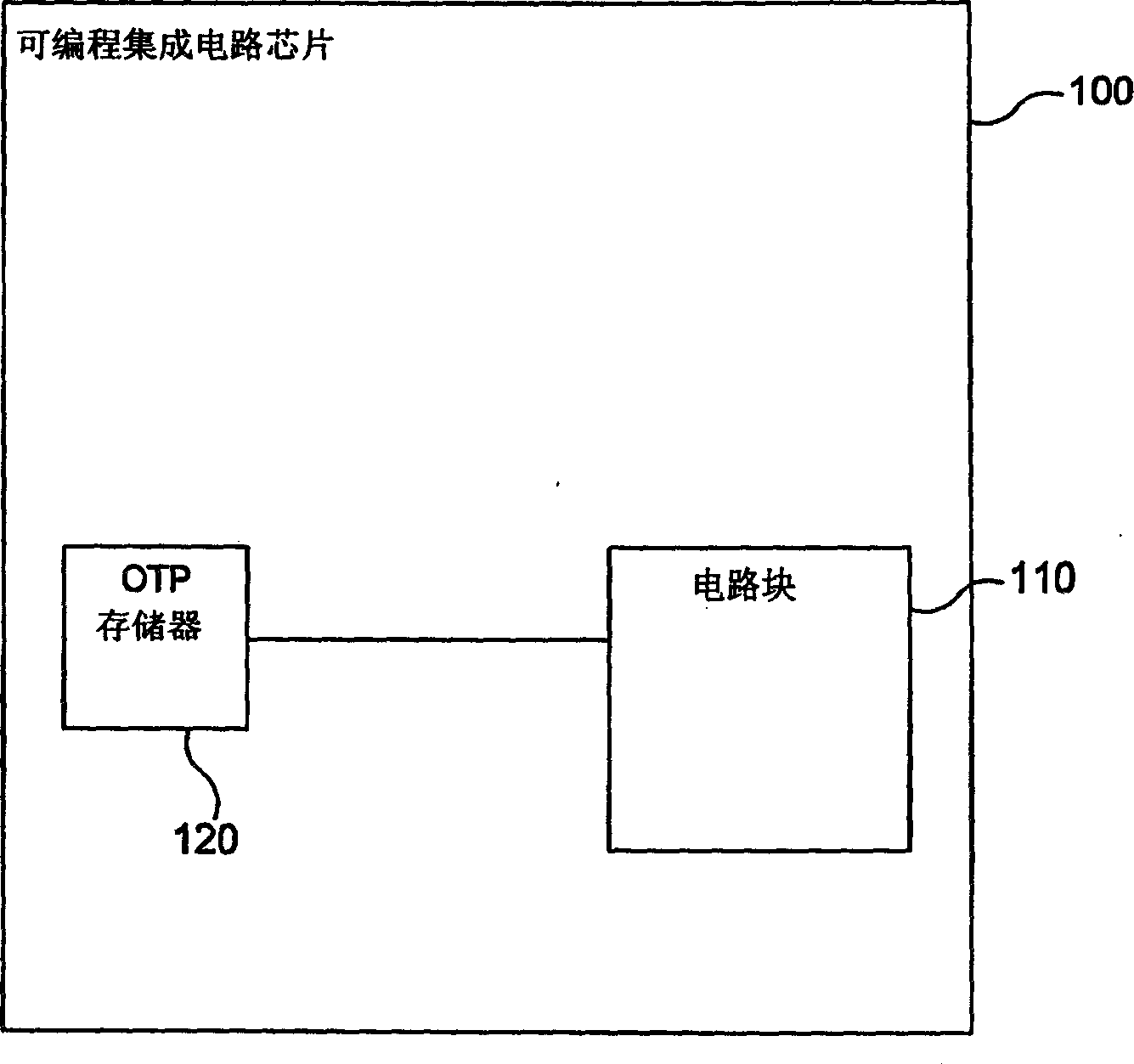

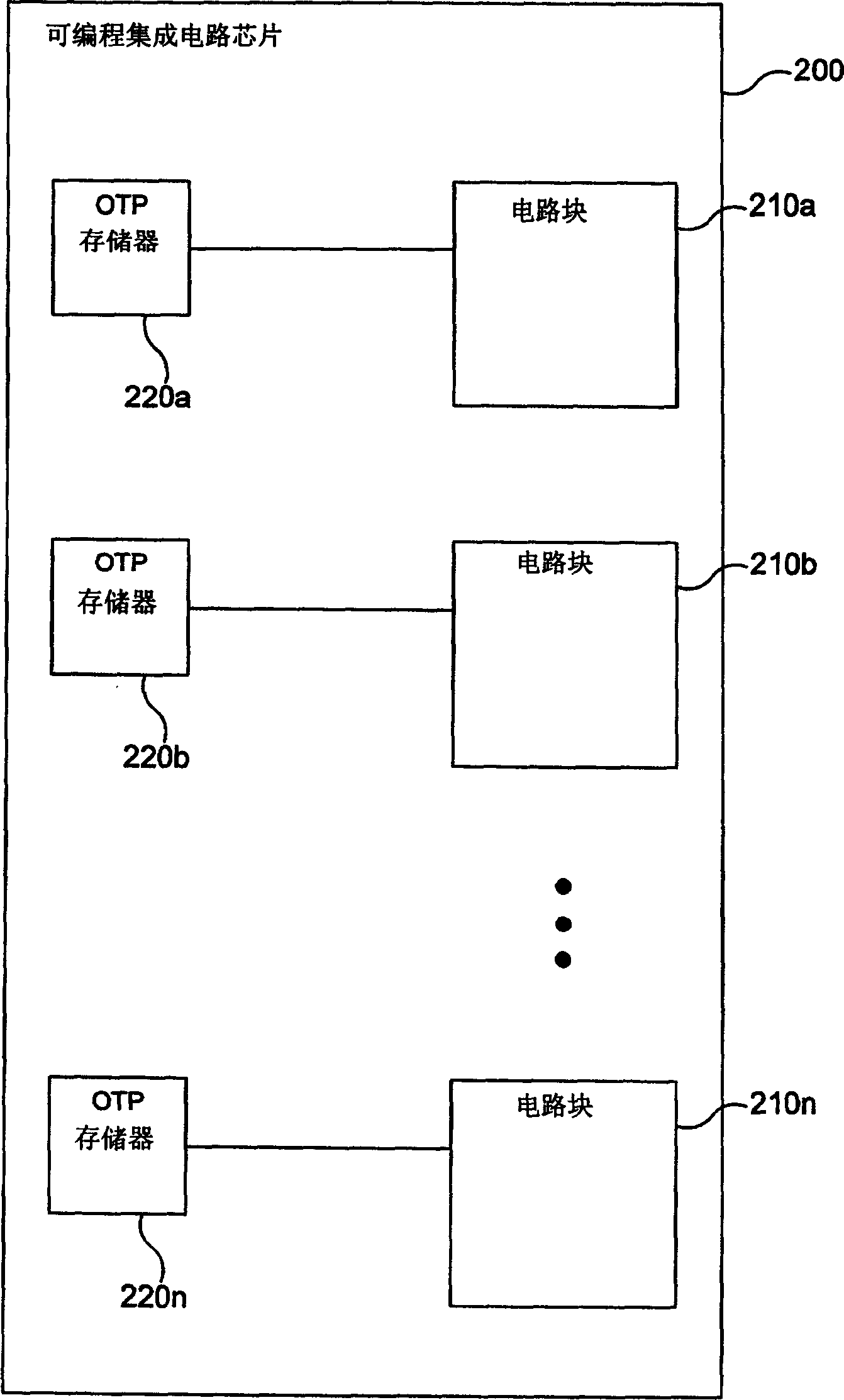

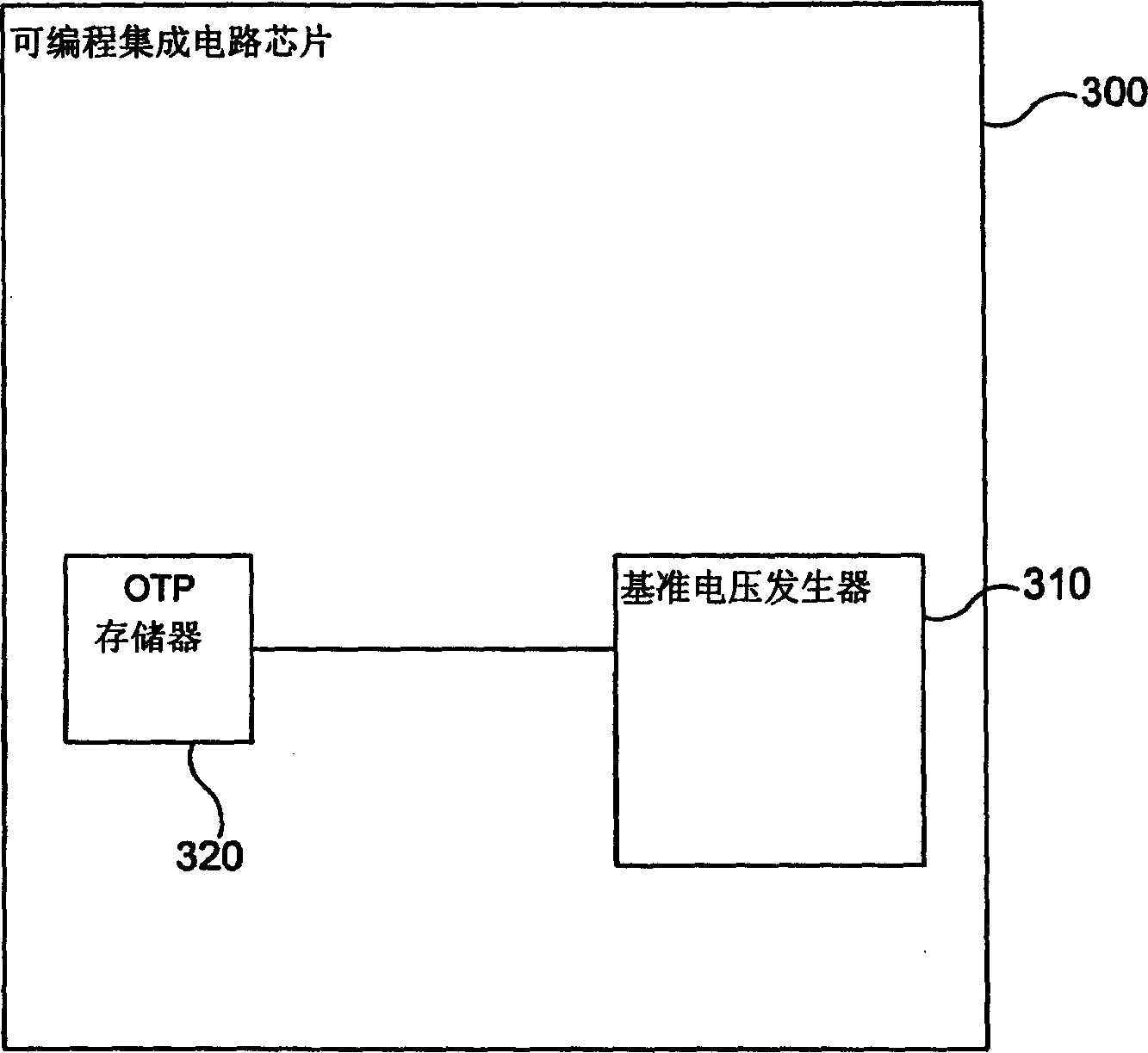

Integrated circuit chip programmable and operation method

ActiveCN1776909ACompensate for the possibility of failureReduce usageSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitOne time programmable

The invention discloses an integrated circuit chip with programmable functions and features and its operating method, wherein a one-time programmable (OTP) memory is used to realize the function of a non-volatile memory. The OTP memory may be based on multi-state fuses and gate oxide fuses. Because the OTP memory is very small, it occupies a smaller package area than metal fuses. In addition, since OTP memory can be implemented as part of a standard CMOS process, this approach is less costly and less complex than using electrically erasable programmable read-only memory (E2PROM).

Owner:AVAGO TECH INT SALES PTE LTD

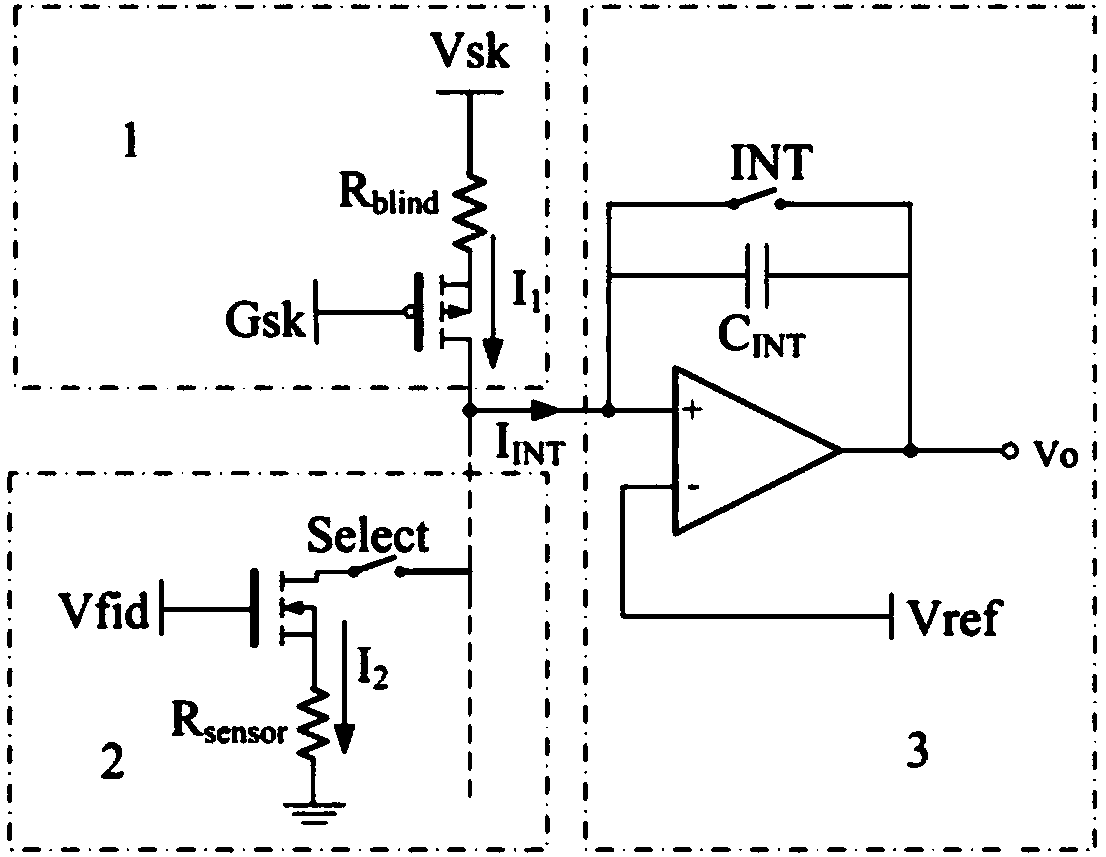

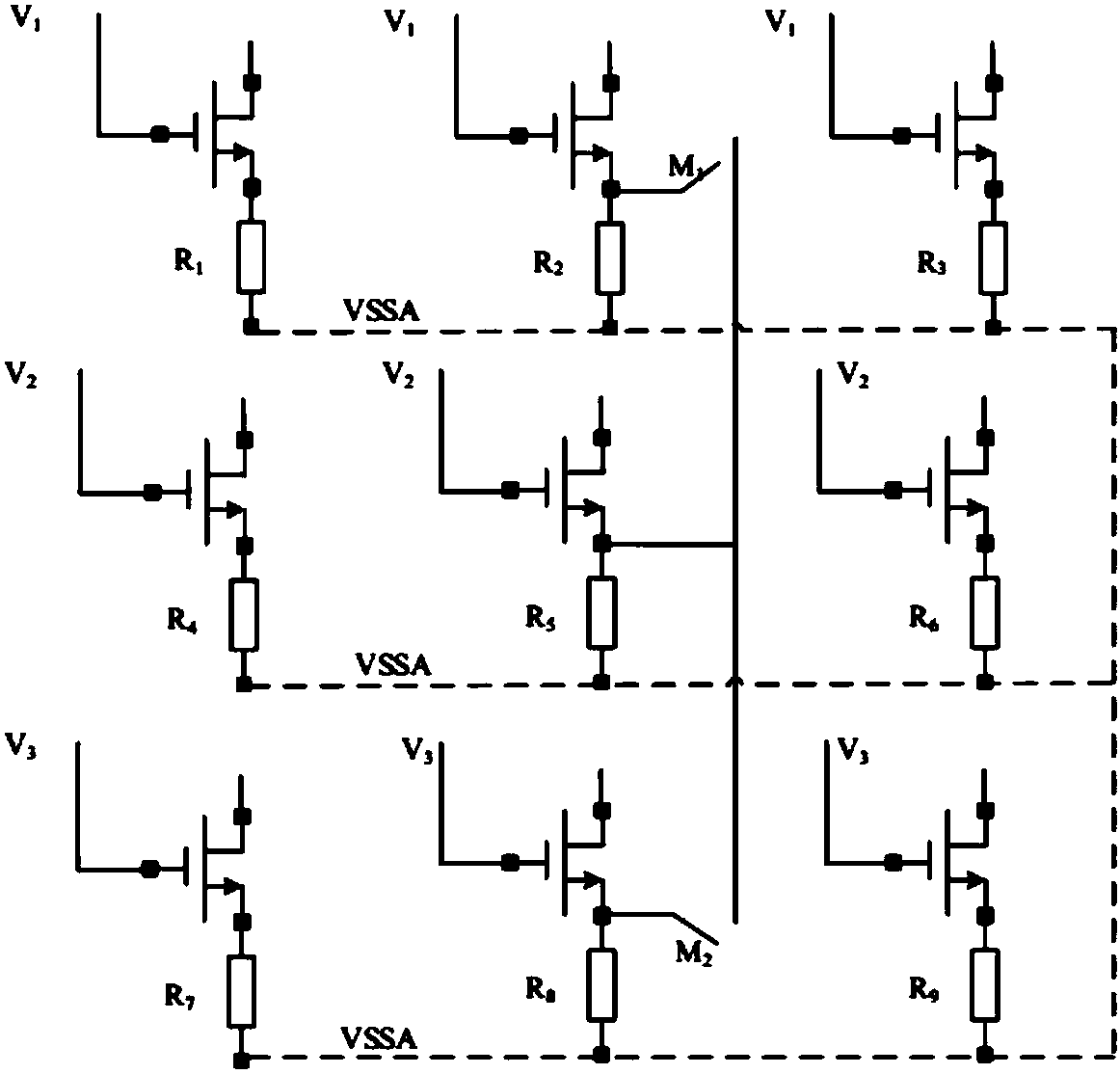

Reading circuit of non-refrigeration infrared focal plane detector and method for improving yield

ActiveCN108414093ACorrect non-uniformity in real timeImprove yieldPyrometry using electric radation detectorsElectrical resistance and conductanceComputer module

The invention discloses a reading circuit of a non-refrigeration infrared focal plane detector and a method for improving the yield. An effective element circuit array is subjected to row gating and column integration through a control module, and a substitute signal is obtained according to the fault signal of the effective element circuit. Effective element resistors and fault effective elementresistors of adjacent rows are connected in parallel, so that the fault effective element circuit works normally, and the image elements of infrared images can be restored in real time. Further, a substitute signal is obtained according to the fault signal of a blind element or a reference element circuit, the adjacent blind element or reference element resistor and fault blind element or reference element resistor are connected in parallel, so as to restore the blind element circuit or reference element circuit. The problem of damaged column line or damaged row line of an infrared focal planeis solved.

Owner:WUHAN GUIDE INFRARED CO LTD

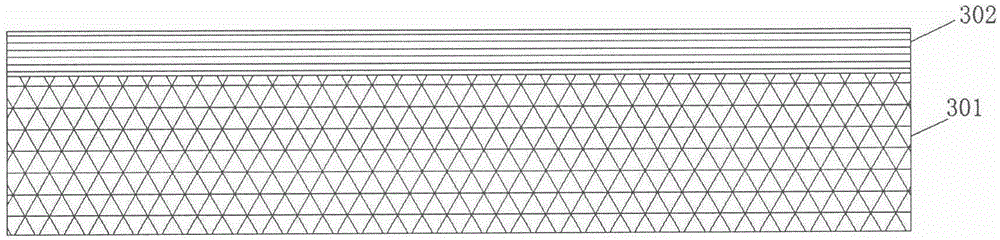

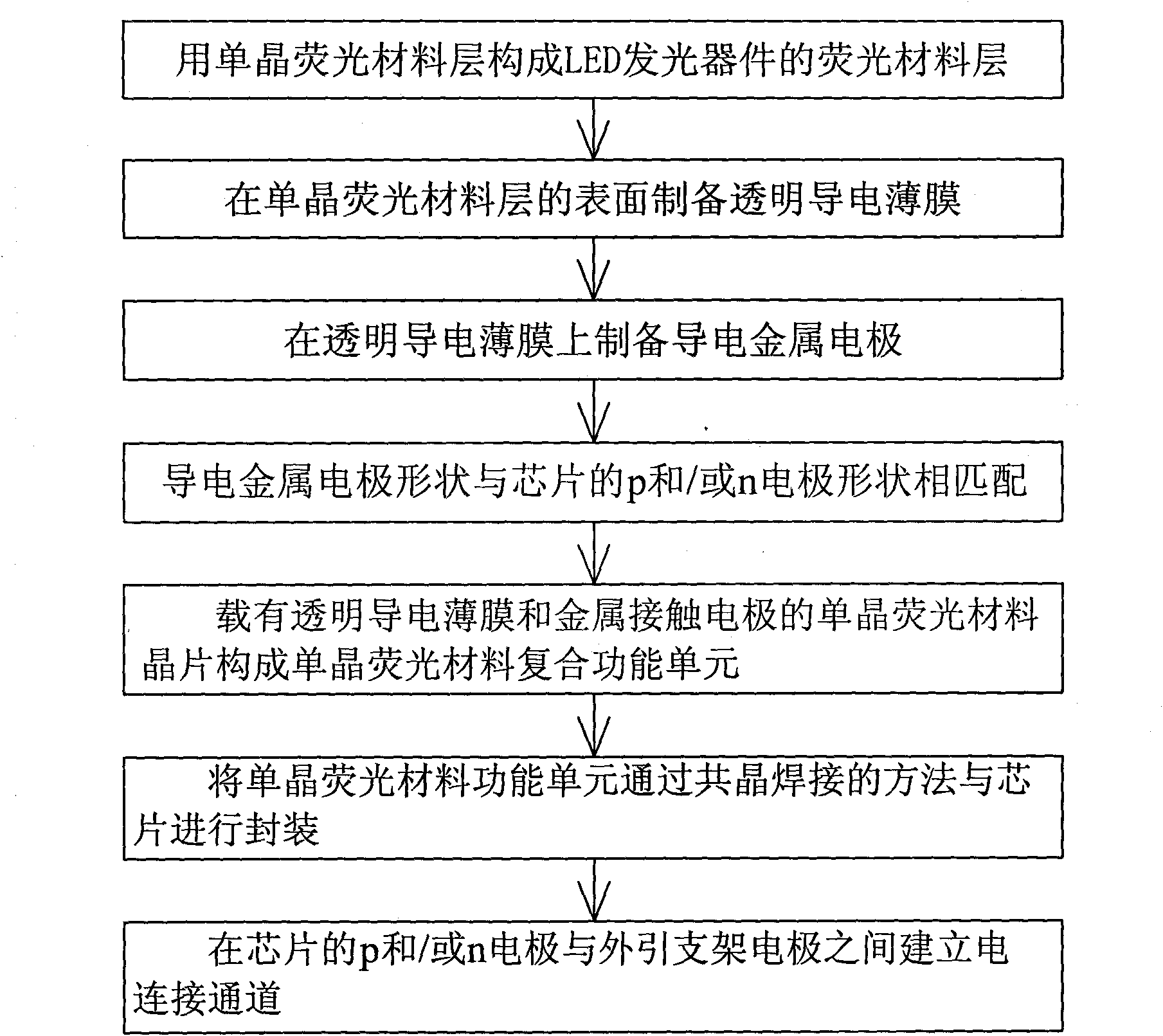

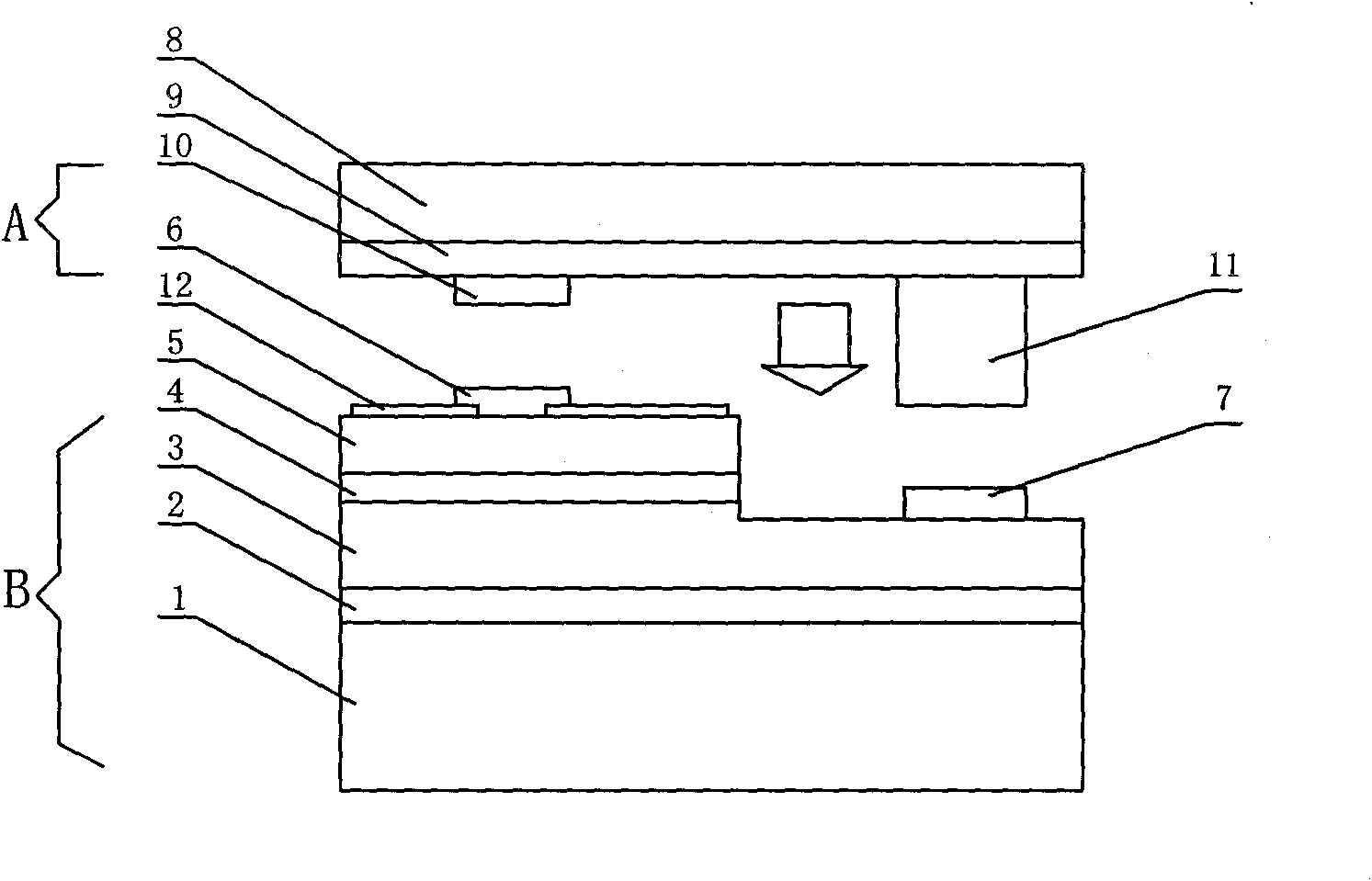

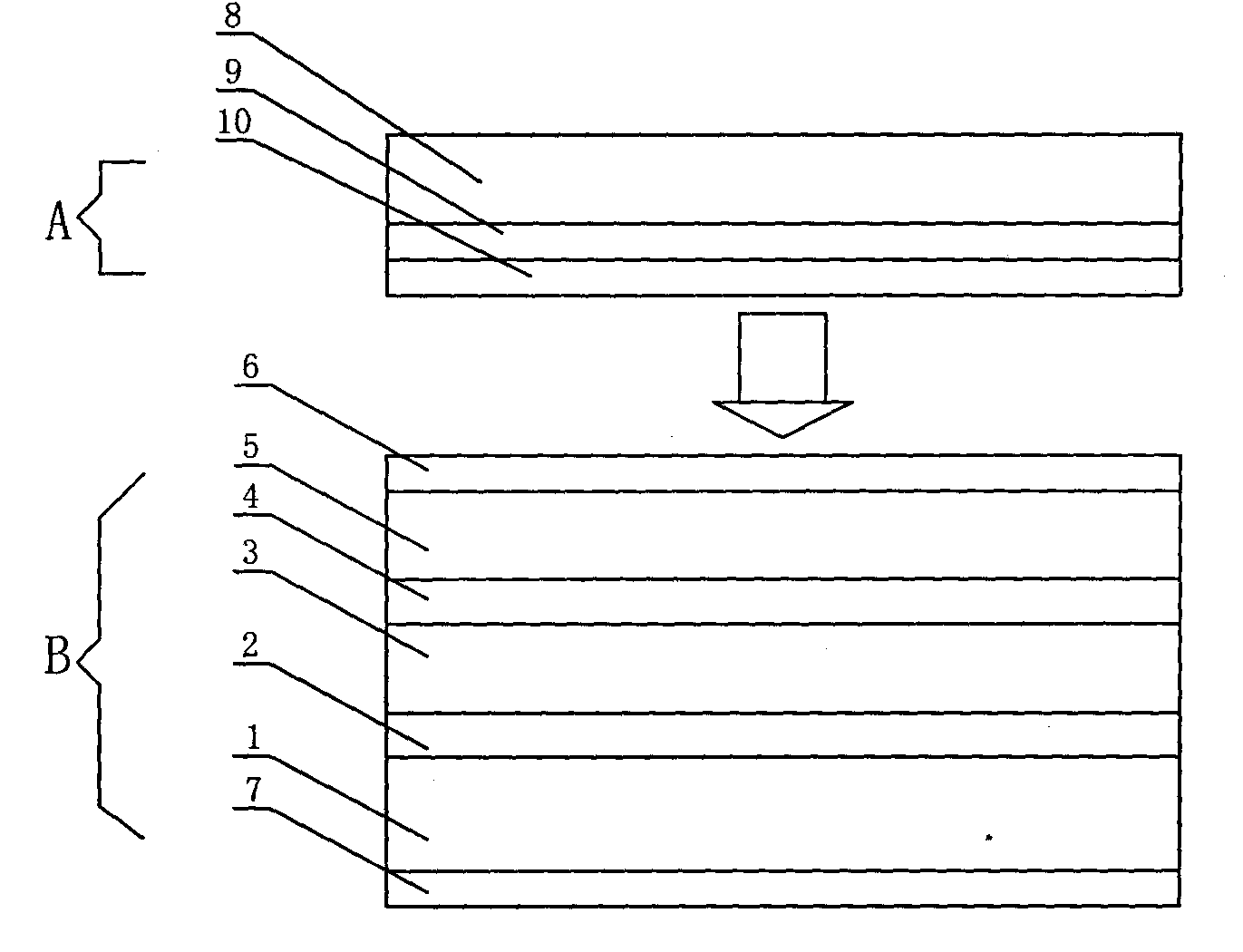

Gold-wire-free encapsulation method of large power white light LED part and white light LED part

ActiveCN101859865AThe process is simpleEfficient processSolid-state devicesSemiconductor devicesElectrically conductiveWhite light

The invention relates to a gold-wire-free encapsulation method of a large power white light LED part and a white light LED part, which belong to the field of the semiconductor luminous part, and comprise a chip is electrically connected with an outer lead bracket electrode, a fluorescent material layer is arranged at one side of the chip, a mono-crystal fluorescent material layer is adopted to form the fluorescent material layer, a transparent conductive film is prepared on the surface of the mono-crystal fluorescent material layer, a conductive metal electrode is arranged on the transparent conductive film, a mono-crystal fluorescent material wafer which carries the transparent conductive film and the conductive metal electrode forms a mono-crystal fluorescent material composite-functionunit, the mono-crystal fluorescent material composite-function unit is encapsulated with the chip through an eutectic welding way, and an electric connection channel is established between a pn electrode of the chip and the outer lead bracket electrode. By adopting the surface contact-type electric connection, the encapsulation reliability of the white light LED part is improved, the service lifeof the LED is remarkably prolonged, and the light-emitting efficiency is improved. The method is particularly applicable to the mass integration encapsulation production process and can effectively reduce the manufacturing cost of the LED luminous part.

Owner:KUSN KAIWEI ELECTRONICS