Multi-chip wafer level fan-out type three-dimensional package structure and packaging process thereof

A three-dimensional, packaging structure technology, applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device manufacturing, etc., can solve the problems of large packaging area, poor precision, and inability to achieve multi-function, etc., to reduce the packaging area and improve integration degree of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

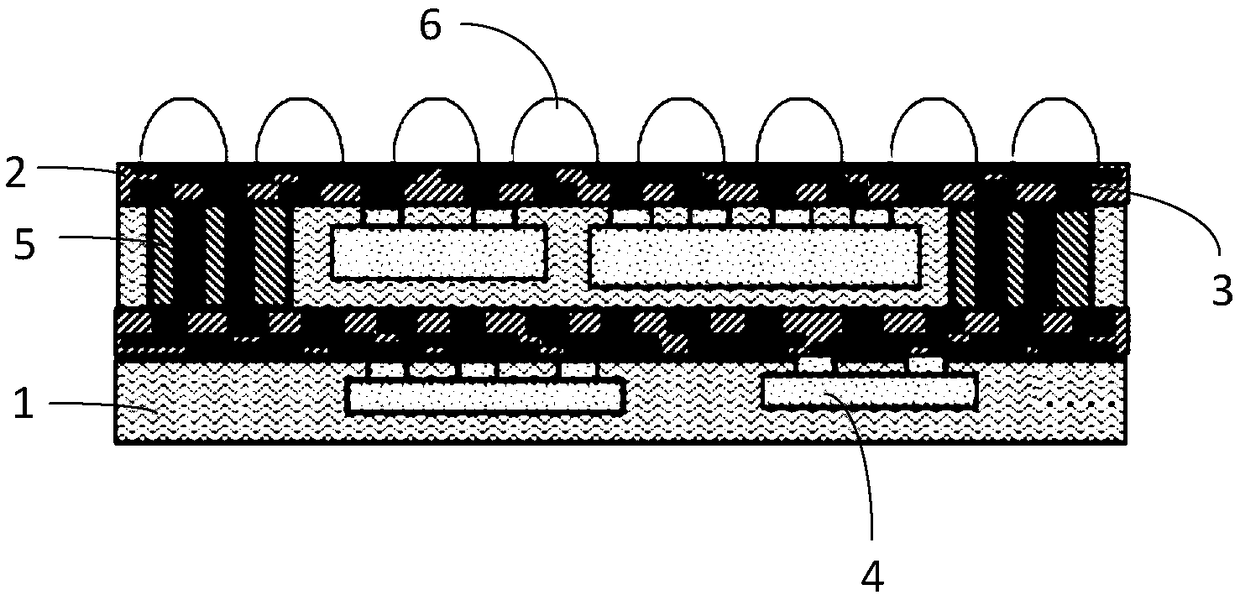

[0066] as attached figure 1 As shown, an integrated packaging structure includes two rewiring layers, the rewiring layer is a dielectric layer 2, and the plastic sealing layer 1, the dielectric layer 2, the plastic sealing layer 1 and the dielectric layer 2 are arranged in sequence from top to bottom, On both sides of the dielectric layer 2, there is a metal connection structure 3 that connects the two sides to cooperate with each other and form an interconnected structure. One end of the metal connection structure 3 is parallel to the plane of the dielectric layer 2, and one end extends out of the dielectric layer 2. The metal contact (not shown) side of the dielectric layer 2 is provided with a plastic sealing layer 1, and a chip 4 (including a bare chip, a packaged chip, etc.) or a passive passive component (not shown) is plastic sealed in the plastic sealing layer 1 , the plastic sealing layer 1 between the two dielectric layers 2 is also provided with a micro-silicon bloc...

Embodiment 2

[0076] An integrated packaging structure, including three layers of rewiring layers, the rewiring layer is a dielectric layer 2, and the plastic packaging layer 1, the dielectric layer 2, the plastic packaging layer 1, the dielectric layer 2, and the plastic packaging layer 1 are arranged in sequence from top to bottom and the dielectric layer 2, on both sides of the dielectric layer 2, there is a metal connection structure 3 that connects the two sides to cooperate with each other and form an interconnected structure. One end of the metal connection structure 3 is parallel to the plane of the dielectric layer 2, and one end extends out The dielectric layer 2 is provided with a plastic sealing layer 1 on one side of the metal contact (not shown) extending out of the dielectric layer 2, and a chip 4 (including a bare chip, a packaged chip, etc.) or a passive passive Components (not shown), the plastic sealing layer 1 between two adjacent dielectric layers 2 is also provided with...

Embodiment 3

[0086] A packaging process for a multi-chip wafer-level fan-out three-dimensional packaging structure as claimed in claim 1, comprising the following steps:

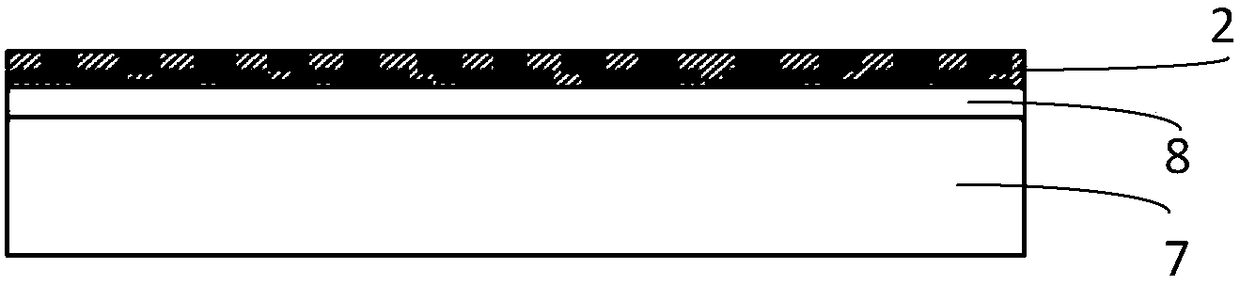

[0087] 1) Adhering a temporary bonding adhesive layer 8 on the surface of the temporary carrier 7;

[0088] The temporary carrier is a light-transmitting carrier (such as quartz, glass, etc.) or an opaque carrier (such as metal, silicon wafer, ceramics, etc.), and the temporary bonding adhesive layer is thermal peeling glue, UV glue or laser Debonding glue.

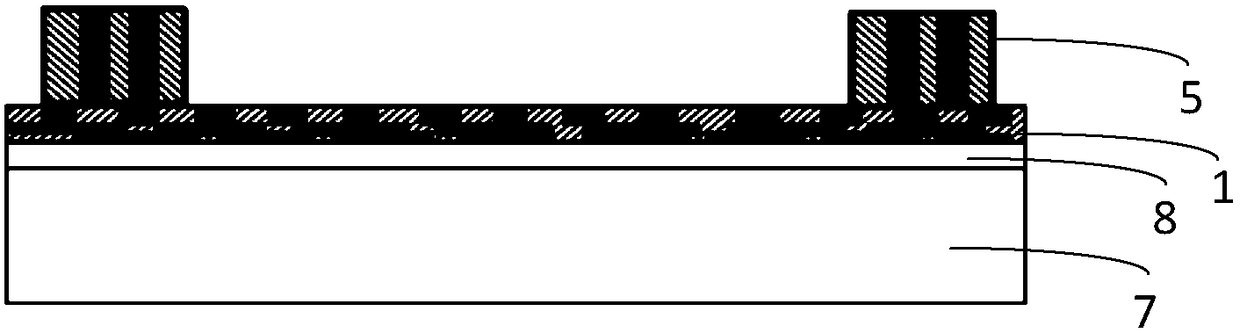

[0089] 2) The surface of the temporary bonding adhesive layer 8 obtained in step 1) is used to make the first layer of rewiring layer with a thin film process. The metal connection structure 3 that cooperates with each other and forms an interconnected structure;

[0090] It is used to interconnect chips and passive components to be packaged in subsequent steps and lead out the formed pins.

[0091] The production of the rewiring layer specifically includes the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More