Three-dimensional multi-chip encapsulation module based on buried substrate and method

A multi-chip packaging and embedding technology, which is applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the thermal and mechanical reliability hazards of large-sized chips, aggravate the thermal expansion and contraction mismatch between the upper and lower layers of the substrate, and the mirror surface of the substrate structure. Symmetry and other issues, to achieve the effect of enhancing the mirror symmetry of the structure, low production cost, and reducing the packaging area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] In order to fully demonstrate the advantages and effects of the present invention, the substantive features and remarkable progress of the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

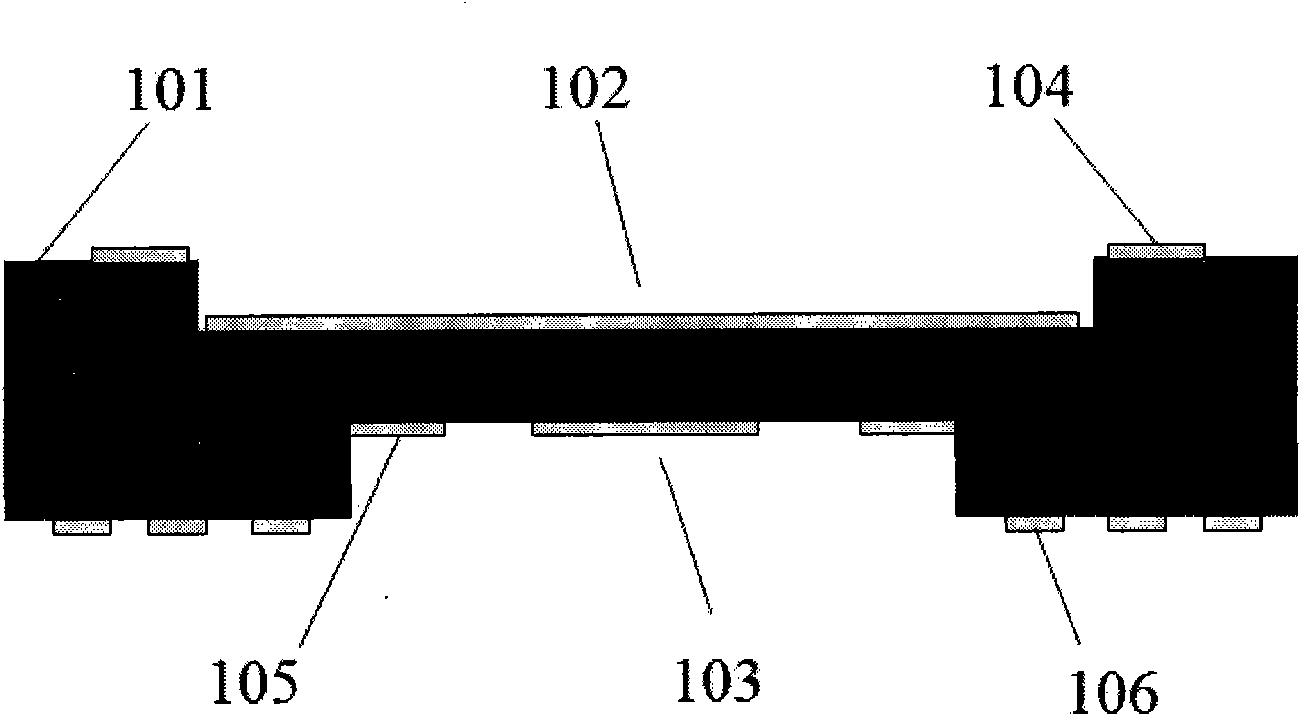

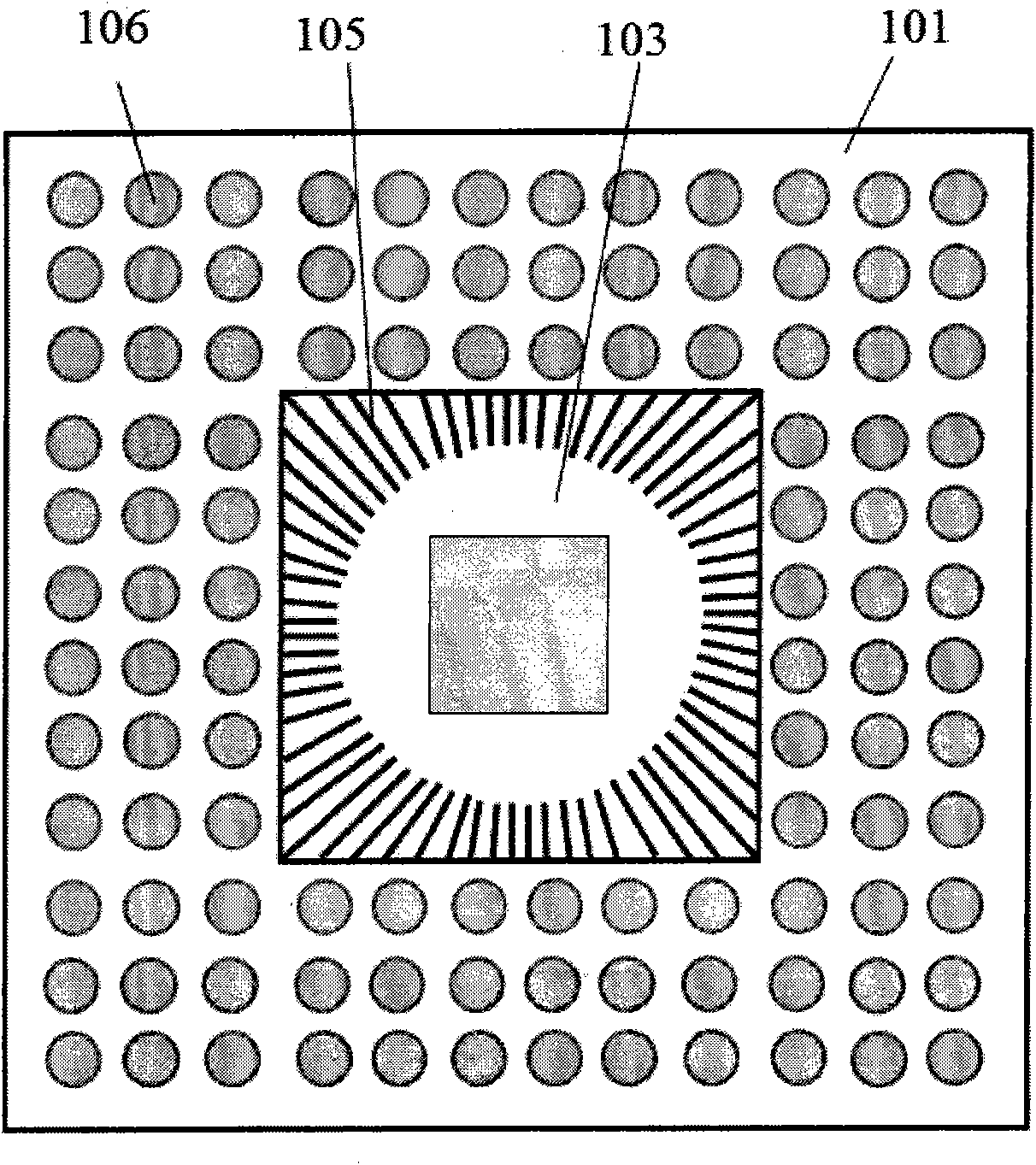

[0048] figure 1 It is a cross-sectional view of an H-shaped embedded substrate. A package substrate 101 made of a multilayer PCB has a recessed cavity 102 in the middle of the upper surface and a recessed cavity 103 in the middle of the lower surface. The package substrate in the cross-sectional view has a typical "H" structure.

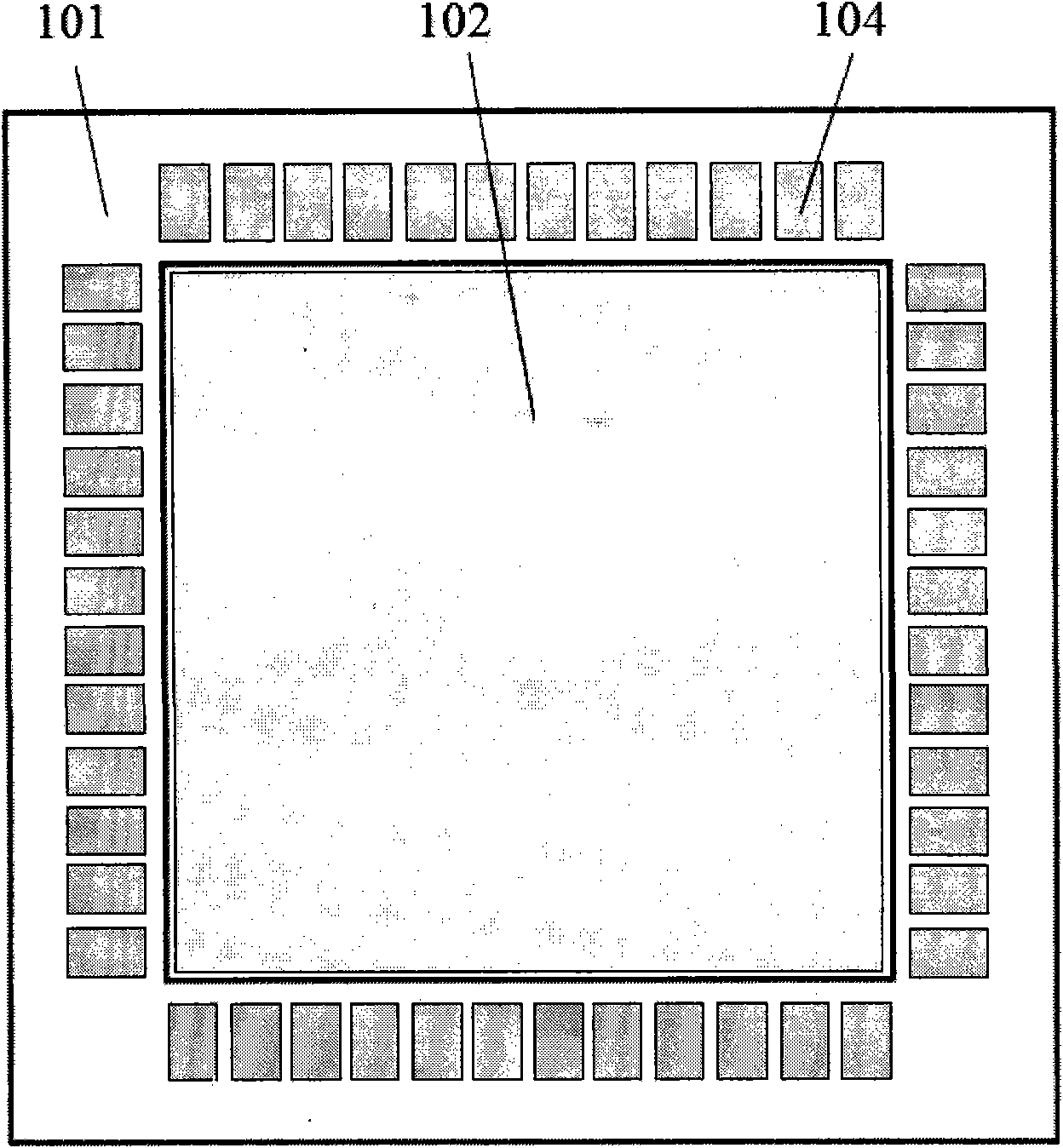

[0049] exist figure 2 Among them, the recessed cavity 102 in the middle of the upper surface of the packaging substrate 101 is a large-sized cavity. The size of the cavity should be just enough to accommodate and mount large-size chips, and the depth of the cavity is equivalent to the thickness of the large-size chip, which can effectively shorten the length of the bonding wire. Wire bondin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More