Manufacturing method of semiconductor structure

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as inability to absorb, wafer warping, falling and breaking, etc., to improve production yield and reduce The effect of changing the value and preventing warping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] It can be seen from the background art that how to eliminate wafer warpage is one of the current problems that need to be solved urgently.

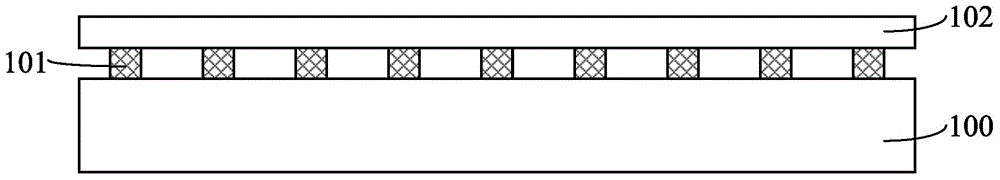

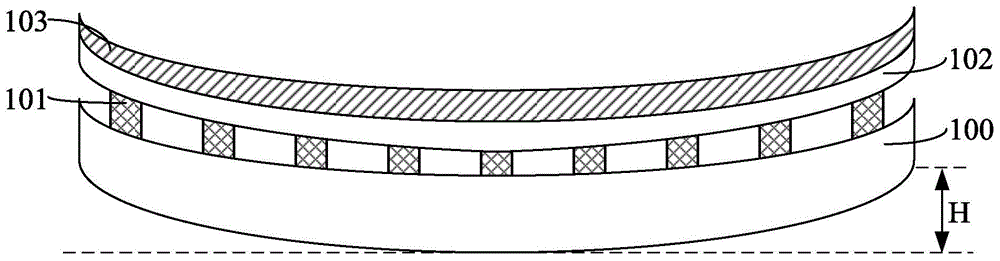

[0036] For research on the fabrication method of semiconductor structures, please refer to figure 1 , provide a support plate 100, bond the support plate 100 and the base 102 through the adhesive layer 101, the support plate 100 improves the mechanical strength of the base 102; please refer to figure 2 , the metal layer 103 is formed on the surface of the base 102. After the metal layer 103 is formed, the support plate 100, the base 102, and the metal layer 103 all warp and deform, and the warpage of the support plate 100, the base 102, and the metal layer 103 ( bow) is H, and the warpage H is the distance between the highest point of the support plate 100 and the line connecting the bottom edge of the support plate 100 .

[0037] After research, it was found that the main reason for the warpage and deformation of the substrate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More