Method of forming a wafer backside interconnecting wire

a backside and interconnecting wire technology, applied in the direction of electrical equipment, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of fp bga package suffering from the stress problem between the die and the substrate, the substrate warpage, and the aforementioned technologies still have some disadvantages or limitations, so as to achieve the effect of reducing the area of the package and low cos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

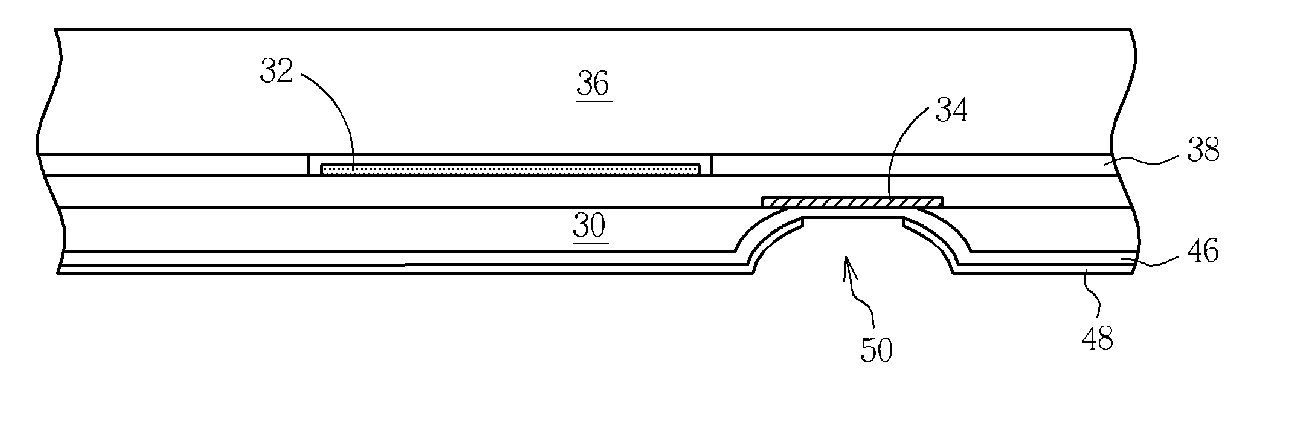

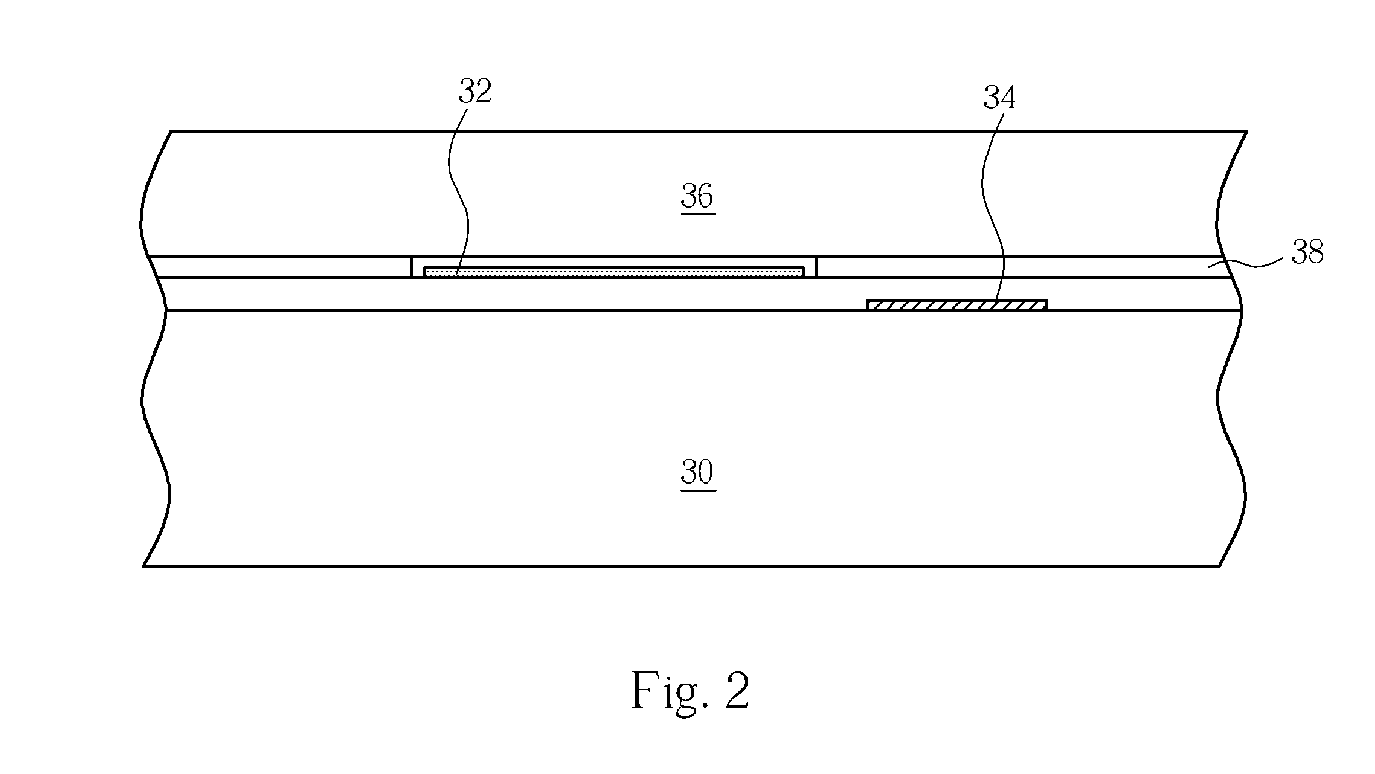

[0015] Please refer to FIG. 2 through FIG. 9. FIG. 2 through FIG. 9 are schematic diagrams illustrating a method of forming a wafer backside interconnecting wire according to a preferred embodiment of the present invention. As shown in FIG. 2, a wafer 30 is provided. The wafer 30 includes at least a circuit element 32 disposed on the front surface of the wafer 30, and at least a metal bonding pad 34 electrically connected to the circuit element 32 positioned on the front surface of the wafer 30. The front surface of the wafer 30 is bonded to a cap wafer 36 with a bonding layer 38. In this embodiment, the material of the bonding layer 38 is particularly selected from commonly used bonding materials, such as photoresist, epoxy, and UV tape, but is not limited to these materials. The cap wafer 36 and the wafer 30 can also be bonded together in another manners, such as by an anode bonding technique or by a plasma enhanced bonding technique. In addition, if the circuit element 32 is an o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More