Multi-substrate region-based package and method for fabricating the same

a multi-substrate region and package technology, applied in the field of semiconductor packages, can solve the problems of inability to meet the requirement of further increase in i/o connections for electronic products nowadays, limited number of i/o connections provided, and out of date conventional bga package configuration. achieve the effect of improving reliability, good compatibility and increasing yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

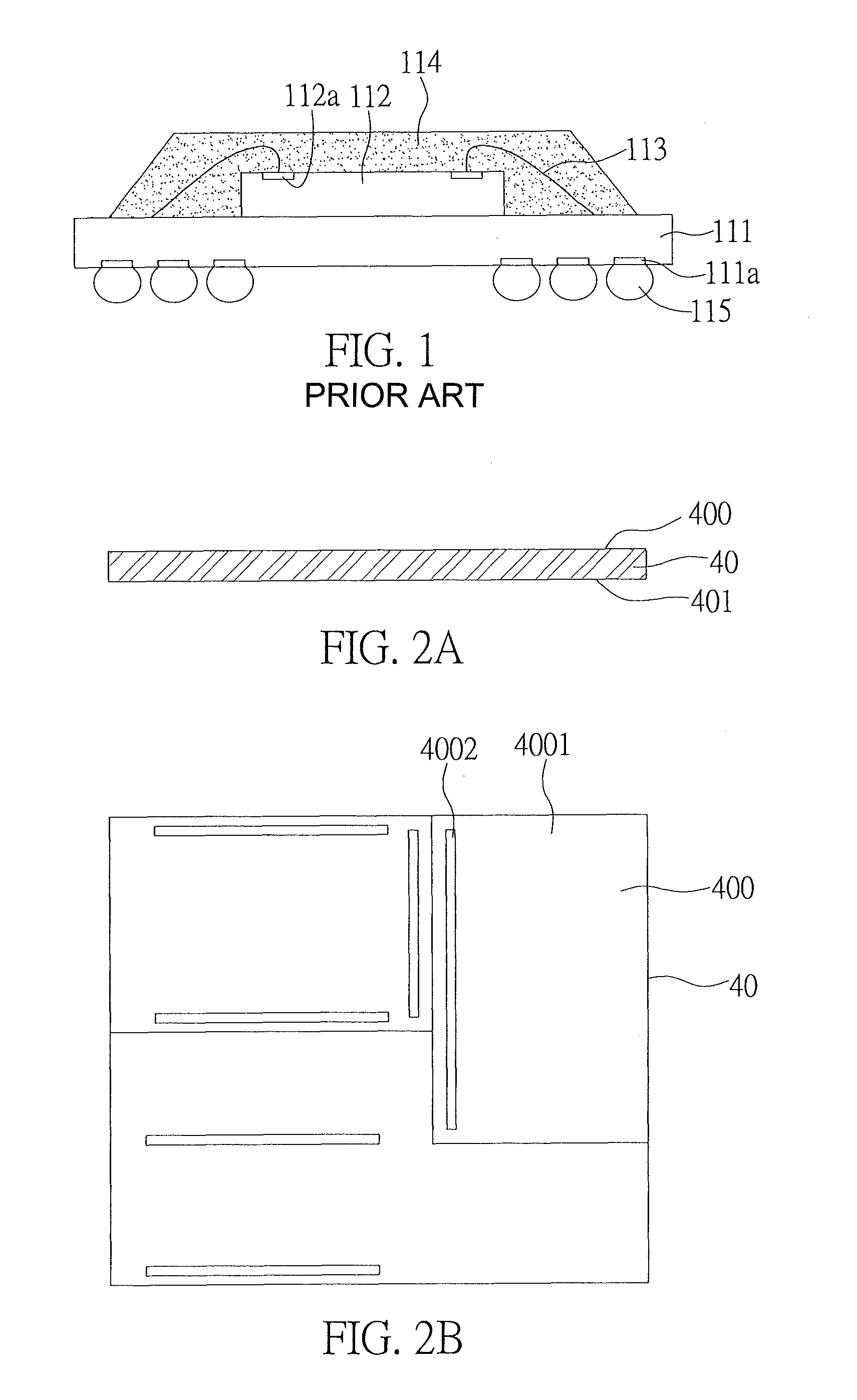

[0029]FIGS. 2A to 2G are schematic diagrams showing a multi-substrate region-based package and a method for fabricating the same according to a first embodiment of the present invention.

[0030]As shown in FIGS. 2A and 2B, a chip 40 having an active surface 400 and a non-active surface 401 is provided. The active surface 400 of the chip 40 is divided into a plurality of functional regions 4001 each having an independent first electrical connecting portion 4002. The first electrical connecting portion 4002 can be situated on one side, two opposite sides or three sides of the functional region 4001. If there is sufficient room, the first electrical connecting portion 4002 may also be situated on four sides of the functional region 4001.

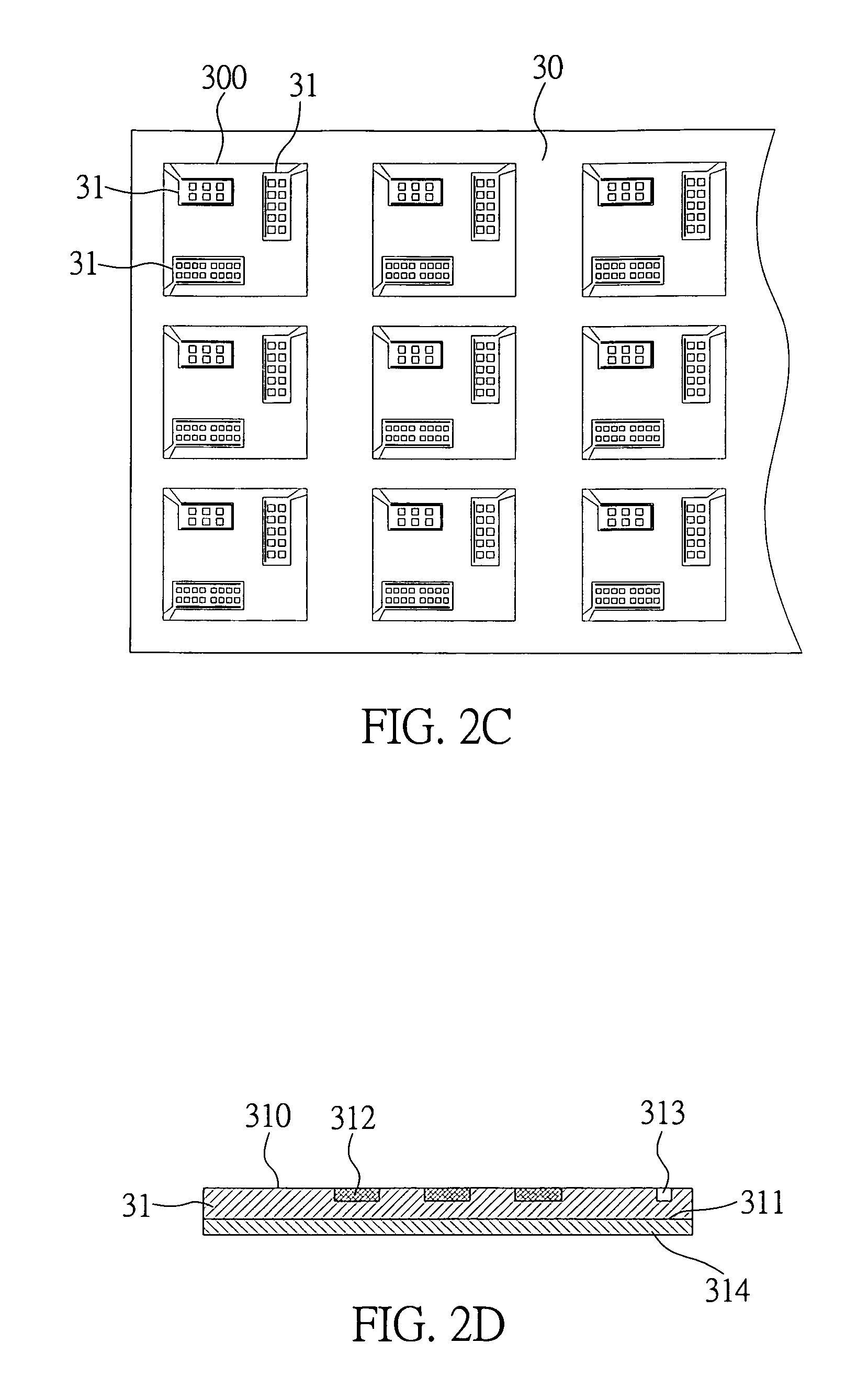

[0031]As shown in FIG. 2C, a substrate strip 30 is provided. The substrate strip 30 is formed with a plurality of openings 300, with a plurality of substrates 31 being disposed in the openings 300 respectively and connected to the substrate strip 30. Refe...

second embodiment

[0039]FIGS. 3A to 3C are schematic diagrams showing a multi-substrate region-based package and a method for fabricating the same according to a second embodiment of the present invention. The second embodiment differs from the above first embodiment in that in the second embodiment, a plurality of stacked chips are disposed in the package.

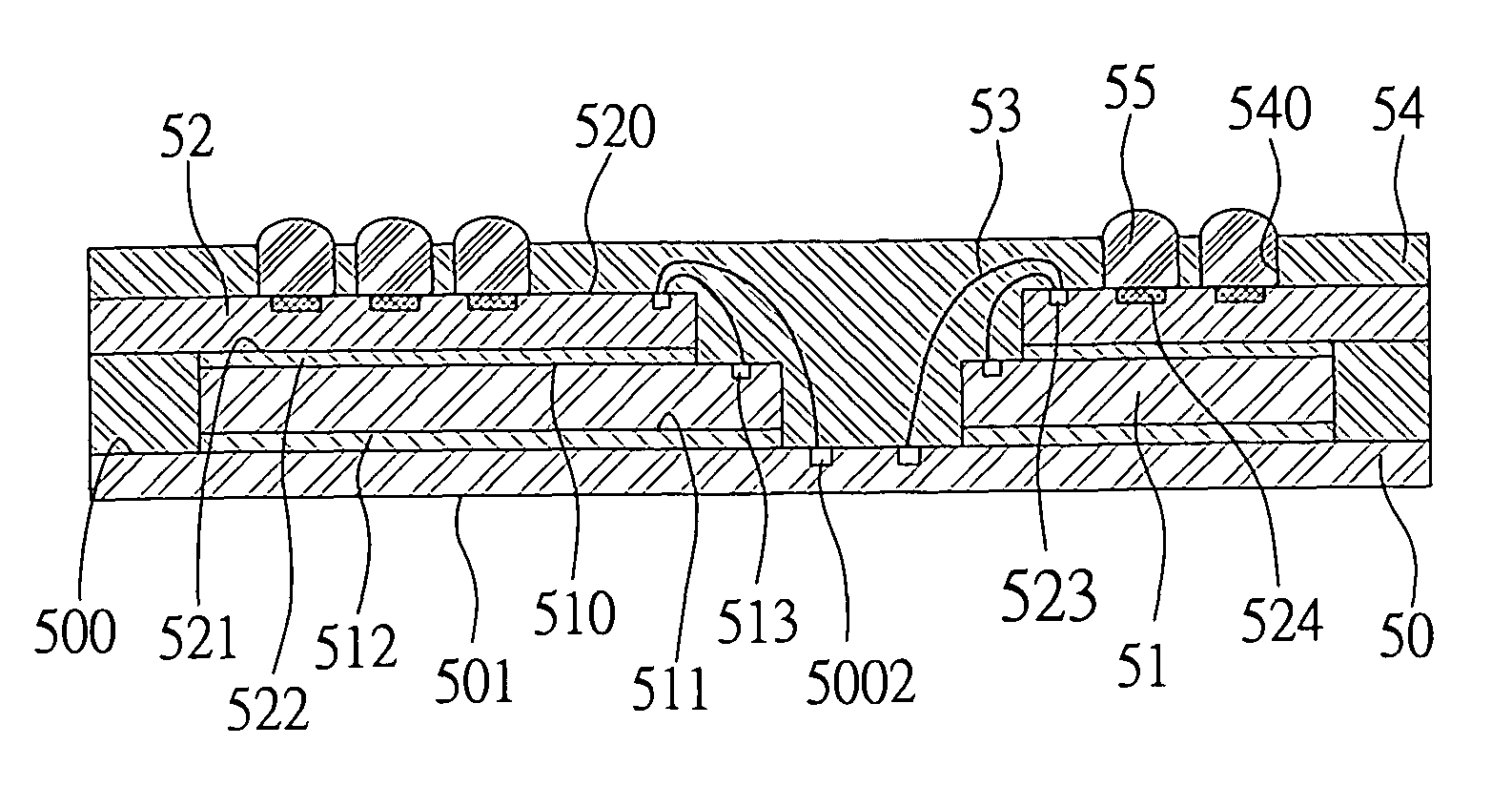

[0040]As shown in FIG. 3A, a chip 50 having an active surface 500 and a non-active surface 501 (referring also to FIG. 3B) is provided. The active surface 500 of the chip 50 is divided into a plurality of functional regions 5001 each having an independent first electrical connecting portion 5002.

[0041]As shown in FIG. 3B, a plurality of sub-chips 51 are provided, each of the sub-chips 51 having an active surface 510 and a non-active surface 511. The active surface 510 of the sub-chip 51 is formed with a third electrical connecting portion 513, and the non-active surface 511 of the sub-chip 51 has an adhesive layer 512 attached thereto, allowing the...

third embodiment

[0045]FIG. 4 is a schematic diagram showing a multi-substrate region-based package according to a third embodiment of the present invention. In the above first and second embodiments, the substrate is smaller in area that that of the corresponding functional region of the chip, while in this third embodiment, the substrate can be larger in size than that of the functional region of the chip.

[0046]As shown in FIG. 4, each of the substrates 61 is larger in area than that of a corresponding one of the functional regions 6000 of the active surface 600 of the chip 60. The second electrical connecting portion 6101 of the ball mounting surface 610 of each of the substrates 61 is electrically connected to the first electrical connecting portion 6001 of the corresponding functional region 6000 of the chip 60, and a conductive material is disposed on the bond pads of each of the substrates 61. The rest of the fabrication processes and structural arrangement are substantially identical to thos...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More