Patents

Literature

108results about How to "Improve package yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

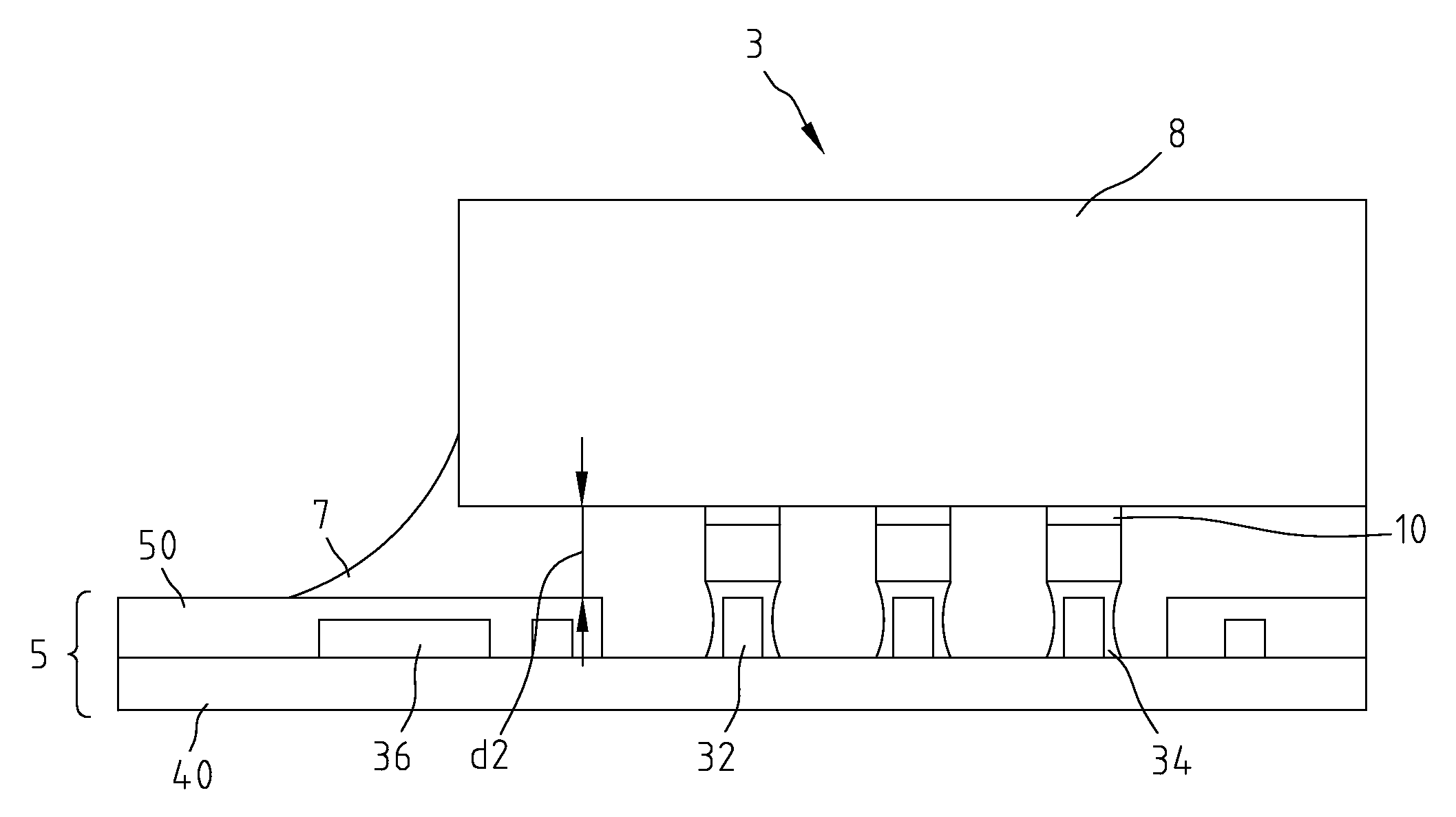

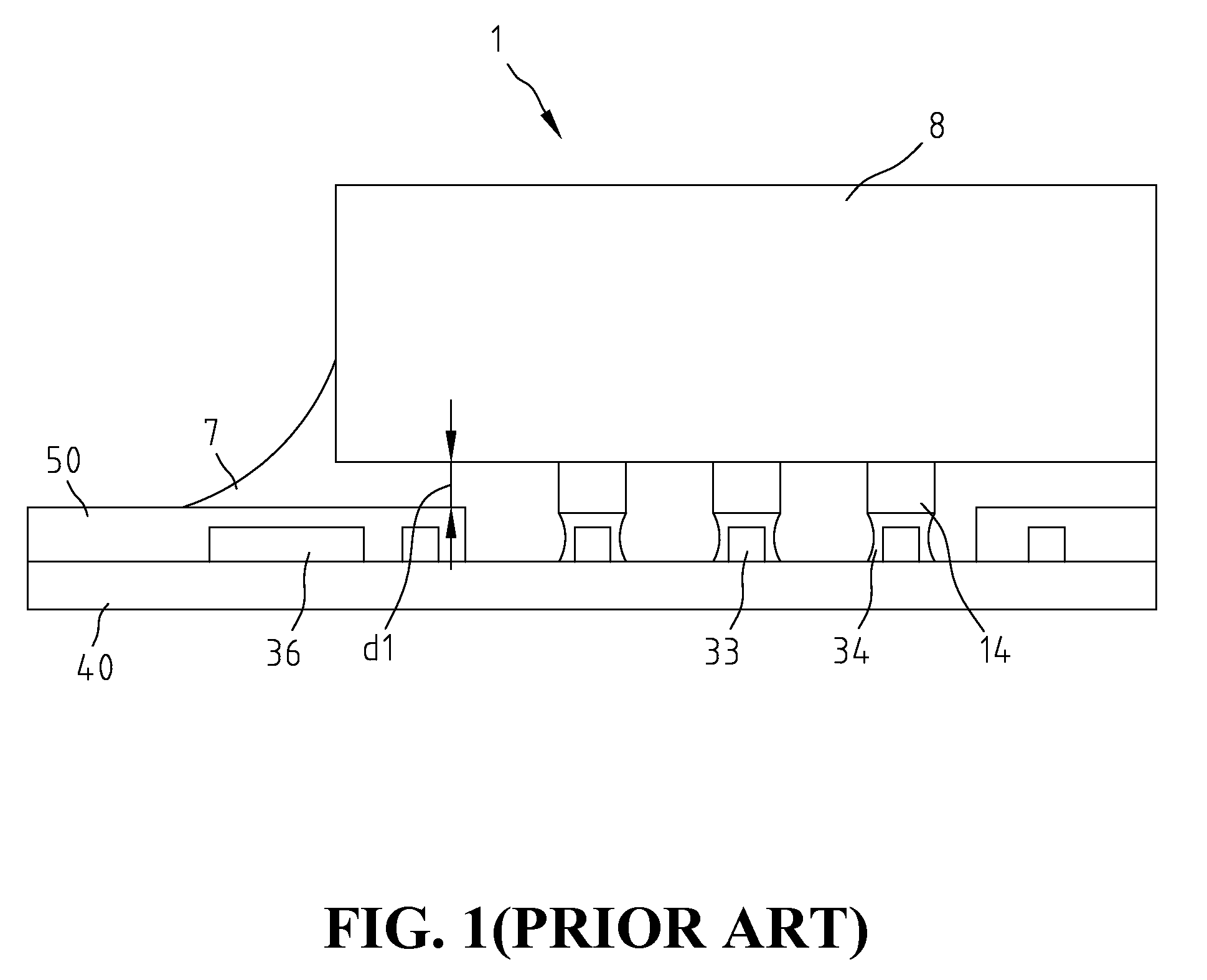

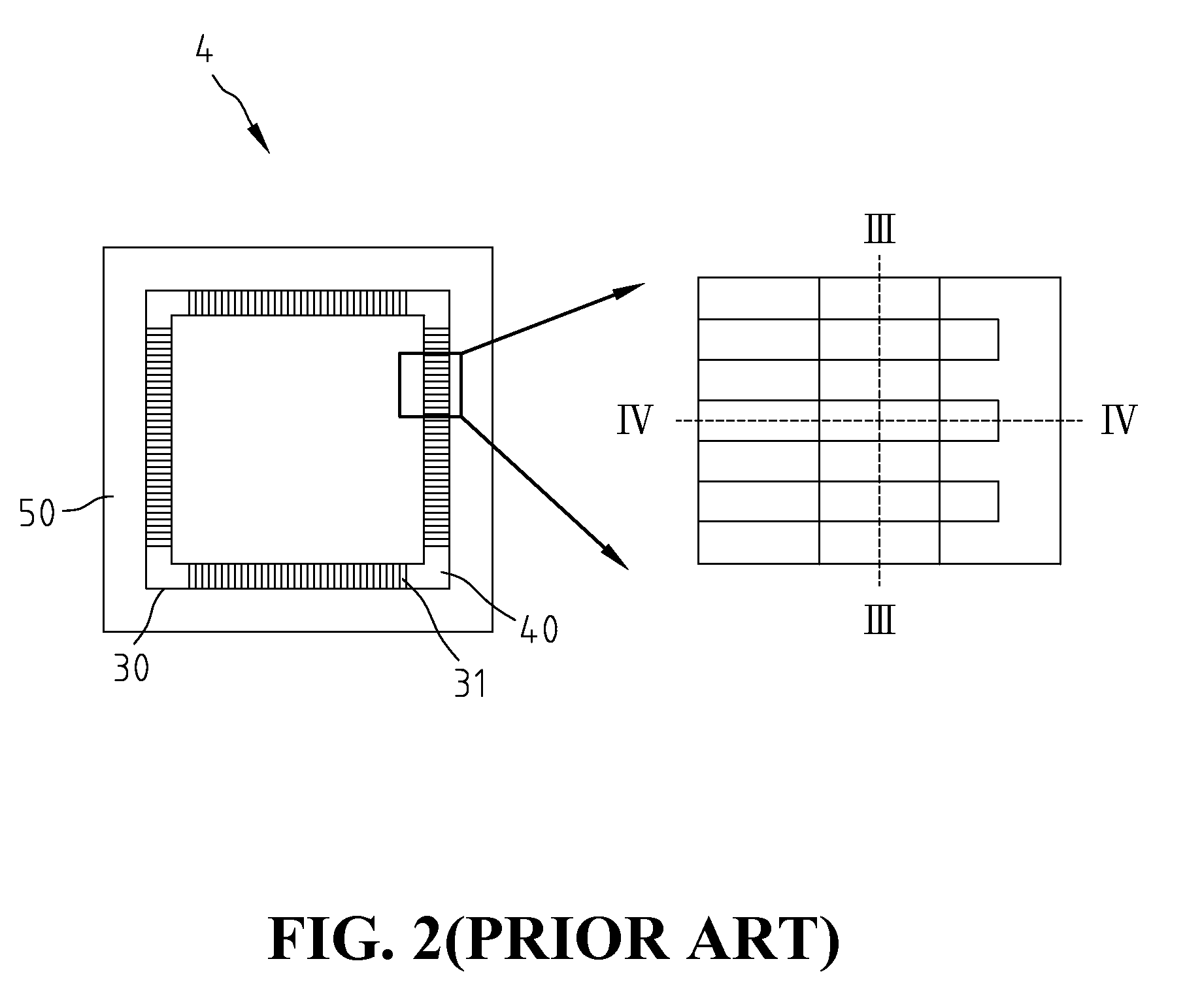

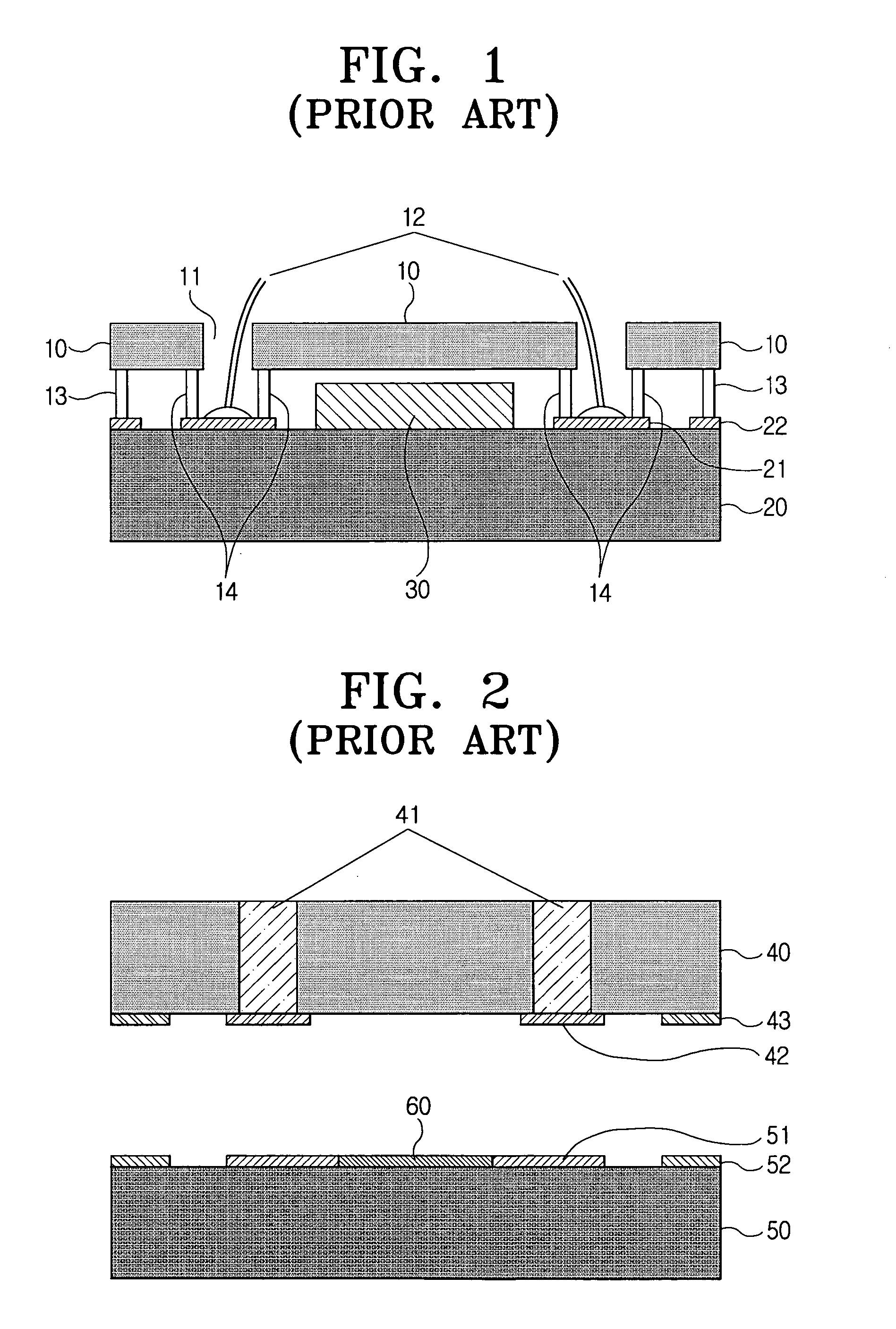

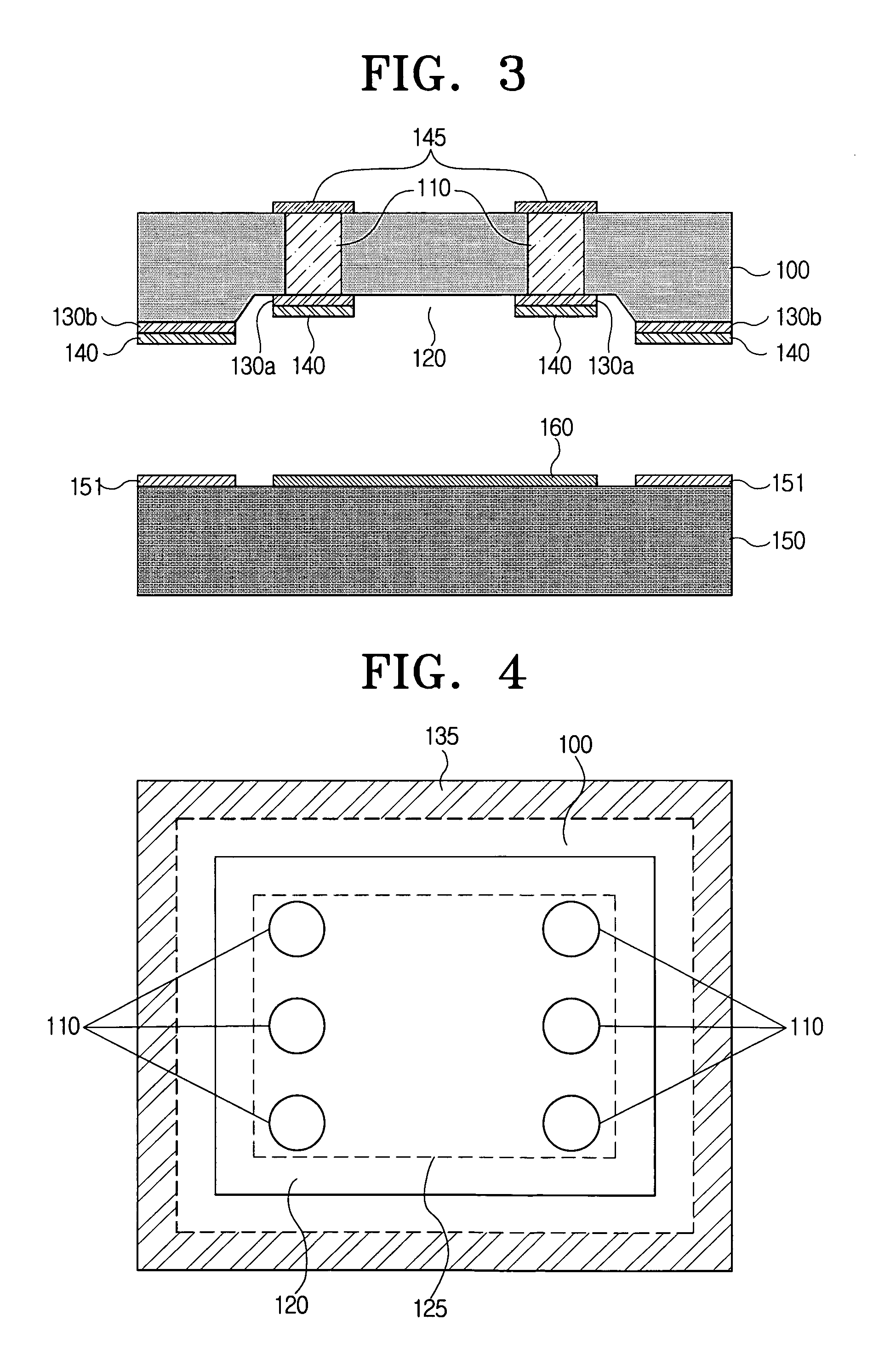

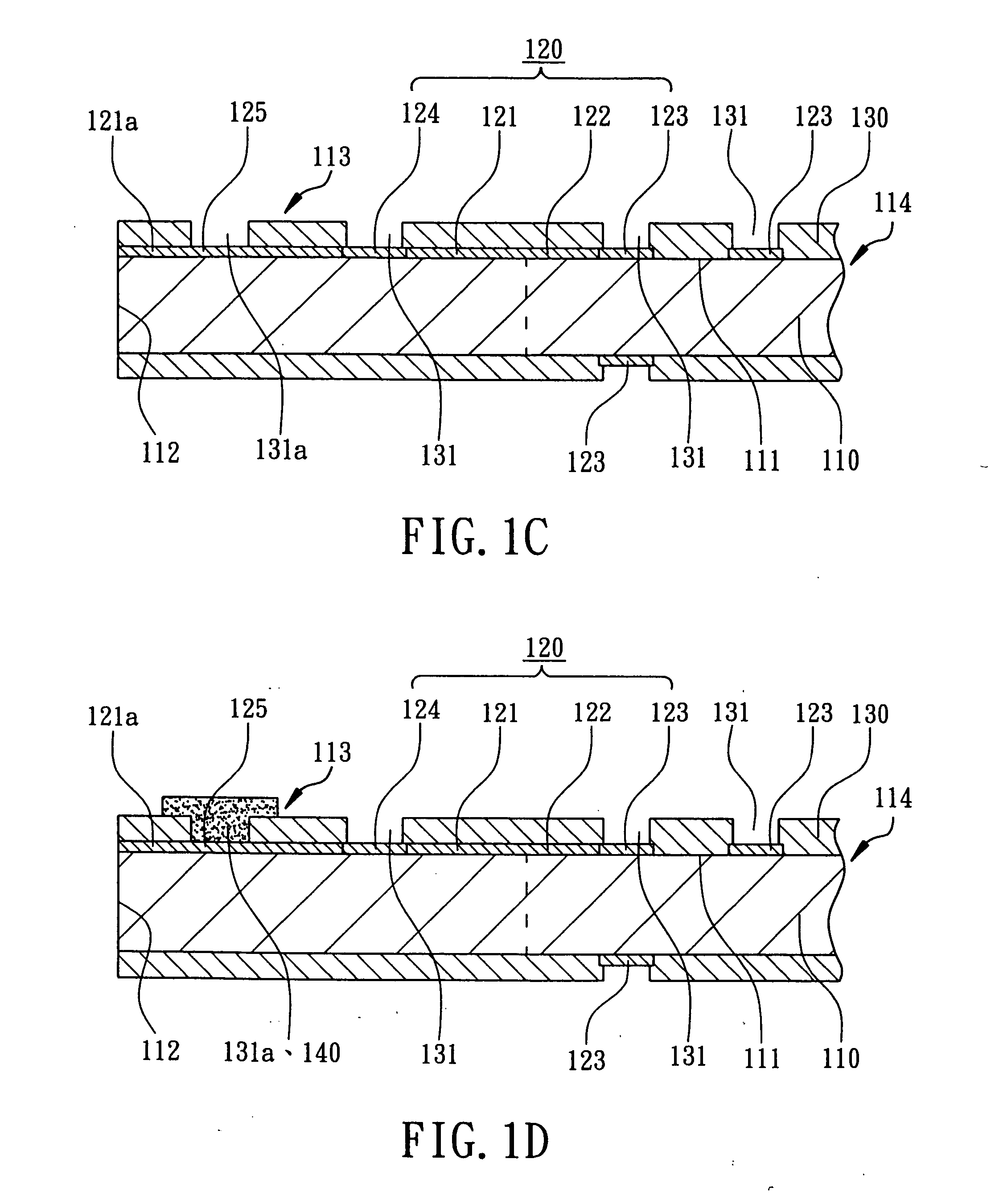

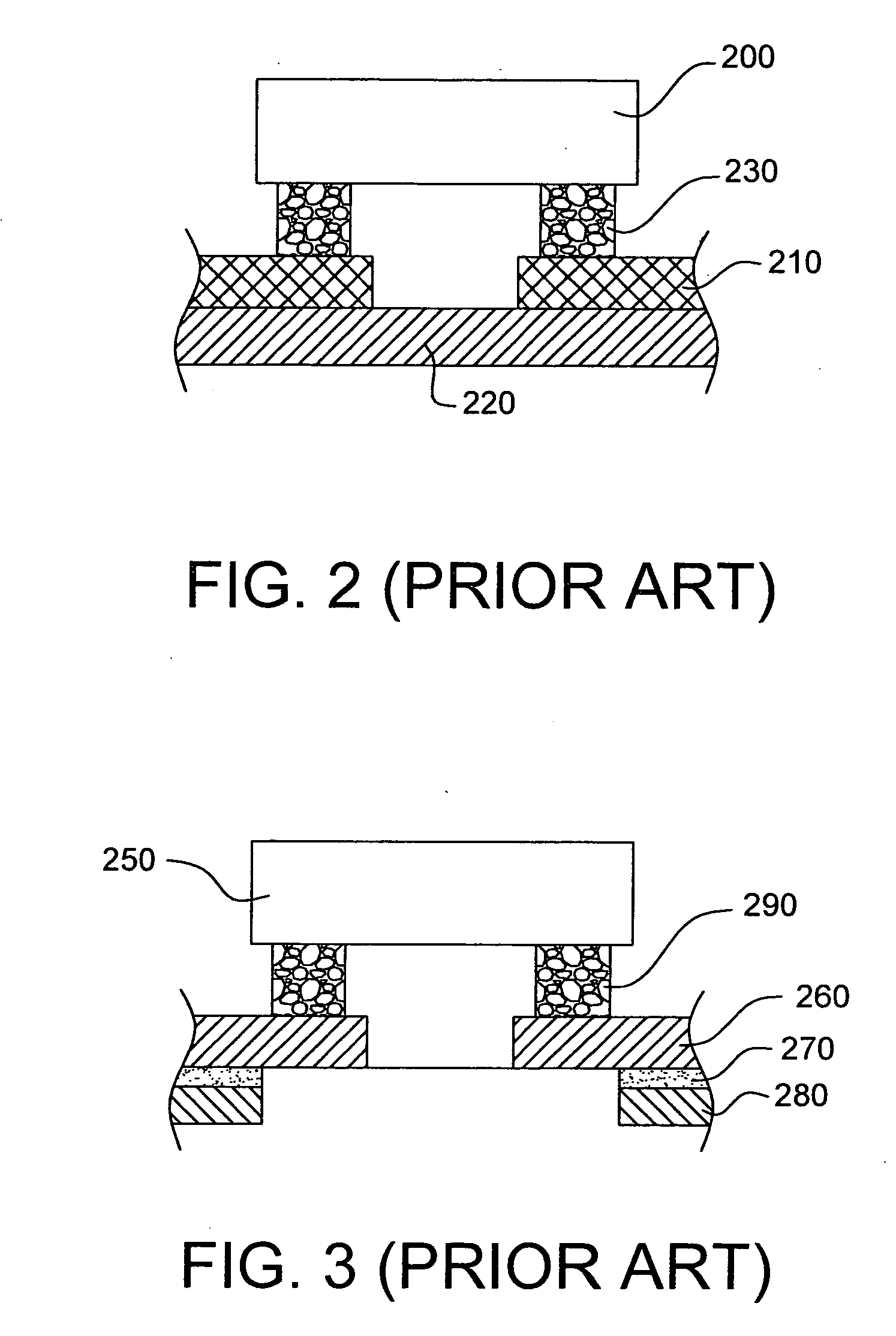

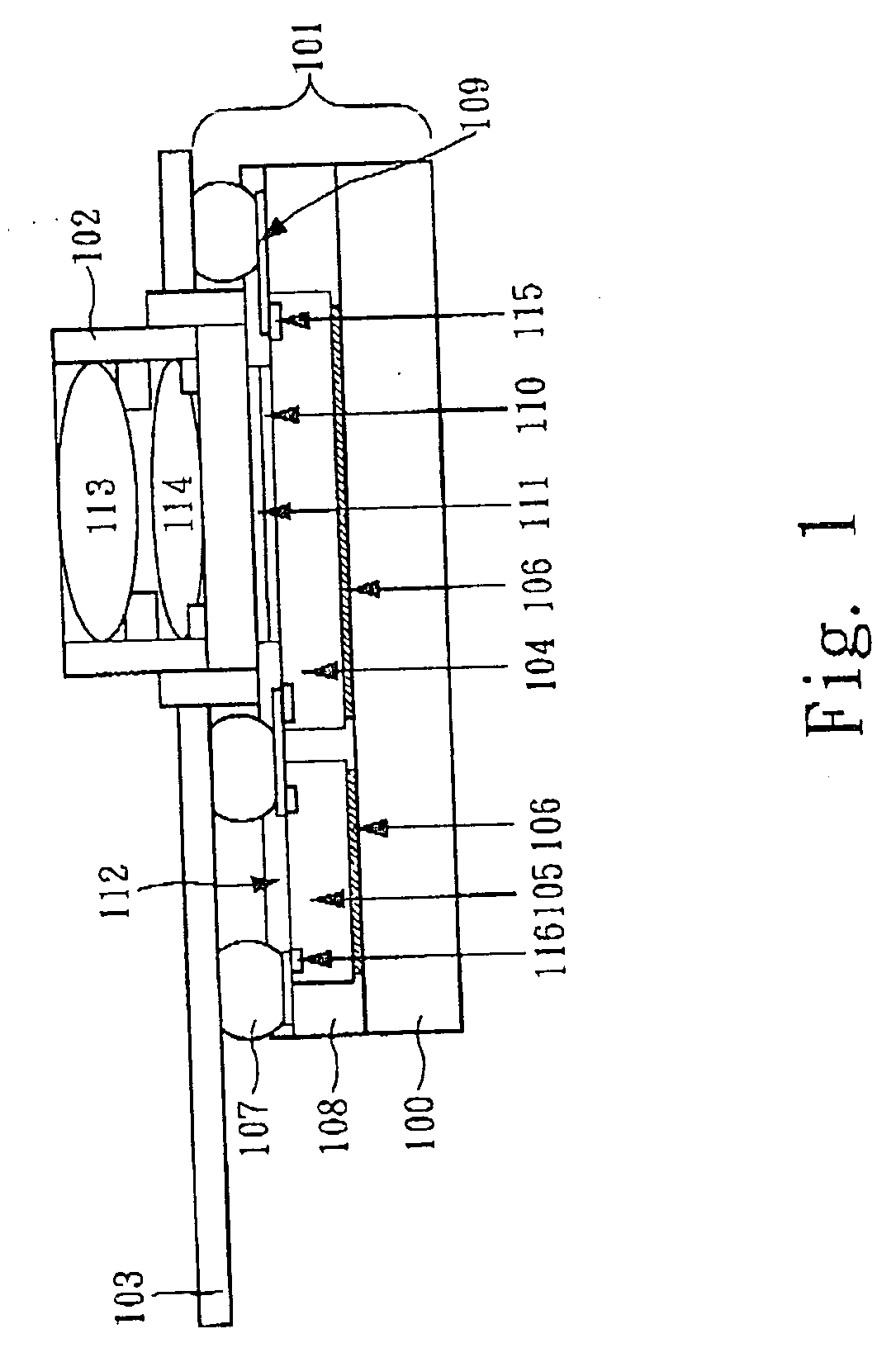

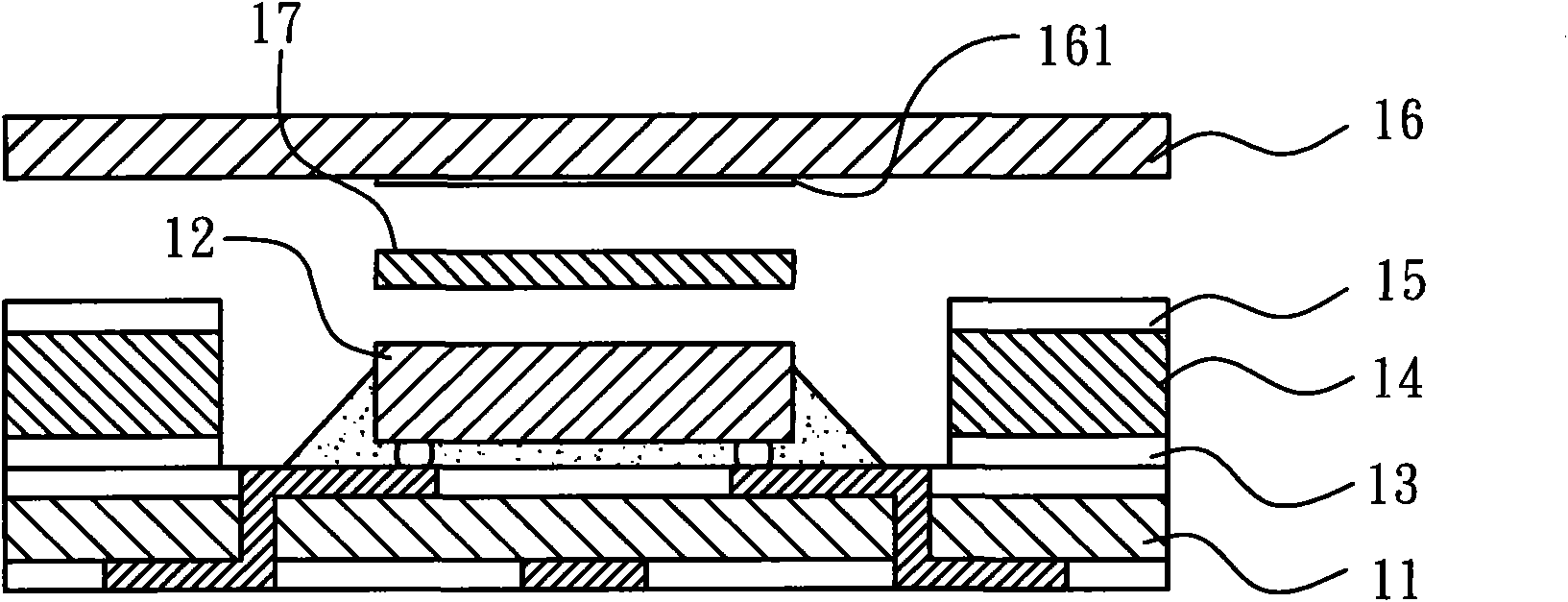

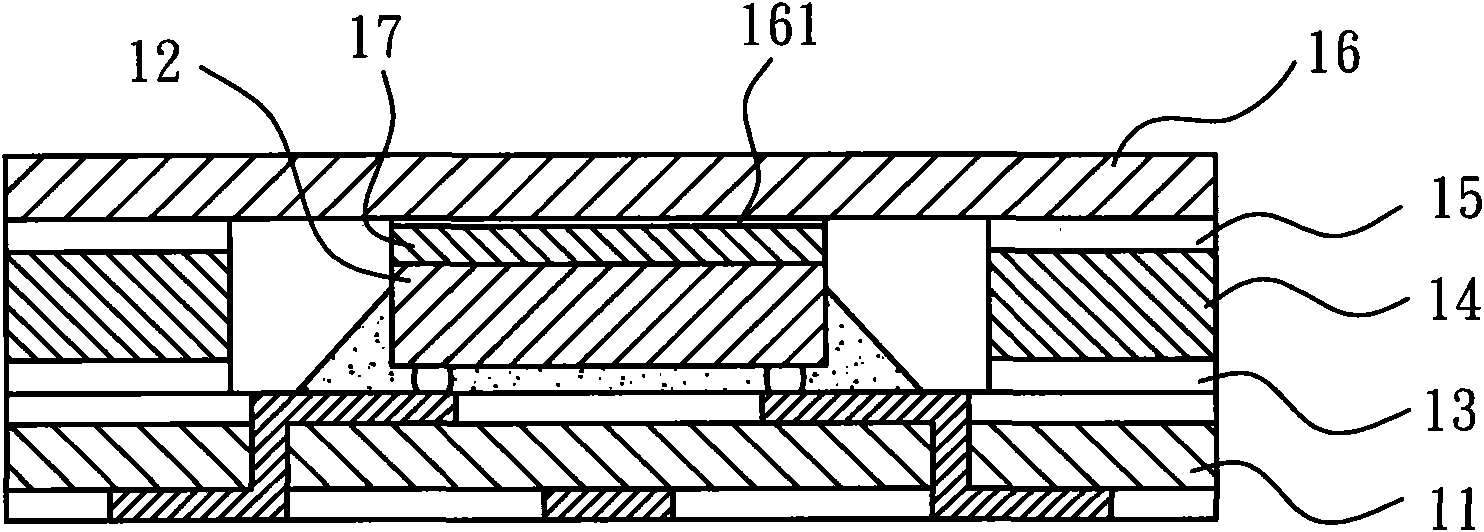

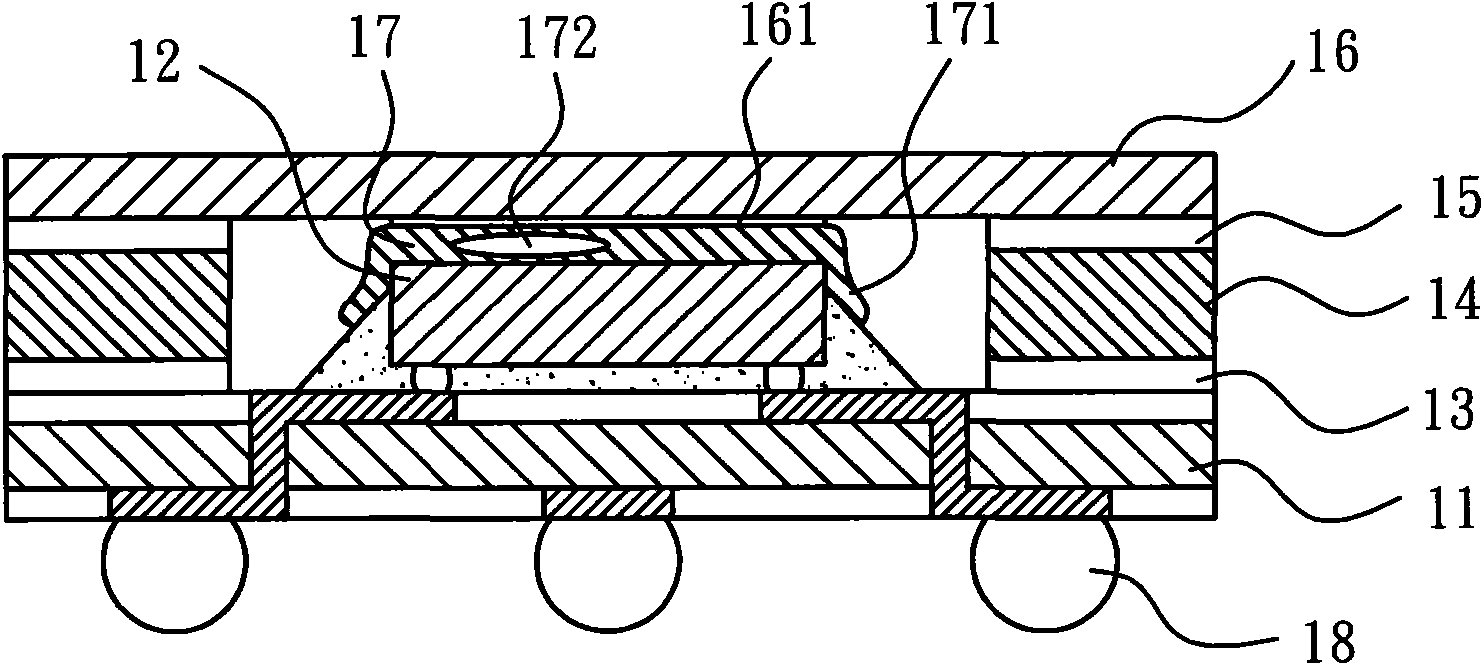

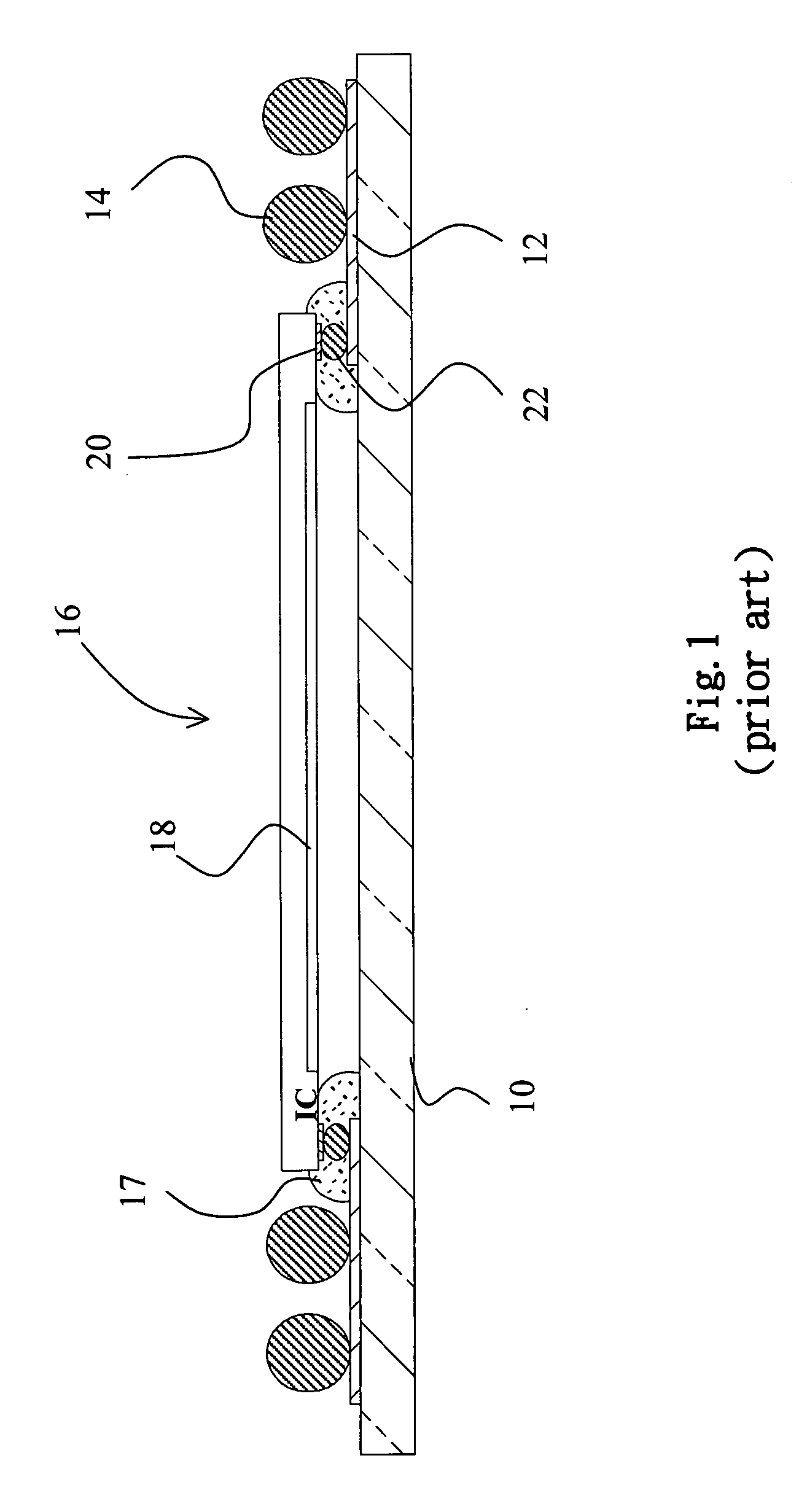

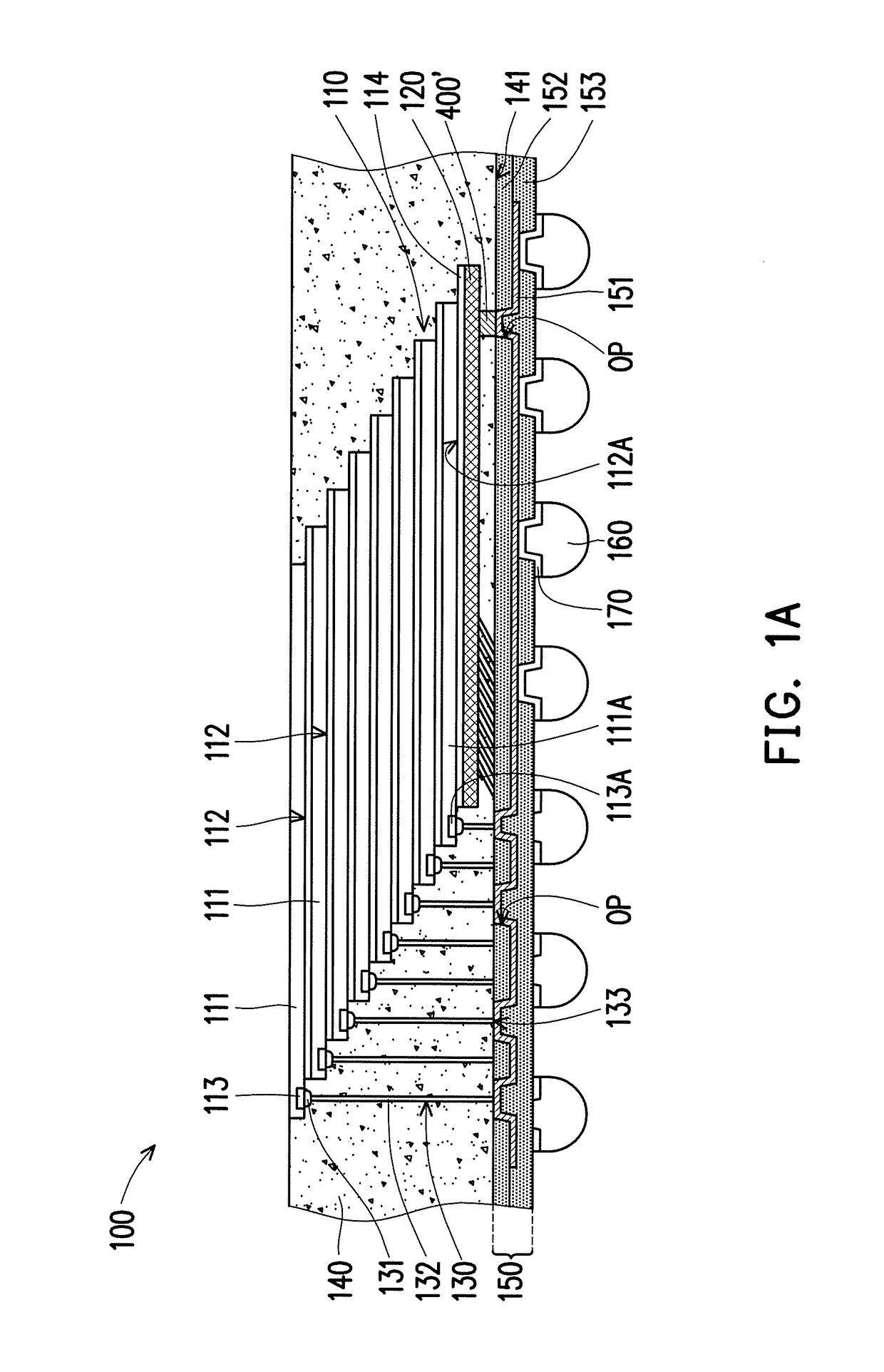

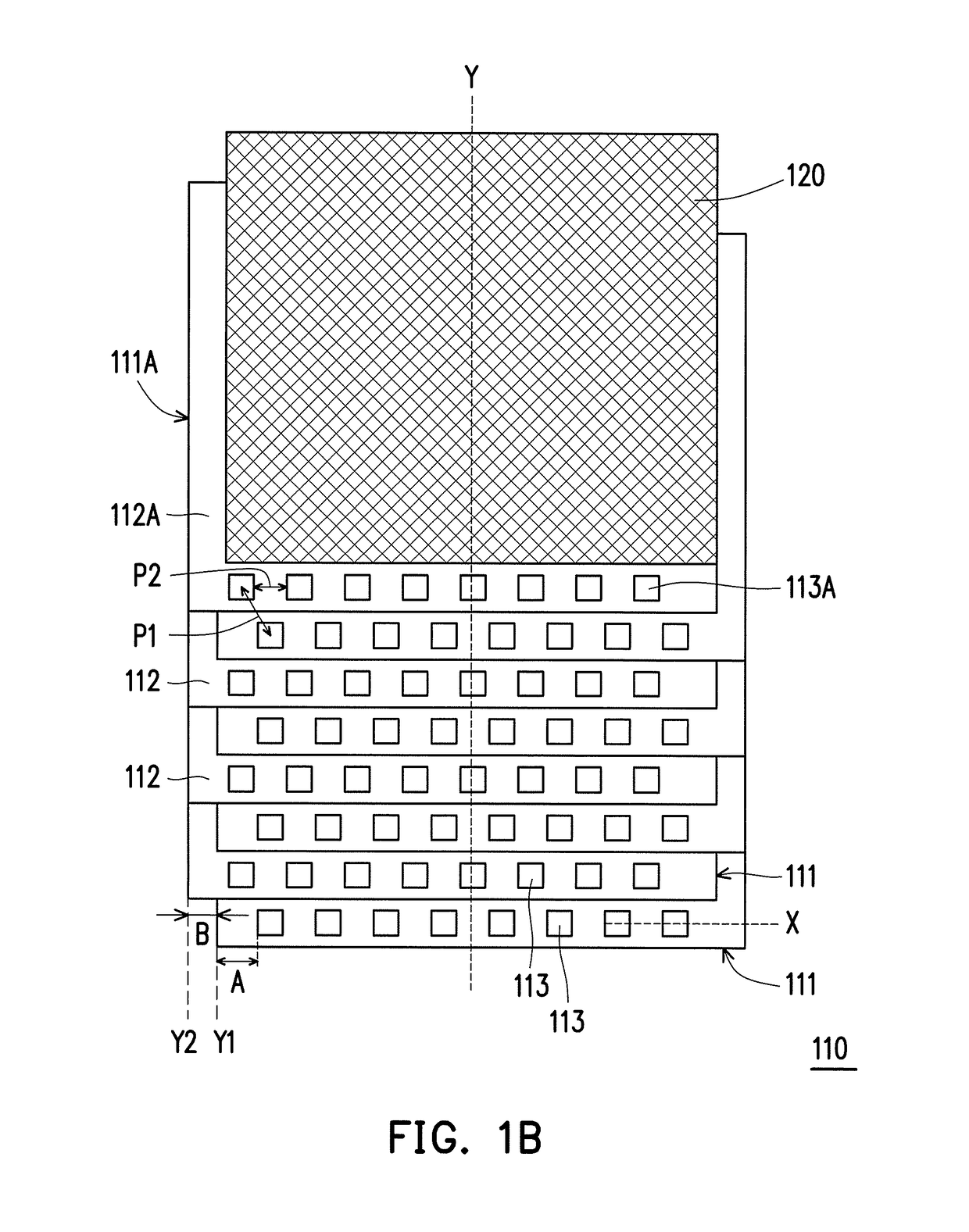

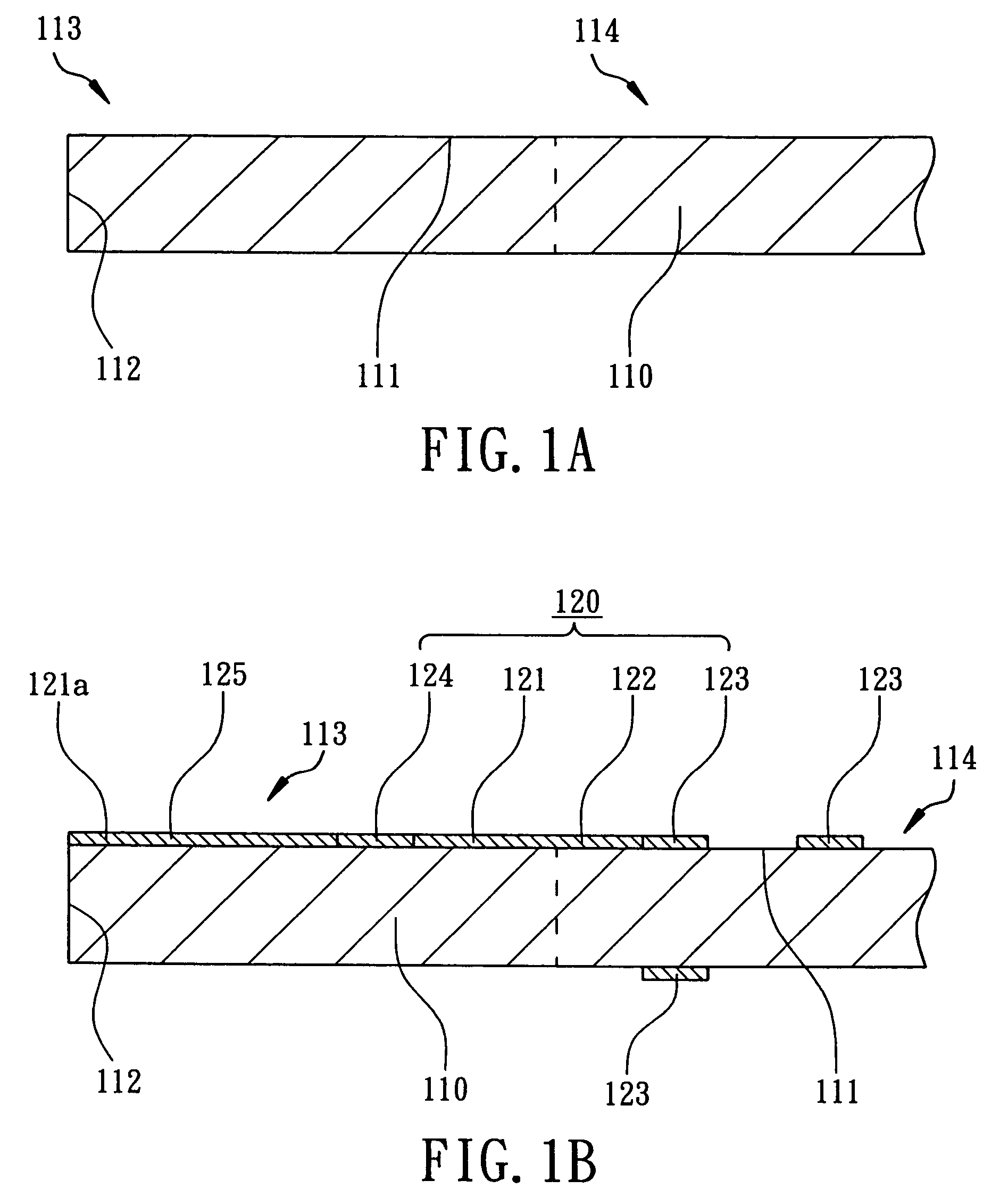

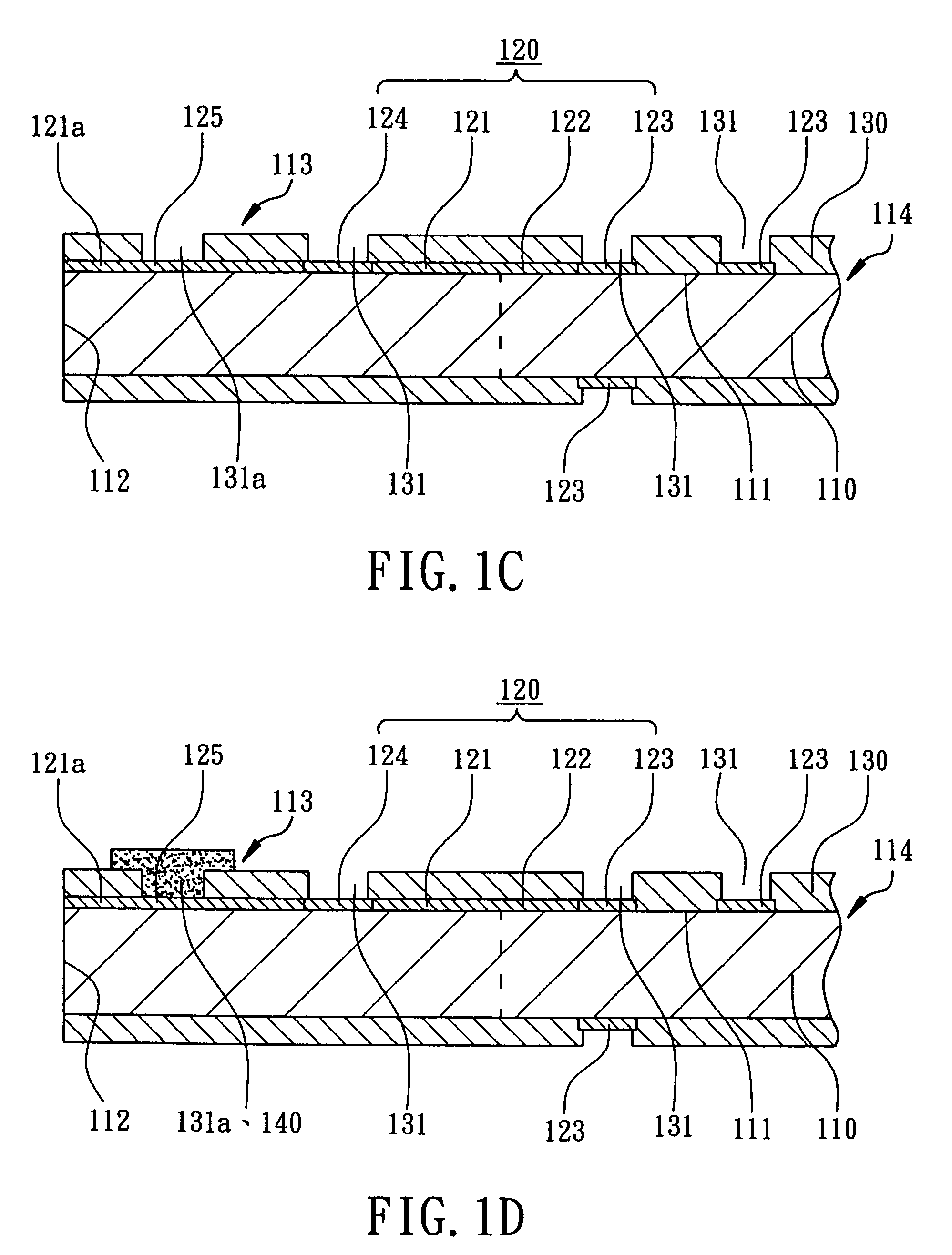

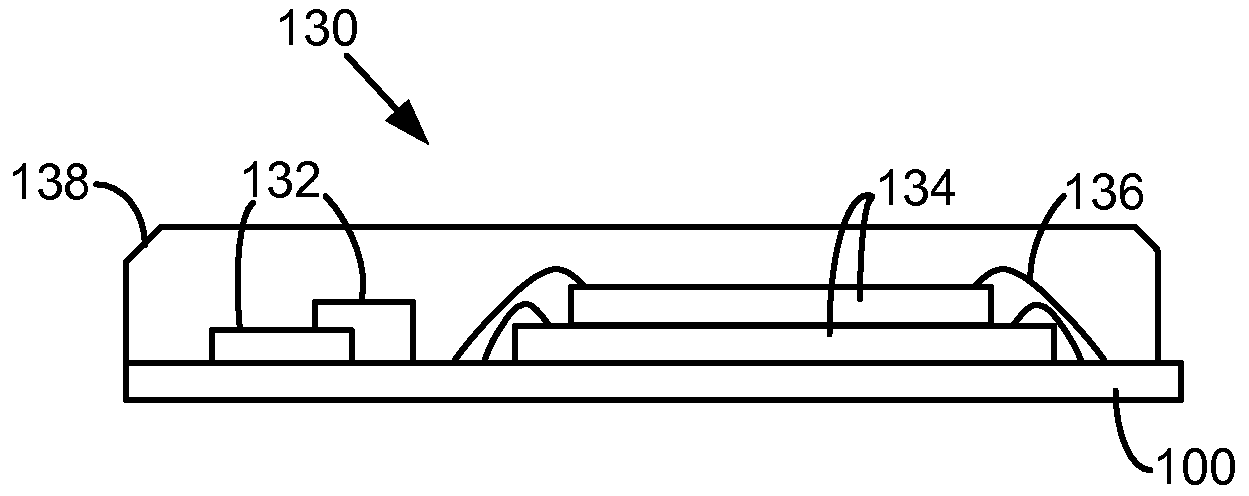

Flip-Chip Package Structure

InactiveUS20110049703A1Save substrate areaMade smallSemiconductor/solid-state device detailsSolid-state devicesSolder maskLead bonding

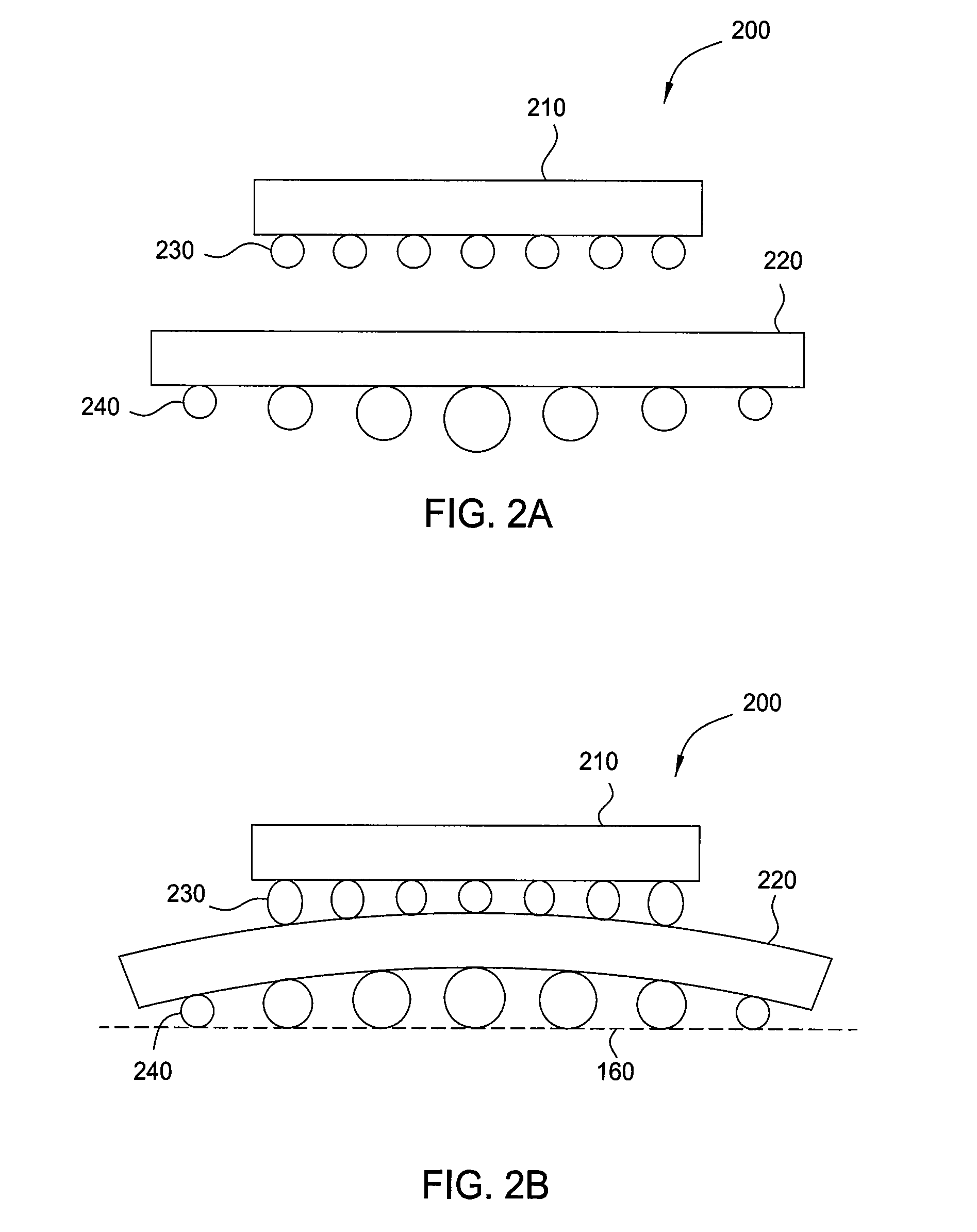

A flip-chip (FC) package structure is provided. The FC package structure includes a substrate, a chip, a plurality of copper platforms, a plurality of copper bumps, a plating layer, a circuit layer and a solder mask layer. The copper bumps are disposed on the substrate. The copper platforms are stacked on the copper bumps. The plating layer covers the copper bumps and the copper platforms, for contacting with chip foot pads configured at a bottom of the chip. The FC package structure does not need to reserve a space for wire bonding, thus saving the area of the substrate. The copper platforms are stacked on the copper bumps, and are higher than the circuit pattern layer. Therefore, the chip is blocked up, and the gap between the chip and the substrate is enlarged, thus preventing the risk of configuring voids when filling the cladding material and improving the packaging yield.

Owner:KINSUS INTERCONNECT TECH

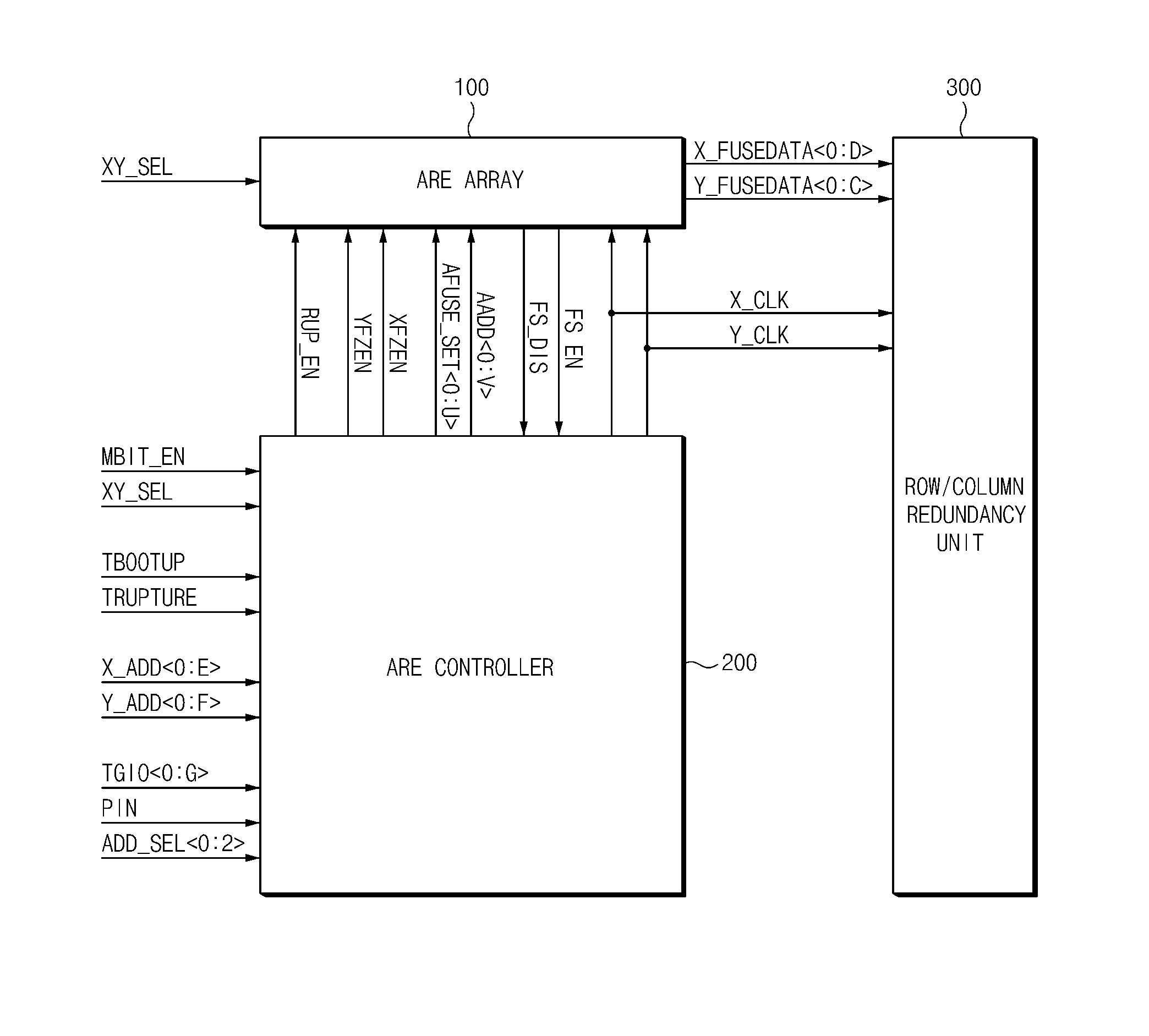

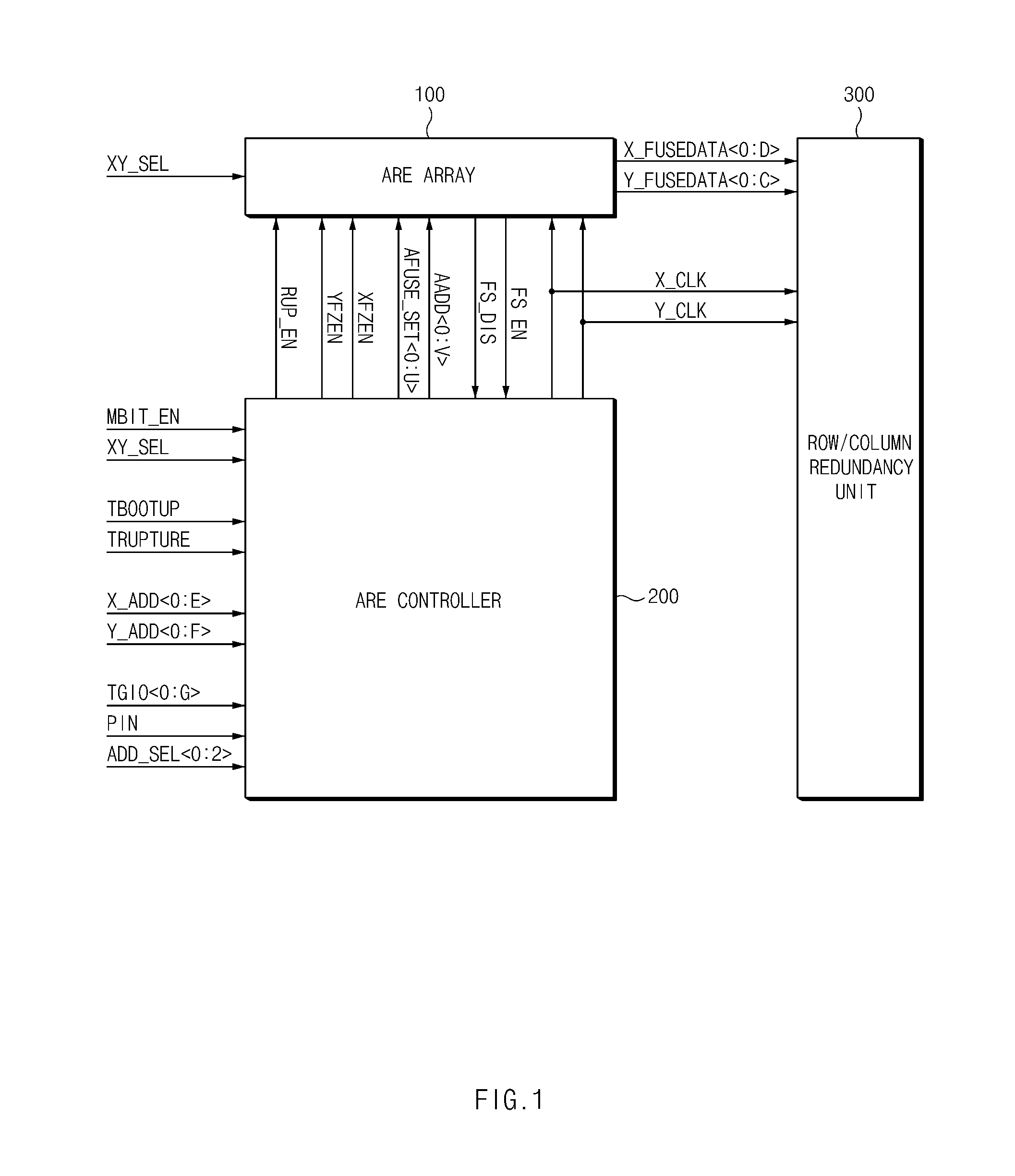

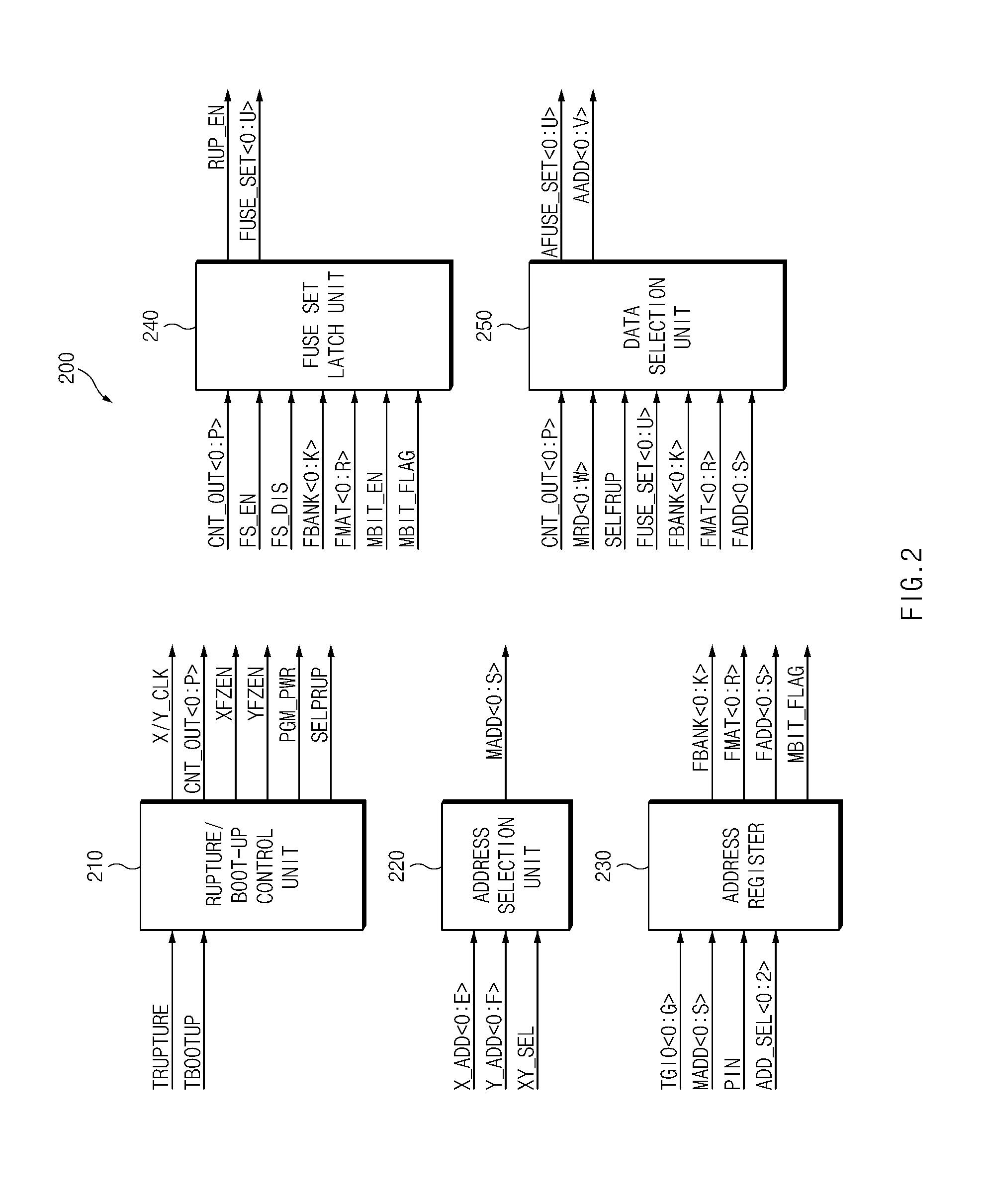

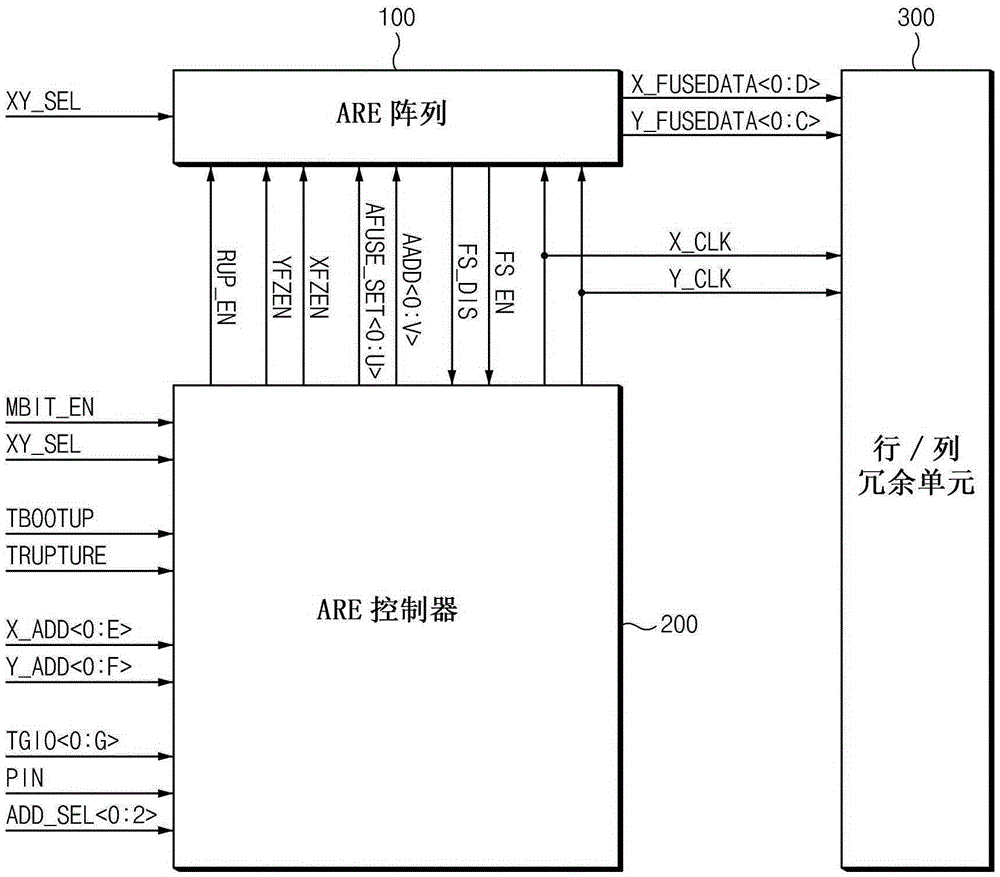

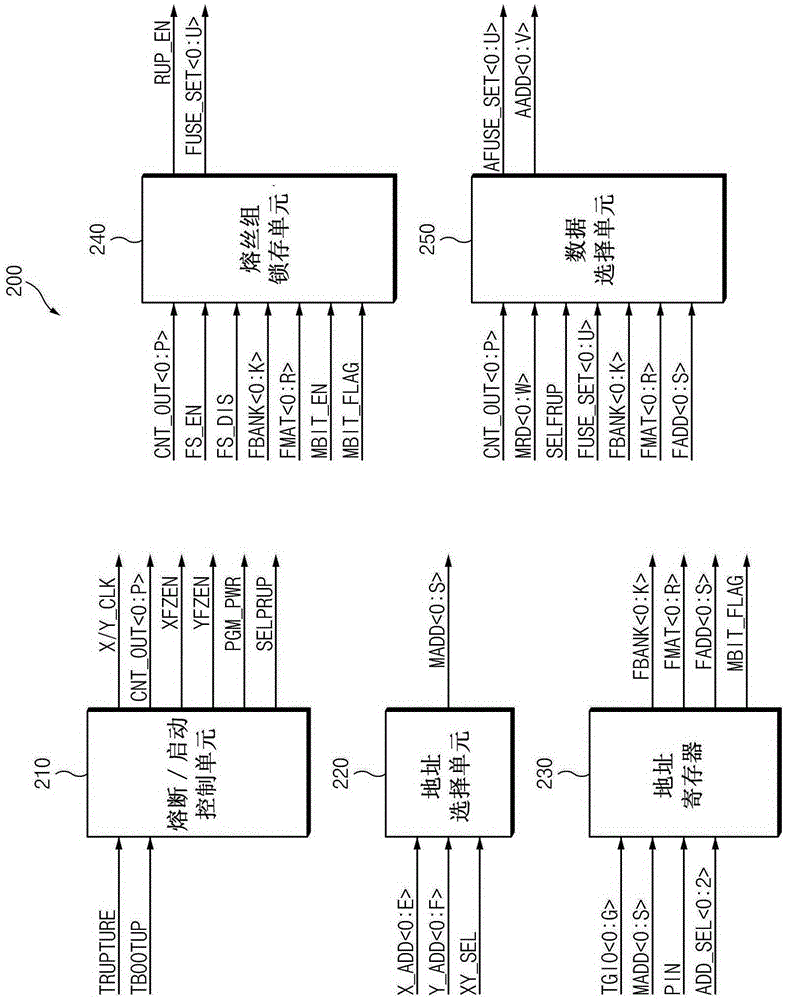

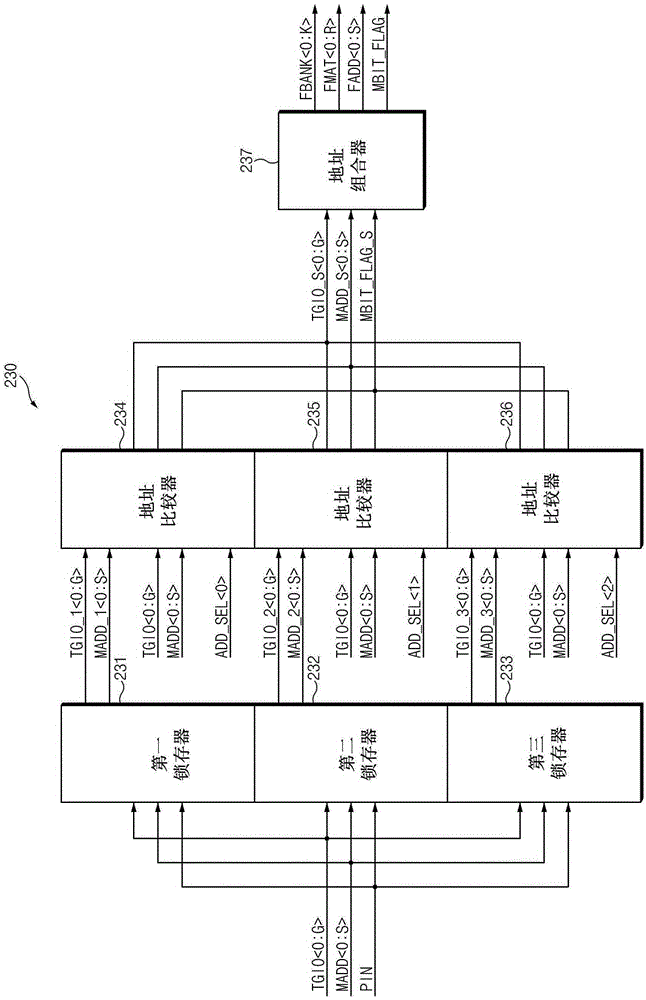

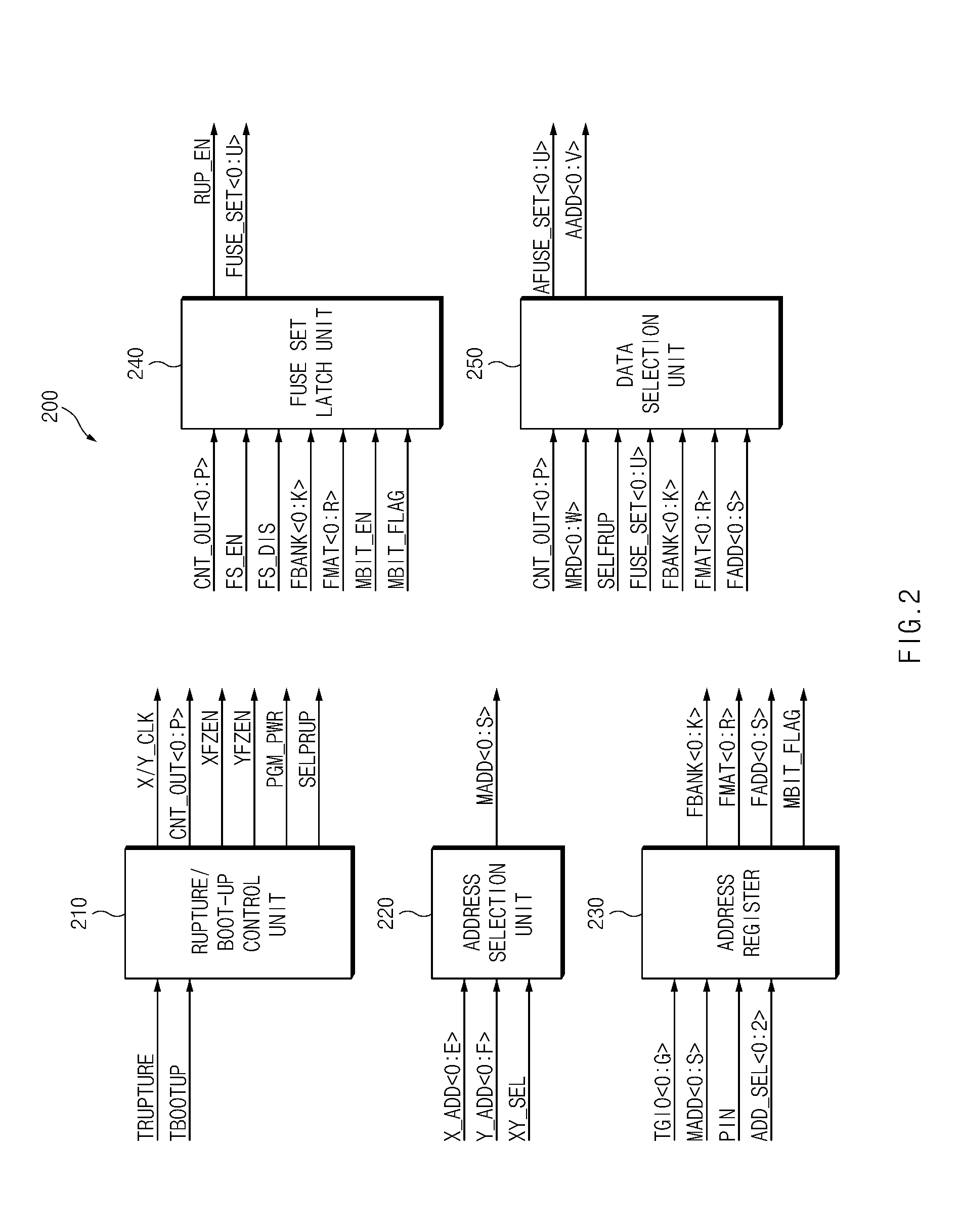

Self repair device and method thereof

A self repair device may include: an electrical fuse array configured to store bit information of a failed address in a fuse; an electrical fuse controller configured to store a row address or column address corresponding to a failed bit when a failure occurs, generate a repair address by comparing a failed address inputted during a test to the address stored therein, output a rupture enable signal for controlling a rupture operation of the electrical fuse array, and output row fuse set data or column fuse set data in response to the failed address; and a row / column redundancy unit configured to perform a row redundancy or column redundancy operation in response to the row fuse set data or the column fuse set data applied from the electrical fuse array.

Owner:SK HYNIX INC

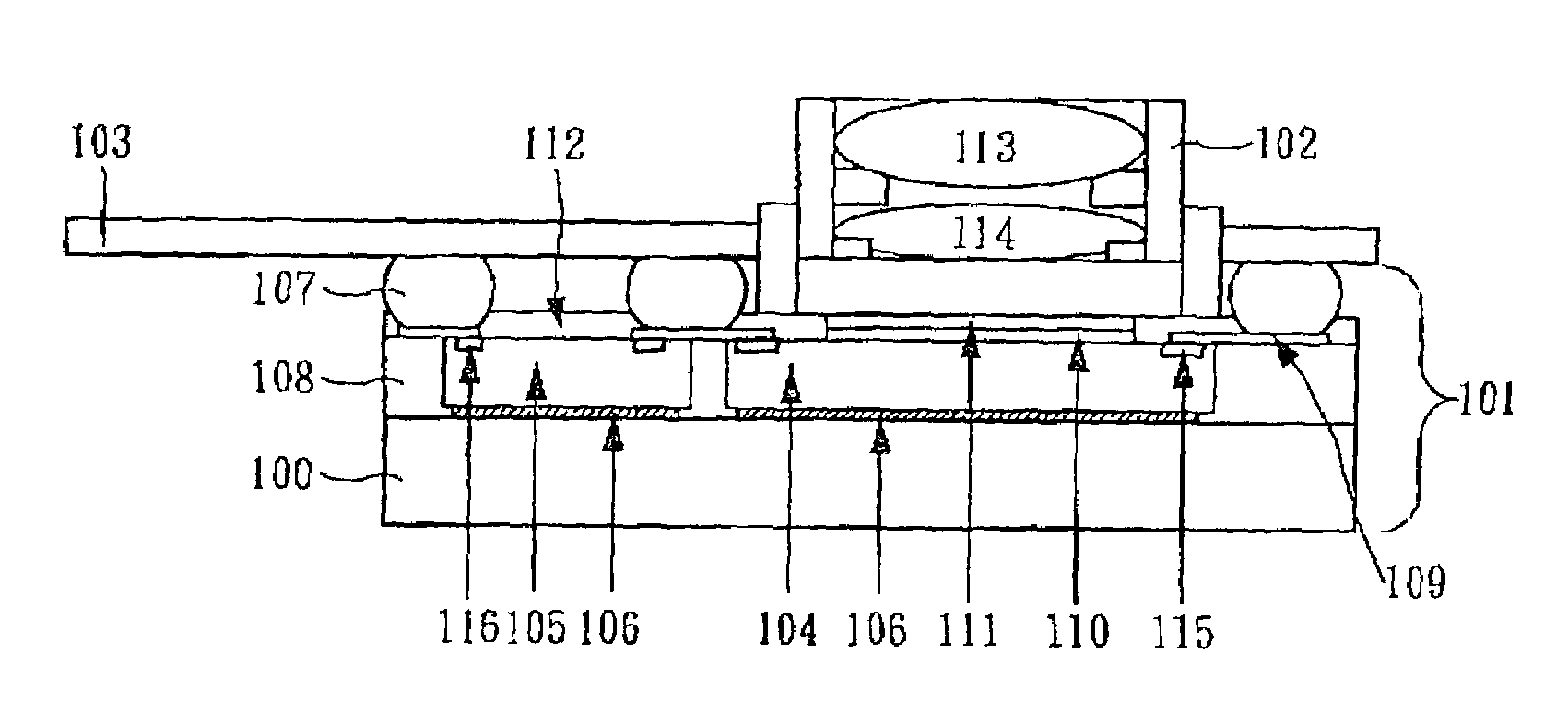

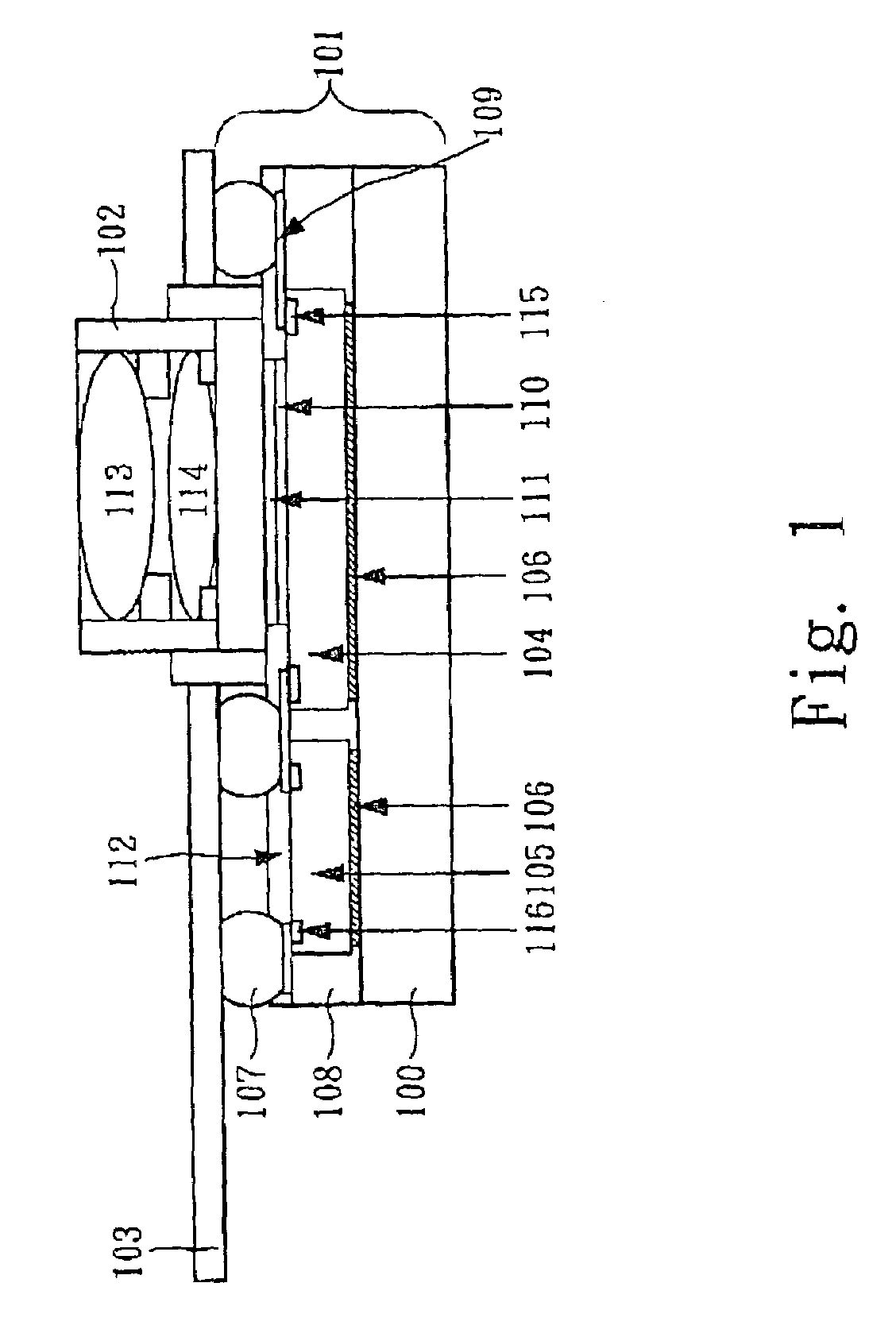

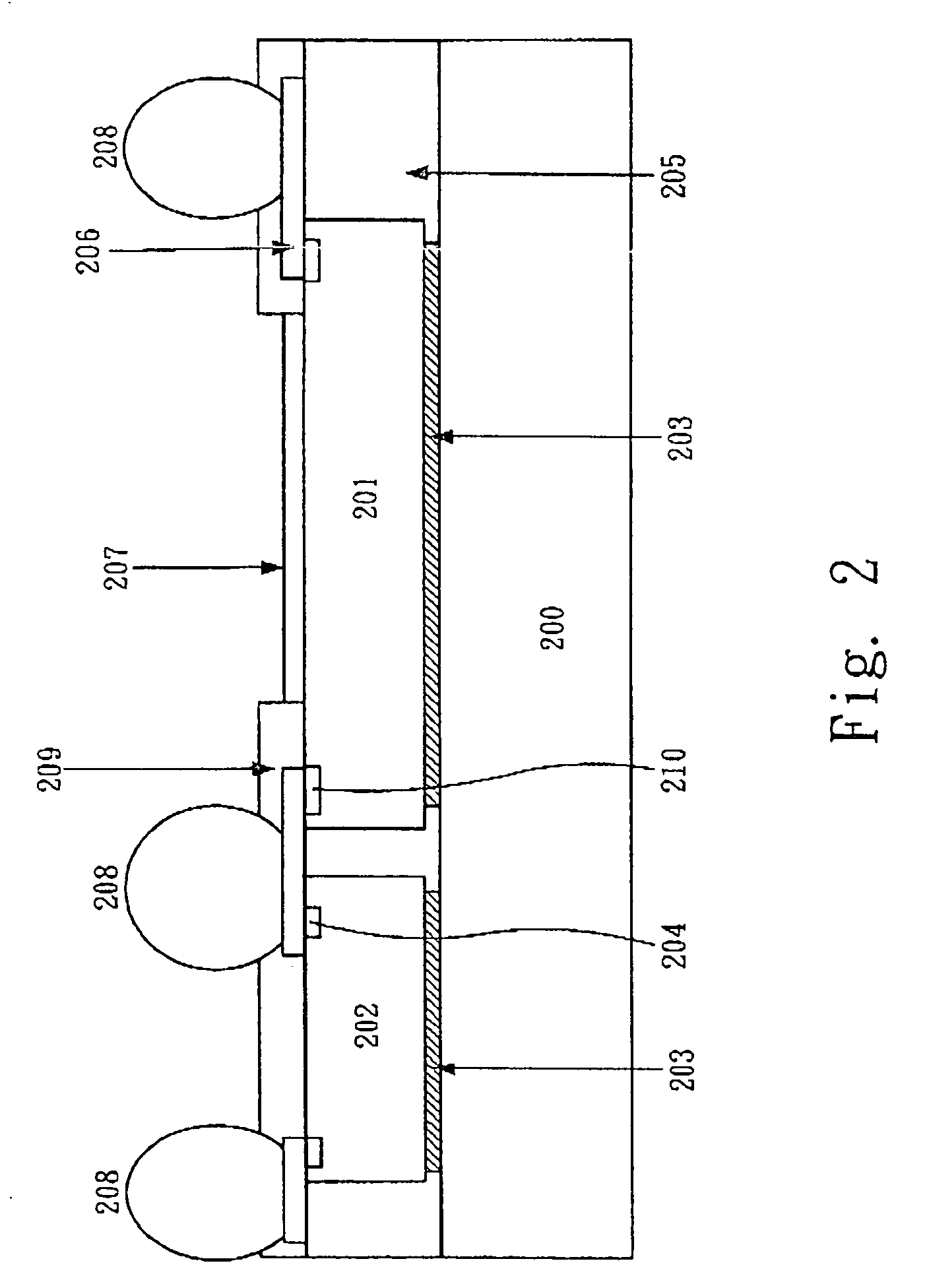

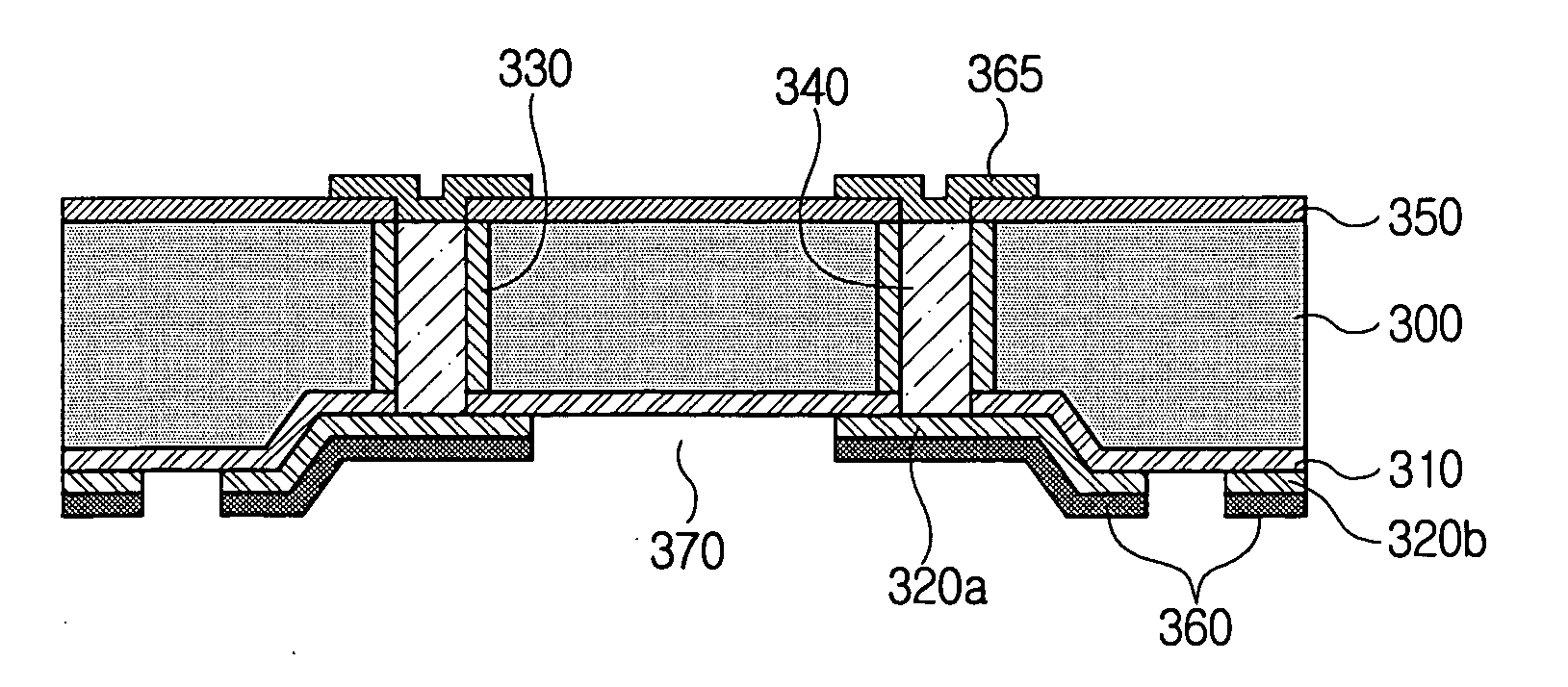

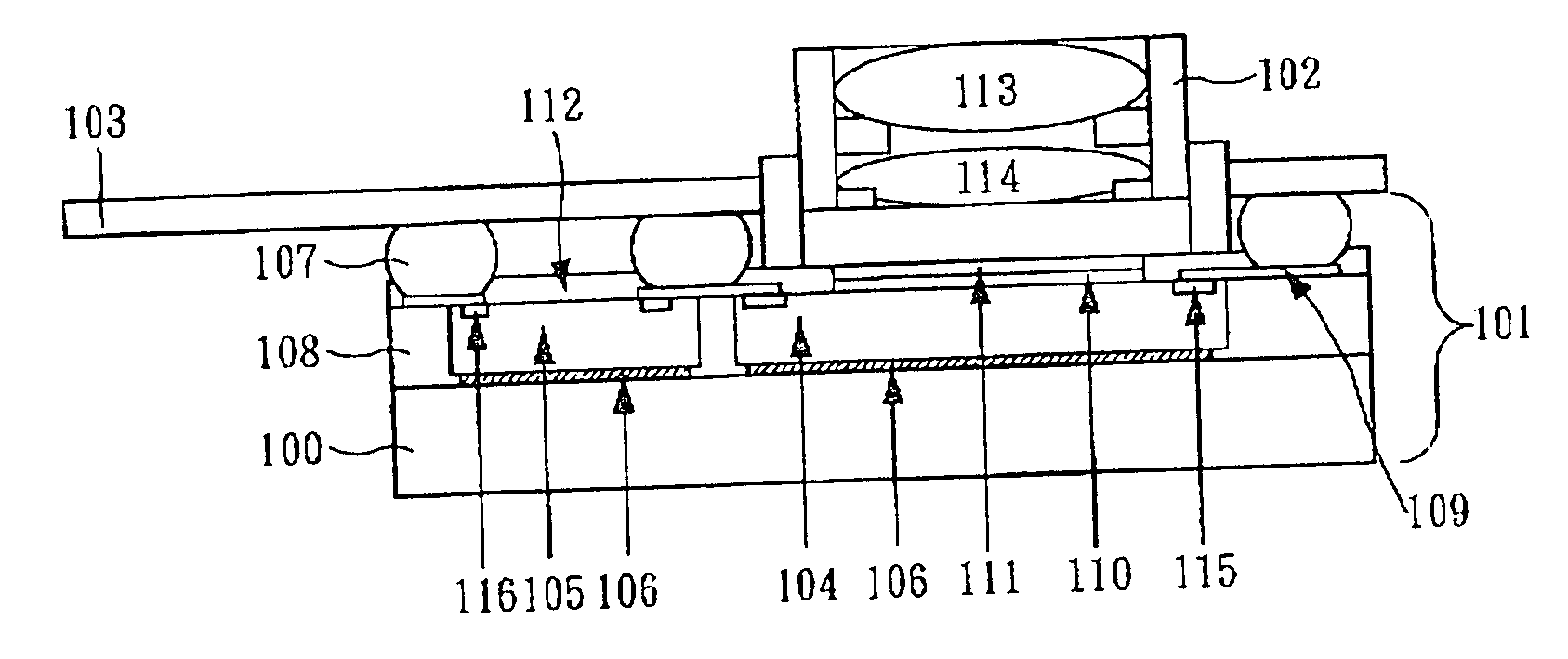

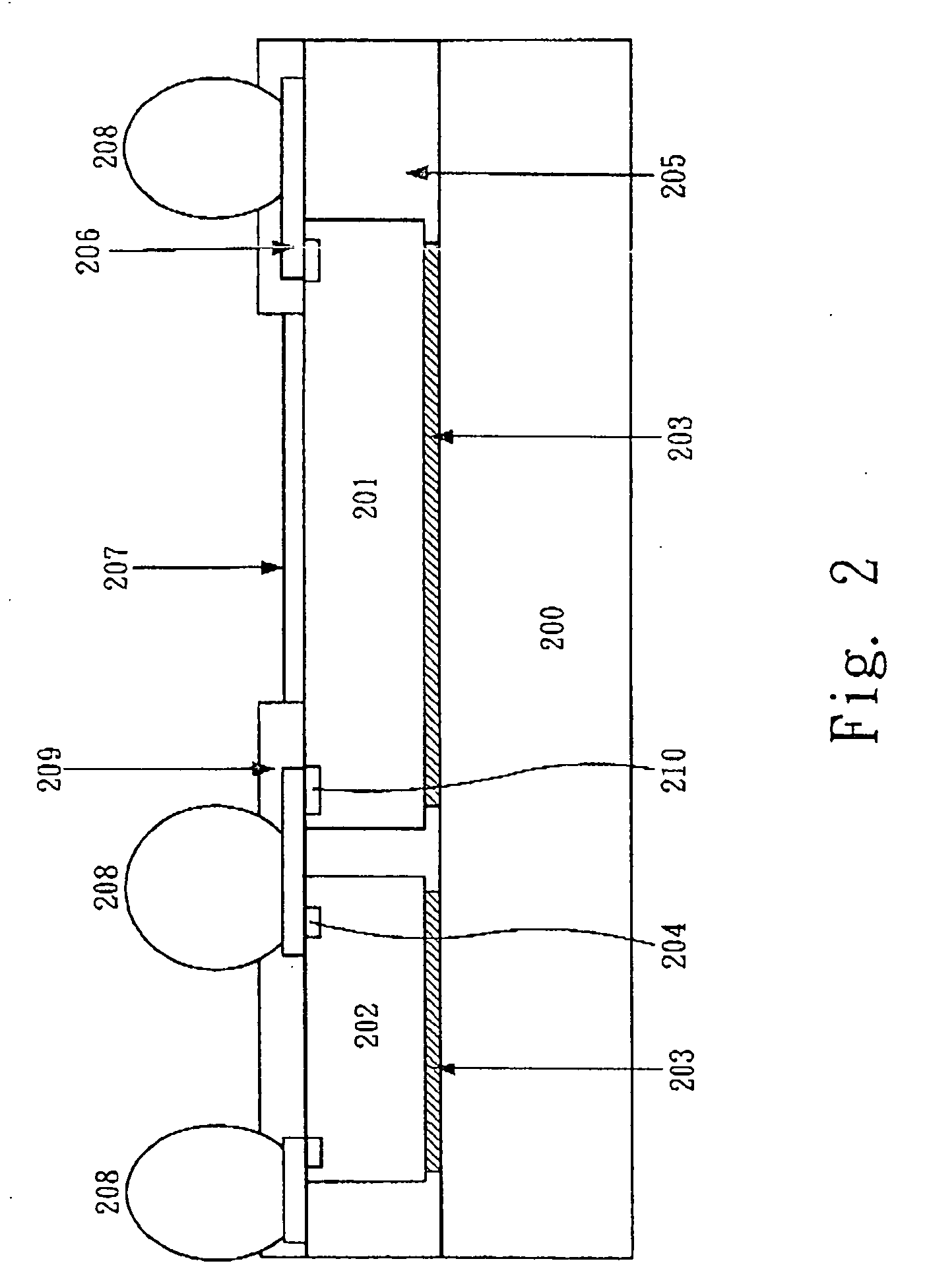

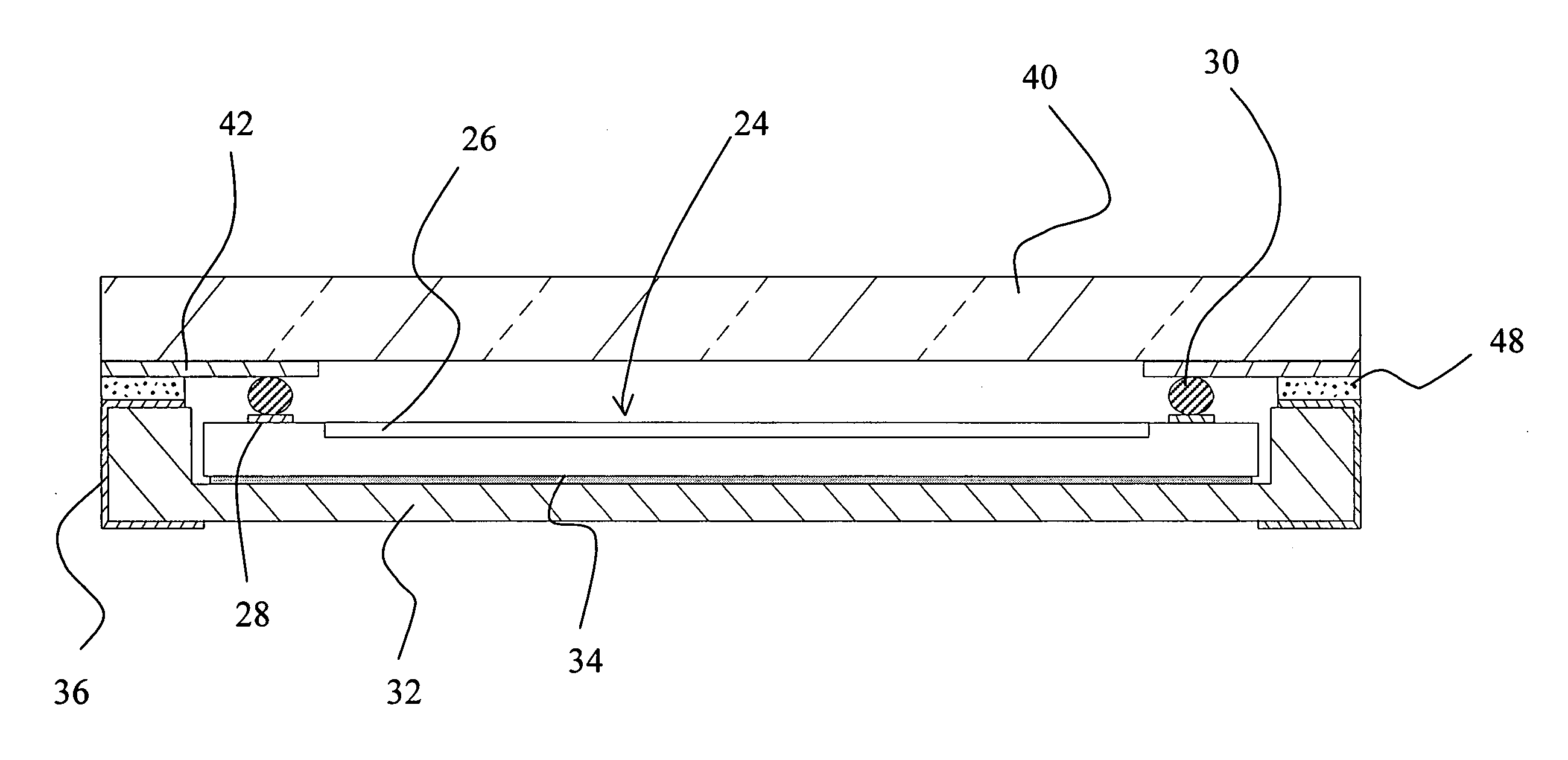

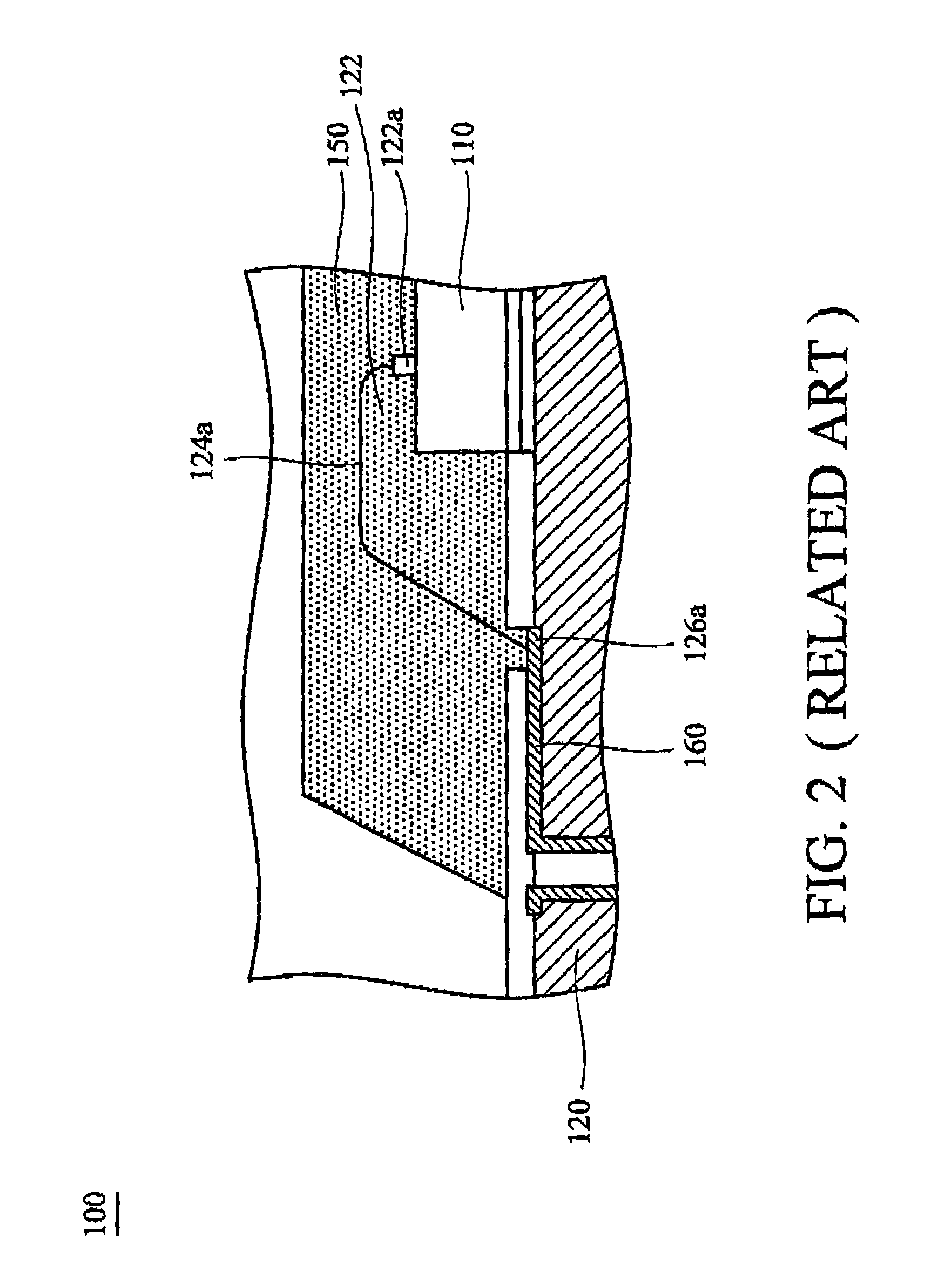

Structure of image sensor module and a method for manufacturing of wafer level package

ActiveUS7061106B2Easy to testLow costTelevision system detailsSemiconductor/solid-state device detailsSolder ballOptoelectronics

The present invention discloses an image sensor module and forming method of wafer level package. The image sensor module comprises an isolating base, a wafer level package, a lens holder, and a F.P.C.. The wafer level package having a plurality of image sensor dies and a plurality of solder balls is attached to the isolating base. A plurality of lens are placed in the lens holder, and the lens holder is located on the image sensor dies. The lens holder is placed in the F.P.C., and the F.P.C. has a plurality of solder joints coupled to the solder balls for conveniently transmitting signal of the image sensor dies. Moreover, the image sensor dies may be packaged with passive components or other dies with a side by side structure or a stacking structure.

Owner:ADL ENERGY CORP

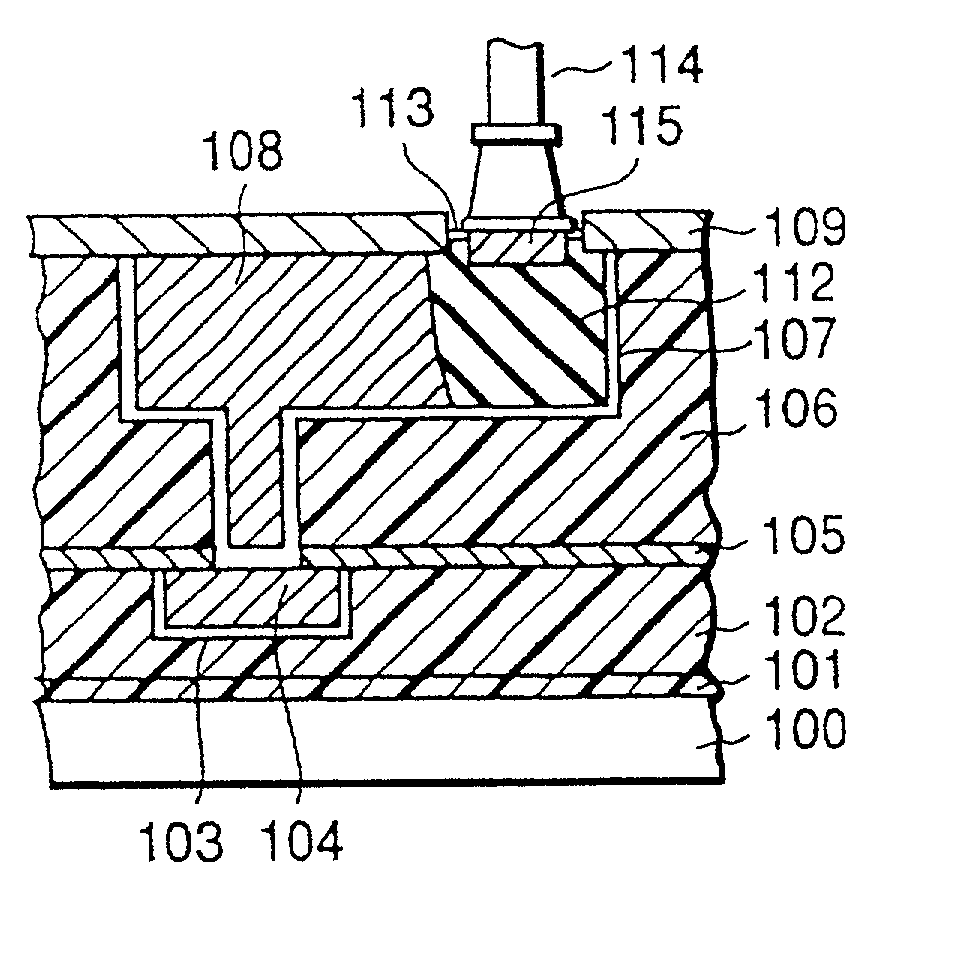

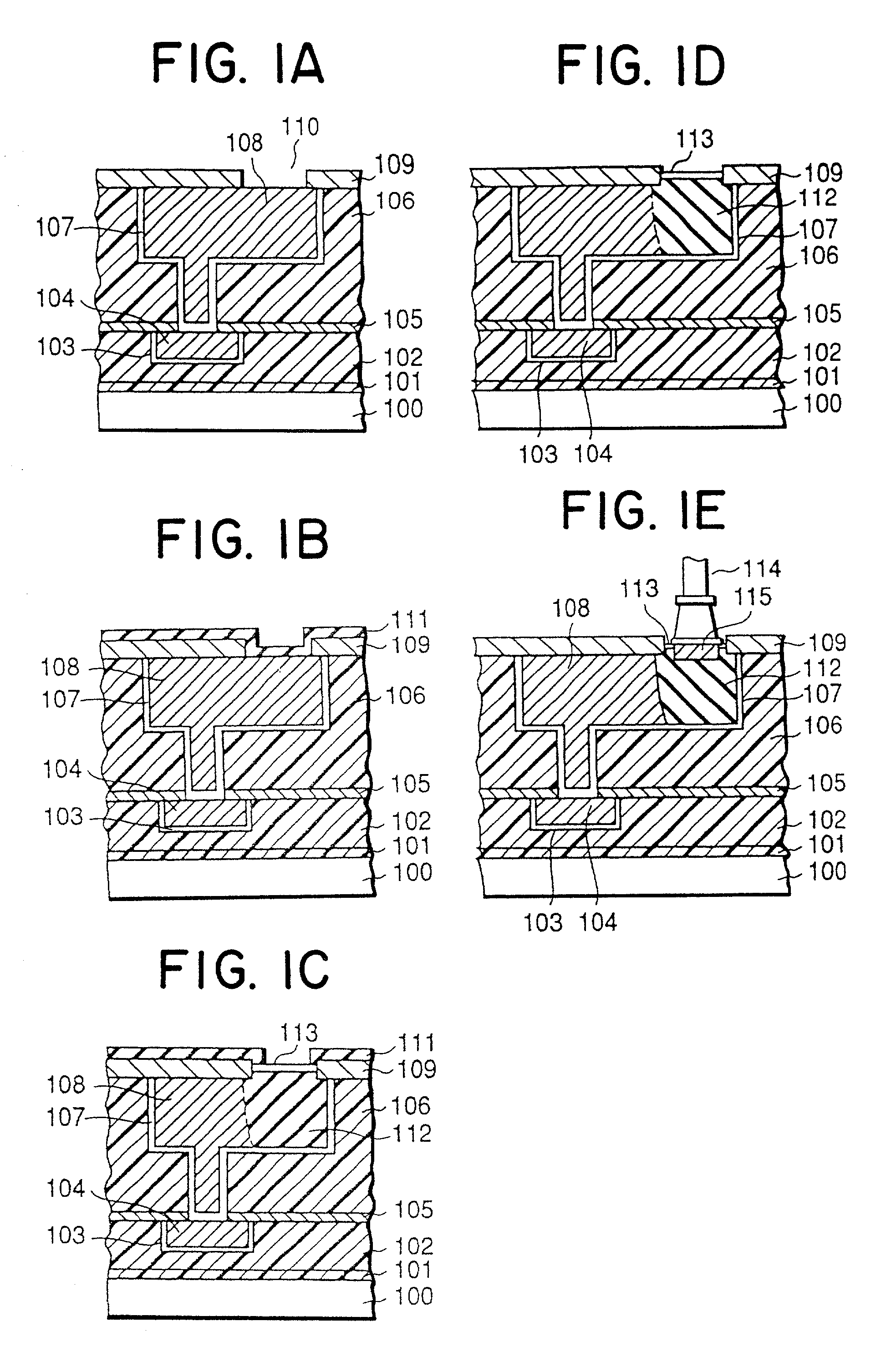

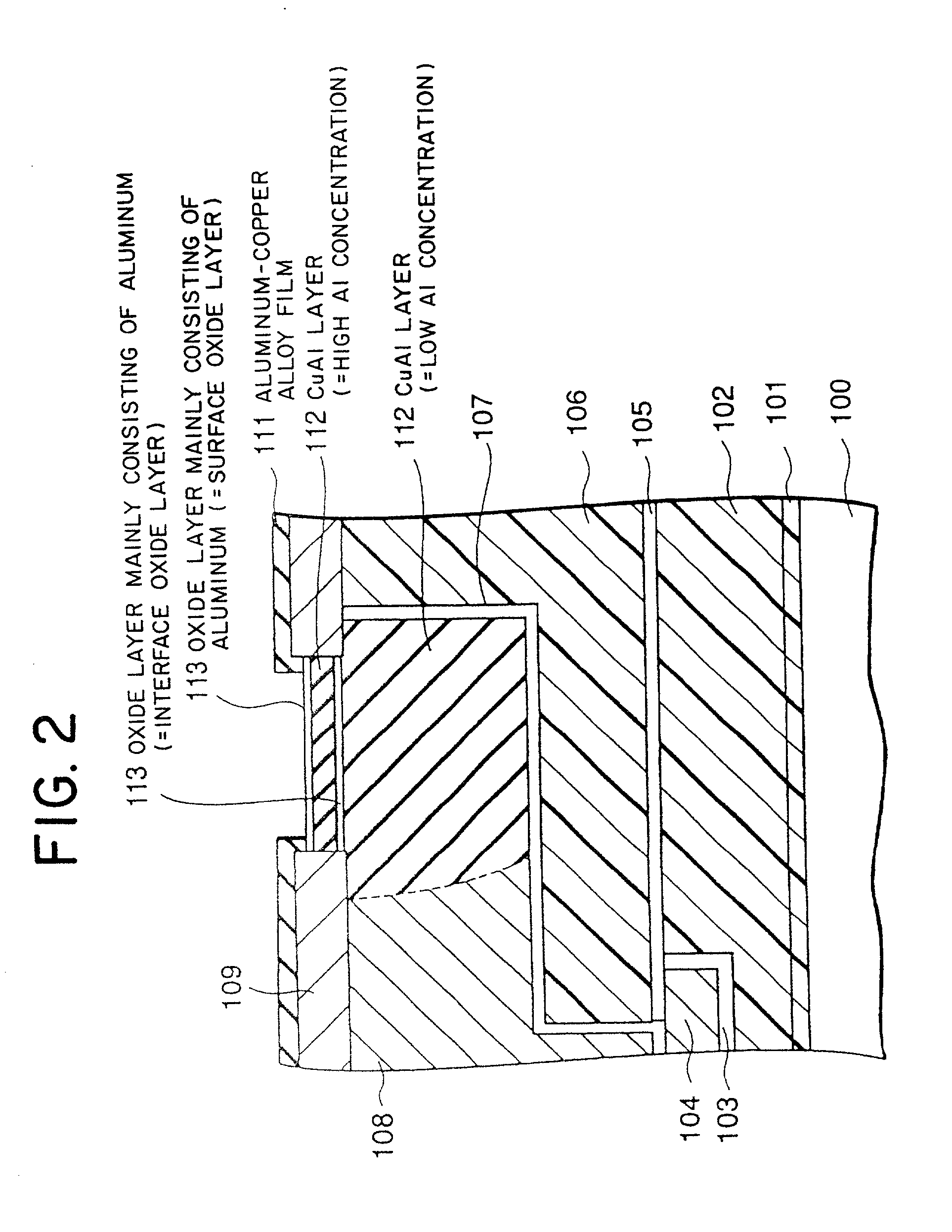

Semiconductor device and manufacturing method of semiconductor device

InactiveUS20020121703A1Dust could be greatly decreasedSolution value is not highSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsDevice materialCopper-wiring

A semiconductor device, which is comprised of a copper wiring layer which is formed above a semiconductor substrate, a pad electrode layer which conducts electrically to the copper wiring layer and has an alloy, which contains copper and a metal whose oxidation tendency is higher than copper, formed to extend to the bottom surface, and an insulating protective film which has an opening extended to the pad electrode layer, is provided.

Owner:KIOXIA CORP

Self repair device and method thereof

A self repair device may include: an electrical fuse array configured to store bit information of a failed address in a fuse; an electrical fuse controller configured to store a row address or column address corresponding to a failed bit when a failure occurs, generate a repair address by comparing a failed address inputted during a test to the address stored therein, output a rupture enable signal for controlling a rupture operation of the electrical fuse array, and output row fuse set data or column fuse set data in response to the failed address; and a row / column redundancy unit configured to perform a row redundancy or column redundancy operation in response to the row fuse set data or the column fuse set data applied from the electrical fuse array.

Owner:SK HYNIX INC

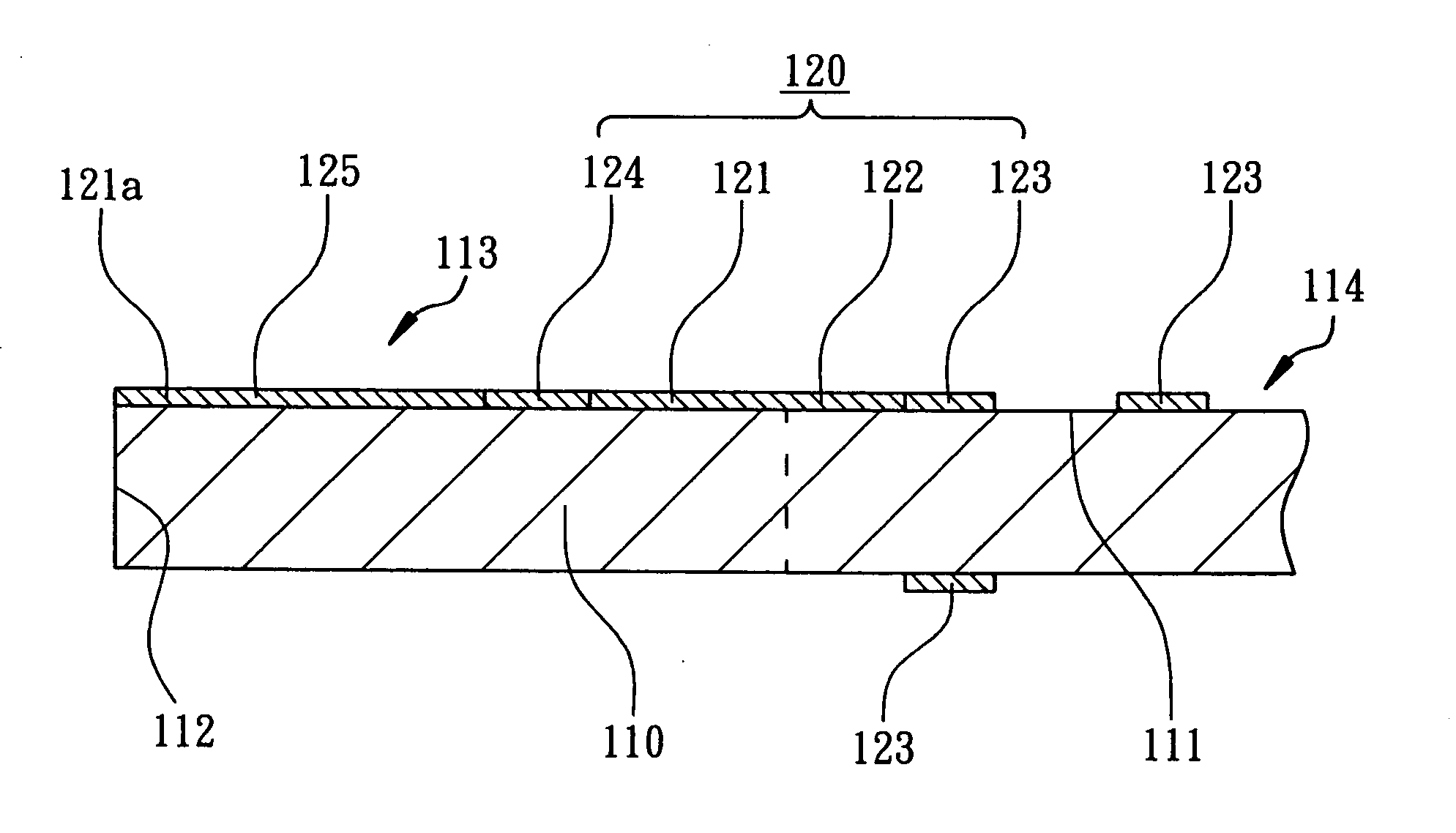

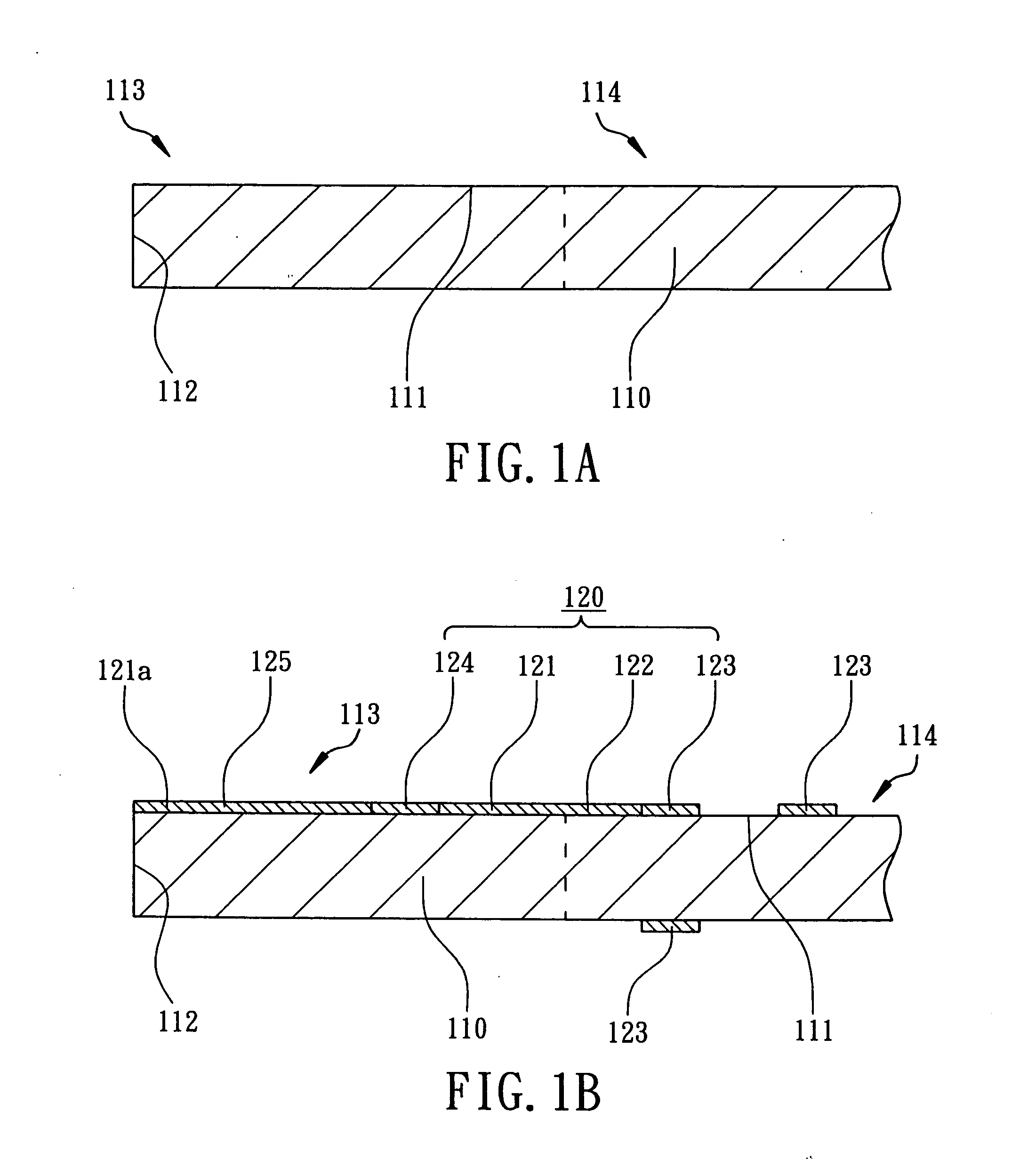

Cap wafer, semiconductor package, and fabricating method thereof

InactiveUS20060022325A1Improve package yieldReduce device sizeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A cap wafer including a cavity, a packaged semiconductor including the cap wafer, and a method of fabricating the cap wafer. The cap wafer includes a cavity formed in an area of a lower surface of the cap wafer; and at least one feed-through penetrating through upper and lower surfaces of the cap wafer so as to be connected to the cavity. The packaged semiconductor includes a base wafer including an upper surface including an area in which a circuit device is formed; a cap wafer including a lower surface including an area in which a cavity having a predetermined size is formed, the cap wafer being combined with the base wafer to position the circuit device in the cavity so as to package the circuit device; and at least one feed-through penetrating through upper and lower portions of the cap wafer so as to be connected to the cavity and electrically connected to the circuit device.

Owner:SAMSUNG ELECTRONICS CO LTD

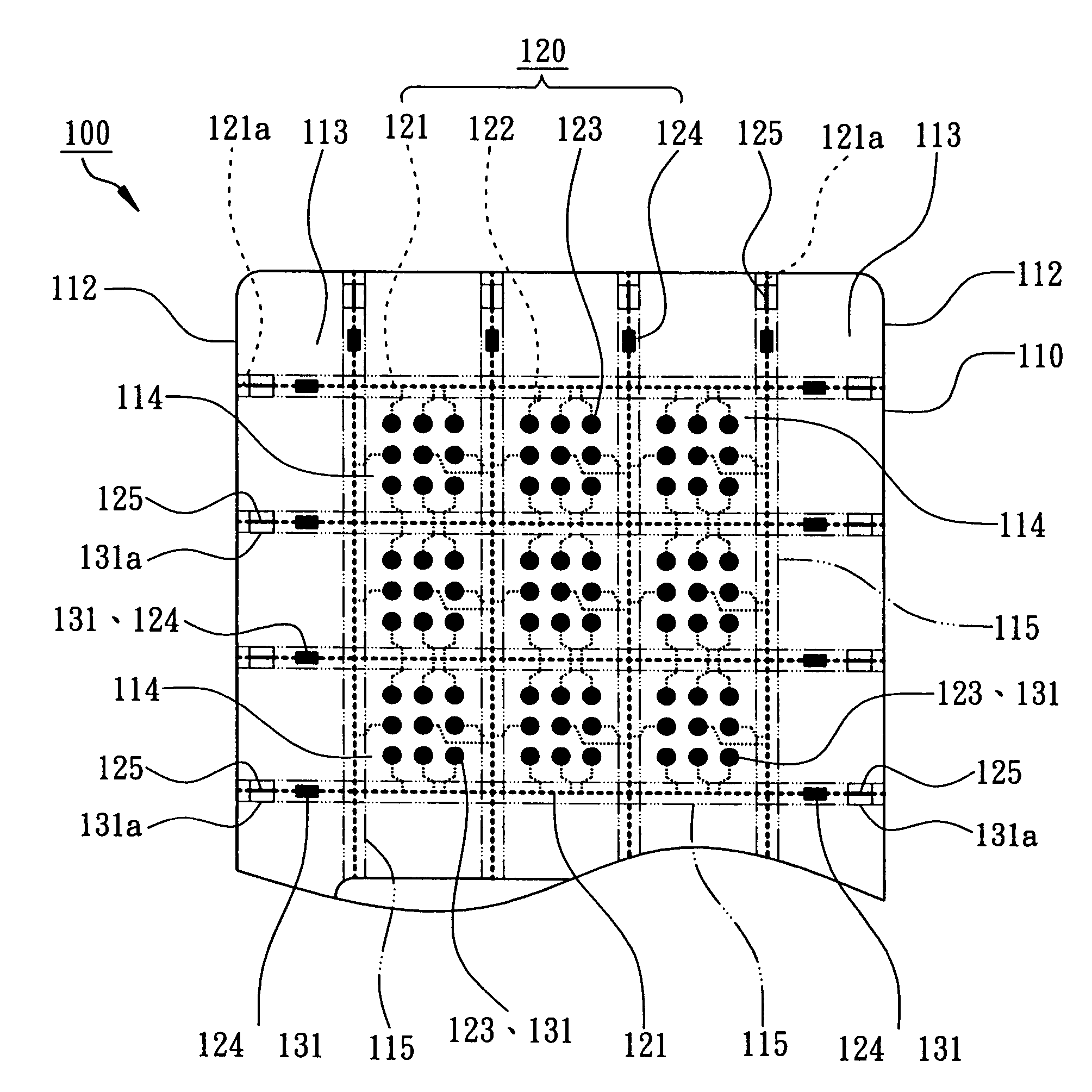

Method and structure for prevention leakage of substrate strip

InactiveUS20050051881A1Large caliberImprove package yieldSemiconductor/solid-state device detailsStacked resist layersSolder maskContact pad

The present invention provides a structure and a method for prevention leakage of a substrate strip. The substrate strip includes an edge portion and a plurality of units. A patterned metal layer on a surface of the substrate strip includes at least one plating bus extended to the edge portion, a plurality of plating lines at the units, a plurality of contact pads at the units and a plurality of fiducial marks at the edge portion. The plating bus has an extended trail having one end exposed out of the sidewall of the substrate strip. The fiducial marks and the contact pads are exposed out of a plurality of first openings of a solder mask. The solder mask also has a second opening at the edge portion exposing a portion of the plating bus to define a breaking hole. After forming a surface layer on the fiducial marks and the contact pads, the exposed portion of the plating bus is void of the surface layer. By removing the exposed portion of the plating bus, the breaking hole is formed to electrically isolate the extended trail from the contact pads in order to prevent a chip on the substrate strip from being damaged by ESD (Electrostatic Discharge) during packaging processes.

Owner:ADVANCED SEMICON ENG INC

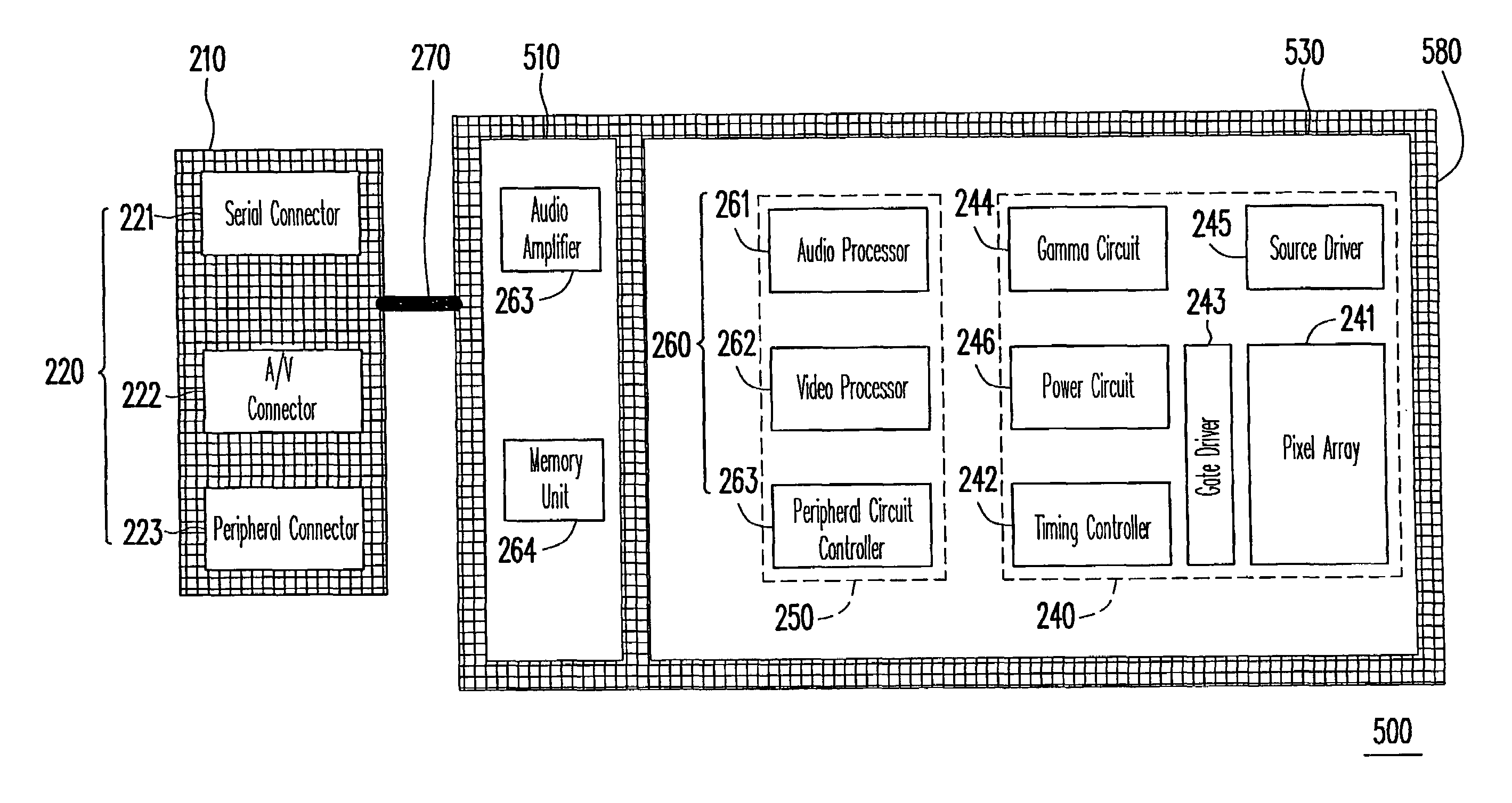

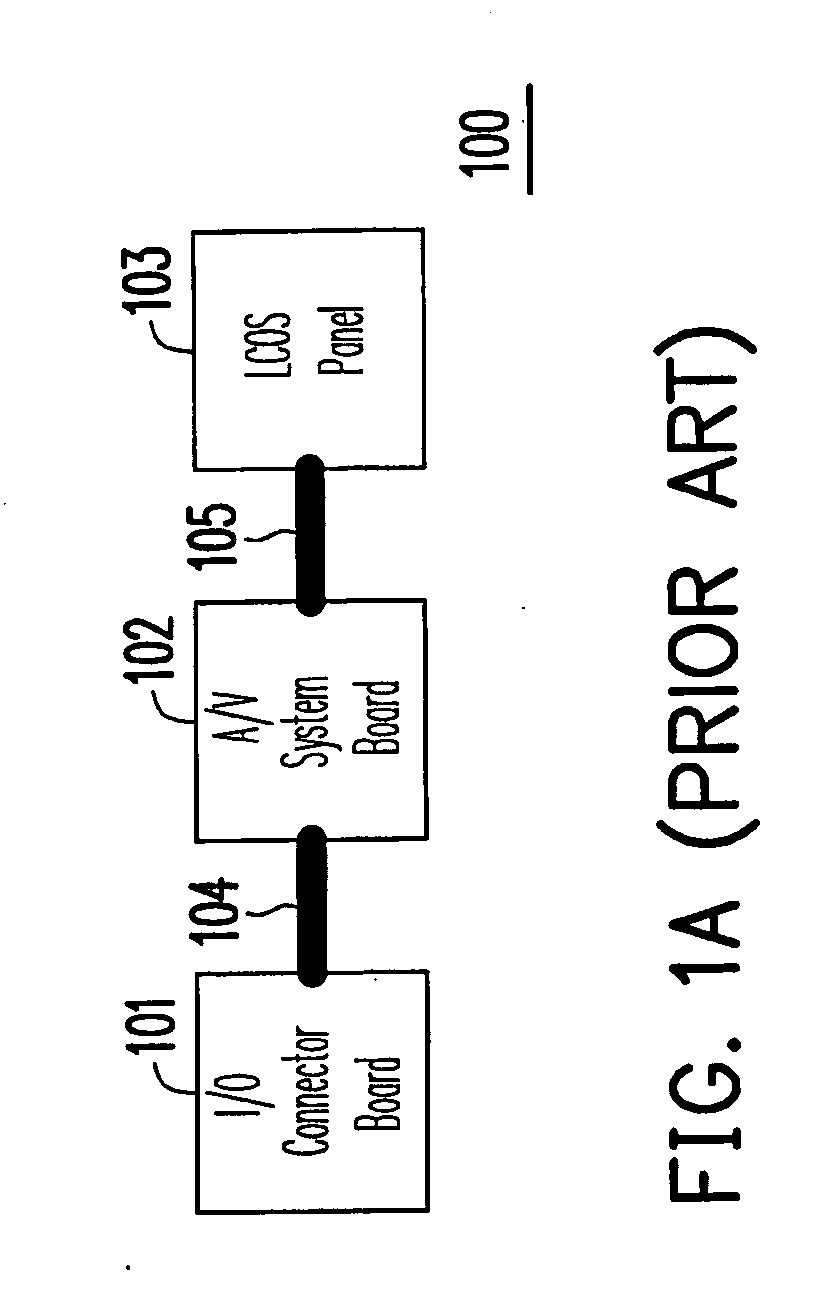

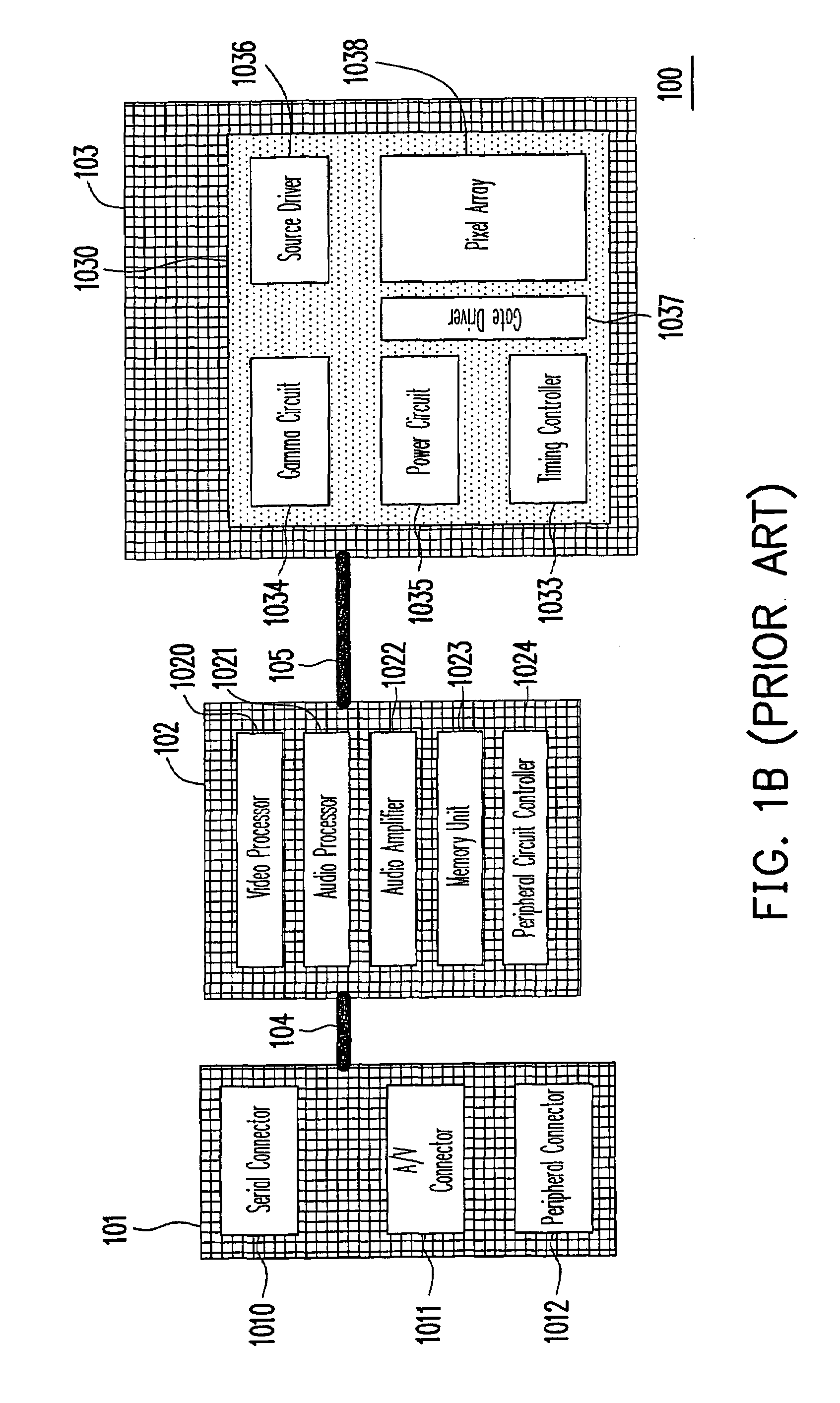

Liquiid crystal on silicon (LCOS) display and package thereof

InactiveUS20080266469A1Improve area efficiencyIncreasing system integrationStatic indicating devicesNon-linear opticsSilicon chipElectric cables

The present invention provides a LCOS display. The display comprises a first PCB, an interface module, a first silicon chip, and a flat cable. The interface module is disposed on the first PCB and used to receive an audio and video signal. The first silicon chip comprises a display area, a processing area, and a metal layer. The display area comprises a pixel array in a LCOS panel formed on the first silicon chip. The processing area comprises a processing unit formed on the first silicon chip. The metal layer is formed on the first silicon chip for electrically connecting the display area with the processing area. The flat cable is used to electrically connect the interface module with the processing unit.

Owner:HIMAX TECH LTD

Semiconductor package

InactiveUS20060081968A1High mechanical strengthRealize functionSemiconductor/solid-state device detailsSolid-state devicesContact padSemiconductor chip

The present invention discloses a semiconductor package comprising a substrate having a plurality of substrate units, a plurality of semiconductor chips respectively disposed on the substrate units, and a plurality of conductive guard lines each disposed between two adjacent substrate units. Each substrate unit is provided with a plurality of contact pads and a plurality of conductive leads respectively connected to the corresponding contact pads. The semiconductor chips are electrically connected to the plurality of contact pads through the conductive leads. Each substrate unit has at least one of the contact pads electrically connected to the conductive guard lines such that the semiconductor package of the present invention can efficiently achieve the function of electrostatic discharge (ESD) protection.

Owner:HIMAX TECH LTD

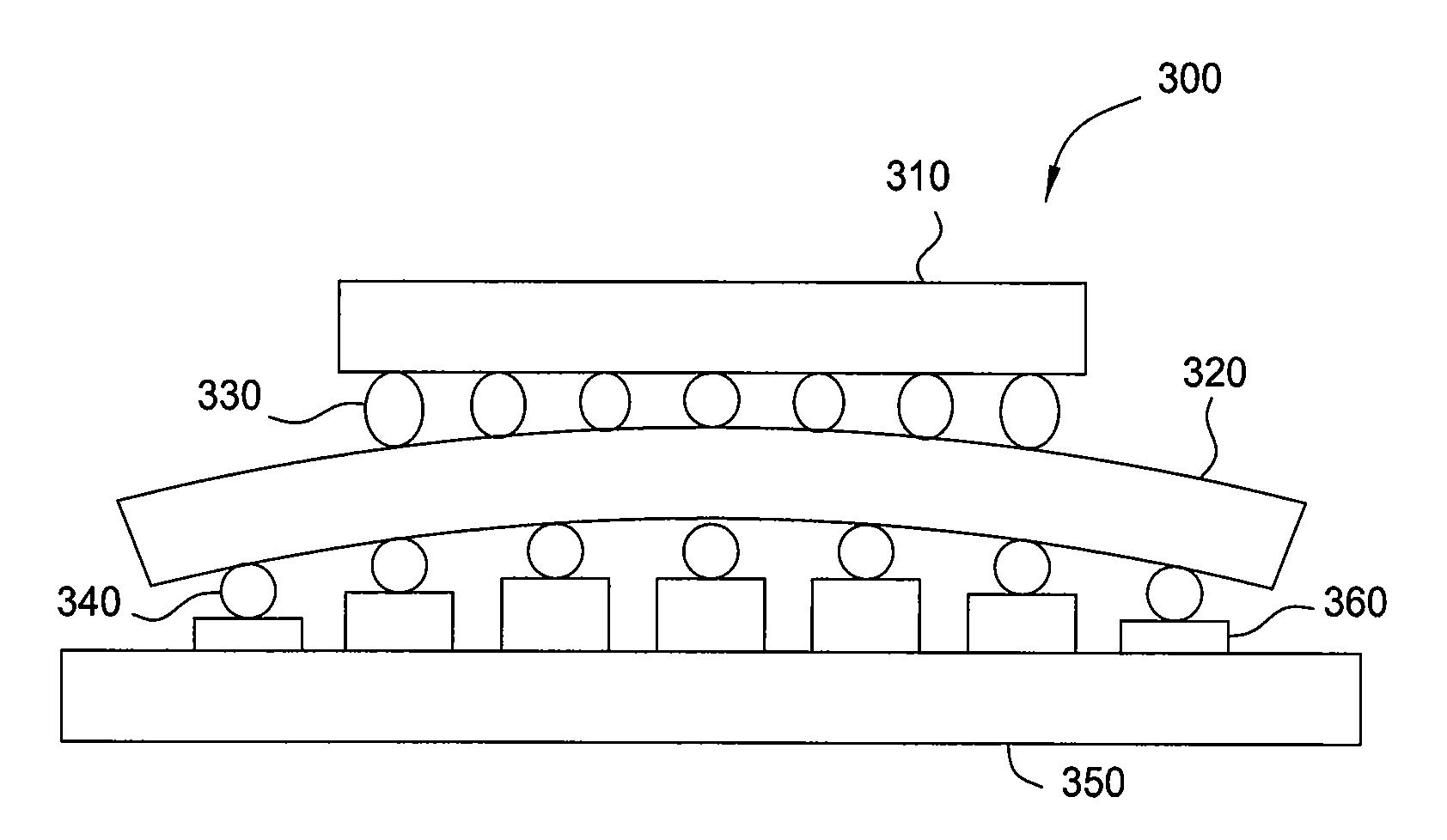

Structure of image sensor module and a method for manufacturing of wafer level package

ActiveUS20050242408A1Easy to testLow costTelevision system detailsSemiconductor/solid-state device detailsSolder ballOptoelectronics

The present invention discloses an image sensor module and forming method of wafer level package. The image sensor module comprises an isolating base, a wafer level package, a lens holder, and a F.P.C.. The wafer level package having a plurality of image sensor dies and a plurality of solder balls is attached to the isolating base. A plurality of lens are placed in the lens holder, and the lens holder is located on the image sensor dies. The lens holder is placed in the F.P.C., and the F.P.C. has a plurality of solder joints coupled to the solder balls for conveniently transmitting signal of the image sensor dies. Moreover, the image sensor dies may be packaged with passive components or other dies with a side by side structure or a stacking structure.

Owner:ADVANCED CHIP ENG TECH

Method for preparing composition of epoxy resin for packaging semiconductor

InactiveCN1687229AReduce viscosityReduce liquidityOther chemical processesSemiconductor/solid-state device detailsEpoxyPorosity

The present invention relates to a preparation method of epoxy resin compound for semiconductor packaging process. Said epoxy resin compound has the advantages of low-viscosity, high-flowability, low water absorption and low porosity, etc. and can be used for packaging various integrated circuits and semiconductor devices.

Owner:HENKEL HUAWEI ELECTRONICS

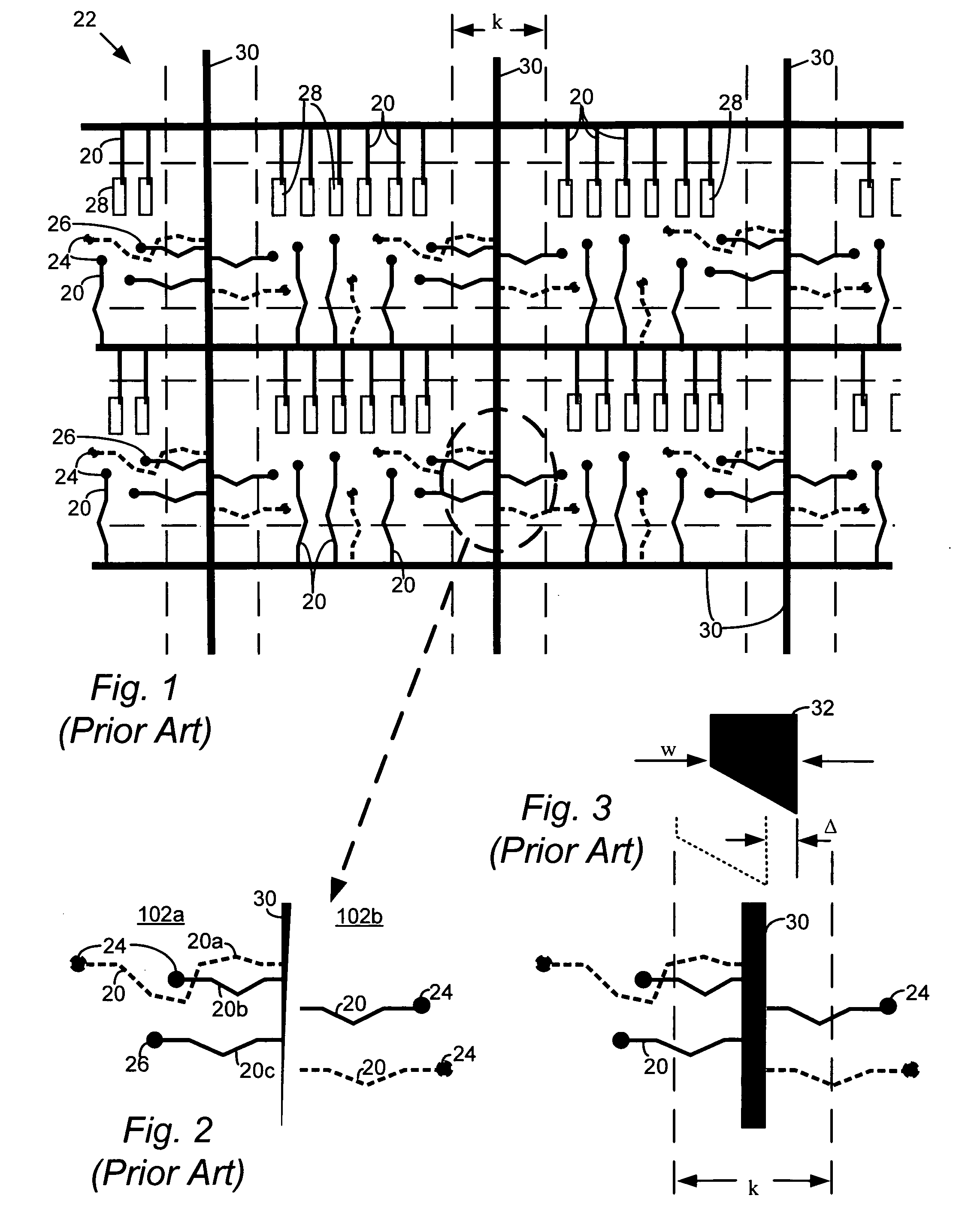

Substrate having minimum kerf width

ActiveUS20070132066A1Reduce widthKerf widthSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageElectrical isolation

A semiconductor die substrate panel is disclosed including a minimum kerf width between adjoining semiconductor package outlines on the panel, while ensuring electrical isolation of plated electrical terminals. By reducing the width of a boundary between adjoining package outlines, additional space is gained on a substrate panel for semiconductor packages.

Owner:SANDISK TECH LLC

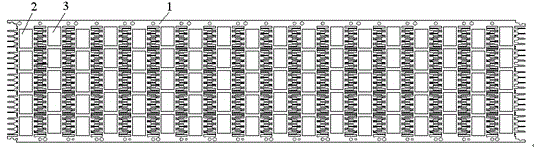

Lead wire framework based on DIP multiple substrates and method of using lead wire framework to manufacture packaging part

ActiveCN104934405ANovel structureLow costSemiconductor/solid-state device detailsSolid-state devicesStructural engineeringLead frame

Provided is a lead wire framework based on DIP multiple substrates and a method of using the lead wire framework to manufacture a packaging part. The lead wire framework comprises a framework body with a plurality of rows of first framework unit sets and a plurality of rows of second framework unit sets, and the two kinds of framework unit sets are arranged at intervals. A framework unit is provided with three substrates, wherein two substrates are in connection with four inner pins of the framework unit through a dam bar, and are located between a third substrate and the dam bar; the third substrate is in connection with the frame of the framework body through a tie bar; the inner pin in the framework unit towards an adjacent framework unit and the inner pin of the adjacent framework unit towards the framework unit are interlaced. A wafer is thinned and sawed, and a chip is adhered to the lead wire framework according to requirements to obtain a packing part through processes including pressure welding, post curing, plastic package, etc. The lead wire framework is conductive to increasing product function integration, and improving product packaging yield, quality and reliability; in addition, the lead wire framework can be extended to multi-row matrix type packaging, and is not limited to a DIP packaging form.

Owner:TIANSHUI HUATIAN TECH

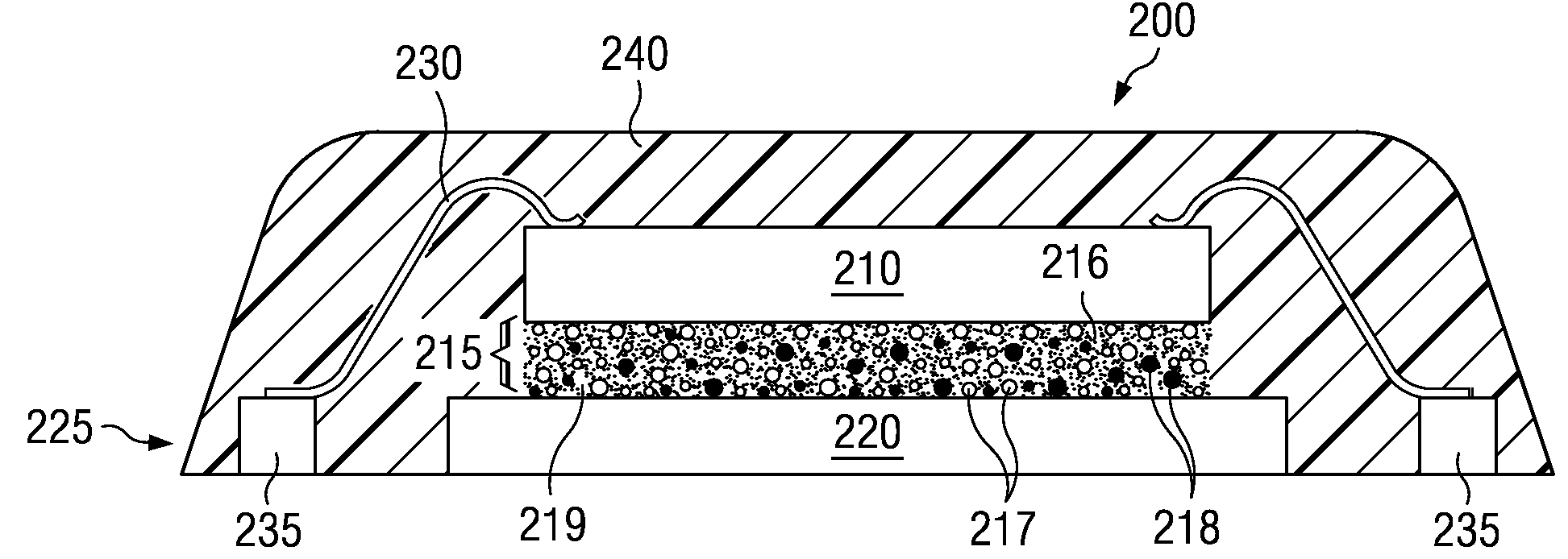

Packaged electronic device having metal comprising self-healing die attach material

ActiveUS20100264553A1High metal to metal contactEvenly distributedSemiconductor/solid-state device detailsSolid-state devicesAdhesiveMetal particle

A method of assembling an electronic device and electronic packages therefrom. A die attach adhesive precursor is placed between a top surface of a workpiece and an IC die. The die attach adhesive precursor includes metal particles, a first plurality of first microcapsules having a polymerizable material inside, and a second plurality of second microcapsules having a polymerization agent inside to form a first polymer upon rupture of first and second microcapsules. A force sufficient to rupture at least a portion of the first plurality of first microcapsules and at least a portion of the second plurality of second microcapsules is applied to form a self-healing die attach adhesive wherein the first polymer binds the plurality of metal particles and the remaining microcapsules and secures the IC die to the top surface of the workpiece. The self-healing die attach adhesive generally includes at least 90 vol. % metal.

Owner:TEXAS INSTR INC

Image sensor package structure and method for fabricating the same

InactiveUS20060024857A1Avoid defectsImprove package yieldSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringIntegrated circuit

A method for fabricating an image sensor package is disclosed, comprising: providing a wafer having a plurality of image sensor integrated circuits, each of which has a photosensitive active region and at least one first bonding pad; joining a transparent protecting material to the wafer wherein the photosensitive active region of the image sensor integrated circuit is covered by the transparent protecting material; forming a plurality of through holes in the transparent protecting material, the through holes being correspondingly to the first bonding pad of the wafer to expose the first bonding pad; and dicing the wafer to form a plurality of image sensor integrated circuit components. The method for fabricating an image sensor package of the present invention decreases the defects of the photosensitive active region and reduces the size of the package structure.

Owner:IND TECH RES INST

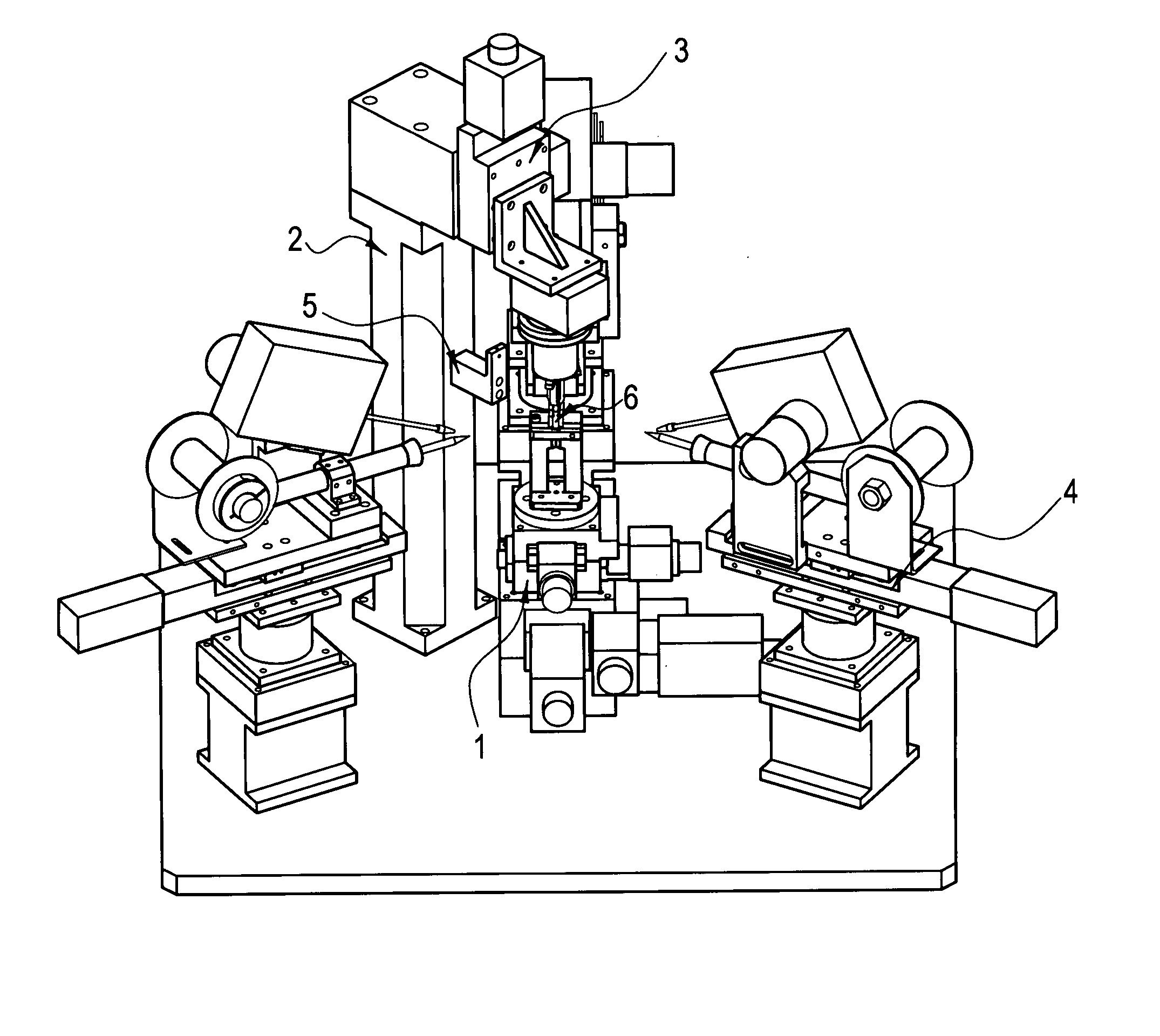

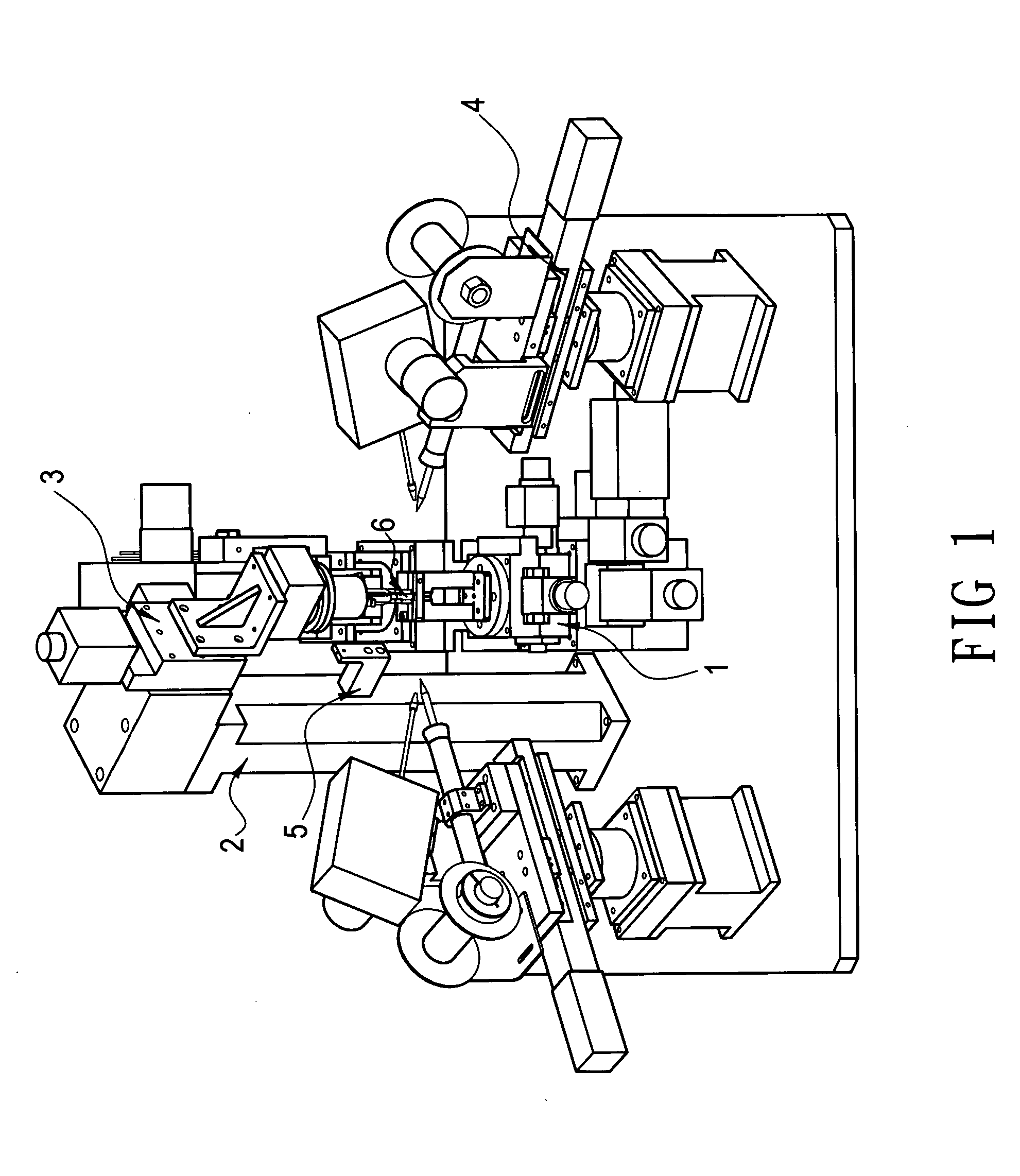

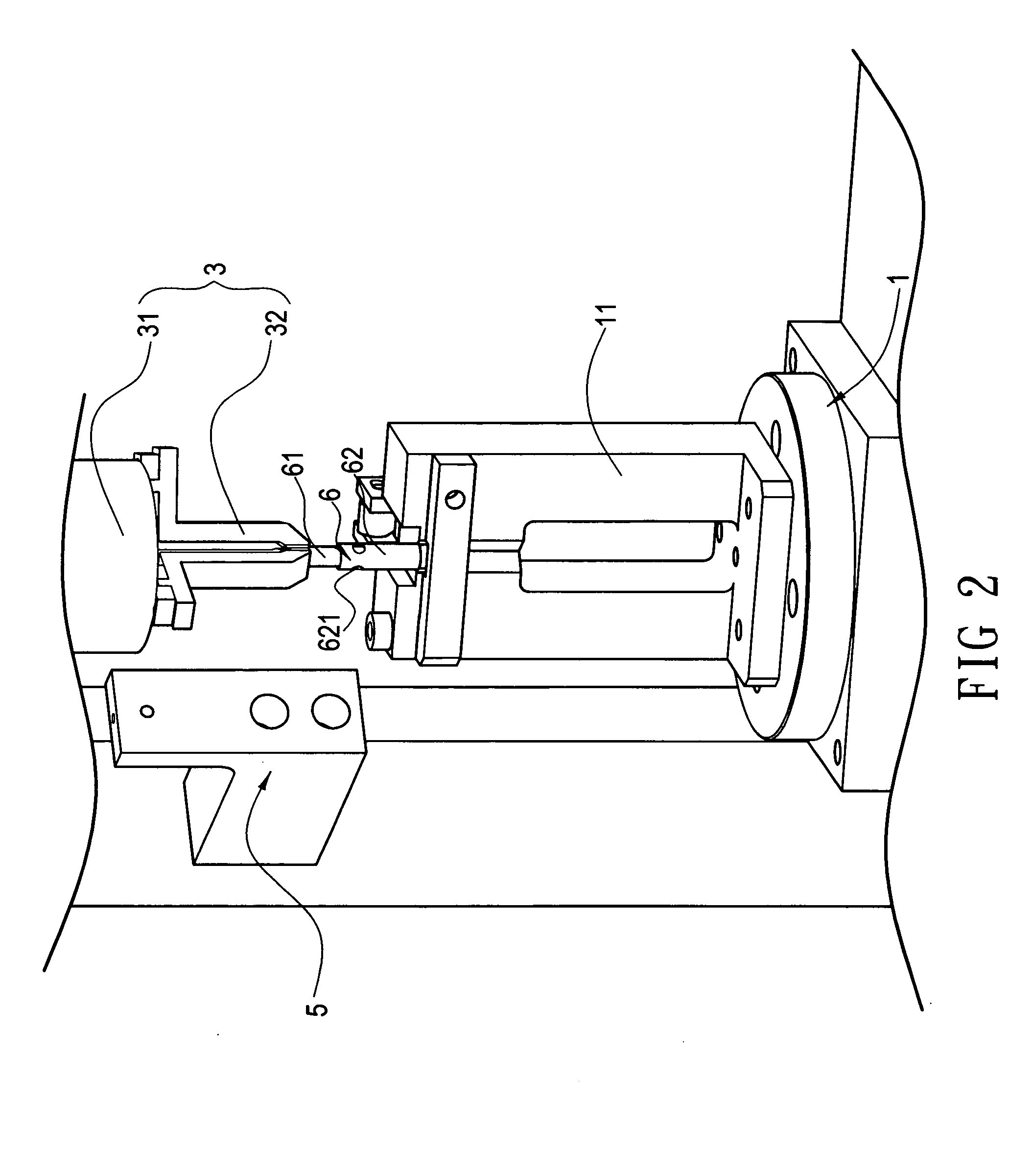

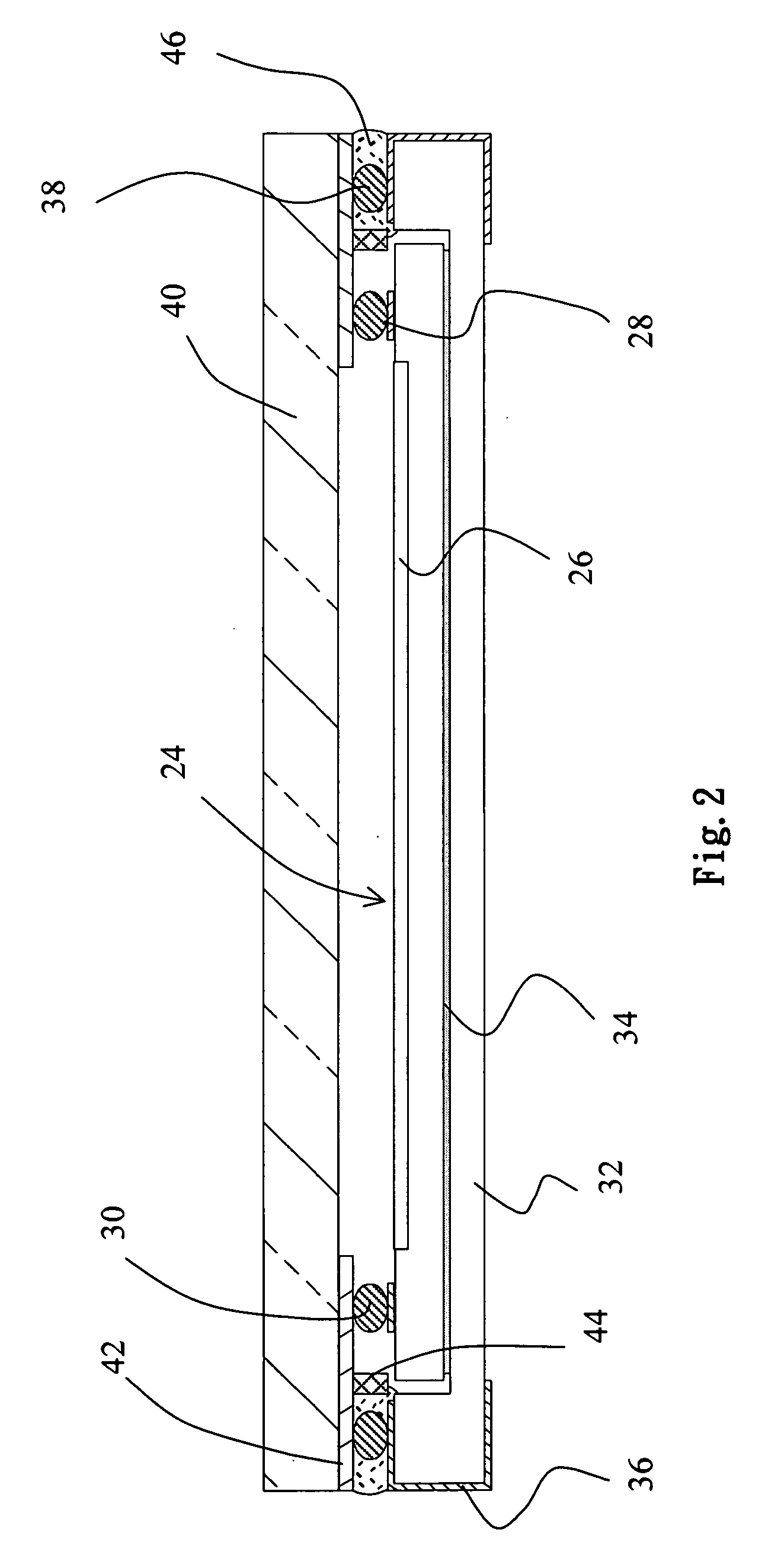

Automated packaging apparatus and method of optical elements

InactiveUS20050139638A1Efficient solutionMinimize thermal strainWelding/cutting auxillary devicesAuxillary welding devicesEngineering

Owner:IND TECH RES INST

Radiating packaging structure of semiconductor chip

InactiveCN101887872APrevent overflowImprove package yieldSemiconductor/solid-state device detailsSolid-state devicesHeat sinkEngineering

The invention discloses a radiating packaging structure of a semiconductor, which comprises a base plate, a frame, a radiating fin and a heat conducting interface material layer, wherein the base plate loads and is electrically connected with at least one chip; the frame is bonded to the periphery of the base plate; the radiating fin is provided with one bonding surface bonded to the frame, the bonding surface is additional provided with one heat conducting area, and the heat conducting area is provided with a barrier wall to surround and form a material limiting space; and the heat conducting interface material layer is arranged in the material limiting space. The chip is provided with a radiating surface stretching into the material limiting space. The heat conducting interface material layer is located between the heat conducting area of the radiating fin and the radiating surface of the chip. The material limiting space is used for preventing the overflow, voids or other defects of the heat conducting interface material layer during high-temperature manufacturing.

Owner:ADVANCED SEMICON ENG INC

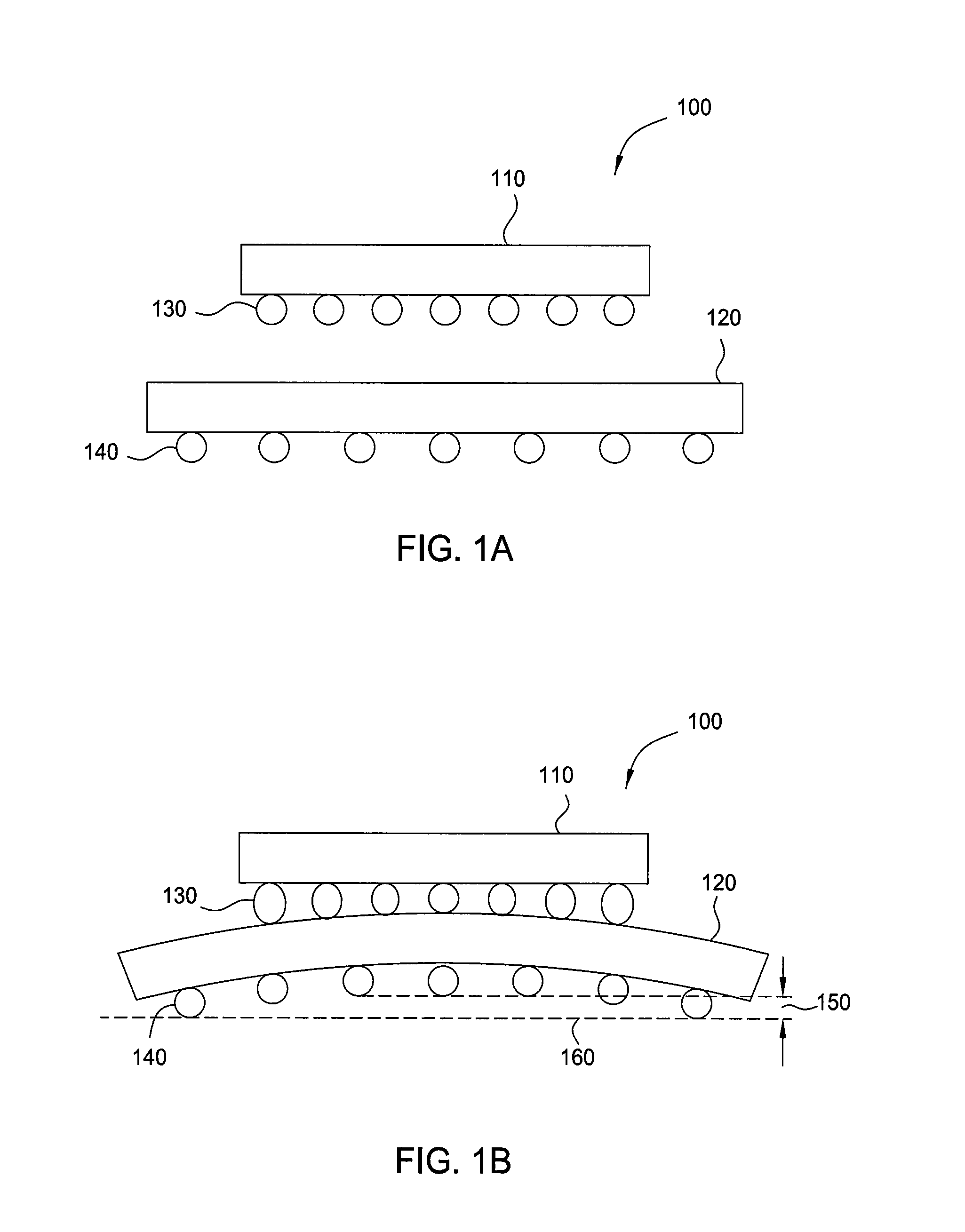

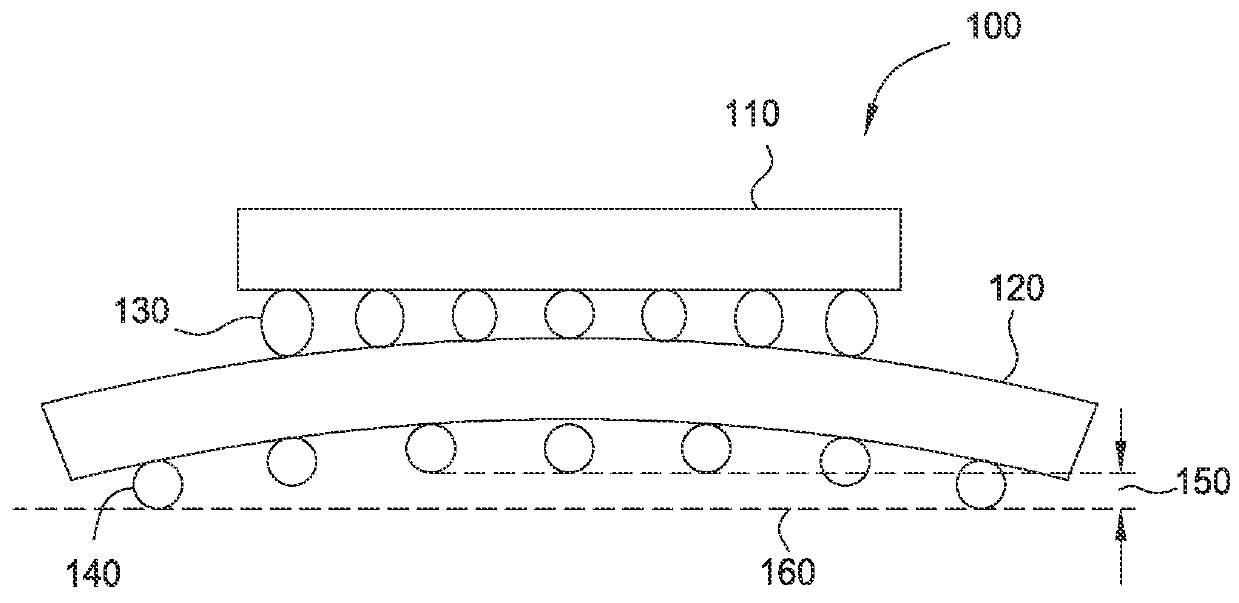

Variable-size solder bump structures for integrated circuit packaging

ActiveUS20140138823A1Improve package yieldSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsIntegrated circuit packagingVariable size

One embodiment of the present invention sets forth an integrated circuit package including a substrate, an integrated circuit die, a first plurality of solder bump structures, and a first plurality of variable-size solder bump structures. The first plurality of solder bump structures electrically couple the integrated circuit die to the substrate. The first plurality of variable-size solder bump structures are disposed on a bottom surface of the substrate. The first plurality of variable-size solder bump structures are sized to be substantially coplanar with a seating plane of the integrated circuit package.

Owner:NVIDIA CORP

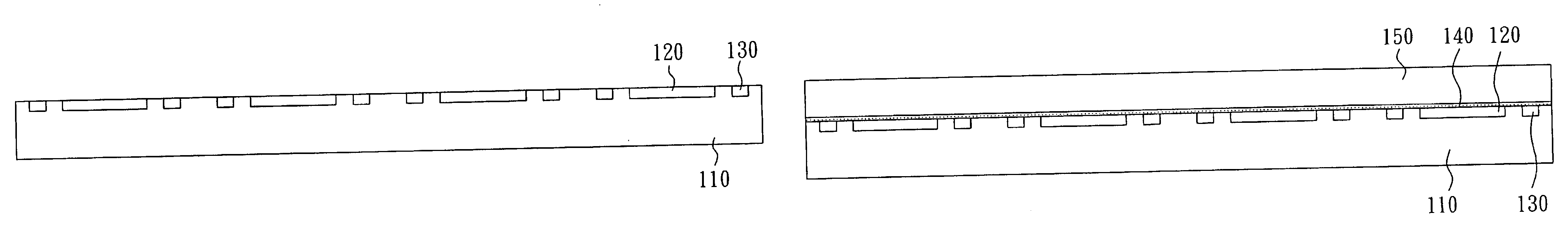

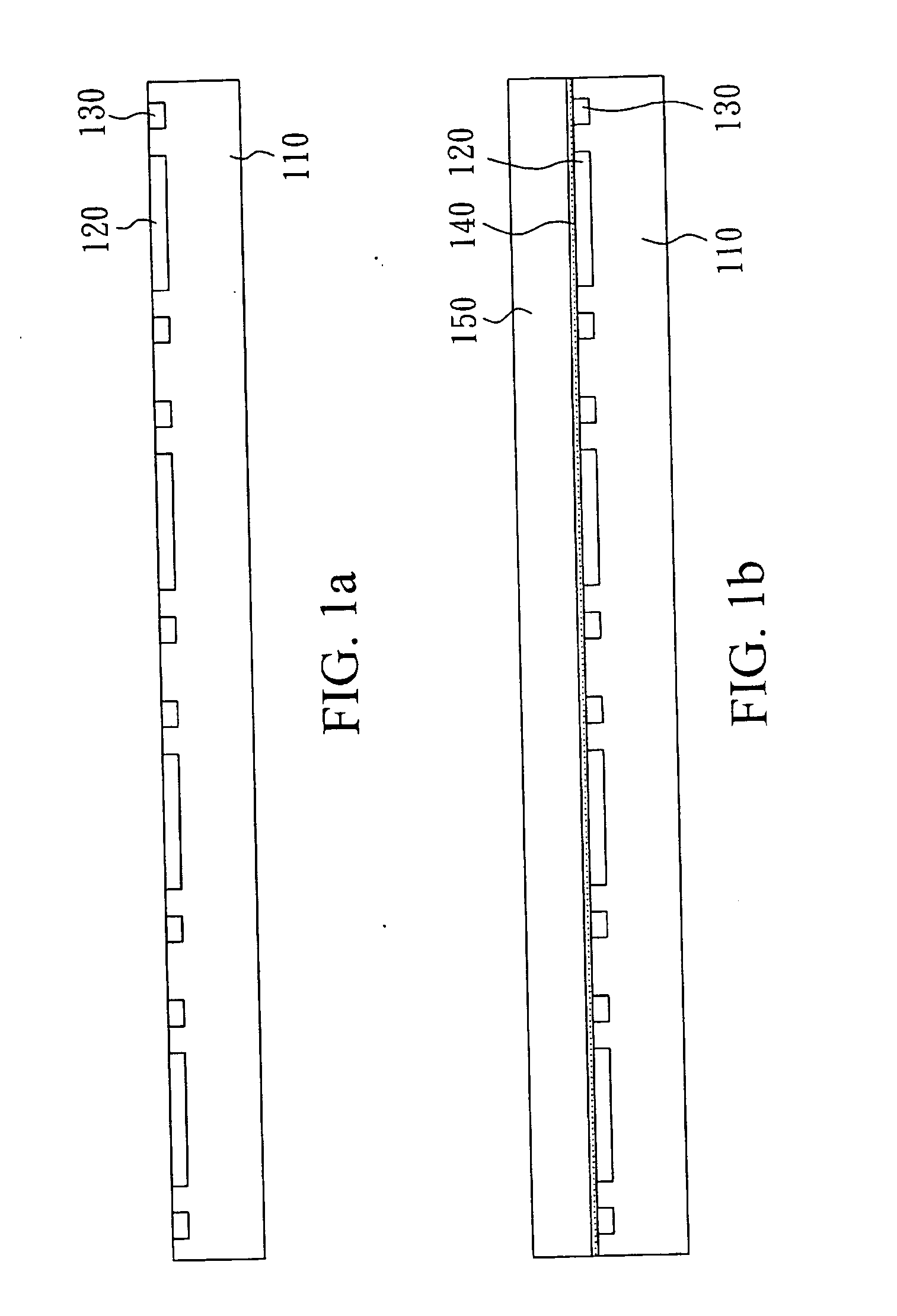

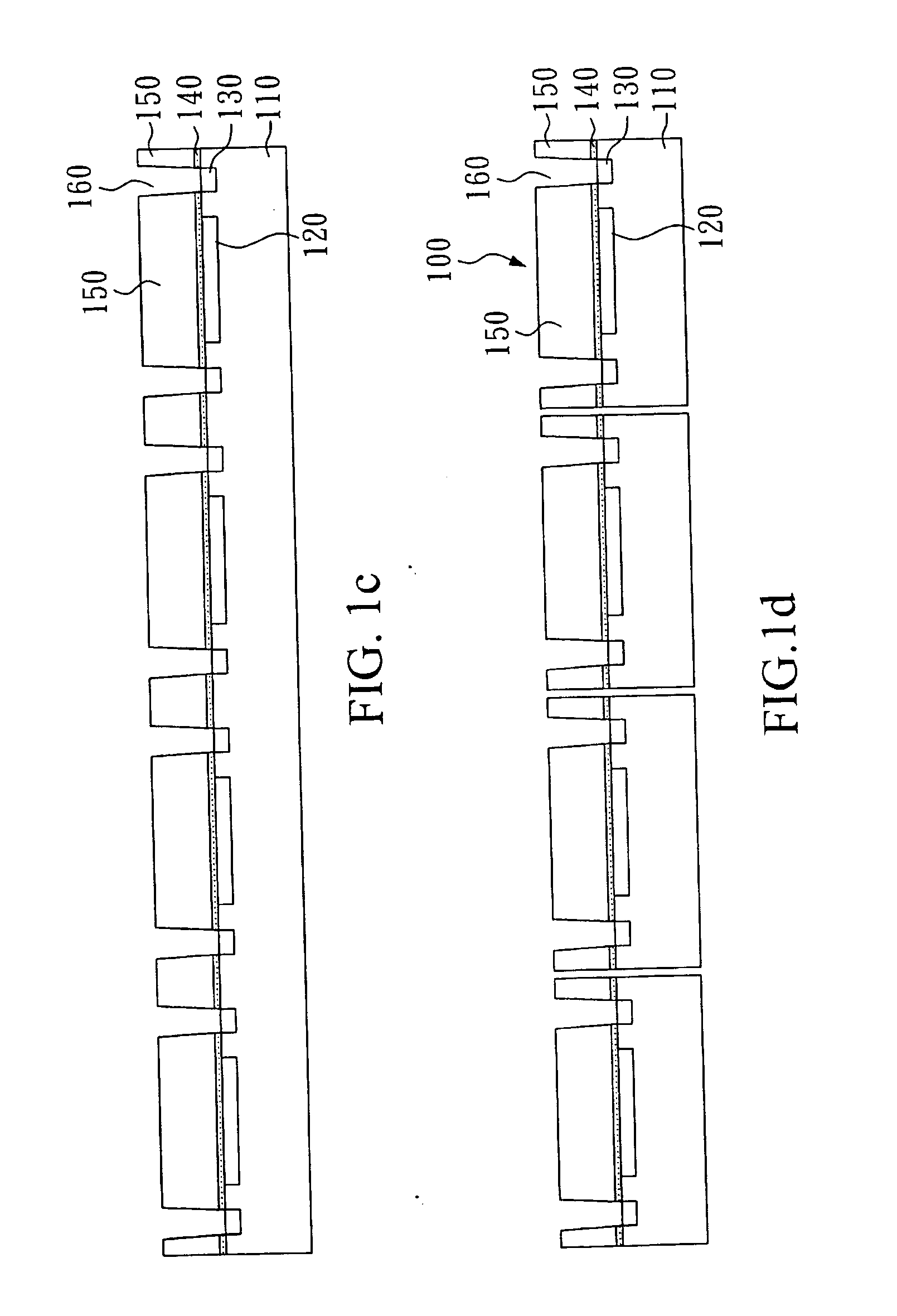

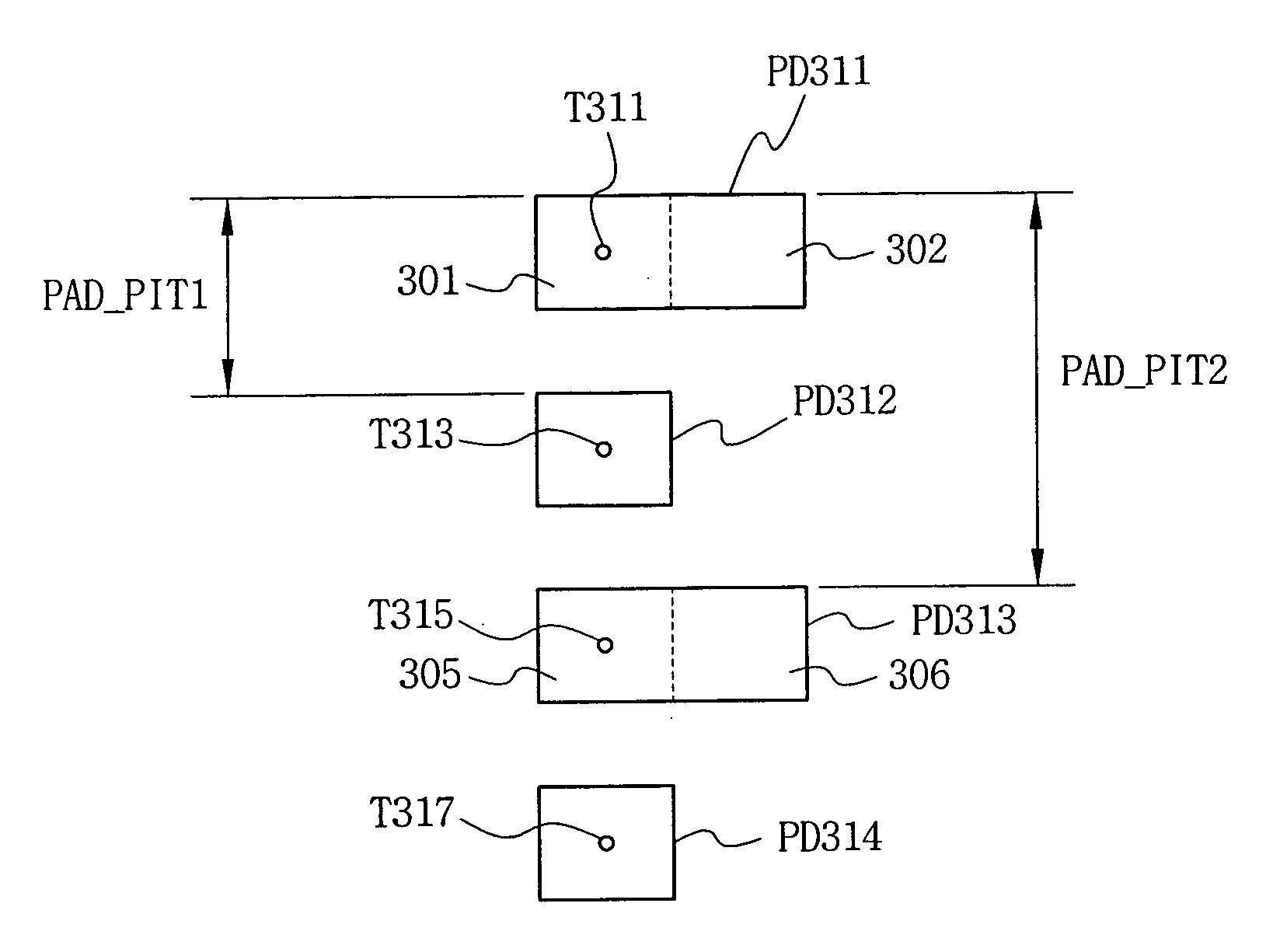

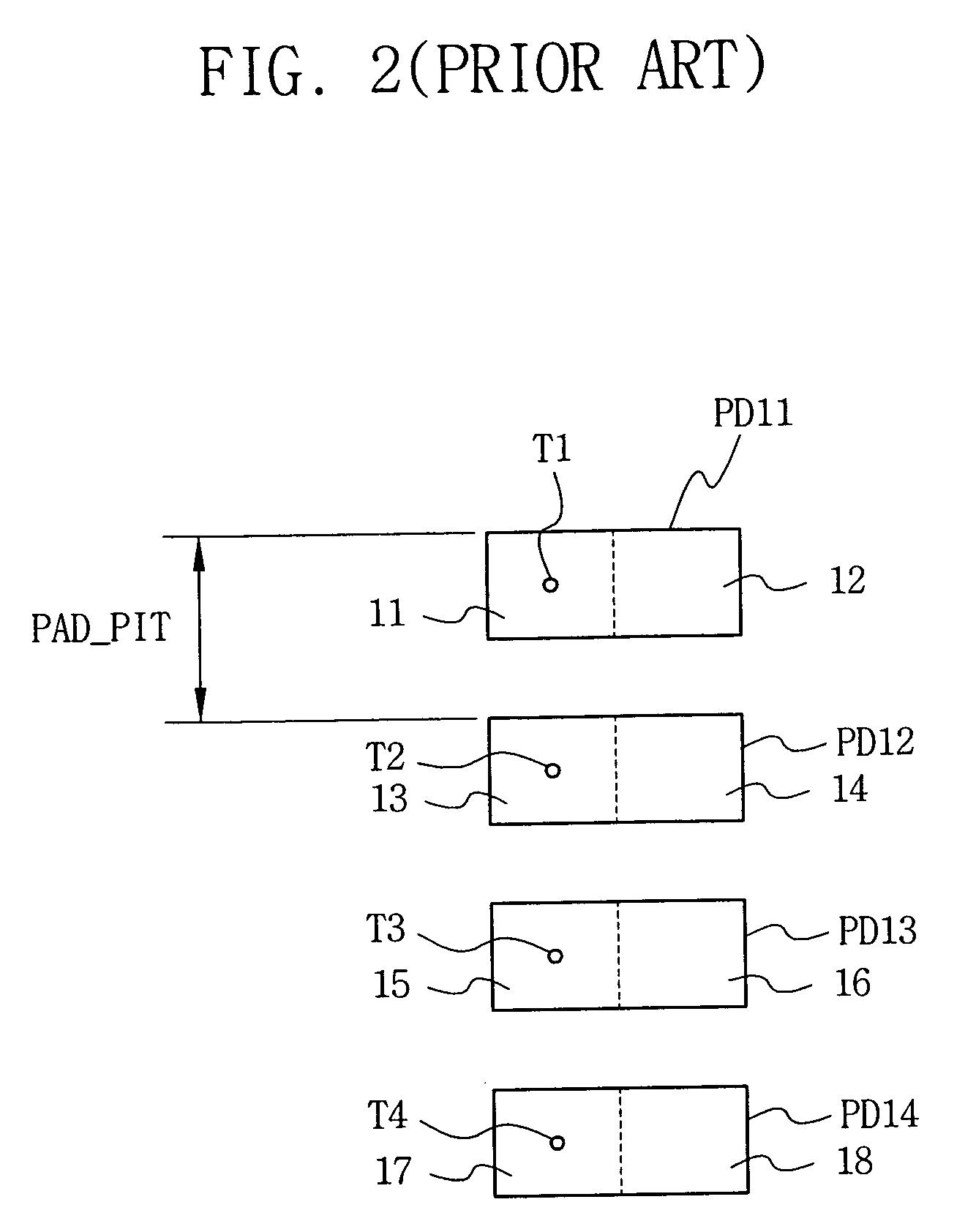

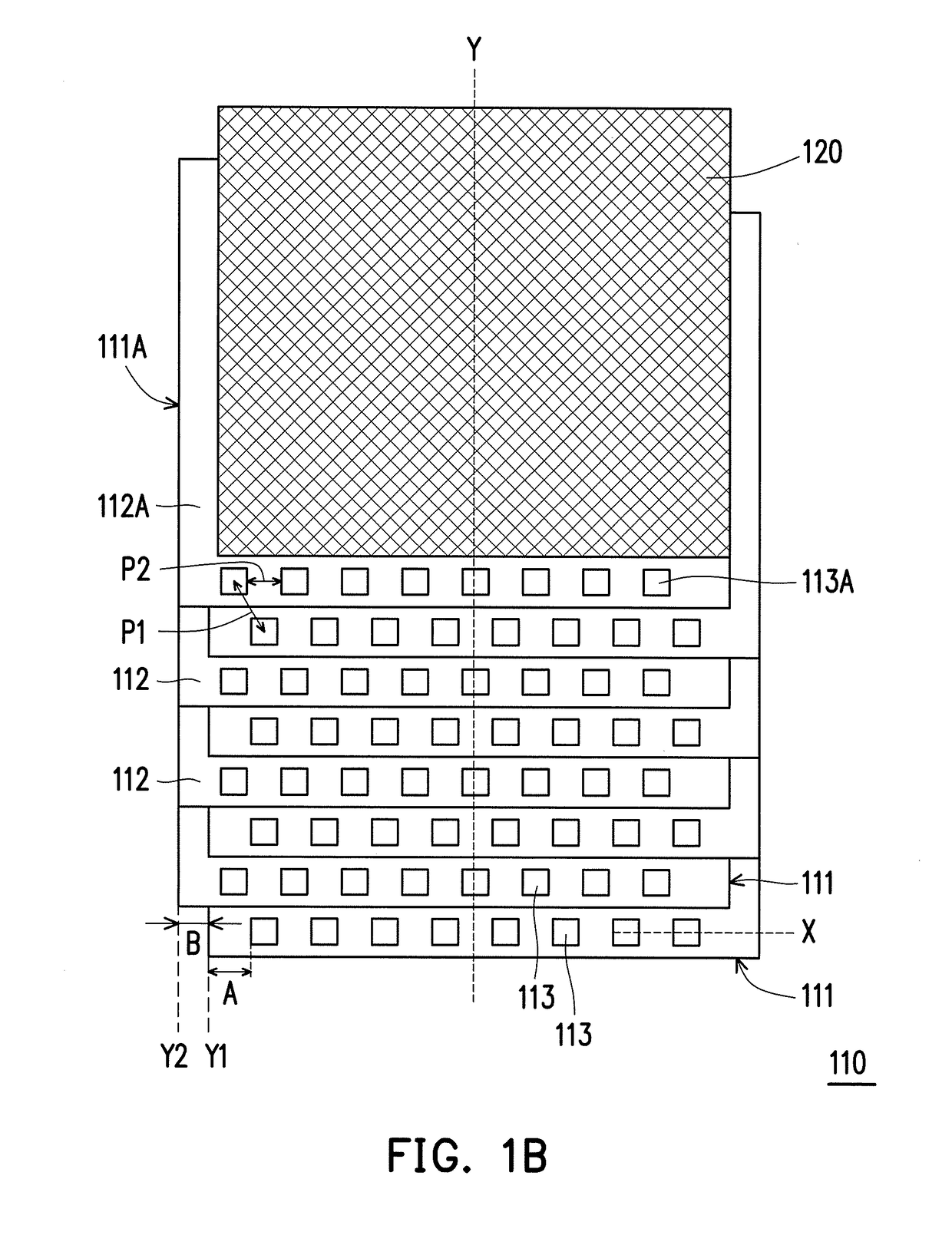

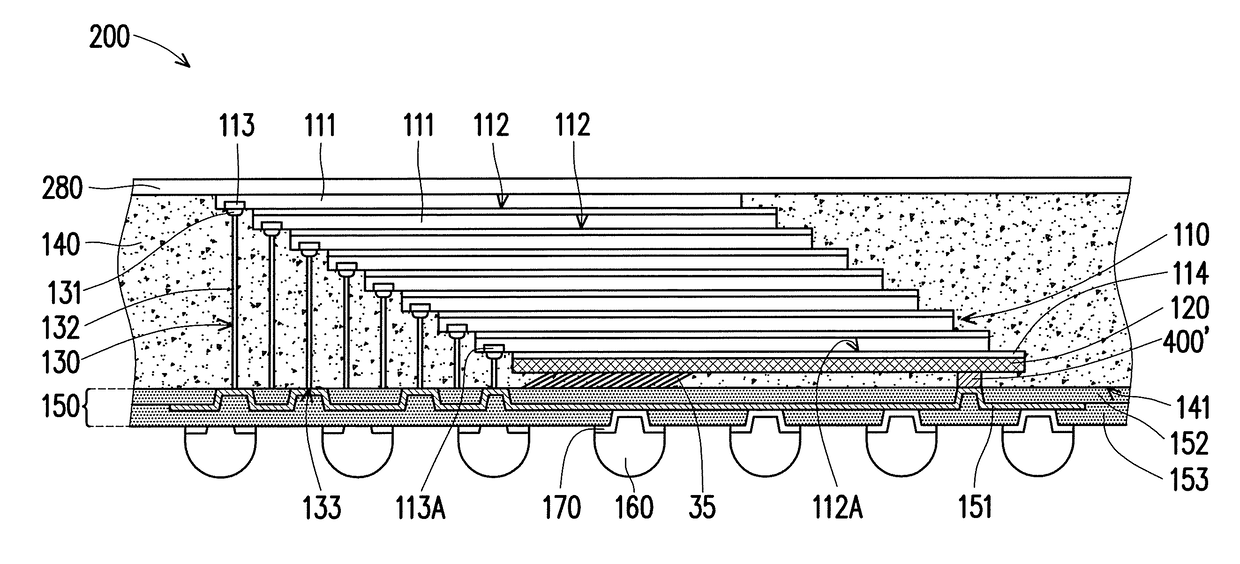

Pad structure, pad layout structure, and pad layout method in semiconductor devices

ActiveUS20060255477A1High integrationReduce areaSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringSemiconductor

In a layout structure of pads and a structure of pad used for a test or wire bonding of a semiconductor device, a size of at least one or more non-wire bonding pads is relatively small as compared with a size of at least one or more pads to be used for wire bonding of the semiconductor device. In the pad structure, a pad includes a wire bonding region that has an embossed surface for a portion of top metal layer within a determined pad size to improve the bonding process, and a probe tip contact region that does not have the embossed surface for a surface portion of the top metal layer within the determined pad size, so as to reduce wear of probe tip during testing of the device. Pad pitch can thereby be increased within a limited region, and peripheral circuits can be further formed in regions that would have been occupied in a conventional pad formation region. Higher integration of semiconductor devices and reduced wear of probe tip in probing is thereby realized.

Owner:SAMSUNG ELECTRONICS CO LTD

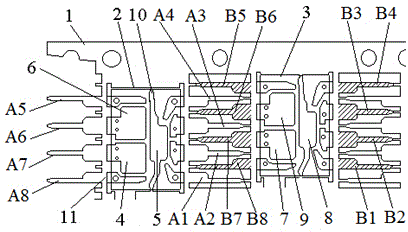

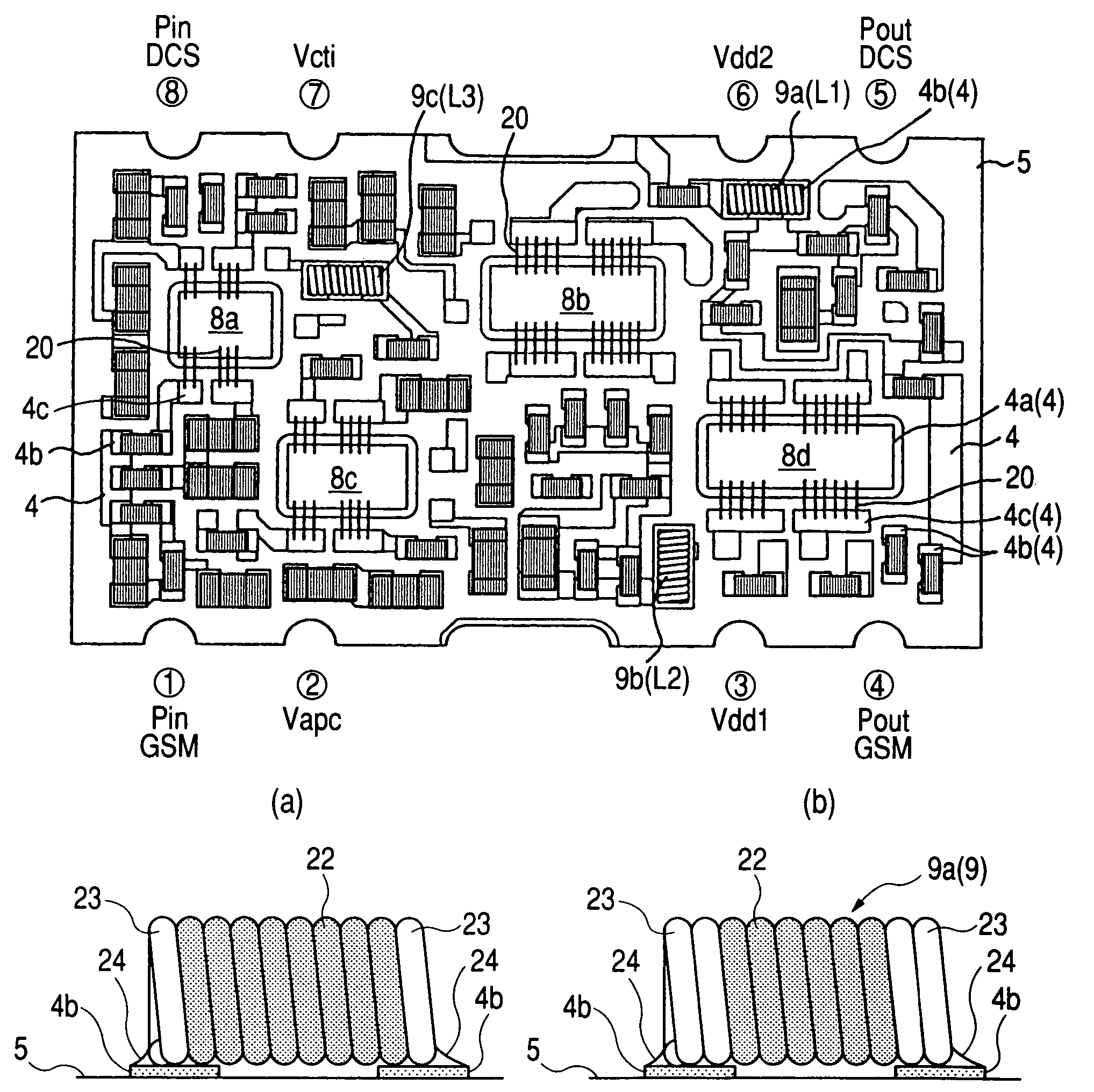

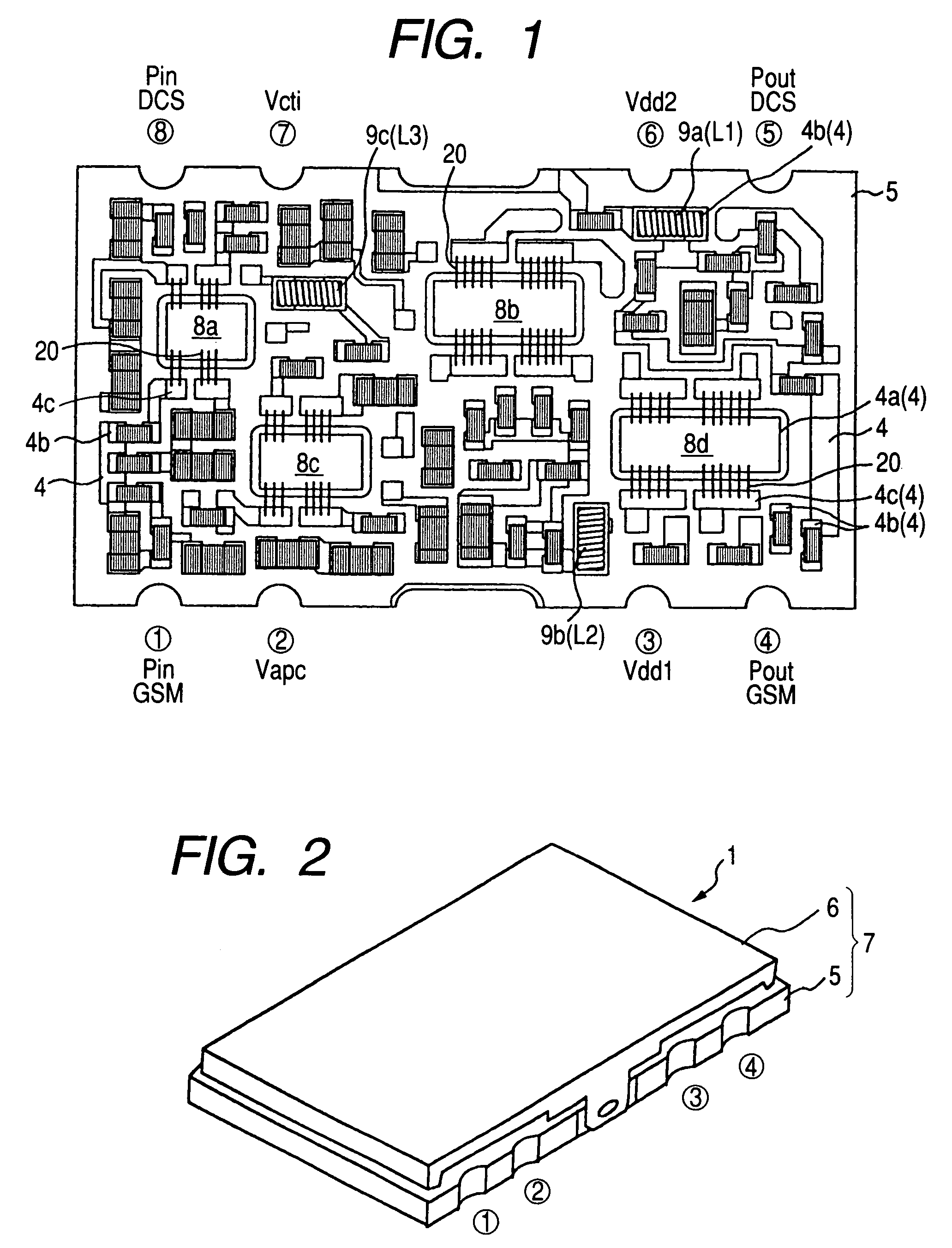

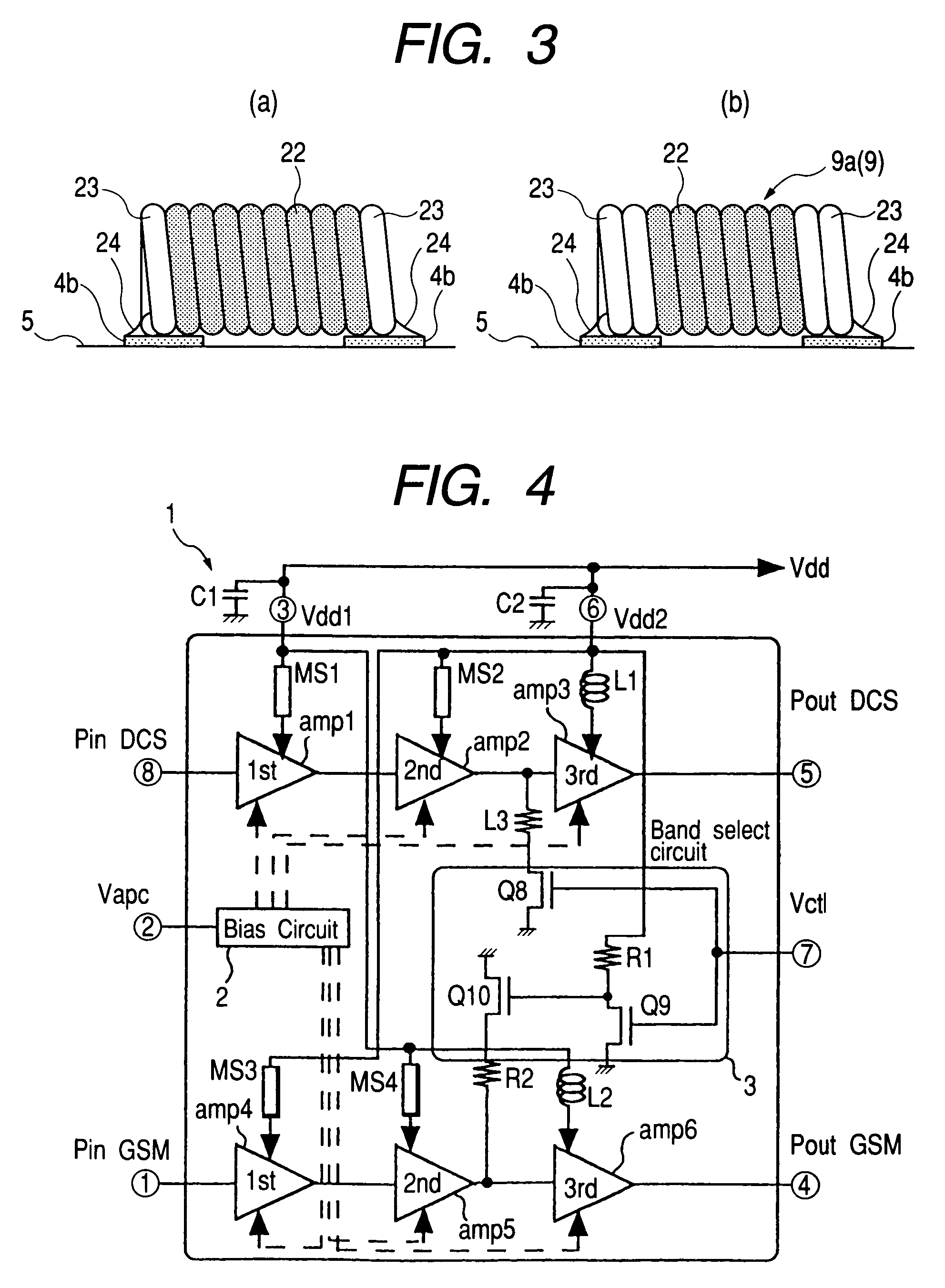

Semiconductor device, and method and apparatus for manufacturing semiconductor device

InactiveUS7262480B2Improve package yieldAccurate and secure packagingFinal product manufactureGated amplifiersHigh frequency powerCopper wire

A high frequency power amplifying device has two amplifying lines. Each amplifying line has a configuration in which a plurality of amplifying stages are connected in cascade having two source voltage terminals, of which one is connected to the first amplifying stage of one amplifying line and to the remaining amplifying stages of the other amplifying line, and the other, to the first amplifying stage of the latter amplifying line and to the remaining amplifying stages of the former amplifying line. An air core coil with a low D.C. resistance, formed by spirally winding a copper wire of about 0.1 mm in diameter, is connected in series between the final amplifying stage of each amplifying line and the source voltage terminal.

Owner:HITACHI LTD +2

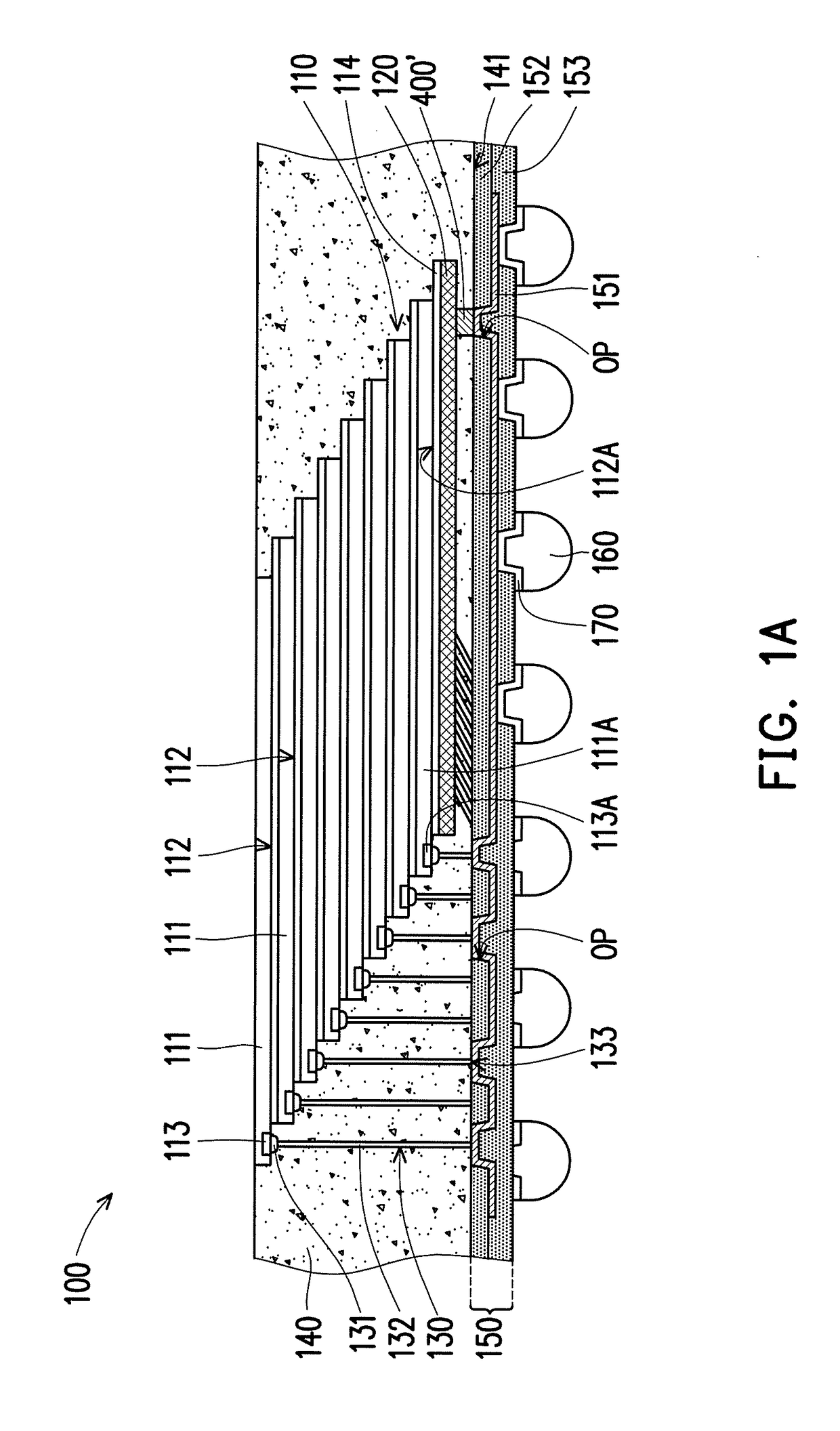

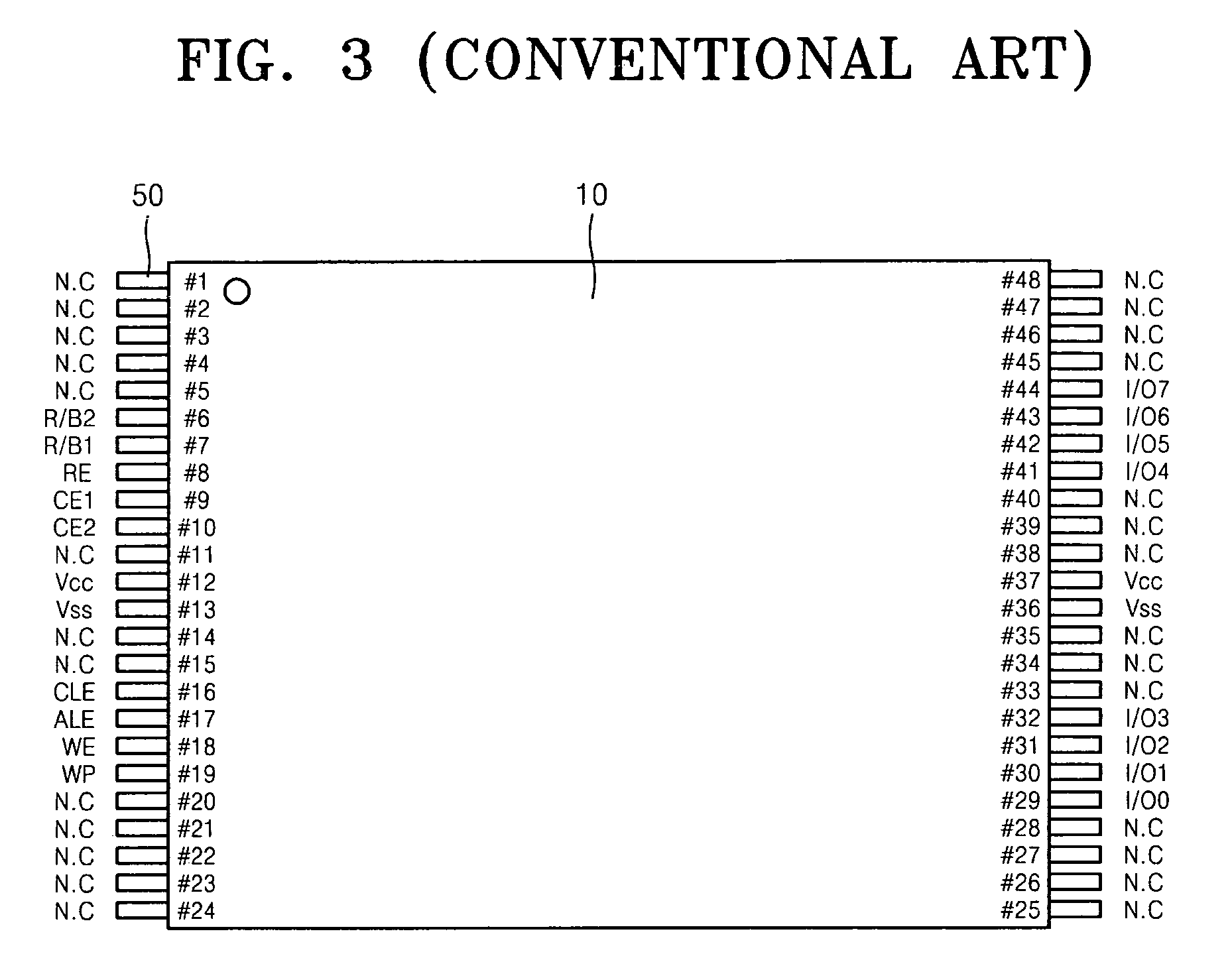

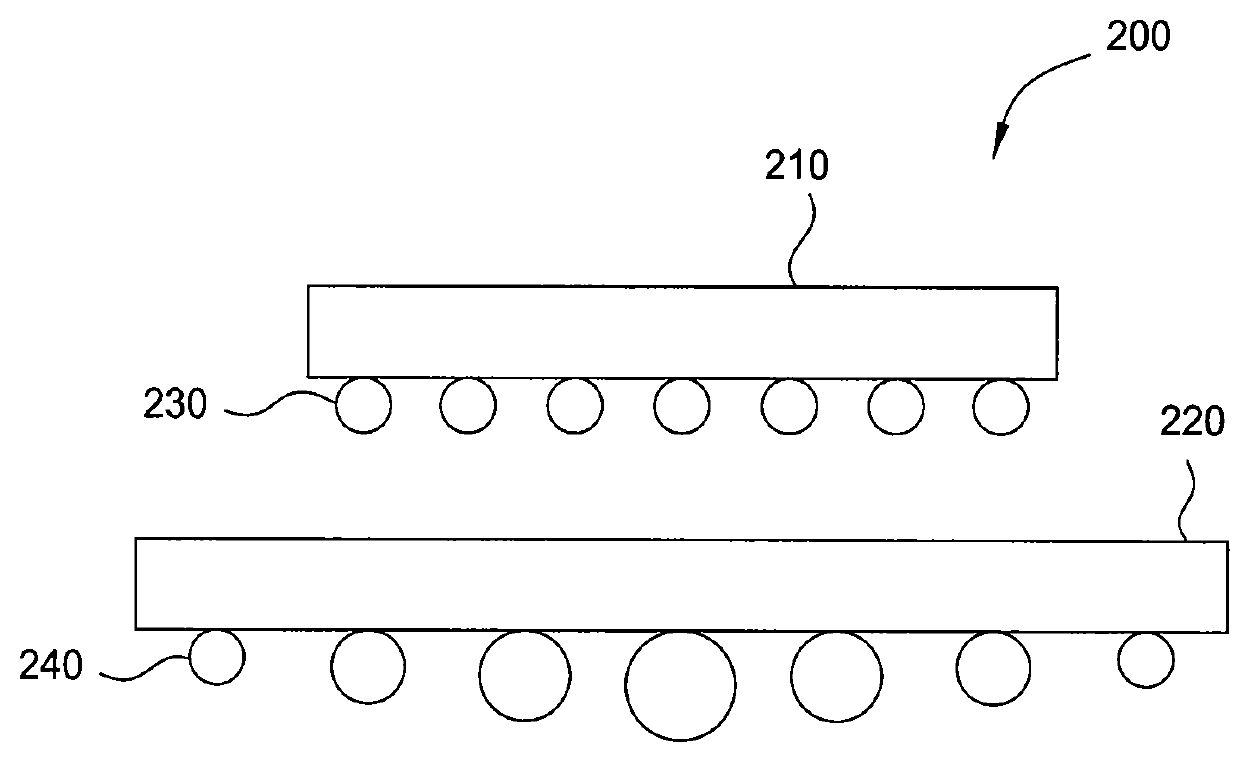

Thin fan-out multi-chip stacked package structure and manufacturing method thereof

ActiveUS20180211936A1Improve package yieldEasy to manufactureSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerEngineering

A thin fan-out multi-chip stacked package structure including a plurality of stacked chips is provided. The electrodes of the stacked chips and the active surface of the top chip are exposed. A dummy spacer and an alignment structure are disposed over the active surface. Each bonding wire has a bonding thread bonded to a chip electrode and an integrally-connected vertical wire segment. A flat encapsulant encapsulates the chip stacked structure and the bonding wires. Polished cross-sectional surfaces of the bonding wires and a surface of the alignment structure are exposed by the flat surface of the encapsulant. A redistribution layer structure is formed on the flat surface. A passivation layer covers the flat surface and exposes the polished cross-sectional surfaces and the alignment structure. Fan-out circuits are formed on the passivation layer and are connected to the polished cross-sectional surfaces of the bonding wires and the alignment structure.

Owner:POWERTECH TECHNOLOGY

Image sensor package structure

InactiveUS20070090478A1Improve package yieldAvoid pollutionSolid-state devicesSemiconductor devicesCMOSSolder ball

An image sensor package structure is proposed, in which an image sensor is fixed on a substrate having metallization traces and an adhesion layer. Electric paths of the package structure are changed from the COG (chip on glass) process to the CIS (CMOS image sensor) process to improve electric characteristics. Moreover, spacers are formed at appropriate positions to prevent glue overflow from contaminating the sensing regions and solder balls. The proposed package structure can also shrink the package area to greatly enhance the yield and quality.

Owner:SIGURD MICROELECTRONICS CORP

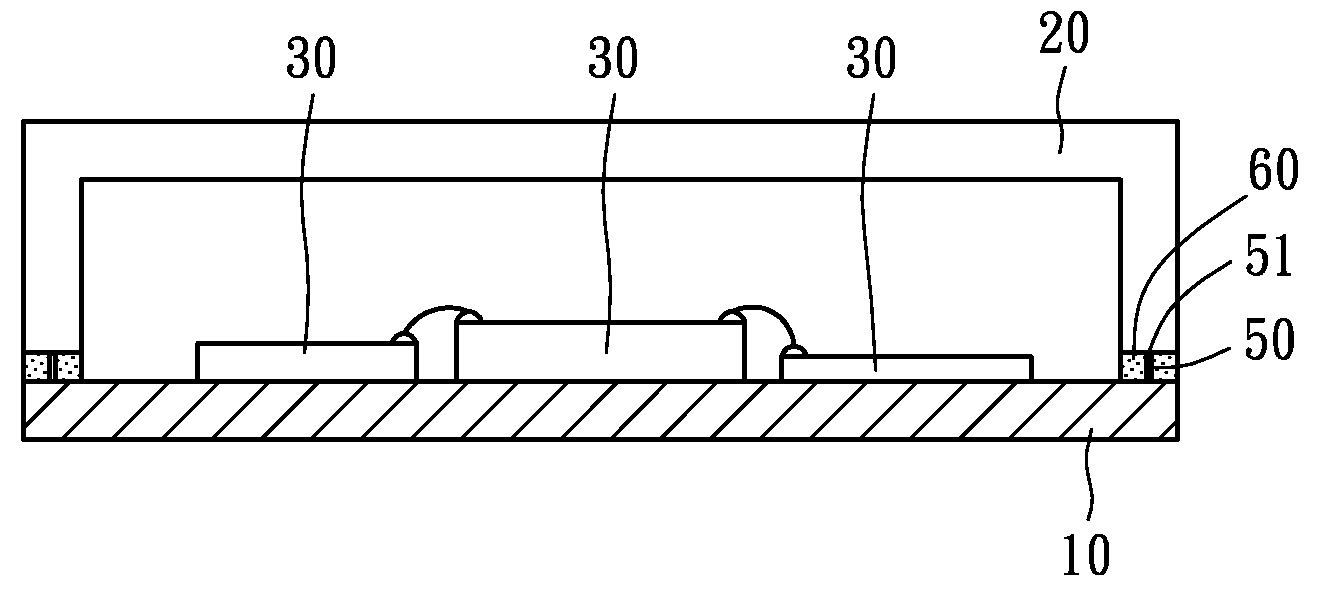

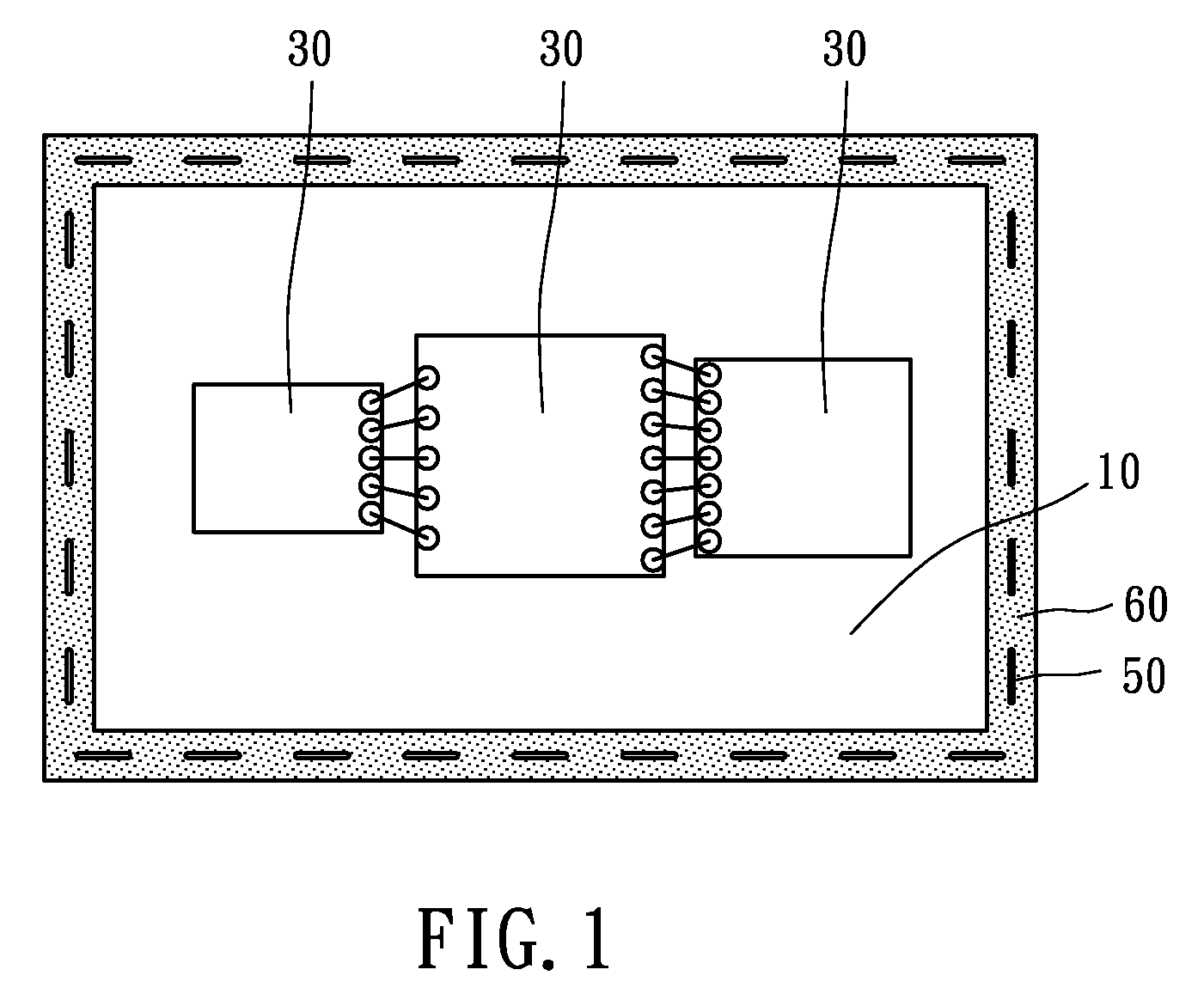

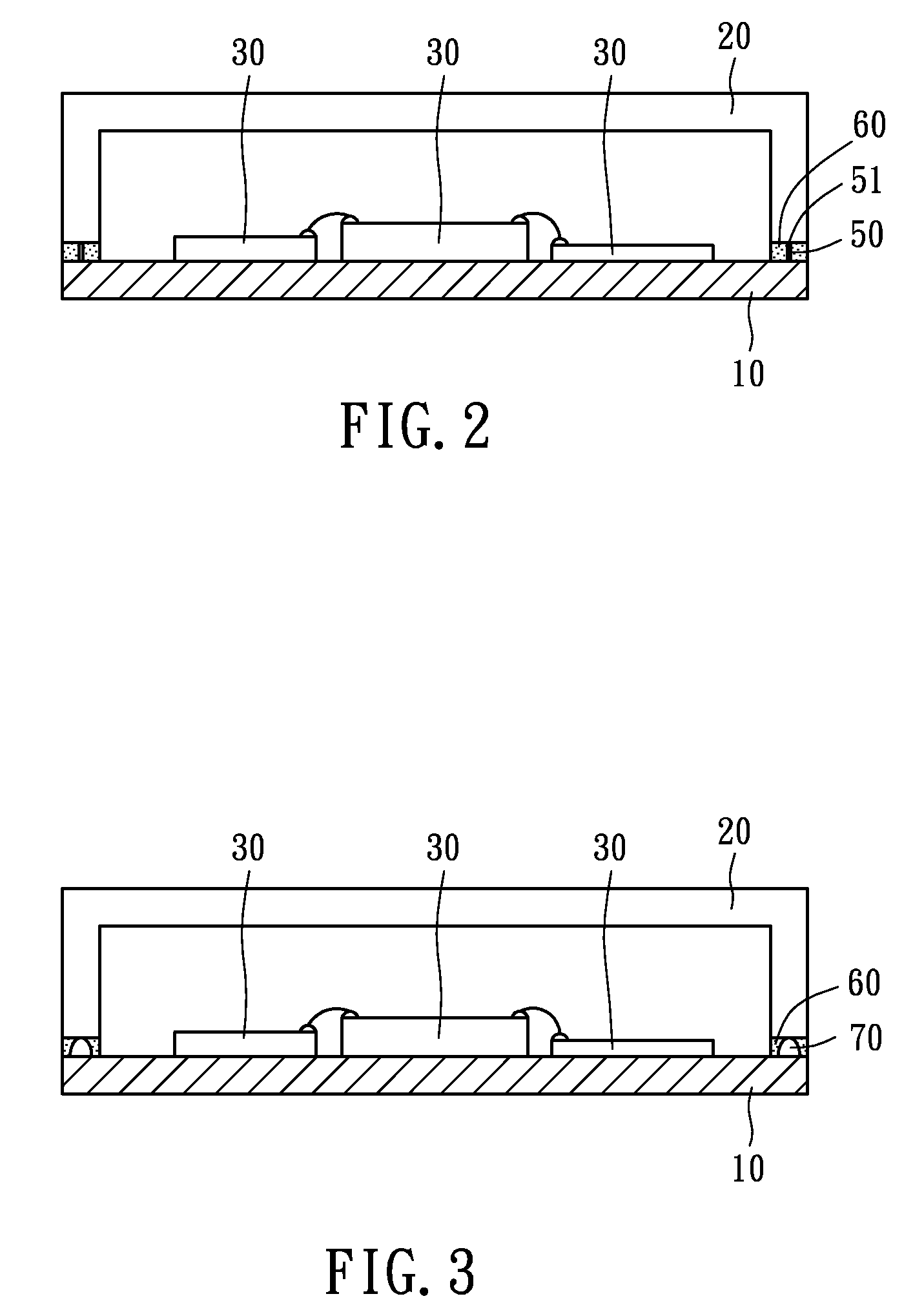

Microelectromechanical system microphone package

InactiveUS20100096711A1Low costImprove package yieldSemiconductor electrostatic transducersSemiconductor/solid-state device detailsAdhesiveEngineering

An MEMS microphone package includes a substrate, a cover, a plurality of conductive members, and an insulative adhesive. The cover is mounted to the substrate. The conductive members are disposed between the substrate and the cover. Each of the conductive members can be a golden wire, a conductive bump, or a conductive metal. Upper ends of the conductive members are connected with the cover and the lower ends of the conductive members are connected with the substrate to enable a conductive loop. The insulative adhesive encapsulates the conductive members. In this way, the substrate, the conductive members, and the cover jointly construct a shielding against EMI.

Owner:LINGSEN PRECISION INDS

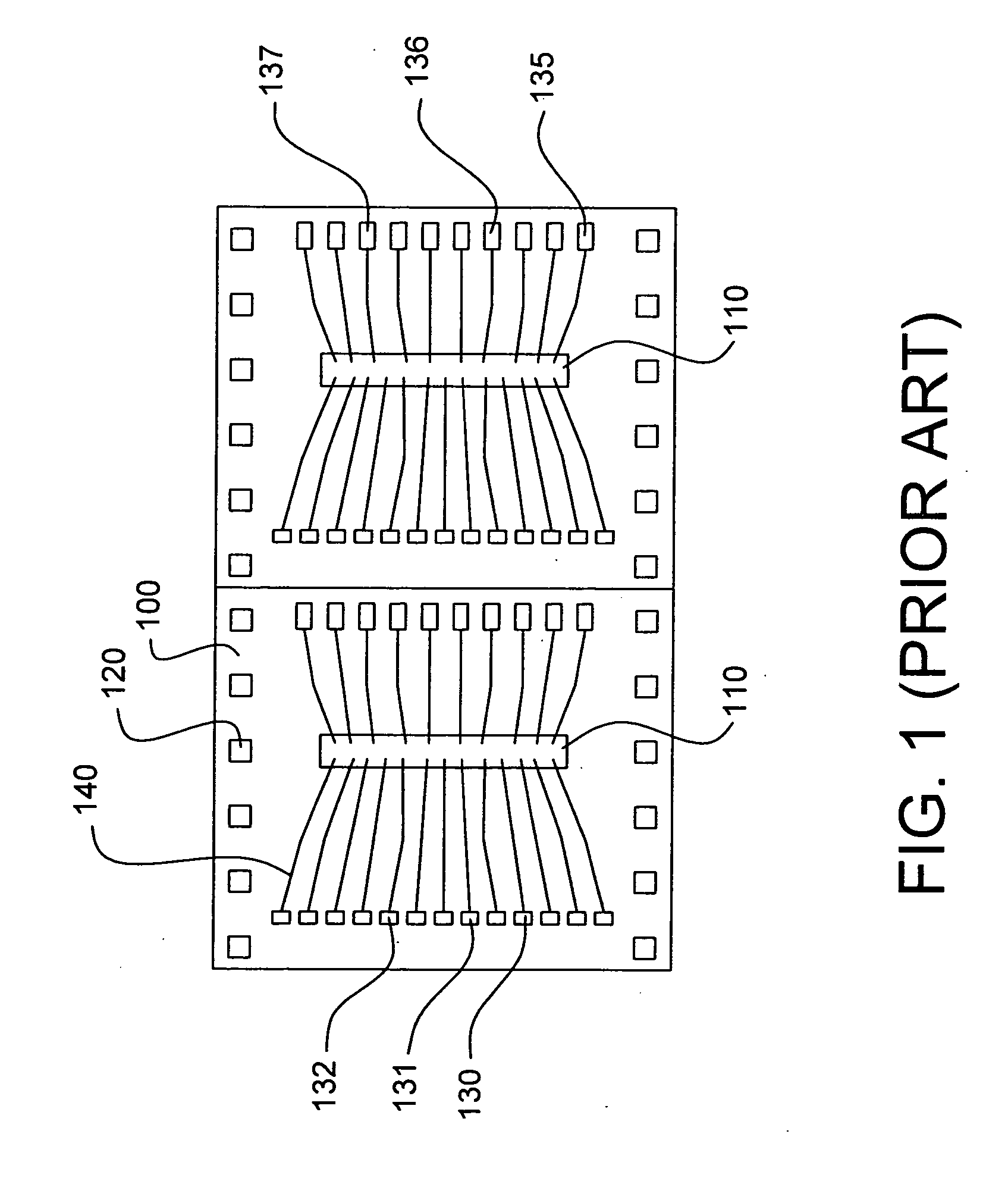

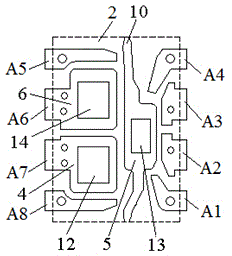

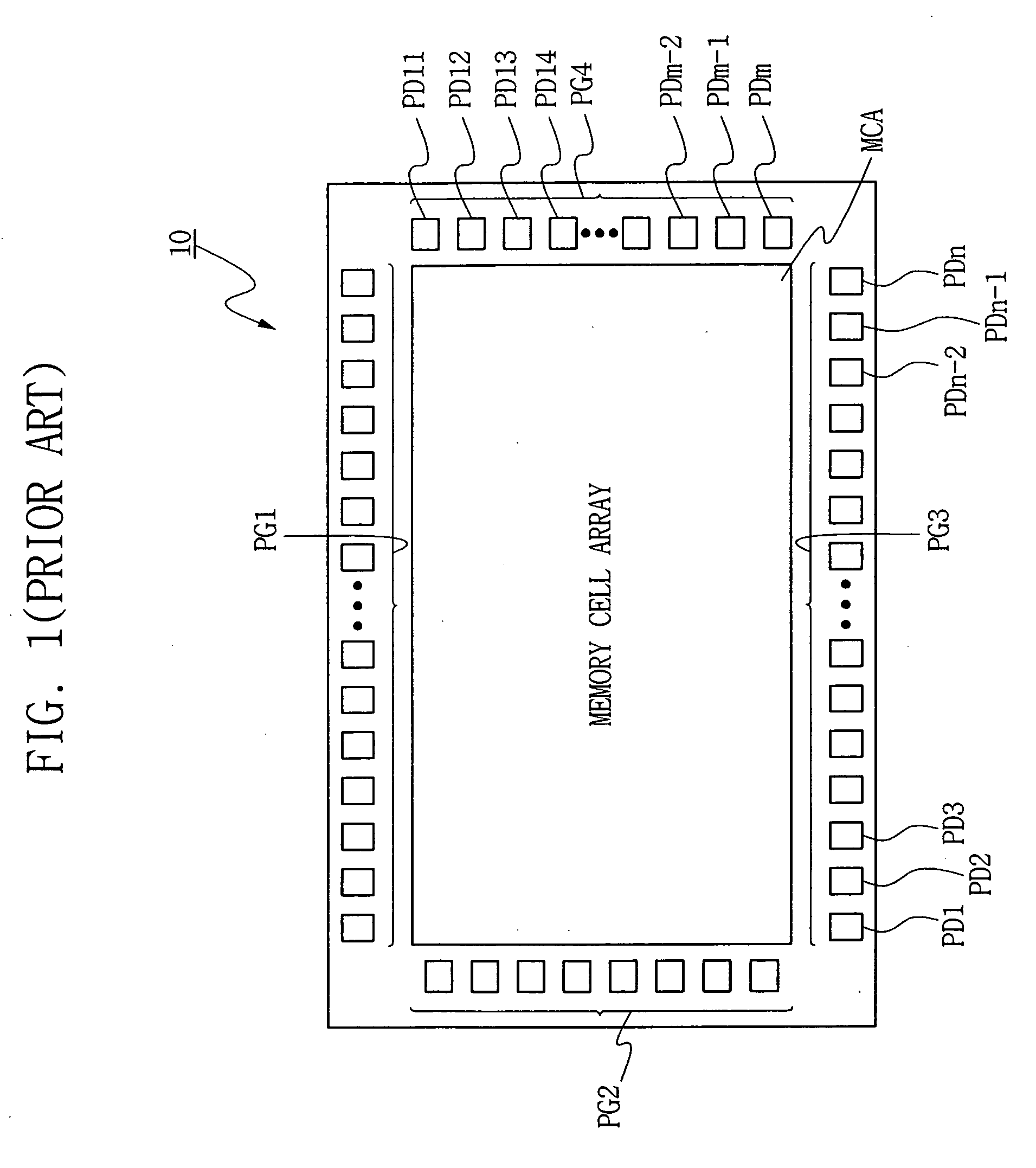

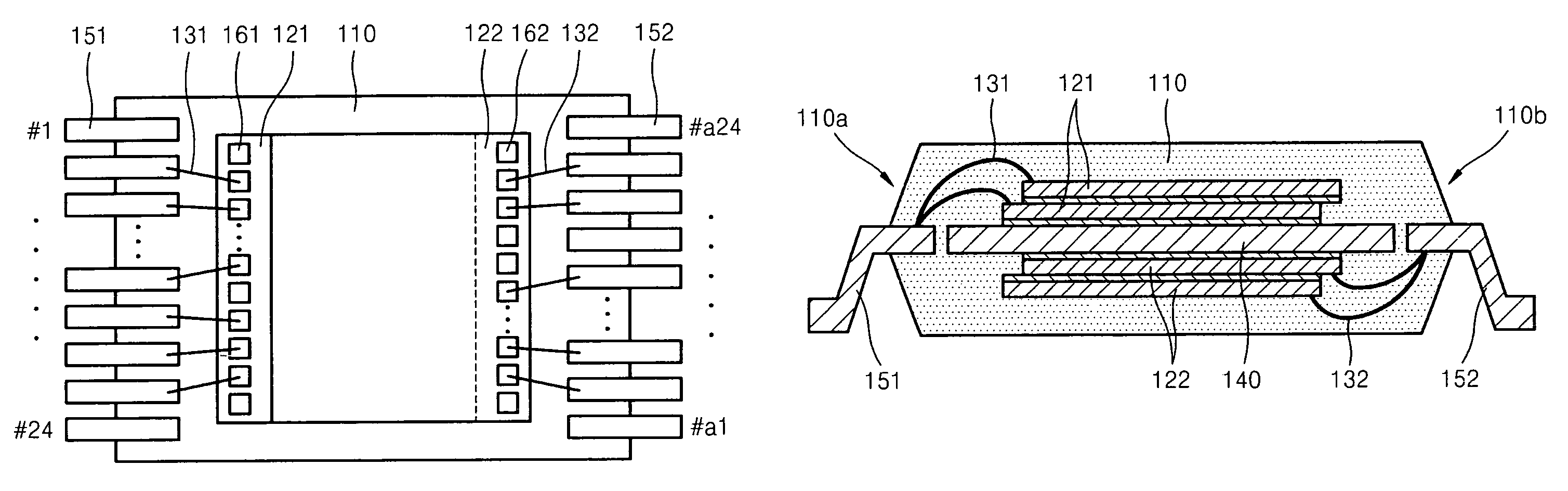

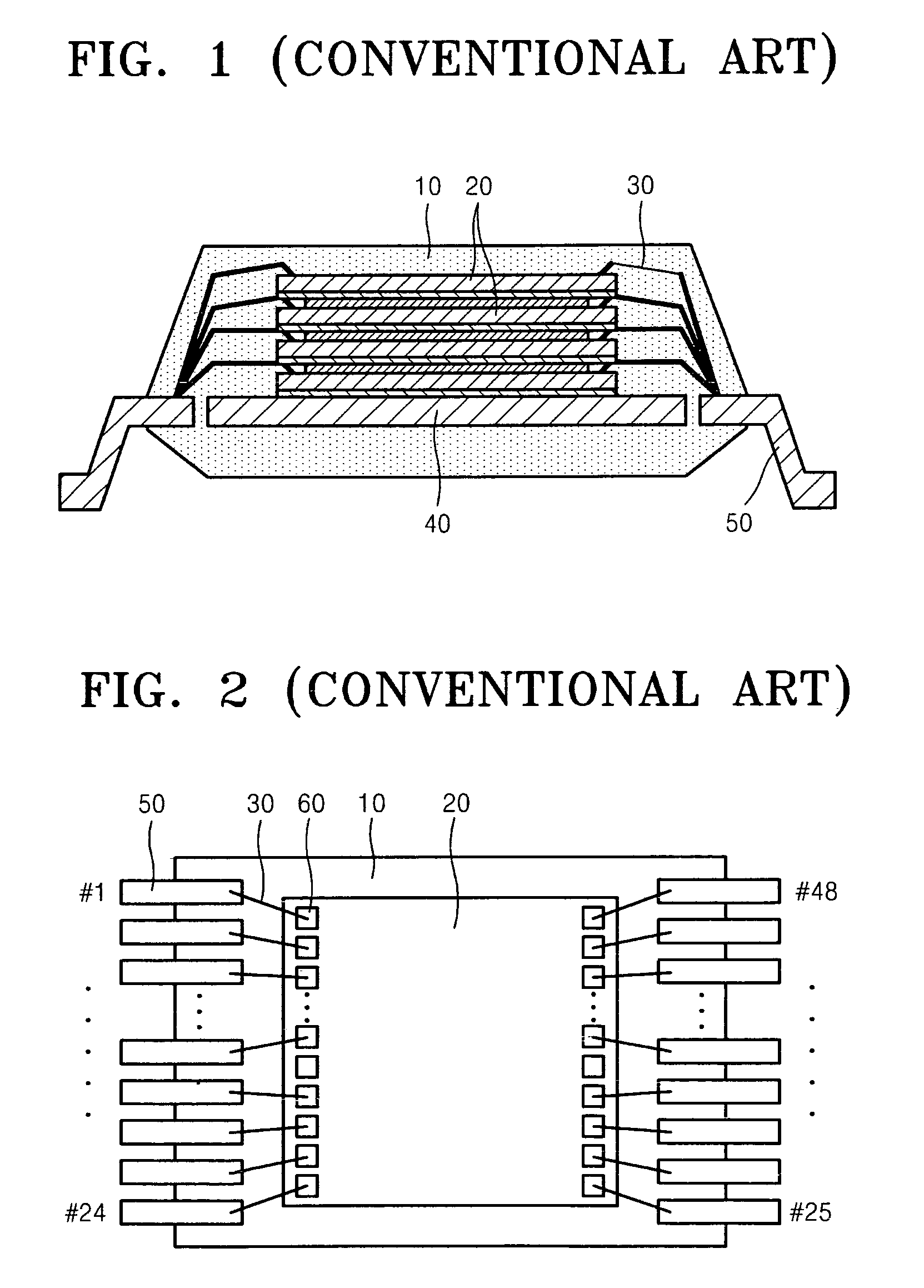

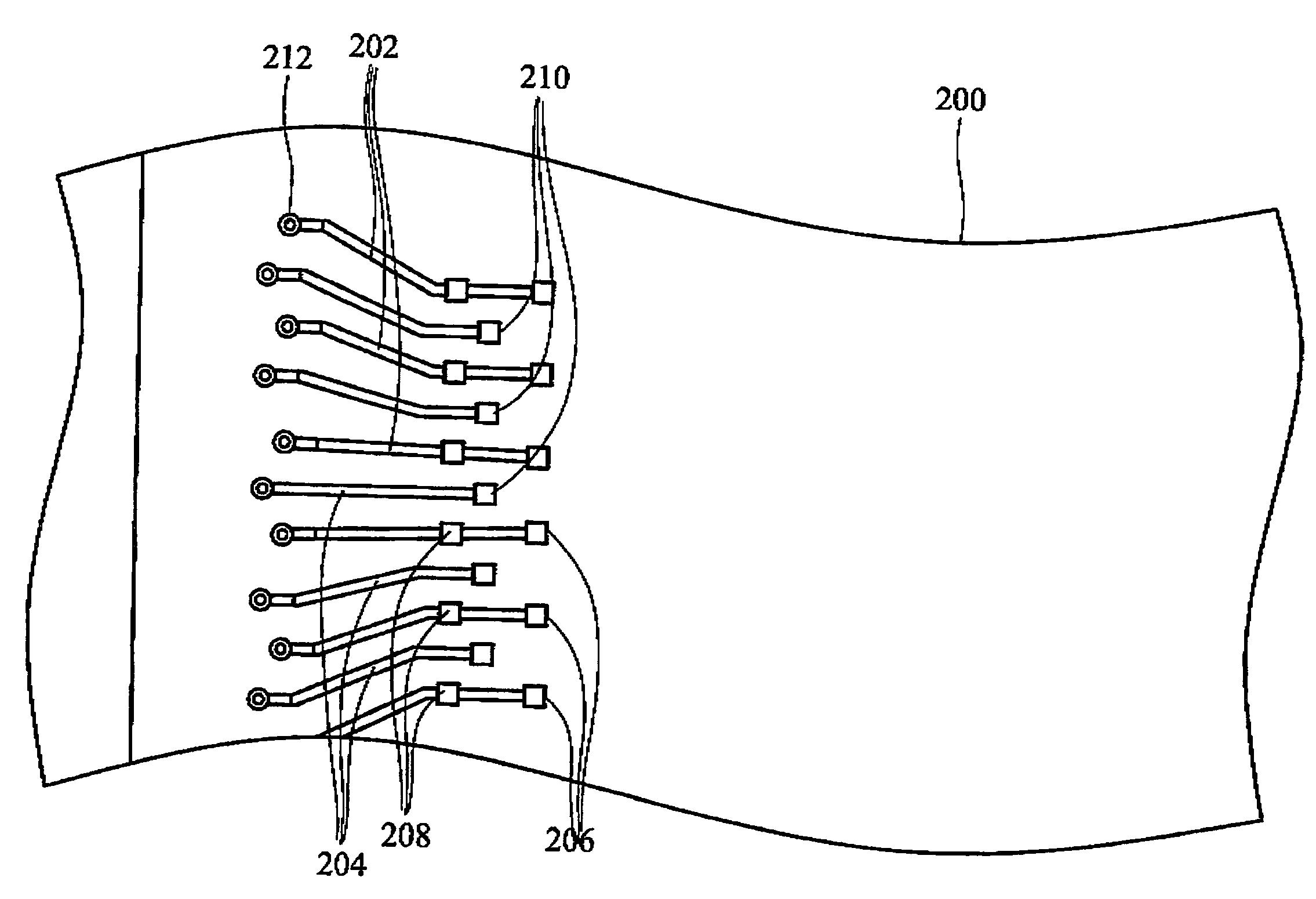

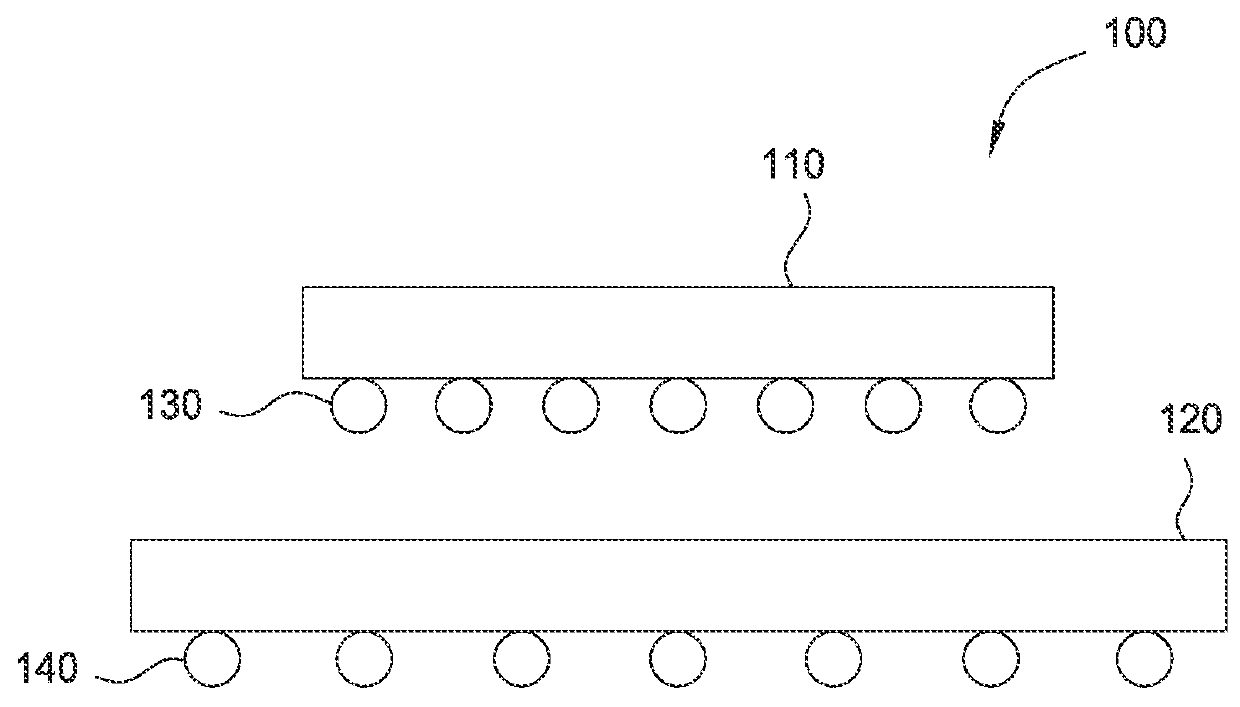

Semiconductor package, semiconductor package module including the semiconductor package, and methods of fabricating the same

ActiveUS7745932B2Improve package yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

Provided are a semiconductor package and a semiconductor package module including the same. The semiconductor package may include a plurality of semiconductor chips, a plurality of leads connected to pads of the semiconductor chips and externally exposed, wherein the plurality of leads may be classified into a plurality of pin groups, and the plurality of semiconductor chips may be classified into a plurality of chip groups, and the pads of the semiconductor chips of like chip groups may be connected to the leads of like pin groups.

Owner:SAMSUNG ELECTRONICS CO LTD

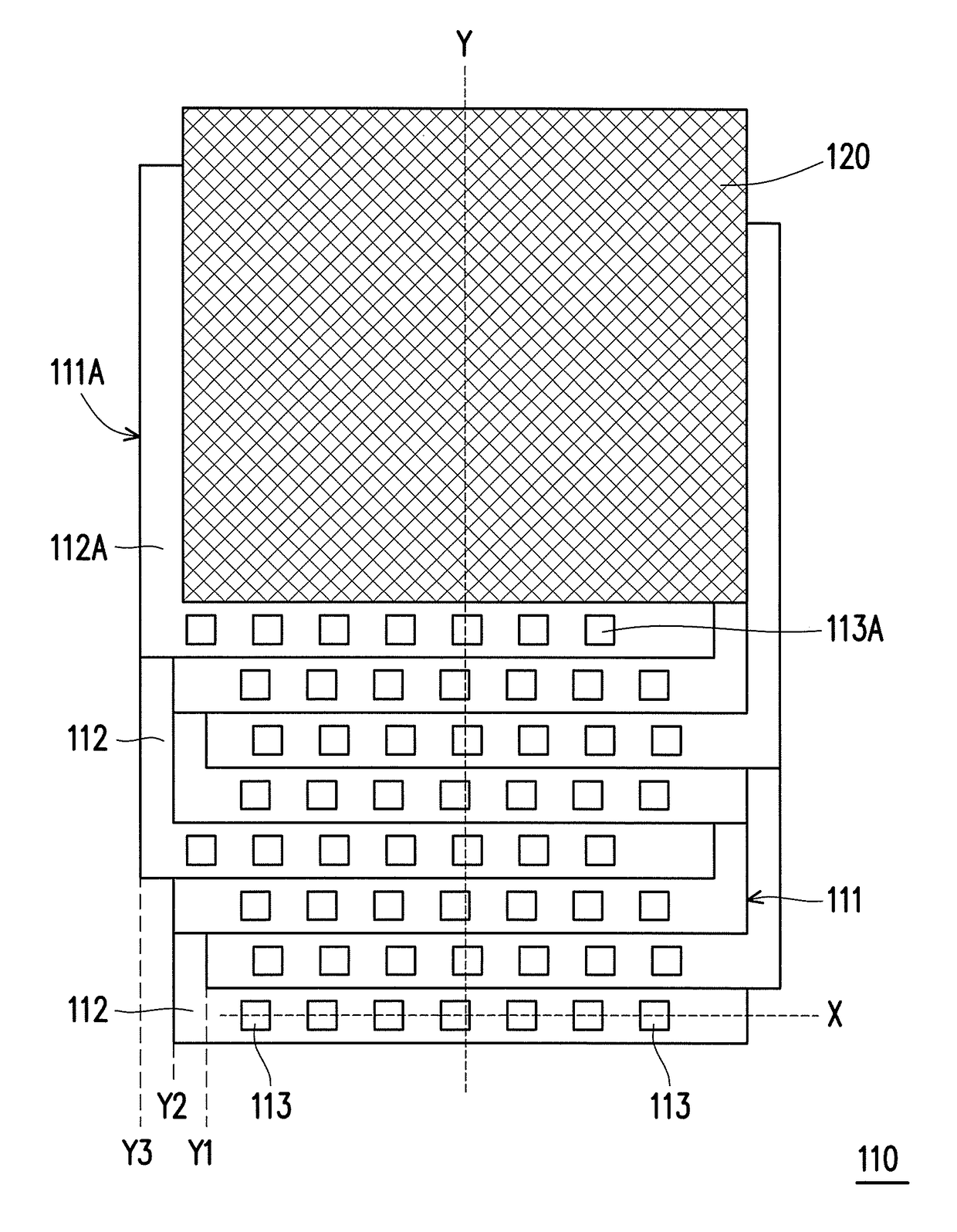

Thin fan-out multi-chip stacked package structure and manufacturing method thereof

ActiveUS10128211B2Reduce bondingPrecise processingSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerEngineering

A thin fan-out multi-chip stacked package structure including a plurality of stacked chips is provided. The electrodes of the stacked chips and the active surface of the top chip are exposed. A dummy spacer and an alignment structure are disposed over the active surface. Each bonding wire has a bonding thread bonded to a chip electrode and an integrally-connected vertical wire segment. A flat encapsulant encapsulates the chip stacked structure and the bonding wires. Polished cross-sectional surfaces of the bonding wires and a surface of the alignment structure are exposed by the flat surface of the encapsulant. A redistribution layer structure is formed on the flat surface. A passivation layer covers the flat surface and exposes the polished cross-sectional surfaces and the alignment structure. Fan-out circuits are formed on the passivation layer and are connected to the polished cross-sectional surfaces of the bonding wires and the alignment structure.

Owner:POWERTECH TECHNOLOGY INC

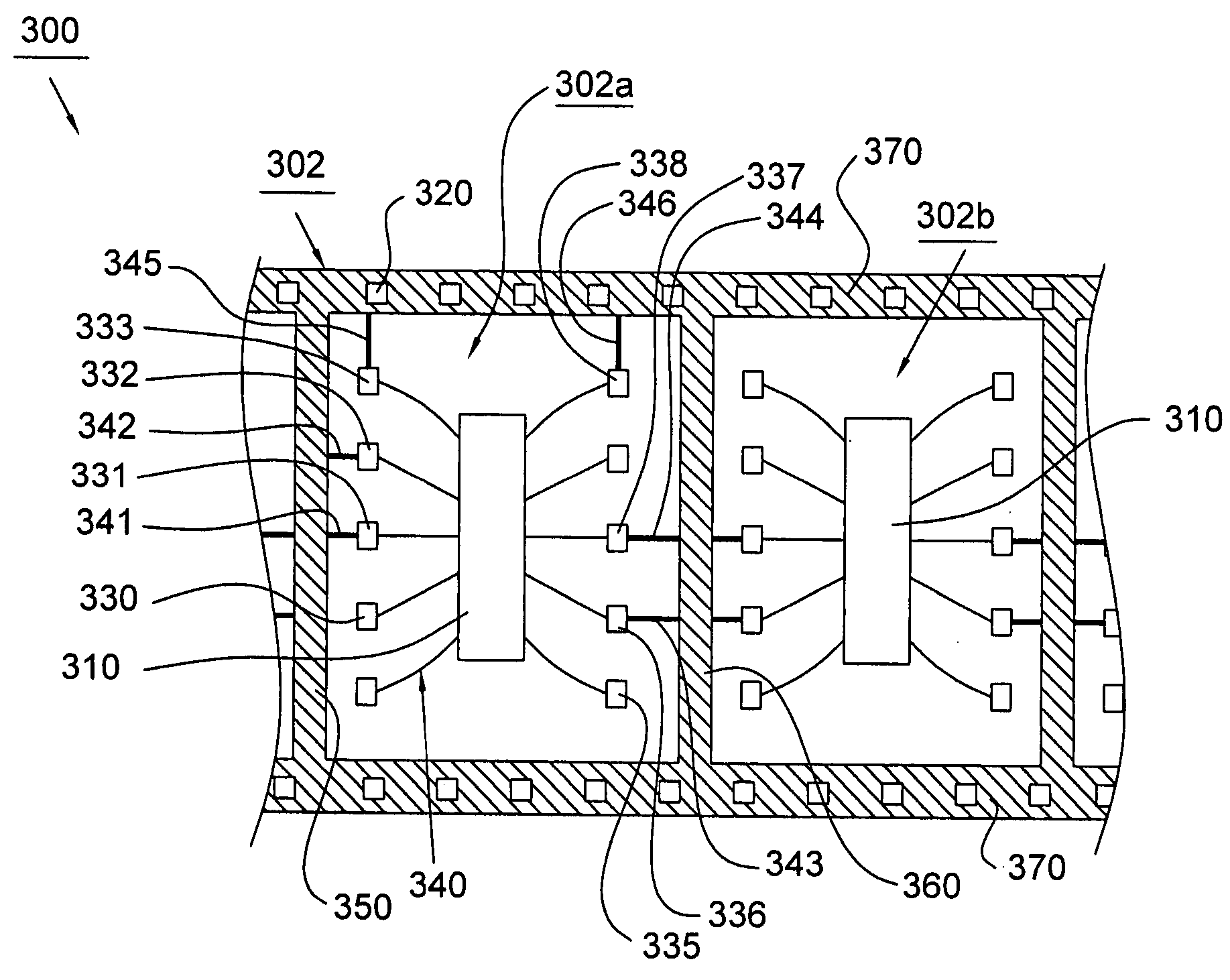

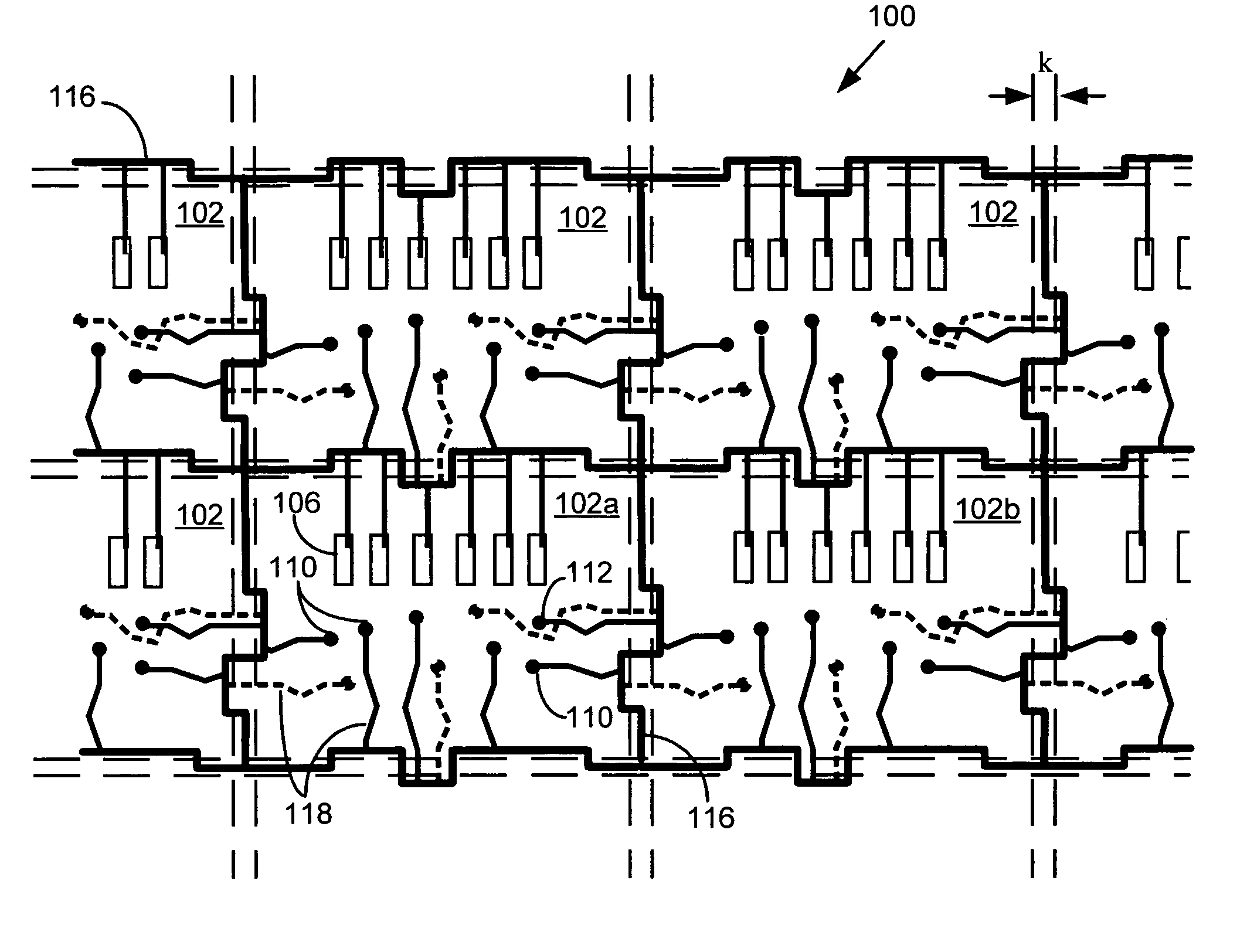

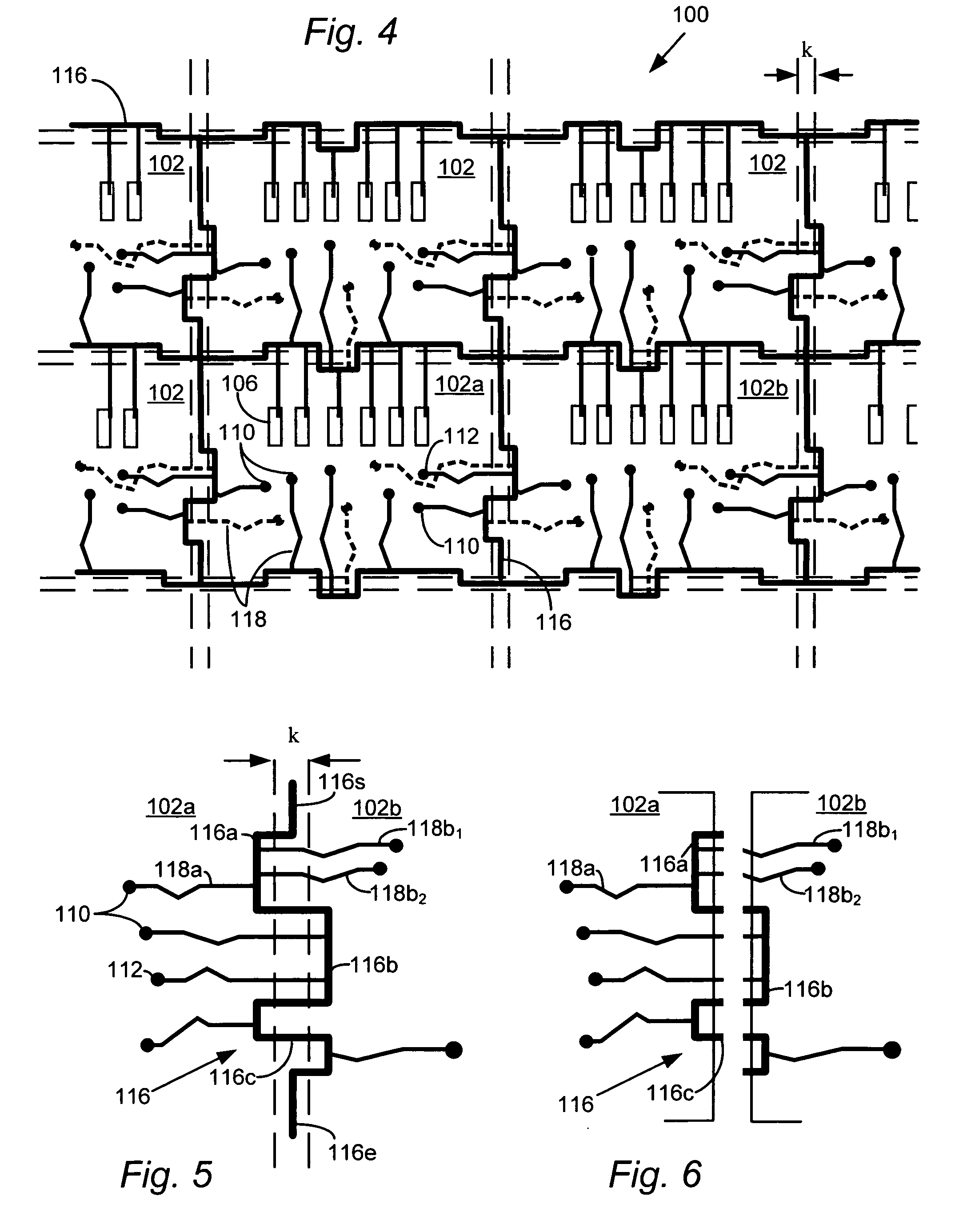

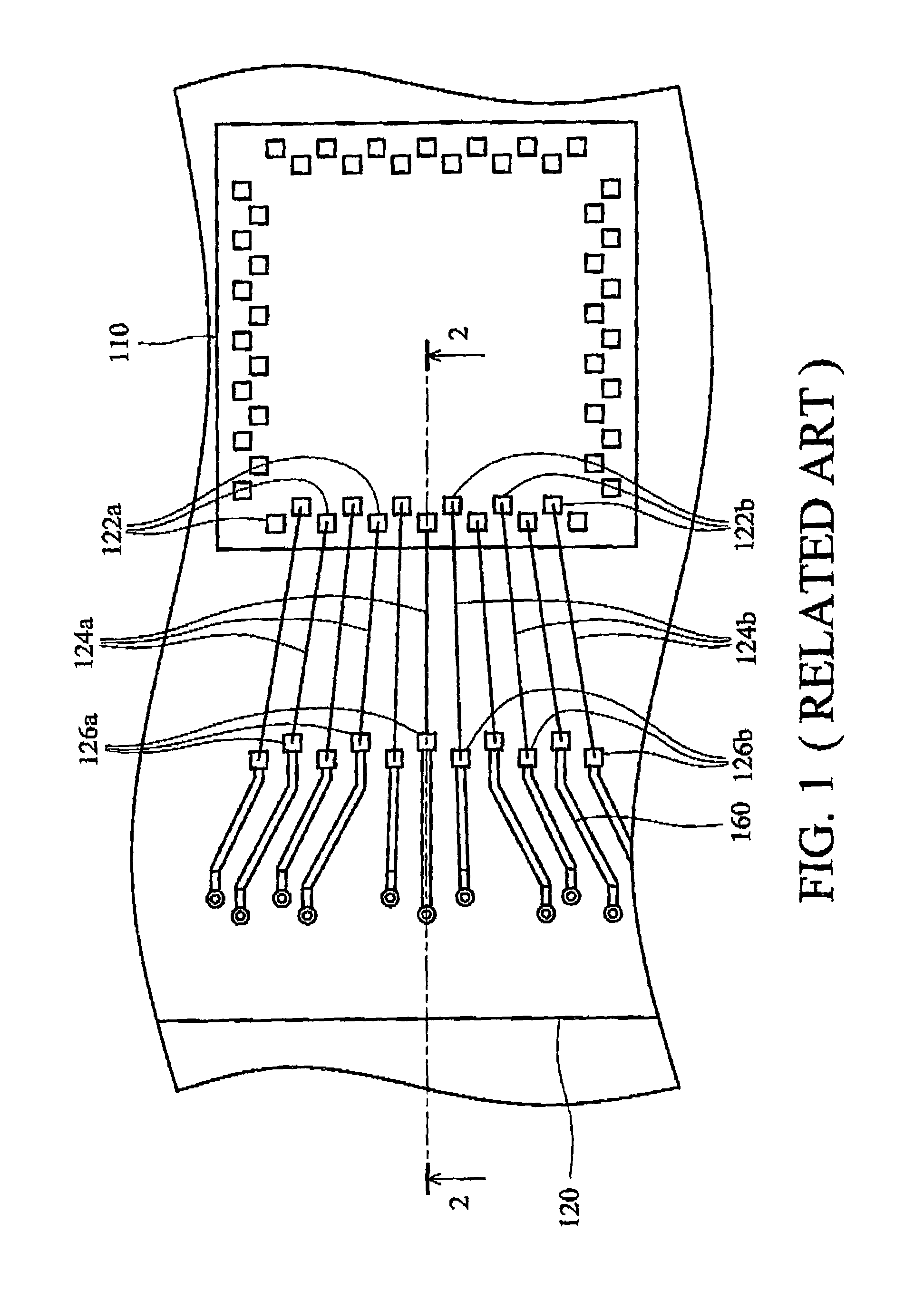

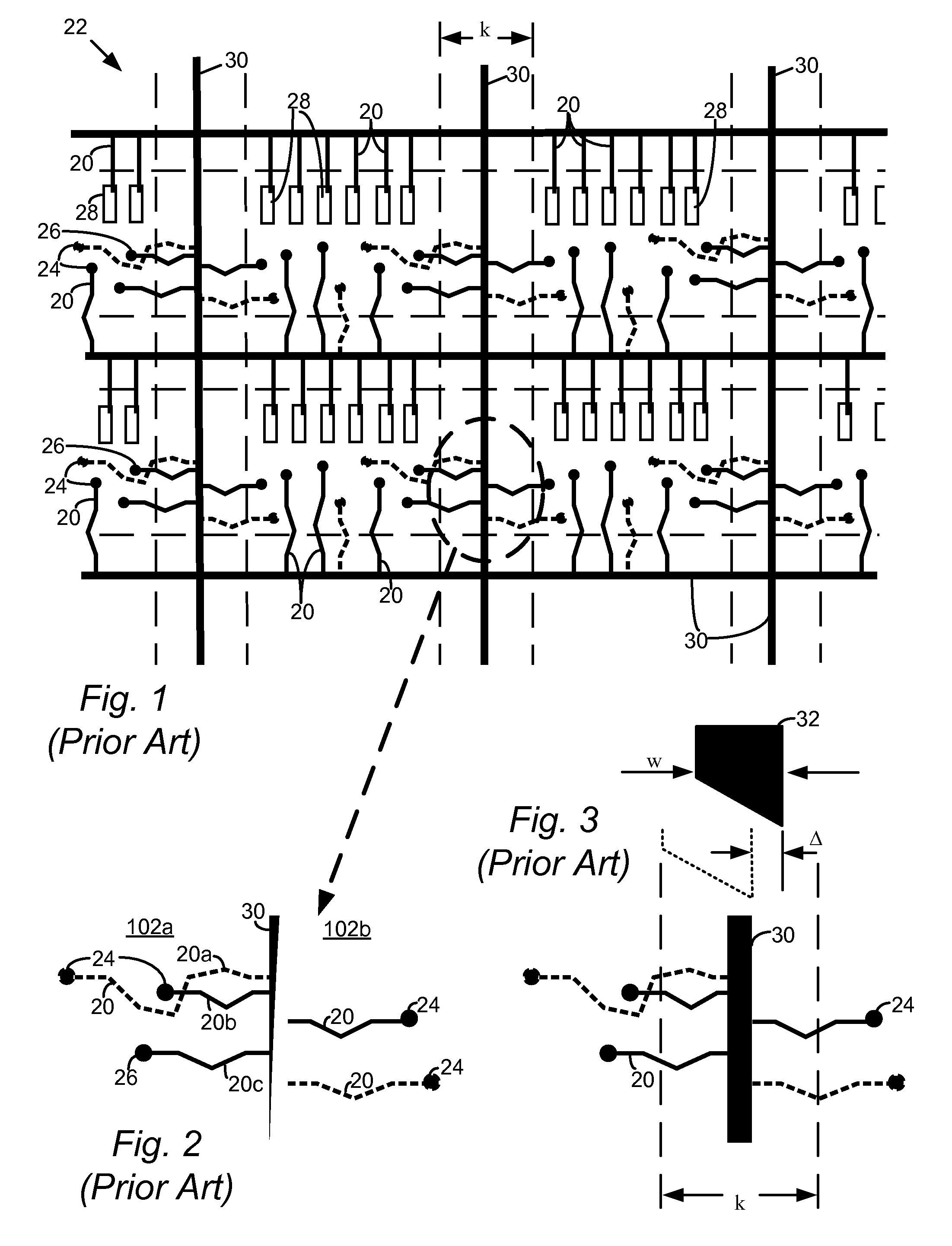

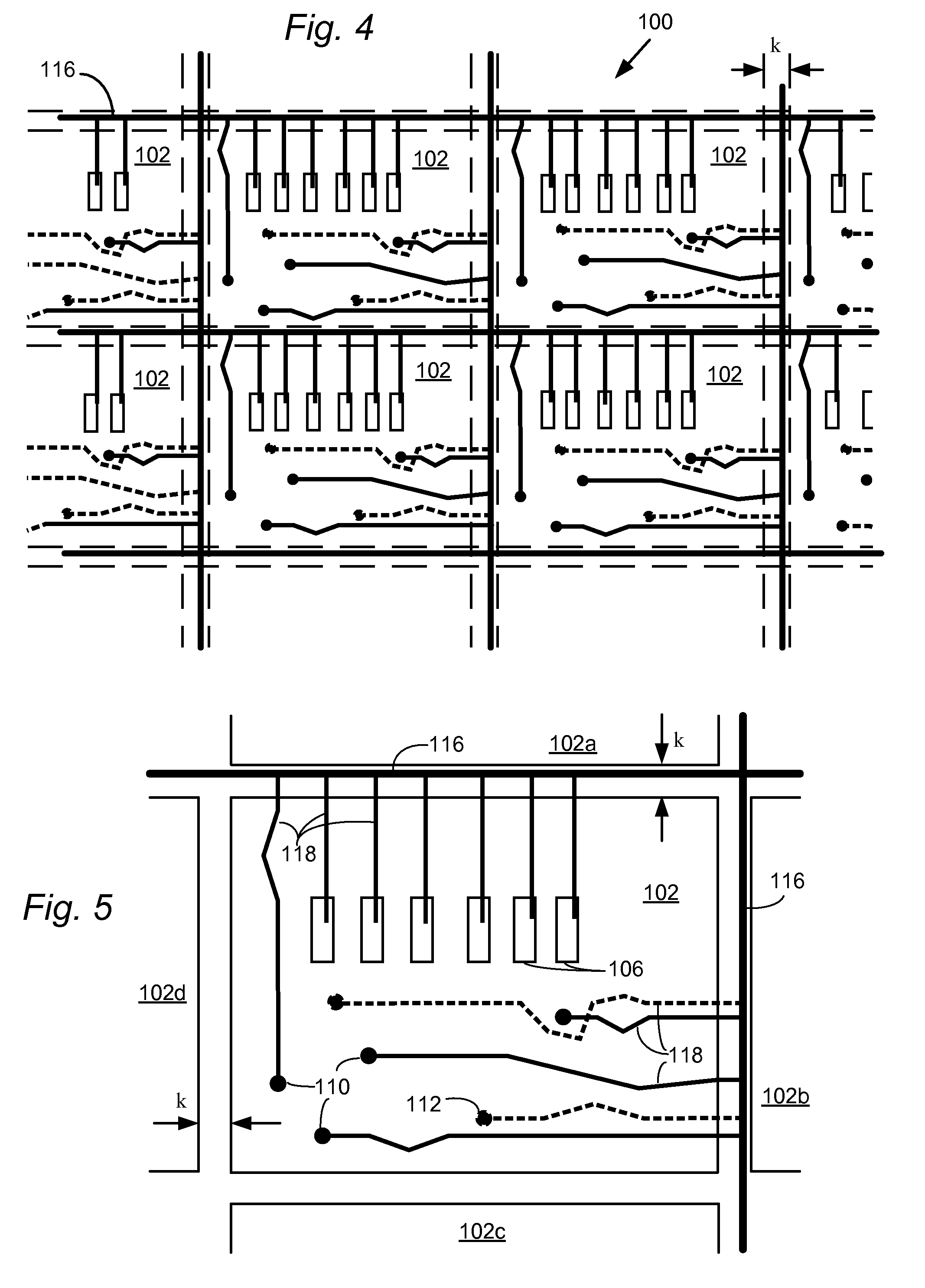

Staggered wirebonding configuration

ActiveUS7411287B2Low costImprove chip efficiencySemiconductor/solid-state device detailsSolid-state devicesEngineeringMechanical engineering

Owner:ADVANCED SEMICON ENG INC

Method and structure for prevention leakage of substrate strip

InactiveUS7091583B2Improve package yieldSimple formatSemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskSurface layer

The present invention provides a structure and a method for prevention leakage of a substrate strip. The substrate strip includes an edge portion and a plurality of units. A patterned metal layer on a surface of the substrate strip includes at least one plating bus extended to the edge portion, a plurality of plating lines at the units, a plurality of contact pads at the units and a plurality of fiducial marks at the edge portion. The plating bus has an extended trail having one end exposed out of the sidewall of the substrate strip. The fiducial marks and the contact pads are exposed out of a plurality of first openings of a solder mask. The solder mask also has a second opening at the edge portion exposing a portion of the plating bus to define a breaking hole. After forming a surface layer on the fiducial marks and the contact pads, the exposed portion of the plating bus is void of the surface layer. By removing the exposed portion of the plating bus, the breaking hole is formed to electrically isolate the extended trail from the contact pads in order to prevent a chip on the substrate strip from being damaged by ESD (Electrostatic Discharge) during packaging processes.

Owner:ADVANCED SEMICON ENG INC

Two-sided substrate lead connection for minimizing kerf width on a semiconductor substrate panel

ActiveUS20080303166A1Reduce widthIncrease spacingSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectrical isolation

A semiconductor die substrate panel is disclosed including a minimum kerf width between adjoining semiconductor package outlines on the panel, while ensuring electrical isolation of plated electrical terminals. By reducing the width of a boundary between adjoining package outlines, additional space is gained on a substrate panel for semiconductor packages.

Owner:SANDISK TECH LLC

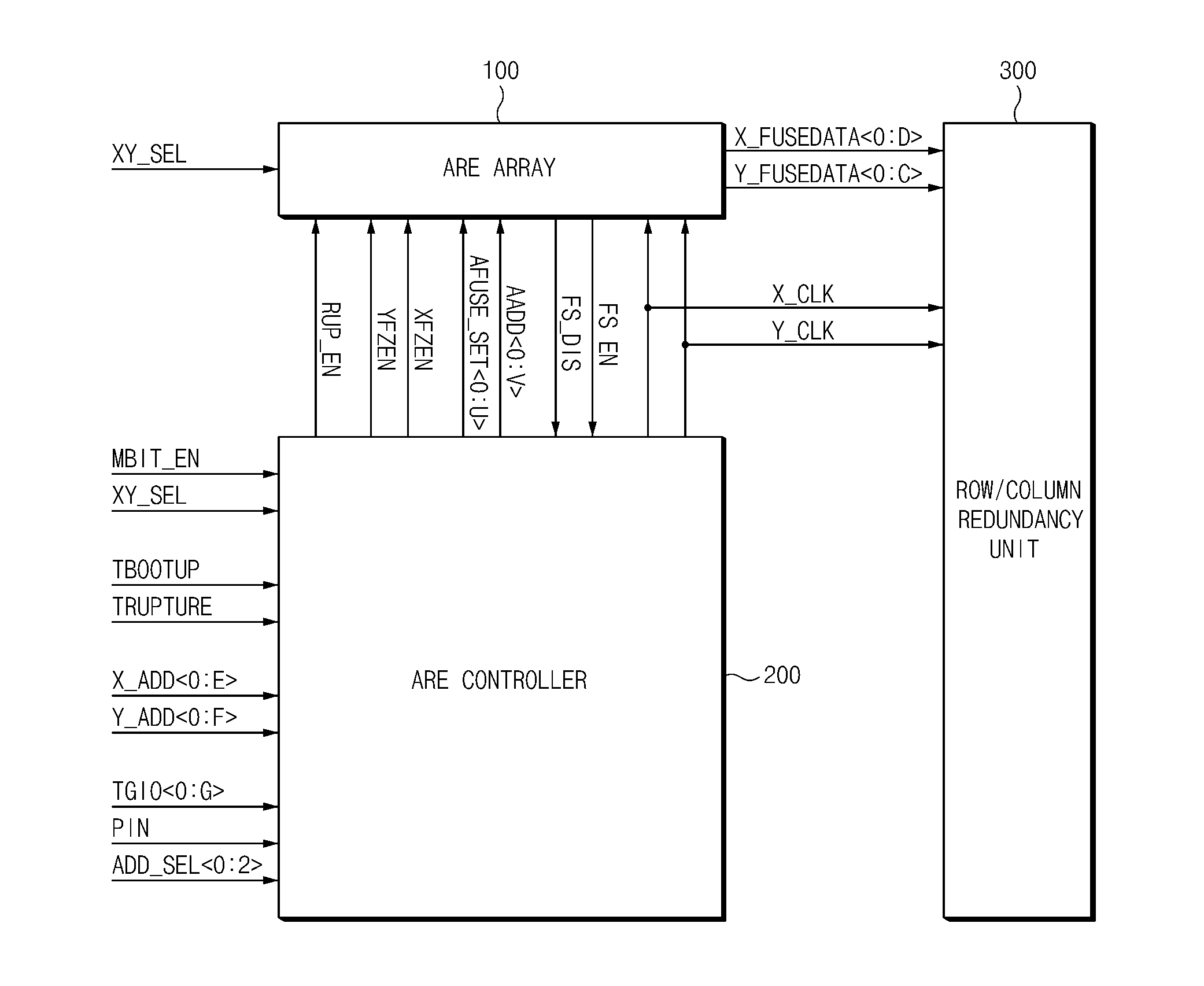

Self repair device and method thereof

ActiveUS20160372214A1Improve maintenance efficiencyImprove package yieldRead-only memoriesElectricityRestoration device

A self repair device may include: an electrical fuse array configured to store bit information of a failed address in a fuse; an electrical fuse controller configured to store a row address or column address corresponding to a failed bit when a failure occurs, generate a repair address by comparing a failed address inputted during a test to the address stored therein, output a rupture enable signal for controlling a rupture operation of the electrical fuse array, and output row fuse set data or column fuse set data in response to the failed address; and a row / column redundancy unit configured to perform a row redundancy or column redundancy operation in response to the row fuse set data or the column fuse set data applied from the electrical fuse array.

Owner:SK HYNIX INC