Patents

Literature

64results about How to "More scalable" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

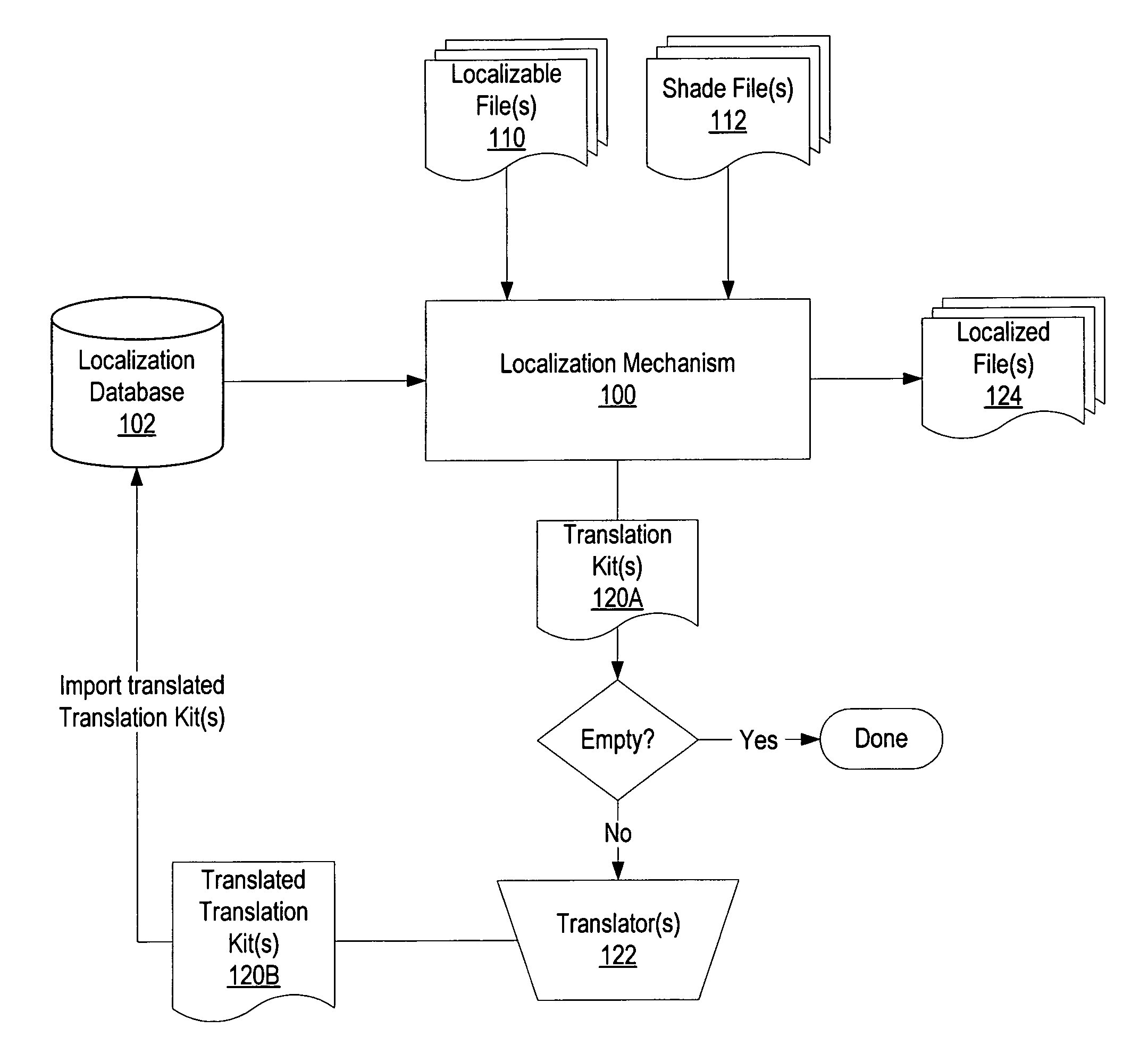

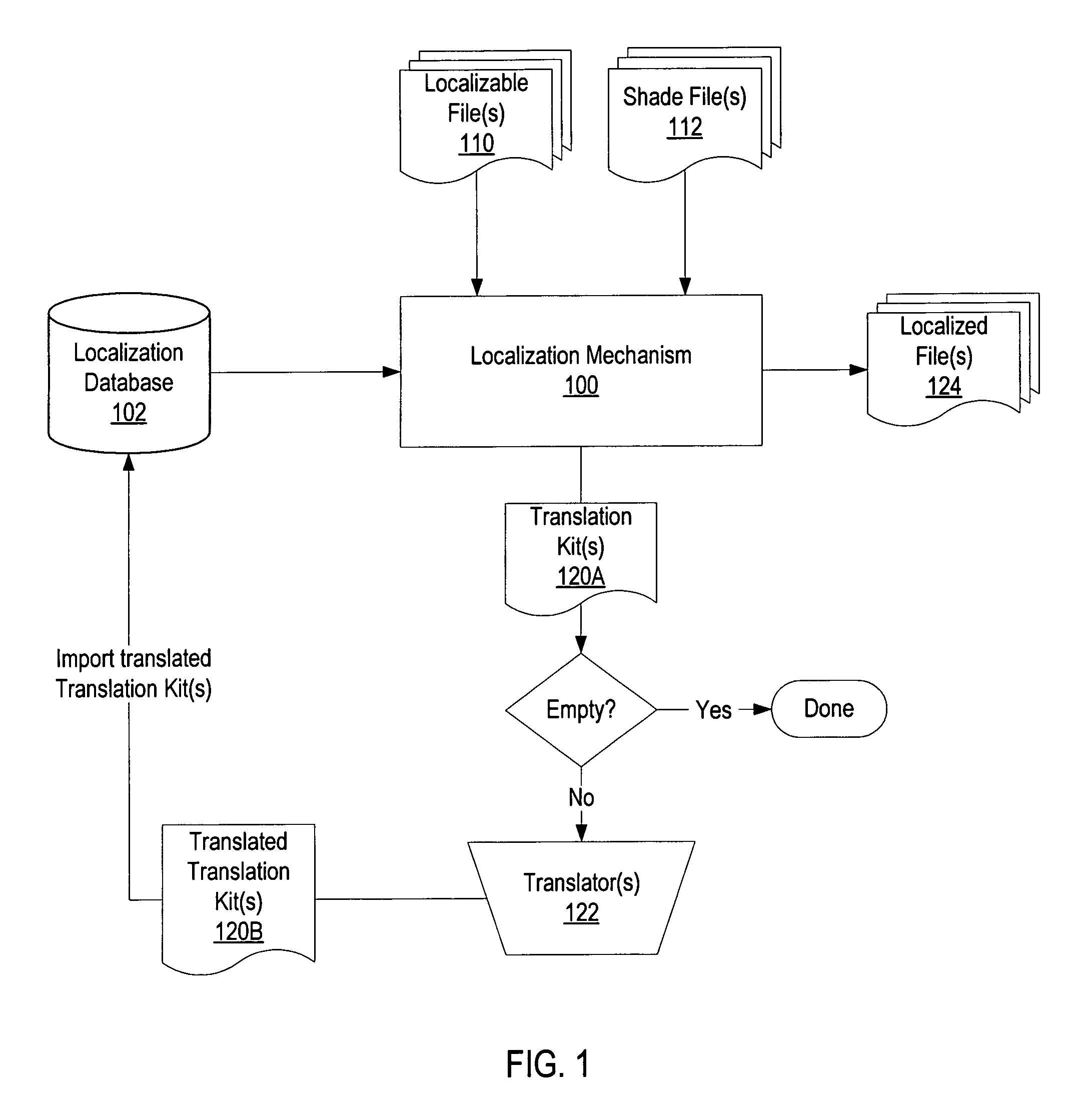

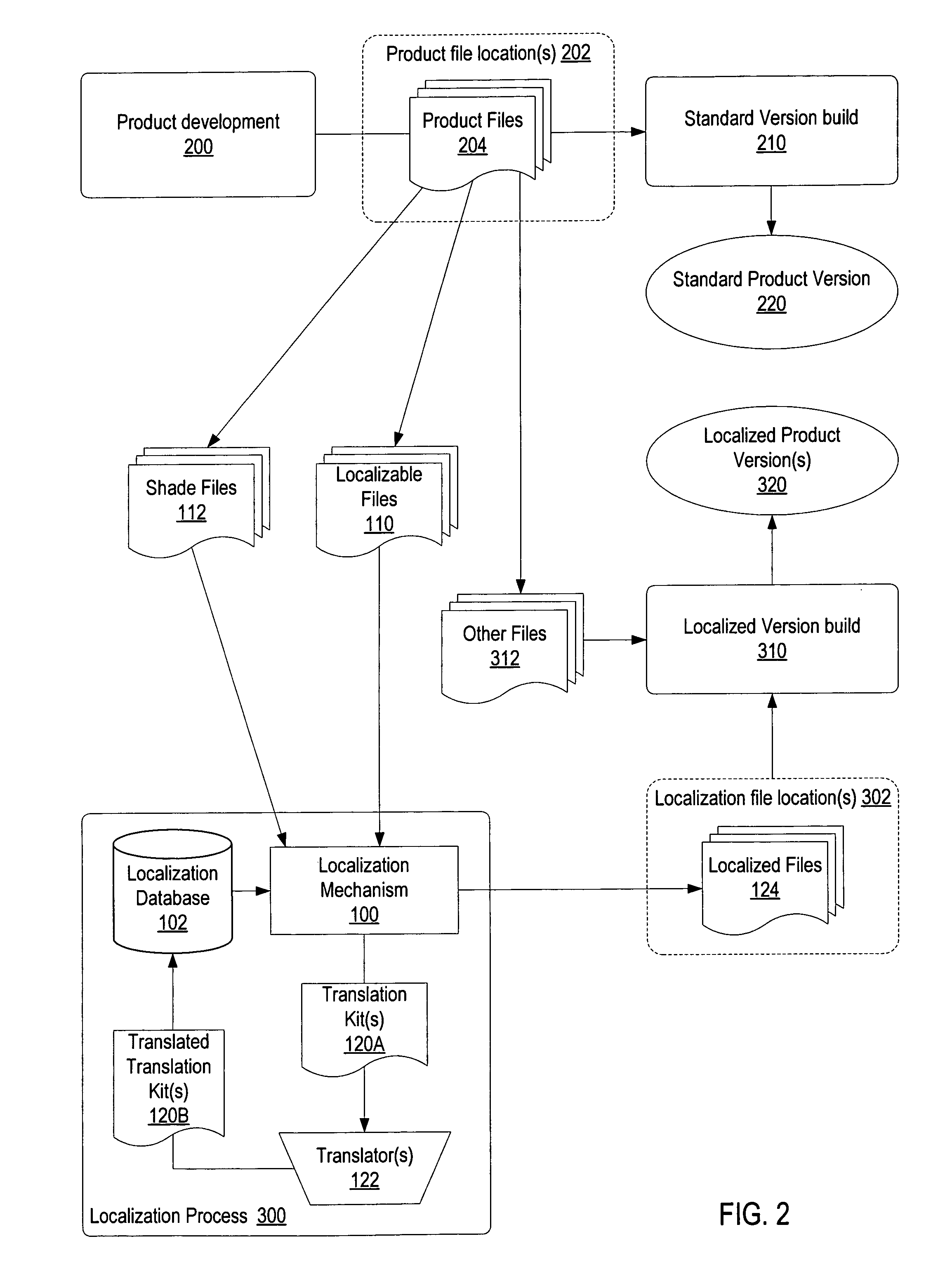

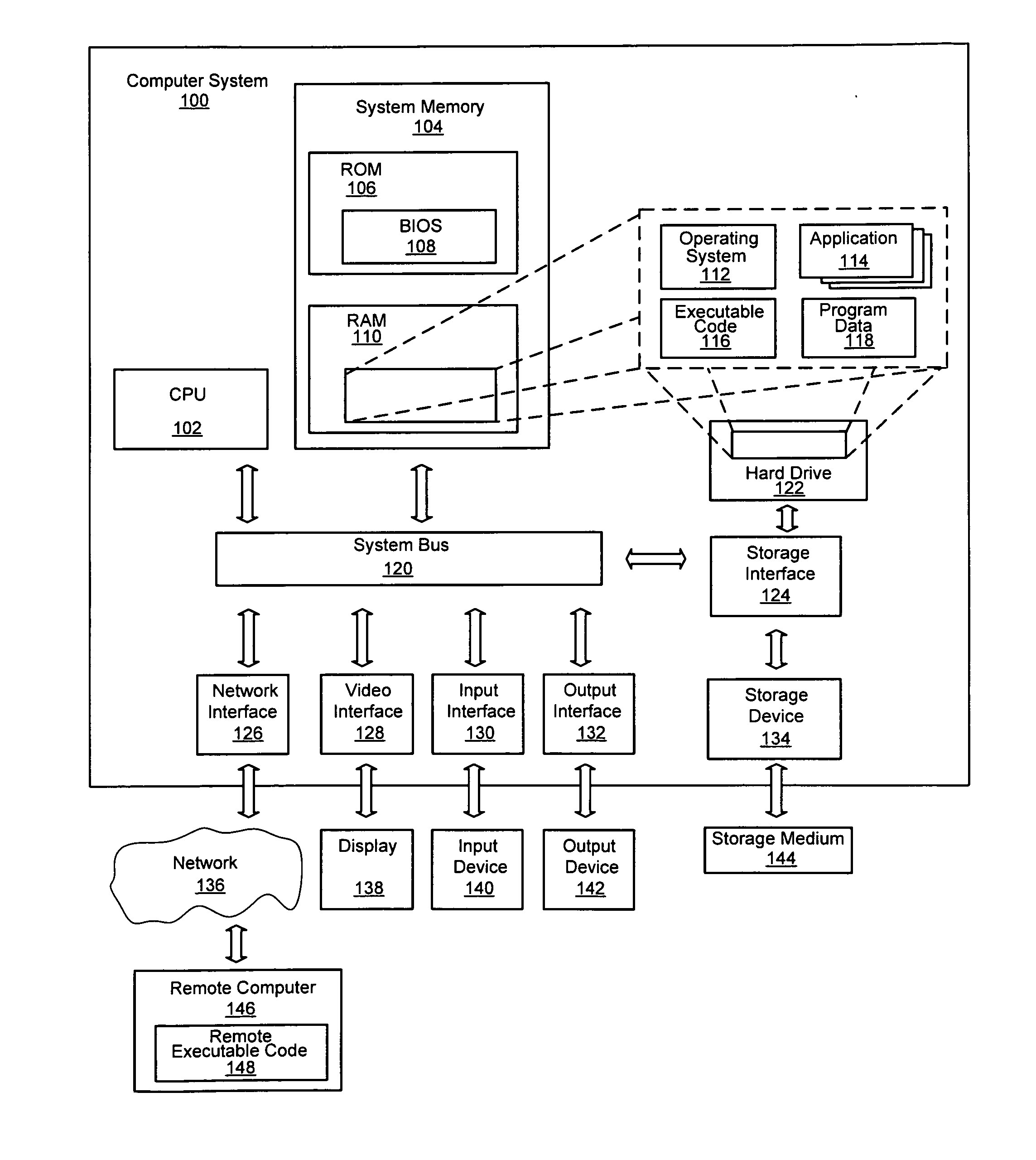

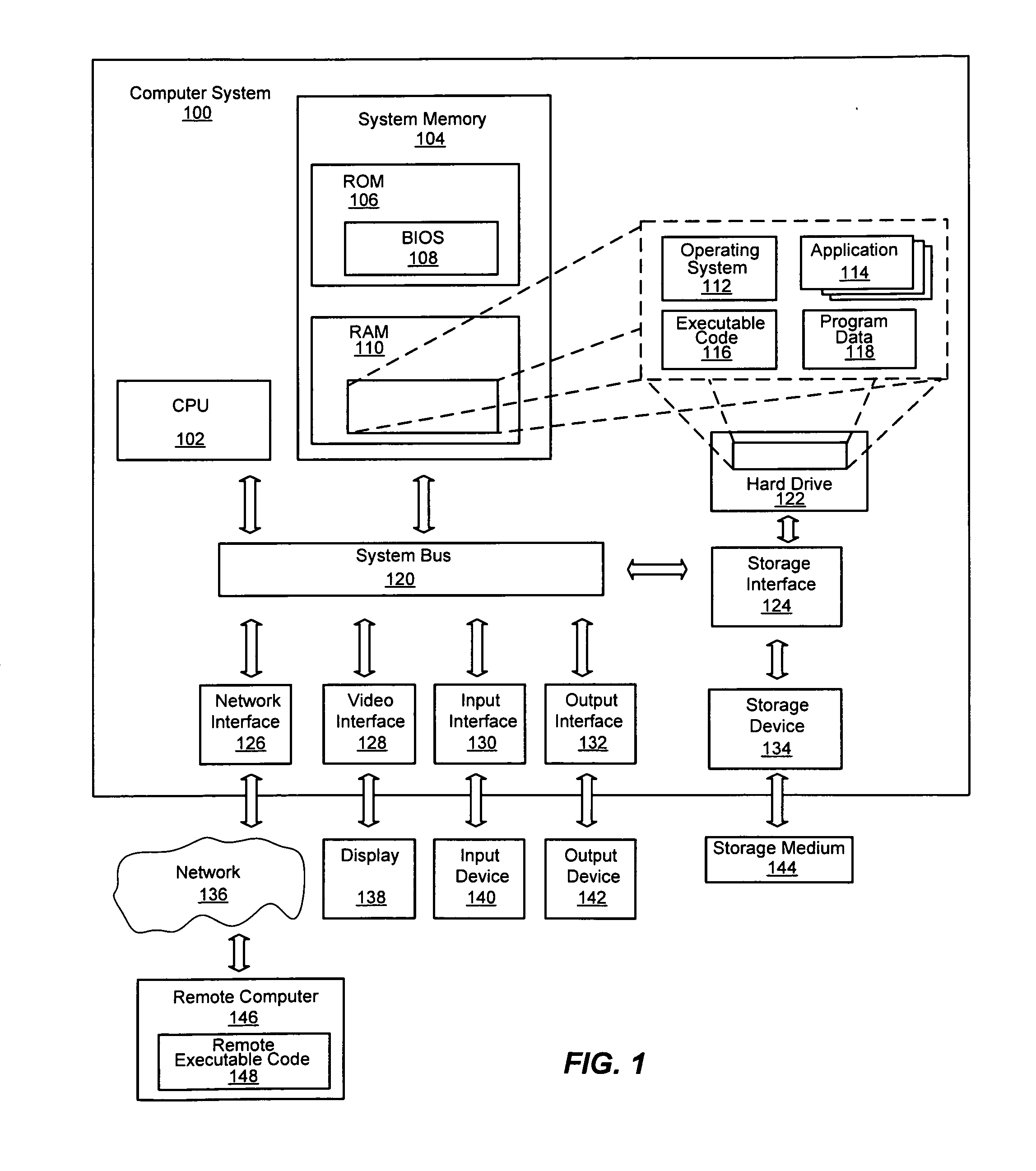

Method and apparatus for on-demand localization of files

ActiveUS7571092B1More scalableReduce or eliminate human-caused errorsSpeech analysisNatural language data processingOn demandFile format

Method and apparatus for the on-demand localization of files. Embodiments may provide a file format-independent localization mechanism that automates the extraction of localizable text content from localizable files, the process of generating translations for the extracted localizable text content, and the generation of localized versions of the localizable files including the translations for the extracted localizable content. The localized versions of the files may be automatically generated with correct structure and content, correct file names, and automatically placed in correct file locations by the localization mechanism, and are thus readily available to and locatable by an automated build process for the localized version of the product, thus reducing or eliminating the necessity for human intervention during the localization process.

Owner:ORACLE INT CORP

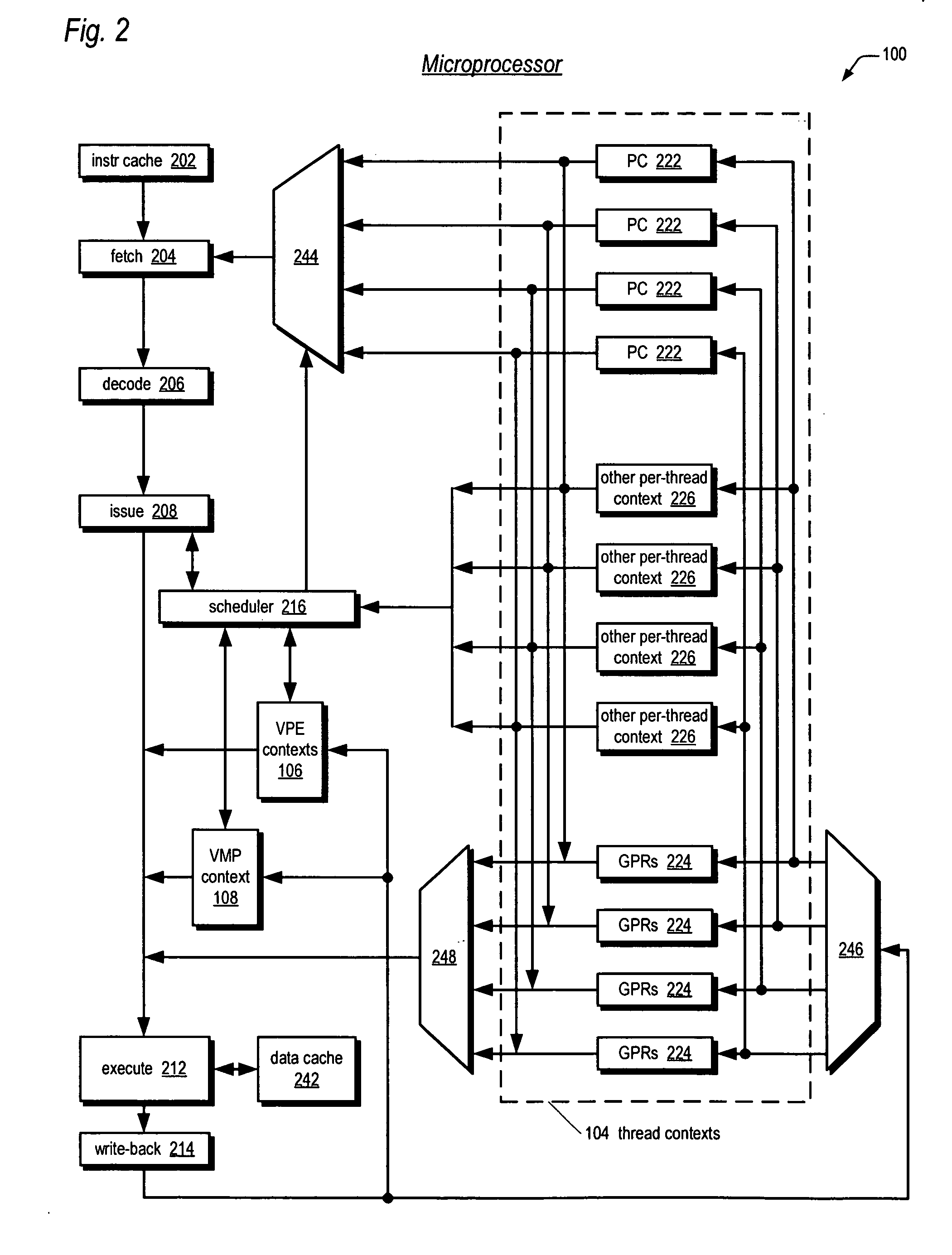

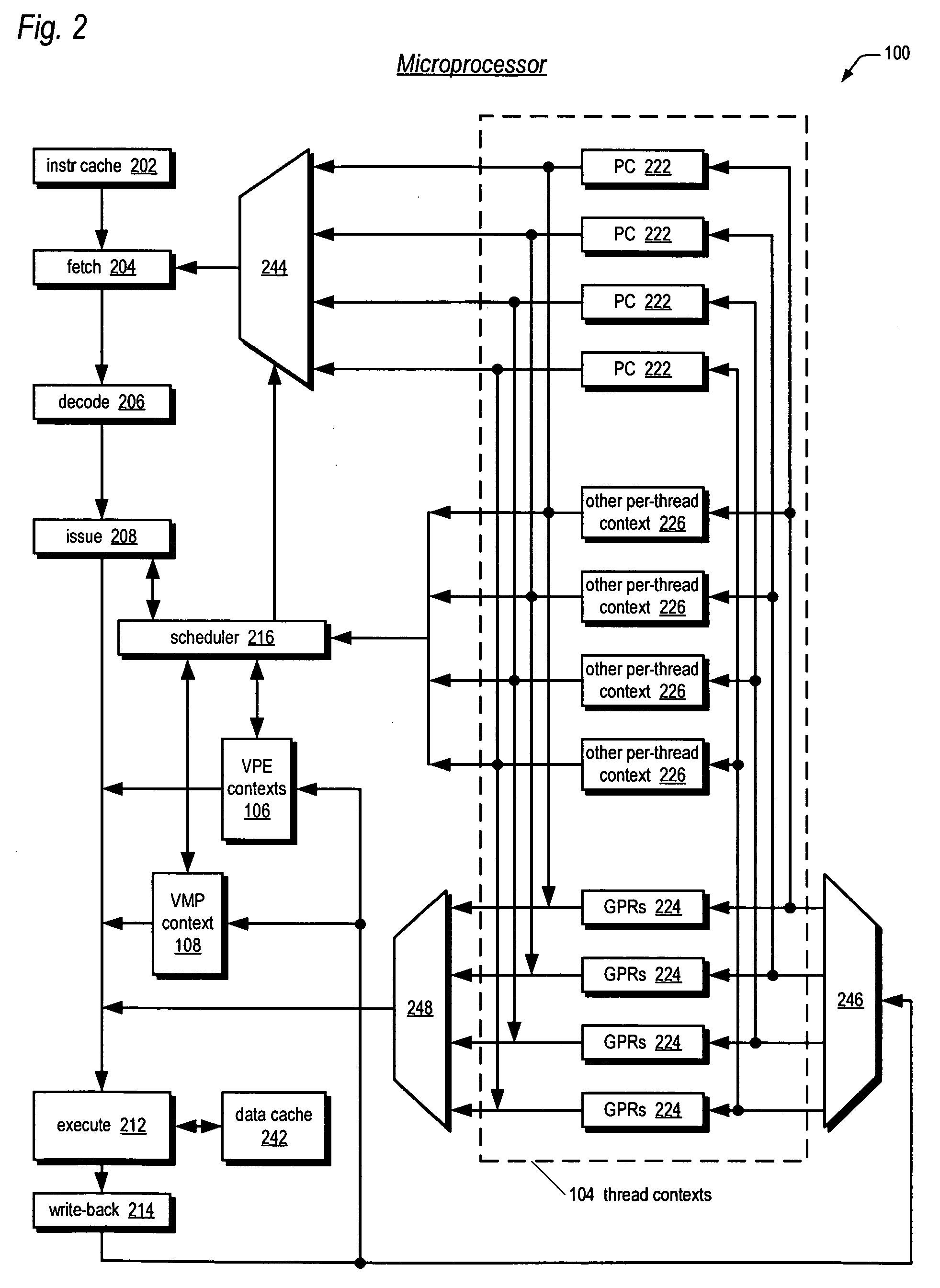

Preemptive multitasking employing software emulation of directed exceptions in a multithreading processor

ActiveUS20060161921A1Save chip area and powerHigh performanceSoftware engineeringRuntime instruction translationNon specificTimer

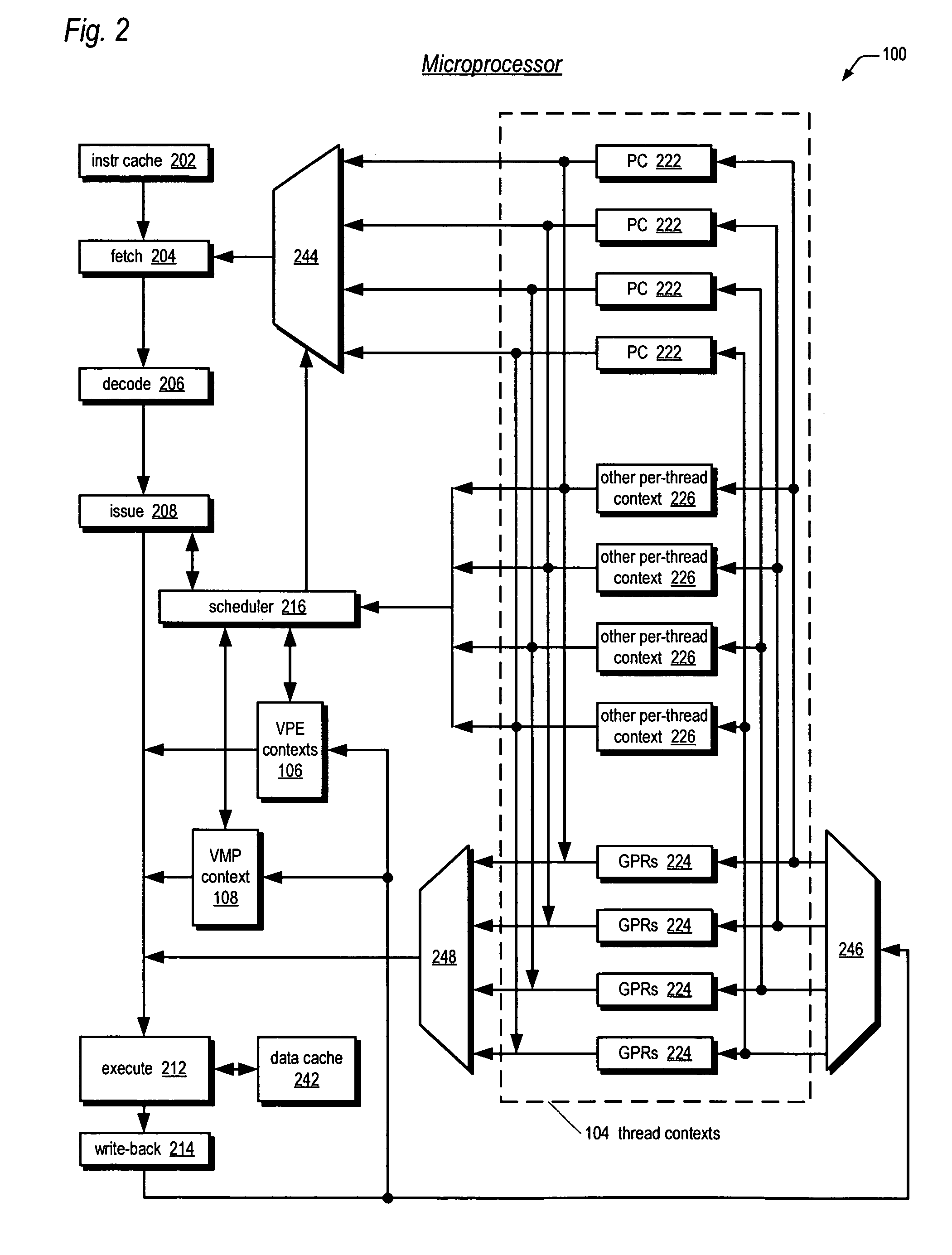

A multiprocessor computer system includes an exception domain having multiple thread contexts (TCs) each having a restart address register, and a timer that generates a periodic interrupt request to the exception domain. The exception domain selects an eligible TC to service the interrupt request, which is non-specific regarding which TC to select. A first interrupt handler executes on the selected TC to service the interrupt request to schedule a set of processes assigned by the SMP OS for execution on the selected TC, and write an address of a second interrupt handler to the restart address register of each TC other than the selected TC. The second interrupt handler schedules a plurality of sets of processes assigned by the SMP OS for execution on respective ones of the TCs other than the selected TC.

Owner:MIPS TECH INC

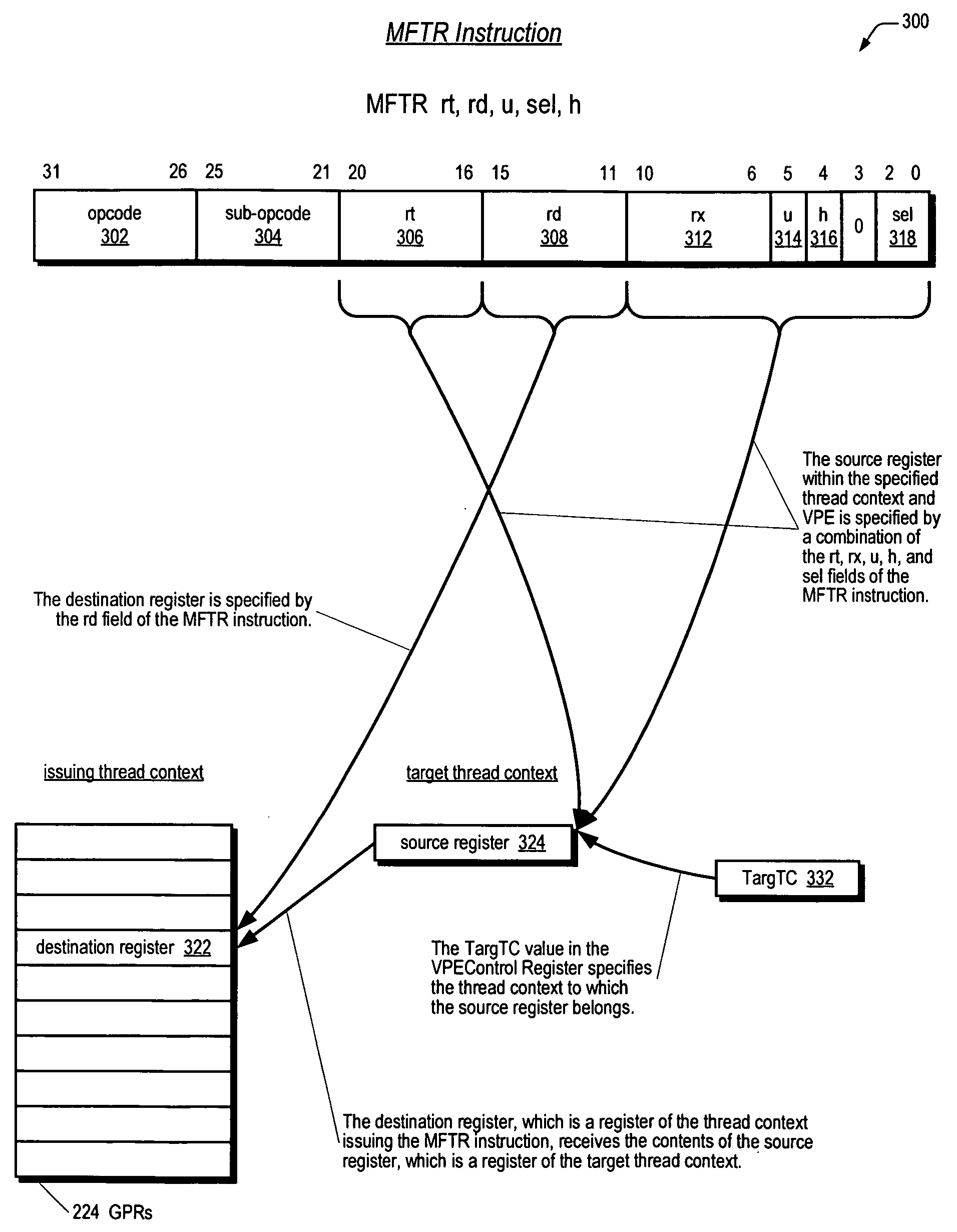

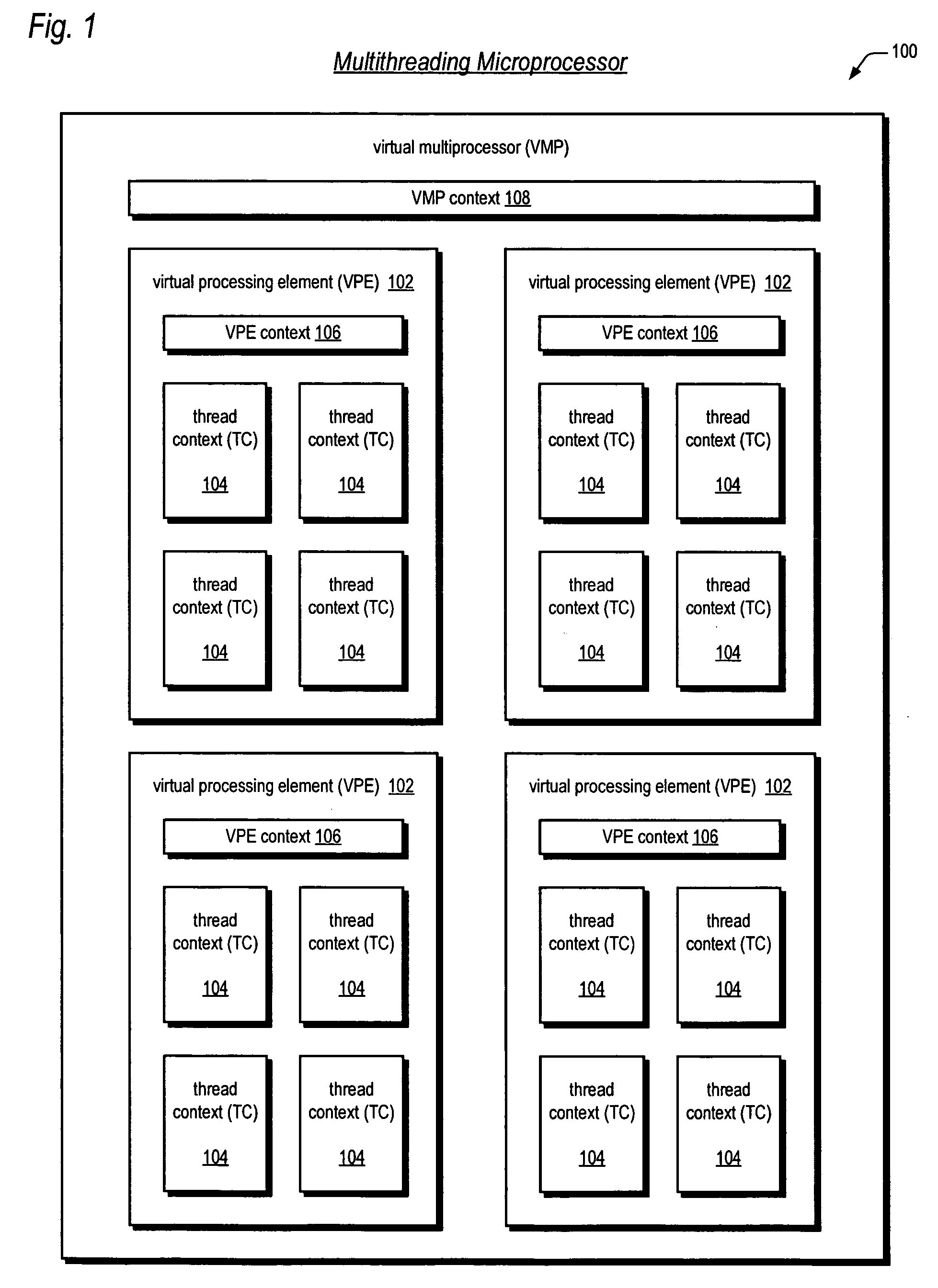

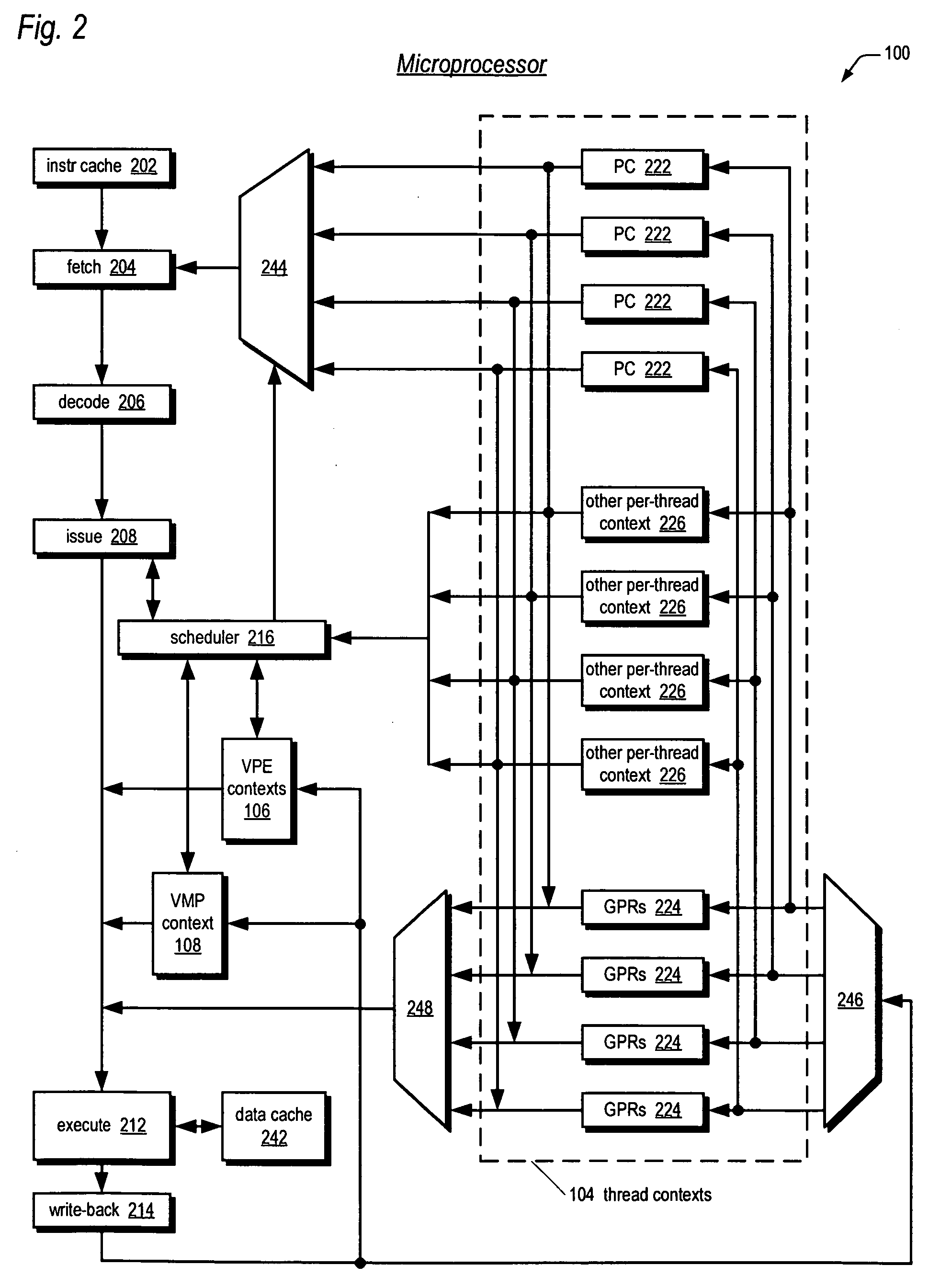

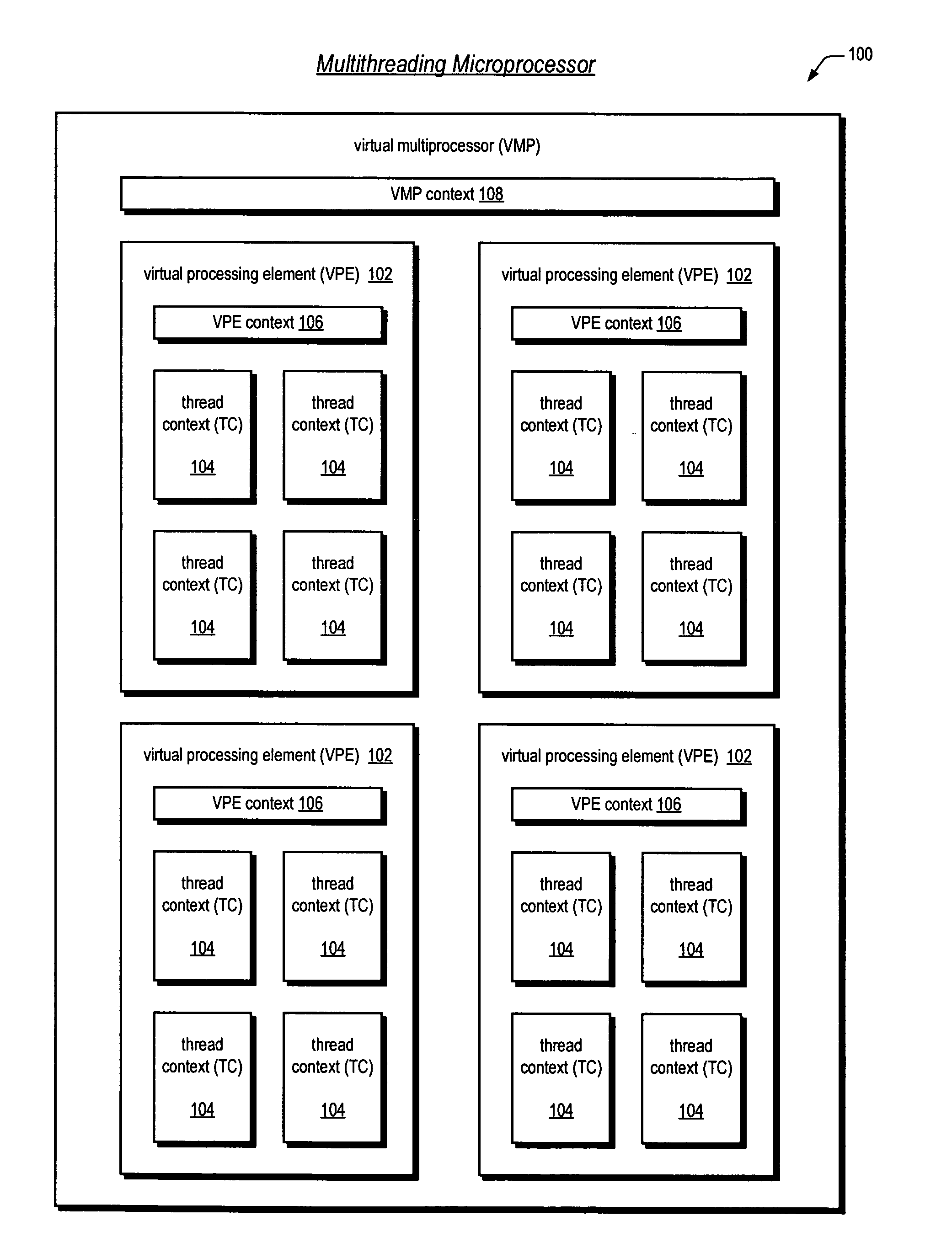

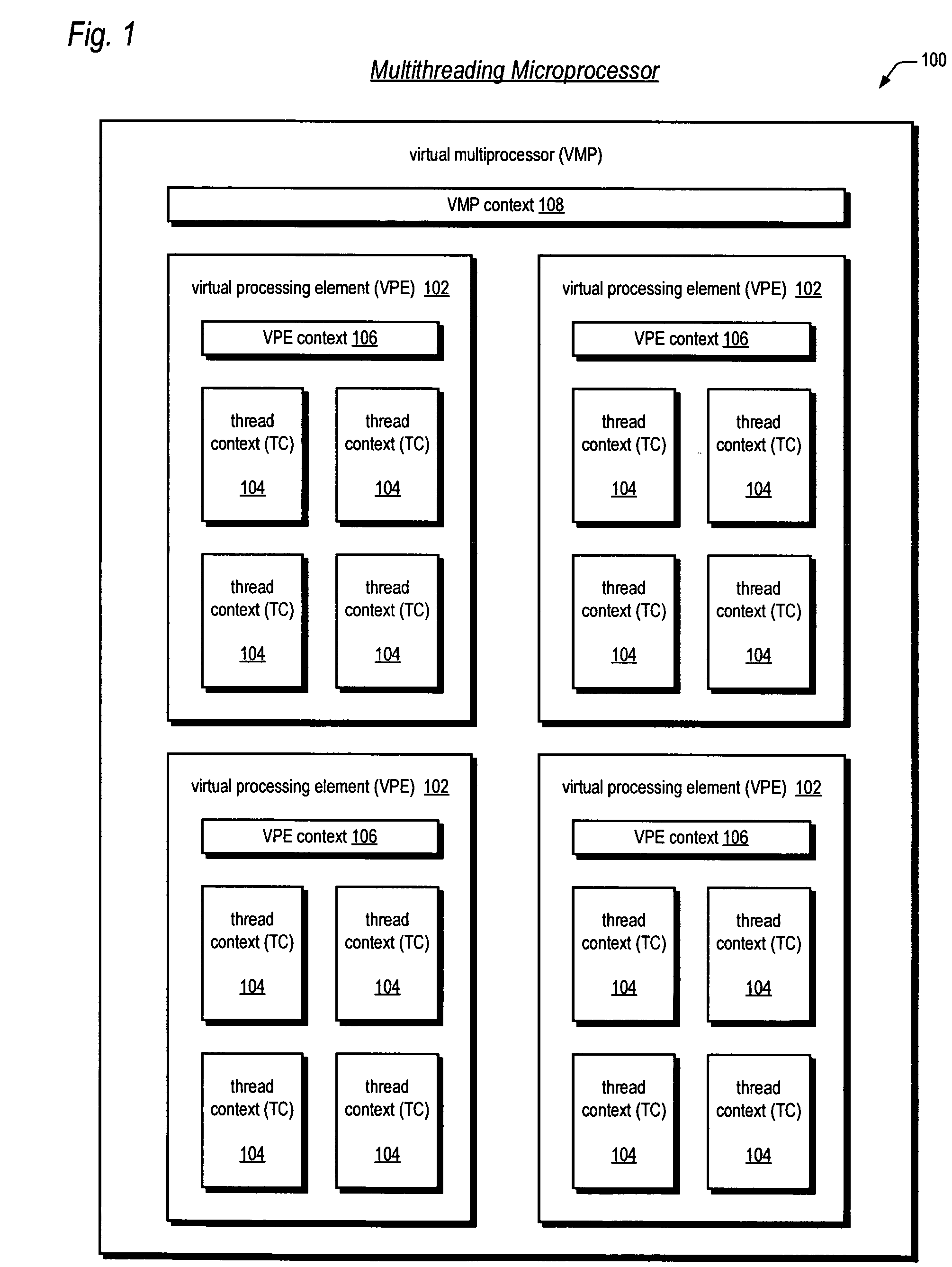

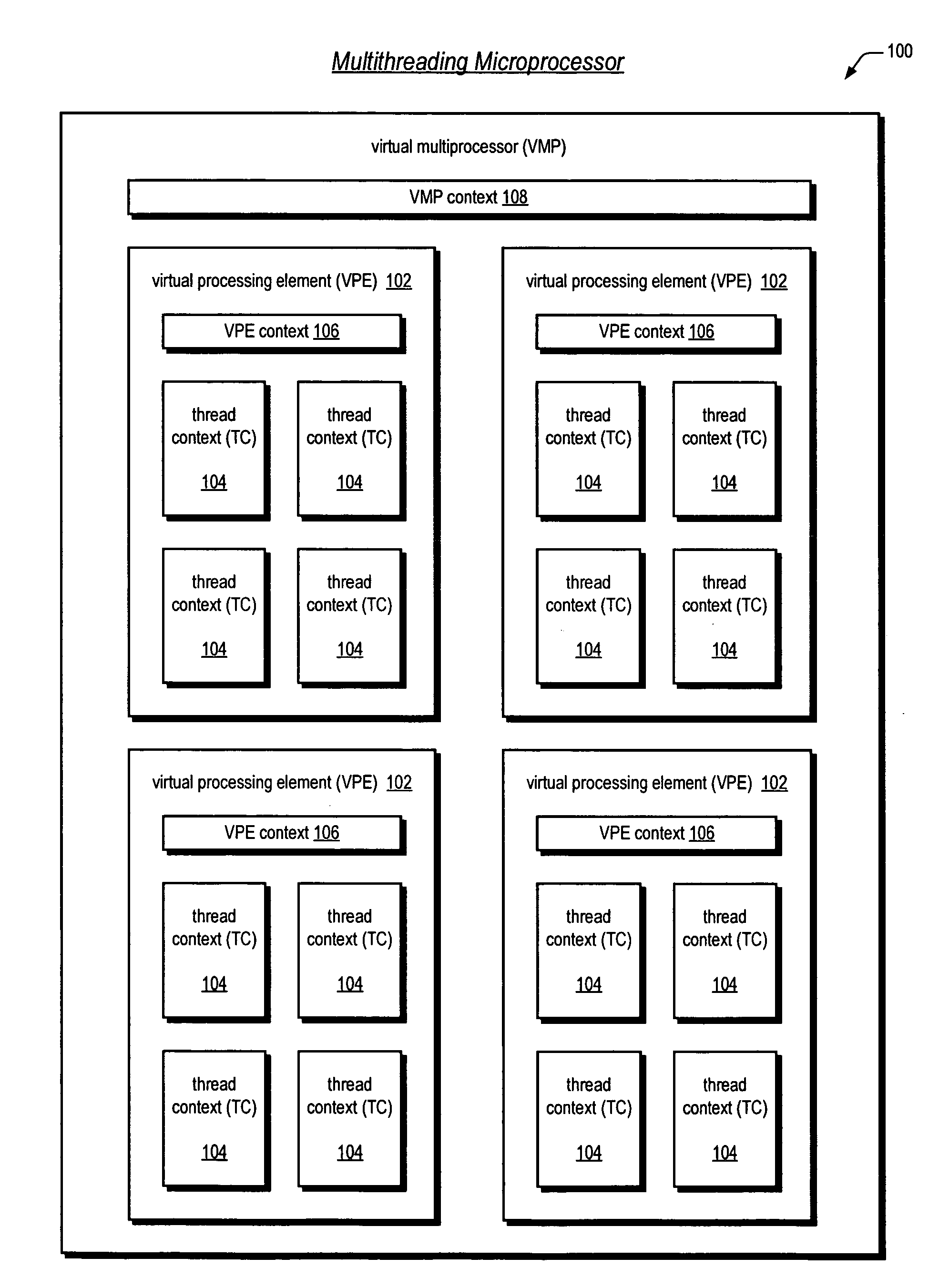

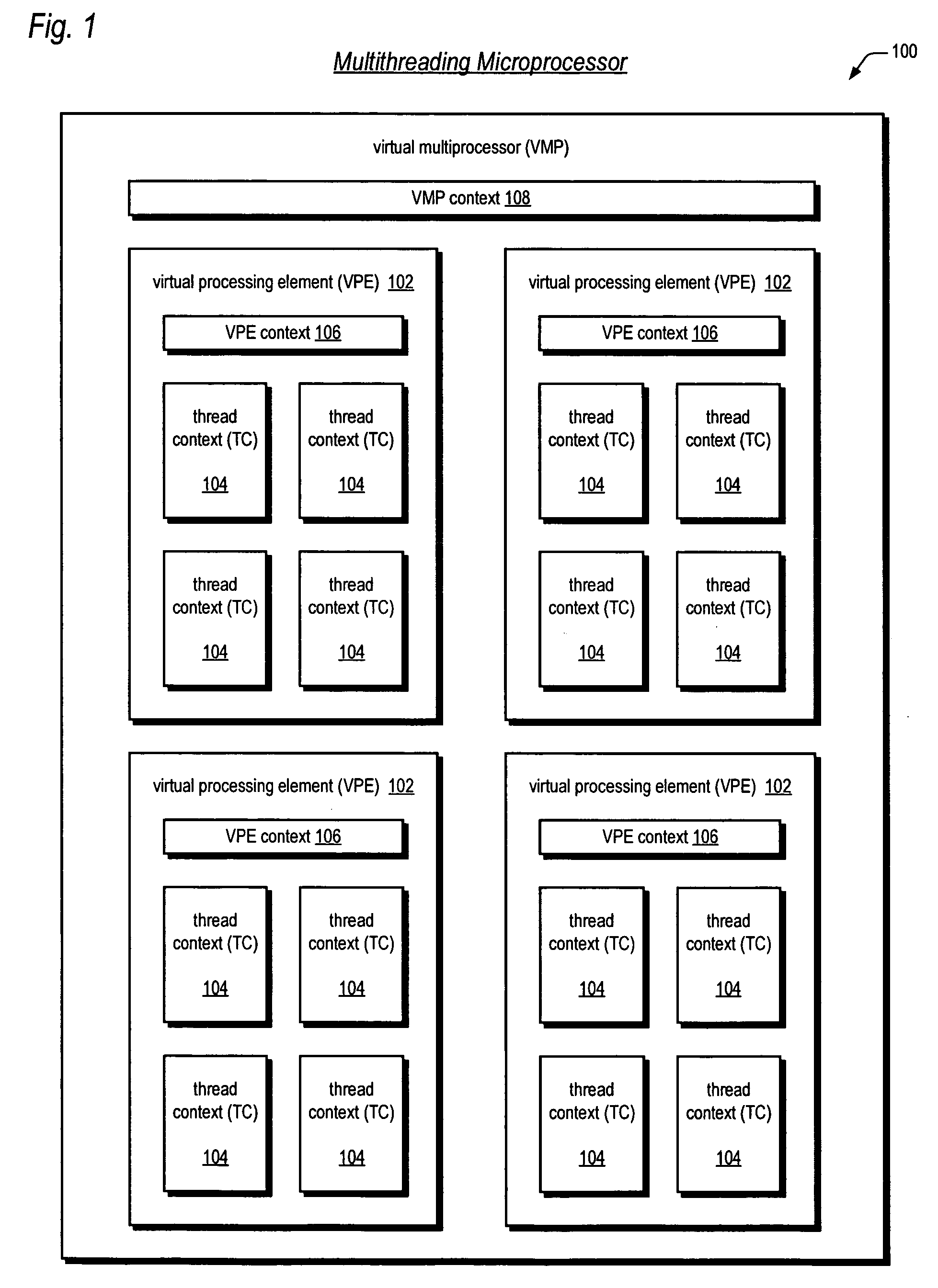

Software emulation of directed exceptions in a multithreading processor

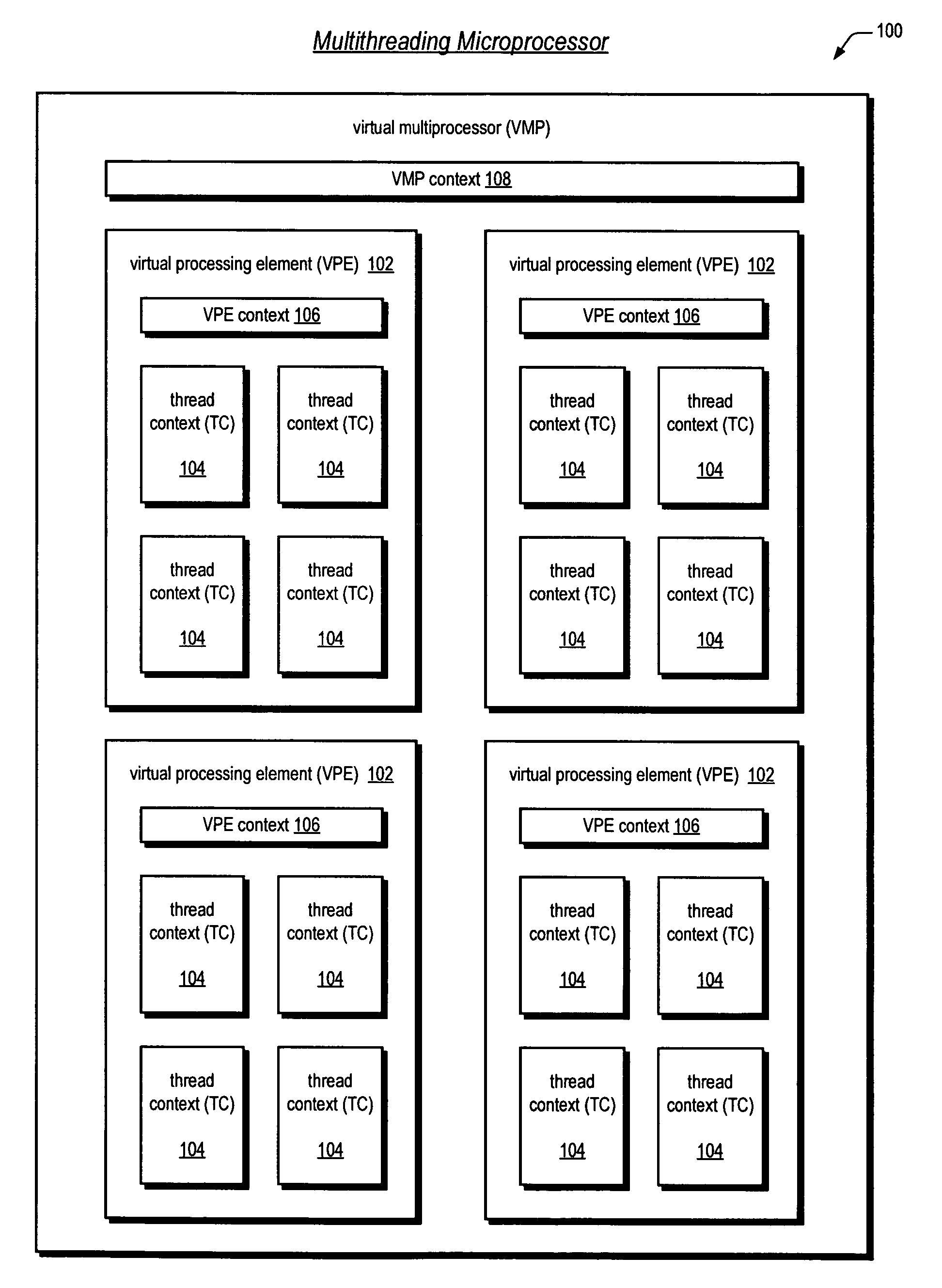

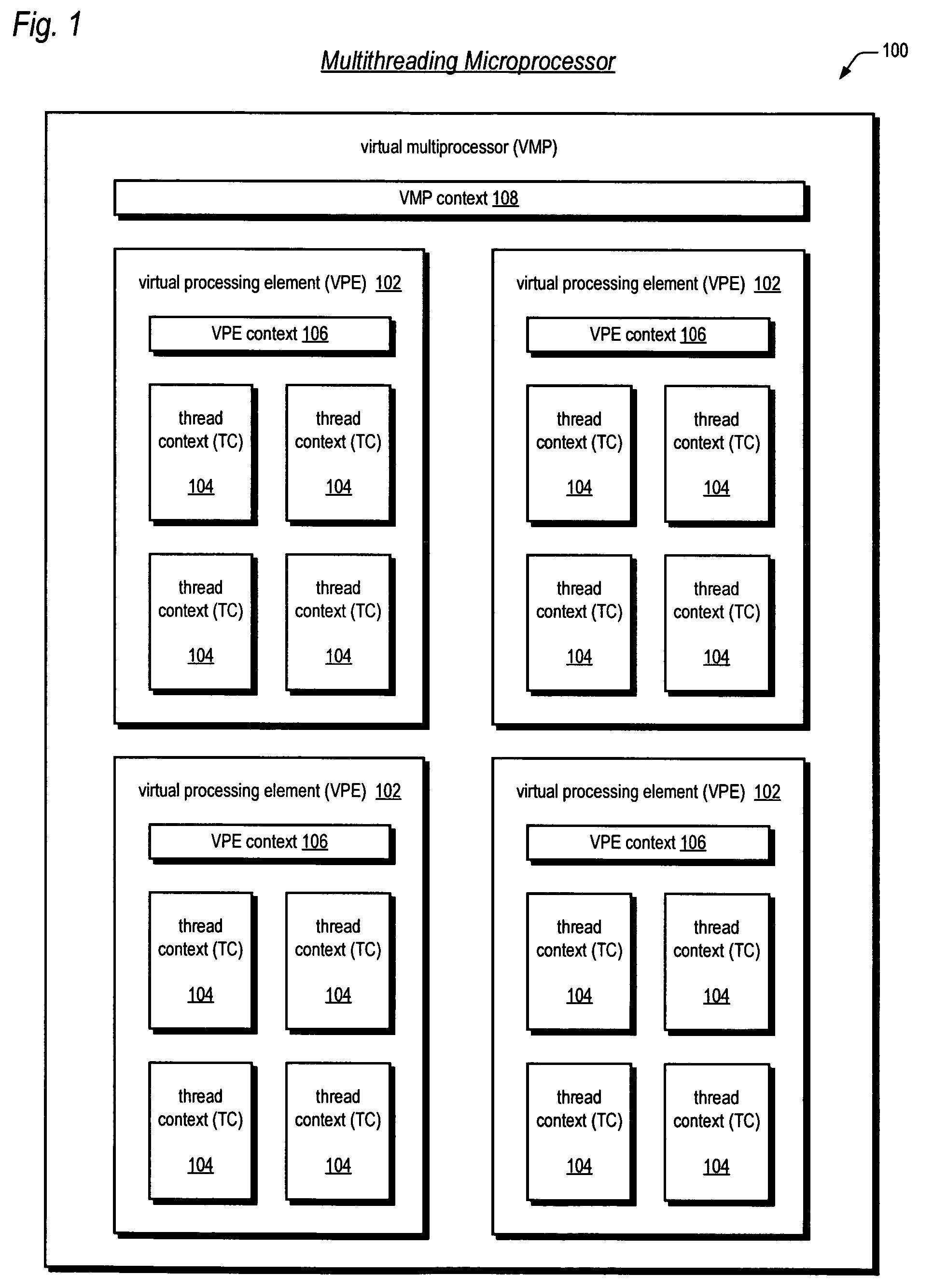

ActiveUS20060161421A1More scalableSave areaDigital computer detailsSoftware simulation/interpretation/emulationGeneral purposeSoftware emulation

A multithreading microprocessor has a plurality of thread contexts (TCs) each including sufficient state, such as general purpose registers and program counter, to execute a separate thread of execution as one of a plurality of symmetric processors controlled by a multiprocessor operating system. However, the microprocessor hardware does not support the ability for one TC to direct an exception to another TC, i.e., to specify to which of the other TCs the exception is directed. A first thread running on a first TC of the operating system executes architected instructions to halt a second thread (either user or kernel thread) running on a second TC, save state of the second TC, write the second TC state to emulate an exception—including writing a restart register with the address of an exception handler, and unhalt the second TC to execute the exception hander.

Owner:MIPS TECH INC

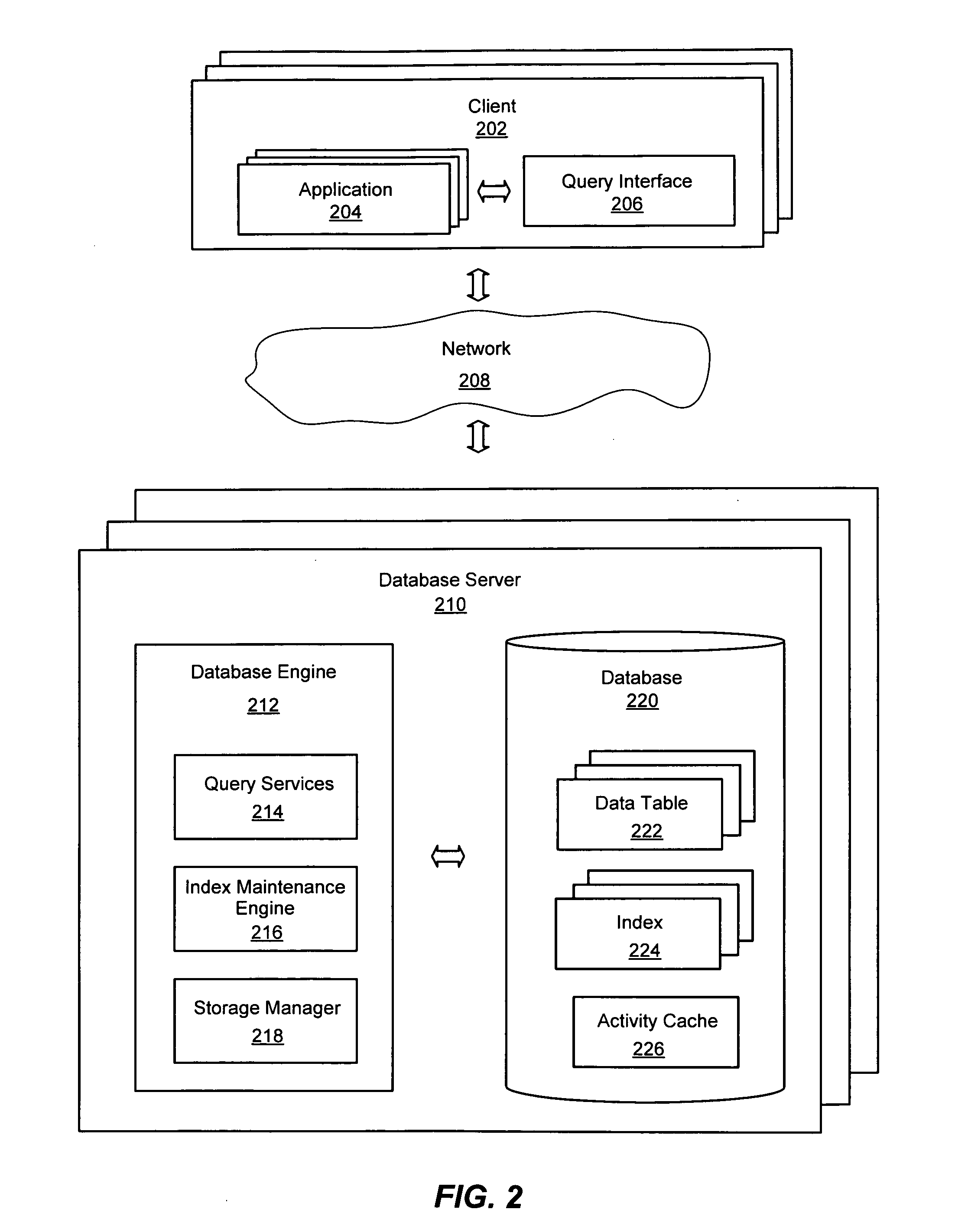

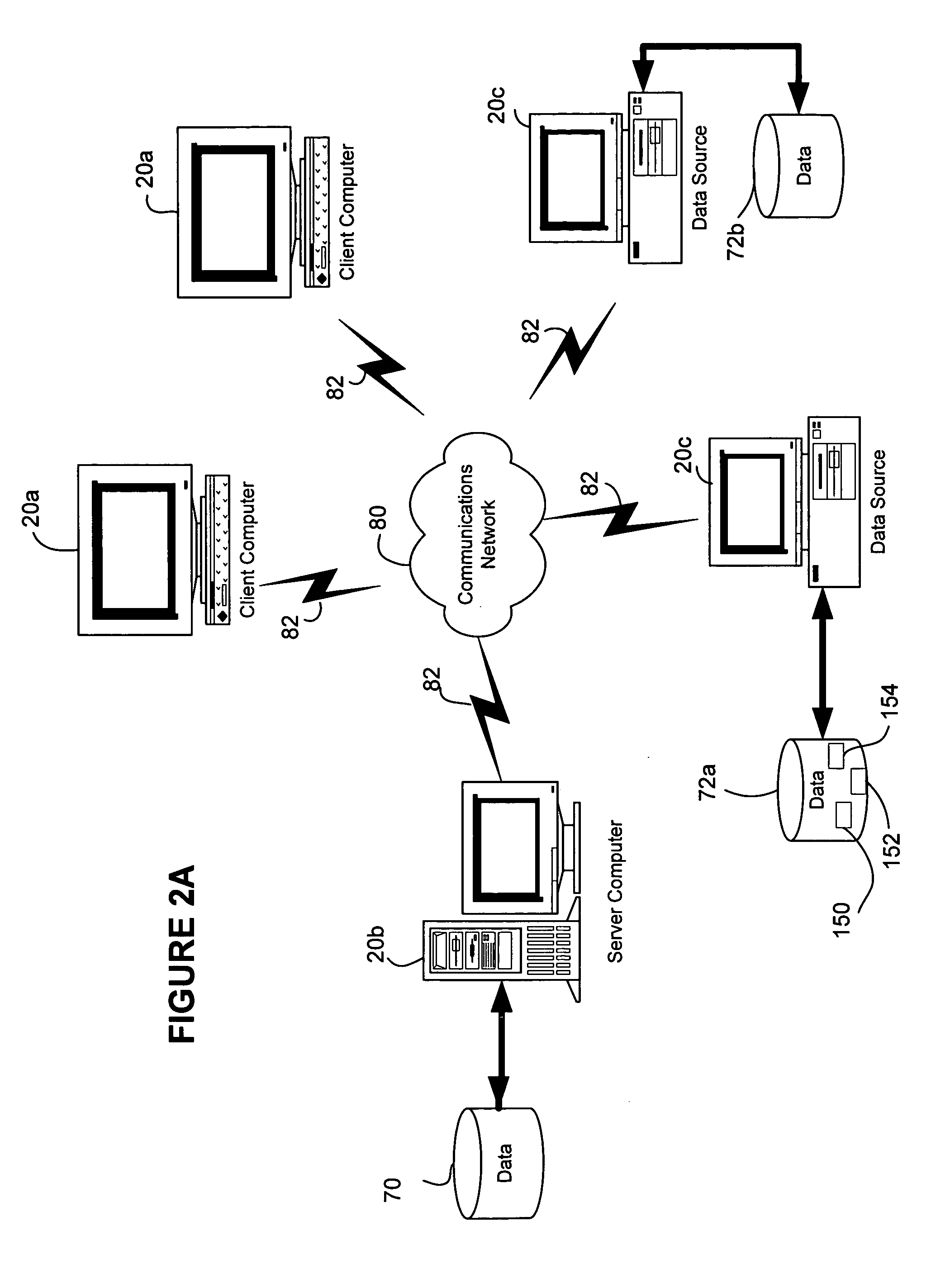

System and method for asynchronous update of indexes in a distributed database

InactiveUS20090210429A1Reduce latencyIncrease throughputDigital data information retrievalSpecial data processing applicationsClient-sideDatabase server

An improved system and method for asynchronous update of indexes in a distributed database is provided. A database server may receive the request to update the data and may update the data in a primary data table of the distributed database. An asynchronous index update of the indexes may be initiated at the time a record is updated in a data table and then control may be returned to a client to perform another data update. An activity cache may be provided for caching the records updated by a client so that when the client requests a subsequent read, the updated records may be available in the activity cache to support the various guarantees for reading the data. Advantageously, the asynchronous index update scheme may provide increased performance and more scalability while efficiently maintaining indexes over database tables in a large scale, replicated, distributed database.

Owner:OATH INC

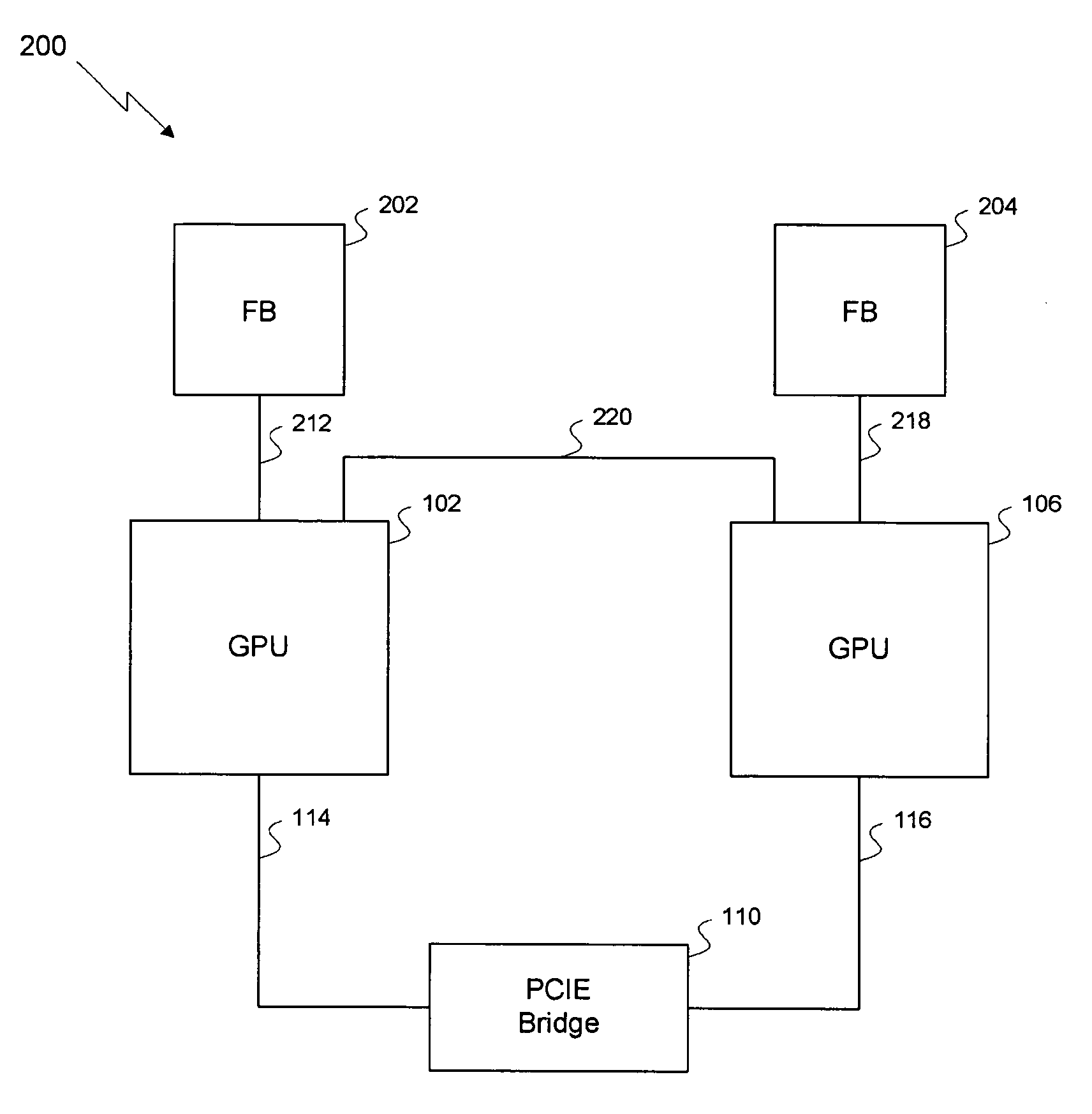

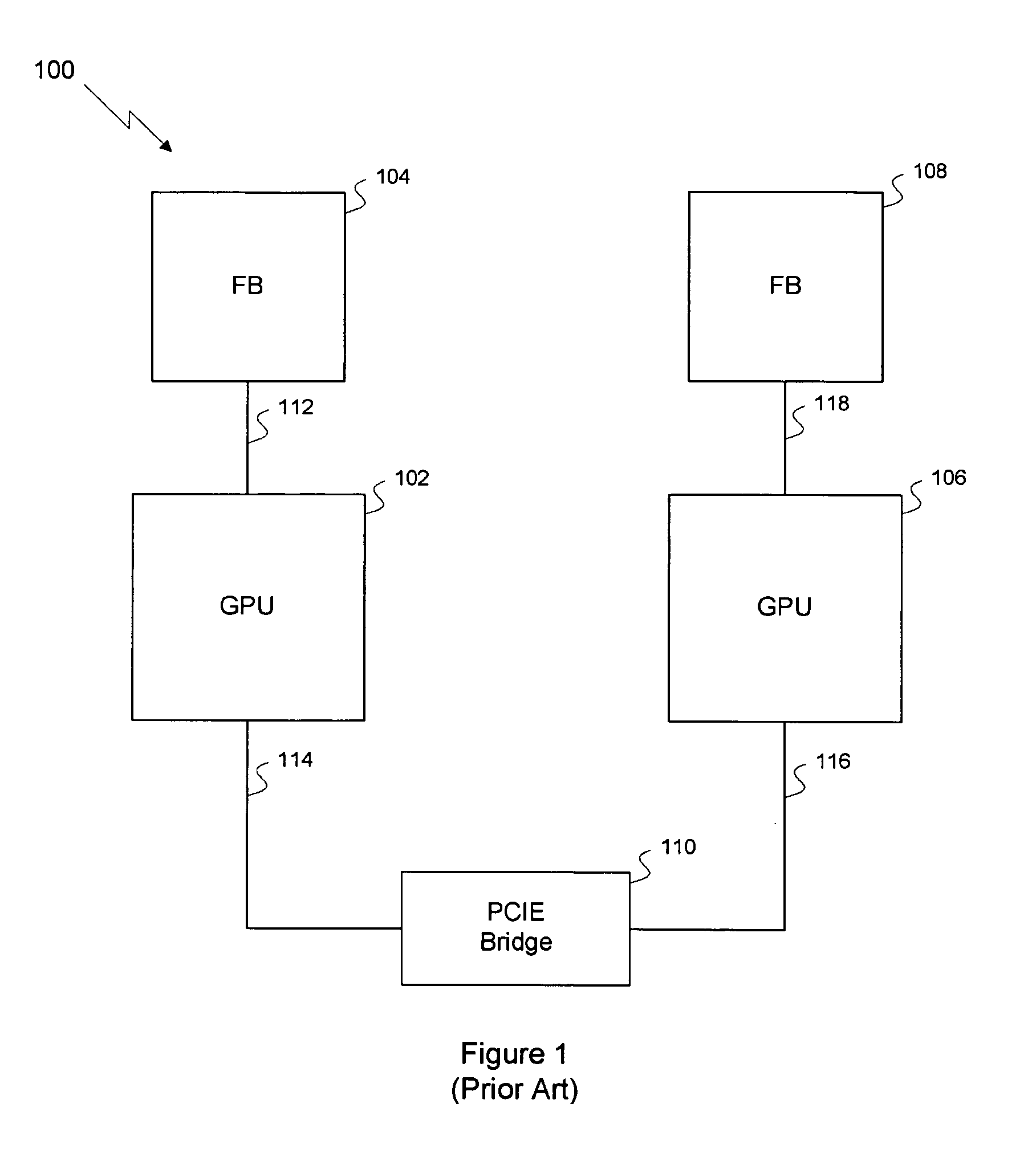

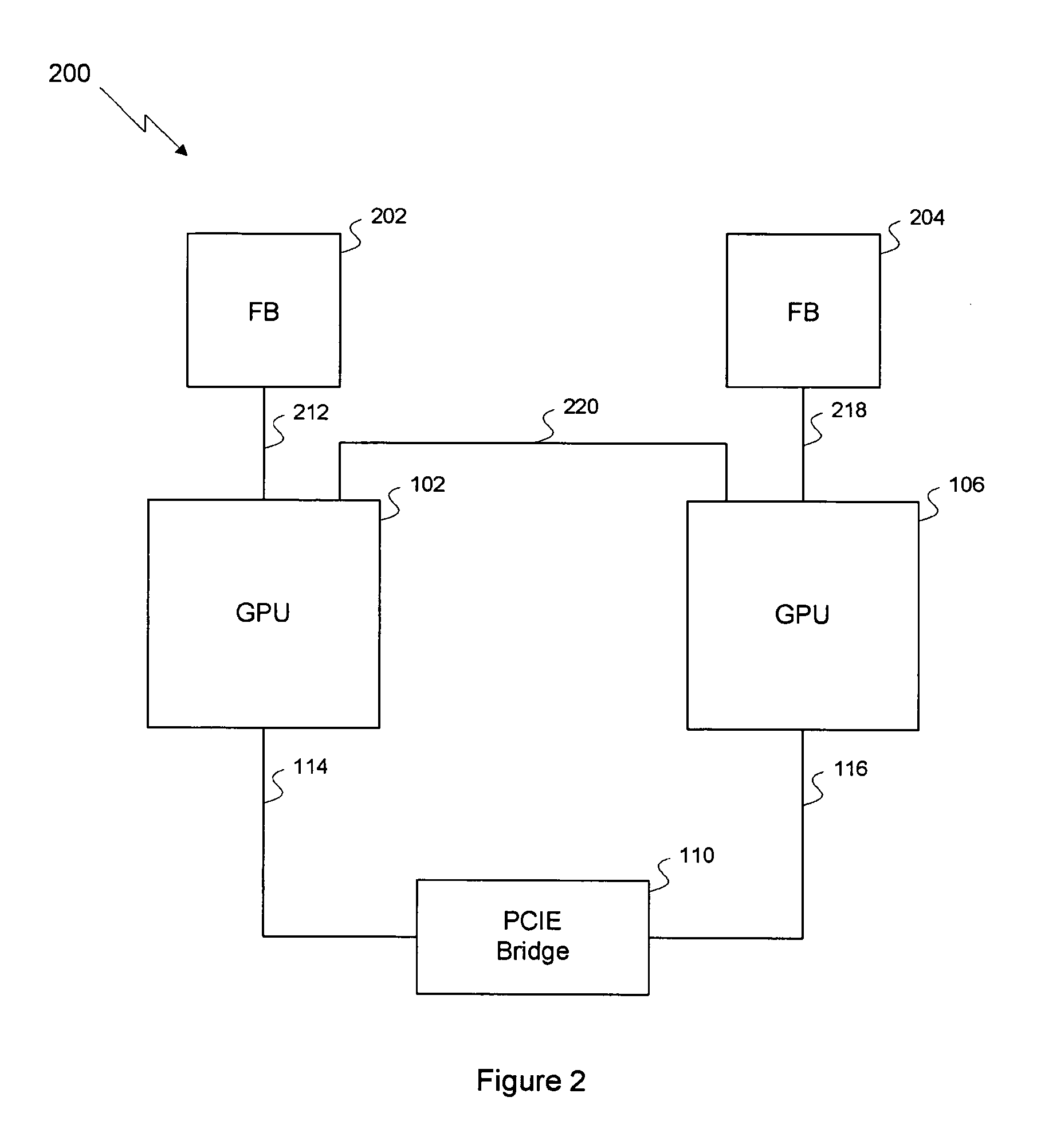

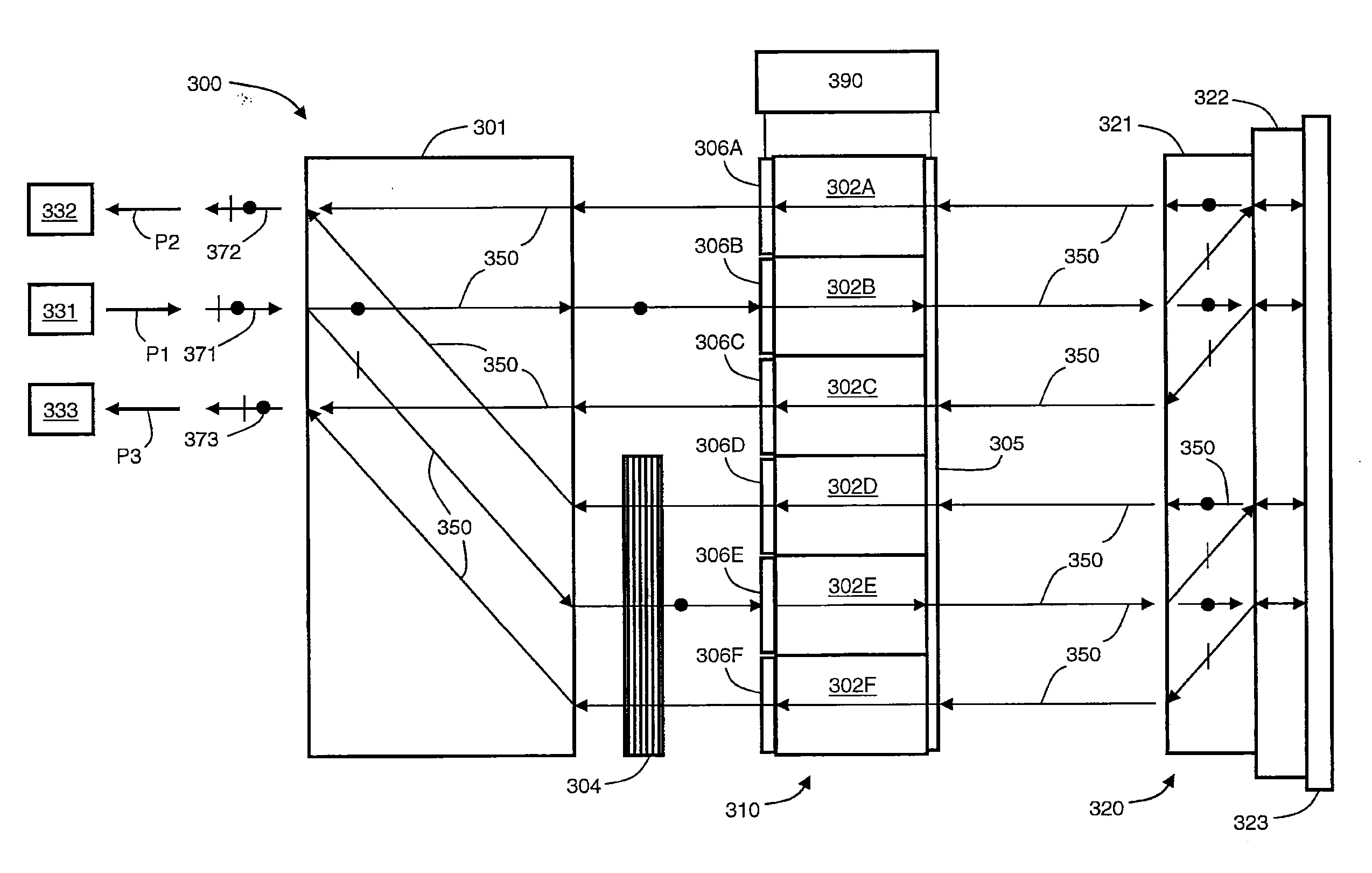

Efficient multi-chip GPU

ActiveUS7616206B1Raise the ratioMore scalableCathode-ray tube indicatorsMultiple digital computer combinationsData compressionExtensibility

One embodiment of the invention sets forth a technique for efficiently combining two graphics processing units (“GPUs”) to enable an improved price-performance tradeoff and better scalability relative to prior art multi-GPU designs. Each GPU's memory interface is split into a first part coupling the GPU to its respective frame buffer and a second part coupling the GPU directly to the other GPU, creating an inter-GPU private bus. The private bus enables higher bandwidth communications between the GPUs compared to conventional communications through a PCI Express™ bus. Performance and scalability are further improved through render target interleaving; render-to-texture data duplication; data compression; using variable-length packets in GPU-to-GPU transmissions; using the non-data pins of the frame buffer interfaces to transmit data signals; duplicating vertex data, geometry data and push buffer commands across both GPUs; and performing all geometry processing on each GPU.

Owner:NVIDIA CORP

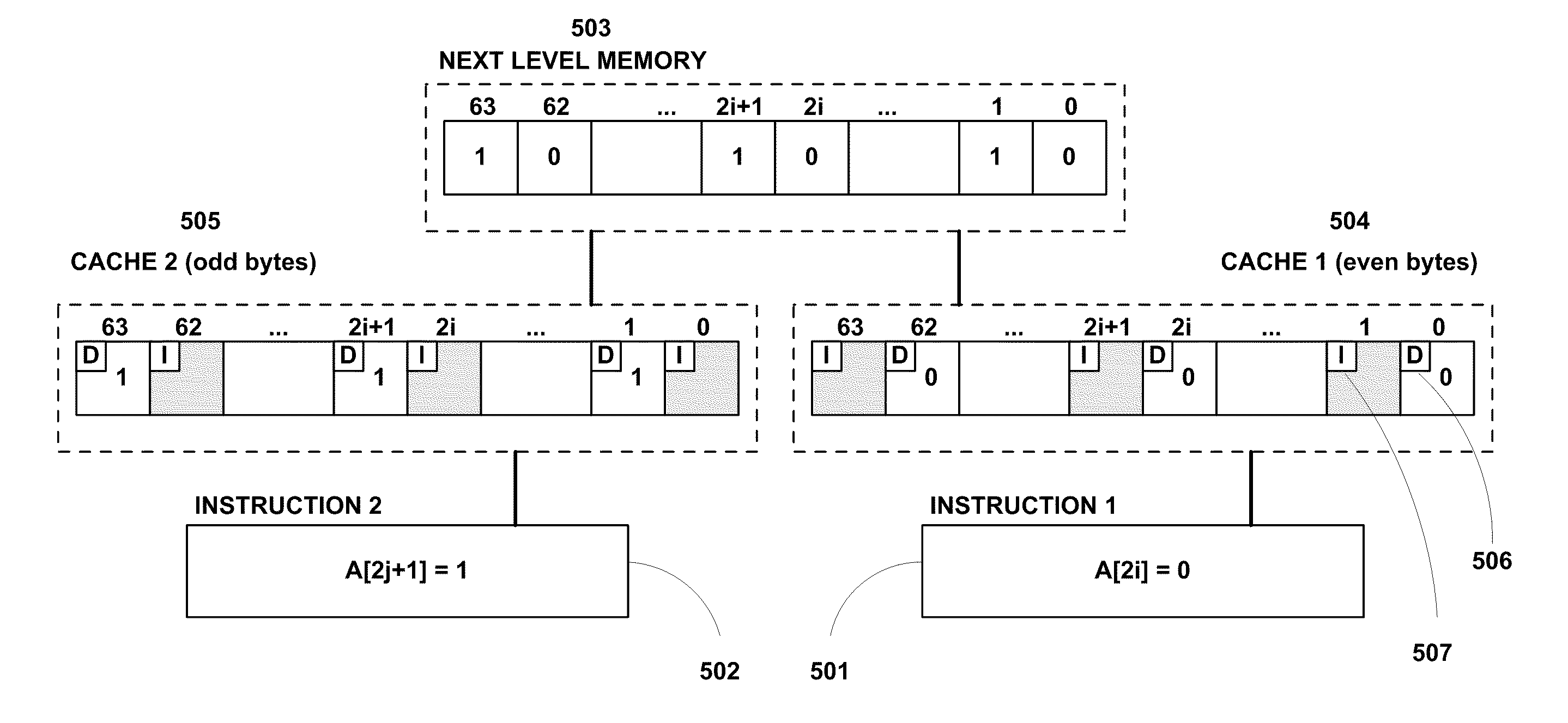

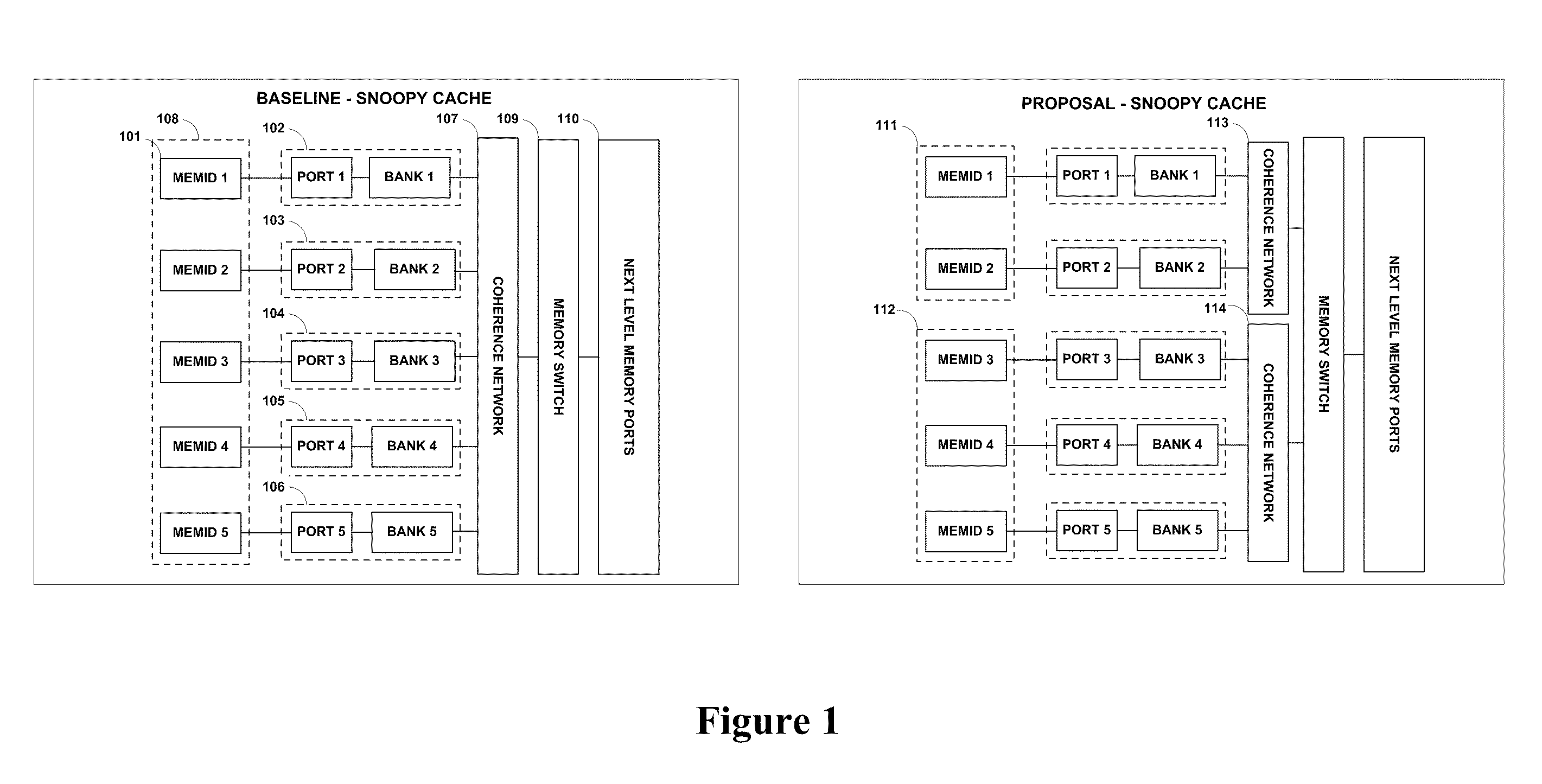

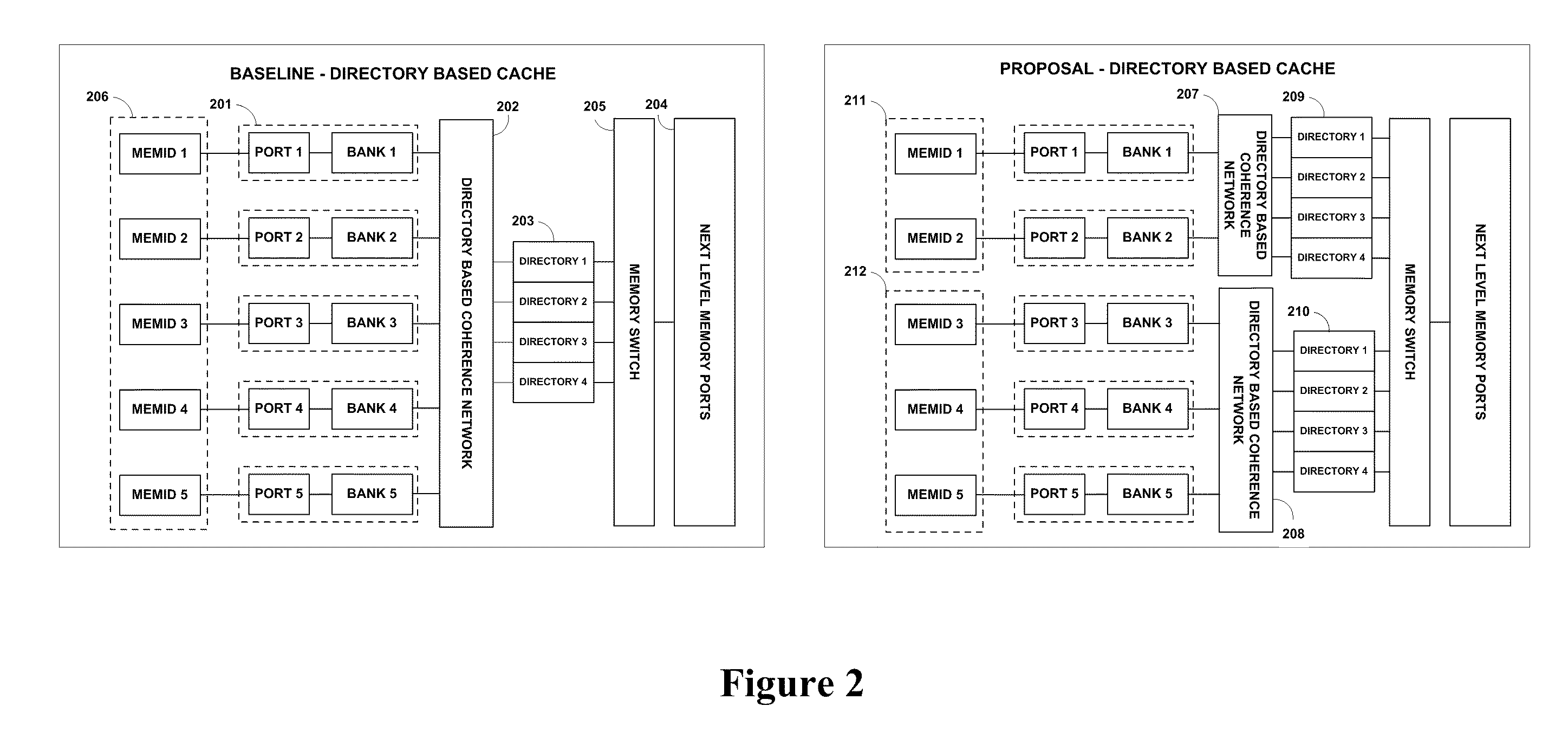

Storage Unsharing

ActiveUS20110307663A1Improve performanceReduce in quantityEnergy efficient ICTMemory adressing/allocation/relocationApplication specificApplication software

A method is described to partition the memory of application-specific hardware compiled from a software program. Applying the invention generates multiple small memories that need not be kept coherent and are defined over a specific region of the program. The invention creates application specific hardware which preserves the memory image and addressing model of the original software program. The memories are dynamically initialized and flushed at the entries and exits of the program region they are defined in.

Owner:GLOBAL SUPERCOMPUTING CORP

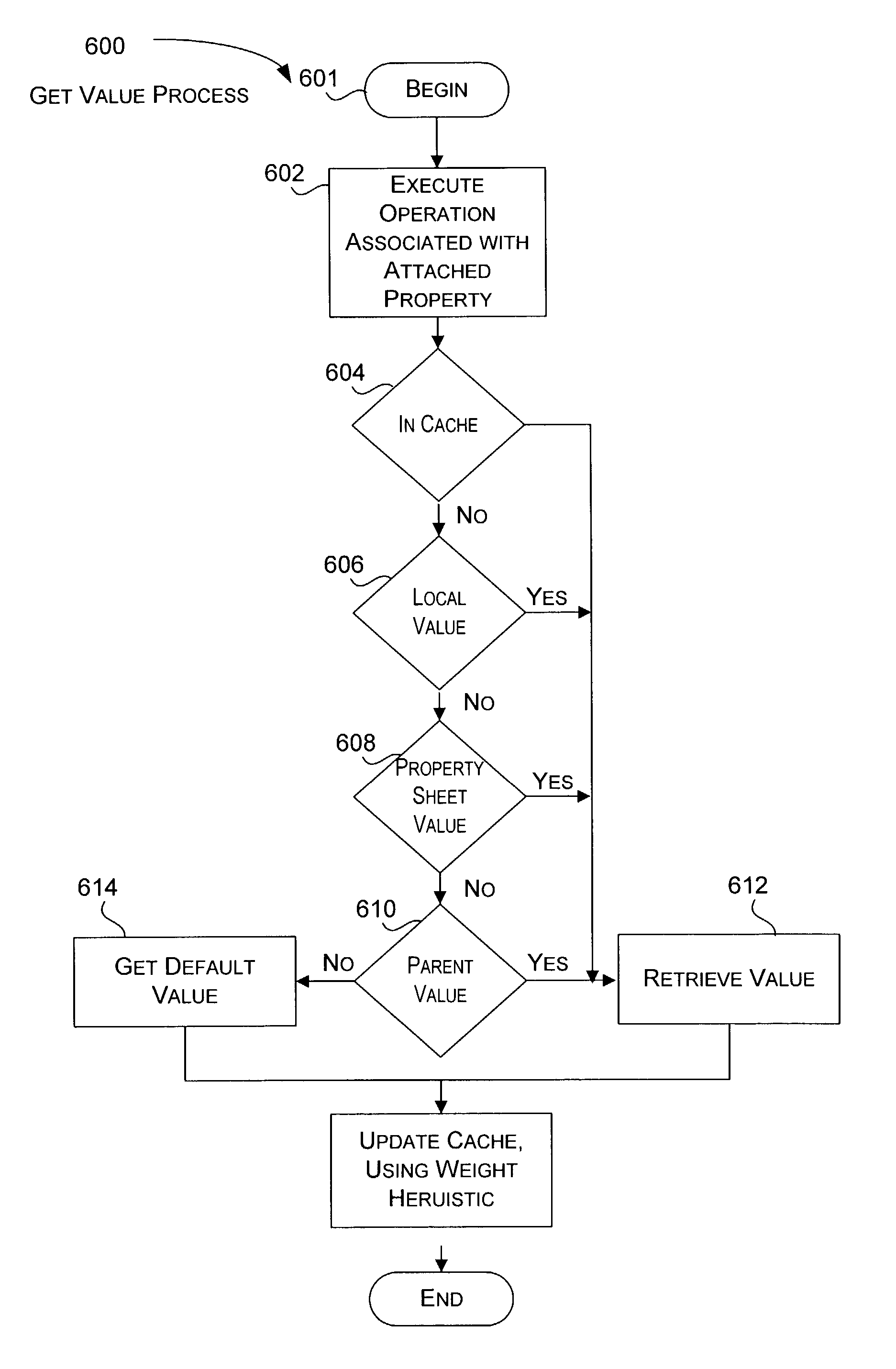

System and method for associating properties with objects

InactiveUS7055132B2Easy maintenanceFunction increaseTransformation of program codeCharacter printing data arrangement from carrierUnique identifierRunning time

Described is a mechanism for allowing new functionality for an object to be expressed as a property that is not built into the class from which the object derives. More specifically, the mechanism associates properties in one class with another class. A computer-readable medium, that includes an object having a property in a first set of properties, further includes a data structure. The data structure includes definitions for each of a second set of properties and includes at least one static method. The static method is associated with one property out of the second set of properties and includes a first parameter. The first parameter uniquely identifies the one property. The static method is operative to associate the one property with the object without specifying an explicit reference to the one property in the object. The property is registered during run-time in order to receive the unique identifier.

Owner:MICROSOFT TECH LICENSING LLC

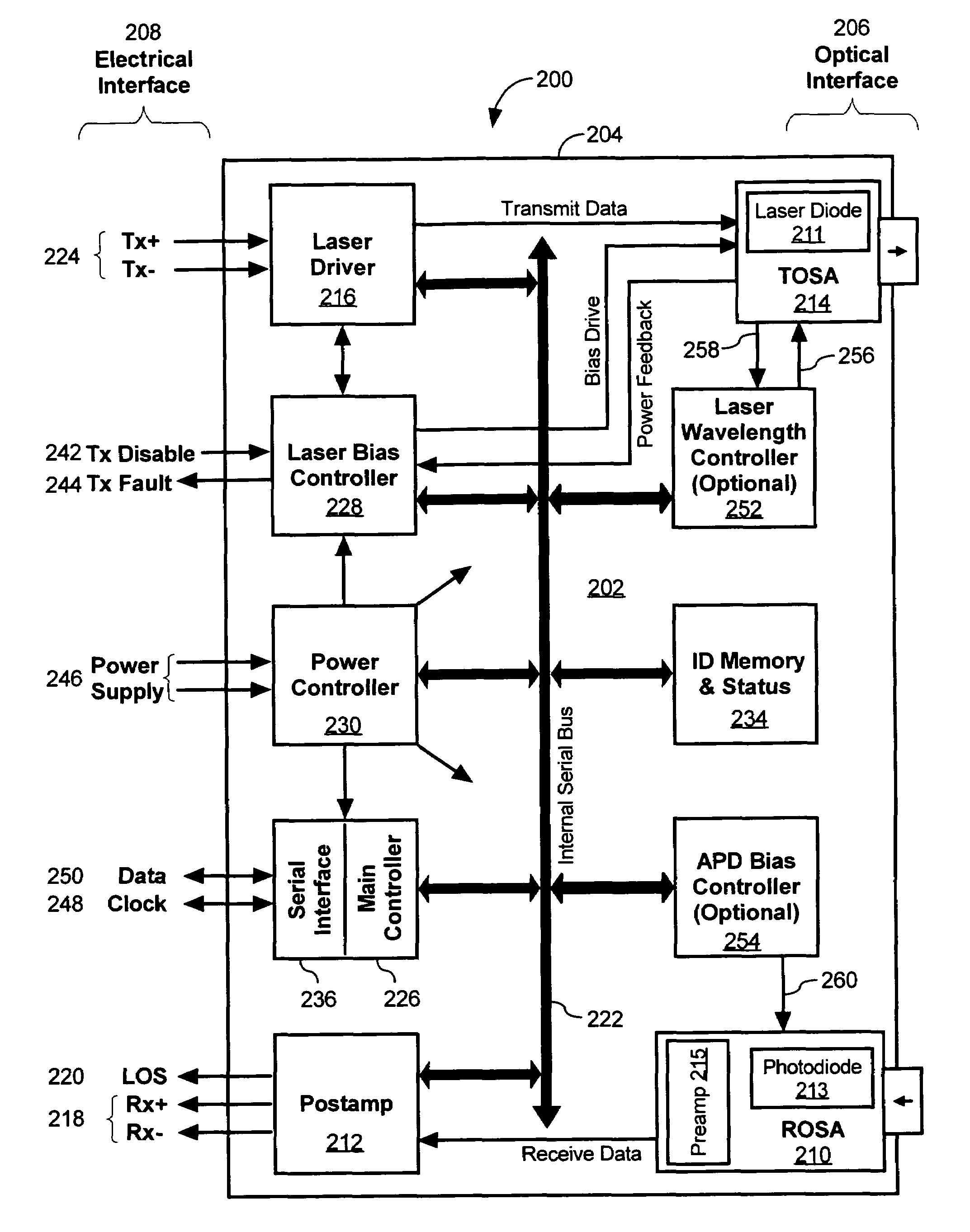

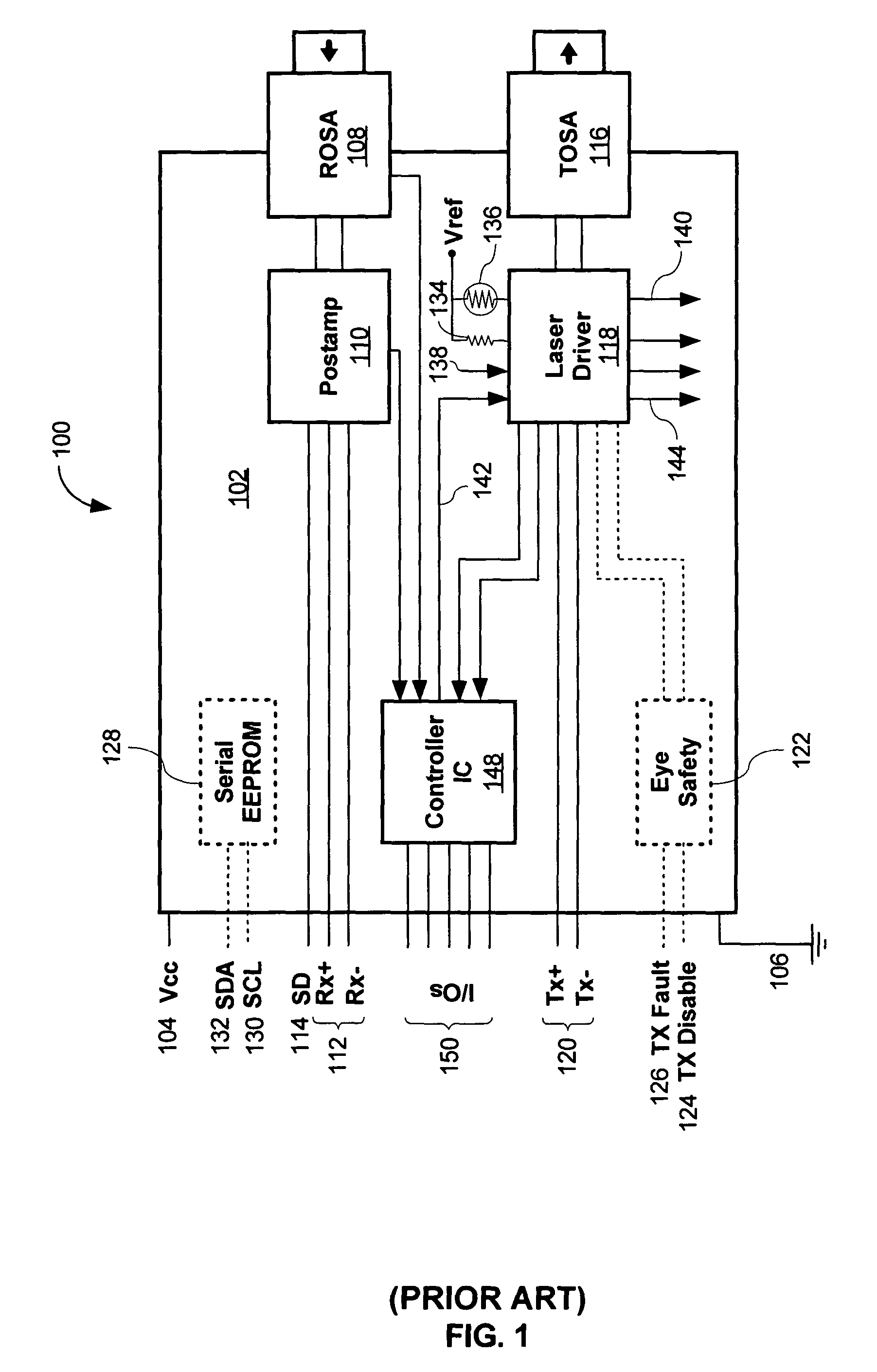

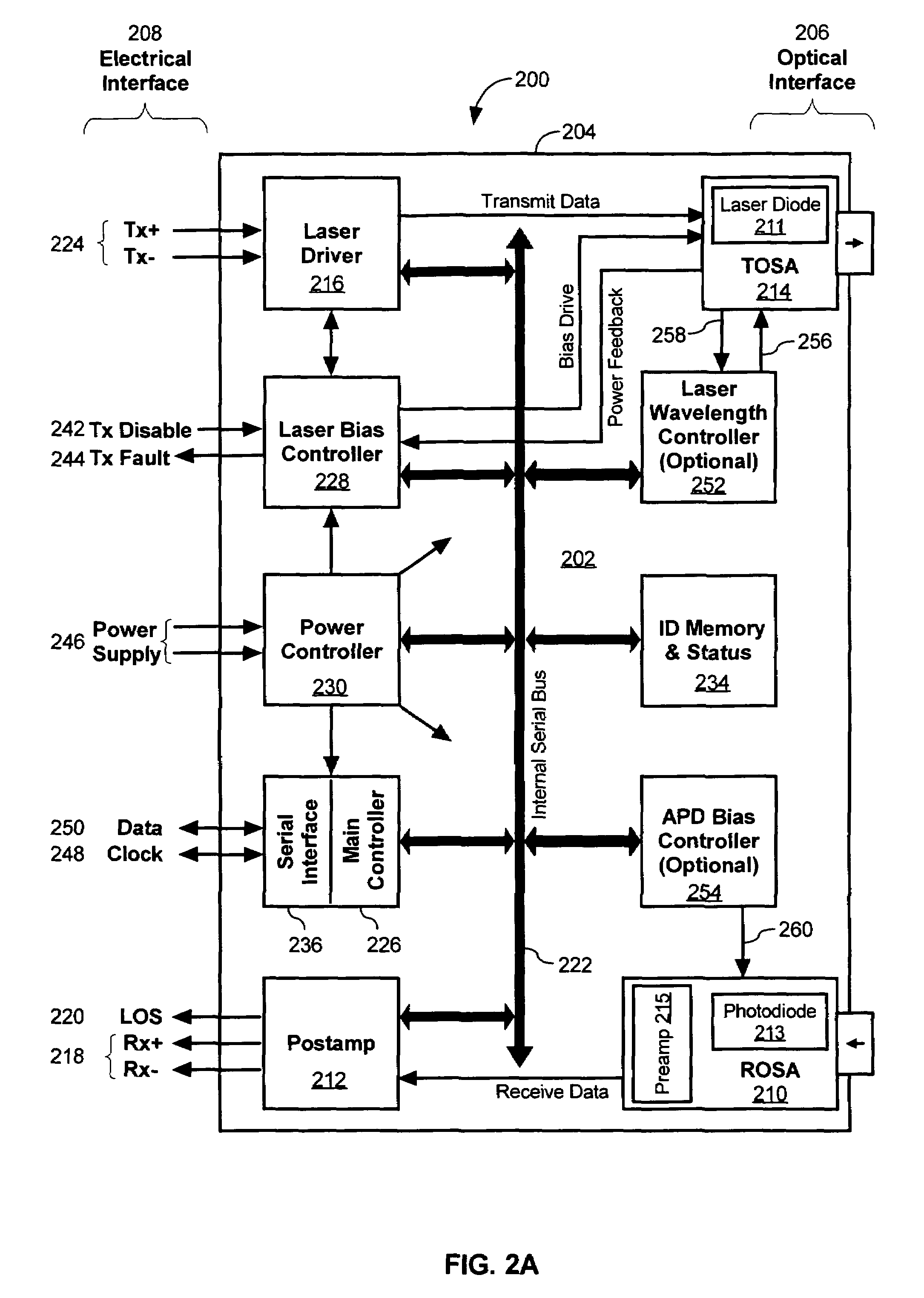

Optical transceiver module with power integrated circuit

InactiveUS7359643B2Reduce system complexityMore compact transceiver moduleCoupling light guidesTransmission monitoringPower controllerElectricity

The optical transceiver module includes a housing and a plurality of components disposed at least partially within the housing. The components include an optical transmitter, an optical receiver, and a power controller integrated circuit (IC). The power controller IC is electrically coupled to at least one of the plurality of components. The power controller IC is configured to perform power supply functions for the optical transceiver module. Also, the power controller IC includes multiple voltage regulators providing power to the components at two or more voltages.

Owner:II VI DELAWARE INC

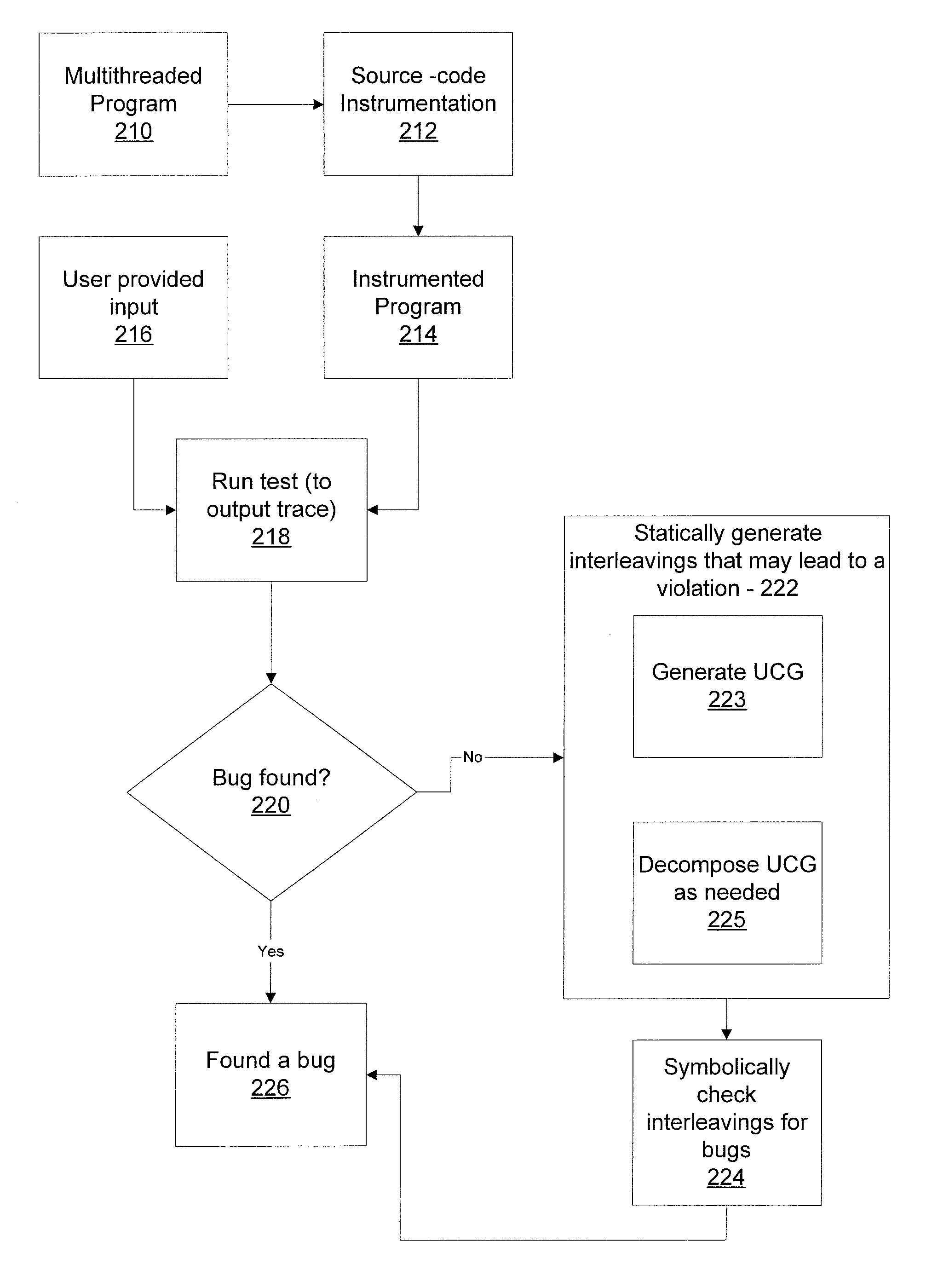

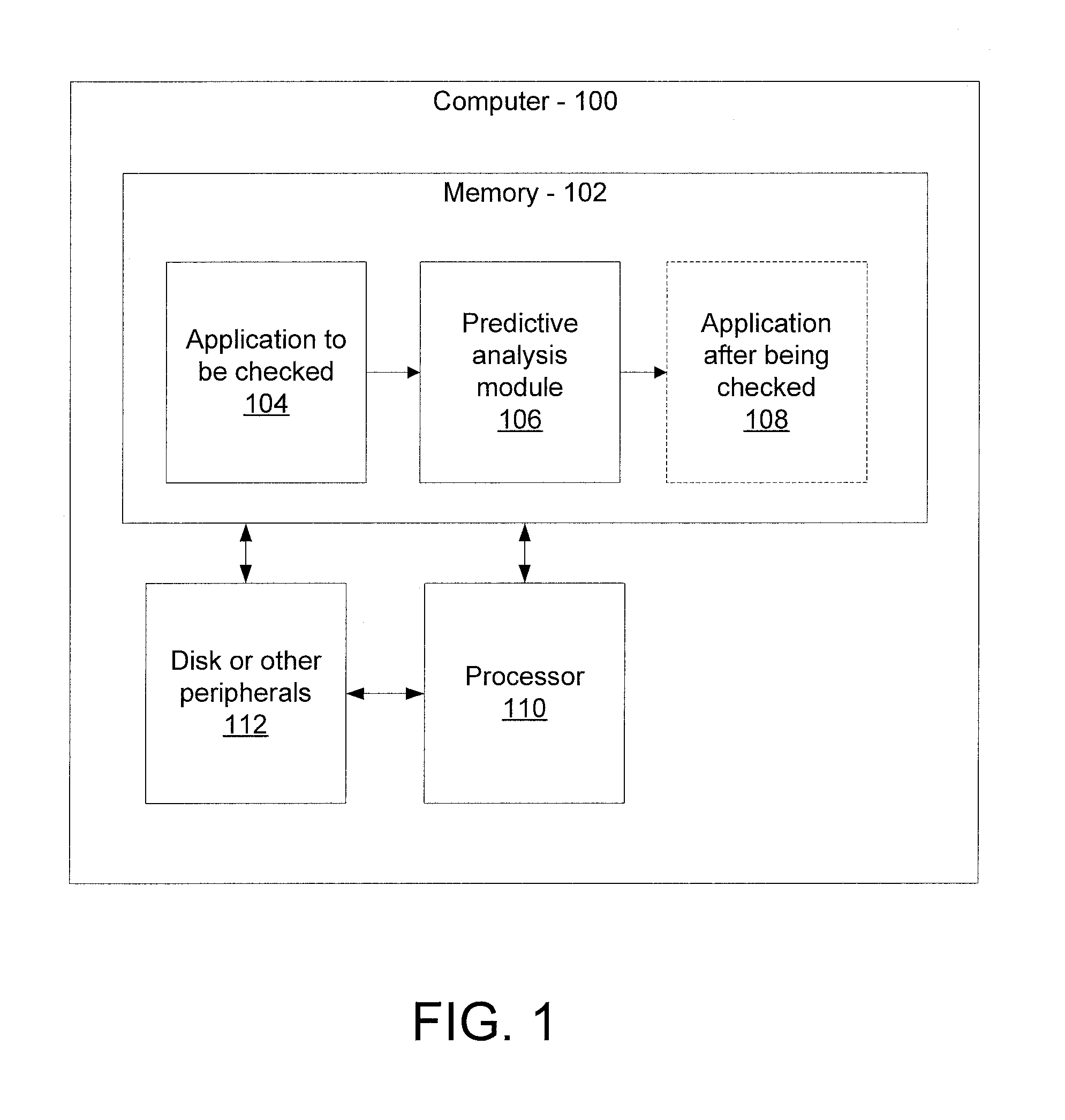

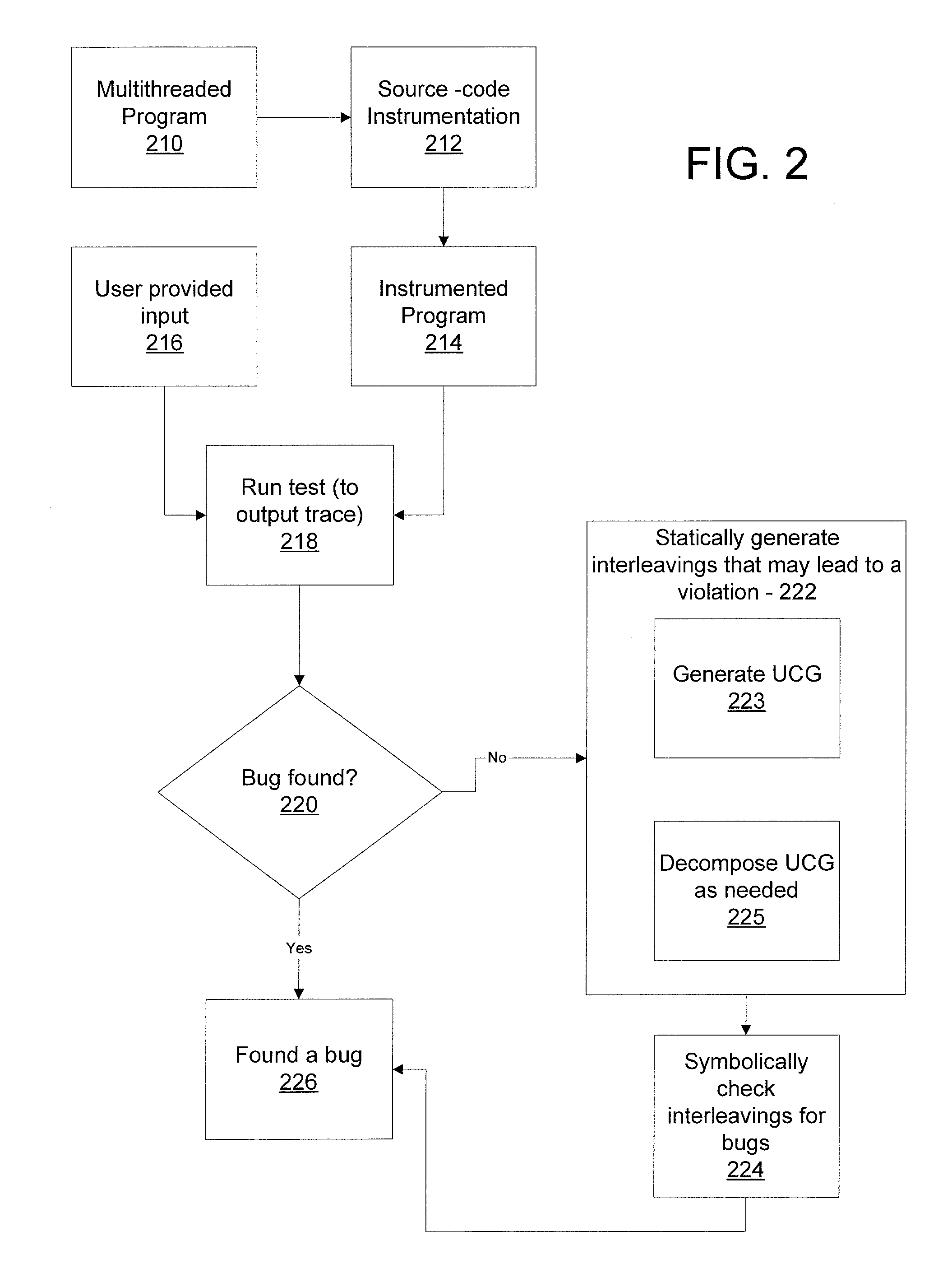

Universal causality graphs for bug detection in concurrent programs

ActiveUS20110167412A1Increase coverageMore scalableError detection/correctionSpecific program execution arrangementsHappened-beforeSource code

A system and method for predictive analysis includes generating an execution trace on an instrumented version of source code for a multithreaded computer program. Interleavings which potentially lead to a violation in the program are statically generated by performing a static predictive analysis using a Universal Causality Graph (UCG) to generate alternative interleavings that might lead to an error. The UCG includes a unified happens-before model for the concurrent program and a property being analyzed. The interleavings are symbolically checked to determine errors in the program.

Owner:NEC CORP

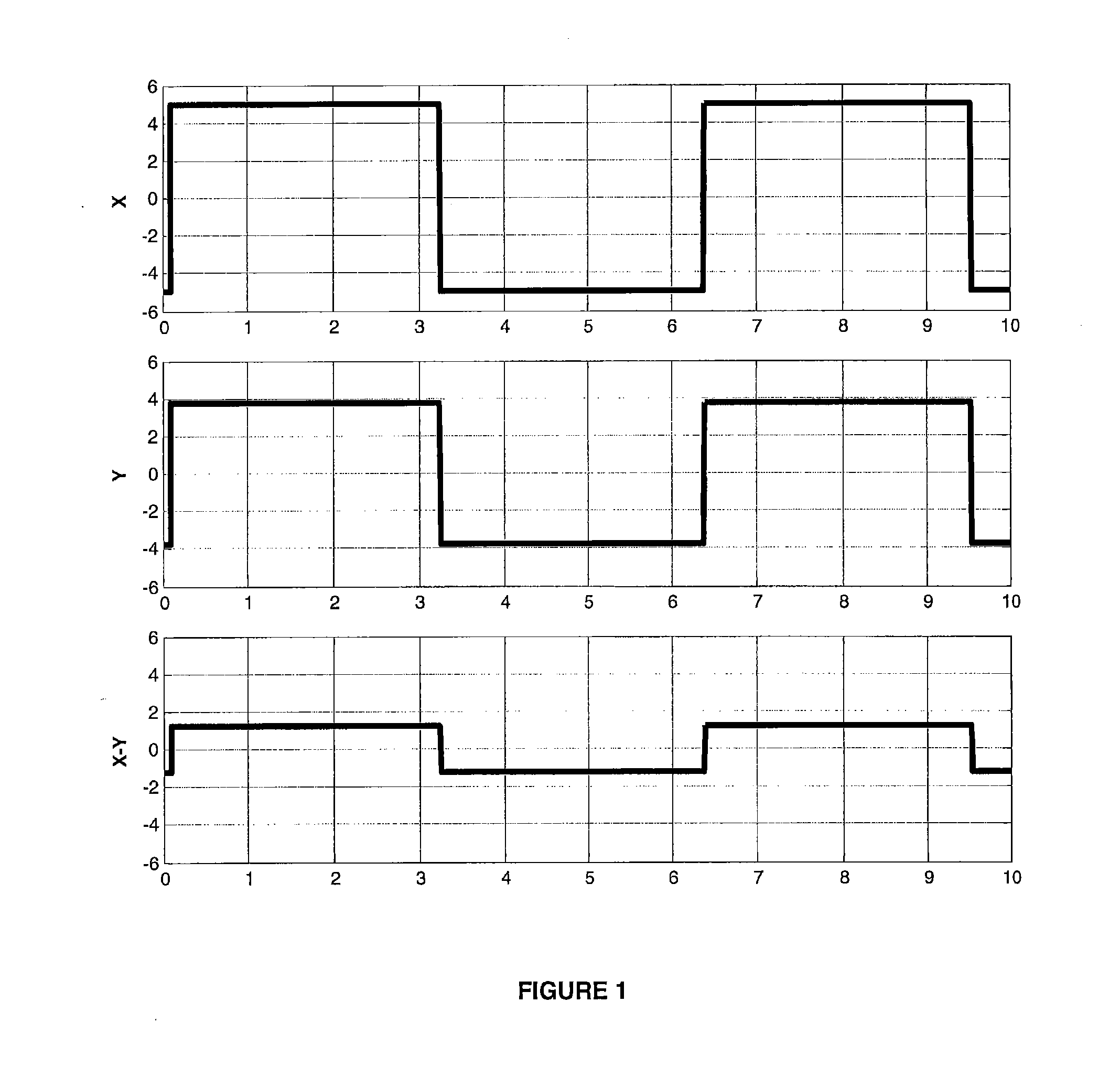

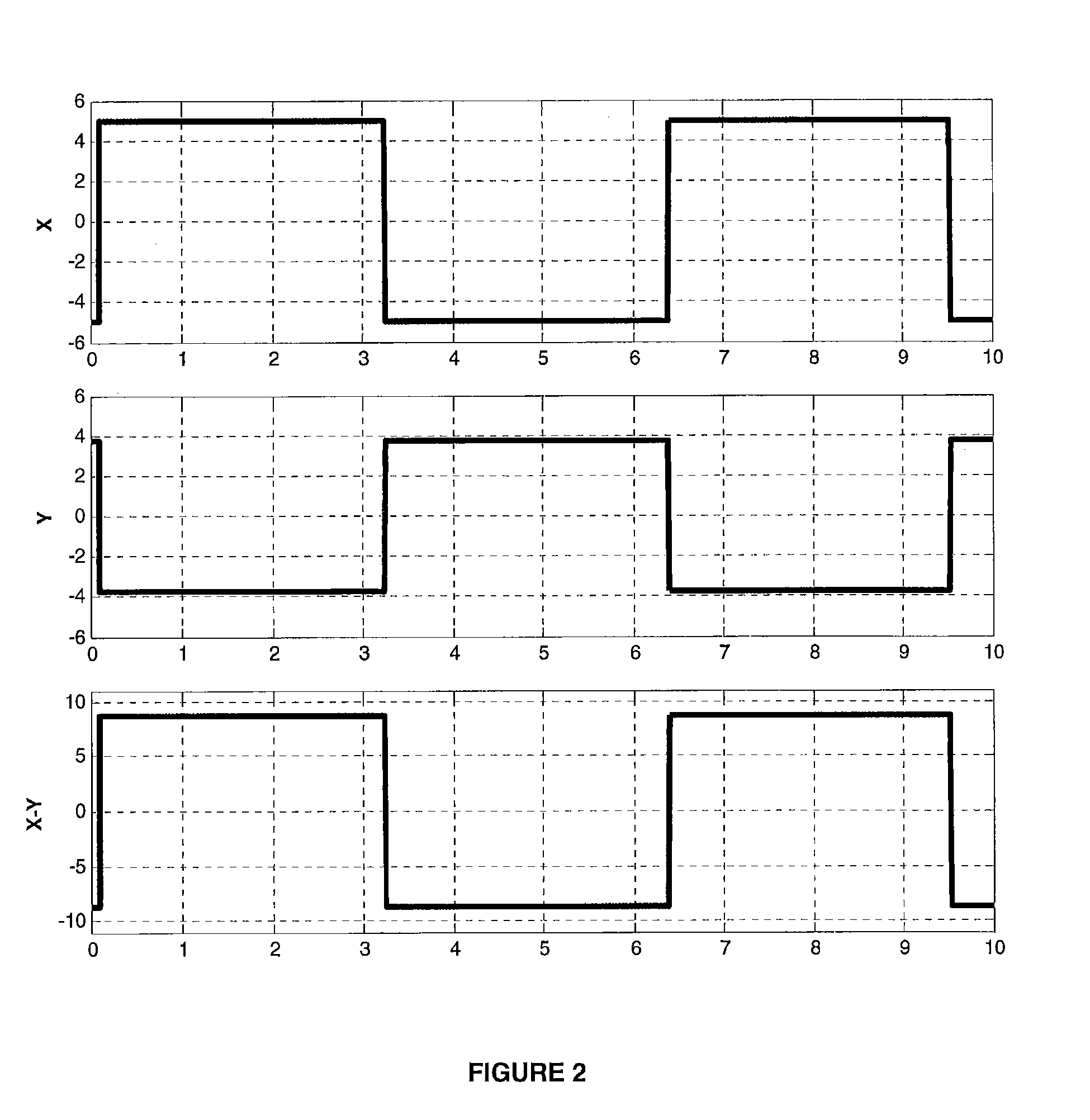

Driving mechanism for liquid crystal based optical device

InactiveUS20110001895A1Simple designLess-costly partStatic indicating devicesNon-linear opticsControl signalEngineering

An optical device with liquid crystal (LC) cells for conditioning the polarization of incident light includes a drive unit for the LC cells that employs a digital technique. According to this digital technique, the drive unit generates control signals for opposing electrodes of the LC cells based on digital signals that have the same period but differ in phase by up to one-half period. By employing digital signals that differ in phase by up to one-half period with high resolution, the differential voltage across the LC cells can be controlled precisely to a desired RMS value.

Owner:AVANEX CORP

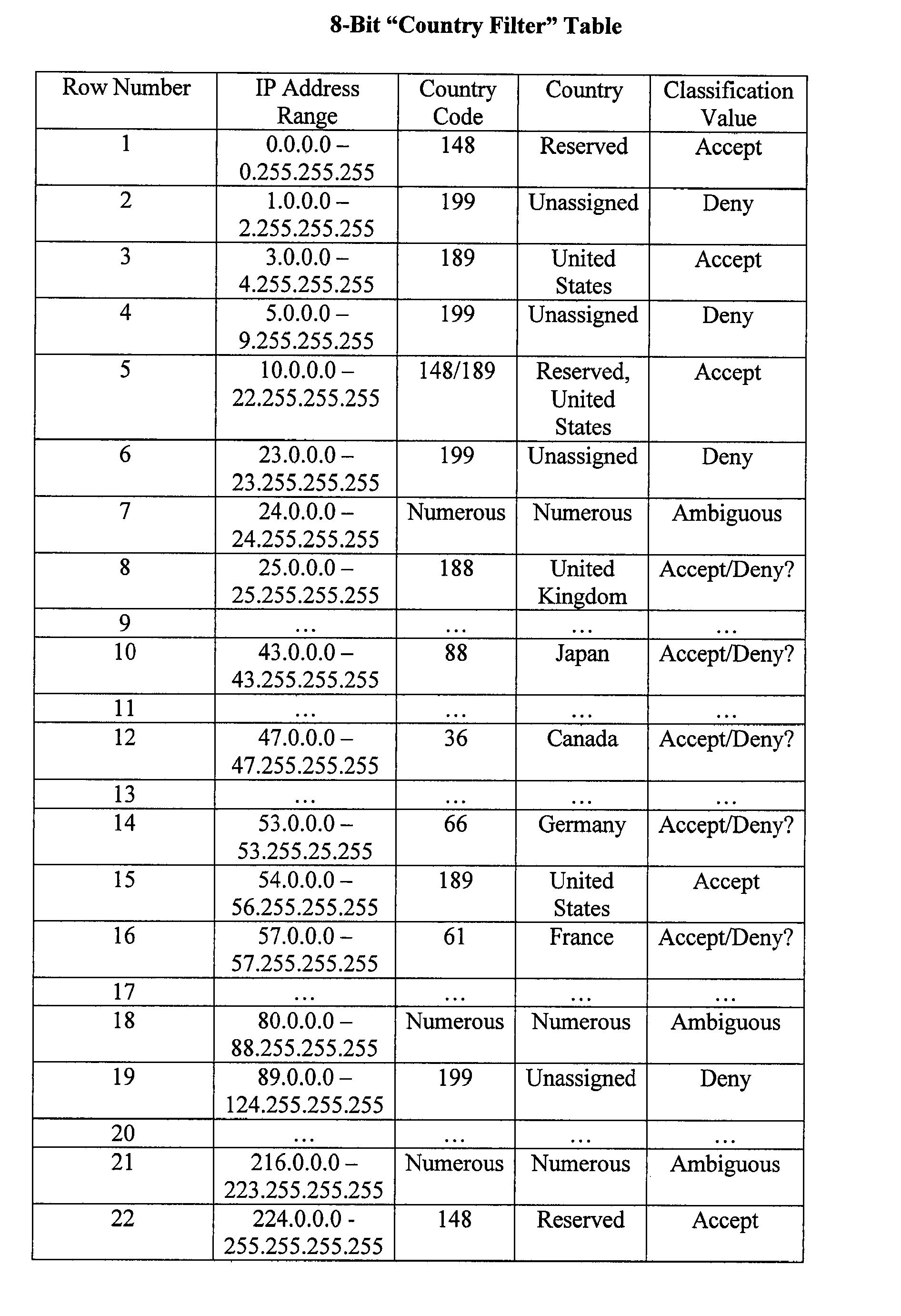

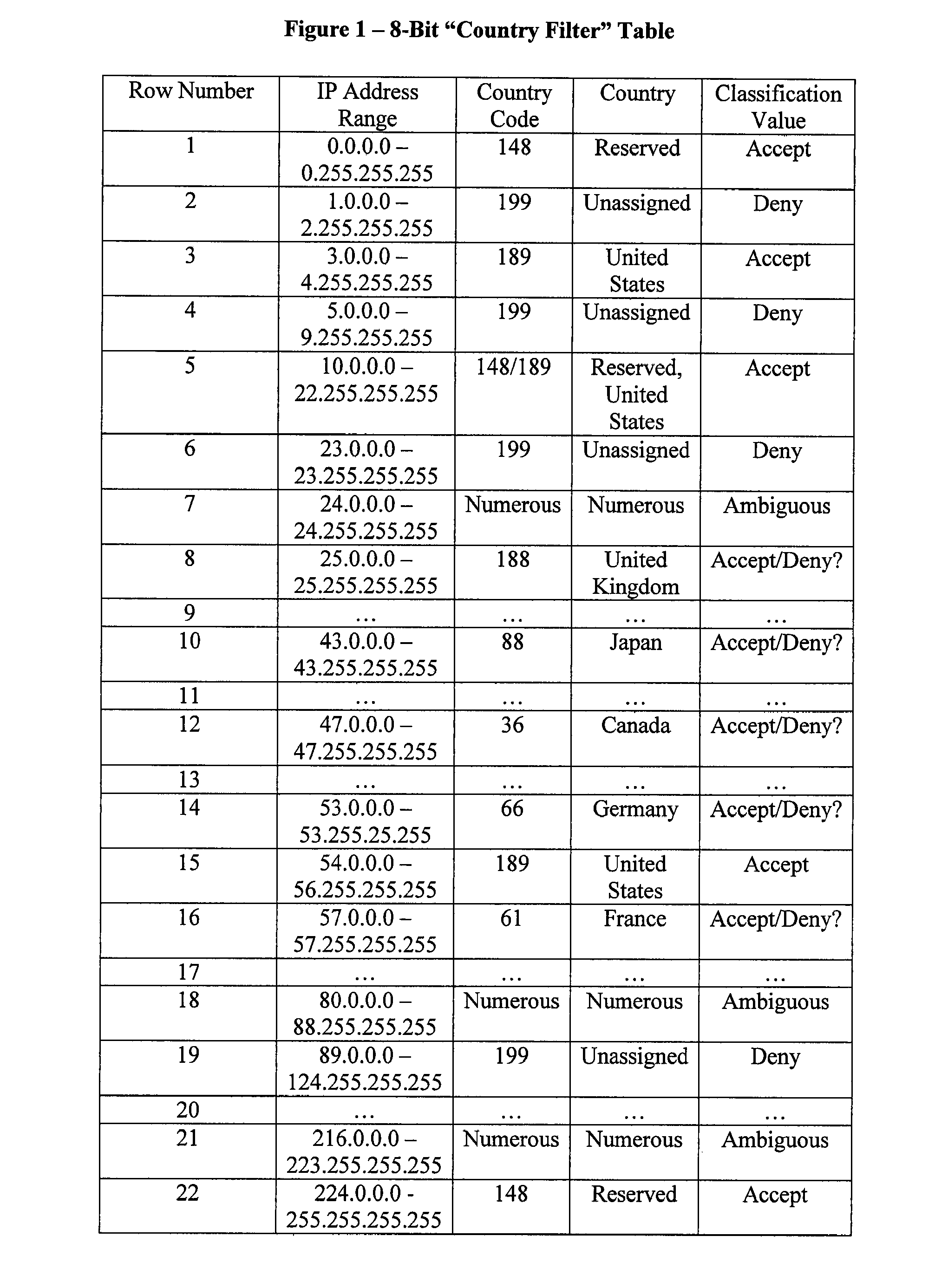

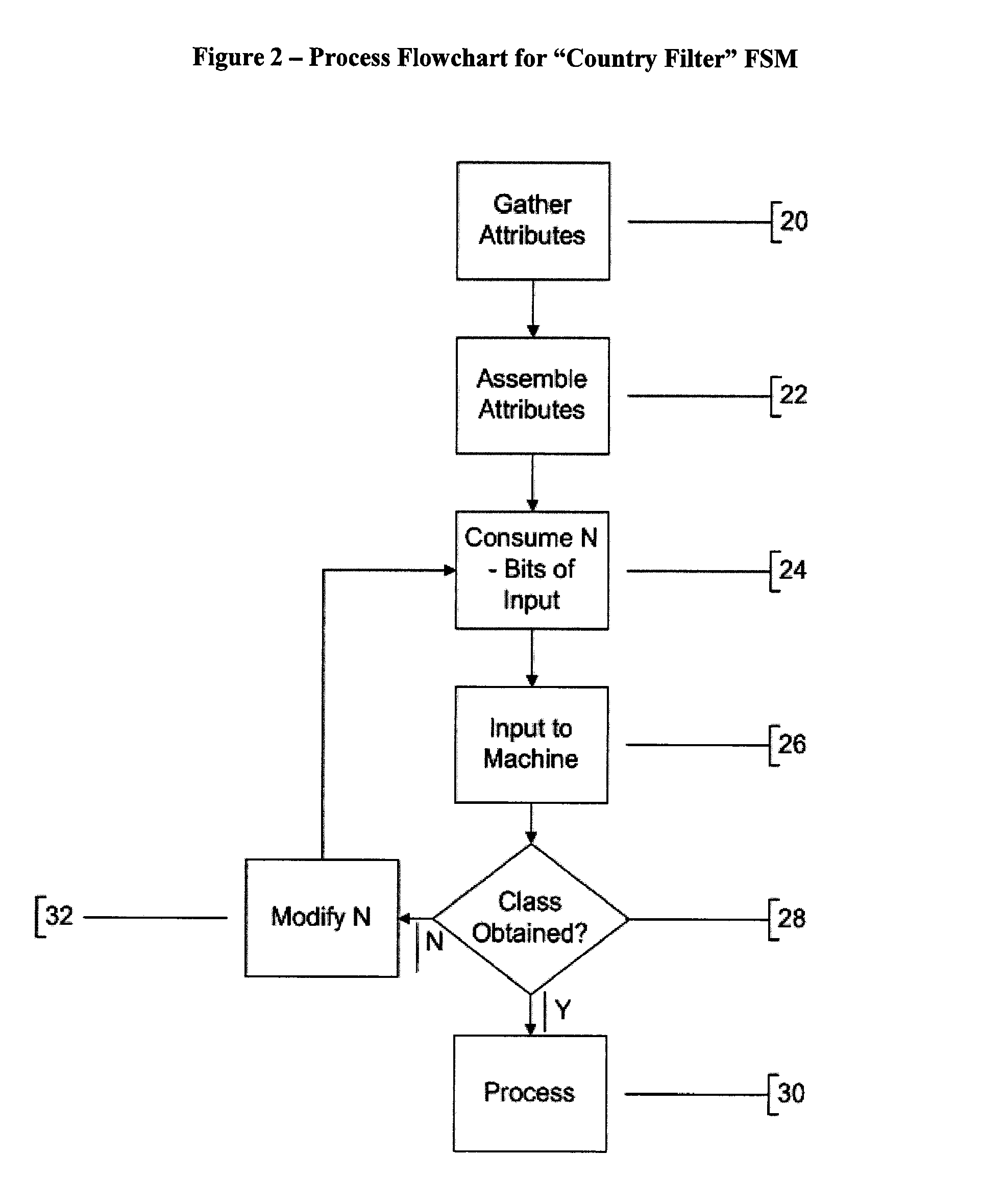

Method and Apparatus for Heuristic/Deterministic Finite Automata

InactiveUS20070271613A1Overcome disadvantagesMore scalableMemory loss protectionError detection/correctionAnti virusExtensibility

One embodiment of the present invention is a method for processing data in a computer or computer communications network that includes the steps of analyzing data using at least a first Heuristic / Deterministic Finite Automata (H / DFA), to classify data based upon pre-programmed programmed classification values assigned to different possible input data and / or pre-trained or dynamically updated heuristic engine output, and to select data for further processing based upon the resultant classification values that the logically interconnected look-up tables and / or heuristic components output given the input data. This exemplary embodiment overcomes disadvantages of previous methods for providing access control list, firewall, intrusion detection, intrusion prevention, spam filtration, anti-spyware, anti-phishing, anti-virus, anti-trojan, anti-worm, other computer security, routing, and / or switching related functionality. Heuristic algorithms, or a combination of logically interconnected look-up tables and heuristic techniques can also implement the H / DFA functionality. There are significant advantages in speed and scalability.

Owner:TECHGUARD SECURITY L L C

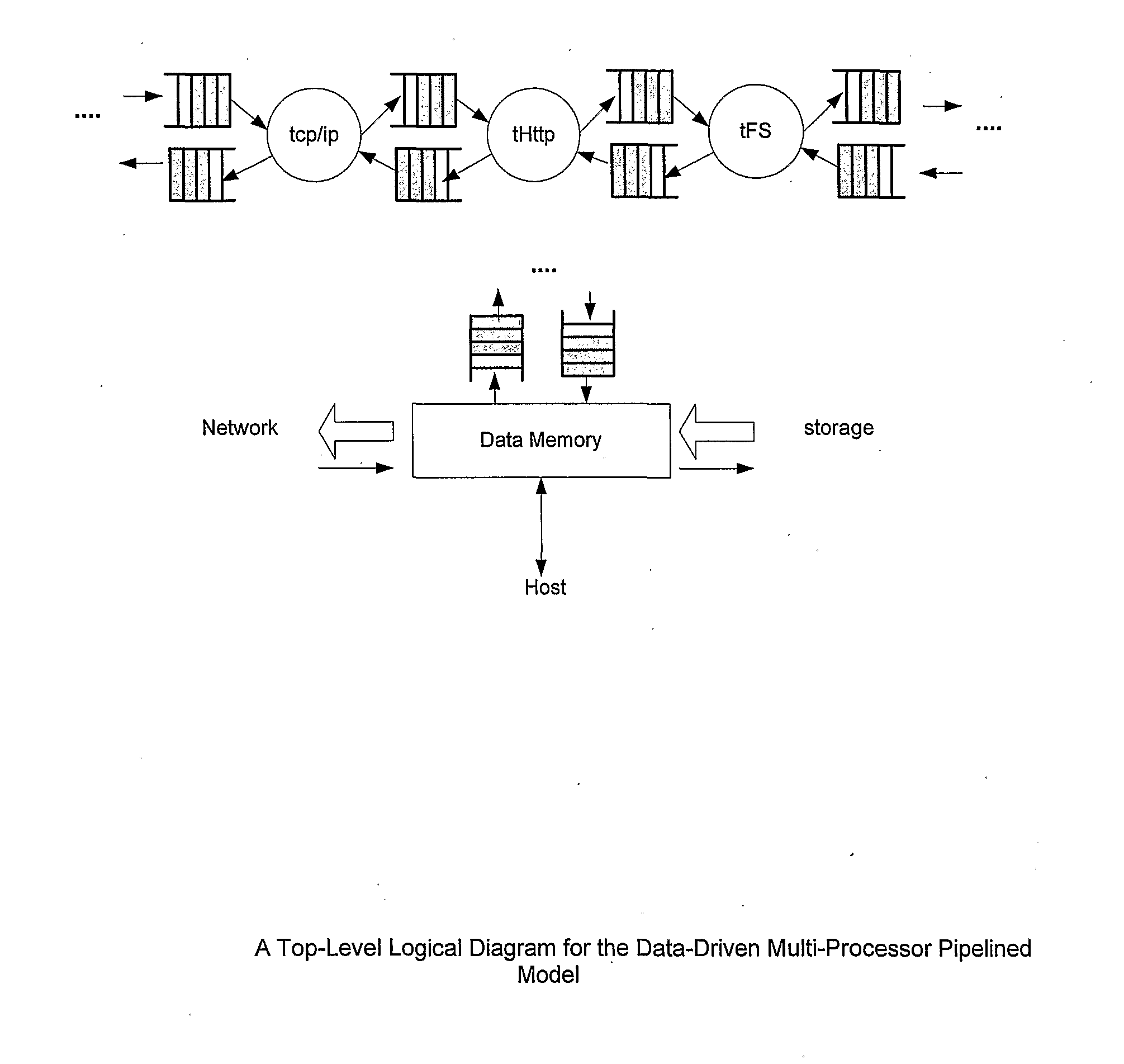

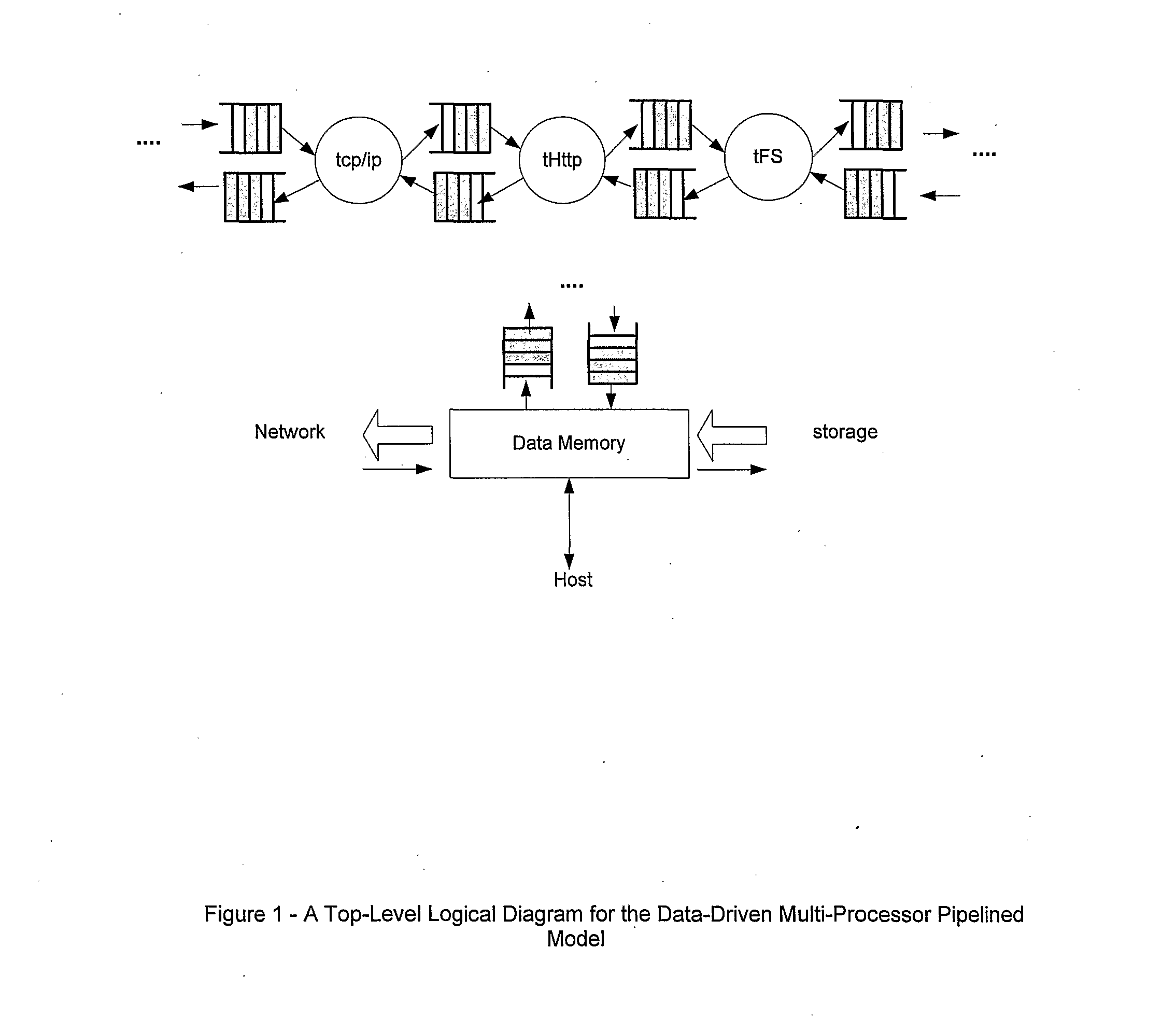

Systems and methods for distributing a workplan for data flow execution based on an arbitrary graph describing the desired data flow

ActiveUS20050278152A1Improve performanceMore resourceDigital data processing detailsMultiple digital computer combinationsData streamParallel computing

Various embodiments of the present invention are directed to the creation of multiple redundant chains of transforms, each on a separate processing thread, for a data flow execution (DFE) of a data transformation pipeline (DTP). For certain of these embodiments, a “distributor” receives a buffer as input and directs that buffer to one of several parallel identical threads to process that buffer. A scheduler would create each of these multiple threads, each thread having an identical (redundant) strings of transforms (chains) downstream from the distributor, and all of which would lead even further downstream to a collector that is responsible for collecting and, if necessary, ordering the buffers processed by the previous redundant chains. In this way, the distributors and collectors provide increased scalability for the pipeline by implicitly partitioning (distributing) individual buffers to one of many threads for at least a part of their execution / processing.

Owner:MICROSOFT TECH LICENSING LLC

Software emulation of directed exceptions in a multithreading processor

ActiveUS7849297B2More scalableSave areaDigital computer detailsProgram loading/initiatingGeneral purposeSoftware emulation

A multithreading microprocessor has a plurality of thread contexts (TCs) each including sufficient state, such as general purpose registers and program counter, to execute a separate thread of execution as one of a plurality of symmetric processors controlled by a multiprocessor operating system. However, the microprocessor hardware does not support the ability for one TC to direct an exception to another TC, i.e., to specify to which of the other TCs the exception is directed. A first thread running on a first TC of the operating system executes architected instructions to halt a second thread (either user or kernel thread) running on a second TC, save state of the second TC, write the second TC state to emulate an exception—including writing a restart register with the address of an exception handler, and unhalt the second TC to execute the exception hander.

Owner:MIPS TECH INC

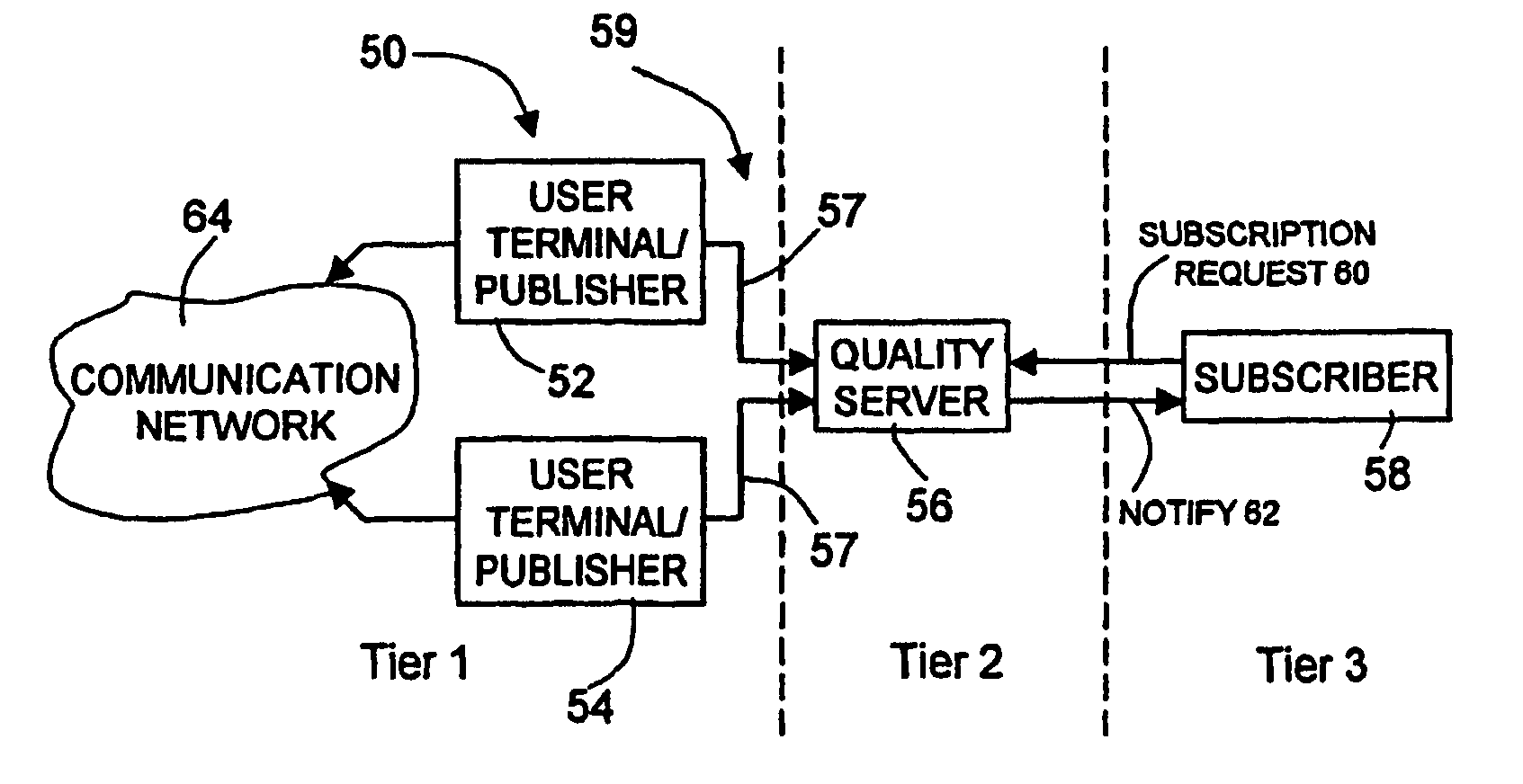

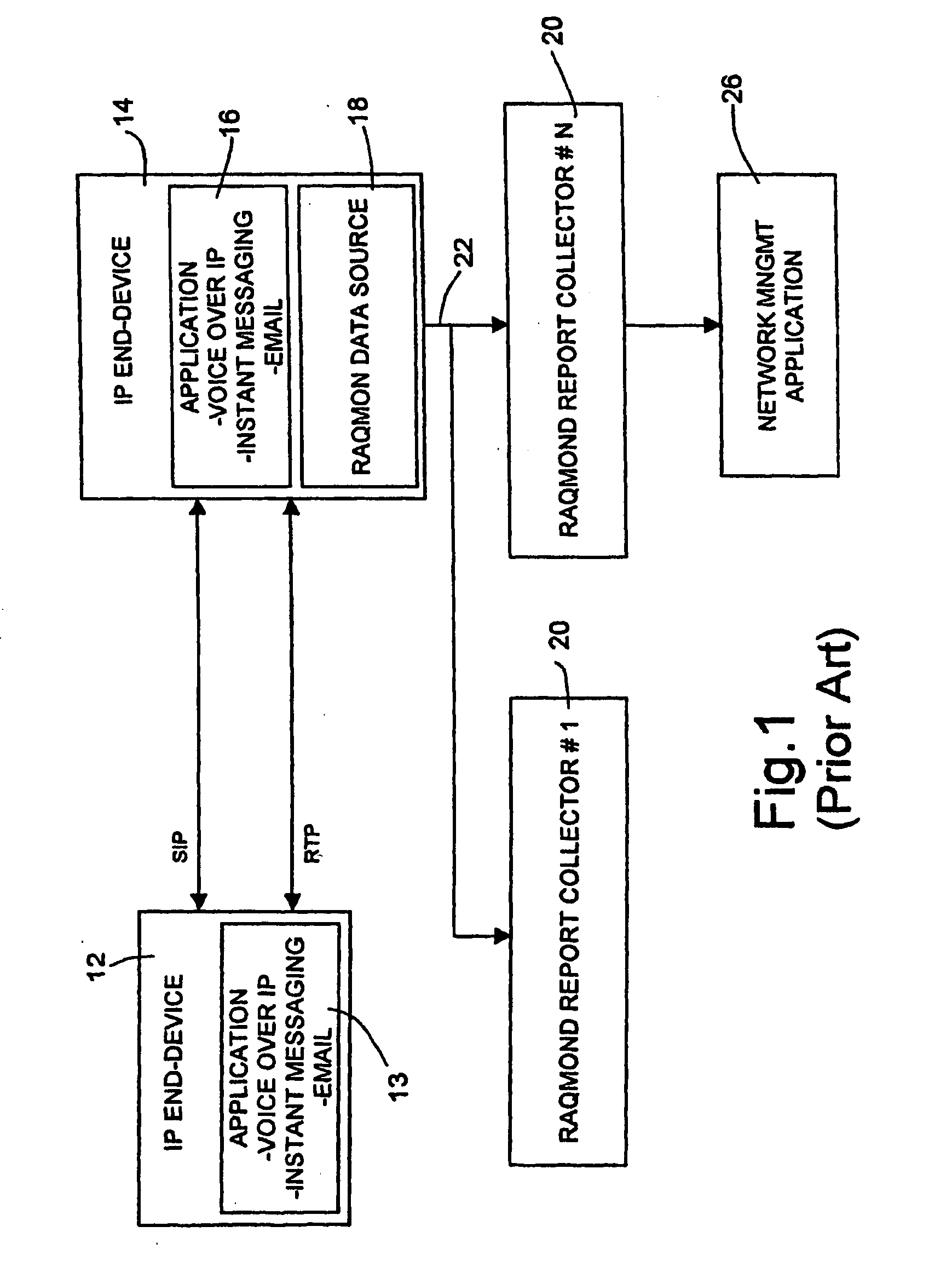

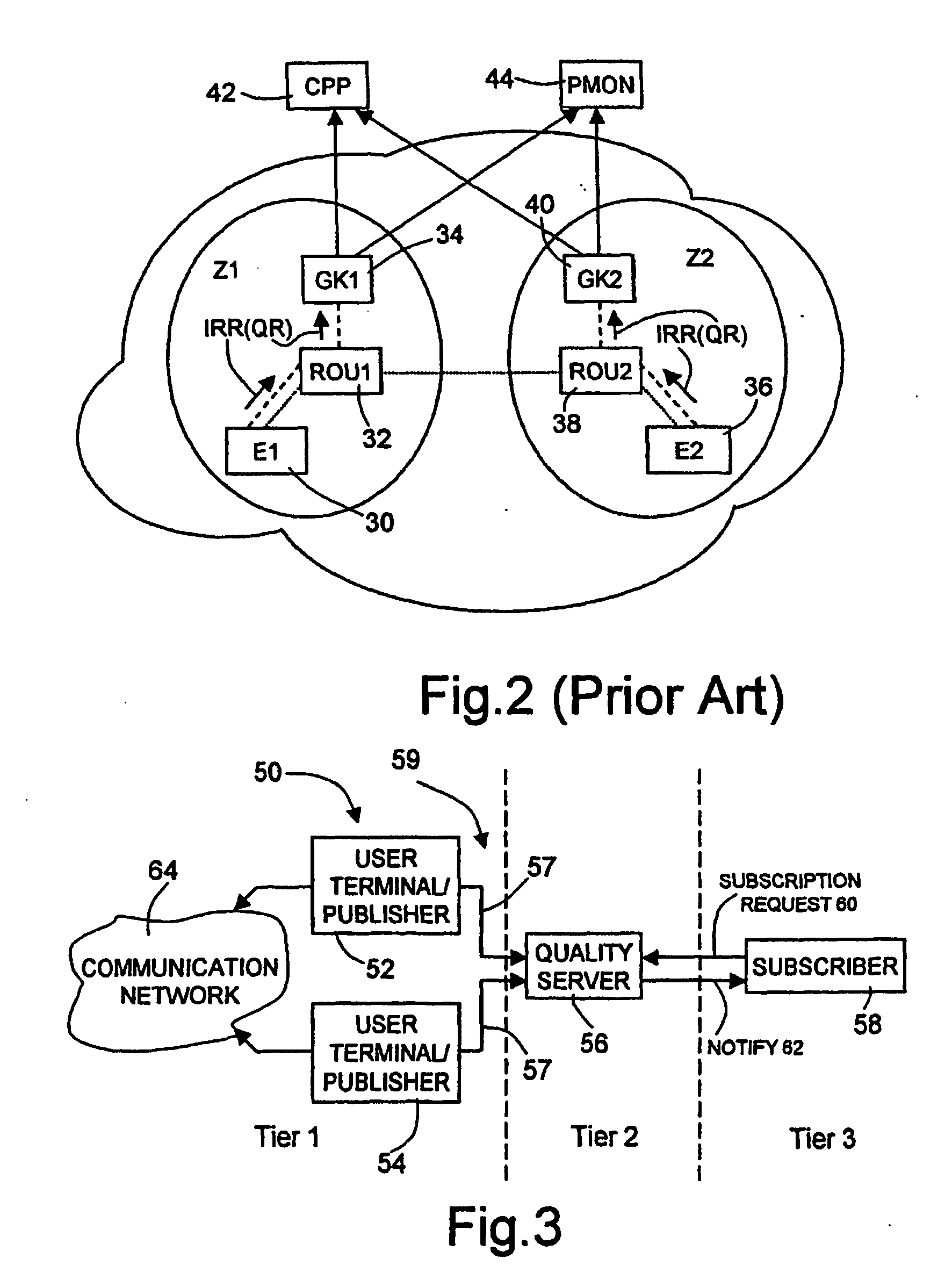

Quality of Service Monitor in a Packet-Based Network

InactiveUS20070288630A1Improve scalabilityLow costMetering/charging/biilling arrangementsDigital computer detailsQuality of serviceMultiple applications

A method and system of monitoring quality of service in a packet-based network includes a three-tier architecture, wherein one or more applications can request customized quality of service reports from a quality server. The customized reports may include, for example, a desired report format or trigger events indicating when the one or more applications should receive the report. The quality server prepares these reports based on quality of service messages received from user terminals and sends the reports in accordance with the request.

Owner:TELECOM ITALIA SPA

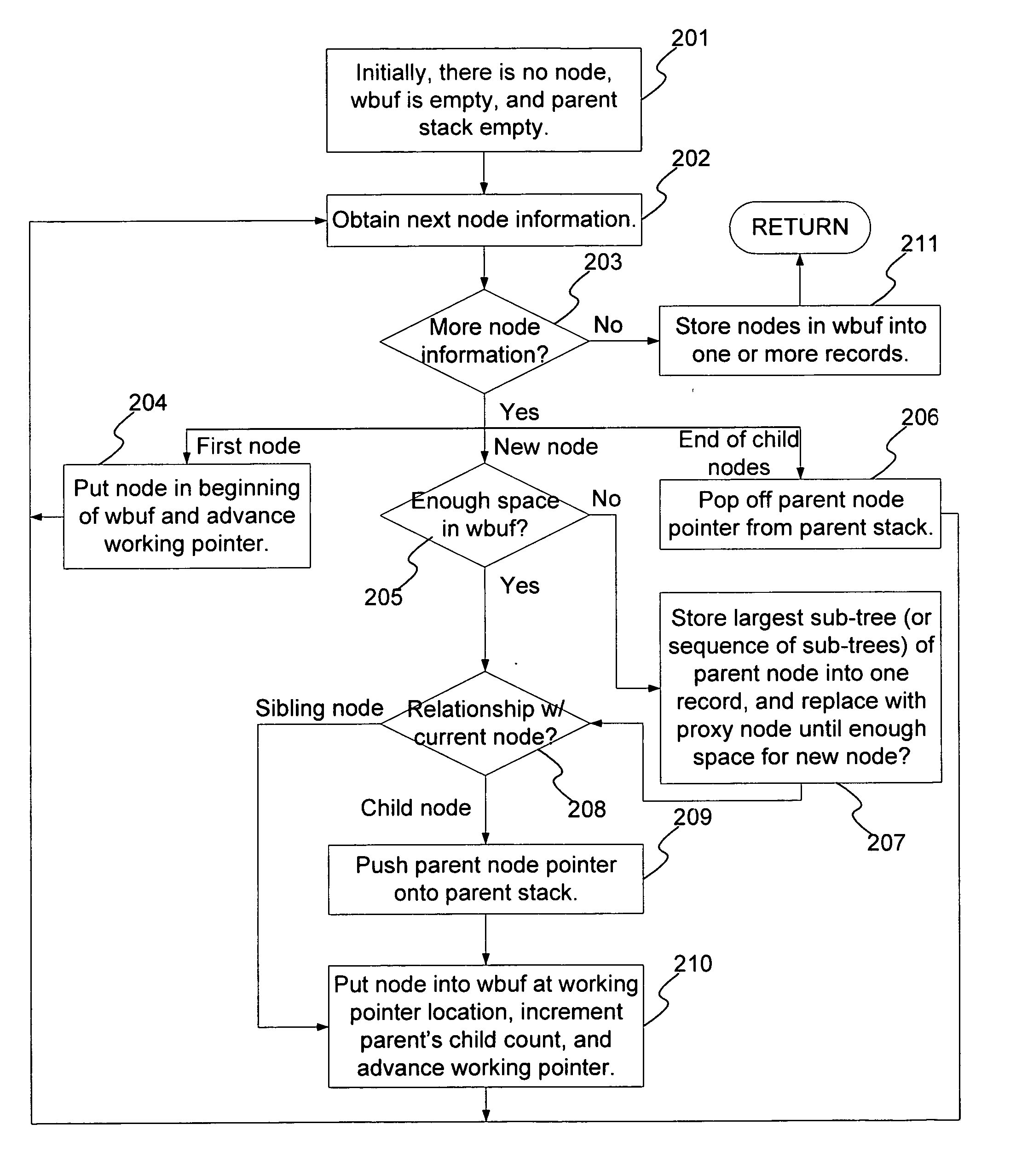

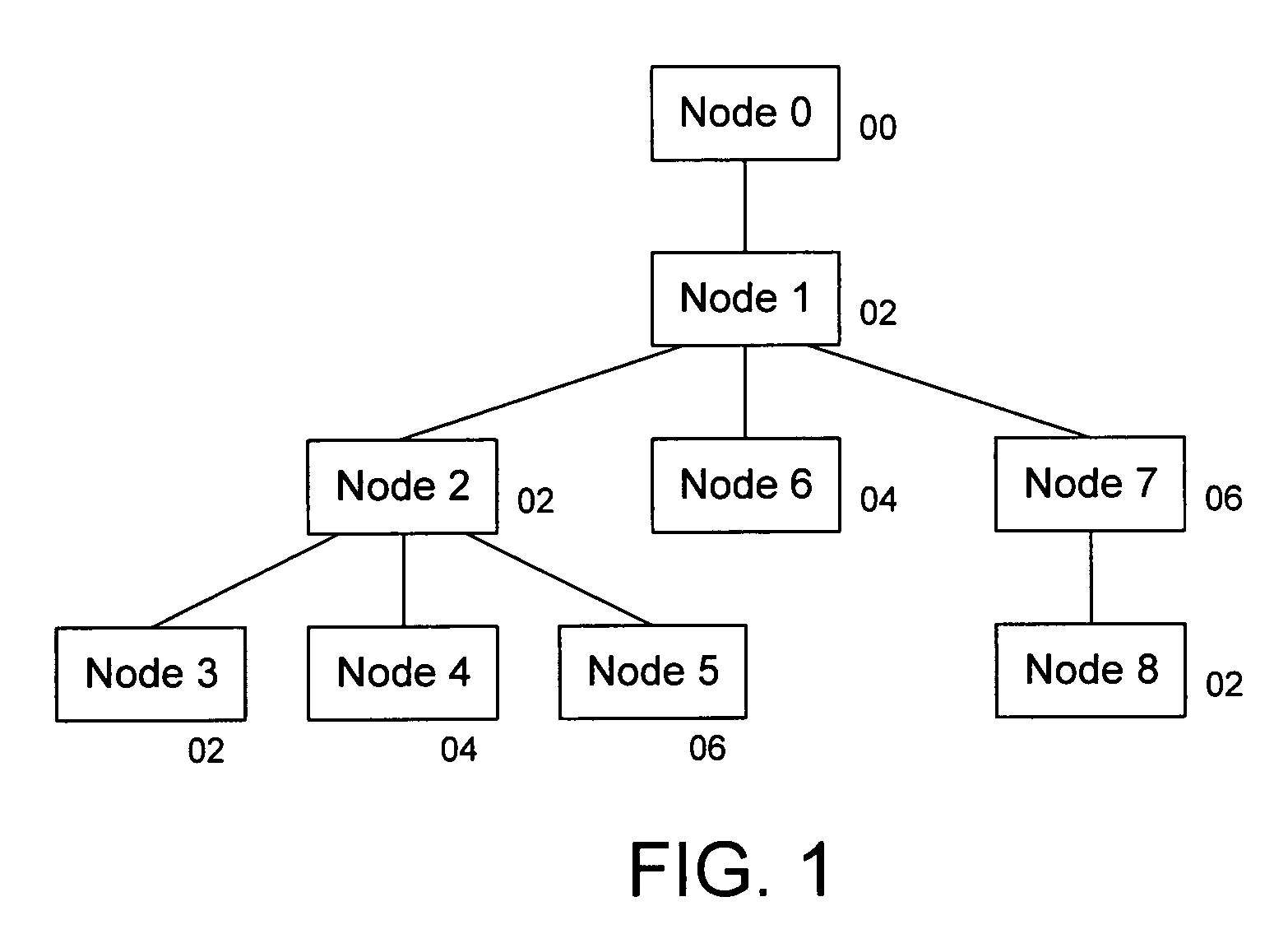

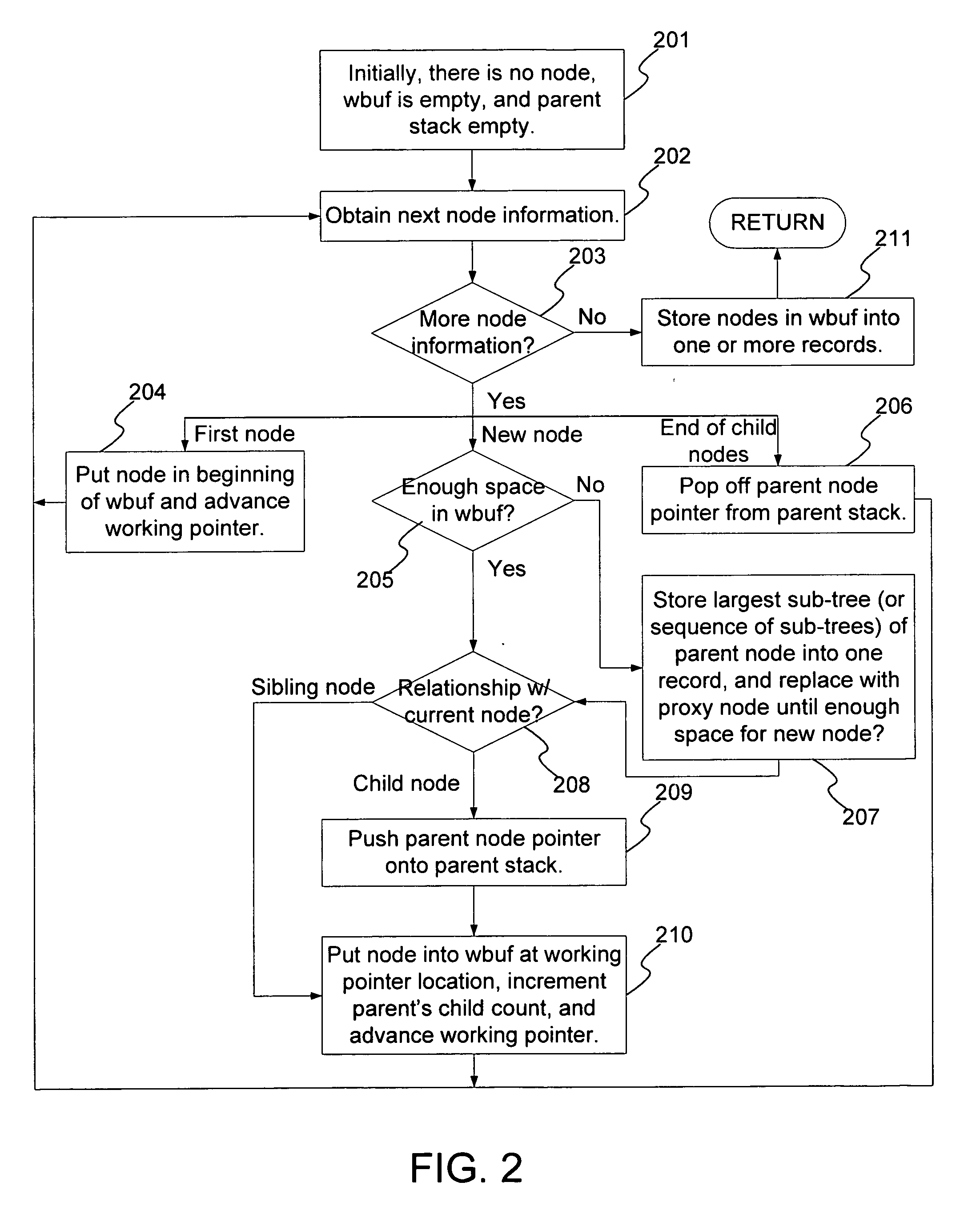

Packing nodes into records to store XML XQuery data model and other hierarchically structured data

InactiveUS20070043743A1Small storage consumptionMore scalableDigital data processing detailsSemi-structured data indexingData pageData model

A storage of nodes of hierarchically structured data uses logical node identifiers to reference the nodes stored within and across record data structures. A node identifier index is used to map each logical node identifier to a record identifier for the record that contains the node. When a sub-tree is stored in a separate record, a proxy node is used to represent the sub-tree in the parent record. The mapping in the node identifier index reflects the storage of the sub-tree nodes in the separate record. Since the references between the records are through logical node identifiers, there is no limitation to the moving of records across pages, as long as the indices are updated or rebuilt to maintain synchronization with the resulting data pages. This approach is highly scalable and has a much smaller storage consumption than approaches that use explicit references between nodes.

Owner:IBM CORP

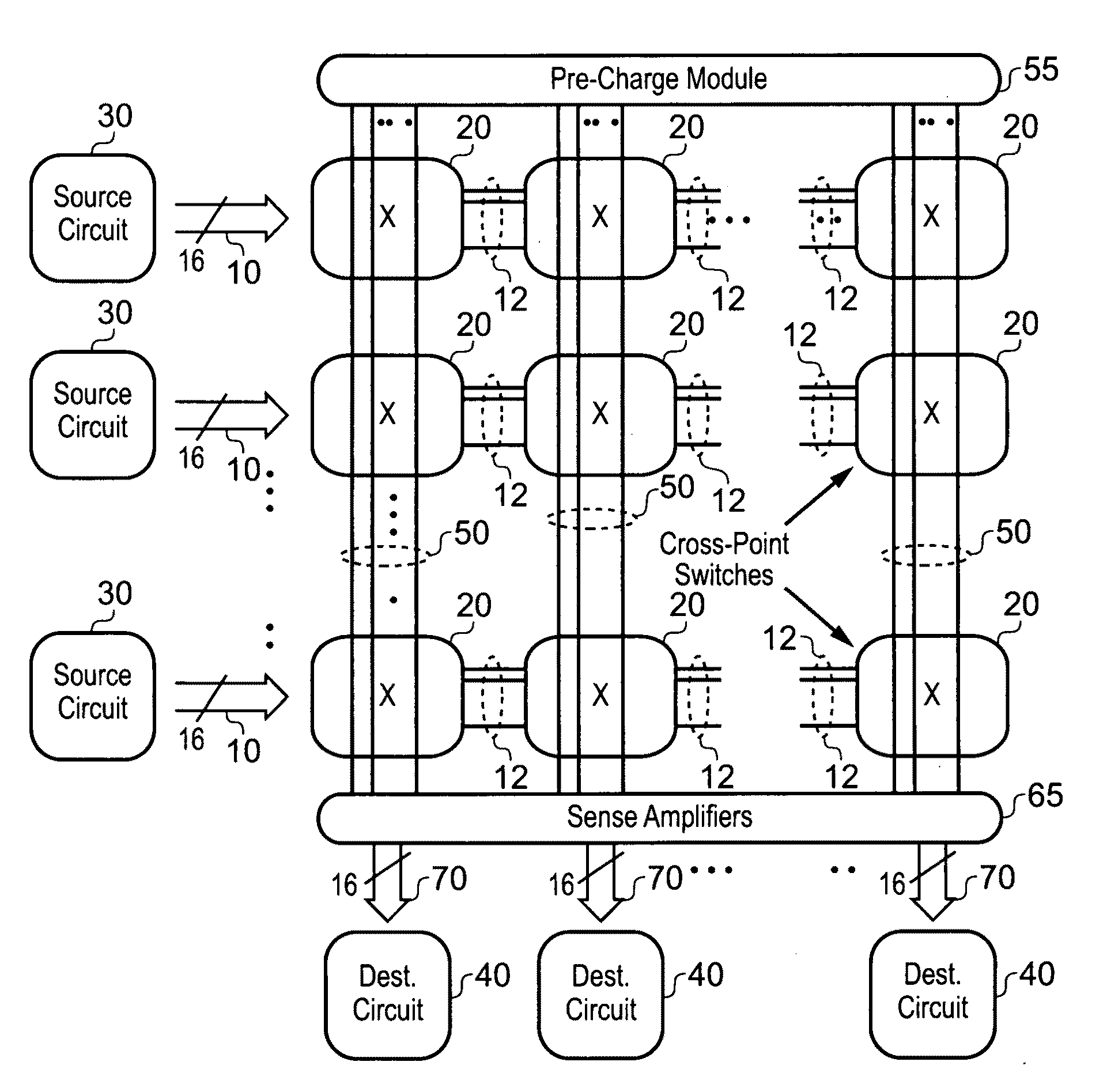

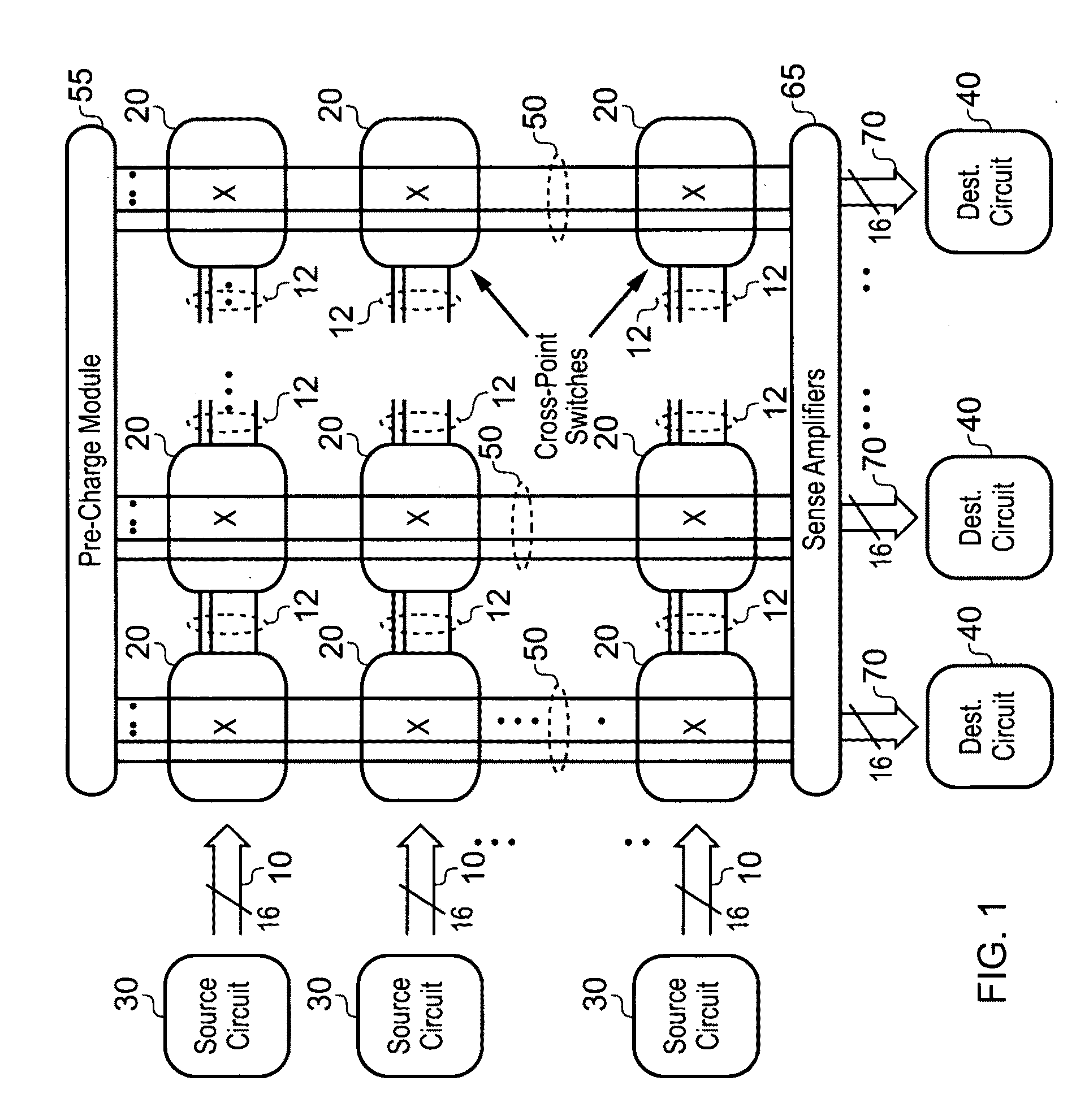

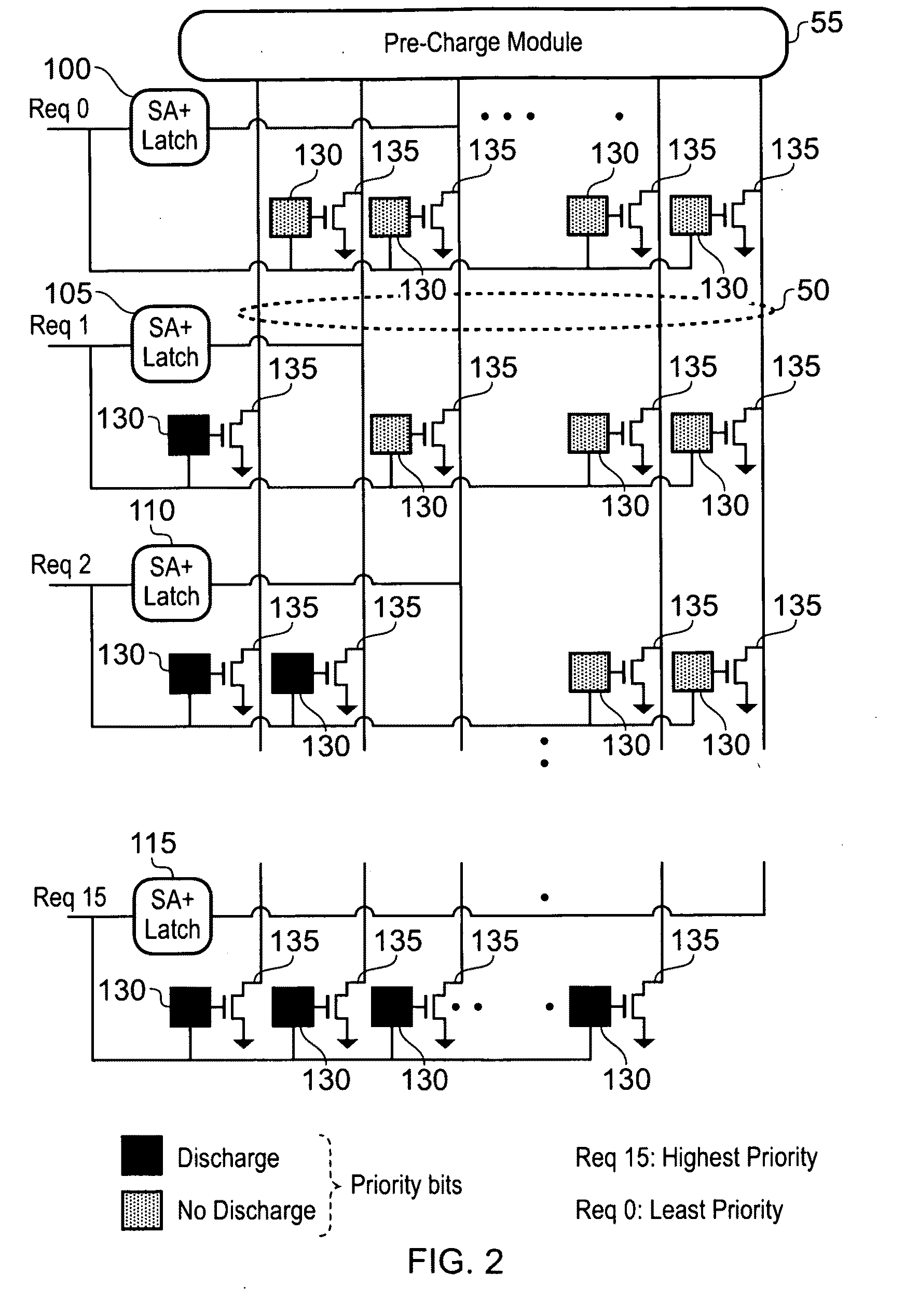

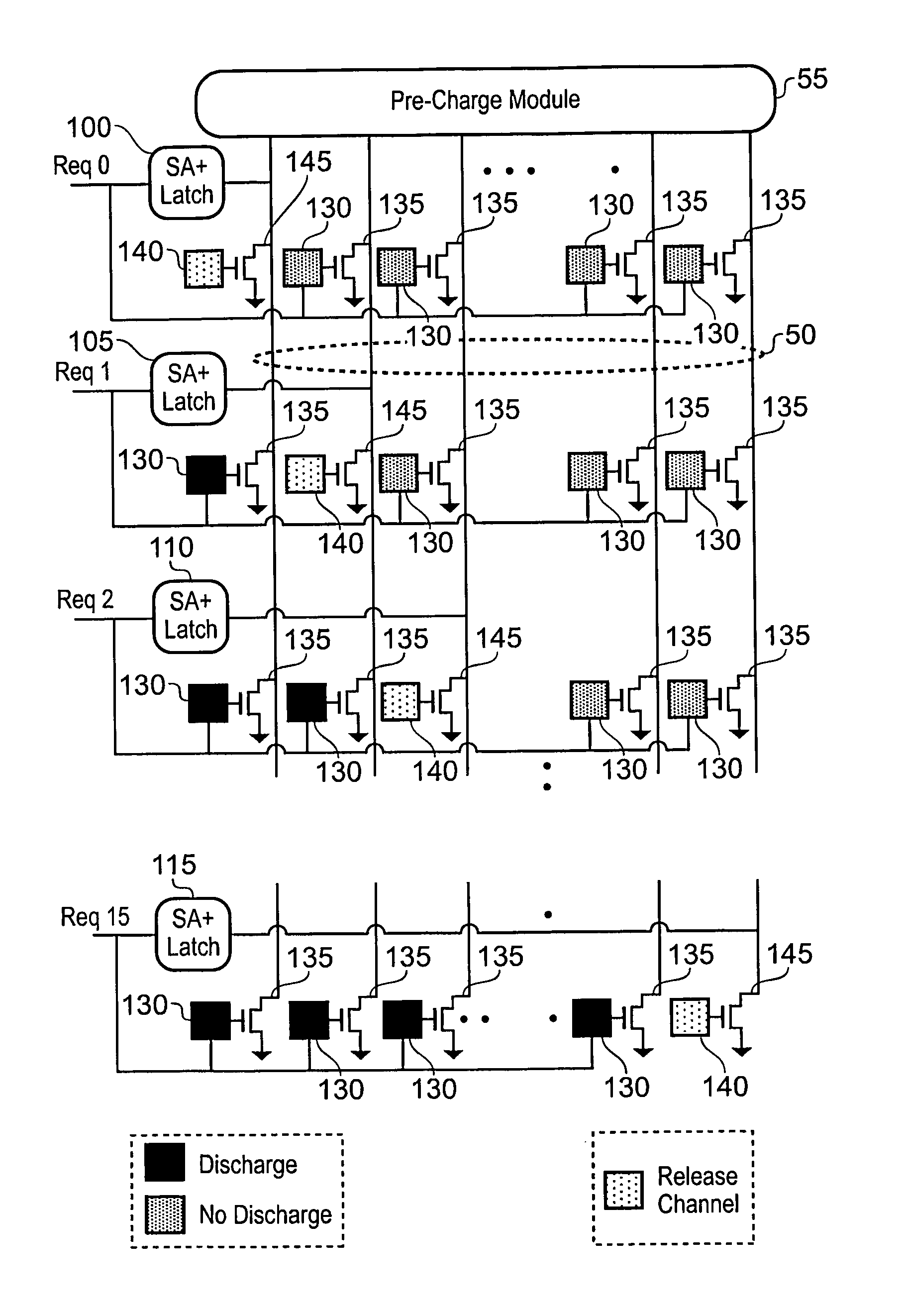

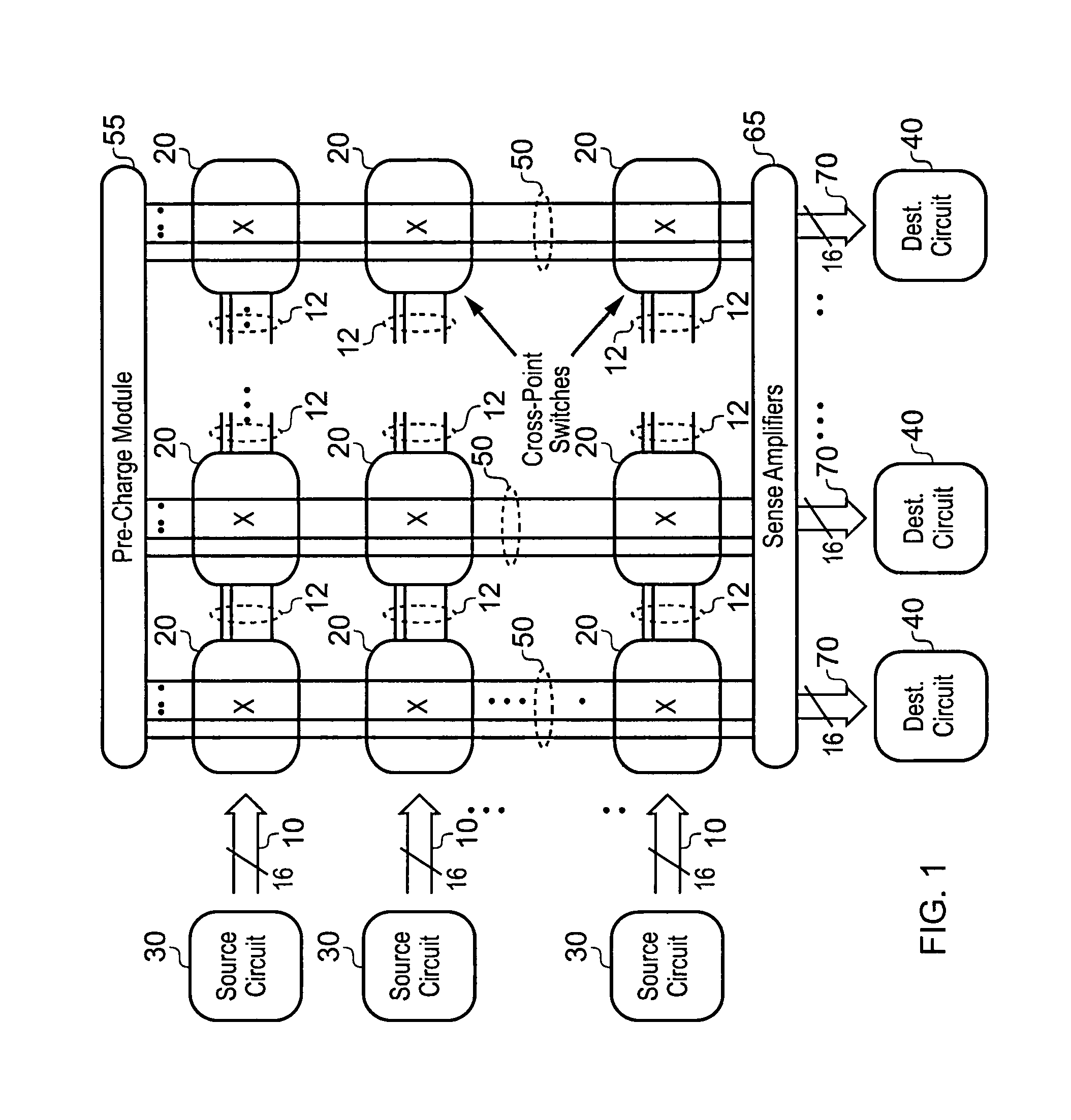

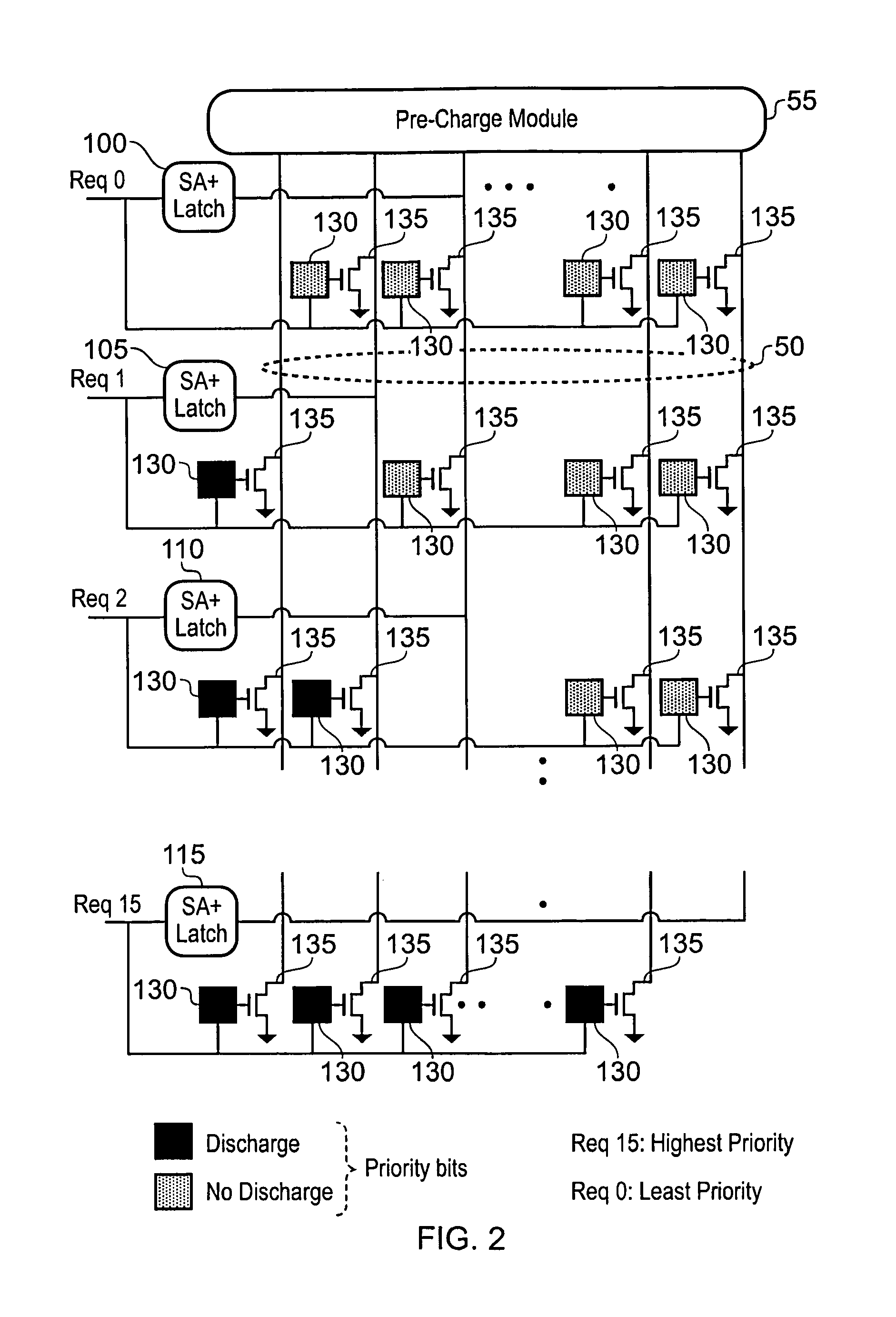

Crossbar circuitry for applying an adaptive priority scheme and method of operation of such crossbar circuitry

ActiveUS20110138098A1Fast and scalable techniqueMore scalableMultiplex system selection arrangementsNext instruction address formationBit lineOperation mode

Crossbar circuitry has an array of data input and output paths where the data output paths are transverse to the data input paths. At each intersection between a data input path and a data output path, a crossbar cell is provided which includes a configuration storage circuit programmable to store a routing value, a transmission circuit, and an arbitration circuit. In a transmission mode of operation, the transmission circuit is responsive to the routing value being a first value, indicating that the data input path should be coupled to the data output path, to detect the data input along the data input path, and to output an indication of that data on the data output path at the associated intersection. In an arbitration mode of operation, the arbitration circuitry is operable to selectively modify the voltage on said plurality of bit lines in order to apply an adaptive priority scheme.

Owner:RGT UNIV OF MICHIGAN

Systems and methods for distributing a workplan for data flow execution based on an arbitrary graph describing the desired data flow

ActiveUS7930432B2Improve performanceMore resourceDigital data processing detailsMultiple digital computer combinationsData streamData transformation

Various embodiments of the present invention are directed to the creation of multiple redundant chains of transforms, each on a separate processing thread, for a data flow execution (DFE) of a data transformation pipeline (DTP). For certain of these embodiments, a “distributor” receives a buffer as input and directs that buffer to one of several parallel identical threads to process that buffer. A scheduler would create each of these multiple threads, each thread having an identical (redundant) strings of transforms (chains) downstream from the distributor, and all of which would lead even further downstream to a collector that is responsible for collecting and, if necessary, ordering the buffers processed by the previous redundant chains. In this way, the distributors and collectors provide increased scalability for the pipeline by implicitly partitioning (distributing) individual buffers to one of many threads for at least a part of their execution / processing.

Owner:MICROSOFT TECH LICENSING LLC

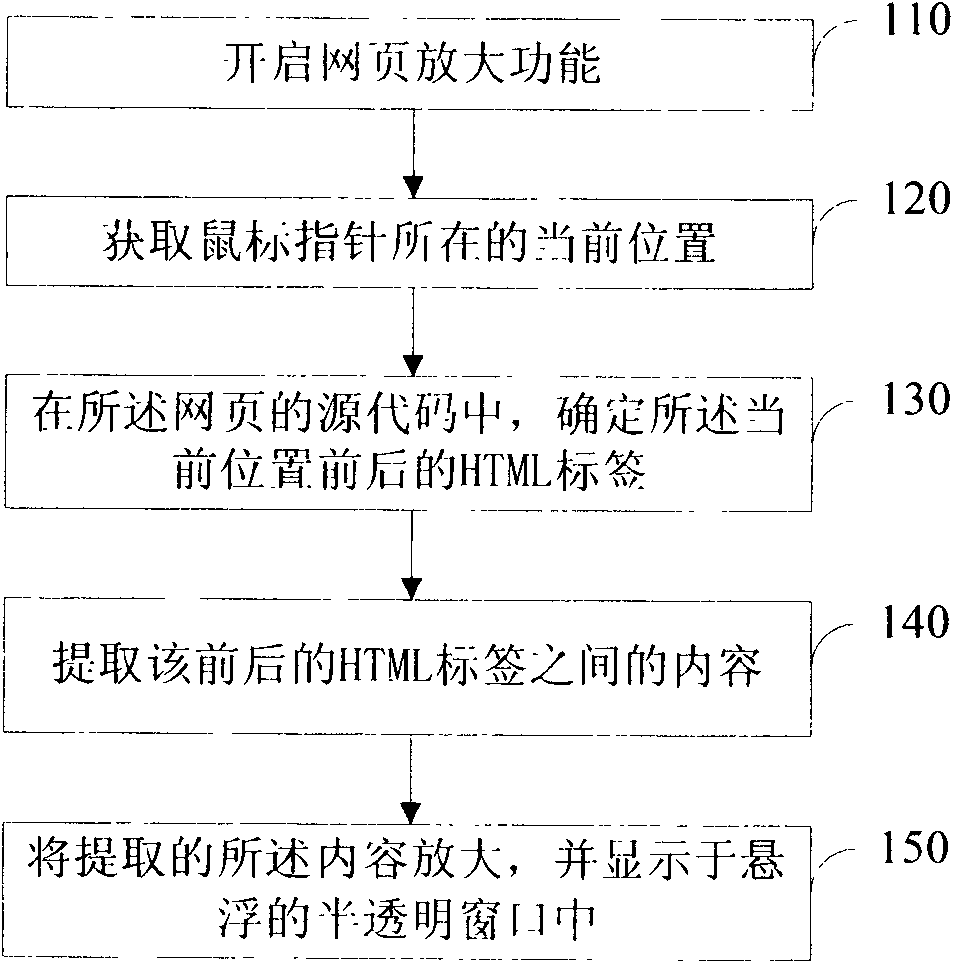

Method, device and browser for magnifying contents of webpage

InactiveCN102023975ALayout changesWill not affect readingSpecial data processing applicationsWeb pageSource code

Owner:LENOVO (BEIJING) CO LTD

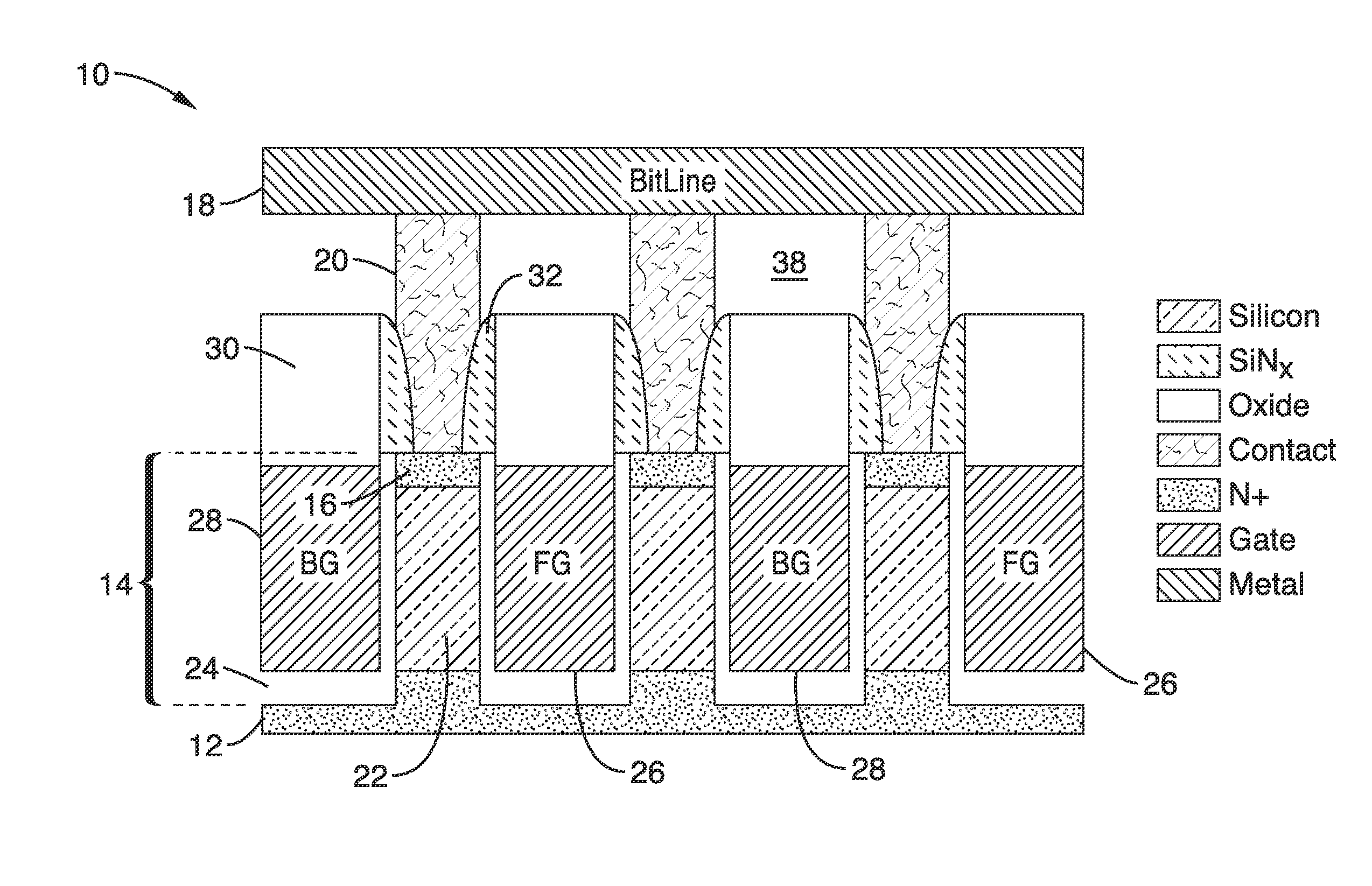

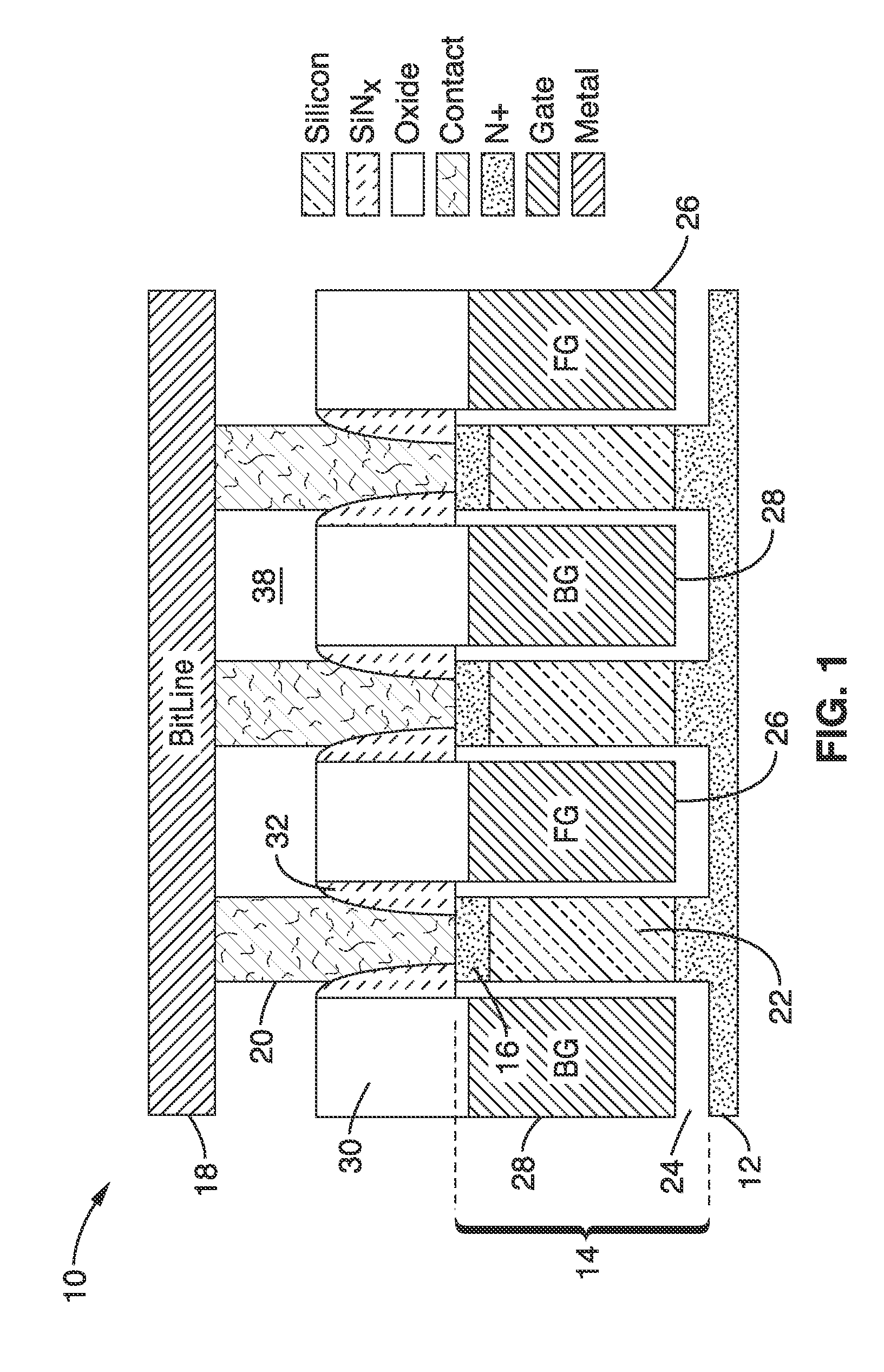

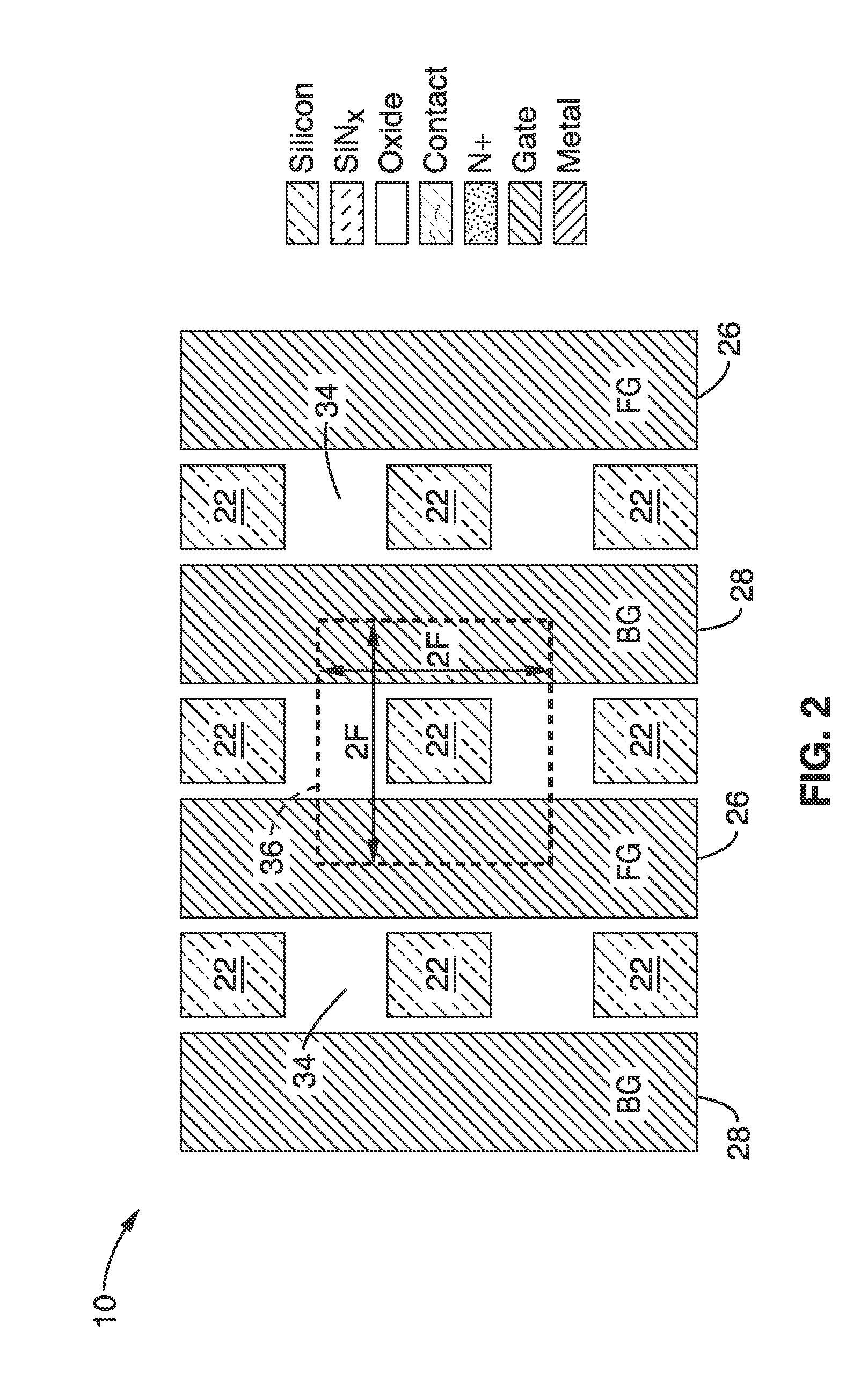

Dram cell utilizing a doubly gated vertical channel

InactiveUS20120161229A1Low costLow cost manufacturingTransistorSolid-state devicesSemiconductor materialsEngineering

A double-gate vertical channel transistor (DGVC) structure is described which is particularly well suited for Dynamic RAM (DRAM) memory (e.g., capacitorless DRAM) wherein the memory cell occupies a small cell area of 4F2, and provides beneficial retention properties including immunity to disturbances. The vertical transistors are arranged in an alternating gate-facing orientation, with a common source formed on a first end and separate drains on their second ends. Word lines comprise alternating front gates and back gates shared by columns of gate-facing transistors on each side of it. The DGVC cell provides enhanced scalability allowing the continued scaling of DRAM technology and can be fabricated using low-cost semiconductor materials and existing fabrication techniques. Fabrication techniques and array biasing are also described for the DGVC cell arrays.

Owner:RGT UNIV OF CALIFORNIA

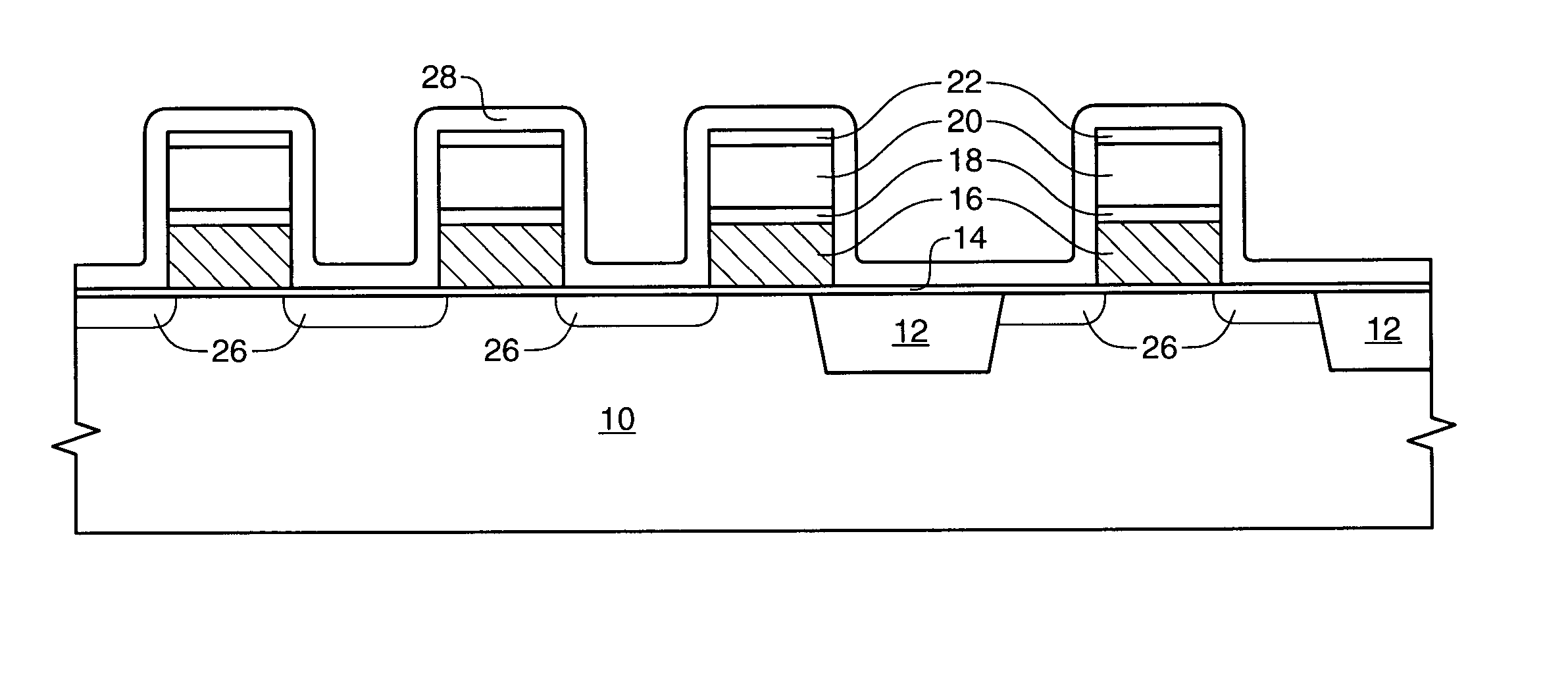

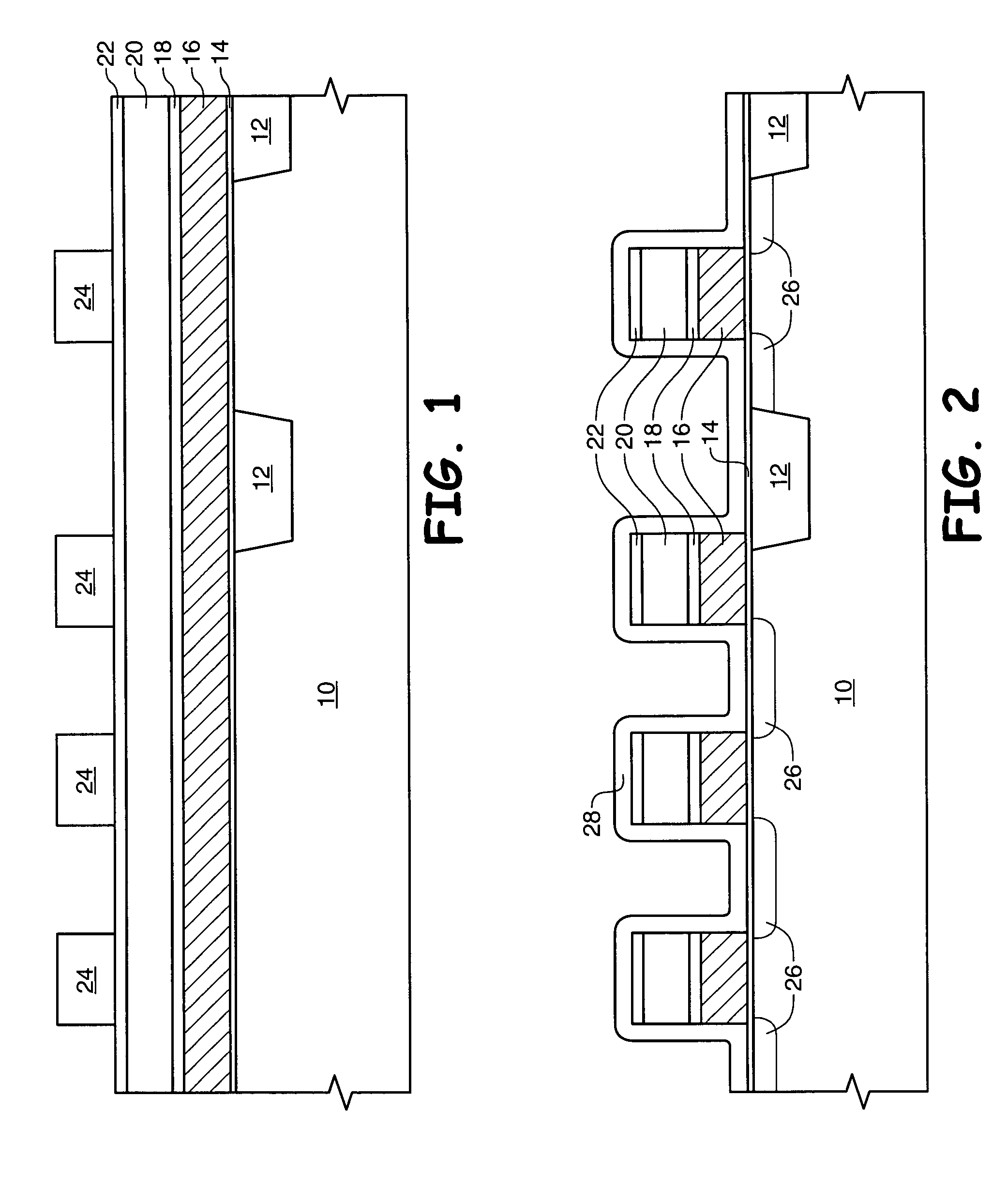

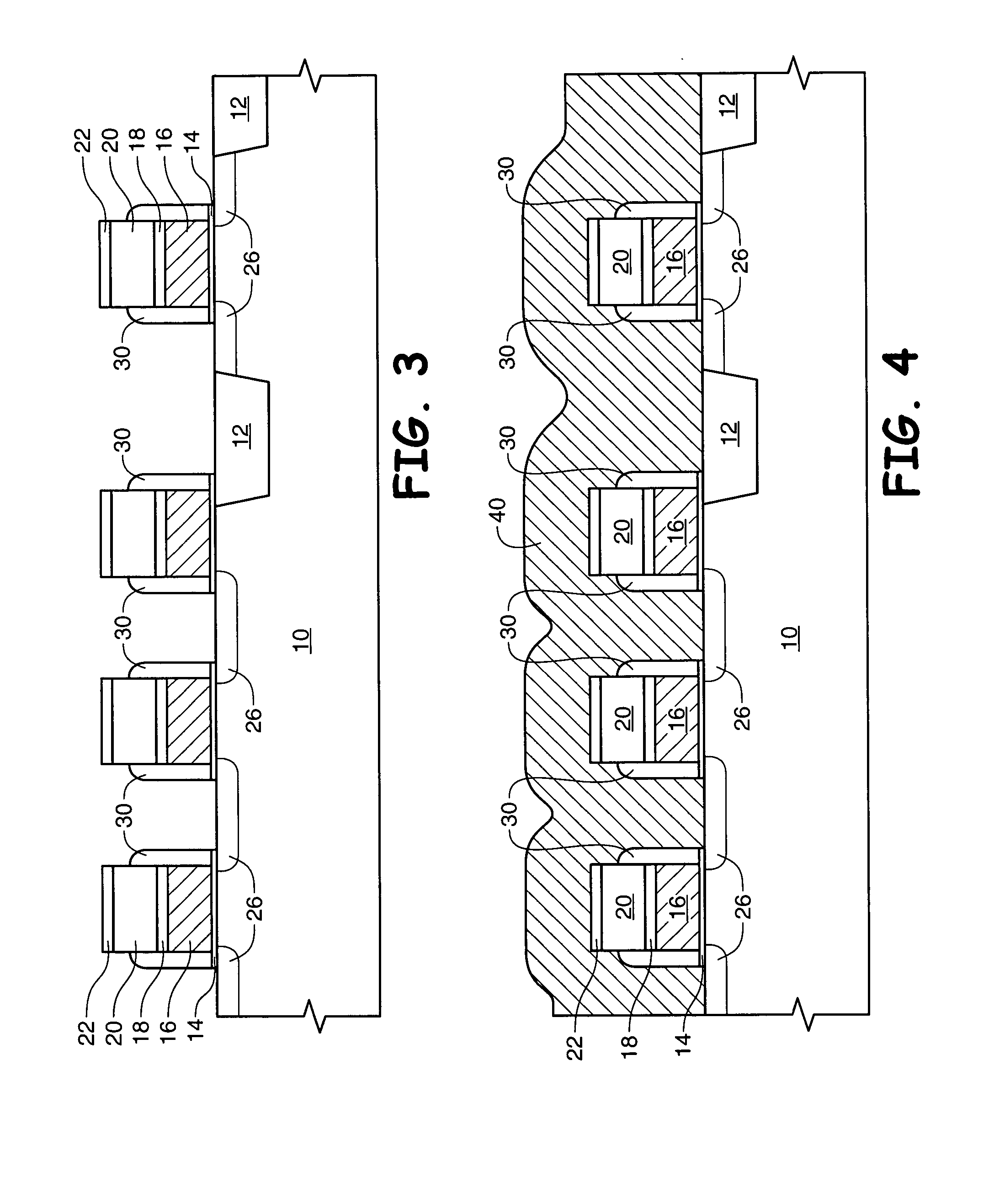

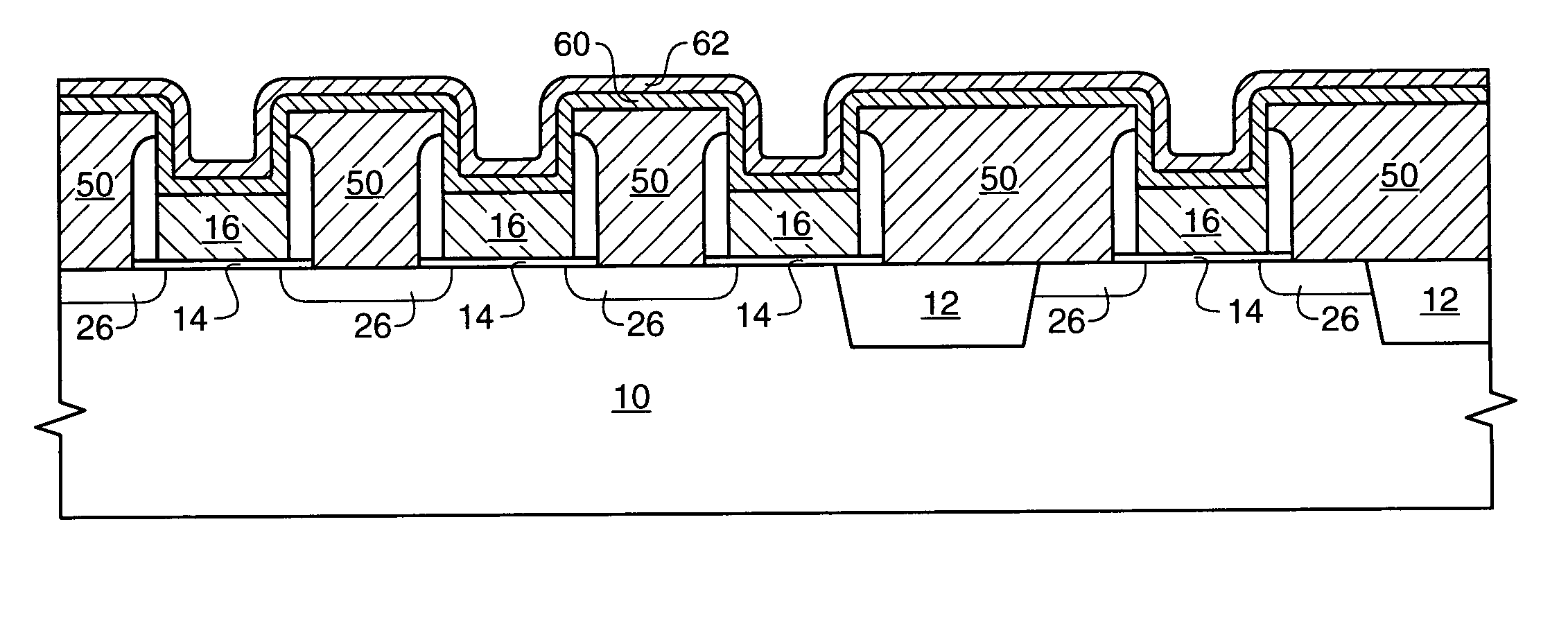

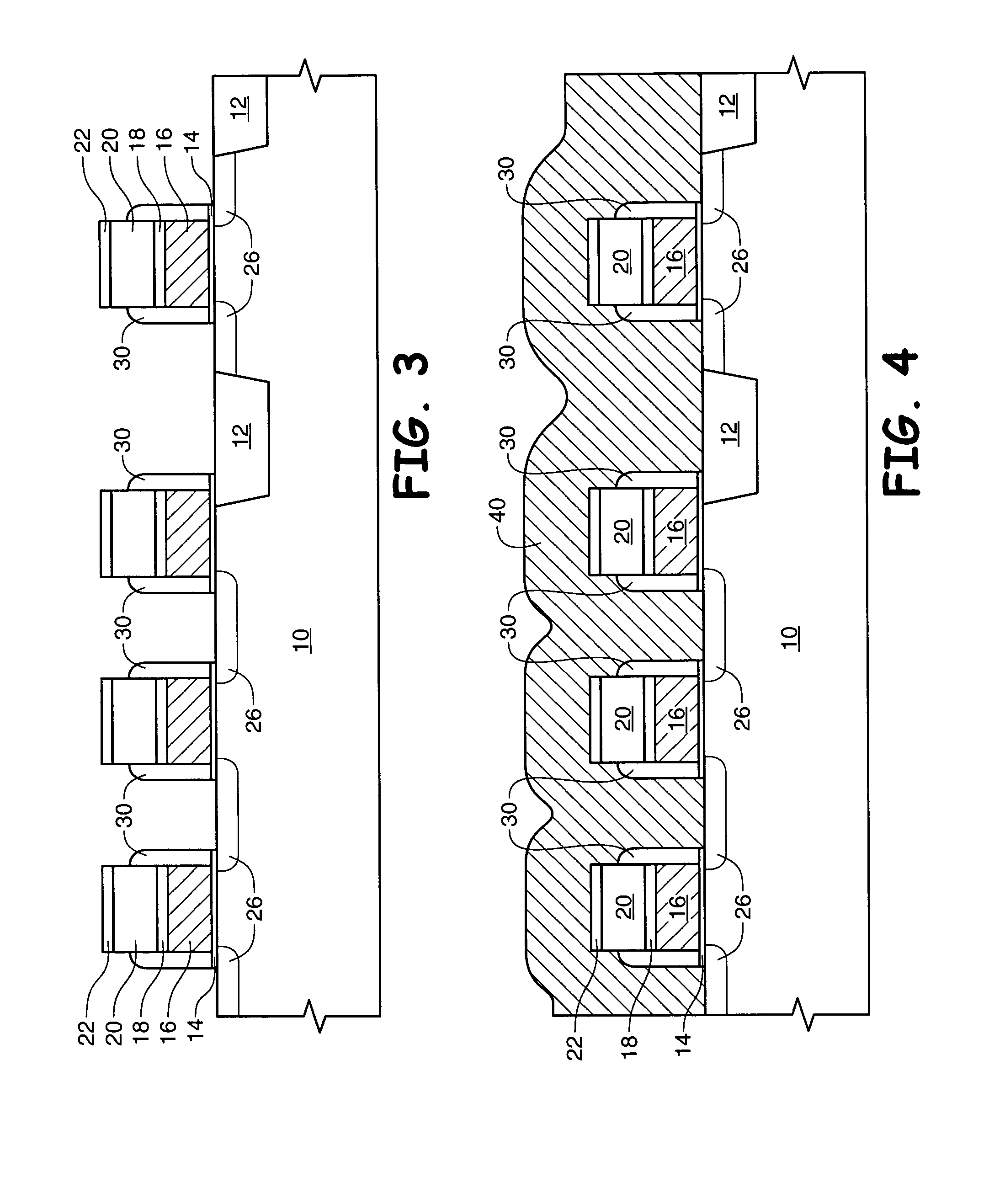

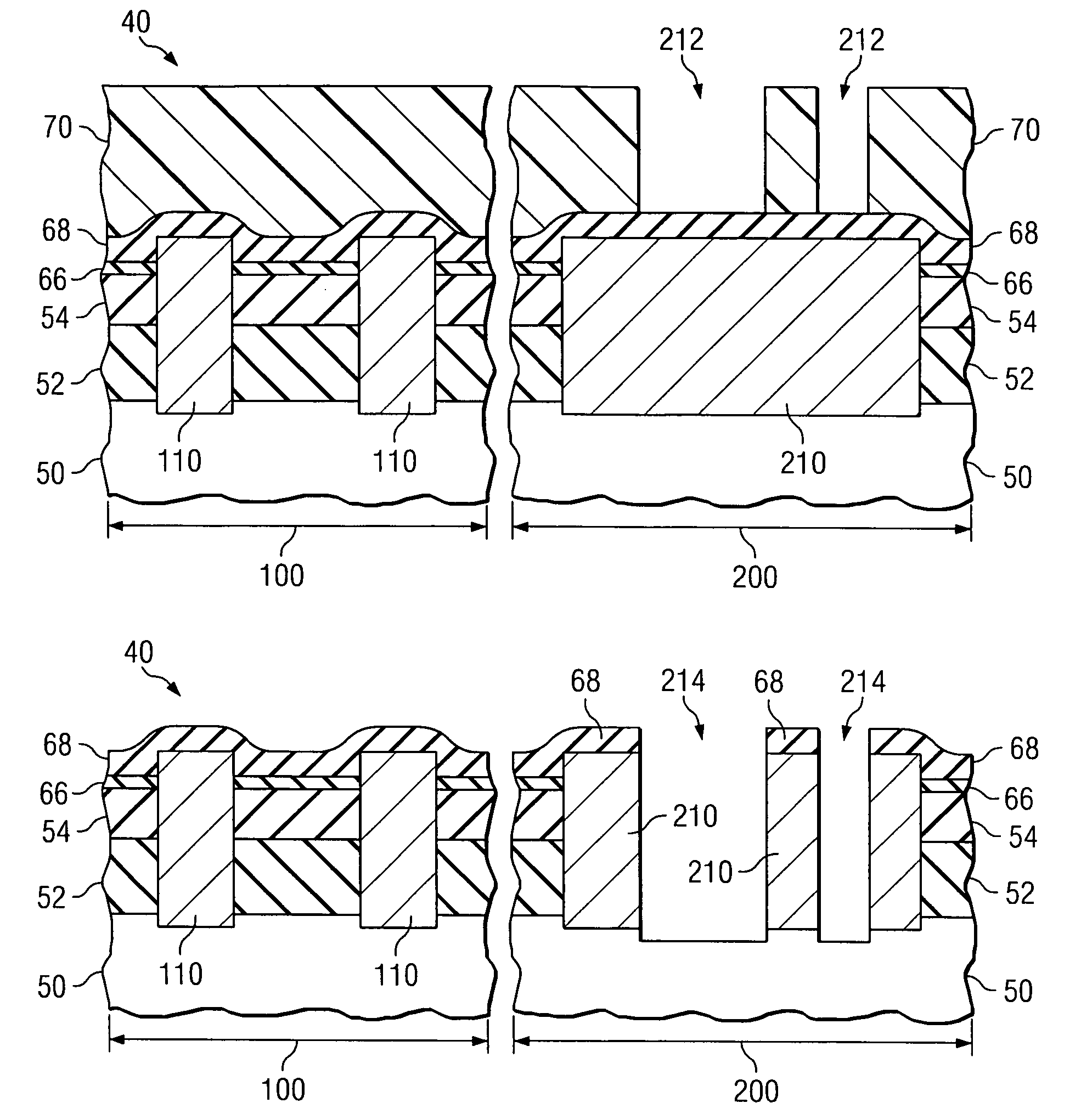

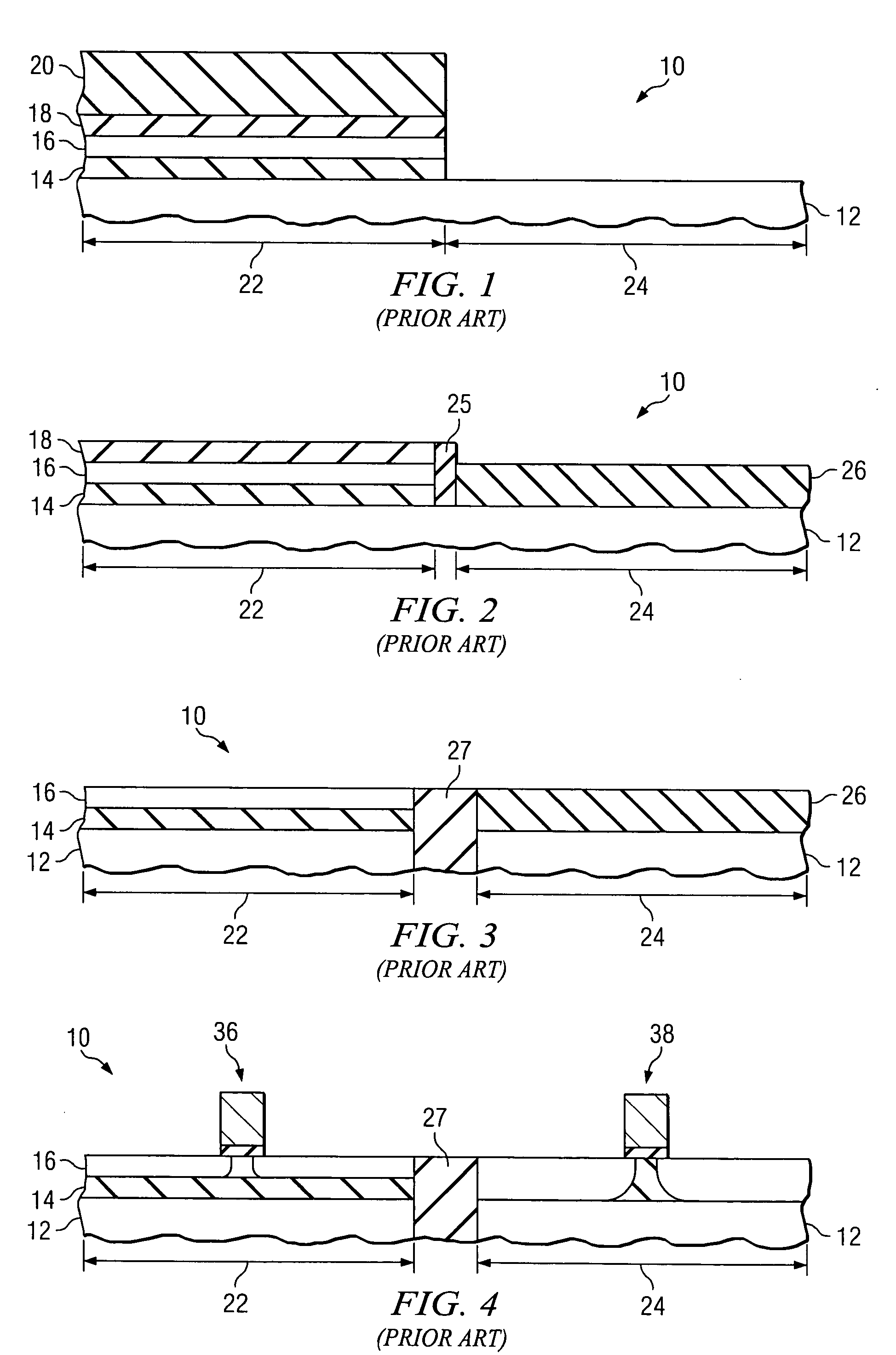

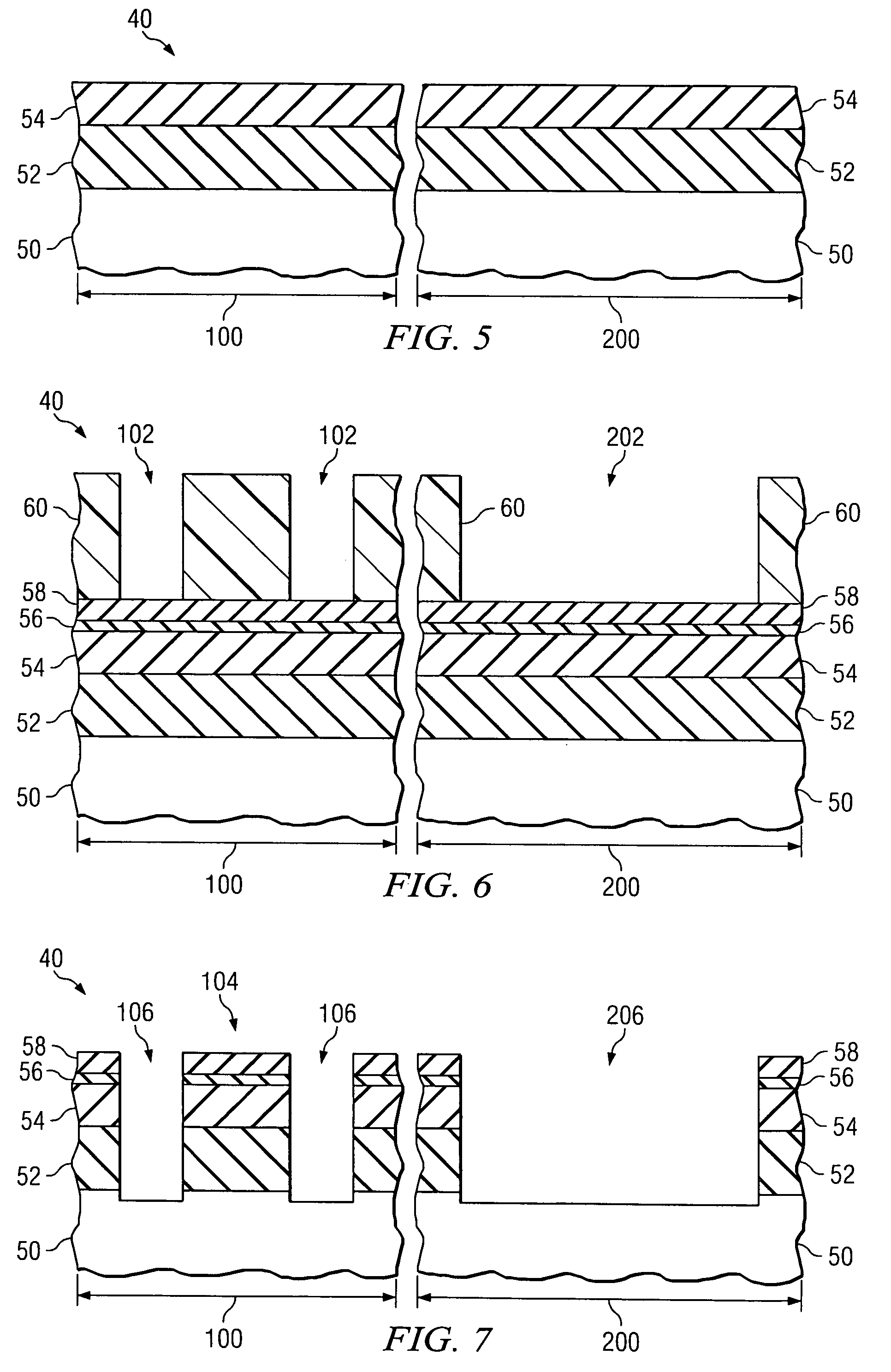

Method and structure for a self-aligned silicided word line and polysilicon plug during the formation of a semiconductor device

ActiveUS20050009343A1Reduce decreaseMore scaleableSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

A method used to form a semiconductor device provides a silicide layer on a plurality of transistor word lines and on a plurality of conductive plugs. In one embodiment, the word lines, one or more sacrificial dielectric layers on the word lines, conductive plugs, and a conductive enhancement layer are formed through the use of a single mask. An in-process semiconductor device which can be formed using one embodiment of the inventive method is also described.

Owner:MICRON TECH INC

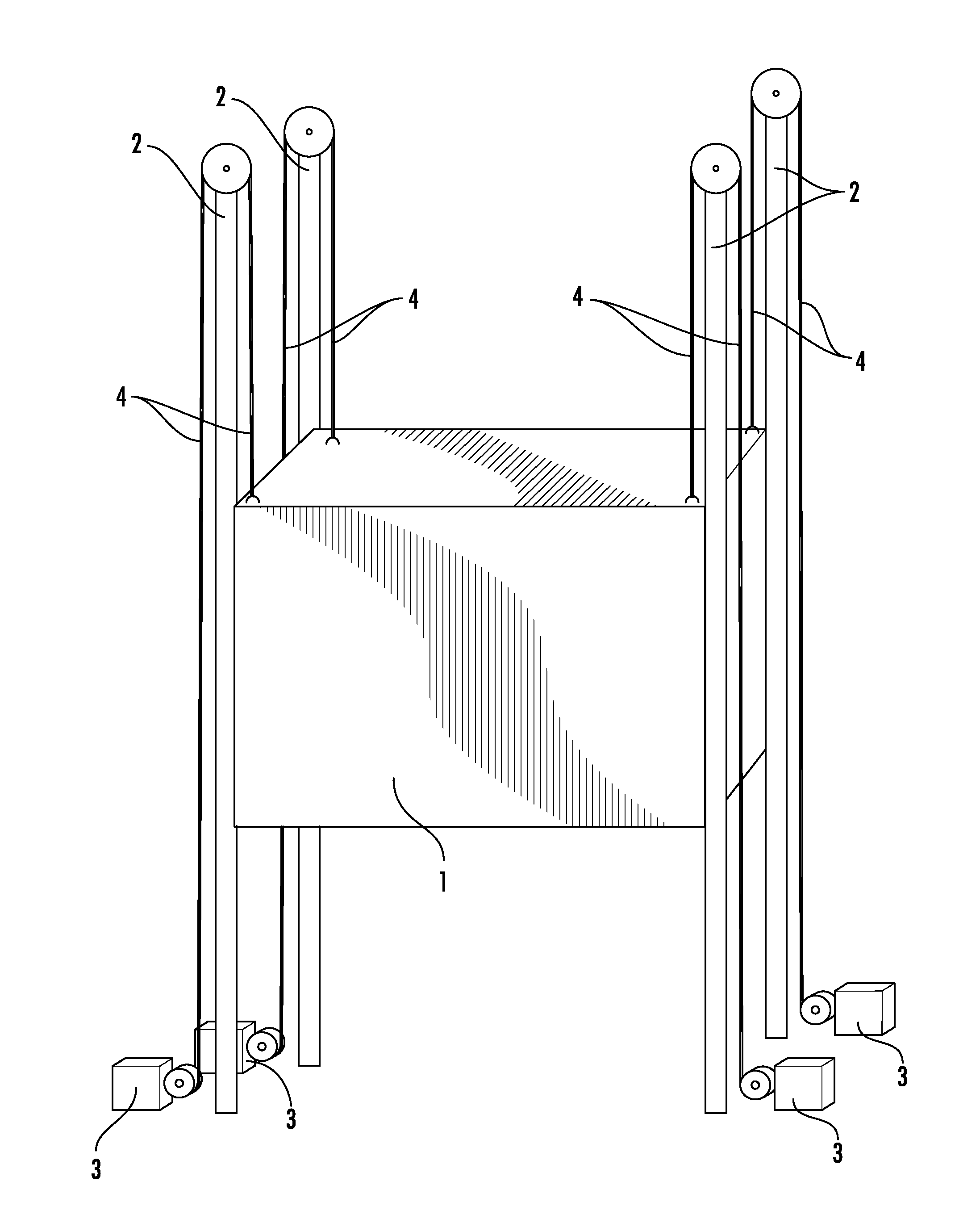

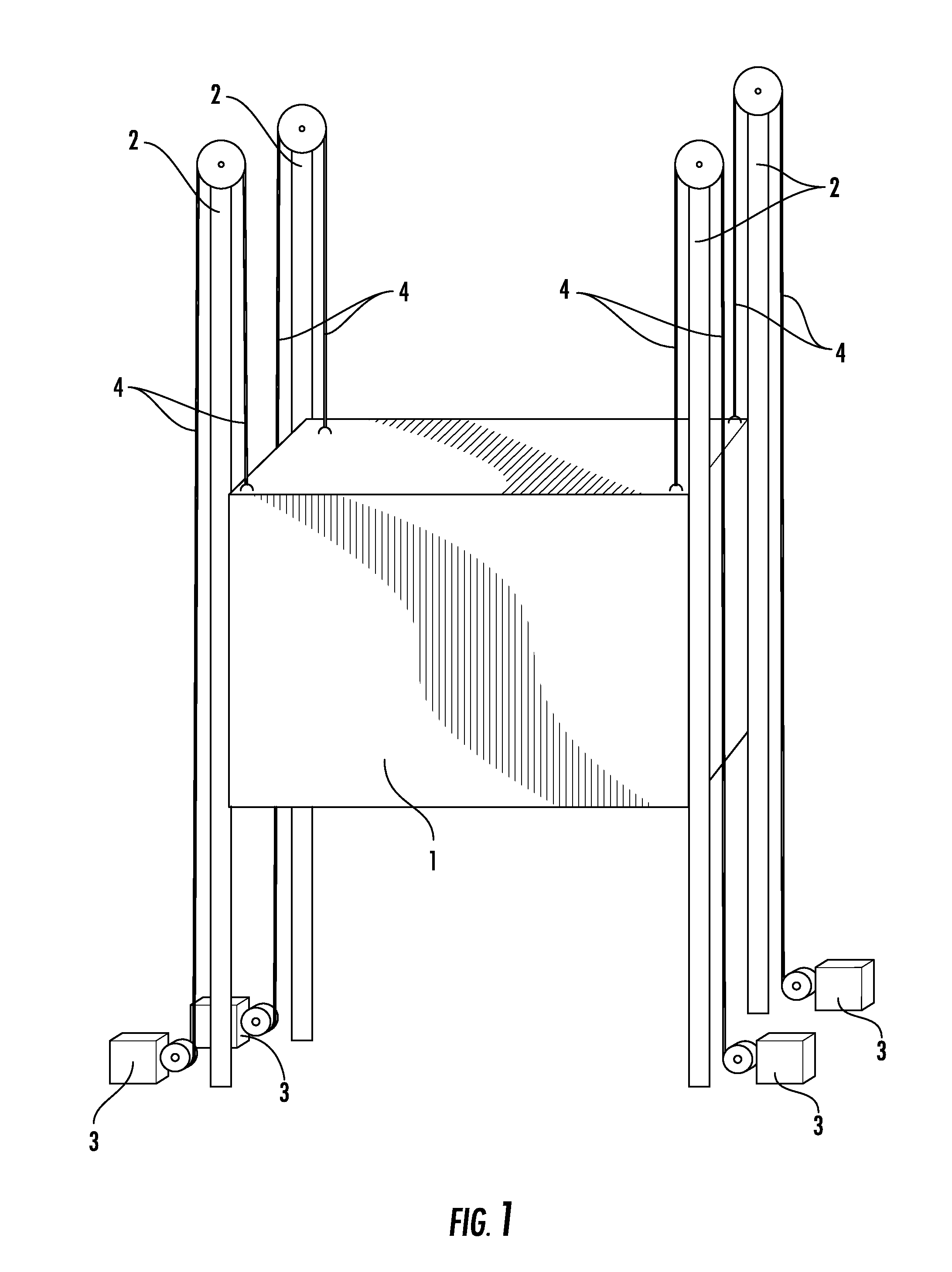

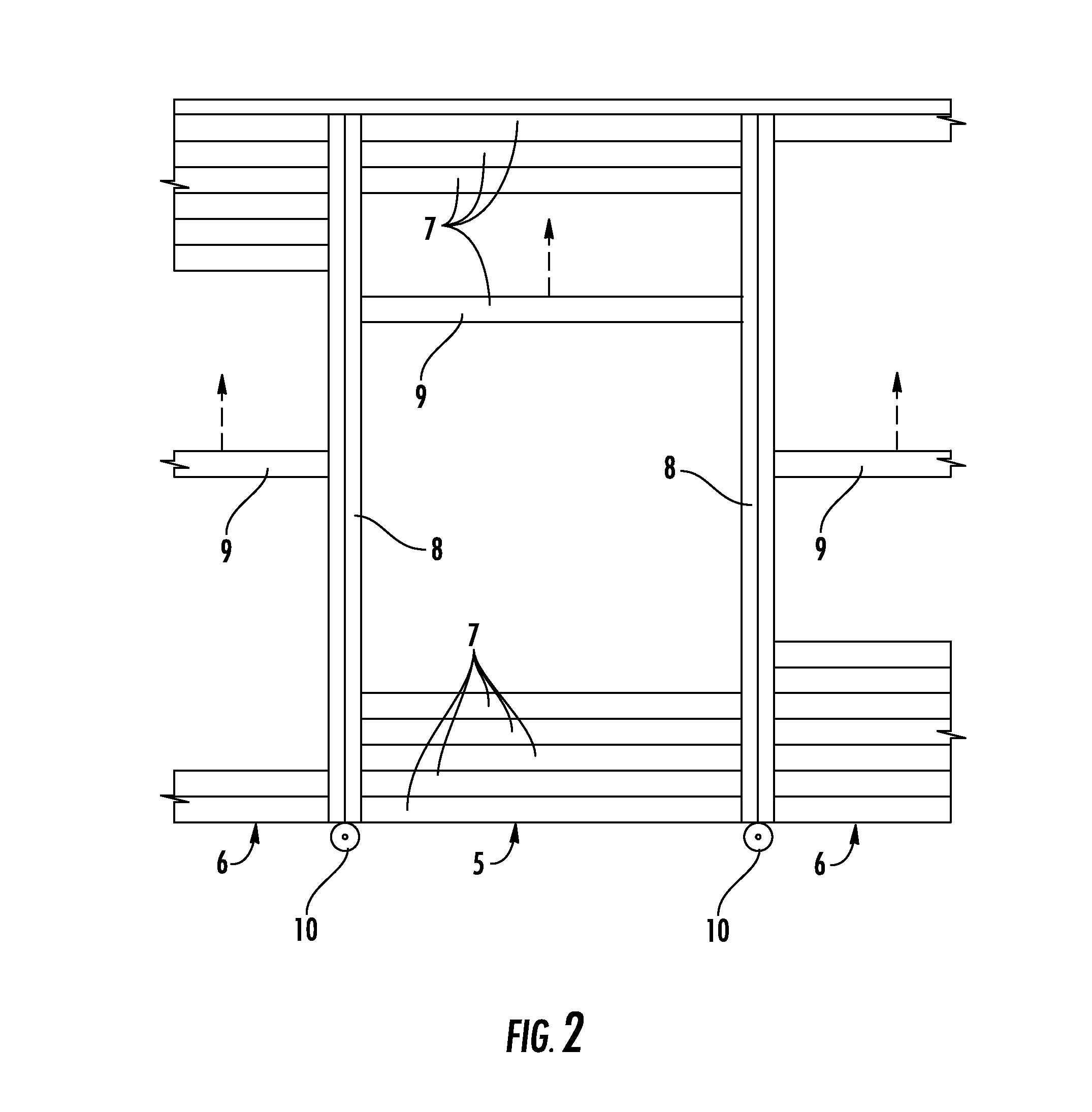

Energy Weight Storage

ActiveUS20160138572A1High costLower energyMachines/enginesMechanical energy handlingEngineeringEnergy storage

A first weight system for storing energy comprises a support platform with a lifting station having a plurality of vertically extending shafts, a cable and a motor located at ground level. This weight system hoists a heavily weighted device upwardly along the vertically extending shafts; holds it in a raised position and then lowers it along these same shafts to turn the motors and generate energy. The weighted device can include one or more flat rectangular containers or a weighted box.A second system employs a pair of containers connected to one another on an inclined track by a cable that can be moved about a guide wheel at a top of the track. The track further includes a media collection area, container filling area and means for conveying media from the bottom to the top of the inclined track.A third system pulls a plurality of large heavy wheels up an inclined track with wind power for subsequent lowering to turn a motor and generate energy.

Owner:BOONE DANIEL N

Preemptive multitasking employing software emulation of directed exceptions in a multithreading processor

ActiveUS9032404B2Multithreading processor more scalableSave areaProgram initiation/switchingSoftware engineeringSoftware emulationMulti processor

Owner:MIPS TECH INC

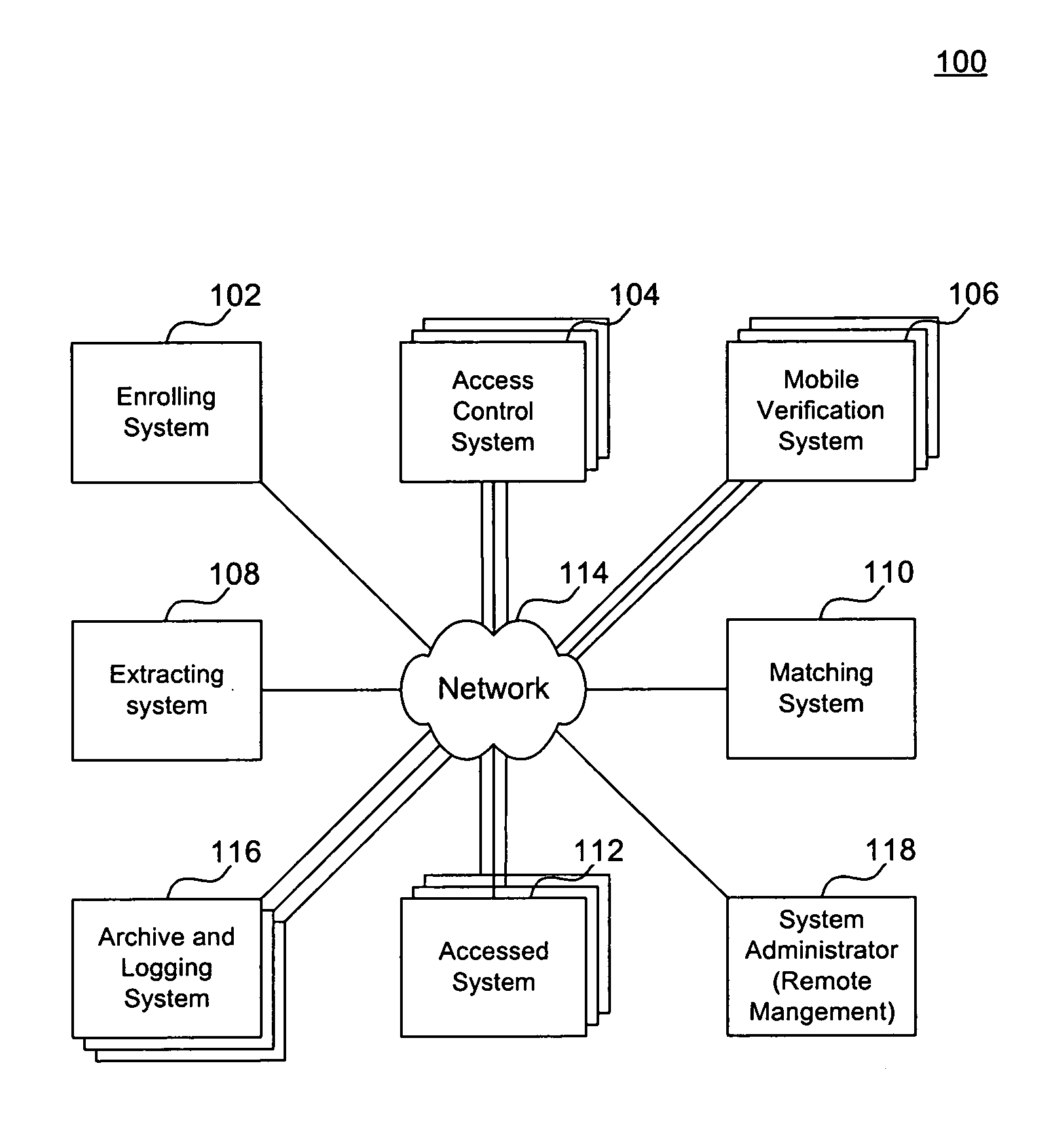

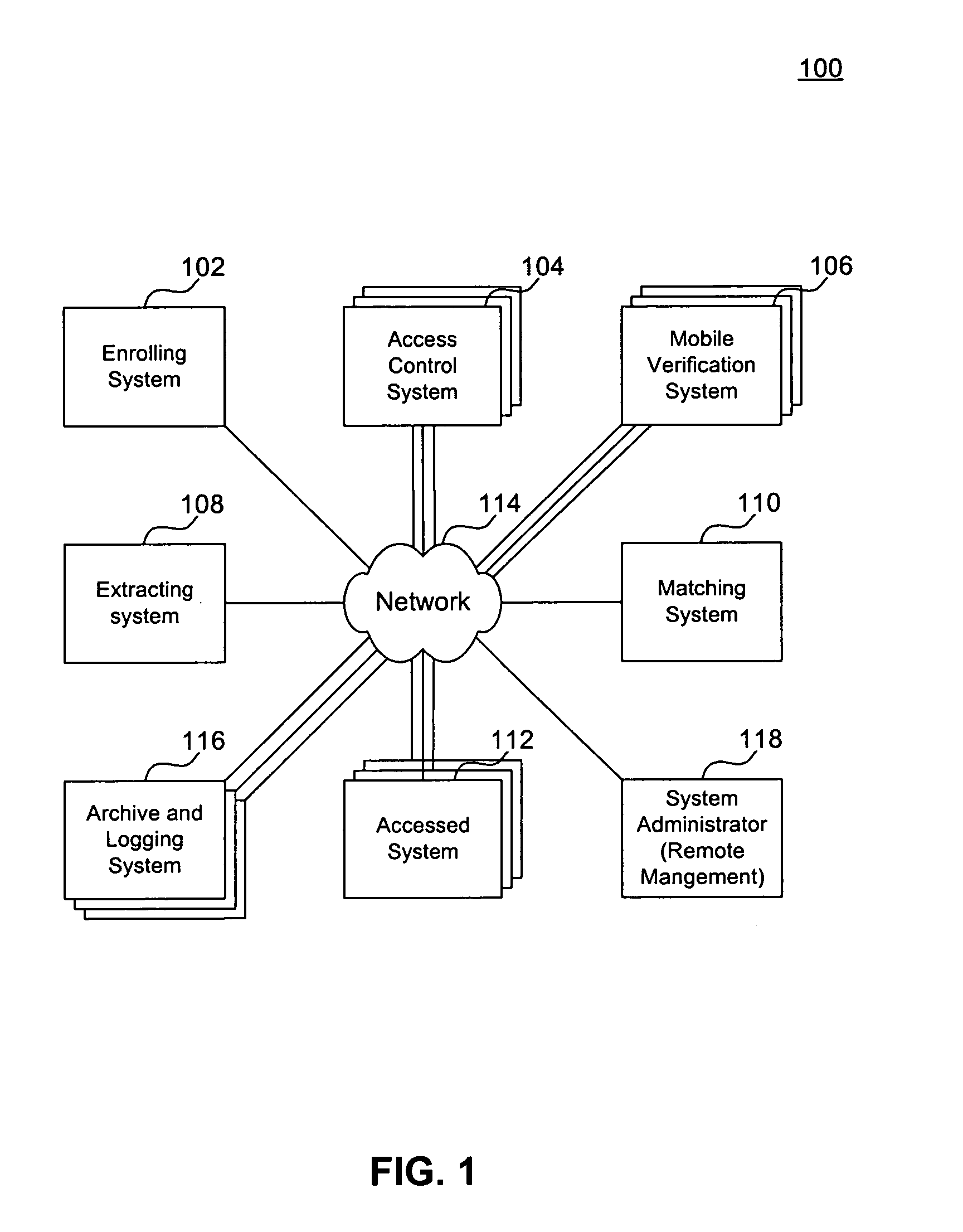

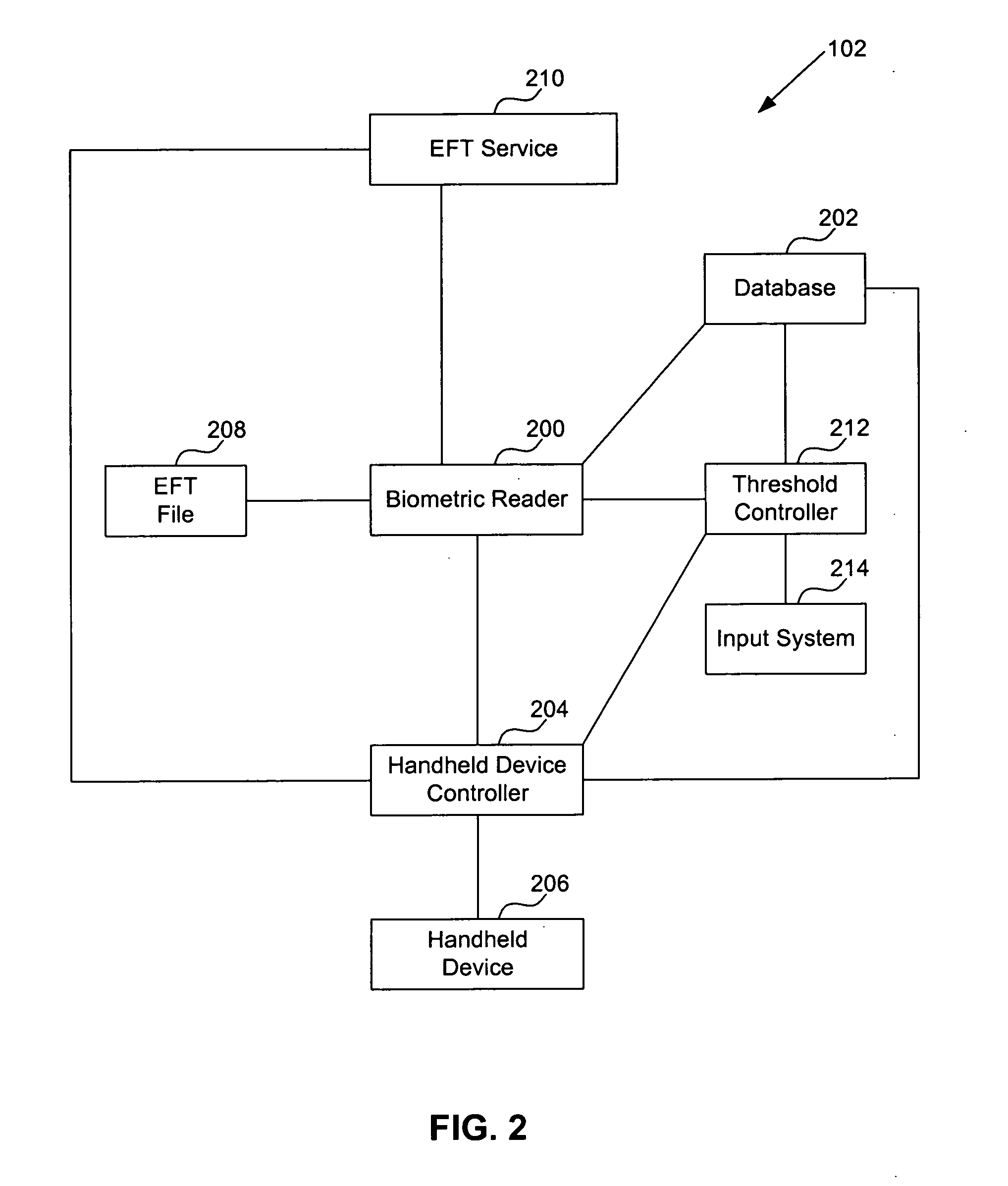

Systems and methods utilizing biometric data

InactiveUS20050264398A1Reduce in quantityIncrease the number ofProgramme controlElectric signal transmission systemsBiometric dataBarcode

Systems and methods perform access control and mobile identity verification utilizing a memory, maybe on a handheld device, that stores at least biometric data, such as minutia. The handheld device may also store other data, such as a threshold value and Wiegand data. The data may be stored in a memory, a magnetic strip, a code, a bar code, or in all of these devices associated with the handheld device. The handheld device may be a SmartCard or the like. The threshold value may be a required value or parameter generated from input criteria based on biometric data read and extracted by an extracting system during an enrolling process. The threshold value is used during extracting, matching, or both, to most accurately determine the identity and characteristics of an individual wanting access to an accessed system or being questioned by law enforcement in the field.

Owner:CROSS MATCH TECH

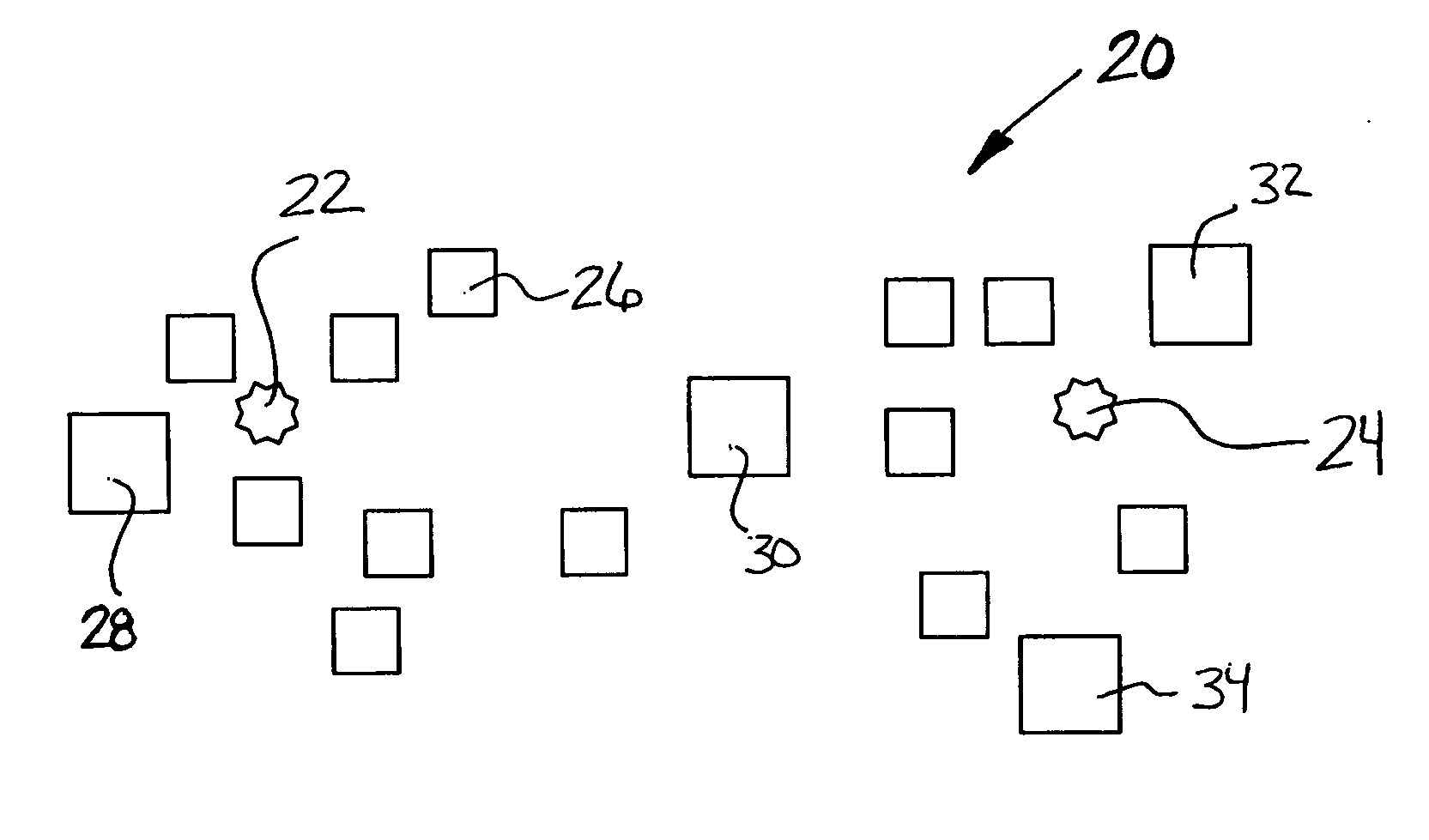

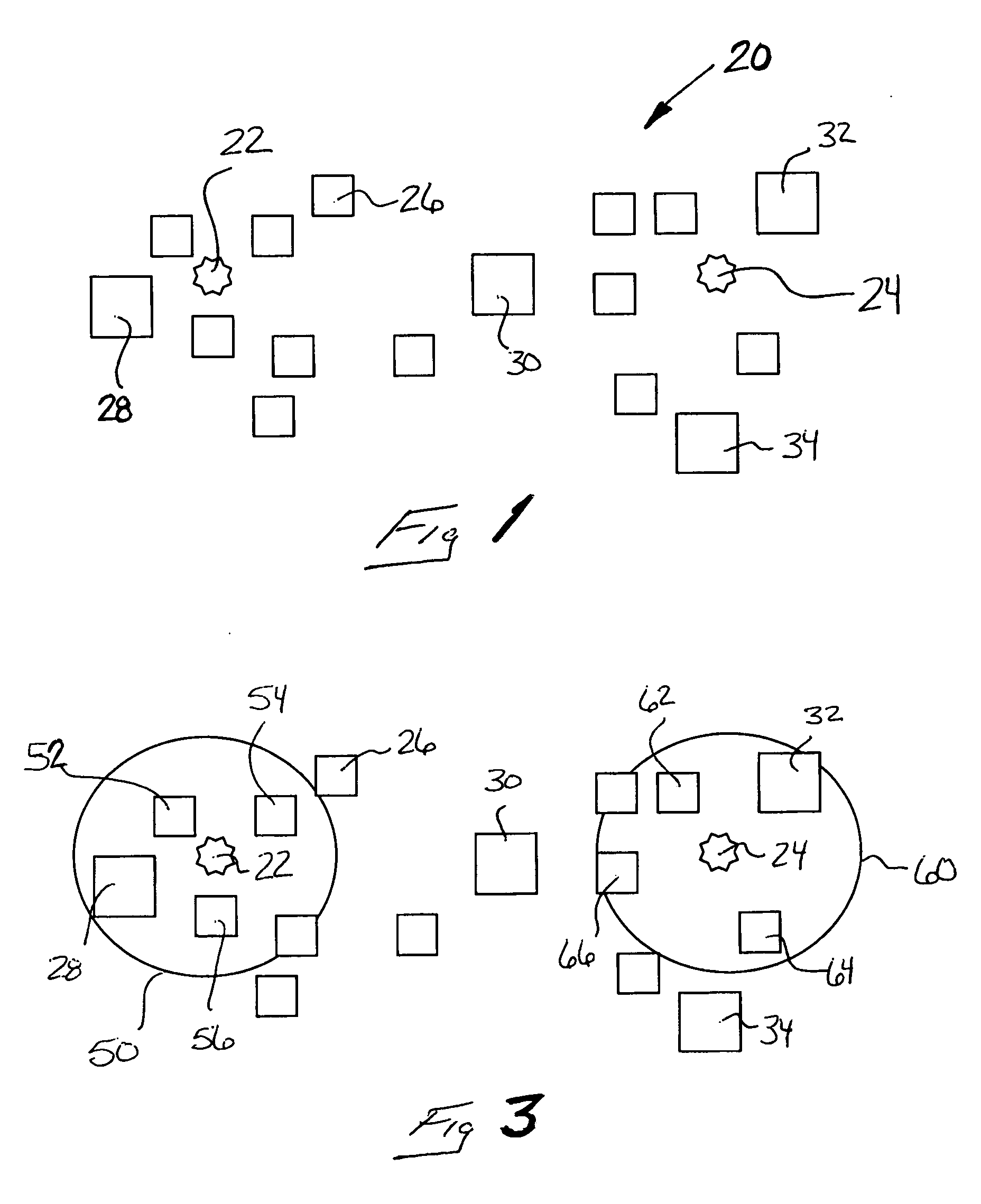

Routing Internet communications using network coordinates

InactiveUS20070097951A1Improve abilitiesLow costData switching by path configurationInternet communicationComputer network

A communication technique includes routing communications over an internet topology using coordinates, which correspond to estimated round trip times, of an origination, a destination and at least one intermediary host or node. A disclosed example includes identifying candidate intermediary nodes based upon selected criteria such as proximity to at least one of the origination or destination for the communication. A disclosed example includes identifying a plurality of intermediary nodes for some applications.

Owner:WSOU INVESTMENTS LLC +1

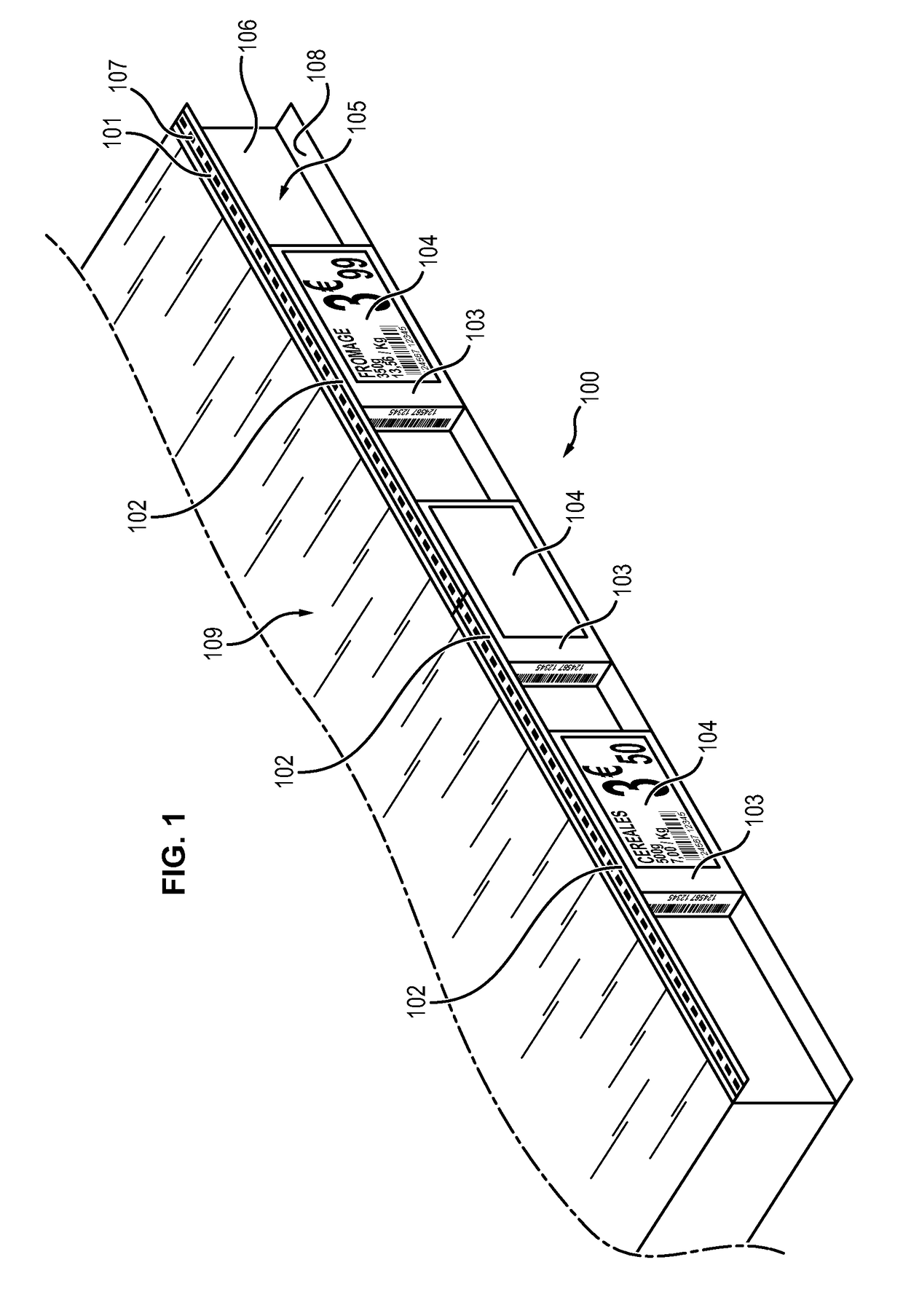

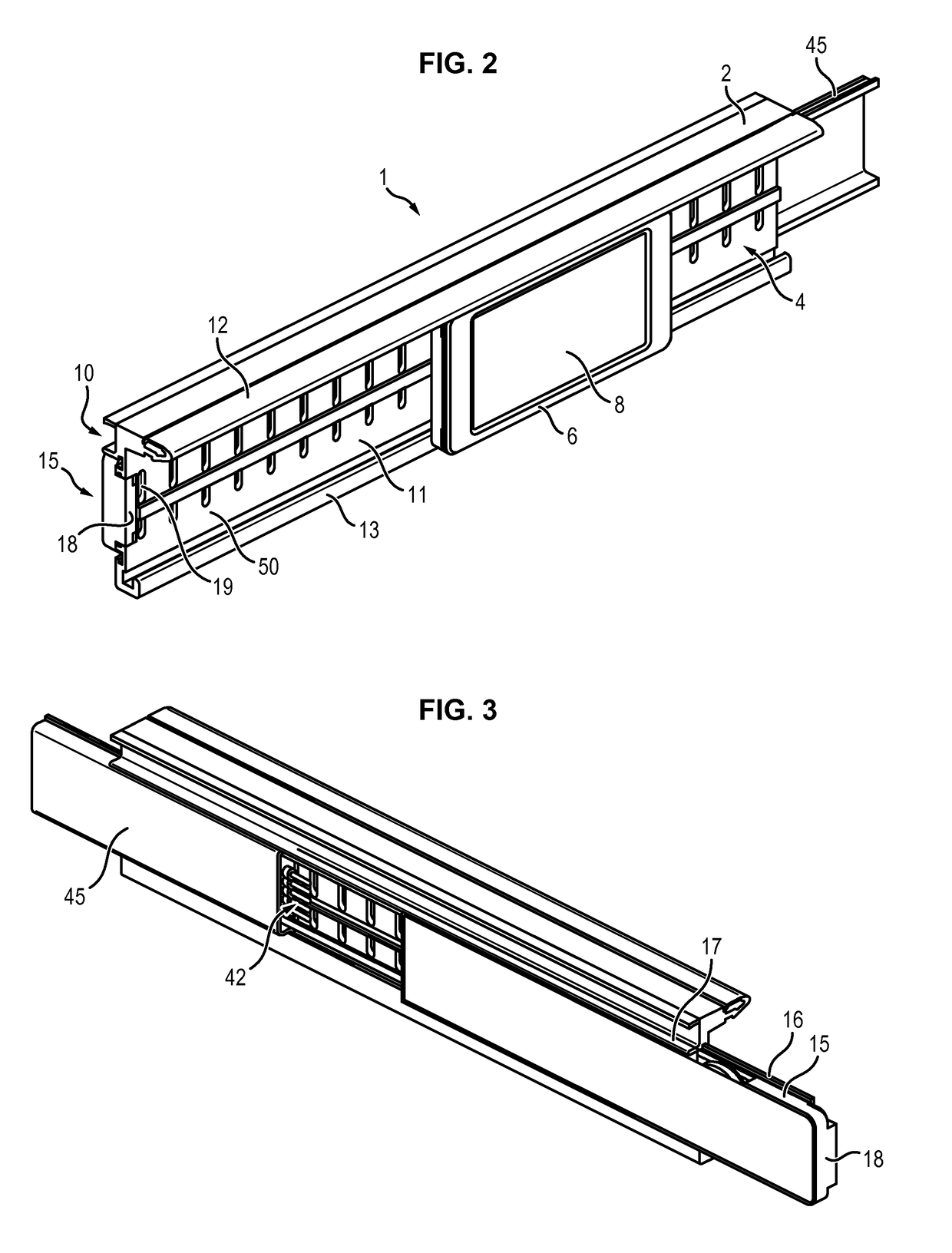

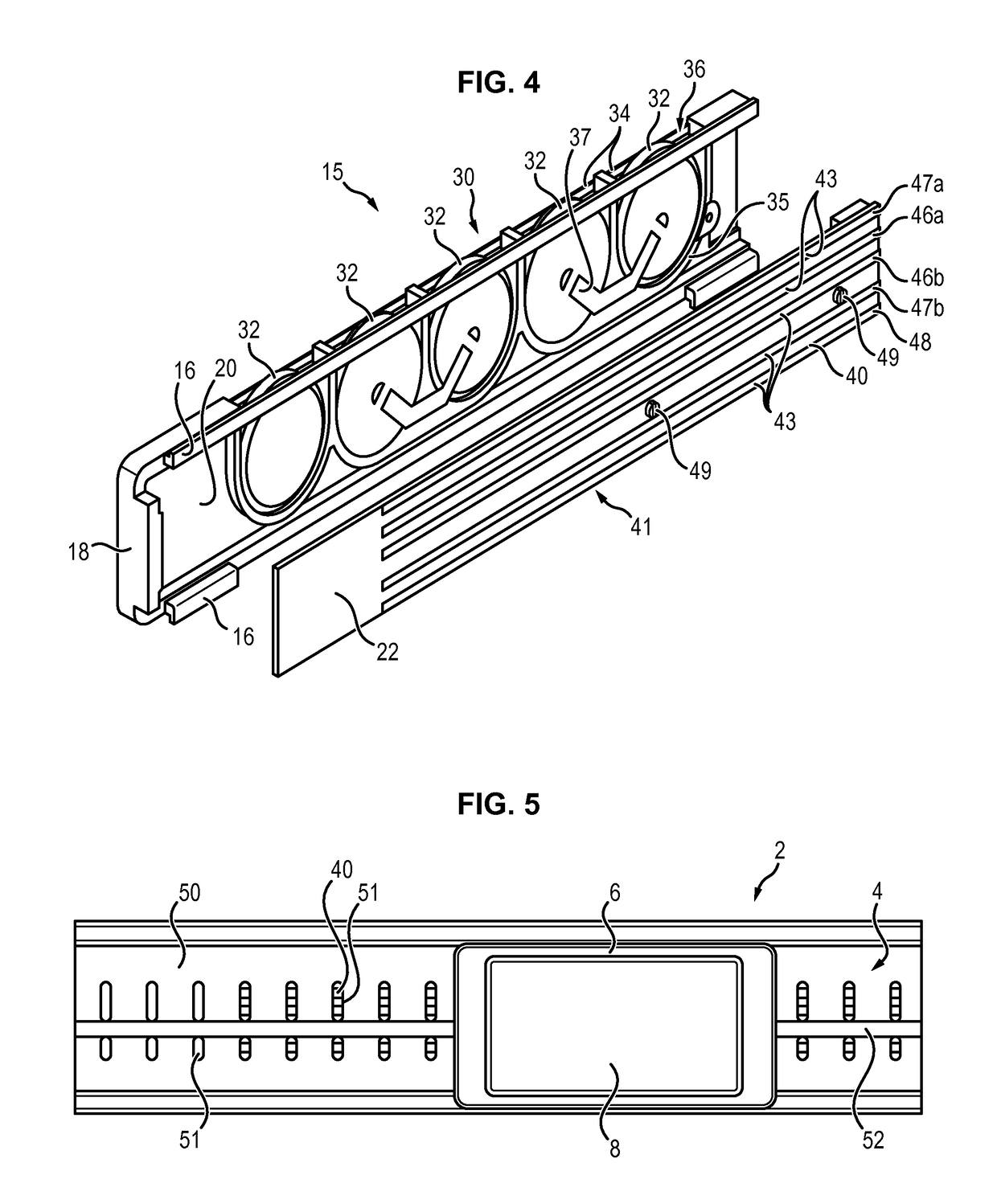

Information Display System In A Sales Area

ActiveUS20190080633A1More scalableLess costlyStampsStatic indicating devicesInformation display systemsElectronic shelf label

The invention concerns an information display system in a sales area, comprising: —a support (2) comprising a module (15) managing electronic shelf labels and connection lines (40) linking the management module to the receiving space; and —a plurality of electronic shelf labels (6) housed in the receiving space of said support, wherein the electronic shelf labels (6) are connected to the connection lines (40) via connectors (63), and wherein the electronic shelf labels (6) are managed by the management module.

Owner:SES IMAGOTAG

Method and structure for a self-aligned silicided word line and polysilicon plug during the formation of a semiconductor device

ActiveUS7119024B2Reduce decreaseMore scalableSolid-state devicesSemiconductor/solid-state device manufacturingDielectric layerSemiconductor

A method used to form a semiconductor device provides a silicide layer on a plurality of transistor word lines and on a plurality of conductive plugs. In one embodiment, the word lines, one or more sacrificial dielectric layers on the word lines, conductive plugs, and a conductive enhancement layer are formed through the use of a single mask. An in-process semiconductor device which can be formed using one embodiment of the inventive method is also described.

Owner:MICRON TECH INC

Storage unsharing

ActiveUS8825982B2Improve performanceReduce in quantityEnergy efficient ICTMemory adressing/allocation/relocationComputer engineeringSoftware

A method is described to partition the memory of application-specific hardware compiled from a software program. Applying the invention generates multiple small memories that need not be kept coherent and are defined over a specific region of the program. The invention creates application specific hardware which preserves the memory image and addressing model of the original software program. The memories are dynamically initialized and flushed at the entries and exits of the program region they are defined in.

Owner:GLOBAL SUPERCOMPUTING CORP

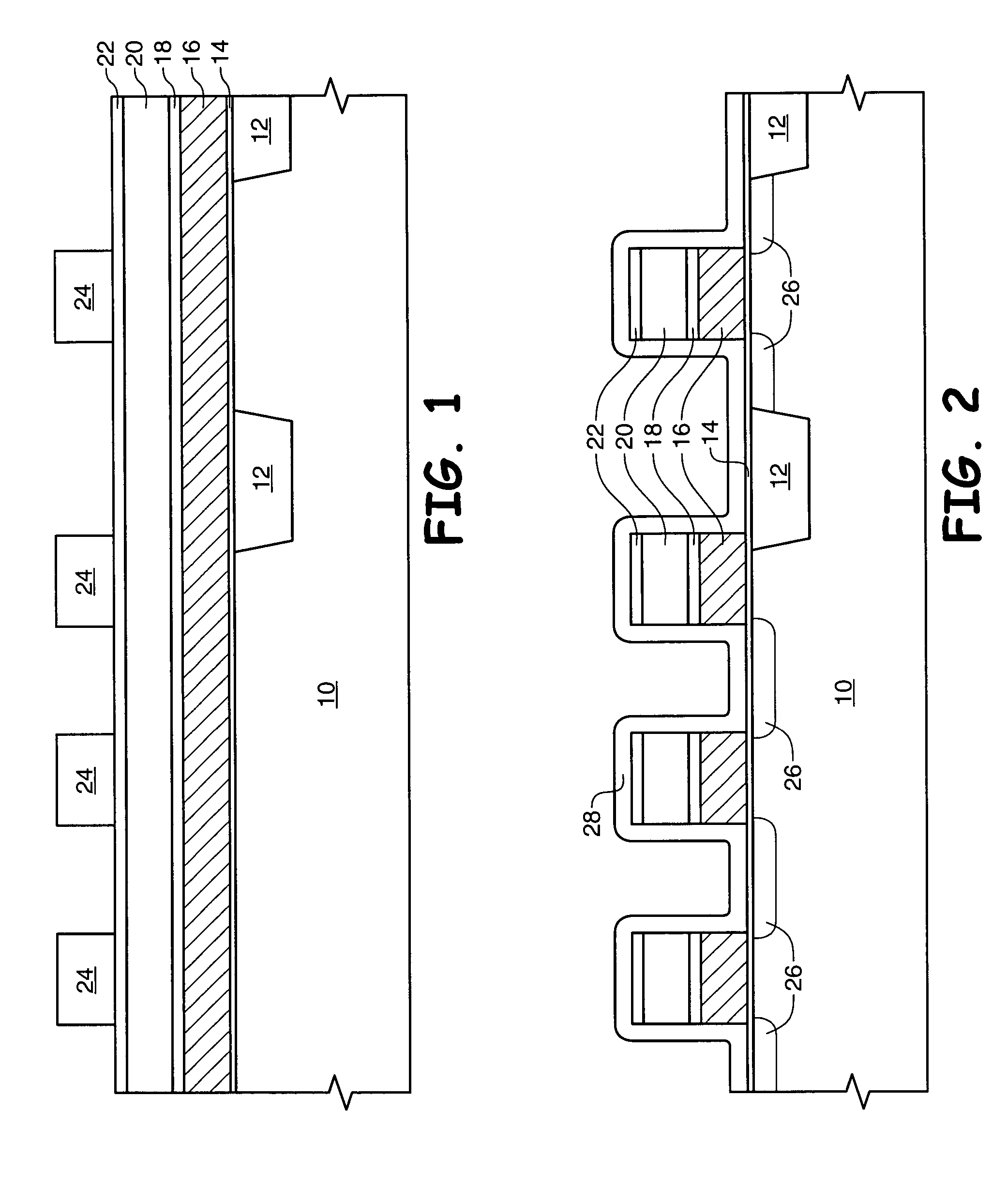

High performance transistors with hybrid crystal orientations

InactiveUS7611937B2Improve performanceMore scalableSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectrical conductor

A method of forming a semiconductor structure having a hybrid crystal orientation and forming MOSFETs having improved performance on the semiconductor structure is provided. The method includes providing a substrate comprising a buried oxide (BOX) on a first semiconductor layer, and a second semiconductor layer on the BOX, wherein the first and second semiconductor layers have a first and a second crystal orientation, respectively, and wherein the substrate comprises a first region and a second region. An isolation structure is formed in the second region extending to the first semiconductor layer. A trench is then formed in the isolation structure, exposing the first semiconductor layer. A semiconductor material is epitaxially grown in the trench. The method further includes forming a MOSFET of a first type on the second semiconductor layer and a MOSFET of an opposite type than the first type on the epitaxially grown semiconductor material.

Owner:TAIWAN SEMICON MFG CO LTD +1

Crossbar circuitry for applying an adaptive priority scheme and method of operation of such crossbar circuitry

ActiveUS8549207B2Fast and scalable techniqueMore scalableMultiplex system selection arrangementsElectronic switchingCrossbar switchOperation mode

Crossbar circuitry has an array of data input and output paths where the data output paths are transverse to the data input paths. At each intersection between a data input path and a data output path, a crossbar cell is provided which includes a configuration storage circuit programmable to store a routing value, a transmission circuit, and an arbitration circuit. In a transmission mode of operation, the transmission circuit is responsive to the routing value being a first value, indicating that the data input path should be coupled to the data output path, to detect the data input along the data input path, and to output an indication of that data on the data output path at the associated intersection. In an arbitration mode of operation, the arbitration circuitry is operable to selectively modify the voltage on said plurality of bit lines in order to apply an adaptive priority scheme.

Owner:RGT UNIV OF MICHIGAN

Devices and methods for reshaping cartilage structures

ActiveUS20120226307A1Reduce system costImprove networkingAdditive manufacturing apparatusEar treatmentRouting tableNetworked system

A networked system in which the majority of data bypass the server (101) to improve end-to-end performance of network access by achieving higher throughput between the network (130) and storage system (110). The apparatus consists of a network interface (120), server computer interface (240), and storage interface (250); and a switching element (201) and a high-layer protocol decoding and control unit (205). Incoming traffic is decoded and compared against a routing table. If there is a matching entry, it will be routed to the storage interface or sent to the server for further processing by default. The routing table entries are set up based on the initial nature of the applications. Subsequently, barring any changes or errors, there will be no data exchange between the server and the device. There may also be a speed matching funcion between the network and storage, load balancing function for servers, and flow control for priority and QOS purposes.

Owner:CHONDROCYTE