Patents

Literature

89results about How to "Avoid long connections" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

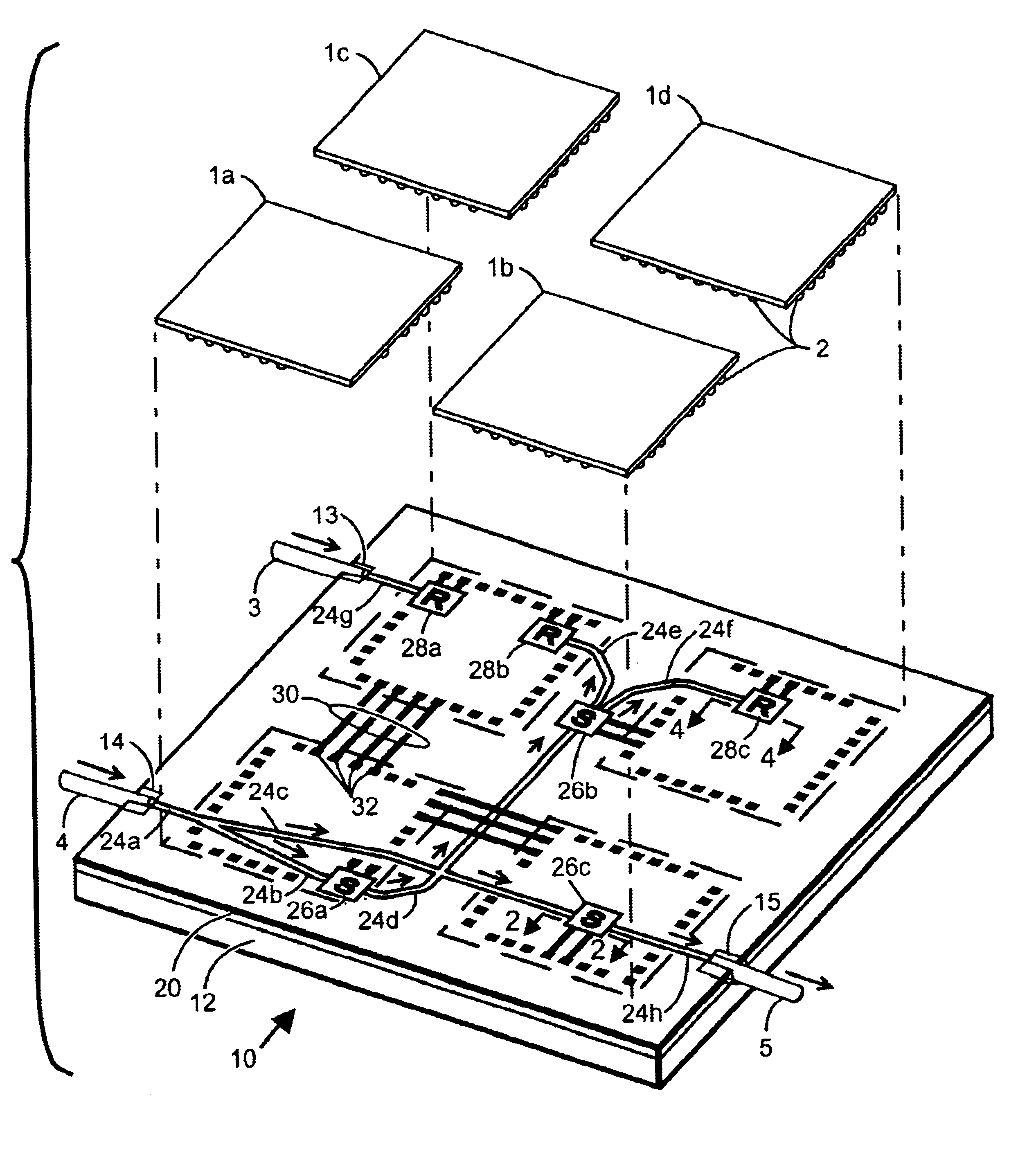

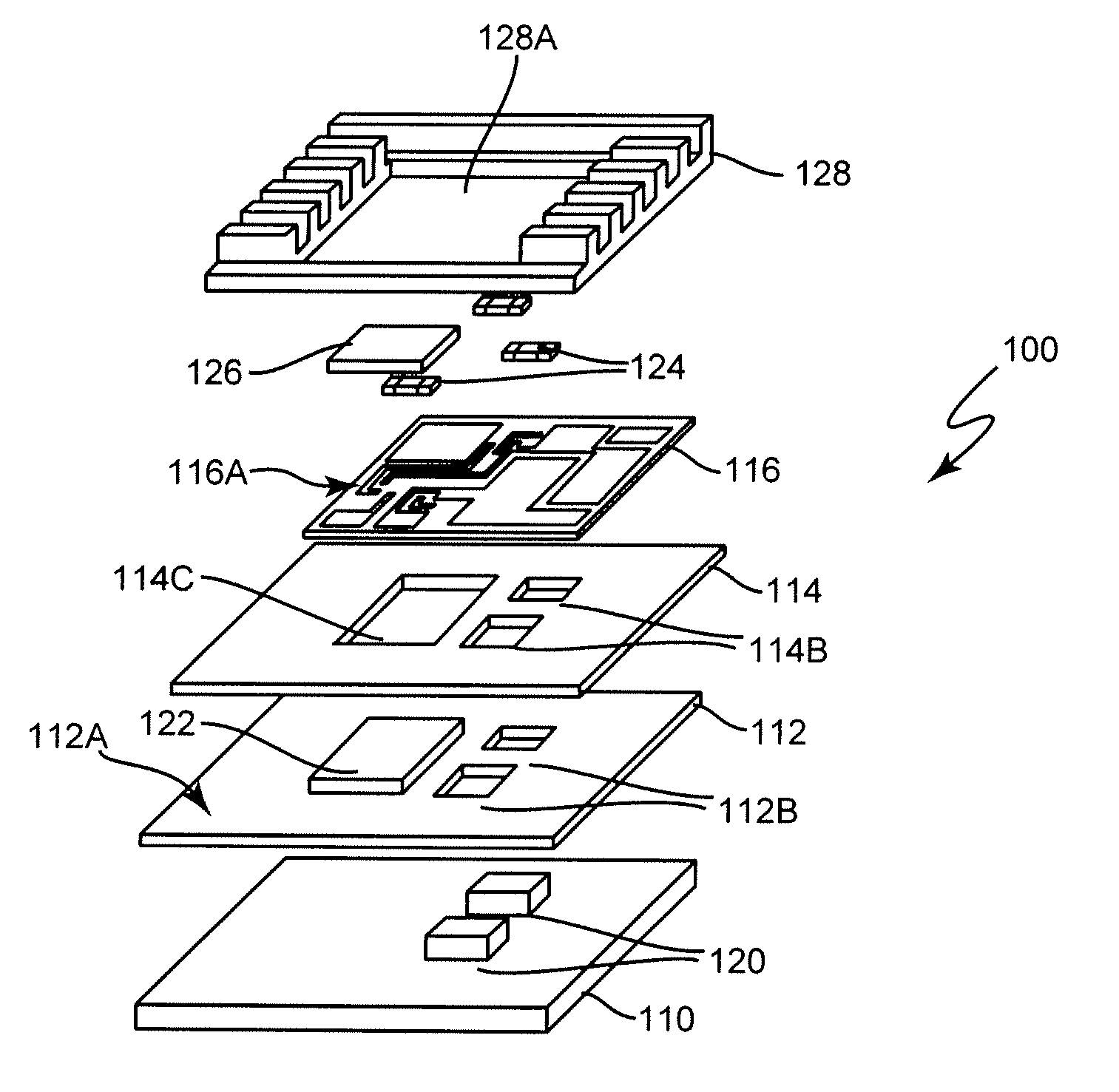

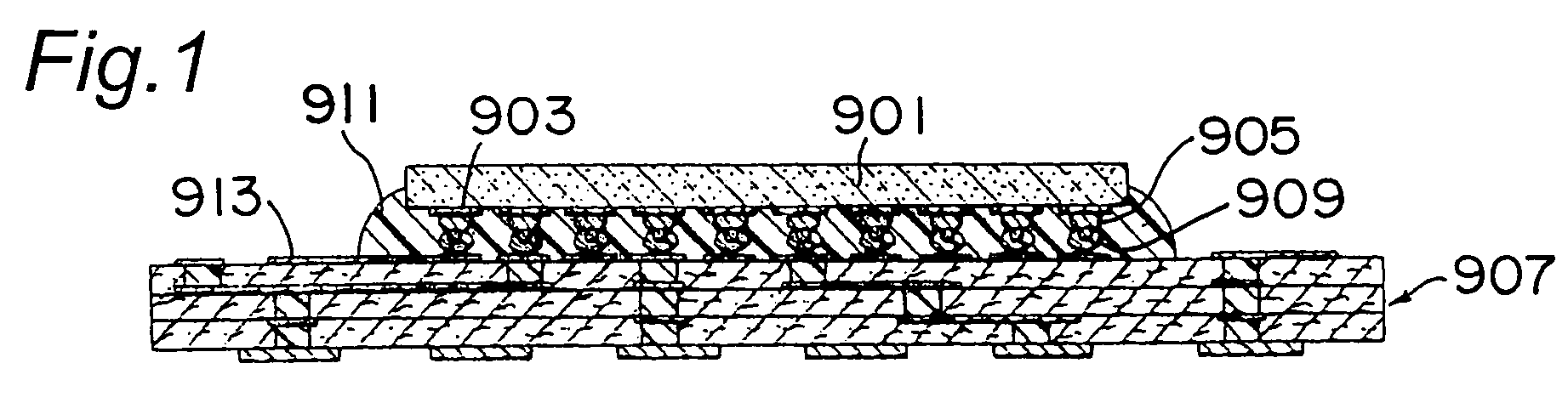

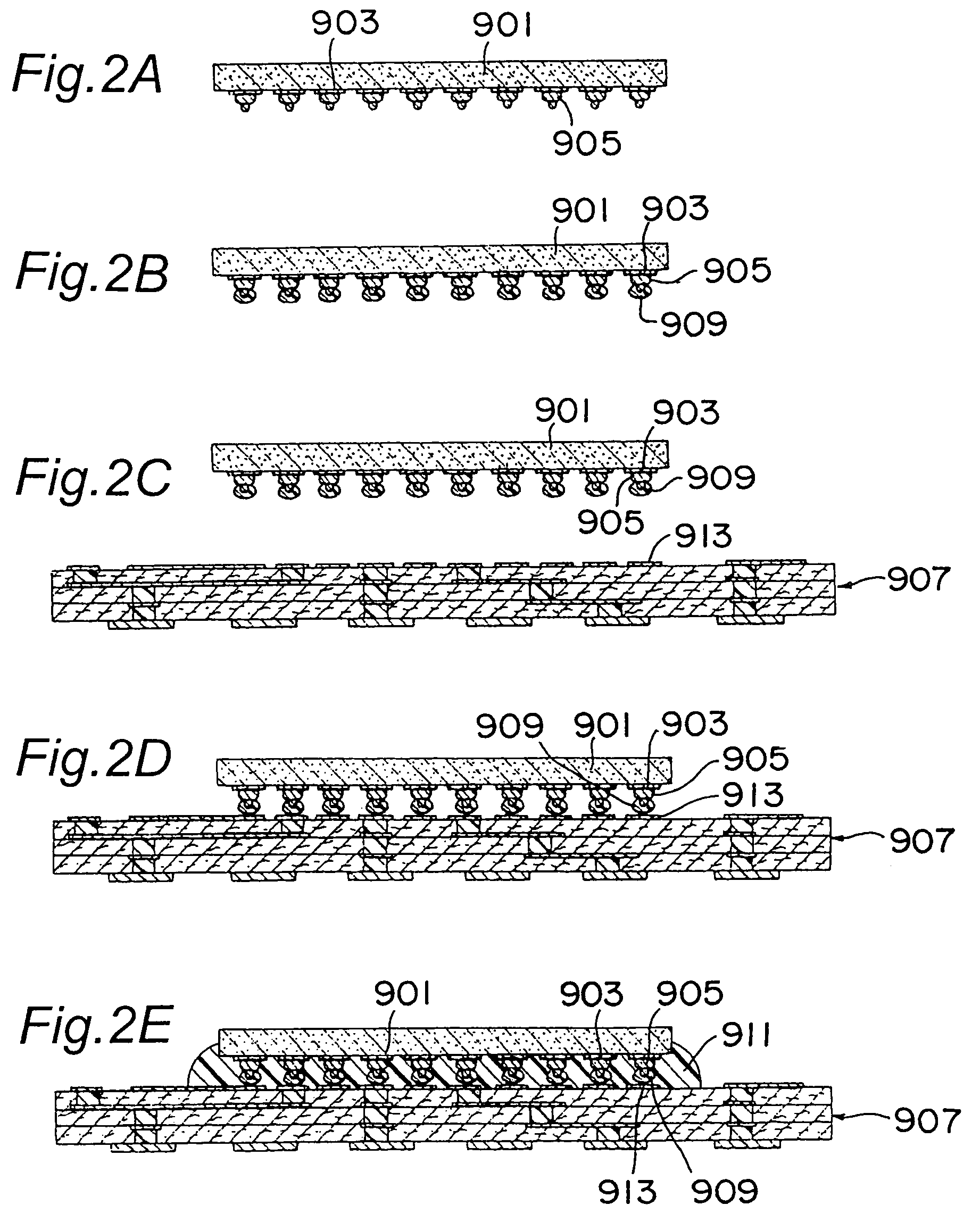

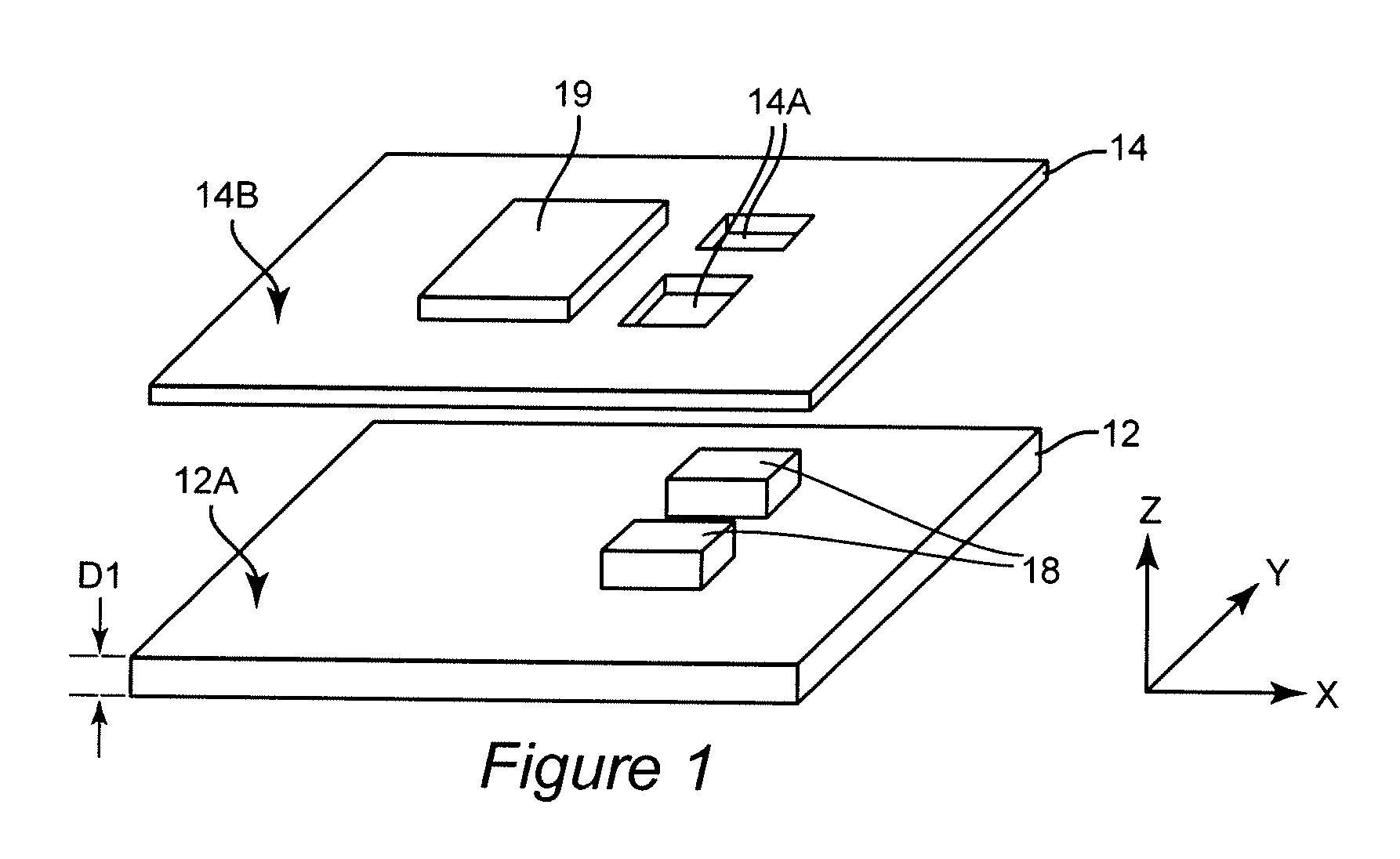

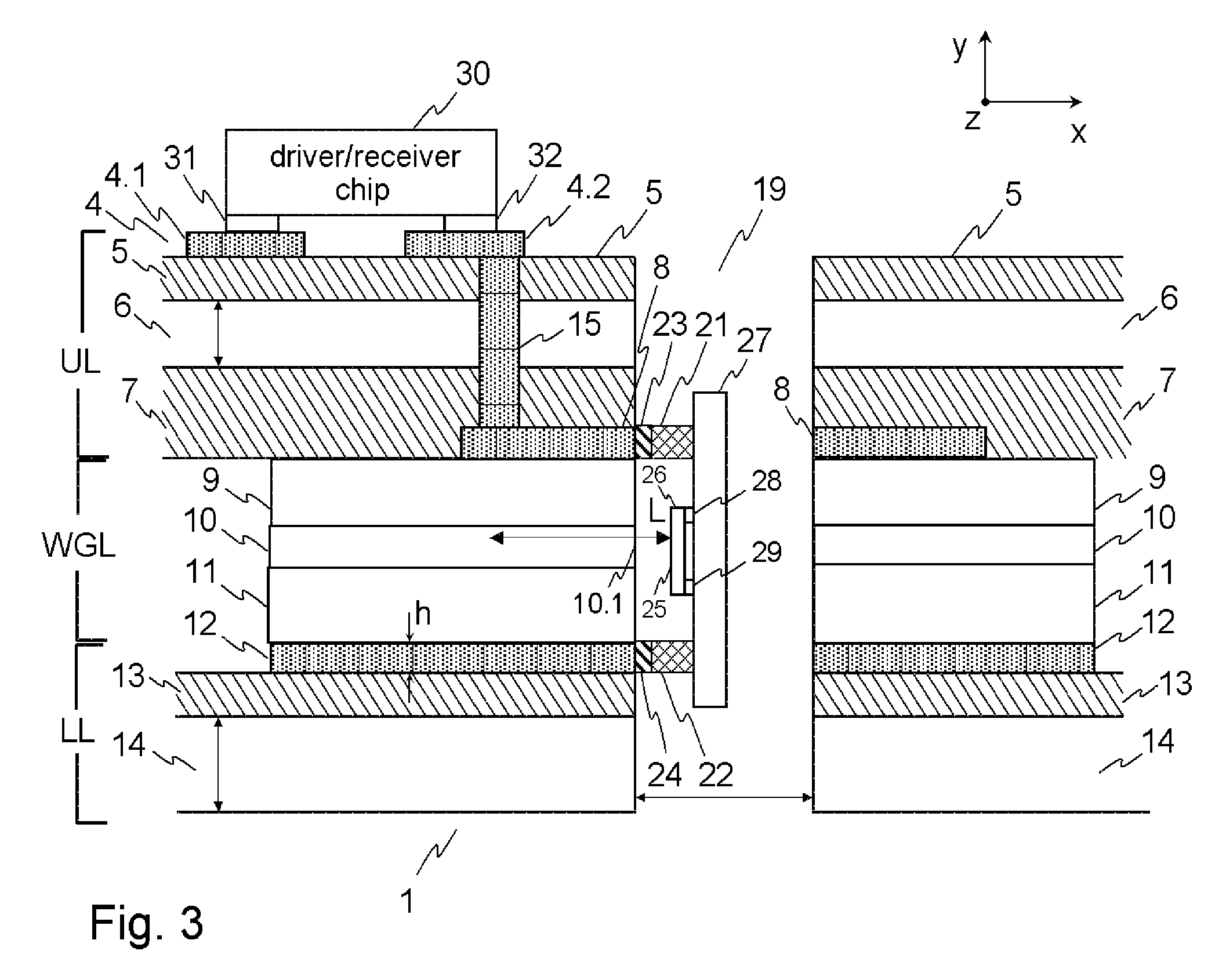

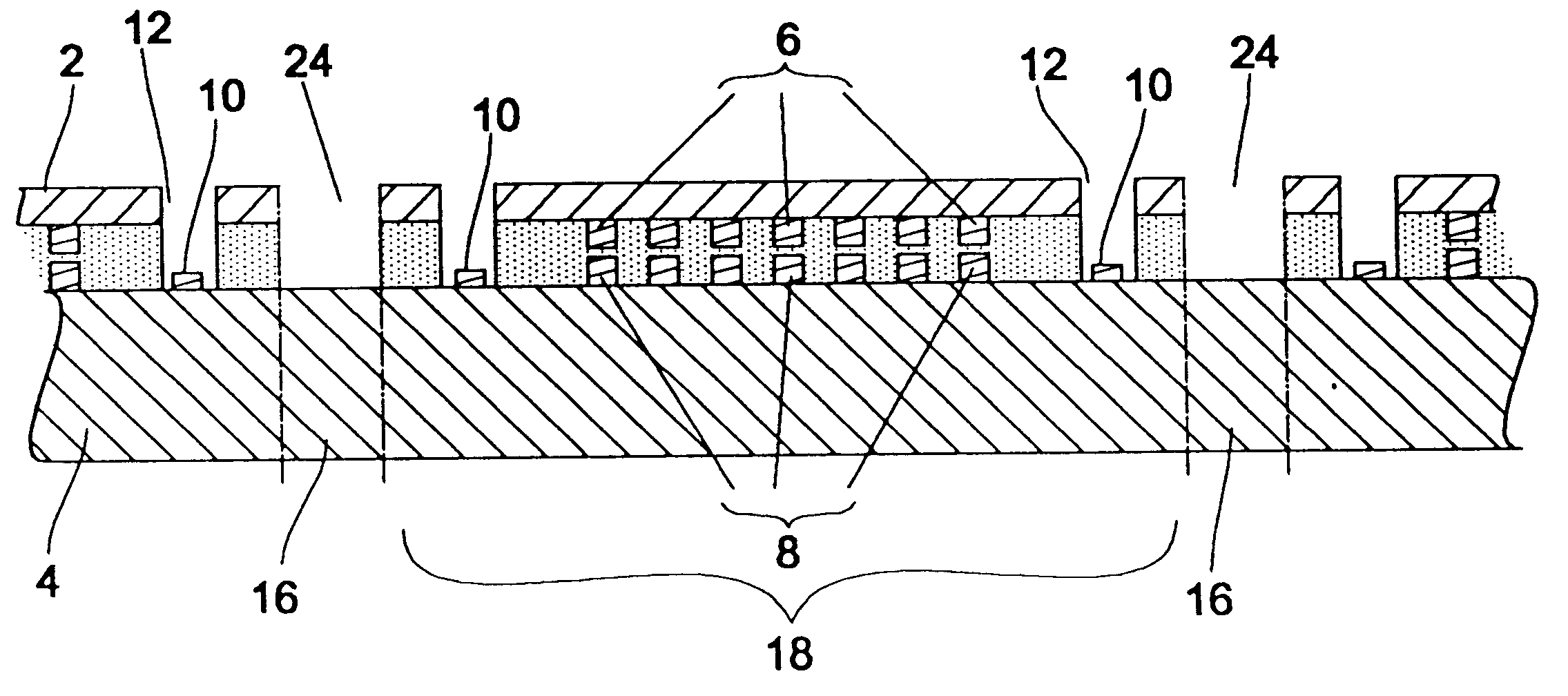

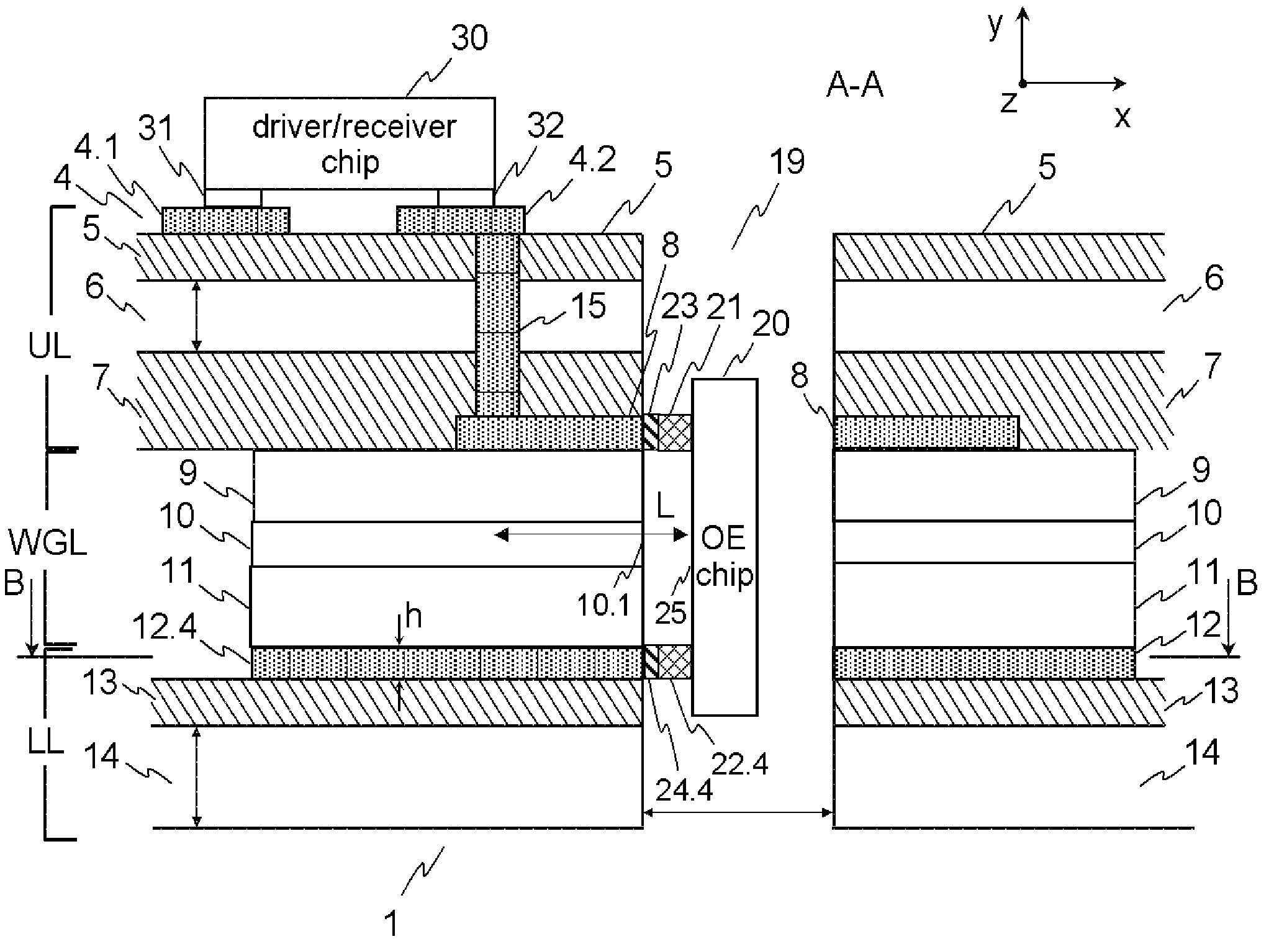

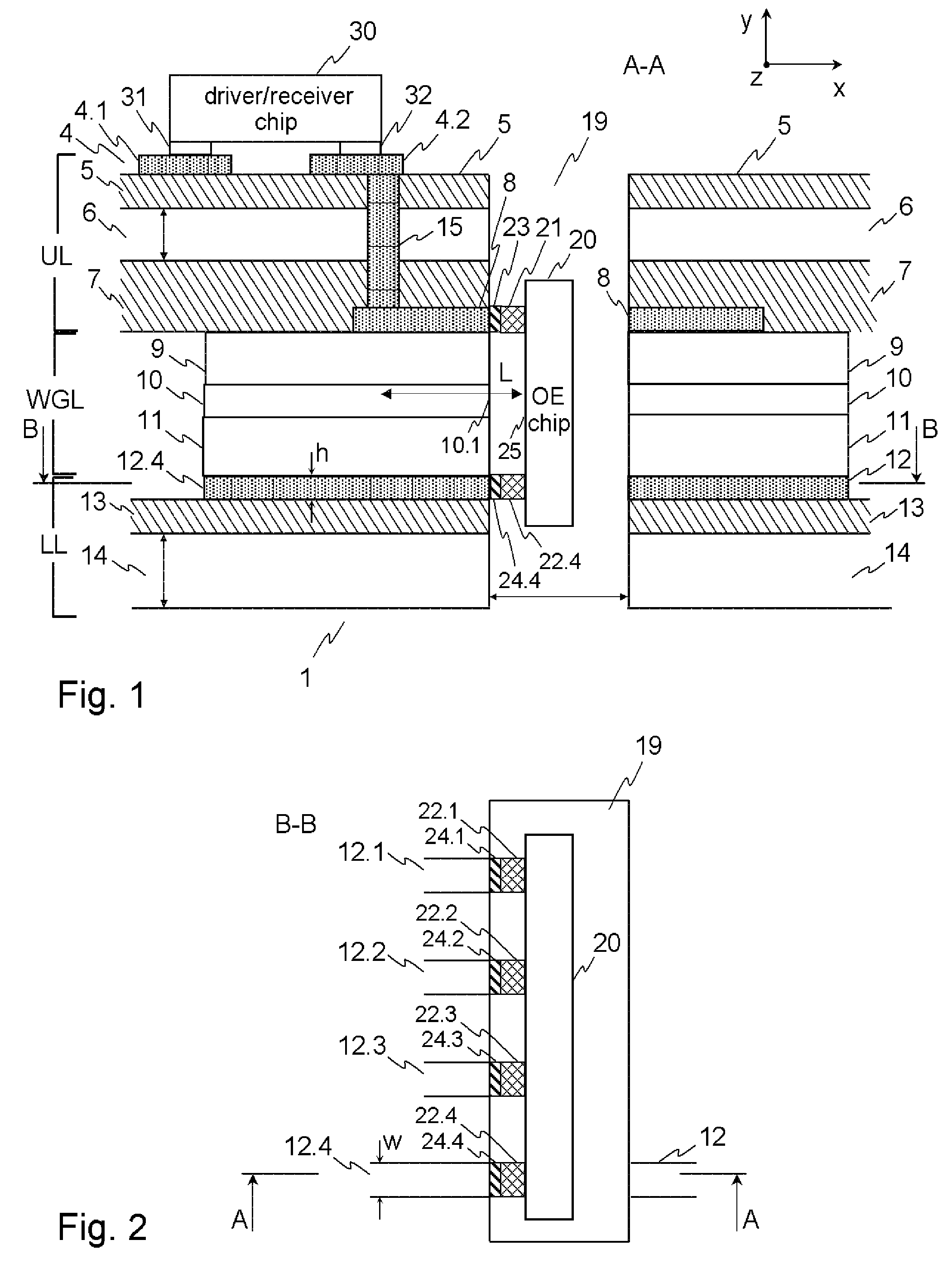

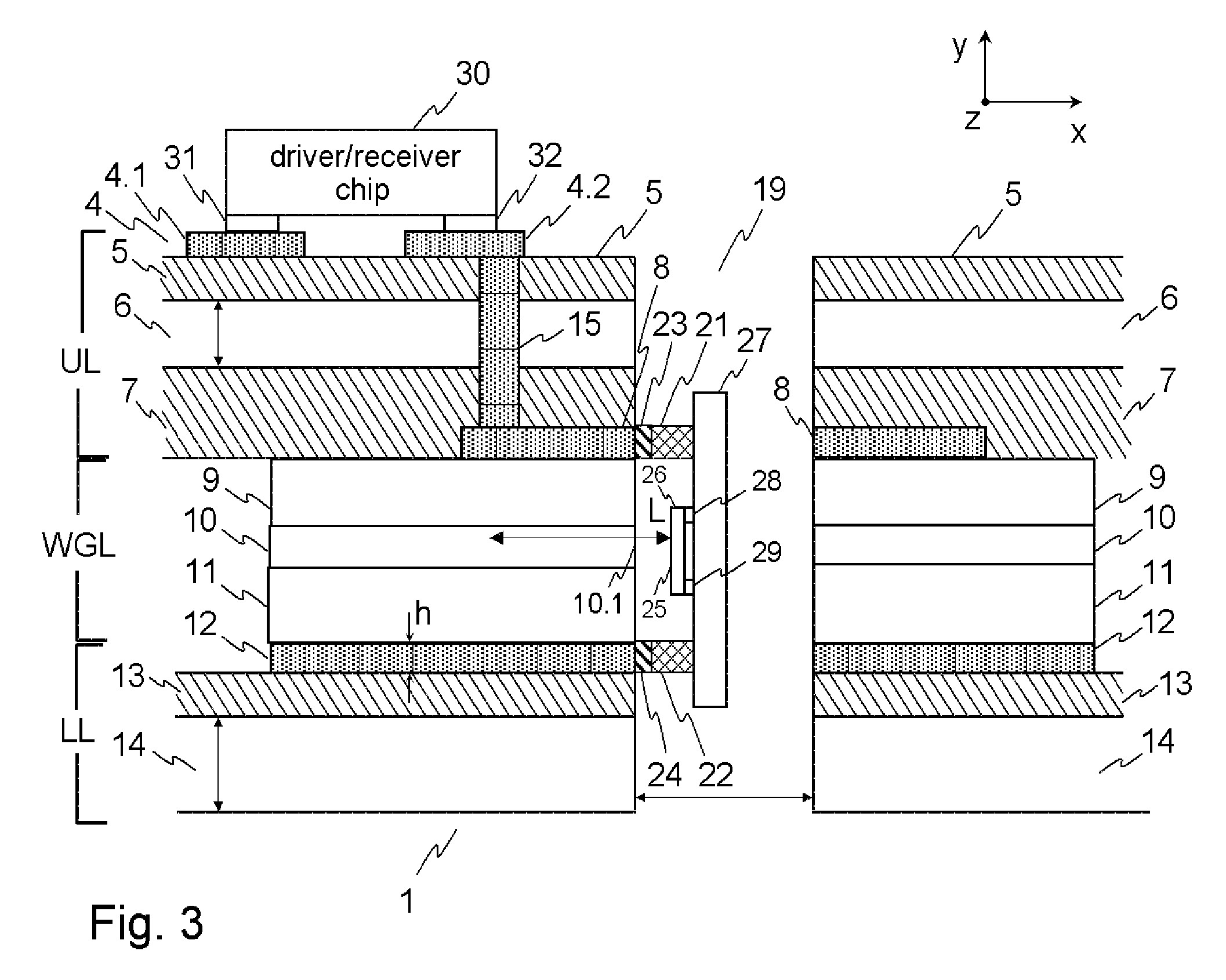

Multi-layer opto-electronic substrates with electrical and optical interconnections and methods for making

InactiveUS6845184B1Reduce area requirementsOptical coupling efficiency improvementSemiconductor/solid-state device detailsSolid-state devicesElectricityThin layer

Opto-electrical systems having electrical and optical interconnections formed in thin layers are disclosed. In one set of preferred embodiments, optical signals are conveyed between layers by respective vertical optical couplers disposed on the layers. In other preferred embodiments, optical signals are conveyed by stack optical waveguide coupling means. Yet other preferred embodiments have electrical via means formed in one or more layers to covey electrical signals between two or more layers.

Owner:FUJITSU LTD

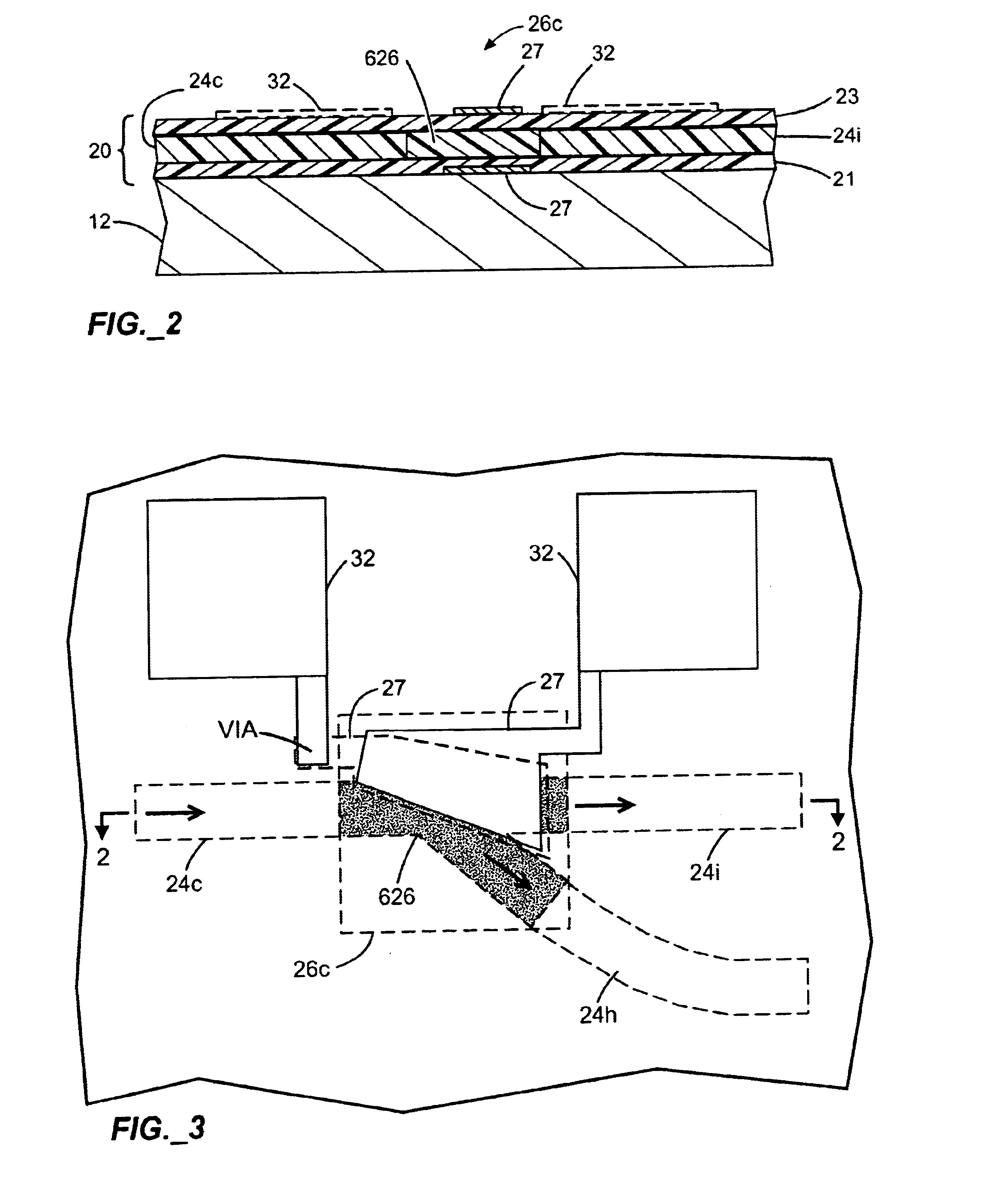

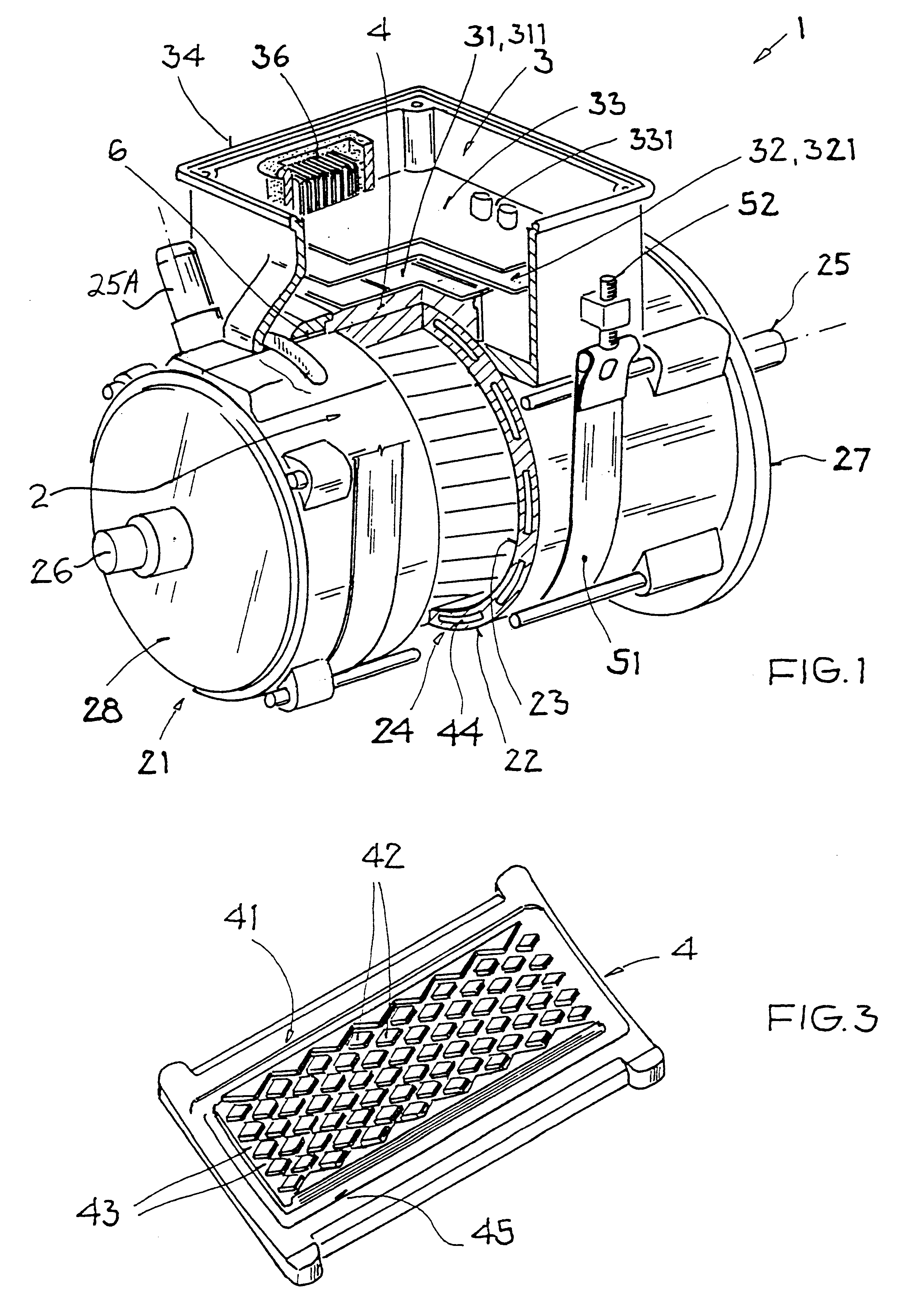

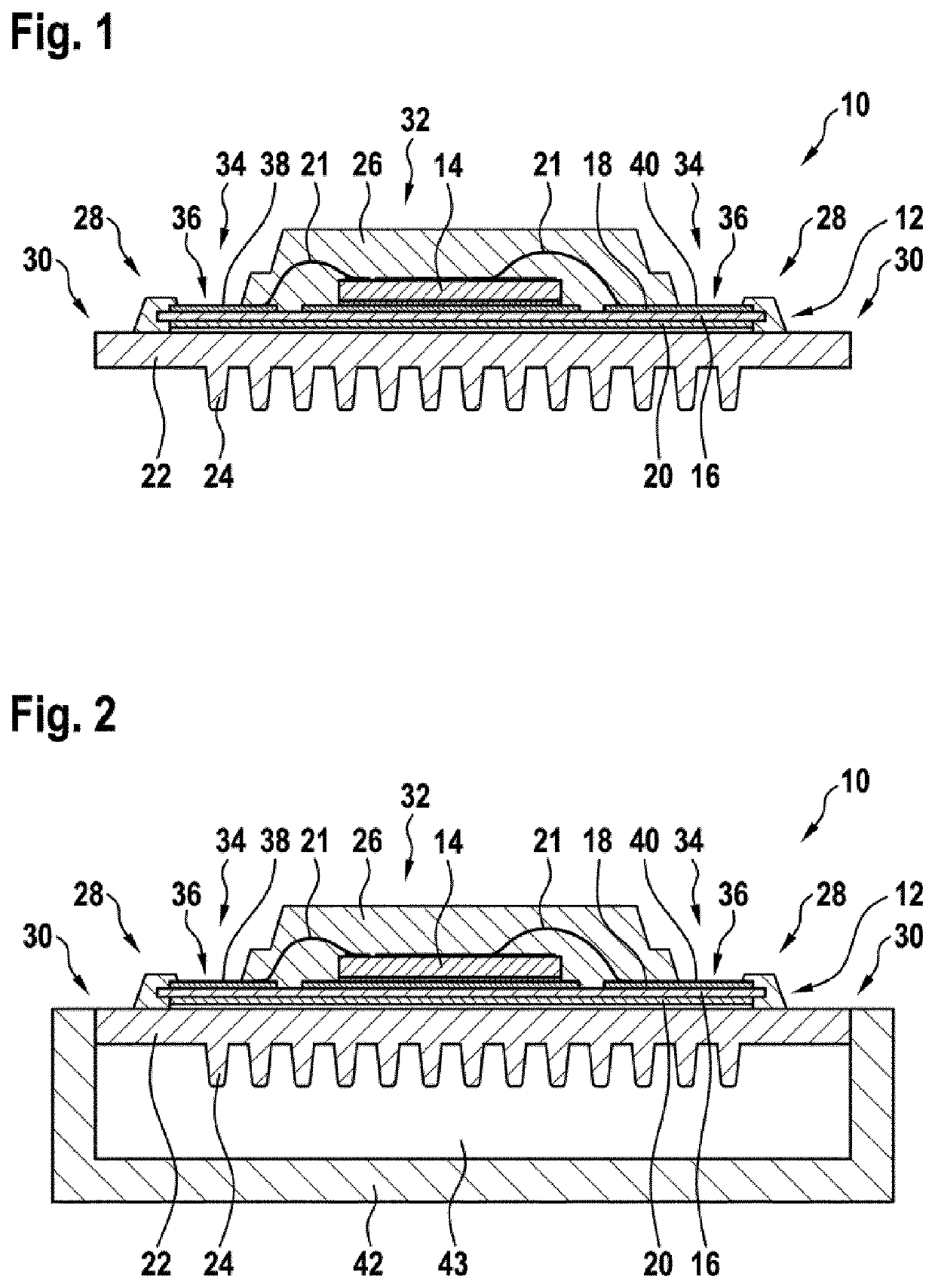

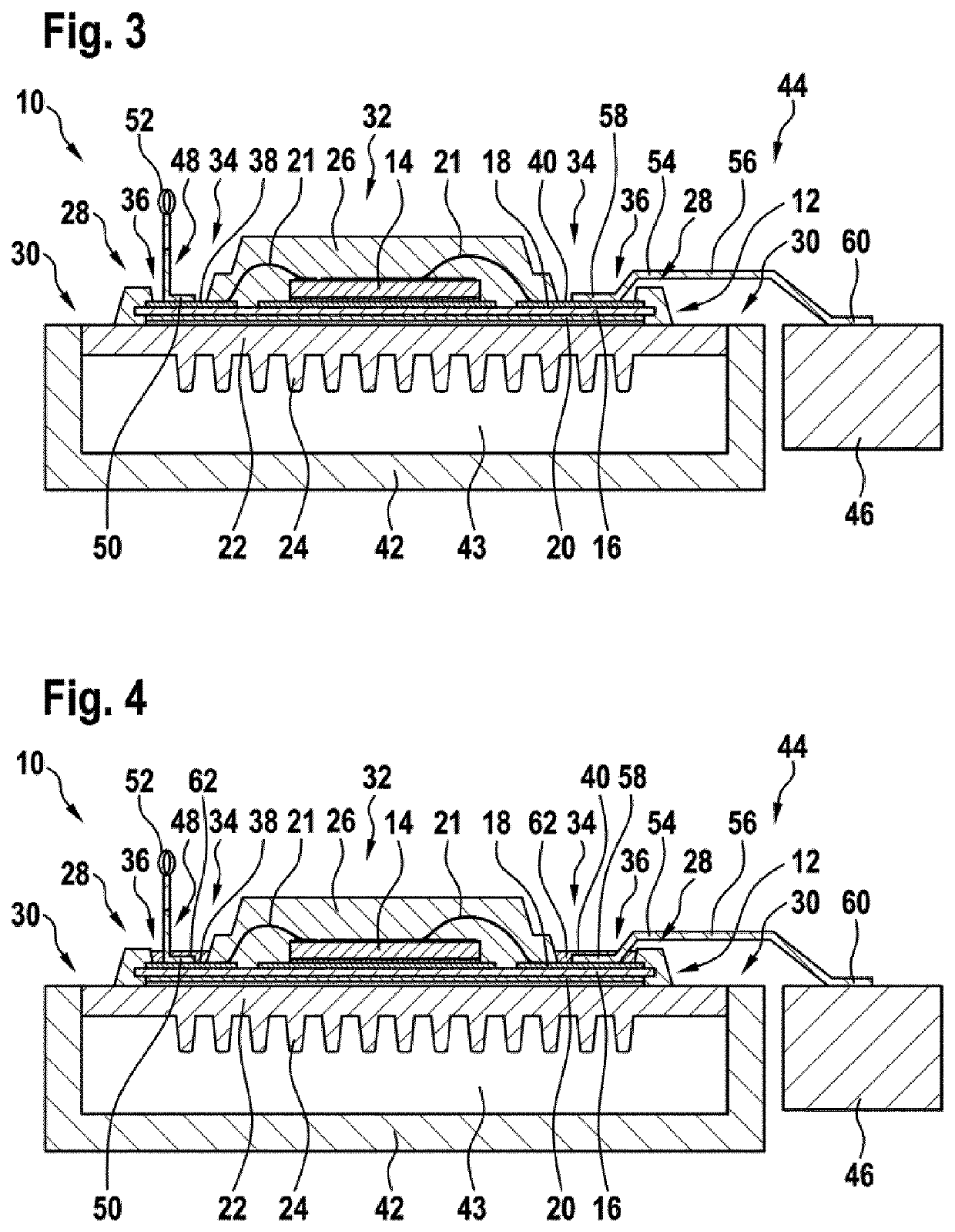

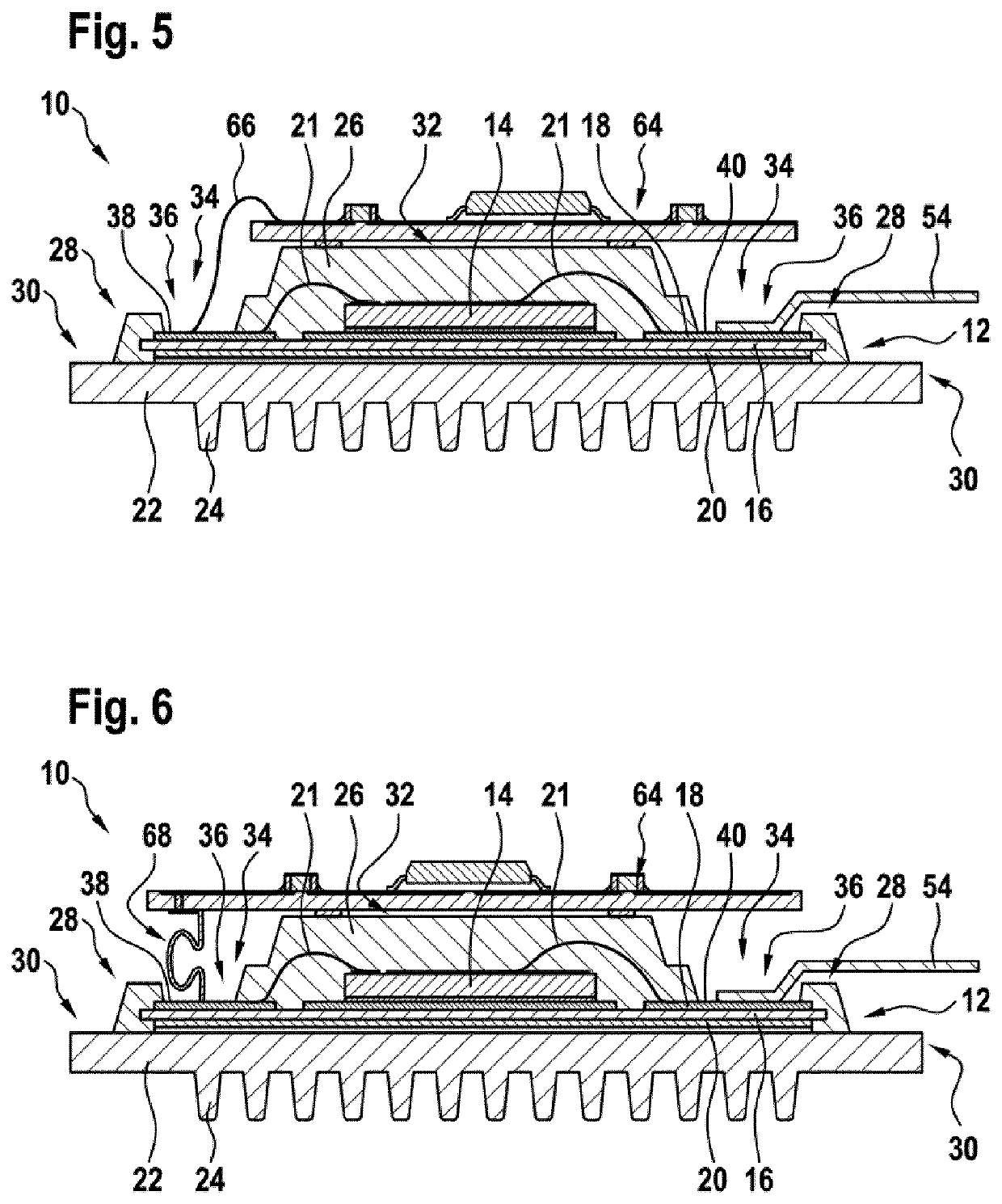

Integrated electric drive unit including an electric motor and an electronic control and monitoring module

InactiveUS6198183B1Small structural installation volumeReduce manufacturing costAssociation with control/drive circuitsMagnetic circuit rotating partsElectricityDouble wall

An electric drive unit includes an electronic control and monitoring module integrally connected to an electric motor. The housing of the electric motor has a double-walled construction to form a water jacket with cooling water passages therein. The electronic module includes at least one high power component that requires cooling. This component is mounted directly on a cooling insert that extends through a recess in the electronic module housing and is inserted in an opening provided in the outer wall of the motor housing. In this manner, the cooling insert is integrated into the water jacket of the motor housing and is directly cooled by the cooling water flowing in the cooling passages. A very compact and reliable construction is achieved, in which the electric motor and the electronic module share a common water cooling circuit. External water hoses and external electrical connections between the electric motor and the electronic module are avoided.

Owner:CONTI TEMIC MICROELECTRONIC GMBH

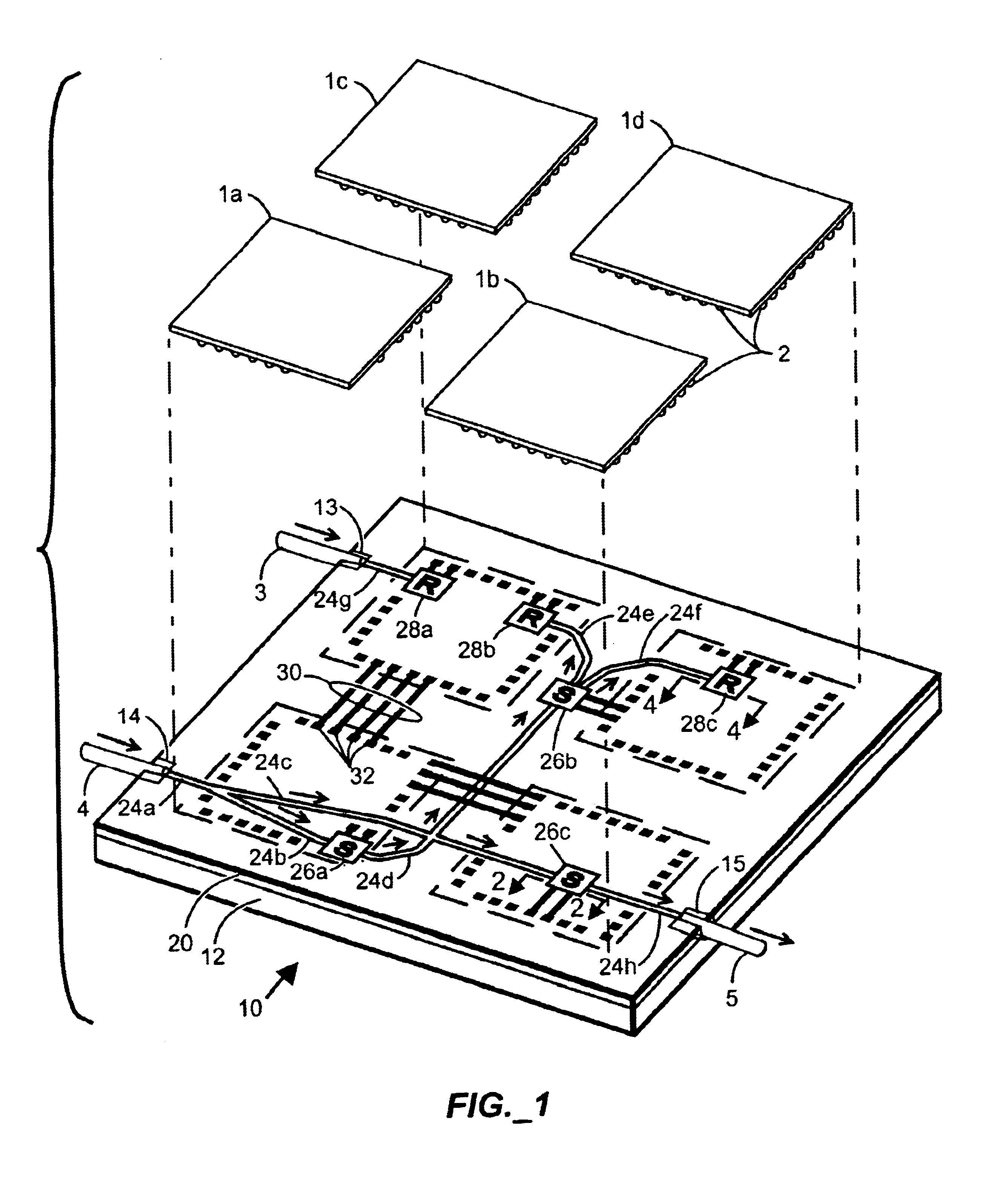

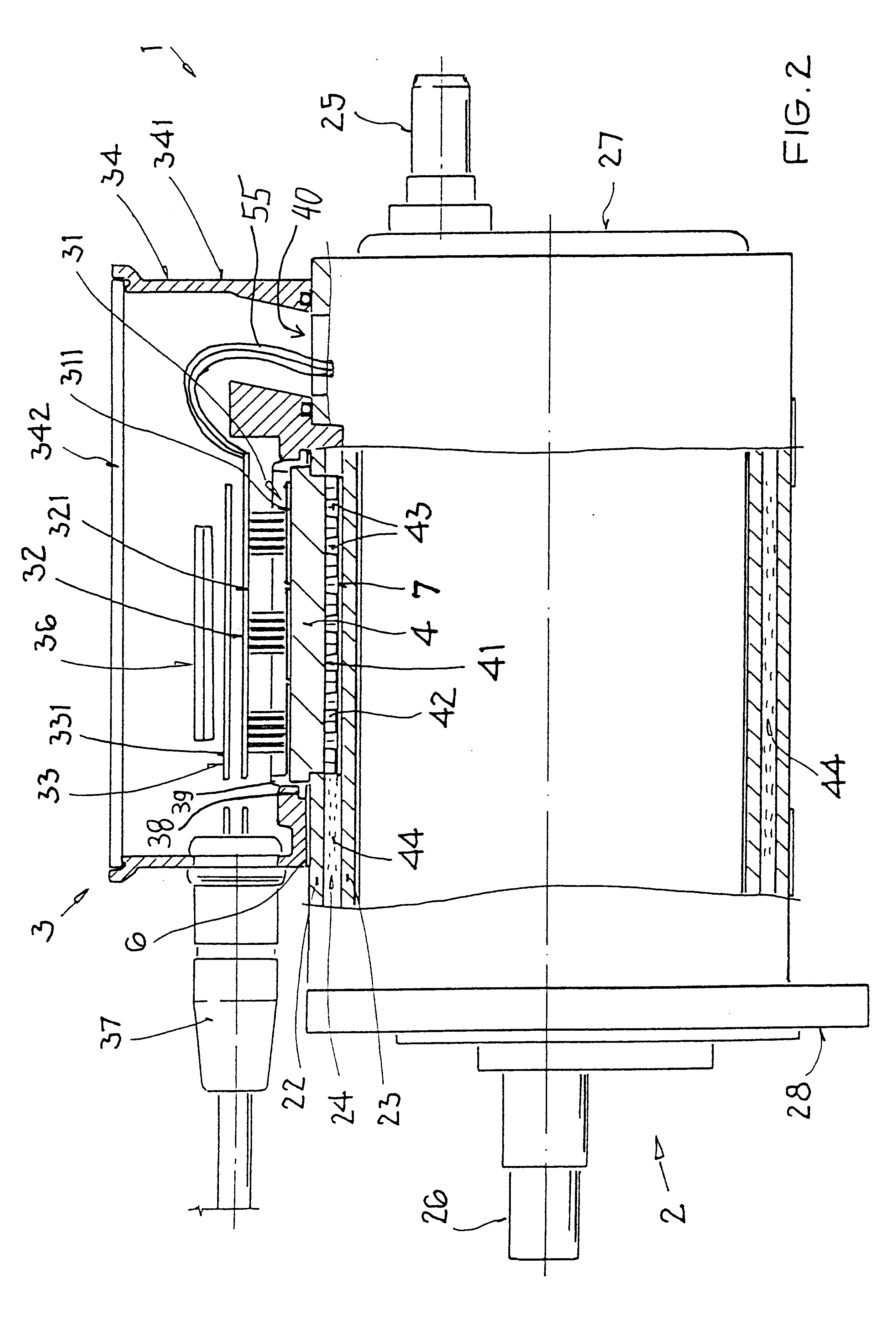

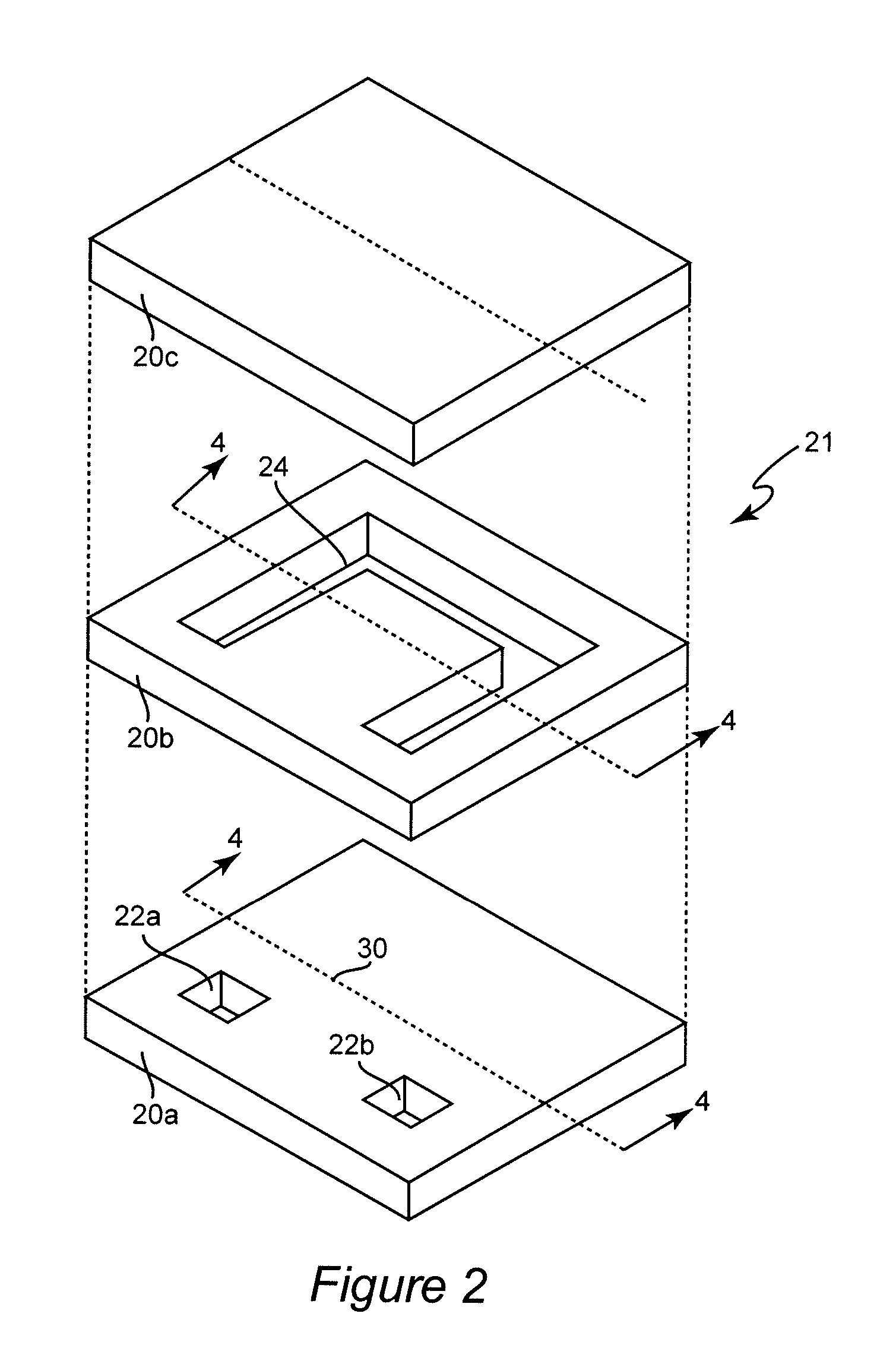

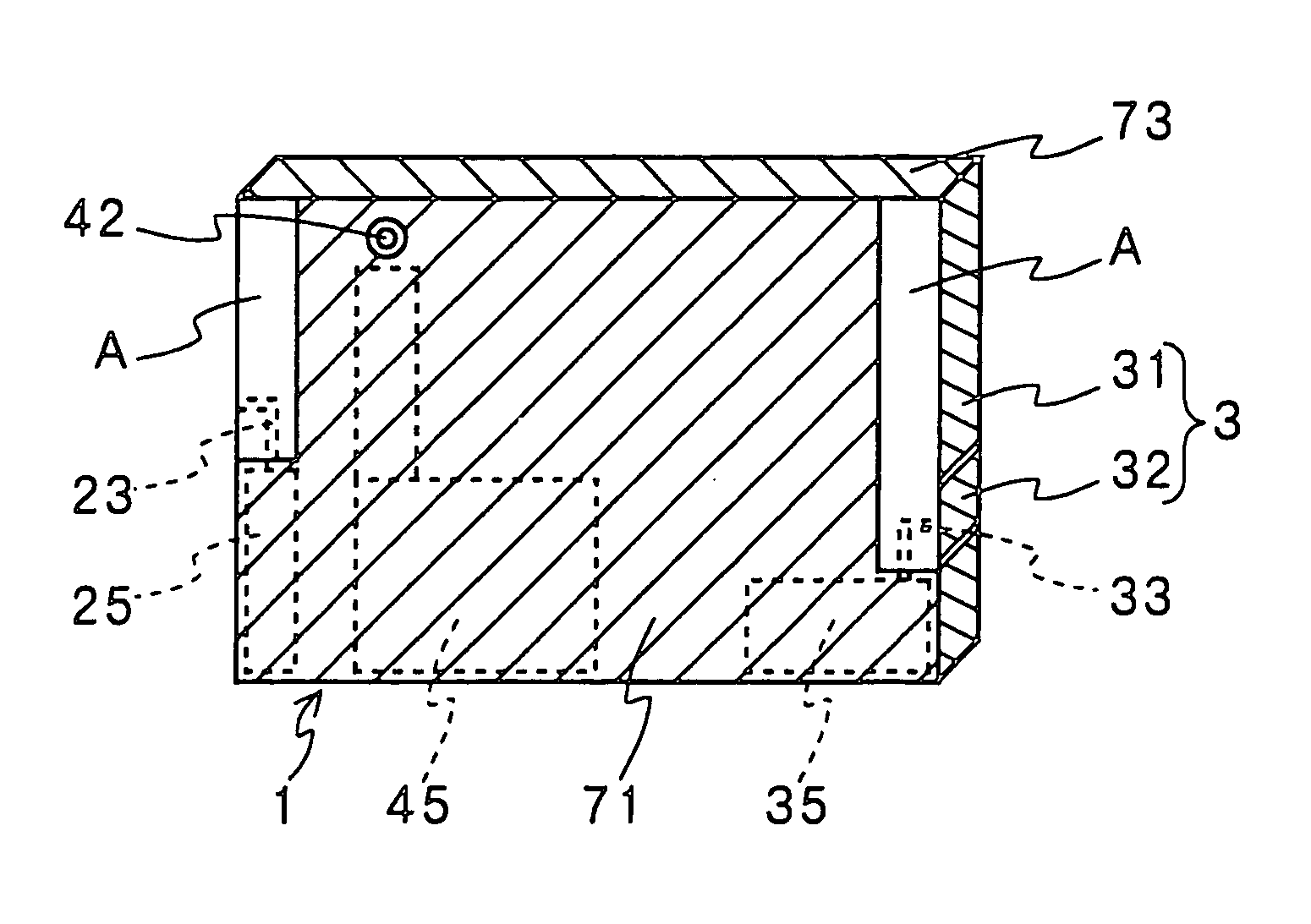

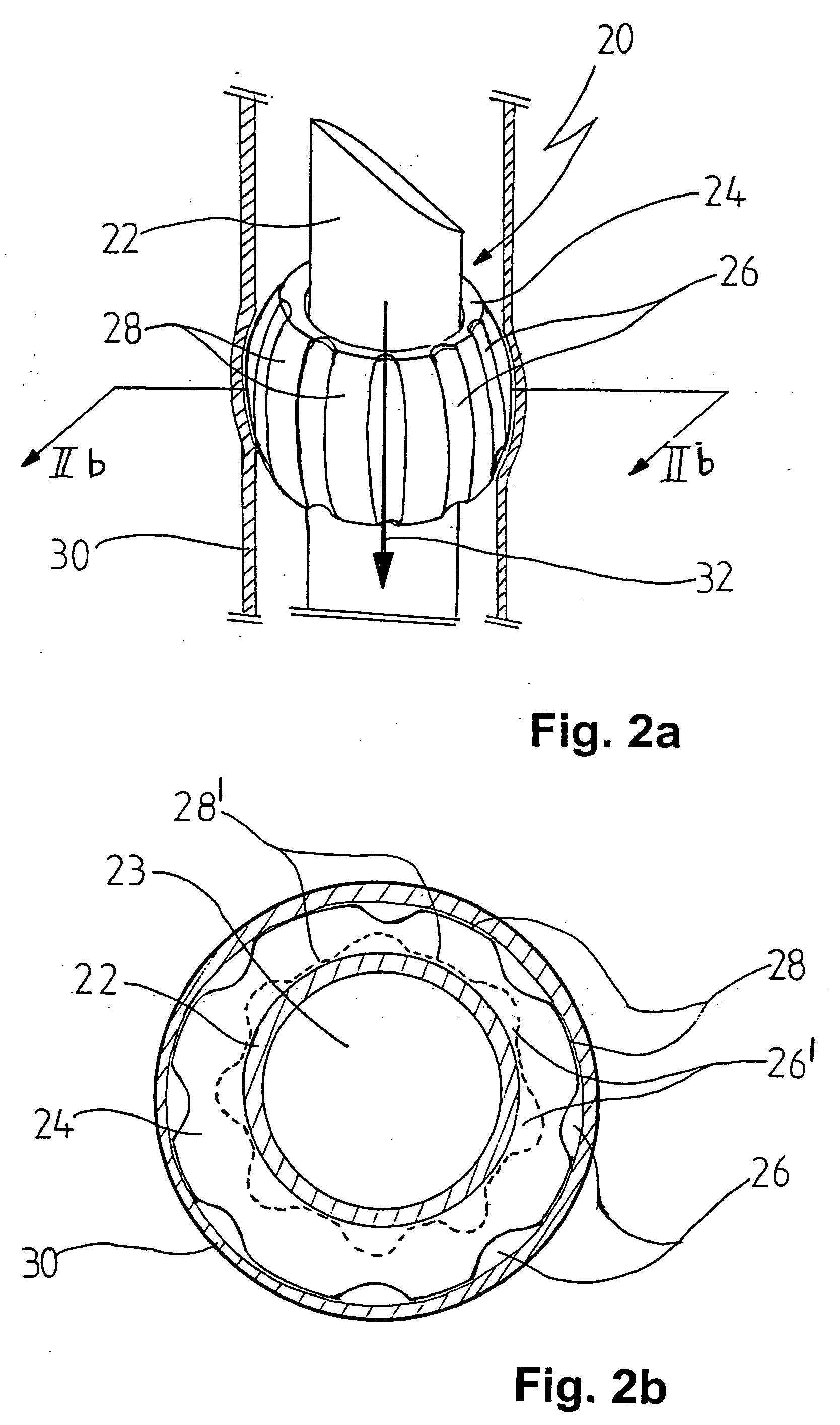

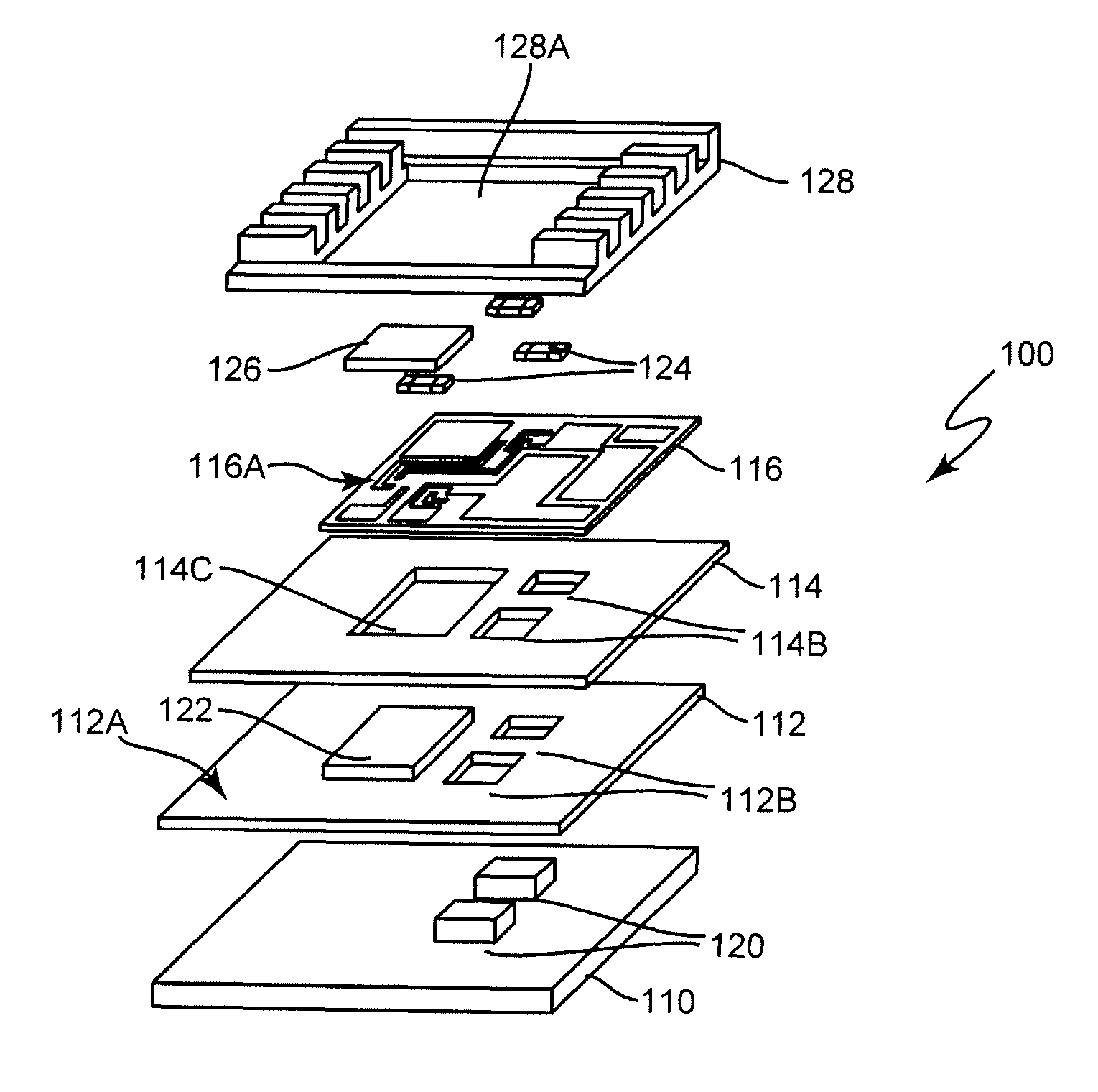

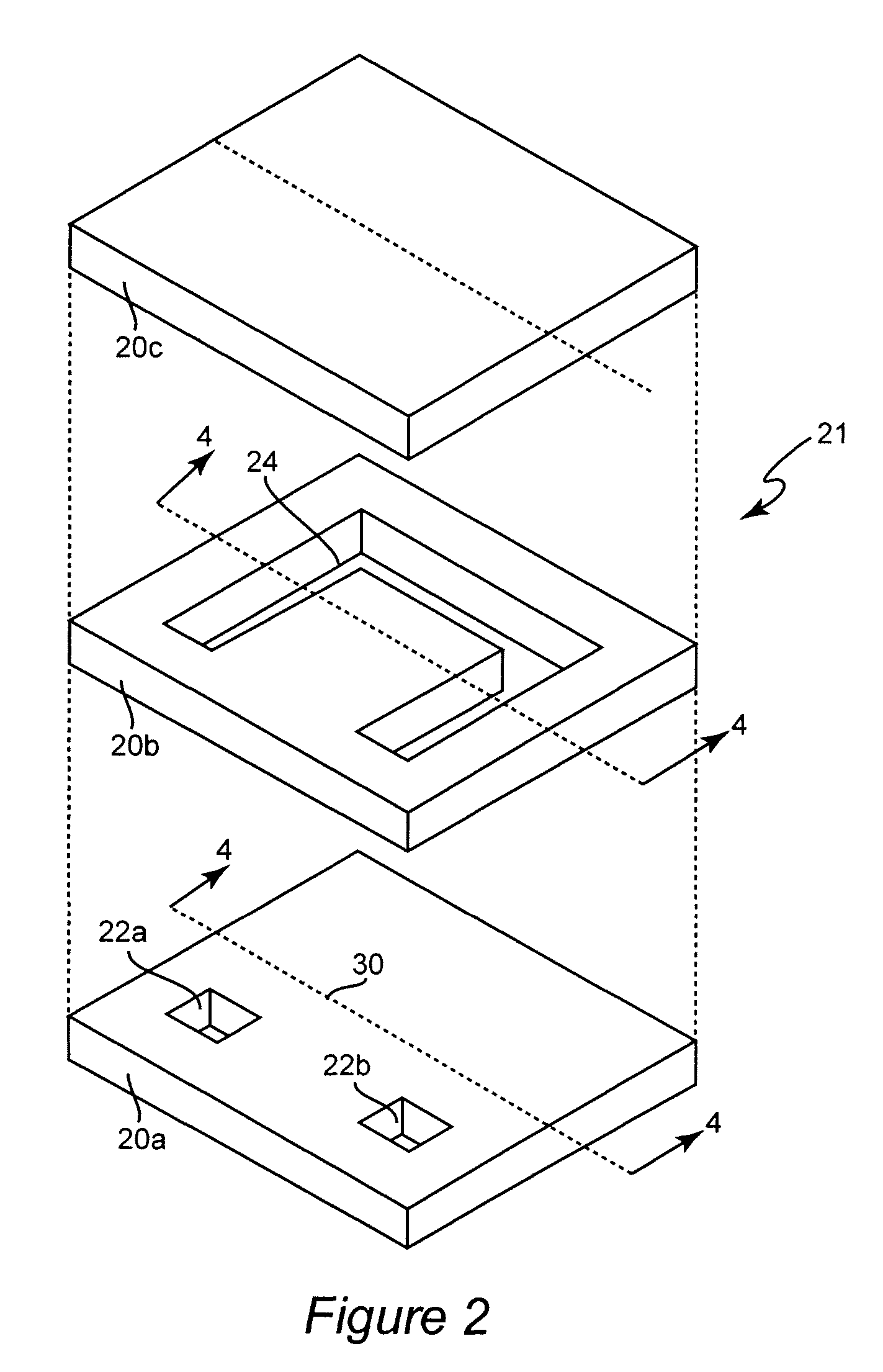

Method and Apparatus for Three-Dimensional Integration of Embedded Power Module

InactiveUS20070230221A1Reduces packaging overheadPackaging overhead is reducedTransformers/inductances coolingTransformers/inductances coils/windings/connectionsCo-fired ceramicInductor

A modified planar Low Temperature Co-Fired Ceramic (LTCC) high conductance inductor, embedding a large cross section conductor, supports a stacked arrangement of heat spreader, inductor and active device layers. Interlayer electrical connections connect the layers. Optionally, a DC-DC converter includes the modified planar LTCC high conductance inductor, embedding a large cross section conductor, supporting a stacked arrangement of heat spreader, capacitor and active device layers, the active devices layer including the switching transistors. The active devices layer may include semiconductor dies embedded in a substrate.

Owner:VIRGINIA TECH INTPROP INC

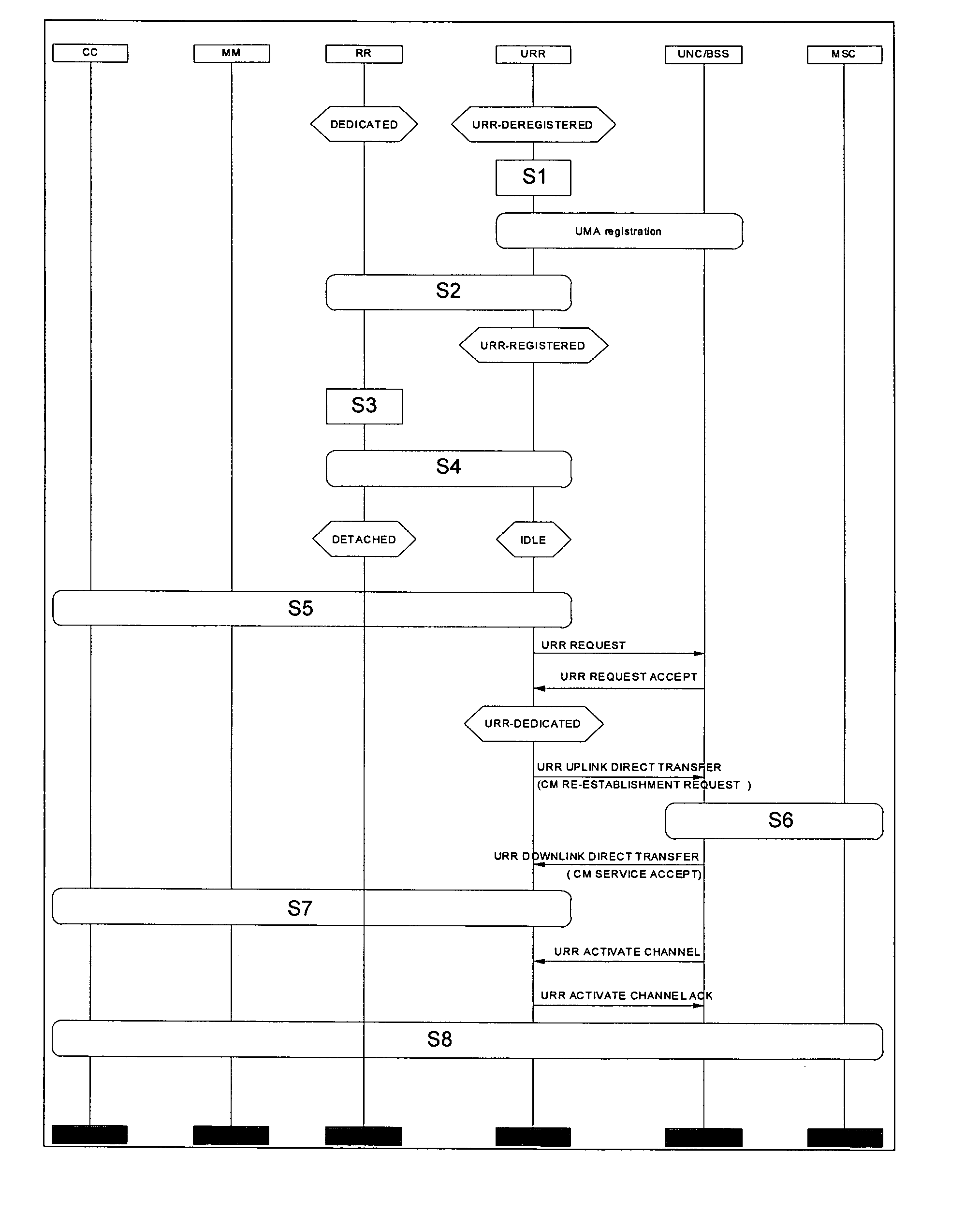

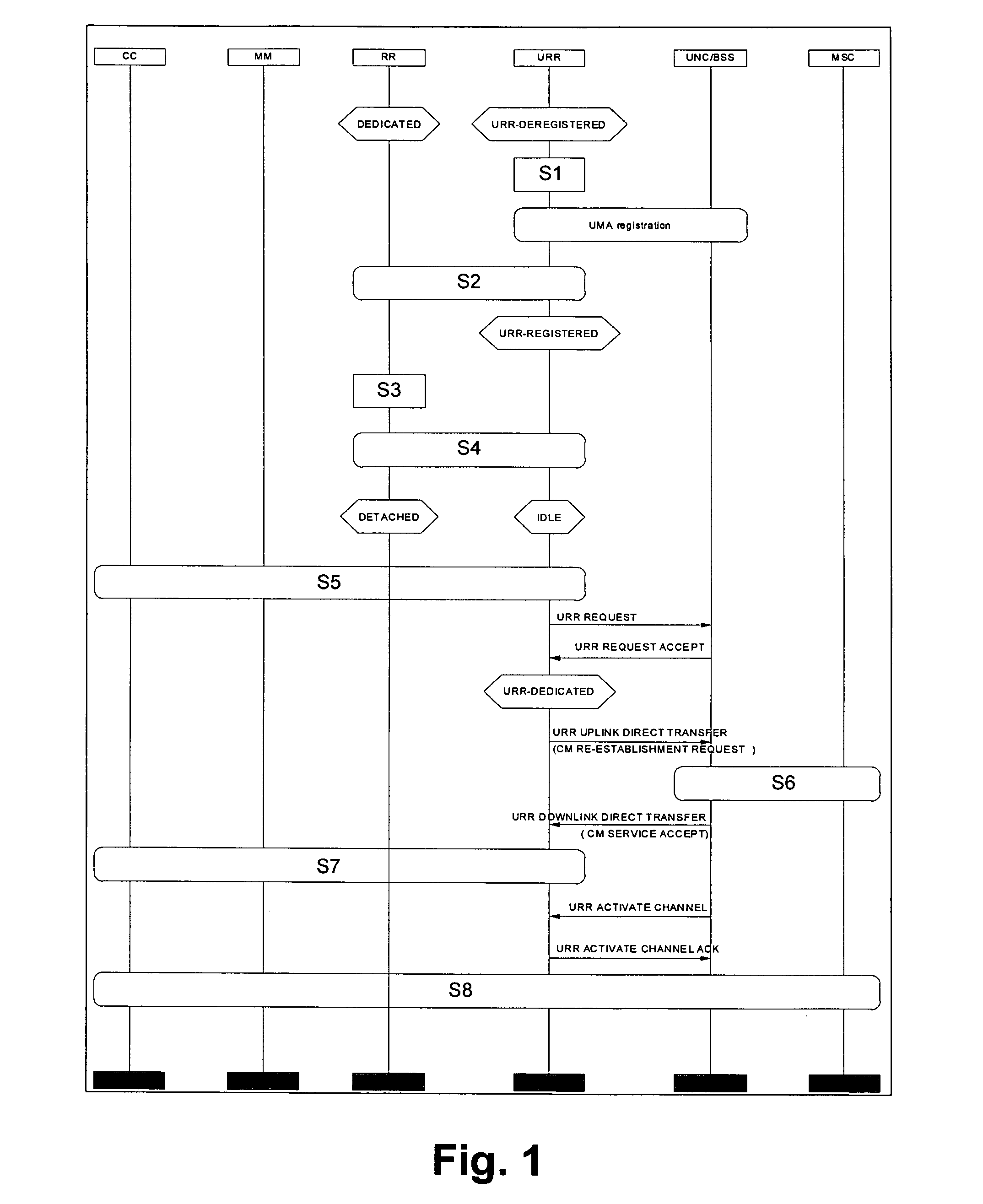

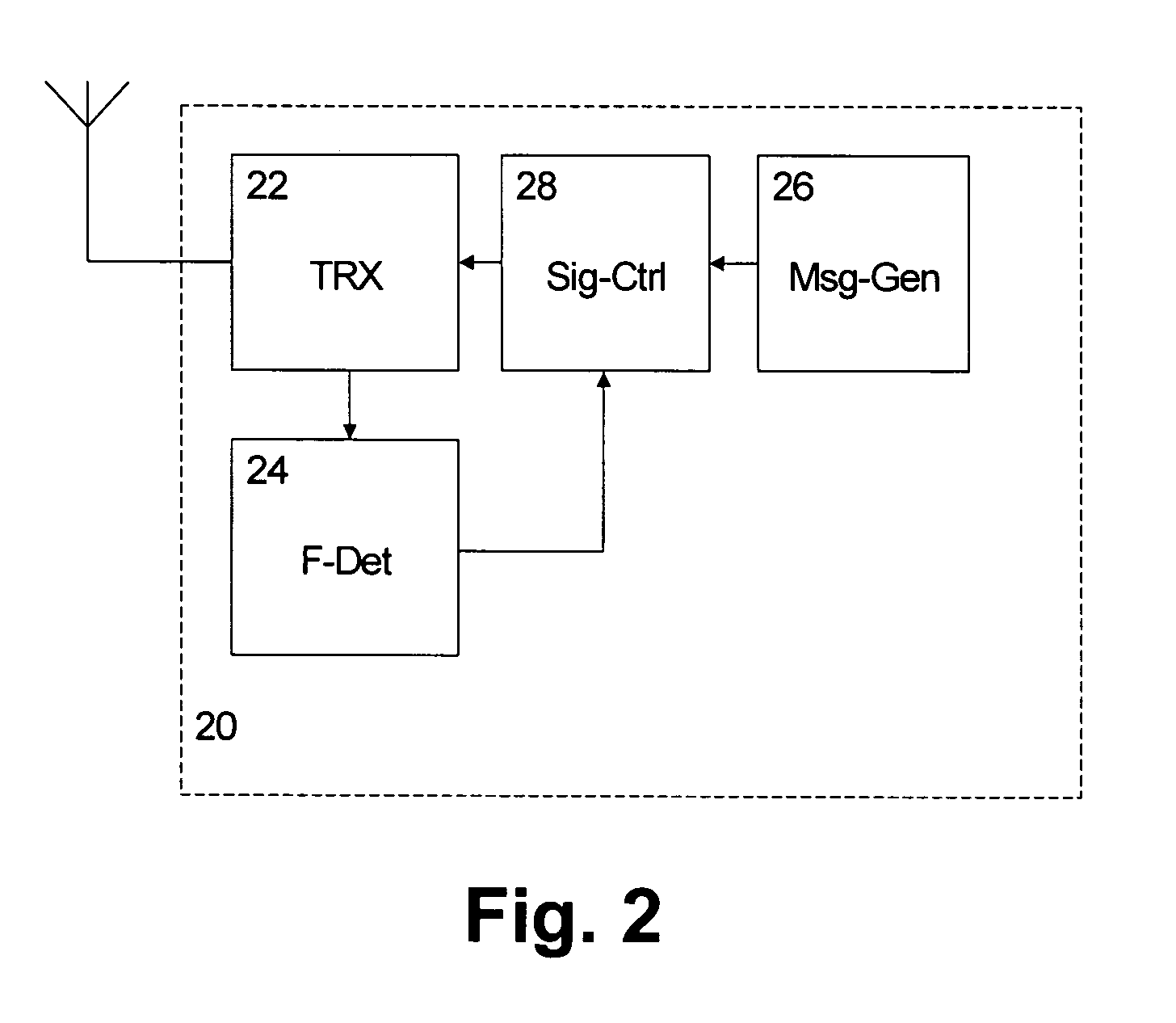

Call-re-establishment via alternative access network

InactiveUS20060209798A1Avoid connection failureImprove user experienceAssess restrictionTime-division multiplexAccess networkTerminal equipment

A terminal device and method of re-establishes a circuit switched call or a packet switched connection in a data network having at least a first access network and a second access network. A failure of the circuit switched call or the packet switched connection established via the first access network is detected at the terminal device and connection re-establishment is initiated via the second access network in response to the result of checking registration to the second access network, if a failure has been detected. Thereby, a new option is provided to avoid connection failures when coverage to another access network is available, especially where call re-establishment via the first access network is not allowed.

Owner:NOKIA CORP

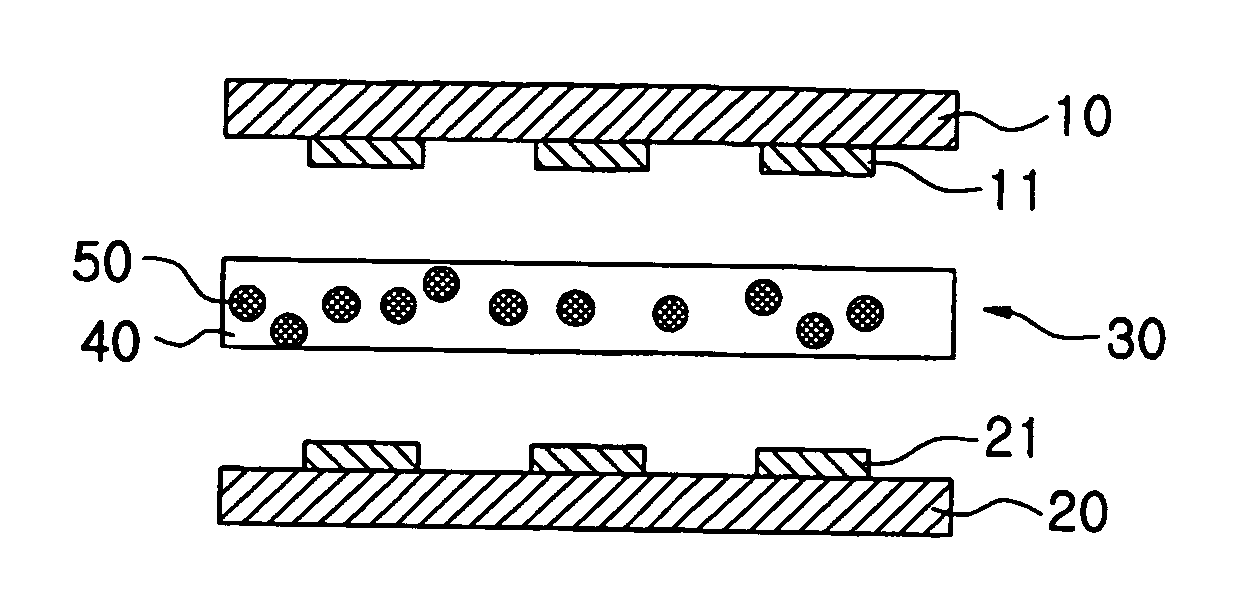

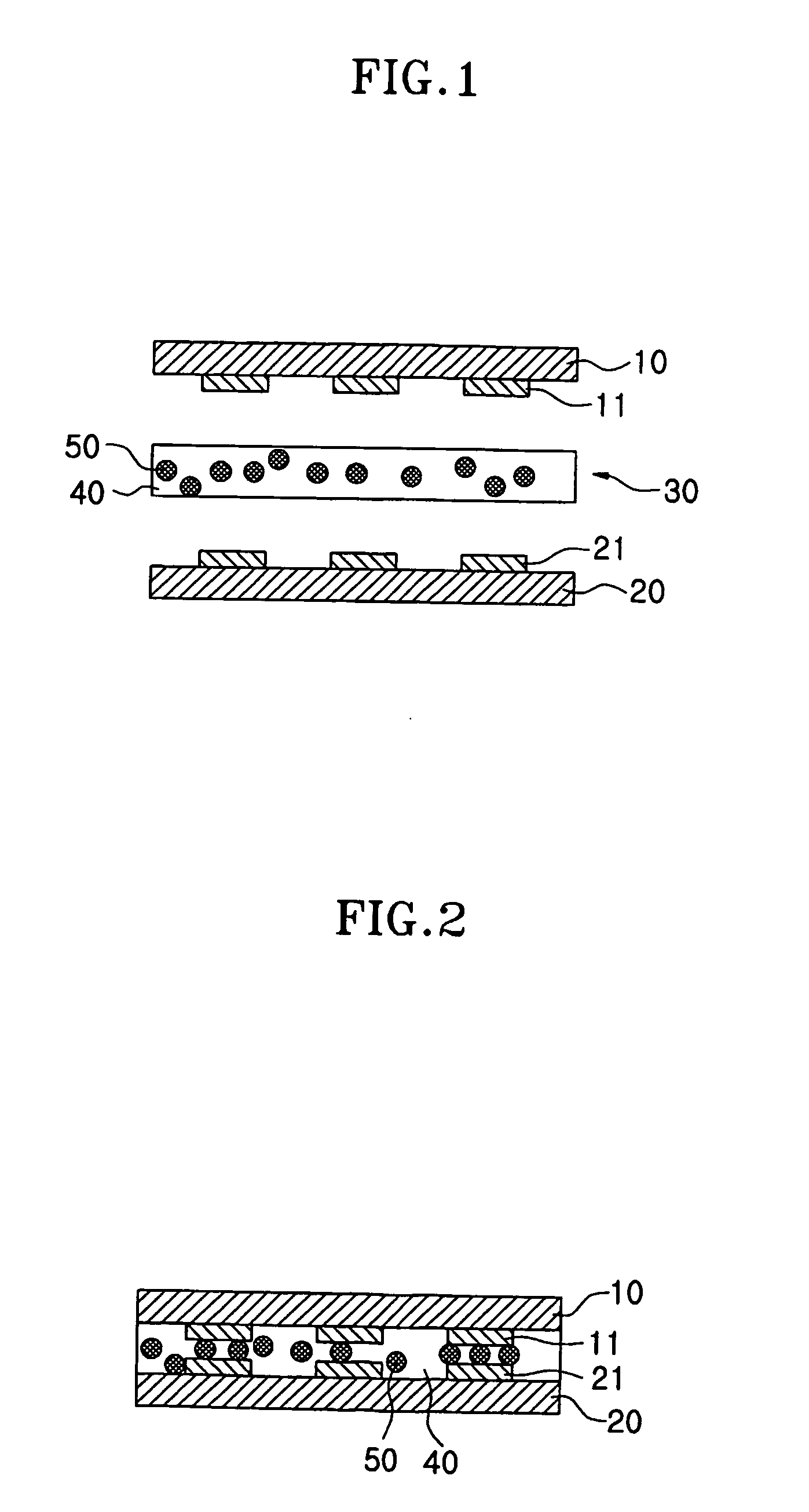

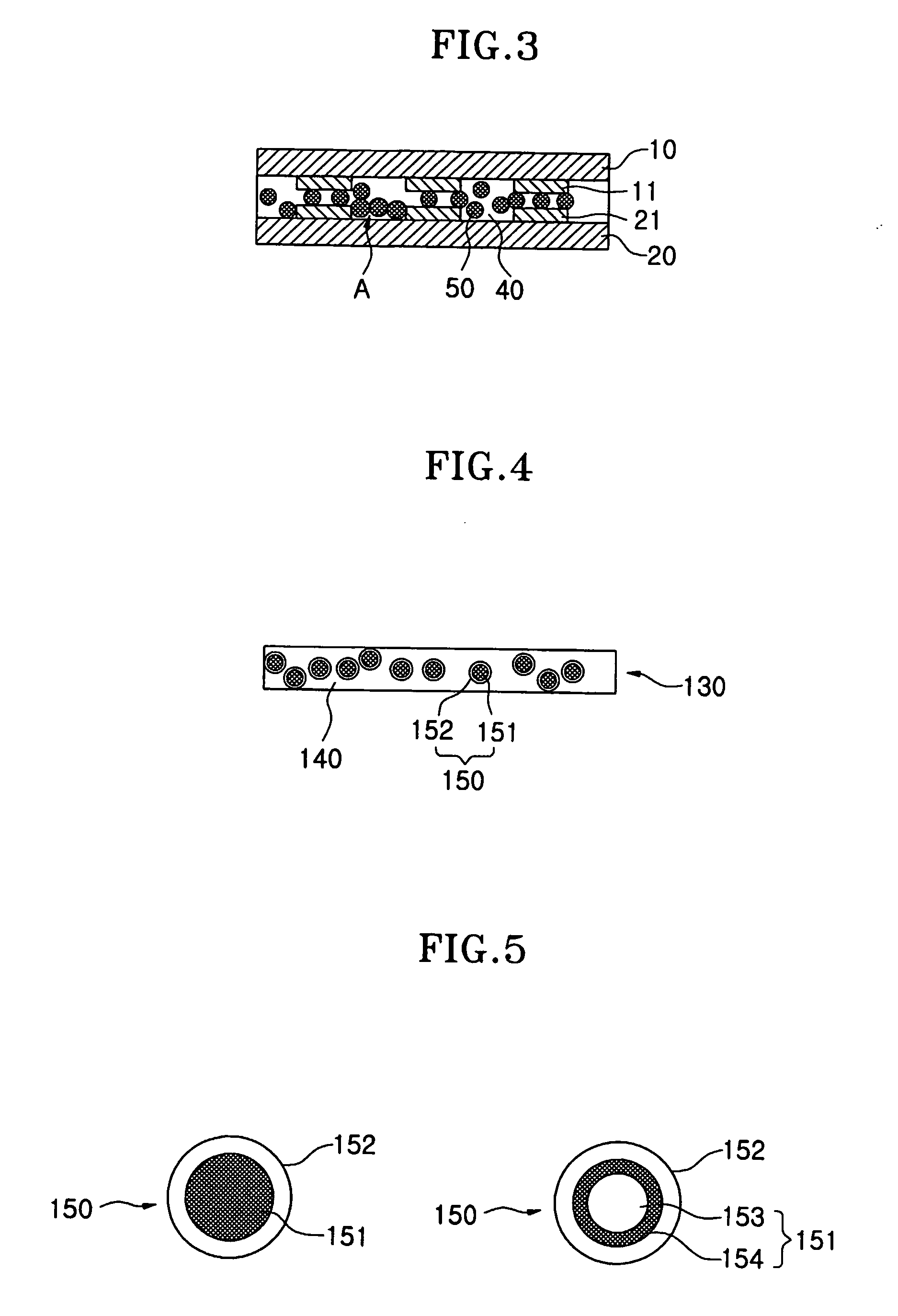

Anisotropic-electroconductive adhesive, circuit connection method and structure using the same

InactiveUS20060054277A1Avoid long connectionsPrevents a short circuitPrinted circuit assemblingLayered productsAdhesivePolymerization

Disclosed is an anisotropic-electroconductive adhesive, which includes an insulating adhesive component containing a radical polymerizable compound and a polymerization initiator; and a plurality of insulating coated electroconductive particles dispersed in the insulating adhesive component, the insulating coated electroconductive particle having a coating layer made of insulating thermoplastic resin on a surface of an electroconductive particle, wherein a softening point of the insulating thermoplastic resin is lower than an exothermic peak temperature of the insulating adhesive component. The anisotropic-electroconductive adhesive enables rapid curing of the insulating adhesive component at a low temperature and is very useful for making a circuit connection structure since it may prevent a short of circuit without connection failure even when the electroconductive particles are condensed.

Owner:LS MTRON LTD

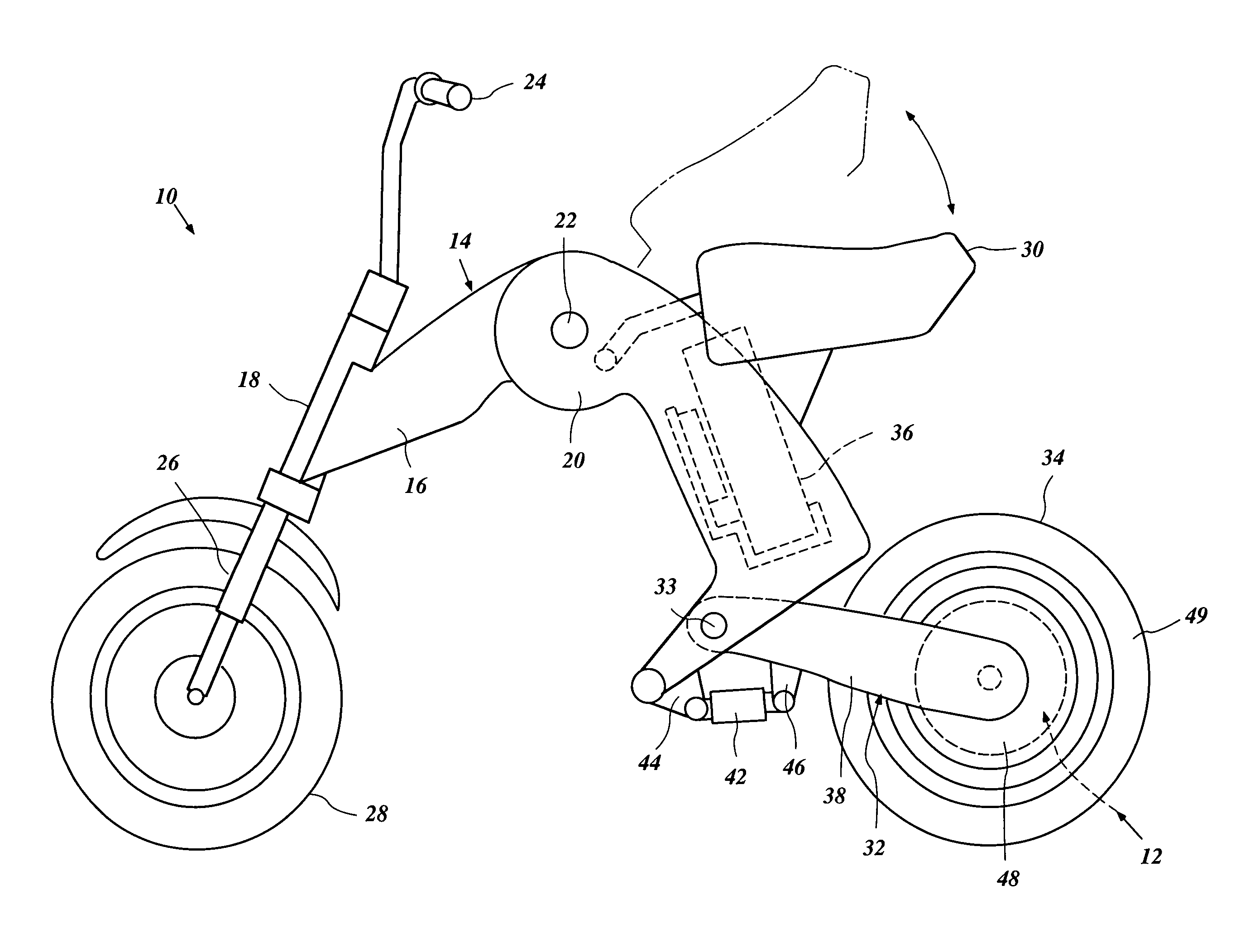

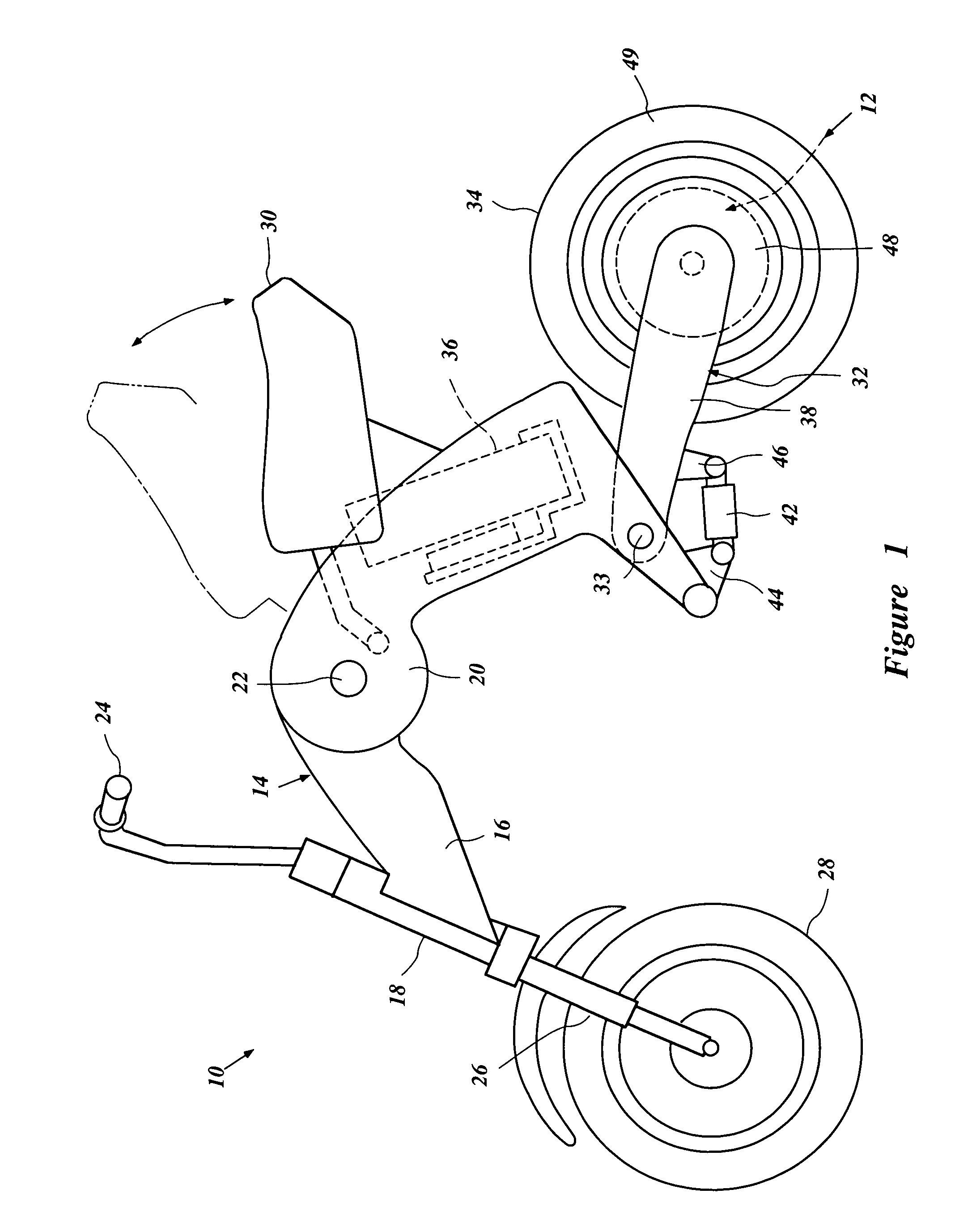

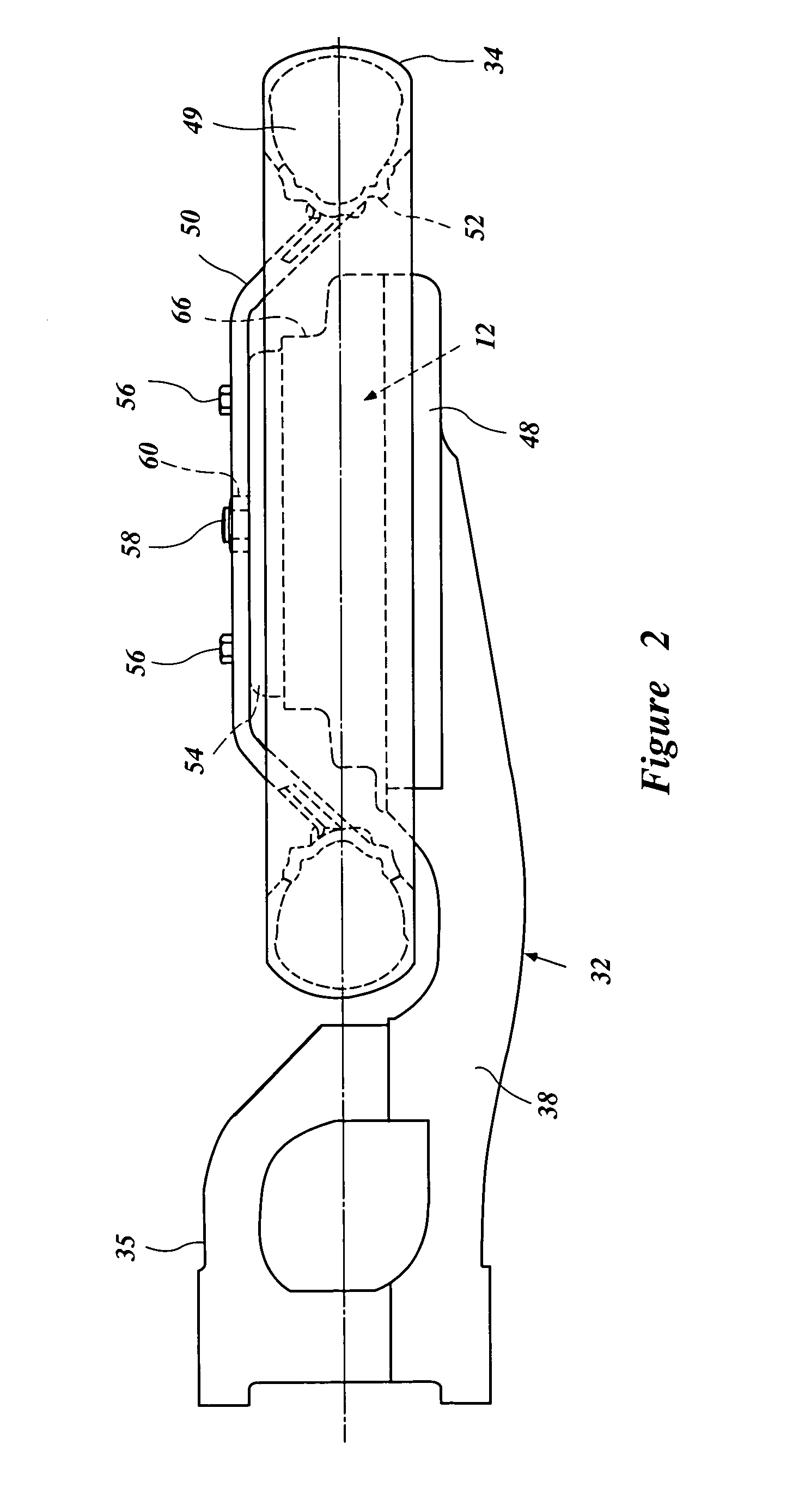

Electrically operated power unit, electric vehicle and electric motorcycle

InactiveUS7017694B2Avoid long connectionsMinimal damageSuspensionsWheel based transmissionElectric machineBattery electric vehicle

An electronically controlled compact motor and planetary transmission system including a compact control unit and wiring for an electrical vehicle or electric motorcycle. The compact motor and integrated transmission system enables the operator to enjoy a powerful, conveniently sized, lightweight vehicle.

Owner:YAMAHA MOTOR CO LTD

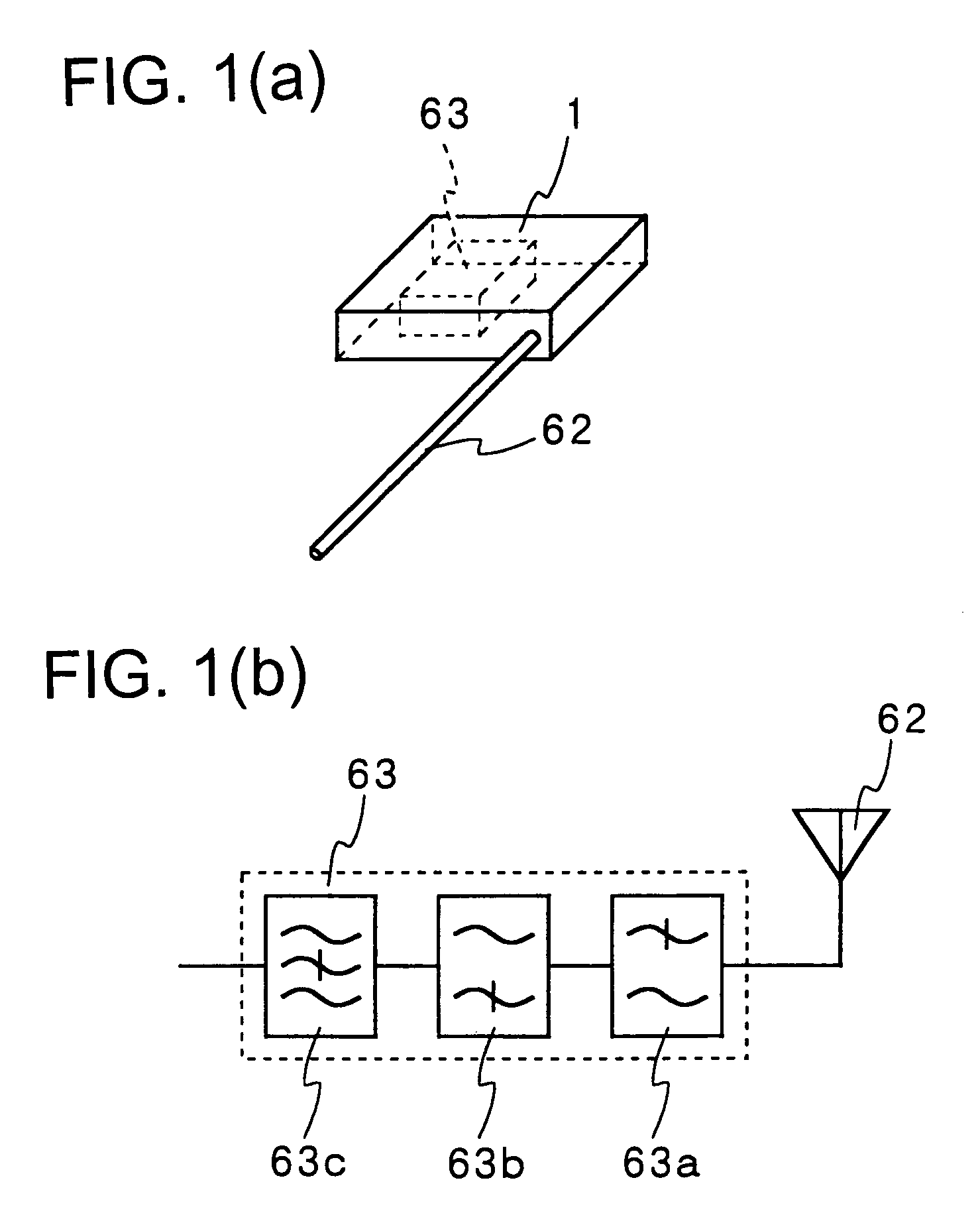

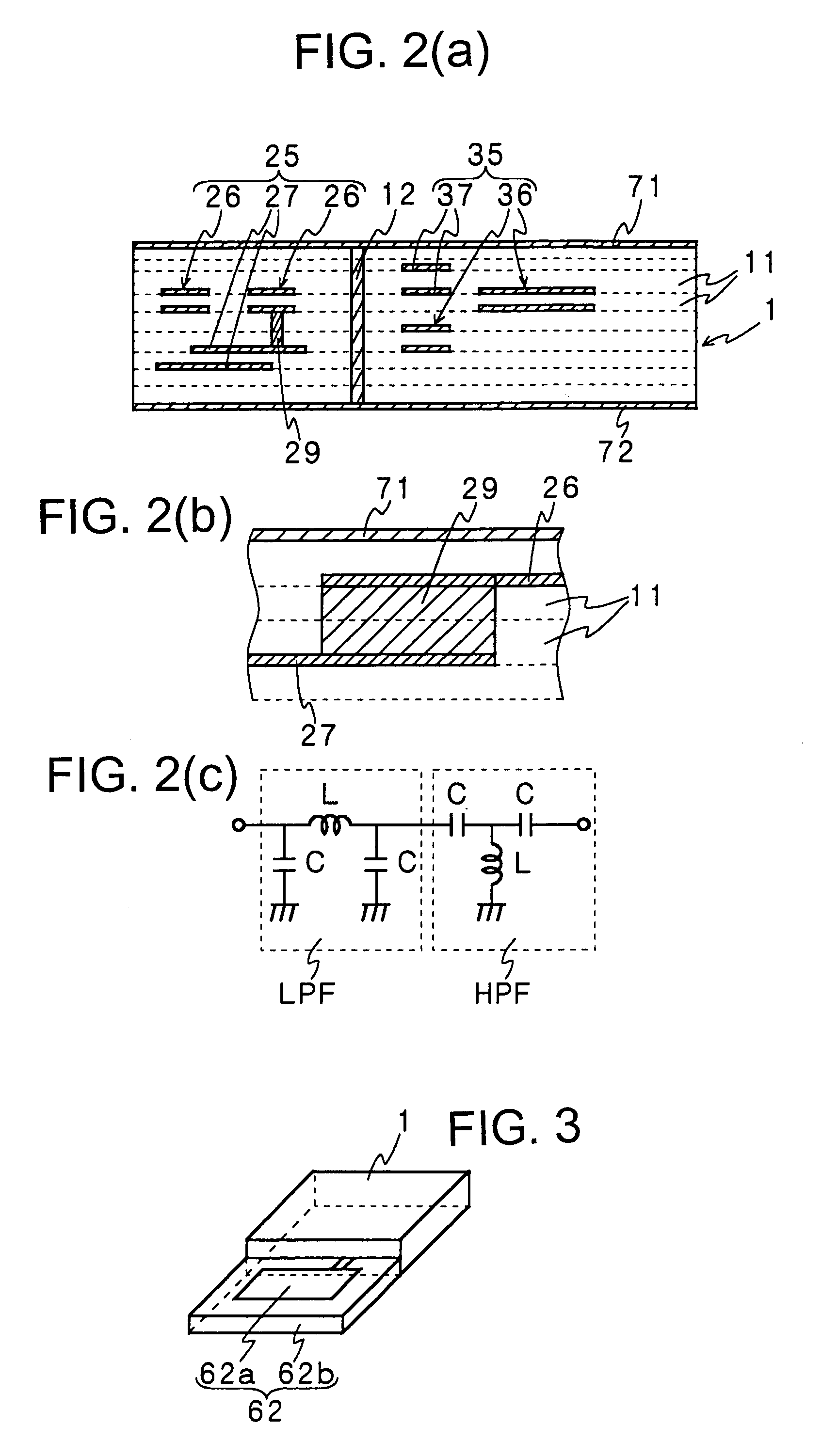

Antenna with built-in filter

InactiveUS7180473B2Simple structureLower resistanceMultiple-port networksSimultaneous aerial operationsSurface mountingHigh-pass filter

At least one filter block (25, 35, 45) is formed in a thin and flat dielectric multilayer structure (21) and fixed with radiation elements (2, 3). Each filter block includes at least one of a low-pass filter, a high-pass filter and a band-eliminating filter. On the surface (one major surface) side and / or the side face of the multilayer structure, at least one radiation element (2, 3) being connected with the filter block is provided and feeding parts (28, 38, 48) for supplying signal to the radiation elements are provided on the rear surface of the multilayer structure. Consequently, the antenna and the filter block are integrated and a small surface mountable antenna with a built-in filter of a structure such that signals are not mixed each other even when signals of a plurality of frequency bands are transmitted / received can be obtained.

Owner:YOKOWO CO LTD +1

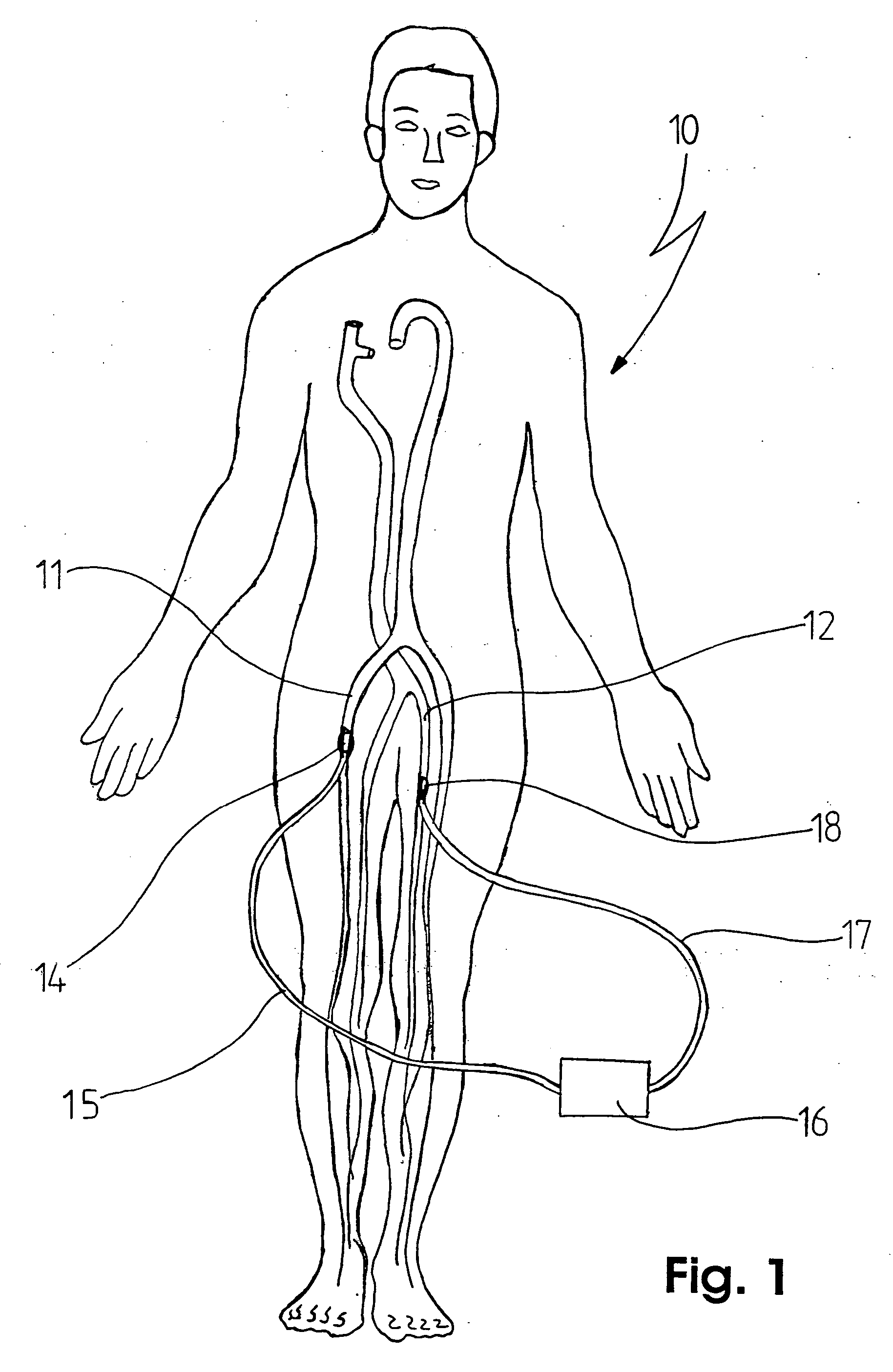

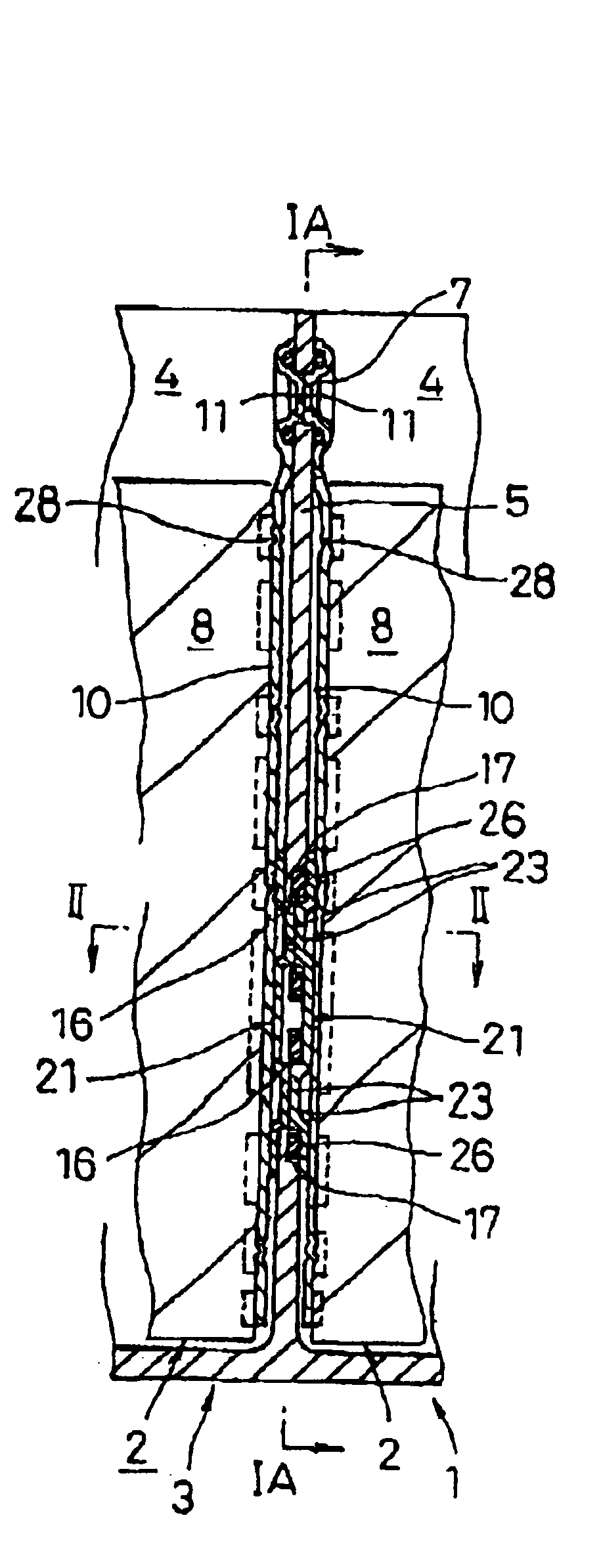

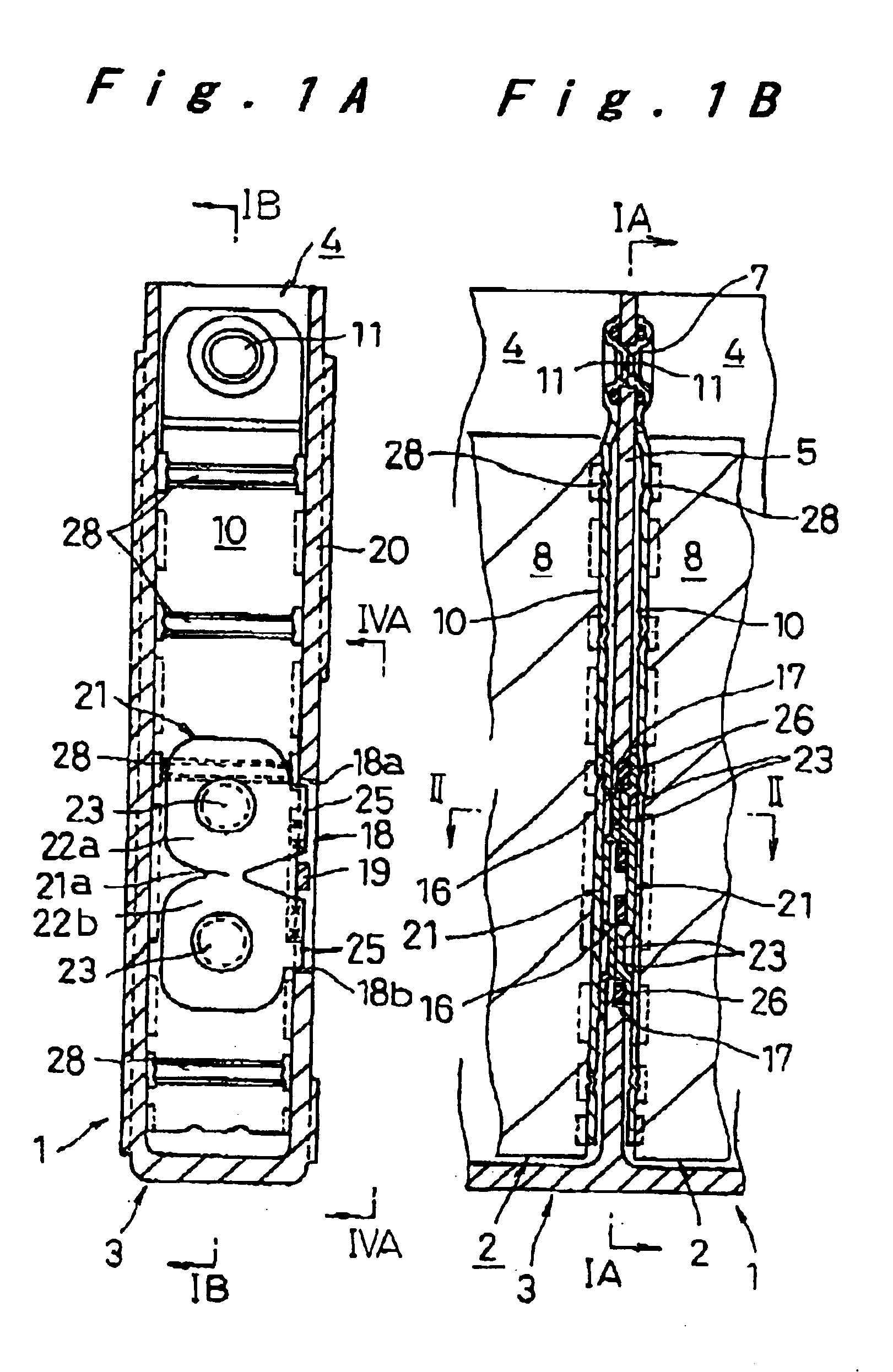

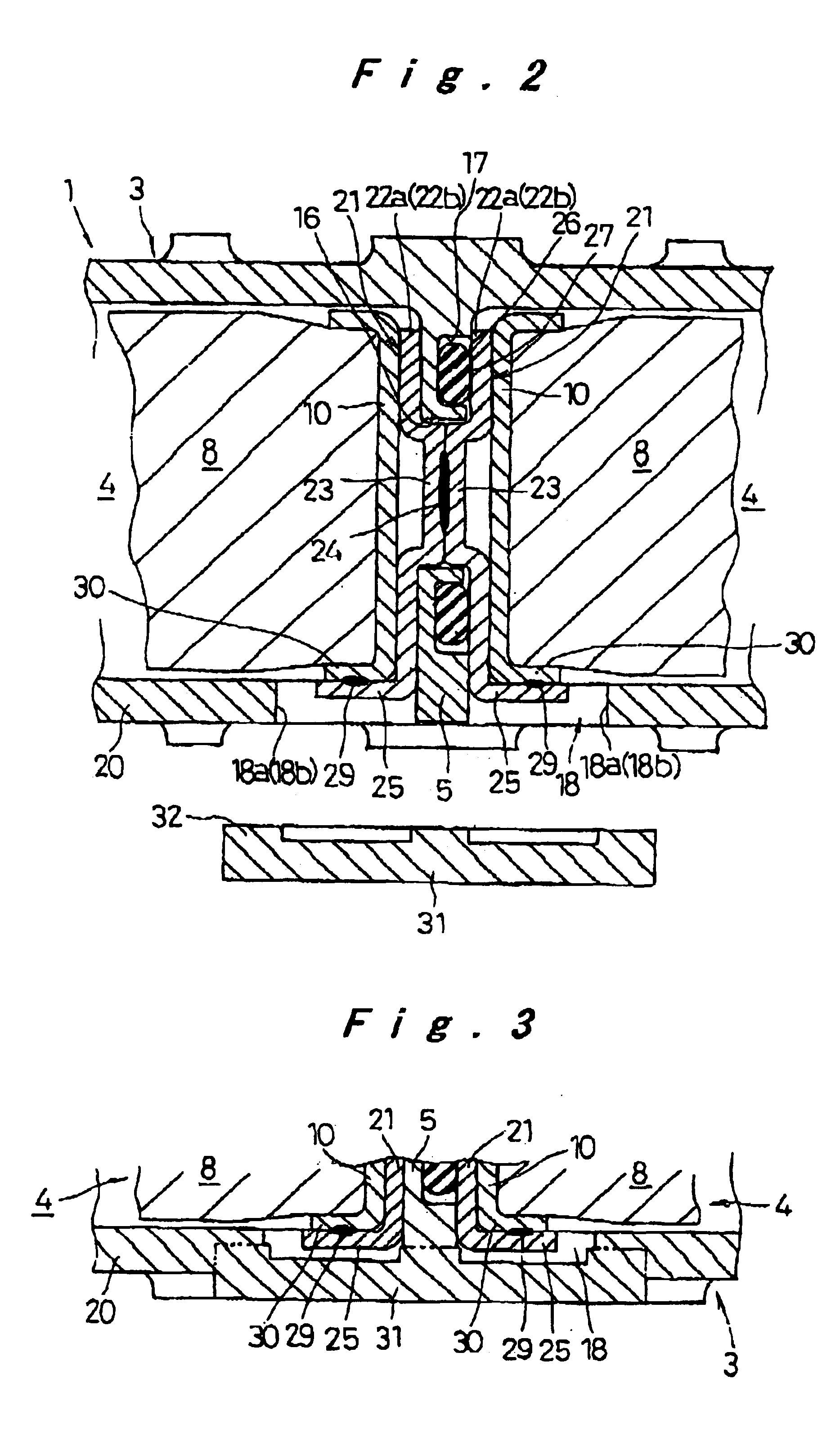

Appliance for cannulation of a blood vessel

InactiveUS20040215142A1Guaranteed supplyBlood trauma can be minimizedBalloon catheterOther blood circulation devicesMedicineBlood vessel spasm

The present invention relates to an appliance for cannulation of a blood vessel with a cannula which, after introduction into the vessel, is in fluidic communication with the vessel. At least one means is also provided to permit a controlled division of the blood into a first subsidiary stream which leaves the vessel through the cannula, and a second subsidiary stream which continues to flow through the vessel.

Owner:NOVALUNG

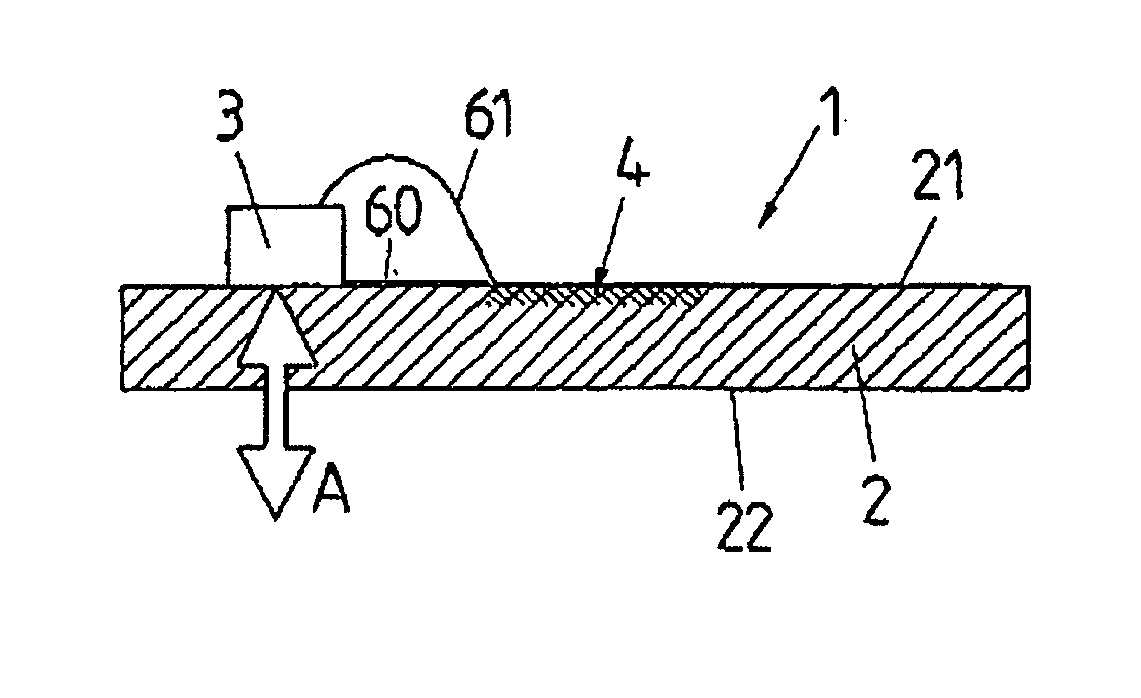

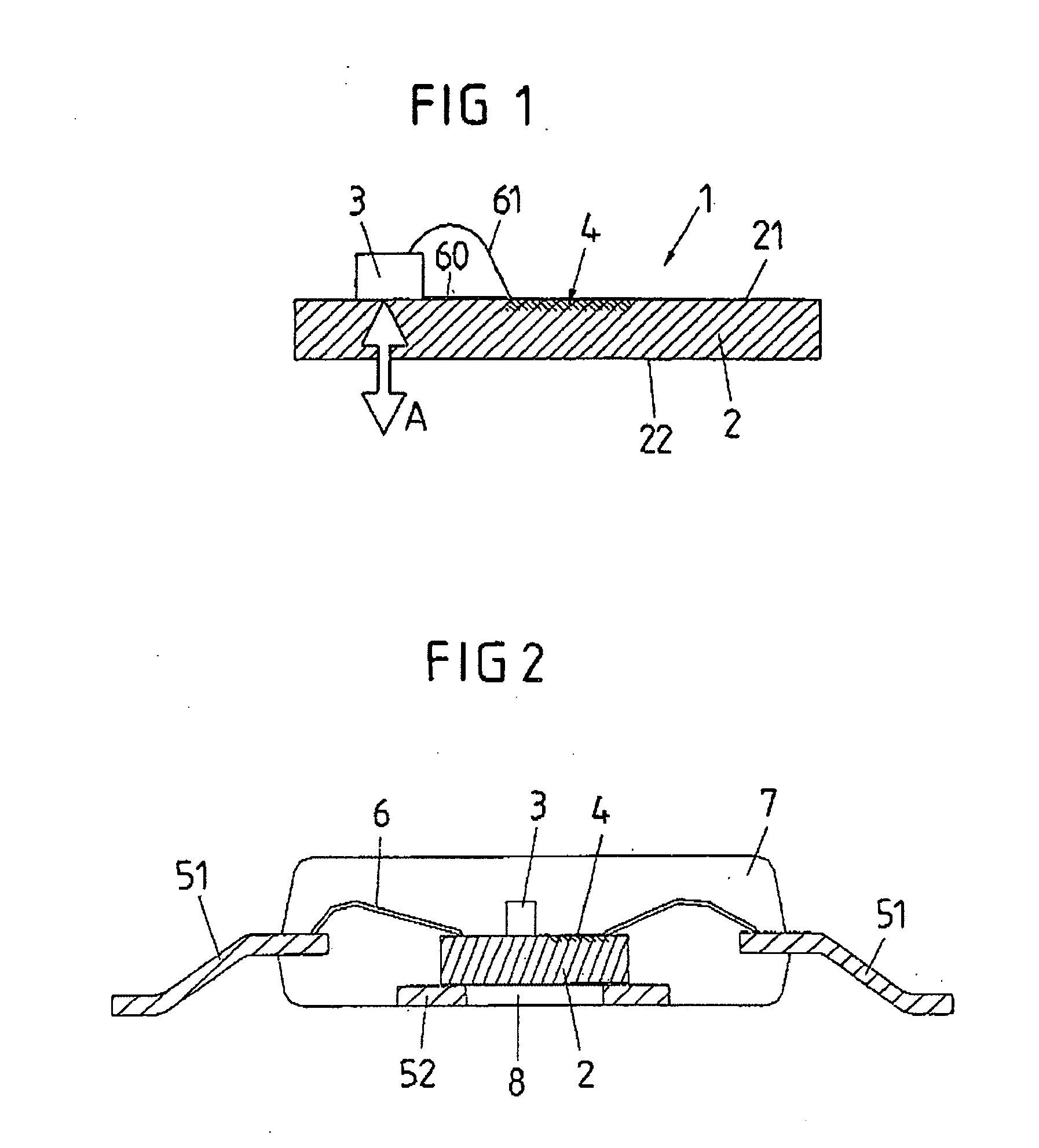

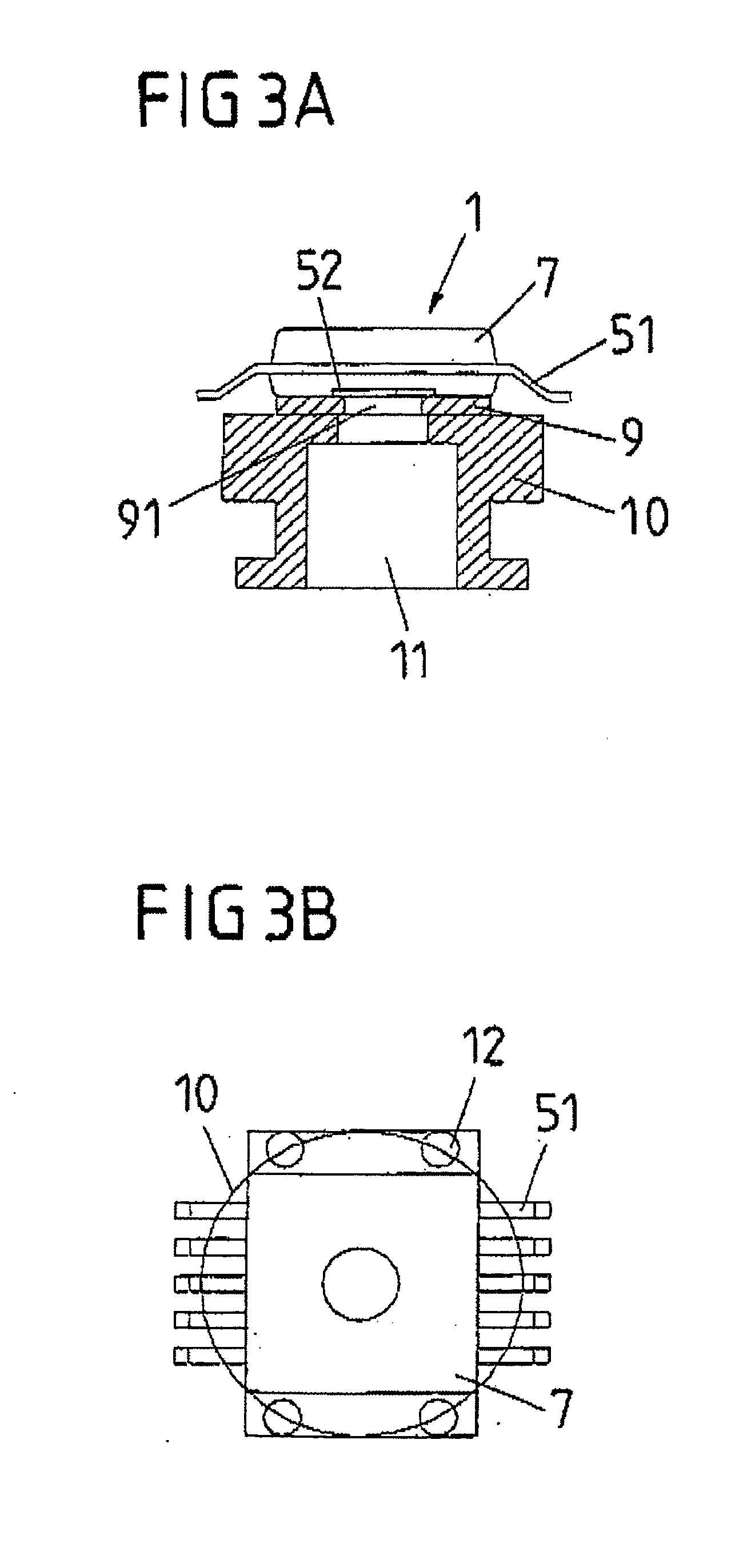

Optoelectronic component and optoelectronic arrangement with an optoelectronic component

InactiveUS20050056851A1Good signal propertyCompact structureSemiconductor/solid-state device detailsSolid-state devicesTransducerEngineering

An optoelectronic component with an optoelectronic transducer device and an electrical circuit electrically connected to the transducer device mounted on a carrier substrate which is optically transparent for specific wavelengths. The transducer device is arranged on the front side of the carrier substrate, and light coupling takes place through the back side. The electrical circuit is formed as a circuit integrated into the carrier substrate or is formed on the carrier substrate using hybrid technology, the terminal contacts of the circuit being arranged on the front side of the carrier substrate. An optoelectronic arrangement with an optoelectronic component includes an at least partly planar-formed mounting element, which is connected by its one side to an outer side of the component or is integrated in the latter and extends at least as far as an outer edge of the component, and includes a mechanical interface for the mechanical connection of the component.

Owner:INFINEON TECH AG

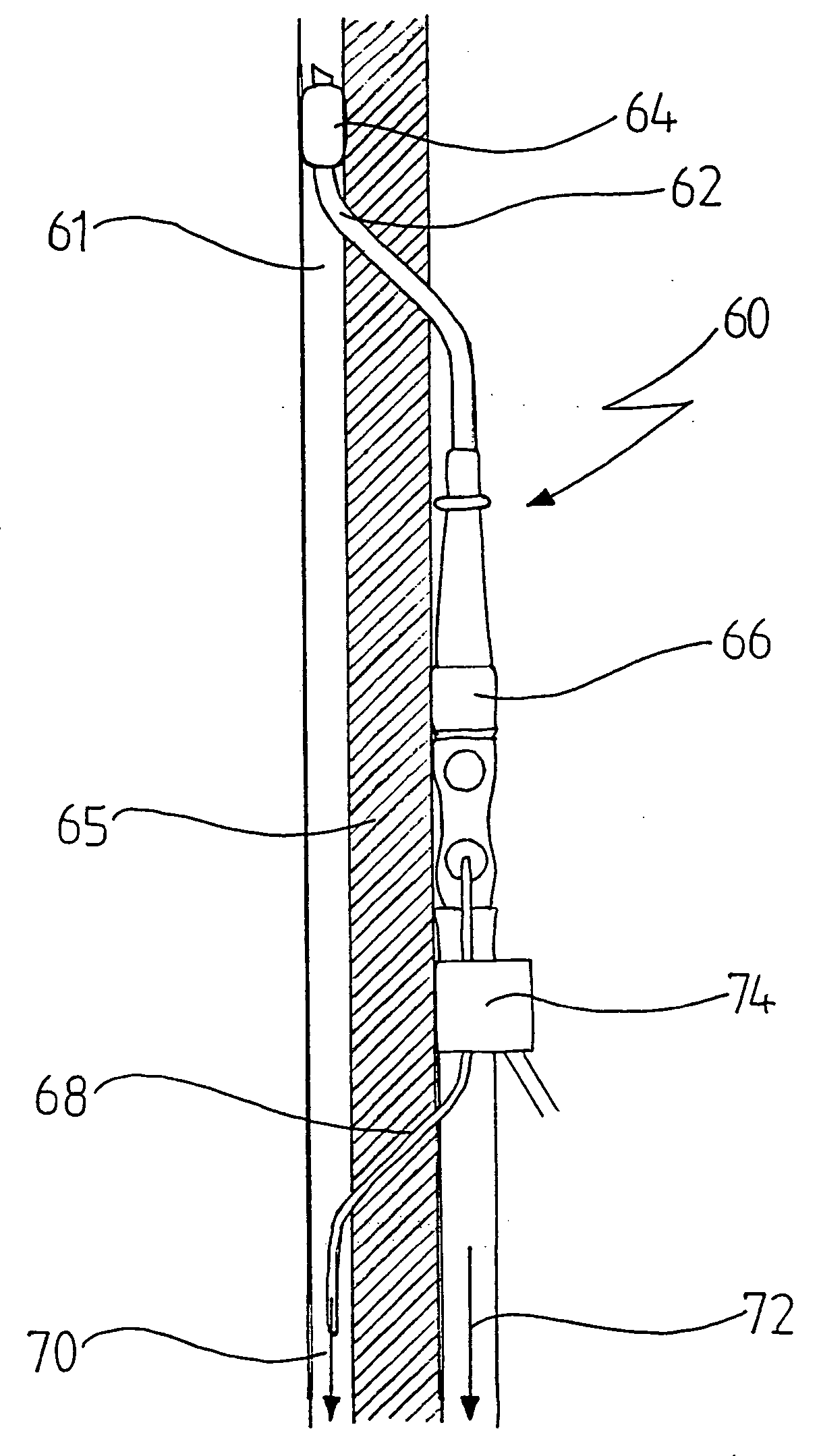

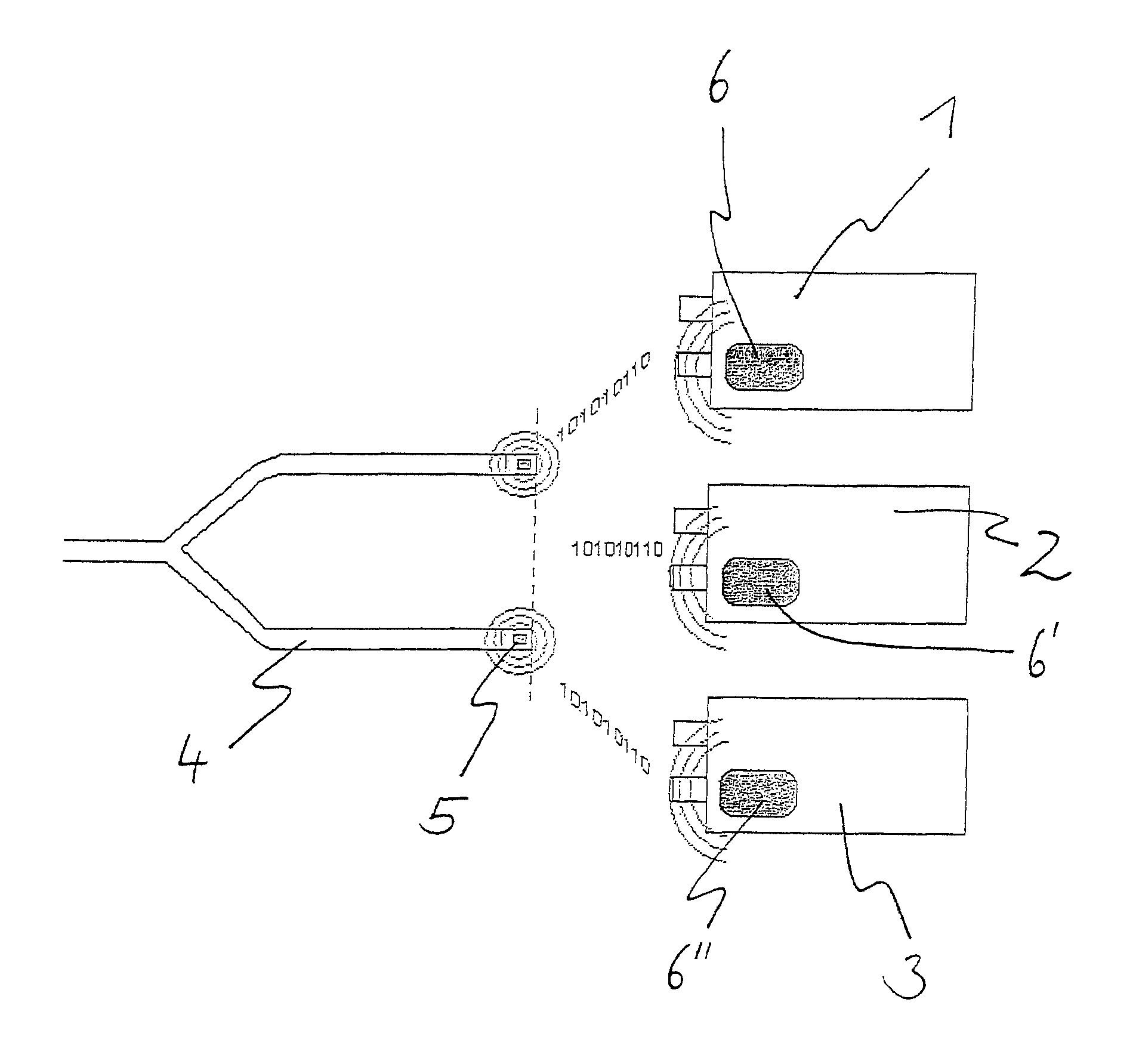

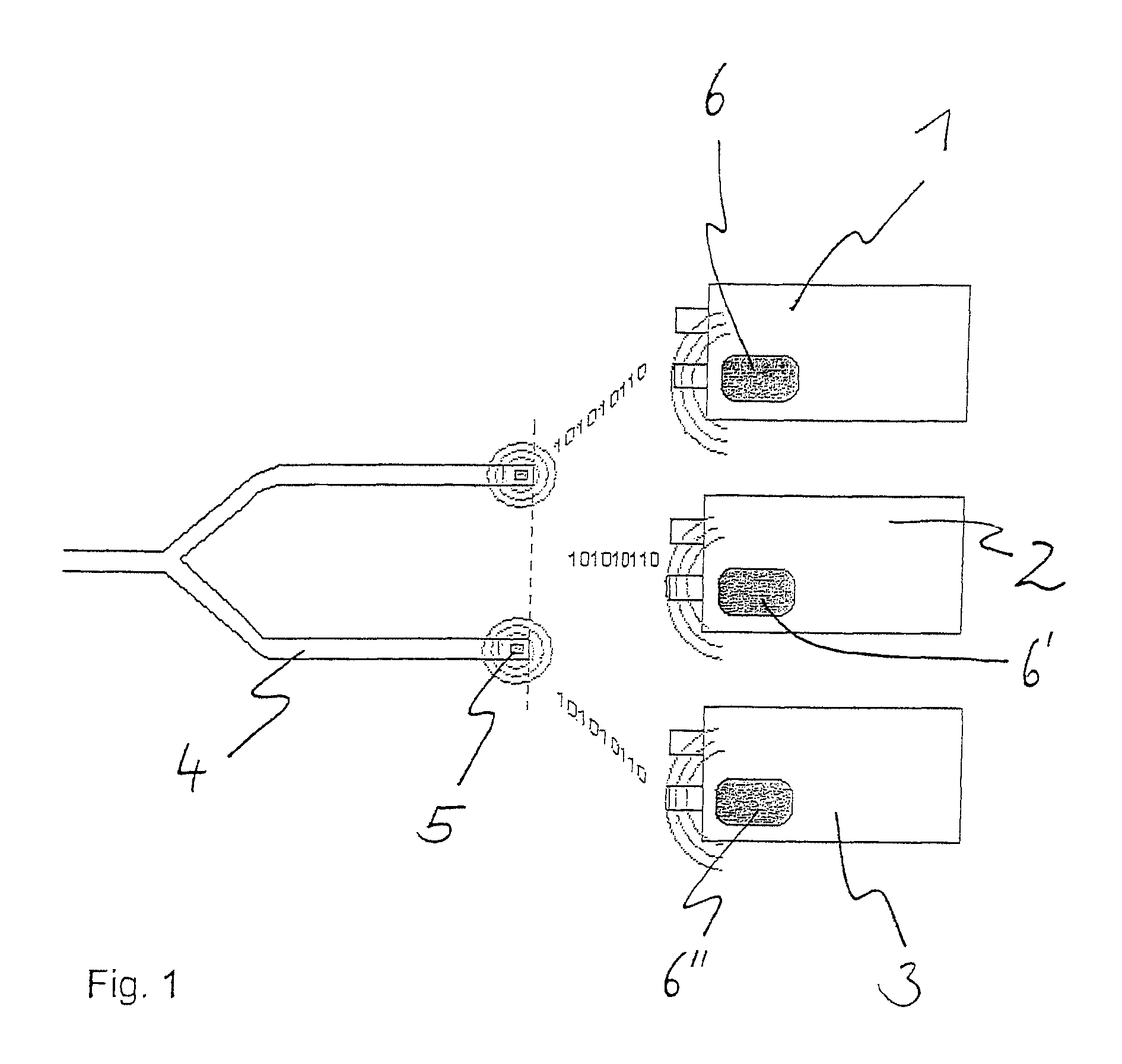

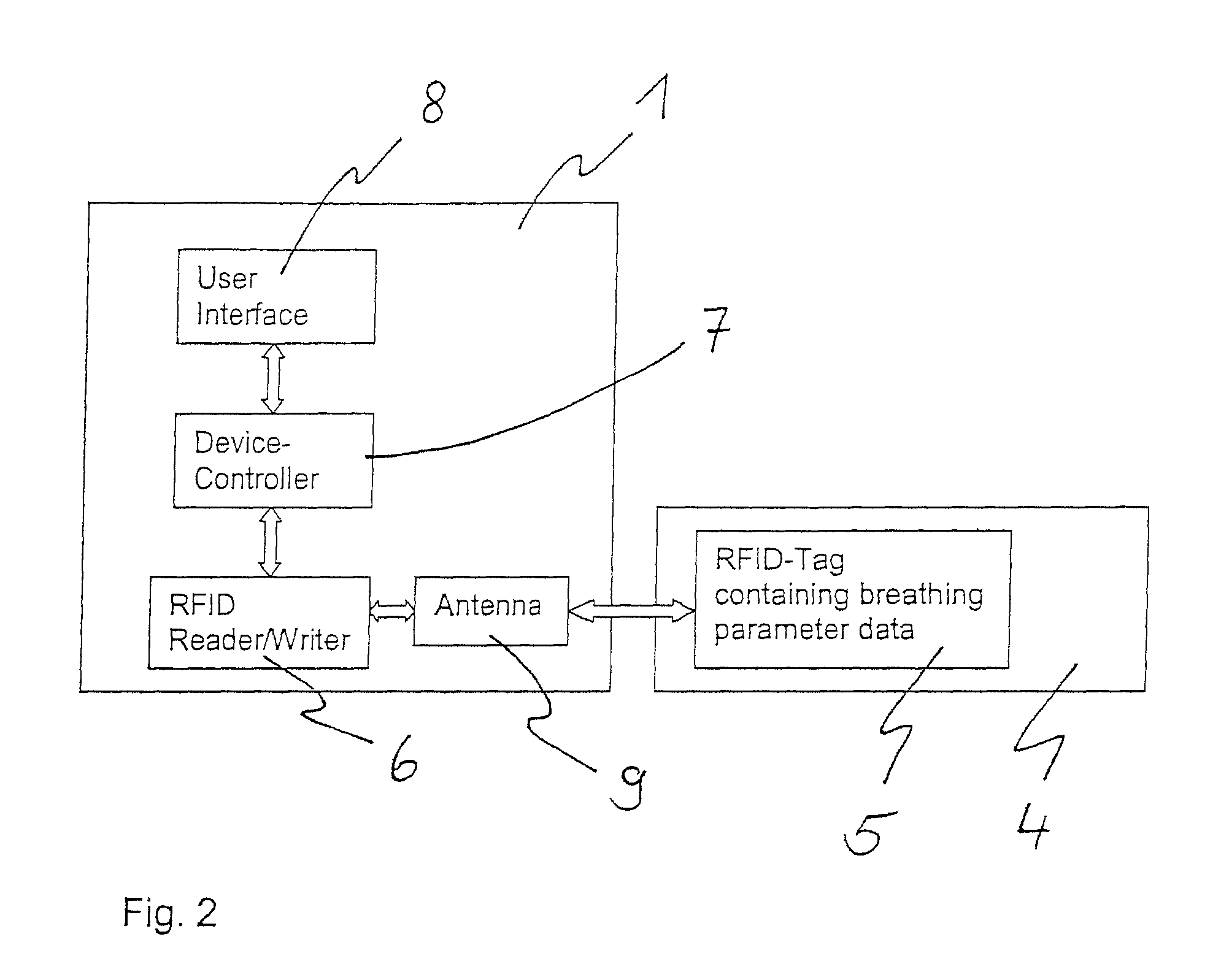

Process and device for the automatic identification of breathing tubes

ActiveUS8496001B2Frequent replacementAvoid long connectionsRespiratorsOperating means/releasing devices for valvesRespiratorBiomedical engineering

A process and a device / system are provided for the automatic identification of the type of a breathing tube. A memory element (5) is connected to the breathing tube (4). The memory element carries stored data identifying the breathing tube (4). The data are read by a reading unit (6), which is part of a respirator (1). The data may be read when the breathing tube (4) is brought into the vicinity of the respirator (1) or connected thereto.

Owner:DRAGERWERK AG

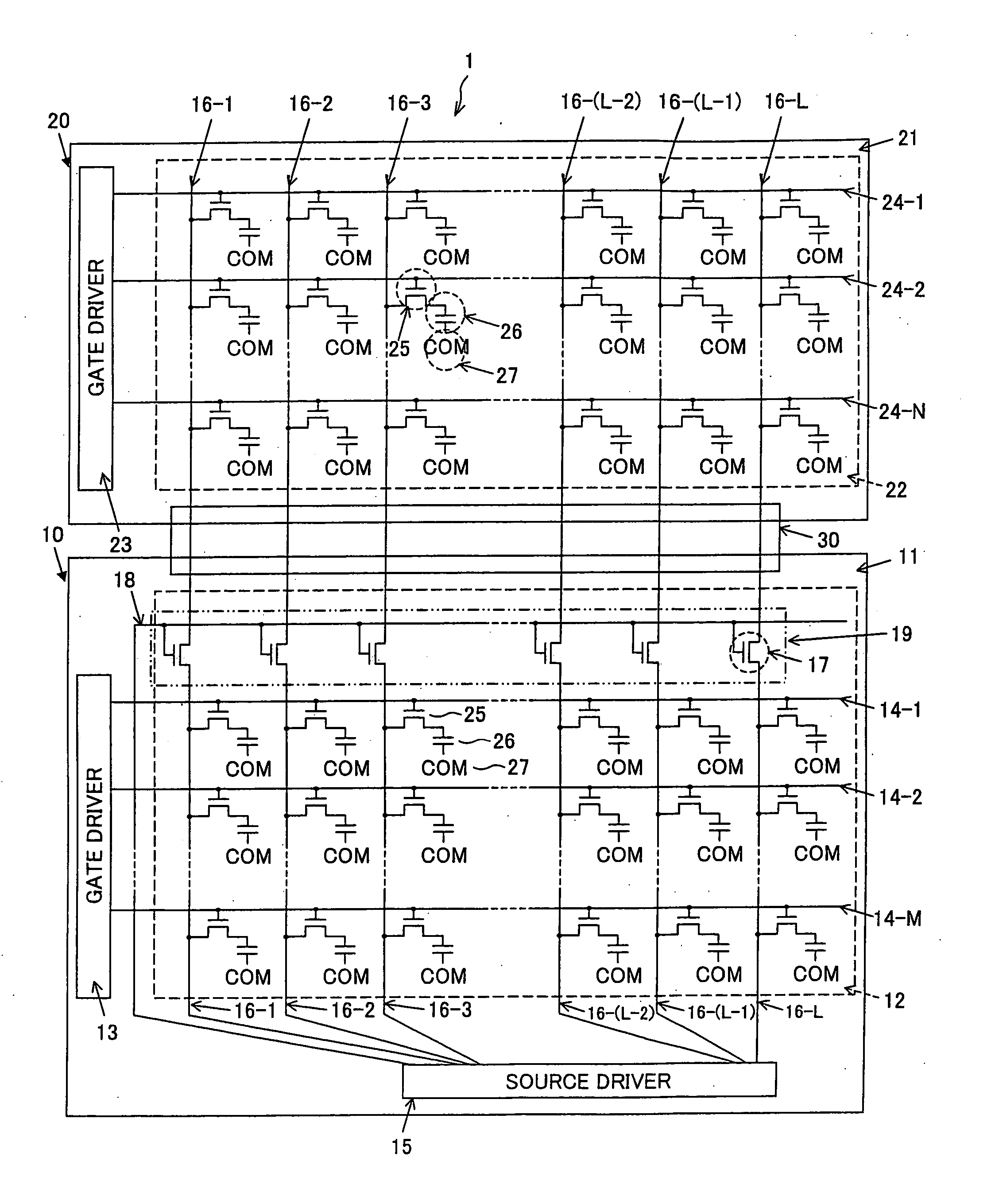

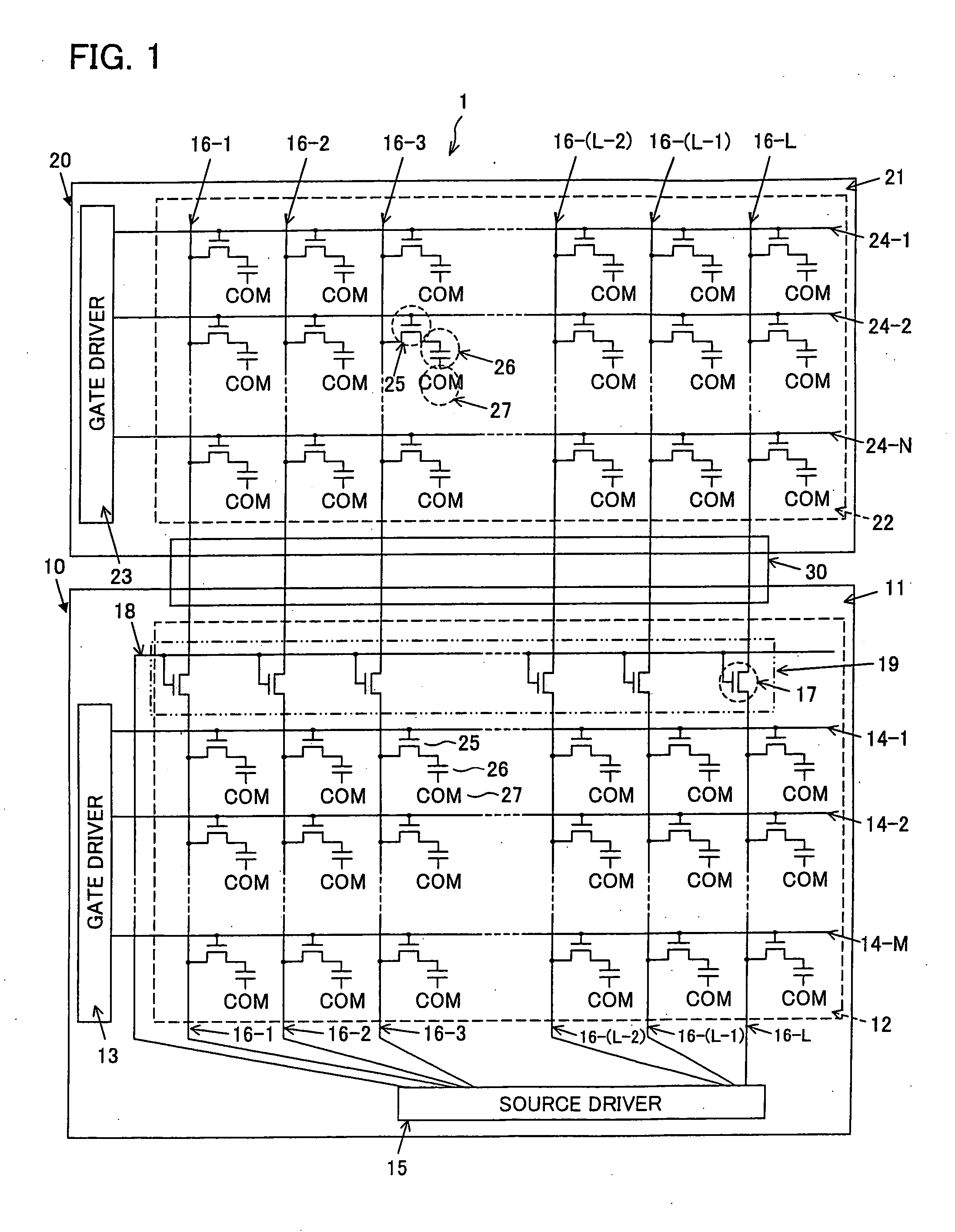

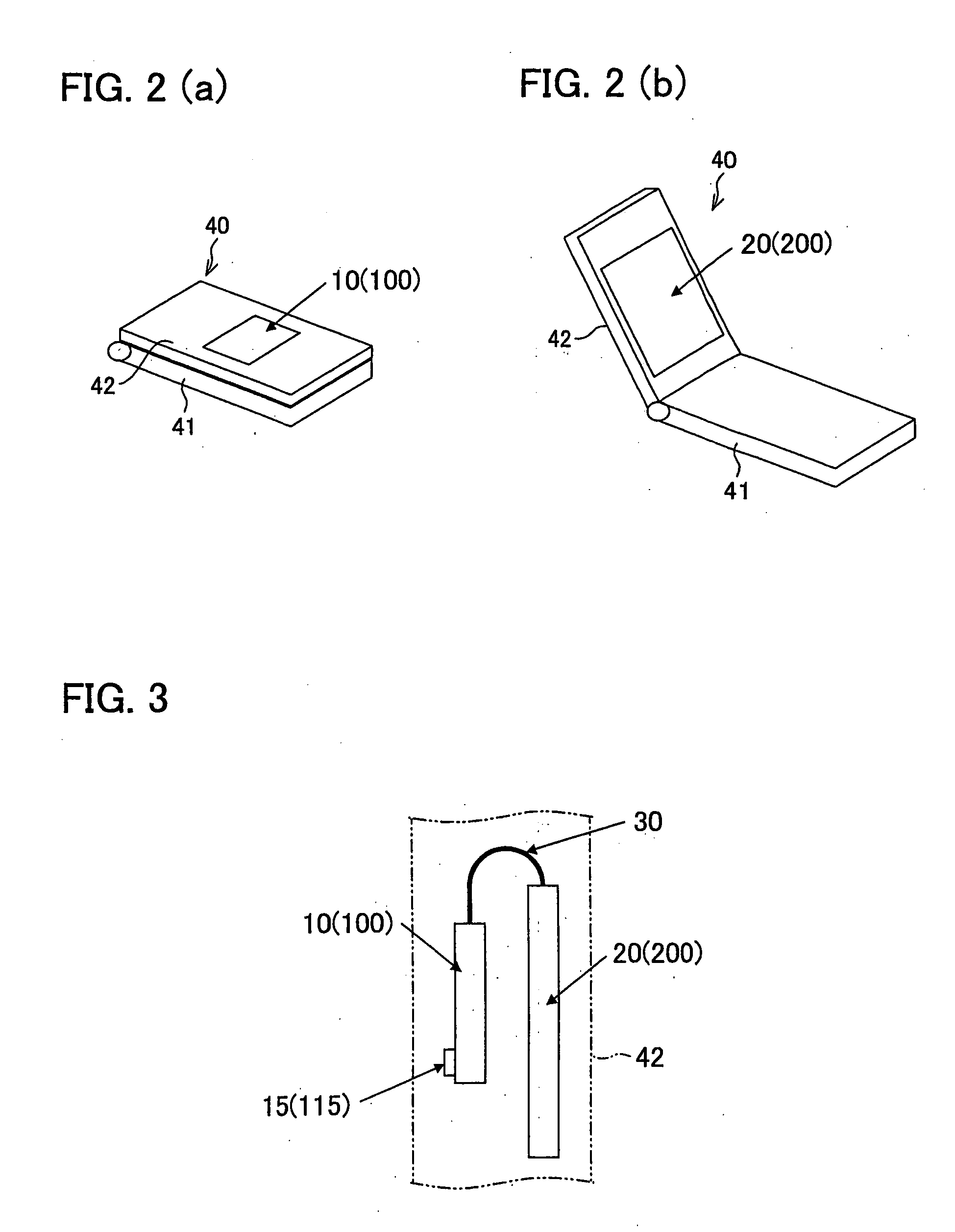

Display device, drive method thereof, and drive system thereof

ActiveUS20050179640A1Reduce power consumptionReduce electricity loadCathode-ray tube indicatorsNon-linear opticsDisplay deviceElectric power

The sub panel 100, having a plurality of gate bus lines 14, source bus lines 16, TFTs 25 and pixel electrodes, is provided with a source driver 15. The main panel 200 has a plurality of gate bus lines 24, source bus lines 16, TFTs 25 and pixel electrodes, each of the source bus lines 16 being connected to the corresponding source bus lines 16 of the first liquid crystal panel 10 through a switching TFT 17. The main panel 200, sharing the source driver 15 with the first liquid crystal panel 10, is less frequently used for display than the first liquid crystal panel 10, and is disconnected by the switching TFT 17 when only the sub panel 100 is used. This makes it possible to device a twin-panel display device low in electric power consumption.

Owner:SHARP KK

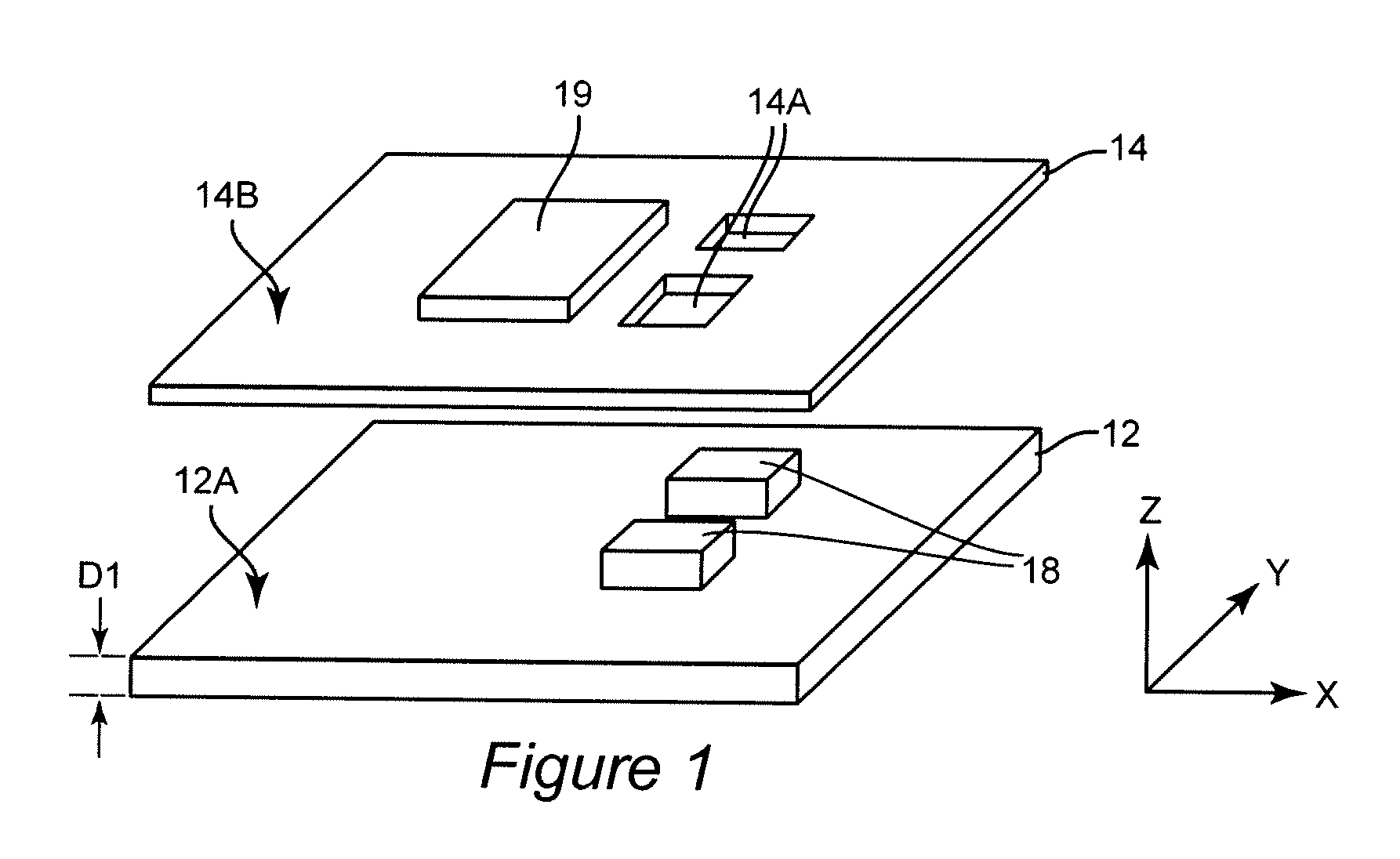

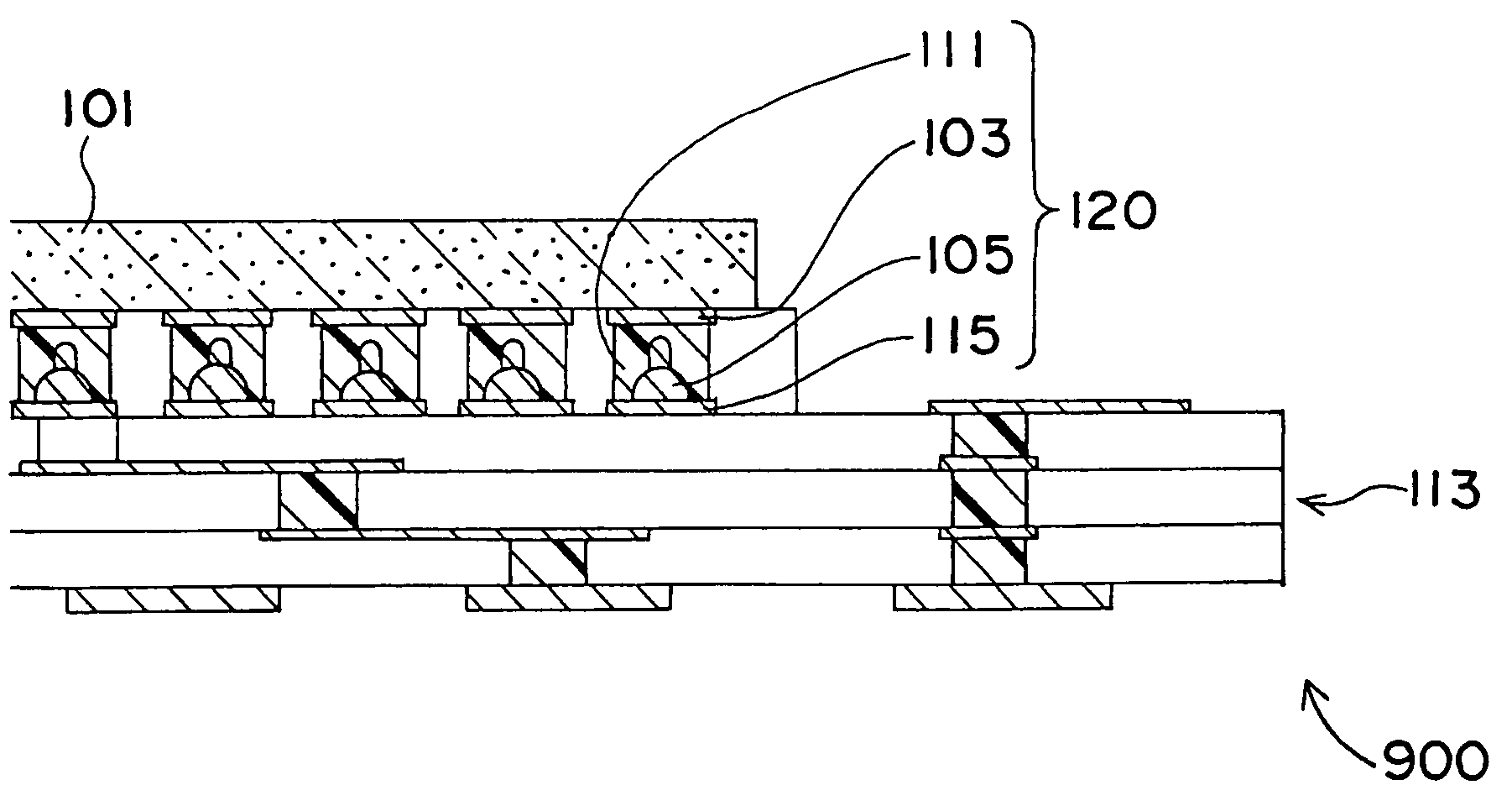

Semiconductor device with intermediate connector

InactiveUS7247508B2Improve reliabilityAvoid long connectionsPrinted circuit assemblingInsulating substrate metal adhesion improvementSemiconductor electrodeConductive paste

A semiconductor element and a circuit substrate each having electrodes disposed at narrow pitch are electrically connected with high reliability by conductive paste. A semiconductor device with a semiconductor section and a circuit substrate electrically connected and a method for manufacturing such semiconductor device are provided. The manufacturing method includes processes of: forming semiconductor electrodes at the semiconductor section; forming substrate electrodes at the circuit substrate; firstly affixing one part of the semiconductor section and circuit substrate to an intermediate connector made of insulating material; forming via holes at intermediate connector according to positions of the semiconductor electrodes and positions of the substrate electrodes; electrically connecting each semiconductor electrode and each substrate electrode via each via hole; and secondly affixing the other part of the semiconductor section and circuit substrate to the intermediate connector.

Owner:PANASONIC CORP

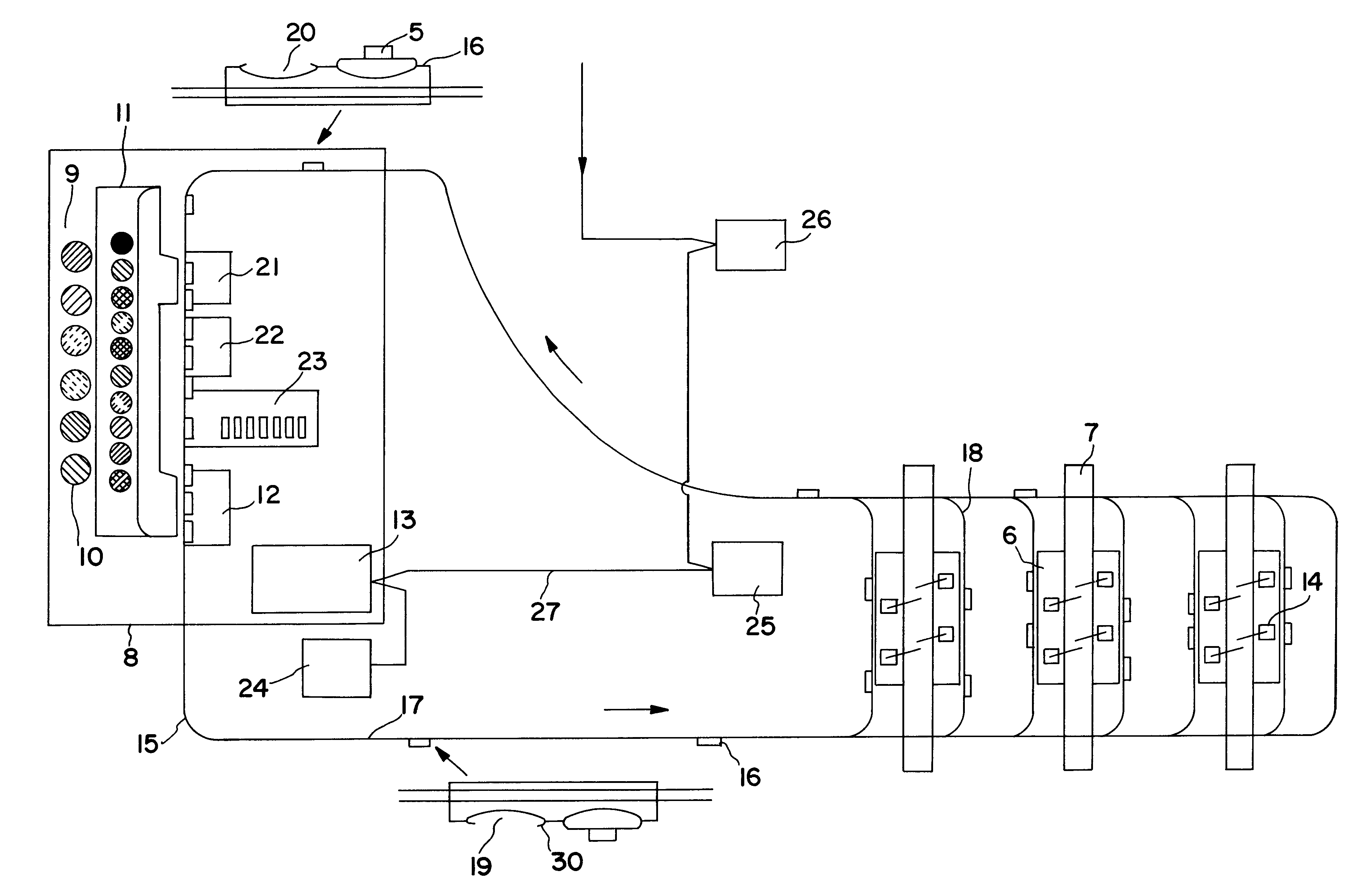

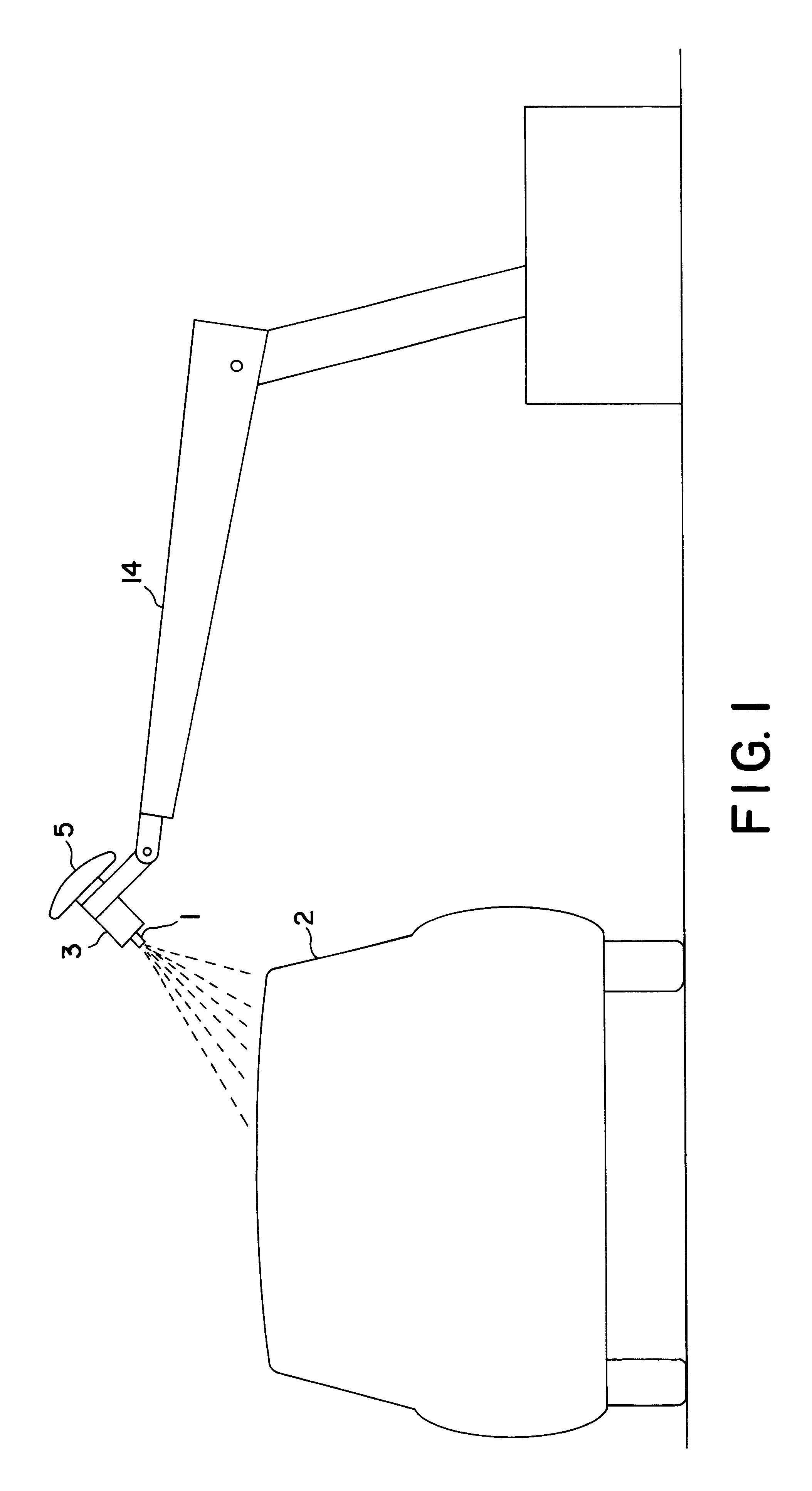

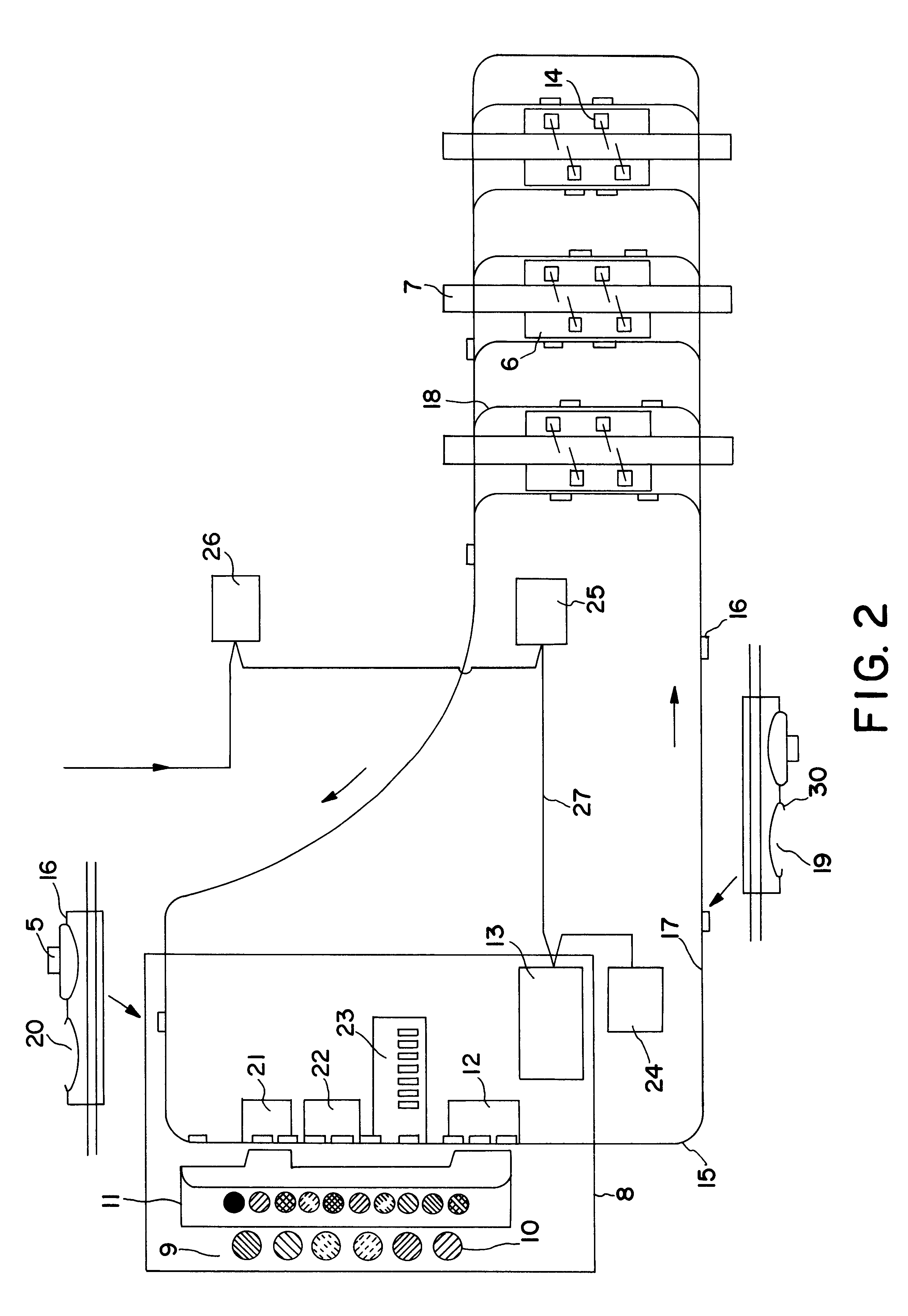

Plant for feeding paint to a spray application apparatus

InactiveUS6309464B1Increase flexibilityIncrease pump powerLiquid surface applicatorsMovable spraying apparatusEngineeringMechanical engineering

A plant is adapted to feed paint to robots for automatic spray application of paint on objects provided with a container (5) made loosenable and removable from the robot for exchange for another such container when there is a desire to have more paint in the container and / or change paint. The plant has a station (8) with containers filled with paint, a transport device (15-18) with means (16) for transporting a container containing paint from said station when said desire arises to the robot and deliver this thereto as well as means adapted to receive a container to be exchanged from the robot and transport it away for taking care thereof.

Owner:ABB FLEXIBLE AUTOMATION AS

Method and apparatus for three-dimensional integration of embedded power module

InactiveUS7932800B2High conductanceImprove abilitiesTransformers/inductances coolingTransformers/inductances coils/windings/connectionsElectrical conductorElectrical connection

A modified planar Low Temperature Co-Fired Ceramic (LTCC) high conductance inductor, embedding a large cross section conductor, supports a stacked arrangement of heat spreader, inductor and active device layers. Interlayer electrical connections connect the layers. Optionally, a DC-DC converter includes the modified planar LTCC high conductance inductor, embedding a large cross section conductor, supporting a stacked arrangement of heat spreader, capacitor and active device layers, the active devices layer including the switching transistors. The active devices layer may include semiconductor dies embedded in a substrate.

Owner:VIRGINIA TECH INTPROP INC

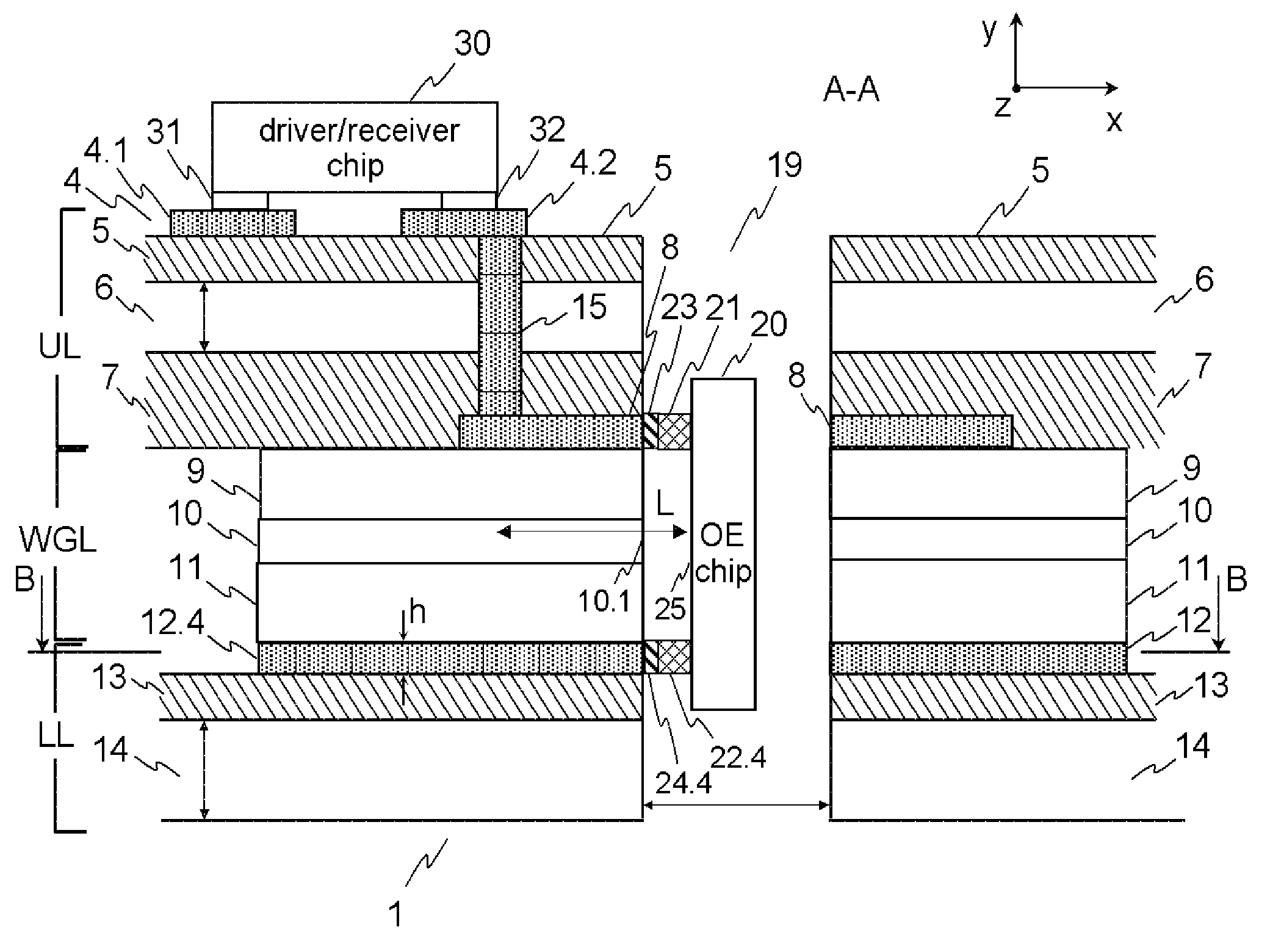

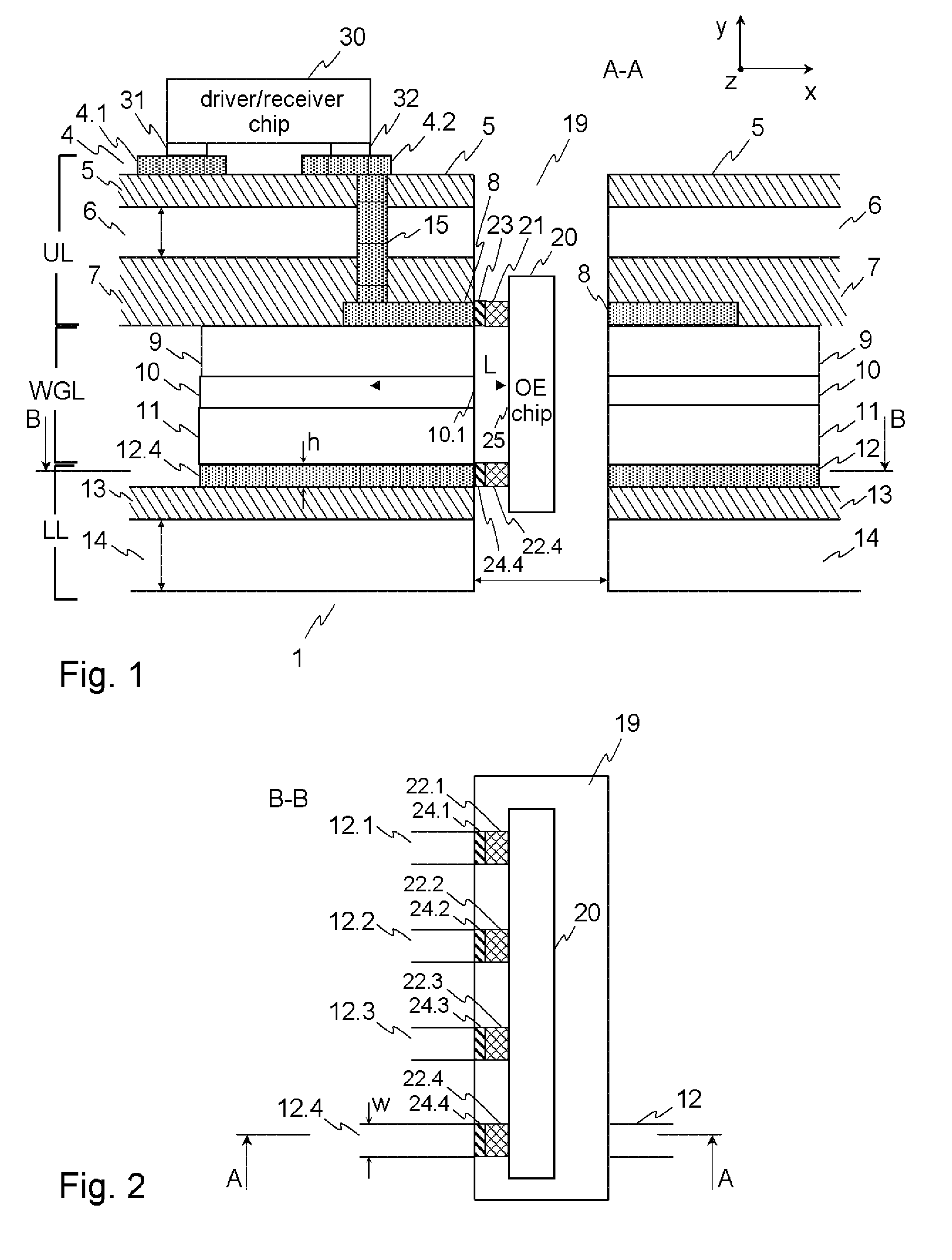

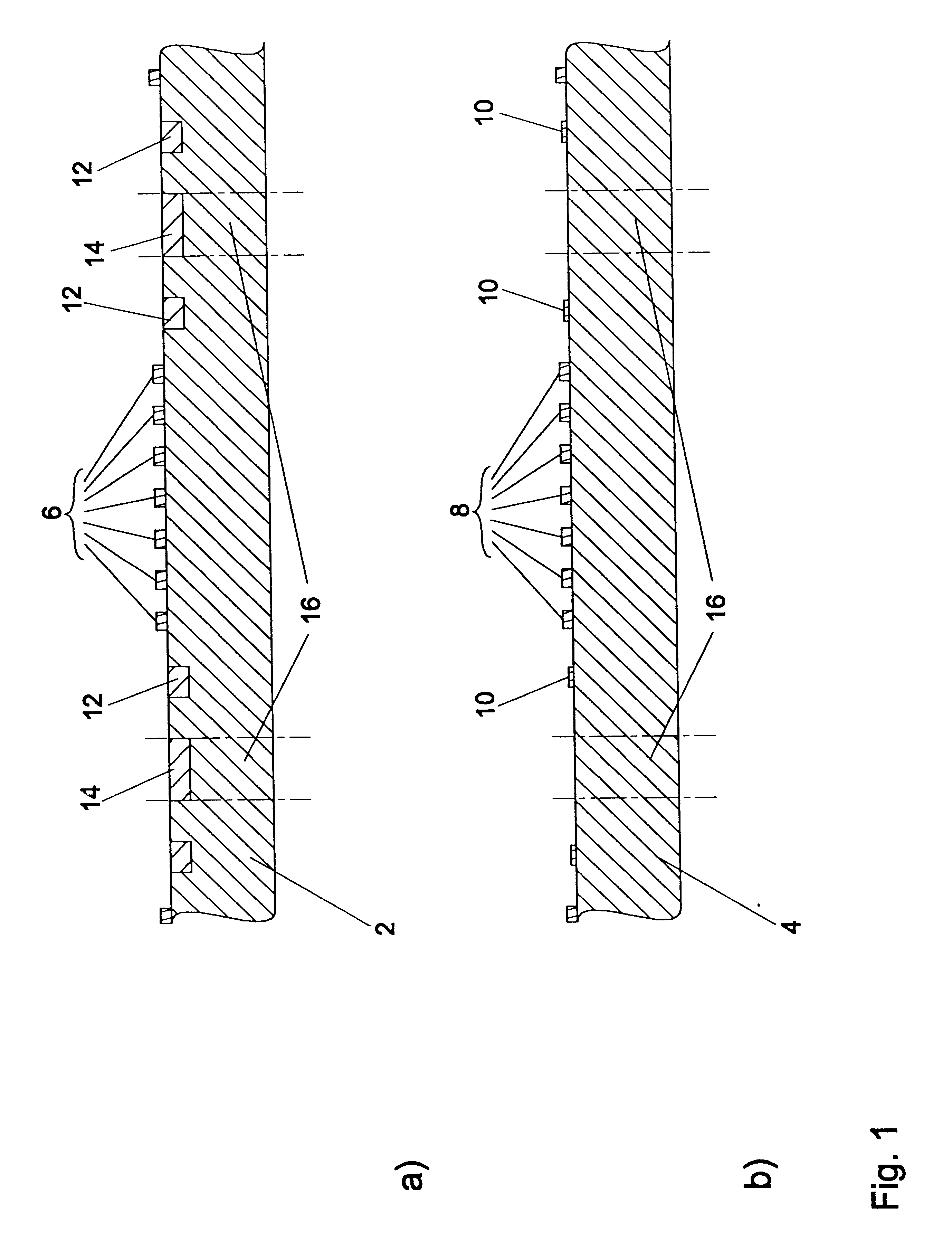

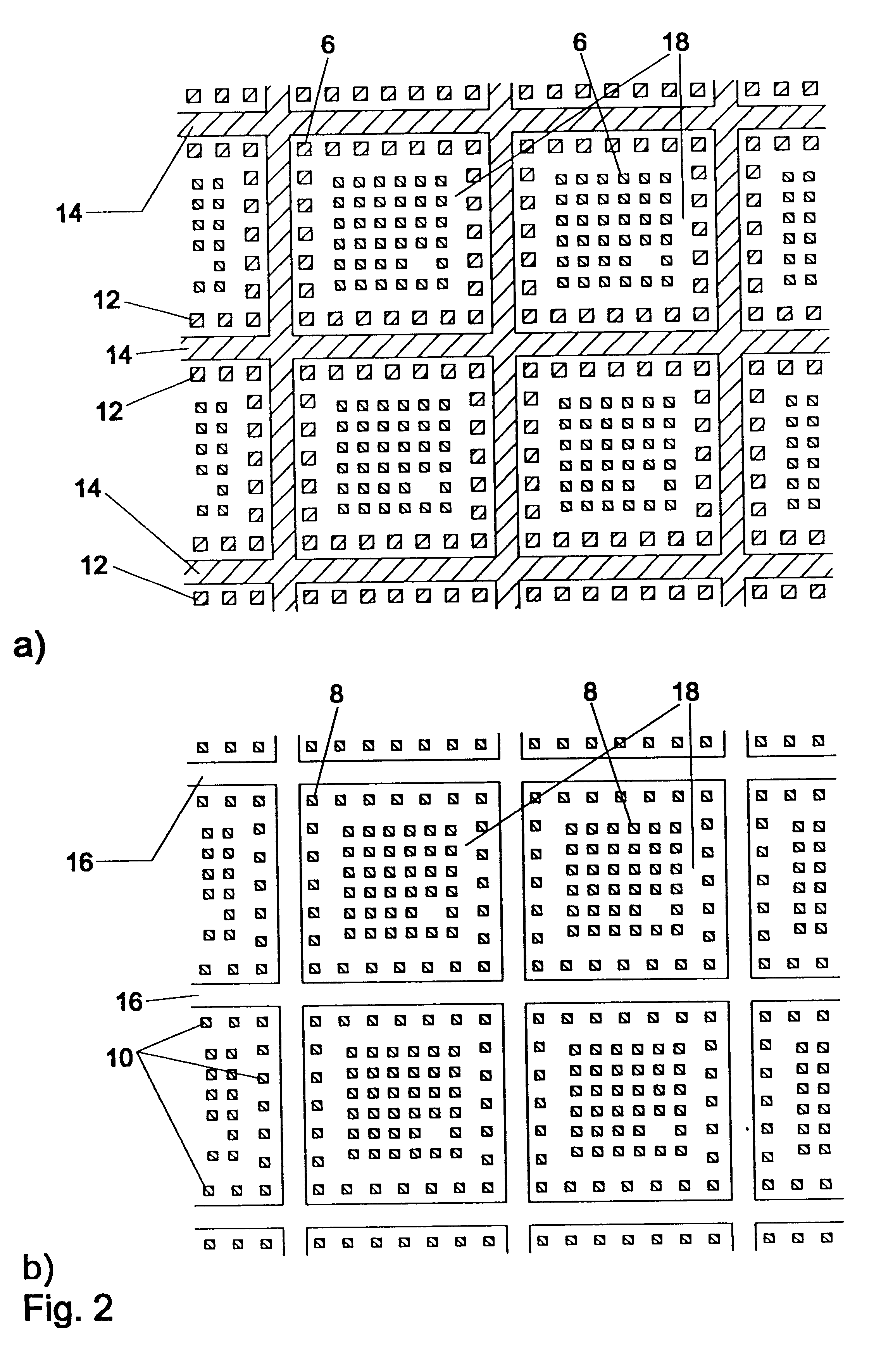

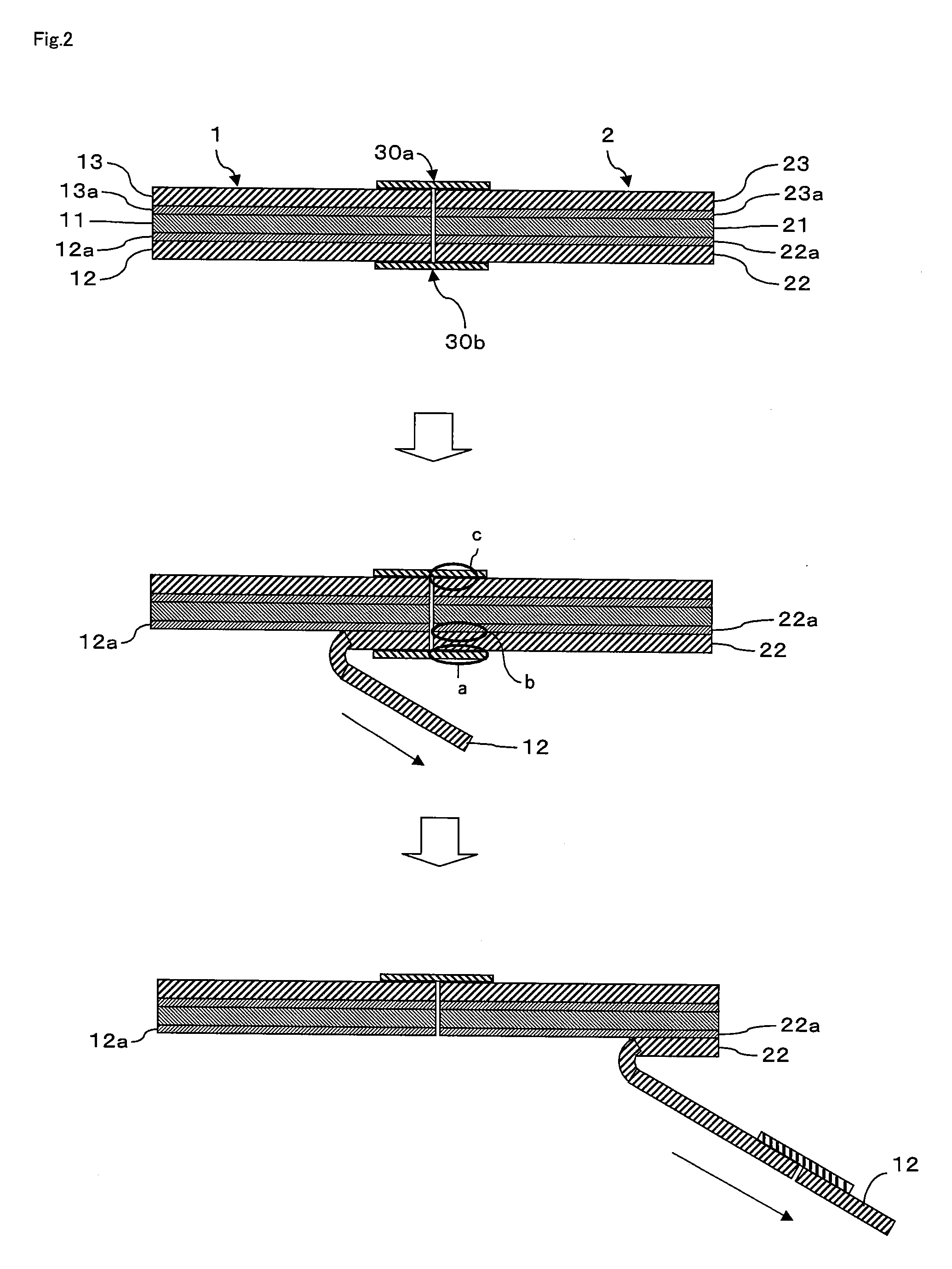

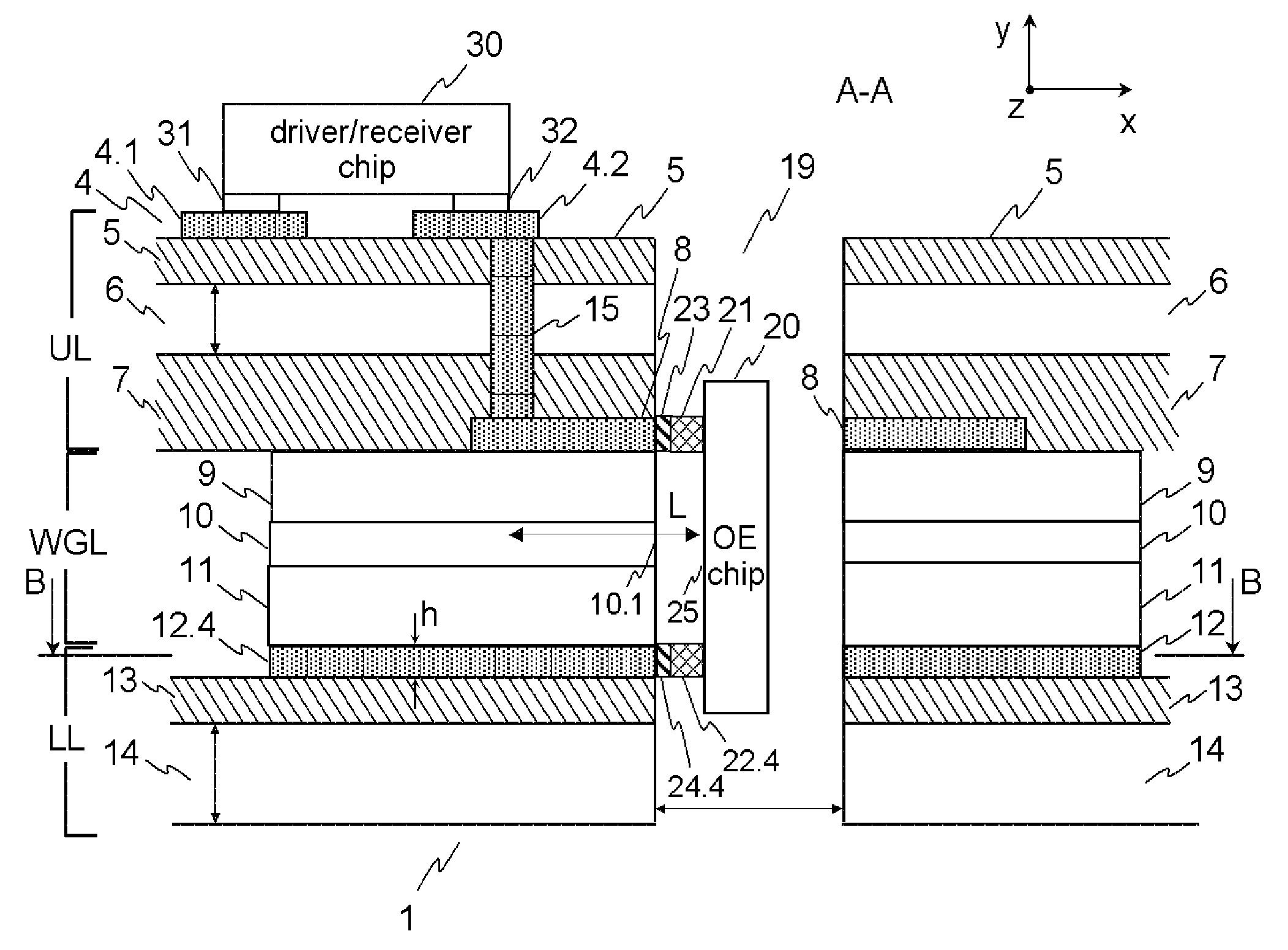

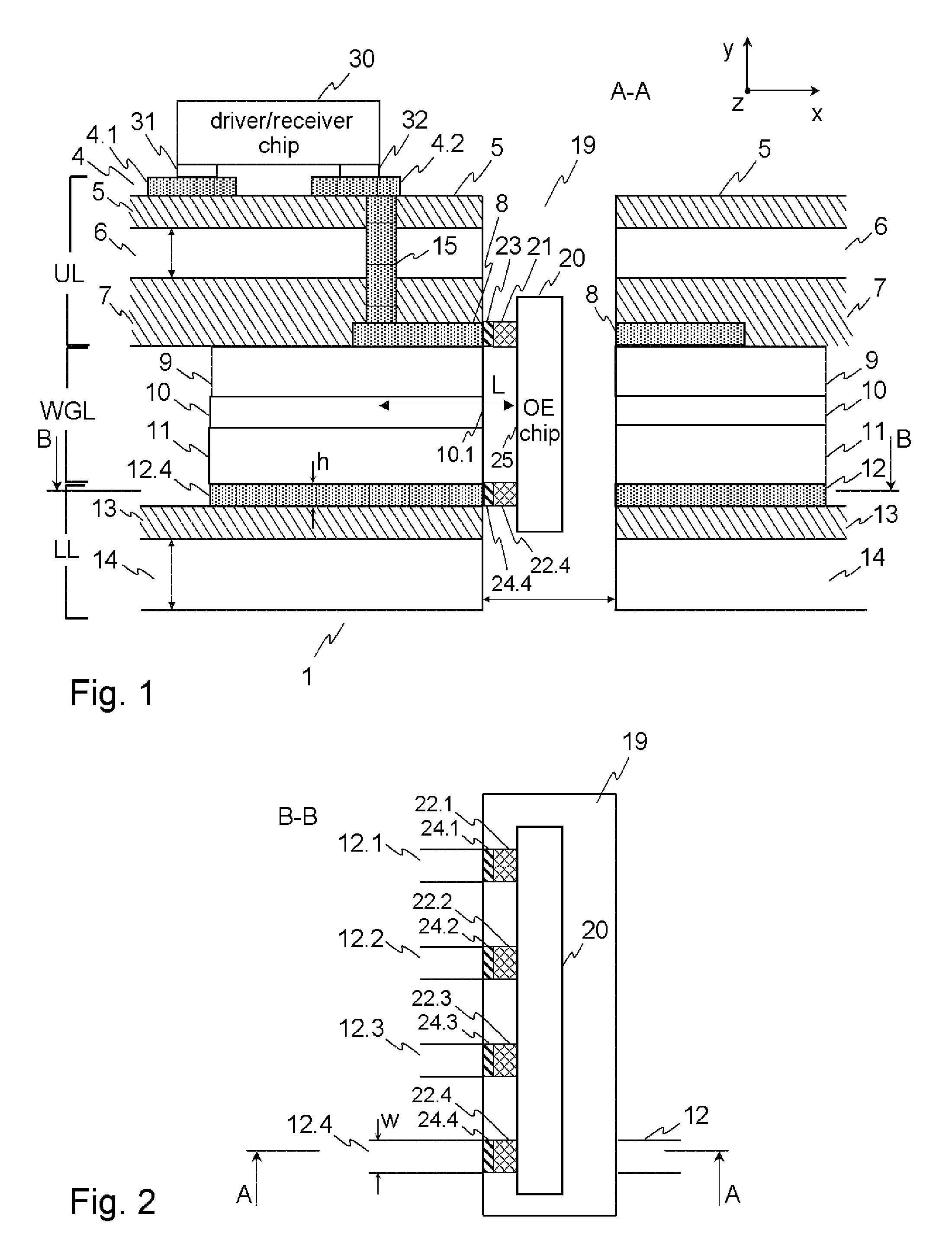

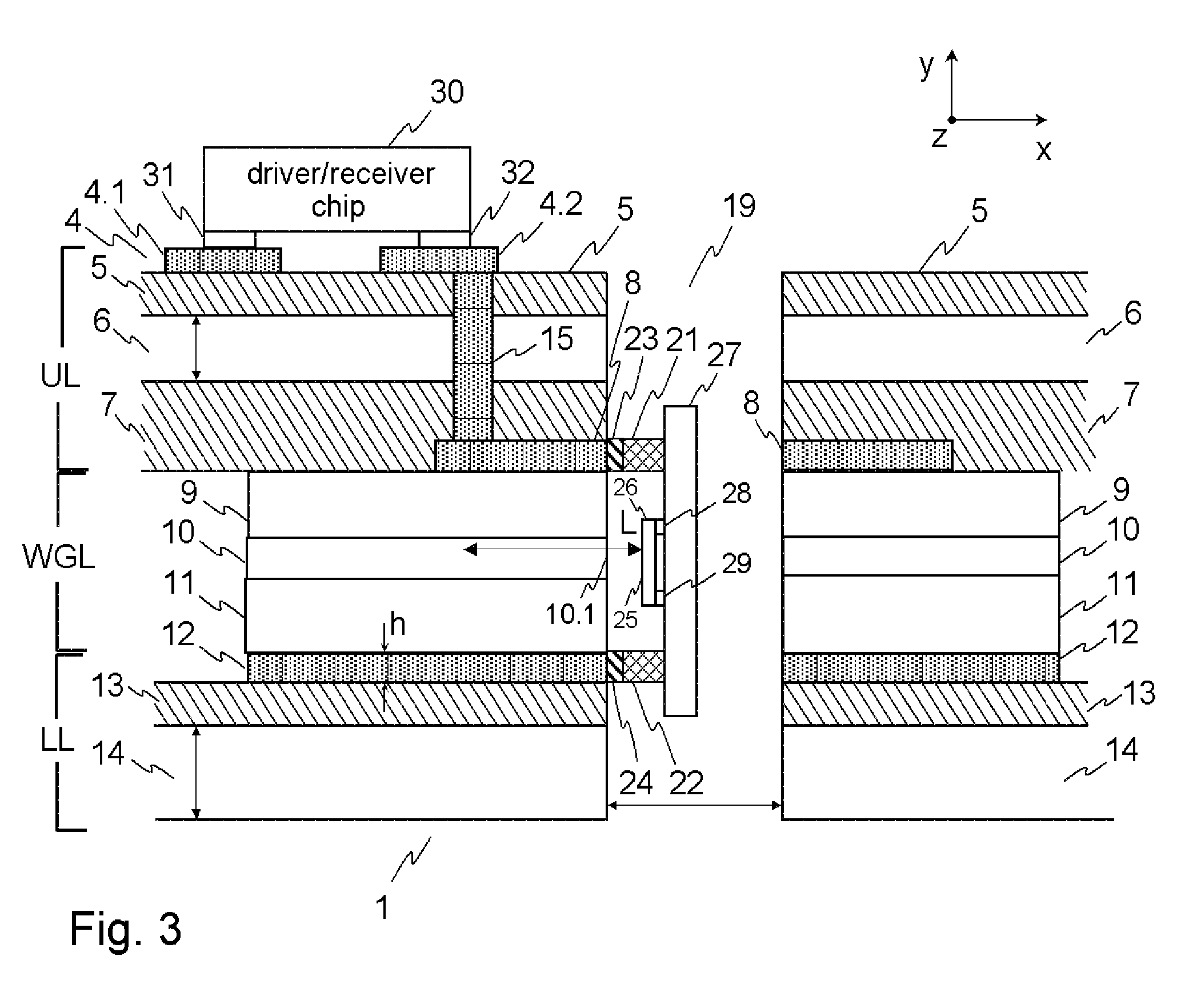

Opto-electronic board

ActiveUS20070147729A1Efficient couplingMechanically better locatedCircuit optical detailsPrinted circuit aspectsEngineeringElectronic board

An opto-electronic board including a printed wiring board with an optical waveguide, a metallic area, and a hole, wherein an abutting face of the optical waveguide and an abutting face of the metallic area form a part of the side face of the hole. The opto-electronic board further comprises an opto-electronic circuit with a bonding pad, wherein the opto-electronic circuit is arranged in the hole and soldered with its bonding pad to the abutting face of the metallic area.

Owner:IBM CORP

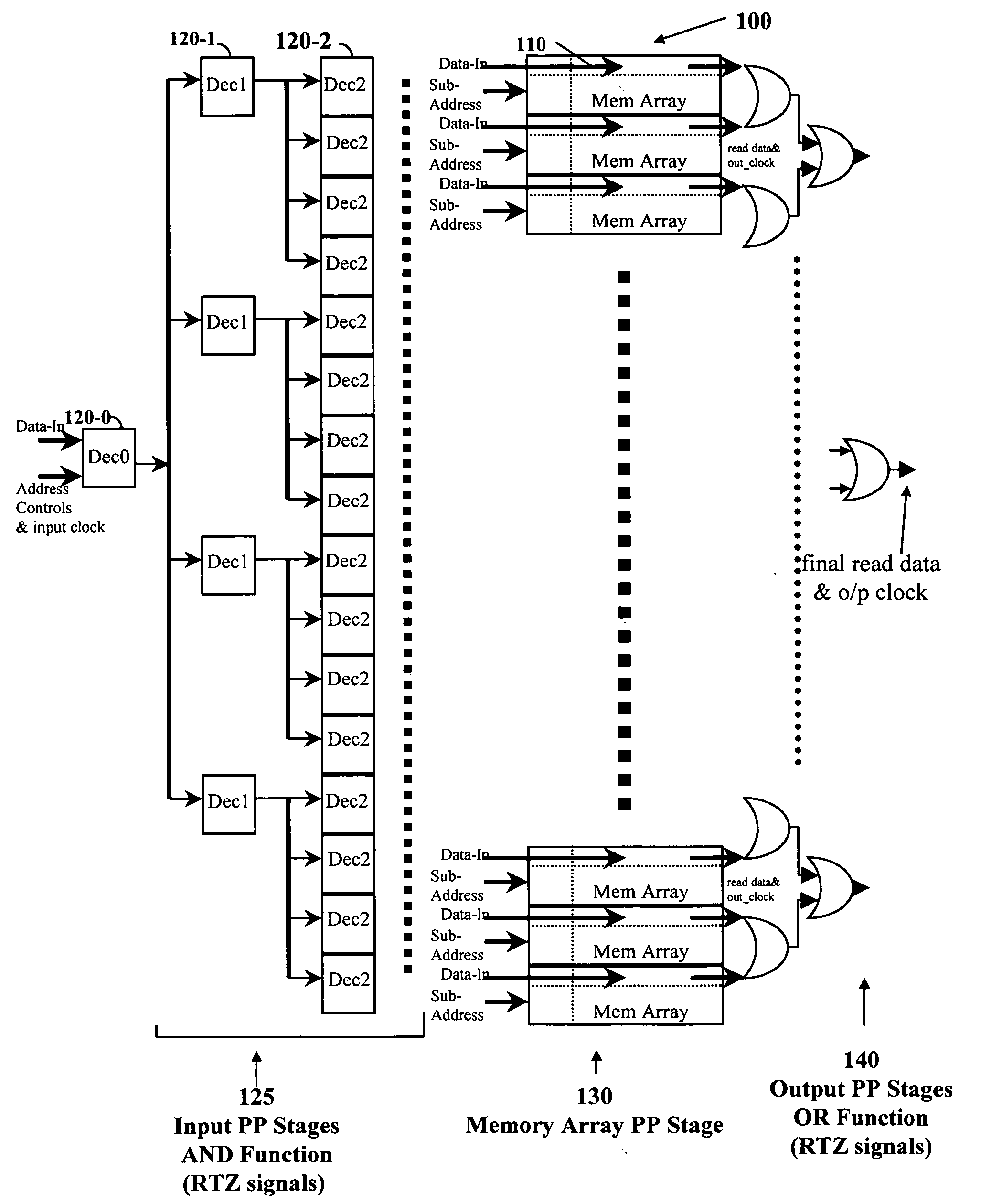

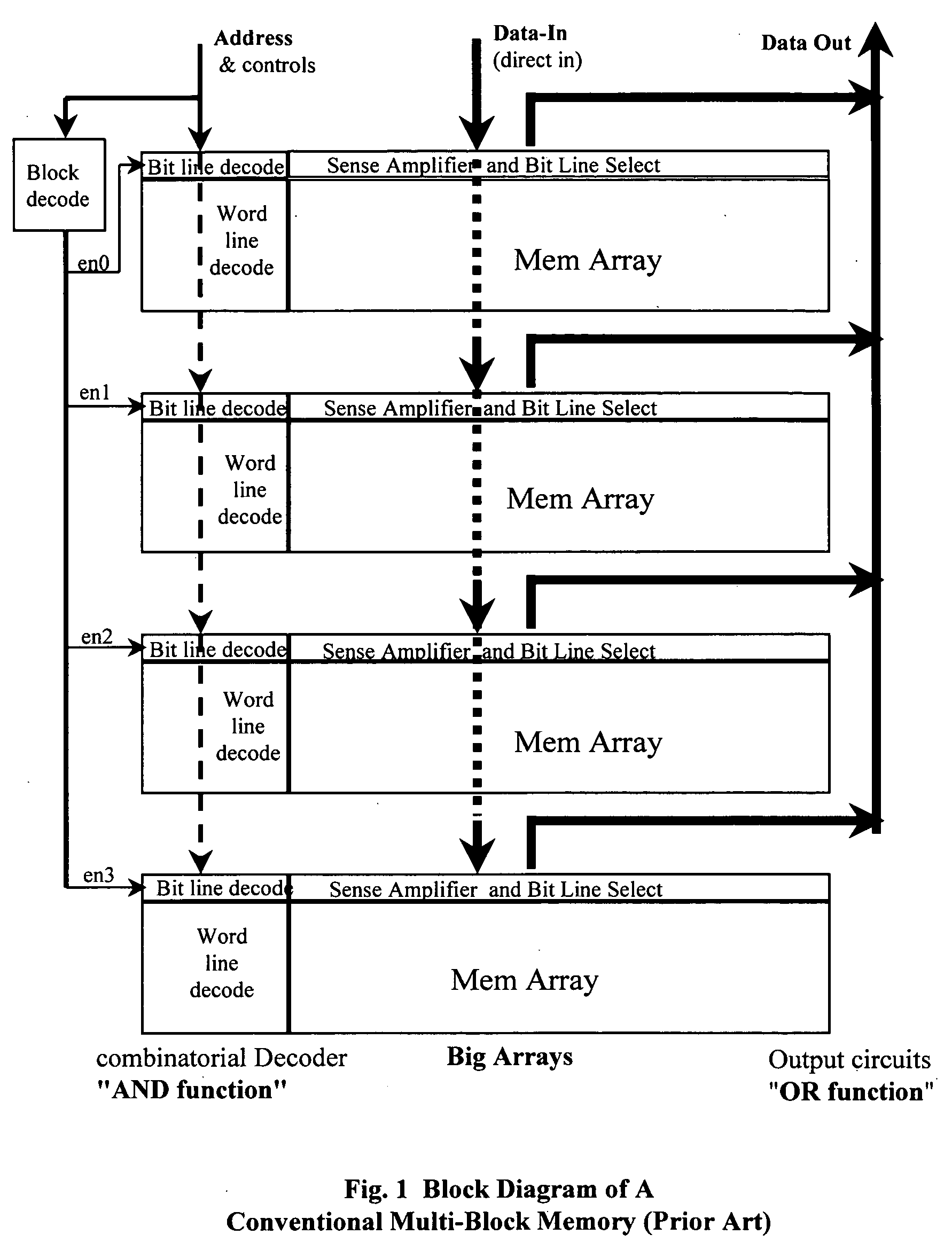

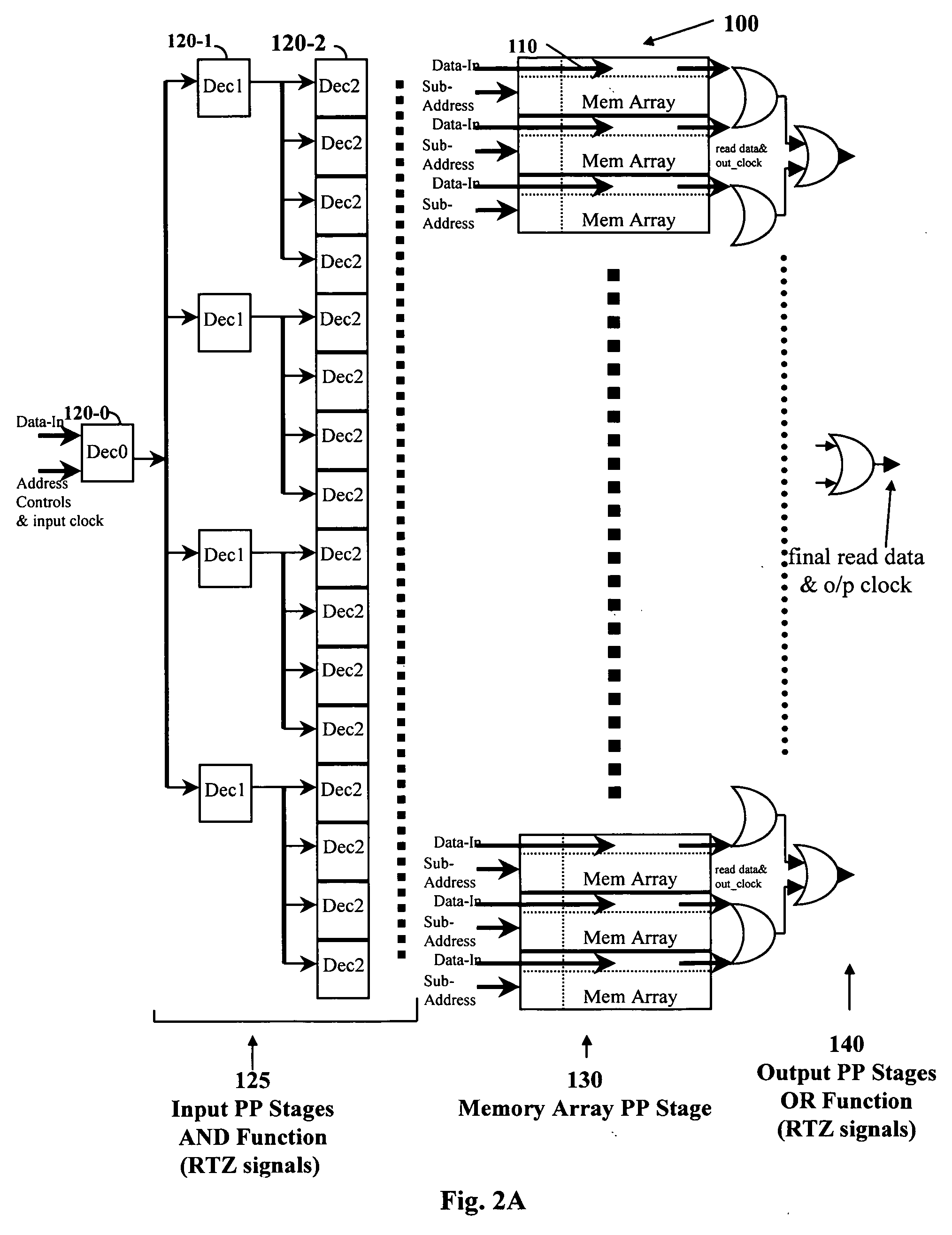

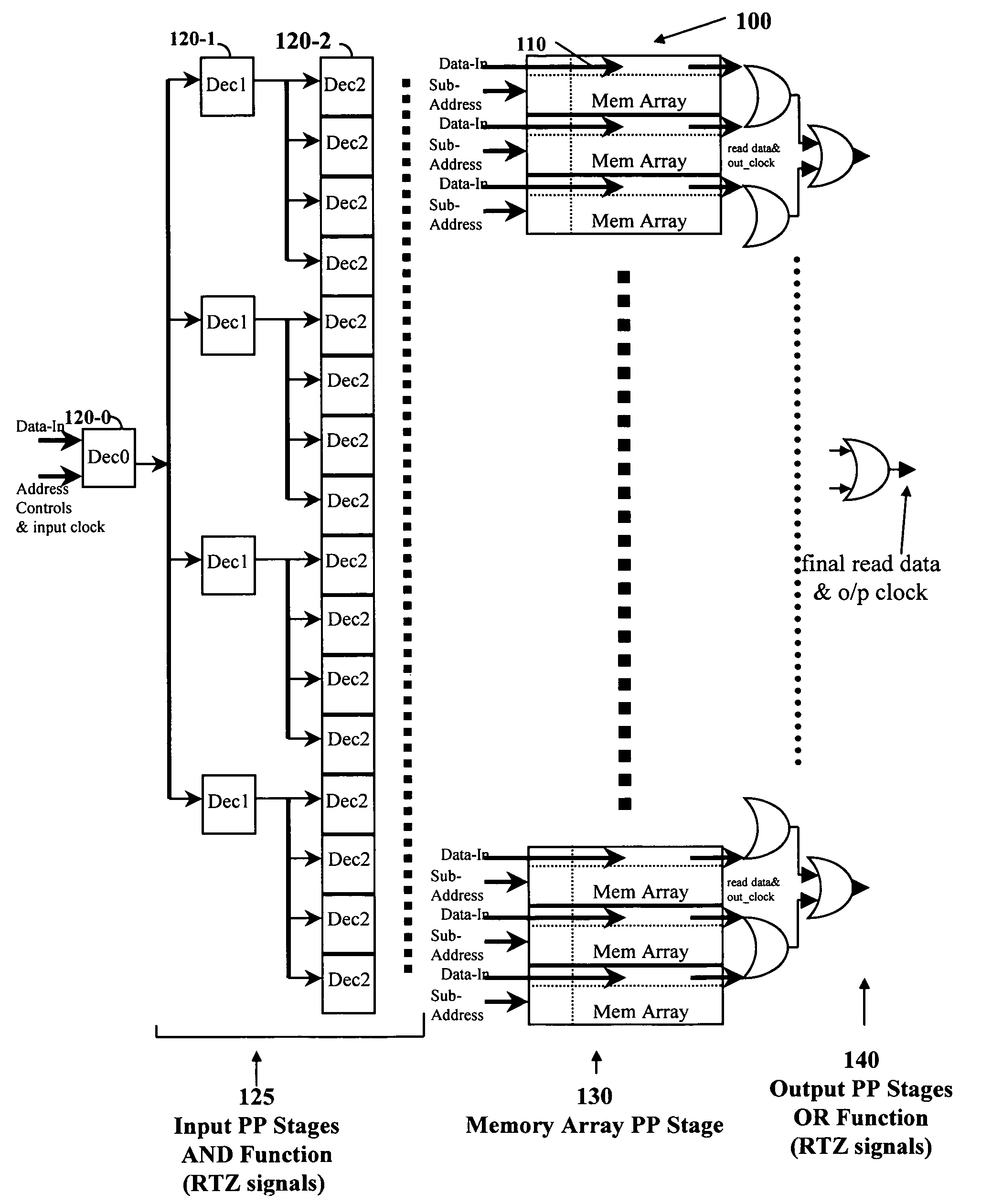

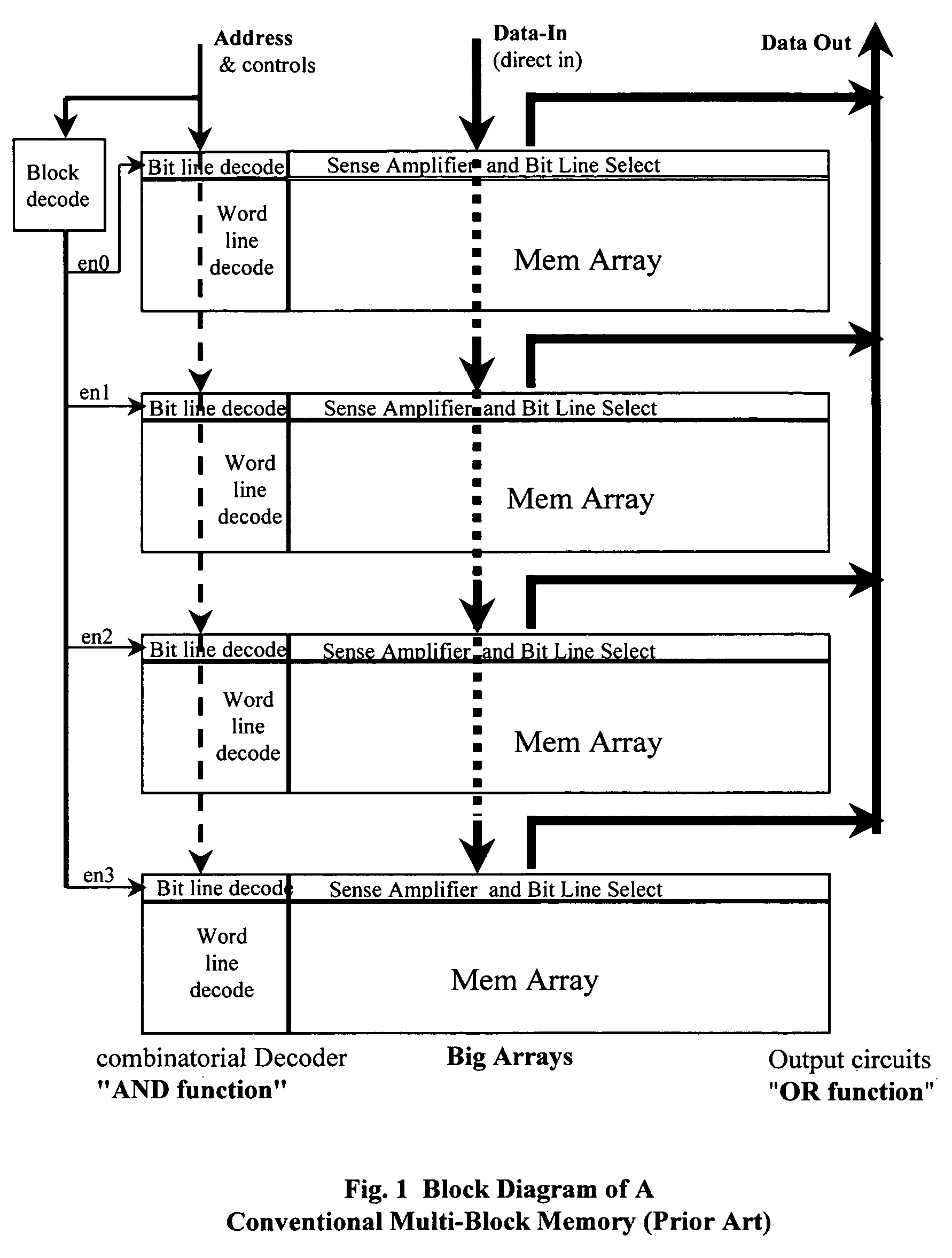

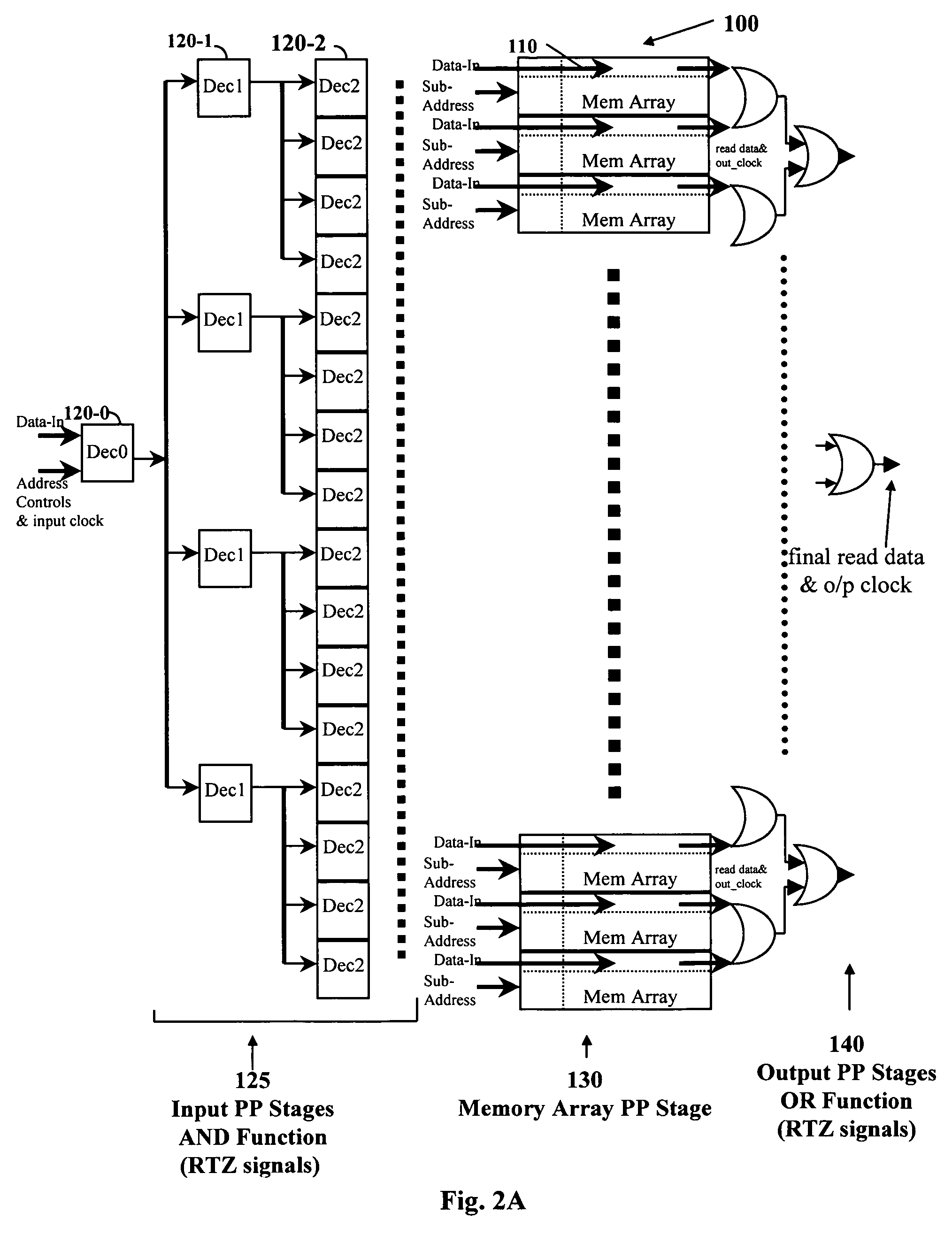

Parallel asynchronous propagation pipeline structure to access multiple memory arrays

A method is disclosed to carry out a data access operation in a data memory device that is subdivided into a plurality of memory arrays each array includes a plurality of memory cells accessible by an identifiable address. The method includes a step of asynchronously propagating in parallel a plurality of data access signals, each through a data access path over multiple propagation stages of signal lines interconnected between the memory arrays and each of the multiple propagation stages implementing an asynchronous local clock for receiving and sending said data access signals for carrying out said data access operation. The method further includes a step of adding a path delay in a selected set of the propagation stages to minimize a length of time difference in carrying out the data access operations through each of the different data access paths. The method further includes a step of generating a pulse train in each of the propagation stages for inputting to the local clock of a subsequent propagation stage for initiating the local clock of the subsequent propagation stage for propagating the data access signals.

Owner:CHEN CHAO WU

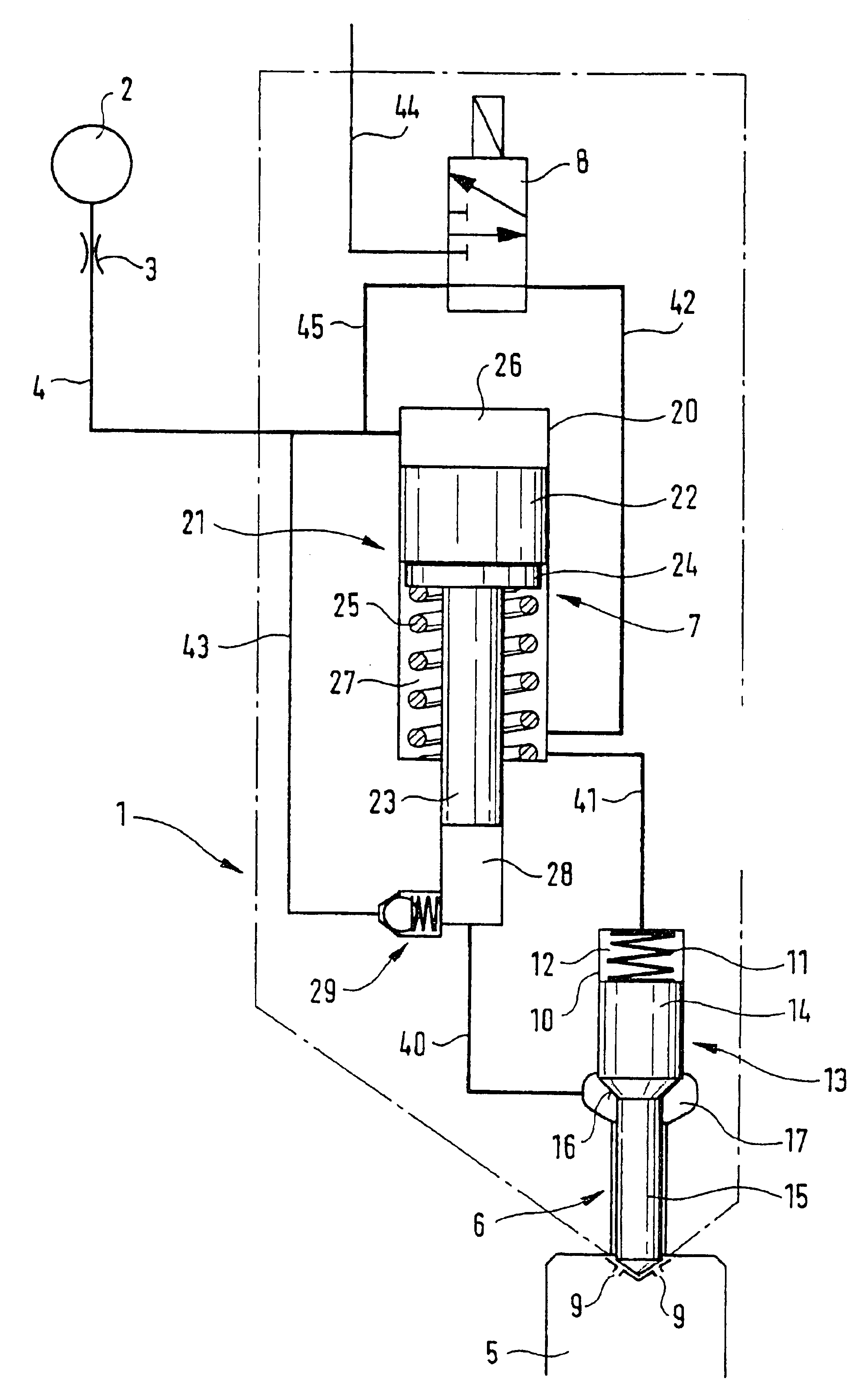

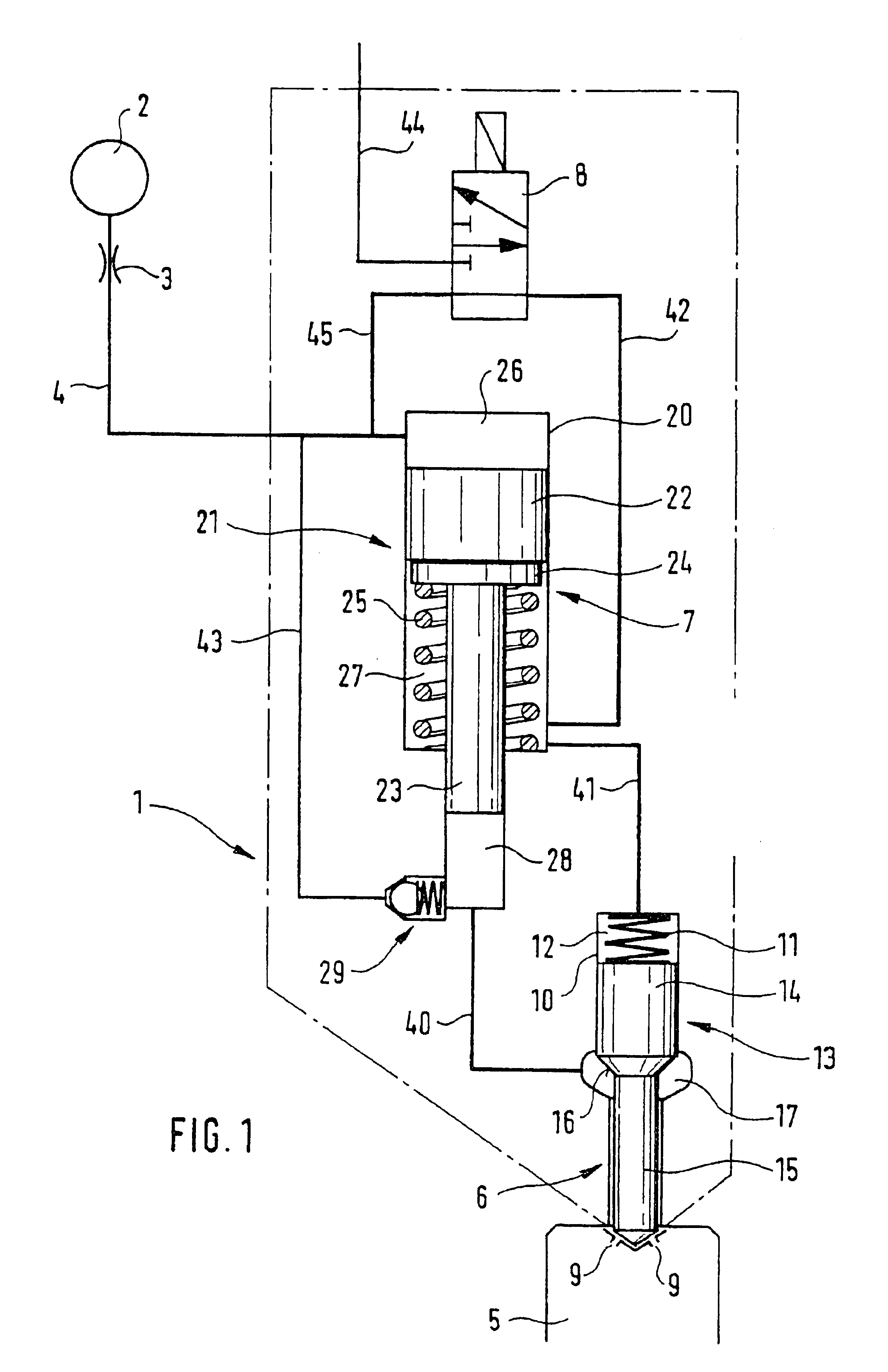

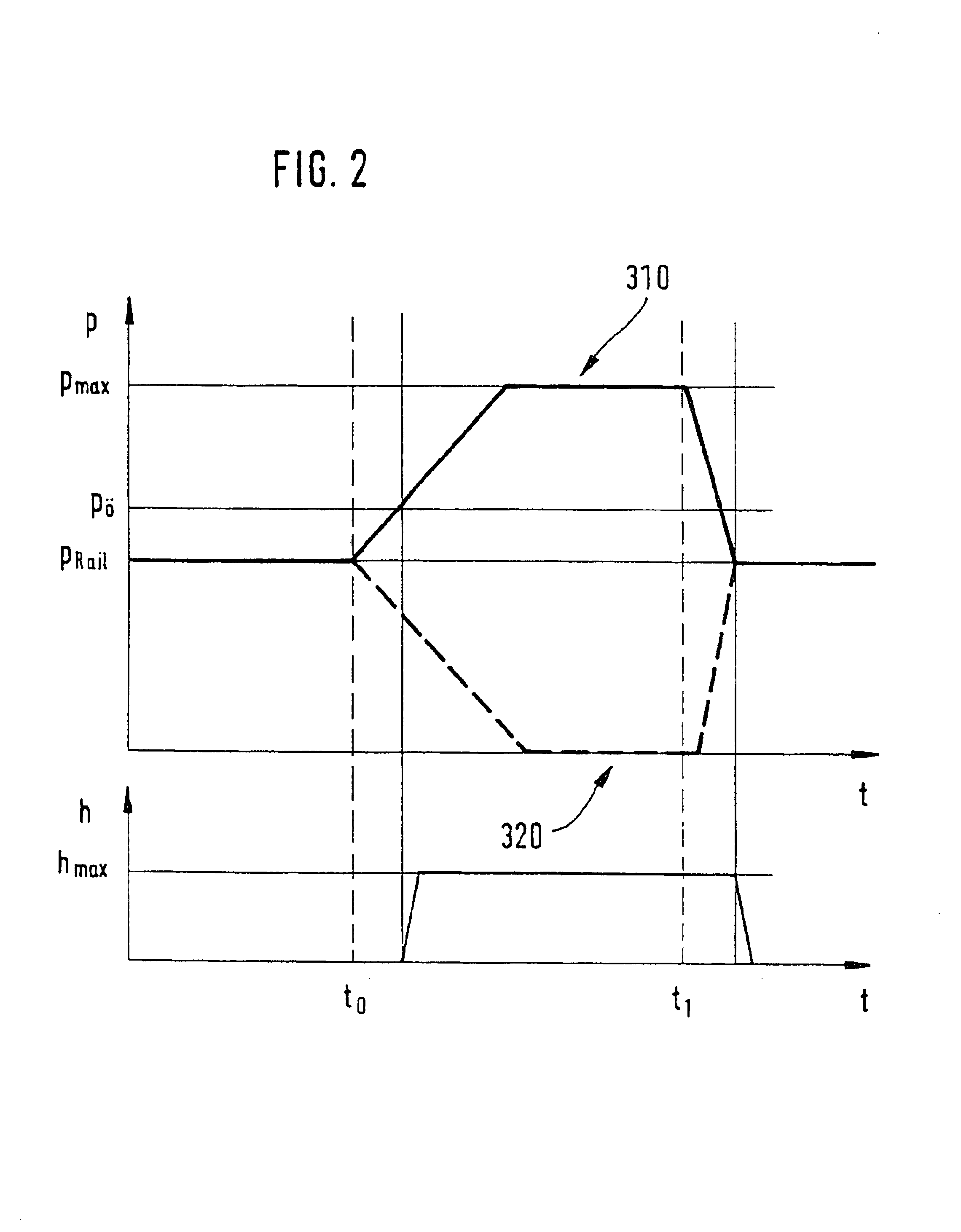

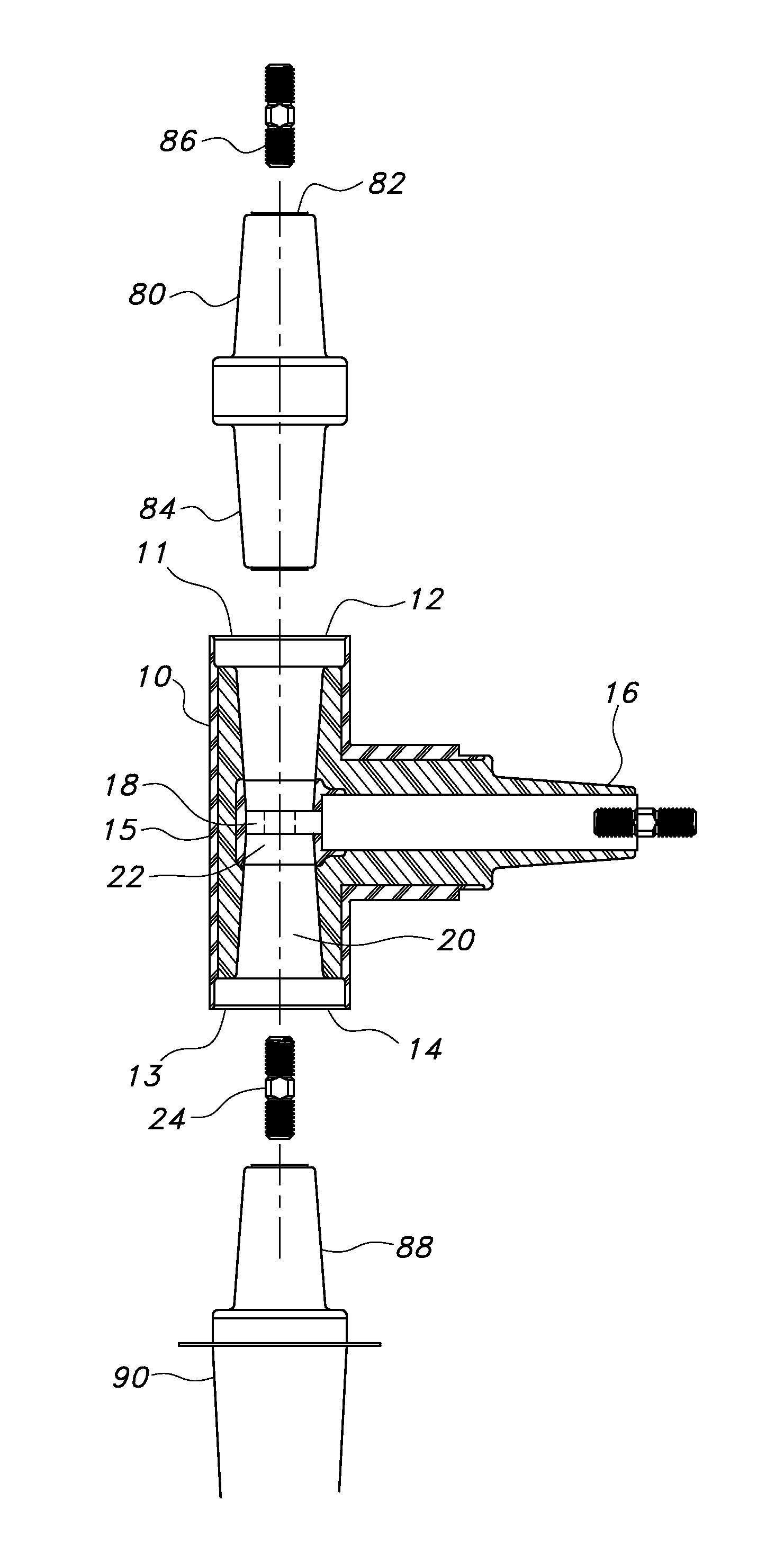

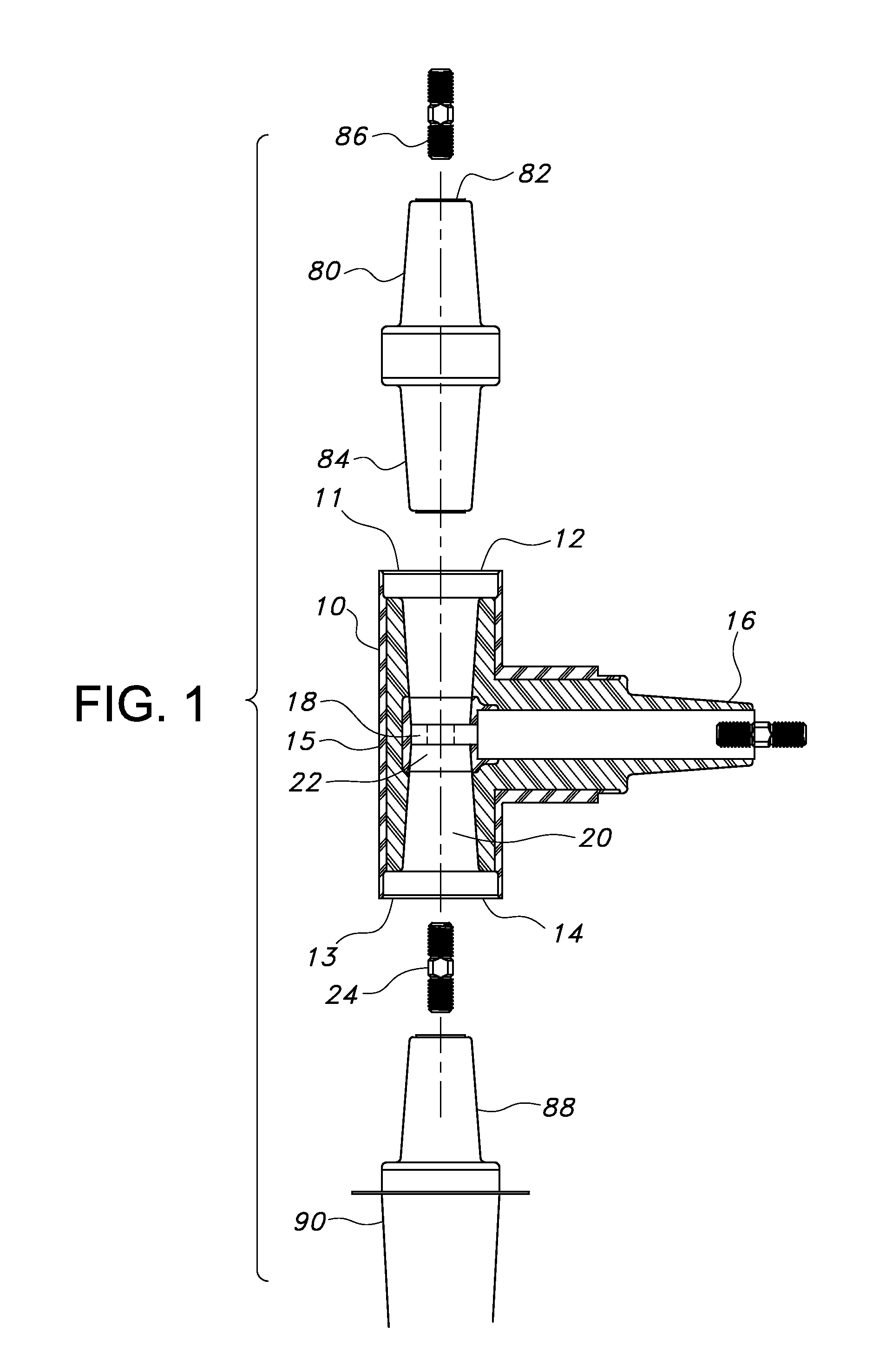

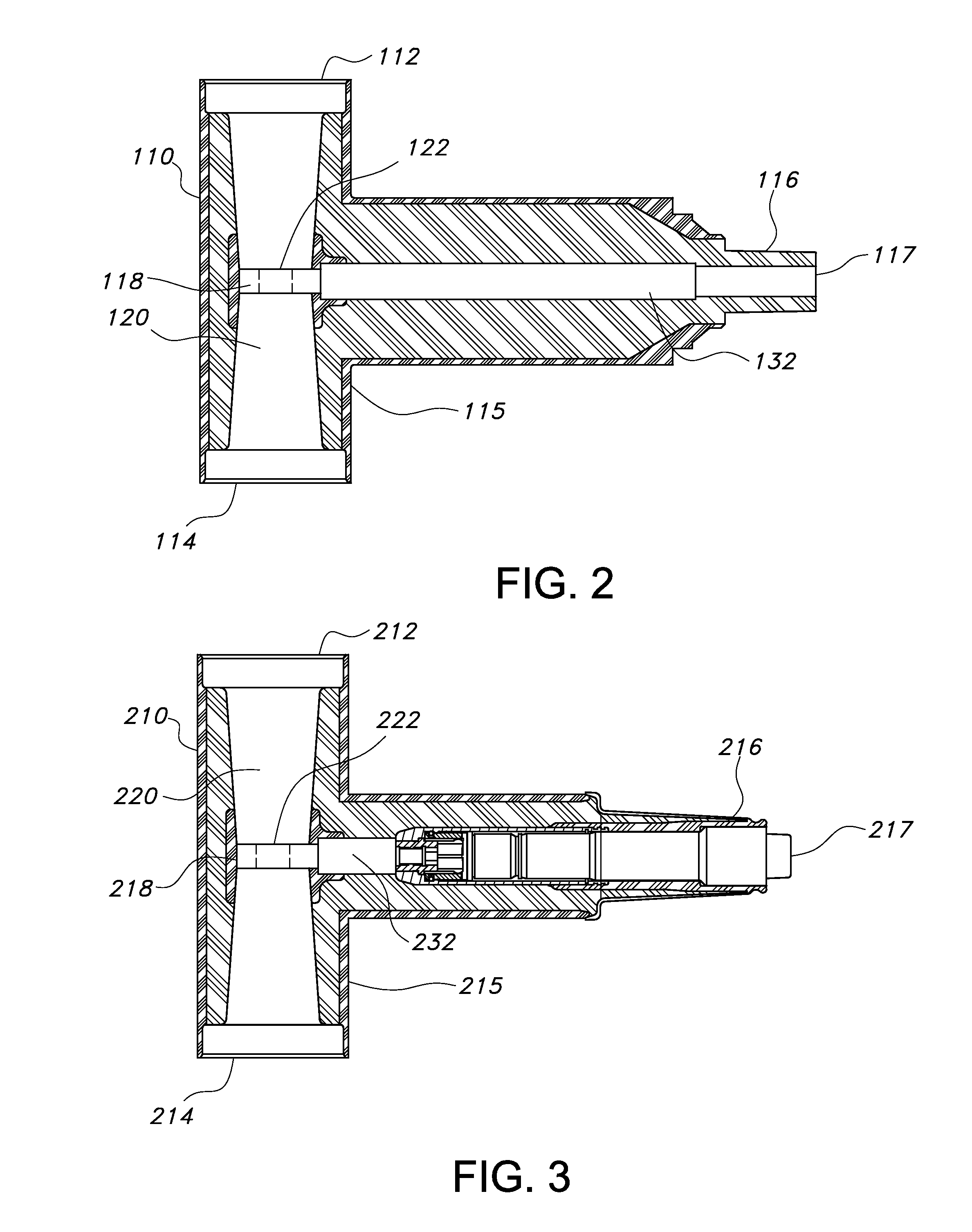

Fuel injection device

InactiveUS6880527B2Low pressure boosting ratioHighly dynamic pressure buildupFuel injection with piezoelectric/magnetostrictive elementsMachines/enginesCombustionEngineering

A fuel injection system for internal combustion engines includes an injector supplied from a high-pressure fuel source and with a pressure booster device, in which the closing piston can be acted upon by fuel pressure to attain a force exerted on the closing piston in the closing direction, and in which the closing pressure chamber and the return chamber of the pressure booster device are formed by a common closing pressure return chamber, and all the portions of the closing pressure return chamber communicate with one another permanently for exchanging fuel, so that despite a low pressure boost by the pressure booster device, a relatively low injection opening pressure is attainable.

Owner:ROBERT BOSCH GMBH

Method for vertically integrating active circuit planes and vertically integrated circuit produced using said method

InactiveUS6444493B1Avoid long connectionsImprove system speedSolid-state devicesSemiconductor/solid-state device manufacturingStandard methodsExternal connection

In a method for vertically integrating active circuit planes, a first substrate having at least one integrated circuit in a first main surface thereof and further having connecting areas for the integrated circuit as well as outer connecting areas on the first main surface is provided in a first step. A second substrate having at least one integrated circuit in a first main surface thereof and further having connecting areas for the integrated circuit as well as open or openable areas on the first main surface is provided. The first main surfaces of the first and second substrates are joined in such a way that the connecting areas of the first substrate are connected to those of the second substrate in an electrically conductive manner in such a way that the outer connecting areas of the first substrate are in alignment with the open or openable areas of the second substrate. Subsequently, the second substrate is thinned and the outer connecting areas are exposed through the open or openable areas. The resultant chips can be further processed making use of standard methods.

Owner:S AQUA SEMICONDUCTOR LLC

Opto-electronic board

ActiveUS7336864B2Efficient couplingMechanically better locatedCircuit optical detailsPrinted circuit aspectsEngineeringElectronic board

An opto-electronic board including a printed wiring board with an optical waveguide, a metallic area, and a hole, wherein an abutting face of the optical waveguide and an abutting face of the metallic area form a part of the side face of the hole. The opto-electronic board further comprises an opto-electronic circuit with a bonding pad, wherein the opto-electronic circuit is arranged in the hole and soldered with its bonding pad to the abutting face of the metallic area.

Owner:INT BUSINESS MASCH CORP

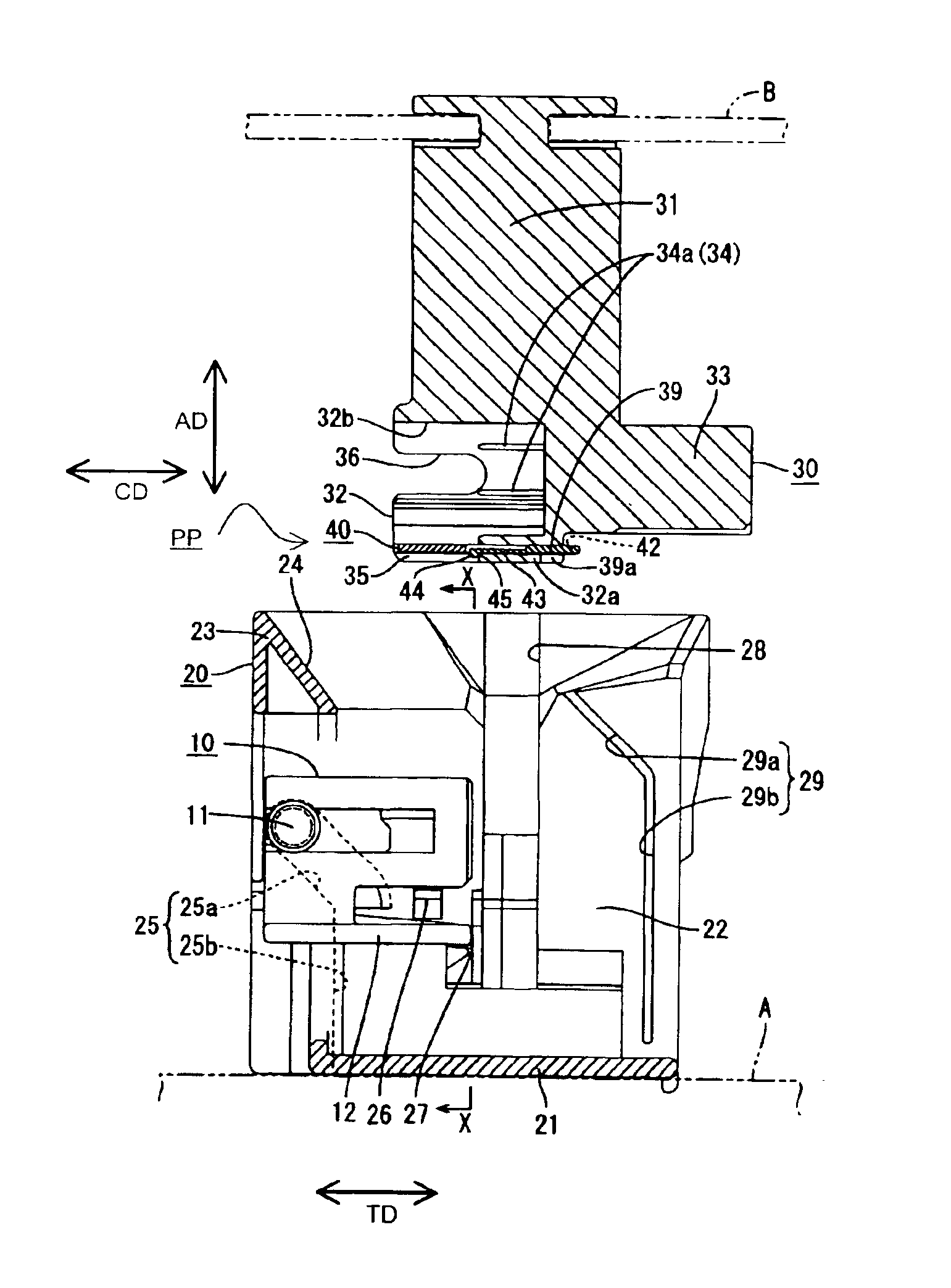

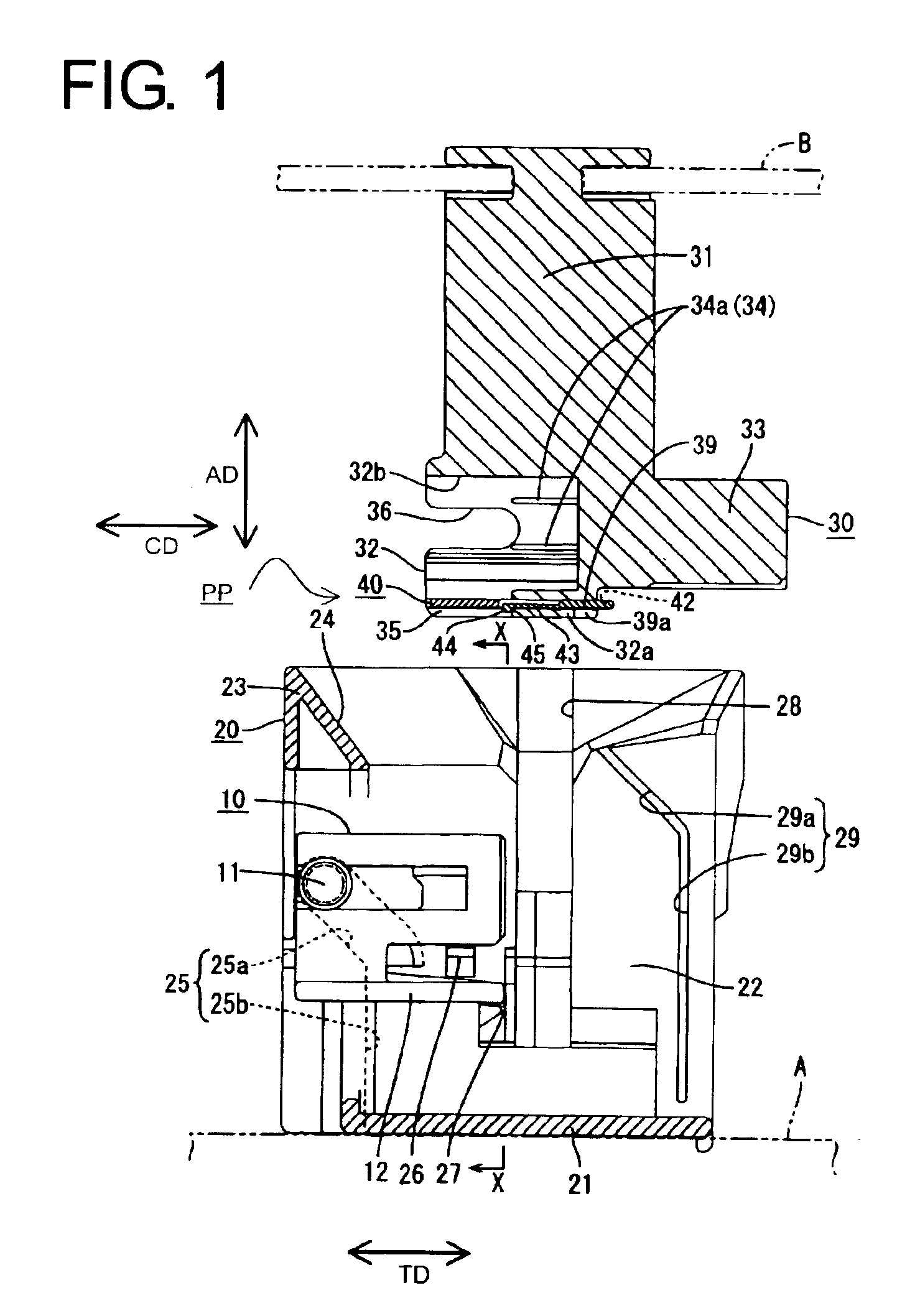

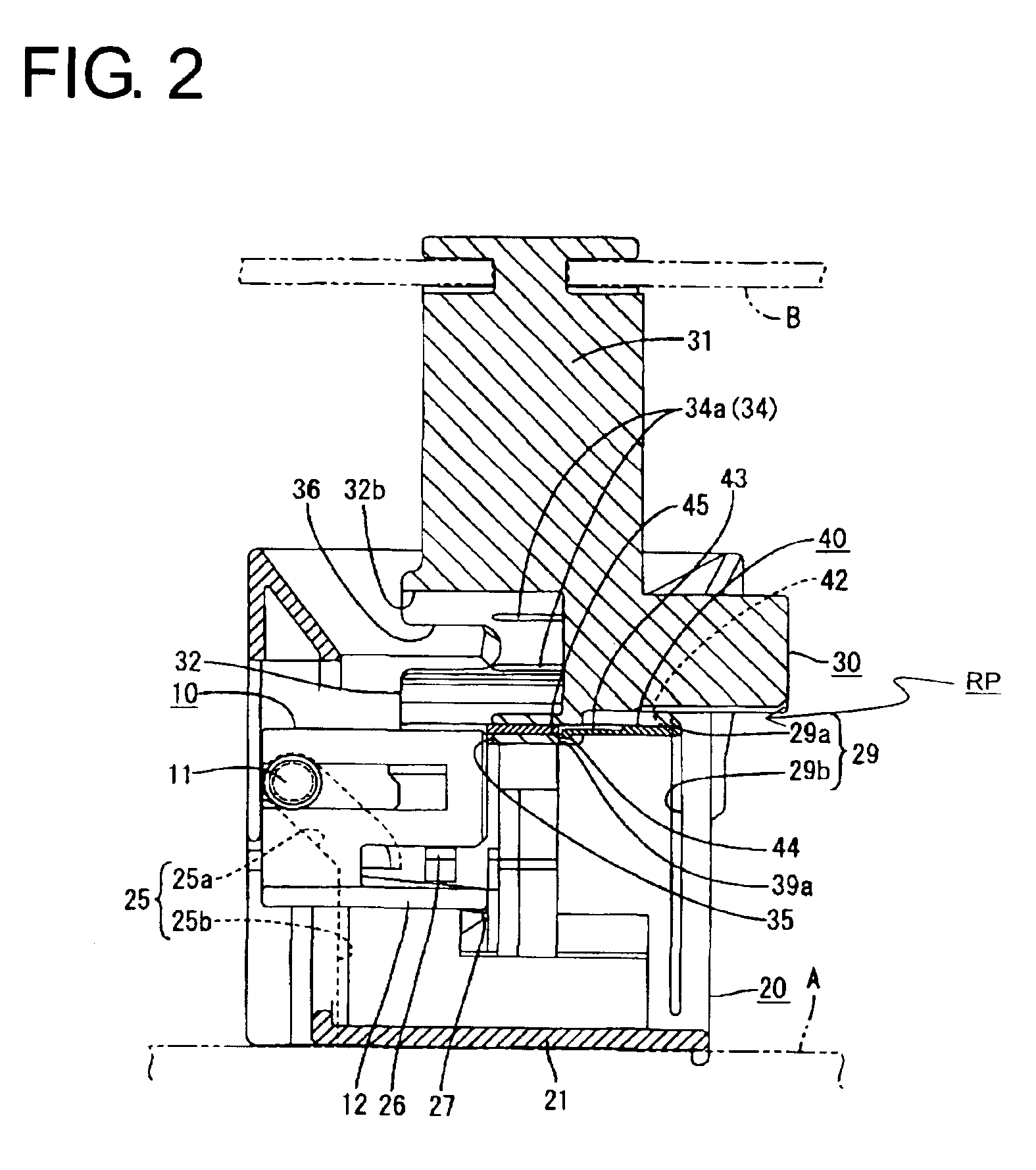

Connector connecting construction and a connector connecting method

InactiveUS6948953B2Connector be smallShorter connectionEngagement/disengagement of coupling partsLive contact access preventionEngineeringMechanical engineering

A female connector (10) is assembled with a holder (20) on a dashboard (A) and a male connector (30) is assembled with an instrument panel (B). The male connector (30) has a receptacle 32 with a cut-out (35) for receiving the female connector (10). Guide pins (11) of the female connector (10) slide along guide grooves (25) of the holder (20) to displace the female connector (10) normal to an assembling direction and to connect the female connector (10) with the male connector (30). A movable protecting portion (40) is displaced from a protecting position where the movable protecting portion (40) covers the cut-out (35) to a retracted position RP where the movable protecting portion (40) is retracted from the cut-out (35) by sliding movements of guide pins (42) of the movable protection portion (40) along guide grooves (29) of the holder (20).

Owner:SUMITOMO WIRING SYST LTD

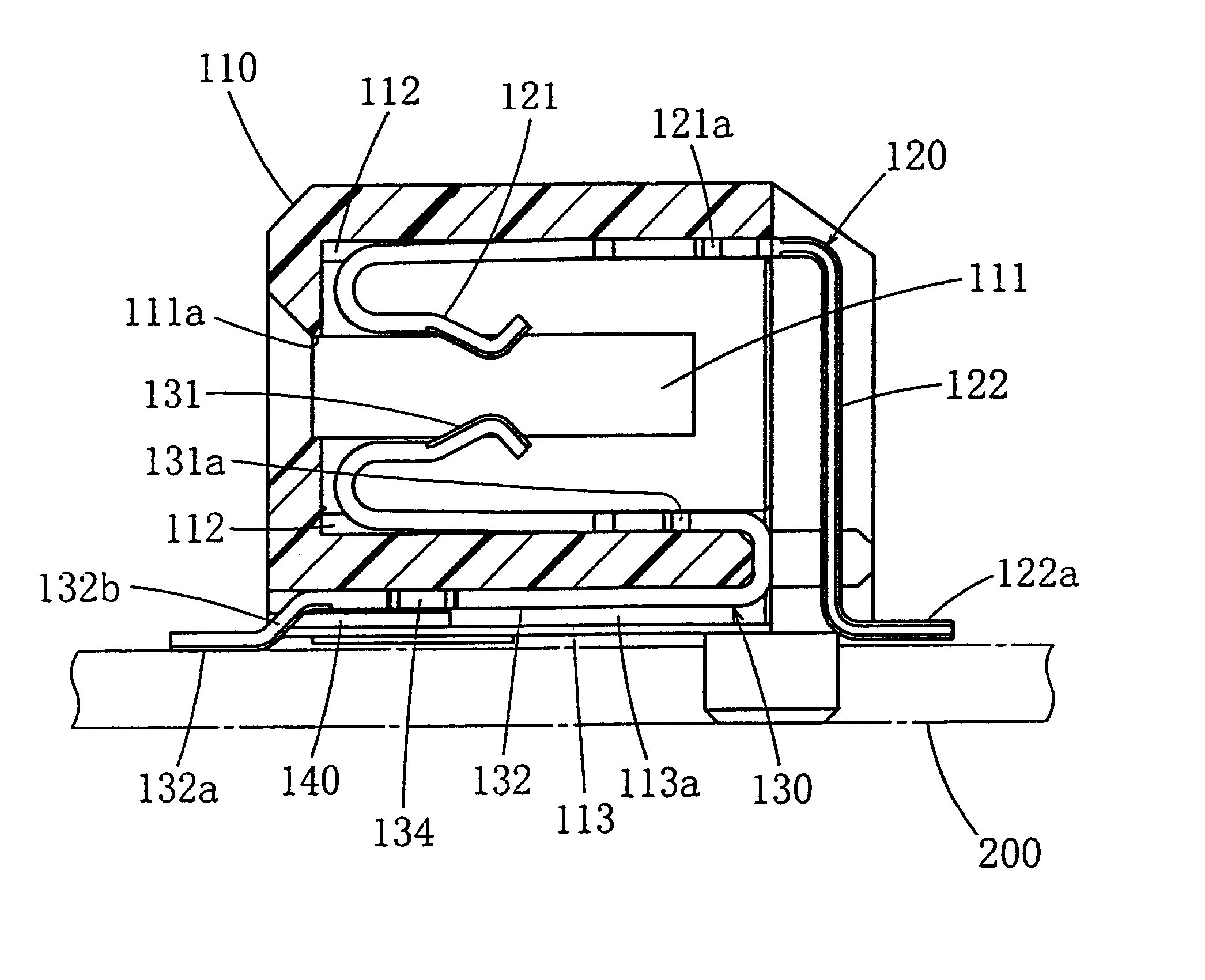

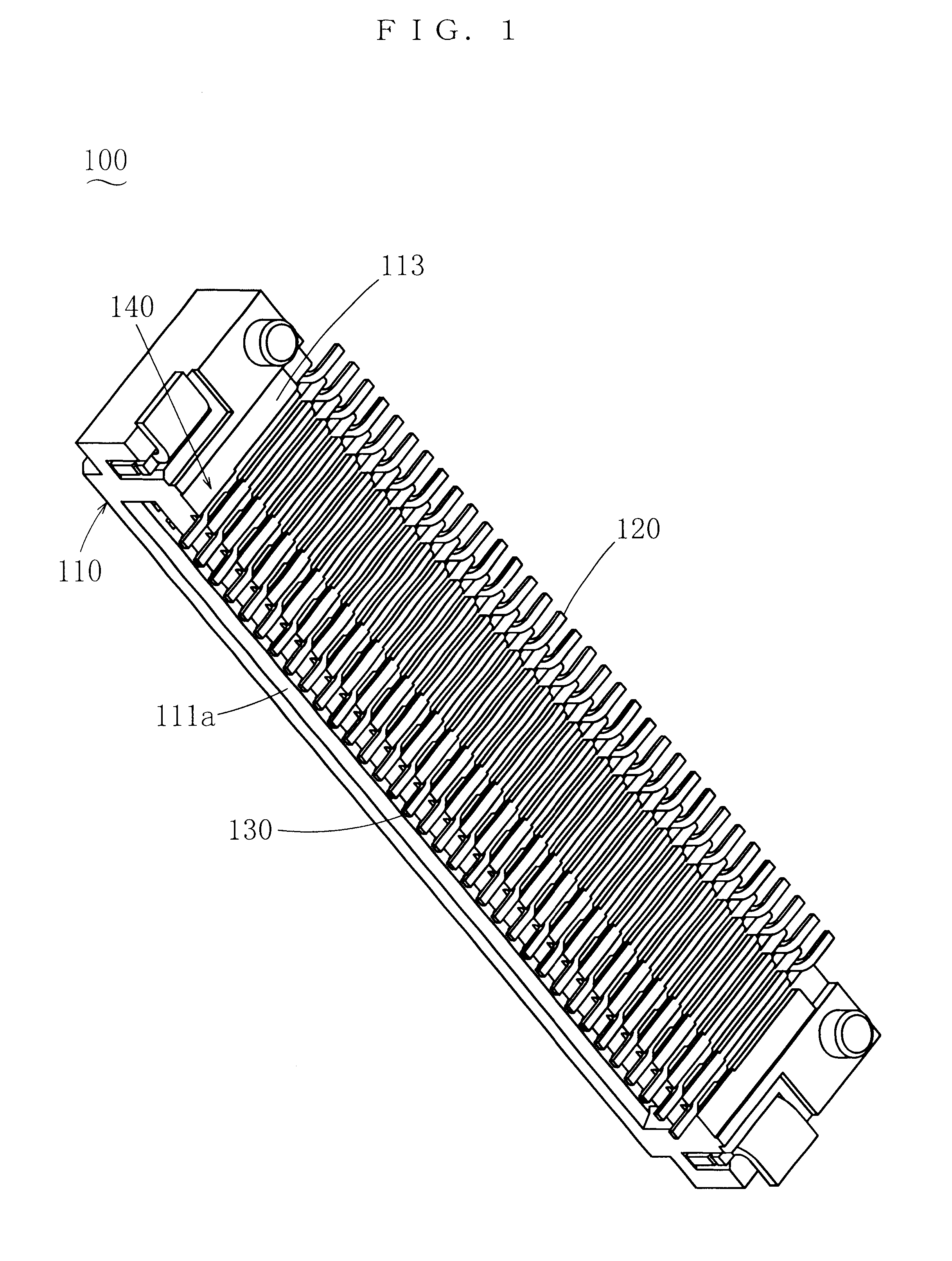

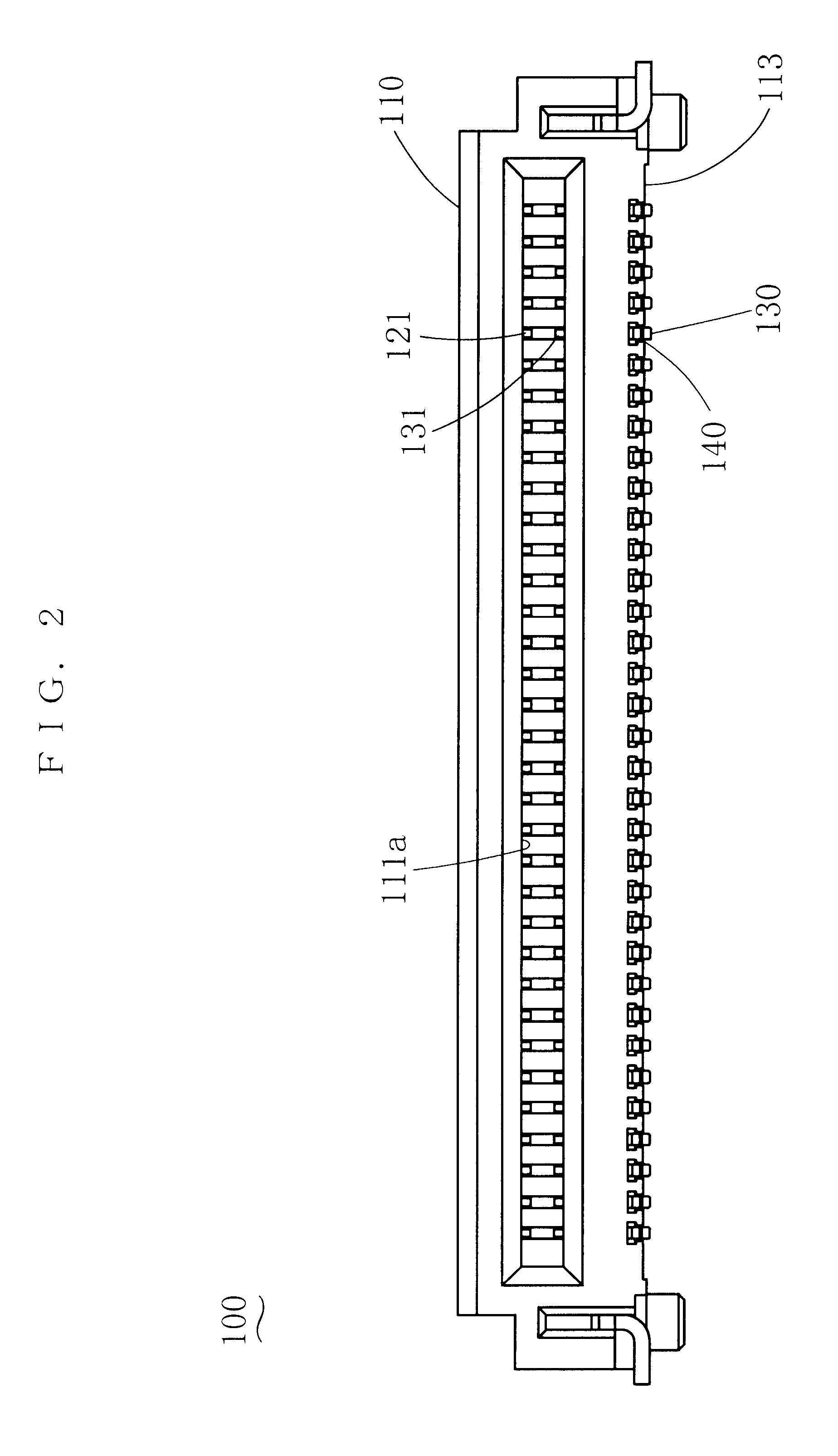

Horizontal electric connector

InactiveUS6702619B2Avoid long connectionsAvoid deformationSecuring/insulating coupling contact membersCouplings bases/casesComing outElectric contact

A horizontal electric connector includes an insulating housing, a first electric contact, with a contacting part that is press-fitted into the housing from the rear and contacts a counterpart conductive part, and a leg that extends from the contacting part, comes out of the housing at the rear and descends, and a second electric contact, with a contacting part that is press-fitted into the housing from the rear at a position lower than the first electric contact and contacts a counterpart conductive part, and a leg that extends from the contacting part, comes out of the housing at the rear and extends forward along the bottom of the housing. A leg supporting part is provided on the bottom of the housing, into which the leg of the second electric contact is press-fitted from the rear, to prevent deformation of the leg.

Owner:JST MFG CO LTD

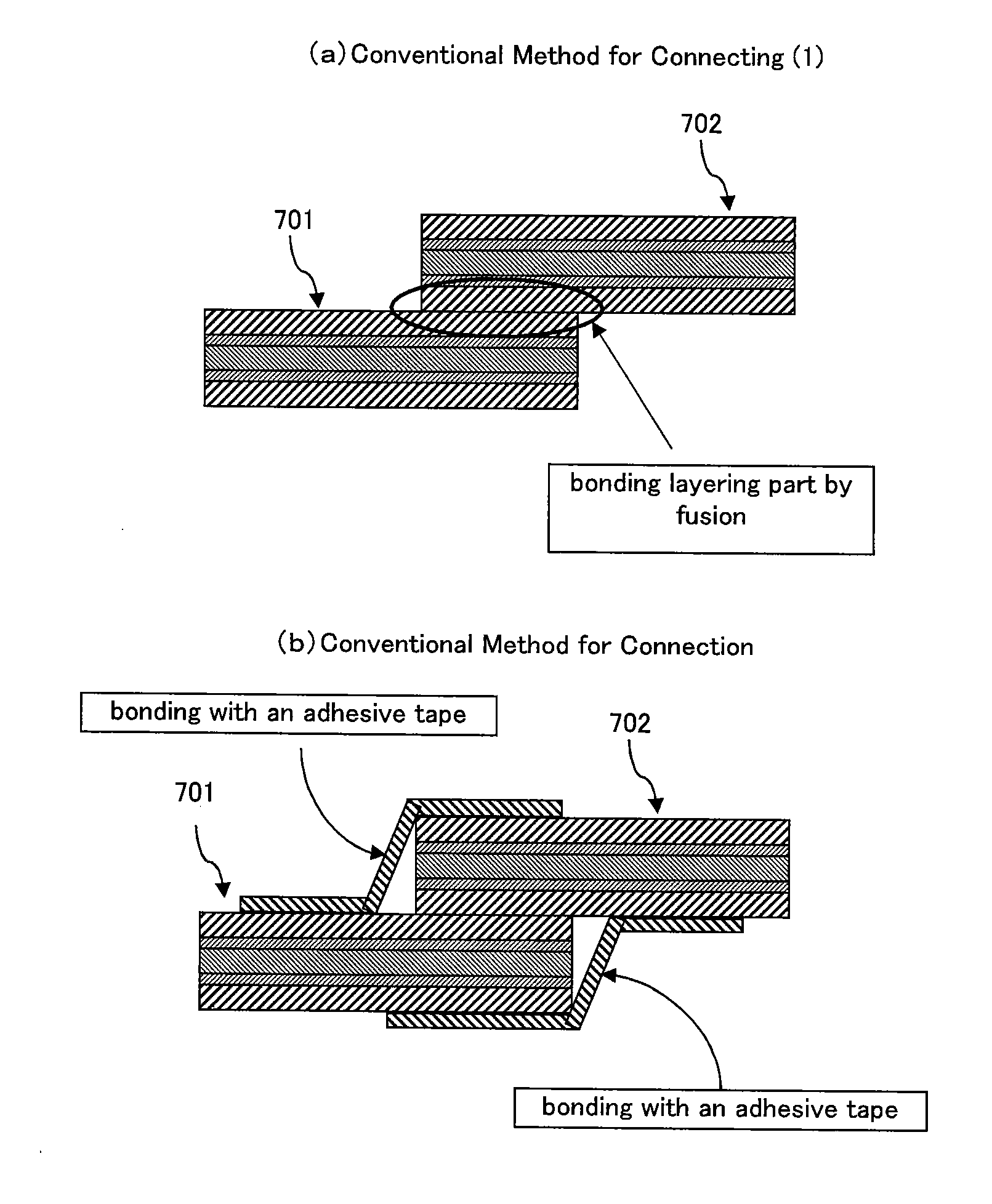

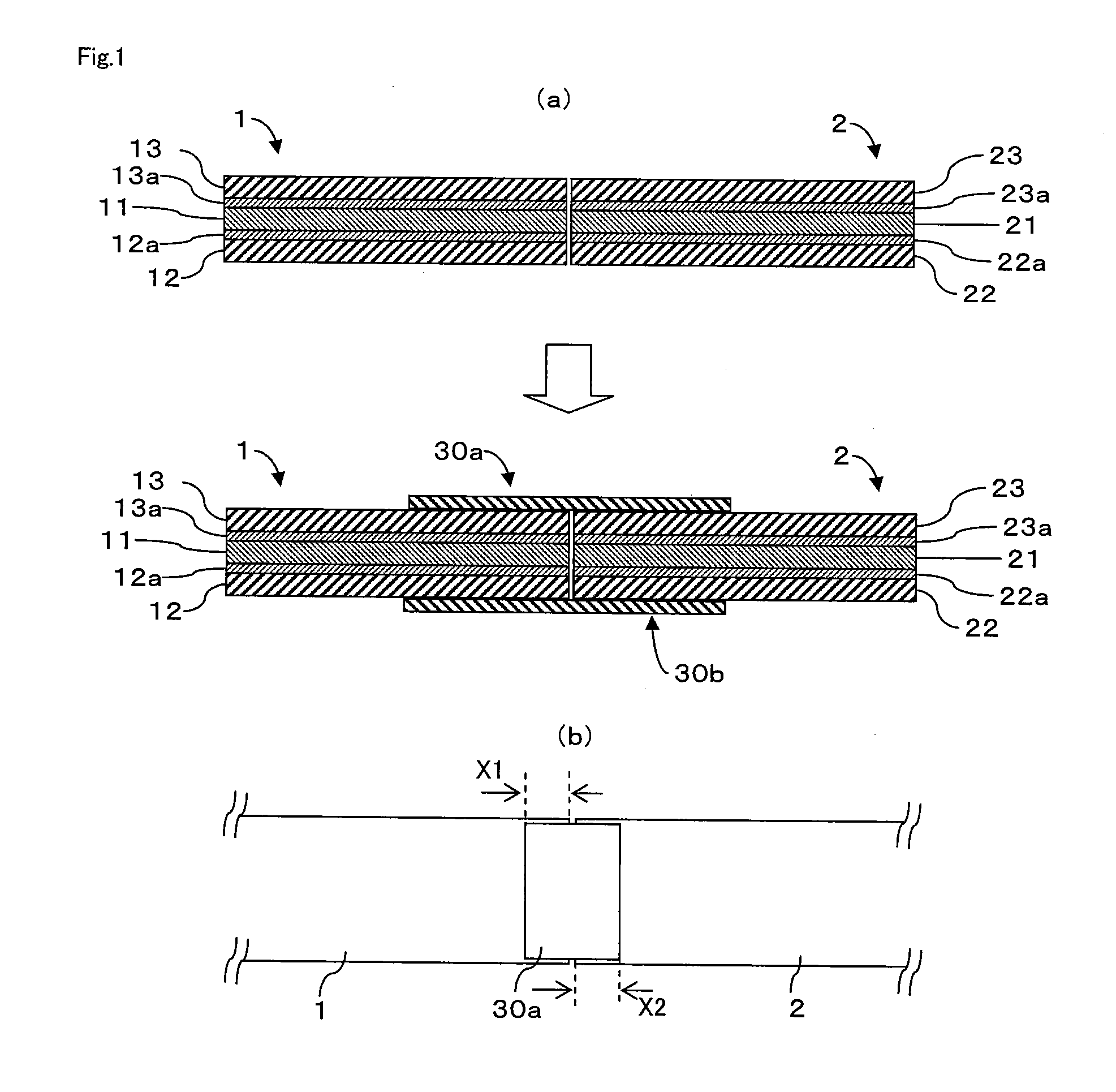

Method for manufacturing connected sheet material, connected sheet material and method for manufacturing optical display unit

ActiveUS20100215884A1Avoid long connectionsImprove productivityMechanical working/deformationLamination ancillary operationsEngineeringBiomedical engineering

The invention is to provide a process for production of a connected sheet product, which makes it possible to connect opposed end faces of two or more sheet products. A process for production of a connected sheet product including sheet products that are connected to one another and each have at least an optical member and a release film provided on one side of the optical member with a pressure-sensitive adhesive interposed therebetween, comprising: opposing a transverse end face of a first sheet product to a transverse end face of a second sheet product; connecting release films of the first and second sheet products with a connecting member (30a); and connecting surface members of the first and second sheet products with a connecting member (30b) on the opposite side from the release films.

Owner:NITTO DENKO CORP

Opto-electronic board

ActiveUS20080247706A1Efficient couplingMechanically better locatedCircuit optical detailsPrinted circuit aspectsEngineeringOpto electronic

An opto-electronic board including a printed wiring board with an optical waveguide, a metallic area, and a hole, wherein an abutting face of the optical waveguide and an abutting face of the metallic area form a part of the side face of the hole. The opto-electronic board further comprises an opto-electronic circuit with a bonding pad, wherein the opto-electronic circuit is arranged in the hole and soldered with its bonding pad to the abutting face of the metallic area.

Owner:INT BUSINESS MASCH CORP

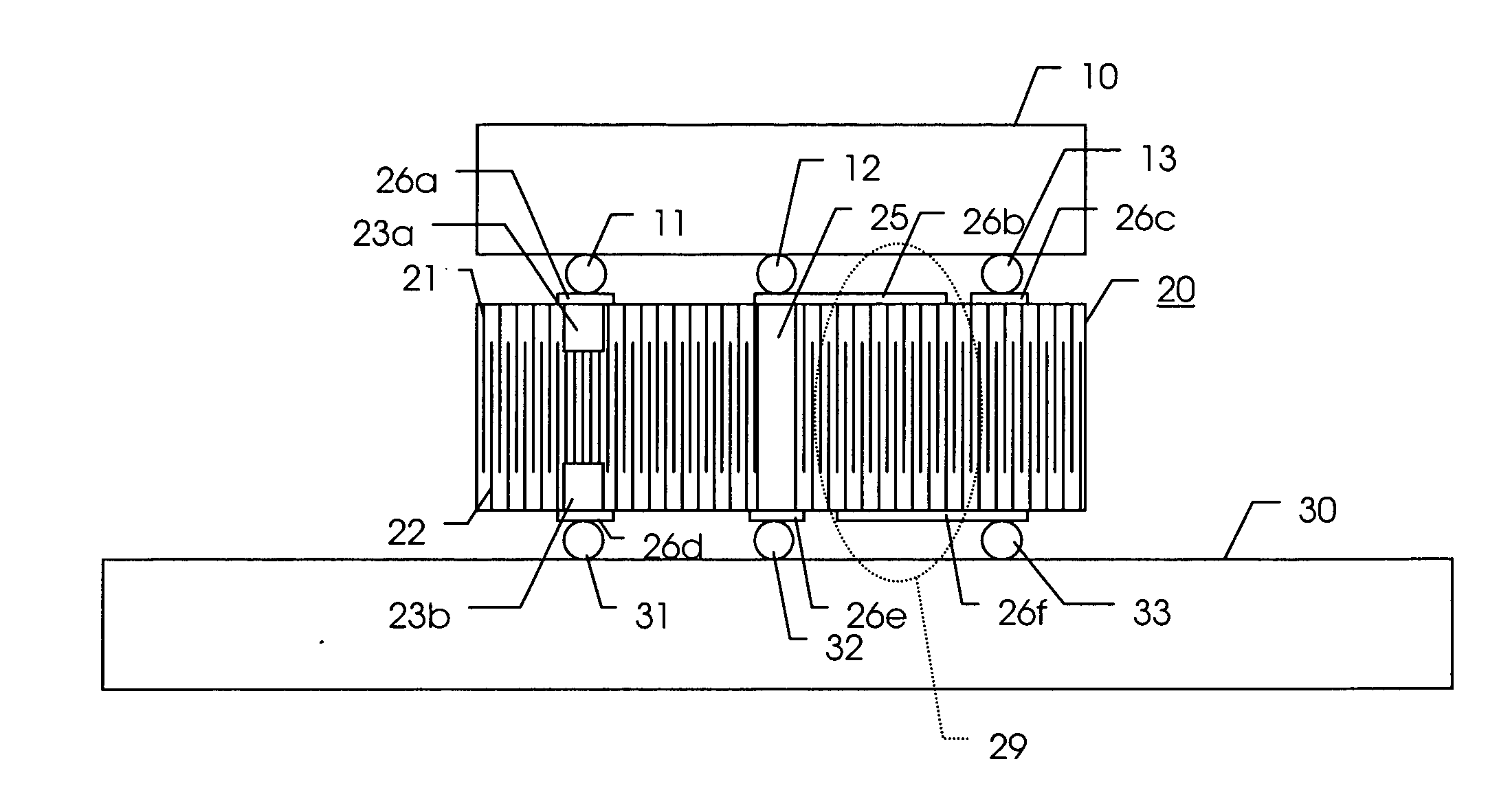

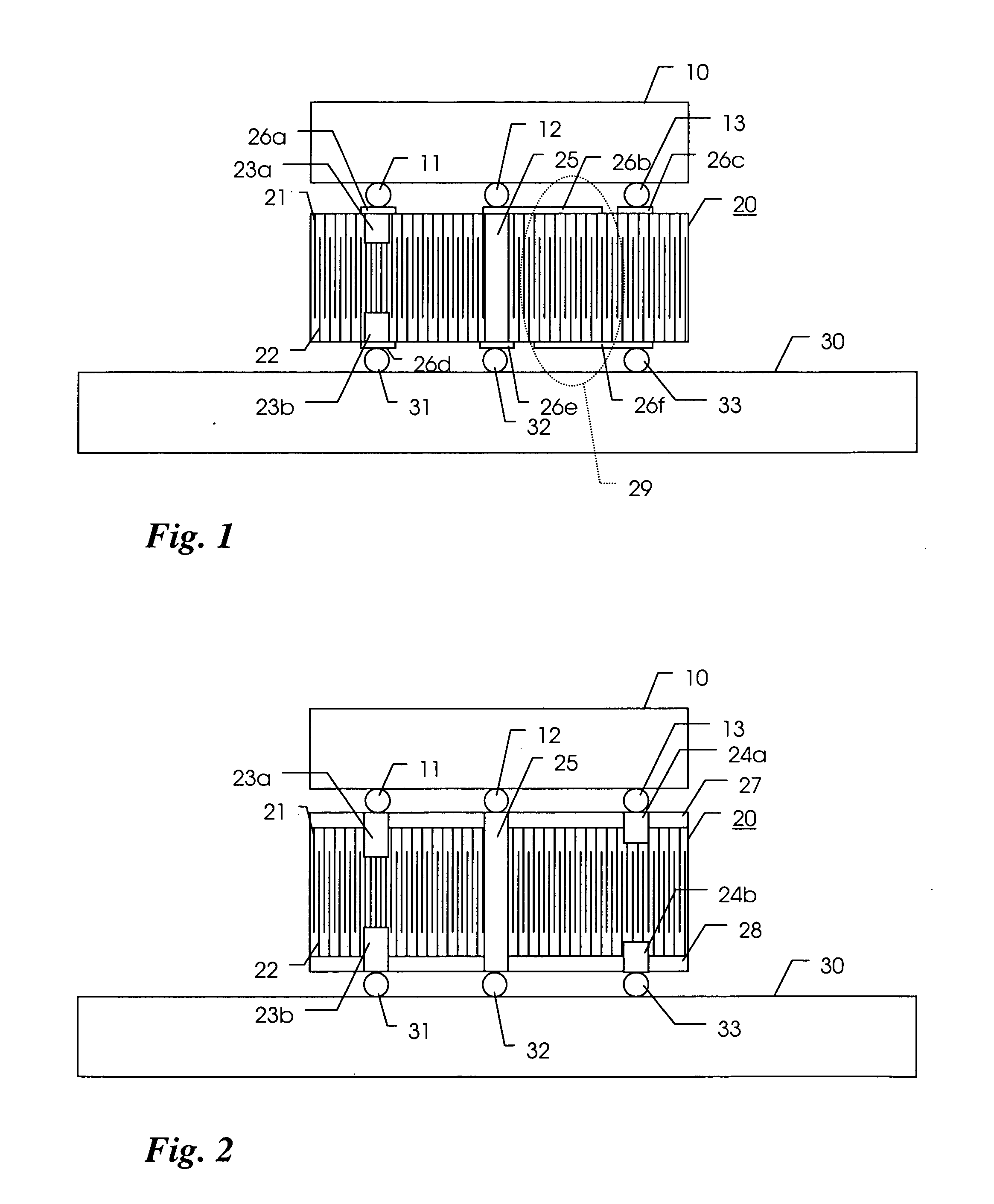

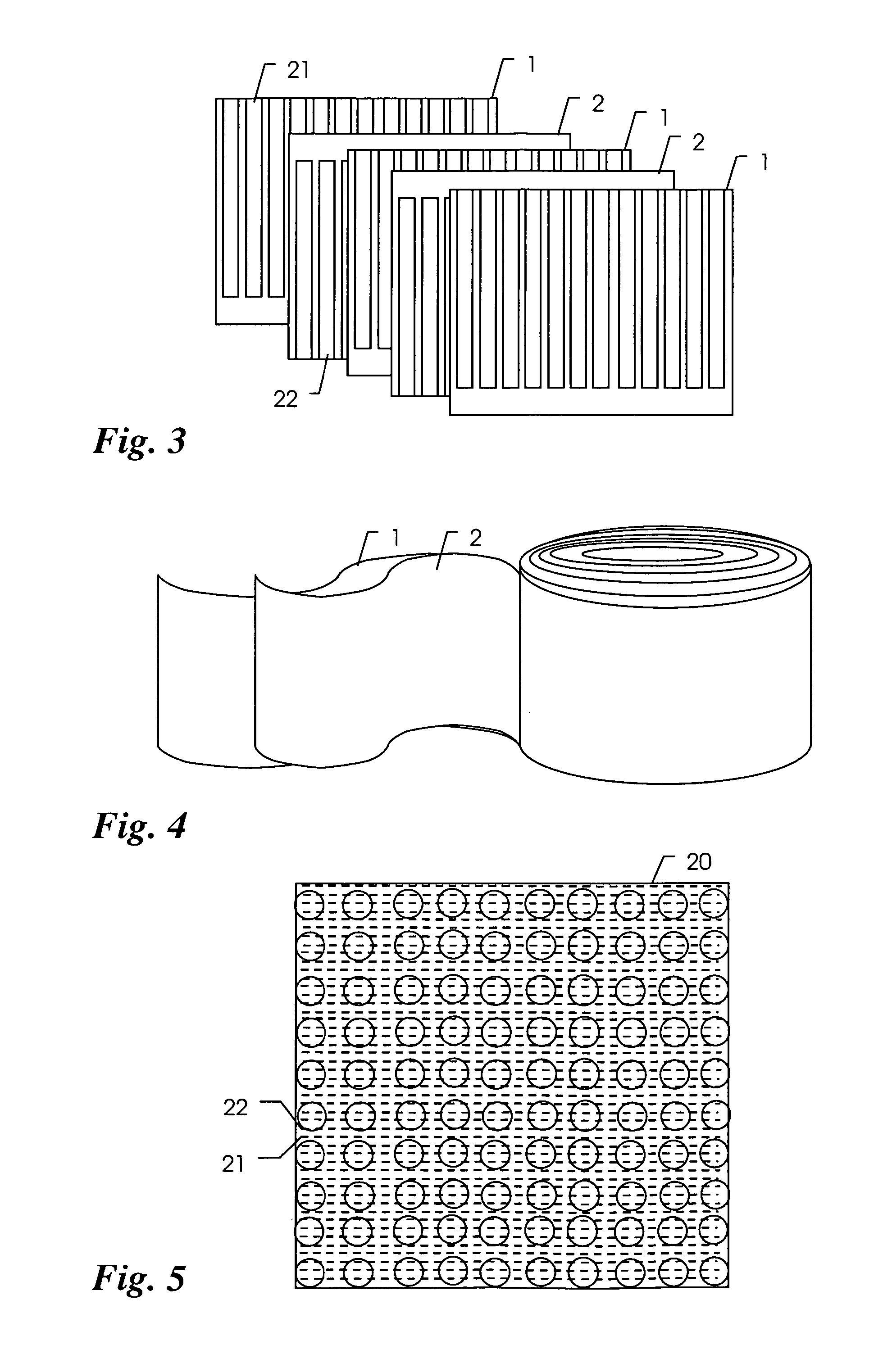

Interposer for decoupling integrated circuits on a circuit board

ActiveUS20060176674A1High capacityShorter connectionCross-talk/noise/interference reductionSemiconductor/solid-state device detailsIntegrated circuitEngineering

An interposer (20) is used for decoupling a microchip (10) on a circuit board (30). The interposer (20) contains on its upper and lower surfaces structured metal layers (26a-26d) for attachment to the microchip (10) and the circuit board (30), respectively. Inside the interposer, there are two sets of mutually isolated metal structures (21, 22) extending substantially perpendicular to the upper and lower surfaces of said interposer (20). The first set (21) extends closer towards the upper surface than the second set (22), while said second set (22) extends closer towards the lower surface than said first set (21).

Owner:ALCATEL LUCENT SAS

Resin encapsulated power semiconductor module with exposed terminal areas

ActiveUS20200066609A1Improve electrical performanceAvoid long connectionsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A power semiconductor module includes a substrate with a metallization layer; at least one power semiconductor chip bonded to the substrate; and a mold encapsulation partially encapsulating the semiconductor chip and the substrate; the mold encapsulation includes at least one window exposing a terminal area of the metallization layer; and a border part of the mold encapsulation between the window and a border of the substrate has a height over the substrate smaller than a maximal height of a central part of the mold encapsulation.

Owner:HITACHI ENERGY SWITZERLAND AG +1

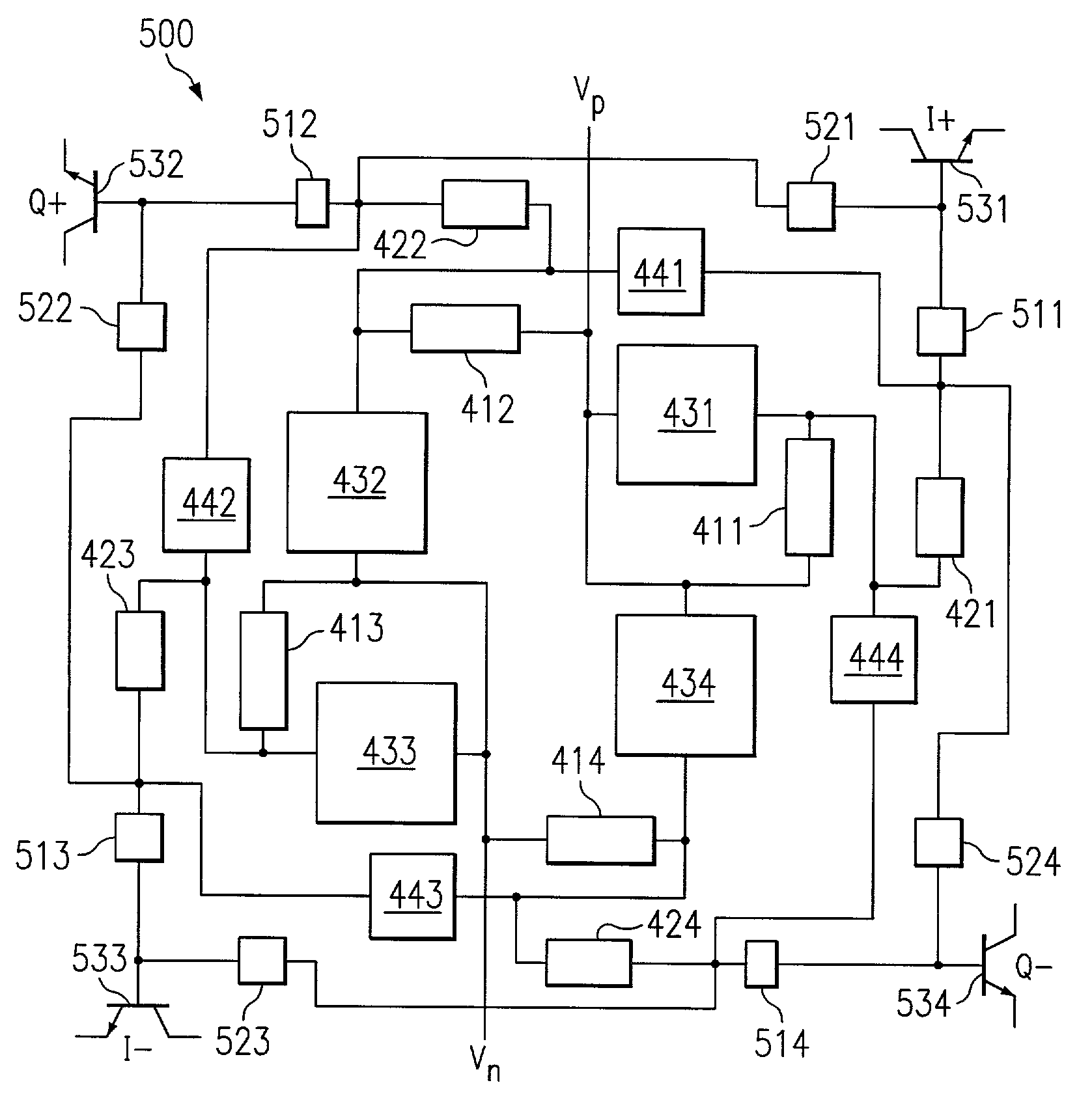

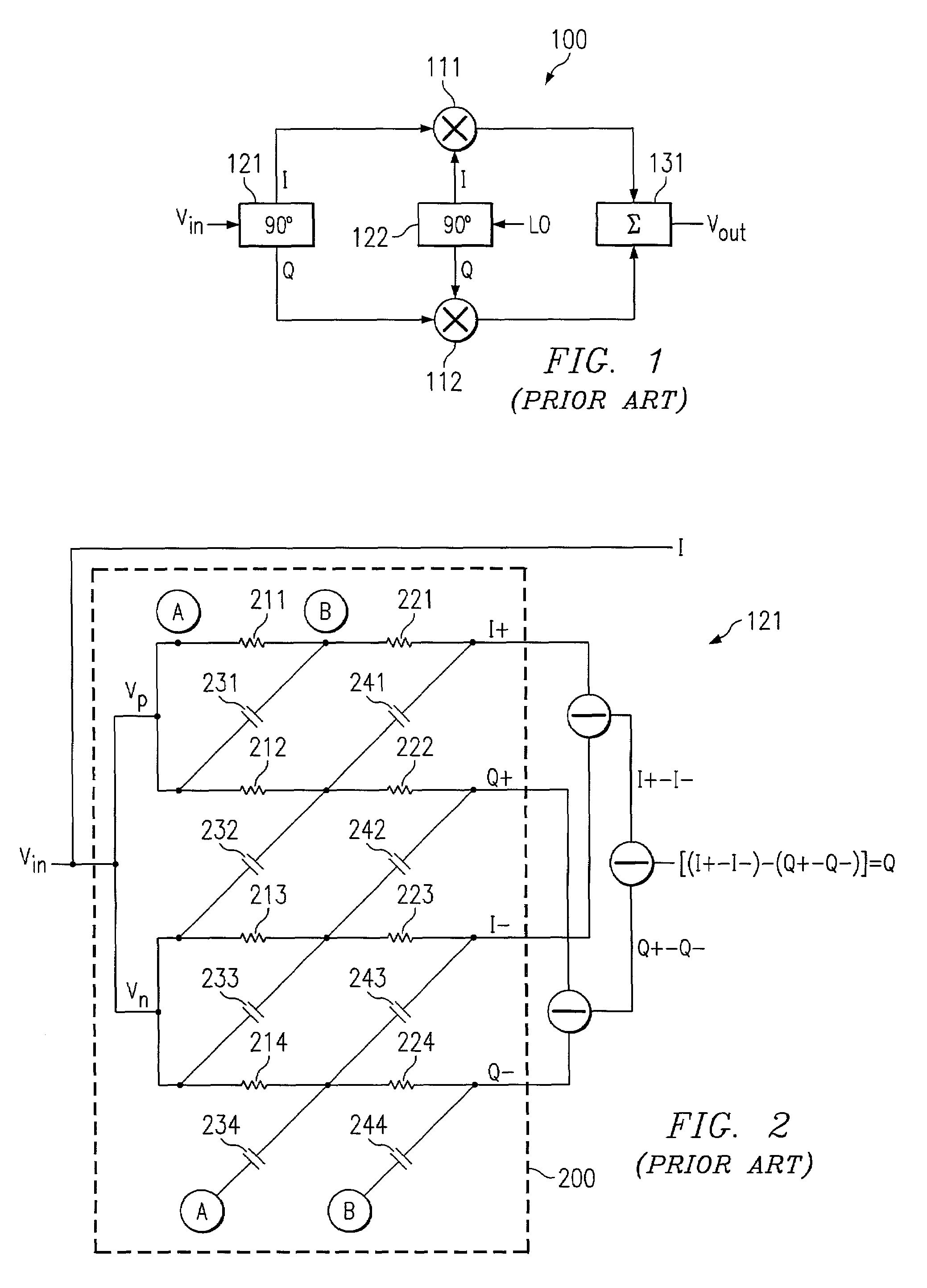

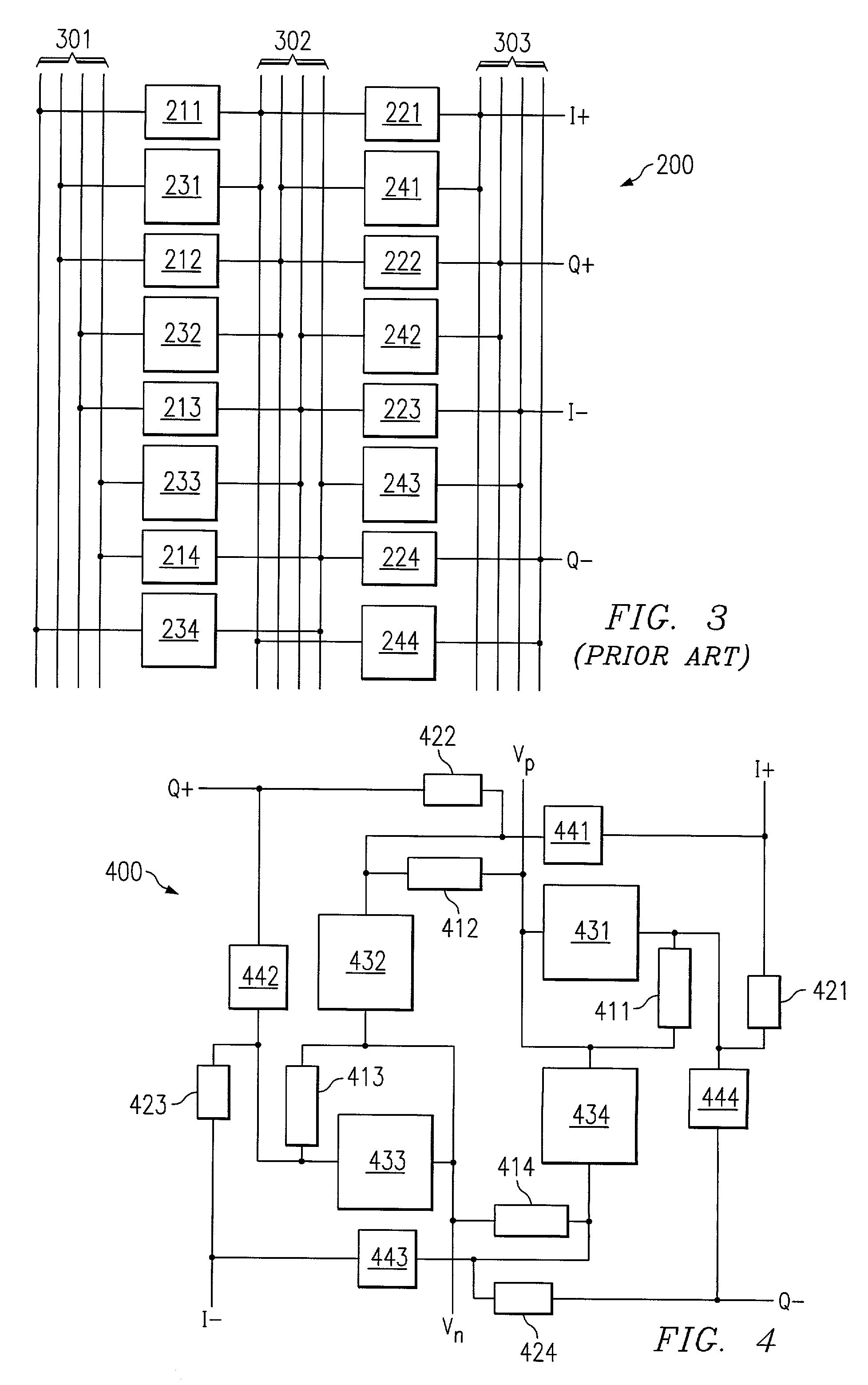

Efficient polyphase filter having a compact structure

ActiveUS7190942B1Minimize signal attenuationMinimize parasitic capacitanceMultiple-port networksTransmissionUltrasound attenuationParasitic capacitance

Disclosed are systems and methods which provide phase shifting of signals while minimizing signal attenuation associated with providing such phase shifting. Preferred embodiments provide a compact polyphase filter structure in which the geometry of the polyphase filter both minimizes parasitic capacitance and signal transmission paths therein. A polyphase filter of a preferred embodiment utilizes a radial pinwheel structure providing a geometry in which successive circuit components are disposed very near one another and in an orientation to accommodate very short connections therebetween. Embodiments may include the use of a buffer at the outputs of the polyphase filter circuit to reduce the amount of parasitics associated with the polyphase filter.

Owner:CSR TECH INC

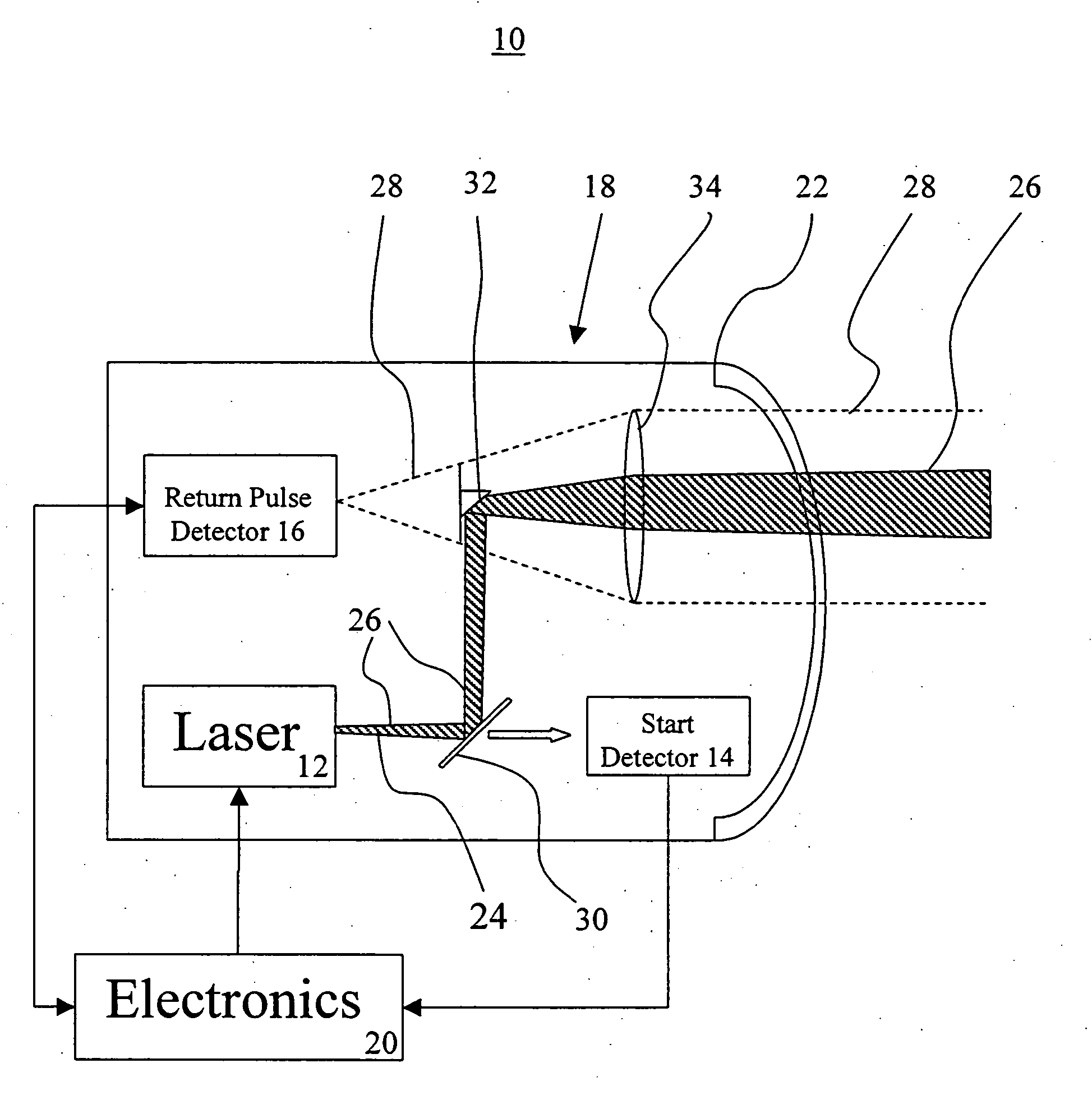

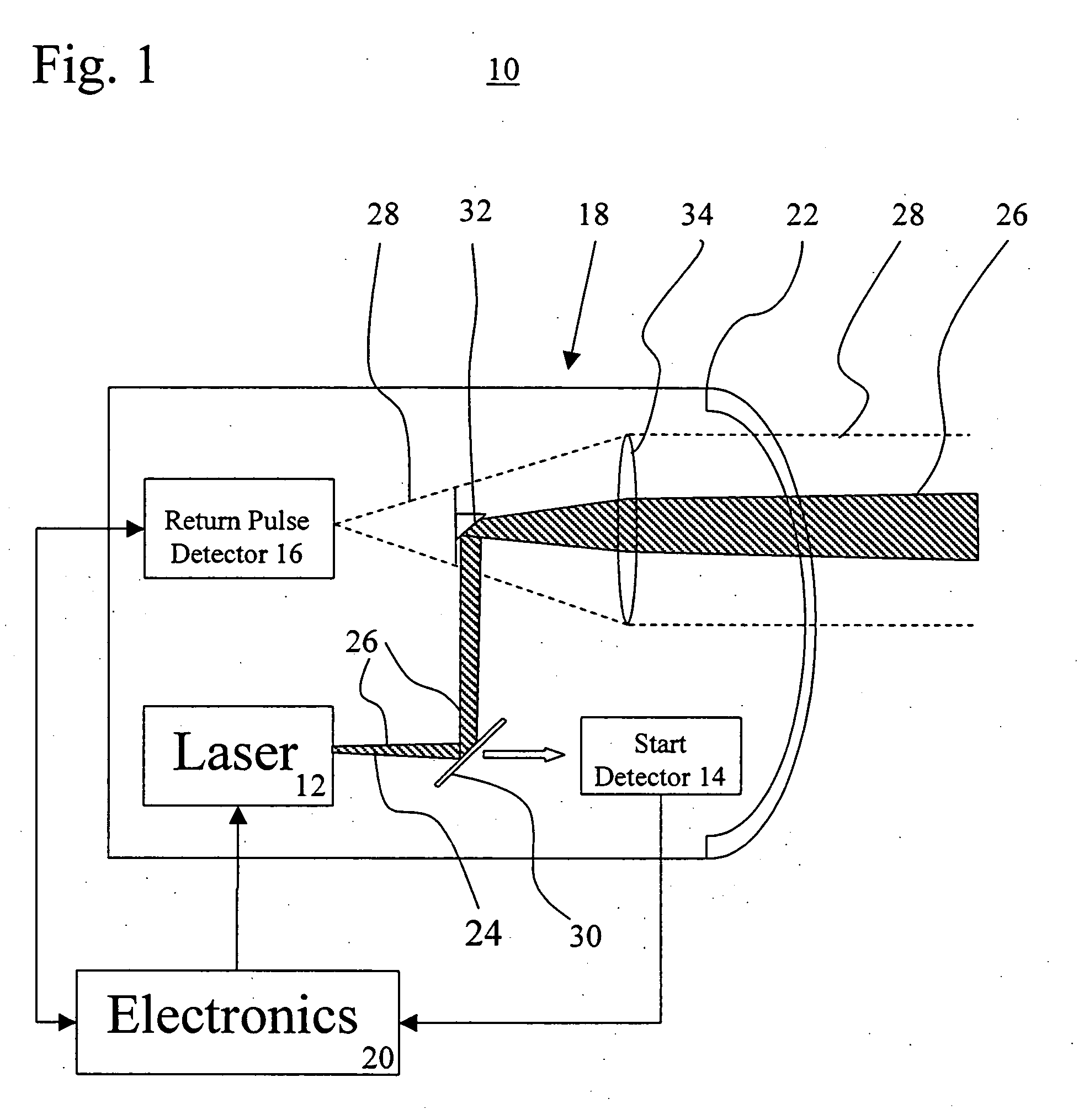

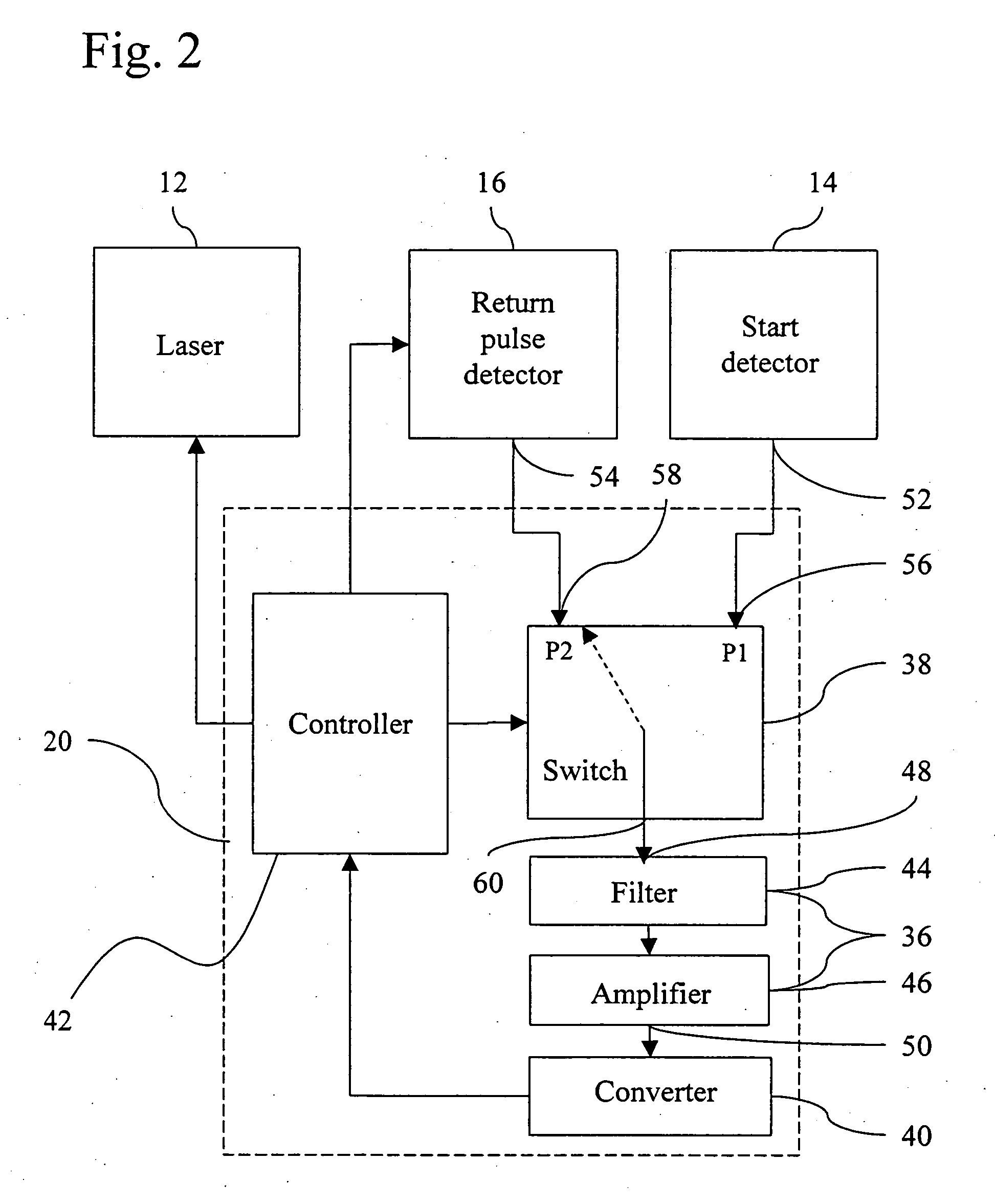

Rangefinder

InactiveUS20060170903A1Avoid long connectionsOptical rangefindersElectromagnetic wave reradiationObject basedTime of flight

A range finder system for determining a range of an object. The system includes a source of laser radiation configured for transmitting a plurality of pulses, a first detector, a second detector, an optical arrangement configured for directing the pulses along an outgoing path and receiving the pulses reflected by the object along a return path. The first detector is deployed to be responsive to the pulses traveling along the outgoing path and the second detector insensitive to the reflections of the pulses from less that the minimum range. The system further includes a controller configured for shorting a connection within the second detector to make the second detector insensitive to the reflections of the pulses from less than a minimum range, and for determining the range of the object based upon a time-of-flight of one or more of the pulses based upon output signals of the first detector and the second detector.

Owner:STATE OF ISRAEL MINIST OF AGRI & RURAL DEV AGRI RES ORG (A R O) (VOLCANI CENT)

Sealed prismatic battery connected via openings with conductive connection plates

InactiveUS6946219B2Lower internal resistanceIncrease powerCell sealing materialsFlat cells groupingEngineeringElectrical and Electronics engineering

A sealed prismatic battery having a battery case made of a plurality of prismatic cell cases coupled together via partition walls, electrode plate groups, and collectors bonded to lead portions on both sides of the electrode plate groups. In at least one side wall of the battery case is formed openings at locations corresponding to the partition walls such as to open to the cell cases on both sides of the partition walls. Pairs of conductive connection plates are connected to each other through the partition walls and formed with connection pieces that face the openings. The collectors are connected together via the conductive connection plates, i.e., they are connected to the connection pieces after the electrode plate groups are encased in the cell cases, and the openings are sealed by sealing plates in a manner that separates the cell cases.

Owner:PANASONIC CORP +1

Electrical connector with multiple interfaces

ActiveUS20140057467A1Avoid long connectionsDistance minimizationSwitchgear arrangementsCoupling contact membersEngineeringElectrical connector

An electrical connector having a body, first and second female interfaces, a female connector, one to four side interfaces and a connecting pin. The body has a longitudinal axis with a passage extending between the first and second female interfaces. The side interfaces extend from the body and are substantially perpendicular to the longitudinal axis. The interfaces have a distal end and a bus electrically connected to the female connector. The ends of the connecting pin are adapted to snugly engage louver-type connectors on male interfaces, which are inserted into the first and second female interfaces. The electrical connector is designed to minimize the distance between the first and second ends of the body. The side interfaces of the electrical connector can be designed to accommodate different high voltage connectors.

Owner:THOMAS & BETTS INT INC

Parallel asynchronous propagation pipeline structure to access multiple memory arrays

A method is disclosed to carry out a data access operation in a data memory device that is subdivided into a plurality of memory arrays each array includes a plurality of memory cells accessible by an identifiable address. The method includes a step of asynchronously propagating in parallel a plurality of data access signals, each through a data access path over multiple propagation stages of signal lines interconnected between the memory arrays and each of the multiple propagation stages implementing an asynchronous local clock for receiving and sending said data access signals for carrying out said data access operation. The method further includes a step of adding a path delay in a selected set of the propagation stages to minimize a length of time difference in carrying out the data access operations through each of the different data access paths. The method further includes a step of generating a pulse train in each of the propagation stages for inputting to the local clock of a subsequent propagation stage for initiating the local clock of the subsequent propagation stage for propagating the data access signals.

Owner:CHEN CHAO WU