Amorphous-oxide thin-film transistor, manufacturing method thereof, and display panel

A technology of amorphous oxide and thin film transistors, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of reduced current drive capability, low threshold voltage, and increased parasitic resistance of source and drain, and achieve improved Driving capability and effect of reduction in parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

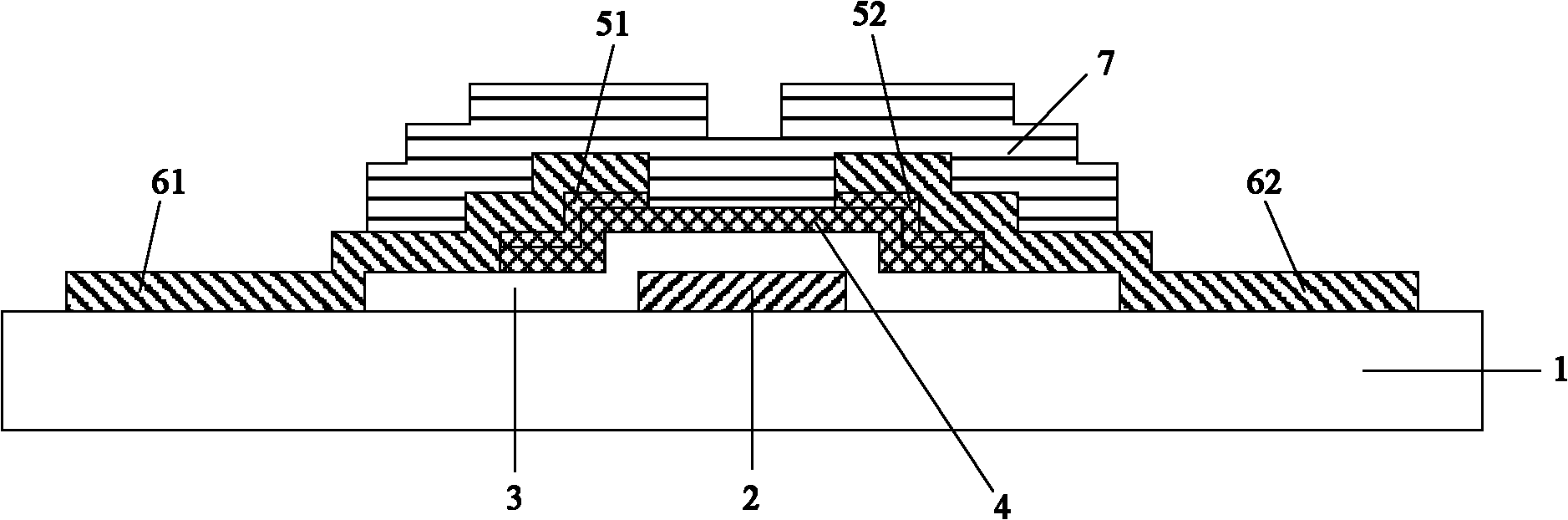

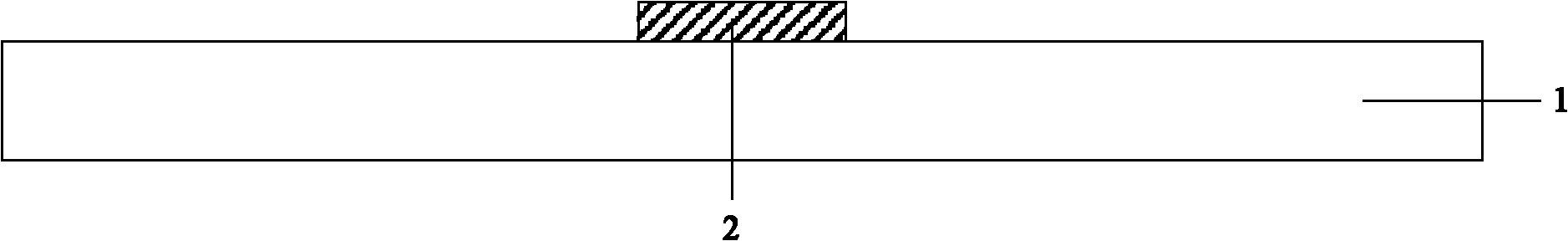

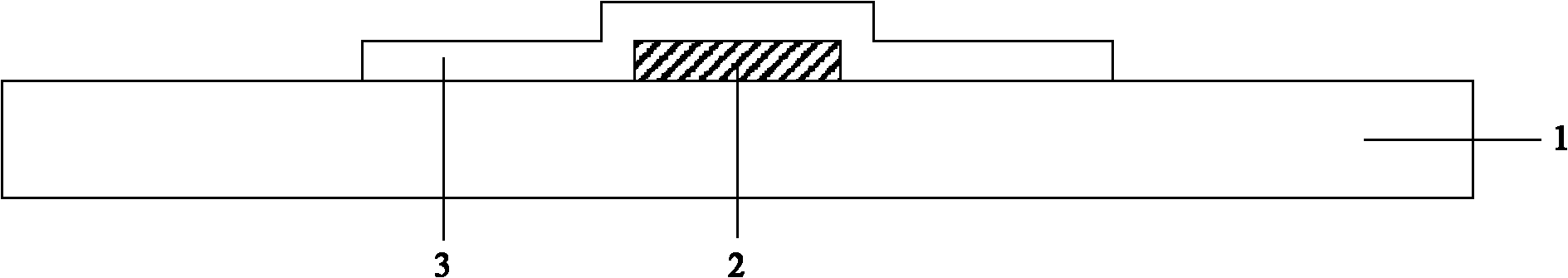

[0036] Such as figure 1 As shown, the embodiment of the present invention provides an amorphous oxide thin film transistor, including: a gate 2, a gate insulating layer 3, a semiconductor active layer, a source 61, a drain 62 and a passivation protection layer 7, the The semiconductor active layer is a double-layer structure of a channel layer 4 and an ohmic contact layer, and the channel layer 4 has a higher oxygen content than the ohmic contact layer;

[0037] The channel layer 4 is bonded to the gate insulating layer 3, the ohmic contact layer is divided into two independent ohmic contact regions 51, 52, and the two independent ohmic contact regions 51, 52 are respectively connected to The source electrode 61 and the drain electrode 62 are bonded together.

[0038] Wherein, the channel layer 4 is formed by sputtering an amorphous oxide material in an oxygen-containing atmosphere; the ohmic contact layer is formed by sputtering an amorphous oxide material in an oxygen-free ...

Embodiment 2

[0088] like Figure 13 As shown, the embodiment of the present invention provides an amorphous oxide thin film transistor, including: a gate 2, a gate insulating layer 3, a semiconductor active layer, a source 61, a drain 62 and a passivation protection layer 7, the The semiconductor active layer is a double-layer structure of a channel layer 4 and an ohmic contact layer, and the channel layer 4 has a higher oxygen content than the ohmic contact layer;

[0089] The channel layer 4 is bonded to the gate insulating layer 3, the ohmic contact layer is divided into two independent ohmic contact regions 51, 52, and the two independent ohmic contact regions 51, 52 are respectively connected to The source electrode 61 and the drain electrode 62 are bonded together;

[0090] An etching protection layer 9 is formed between the two independent ohmic contact regions 51 , 52 , and the etching protection layer 9 is located between the channel layer 4 and the passivation protection layer 7...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com