Array substrate, manufacturing method thereof and display device

A technology of an array substrate and a manufacturing method, applied in the display field, can solve the problem that polysilicon thin film transistors cannot be applied to the production of large-size display panels and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

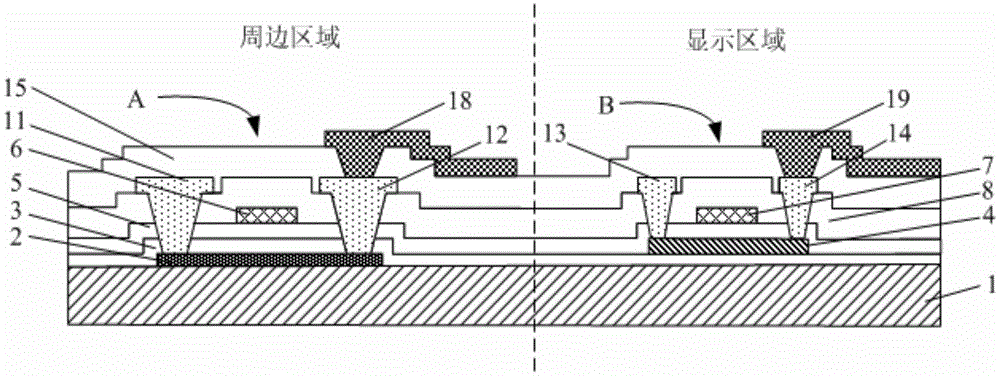

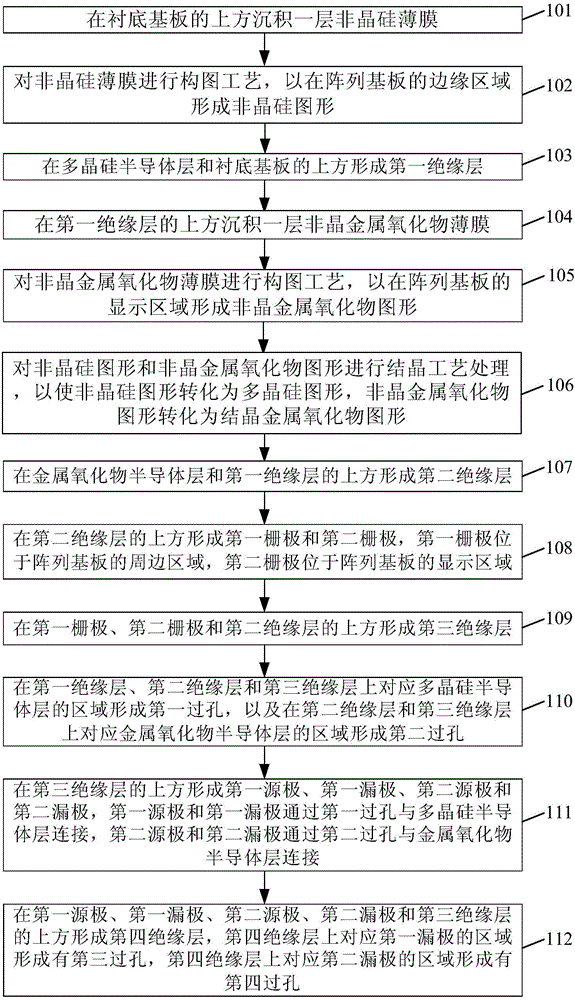

[0094] figure 1 A schematic cross-sectional view of the array substrate provided in Embodiment 1 of the present invention, as shown in figure 1 As shown, the array substrate includes: a first thin film transistor A and a second thin film transistor B, the first thin film transistor A and the second thin film transistor B are formed above the base substrate 1, the first thin film transistor A is a polysilicon thin film transistor, The second thin film transistor B is a metal oxide thin film transistor, the first thin film transistor A is located in the peripheral area of the array substrate, and the second thin film transistor is located in the display area B of the array substrate.

[0095] In this embodiment, on the one hand, a polysilicon thin film transistor with relatively high electron mobility (electron mobility at 30 cm 2 / Vs or so) is arranged in the peripheral area of the array substrate, which can meet the high requirements of the peripheral area of the large-...

Embodiment 2

[0133] Figure 4 A schematic cross-sectional view of the array substrate provided in Embodiment 1 of the present invention, as shown in Figure 4 As shown, the array substrate includes: a first thin film transistor C and a second thin film transistor D, the first thin film transistor C and the second thin film transistor D are formed above the base substrate 1, the first thin film transistor C is a polysilicon thin film transistor, The second thin film transistor D is an amorphous silicon thin film transistor, the first thin film transistor C is located in the peripheral area of the array substrate, and the second thin film transistor D is located in the display area of the array substrate.

[0134] In this embodiment, on the one hand, polysilicon thin film transistors with relatively high electron mobility are arranged in the peripheral area of the array substrate, which can meet the high requirement of the electronic mobility of the components in the peripheral area of...

Embodiment 3

[0163] Embodiment 3 of the present invention provides a display device. The display device includes an array substrate. The array substrate adopts the array substrate provided in Embodiment 1 or Embodiment 2 above. For details, please refer to the above-mentioned Embodiment 1 and Embodiment 2. description and will not be repeated here.

[0164] The display device in this embodiment can be any product or component with a display function, such as a liquid crystal panel, an electronic paper, an OLED panel, a mobile phone, a tablet computer, a television set, a monitor, a notebook computer, a digital photo frame, or a navigator.

[0165] Since the display device provided in the third embodiment includes the array substrate in the first or second embodiment above, this embodiment has the beneficial technical effects described in the first or second embodiment above.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More