Sull transistor with etching barrier layer and preparation method thereof

A technology for etching barrier layers and oxide films, used in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as easy leakage, and achieve the effect of avoiding influence and ensuring electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

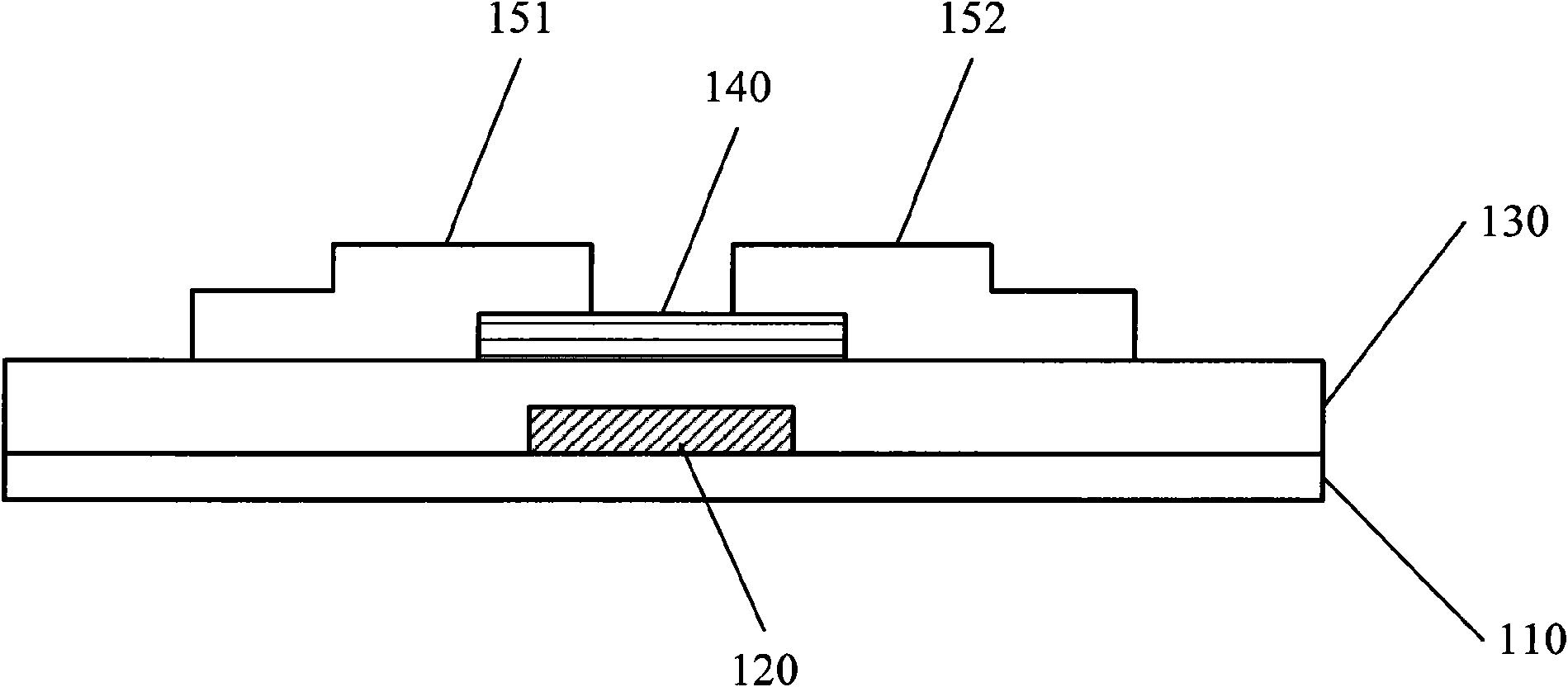

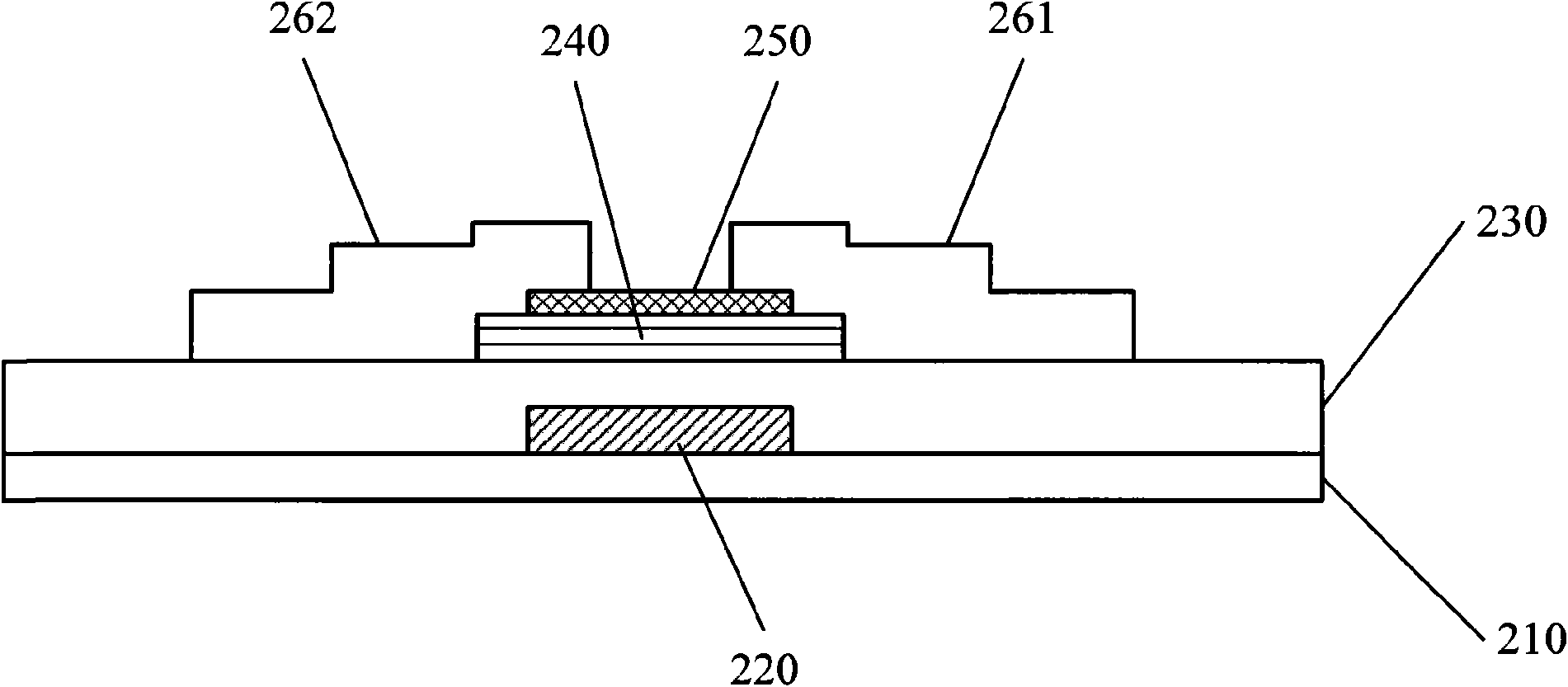

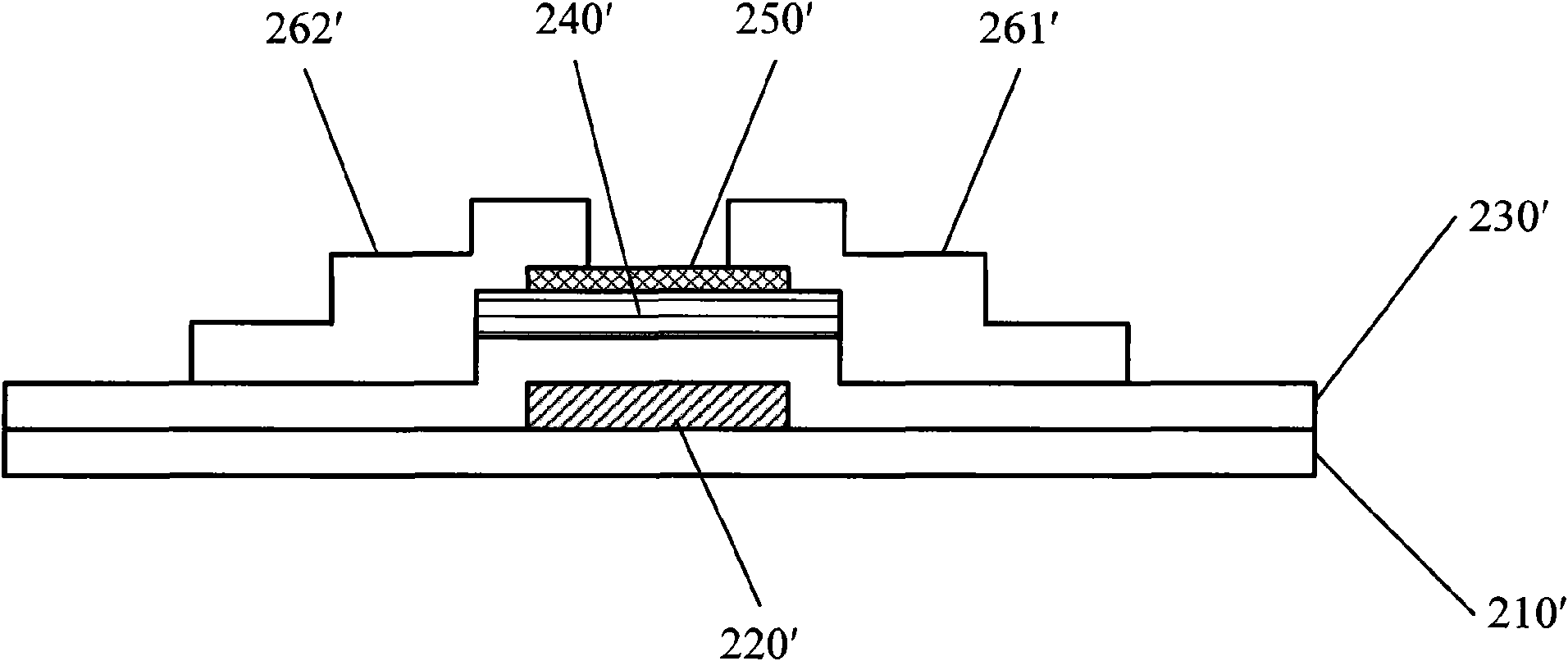

[0016] An oxide thin film transistor with an etching stopper layer and a manufacturing method thereof provided by the present invention will be described in detail below with reference to the accompanying drawings.

[0017] attached Figure 4 It is a structural schematic diagram of the thin film transistor described in this specific embodiment, including: a substrate 310; a gate 320, the gate 320 is arranged on the surface of the substrate 310; an insulating layer 330, the insulating layer 330 covers the surface of the gate 320 Covering all; the conductive channel 340 , the conductive channel 340 is disposed on the surface of the insulating layer 330 away from the gate 320 , and corresponds to the position of the gate 320 . The material of the conductive channel 340 is an oxide semiconductor, preferably an oxide material (InGaZnO) containing metal indium, gallium and zinc.

[0018] The structure described in this specific embodiment further includes an etching barrier layer 3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More