Longitudinal channel SOI (silicon on insulator) nLDMOS (n-type laterally diffused metal oxide semiconductor) device unit with p buried layer

A channel and device technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problem of thermal stability affecting the heat dissipation and electrical characteristics of the device, adverse device and system reliability and stability, affecting the withstand voltage performance of the device, etc. to reduce the self-heating effect, improve thermal stability, and improve heat dissipation performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

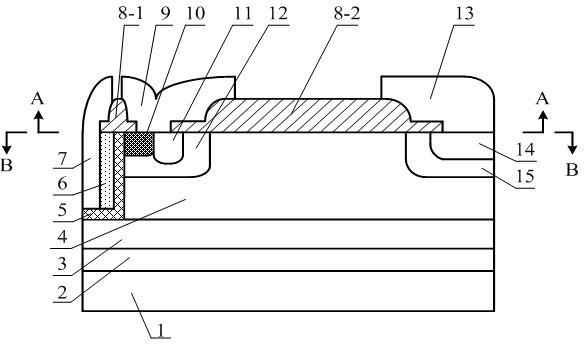

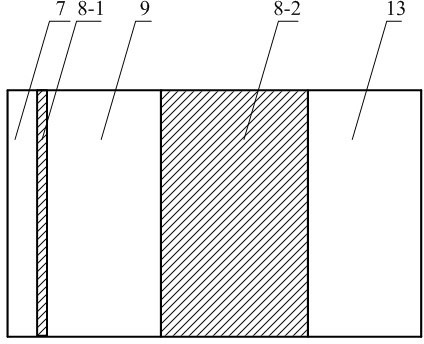

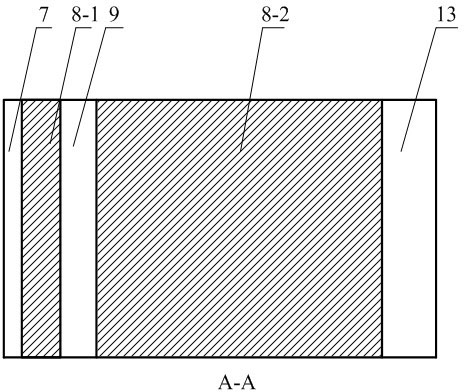

[0014] Such as figure 1 , 2 , 3 and 4, a vertical channel SOI nLDMOS device unit with a p-buried layer, including a p-type semiconductor substrate 1, a buried oxide layer 2, a p-buried layer region 3, and an n-type lightly doped drift region 4 , a gate oxide layer 5, a buried oxide layer 2 covering the p-type semiconductor substrate 1, a p-buried layer region 3 covering the buried oxide layer 2, an n-type lightly doped drift region 4 and a gate oxide layer 5 arranged side by side On the p buried layer region 3, the n-type lightly doped drift region 4 is in contact with the gate oxide layer 5, and the n-type heavily doped polysilicon gate 6 is arranged next to the gate oxide layer 5, and one side of the n-type heavily doped polysilicon gate 6 It is in contact with the gate oxide layer 5.

[0015] On both sides of the top of the n-type lightly doped drift region 4, a p-type well region 12 and an n-type buffer area 15 are respectively embedded, wherein the p-type well region 12...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com