High-voltage LDMOS (laterally-diffused metal oxide semiconductor) device

A high-voltage, device technology, applied in the field of high-voltage LDMOS devices, can solve the problems of not being able to simultaneously meet the forward requirements of high withstand voltage and low on-resistance, and the long time of pushing well in the N-type drift region.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be described in detail below in conjunction with the implementations shown in the drawings, but it should be noted that these implementations are not limitations of the present invention, and those of ordinary skill in the art based on the functions, methods, or structural changes made by these implementations Equivalent transformations or substitutions all fall within the protection scope of the present invention.

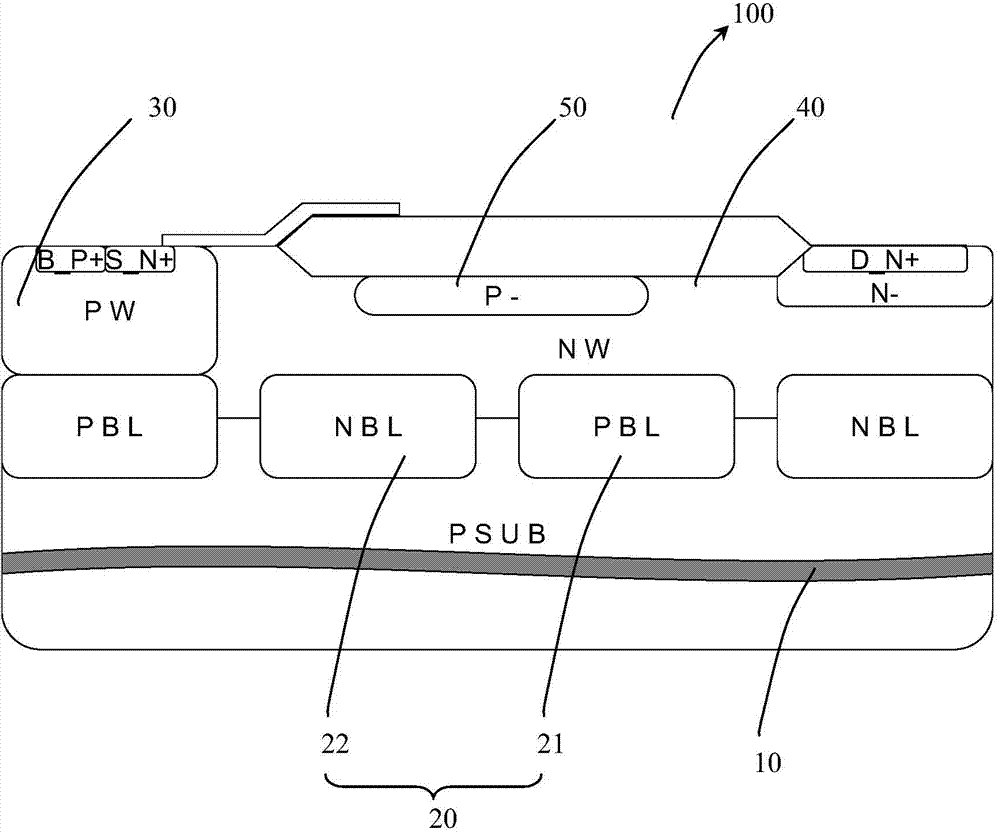

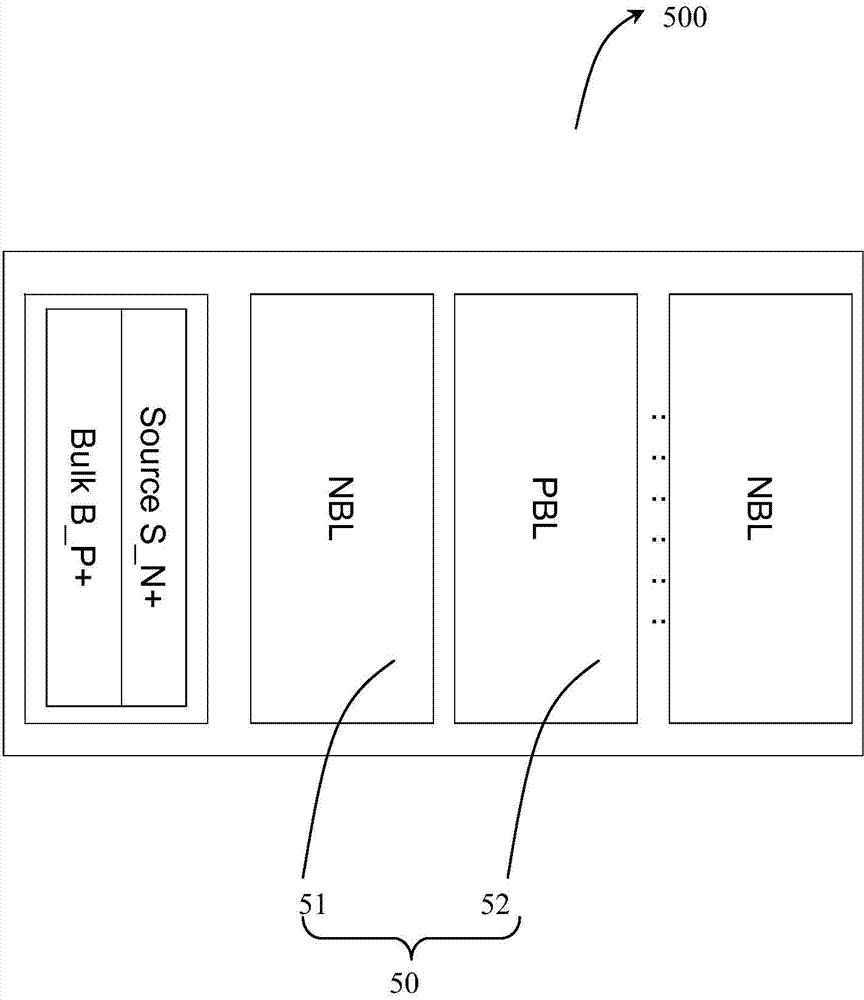

[0019] figure 1 is a schematic diagram of a high-voltage LDMOS device 100 in the first embodiment of the present invention, which includes a P-type substrate 10, a withstand voltage layer 20 located above the P-type substrate, a P-type channel region 30 located above the withstand voltage layer 20, and a N type drift region 40 and a P-type drop field layer 50 above the N-type drift region.

[0020] The P-type substrate 10 is used as the base of the high-voltage LDMOS device 100, and the P-type substrate is arranged below the volt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com