Patents

Literature

33results about How to "Increase the output capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

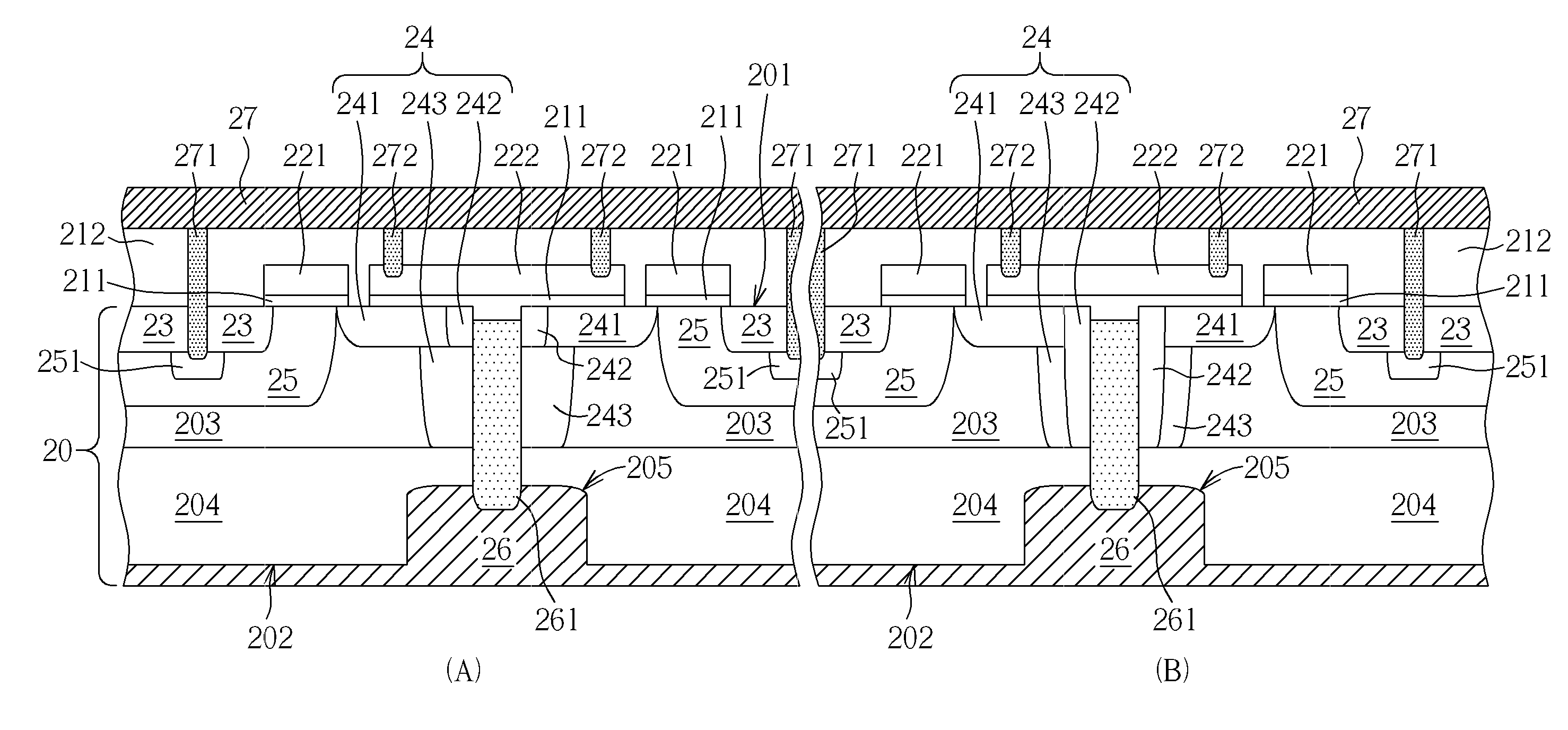

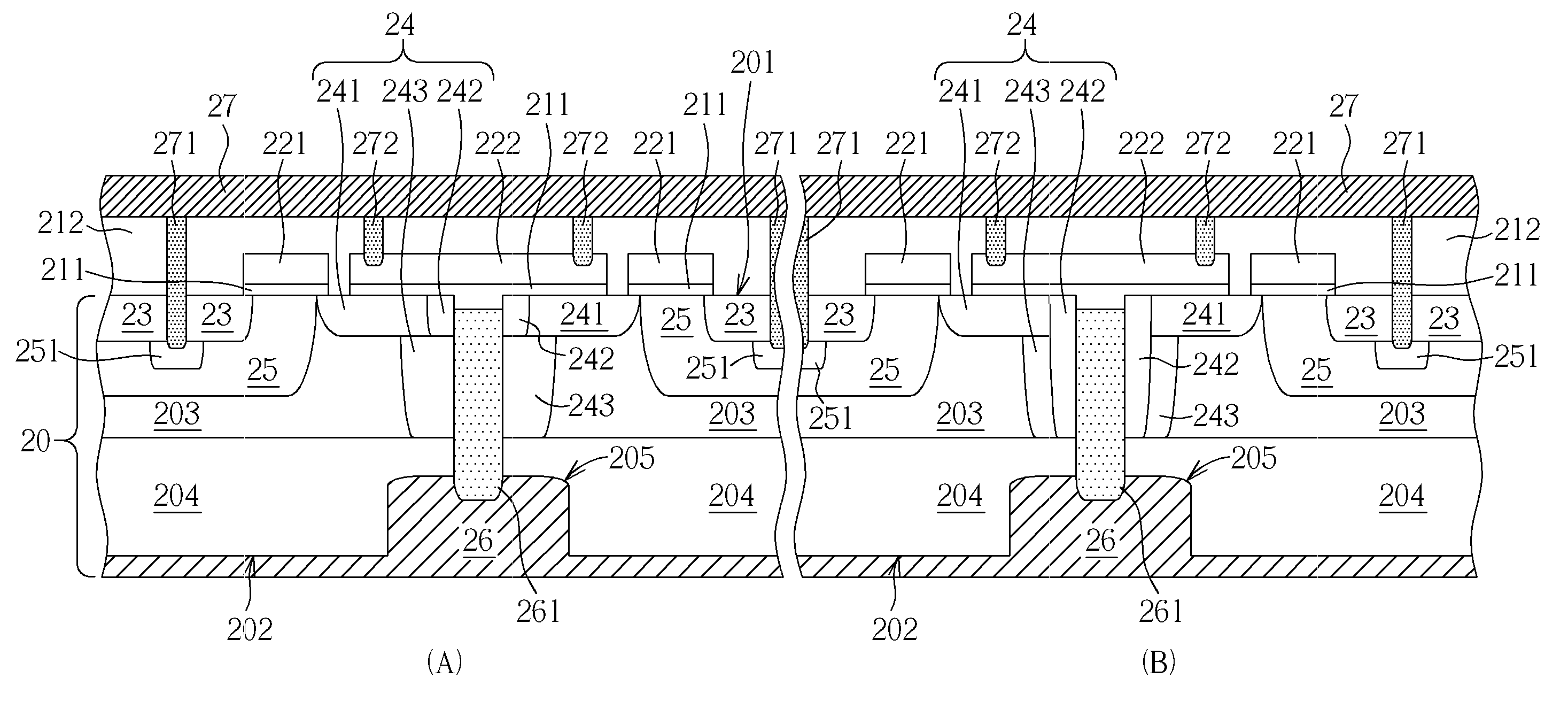

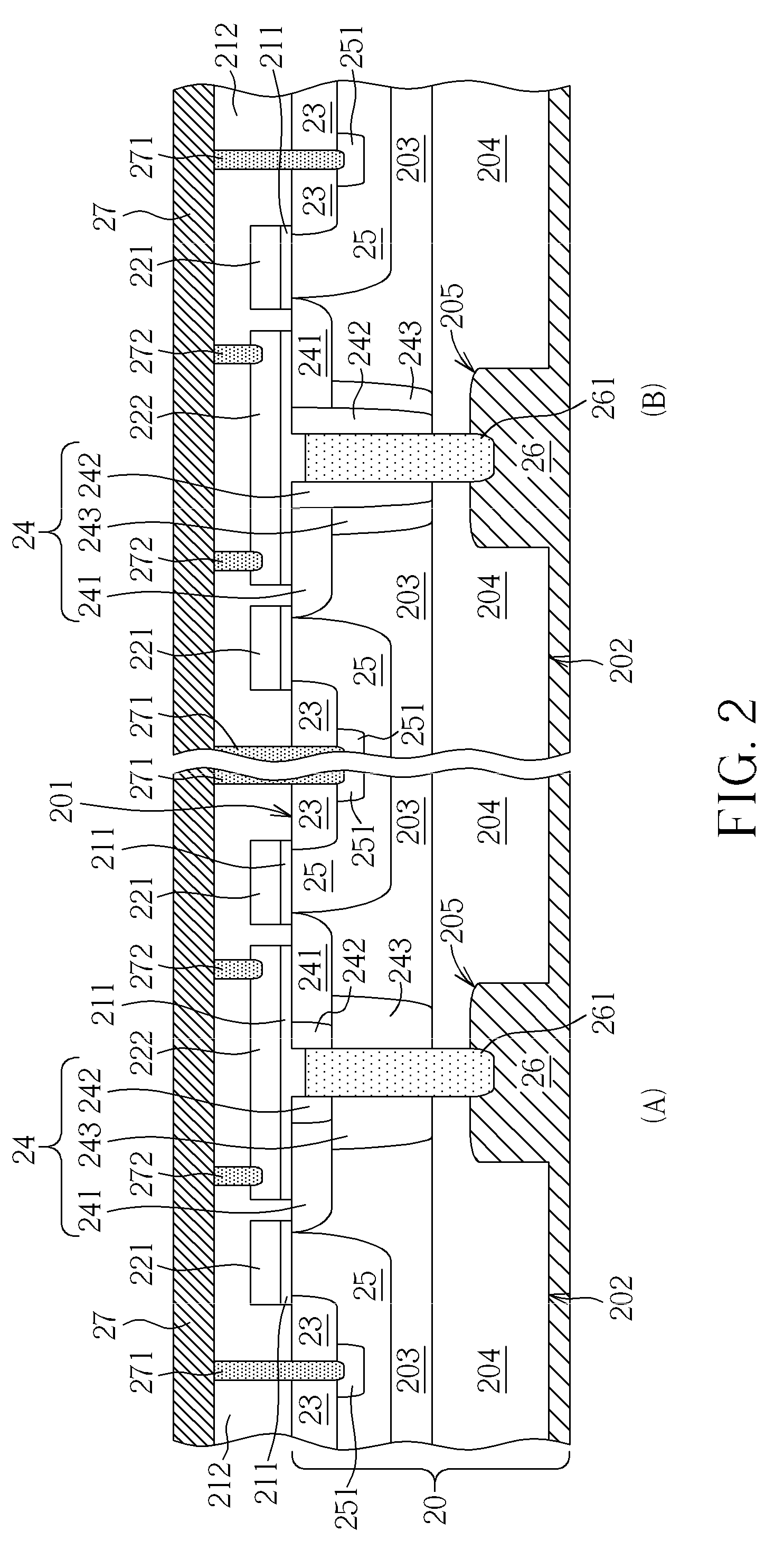

Semiconductor device having extra capacitor structure and manufacturing method thereof

ActiveUS20120049263A1Increasing output capacitanceReduce voltage spikesTransistorSolid-state devicesPhysicsPower semiconductor device

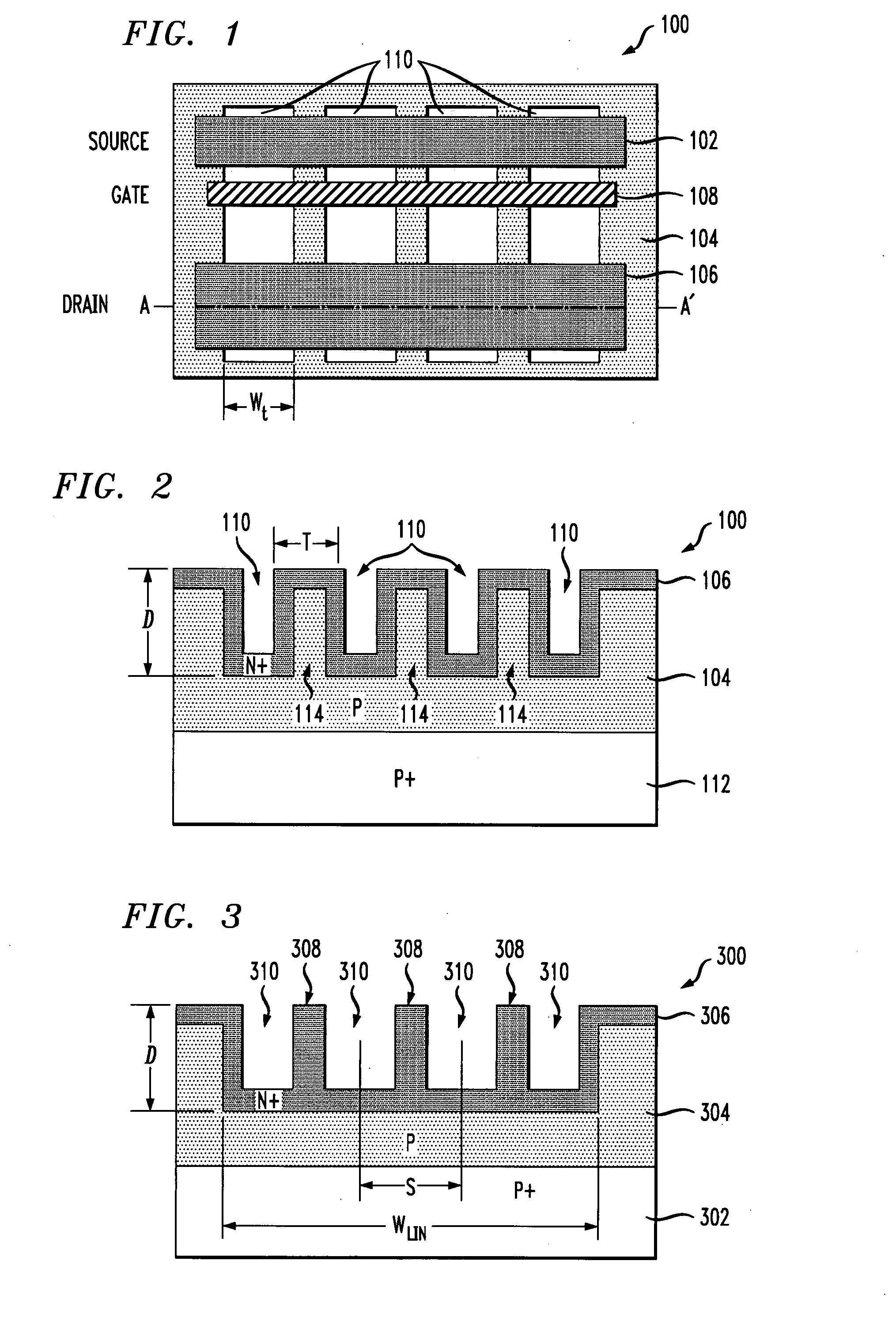

A semiconductor device includes a semiconductor substrate having a conductive type, a source metal layer, a gate metal layer, at least one transistor device, a heavily doped region having the conductive type, a capacitor dielectric layer, a conductive layer. The source metal layer and the gate metal layer are disposed on the semiconductor substrate. The transistor device is disposed in the semiconductor substrate under the source metal layer. The heavily doped region, the capacitor dielectric layer and the conductive layer constitute a capacitor structure, disposed under the gate metal layer, and the capacitor structure is electrically connected between a source and a drain of the transistor device.

Owner:SINOPOWER SEMICON

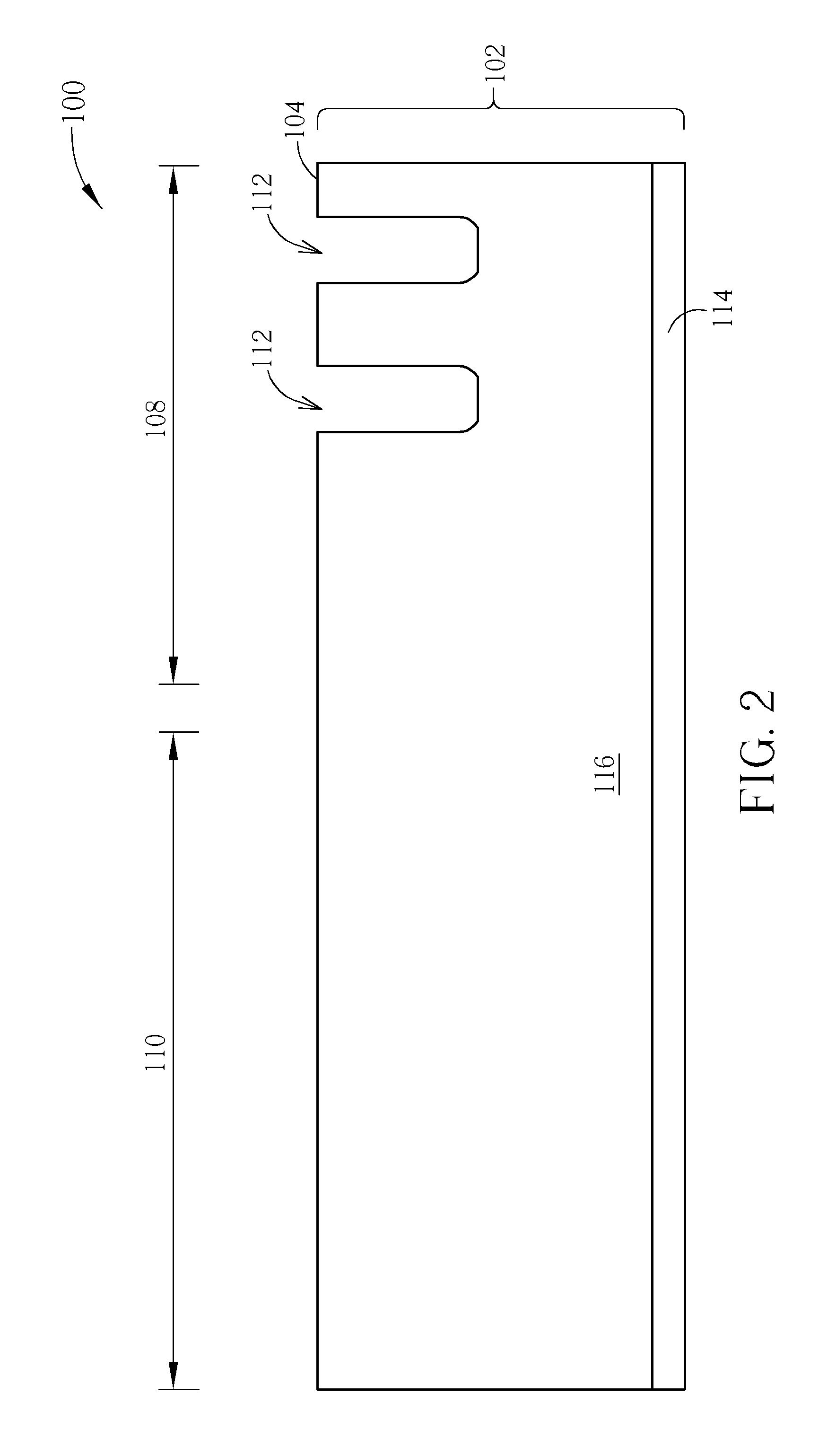

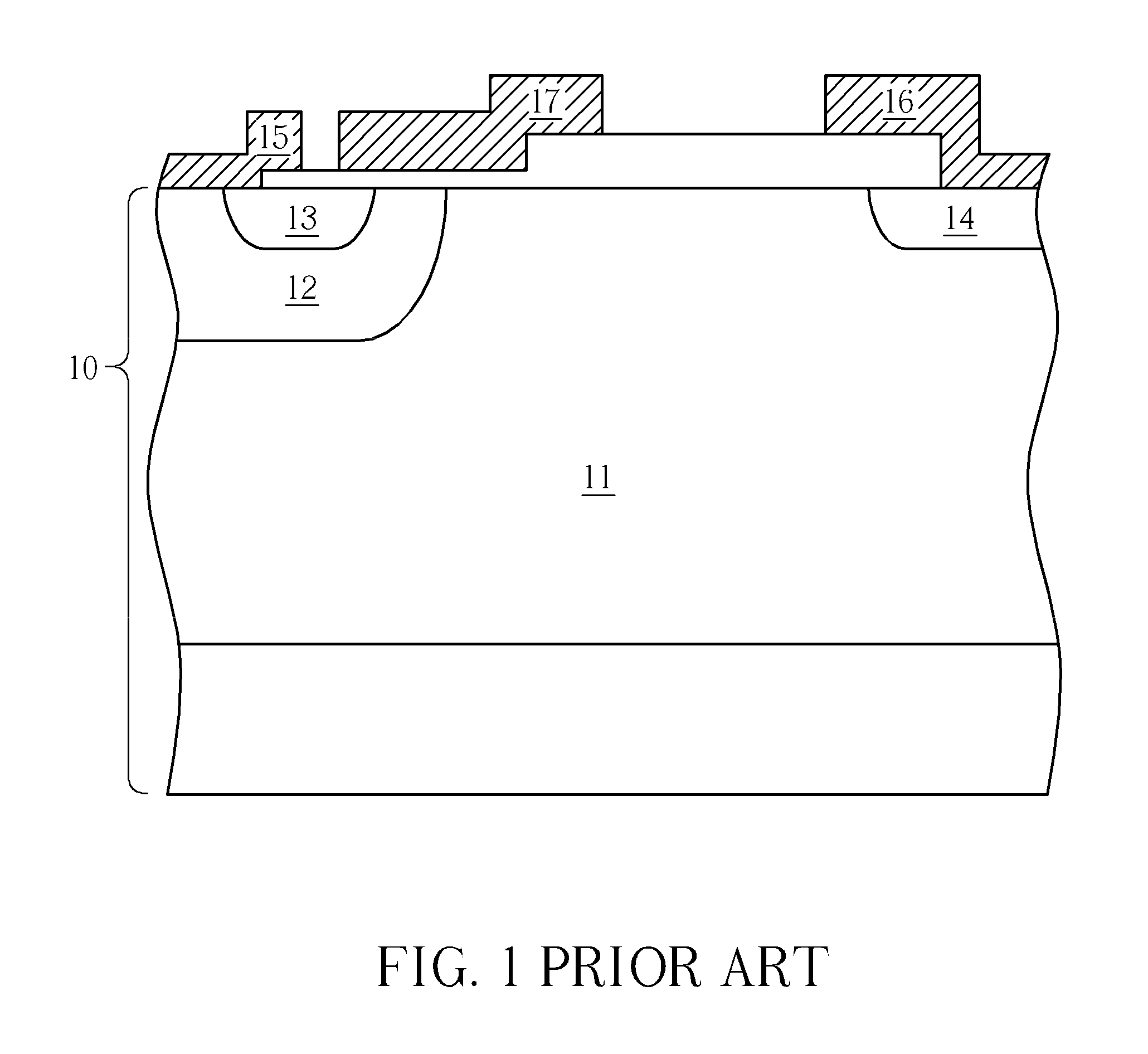

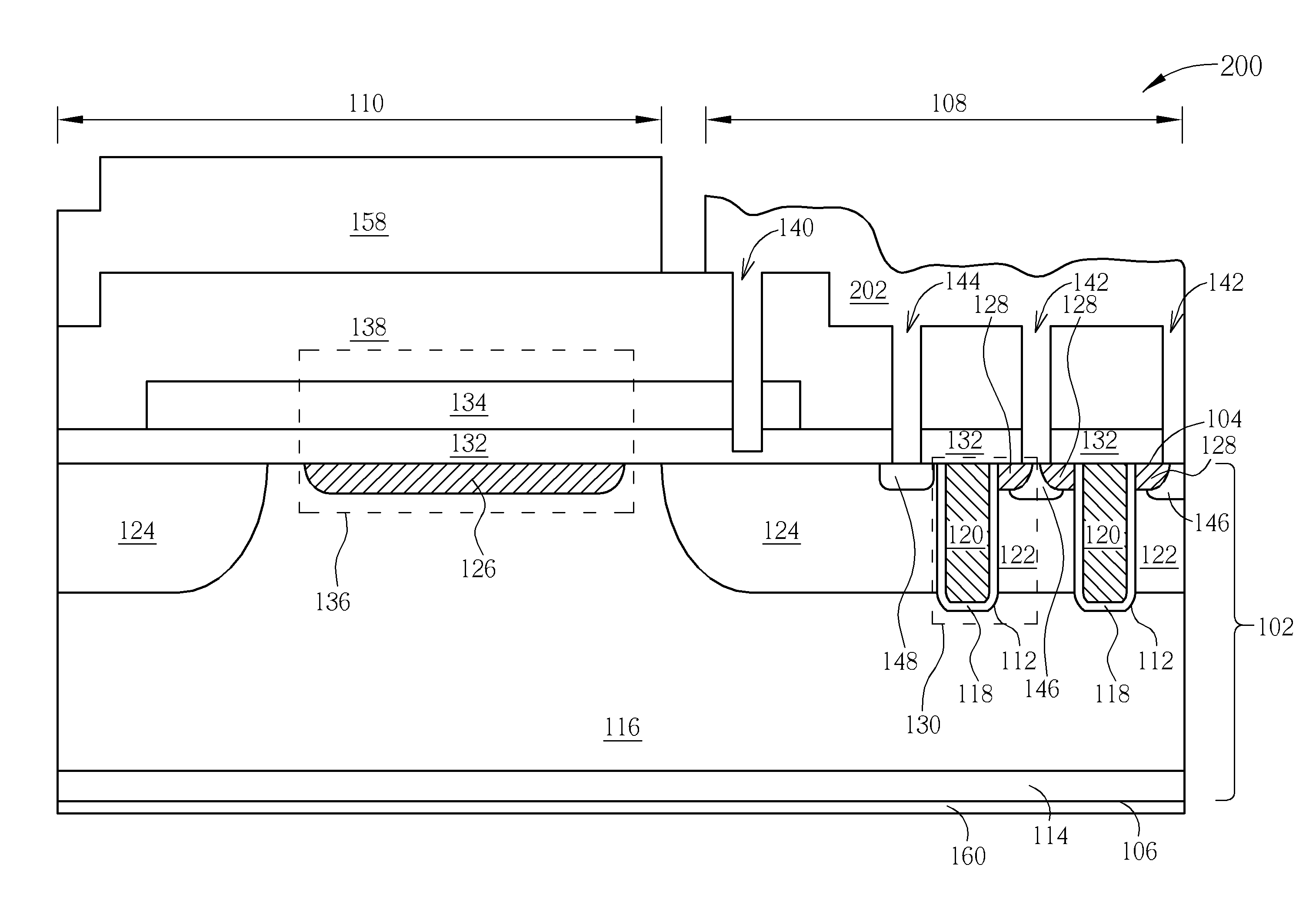

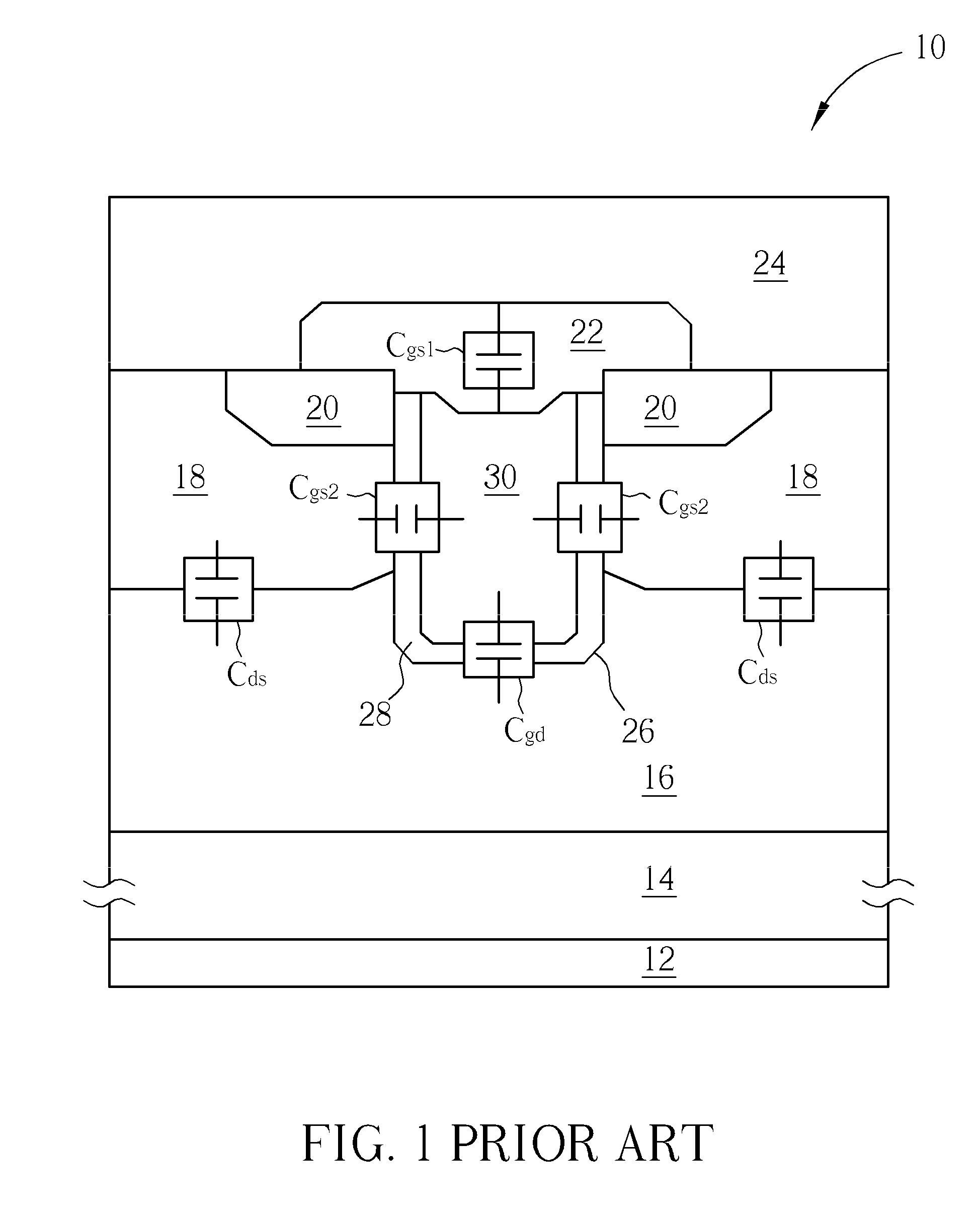

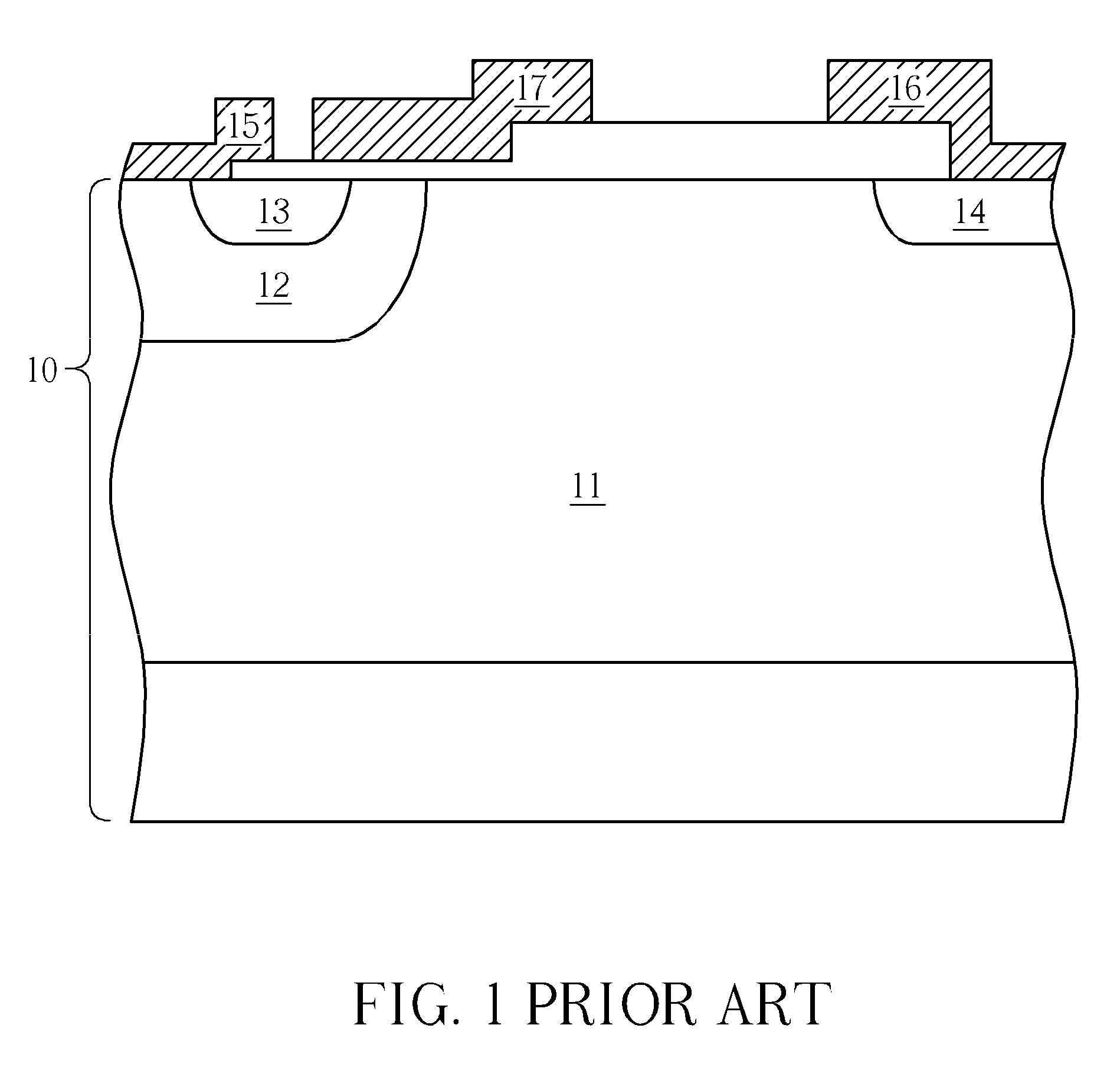

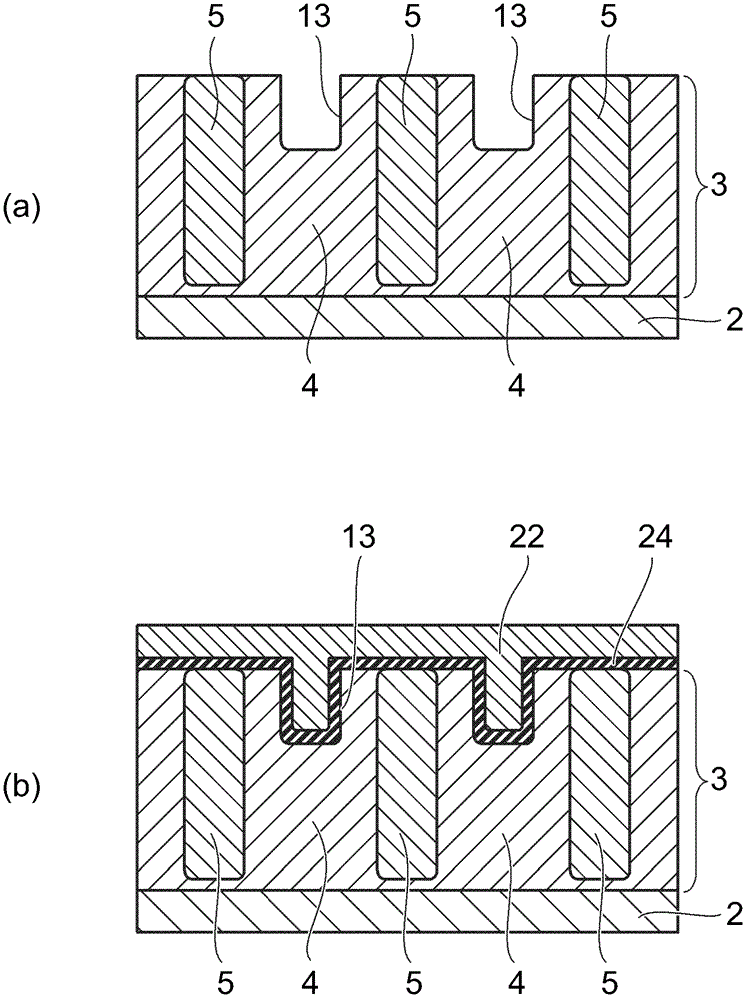

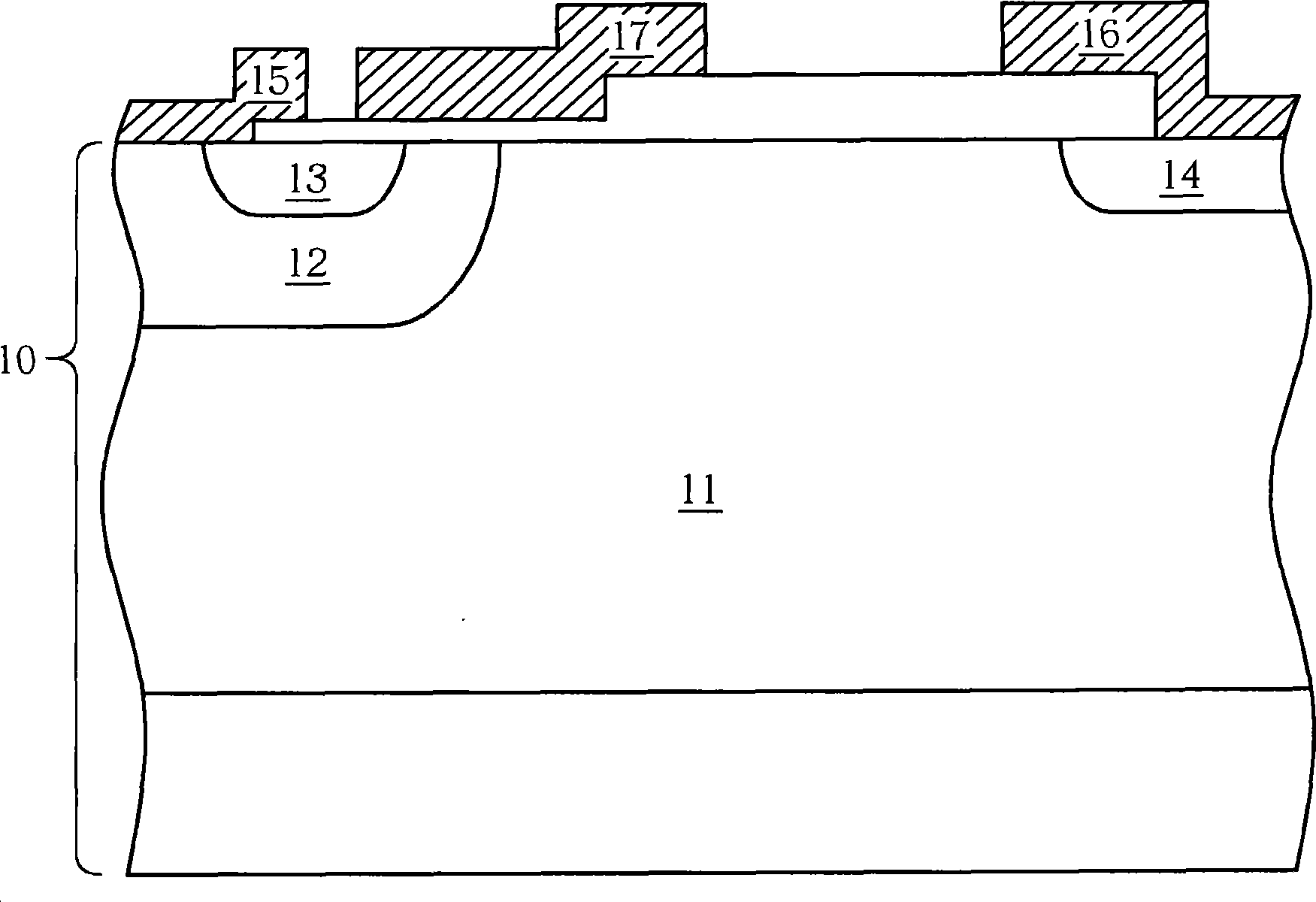

Metal-oxide-semiconductor device having trenched diffusion region and method of forming same

ActiveUS20080093667A1Lower on-state resistanceIncrease the output capacitanceTransistorSolid-state devicesSemiconductorMetal

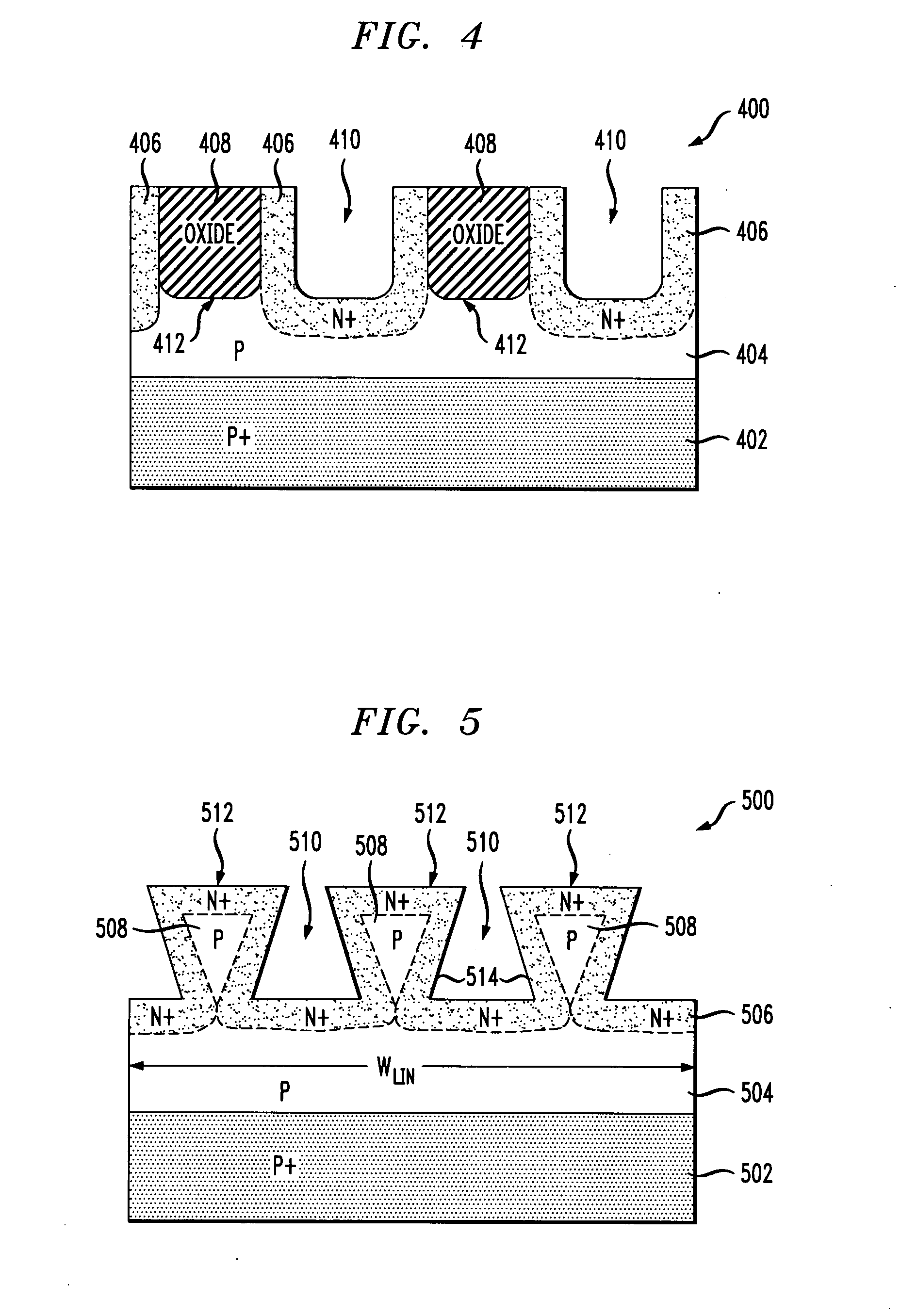

An MOS device includes a semiconductor layer of a first conductivity type and first and second source / drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer. The first and second source / drain regions are spaced apart relative to one another. A gate is formed above and electrically isolated from the semiconductor layer, at least partially between the first and second source / drain regions. At least a given one of the first and second source / drain regions is configured having an effective width that is substantially greater than a width of a junction between the semiconductor layer and the given source / drain region.

Owner:BELL SEMICON LLC

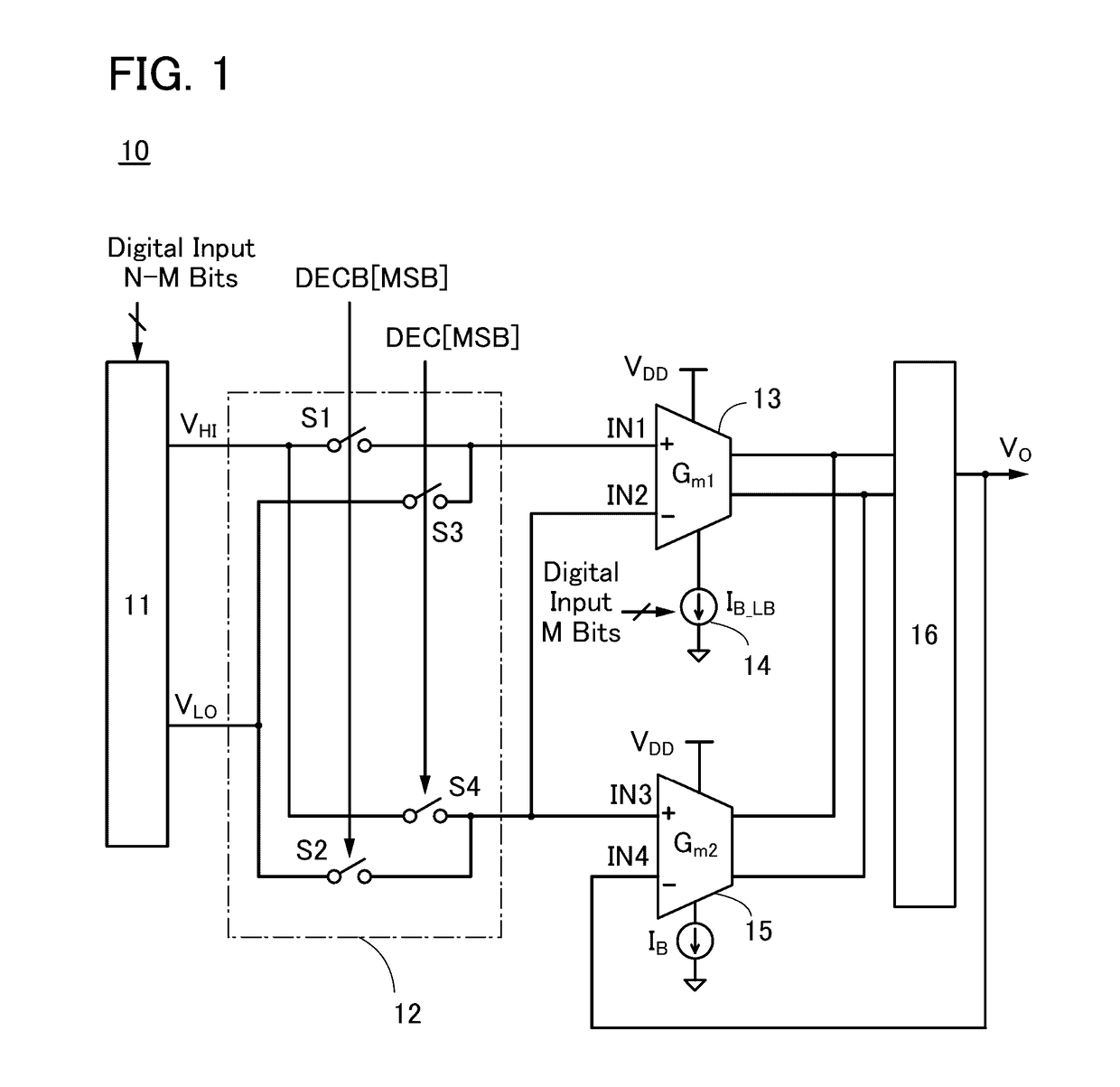

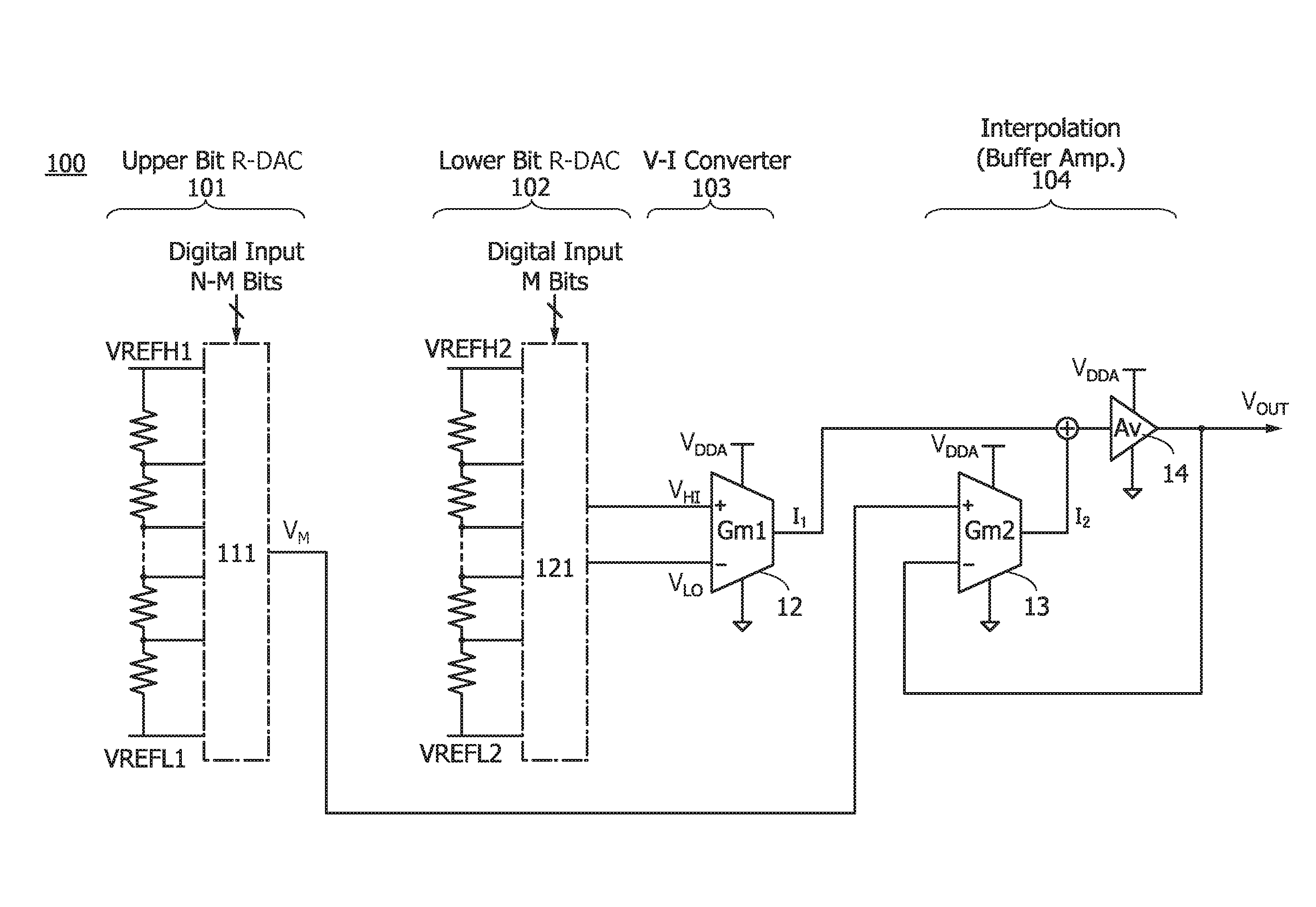

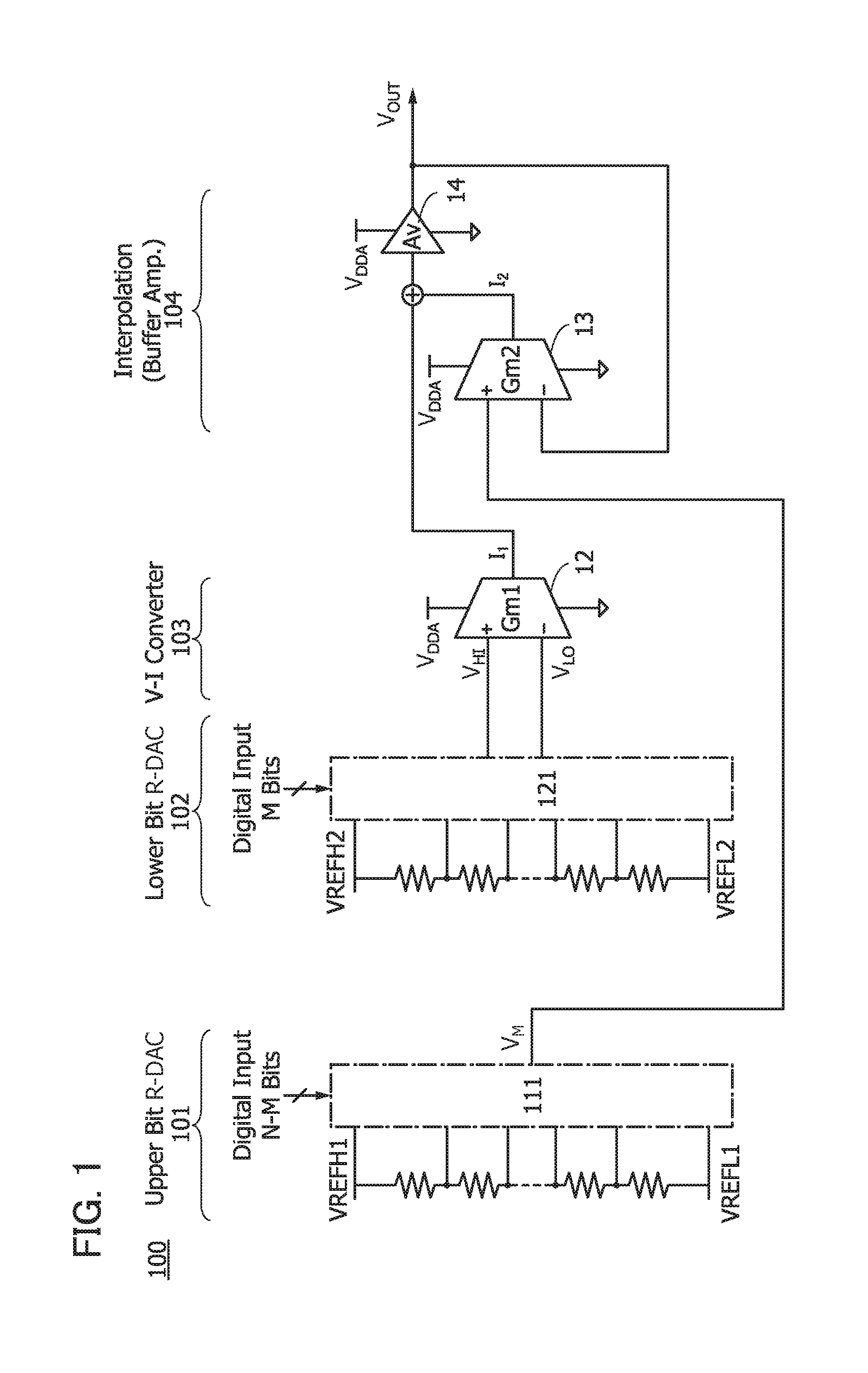

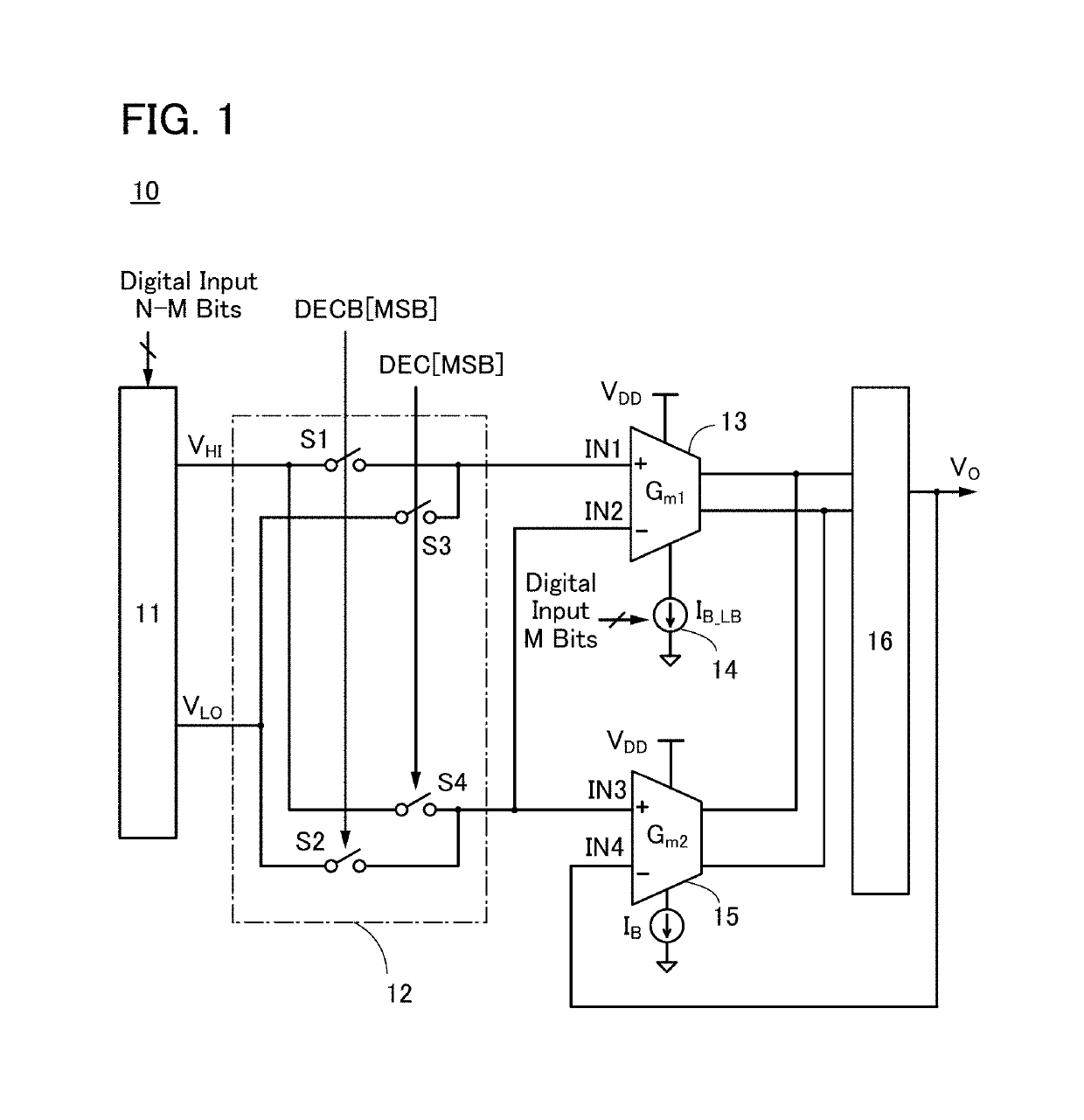

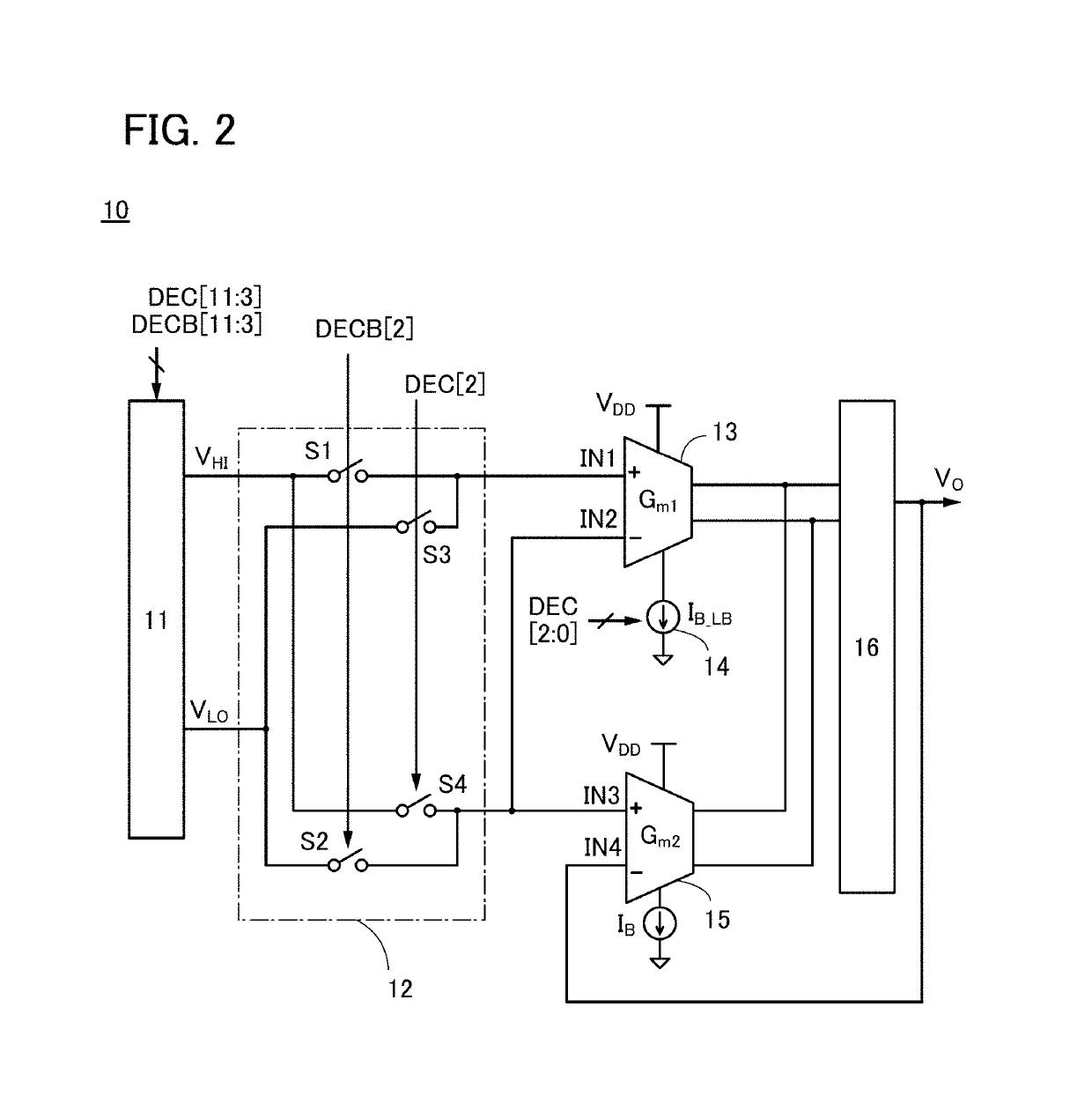

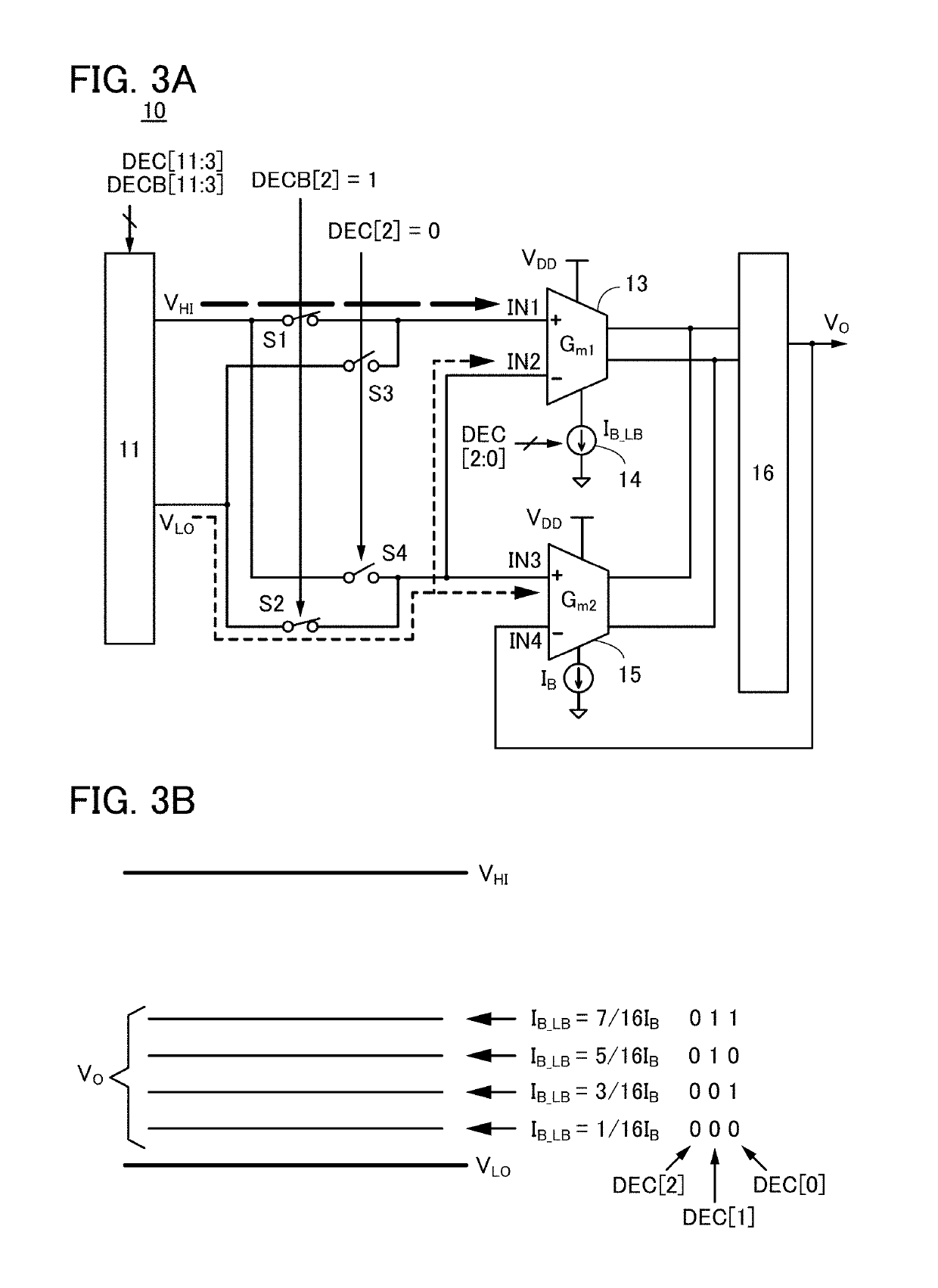

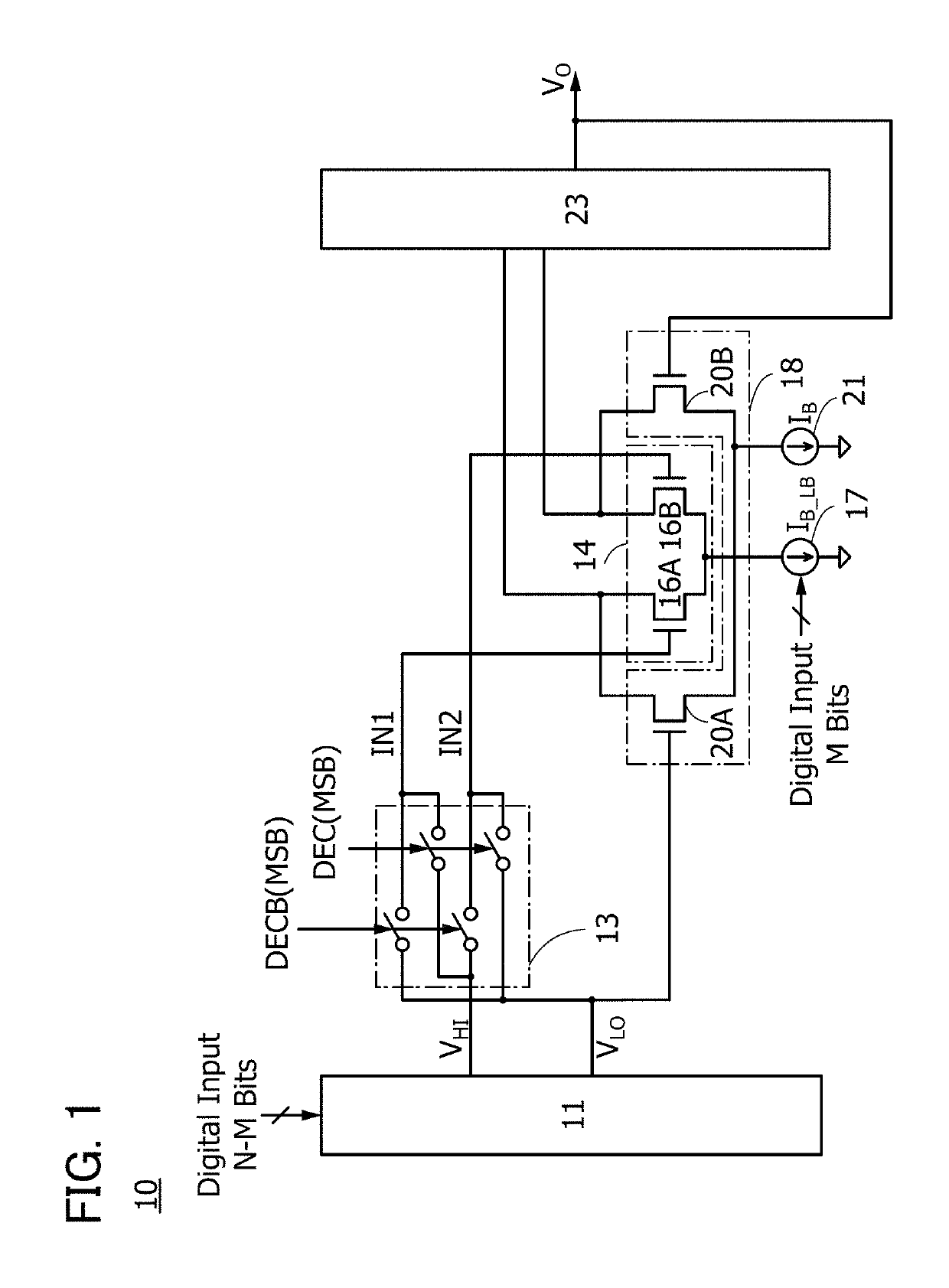

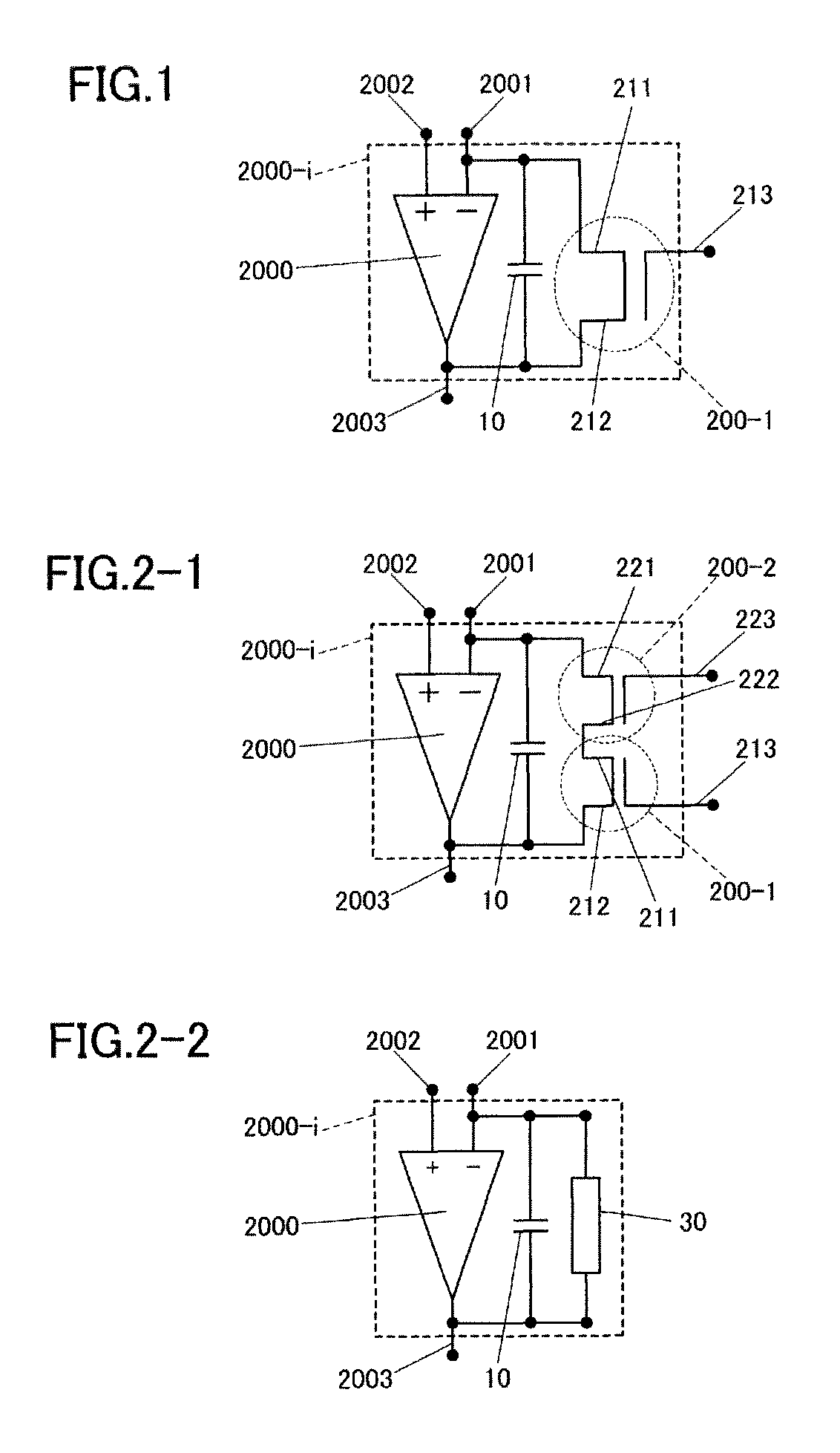

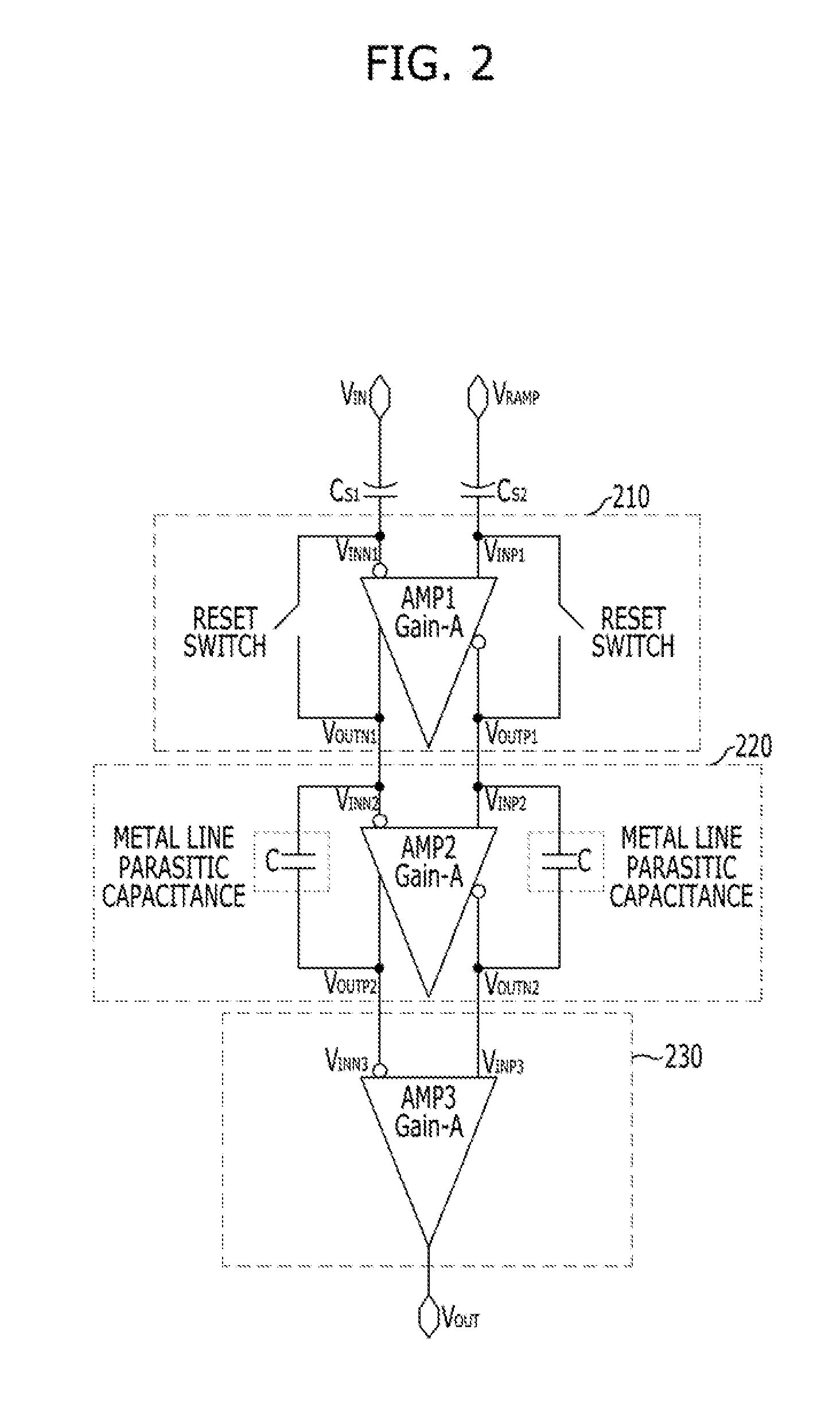

Semiconductor device, display panel, and electronic device

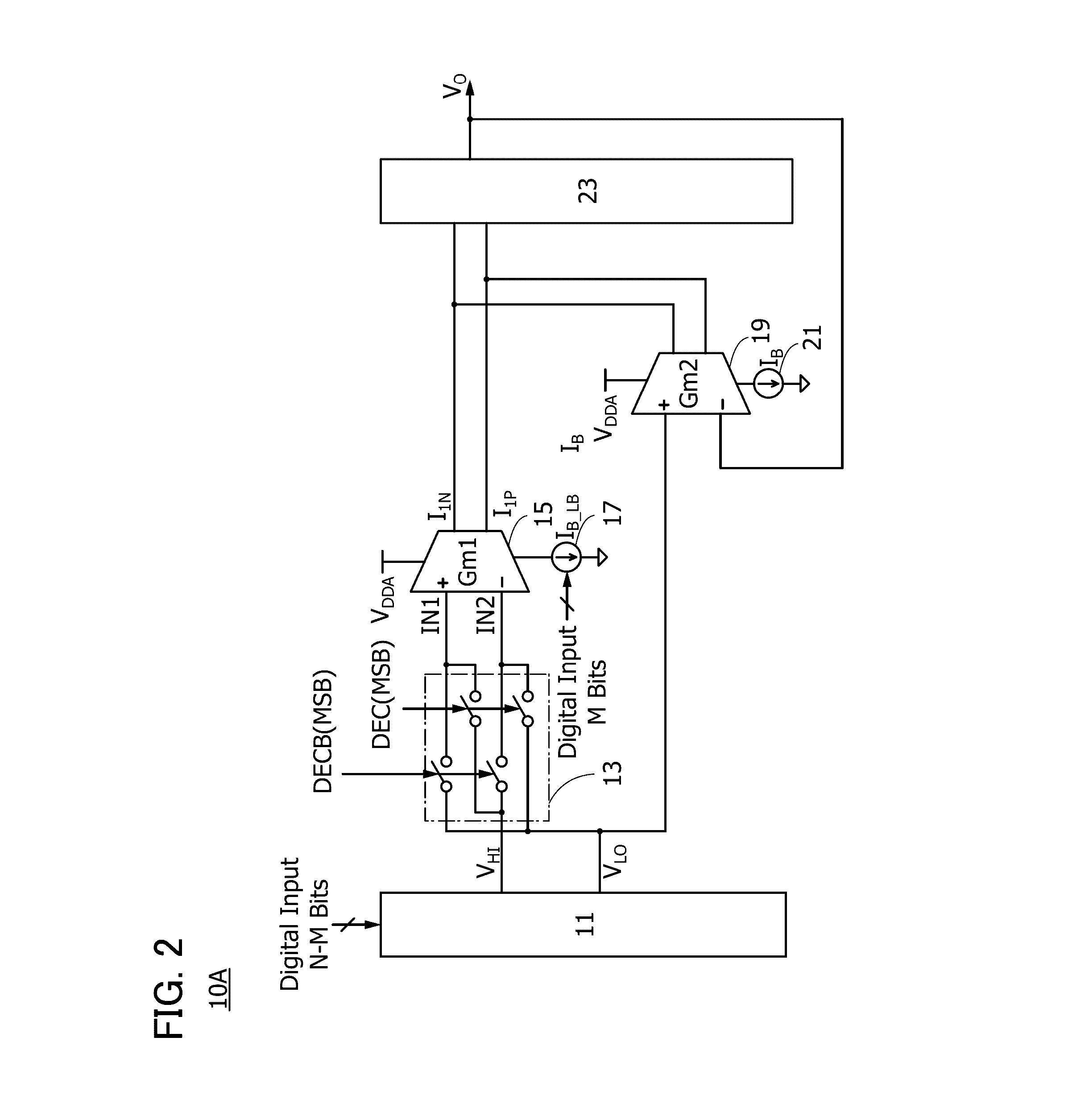

ActiveUS20170053584A1High degree of freedom of choiceNovel structureStatic indicating devicesDigital-analogue convertorsPower semiconductor deviceAudio power amplifier

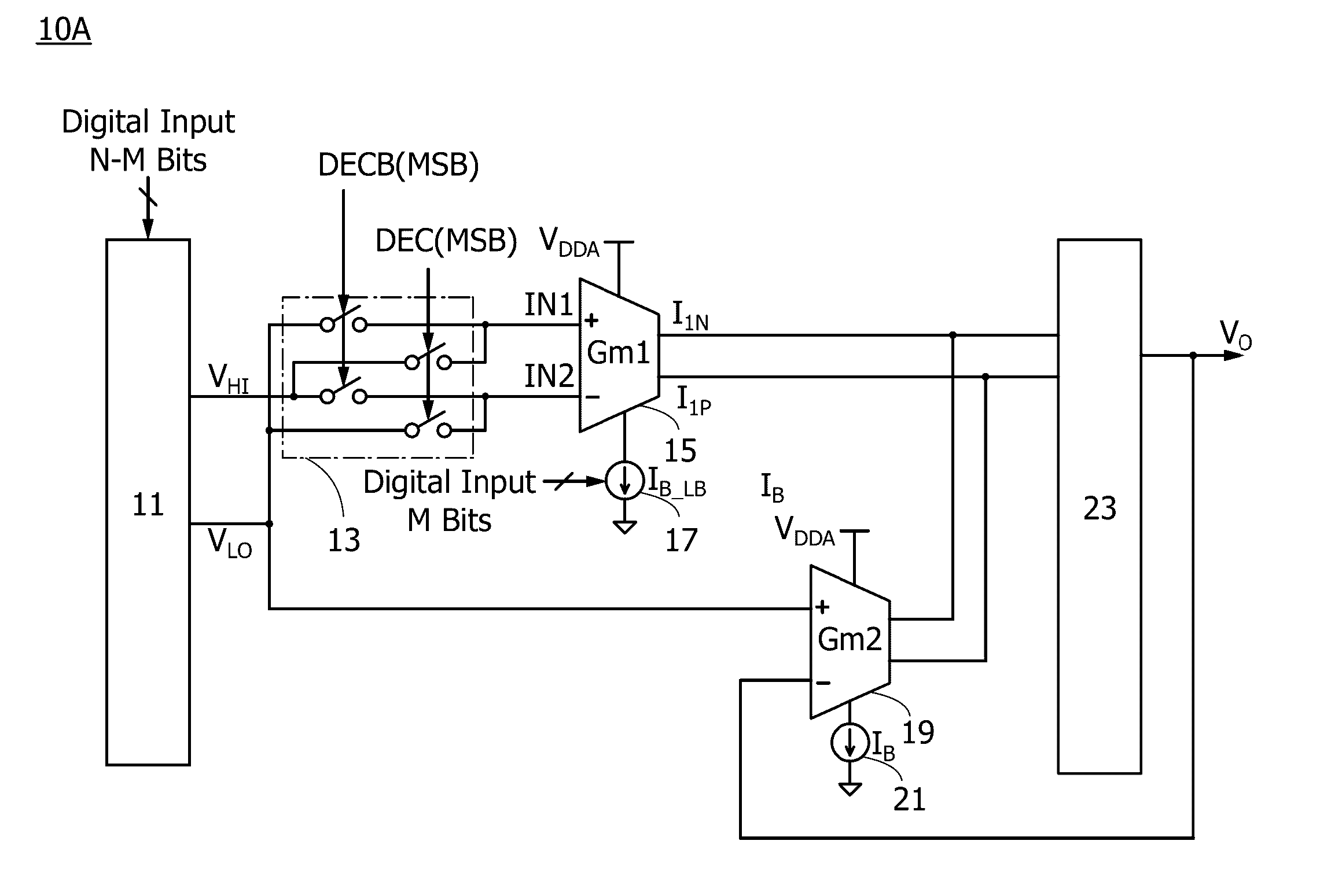

A semiconductor device having a novel structure is provided. Fluctuation in the grayscale voltage due to an offset voltage is suppressed. When a current corresponding to a lower-bit grayscale voltage is generated in a transconductance amplifier, voltages VHI and VLO supplied to the transconductance amplifier are alternately input to two input terminals in accordance with a digital signal of the most significant bit of lower bits. Since a change corresponding to the offset voltage is added to both the maximum and minimum values of the current output from the transconductance amplifier, fluctuation in the grayscale voltage due to the offset voltage can be suppressed.

Owner:SEMICON ENERGY LAB CO LTD

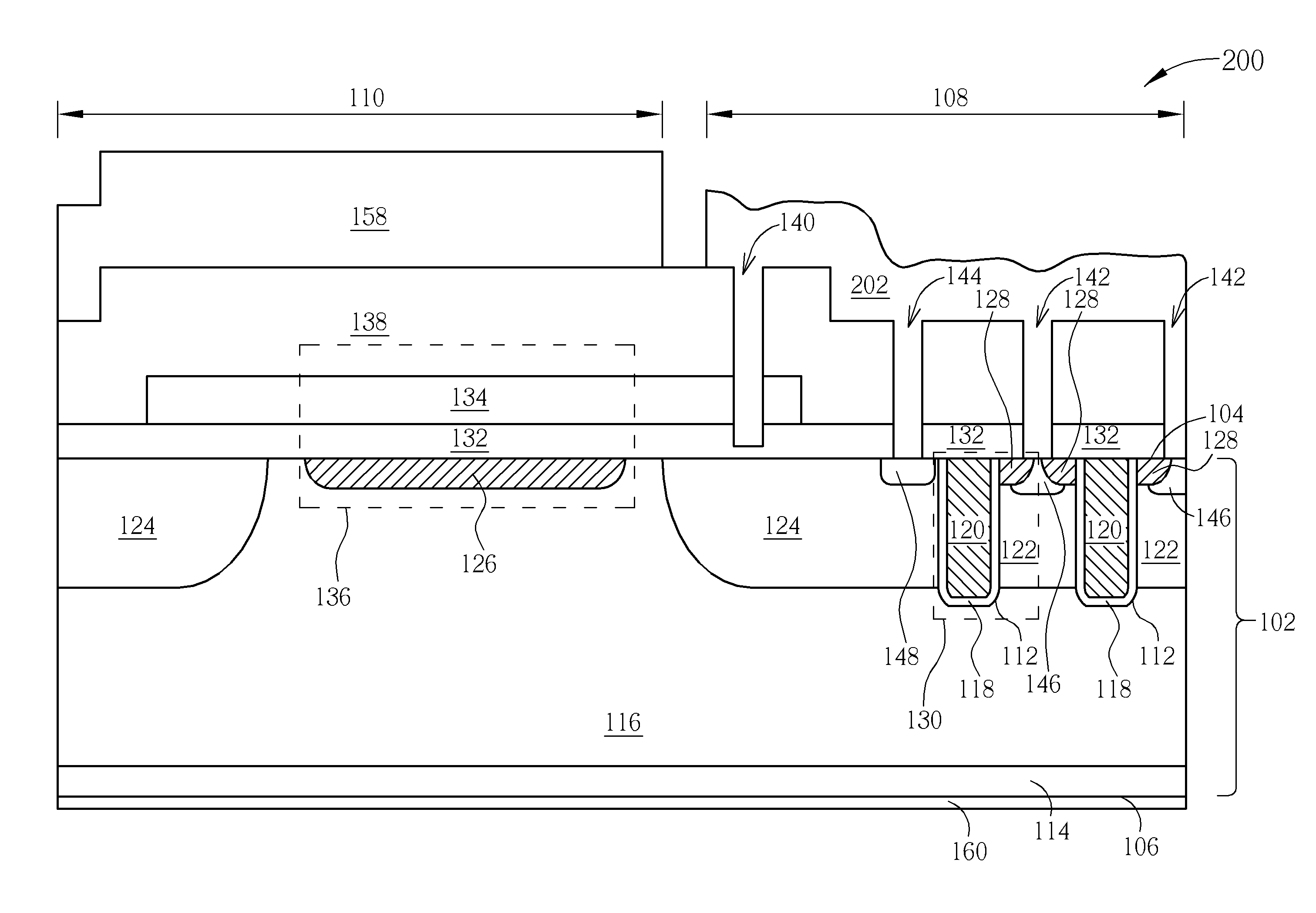

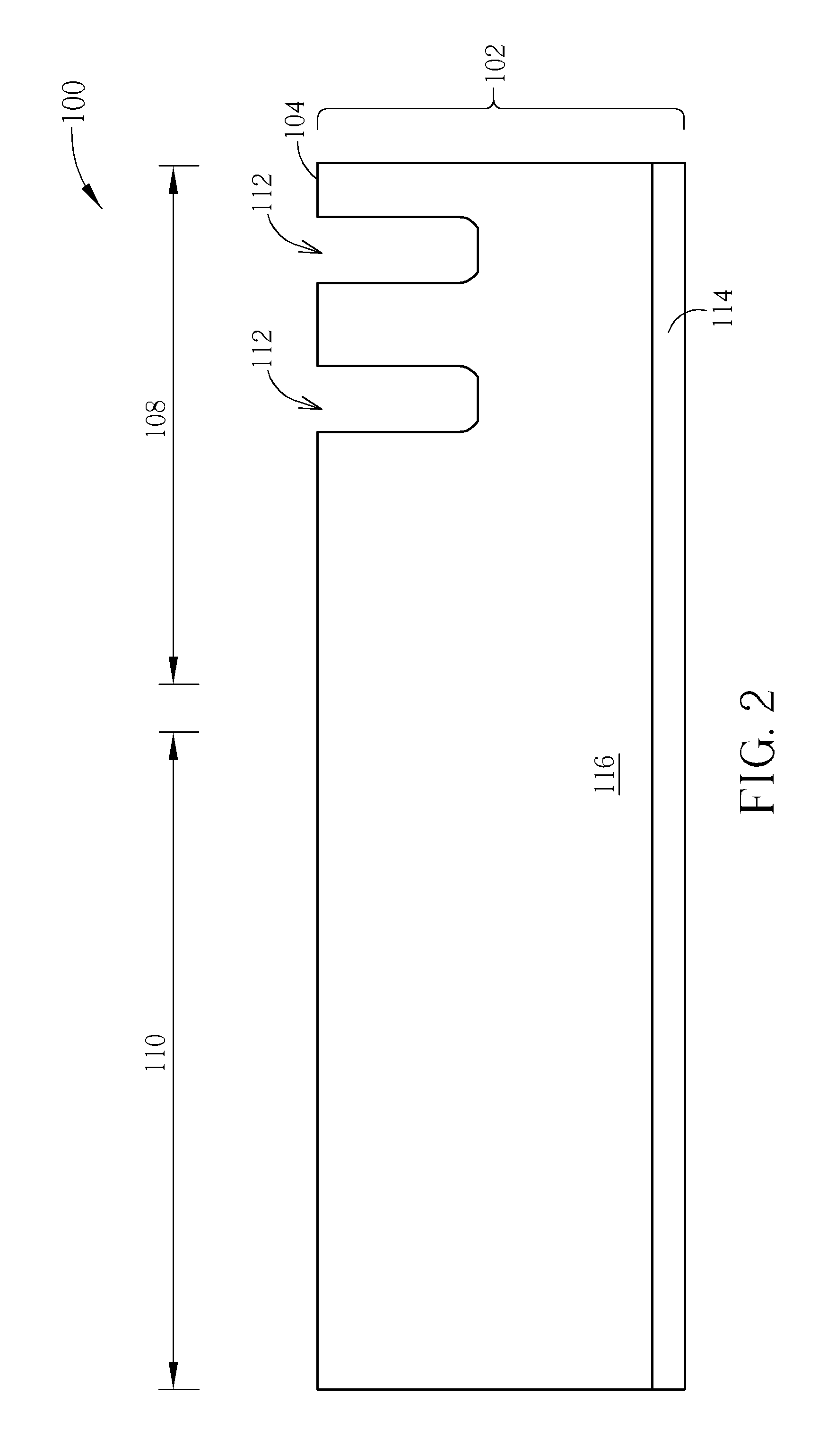

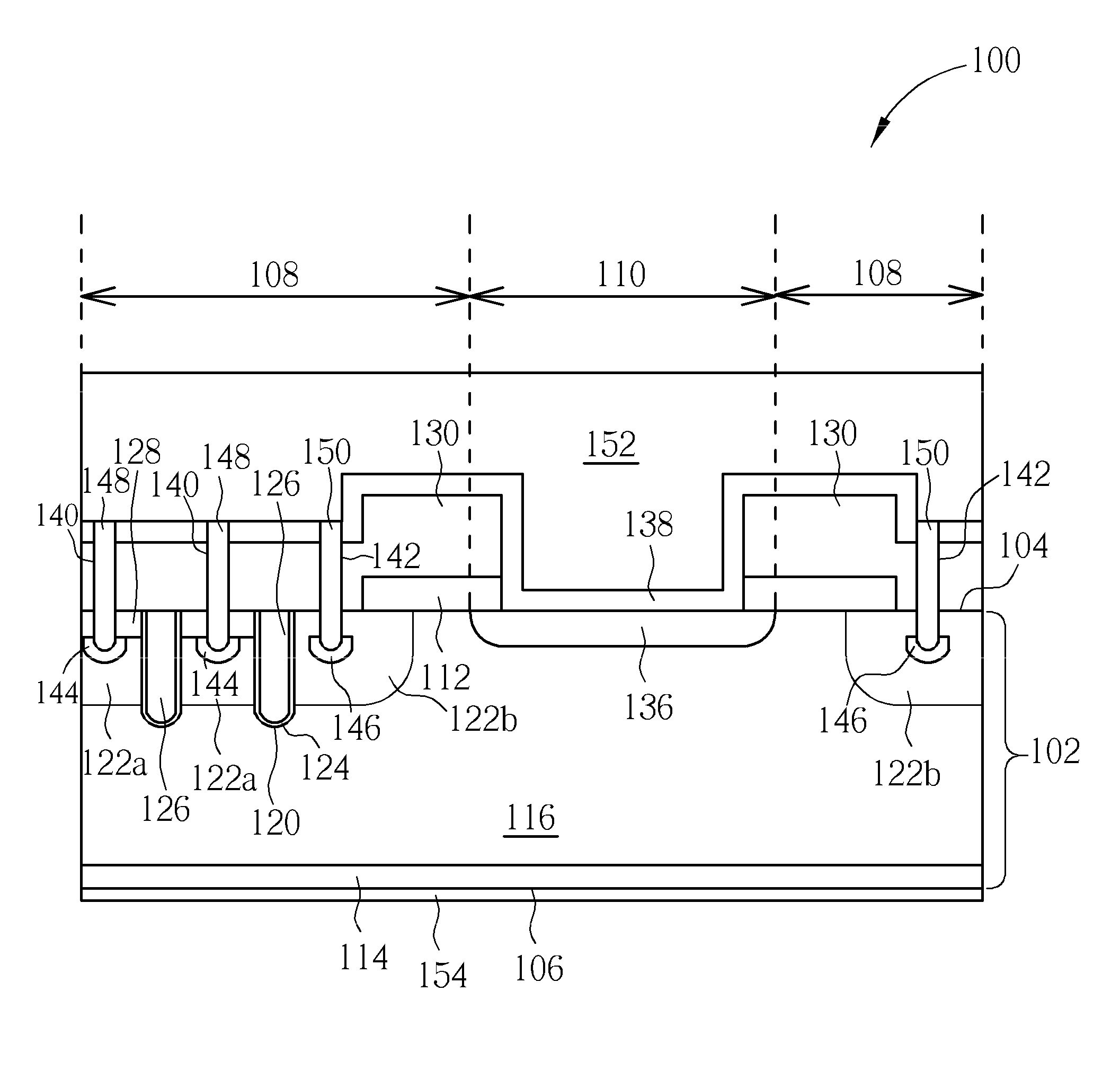

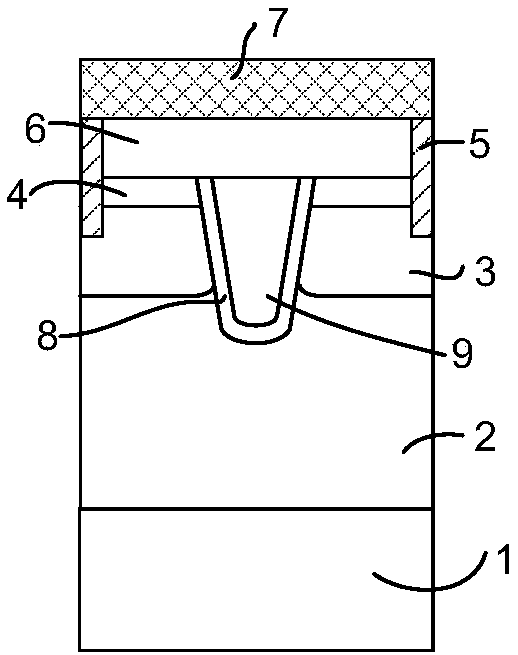

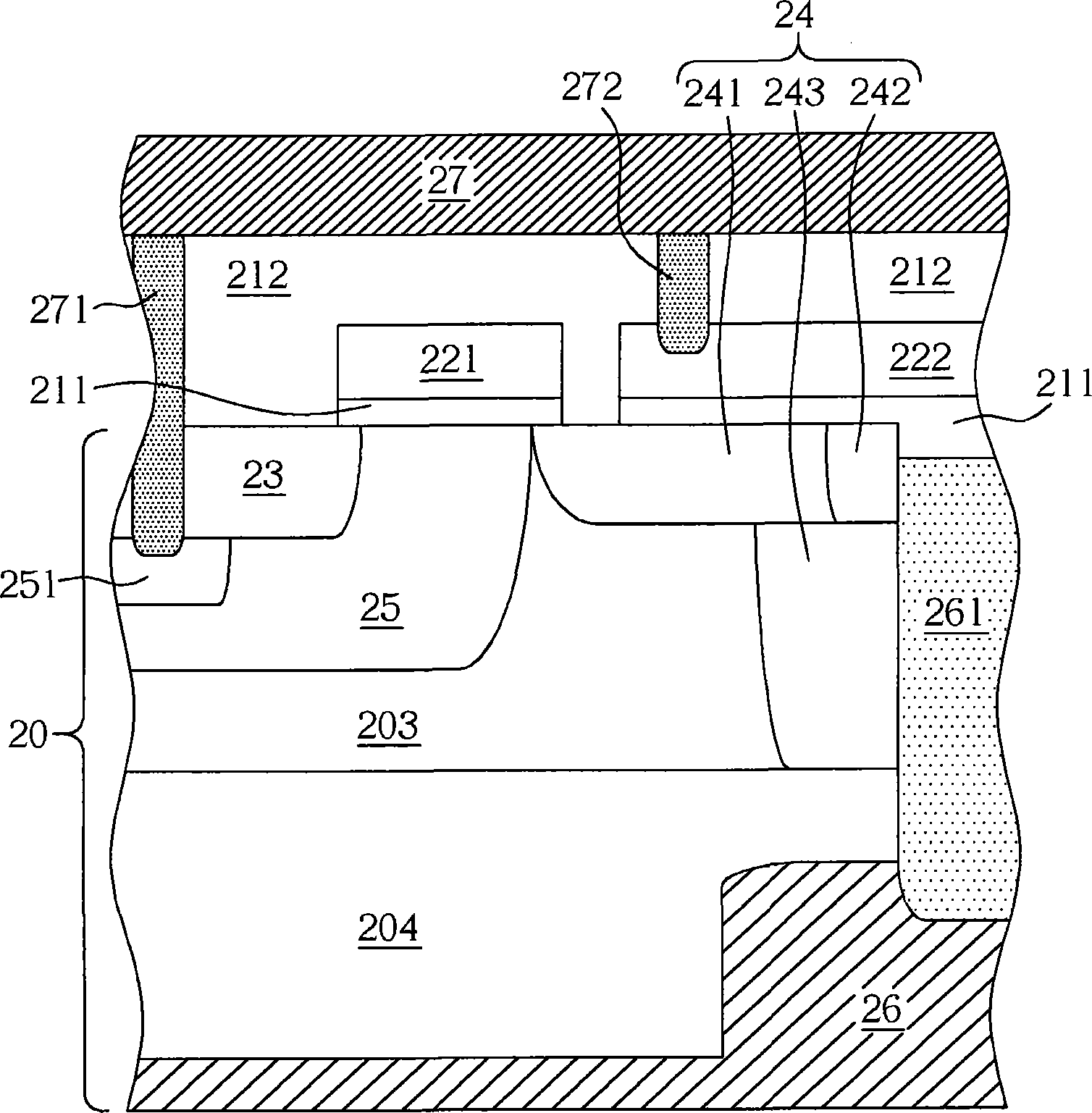

Laterally diffused metal-oxide-semiconductor device

A laterally diffused metal-oxide-semiconductor device includes a substrate, a gate dielectric layer, a gate polysilicon layer, a source region, a drain region, a body region, a first drain contact plug, a source polysilicon layer, an insulating layer, and a source metal layer. The source polysilicon layer disposed on the gate dielectric layer above the drain region can serve as a field plate to enhance the breakdown voltage and to increase the drain-to-source capacitance. In addition, the first drain contact plug of the present invention can reduce the drain-to-source on-resistance and the horizontal extension length.

Owner:SINOPOWER SEMICON

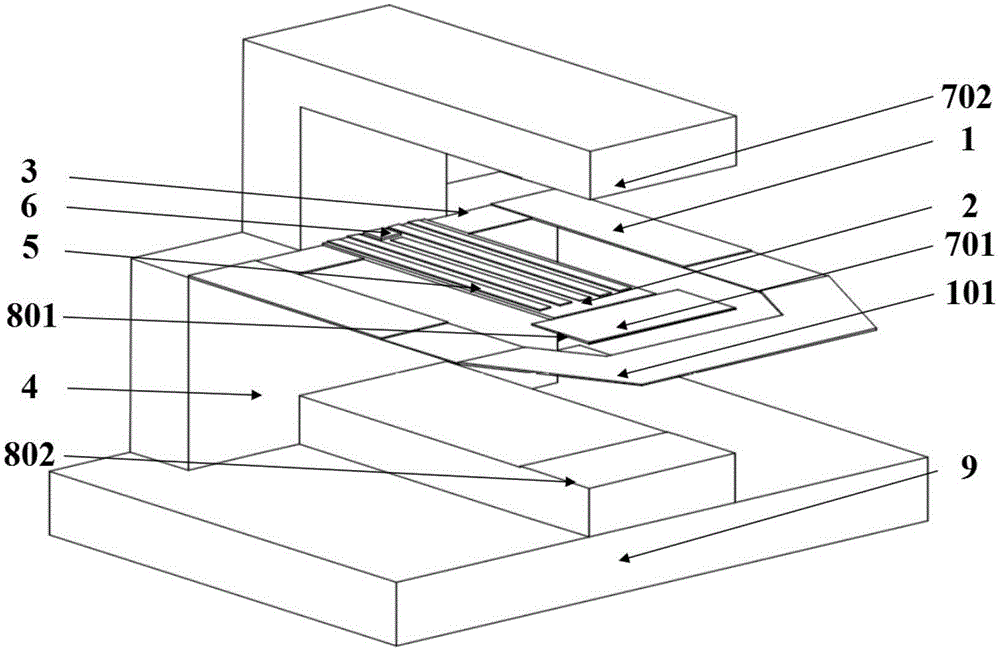

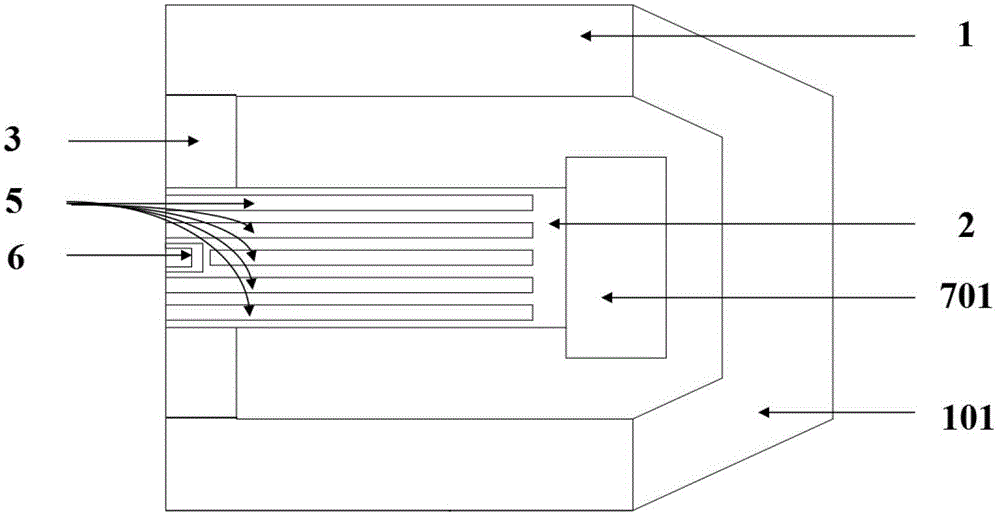

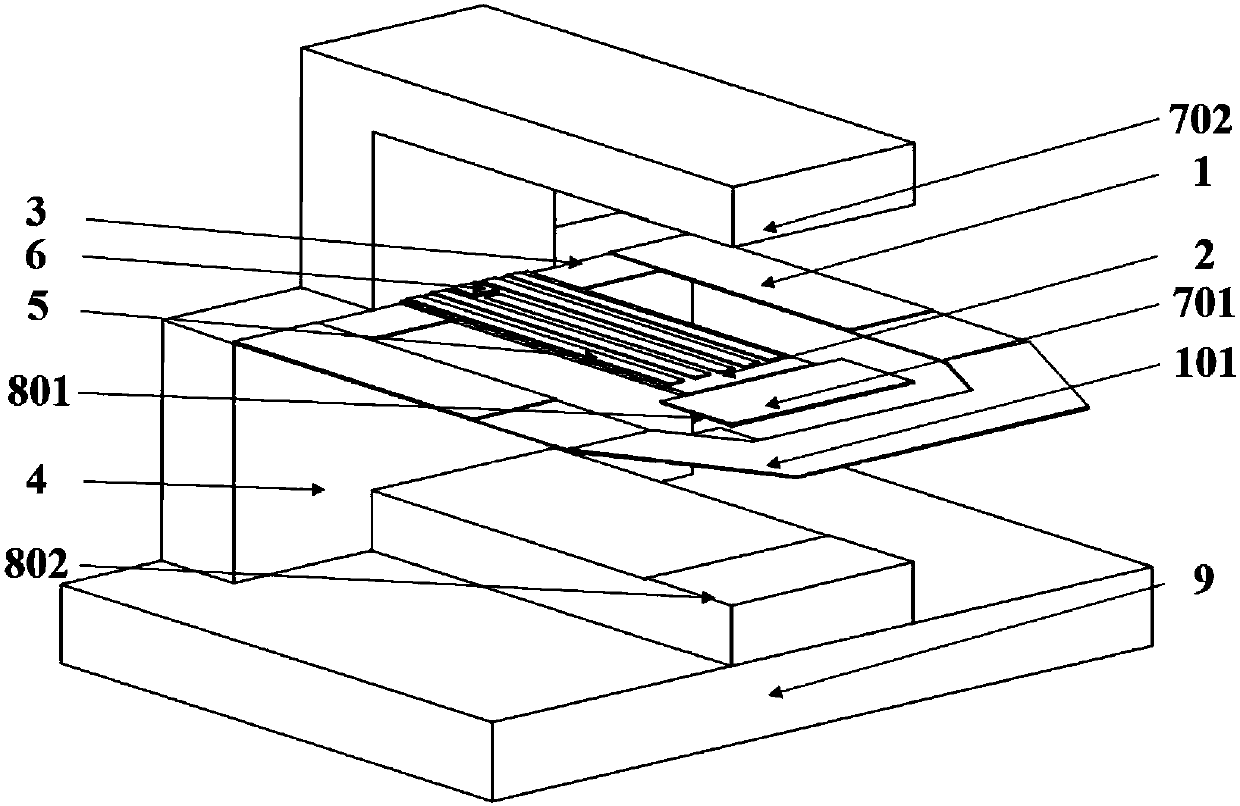

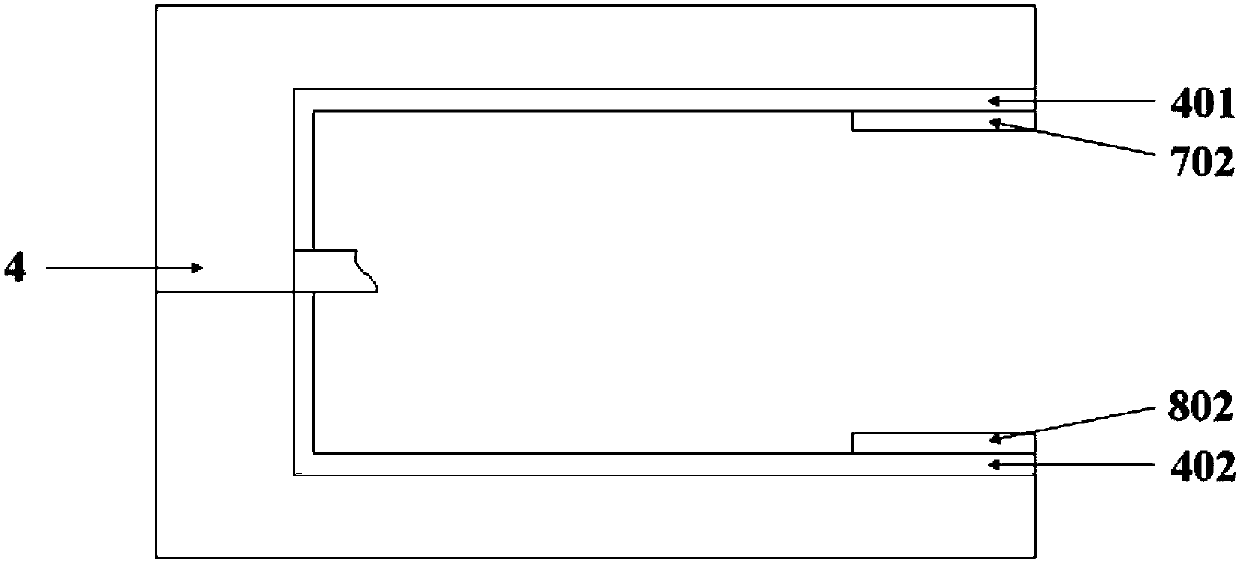

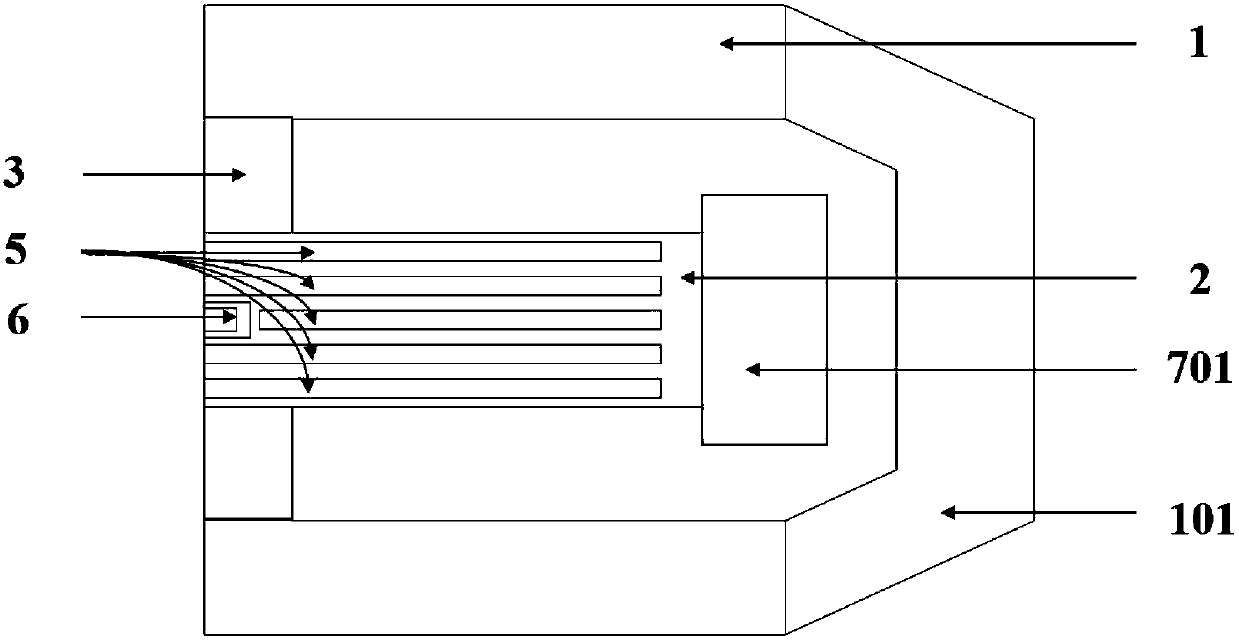

Synchronous resonance-based high-sensitivity voltage, resistance and capacitance superposition force sensor

The invention relates to a synchronous resonance-based high-sensitivity voltage, resistance and capacitance superposition force sensor and belongs to the field of synchronous resonance cantilever force sensors capable of realizing voltage, resistance and capacitance superposition. The lower part of a C-shaped supporting structure is fixedly connected with a piezoelectric excitation structure; the middle part of the C-shaped supporting structure is connected with a U-shaped beam, a T-shaped beam and a synchronous coupling beam; two sides of the T-shaped beam is connected with the synchronous coupling beam; the inner side of the U-shaped beam is connected with the synchronous coupling beam; a plurality of piezoelectric vibration pick-up structures are deposited on the surface of the T-shaped beam; the surface of the fixed end of the T-shaped beam is provided with a piezoresistance vibration pick-up structure; and two capacitance vibration pick-up structures form a differential capacitance vibration pick-up structure. The force sensor of the invention is novel in structure. Based on simple structure design, the piezoelectric, piezoresistance and capacitance vibration pick-up structures are integrated in the same structure, the output signals of the three structures are superposed, and therefore, output voltage can be further amplified, and the detection sensitivity of the sensor can be improved.

Owner:JILIN UNIV

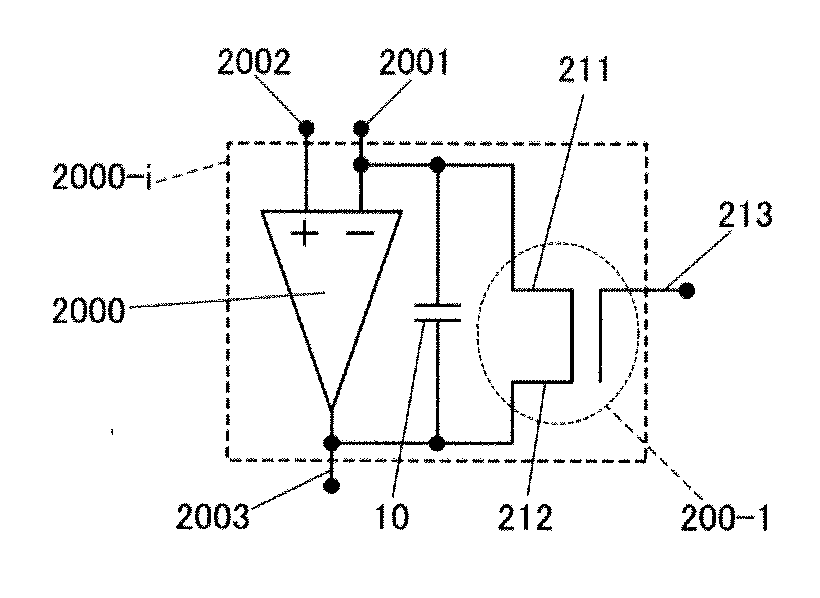

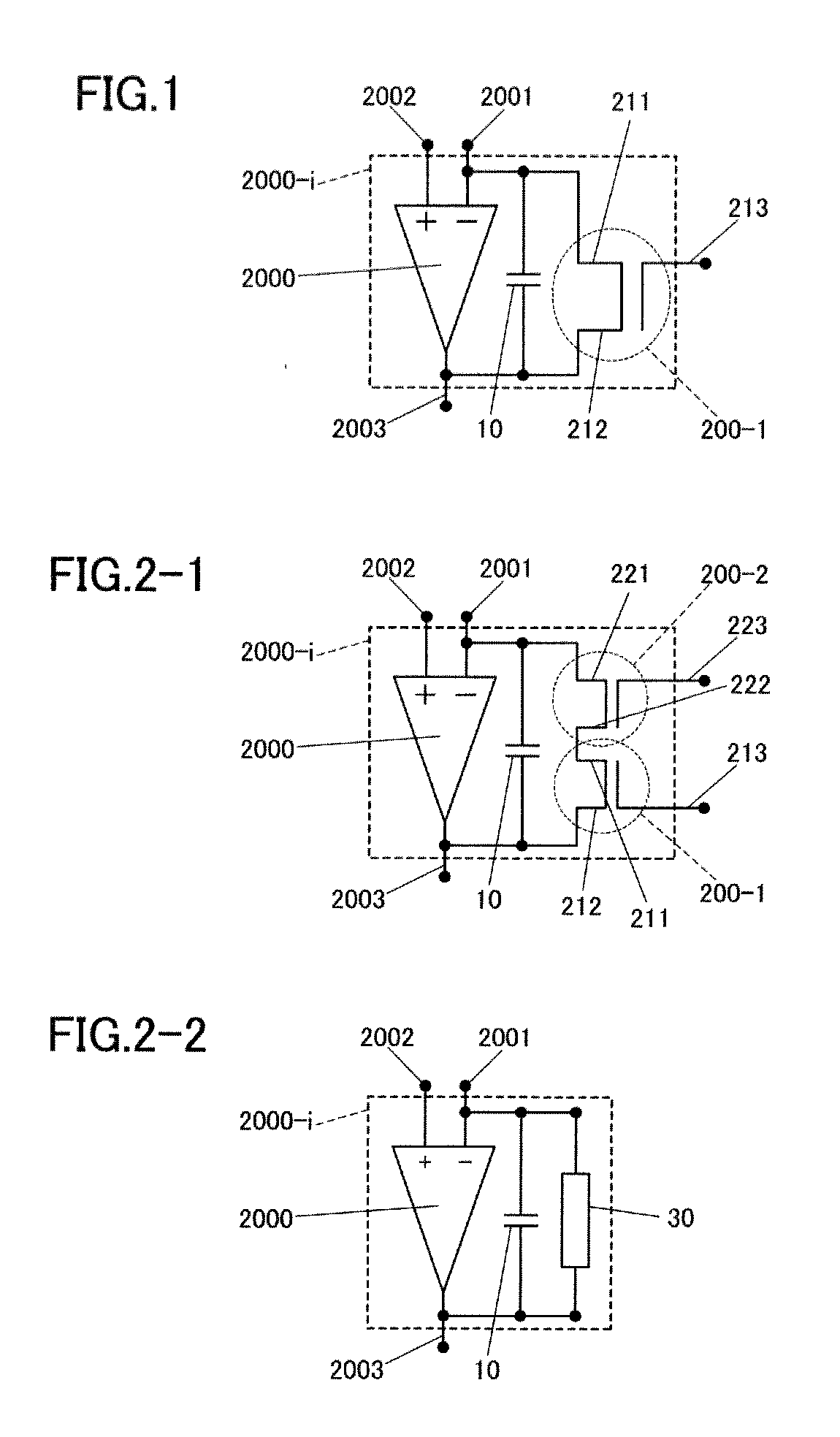

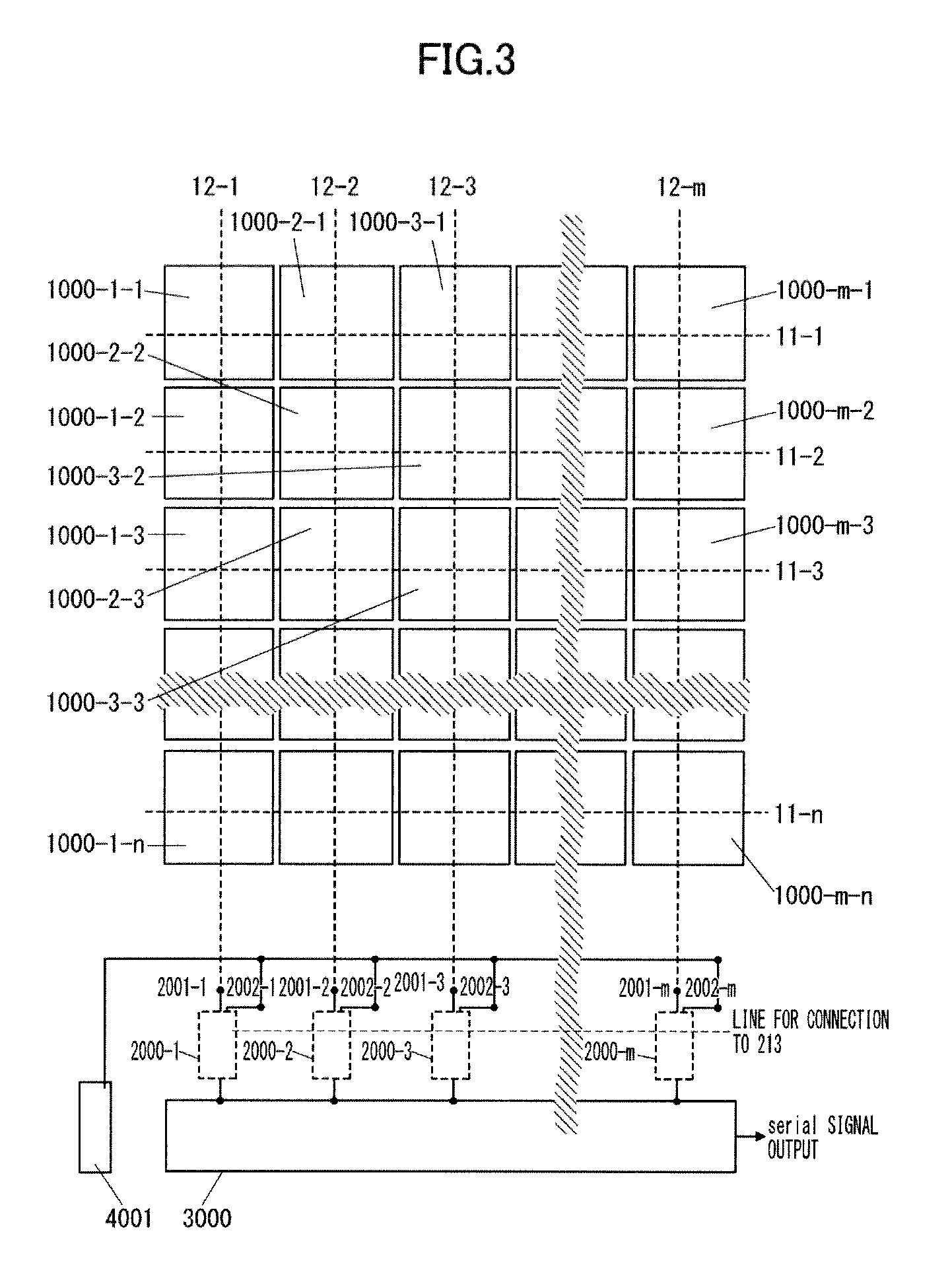

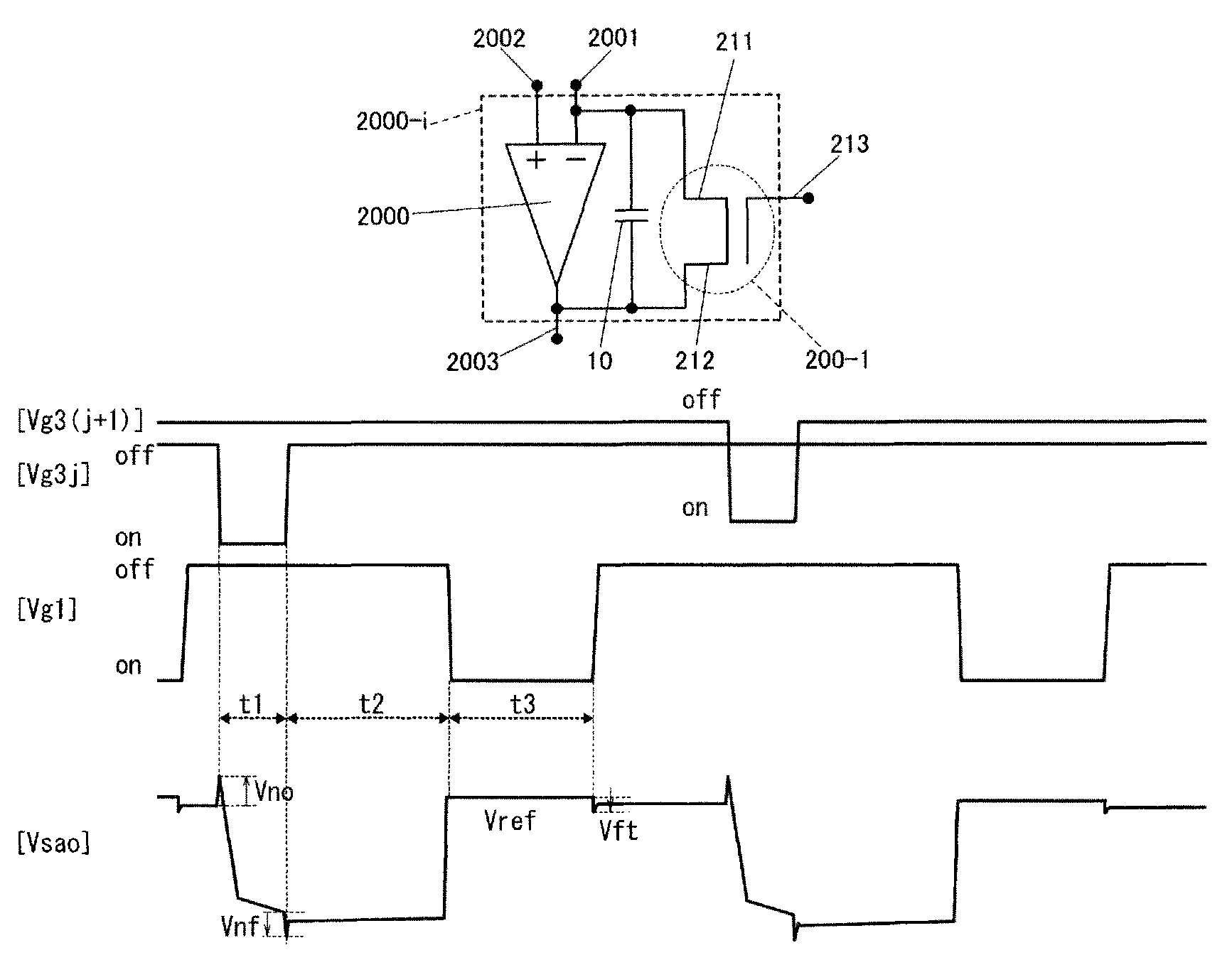

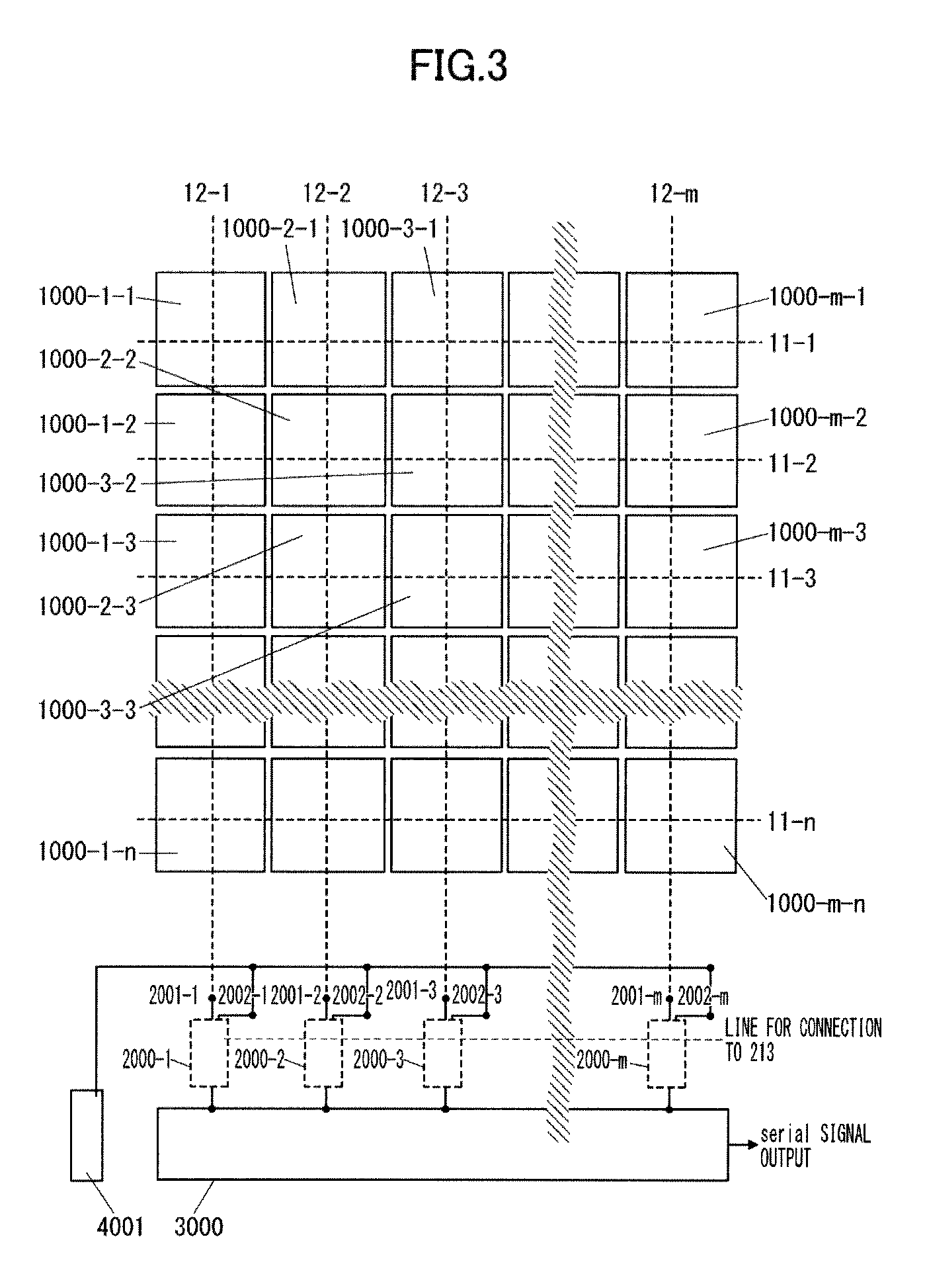

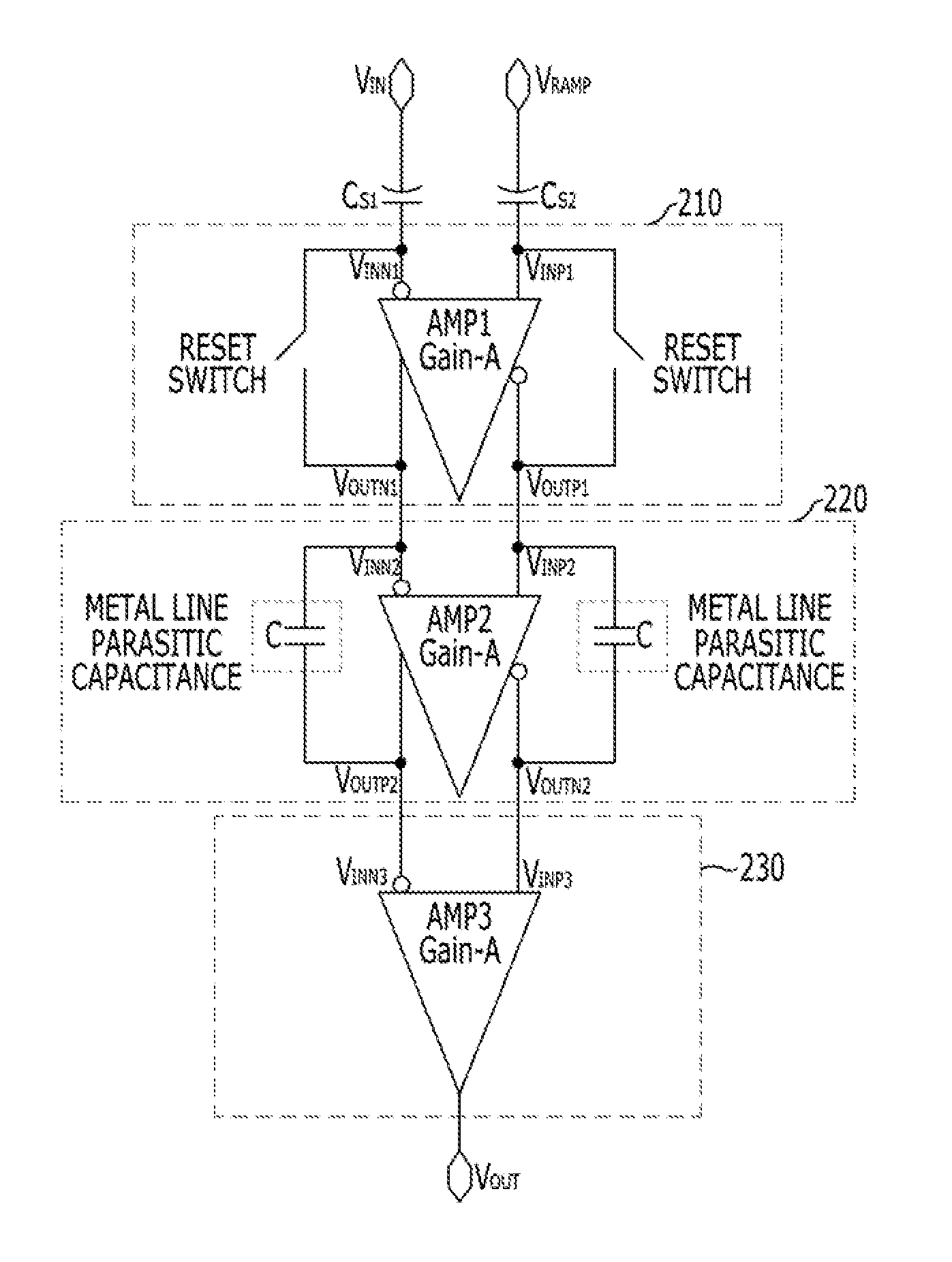

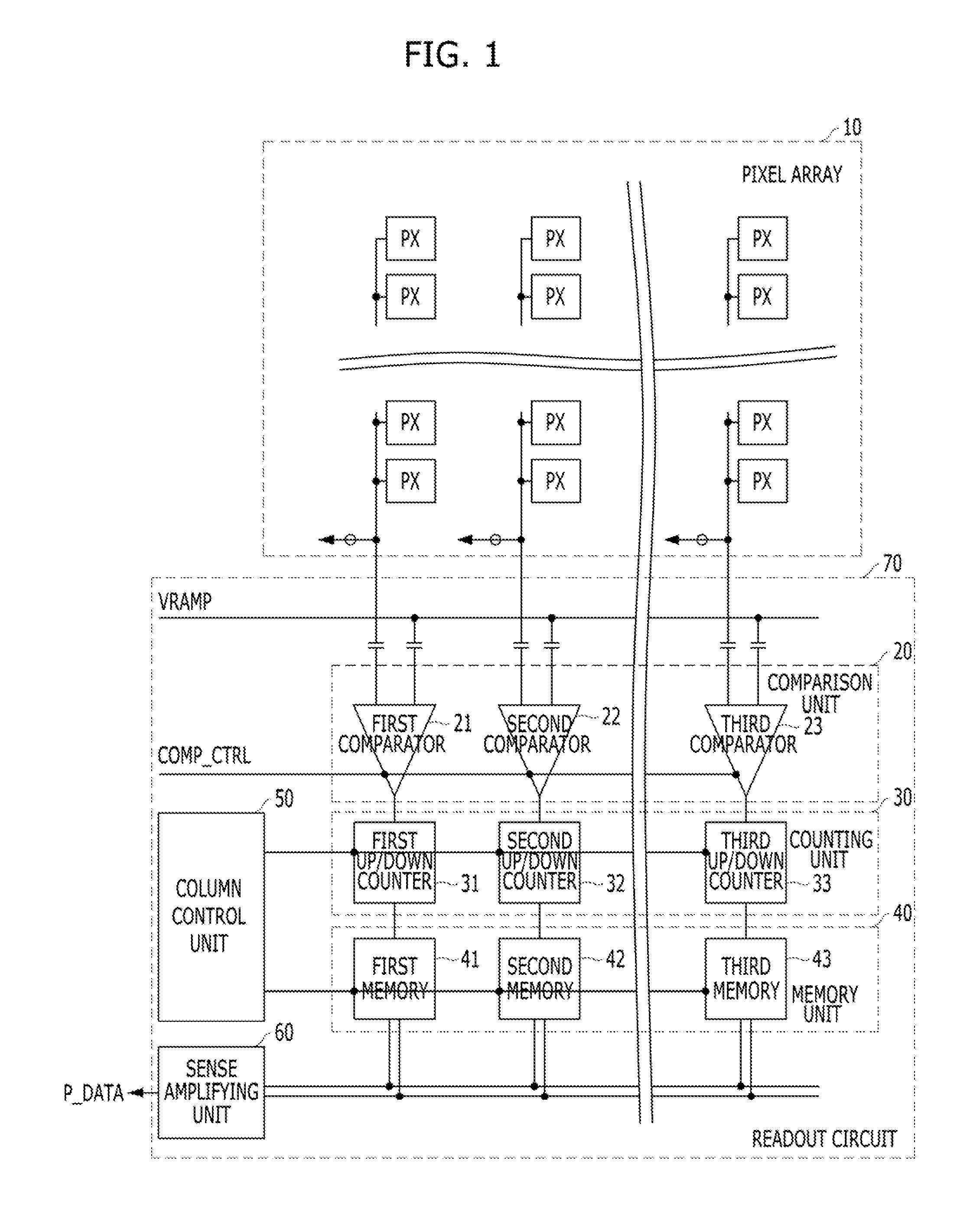

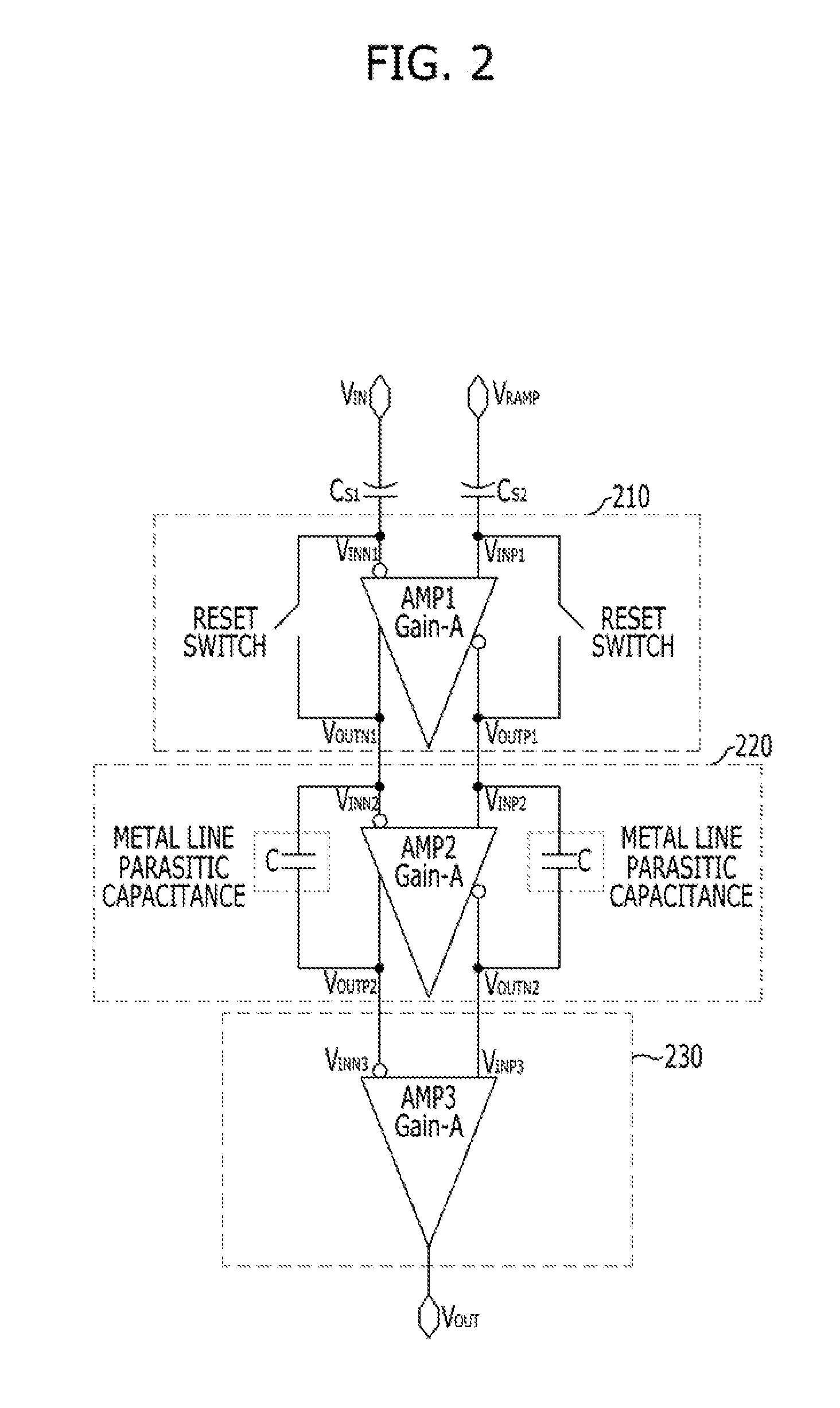

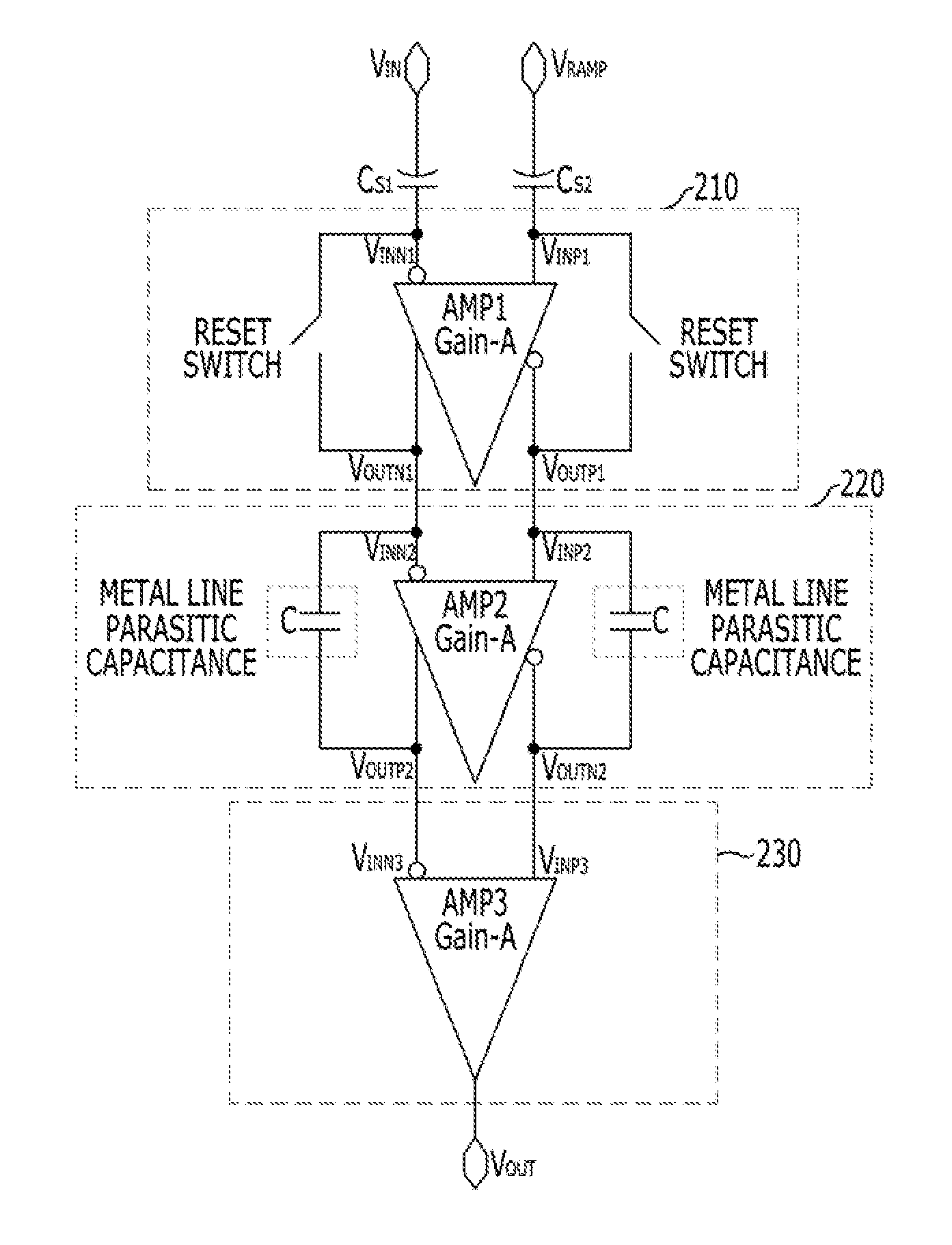

Sense circuit and method of operation thereof and photoelectric conversion array

InactiveUS20130187030A1SpeedShorten the timeTelevision system detailsMaterial analysis by optical meansPhotoelectric conversionField-effect transistor

A sense circuit includes a differential amplifier circuit including an inverting input section, a non-inverting input section and an output section, an electrical capacitor connected between the inverting input section and the output section, and a field effect transistor including a source, a drain, and a gate. One of the source and the drain is connected to the inverting input section, and the other of the source and the drain is connected to the output section. A reference potential is supplied to the non-inverting input section, and an output section of a photoelectric conversion cell having an added switching function is connected to the inverting input section.

Owner:NAT INST OF ADVANCED IND SCI & TECH +1

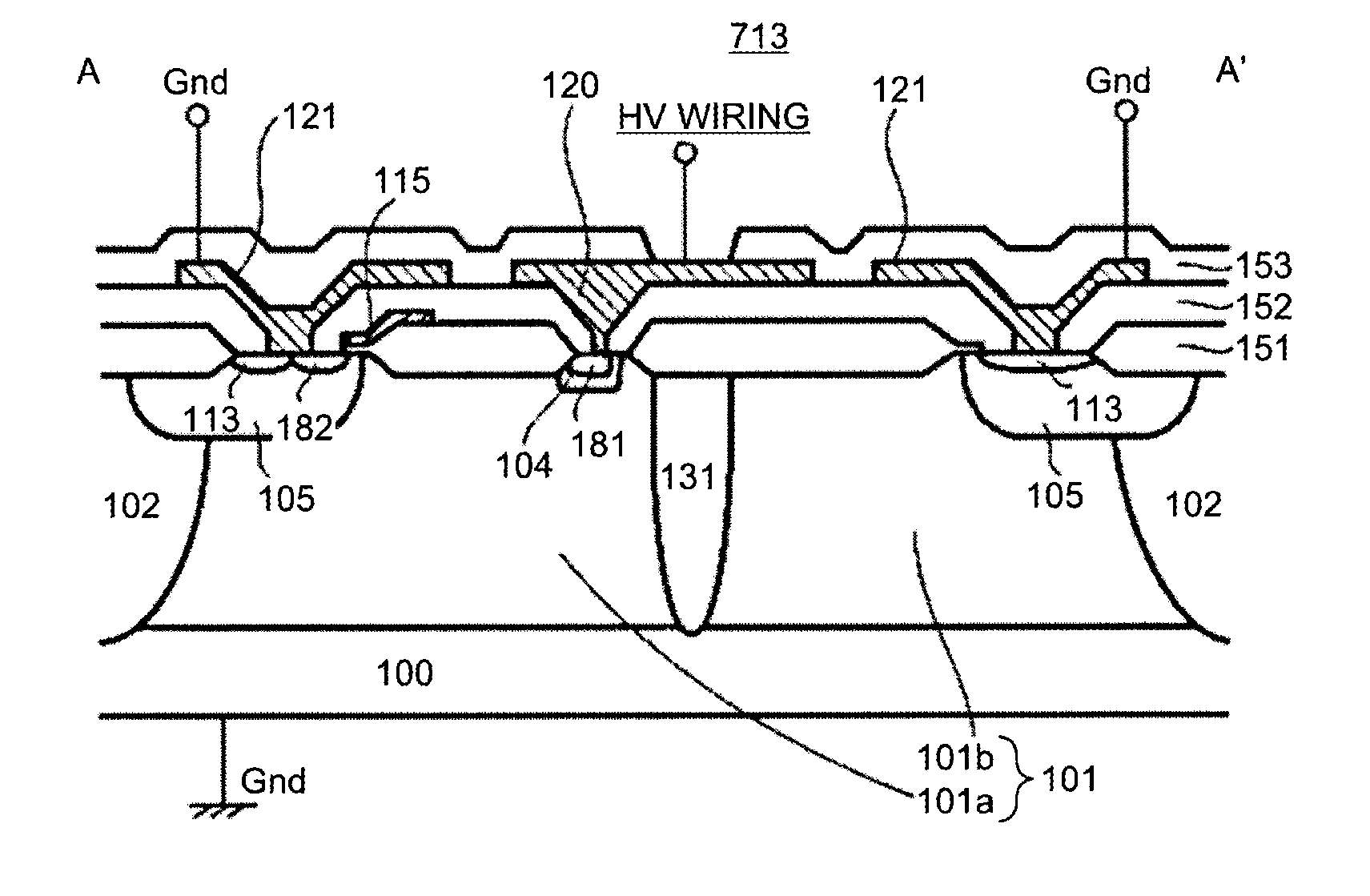

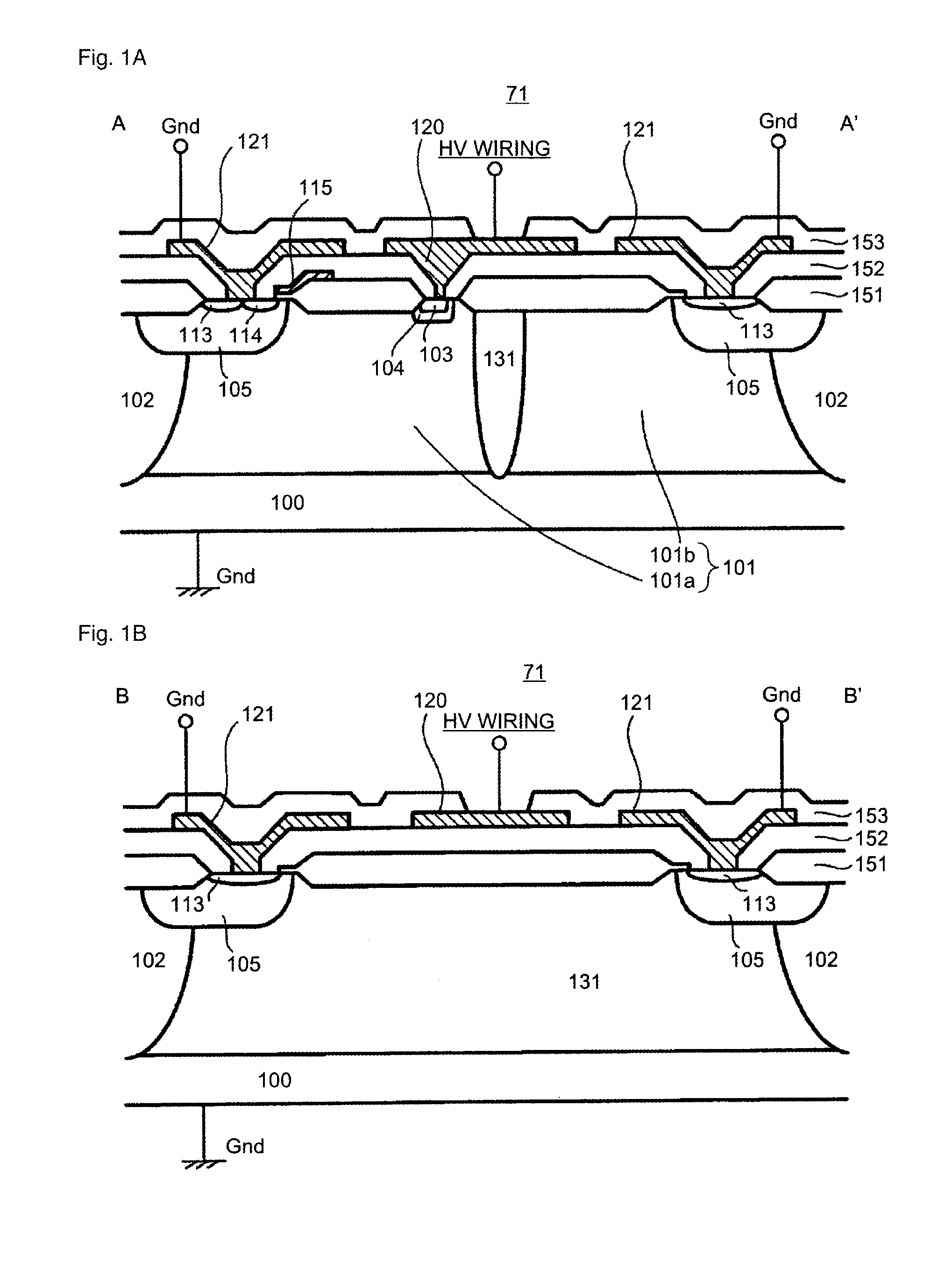

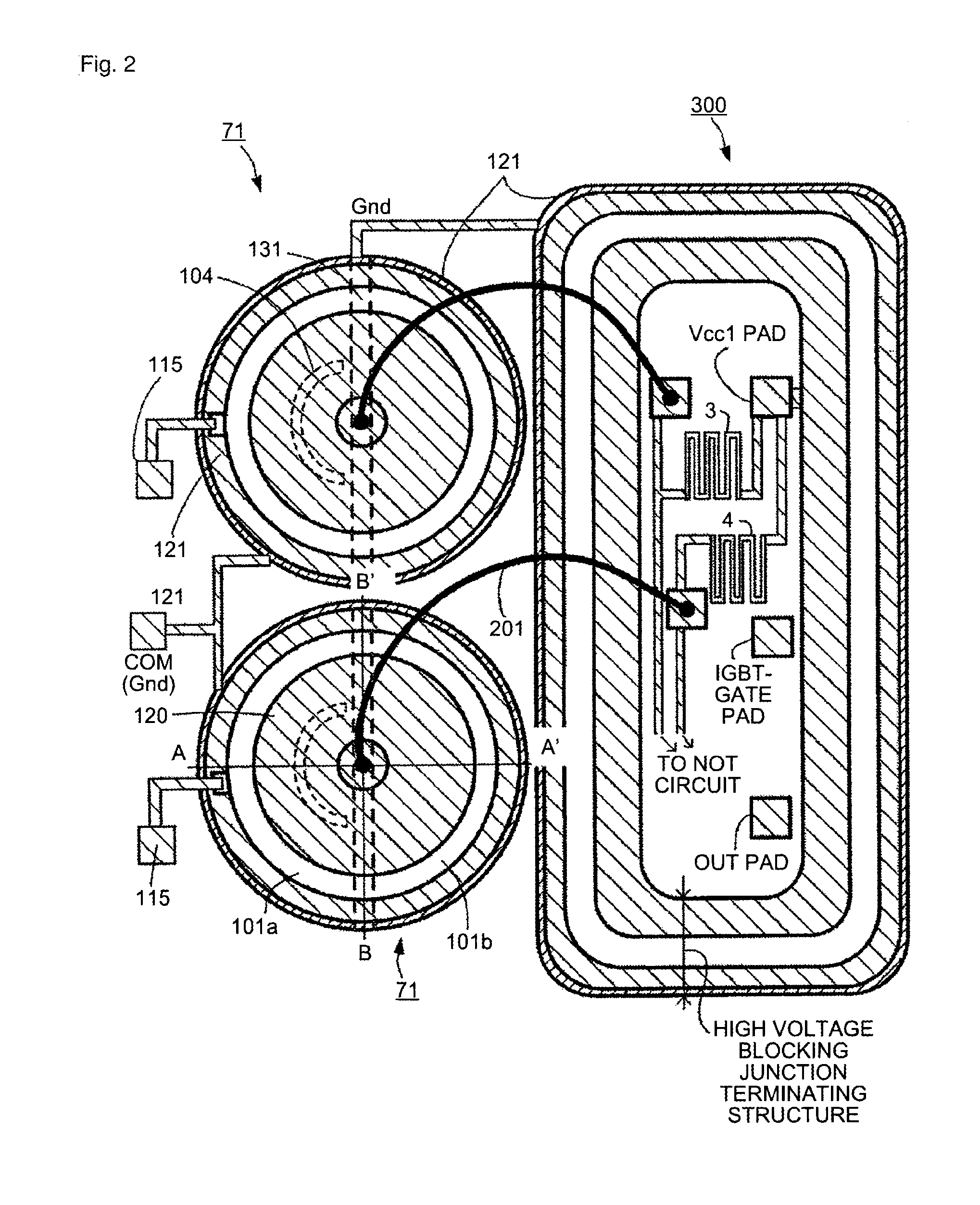

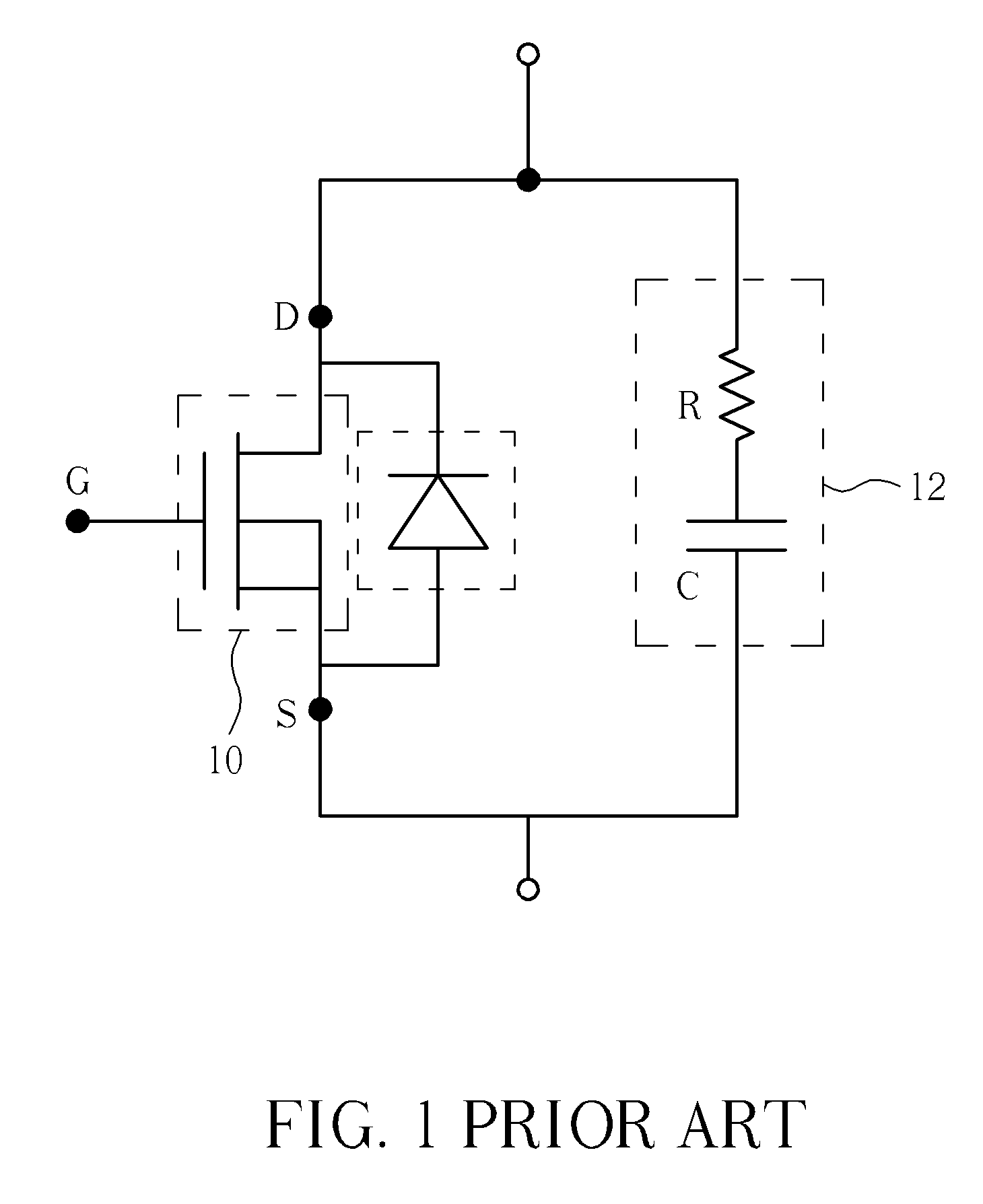

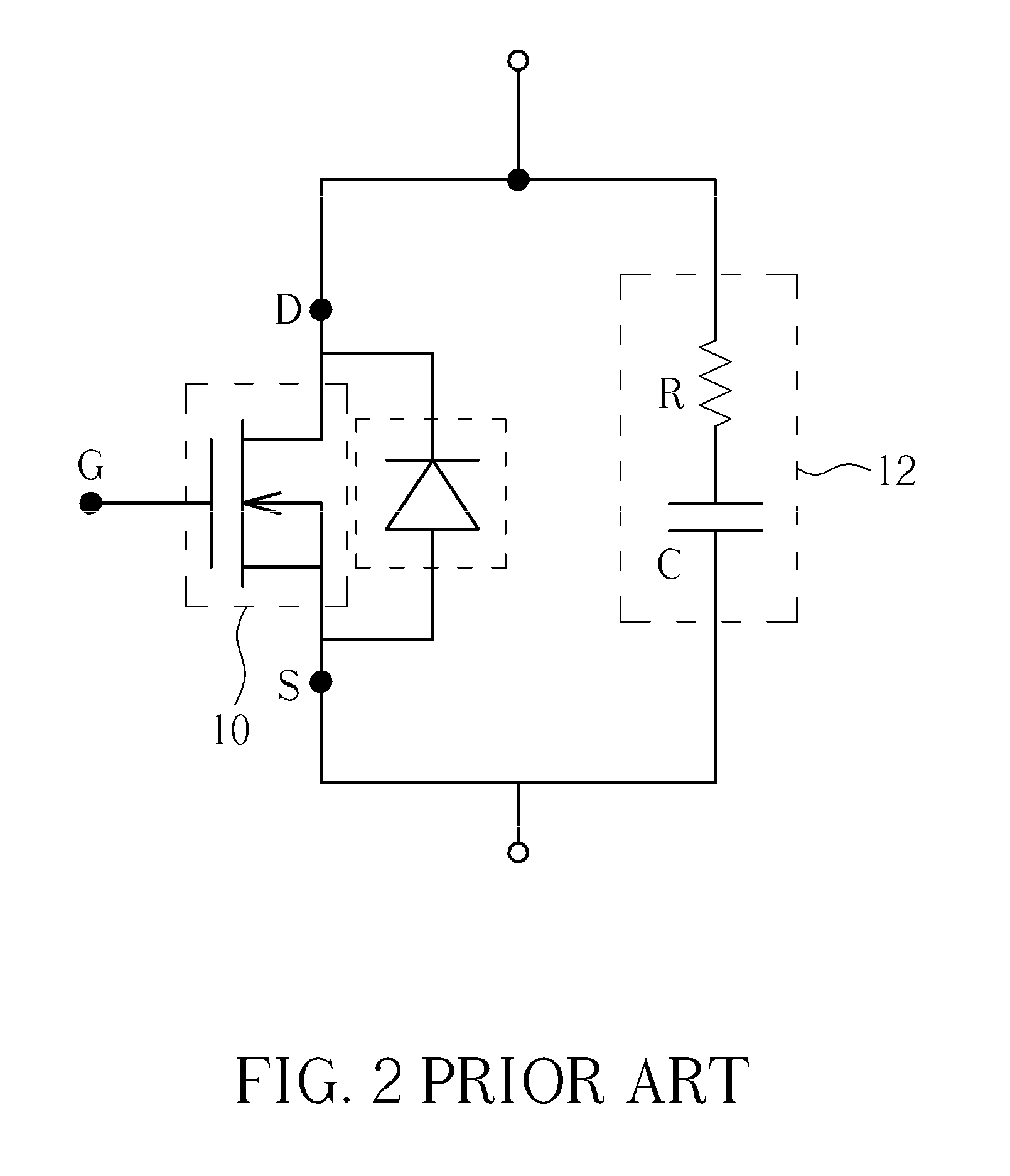

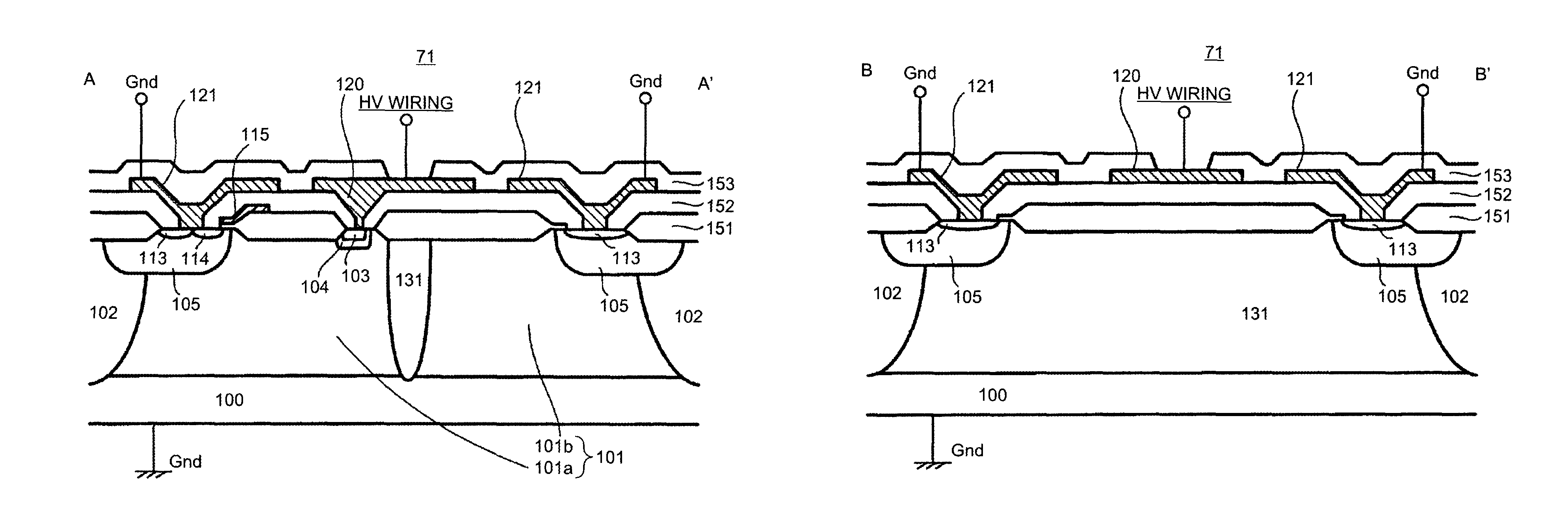

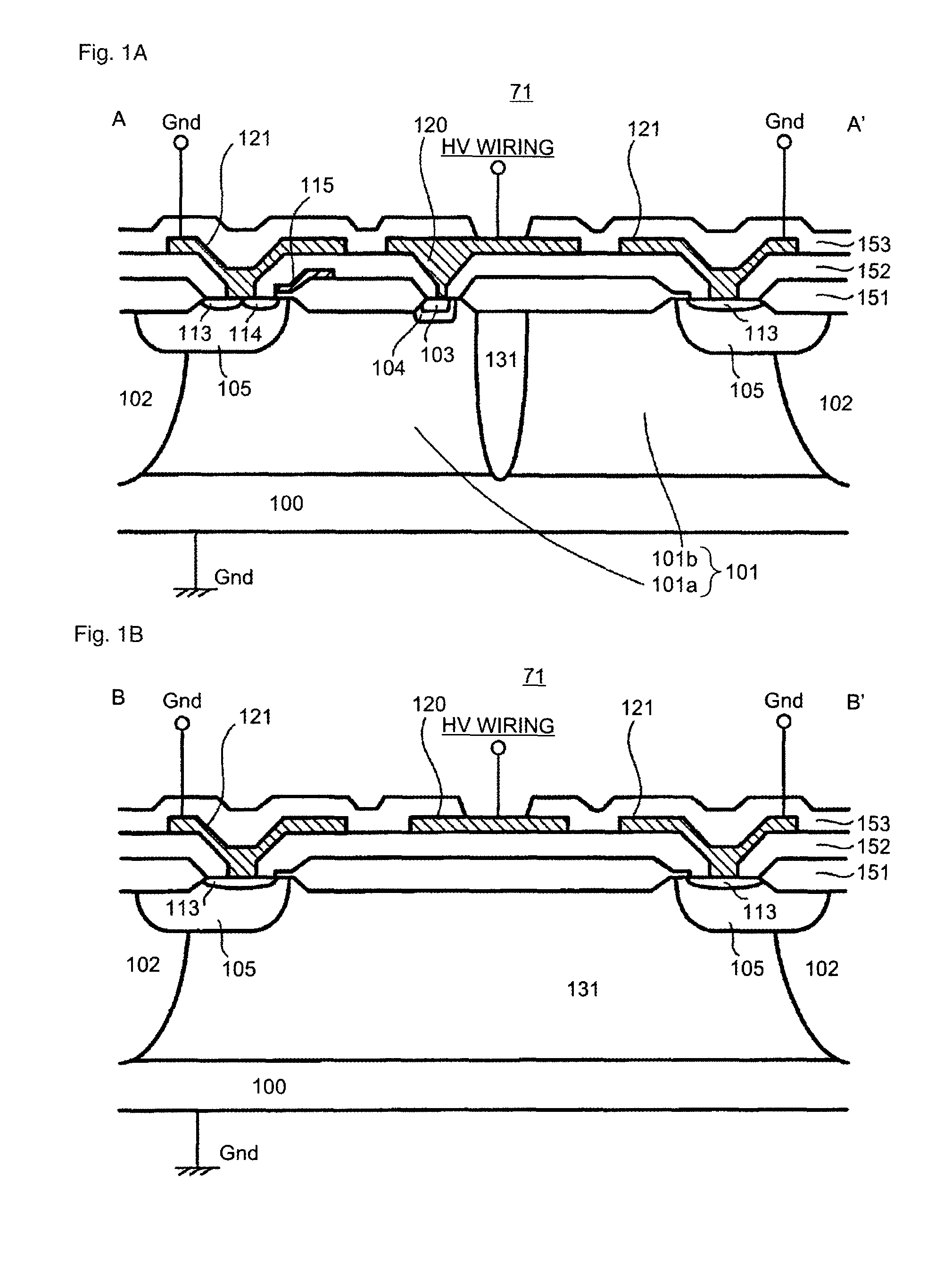

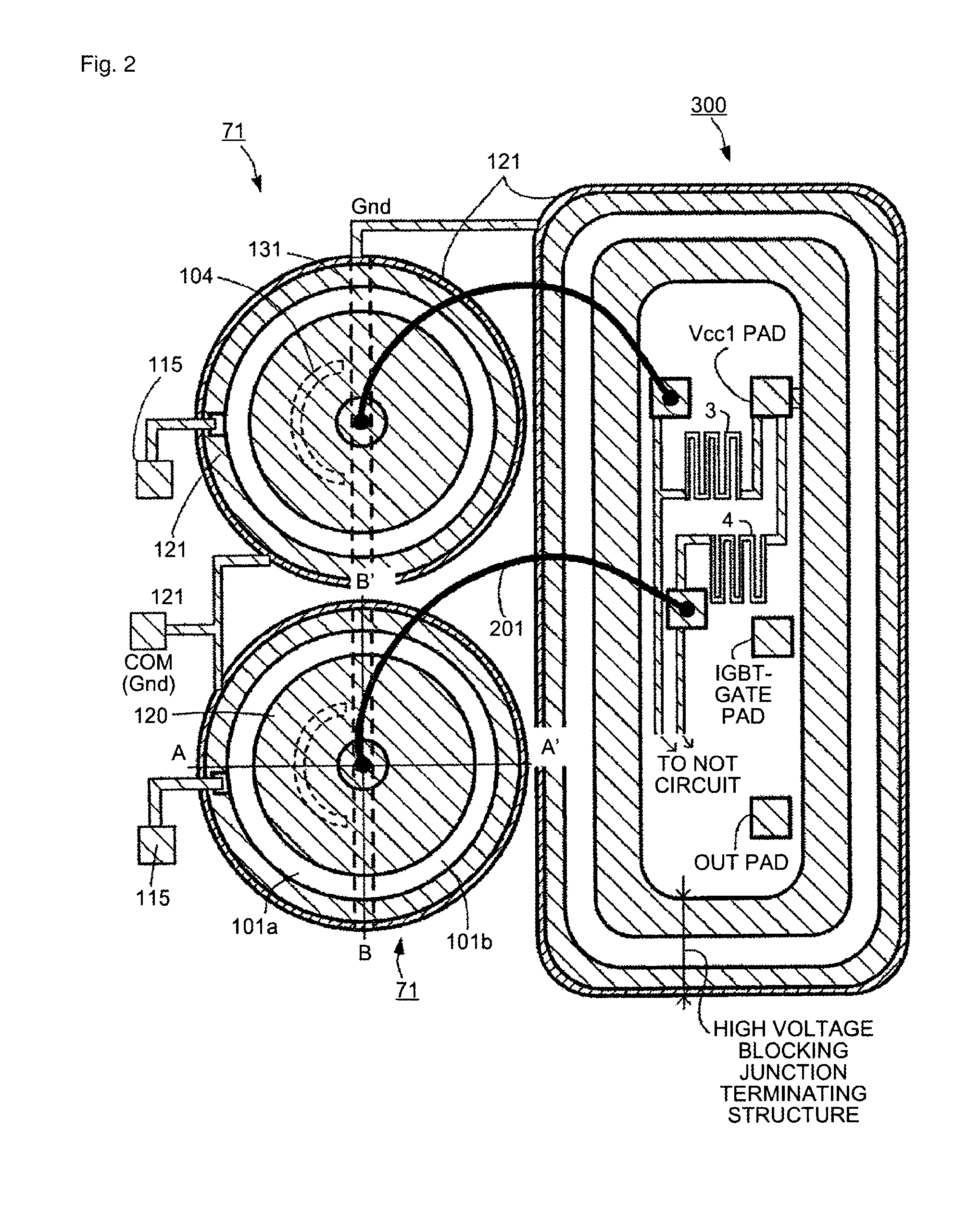

High voltage semiconductor device and driving circuit

ActiveUS20120235712A1Reduce power lossQuick responseTransistorSolid-state devicesDriver circuitDevice material

A high voltage semiconductor device is provided and includes an n−-type region encompassed by a p− well region and is provided on a p−-type silicon substrate. A drain n+-region is connected to a drain electrode. A p base region is formed so as to be separate from and encompass the drain n+-region. A source n+-region is formed in the p base region. Further, a p−-region is provided that passes through the n−-type region to the silicon substrate. The n−-type region is divided, by the p−-region, into a drift n−-type region having the drain n+-region and a floating n−-type region having a floating electric potential.

Owner:FUJI ELECTRIC CO LTD

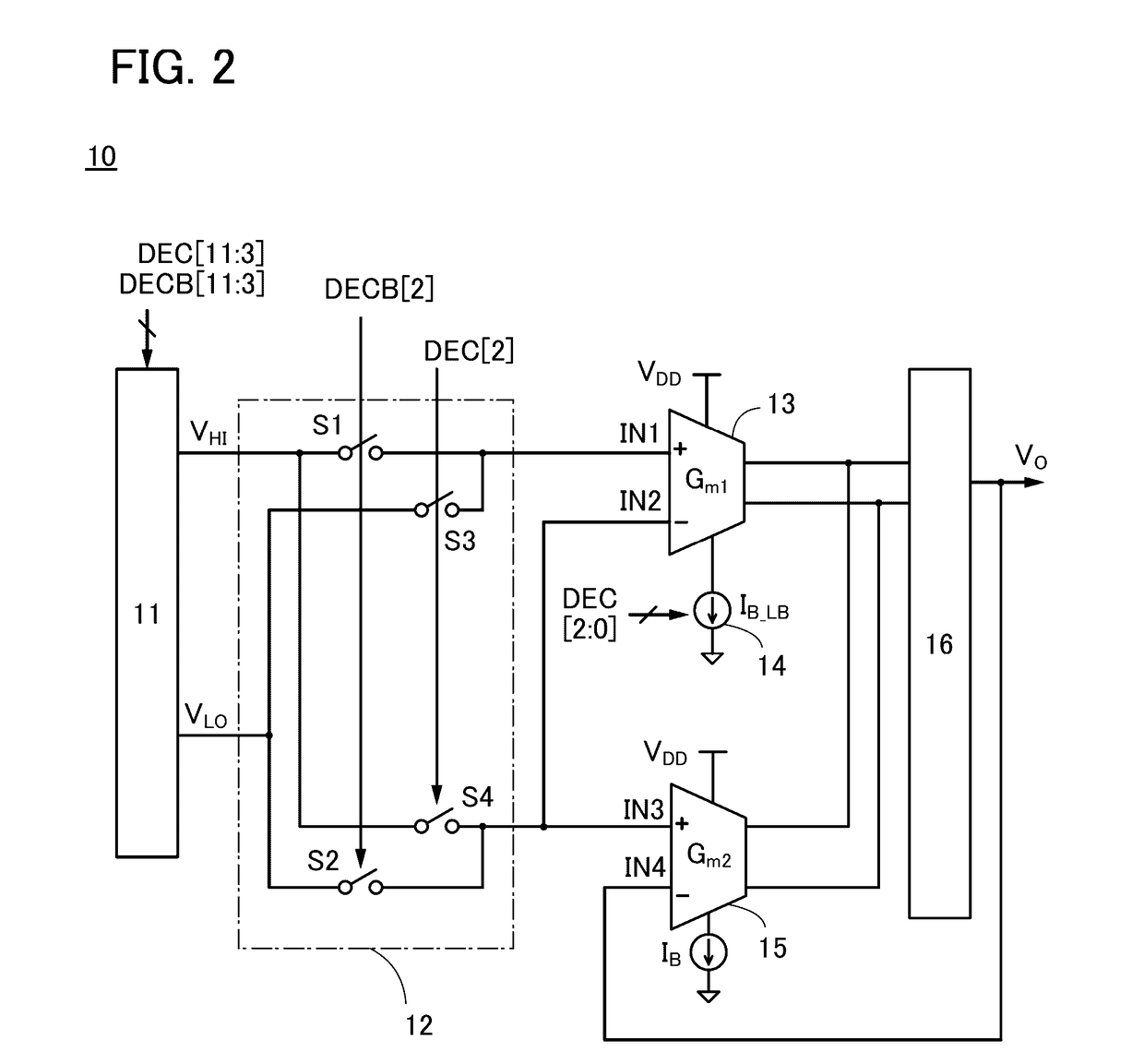

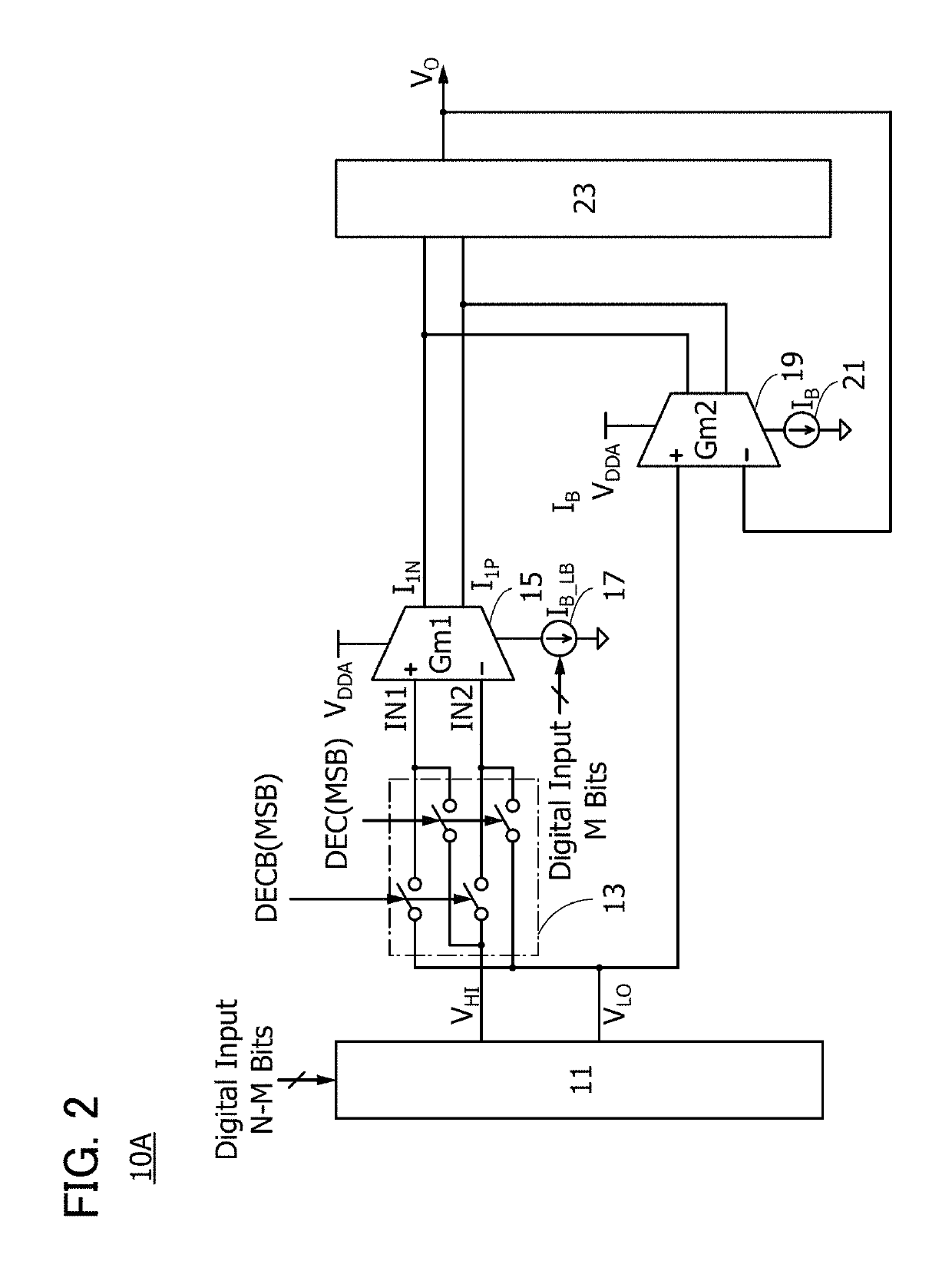

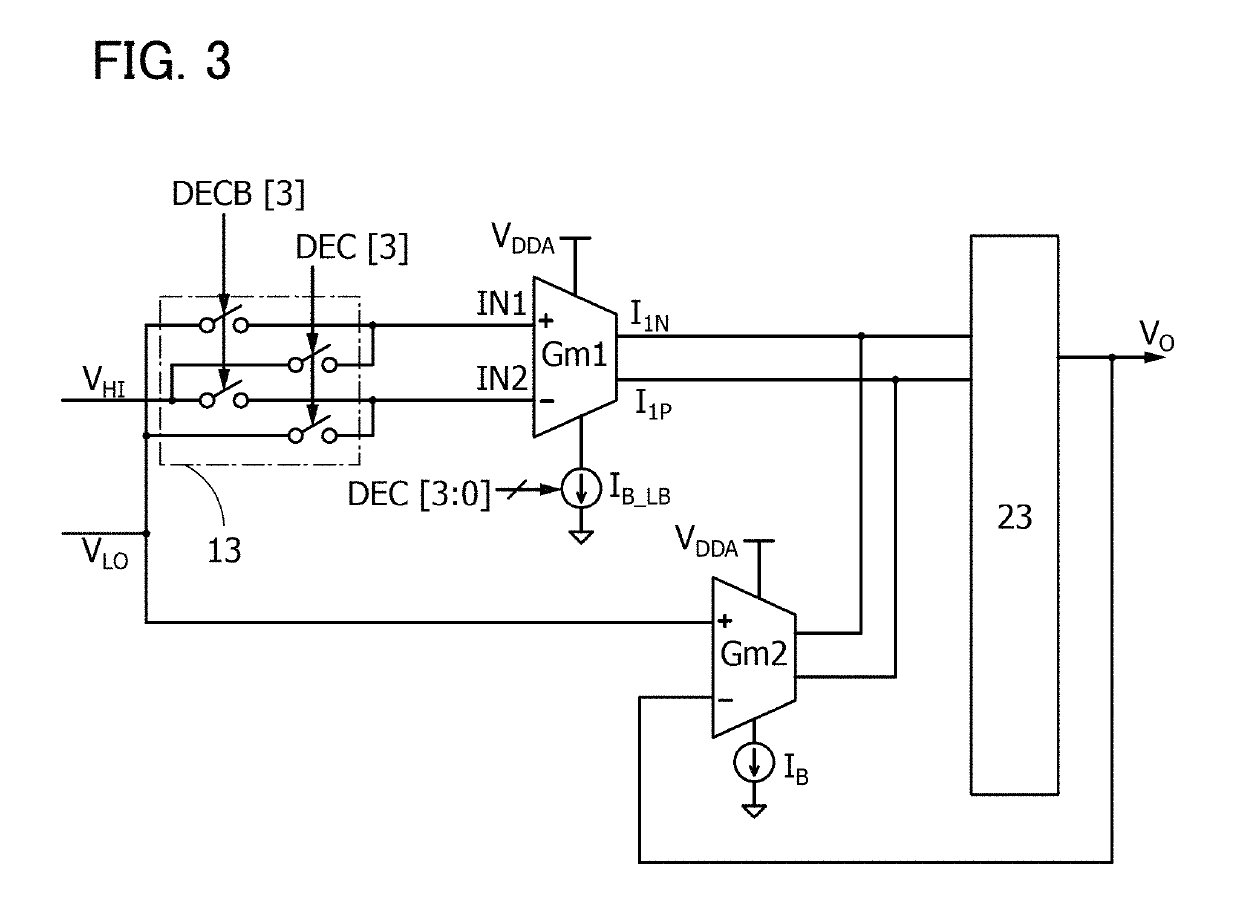

Semiconductor device, display panel, and electronic device

ActiveUS20170154560A1Large circuit areaIncrease parasitic capacitanceStatic indicating devicesCasings with display/control unitsPower semiconductor devicePower flow

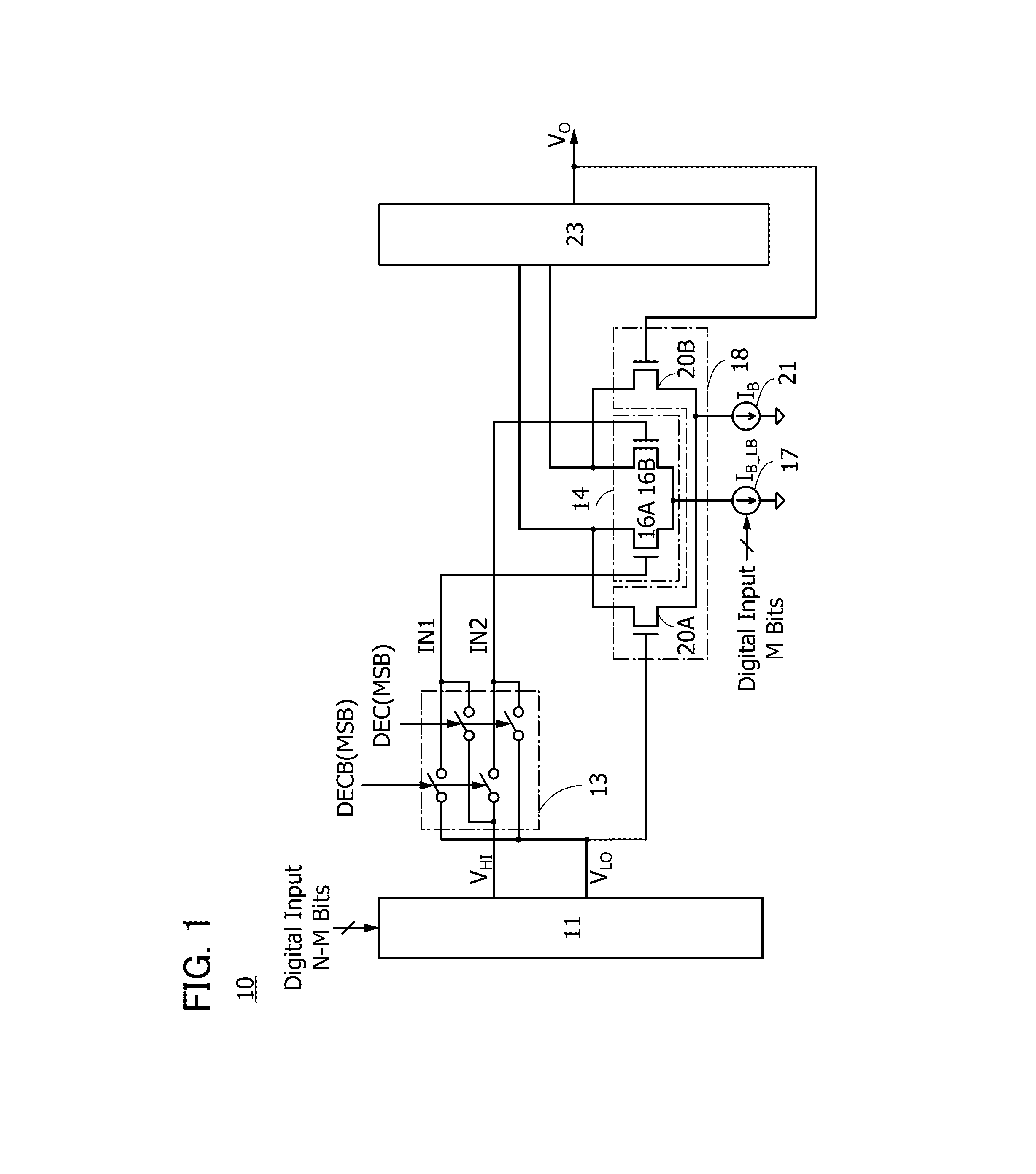

A grayscale voltage generator circuit that is less likely to be influenced by the offset voltage is provided. The grayscale voltage generator circuit is a semiconductor device that includes a D / A converter circuit, a first Gm amplifier, a second Gm amplifier, a current control circuit, an output buffer, and a selector circuit. The D / A converter circuit generates a first voltage and a second voltage from an upper bit of a digital signal. The current control circuit generates a first current from a lower bit of the digital signal and functions as a current source of the first Gm amplifier. The output buffer generates a third voltage from currents output from the first Gm amplifier and the second Gm amplifier. The third voltage is input to the second Gm amplifier. The selector circuit selects voltages that are to be input to the first Gm amplifier and the second Gm amplifier.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device having extra capacitor structure

ActiveUS8258555B2Increase the output capacitanceReduce voltage spikesTransistorSolid-state devicesDielectric layerCapacitor

A semiconductor device includes a semiconductor substrate having a conductive type, a source metal layer, a gate metal layer, at least one transistor device, a heavily doped region having the conductive type, a capacitor dielectric layer, a conductive layer. The source metal layer and the gate metal layer are disposed on the semiconductor substrate. The transistor device is disposed in the semiconductor substrate under the source metal layer. The heavily doped region, the capacitor dielectric layer and the conductive layer constitute a capacitor structure, disposed under the gate metal layer, and the capacitor structure is electrically connected between a source and a drain of the transistor device.

Owner:SINOPOWER SEMICON

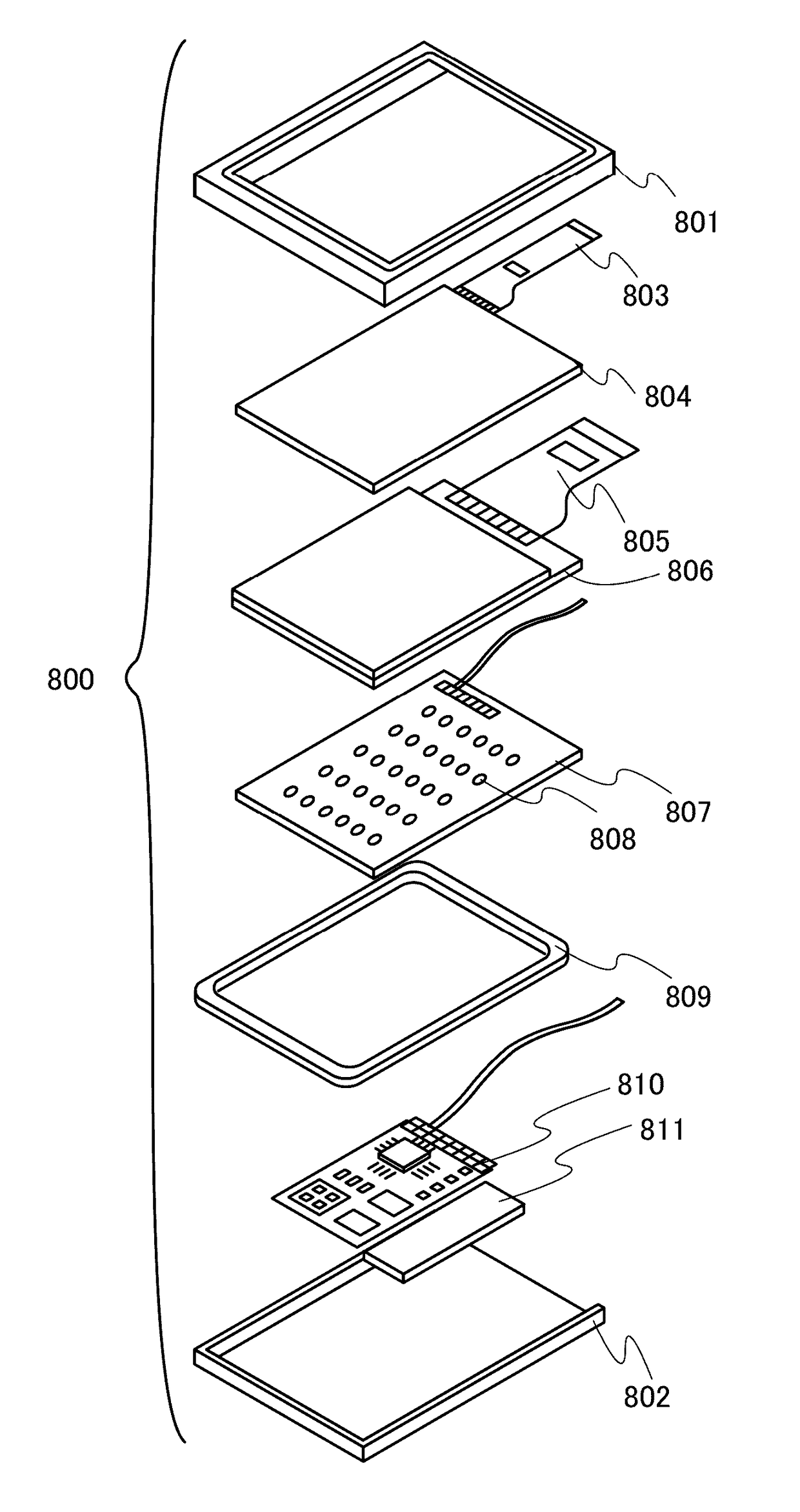

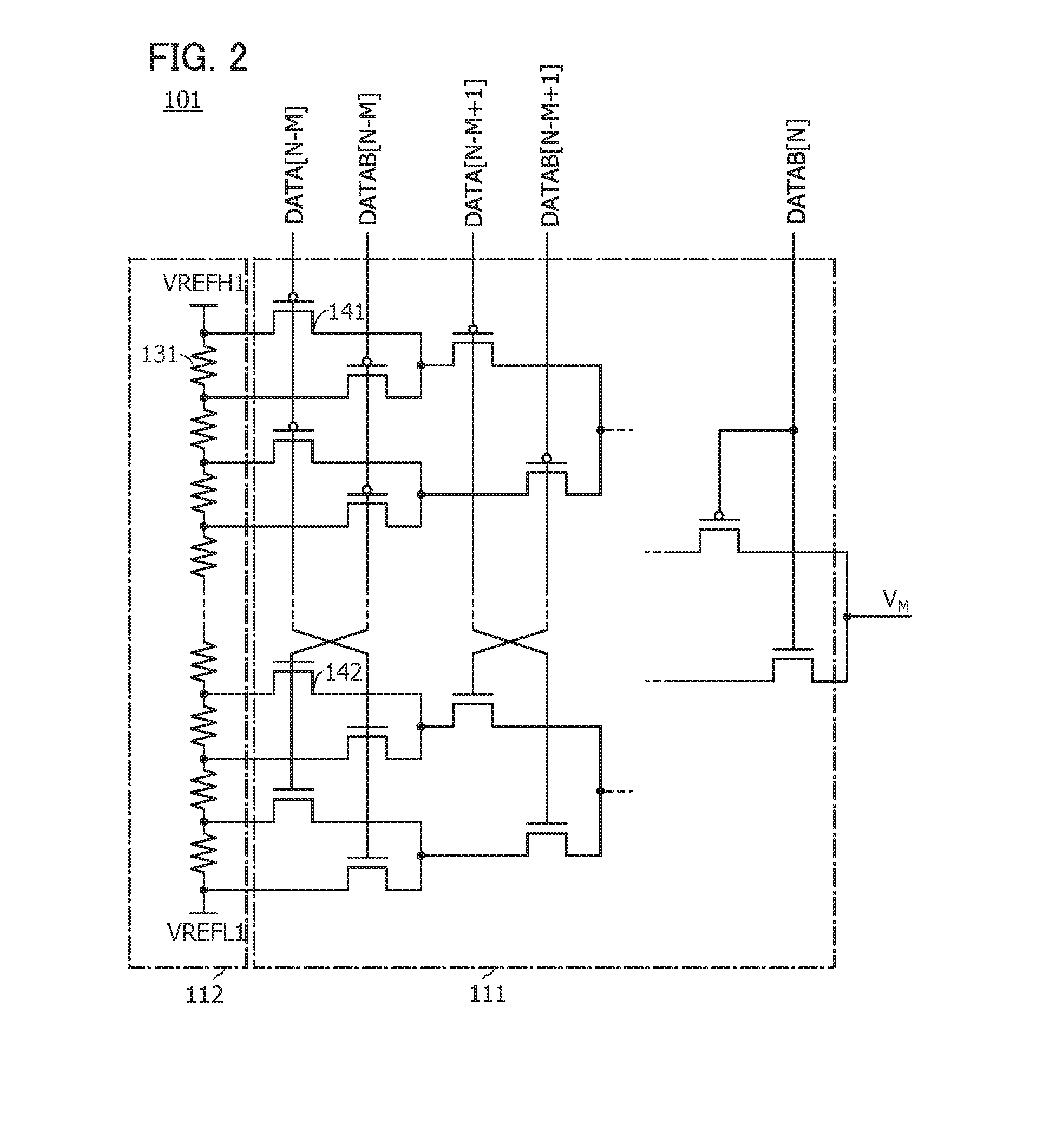

Semiconductor device, electronic component, and electronic device

InactiveUS20160241255A1High degree of freedom of choiceNovel structureStatic indicating devicesSingle output arrangementsParasitic capacitanceElectronic component

A semiconductor device with a novel structure. An upper-bit grayscale voltage and a lower-bit grayscale voltage are separately produced, and then the grayscale voltages are converted into currents and the currents are synthesized. The obtained current is converted into a voltage, and thus an intended grayscale voltage is obtained. The upper-bit grayscale voltage and the lower-bit grayscale voltage are generated using respective D / A converter circuits each including a resistor string circuit and a pass transistor logic. The increase in the number of transistors supplied with high voltage, which occurs along with the increase in the number of digital signal bits, is prevented. Thus, the increase in parasitic capacitance can be suppressed, and a smaller circuit area and higher response speed are obtained.

Owner:SEMICON ENERGY LAB CO LTD

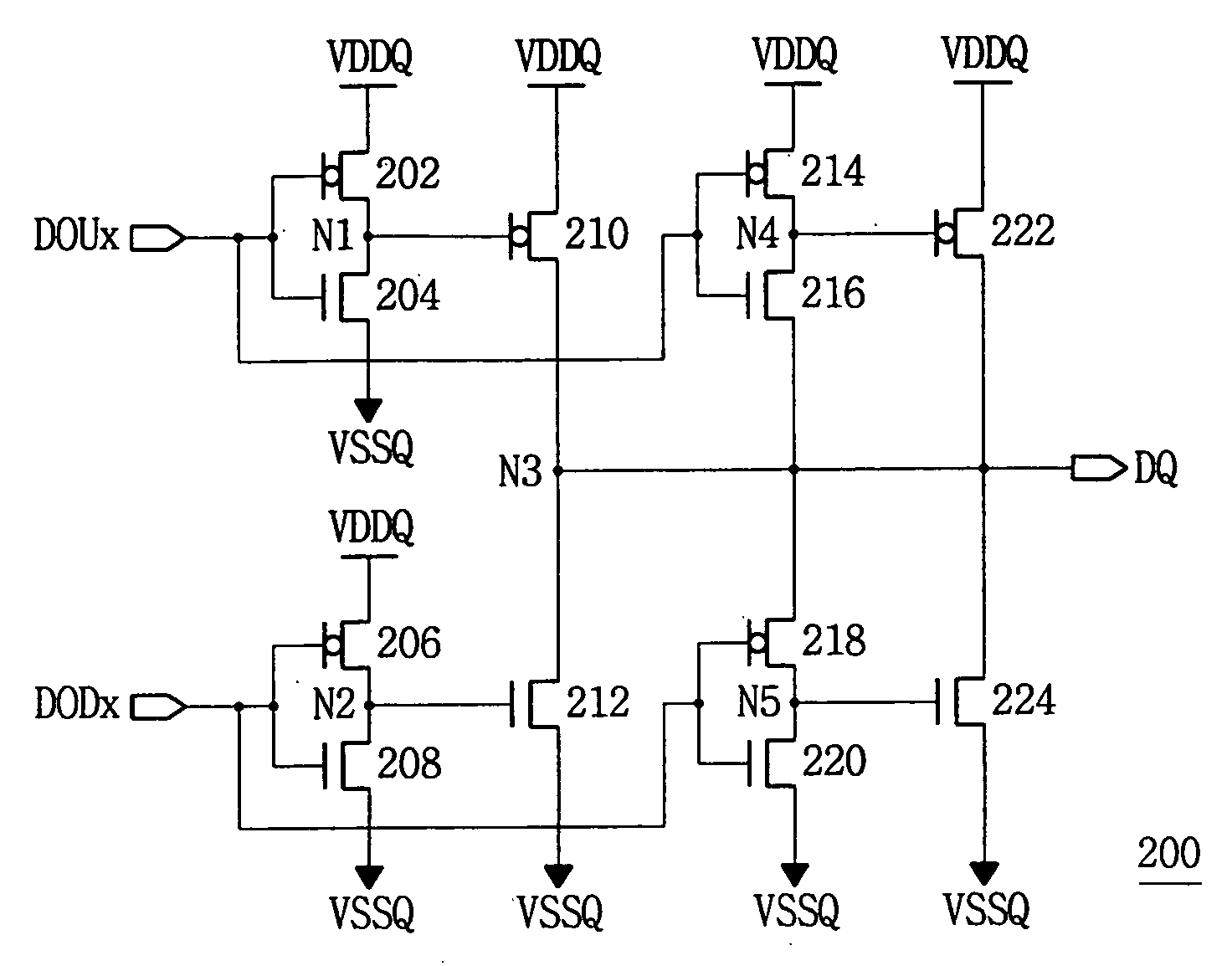

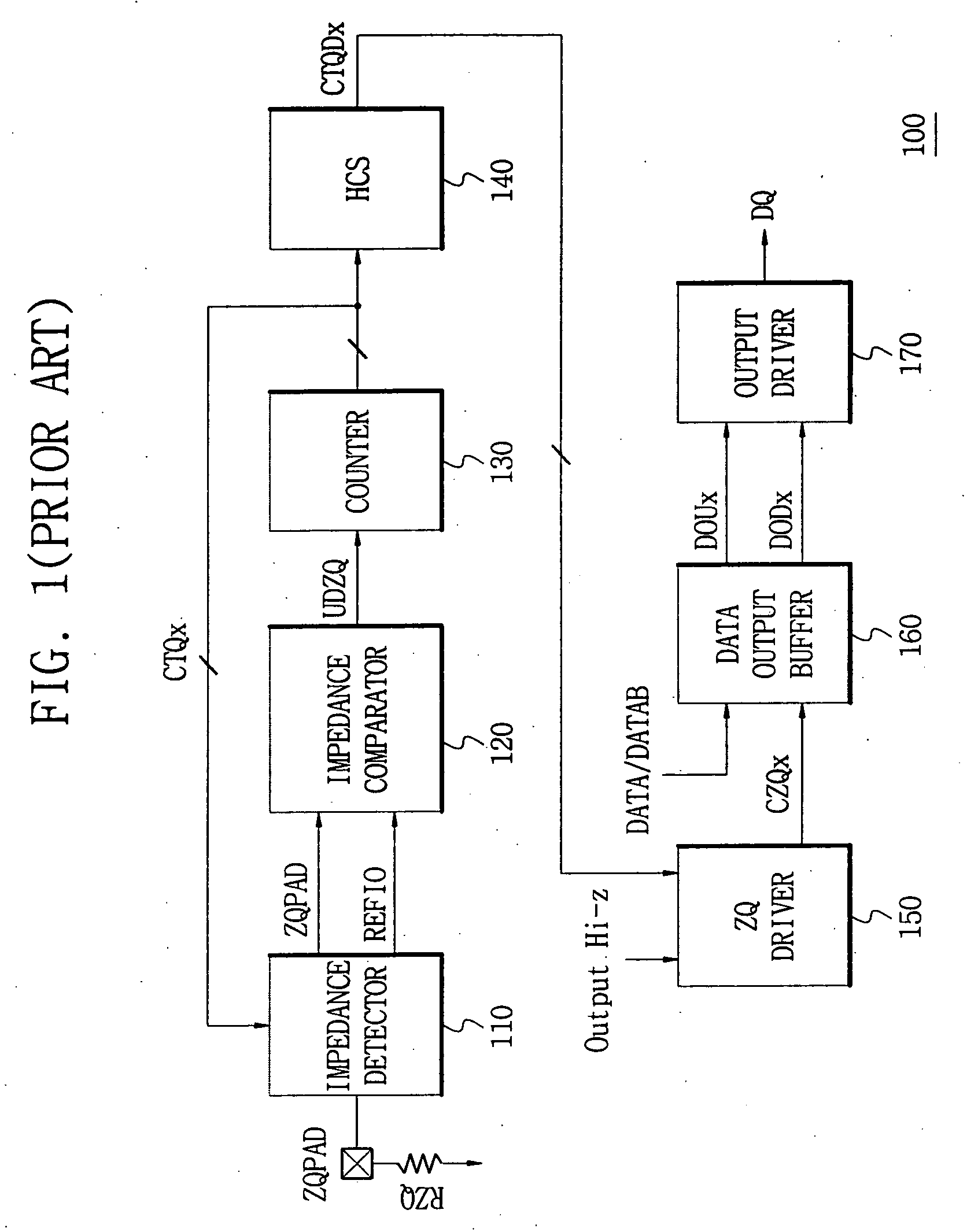

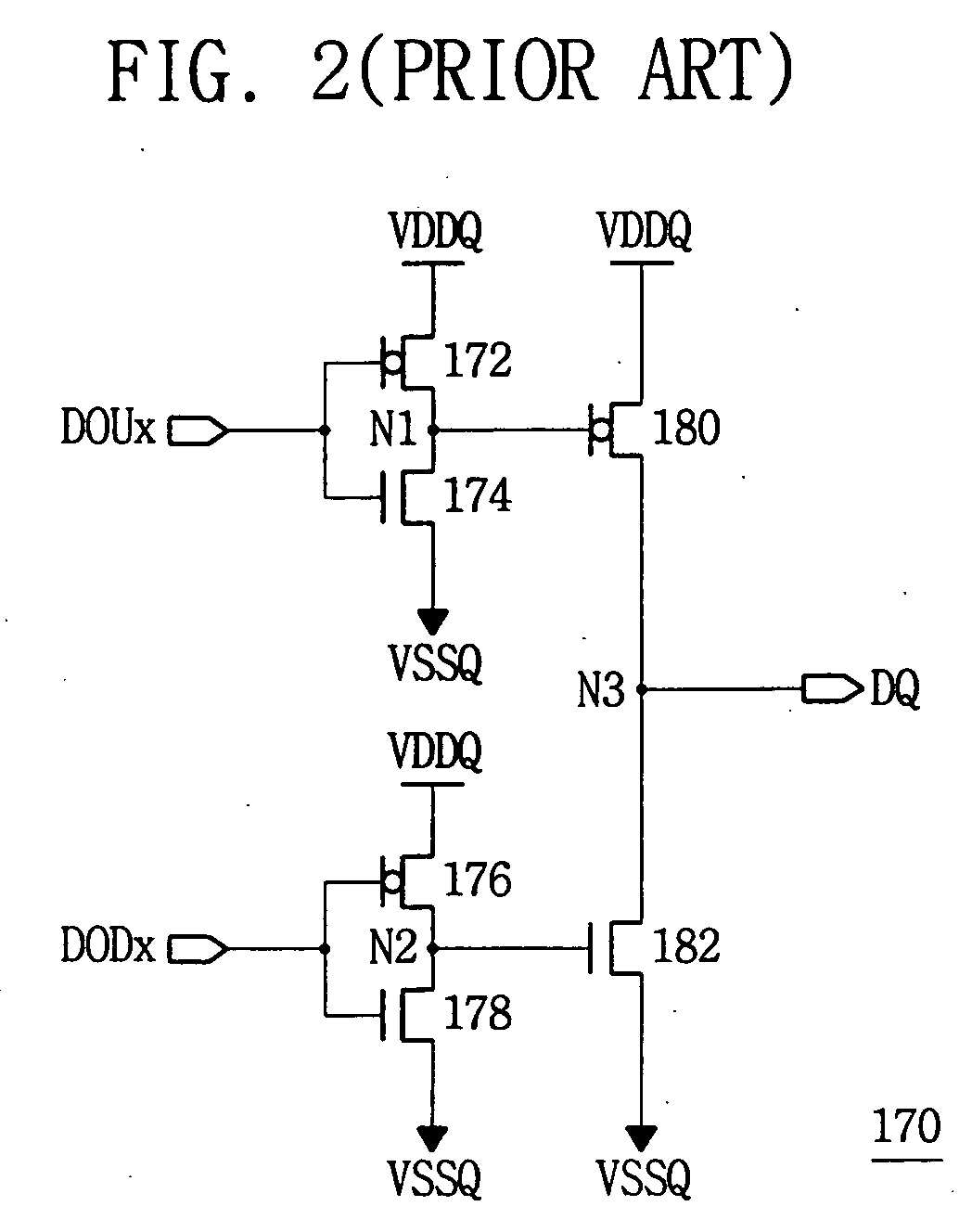

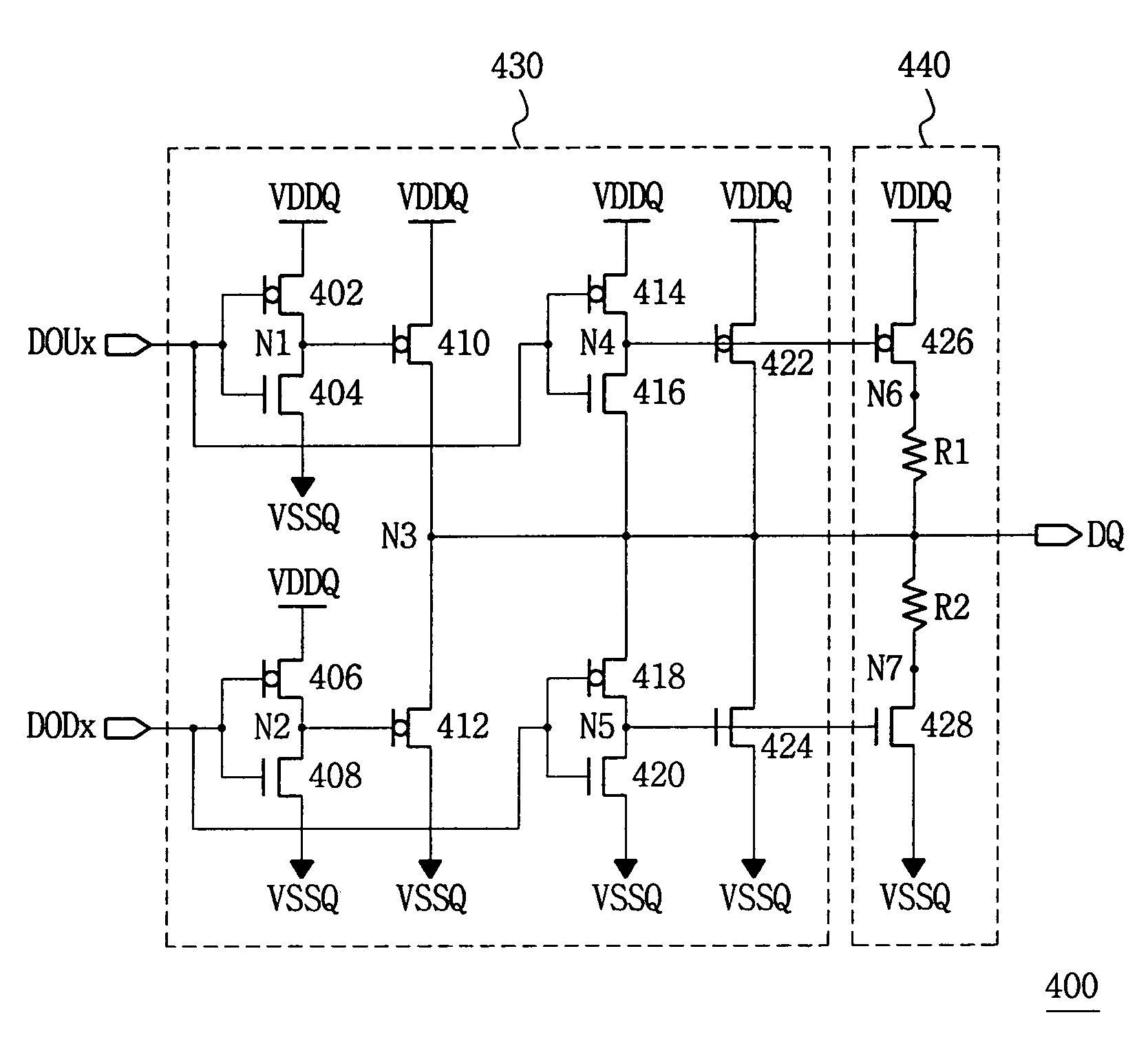

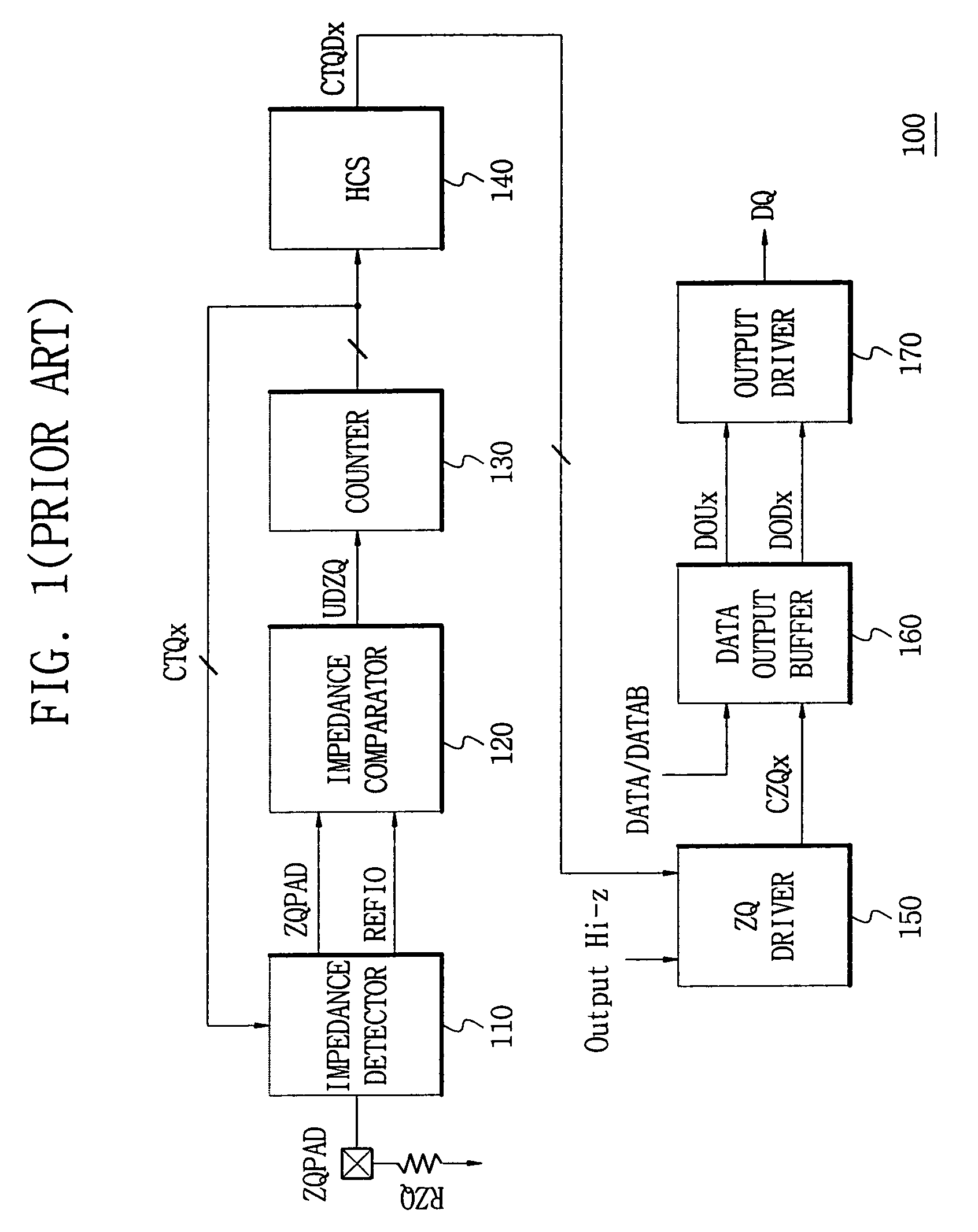

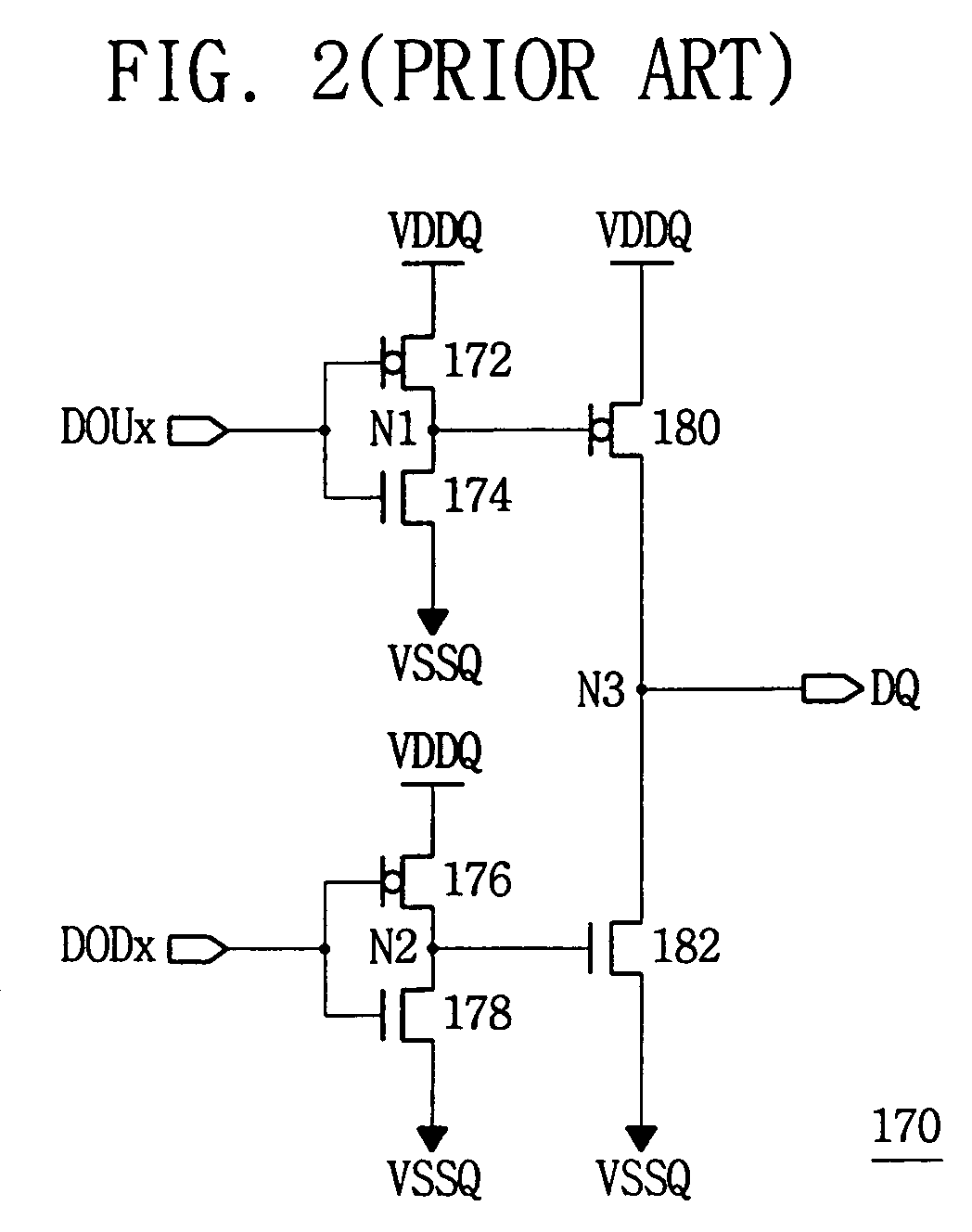

Output driver for use in semiconductor device

ActiveUS20050151561A1Reduced change in impedanceIncrease capacitanceReliability increasing modificationsFilament handlingDevice materialEngineering

There is provided an output driver for use in a semiconductor device capable of remarkably improving linearity of impedance by reducing or minimizing a change of an impedance for output data caused due to a change of an external power supply. The output driver for outputting internal data of a semiconductor device to the exterior of a chip comprises a first driving section including a driving transistor to maintain an impedance for applied data at a certain level in response to the data; and a second driving section for compensating for linearity of the impedance in response to an operation signal from the driving transistor of the first driving section and providing an output terminal with the data.

Owner:SAMSUNG ELECTRONICS CO LTD

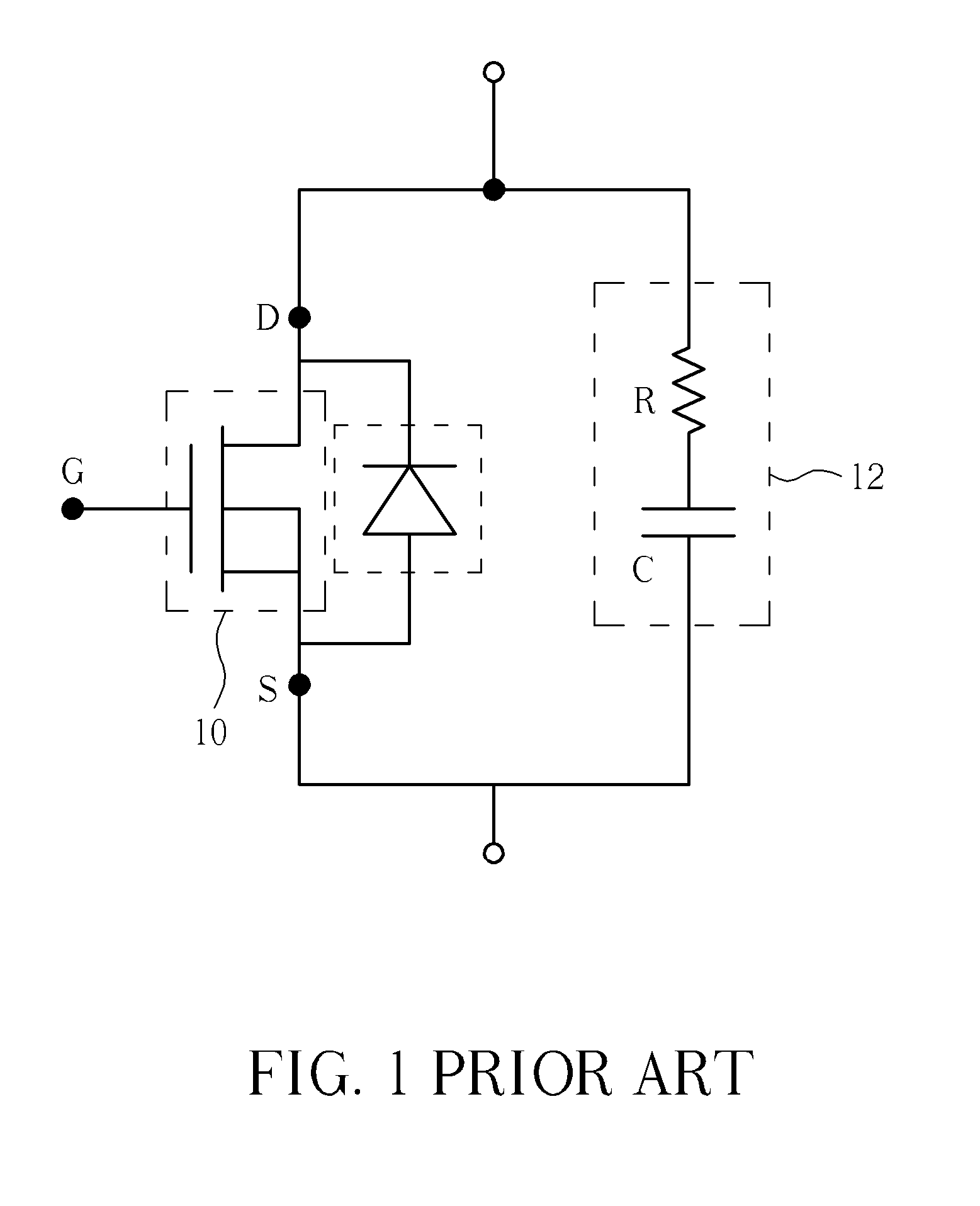

Power semiconductor device having adjustable output capacitance

InactiveUS8362529B2Increase the output capacitanceReduce electricity costsTransistorSolid-state devicesPower semiconductor deviceSnubber capacitor

A power semiconductor device having adjustable output capacitance includes a semiconductor substrate having a first device region and a second device region defined thereon, at lest one power transistor device disposed in the first device region, a heavily doped region disposed in the semiconductor substrate of the second device region, a capacitor dielectric layer disposed on the heavily doped region, a source metal layer disposed on a top surface of the semiconductor substrate and electrically connected to the power transistor device, and a drain metal layer disposed on a bottom surface of the semiconductor substrate. The source metal layer in the second device, the capacitor dielectric layer and the heavily doped region form a snubber capacitor.

Owner:ANPEC ELECTRONICS CORPORATION

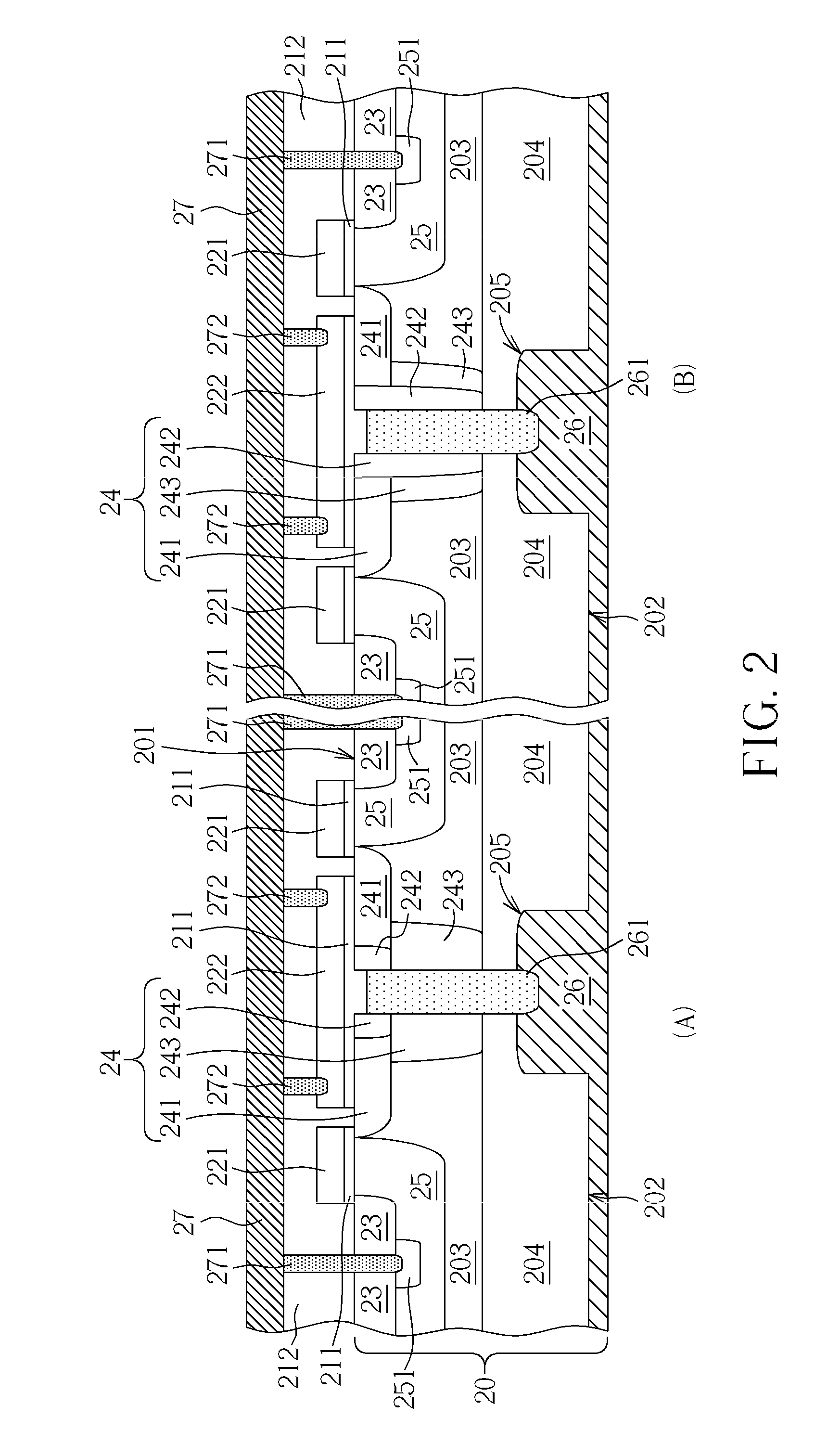

Laterally diffused metal-oxide-semiconductor device

A laterally diffused metal-oxide-semiconductor device includes a substrate, a gate dielectric layer, a gate polysilicon layer, a source region, a drain region, a body region, a first drain contact plug, a source polysilicon layer, an insulating layer, and a source metal layer. The source polysilicon layer disposed on the gate dielectric layer above the drain region can serve as a field plate to enhance the breakdown voltage and to increase the drain-to-source capacitance. In addition, the first drain contact plug of the present invention can reduce the drain-to-source on-resistance and the horizontal extension length.

Owner:SINOPOWER SEMICON

Semiconductor device, display panel, and electronic device

ActiveUS10325542B2Improve pressure resistanceIncrease the number ofStatic indicating devicesCasings with display/control unitsVoltage generatorAudio power amplifier

A grayscale voltage generator circuit that is less likely to be influenced by the offset voltage is provided. The grayscale voltage generator circuit is a semiconductor device that includes a D / A converter circuit, a first Gm amplifier, a second Gm amplifier, a current control circuit, an output buffer, and a selector circuit. The D / A converter circuit generates a first voltage and a second voltage from an upper bit of a digital signal. The current control circuit generates a first current from a lower bit of the digital signal and functions as a current source of the first Gm amplifier. The output buffer generates a third voltage from currents output from the first Gm amplifier and the second Gm amplifier. The third voltage is input to the second Gm amplifier. The selector circuit selects voltages that are to be input to the first Gm amplifier and the second Gm amplifier.

Owner:SEMICON ENERGY LAB CO LTD

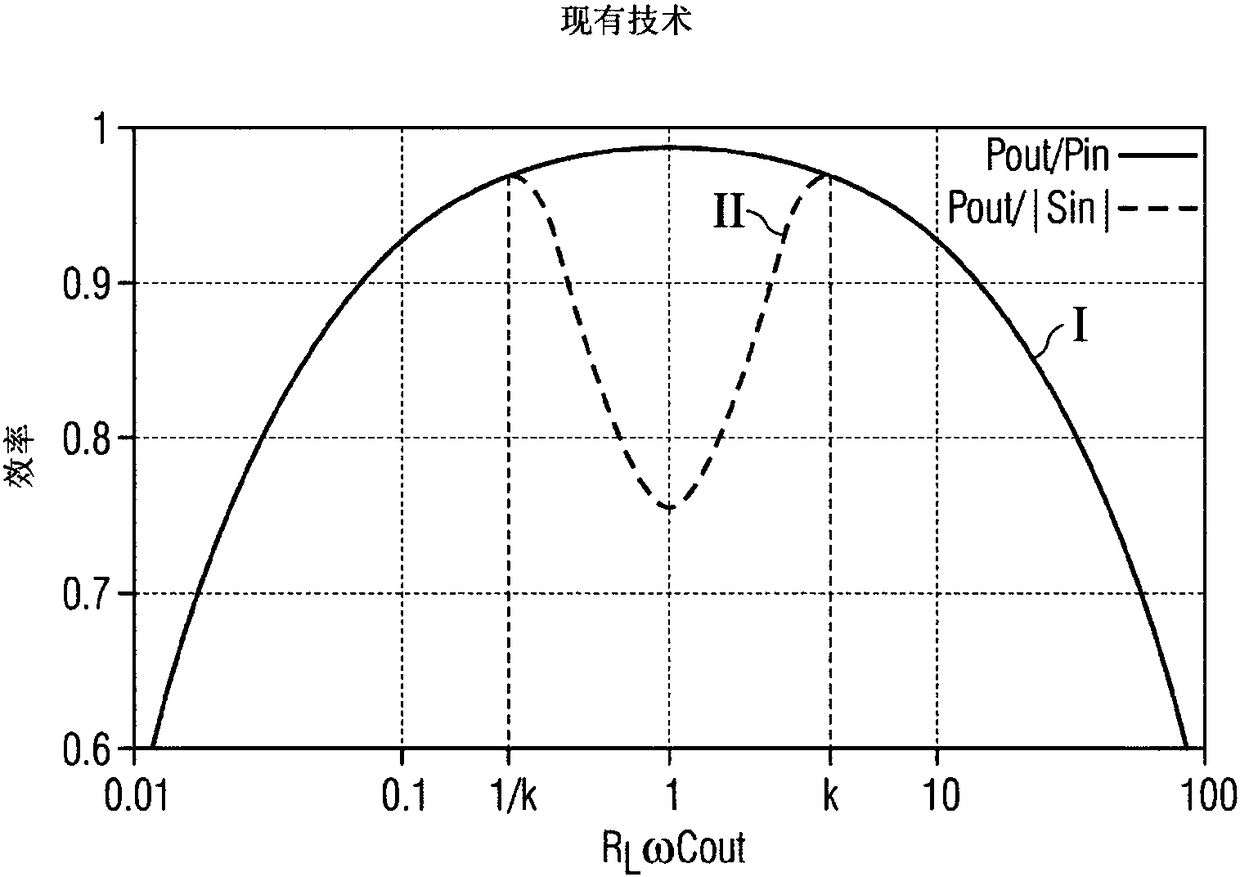

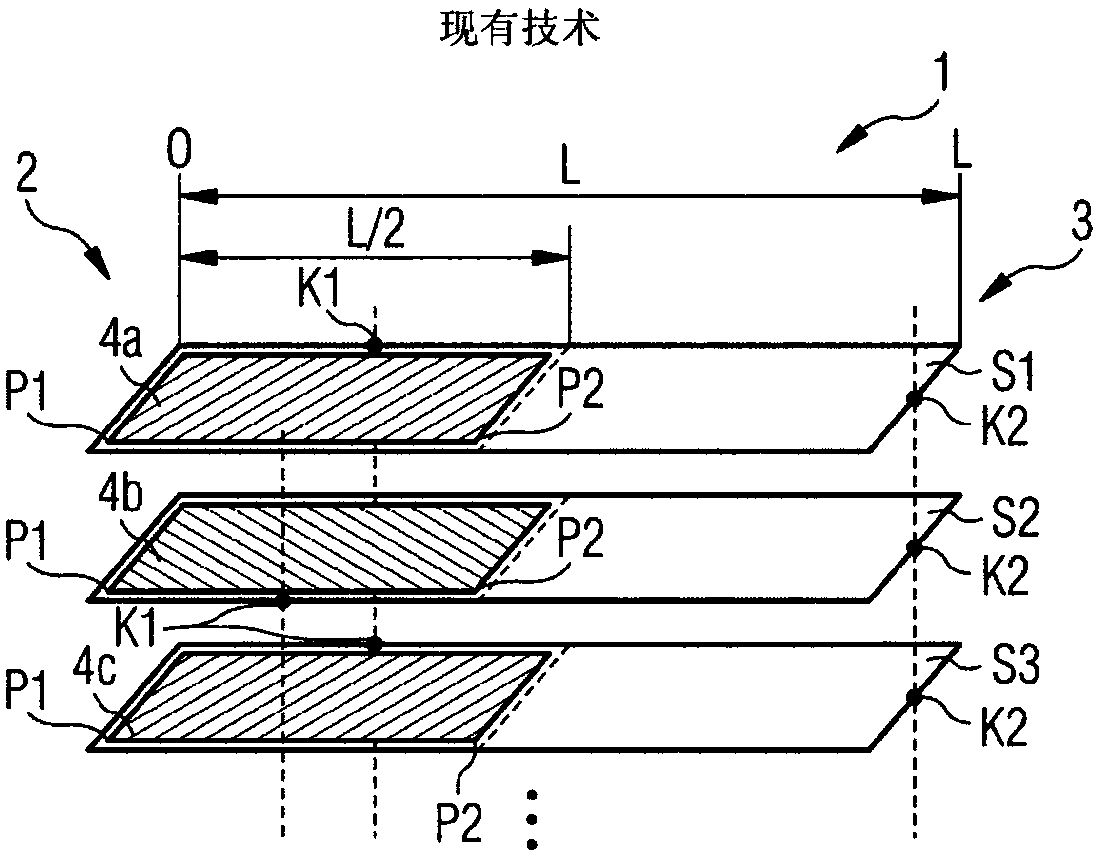

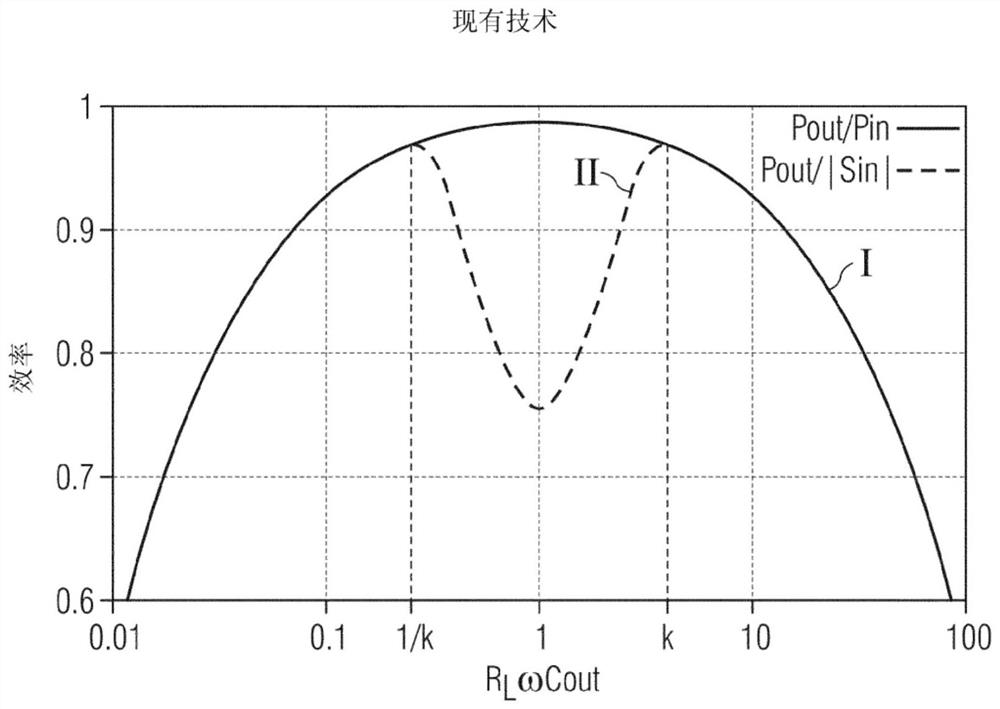

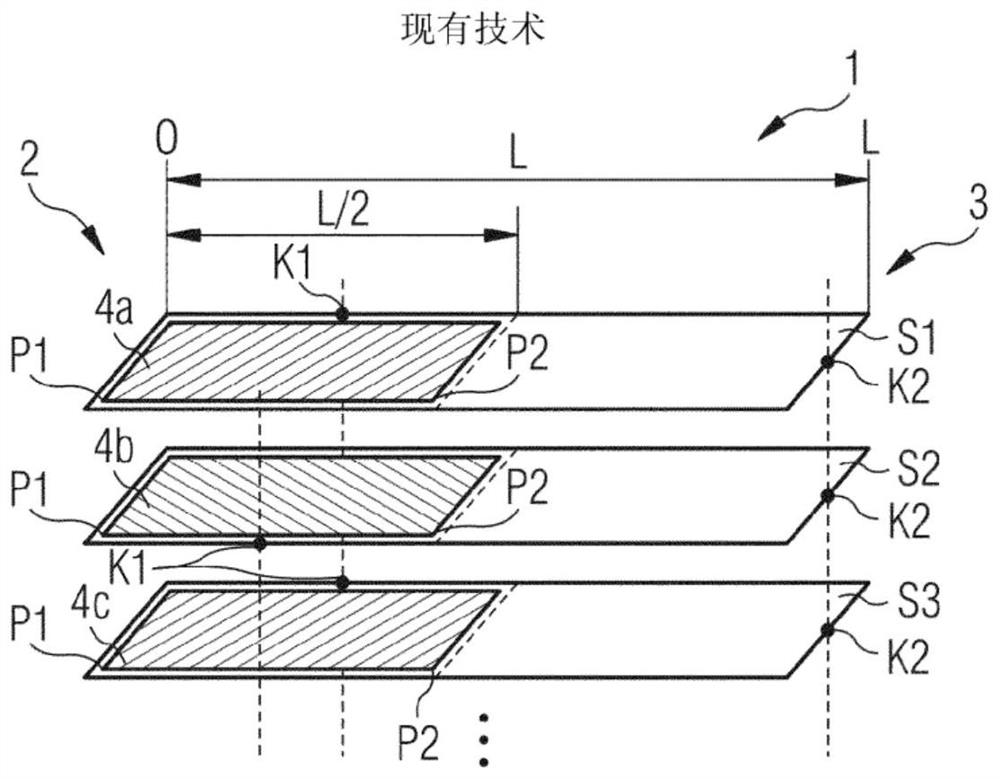

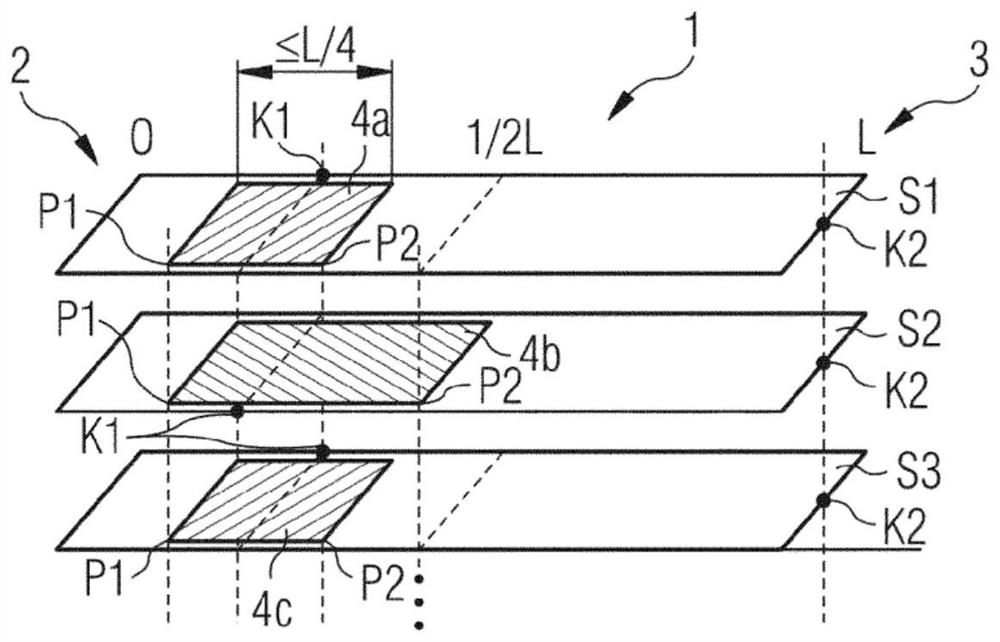

Piezoelectric transformer

ActiveCN108140719AReduce input capacitanceIncrease the output capacitancePiezoelectric/electrostrictive/magnetostrictive devicesCapacitancePiezoelectric transformer

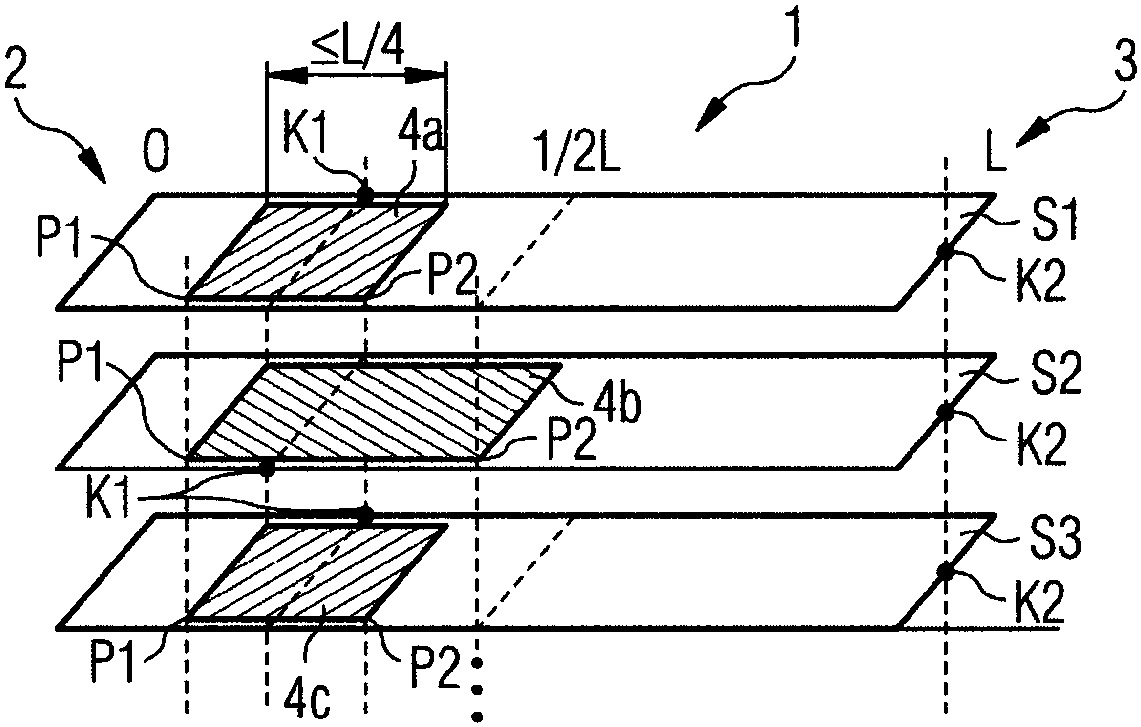

The invention relates to a piezoelectric transformer comprising a piezoelectric element (1) of length L, wherein an input voltage Uin can be applied at an input side (2) for transformation into an output voltage Uout at an output side (3) according to a transformation ratio formula (I). The piezoelectric element (1) has multiple plies (4a, 4b, 4c) of inner electrodes, which are arranged in multiple different layers (S1, S2, S3). Each ply (4a, 4b, 4c) of inner electrodes extends along at least one predetermined sub-section of a predetermined length, wherein sub-sections of plies (4a, 4c) of a first group of layers (S1, S3) and sub-sections of plies (4b) of a second group of layers (S2) have different dimensions, such that the piezoelectric transformer satisfies the following condition: Cin<=N2Cout, wherein Cin represents the input capacity, Cout represents the output capacity and N represents the transformation ratio of the ideal transformer.

Owner:EPCOS AG

High voltage semiconductor device and driving circuit

ActiveUS8674729B2Reduce power lossQuick responseSolid-state devicesSemiconductor/solid-state device manufacturingHigh pressureSemiconductor

Owner:FUJI ELECTRIC CO LTD

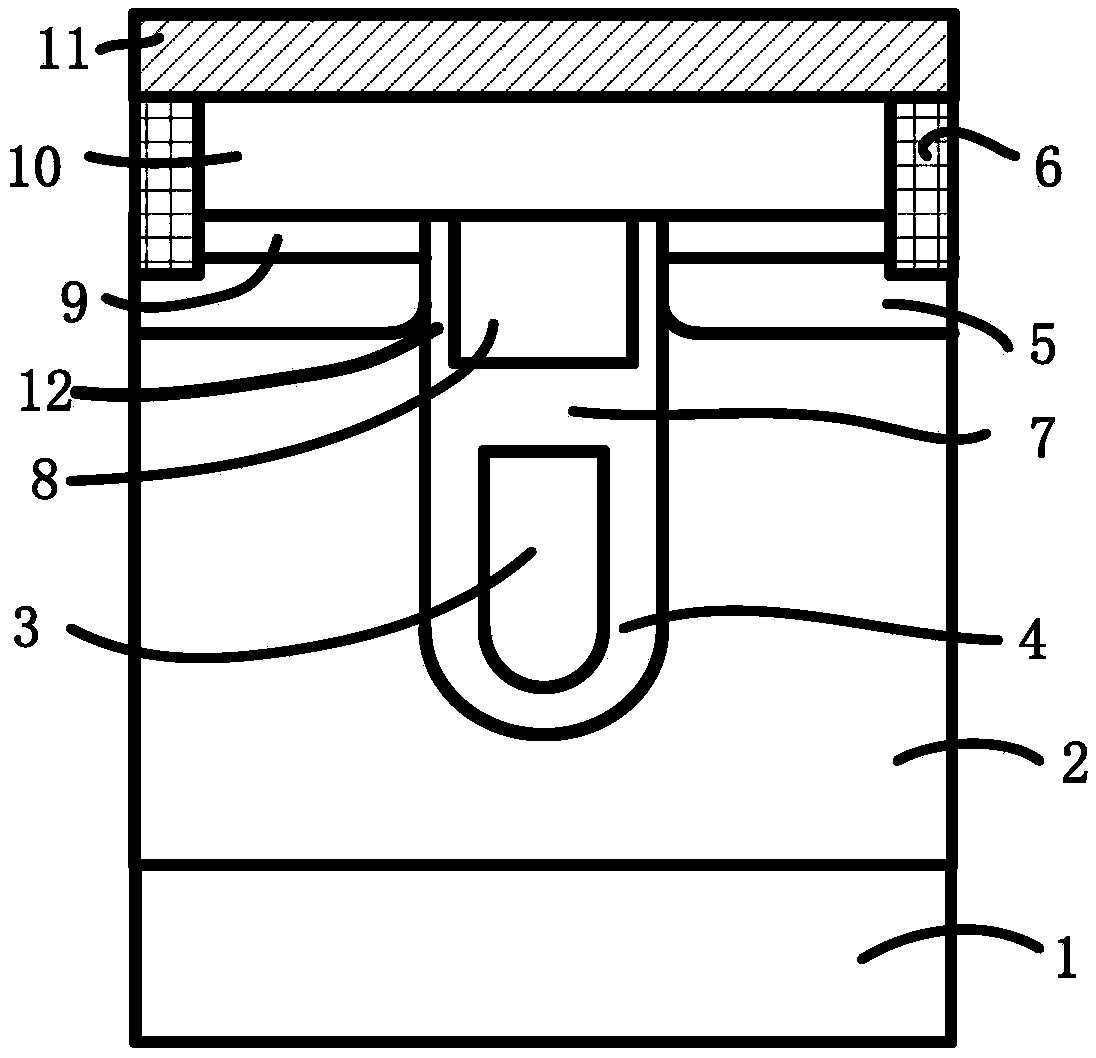

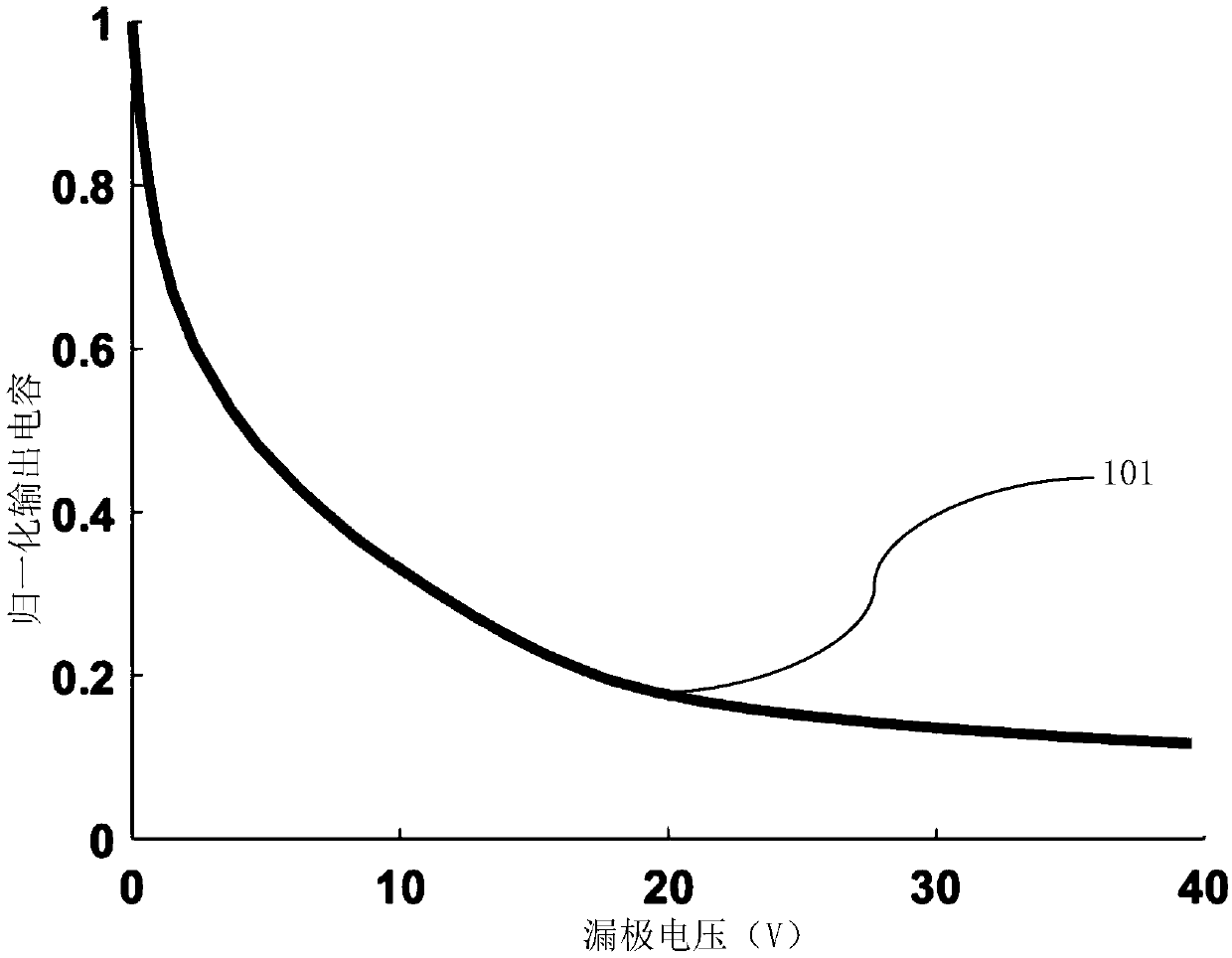

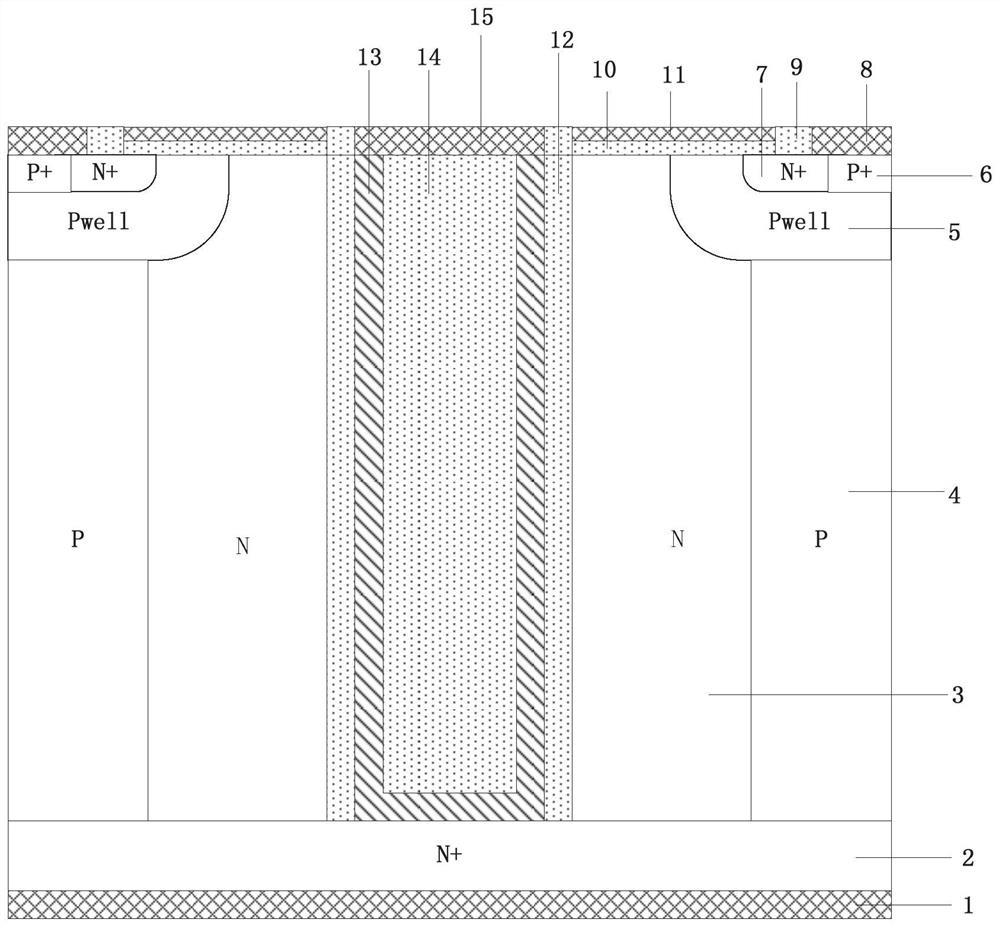

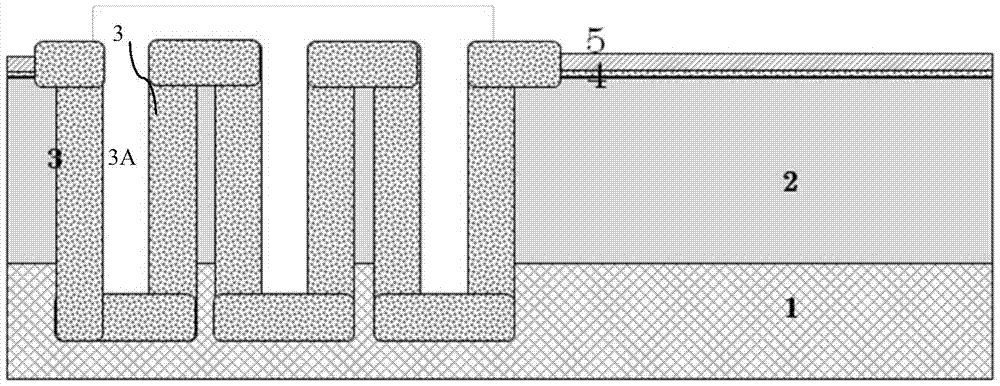

Shield gate trench MOSFET

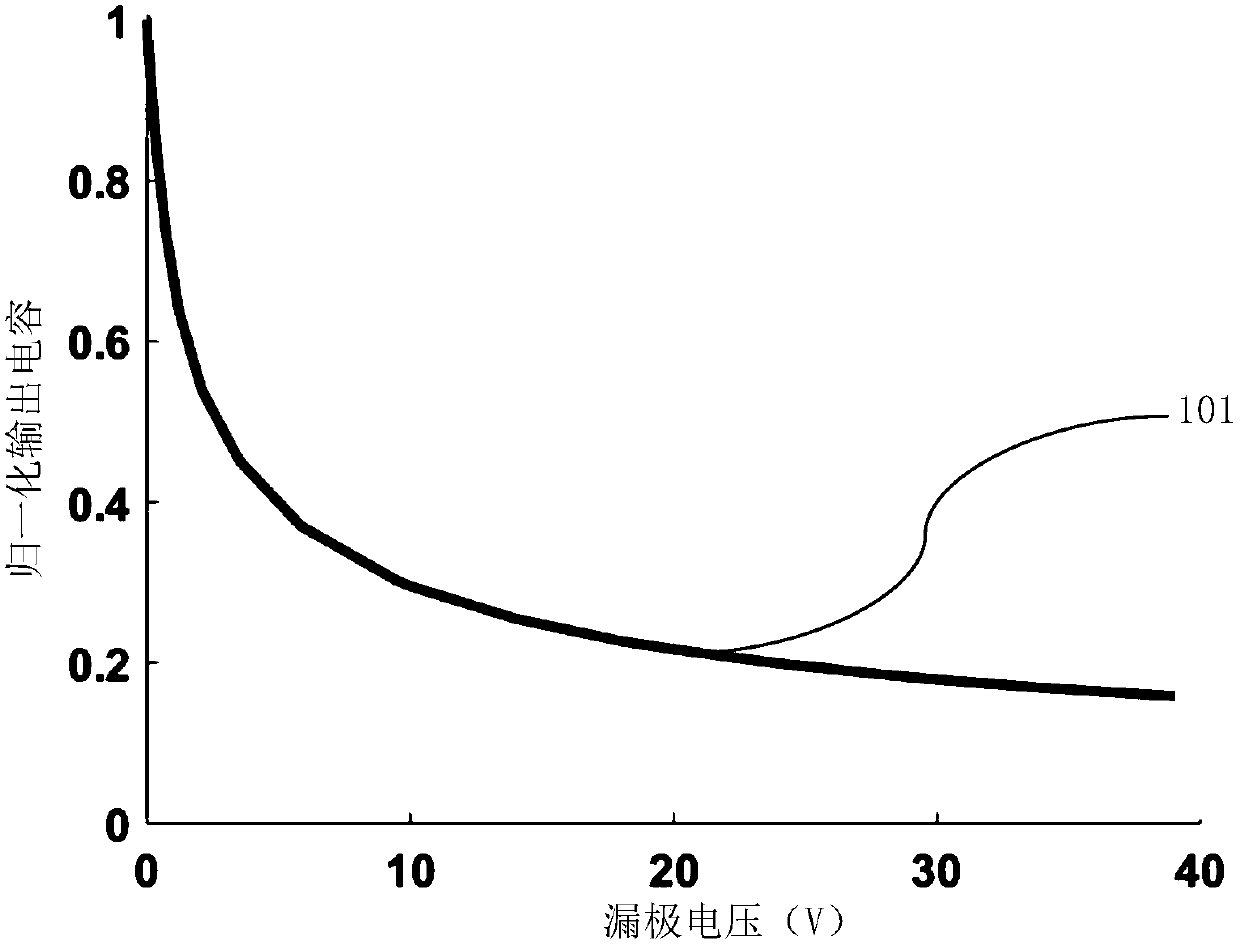

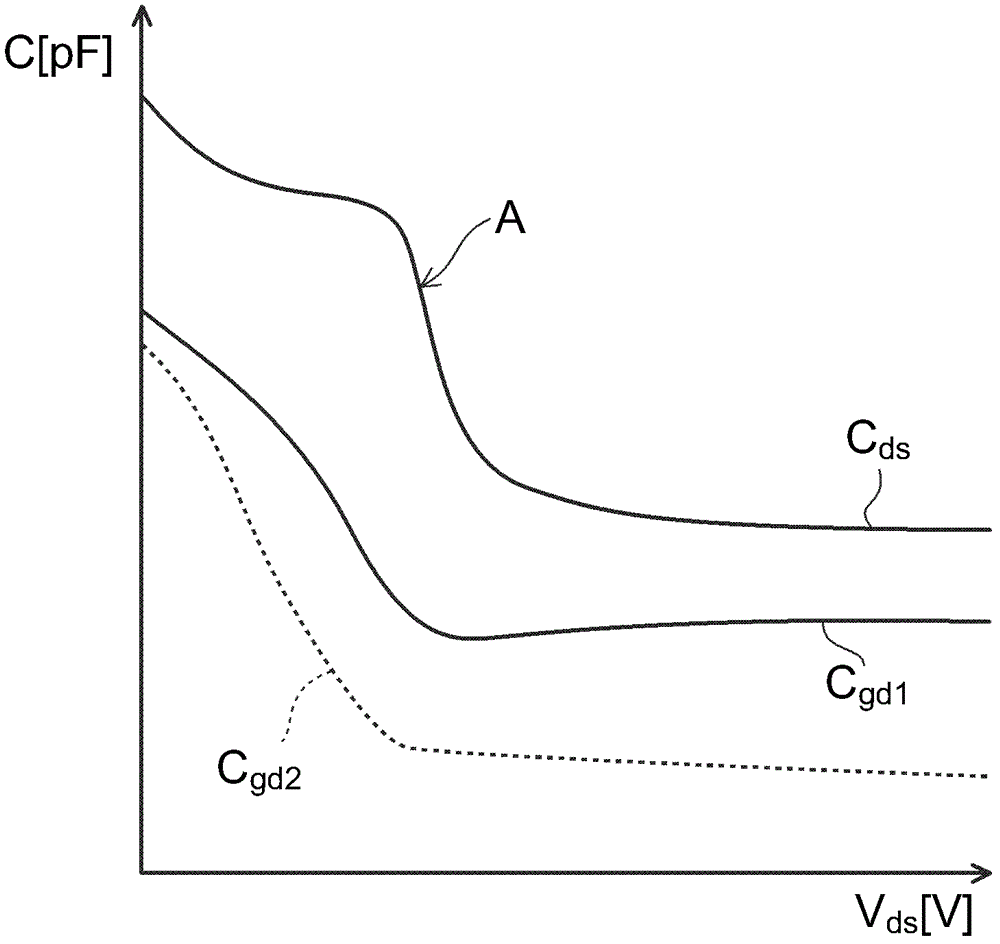

PendingCN111223930ADoes not take up additional spaceIncrease the output capacitanceSemiconductor devicesCapacitanceTrench mosfet

The invention discloses a shield gate trench metal oxide semiconductor field effect transistor (MOSFET). The structure comprises a primitive cell region and a peripheral region, a device unit structure of a shield gate trench MOSFET is formed in the primitive cell region, a trench MOS capacitor used for reducing nonlinearity of output capacitance of the shield gate trench MOSFET is formed in the peripheral region, and the trench MOS capacitor comprises a second gate structure which is formed in a second trench and comprises a second polycrystalline silicon shield field plate, wherein the second trench is formed in a first epitaxial layer doped with the first conductivity type, and a second shielding dielectric layer is isolated between the second polycrystalline silicon shielding field plate and the first epitaxial layer, the source region is not formed on the surface of the first epitaxial layer covered on the side surface of the second trench, and the first epitaxial layer on the side surface of the second trench and the first epitaxial layer of the primitive cell region form the drift region of the whole device; the drain region of the whole device is formed at the bottom of thefirst epitaxial layer; and the top of the second polycrystalline silicon shielding field plate is connected to the source electrode through a contact hole. According to the invention, the minimum value of the output capacitance can be improved, and the nonlinearity of the output capacitance is improved.

Owner:SHENZHEN SANRISE TECH CO LTD

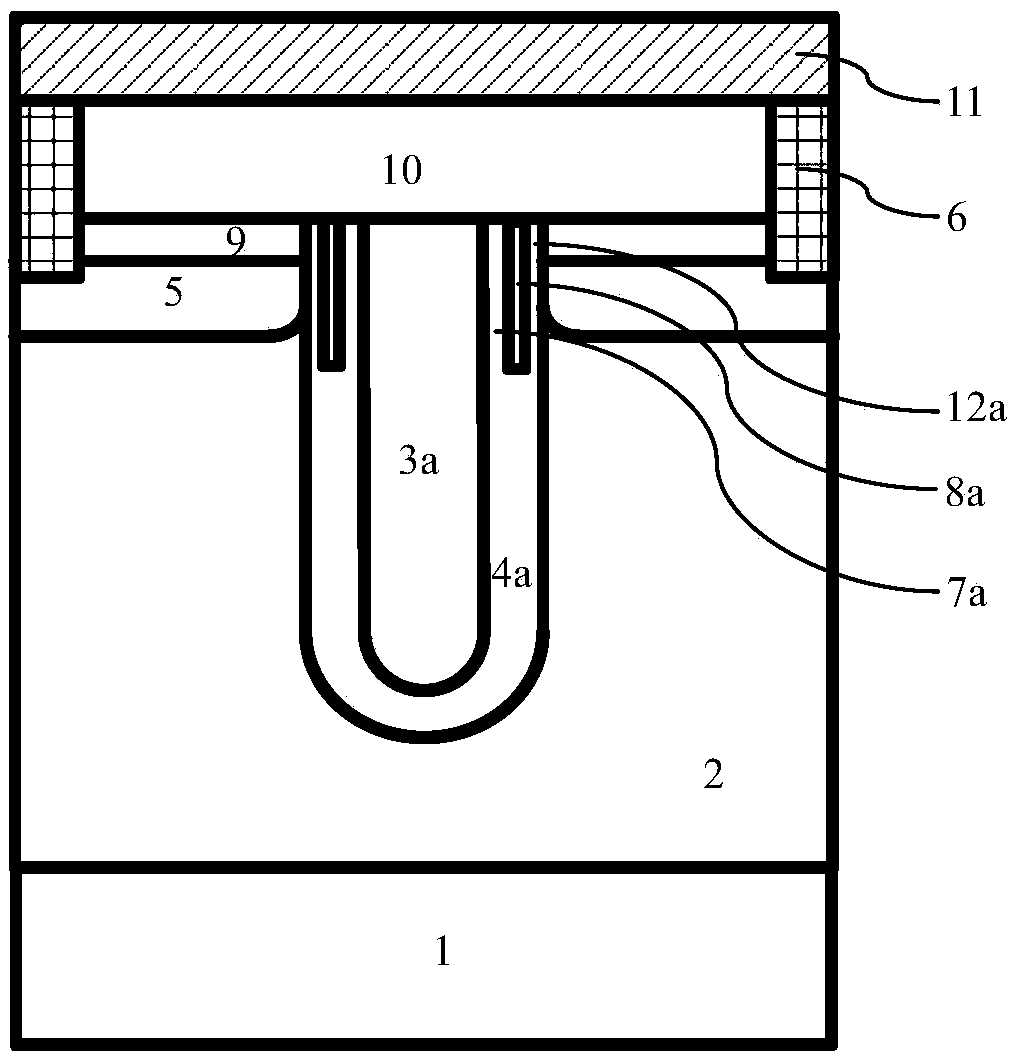

Trench MOSFET and manufacturing method thereof

PendingCN111223931AIncrease the output capacitanceReduce non-linearitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsOxide semiconductor

The invention discloses a trench metal oxide semiconductor field effect transistor (MOSFET). The structure comprises a primitive cell region and a peripheral region, wherein a device unit structure ofa trench MOSFET is formed in the primitive cell region, a trench MOS capacitor used for reducing the nonlinearity of the output capacitance of the trench MOSFET is formed in the peripheral region, and the trench MOS capacitor comprises a second trench gate formed by superposing a second gate dielectric layer and a second polysilicon gate which are formed in a second trench; a source region is notformed on the surface of the first epitaxial layer covered on the side surface of the second polysilicon gate, a drift region formed by the first epitaxial layer extends into the whole primitive cellregion and the peripheral region, and a drain region is formed on the back surface of the drift region; the top of the second polysilicon gate is connected to the source electrode through a contact hole; the trench MOS capacitor and the device unit structure form a parallel structure, and the output capacitance of the whole trench MOSFET is improved and the nonlinearity of the output capacitanceis reduced when the device is reversely biased. The invention further discloses a manufacturing method of the trench MOSFET.

Owner:SHENZHEN SANRISE TECH CO LTD

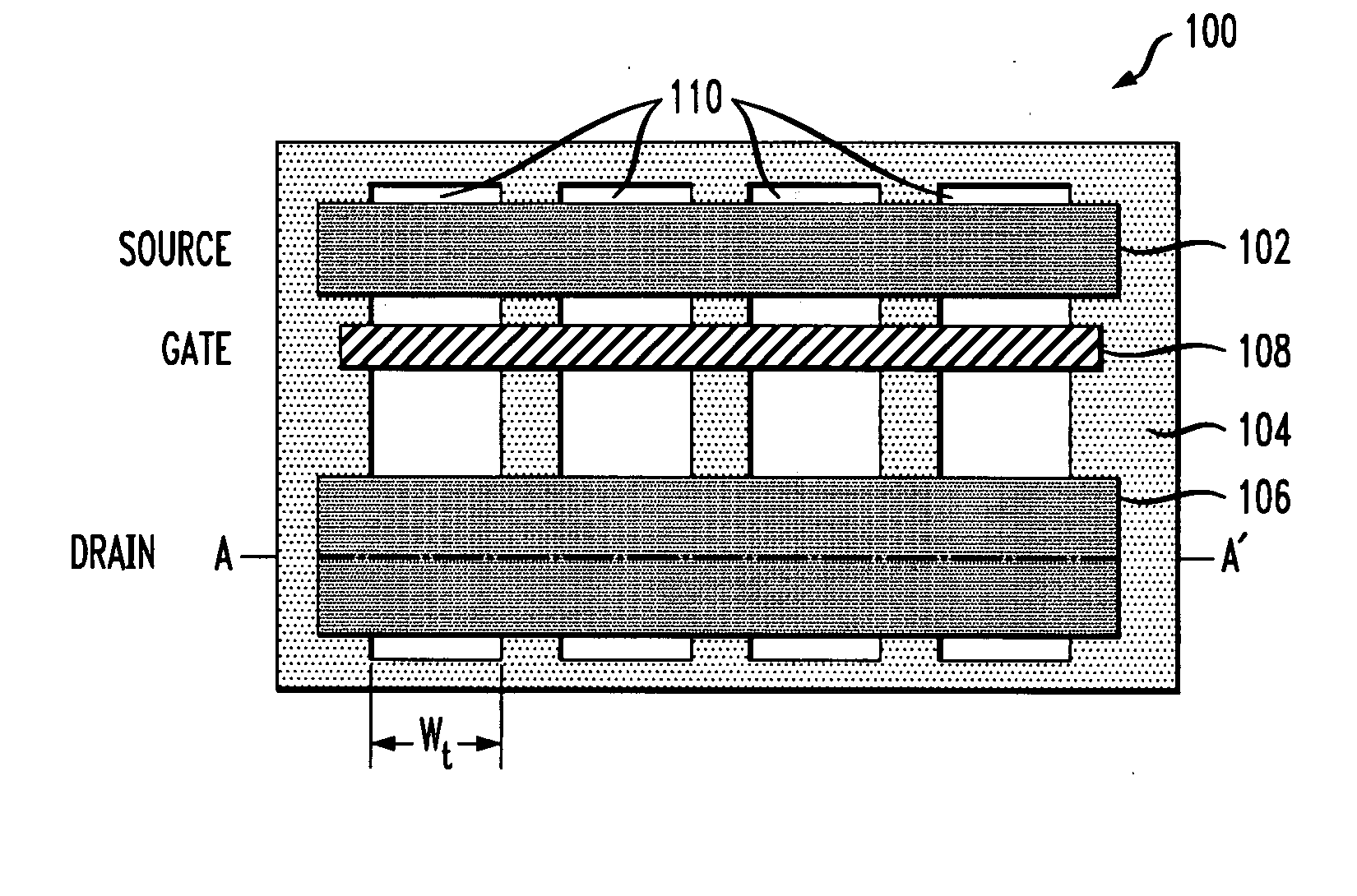

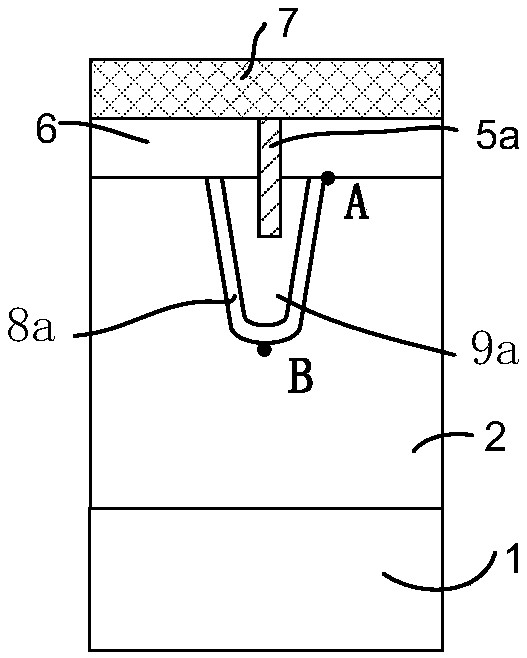

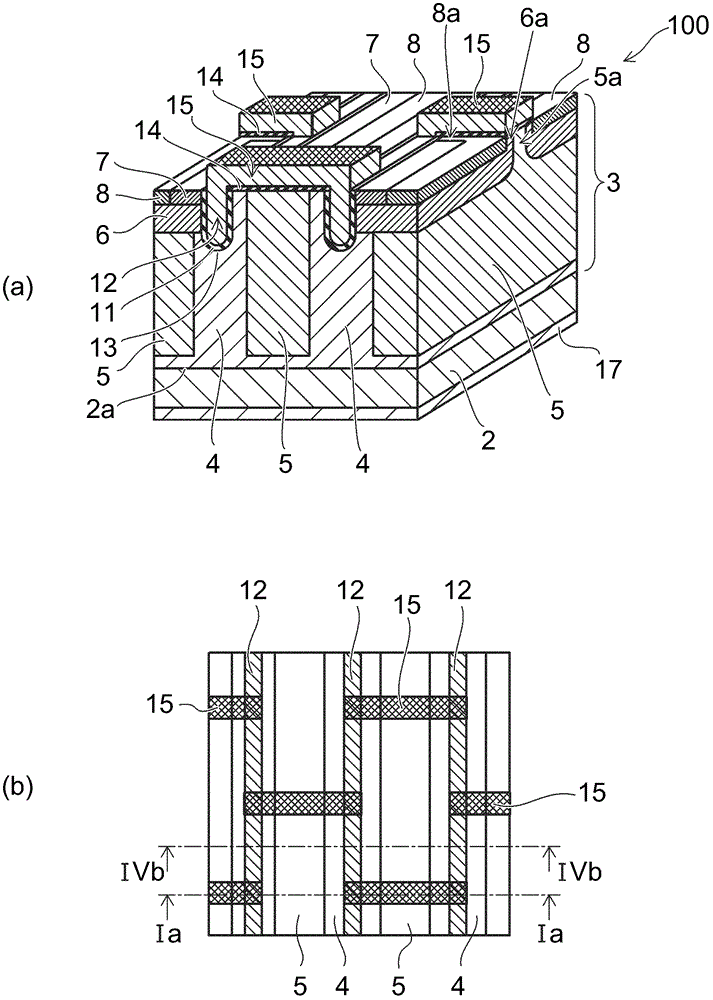

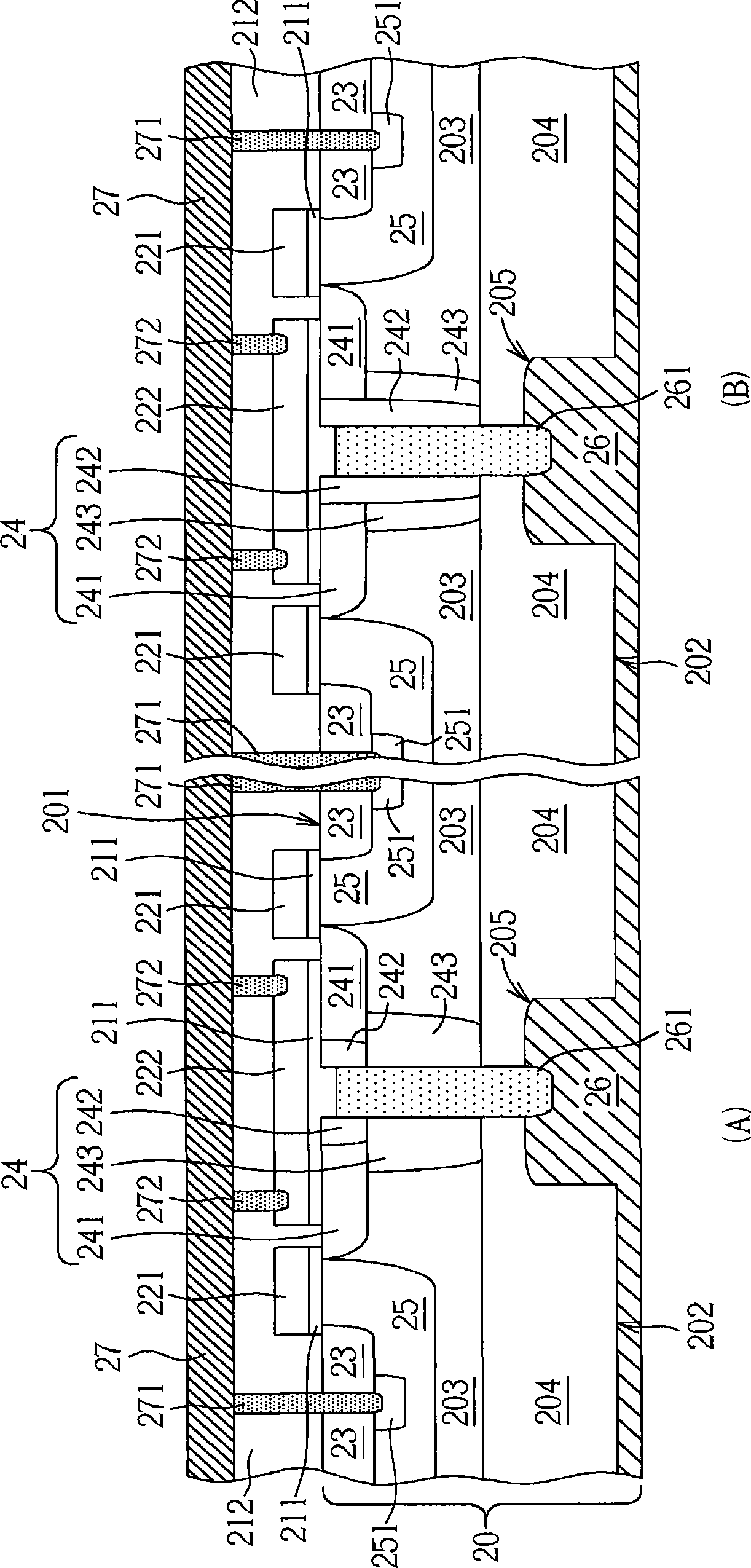

Semiconductor Element And Manufacturing Method Thereof

ActiveCN102412298BIncrease the output capacitanceReduce switching noiseSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorEngineering

The invention provides a semiconductor element and a manufacturing method thereof. The semiconductor element includes a second semiconductor layer comprising first columns in a first conductive type and second columns in a second conductive type arranged alternately in a direction of a main surface of the first semiconductor layer; a first control electrode embedded in a groove arranged in a direction from the surface of the second semiconductor layer to the first semiconductor layer; and a second control electrode arranged on the second semiconductor layer connecting with the first control electrode. A first semiconductor area in the second conductive type is arranged on the surface of the second semiconductor except a part covered by the second control electrodes. A second semiconductor area in the first conductive type are arranged selectively and separately with the surface of the second semiconductor layer covered by the second control electrodes on the surface of the first conductive area. Besides, a third semiconductor area in the second conductive type neighboring to the second semiconductor area is arranged on the surface of the first semiconductor area selectively.

Owner:KK TOSHIBA

Semiconductor device, display panel, and electronic device

ActiveUS10360855B2High degree of freedom of choiceNovel structureStatic indicating devicesSolid-state devicesAudio power amplifierLeast significant bit

A semiconductor device having a novel structure is provided. Fluctuation in the grayscale voltage due to an offset voltage is suppressed. When a current corresponding to a lower-bit grayscale voltage is generated in a transconductance amplifier, voltages VHI and VLO supplied to the transconductance amplifier are alternately input to two input terminals in accordance with a digital signal of the most significant bit of lower bits. Since a change corresponding to the offset voltage is added to both the maximum and minimum values of the current output from the transconductance amplifier, fluctuation in the grayscale voltage due to the offset voltage can be suppressed.

Owner:SEMICON ENERGY LAB CO LTD

Anti-EMI super-junction VDMOS device and preparation method thereof

PendingCN114093951AImprove breakdown voltageReduce Switching ShockSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

The invention provides an anti-EMI super-junction VDMOS device and a preparation method thereof. The device is provided with a composite dielectric layer consisting of an oxide layer (SiO2), a semi-insulating polycrystalline silicon layer (SIPOS) and an oxide layer (SiO2) in a super-junction drift region, wherein the oxide layer isolates a drift region from the SIPOS layer, the lower portion of the SIPOS layer is connected with the device drain electrode metal, and the upper portion of the SIPOS layer is connected with the device source electrode metal. When the device is in a turn-off state, the composite dielectric layer assists in depletion of the super junction drift region, so that the doping concentration of the drift region can be greatly improved, and the phenomenon that the withstand voltage is reduced due to mismatch between a super junction P column and an N column can be relieved; and in the switching process of the device, because the SIPOS is directly connected with the source electrode and the drain electrode of the device, the output capacitance Coss of the device is greatly improved, the switching oscillation is reduced, and thus the voltage oscillation dV / dt failure possibility and the EMI noise of the device are reduced.

Owner:济南市半导体元件实验所

Sense circuit and method of operation thereof and photoelectric conversion array connected to inverting input of sense circuit

InactiveUS9571770B2SpeedShorten the timeTelevision system detailsMaterial analysis by optical meansPhotoelectric conversionEngineering

A sense circuit includes a differential amplifier circuit including an inverting input section, a non-inverting input section and an output section, an electrical capacitor connected between the inverting input section and the output section, and a field effect transistor including a source, a drain, and a gate. One of the source and the drain is connected to the inverting input section, and the other of the source and the drain is connected to the output section. A reference potential is supplied to the non-inverting input section, and an output section of a photoelectric conversion cell having an added switching function is connected to the inverting input section.

Owner:NAT INST OF ADVANCED IND SCI & TECH +1

piezoelectric transformer

ActiveCN108140719BIncrease the output capacitancePiezoelectric/electrostrictive/magnetostrictive devicesCapacitancePiezoelectric transformer

The invention relates to a piezoelectric transformer comprising a piezoelectric element (1) of length L, wherein an input voltage U can be applied to the input side (2) in To be converted to the output voltage U on the output side (3) according to the transformation ratio formula (1) out . The piezoelectric element (1) has a plurality of layers (4a, 4b, 4c) of internal electrodes, which are arranged in a plurality of different layers (S1, S2, S3). Each ply (4a, 4b, 4c) of the internal electrode extends along at least one predetermined subsection of a predetermined length, wherein subsections of plies (4a, 4c) of the first set of layers (S1, S3) and the subsections of the plies (4b) of the second set of layers (S2) have different dimensions such that the piezoelectric transformer satisfies the following condition: C in ≤N 2 C out , where C in Indicates the input capacitance, C out denotes the output capacitance, and N denotes the transformation ratio of the ideal transformer.

Owner:EPCOS AG

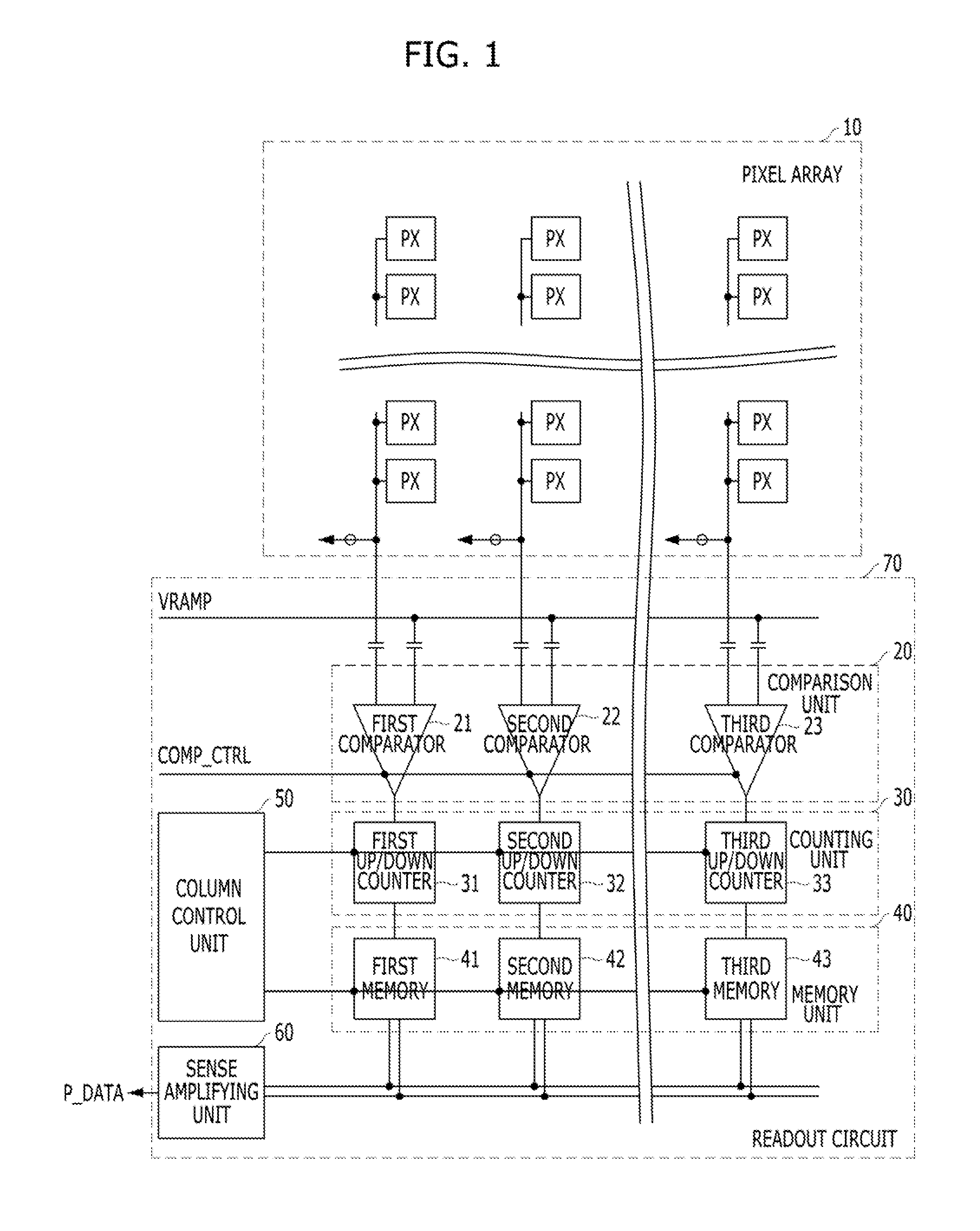

Method for reducing noise using layout scheme and comparing device

ActiveUS20150270834A1Horizontal noise be reduceReduce noiseMultiple input and output pulse circuitsInstant pulse delivery arrangementsEngineeringElectrical and Electronics engineering

A comparing device includes a first stage comparator and a second stage comparator serially coupled to the first stage comparator, wherein output lines of the second stage comparator are disposed to be overlapped with respective input lines of the second stage comparator.

Owner:SK HYNIX INC

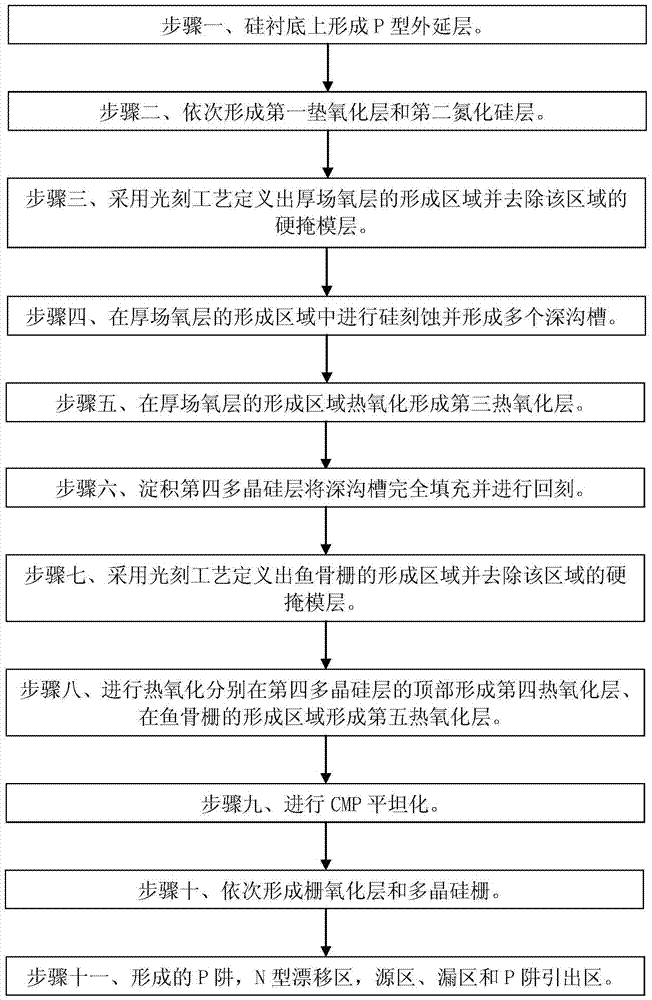

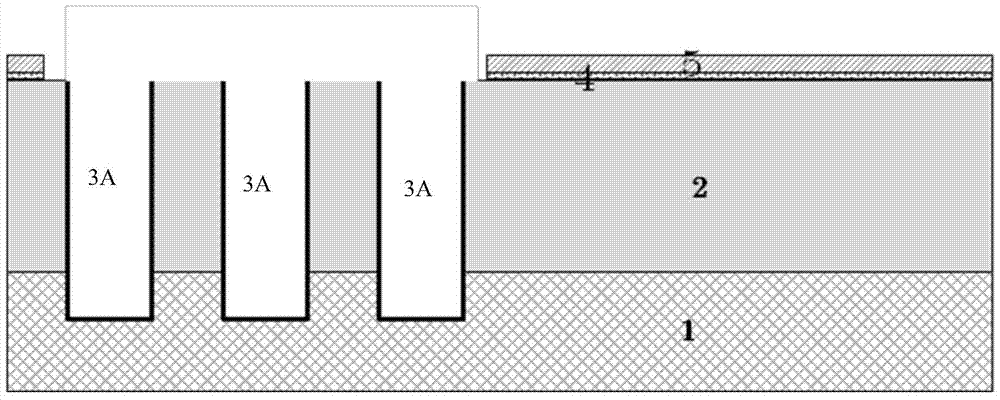

Fabrication method of rfldmos device

ActiveCN104576393BSimple preparation processReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesRadio frequencyPolysilicon gate

The invention discloses a manufacturing method of an RFLDMOS (radio frequency laterally diffused metal oxide semiconductor) device. The manufacturing method comprises steps as follows: a P-type epitaxial layer is formed on a silicon substrate; a first liner oxide layer and a second silicon nitride layer are sequentially formed; a forming region of a thick field oxide layer is defined, and a hard mask layer in the region is removed; multiple deep grooves are formed in the forming region of the thick field oxide layer; third thermal oxidation layers are formed in the forming region of the thick field oxide layer; fourth polycrystalline silicon layers are deposited, the deep grooves are completely filled with the fourth polycrystalline silicon layers, and an etch-back process is performed; a forming region of a fishbone gate is defined, and a hard mask layer in the region is removed; thermal oxidation is performed, fourth thermal oxidation layers are formed at the tops of the fourth polycrystalline silicon layers and a fifth thermal oxidation layer is formed in the forming region of the fishbone region; CMP (chemical mechanical polishing) flattening is performed; a gate oxide layer and a polysilicon gate are sequentially formed; a P well, an N-type drift region, a source region, a drain region and a P-well extraction region are formed. The manufacturing method enables a manufacturing process of the liner oxide layer under the fishbone gate to be simple and reduces the process cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Output driver for use in semiconductor device

ActiveUS7292068B2Reduced change in impedanceIncrease capacitanceReliability increasing modificationsFilament handlingDevice materialElectrical impedance

There is provided an output driver for use in a semiconductor device capable of remarkably improving linearity of impedance by reducing or minimizing a change of an impedance for output data caused due to a change of an external power supply. The output driver for outputting internal data of a semiconductor device to the exterior of a chip comprises a first driving section including a driving transistor to maintain an impedance for applied data at a certain level in response to the data; and a second driving section for compensating for linearity of the impedance in response to an operation signal from the driving transistor of the first driving section and providing an output terminal with the data.

Owner:SAMSUNG ELECTRONICS CO LTD

High-sensitivity piezo-resistive-capacitance superimposed force-sensitive sensor based on synchronous resonance

ActiveCN105628264BSuperimposed output voltage maximizationNovel structureForce measurementCapacitanceElectricity

The invention relates to a synchronous resonance-based high-sensitivity voltage, resistance and capacitance superposition force sensor and belongs to the field of synchronous resonance cantilever force sensors capable of realizing voltage, resistance and capacitance superposition. The lower part of a C-shaped supporting structure is fixedly connected with a piezoelectric excitation structure; the middle part of the C-shaped supporting structure is connected with a U-shaped beam, a T-shaped beam and a synchronous coupling beam; two sides of the T-shaped beam is connected with the synchronous coupling beam; the inner side of the U-shaped beam is connected with the synchronous coupling beam; a plurality of piezoelectric vibration pick-up structures are deposited on the surface of the T-shaped beam; the surface of the fixed end of the T-shaped beam is provided with a piezoresistance vibration pick-up structure; and two capacitance vibration pick-up structures form a differential capacitance vibration pick-up structure. The force sensor of the invention is novel in structure. Based on simple structure design, the piezoelectric, piezoresistance and capacitance vibration pick-up structures are integrated in the same structure, the output signals of the three structures are superposed, and therefore, output voltage can be further amplified, and the detection sensitivity of the sensor can be improved.

Owner:JILIN UNIV

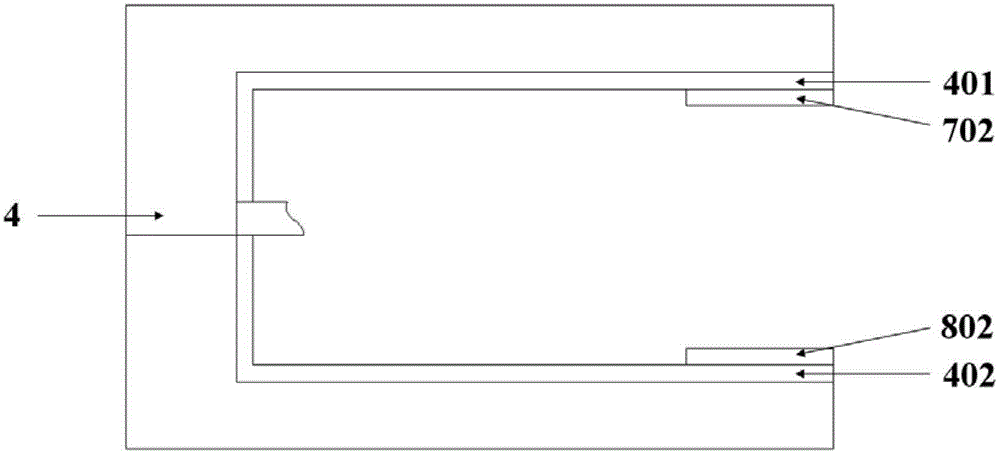

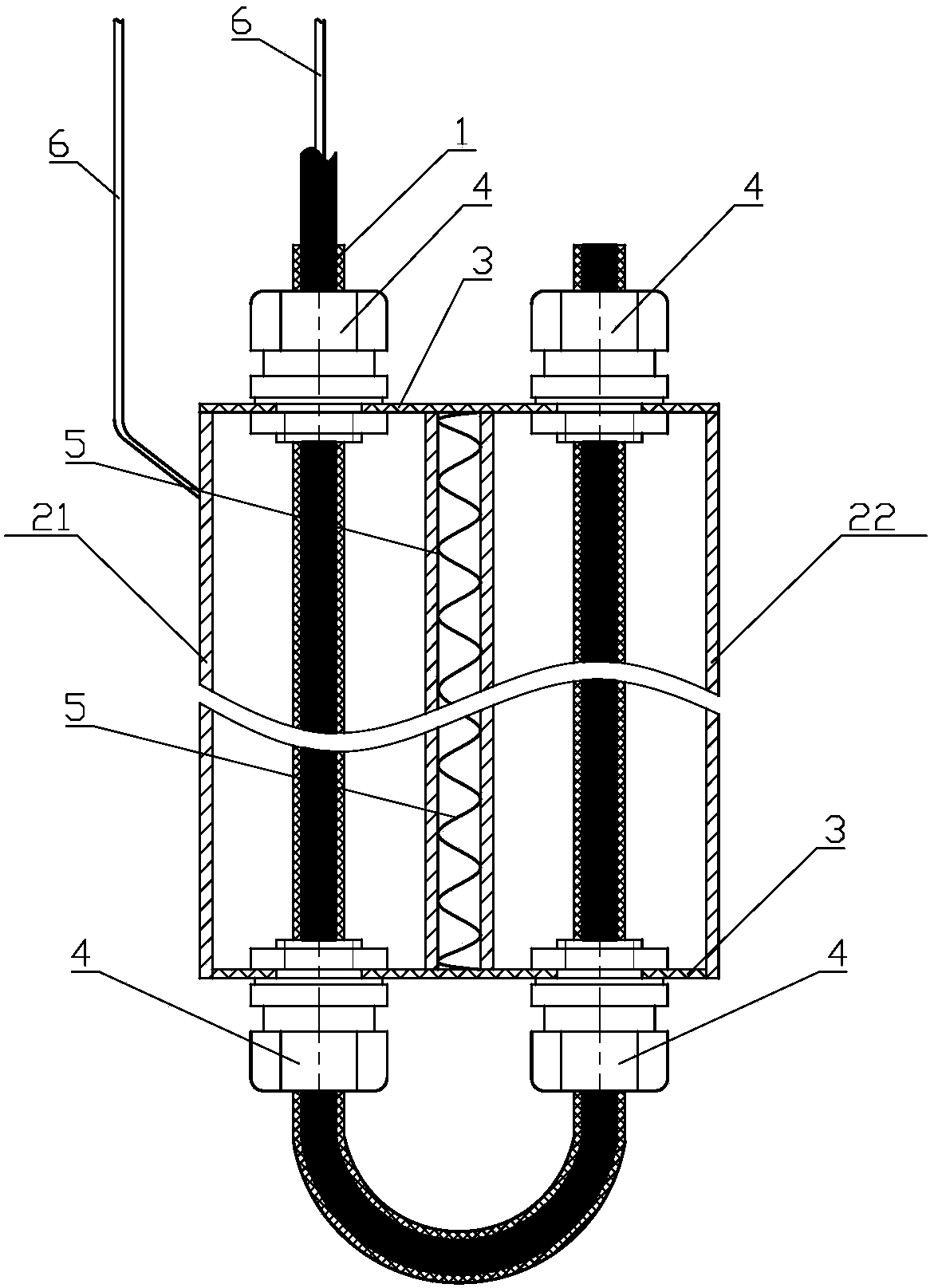

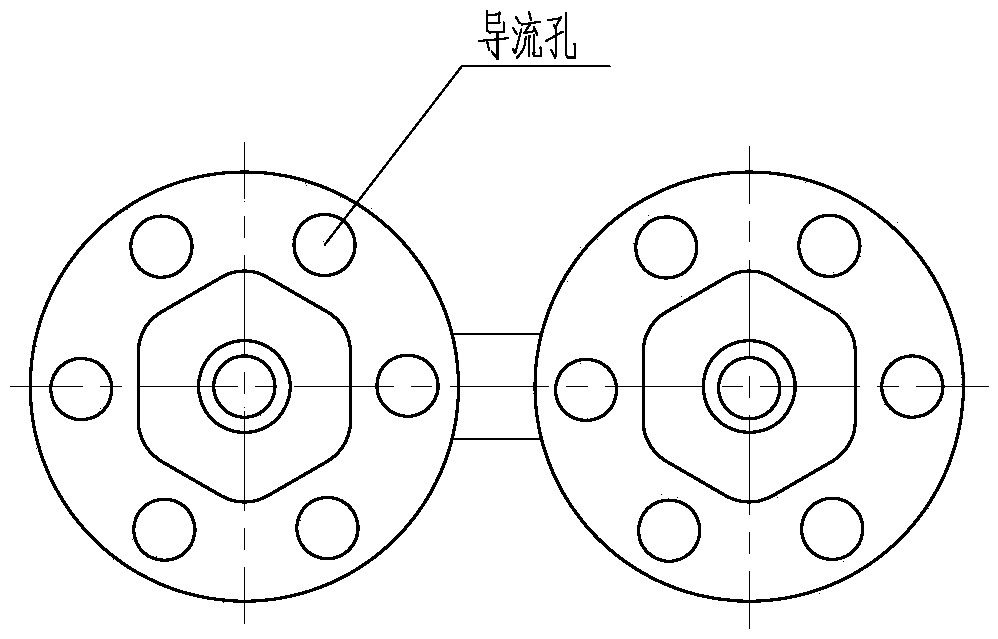

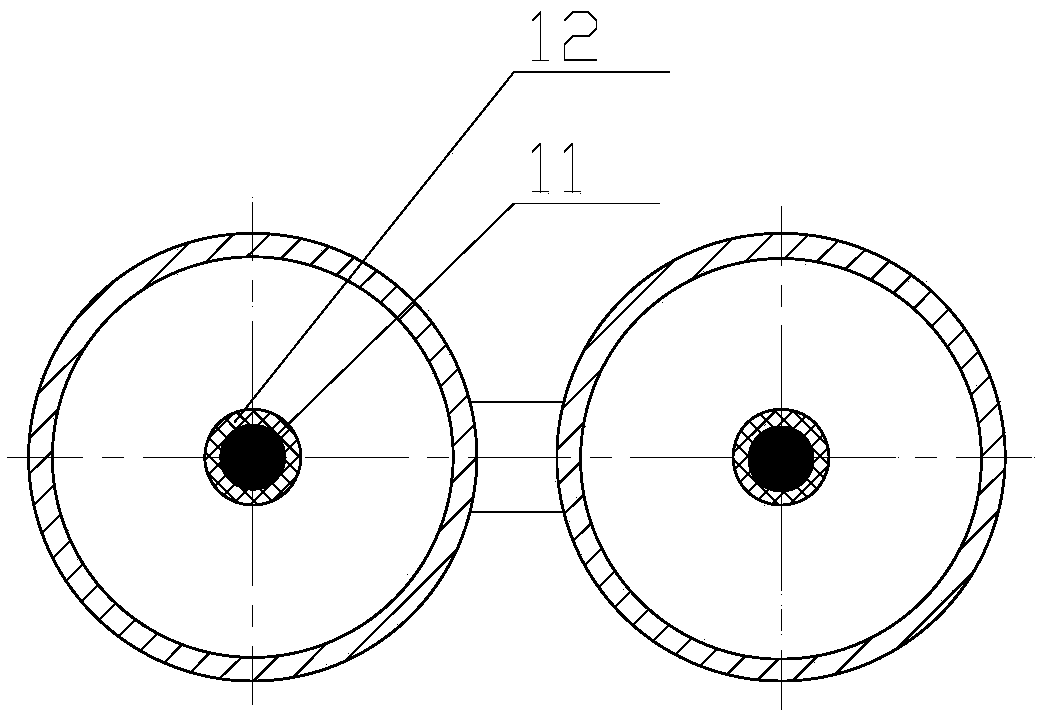

A double-tube flexible capacitive liquid level sensor and its measurement method

ActiveCN106768174BIncrease the output capacitanceHigh measurement accuracyLevel indicators by physical variable measurementCapacitanceMetallic electrode

The invention provides a double-tube flexible capacitive liquid level sensor and a measuring method thereof. The double-tube flexible capacitive liquid level sensor is provided with a single-stranded insulating copper core wire, two cylinders, end plates, cable head clamping assemblies, a spring and signal outgoing cables. The two cylinders are installed side by side at the same height, and the two end plates are installed at the two ends of the cylinders respectively and used for fixing the cable head clamping assemblies. The spring is placed between the two cylinders, and the spring is fixed to the end plates at the upper ends of the cylinders. The single-stranded insulating copper core wire penetrates through the two cylinders in a U shape and is fixed through the cable head clamping assemblies to serve as a metal electrode. The cylinders or a conducting medium serves as another electrode. The signal outgoing cables are arranged on the side walls of the first cylinder and the second cylinder. The double-tube flexible capacitive liquid level sensor is simultaneously suitable for measuring the liquid levels of the conducting medium, a non-conducting medium and different kinds of liquid, the measuring range can be adjusted according to the practical working condition, and the advantages that output capacitance is large, measuring precision is high, and the measuring range is convenient to adjust are achieved.

Owner:BEIJING RES INST OF TELEMETRY +1

Method for reducing noise using layout scheme and comparing device

ActiveUS9413343B2Reduce noiseIncrease capacitanceMultiple input and output pulse circuitsComparatorElectrical and Electronics engineering

A comparing device includes a first stage comparator and a second stage comparator serially coupled to the first stage comparator, wherein output lines of the second stage comparator are disposed to be overlapped with respective input lines of the second stage comparator.

Owner:SK HYNIX INC

Lateral diffusion metal oxide semiconductor assembly

ActiveCN102299179BReduced pressure resistanceImprove pressure resistanceSemiconductor devicesCapacitanceGate dielectric

The invention discloses a lateral diffusion metal oxide semiconductor assembly. The lateral diffusion metal oxide semiconductor assembly comprises a substrate, a gate dielectric layer, a gate polycrystalline silicon layer, a source region, a drain region, a matrix region, a first drain contact plug, a source polycrystalline silicon layer, an insulating layer and a source metal layer, wherein the source polycrystalline silicon layer arranged on the gate dielectric layer above the drain region is utilized to be served as a field plate so as to advance the breakdown voltage and improve the capacitance between a drain electrode and a source electrode. Besides, the first drain contact plug in the invention can effectively reduce the extended length of an on-resistance and the lateral between the drain electrode and the source electrode, thus the power consumption can be reduced and the assembly integration can be increased.

Owner:SINOPOWER SEMICON