Trench MOSFET and manufacturing method thereof

A manufacturing method and trench technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as input capacitance drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

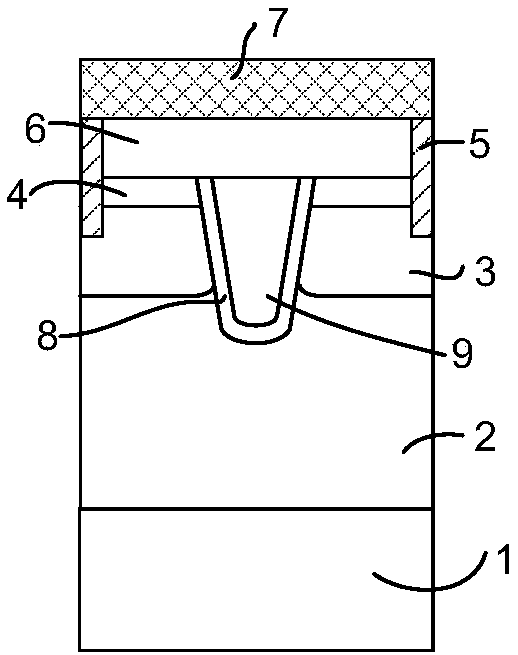

[0077] Trench MOSFET according to the first embodiment of the present invention:

[0078] The trench MOSFET according to the first embodiment of the present invention includes: a primitive cell region and a peripheral region, and the peripheral region is located on the periphery of the primitive cell region.

[0079] The device unit structure of the trench MOSFET is formed in the original cell area, and the device unit structure of each device please refer to figure 1 As shown, each of the device unit structures includes:

[0080] The first trench gate is formed by stacking the first gate dielectric layer 8 and the first polysilicon gate 9 formed in the first trench.

[0081] The drift region 2 is composed of the first epitaxial layer 2 doped with the first conductivity type.

[0082] The body region 3 is composed of a doped region of the second conductivity type formed on the surface of the drift region 2 .

[0083] The source region 4 is composed of a heavily doped region...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More