Tunneling field effect transistor and forming method thereof

A tunneling field effect, transistor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as poor driving ability and low operating current, and achieve improved driving ability, increased operating current, and speed. quick effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

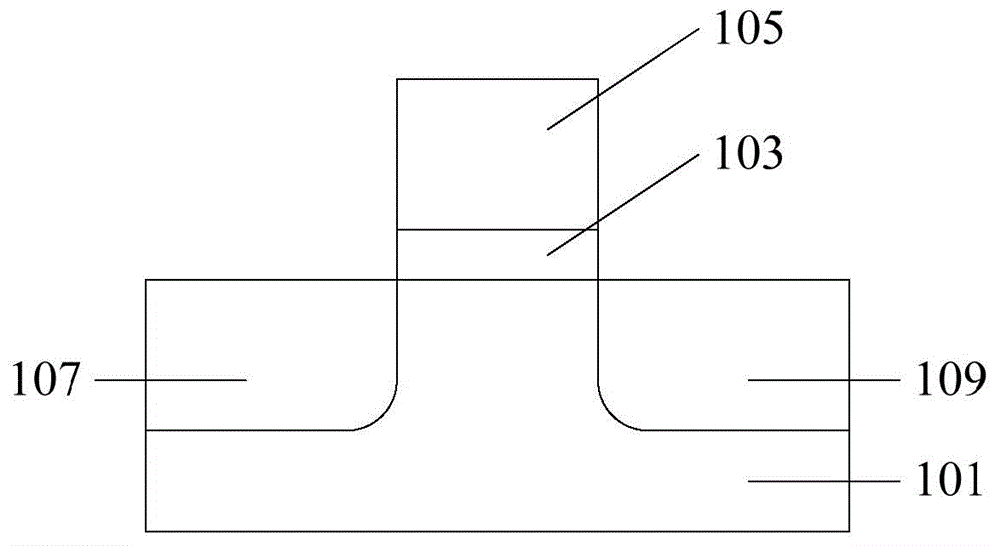

[0029] refer to figure 1 , is a schematic cross-sectional structure diagram of a P-type tunneling field effect transistor in the prior art, including: a semiconductor substrate 101; a gate structure located on the semiconductor substrate 101, the gate structure comprising a high The k dielectric layer 103 and the metal gate 105 located on the high-k dielectric layer 103; the source 107 is located in the semiconductor substrate 101 on one side of the gate structure; the drain 109 is located between the gate structure and In the semiconductor substrate 101 on the side opposite to the source. Wherein, the conductivity type of the semiconductor substrate 101 and the drain 109 is P type, and the conductivity type of the source 107 is N type. Since the operating current of the tunneling field effect transistor is proportional to the tunneling area of the PN junction in the tunneling field effect transistor, and figure 1 The PN junction tunneling area of the medium tunneling fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More