Field-effect transistor and preparation method thereof

A technology of field effect transistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems that reliability has not been well studied, and achieve fast switching speed, small leakage current, and shock The effect of high breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

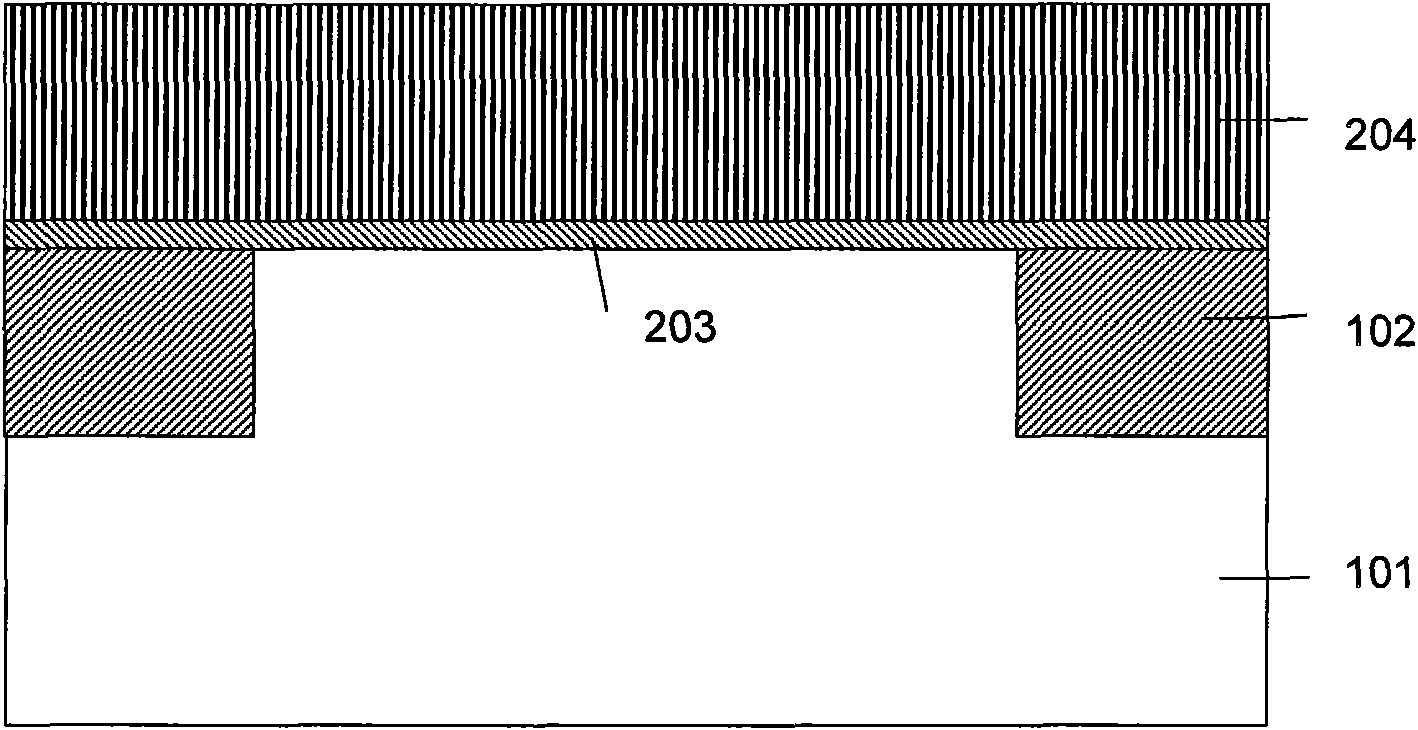

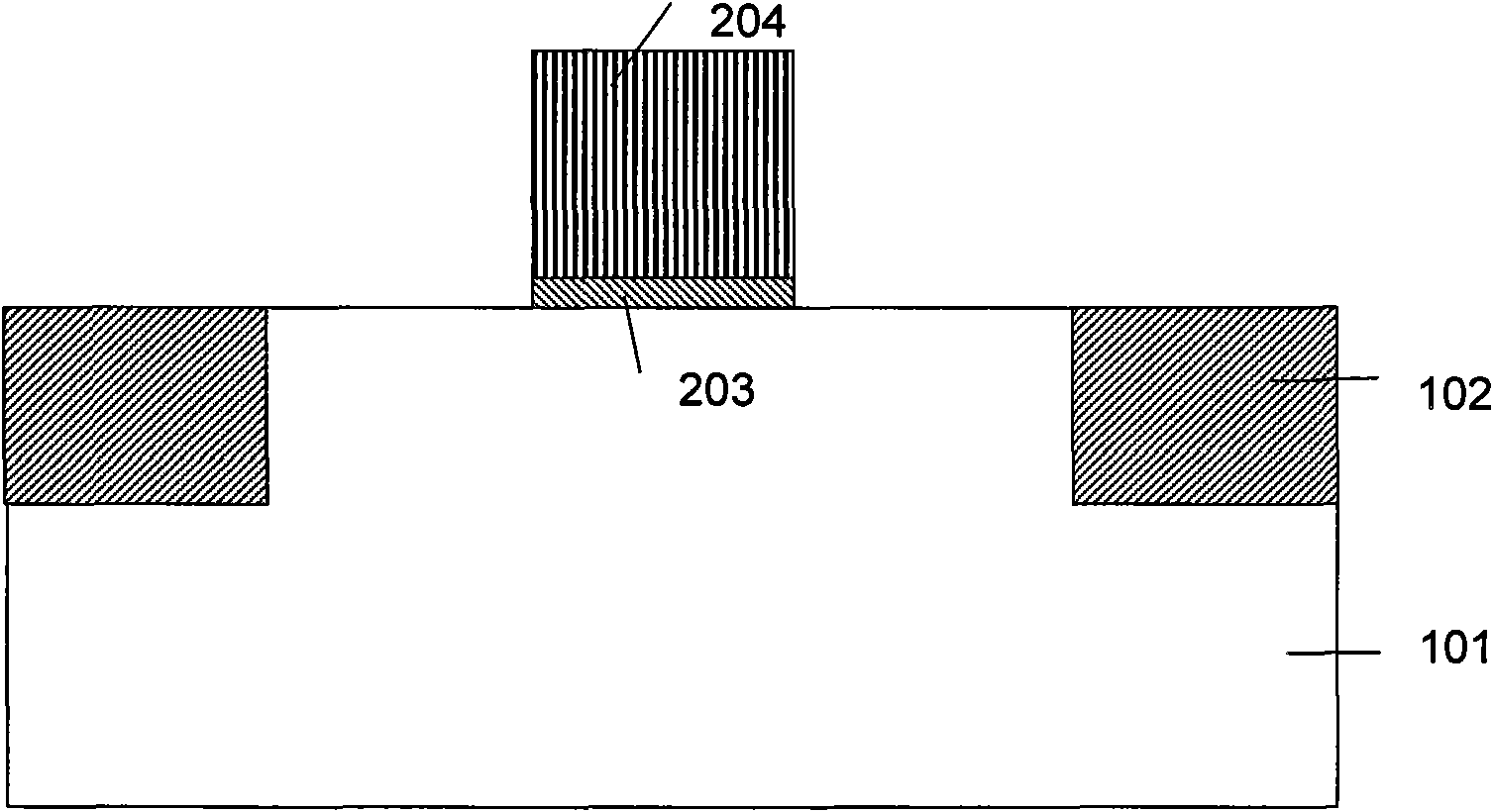

[0048]The structure and manufacturing process of the asymmetric source-drain field effect transistor proposed by the present invention will be described in detail below with reference to the accompanying drawings. In the following description, the same reference numerals denote the same components, and repeated description thereof will be omitted. In the following reference drawings, for convenience of description, the sizes of different layers and regions are enlarged or reduced, so the shown sizes do not necessarily represent actual sizes, nor do they reflect the proportional relationship of sizes.

[0049] It should be noted that many widely different embodiments may be constructed without departing from the spirit and scope of the present invention. It should be understood that the invention is not limited to the specific examples described in the specification, except as defined in the appended claims.

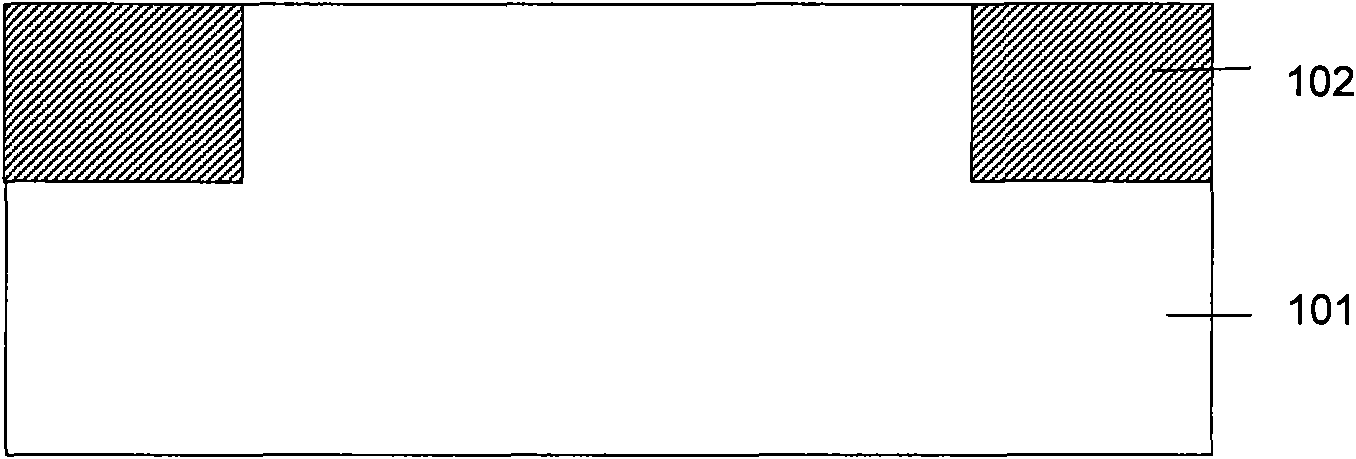

[0050] figure 1 is a schematic cross-sectional view of a semicondu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More