Aluminum oxide gate dielectric double gate graphene transistor on silicon substrate and preparation method thereof

A technology of aluminum oxide and graphene, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems affecting device performance, growth, and inability to play an insulating role, so as to simplify the manufacturing process and improve modulation effect, the effect of suppressing the scattering effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

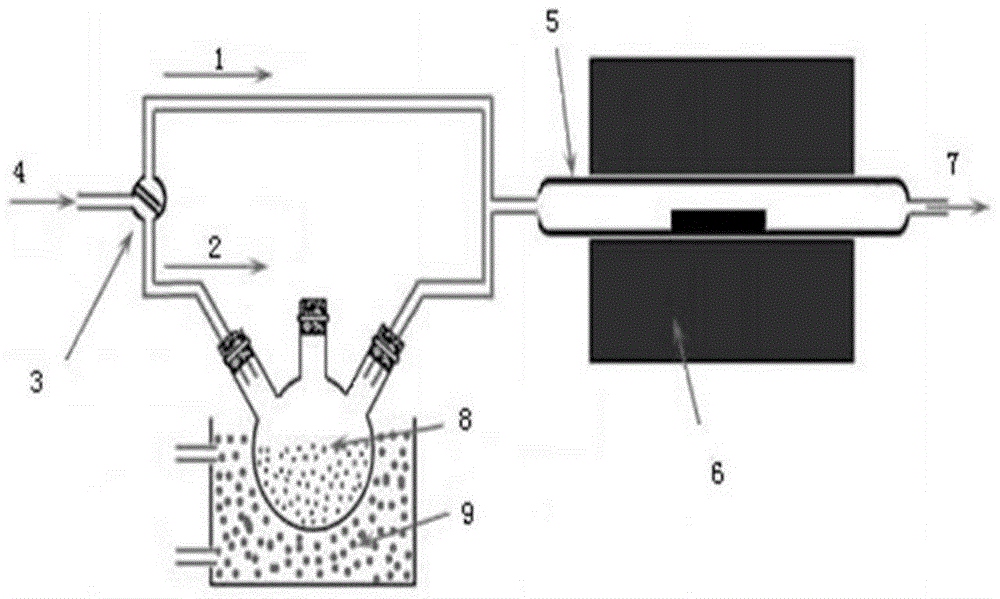

[0038] Step 1: Clean the Si substrate sample to remove surface contaminants such as Figure 4 (a) shown.

[0039] (1.1) Use NH on the Si substrate sample 4 OH+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove the organic residue on the surface of the sample;

[0040] (1.2) Use HCl+H on the Si substrate sample after removing the surface organic residues 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove ionic pollutants.

[0041] Step 2: Grow the carbonized layer, such as Figure 4 (b) shown.

[0042] Put the Si substrate substrate into the reaction chamber of the chemical vapor deposition CVD system, and evacuate the reaction chamber to 10 -7 mbar level; at H 2 In the case of protection, the temperature of the reaction chamber is raised to the carbonization temperature of 900 ° C, and then the flow rate of 30 sccm is introduced into the reaction chamber. 3 h 8 , grow a layer of carbonized layer...

Embodiment 2

[0075] Step 1: same as step 1 of embodiment 1.

[0076] Step 2: growing a carbonized layer on the Si substrate, such as Figure 4 (b).

[0077]Put the Si substrate substrate into the reaction chamber of the chemical vapor deposition CVD system, and evacuate the reaction chamber to 10 -7 mbar level; at H 2 In the case of protection, the temperature of the reaction chamber is raised to the carbonization temperature of 1100 ° C, and then the flow rate of 30 sccm is introduced into the reaction chamber. 3 h 8 , grow a layer of carbonized layer on the Si substrate, the growth time is 6min.

[0078] Step 3: Epitaxial growth of 3C-SiC film, such as Figure 4 (c).

[0079] Raise the temperature of the reaction chamber rapidly to the growth temperature of 1300°C, and feed SiH with flow rates of 30sccm and 60sccm respectively. 4 and C 3 h 8 , carry out 3C-SiC film heteroepitaxial growth, the growth time is 45min; then in H 2 The temperature is gradually lowered to room tempera...

Embodiment 3

[0098] Step A: same as step 1 of embodiment 1.

[0099] Step B: Put the Si substrate substrate into the chemical vapor deposition CVD system reaction chamber, and vacuumize the reaction chamber to reach 10 -7 mbar level; at H 2 In the case of protection, the temperature of the reaction chamber is raised to 1200 ° C, and then the flow rate of 30 sccm is introduced into the reaction chamber. 3 h 8 , grow a layer of carbonized layer on the Si substrate, the growth time is 4min, the generated carbonized layer is as follows Figure 4 (b) shown.

[0100] Step C: Rapidly raise the temperature of the reaction chamber to 1350° C., and feed SiH at flow rates of 35 sccm and 70 sccm respectively 4 and C 3 h 8 , carry out 3C-SiC film heteroepitaxial growth, the growth time is 60min; then in H 2 Under protection, the temperature is gradually lowered to room temperature, and the growth of the 3C-SiC film is completed. The resulting 3C-SiC film is as follows: Figure 4 (c) shown.

[...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More