Double-gate graphene transistor using aluminum oxide as gate dielectric and preparation method thereof

A technology of aluminum oxide and graphene, which is applied in the field of microelectronics, can solve problems such as growth, affecting device performance, and inability to play an insulating role, and achieve the effects of improving modulation, simplifying the manufacturing process, and suppressing scattering effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

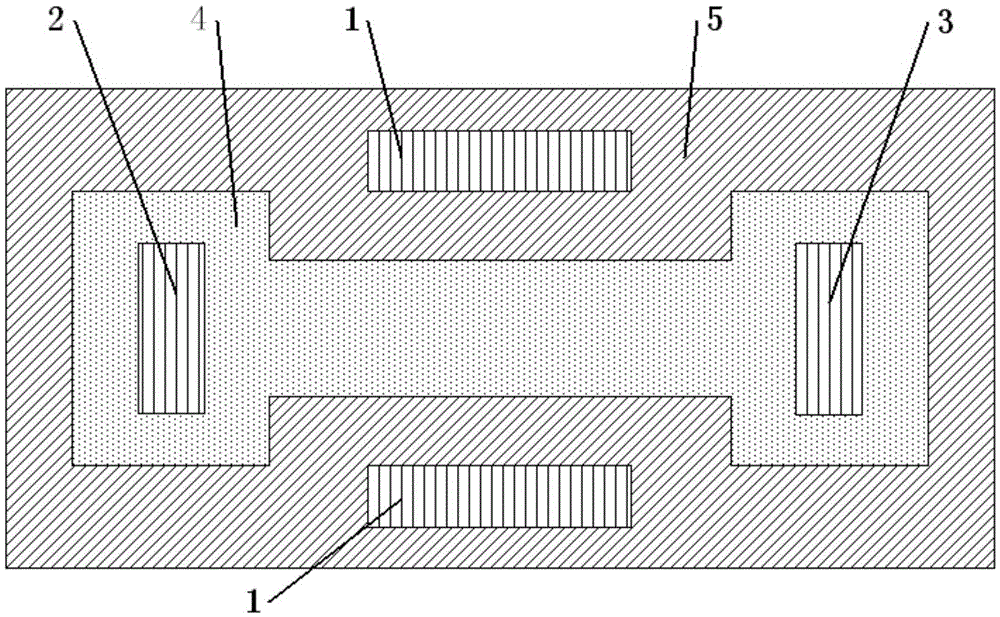

[0038] Step 1: Wash the 6H-SiC sample to remove surface contaminants such as Figure 4 (a).

[0039] (1.1) Use NH for 6H-SiC samples 4 OH+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove the organic residue on the surface of the sample;

[0040] (1.2) Use HCl+H on the 6H-SiC sample after removing the surface organic residues 2 o 2 The reagent soaked the sample for 10 minutes, took it out and dried it to remove ionic contamination.

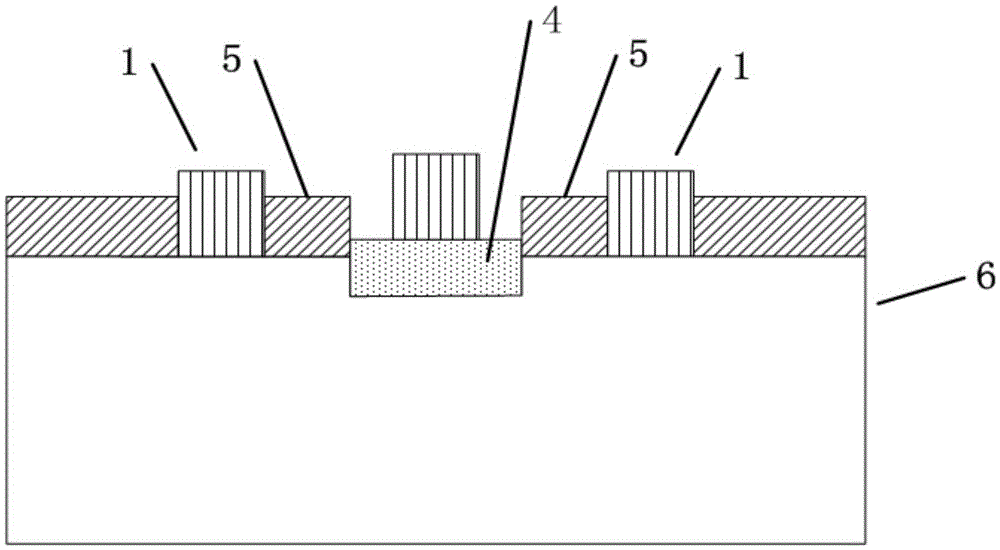

[0041] Step 2: Deposit a layer of Al on the surface of the 6H-SiC sample 2 o 3 ,Such as Figure 4 (b).

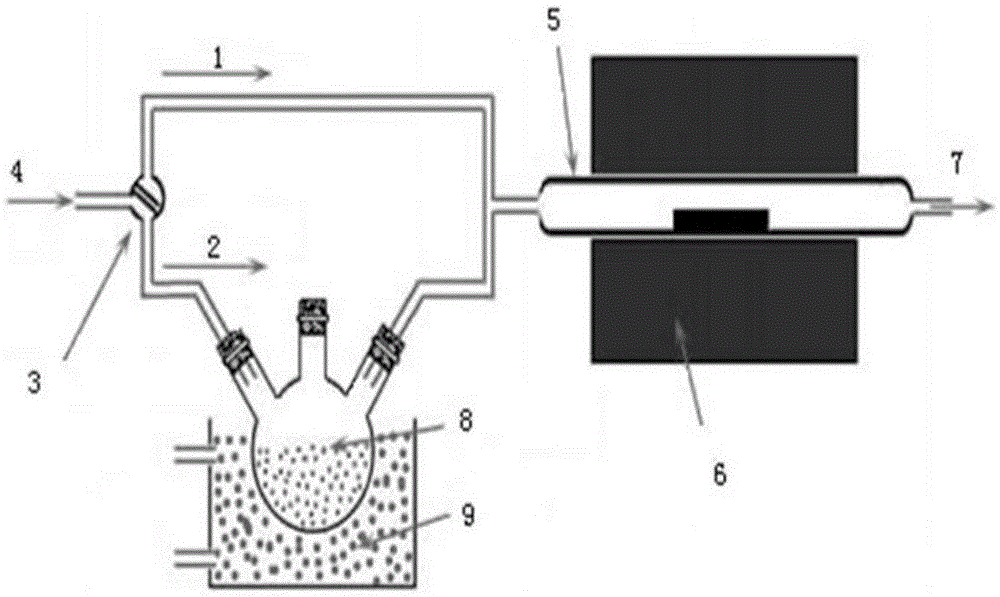

[0042] (2.1) Put the SiC sample into the growth chamber, and flow N into the growth chamber with a flow rate of 10 sccm 2 Perform a 2-minute purge and repeat the cycle 5 times;

[0043] (2.2) Turn on the thermostat, heat the growth chamber to 250°C, and heat the gas path to 40°C for 60 minutes;

[0044] (2.3) Introduce N with a flow rate of 10 sccm into the growth chamber 2 A 2 min purge was pe...

Embodiment 2

[0072] Step 1: Clean the 4H-SiC sample to remove surface contaminants such as Figure 4 (a).

[0073] Use NH for 4H-SiC samples 4 OH+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove the organic residue on the surface of the sample; use HCl+H 2 o 2 The reagent soaked the sample for 10 minutes, took it out and dried it to remove ionic contamination.

[0074] Step 2: Deposit a layer of Al on the surface of the 4H-SiC sample 2 o 3 ,Such as Figure 4 (b).

[0075] 2a) Put the SiC sample into the growth chamber, and flow 10 sccm of N into the growth chamber 2 Perform a 2-minute purge and repeat the cycle 5 times;

[0076] 2b) Turn on the thermostat, heat the growth chamber to 250°C, and heat the gas path to 40°C for 60 minutes;

[0077] 2c) Flow 10 sccm of N into the growth chamber 2 A 2 min purge was performed and the cycle was repeated 3 times. Thereafter, the flow rate of 15 sccm of N was continuously passed into the growth cham...

Embodiment 3

[0095] Step A: Use NH on the 4H-SiC substrate substrate 4 OH+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove the organic residue on the surface of the sample; use HCl+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove ionic contaminants such as Figure 4 (a).

[0096] Step B: Deposit a layer of Al on the surface of the 4H-SiC sample 2 o 3 film, such as Figure 4 (b)

[0097] B1) Put the SiC sample into the growth chamber, and flow 10 sccm of N into the growth chamber 2 Perform a 2-minute purge and repeat the cycle 5 times;

[0098] B2) Turn on the thermostat, heat the growth chamber to 250°C, and heat the air circuit to 40°C for 60 minutes;

[0099] B3) Infuse N with a flow rate of 10 sccm into the growth chamber 2 Carry out the purging of 2 minutes, repeat cycle 3 times, thereafter, feed the N that the flow rate is 15 sccm continuously to the growth chamber 2 ;

[0100] B4) Introduce wat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More