Ion sensitive field effect transistor and preparation process thereof

A field-effect transistor, ion-sensitive technology, applied in measurement devices, material analysis by electromagnetic means, instruments, etc., can solve the problems of reducing the accuracy and sensitivity of measuring ion concentration, reducing the signal-to-noise ratio of devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

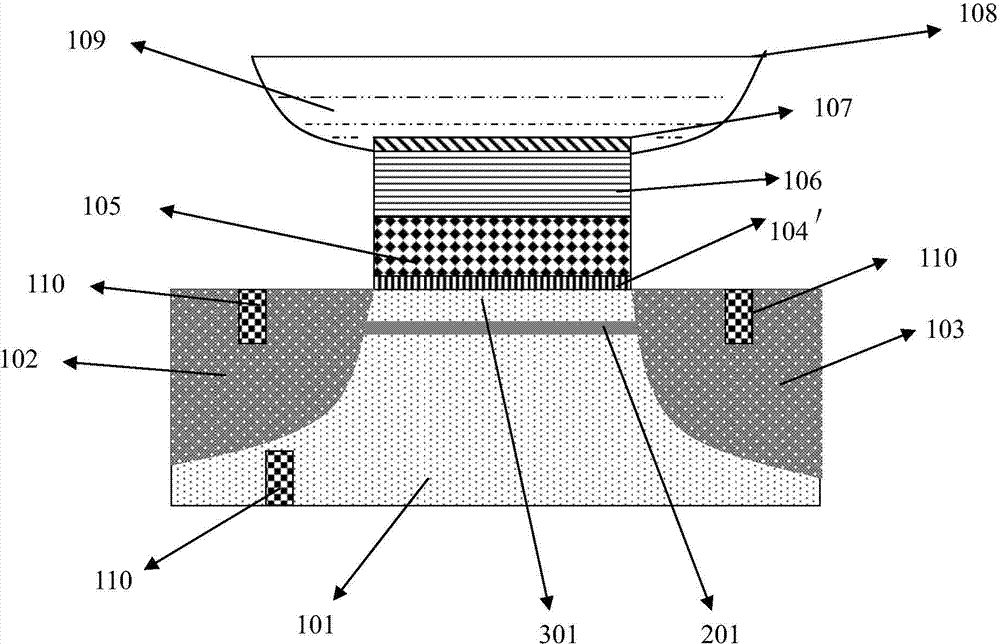

[0075] In this embodiment, since the conduction band positions of the energy bands of Si and SiGe are relatively close, and the forbidden band width of the SiGe material is smaller than that of the silicon material, holes can be gathered in the valence band region. When a current is formed between the source 102 and the drain 103 , holes tend to pass through the SiGe material with a lower forbidden band width rather than through the substrate extension layer 301 made of silicon. Compared with the first embodiment, there is no dopant ion of the same doping type as the buried channel in the substrate extension layer 301 in this embodiment, and the holes tend to all come from the SiGe buried channel with a smaller forbidden band width. 201 passes, and the mobility of holes in SiGe is greater than that in Si material, so that the current density will increase, and the sensitivity and accuracy of the current measurement of the entire device will be improved.

[0076] This embodimen...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More