Building-out circuit and testing method for testing negative bias temperature instability

A technology of negative bias temperature and instability, applied in the direction of single semiconductor device testing, etc., can solve the problems of inability to provide On-the-Fly special conditions, high cost of replacement equipment, etc., to achieve the suppression of recovery effects and accurate measurement results Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

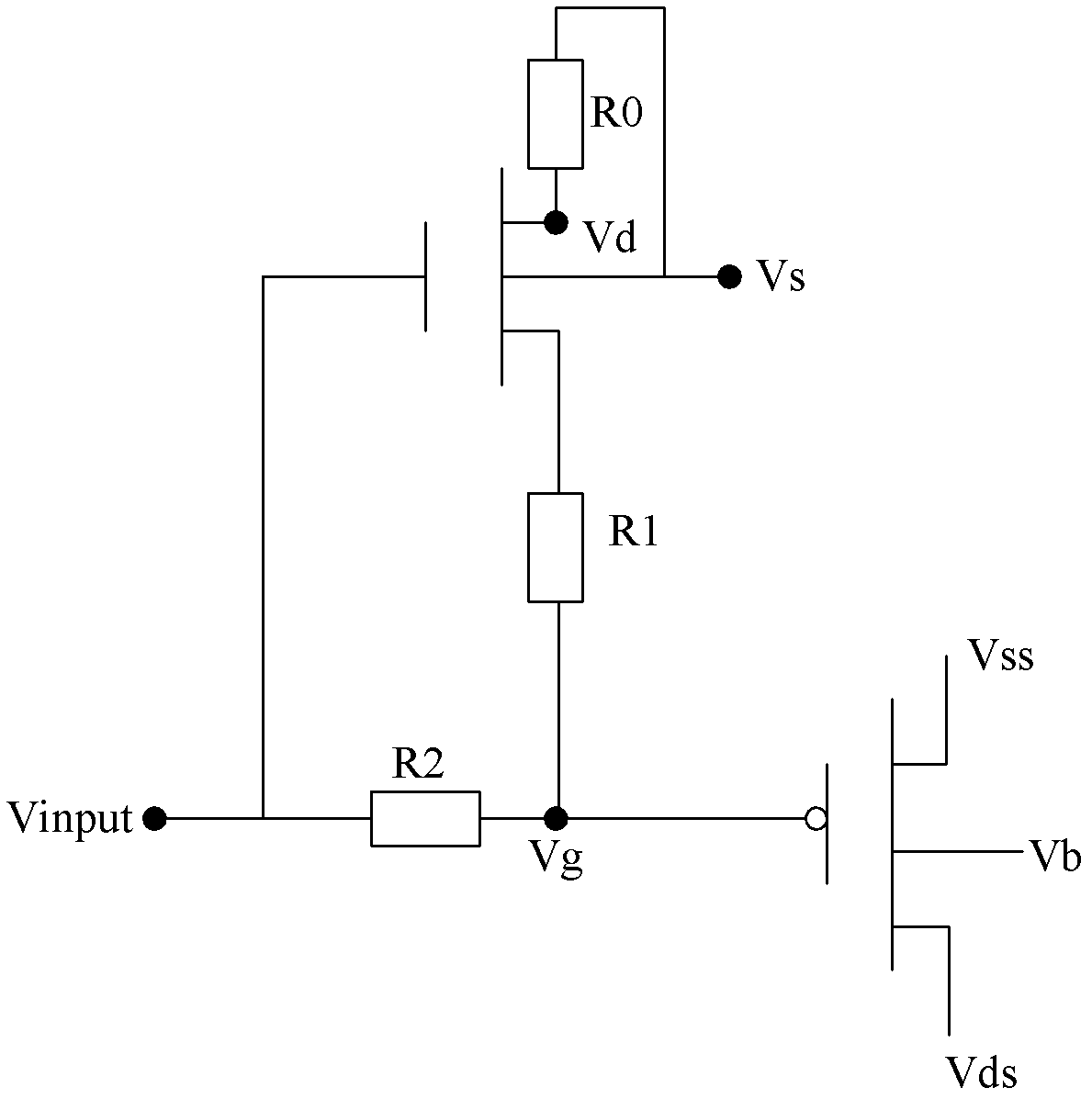

[0024] Such as image 3 A kind of NBTI test additional circuit of the present invention shown, comprises an NMOS; Wherein, the base of NMOS is electrically connected with the source of NMOS through resistance R0; The drain of NMOS is electrically connected with the PMOS gate to be tested through resistance R1; The gate of the NMOS is electrically connected to the gate of the PMOS to be tested through the resistor R2; the potential of the base of the NMOS is set to be less than 0V, and the voltage input terminal of the source-measurement unit is connected to the gate of the NMOS.

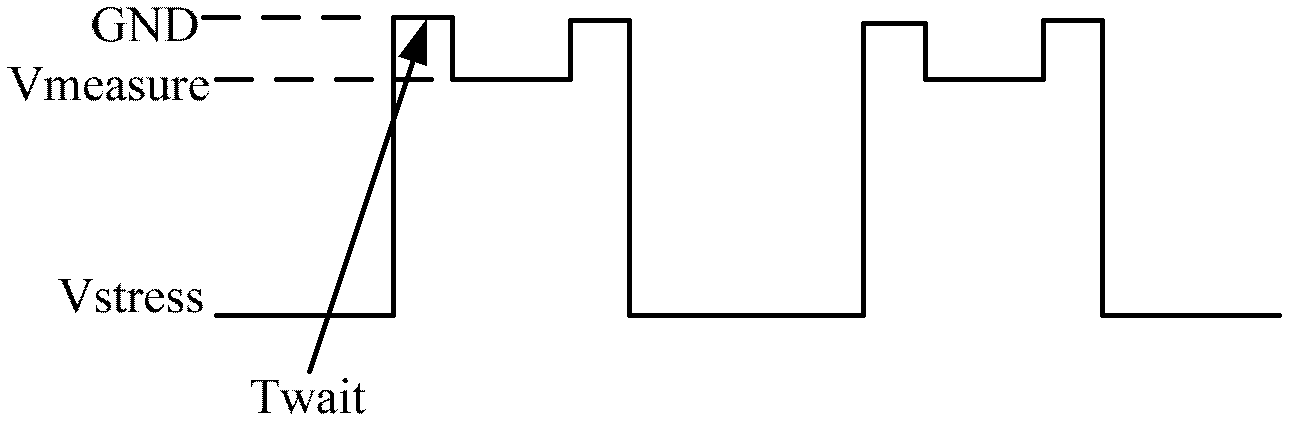

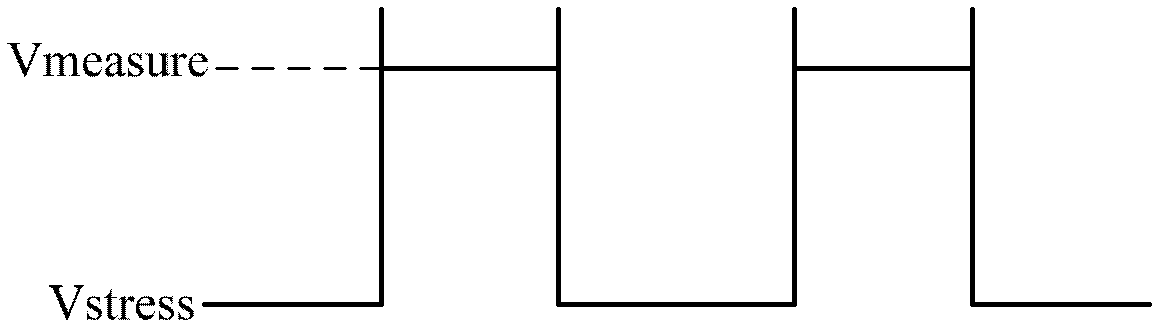

[0025] The voltage input terminal voltage of the source-measurement unit is less than or equal to 0V; the source, drain and base potentia...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More