Multifunctional test circuit of integrated circuit stress degradation and test method thereof

A multi-functional testing, integrated circuit technology, applied in the direction of electronic circuit testing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

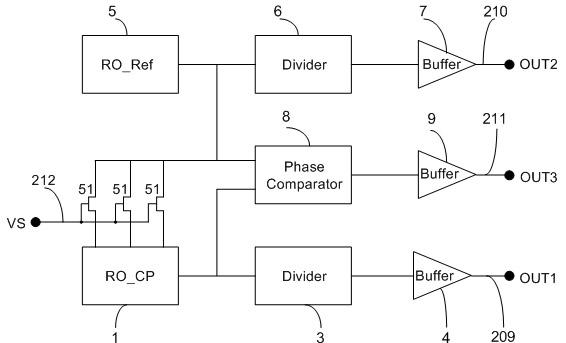

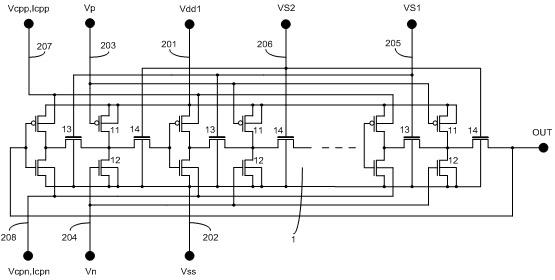

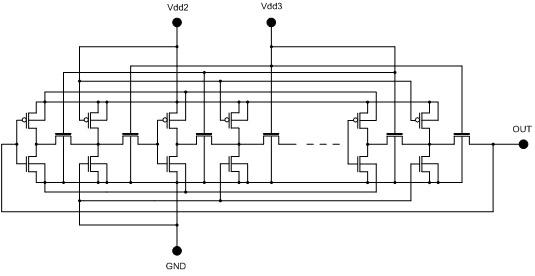

[0033] The circuit and method of the invention are used for reliability testing of integrated circuits, especially for degradation testing of CMOSFETs in integrated circuits under NBTI, PBTI, HCI and dynamic stress. The test parameters include the frequency change caused by the stress degradation of CMOSFETs in the ring oscillator inverter, and also include the CP current generated by the CMOSFETs under stress. The overall circuit as figure 1 As shown, there are a total of 15 external contact pads (Pad), which are the high power supply terminal Vdd1 of the core circuit, the low power supply terminal Vss of the core circuit, and the high power supply terminal commonly used by the reference circuit, frequency divider, buffer and phase comparator. Vdd2, the low power terminal GND commonly used by the reference circuit, frequency divider, buffer and phase comparator, the control terminal Vdd3 of all switches in the reference circuit, the control terminals VS, VS1, VS2 of the switc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More