Patents

Literature

90results about How to "Reduce chip cost" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

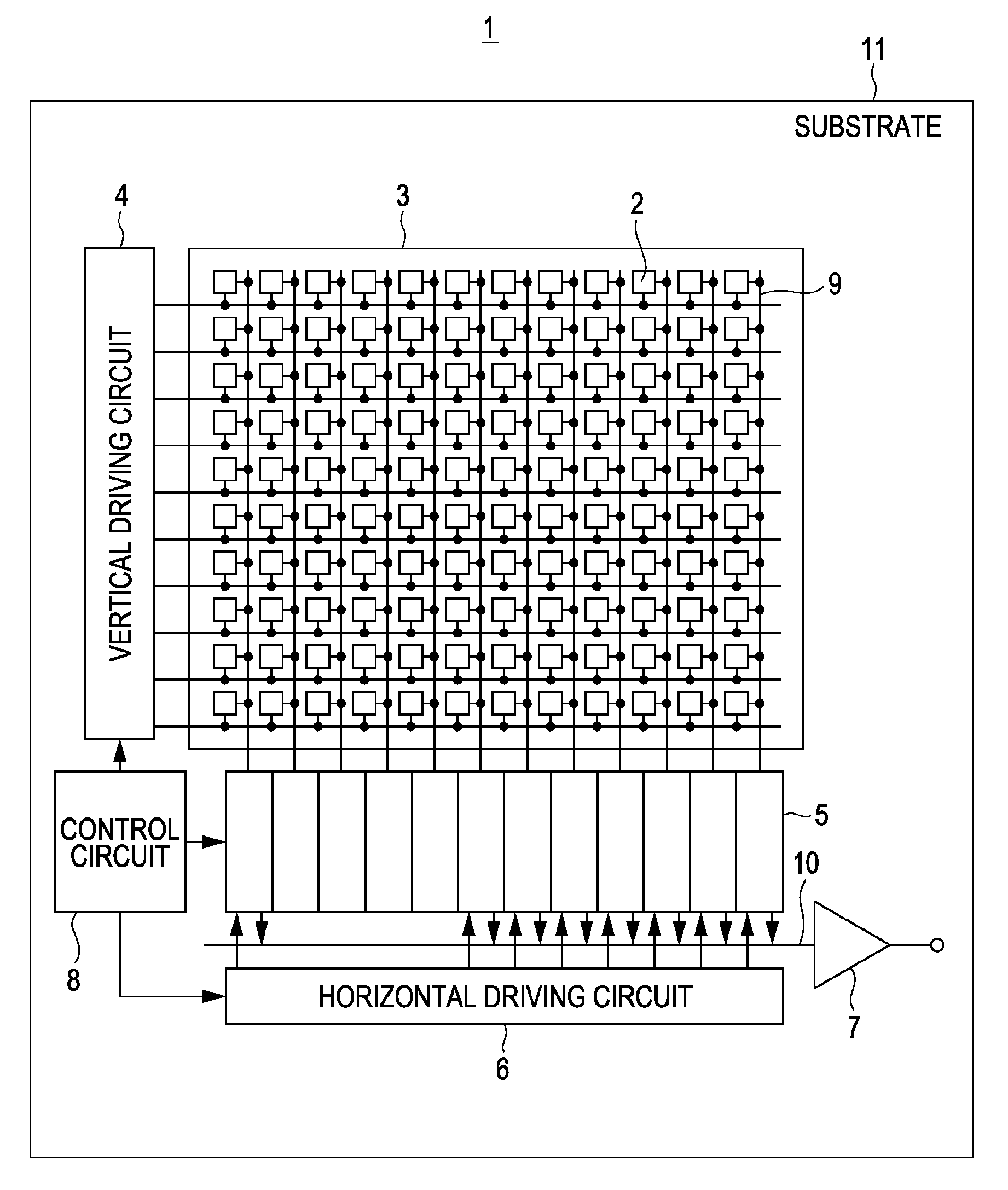

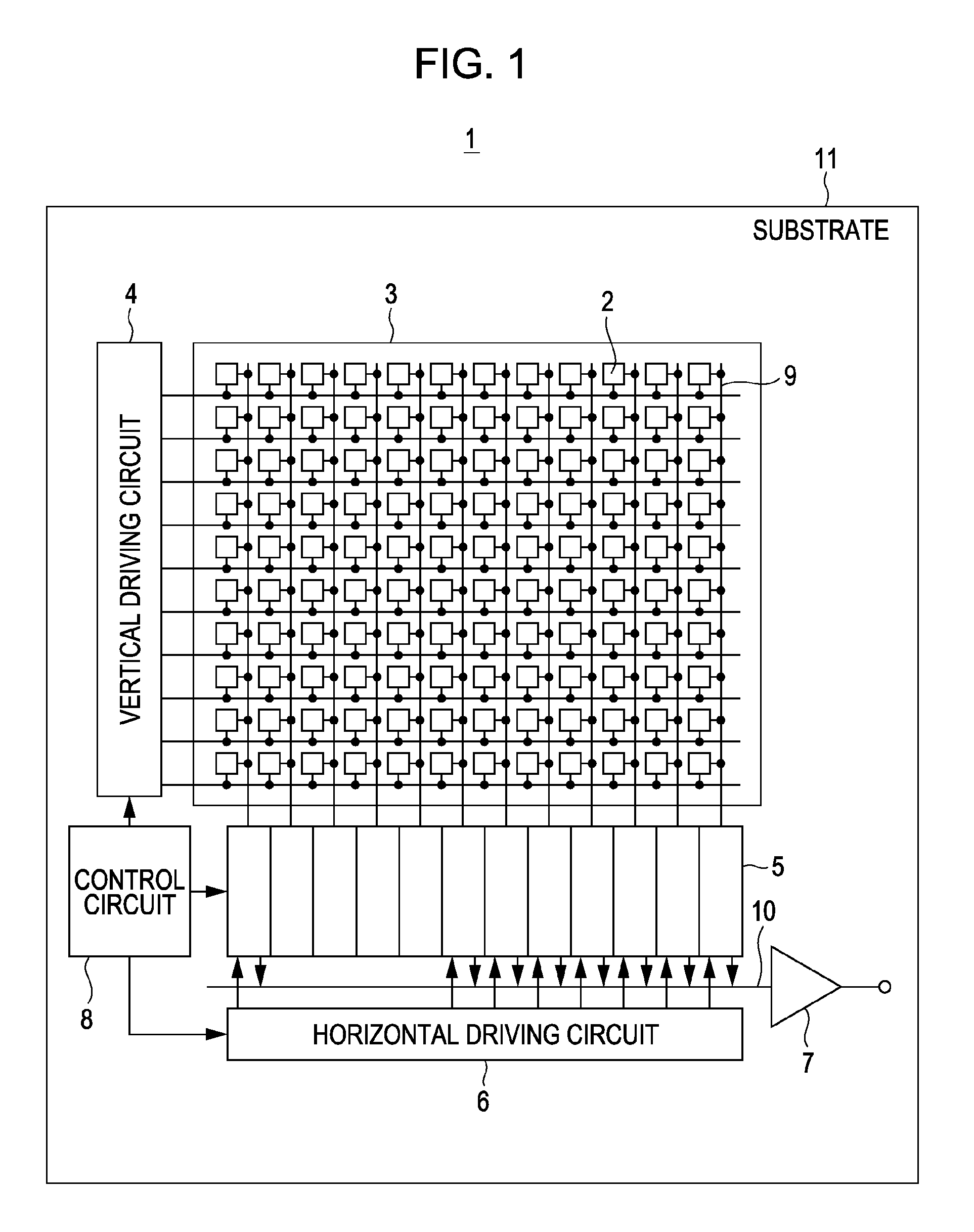

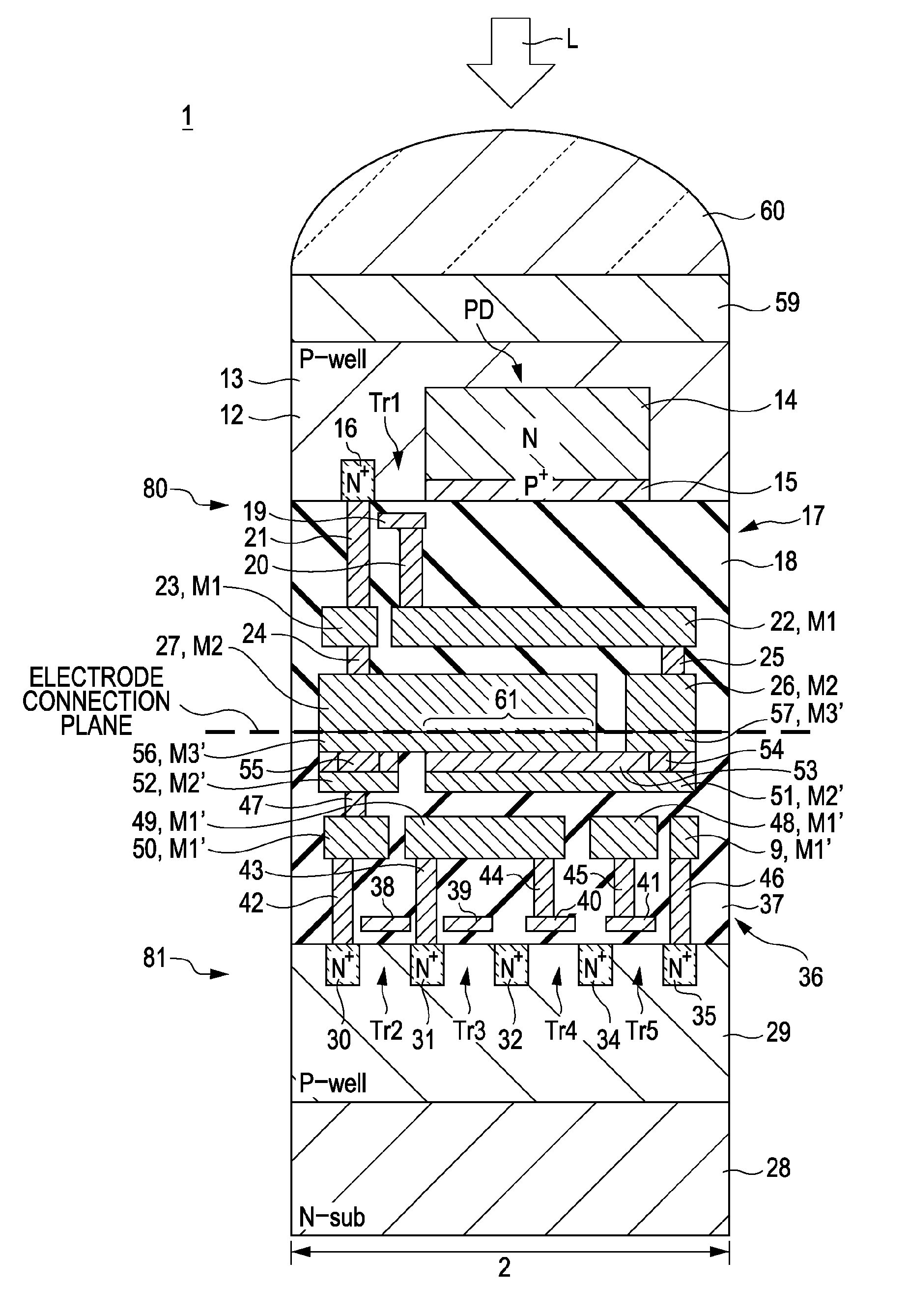

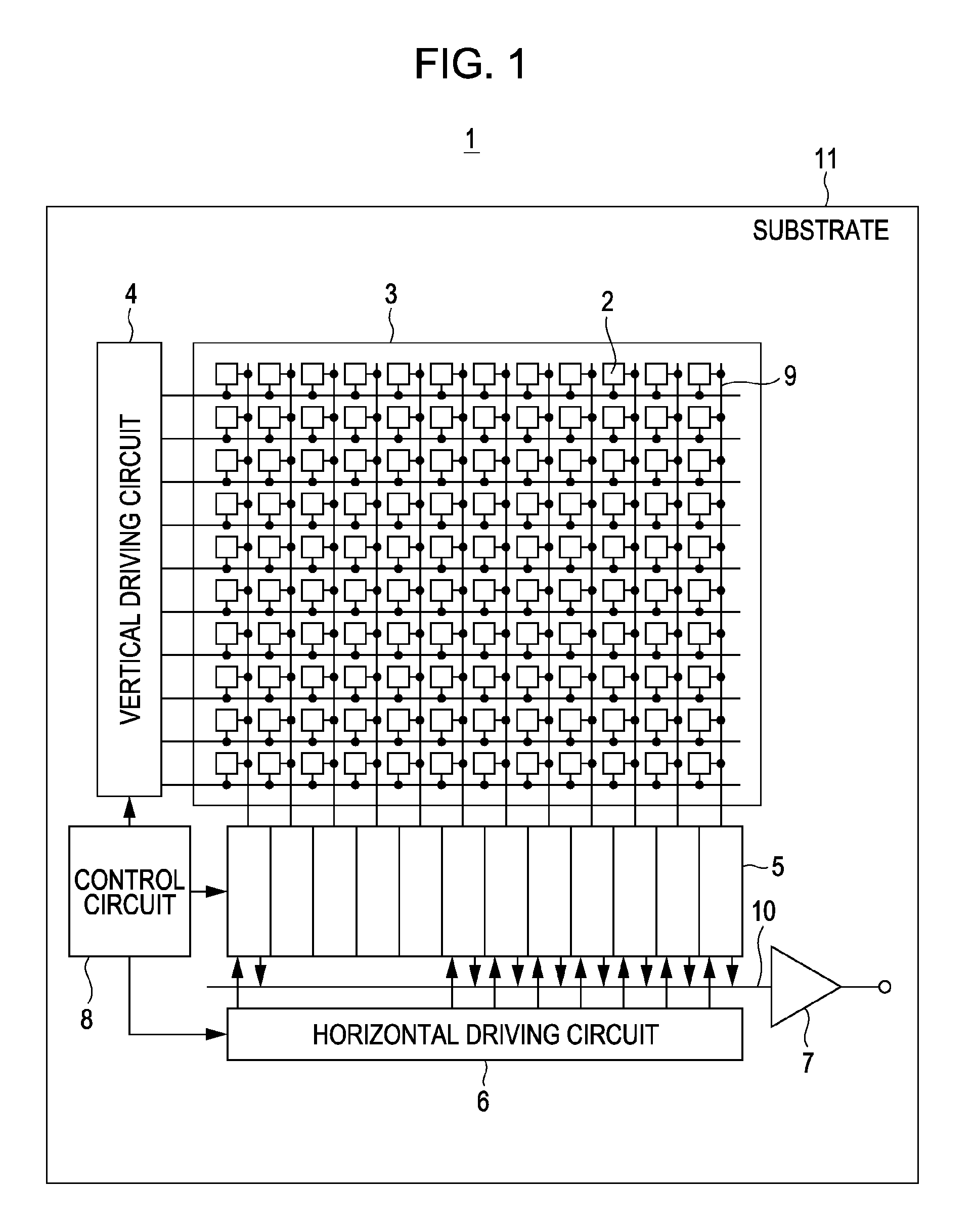

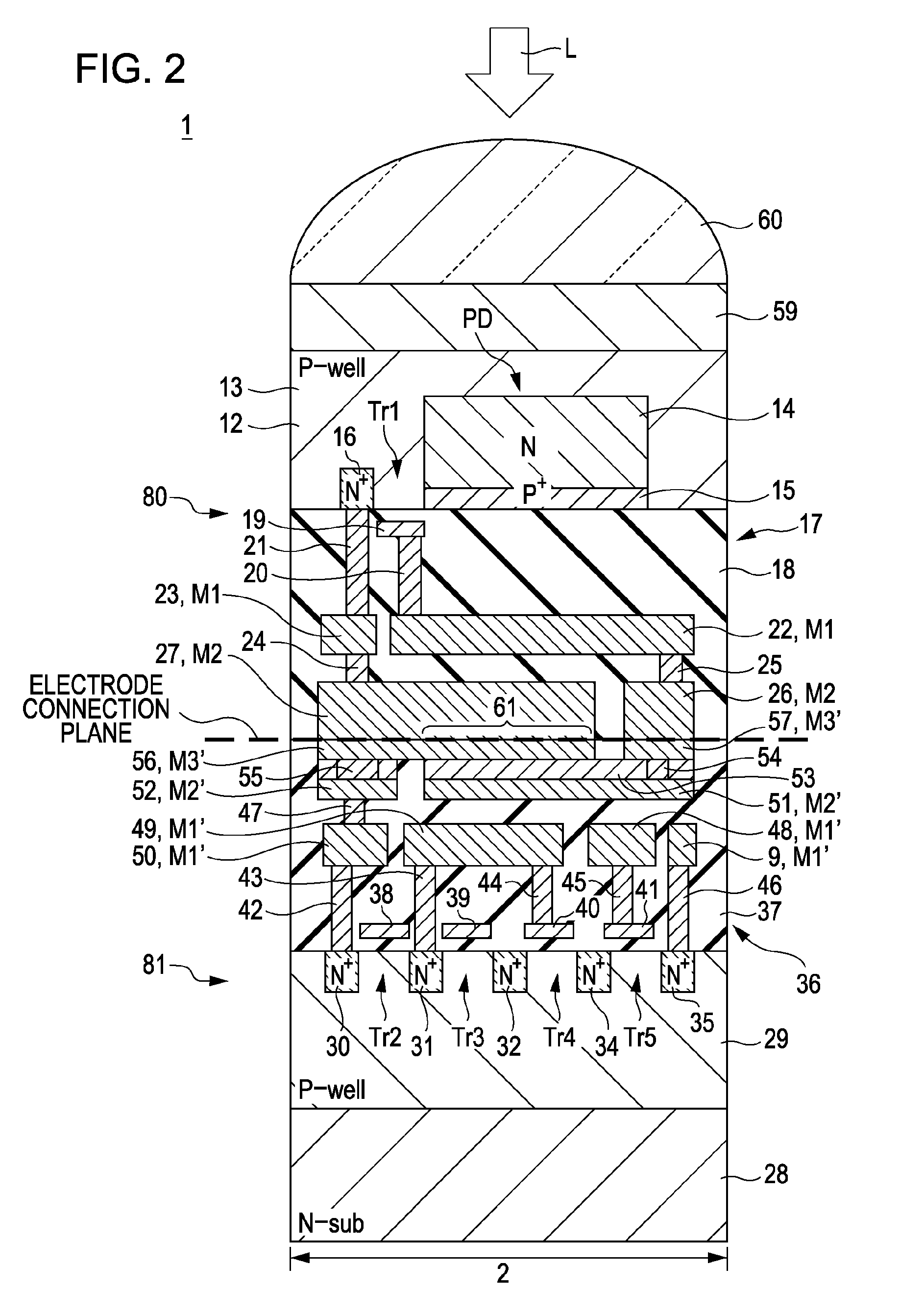

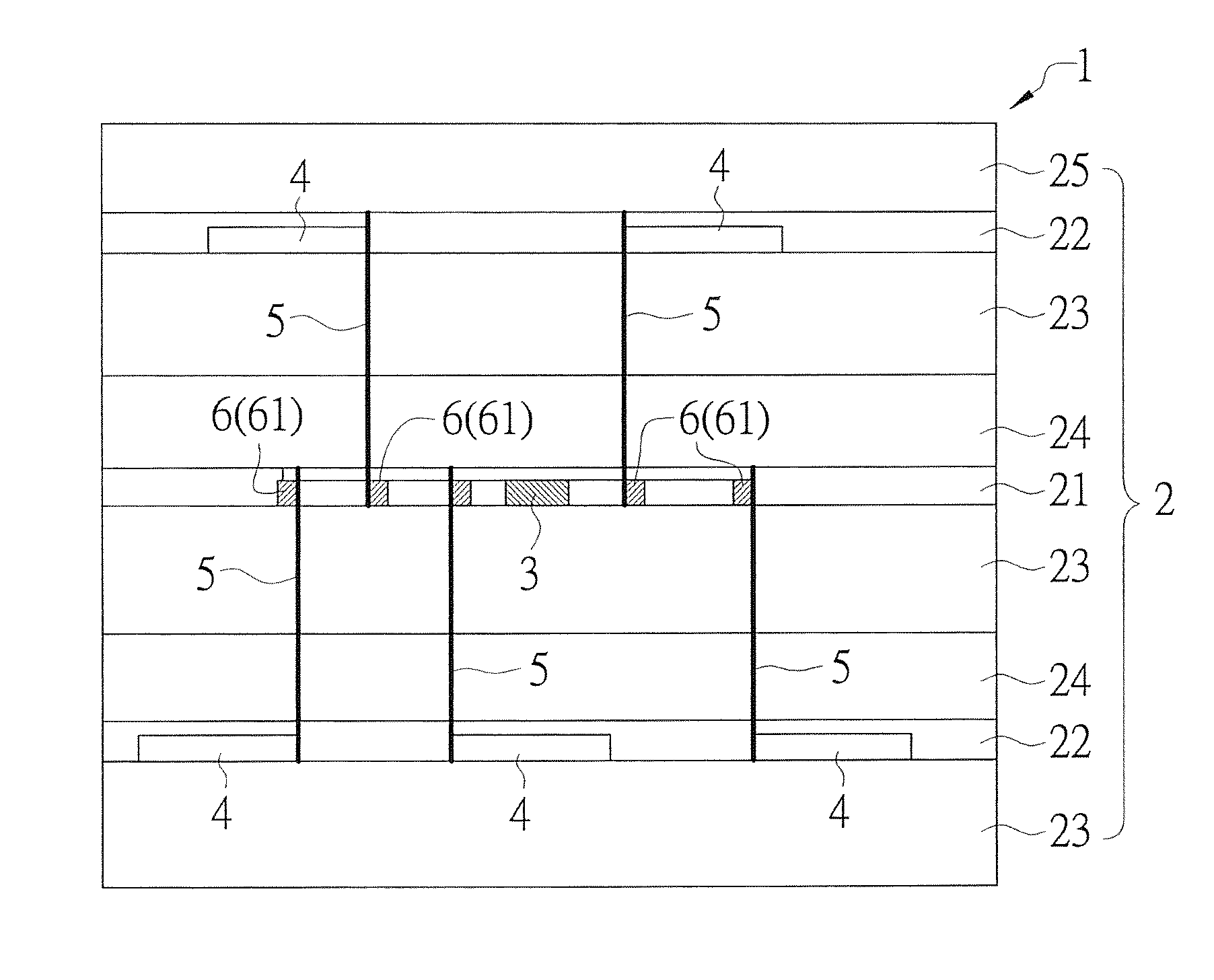

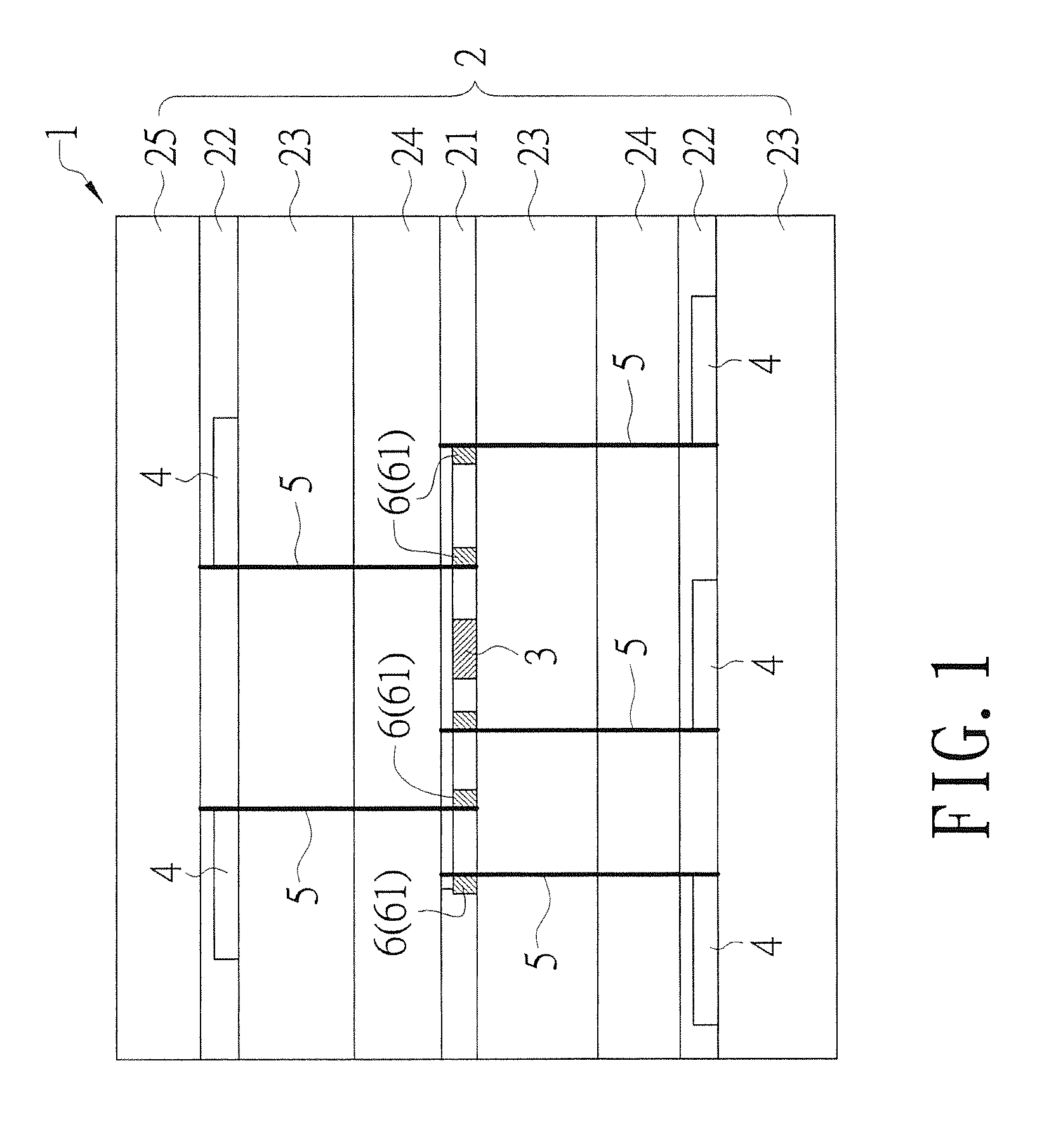

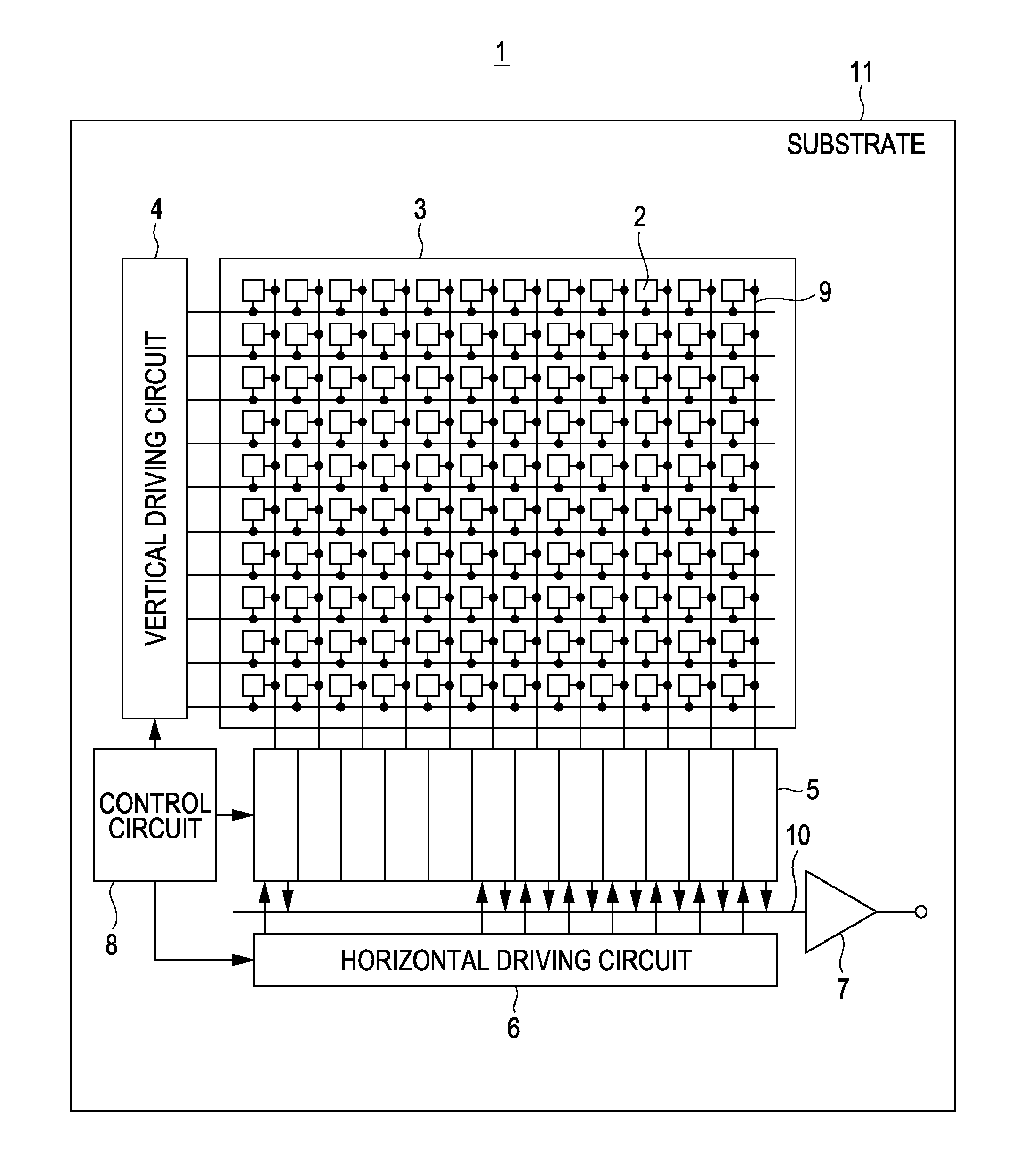

Solid-state imaging device, method of manufacturing the same, method of driving the same, and electronic apparatus

ActiveUS20100238334A1Reduce chip sizeReduce chip costTelevision system detailsTelevision system scanning detailsEngineeringElectron

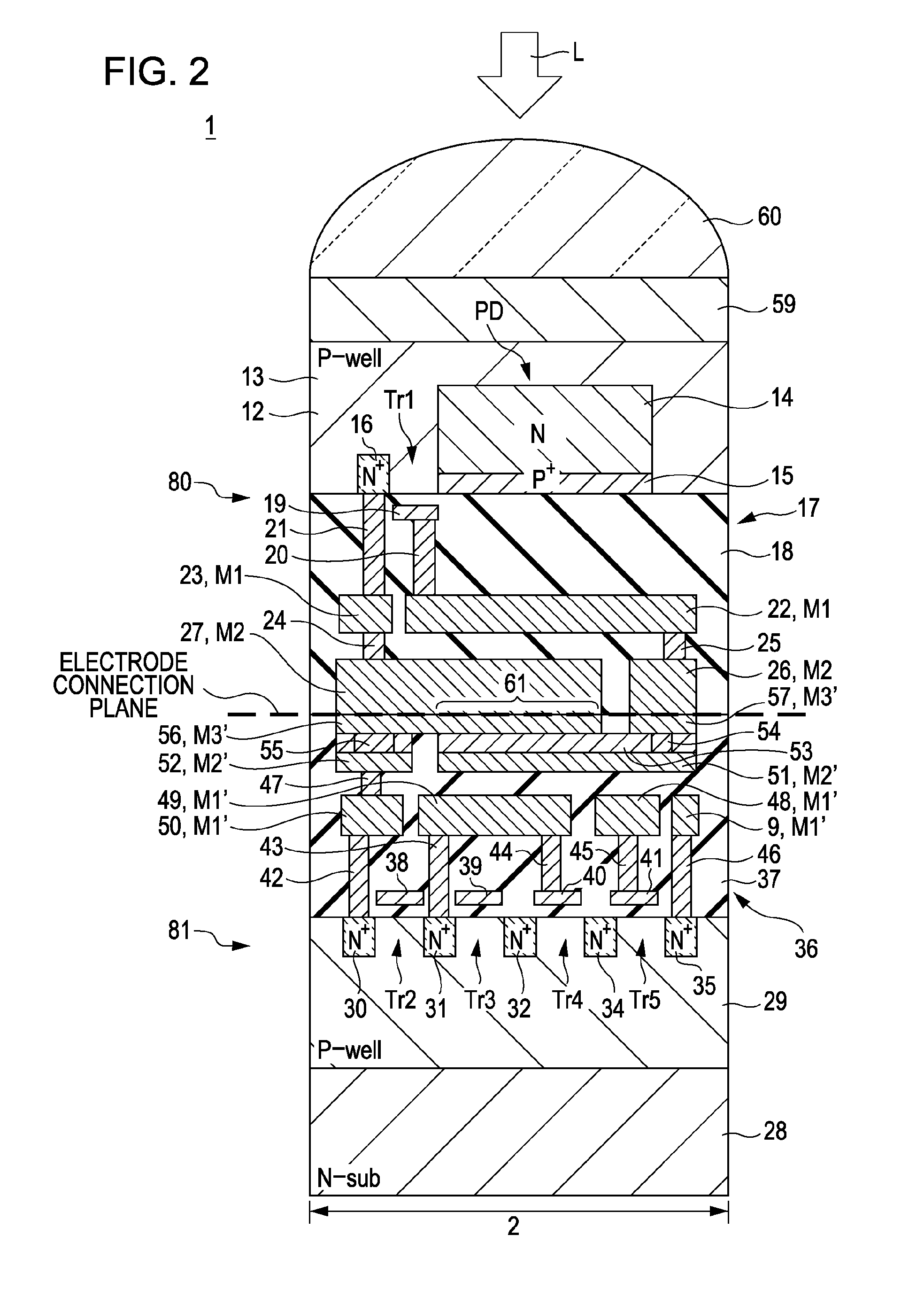

A solid-state imaging device includes a plurality of pixels, each of which includes a photoelectric converter section formed on a first substrate to generate and accumulate signal charges corresponding to incident light, a charge accumulation capacitor section formed on the first substrate or a second substrate to temporarily hold the signal charges transferred from the photoelectric converter section, and a plurality of MOS transistors formed on the second substrate to transfer the signal charges accumulated in the charge accumulation capacitor section, connection electrodes formed on the first substrate, and connection electrodes formed on the second substrate and electrically connected to the connection electrodes formed on the first substrate.

Owner:SONY CORP

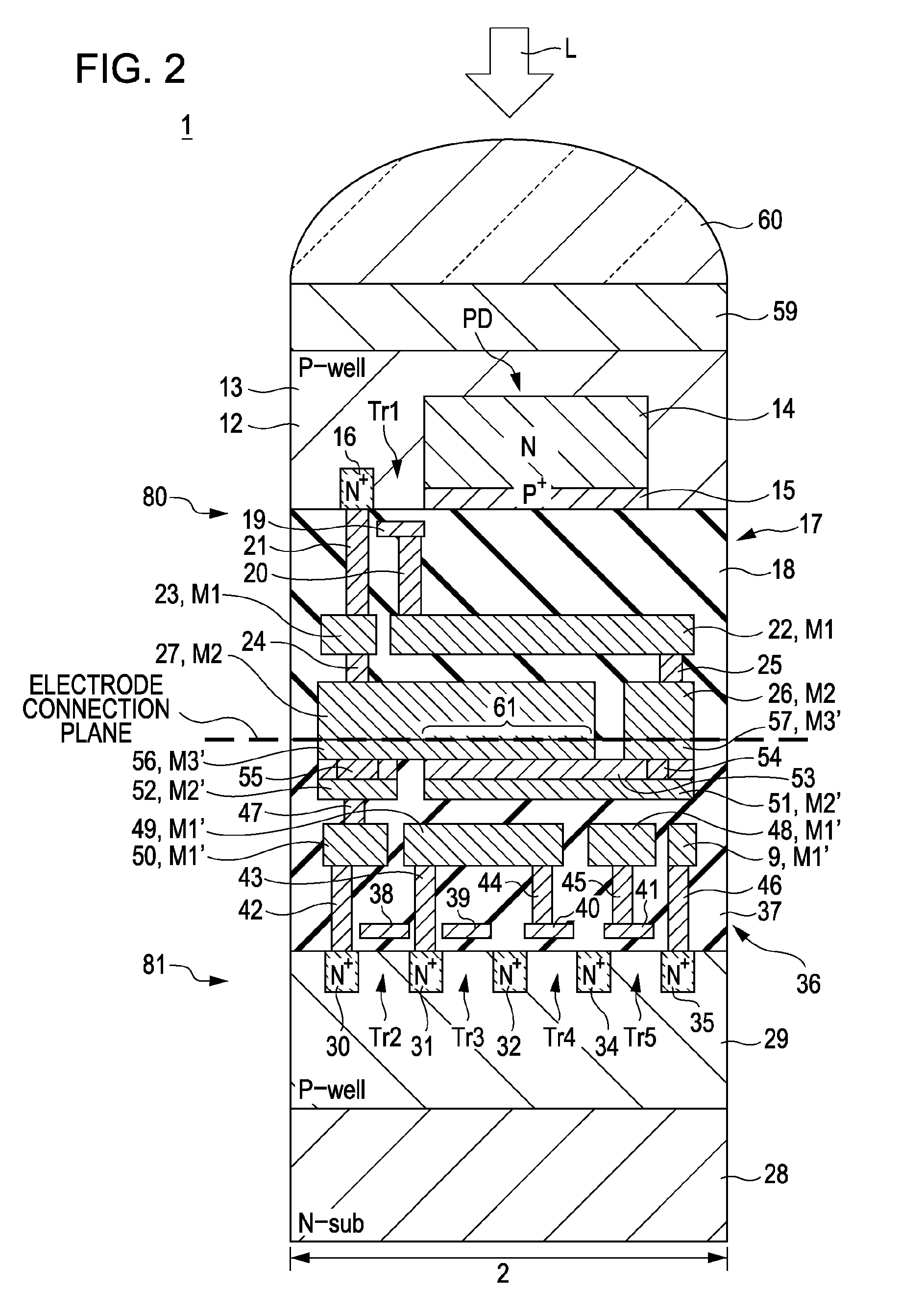

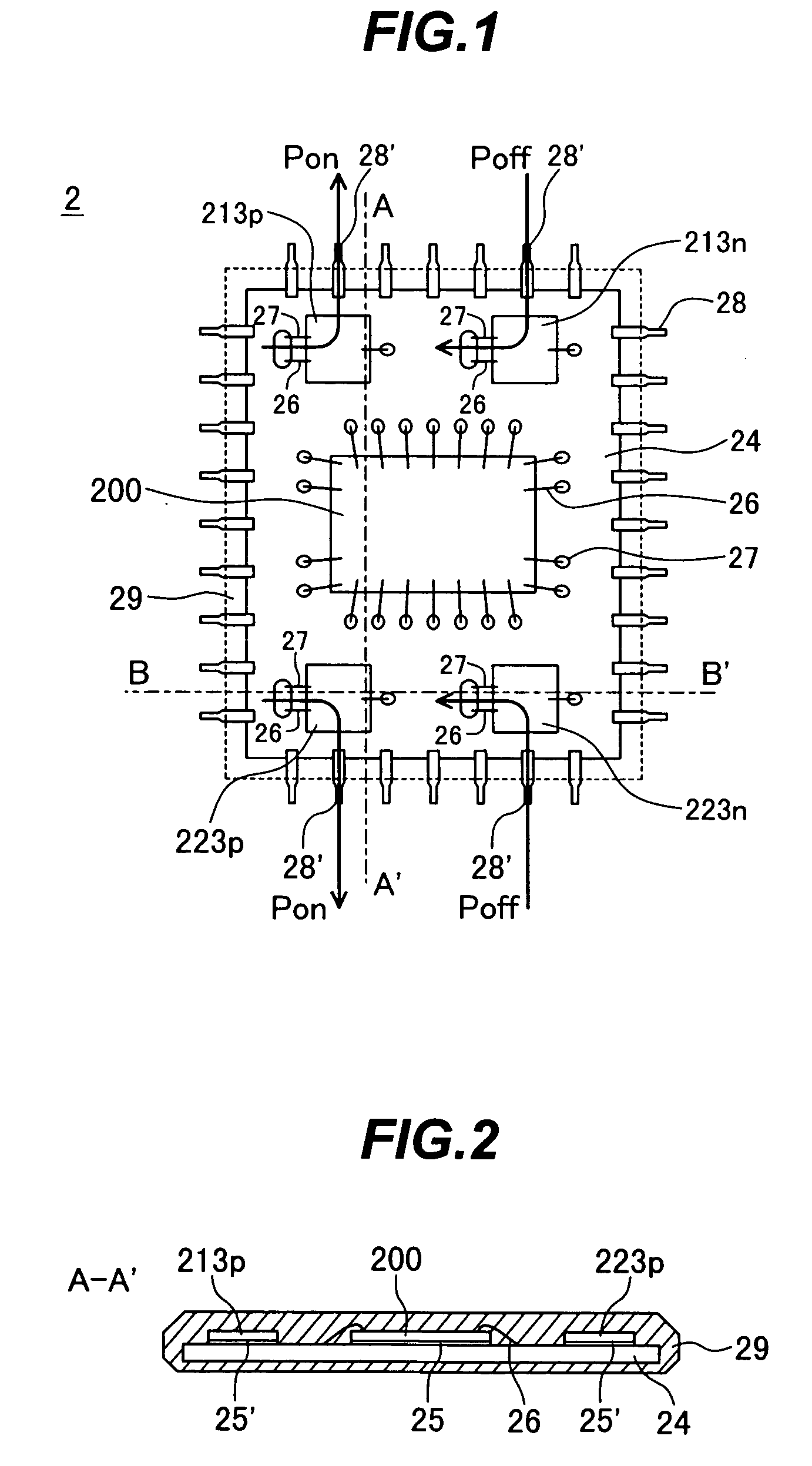

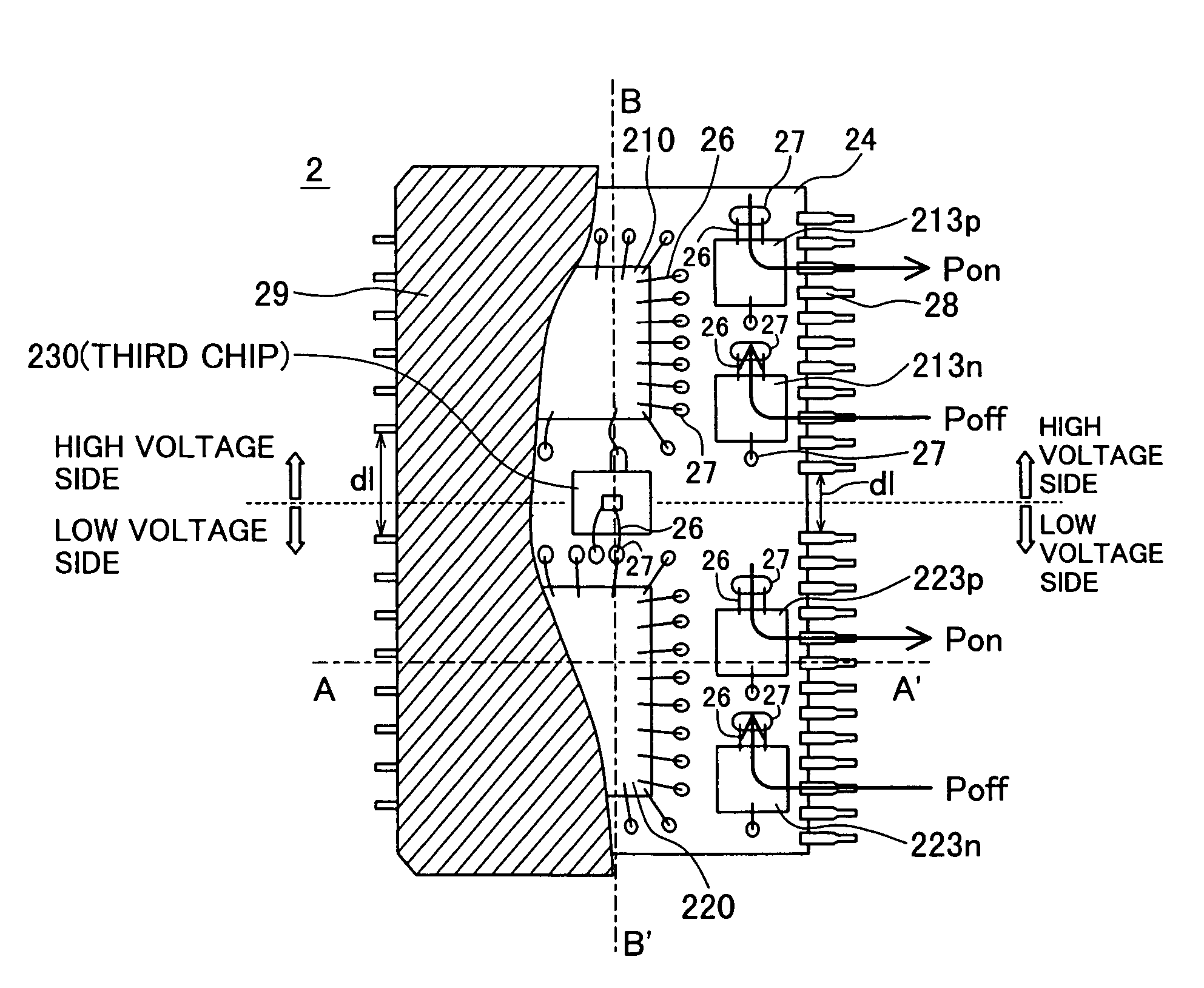

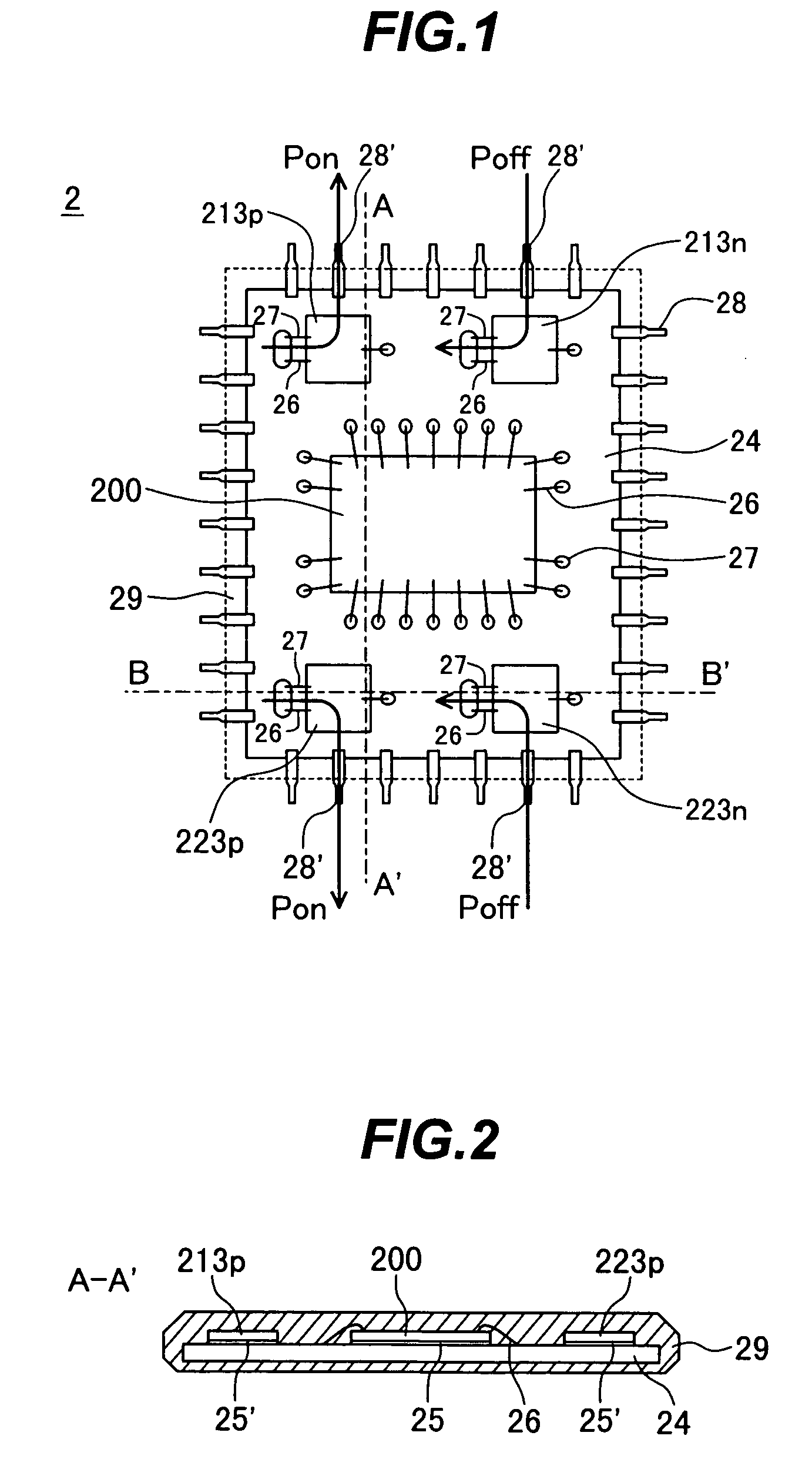

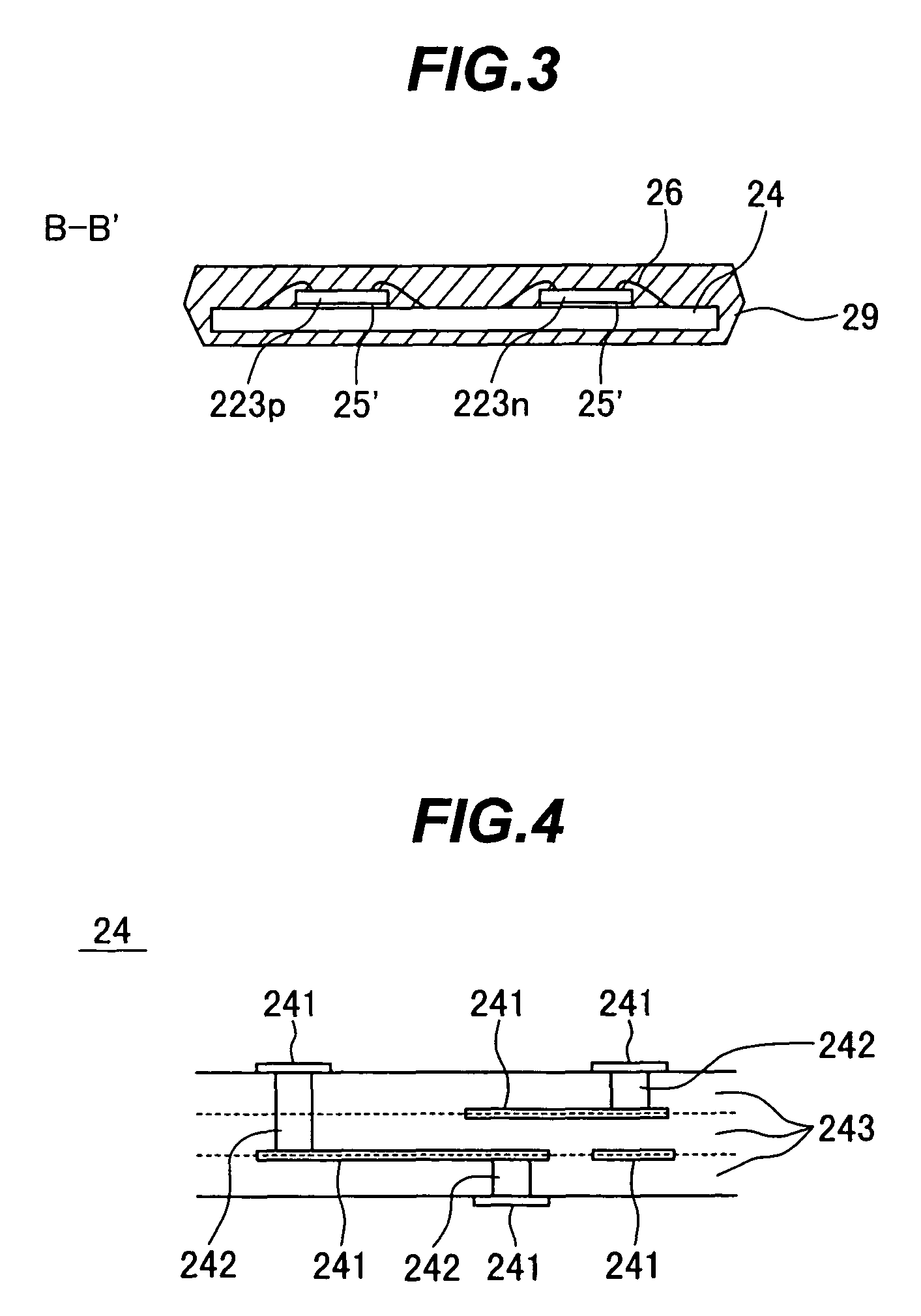

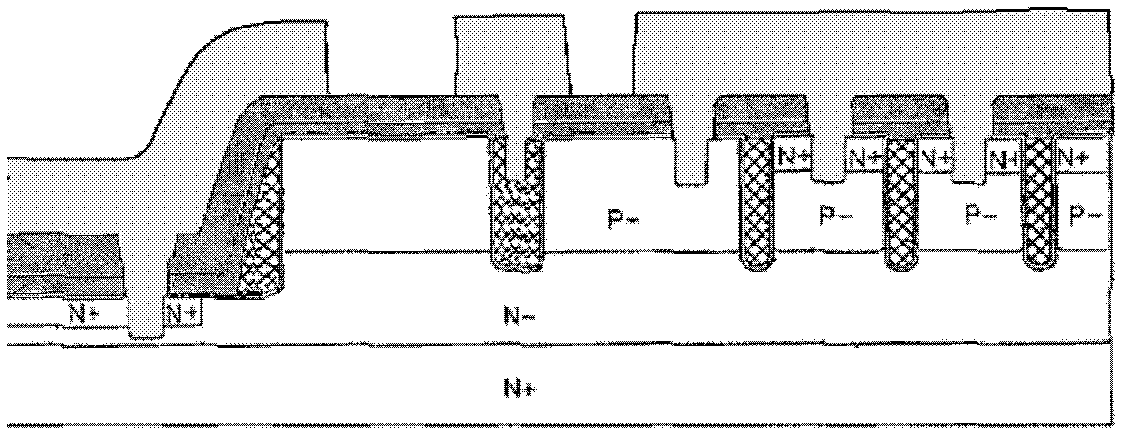

Integrated circuit for driving semiconductor device and power converter

InactiveUS20070008679A1Increase chip areaIncrease in development periodSubstation/switching arrangement detailsSolid-state devicesSignal processing circuitsEngineering

An integrated circuit for driving a semiconductor device, which is adaptable for demands, such as a higher output (larger current), a higher voltage, and a smaller loss, and has a small size, is produced at a low cost, and has high reliability. A power converter including such an integrated circuit is also provided. Circuit elements constituting a drive section of an upper arm drive circuit 212, a level shift circuit 20 including a current sensing circuit 210, a drive section of a lower arm drive circuit 222, and a drive signal processing circuit 224 are integrated and built in one high withstand voltage IC chip 200. Circuit elements constituting a final output stage buffer section 213 of the upper arm drive circuit 212 are built in a vertical p-channel MOS-FET chip 213p and a vertical n-channel MOS-FET chip 213n. Circuit elements constituting a final output stage buffer section 223 of the lower arm drive circuit 222 are built in a vertical p-channel MOS-FET chip 223p and a vertical n-channel MOS-FET chip 223n. Thus, a driver IC 2 is fabricated.

Owner:HITACHI LTD

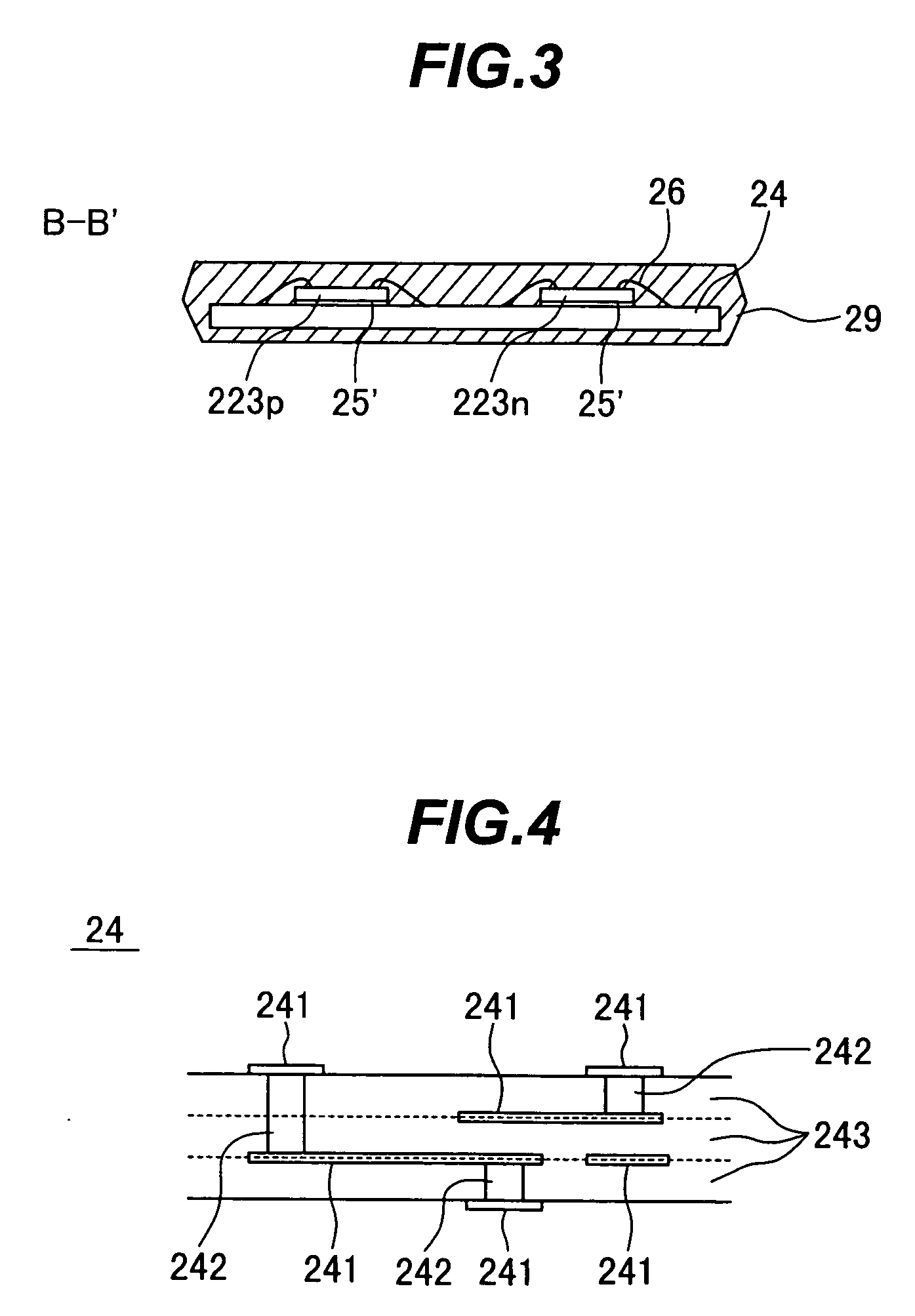

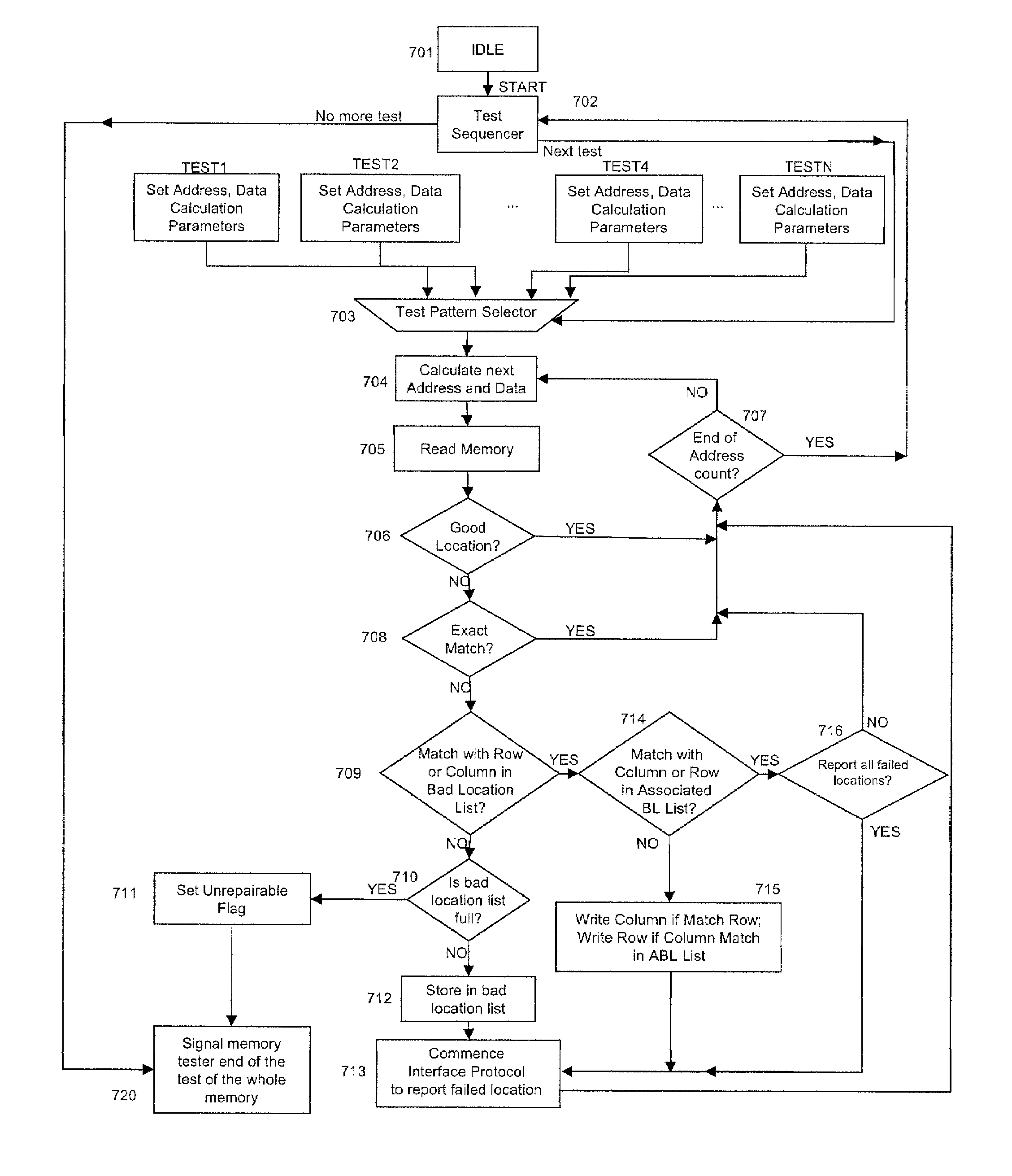

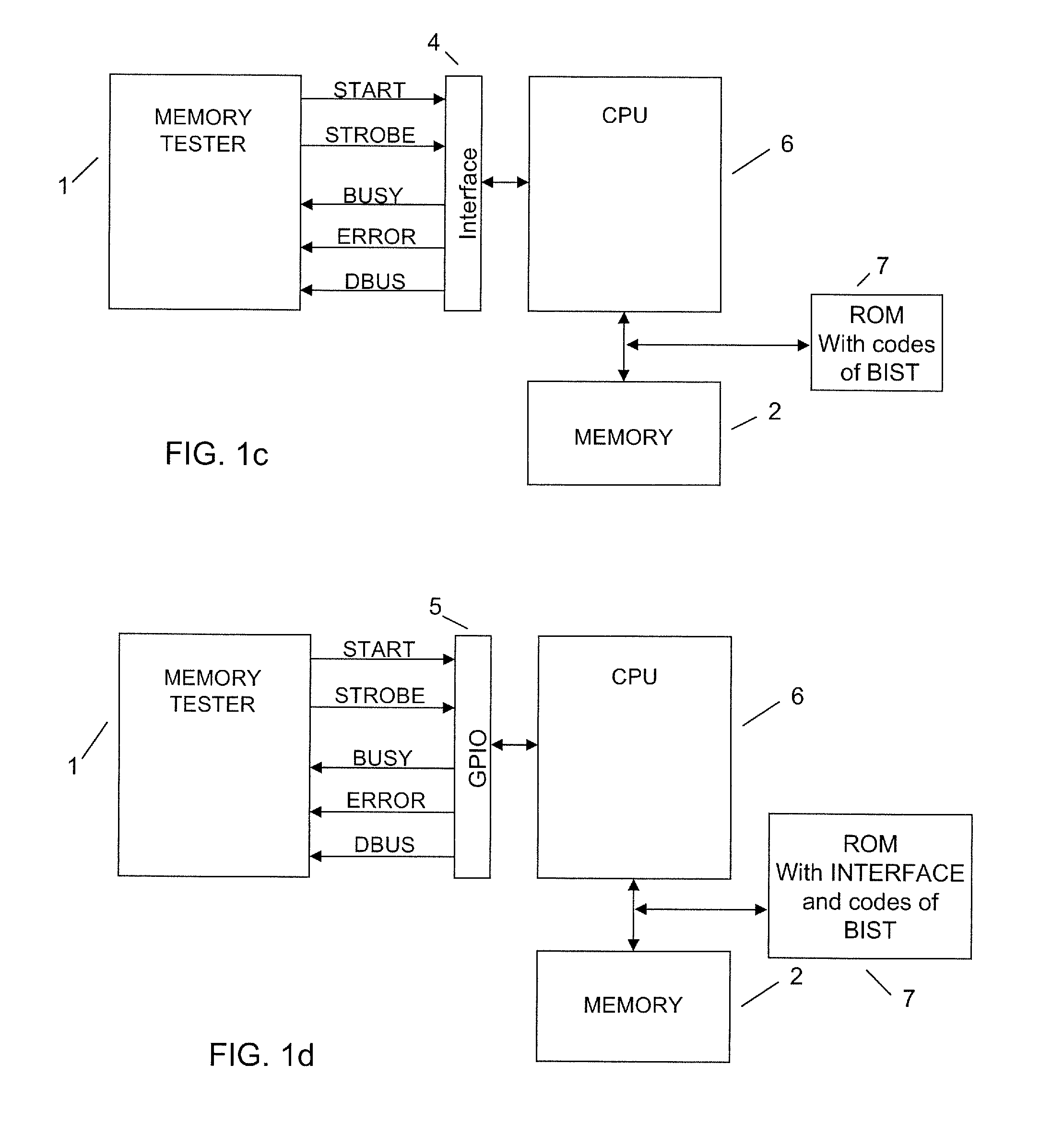

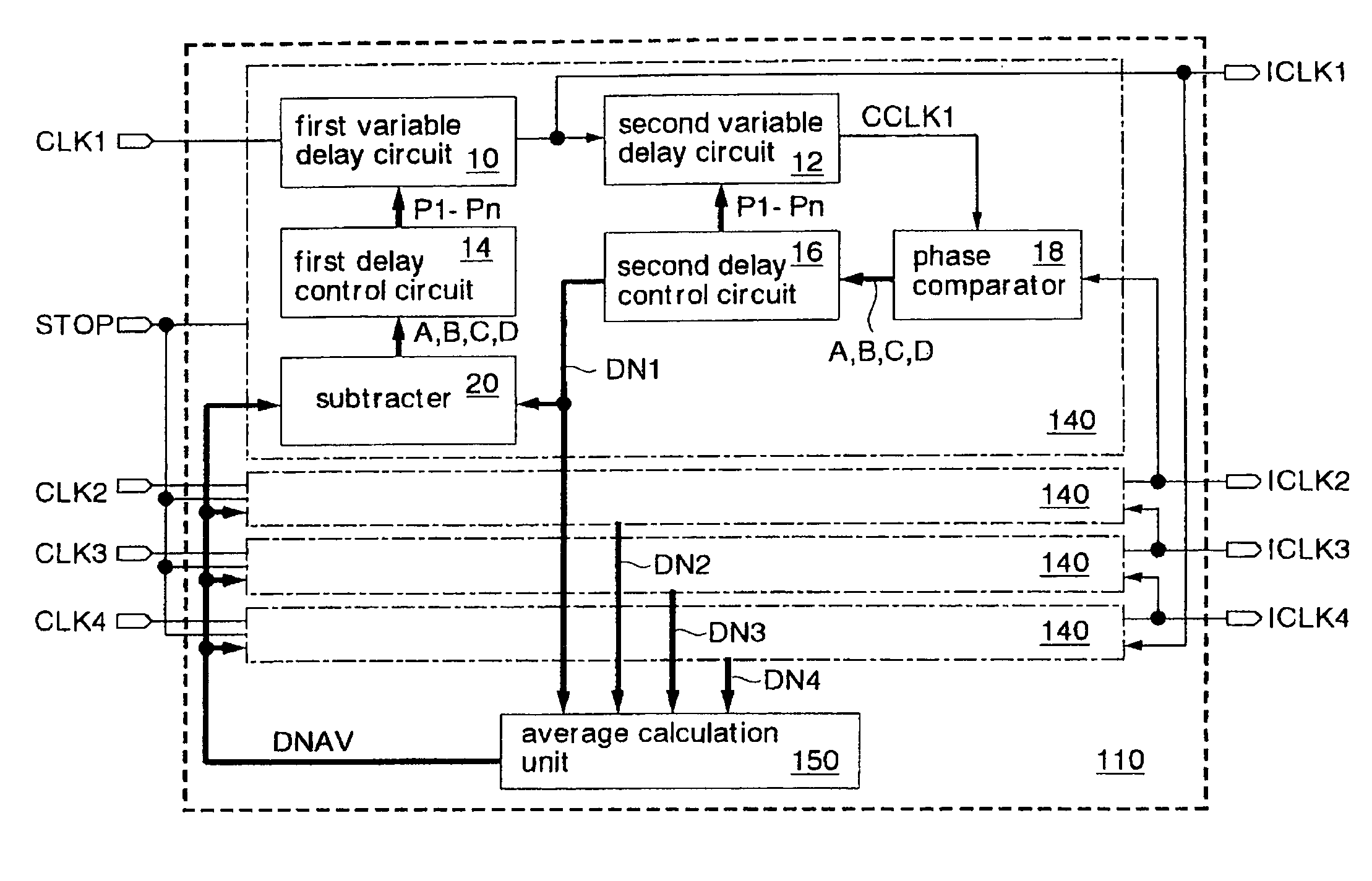

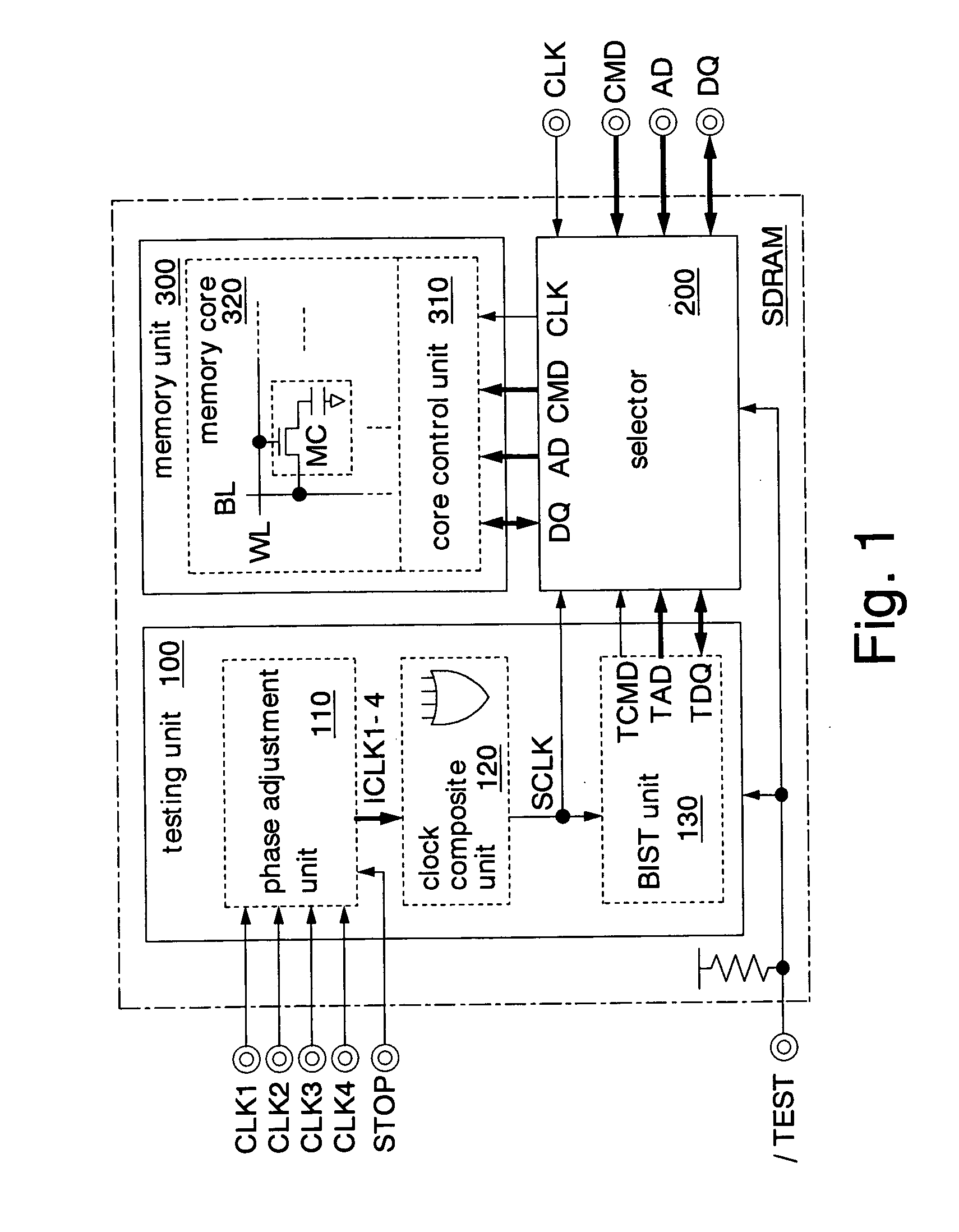

Method and system for memory testing and test data reporting during memory testing

ActiveUS7734966B1Reduced pin countNarrow interfaceElectronic circuit testingError detection/correctionAnalysis dataHigh memory

The present invention provides a method and system for improving memory testing efficiency, raising the speed of memory testing, detecting memory failures occurring at the memory operating frequency, and reducing data reported for redundancy repair analysis. The memory testing system includes a first memory tester extracting failed memory location information from the memory at a higher memory operating frequency, an external memory tester receiving failed memory location information at a lower memory tester frequency, and an interface between the first memory tester and the external memory tester. The memory testing method uses data strobes at the memory tester frequency to clock out failed memory location information obtained at the higher memory operating frequency. In addition, the inventive method reports only enough information to the external memory tester for it to determine row, column and single bit failures repairable with the available redundant resources. The present invention further provides a redundant resource allocation system, which uses a bad location list and an associated bad location list to classify failed memory locations according to a predetermined priority sequence, and allocates redundant resources to repair the failed memory locations according to the priority sequence.

Owner:MARVELL ASIA PTE LTD

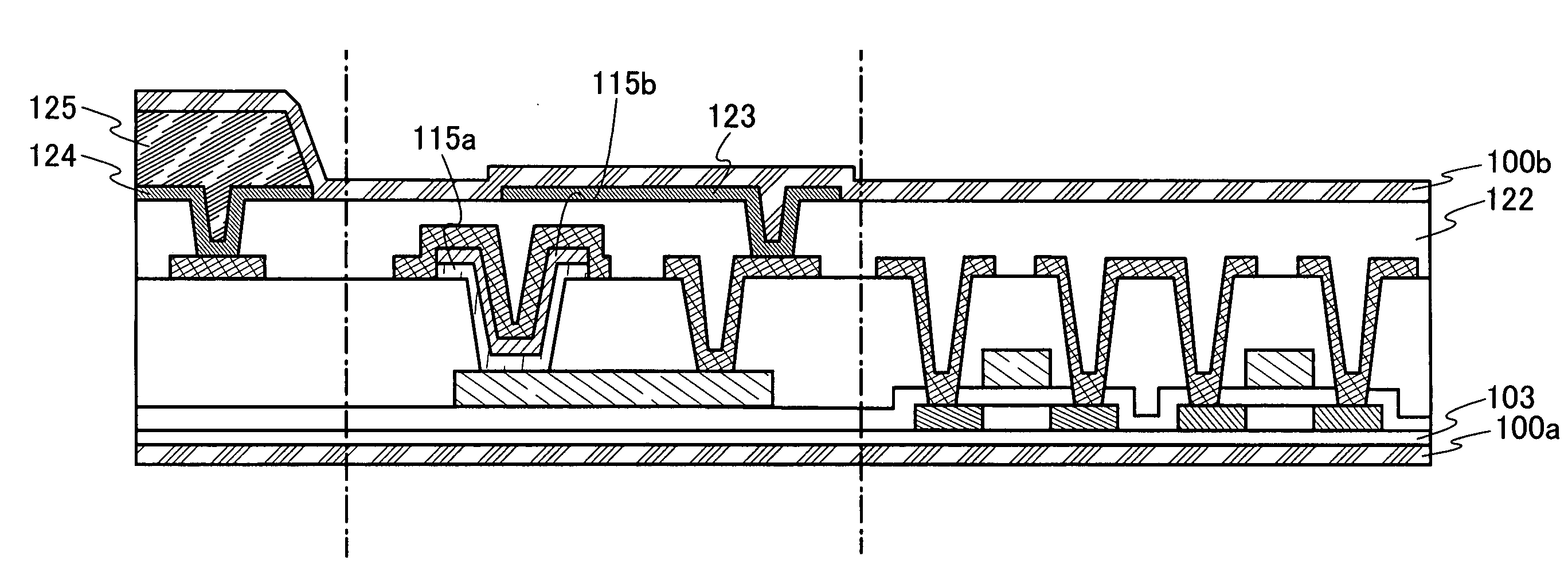

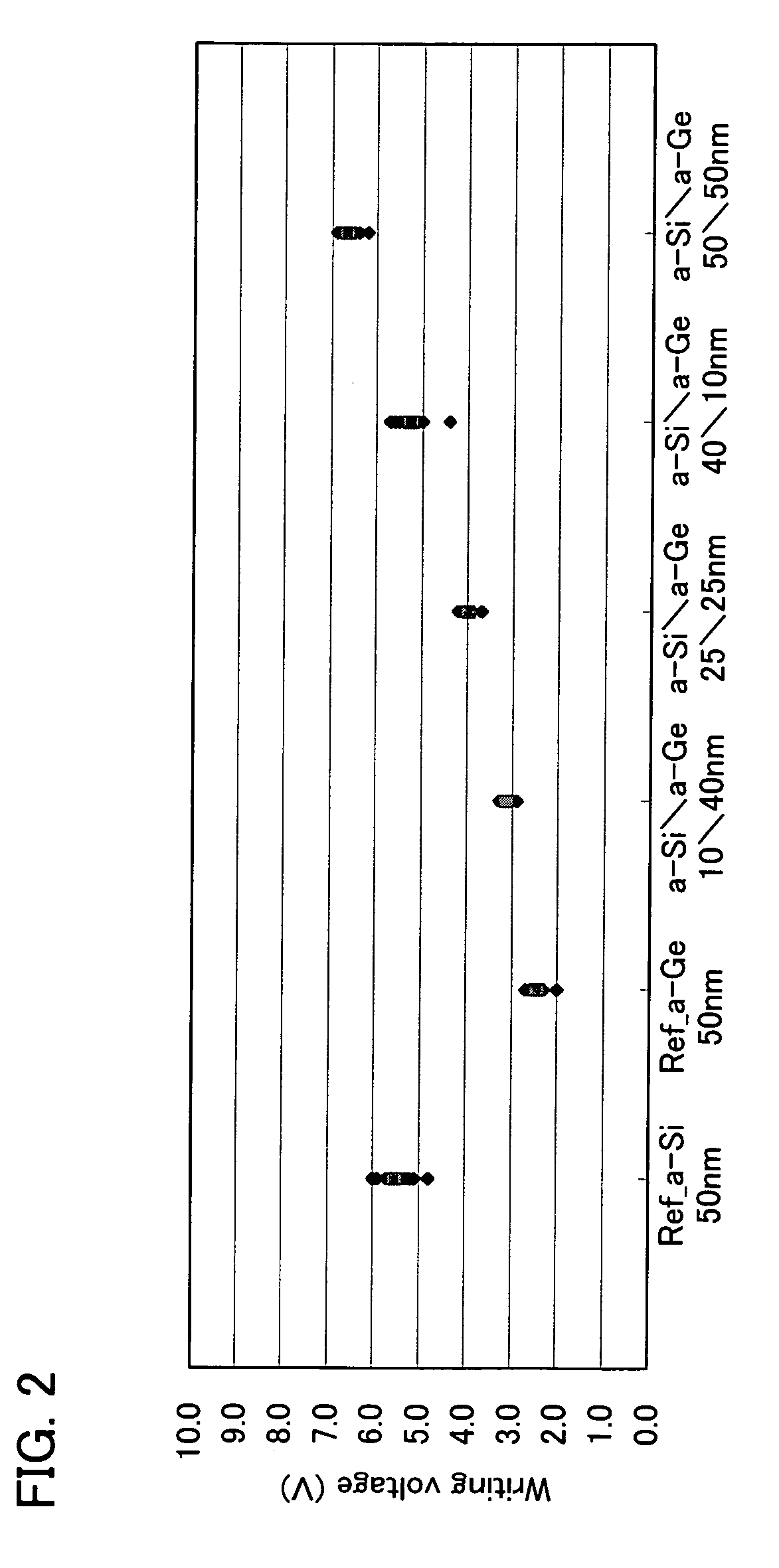

Semiconductor device and manufacturing method thereof

InactiveUS20080224140A1Reduce chip costReduce variationTransistorSolid-state devicesDriver circuitAntifuse

It is an object of the present invention to provide a semiconductor device mounted with a memory which can be driven in the ranges of a current value and a voltage value which can be generated from a wireless signal. It is another object to provide a write-once read-many memory into which data can be written anytime after manufacture of a semiconductor device. An antenna, an antifuse-type ROM, and a driver circuit are formed over a substrate having an insulating surface. A stacked layer of a silicon film and a germanium film is interposed between a pair of electrodes included in the antifuse-type ROM. The antifuse-type ROM having this stacked layer can reduce fluctuation in writing voltage.

Owner:SEMICON ENERGY LAB CO LTD

Solid-state imaging device with charge transfer transistor on different substrates

ActiveUS8792034B2Reduce chip sizeReduce chip costTelevision system detailsTelevision system scanning detailsElectricityEngineering

A solid-state imaging device includes a plurality of pixels, each of which includes a photoelectric converter section formed on a first substrate to generate and accumulate signal charges corresponding to incident light, a charge accumulation capacitor section formed on the first substrate or a second substrate to temporarily hold the signal charges transferred from the photoelectric converter section, and a plurality of MOS transistors formed on the second substrate to transfer the signal charges accumulated in the charge accumulation capacitor section, connection electrodes formed on the first substrate, and connection electrodes formed on the second substrate and electrically connected to the connection electrodes formed on the first substrate.

Owner:SONY CORP

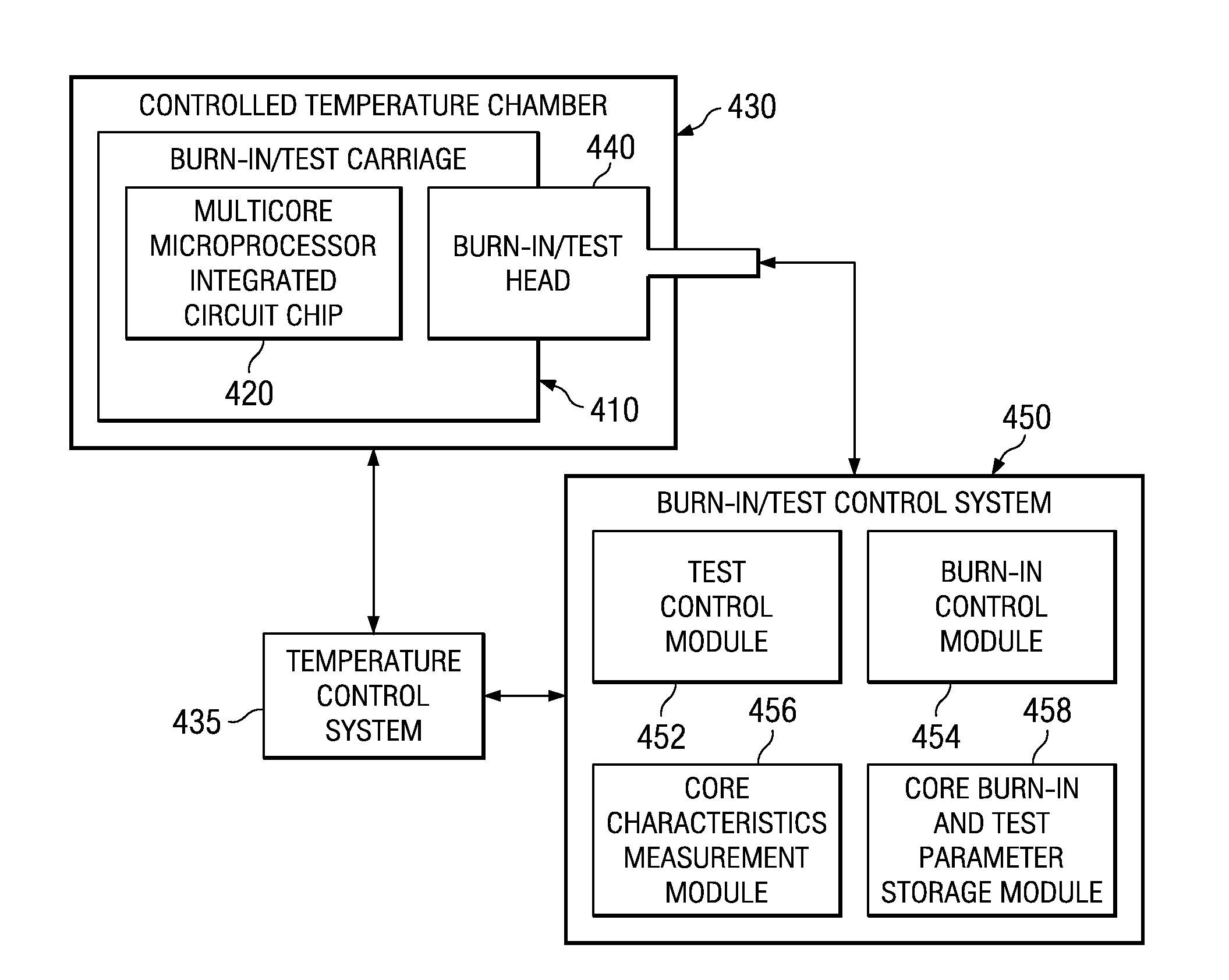

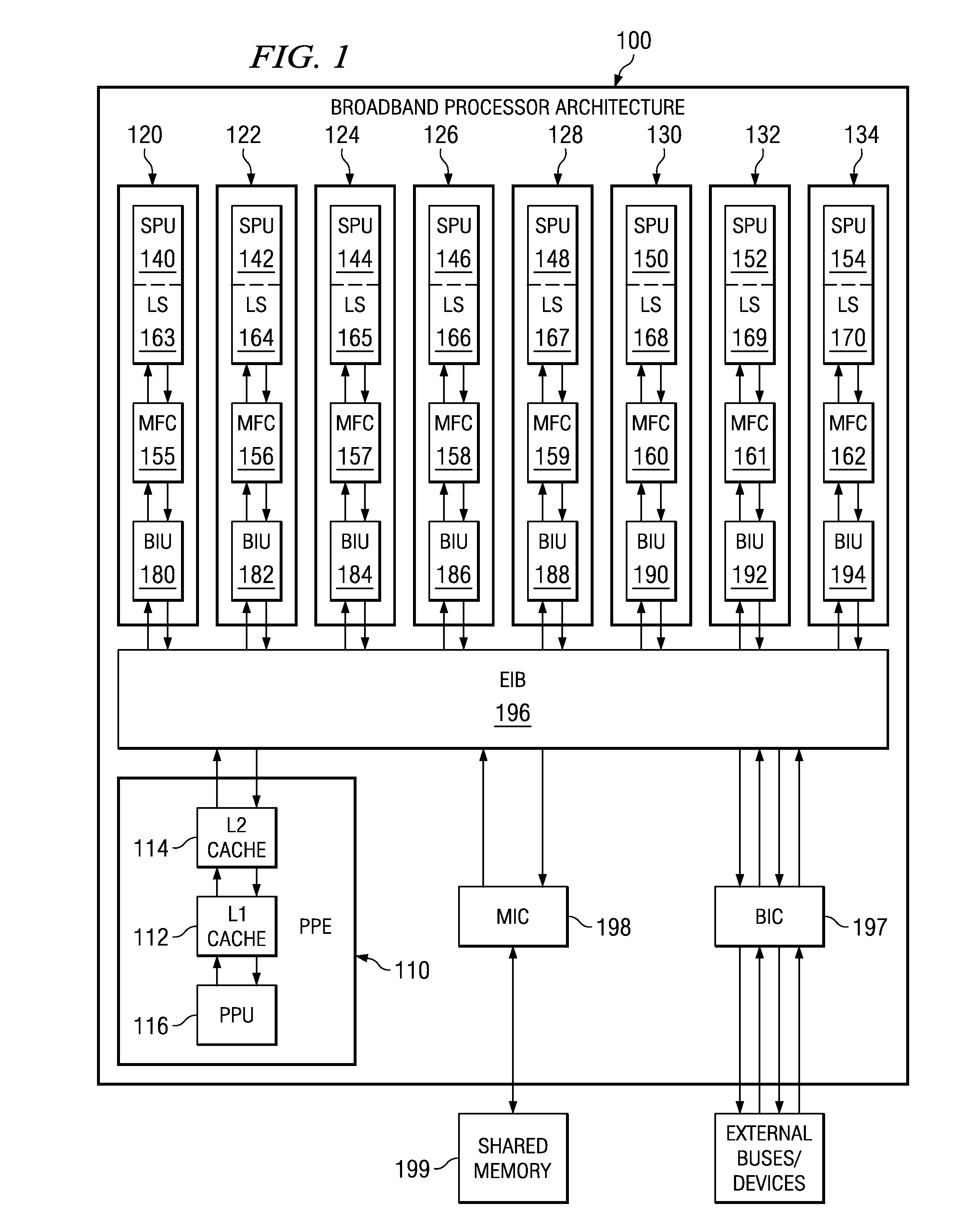

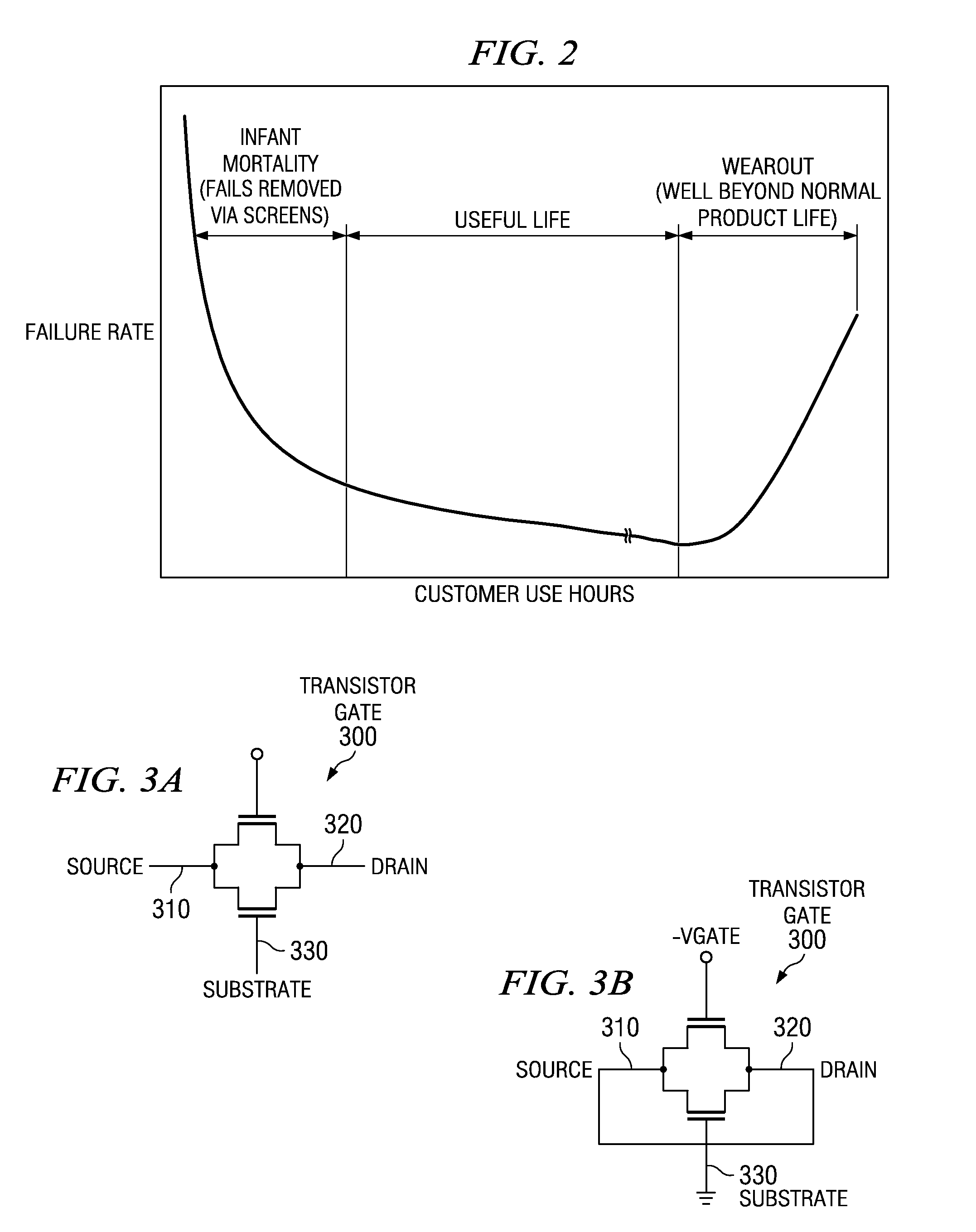

Apparatus and method for customized burn-in of cores on a multicore microprocessor integrated circuit chip

InactiveUS7268570B1Reduce chip costUniform powerFault location by increasing destruction at faultPeak valueEngineering

An apparatus and method for providing a multi-core integrated circuit chip that reduces the cost of the package and board while optimizing performance of the cores for use with a single voltage plane. The apparatus and method of the illustrative embodiments make use of a dynamic burn-in technique that optimizes all of the cores on the chip to run at peak performance at a single voltage. Each core is burned-in with a customized burn-in voltage that provides uniform power and performance across the whole chip. This results in a higher burn-in yield and lower overall power in the integrated circuit chip. The optimization of the cores to run at peak performance at a single voltage is achieved through use of the negative bias temperature instability affects on the cores imparted by the burn-in voltages applied.

Owner:GOOGLE LLC

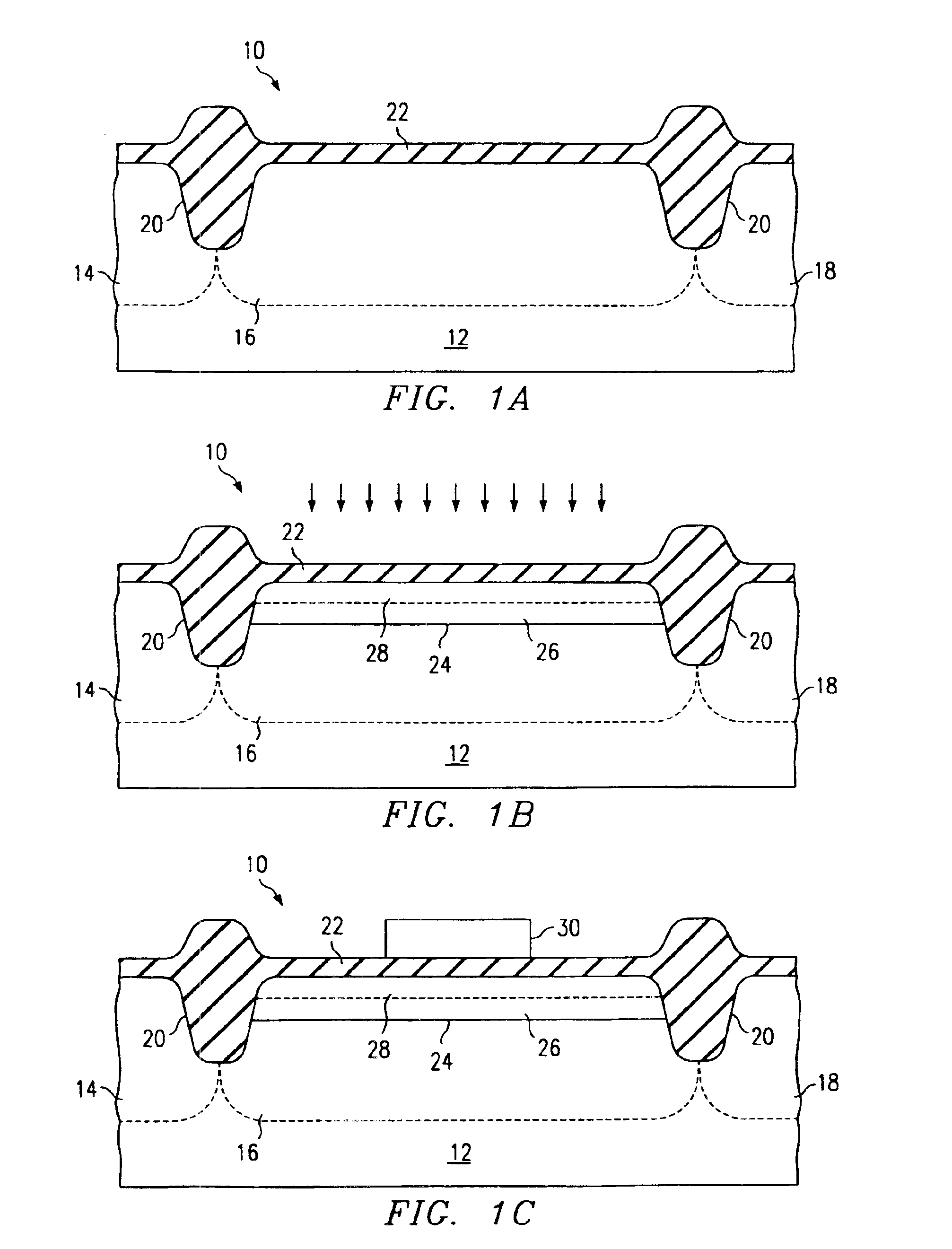

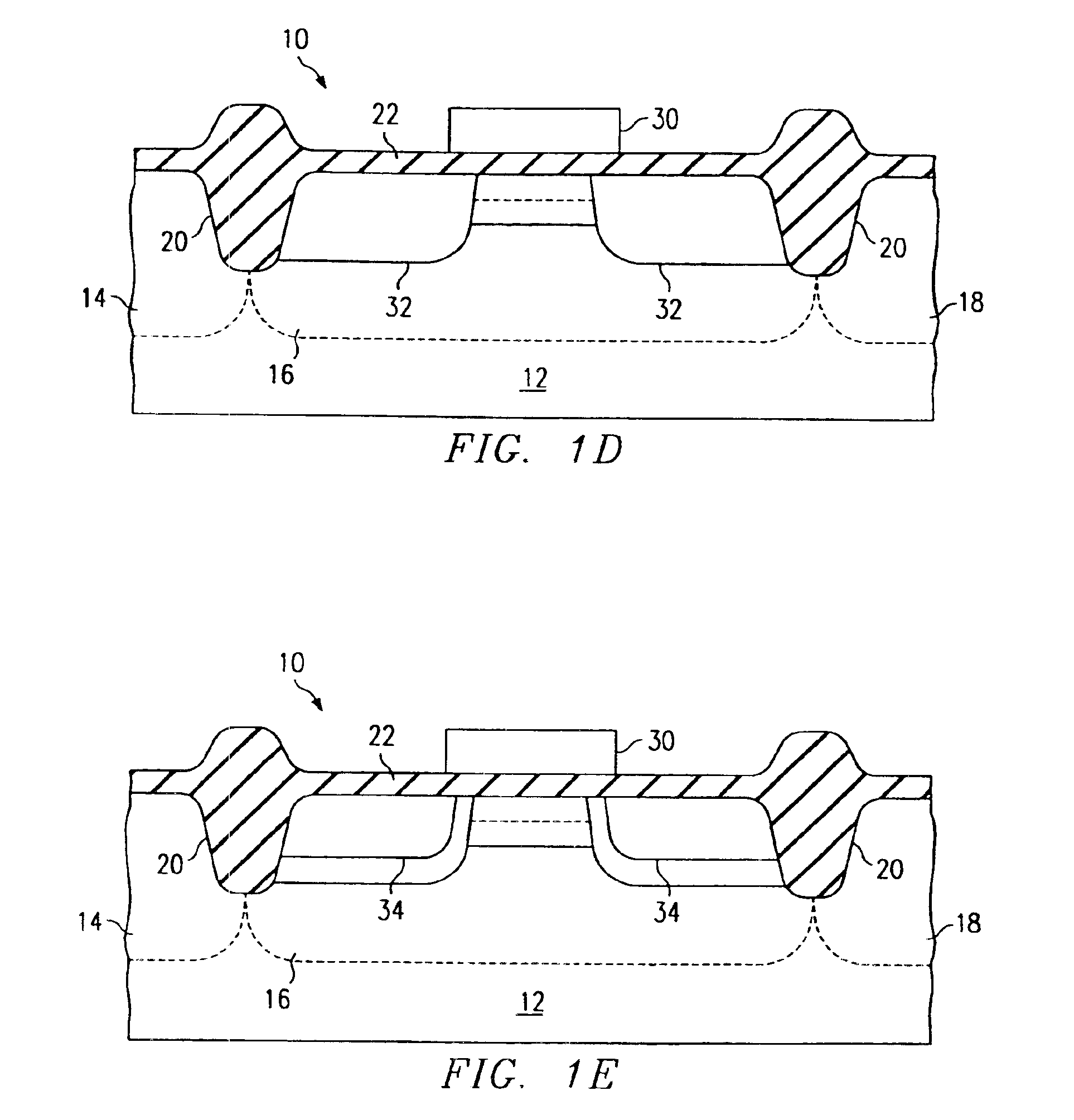

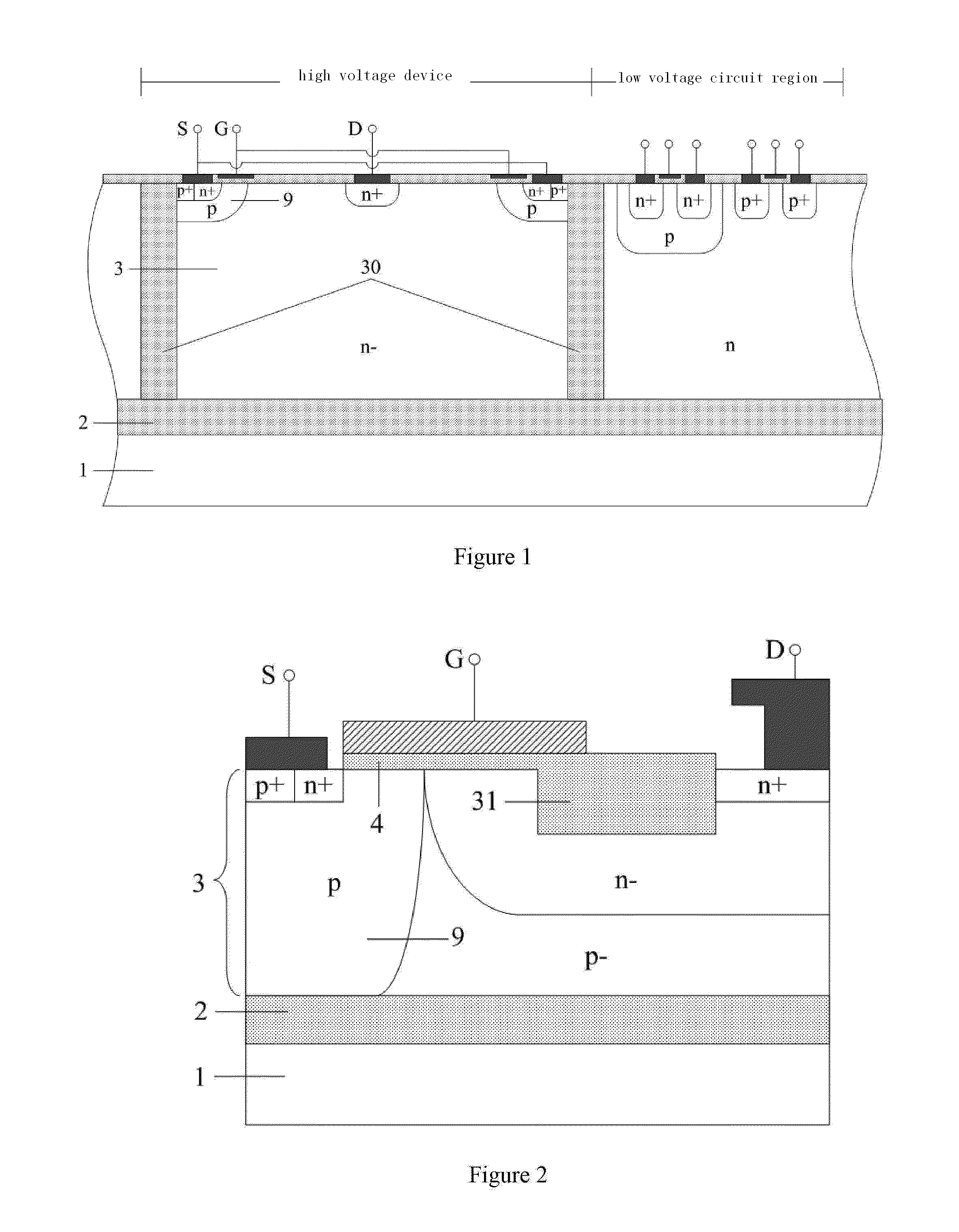

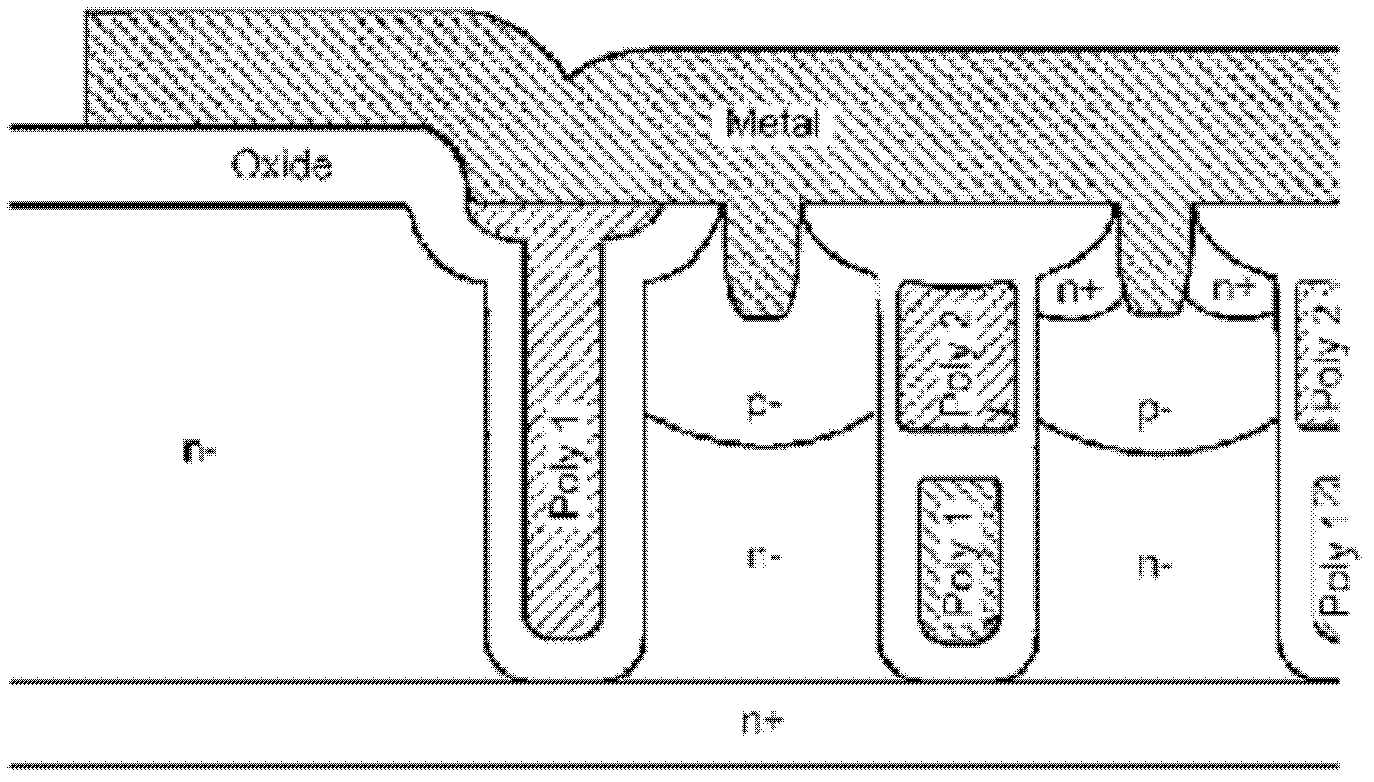

Dual-counterdoped channel field effect transistor and method

InactiveUS6960499B2High carrier mobilityReduce doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesDopantCapacitance

A field effect transistor with a dual-counterdoped channel is disclosed. The transistor features a channel comprising a first doped region (28) and a second doped region (26) underlying the first doped region. A source and drain (32) are formed adjacent to the channel. In one embodiment of the present invention, the first doped region (28) is doped with arsenic, while the second doped region (26) is doped with phosphorus. The high charge-carrier mobility of the subsurface channel layer (28) allowing a lower channel dopant concentration to be used, which in turn allows lower source / drain pocket doping. This reduces the capacitance and response time of the transistor.

Owner:TEXAS INSTR INC

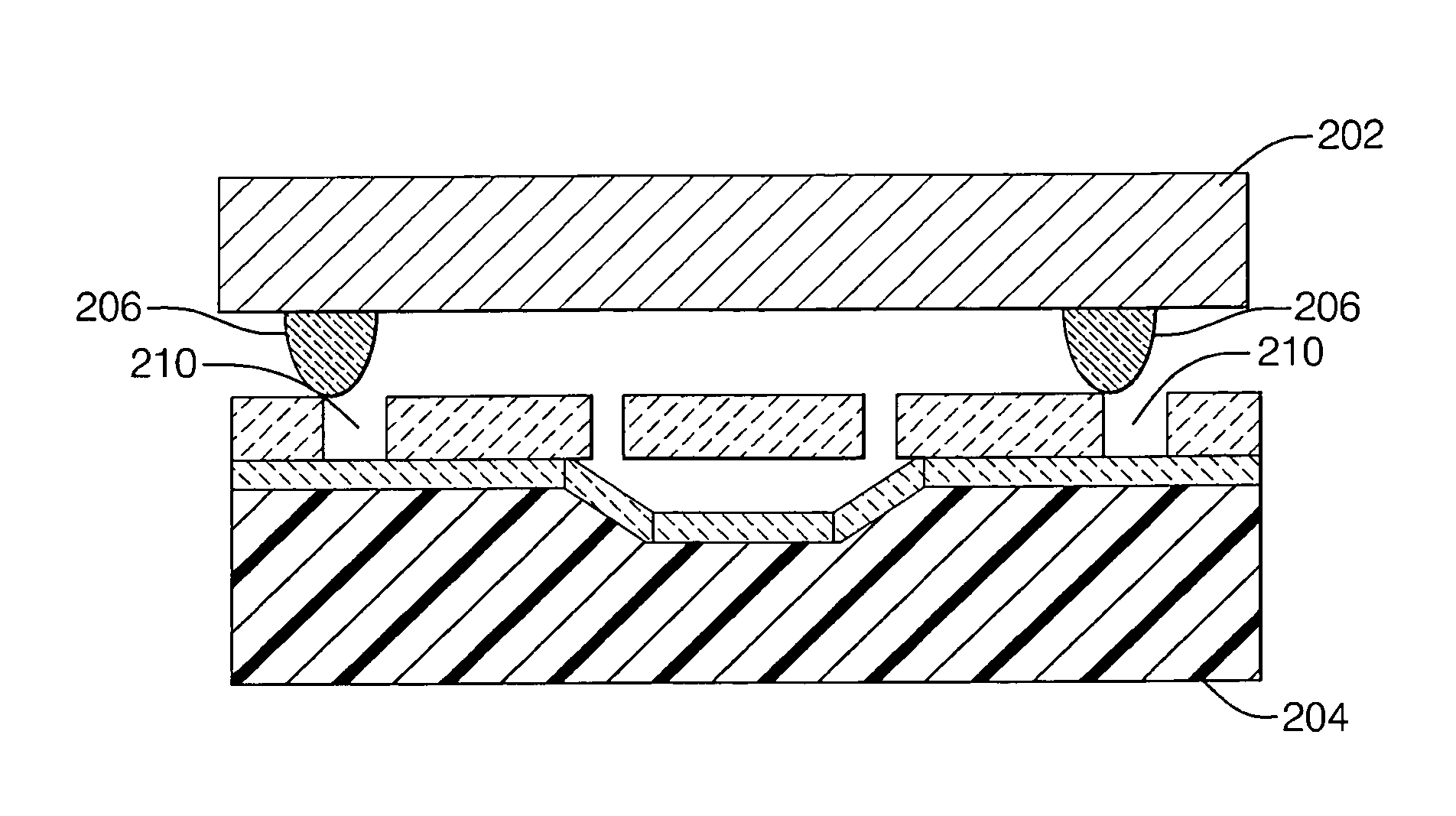

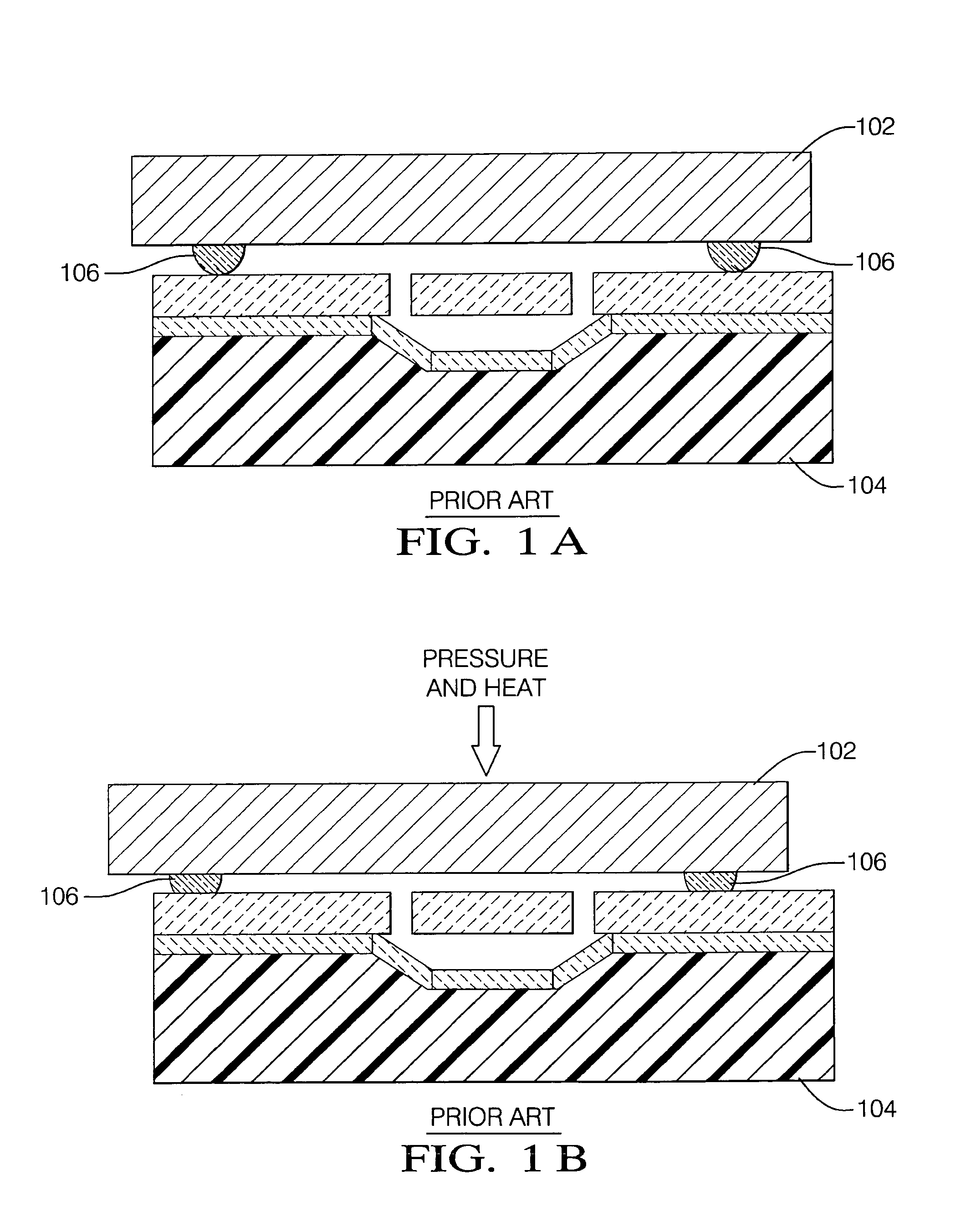

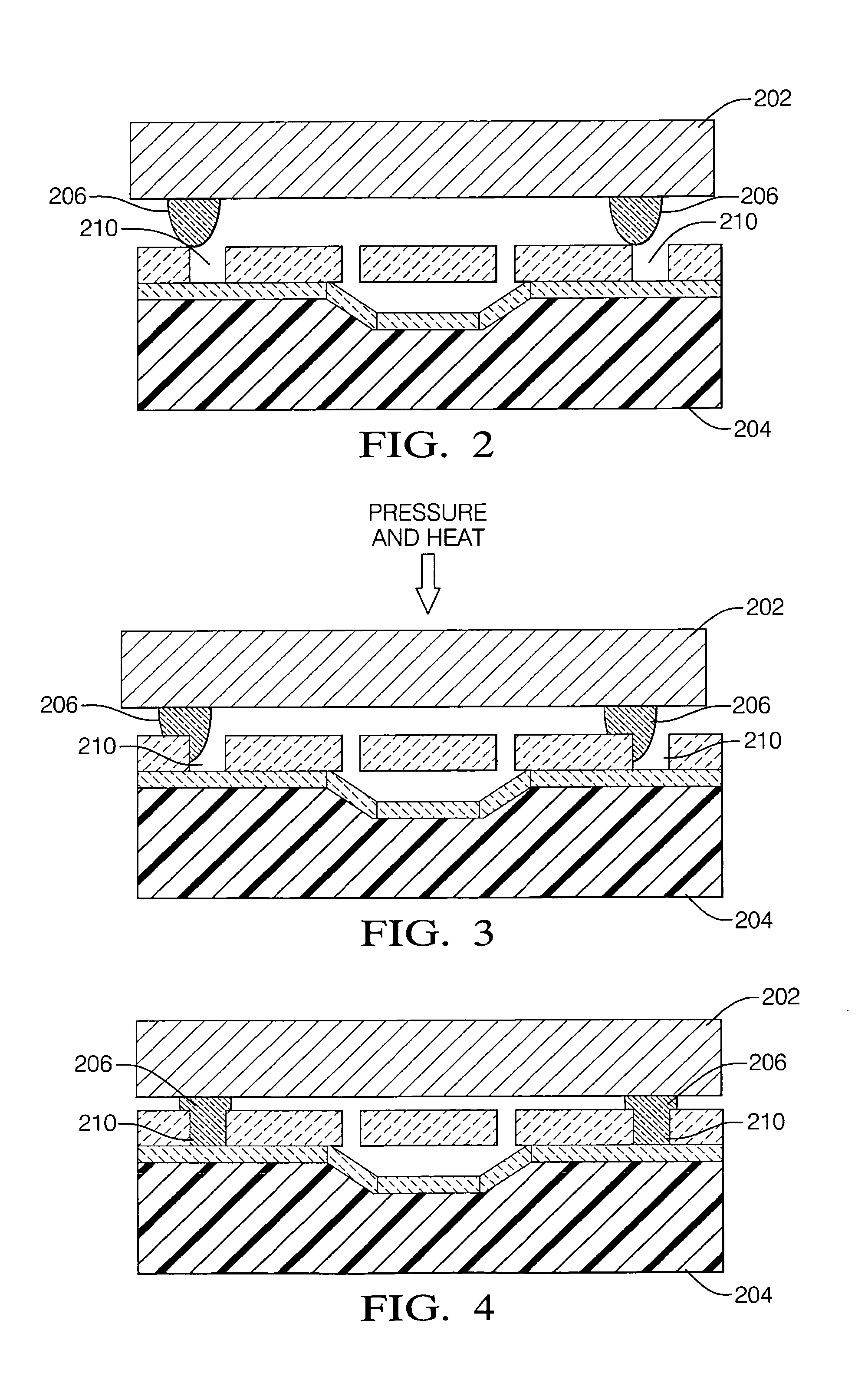

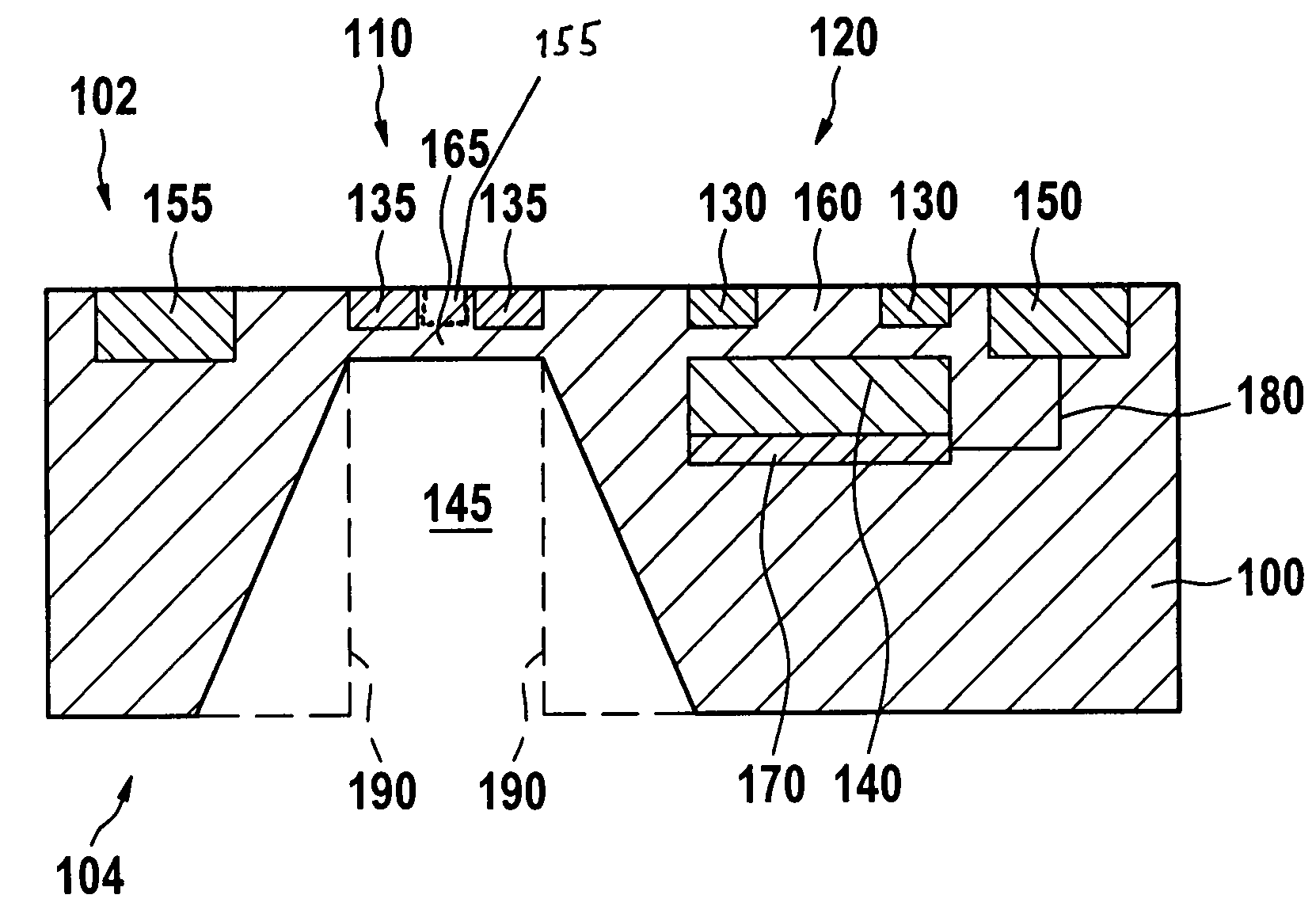

Alignment of a cap to a MEMS wafer

InactiveUS20080131662A1Alignment tolerancePrecise processingLayered productsPretreated surfacesHermetic sealBonding process

An apparatus and method is provided to accurately align a cap wafer relative to a microelectromechanical systems (MEMS) wafer during a bonding process. Other materials may be accurately aligned as well. A trench is established in the MEMS wafer, and a printed substance, secured to the cap wafer, flows into the trench when a pressure is applied to the cap wafer at bond temperature. Natural forces aid in shifting the materials into a lowest energy state and self-aligns the materials into a desired position. The trench also serves as a collection trench for the flowing substance by helping to shape the substance. The trench dimensions may be used to aid in creating a hermetic seal. The alignment tolerances required conventionally during the device design stage are decreased, since the present invention provides a repeatable and accurate alignment bonding process. Chip multiple is increased and therefore chip costs are decreased.

Owner:DELPHI TECH INC

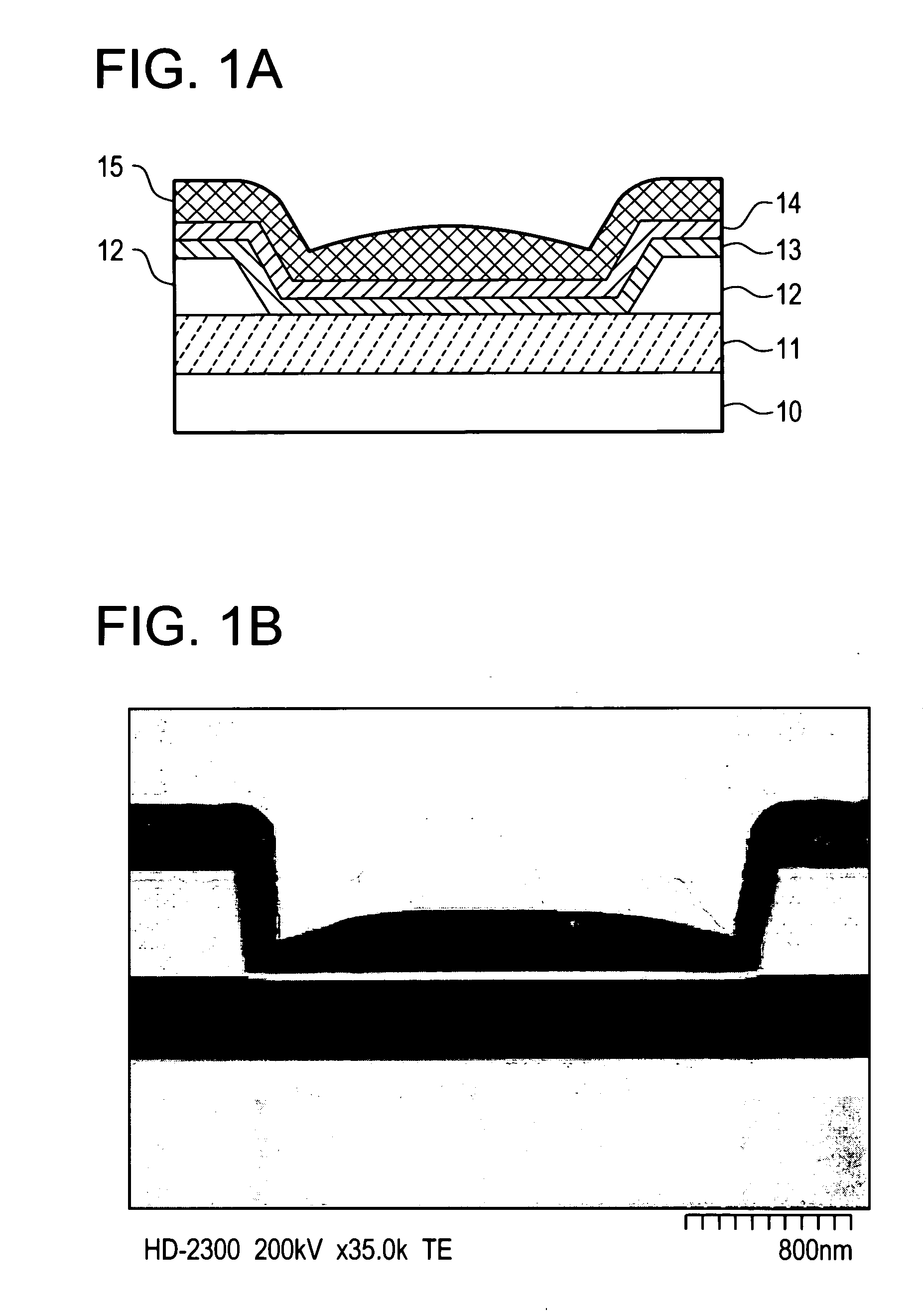

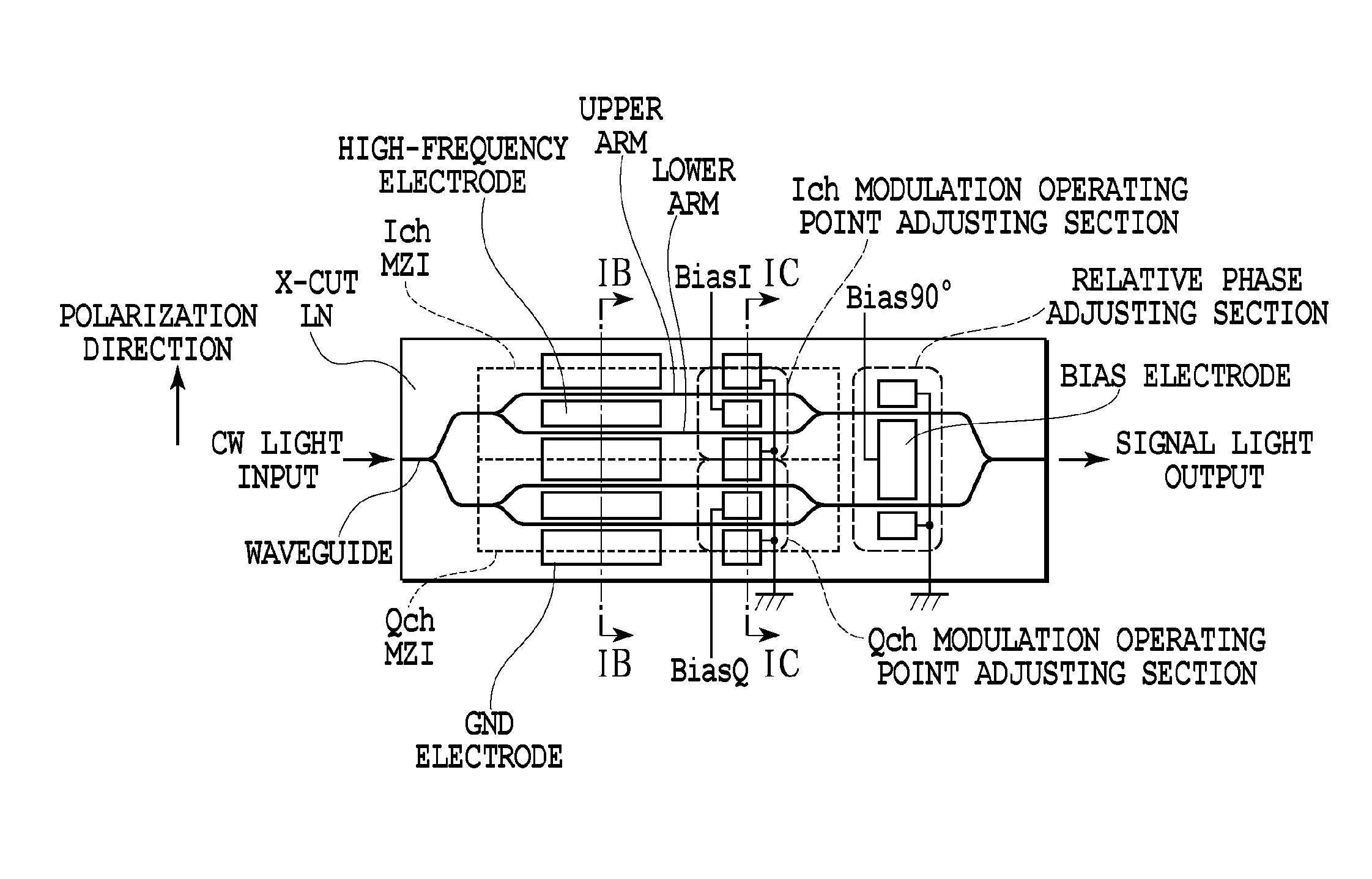

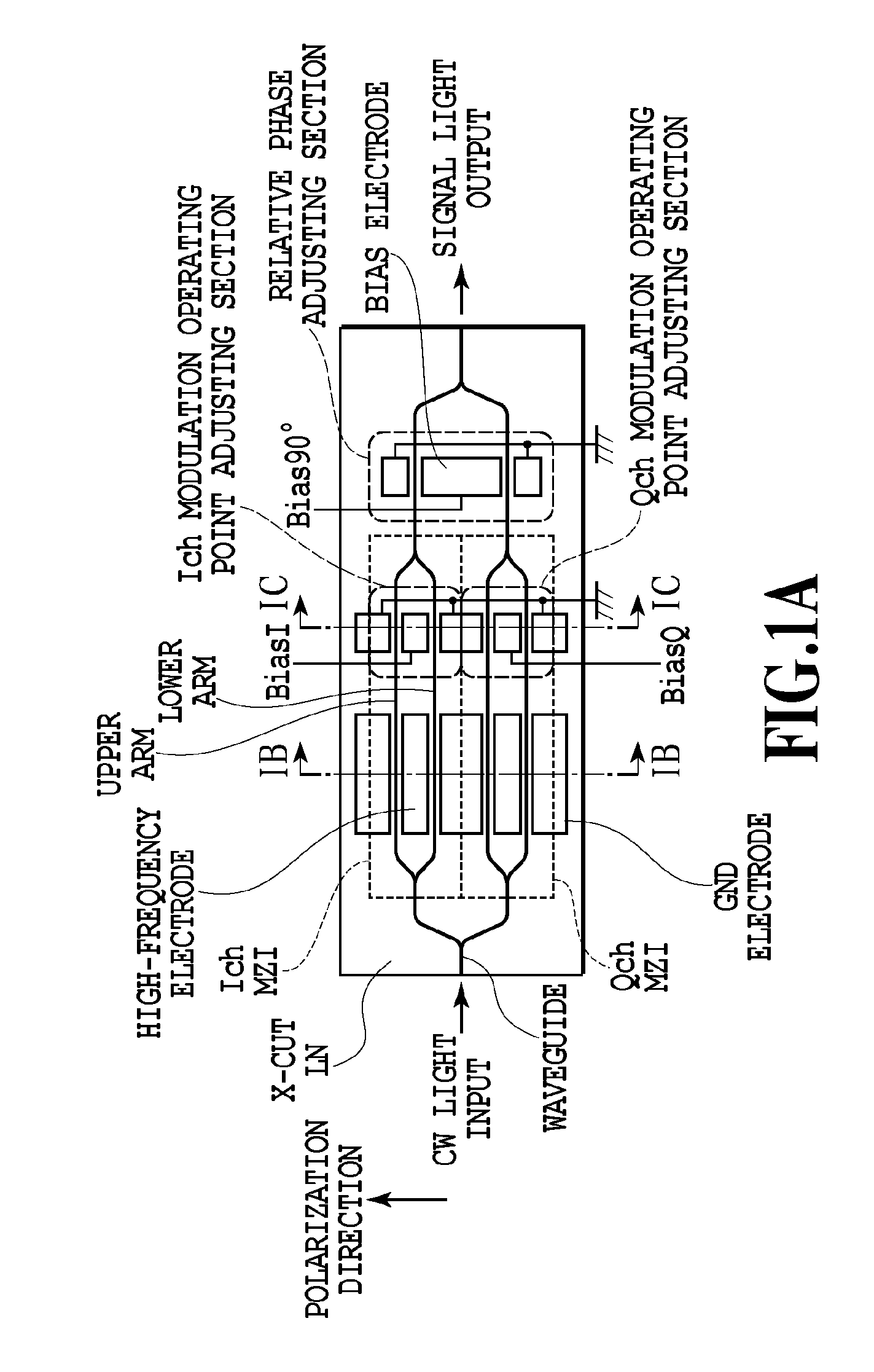

Optical modulator

ActiveUS20120106888A1Reduce chip costEliminate needOptical light guidesNon-linear opticsRelative phasePhase change

In a nest MZI modulator in which each arm includes a child MZI, the power consumption is reduced. The hybrid integrated-type nest MZI modulator of the embodiment 1a is configured so that, instead of placing a relative phase adjusting section in a parent MZI, a bias electrode Bias 90° in which an electric field is applied in the same direction to the polarization direction in both of the upper and lower arms is placed in each child MZI (see FIG. 4B). The bias electrode Bias 90° provided in each child MZI constitute the entirety of a relative phase adjusting section. The optical signals are subjected to a phase change after the output from the child MZI (see FIG. 1A), because such relative phase adjusting section can subject the optical signals of the upper and lower arms of the child MZI to a shift change in the same direction, respectively.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

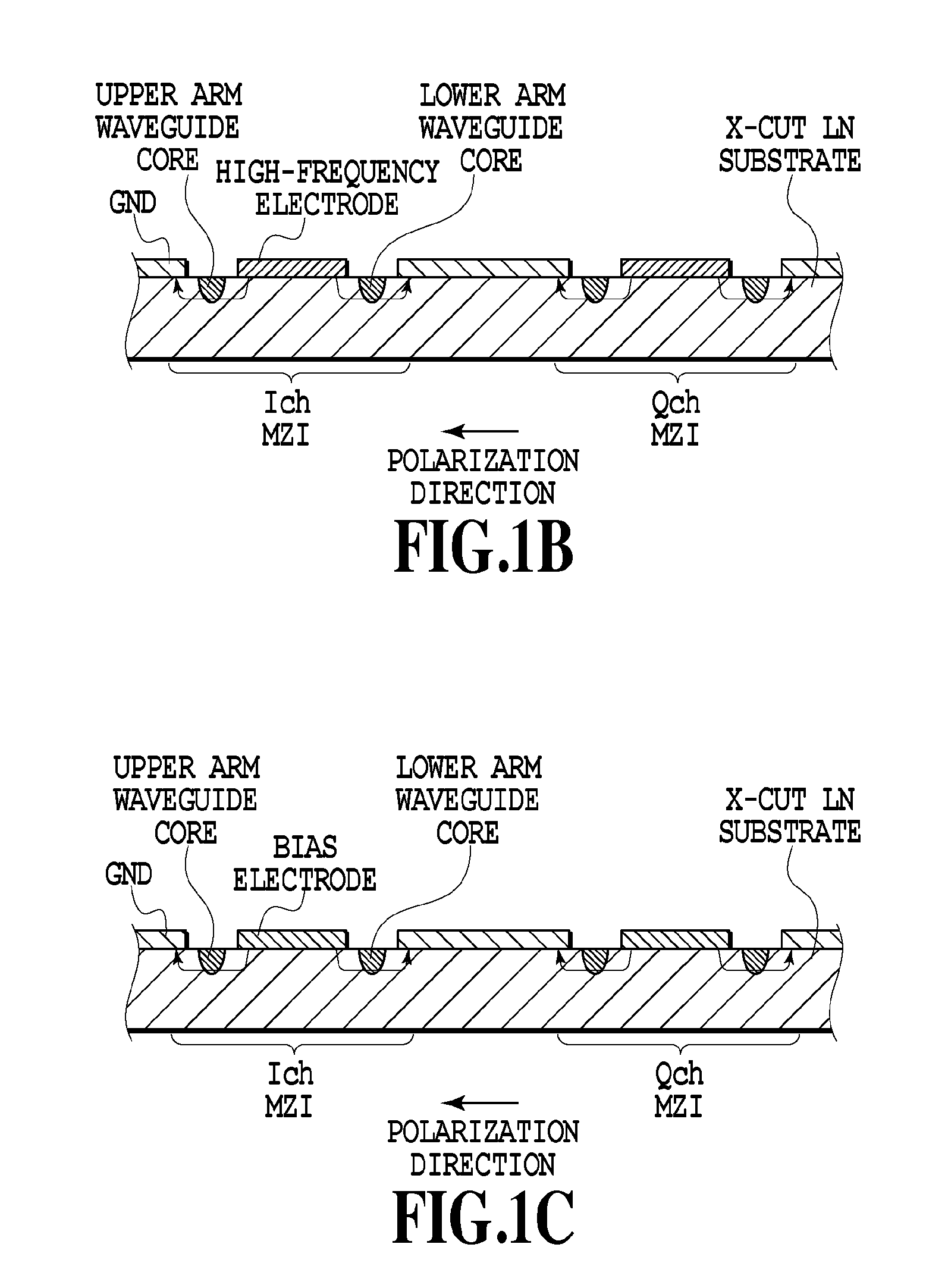

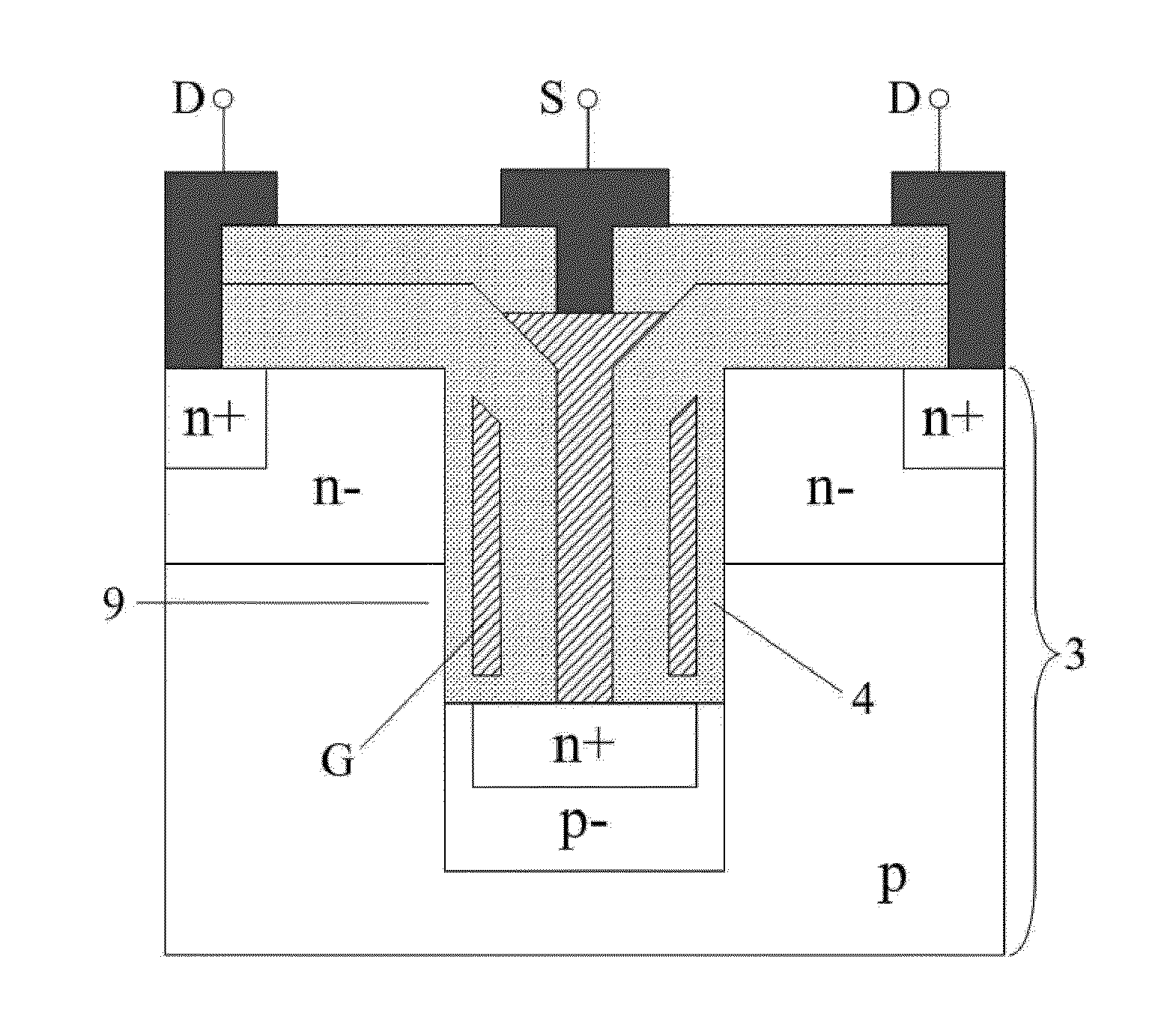

Soi lateral mosfet devices

InactiveUS20130193509A1High critical electric filedIncrease the electric field strengthSolid-state devicesSemiconductor devicesMOSFETPermittivity

The present invention relates to a semiconductor power device and power integrated circuits (ICs). The lateral SOI MOSFET in the present comprises a trench gate extended to the dielectric buried layer, one or multiple dielectric trenches in the drift region, and a buried gate in said dielectric trench. The permittivity of the dielectric in said dielectric trench is lower than that of said active layer. Firstly, said dielectric trench not only greatly improves breakdown voltage, but also reduces pitch size. Secondly, the trench gate widens the effective conductive region in the vertical direction. Thirdly, dual gates of said trench gate and buried gate increase channel and current densities. Thereby, specific on-resistance and the power loss are reduced. The device of the present invention has many advantages, such as high voltage, high speed, low power loss, low cost and ease of integration. The device in the present invention is particularly suitable for power integrated circuits and RF power integrated circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

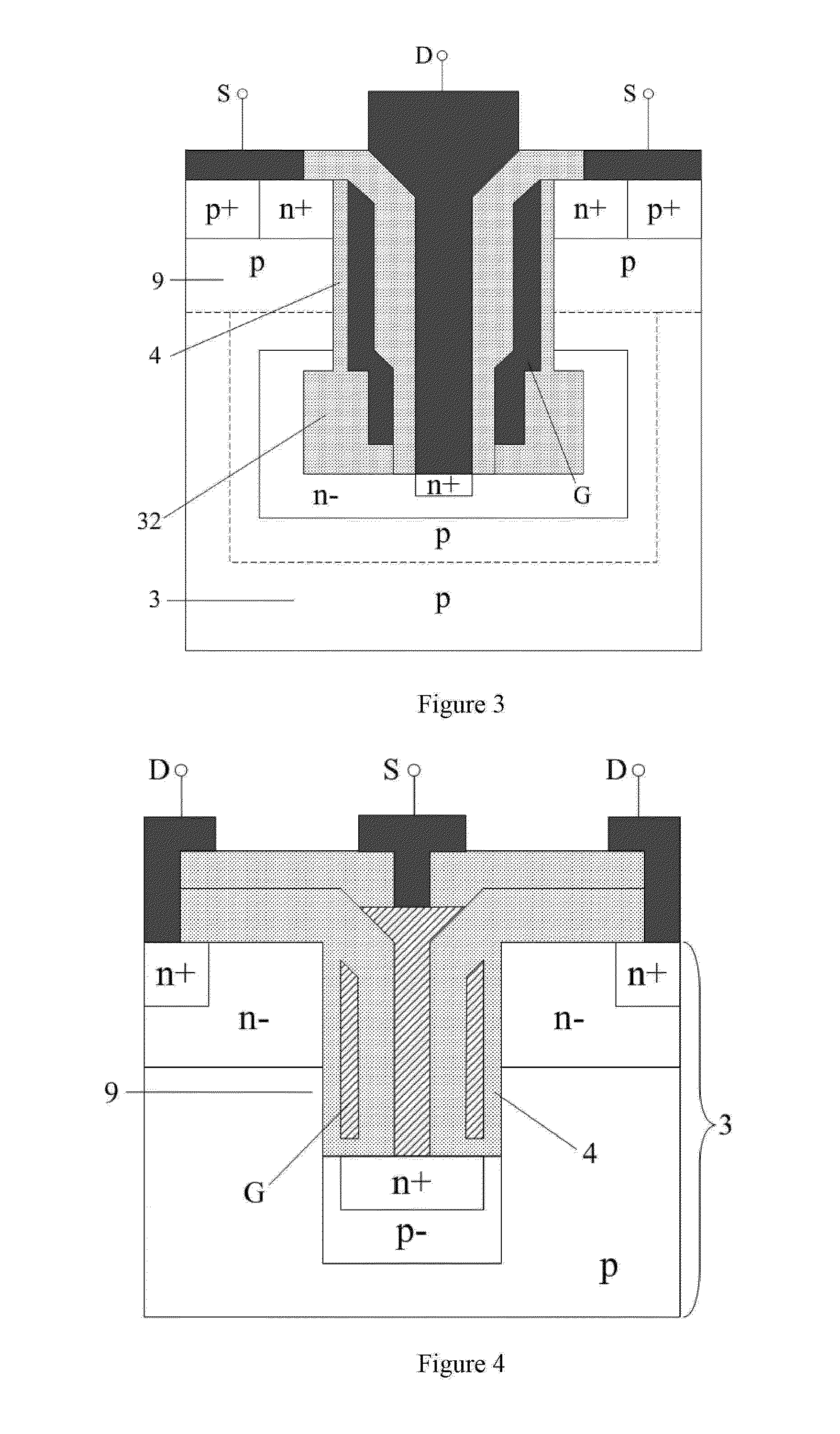

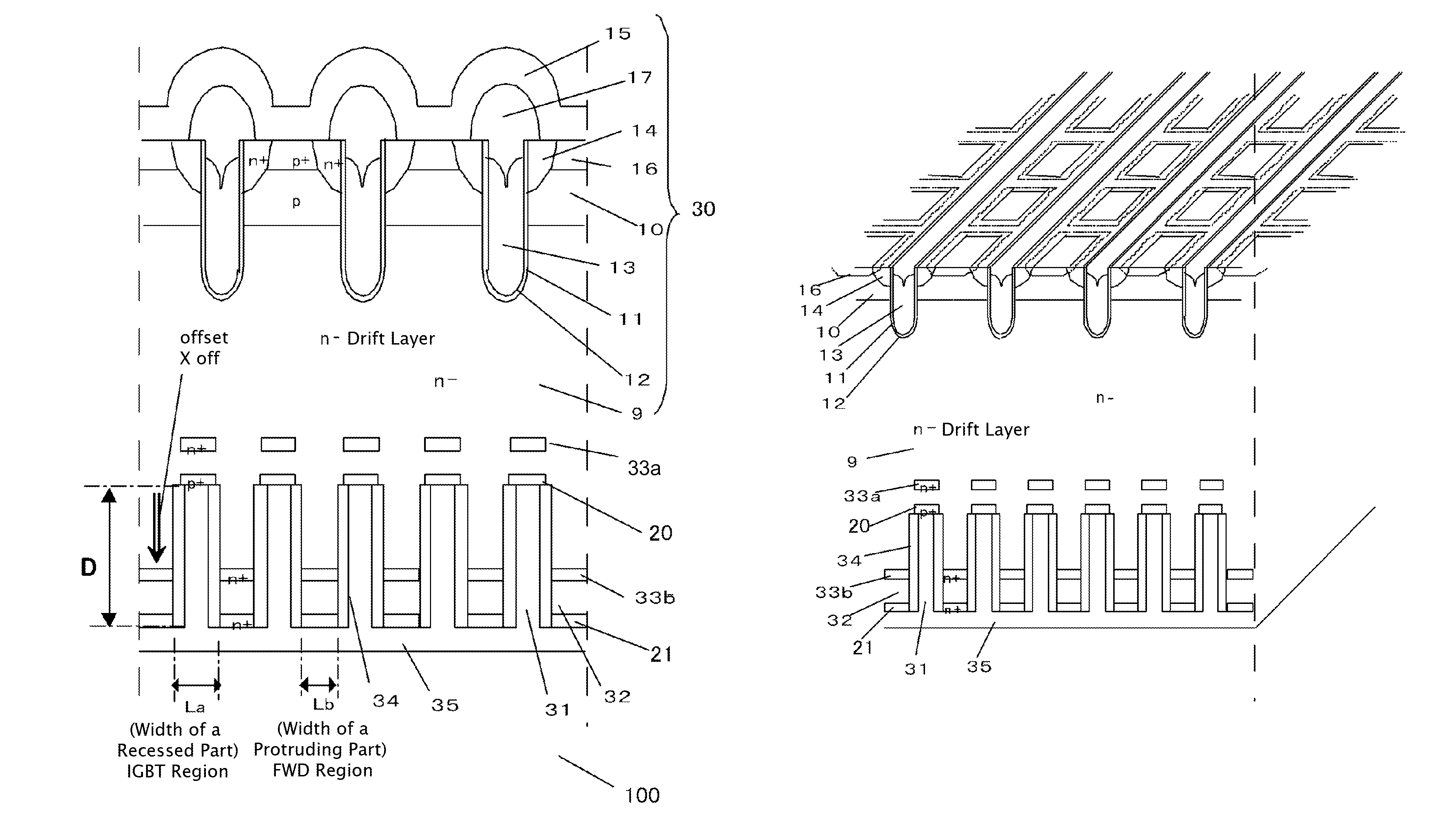

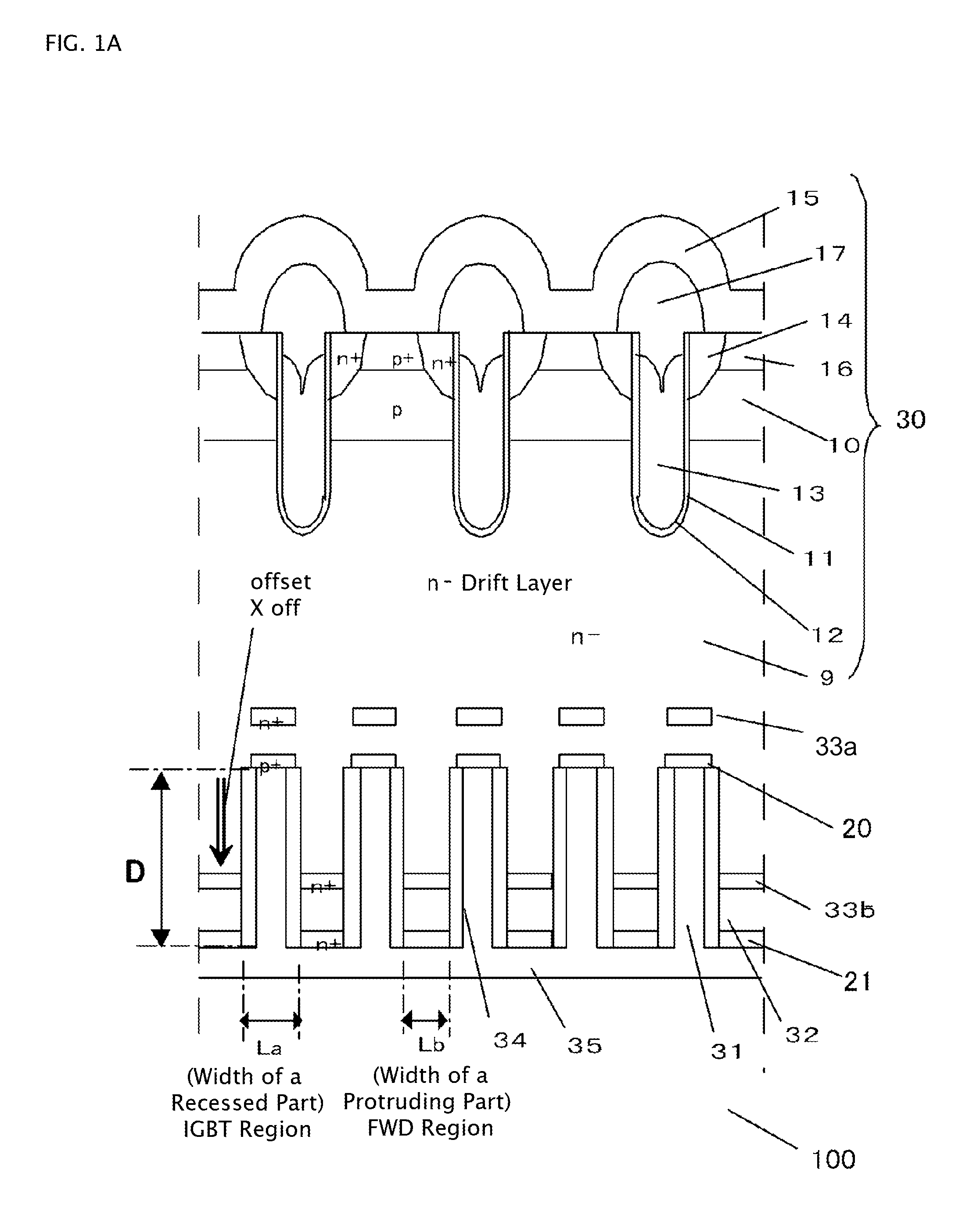

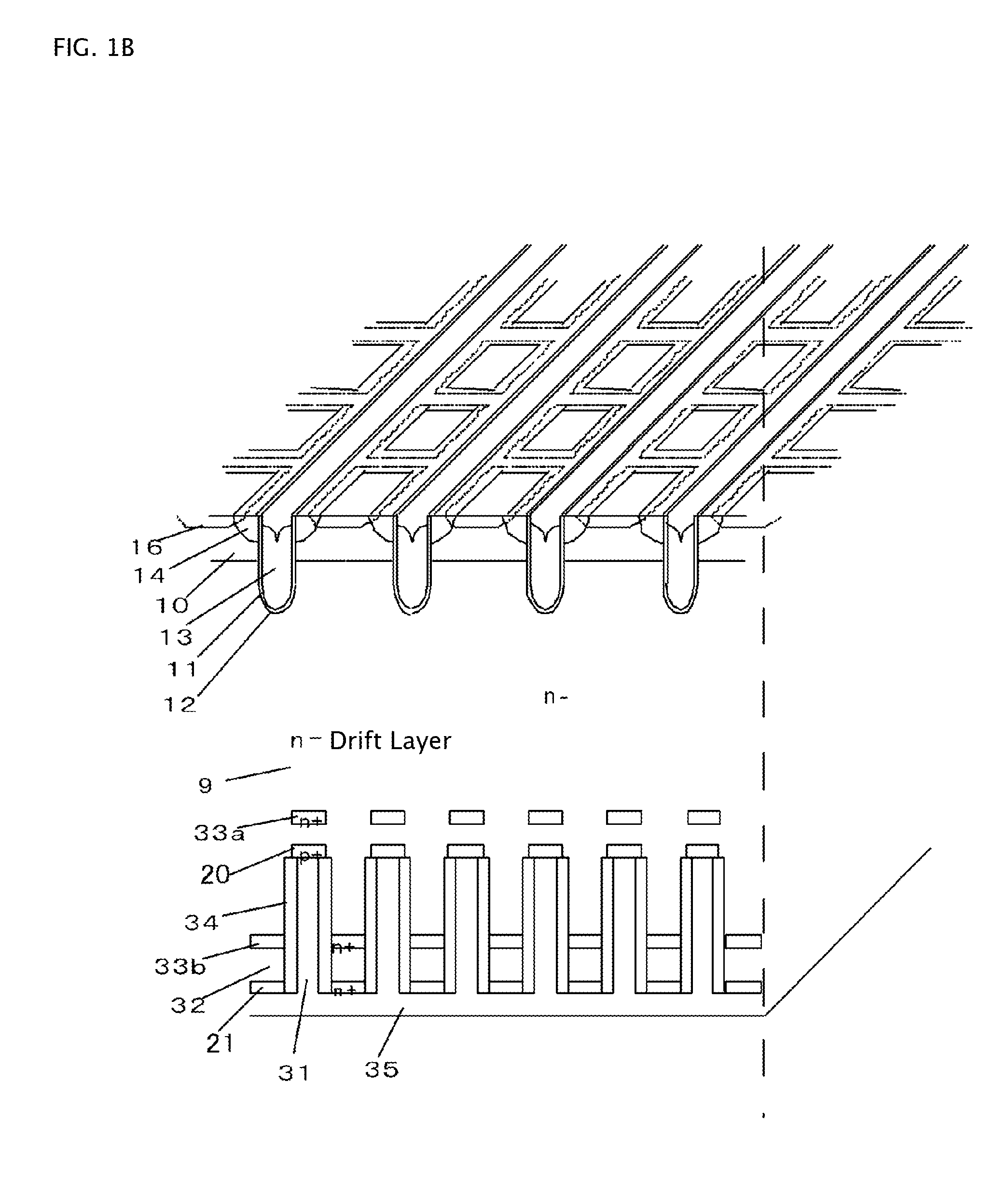

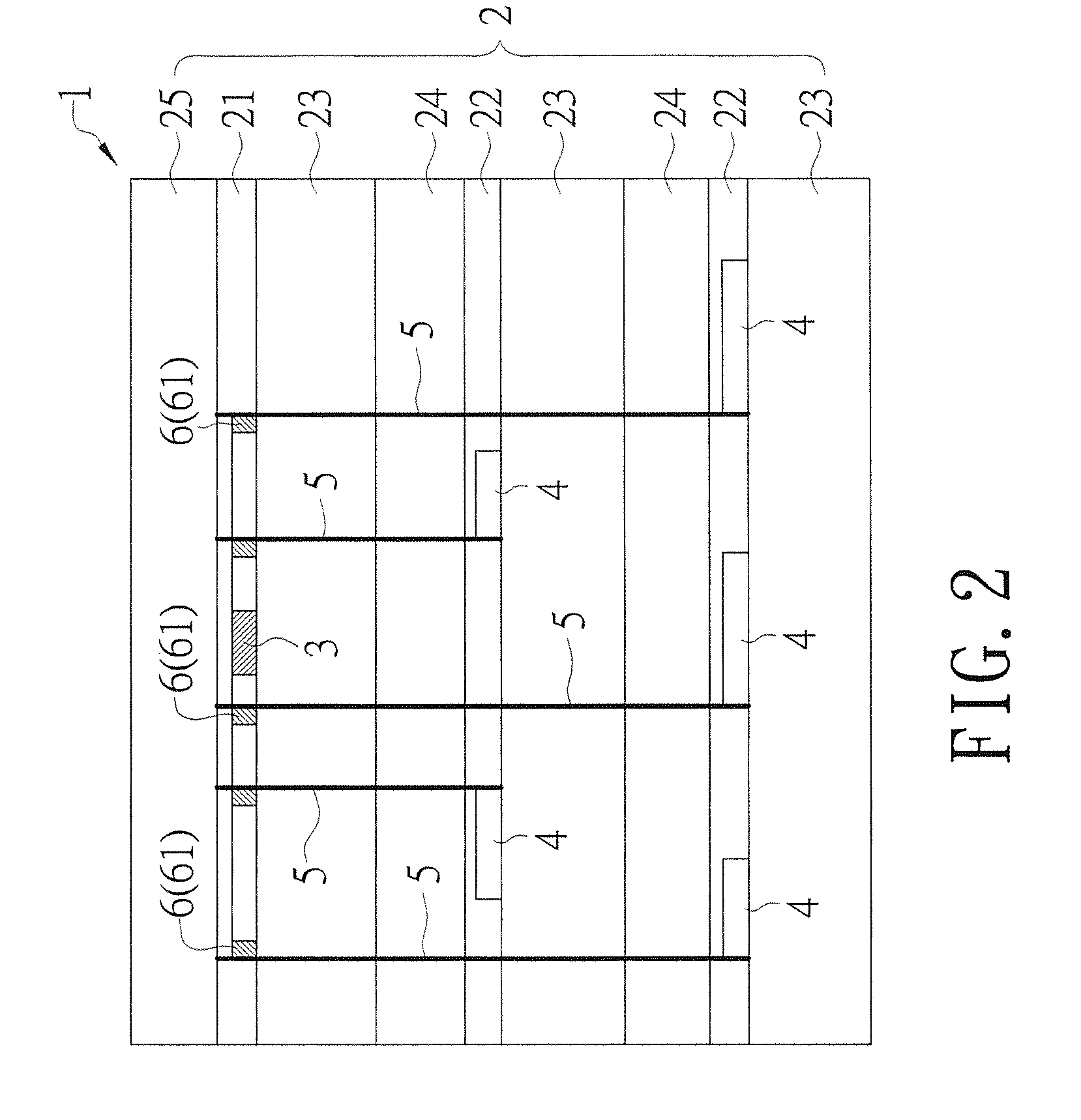

Reverse-conducting insulated gate bipolar transistor

InactiveUS8502345B2Reduce chip costSemiconductor/solid-state device manufacturingBorehole/well accessoriesEngineeringSemiconductor

Reverse-conducting insulated gate bipolar transistor in which IGBT region and FWD region are integrated into a single body in a semiconductor substrate with a common active region is disclosed. MOS gate structure is on a first major surface side. Rear surface side structure is in a second major surface side of the semiconductor substrate and includes a plurality of recessed parts vertical to the second major surface, which are repeated periodically along the second major surface. A plurality of protruding parts are interposed between the recessed parts. Rear surface side structure includes p type collector region on a bottom surface of the recessed part, n type first field stop region at a position deeper than the collector region, n type cathode region on the top surface of the protruding part, and n type second field stop region in the protruding part at a position deeper than the cathode region.

Owner:FUJI ELECTRIC CO LTD

Combined absolute-pressure and relative-pressure sensor

InactiveUS7270011B2Save spaceImprove system reliabilityFluid pressure measurement by electric/magnetic elementsPressure difference measurement between multiple valvesRelative pressureSemiconductor materials

Owner:ROBERT BOSCH GMBH

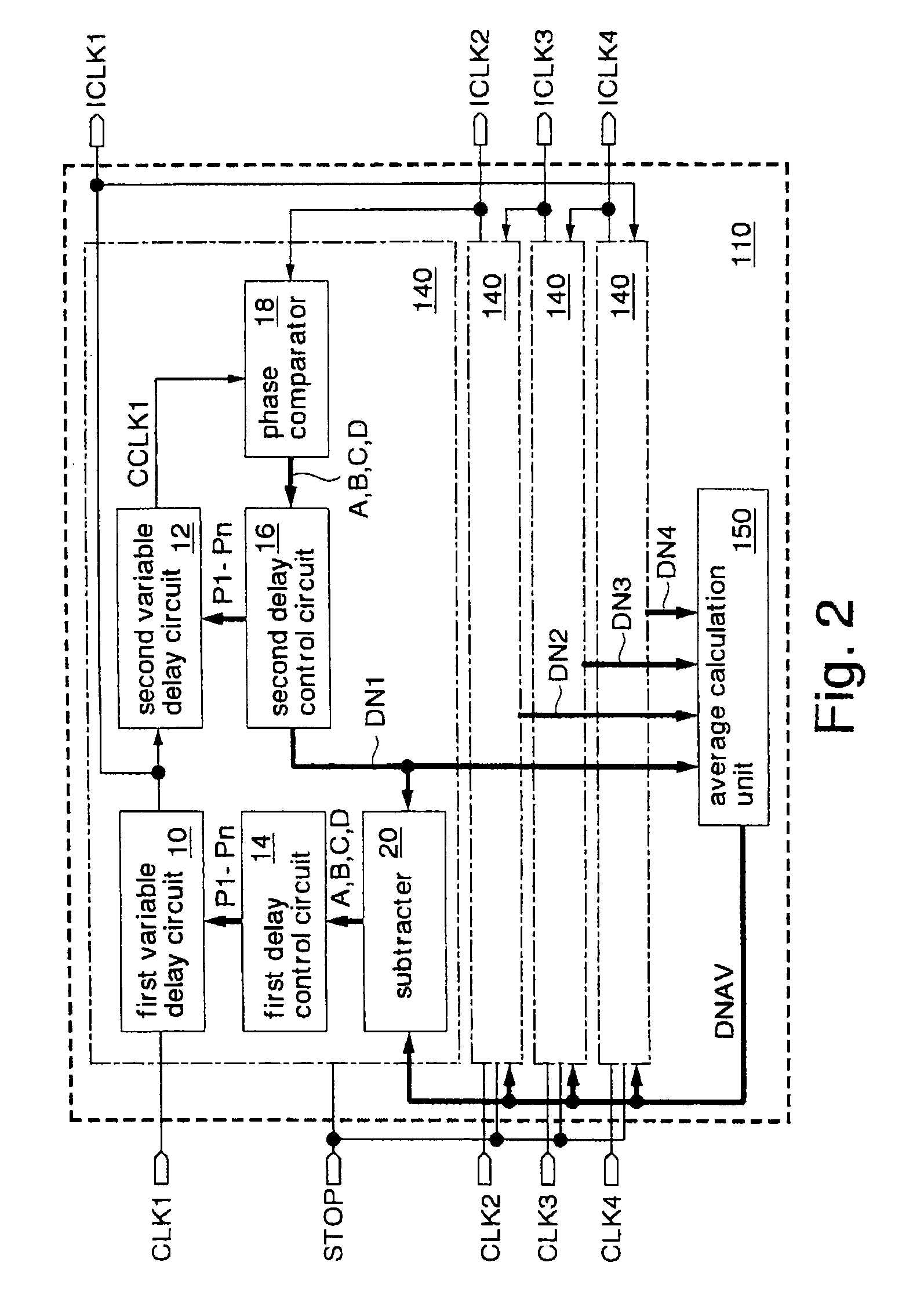

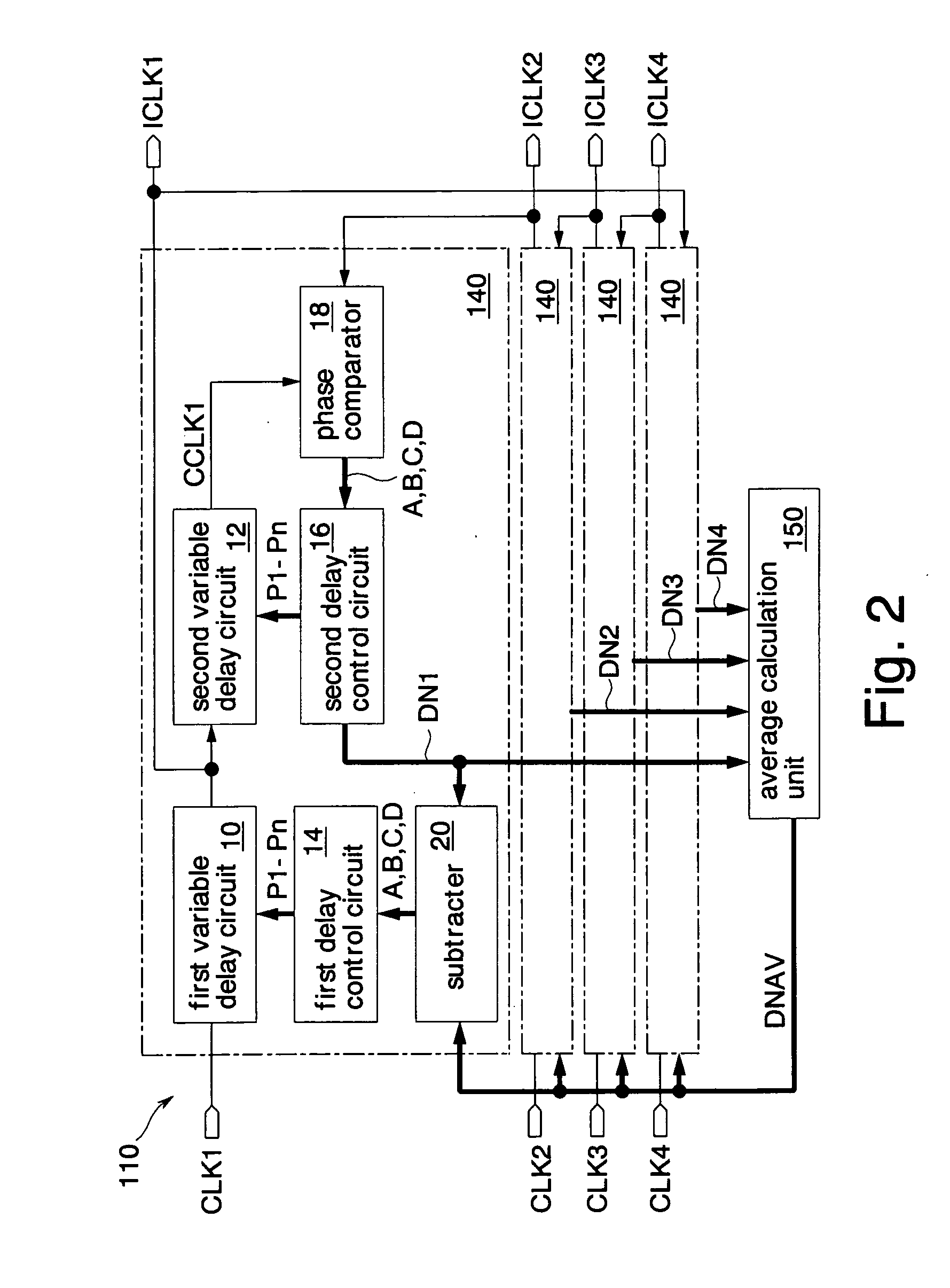

Semiconductor integrated circuit

InactiveUS7319349B2Low costReduce testing costsMultiple input and output pulse circuitsPulse automatic controlPhase differenceClock rate

Owner:SOCIONEXT INC

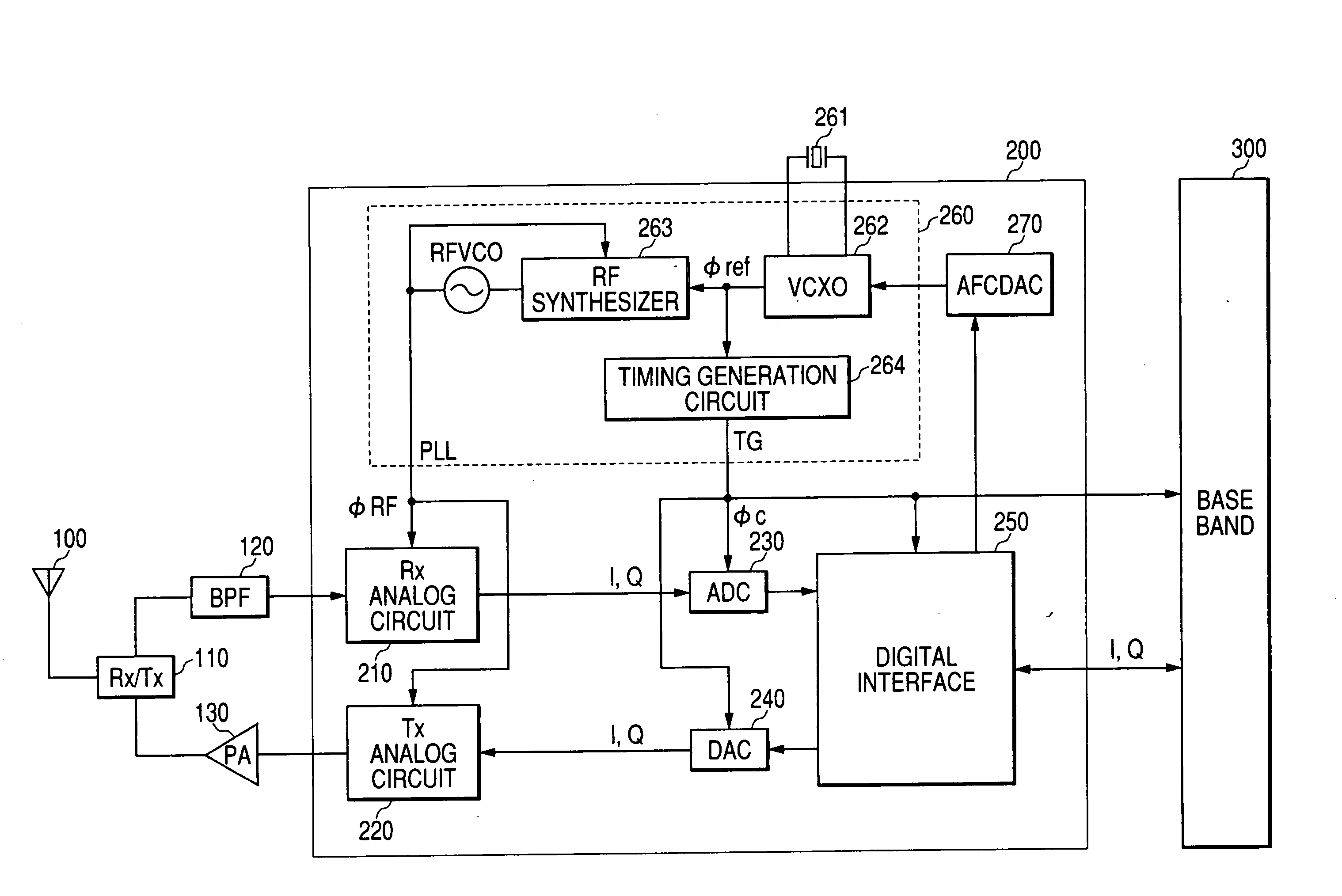

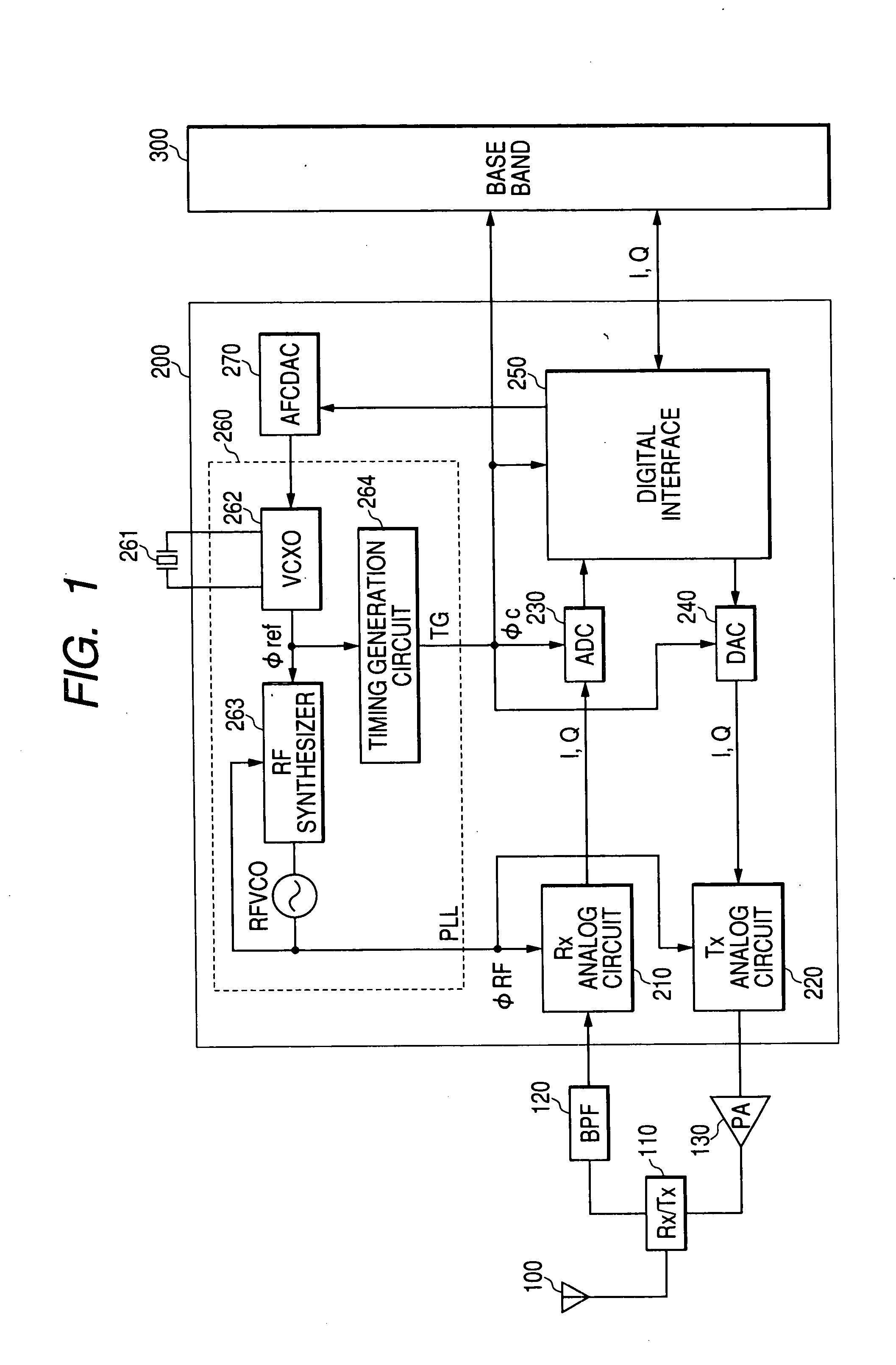

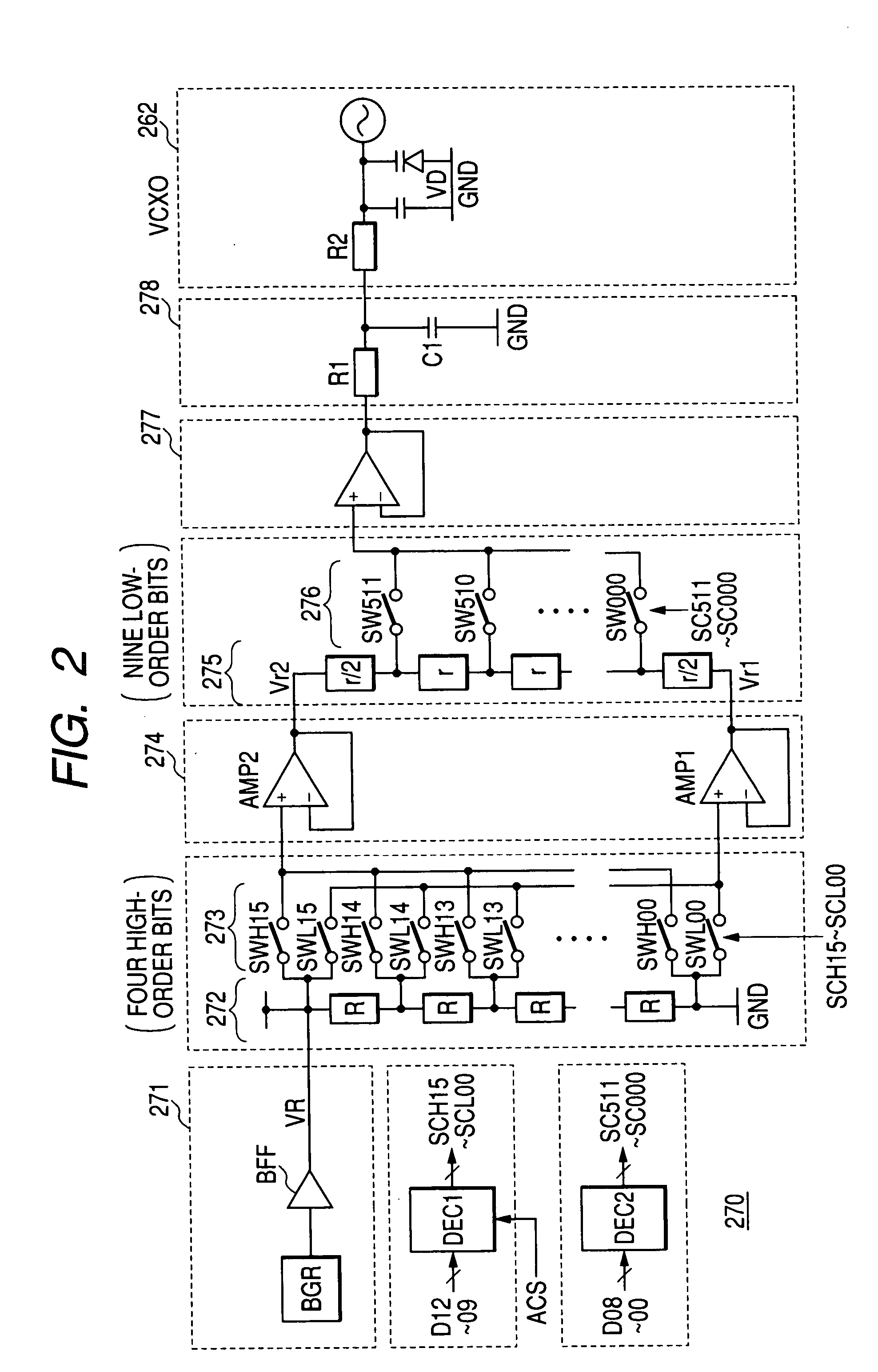

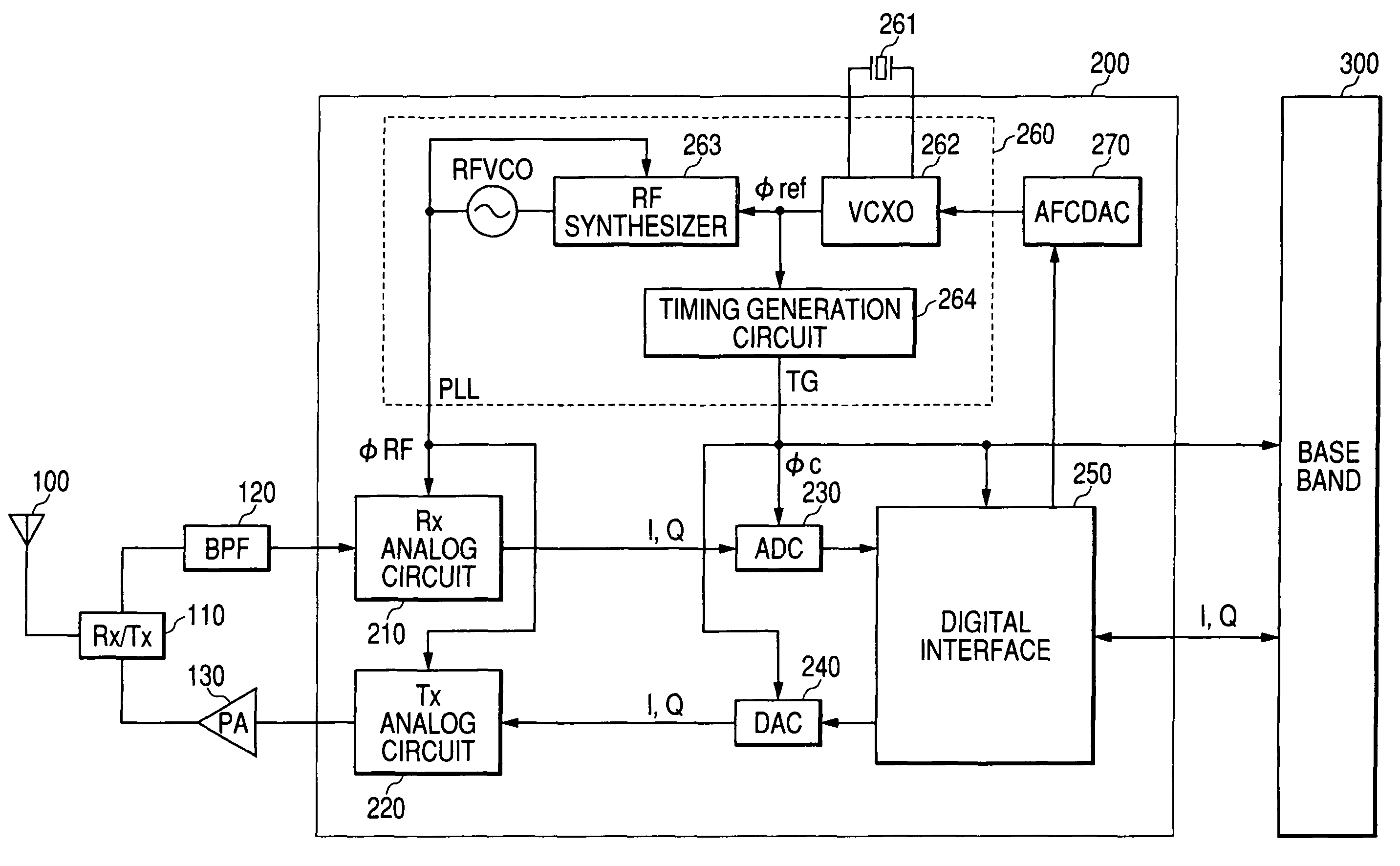

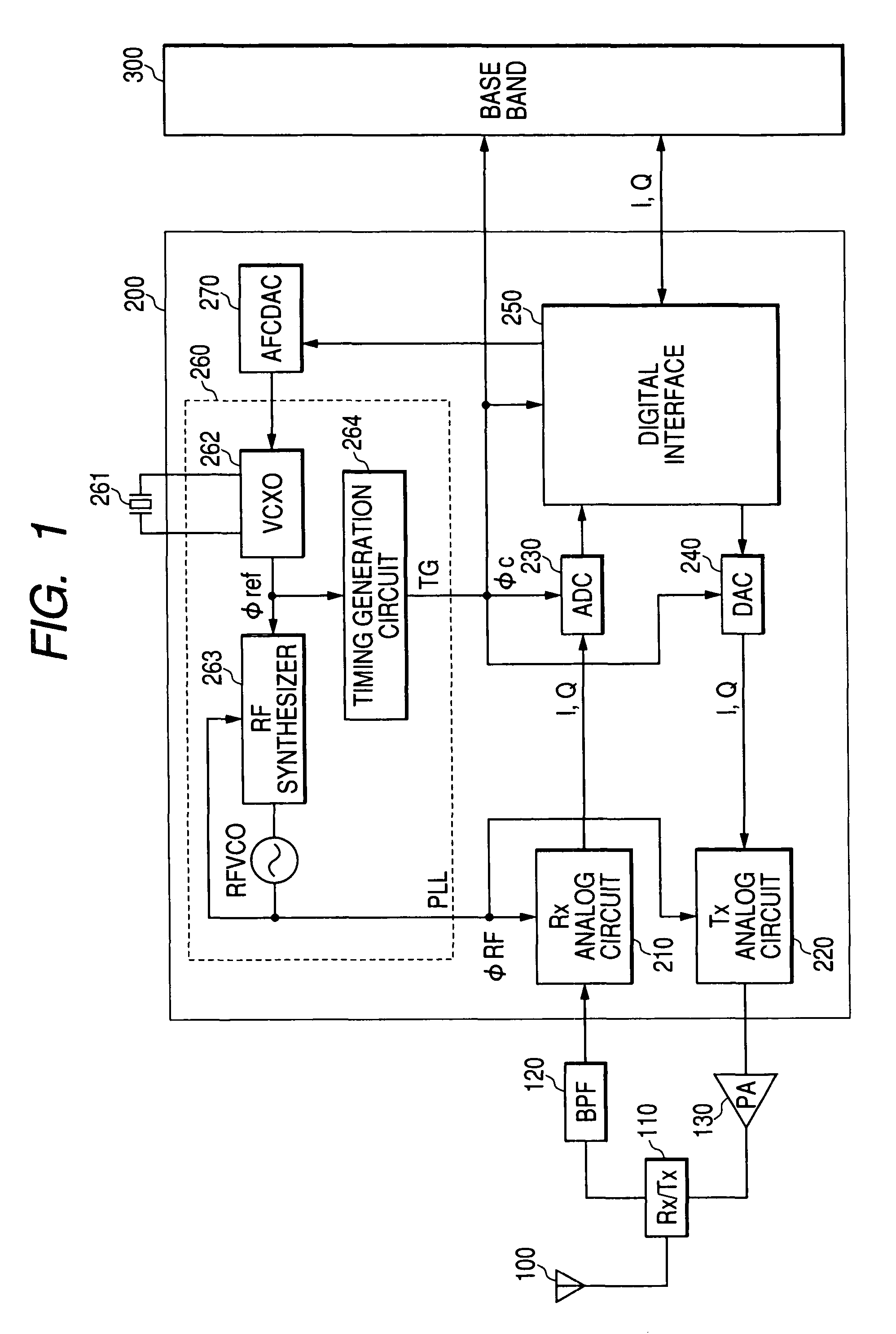

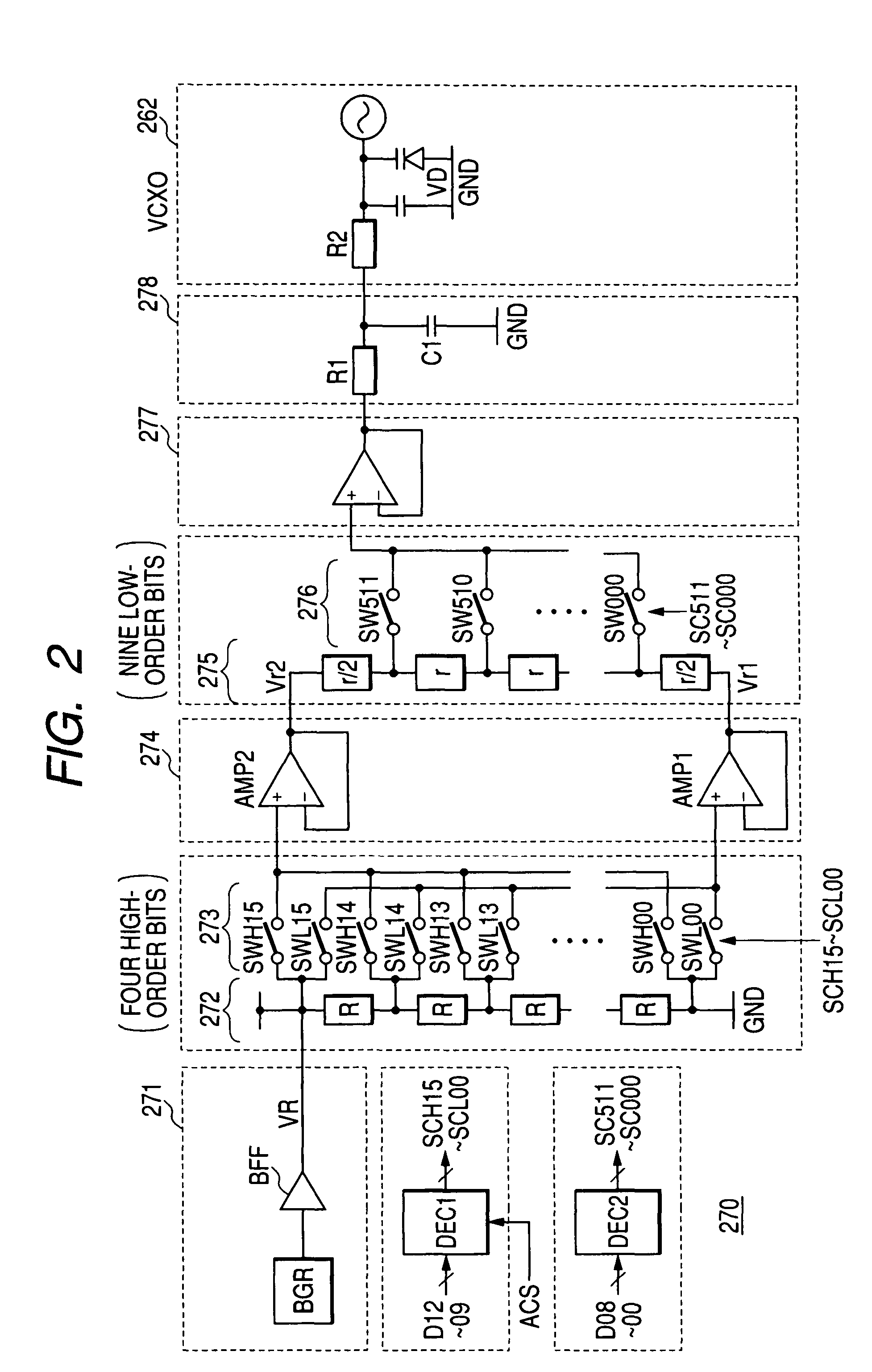

Semiconductor integrated circuit and radio communication apparatus for communication

InactiveUS20060255874A1Raise the ratioReduce chip costAnalogue/digital conversionEnergy efficient ICTEngineeringVoltage control

A total power consumption of a radio communication apparatus is reduced, the radio communication apparatus including a semiconductor integrated circuit (high-frequency IC) which has a clock generation circuit which generates a reference clock signal for use in modulating a transmit signal and demodulating a received signal. The clock generation circuit is provided with a voltage-controlled oscillator circuit (VCXO) which oscillates, when a quartz oscillator is connected thereto, at a frequency dependent on a natural frequency of the quartz oscillator and a control voltage applied thereto. The voltage-controlled oscillator circuit is configured such that a result obtained by converting, in an internal DA converter circuit, digital frequency control information supplied from the baseband circuit is applied as the control voltage to the voltage-controlled oscillator circuit and such that the voltage-controlled oscillator circuit oscillates at a frequency corresponding to the control voltage.

Owner:RENESAS ELECTRONICS CORP

Integrated circuit for driving semiconductor device and power converter

InactiveUS7763974B2Reduce chip costIncreasing the thicknessSubstation/switching arrangement detailsSemiconductor/solid-state device detailsSignal processing circuitsP channel

An integrated circuit for driving a semiconductor device, which is adaptable for demands, such as a higher output (larger current), a higher voltage, and a smaller loss, and has a small size, is produced at a low cost, and has high reliability. A power converter including such an integrated circuit is also provided. Circuit elements constituting a drive section of an upper arm drive circuit 212, a level shift circuit 20 including a current sensing circuit 210, a drive section of a lower arm drive circuit 222, and a drive signal processing circuit 224 are integrated and built in one high withstand voltage IC chip 200. Circuit elements constituting a final output stage buffer section 213 of the upper arm drive circuit 212 are built in a vertical p-channel MOS-FET chip 213p and a vertical n-channel MOS-FET chip 213n. Circuit elements constituting a final output stage buffer section 223 of the lower arm drive circuit 222 are built in a vertical p-channel MOS-FET chip 223p and a vertical n-channel MOS-FET chip 223n. Thus, a driver IC 2 is fabricated.

Owner:HITACHI LTD

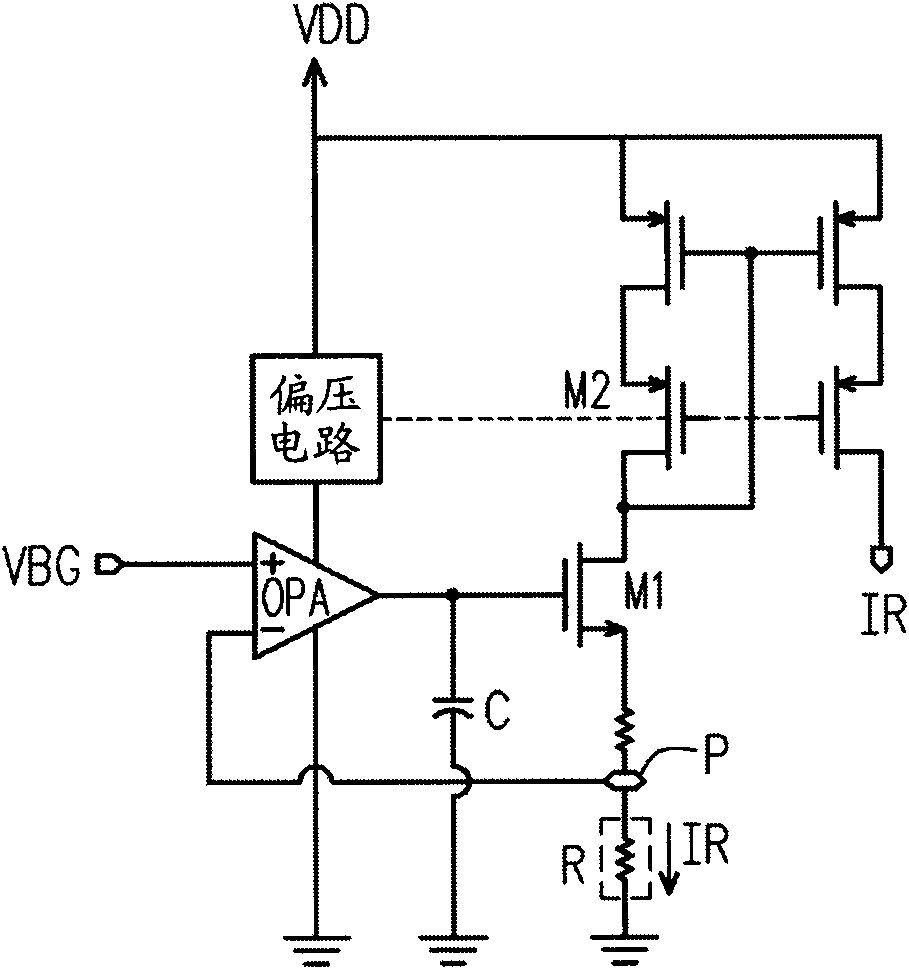

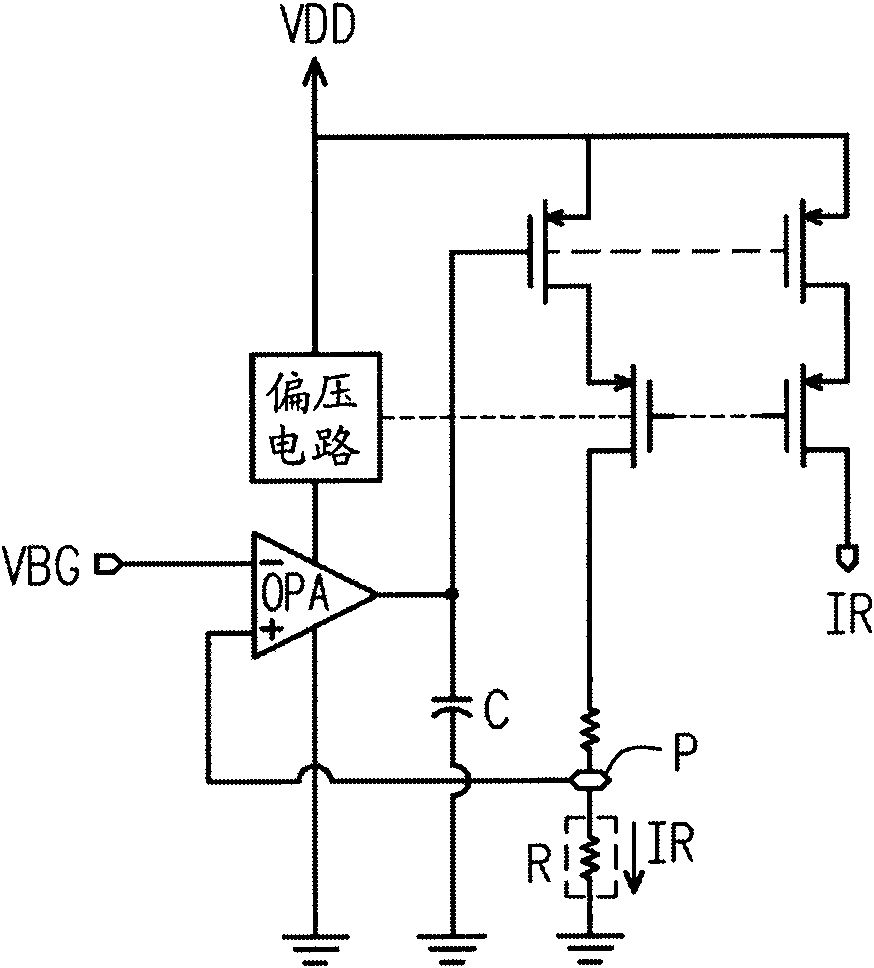

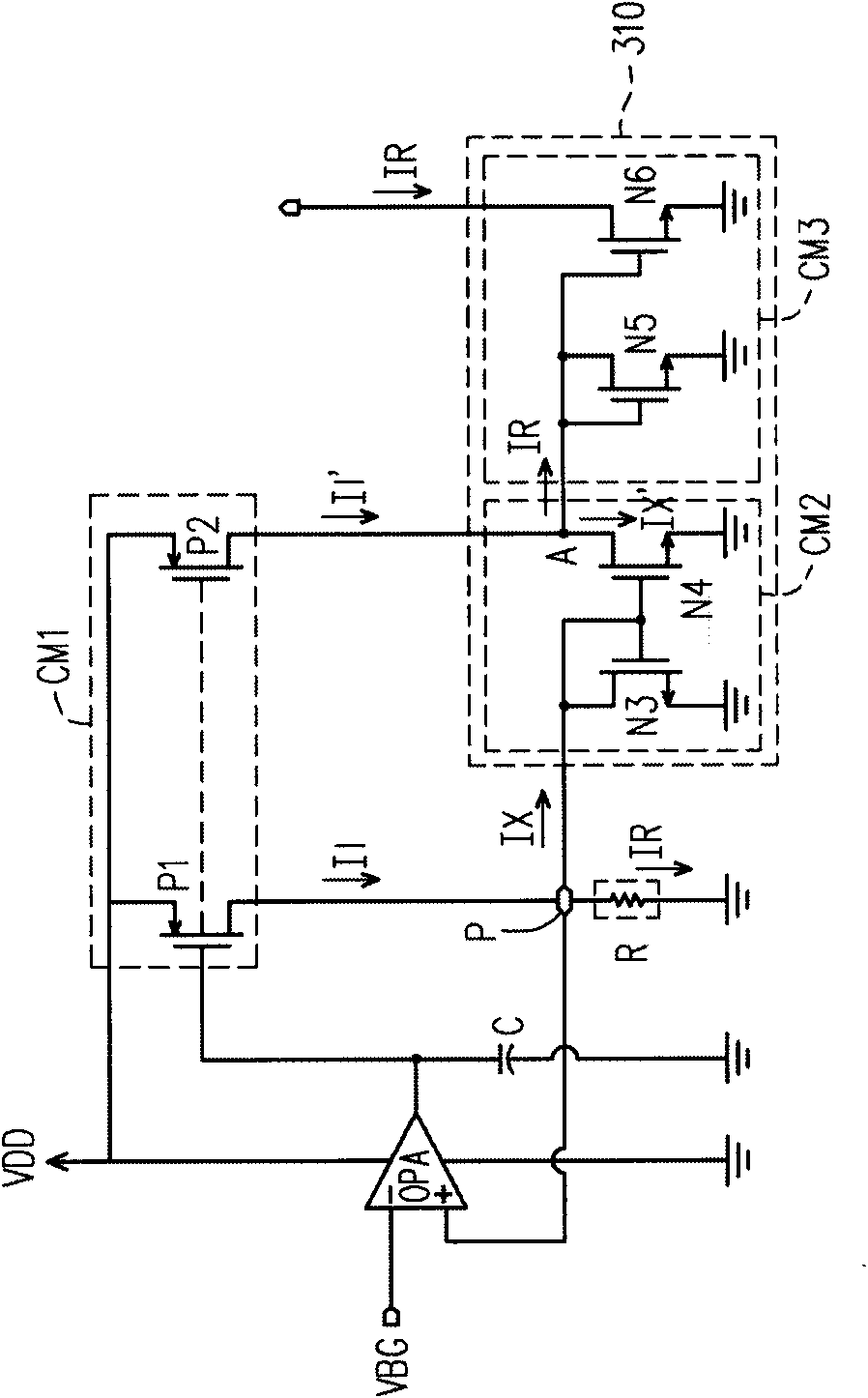

Reference current generating circuit applied to low operating voltage

ActiveCN101676828AImprove phase marginReduce chip areaElectric variable regulationElectrical resistance and conductanceCapacitance

A reference current generating circuit applied to low operating voltage is arranged in a chip and utilizes precise reference voltage and precise external resistance to generate precise reference current. The reference current generating circuit utilizes an equivalent resistance to be connected with the external resistance in parallel, so as to provide resistance compensation and reduce the resistance from chip pad to the interior of the chip. Moderate capacitance compensation is added, phase margin of the reference current generating circuit can be improved, and the aim of stable loop is achieved, thus reducing chip area and cost in application of low operating voltage. In addition, the reference current generating circuit utilizes a current mirror to copy the reference current generated by the external resistance, so at to solve the problem that current is influenced by parallel connection of the equivalent resistance and the external resistance.

Owner:FARADAY TECH CORP

Semiconductor integrated circuit and radio communication apparatus for communication

InactiveUS7929594B2Raise the ratioReduce chip costAnalogue/digital conversionEnergy efficient ICTFrequency oscillationSemiconductor

A total power consumption of a radio communication apparatus is reduced, the radio communication apparatus including a semiconductor integrated circuit (high-frequency IC) which has a clock generation circuit which generates a reference clock signal for use in modulating a transmit signal and demodulating a received signal. The clock generation circuit is provided with a voltage-controlled oscillator circuit (VCXO) which oscillates, when a quartz oscillator is connected thereto, at a frequency dependent on a natural frequency of the quartz oscillator and a control voltage applied thereto. The voltage-controlled oscillator circuit is configured such that a result obtained by converting, in an internal D / A converter circuit, digital frequency control information supplied from the baseband circuit is applied as the control voltage to the voltage-controlled oscillator circuit and such that the voltage-controlled oscillator circuit oscillates at a frequency corresponding to the control voltage.

Owner:RENESAS ELECTRONICS CORP

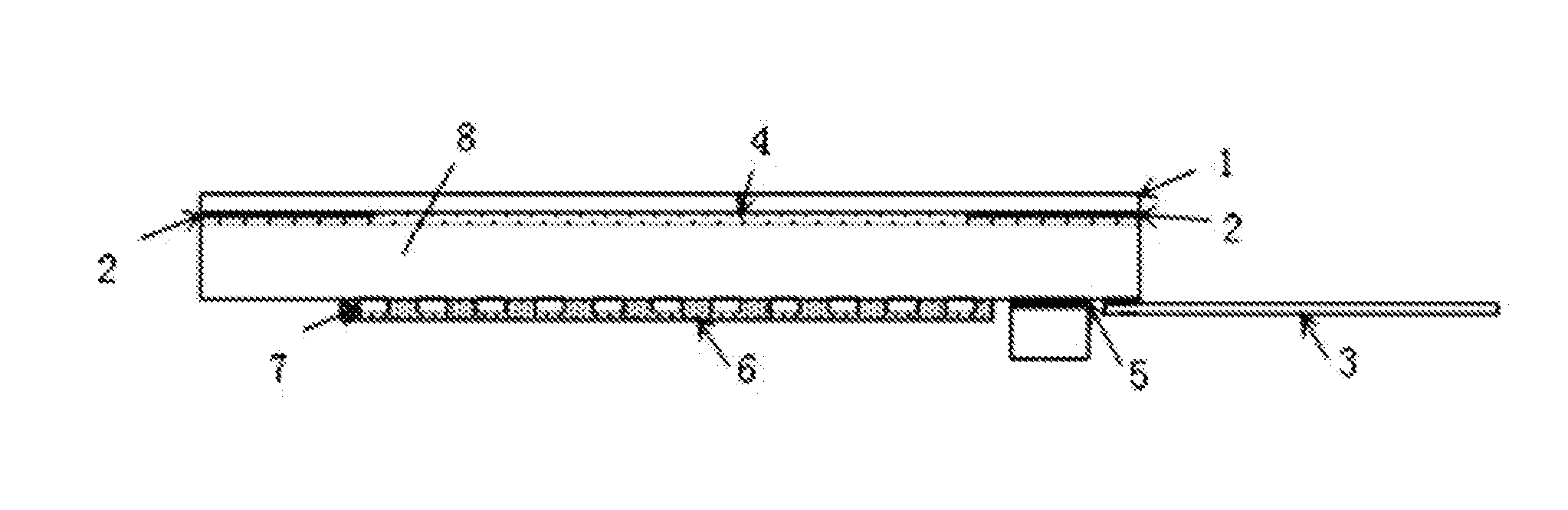

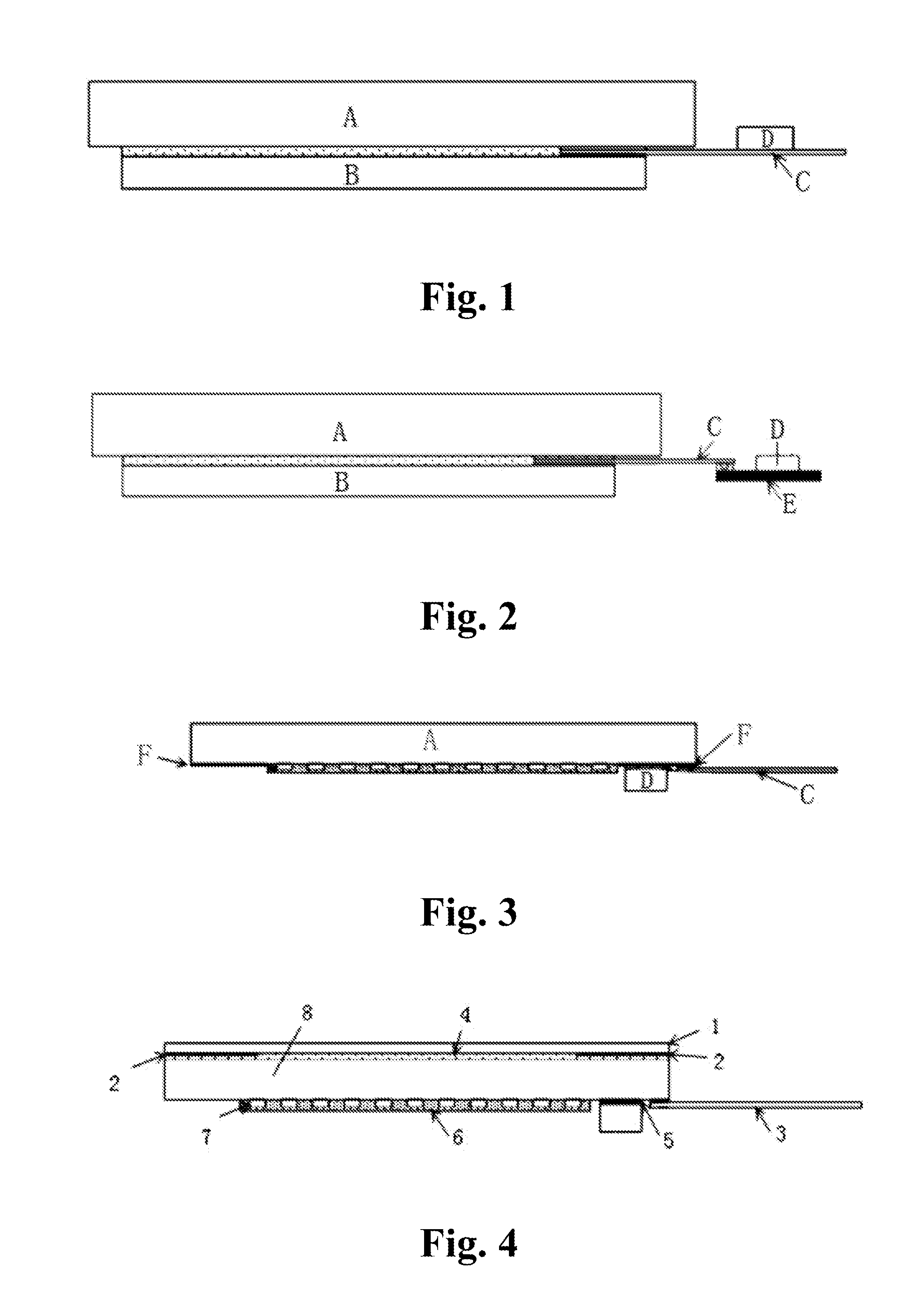

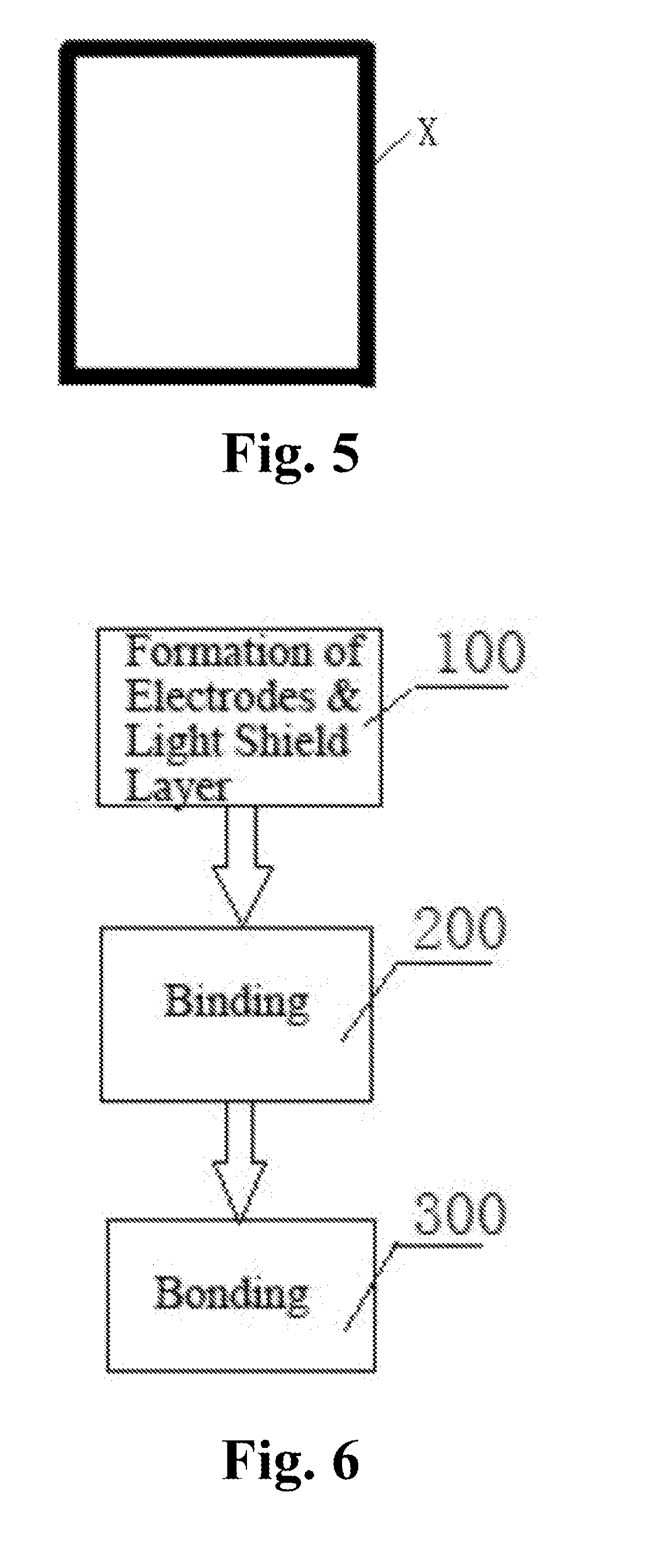

Capacitive touch screen and manufacturing method thereof

InactiveUS20130257791A1Reduce chip areaEasy to produceSynthetic resin layered productsLaminationEngineeringElectrical and Electronics engineering

The invention relates to a capacitive touch screen and a manufacturing method thereof, wherein a touch chip does not need package test and only needs a chip wafer. Therefore, compared with the traditional touch chip for a touch screen module, the package cost and the package test cost of the chip are reduced. Meanwhile, due to small area of the chip, the amount of space is small compared with the traditional touch chip with a package outline. The invention has the advantages that: the overall material cost of the capacitive touch screen can be effectively reduced; the capacitive touch screen is easy to produce; the requirements on the manufacturing processes of the capacitive touch screen are reduced; and the product yield is improved.

Owner:FOCALTECH SYST LTD

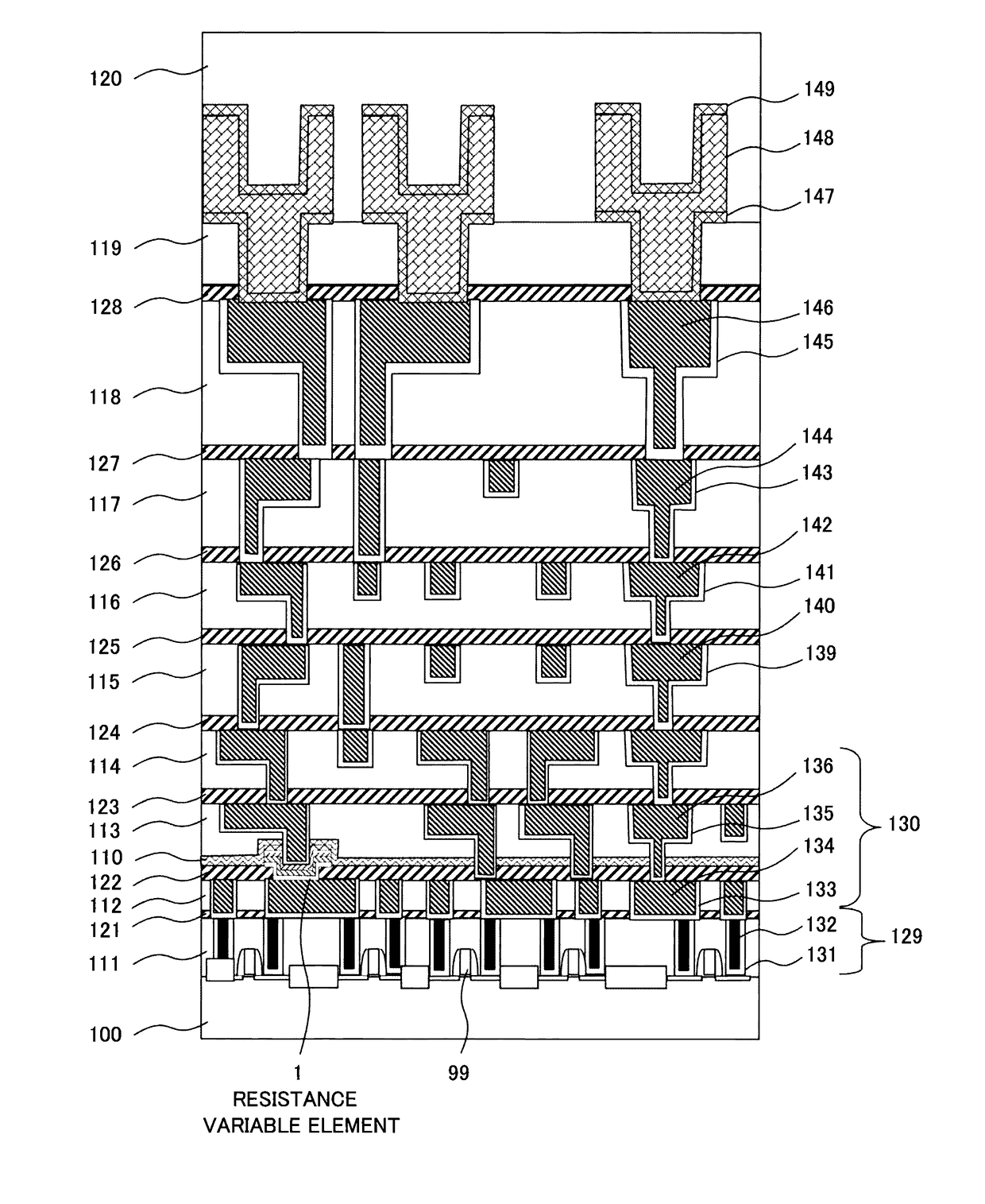

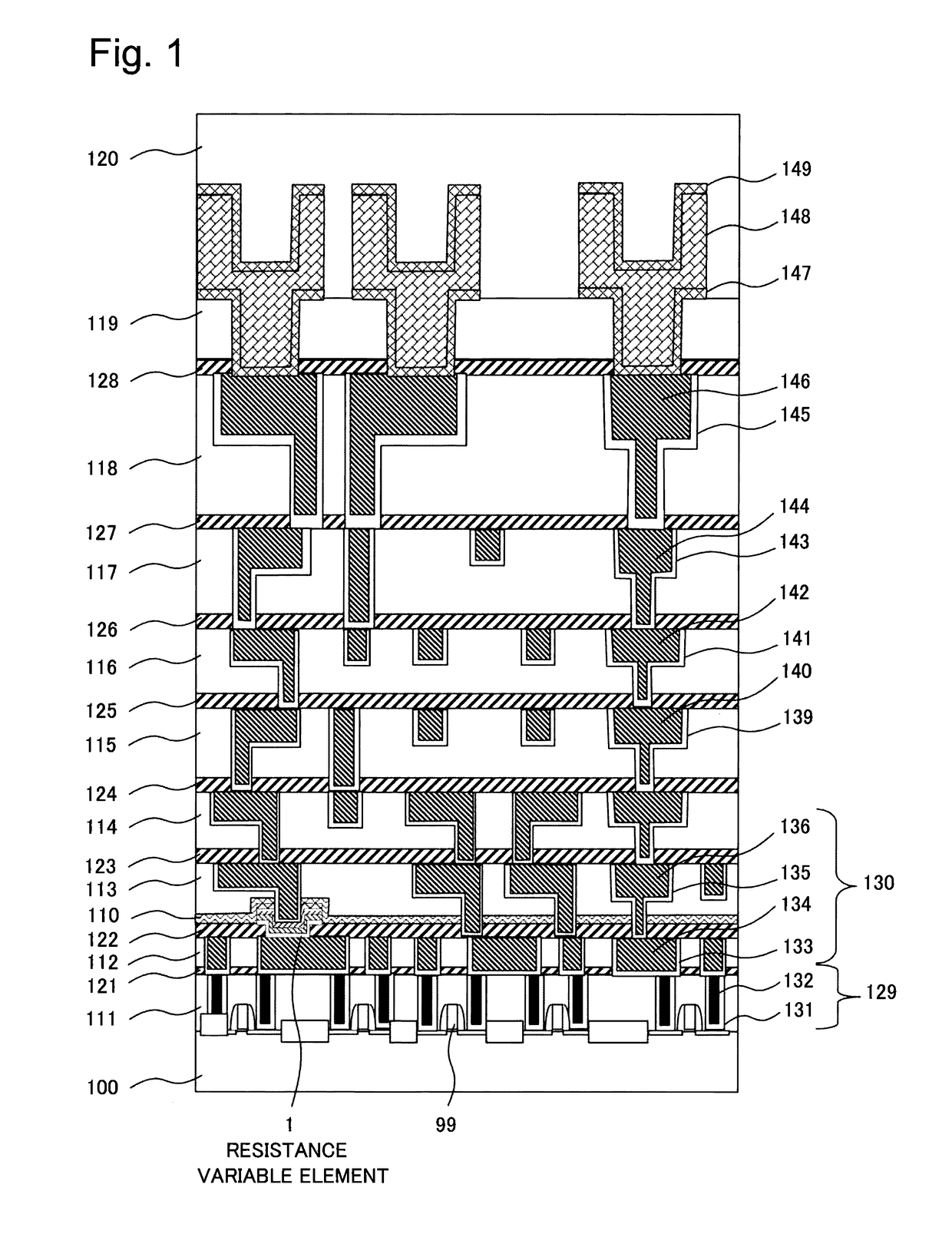

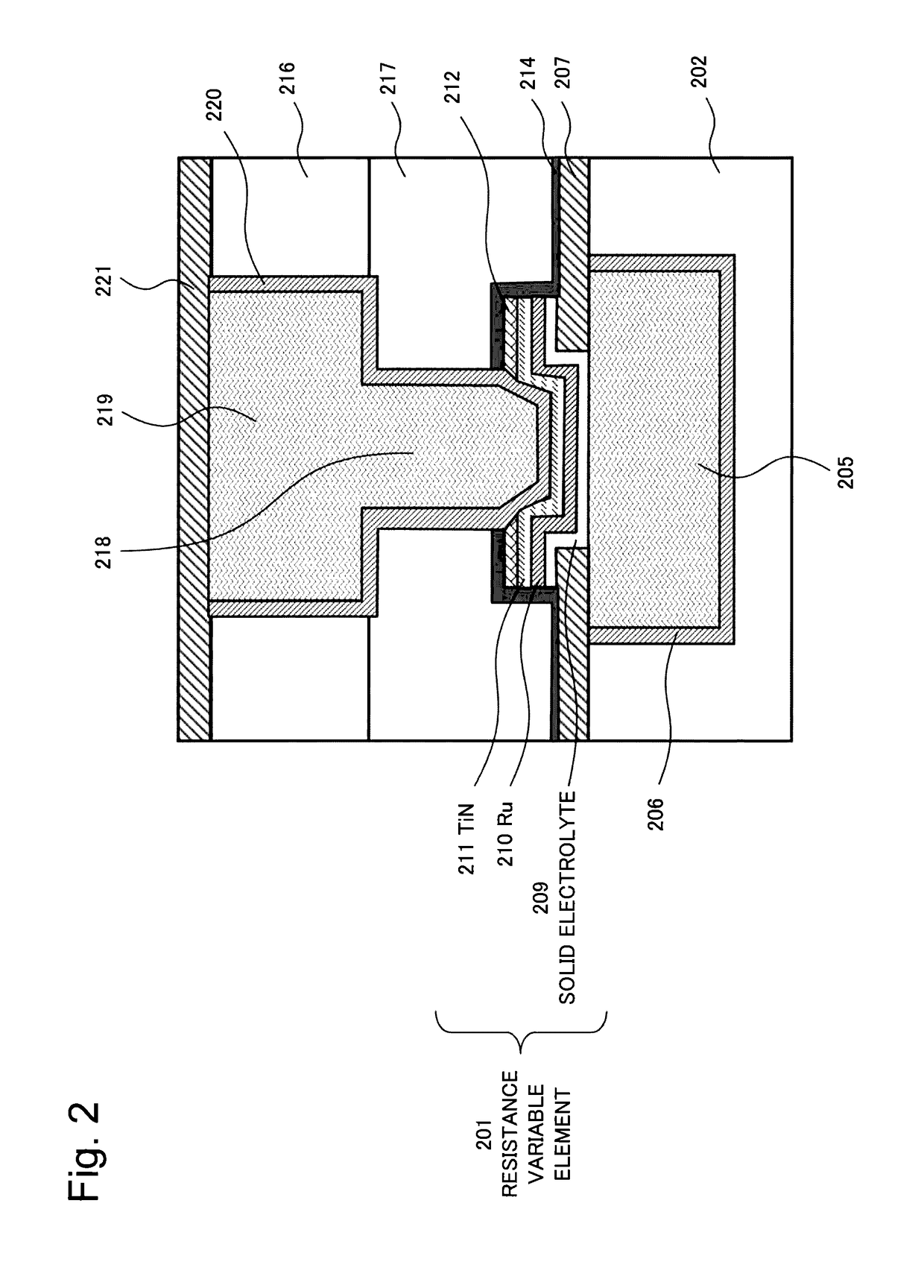

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20170141125A1Low costReduce electric powerSolid-state devicesCAD circuit designEngineeringSemiconductor

Provided are a semiconductor device and a method of manufacturing the semiconductor device which enable a hard copy of a reconfigurable circuit, which employs a resistance variable element, to be formed at low cost. The method of manufacturing a semiconductor device is for manufacturing a hard copy from a reconfigurable circuit chip that employs a resistance-variable non-volatile element formed inside a multi-layered wiring layer on a semiconductor substrate, wherein the hard copy is manufactured by using a semiconductor substrate base that is the same as that of the semiconductor substrate for forming the reconfigurable circuit chip.

Owner:NANOBRIDGE SEMICON INC

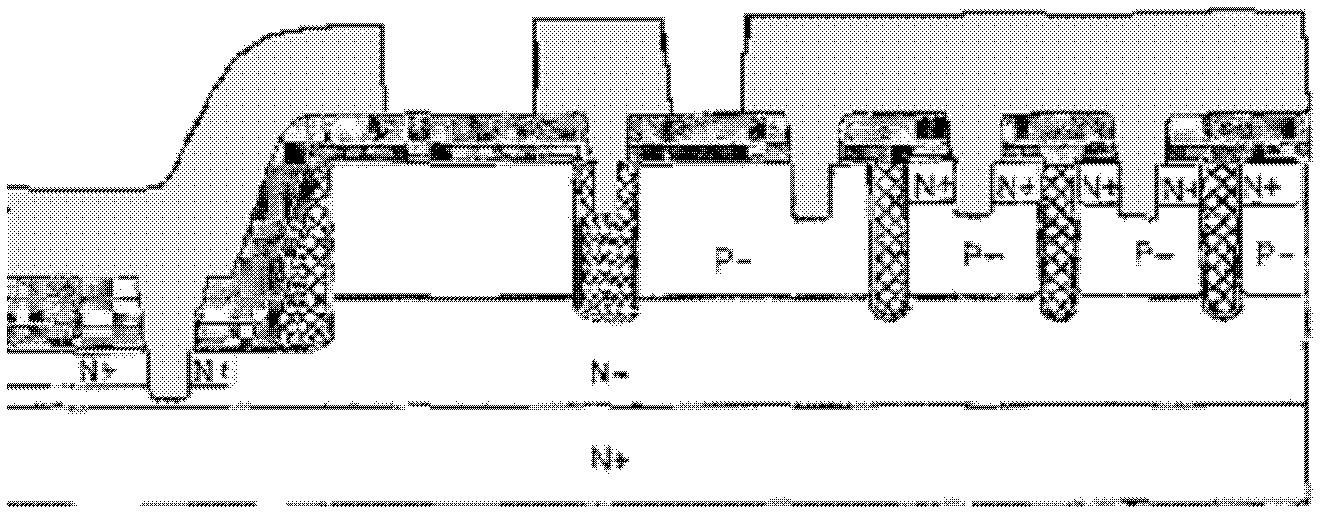

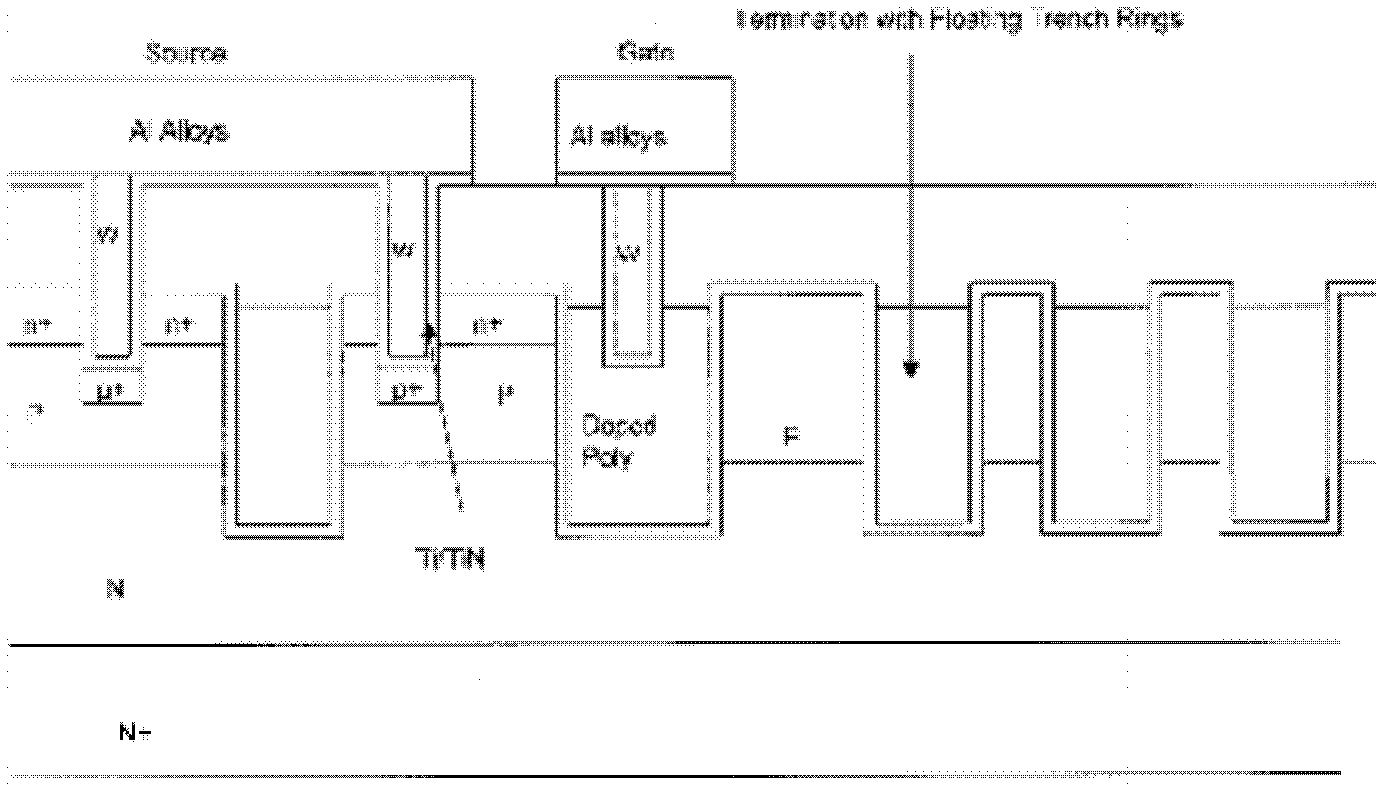

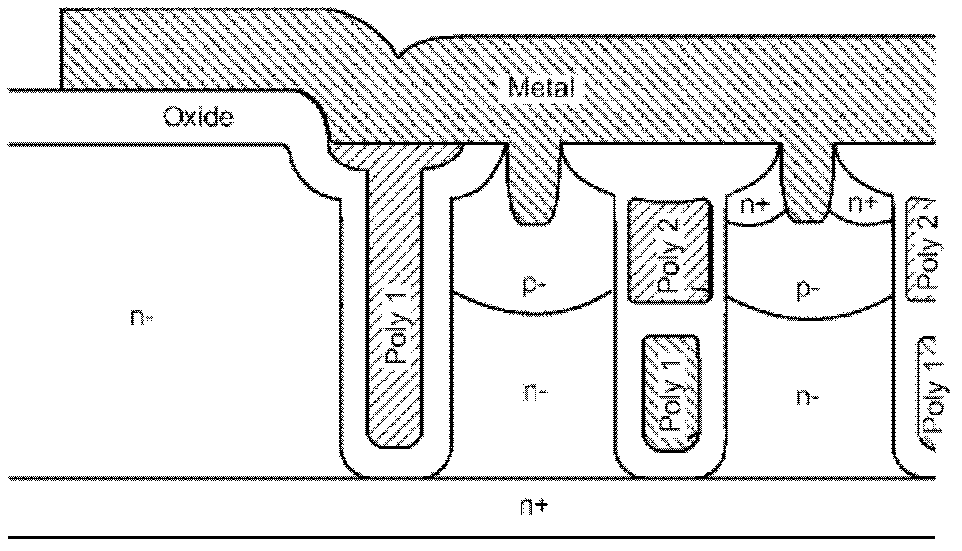

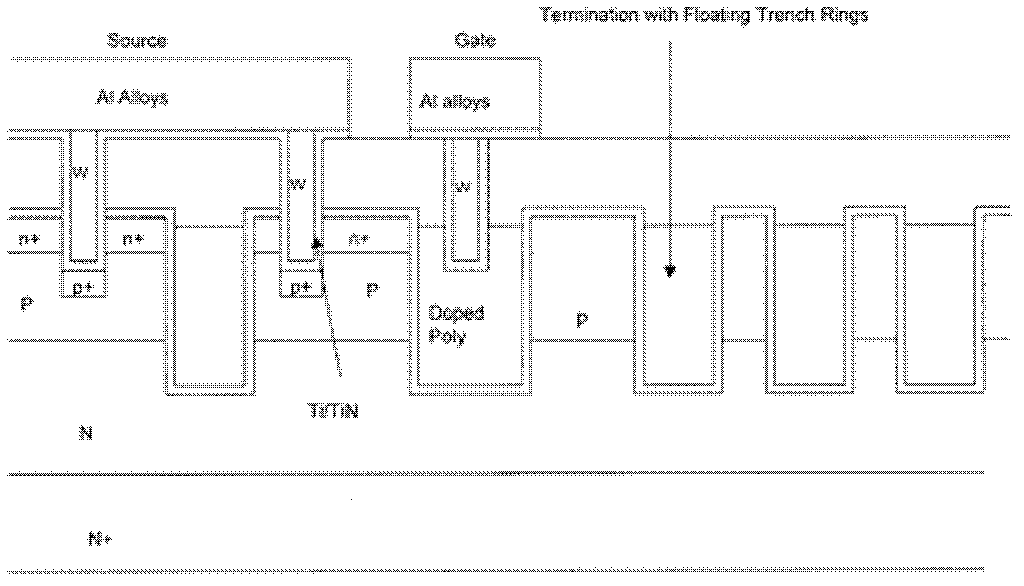

Terminal structure of splitting gate groove power modular operating system (MOS) device and manufacturing method thereof

InactiveCN102569403ALower on-resistanceReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic capacitanceProcess manufacturing

The invention provides a terminal structure of a splitting gate groove power modular operating system (MOS) device and a manufacturing method thereof. The terminal structure comprises a grid leading-out electrode (101), a grid electrode lower part suspended polycrystalline silicon electrode (102), a thick oxidized layer (103), grid electrode connecting metal (104), a source electrode (105), a floating area (N-) (106) and a drain electrode (107); and the grid electrode leading-out electrode (101), the grid electrode lower part suspended polycrystalline silicon electrode (102) and the thick oxidized layer (103) are assembled to form the device terminal and are formed through a same mask plate and same technique. The splitting gate groove power MOS device structure is realized through a process manufacturing flow of five photoetching plates, so the breakdown voltage and parasitic capacitance of the device are not influenced, while ultralow conducting resistance of the device can be guaranteed; and the production cost of the device can be reduced, while the process manufacturing flow is optimized.

Owner:HARBIN ENG UNIV

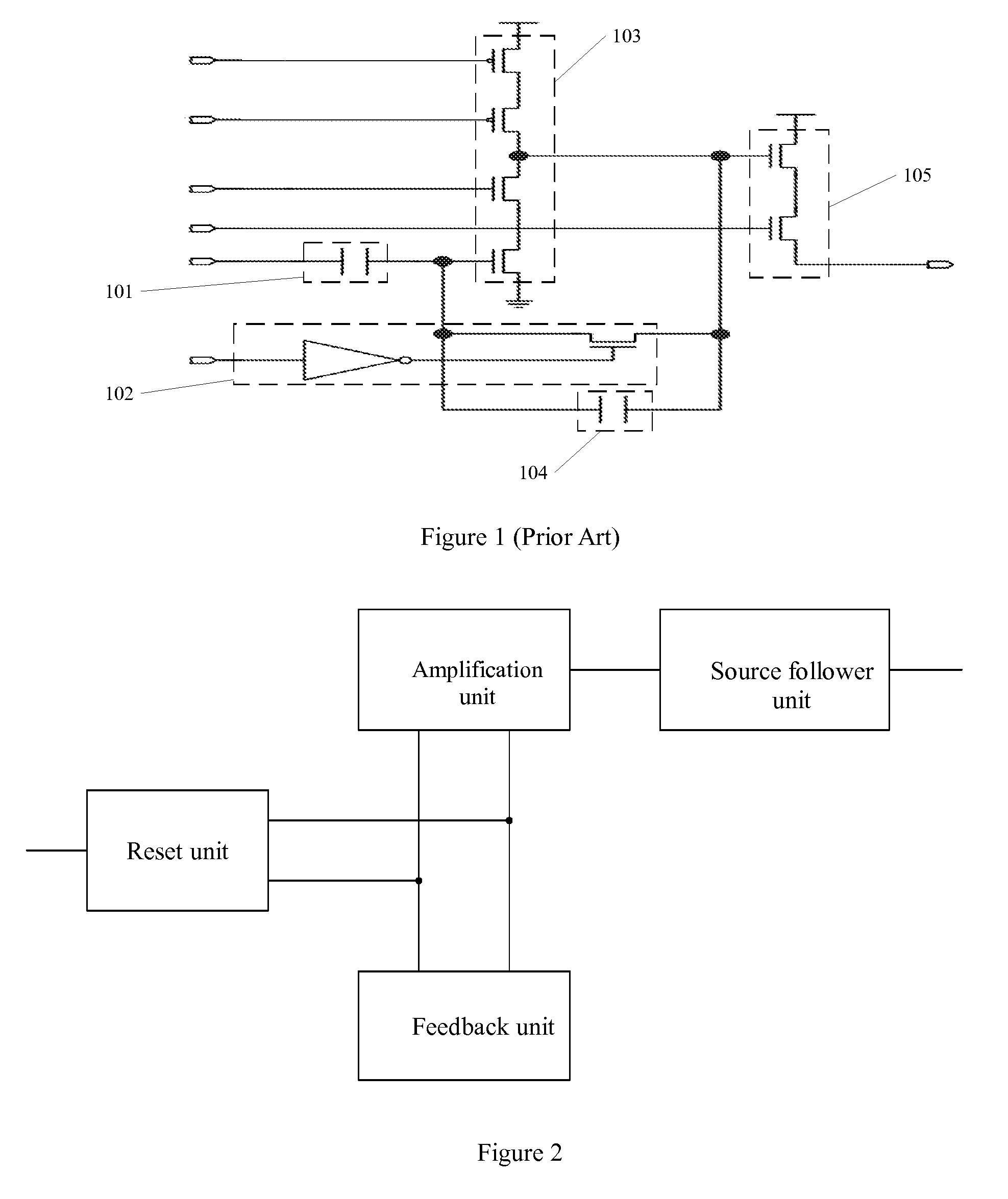

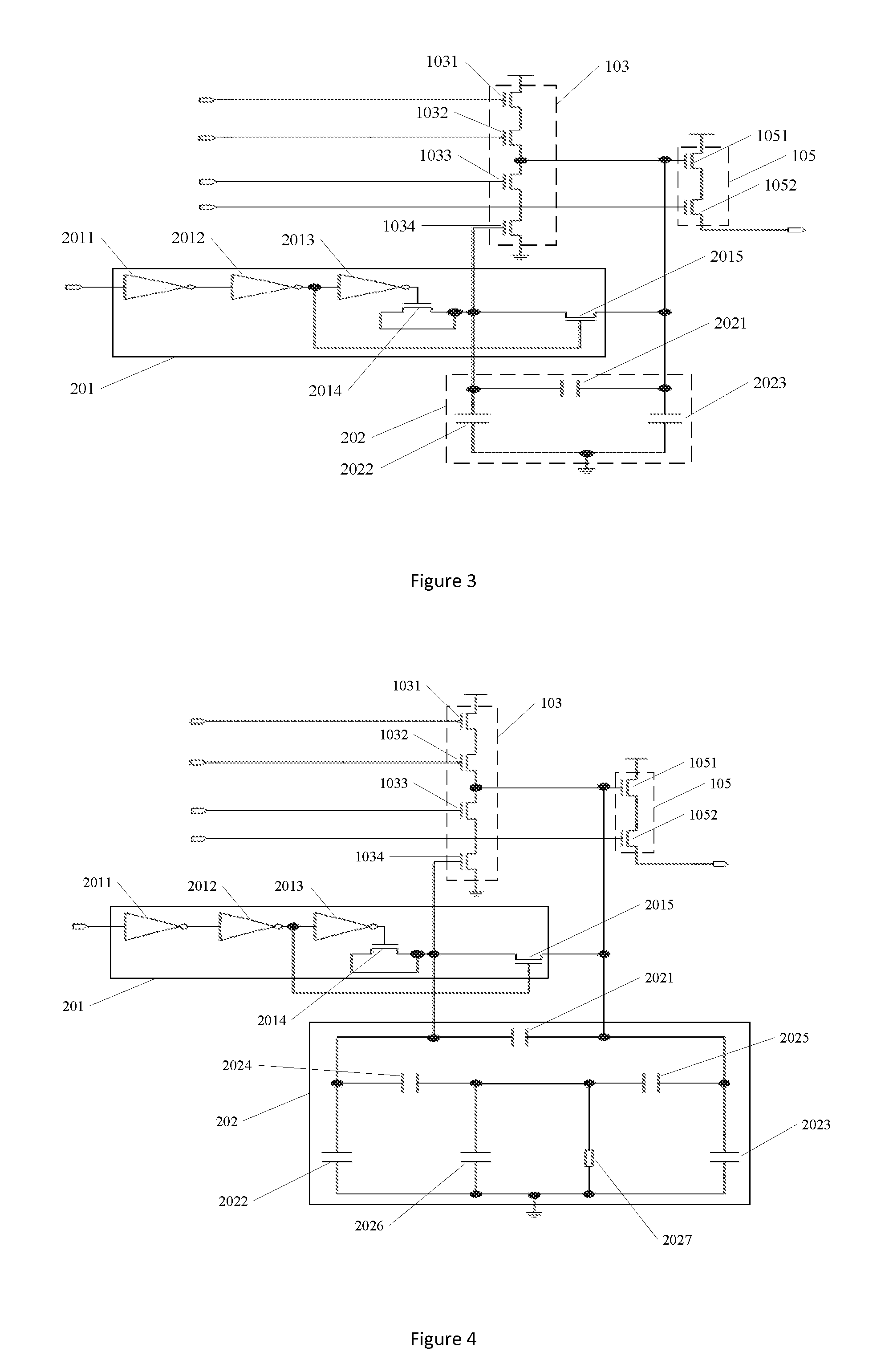

Fingerprint information detection circuit

ActiveUS20160275331A1Accurate representationAccurate distanceTransistorSolid-state devicesLevel shiftingCharge injection

The present invention relates to a chip design and discloses a fingerprint information detection circuit. The invention includes a reset unit, a feedback unit, an amplification unit and a source follower unit; the reset unit is connected to the feedback unit and amplification unit, while the feedback unit is connected to the amplification unit, and the amplification unit is connected to the source follower unit; when the reset transistor built-into the reset unit is on, it stores an electric charge, and resets the feedback unit; when the reset transistor is off, the stored electric charge is injected into the feedback unit and amplification unit; the feedback unit receives the electric charge, and outputs the second voltage signal generated when it detects fingerprints to the source follower unit; the amplification unit amplifies the received signal and outputs it to the source follower unit; the source follower unit receives the signal, performs voltage level shifting before outputting the first voltage signal that carries the detected fingerprint information. The present invention enables the circuit to use a reduced chip area, hence, saving the cost of the chip.

Owner:SILEAD

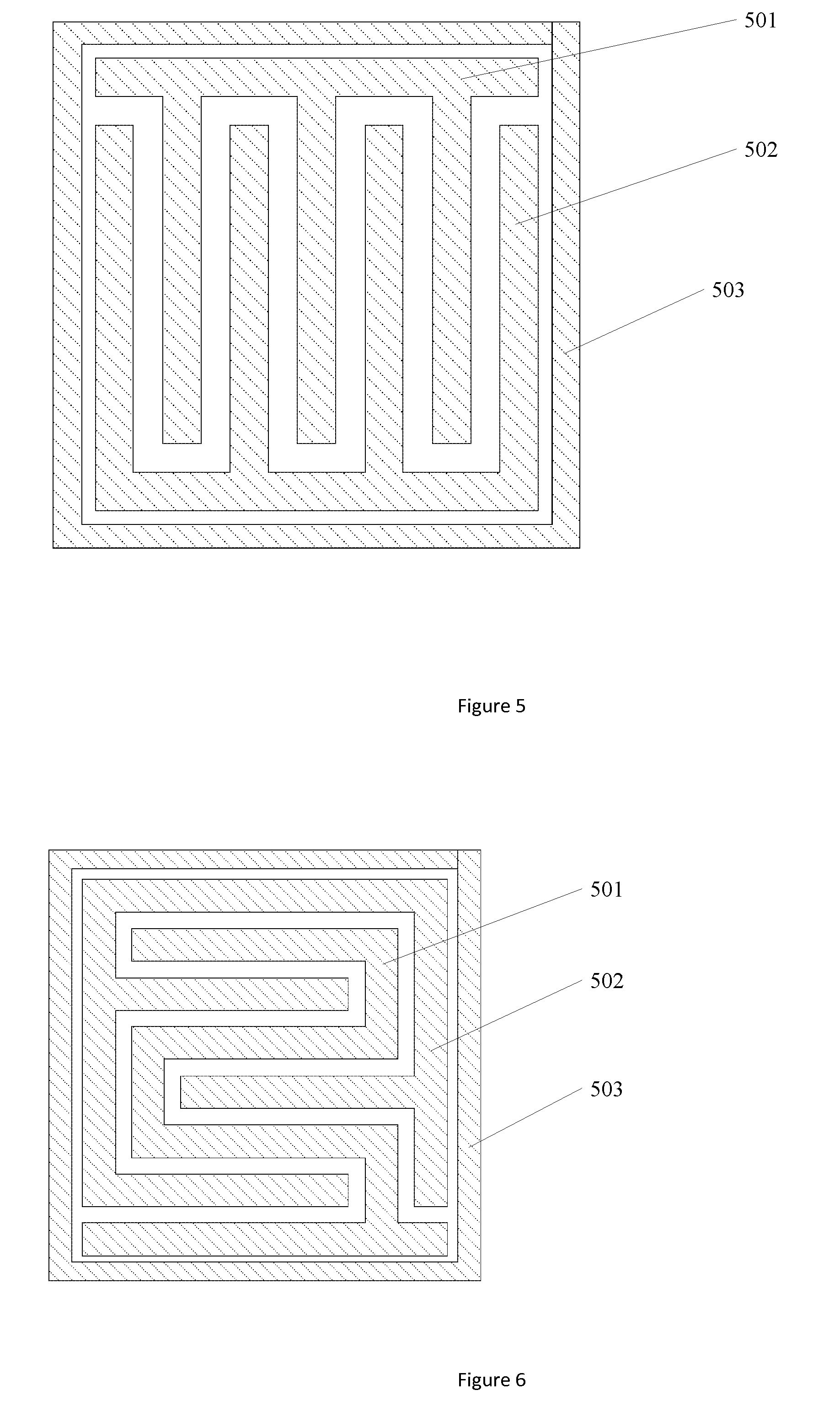

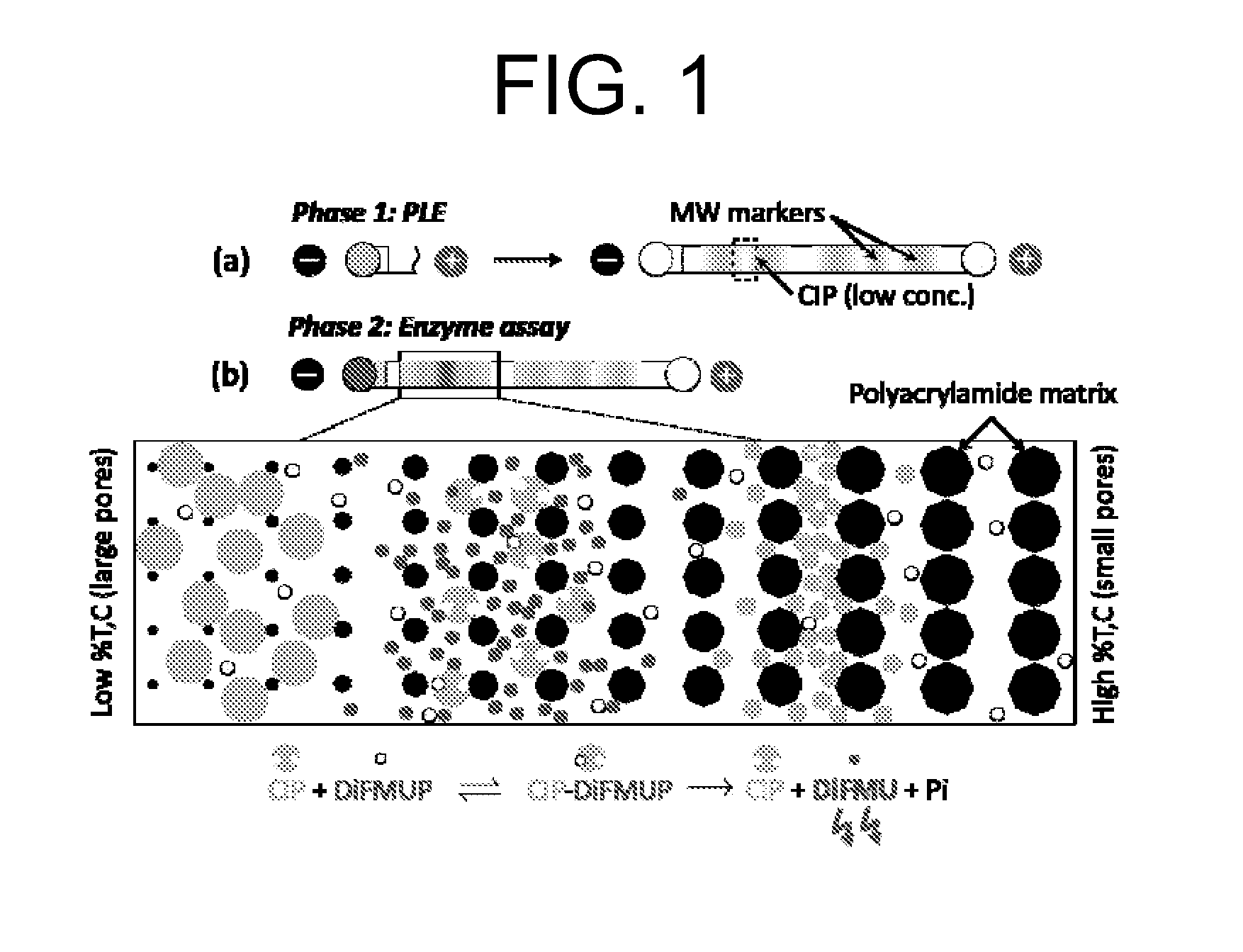

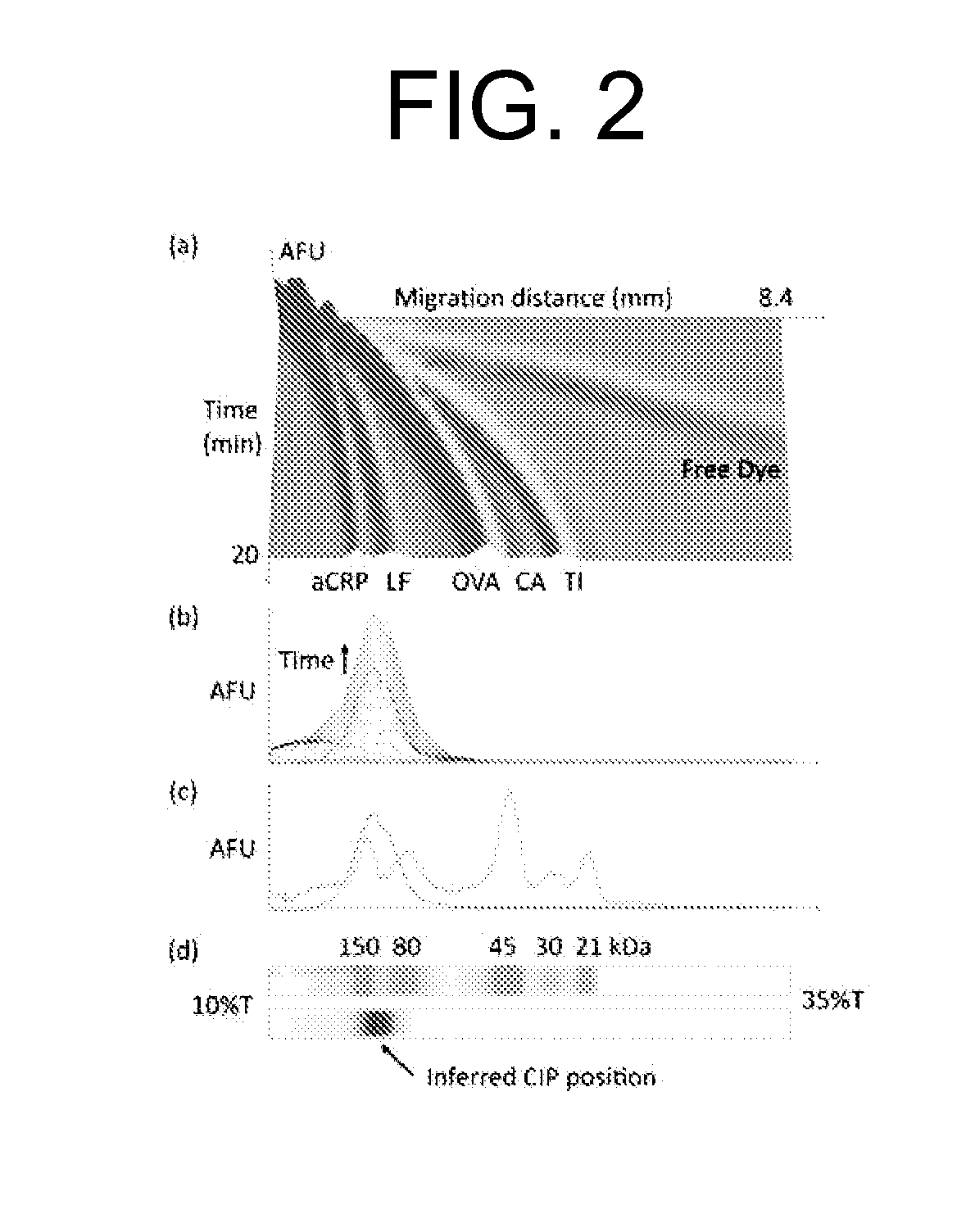

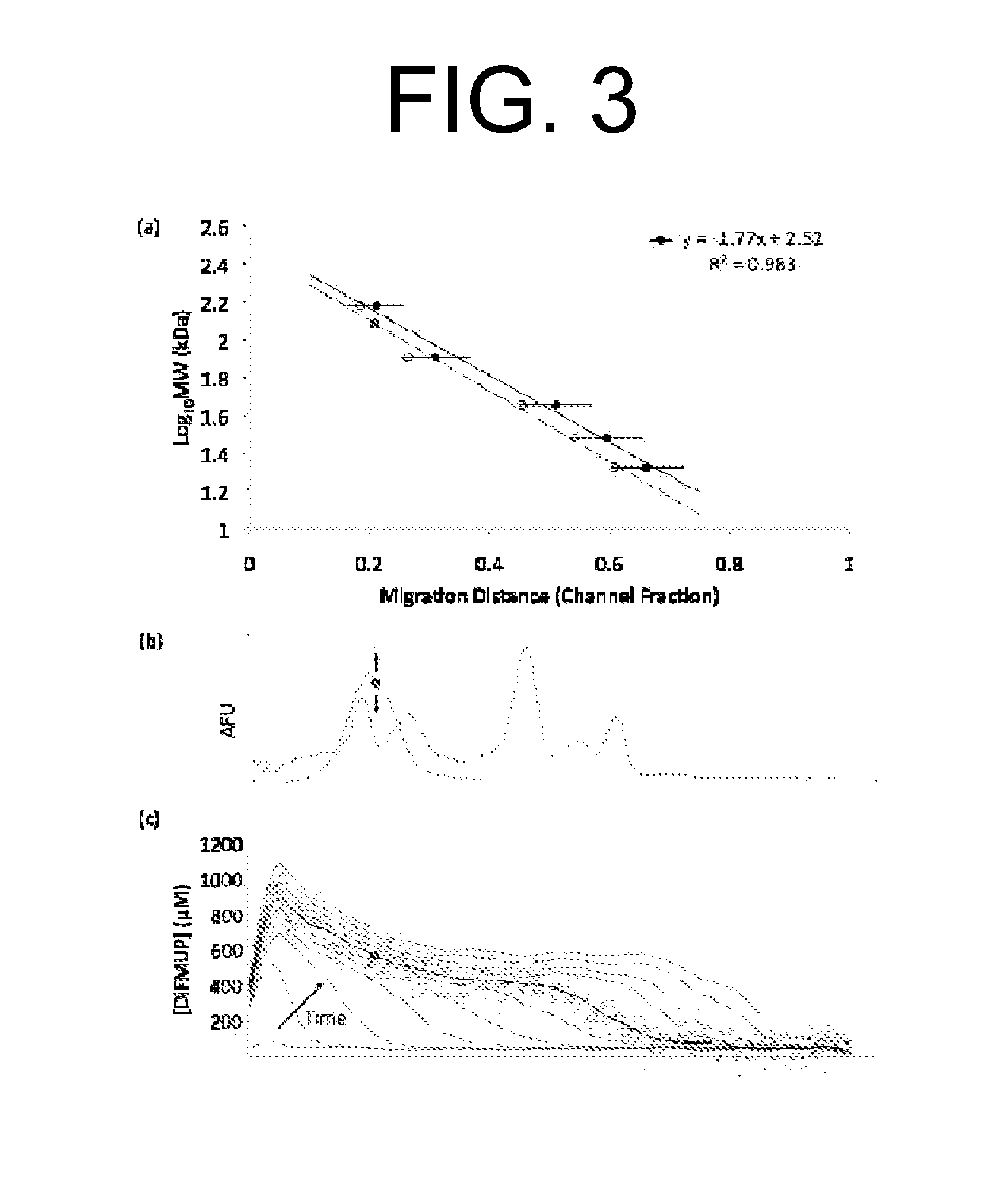

Pore-Limit Electrophoresis (PLE) Microchannel Assays

InactiveUS20130078663A1Simple designReduce chip costMicrobiological testing/measurementMaterial analysis by electric/magnetic meansImmuno assayAssay

Pore-limit electrophoresis (PLE) microchannel assay methods are provided. Aspects of the methods include sequentially introducing samples at least suspected of containing first and second assay members into a PLE microchannel and then evaluating the microchannel for interaction between the first and second assay members. Aspects of the invention further include devices, systems and kits configured for practicing methods of invention. The methods, devices, systems and kits of the invention find use in a variety of different applications, including enzyme activity assays and immunoassays.

Owner:RGT UNIV OF CALIFORNIA

System and method for temperature sensing of three-dimensional integrated circuit

ActiveUS20150369764A1Minimizing chip sizeReduce Design ComplexityThermometer detailsMaterial thermal conductivitySpecific functionEngineering

A system and a method for temperature sensing of three-dimensional integrated circuits are revealed. The three-dimensional integrated circuit is formed by stacking of a plurality of chip layers that execute specific functions. The chip layer includes a master layer and at least one slave layer. The master layer is disposed with a master temperature sensor while a first thermal conductive part is arranged at the slave layer where heat is detected. The first thermal conductive part and the master temperature sensor are connected by a thermal conductive structure. Thereby temperature of various points at different chip layers is conducted to the same chip layer by Through Silicon Vias to be measured and calibrated. The design complexity and the implementation cost of the temperature sensing system are significantly reduced.

Owner:NAT CHENG KUNG UNIV

Terminal structure of channel power metal oxide semiconductor (MOS) device and manufacture method of terminal structure

InactiveCN102637731AProtection breakdown voltageEfficient separationSemiconductor/solid-state device manufacturingSemiconductor devicesChannel powerParasitic capacitance

The invention provides a terminal structure of a channel power metal oxide semiconductor (MOS) device and a manufacture method of the terminal structure. The terminal structure comprises a grid electrode lead-out electrode (101), wherein a suspension polycrystalline silicon electrode (102) is arranged under the grid electrode lead-out electrode (101) and is positioned inside a thick oxidation layer (103), a grid electrode connecting metal (104) is arranged above the grid electrode lead-out electrode (101), a source electrode (105) of a device active region is arranged on the top of a cell structure, a drift region (106) adopts N type doping, a drain electrode (107) adopts N type heavy doping, and a combined structure of the grid electrode lead-out electrode (101), a grid electrode lower part suspension polycrystalline silicon electrode (102) and the thick oxidation layer (103) realizes the effect of a device terminal and is formed in the same mask and the same process. The ultra-low conducting resistance of the device is ensured, the breakdown voltage and the parasitic capacitance of the device cannot be influenced, the process manufacture flow process is optimized, and meanwhile, the manufacture cost of the device is reduced.

Owner:HARBIN ENG UNIV

Solid-state imaging device, method of manufacturing the same, method of driving the same, and electronic apparatus

ActiveUS20140312392A1Reduce chip sizeReduce chip costTelevision system detailsSemiconductor/solid-state device detailsEngineeringElectron

A solid-state imaging device includes a plurality of pixels, each of which includes a photoelectric converter section formed on a first substrate to generate and accumulate signal charges corresponding to incident light, a charge accumulation capacitor section formed on the first substrate or a second substrate to temporarily hold the signal charges transferred from the photoelectric converter section, and a plurality of MOS transistors formed on the second substrate to transfer the signal charges accumulated in the charge accumulation capacitor section, connection electrodes formed on the first substrate, and connection electrodes formed on the second substrate and electrically connected to the connection electrodes formed on the first substrate.

Owner:SONY CORP

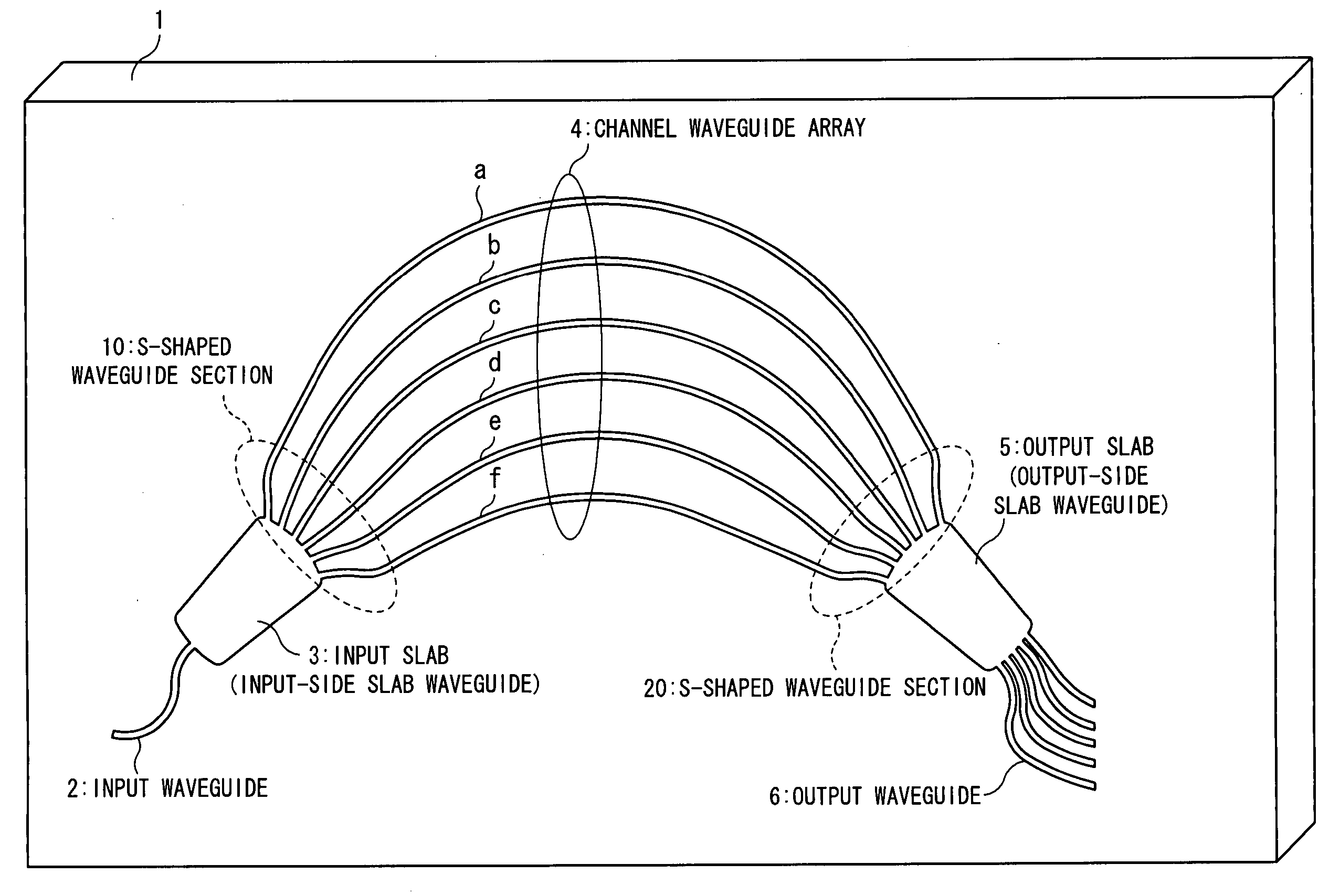

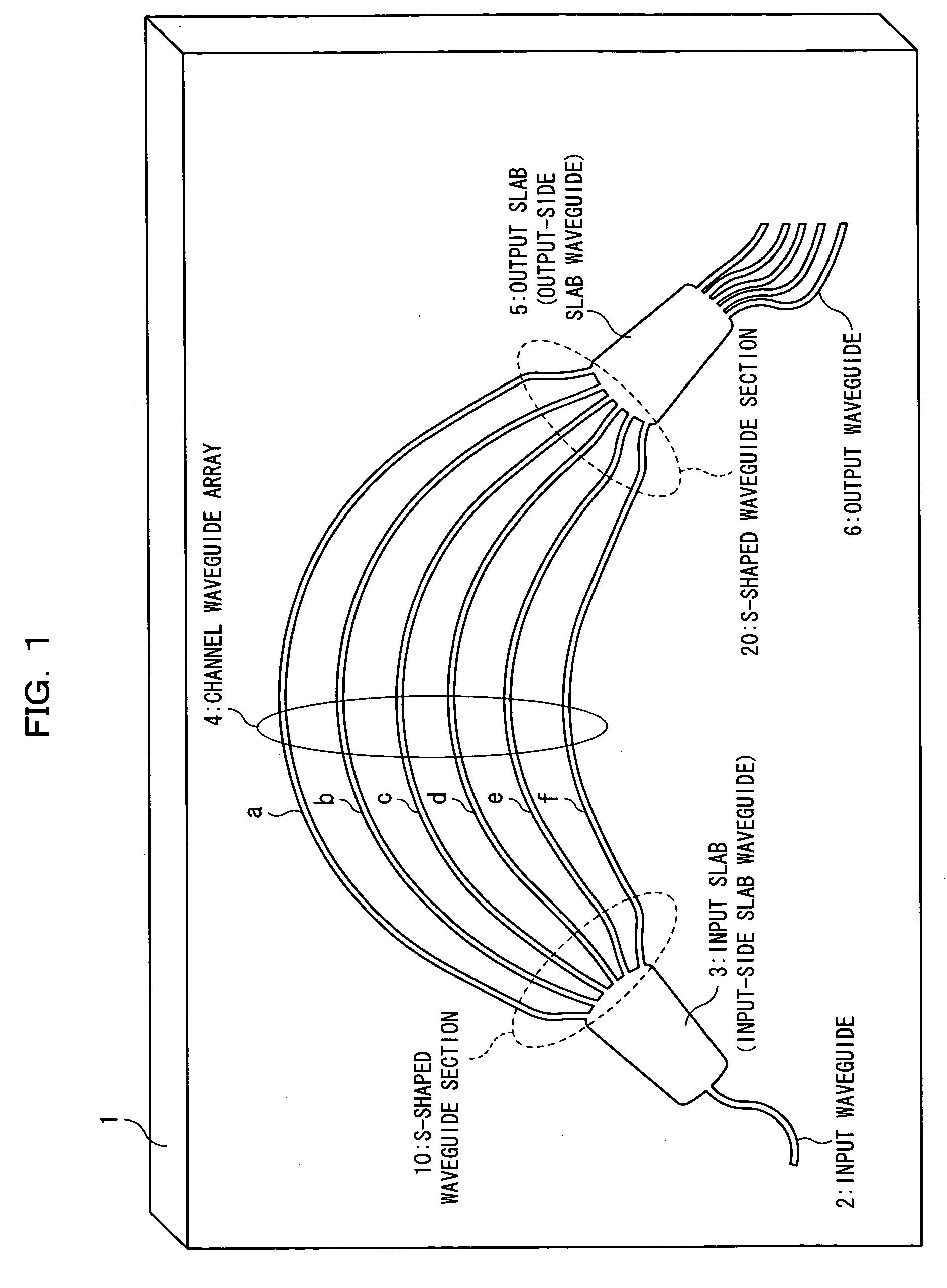

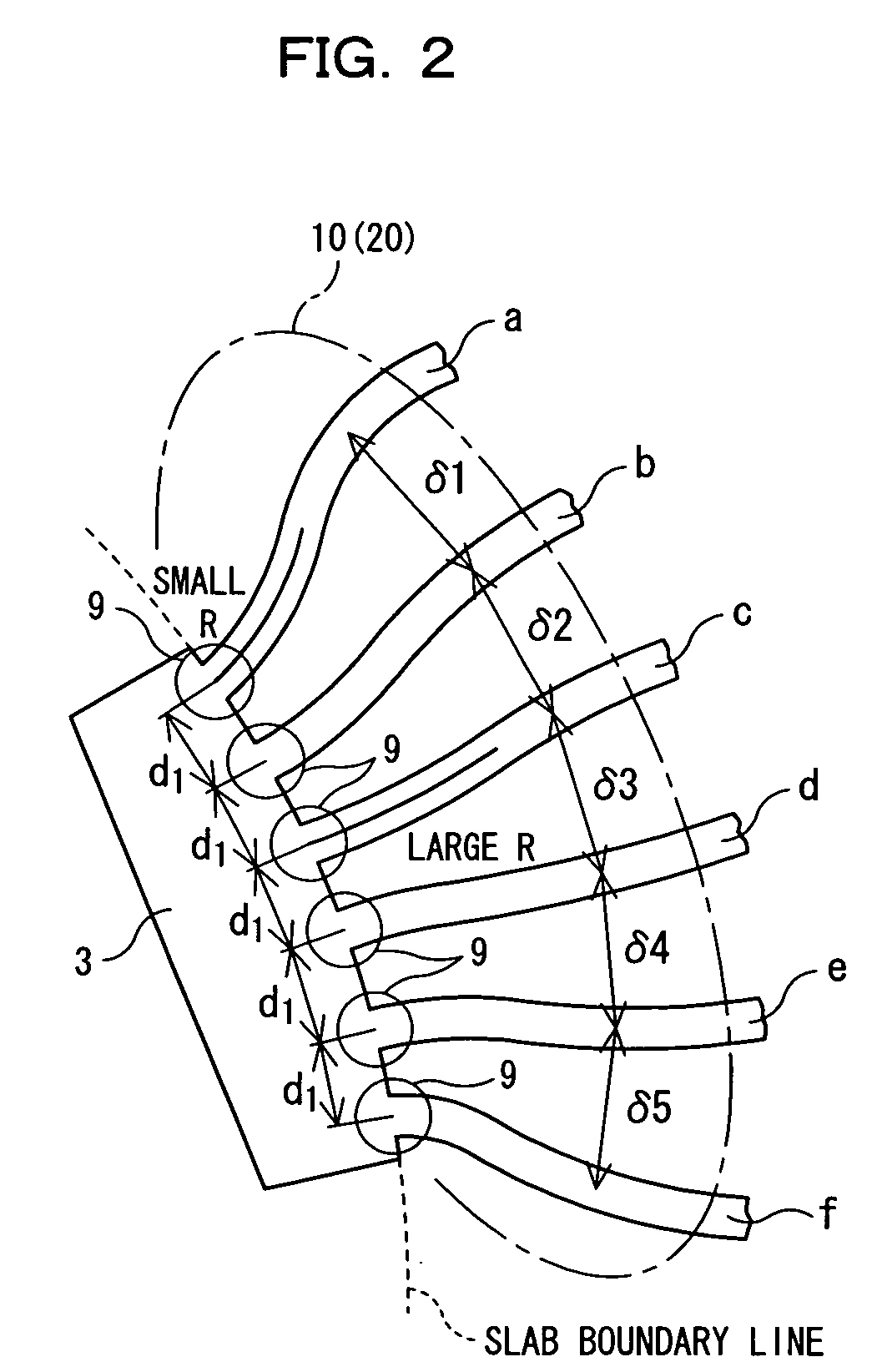

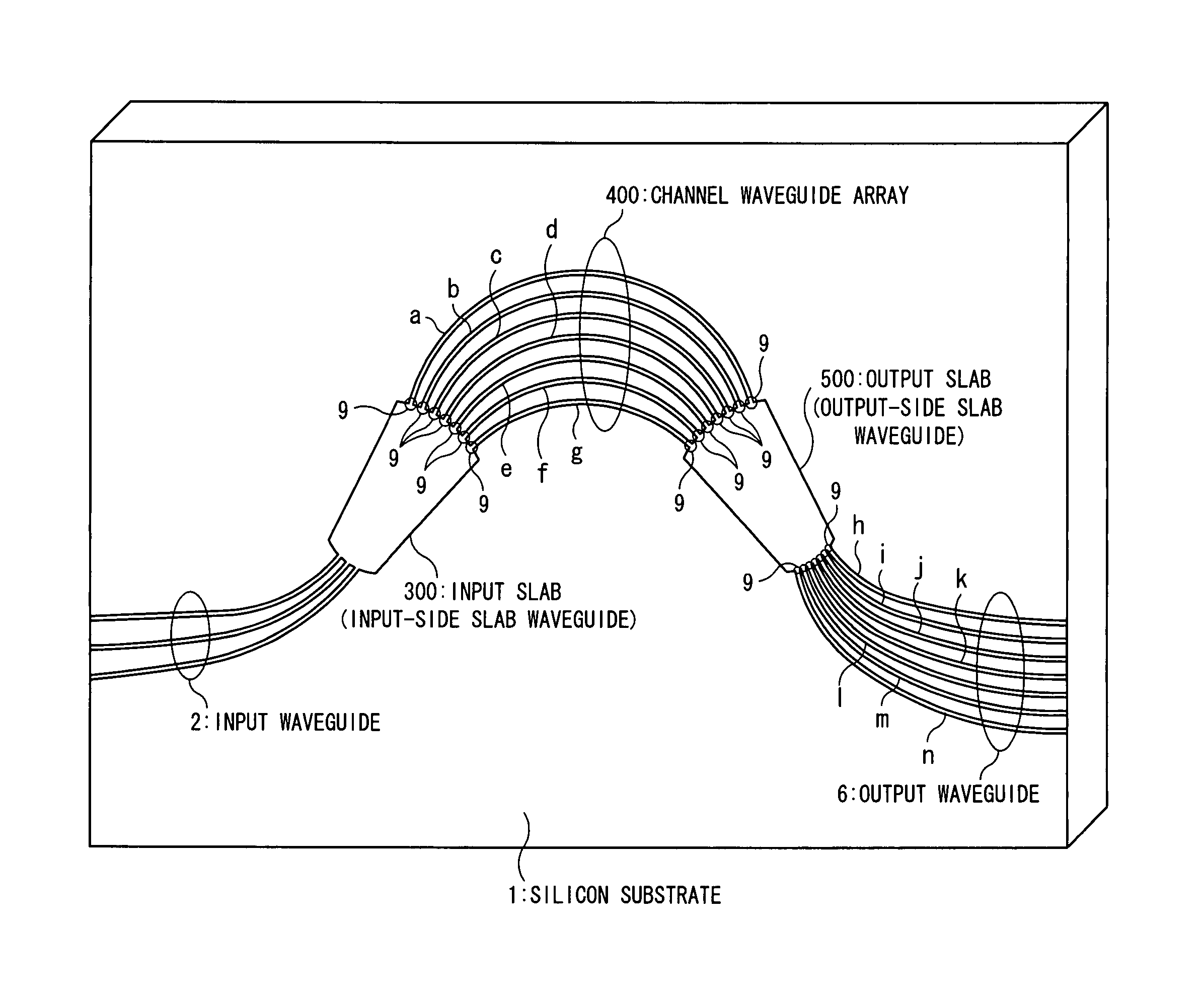

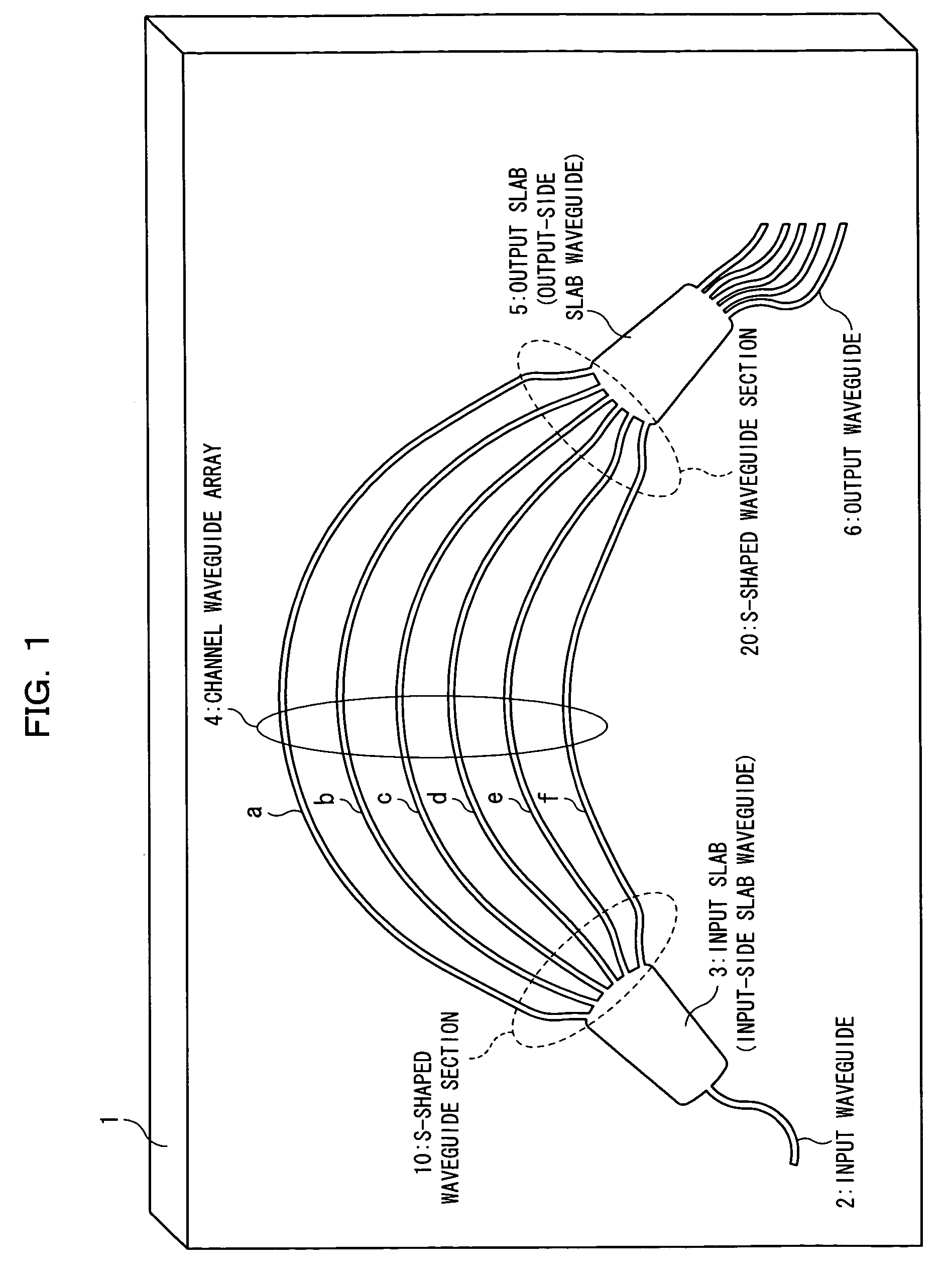

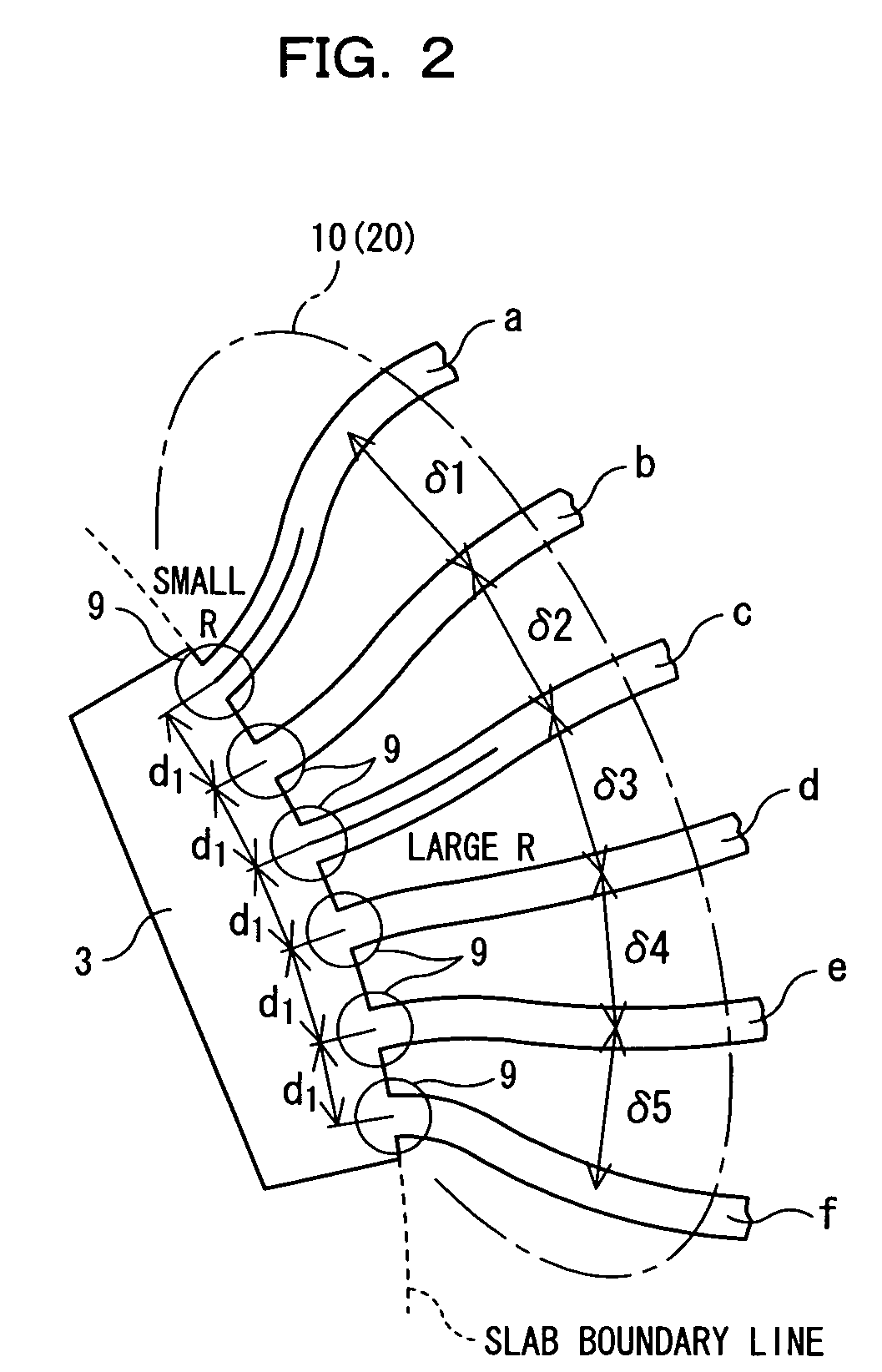

Arrayed waveguide wavelength multiplexing apparatus and optical transmitter

InactiveUS20050141813A1Increase profitHigh bulk densityCoupling light guidesElectromagnetic transmissionMultiplexingChip size

For a WDM optical communication, on a substrate of an arrayed waveguide type wavelength multiplexing / demultiplexing device, input waveguide propagates a plurality of light and outputs WDM light; a first slab diffuses the WDM light outputted from the input waveguide; a channel waveguide array separates the WDM light and causes the separated six lights to propagate; a second slab condenses the separated six lights having propagated through the channel waveguide array; output waveguides causes the separated six lights condensed to propagate, and a waveguide interval in first neighborhoods connected to the first slab is set to become wider than a first waveguide interval in a first connection section for connecting the channel waveguide array to the first slab, which achieves a reduced chip size, cost-reduction of chips, and reduces loss.

Owner:FUJITSU LTD

Arrayed waveguide wavelength multiplexing apparatus and optical transmitter

InactiveUS6985657B2Reduce chip sizeHighly desirable waveguide characteristicCoupling light guidesElectromagnetic transmissionMultiplexingChip size

For a WDM optical communication, on a substrate of an arrayed waveguide type wavelength multiplexing / demultiplexing device, input waveguide propagates a plurality of light and outputs WDM light; a first slab diffuses the WDM light outputted from the input waveguide; a channel waveguide array separates the WDM light and causes the separated six lights to propagate; a second slab condenses the separated six lights having propagated through the channel waveguide array; output waveguides causes the separated six lights condensed to propagate, and a waveguide interval in first neighborhoods connected to the first slab is set to become wider than a first waveguide interval in a first connection section for connecting the channel waveguide array to the first slab, which achieves a reduced chip size, cost-reduction of chips, and reduces loss.

Owner:FUJITSU LTD

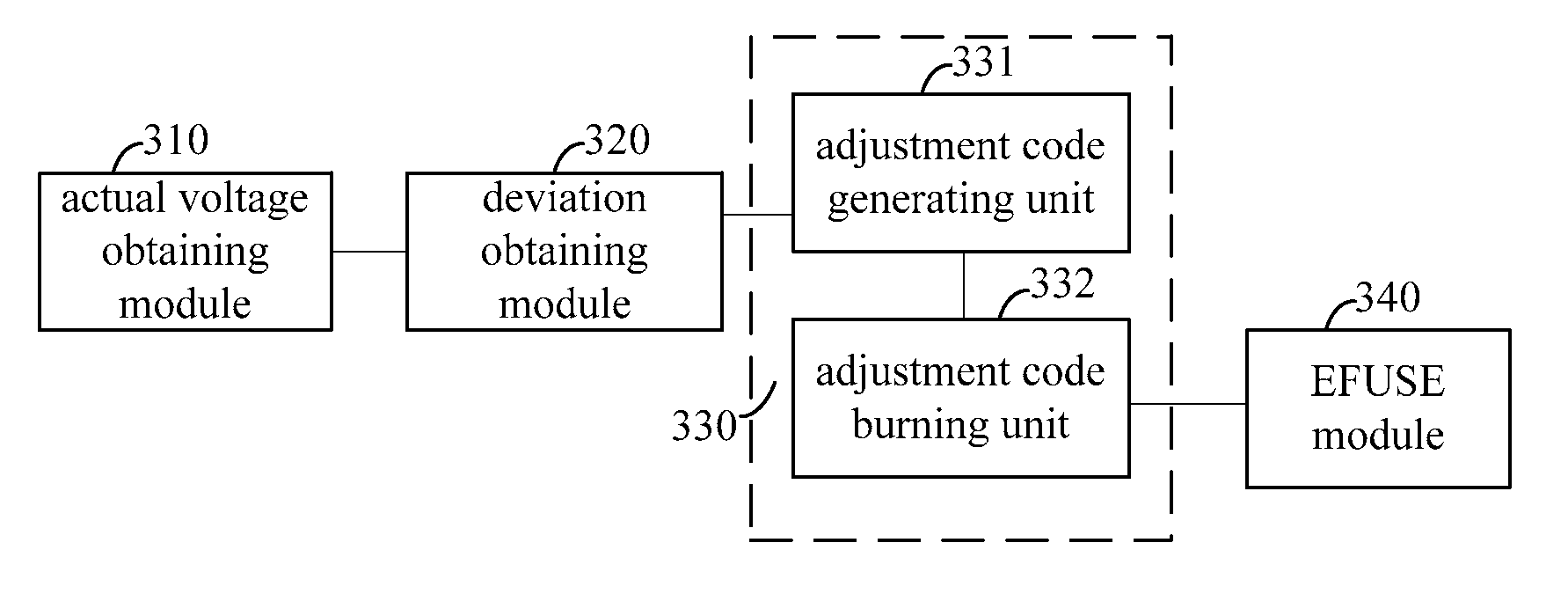

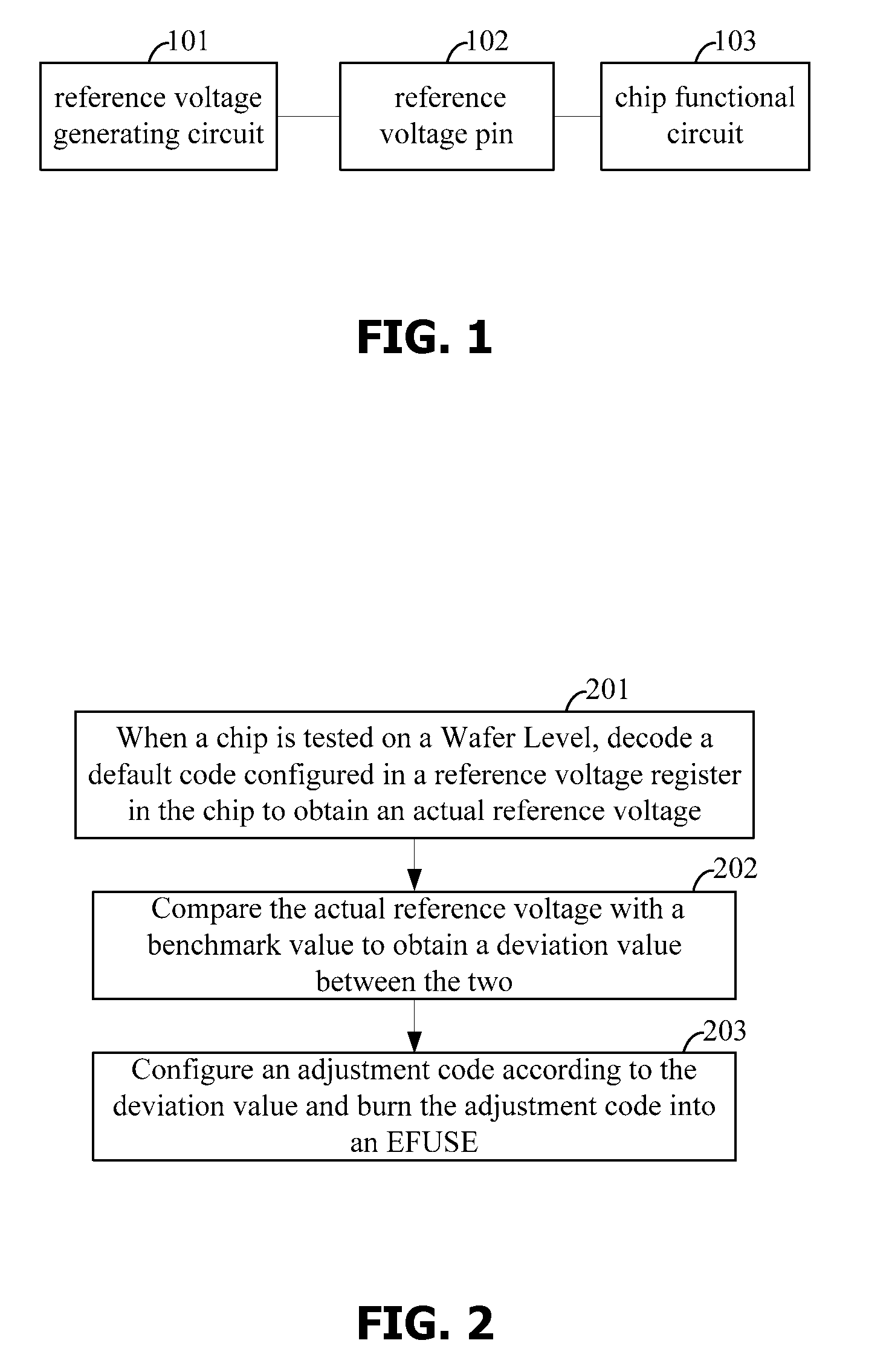

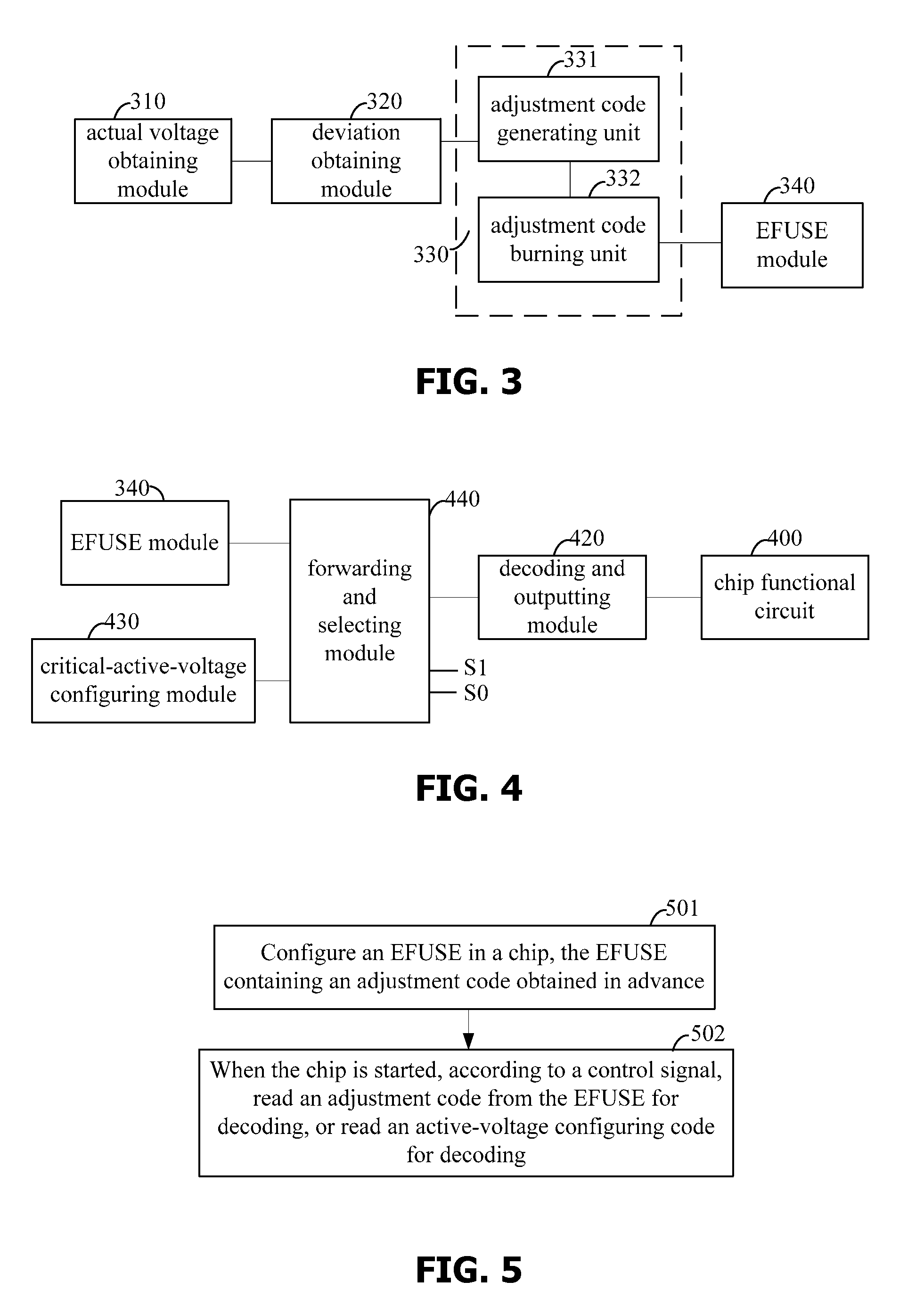

Method and Device for Correcting and Obtaining Reference Voltage

ActiveUS20100188881A1Improve circuit stabilityReduce chip costRead-only memoriesElectrical testingExternal referenceVoltage reference

The present invention discloses a method for adjusting a reference voltage, including: decoding a default code configured in a reference voltage register in a chip to obtain an actual reference voltage; comparing the actual reference voltage with a benchmark value to obtain a deviation value between the two; configuring an adjustment code according to the deviation value; and, burning the adjustment code into a nonvolatile storage medium. The present invention also discloses an apparatus for adjusting a reference voltage. According to the method and apparatus for adjusting a reference voltage provided by embodiments of the present invention, the reference voltage need not be adjusted according to an external power supply's different application schemes. Thus, adjustment on the reference voltage of the chip is standardized and costs of the chip's application schemes are saved. Embodiments of the present invention further provide a method and apparatus for obtaining a reference voltage, which makes it not necessary to configure a dedicated reference voltage pin in the chip for introducing an external reference voltage, and thus stability of the circuit's working is improved and costs of the chip's applications are decreased.

Owner:ACTIONS ZHUHAI TECH CO

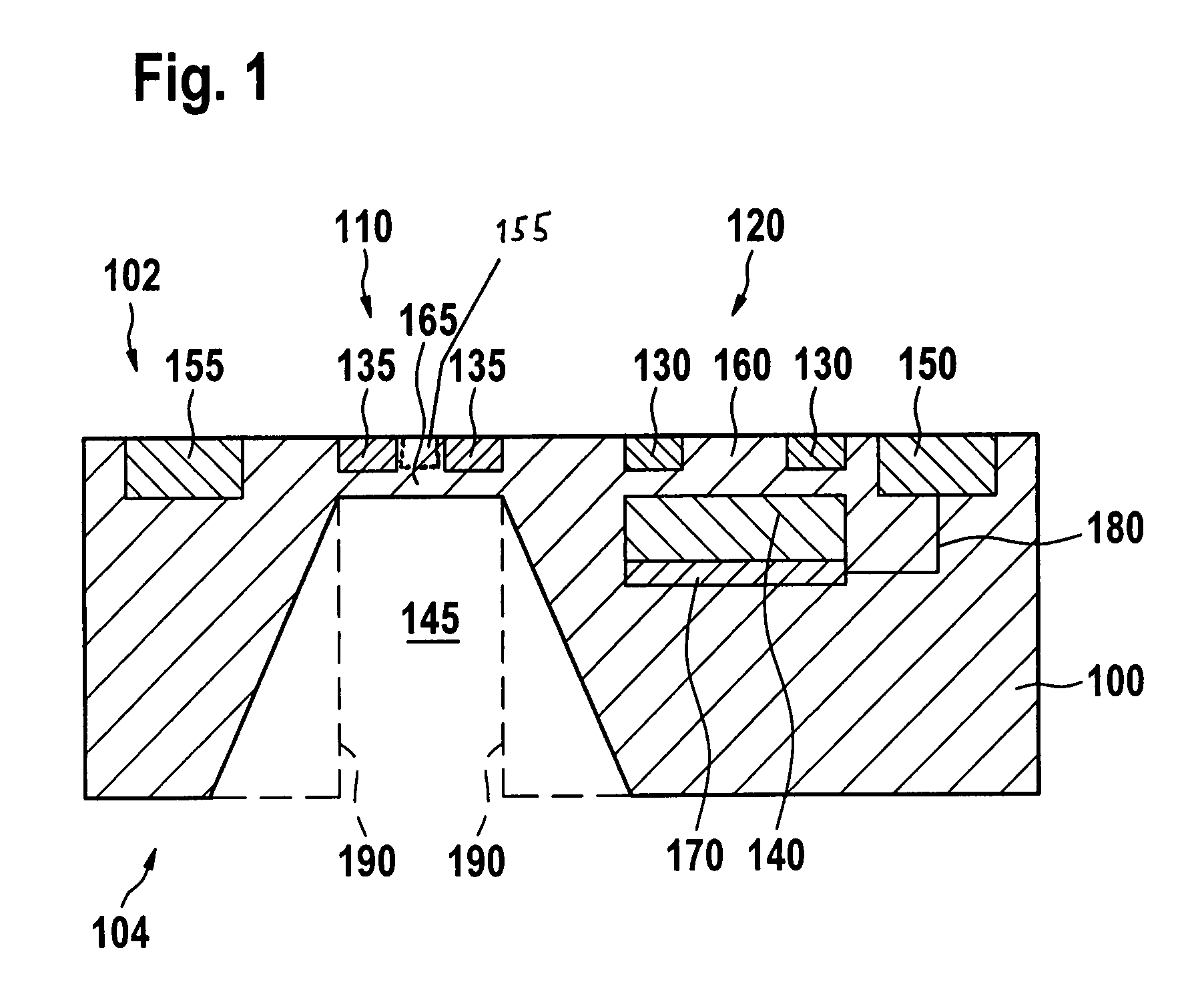

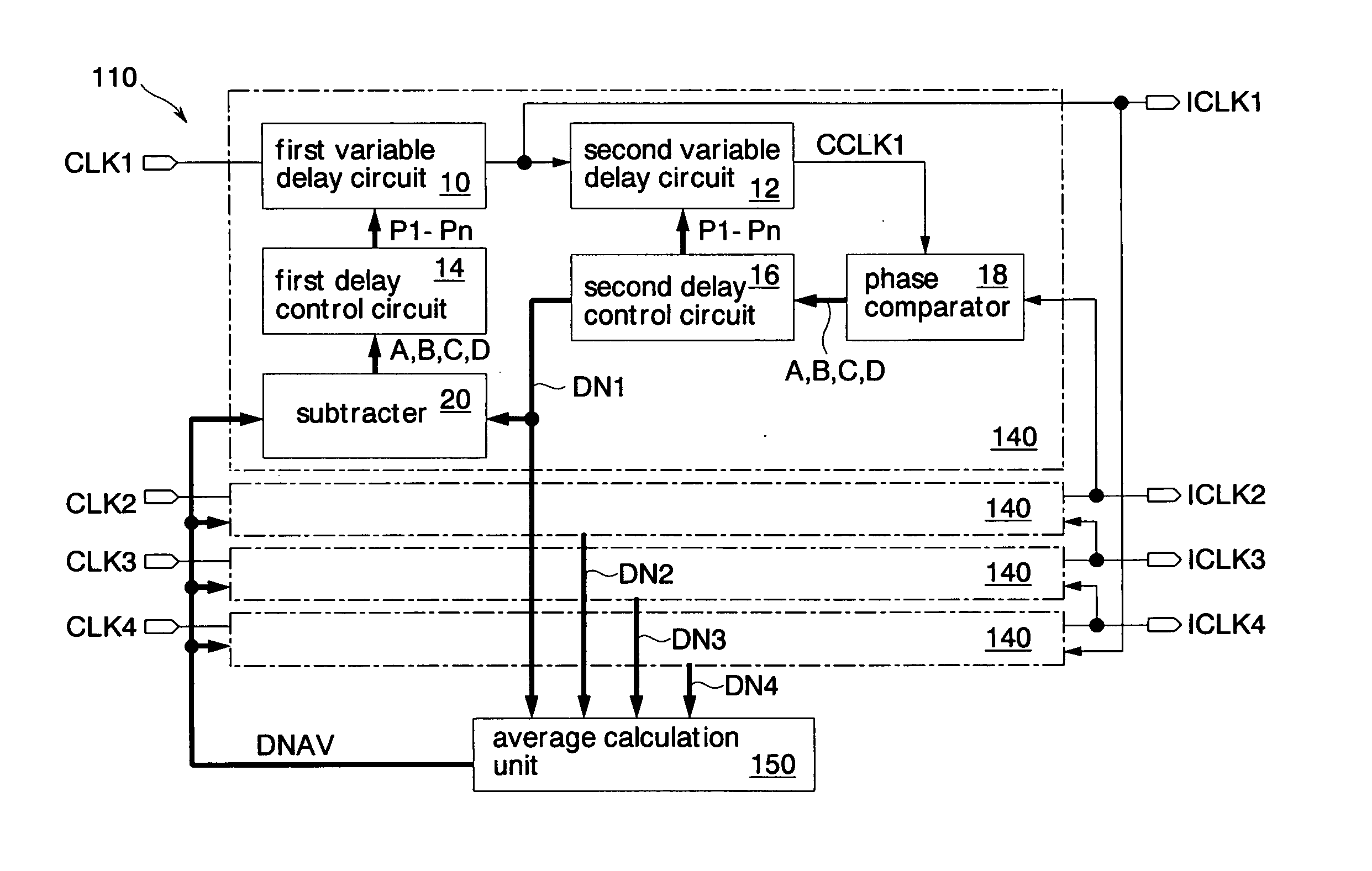

Semiconductor integrated circuit

InactiveUS20060066374A1Low costReduce testing costsMultiple input and output pulse circuitsPulse automatic controlClock ratePhase difference

A phase adjustment unit adjusts the phases of a plurality of external clocks successively shifted in phase, thereby generating a plurality of internal clocks having an equal phase difference between every adjacent transition edges thereof. The internal clocks are synthesized to generate a composite clock having equal pulse intervals. Thus, even when the semiconductor integrated circuit is supplied with external clocks of lower frequencies, it is possible to operate the semiconductor integrated circuit at high speed. For example, the internal circuit can be operated and tested at high speed by using a low-cost LSI tester having a low clock frequency. This can reduce the testing cost of the semiconductor integrated circuit, allowing a reduction in chip cost.

Owner:SOCIONEXT INC

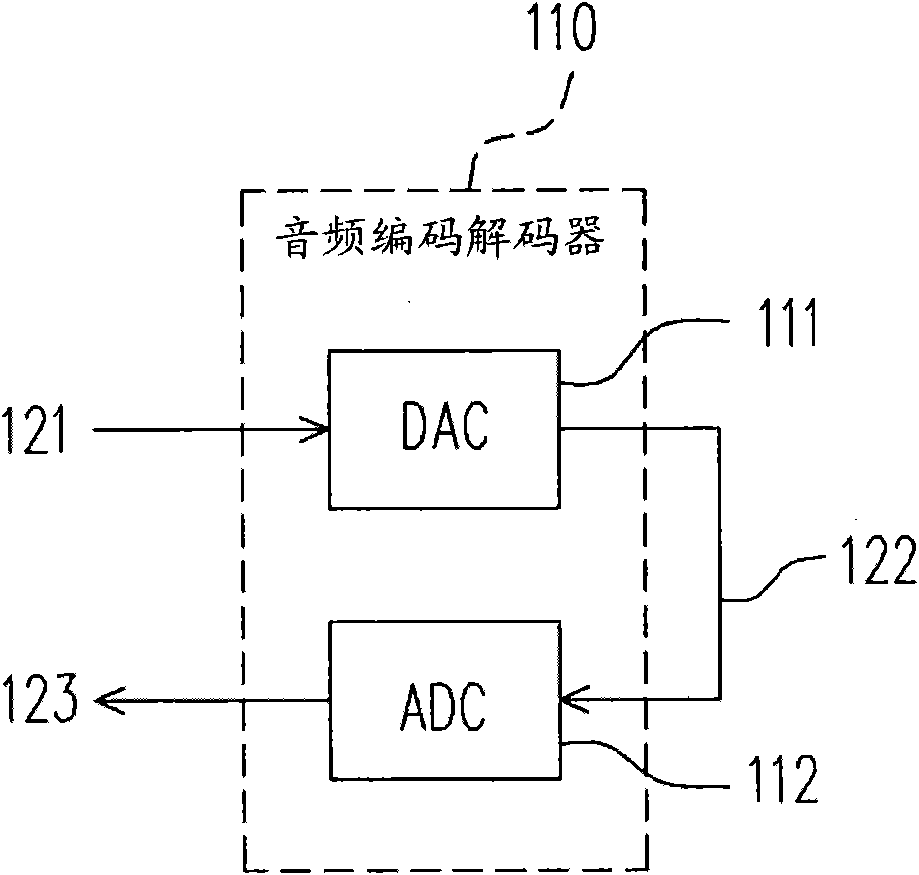

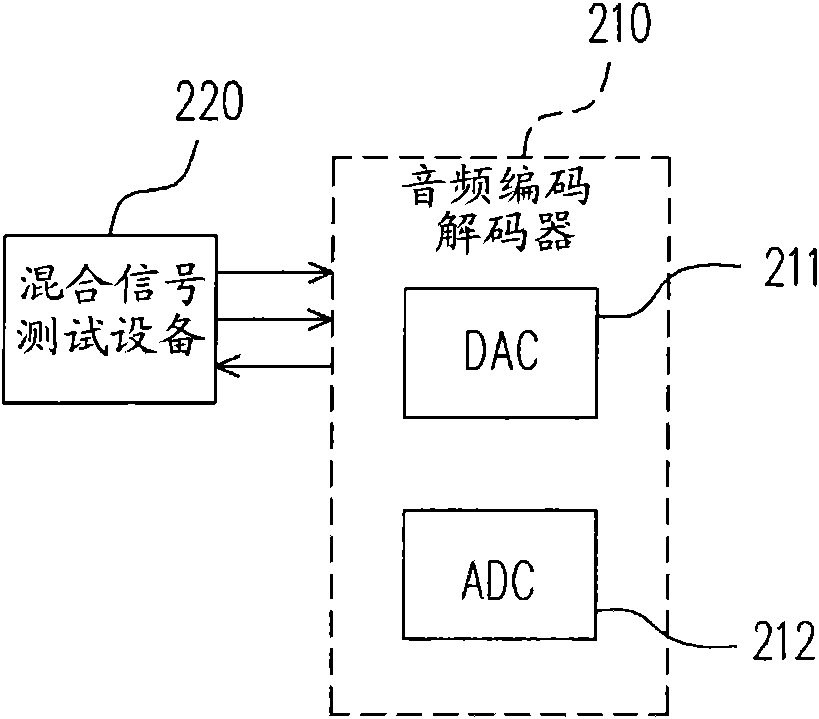

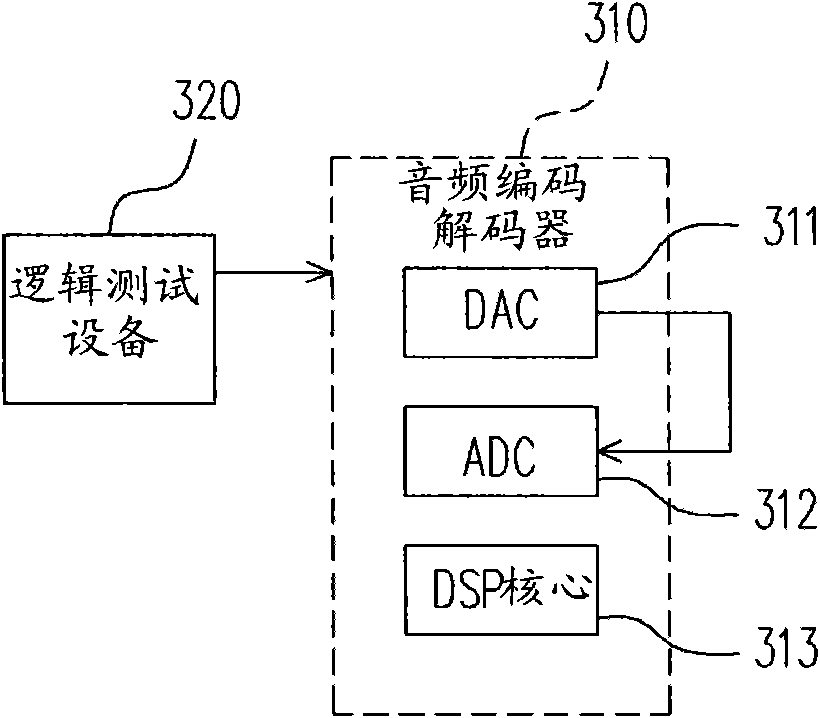

Audio coder-decoder and self-testing method thereof

InactiveCN101577119AReduce chip areaReduce chip costSpeech analysisAnalogue/digital conversion calibration/testingFrequency spectrumAnalog signal

The invention relates to an audio coder-decoder and a self-testing method thereof. The self-testing method comprises the following steps: firstly, a test signal is converted into an analog signal by a first sound channel D / A converter of the audio coder-decoder; secondly, the analog signal is converted into a digital signal by a first sound channel A / D converter of the audio coder-decoder; and thirdly, amplitudes of a plurality of discrete Fourier transform spectrum components of the digital signal are counted by a digital arithmetic unit of a second sound channel D / A converter and a digital arithmetic unit of a second sound channel A / D converter of the audio coder-decoder. Whether the audio coder-decoder passes through a test or not is determined according to the amplitudes of the spectrum components.

Owner:FARADAY TECH CORP