Patents

Literature

90results about How to "Increase chip area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

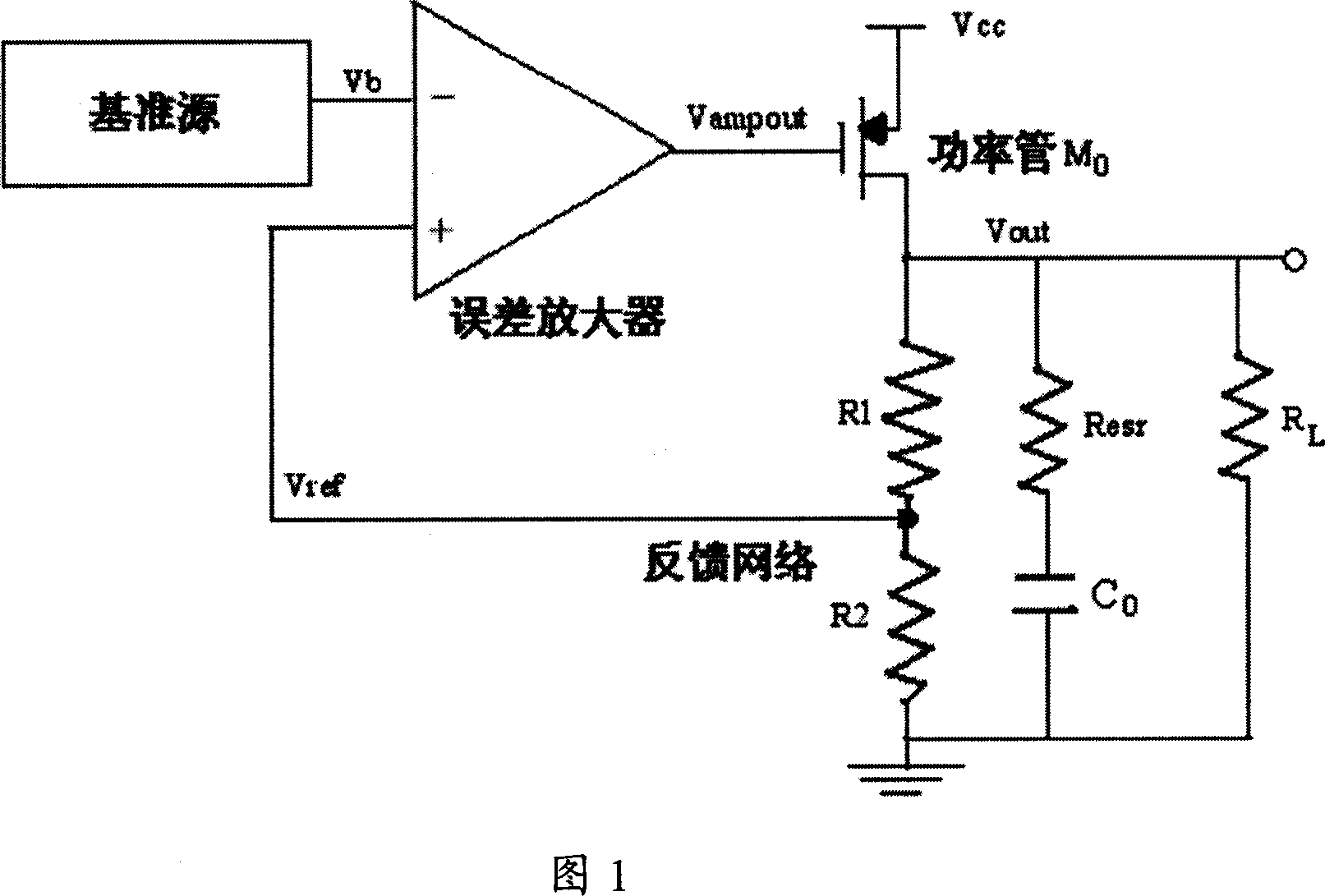

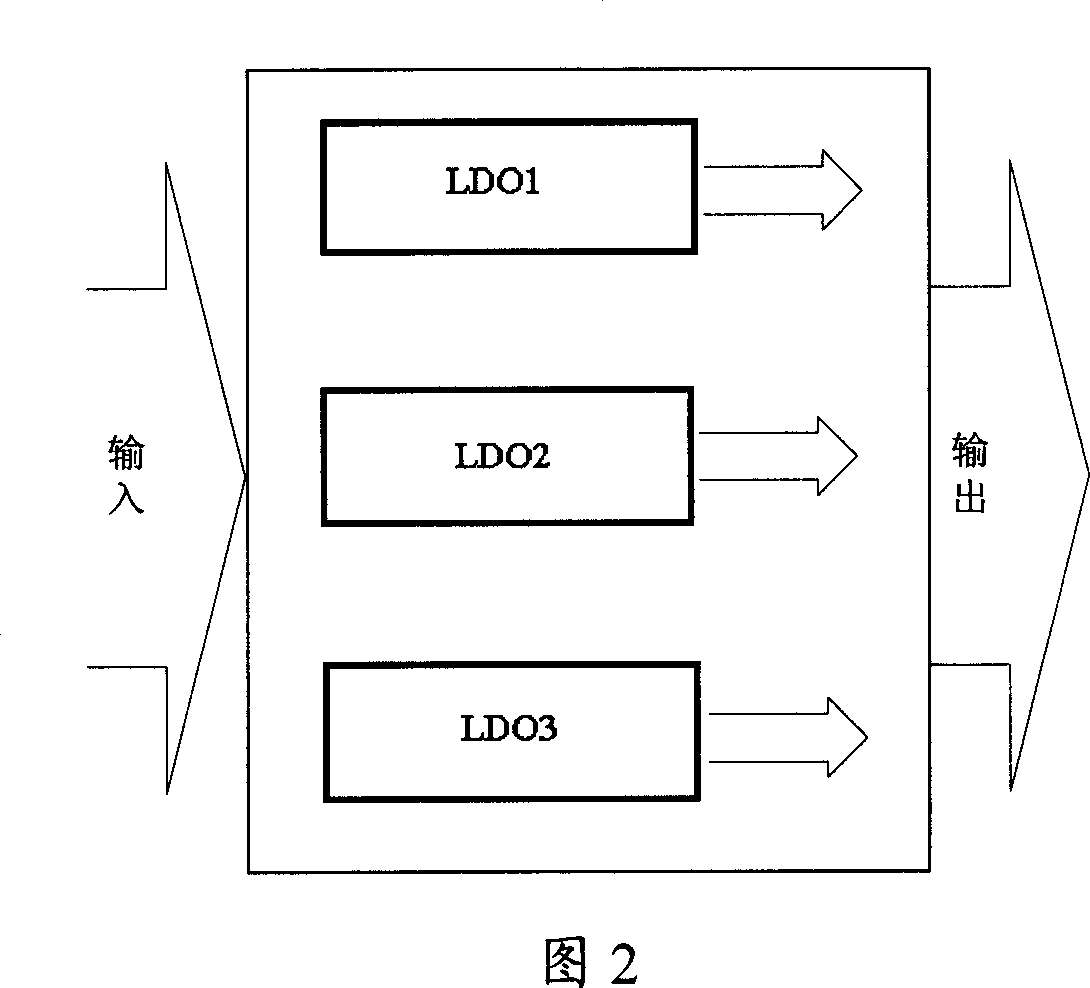

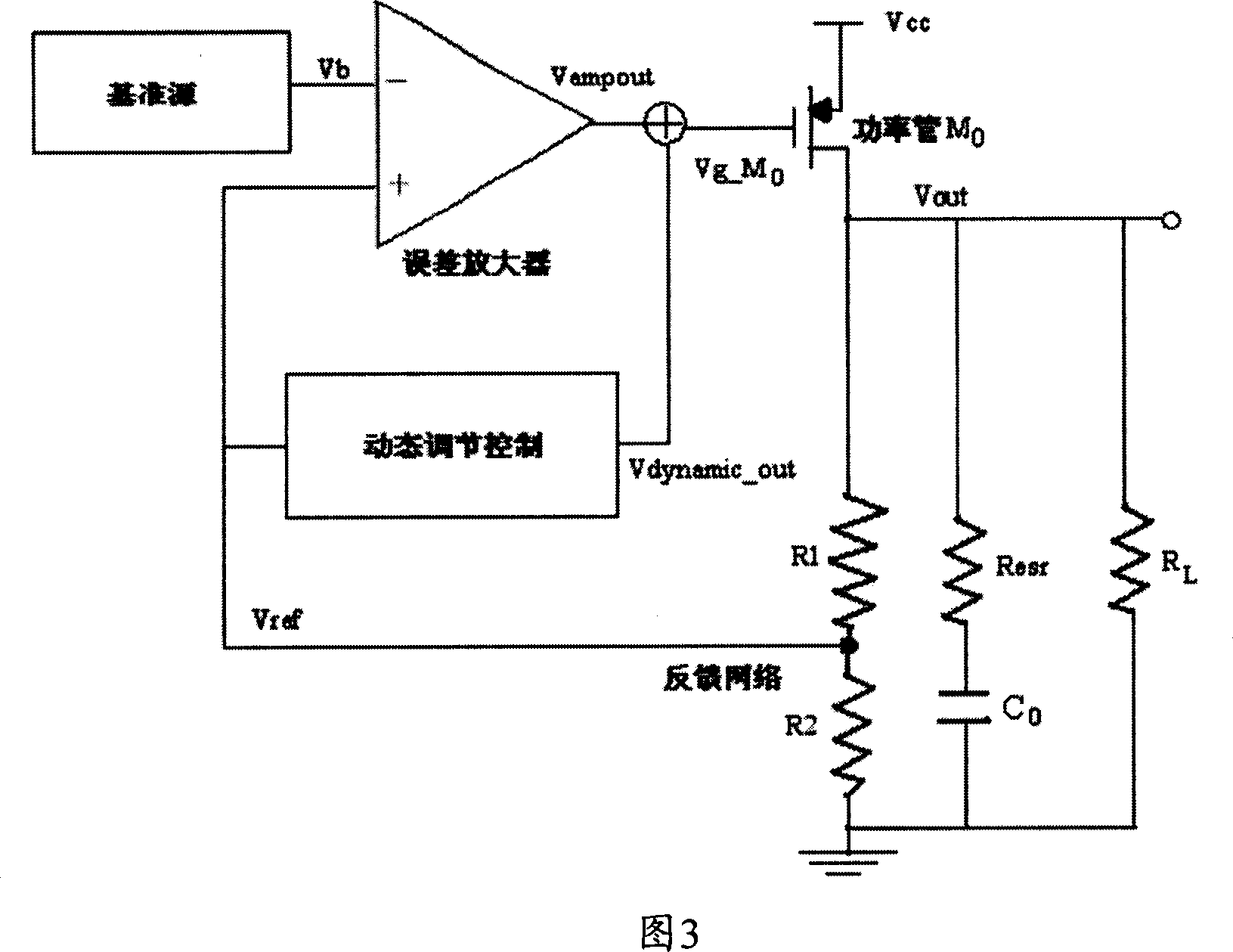

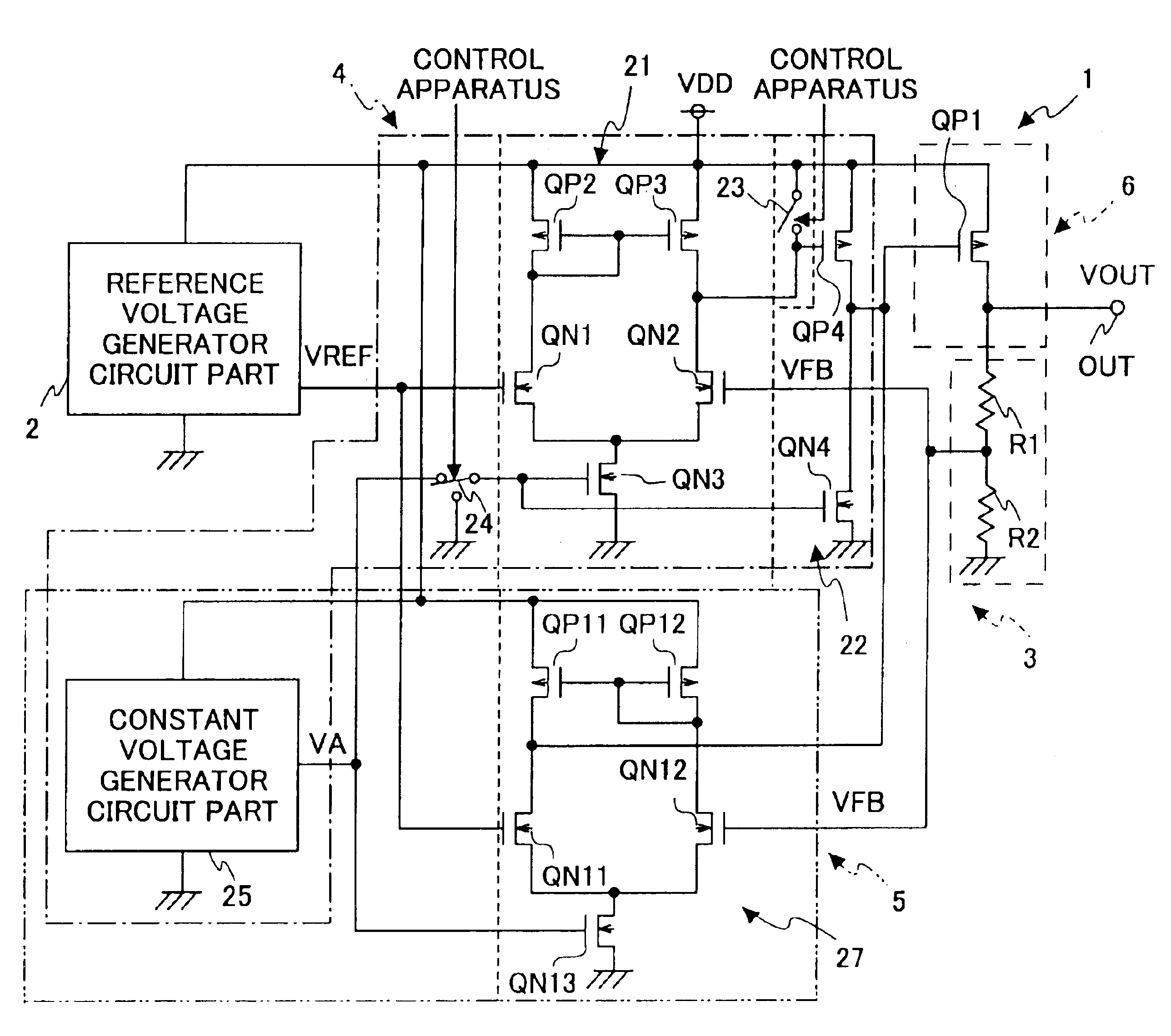

Low-voltage linear adjuster

ActiveCN101075143AIncrease chip areaIncrease power consumptionElectric variable regulationVoltage regulationLow stress

A voltage regulator of low voltage linear type consists of an error amplifier with its reverse phase input end being connected to a reference voltage source, a p type of power tube with its grid being connected to output end of said amplifier and its drain electrode being used as output end of said voltage regulator, a dynamic control unit with its input end being connected to the same phase input end of said amplifier and its output end being connected to grid or drain electrode of power tube. Its regulating method is also disclosed.

Owner:ANYKA (GUANGZHOU) MICROELECTRONICS TECH CO LTD

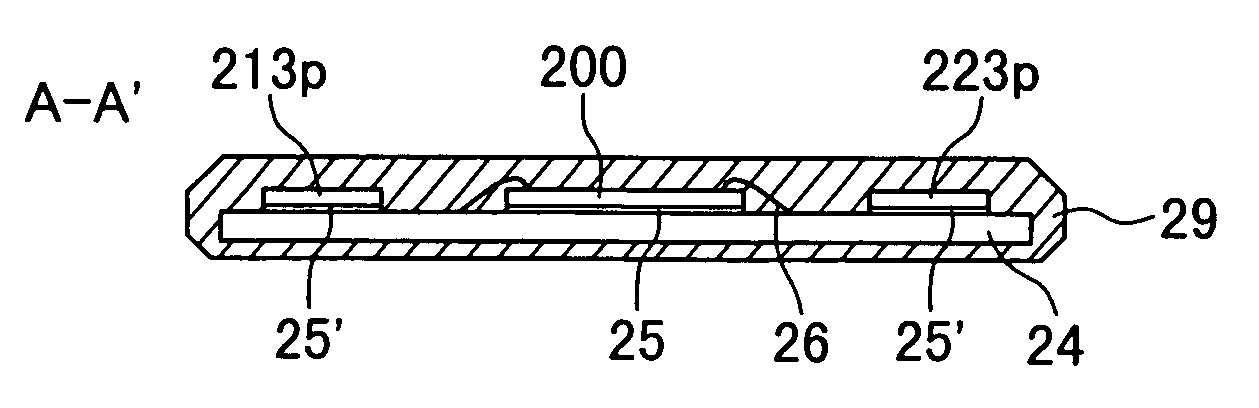

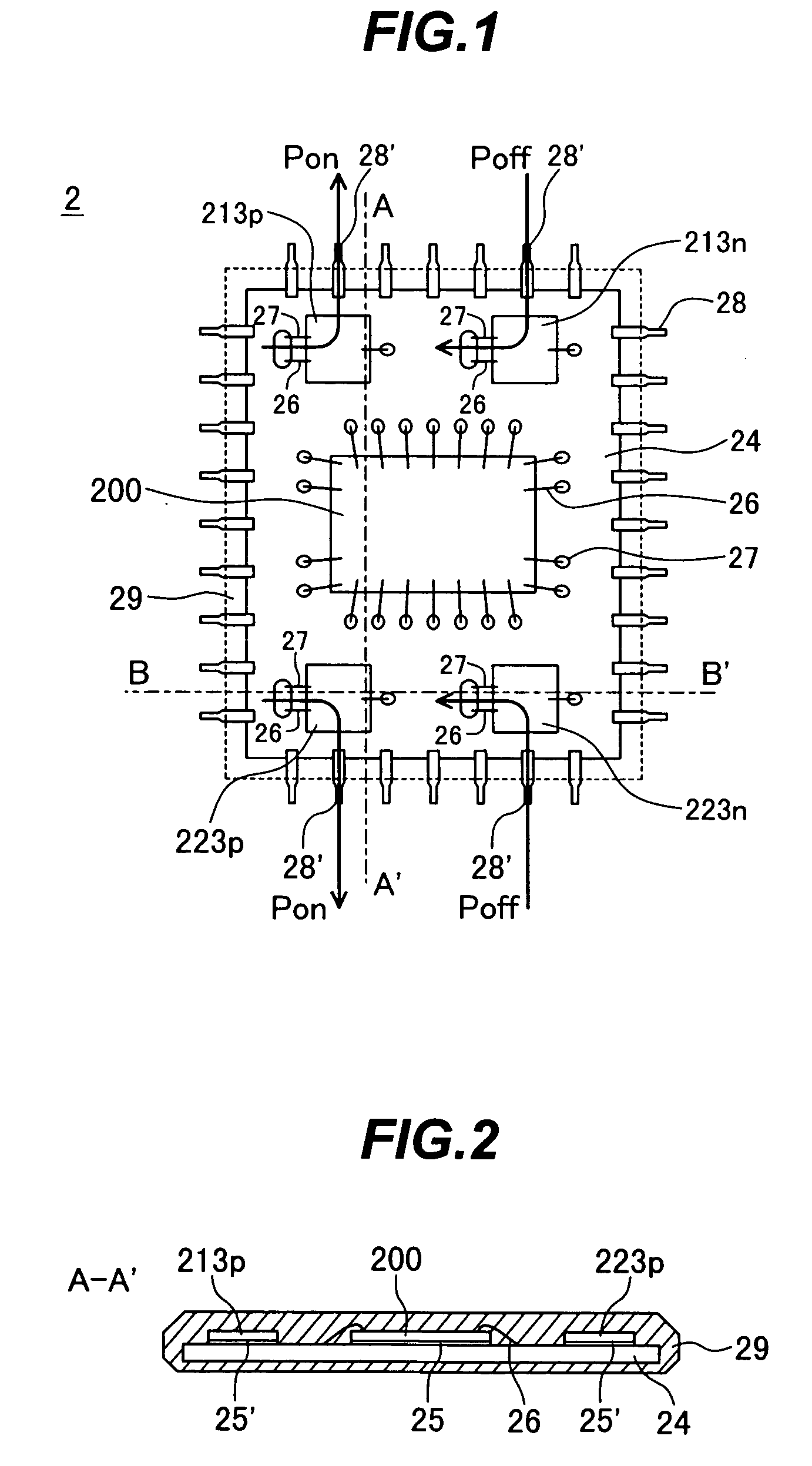

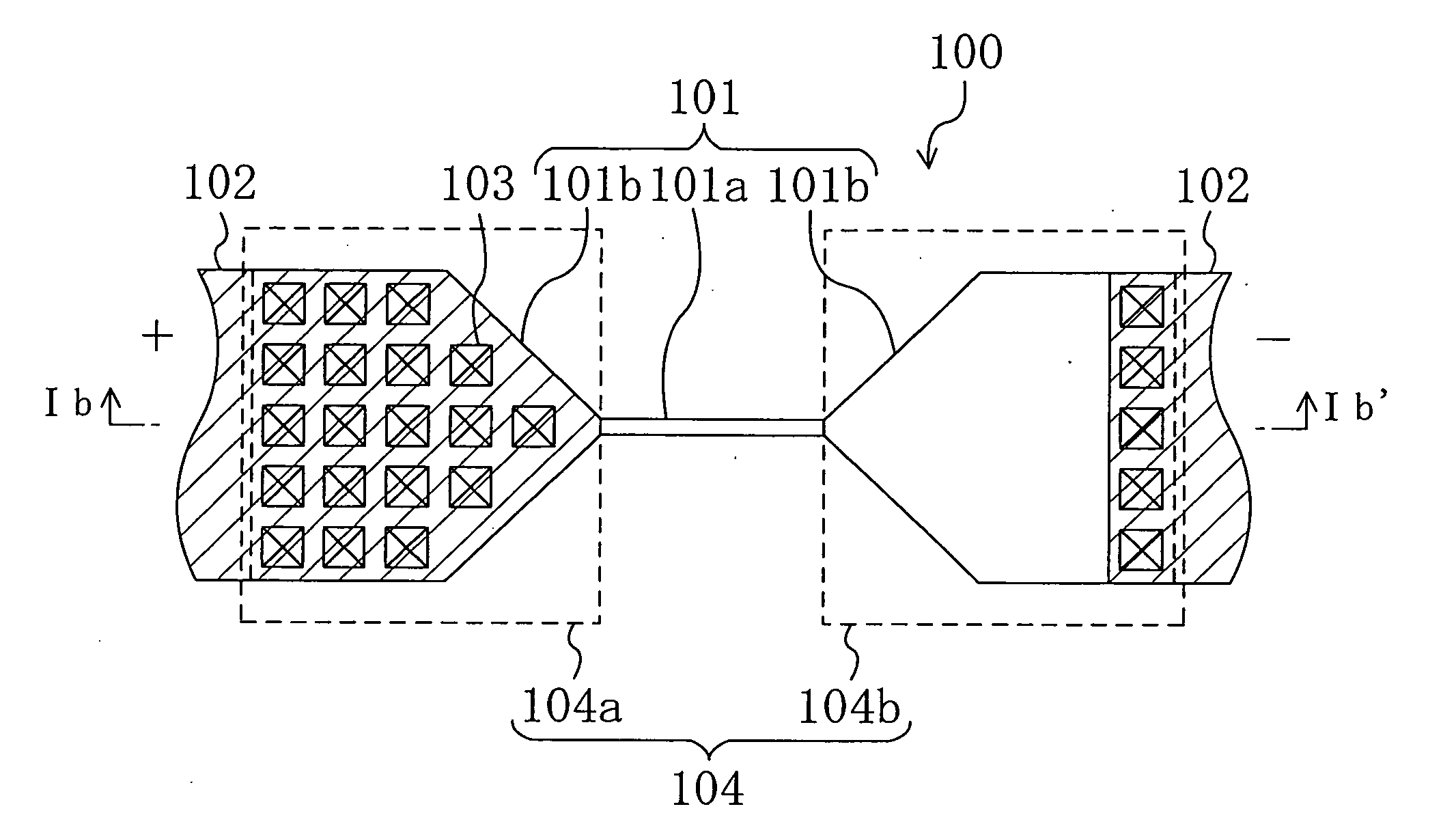

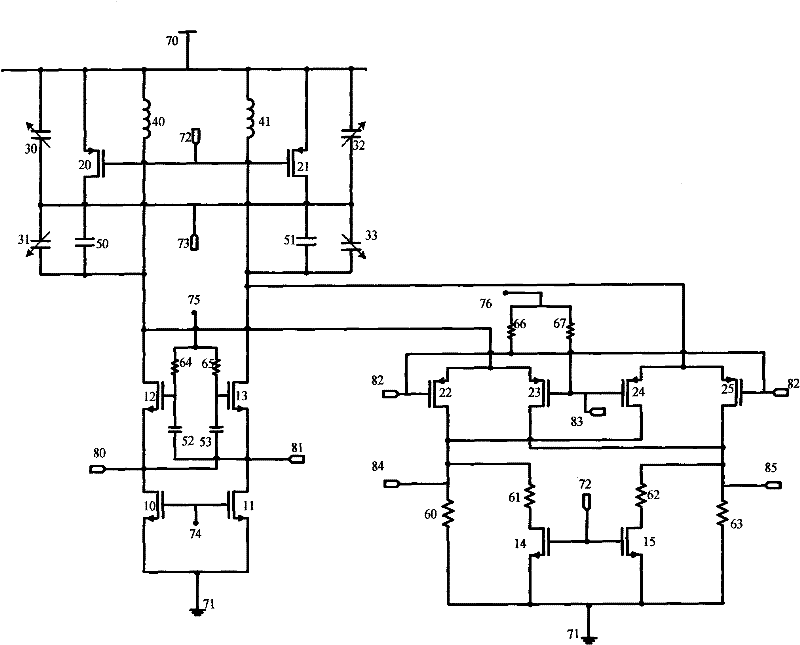

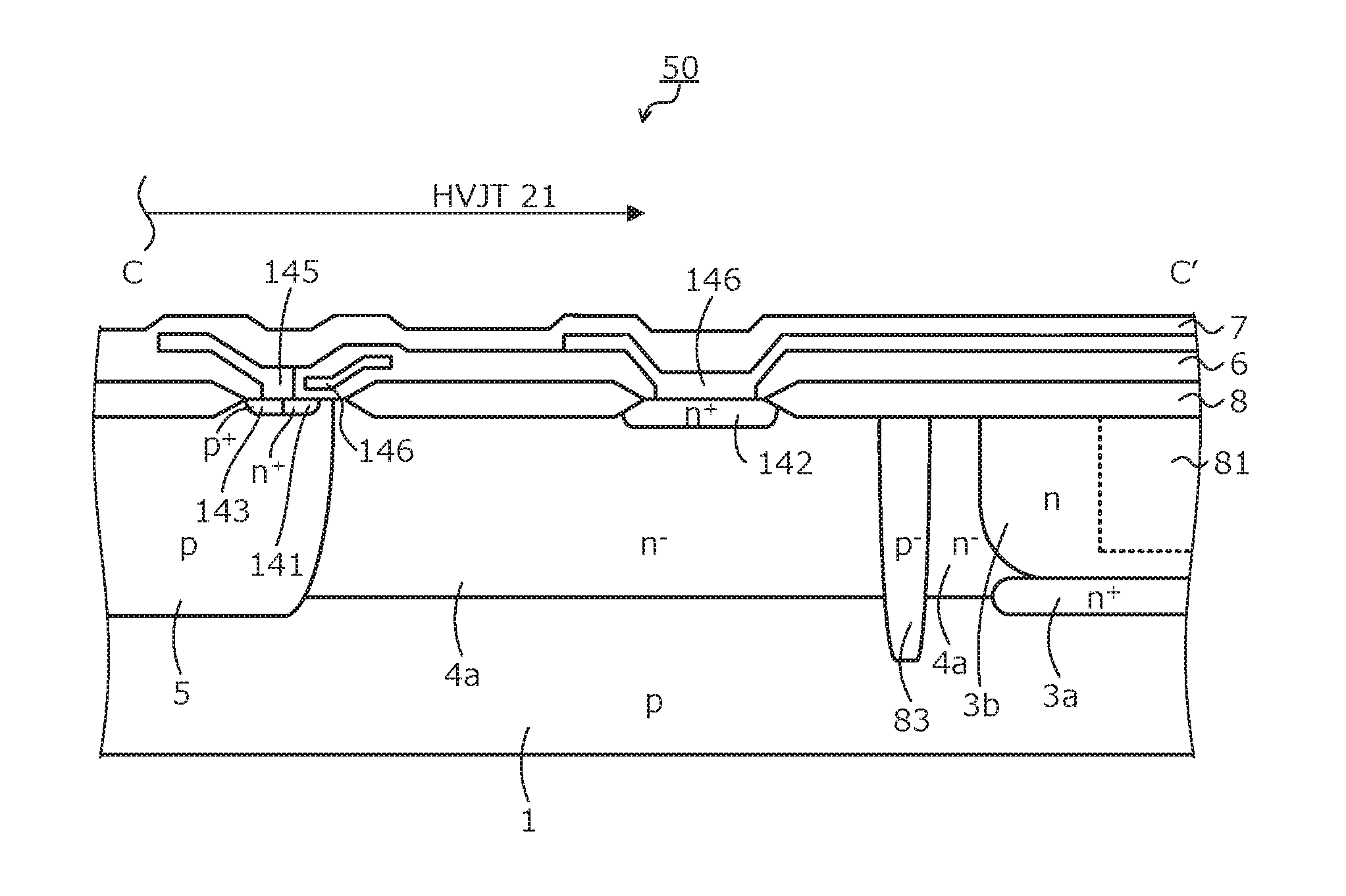

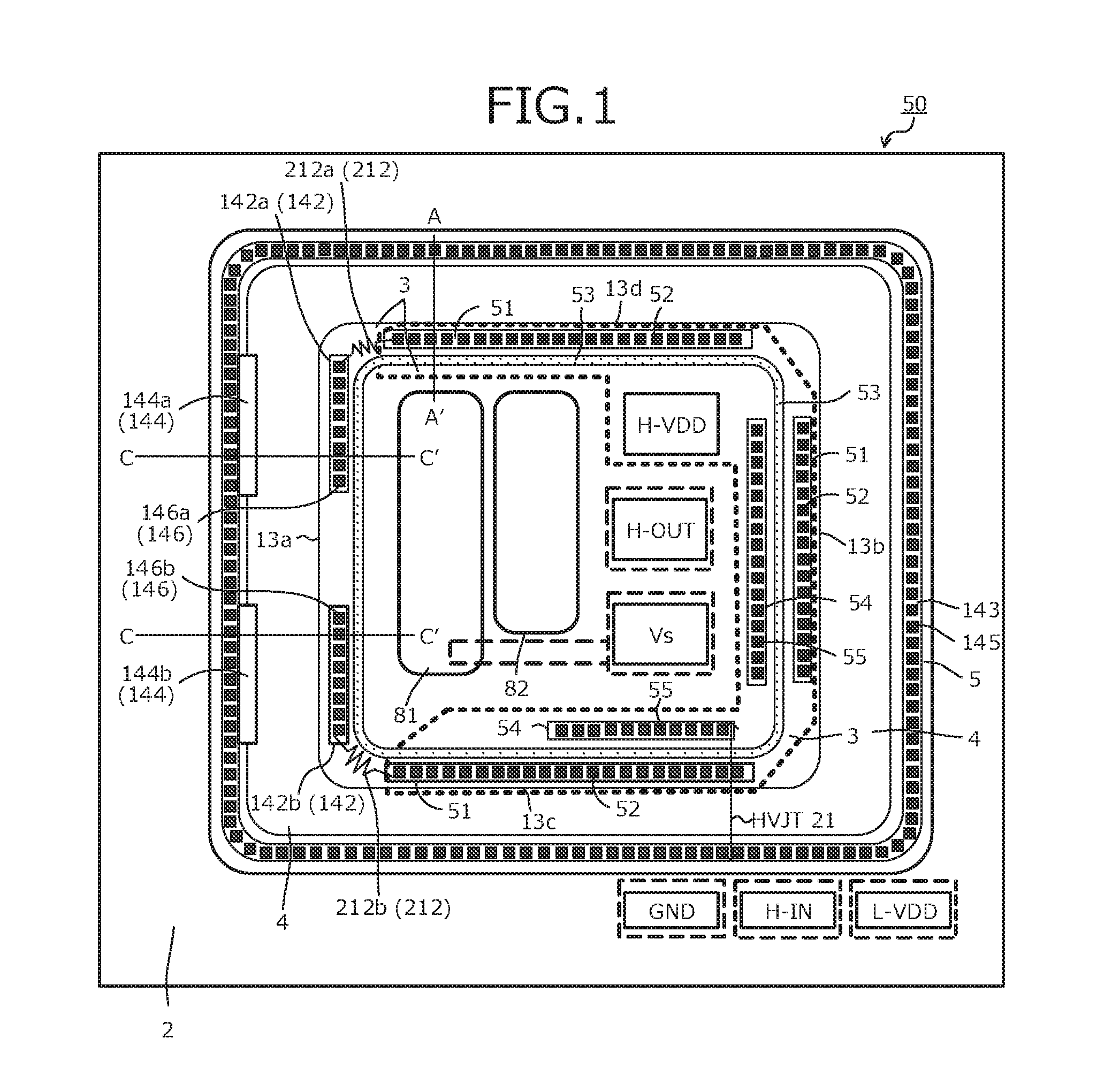

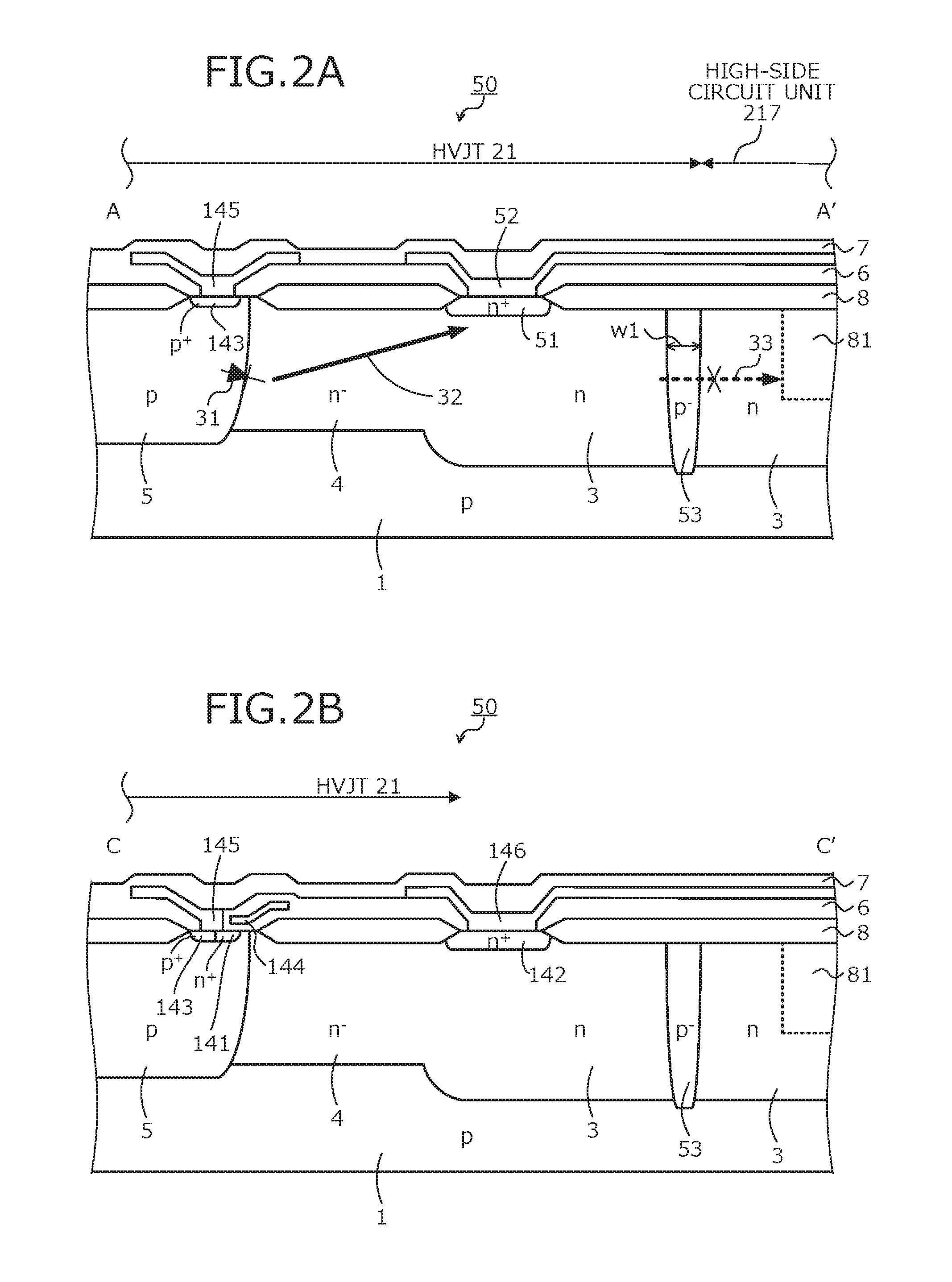

Integrated circuit for driving semiconductor device and power converter

InactiveUS20070008679A1Increase chip areaIncrease in development periodSubstation/switching arrangement detailsSolid-state devicesSignal processing circuitsEngineering

An integrated circuit for driving a semiconductor device, which is adaptable for demands, such as a higher output (larger current), a higher voltage, and a smaller loss, and has a small size, is produced at a low cost, and has high reliability. A power converter including such an integrated circuit is also provided. Circuit elements constituting a drive section of an upper arm drive circuit 212, a level shift circuit 20 including a current sensing circuit 210, a drive section of a lower arm drive circuit 222, and a drive signal processing circuit 224 are integrated and built in one high withstand voltage IC chip 200. Circuit elements constituting a final output stage buffer section 213 of the upper arm drive circuit 212 are built in a vertical p-channel MOS-FET chip 213p and a vertical n-channel MOS-FET chip 213n. Circuit elements constituting a final output stage buffer section 223 of the lower arm drive circuit 222 are built in a vertical p-channel MOS-FET chip 223p and a vertical n-channel MOS-FET chip 223n. Thus, a driver IC 2 is fabricated.

Owner:HITACHI LTD

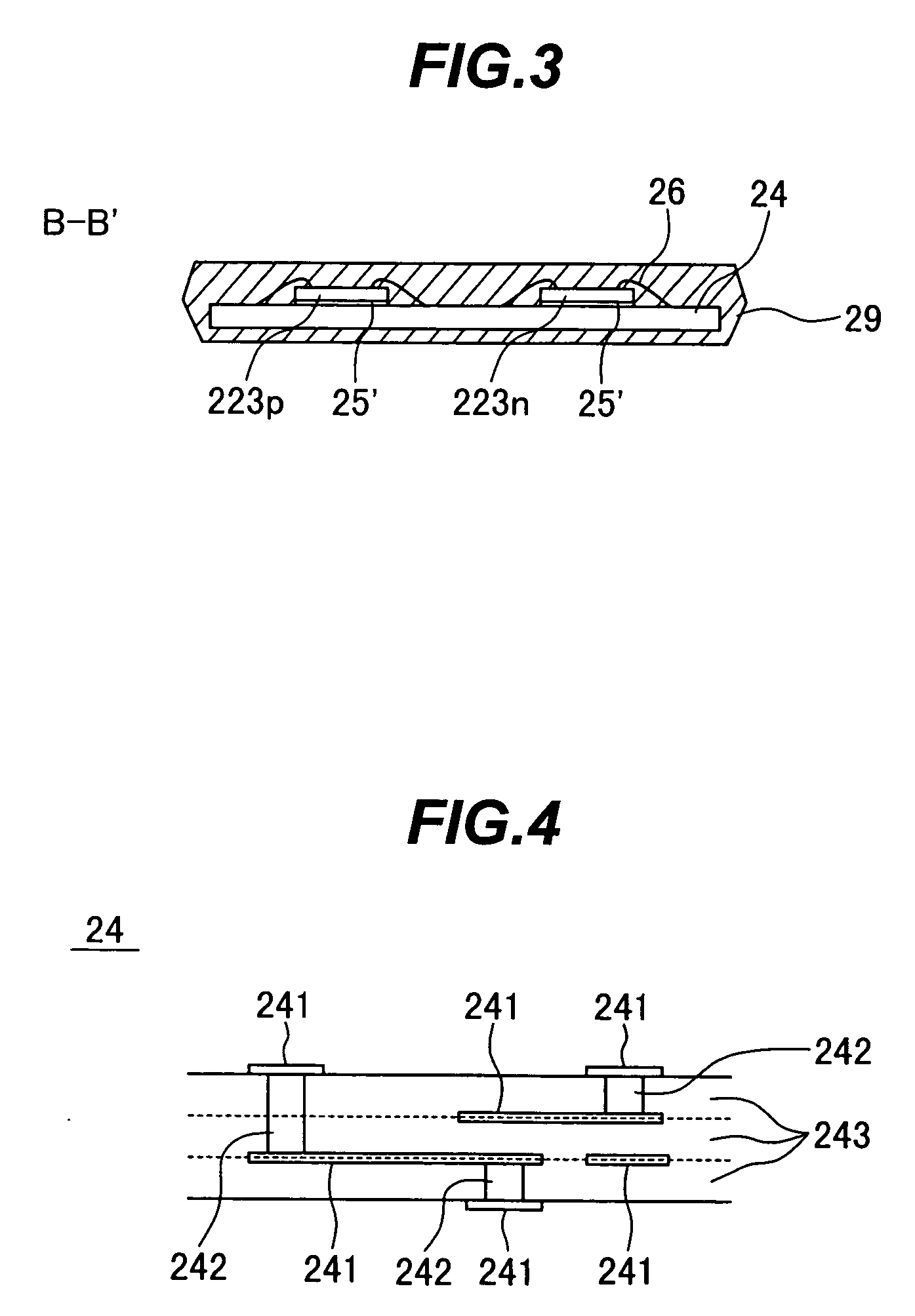

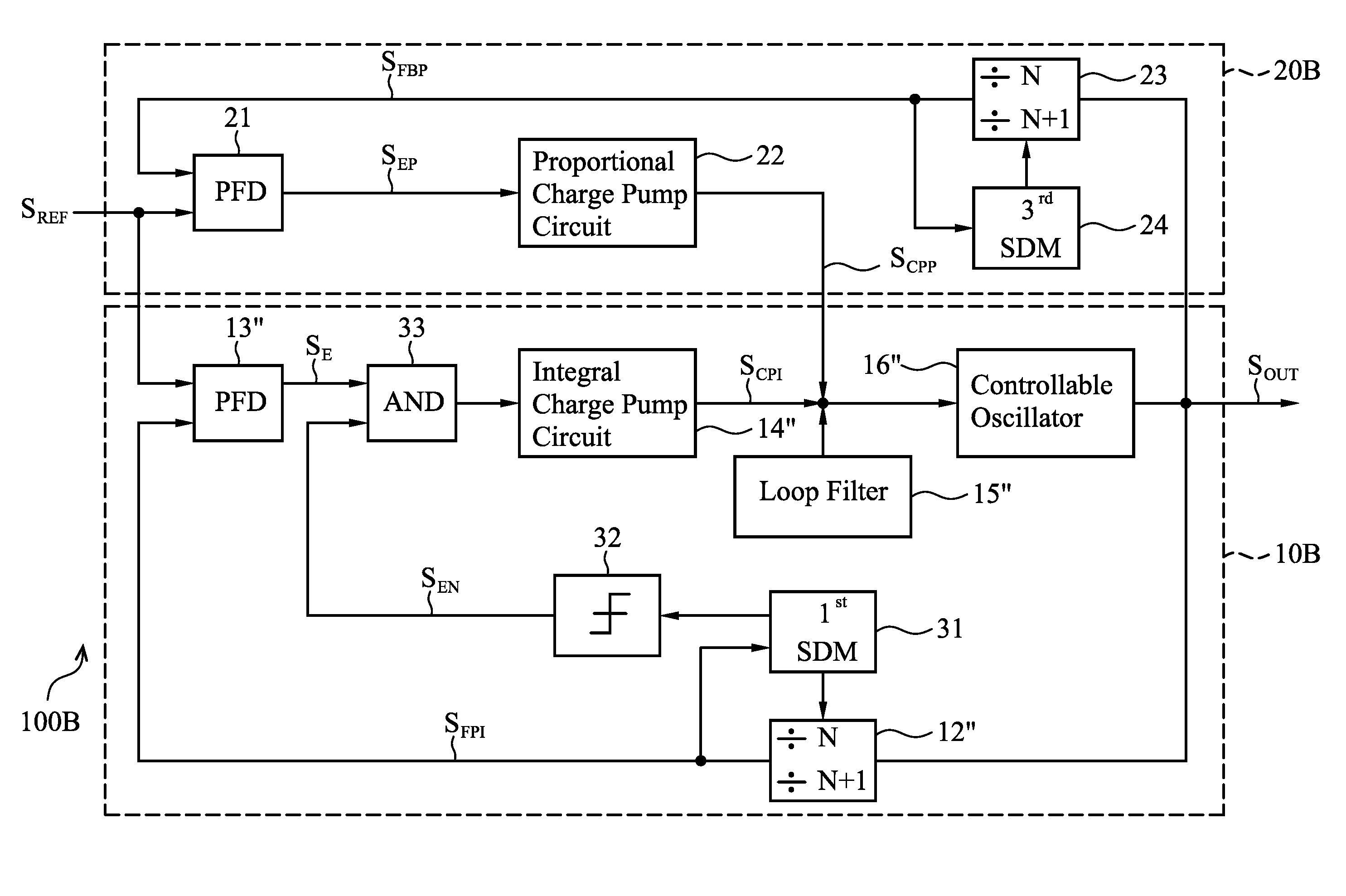

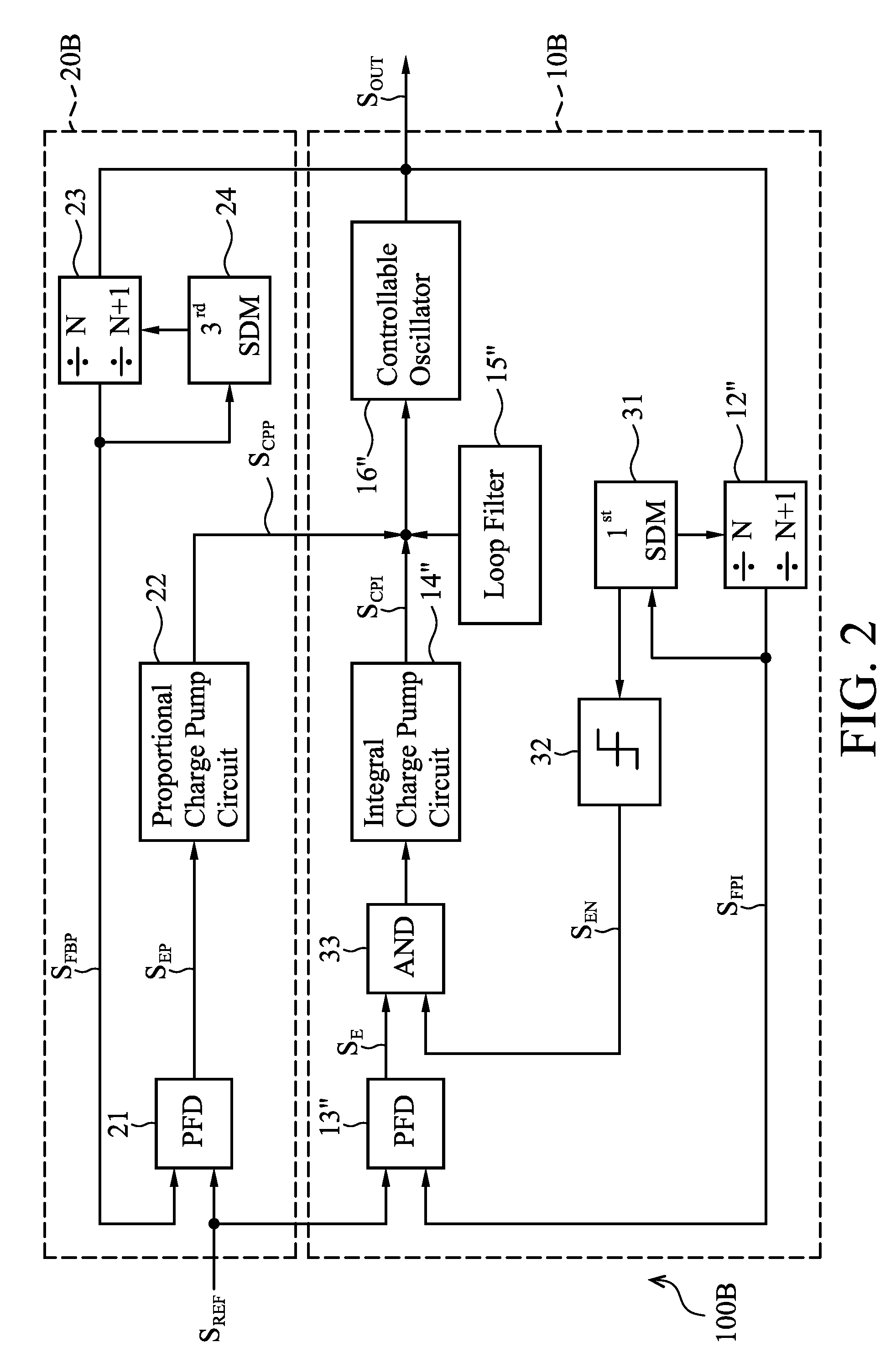

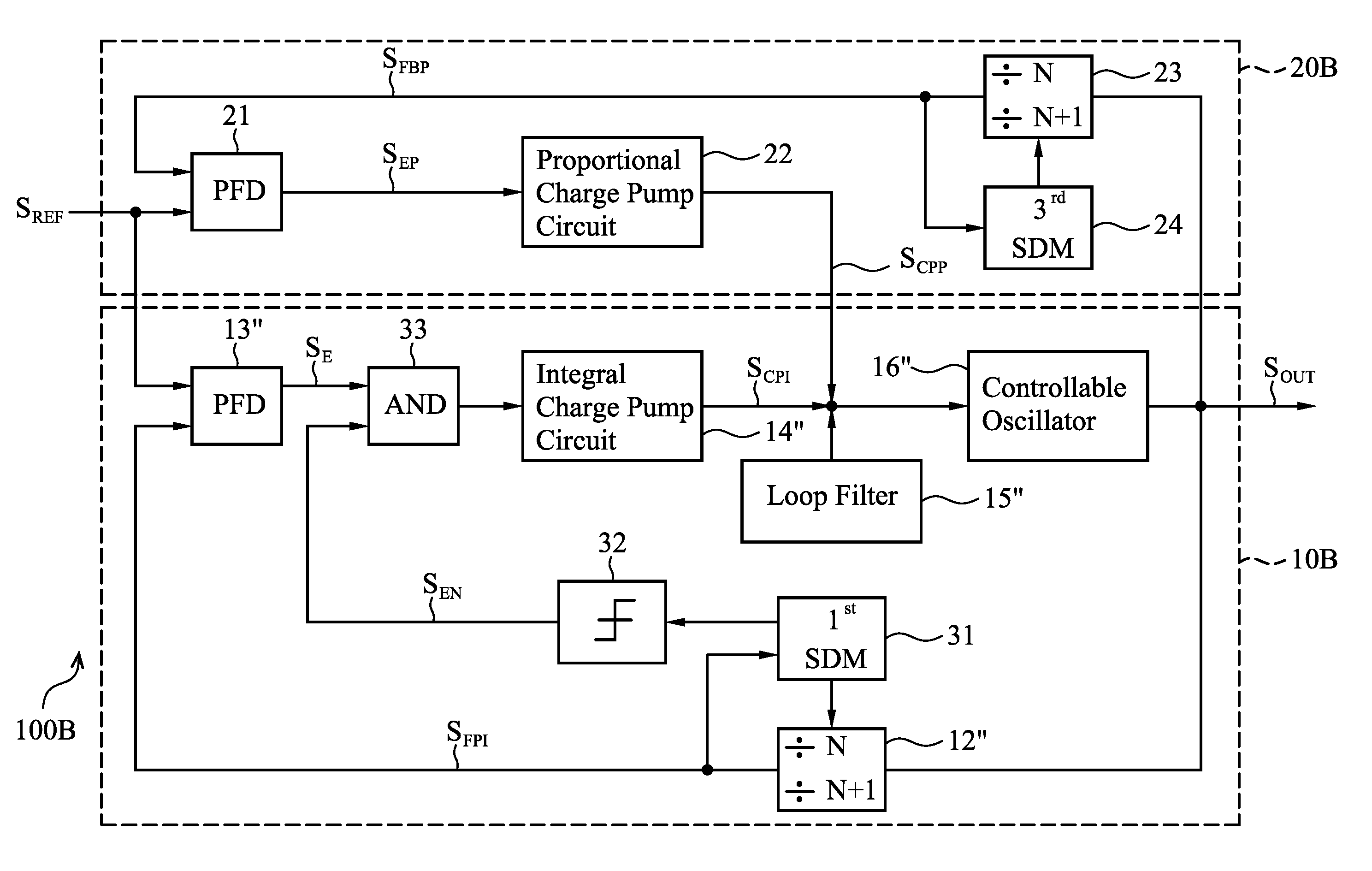

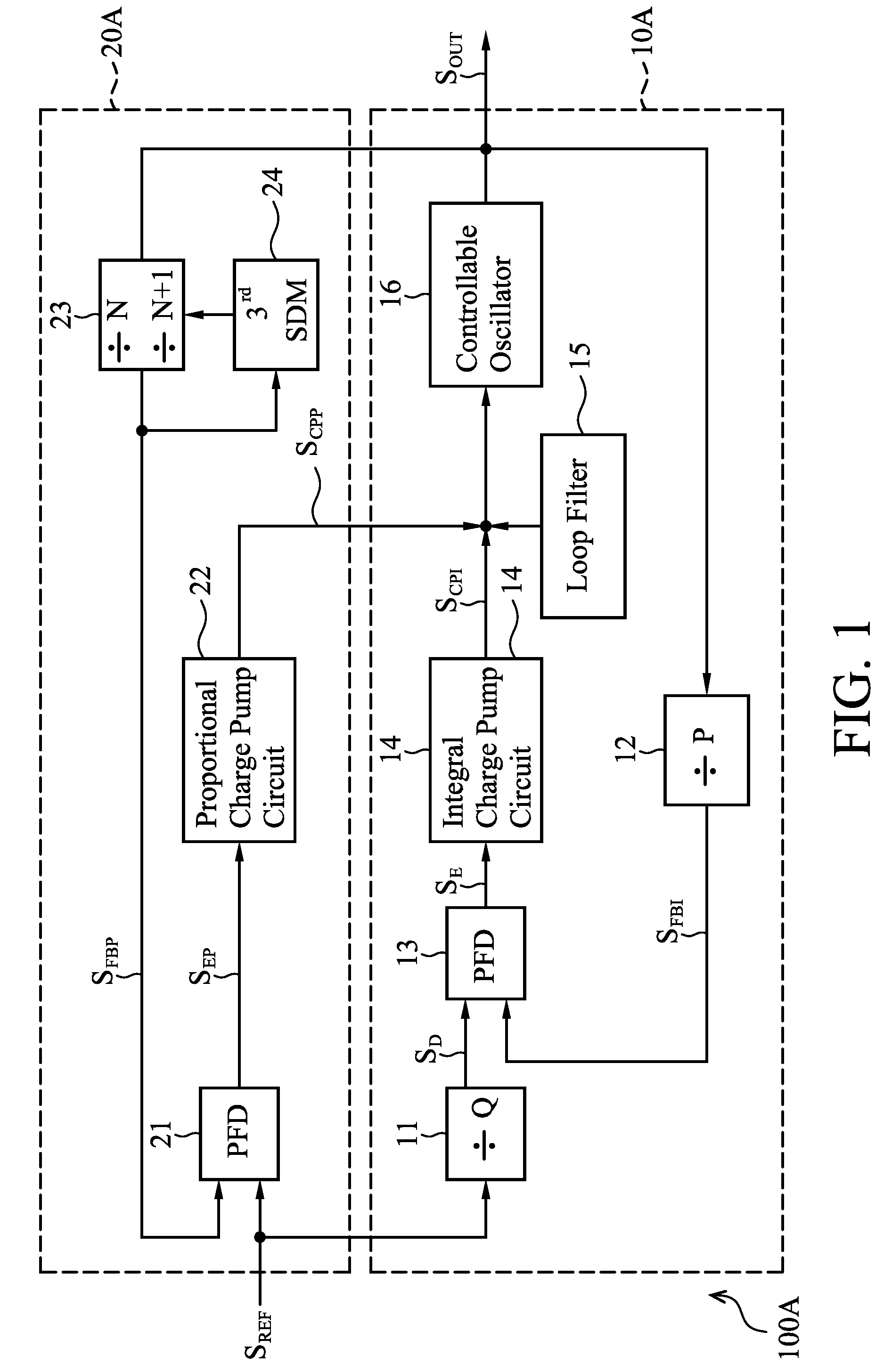

Phase locked loop

InactiveUS8063707B2Improve stabilityIncrease chip areaPulse automatic controlControl signalPhase locked loop circuit

Phase locked loop circuits capable of increasing an equivalent capacitance thereof to improve stability are provided, in which an integral part comprises a first phase frequency detector providing a phase error signal, a first charge pump circuit generating a control signal according to the phase error signal, a controllable oscillator providing an output clock according to the control signal, and a sampling adjustment unit decreasing the number of times the control signal is updated according to the phase error signal. A proportional part is coupled between the controllable oscillator and a reference clock and operated in a fraction mode.

Owner:MEDIATEK INC

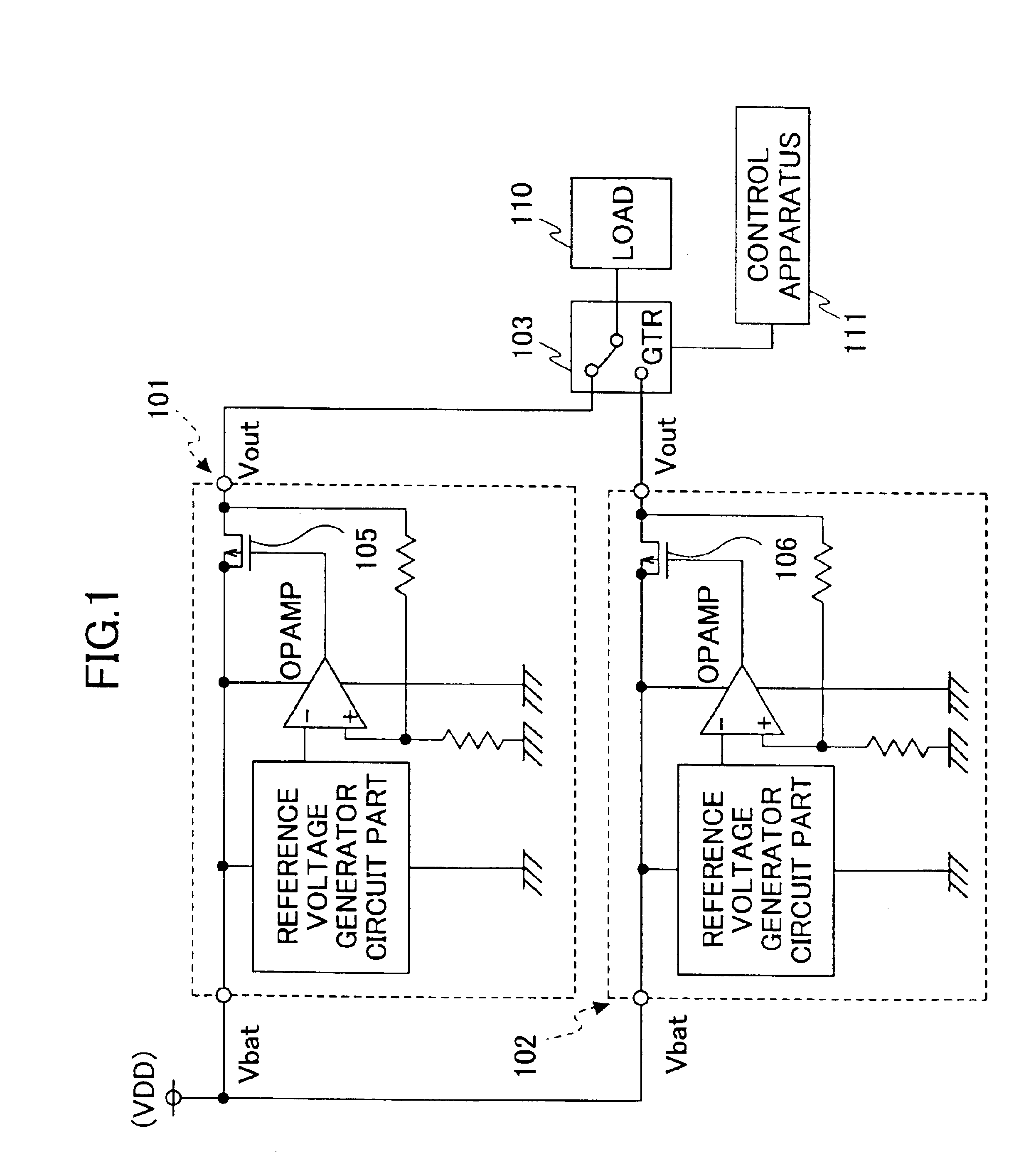

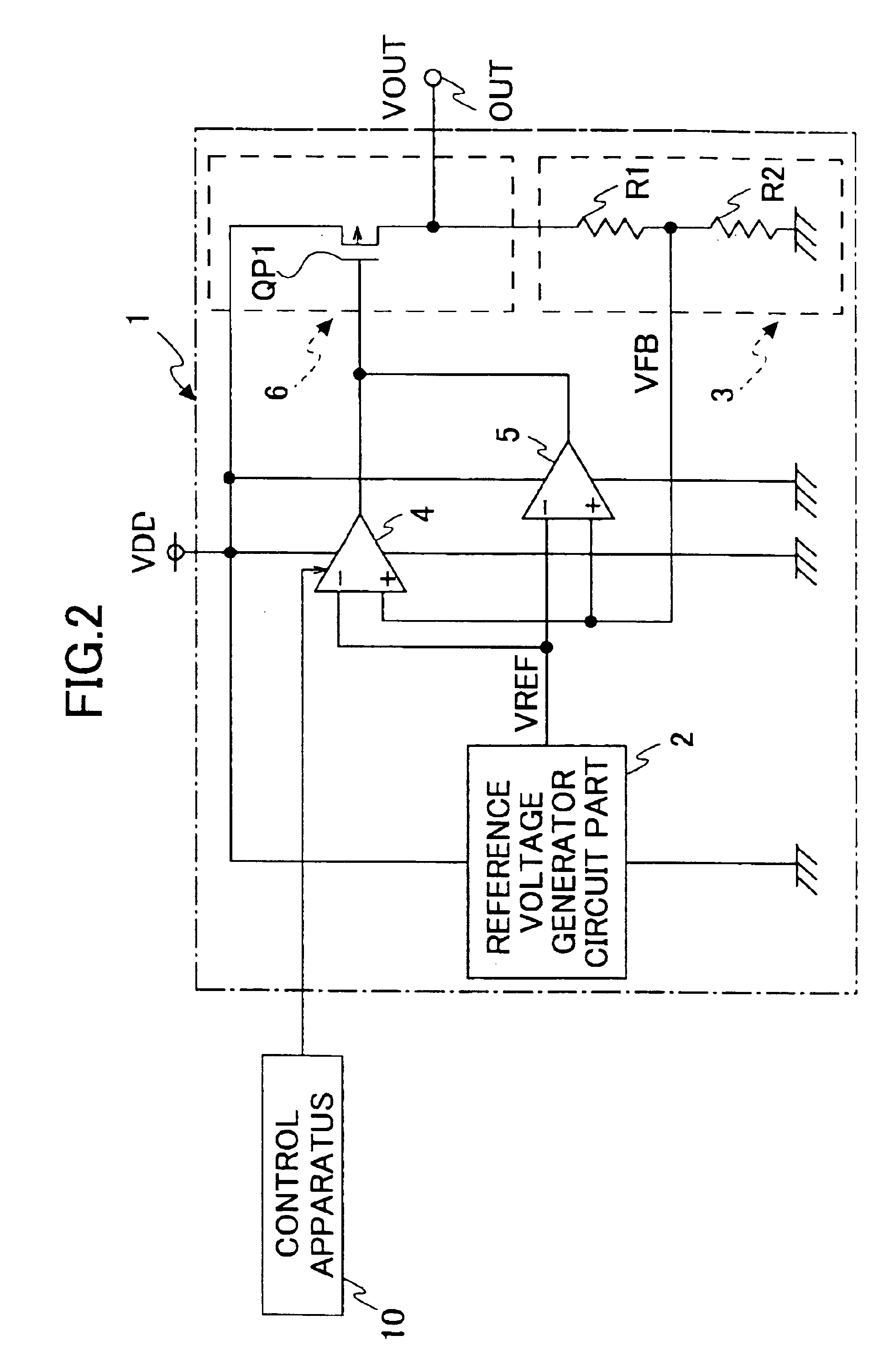

Voltage regulator using two operational amplifiers in current consumption

InactiveUS7002329B2Easy to respond quicklyLower average currentElectric variable regulationAudio power amplifierControl signal

A voltage regulator, which generates and outputs a given voltage based on a preset reference voltage, includes: a detection circuit part detecting the output voltage and generating and outputting a voltage based on the detected voltage; first and second operational amplifiers each comparing the output voltage of said detection circuit part and the preset reference voltage and outputting a voltage representing a comparison result, the first operational amplifier being controlled based on control signals supplied externally and consuming a larger amount of electric current than the second operational amplifier; and an output circuit part comprising an output transistor outputting an electric current based on the output voltages of the first and second operational amplifiers.

Owner:RICOH ELECTRONIC DEVICES CO LTD

Phase locked loop

InactiveUS20100283549A1Improve stabilityIncrease chip areaPulse automatic controlControl signalPhase locked loop circuit

Phase locked loop circuits capable of increasing an equivalent capacitance thereof to improve stability are provided, in which an integral part comprises a first phase frequency detector providing a phase error signal, a first charge pump circuit generating a control signal according to the phase error signal, a controllable oscillator providing an output clock according to the control signal, and a sampling adjustment unit decreasing the number of times the control signal is updated according to the phase error signal. A proportional part is coupled between the controllable oscillator and a reference clock and operated in a fraction mode.

Owner:MEDIATEK INC

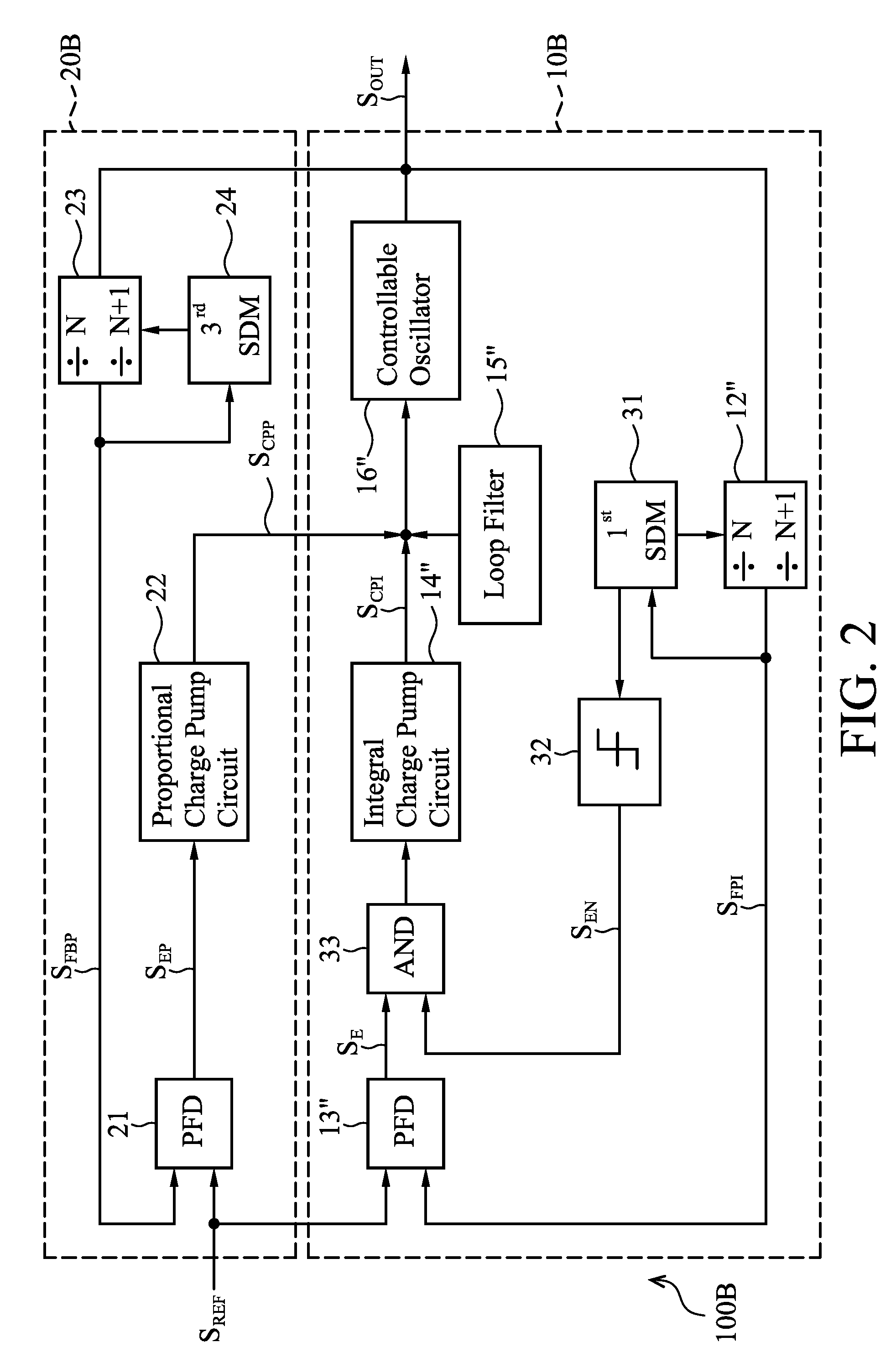

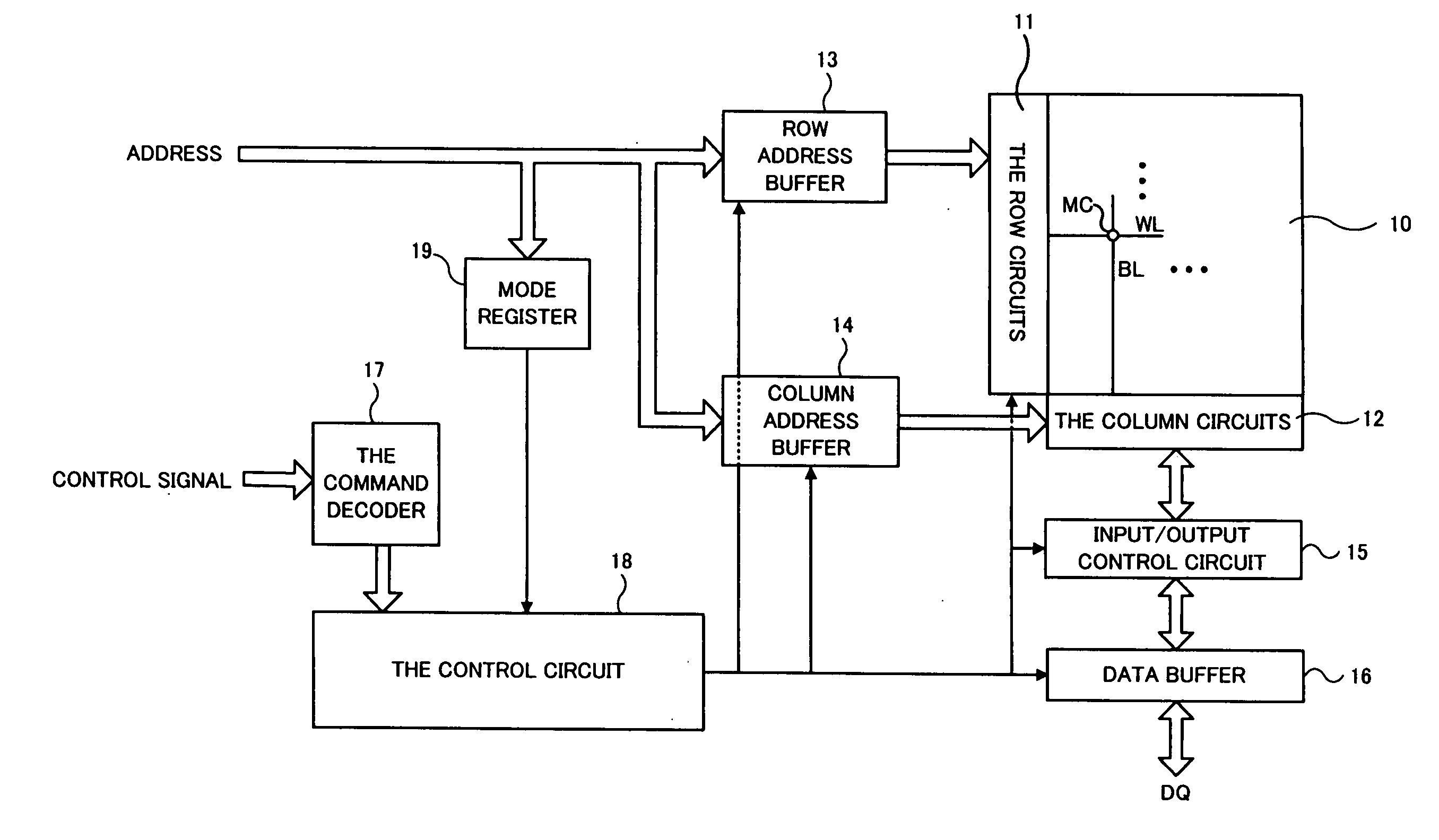

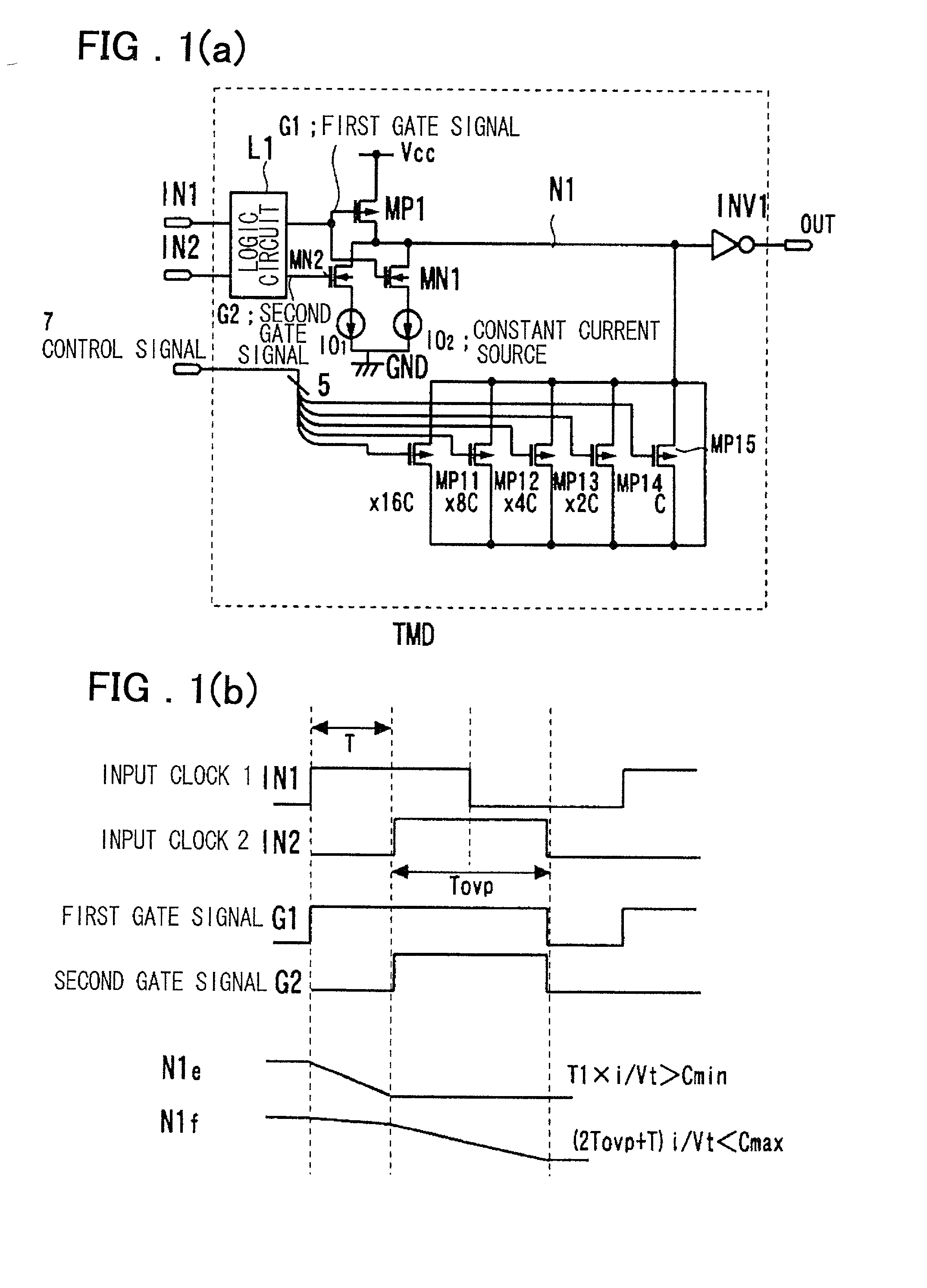

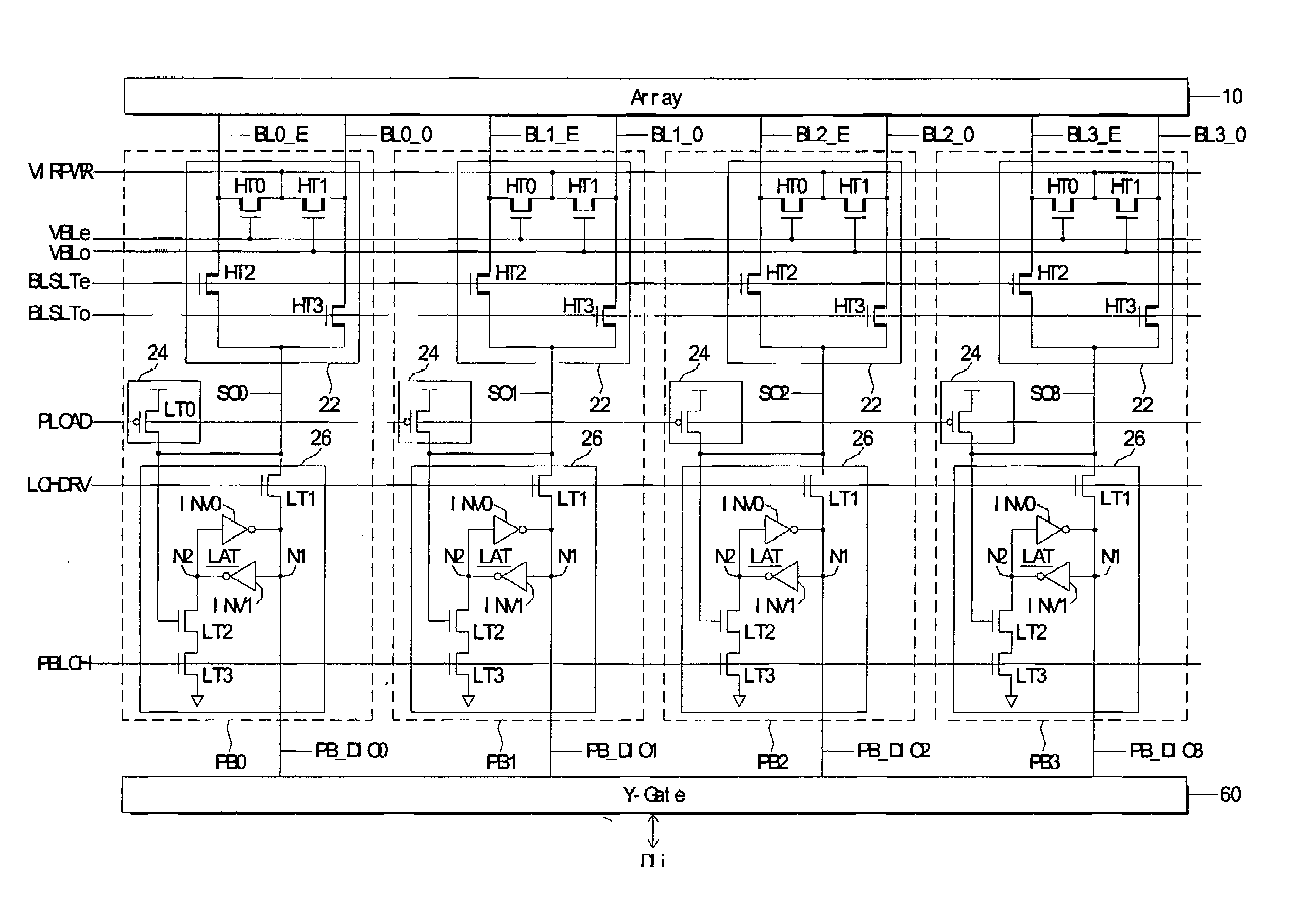

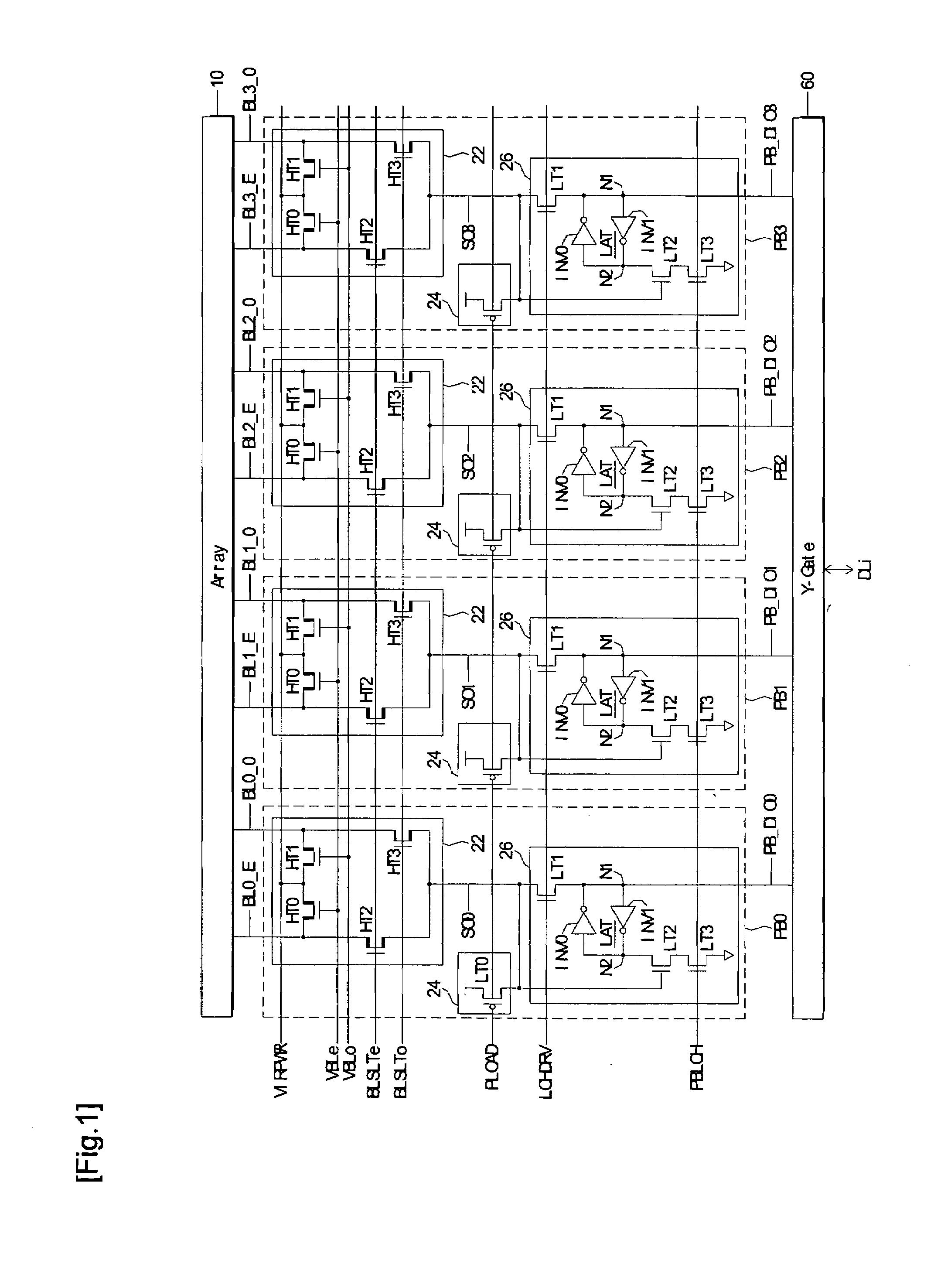

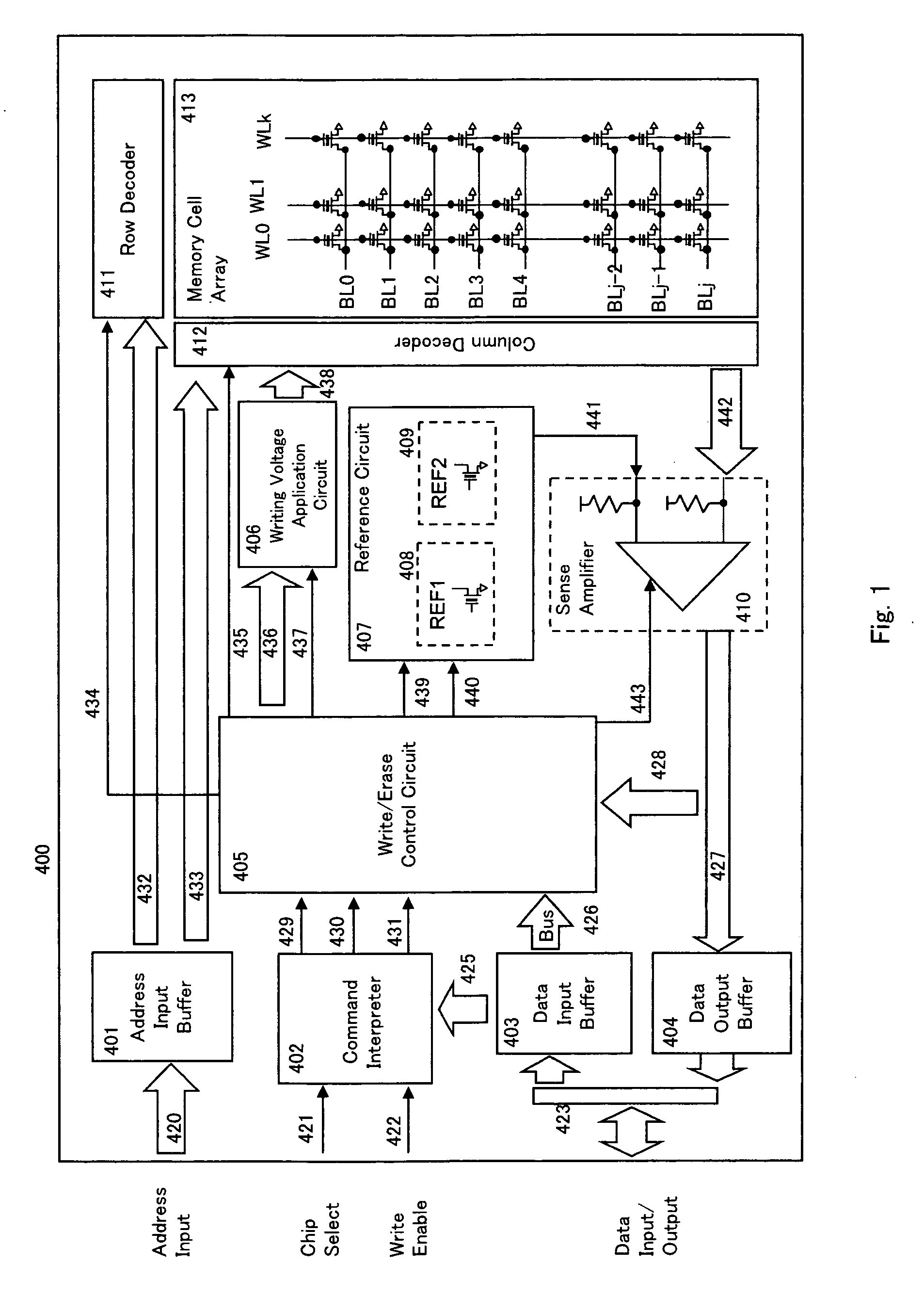

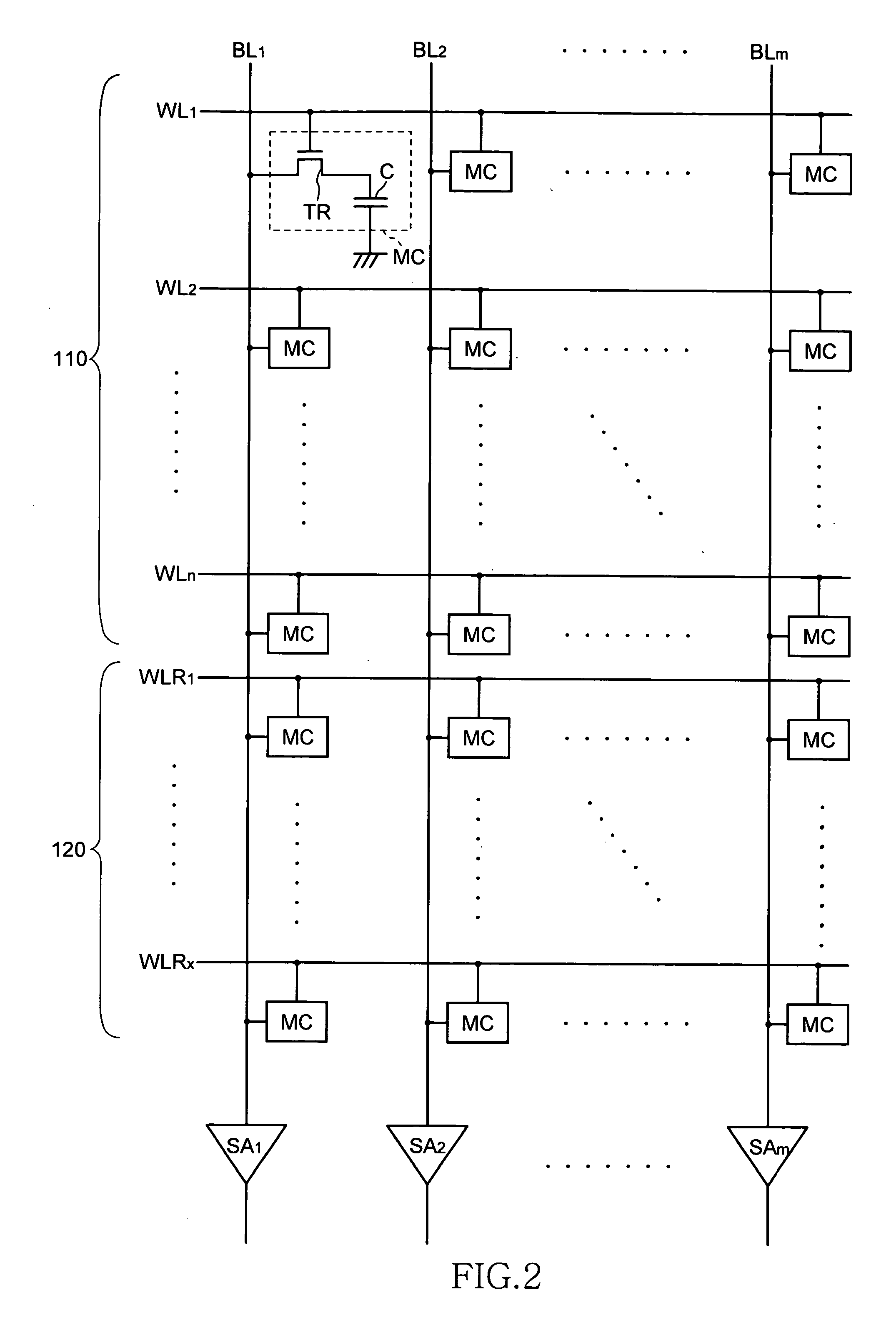

Semiconductor memory device and electronic equipment

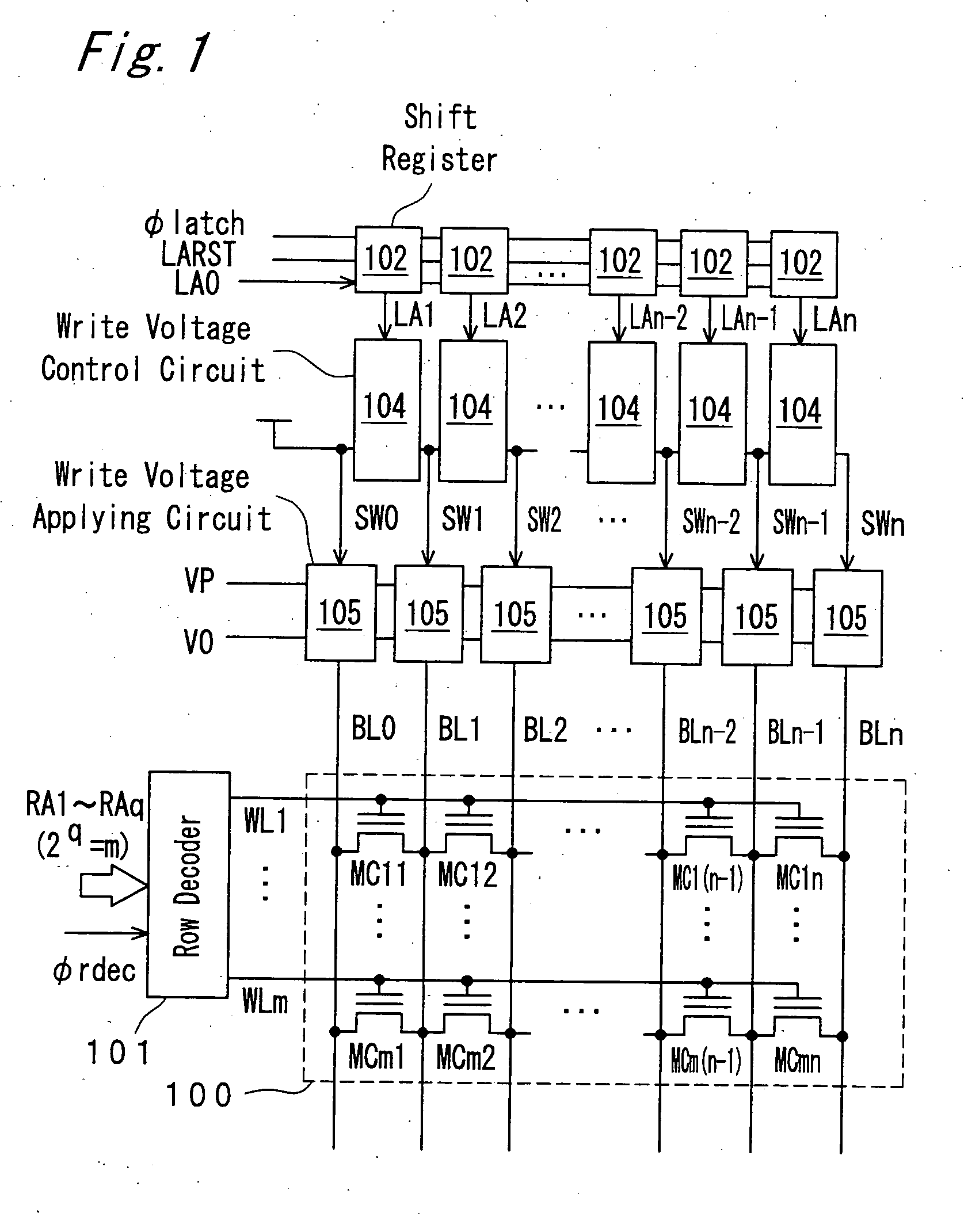

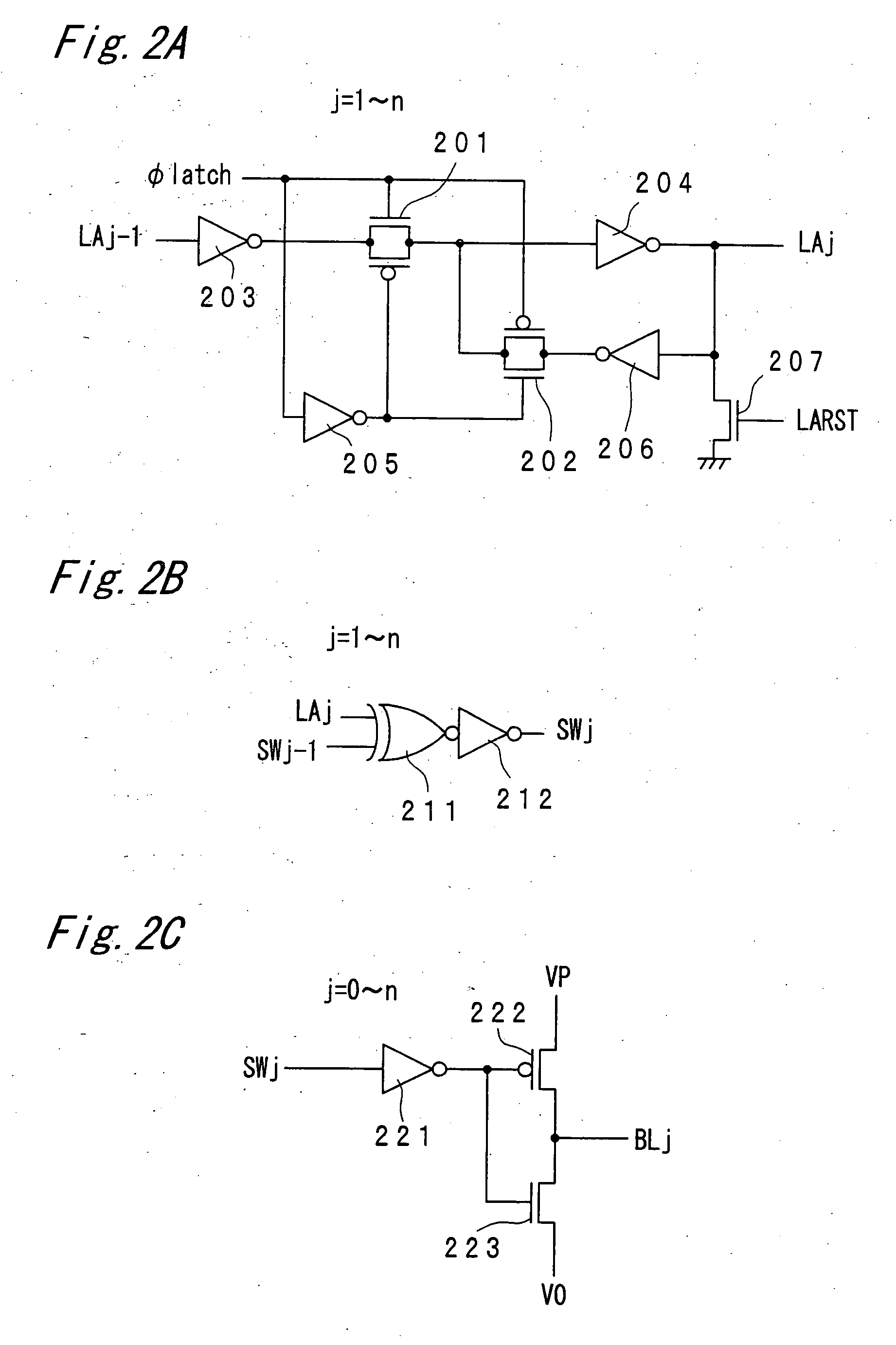

InactiveUS20060239071A1Simple configurationImprove accuracyRead-only memoriesDigital storageShift registerBit line

A semiconductor memory device has a memory cell array in which a plurality of nonvolatile memory cells are arranged. The memory device also has word lines, bit lines connected with the memory cells by a virtual grounding scheme, a row decoder, shift registers, a write voltage control circuit for controlling voltages to be applied to bit lines, and a write voltage applying circuit for applying voltages to the bit lines. The write voltage control circuit controls the write voltage applying circuit such that when writing data 1 to a memory cell, different voltages V0 and VP are applied to two bit lines associated with the memory cell, while a same voltage V0 or VP is applied to the two bit lines when writing data 0 to the memory cell.

Owner:SHARP KK

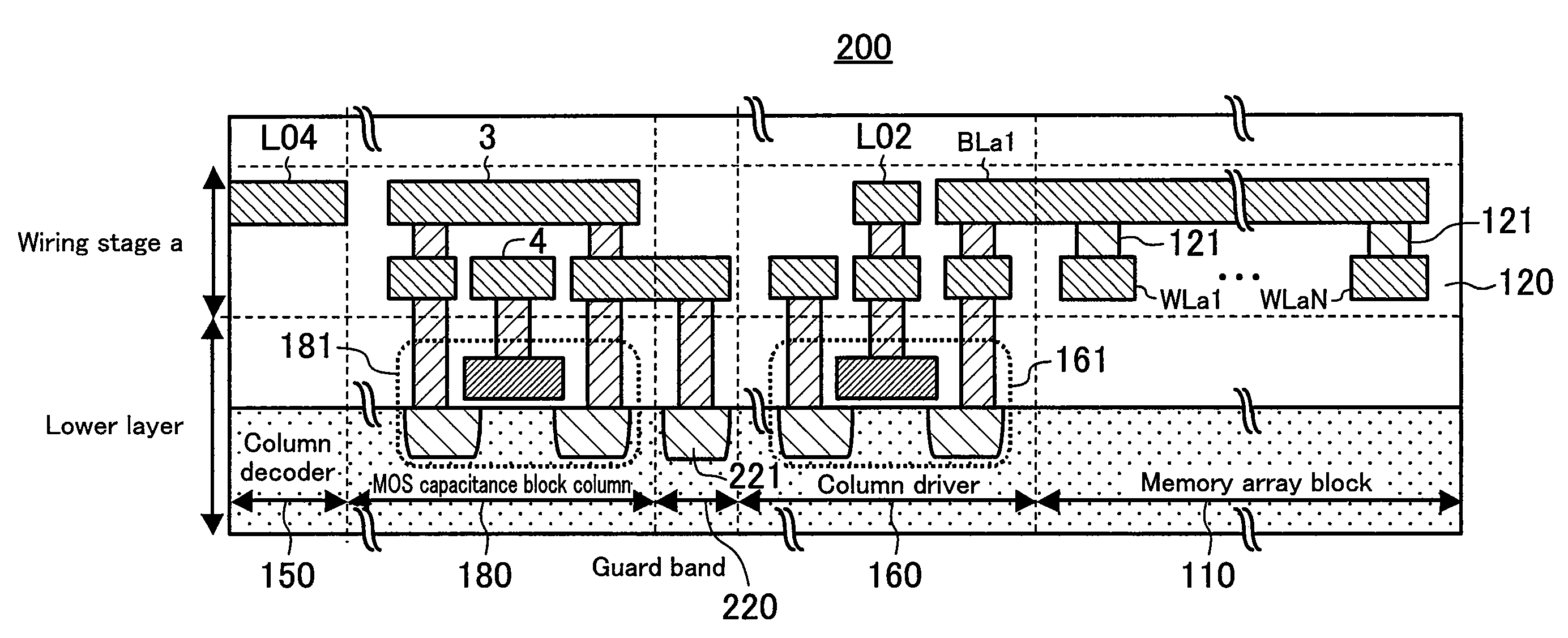

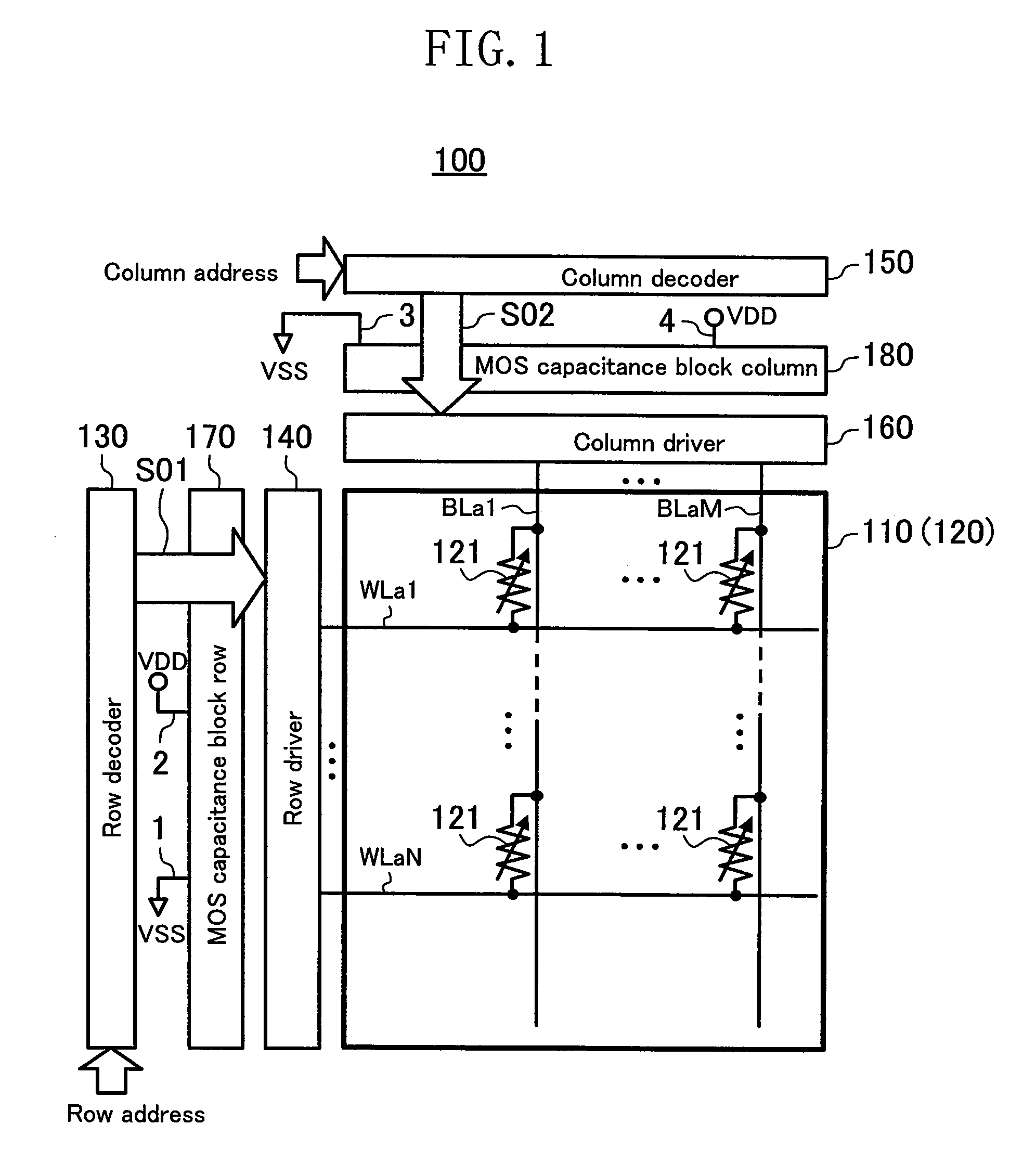

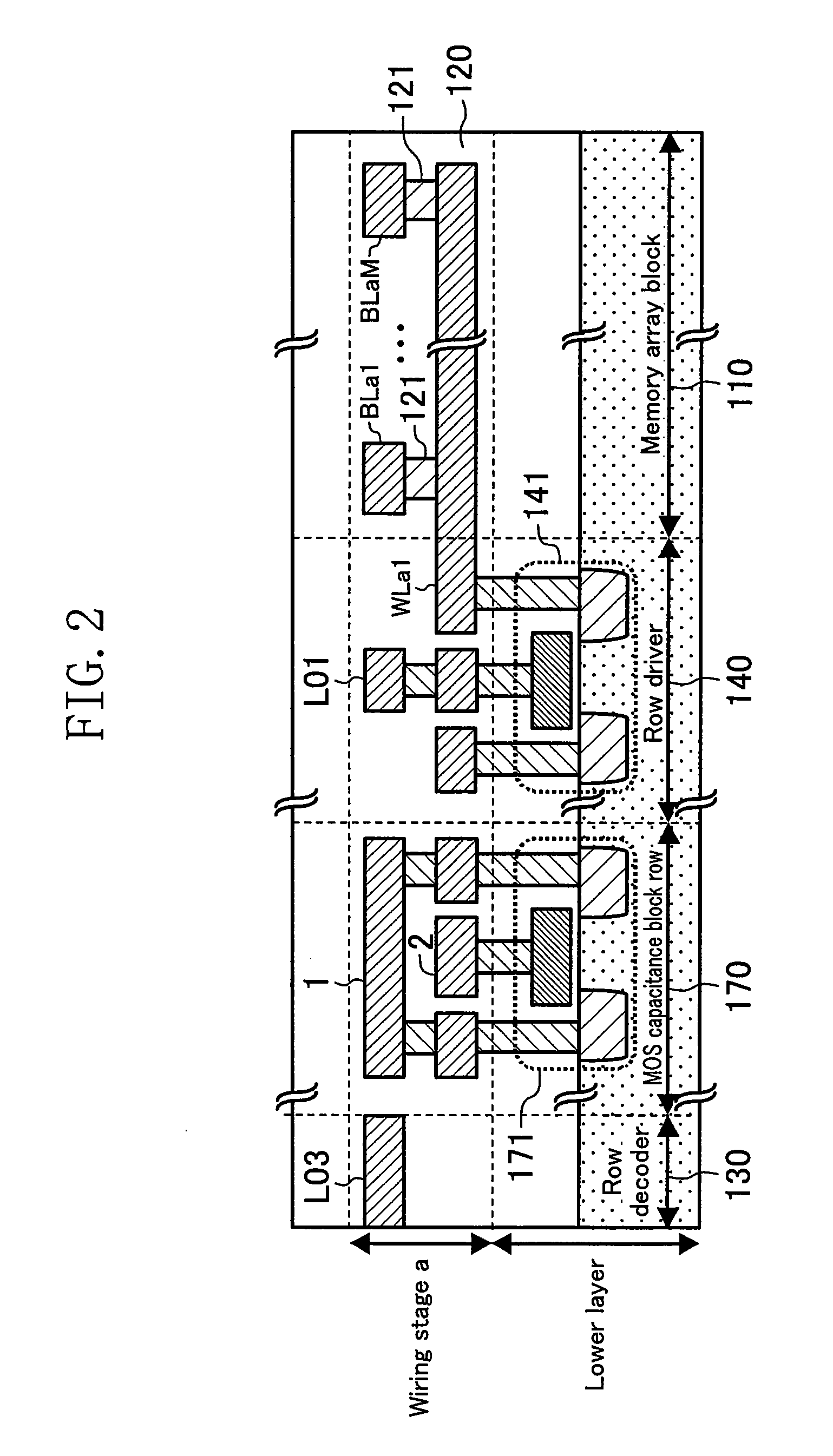

Semiconductor memory device, memory-mounted LSI and fabrication method for semiconductor memory device

InactiveUS20090040802A1Improve scalabilityUnit price increaseTransistorNanoinformaticsEngineeringMos capacitor

The semiconductor memory device includes a memory cell array block having one or more stages of memory cell arrays stacked one on another, each memory cell array including a plurality of memory cells placed in a matrix at respective intersections of a plurality of word lines and a plurality of bit lines. A plurality of MOS transistor blocks are provided which are same in the configuration of circuit elements and include MOS transistors as one kind of the circuit elements. In part of the plurality MOS transistor blocks, the MOS transistors are used for drive of the word lines or the bit lines, while in at least part of the remaining MOS transistor blocks, the MOS transistors are used as MOS capacitors.

Owner:PANASONIC CORP

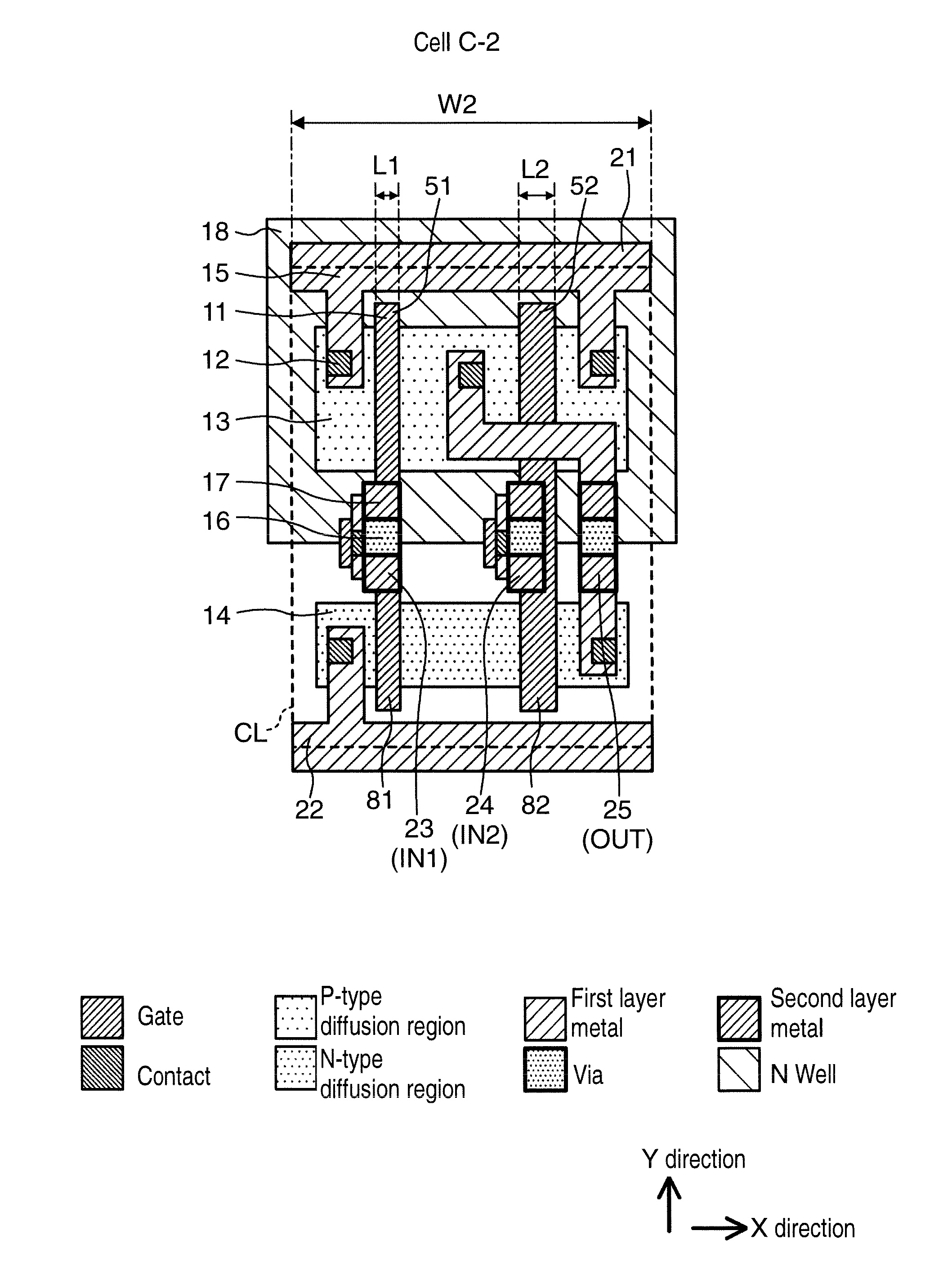

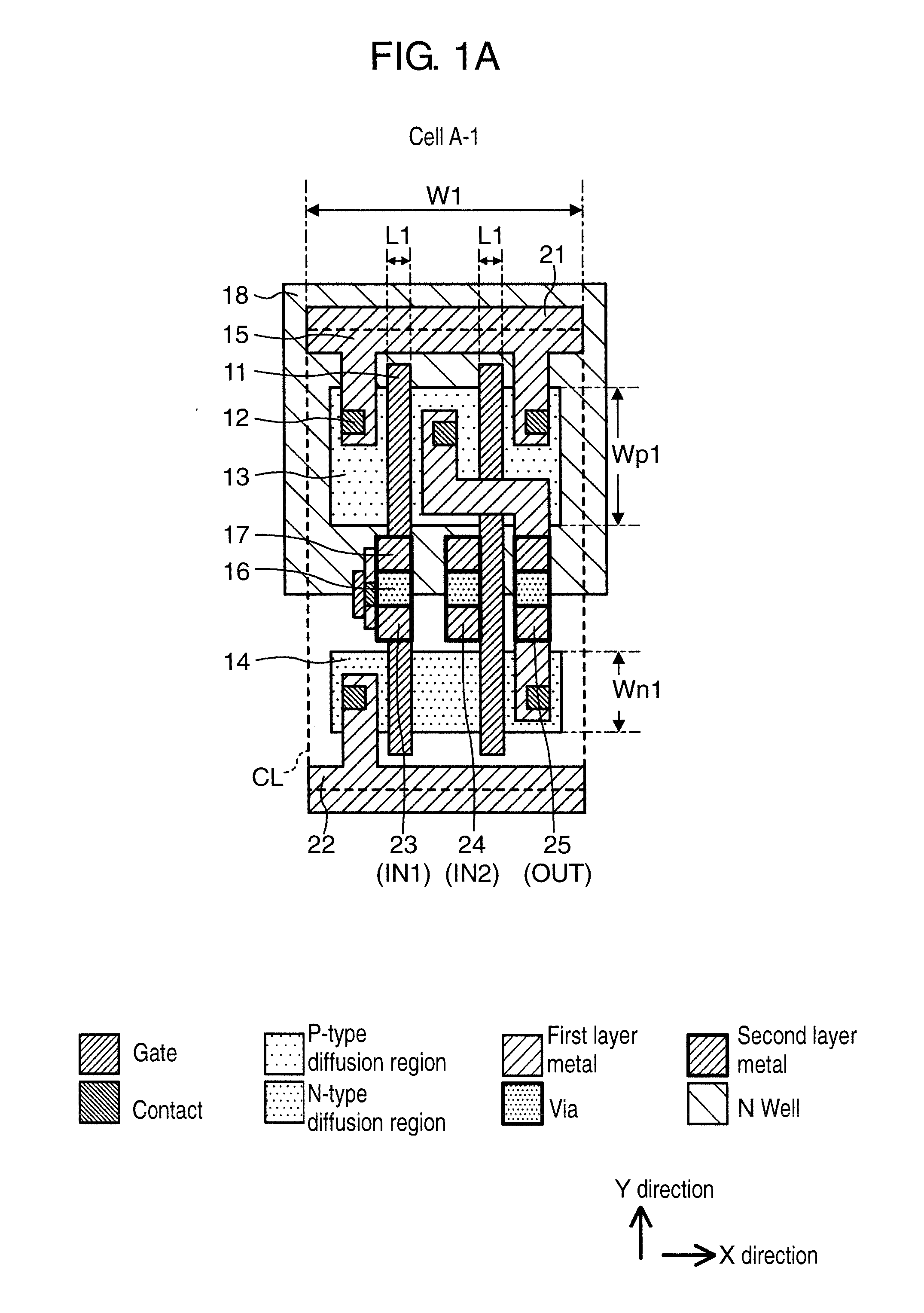

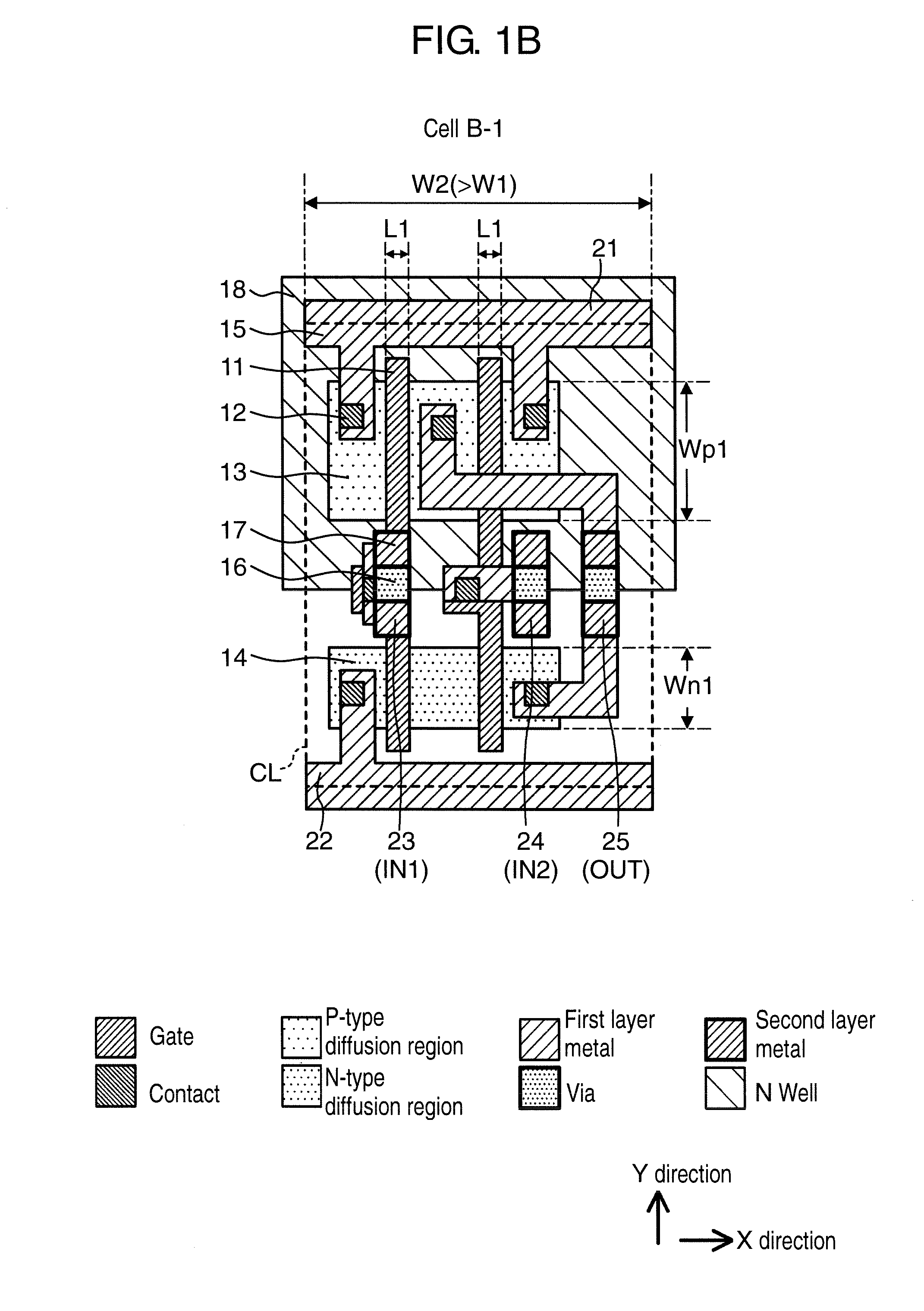

Semiconductor integrated circuit device

InactiveUS20130027083A1Efficiently suppress leak current without increasing a chip areaIncrease chip areaSolid-state devicesSemiconductor/solid-state device manufacturingCircuit delaySemiconductor

A semiconductor integrated circuit device includes cells A-1, B-1, and C-1 that have the same logic. Cell B-1 has cell width W2 larger than a cell width of cell A-1, but gate length L1 of a MOS transistor is equal to that of cell A-1. Cell C-1 has cell width W2 equal to a cell width of cell B-1, but has a MOS transistor having large gate length L2. A circuit delay of cell C-1 becomes large as compared with that of cells A-1 and B-1, but leak current becomes small. Therefore, by replacing cell A-1 adjacent to a space area with cell B-1, and by replacing cell B-1 in a path having room in timing with cell C-1, for example, leak current can be suppressed without increasing a chip area.

Owner:SOCIONEXT INC

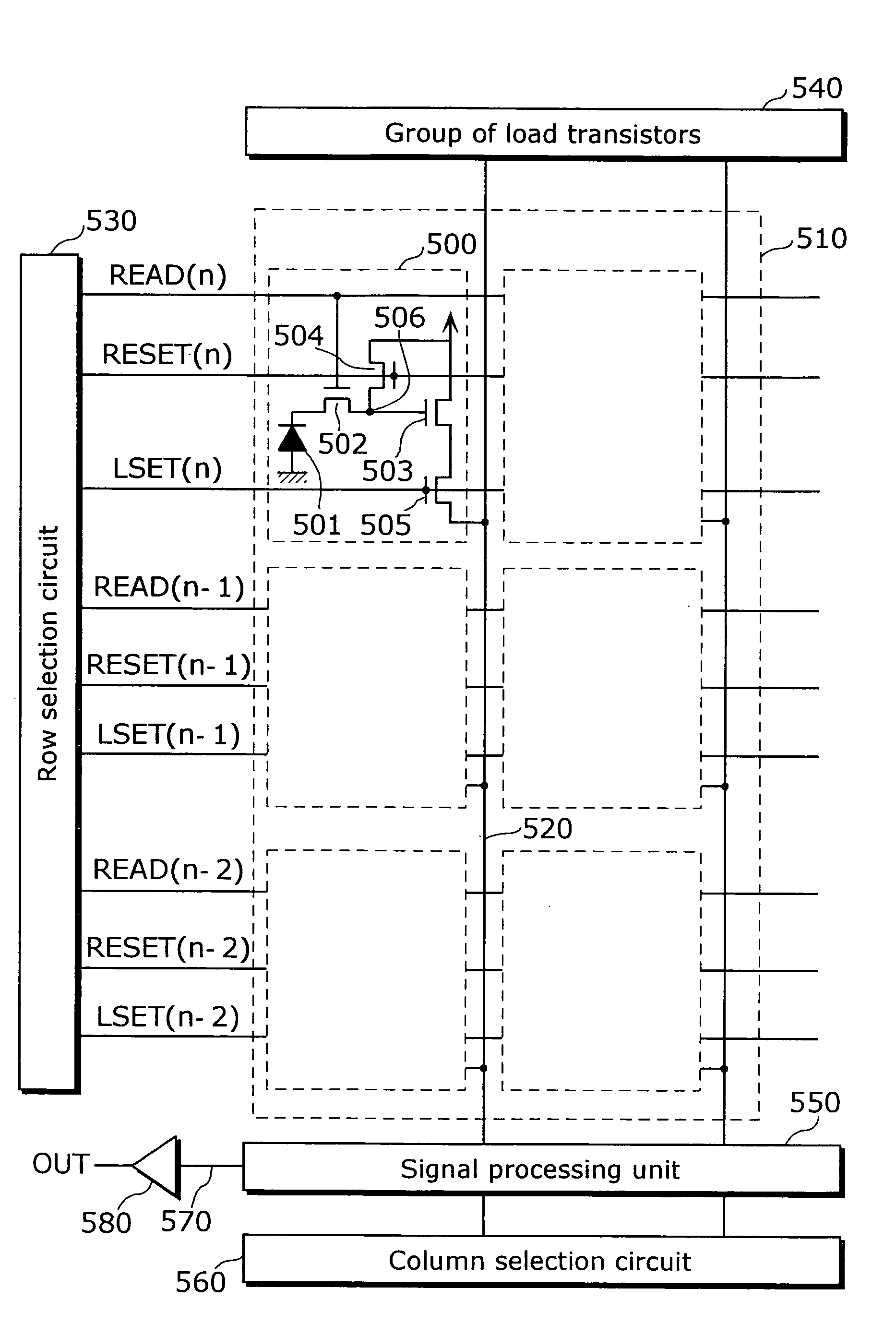

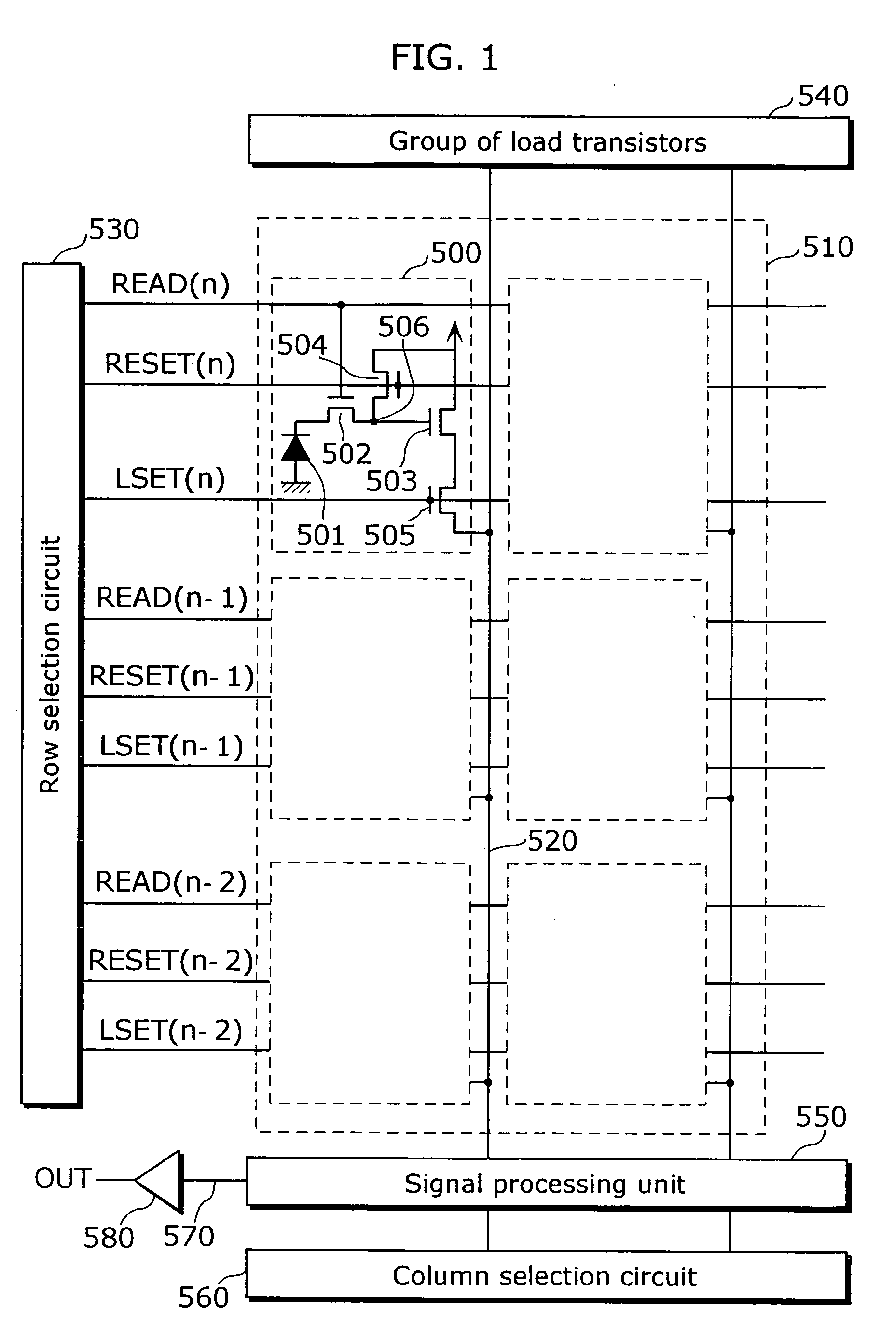

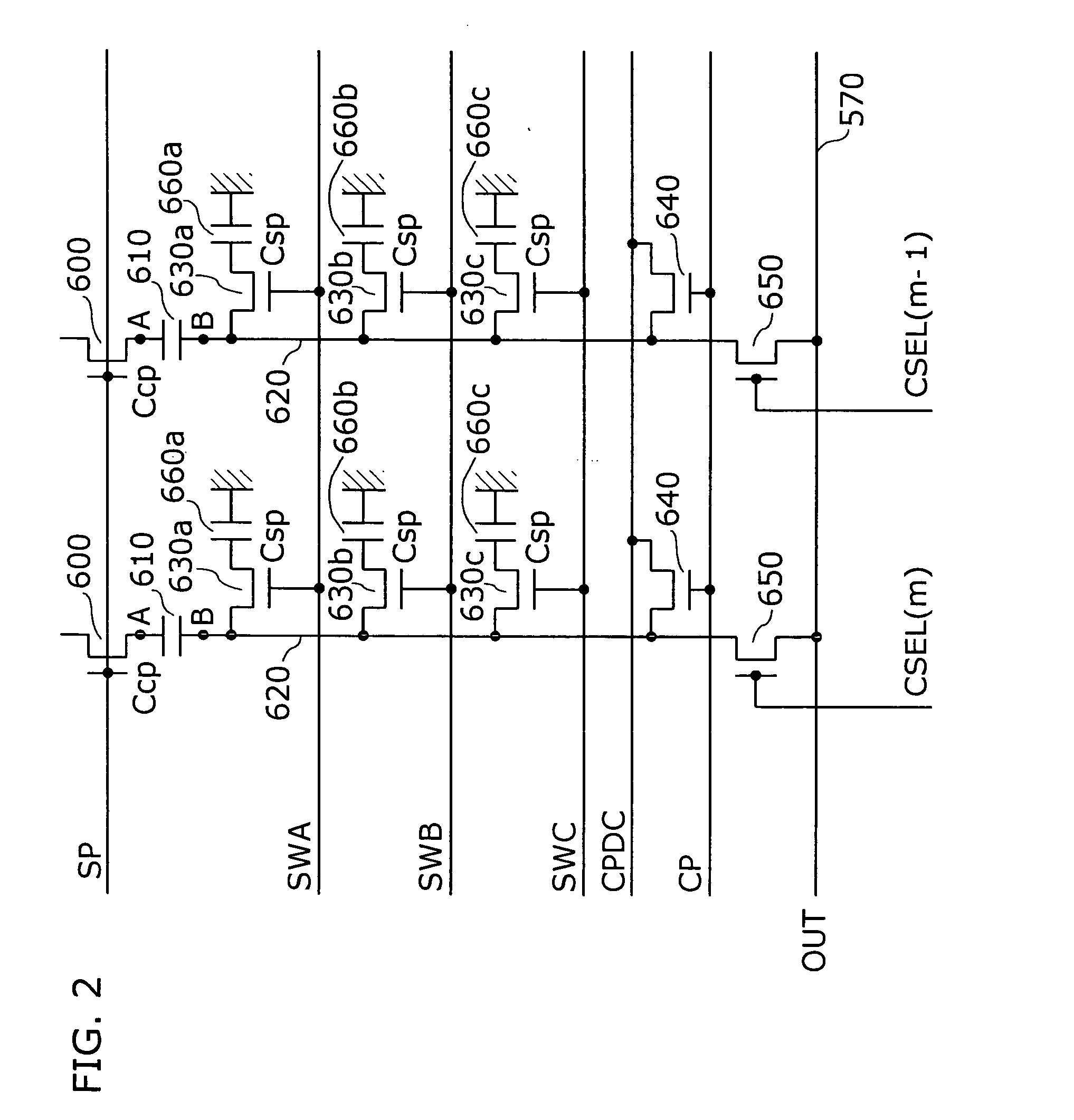

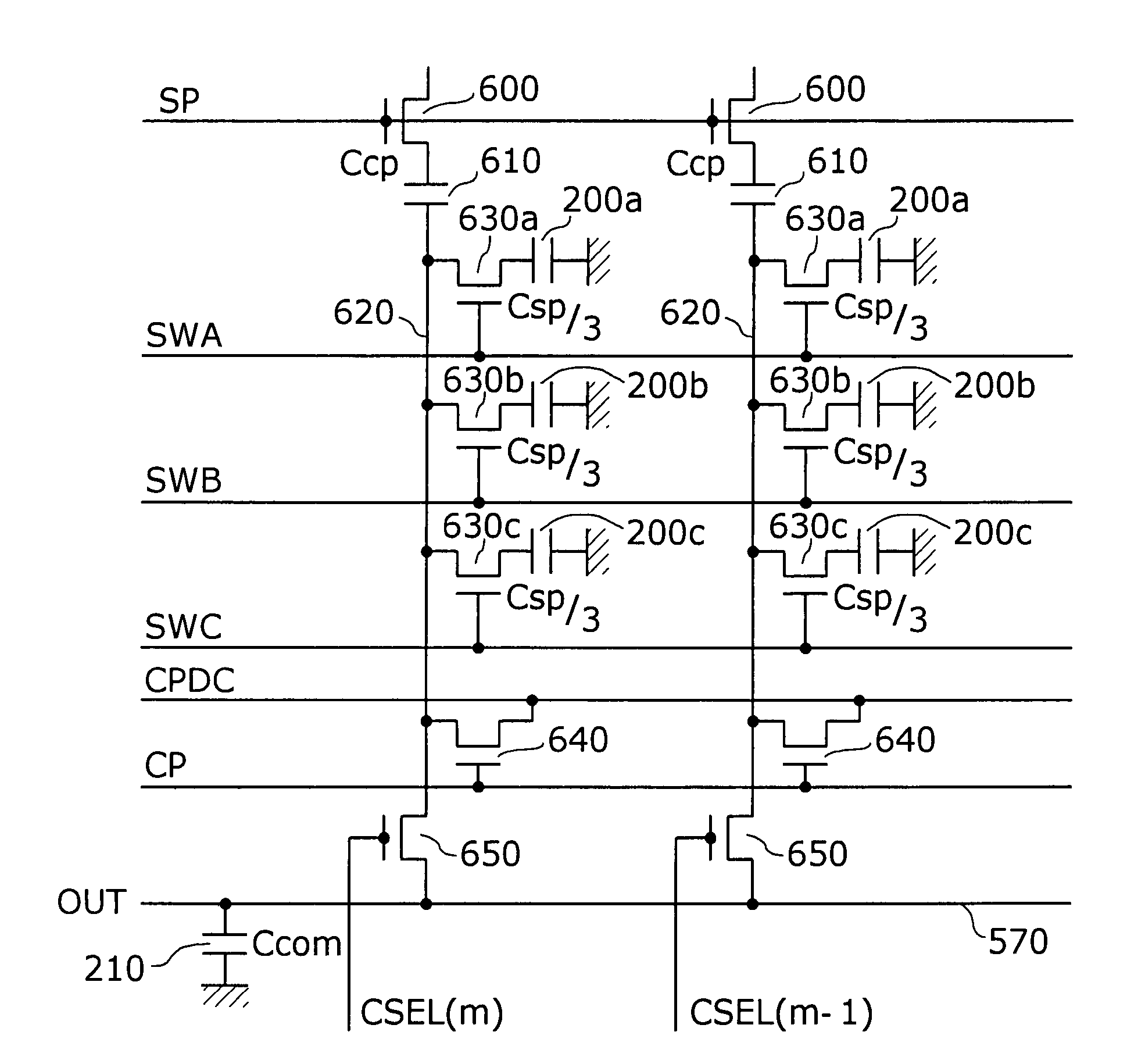

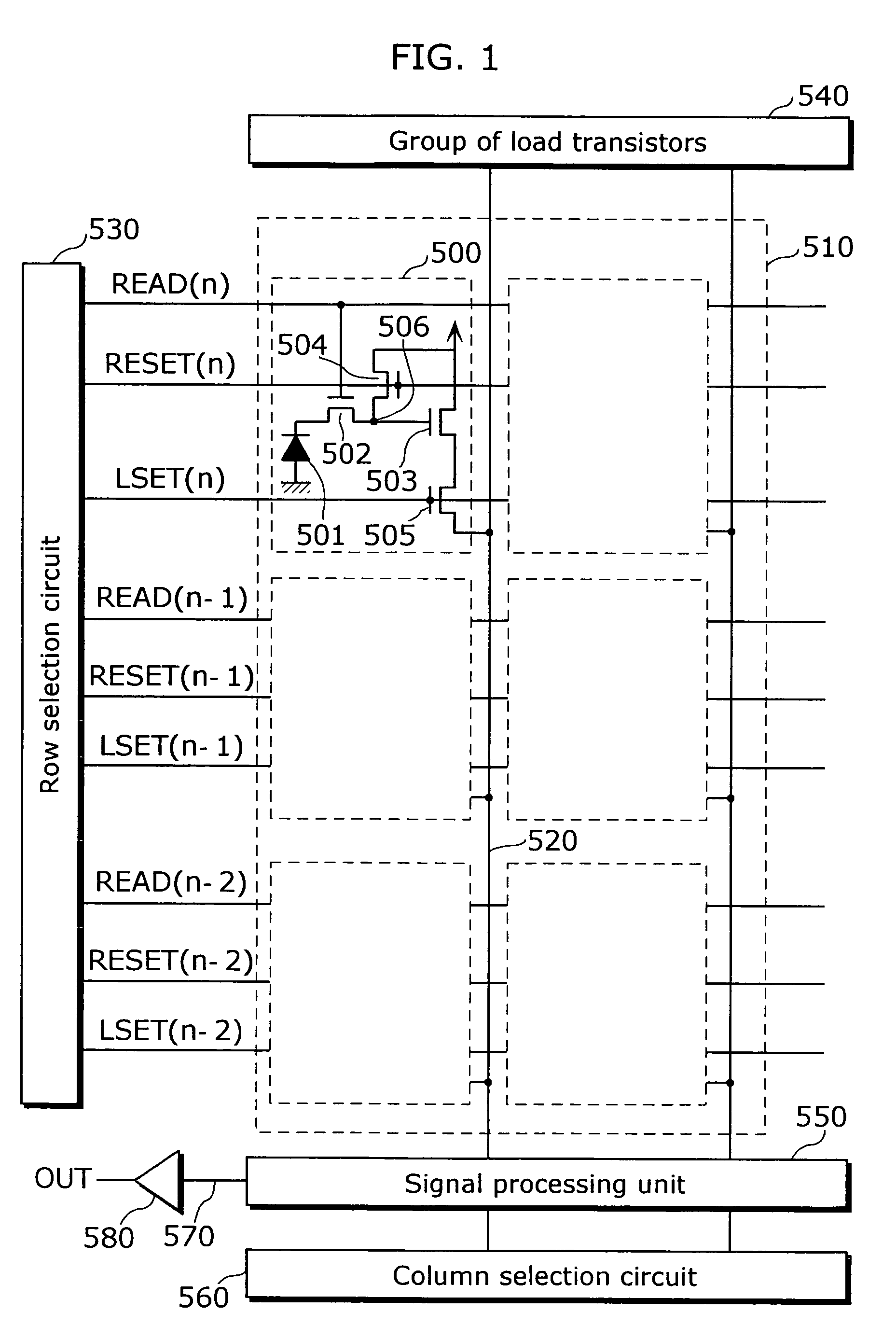

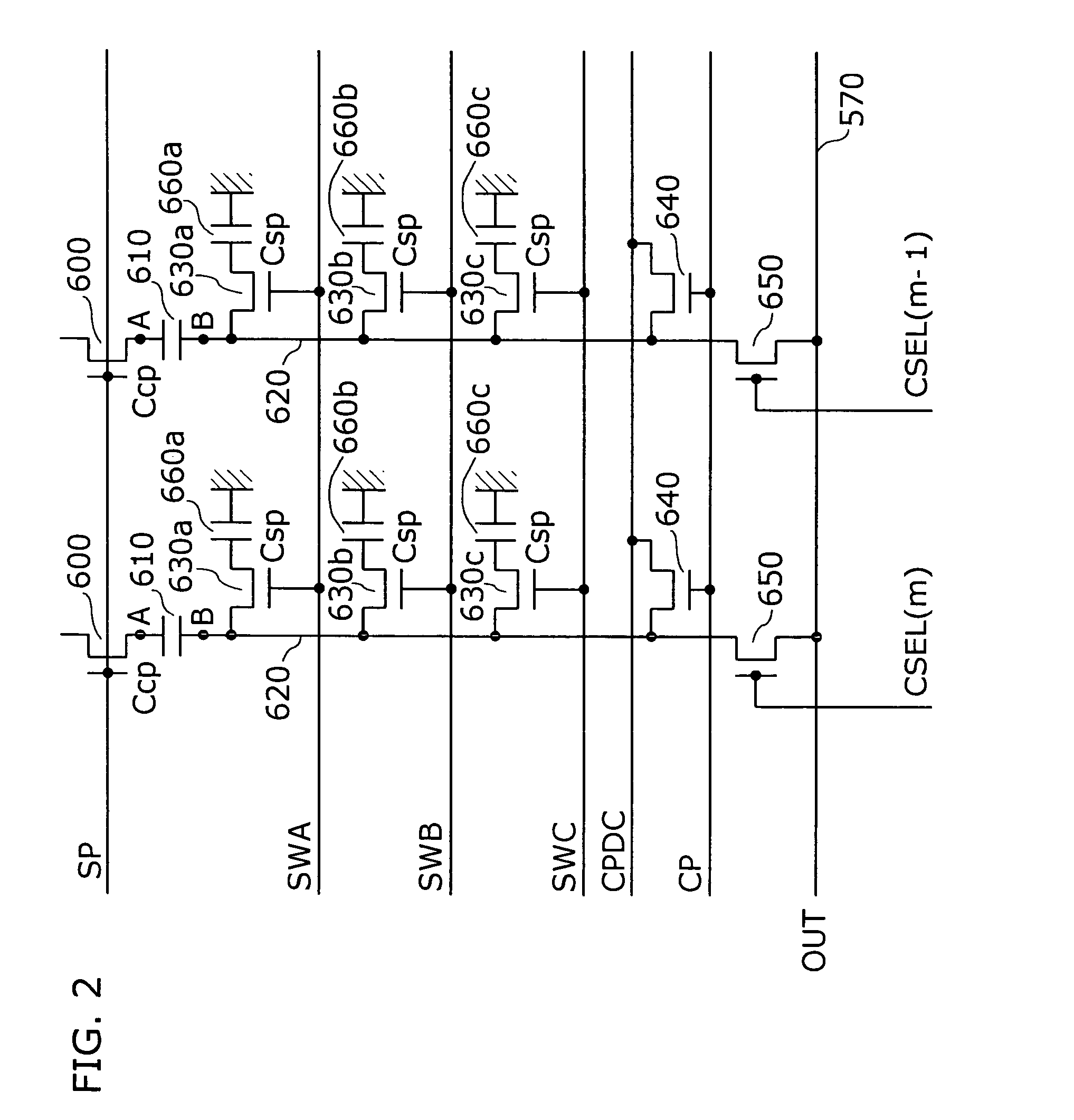

Solid-state image sensing apparatus and driving method thereof

InactiveUS20040183930A1Increase chip areaImprove signal-to-noise ratioTelevision system detailsOther printing matterCapacitanceSignal processing

A solid-state image sensing apparatus which can improve the S / N ratio without enlarging the chip area in both of the mode in which pixel signals are summed and the mode in which pixel signals are not summed is provided. The solid-state image sensing apparatus includes an image sensing region 510 in which a plurality of unit cells 500 is laid out two-dimensionally, the first vertical signal line 520, a row selection circuit 530, a column selection circuit 560, a horizontal signal line 570 and a signal processing unit 100, having a sampling capacitors which accumulate signals corresponding to amplified signals of the unit cells, which selects the case of summing the signals or the case of not summing the signals, wherein the capacitance of the sampling capacitor which accumulates a signal corresponding to an amplified signal of a unit cell for each row when the sum is performed is smaller than the capacitance required for reading out the signal from said capacitor.

Owner:COLLABO INNOVATIONS INC

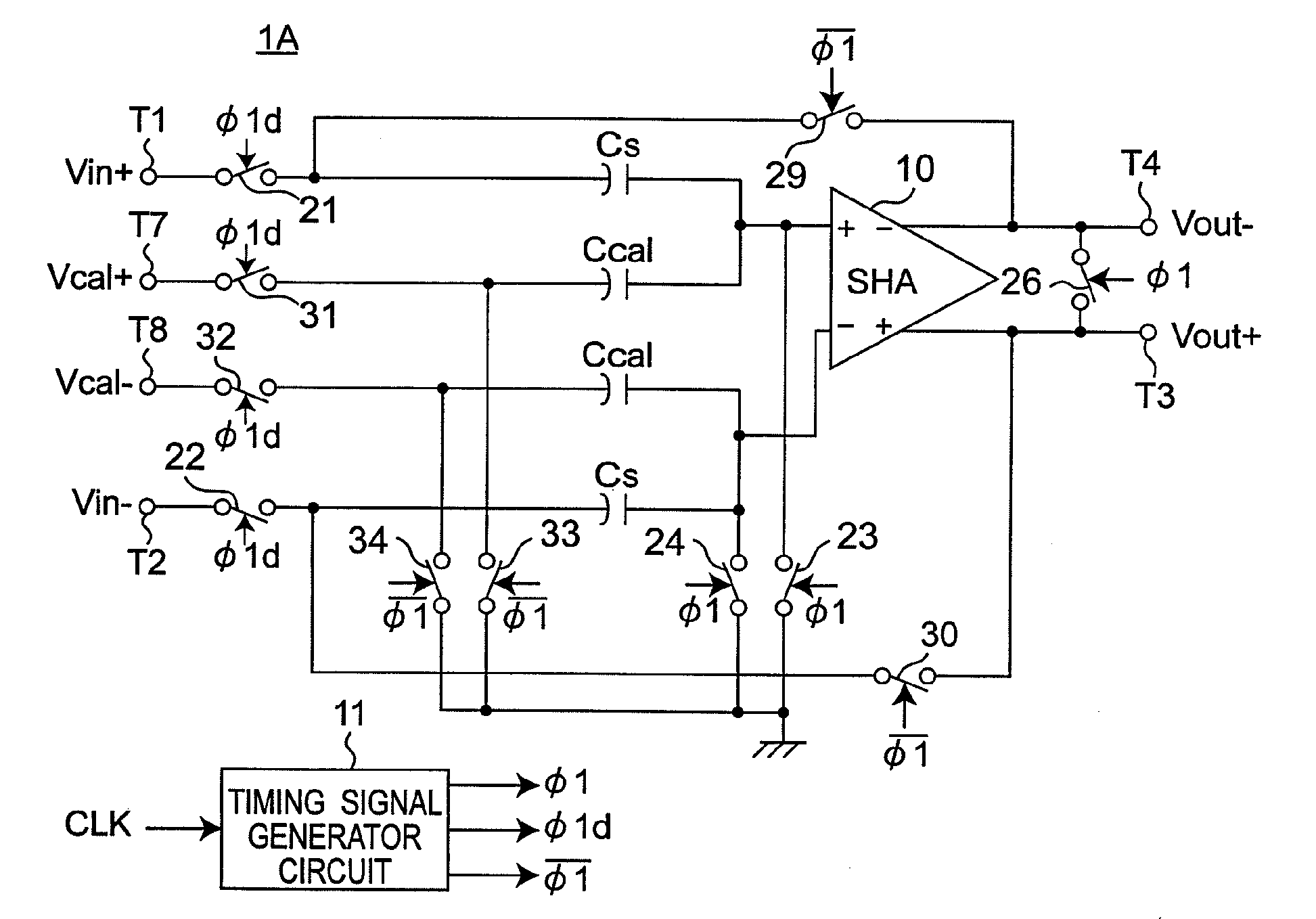

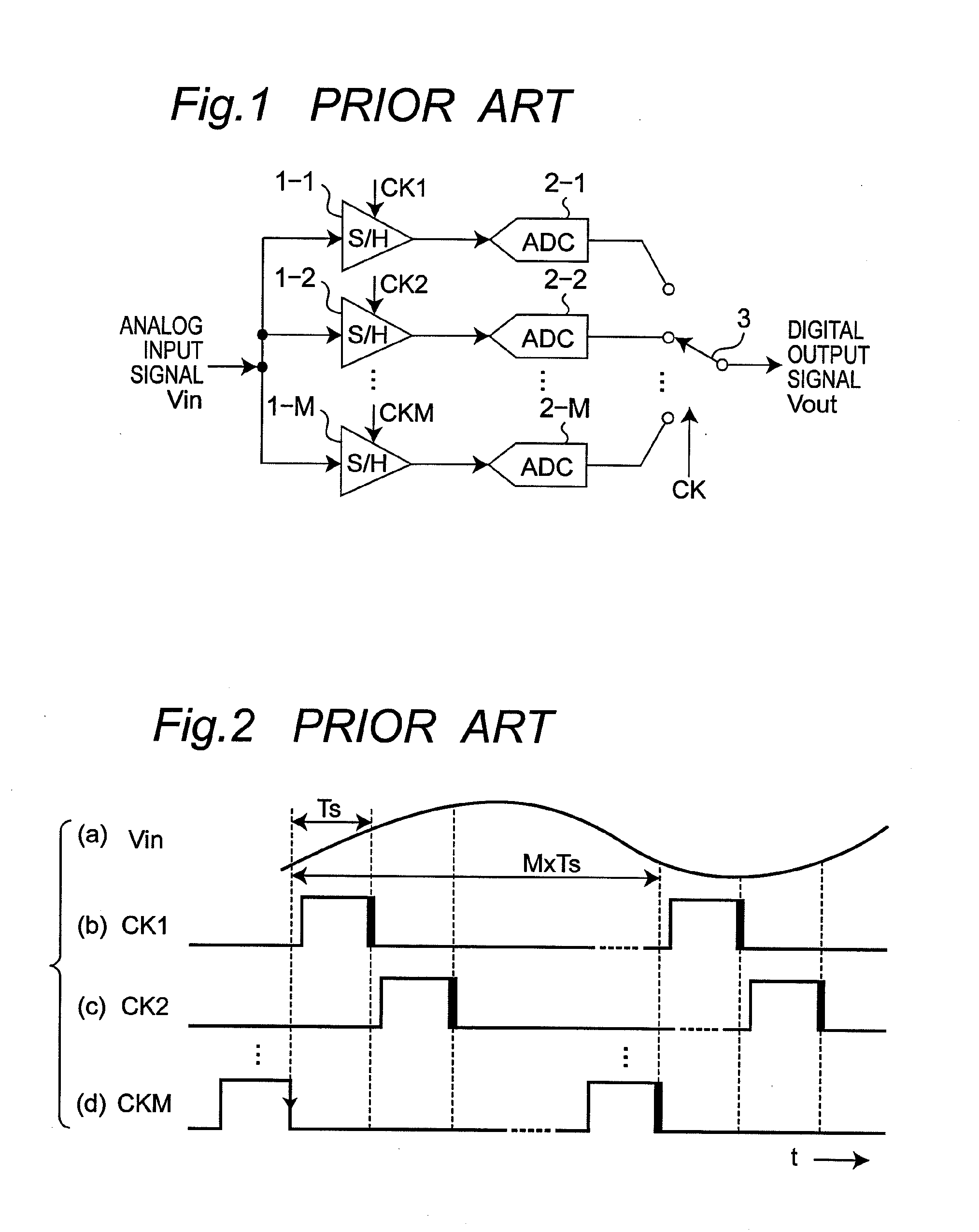

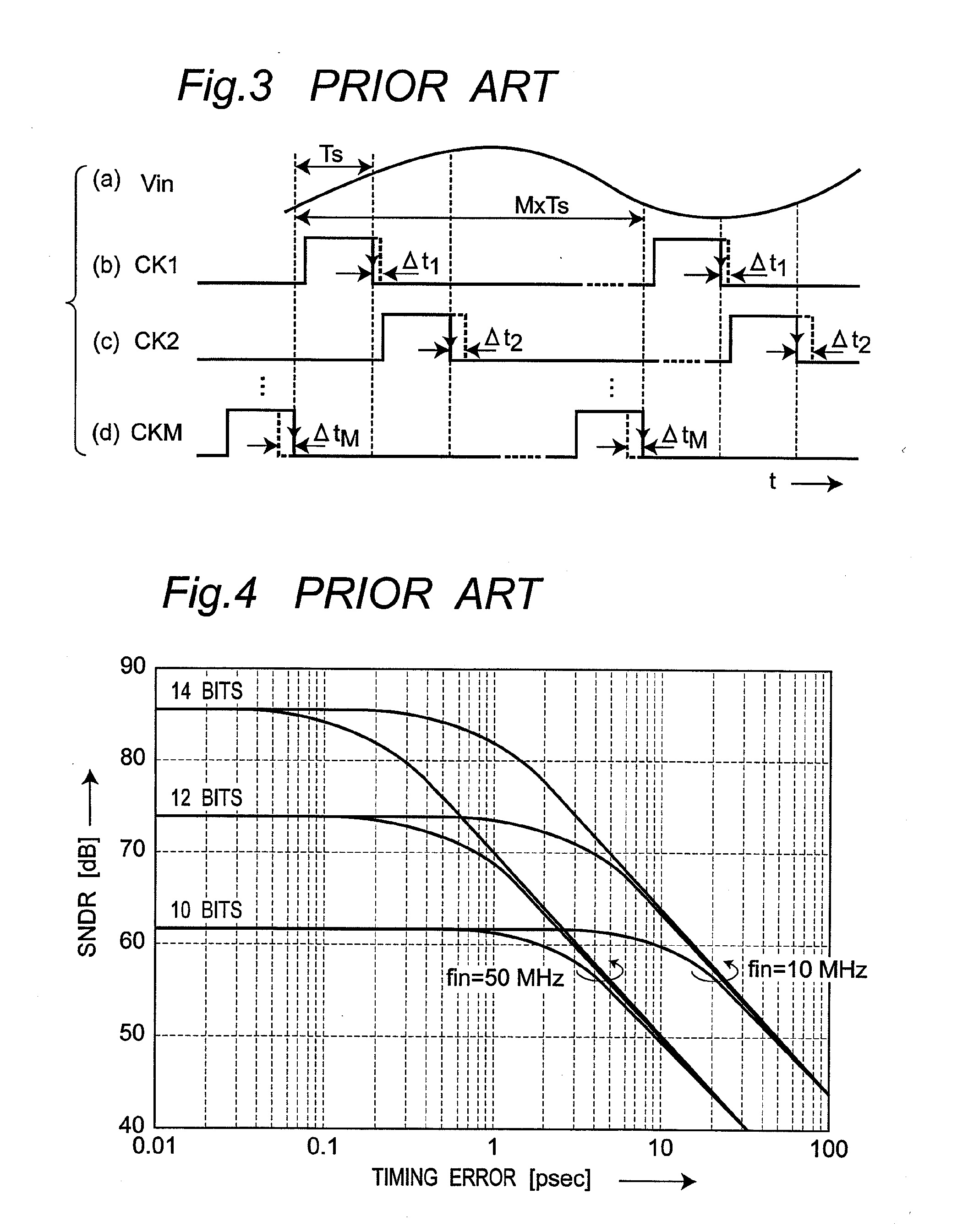

Sample hold circuit for use in time-interleaved a/d converter apparatus including paralleled low-speed pipeline a/d converters

InactiveUS20090278716A1Minimize clock skewIncrease chip areaElectric signal transmission systemsElectric analogue storesCapacitanceAudio power amplifier

A sample hold circuit is provided for use in a time-interleaved A / D converter apparatus including a plurality of low-speed pipeline A / D converters which are parallelized. The sample hold circuit includes a sampling capacitor and a sample hold amplifier, and operates to sample and hold an input signal by using a switched capacitor. An adder circuit of the sample hold circuit adds a ramp calibration signal to the input signal, by inputting the ramp calibration signal generated to have a frequency identical to that of a sampling clock signal and a predetermined slope based on the sampling clock signal, into a sample hold amplifier via a calibration capacitor having a capacitance smaller than that of the sampling capacitor.

Owner:SEMICON TECH ACADEMIC RES CENT

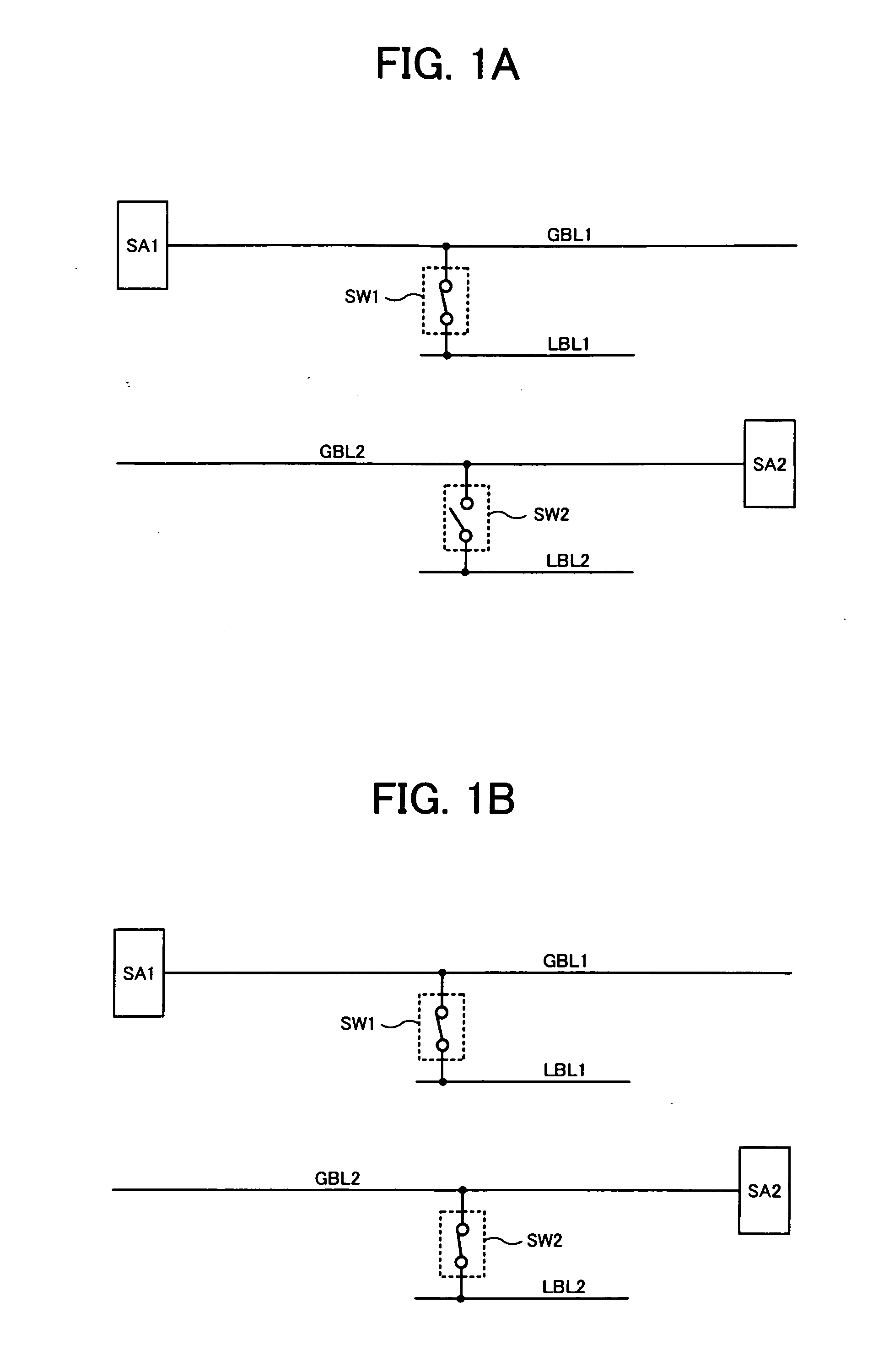

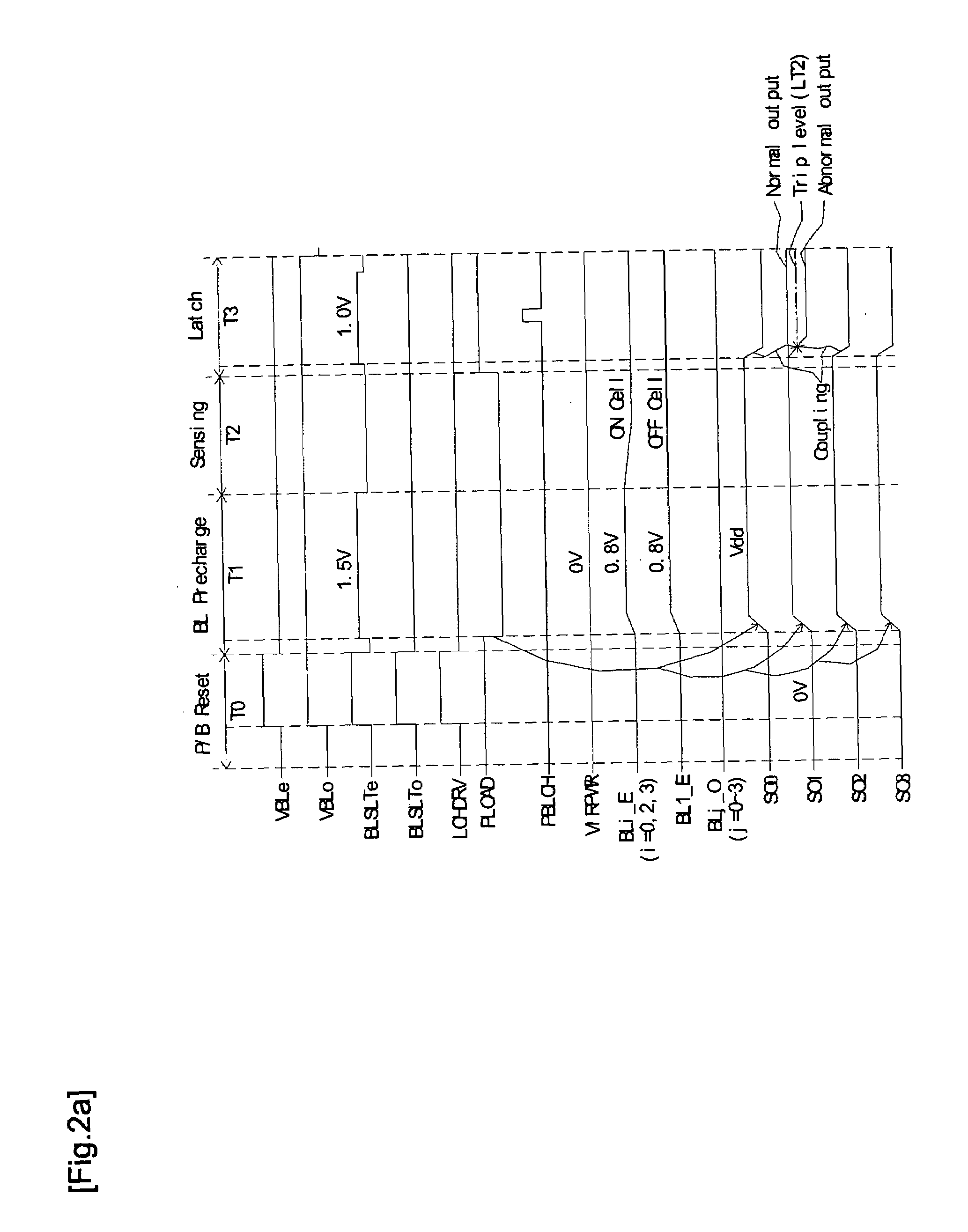

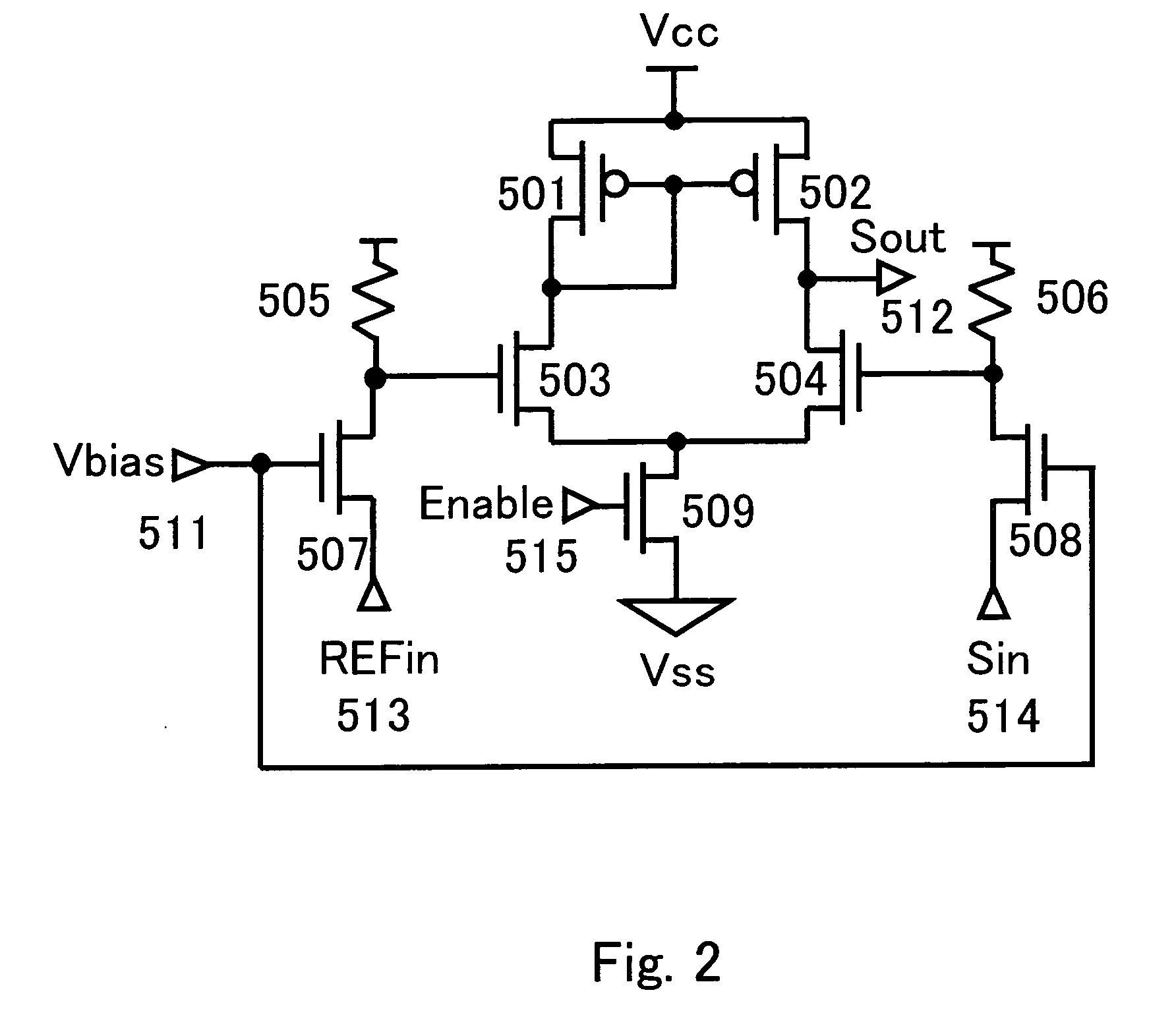

Semiconductor device and control method thereof

InactiveUS20120063241A1Improving sensing margin of senseAvoid influenceDigital storageBit lineAudio power amplifier

Owner:LONGITUDE SEMICON S A R L

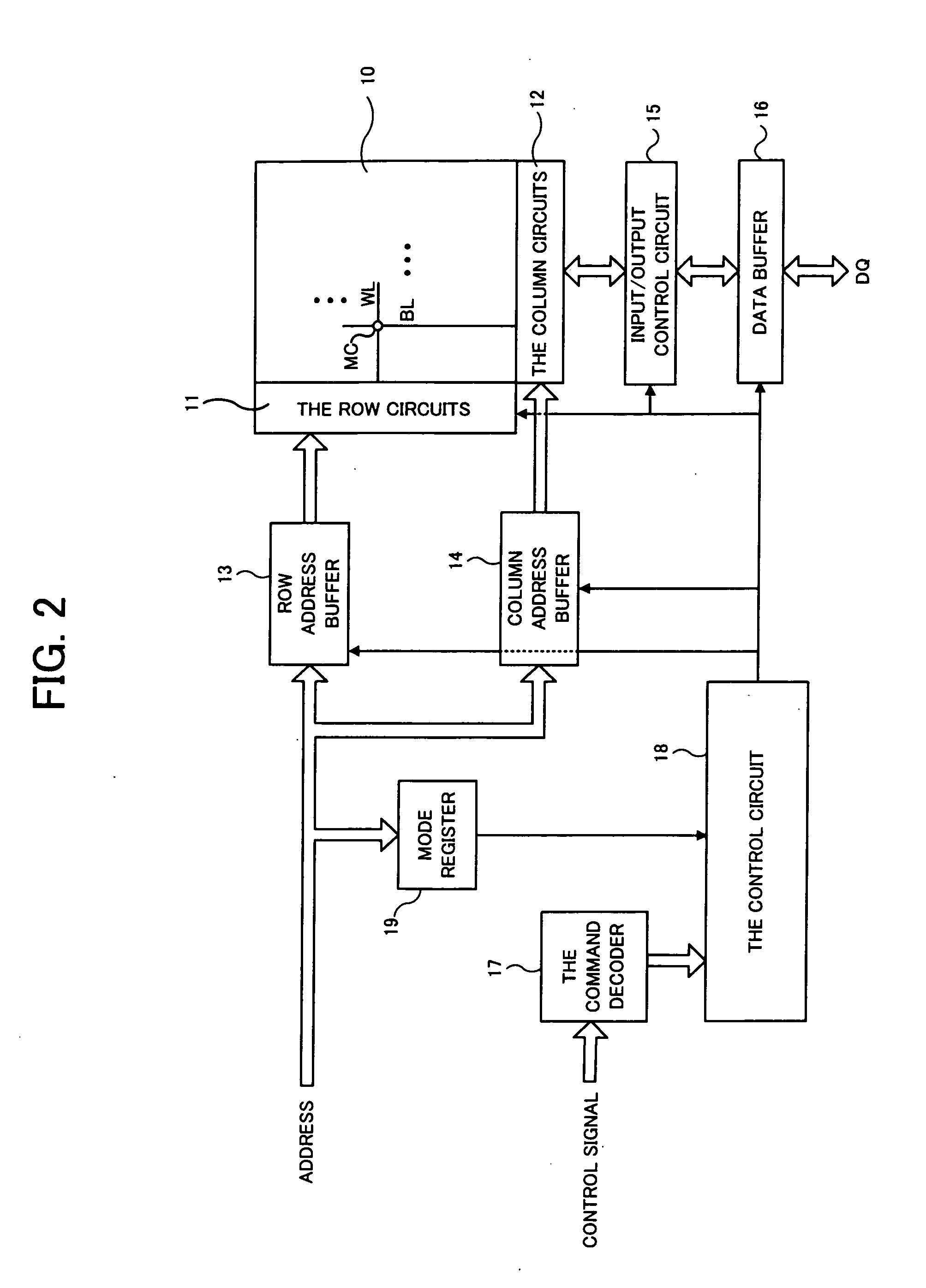

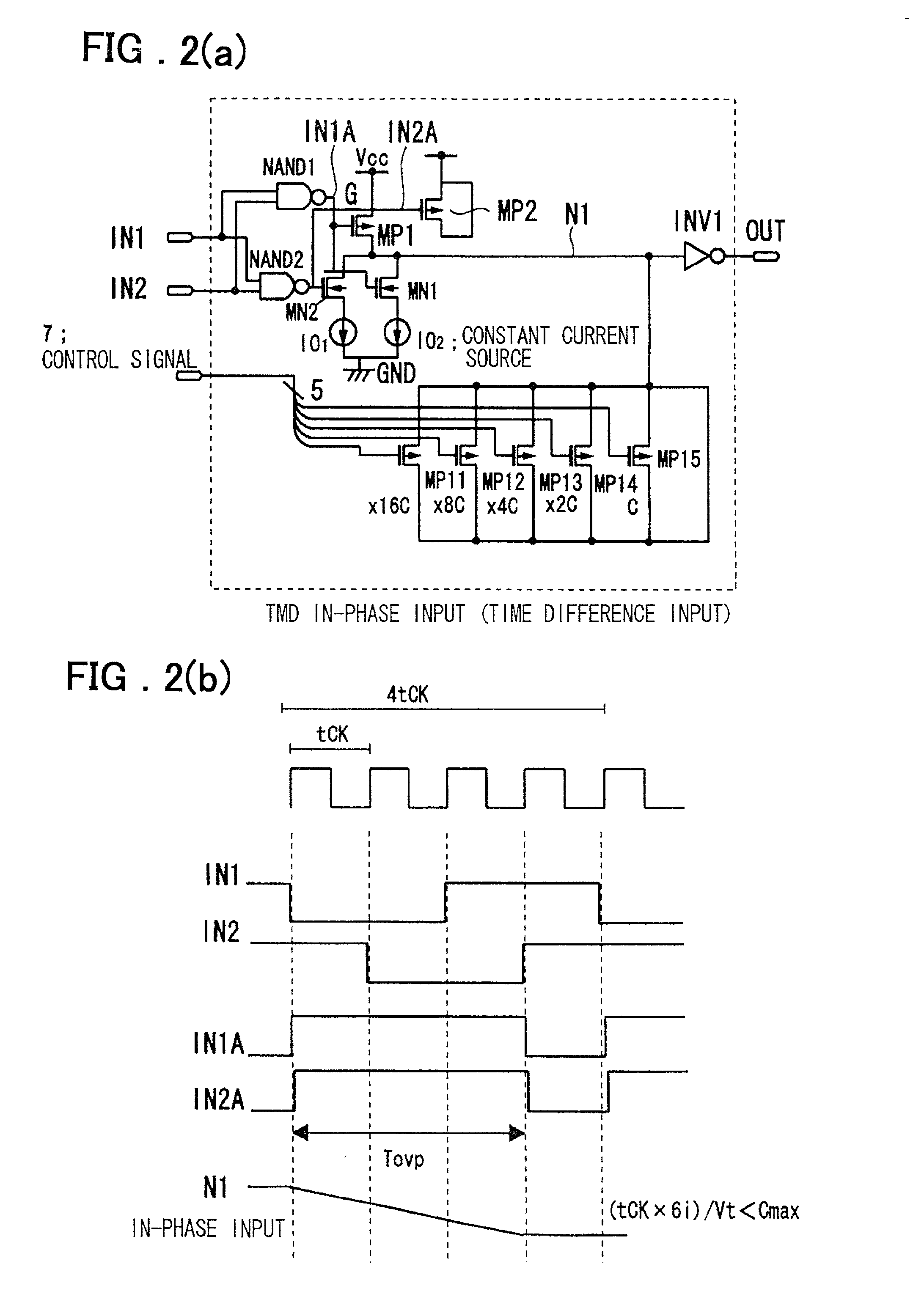

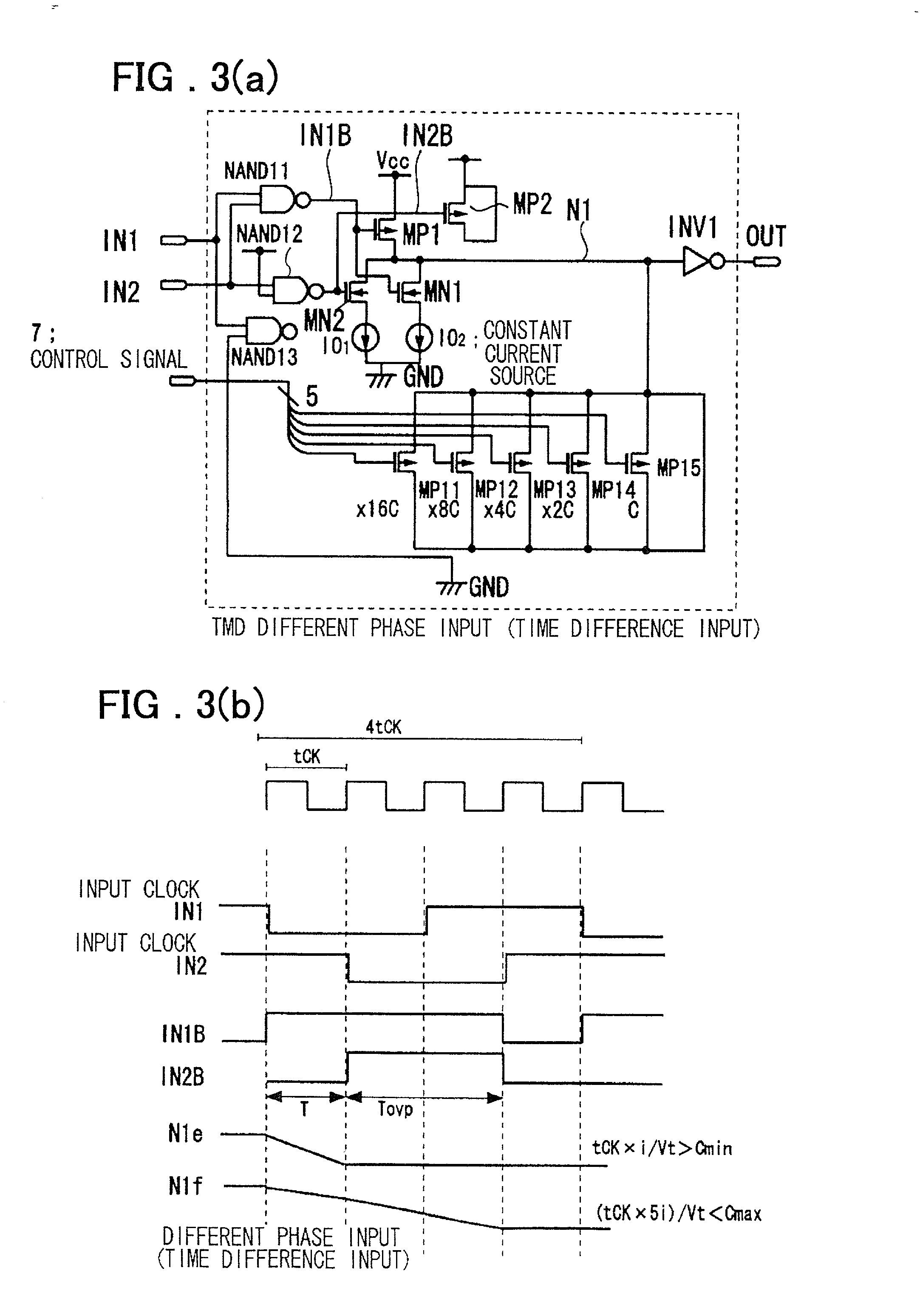

Timing difference division circuit and signal controlling method and apparatus

InactiveUS20010045853A1Increase chip areaHigh speedElectronic switchingSingle output arrangementsCapacitanceControl signal

Timing difference division circuit with a high operating speed and a small area, assuring broadband operation. The circuit includes a logic circuit L1 generating a first gate signal and a second gate signal based on a first input signal and a second input signal, a first switch element connected across a first power source and an inner node and having a control terminal to which is fed the first gate signal, a first series circuit made up of a second switch element and a first constant current source and a second series circuit made up of a third switch element and a second constant current source. The first and second series circuits are connected in parallel across the inner node and the second power source. The first and second gate signals are connected to control terminals of the second and third switches, respectively. The circuit also includes a plurality of MOS capacitors, connection of which to the inner node is separately controlled by a control signal, and a buffer circuit an input end of which is connected to the inner node and the value of an output signal of which is determined based on the relative magnitude of the potential of the inner node and a threshold voltage. An overlap period during which the first and second gate signals output from the logic circuit are both activated to turn on the second and third switch elements is set to an optional value.

Owner:RENESAS ELECTRONICS CORP

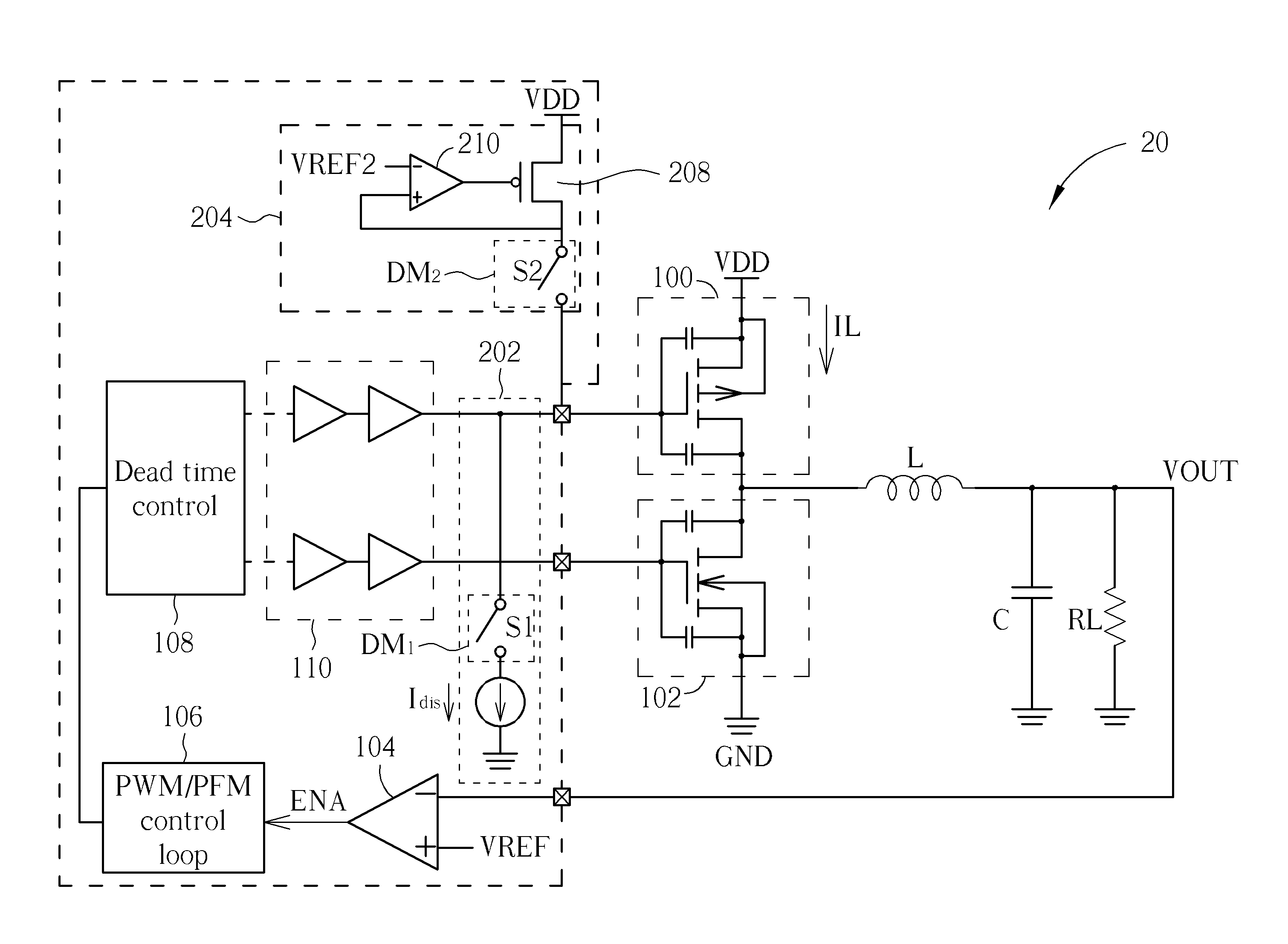

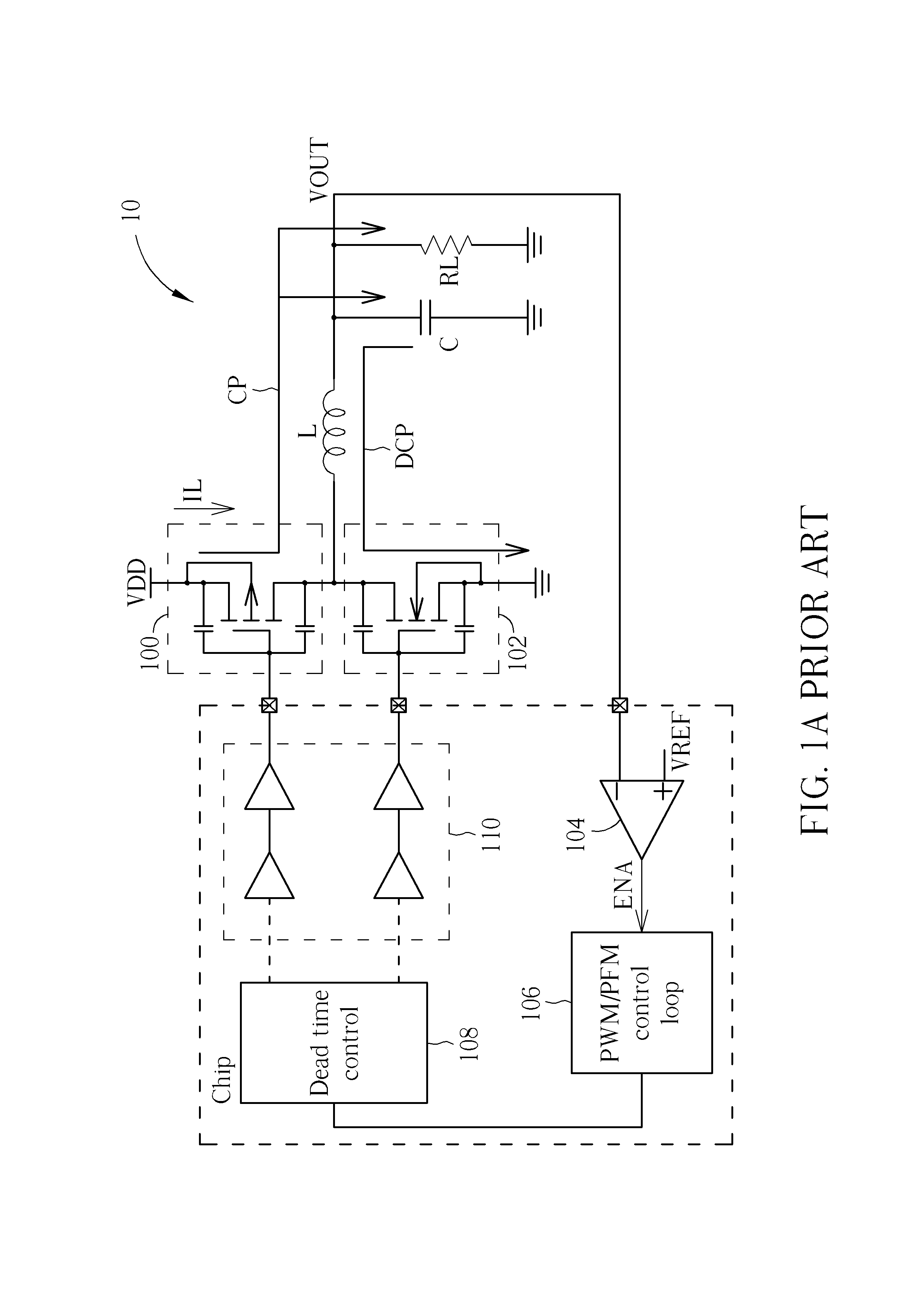

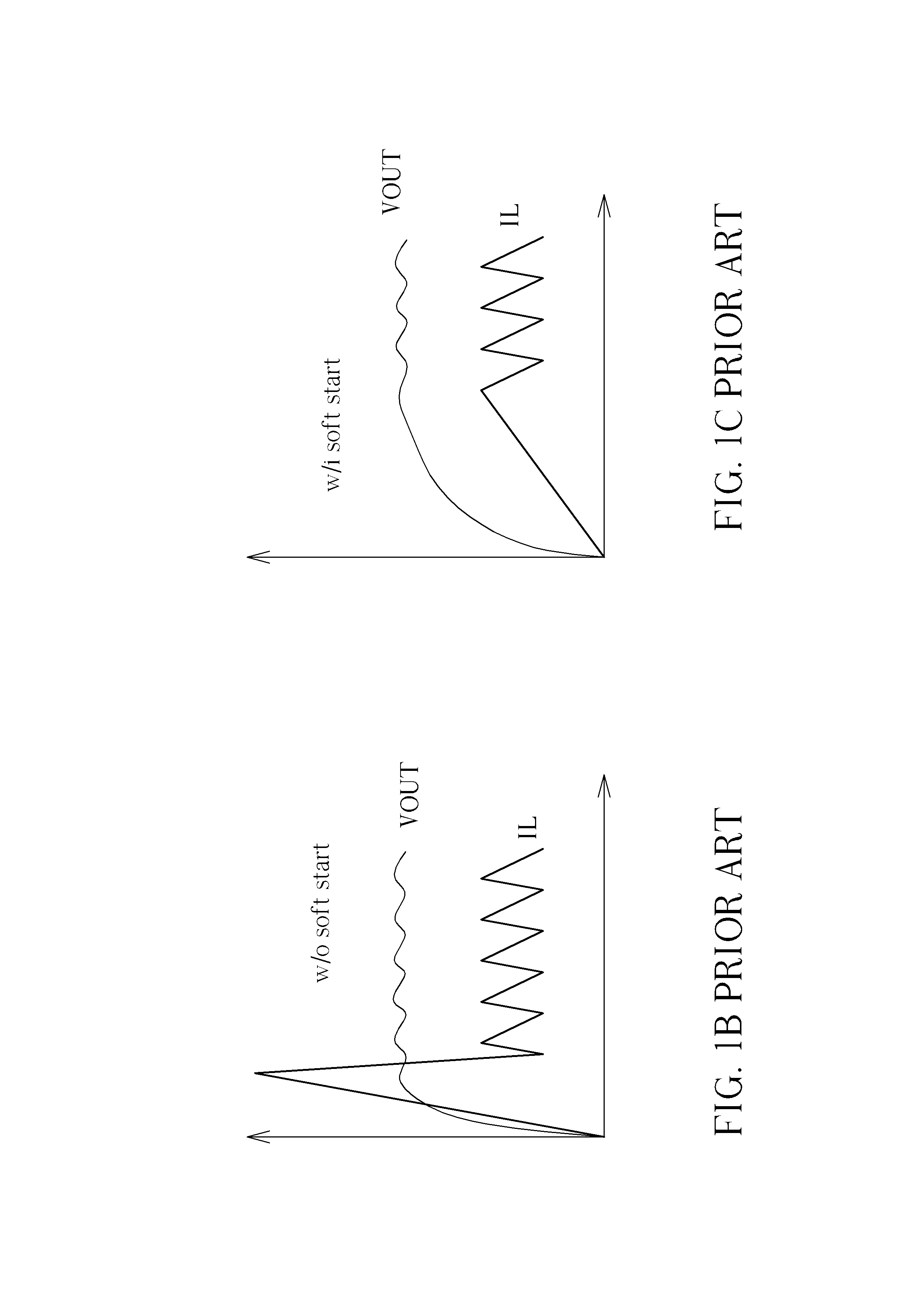

Soft Start Circuit and Power Supply Device Using the Same

InactiveUS20130176008A1Increasing chip areaIncrease chip areaEfficient power electronics conversionDc-dc conversionCurrent sourceDischarge current

The present invention discloses a soft start circuit for a power supply device comprising an external P-type transistor for charging an output capacitor to provide an output voltage. The soft start circuit includes a current source, for providing a discharge current; and a disabling means, coupled to the current source, for discharging an equivalent total parasitic capacitor of the external P-type transistor during an activation period according to the discharge current.

Owner:RALINK TECHNOLOGY CORP

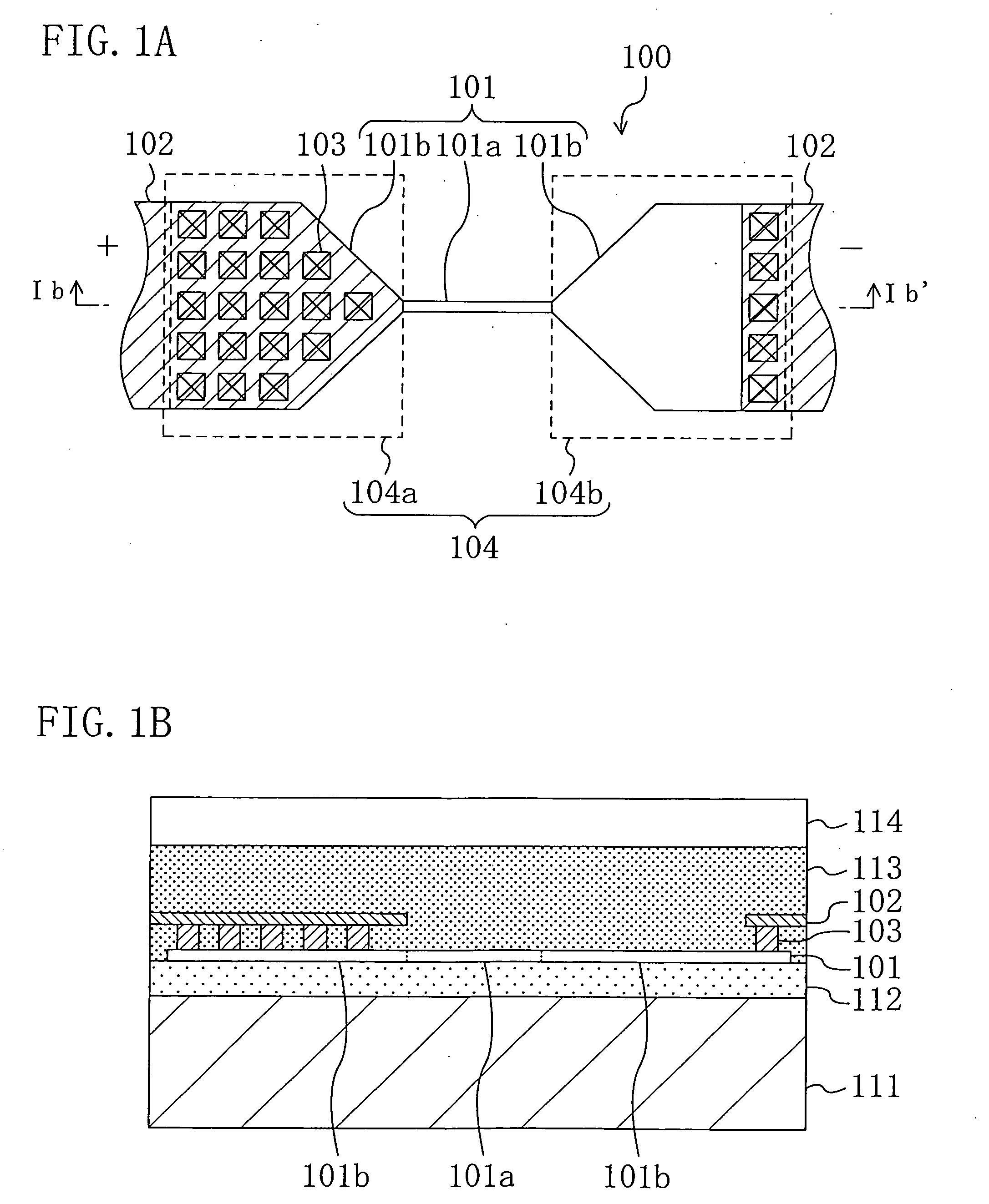

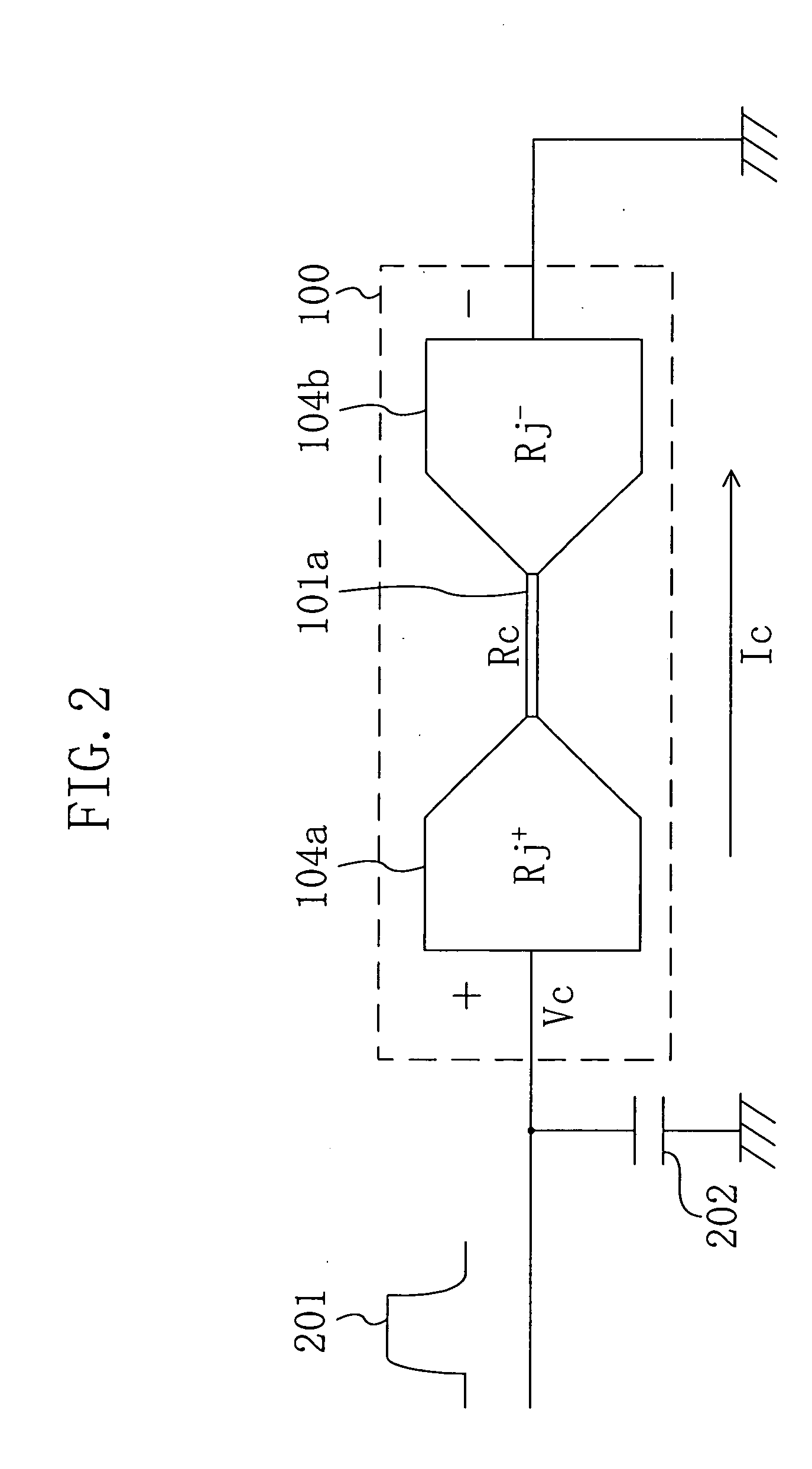

Fuse and write method for fuse

InactiveUS20050274966A1Increase cell areaTotal current dropSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceCurrent limiting

A polysilicon fuse includes a fusing part to be fused through voltage application, a positive terminal side joint connected to one end of the fusing part and a negative terminal side joint connected to the other end of the fusing part. The positive terminal side joint that attains a high voltage through the voltage application has lower resistance and higher heat conductivity than the negative terminal side joint. Furthermore, a write operation is performed, with a current limiting resistance serially connected to a positive terminal side joint of a polysilicon fuse, by applying a voltage pulse to the polysilicon fuse through the current limiting resistance. Thus, a current flowing to the polysilicon fuse in fusing the fusing part is limited to a given range.

Owner:PANASONIC CORP

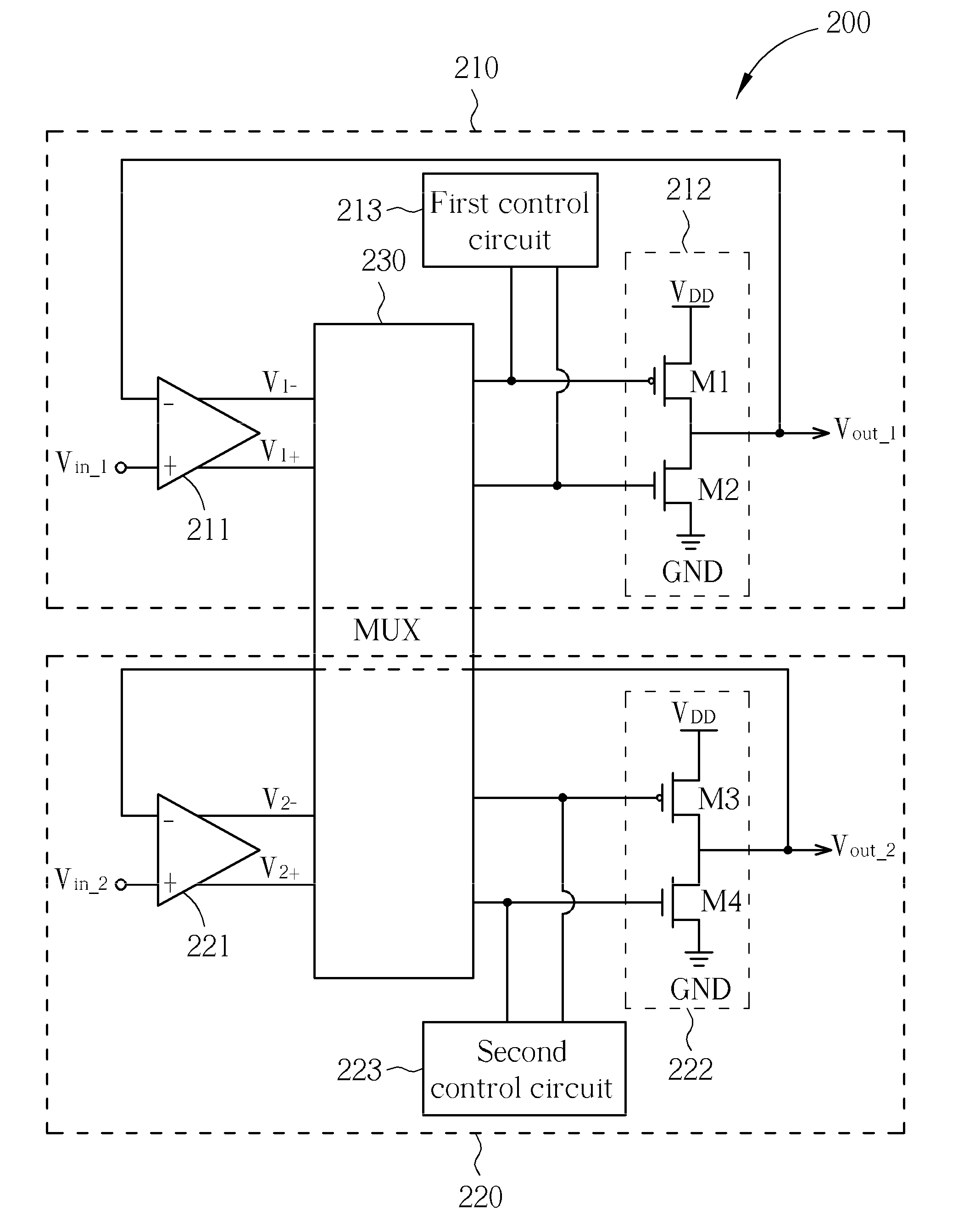

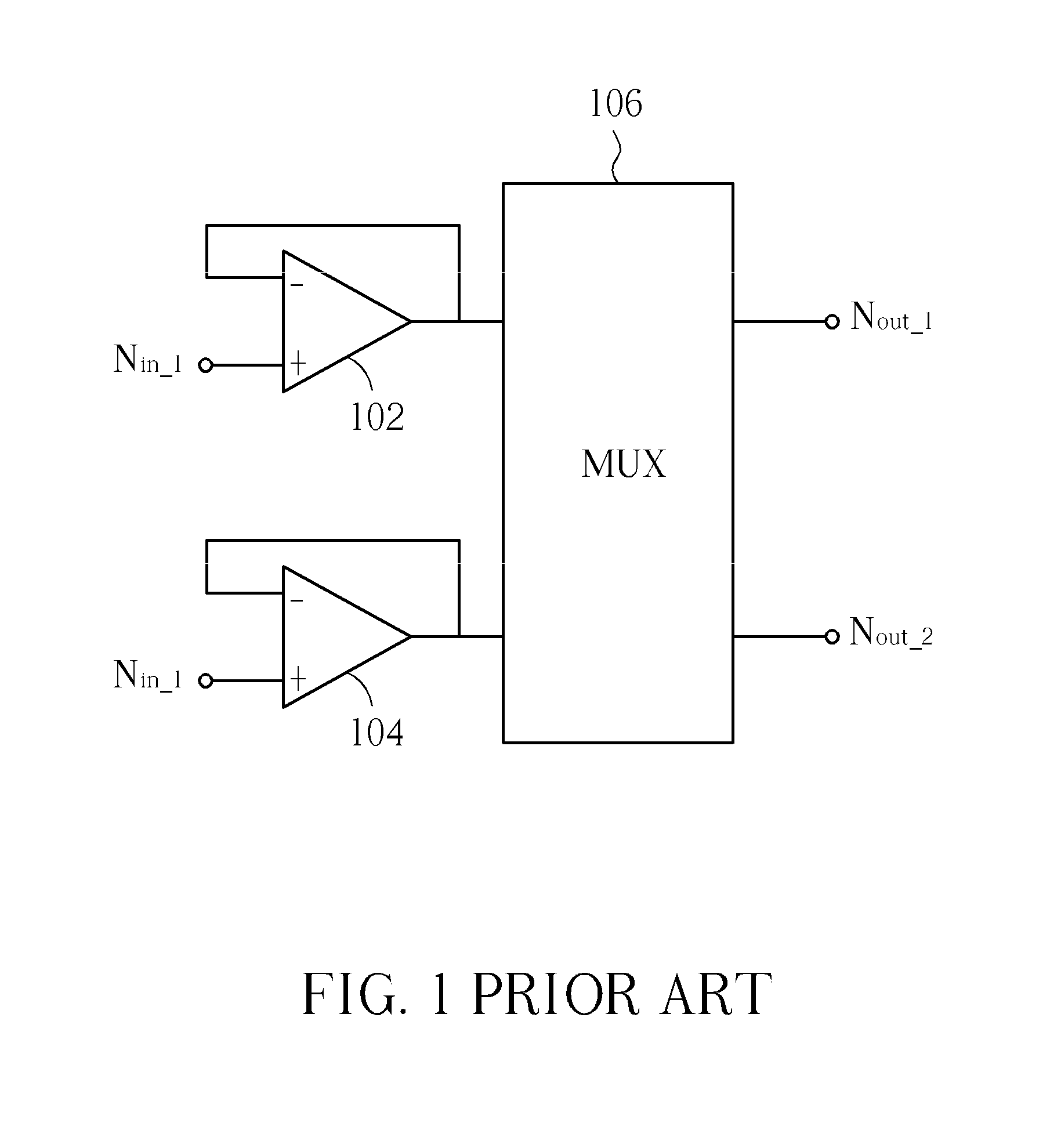

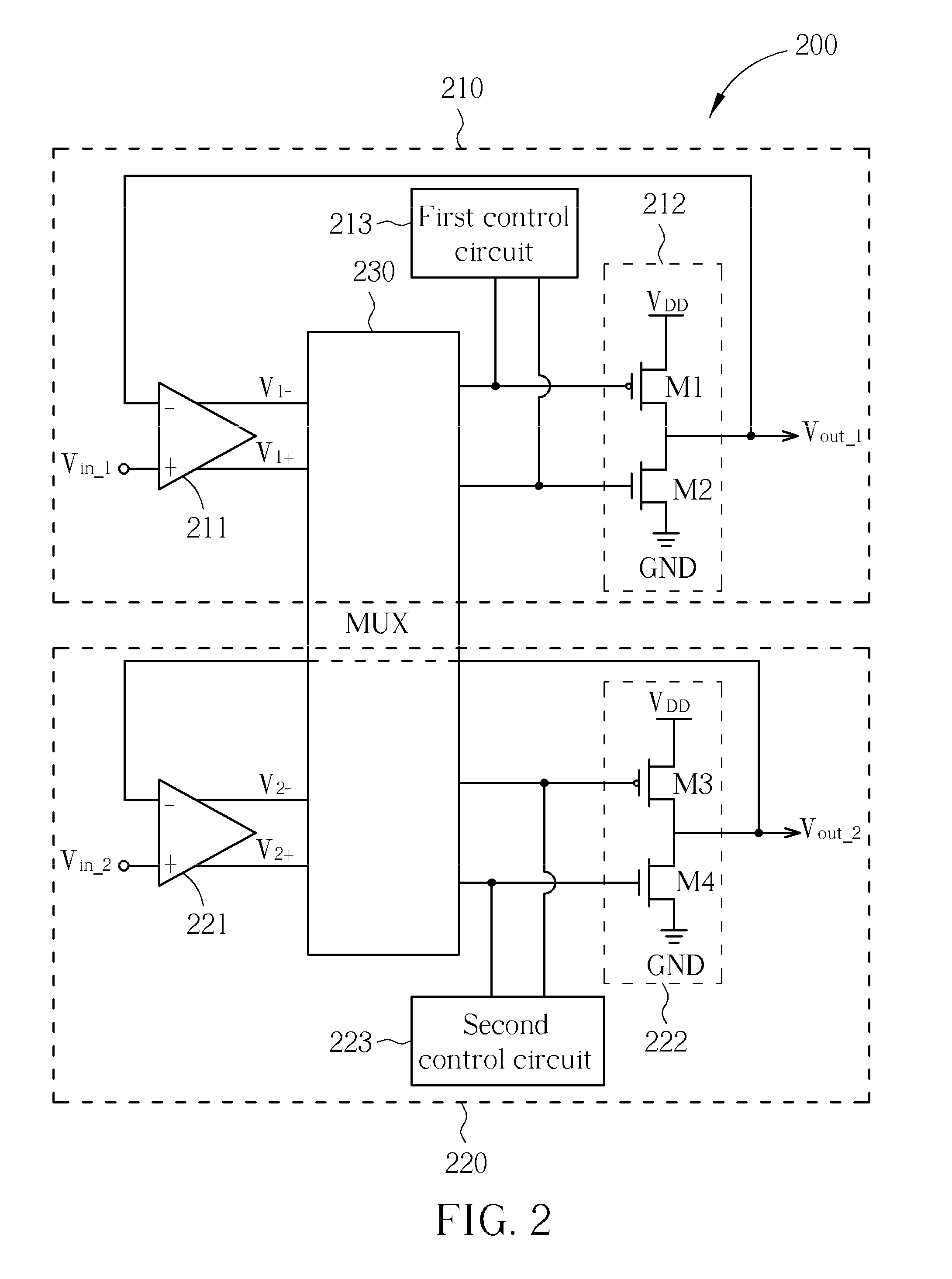

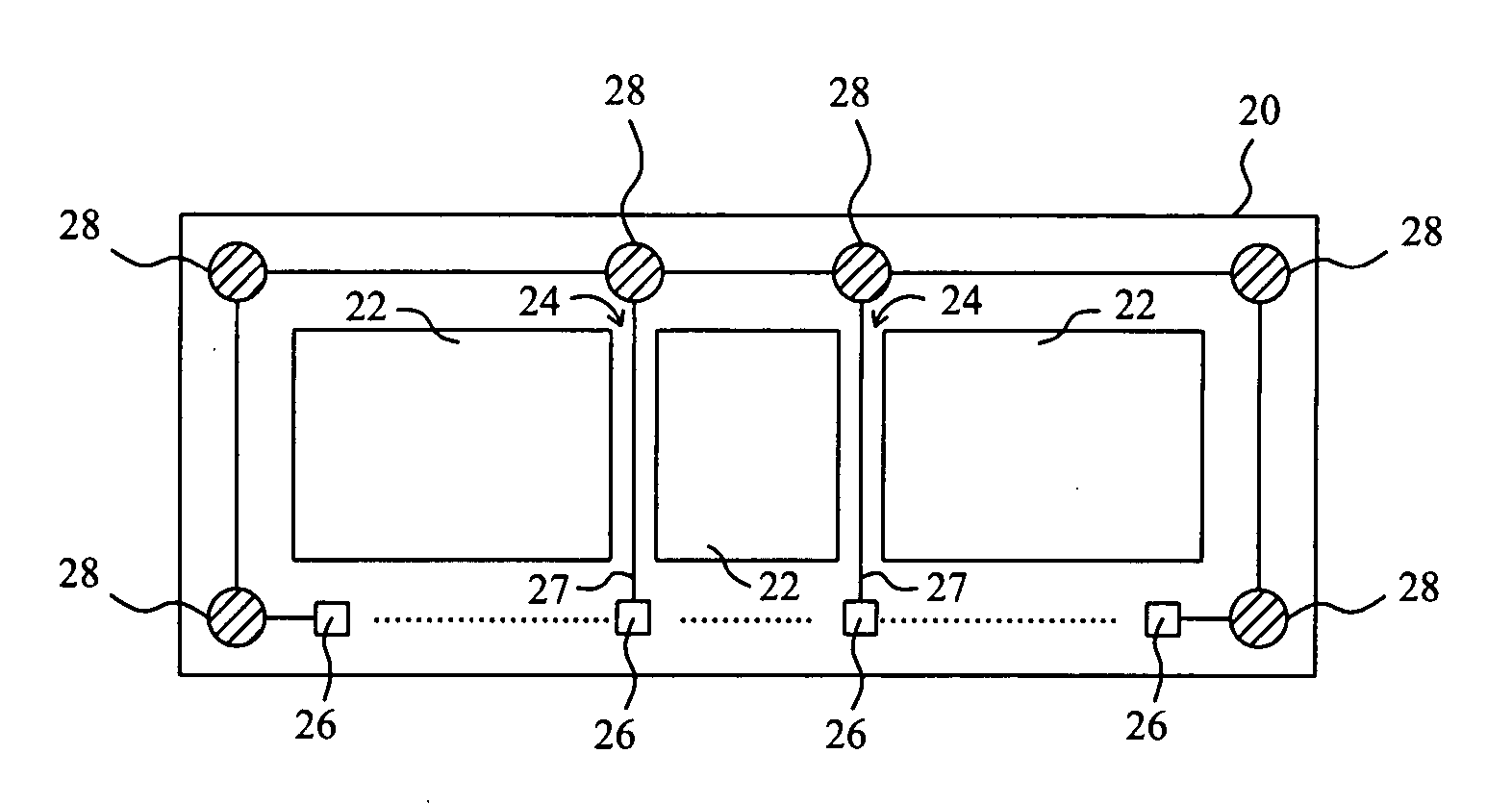

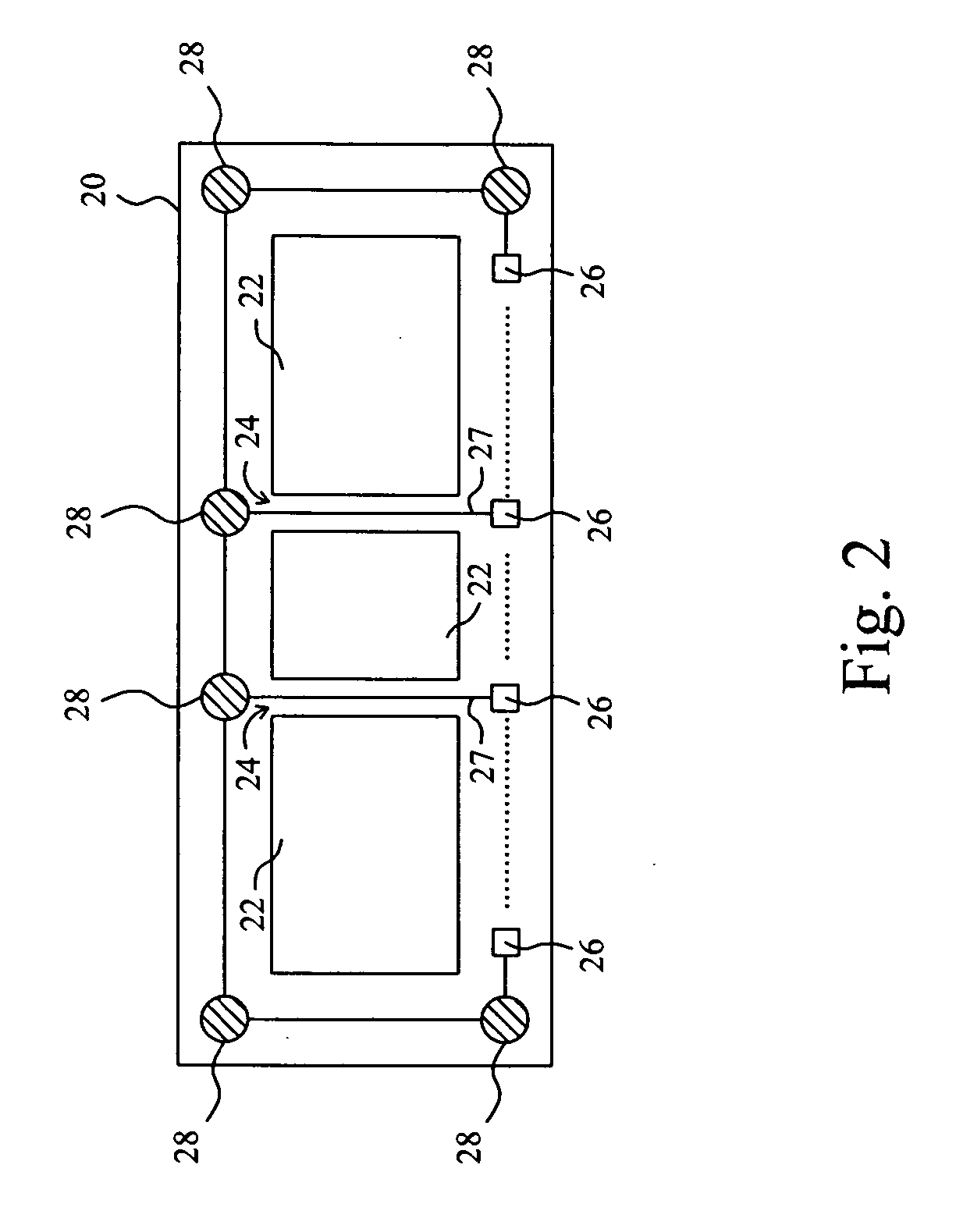

Source driver and associated driving method

ActiveUS20110157150A1Improve drivabilityIncrease chip areaGated amplifiersAmplifier combinationsMultiplexerEngineering

A source driver includes a first differential amplifier, a first output stage, a second differential amplifier, a second output stage and a multiplexer. The first differential amplifier is utilized for receiving a first differential input signal pair to generate a first differential output signal pair. The second differential amplifier is utilized for receiving a second differential input signal pair to generate a second differential output signal pair. The multiplexer couples the first differential amplifier to the first output stage and couples the second differential amplifier to the second output stage under a first configuration, and couples the first differential amplifier to the second output stage and couples the second differential amplifier to the first output stage under a second configuration.

Owner:HIMAX TECH LTD

Solid-state image sensing apparatus and driving method thereof

InactiveUS7379109B2Increase chip areaImprove signal-to-noise ratioTelevision system detailsOther printing matterCapacitanceEngineering

A solid-state image sensing apparatus which can improve the S / N ratio without enlarging the chip area in both of the mode in which pixel signals are summed and the mode in which pixel signals are not summed is provided. The solid-state image sensing apparatus includes an image sensing region 510 in which a plurality of unit cells 500 is laid out two-dimensionally, the first vertical signal line 520, a row selection circuit 530, a column selection circuit 560, a horizontal signal line 570 and a signal processing unit 100, having a sampling capacitors which accumulate signals corresponding to amplified signals of the unit cells, which selects the case of summing the signals or the case of not summing the signals, wherein the capacitance of the sampling capacitor which accumulates a signal corresponding to an amplified signal of a unit cell for each row when the sum is performed is smaller than the capacitance required for reading out the signal from said capacitor.

Owner:COLLABO INNOVATIONS INC

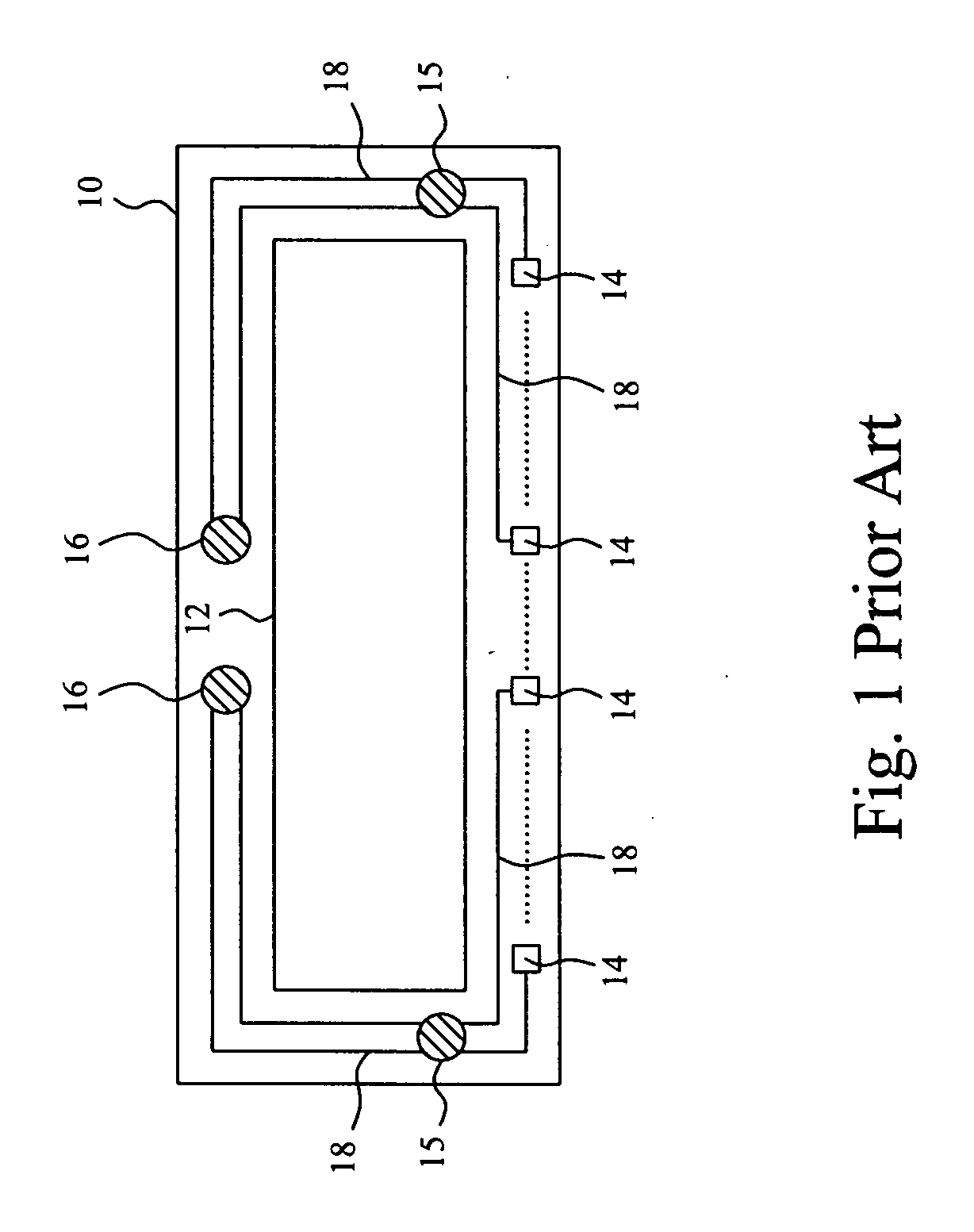

LCD source driver for improving electrostatic discharge

InactiveUS20070057327A1Improve ESD performanceIncrease chip areaSemiconductor/solid-state device detailsSolid-state devicesElectrostatic dischargePower cord

In an LCD source driver, to enhance the ESD performance thereof, there is provided a path in a device area penetrating thereacross such that an internal power wire or an internal ground wire to connect between an output pad and a power-rail ESD clamp circuit on two margins, respectively, of the LCD source driver could pass through the path to shorten the internal power wire or the internal ground wire and thereby to avoid chip area increase for the ESD mechanism.

Owner:ELAN MICROELECTRONICS CORPORATION

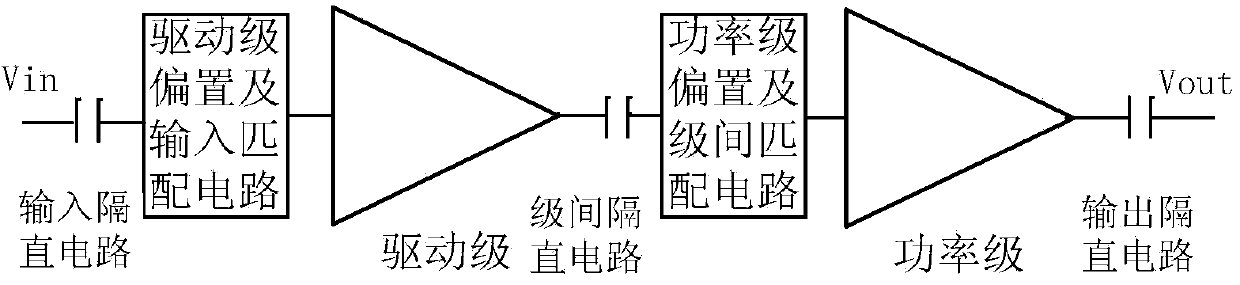

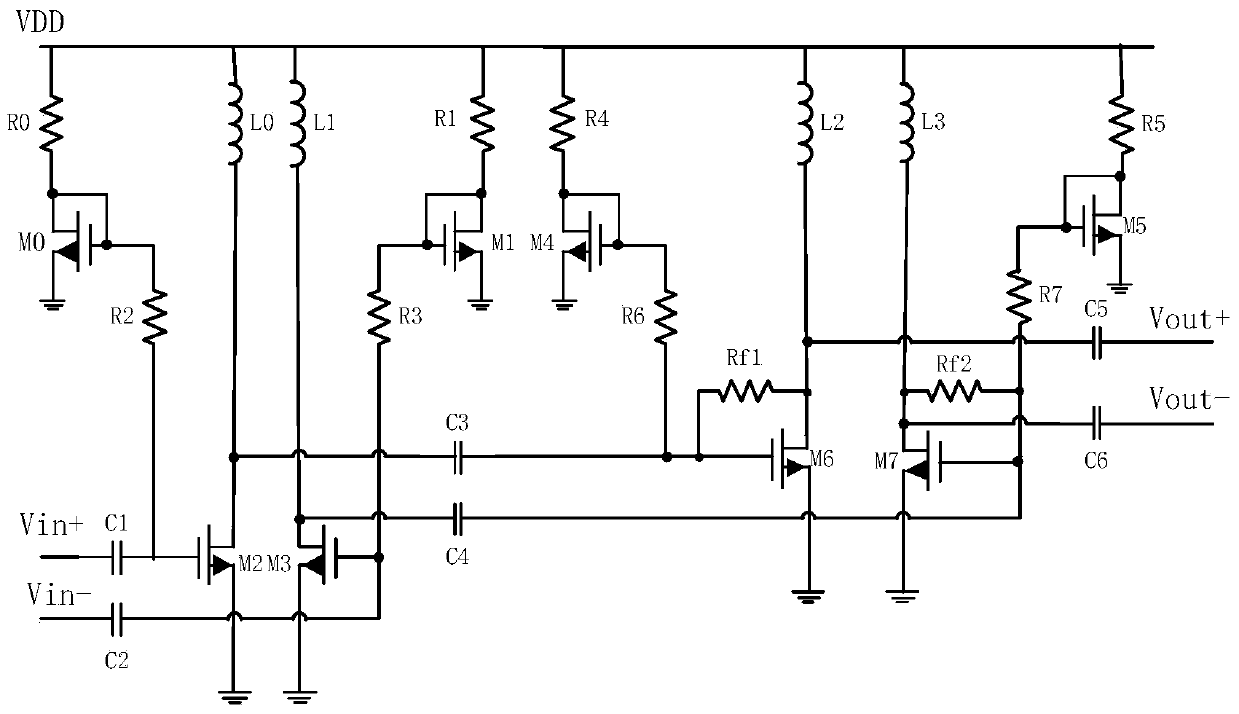

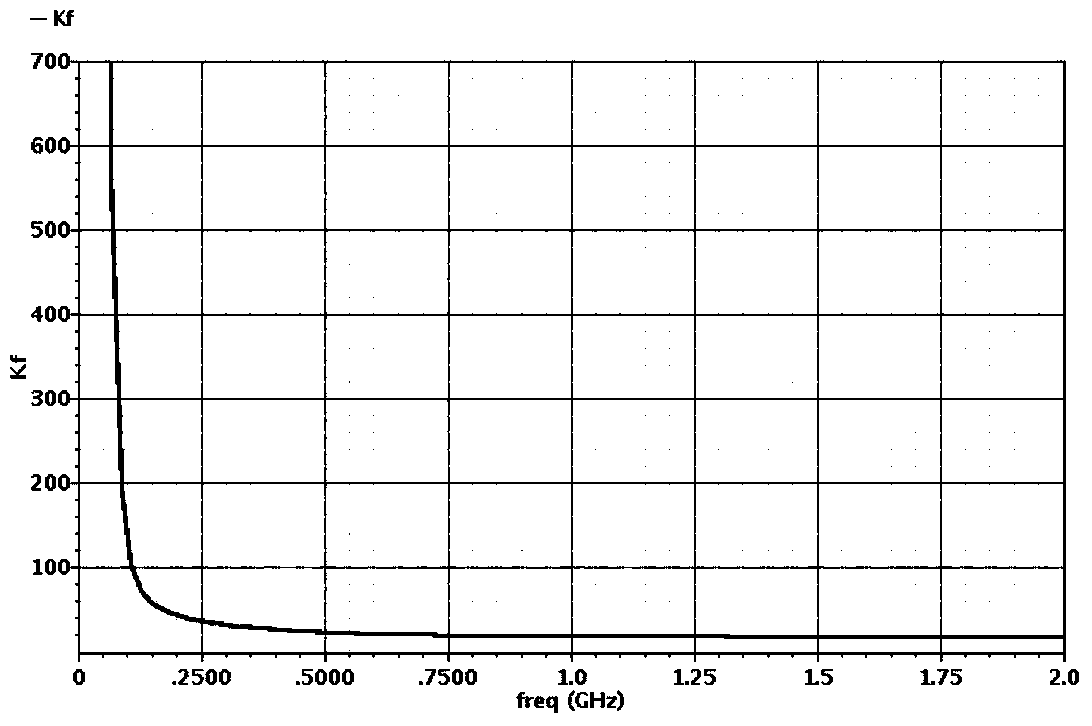

Differential power amplifier for CMOS with radio frequency of 0.1-1.2GHz

InactiveCN103746666AReduce areaIncrease output powerHigh frequency amplifiersPower amplifiersEngineeringRadio frequency

The invention discloses a differential power amplifier for a CMOS with the radio frequency of 0.1-1.2GHz. The differential power amplifier comprises an input blocking circuit, a drive stage polarization and input match circuit, a drive stage, an inter-stage blocking circuit, a power stage polarization and inter-stage match circuit, and a power stage and input blocking circuit. The drive stage provides drive gain and good input match. A power stage amplifying circuit provides power gain and good output match. The drive stage and the power stage amplifying circuit respectively comprise two NMOS tubes, two inductors, two current polarization circuits and two outer blocking capacitors. The power output stage comprises two feedback resistors and an inter-stage blocking capacitor. A common source structure is adopted, and the area of a chip is small. In the whole differential structure circuit, parameters of an adopted component can be determined after indexes of items such as the whole circuit gain, the bandwidth and the output power are integrated, and therefore the high gain, the high linearity and the high output power within 0.1-1.2GHz can be achieved.

Owner:TIANJIN UNIV

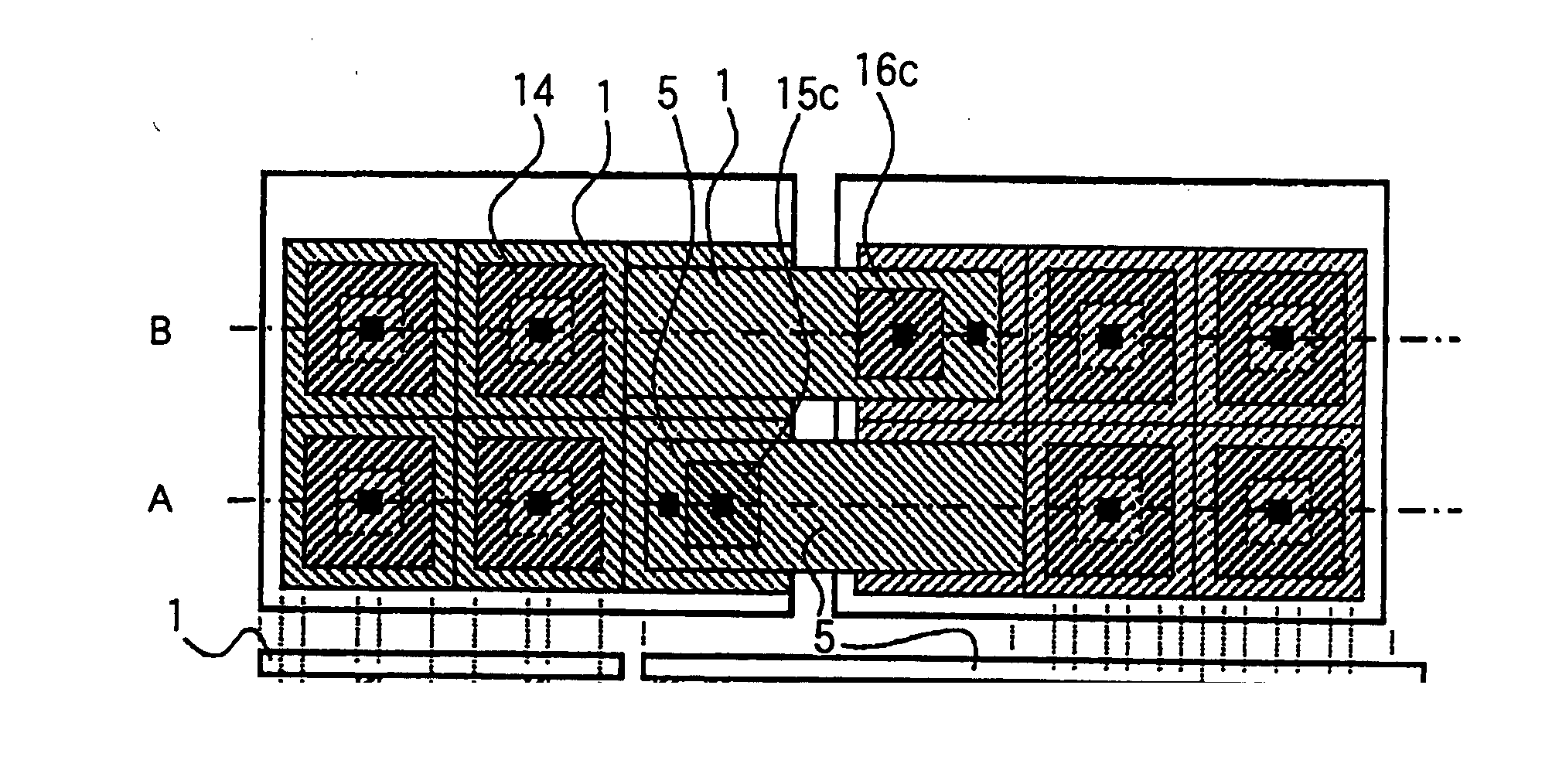

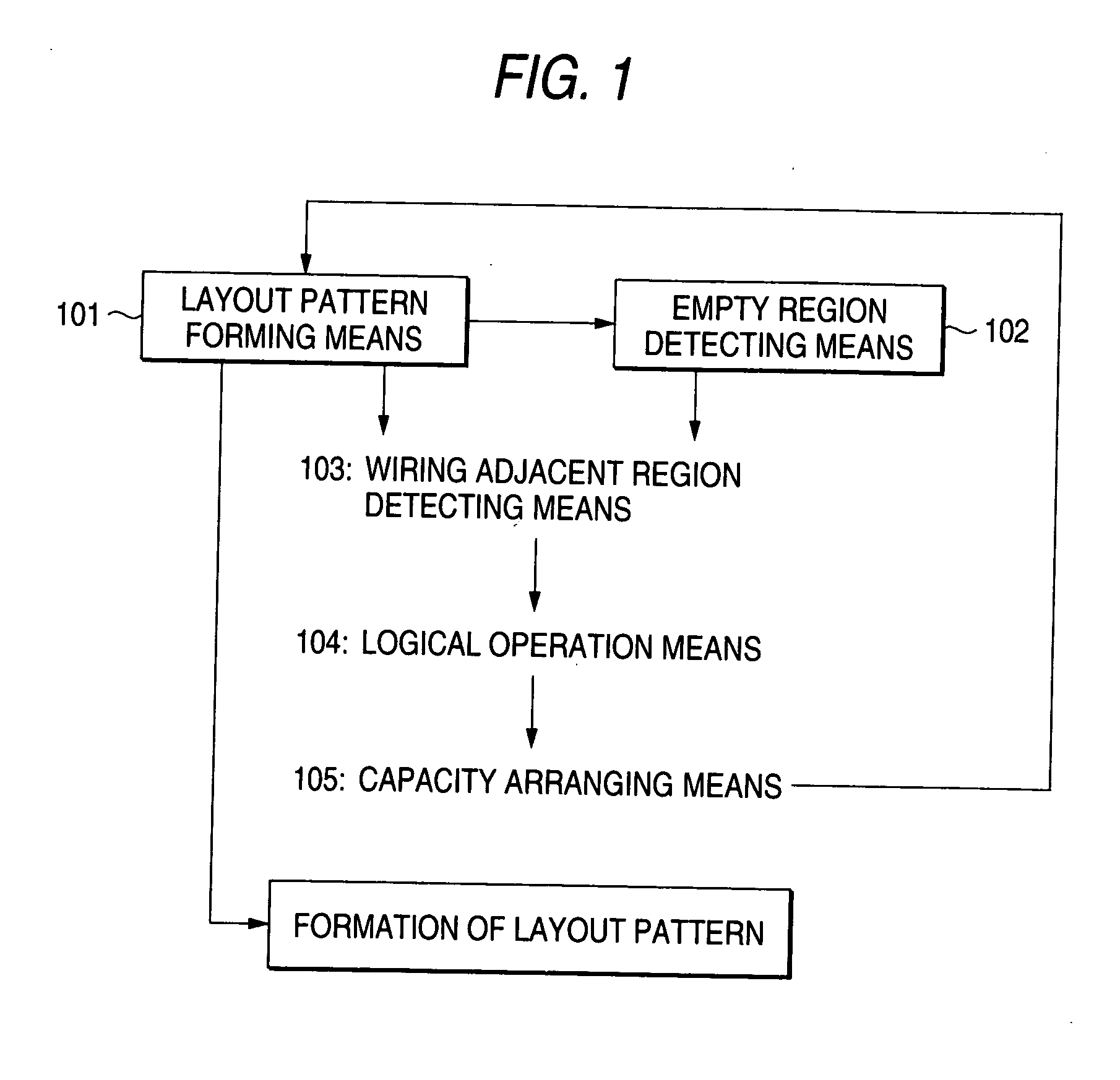

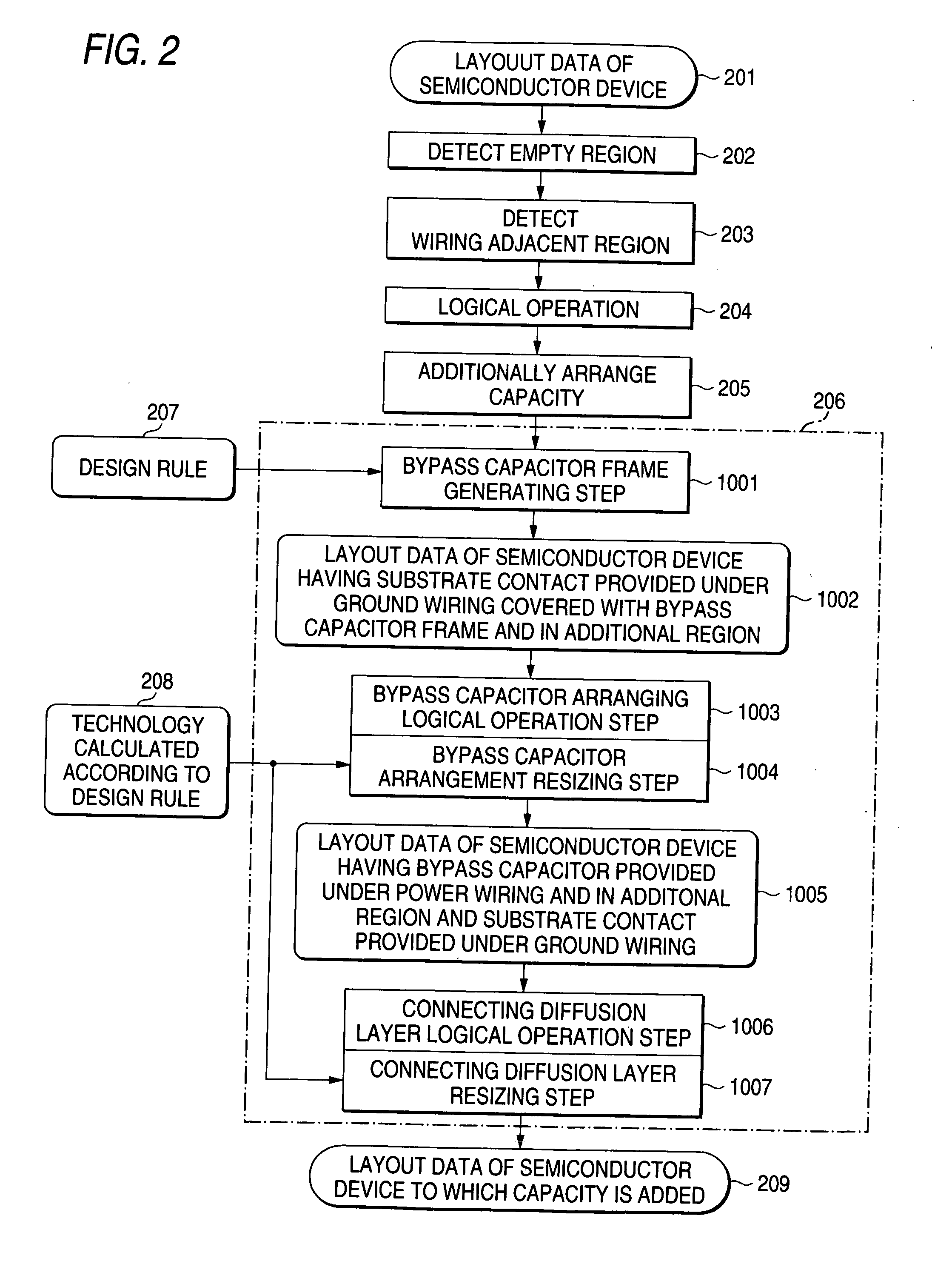

Semiconductor device method of generating semiconductor device pattern method of semiconductor device and pattern generator for semiconductor device

ActiveUS20050017320A1Large capacityReduce Power NoiseTransistorSolid-state devicesCapacitanceDevice material

It is an object of the invention to effectively absorb a power noise and to implement the stable operation of a circuit. The invention provides a semiconductor device comprising a bypass capacitor including an MOS structure having a gate electrode formed to be extended from a power wiring region to a portion provided under an empty region which is adjacent to the power wiring region and has no other functional layer, and formed through a capacitive insulating film on a diffusion region having one conductivity type, and a substrate contact formed under a ground wiring region and fixing a substrate potential, wherein the bypass capacitor has a contact to come in contact with the power wiring which is formed on a surface of the gate electrode and has the diffusion region having the one conductivity type and a diffusion region of the substrate contact connected to each other.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

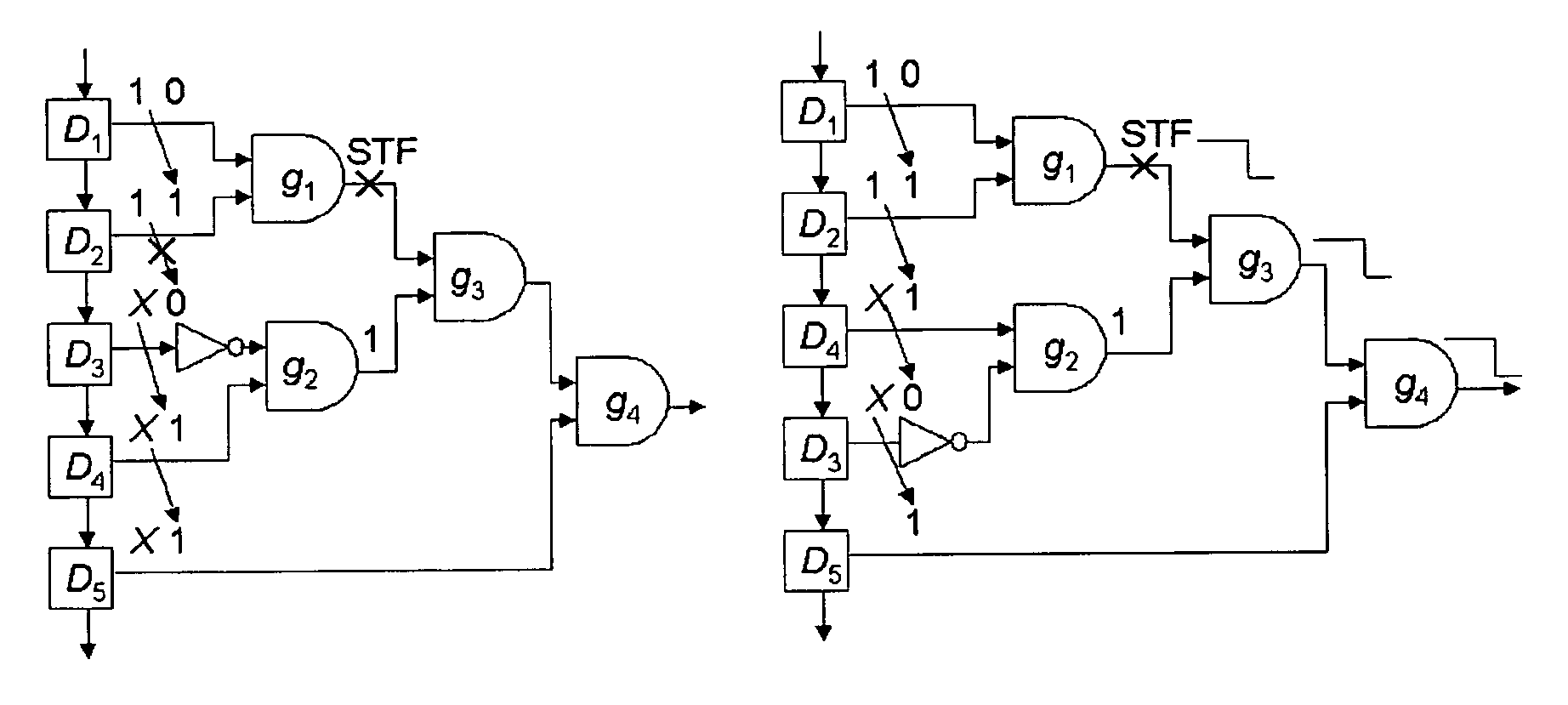

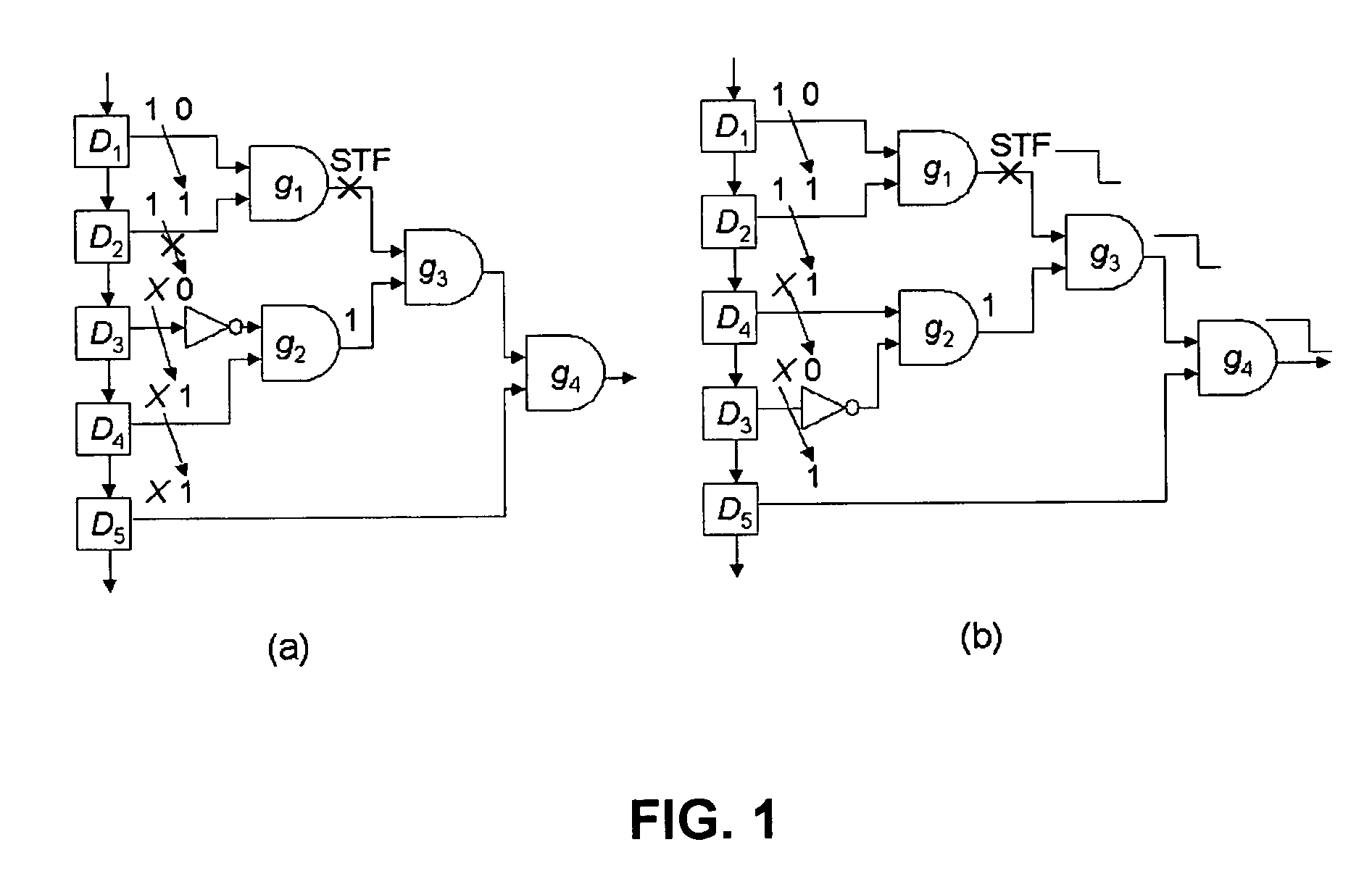

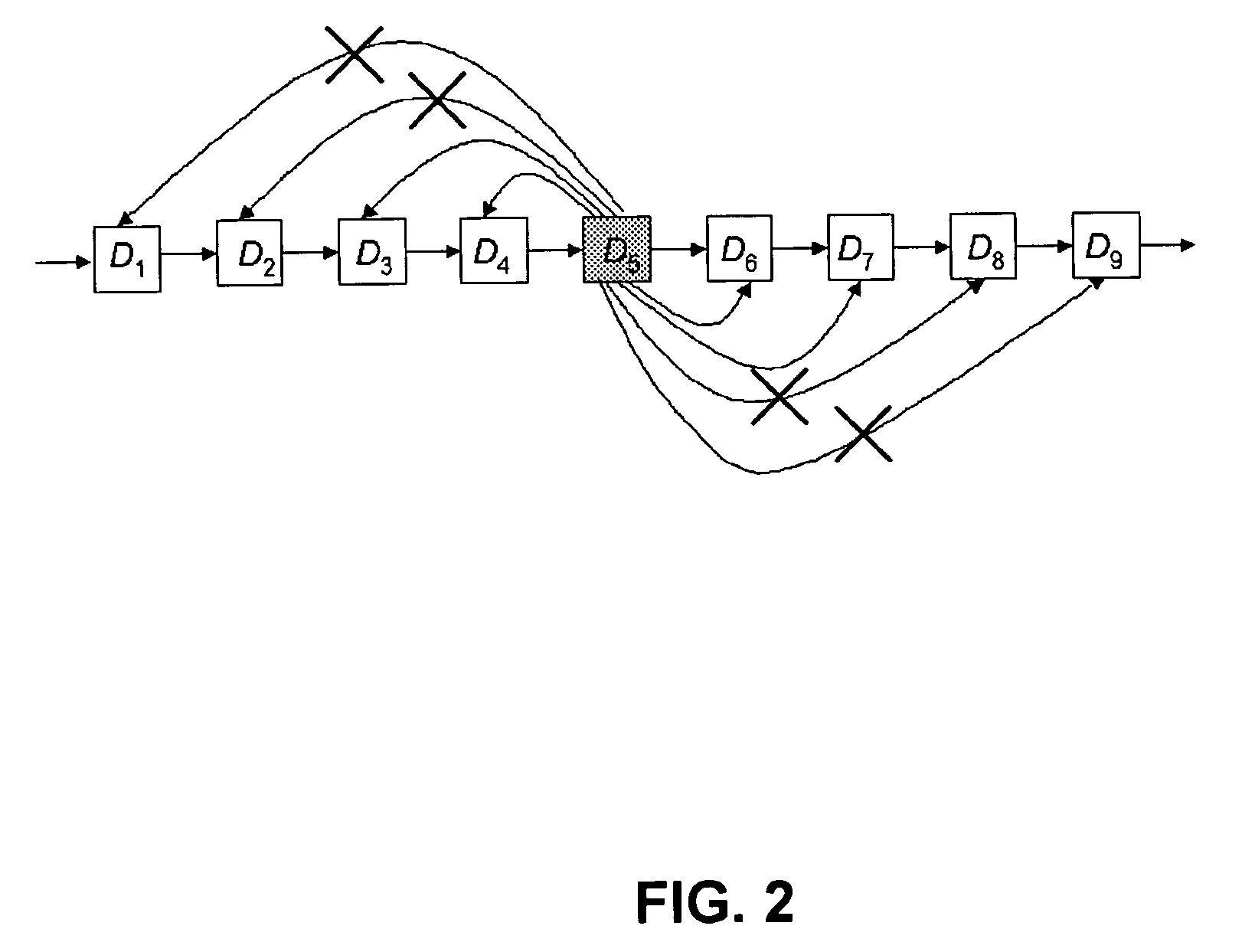

Restricted scan reordering technique to enhance delay fault coverage

InactiveUS20050235183A1Enhance delay fault coverageReasonable CPU timeElectronic circuit testingSpecial data processing applicationsFault coverageScan chain

The present invention is directed to improved delay fault testing by optimizing the order of scan cells in a scan chain.

Owner:NEC CORP

Semiconductor device for reducing coupling noise

Semiconductor devices, semiconductor memory device, or flash memories including a high voltage region including high voltage elements, a low voltage region including low voltage elements, and a switch transistor, such as a low voltage switch transistor, connecting the high voltage region and the high voltage region. The switch transistor reduces or eliminates coupling noise between sense nodes without increasing chip area.

Owner:SAMSUNG ELECTRONICS CO LTD

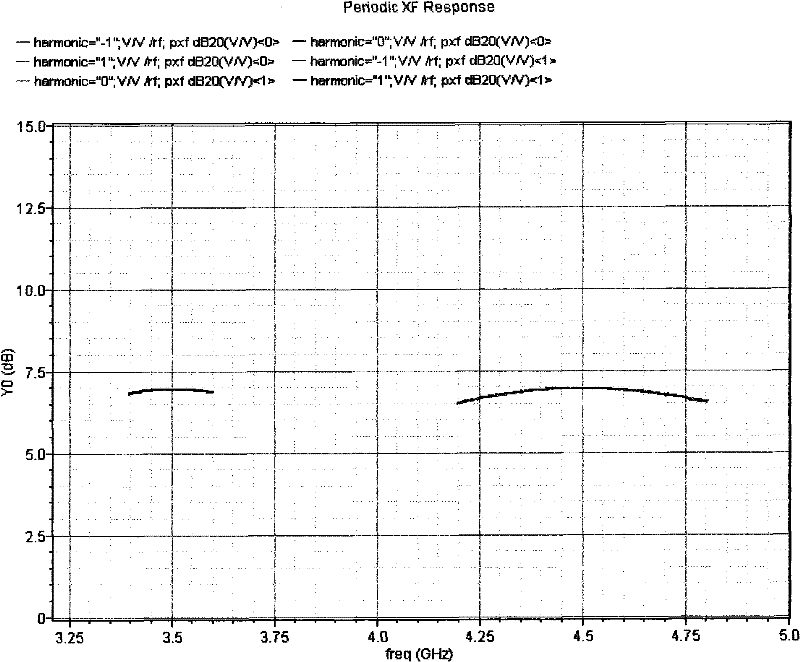

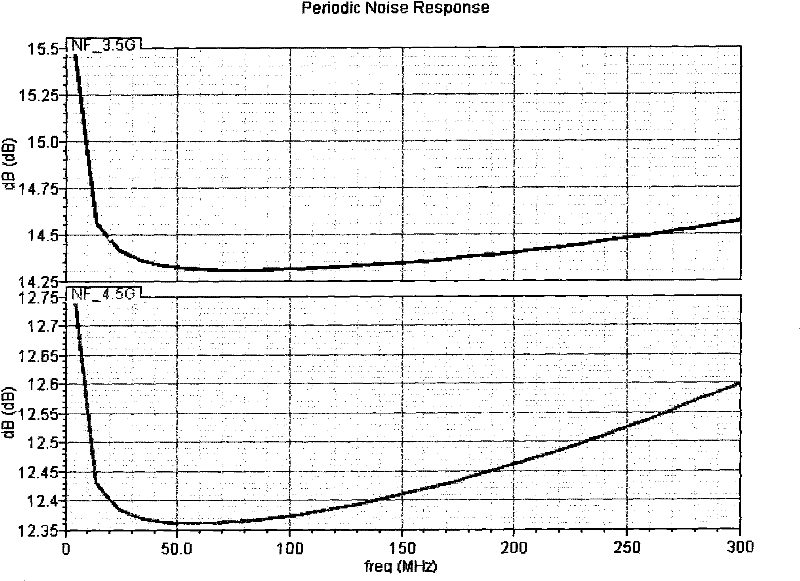

Integrated circuit chip of dual frequency band reconfigurable frequency mixer

InactiveCN102130654AReduce adverse effectsReduce working bandwidthModulation transferenceCapacitanceSwitching frequency

The invention designs an integrated circuit chip of a reconfigurable frequency mixer, in particular an integrated circuit chip of a dual frequency band reconfigurable frequency mixer, which is applied to two systems, namely advanced international mobile communication (IMT-Advanced) and ultra-wide band (UWB) communication. By adoption of an adjustable capacitor and a resistance network structure, reconfiguration between two frequency bands can be realized; compared with other frequency mixers reported at present, the circuit is arranged into a switch frequency selection tuning network; and the circuit can be switched between two working modes by adjusting an external control voltage; at the same time, the two frequency bands of the circuit can be optimized simultaneously by adjusting element parameters in the circuit. Factors, such as linearity, variable gain flatness, complexity, chip area, power consumption and the like, are taken into consideration, so the design compared with other reported technologies is improved greatly. The feasibility of the integrated circuit chip is tested in China by using a 0.13-millimeter mixed signal complementary metal-oxide-semiconductor process of SMIC Company.

Owner:SOUTHEAST UNIV +1

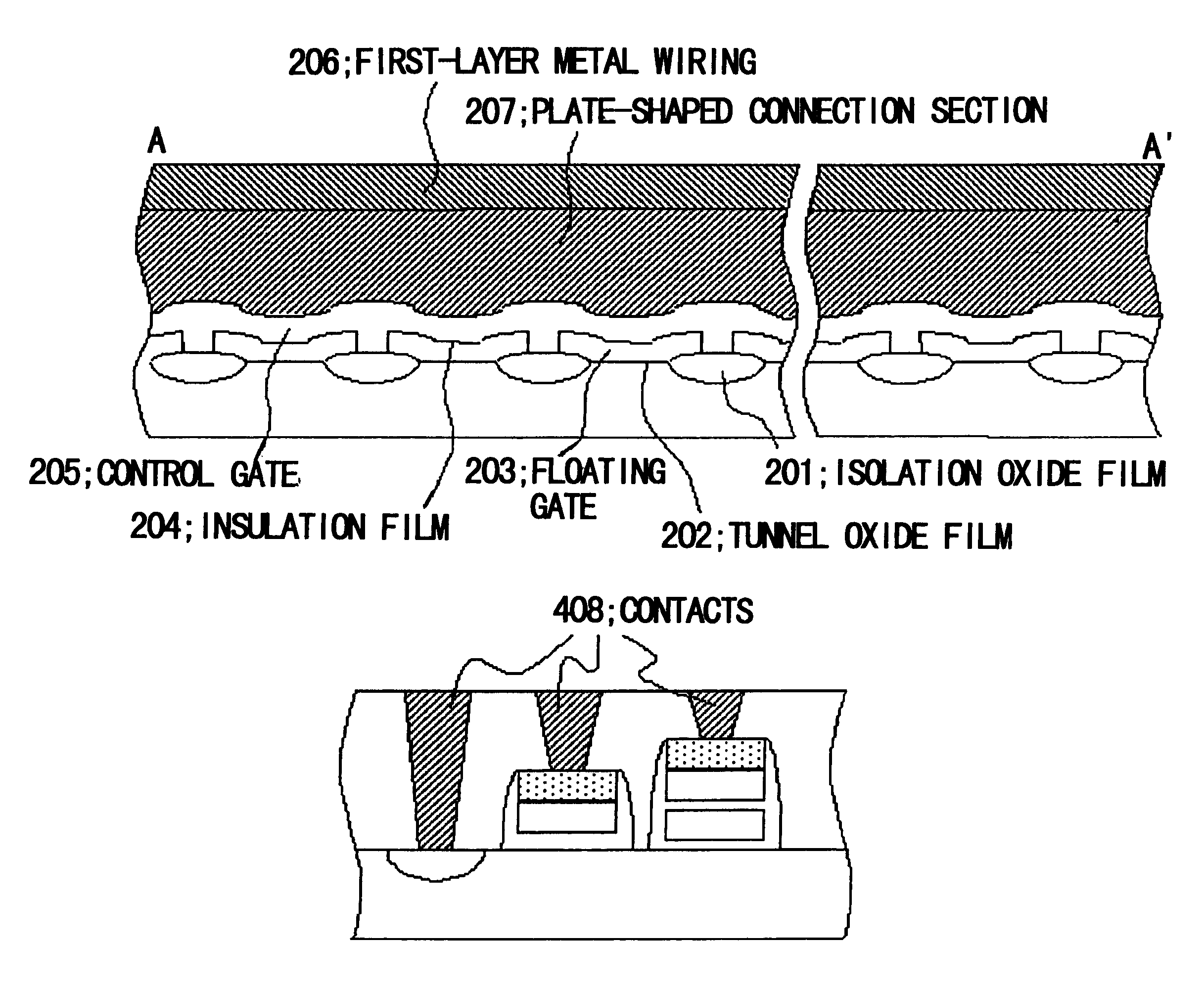

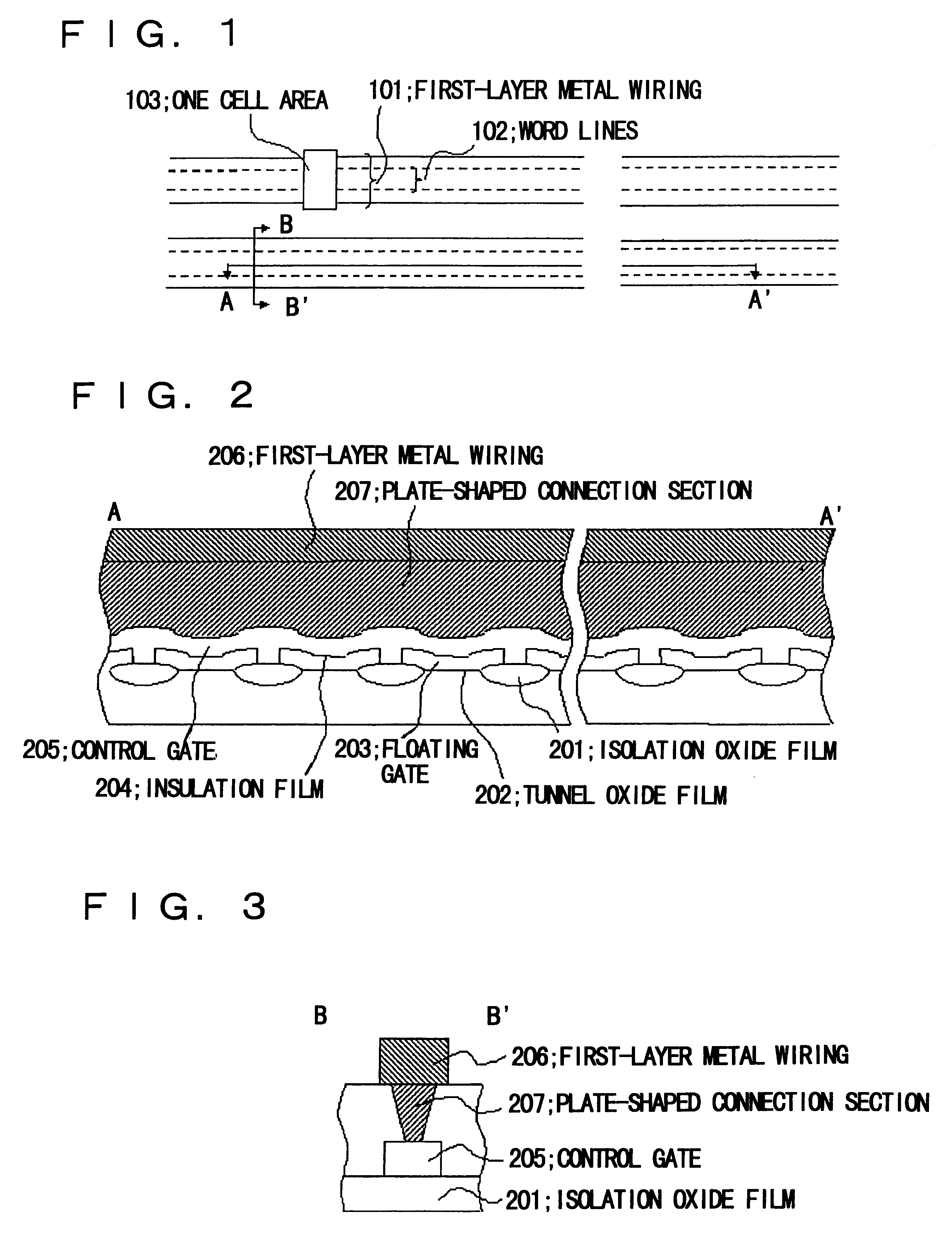

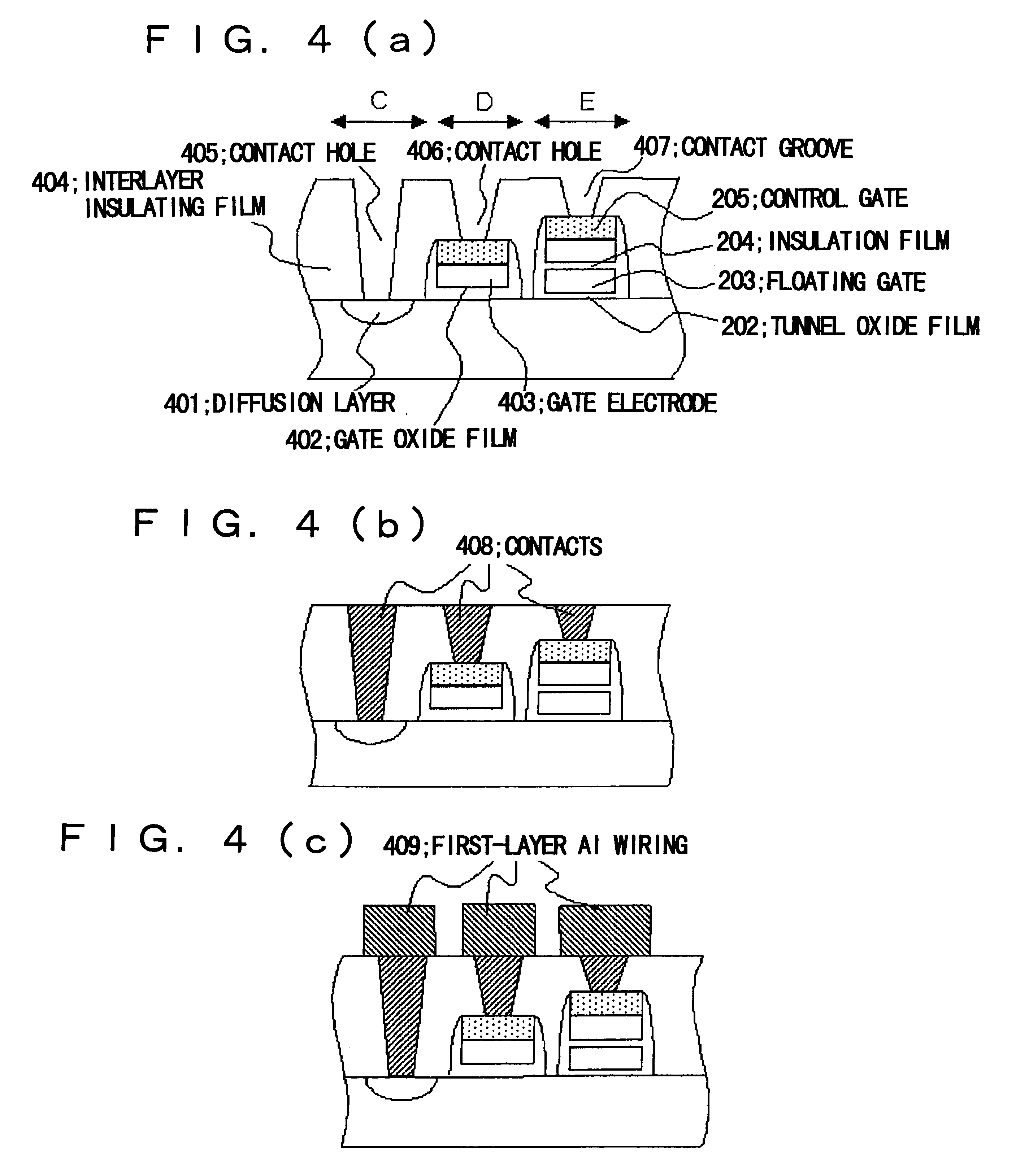

Non-volatile semiconductor memory device with reduced line resistance and method of manufacturing

InactiveUS6437394B1Increase readout speedIncrease chip areaTransistorSolid-state devicesElectrical resistance and conductanceLine resistance

To provide a non-volatile semiconductor memory device in which the word line resistance can be decreased in resistance without being accompanied by increase in chip area, and a manufacturing method for the non-volatile semi conductor memory device. In a non-volatile semiconductor memory device having a floating gate (203 of FIG. 2) and a control gate (205 of FIG. 2), a contact groove (407 of FIG. 4a) extending in the direction of a word line (102 of FIG. 1) is provided on an interlayer insulating film (404 of FIG. 4a) formed as an upper layer of the control gate, and an electrically conductive member of, for example, tungsten, is embedded in the contact groove to establish electrical connection between the wiring metal (409 of FIG. 4d) formed as an upper layer of the interlayer insulating film and the control gate with a large contact area.

Owner:NEC ELECTRONICS CORP

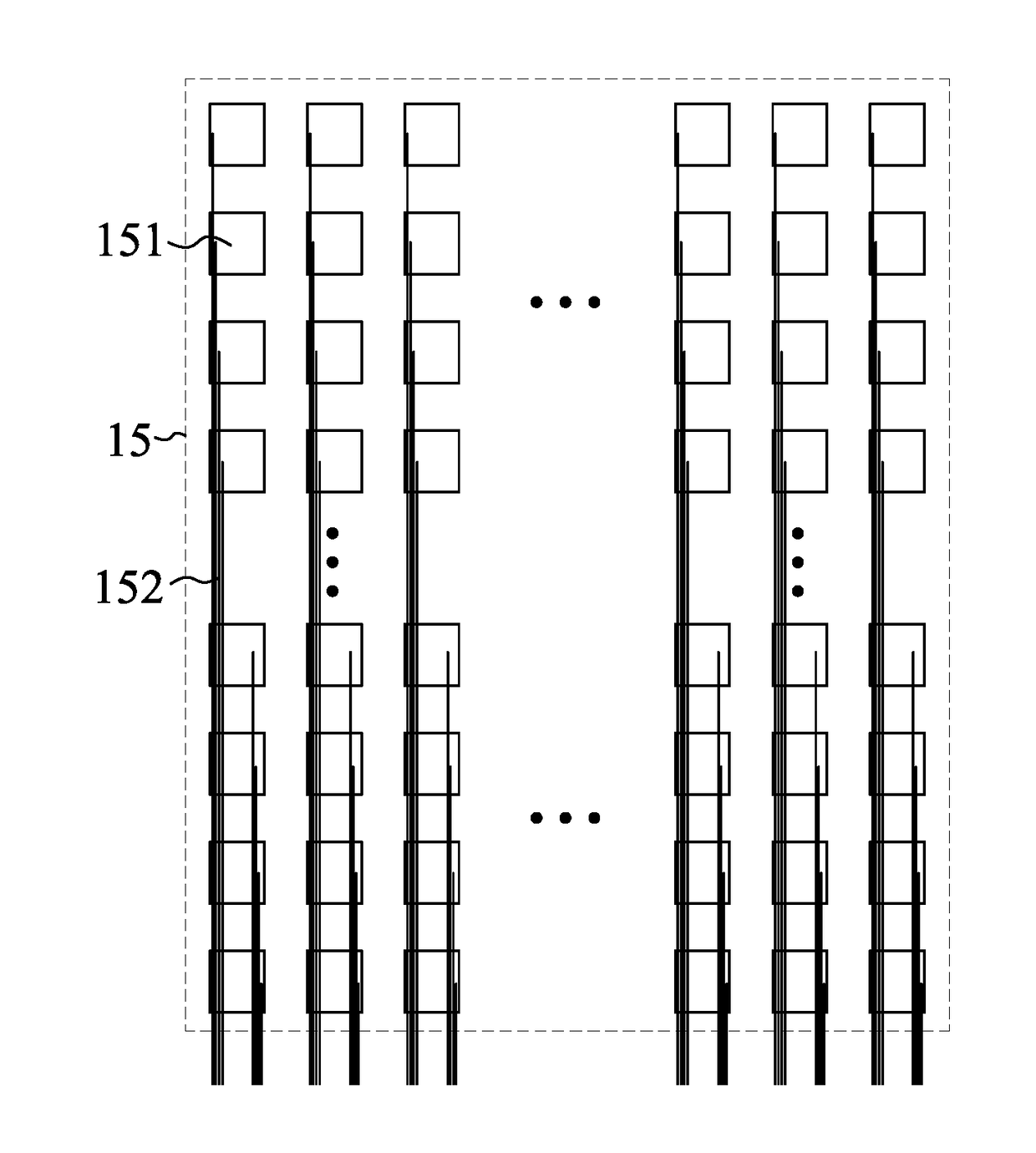

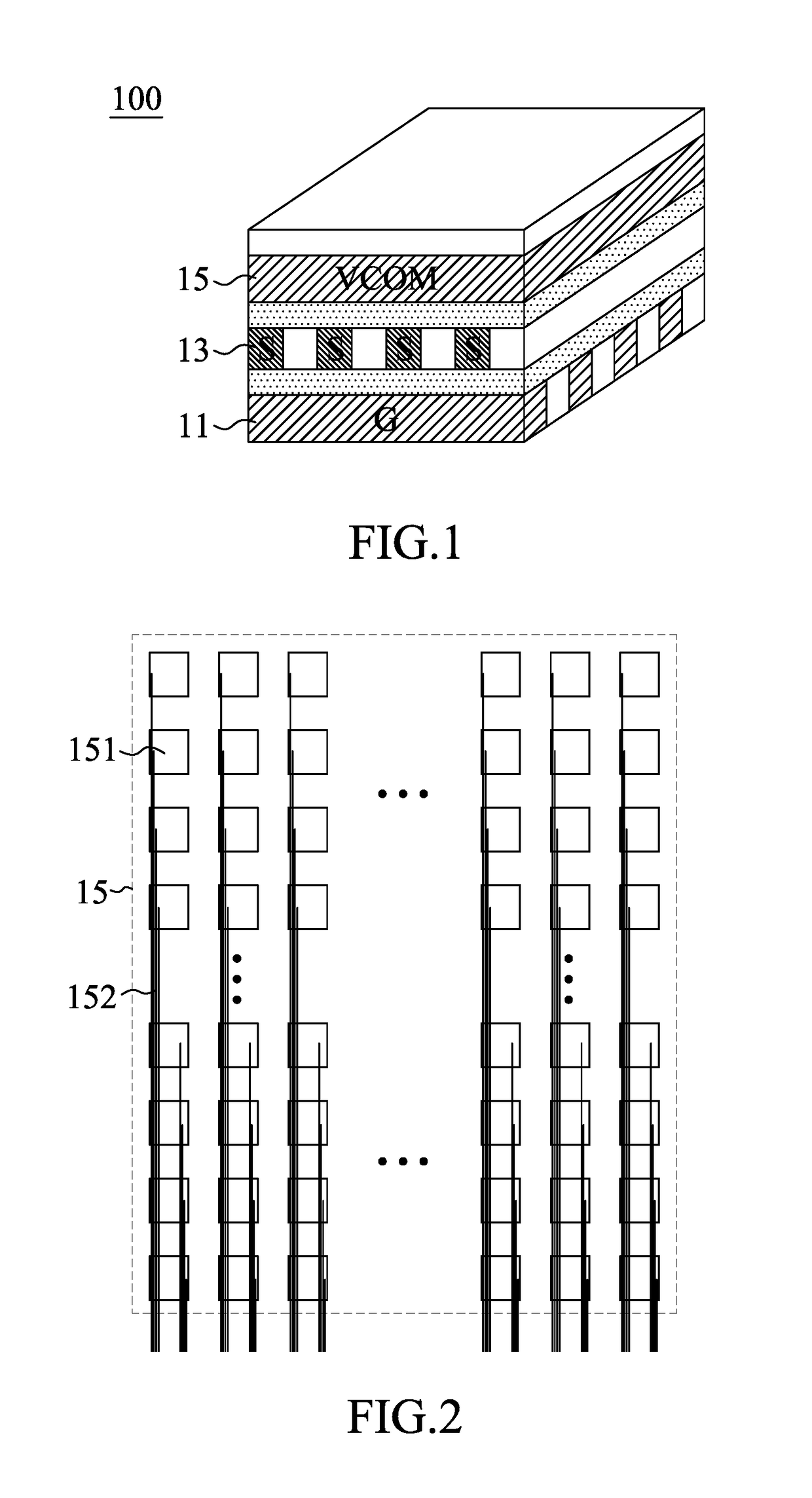

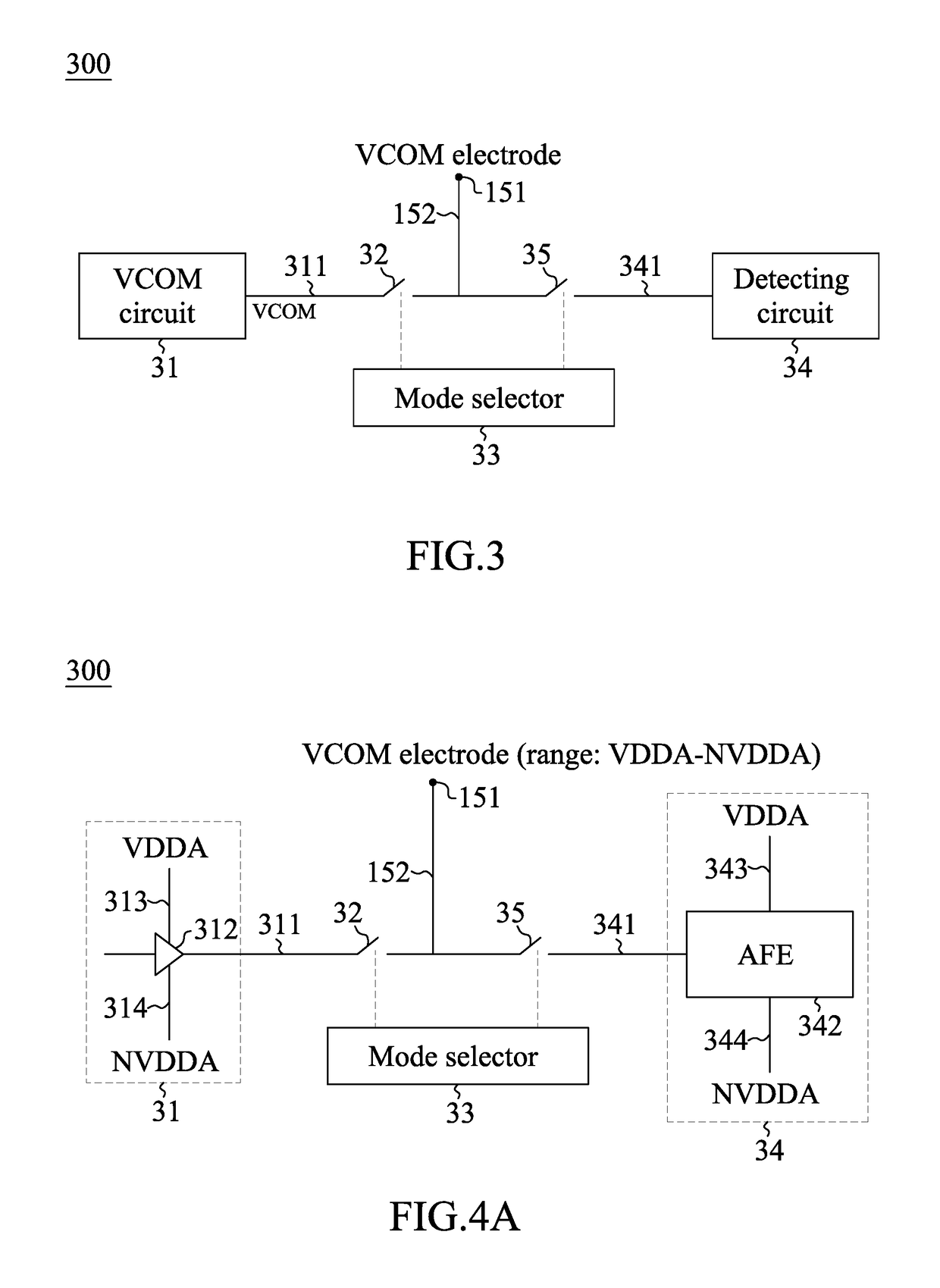

In-cell touch screen and a controller adapted thereto

ActiveUS20170139523A1Reduce chip areaAvoid problemsElectronic switchingInput/output processes for data processingTouch SensesEngineering

A controller adapted to an in-cell touch screen includes a common voltage (VCOM) circuit generating a common voltage at an output node of the VCOM circuit, and a detecting circuit receiving a sensing signal at an input / output node of the detecting circuit. A display-mode switch is closed in a display mode such that a VCOM electrode is set at the common voltage, and a touch-sensing-mode switch is closed in a touch sensing mode such that the sensing signal from the VCOM electrode is received and processed by the detecting circuit. The detecting circuit has full-swing power that contains full-swing power of the VCOM circuit.

Owner:HIMAX TECH LTD

Semiconductor integrated circuit and method of designing semiconductor integrated circuit

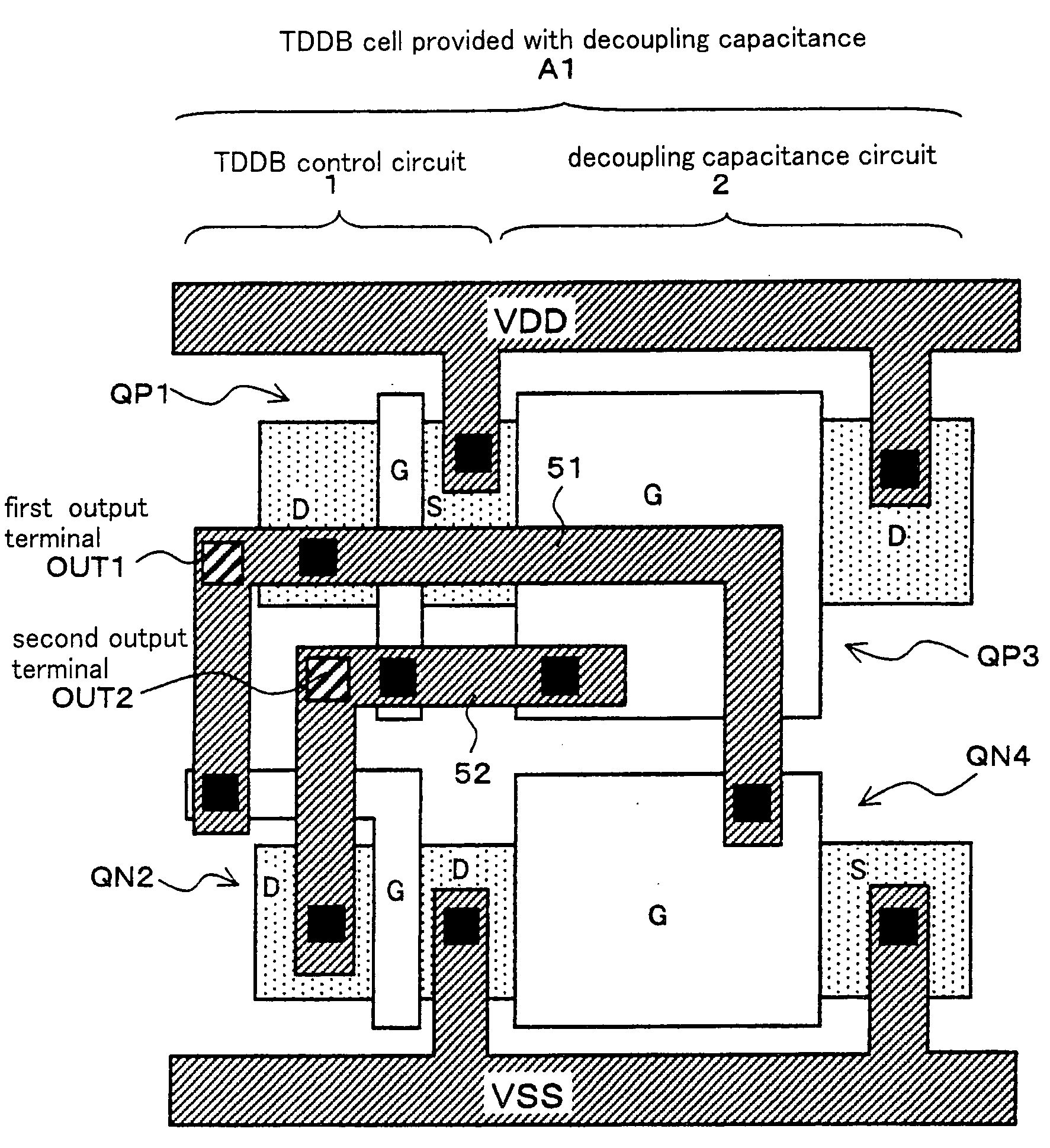

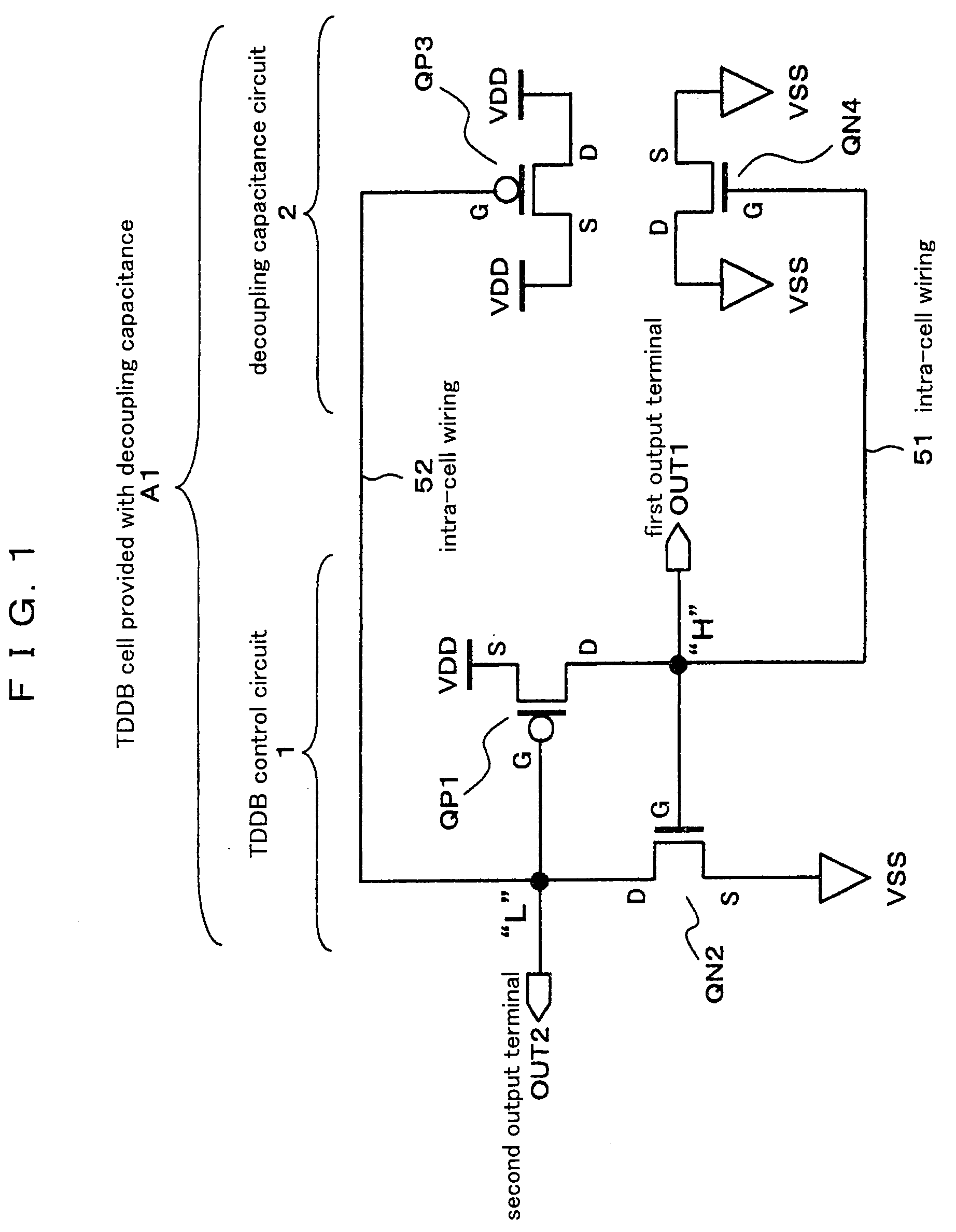

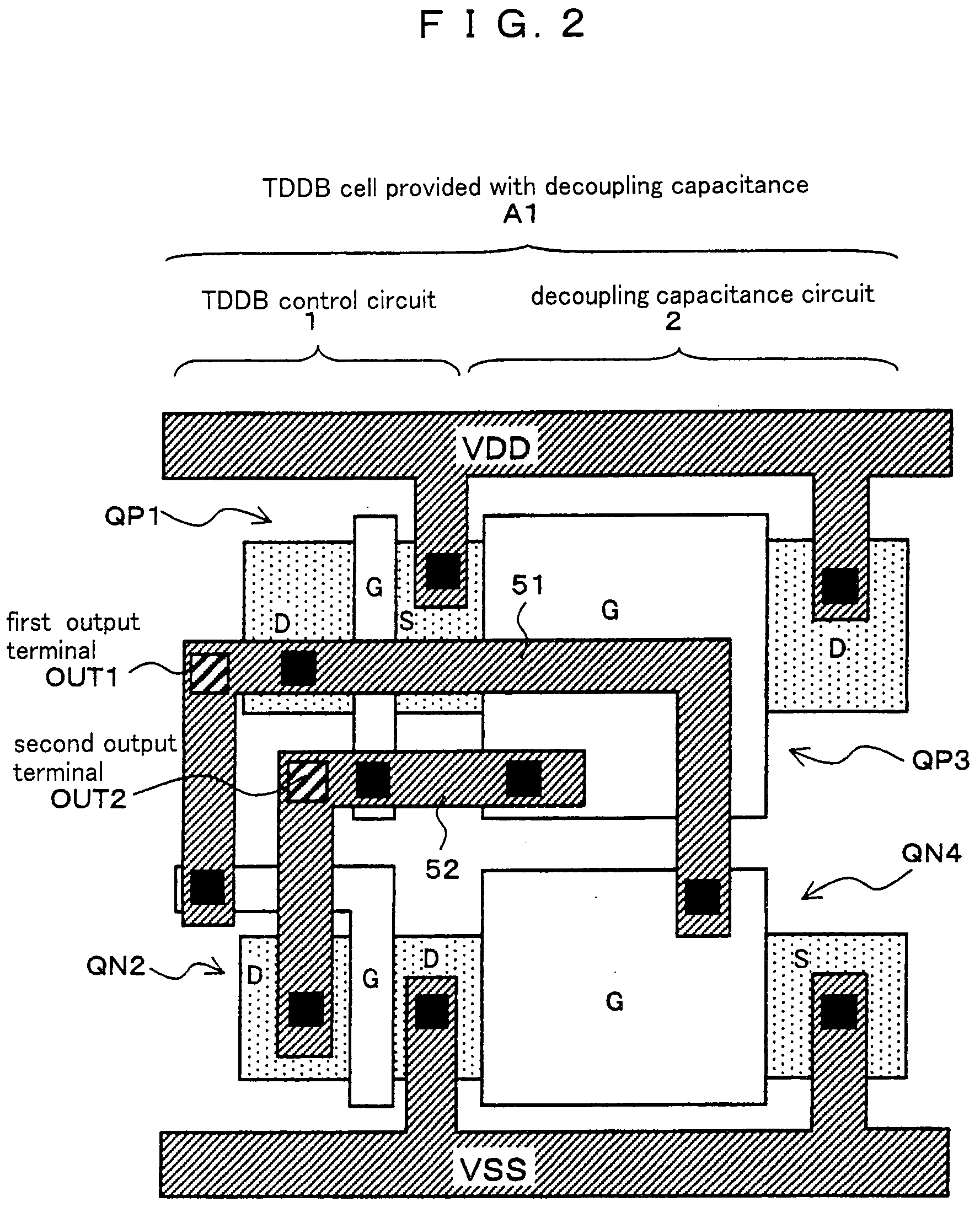

ActiveUS20070205451A1Inhibit deteriorationIncrease chip areaTransistorSolid-state devicesCapacitanceEngineering

In the present invention, a decoupling capacitance circuit, a first output terminal and a second output terminal are provided. The decoupling capacitance circuit comprises a TDDB control circuit consisting of a first Tr and a second Tr, and a third Tr. Conductivity types of the first and second Trs are different from each other. A source of the first Tr is connected to a first power supply wiring, and a drain of the first Tr is connected to a gate of the second Tr. A source of the second Tr is connected to a second power supply wiring, and a drain of the second Tr is connected to a gate of the first Tr. The third and first Trs have the same conductivity type. A source and a drain of the third Tr are connected to the first power supply wiring, and a gate of the third Tr is connected to the drain of the second Tr. The first output terminal is connected to the drain of the first Tr, and the second output terminal is connected to the drain of the second Tr.

Owner:SOCIONEXT INC

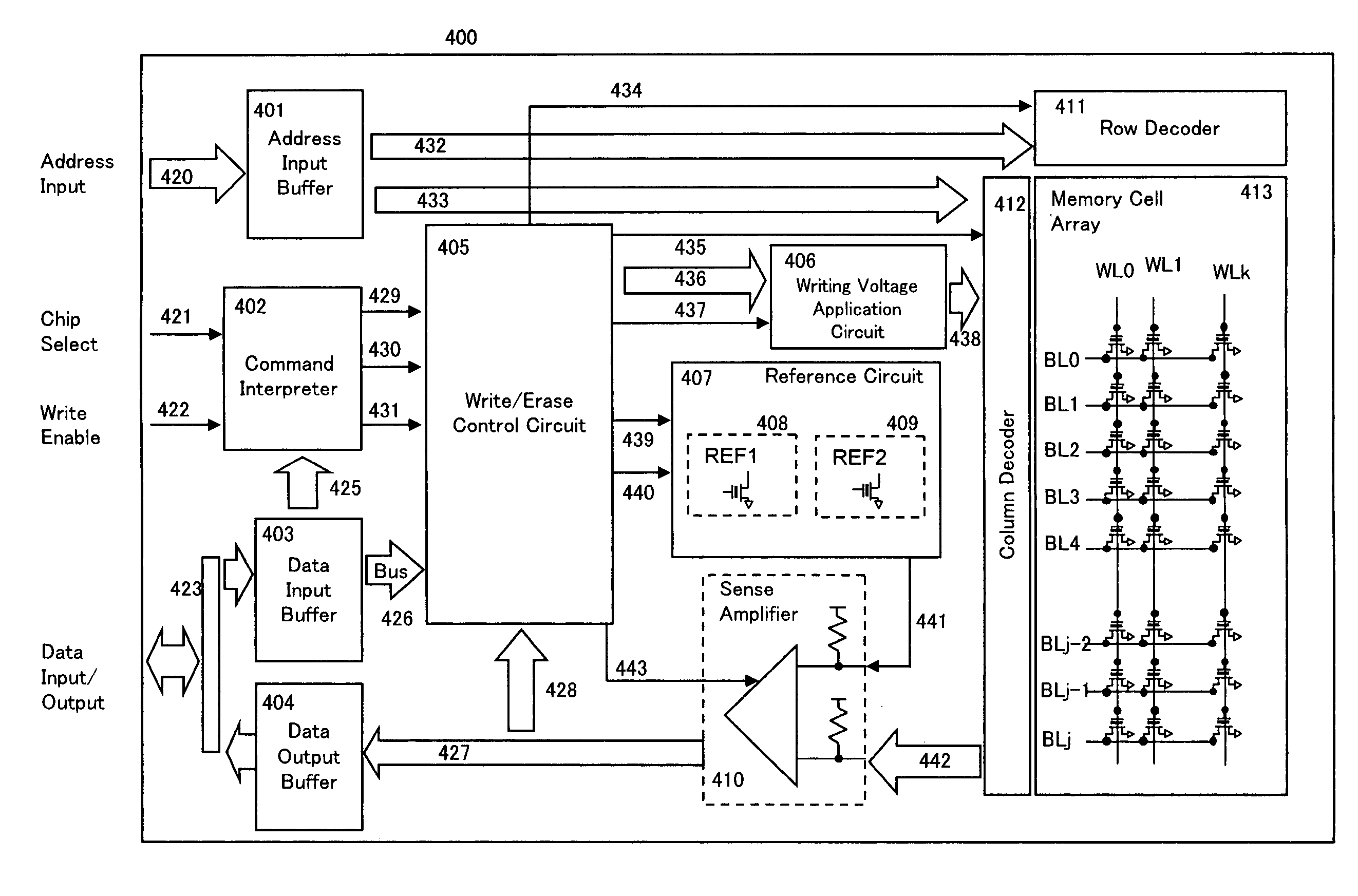

Nonvolatile semiconductor memory device and its writing method

InactiveUS20070121392A1Prevent threshold voltage distributionIncrease chip areaRead-only memoriesDigital storageMiniaturizationEngineering

There is provided a nonvolatile semiconductor memory device and its writing method capable of controlling an increase in threshold voltage due to effects of adjacent memory cells and performing stable readout operations even if miniaturization of semiconductor memory devices proceeds further. The device comprises a memory cell array 411 having memory cells in a row and column directions, a row selection circuit 412, a column selection circuit 411, and a control circuit 405 for exercising writing control on a selected memory cell by an external command input. The control circuit performs a threshold voltage control for writing a memory cell selected as a writing target to a first predetermined threshold voltage when receiving a first external write command, and performs another threshold voltage control for writing the selected memory cell to a second predetermined threshold voltage different from the first threshold voltage when receiving a second external write command.

Owner:SHARP KK

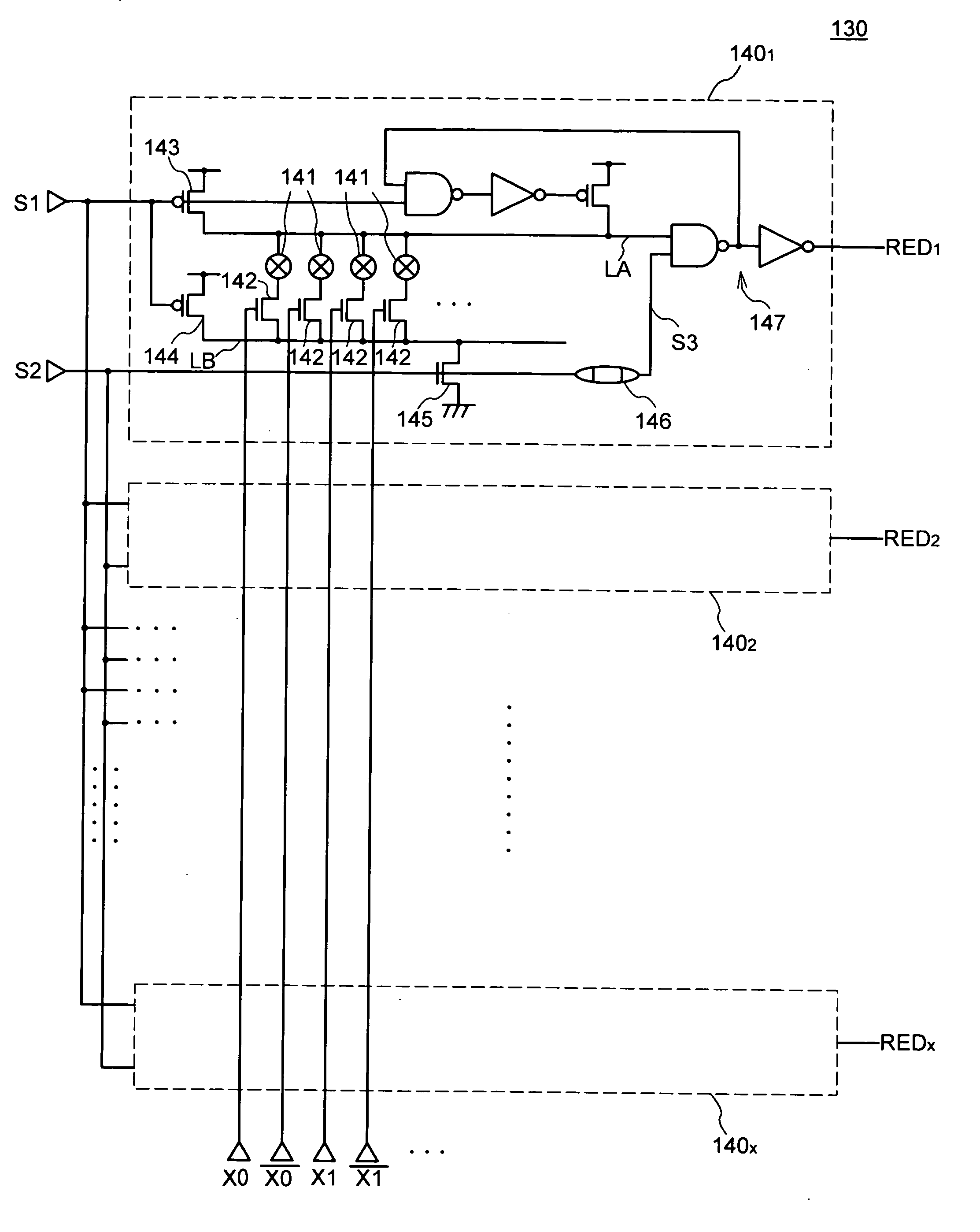

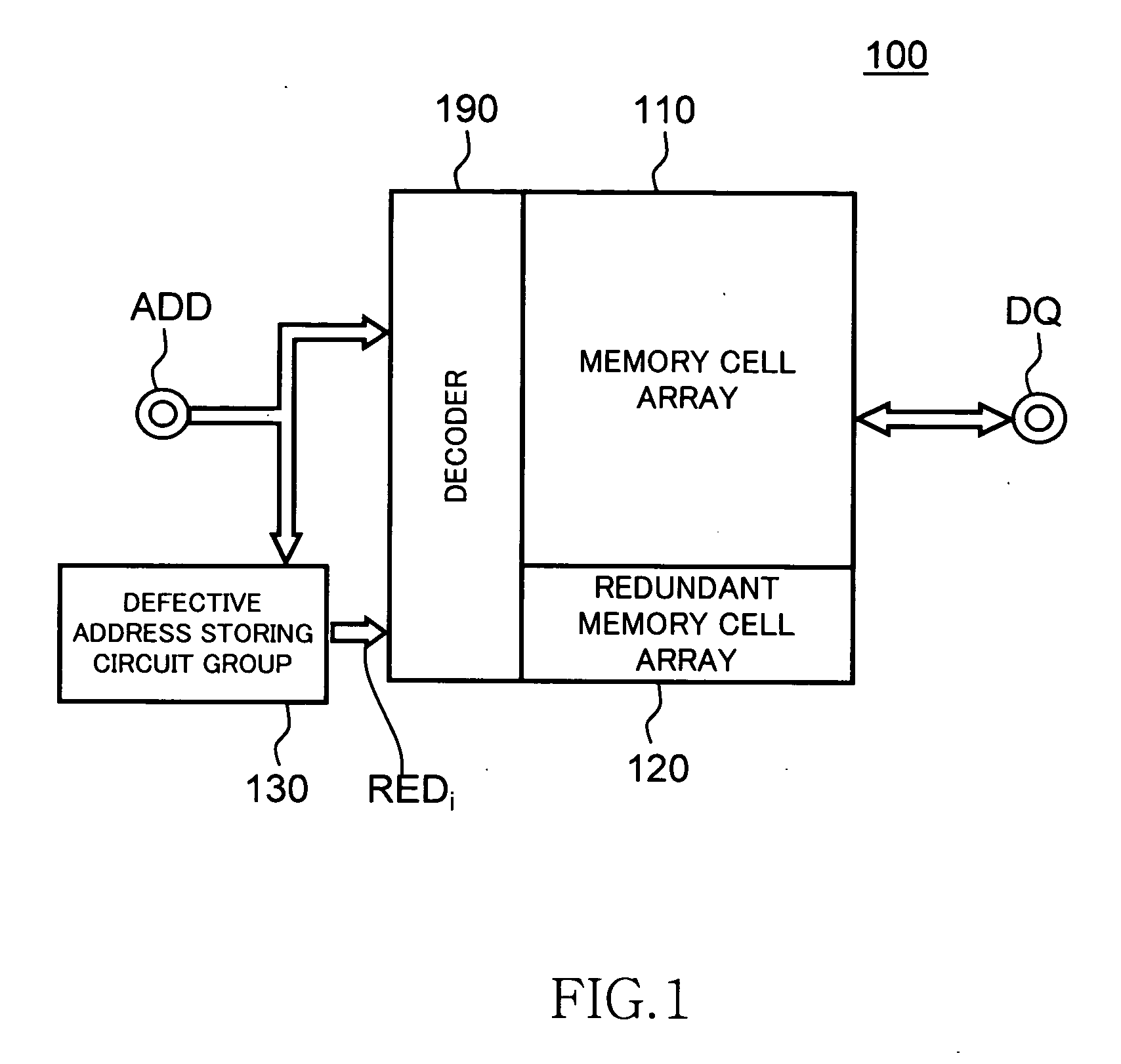

Chip information managing method, chip information managing system, and chip information managing program

ActiveUS20060268634A1Information obtainedIncrease chip areaDigital storageVery large databaseComputer science

In replacing word lines having defective addresses with redundant word lines, information is held in a relationship between the word lines and the redundant word lines. In other words, information is held in a replacement rule. With this arrangement, information such as a lot number, a wafer number within the lot, and a position of a chip within the wafer can be held in the chip, without increasing the chip area at all and without using a large database.

Owner:MICRON TECH INC

Semiconductor integrated circuit device

ActiveUS20160308534A1Increase chip areaTransistorConversion constructional detailsHigh concentrationCondensed matter physics

A semiconductor integrated circuit device, including a semiconductor layer of a first conductivity type, a first well region of a second conductivity type, a second well region of the second conductivity type, and a third well region of the first conductivity type. The device further includes an isolation region electrically isolating a predetermined region in the first well region, a first high-concentration region of the second conductivity type, disposed outside the isolation region and inside one of the first well region and the second well region, and a second high-concentration region of the second conductivity type, disposed inside the isolation region and inside one of the first well region and the second well region. The first and second high-concentration regions each have an impurity concentration that is higher than that of the first well region.

Owner:FUJI ELECTRIC CO LTD

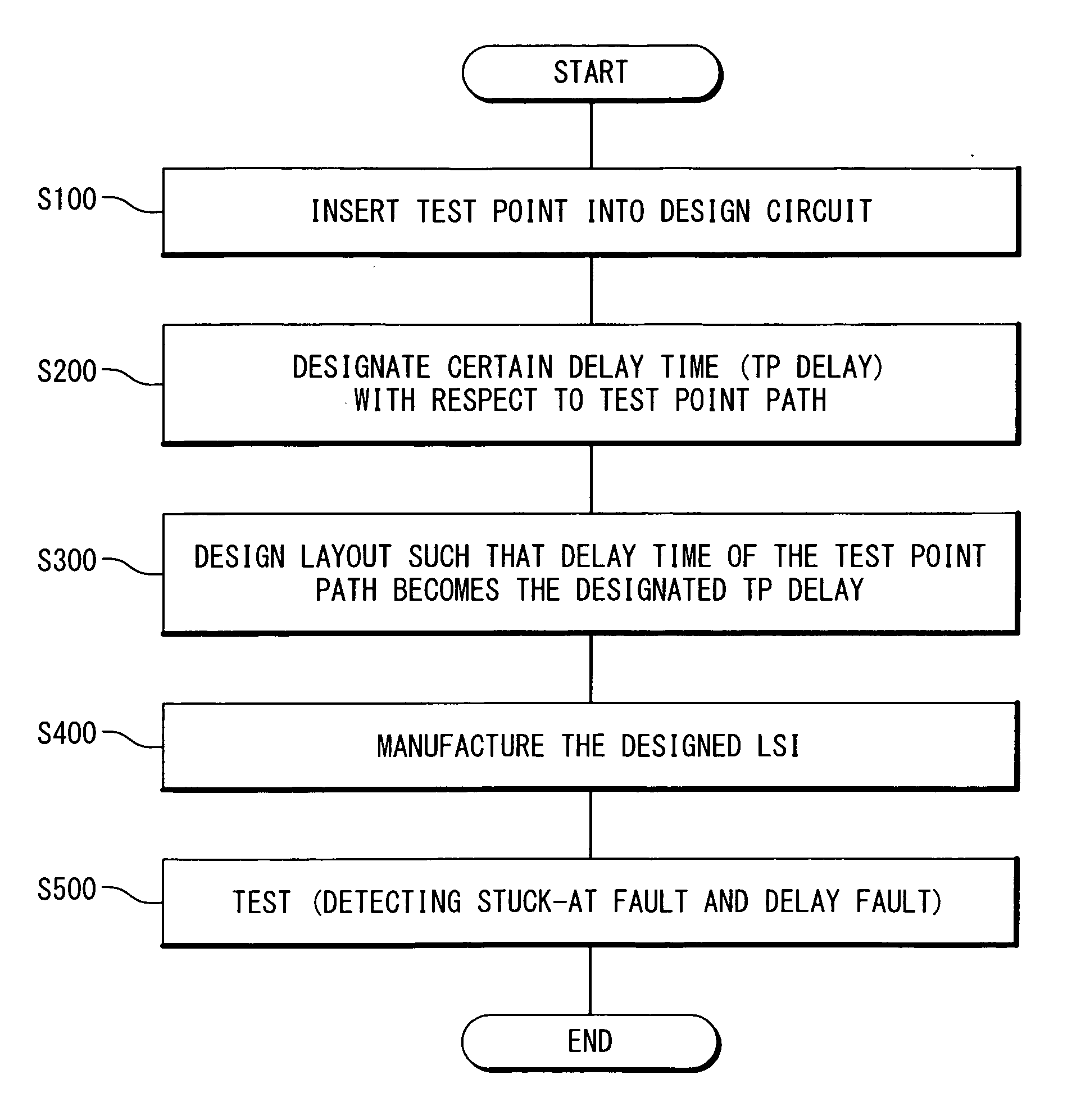

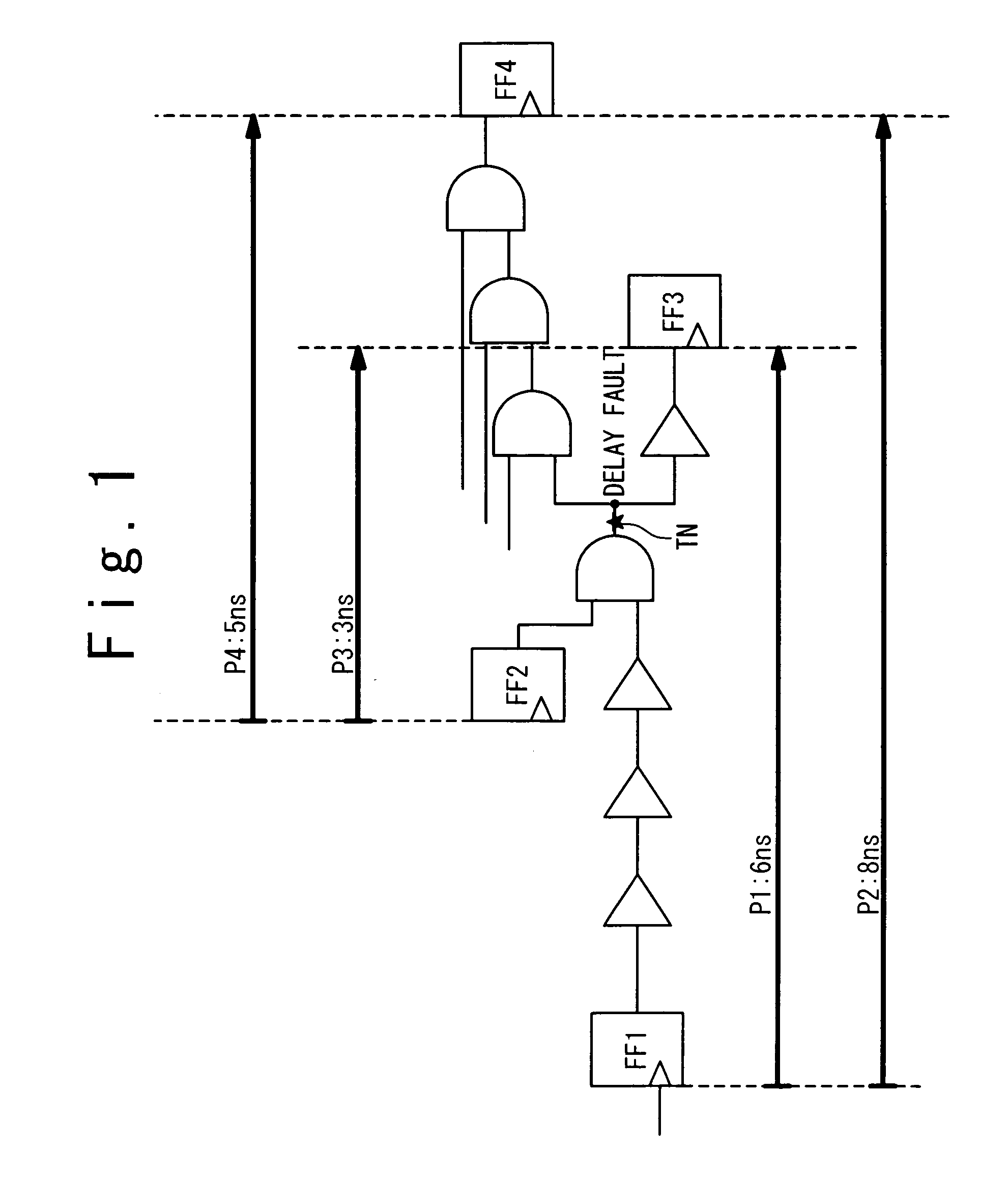

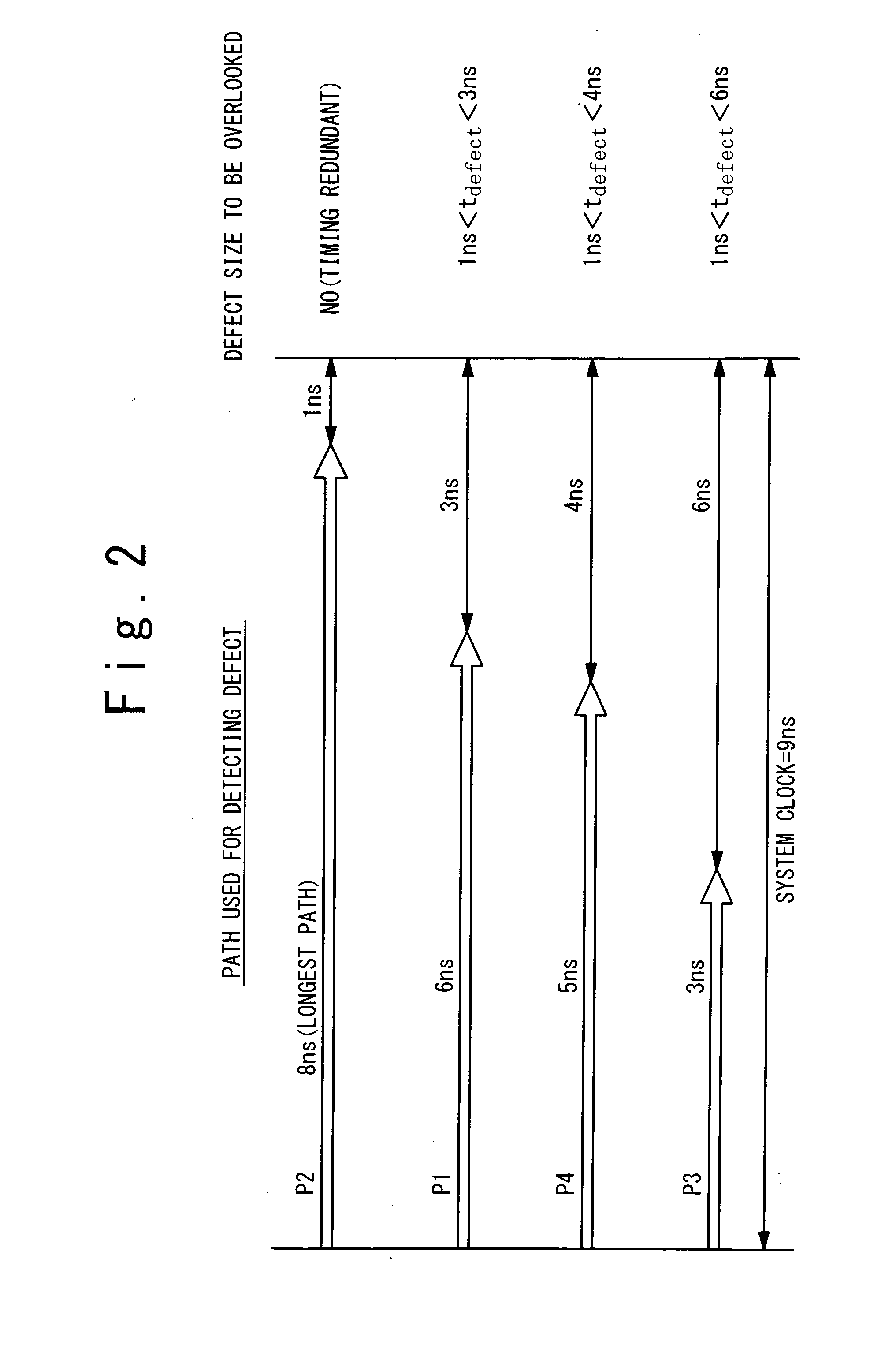

Semiconductor integrated circuit and method of designing thereof based on TPI

InactiveUS20080295050A1To overcome the large delayReduce in quantityElectrical testingSoftware simulation/interpretation/emulationDelayed timeDesign methods

A method of designing a semiconductor integrated circuit based on the TPI technique, comprising: (A) selecting a target node from a plurality of nodes included in a design circuit; (B) inserting a test point at the target node; (C) designating a delay time with respect to a test point path that is a path connected to the test point; and (D) laying out the design circuit such that a delay time of the test point path becomes the designated delay time. The (A) selecting includes: (A1) calculating delay times of fan-in paths and fan-out paths with respect to each of the plurality of nodes; and (A2) selecting the target node from the plurality of nodes based on the calculated delay times.

Owner:RENESAS ELECTRONICS CORP

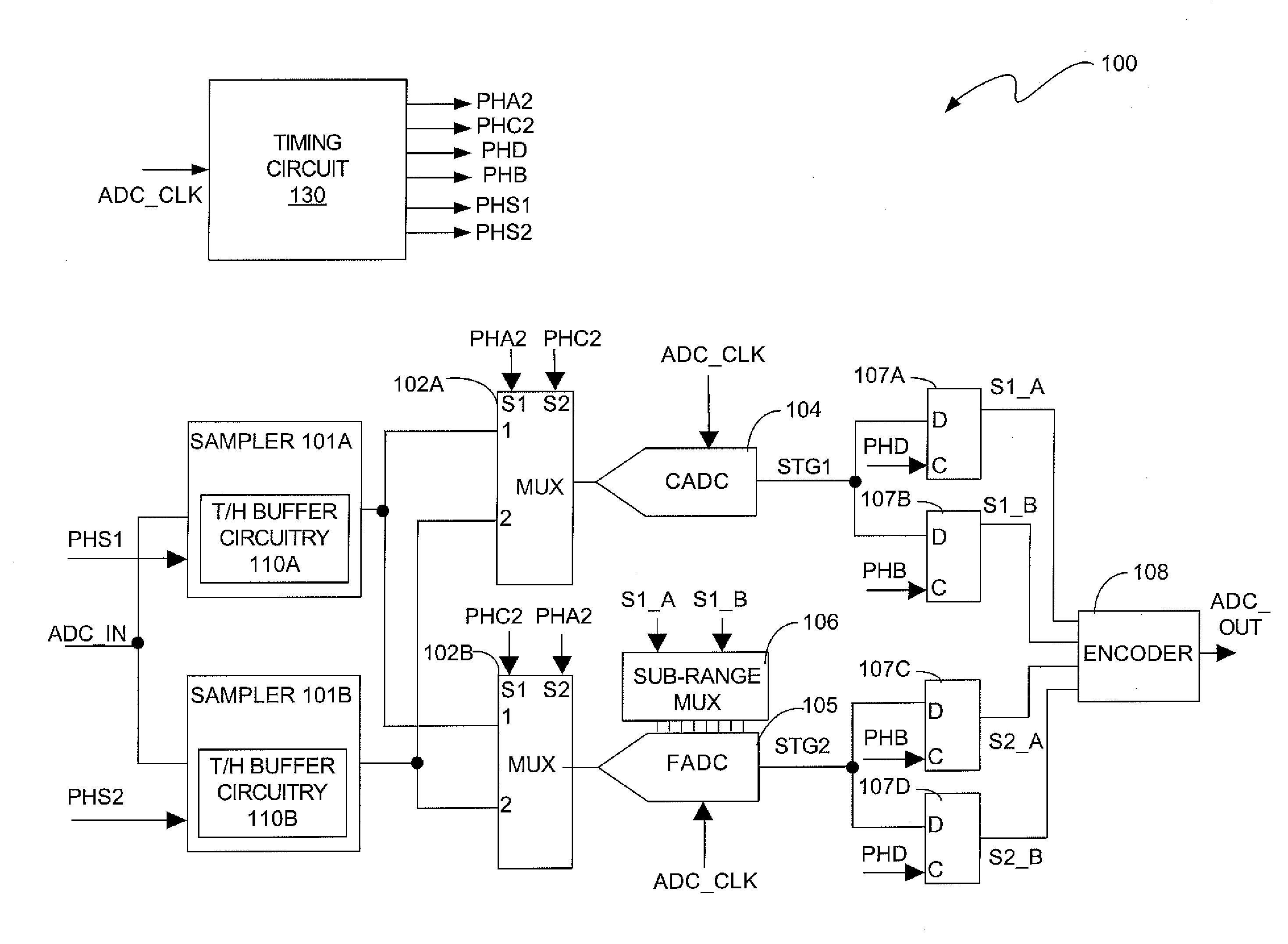

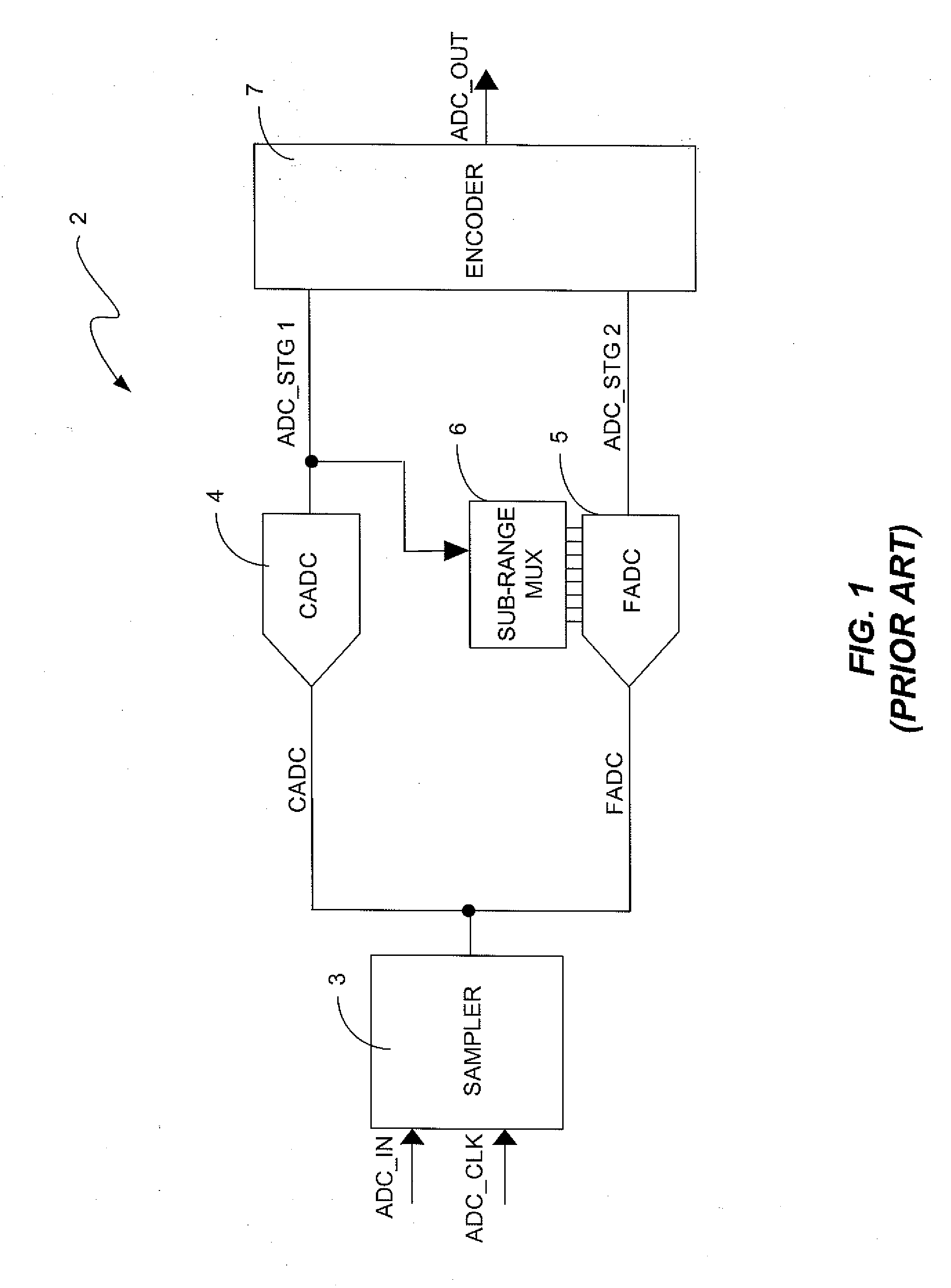

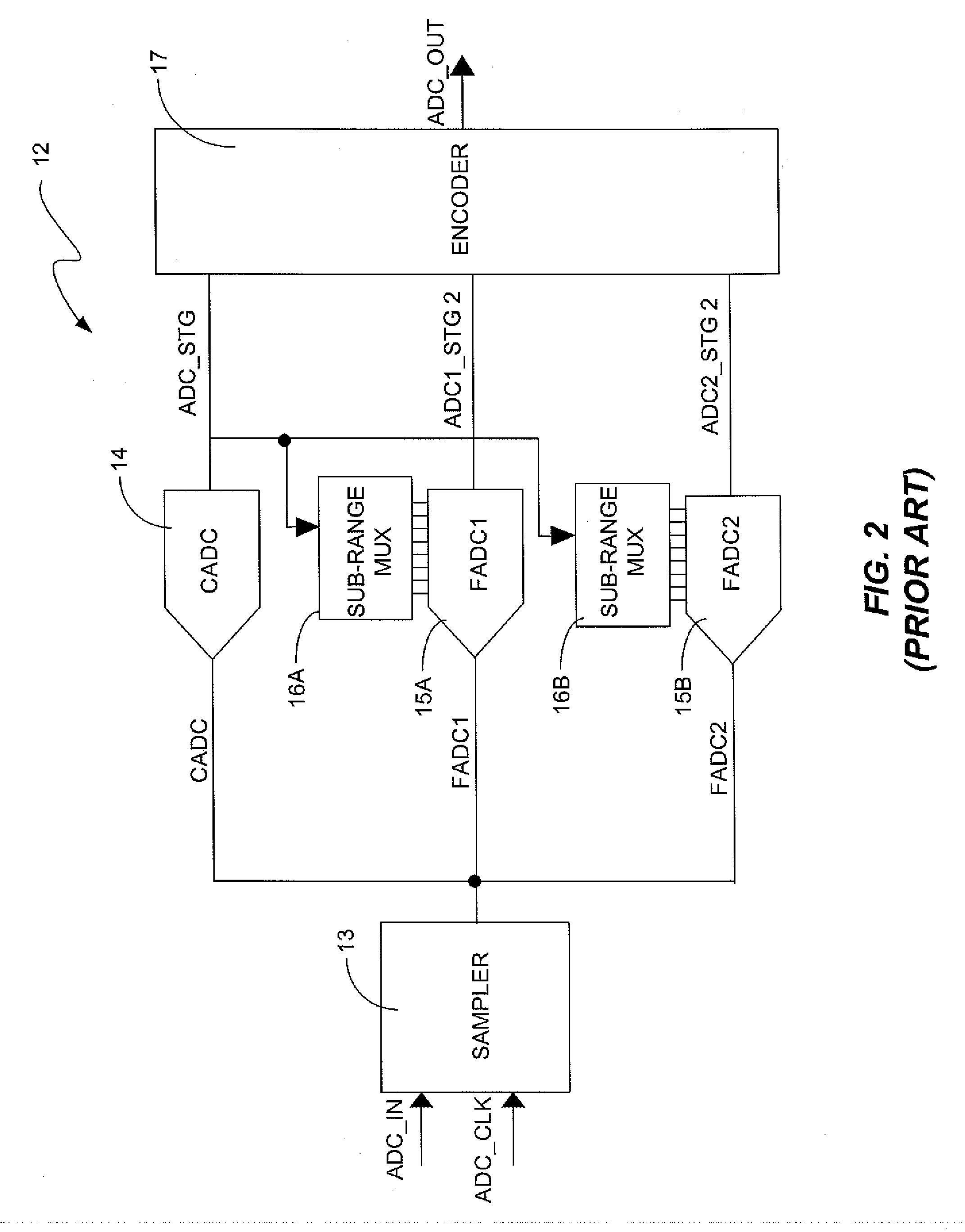

Two-step sub-ranging analog-to-digital converter and method for performing two-step sub-ranging in an analog-to-digital converter

InactiveUS20100103010A1Increased power consumptionExtension of timeElectric signal transmission systemsAnalogue-digital convertersDigital down converterAnalog-to-digital converter

A two-step ADC is provided that achieves significant improvements in the settling time window available for CDAC conversion, FADC sub-ranging and FADC conversion without increasing the amount of chip area or power that are consumed by the ADC. The ADC uses interleaved sampler / buffer circuits to sample the incoming analog signal on different phases of the clock signal. MUXes provide the samples obtained by the sampler / buffer circuits to the CADC and FADC circuits in ping pong fashion in such a way that the CADC and FADC circuits are converting during every clock period. In addition, these improvements are achieved without increasing the number of potential sources of bit decision mismatches in the two-step sub-ranging ADC.

Owner:BROADCOM INT PTE LTD