Patents

Literature

108results about How to "Increase readout speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

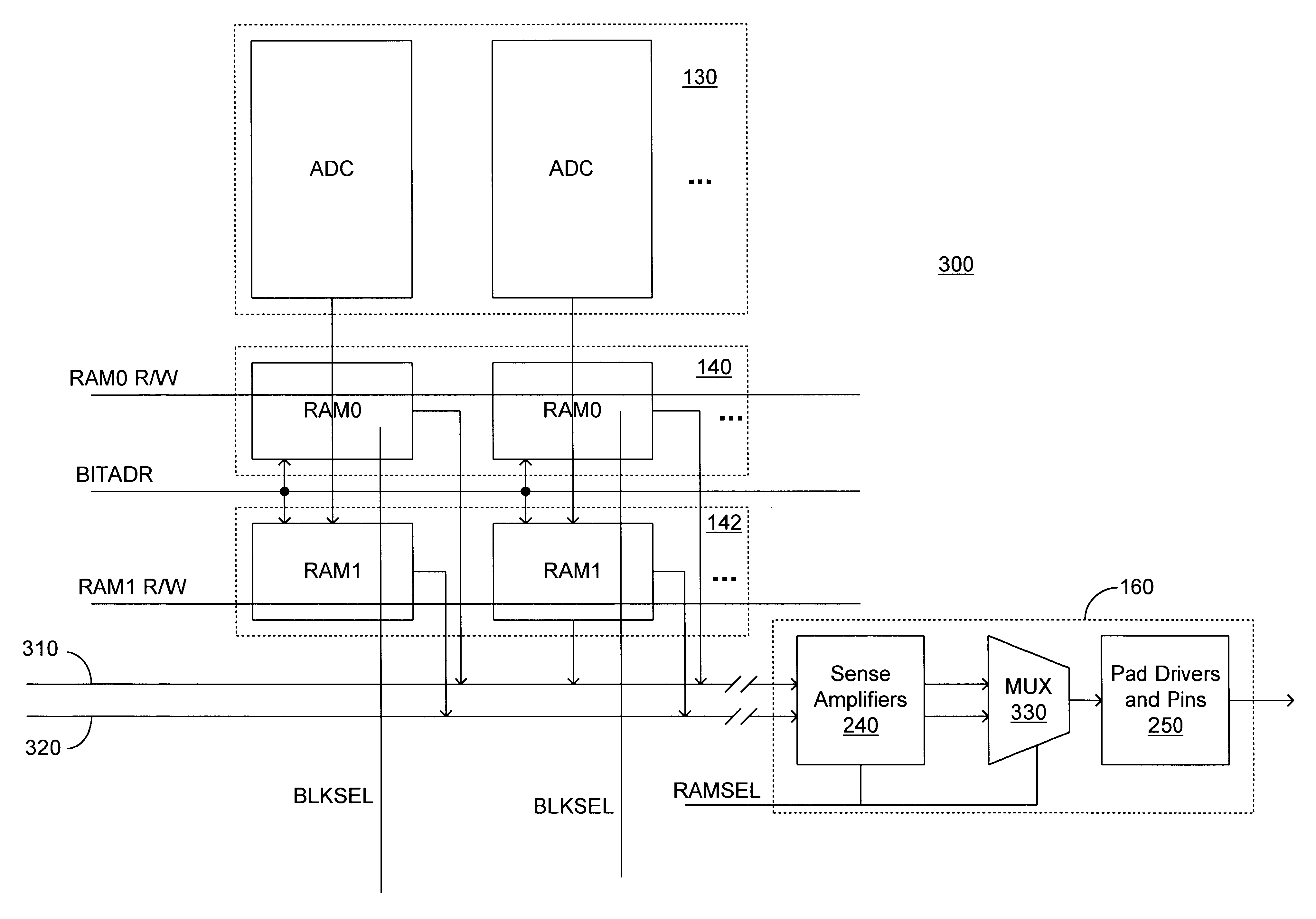

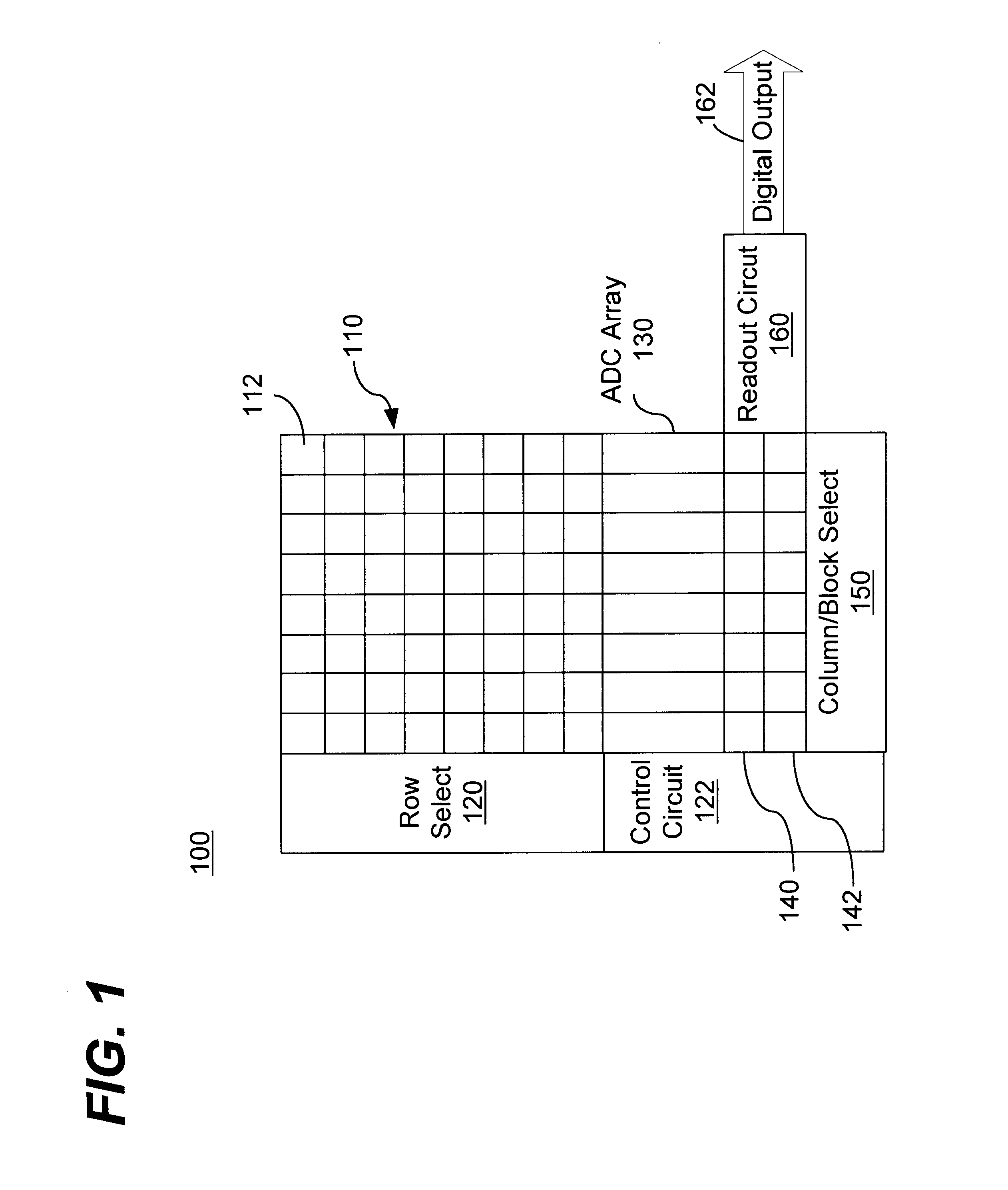

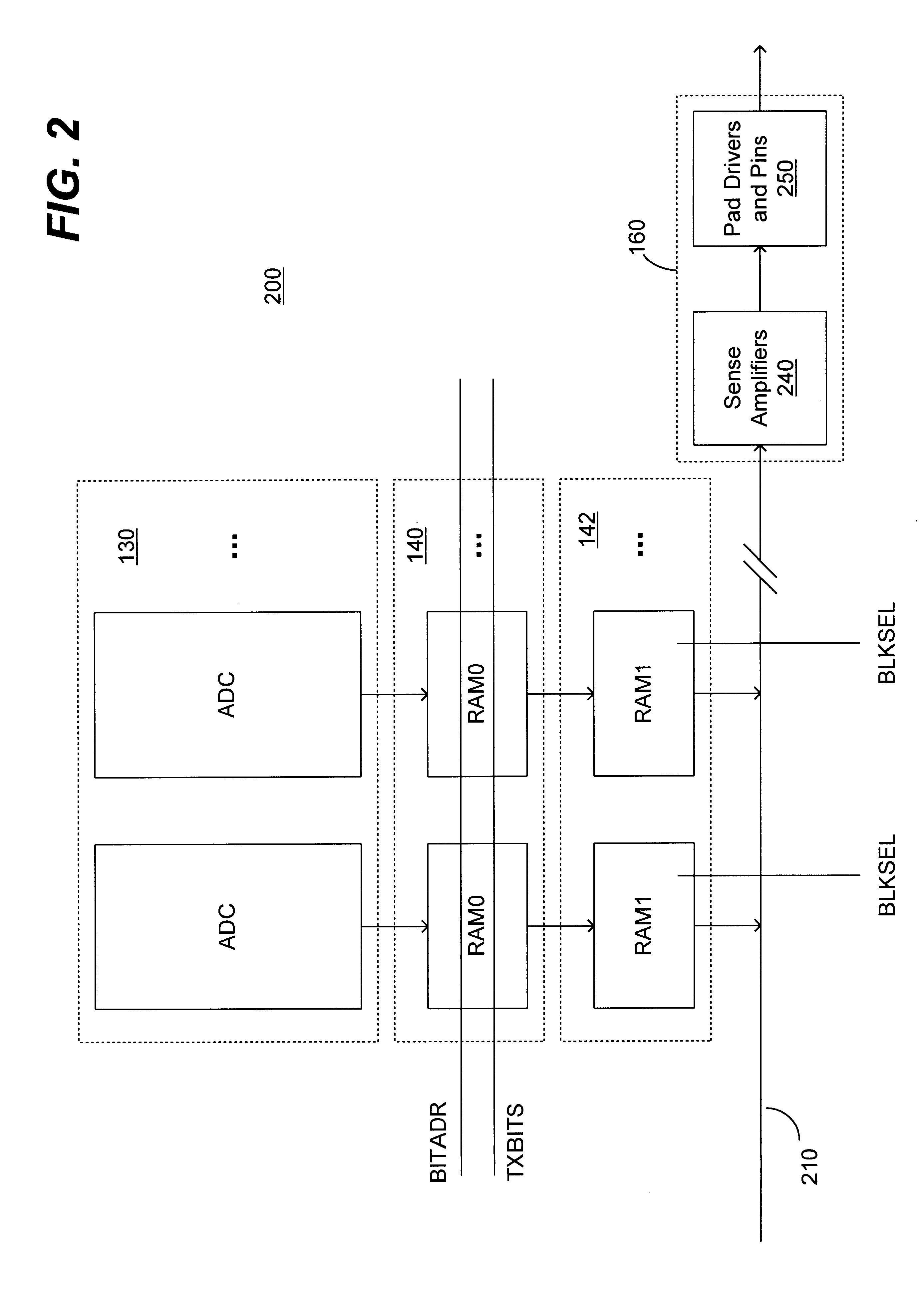

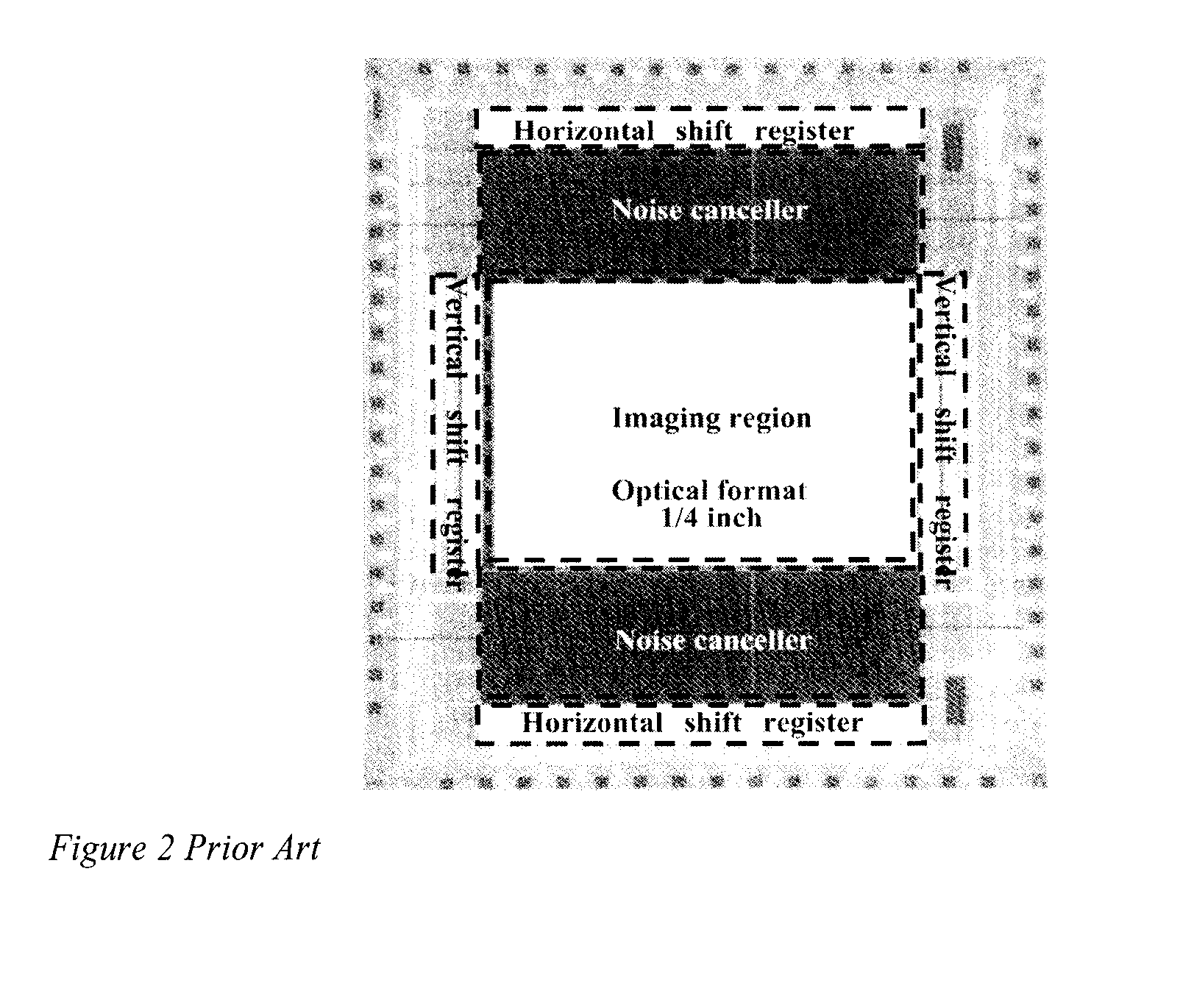

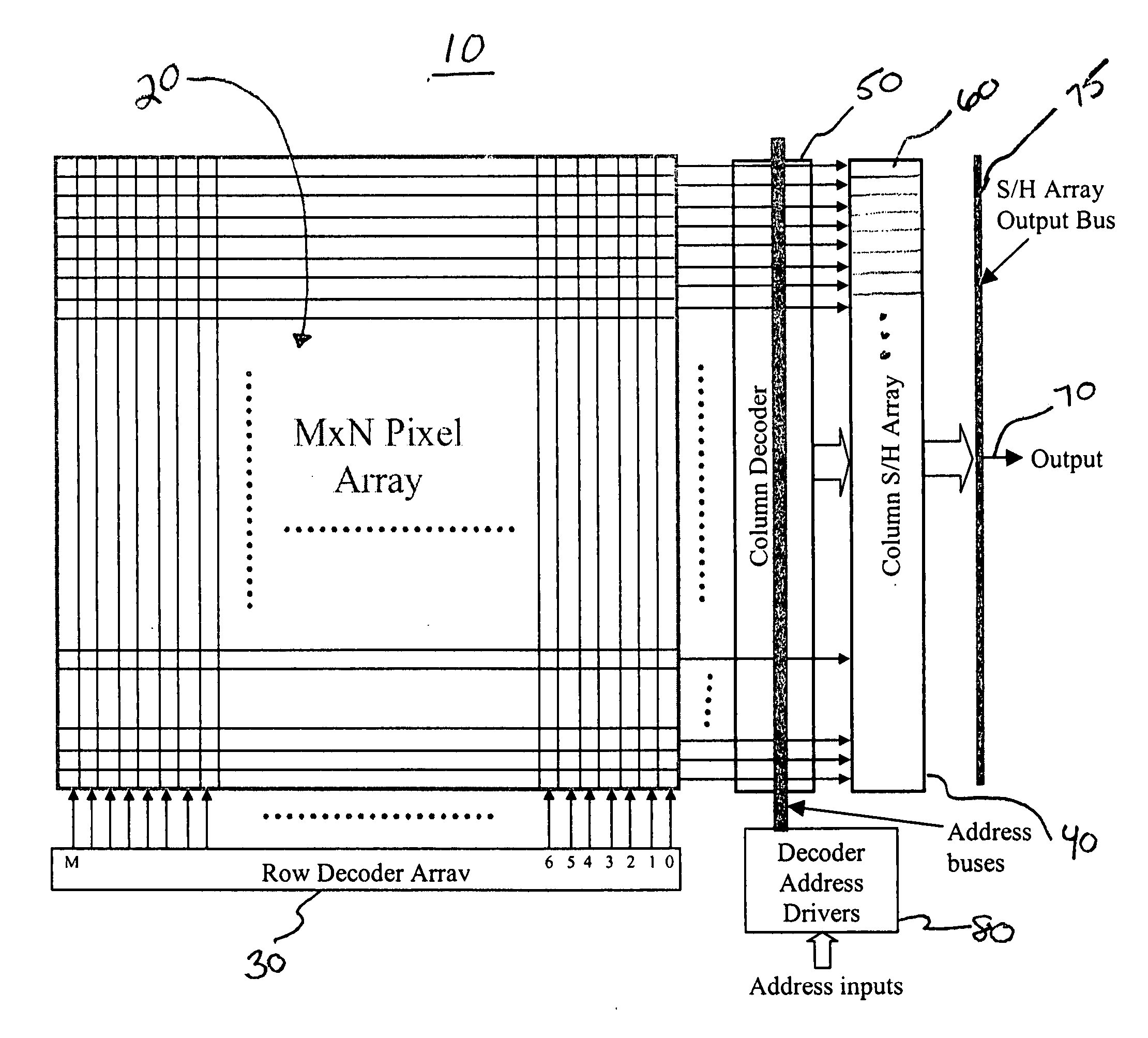

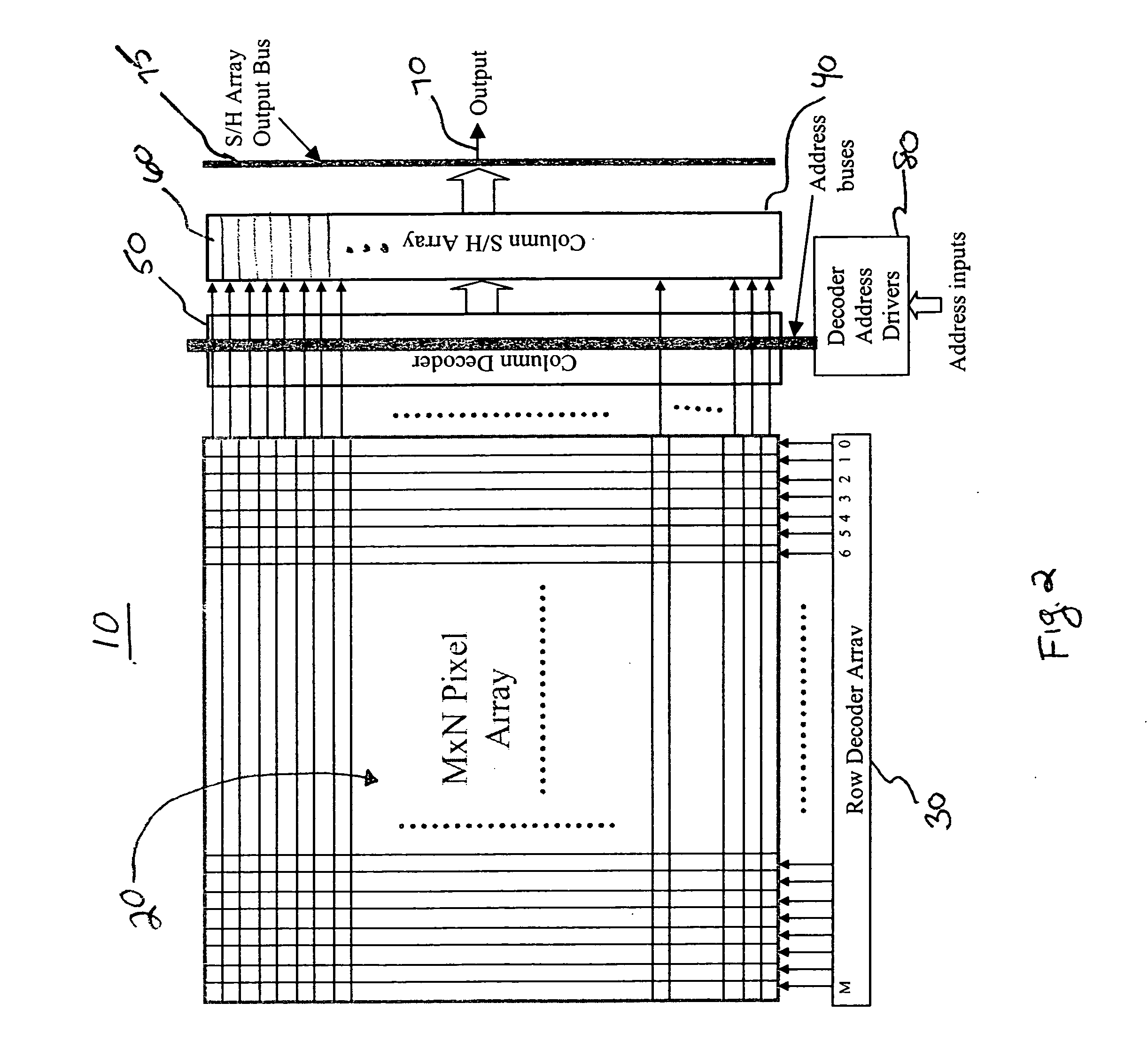

Semiconductor imaging sensor array devices with dual-port digital readout

InactiveUS6870565B1Increase speedReduce delaysTelevision system detailsTelevision system scanning detailsSensor arraySemiconductor

Owner:APTINA IMAGING CORP

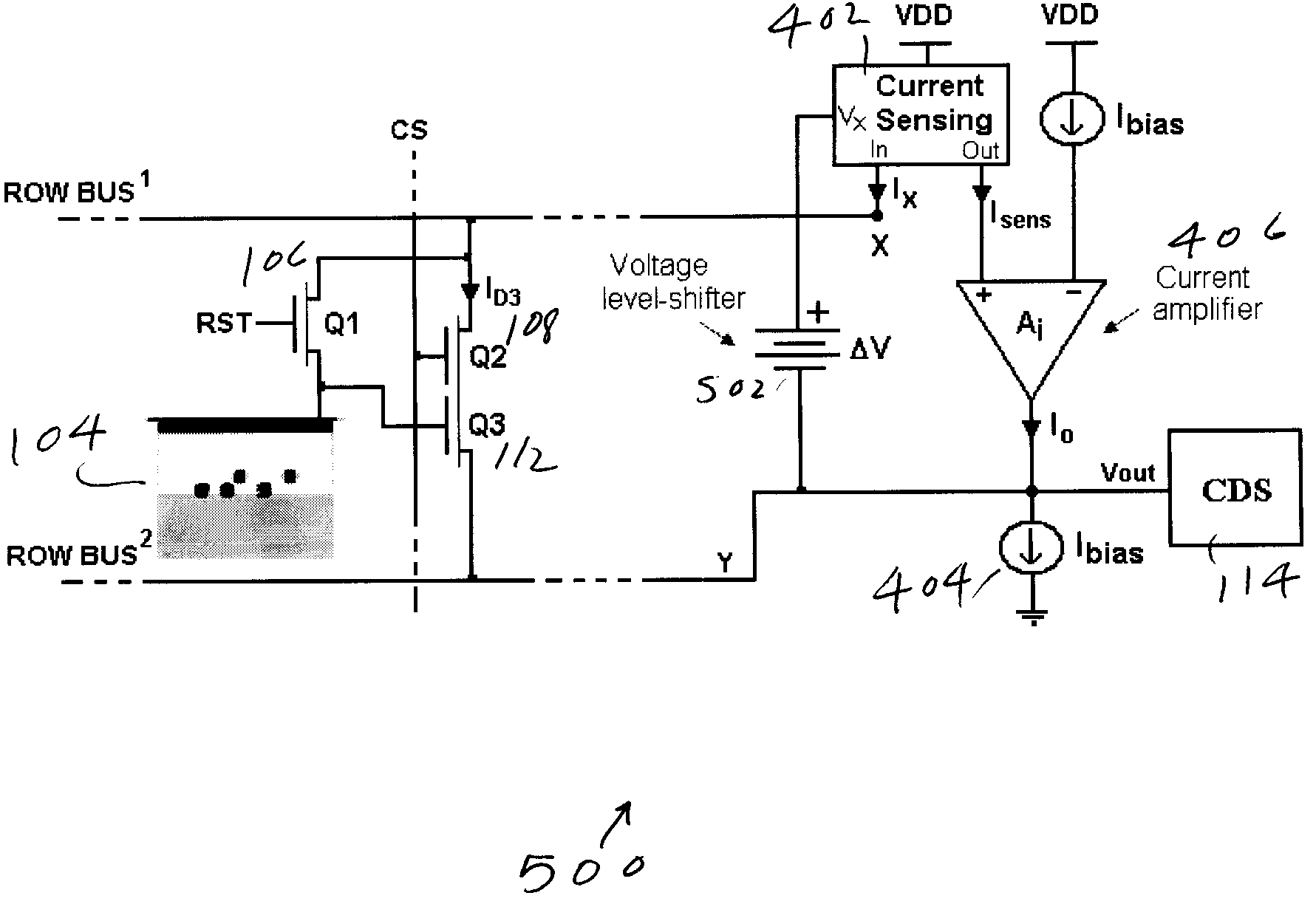

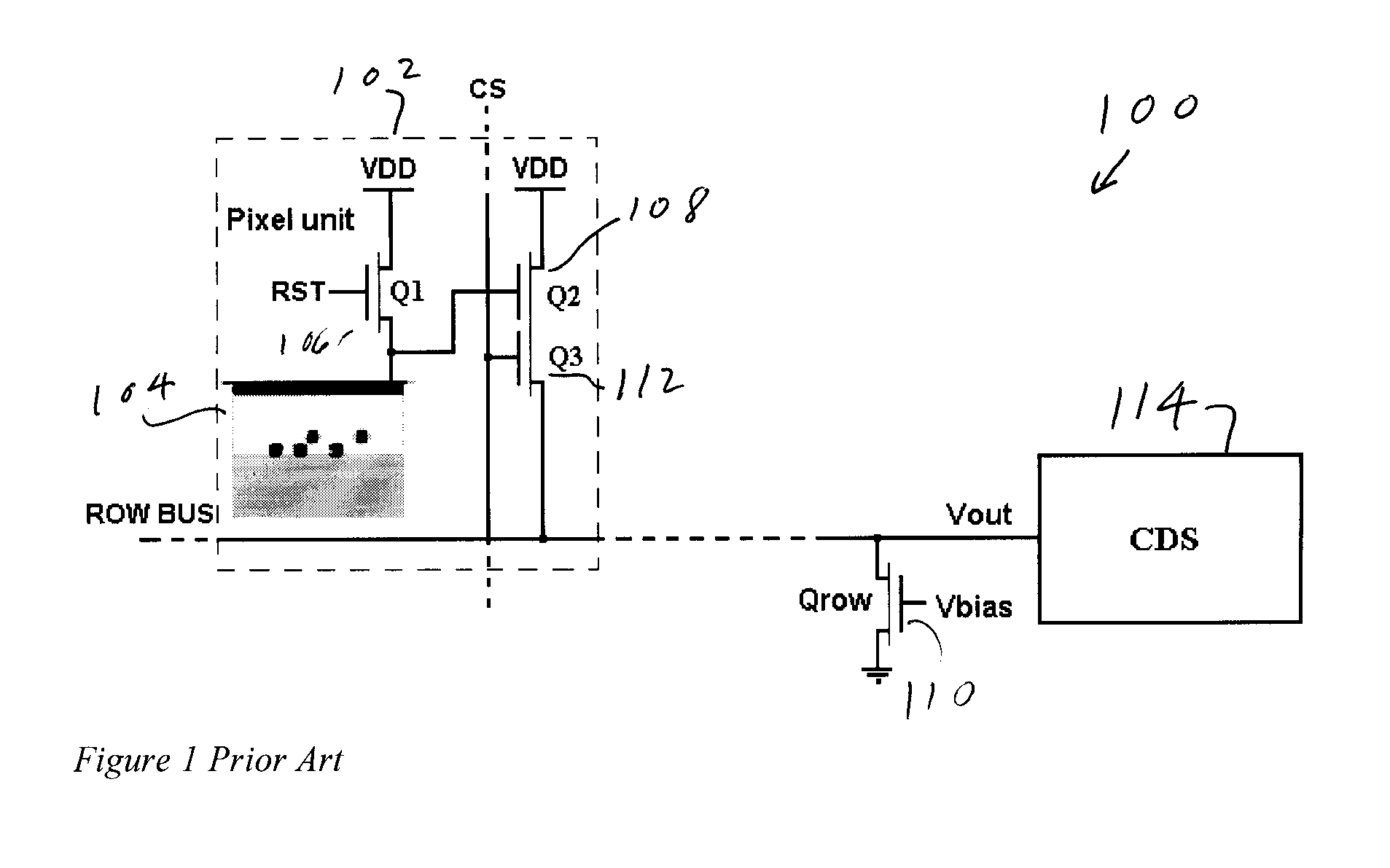

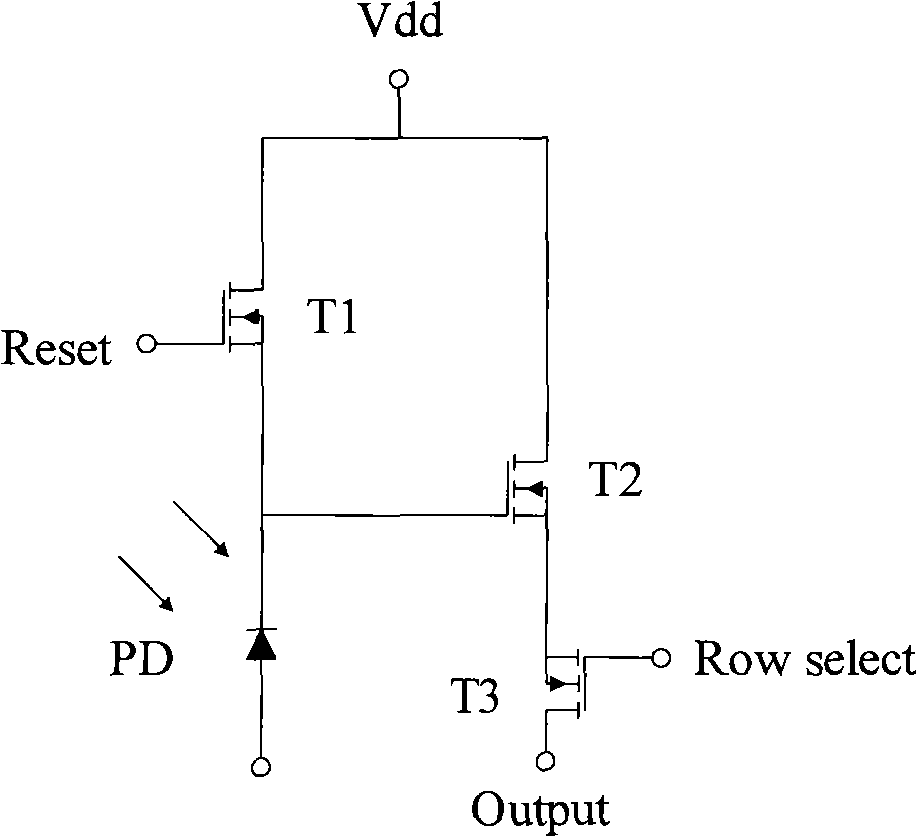

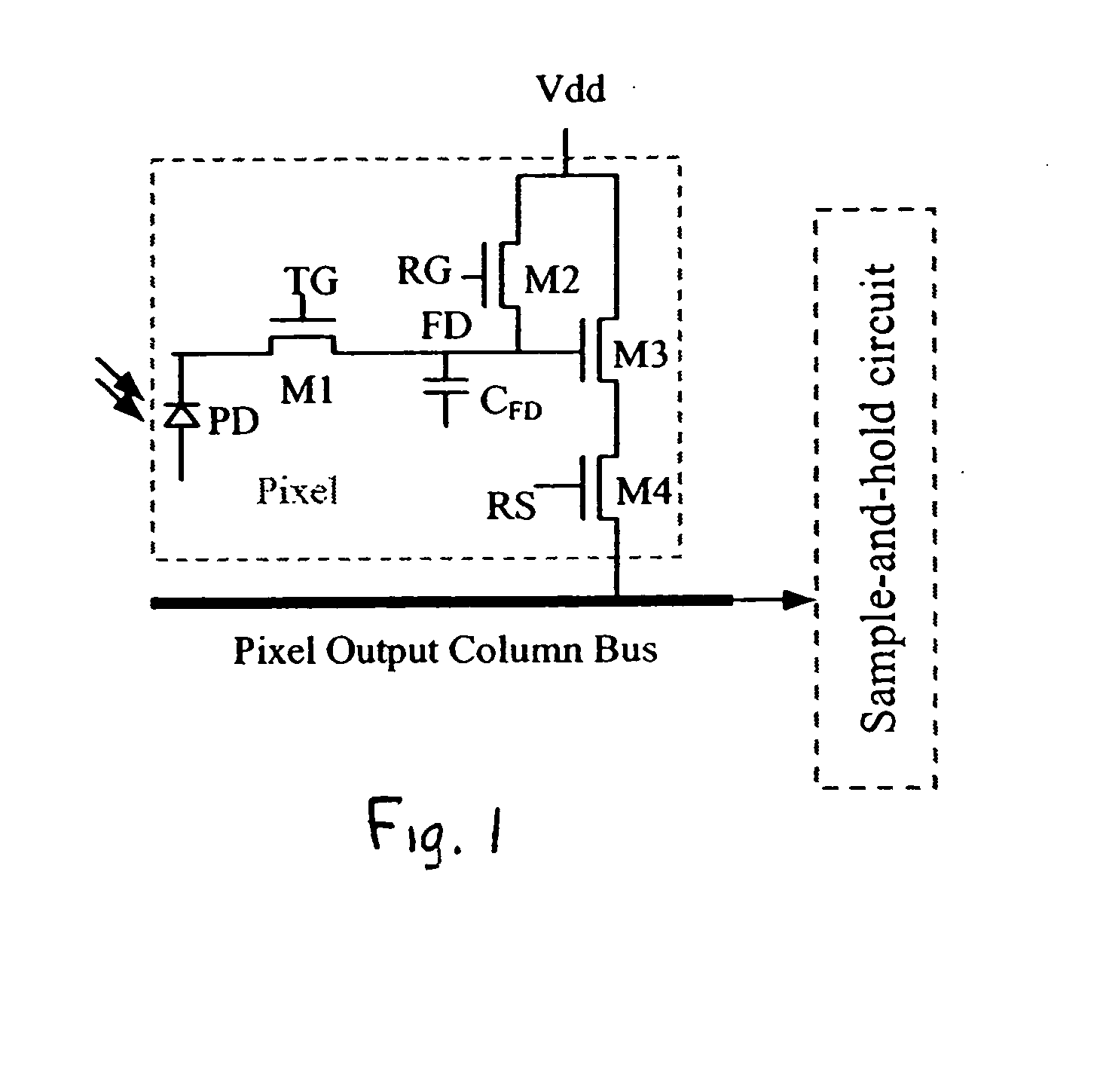

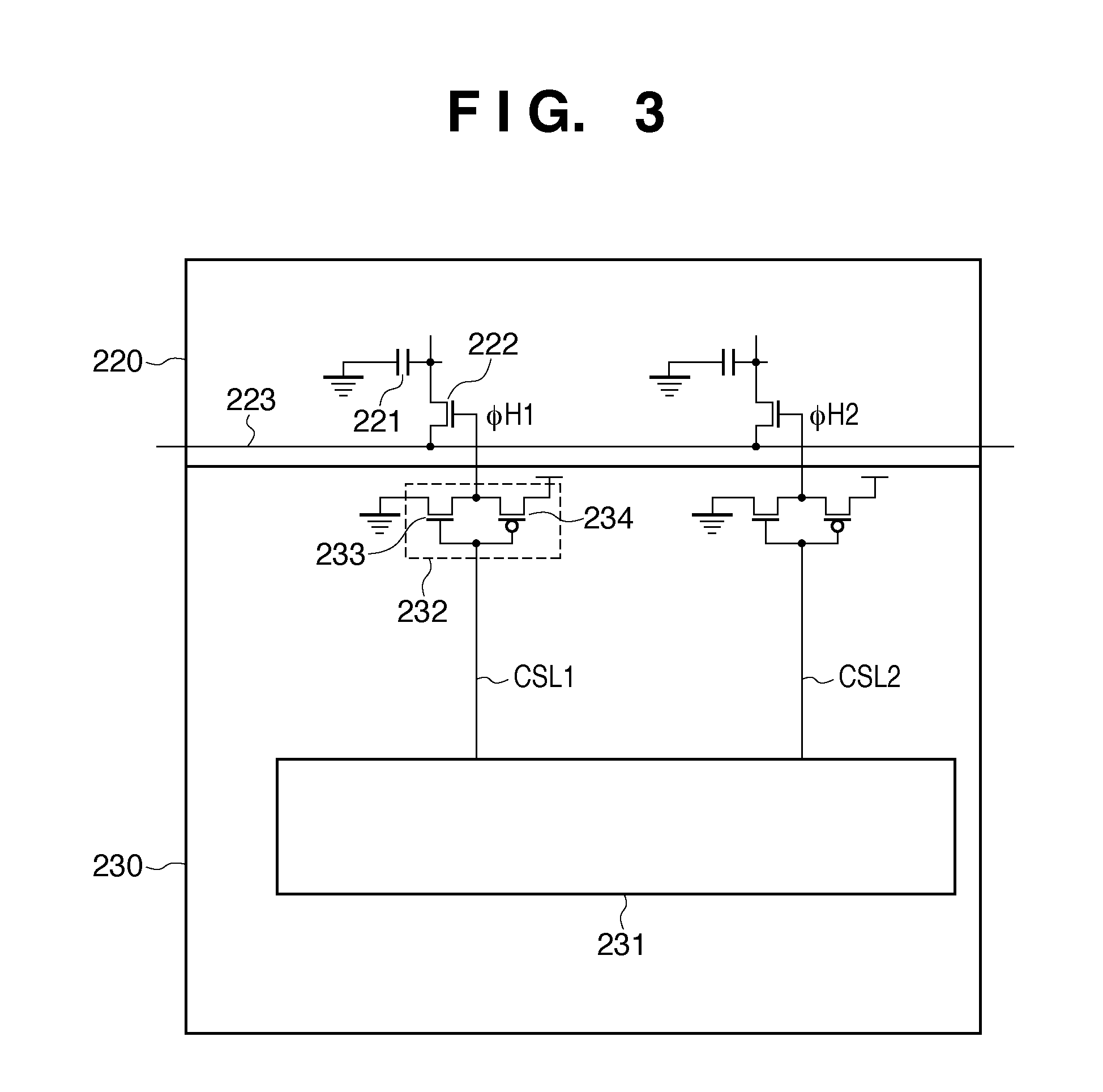

CMOS image sensor readout employing in-pixel transistor current sensing

ActiveUS7847846B1Reduce read noiseIncrease frame rateTelevision system detailsTelevision system scanning detailsCMOSParasitic capacitance

In an image sensor, the current through the in-pixel readout transistor is sensed by a circuit that is external to the pixel, and according to the measured current value a feedback current is supplied to charge the read-line parasitic capacitance. The feedback current is supplied by a circuit that also is external to the pixel area. The amplifier structure is reconfigurable so that it can be used both to read out and to reset the pixel.

Owner:UNIVERSITY OF ROCHESTER

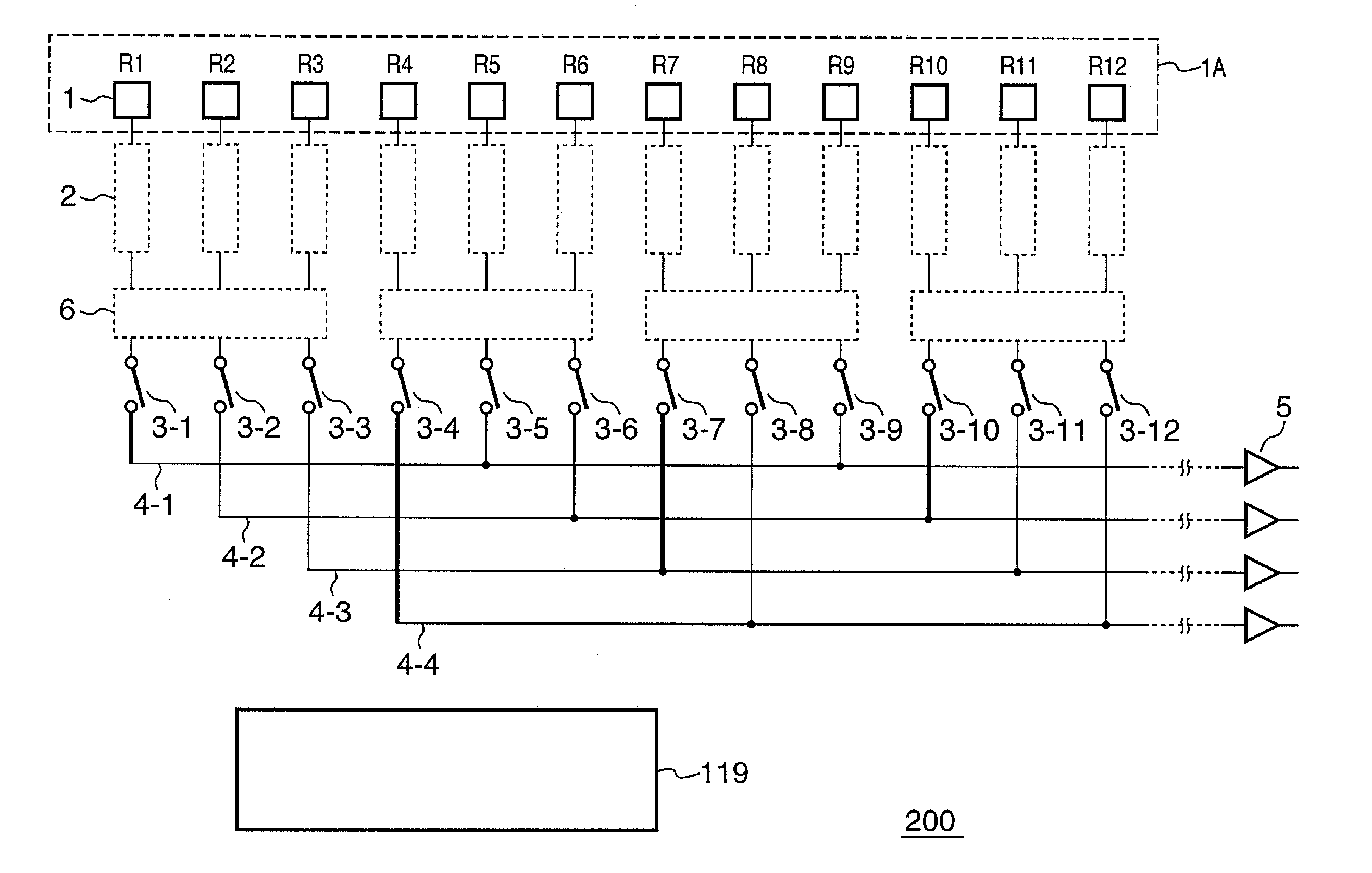

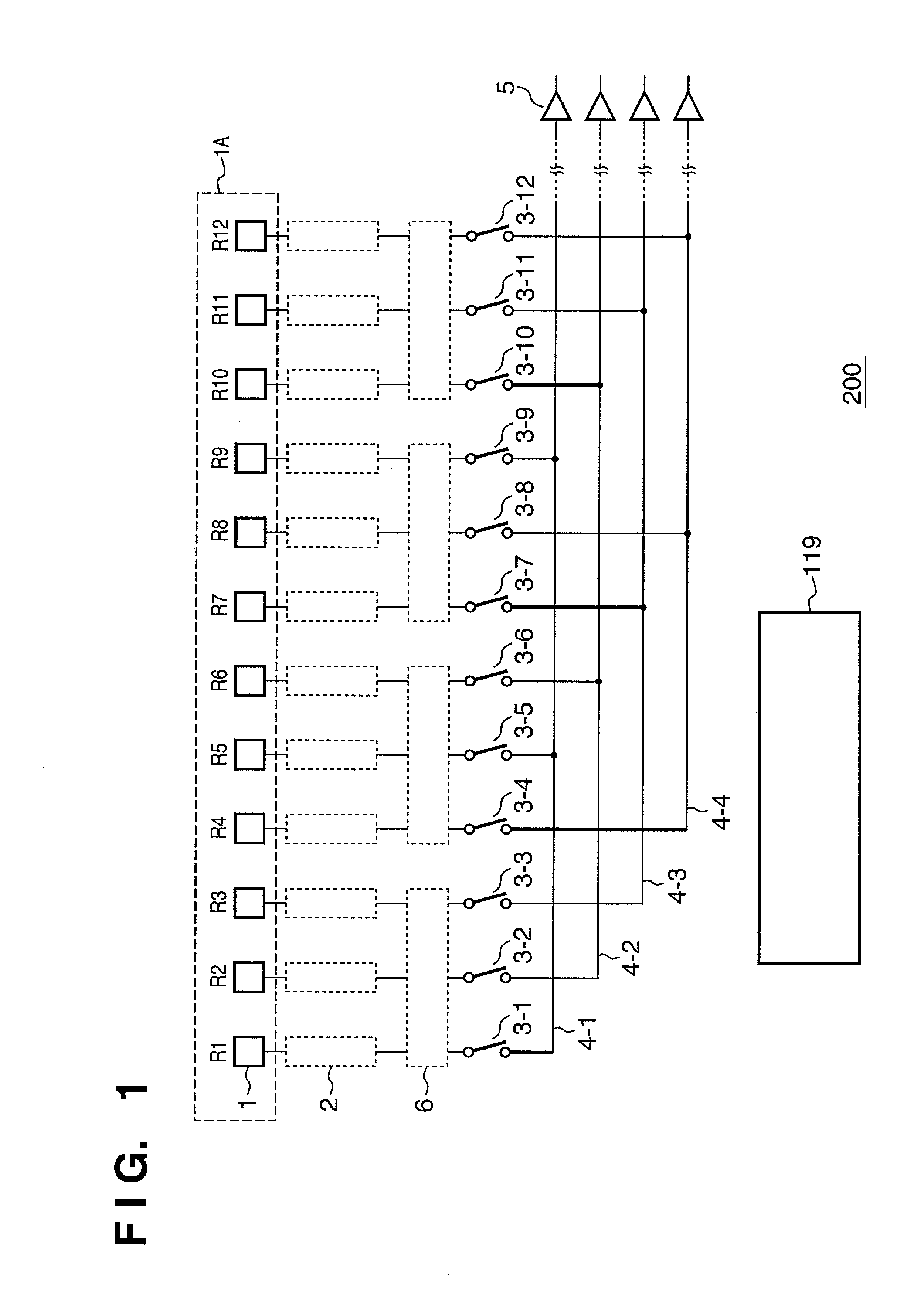

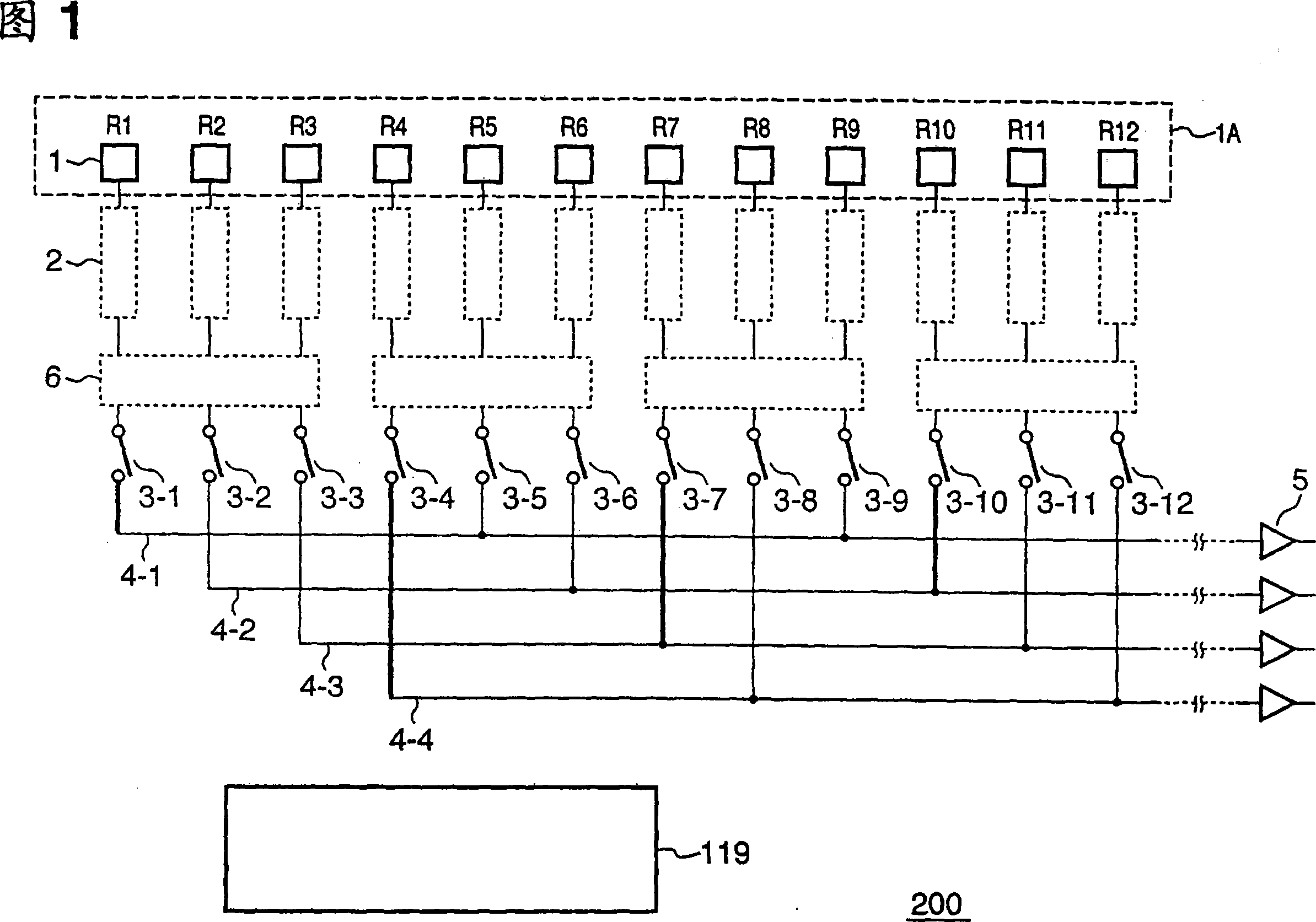

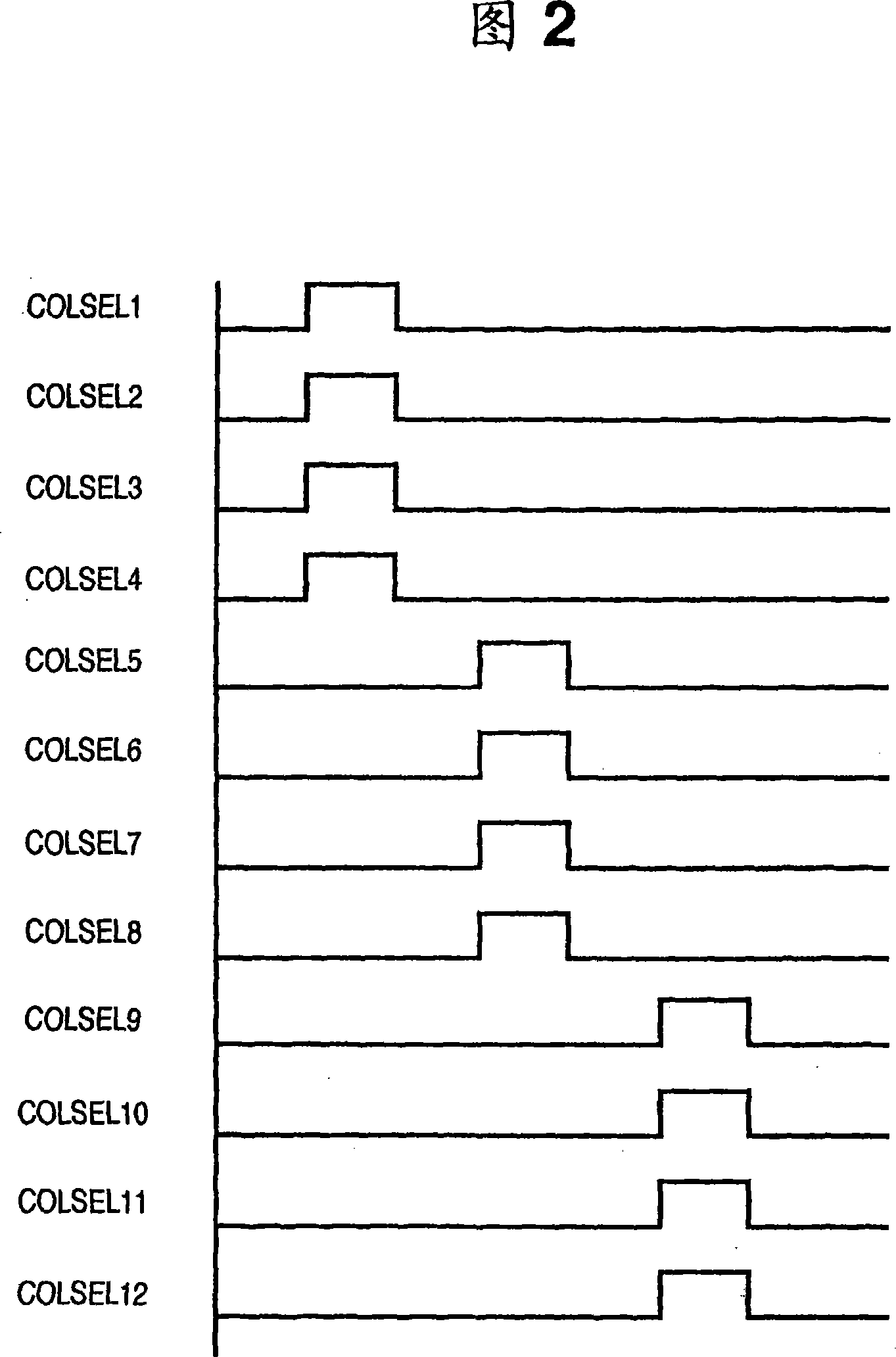

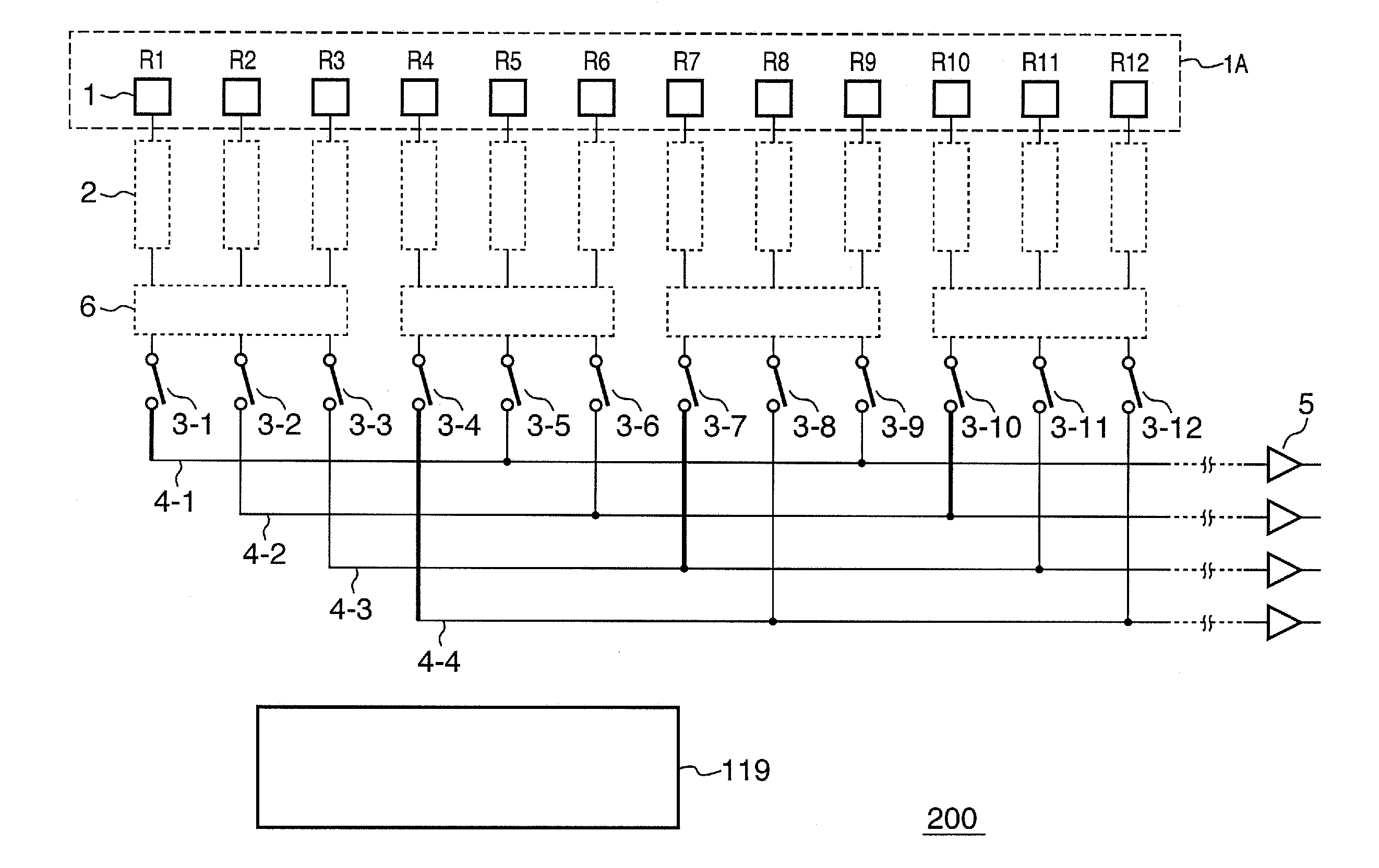

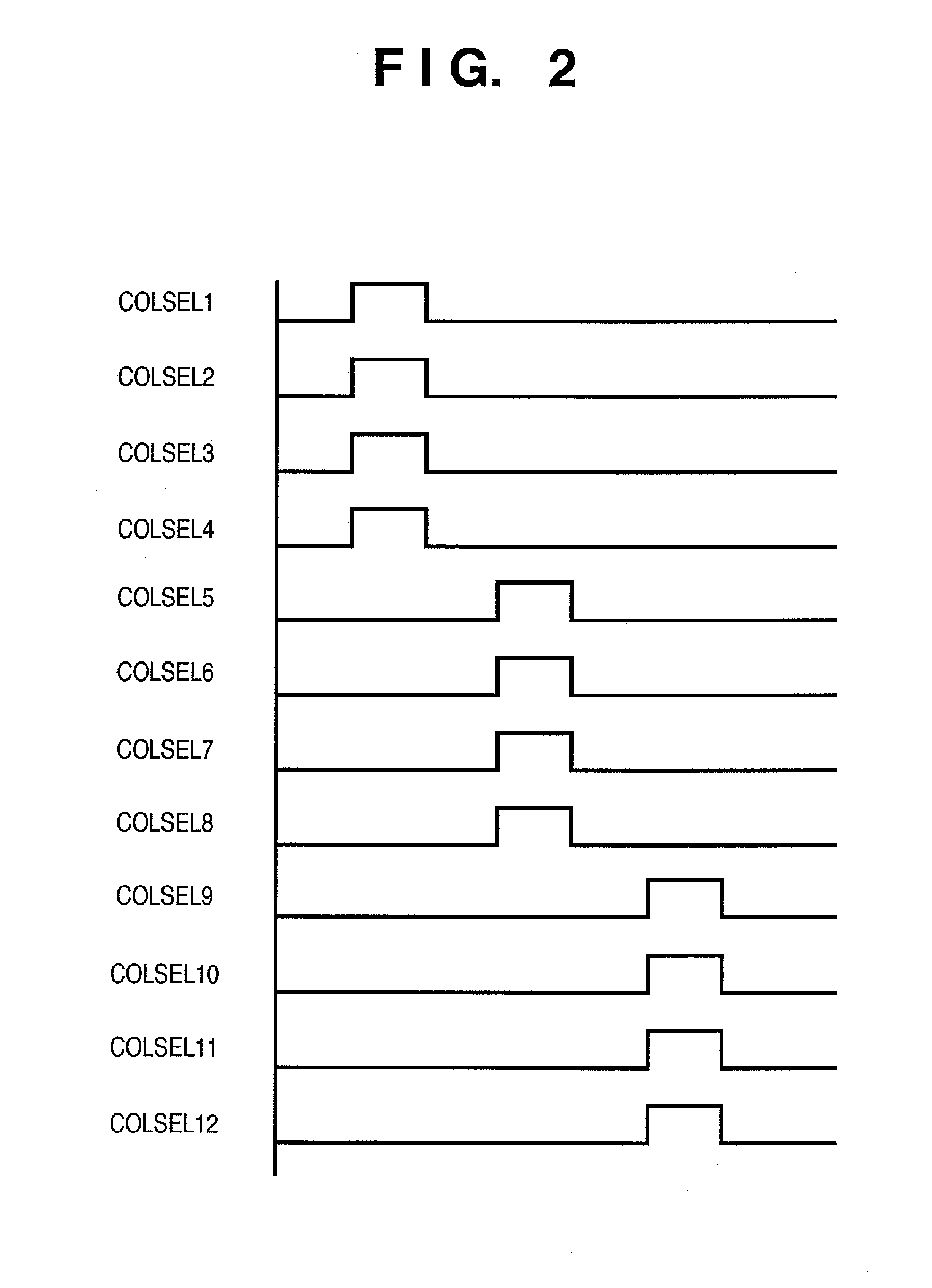

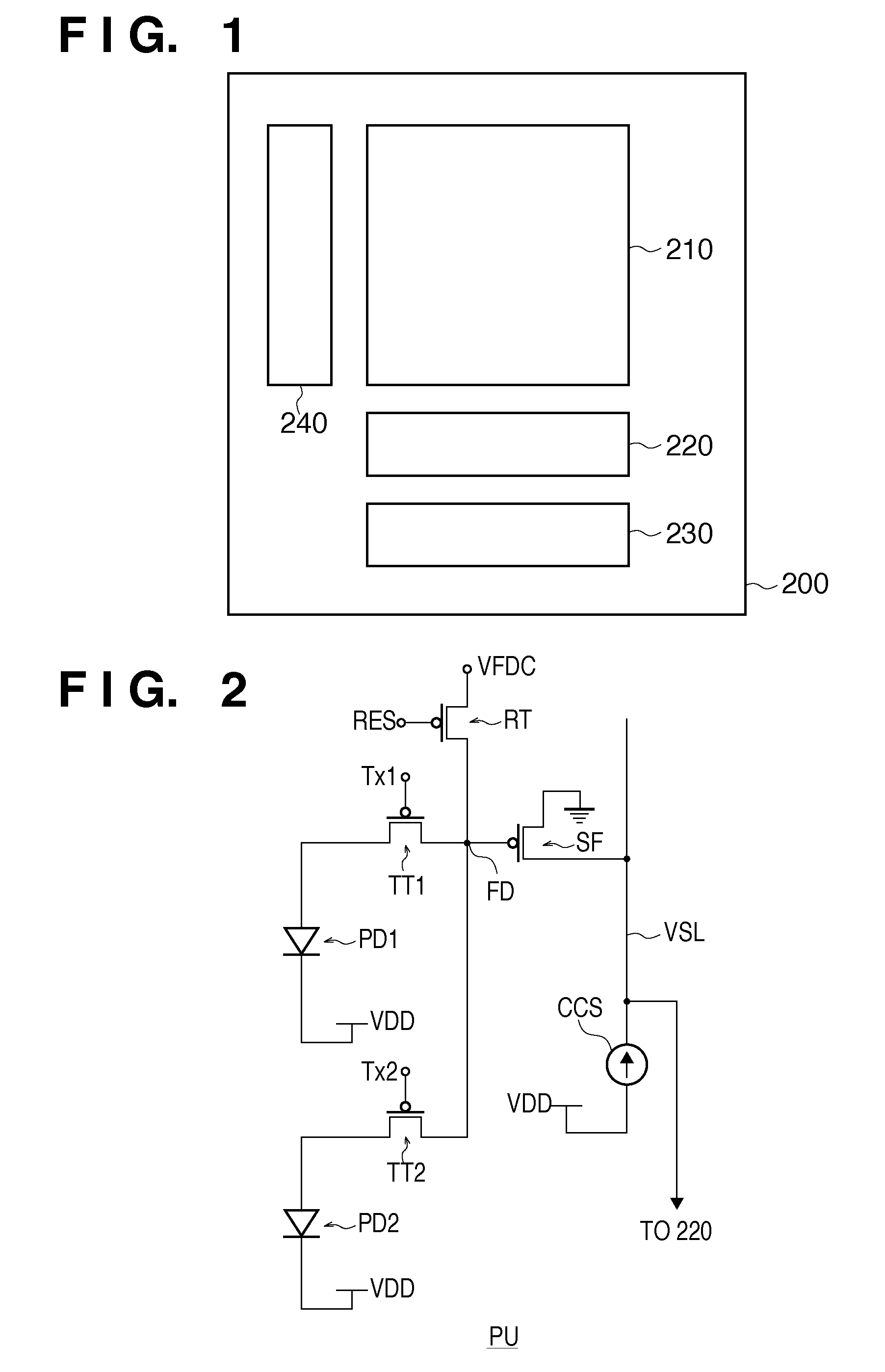

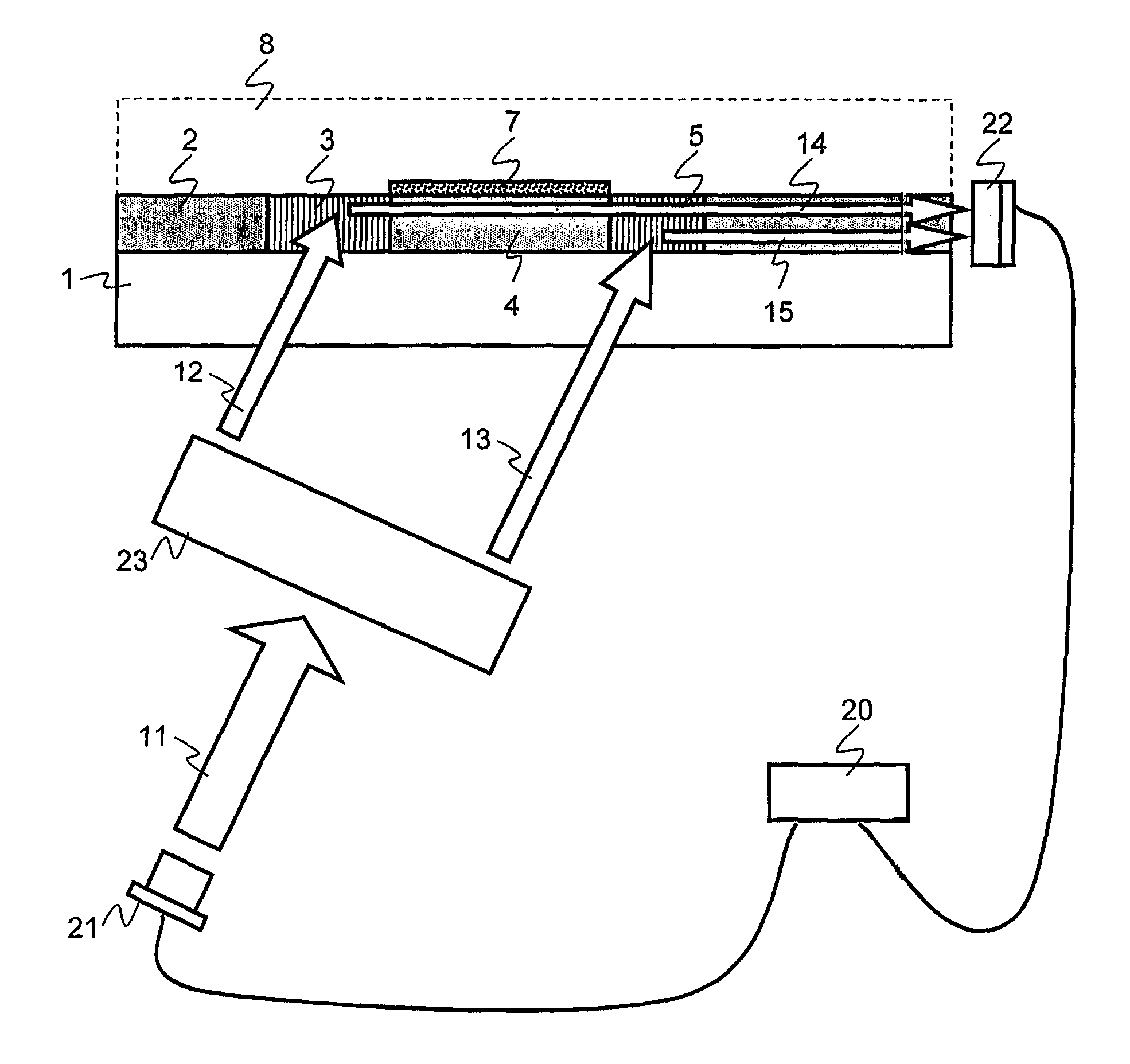

Image sensor

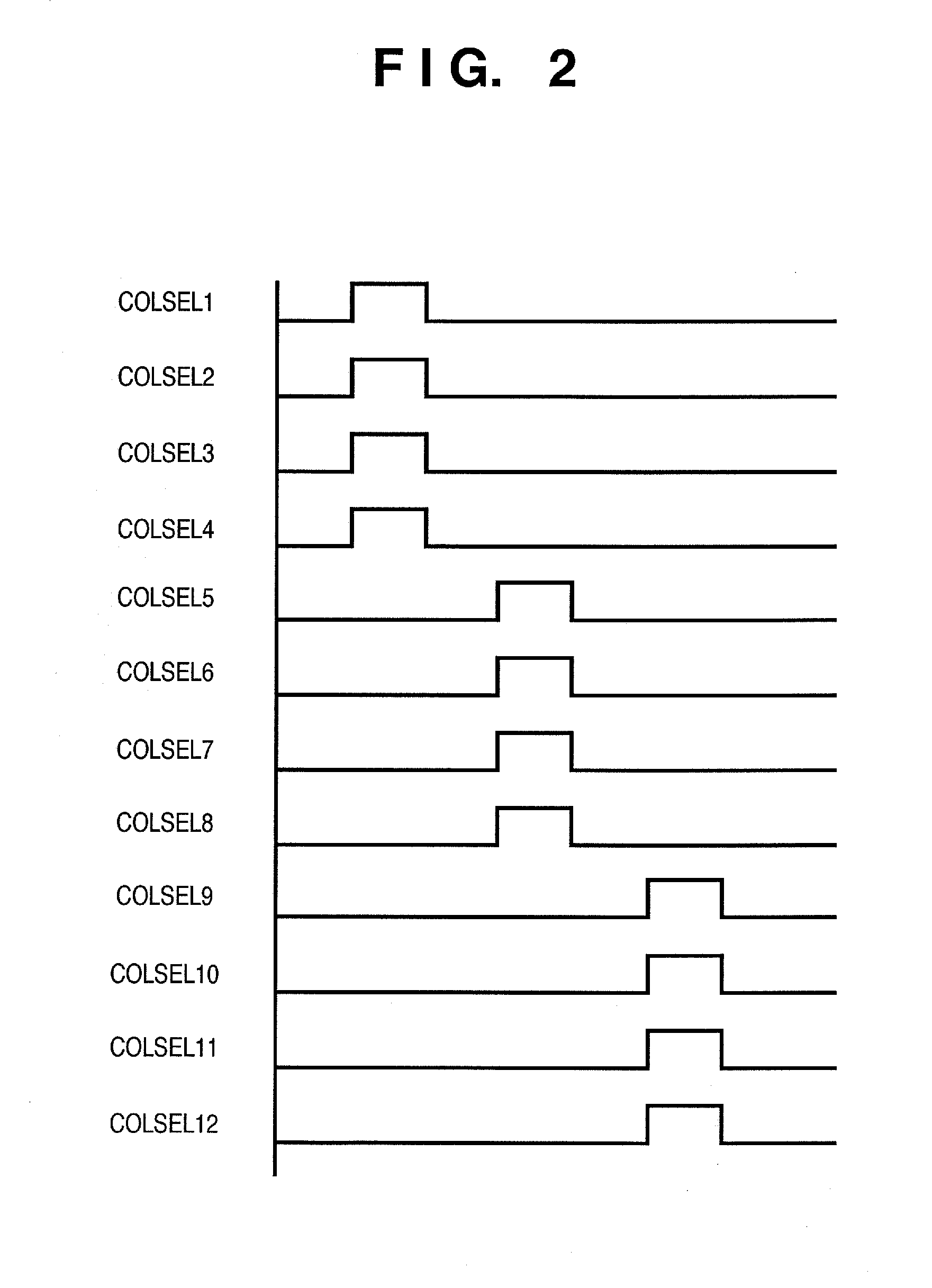

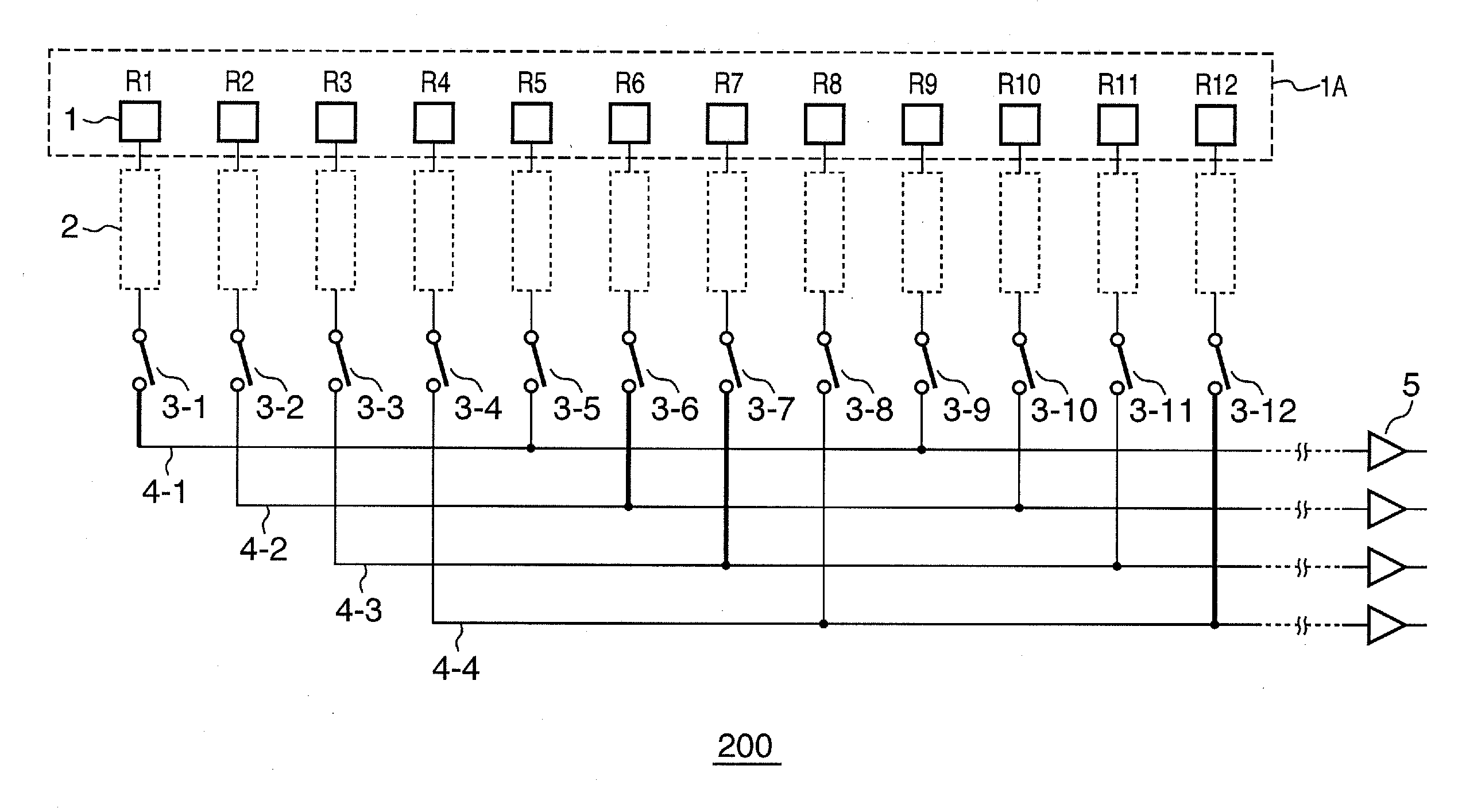

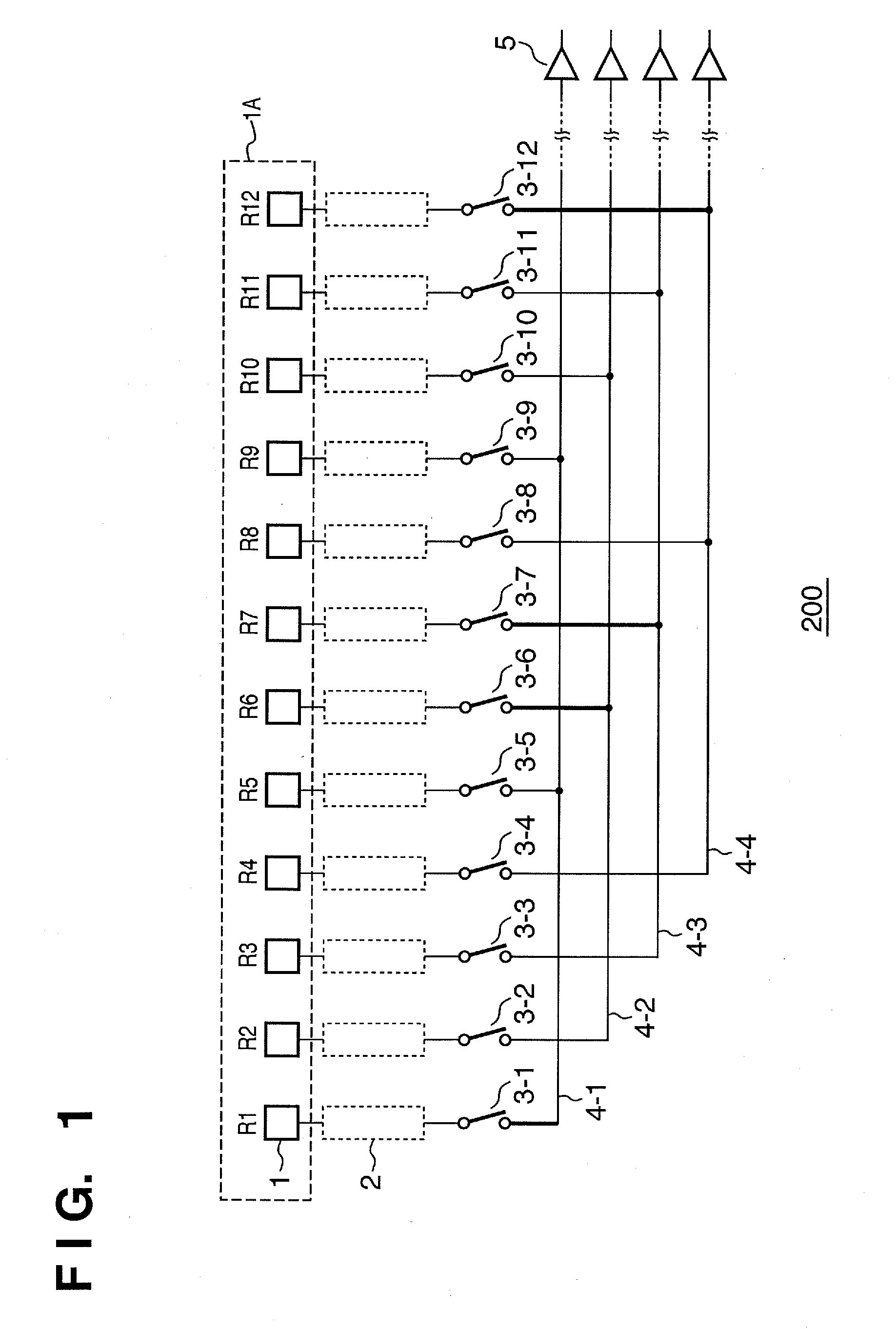

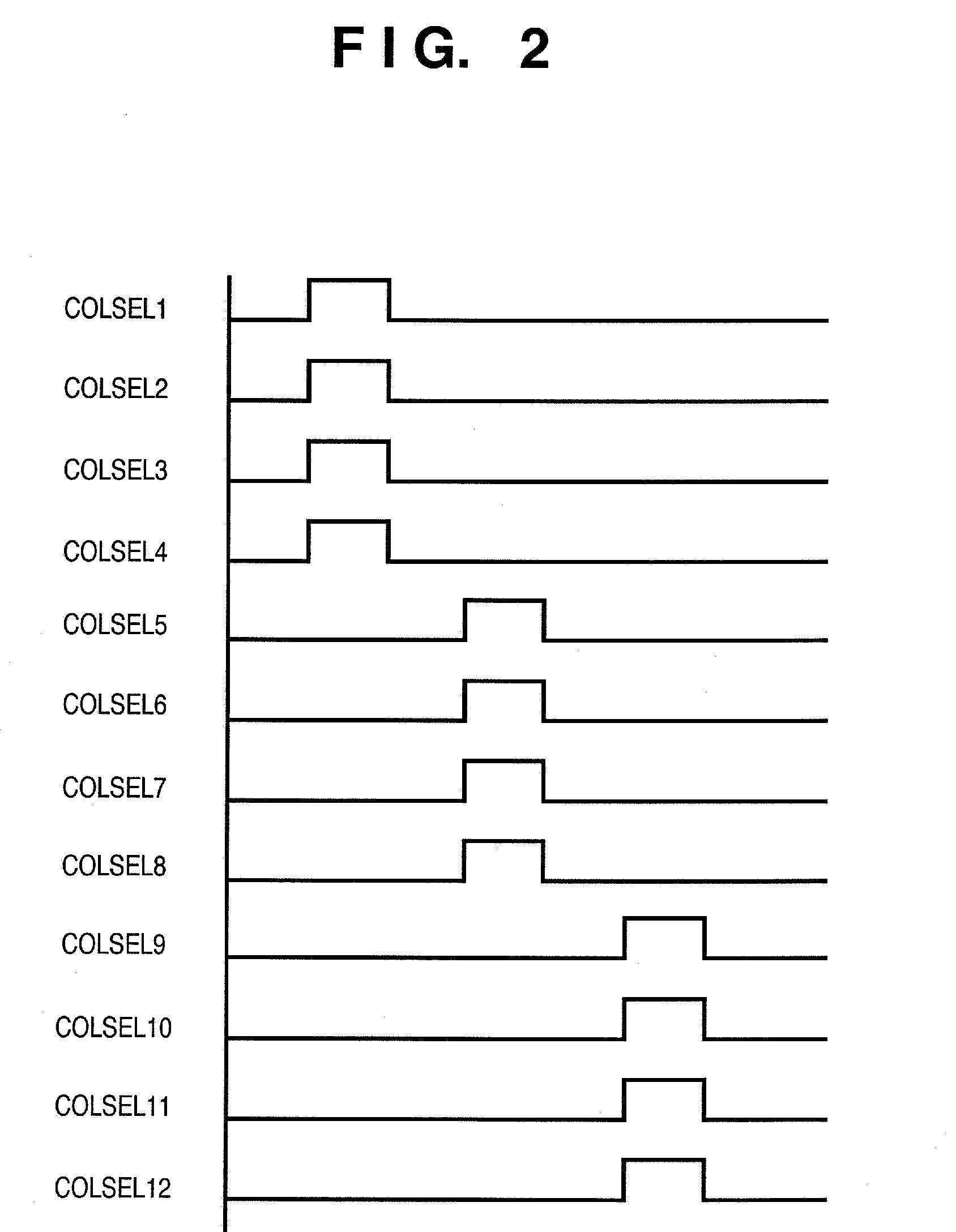

ActiveUS20070229687A1Inhibit productionIncrease readout speedTelevision system detailsTelevision system scanning detailsControl circuitComputer science

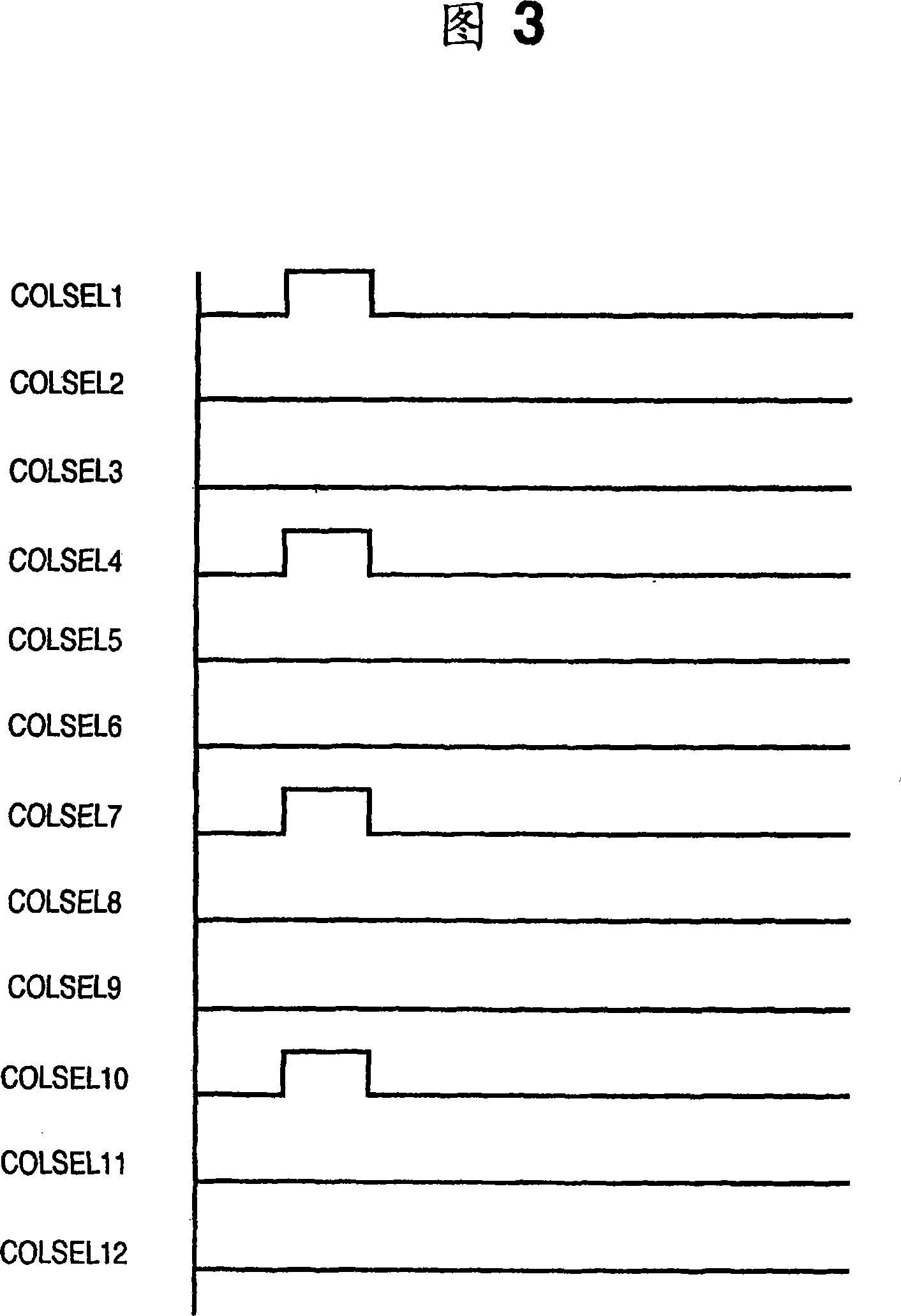

An image sensor includes a plurality of operation circuits. The operation circuit operates pixel signals read out from a group of pixels included in a readout area to generate a pixel signal in the thinning readout mode. A plurality of column selecting switches are arranged between the output terminals of the plurality of operation circuits and a plurality of output channels. A control circuit controls the plurality of column selecting switches such that pixel signals the number of which is equal to the number of the plurality of output channels are output to the plurality of output channels in parallel in the thinning readout mode. The circuit arrangements, each included in the corresponding one of the plurality of operation circuits and each viewed from the corresponding one of the column selecting switches used in the thinning readout mode, are equivalent to each other.

Owner:CANON KK

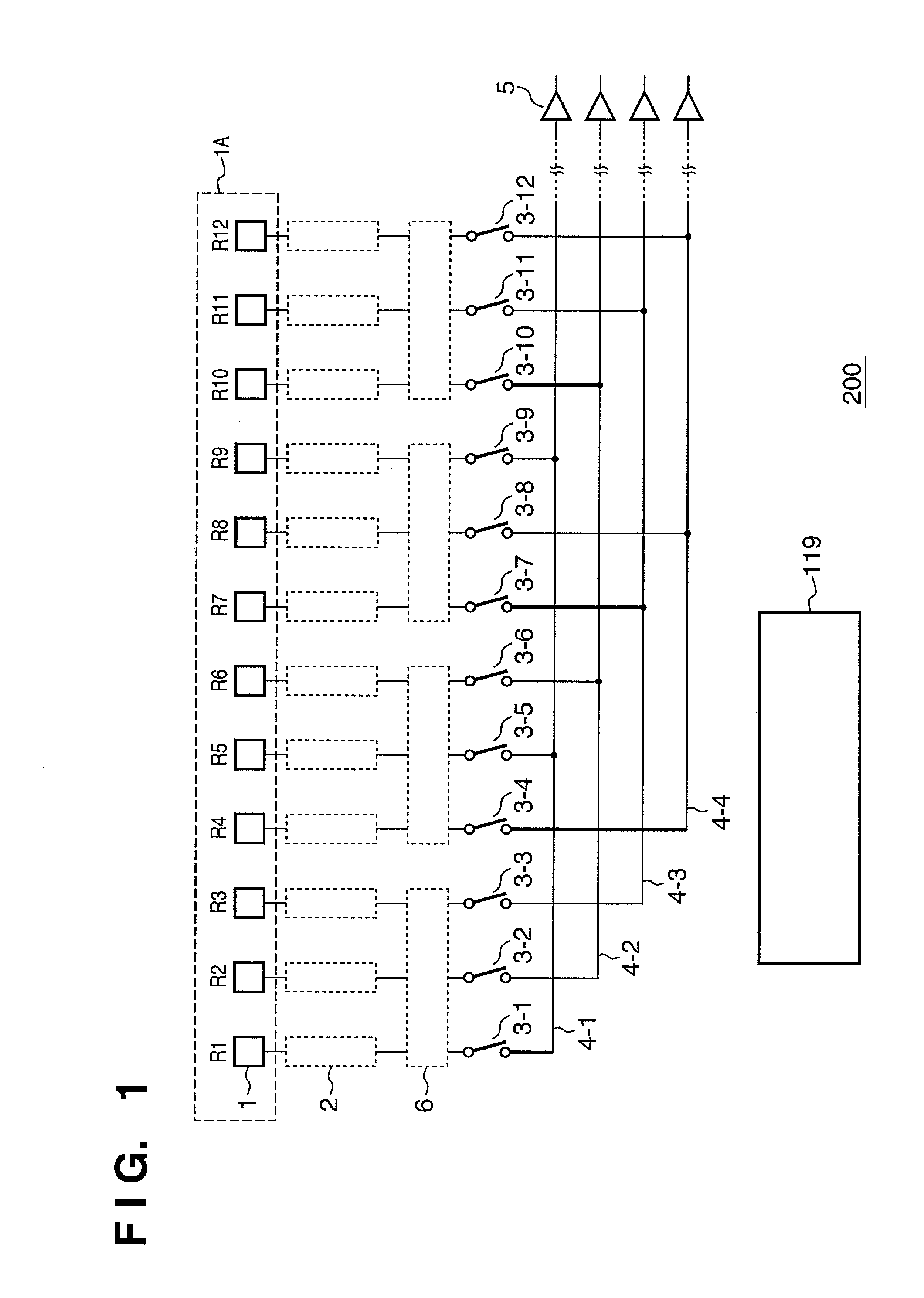

Image sensor

ActiveUS20070229686A1Reduce loadIncrease readout speedTelevision system detailsTelevision system scanning detailsEngineeringControl circuit

An image sensor has a plurality of pixels arrayed to form a plurality of columns. The sensor includes a plurality of readout circuits which generate pixel signals based on signals supplied from the pixels of respective columns, a plurality of output channels, a plurality of column selecting switches, and a control circuit which controls the plurality of column selecting switches. The control circuit controls the plurality of column selecting switches so as to output the pixel signals of target readout pixels to output channels selected based on a selection rule in the spatial order of the pixels in the full pixel readout mode. The control circuit controls the plurality of column selecting switches so as to output the thinned-out pixel signals of target readout areas to output channels selected based on the same rule as the selection rule in the spatial order of the areas in the thinning readout mode.

Owner:CANON KK

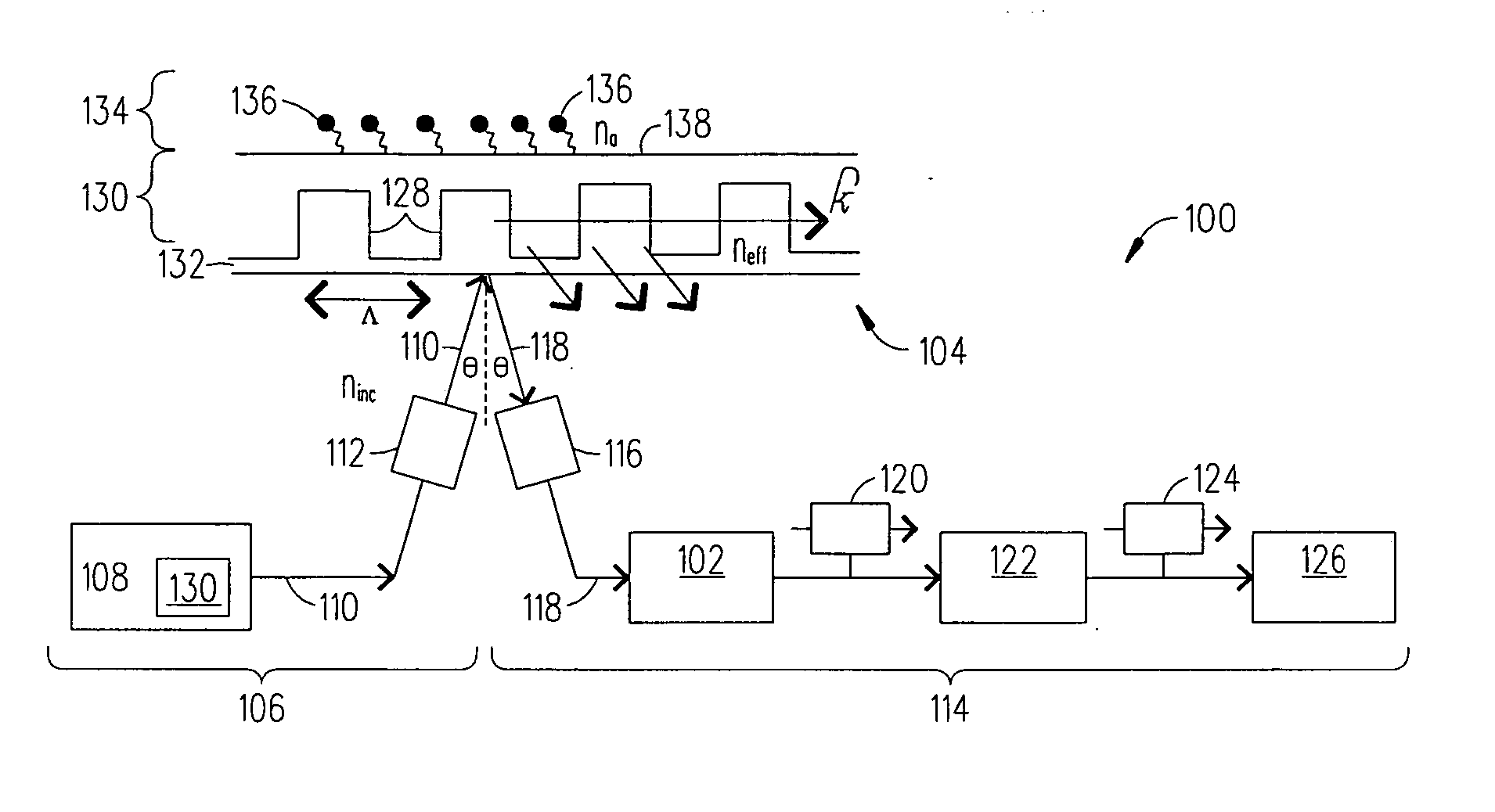

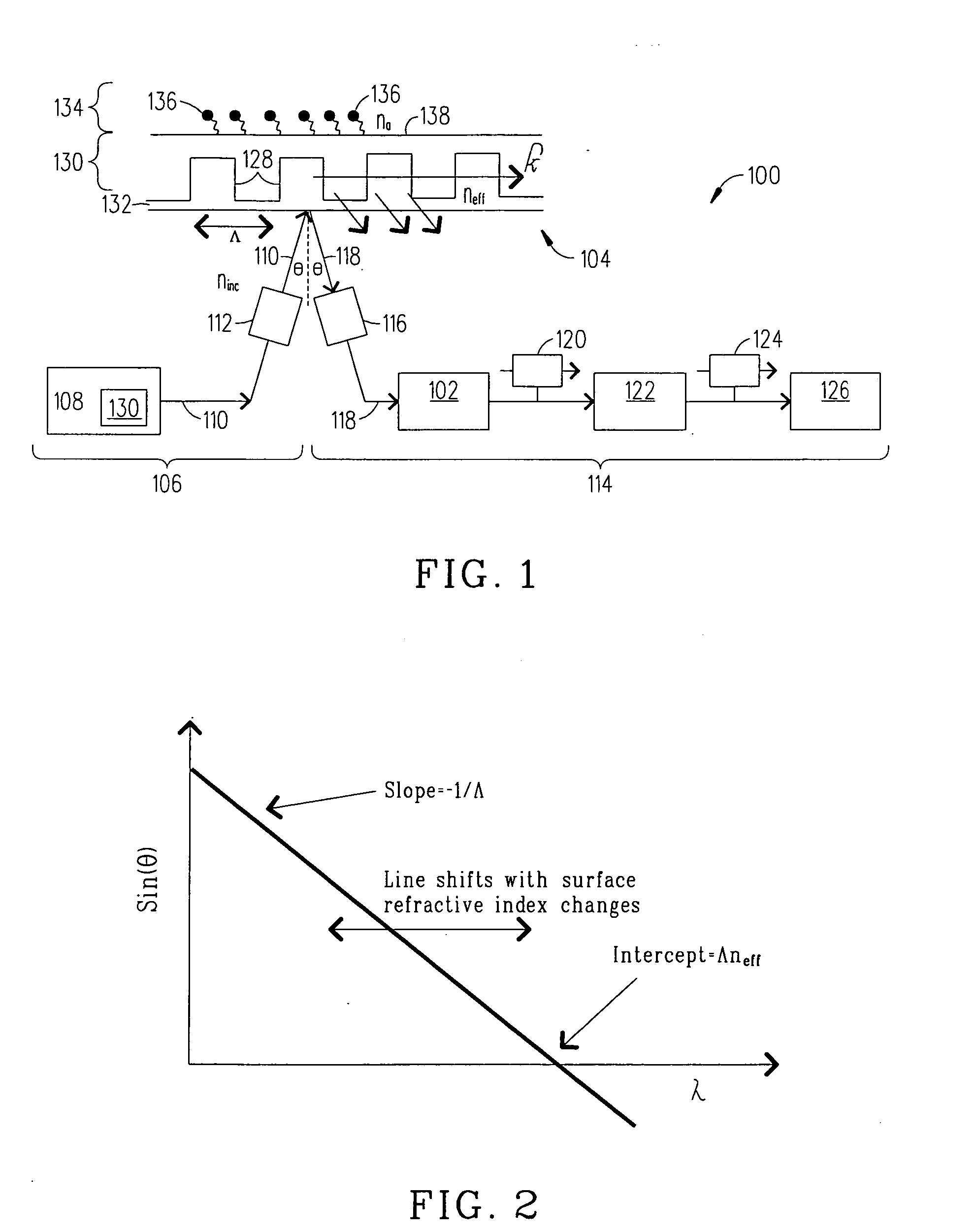

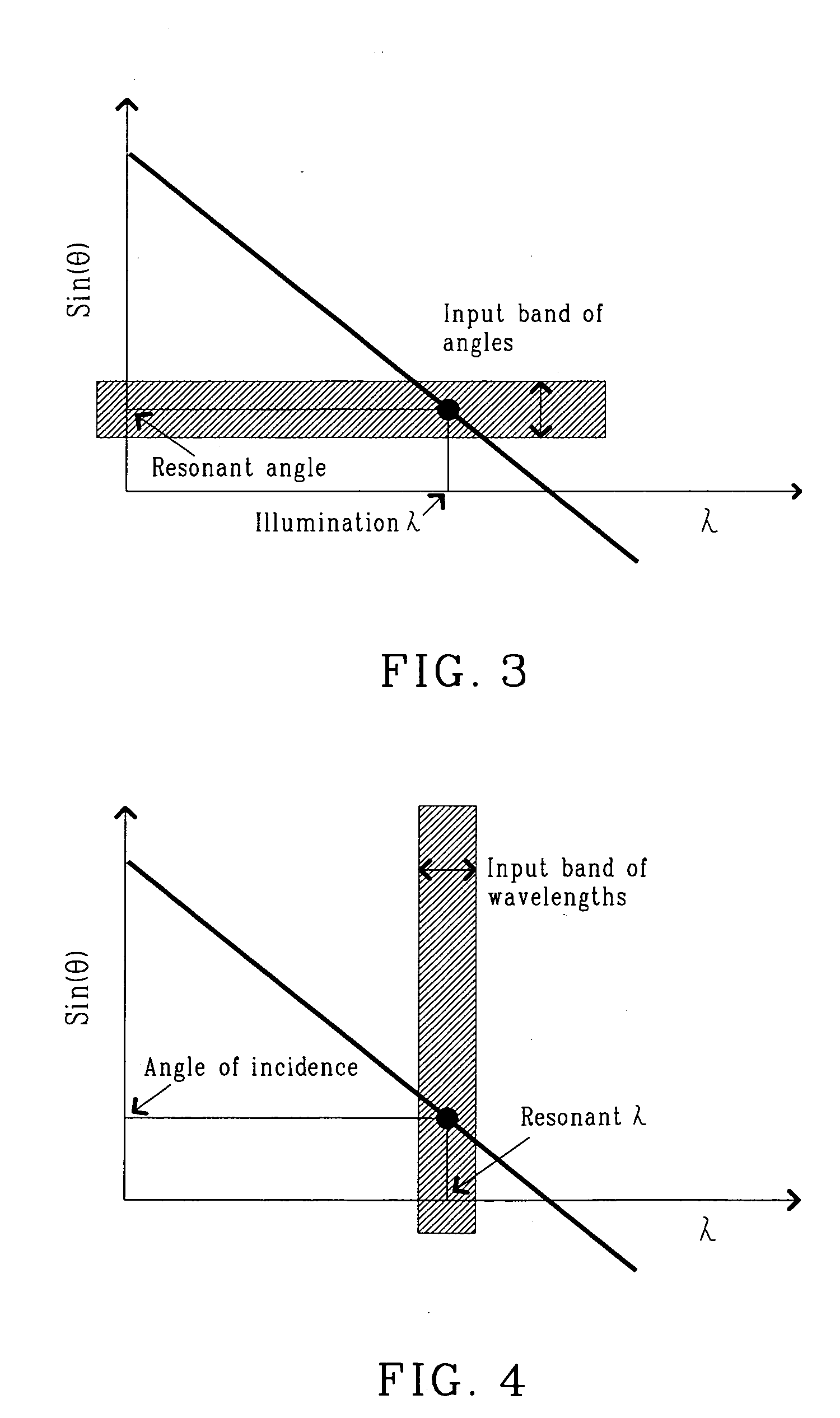

Optical interrogation system and method for increasing a read-out speed of a spectrometer

InactiveUS20070031291A1Increase readout speedEasy to detectBeam/ray focussing/reflecting arrangementsInvestigating moving sheetsPhysicsOptical power

Owner:CORNING INC

Anti-stokes fluorescent compositions and methods of use

InactiveUS6841092B2Increase readout speedOther printing matterPaper-money testing devicesLutetiumElectromagnetic radiation

The present invention provides a secured document including a composition capable of anti-Stokes fluorescence containing an ion capable of absorption of electromagnetic radiation, an ion capable of emitting electromagnetic radiation, and a matrix composition comprising gadolinium, yttrium, lanthanum, and lutetium, wherein the wavelength of the emitted electromagnetic radiation is shorter than the wavelength of the absorbed electromagnetic radiation, and wherein the concentrations of the absorbing and emitting ions are adjusted to achieve concentration quenching of anti-Stokes luminescence.

Owner:FA LEUCHTSTOFFWERK BREITUNGEN +1

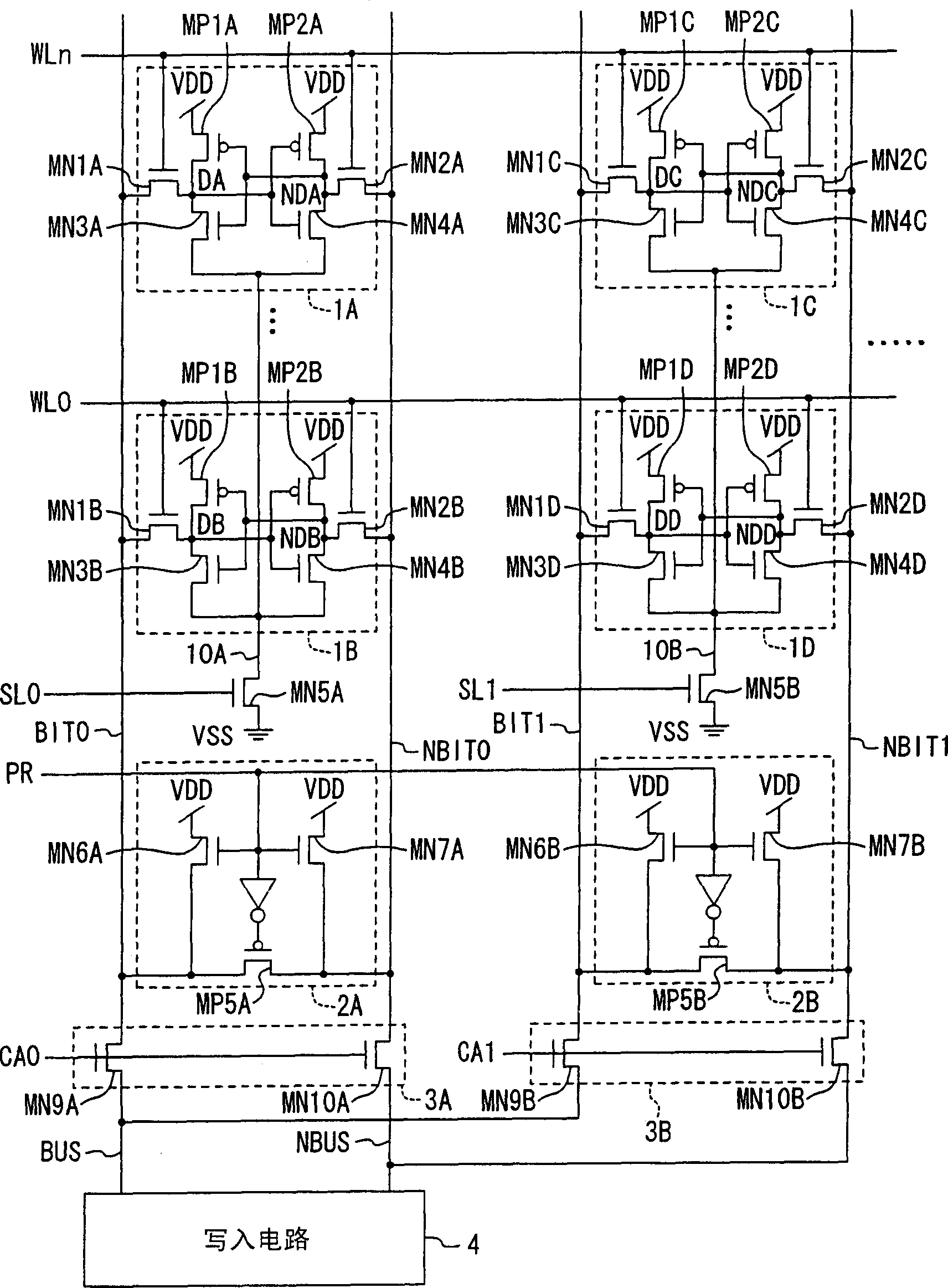

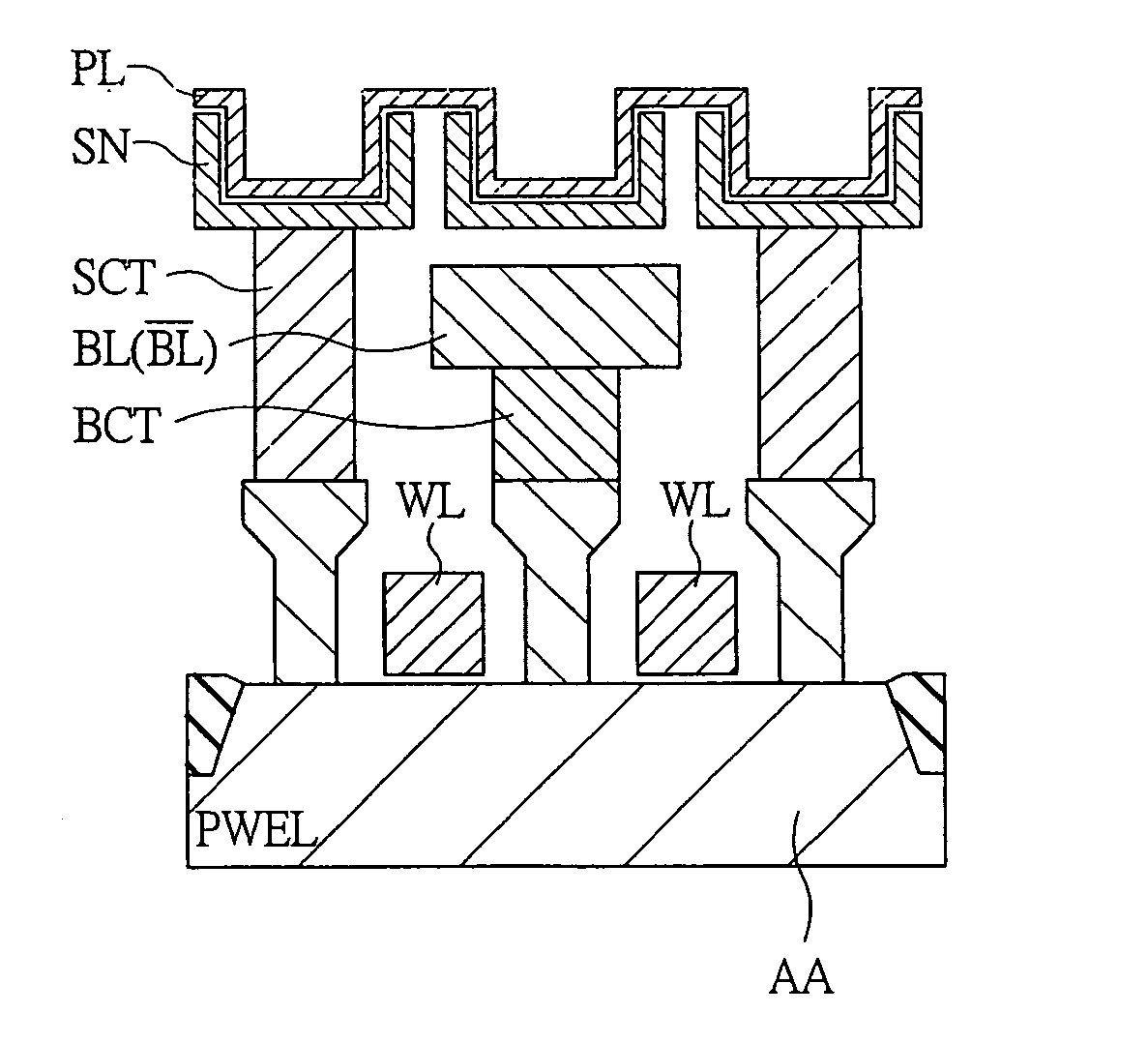

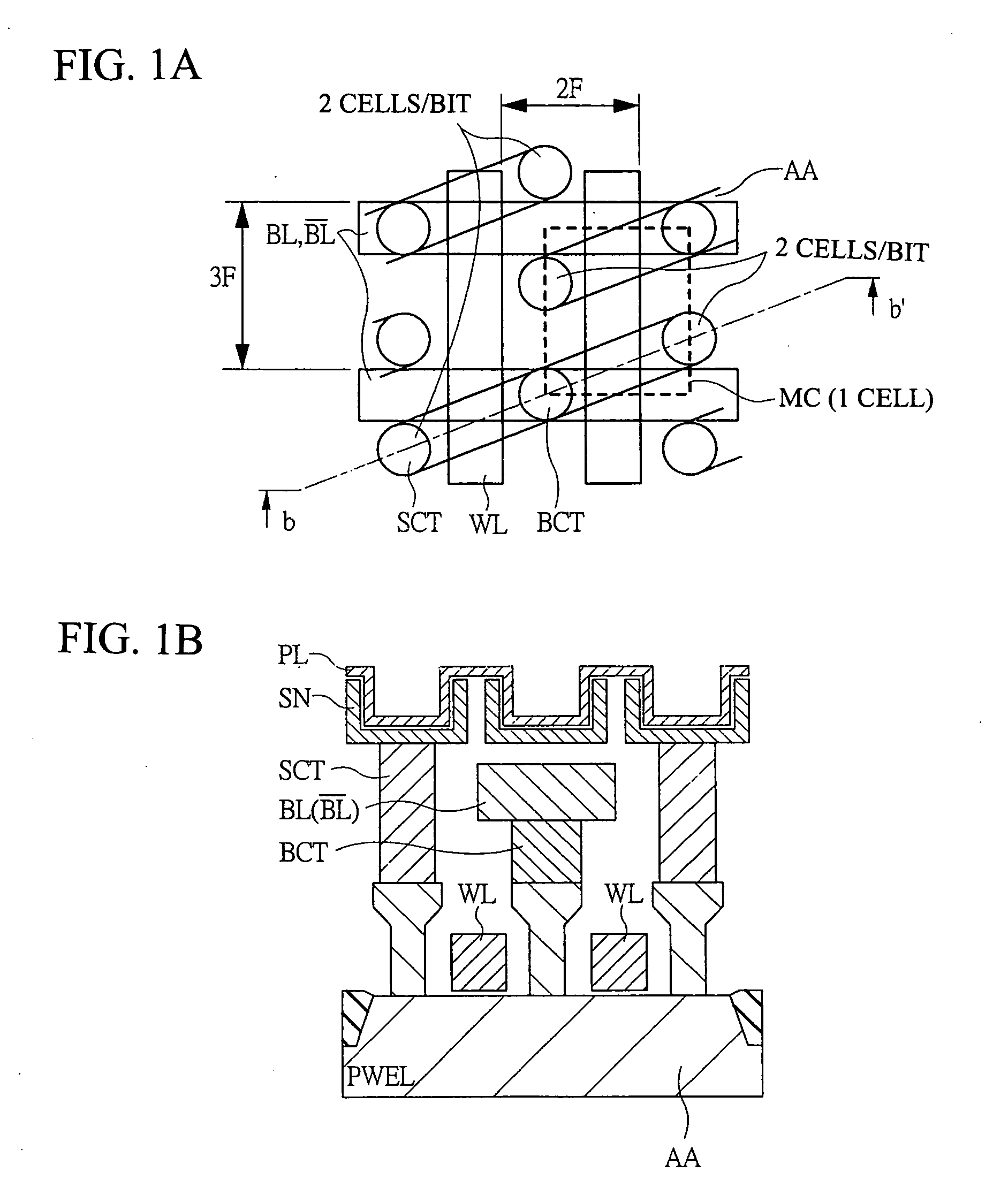

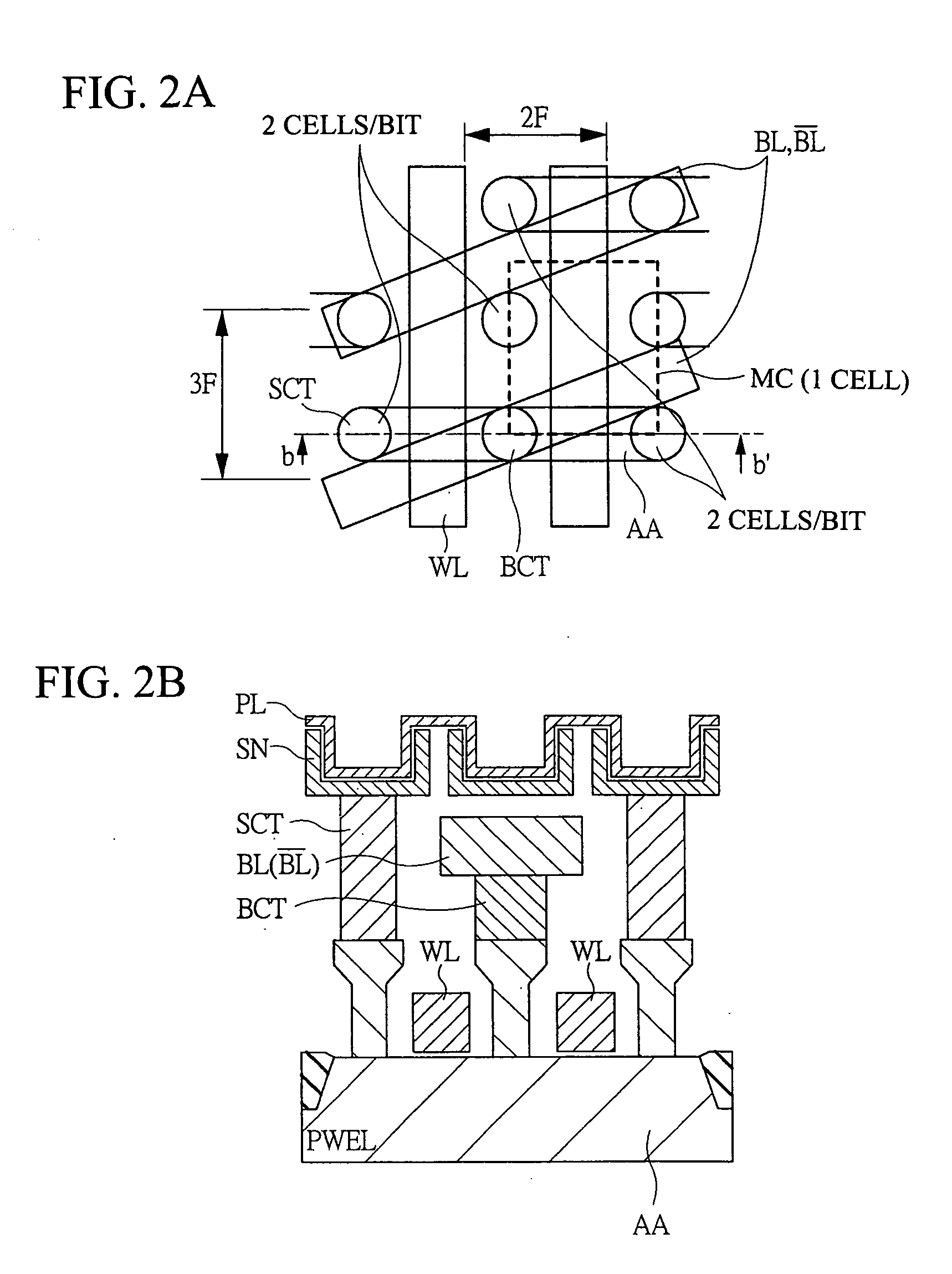

Semiconductor memory device

InactiveUS6992343B2Easy to integrateUltra-high speed operationTransistorSolid-state devicesBit lineUltra high speed

Owner:LONGITUDE SEMICON S A R L

Anti-stokes fluorescent compositions and methods of use

InactiveUS20020130304A1Increase readout speedOther printing matterPaper-money testing devicesLutetiumGadolinium

The present invention provides a secured document including a composition capable of anti-Stokes fluorescence containing an ion capable of absorption of electromagnetic radiation, an ion capable of emitting electromagnetic radiation, and a matrix composition comprising gadolinium, yttrium, lanthanum, and lutetium, wherein the wavelength of the emitted electromagnetic radiation is shorter than the wavelength of the absorbed electromagnetic radiation, and wherein the concentrations of the absorbing and emitting ions are adjusted to achieve concentration quenching of anti-Stokes luminescence.

Owner:FA LEUCHTSTOFFWERK BREITUNGEN +1

Image sensor

ActiveCN101047797AIncrease readout speedSuppress noiseTelevision system detailsTelevision system scanning detailsControl circuitComputer science

An image sensor includes a plurality of operation circuits. The operation circuit operates pixel signals read out from a group of pixels included in a readout area to generate a pixel signal in the thinning readout mode. A plurality of column selecting switches are arranged between the output terminals of the plurality of operation circuits and a plurality of output channels. A control circuit controls the plurality of column selecting switches such that pixel signals the number of which is equal to the number of the plurality of output channels are output to the plurality of output channels in parallel in the thinning readout mode. The circuit arrangements, each included in the corresponding one of the plurality of operation circuits and each viewed from the corresponding one of the column selecting switches used in the thinning readout mode, are equivalent to each other.

Owner:CANON KK

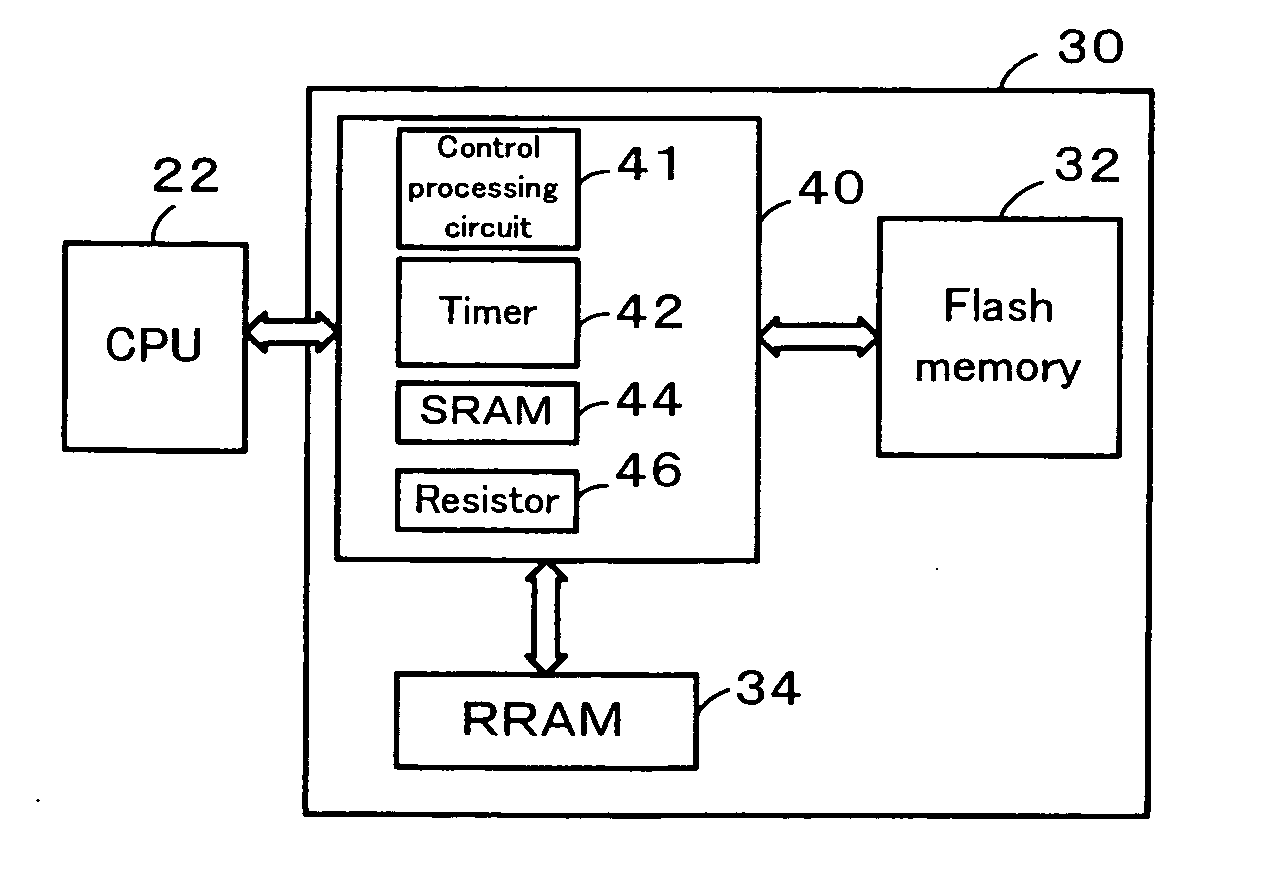

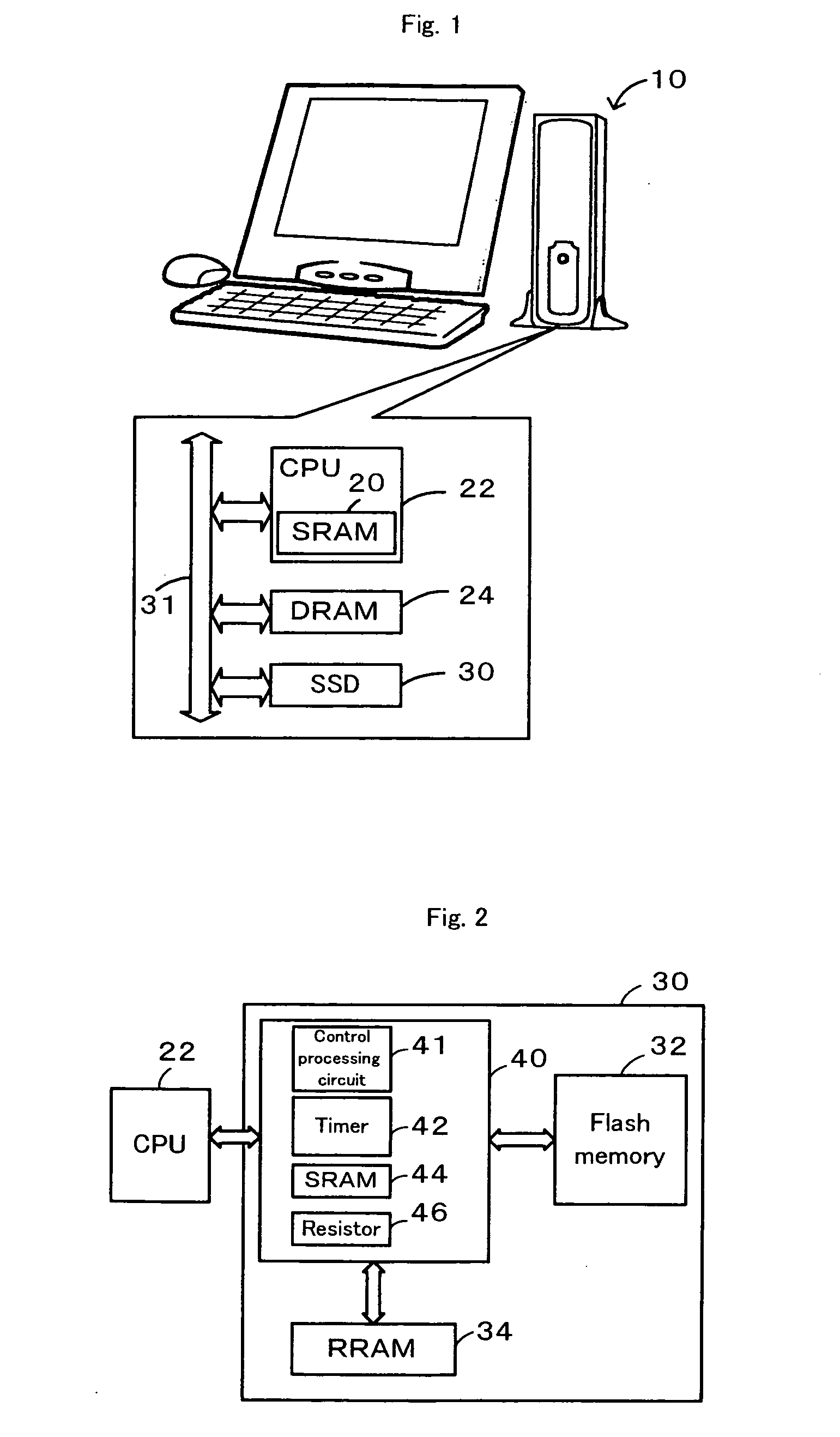

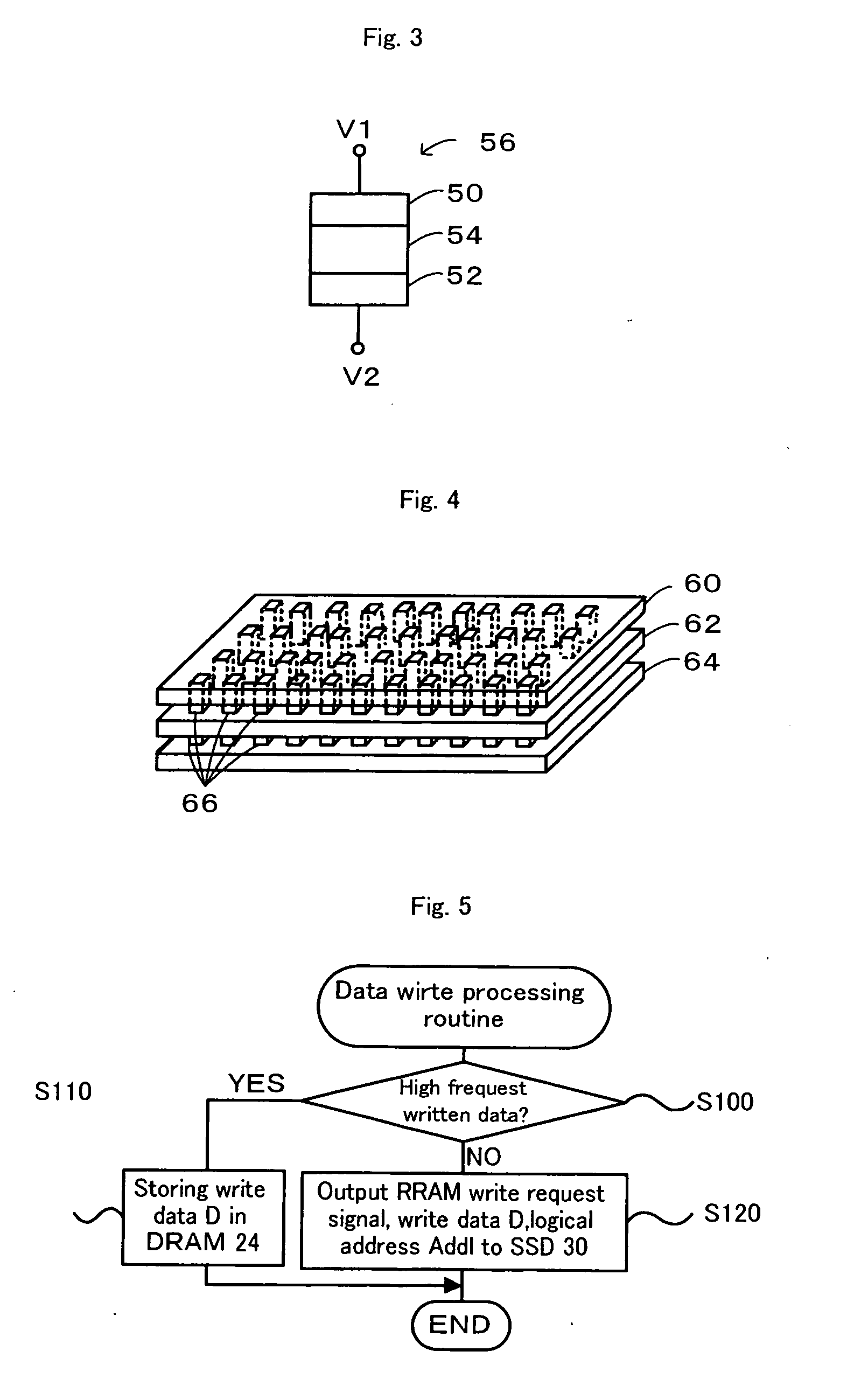

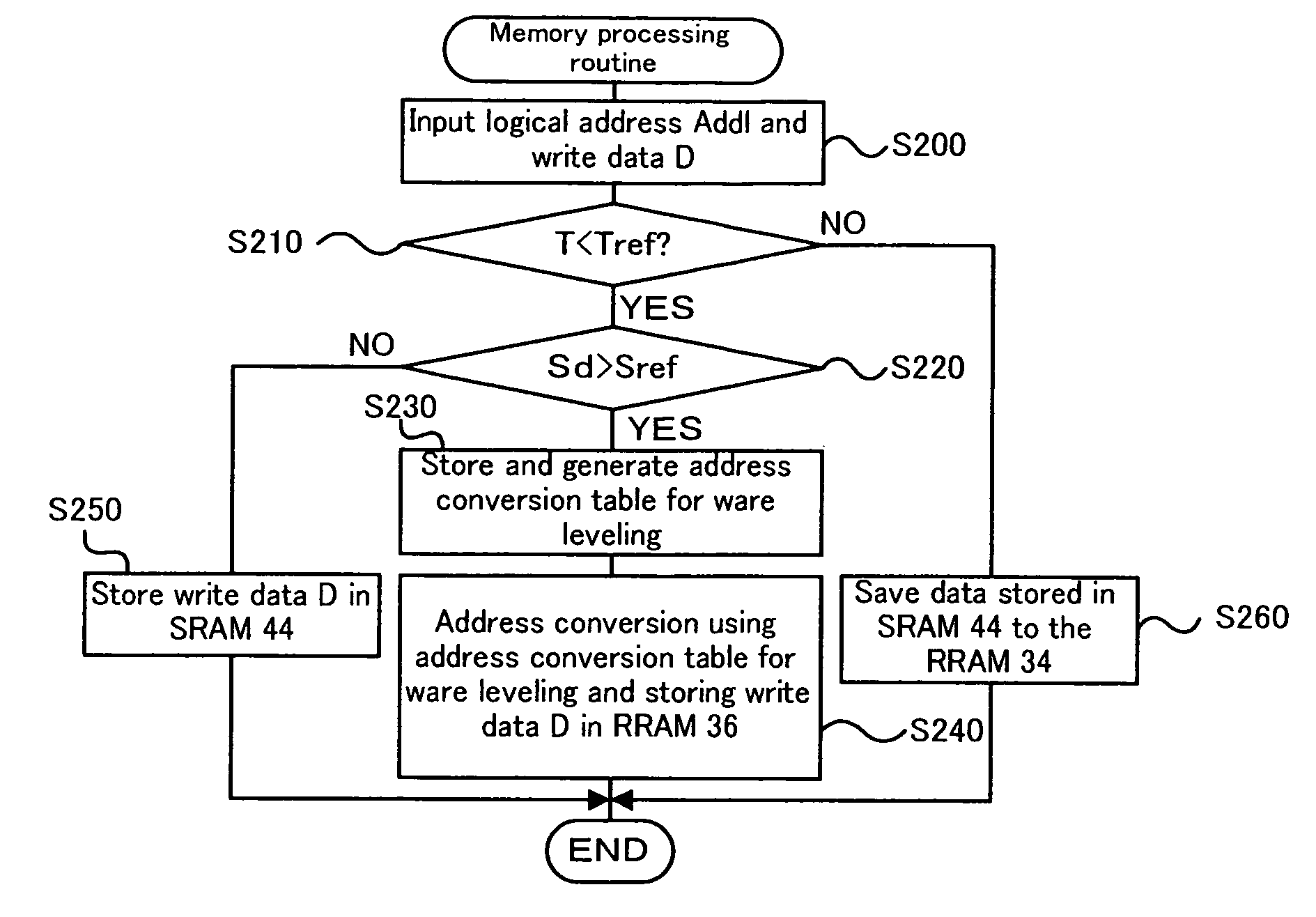

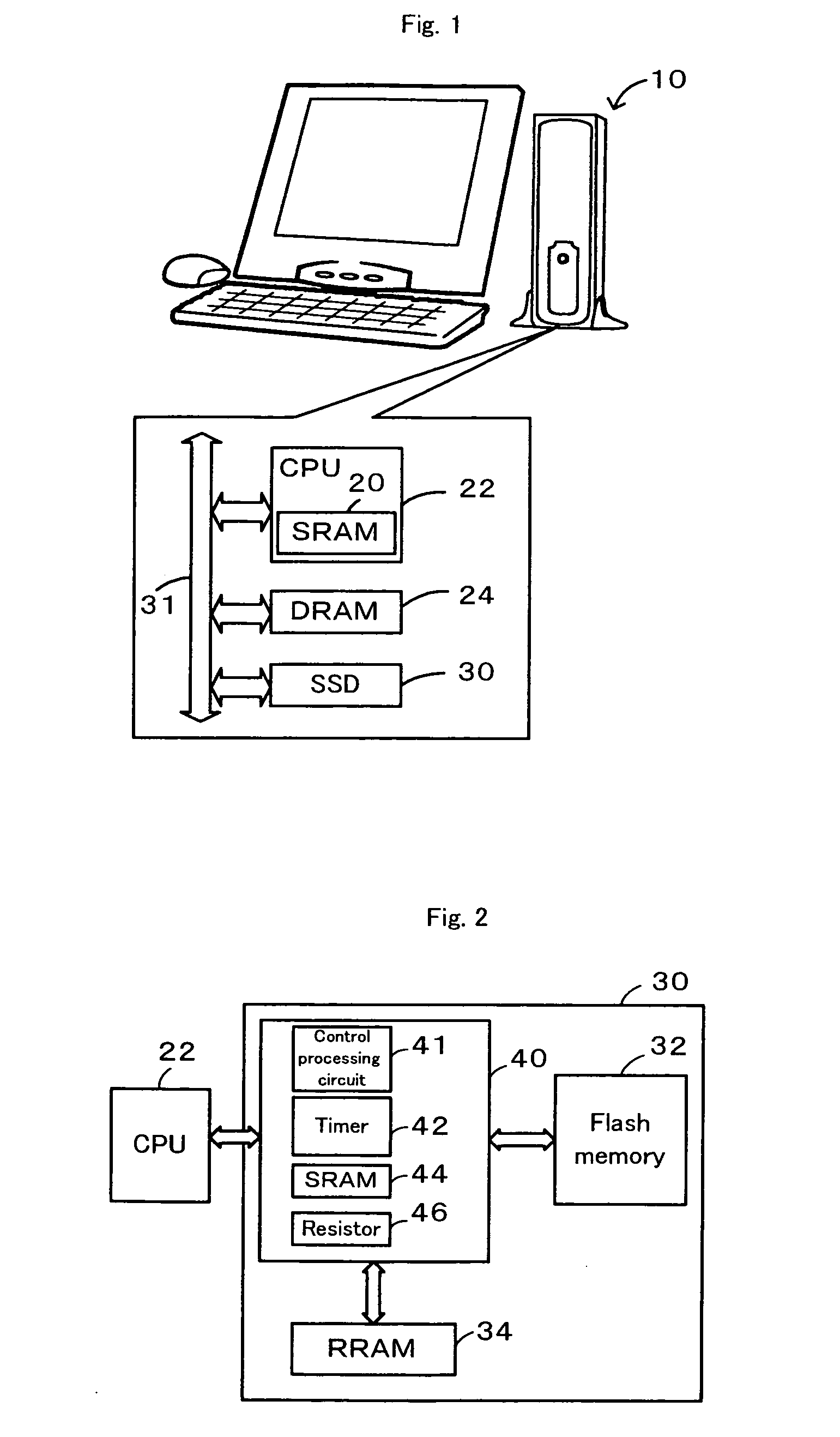

Data processing apparatus, control device and data storage device

InactiveUS20120072801A1Increase speedIncrease readout speedEnergy efficient ICTDigital data processing detailsMemory controllerData storing

When write data D is high rewritten data, a PC 10 controls a DRAM 24 to store the write data D (steps S100 and S110). When the write data D is not the high rewritten data, the PC 10 outputs an RRAM write request signal and the write data D to an SSD (step S100 and S120). A memory controller of the SSD input the RRAM write request signal controls the RRAM and an SRAM to store the write data D in the RRAM or the SRAM. This treatment enables data stored in the DRAM to be rewritten frequently. Therefore, the decrease of number of times of refresh operation of the DRAM and the decrease of power consumption are accomplished.

Owner:THE UNIV OF TOKYO

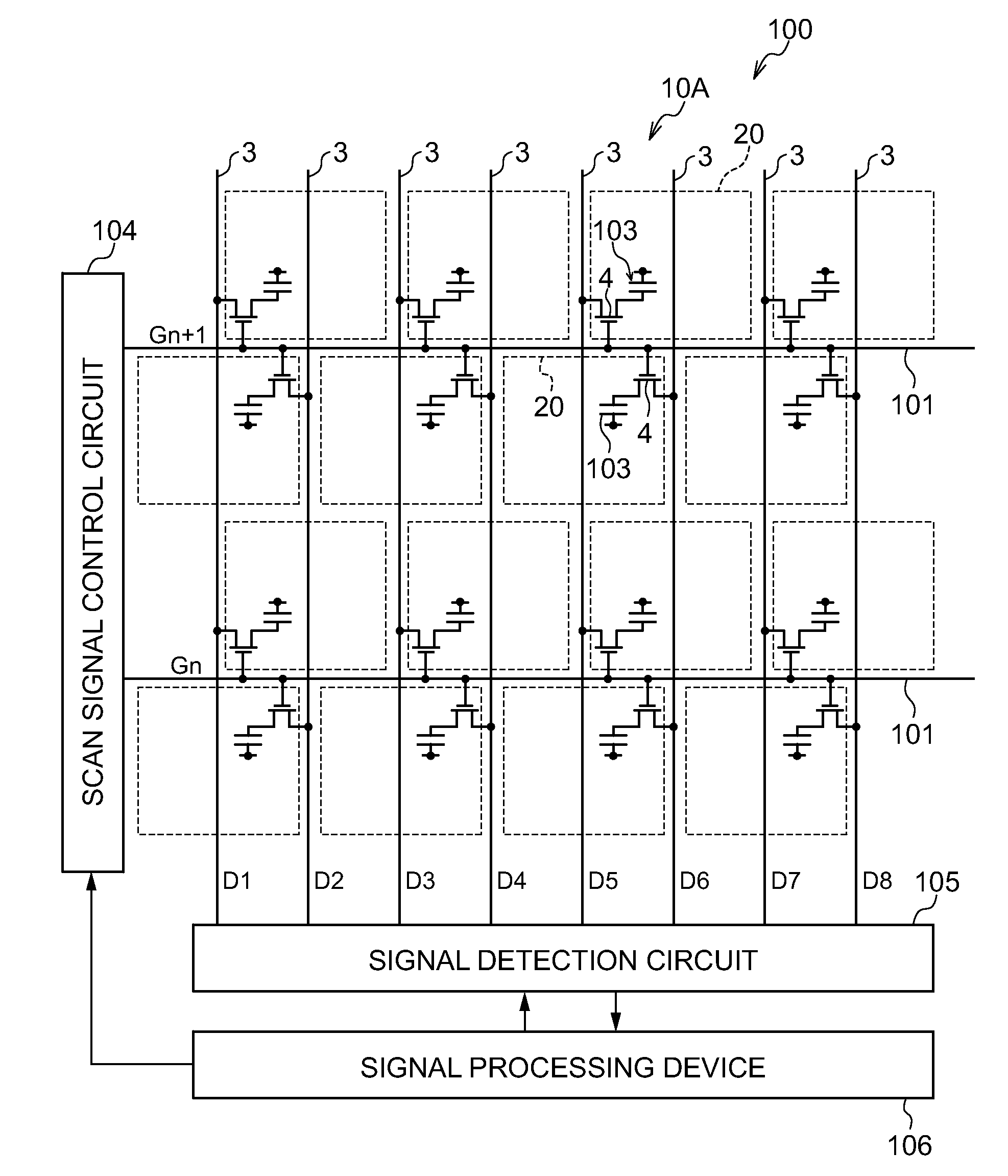

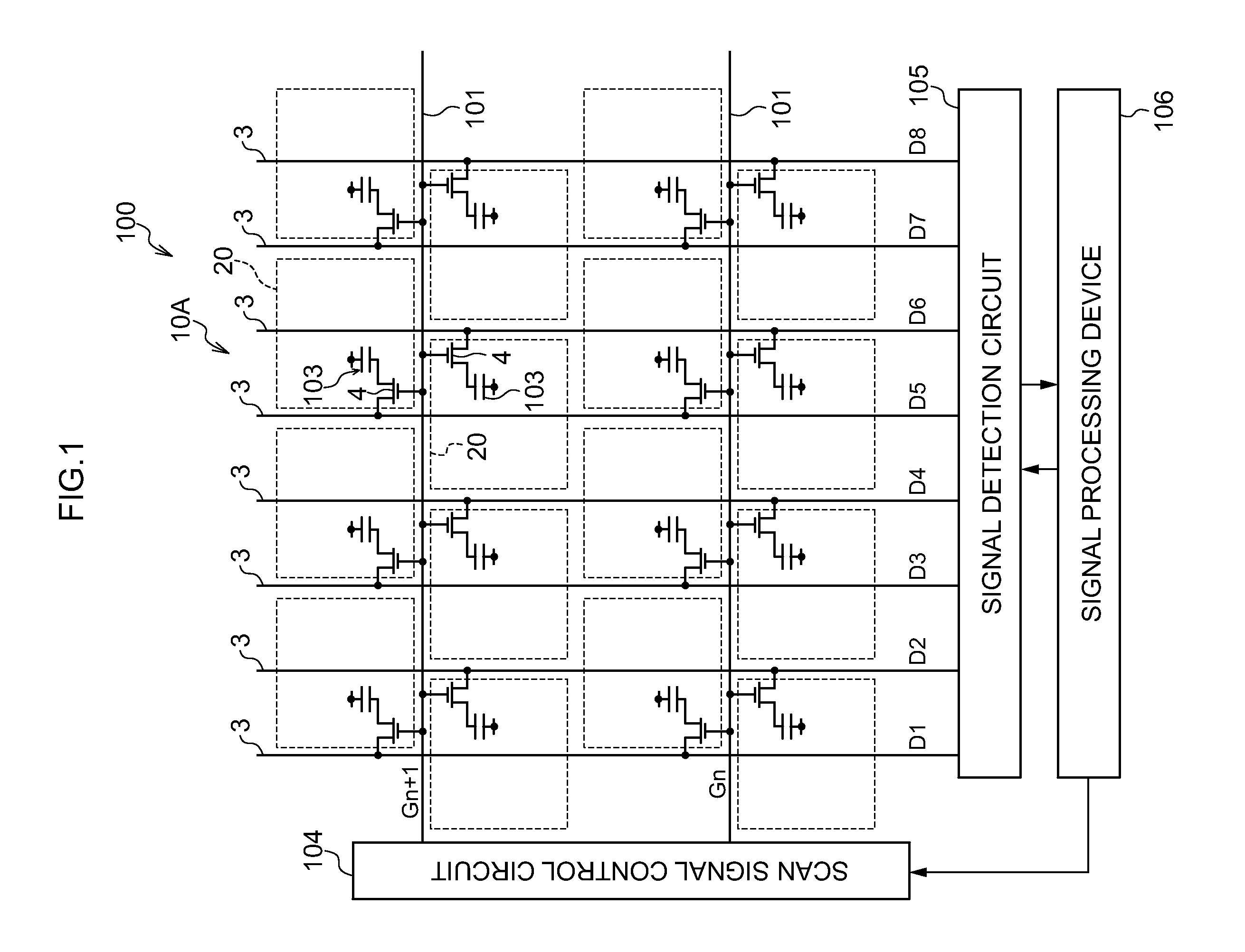

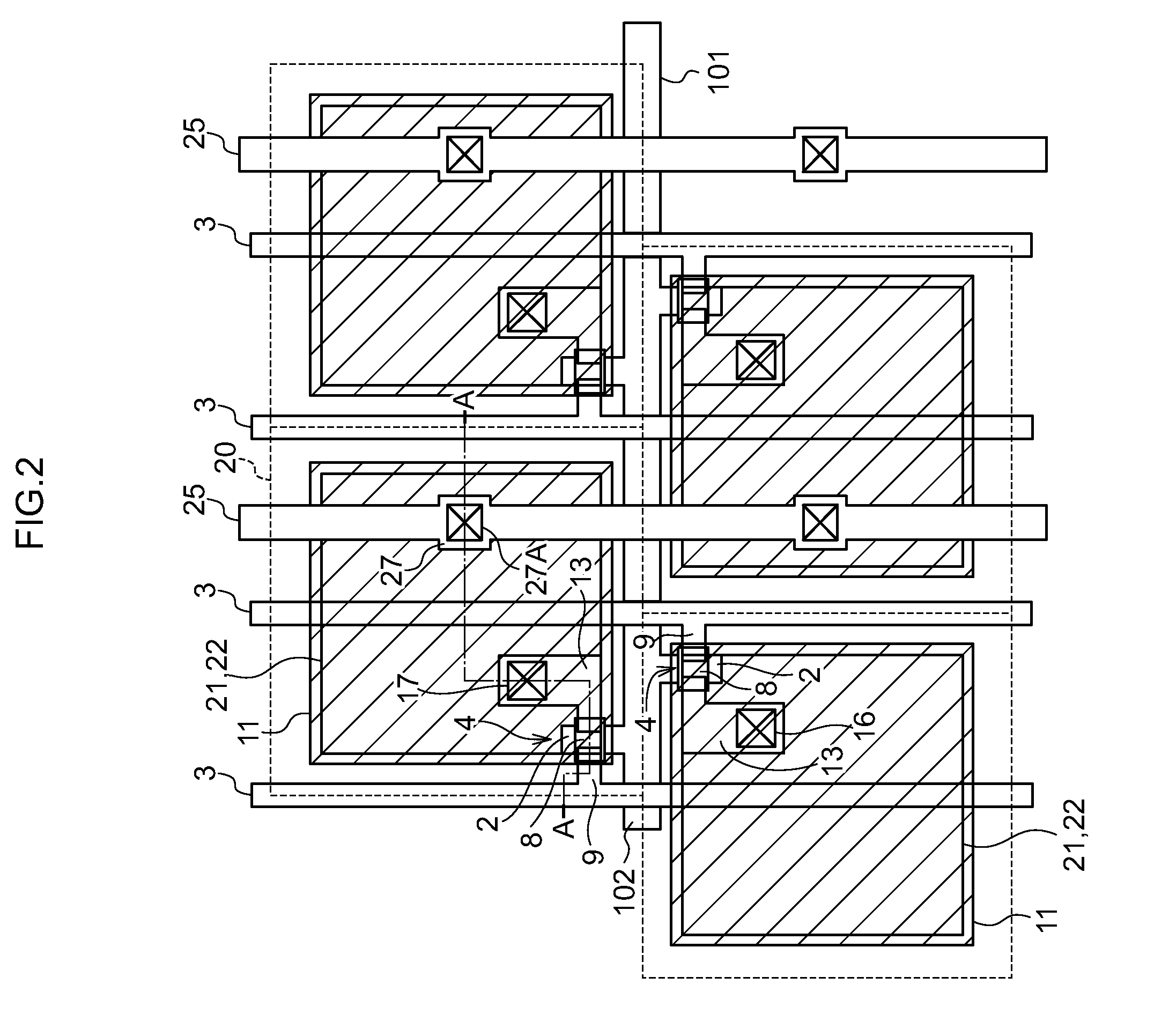

Radiation detector

InactiveUS20110121189A1Increase speedAvoid differencesTelevision system detailsSolid-state devicesScan lineEngineering

Scan lines, each disposed to plural pixel lines for each of the pixel lines in a row direction of plural pixels disposed in a matrix, that switch each TFT switch provided at respective pixels in the plural pixel lines. Plural signal lines are each disposed to each of the pixel lines in the row direction of the matrix array. In each of the pixel lines in the row direction, respective signal line is connected to different TFT switch from the TFT switches that are connected to the same respective scan line, and charges accumulated in charge storage capacitors is read out according to the states of the TFT switches. The pixels or the signal lines at a subset of the pixel lines in one direction are disposed shifted in the one direction, such that the signal lines are disposed between pixels of the pixel lines.

Owner:FUJIFILM CORP

Data processing apparatus, control device and data storage device

InactiveUS8635511B2Increase speedIncrease readout speedEnergy efficient ICTDigital data processing detailsMemory controllerData storing

Owner:THE UNIV OF TOKYO

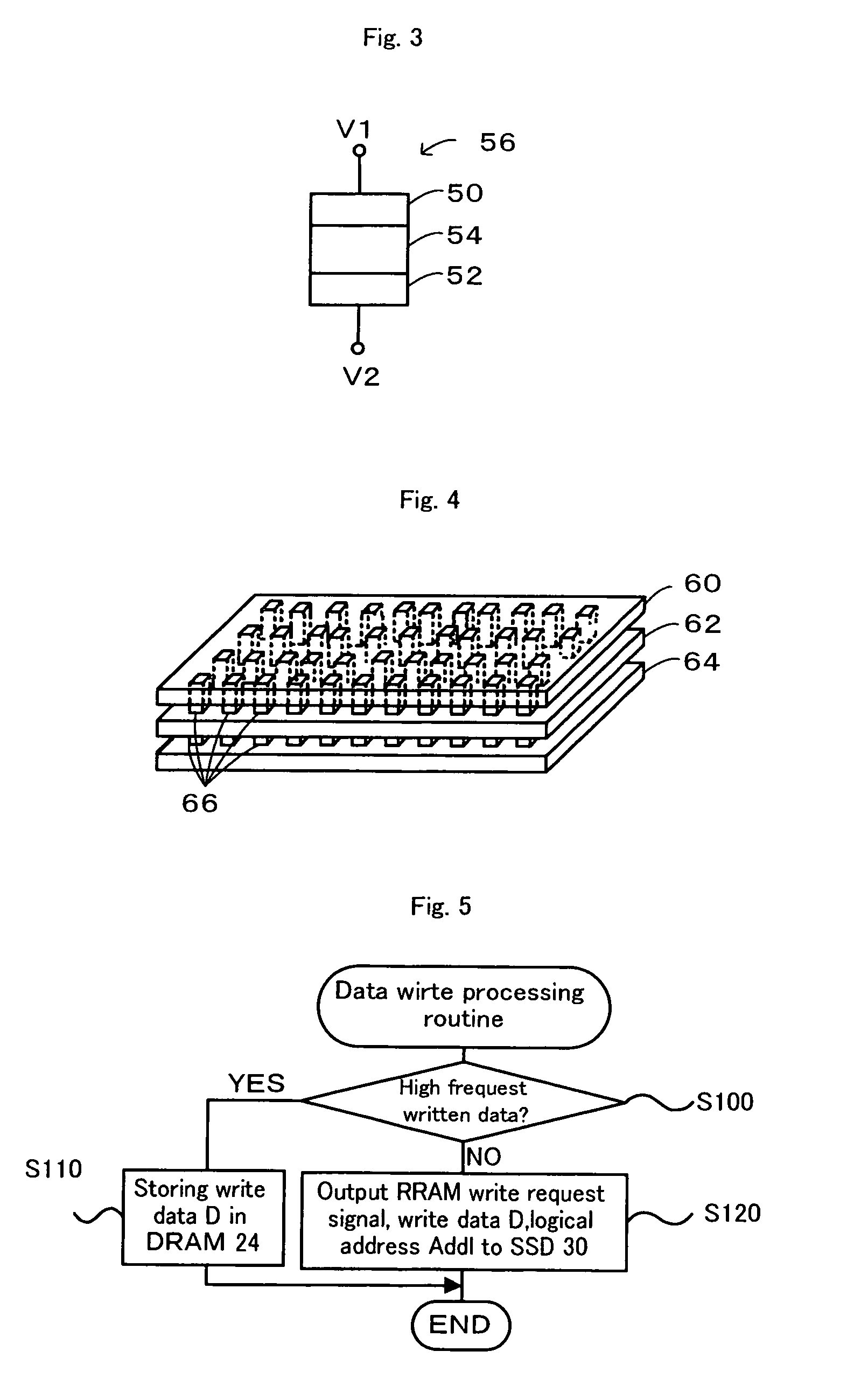

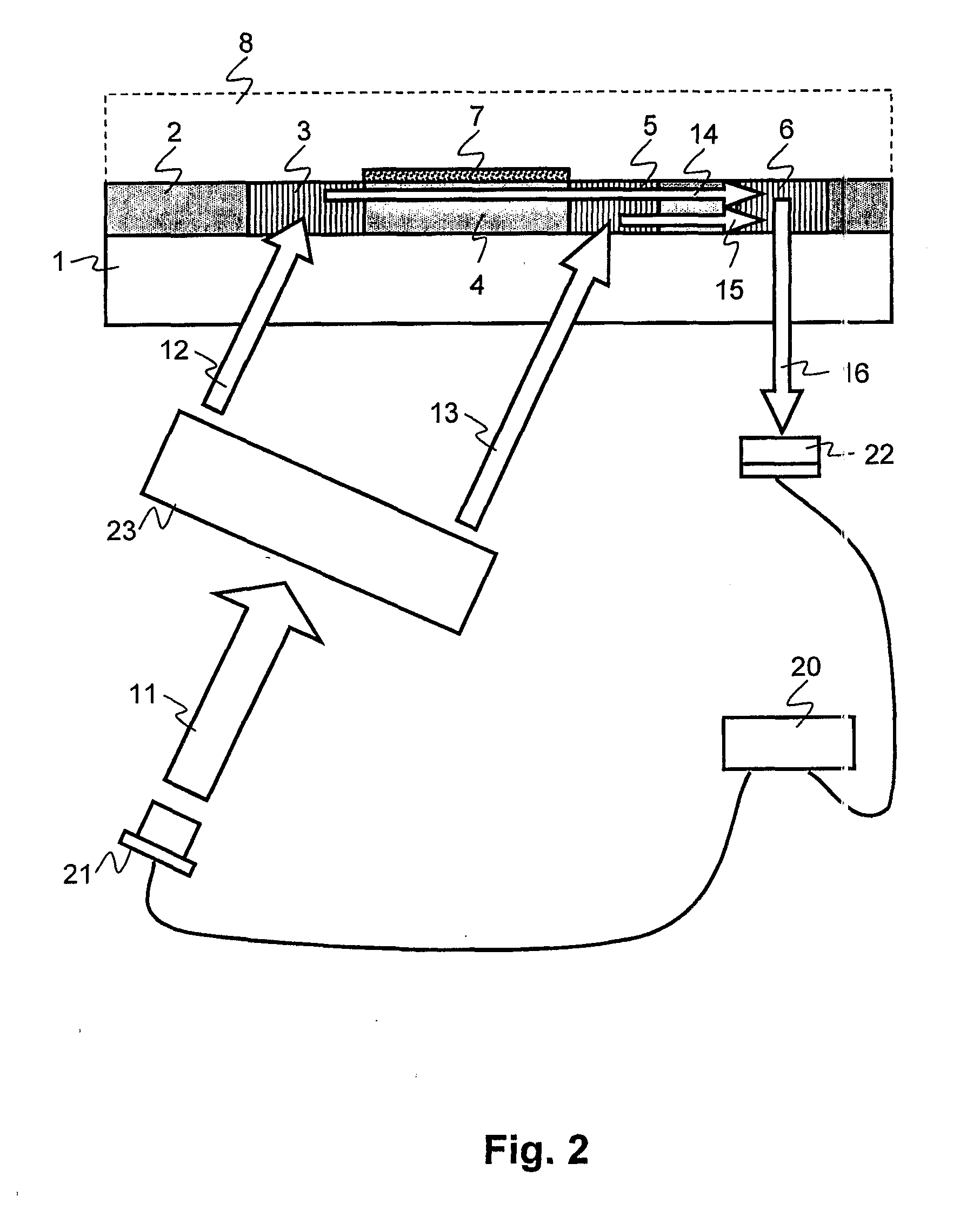

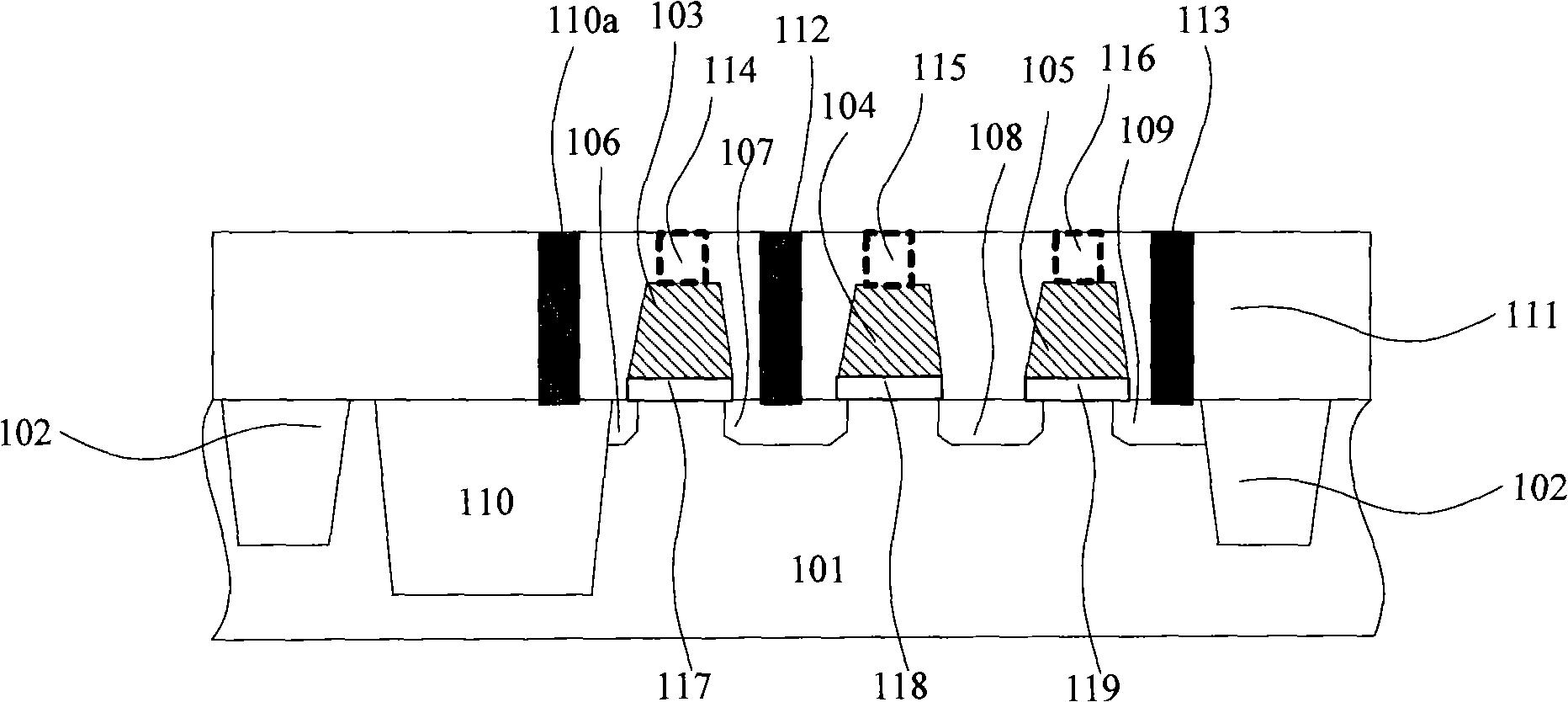

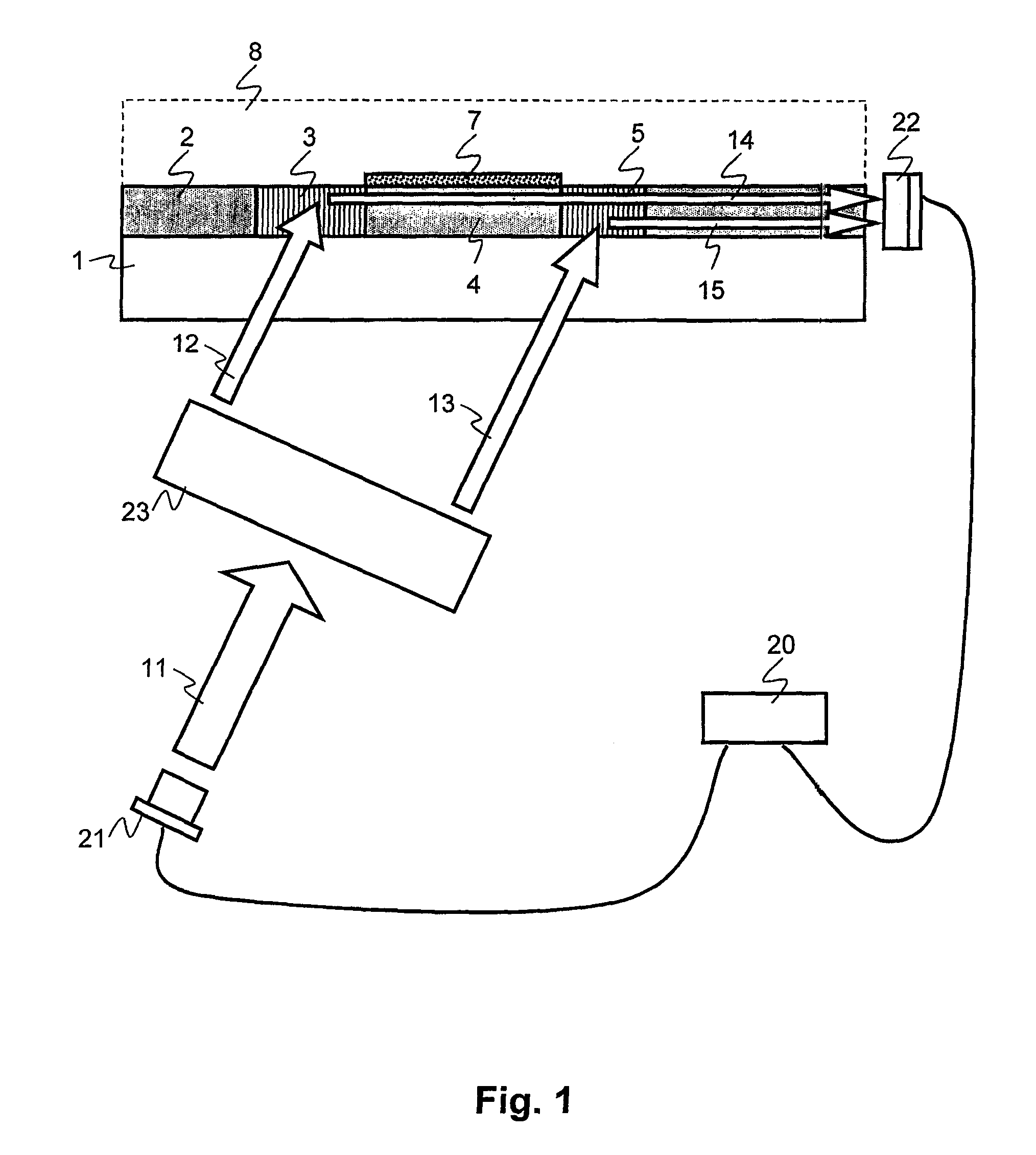

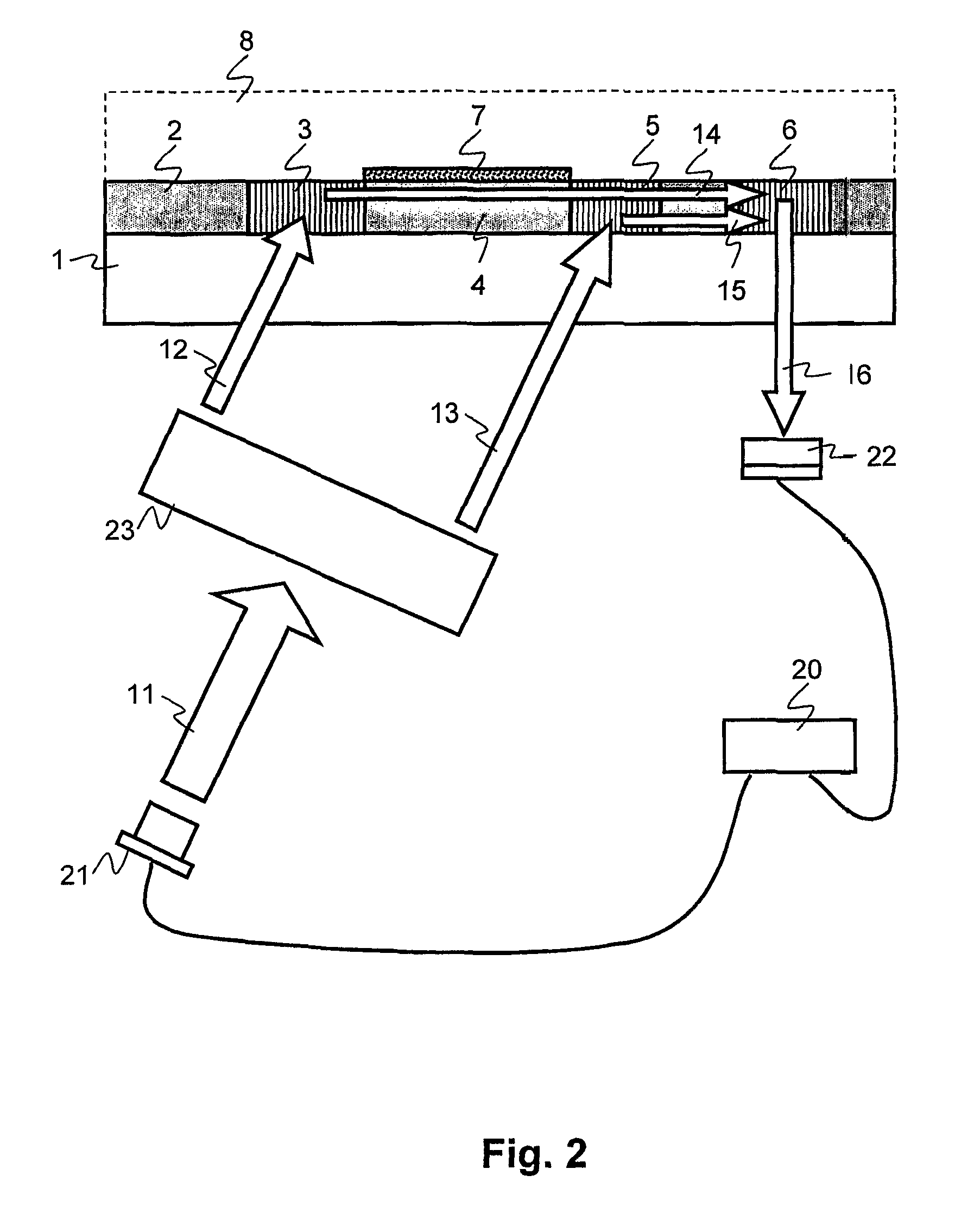

Integrated optical sensor

ActiveUS20100103429A1High and adjustable sensitivityLow costPhase-affecting property measurementsUsing optical meansEngineeringWaveguide

An integrated optical sensor for, for example, a (bio)chemical sensor has an optical waveguide (2) having at least two coupling regions (3, 5), which are separated by at least one measurement region (4). A first wave is excited in the waveguide (2) by the first coupling region (3) and passes through the measurement region (4) and the second coupling region (5). A second wave is excited in the second coupling region (5) and subsequently interferes with the first wave. Here, the reduction in amplitude of the first wave by the second coupling region (5) is less than 95%.

Owner:CREOPTIX

Image sensor

ActiveUS7728891B2Inhibit productionIncrease readout speedTelevision system detailsTelevision system scanning detailsControl circuitComputer science

An image sensor includes a plurality of operation circuits. The operation circuit operates pixel signals read out from a group of pixels included in a readout area to generate a pixel signal in the thinning readout mode. A plurality of column selecting switches are arranged between the output terminals of the plurality of operation circuits and a plurality of output channels. A control circuit controls the plurality of column selecting switches such that pixel signals the number of which is equal to the number of the plurality of output channels are output to the plurality of output channels in parallel in the thinning readout mode. The circuit arrangements, each included in the corresponding one of the plurality of operation circuits and each viewed from the corresponding one of the column selecting switches used in the thinning readout mode, are equivalent to each other.

Owner:CANON KK

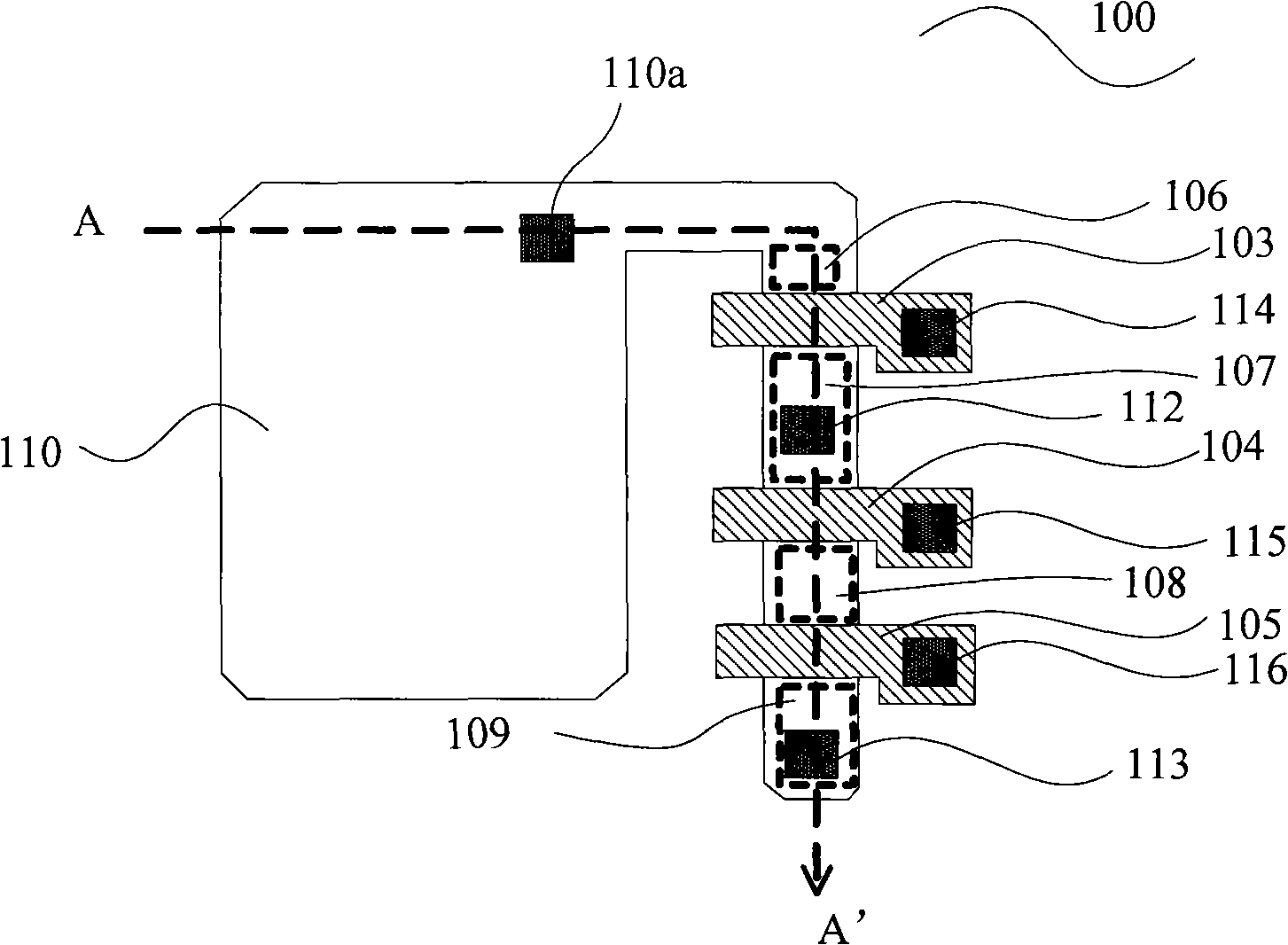

CMOS image sensor and method for forming same

ActiveCN101312201AFree spaceReduced output contact holesSemiconductor/solid-state device detailsSolid-state devicesOptical pathCMOS

A CMOS image sensor comprises at least one CMOS image sensor pixel unit pair which comprises a first pixel unit and a second pixel unit. Each pixel unit in the CMOS image sensor comprises a photodiode area and a drive circuit area, wherein the drive circuit area comprises output transistors. Drain electrodes of the two output transistors adjacent to the first pixel unit and the second pixel unit are connected to be a common output end. The invention further provides another CMOS image sensor, wherein the amount of effective contact holes can be reduced through an output contact hole and a power contact hole of a common output transistor of the adjacent pixel units, thereby effectively decreasing the amount of the contact holes. The structure enables pixel units with smaller dimension to be designed under the condition of unreduced technical nodes without modifying a peripheral circuit and the processing parameter, which can not increase the mask and processing cost, but reduces the output capacitance and increases the filling ratio and the optical path.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

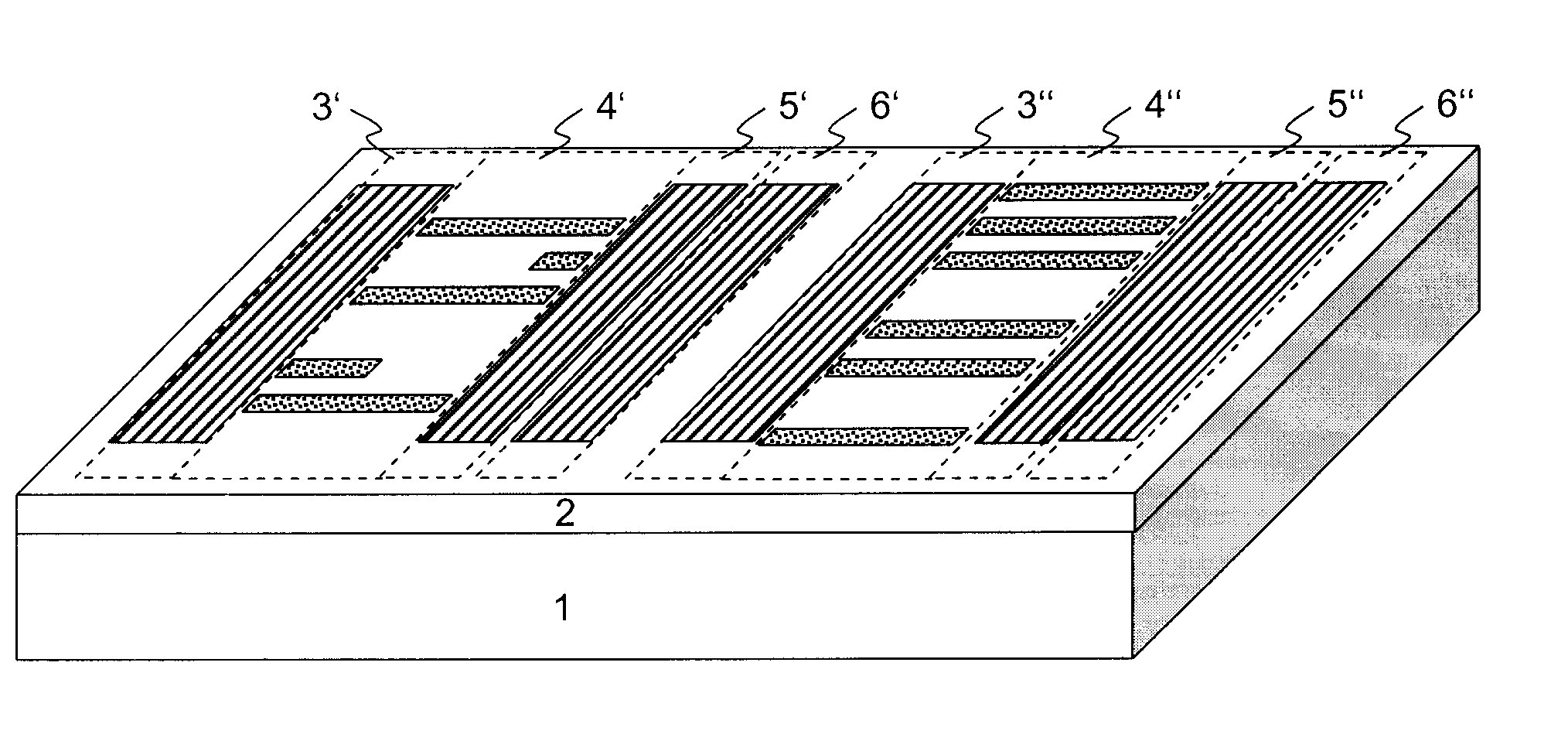

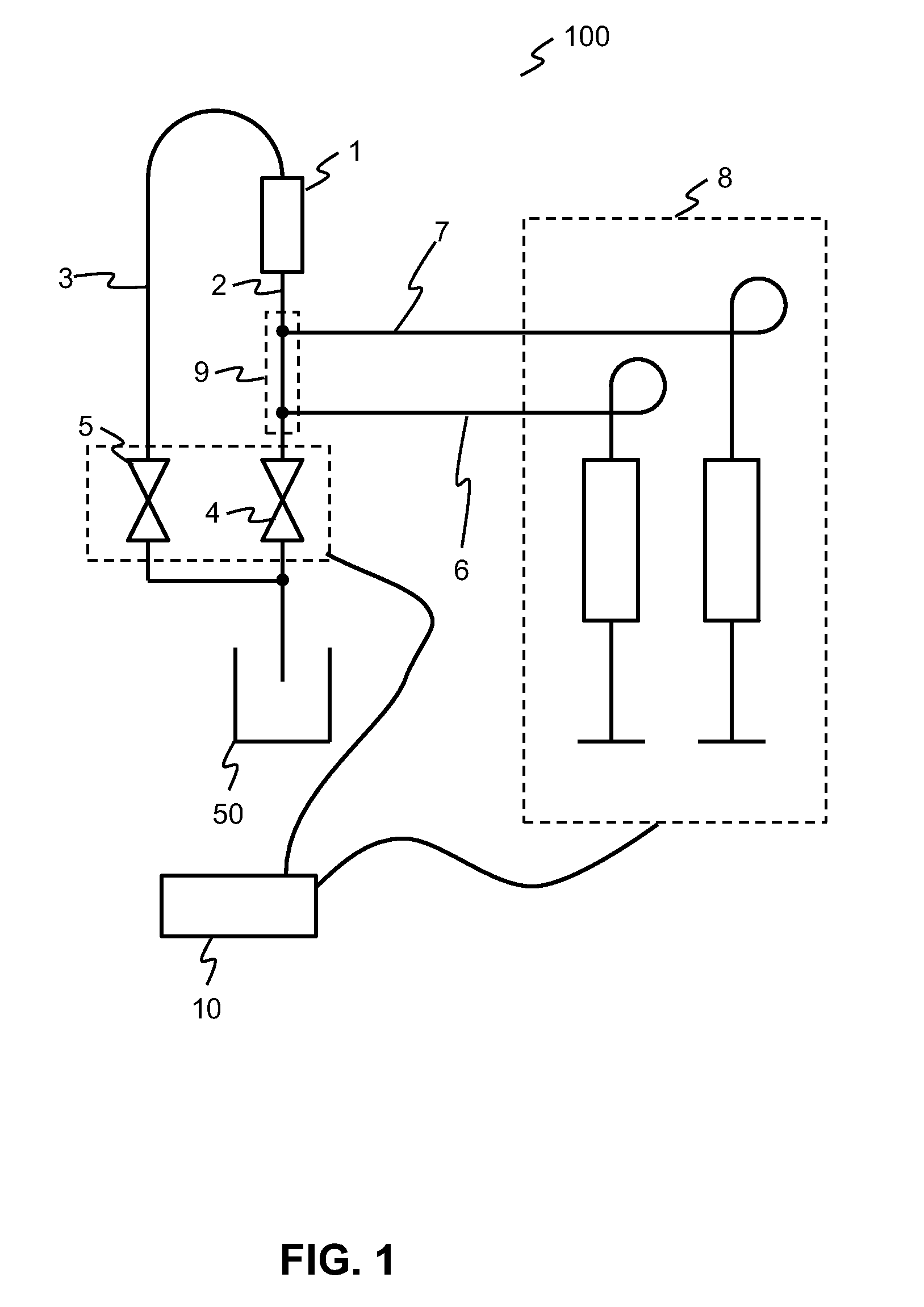

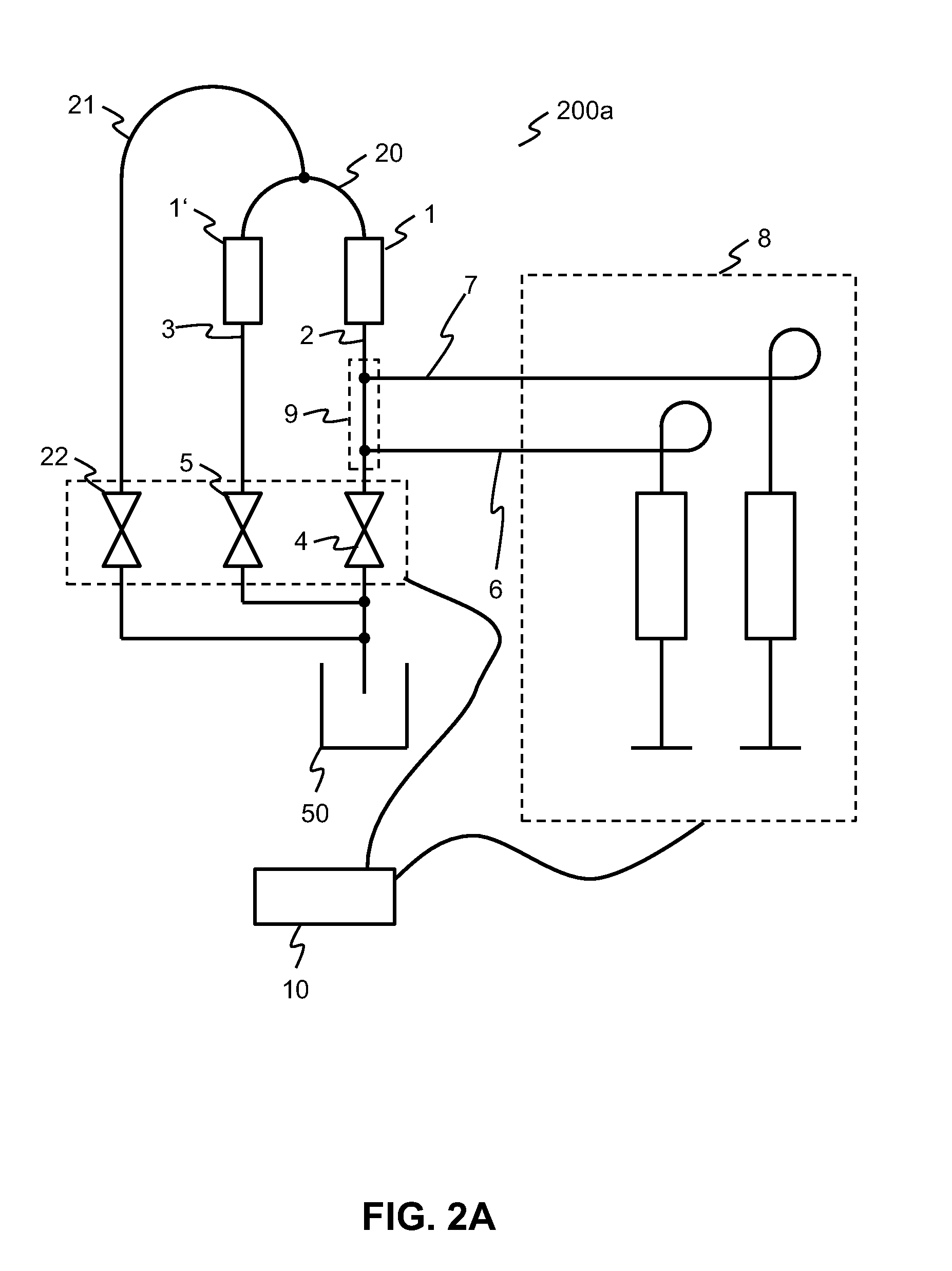

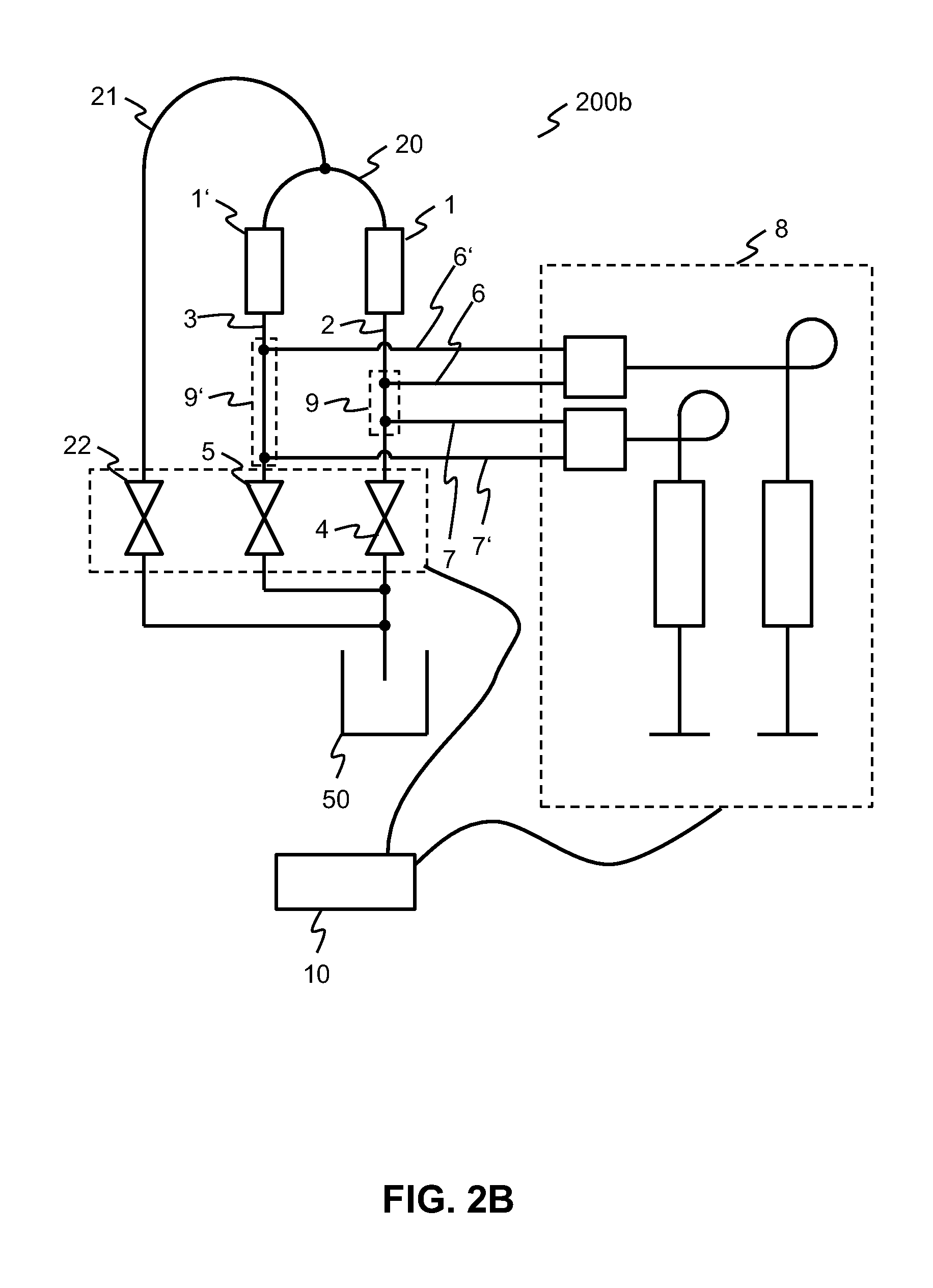

Flow conduit system for a biochemical sensor

ActiveUS20150192574A1Fast transitionHigh sensitivityComponent separationBiological testingBiomedical engineeringStreamflow

A flow conduit system (100,200a,200b) suitable for biochemical sensing, the flow conduit system (100,200a,200b) comprising, a first flow cell conduit (1) comprising one or more sensing areas for biochemical sensing; a first selector valve (4); a first inlet / outlet conduit (2) which fluidly connects the first flow cell conduit (1) to the first selector valve (4); a first injection conduit (6) having a first end and a second end; a second injection conduit (7) having a first end and a second end; a fluid injecting means (8) fluidly connected to the second ends of each of the first and second injection conduits (6, 7) so that the fluid injecting means can selectively inject fluids into the first and / or second injection conduits (6,7); wherein the first injection conduit (6) is fluidly connected, at its first end, to the first inlet / outlet conduit (2) by a valveless junction (9), and the second injection conduits (6) is fluidly connected, at its first end, to the first inlet / outlet conduit (2) by a valveless junction (9).

Owner:CREOPTIX

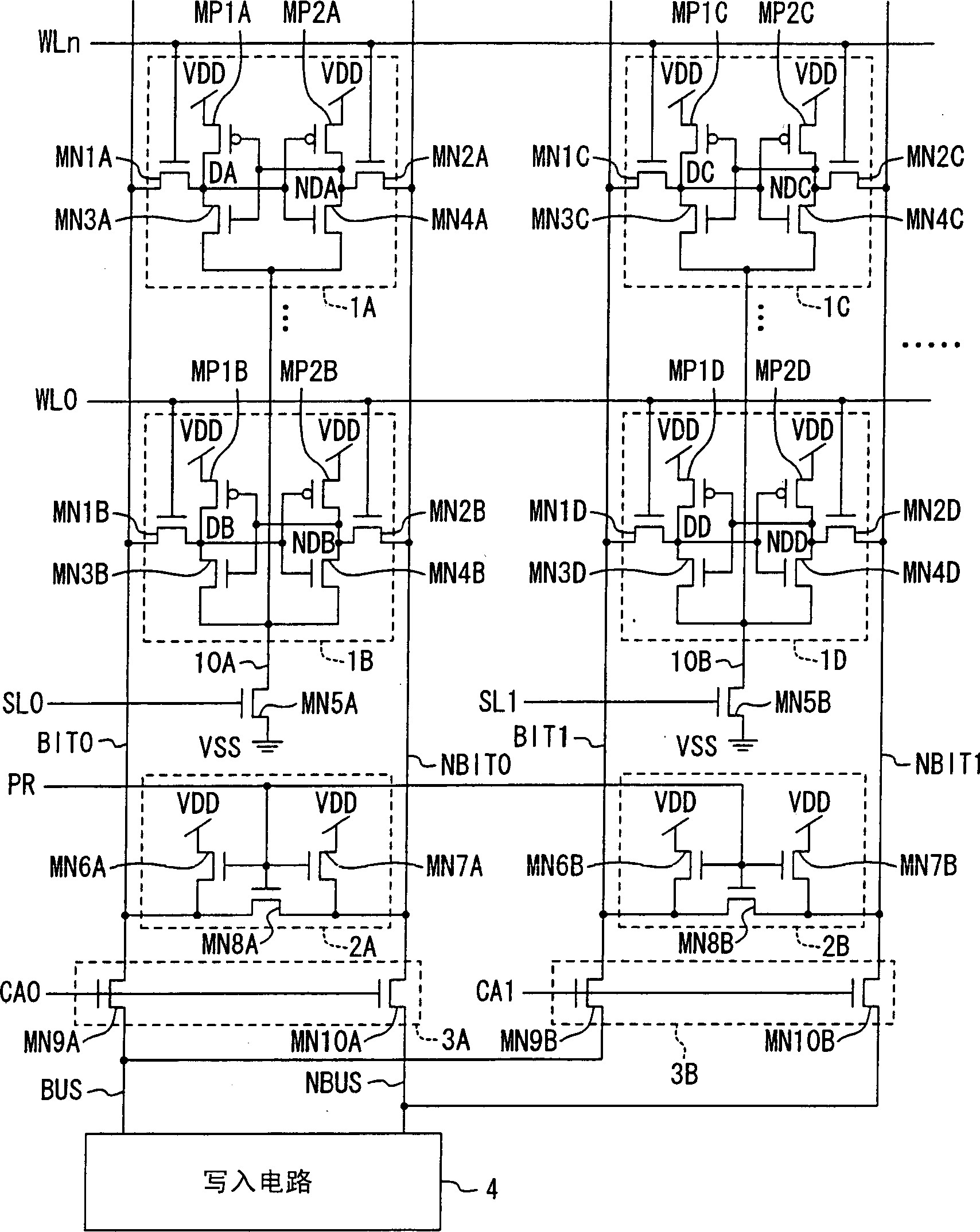

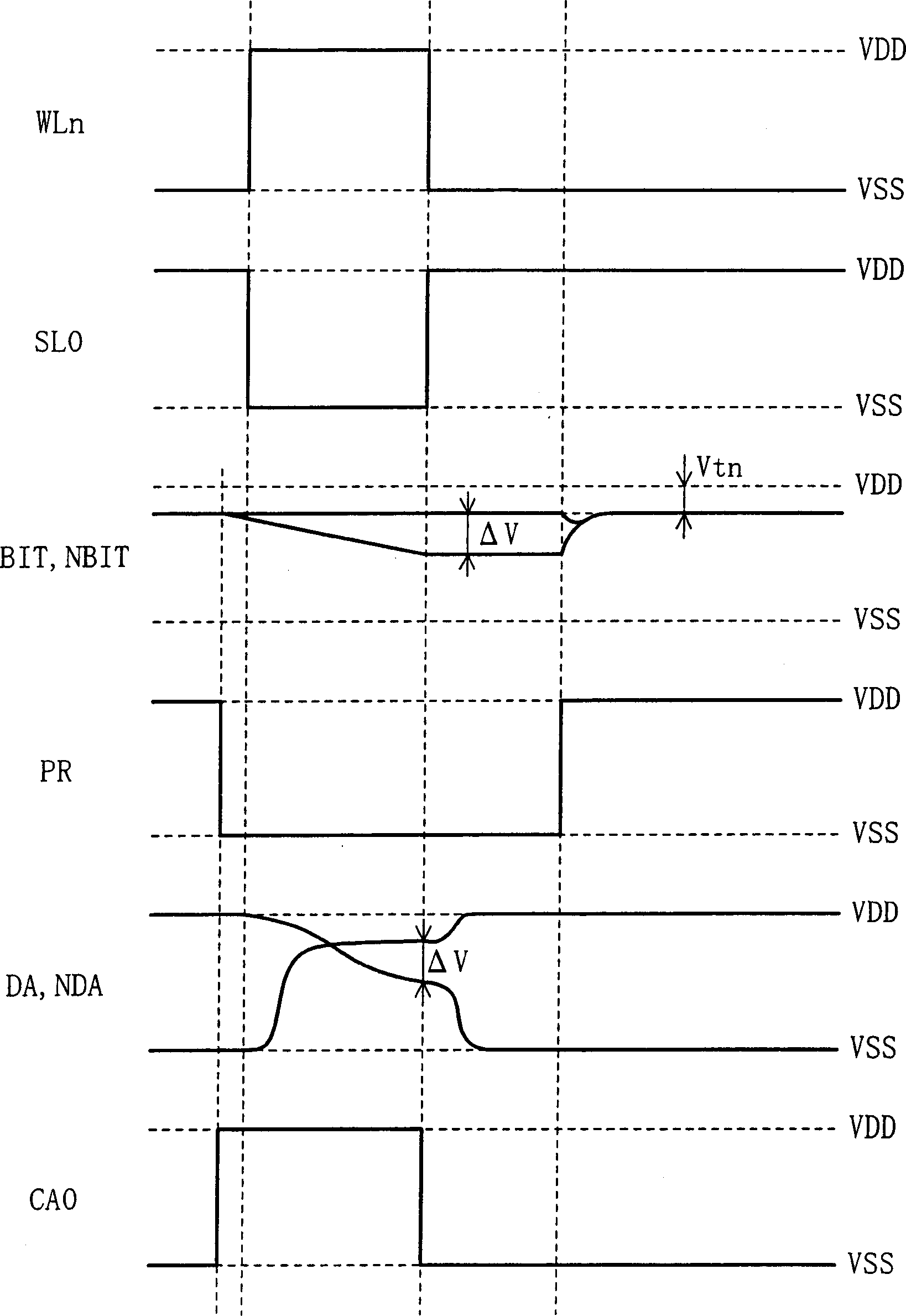

Semiconductor storage

InactiveCN1516196AGuaranteed dataReduce current consumptionSolid-state devicesDigital storageBit lineLow voltage

The respective sources of drive transistors included in memory cells that are located in each of multiple columns and connected to a corresponding one of bit line pairs are connected commonly to a low voltage power supply VSS via an assertion transistor. When data is written, the assertion transistor for the memory cells connected to a selected one of the bit line pairs and located in the identical column is negated, so that the sources of the drive transistors in the memory cells in that column are allowed to float. Consequently, even with a low power supply voltage, it is possible to write the data into a single selected memory cell, while data in the unselected memory cells can be retained favorably.

Owner:SOCIONEXT INC

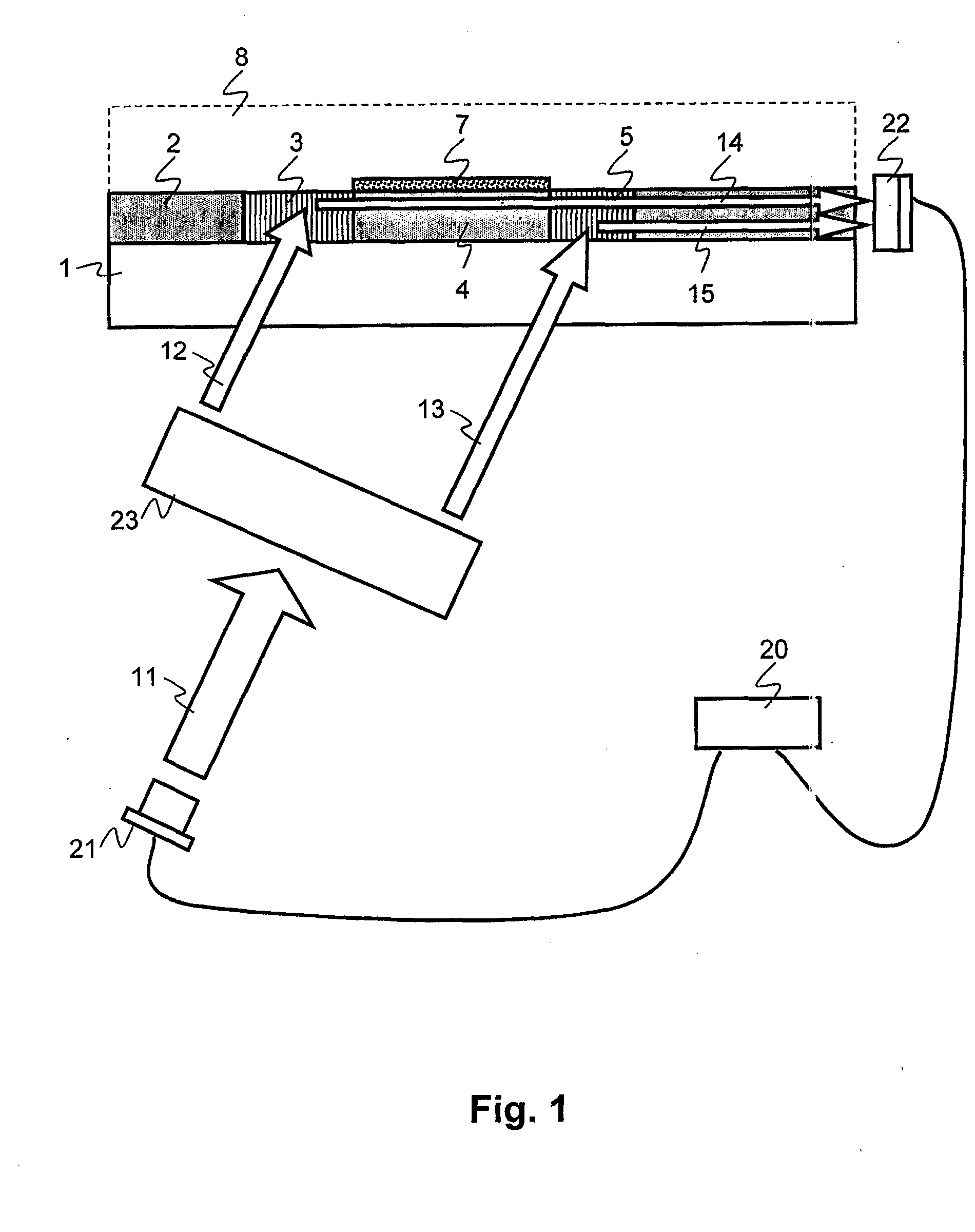

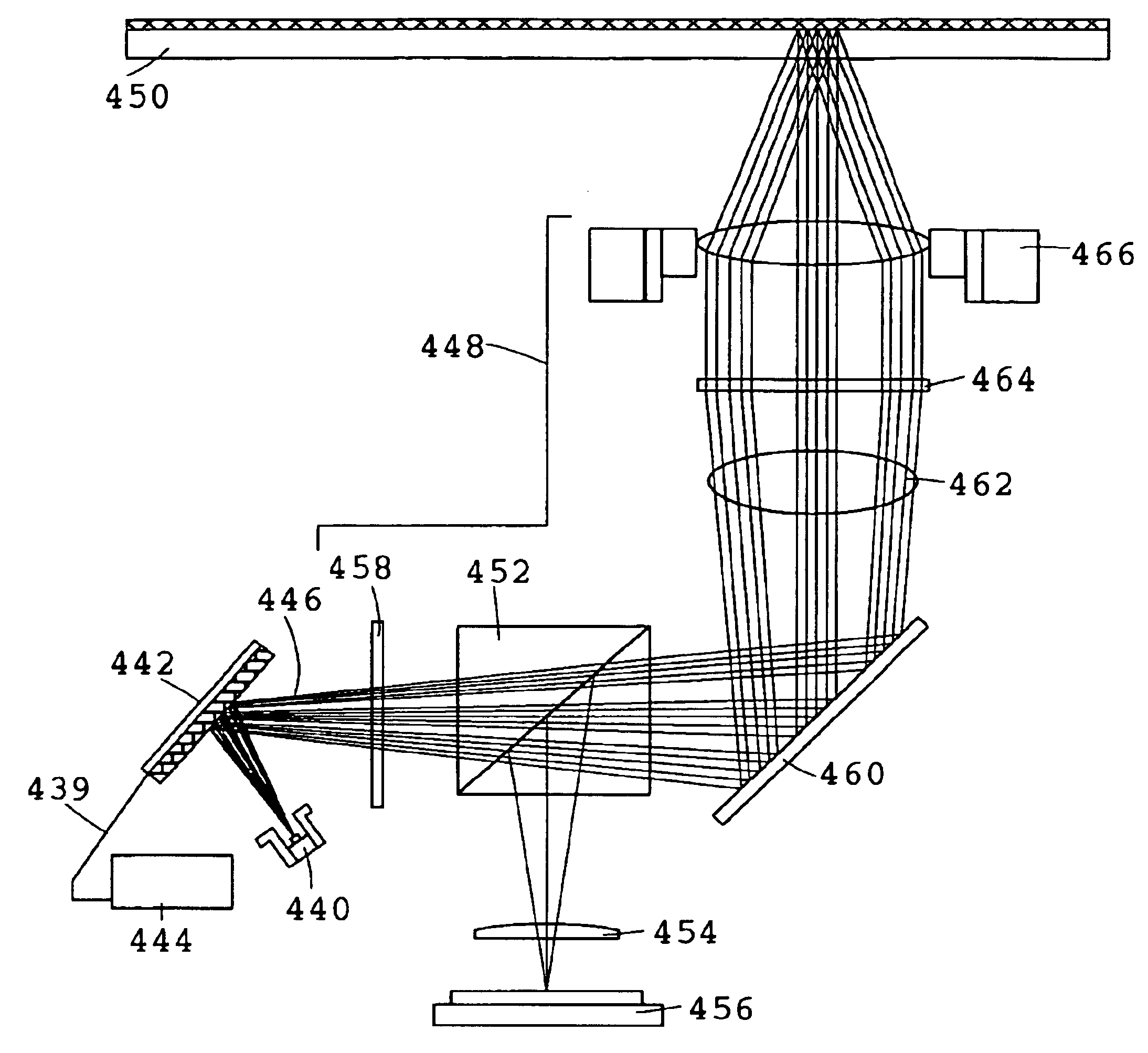

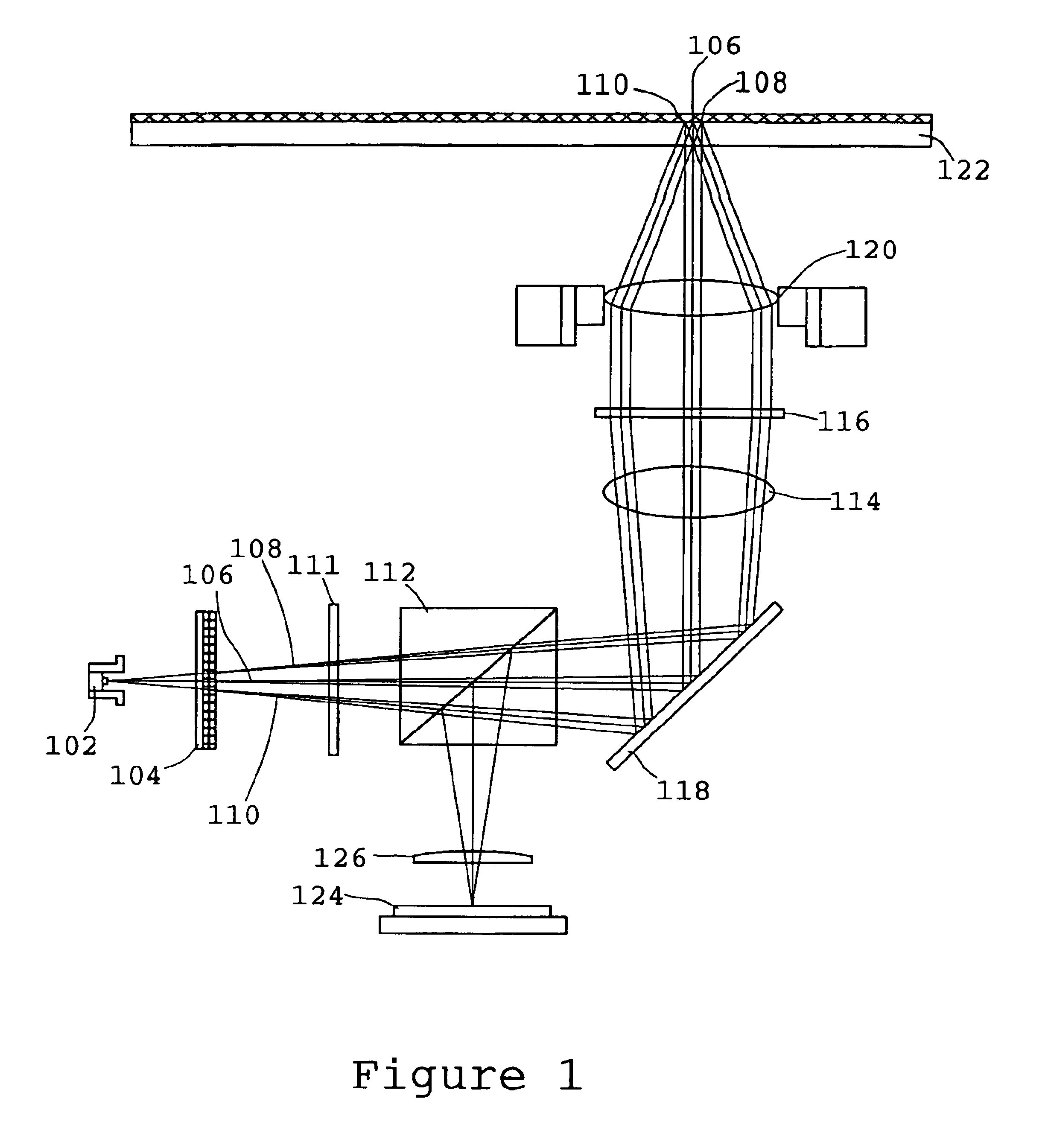

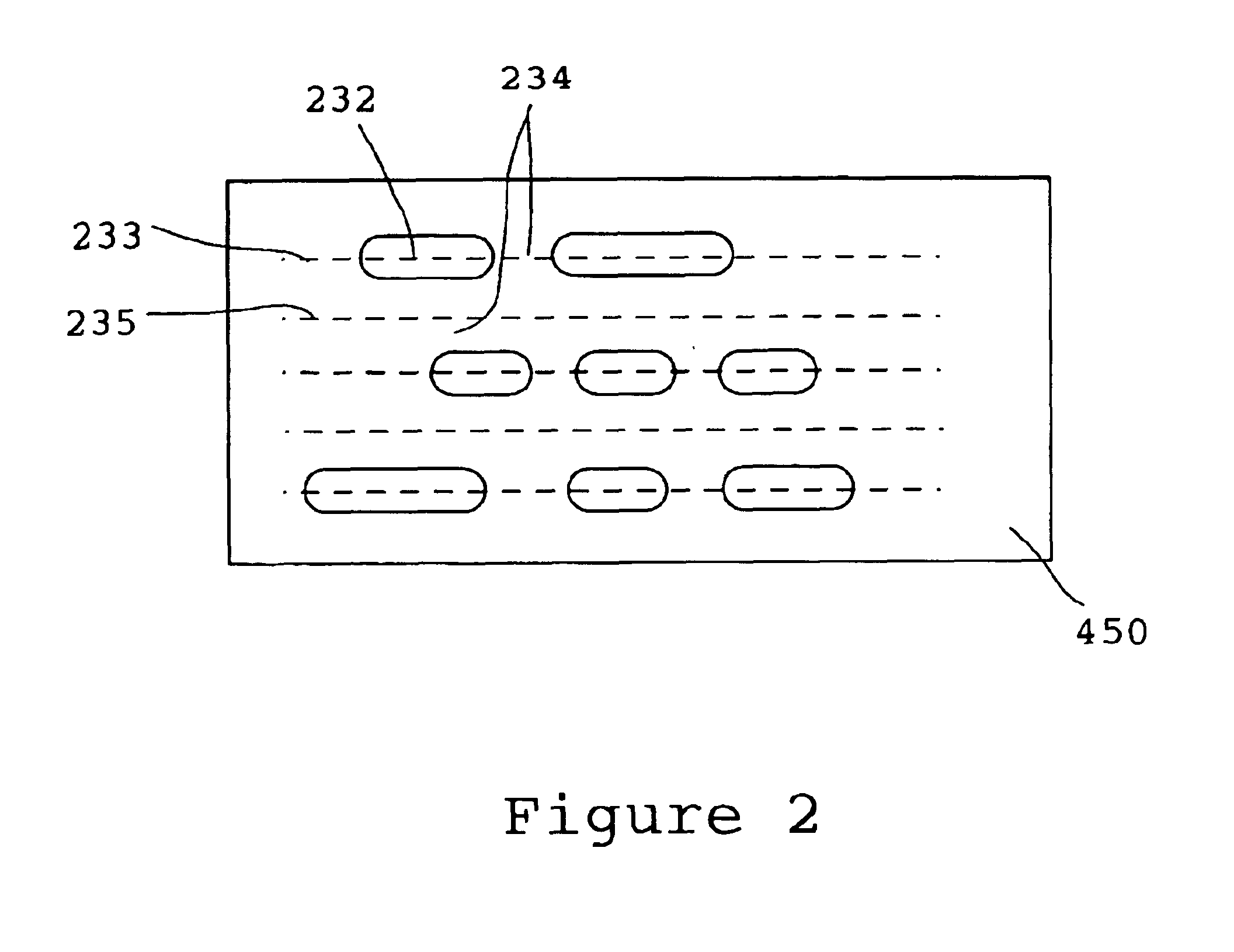

Optical pickup apparatus and method

InactiveUS6891791B1Improve storage densityIncrease readout speedRecord information storageOptical beam guiding meansOptical storageOptical pickup

The present invention provides an improved optical pickup device based on the developing electronically reconfigurable diffraction grating MEMS technology. The improved optical pickup device has applications that include but are not limited to CD and DVD for audio, video and computer technology. The present invention can provide improvements to this current and future technology with higher data storage density and faster retrieval. In a preferred embodiment, the optical pickup apparatus comprises an electronically reconfigurable diffraction grating modulating relative light intensities as among at least two different diffraction orders of light diffracted by the electronically reconfigurable diffraction grating; focusing optics for focusing the light diffracted by the electronically reconfigurable diffraction grating into diffractive spots corresponding with each of the diffraction orders and onto an optical storage medium, which light is then reflected by the optical storage medium; and a detector for detecting the light reflected by the optical storage medium and striking said detector.

Owner:INTERSCI

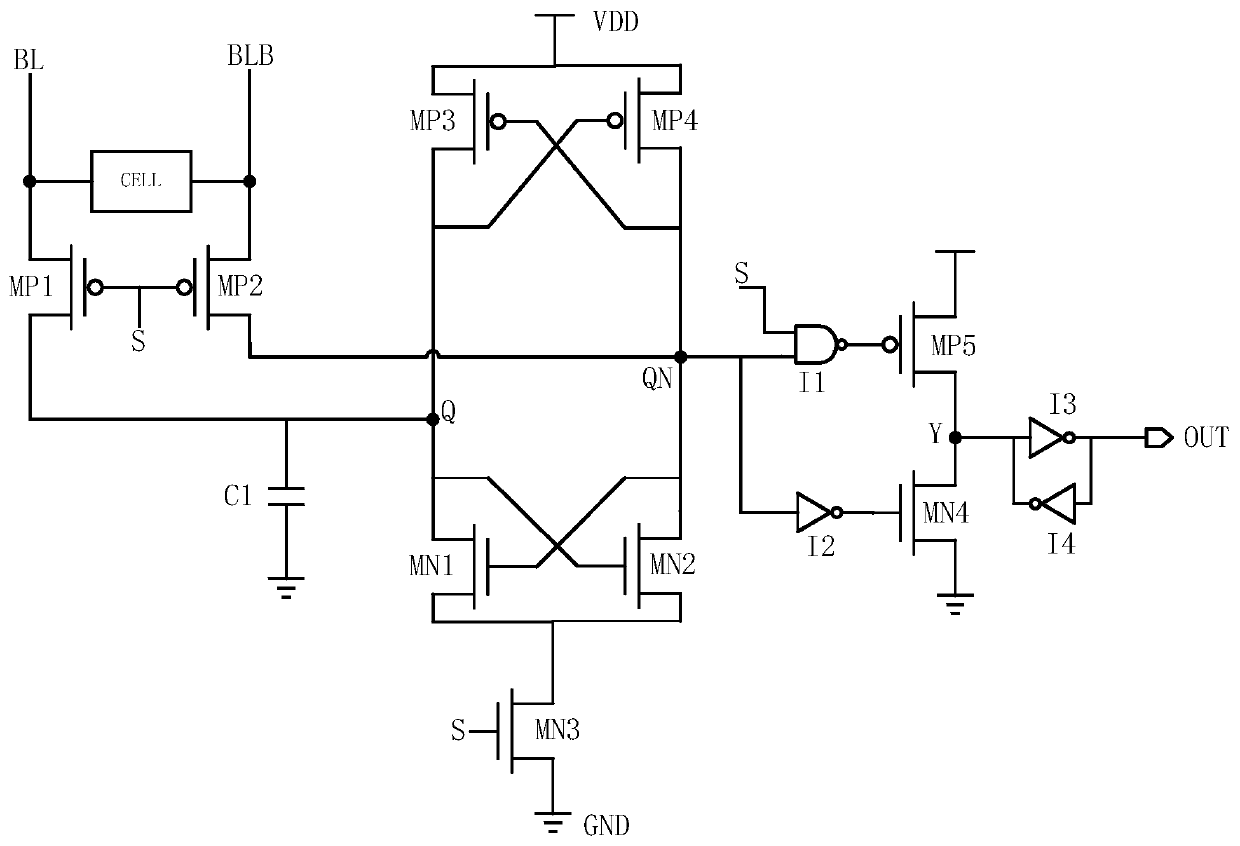

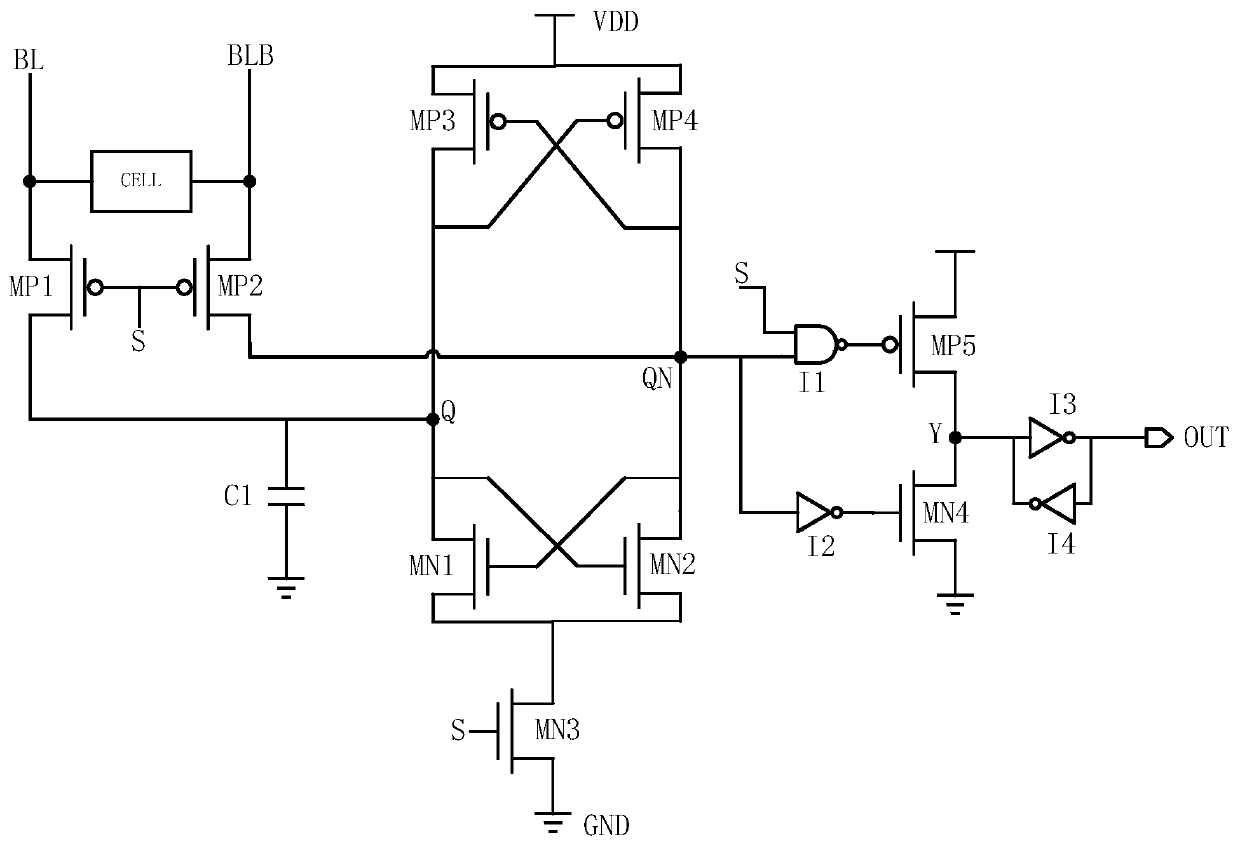

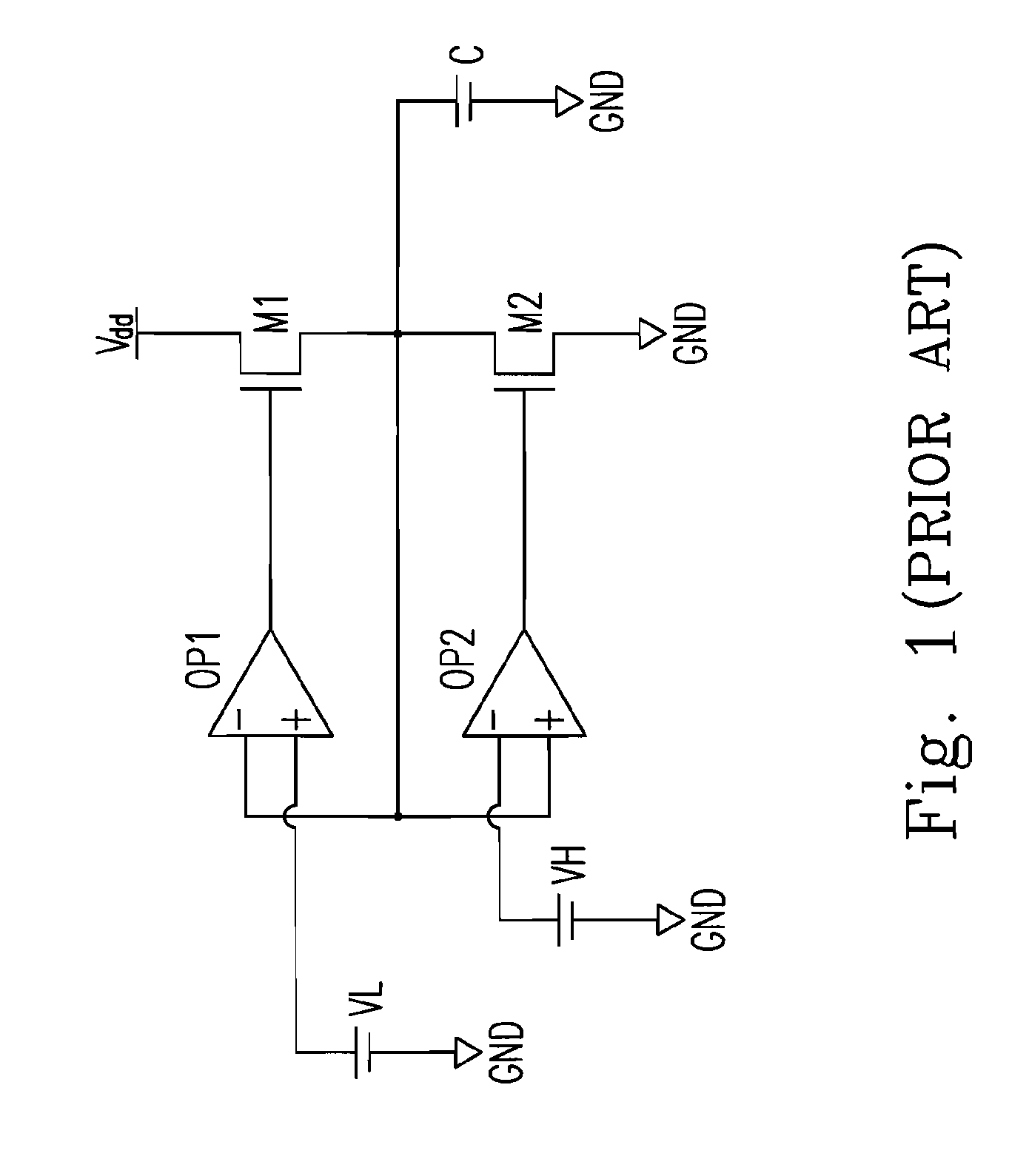

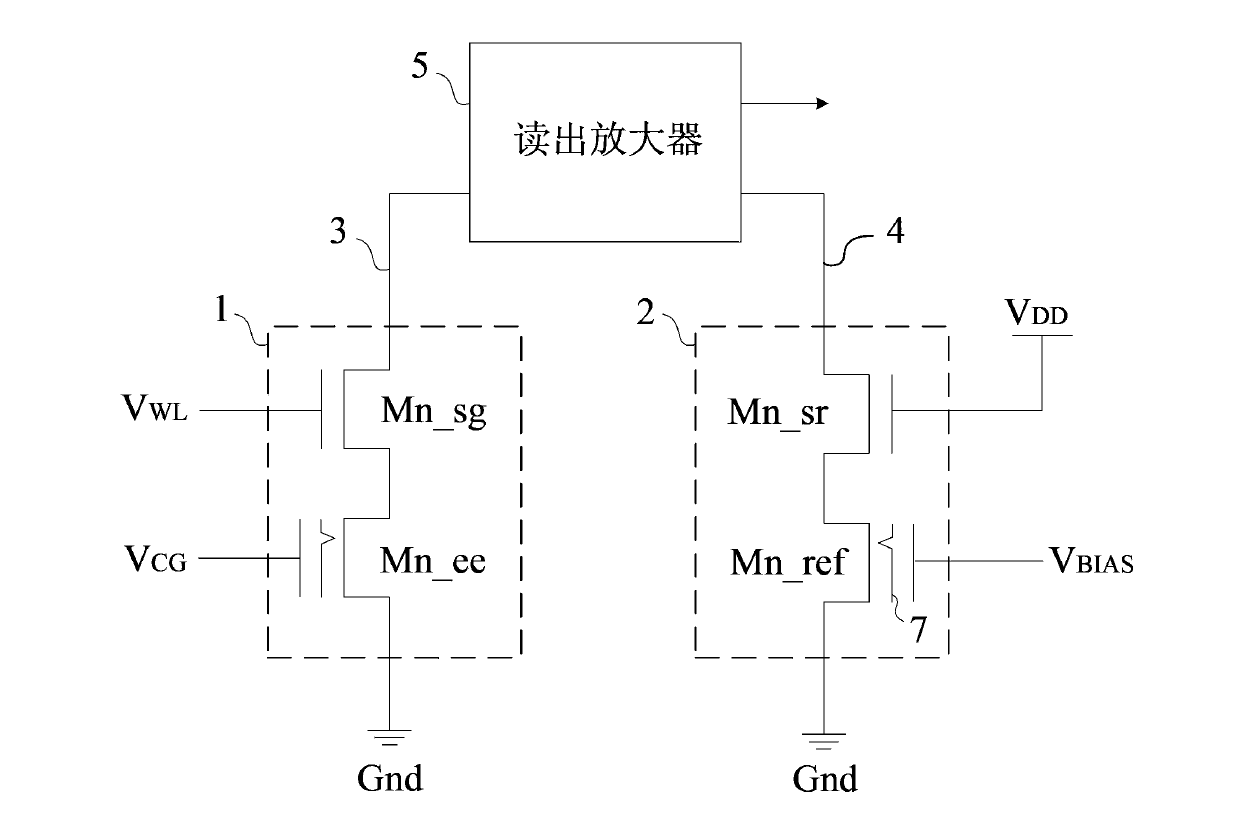

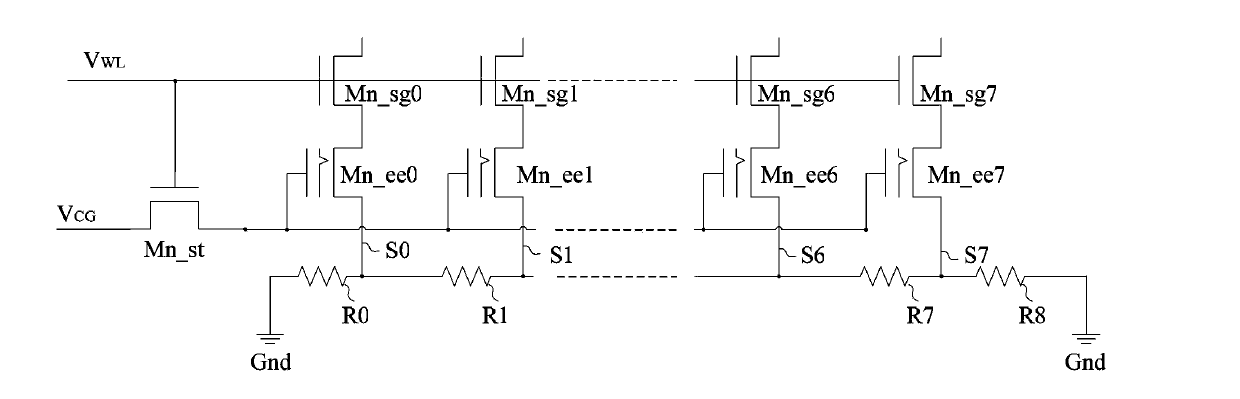

A high-speed sense amplifier circuit of an SRAM type memory

The invention relates to a high-speed sensitive amplifier circuit of an SRAM (Static Random Access Memory) type memory, which accelerates the overall response speed of a latch amplifier through positive feedback by virtue of the charge retention characteristic of a capacitor C1 when reading a '1' memory cell, so that the requirement of the amplifier on the input voltage difference is greatly reduced, and the speed of the SRAM type memory for reading the '1' is accelerated; When the '0' storage unit is read, the storage data is read by virtue of the fast pull-up action of the transistor MP5 through the control on the NAND gate I1 by the hopping of the read enable signal S, so that the requirement on the input voltage difference is greatly reduced, the reading speed of the sense amplifier isaccelerated, and the speed of the SRAM for reading the '0' is accelerated. The requirement of the sensitive amplifier for the input voltage difference is reduced, and the reaction speed and the processing capacity of the sensitive amplifier are improved.

Owner:BEIJING MXTRONICS CORP +1

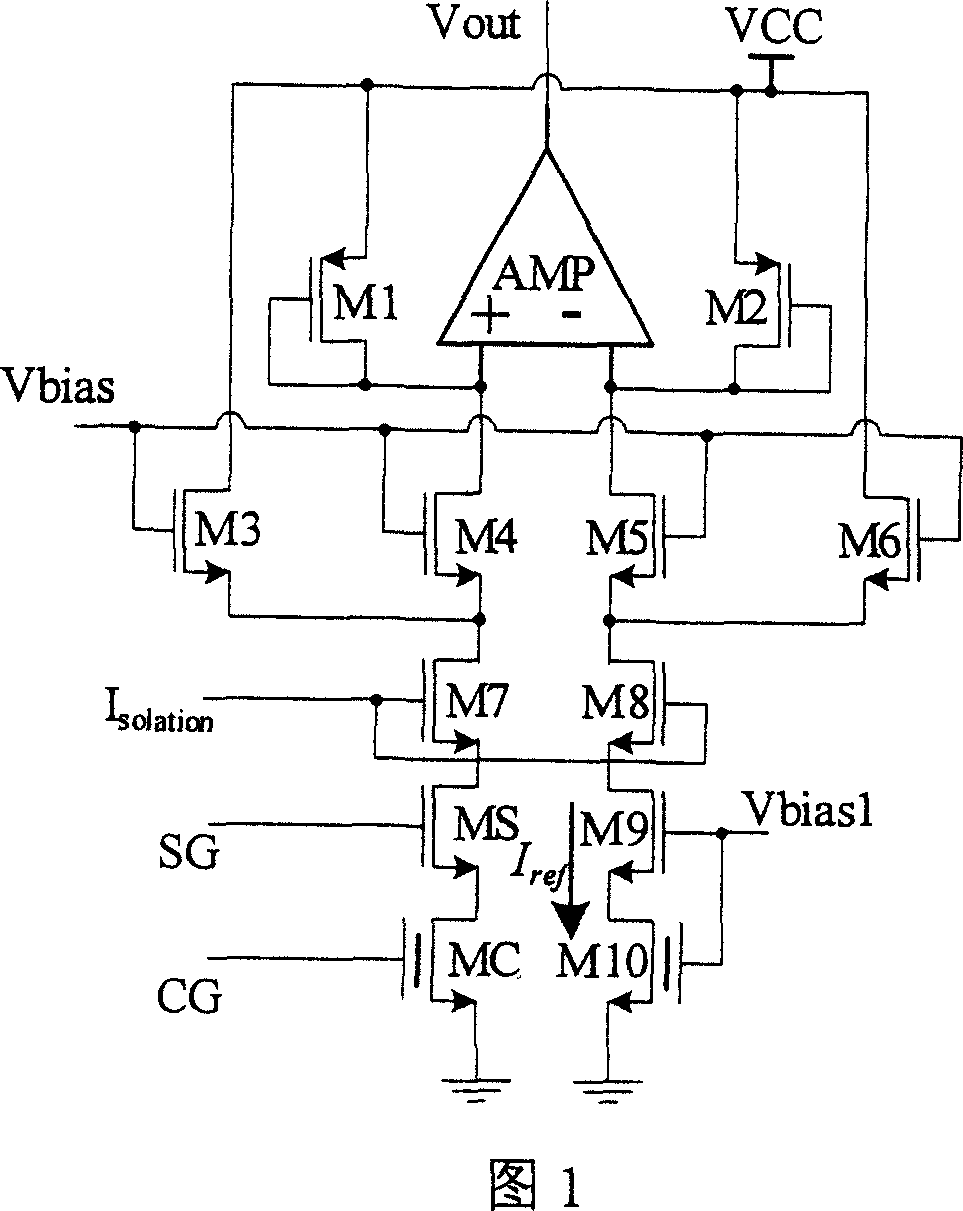

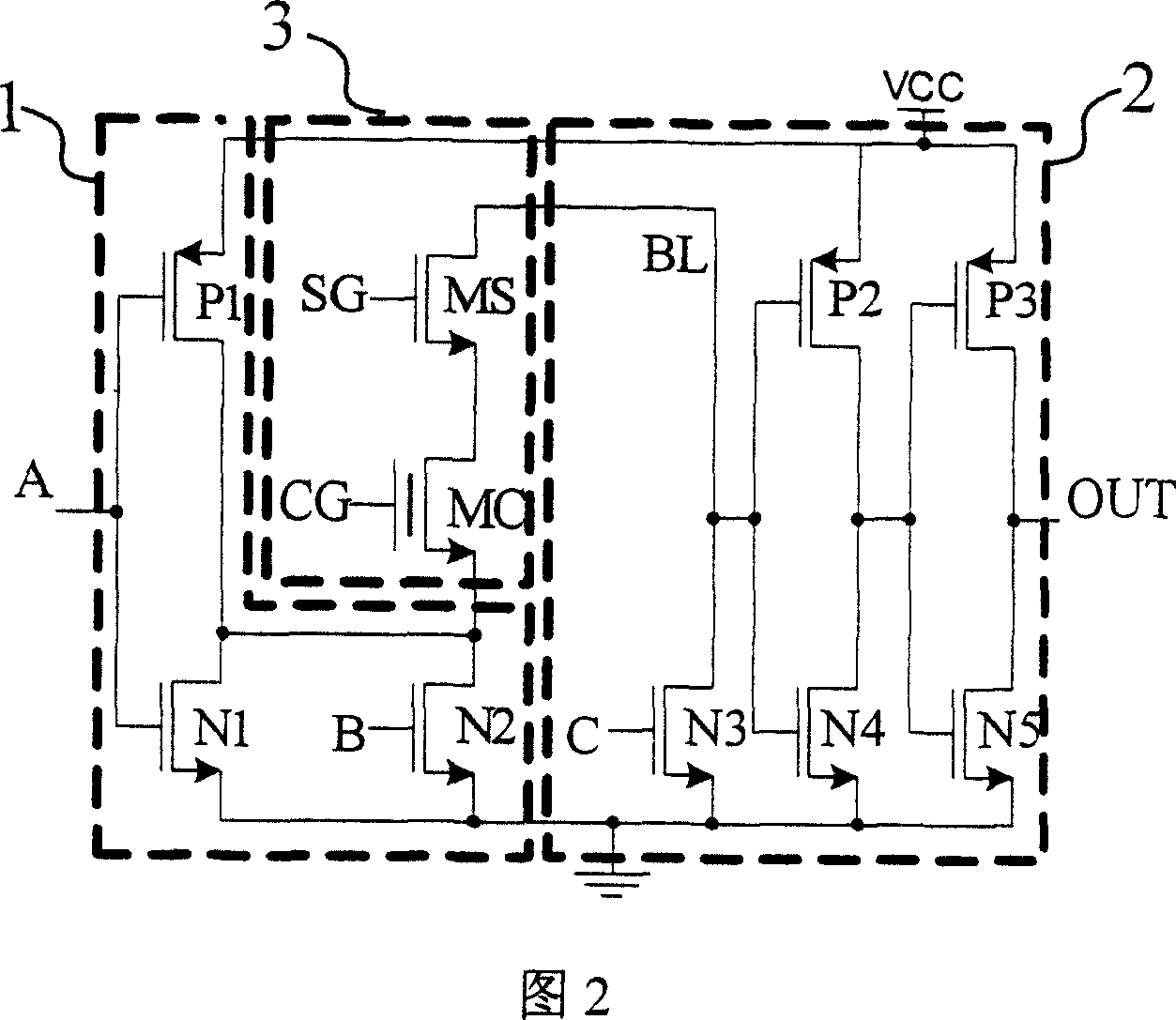

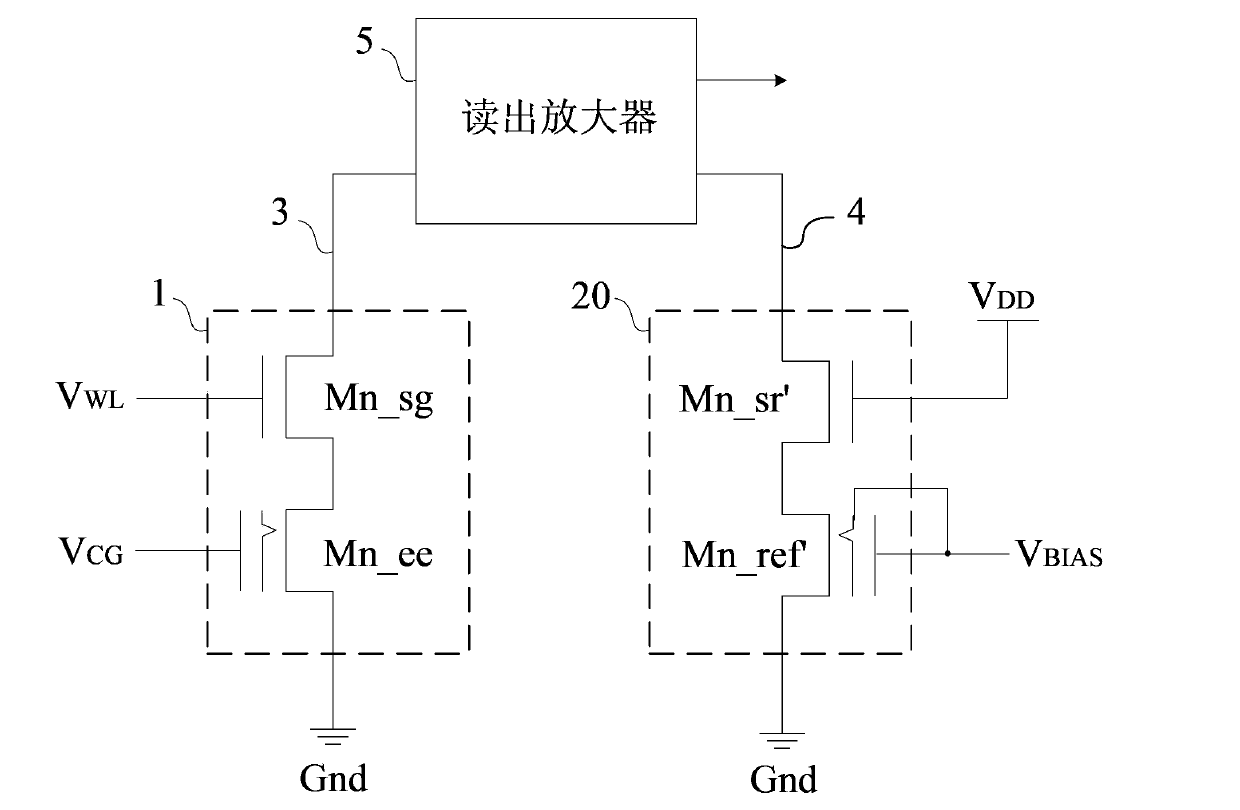

Sensitive amplifier for electric EPROM

InactiveCN1949394AReduce power consumptionAvoid Interfering ChargesRead-only memoriesAudio power amplifierHemt circuits

The invention discloses a sensitivity amplifier for EEPROM. It includes charge control circuit and detecting output circuit. The charge control circuit includes PMOS tube P1 and NMOS tubes N1, N2. Detecting output circuit includes PMOS tubes P2, P3 and NMOS tubes N3, N4, N5. The invention uses the bidirectional ducting ability of MOS tube to take charge to drain electrode. The source electrodes of floating grid tube are connected to each other to decrease charging circuit quantity. By modifying the reverse threshold value of the inverter, the charging voltage would be decreased, and read speed would be improved. The invention is especially suitable for embedded EEPROM.

Owner:HUAZHONG UNIV OF SCI & TECH

Delay management circuit for reading out large S/H arrays

ActiveUS20070200942A1Increases effective sensor readout speedReduces mis-samplingTelevision system detailsTelevision system scanning detailsComputer scienceSample and hold

An image sensor includes a plurality of pixels for capturing an image; a sample and hold circuit array having a plurality of units for receiving signals from the plurality of pixels representing the captured image; a decoder for selecting each of the units of the sample and hold circuit array for output; and a delay circuit that includes an adjustable time delay to the decoder for compensating for time delays.

Owner:OMNIVISION TECH INC

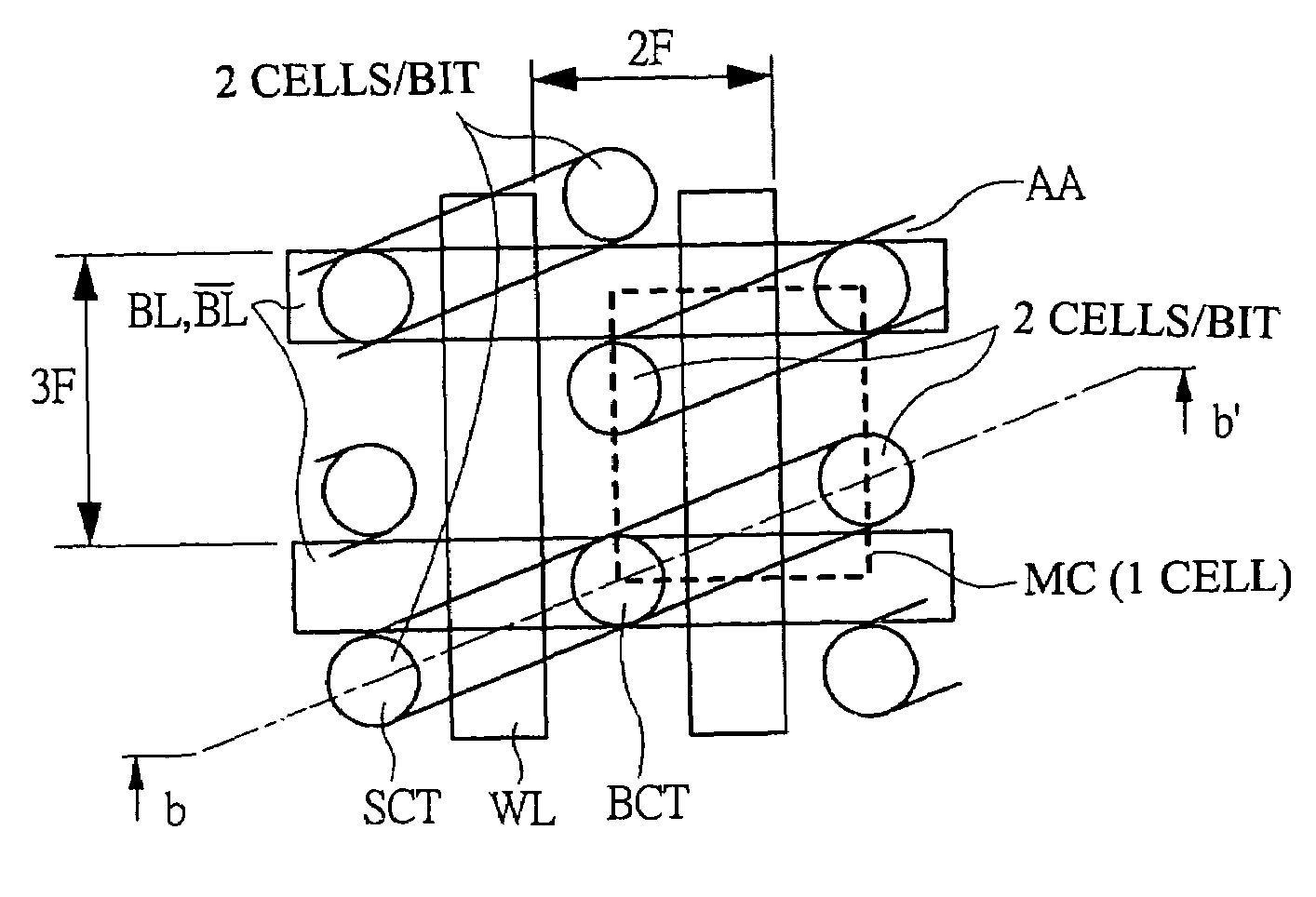

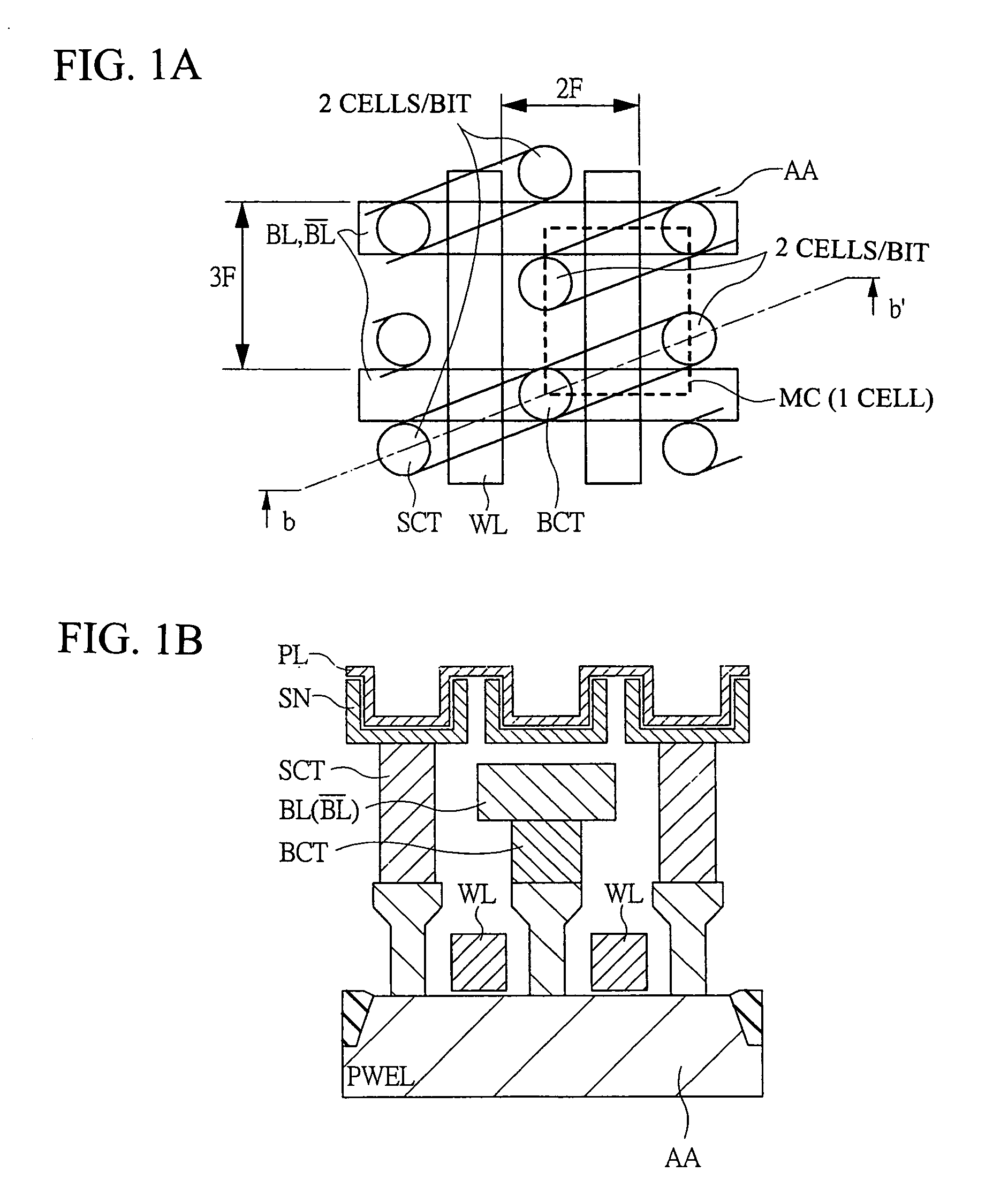

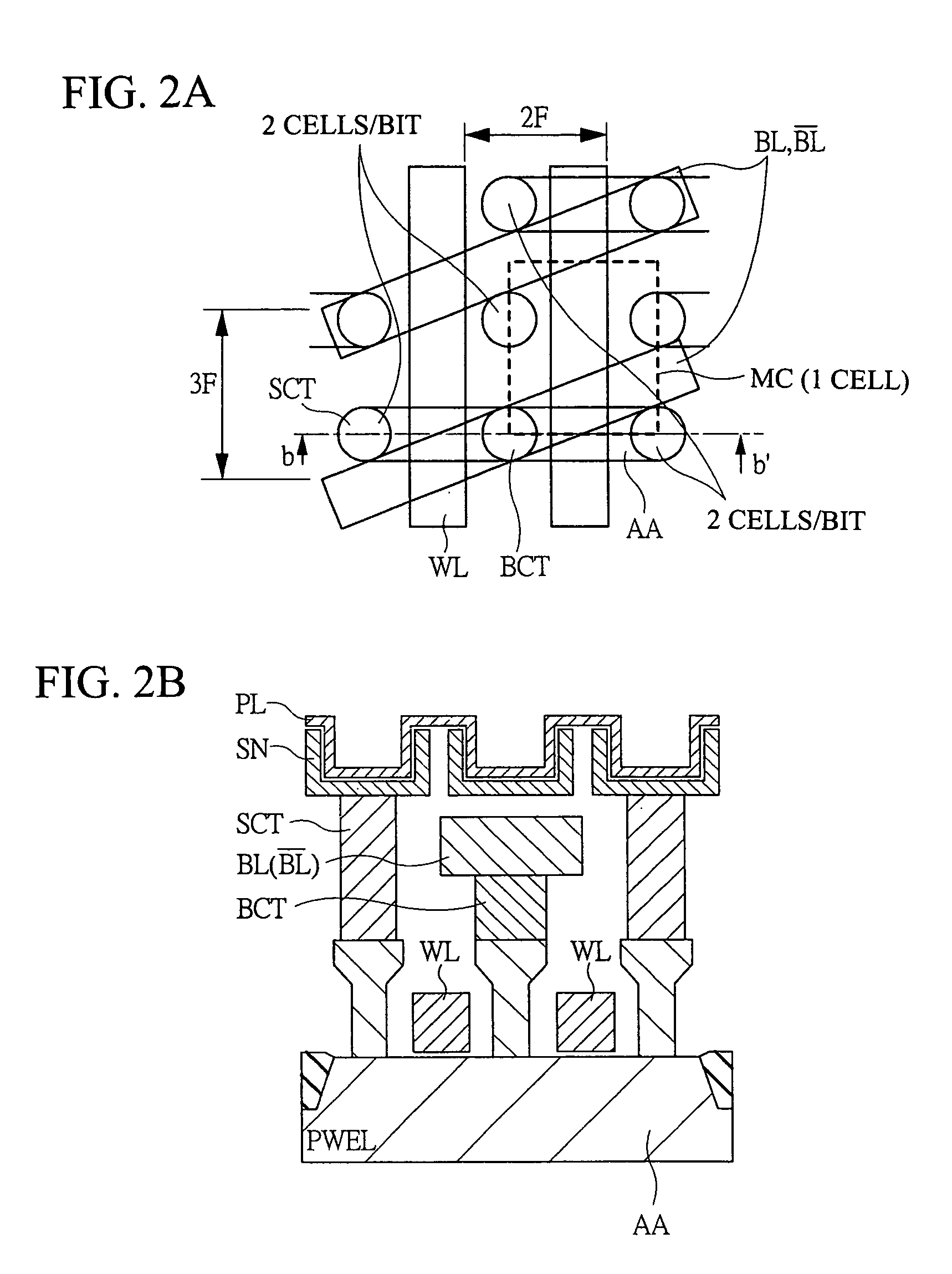

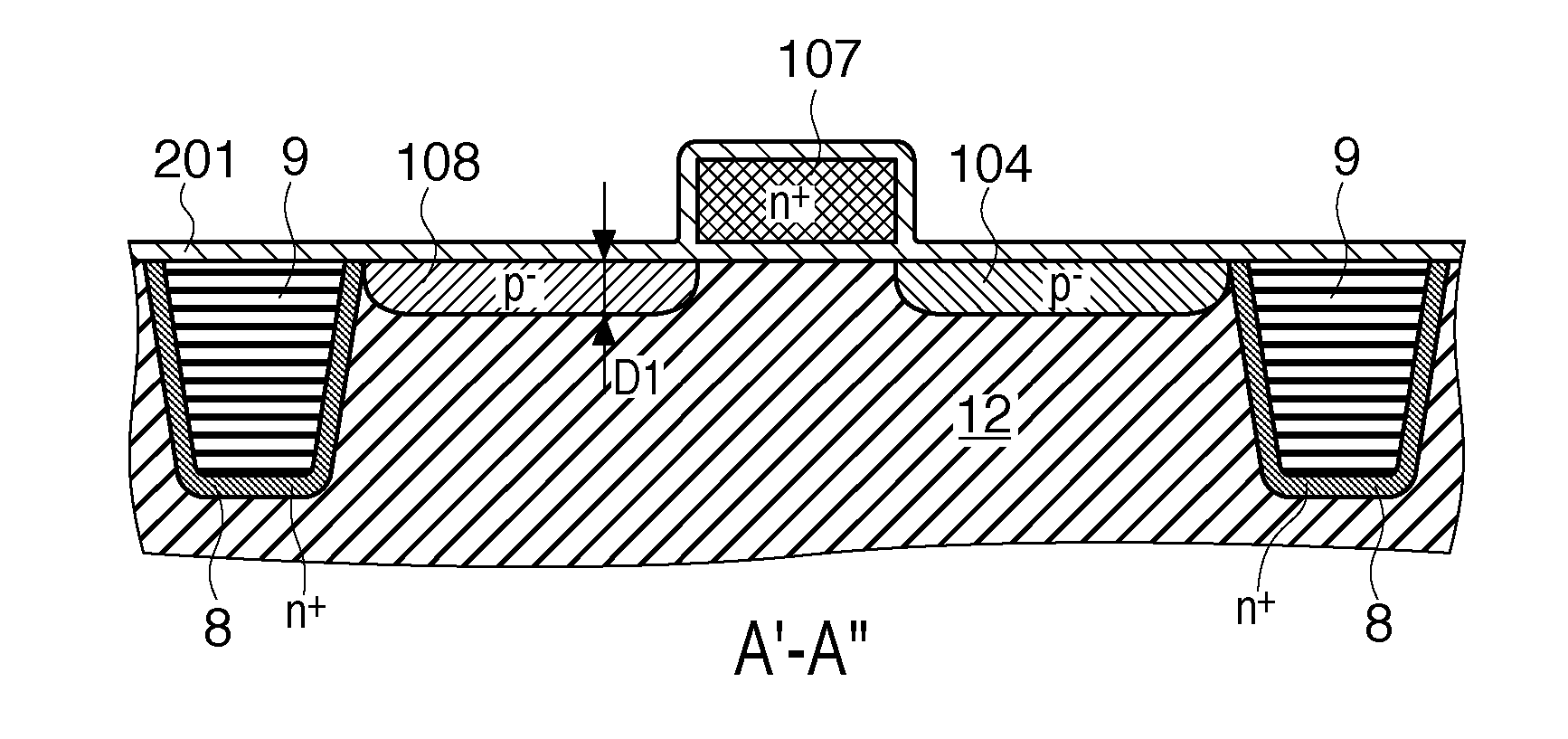

Semiconductor memory device

InactiveUS20050056876A1Guaranteed high-speed and stable operationExtended maintenance periodTransistorSolid-state devicesUltra high speedBit line

A semiconductor memory device is provided which can achieve the high integration, ultra-high speed operation, and significant reduction of power consumption during the information holding time, by reducing the increase in the area of a memory cell and obtaining a period of the ultra-high speed readout time and ensuring a long refresh period at the time of the self refresh. A DRAM employing a one-intersection cell·two cells / bit method has a twin cell structure employing a one-intersection 6 F2 cell, the structure in which: memory cells are arranged at positions corresponding to all of the intersections between a bit-line pair and a word line; and when a half pitch of the word line is defined as F, a pitch of each bit line of the bit-line pair is larger than 2 F and smaller than 4 F. Further, an active region in the silicon substrate, on which a source, channel and drain of the transistor of each memory cell are formed, is obliquely formed relative to the direction of the bit-line pair.

Owner:LONGITUDE SEMICON S A R L

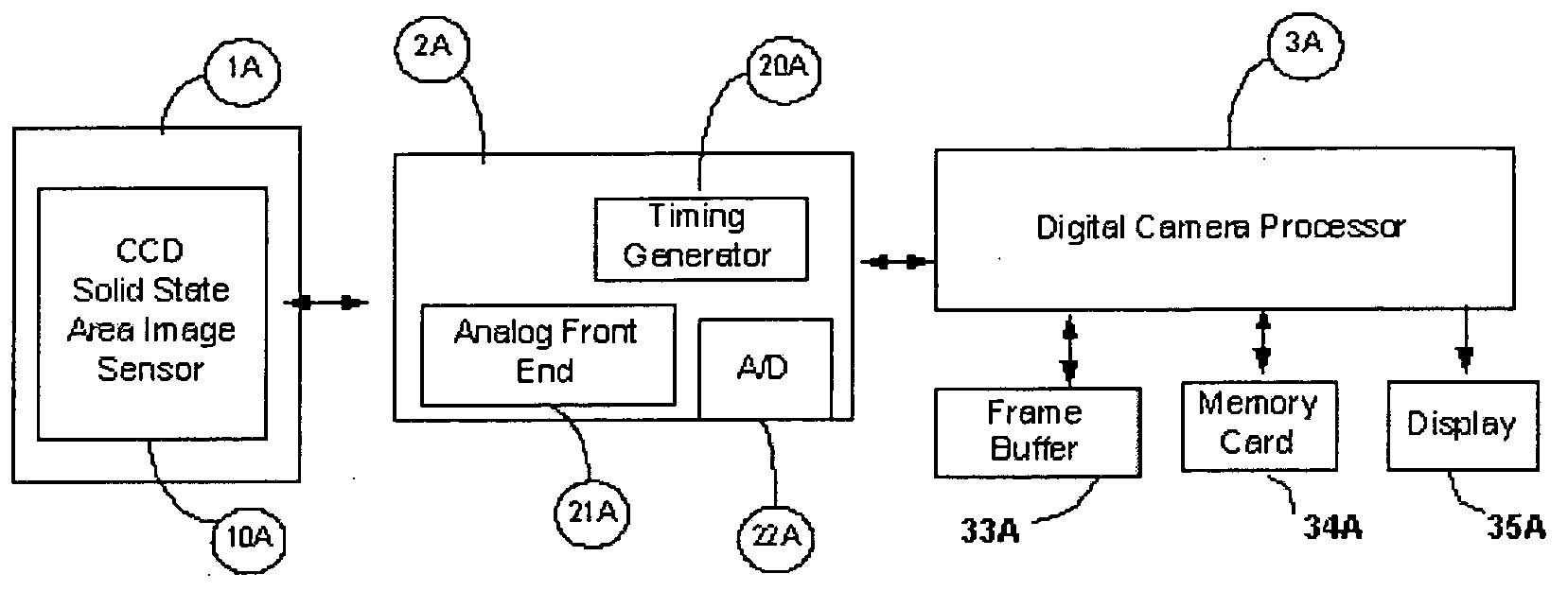

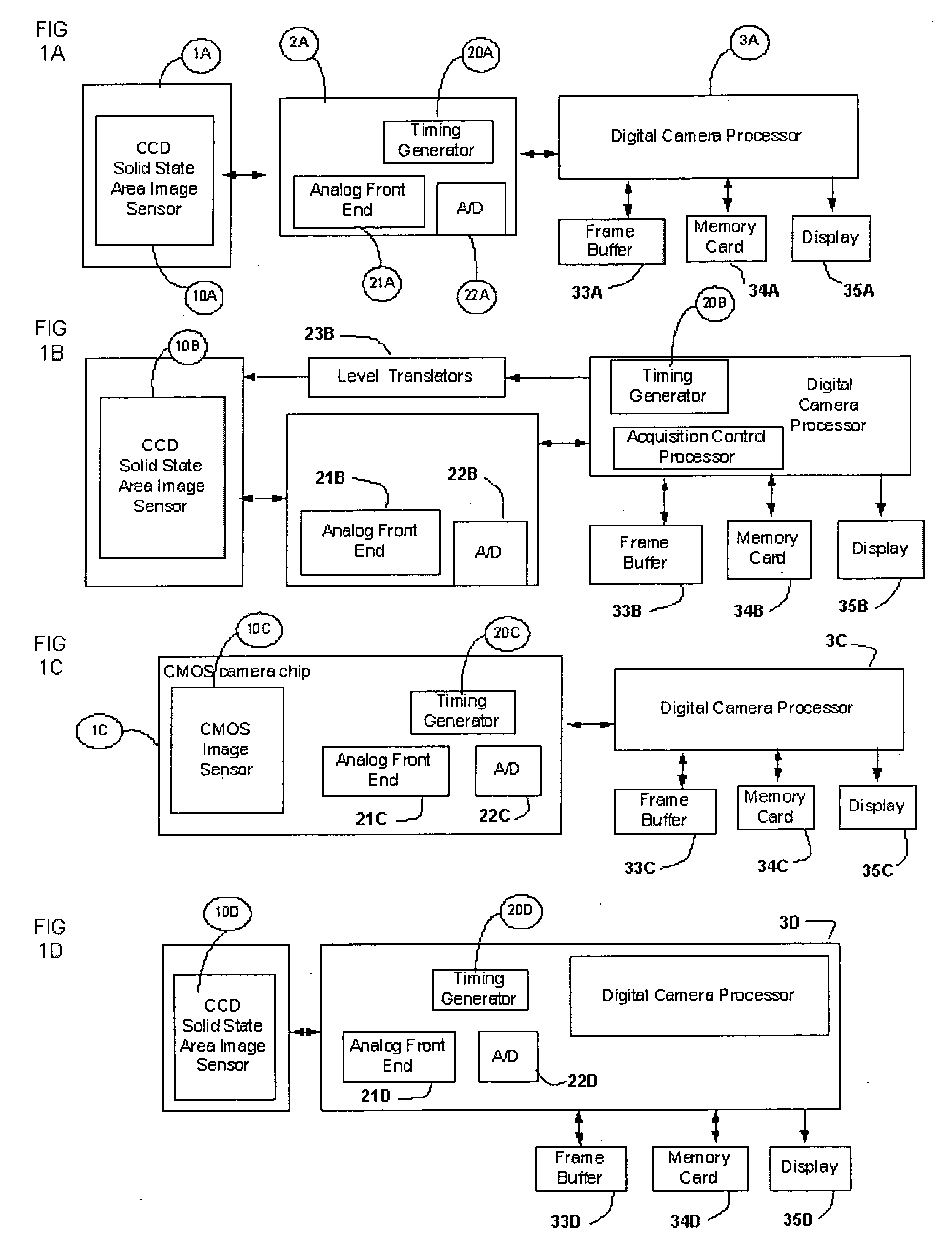

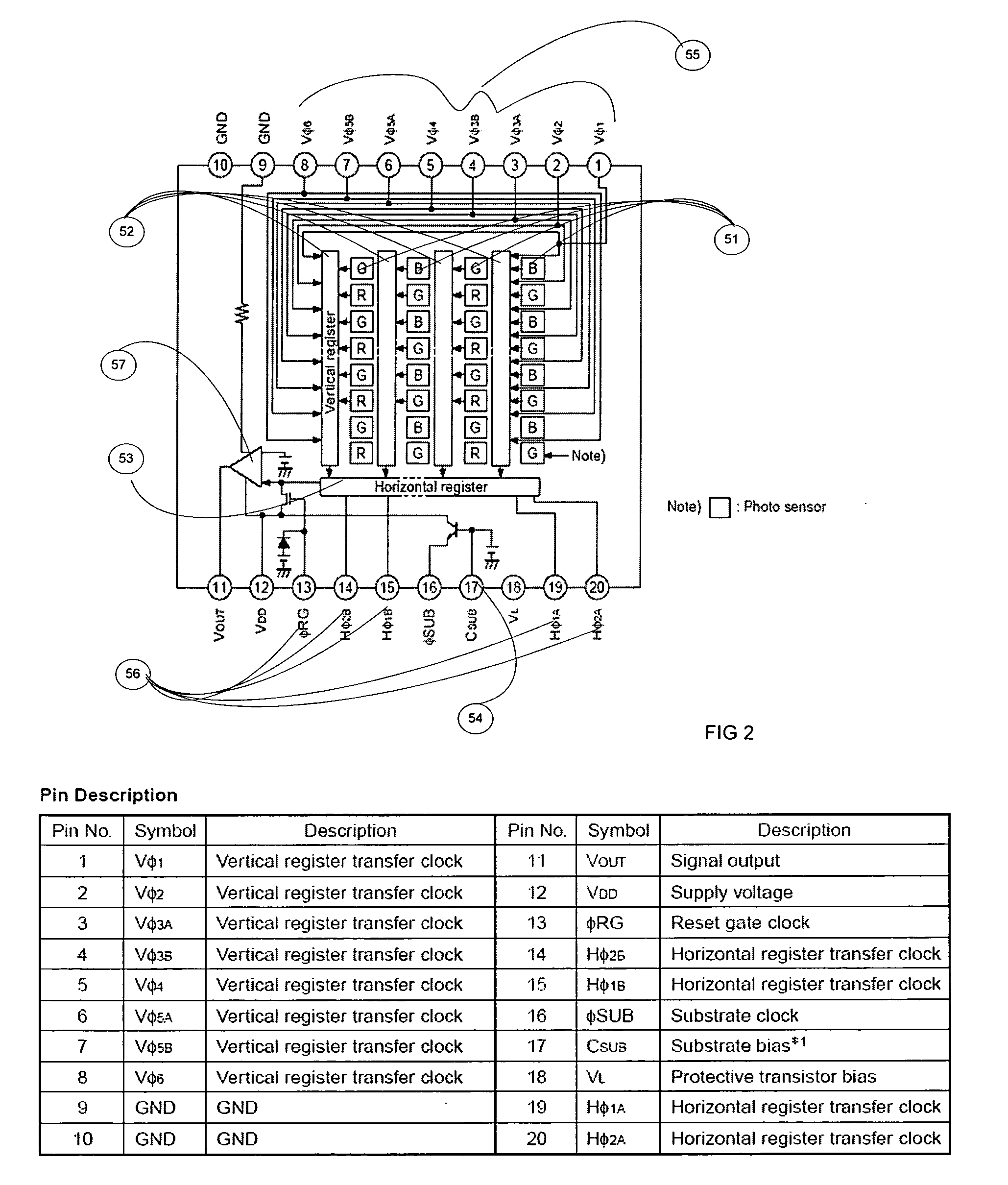

Solid-state area image sensor readout methods for illuminat discrimination and automatic white balance in digital cameras

InactiveUS20050195289A1High magnitudeAdditional costTelevision system detailsColor signal processing circuitsCombined useLight source

A method and apparatus is provided which obtains the temporal signature of artificial illuminants using a single imaging path, by controlling and reading the actual solid stage area imager. When using the solid-state area sensor to sample the temporal characteristics of artificial illuminants it may be necessary to greatly increase solid-state area sensor readout speed and to also increase the solid-state area sensors effective sensitivity to light. A method and apparatus is provided for discriminating artificial illuminants reliably through-the-lens (TTL) without the cost and bulkiness and other disadvantages of an additional sensor. This method and apparatus may be used independently or can be used in combination with the white pixel discrimination or scene analysis methods described earlier and embodied in the prior art.

Owner:JACOBS WILLIAM S +1

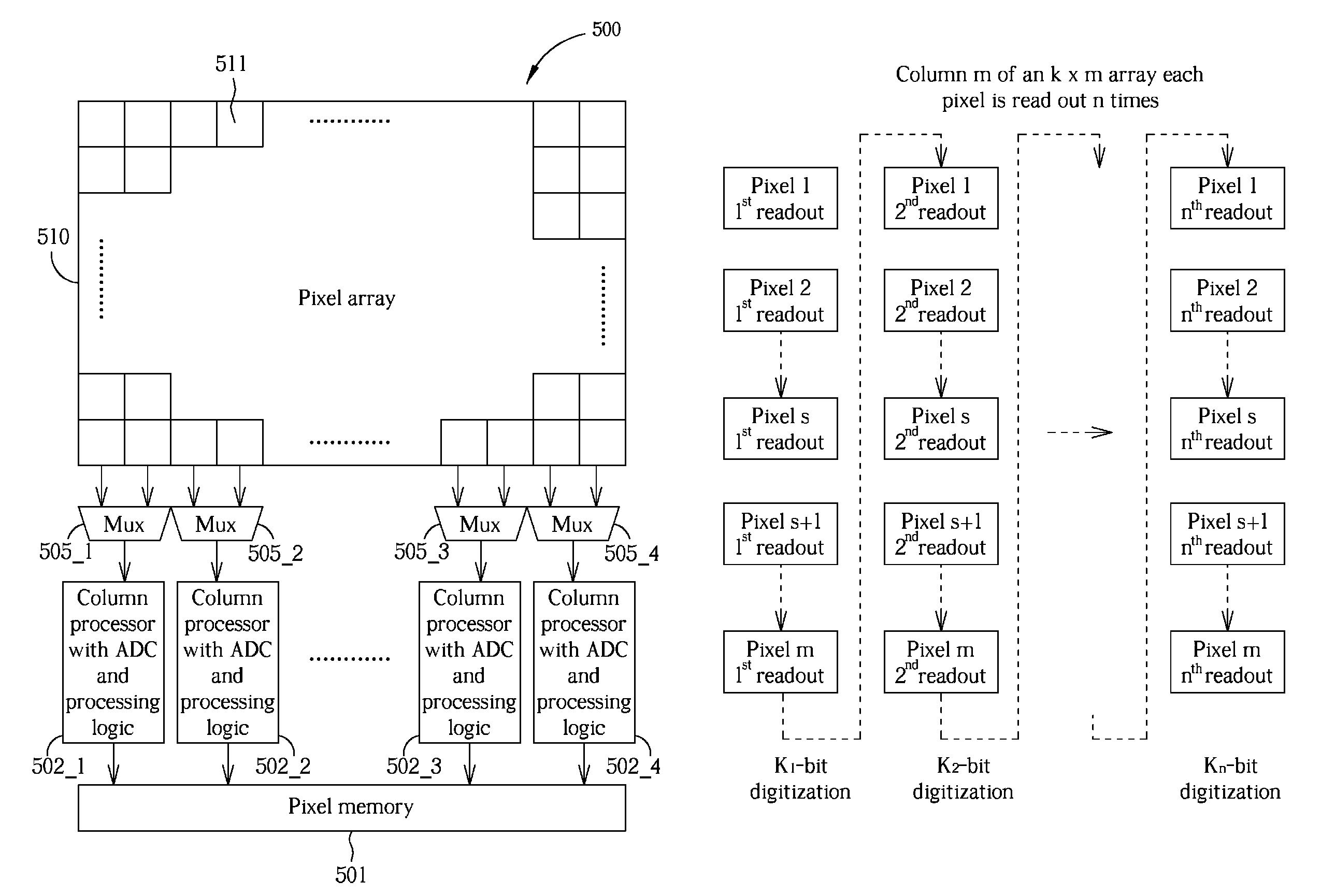

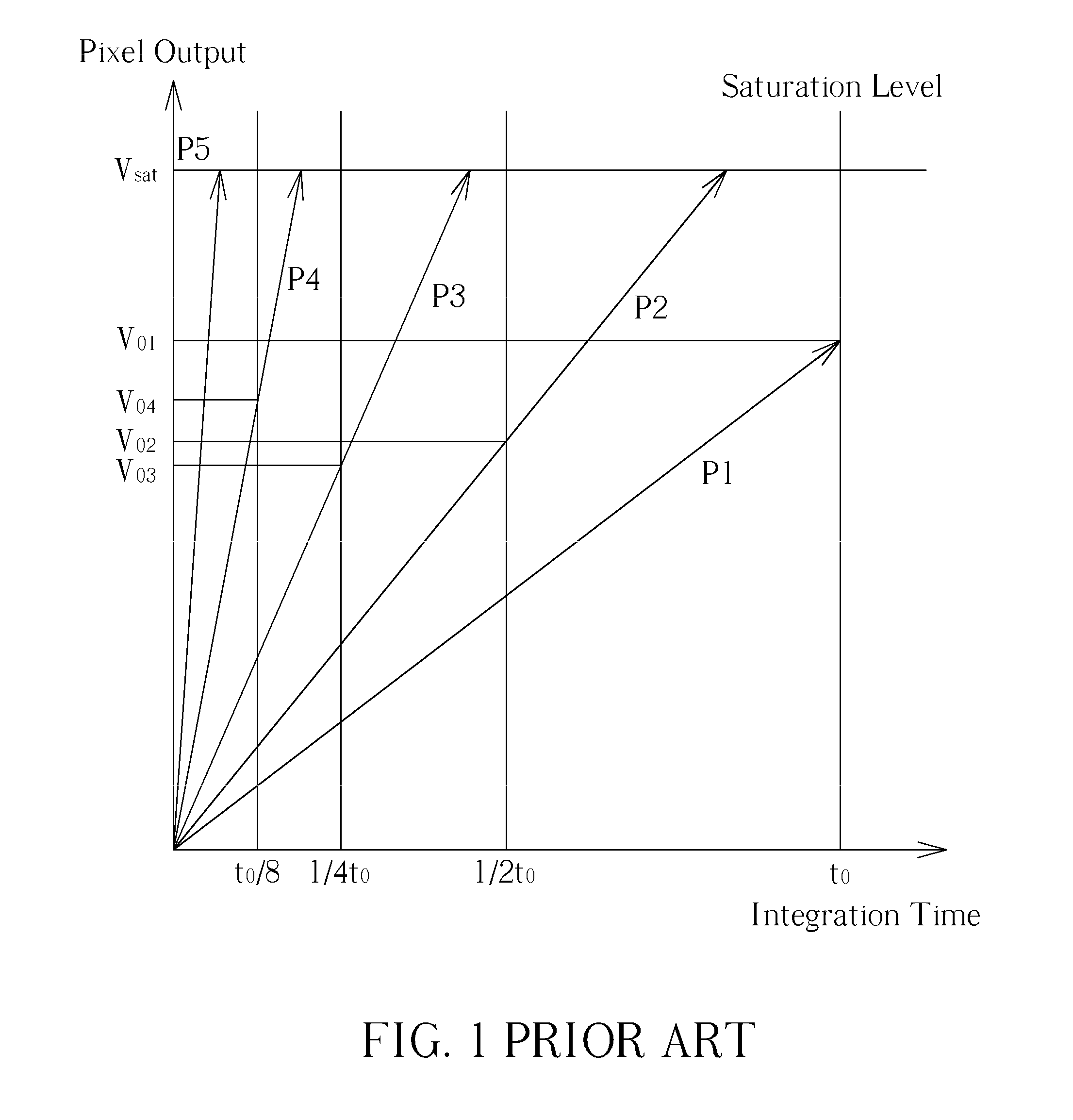

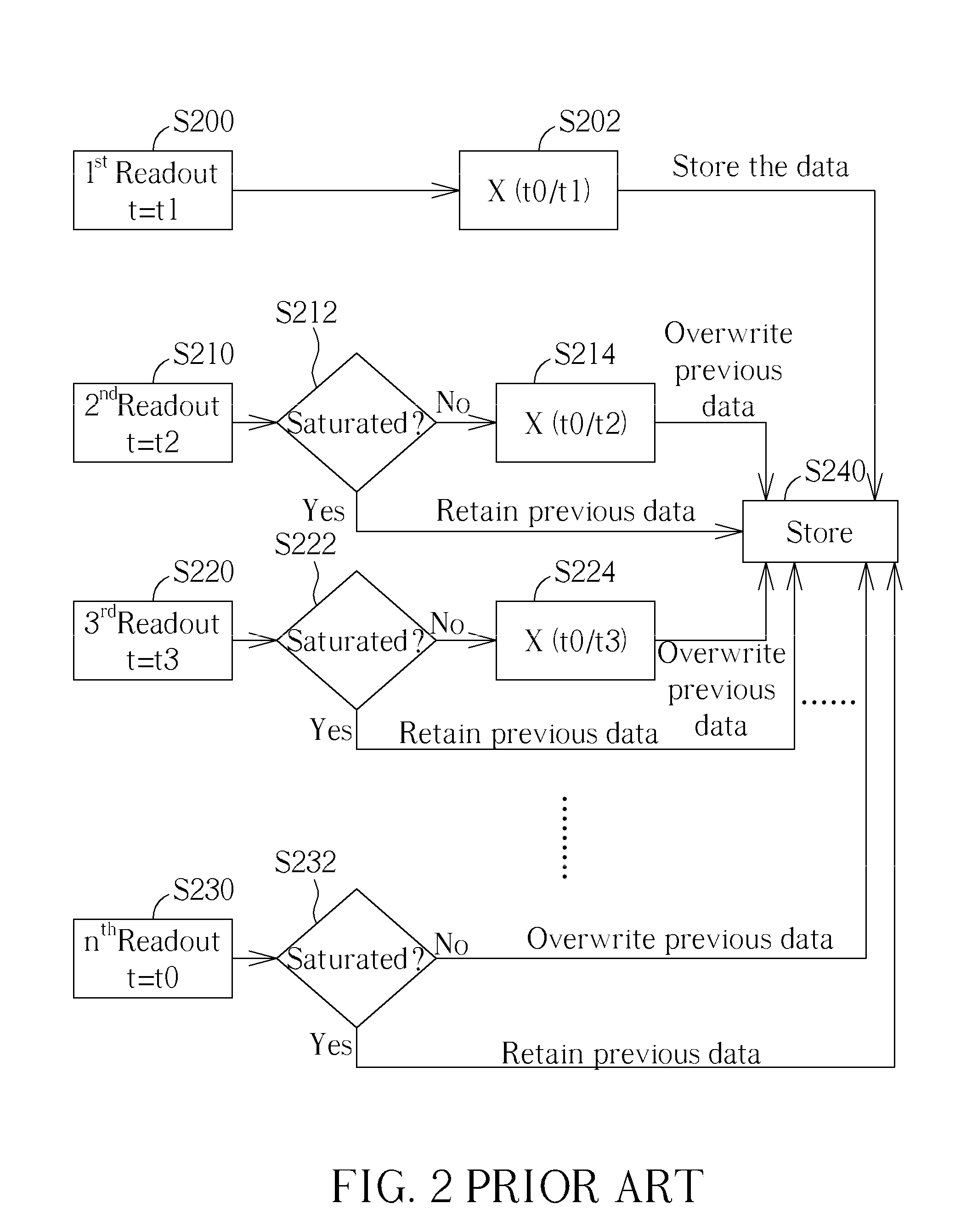

Method and apparatus of using processor with analog-to-digital converter within image sensor to achieve high dynamic range of image sensor

ActiveUS8144215B2Extended imaging rangeImprove performanceTelevision system detailsTelevision system scanning detailsDigital dataDigital down converter

A scheme is provided that enhances the dynamic range performance of images via multiple readouts during one exposure. The readout process circuit structure includes at least an analog-to-digital converter (ADC). The analog-to-digital converter converts analog data generated from an image sensor into digital data, allowing sub-frame readouts for improving a dynamic range of the image sensor. Additionally, methods of partial digitization (not a full number of bits) and image array are provided.

Owner:HIMAX IMAGING LIMITED

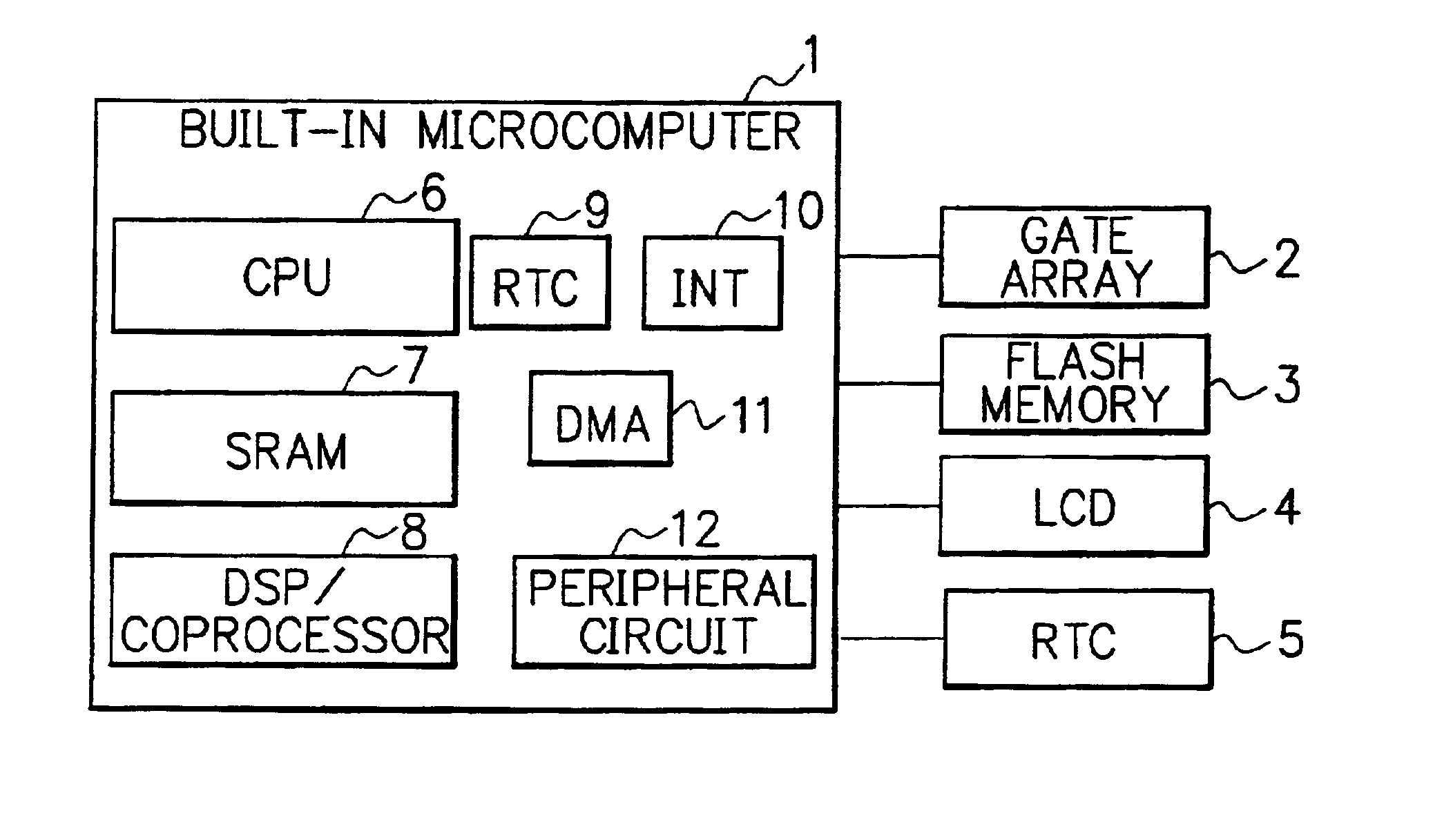

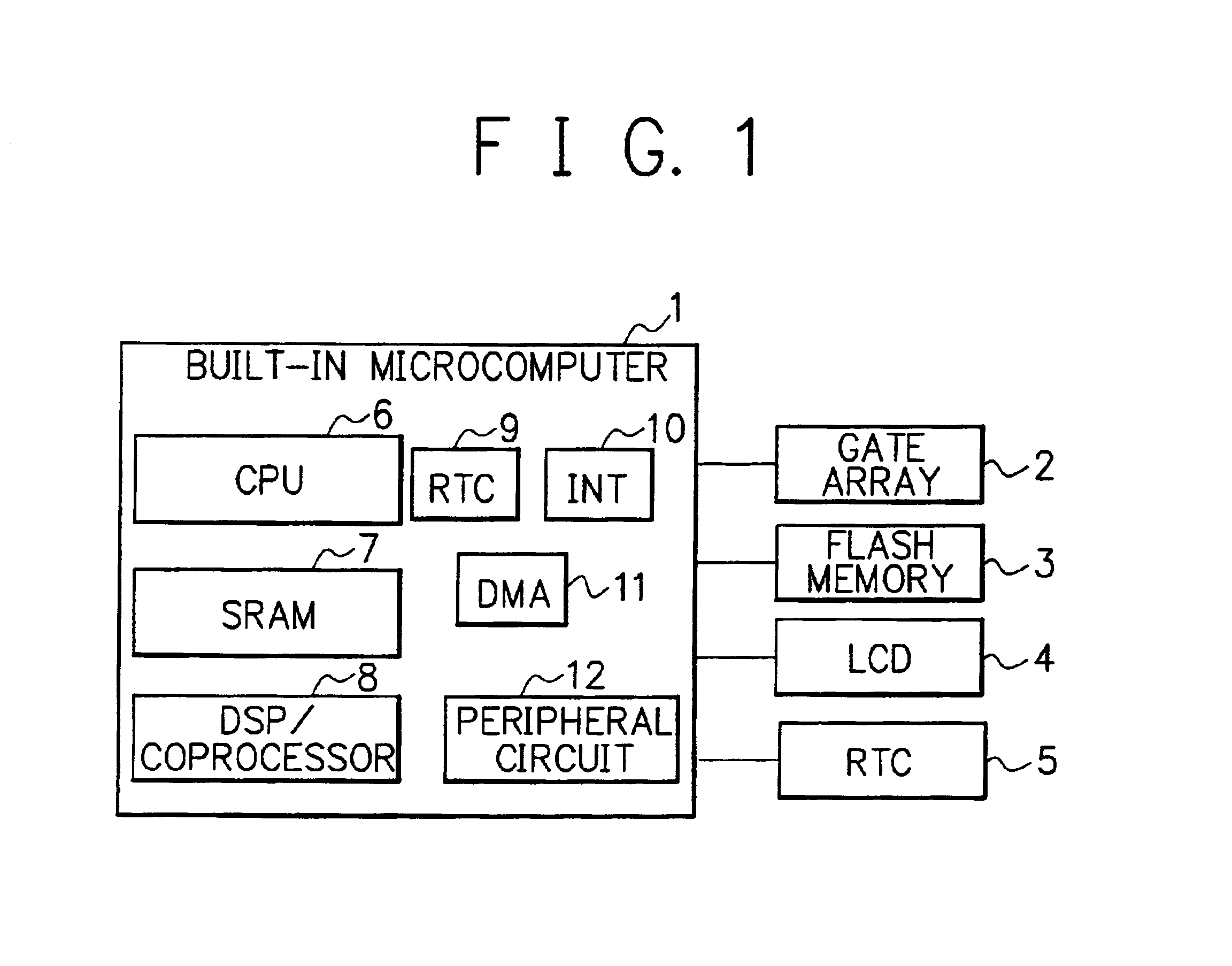

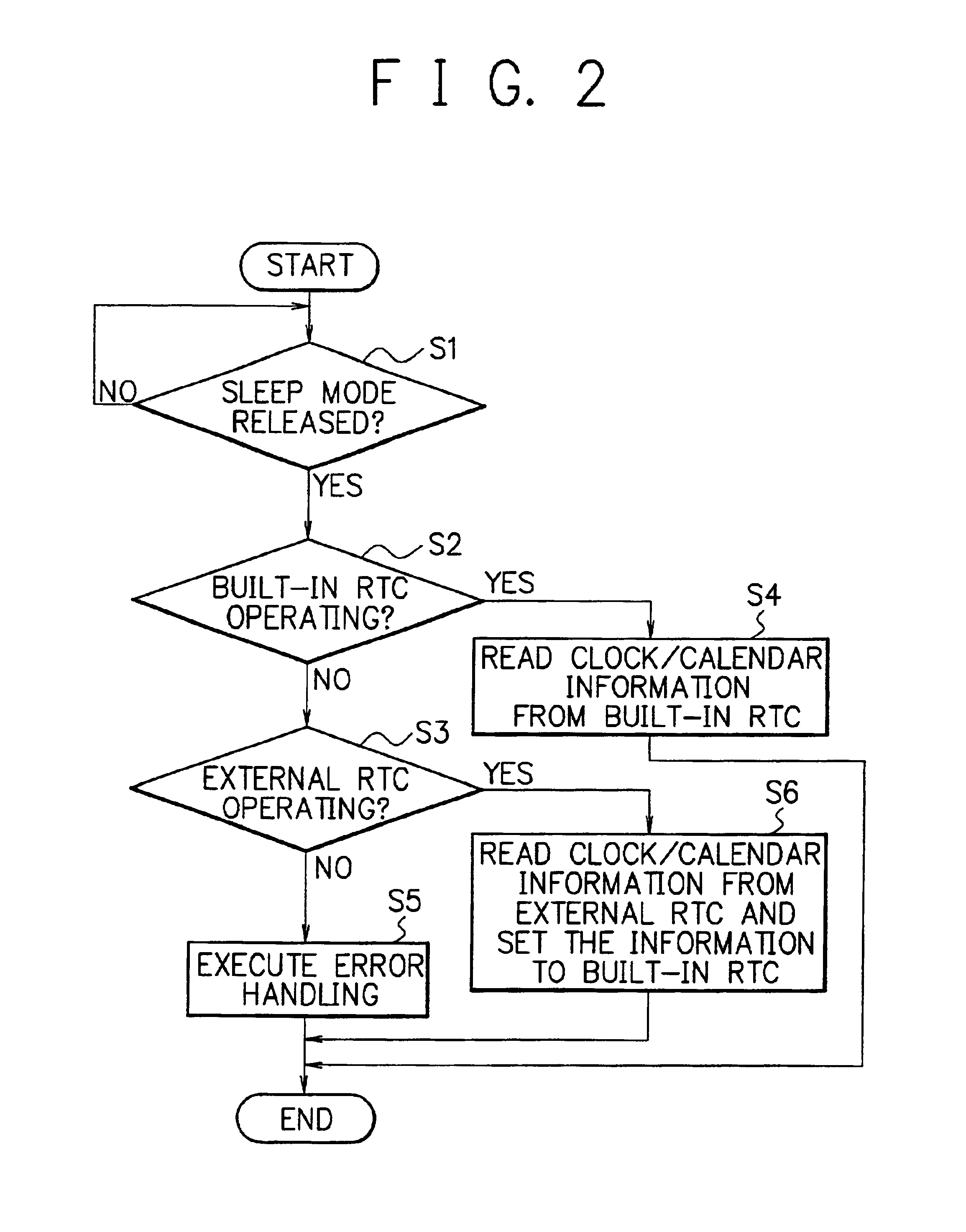

Terminal device and real-time clock control method therefor enabling preservation of clock/calendar information and high information readout speed

InactiveUS6938178B2Minimal additionIncrease readout speedElectric windingSetting time indicationMicrocomputerReal-time clock

A terminal device such as a mobile terminal is provided with two real-time clocks which are powered by different power sources: a first real-time clock which is built in a control section (built-in microcomputer 1, for example) of the terminal device; and a second real-time clock which is provided outside the control section. At power-on of the mobile terminal or on recovery from failure such as a power cut, clock / calendar information is read out from the second real-time clock and is set to the first real-time clock, and thereafter, the control section obtains the clock / calendar information from the first real-time clock. The second real-time clock is connected to the control section directly by a signal line or via a functional device, or the second real-time clock is built in a functional device which is connected to the control section. By such composition and operation, the clock / calendar information can be maintained reliably and correctly even if failure occurred to the control section. The readout of the clock / calendar information is carried out usually from the first real-time clock (built-in RTC), therefore, high readout speed can be realized.

Owner:LENOVO INNOVATIONS LTD HONG KONG

Image sensing device and camera

InactiveUS8482646B2Increase readout speedReduce noiseTelevision system detailsTelevision system scanning detailsEngineeringFloating diffusion

An image sensing device comprises a pixel array, and a peripheral circuit, a column selecting circuit, and a readout, wherein each pixel includes a photodiode, a floating diffusion, a transfer PMOS transistor to the floating diffusion, an amplifier PMOS transistor, and a reset PMOS transistor, the amplifier PMOS transistor has a gate which is formed by an n-type conductive pattern, and is isolated by a first element isolation region and an n-type impurity region which covers at least a lower portion of the first element isolation region, and each PMOS transistor included in the column selecting circuit has a gate which is formed by a p-type conductive pattern and is isolated by a second element isolation region, and an n-type impurity concentration in a region adjacent to a lower portion of the second element isolation region is lower than that in the n-type impurity region.

Owner:CANON KK

Integrated optical sensor

ActiveUS8325347B2High and adjustable sensitivityLow costPhase-affecting property measurementsUsing optical meansCouplingWaveguide

An integrated optical sensor for, for example, a (bio)chemical sensor has an optical waveguide (2) having at least two coupling regions (3, 5), which are separated by at least one measurement region (4). A first wave is excited in the waveguide (2) by the first coupling region (3) and passes through the measurement region (4) and the second coupling region (5). A second wave is excited in the second coupling region (5) and subsequently interferes with the first wave. Here, the reduction in amplitude of the first wave by the second coupling region (5) is less than 95%.

Owner:CREOPTIX

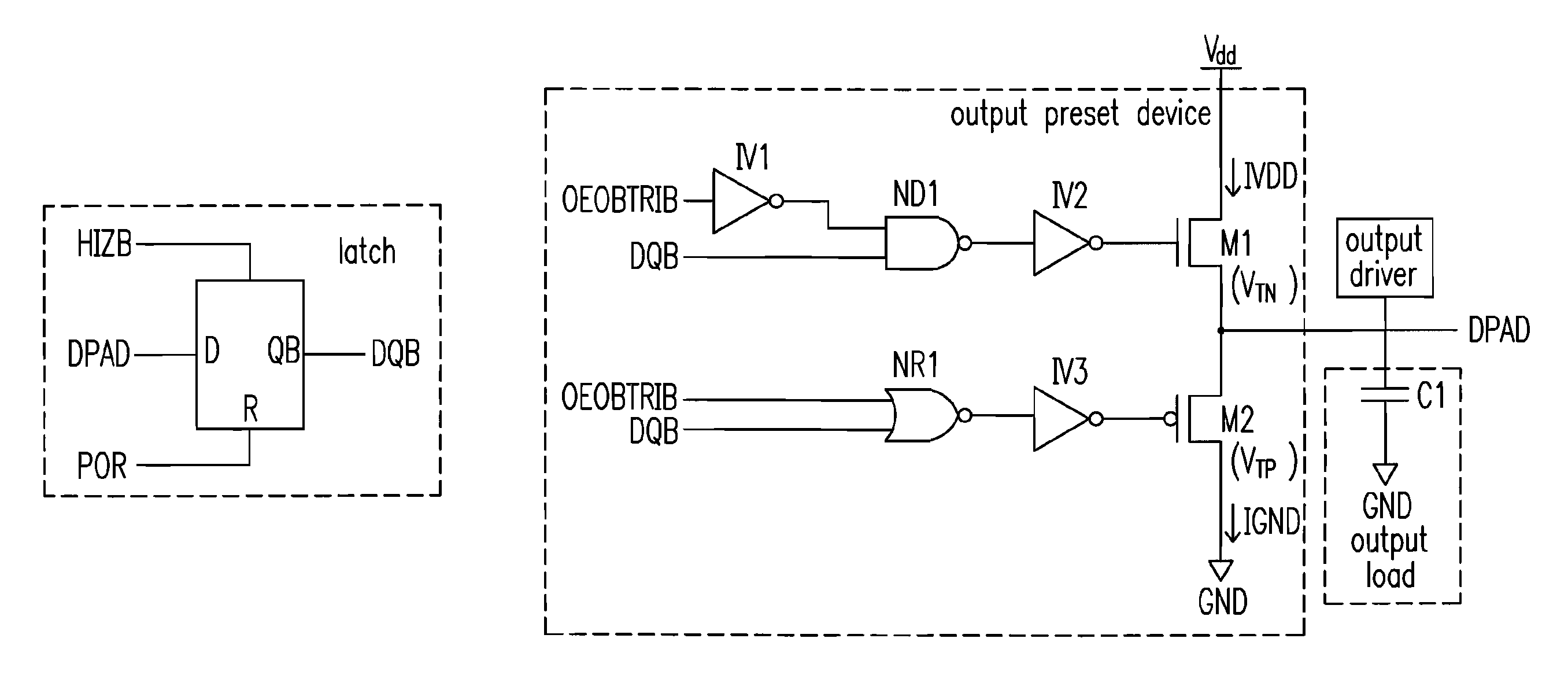

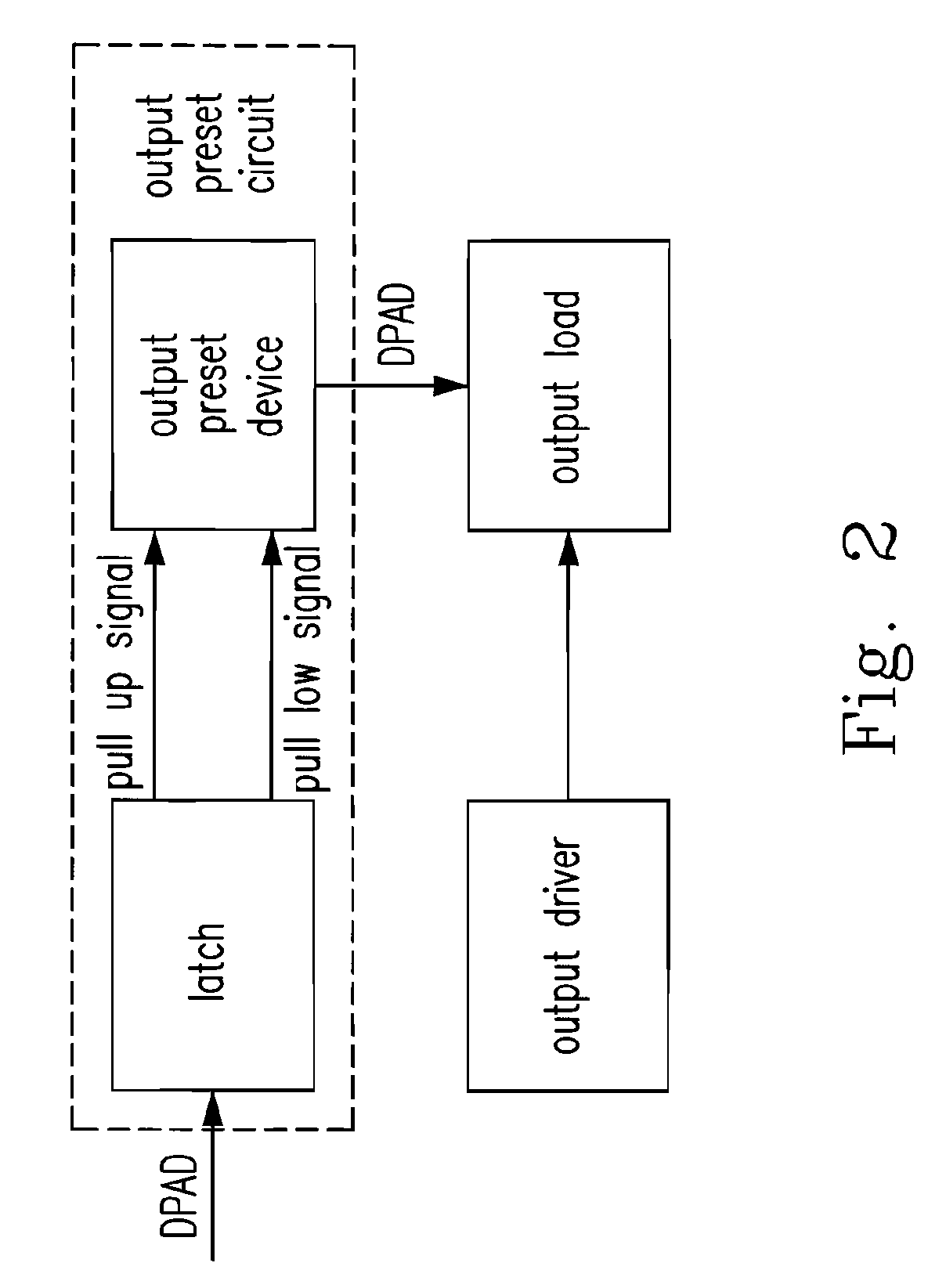

Output driver circuit with output preset circuit and controlling method thereof having lower power consumption

ActiveUS7714618B2Increase readout speedReduce noiseReliability increasing modificationsPower consumption reductionDriver circuitEngineering

Owner:MACRONIX INT CO LTD

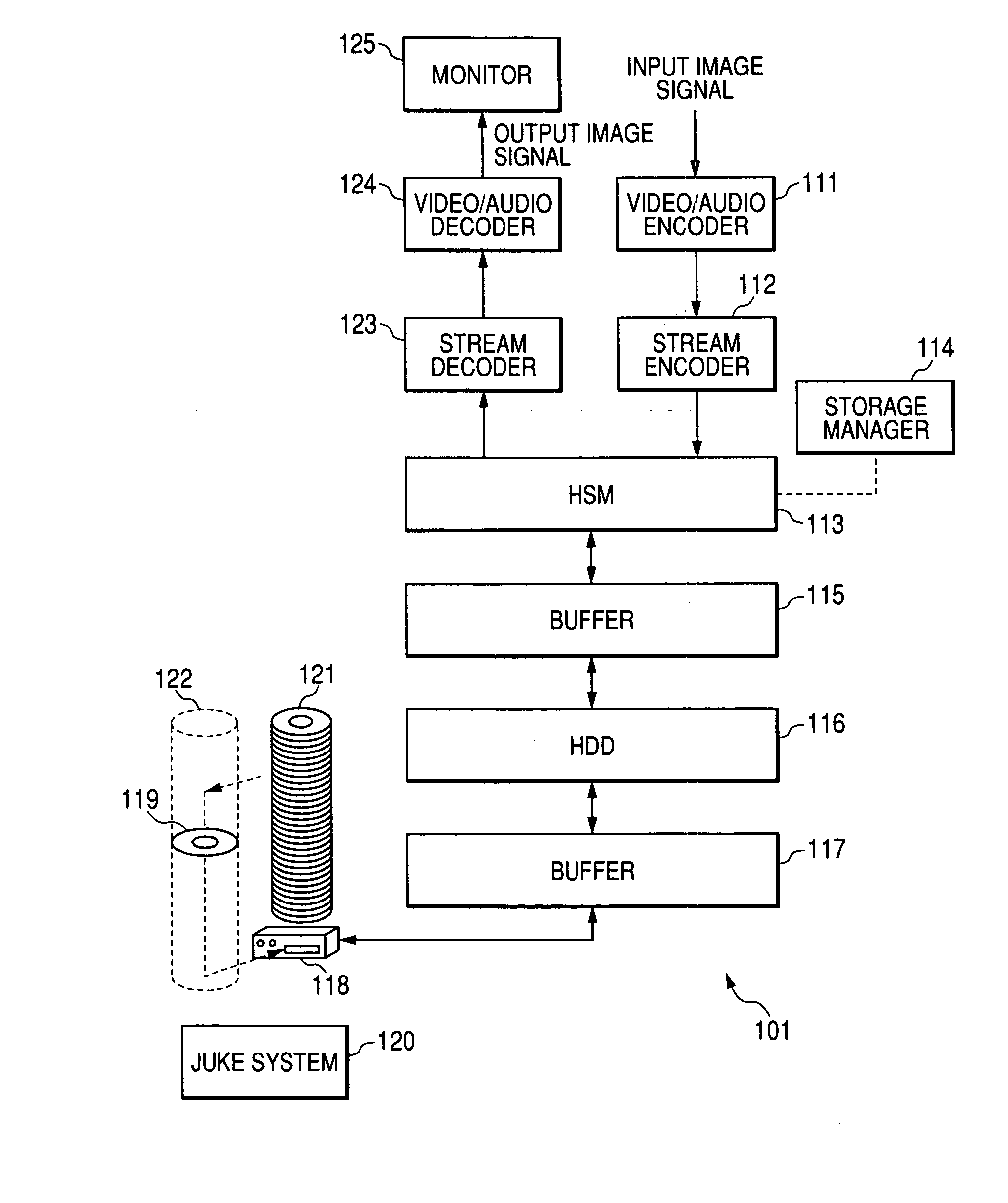

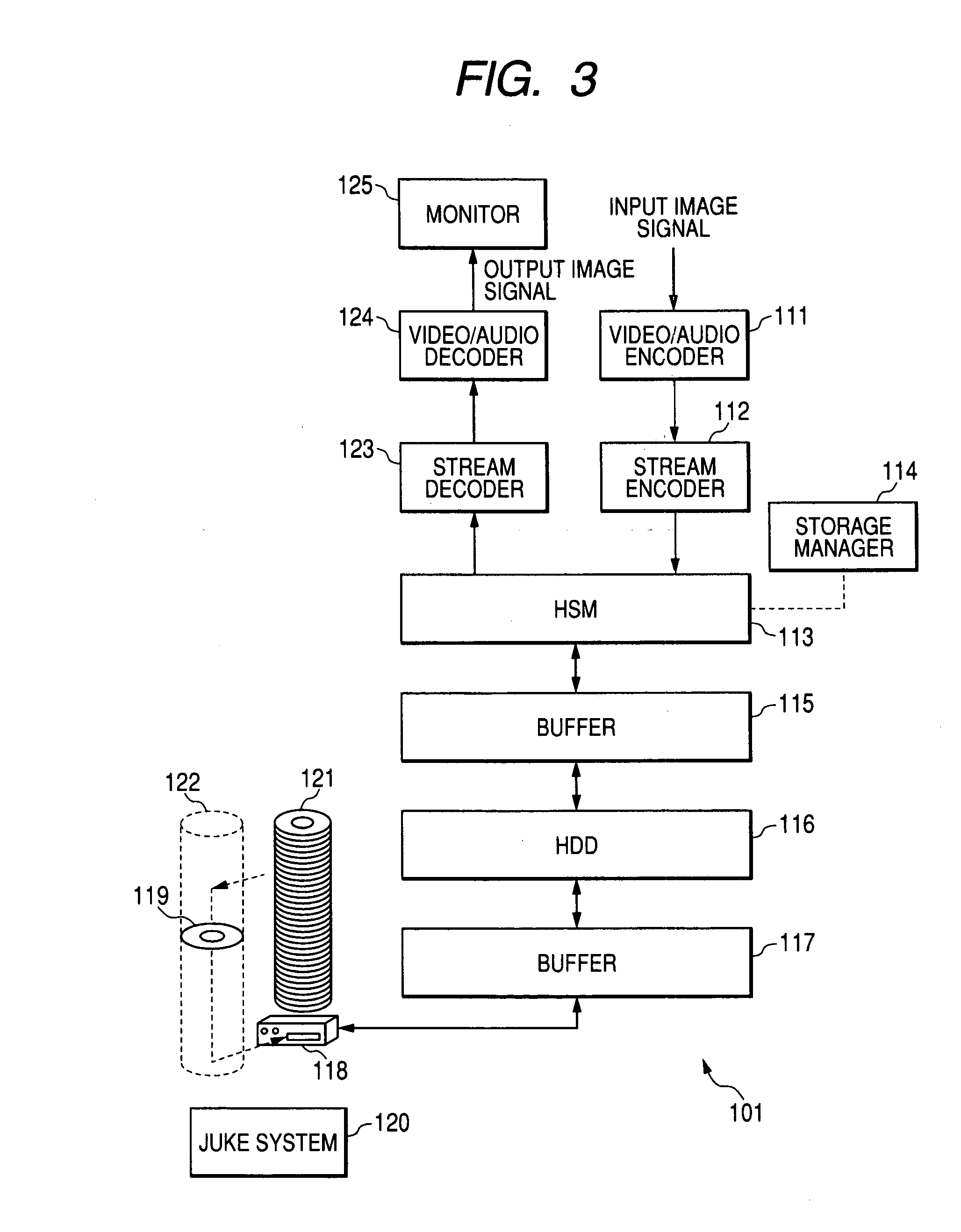

Readout device, readout method, program, and program recording medium

InactiveUS20070019520A1Reduce occurrenceIncrease readout speedDisc-shaped record carriersRecording carrier detailsComputer hardwareControl unit

A readout device includes a first recording medium having recorded therein data of arbitrary plural portions of a period of a predetermined length in temporally continuous content; a second recording medium having recorded therein data of the entire content; and a readout control unit that controls, when the readout of data of the content is requested, the readout of data from the first recording medium and from the second recording medium such that data of any one of the portions recorded in the first recording medium is read out and data following the data read out from the first recording medium is read out from the second recording medium.

Owner:SONY CORP

Read amplification circuit for nonvolatile memory and memory

ActiveCN103377708AThreshold Voltage StabilityEliminate errorsRead-only memoriesDigital storageAudio power amplifierComputer science

The invention relates to a read amplification circuit for a nonvolatile memory and a memory. The read circuit comprises a basic physical unit composed of a plurality of storage units, a reference unit set and a read amplifier, wherein the storage units are correspondingly connected to respective read bit lines; the basic physical unit is gated via a first gate tube; the reference unit set has the same configuration as the basic physical unit and is composed of a plurality of reference units; the reference units and the storage units are one-to-one correspondence; the reference units are correspondingly connected with respective reference voltage lines, and respectively have the same structure as the corresponding storage units; the reference unit set is gated via a second gate tube; the second gate tube has the same structure as the first gate tube; the read amplifier is connected with the read bit lines and the reference voltage lines, and outputs corresponding read data according to the comparative result between the read bit lines and the voltages on the corresponding reference voltage lines. The read amplification circuit can enhance the data read speed when reading the memory, and prolong the service life of the memory.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP