Device and method thereof for testing bias temperature instability degrading of MOS (metal oxide semiconductor) device

A MOS device, bias temperature technology, applied in the direction of single semiconductor device testing, etc., can solve the problems of circuit power consumption and chip area increase, and achieve the effect of high test accuracy and simple circuit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described in detail in conjunction with the following specific embodiments and accompanying drawings. The process, conditions, experimental methods, etc. for implementing the present invention, except for the content specifically mentioned below, are common knowledge and common knowledge in this field, and the present invention has no special limitation content.

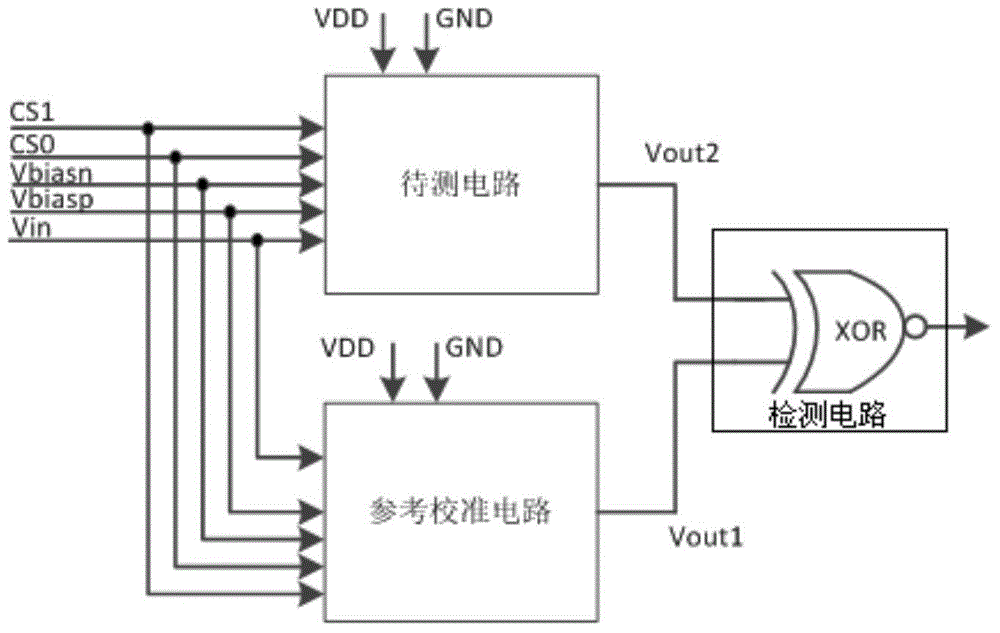

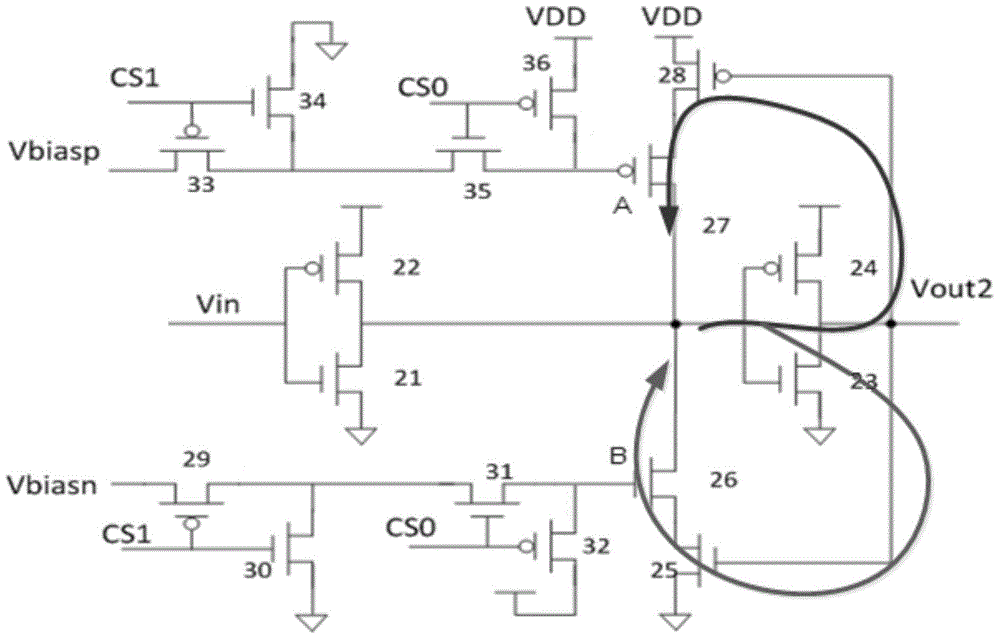

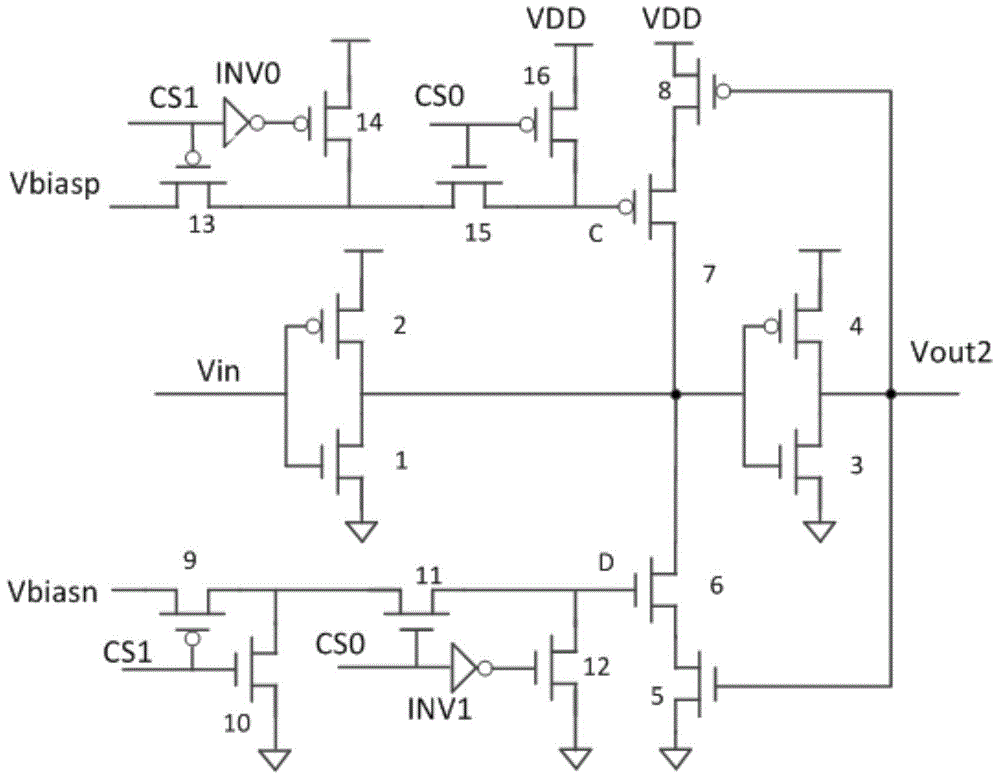

[0024] refer to figure 1 The test device for the degradation of MOS device bias temperature instability of the present invention comprises a circuit to be tested, a reference calibration circuit and a detection circuit; the outputs of the circuit to be tested and the reference calibration circuit are connected to the detection circuit at the same time; the internal setting of the circuit to be tested is the first The feedback control component is connected to the first Schmitt trigger, the first feedback control component is connected to the first Schmitt trigger, and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More