Semiconductor device and method for forming the same

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, to achieve the effect of reducing the problem of noise coupling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

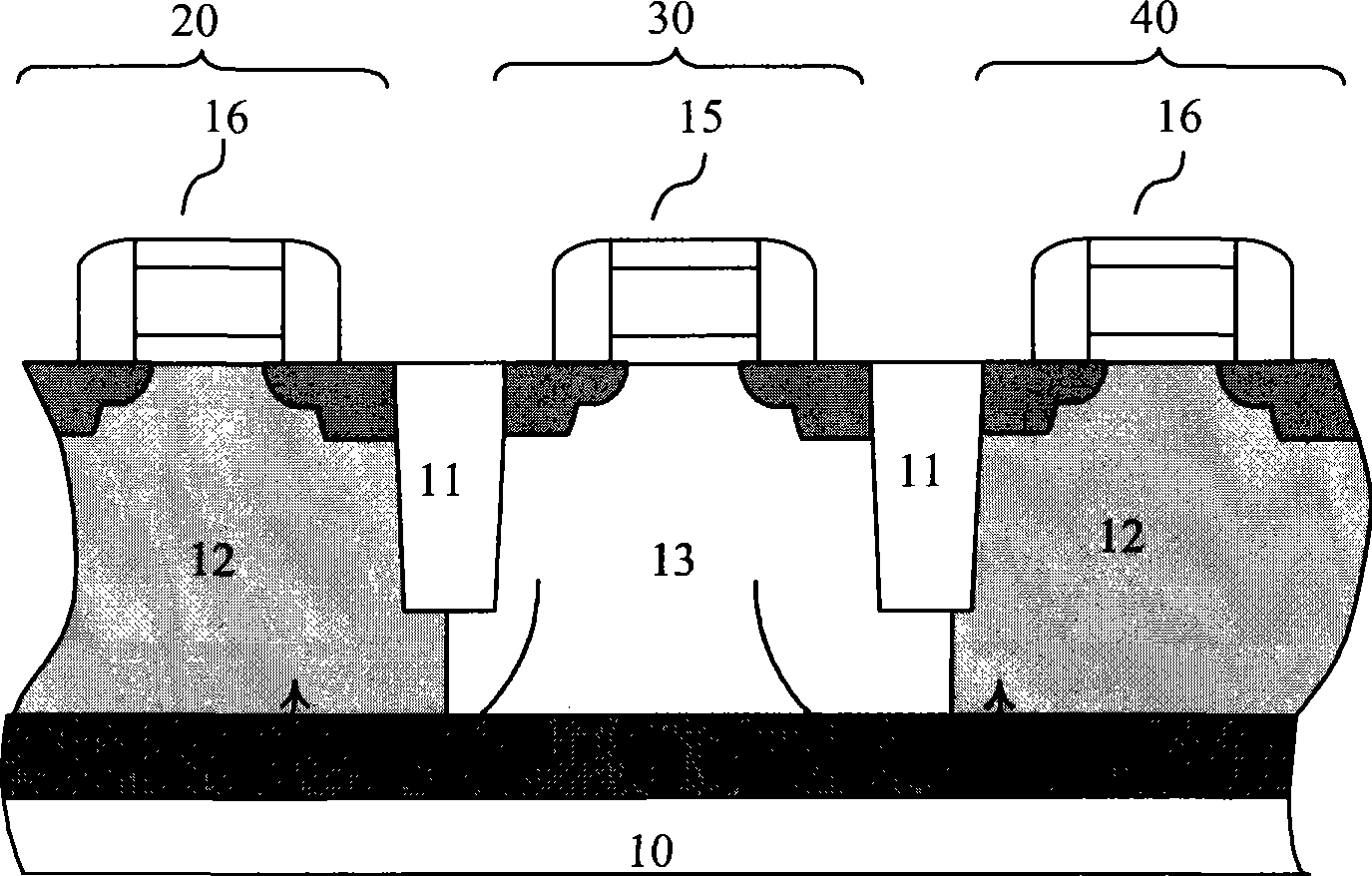

[0026] The present invention provides a semiconductor device. By forming a deep n-type doped well only in the region where the NMOS transistor is located in the semiconductor substrate, the longitudinal isolation of the NMOS transistor and the semiconductor substrate and the lateral isolation of the PMOS transistors on both sides are realized, reducing the Minimizes noise coupling problems in semiconductor substrates in hybrid circuits.

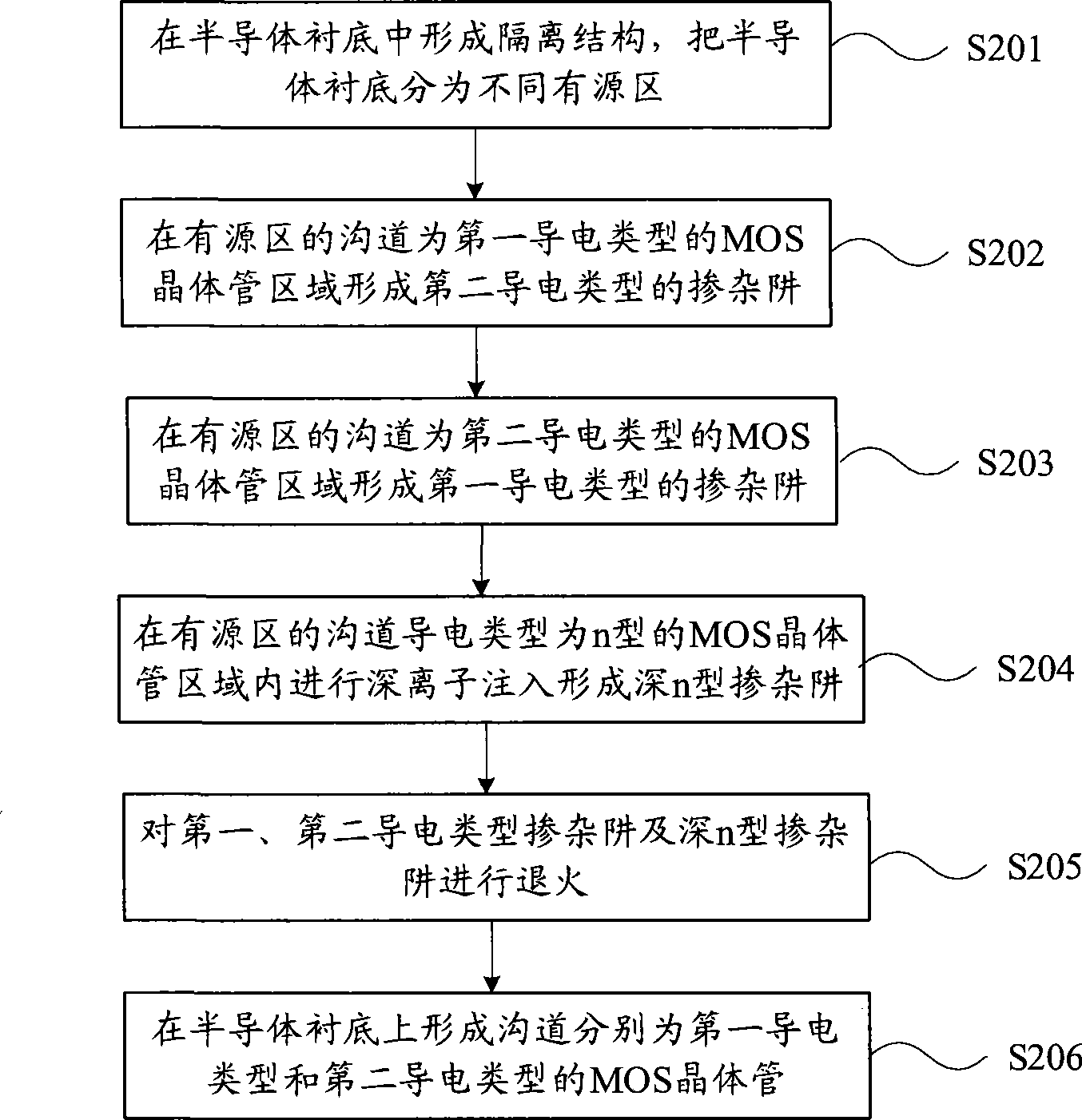

[0027] refer to figure 2 , first provide a schematic flow chart of forming the semiconductor device, including the following steps: performing step S201, forming an isolation structure in the semiconductor substrate, and dividing the semiconductor substrate into different active regions; performing step S202, forming an isolation structure in the active region. Forming a doped well of the second conductivity type in the MOS transistor region of the first conductivity type in the channel; performing step S203, forming a doped well of the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More