Patents

Literature

188results about How to "Improve joint reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

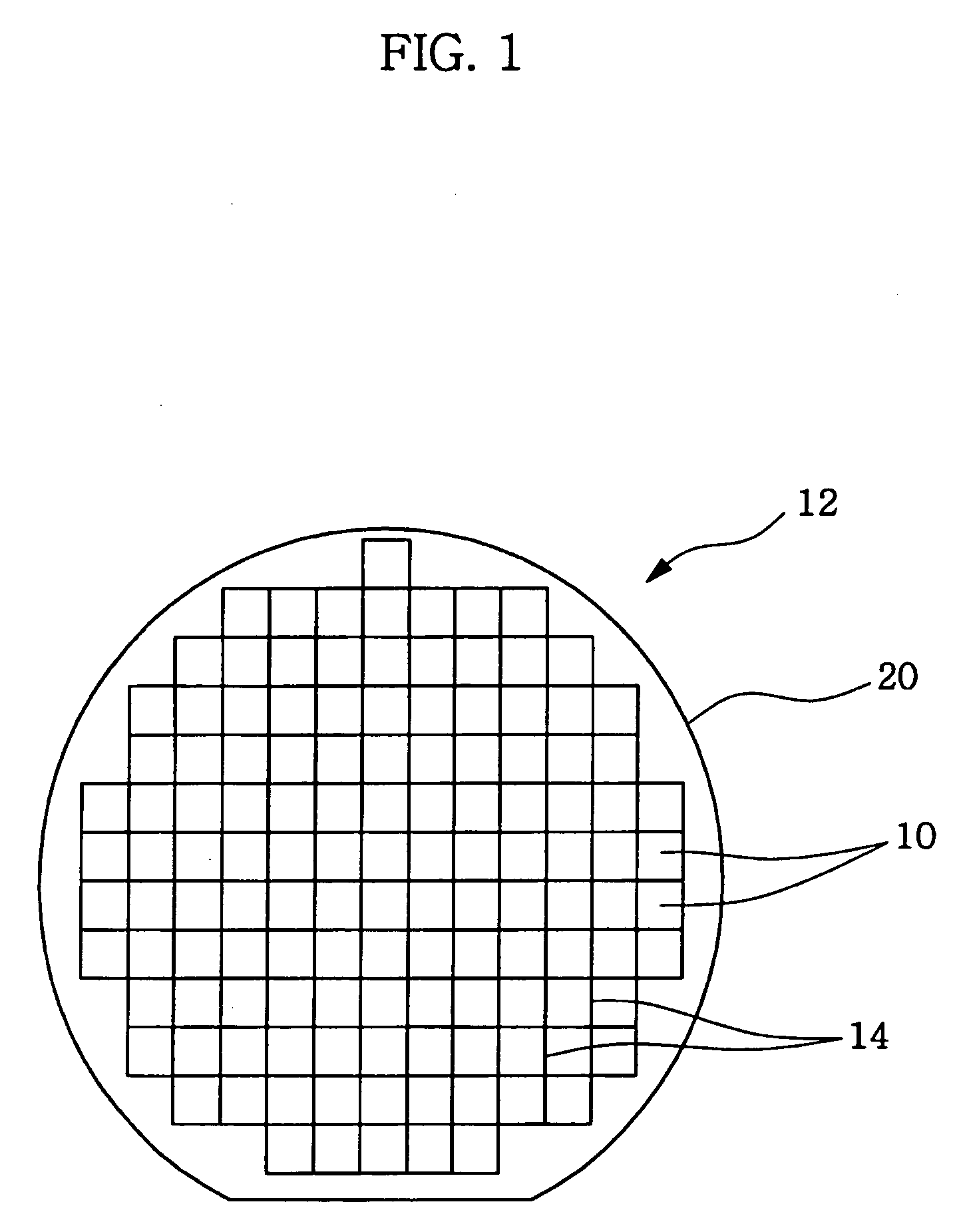

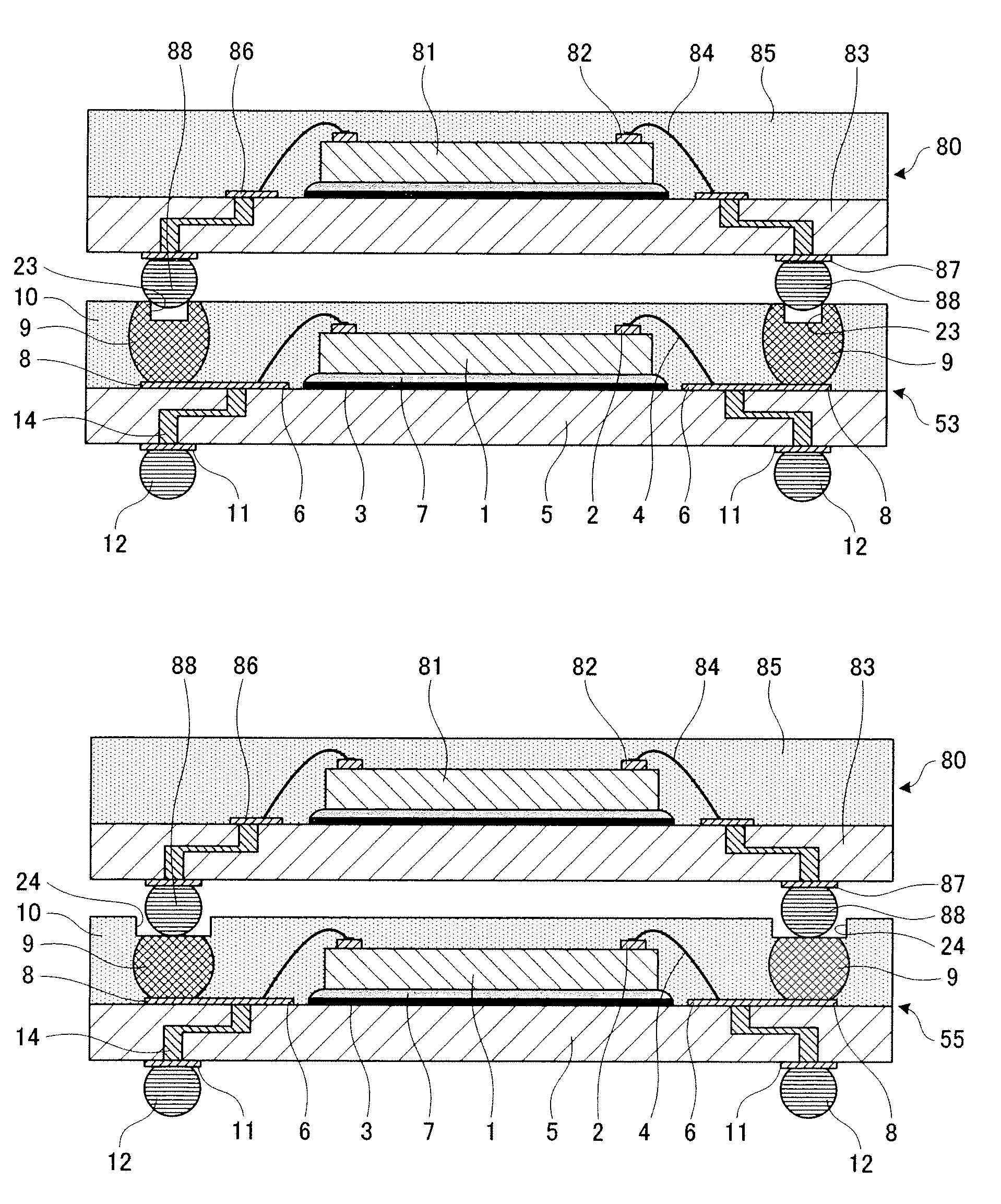

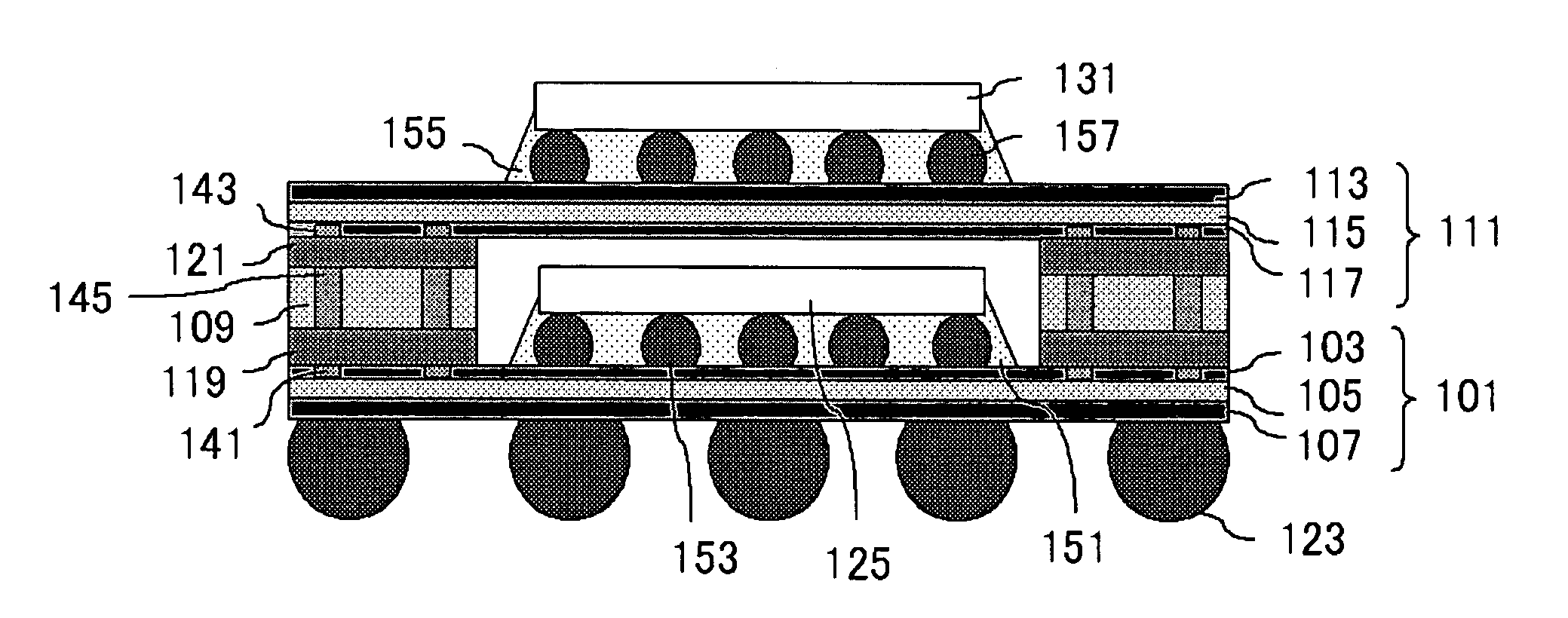

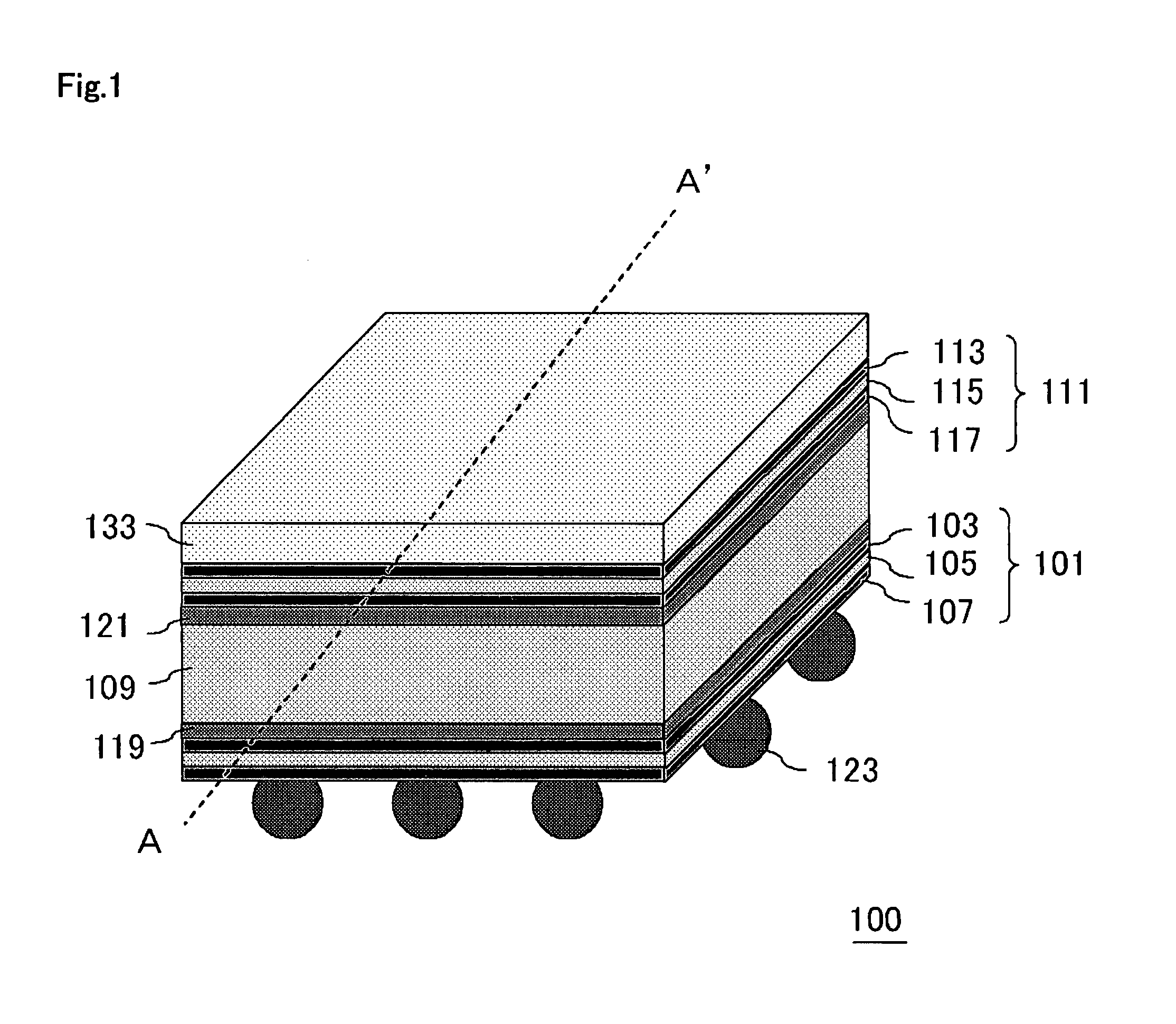

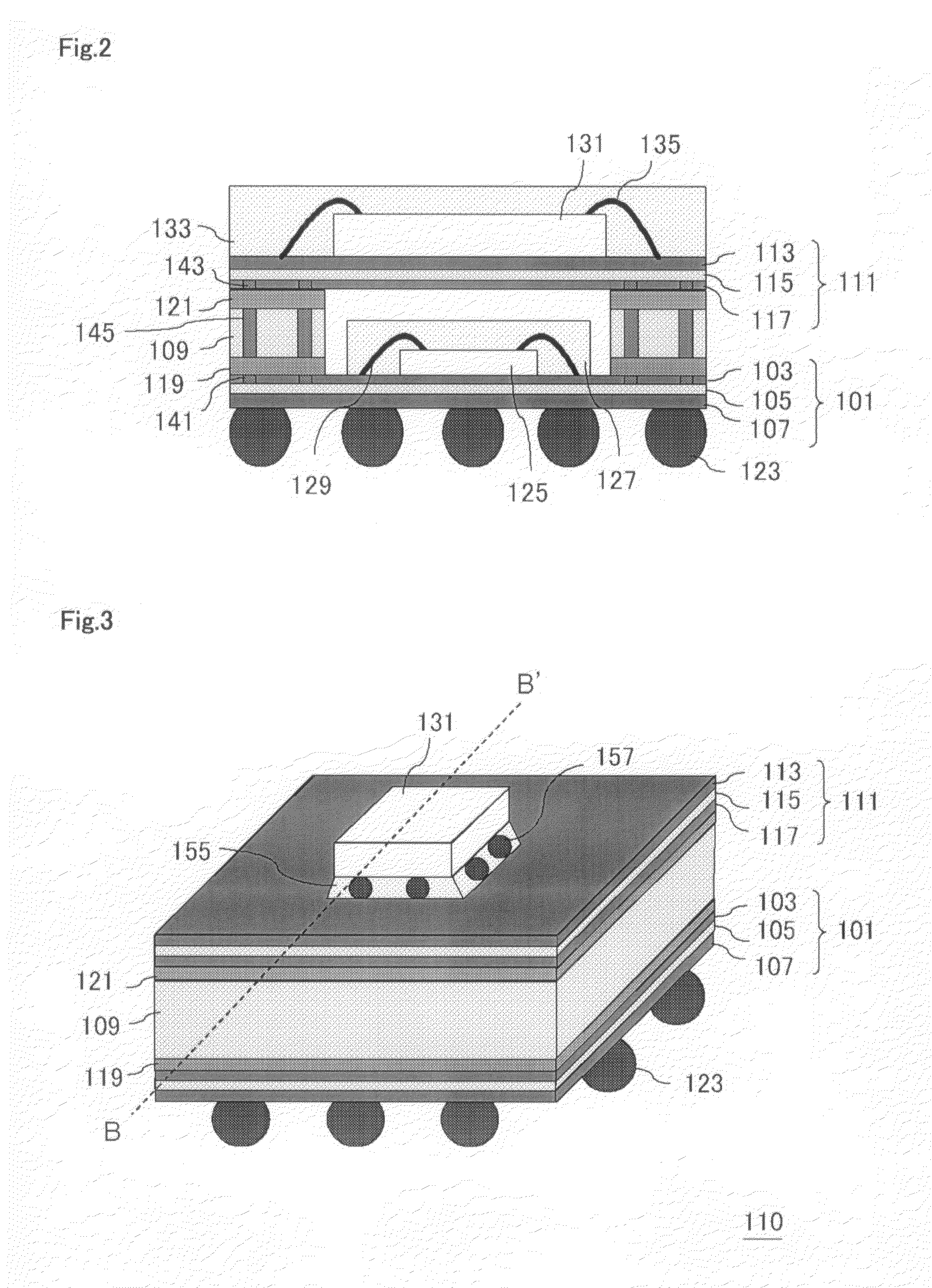

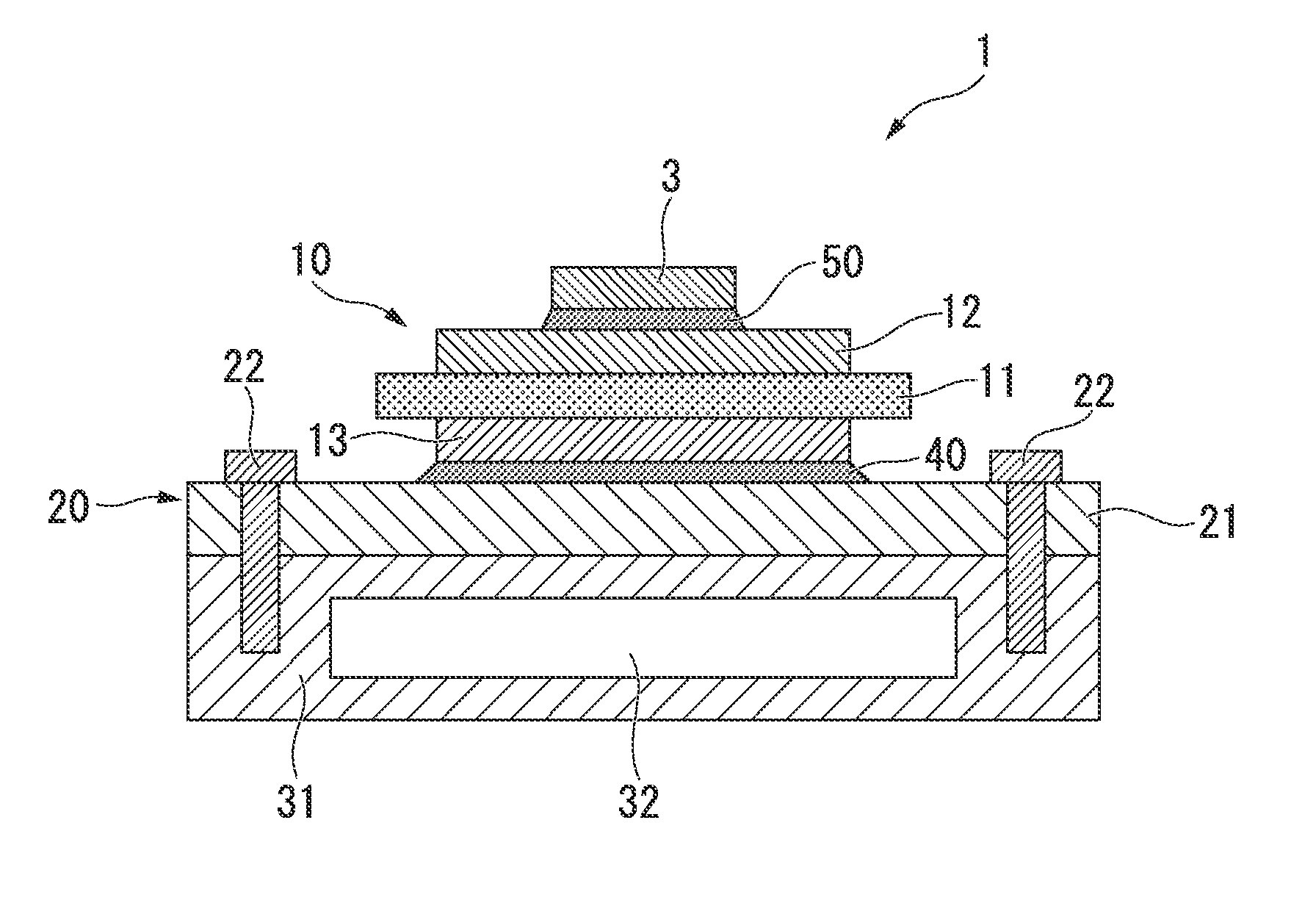

Semiconductor Device and Method for Manufacturing Semiconductor Device

InactiveUS20090243065A1Improve joint reliabilityLower elastic modulusSemiconductor/solid-state device detailsSolid-state devicesSurface mountingSemiconductor chip

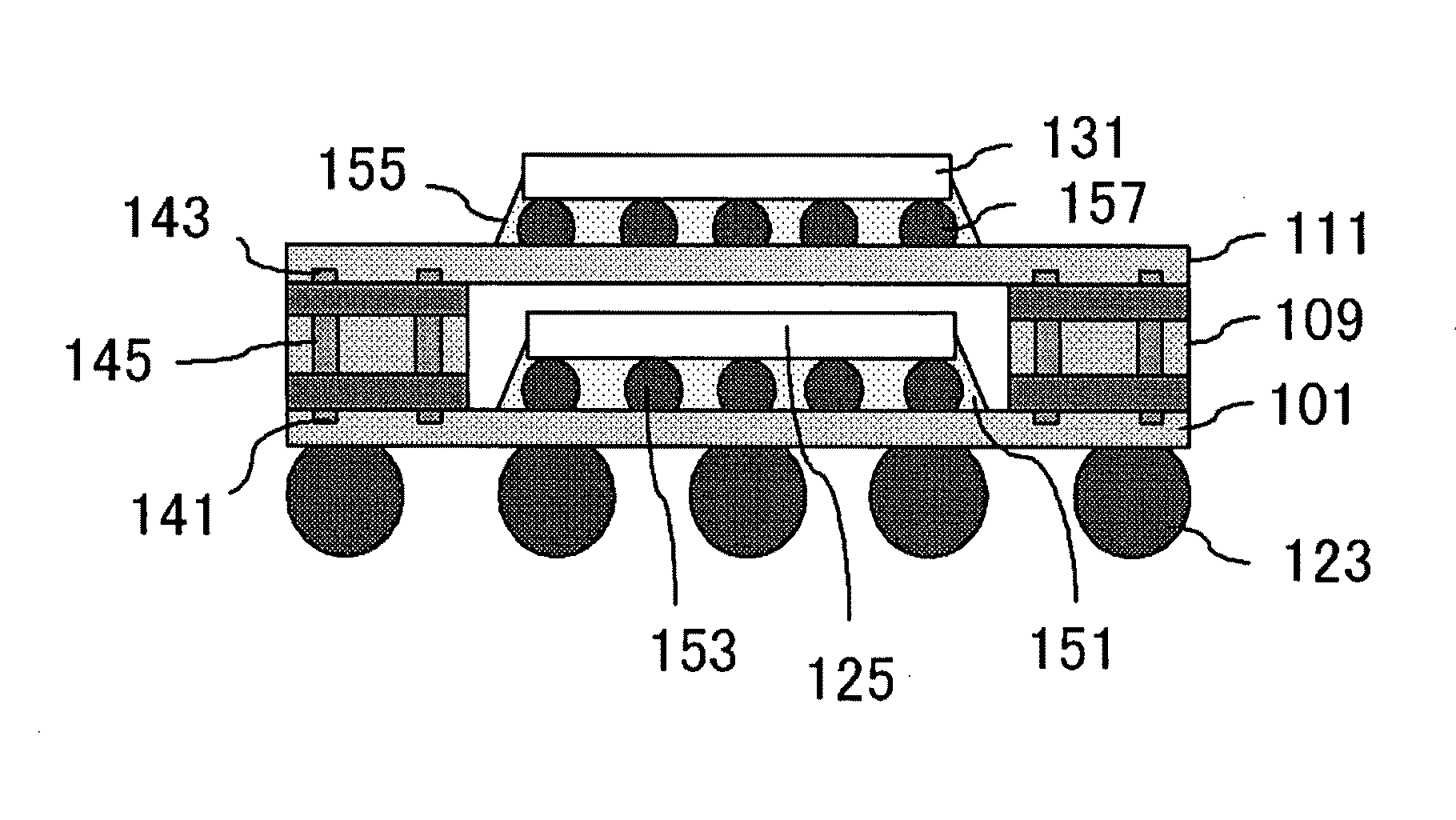

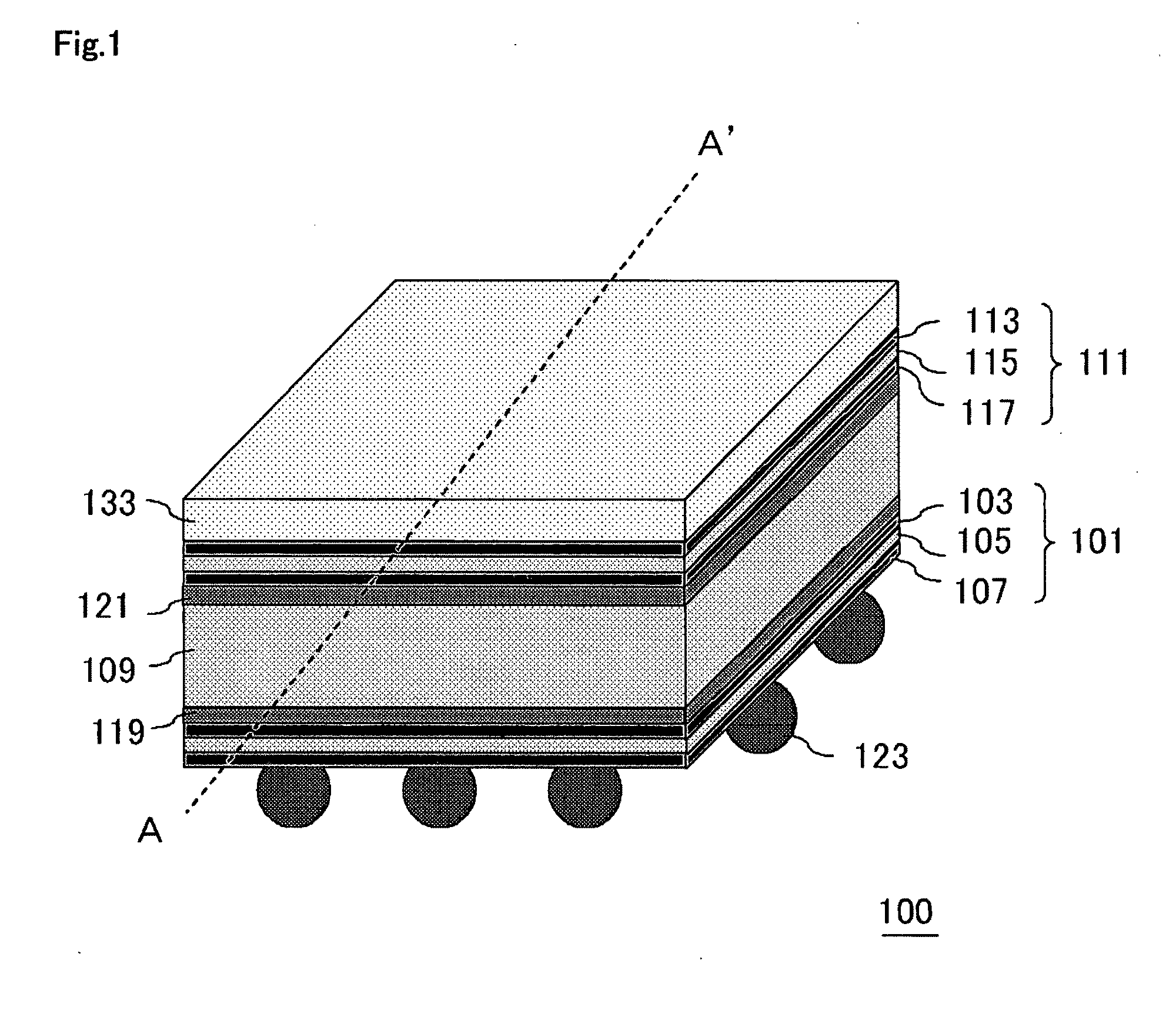

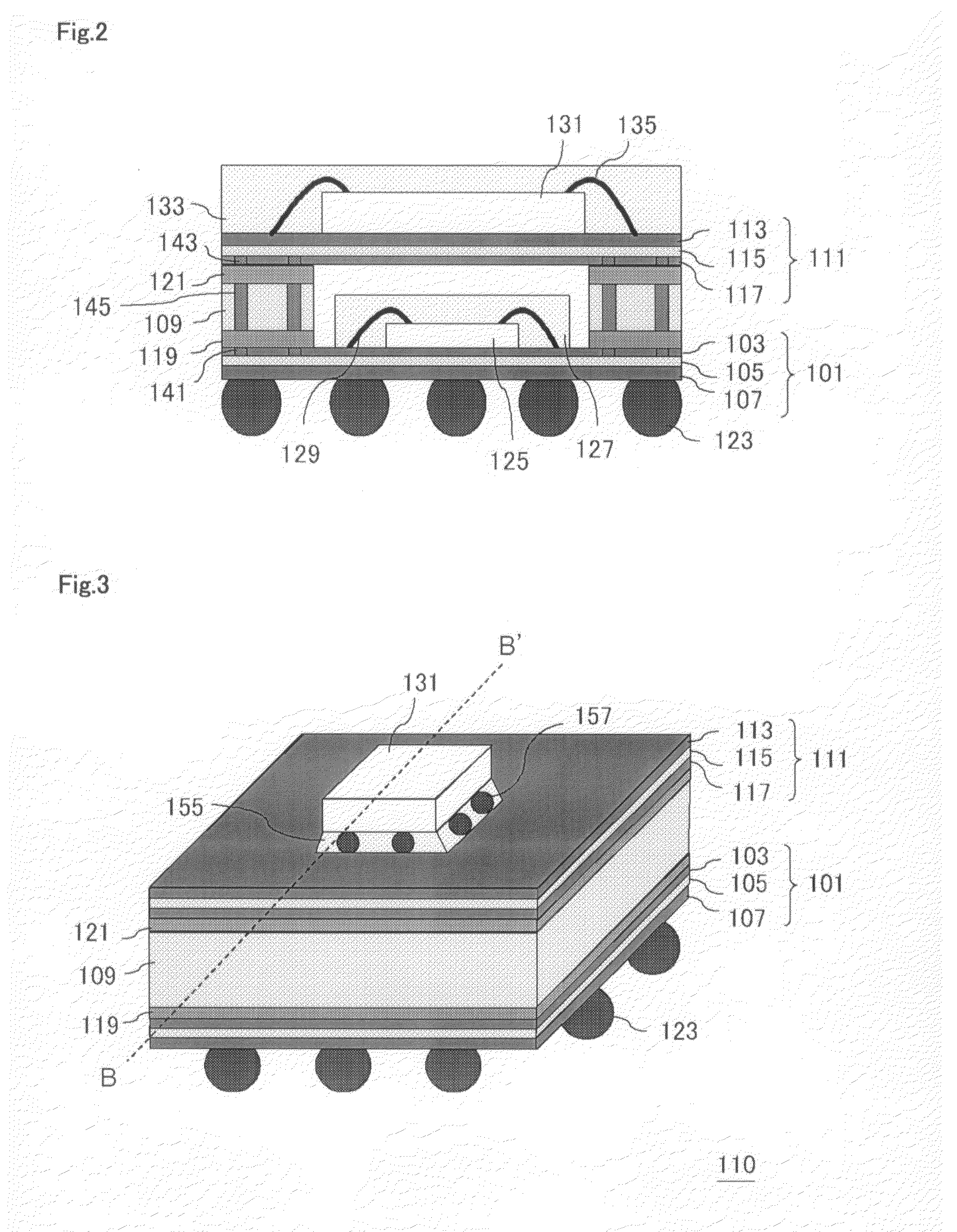

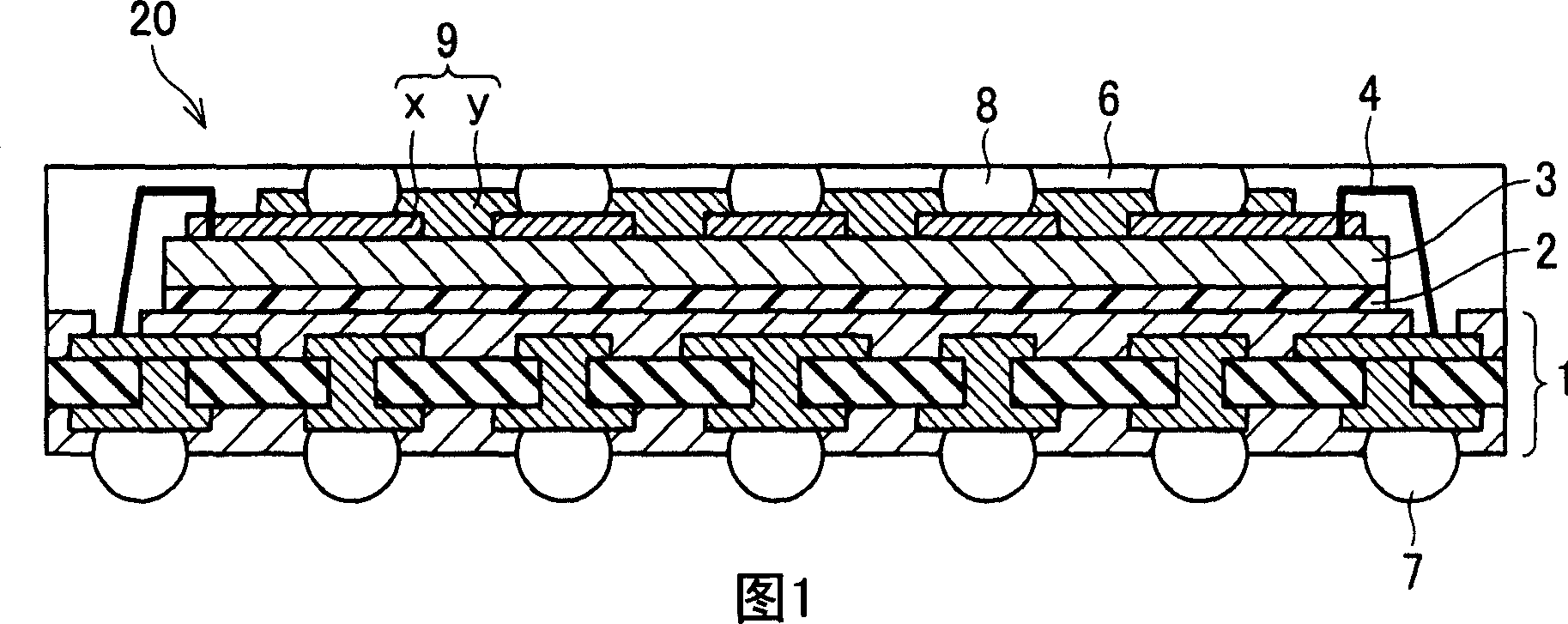

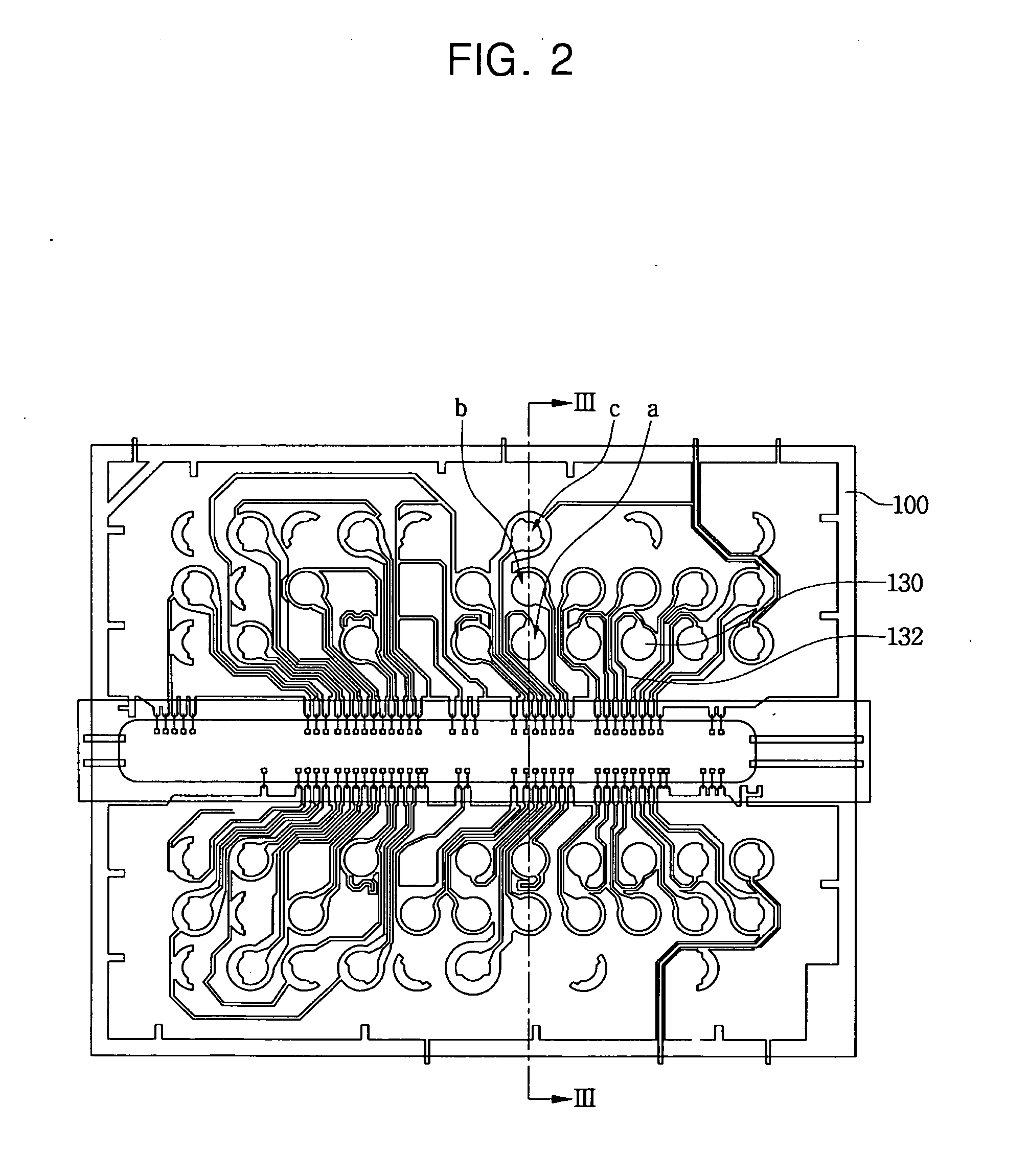

A semiconductor device (100) comprises a first resin substrate (101) on which a first semiconductor chip (125) is mounted a surface thereof; a second resin substrate (111) on which a second semiconductor chip (131) is mounted on a surface thereof; and a resin base material (109), joined to a front surface of the first resin substrate (101) and to a back surface of the second resin substrate (111), so that these surfaces are electrically connected. The resin base material (109) is disposed in a circumference of the first resin substrate (101) in the surface of the first resin substrate (101). Further, the first semiconductor chip (125) is disposed in a space section provided among the first resin substrate (101), the second resin substrate (111) and the resin base material (109) in the surface of the first resin substrate (101).

Owner:SUMITOMO BAKELITE CO LTD

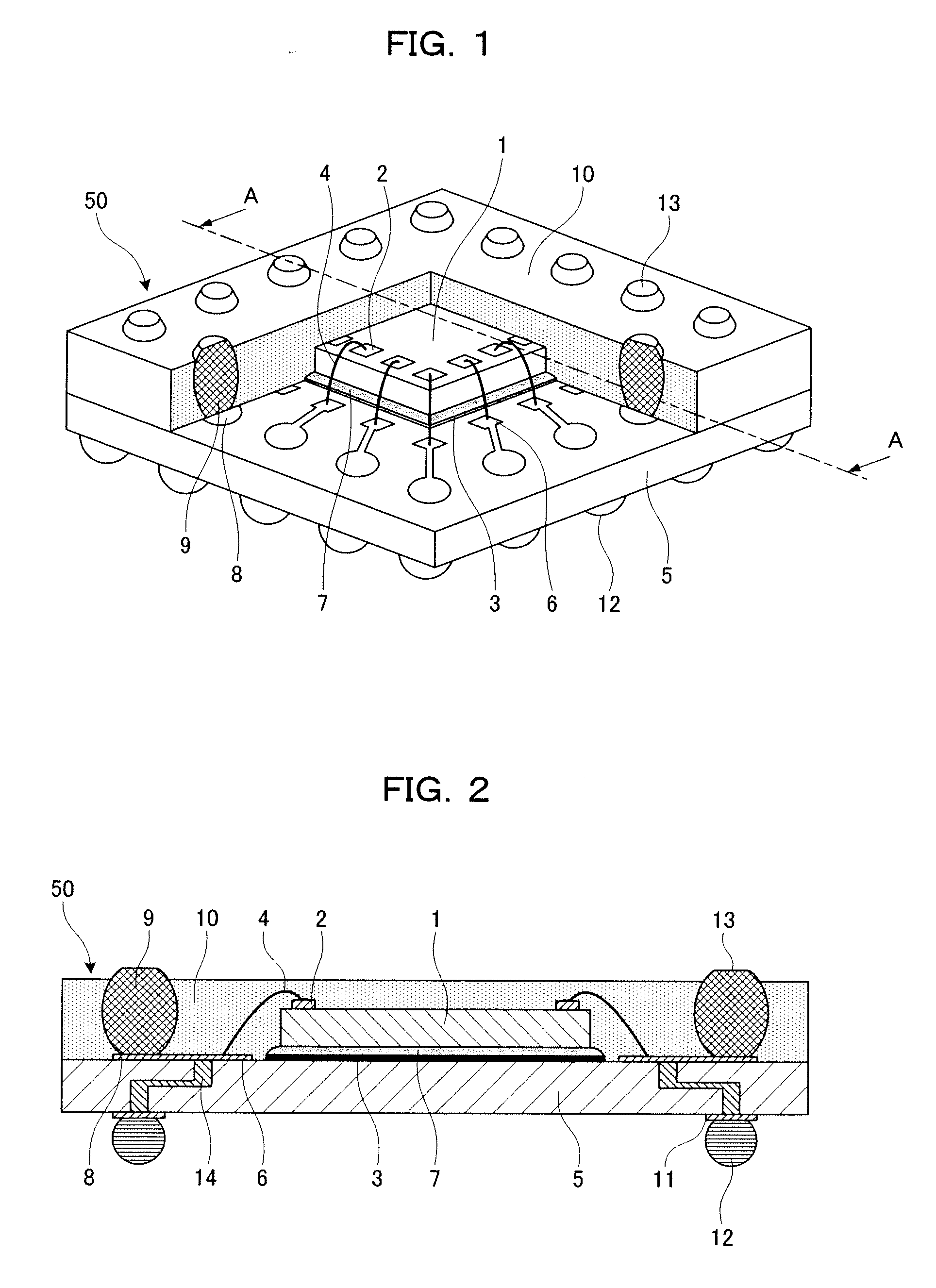

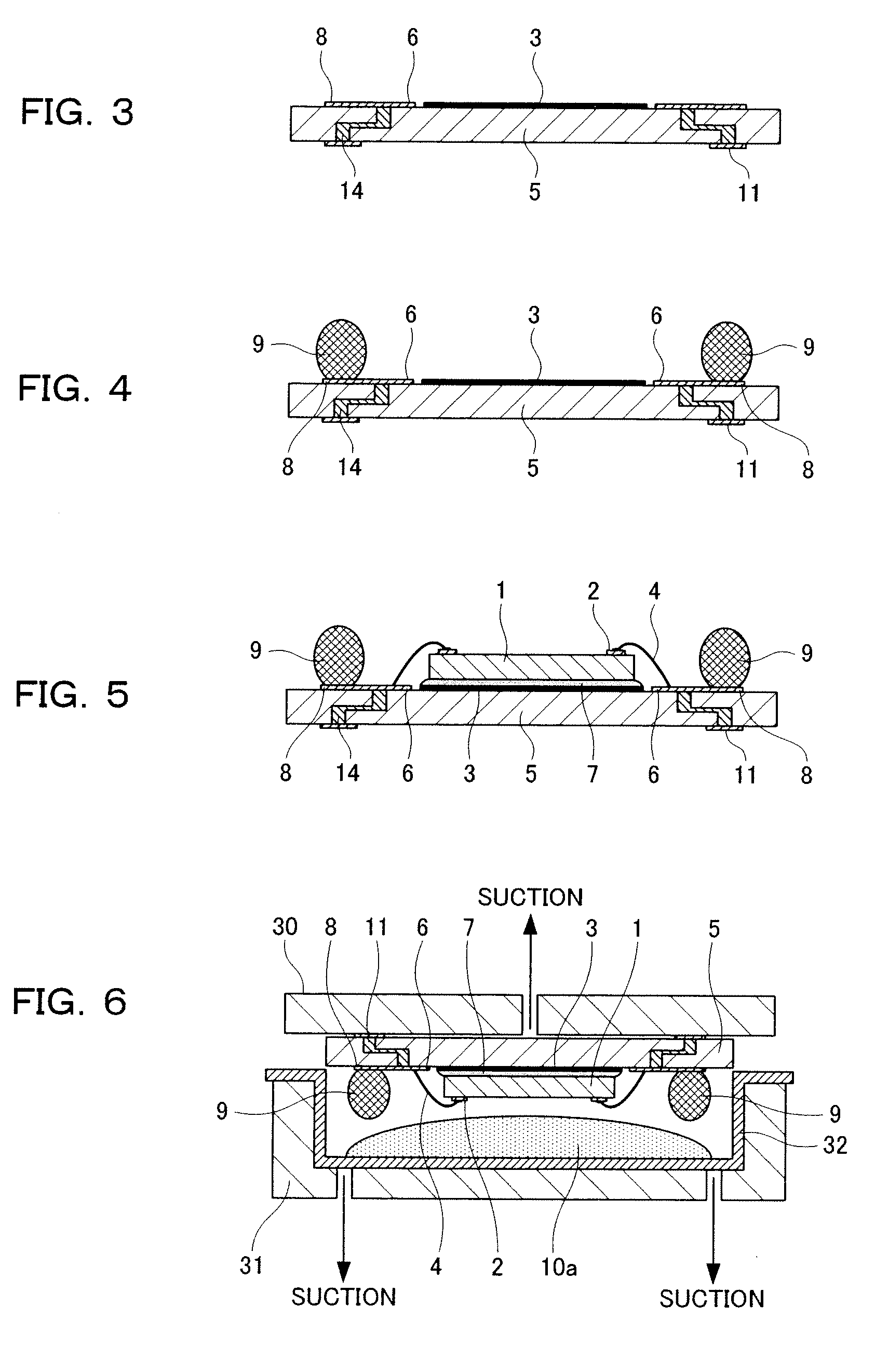

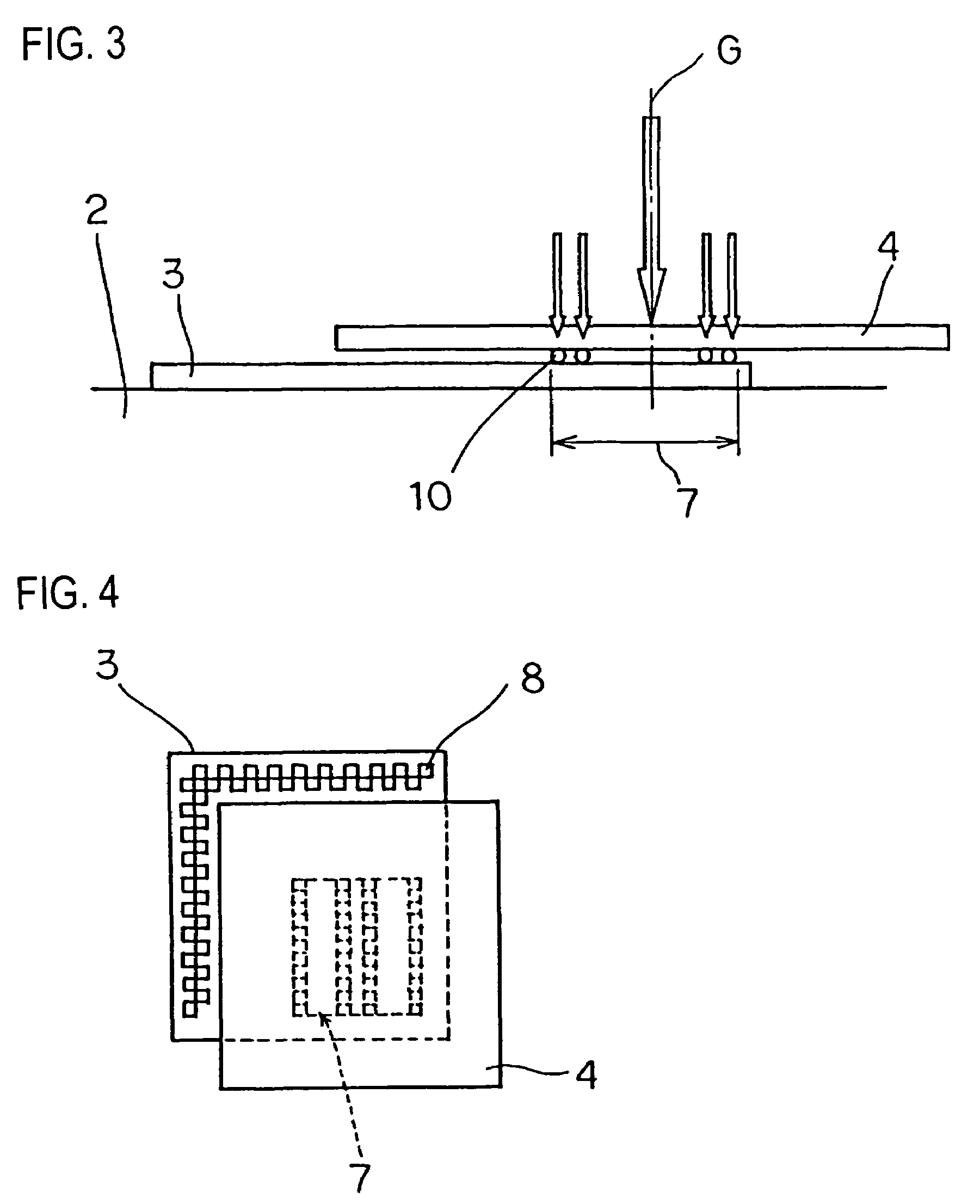

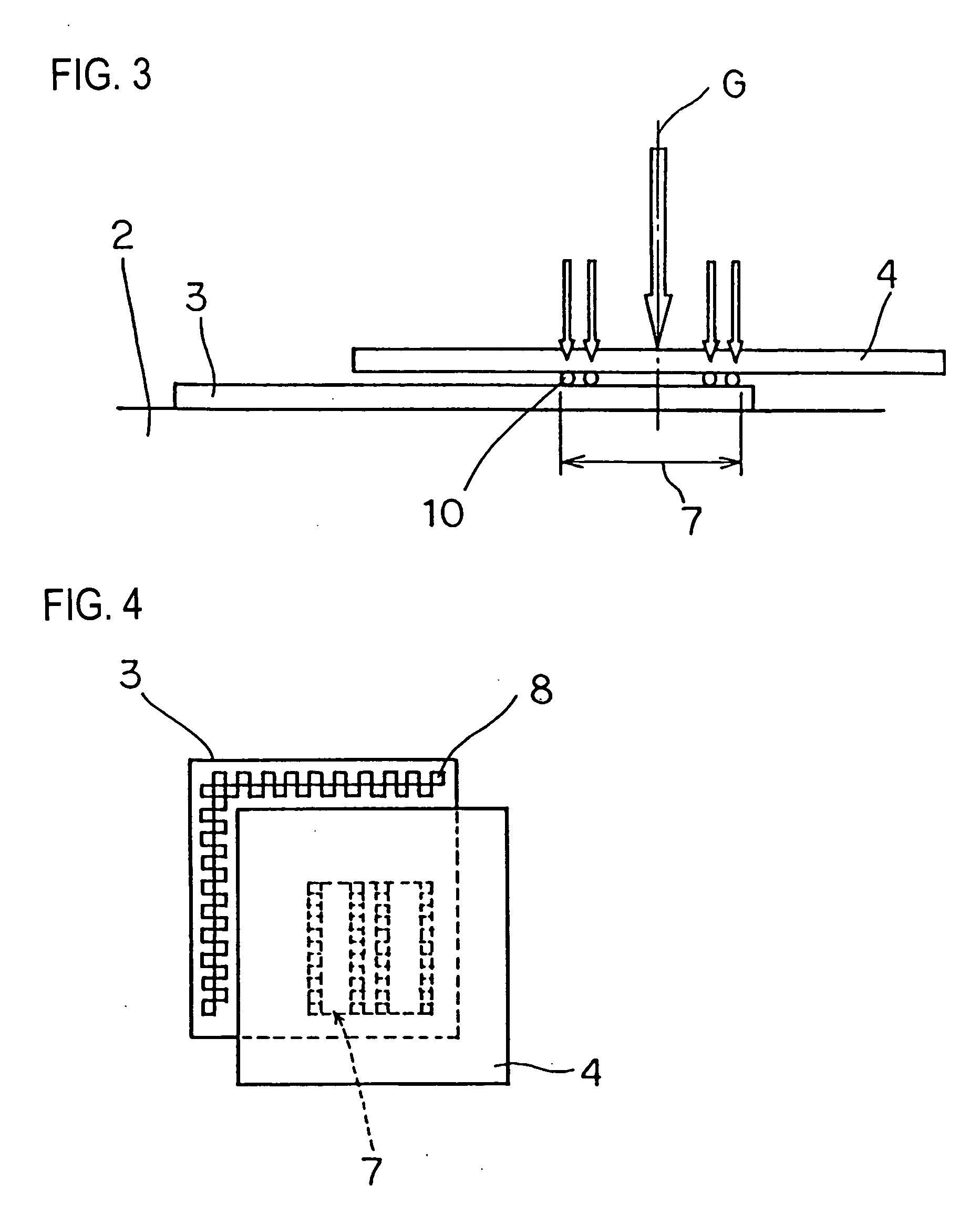

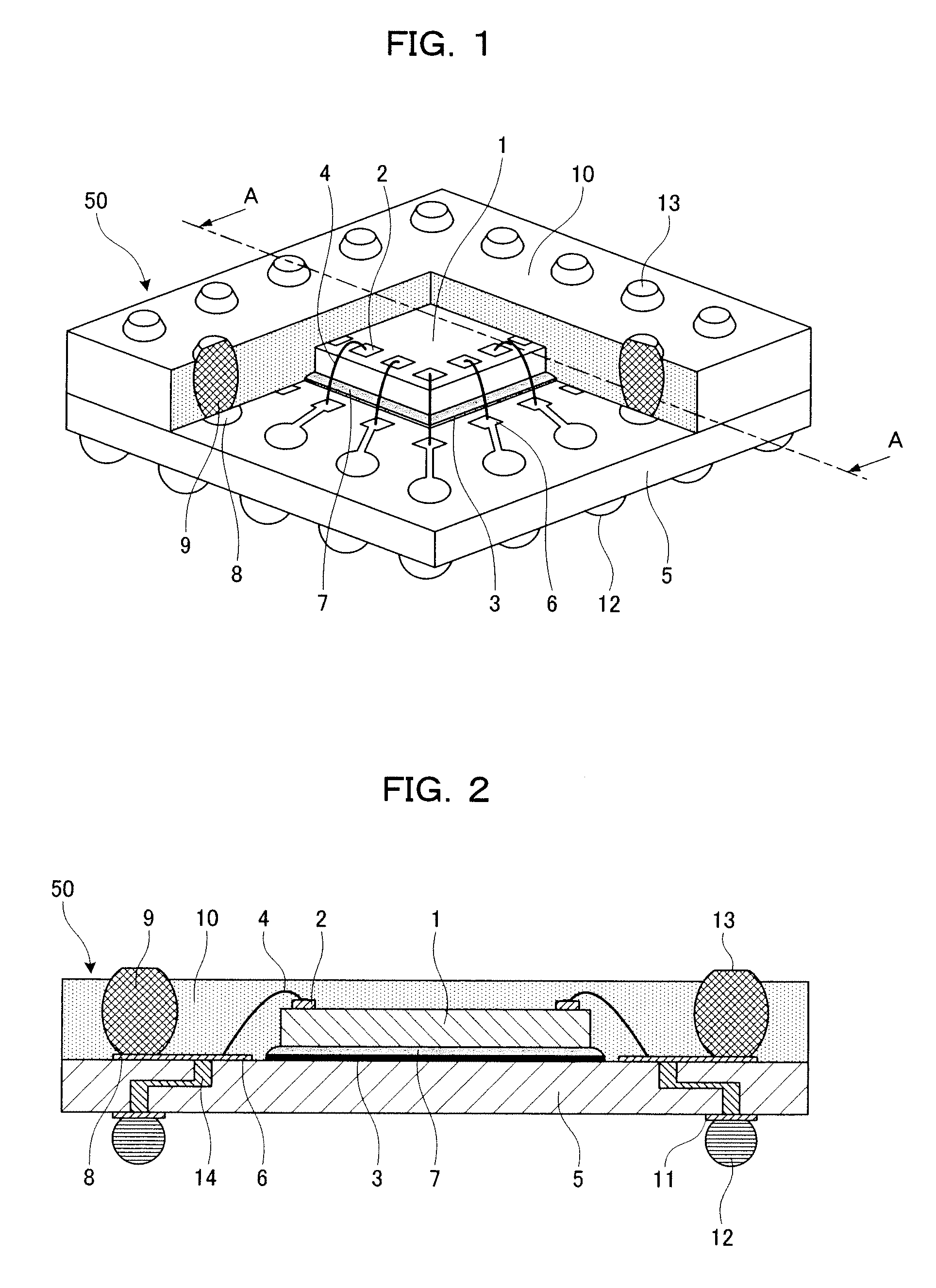

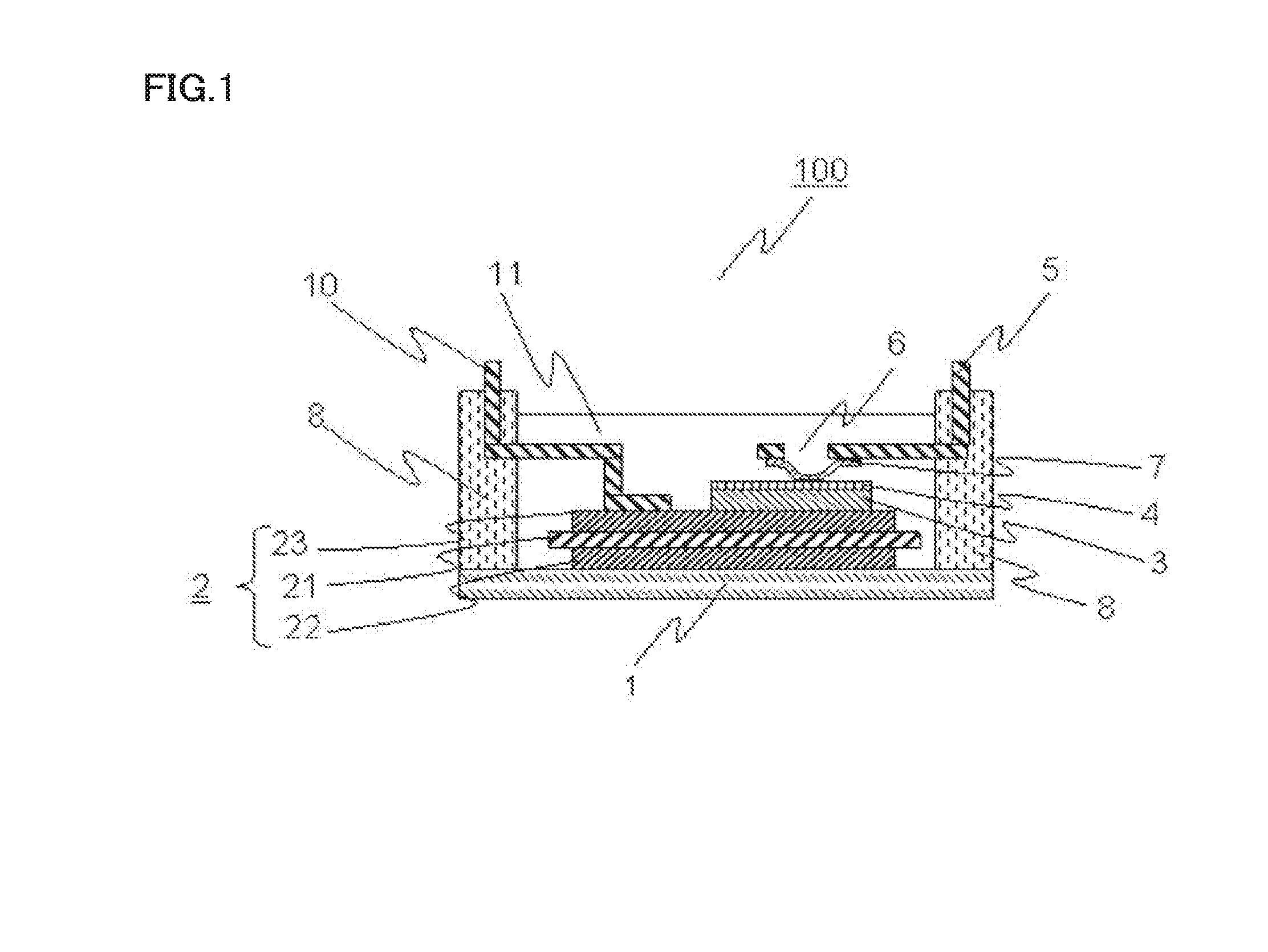

Semiconductor device and method of manufacturing the same

ActiveUS20090146301A1Highly reliable three-dimensional mounting structureOptimizationInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsEngineeringSemiconductor

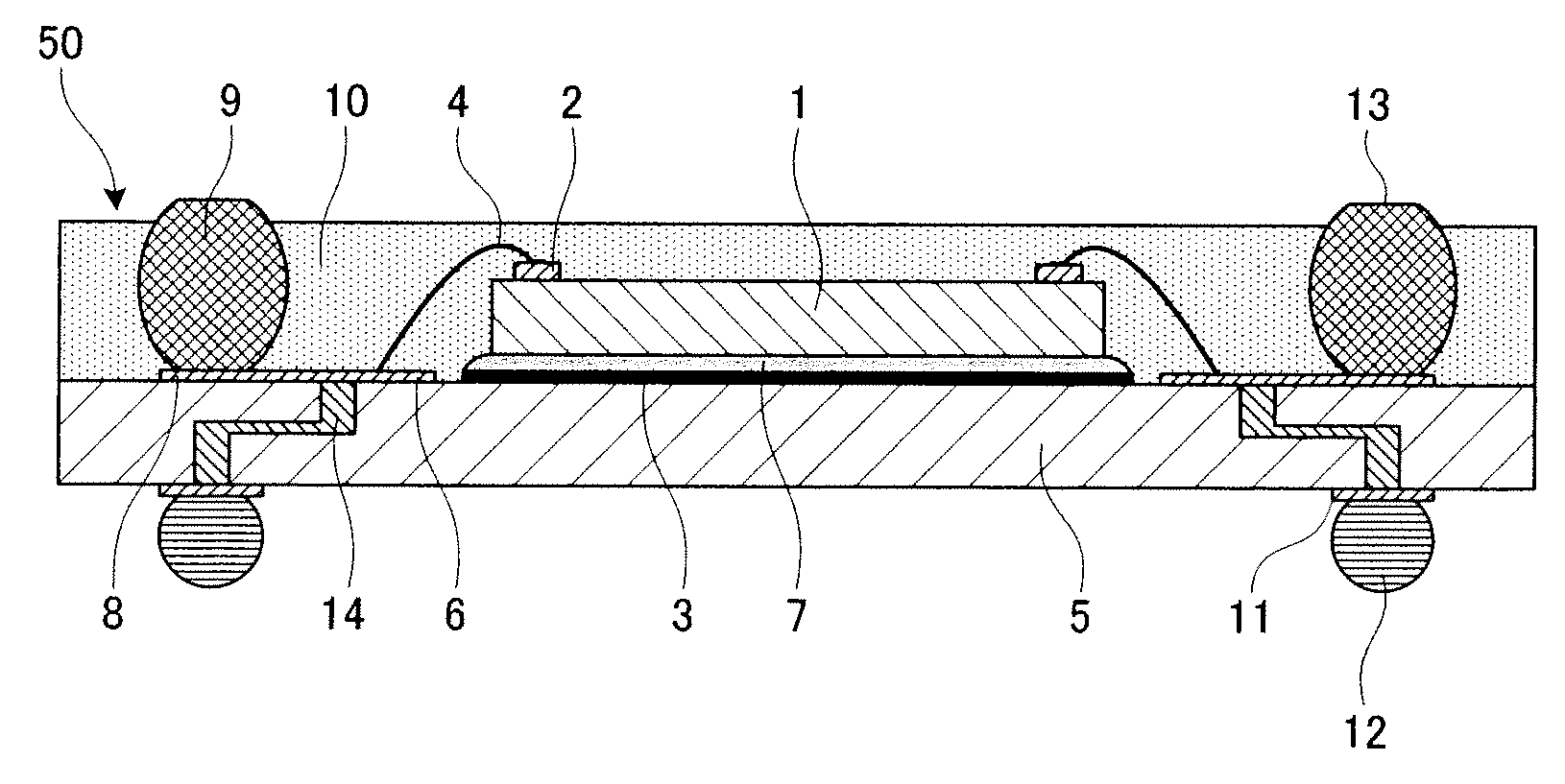

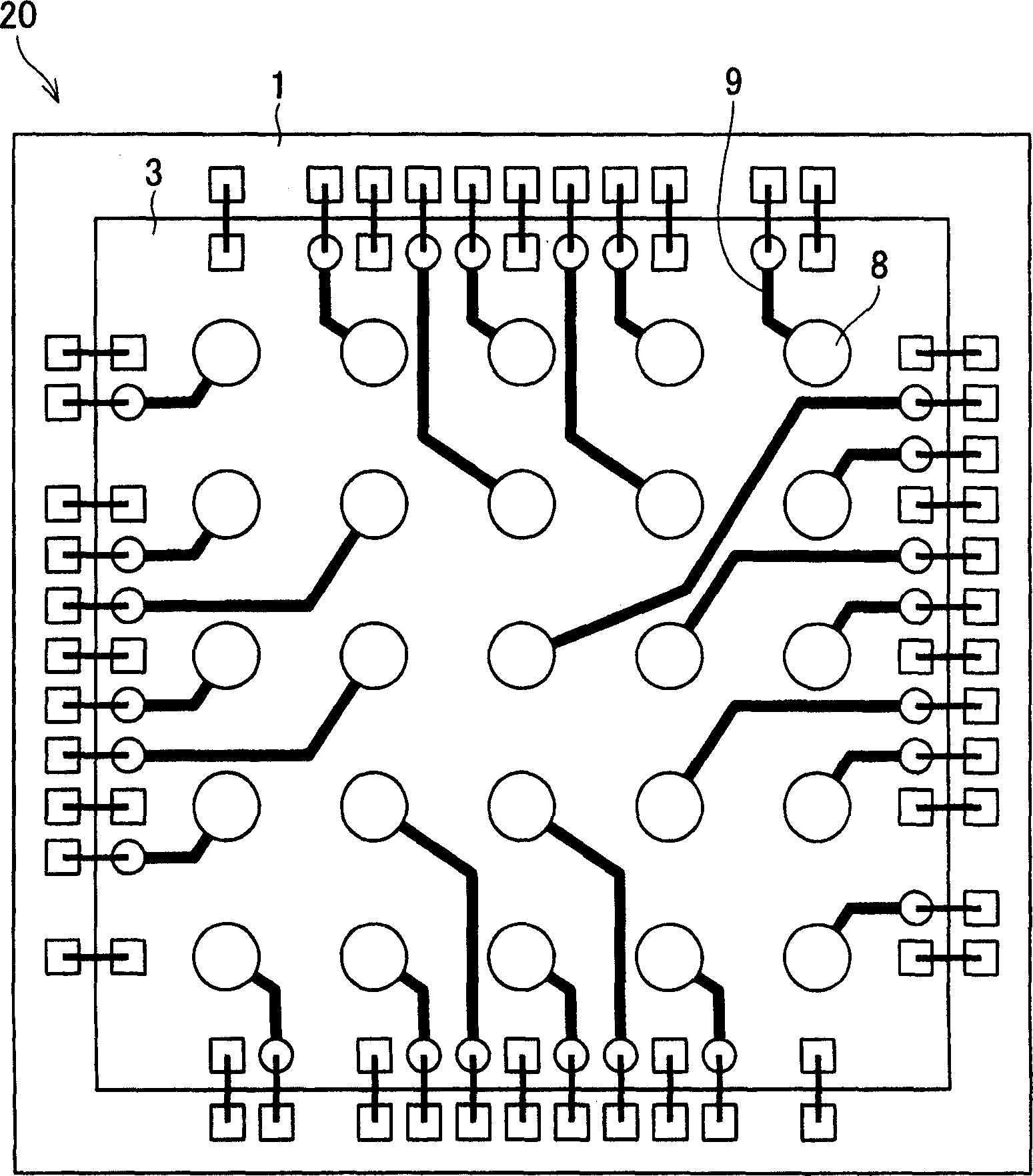

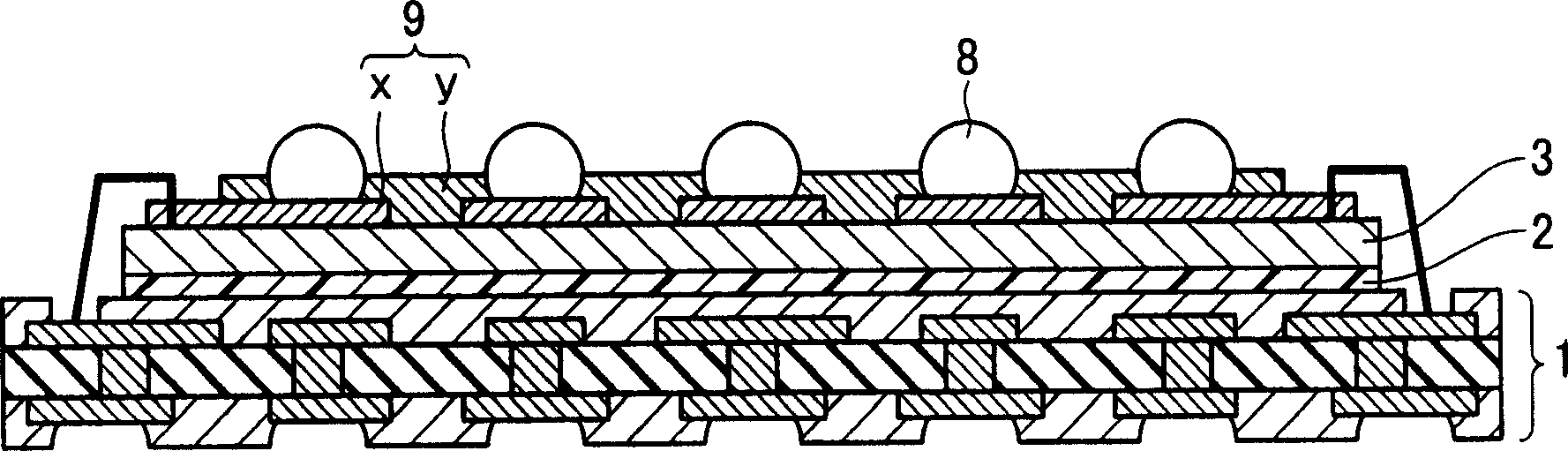

A semiconductor device capable of realizing highly reliable three-dimensional mounting, and a method of manufacturing the same, are provided. A projected electrode 9 is formed in a region outside of an element mounting region of a substrate 5. The projected electrode 9 includes a protruding portion that protrudes from the front face of a molding resin portion 10. The distal end of the protruding portion is a flat face 13. In addition, a portion of the projected electrode 9 whose cross section is larger than the protruding portion is positioned inside the molding resin portion 10.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

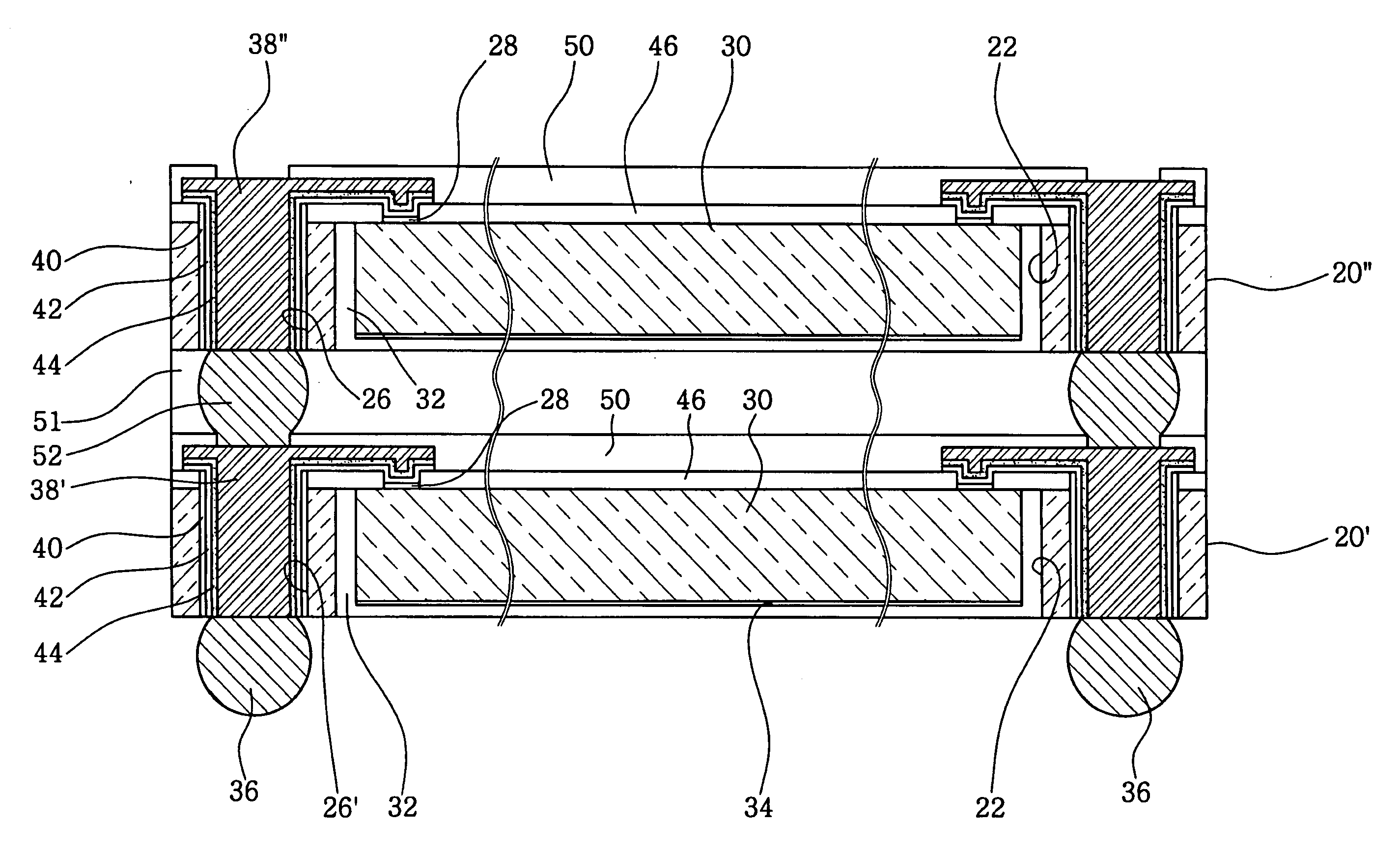

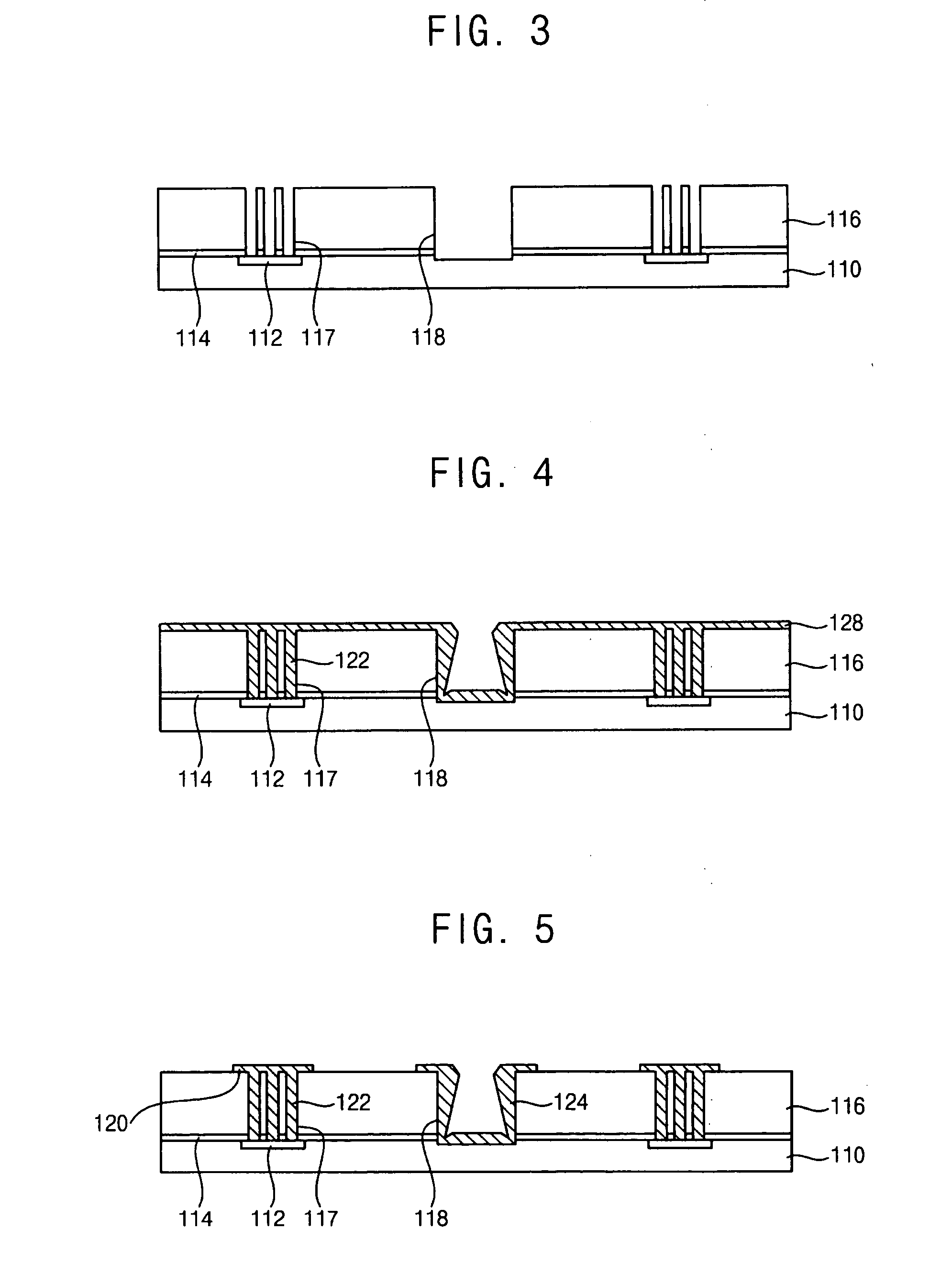

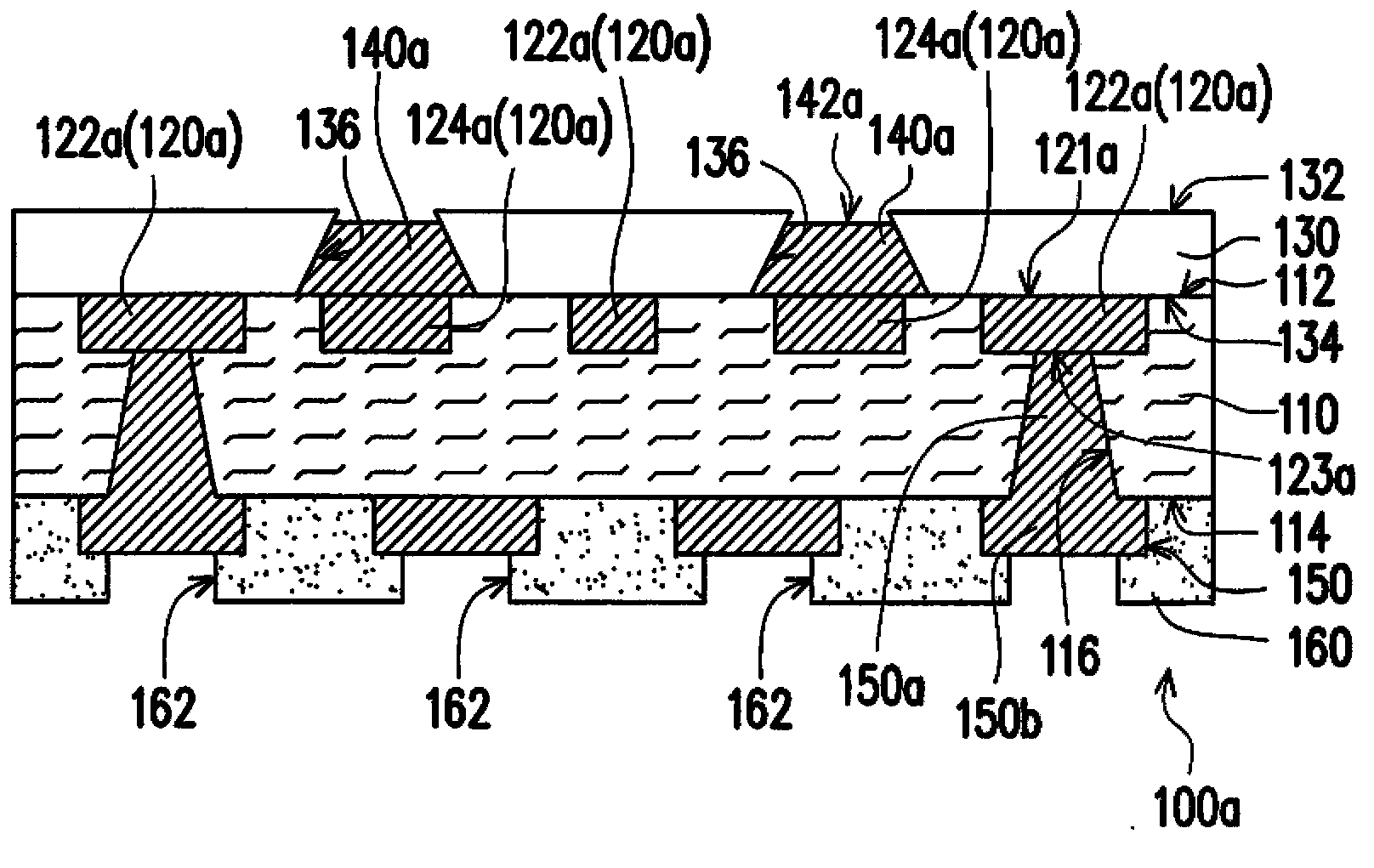

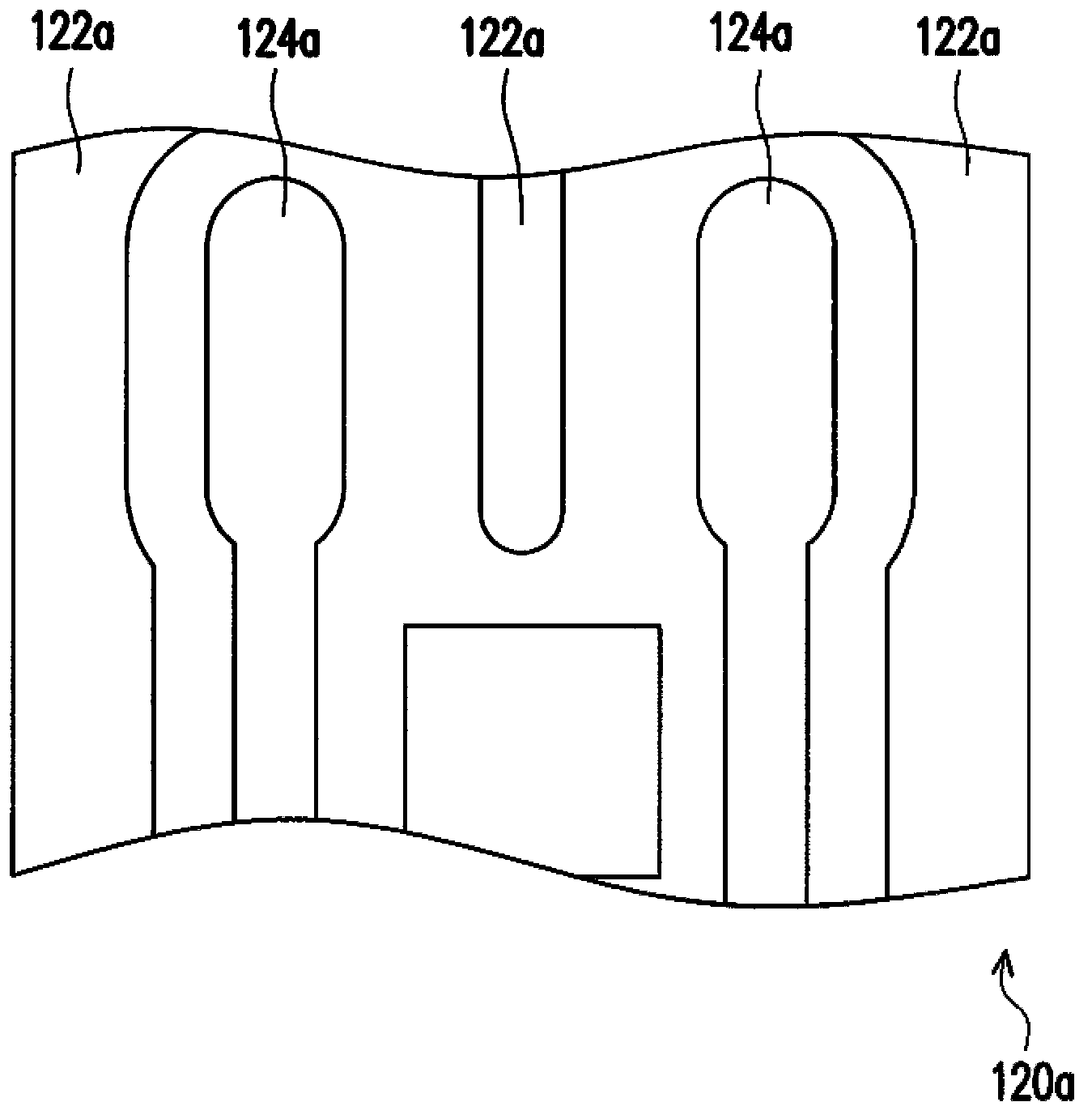

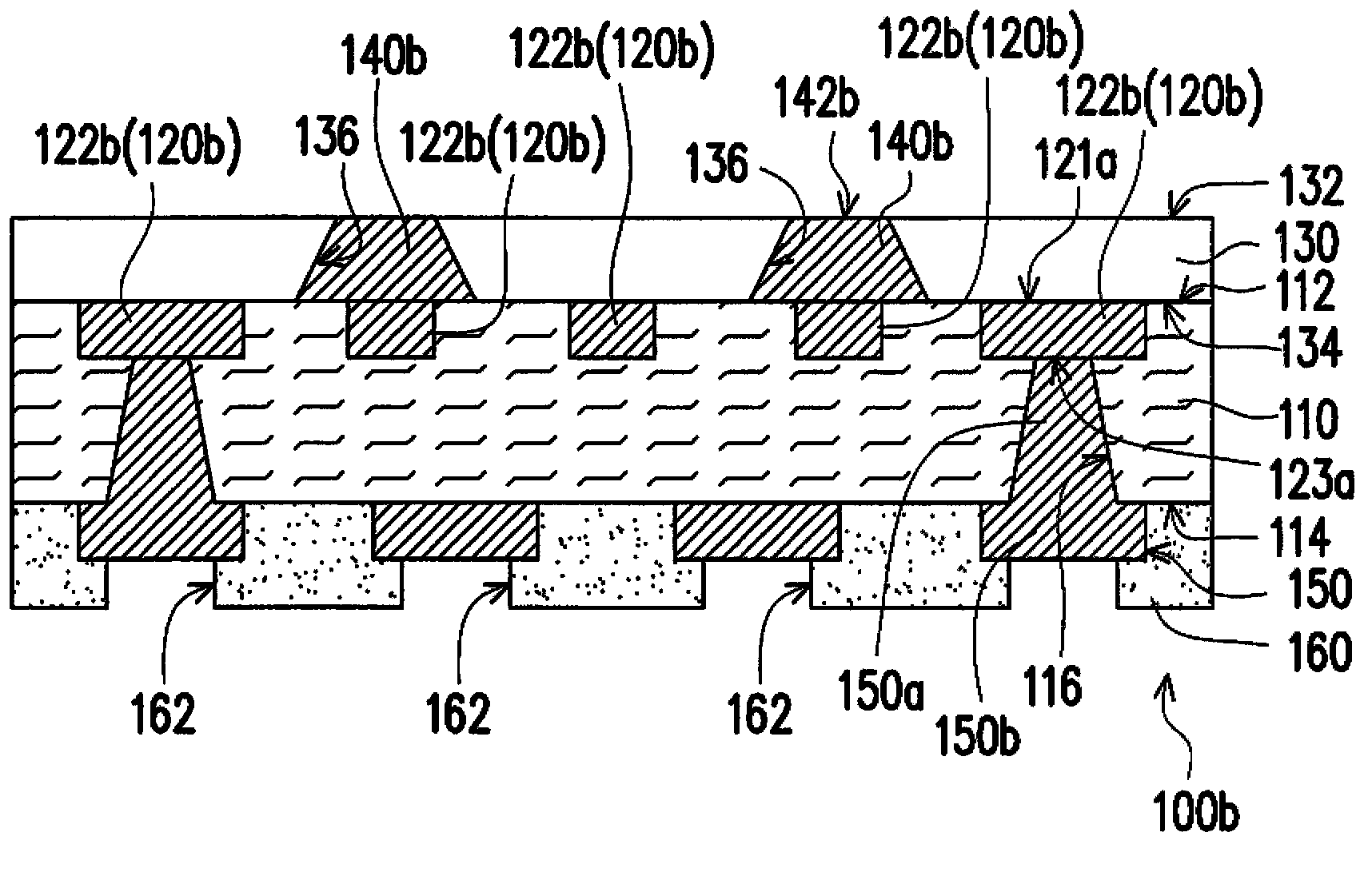

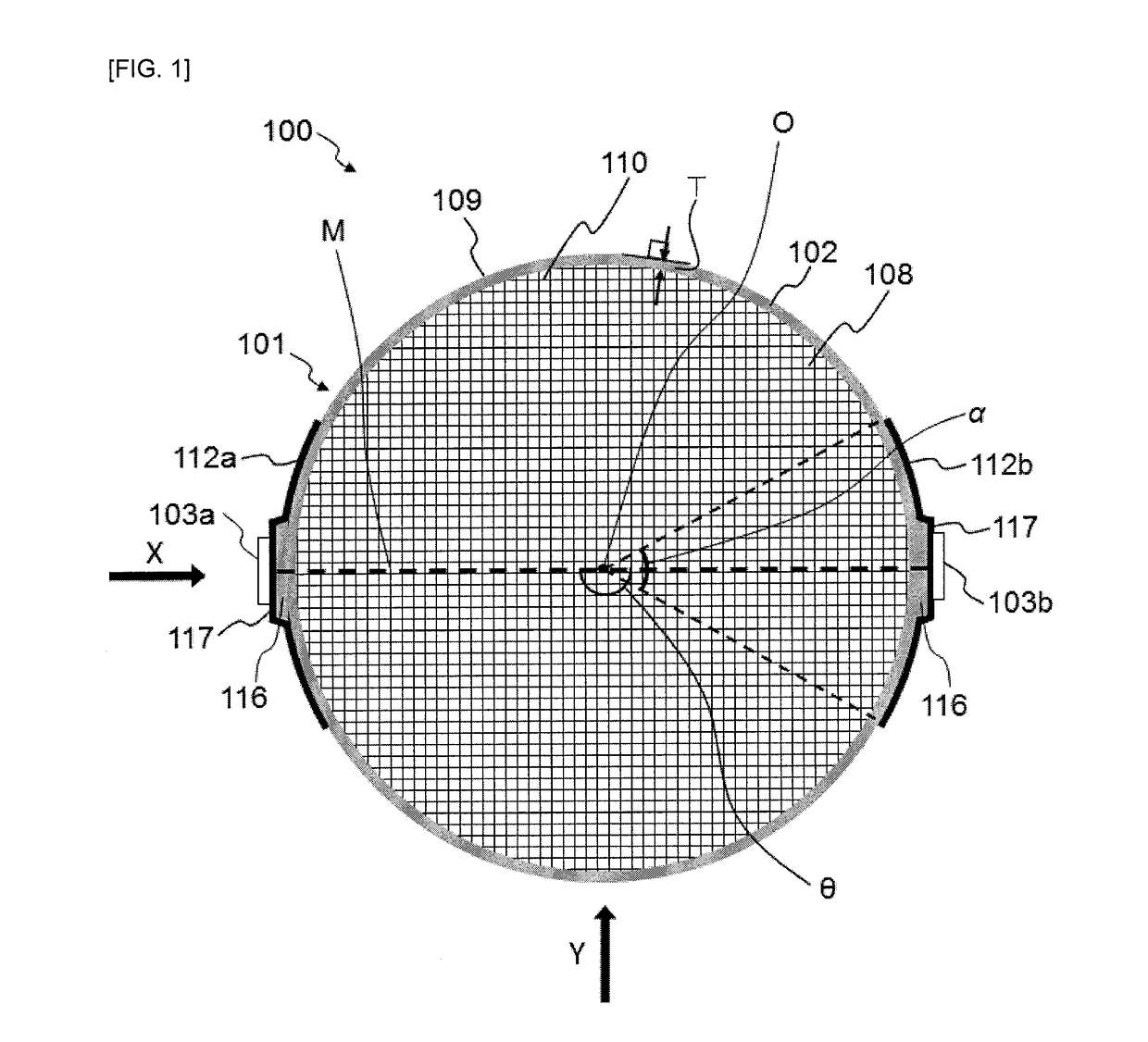

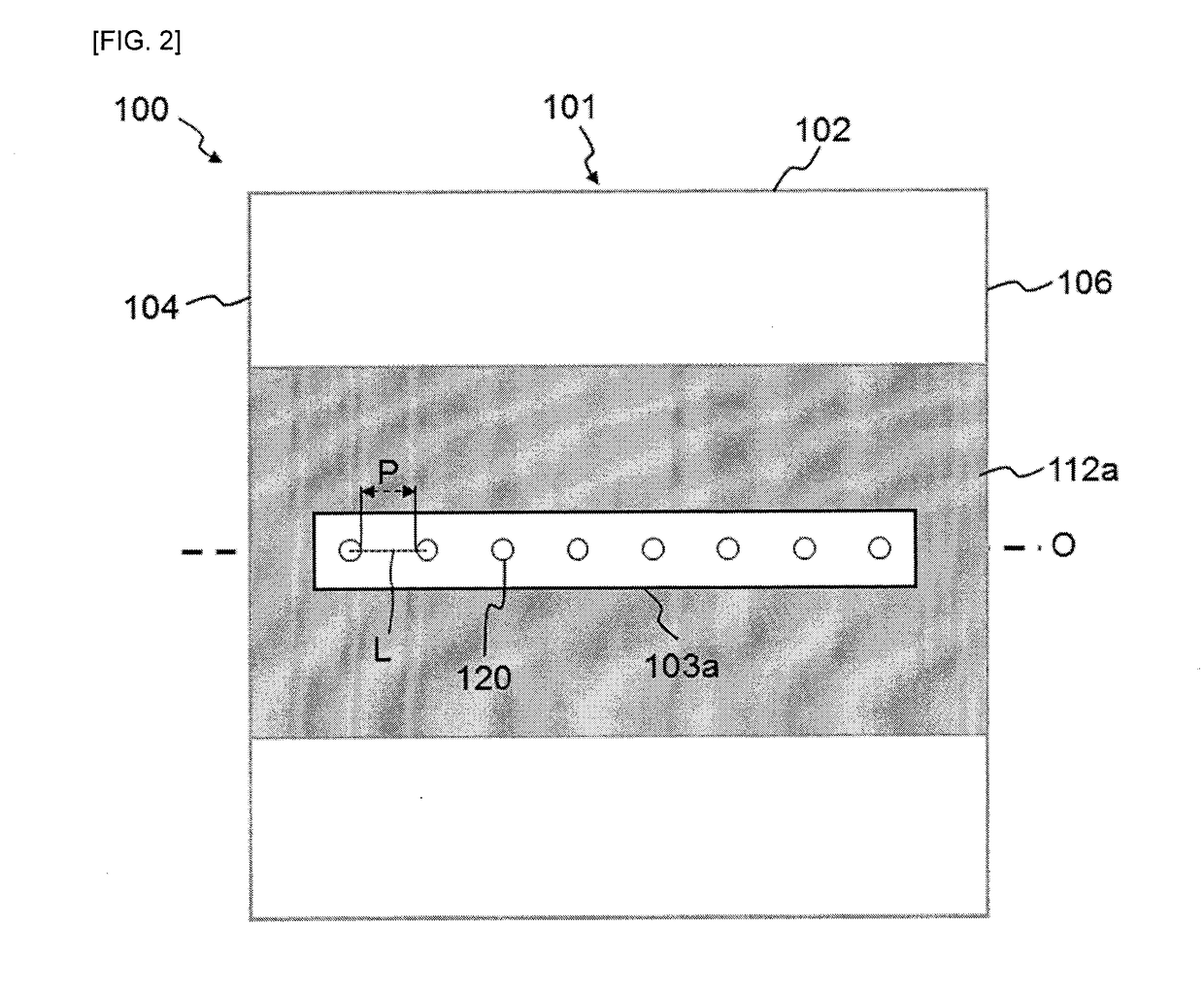

Semiconductor package having a semiconductor chip in a substrate and method of fabricating the same

InactiveUS20080169548A1Improve joint reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

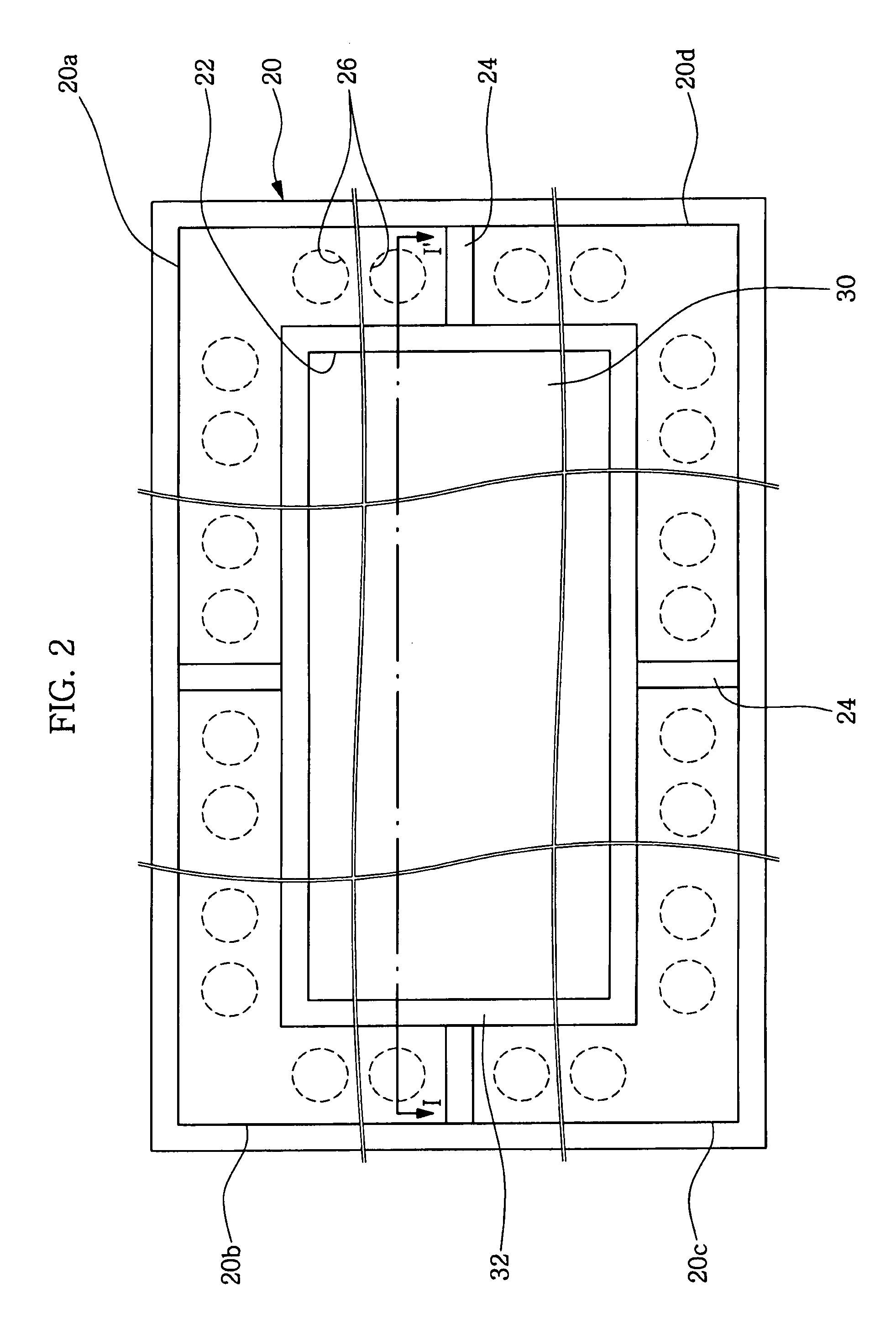

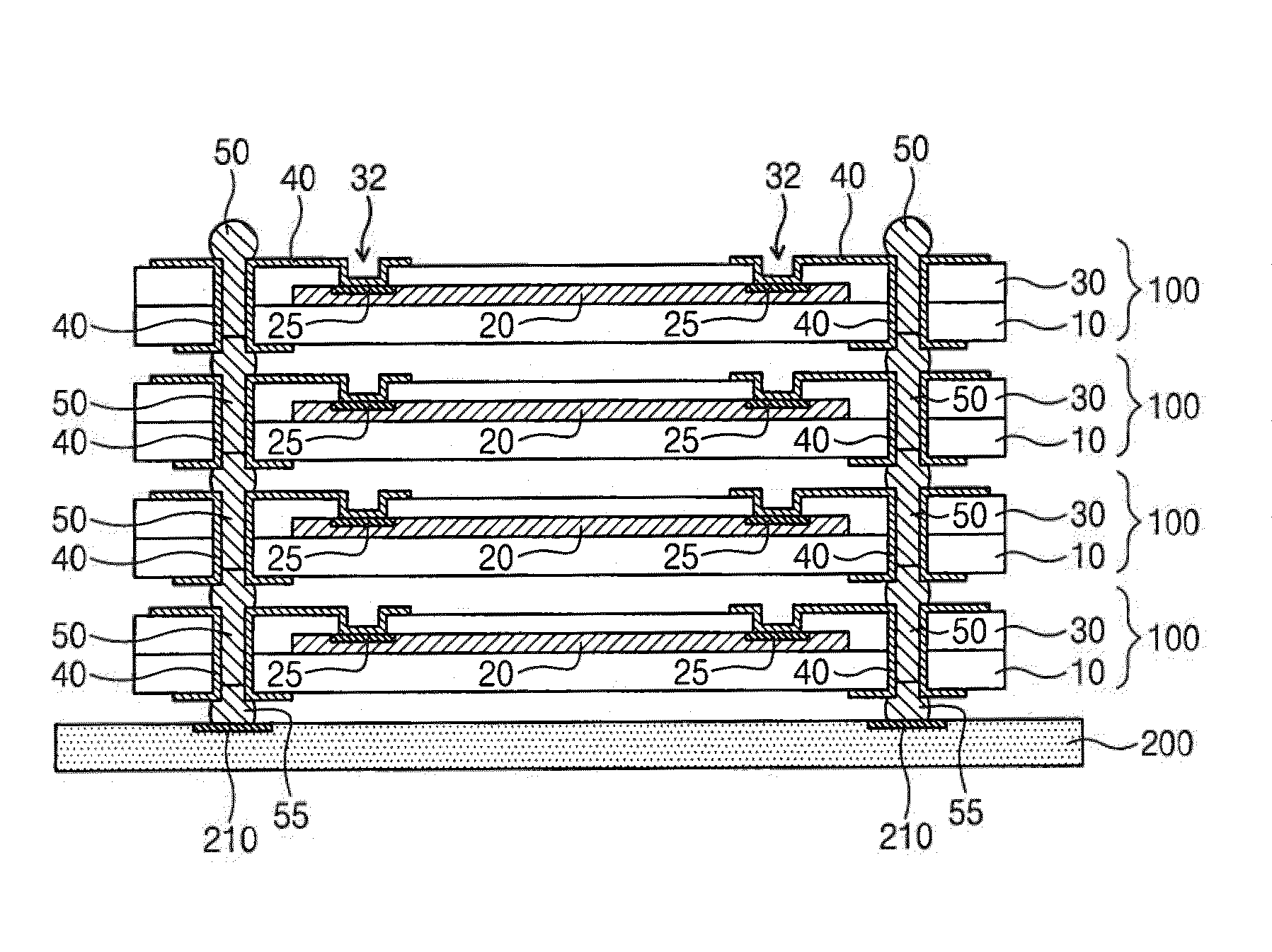

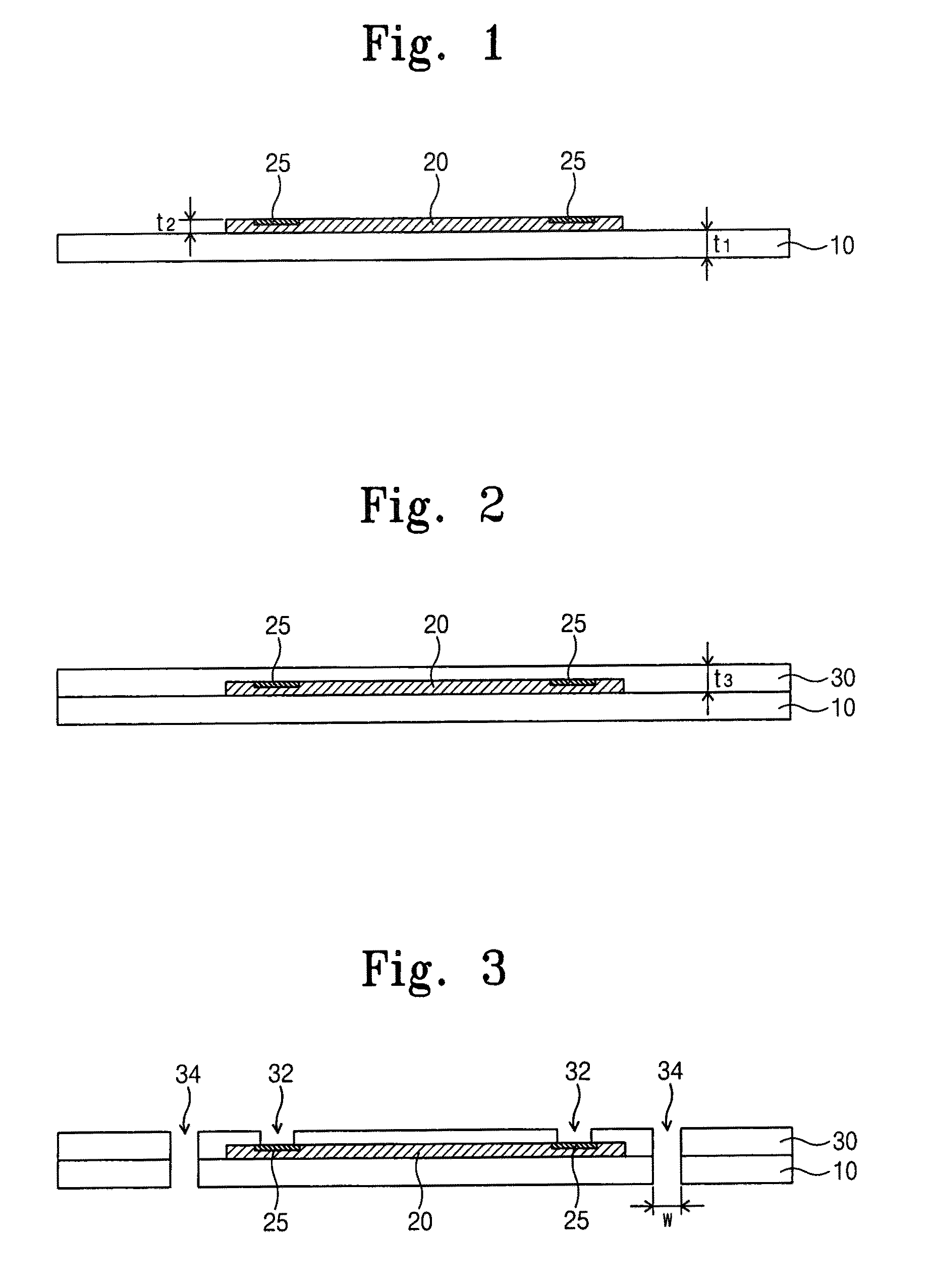

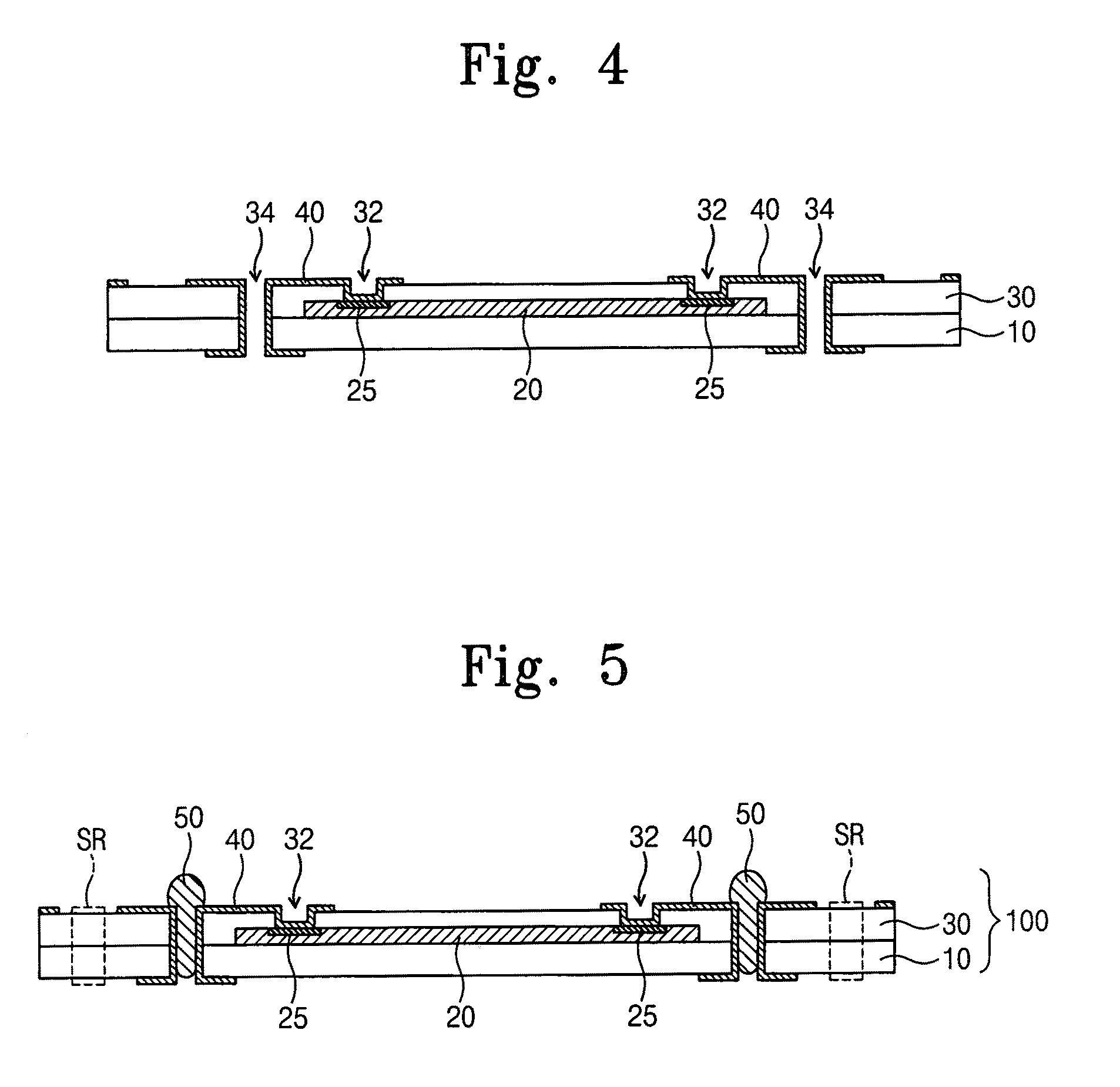

Example embodiments relate to a semiconductor package having a semiconductor chip provided in a substrate and a method of fabricating the same. The semiconductor package may include a semiconductor substrate having a first through hole and a plurality of second through holes spaced apart from the first through hole. A semiconductor chip having a plurality of pads may be disposed in the first through hole. Solder balls electrically connected to the pads may be attached to end portions of the second through holes. A plurality of the above semiconductor substrates may be stacked to form a multi-chip package.

Owner:SAMSUNG ELECTRONICS CO LTD

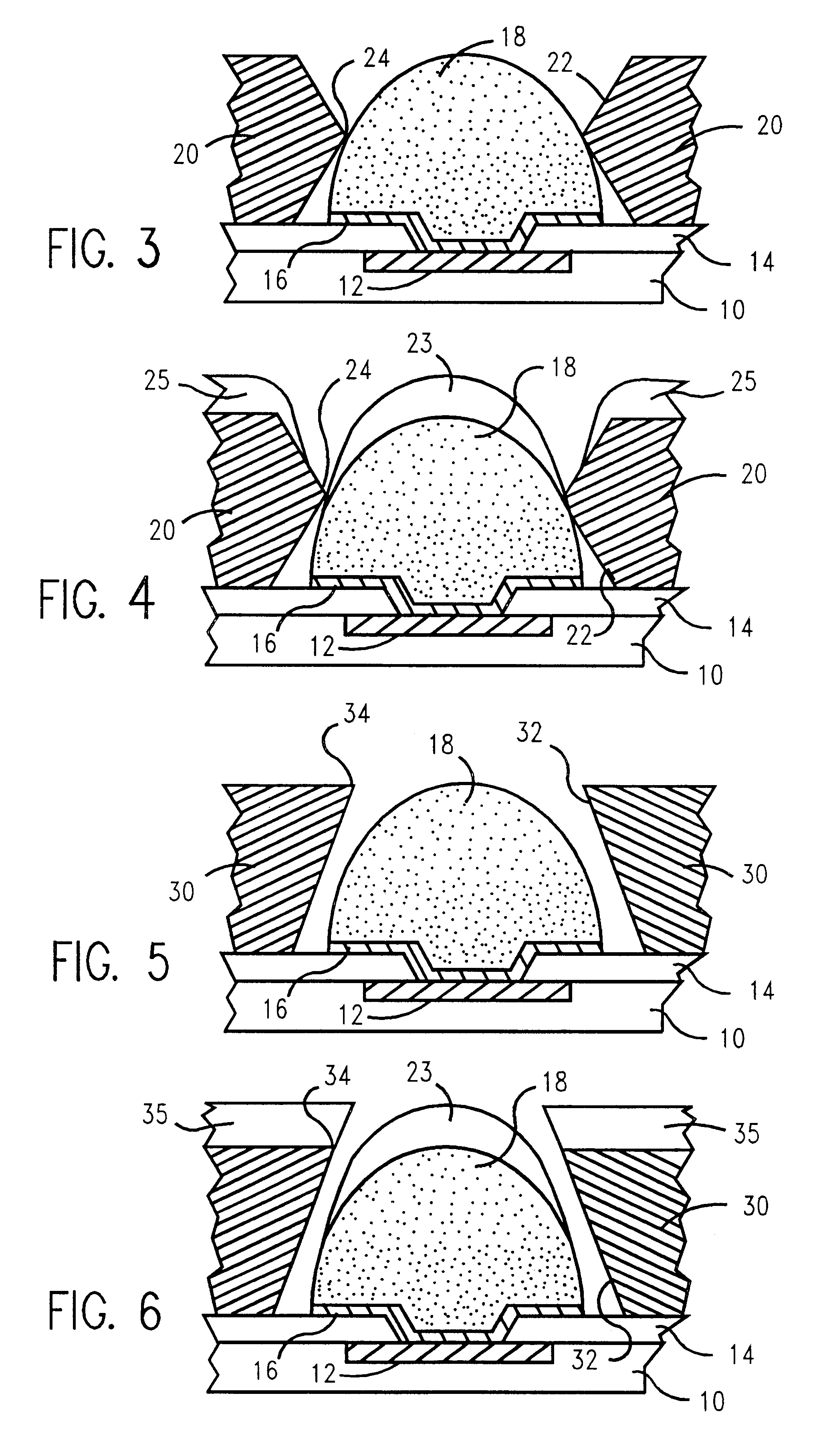

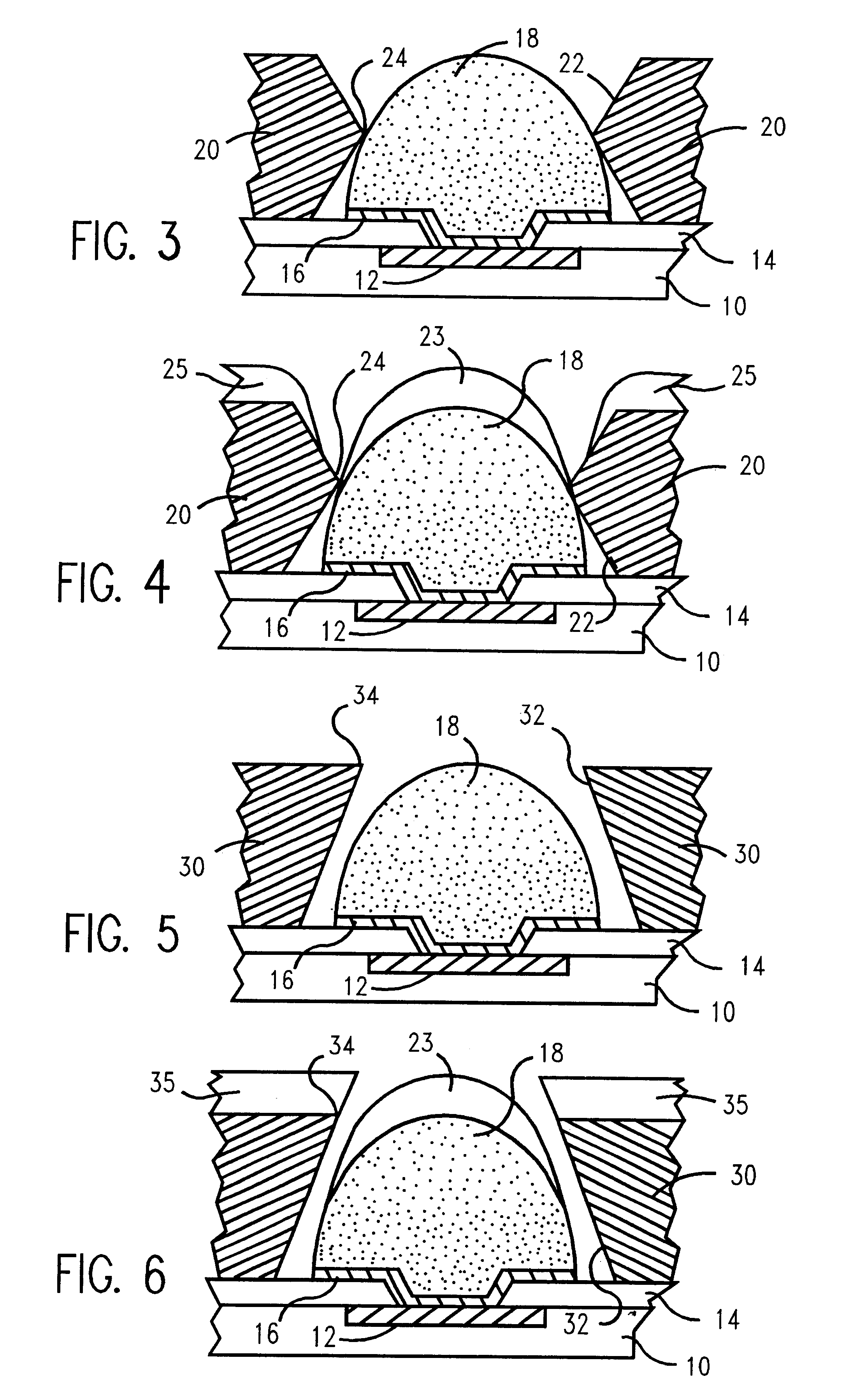

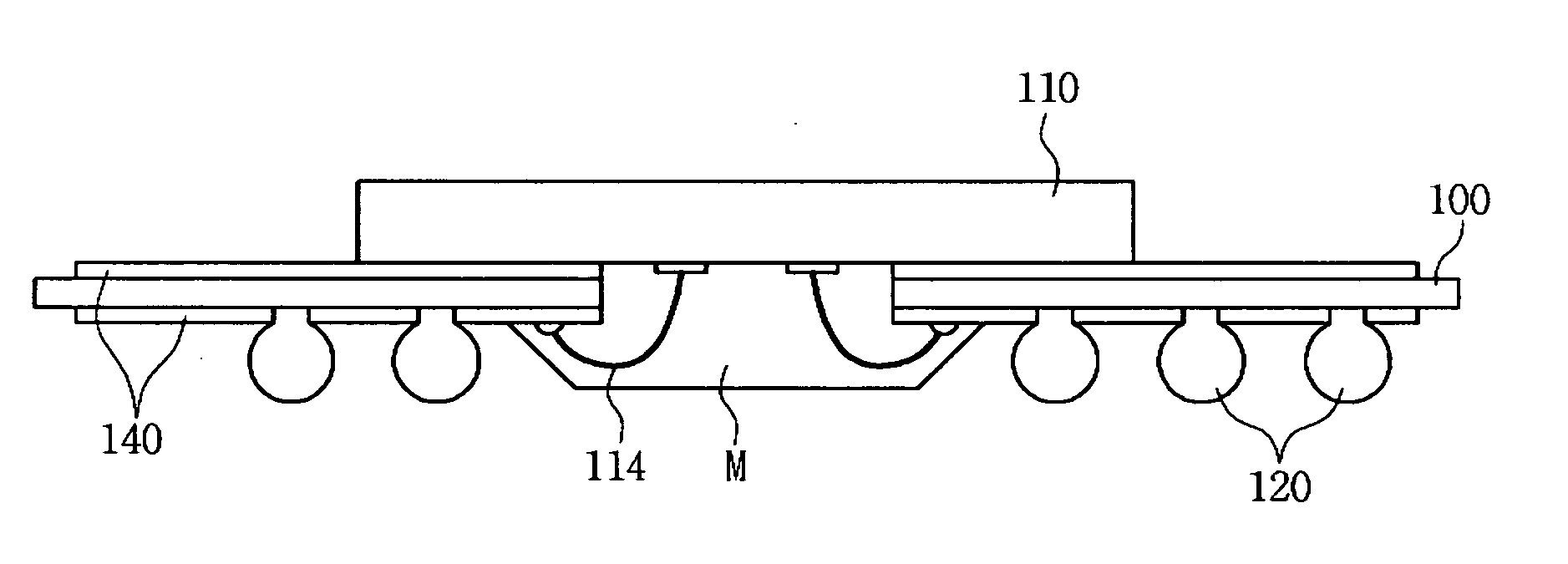

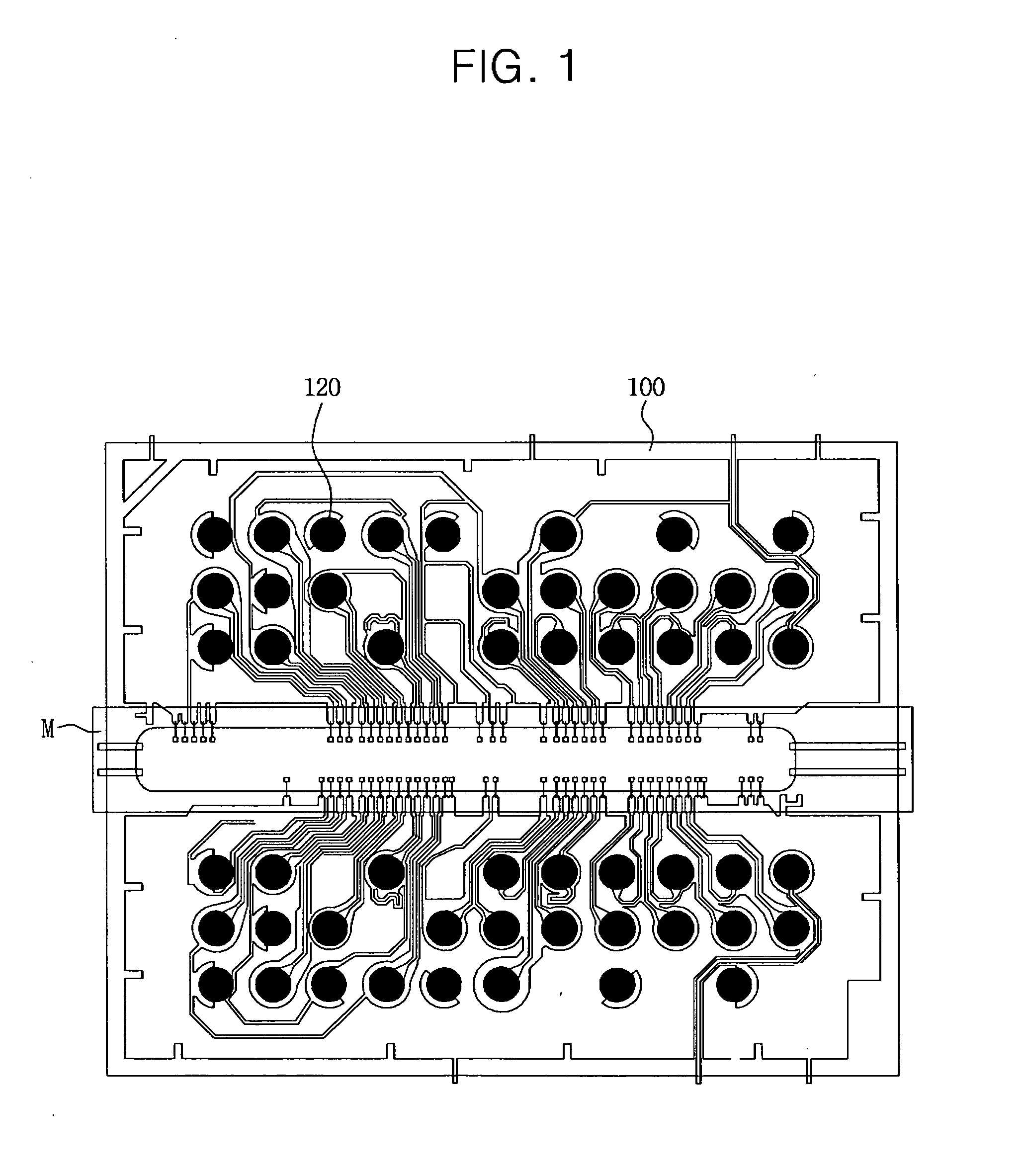

Semiconductor packages with enhanced joint reliability and methods of fabricating the same

ActiveUS7598607B2Improve joint reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

Owner:SAMSUNG ELECTRONICS CO LTD

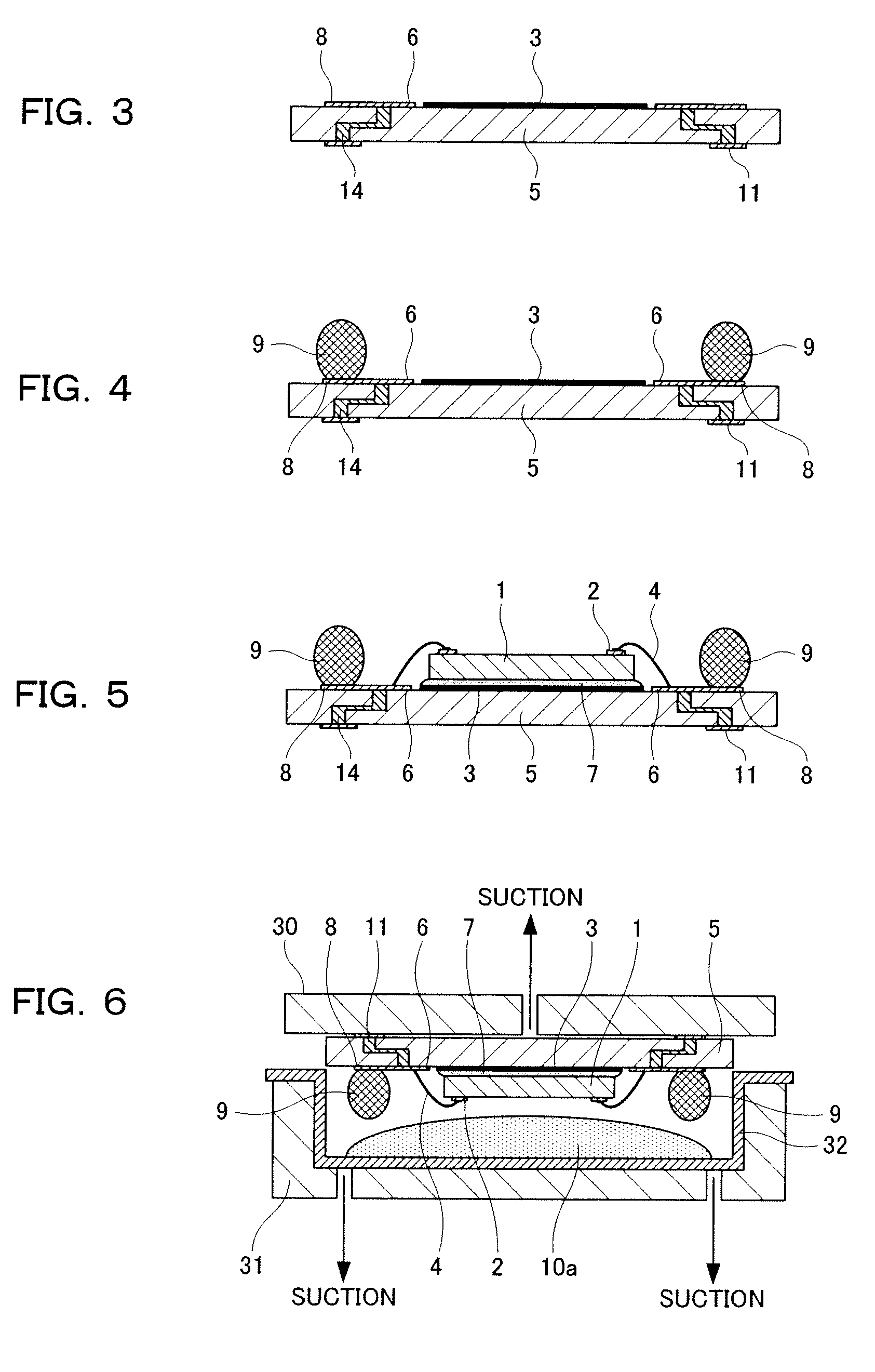

Semiconductor device, stacked semiconductor device, and manufacturing method for semiconductor device

InactiveCN1877824AEasy to manufactureImprove joint reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

The invention provides a semiconductor device, a stacked semiconductor device, and a manufacturing method for semiconductor device. A semiconductor device includes: a base substrate; a semiconductor chip formed on the base substrate in such a manner that an adhesive layer is interposed between the semiconductor chip and the base substrate; a resin layer covering at least a portion of the semiconductor chip; and an external connection terminal electrically connected to the base substrate via a wiring layer. The external connection terminal is in the same plane as the surface of the resin layer, and is exposed from the resin layer. With this configuration, it is possible to provide a semiconductor device of a lower stage, and a stacked semiconductor device, each of which is high in connection reliability in a case of stacking plural semiconductor devices, no matter if a connection terminal of a semiconductor device stacked on an upper stage is low.

Owner:SHARP KK

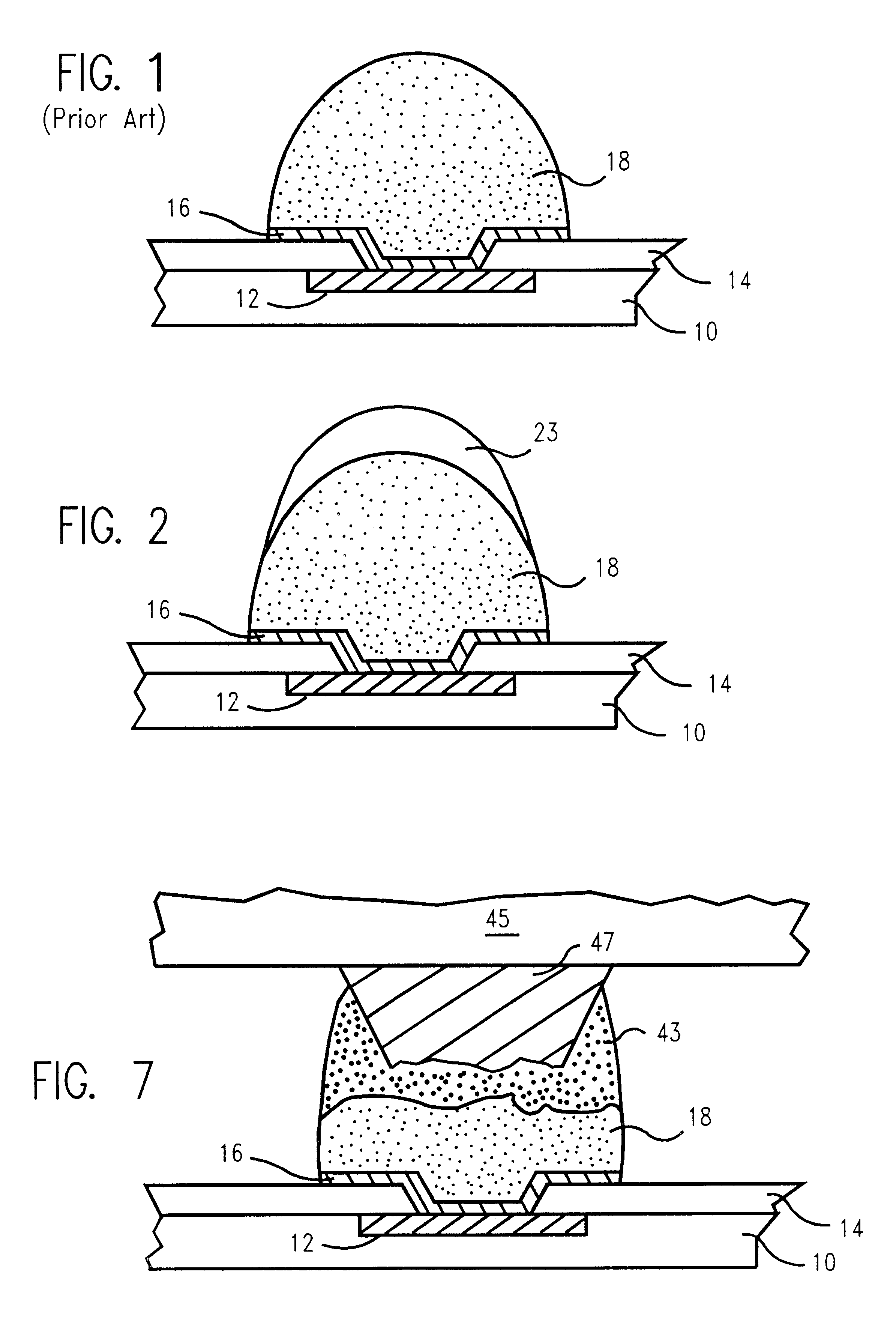

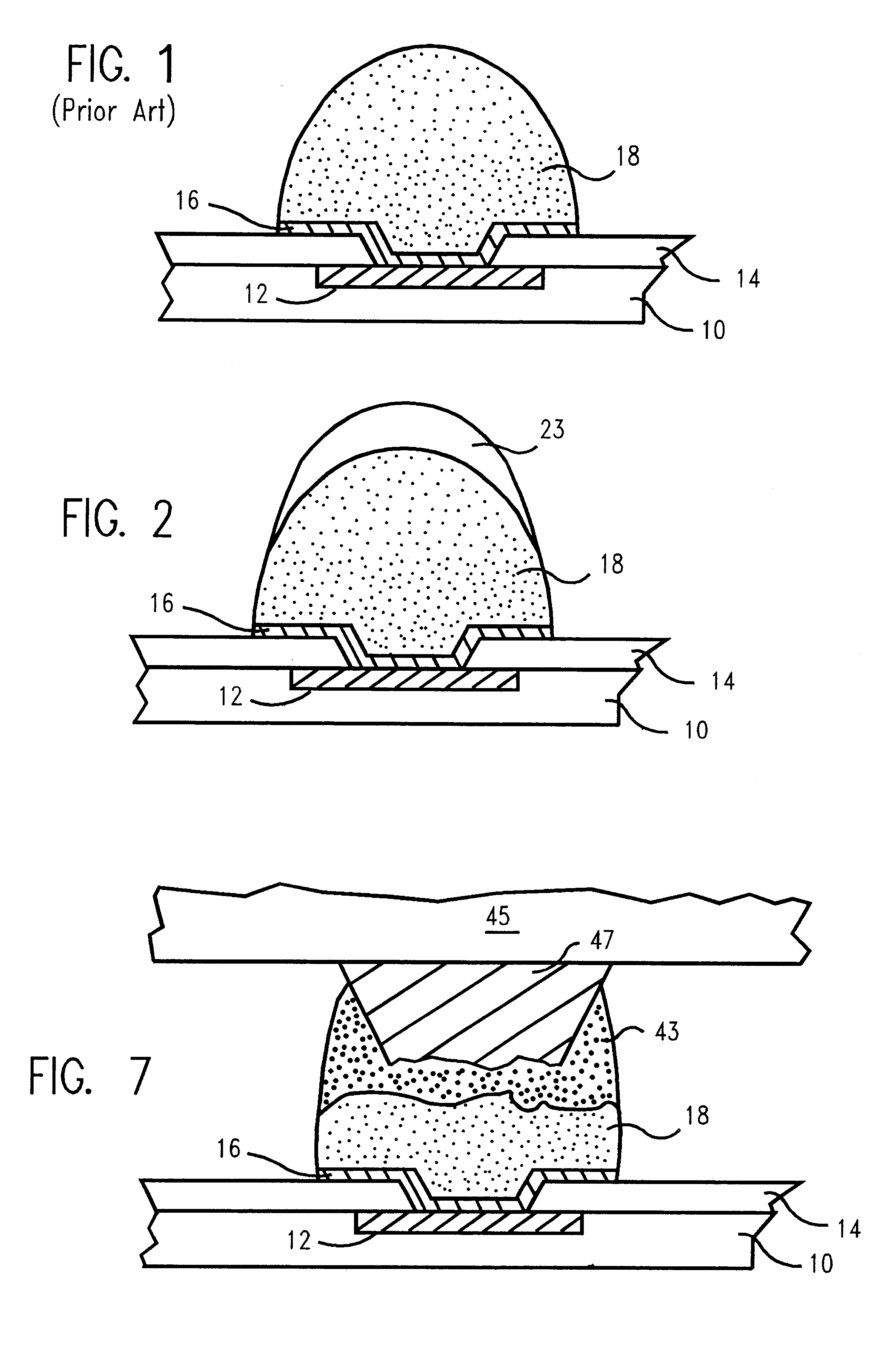

Method for forming reflowed solder ball with low melting point metal cap

InactiveUS6344234B1Reduce the hole diameterMinimal diameterFinal product manufactureSemiconductor/solid-state device detailsTinningIndium

A method and structure for a solder interconnection, using solder balls for making a low temperature chip attachment directly to any of the higher levels of packaging substrate is disclosed. After a solder ball has been formed using standard methods it is reflowed to give the solder ball a smooth surface. A layer of low melting point metal, such as, bismuth, indium or tin, preferably, pure tin, is deposited on the top of the solder balls. This structure results in localizing of the eutectic alloy, formed upon subsequent low temperature joining cycle, to the top of the high melting solder ball even after multiple low temperature reflow cycles. This method does not need tinning of the substrate to which the chip is to be joined, which makes this method economical. It has also been noticed that whenever temperature is raised slightly above the eutectic temperature, the structure always forms a liquid fillet around the joint with copper wires. This liquid fillet formation results in substantial thermal fatigue life improvement for reduced stress at interface; and secondly, provides an easy means to remove chip for the purpose of chip burn-in, replacement or field repairs.

Owner:ULTRATECH INT INC

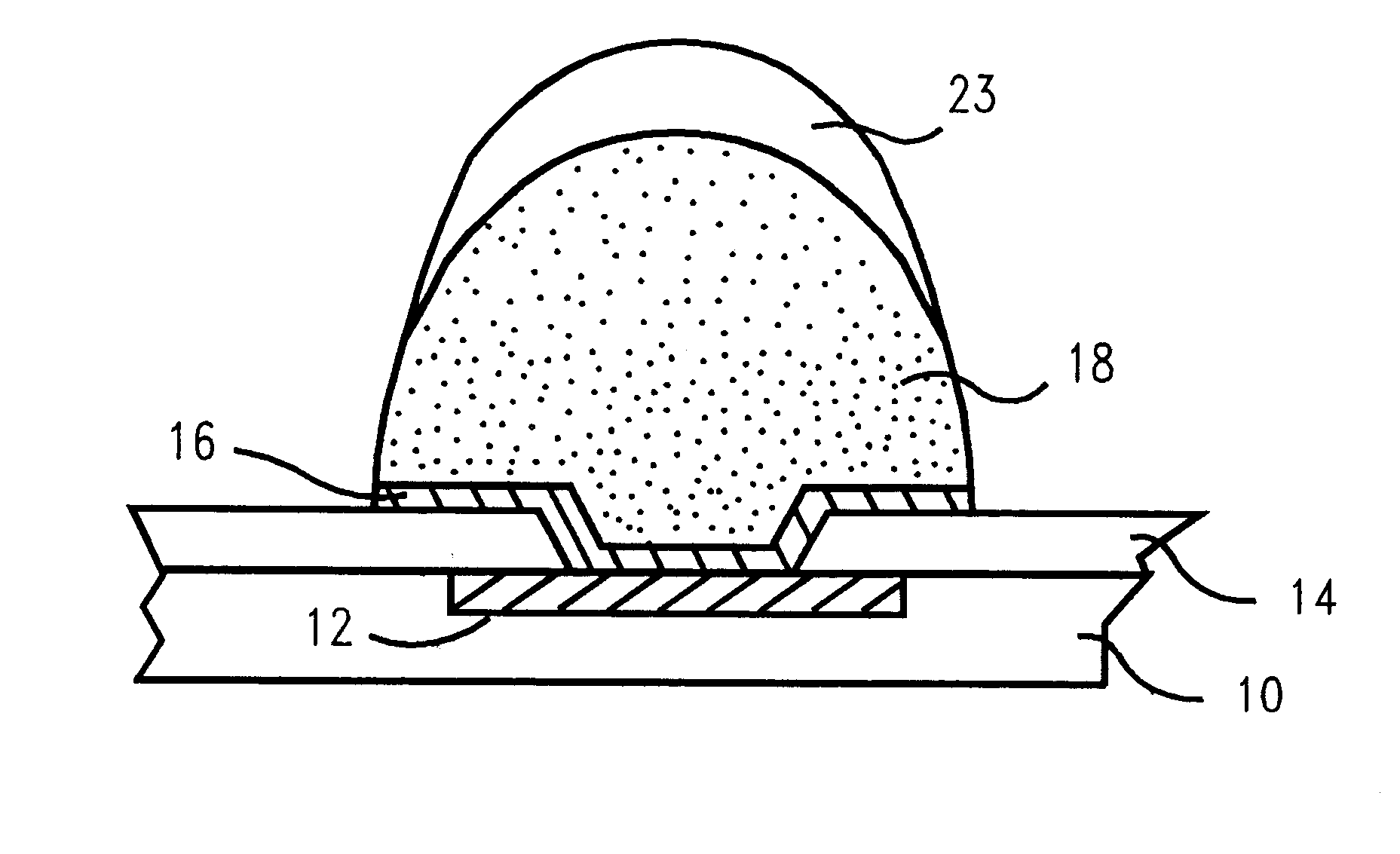

Reflowed solder ball with low melting point metal cap

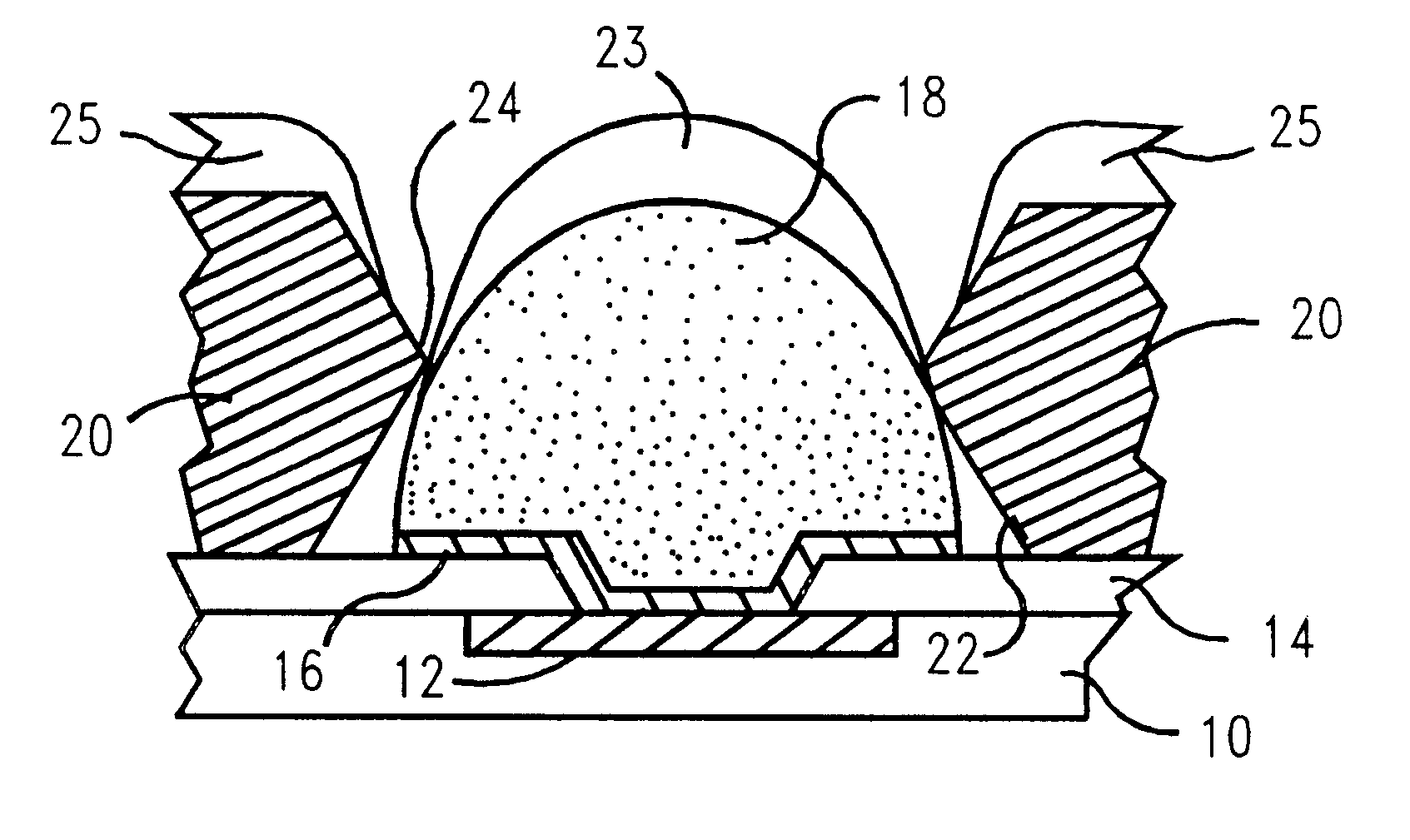

InactiveUS6259159B1Low costEasy to buildPrinted circuit assemblingFinal product manufactureTinningIndium

A method and structure for a solder interconnection, using solder balls for making a low temperature chip attachment directly to any of the higher levels of packaging substrate is disclosed. After a solder ball has been formed using standard methods it is reflowed to give the solder ball a smooth surface. A layer of low melting point metal, such as, bismuth, indium or tin, preferably, pure tin, is deposited on the top of the solder balls. This structure results in localizing of the eutectic alloy, formed upon subsequent low temperature joining cycle, to the top of the high melting solder ball even after multiple low temperature reflow cycles. This method does not need tinning of the substrate to which the chip is to be joined, which makes this method economical. It has also been noticed that whenever temperature is raised slightly above the eutectic temperature, the structure always forms a liquid fillet around the joint with copper wires. This liquid fillet formation results in substantial thermal fatigue life improvement for reduced stress at interface; and secondly, provides an easy means to remove chip for the purpose of chip burn-in, replacement or field repairs.

Owner:IBM CORP

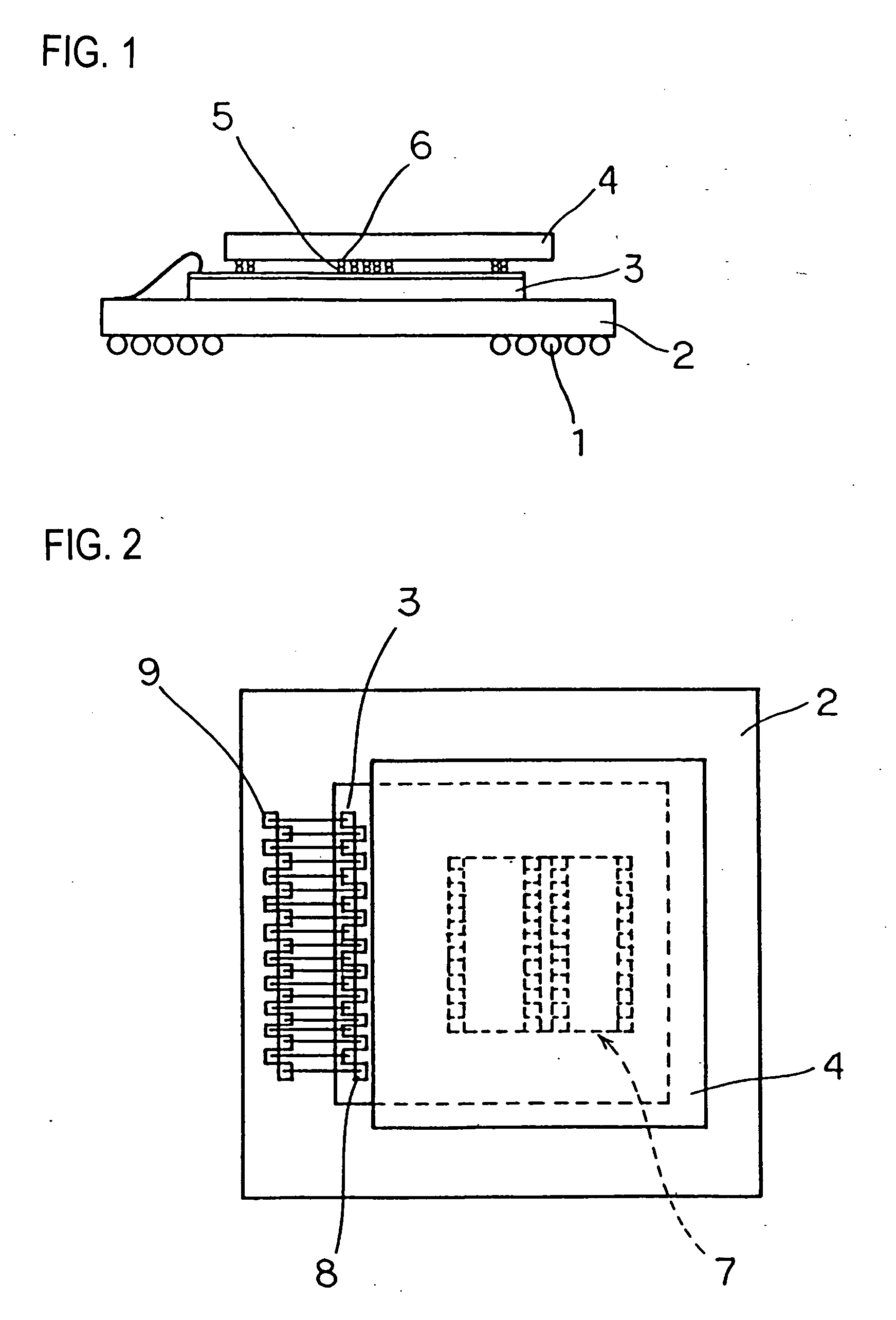

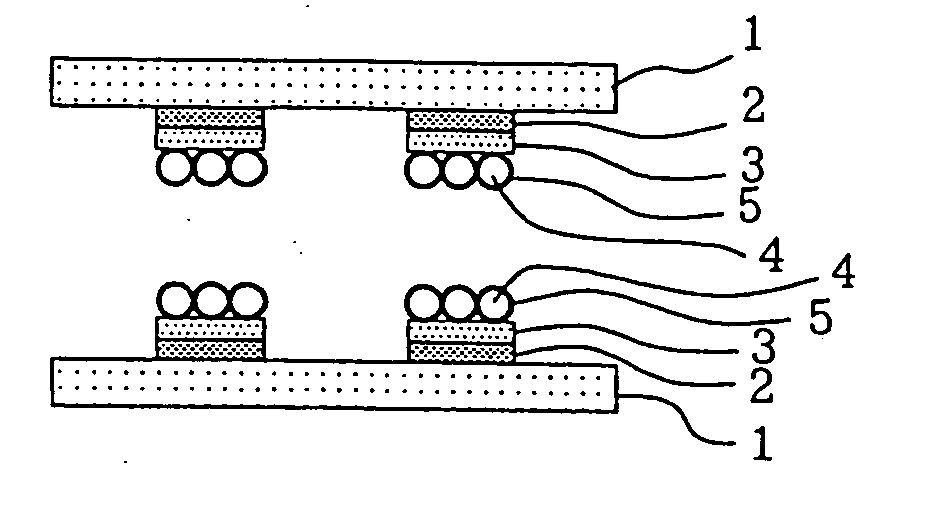

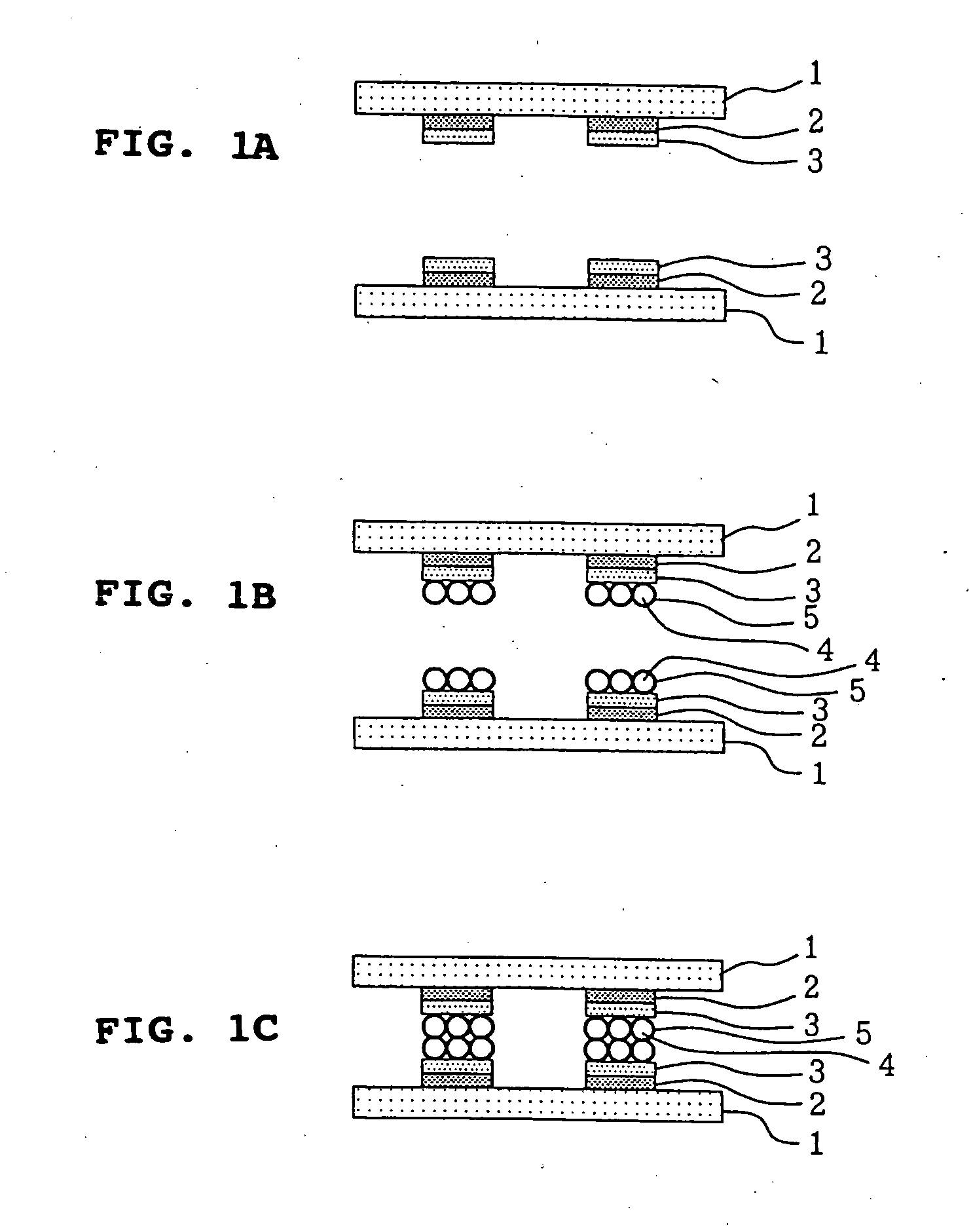

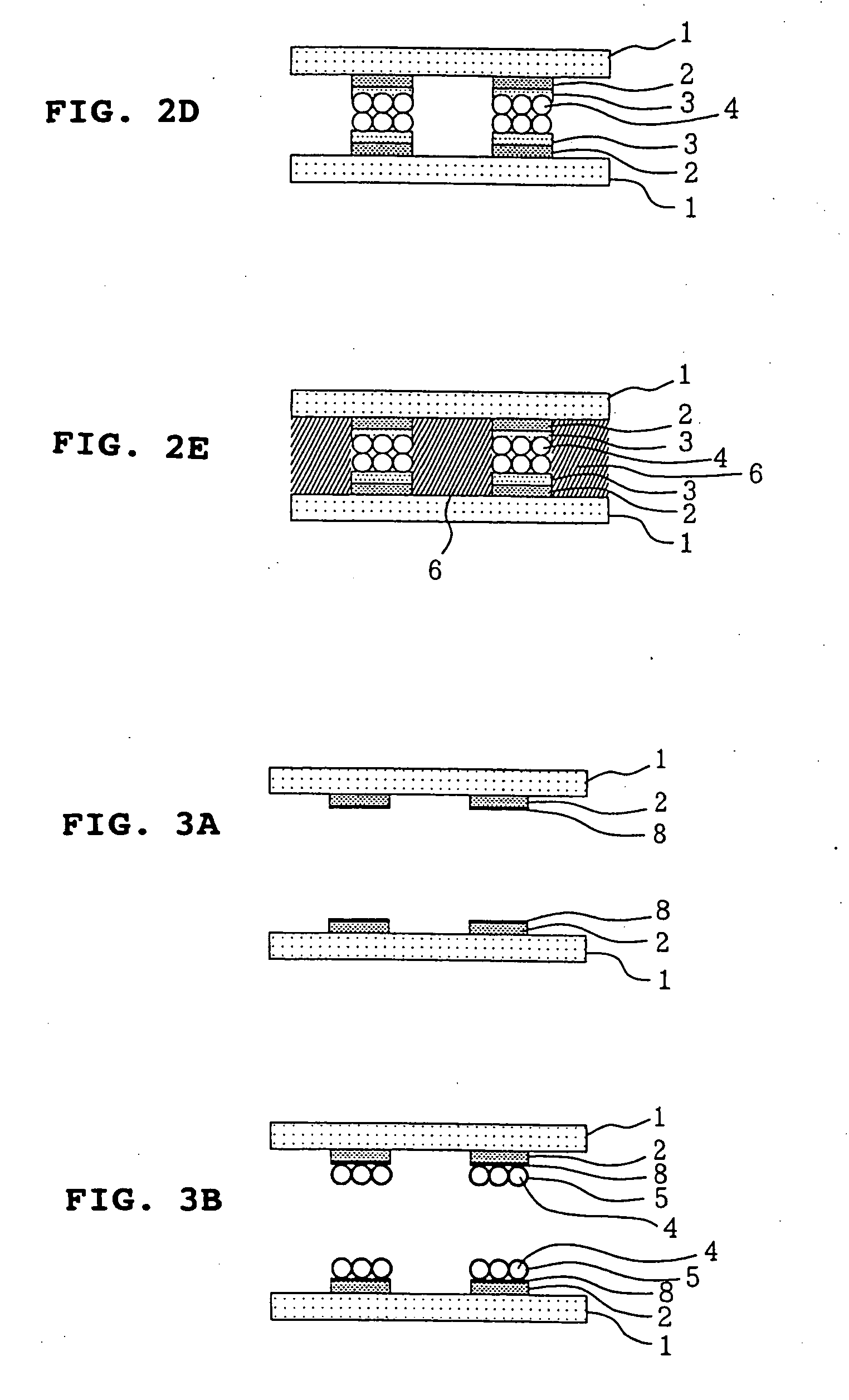

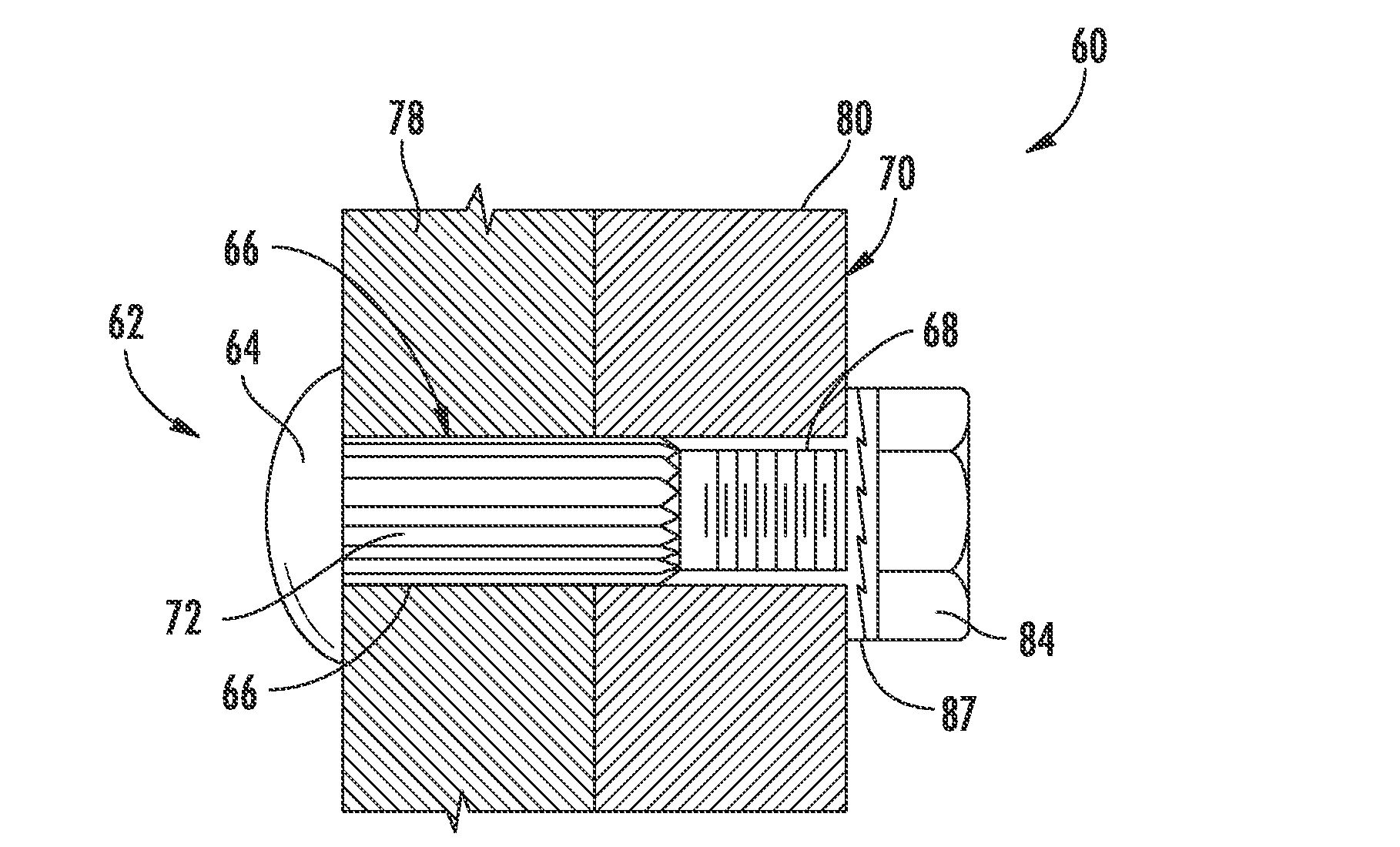

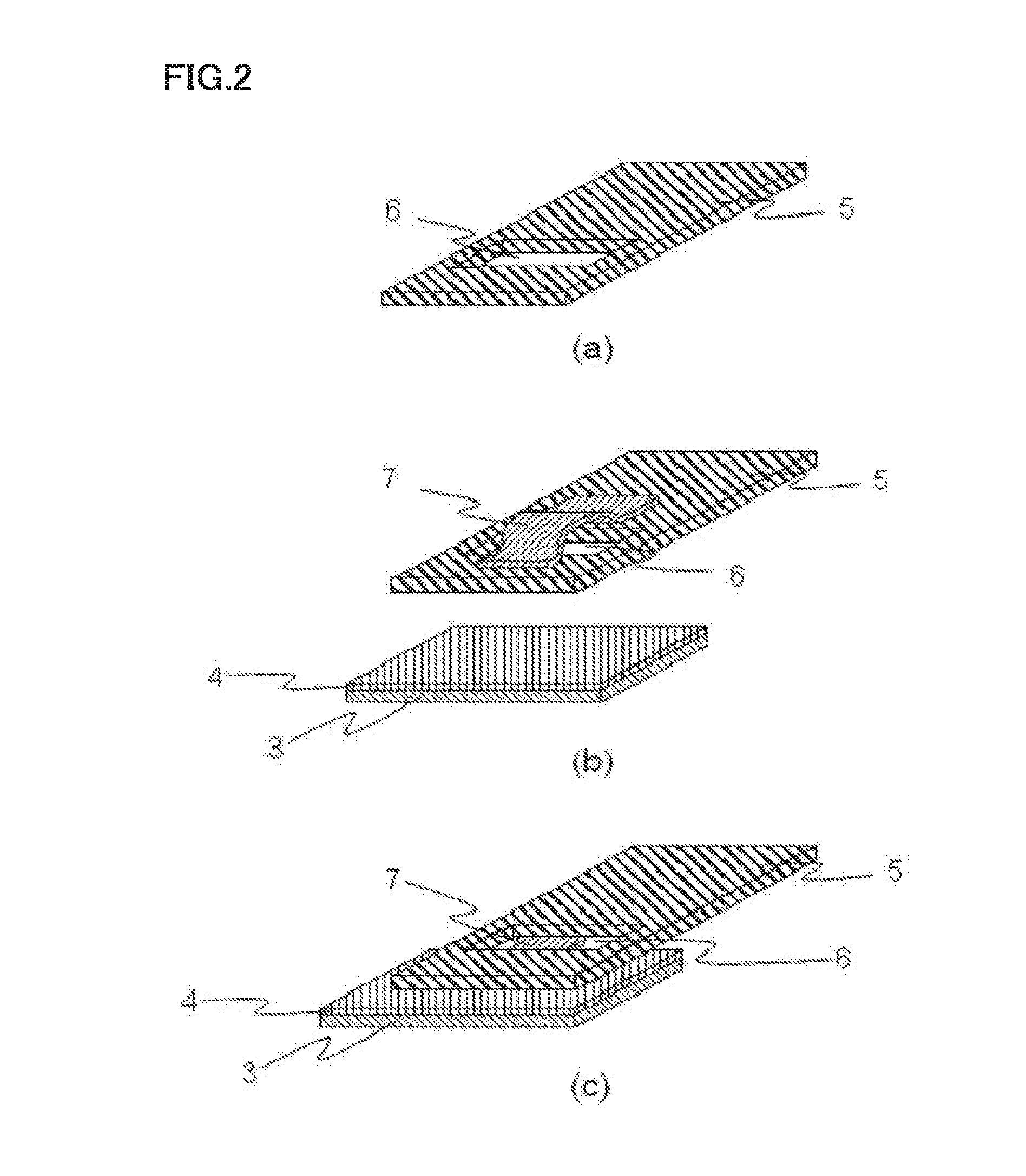

Offset-bonded, multi-chip semiconductor device

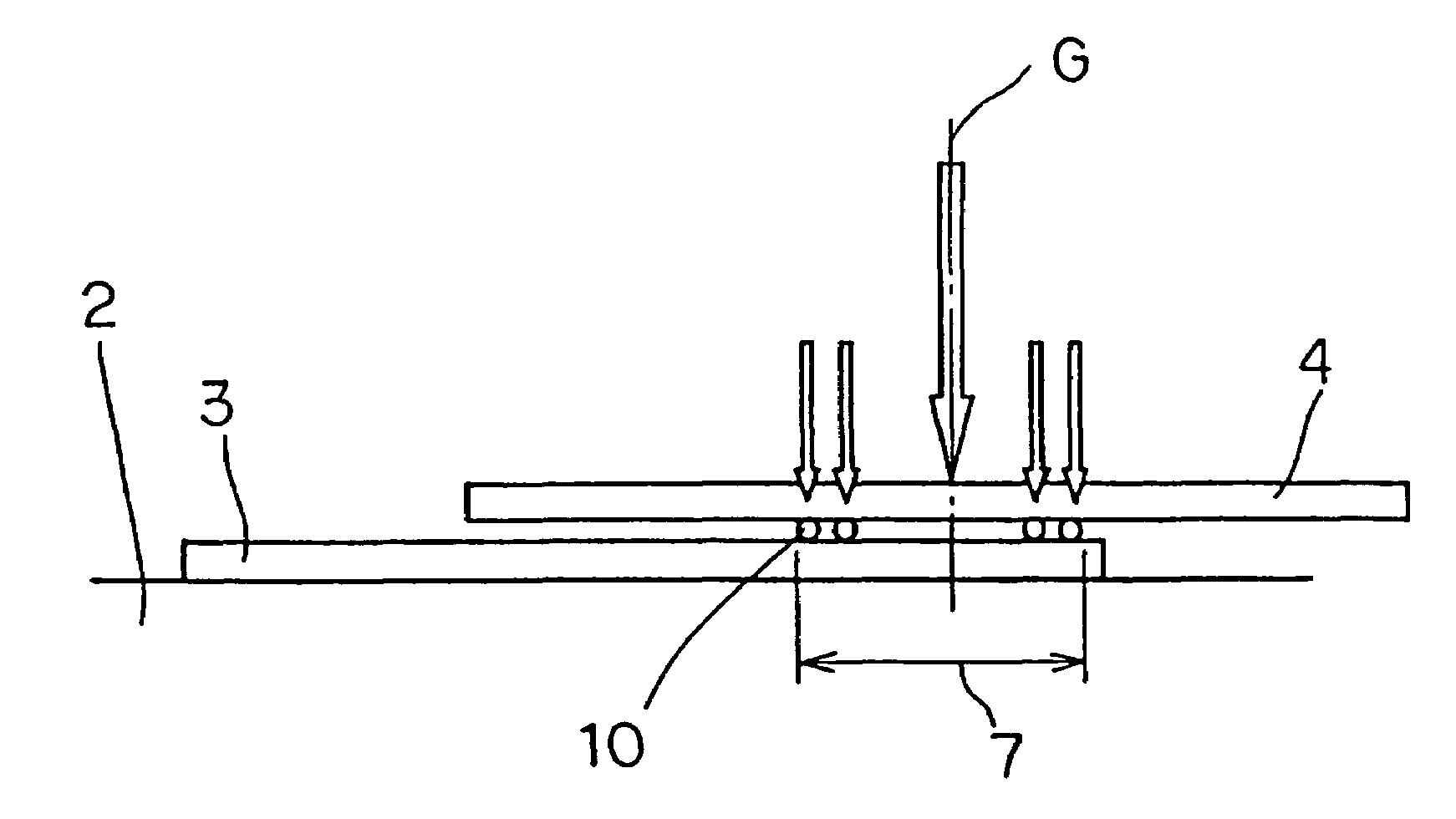

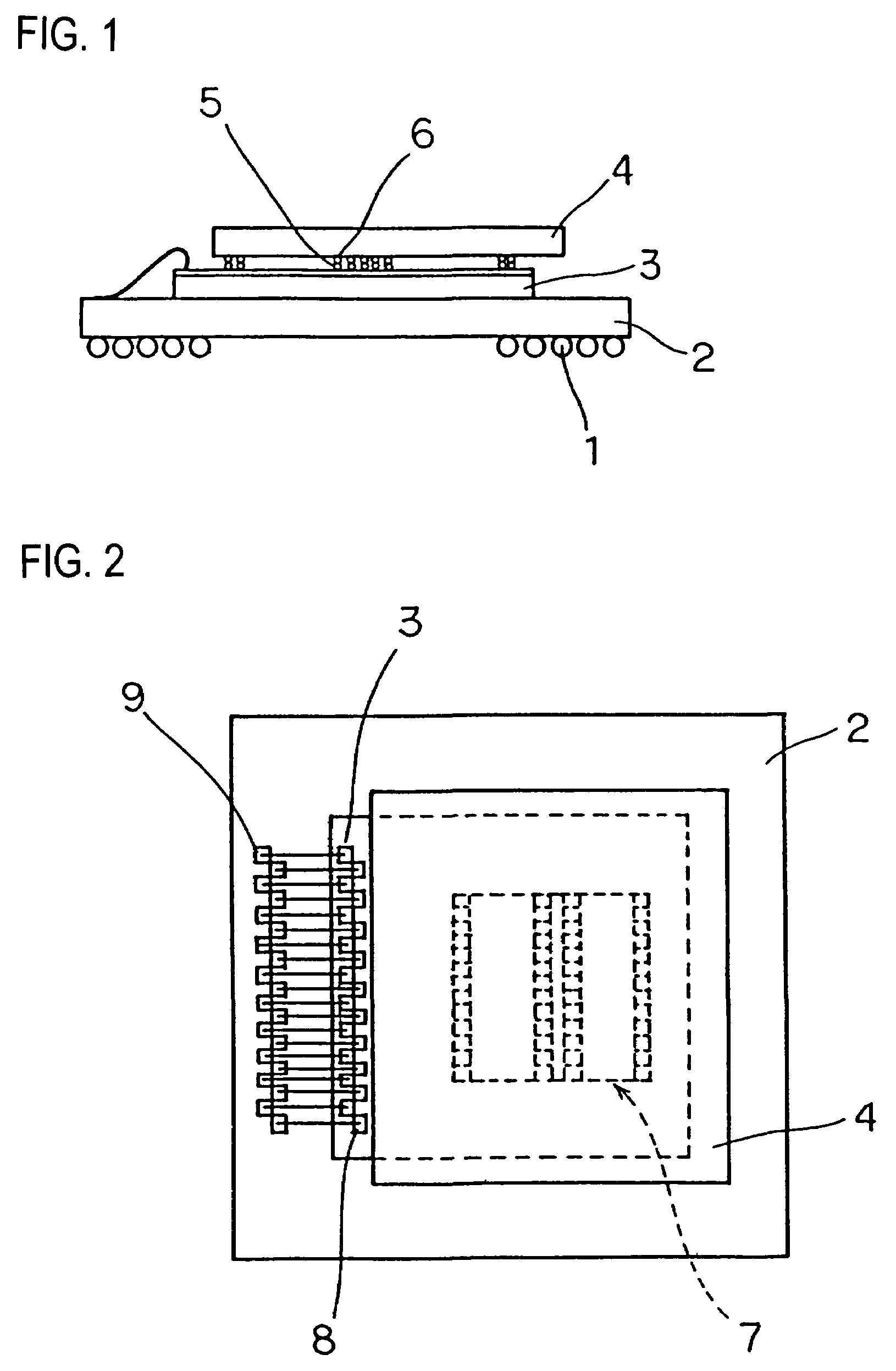

InactiveUS7145247B2Improve joint reliabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

The present invention is aimed at bonding a lower chip and an upper chip through bumps in a highly reliable manner, while ensuring a sufficient area for an external connection terminal region, by offsetting the upper chip to the lower chip. The substrate 2 has bumps 1 arranged on one surface thereof, and has a first chip 3 mounted on the other surface thereof. A second chip 4 is bonded to the first chip 3 through bumps 5, 6 while offsetting the second chip 4 to the first chip 3 in parallel. In the bonded state of the first chip 3 and the second chip 4, a part of the first chip 3 and a part of the second chip 4 are overlapped without aligning the centers of the both. The center of gravity of the second chip 4 falls inside a region surrounded by the outermost bumps between the first chip 3 and the second chip 4.

Owner:RENESAS ELECTRONICS CORP

Offset-bonded, multi-chip semiconductor device

InactiveUS20050121802A1Improve joint reliabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

The present invention is aimed at bonding a lower chip and an upper chip through bumps in a highly reliable manner, while ensuring a sufficient area for an external connection terminal region, by offsetting the upper chip to the lower chip. The substrate 2 has bumps 1 arranged on one surface thereof, and has a first chip 3 mounted on the other surface thereof. A second chip 4 is bonded to the first chip 3 through bumps 5, 6 while offsetting the second chip 4 to the first chip 3 in parallel. In the bonded state of the first chip 3 and the second chip 4, a part of the first chip 3 and a part of the second chip 4 are overlapped without aligning the centers of the both. The center of gravity of the second chip 4 falls inside a region surrounded by the outermost bumps between the first chip 3 and the second chip 4.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method of manufacturing the same

ActiveUS8390117B2Highly reliable three-dimensional mounting structureOptimizationInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsEngineeringSemiconductor

A semiconductor device capable of realizing highly reliable three-dimensional mounting, and a method of manufacturing the same, are provided. A projected electrode 9 is formed in a region outside of an element mounting region of a substrate 5. The projected electrode 9 includes a protruding portion that protrudes from the front face of a molding resin portion 10. The distal end of the protruding portion is a flat face 13. In addition, a portion of the projected electrode 9 whose cross section is larger than the protruding portion is positioned inside the molding resin portion 10.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

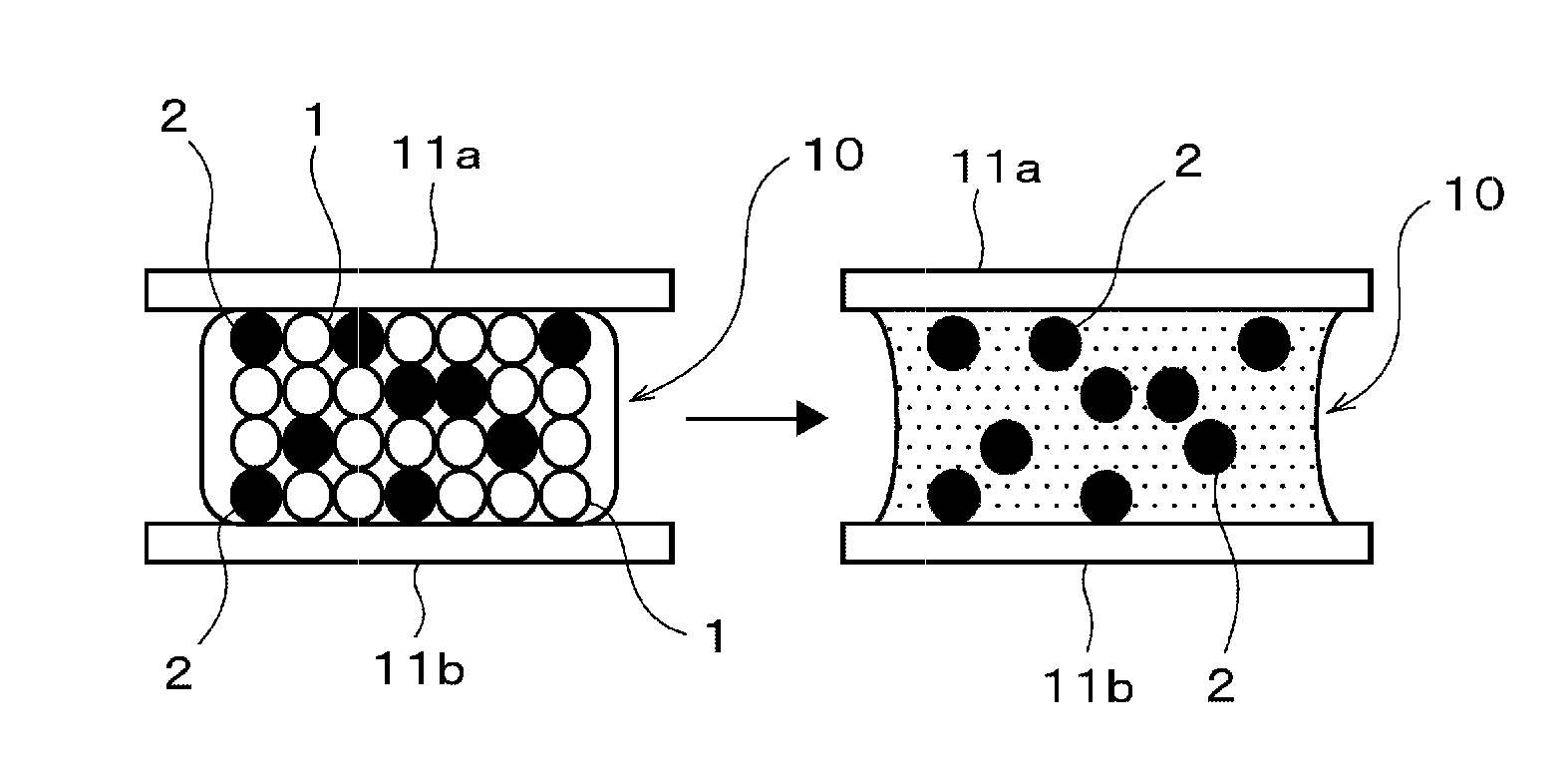

Electronic device and method for producing the same

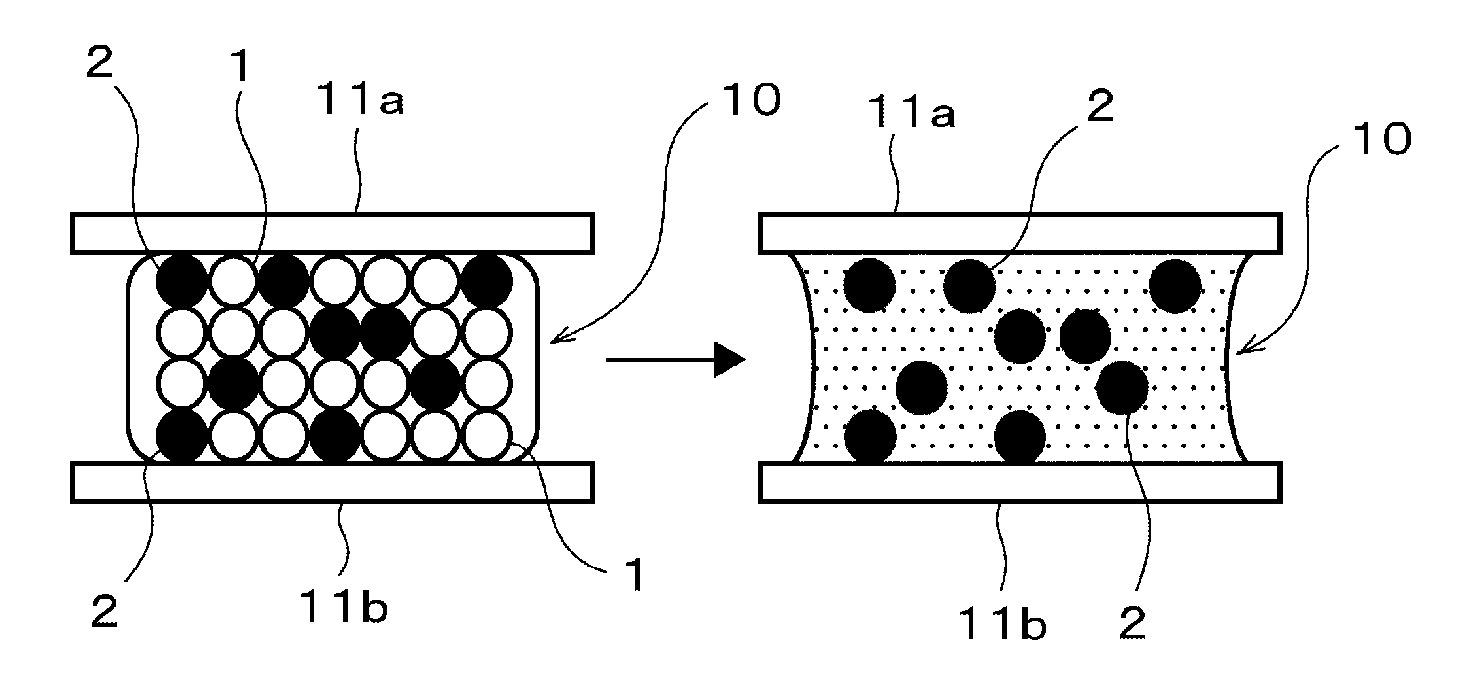

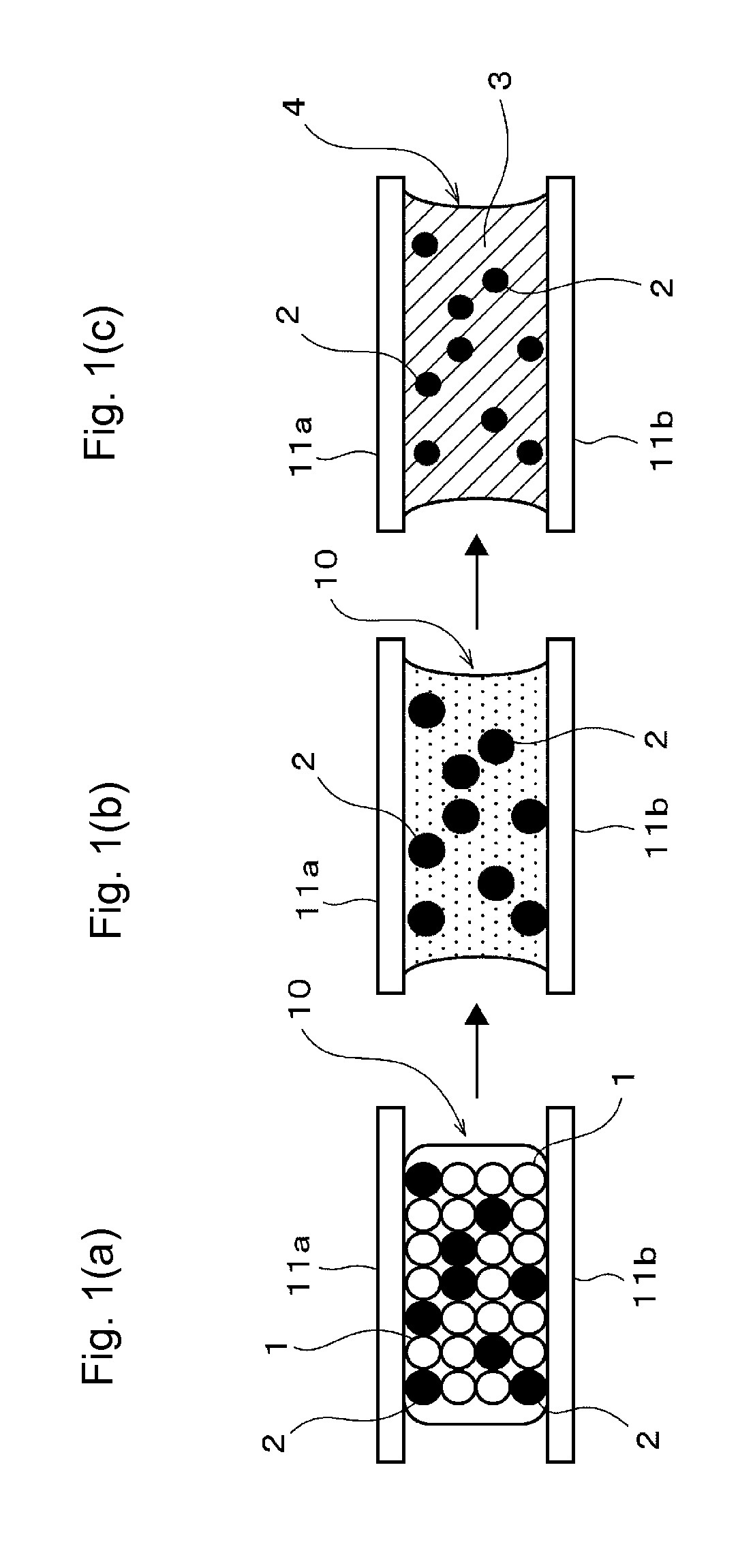

InactiveUS20050150684A1Improve bonding reliabilityLow production costMaterial nanotechnologyPrinted circuit assemblingNanometreElectrical and Electronics engineering

An electronic device includes a plurality of components, nanoparticles to bond the components, and a receiving layer for holding the nanoparticles, the receiving layer being disposed on at least one of the bonded components. The electronic device may further include an electrode disposed on at least one of the plurality of components. The receiving layer is disposed on the surface of the electrode. Conductive particles etc. are mixed in the receiving layer.

Owner:138 EAST LCD ADVANCEMENTS LTD

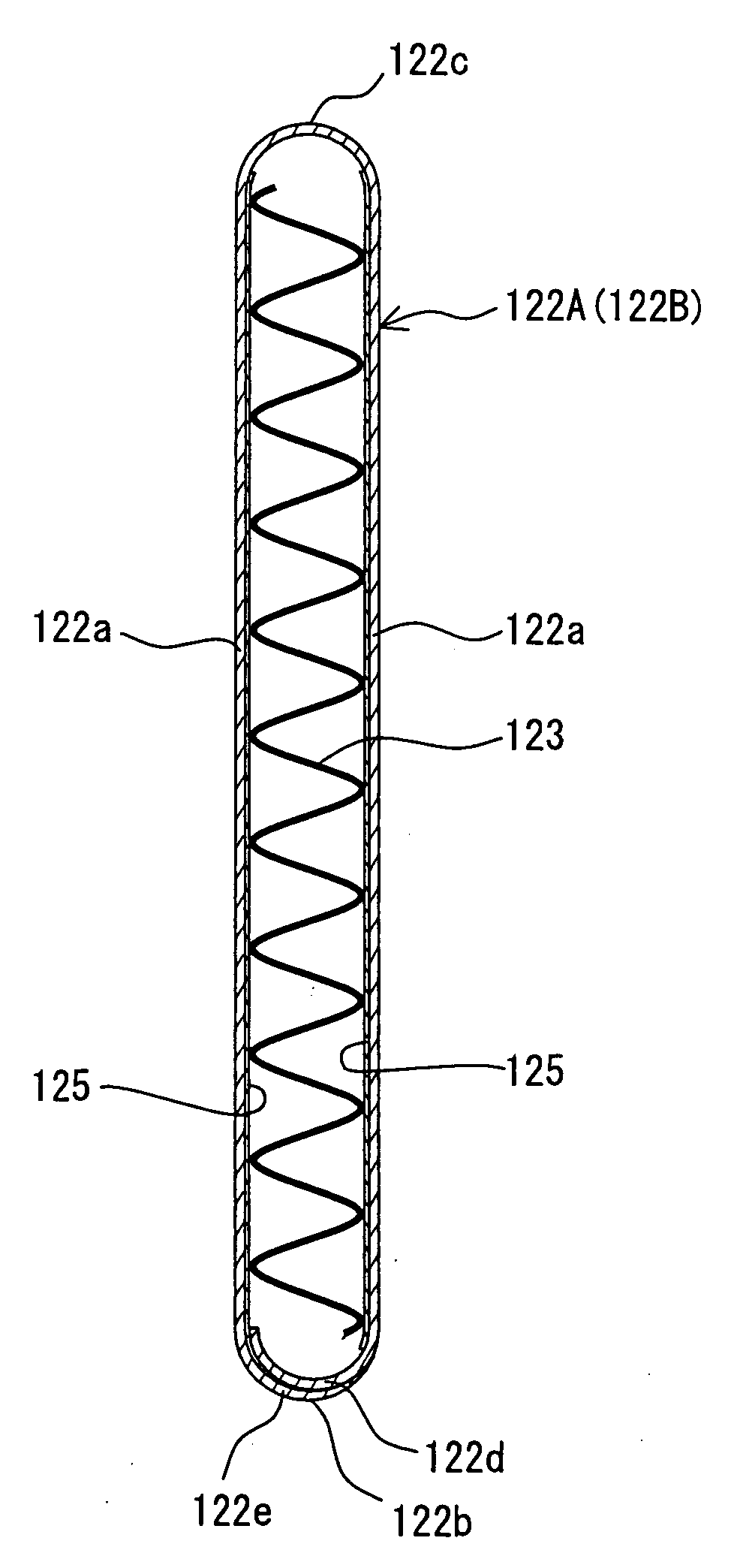

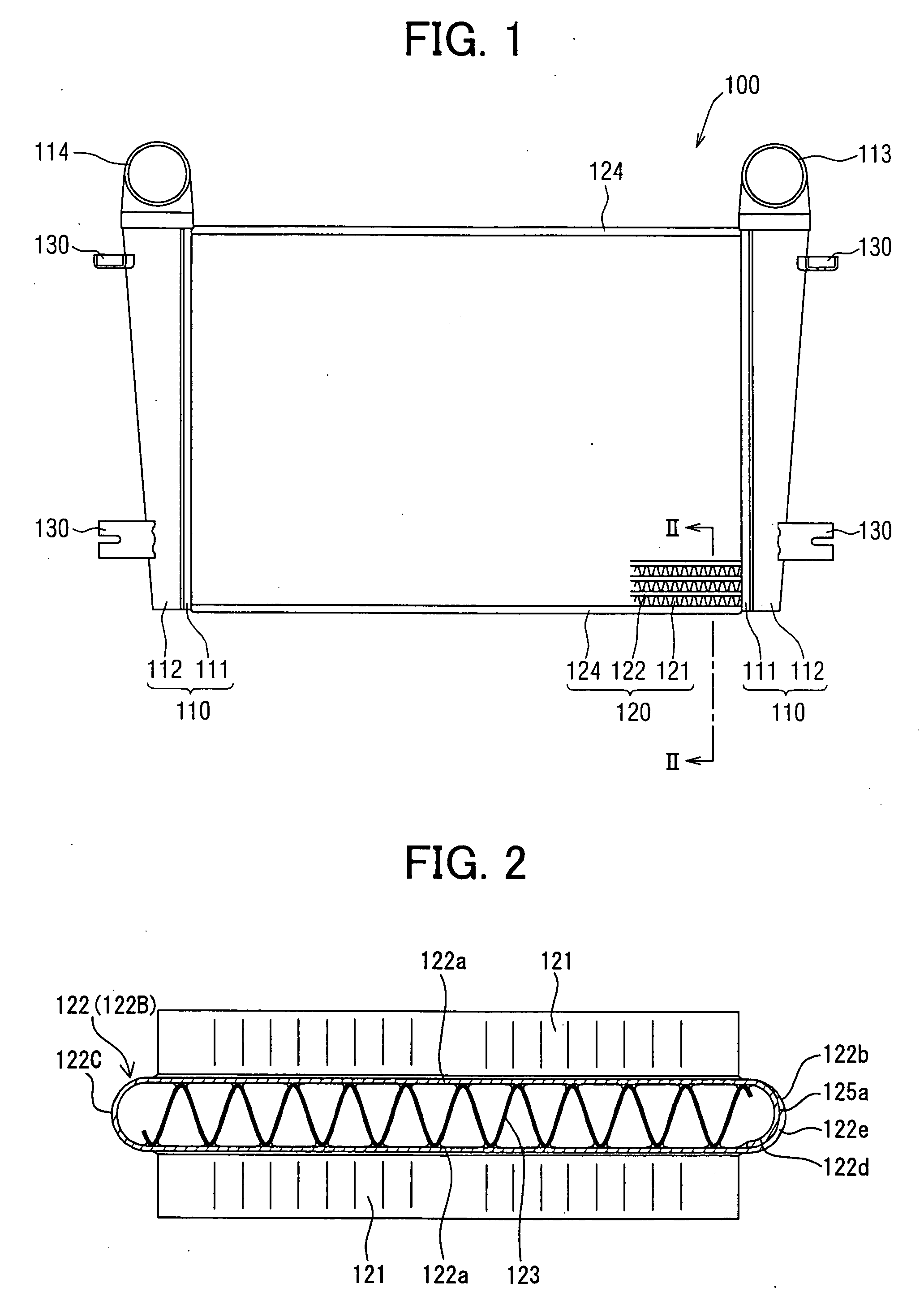

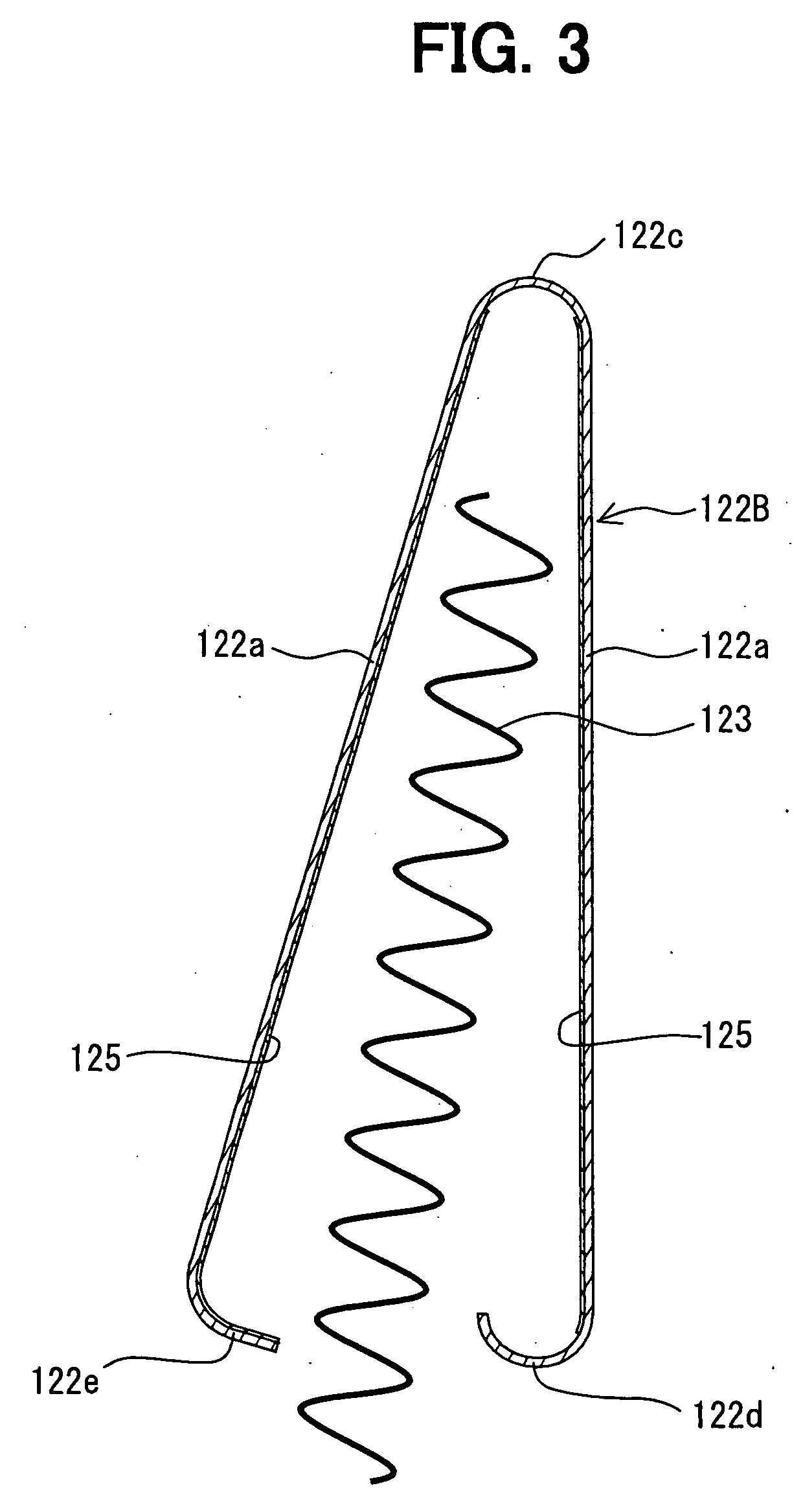

Heat exchanger and method of manufacturing the same

InactiveUS20060086491A1Improve joint reliabilityMaintain performanceSoldering apparatusStationary conduit assembliesEllipseEngineering

A heat exchanger includes at least one tube provided with an inner fin in a fluid passage which is defined by the tube therein and has a substantially ellipse-shaped cross section. A plate member for constructing the tube has two edge portions, which overlap each other and are integrally joined at a single joint disposed at a major-axis direction end of the tube. The inner fin is arranged in the tube before the forming of the joint, thus improving an arrangement performance of the inner fin. Moreover, there exists the single joint positioned at the one end of the tube so that a joint reliability of the tube is enhanced.

Owner:DENSO CORP

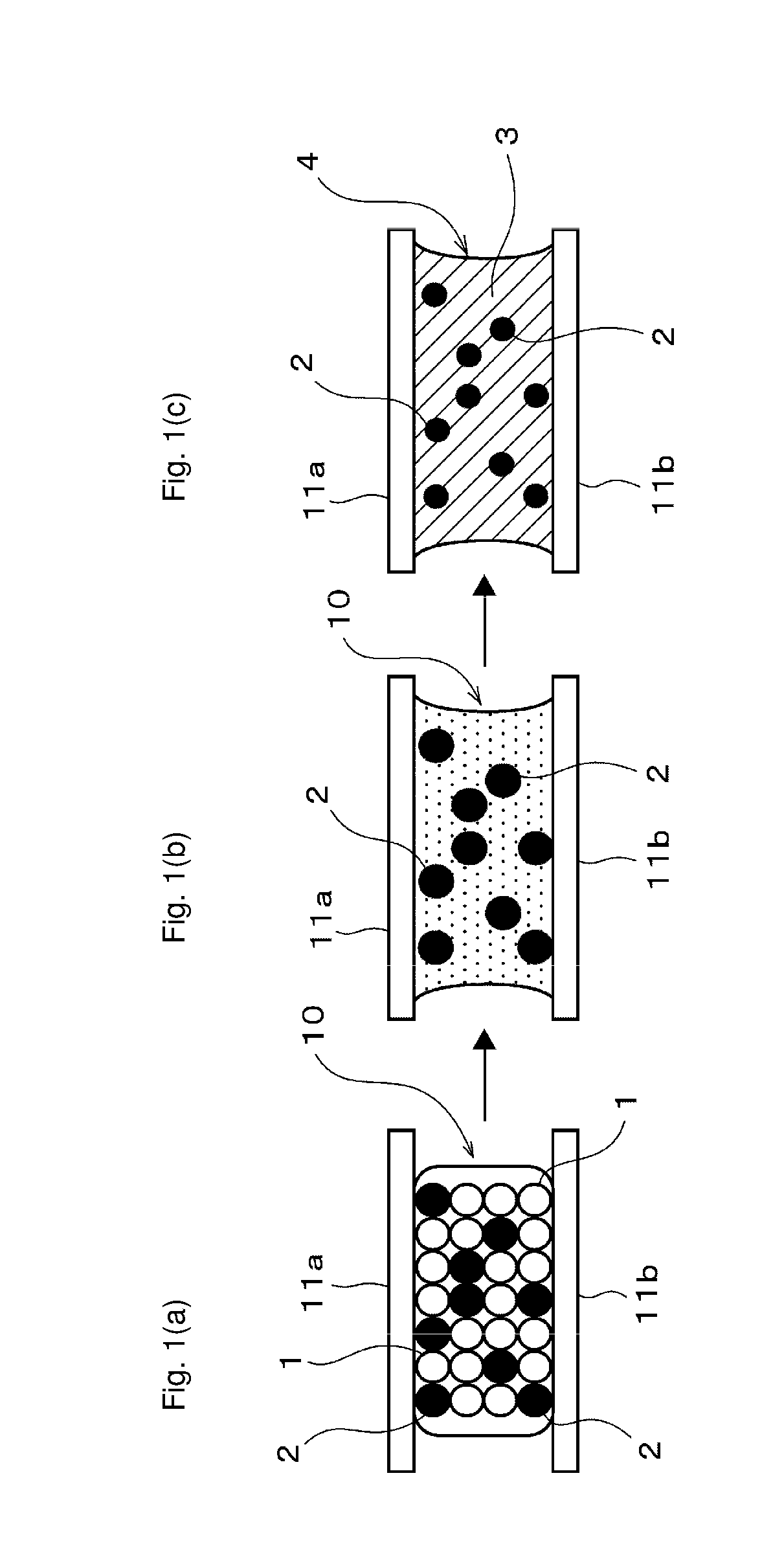

Conductive material, bonding method using the same, and bonded structure

ActiveUS20130233618A1High strengthShort timeCooking-vessel materialsTransportation and packagingAlloyConductive materials

A conductive material that includes a metal component consisting of a first metal and a second metal having a melting point higher than that of the first metal, wherein the first metal is Sn or an alloy containing 70% by weight or more of Sn, and the second metal is a metal or alloy which forms an intermetallic compound having a melting point of 310° C. or higher with the first metal and has a lattice constant difference of 50% or greater between itself and the intermetallic compound generated at the circumference of the second metal.

Owner:MURATA MFG CO LTD

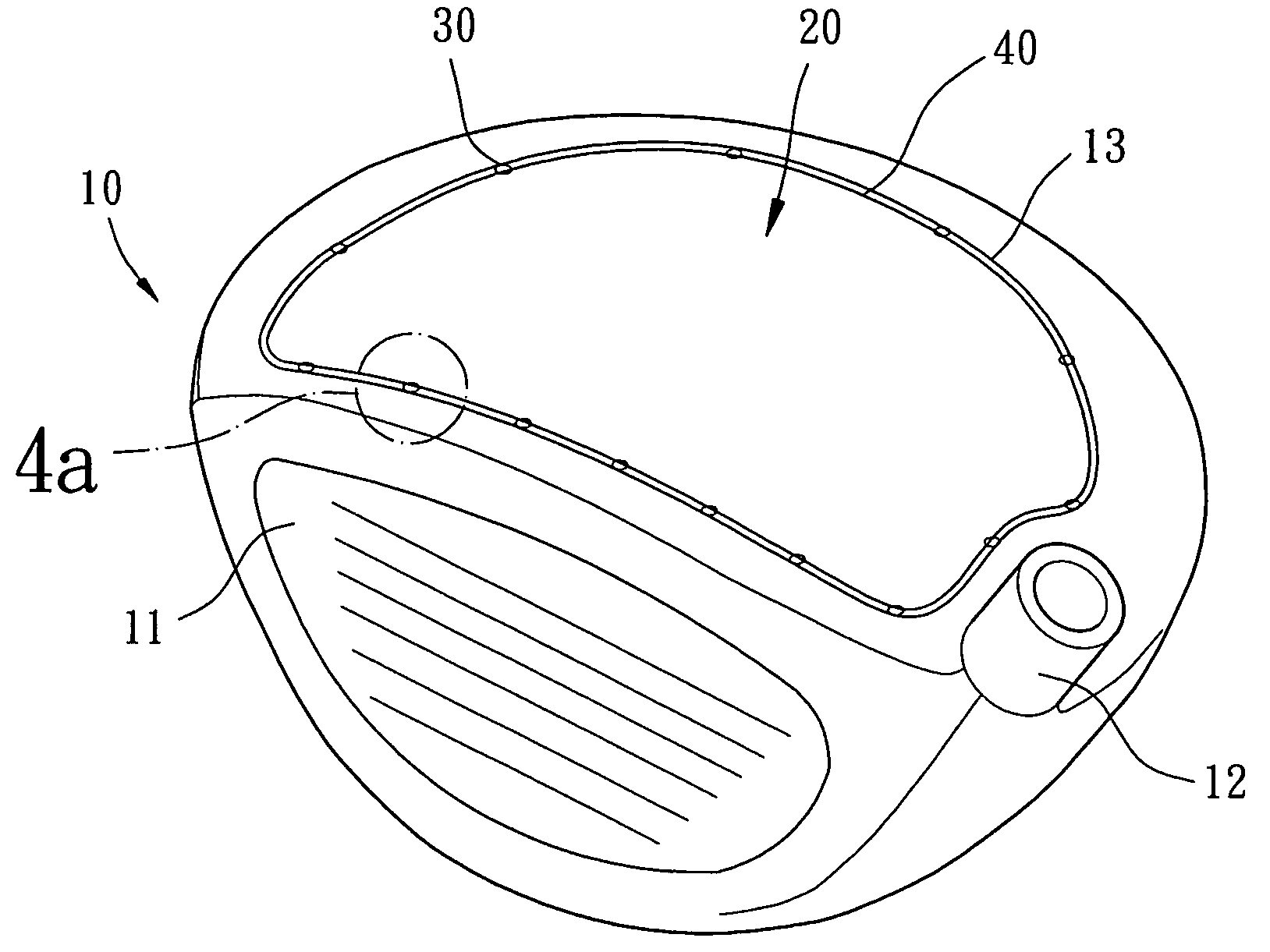

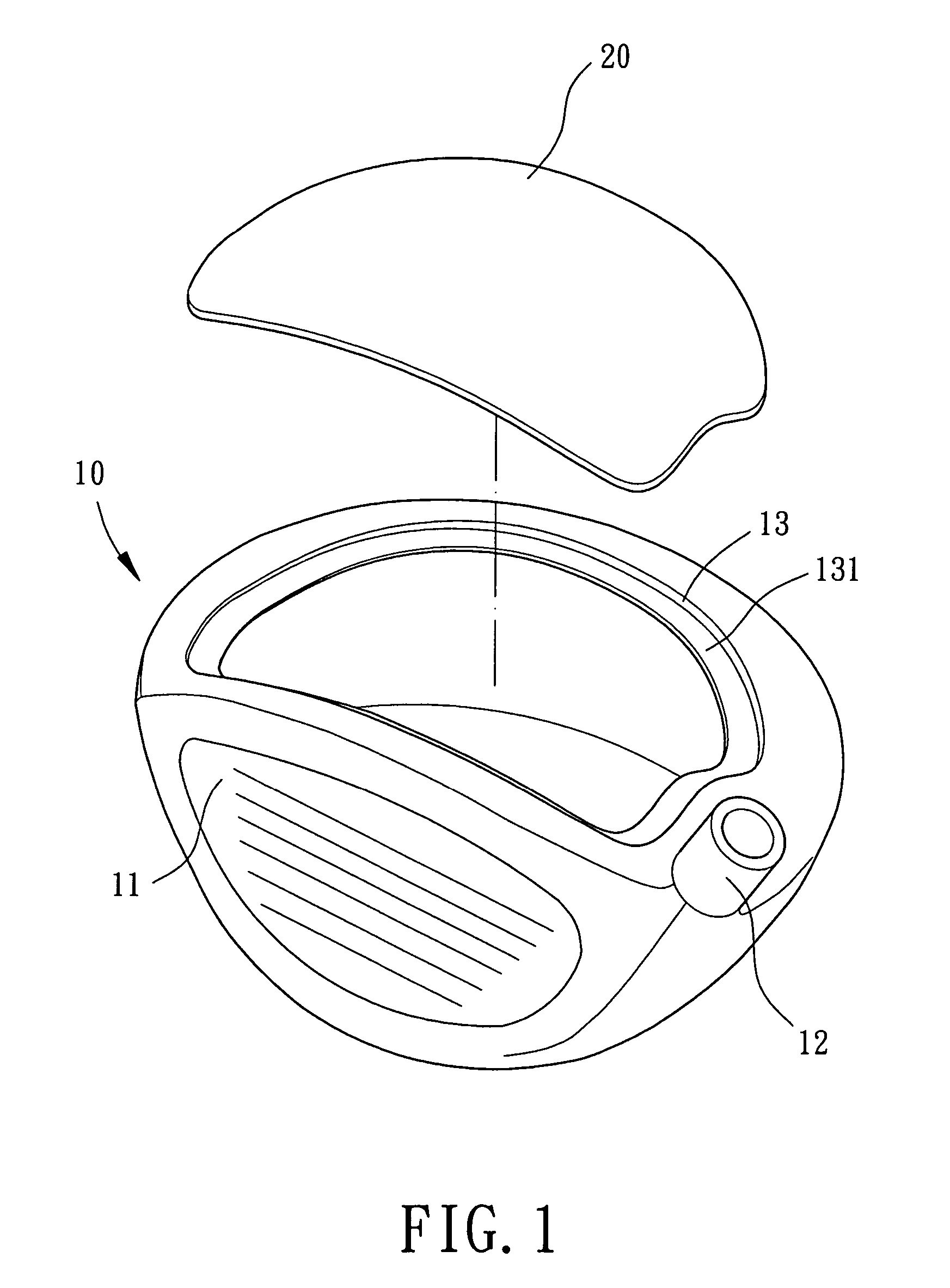

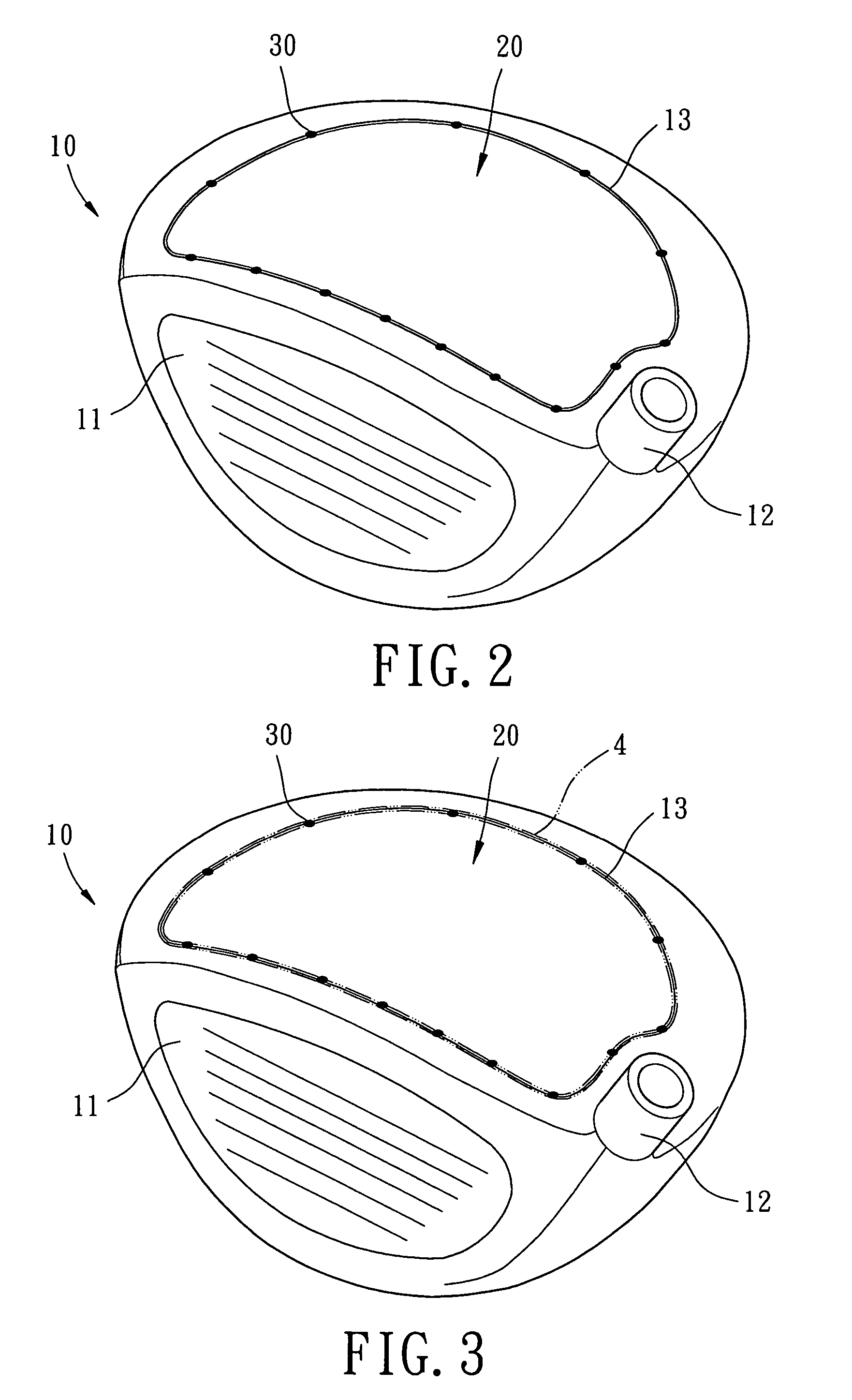

Golf club head and manufacturing method therefor

InactiveUS7396291B2Improve joint reliabilitySimple structureGolf clubsRacket sportsEngineeringGolf Ball

A golf club head includes a body having at least one assembling opening and at least one cover plate mounted in the at least one assembling opening. A plurality of spaced spot welding points are provided along a joint area between the cover plate and the perimeter wall of the assembling opening. A brazing bonding portion is located between a pair of the spaced spot welding points adjacent to each other. The spot welding points and the brazing bonding portions securely fix the cover plate in the assembling opening to improve the bonding reliability.

Owner:FUSHENG PRECISION

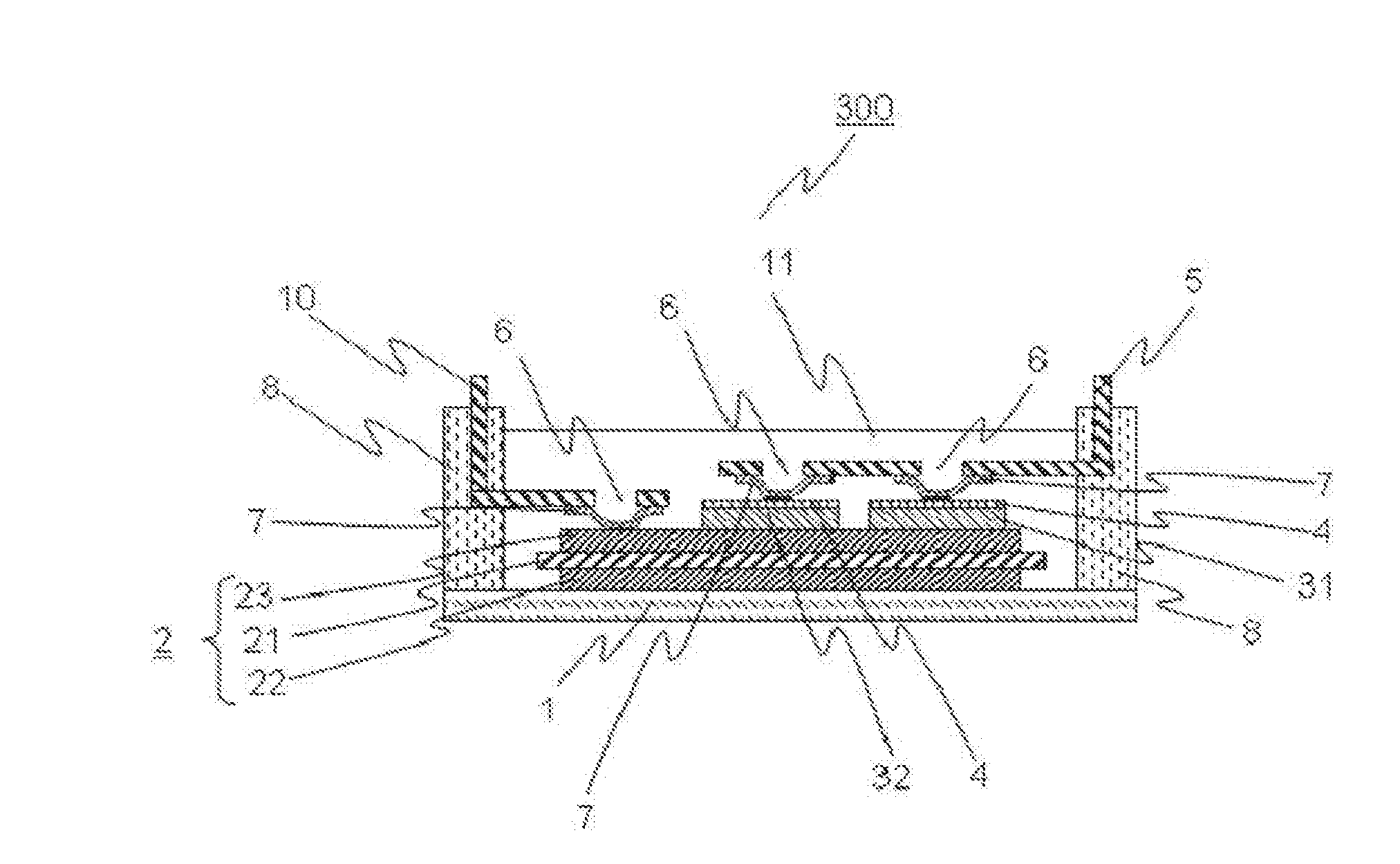

Semiconductor device and method for manufacturing semiconductor device

InactiveUS7829992B2Inhibition is effectiveImprove joint reliabilitySemiconductor/solid-state device detailsSolid-state devicesSurface mountingSemiconductor chip

A semiconductor device (100) comprises a first resin substrate (101) on which a first semiconductor chip (125) is mounted a surface thereof; a second resin substrate (111) on which a second semiconductor chip (131) is mounted on a surface thereof; and a resin base material (109), joined to a front surface of the first resin substrate (101) and to a back surface of the second resin substrate (111), so that these surfaces are electrically connected. The resin base material (109) is disposed in a circumference of the first resin substrate (101) in the surface of the first resin substrate (101). Further, the first semiconductor chip (125) is disposed in a space section provided among the first resin substrate (101), the second resin substrate (111) and the resin base material (109) in the surface of the first resin substrate (101).

Owner:SUMITOMO BAKELITE CO LTD

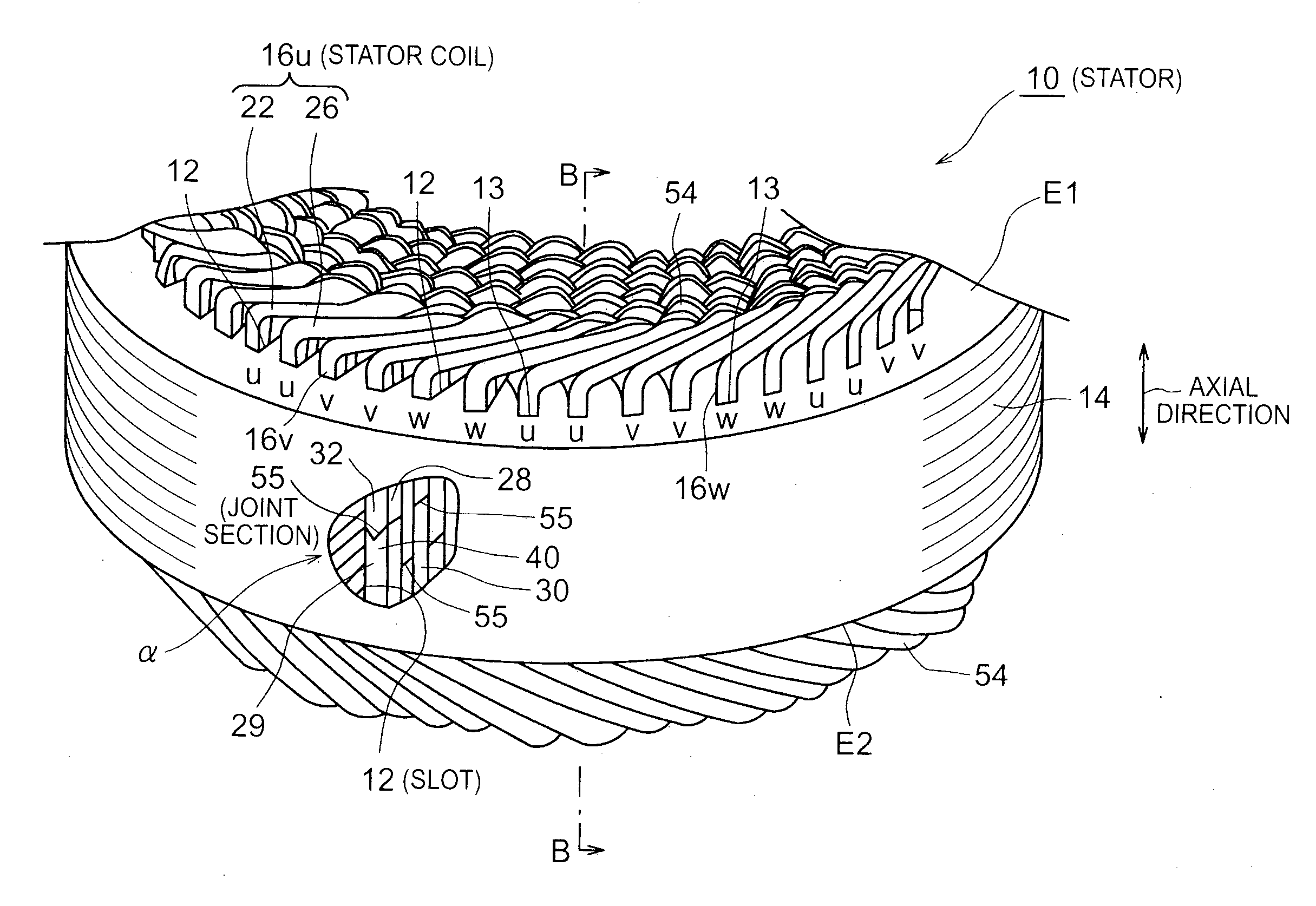

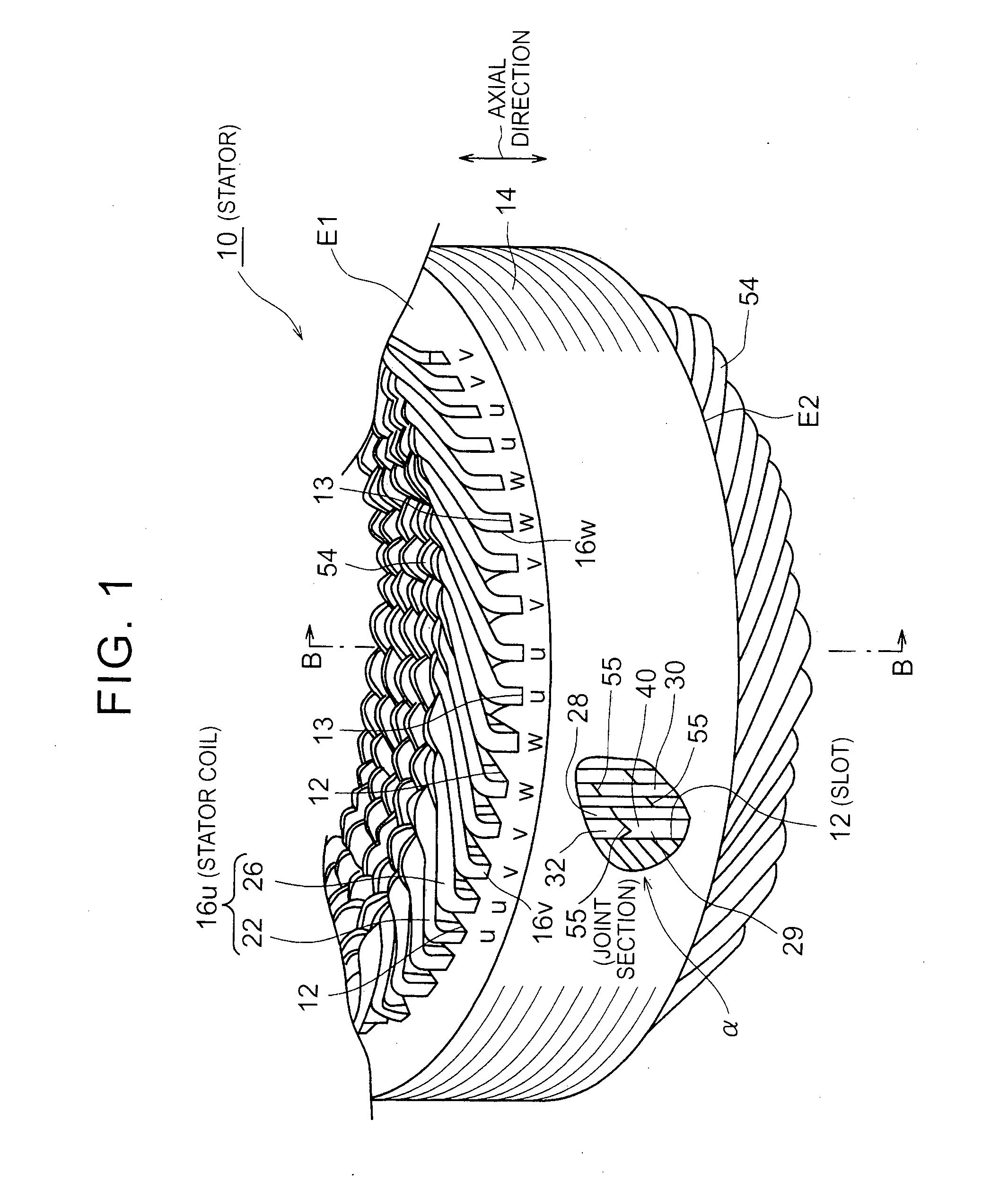

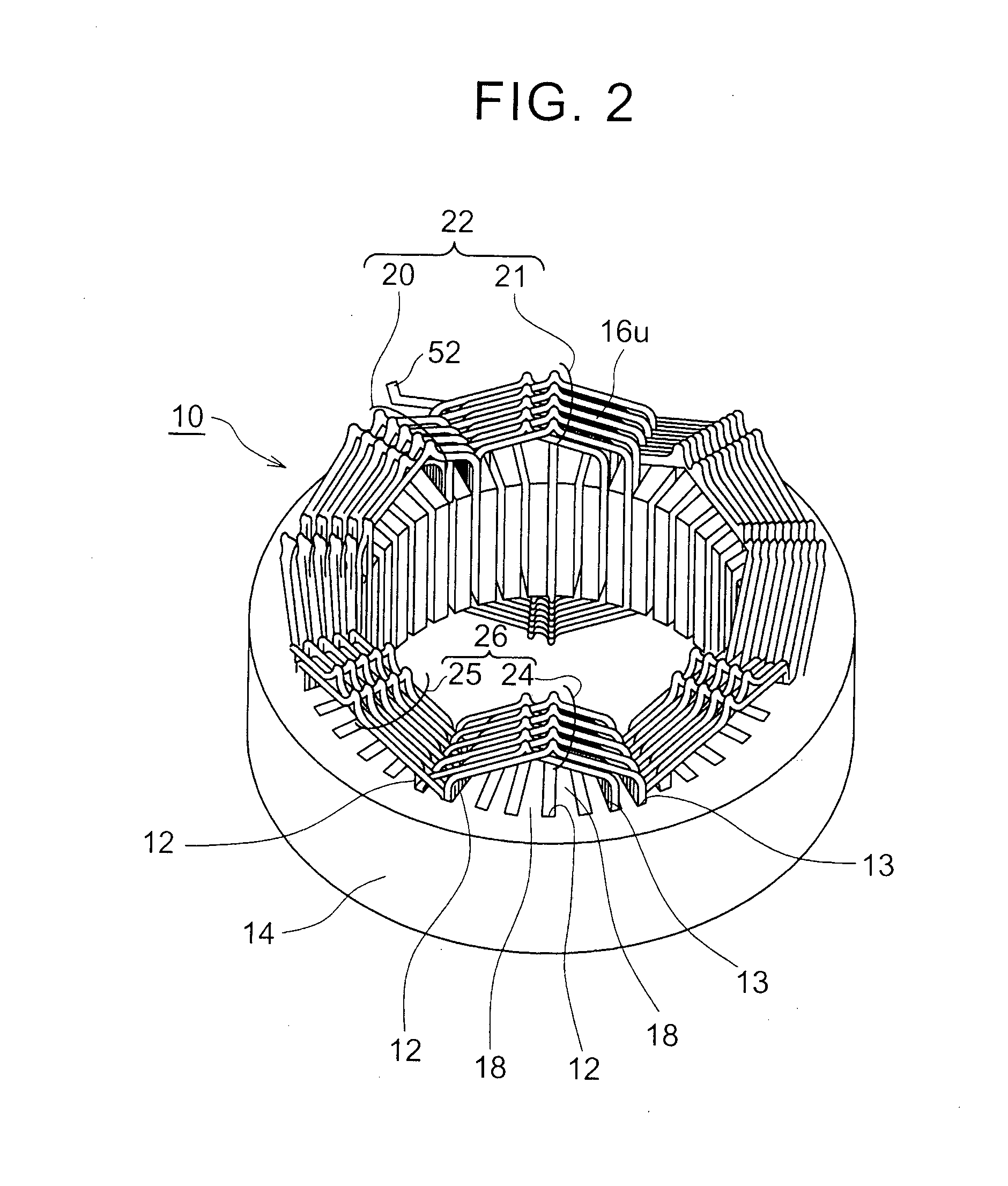

Stator for rotary electric machine and method for manufacturing the same

InactiveUS20160172919A1Improve joint reliabilitySmall sizeSynchronous machinesAsynchronous induction motorsElectrical conductorElectric machine

Stator for rotary electric machine has stator core and stator coil. The stator core has plural slots. The stator coil has a one-side conductor segment, a first other-side conductor segment, and a second other-side conductor segment. In the one-side conductor segment, a first leg and a second leg are inserted in first and second slots from one axial end side of the stator core. In the first other-side conductor segment, a third leg is inserted in the first slot from another axial end side of the stator core. In the second other-side conductor segment, a fourth leg is inserted in the second slot from the other axial end side of the stator core. The stator coil is formed such that the opposing legs are joined in each of the slots and a plurality of the one-side conductor segment and a plurality of the other-side conductor segment are sequentially joined.

Owner:TOYOTA JIDOSHA KK

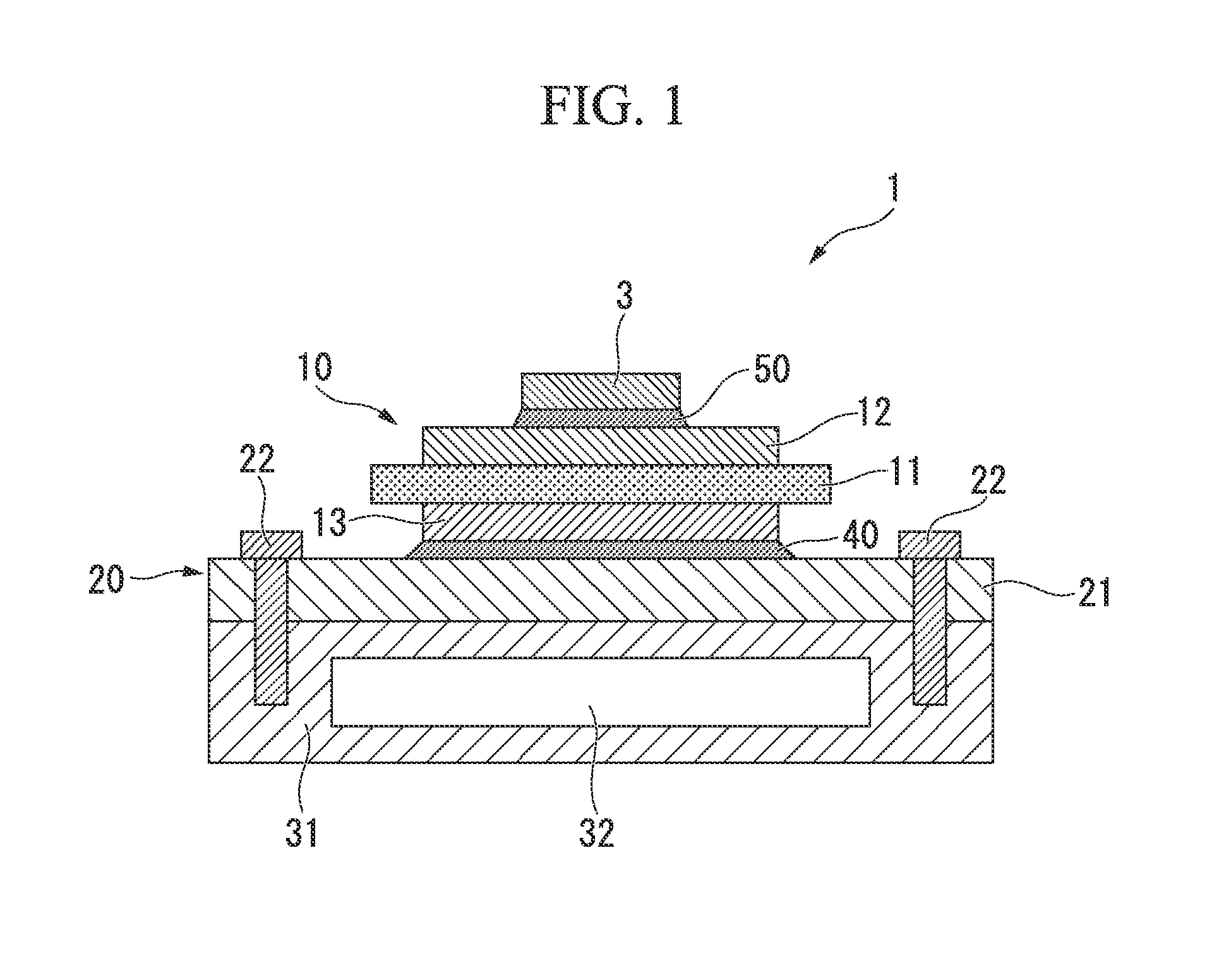

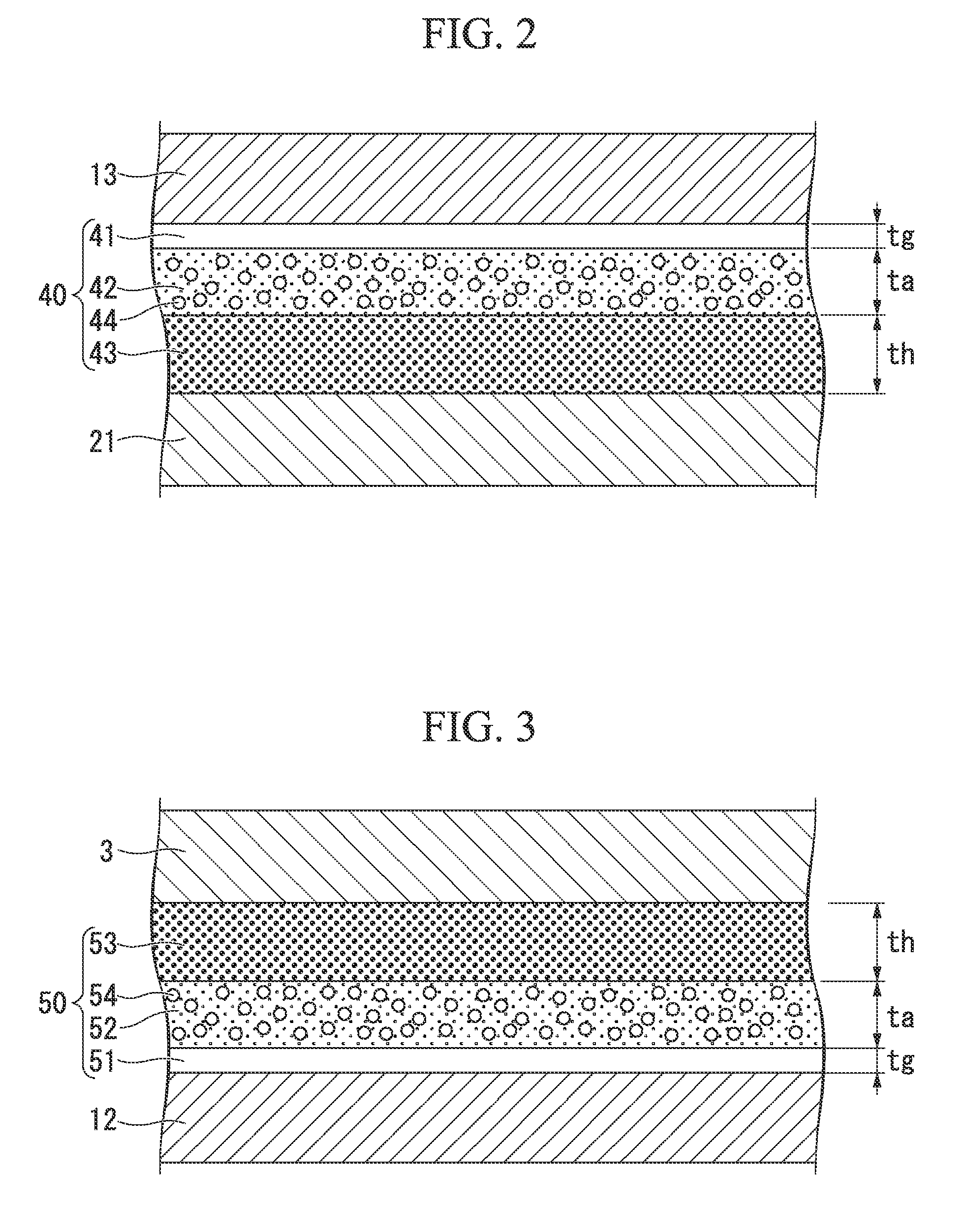

Solder joint structure, power module, power module substrate with heat sink and method of manufacturing the same, and paste for forming solder base layer

ActiveUS20150035137A1InhibitionImprove joint reliabilitySemiconductor/solid-state device detailsSolid-state devicesPower cycleSolder paste

There are provided a solder joint structure, a power module using the joint structure, a power module substrate with a heat sink and a method of manufacturing the same, as well as a solder base layer forming paste which is disposed and fired on a metal member to thereby react with an oxide film generated on the surface of the metal member and form the solder base layer on the metal member, capable of suppressing the occurrence of waviness and wrinkles on the surface of the metal member even at the time of loading the power cycle and heat cycle and improving the joint reliability with a joint member.

Owner:MITSUBISHI MATERIALS CORP

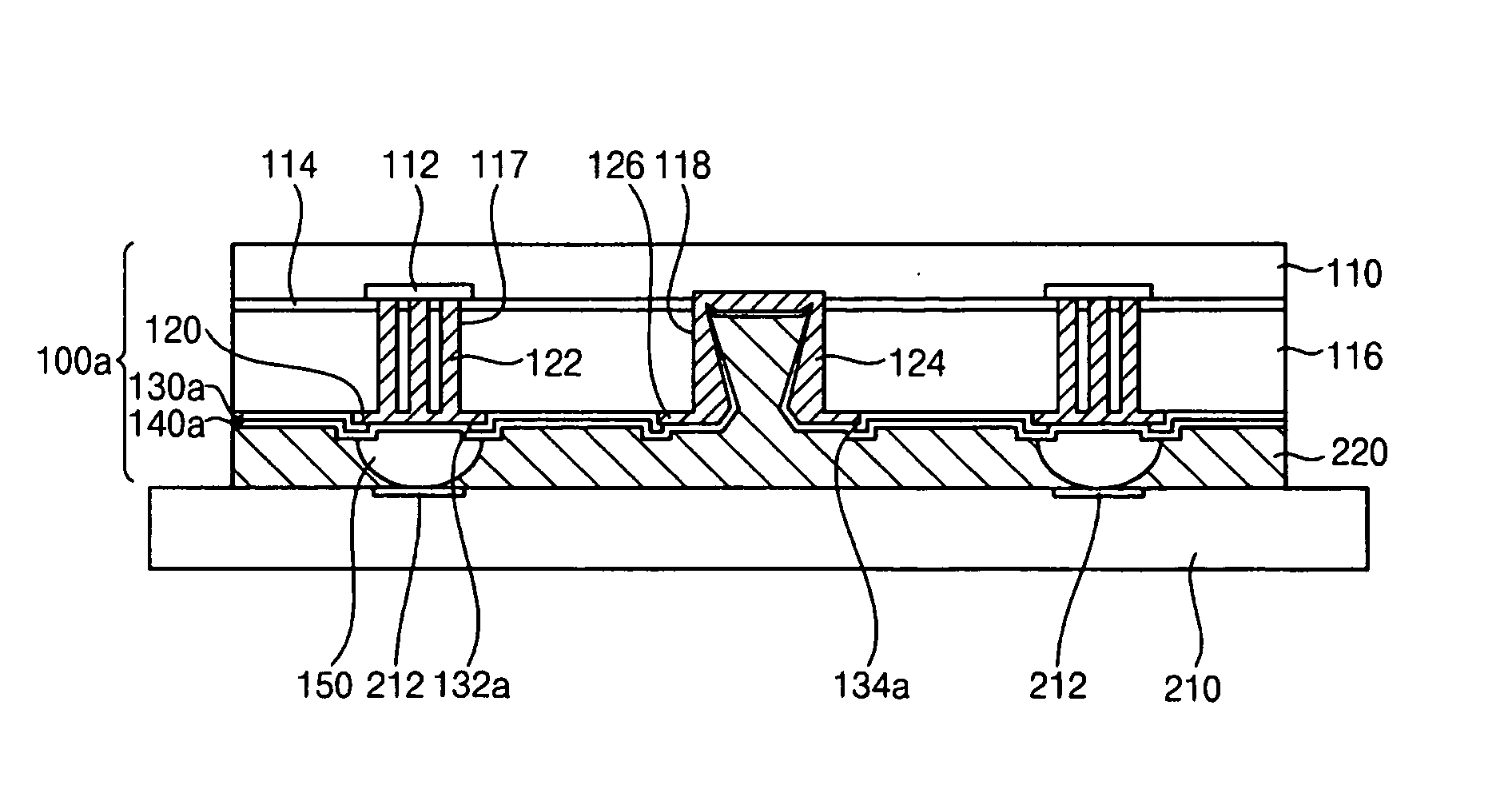

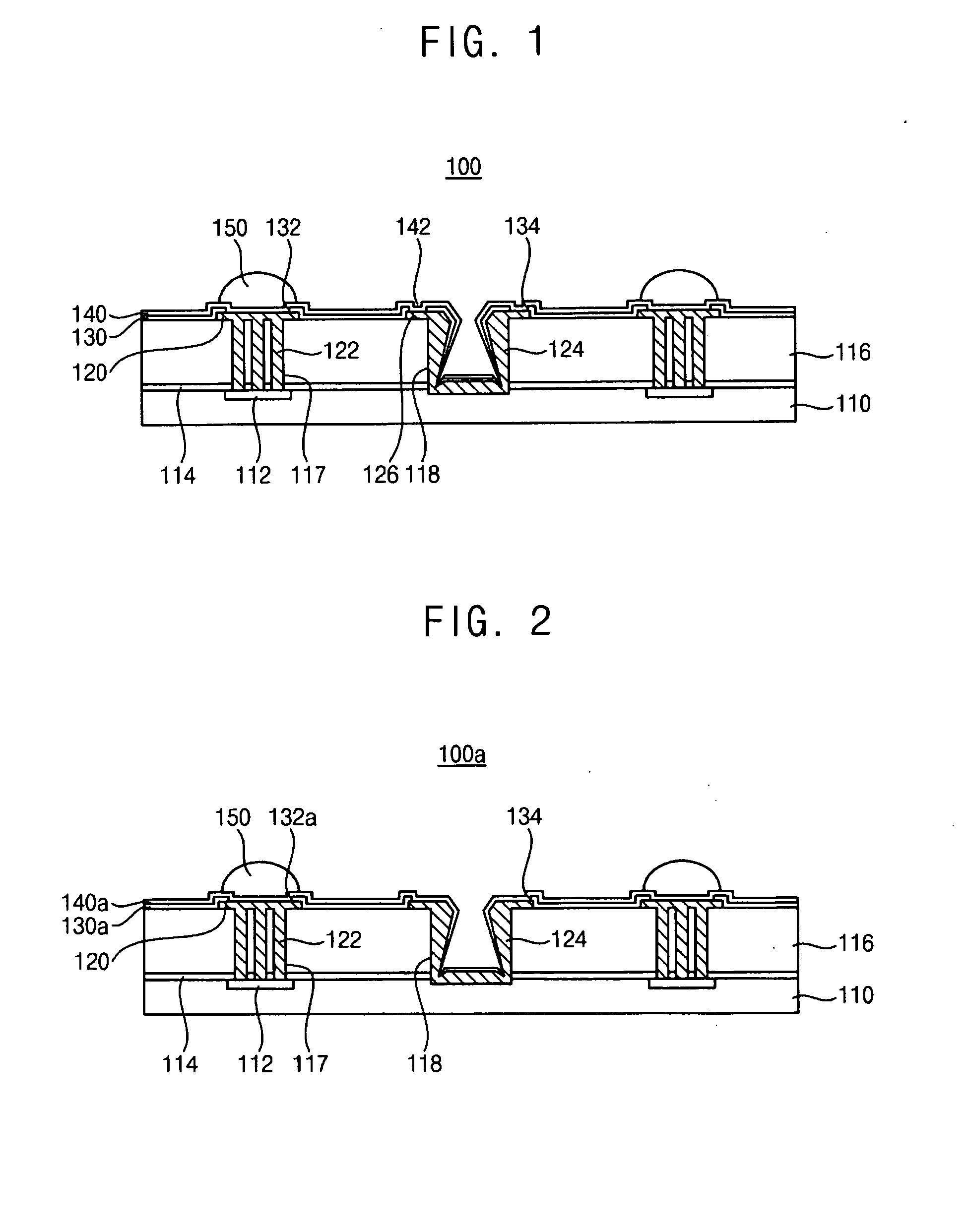

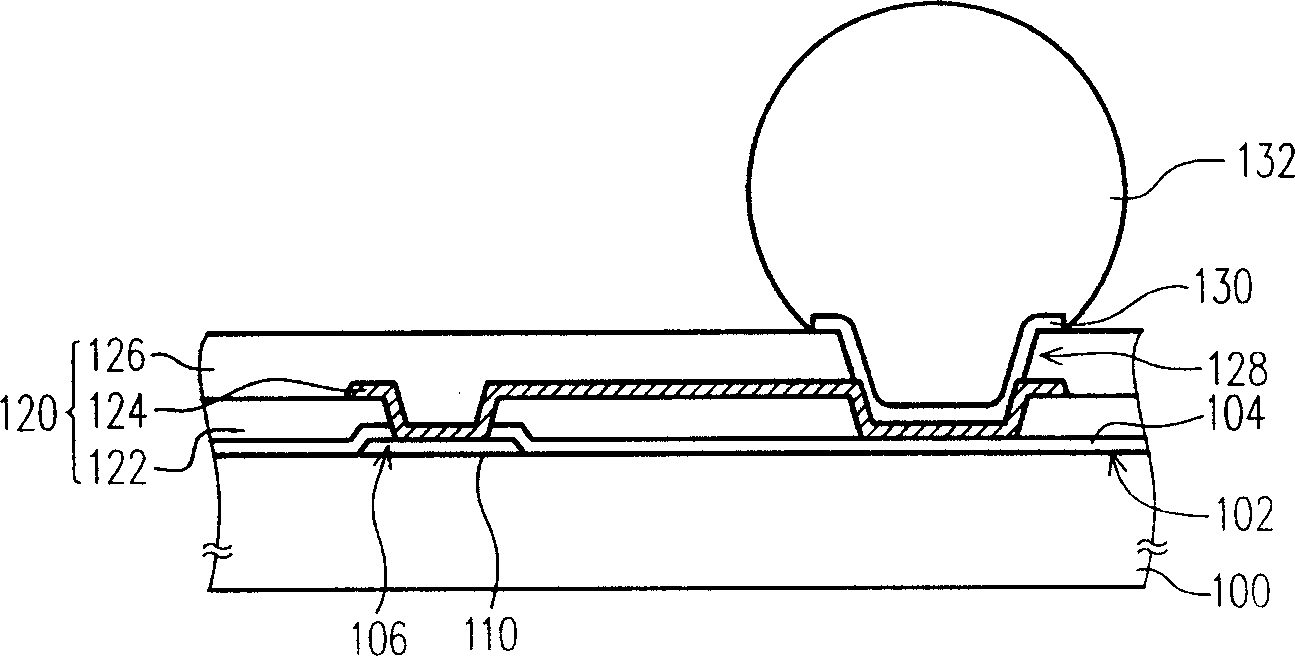

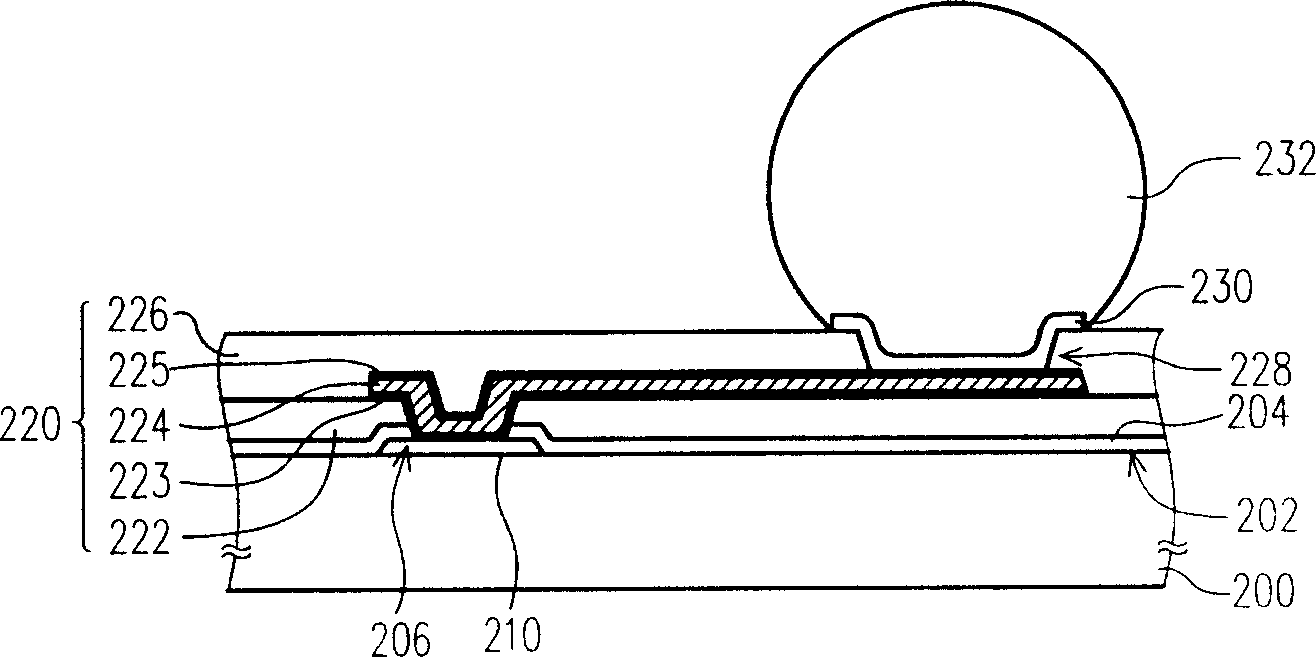

Semiconductor device, method of manufacturing the semiconductor device, flip chip package having the semiconductor device and method of manufacturing the flip chip package

ActiveUS20090057922A1Uniform sizeImprove joint reliabilitySemiconductor/solid-state device detailsSolid-state devicesUnder bump metallurgyEngineering

A semiconductor device can include a semiconductor chip, a protective layer pattern, an under bump metallurgy (UBM) layer, and conductive bumps. The semiconductor chip can include a pad and a guard ring. The protective layer pattern can be formed on the semiconductor chip to expose the pad and the guard ring. The UBM layer can be formed on the protective layer and can directly make contact with the pad and the guard ring. The conductive bumps can be formed on a portion of the UBM layer on the pad. Thus, the UBM layer and the guard ring can directly make contact with each other, so that a uniform current can be provided to the UBM layer on the pad regardless of a thick difference of different portions of the UBM layer.

Owner:SAMSUNG ELECTRONICS CO LTD

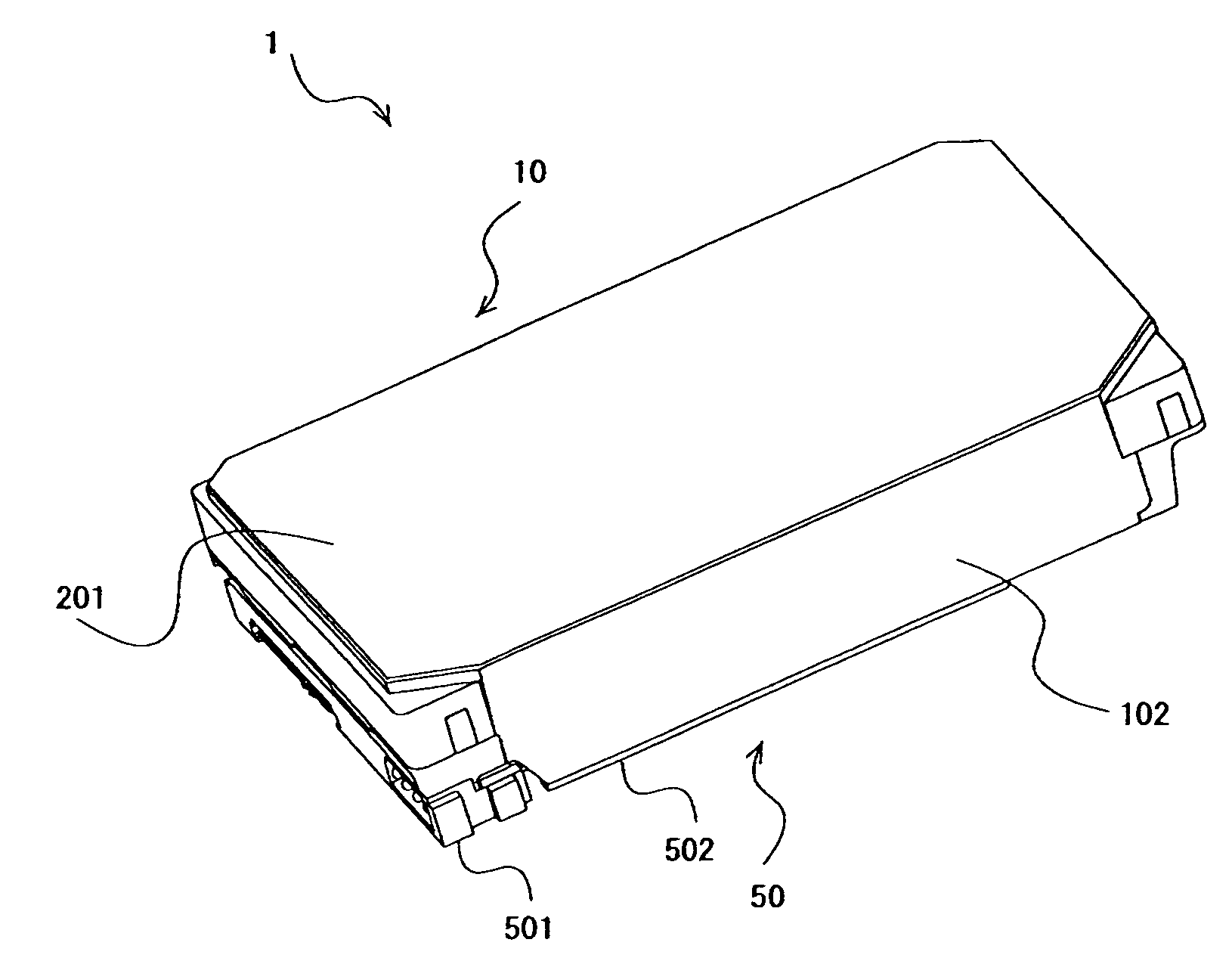

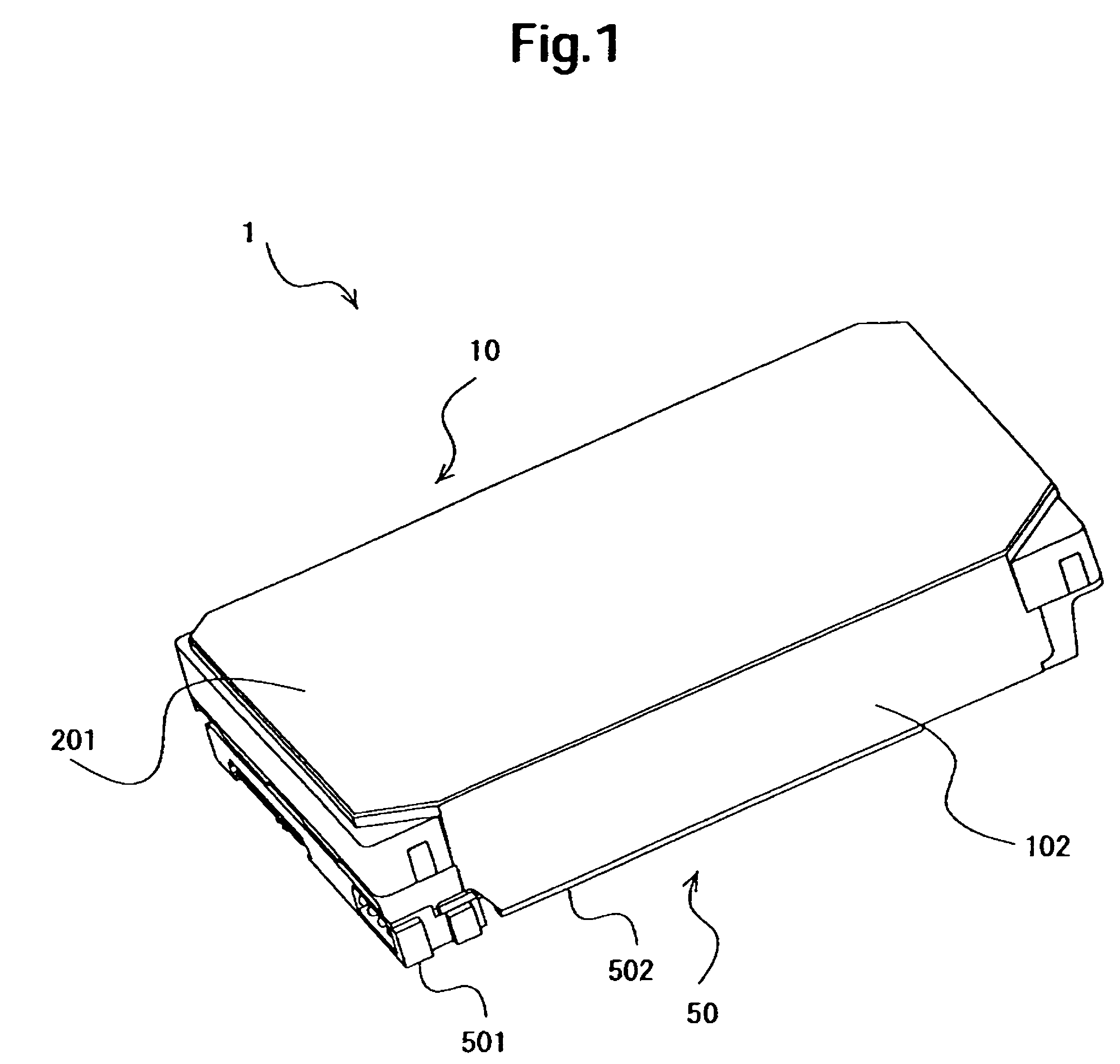

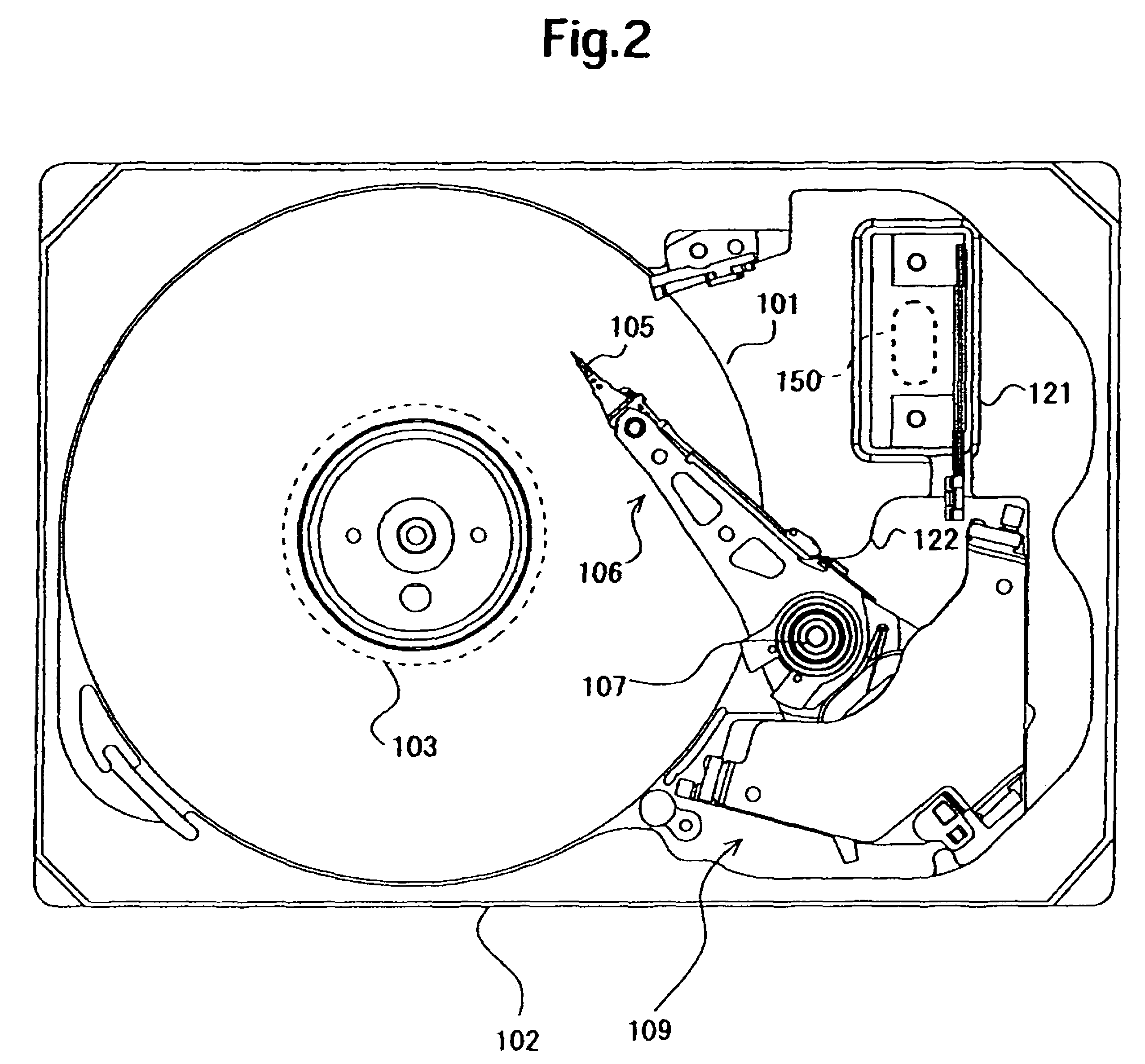

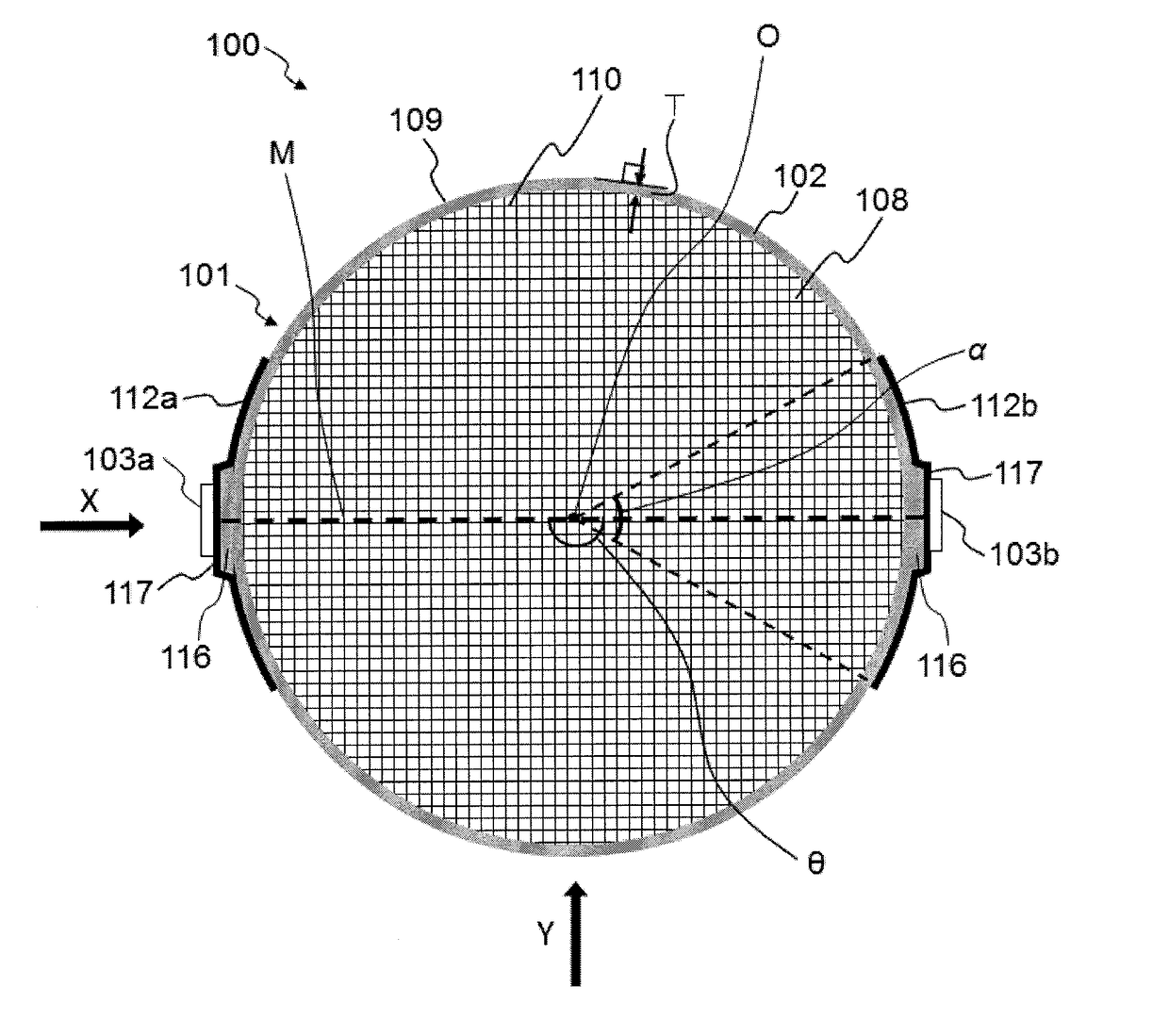

Disk drive device

ActiveUS7872836B2Improve joint reliabilityImprove thermal stressUndesired vibrations/sounds insulation/absorptionRecord information storageInterior spaceEngineering

In a disk drive device in which low-density gas is sealed, embodiments of the present invention help to improve joint reliability at a solder joint section between a feedthrough and an enclosure with respect to stress applied by deformation due to changes in temperature environment in use. According to one embodiment, helium gas is sealed in an interior space of an HDD. A feedthrough is solder jointed to a feedthrough mounting surface of a base. At a part with relatively large thermal stress, a width of the feedthrough mounting surface is increased, and at a part with relatively small thermal stress, a width of the feedthrough mounting surface is decreased. This prevents a crack penetrating path from being generated at the solder joint section due to the thermal stress and prevents the solder joint section from contacting pins.

Owner:WESTERN DIGITAL TECH INC

Bonding structure and method for bonding members

InactiveUS20050230042A1High bonding reliabilityAvoid damageTransportation and packagingSemiconductor/solid-state device detailsNanoparticleEngineering

Owner:SEIKO EPSON CORP

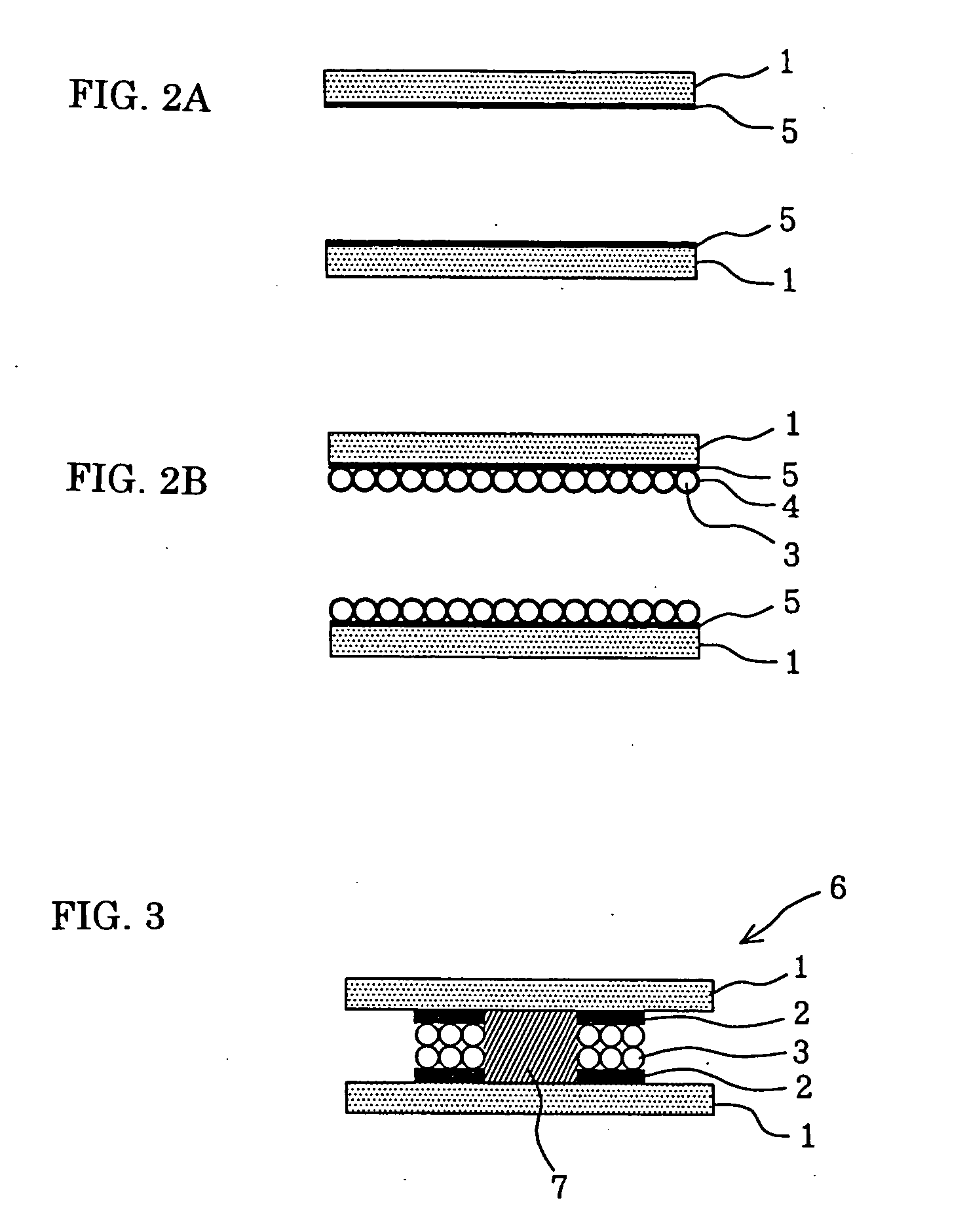

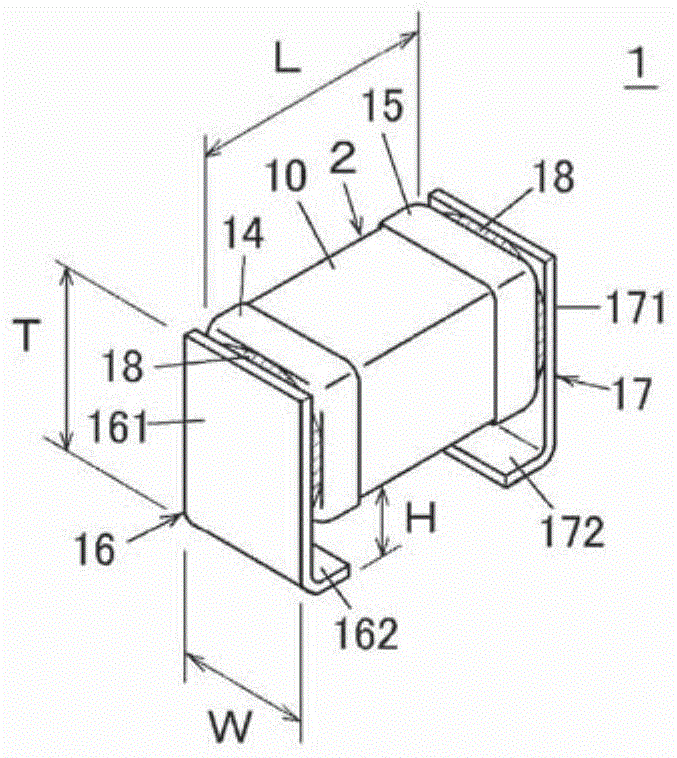

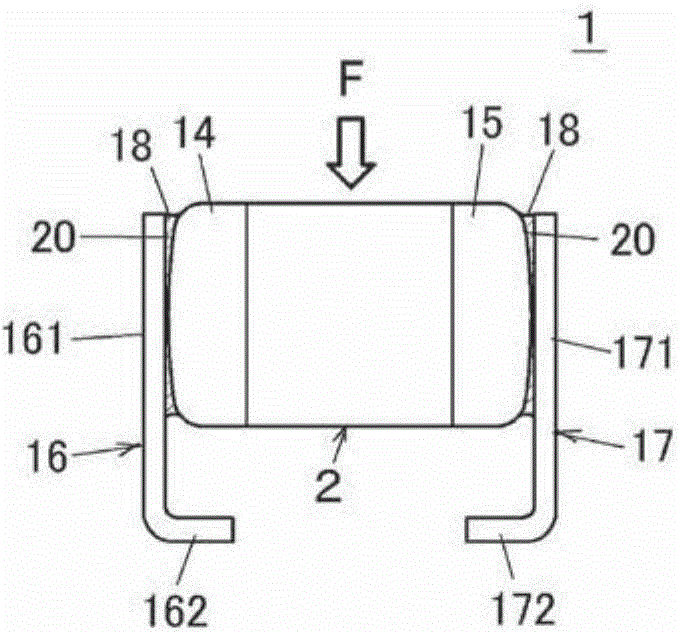

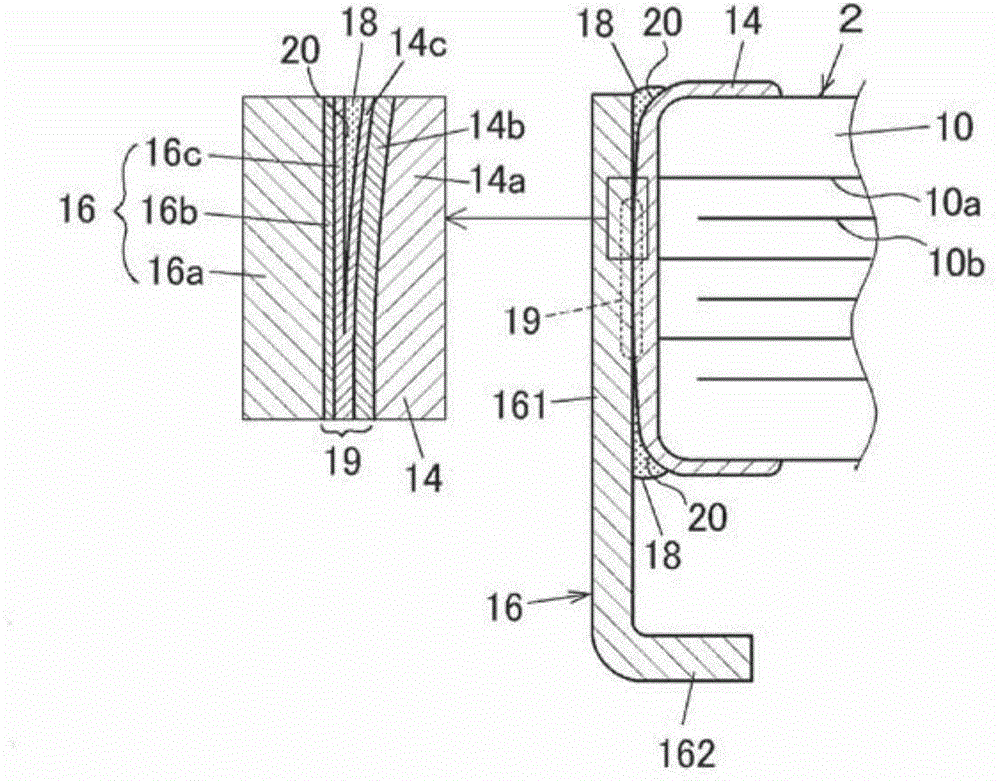

Method for manufacturing terminal-strip-equipped electronic component and terminal-strip-equipped electronic component

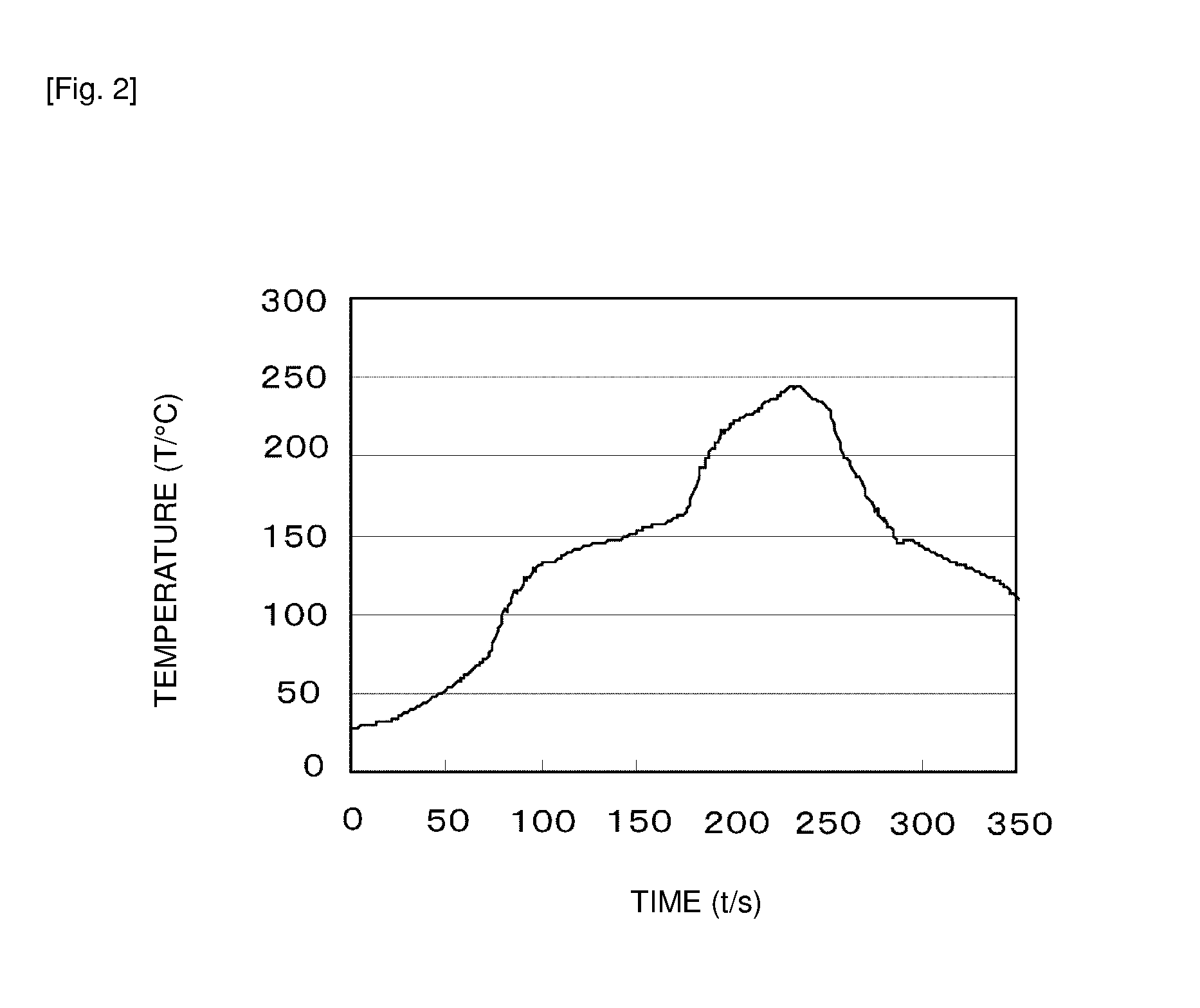

ActiveCN104425137AReduce residual stressHigh bonding strengthFixed capacitor dielectricStacked capacitorsHeating furnaceElectronic component

A method for manufacturing a terminal-strip-equipped electronic component in which terminal strips made of a metal plate are bonded with solder to terminal electrodes of an electronic chip component on two opposing end surfaces. Solder cream is applied to outer surfaces of the terminal electrodes. The terminal strips are thermocompression bonded to the terminal electrodes by placing the electronic chip component between the terminal strips and pressing the terminal strips against the terminal electrodes using a pair of heating elements so as to obtain an electronic component to which the terminal strips are temporarily fixed. The terminal strips are fully fixed to the electronic component by melting the solder cream as a result of heating the electronic component in a heating furnace so as to obtain a terminal-strip-equipped electronic component.

Owner:MURATA MFG CO LTD

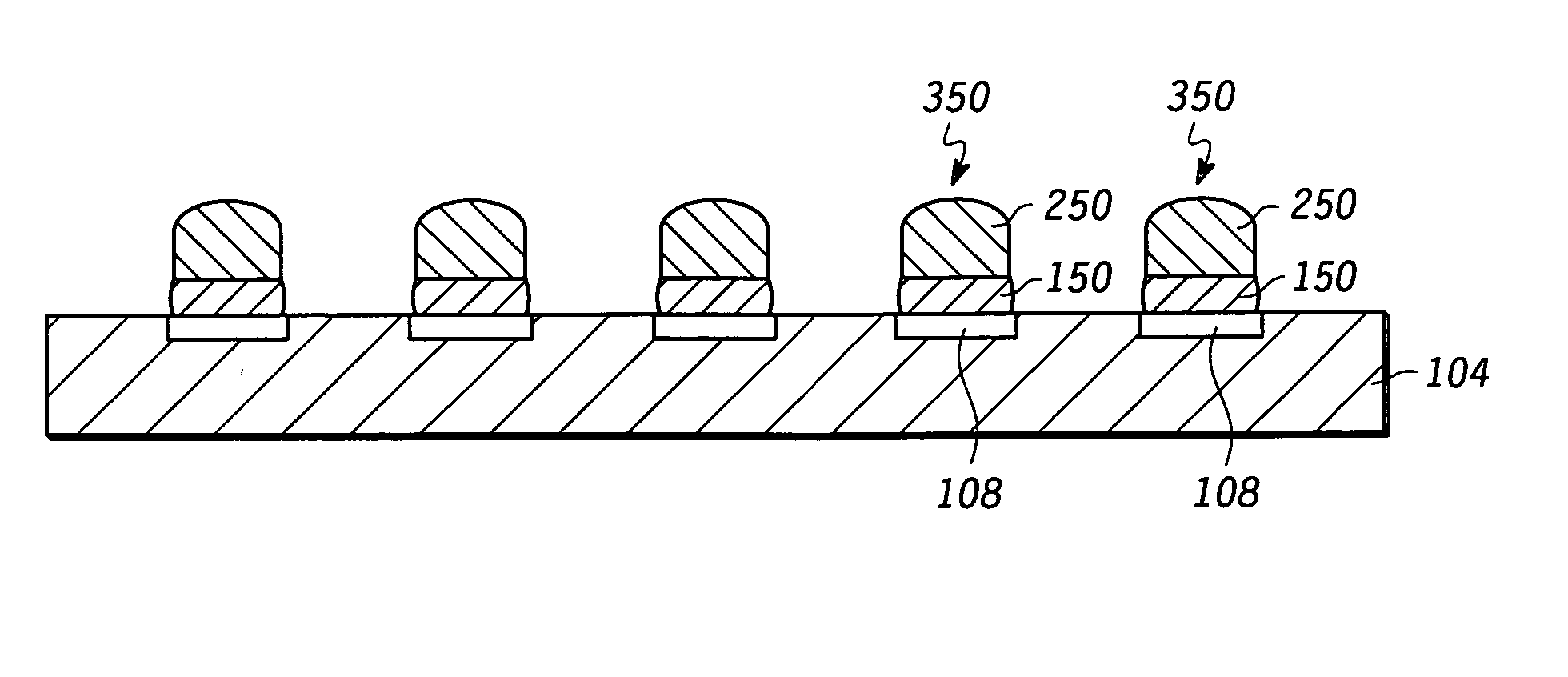

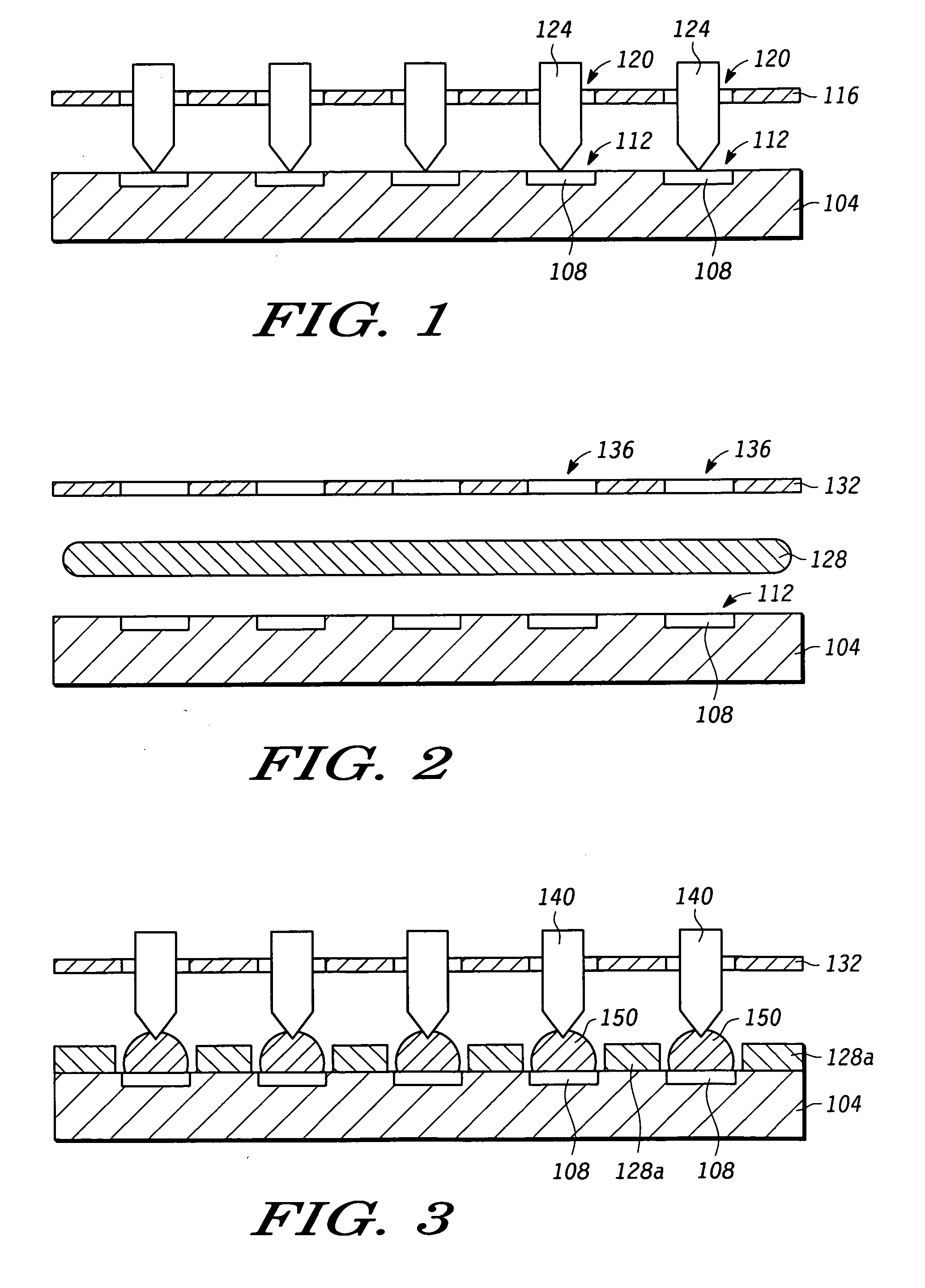

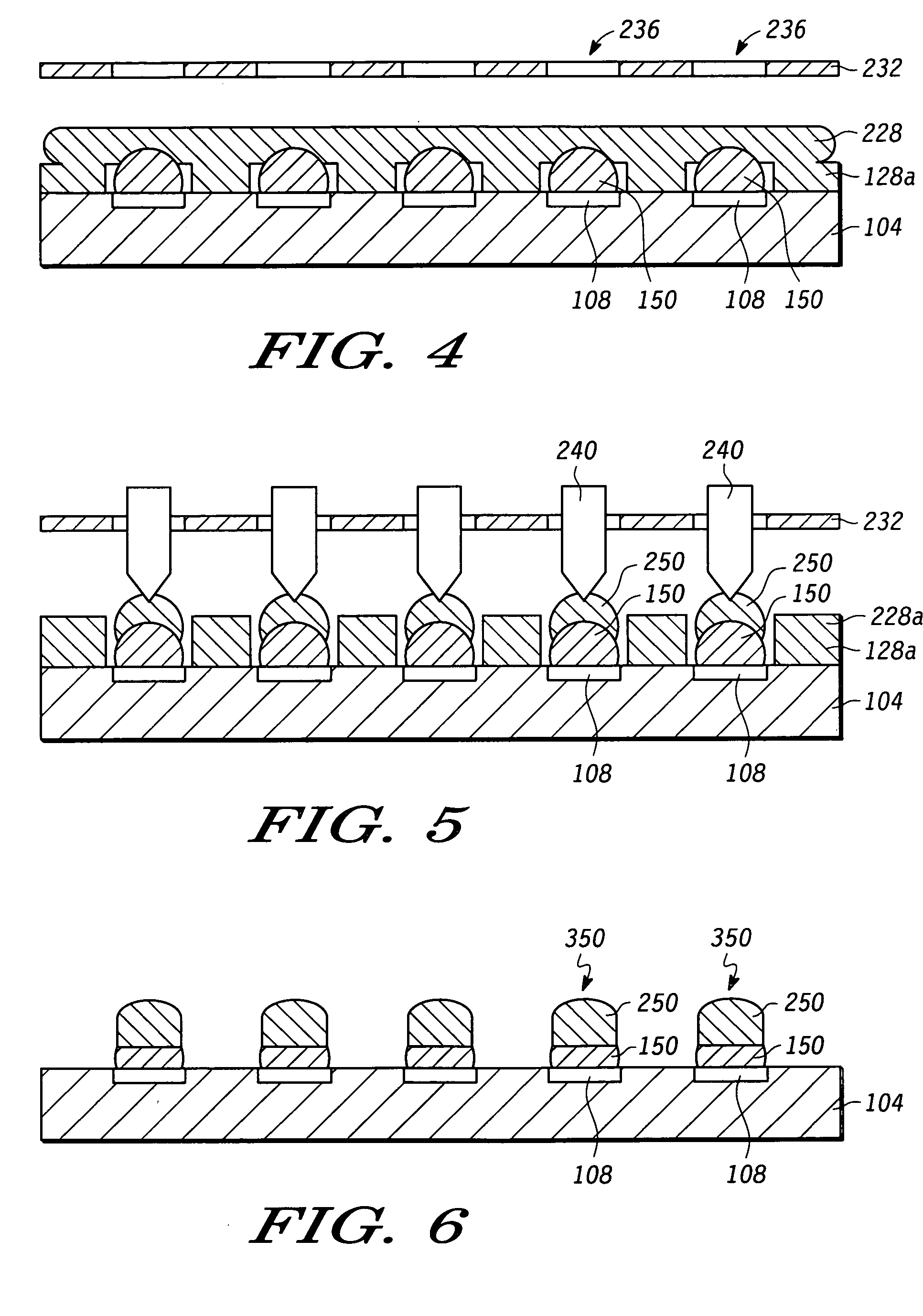

Method for forming multi-layer bumps on a substrate

InactiveUS20070099413A1High standoffImprove joint reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsCompound (substance)Metal powder

A method for forming multi-layer bumps on a substrate includes depositing a first metal powder on the substrate, and selectively melting or reflowing a portion of the first metal powder to form first bumps. A second metal powder is then deposited on the first bumps, and melted to form second bumps on the first bumps. A masking plate is disposed over the substrate to select the portions of the metal powders that are melted and the metal powders are melted via an irradiation beam. The multi-layer bump is formed without the need for any wet chemicals.

Owner:NXP USA INC

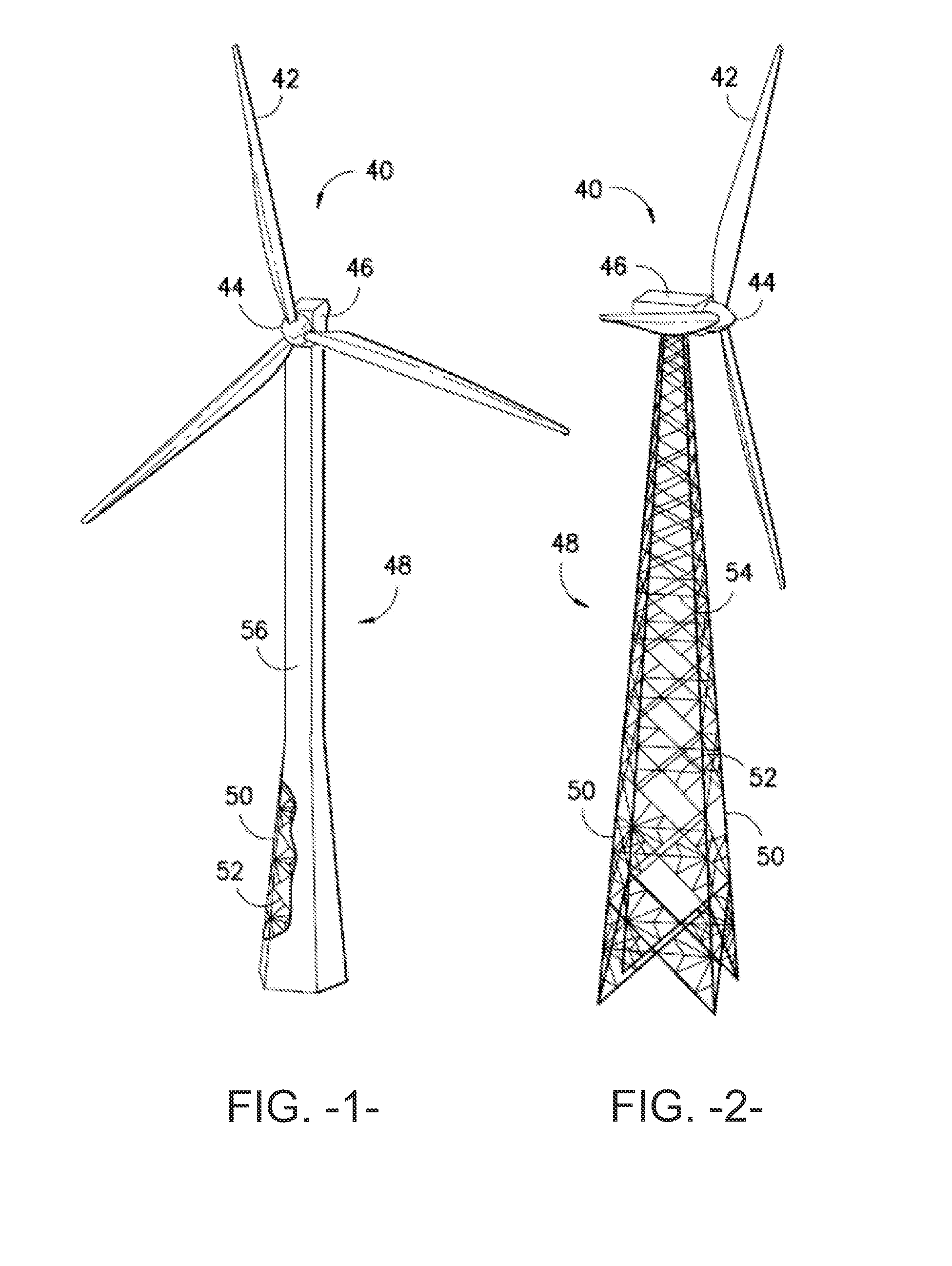

Bolt connection assembly for a wind turbine lattice tower structure

InactiveUS20140331568A1Improve joint reliabilityEvenly loadedEngine manufactureFinal product manufactureEngineeringTurbine

A bolt connection assembly is provided that is particularly well-suited for connecting structural members of a lattice tower structure for a wind turbine. The bolt connection assembly includes a bolt component having a head and a shaft and a structural bore component having a bore defined therethrough for receipt of the bolt component. The shaft includes a knurled surface such that the knurled surface defines an outermost shaft diameter. Moreover, the knurled surface includes a plurality of knurls, each defining a non-arcuate edge. The bore defines a bore diameter, wherein the outermost shaft diameter is greater than the bore diameter. In an assembled state of the bolt component and the structural bore component, the bolt component may be inserted within the bore such that the knurled surface may be deformed to friction fit within the bore diameter.

Owner:GENERAL ELECTRIC CO

Bearing substrate and manufacturing method thereof

ActiveCN104168706AImprove joint reliabilityAvoid oxidationPrinted circuit assemblingElectrical connection printed elementsElectrical and Electronics engineeringOpen hole

The invention discloses a bearing substrate and a manufacturing method thereof. The bearing substrate comprises a dielectric layer, a first line layer, an insulating layer, a plurality of conductive blocks and a first conductive structure. The dielectric layer has a first surface, a second surface and a plurality of blind holes. The first line layer is internally buried in the first surface, and the blind holes extend to the first line layer from the second surface. The insulating layer is arranged on the first surface and is provided with a third surface, a fourth surface and a plurality of first open holes. The first open holes expose the first line layer, and the diameter of each first open hole increases gradually from the third surface to the fourth surface. The conductive blocks are filled in the conductive blocks and are connected with the first line layer. The first conductive structure comprises a plurality of conductive holes filling to the blind holes and second line layers arranged on a part of the second surface.

Owner:UNIMICRON TECH CORP

Duplexing wiring layer and its circuit structure

InactiveCN1855461AImprove delaminationImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorEngineering

The invention is designed for use in a wafer to define a circuit and a contact window required by next bumping process. The re-wiring layer is located on a wafer's active side and has a line construction mainly comprising a first metal layer, a second metal layer and a conducting layer. Wherein, said conducting layer is mad of aluminum material, and said first and second metal layer are respectively overlapped on each of two side of said conducting layer. The connectivity between the first and second metal layers and a high polymer is higher than the one between said conducting layer and said high polymer. Said first and second metal layer can notably avoid the delaminating between a circuit layer and dielectric layer, and improve the reliability of wafer package.

Owner:ADVANCED SEMICON ENG INC

Power module and method of manufacturing power module

ActiveUS20160300770A1Improve joint reliabilityRelieve stressSemiconductor/solid-state device detailsSolid-state devicesElectricityElectrical connection

A power module providing an improved manufacture yield and having an ensured stable joint strength and accordingly improved reliability is provided. The power module includes: a base portion having one surface on which an electrode portion is formed; a conductor portion disposed to face the one surface of the base portion on which the electrode portion is formed, for making electrical connection with the outside; and an interconnect portion connected to the electrode portion formed on the one surface of the base portion and to the surface of the conductor portion facing the one surface of the base portion for electrically connecting the electrode portion to the conductor portion.

Owner:MITSUBISHI ELECTRIC CORP

Conductive honeycomb structure

ActiveUS20180280872A1Improve joint reliabilityShortening of production timeInternal combustion piston enginesExhaust apparatusHoneycomb structureMetal

A conductive honeycomb structure, comprising: a columnar ceramic honeycomb structure portion comprising an outer peripheral side wall and partition walls each disposed inside the outer peripheral side wall and defining a plurality of cells penetrating from one bottom surface to another bottom surface to form flow paths; a pair of electrode layers disposed on an outer surface of the outer peripheral side wall across a central axis of the honeycomb structure portion; and a pair of metal terminals joined to the respective electrode layers via one or more welded portions, wherein each of the one or more welded portions comprises a welded area of from 2 to 50 mm2.

Owner:NGK INSULATORS LTD

Ball land structure having barrier pattern

InactiveUS20100164101A1Improve joint reliabilityPreventing and retarding propagation of crackSemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskCivil engineering

Disclosed is a ball land structure suitable for use with a semiconductor package. The ball land structure includes a ball land and a barrier on a core. The barrier may be configured to connect to the ball land so as to form a barrier hole between an edge of the ball land and an edge of the barrier thus exposing a portion of the core. A solder mask may be deposited on the ball land and a portion of the core exposed by the barrier hole so as to partially expose the core.

Owner:SAMSUNG ELECTRONICS CO LTD

Solder paste, joining method using the same and joined structure

ActiveUS20150239069A1Diffusibility in a soldering stepShort timePrinted circuit aspectsSolid-state devicesSolder pasteMetal powder

A solder paste including a metal component consisting of a first metal powder and a second metal powder having a melting point higher than that of the first metal, and a flux component. The first metal is Sn or an alloy containing Sn, the second metal is one of (1) a Cu—Mn alloy in which a ratio of Mn to the second metal is 5 to 30% by weight and (2) a Cu—Ni alloy in which a ratio of Ni to the second metal is 5 to 20% by weight, and a ratio of the second metal to the metal component is 36.9% by volume or greater.

Owner:MURATA MFG CO LTD

Multi-layer flexible printed circuit board, and method for fabricating it

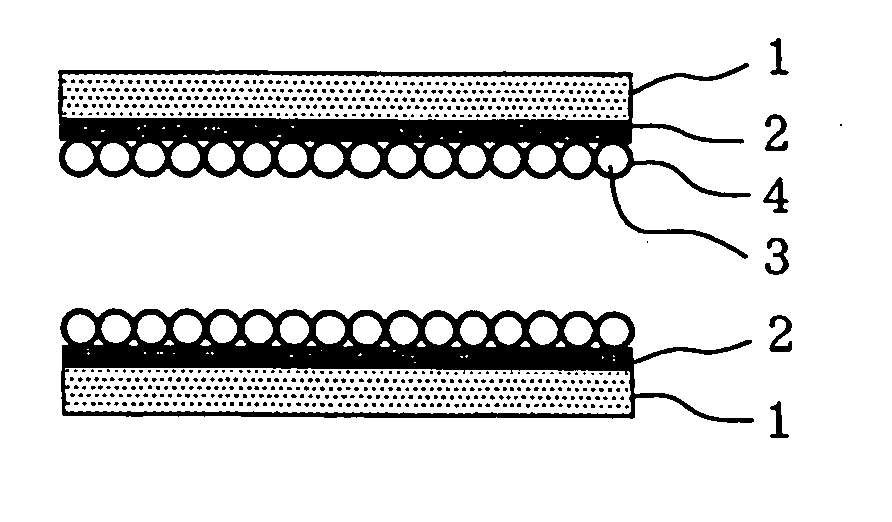

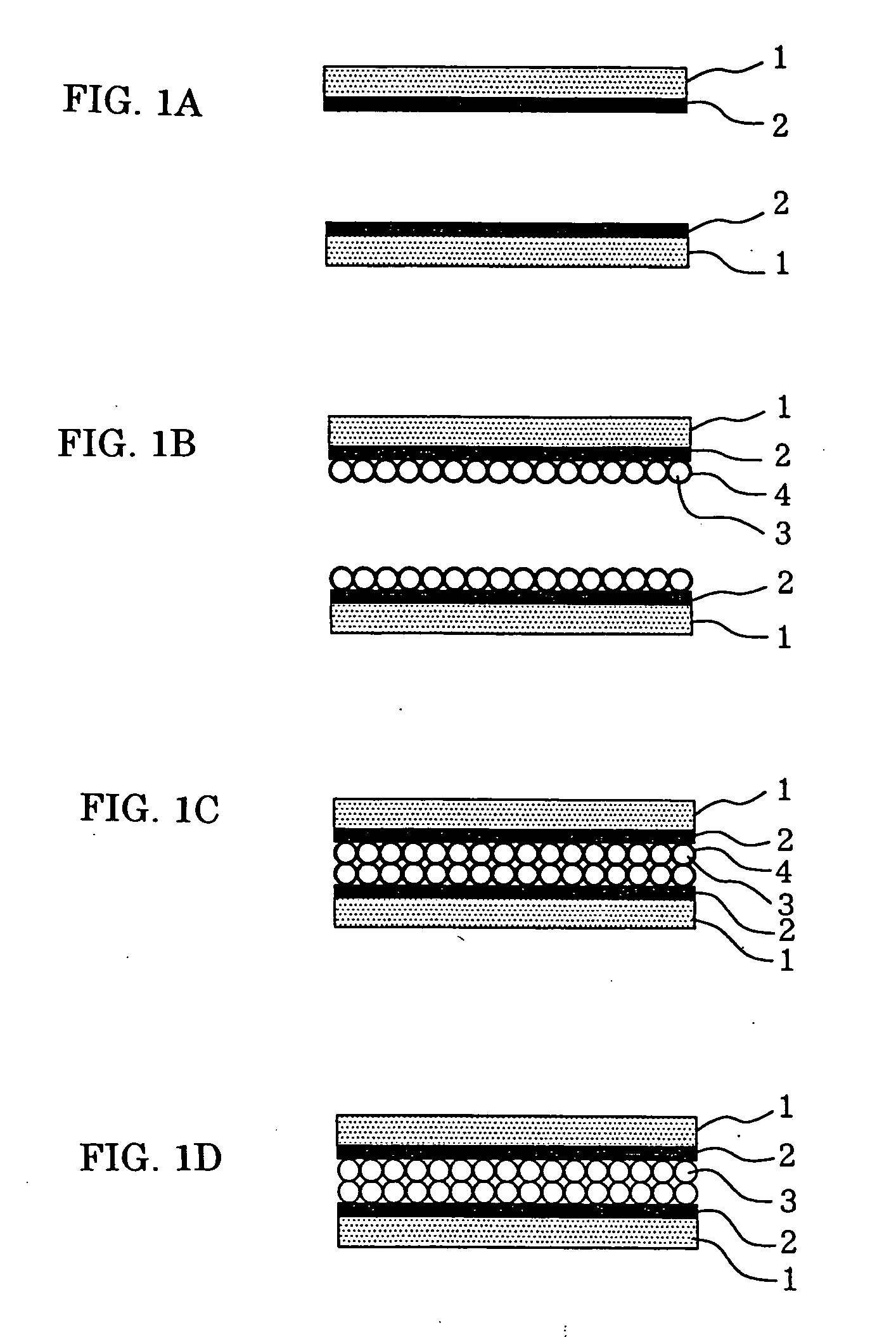

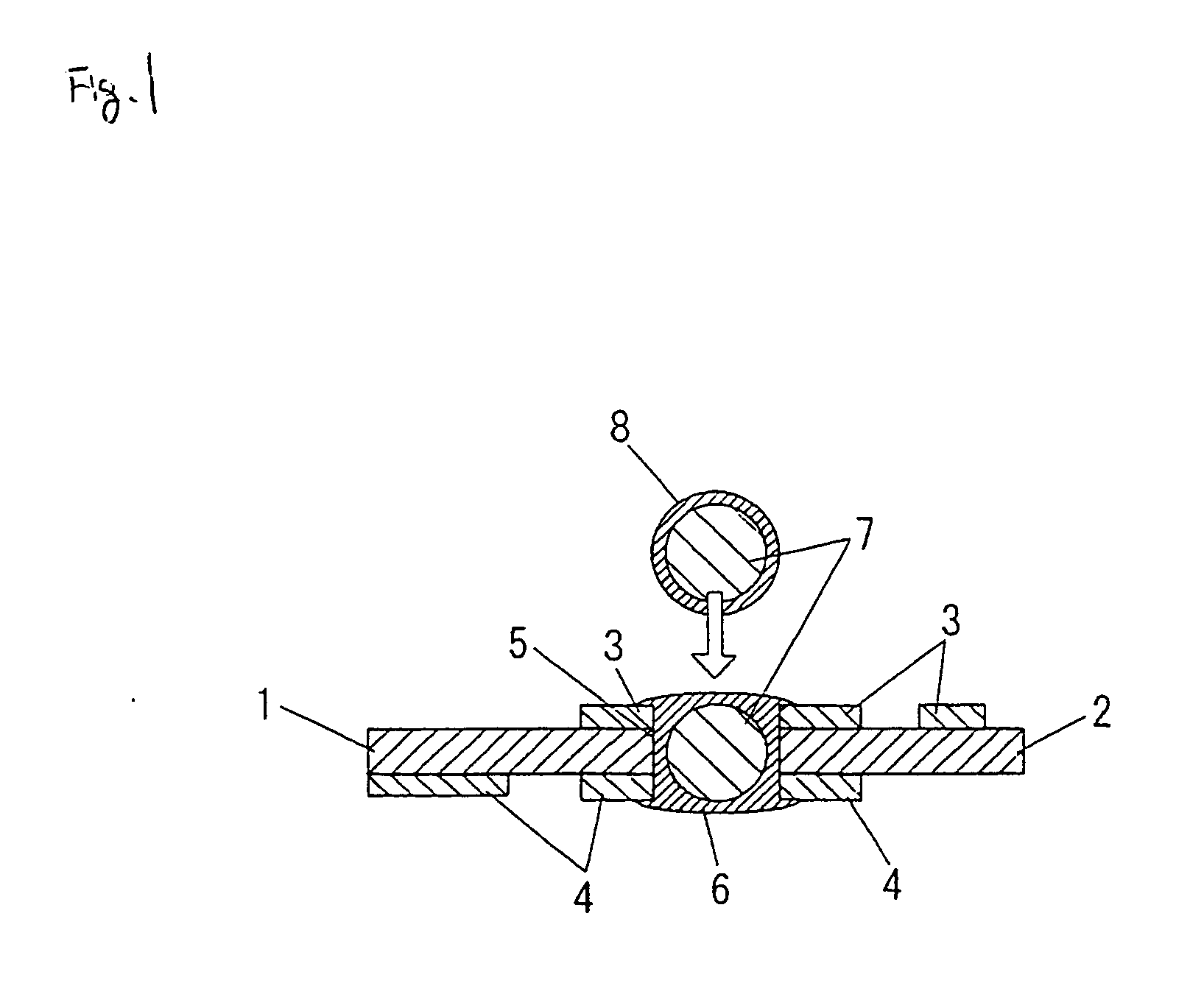

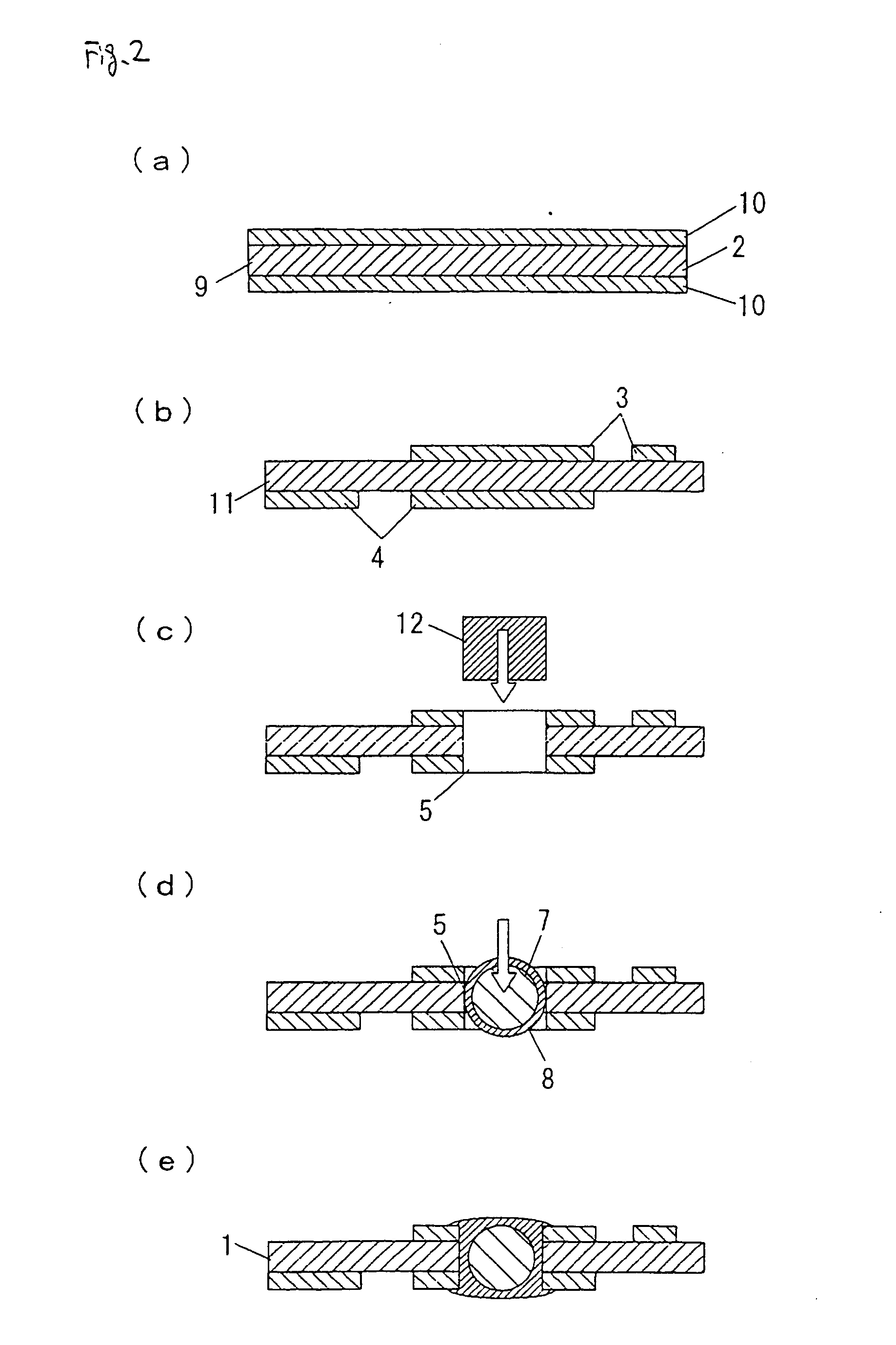

InactiveUS20050011677A1Improve joint reliabilityOptimized coefficientPrinted circuit assemblingElectrically conductive connectionsElectrical conductorSolder ball

To provide an interlayer-connected, multi-layer flexible printed circuit board having high bonding reliability and most suitable for micropatterning the circuit layers in the device; and to provide a high-productivity method for fabricating the device. A multi-layer flexible printed circuit board, wherein a conductor is filled in the through-holes formed in the insulating layer in the direction of the thickness thereof so as to electrically interconnect the circuit layers formed on both faces of the insulating layer, and wherein the conductor contains inside it, a copper-core solder ball having a copper ball as a core thereof.

Owner:PANASONIC CORP