Duplexing wiring layer and its circuit structure

A technology for rewiring layers and circuit structures, applied in the structural field of multi-layer metal layers, which can solve problems such as cracks, delamination, and inconvenience

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

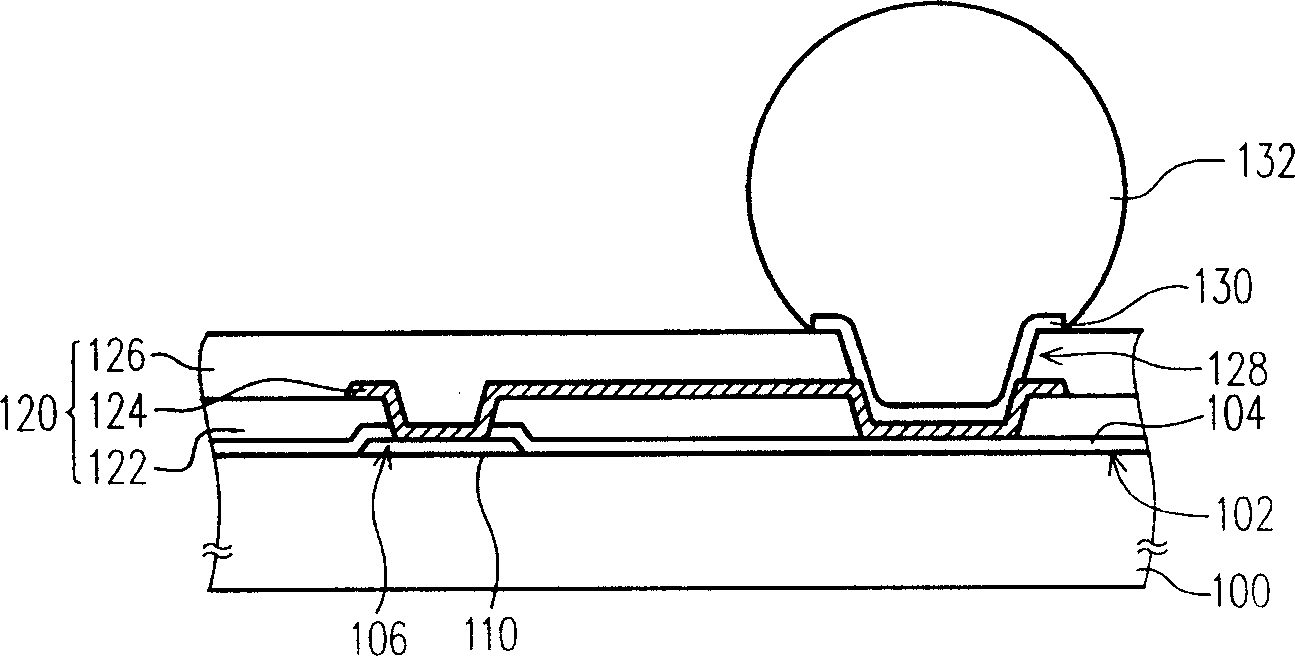

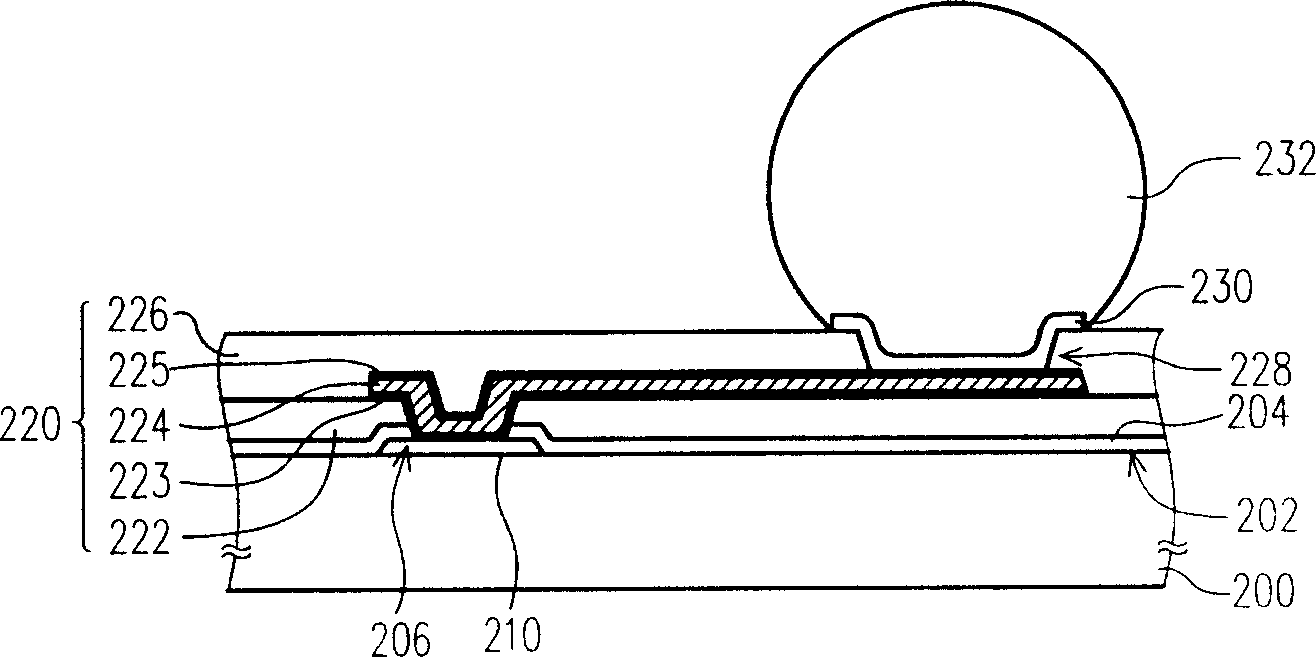

[0042] In order to further explain the technical means and effects of the present invention to achieve the intended purpose of the invention, the specific implementation, structure, and characteristics of the redistribution layer and its circuit structure proposed according to the present invention will be described below in conjunction with the accompanying drawings and preferred embodiments. And its effect, detailed description is as follows.

[0043] see figure 2 Shown is a schematic diagram of a redistribution layer according to a preferred embodiment of the present invention to define the lines and contact windows required for the subsequent bumping process. exist figure 2 Among them, there is a protective layer 204 on the active surface 202 of the wafer 200, and the protective layer 204 can be deposited from an organic protective material or an inorganic protective material, which covers the active surface 202 of the wafer 200, and the common protection Layer 204 , s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More