Patents

Literature

240results about How to "High process yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Structure of an optical interference display unit

InactiveUS6958847B2Avoid pollutionIncreased process complexityTelevision system detailsColor television detailsLight reflectionReflective layer

Owner:SNAPTRACK

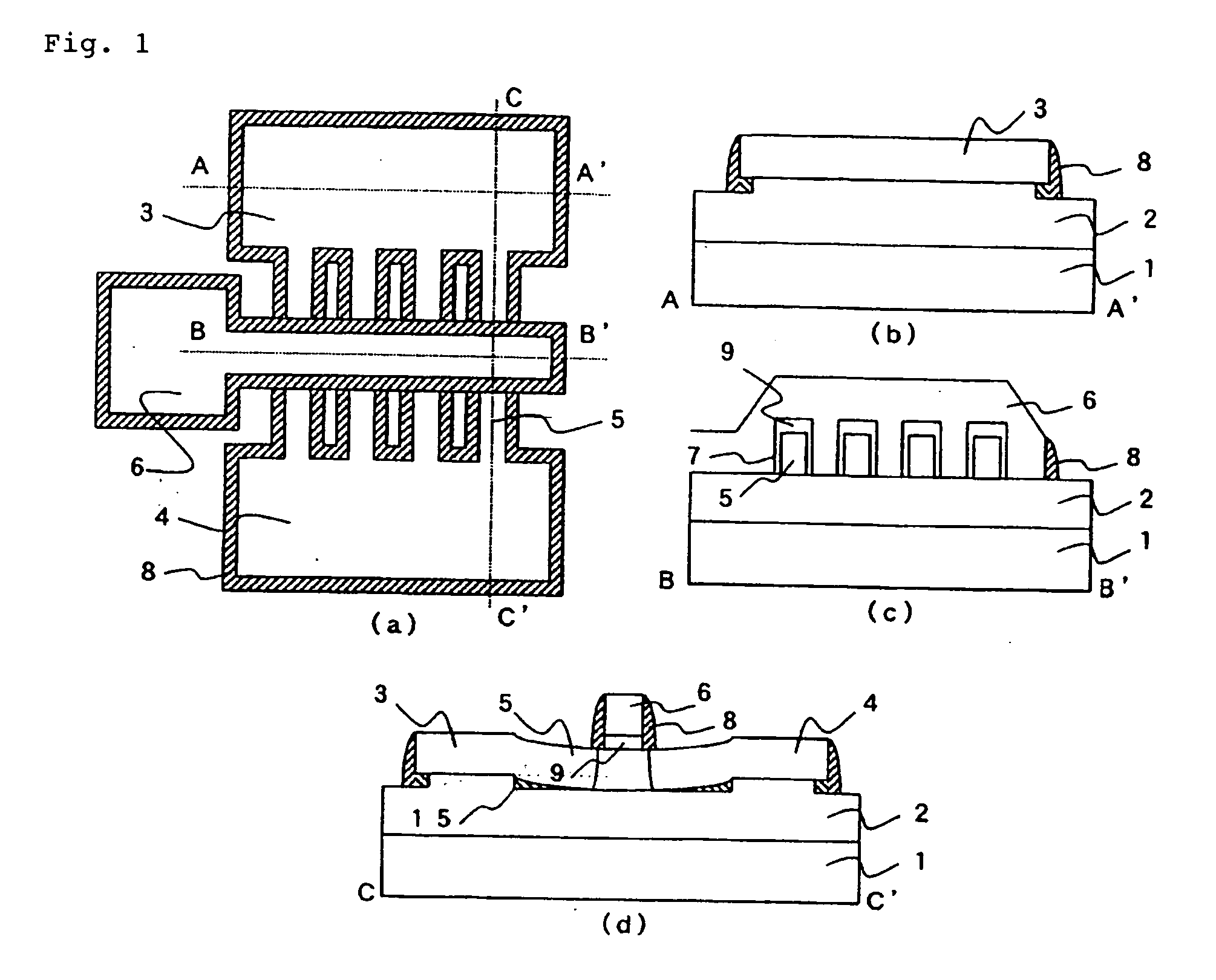

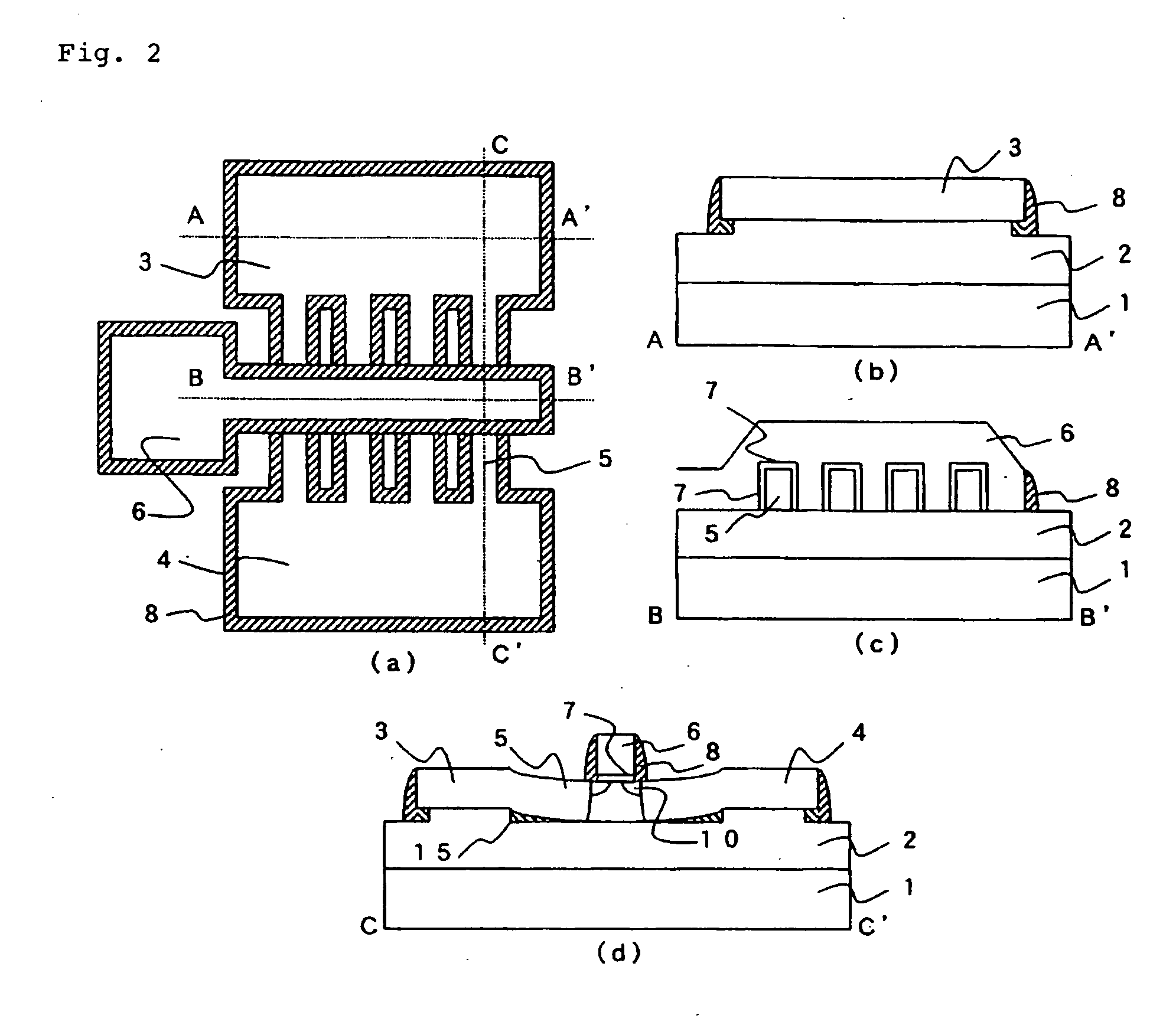

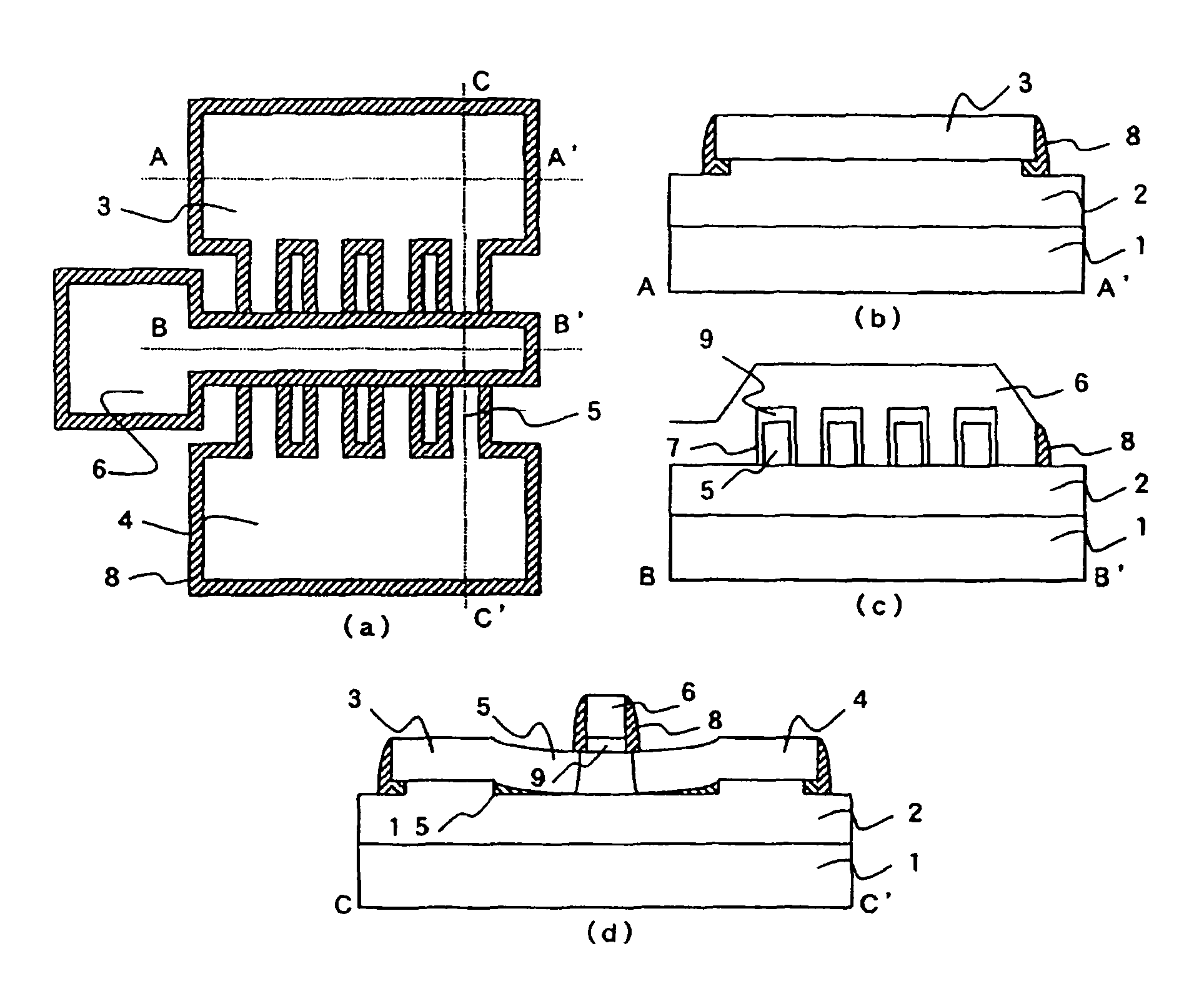

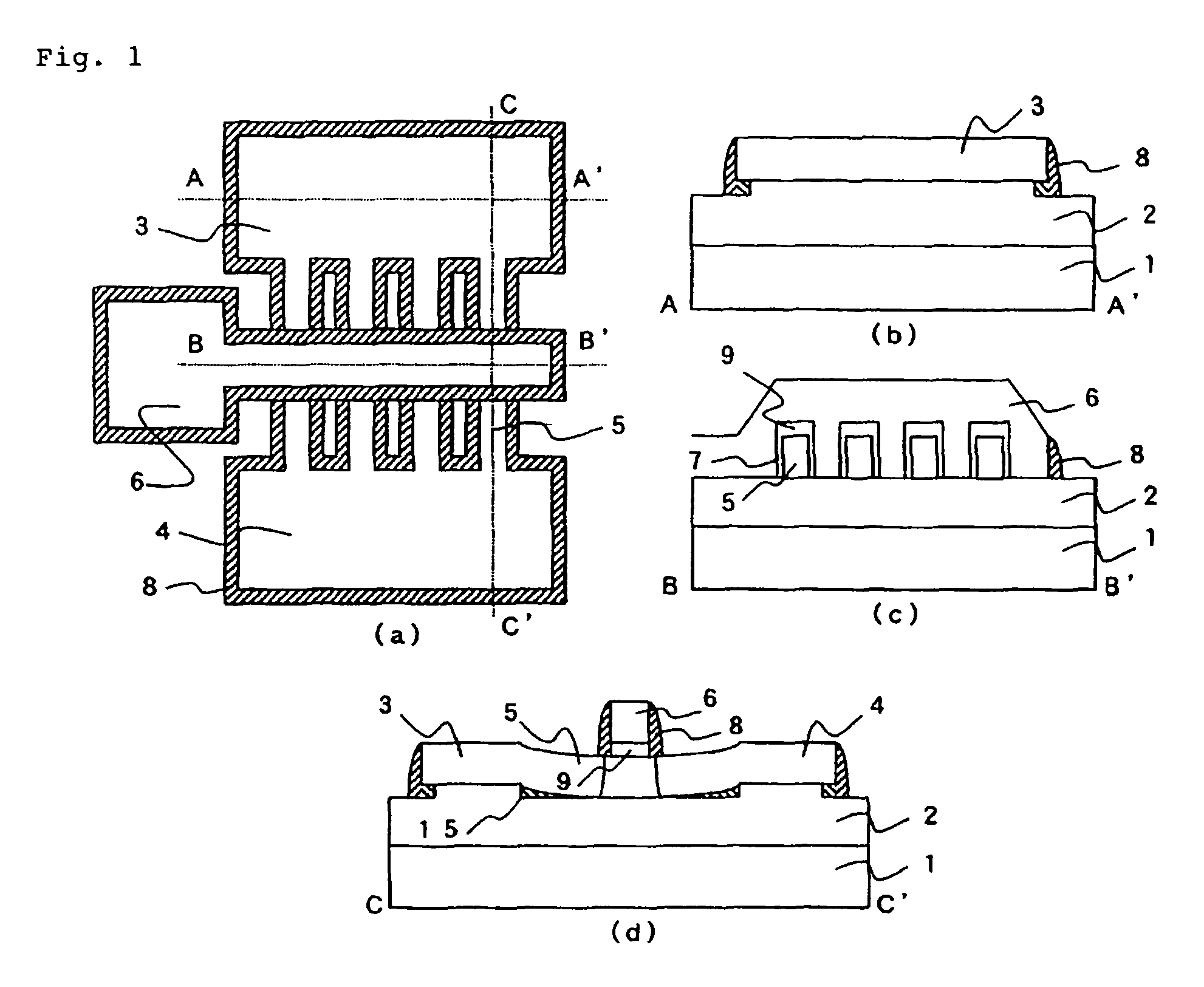

Semiconductor Device and Manufacturing Process Therefor

ActiveUS20070241414A1Less dislocation and defectControlled amount of strainTransistorSolid-state devicesManufacturing technologyDevice material

This invention relates to a semiconductor device having a beam made of a semiconductor to which strain is introduced by deflection, and a current is permitted to flow in the beam.

Owner:GK BRIDGE 1

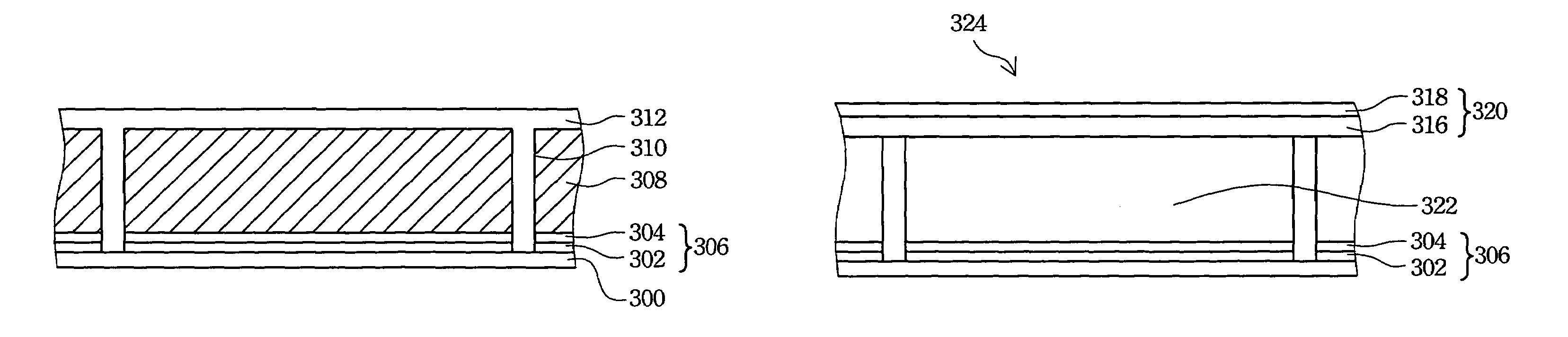

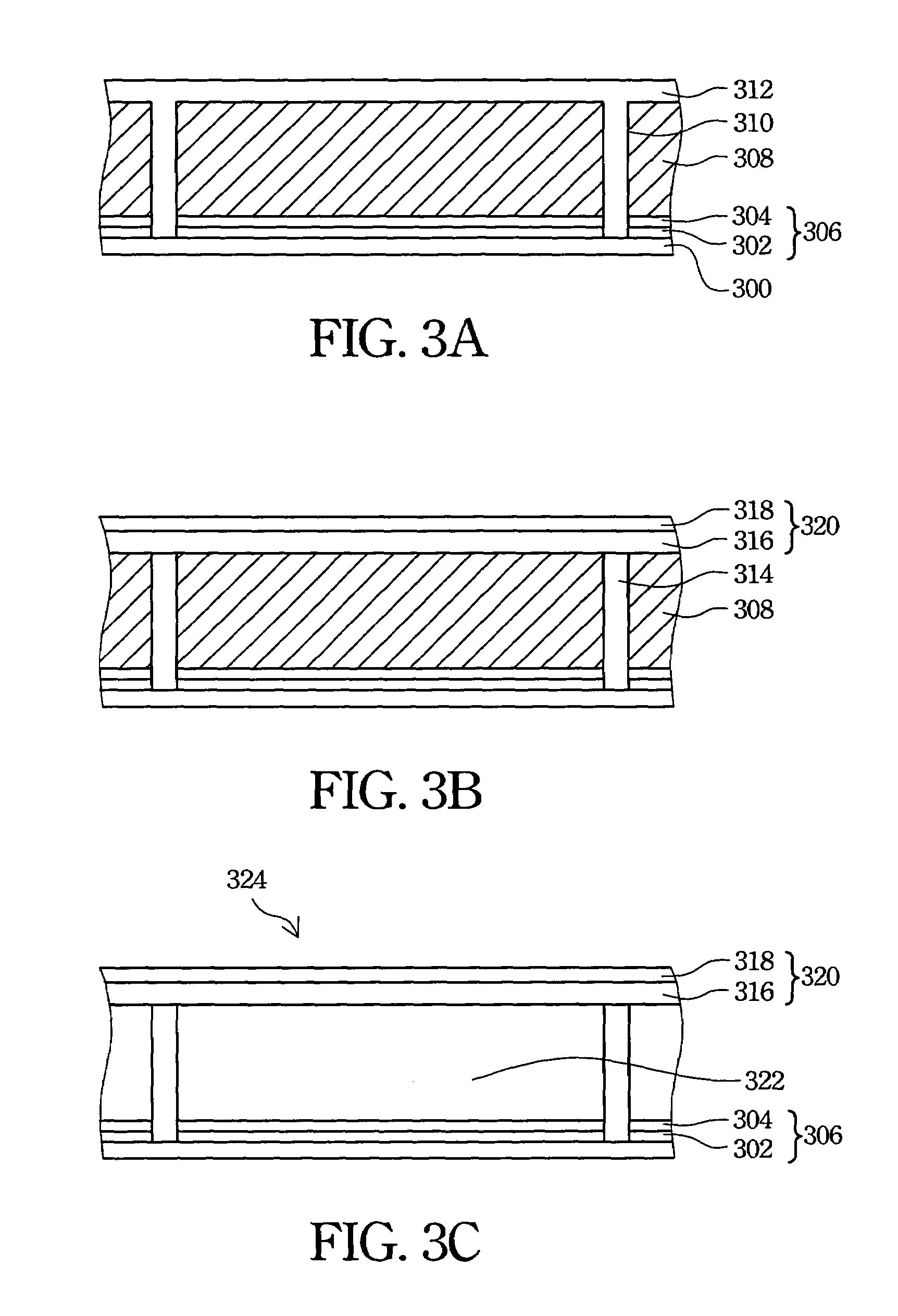

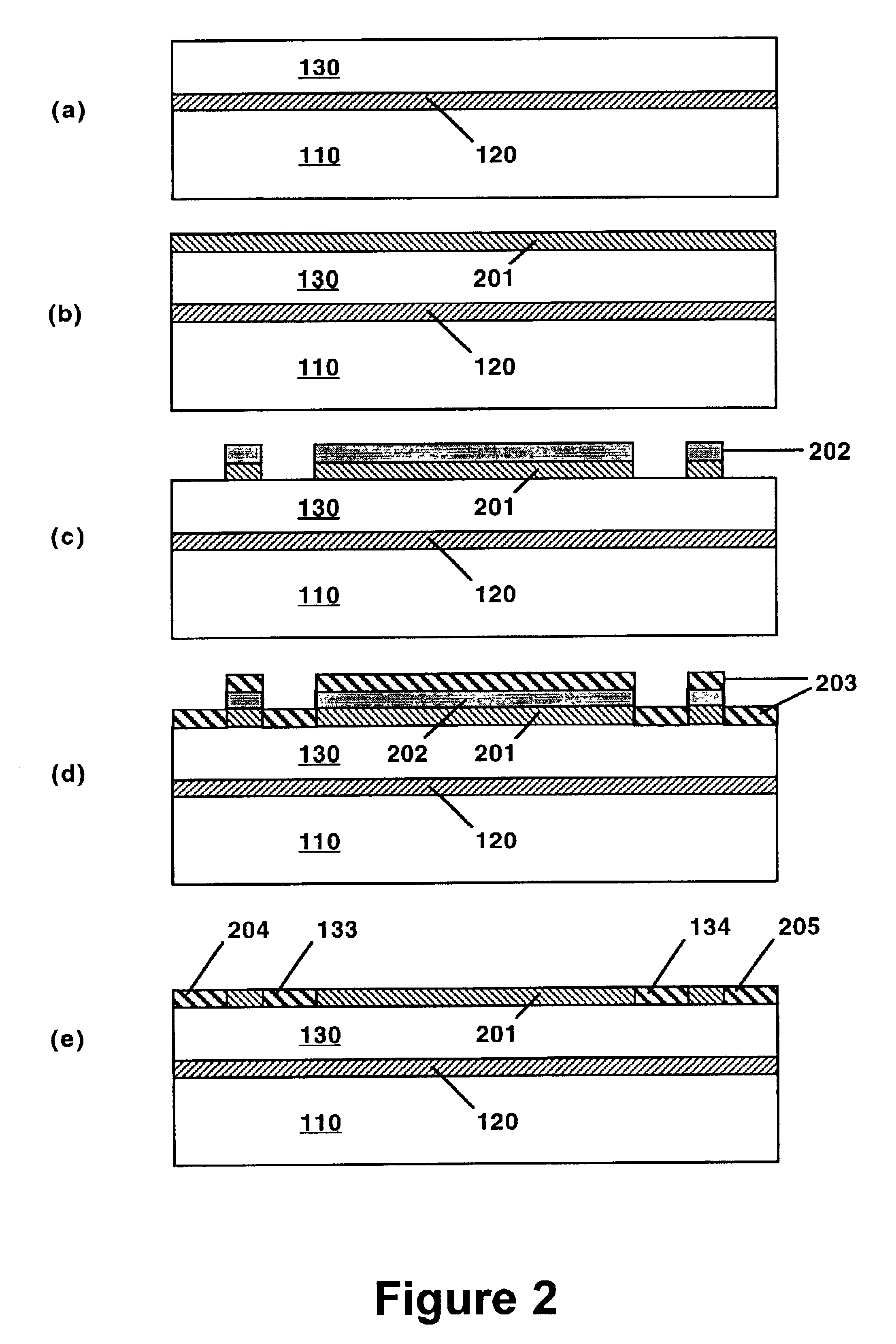

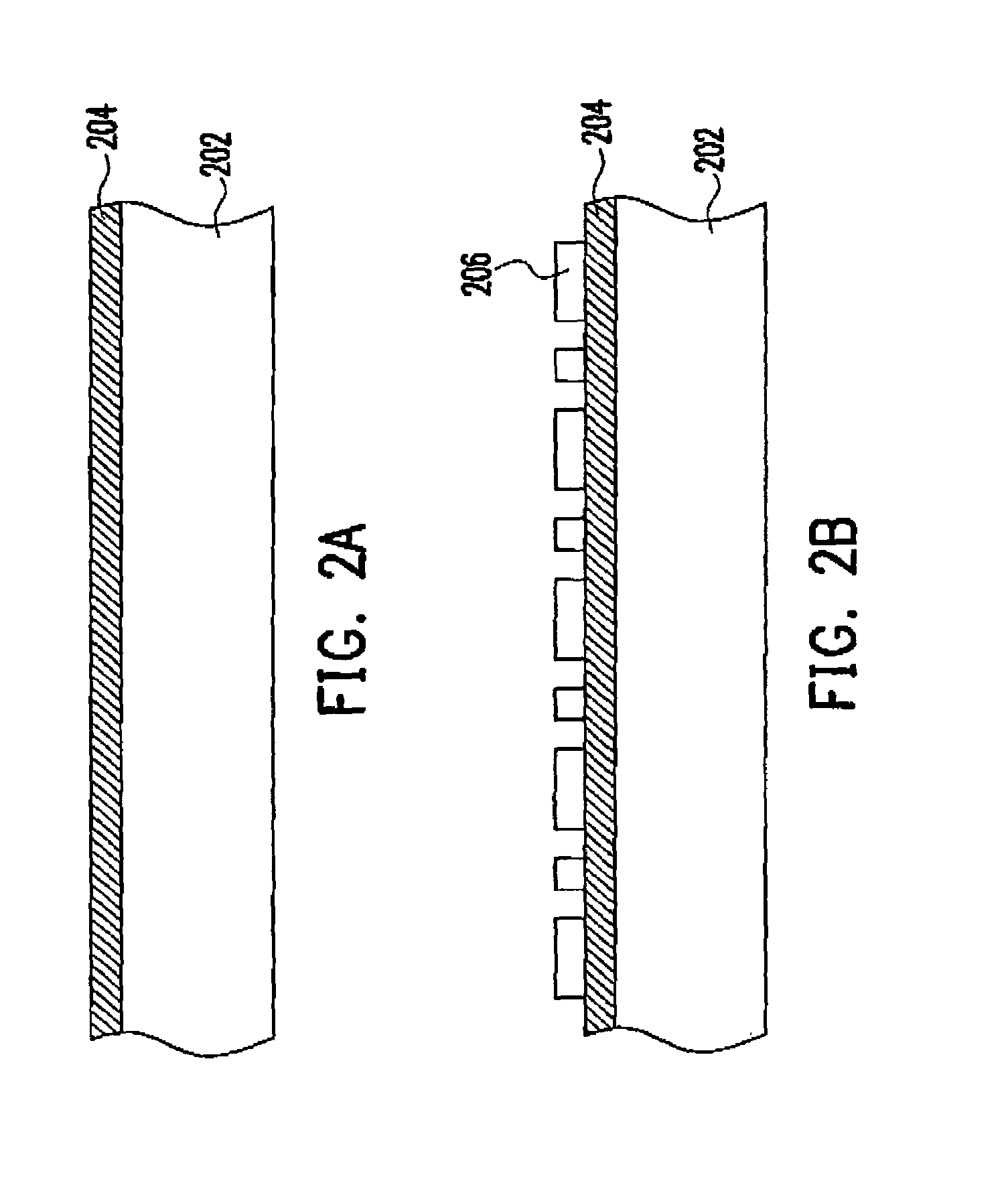

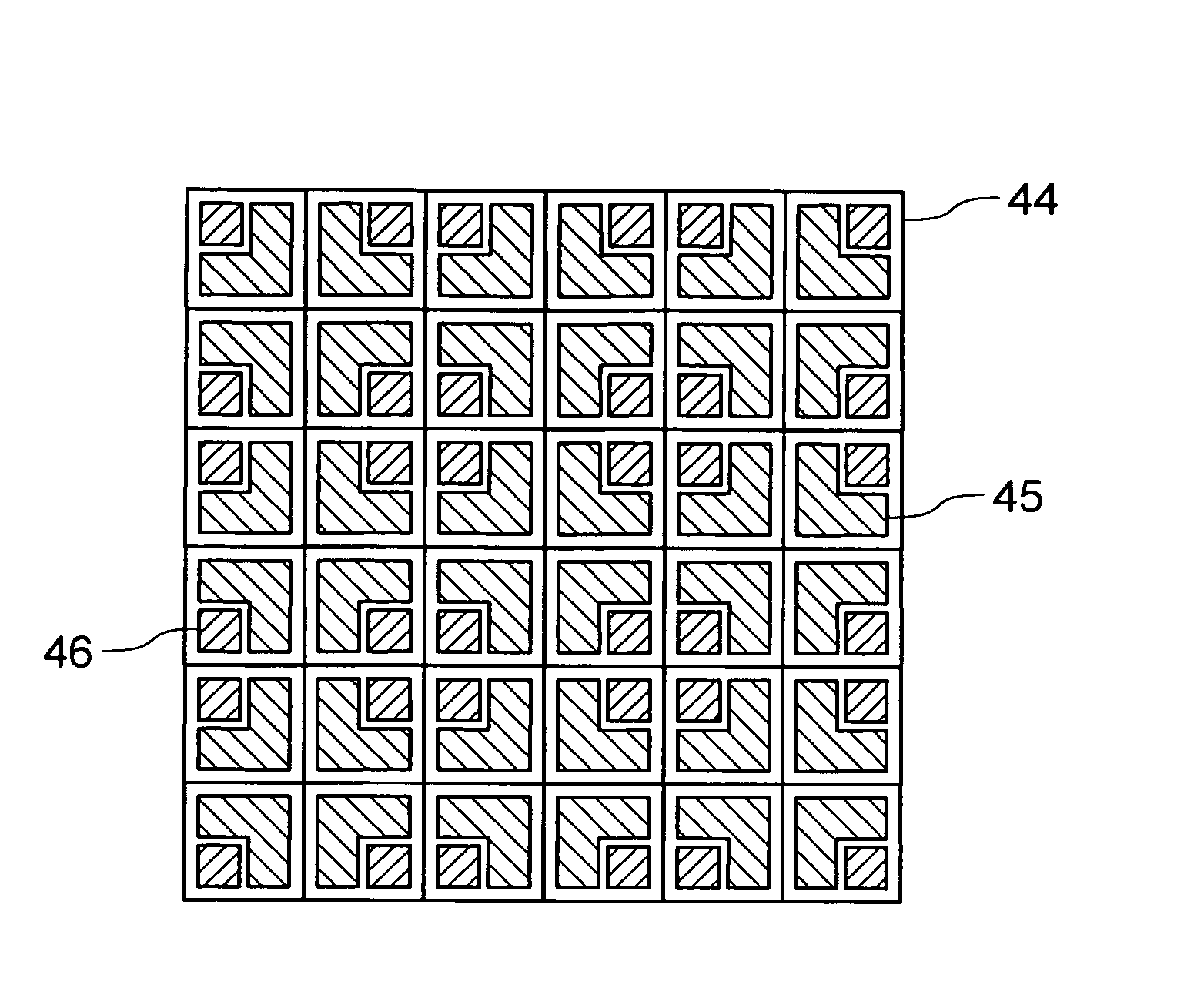

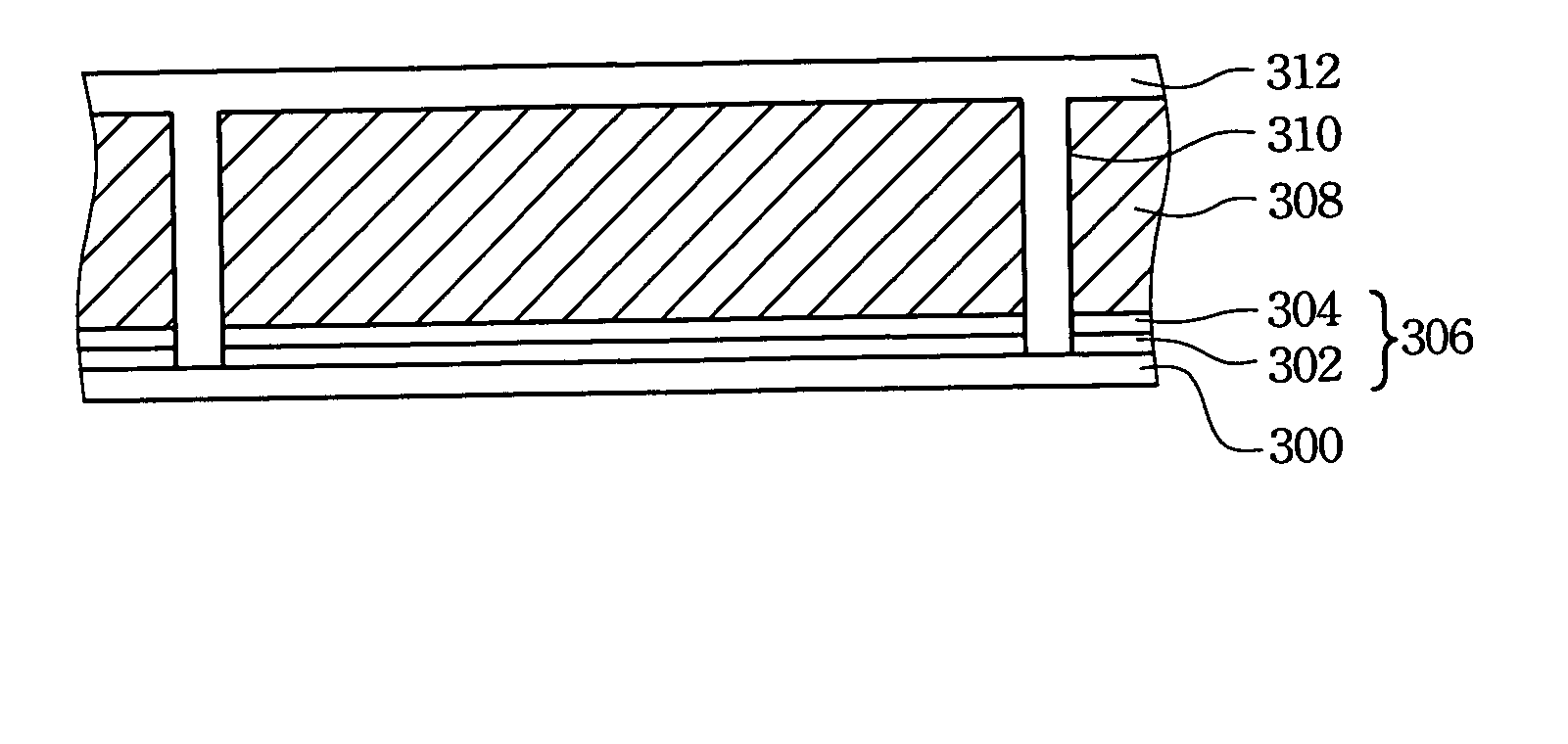

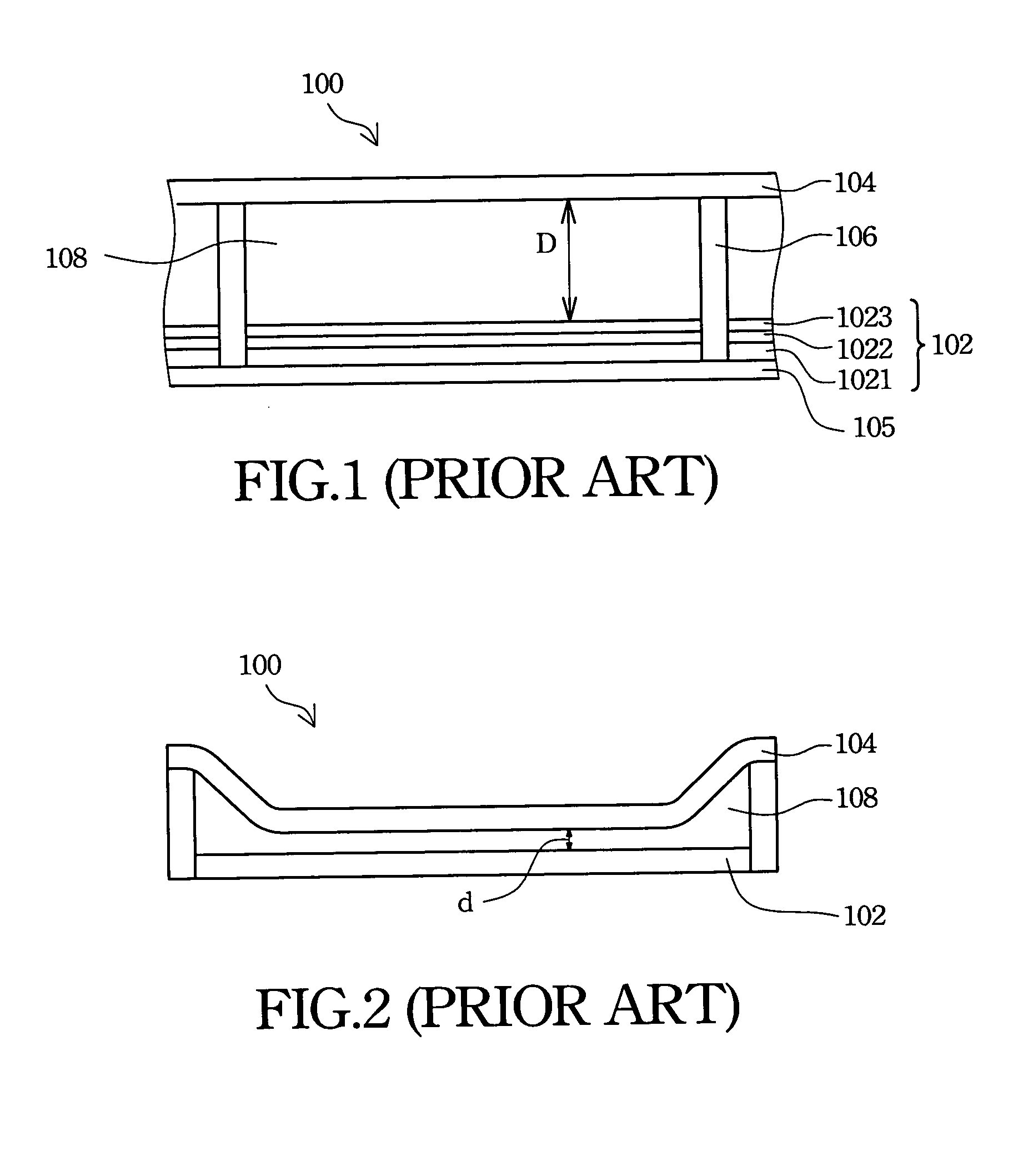

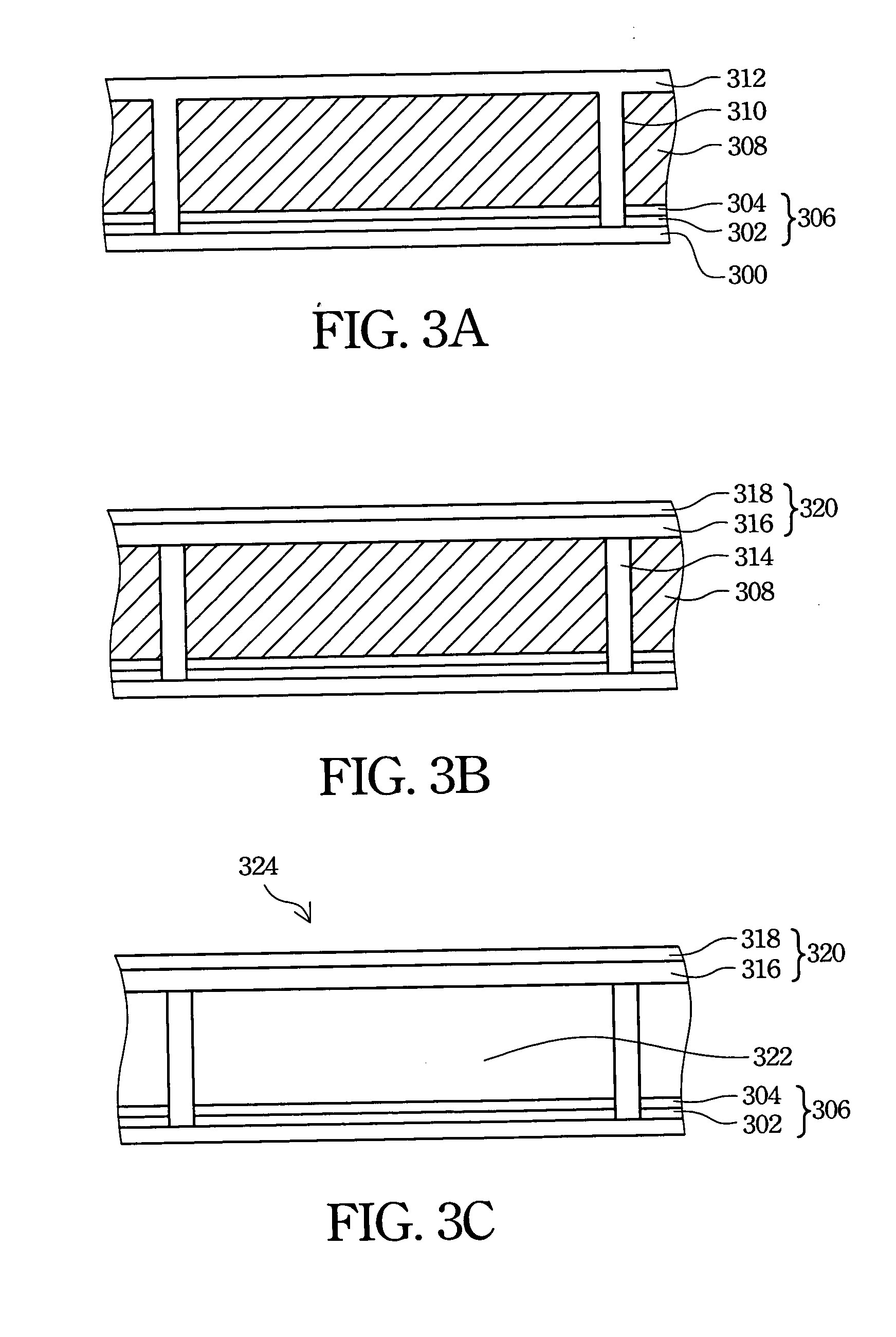

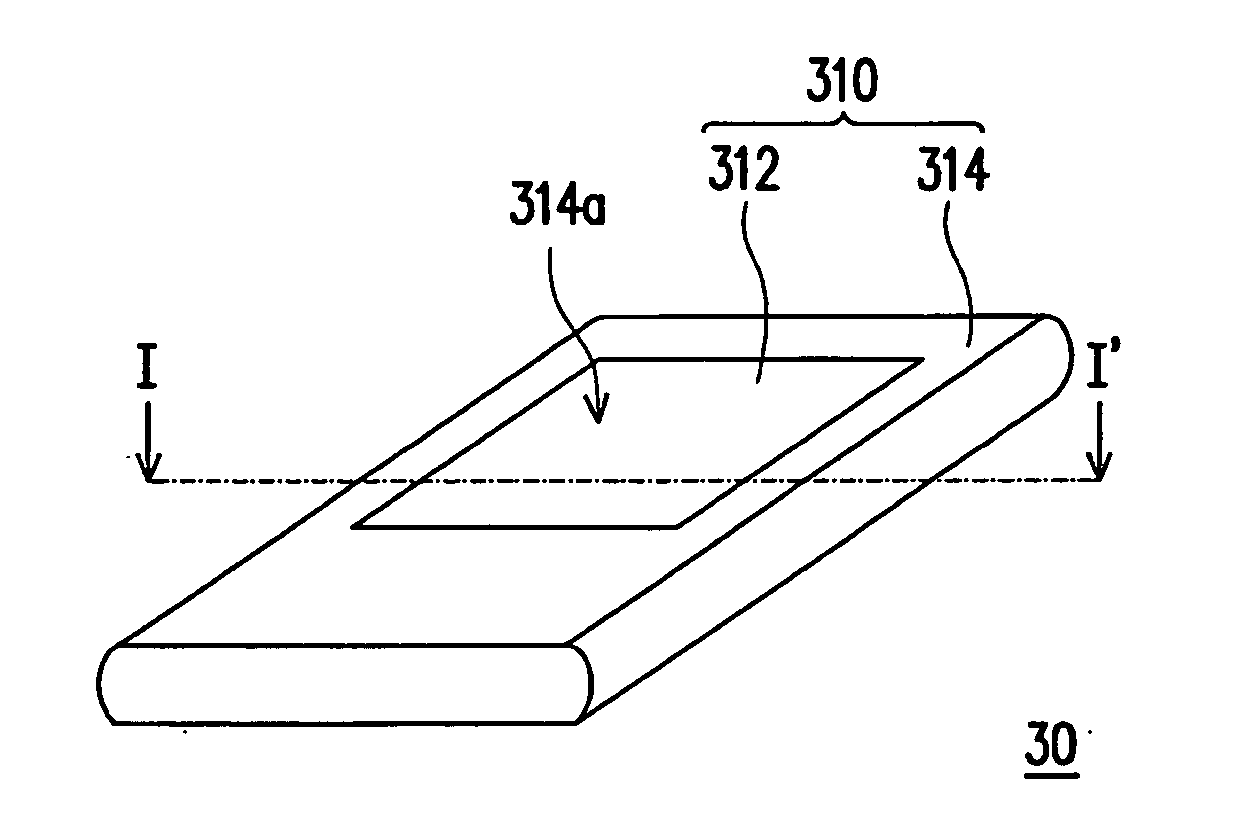

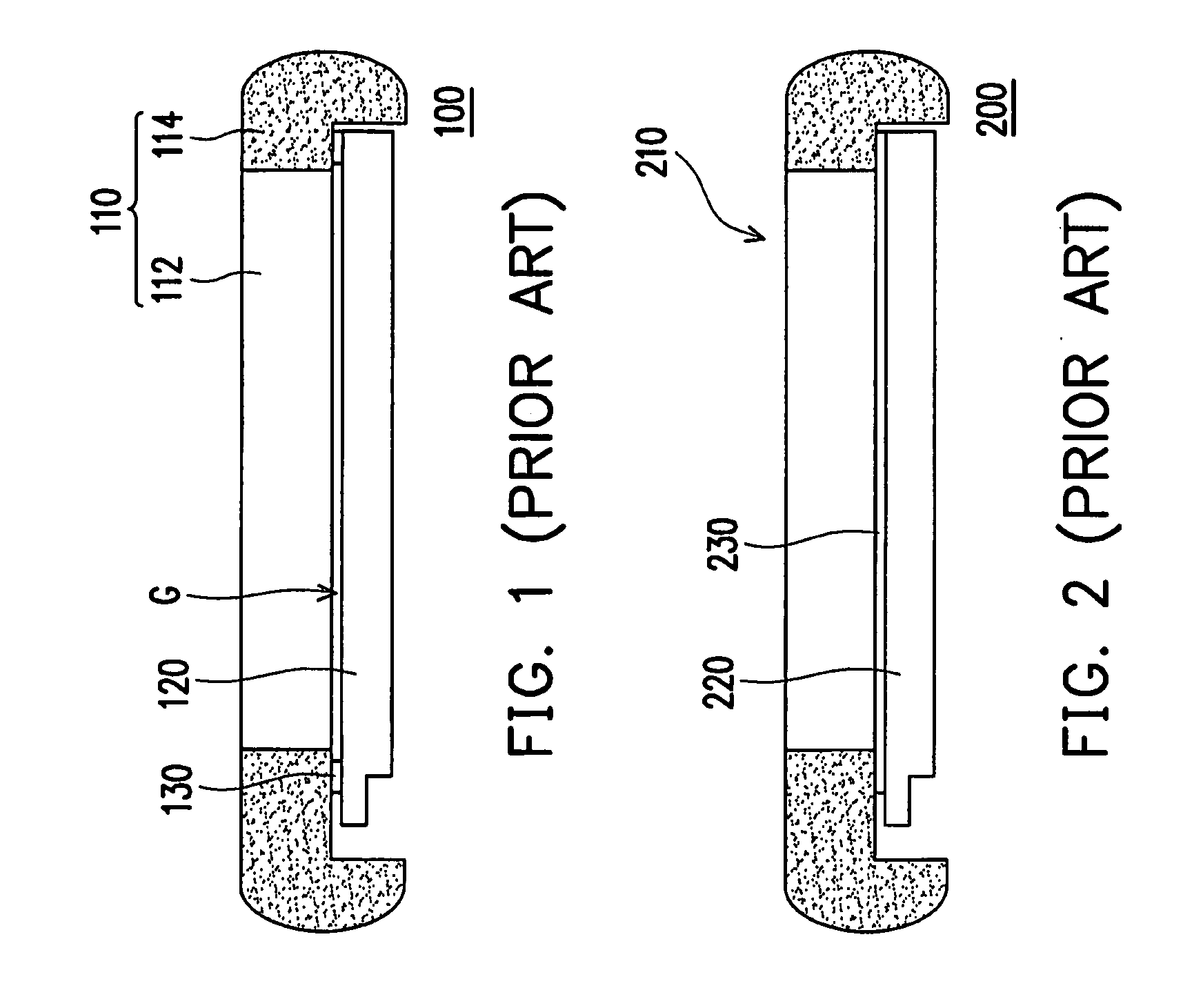

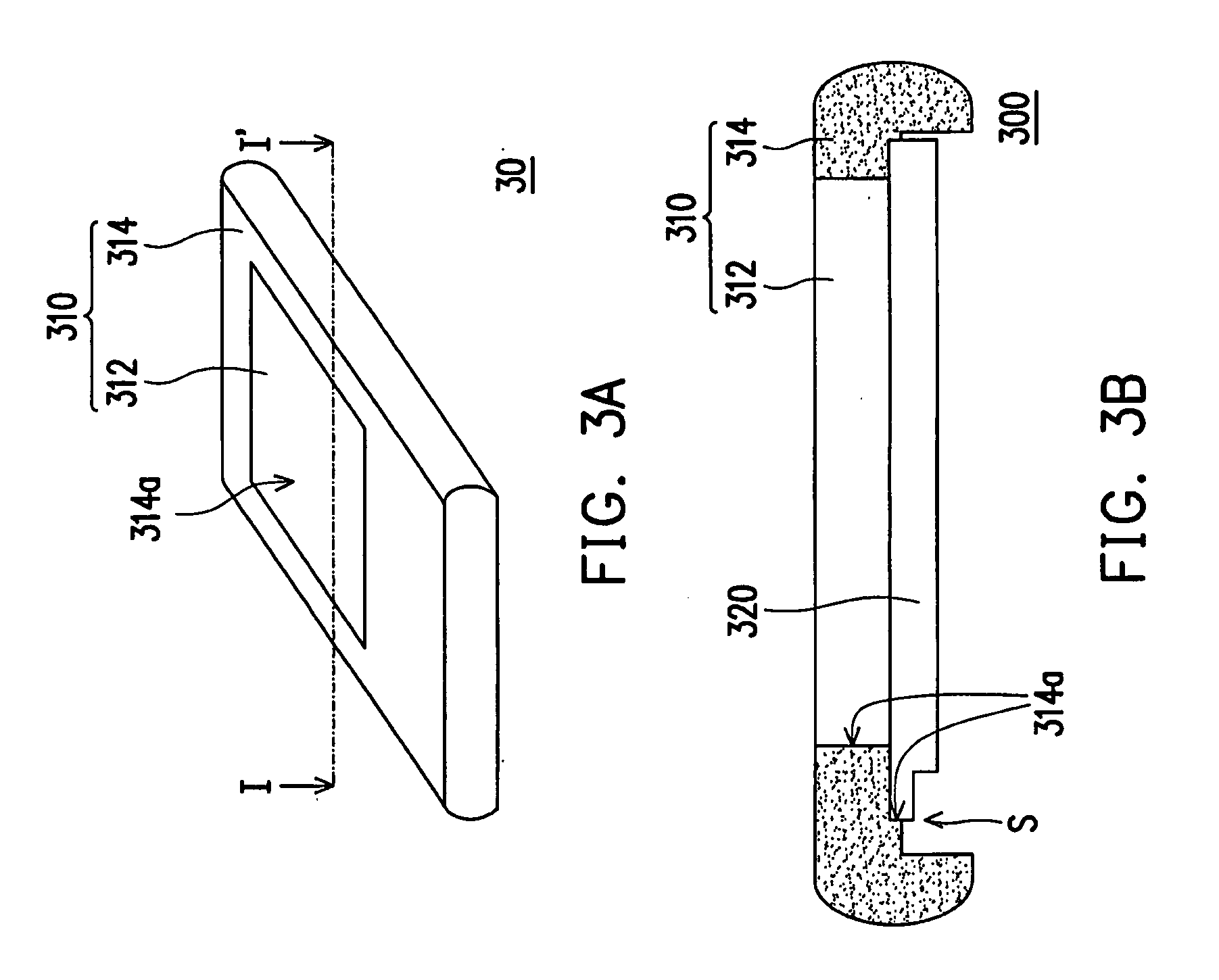

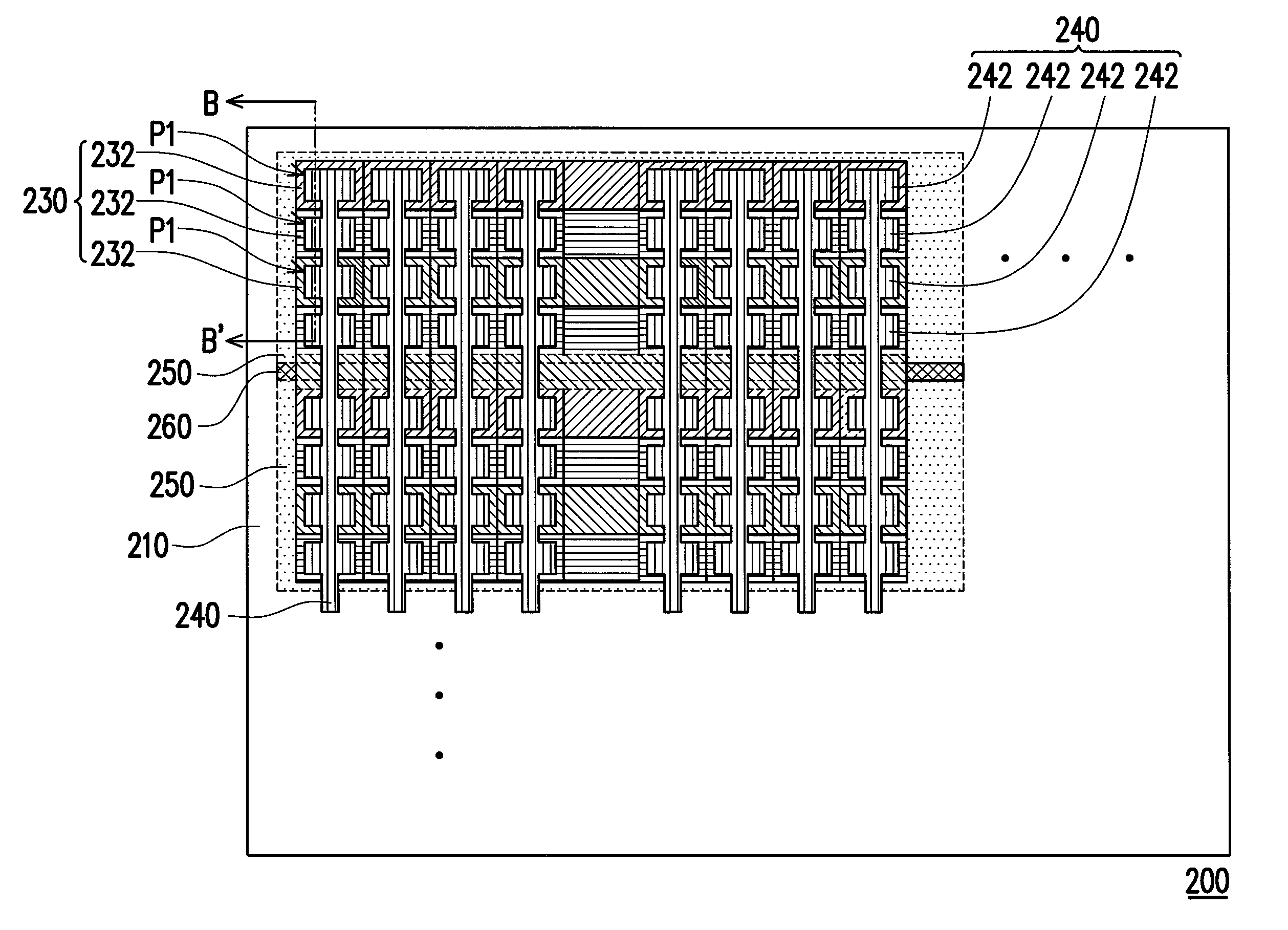

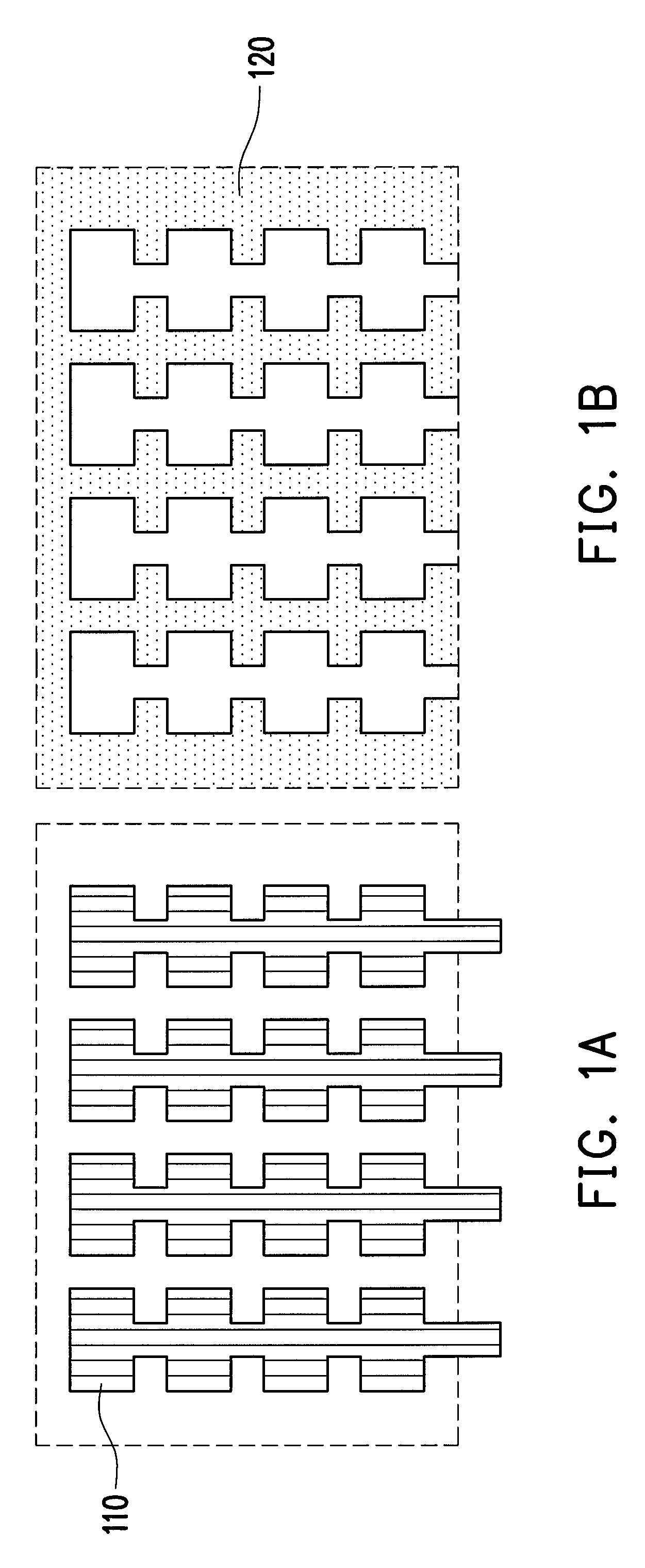

Touch sensing display panel, touch sensing color filter and fabricating method thereof

ActiveUS20090322702A1Touch sensing resolutionSimplify the manufacturing processCathode-ray tube indicatorsInput/output processes for data processingTouch SensesColor filter array

A touch sensing color filter including a substrate, a black matrix, a color filter layer and a second sensing electrode layer is provided. The black matrix is disposed on the substrate to define a plurality of sub-pixel areas. The black matrix includes a first sensing electrode layer, and the first sensing electrode layer has a plurality of openings corresponding to the sub-pixel areas. The color filter layer includes a plurality of color filter units disposed in the sub-pixel areas respectively. The second sensing electrode layer is disposed on the substrate, and the second sensing electrode layer includes a plurality of sub patterns corresponding to the sub-pixel areas. A method for fabricating the touch sensing color filter and a display panel using the same are further provided.

Owner:AU OPTRONICS CORP

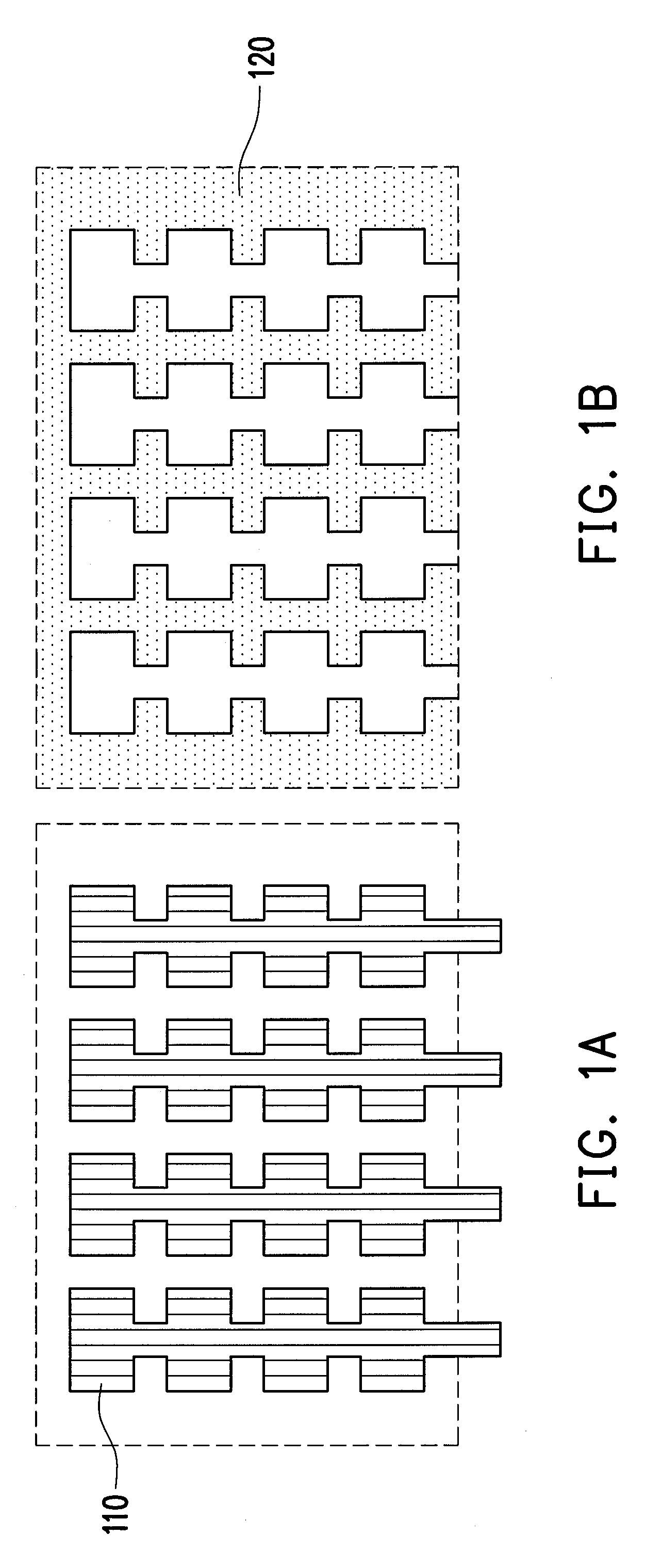

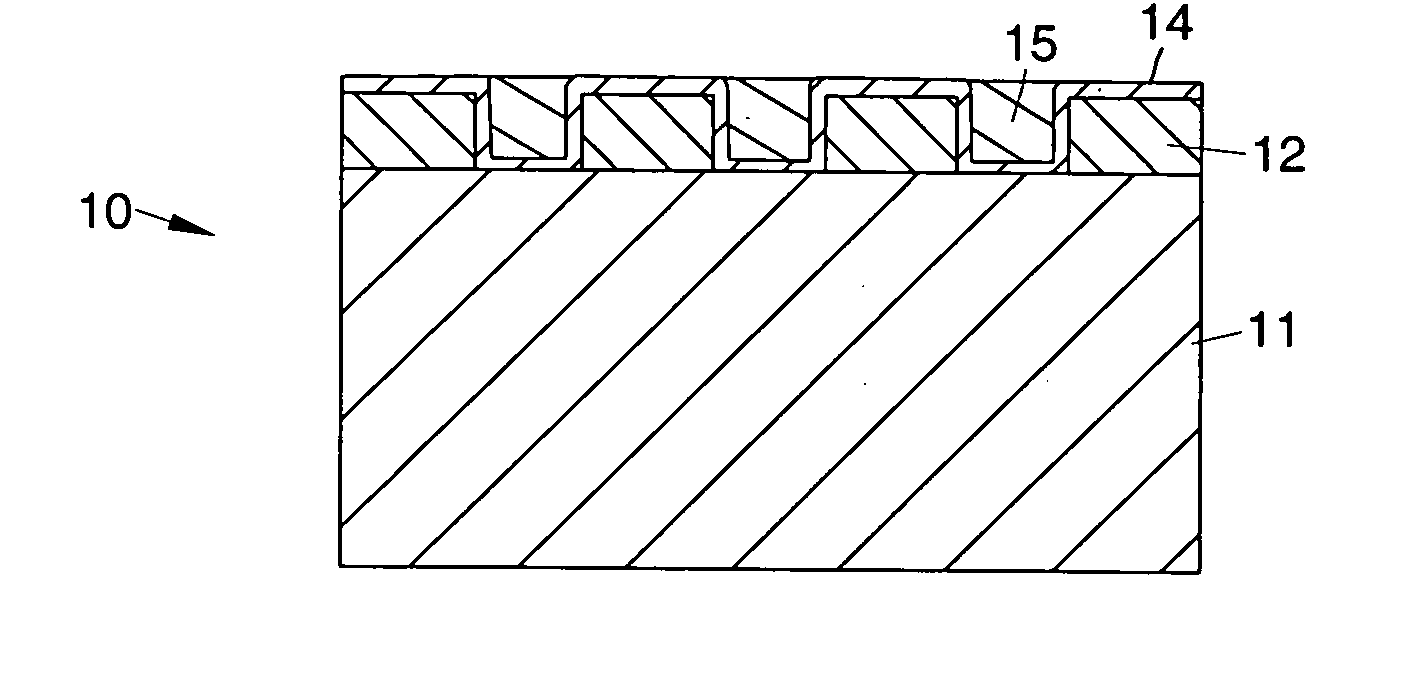

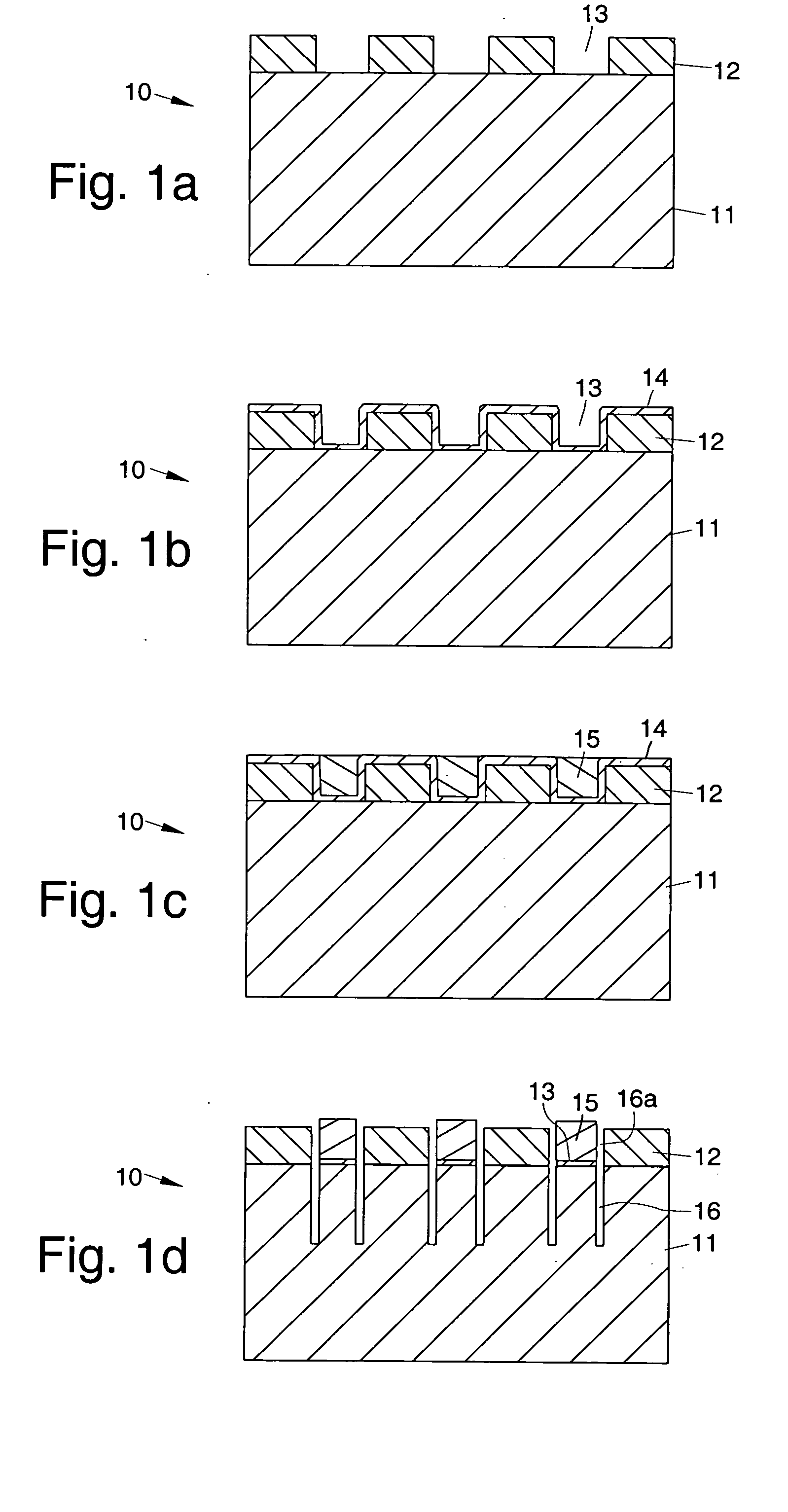

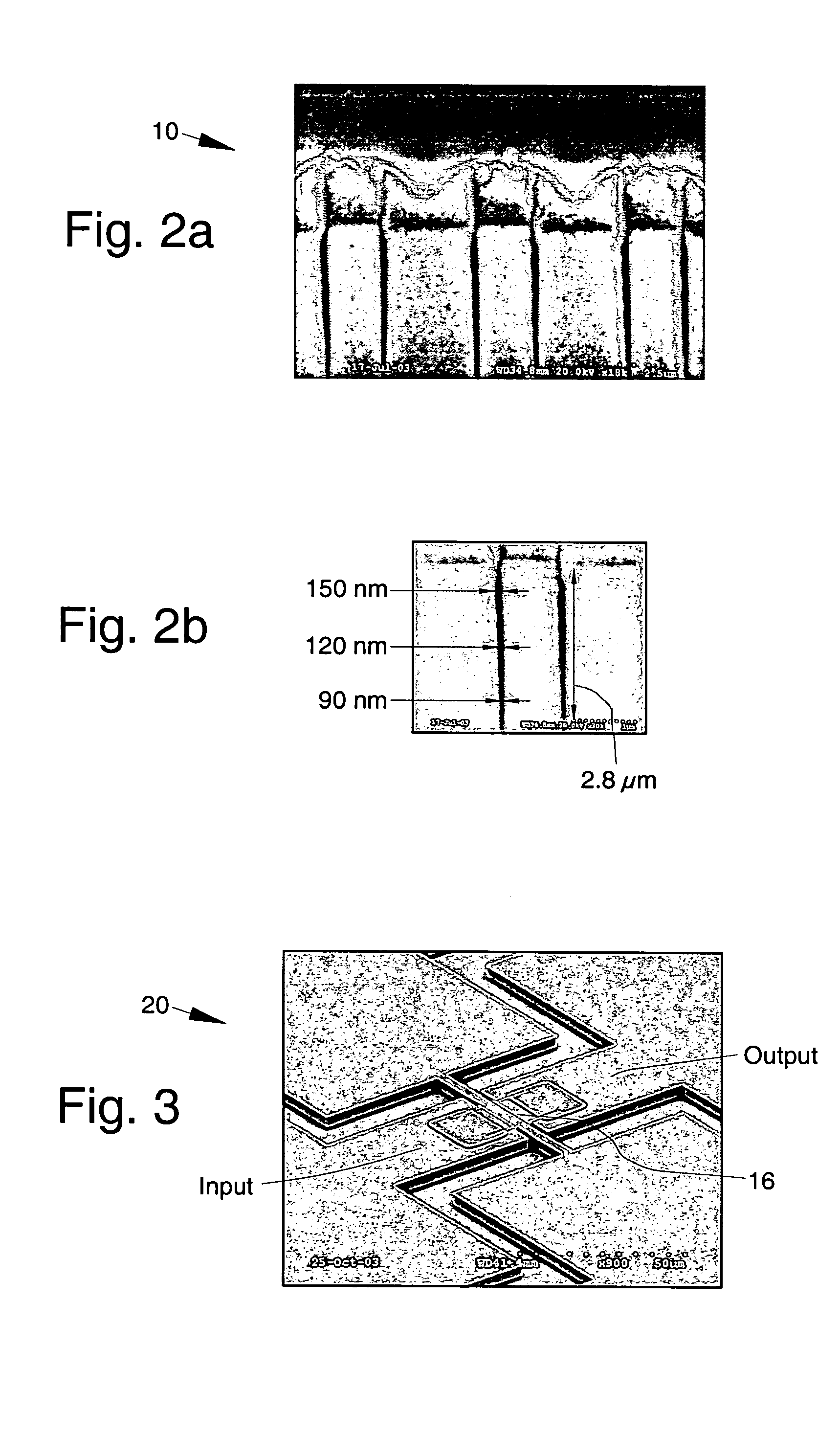

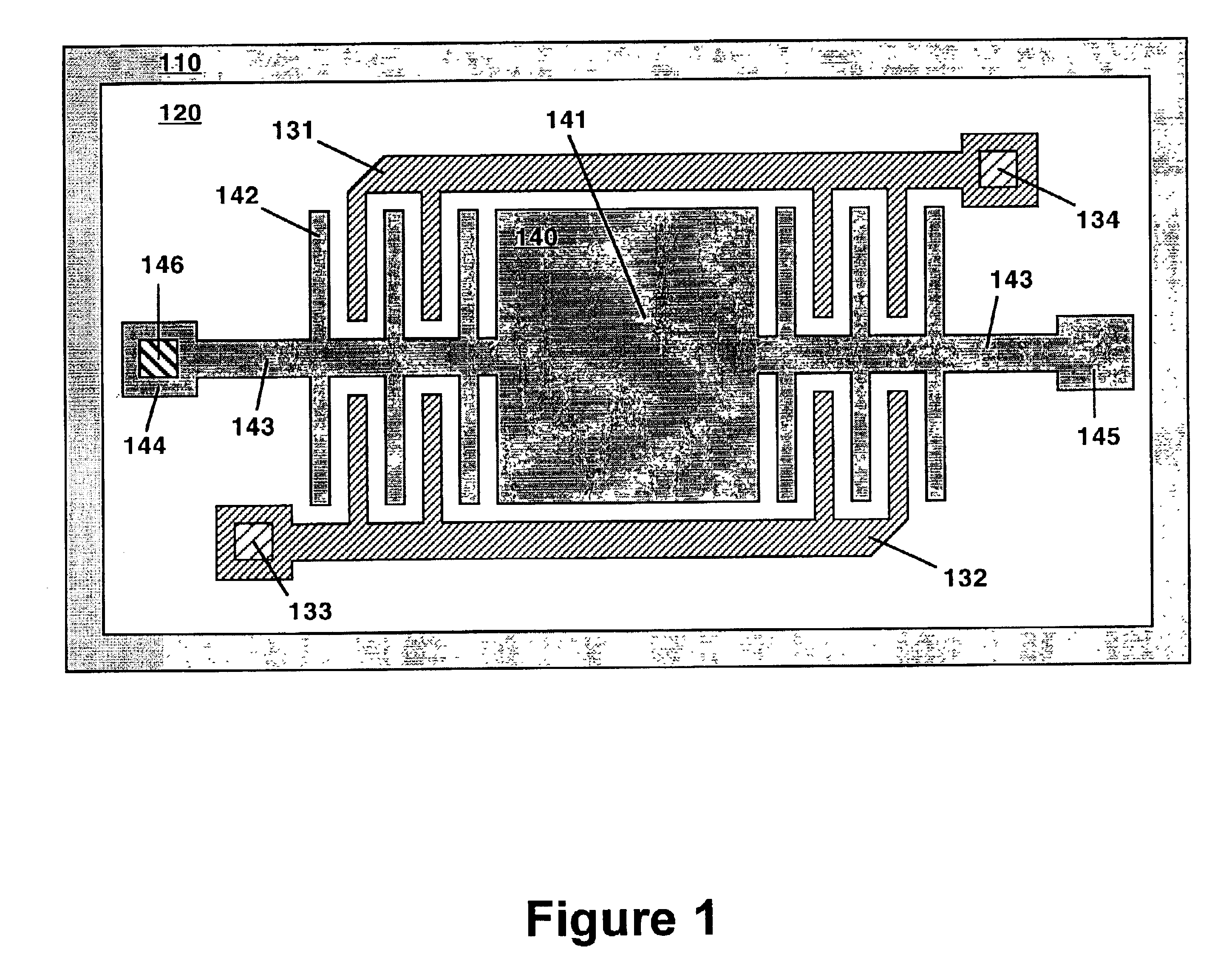

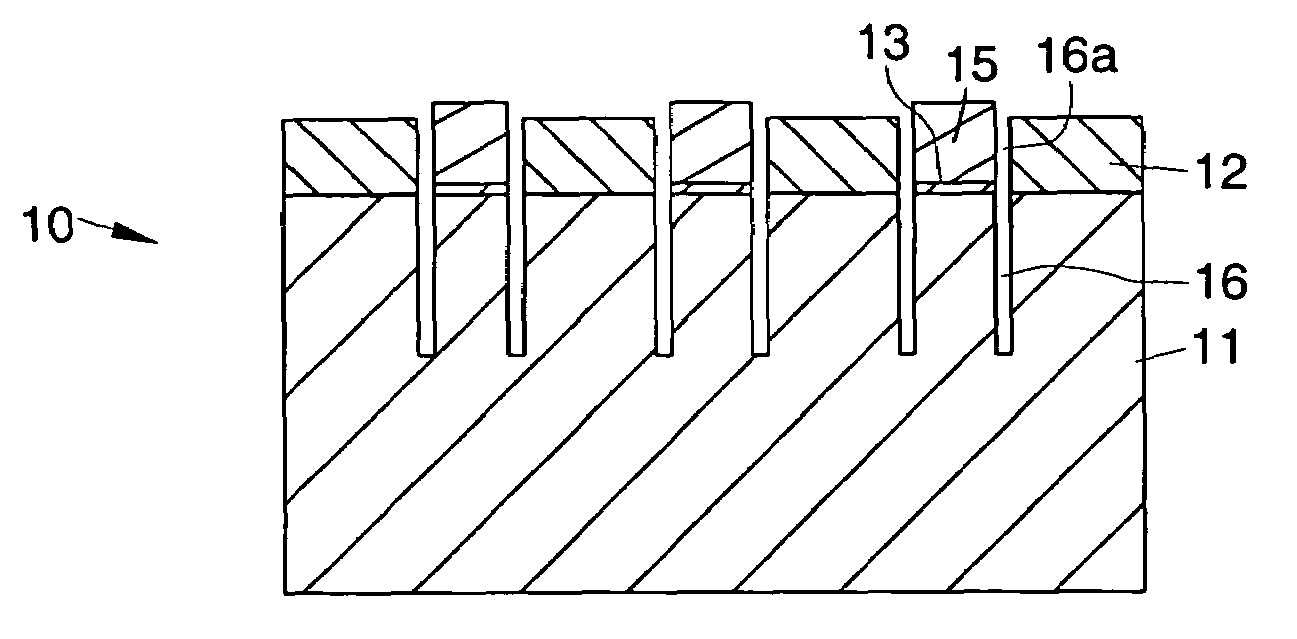

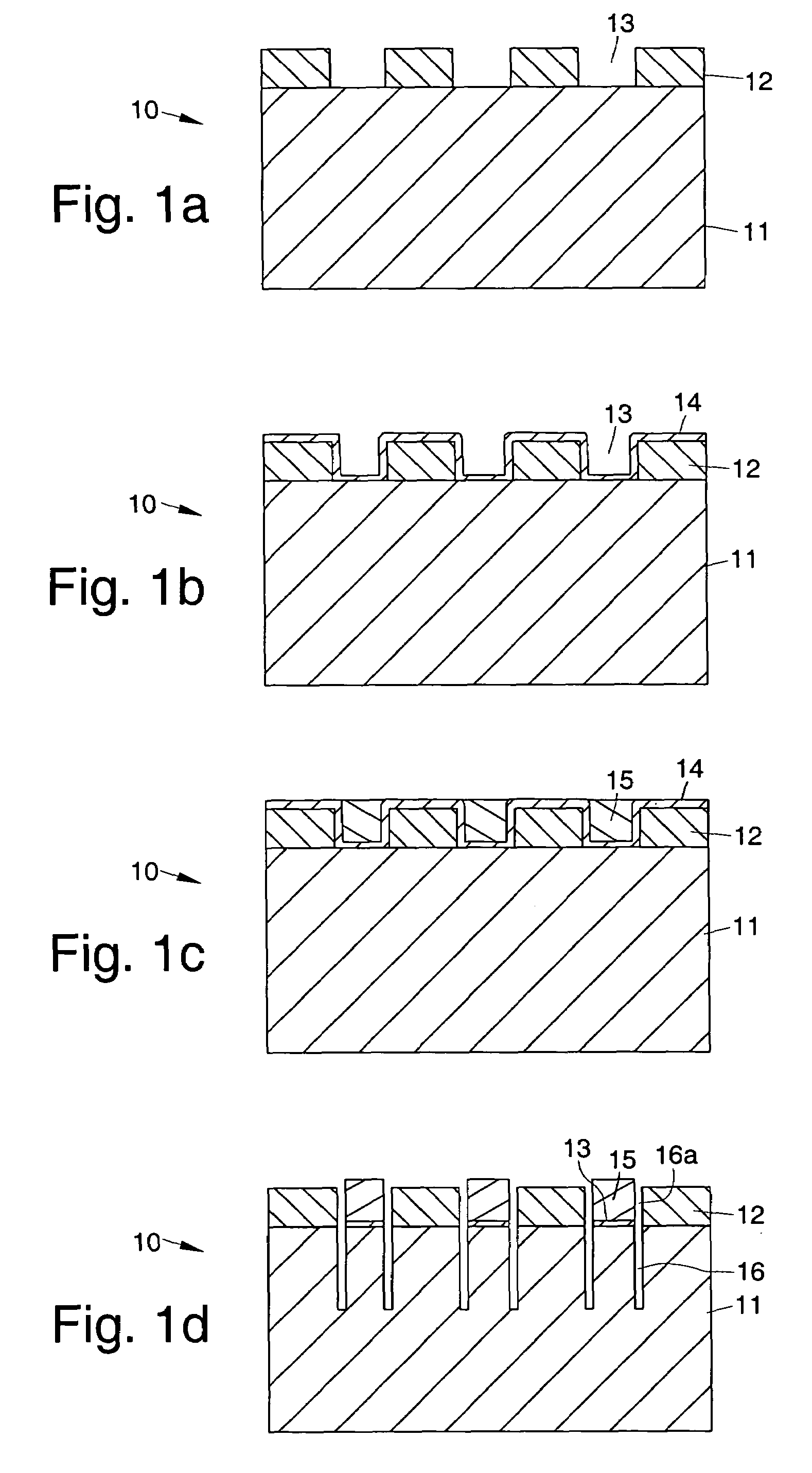

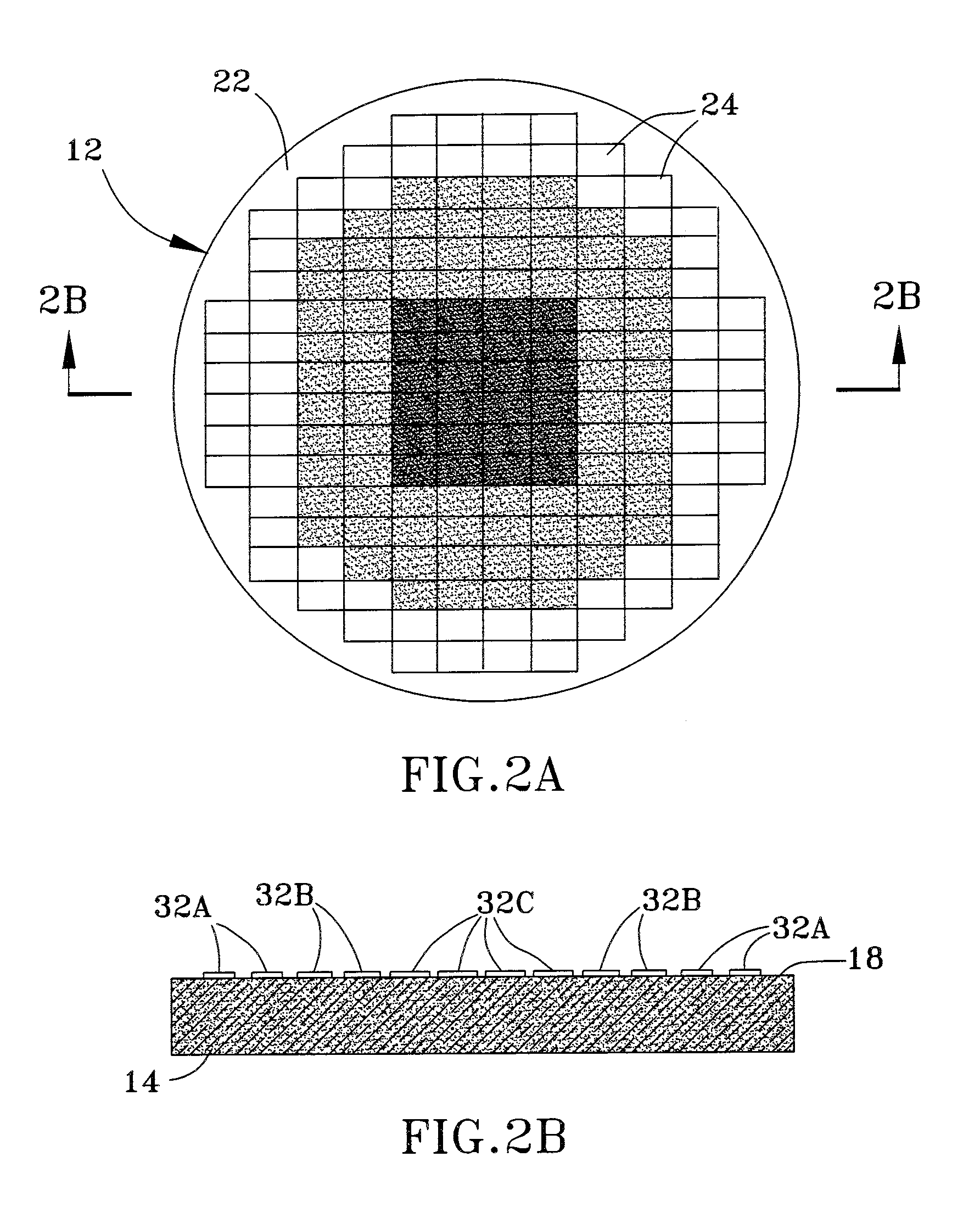

Methods of forming oxide masks with submicron openings and microstructures formed thereby

ActiveUS20050124135A1High process yieldHigh quality factorSemiconductor/solid-state device manufacturingMicrostructural device manufactureSingle crystalPhotolithography

Processing techniques are disclosed for batch fabrication of microstructures comprising an oxide mask on a substrate with submicron openings formed therein, and microstructures having deep-submicron, high aspect-ratio etched trenches, using conventional optical photolithography. Exemplary high aspect-ratio etched-trench microstructures that may be produced include single crystal resonators and sensors.

Owner:GEORGIA TECH RES CORP

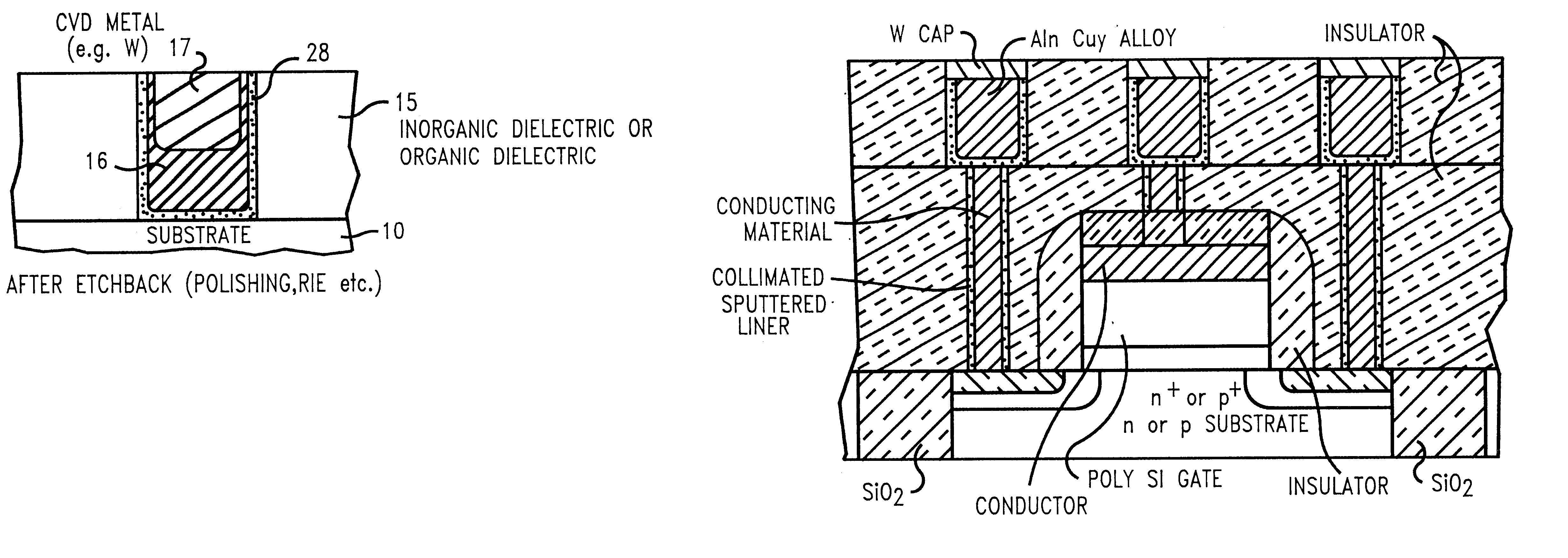

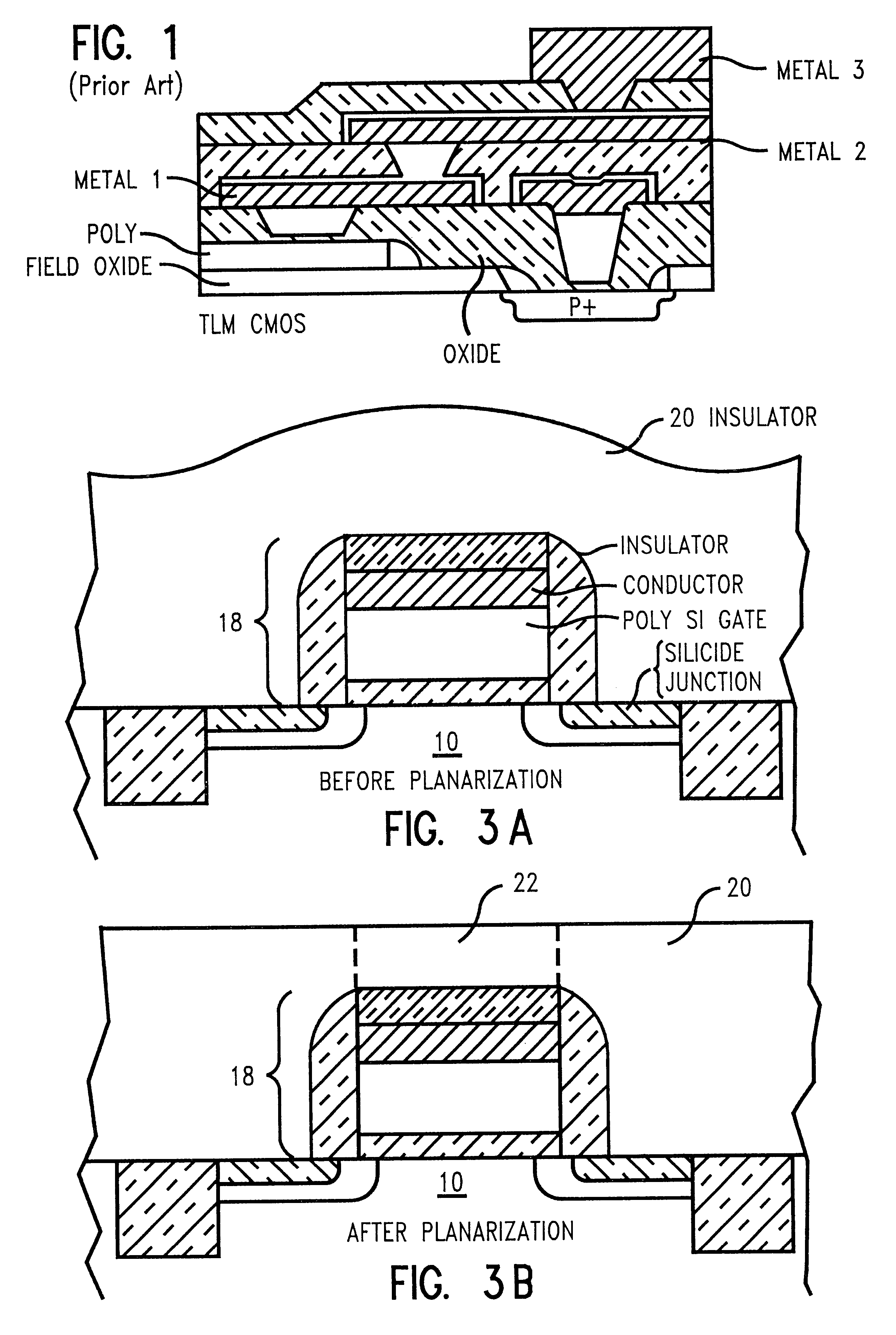

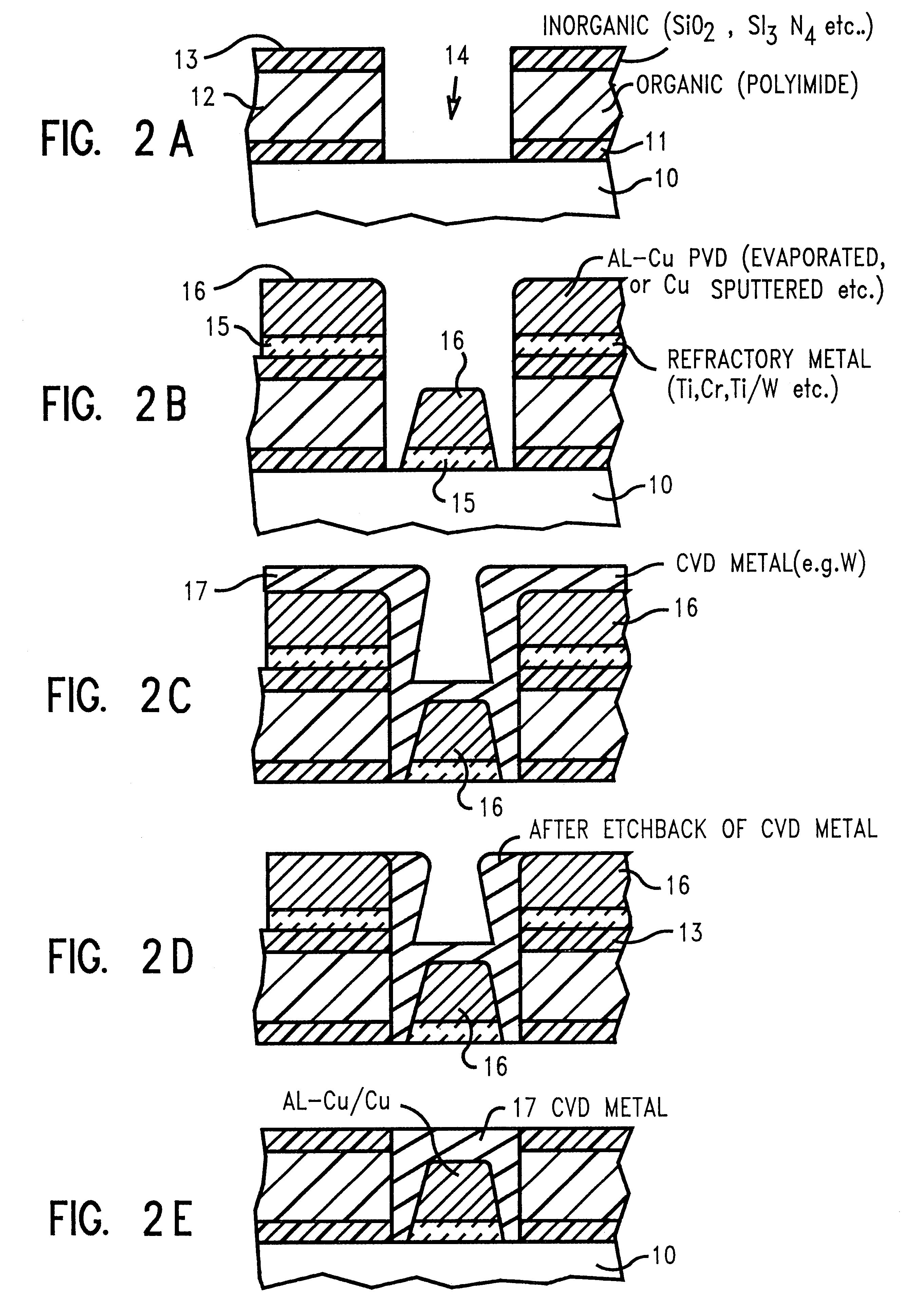

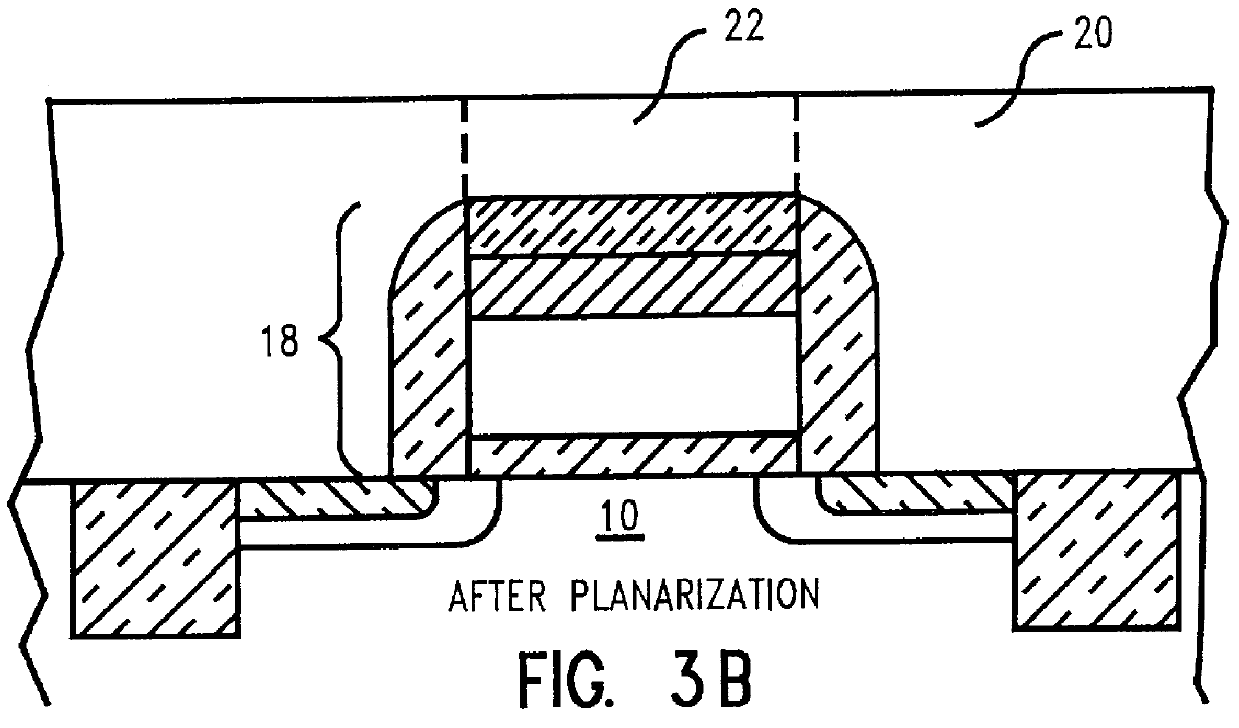

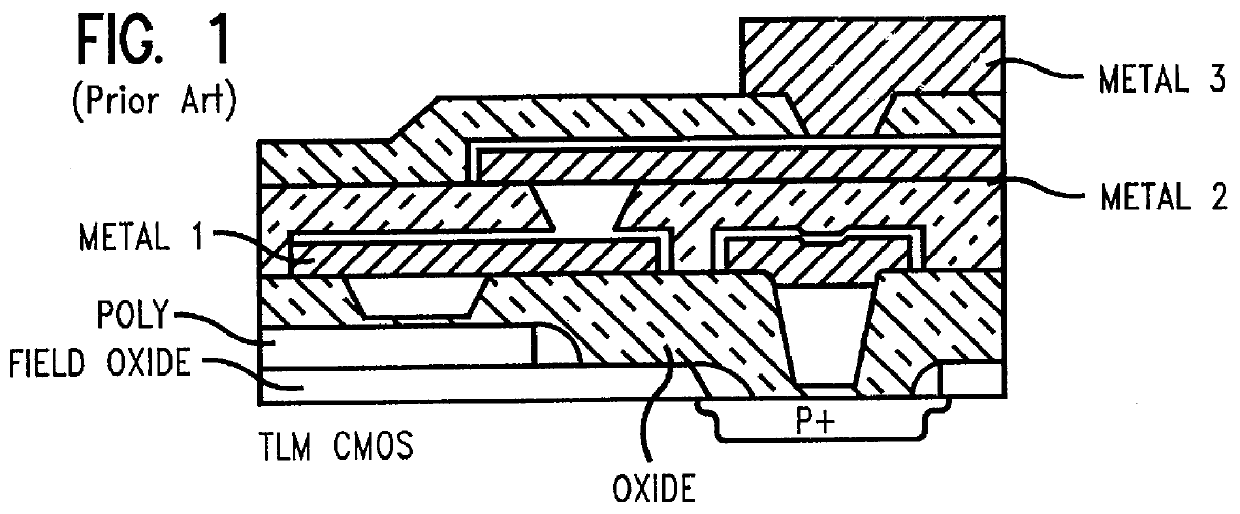

Refractory metal capped low resistivity metal conductor lines and vias formed using PVD and CVD

InactiveUS6323554B1High process yieldSemiconductor/solid-state device detailsSolid-state devicesDielectricGas phase

Capping a low resistivity metal conductor line or via with a refractory metal allows for effectively using chemical-mechanical polishing techniques because the hard, reduced wear, properties of the refractory metal do not scratch, corrode, or smear during chemical-mechanical polishing. Conductive lines and vias are created using a combination of both physical vapor deposition (e.g., evaporation or collimated sputtering) of a low resistivity metal or alloy followed by chemical vapor deposition (CVD) of a refractory metal and subsequent planarization. Altering a ratio of SiH4 to WF6 during application of the refractory metal cap by CVD allows for controlled incorporation of silicon into the tungsten capping layer. Collimated sputtering allows for creating a refractory metal liner in an opening in a dielectric which is suitable as a diffusion barrier to copper based metalizations as well as CVD tungsten. Ideally, for faster diffusing metals like copper, liners are created by a two step collimated sputtering process wherein a first layer is deposited under relatively low vacuum pressure where directional deposition dominates (e.g., below 1 mTorr) and a second layer is deposited under relatively high vacuum pressure where scattering deposition dominates (e.g., above 1 mTorr). For refractory metals like CVD tungsten, the liner can be created in one step using collimated sputtering at higher vacuum pressures.

Owner:GLOBALFOUNDRIES INC

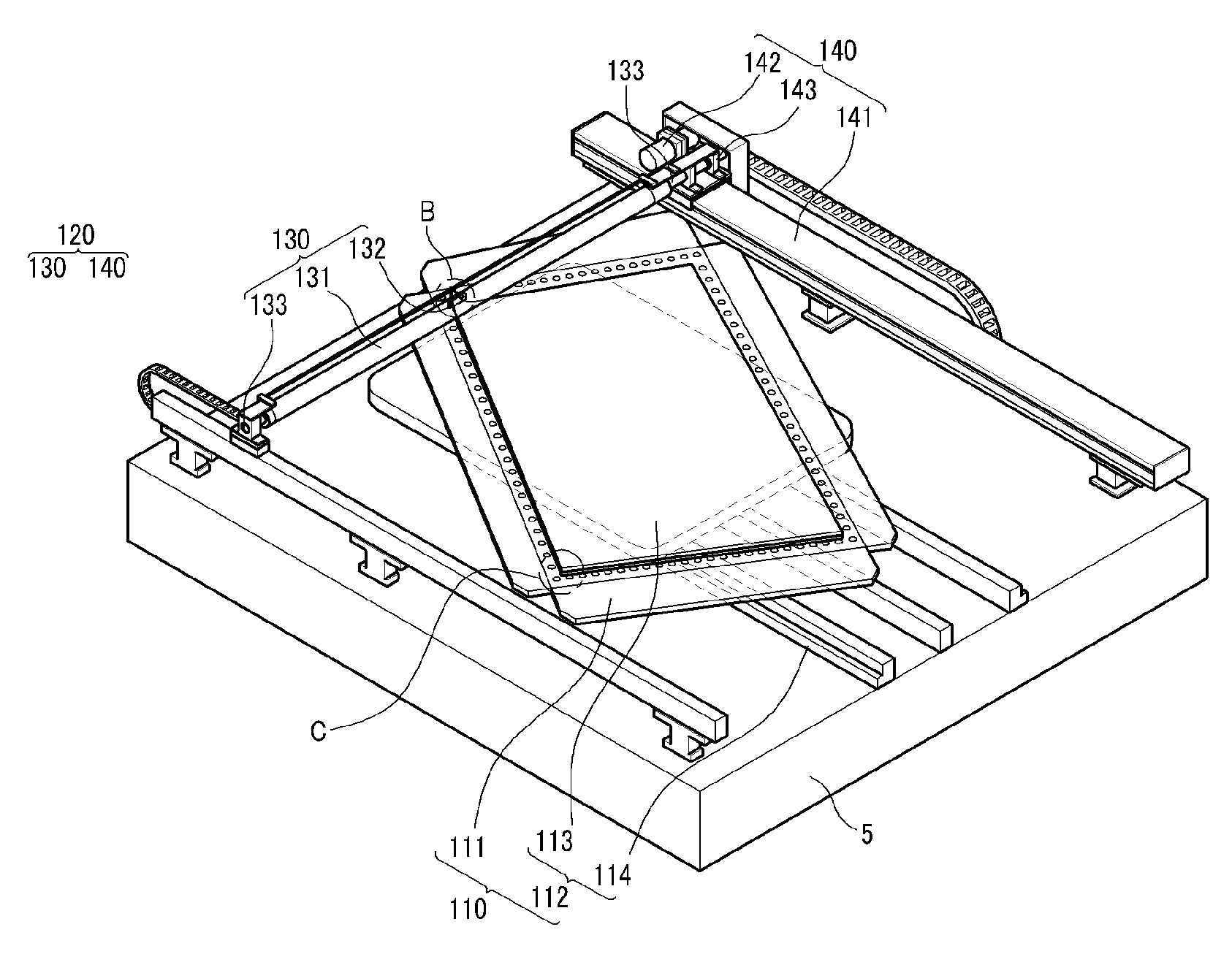

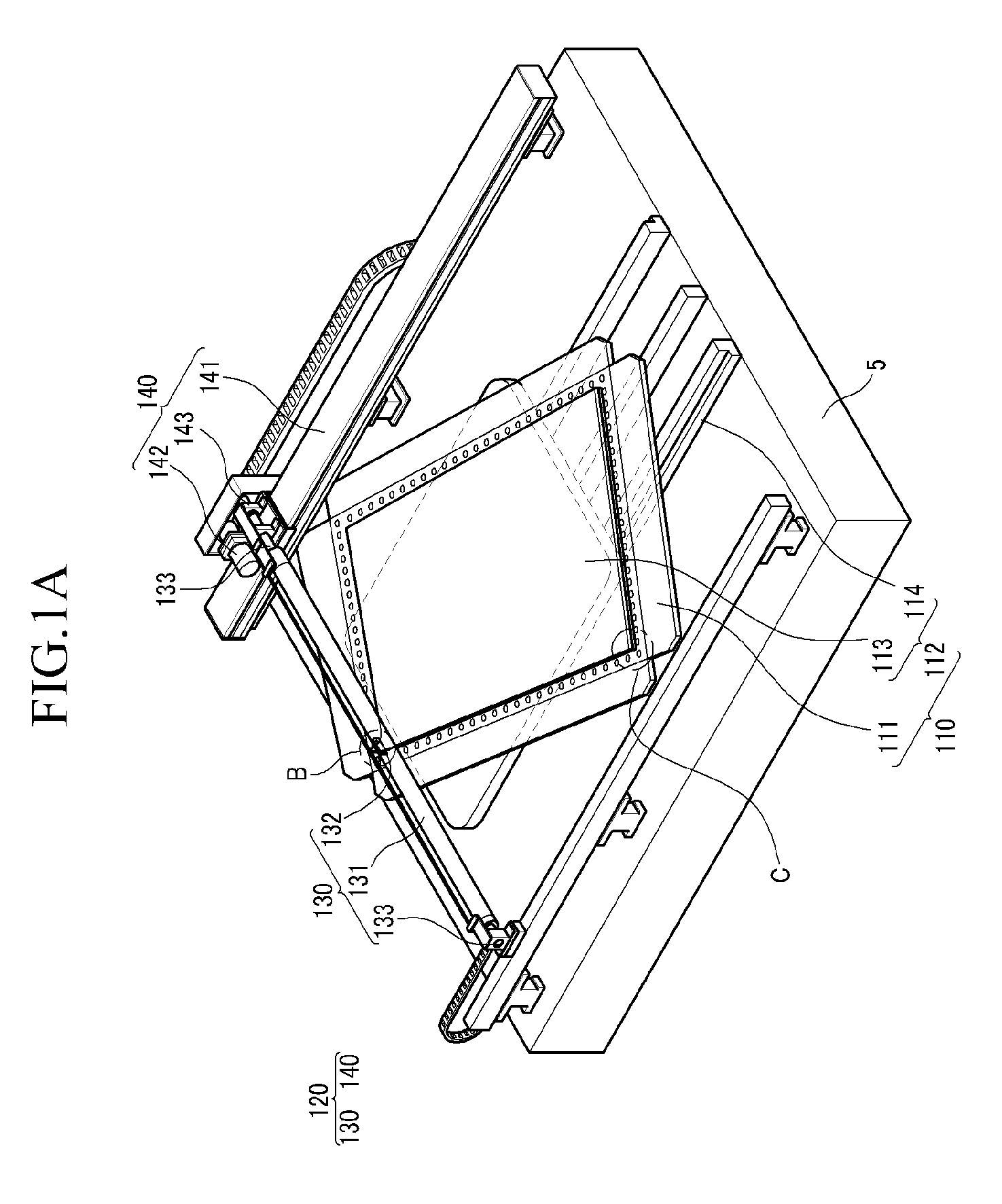

Apparatus for removing a polarizer and method thereof

InactiveUS20080236743A1Improve productivityHigh process yieldLamination ancillary operationsLaminationLiquid-crystal displayEngineering

An apparatus for removing a polarizer of a liquid crystal display includes a roller portion including a rotating exfoliating roller and a gripping portion disposed on the exfoliating roller and gripping an edge of the polarizer, and a roller moving portion exfoliating the polarizer from a liquid crystal panel, the roller moving portion rotating and moving the roller portion. A rotating direction of the exfoliating roller is the same as a moving direction of the exfoliating roller.

Owner:SAMSUNG ELECTRONICS CO LTD

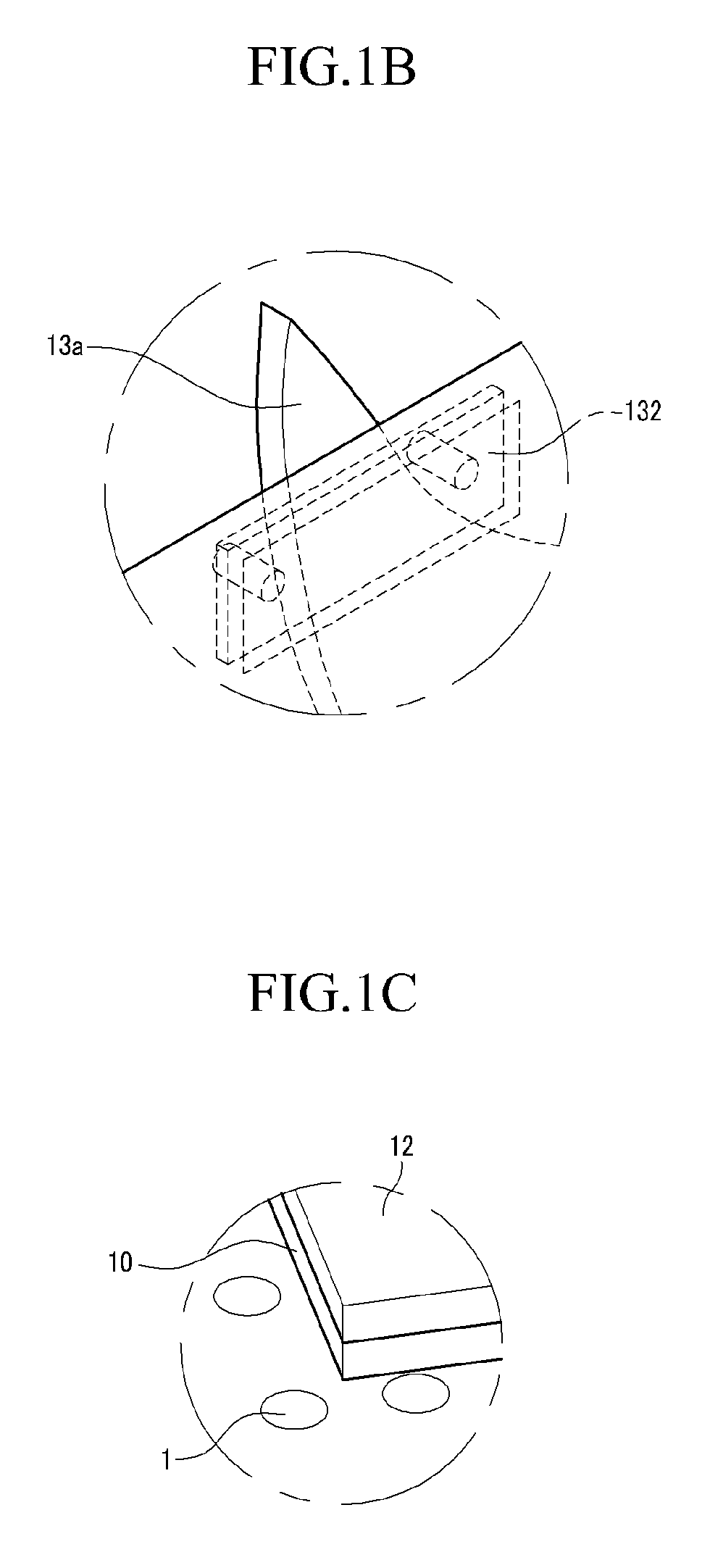

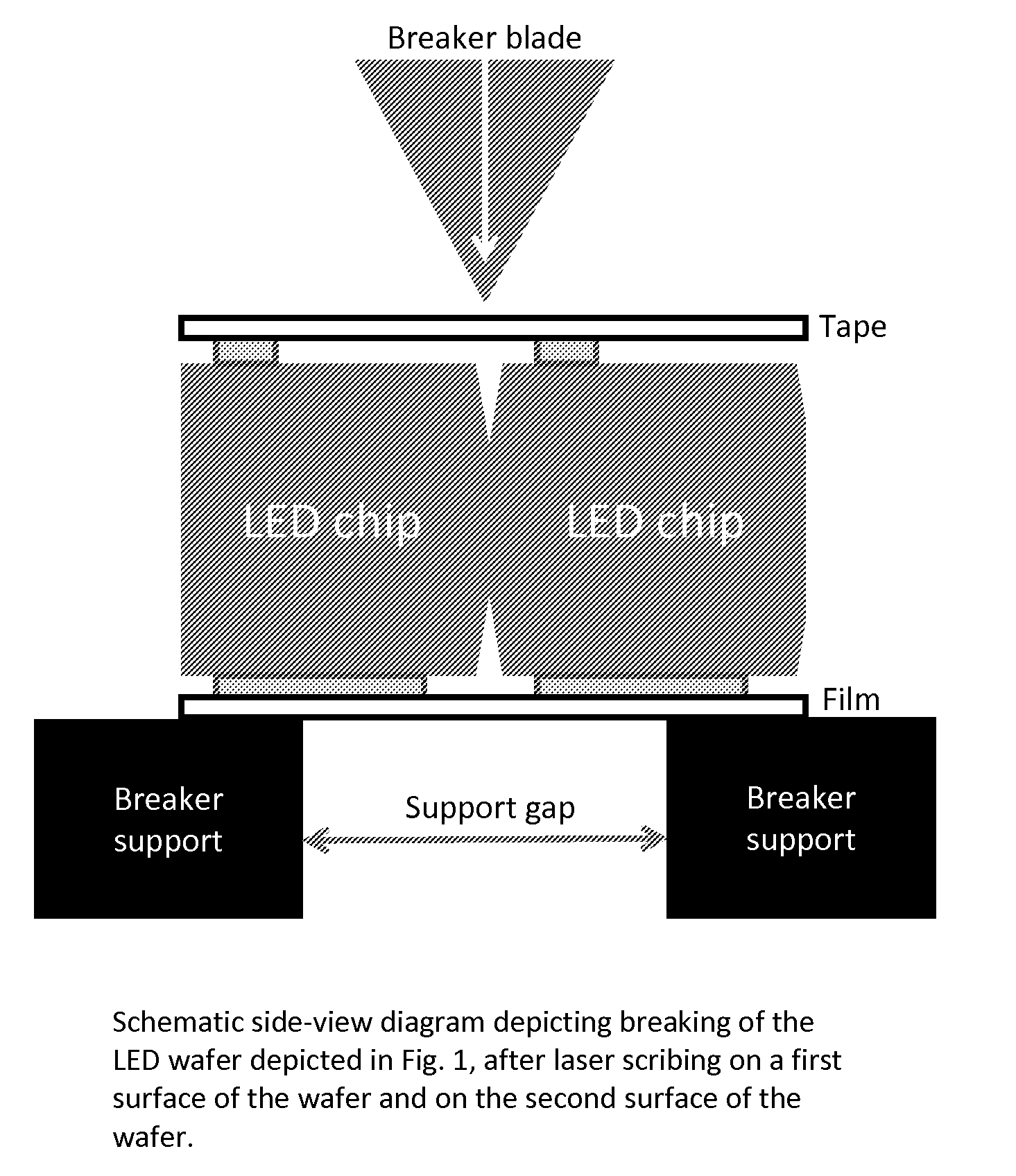

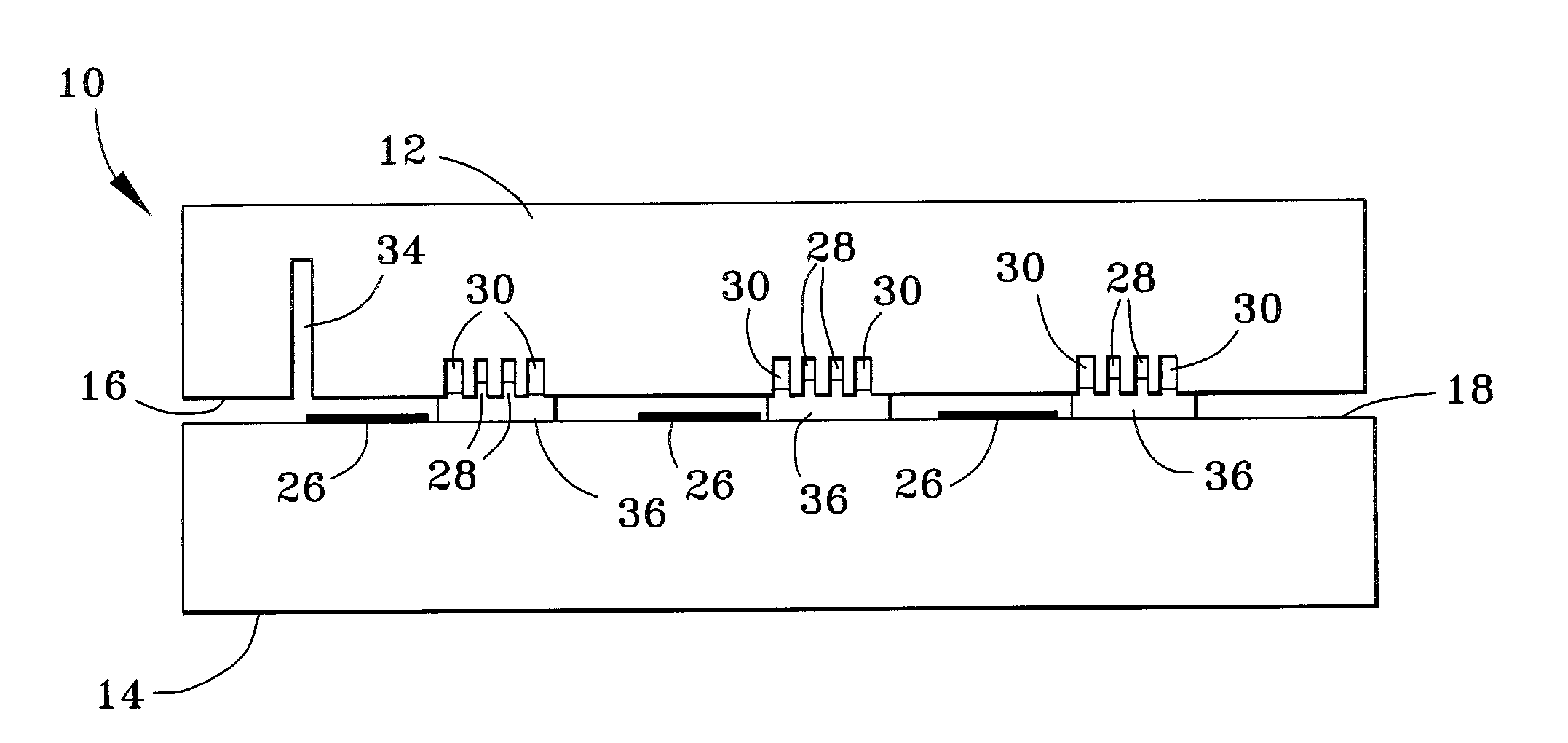

Process for high yield fabrication of MEMS devices

ActiveUS6872319B2Thickness minimizationExceptionally precise layer to layer alignmentSemi-permeable membranesPrecision positioning equipmentEngineeringSilicon

A MEMS fabrication process eliminates through-wafer etching, minimizes the thickness of silicon device layers and the required etch times, provides exceptionally precise layer to layer alignment, does not require a wet etch to release the moveable device structure, employs a supporting substrate having no device features on one side, and utilizes low-temperature metal-metal bonding which is relatively insensitive to environmental particulates. This process provided almost 100% yield of scanning micromirror devices exhibiting scanning over a 12° optical range and a mechanical angle of ±3° at a high resonant frequency of 2.5 kHz with an operating voltage of only 20 VDC.

Owner:TELEDYNE SCI & IMAGING

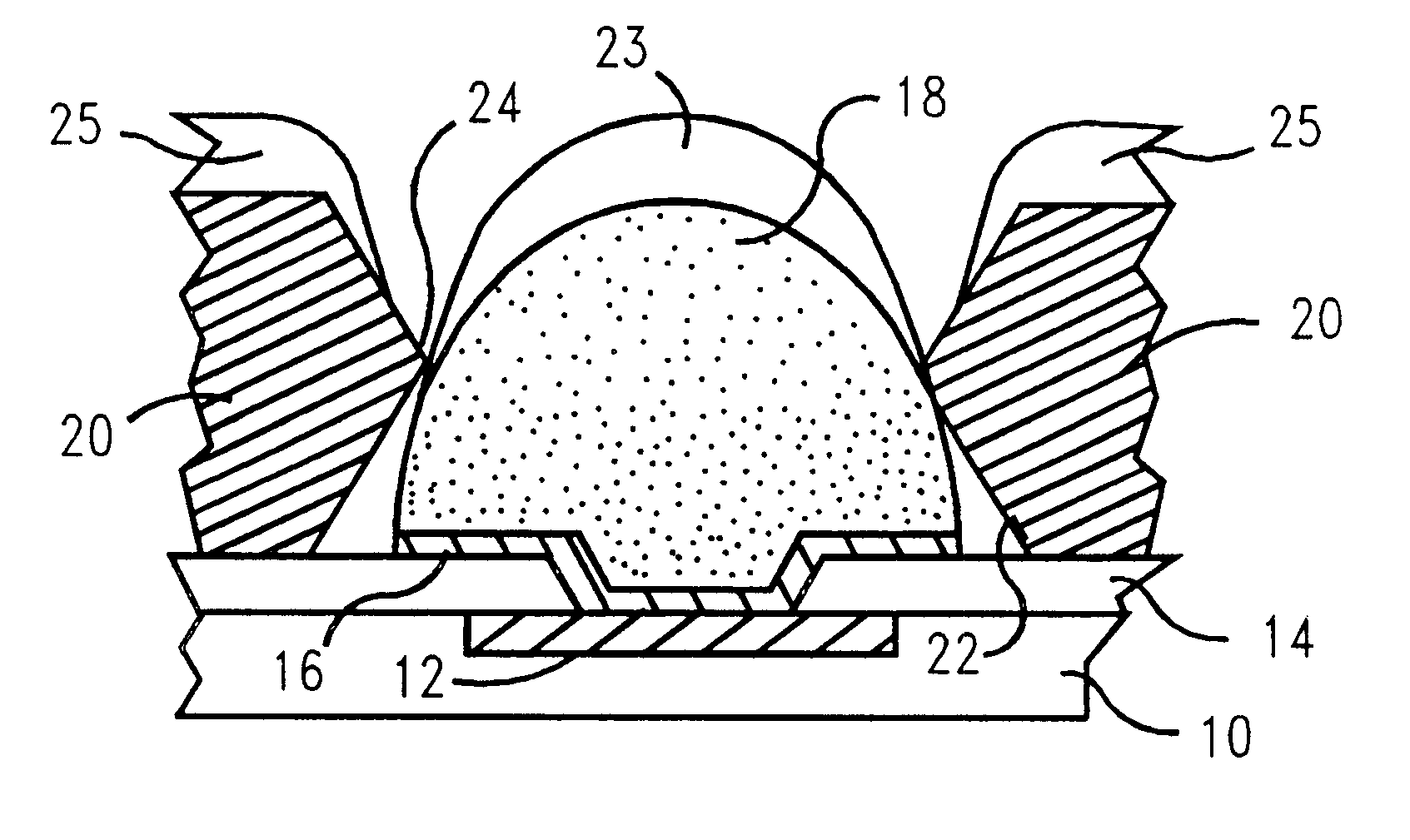

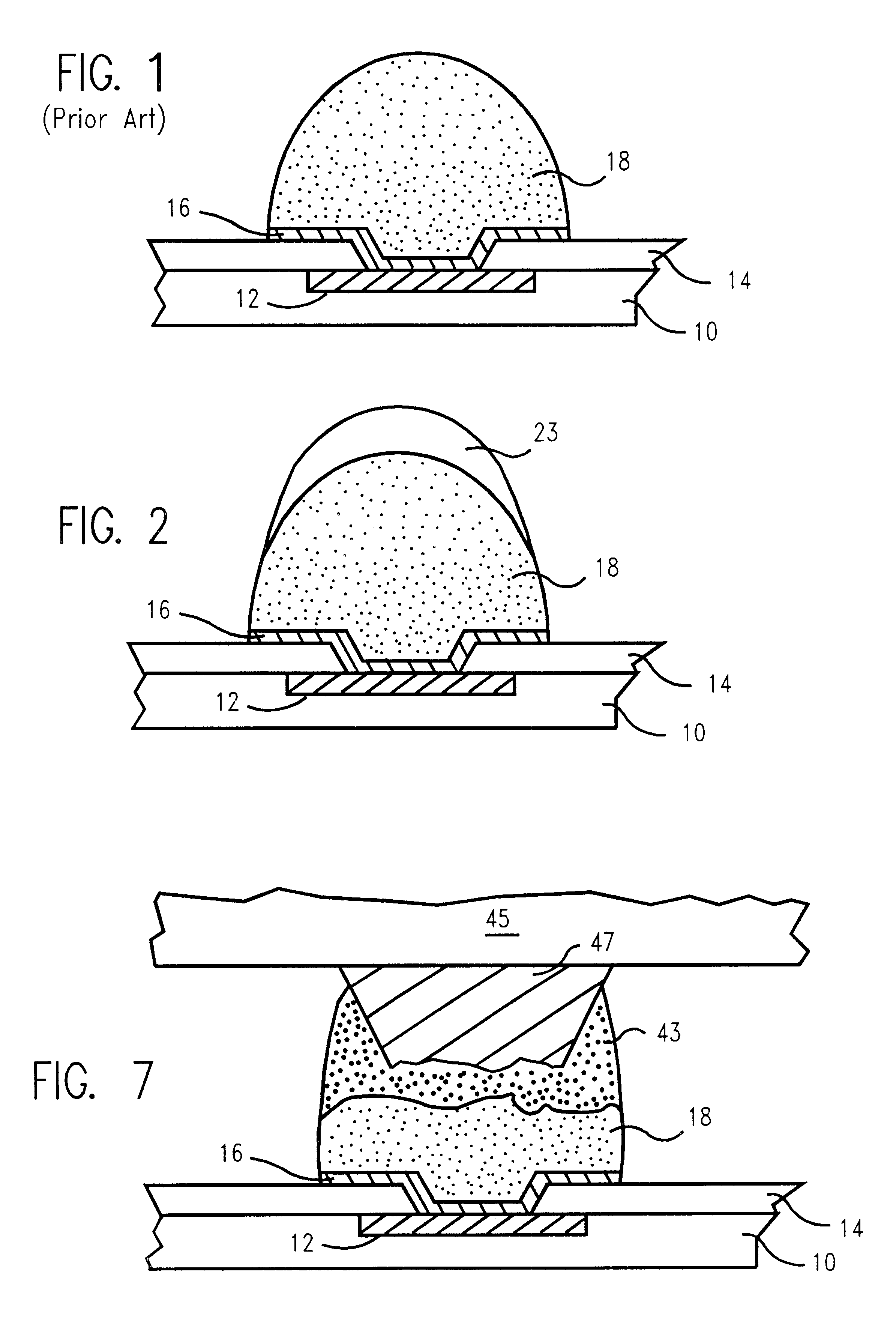

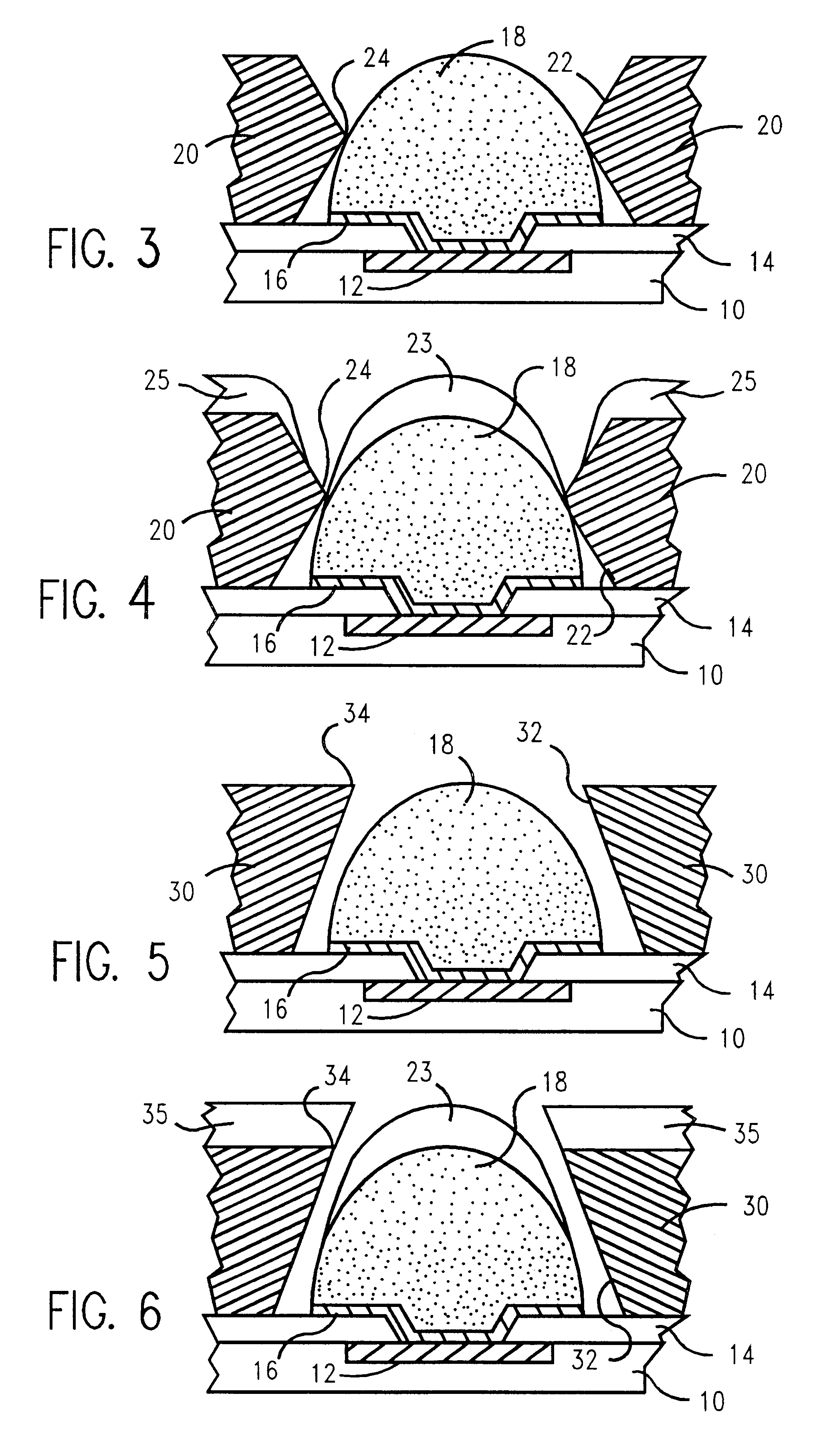

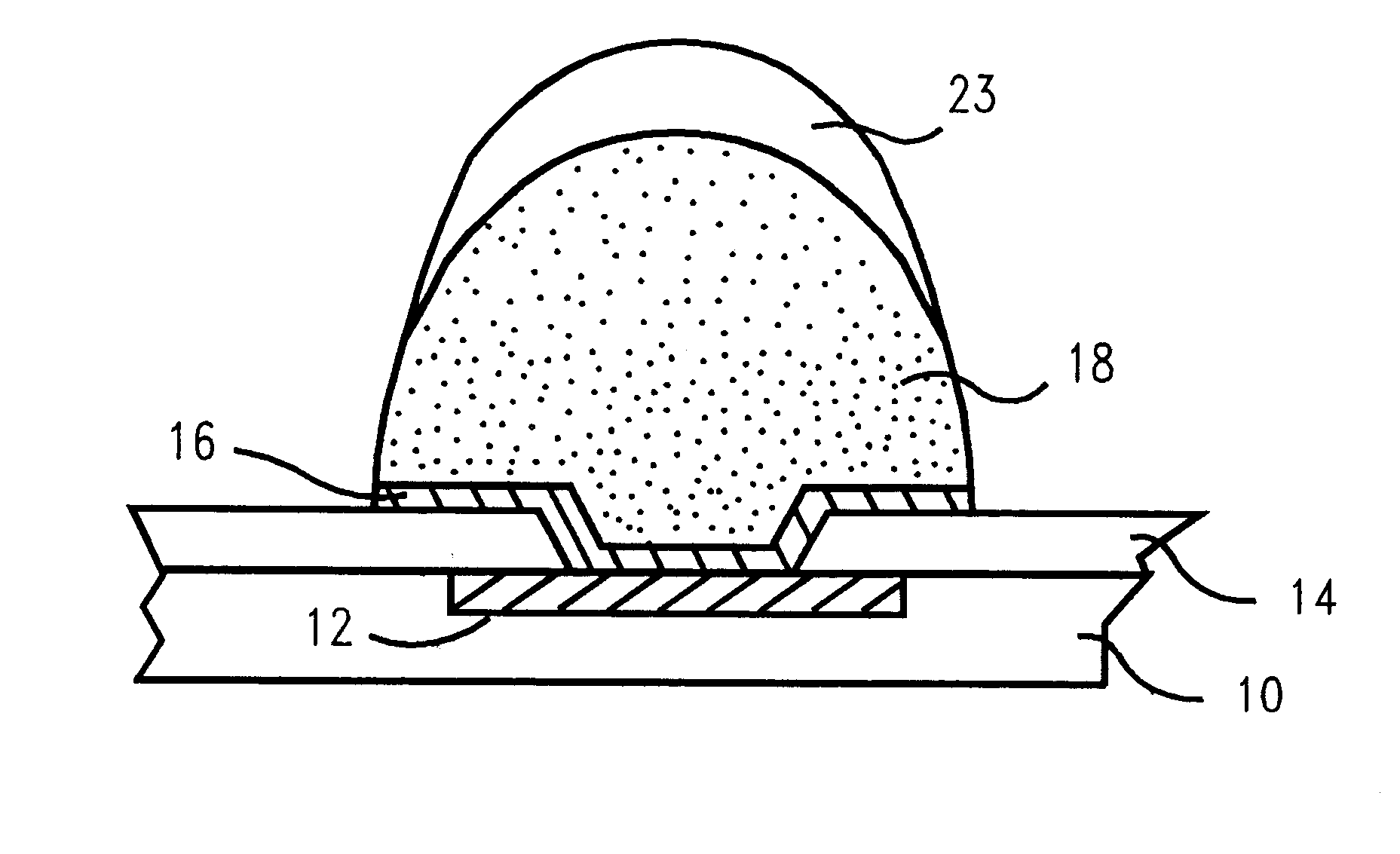

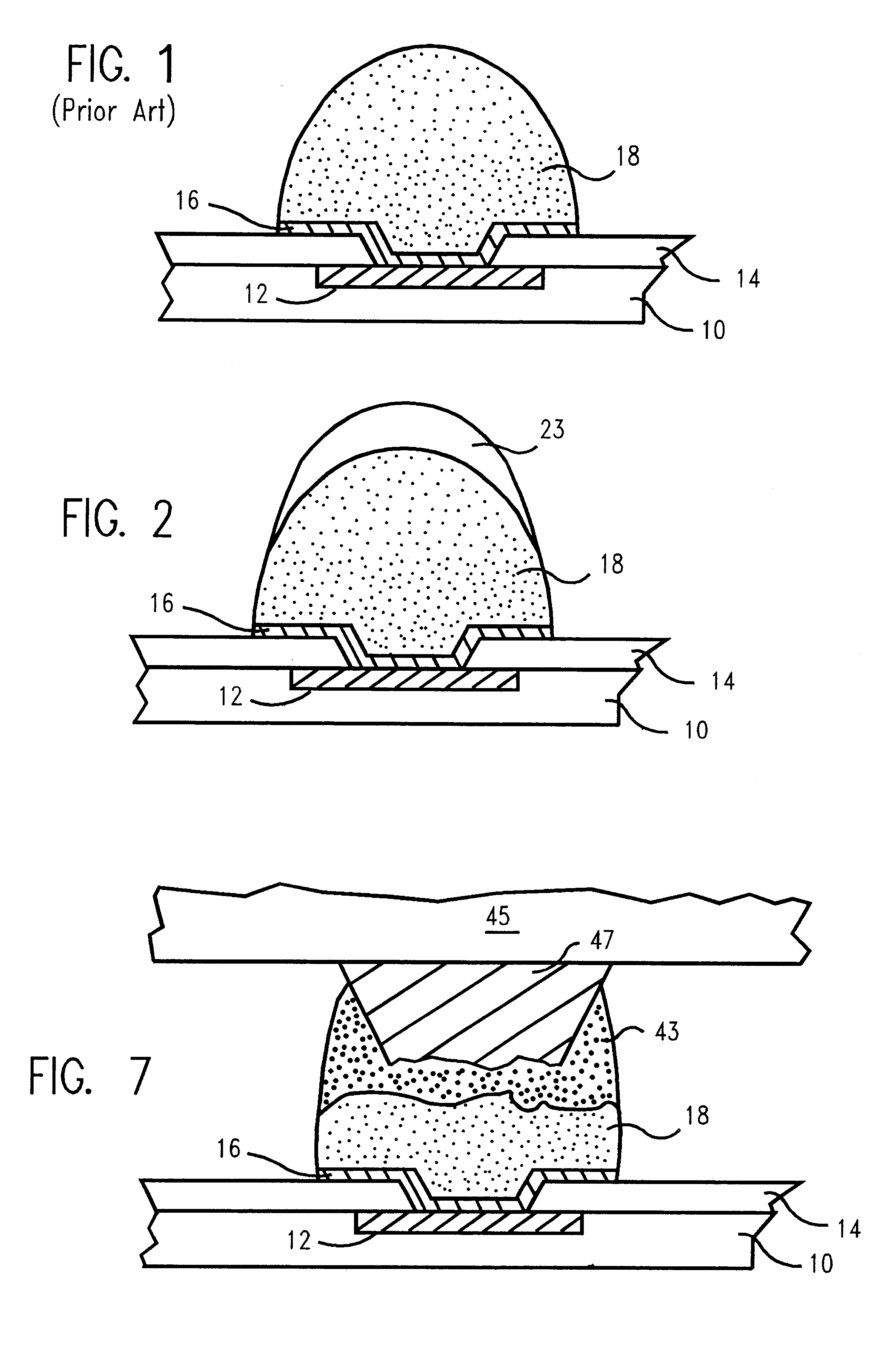

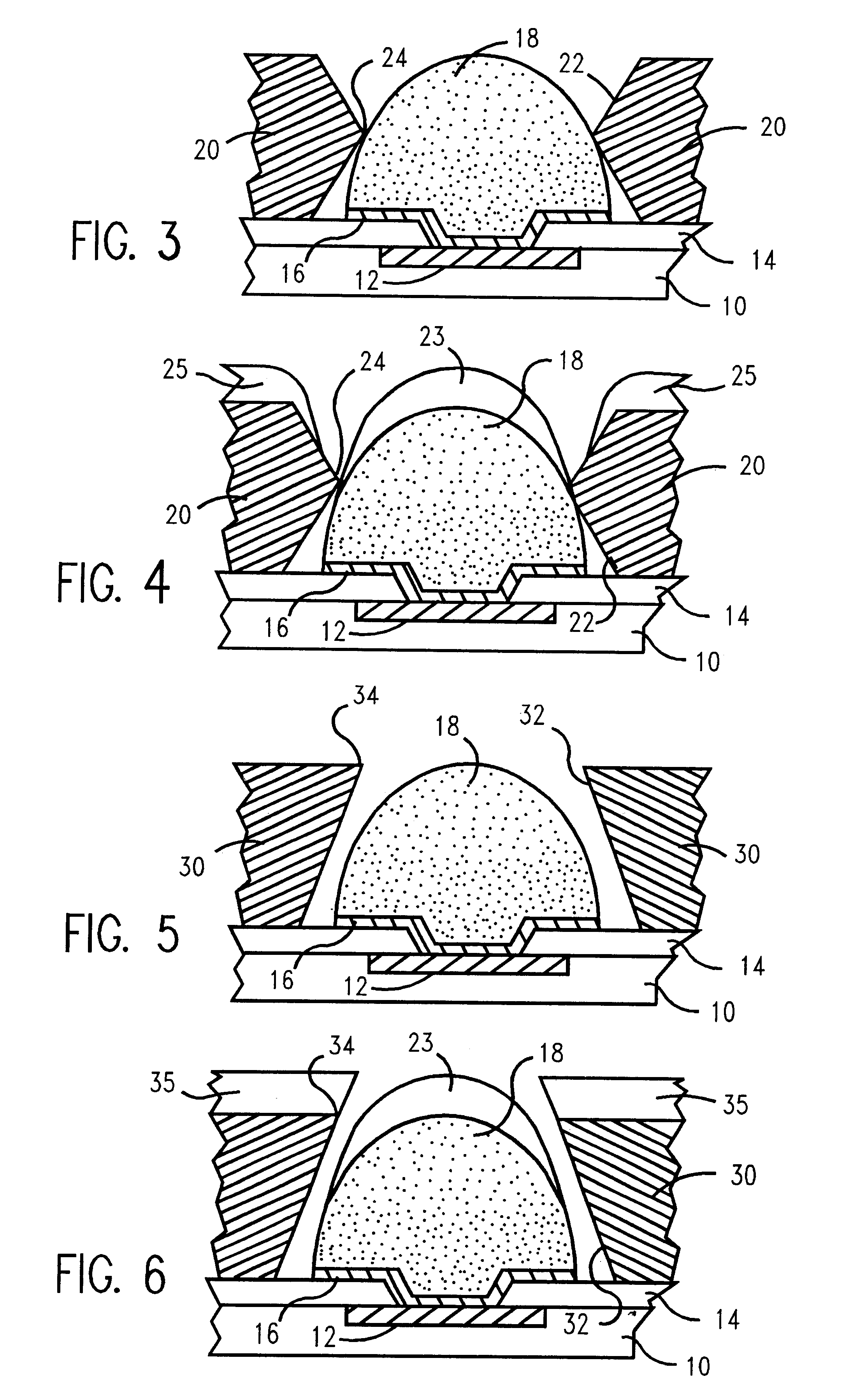

Method for forming reflowed solder ball with low melting point metal cap

InactiveUS6344234B1Reduce the hole diameterMinimal diameterFinal product manufactureSemiconductor/solid-state device detailsTinningIndium

A method and structure for a solder interconnection, using solder balls for making a low temperature chip attachment directly to any of the higher levels of packaging substrate is disclosed. After a solder ball has been formed using standard methods it is reflowed to give the solder ball a smooth surface. A layer of low melting point metal, such as, bismuth, indium or tin, preferably, pure tin, is deposited on the top of the solder balls. This structure results in localizing of the eutectic alloy, formed upon subsequent low temperature joining cycle, to the top of the high melting solder ball even after multiple low temperature reflow cycles. This method does not need tinning of the substrate to which the chip is to be joined, which makes this method economical. It has also been noticed that whenever temperature is raised slightly above the eutectic temperature, the structure always forms a liquid fillet around the joint with copper wires. This liquid fillet formation results in substantial thermal fatigue life improvement for reduced stress at interface; and secondly, provides an easy means to remove chip for the purpose of chip burn-in, replacement or field repairs.

Owner:ULTRATECH INT INC

Semiconductor device including a deflected part

ActiveUS7989855B2Less dislocation and defectControlled amount of strainTransistorSolid-state devicesLight beamSemiconductor

This invention relates to a semiconductor device having a beam made of a semiconductor to which strain is introduced by deflection, and a current is permitted to flow in the beam.

Owner:GK BRIDGE 1

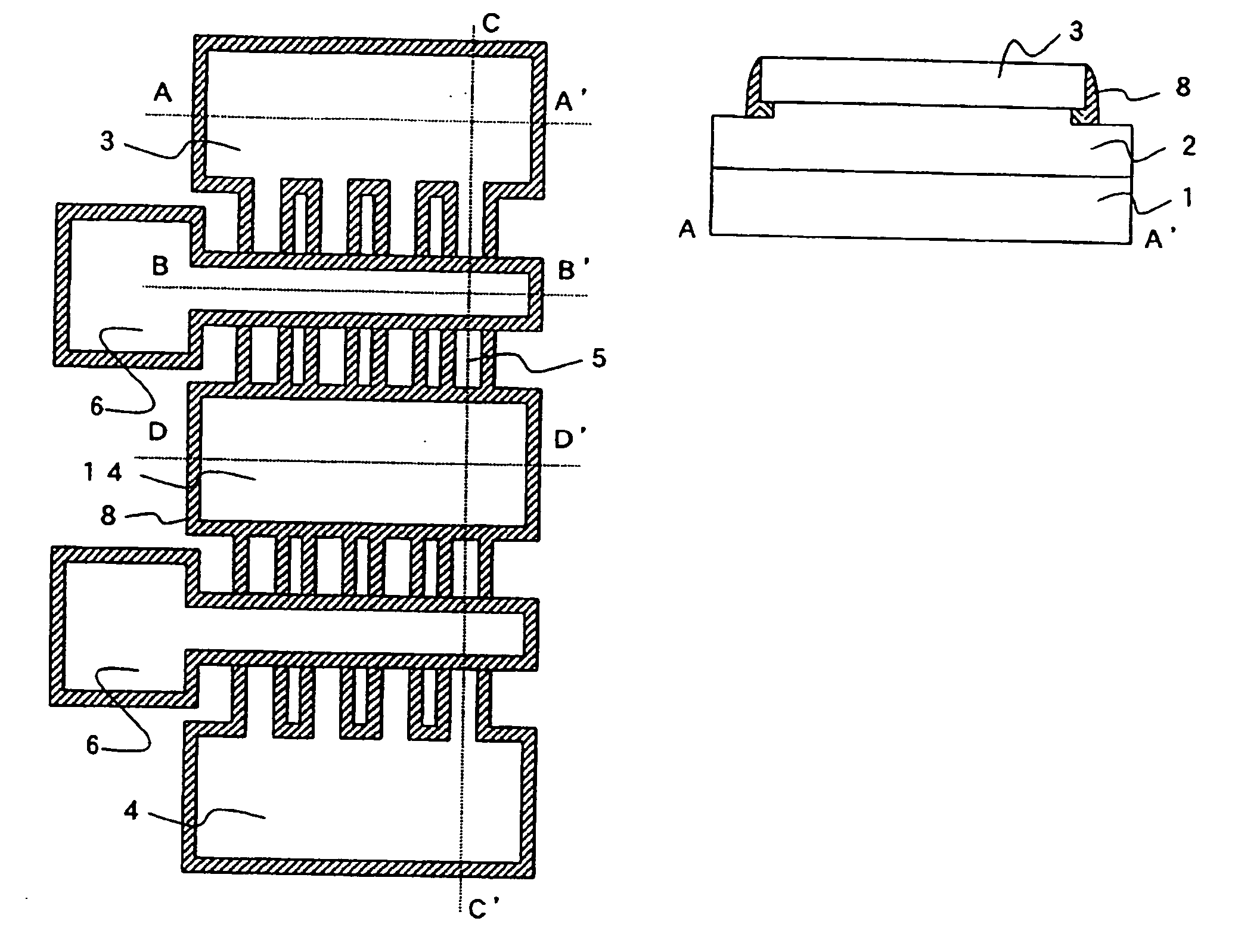

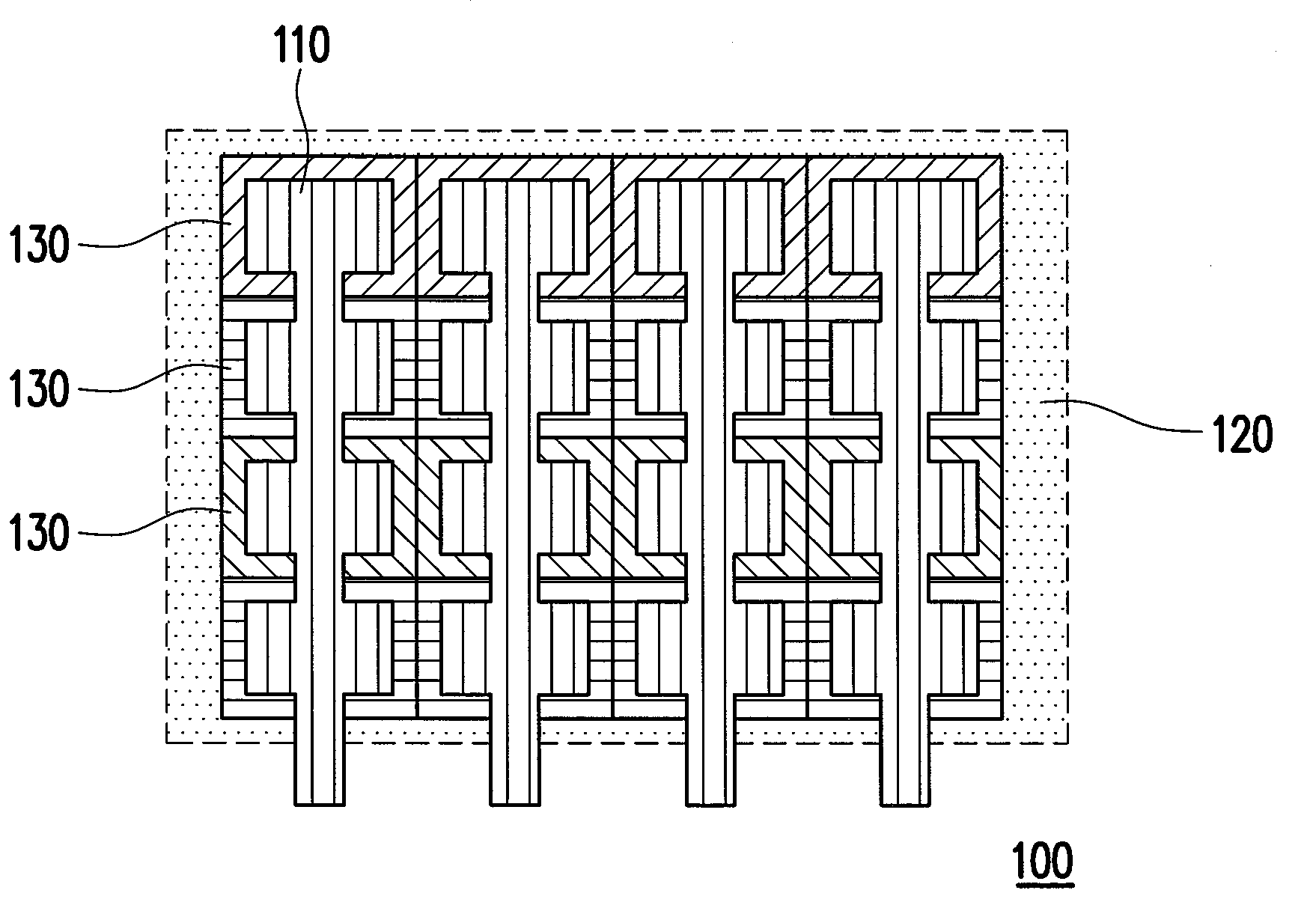

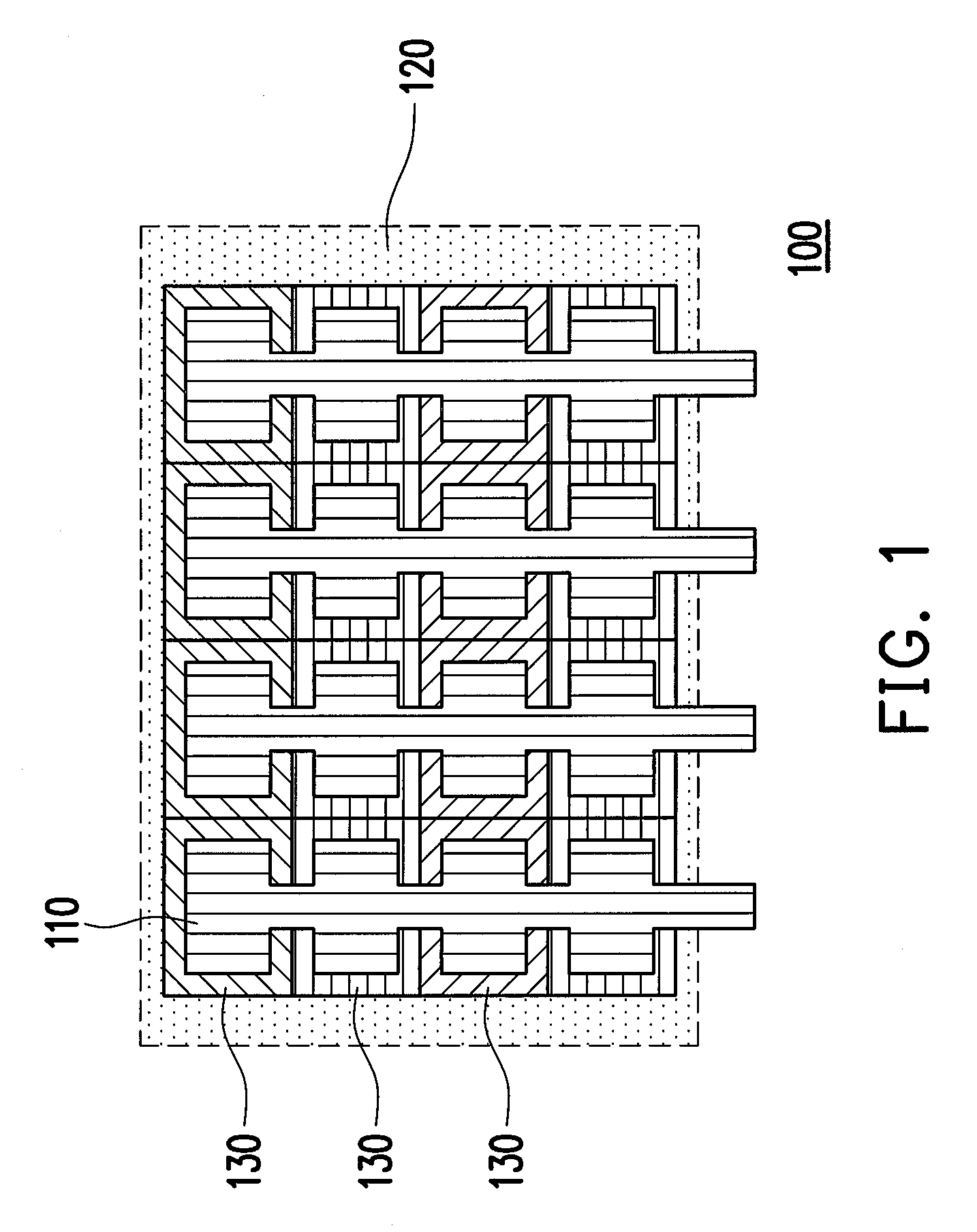

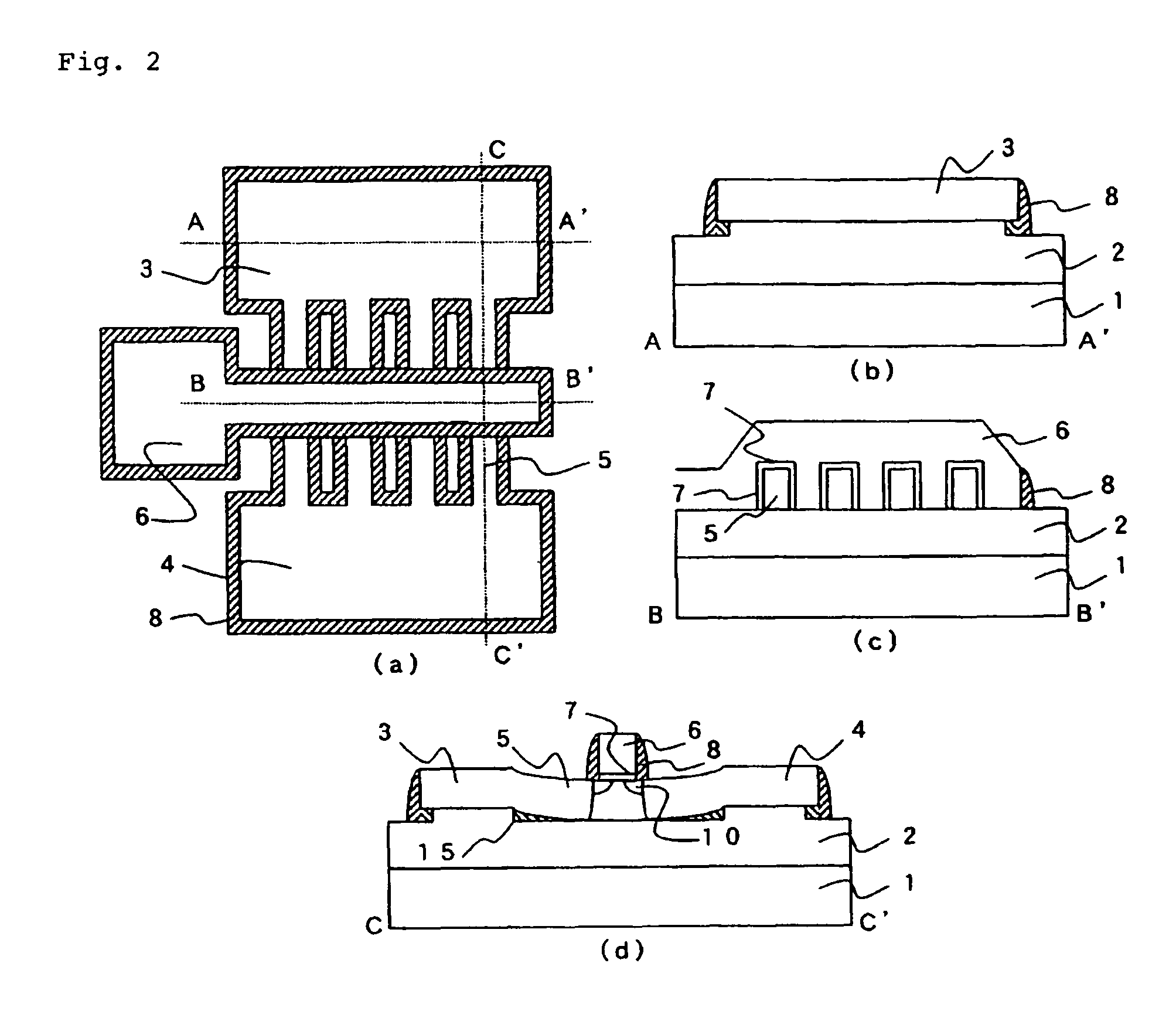

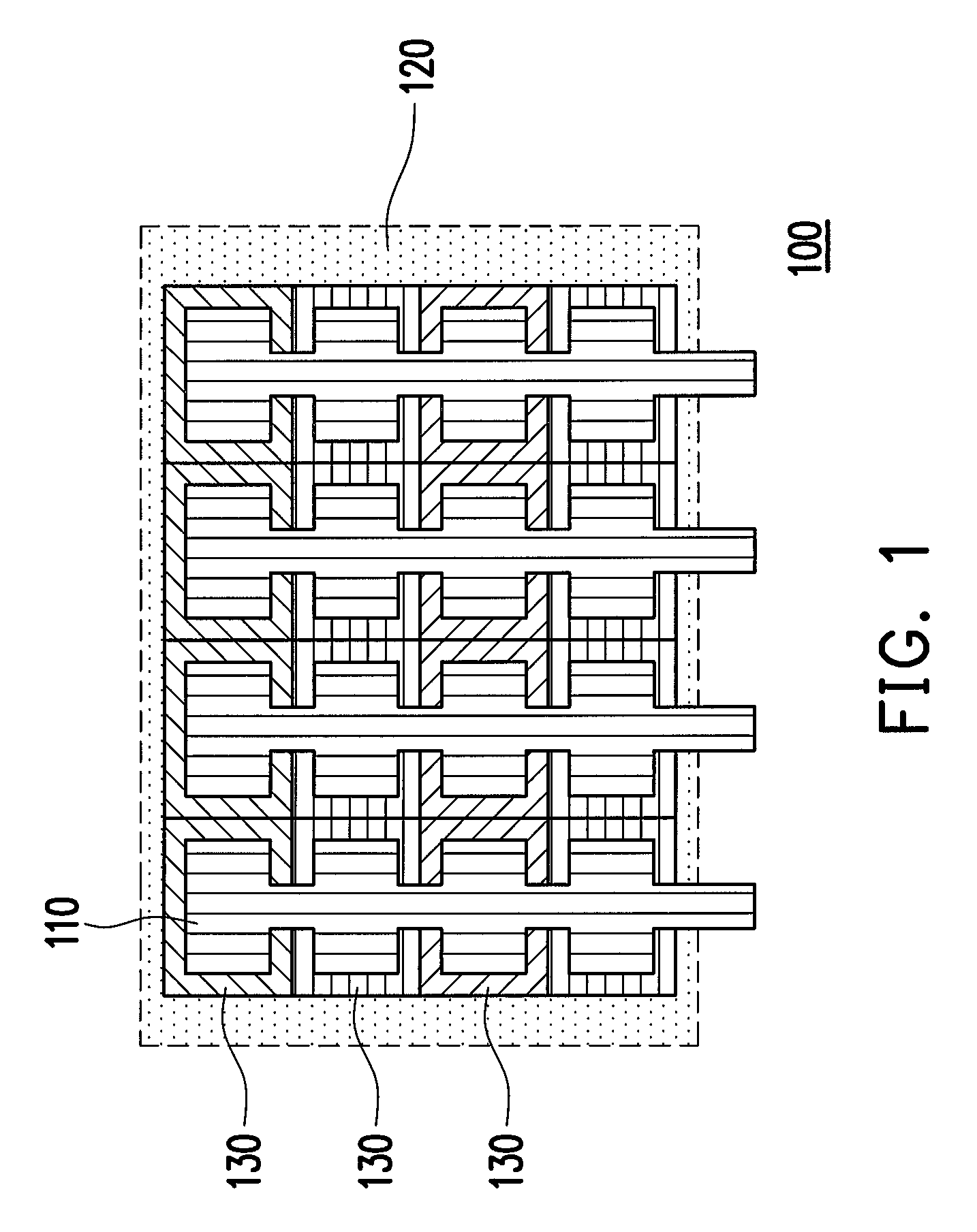

High density laminated substrate structure and manufacture method thereof

InactiveUS6977348B2Improve circuit densityHigh densityPrinted circuit aspectsElectrical connection printed elementsEngineeringHigh density

A laminated substrate structure composed of a plurality of dielectric layers and a plurality of circuit layers stacked with each other. Each of the dielectric layers has a plurality of via studs, and the circuit layers are electrically coupled with each other through the via studs. The laminated substrate structure of the present invention is characterized by adopting the embedded structure landless design that provides high reliability and better adherence. The present invention also provides a laminated substrate manufacture method. The dielectric layers having the patterned circuit and the dielectric layers having the via holes are formed first, and after the dielectric layers having the patterned circuit and the dielectric layers having the via holes are formed, they are aligned and laminated synchronously to complete the manufacture of the laminated substrate.

Owner:VIA TECH INC

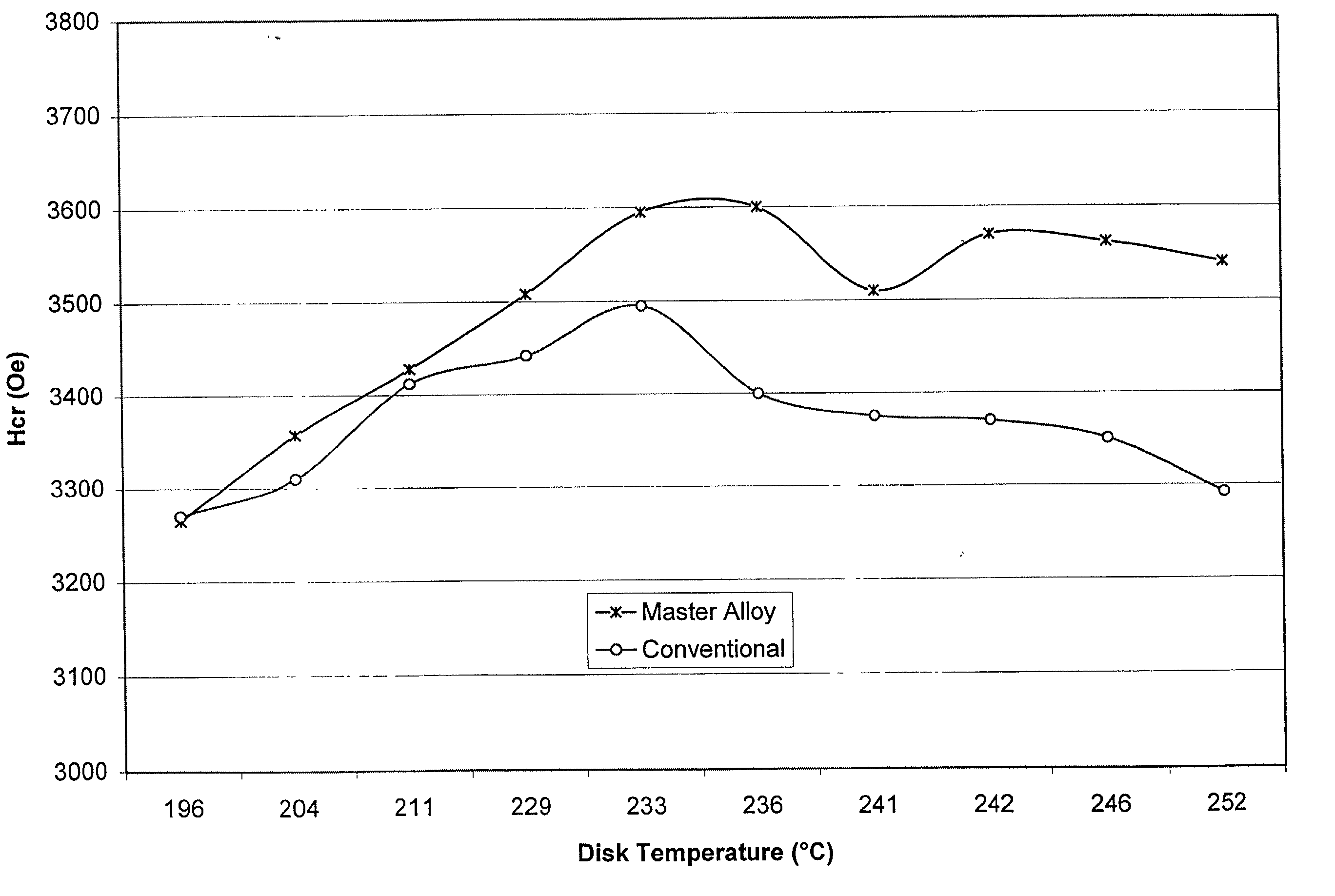

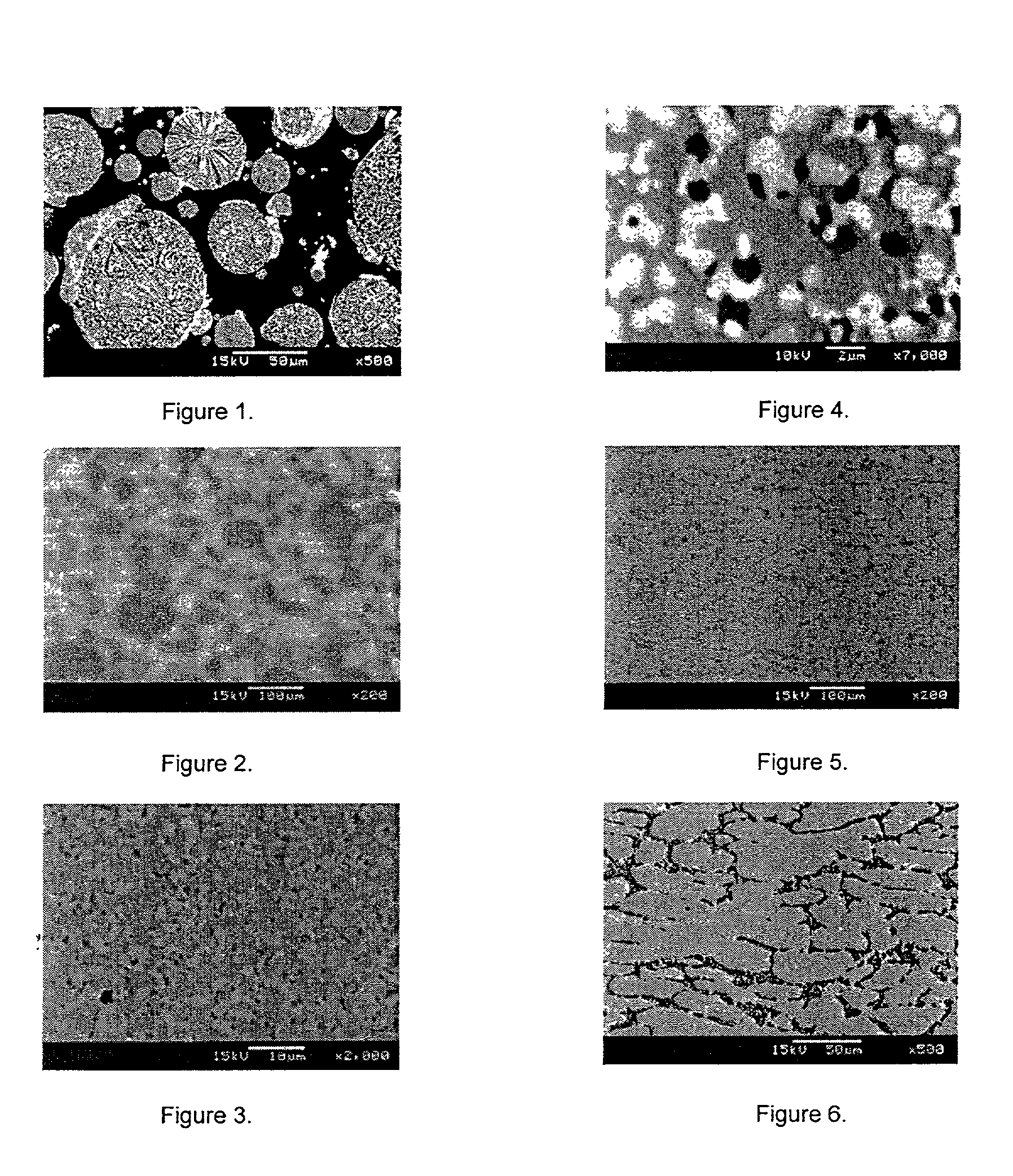

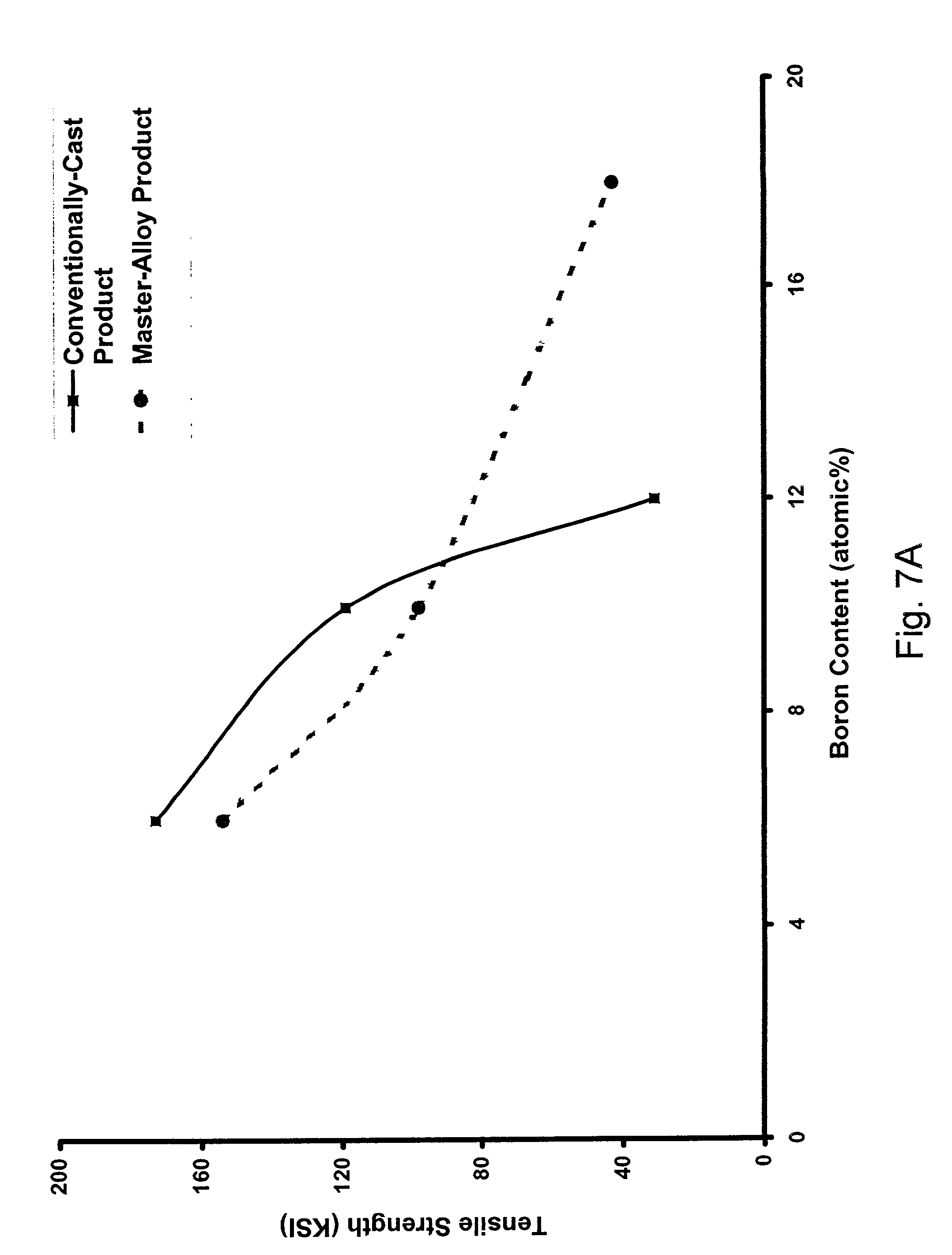

Mechanically alloyed precious metal magnetic sputtering targets fabricated using rapidly solidified alloy powders and elemental Pt metal

InactiveUS20020170821A1Improve featuresImprove manufacturabilityCellsVacuum evaporation coatingPlatinumAlloy

A cobalt-chromium-boron-platinum sputtering target alloy having multiple phases. The alloy can include Cr, B, Ta, Nb, C, Mo, Ti, V, W, Zr, Zn, Cu, Hf, O, Si or N. The alloy is prepared by mixing Pt powder with a cobalt-chromium-boron master alloy, ball milling the powders and HIP'ing to densify the powder into the alloy.

Owner:HERAEUS INC

Reflowed solder ball with low melting point metal cap

InactiveUS6259159B1Low costEasy to buildPrinted circuit assemblingFinal product manufactureTinningIndium

A method and structure for a solder interconnection, using solder balls for making a low temperature chip attachment directly to any of the higher levels of packaging substrate is disclosed. After a solder ball has been formed using standard methods it is reflowed to give the solder ball a smooth surface. A layer of low melting point metal, such as, bismuth, indium or tin, preferably, pure tin, is deposited on the top of the solder balls. This structure results in localizing of the eutectic alloy, formed upon subsequent low temperature joining cycle, to the top of the high melting solder ball even after multiple low temperature reflow cycles. This method does not need tinning of the substrate to which the chip is to be joined, which makes this method economical. It has also been noticed that whenever temperature is raised slightly above the eutectic temperature, the structure always forms a liquid fillet around the joint with copper wires. This liquid fillet formation results in substantial thermal fatigue life improvement for reduced stress at interface; and secondly, provides an easy means to remove chip for the purpose of chip burn-in, replacement or field repairs.

Owner:IBM CORP

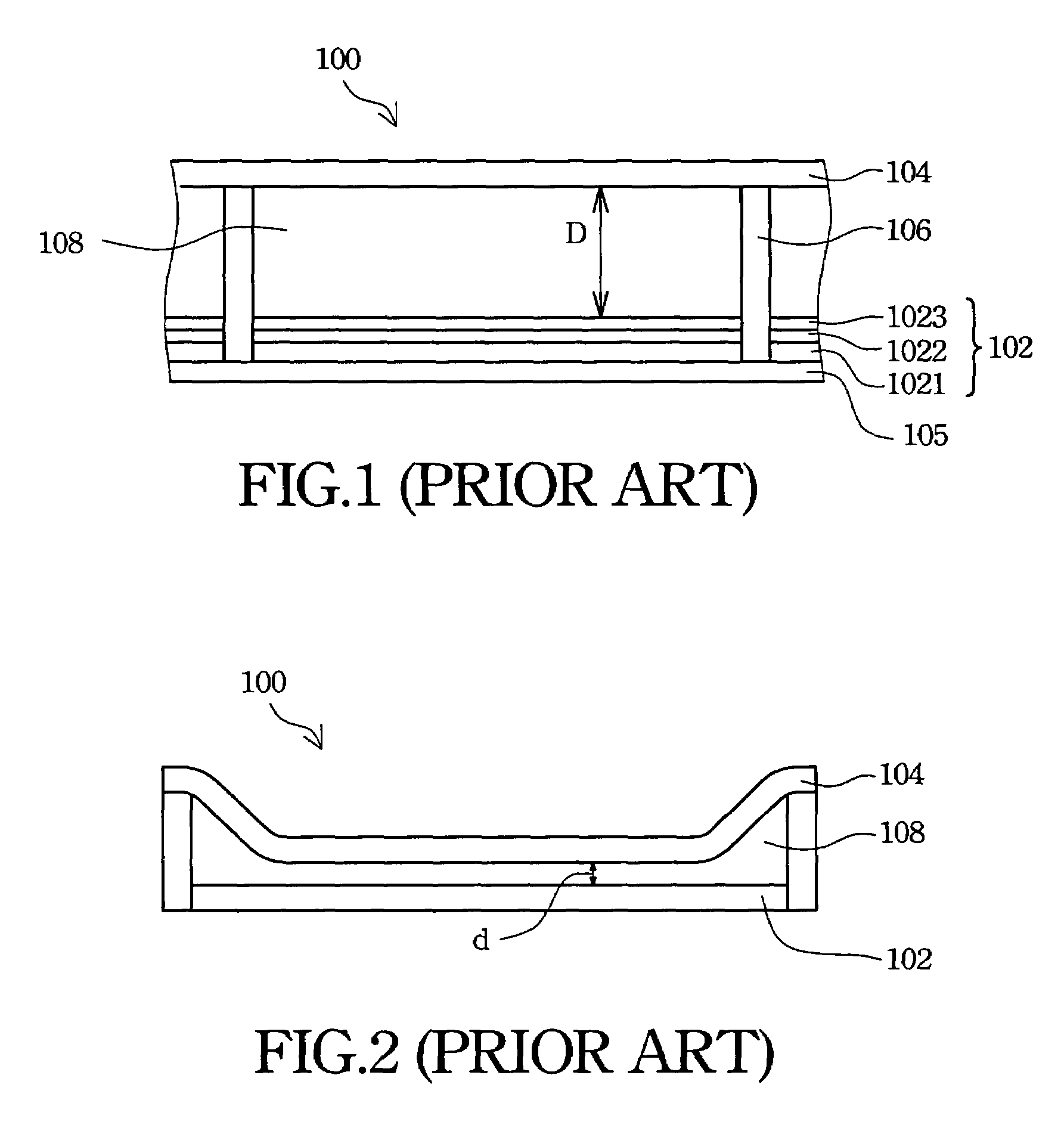

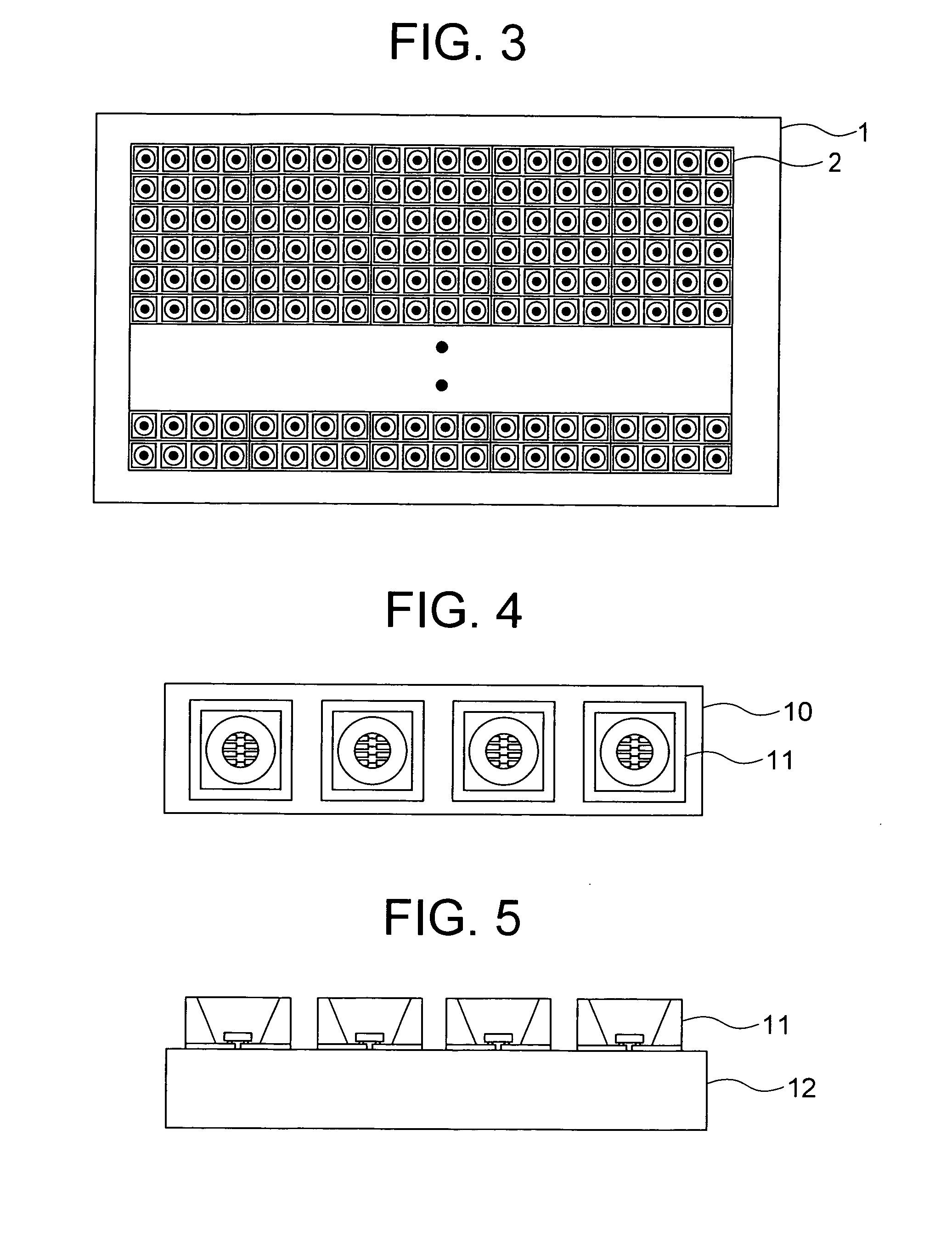

Liquid crystal display apparatus

ActiveUS20070085944A1Increase brightnessIncrease in sizeSolid-state devicesNon-linear opticsCold cathodeEngineering

A cold-cathode tube has hitherto been used as a backlight for supplying illumination to a liquid crystal television but recently, light emitting diode pieces have been used for a backlight of a large-size liquid crystal television. For the purpose of improving the emission efficiency, flip chip mounting of the light emitting diode piece is advantageous but the mounting yield is restricted by the piece size, electrode structure and wire pattern structure, facing situations having difficulties in realizing simplified mounting and reduction of costs of members. In a liquid crystal display apparatus having a liquid crystal panel, an optical system and a light source, the light source includes a light emitting element structure having positive and negative electrodes, at least one of them being plural, and wires mounted to the positive and negative electrodes through flip chip mounting by making electrical correspondence to individual regions of the positive and negative electrodes.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

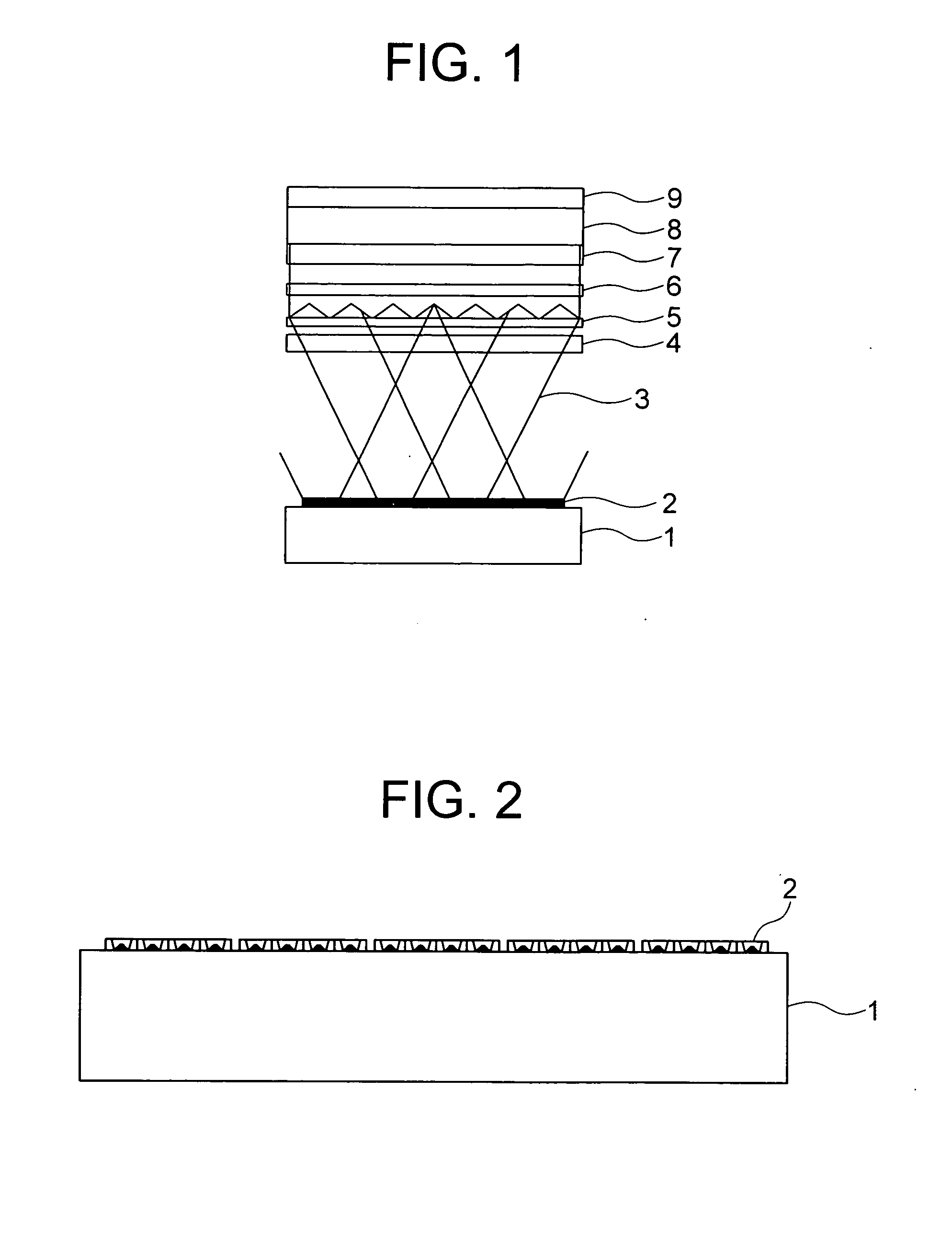

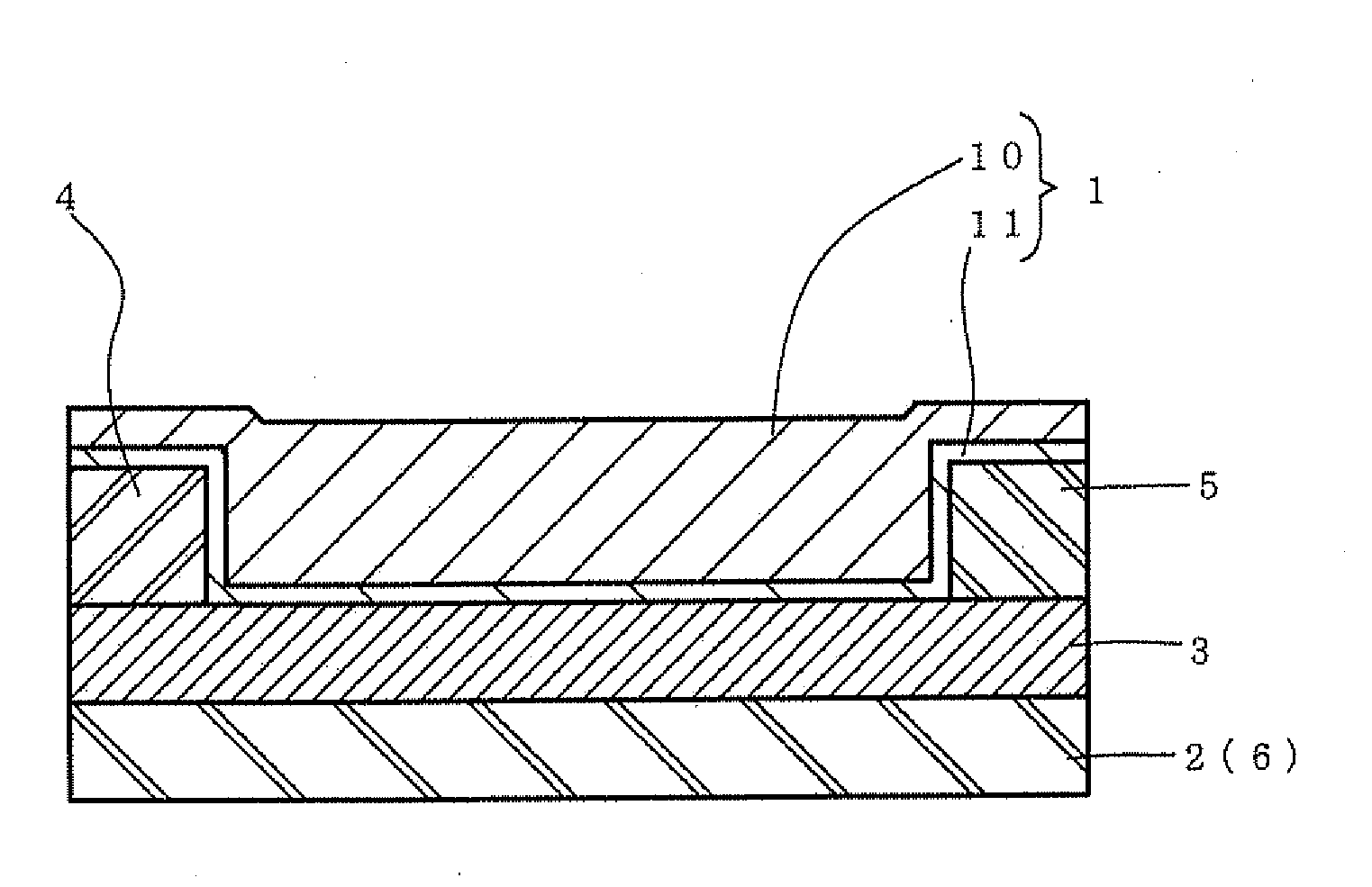

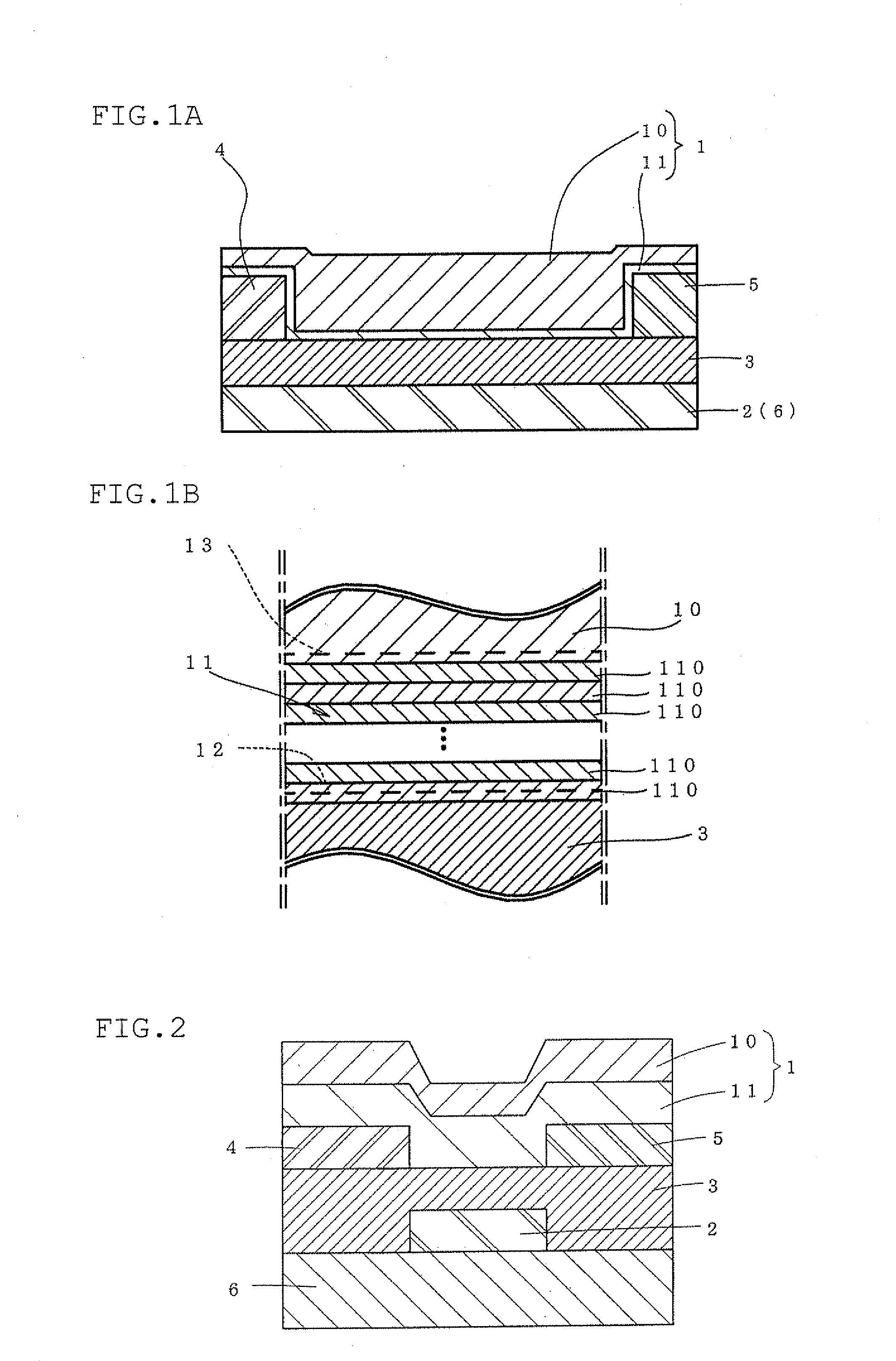

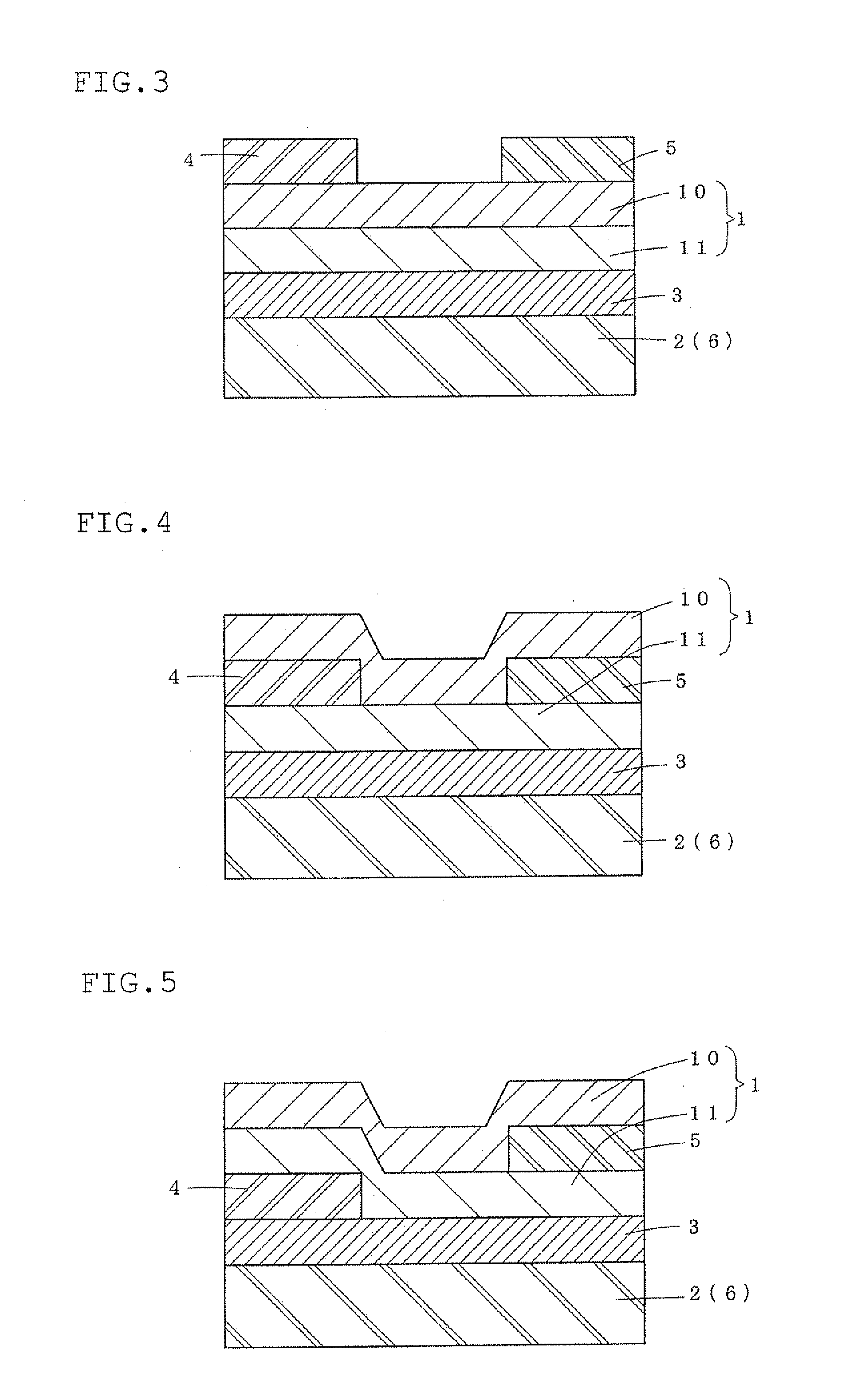

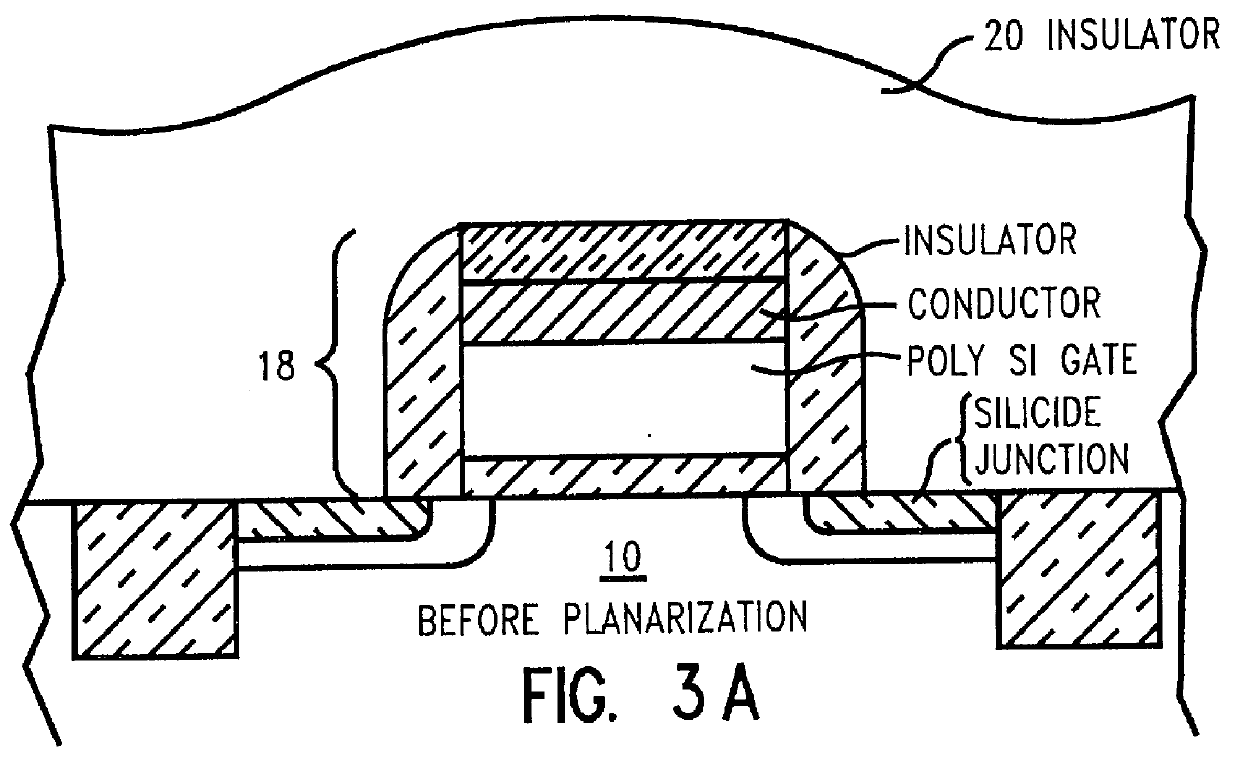

Semiconductor device, method for manufacturing semiconductor device, and display

InactiveUS20100140599A1Intuitive displayEasy to produceSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOrganic semiconductor

A semiconductor device includes an organic semiconductor layer 10 and an oxide semiconductor layer 11, and emits light.

Owner:IDEMITSU KOSAN CO LTD +1

Refractory metal capped low resistivity metal conductor lines and vias

InactiveUS6147402AHigh process yieldSemiconductor/solid-state device detailsSolid-state devicesDielectricElectrical conductor

Capping a low resistivity metal conductor line or via with a refractory metal allows for effectively using chemical-mechanical polishing techniques because the hard, reduced wear, properties of the refractory metal do not scratch, corrode, or smear during chemical-mechanical polishing. Superior conductive lines and vias are created using a combination of both physical vapor deposition (e.g., evaporation or collimated sputtering) of a low resistivity metal or alloy followed by chemical vapor deposition (CVD) of a refractory metal and subsequent planarization. Altering a ratio of SiH4 to WF6 during application of the refractory metal cap by CVD allows for controlled incorporation of silicon into the tungsten capping layer. Collimated sputtering allows for creating a refractory metal liner in an opening in a dielectric which is suitable as a diffusion barrier to copper based metalizations as well as CVD tungsten. Ideally, for faster diffusing metals like copper, liners are created by a two step collimated sputtering process wherein a first layer is deposited under relatively low vacuum pressure where directional deposition dominates (e.g., below 1 mTorr) and a second layer is deposited under relatively high vacuum pressure where scattering deposition dominates (e.g., above 1 mTorr). For refractory metals like CVD tungsten, the liner can be created in one step using collimated sputtering at higher vacuum pressures.

Owner:GLOBALFOUNDRIES INC

Structure of an optical interference display unit

InactiveUS20050157364A1Good uniformity and qualityIncrease mechanical stressTelevision system detailsColor television detailsLight reflectionReflective layer

An optical interference display unit, at least comprises a light-incidence electrode and a light-reflection electrode located on a transparent substrate. The light-incidence electrode at least comprises a transparent conductive layer and a dielectric layer. The light-reflection electrode at least comprises an absorption layer and a reflective layer.

Owner:SNAPTRACK

Touch panel module and method of fabricating the same

InactiveUS20080117186A1Transmittance be wellHigh process yieldInput/output processes for data processingTouch panelTouchpad

A touch panel module including a cover and a transparent touch panel is provided. At least a portion of the transparent touch panel is directly connected to the cover. A method of fabricating the touch panel module including the following steps is also provided. First, a transparent touch panel is provided. Next, the cover is formed using injection molding technology such that at least a portion of the transparent touch panel is directly connected to the cover.

Owner:WINTEK CORP

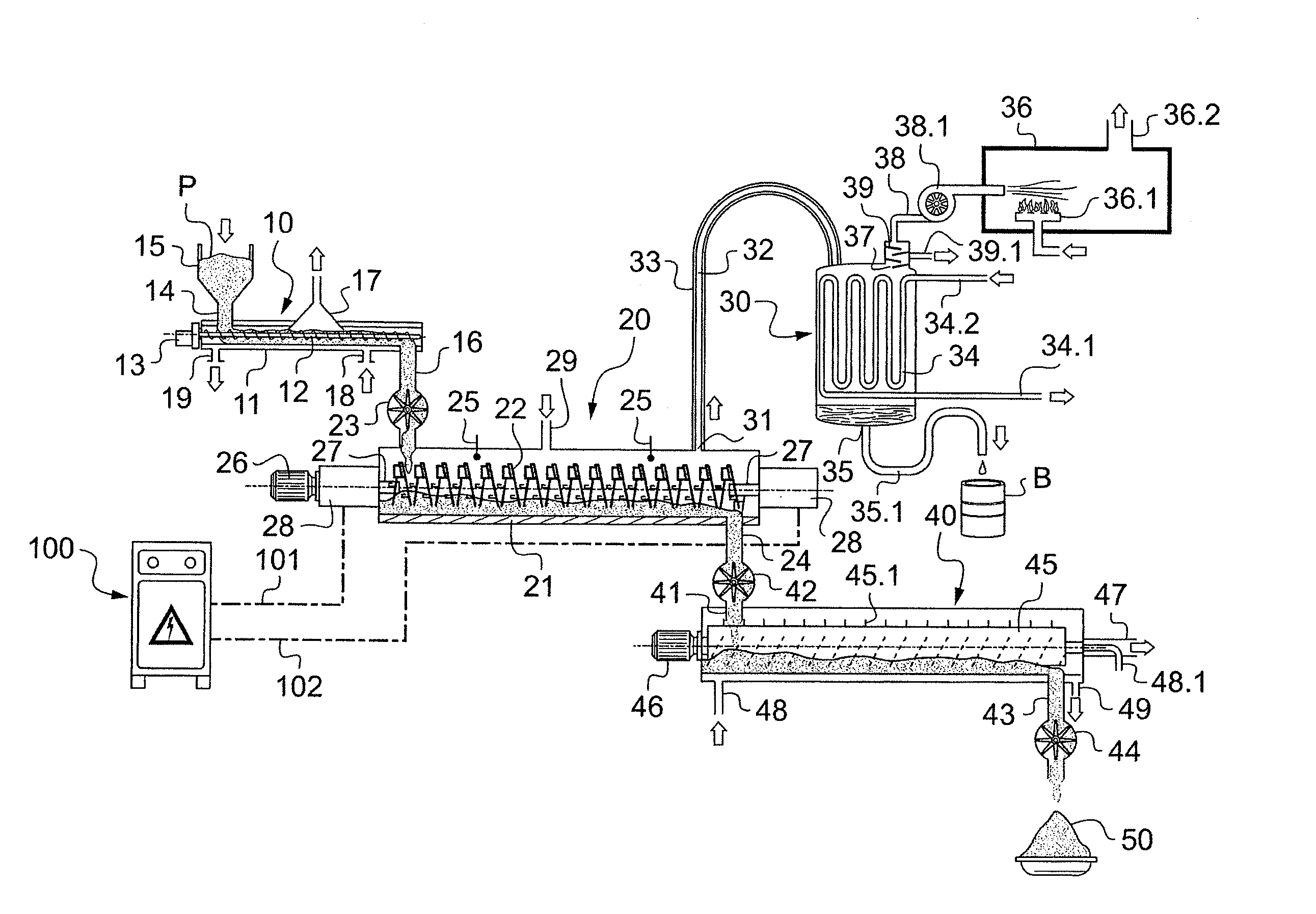

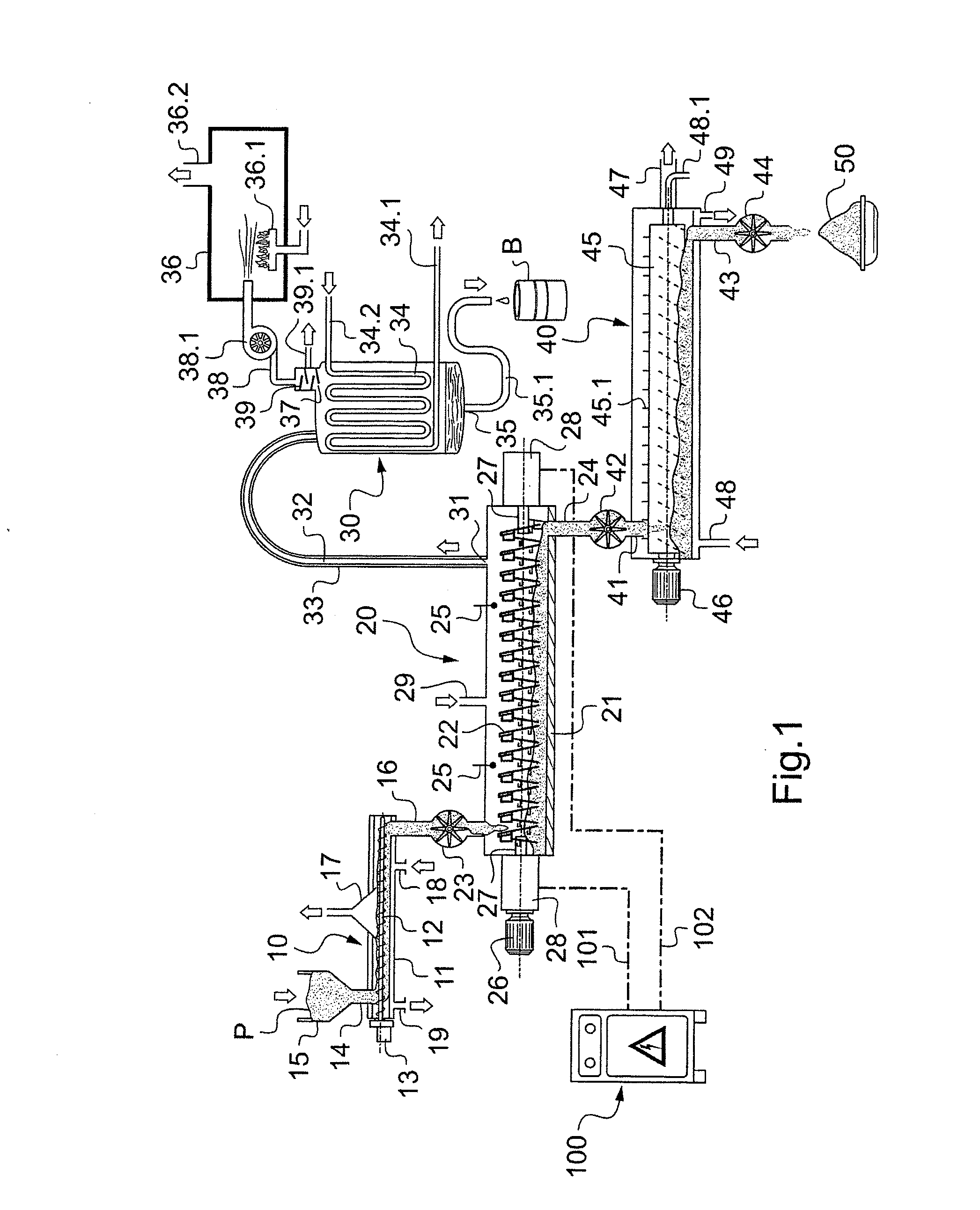

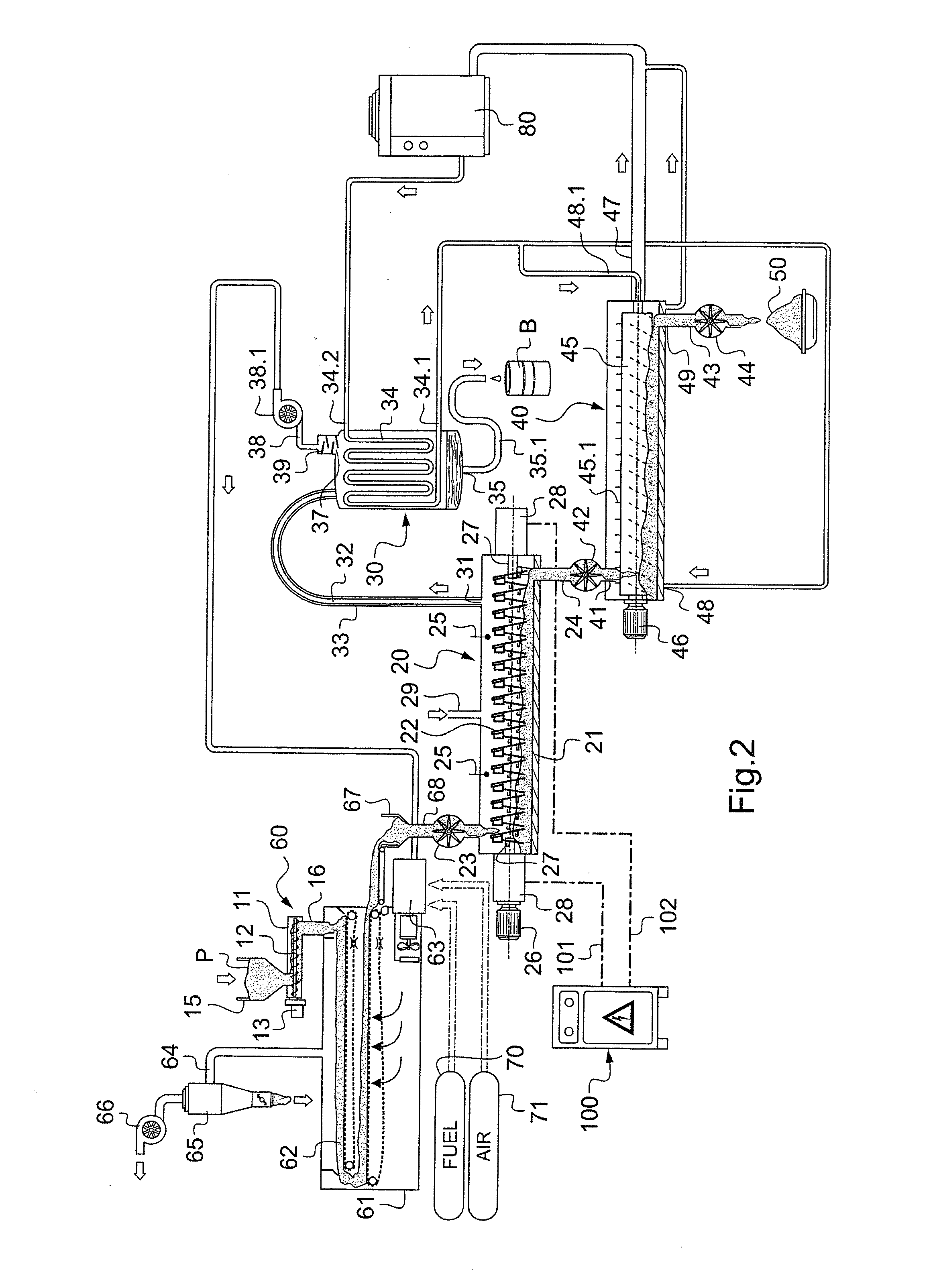

Method and apparatus for the energy densification of a material in the form of divided solids, with a view to obtaining pyrolysis oils for energy purposes

ActiveUS20120043194A1High calorific valueImprove operating conditionsMechanical conveying coke ovensElectrical coke oven heatingPre treatmentRelative humidity

A method and installation for energy densification of a material to obtain pyrolytic oils for energy. The method includes preconditioning the material by heating and drying to raise the material temperature close to 100° C. and a relative humidity not exceeding about 10%; pyrolyzing the material that is subsequently caused to flow through a substantially hermetic reactor containing at least one transfer screw or vibrating tube heated by the Joule effect, the material heated progressively in the range of 300° C. to 850° C., the electrical power passing through the transfer screw or the vibrating tube for providing heating regulated as a function of the material in order to obtain the desired temperature level during the transit time of the material through the reactor; extracting pyrolysis gas from a high portion of the reactor for rapid recondensation in a vertical condenser; and recovering pyrolytic oils from a low portion of the vertical condenser.

Owner:LEPEZ CONSEILS FINANCE INNOVATIONS LCFI +1

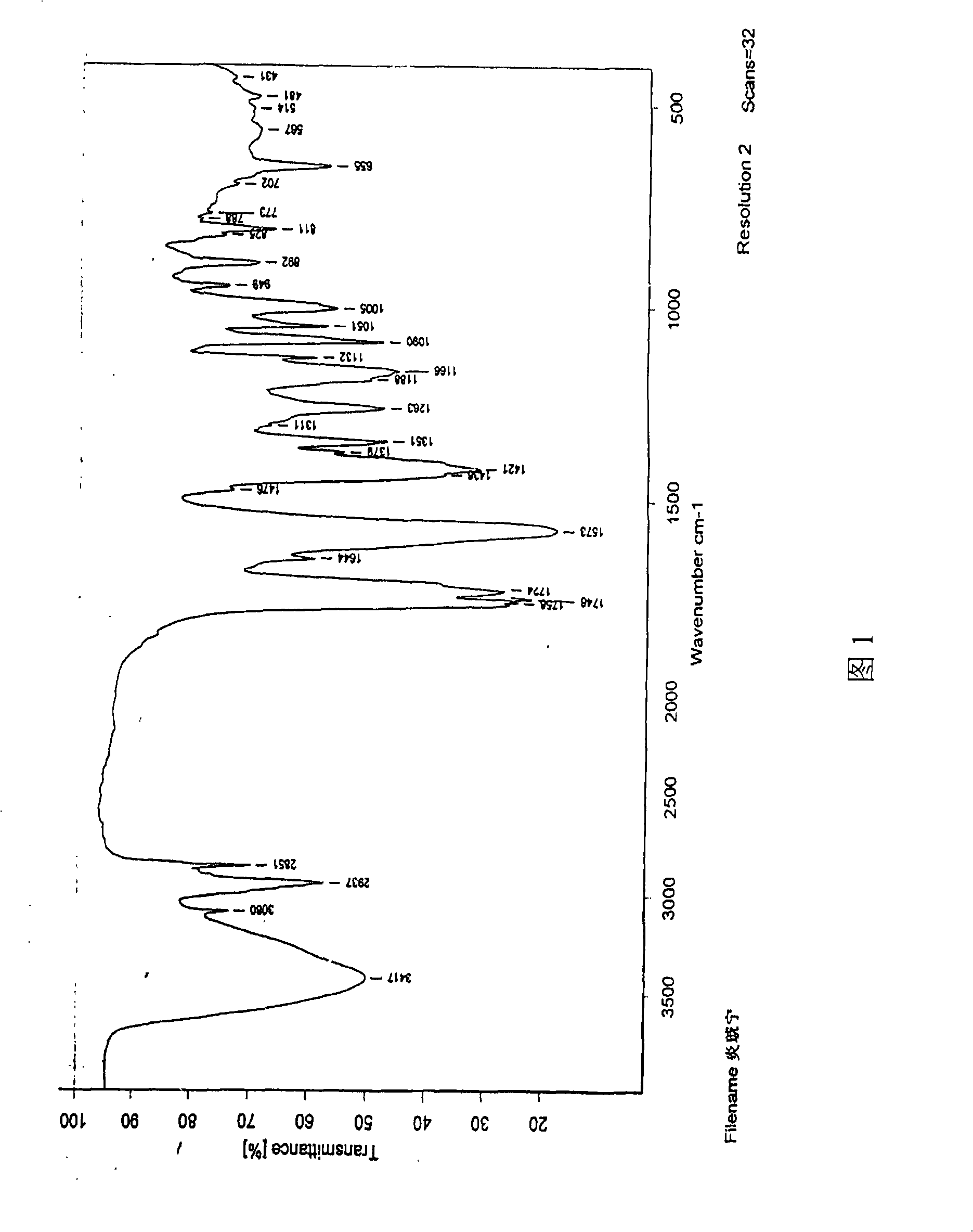

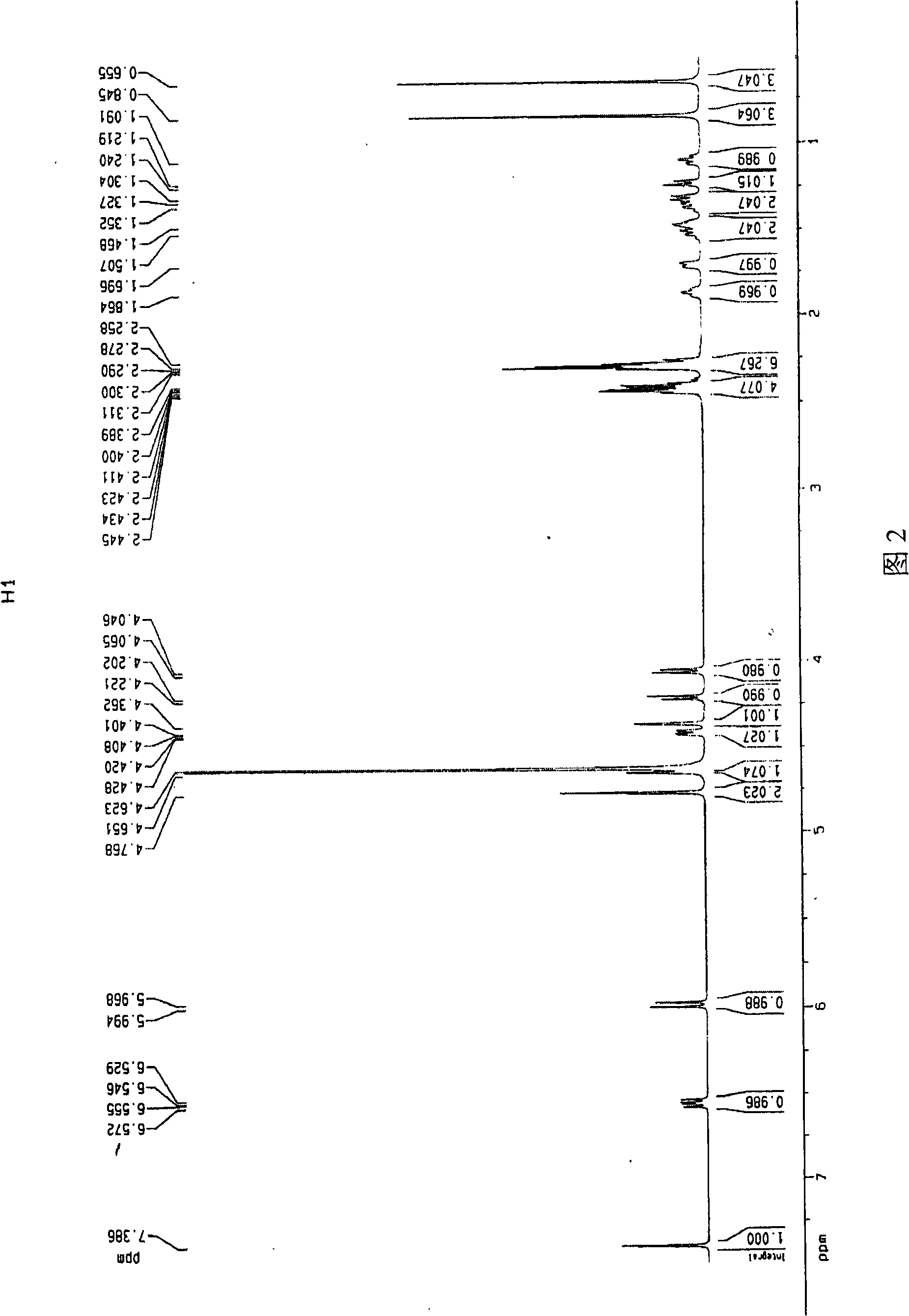

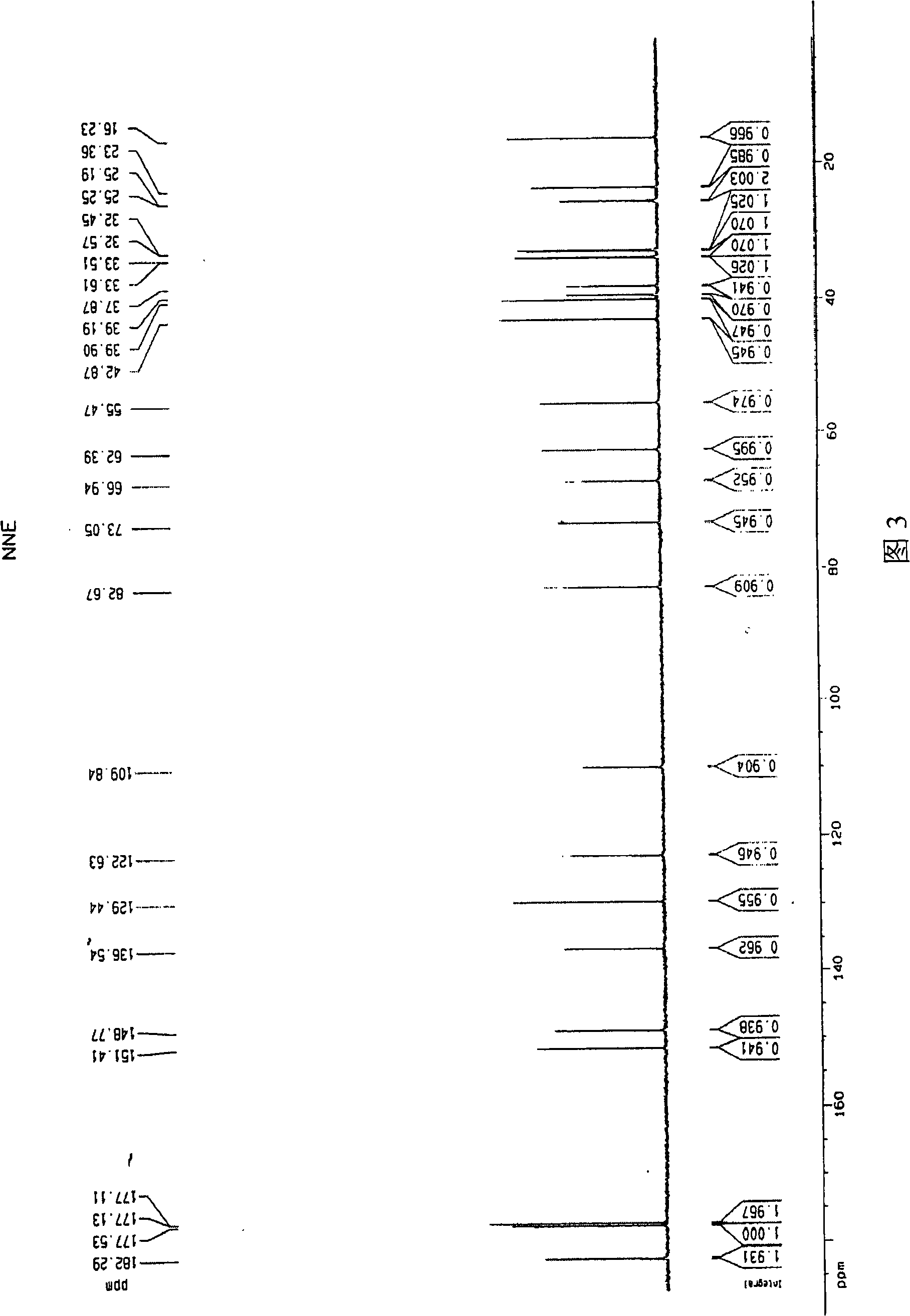

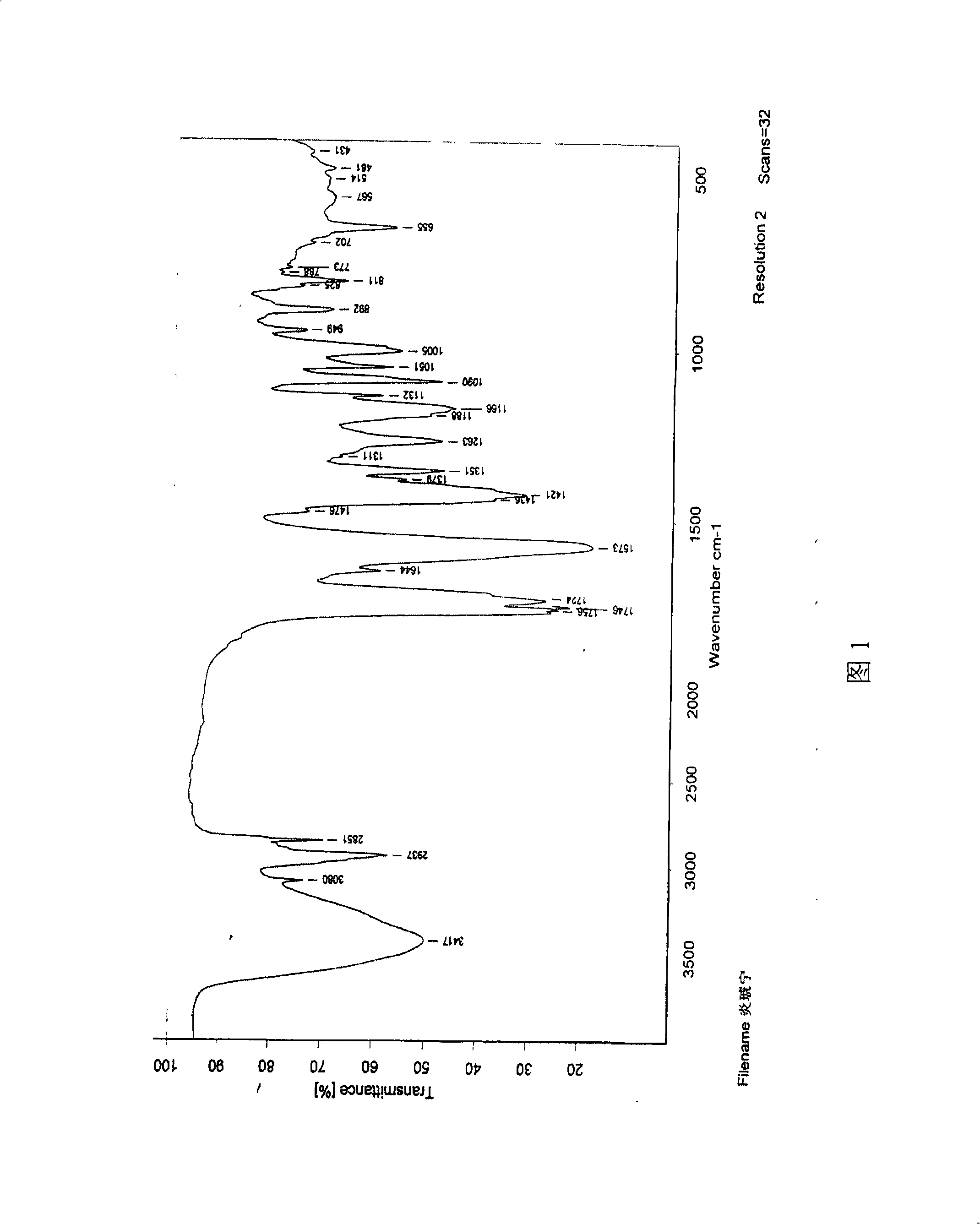

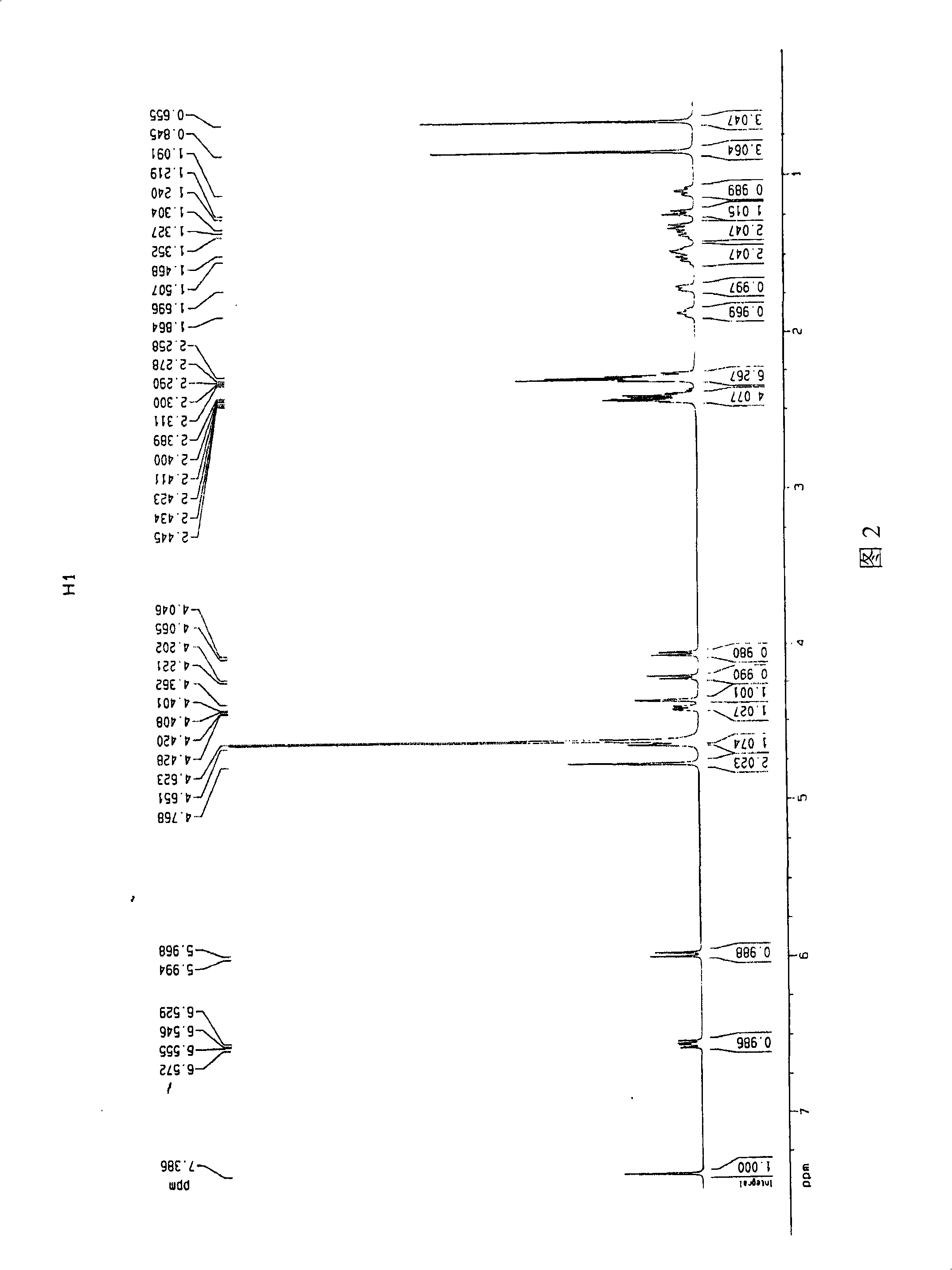

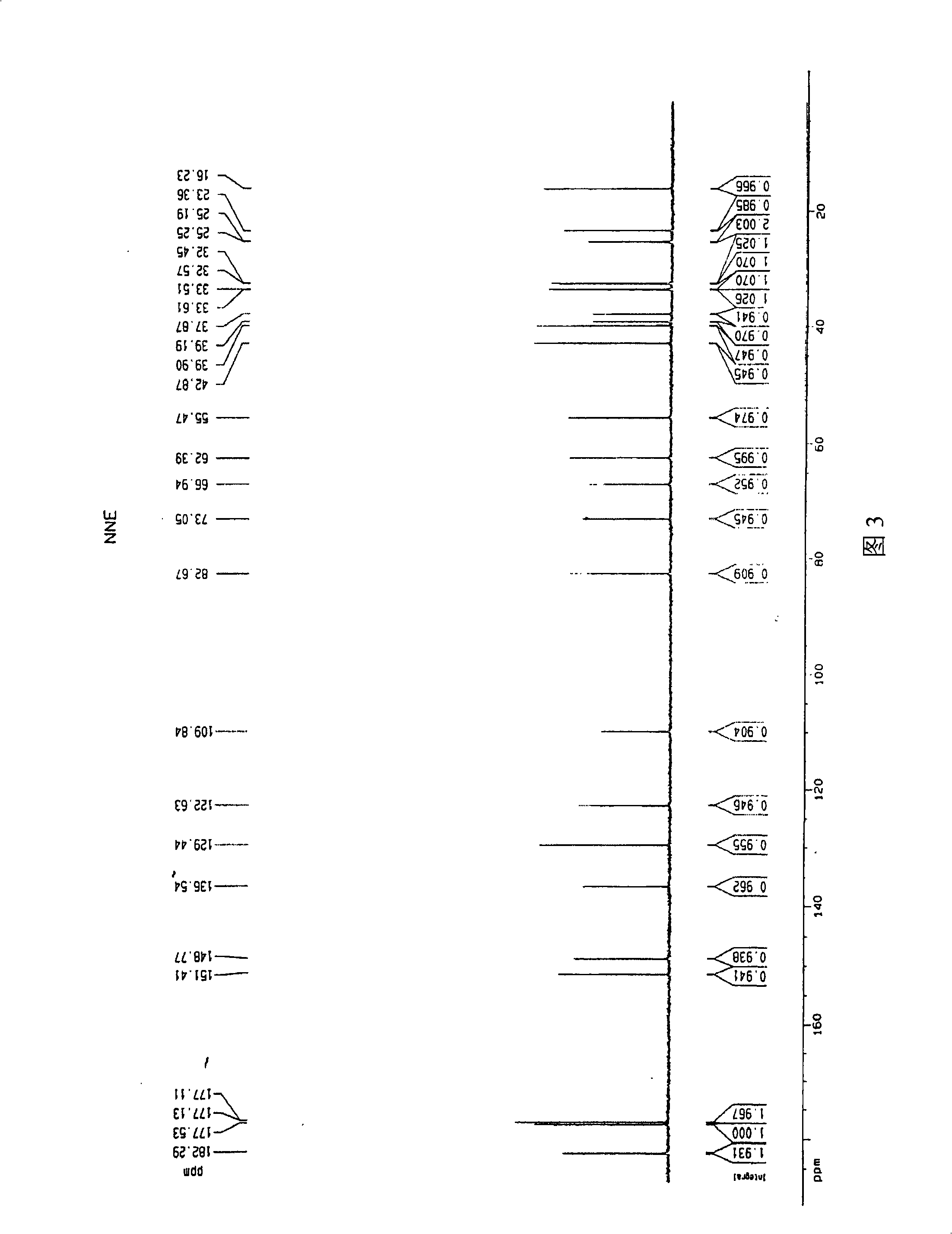

Technique for preparing potassium sodium dehydroandroandrographolide succinic by using potassium dehydroandrographolide succinate

The invention discloses a process of preparing Dehydroandrographolide Succinate Sodium and Potassium salts with Potassium Dehydroandrograpolide Succinate. The process comprises the steps of: weighing right amount of Potassium Dehydroandrograpolide Succinate, adding absolute ethyl alcohol about 3 to 6 times to make suspension; weighting mole Sodium bicarbonate in equal weight, adding water to dissolve, dripping slowly Sodium bicarbonate solution in potassium dehydroandrograpolide succinate suspension in a water bath at a temperature of between 40 and 60 DEG C, mixing into liquid medicine and defecating, dissolving impurity and filtering, putting on a 0.22 mu m filter membrane, adding absolute ethyl alcohol about 7 to 12 times while mixing, after 10 to 30 minutes of mixing, natural crystallization seeds out after 13 to 18 hours standing in room temperature; filtering and washing 2 to 3 times with right amount of absolute ethyl alcohol; filtering and drying with less pressure. The invention provides a process route of preparing potassium sodium dehydroandroan drographolide succinate for injection with high purity, which is high in process yields, high in product purity, good in solubility, less in impurity and complete in combination of Potassium and Sodium; no obvious toxic and side effect in clinic application, the preparation is more stable compared with the similar and can be prepared into various preparations.

Owner:CHANGCHUN MAILING BIOLOGICAL ENG CO LTD

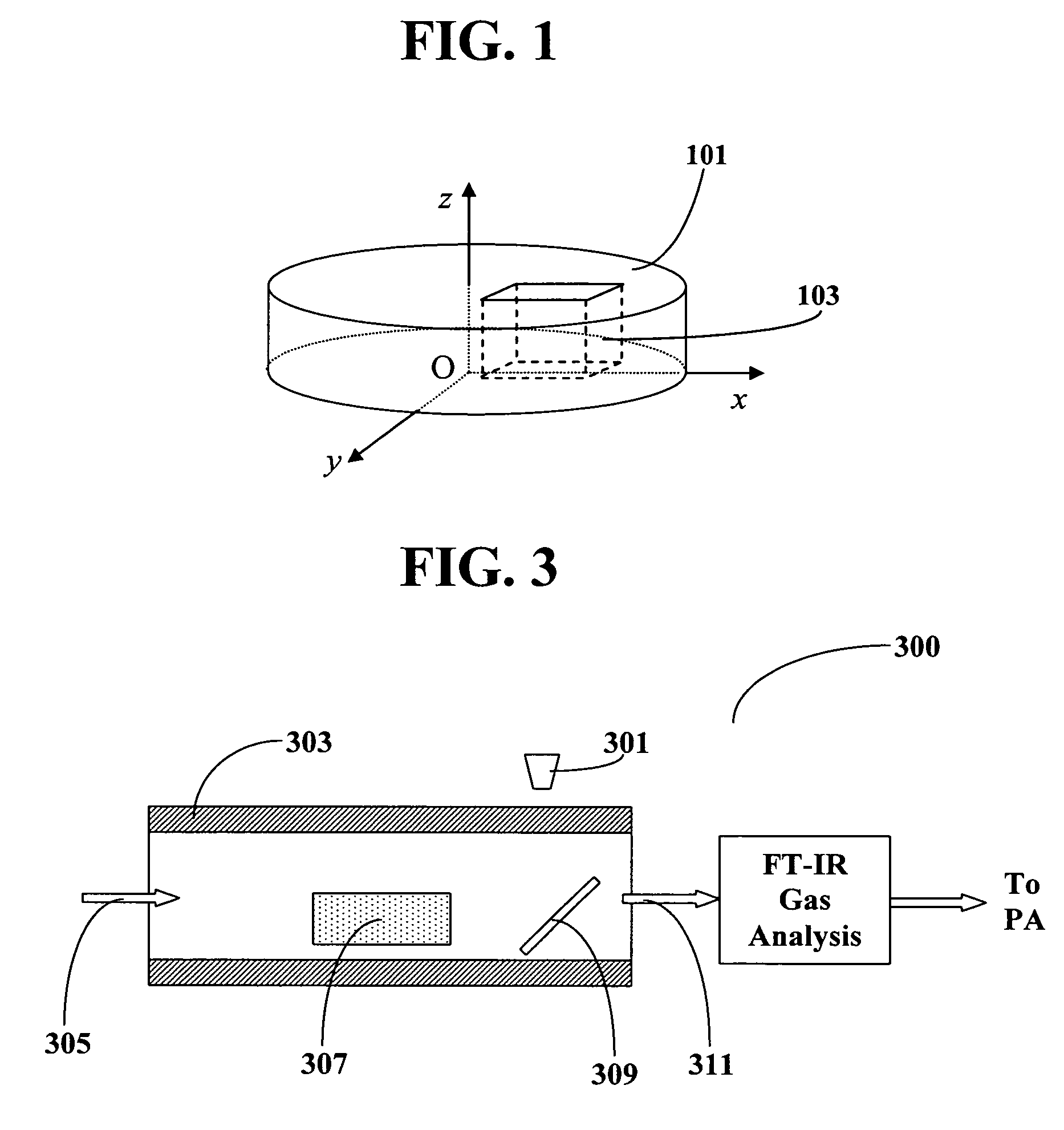

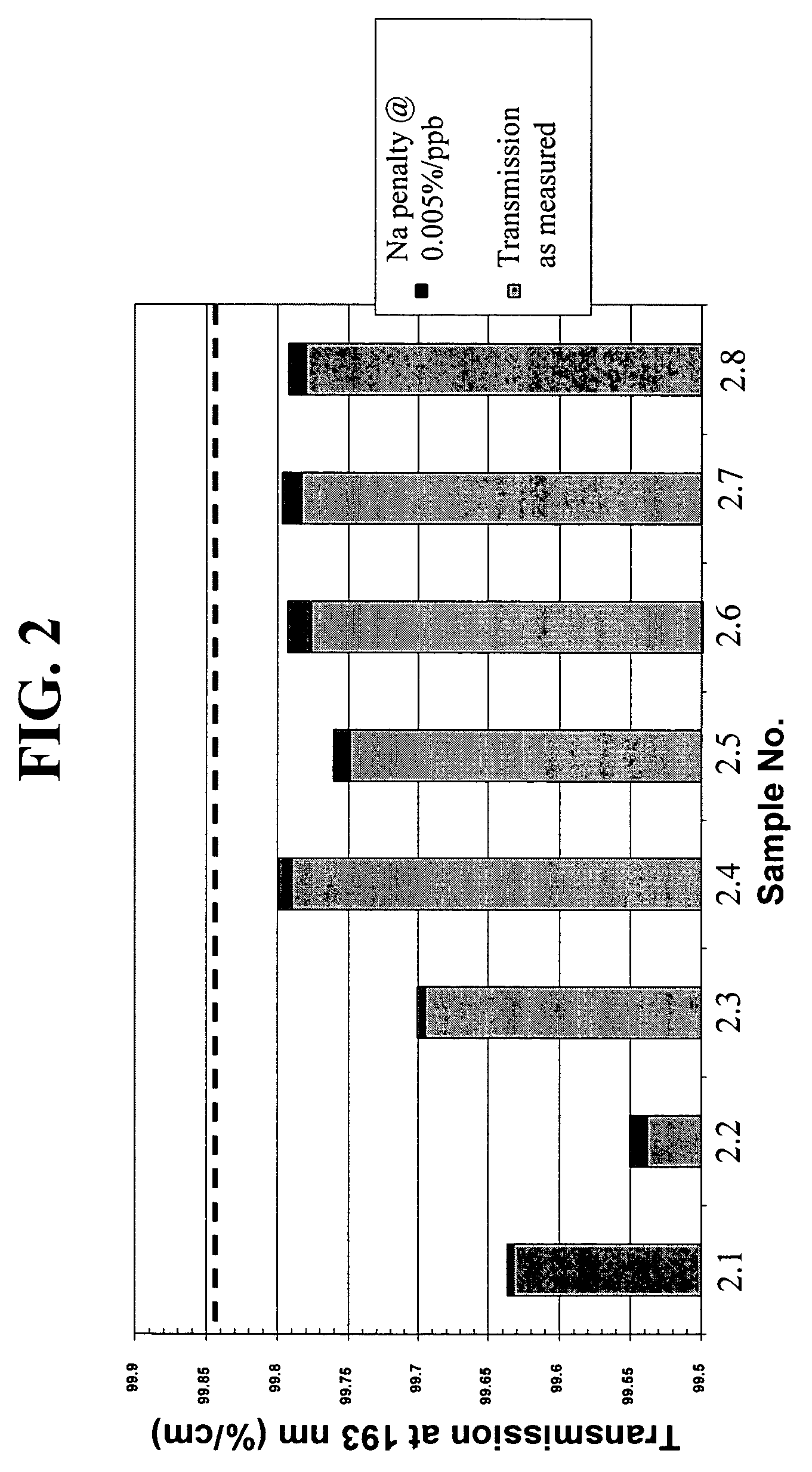

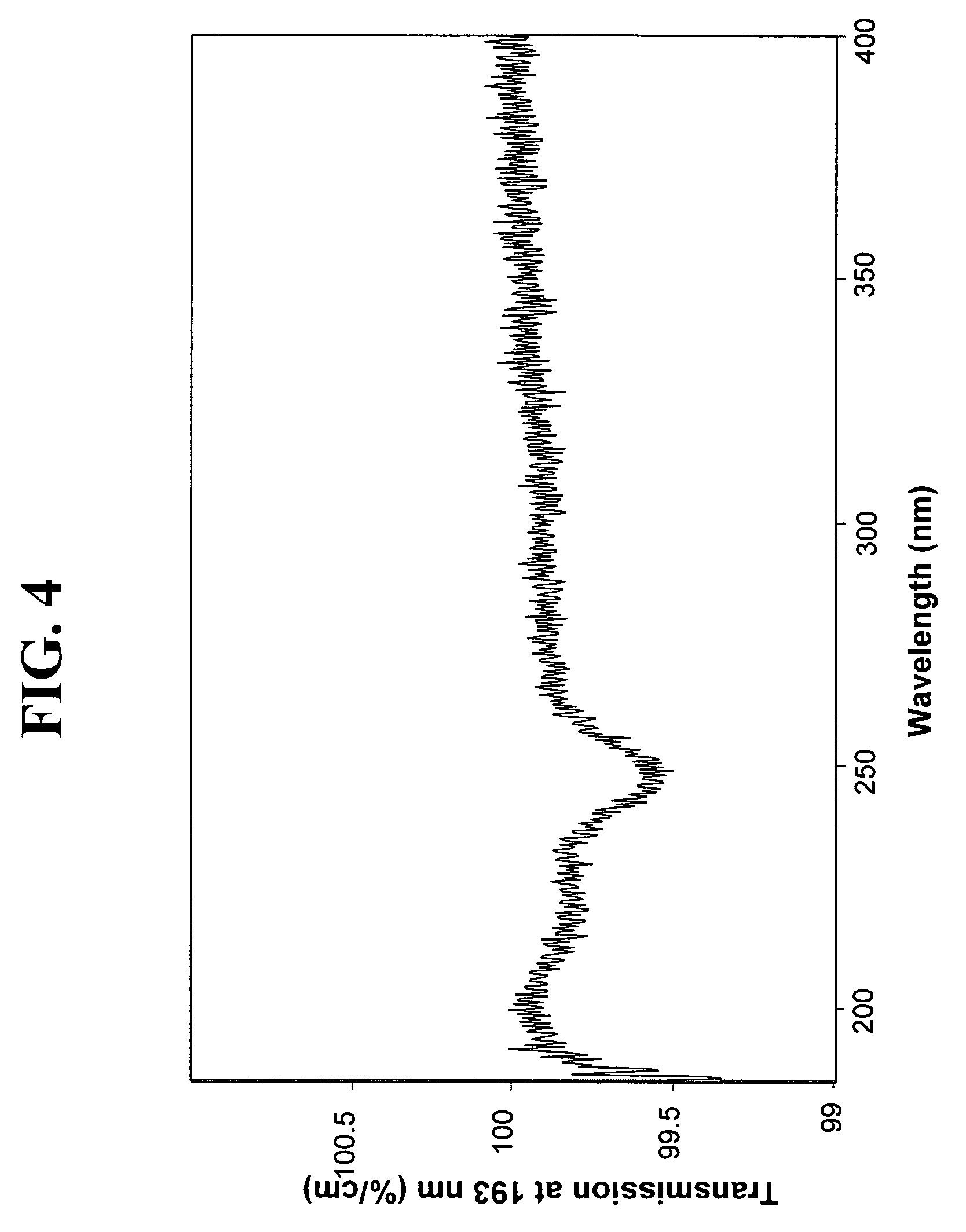

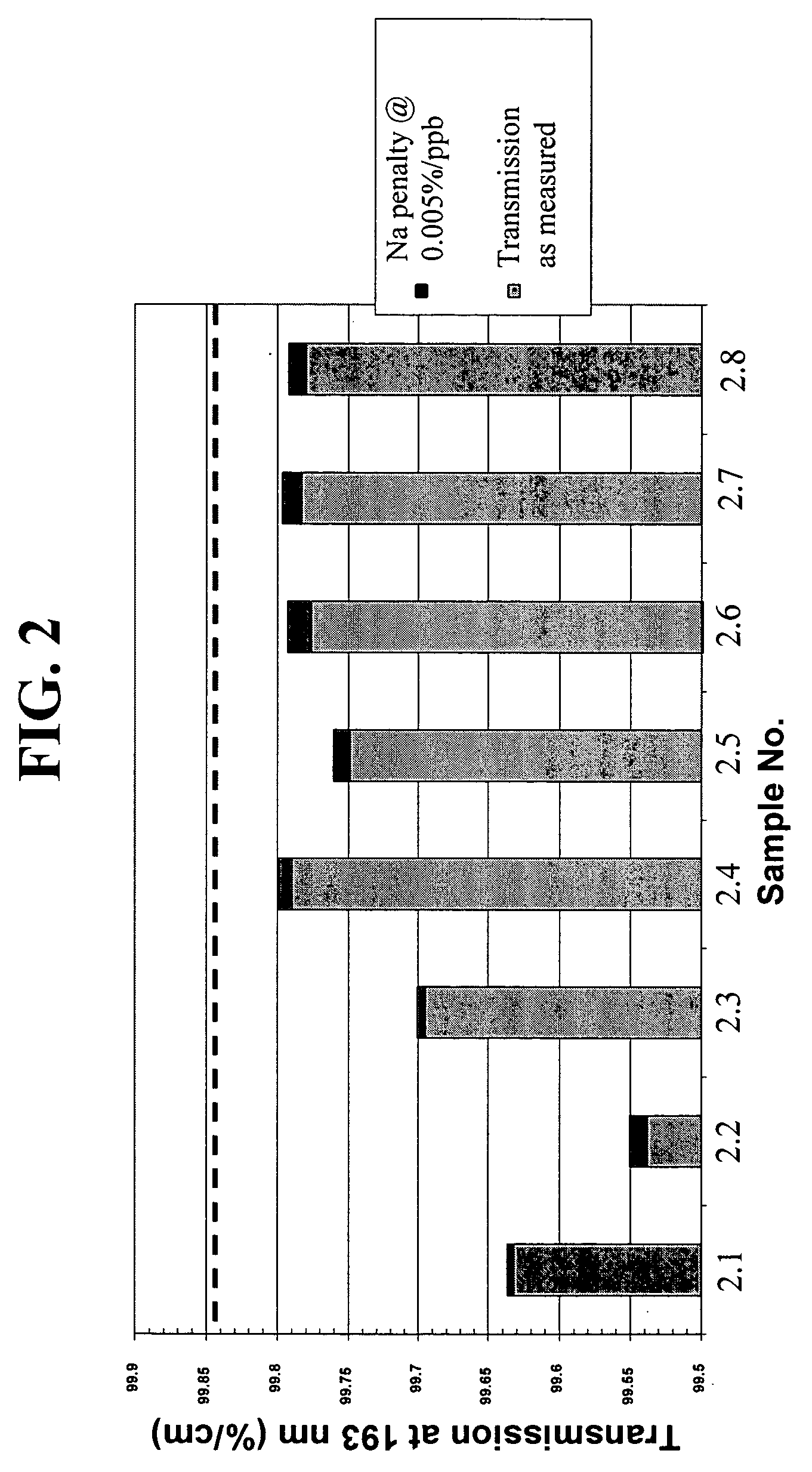

High transmission synthetic silica glass and method of making same

InactiveUS7506521B2Improve homogeneityIncrease the areaPhotomechanical apparatusGlass shaping apparatusPolymer scienceOptical axis

Owner:CORNING INC

Methods of forming oxide masks with submicron openings and microstructures formed thereby

ActiveUS7056757B2High quality factorHigh process yieldSemiconductor/solid-state device manufacturingMicrostructural device manufactureSingle crystalPhotolithography

Processing techniques are disclosed for batch fabrication of microstructures comprising an oxide mask on a substrate with submicron openings formed therein, and microstructures having deep-submicron, high aspect-ratio etched trenches, using conventional optical photolithography. Exemplary high aspect-ratio etched-trench microstructures that may be produced include single crystal resonators and sensors.

Owner:GEORGIA TECH RES CORP

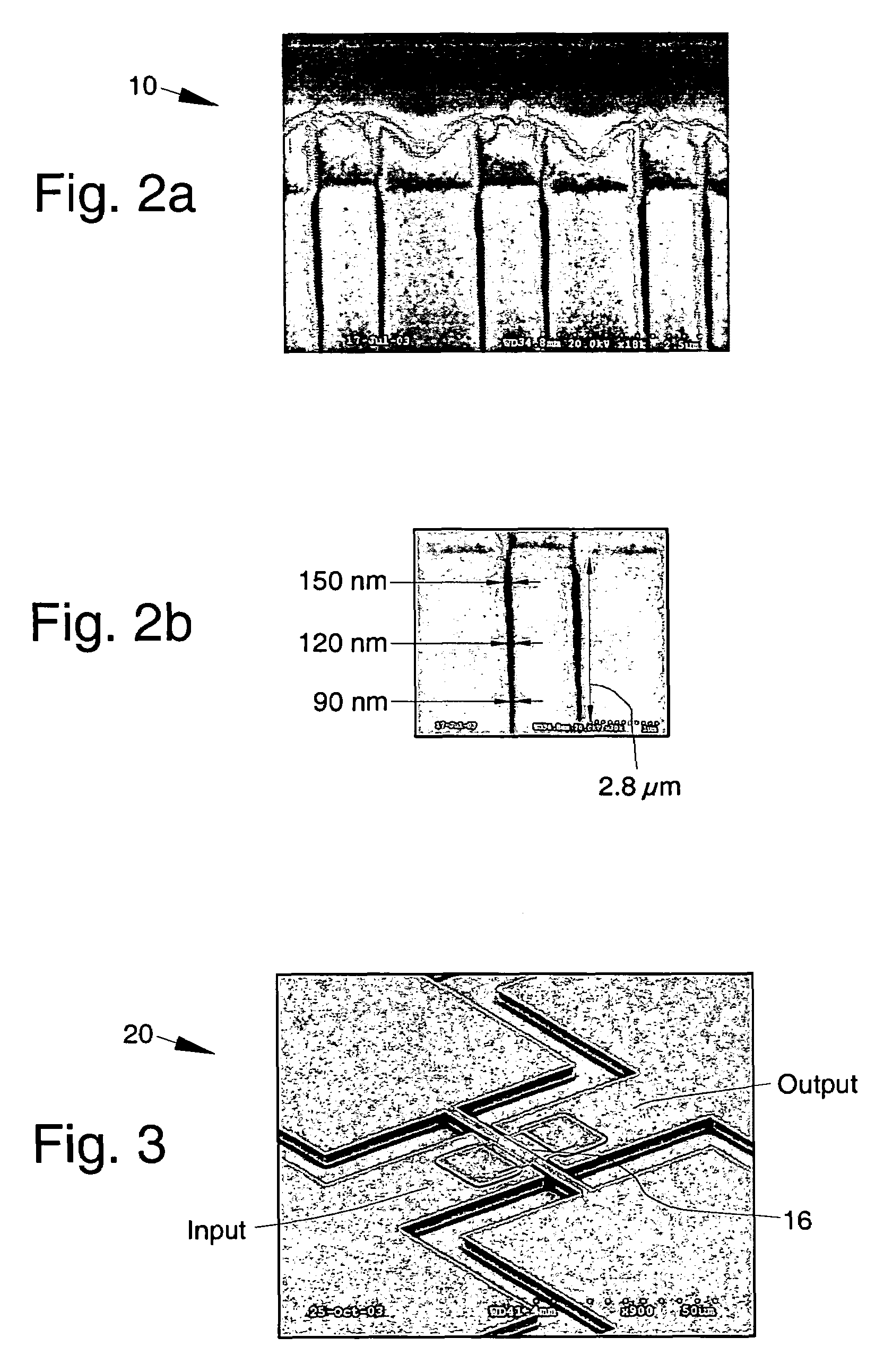

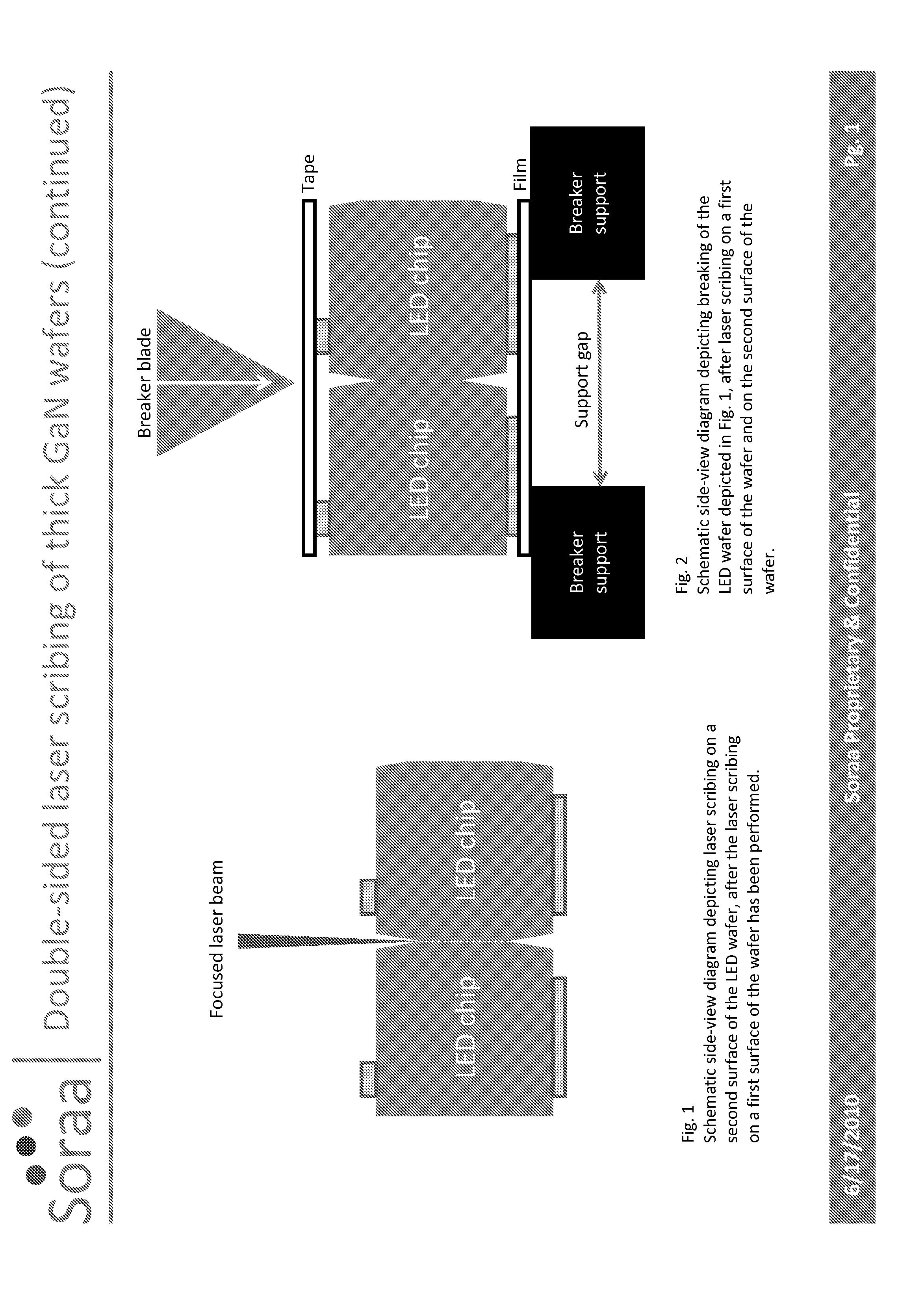

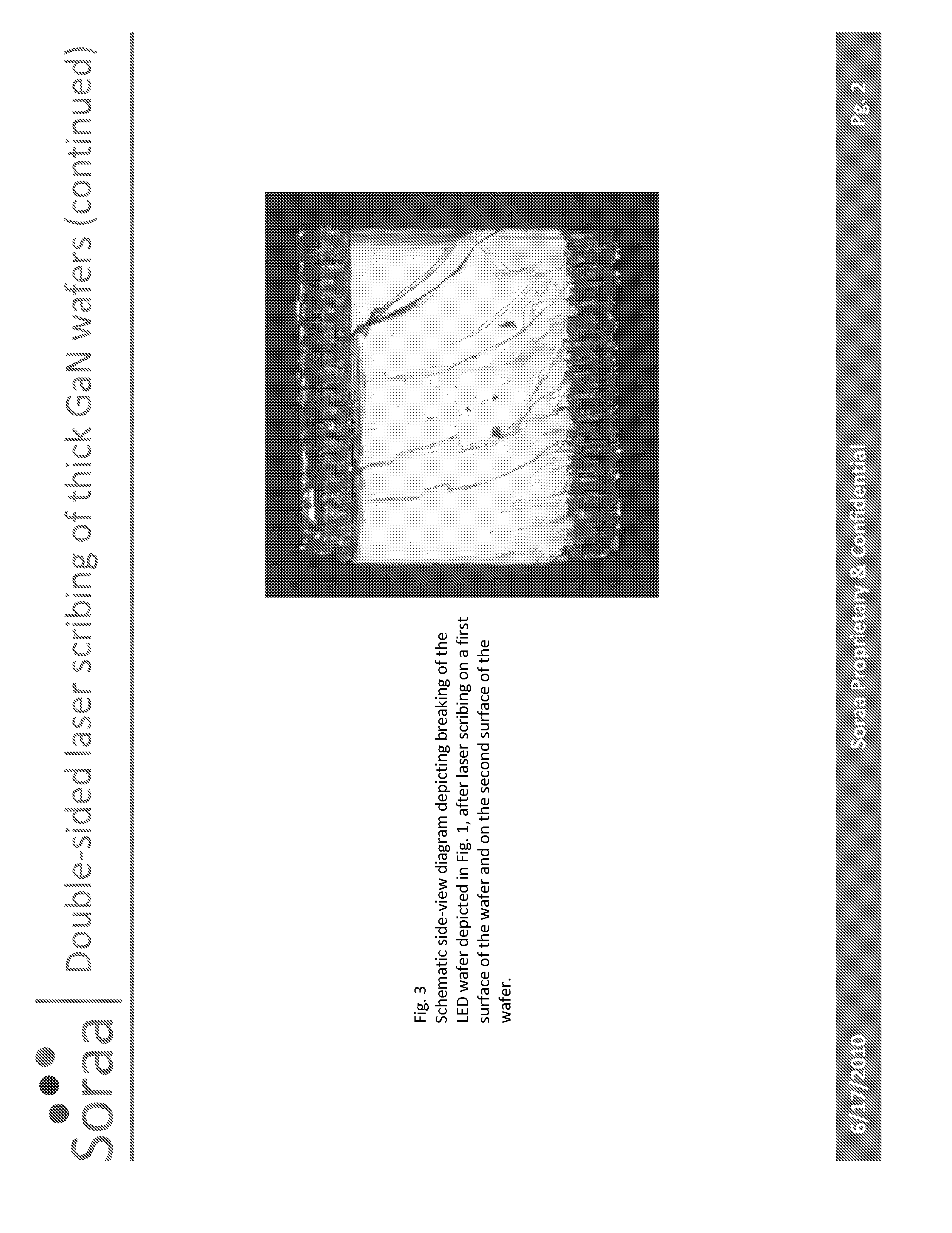

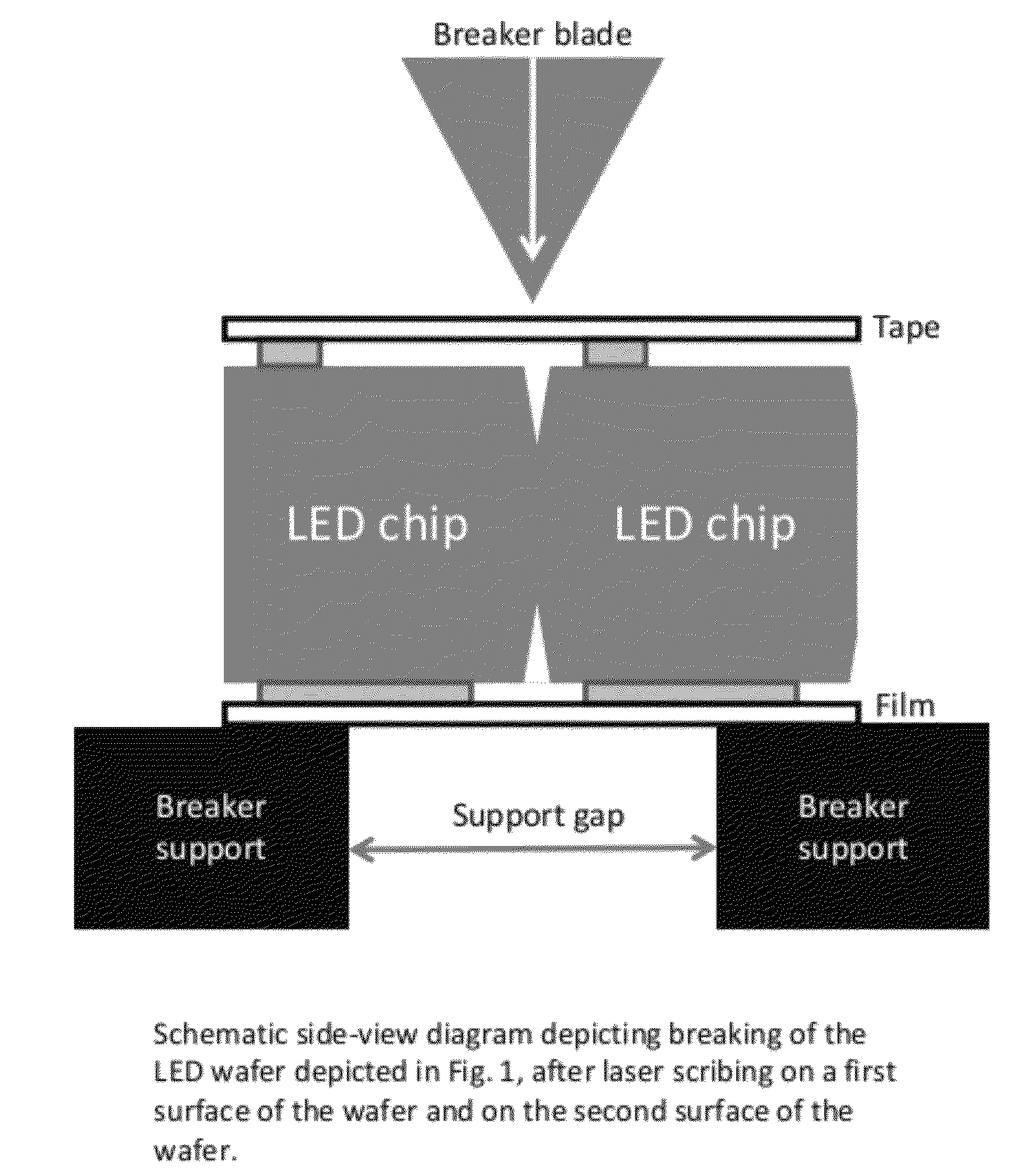

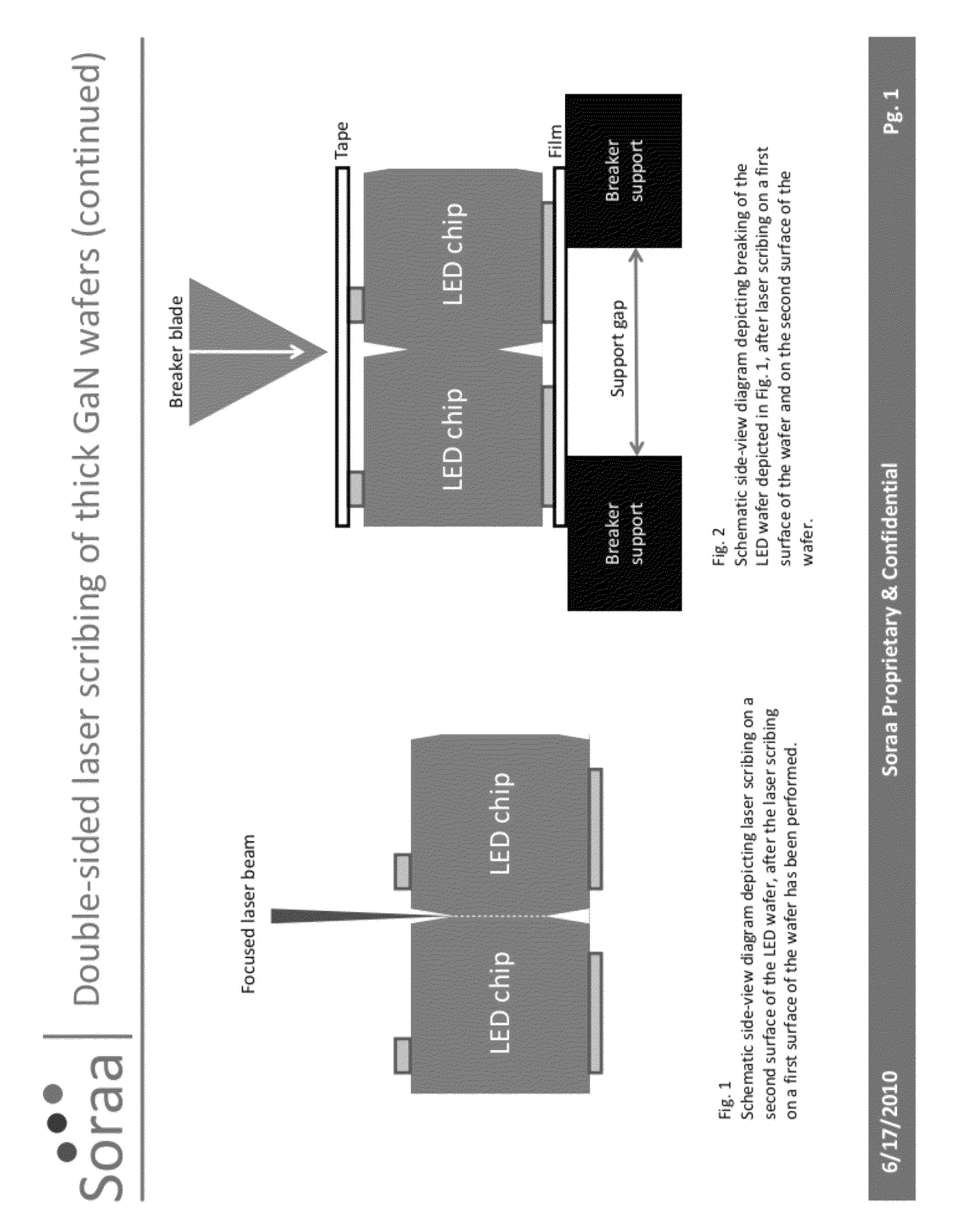

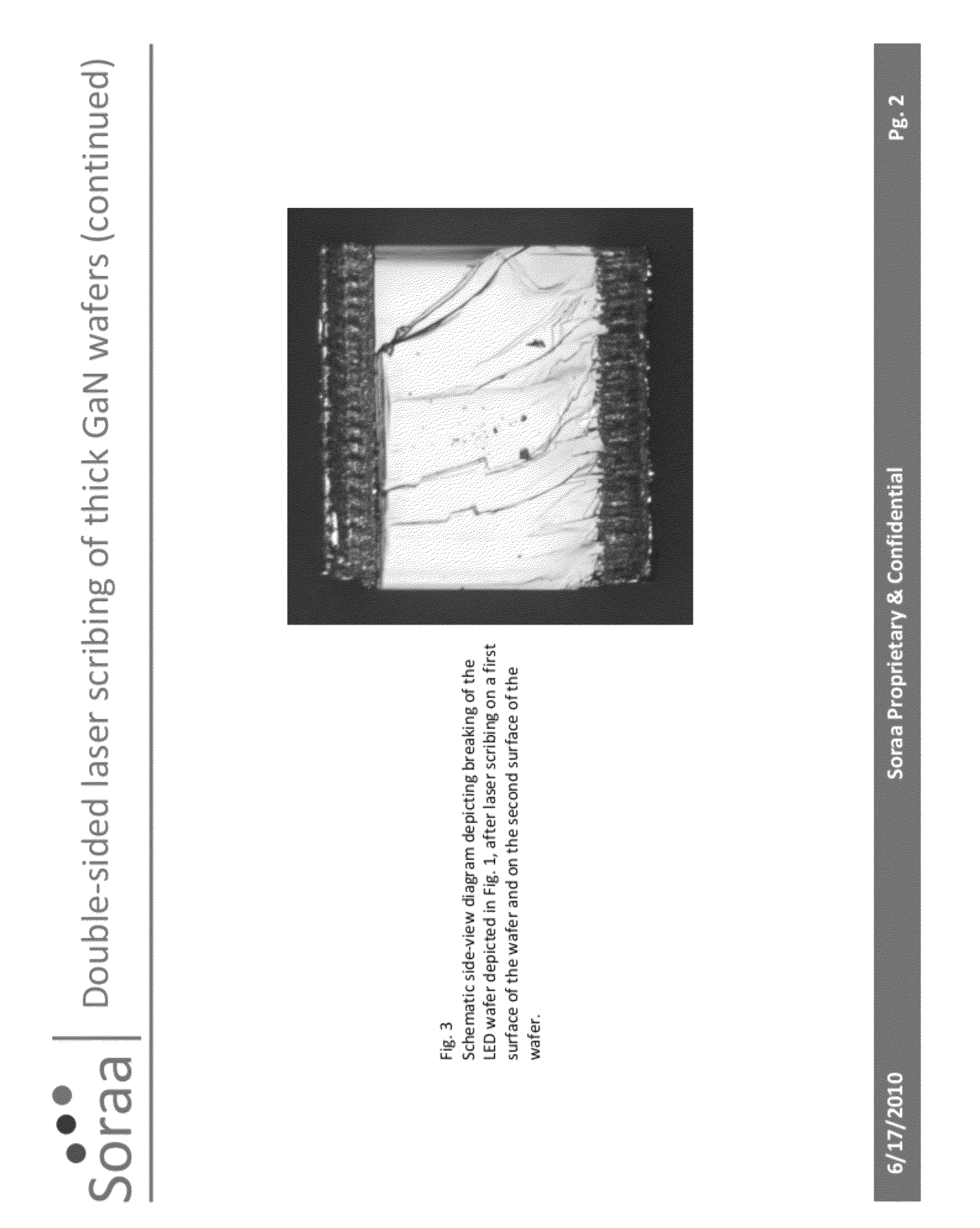

Singulation Method and Resulting Device of Thick Gallium and Nitrogen Containing Substrates

InactiveUS20110309373A1Eliminate needReduce morbiditySemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenEngineering

A method for singulation of thick GaN wafers (e.g., 300-400 um) through the use of a double-side laser-scribe process. In a preferred embodiment, the patterned GaN substrate is processed using a laser-scribe on each side of the substrate to form scribe lines. The scribe lines are aligned to each other. In a preferred embodiment, the substrate has not been subjected to a thinning or polishing process for reducing its thickness.

Owner:KORRUS INC

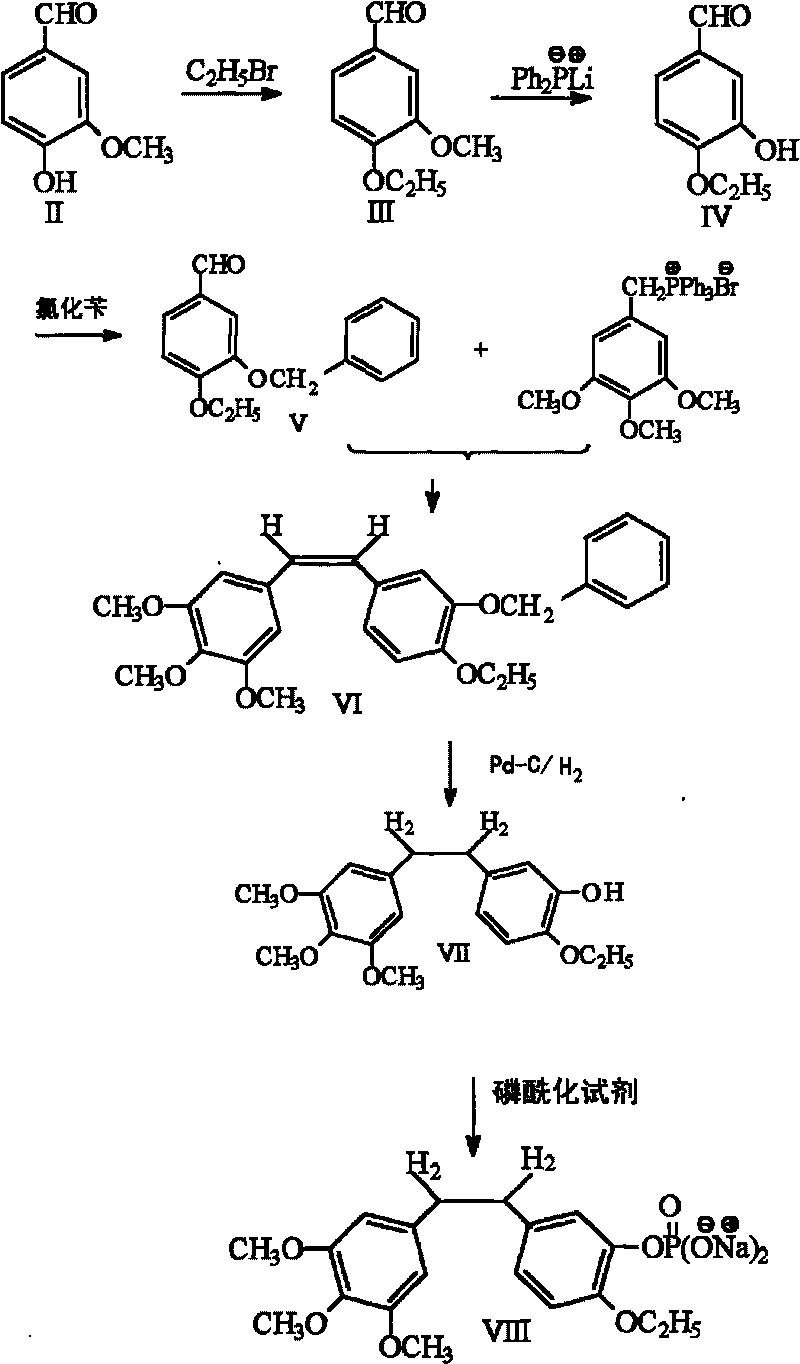

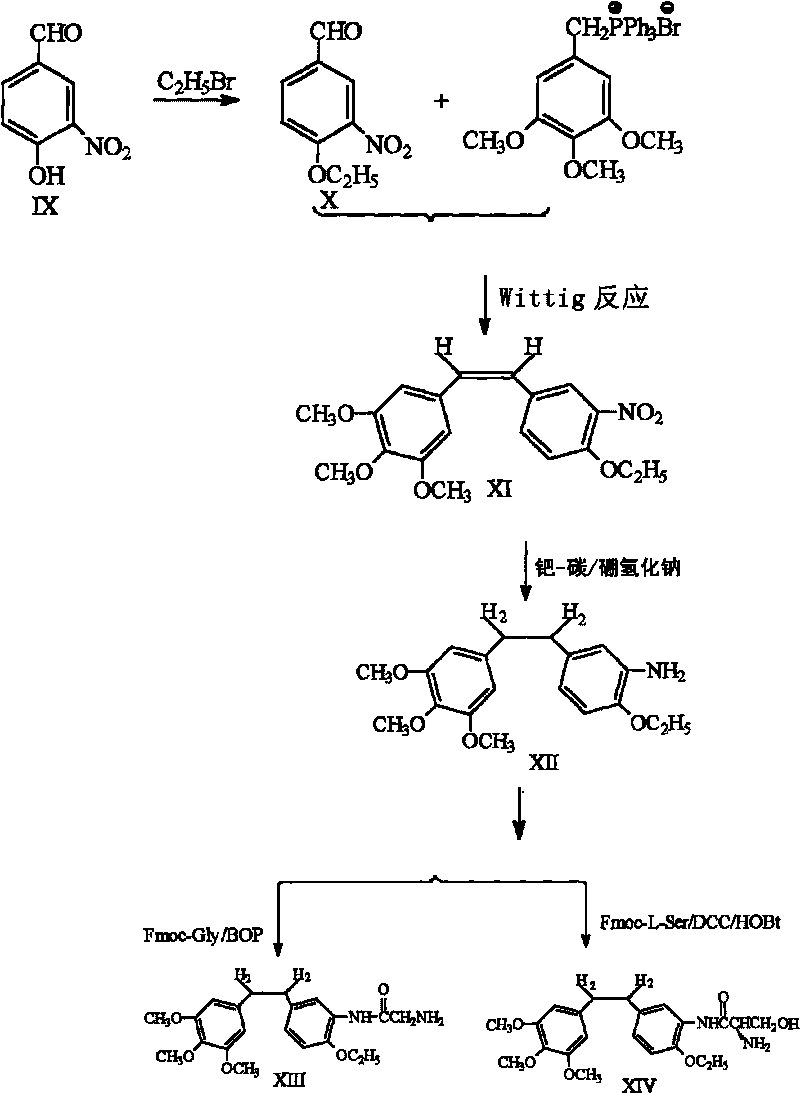

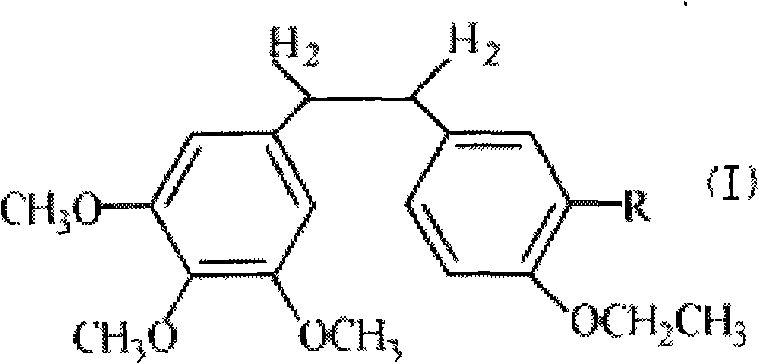

Ethoxy diphenyl ethane derivative and preparation method and application thereof

InactiveCN101723813AImprove stabilityReduce lossGroup 5/15 element organic compoundsEther/acetal active ingredientsAmino acid side chainLymphatic Spread

The invention discloses an ethoxy diphenylethane derivative and a preparation method and application thereof. The 4, position of a B aromatic ring of phenylethane is chemically modified by an ethoxyl group, and simultaneously, a hydroxyl group at the 3, position of the B aromatic ring of the phenylethane is modified into water-soluble pro-drugs such as phosphate and the like, and likewise, an amino acid side chain is introduced into an amino group at the 3, position to form an amino acid amide water-soluble pre-drug having a structure as shown by a structural formula (I). An ethoxy phenylethane derivative and a pre-drug thereof have strong capacity of inhibiting tubulin aggregation, have obvious targeted destructive functions to tumor vessels, selectively cause the tumor vessels to have dysfunctions and structural damages, induce the apoptosis of vascular endothelial cells so that tumor cells lose the support of nutrition and oxygen gas, and give play to the functions of killing and wounding the tumor cells or inhibiting the tumor metastasis.

Owner:SHANGHAI ECUST BIOMEDICINE CO LTD +1

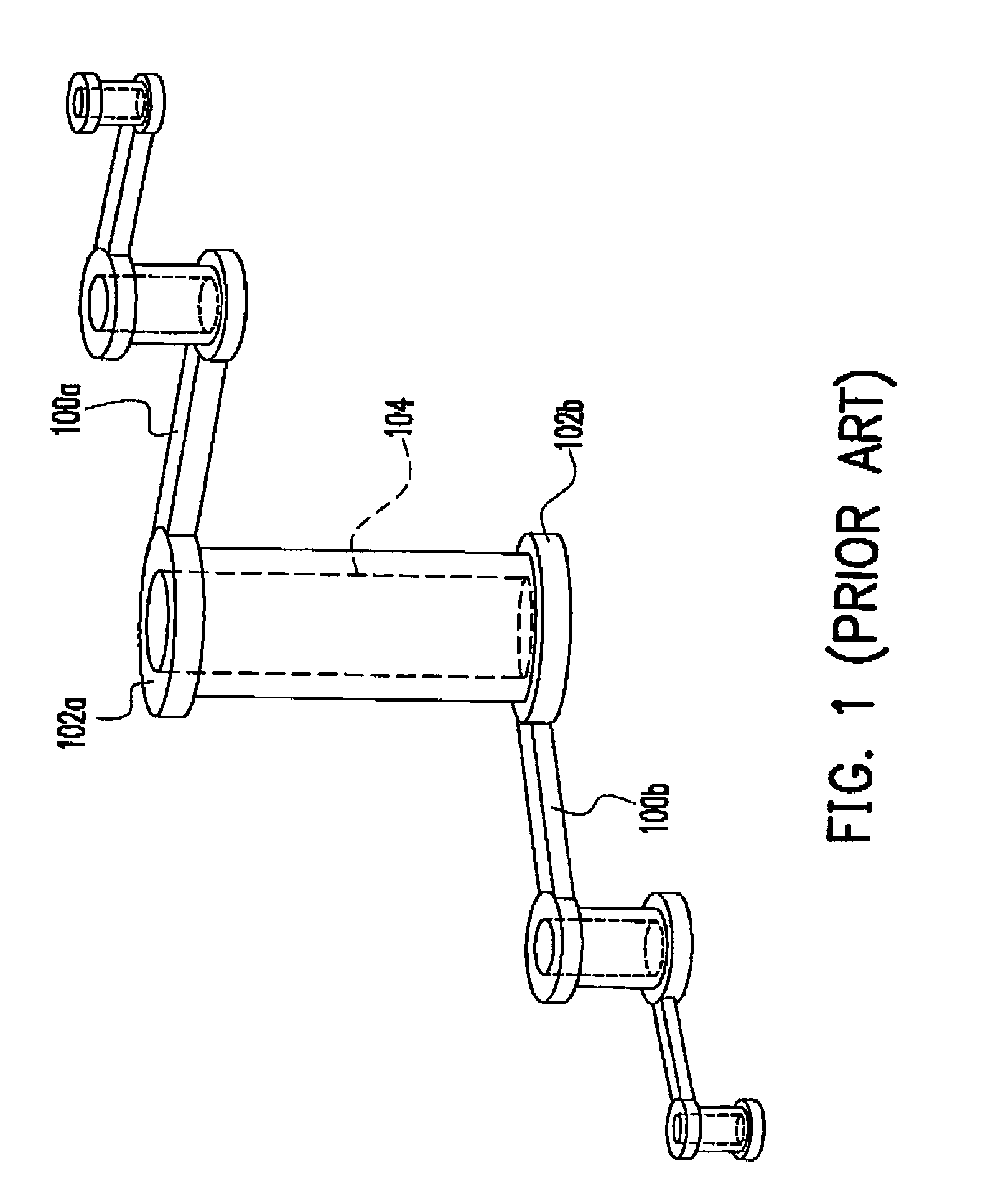

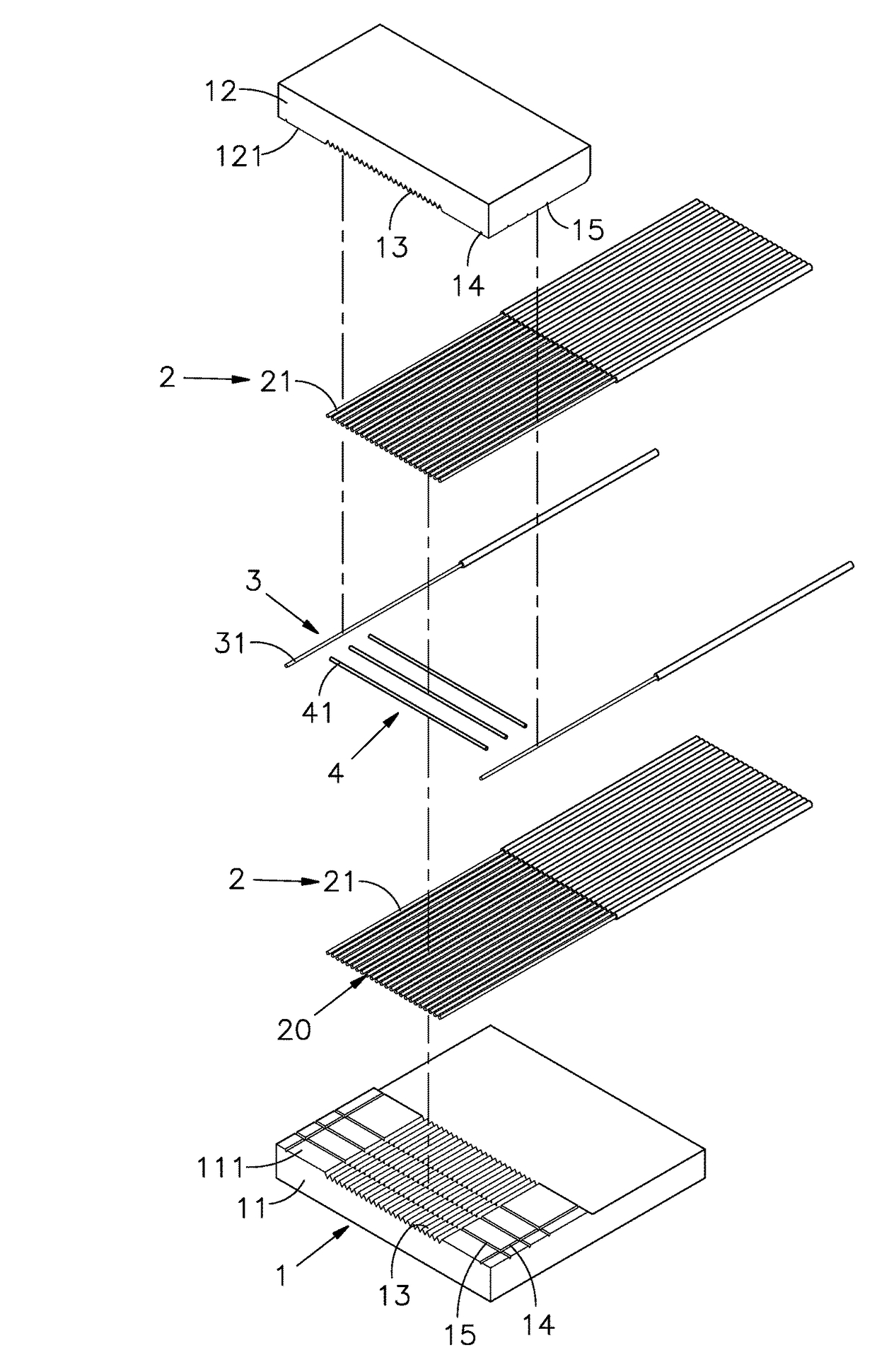

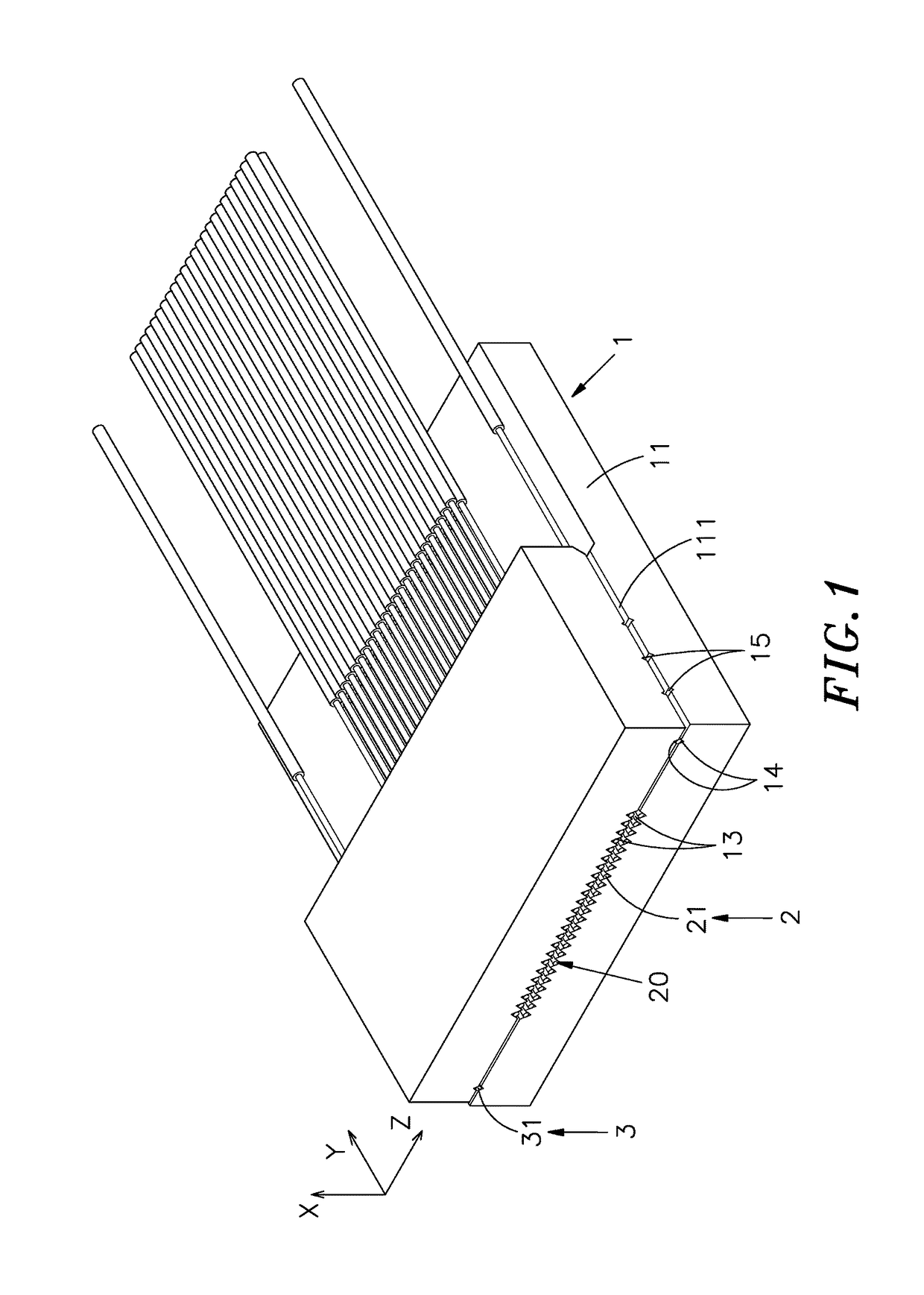

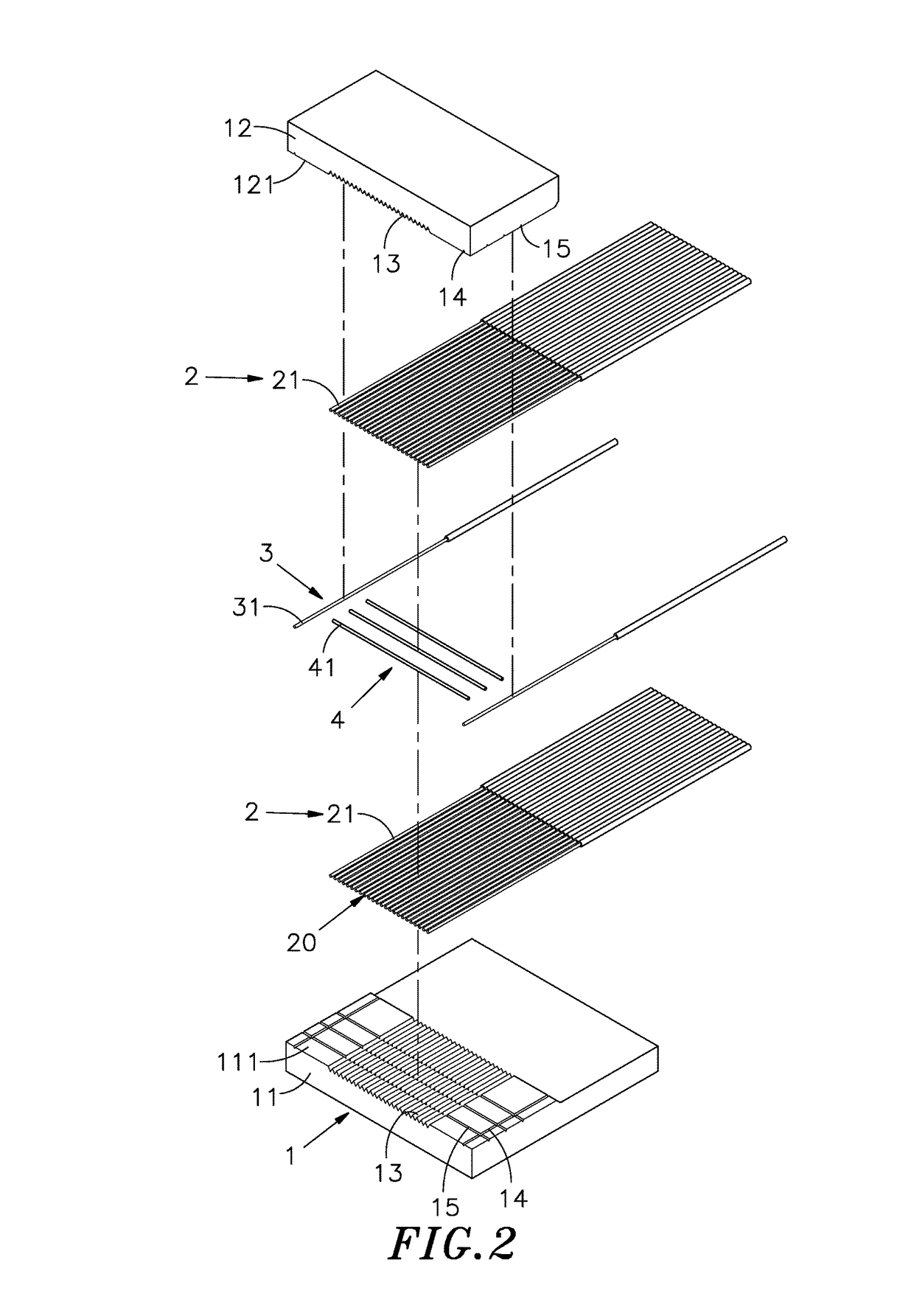

2-dimensional fiber array structure

ActiveUS9709750B1Accurate separationExtra precise machiningCoupling light guidesPosition toleranceFiber array

The present disclosure relates to a two-dimensional fiber array structure including a base which includes a baseboard, a cover board and a spacer layer, and an optical fiber cable is positioned between the baseboard and the cover board, positioning fibers are positioned at two external sides of the optical fiber cable, the spacer layer is abutted with two adjacent fiber layers of the optical fiber cable to reduce the position tolerance along X axis for further improving accuracy, whereby ensuring quality and stability of transmitting optical signal.

Owner:ALLIAN FIBER OPTIC PROD INC

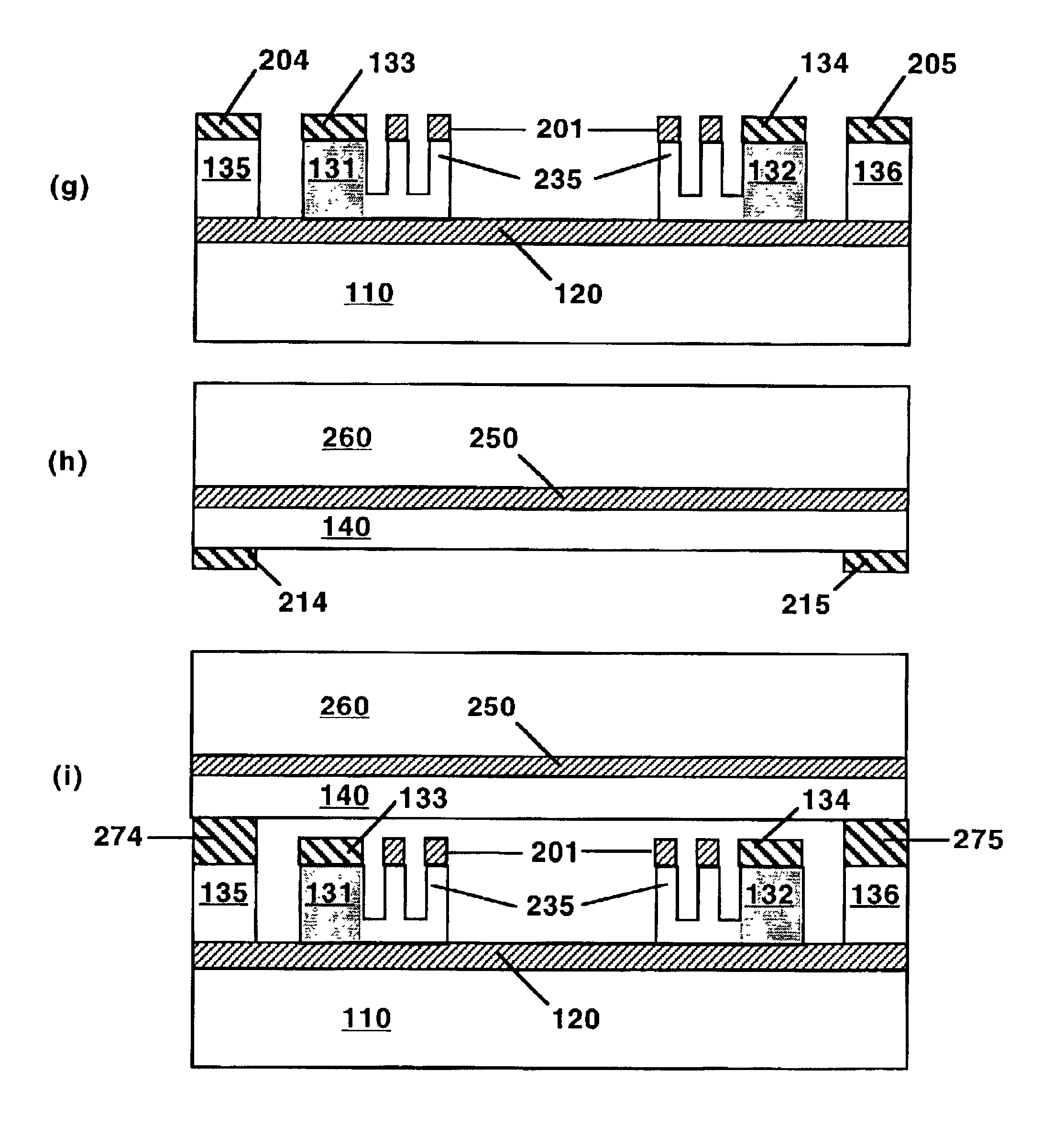

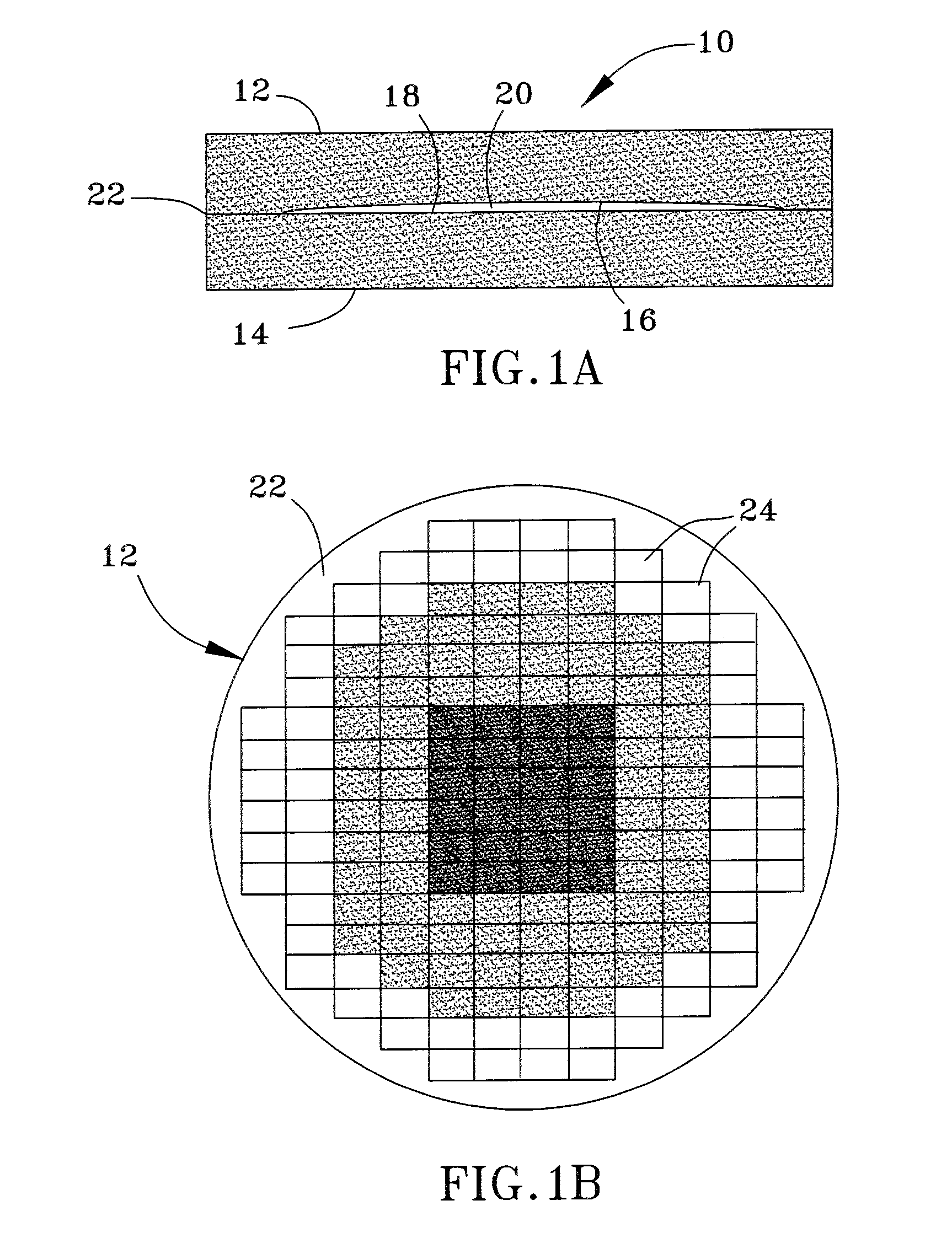

Wafer bonding method and wafer stack formed thereby

ActiveUS20100072555A1Minimize and eliminate detrimental effectLimit electrical shortingSolid-state devicesSemiconductor/solid-state device manufacturingBonding processWafer stacking

A wafer bonding process that compensates for curvatures in wafer surfaces, and a wafer stack produced by the bonding process. The process entails forming a groove in a surface of a first wafer, depositing a bonding stack on a surface of a second wafer, aligning and mating the first and second wafers so that the bonding stack on the second wafer contacts a bonding site on the first wafer, and then heating the first and second wafers to reflow the bonding stack. The groove either surrounds the bonding site or lies entirely within the bonding site, and the heating step forms a molten bonding material, causes at least a portion of the molten bonding material to flow into the groove, and forms a bonding structure that bonds the second wafer to the first wafer. Bonding stacks having different lateral surface areas can be deposited to form bonding structures of different heights to compensate for variations in the wafer gap.

Owner:MICRO INERTIAL LLC

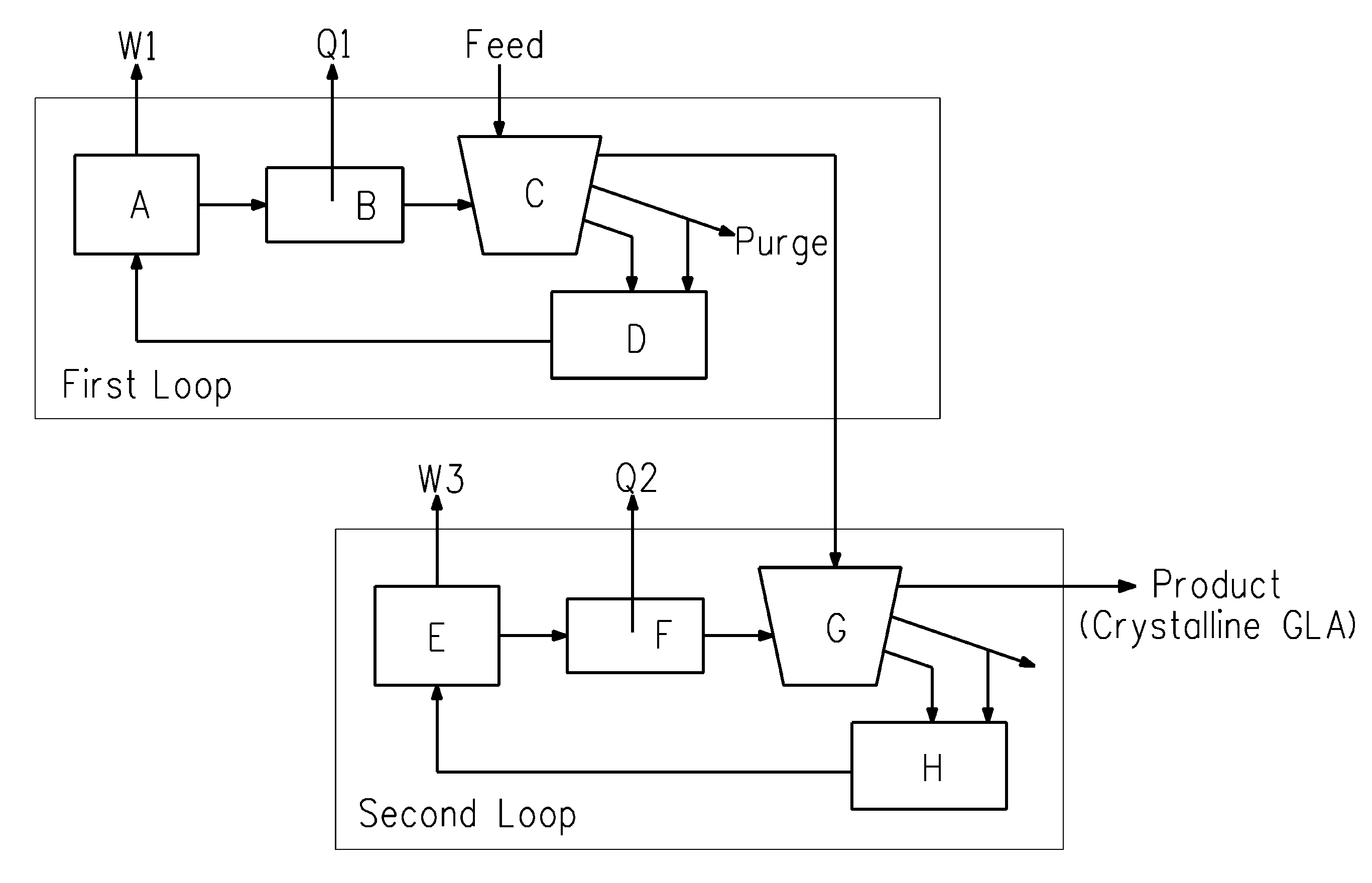

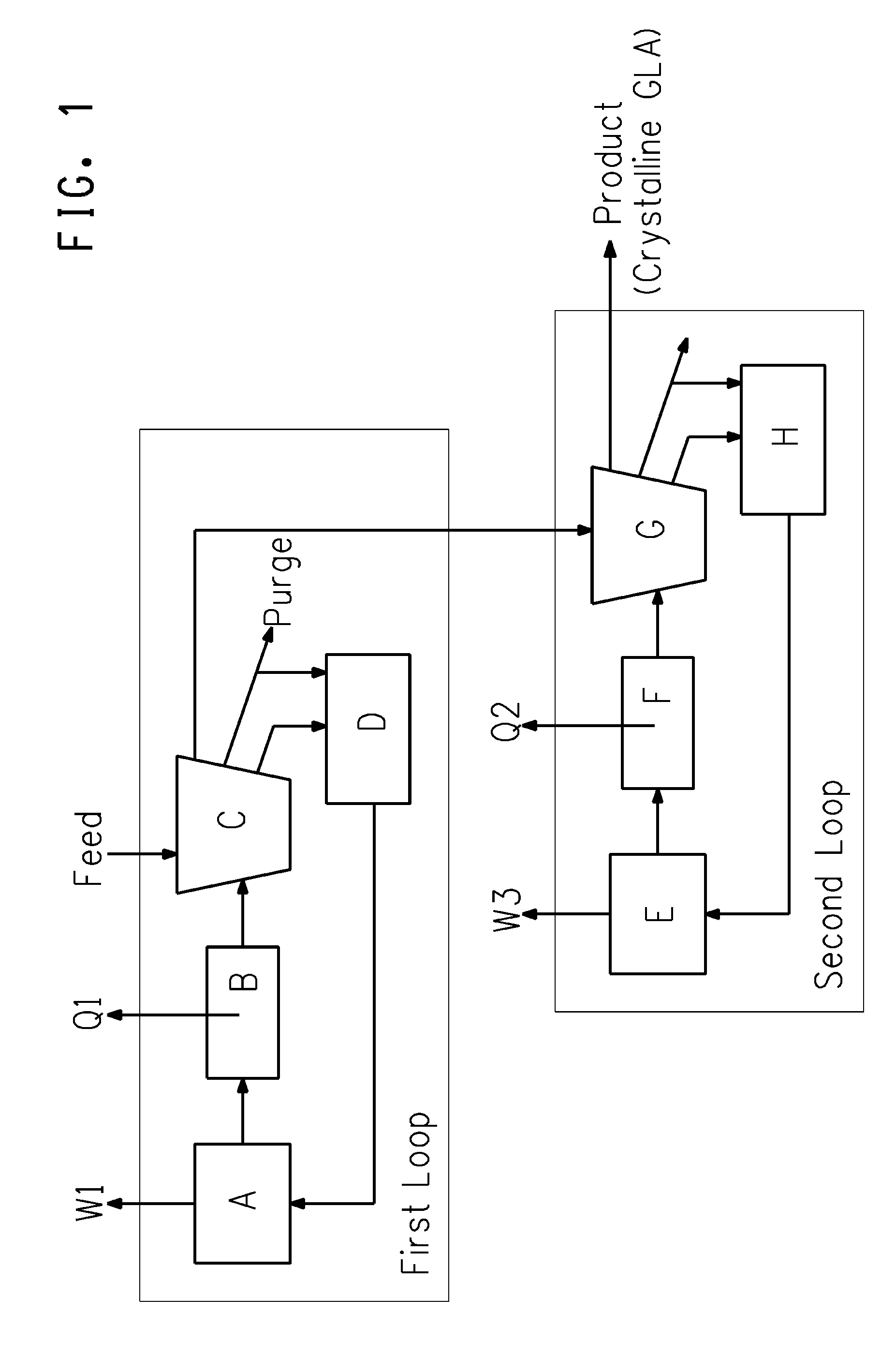

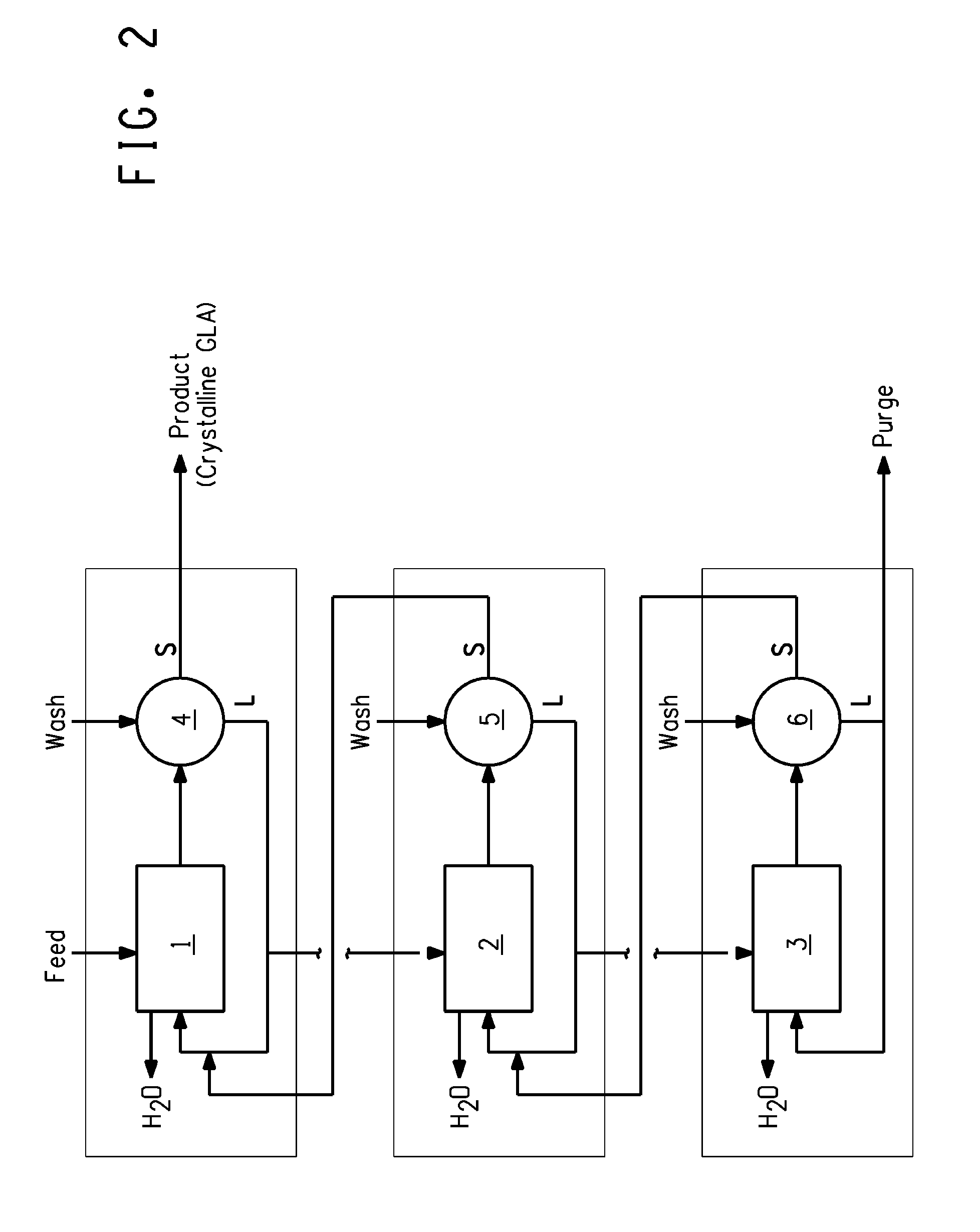

Multi-stage glycolic acid crystallization

ActiveUS7439391B2High yieldLow levelOrganic compound preparationCrystallization by component evaporationGlycollic acidCrystallization

The present invention relates to a high yield process to prepare high purity crystalline glycolic acid using a multi-loop crystallization process characterized by high liquid and / or solid recycle, said process suitable for large scale purification and producing high purity glycolic acid with low diglycolic acid content.

Owner:PURETECH SCI LLC

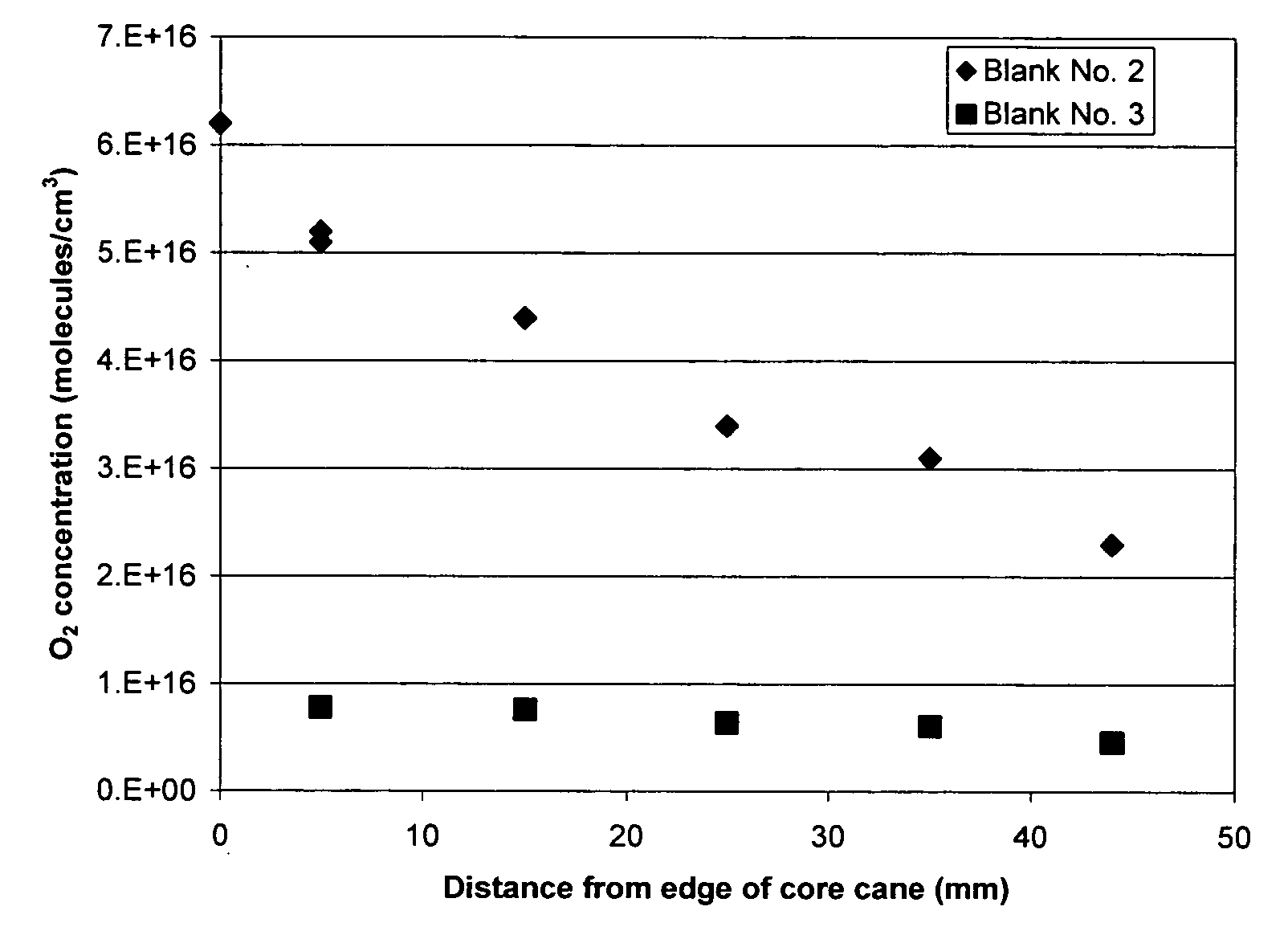

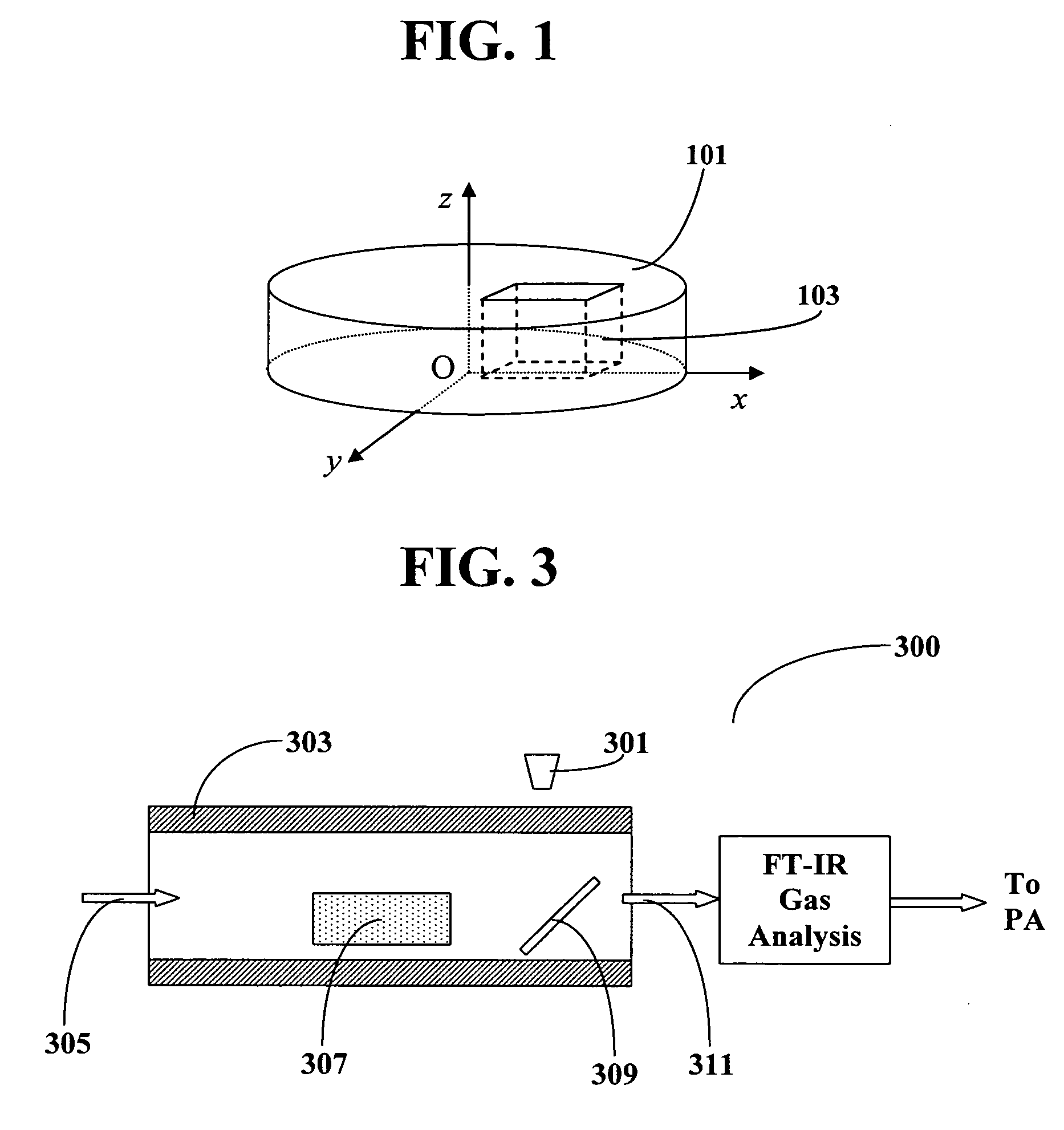

High transmission synthetic silica glass and method of making same

InactiveUS20060137397A1Improve homogeneityIncreased aperture areaPhotomechanical apparatusGlass shaping apparatusPolymer scienceOptical axis

Disclosed are high purity synthetic silica material having an internal transmission at 193 nm of at least 99.65% / cm and method of preparing such material. The material is also featured by a high compositional homogeneity in a plane transverse to the intended optical axis. The soot-to-glass process for making the material includes a step of consolidating the soot preform in the presence of H2O and / or O2.

Owner:CORNING INC

Technique for preparing potassium sodium dehydroandroandrographolide succinate

ActiveCN101260098ASolve the problem of unstable pHFully combinedOrganic chemistryAntipyreticSodium bicarbonateWater baths

The invention discloses a process of preparing Dehydroandrographolide Succinate Sodium and Potassium salts. The process includes: heating and dissolving Dehydroandrographolide Succinate with 3 to 6 times of absolute ethyl alcohol; adding mole KHCO3 and NaHCO3 in equal weight into water and dissolving in a water bath; dripping slowly while mixing in the temperature of between 50 and 80 DEG C until solution defecates, filtering and putting on a 0.22 mu m filter membrane, adding 7 to 11 times of absolute ethyl alcohol while mixing until the solution is even, standing in room temperature until natural crystallization seeds out, filtering and washing 2 to 3 times with absolute ethyl alcohol, fitering and drying with less pressure to obtain a canary solid. The invention provides a process route of preparing potassium sodium dehydroandroan drographolide succinate for injection with high purity, which uses Dehydroandrographolide Succinate as the raw material, is added with potassium bicarbonate and sodium bicarbonate directly to compose Potassium Sodium Dehydroandroan drographolide Succinate, which is high in process yields, high in product purity, good in solubility, less in impurity and complete in combination of Potassium and Sodium; the product is high in purity and good in solubility without obvious toxic and side effect in clinic application, the preparation is more stable compared with the similar and can be prepared into various preparations.

Owner:CHANGCHUN MAILING BIOLOGICAL ENG CO LTD

Singulation method and resulting device of thick gallium and nitrogen containing substrates

InactiveUS8313964B2Eliminate needReduce morbiditySemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenEngineering

A method for singulation of thick GaN wafers (e.g., 300-400 um) through the use of a double-side laser-scribe process. In a preferred embodiment, the patterned GaN substrate is processed using a laser-scribe on each side of the substrate to form scribe lines. The scribe lines are aligned to each other. In a preferred embodiment, the substrate has not been subjected to a thinning or polishing process for reducing its thickness.

Owner:KORRUS INC

Touch sensing display panel, touch sensing color filter and fabricating method thereof

ActiveUS8134527B2Touch sensing resolutionSimplify the manufacturing processCathode-ray tube indicatorsInput/output processes for data processingTouch SensesComputer science

Owner:AU OPTRONICS CORP