Patents

Literature

99 results about "Partial alignment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

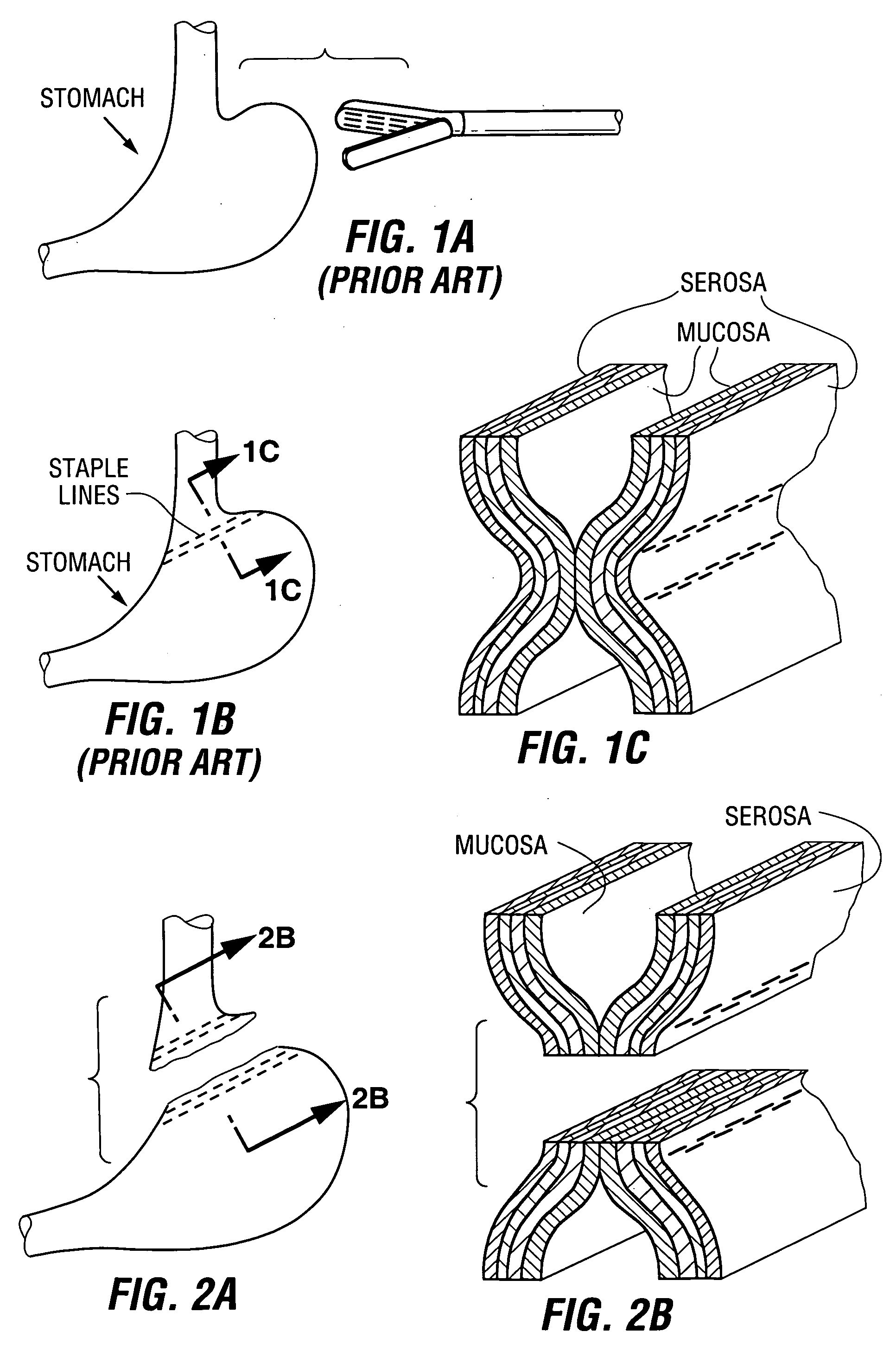

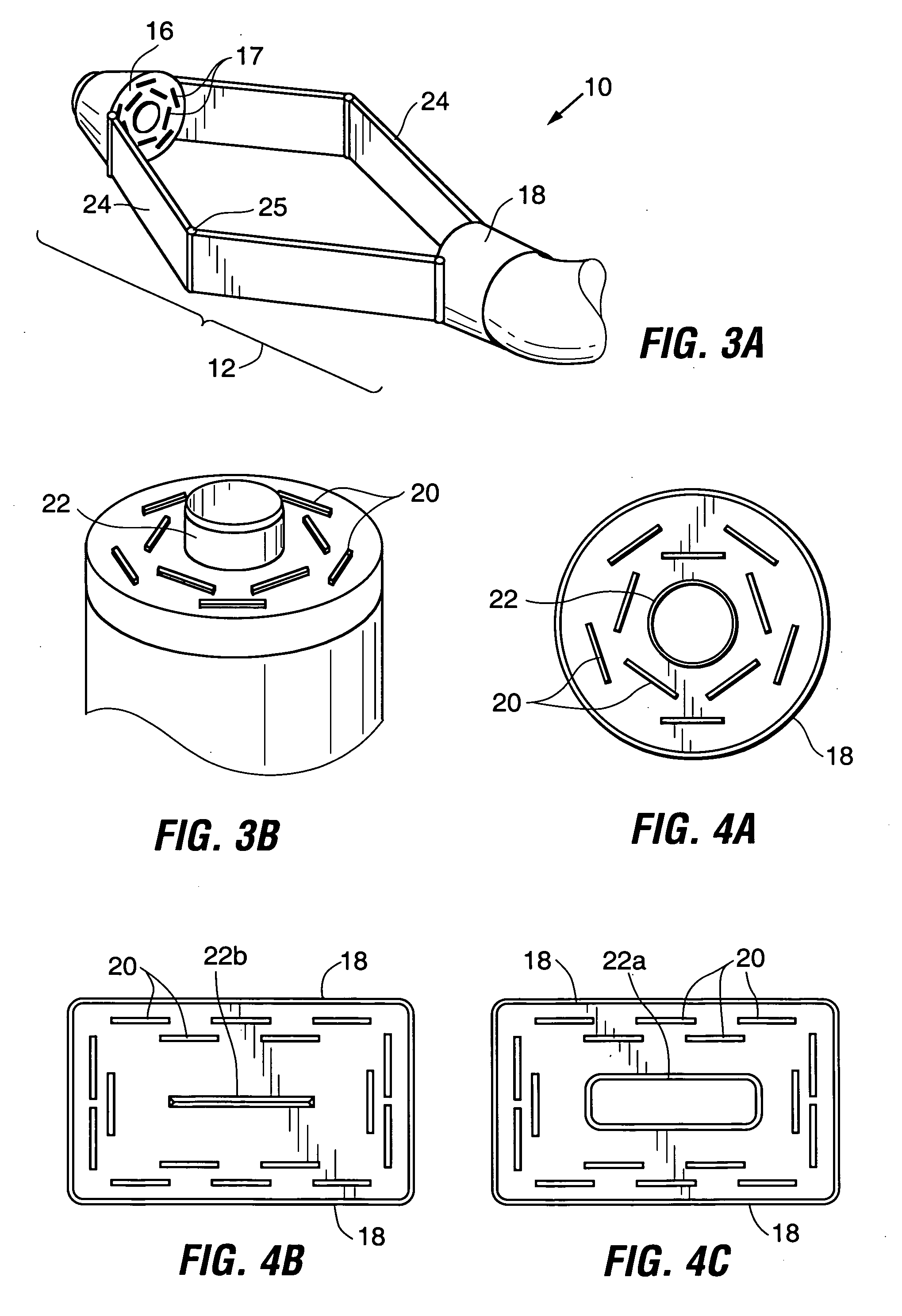

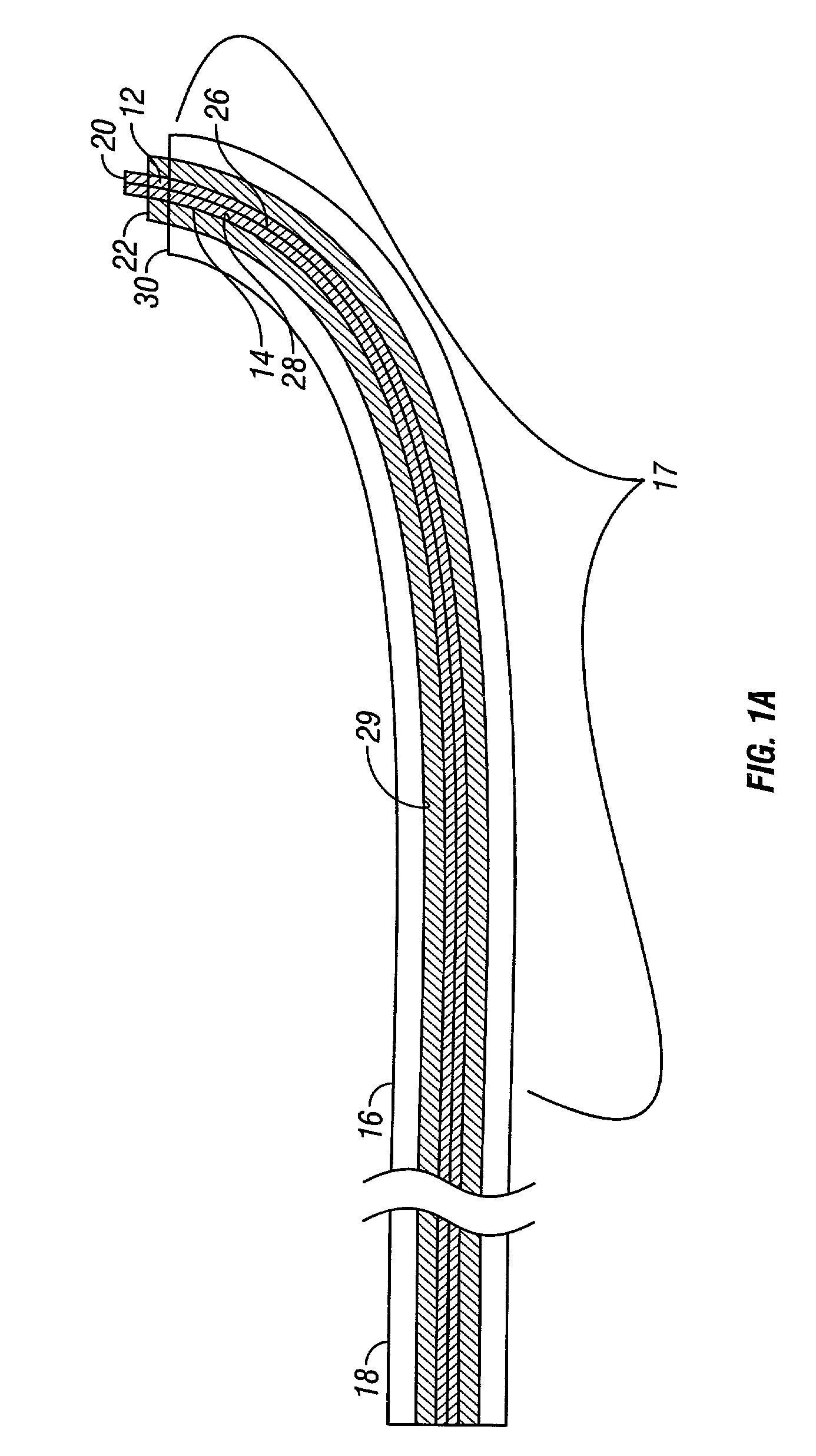

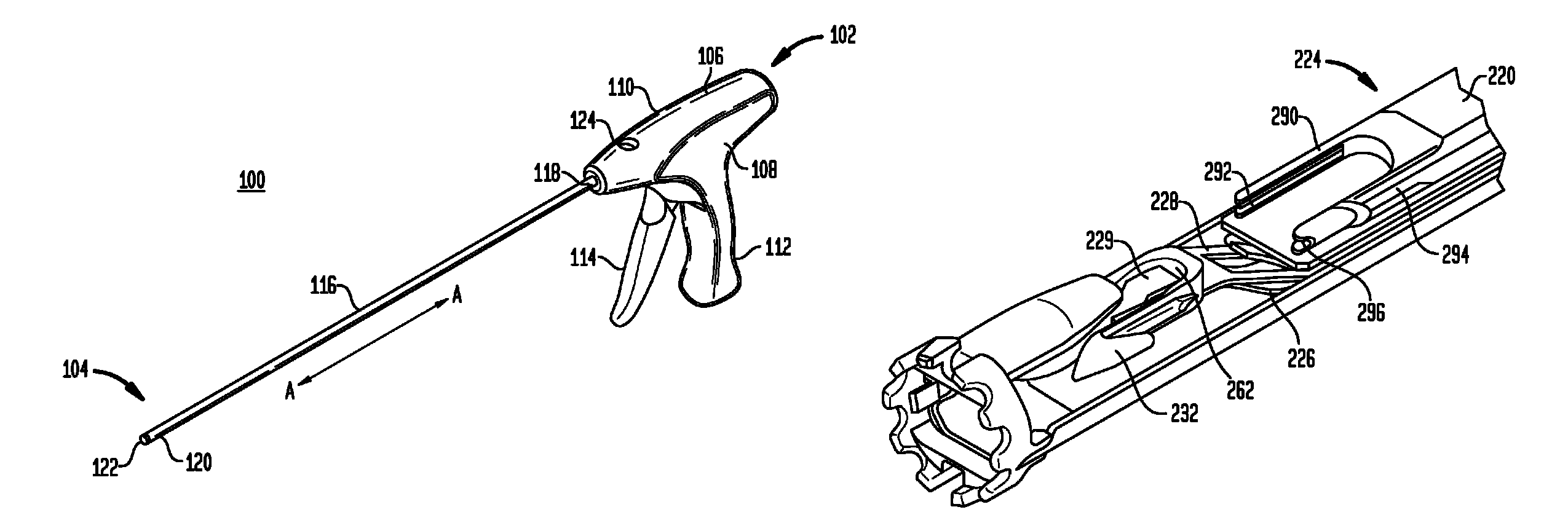

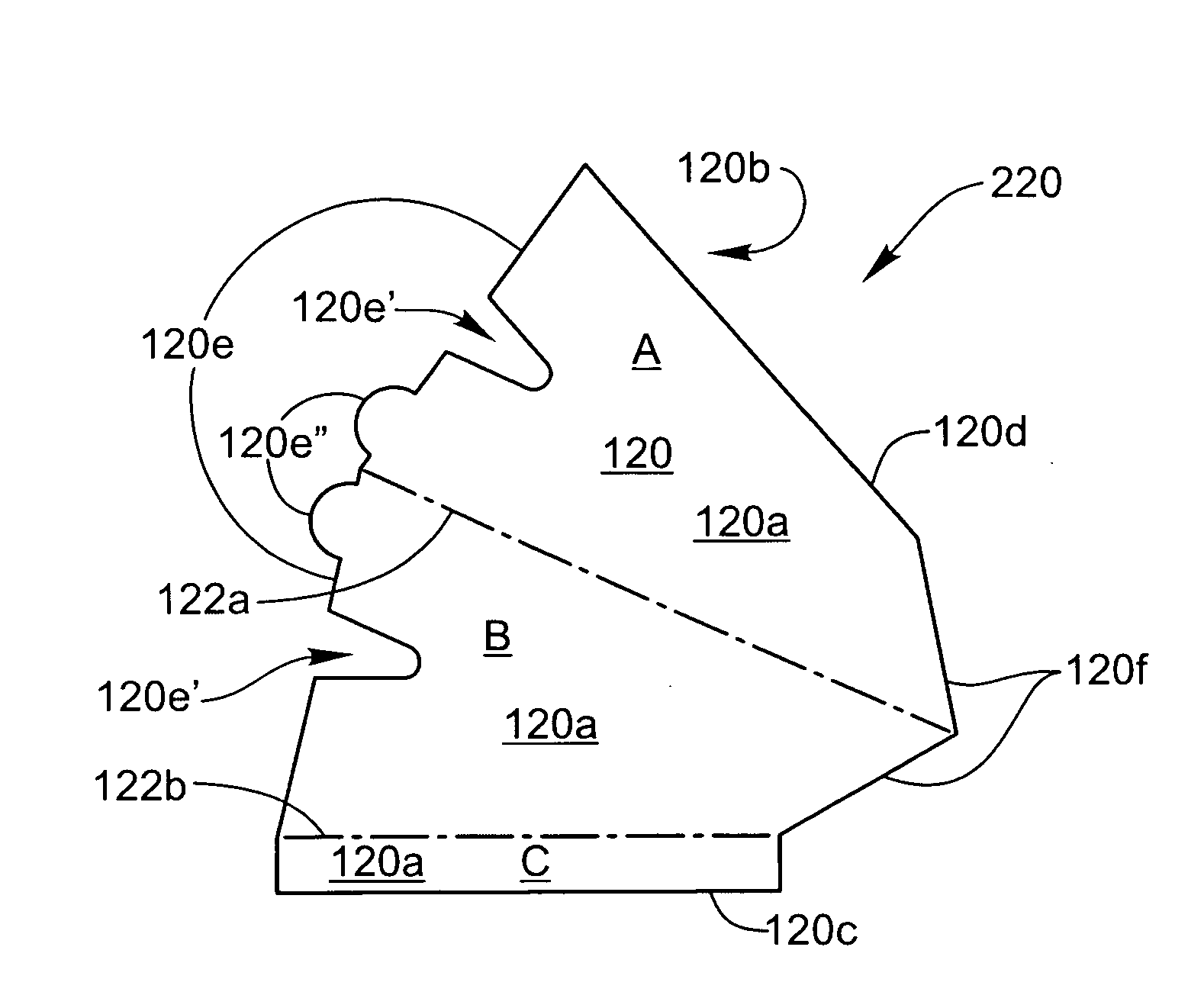

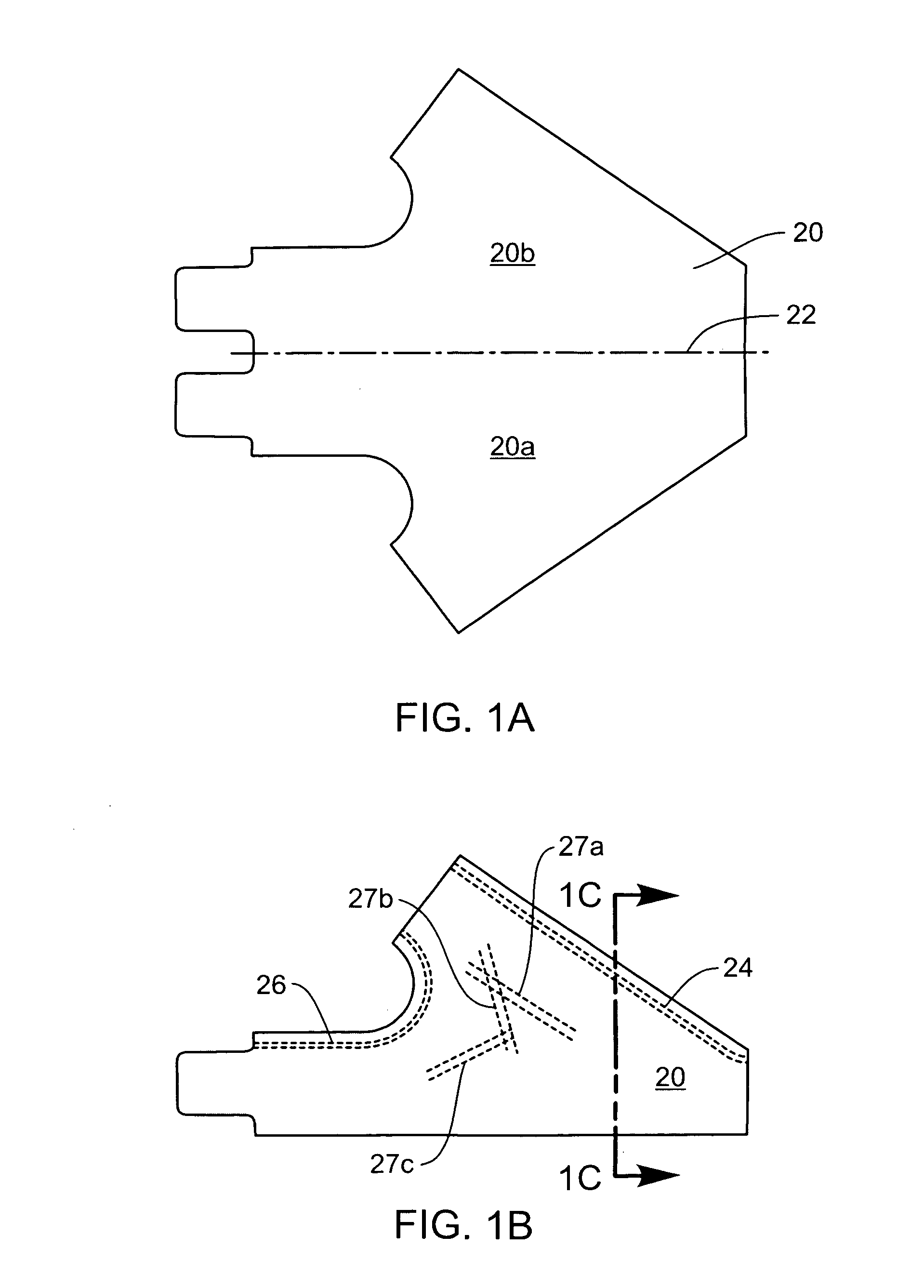

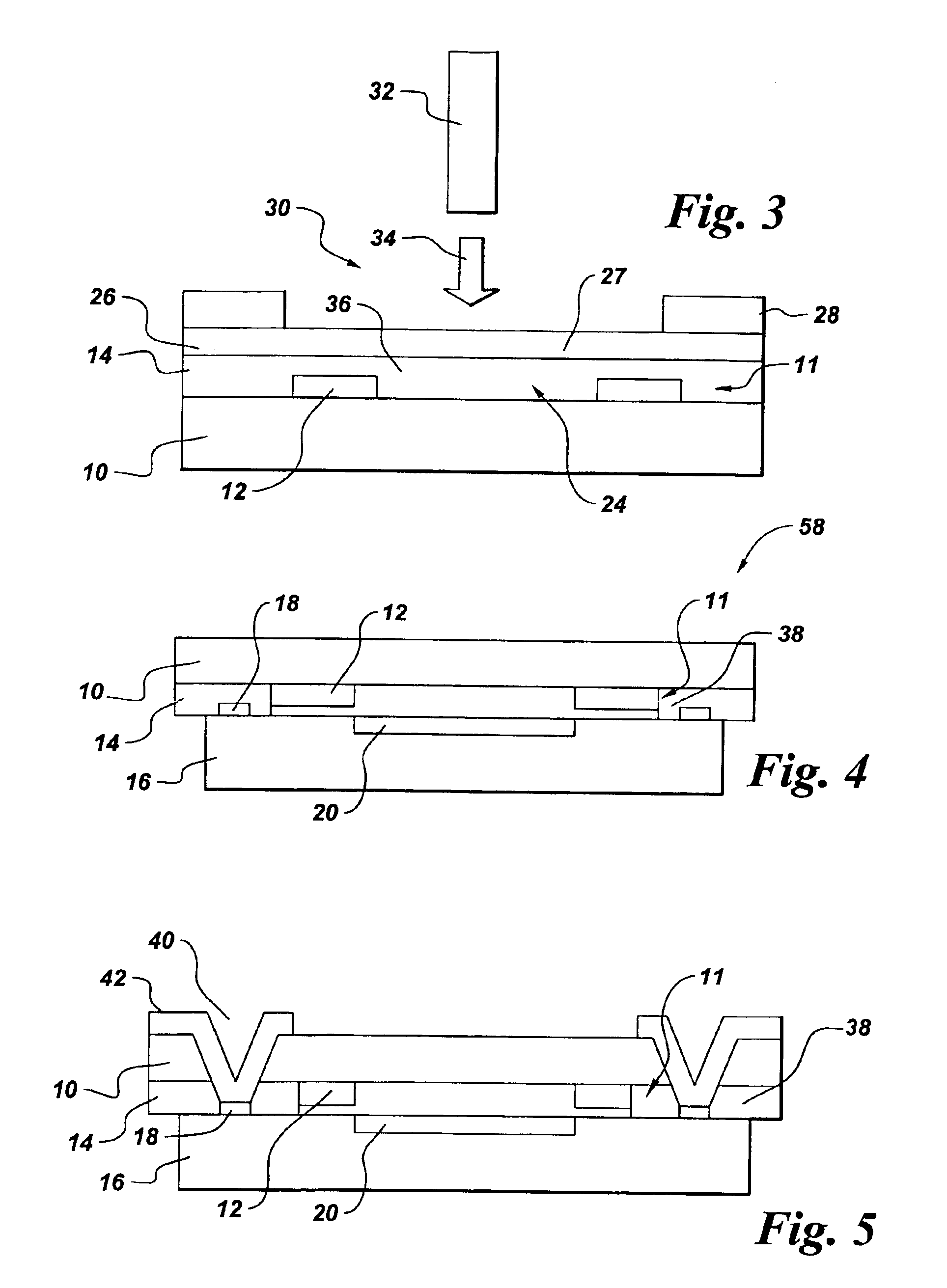

Devices and methods for stomach partitioning

A device and method for remodeling or partitioning a body cavity, hollow organ or tissue tract includes graspers operable to engage two or more sections of tissue within a body cavity and to draw the engaged tissue between a first and second members of a tissue remodeling tool. The two or more pinches of tissue are held in complete or partial alignment with one another as staples or other fasteners are driven through the pinches, thus forming a four-layer tissue plication. Over time, adhesions formed between the opposed serosal layers create strong bonds that can facilitate retention of the plication over extended durations, despite the forces imparted on them by stomach movement. A cut or cut-out may be formed in the plication during or separate from the stapling step to promote edge-to-edge healing effects that will enhance tissue knitting / adhesion.

Owner:BAROSENSE

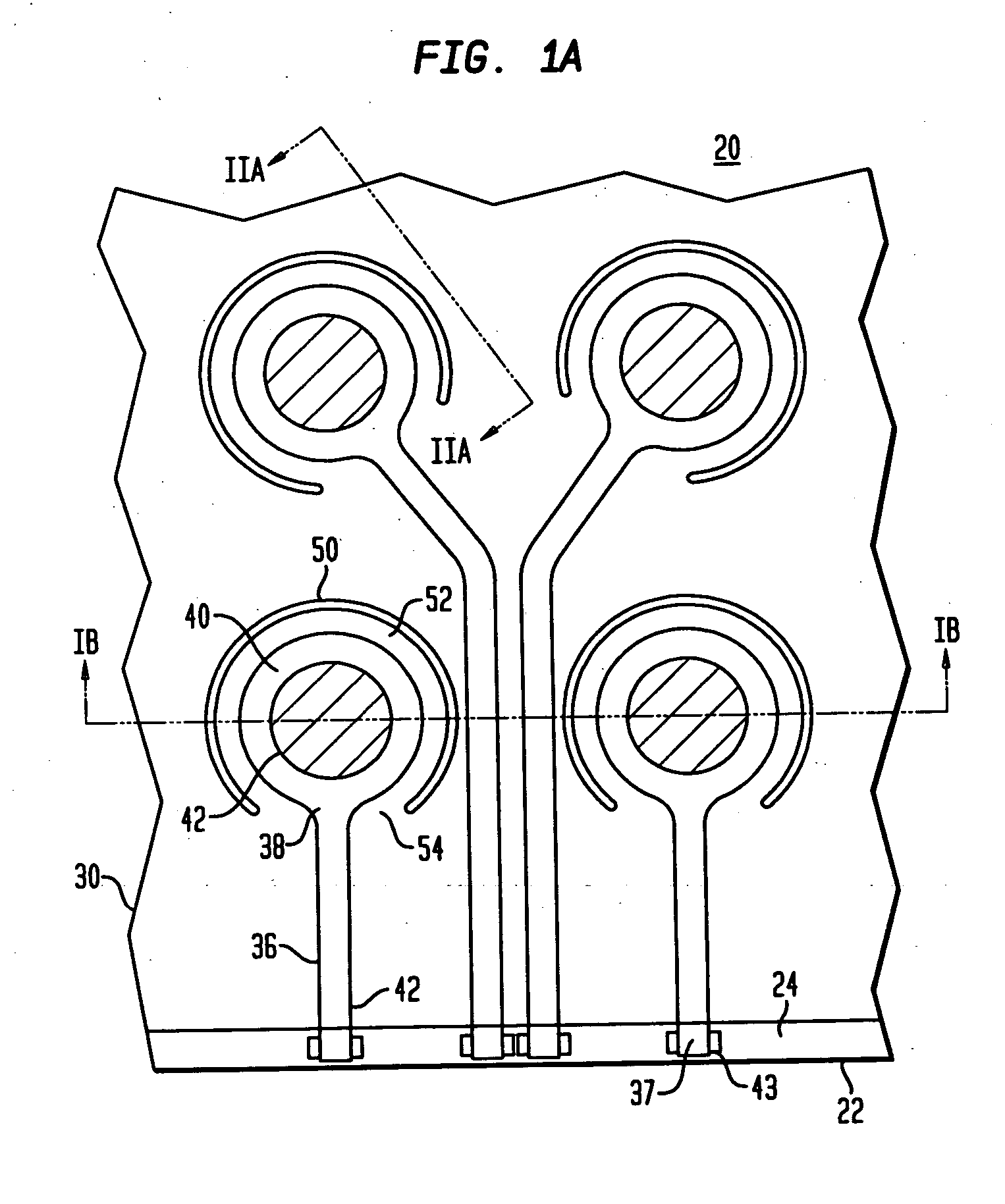

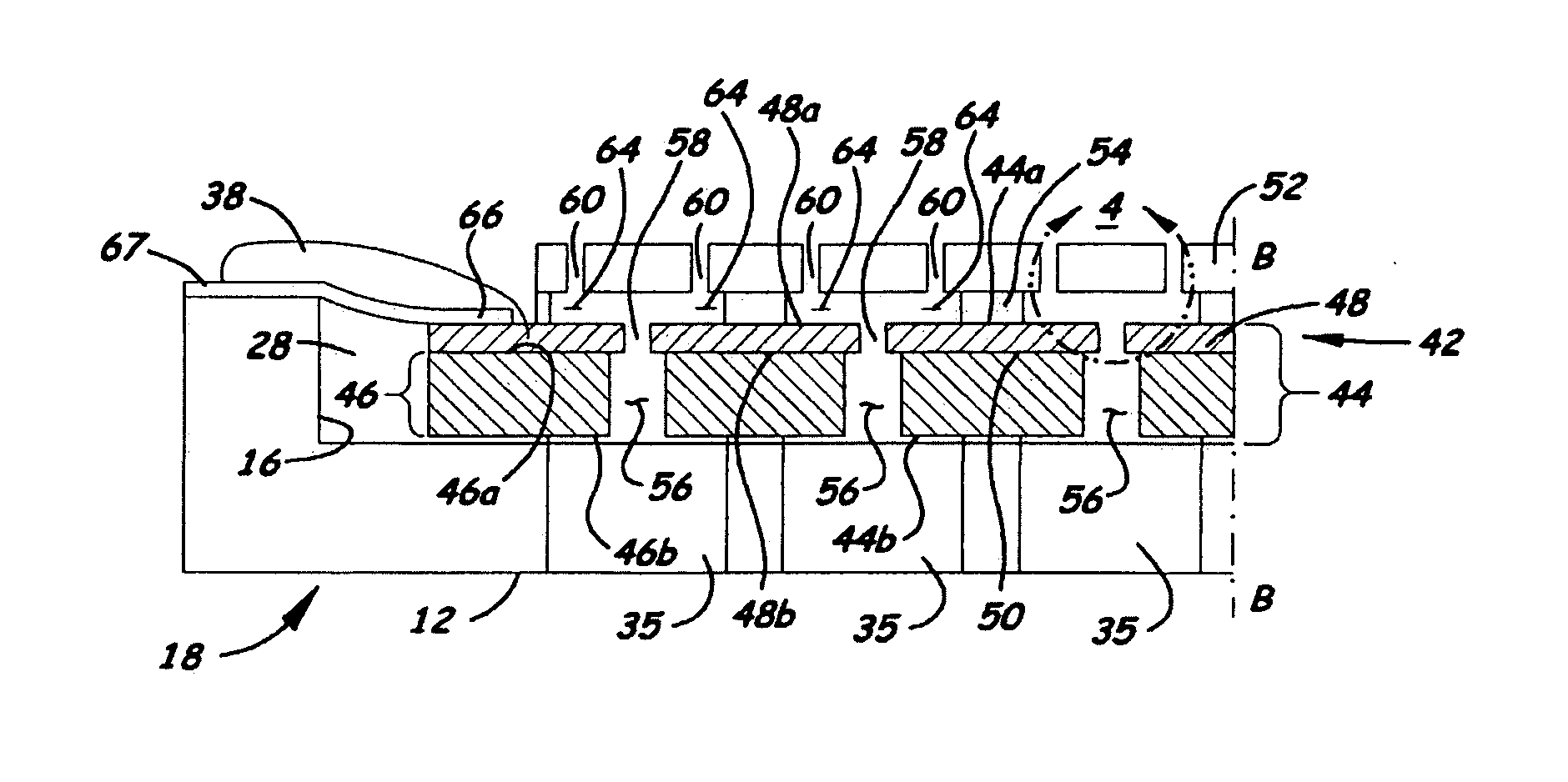

Micro pin grid array with pin motion isolation

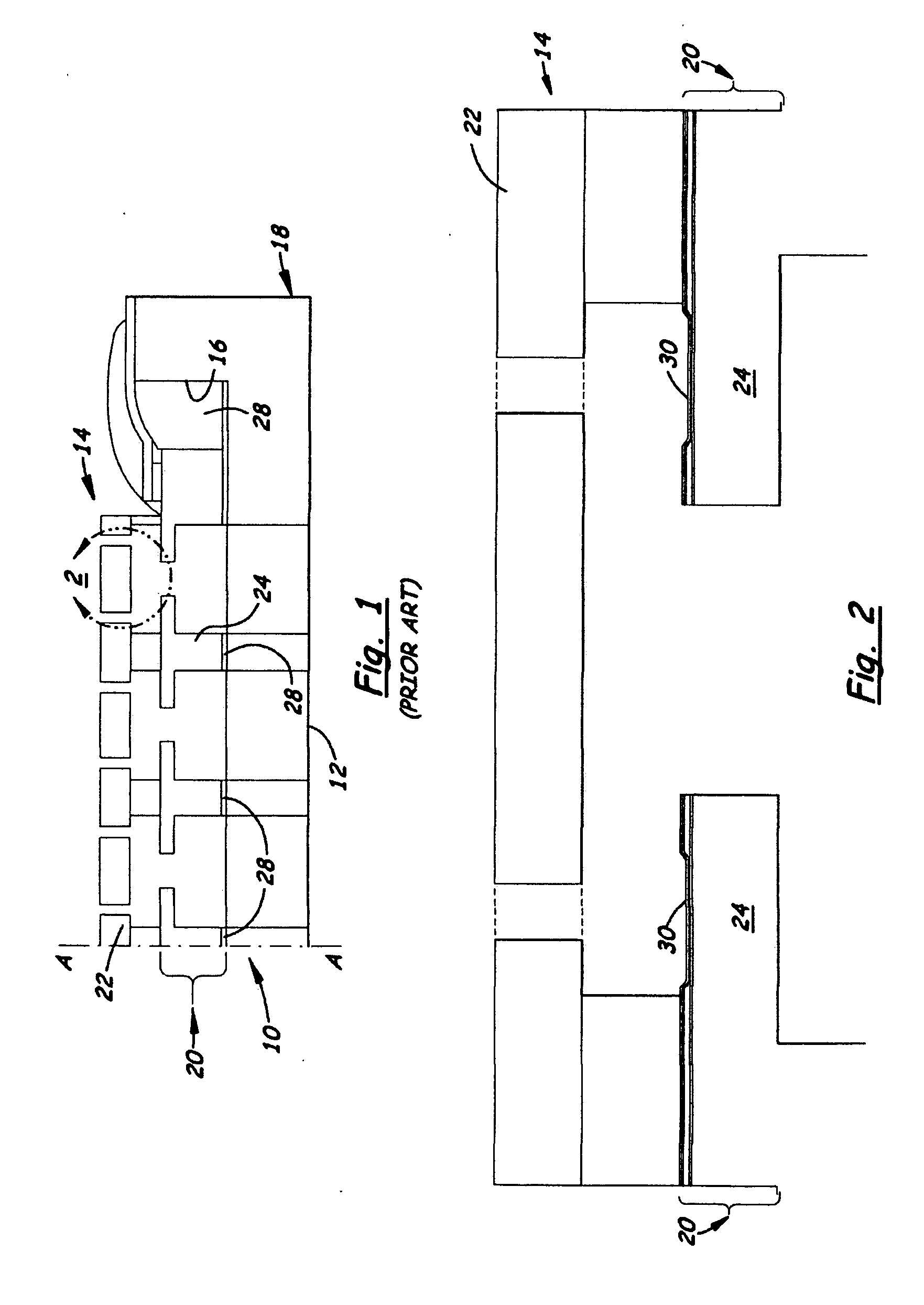

InactiveUS20050173805A1Promote sportsFacilitates flexing of the substratePrinted circuit assemblingSemiconductor/solid-state device detailsPin grid arrayPartial alignment

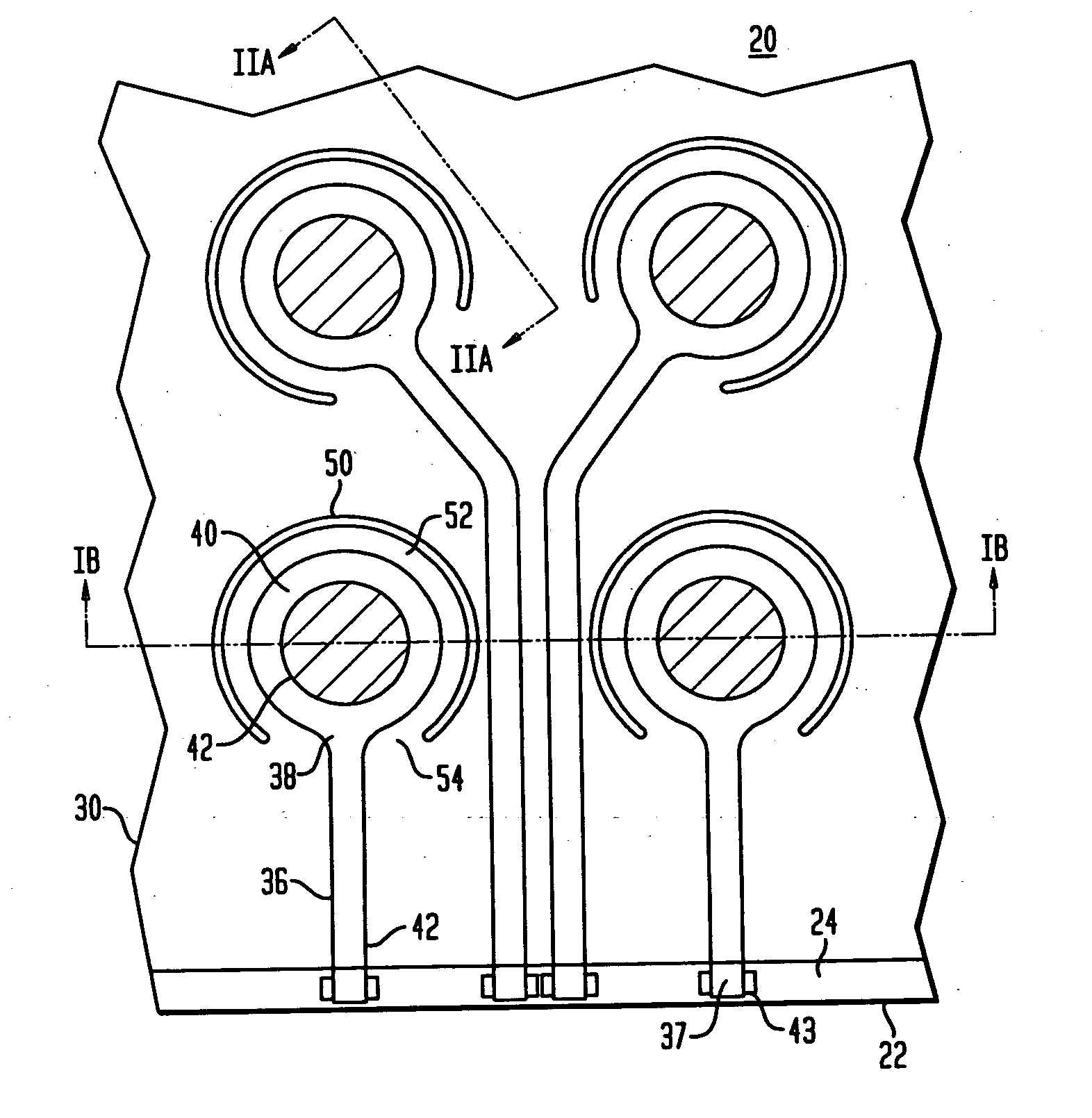

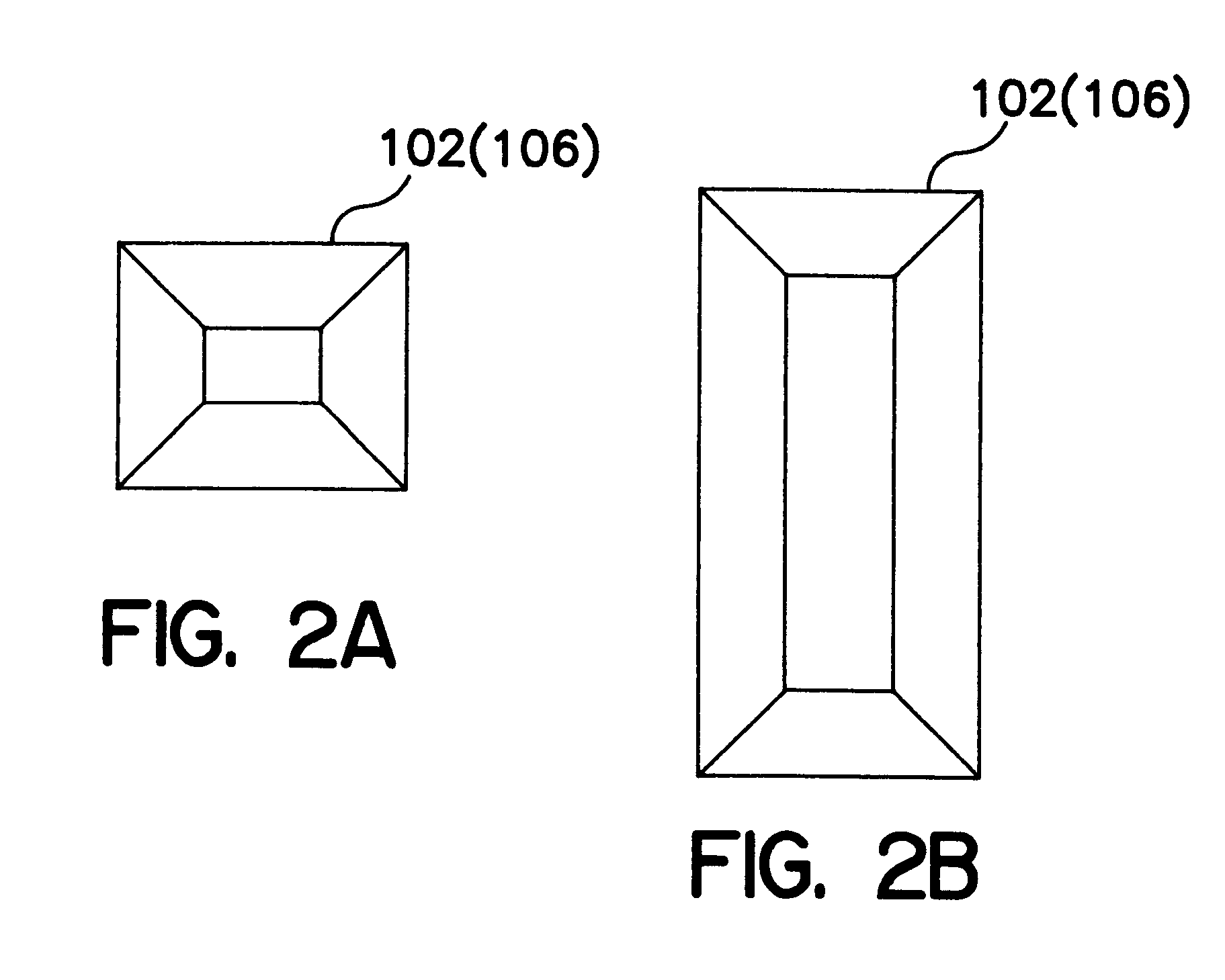

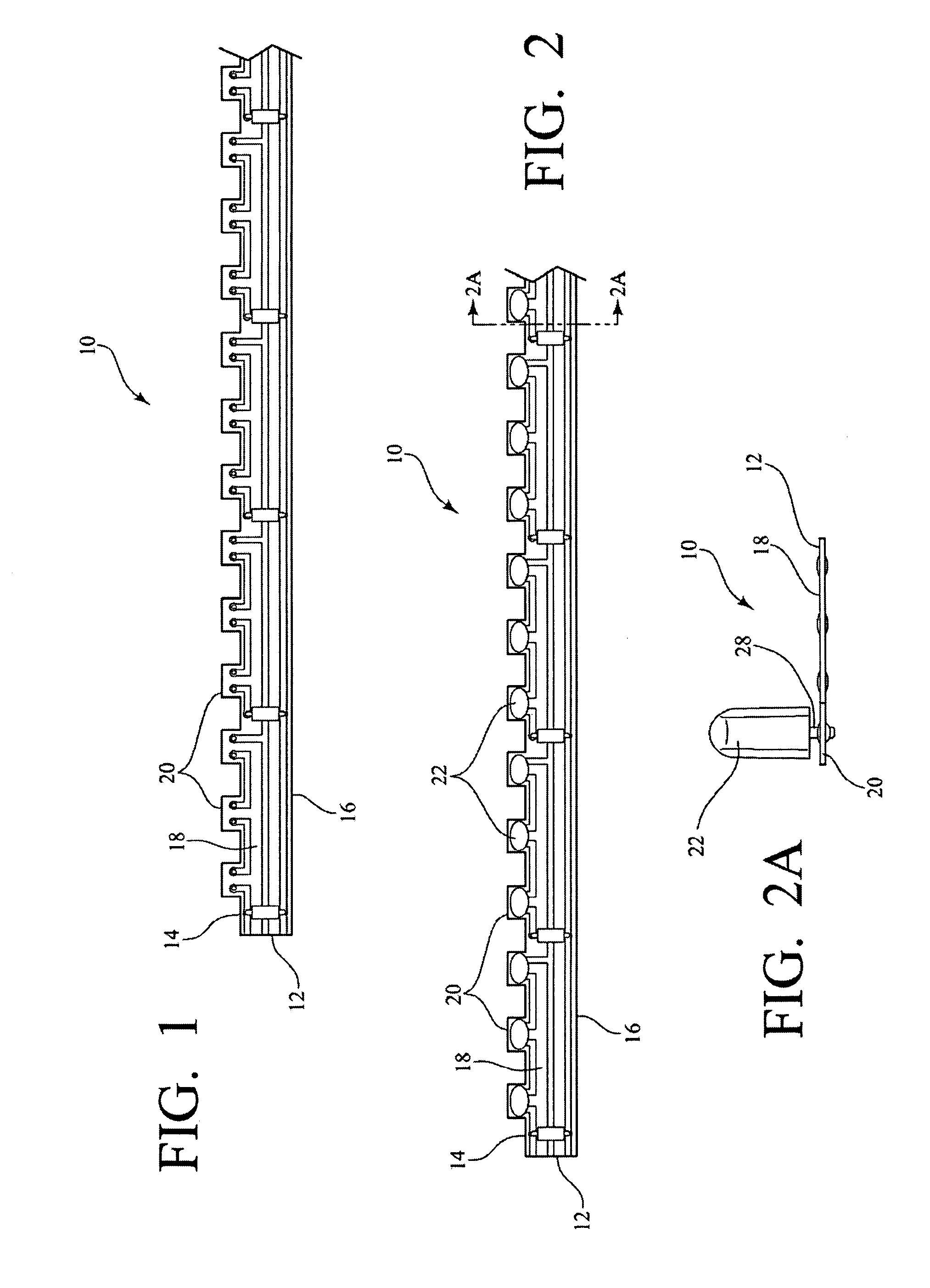

A microelectronic package includes a microelectronic element having faces and contacts, a flexible substrate overlying and spaced from a first face of the microelectronic element, and a plurality of conductive terminals exposed at a surface of the flexible substrate. The conductive terminals are electrically interconnected with the microelectronic element and the flexible substrate includes a gap extending at least partially around at least one of the conductive terminals. In certain embodiments, the package includes a support layer, such as a compliant layer, disposed between the first face of the microelectronic element and the flexible substrate. In other embodiments, the support layer includes at least one opening that is at least partially aligned with one of the conductive terminals.

Owner:TESSERA INC

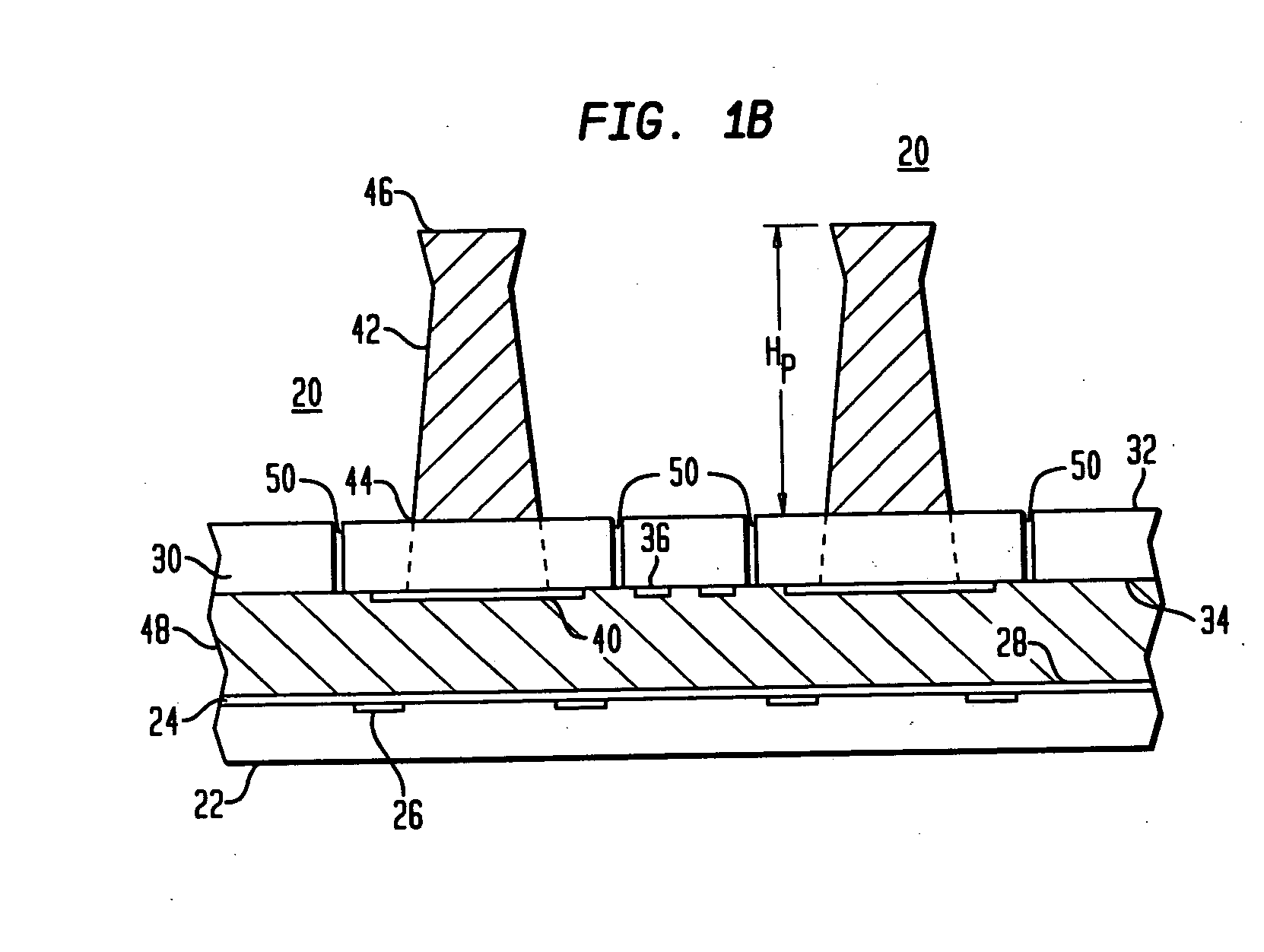

Telescopic introducer with a compound curvature for inducing alignment and method of using the same

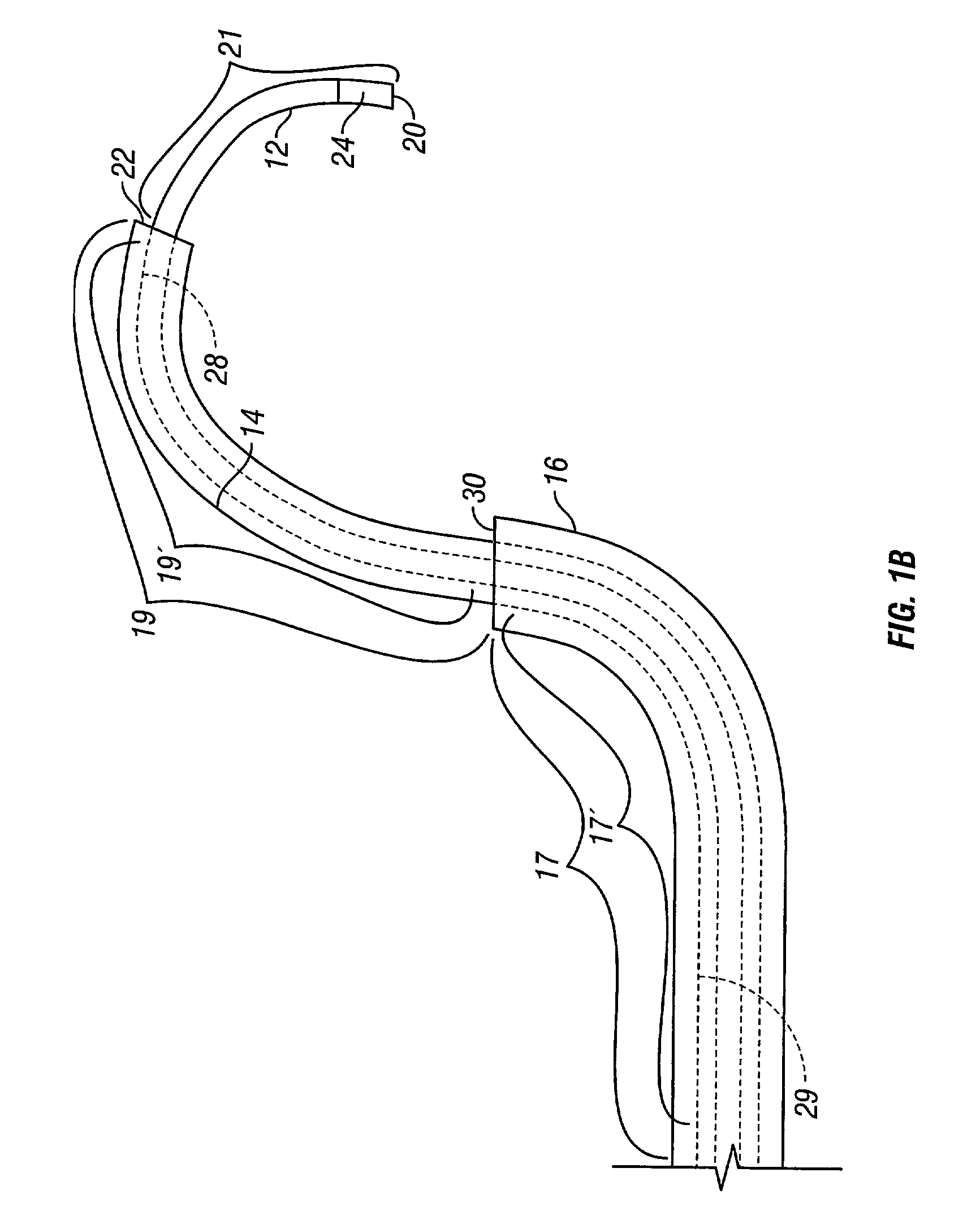

An introducer system for implantation of pacemaker leads into the venous system of the human heart through the coronary sinus is comprised of a flexible, elongate, outer elongate element having a first shape or bias along a portion. The first shape on the outer element may be prebiased or may be initially straight and subsequently biased once deployed in the body chamber. A flexible, elongate, telescopic inner elongate element has a second shape or bias on its distal portion and has the first shape or bias on a more proximal portion. The inner elongate element is telescopically disposed in the outer sheath. The outer and inner elongate elements are rotatable with respect to each other, such that when the inner elongate element is distally extended from the outer sheath, there exists an angular orientation between the inner and outer sheaths which is congruent, when there is at least partial alignment between the distal portion of the outer elongate element and the more proximal portion of the inner sheath, both having the first shape or bias. This results in the rotation of the distal second shape or curve of the inner elongate element into a predetermined three dimensional location.

Owner:PRESSURE PROD MEDICAL SUPPLIES INC

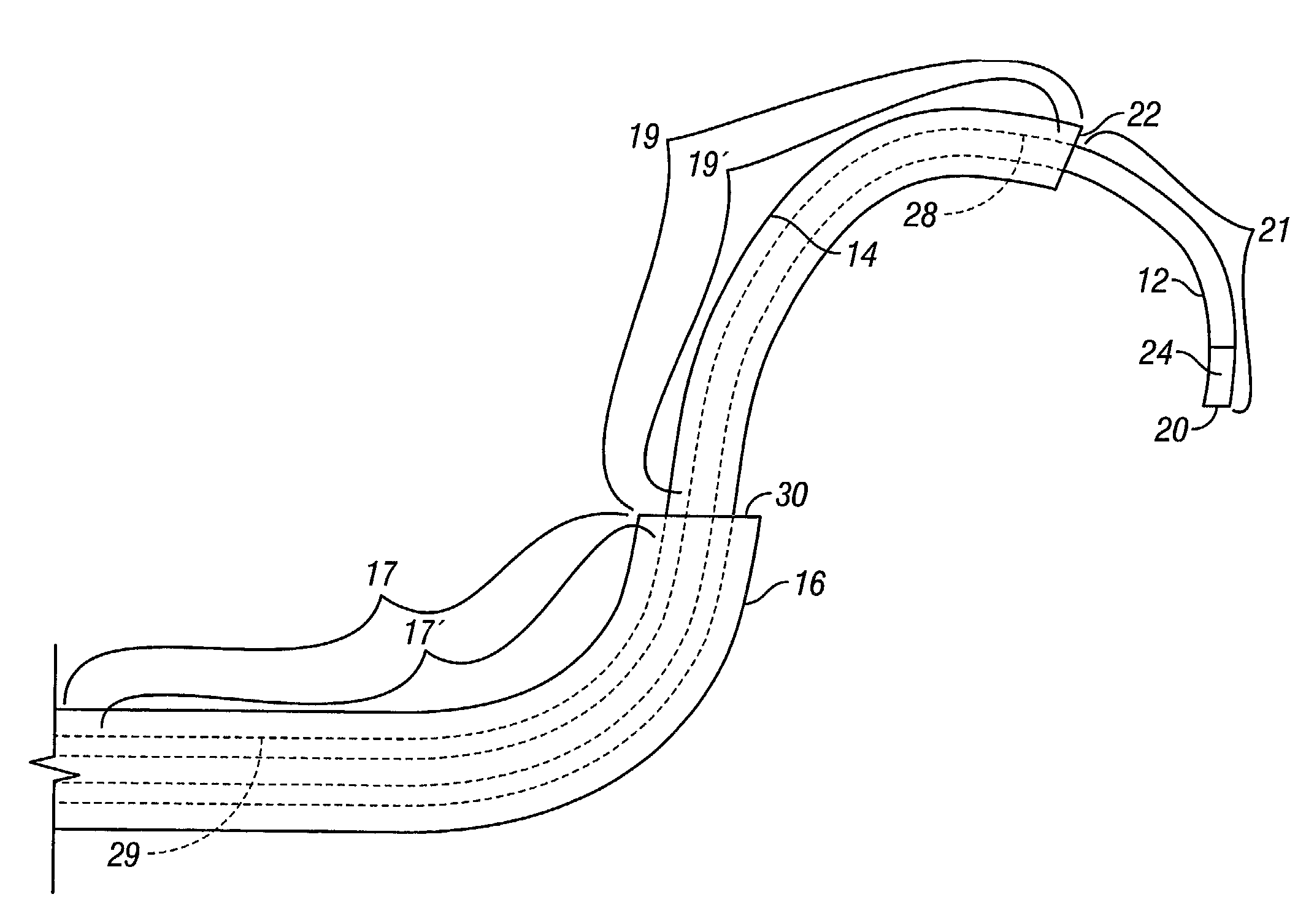

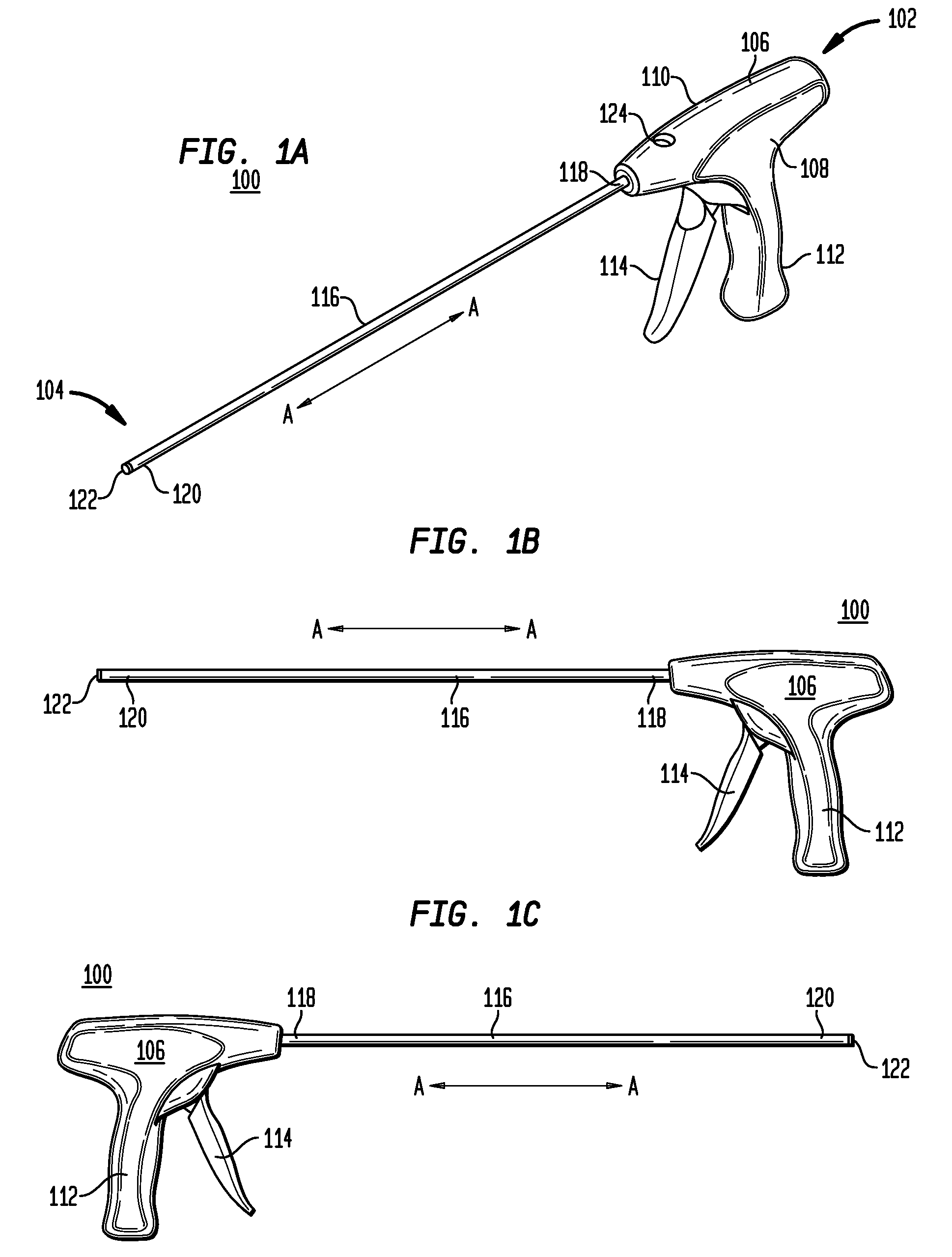

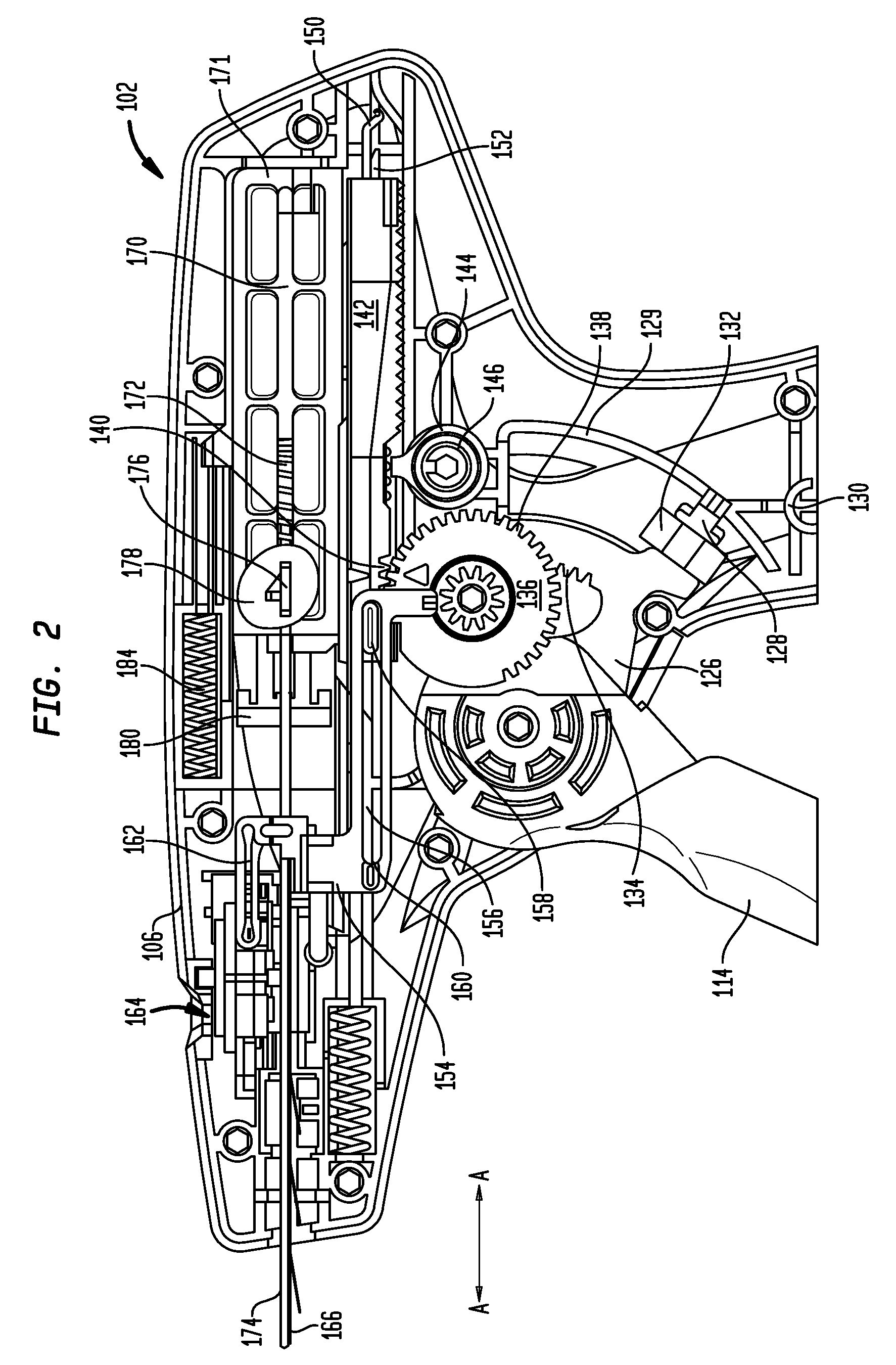

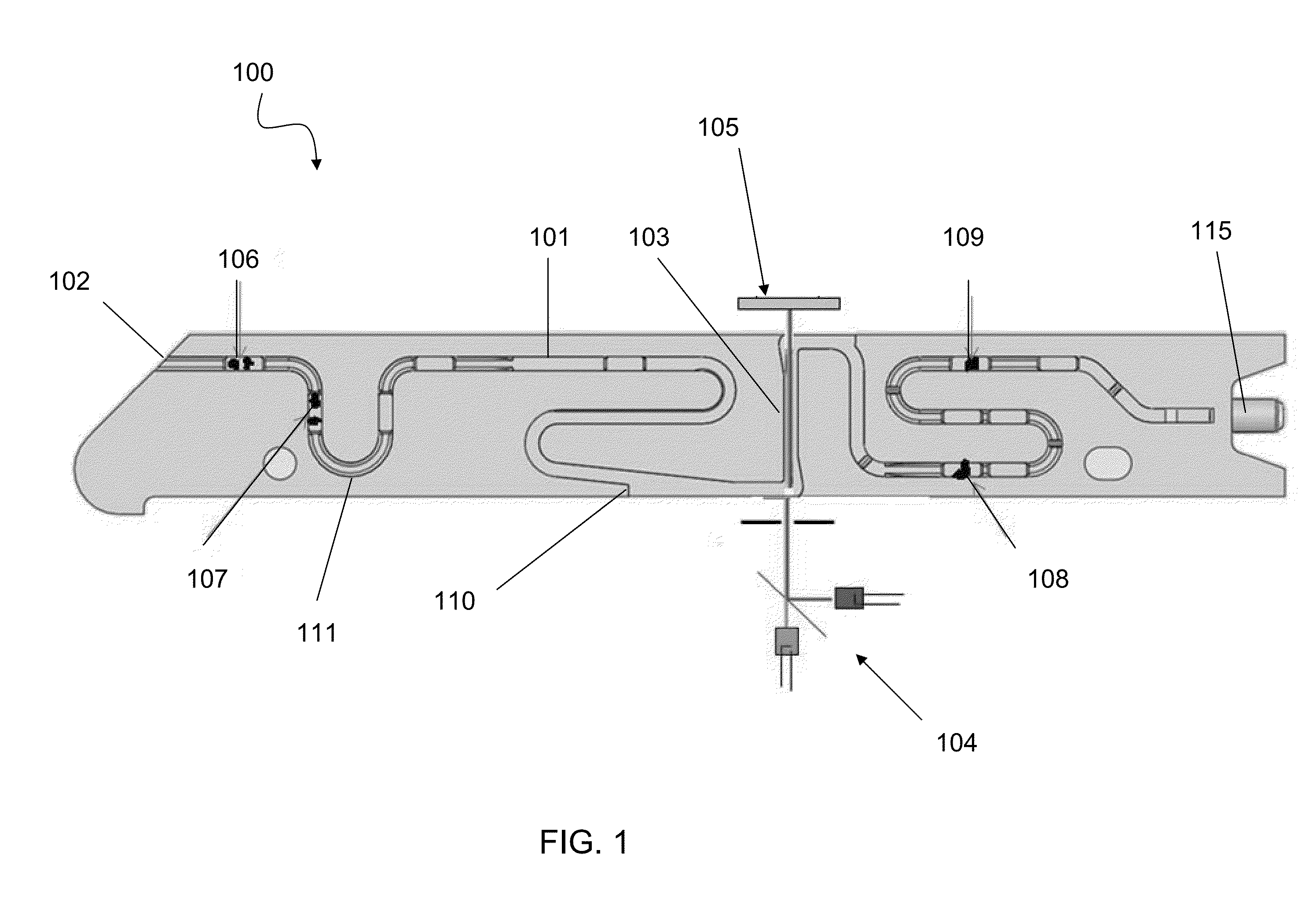

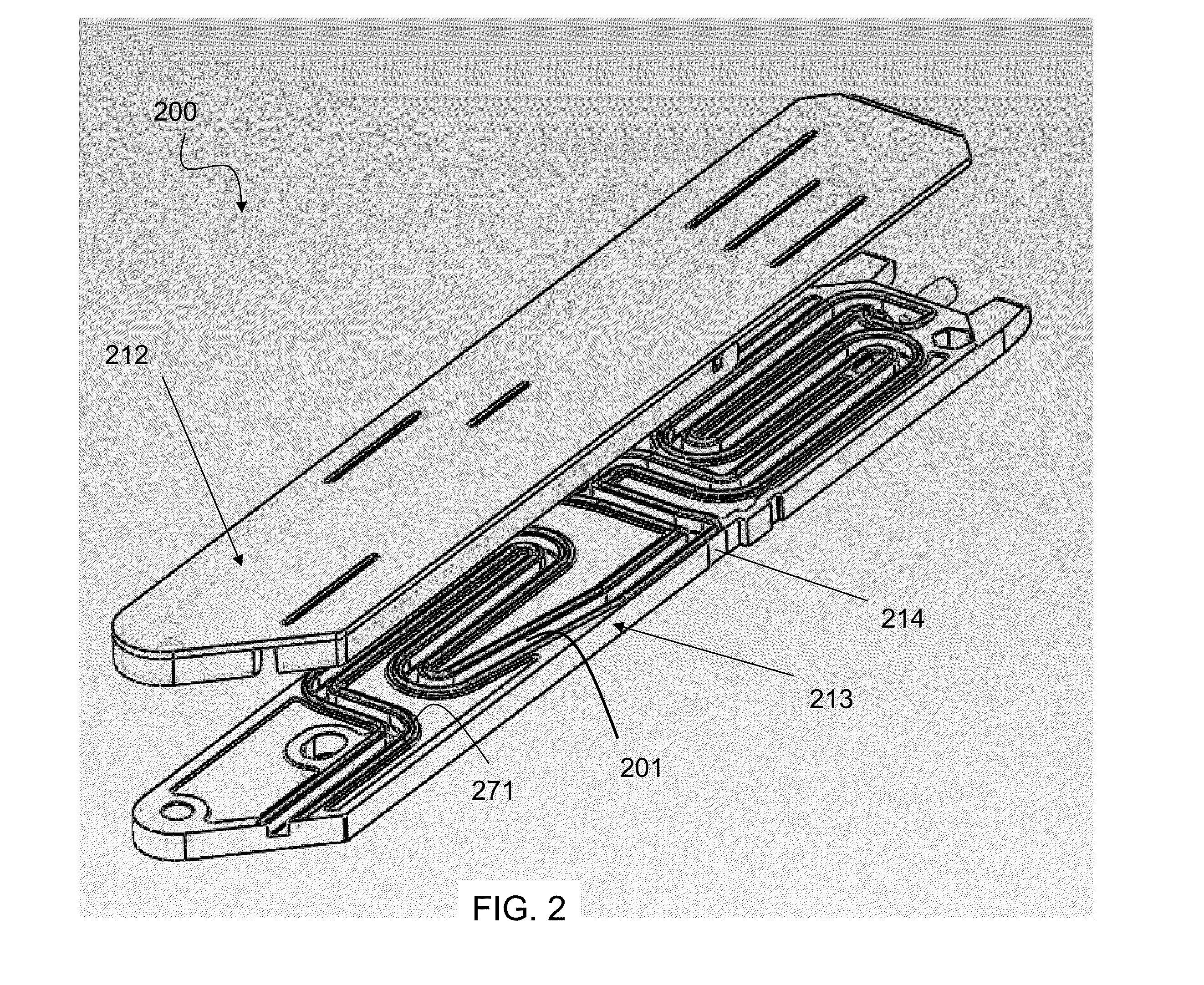

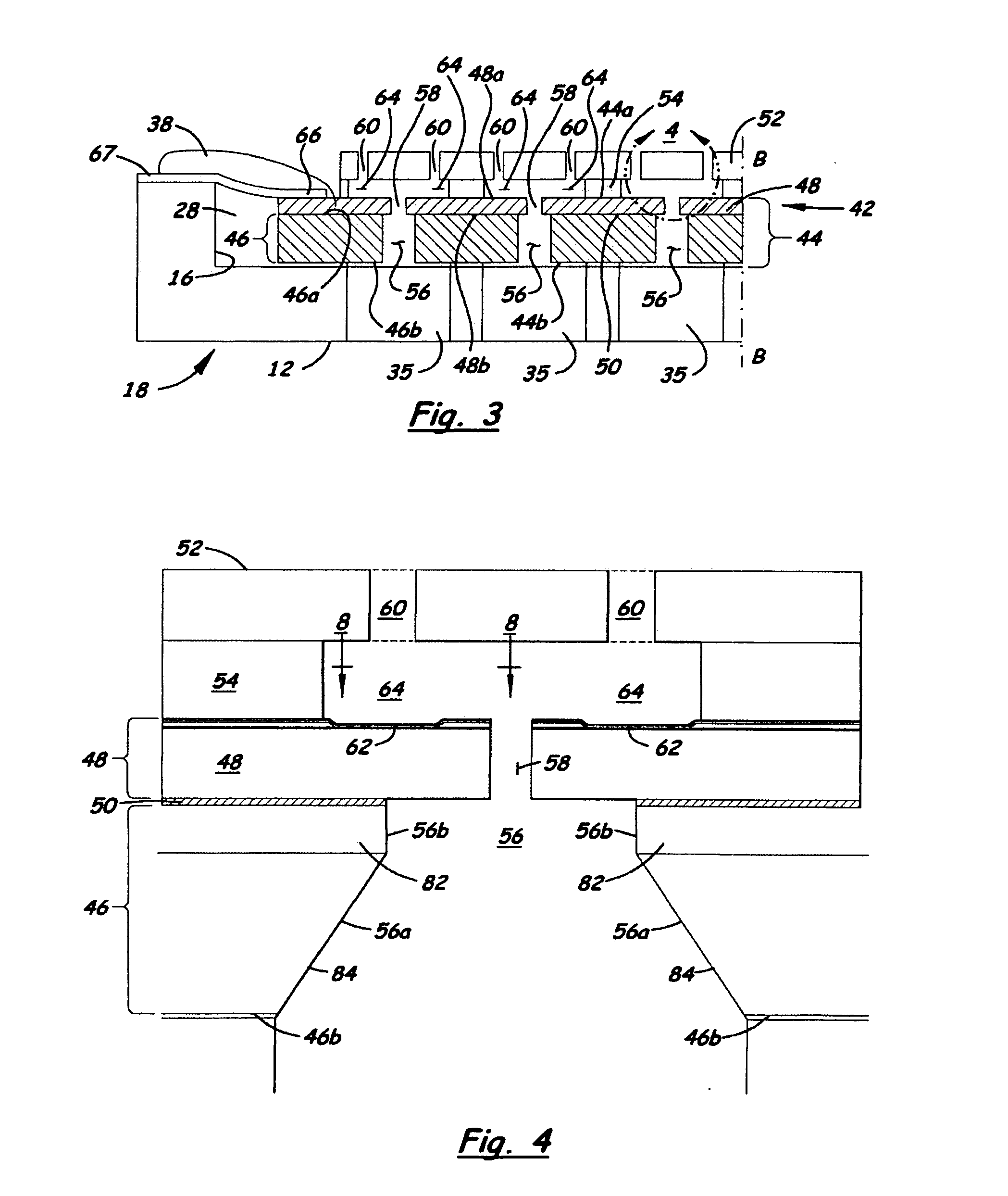

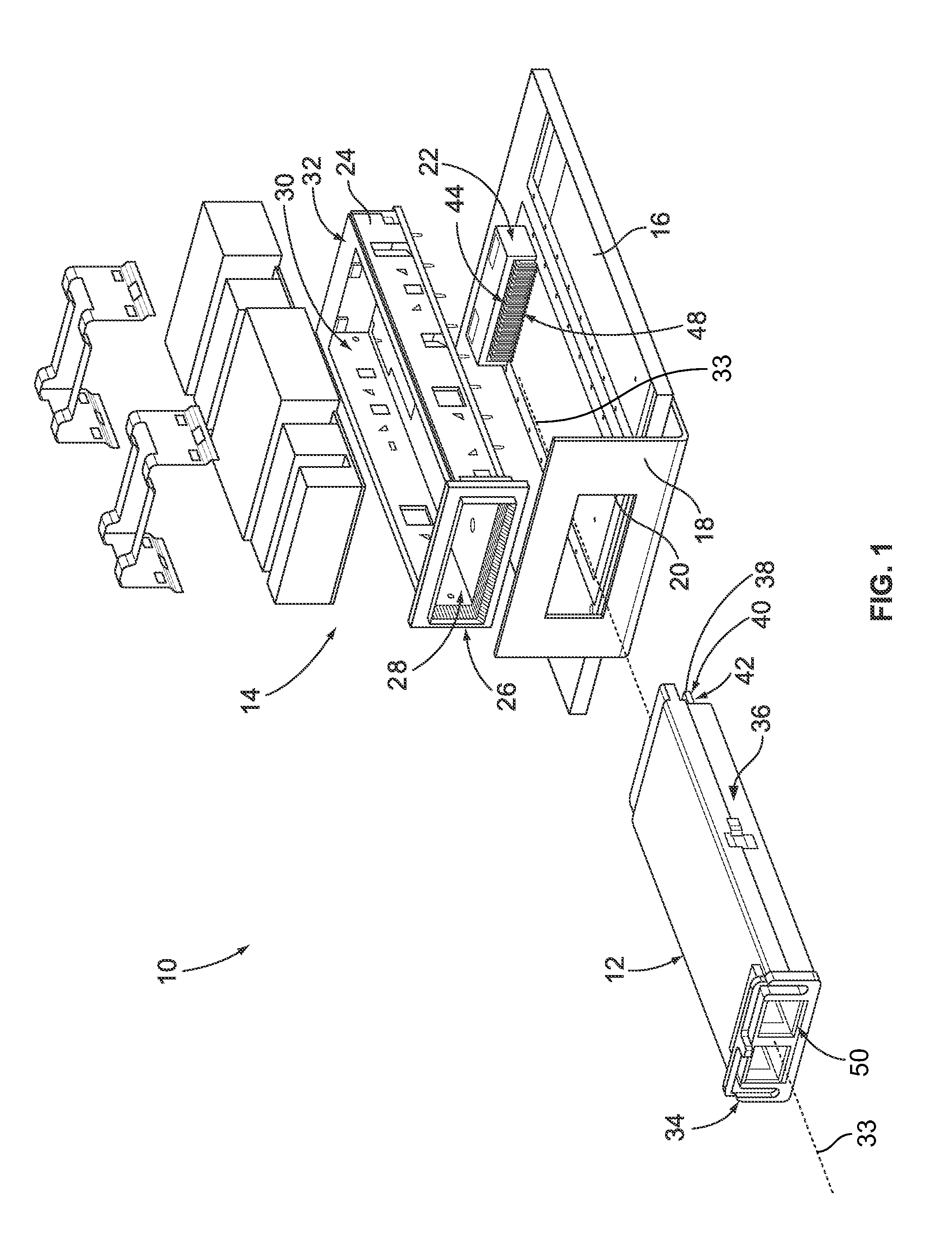

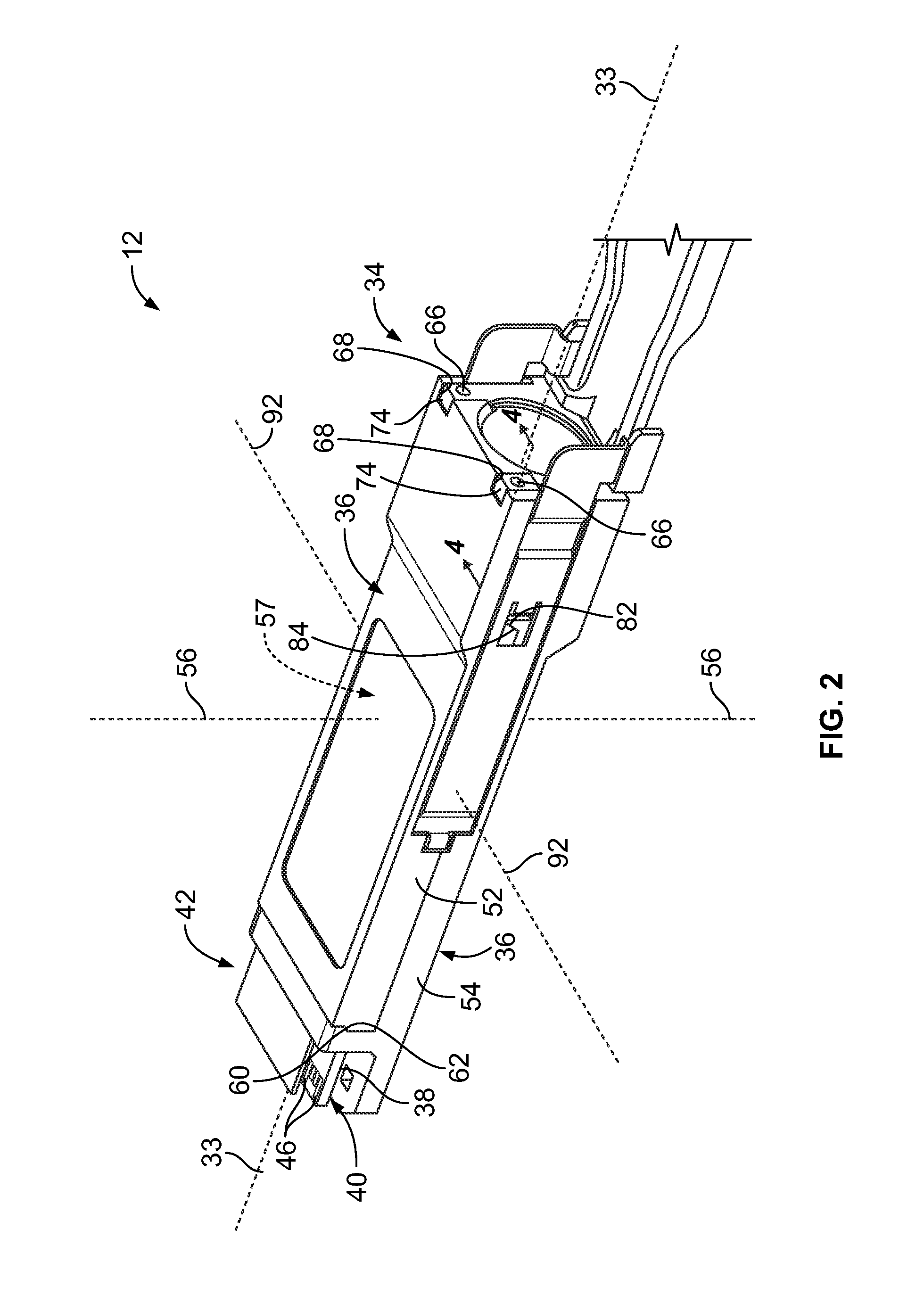

Surgical fasteners, applicator instruments, and methods for deploying surgical fasteners

ActiveUS20100292712A1Easy to collapseImprove abilitiesDiagnosticsSurgical staplesPartial alignmentBiomedical engineering

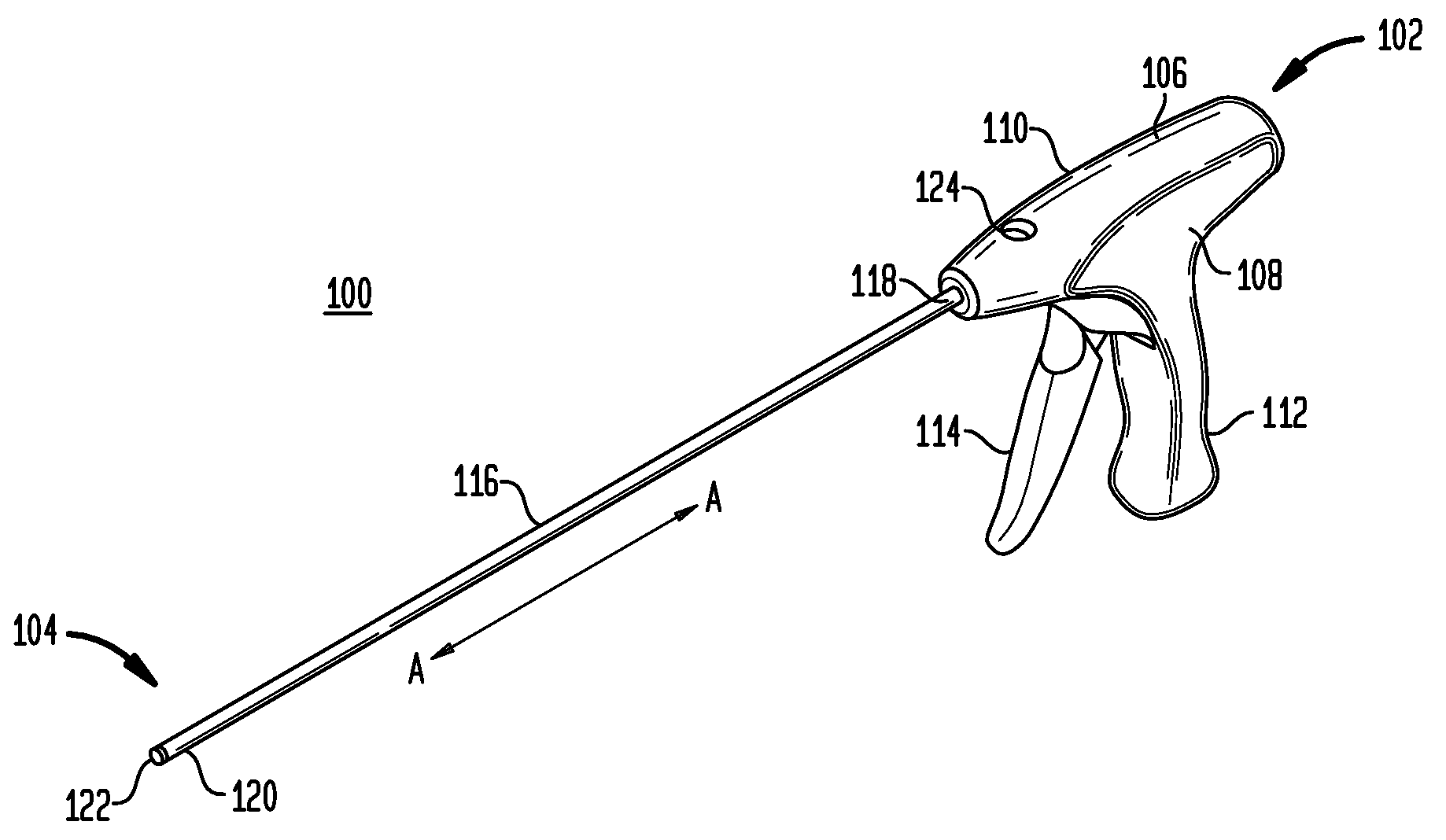

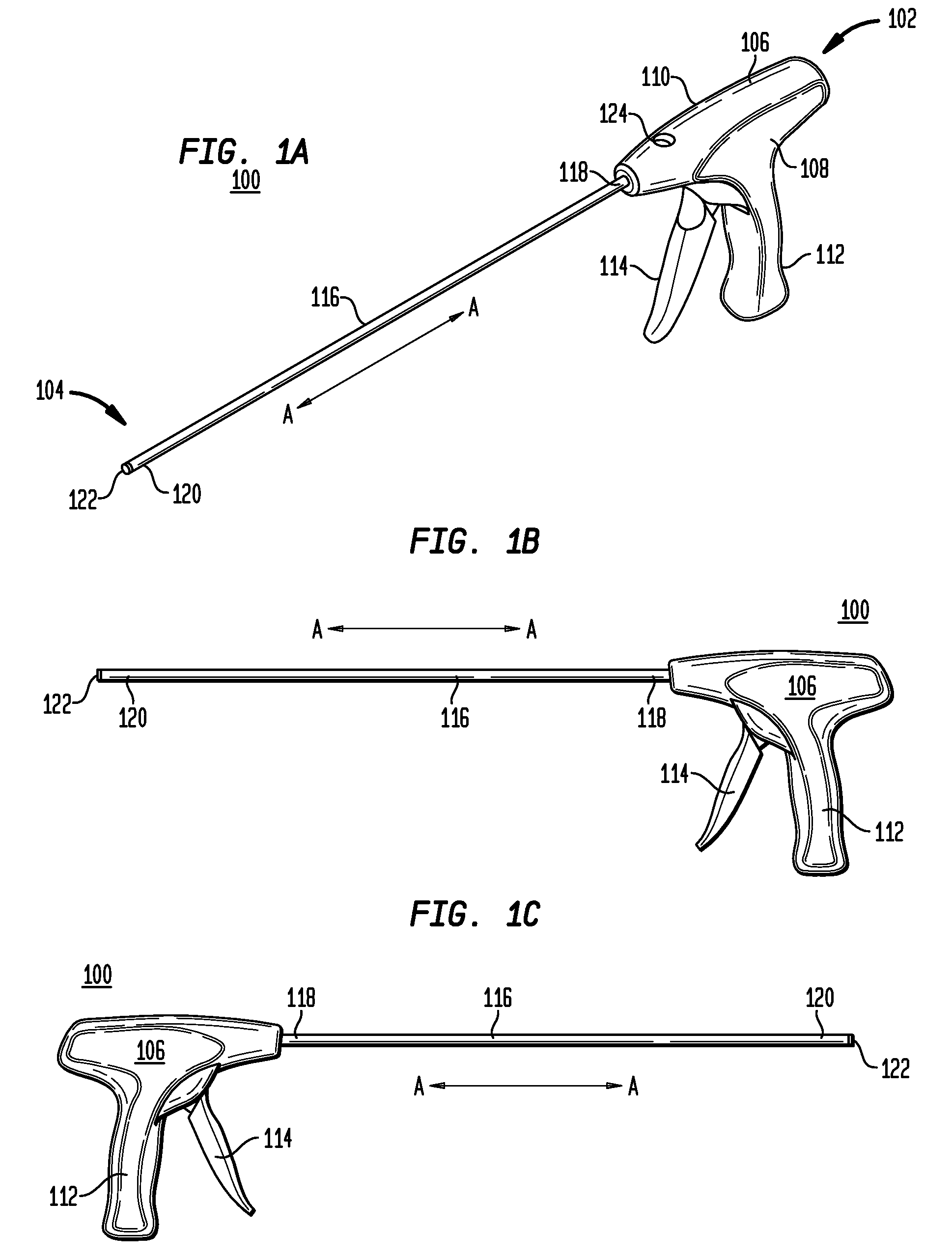

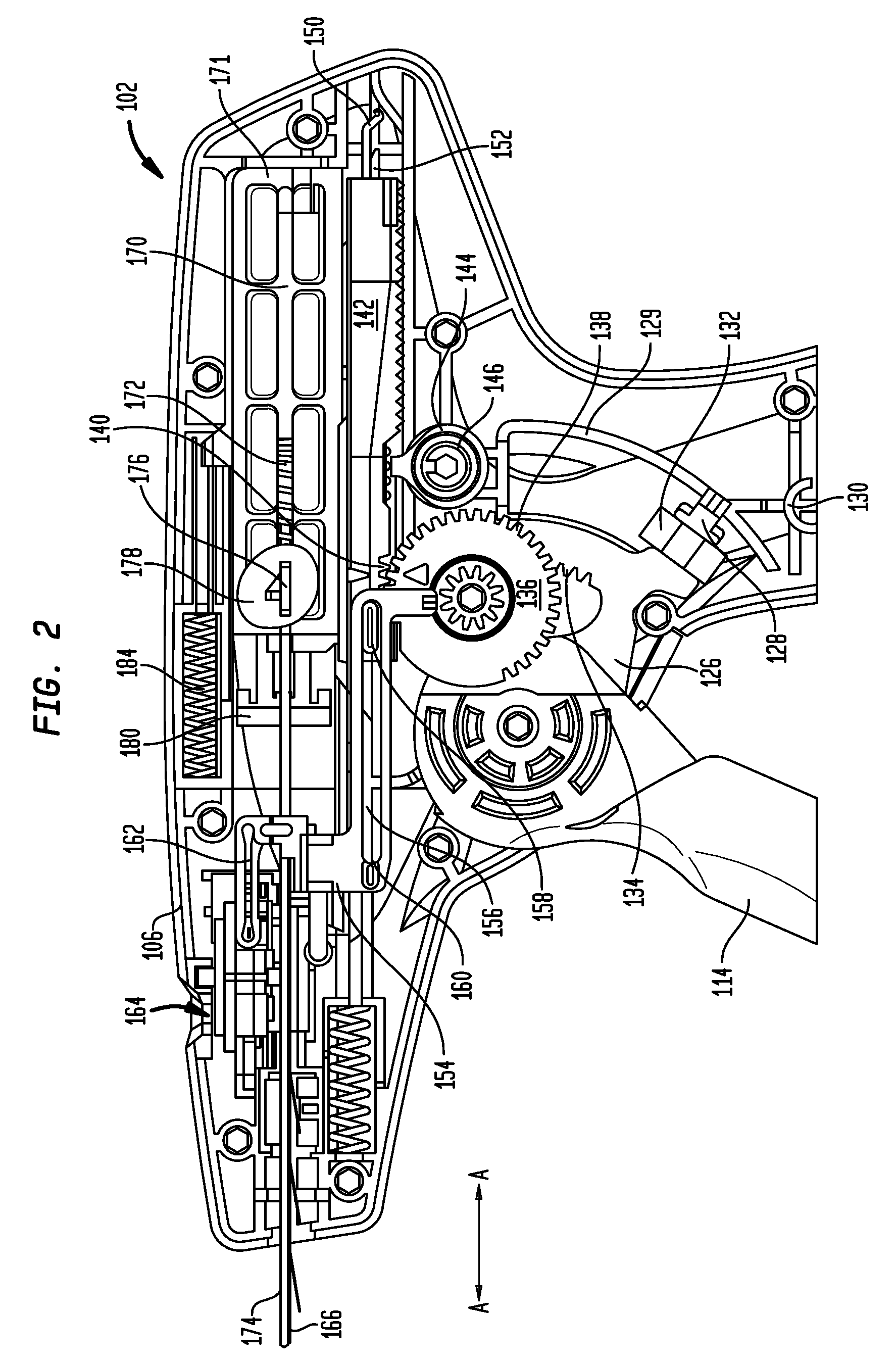

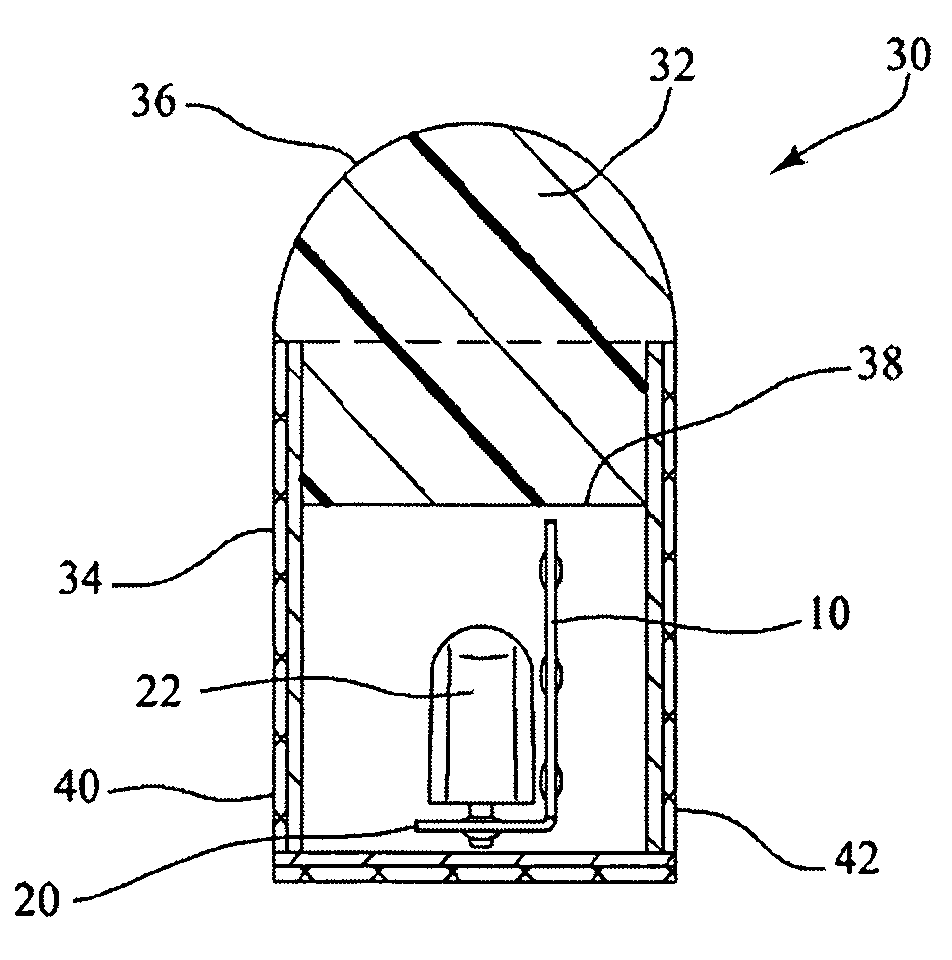

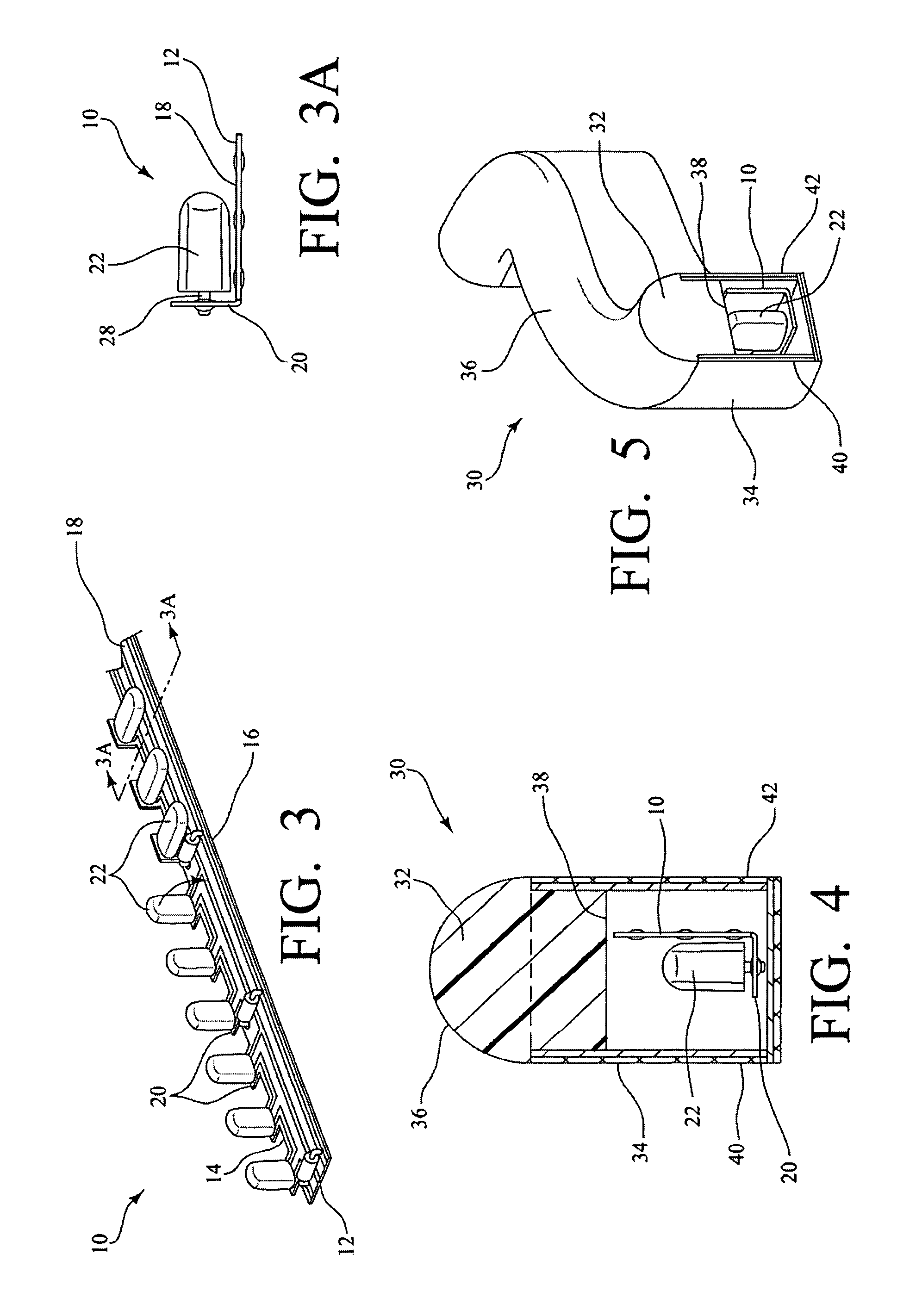

An applicator instrument for dispensing surgical fasteners includes a housing, an elongated shaft extending from the housing, a firing rod disposed inside the elongated shaft and being movable within a first plane between a retracted position and an extended position, an advancer disposed inside the elongated shaft and being moveable within a second plane between a retracted position and an extended position, and a staging assembly located adjacent the distal end of the elongated shaft and being adapted to align surgical fasteners with a distal end of the firing rod. The staging assembly is held below the second plane by the advancer when the advancer is in the extended position and the staging assembly is adapted to move into at least partial alignment with the distal end of the firing rod when the advancer is in the retracted position.

Owner:ETHICON INC

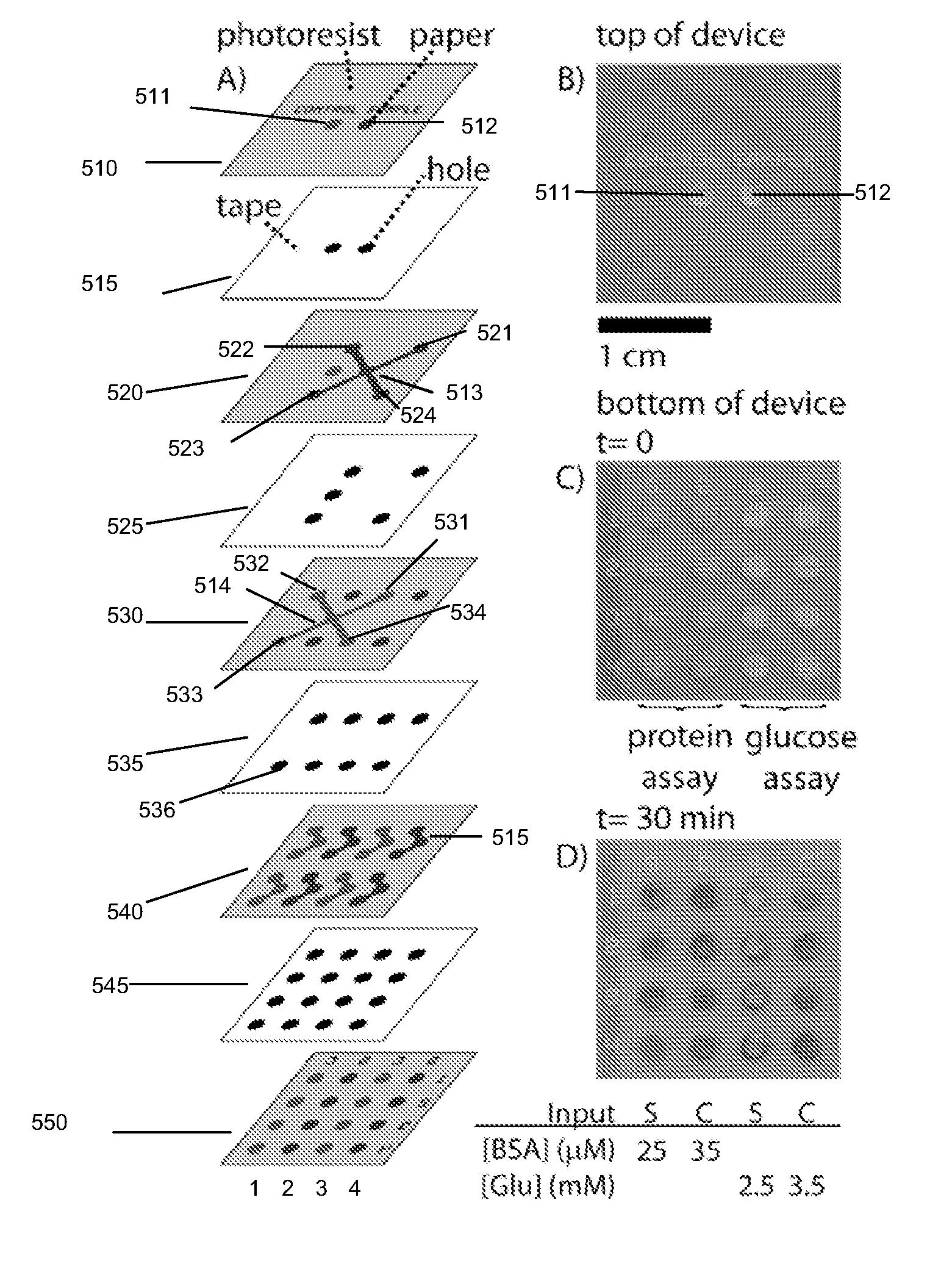

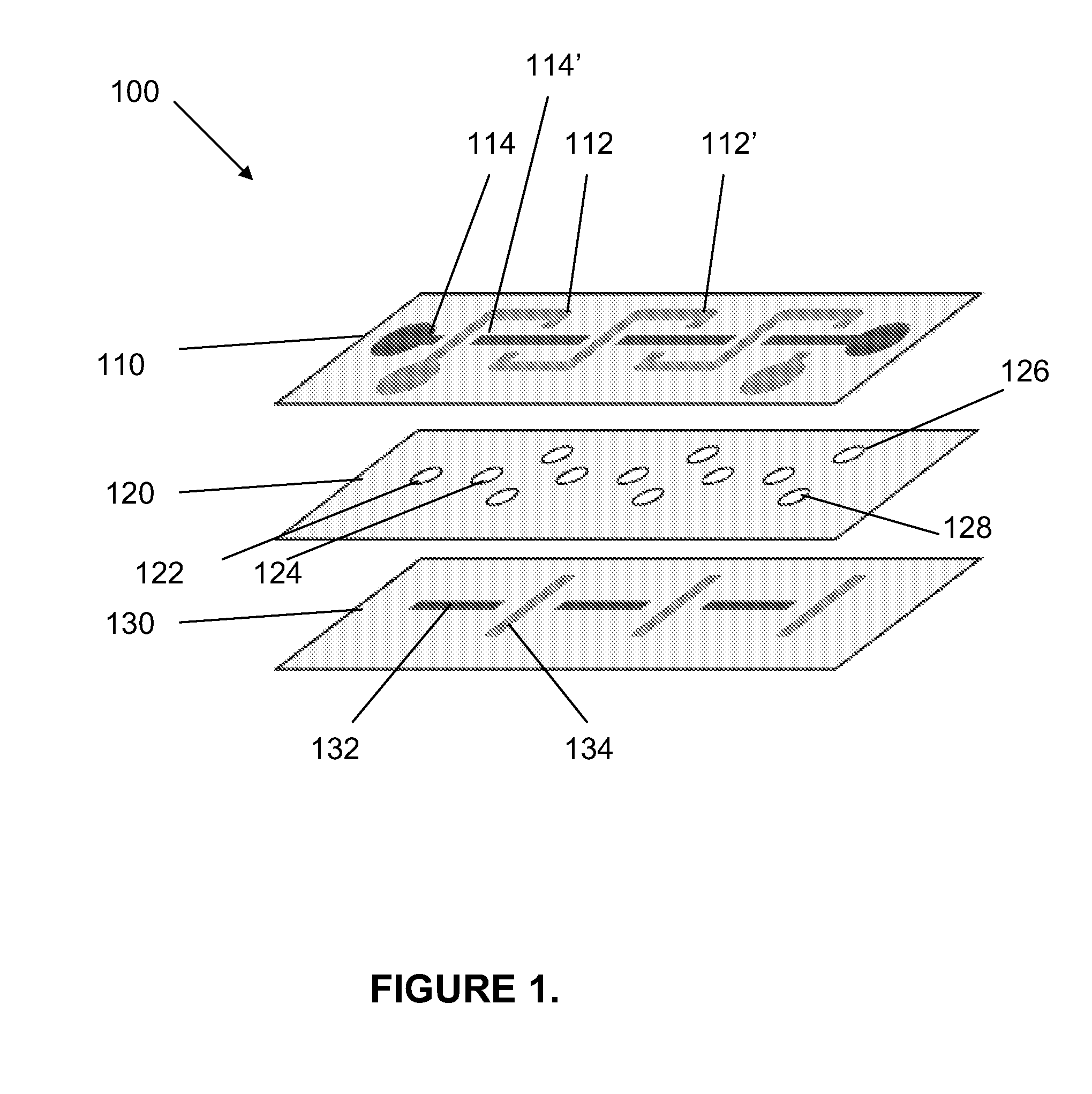

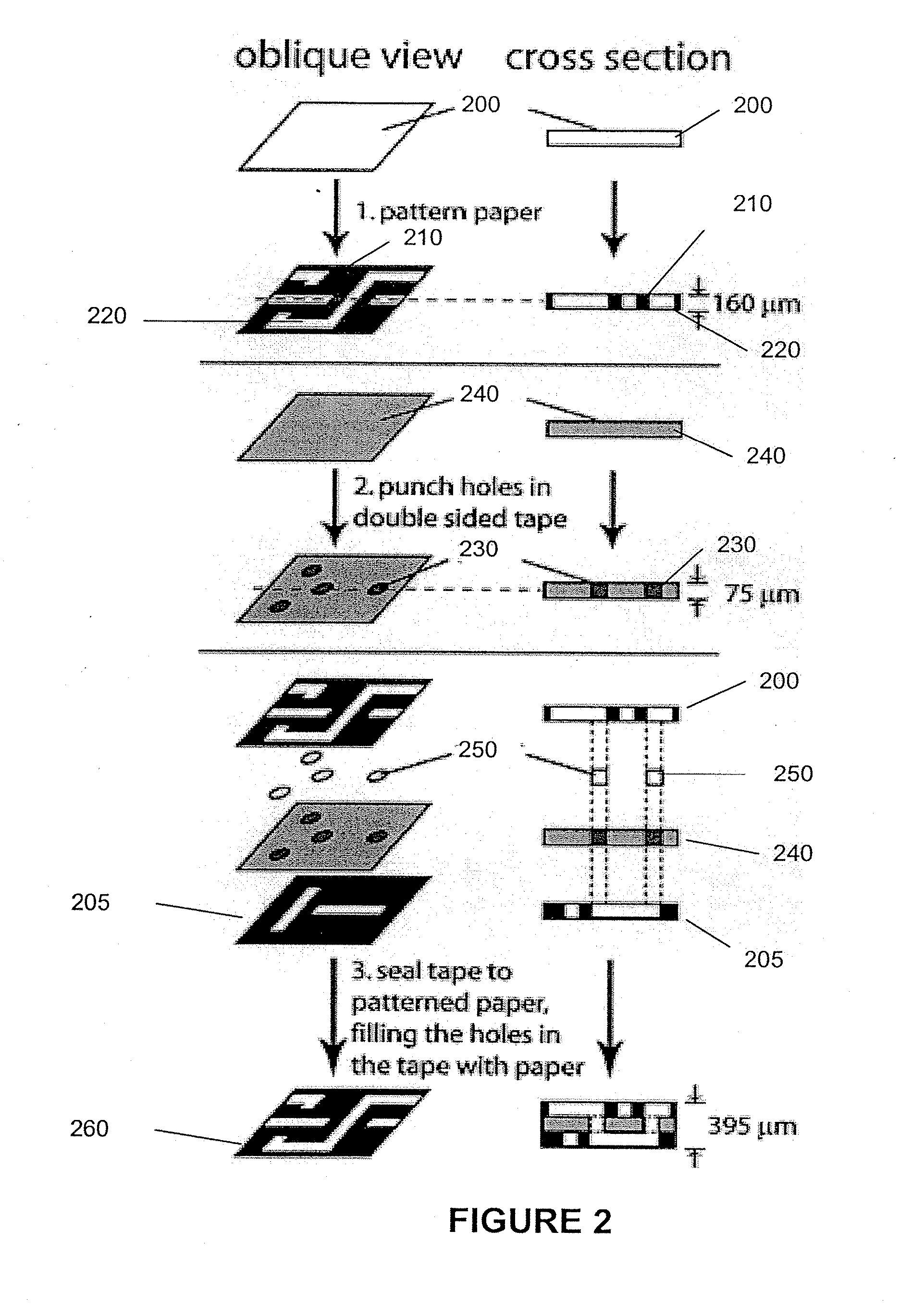

Three-dimensional microfluidic devices

Three-dimensional microfluidic devices including by a plurality of patterned porous, hydrophilic layers and a fluid-impermeable layer disposed between every two adjacent patterned porous, hydrophilic layers are described. Each patterned porous, hydrophilic layer has a fluid-impermeable barrier which substantially permeates the thickness of the porous, hydrophilic layer and defines boundaries of one or more hydrophilic regions within the patterned porous, hydrophilic layer. The fluid-impermeable layer has openings which are aligned with at least part of the hydrophilic region within at least one adjacent patterned porous, hydrophilic layer. Microfluidic assay device, microfluidic mixer, microfluidic flow control device are also described.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Surgical fasteners, applicator instruments, and methods for deploying surgical fasteners

ActiveUS8579920B2Accurate insertionGuarantees proper engagementDiagnosticsSurgical staplesPartial alignmentEngineering

Owner:ETHICON INC

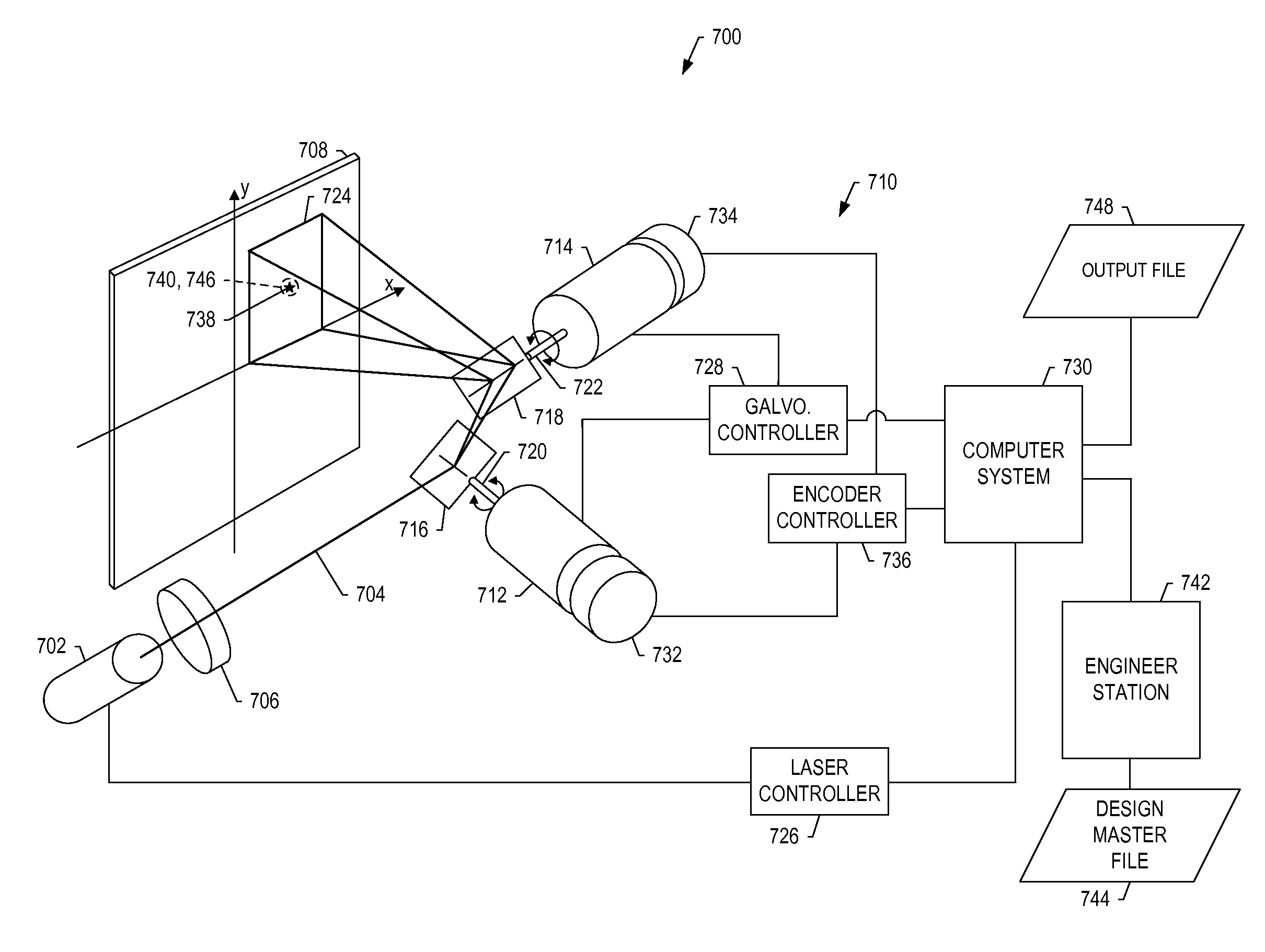

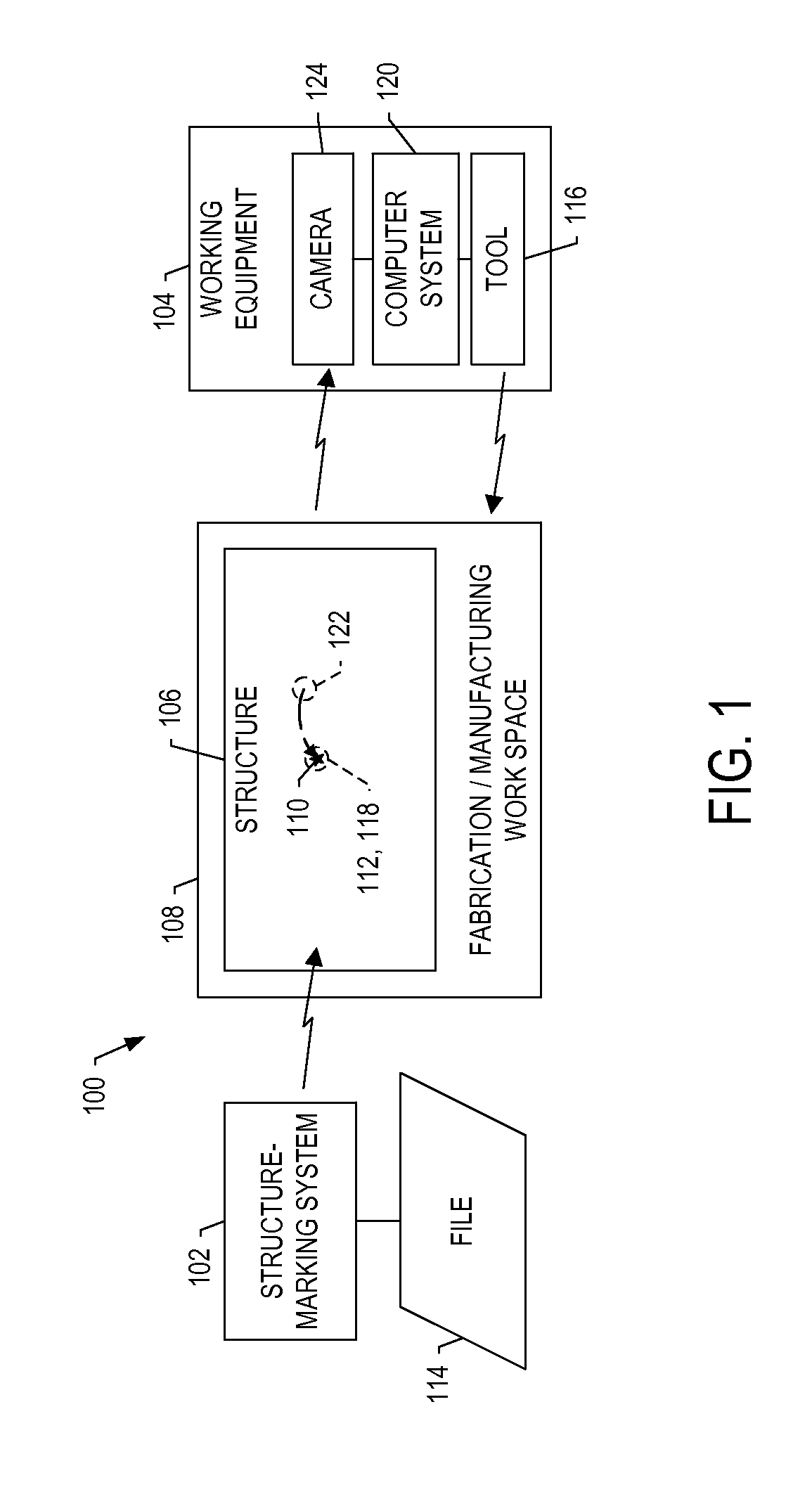

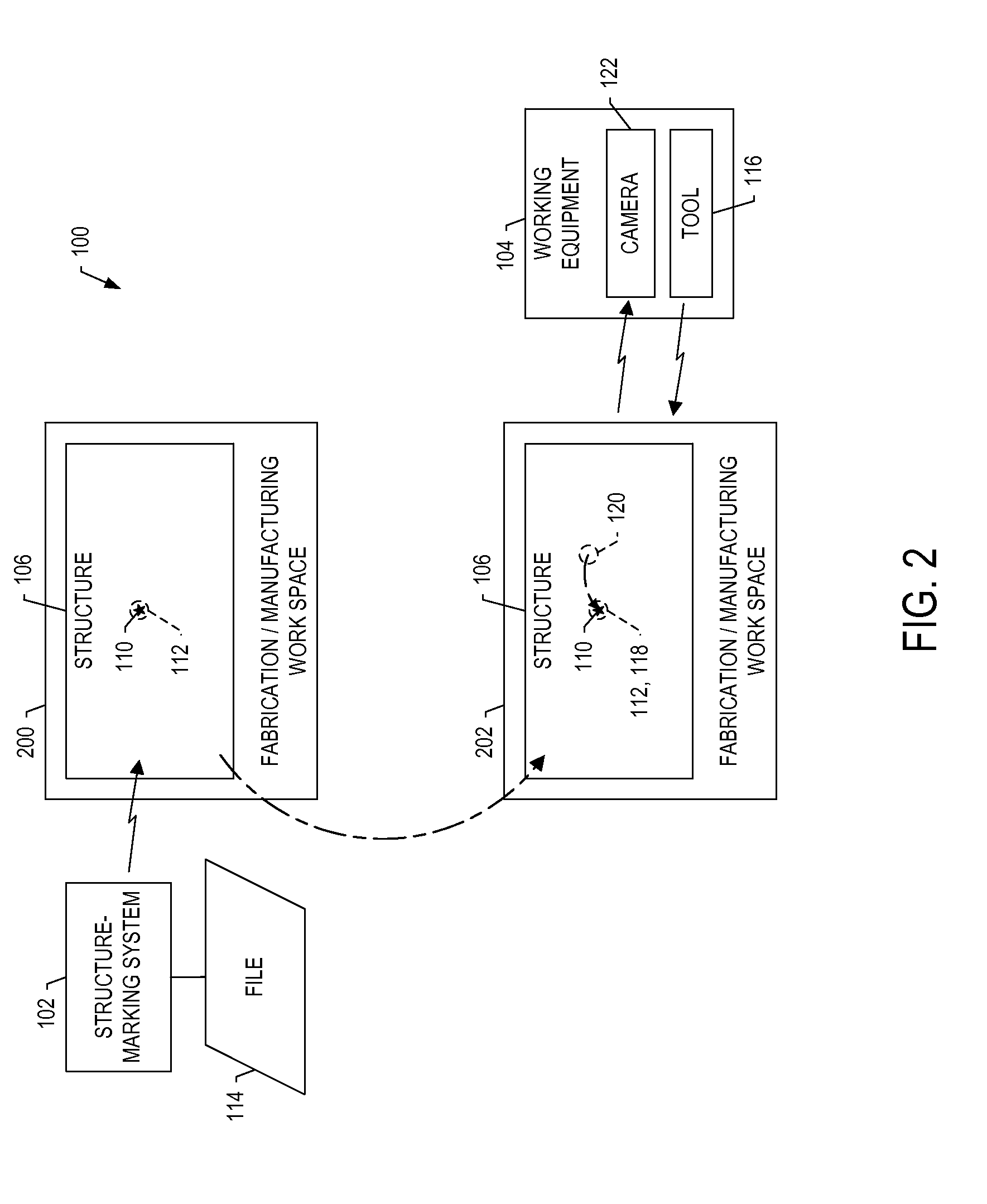

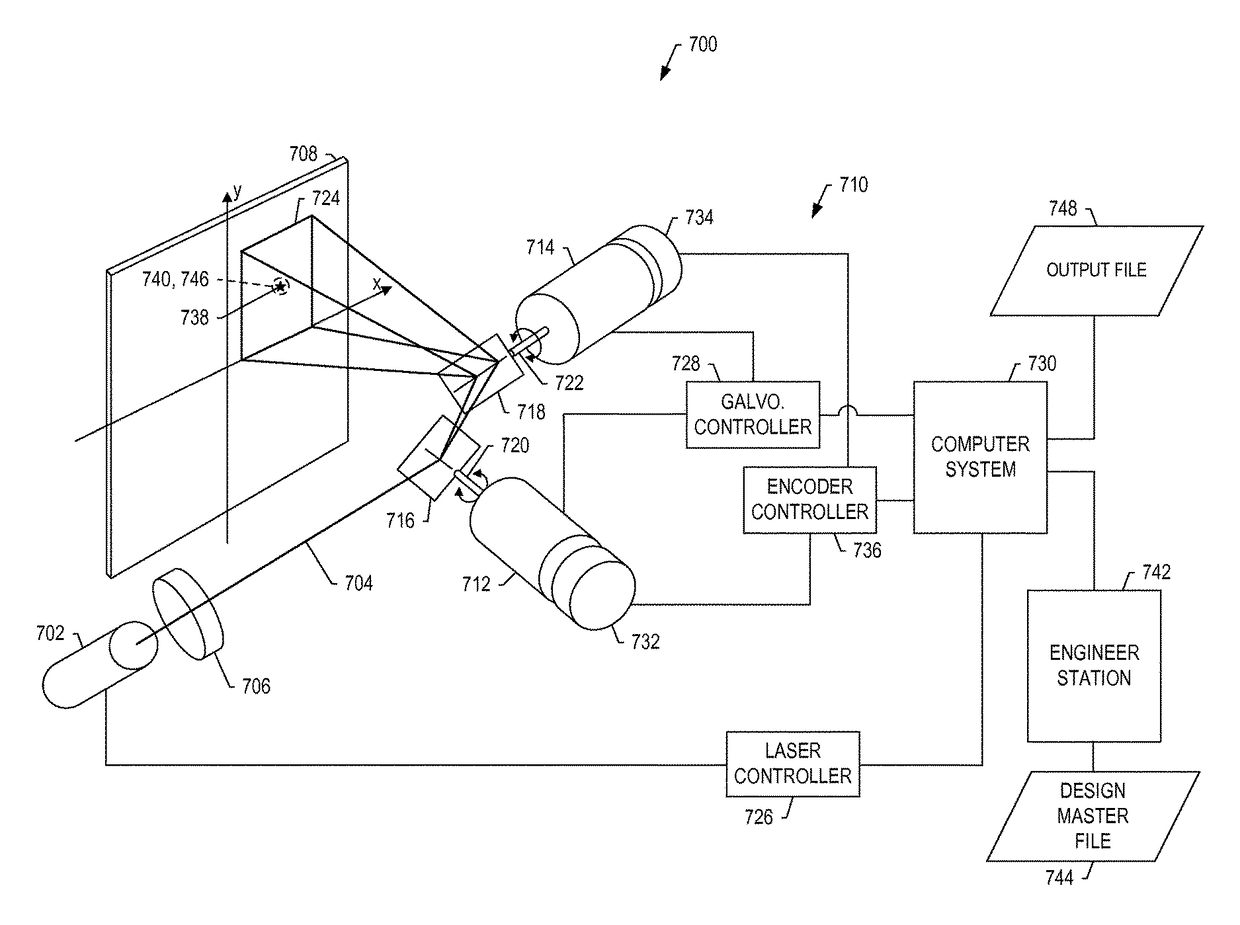

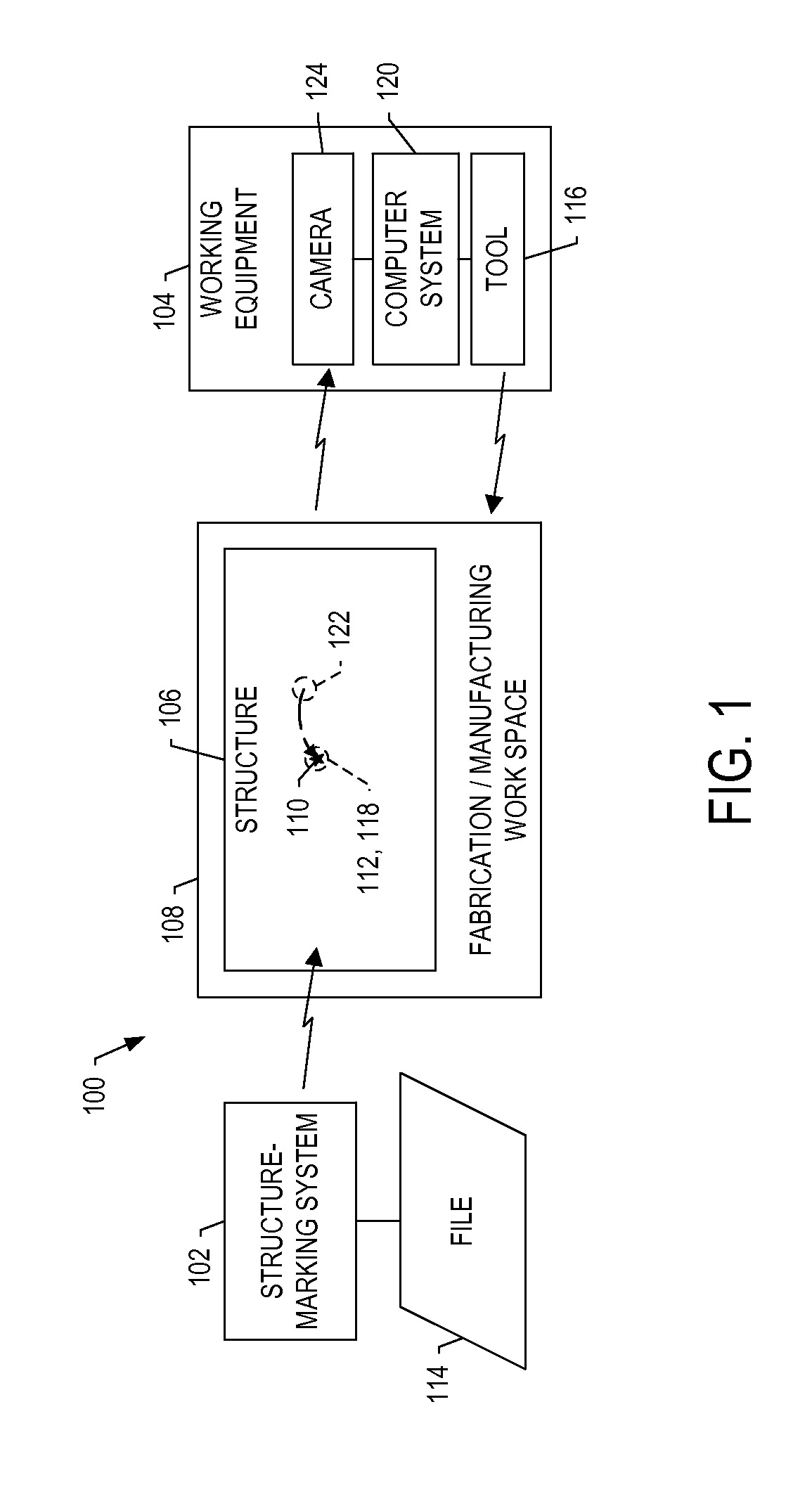

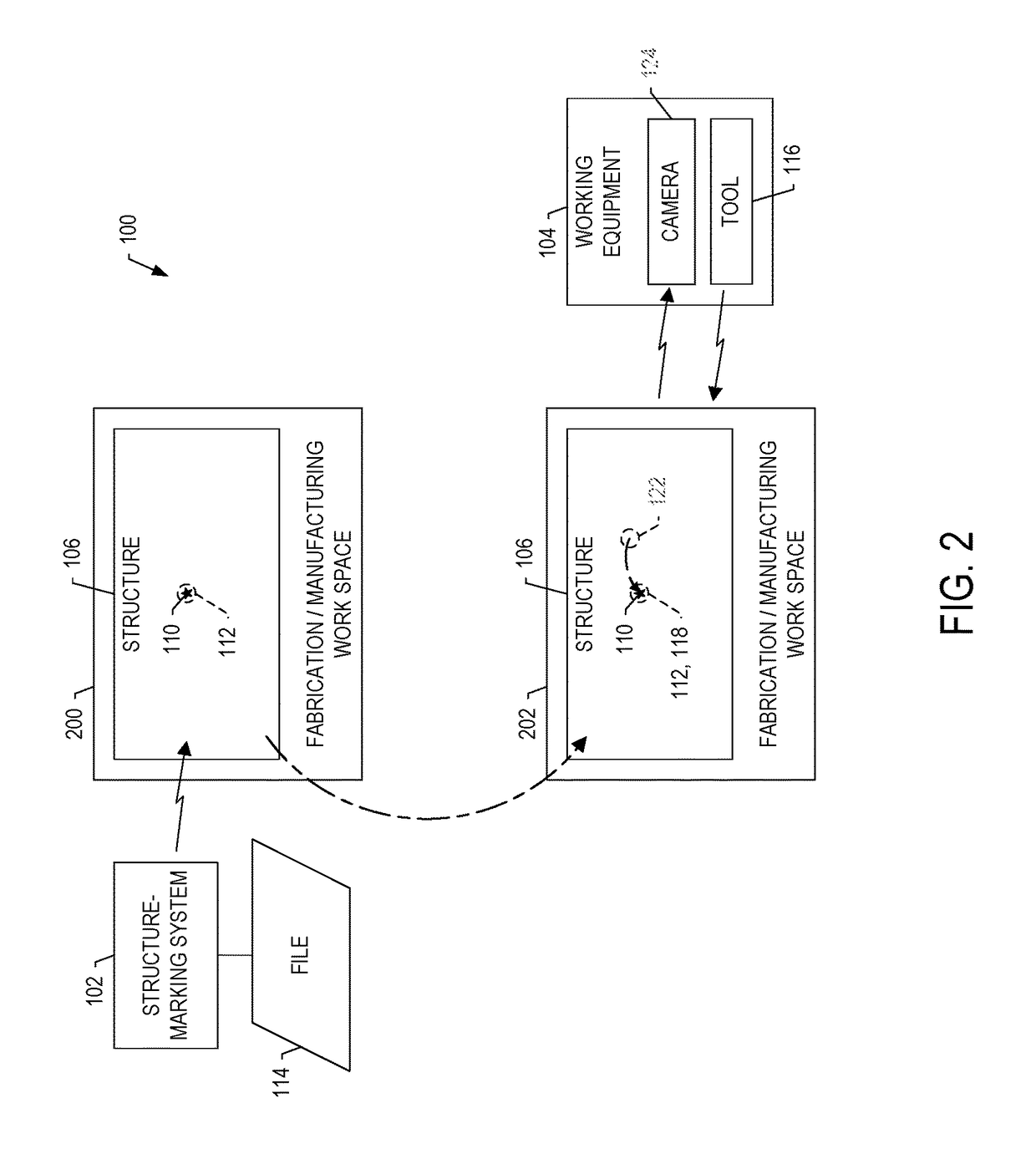

Apparatuses and methods for accurate structure marking and marking-assisted structure locating

Working equipment includes a tool configured to work a structure at a working location thereon, with the structure having an applied marking at a known location with a known relationship with the working location. A computer system is configured to determine placement of the structure, and accordingly position the tool into at least partial alignment with the working location, and which in at least one instance, the tool is aligned with a second, offset location. A camera is configured to capture an image of the structure and including the marking, and further including the second location with which the tool is aligned. And the computer system is configured to process the image to locate the working location, reposition the tool from the second location and into greater alignment with the located working location, and control the repositioned tool to work the structure at the located working location.

Owner:THE BOEING CO

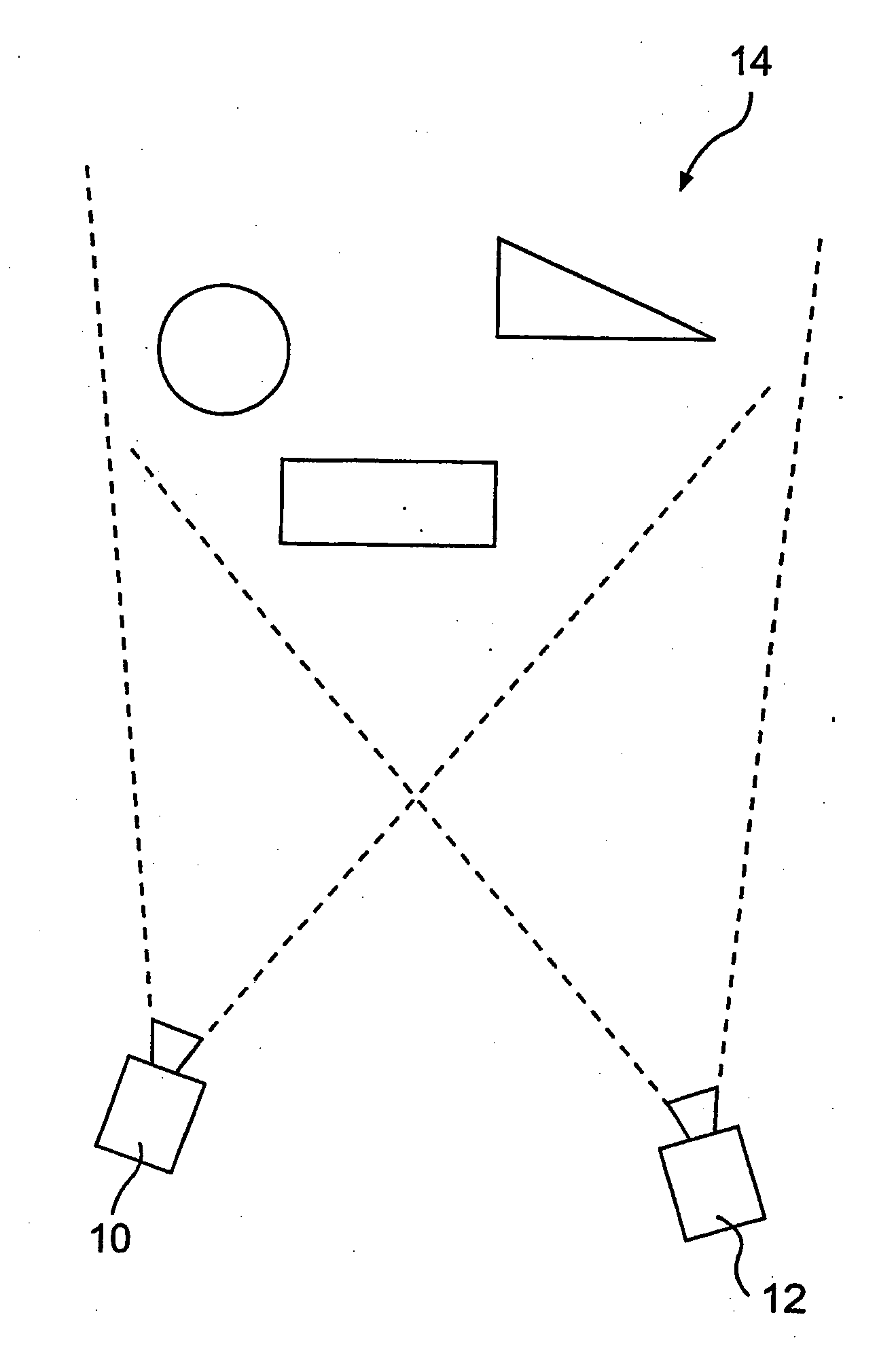

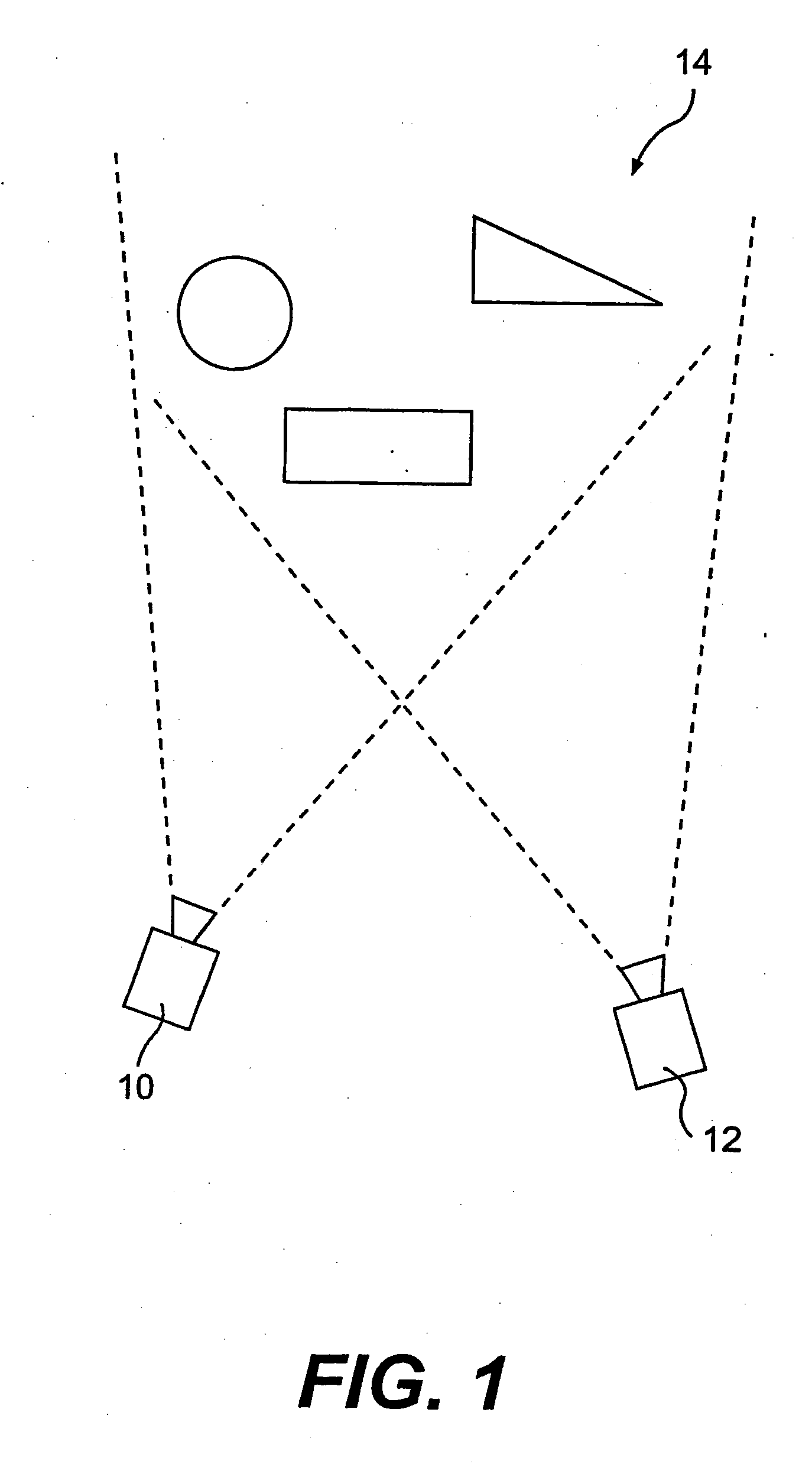

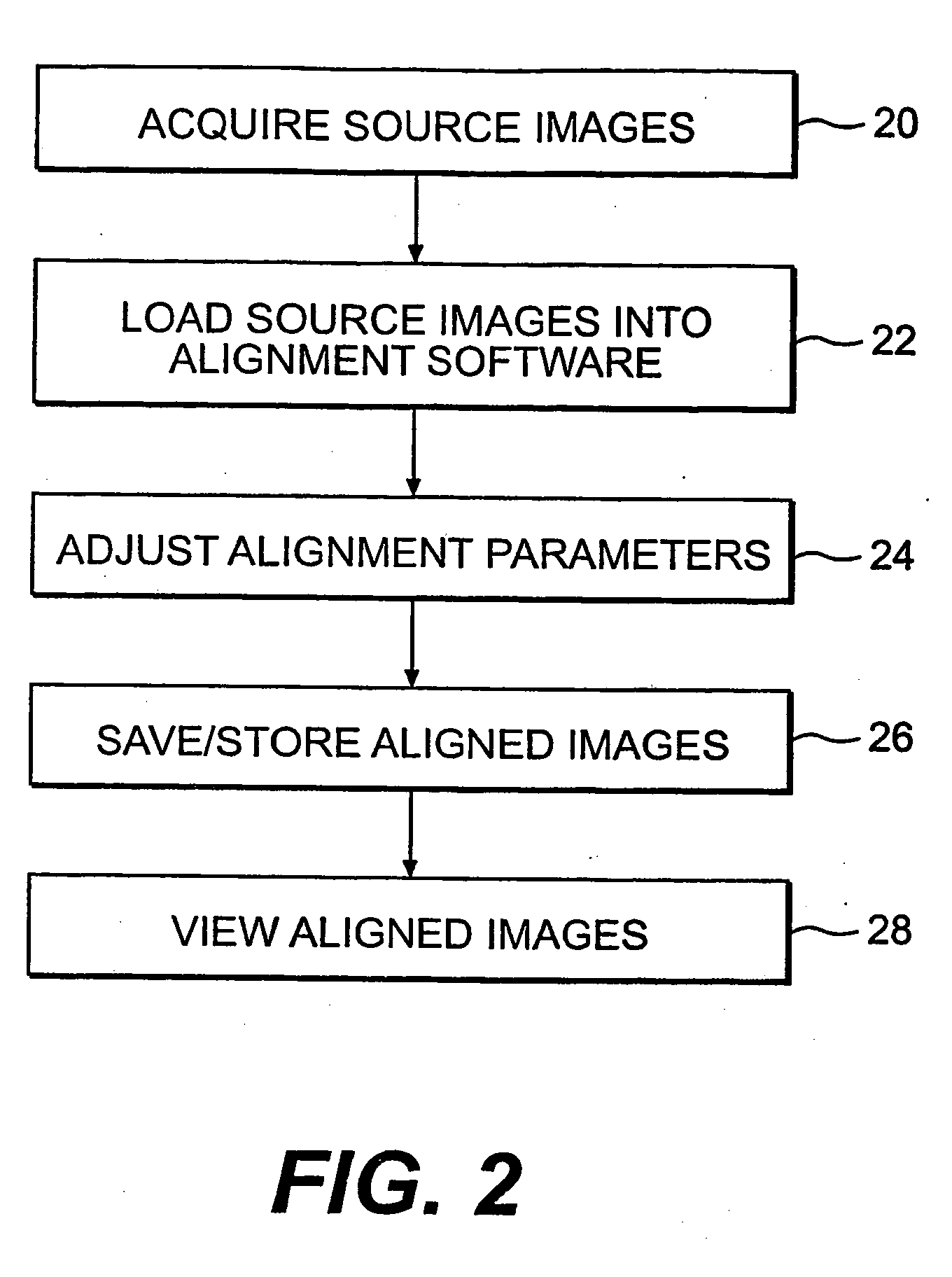

Critical alignment of parallax images for autostereoscopic display

A method is provided for generating an autostereoscopic display. The method includes acquiring a first parallax image and at least one other parallax image. At least a portion of the first parallax image may be aligned with a corresponding portion of the at least one other parallax image. Alternating views of the first parallax image and the at least one other parallax image may be displayed.

Owner:VISION III IMAGING

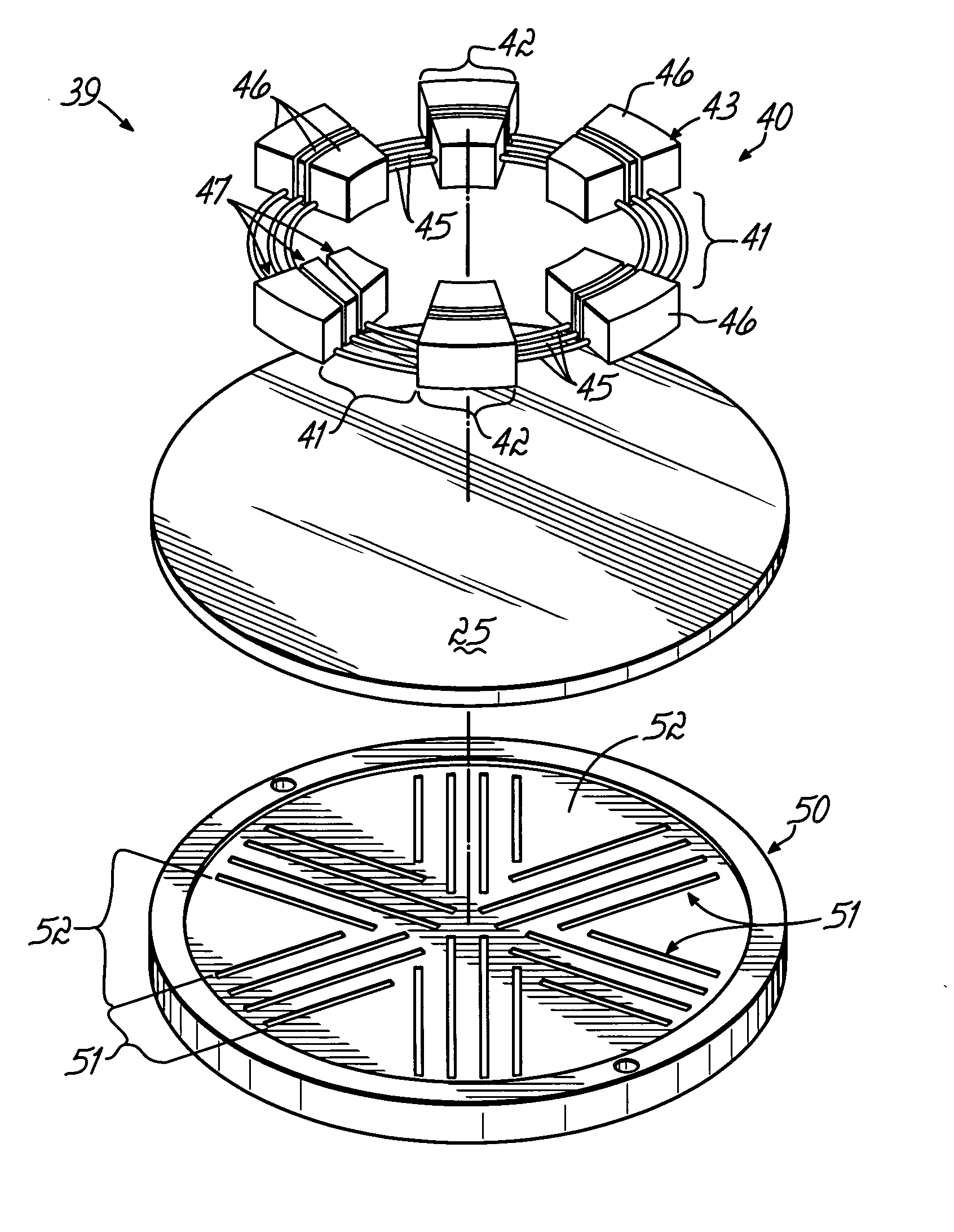

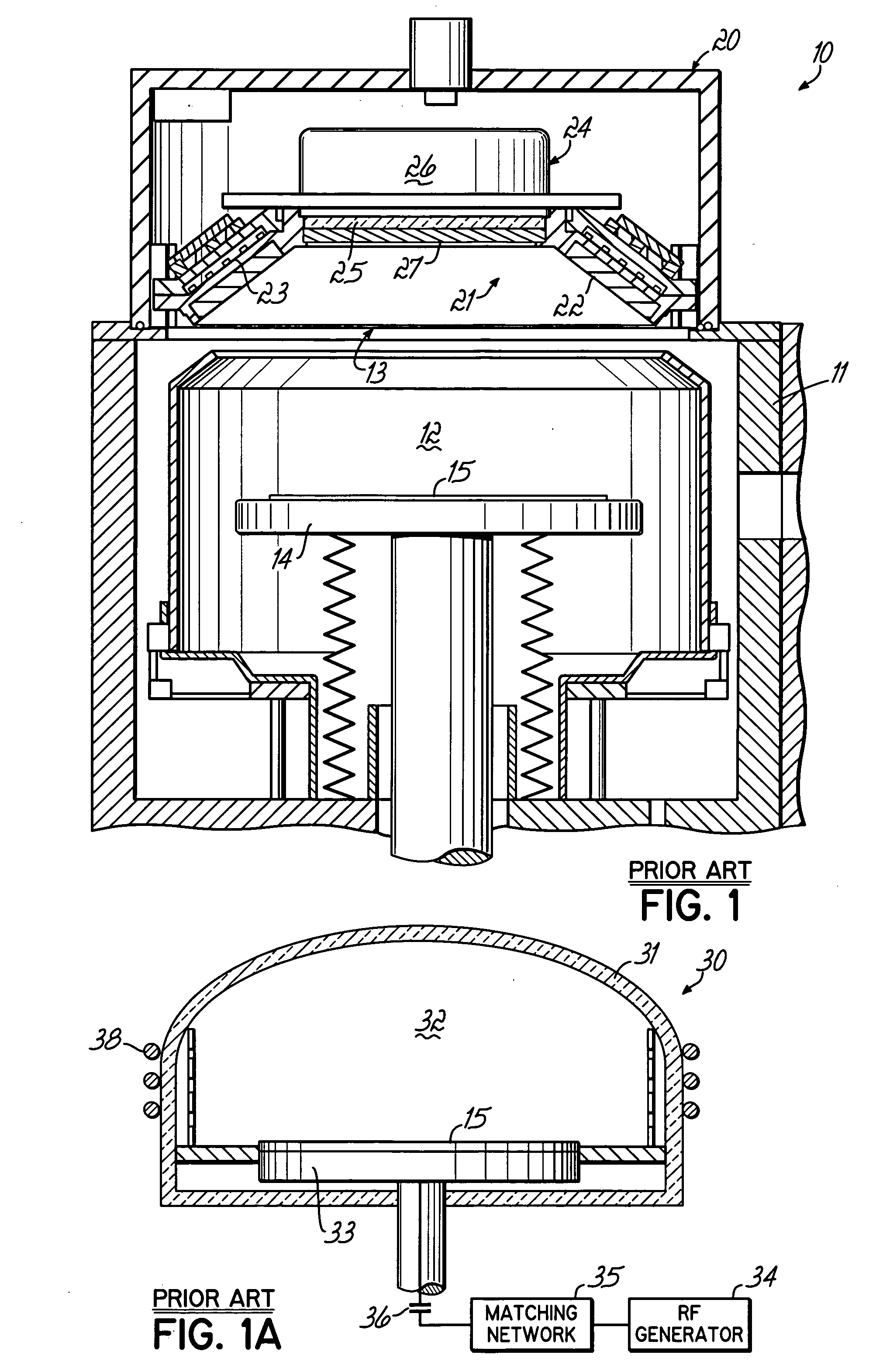

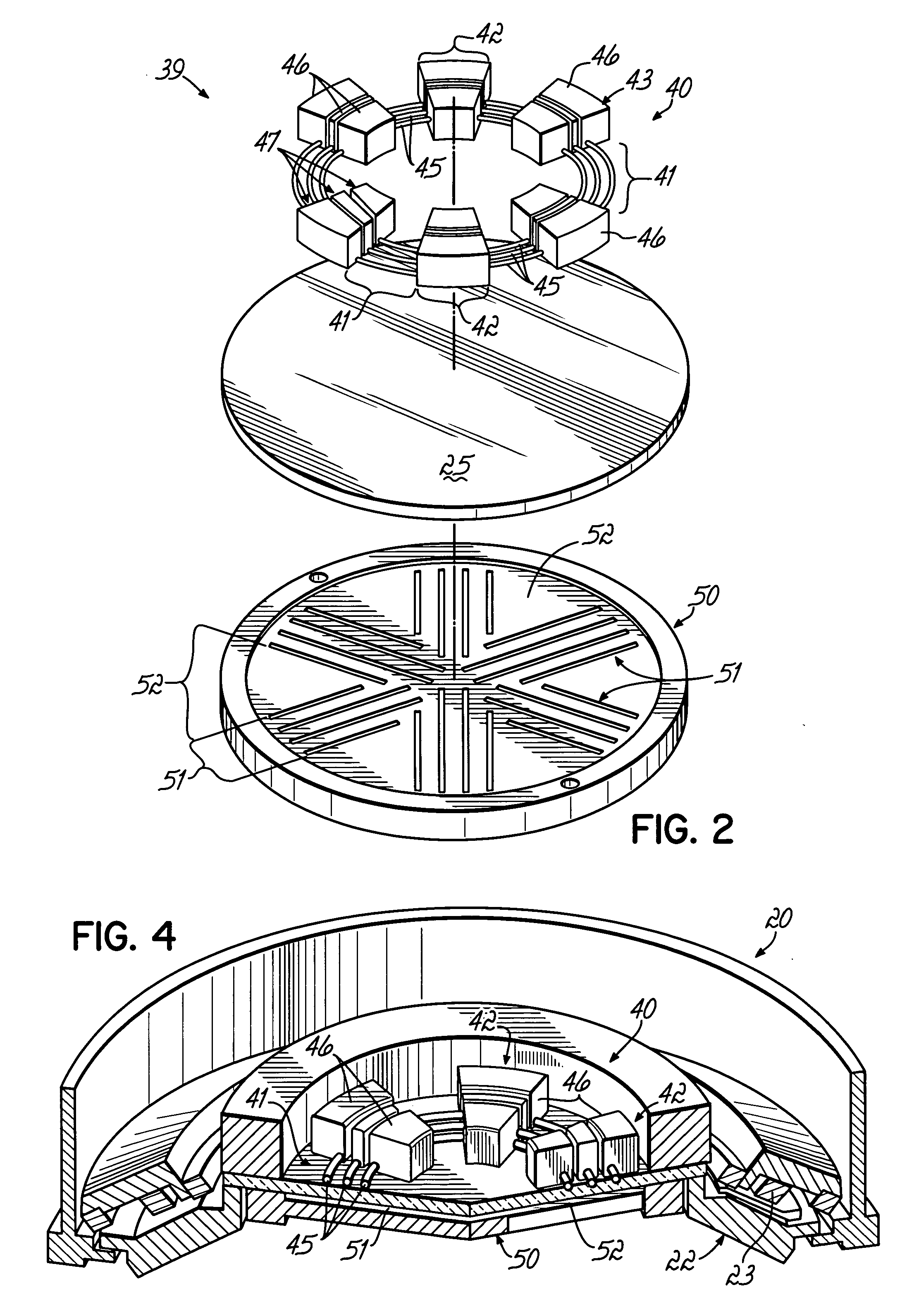

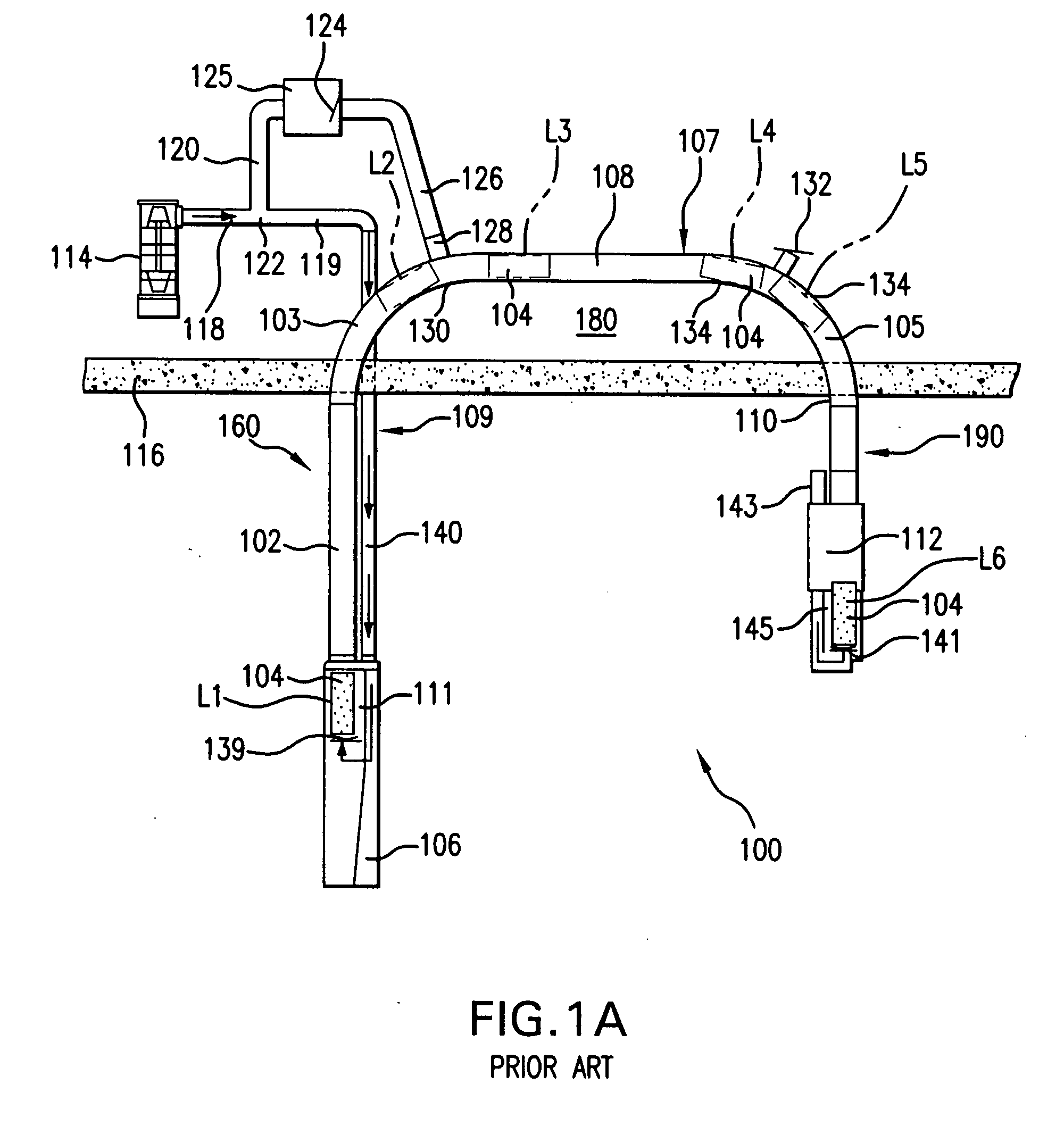

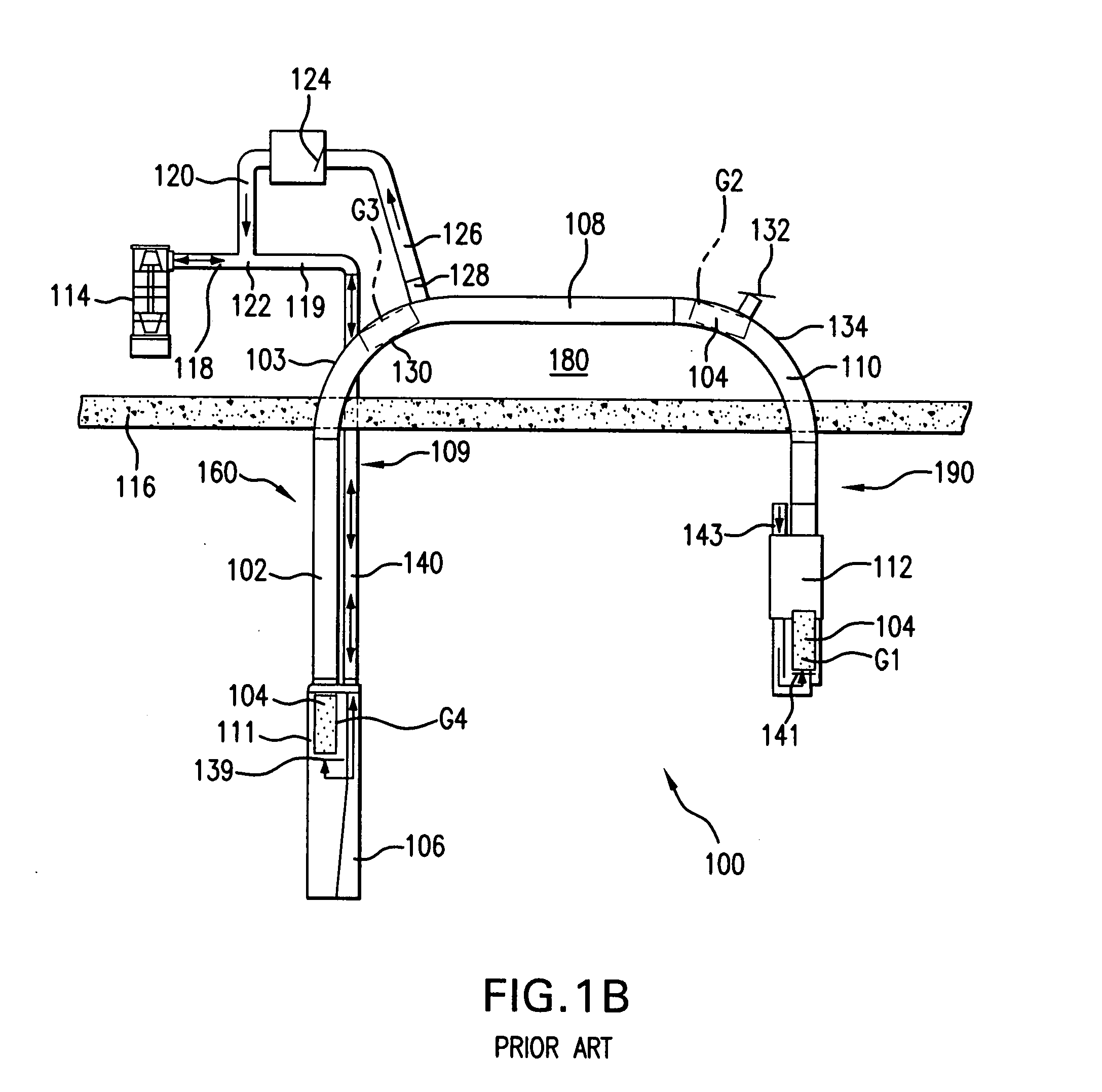

Plasma processing system with locally-efficient inductive plasma coupling

InactiveUS20050103445A1Improving uniformity of plasma processElectric discharge tubesVacuum evaporation coatingElectrical conductorEtching

An inductively coupled plasma source is provided with a peripheral ionization source for producing a high-density plasma in a vacuum chamber for semiconductor wafer coating or etching. The source includes a segmented configuration having high and low radiation segments and produces a generally ring-shaped array of energy concentrations in the plasma around the periphery of the chamber. Energy is coupled from a segmented low inductance antenna through a dielectric window or array of windows and through a segmented shield or baffle. The antenna has concentrated conductor segments through which current flows in one or more small cross-section conductors to produce high magnetic fields that couple through the high-transparency shield segments into the chamber, while alternating distributed conductor segments, formed of large cross-section conductor portions or diverging small conductor sections, permit magnetic fields to pass through or between the conductors and deliver only weak fields, which are aligned with opaque shield sections and couple insignificant energy to the plasma. The source provides spatial control of plasma energy distribution, which aids in control of the uniformity of plasma processing across the surface of the semiconductor being processed.

Owner:TOKYO ELECTRON LTD

Mobile water analysis

ActiveUS20130330245A1Increase alkalinityFacilitate in-field chemical analysisAnalysis using chemical indicatorsMaterial analysis by observing effect on chemical indicatorCuvettePartial alignment

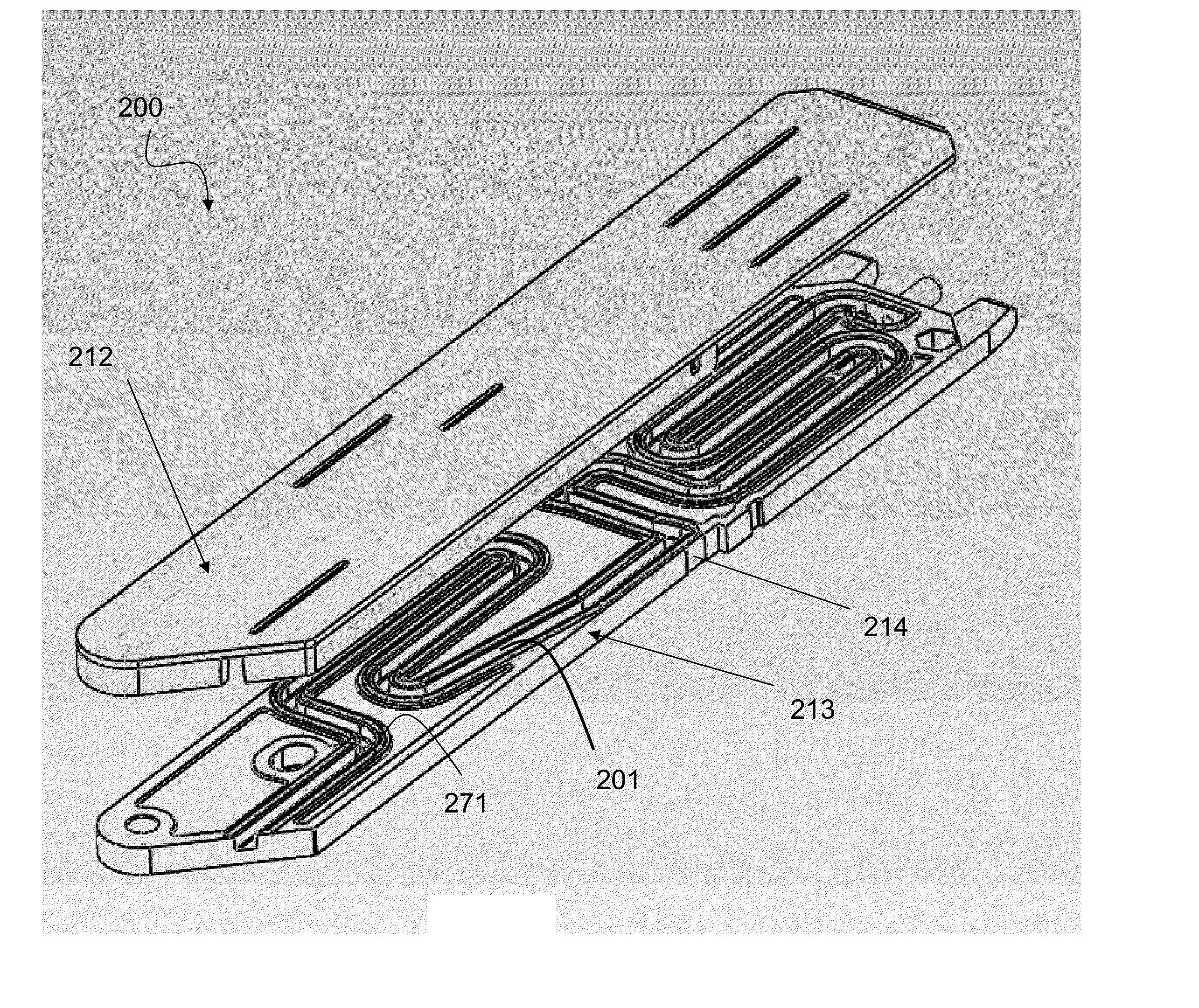

An embodiment provides a cuvette apparatus including: a lid and a body, the body including a fluid channel disposed therein; and the lid including at least one opening aligned with a portion of the fluid channel, thereby providing access to the fluid channel in the body. Other aspects are described and claimed.

Owner:HACH CO

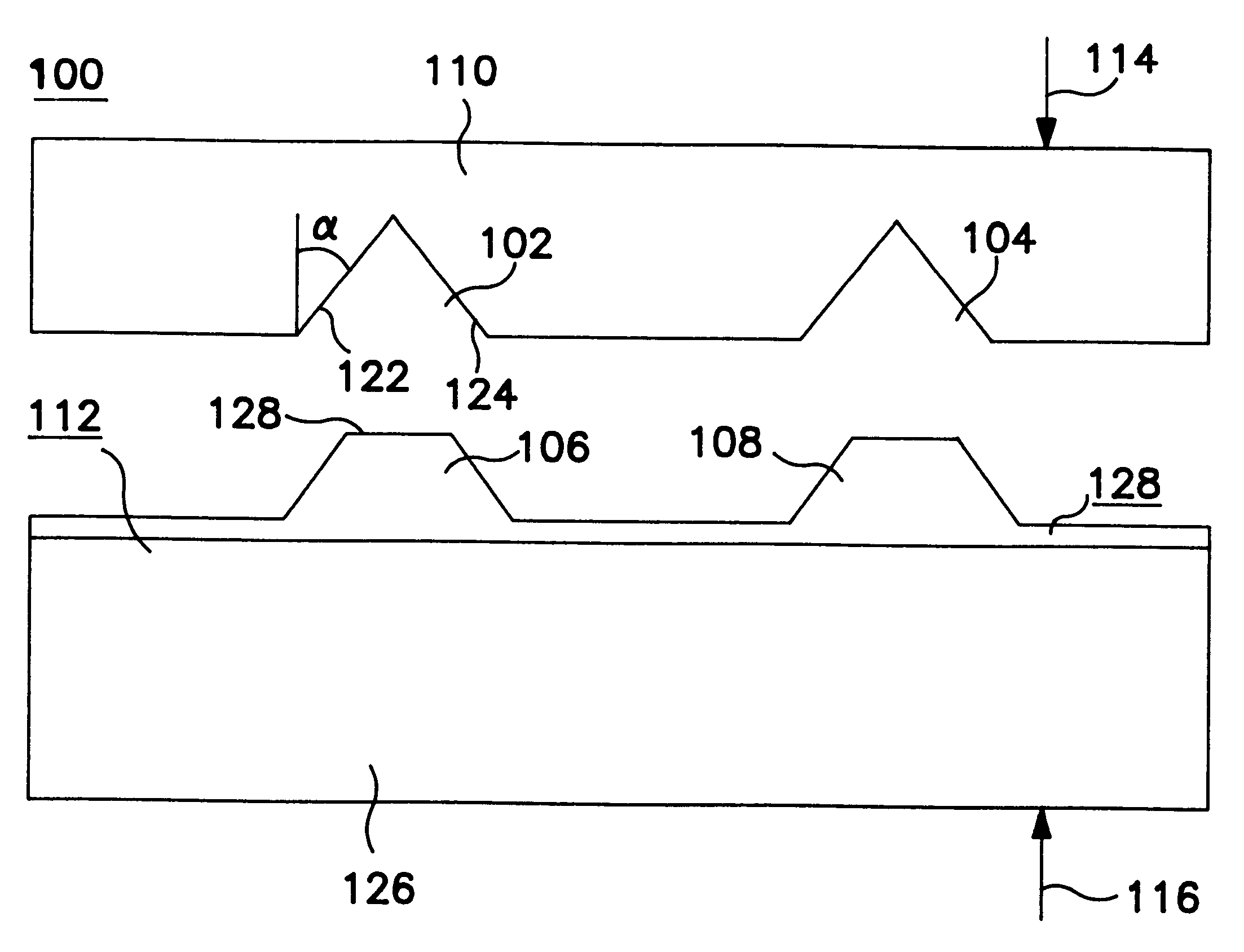

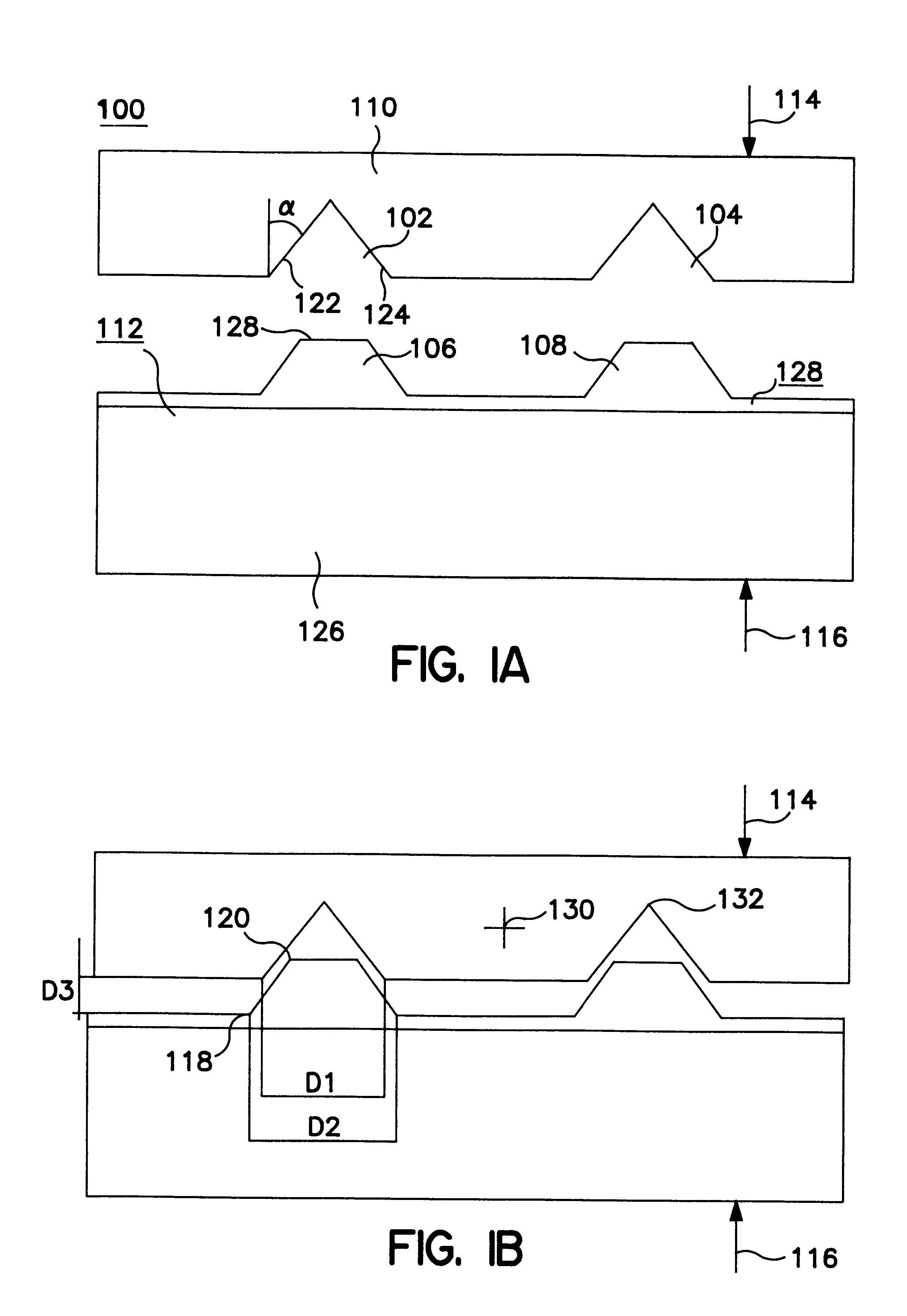

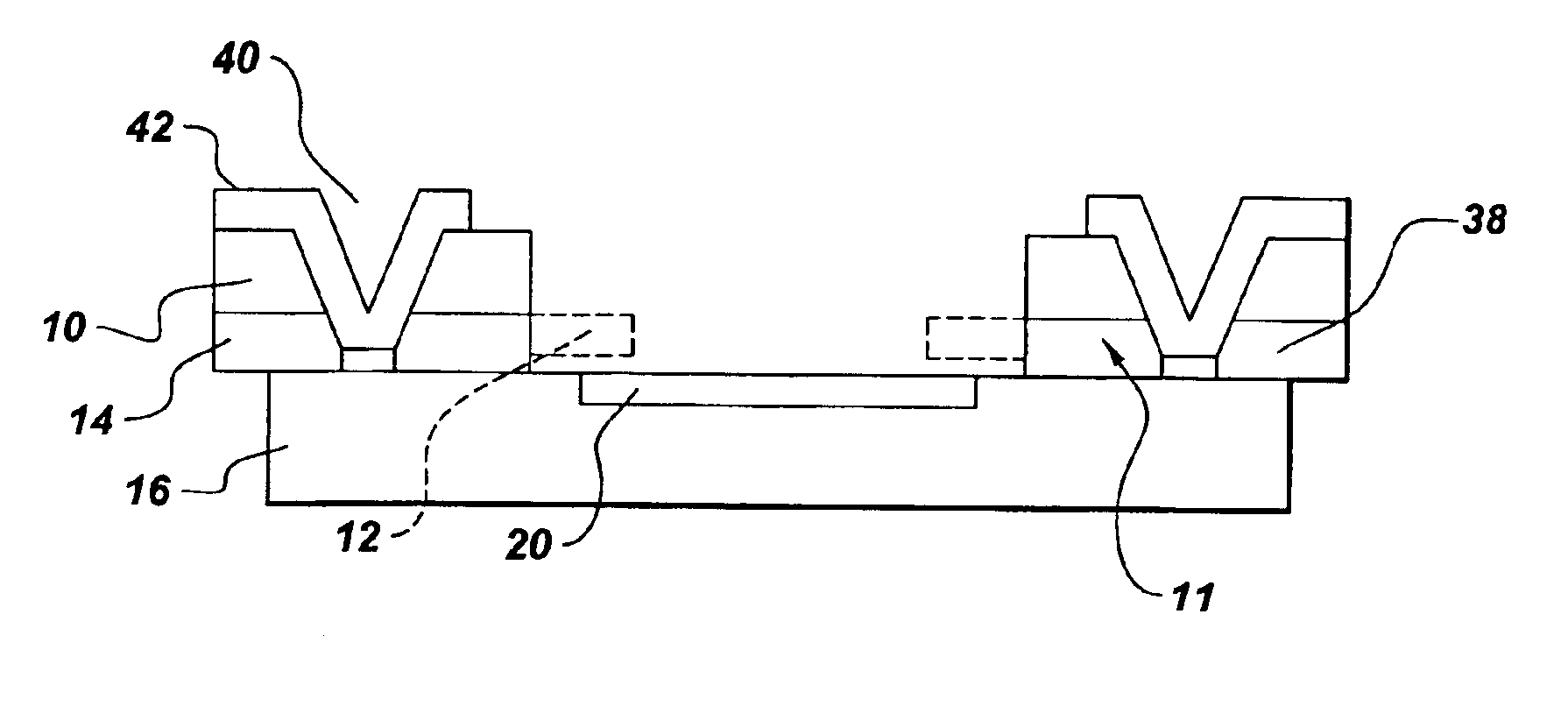

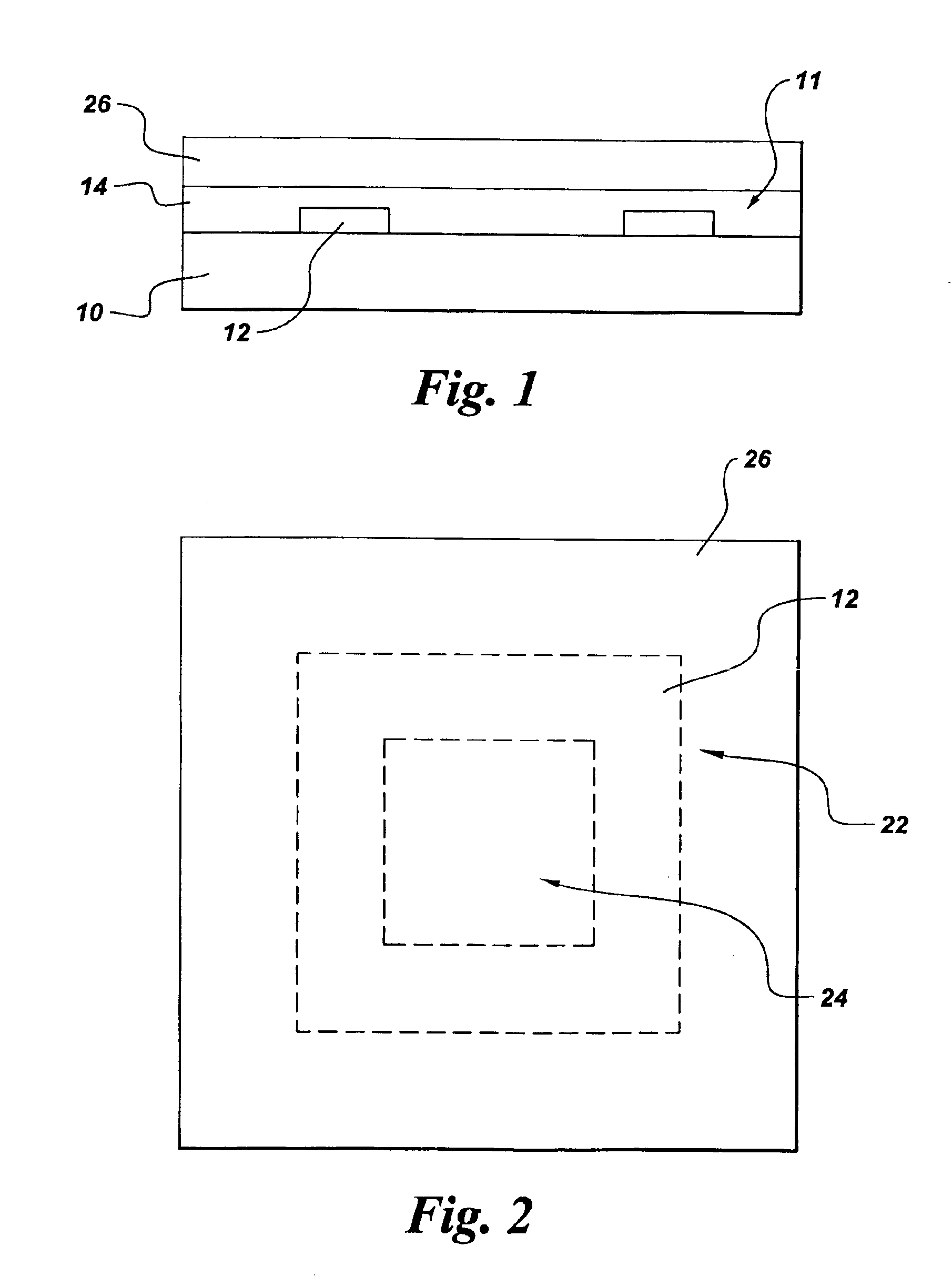

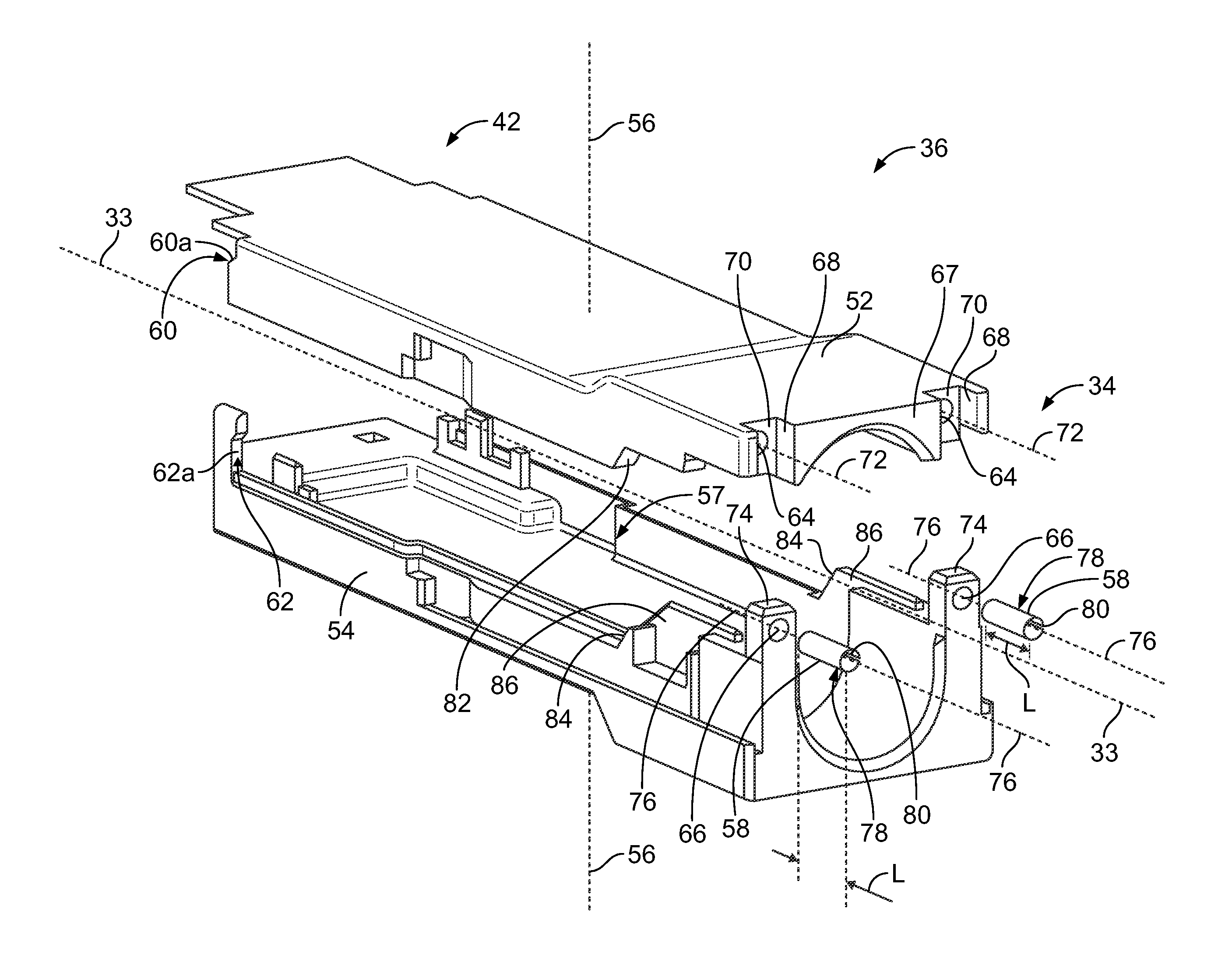

Bumps in grooves for elastic positioning

InactiveUS6188138B1Precise alignmentSimple technologySemiconductor/solid-state device detailsSolid-state devicesPartial alignmentEngineering

This invention belong to a mounting technology for aligning parts, a self-aligned elastic positioning. A problem this invention solves is alignment of parts without using mechanical fine pre-alignment. Wherein one part has elastic bumps, another part has V-grooves and the parts fit into each other. The invention is using elastic material for the bumps to fit the V-grooves. Whereas the bumps are made of elastic material and shaped partly to the V-bumps by moulding. The two parts can slide along in the direction perpendicular to the plane of the surface of the part. The movement in the perpendicular direction can be controlled by an external force. This means that the bumps and V-grooves have good alignment in xy-orientation and are also partial aligned in z-orientation. The elasticity of the bumps allows for thermal expansion differences without stresses to the parts while maintaining high precision alignment at a point. By using this type of parts they can be disassembled and be replaced without destroying the alignment features.

Owner:INFINEON TECH AG

Tabbed circuit board and method for manufacturing same

InactiveUS7377787B1Compact profileSmall housingPoint-like light sourceElectric lightingPartial alignmentEngineering

Owner:ILIGHT TECH INC

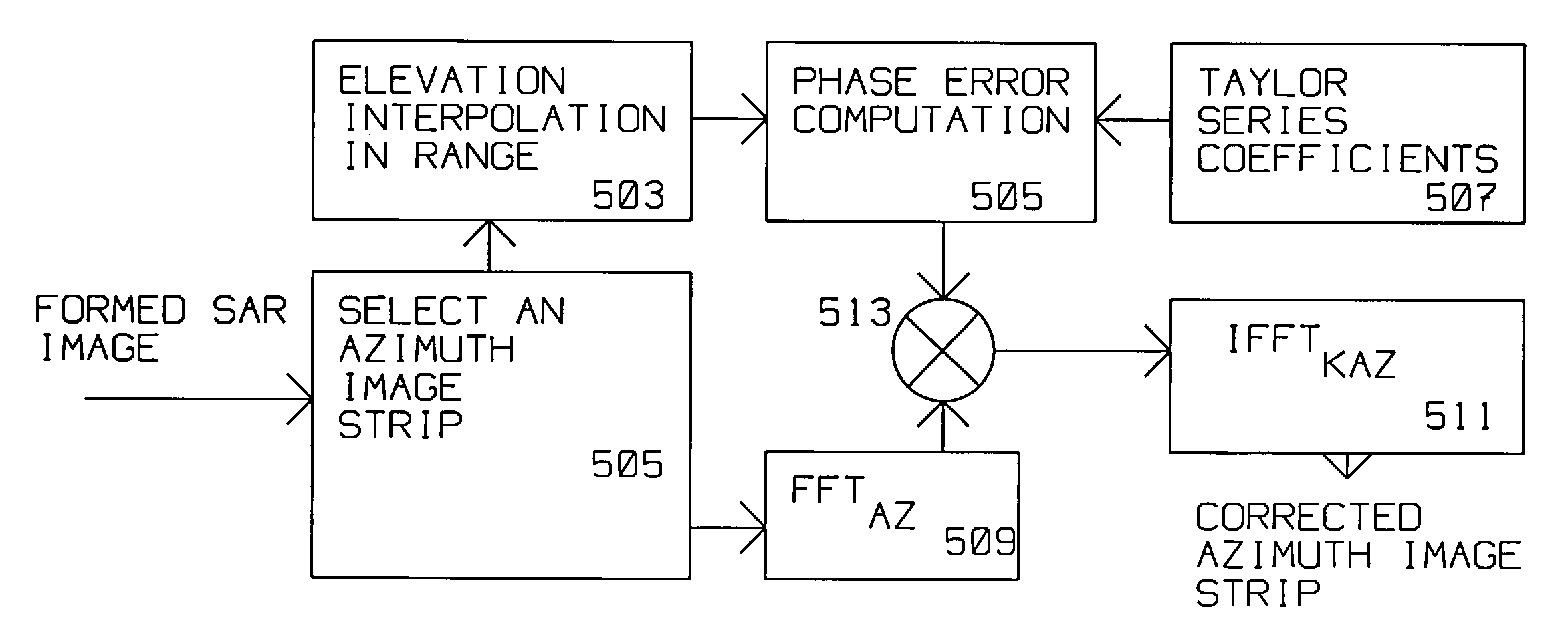

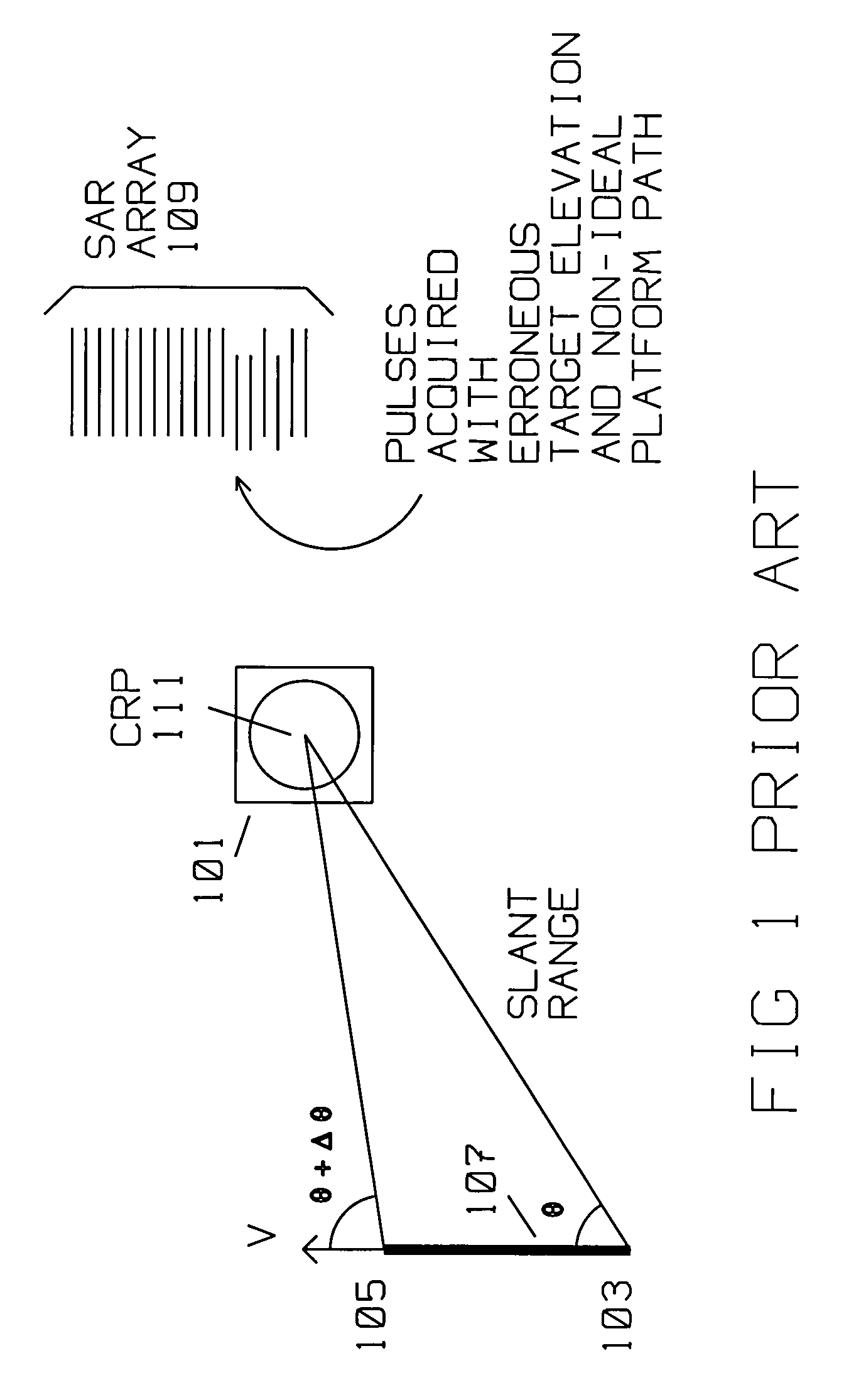

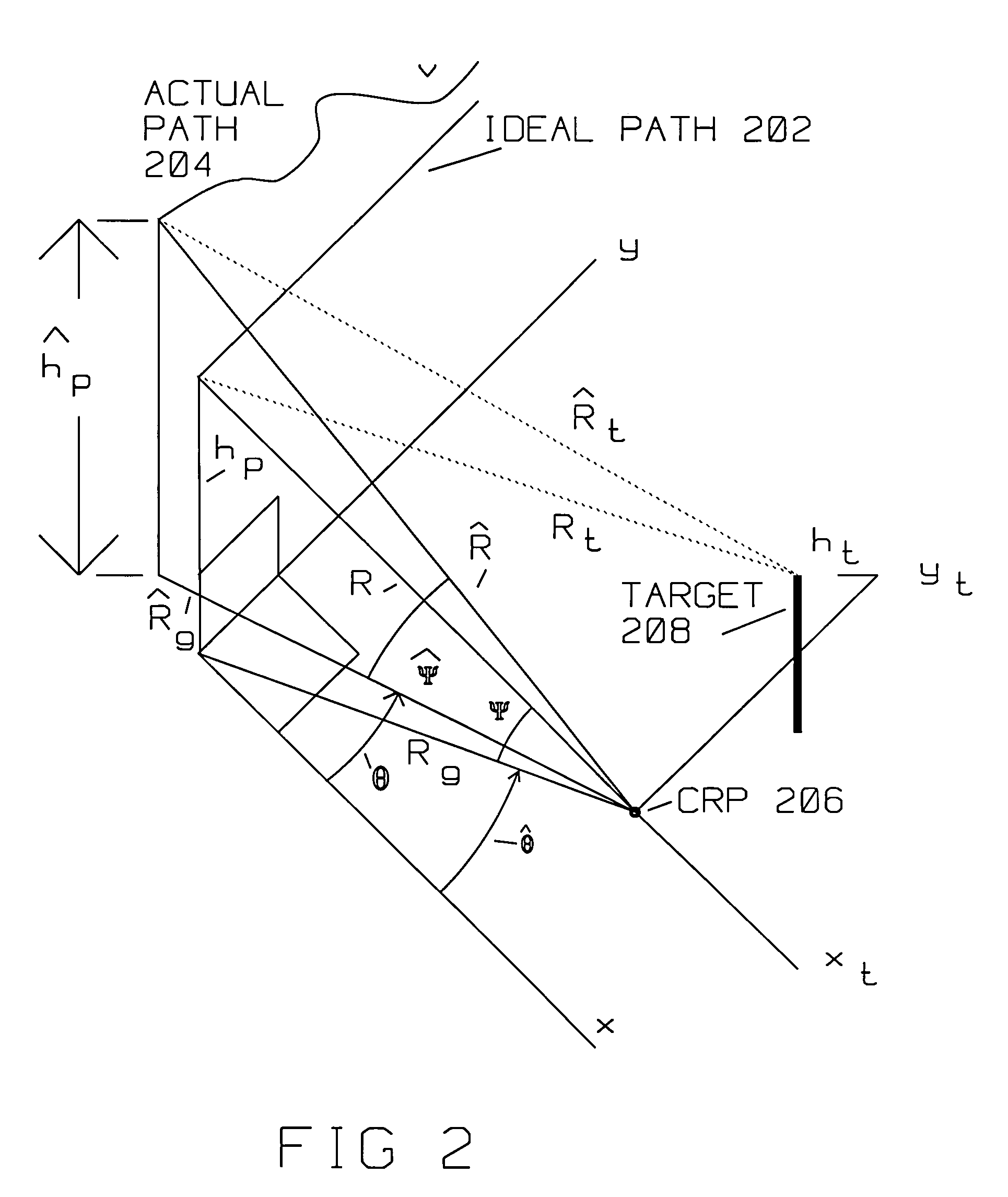

Compensation of flight path deviation for spotlight SAR

ActiveUS7277042B1Enhance the imageRadio wave reradiation/reflectionArray data structureFourier transform on finite groups

A radar acquires a formed SAR image of radar scatterers in an area around a central reference point (CRP). Target(s) are within the area illuminated by the radar. The area covers terrain having a plurality of elevations. The radar is on a moving platform, where the moving platform is moving along an actual path. The actual path is displaced from an ideal SAR image acquisition path. The radar has a computer that divides the digital returns descriptive of the formed SAR image into multiple blocks, such as a first strip and an adjacent strip. The first strip is conveniently chosen, likely to generally align with a part of the area, at a first elevation. An adjacent strip covers a second part of the area at a second elevation. The first strip is overlapping the adjacent strip over an overlap portion. The first and second elevation are extracted from a terrain elevation database (DTED). Horizontal displacement of returns (range deviation) is computed for each strip using the elevation information from the terrain elevation database. Taylor series coefficients are computed for the horizontal displacement due to terrain elevation using the ideal path, the actual path and central reference point. Actual flight path deviation is available at each pulse position while azimuth frequency is given in azimuth angle off mid angle point. Remapping between indices in two arrays is also computed. Phase error compensation and compensation in azimuth (spacial frequency) is computed using the Taylor series coefficients, a Fast Fourier Transform and an inverse Fast Fourier Transform for each strip. Phase error compensation is applied to the digital returns from each strip to obtain the SAR image. The SAR image is further improved by having the first strip corrected data and the second strip corrected data merged over the overlap portion to generate a relatively seamless SAR image.

Owner:RAYTHEON CO

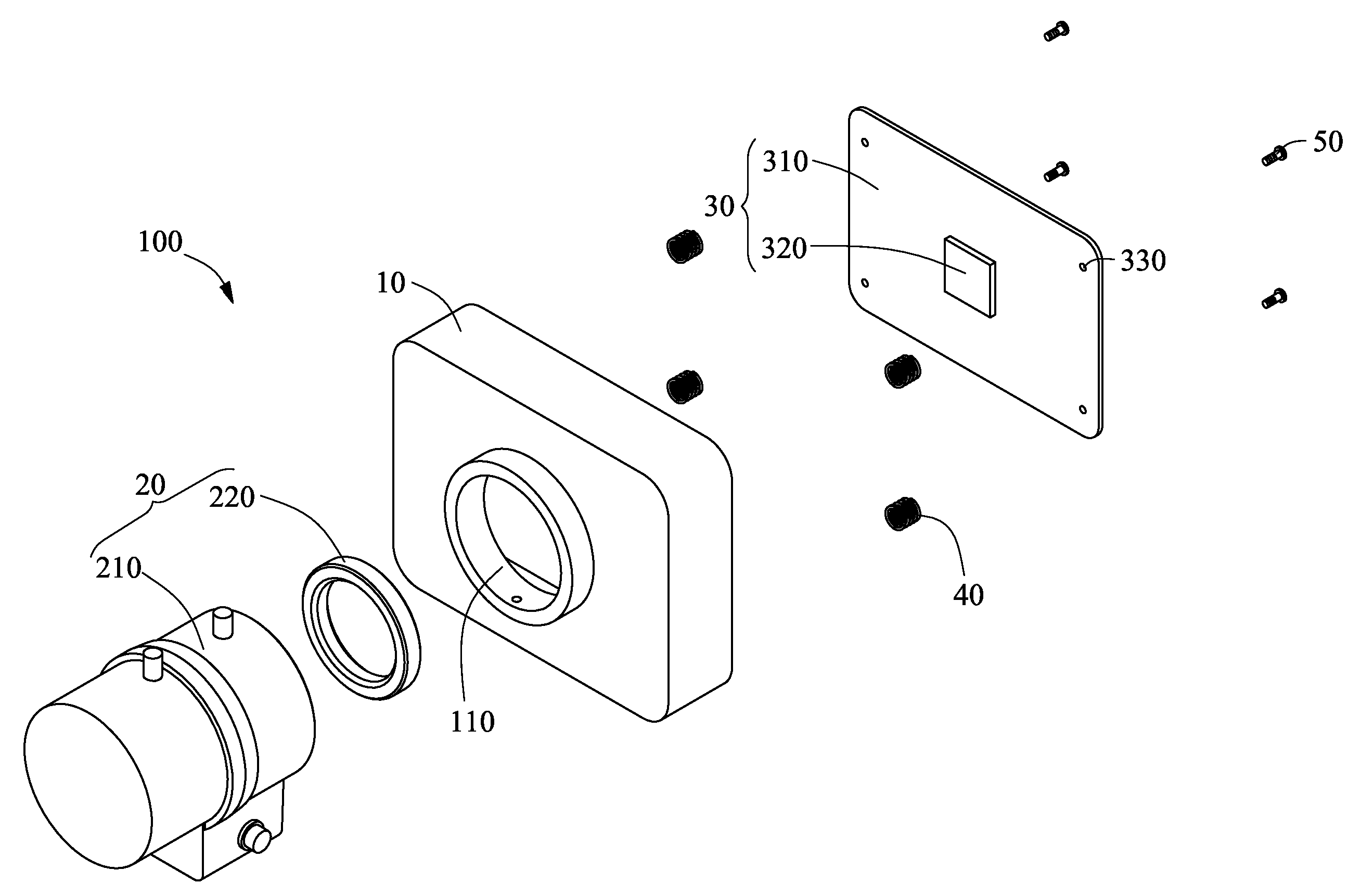

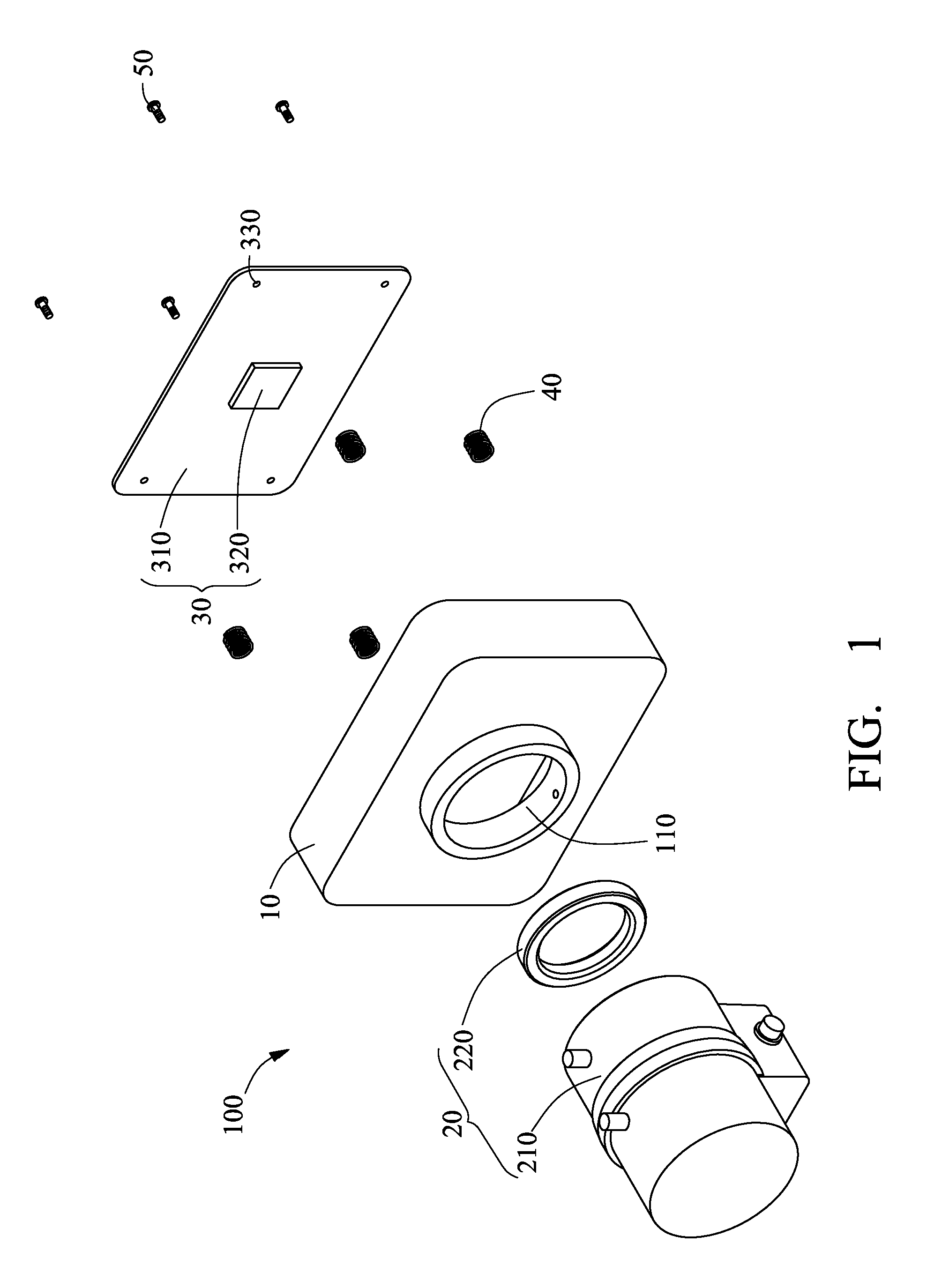

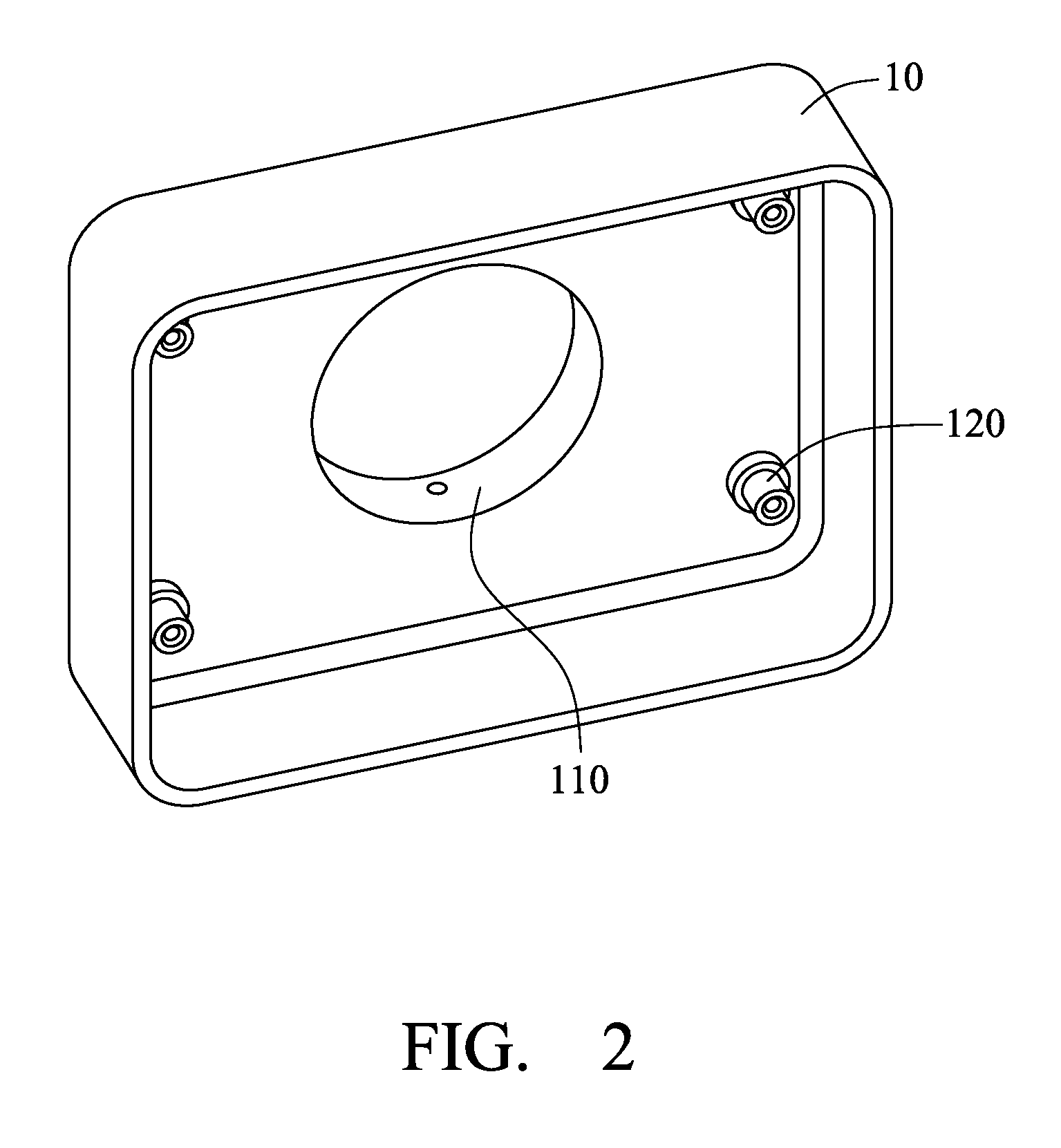

Image capture assembly

InactiveUS20090324213A1Television system detailsColor television detailsPartial alignmentImage detection

An image capture assembly is disclosed. The image capture assembly includes a housing, a lens unit, an image detection unit, three screws, and three elastic members. The housing includes a lens-receiving portion, and three screw-receiving portions on an inner surface of the housing and surrounding the lens-receiving portion, an end surface of each screw-receiving portion defining a threaded hole. The lens unit is received in the lens-receiving portion. The image detection unit includes a substrate and an image sensor. The substrate facing the inner surface of the housing defines three through holes therein aligned with the three screw-receiving portions respectively. The image sensor is fixed to the substrate and faces the lens-receiving portion. The screws extend through the through holes of the substrate and into the threaded holes of the screw-receiving portions respectively. The elastic members surround the screw-receiving portions respectively and are compressed between the housing and the substrate.

Owner:HON HAI PRECISION IND CO LTD

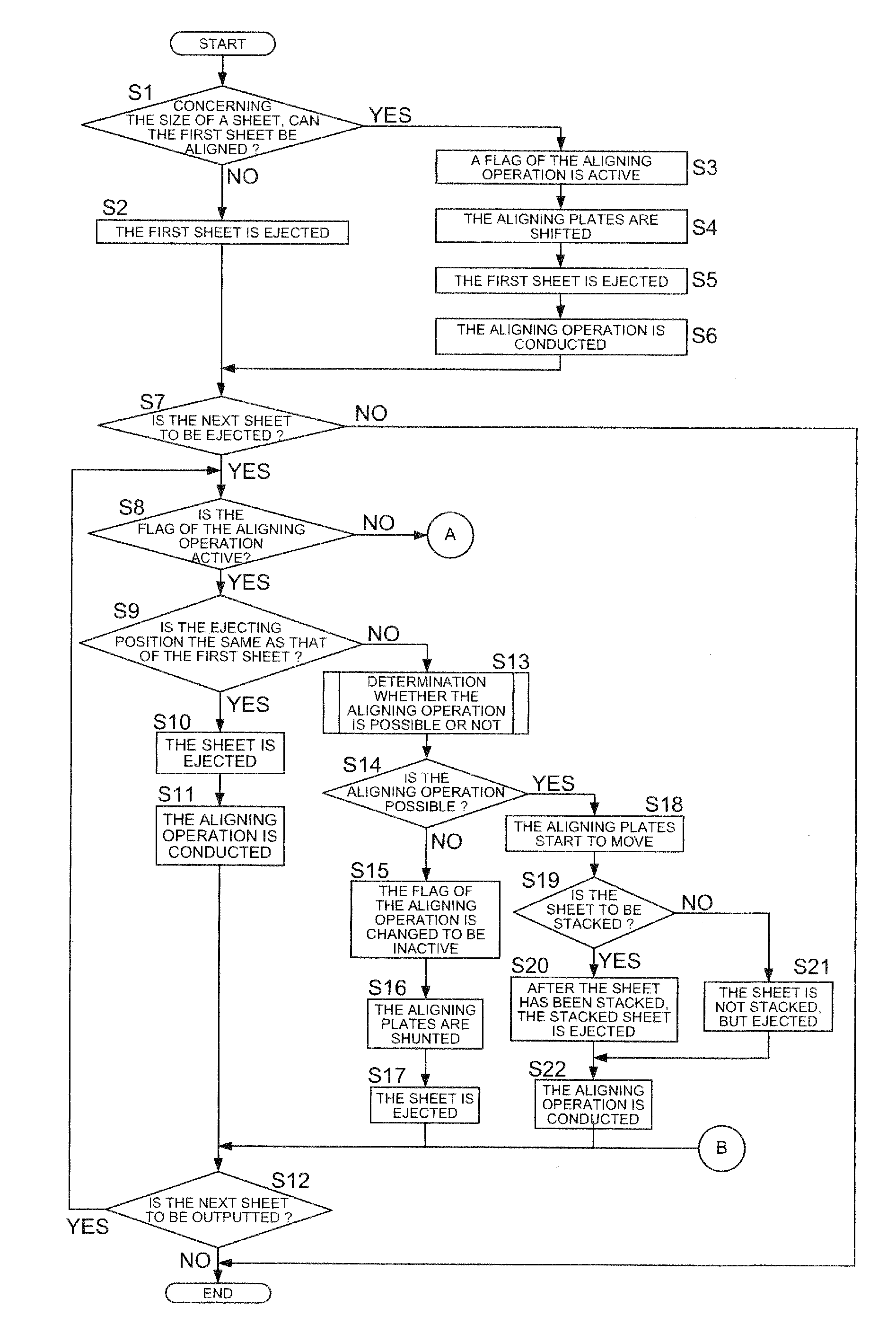

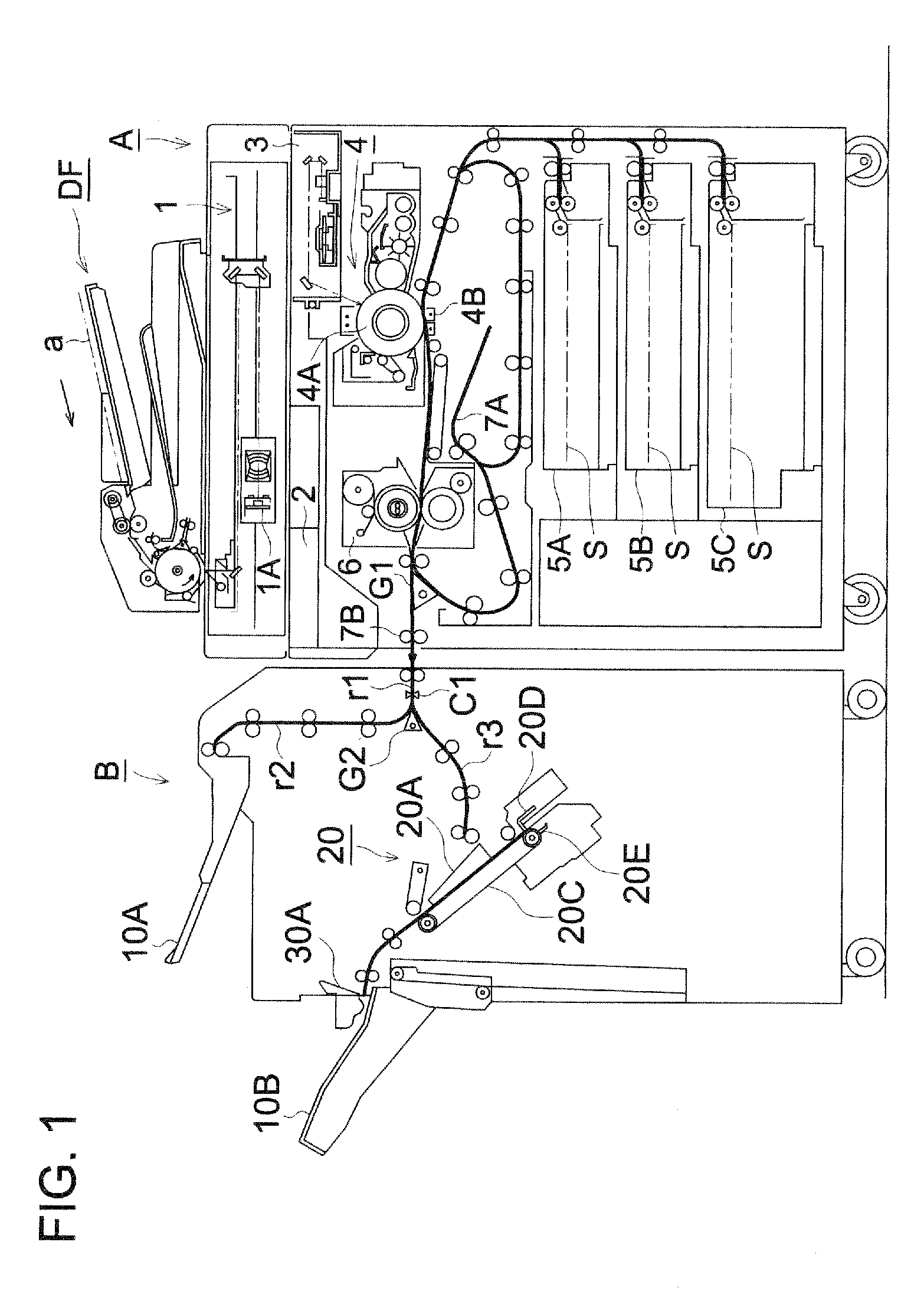

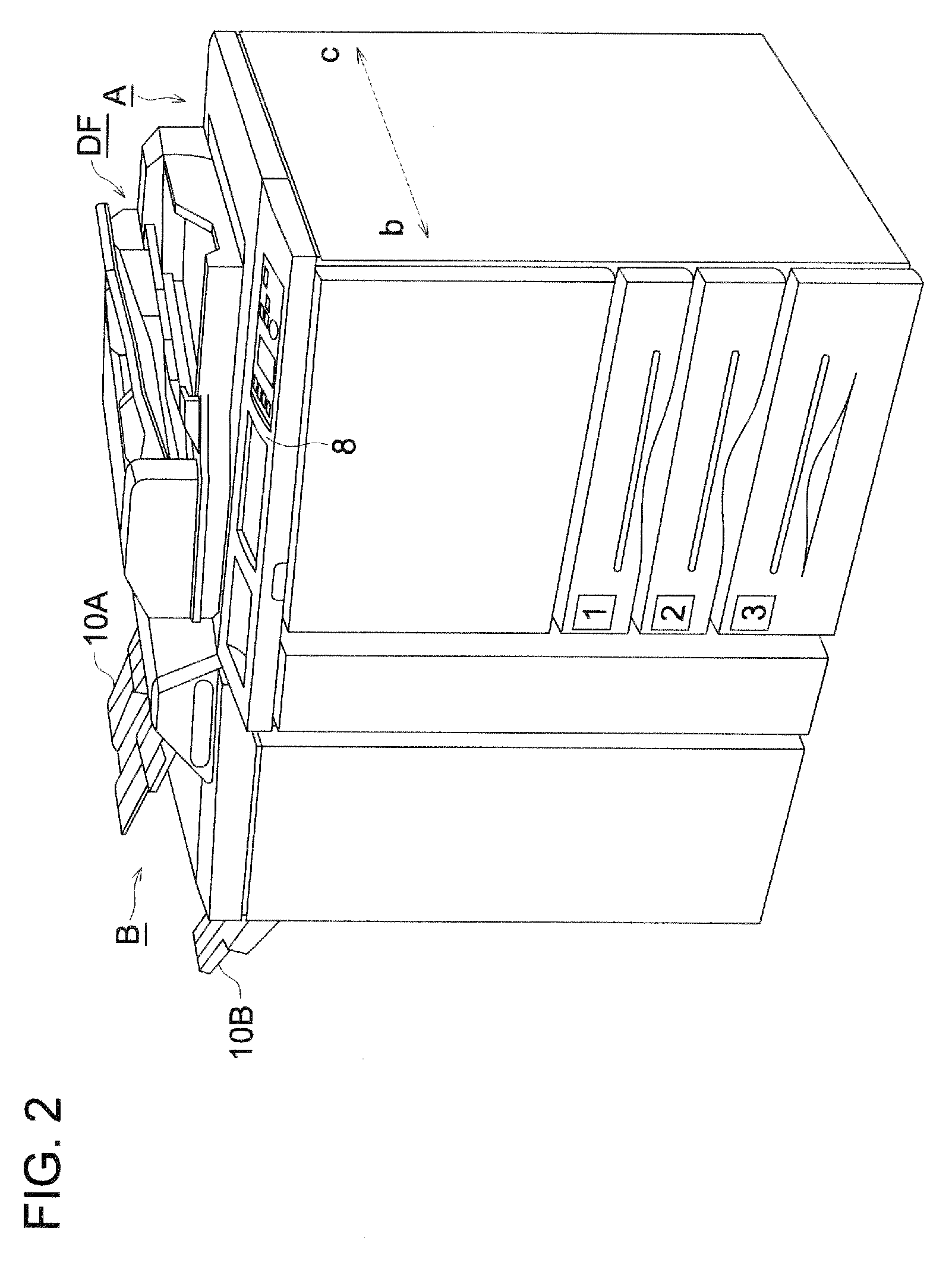

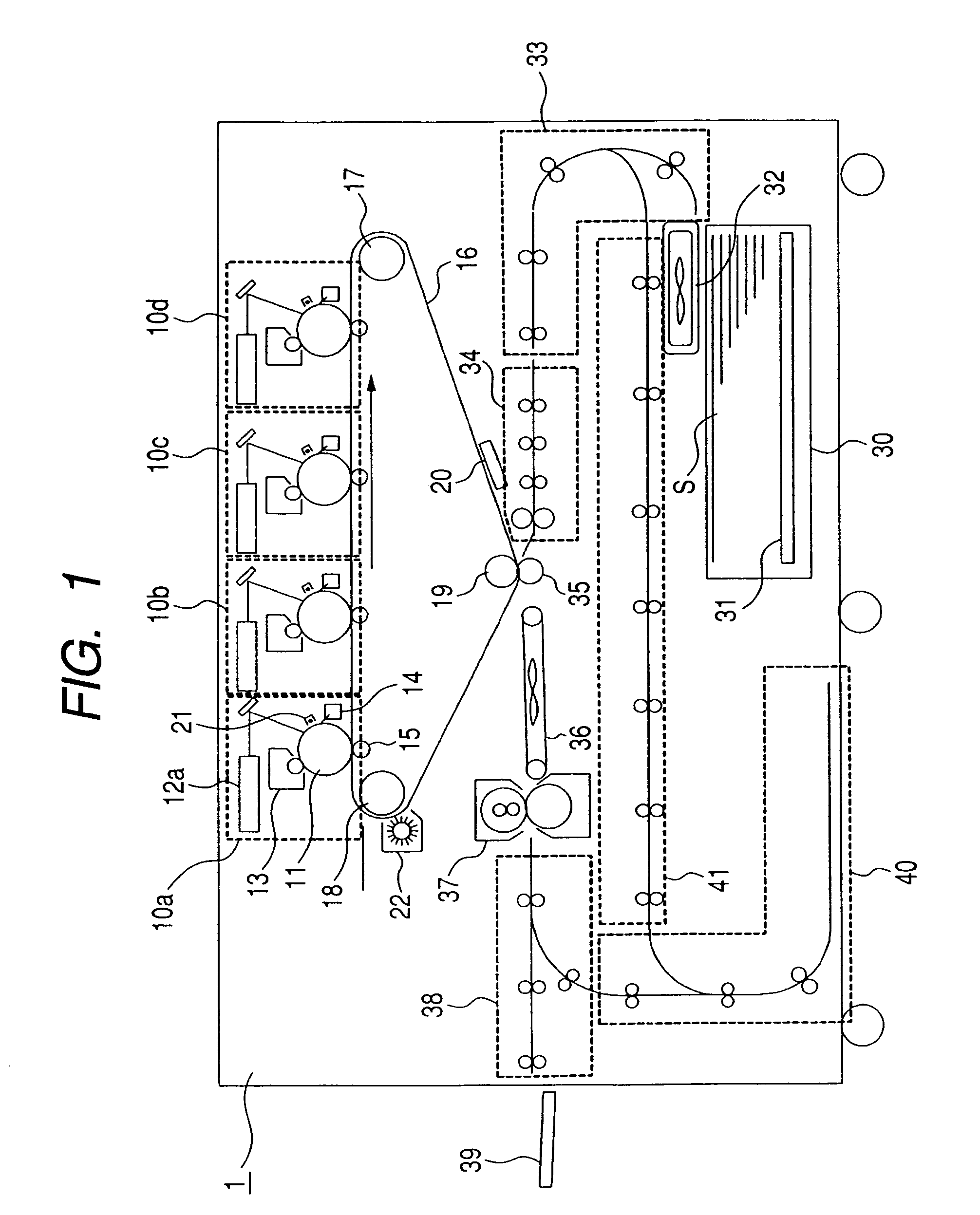

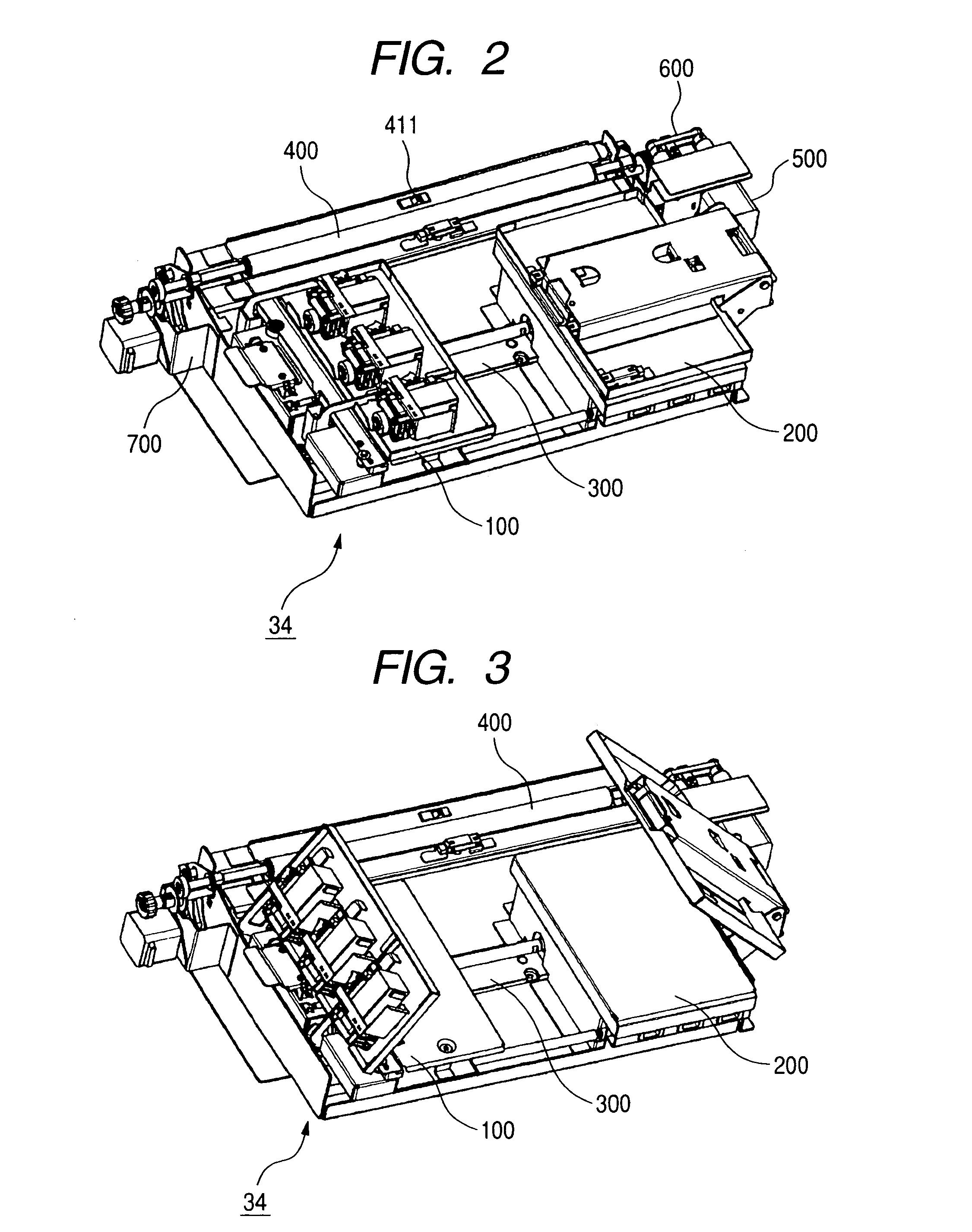

Sheet stacking apparatus and image forming system using the same

ActiveUS20090243198A1Function indicatorsElectrographic process apparatusImage formationPartial alignment

Owner:KONICA MINOLTA BUSINESS TECH INC

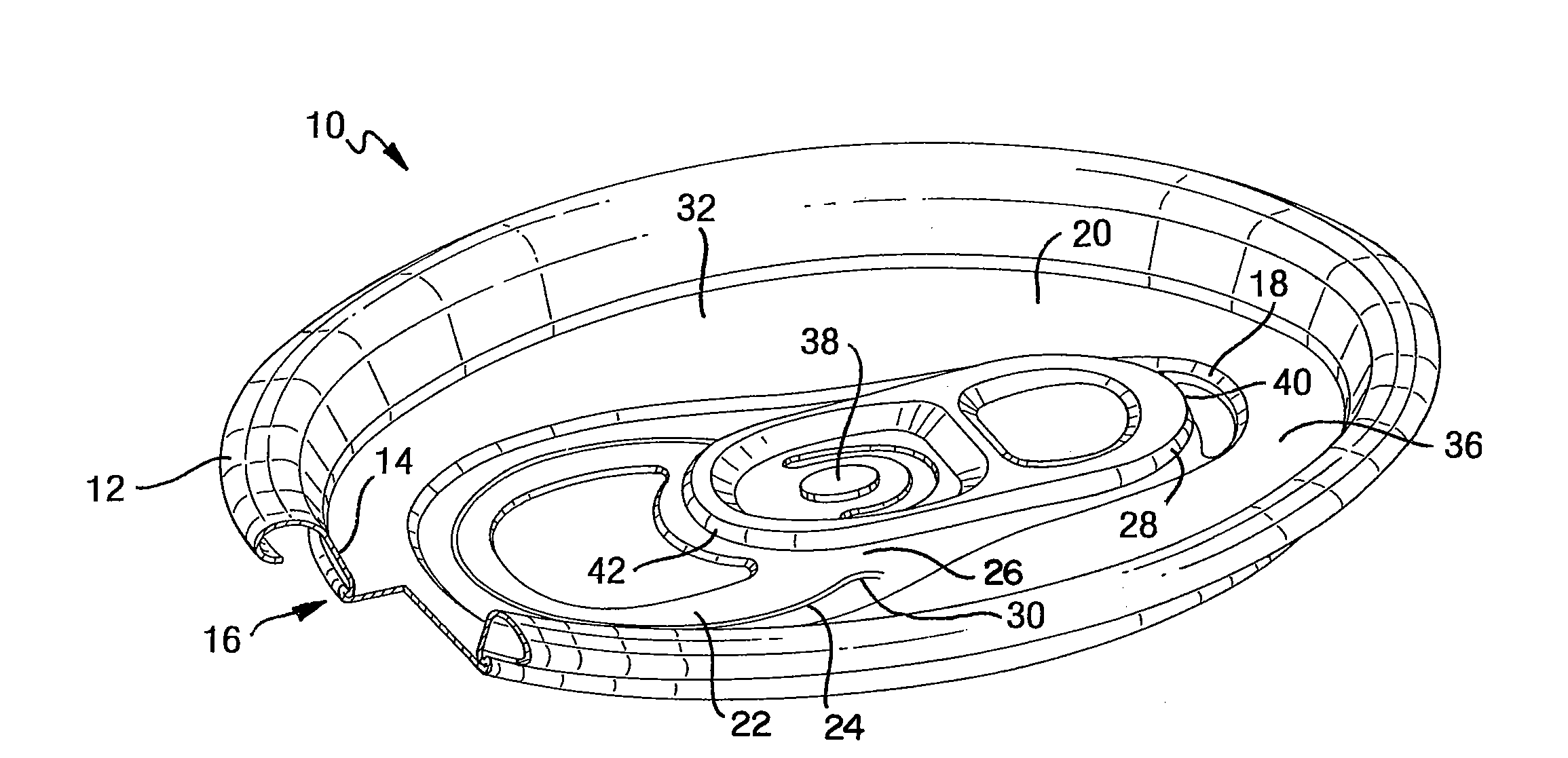

Can end

InactiveUS20090269169A1High strengthImprove featuresRemovable lids/coversRefuse receptaclesPartial alignmentCircular segment

In a method of forming a beverage can end wherein a beverage can end shell has a curl defining a perimeter of the can end, a chuckwall extending downwardly and radially inwardly from the curl, a generally U-shaped countersink joining the chuckwall to an outer peripheral edge of a center panel, a method of forming an arcuate chuckwall in the beverage can end shell is described. The method of forming the arcuate chuckwall comprises the steps of providing a partially formed can end, providing an upper tooling having an annular, generally arcuate segment, and providing a lower tooling having a circumferential, generally arcuate, outwardly convex segment in at least partial alignment with the annular, generally arcuate segment of the upper tooling. The annular, generally arcuate segment of the upper tooling and the circumferential, generally arcuate, outwardly convex segment of the lower tooling are brought into engagement with a public side and a product side of the partially formed can end, respectively. A portion of the partially formed can end is reformed to form a circumferential, generally arcuate, outwardly convex segment located between an upper bend in the can end having a center of curvature above a public side of the can end and a lower bend in the partially formed can end having a center of curvature below the public side of the partially formed can end.

Owner:REXAM BEVERAGE CAN

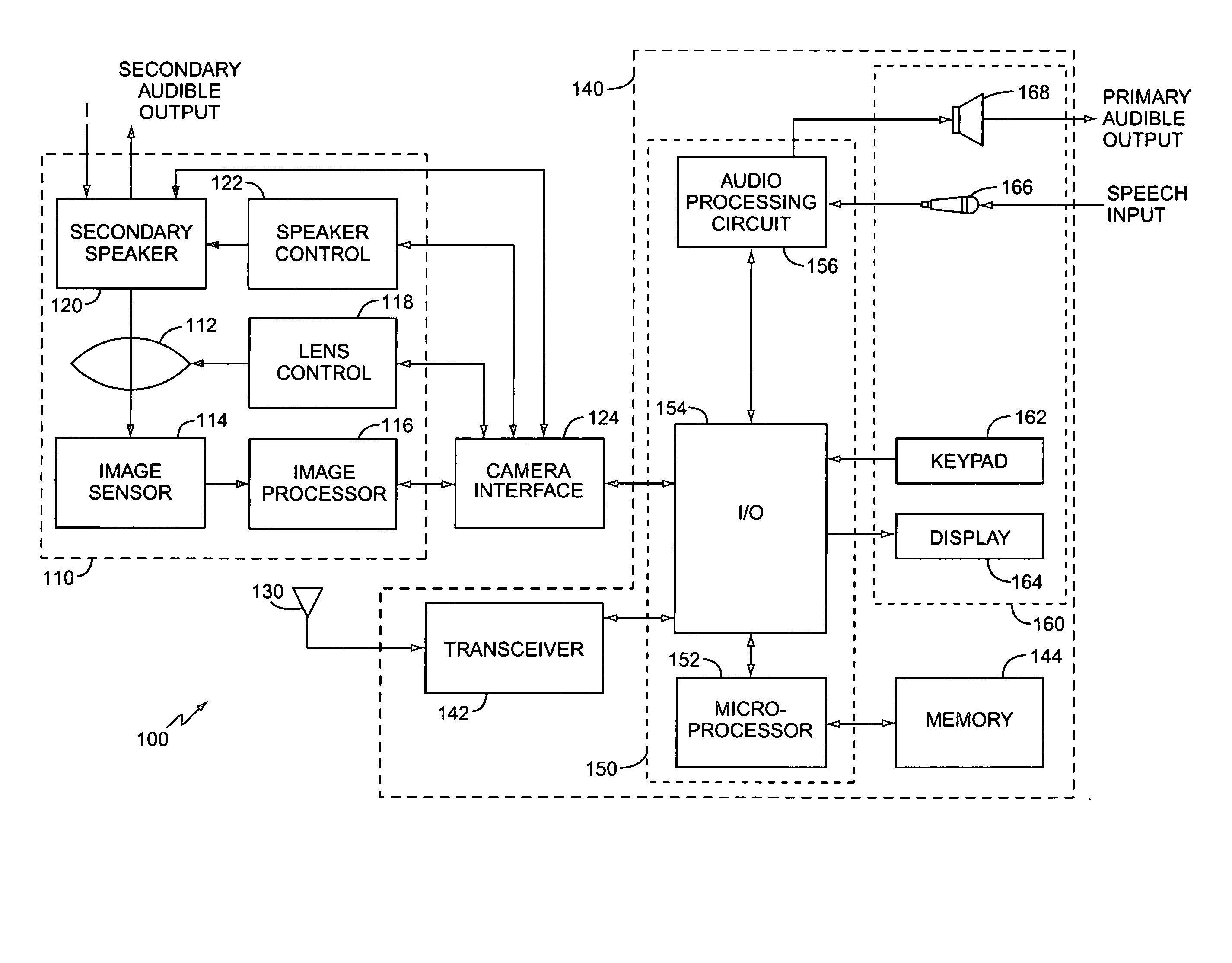

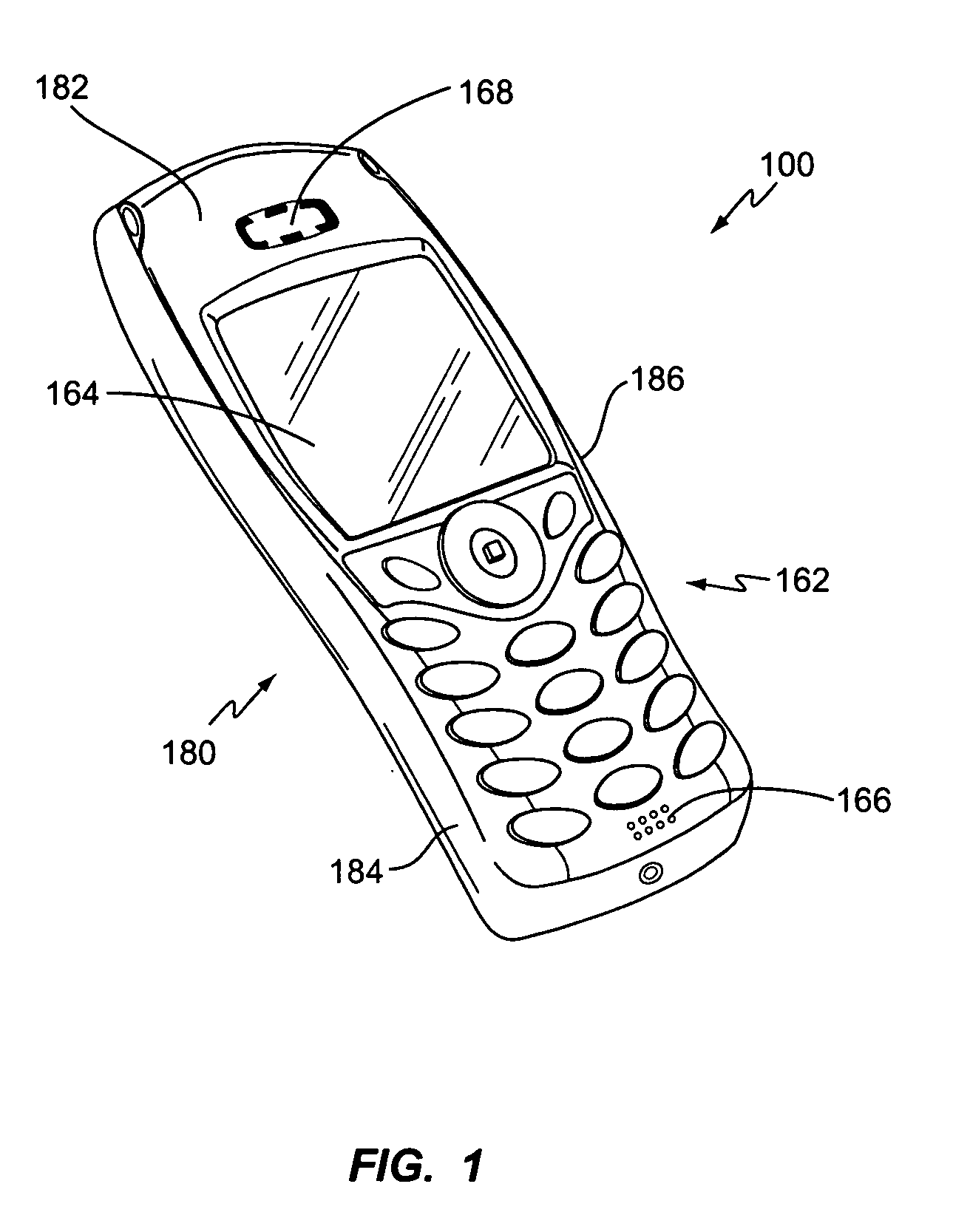

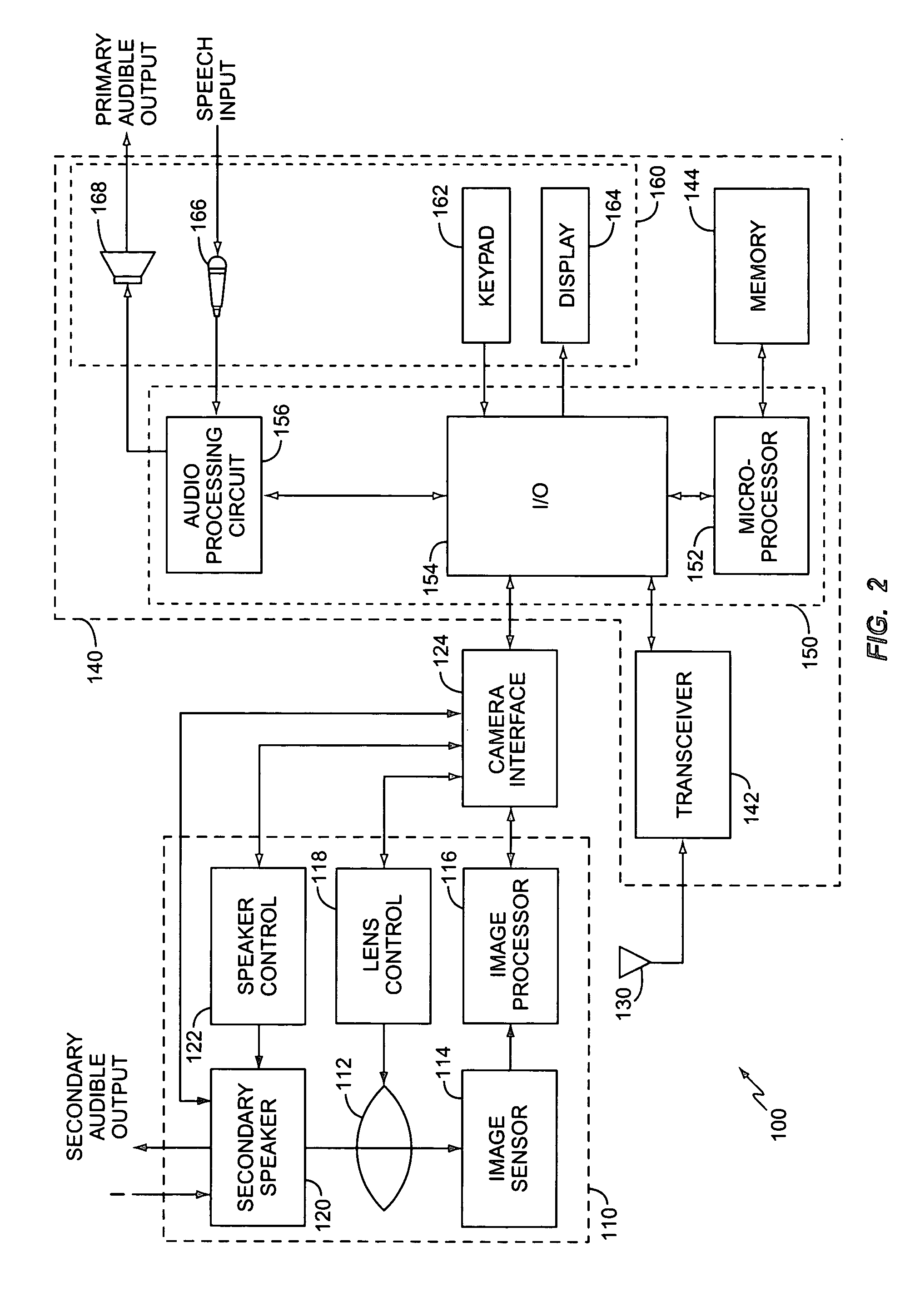

Mobile device with a combination camera and loudspeaker

InactiveUS20050128322A1Television system detailsPicture reproducers using cathode ray tubesCamera lensOptical property

A combination camera and loudspeaker is described herein. The combination camera and loudspeaker includes a lens for selectively manipulating an image and a loudspeaker assembly disposed proximate the lens for projecting audible sounds. In one embodiment, a transparent piezo-electric aligned with at least a portion of the lens projects audible sound based on electrical signals applied to the piezo-electric diaphragm. In another embodiment, a speaker coil and magnet within the loudspeaker assembly encircles an outer perimeter of the lens, while a transparent diaphragm connected to the speaker coil and aligned with at least a portion of the lens projects audible sound based on the interaction between the speaker coil and magnet. The camera captures an image when light is transmitted through the transparent diaphragm to the camera lens. Further, the combination camera and loudspeaker may include a controller for selectively controlling optical properties of the transparent diaphragm.

Owner:SONY ERICSSON MOBILE COMM AB

Sheet conveying apparatus and image forming apparatus

A sheet conveying apparatus with a skew feed correcting device including a first guide supporting one side edge of the sheet, an aligning device provided in the first guide and having an abutment portion and a first roller pair for causing the sheet to abut the abutment portion, a contact-separation device for separating and contacting the first roller pair, a second guide supporting the other side edge of the sheet, a positioning device for moving the first guide in a direction substantially perpendicular to a sheet conveying direction, a second roller pair downstream of the first and second guides, a slide device for moving the second roller pair in the direction, and a sheet detector. When conveying the sheet, the positioning device moves the first guide such that the abutment portion is at a predetermined distance from the side edge of the sheet, the sheet is conveyed while aligned by abutted against the abutment portion by the first roller pair, the first roller pair is separated by the contact-separation device based on the detection of the sheet detector, and the sheet is moved by the slide device so as to be returned by the predetermined distance while held by the second roller pair.

Owner:CANON KK

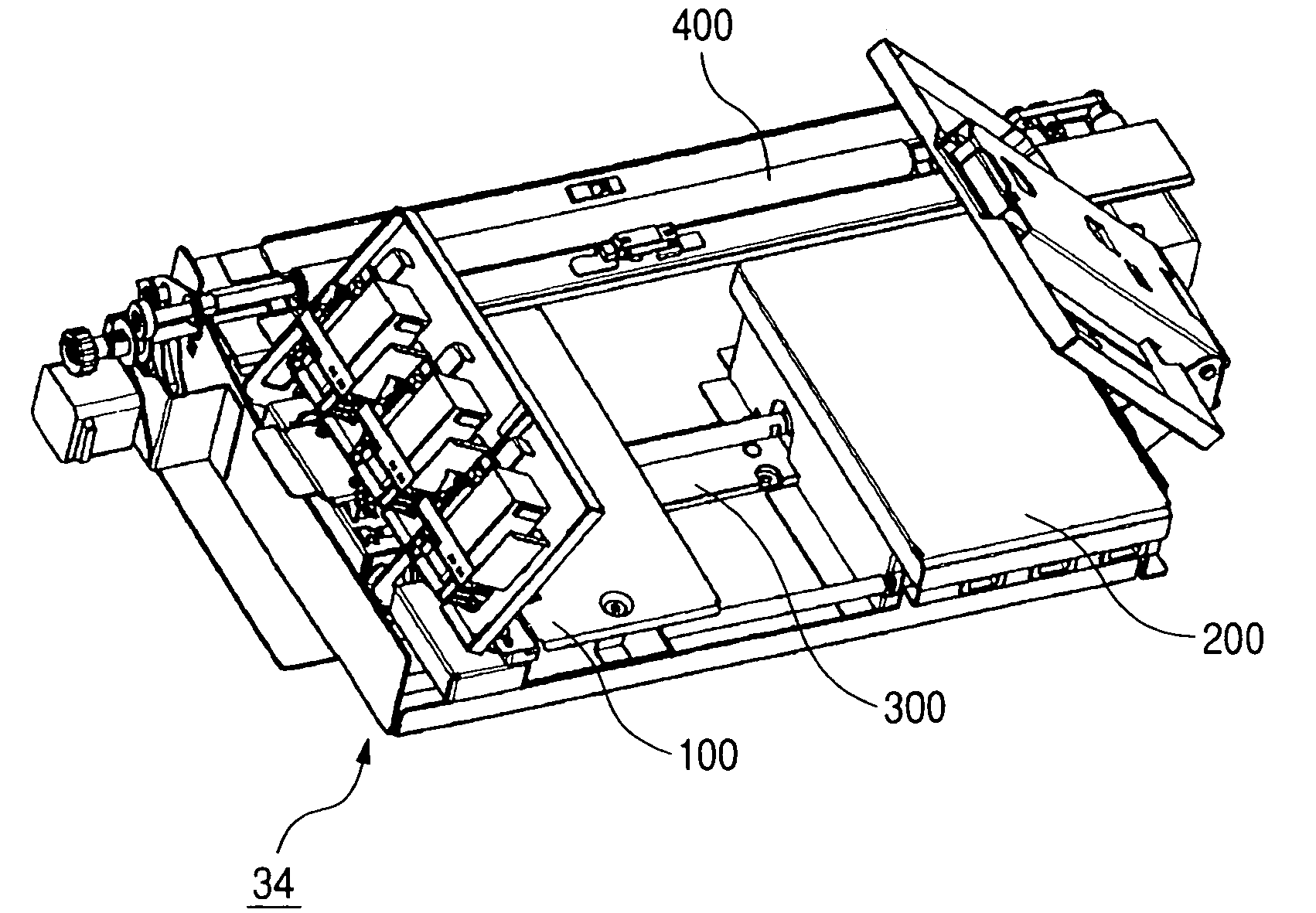

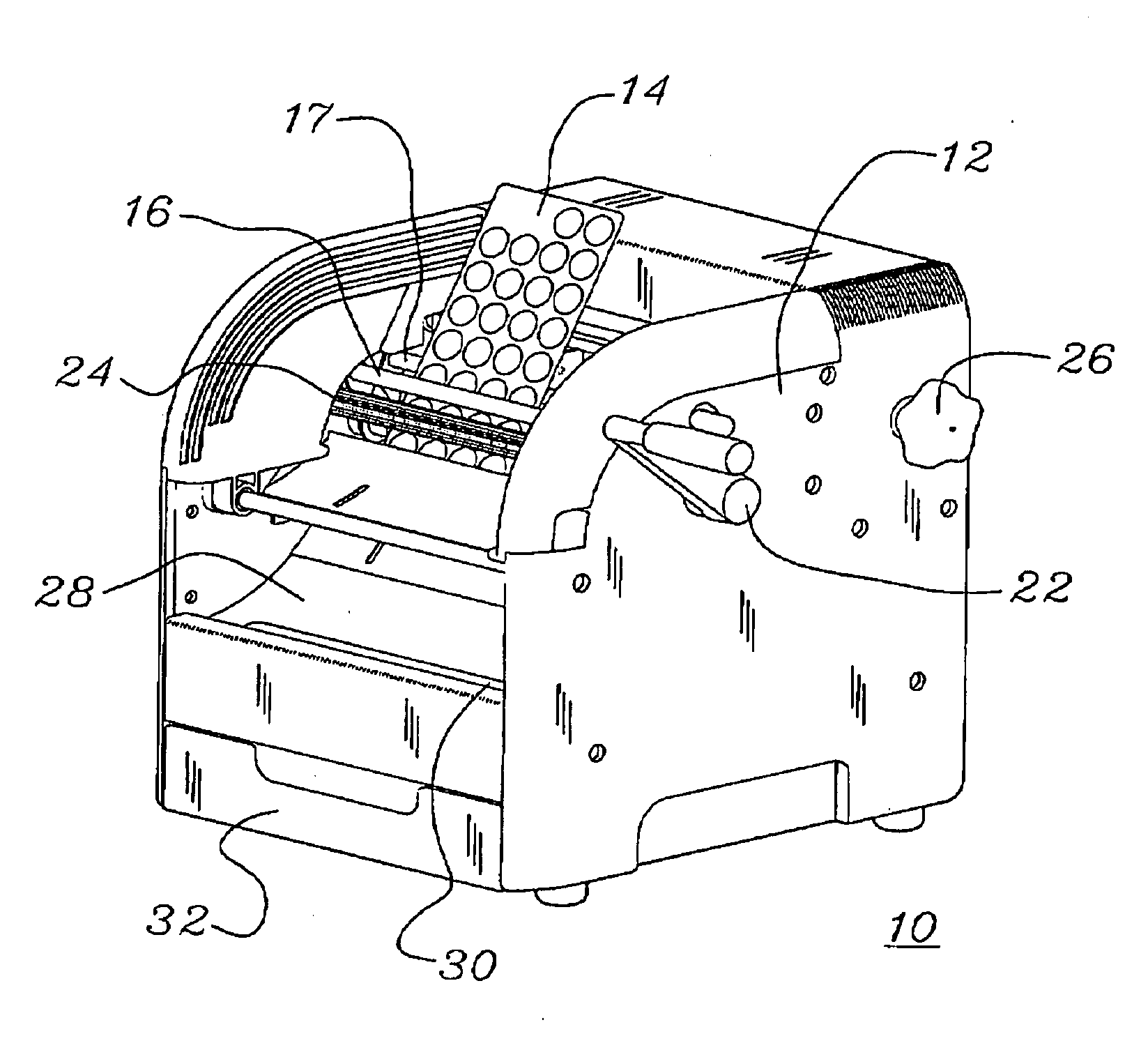

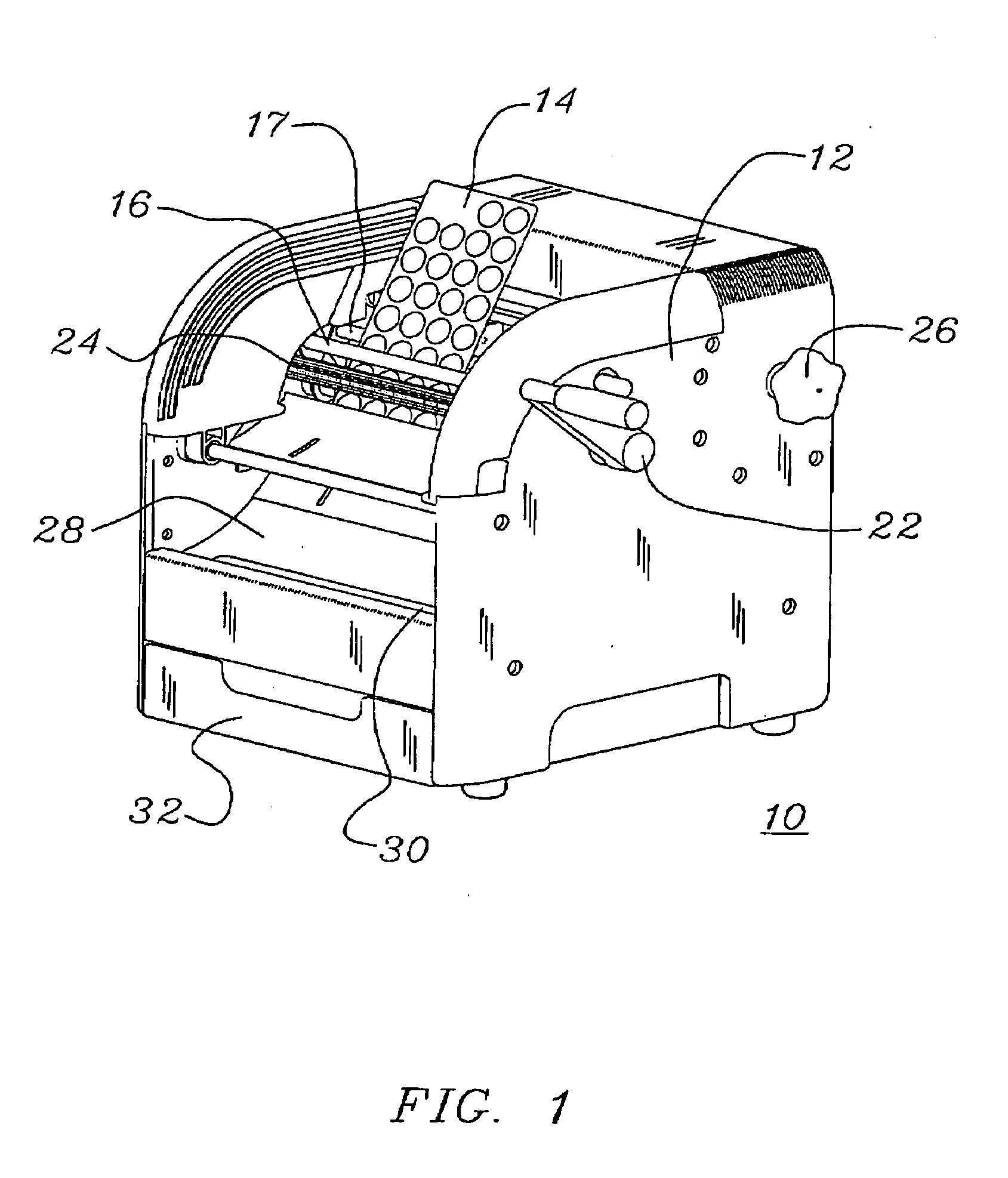

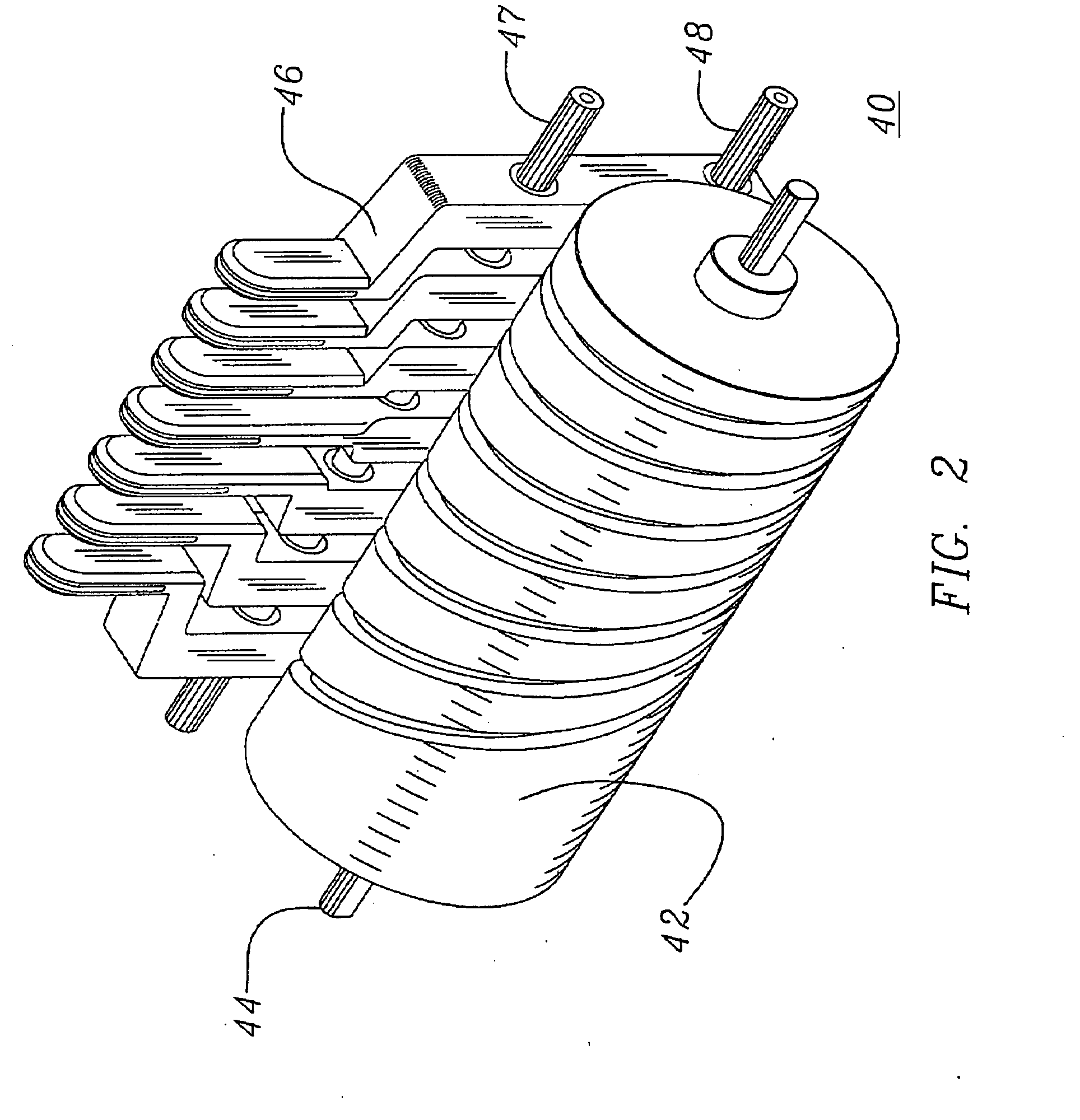

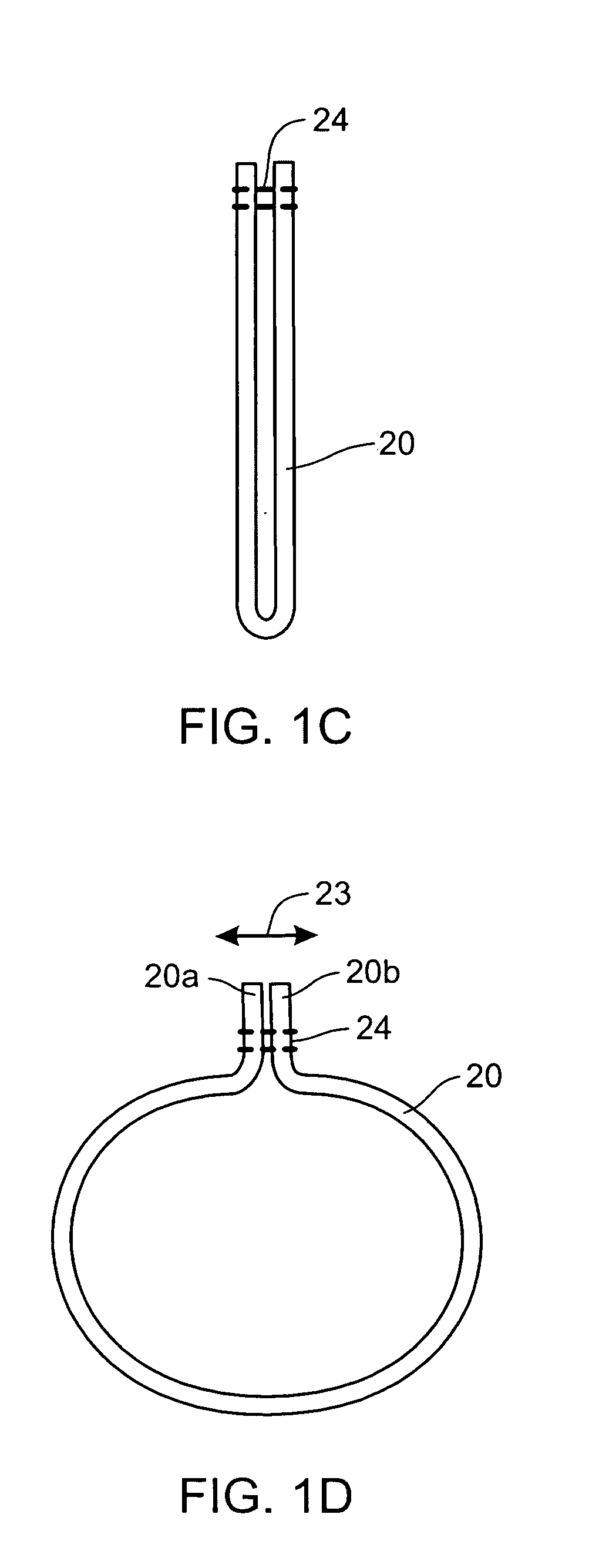

Systems and methods for removing medication from packaging

ActiveUS20080257904A1Easy to removeSmooth rotationSmall article dispensingRacksAutomatic controlIndividual dose

Improved solid pharmaceutical dispensing systems and methods provide direct transfer of doses from bulk blister packaging material. In a preferred embodiment, the invention comprises a positioning mechanism that alters the spacing between portions of a de-blister apparatus. The de-blister apparatus comprises a de-blister roller, cylinder or elongated cylindrical toothed gear which pushes against a first side of packaging material to remove individual doses from a conventional blister package. The apparatus may operate under manual or automatic control and preferably includes adjustable or movable package holding rollers which are preferably aligned with portions of packaging material between the rows of blister cavities at a side of the packaging material opposite the side at which the roller or cylinder is located. The de-blister apparatus enables the rapid removal of solid pharmaceutical or nutraceutical products from blister cavities and provides a convenient mechanism for altering the device in order to accommodate different sizes of packaging material.

Owner:MTS MEDICATION TECH

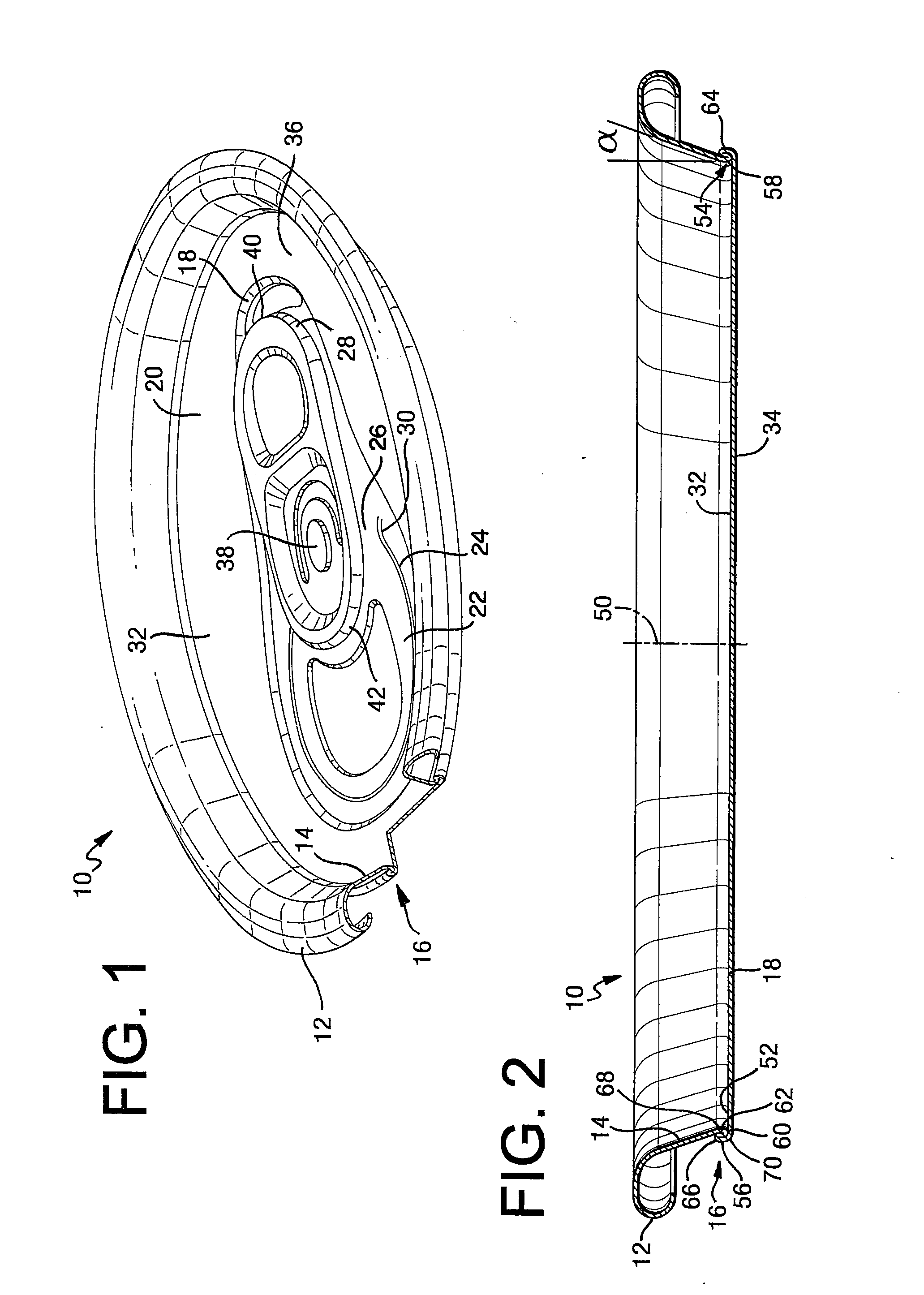

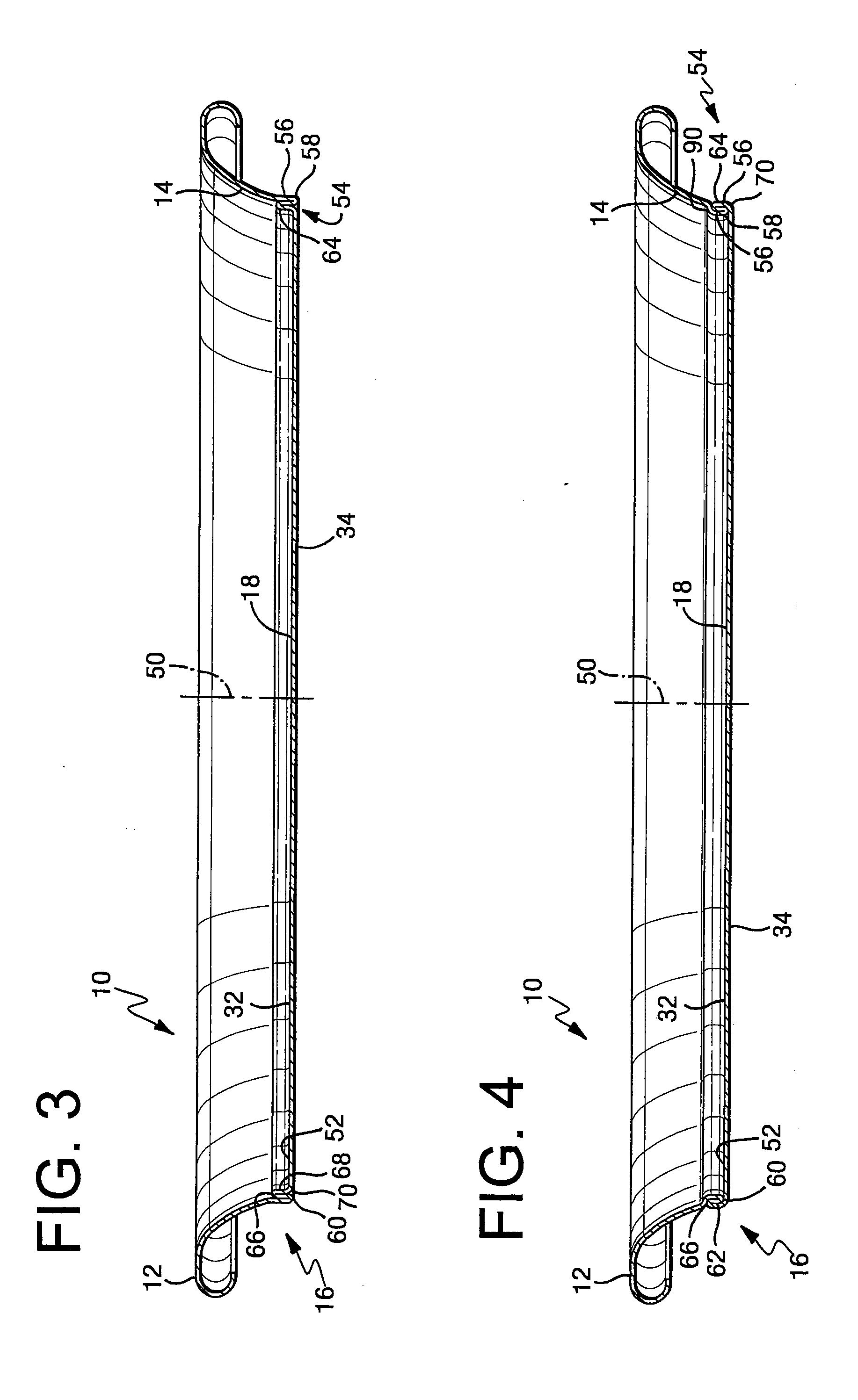

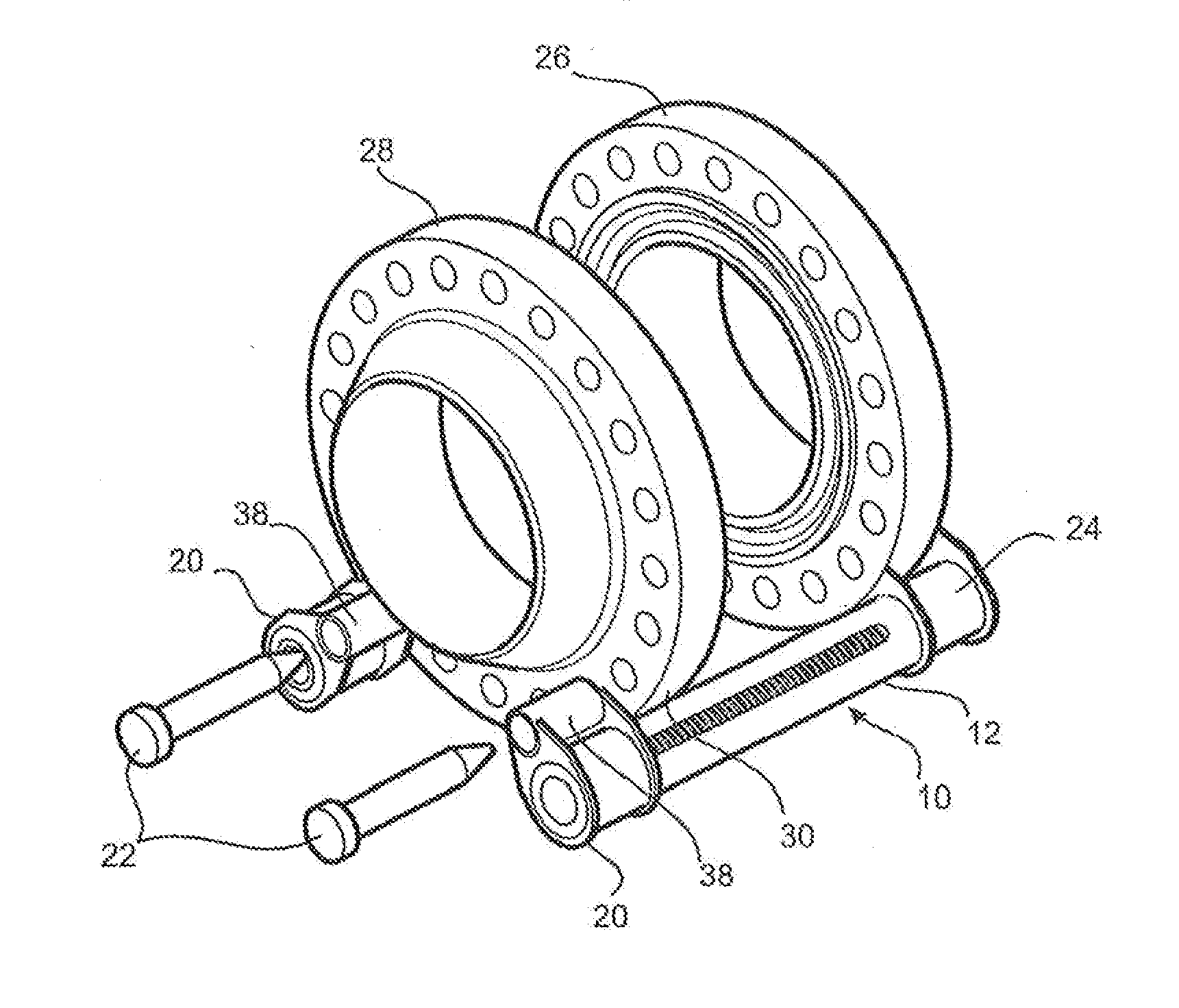

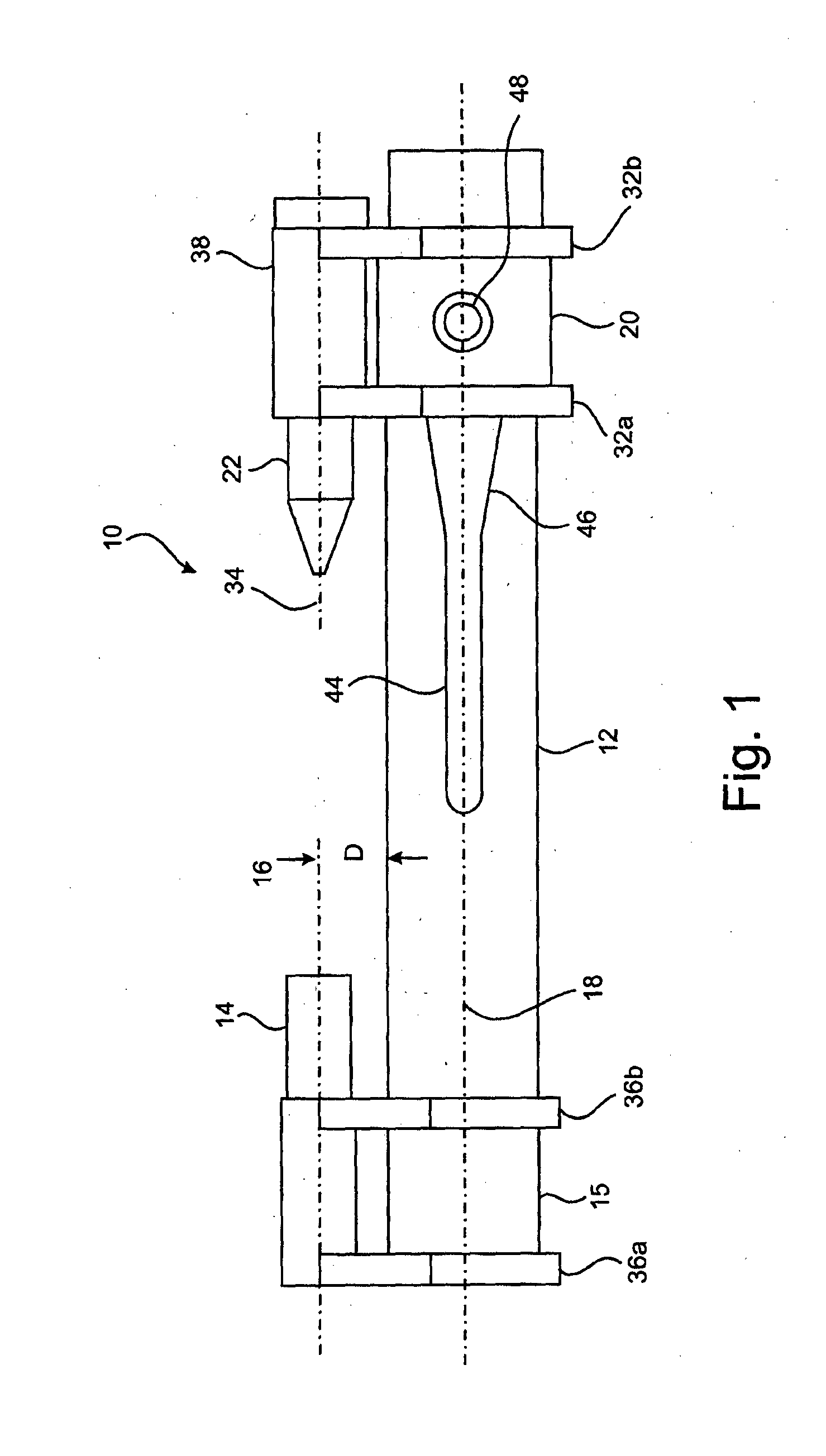

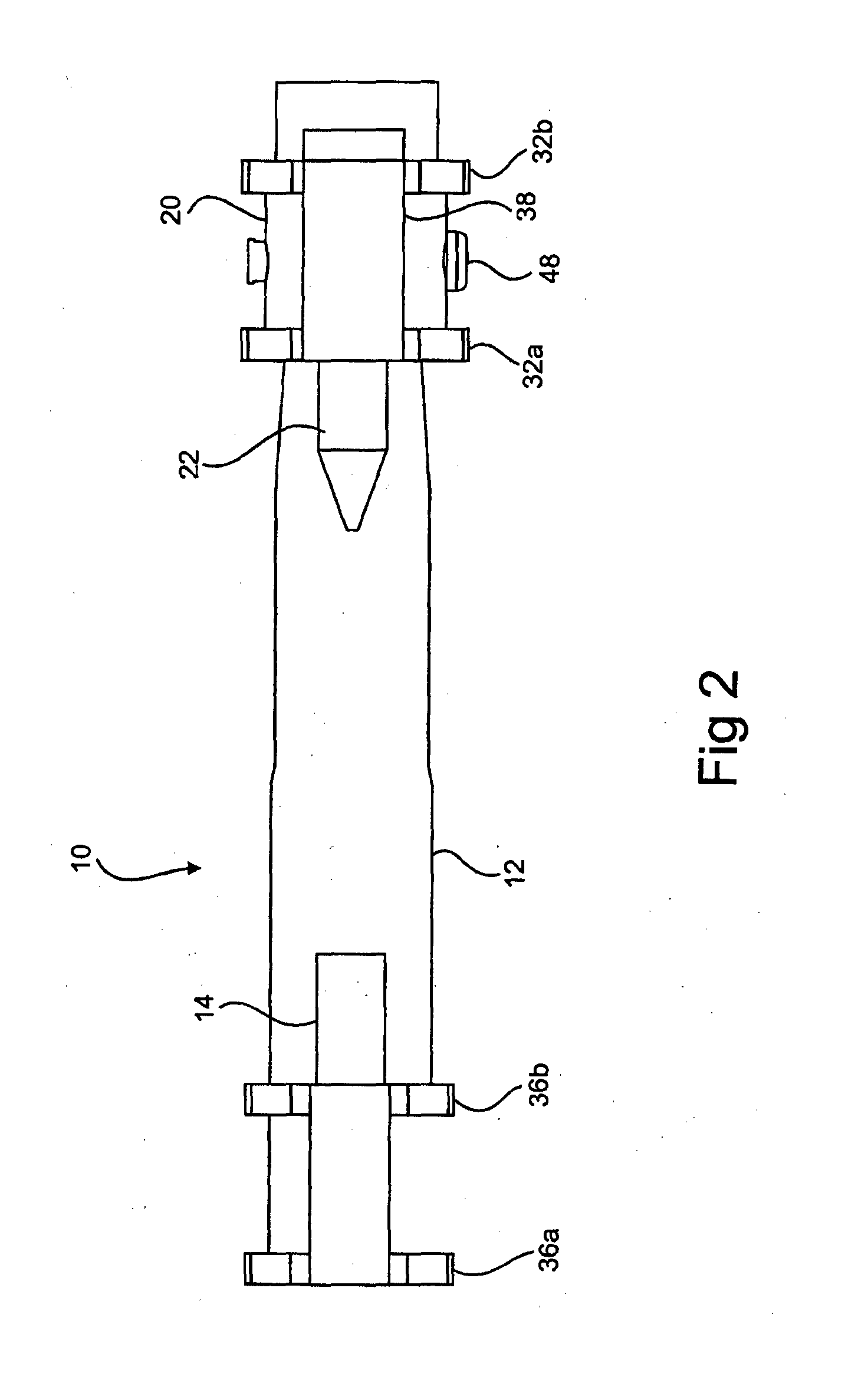

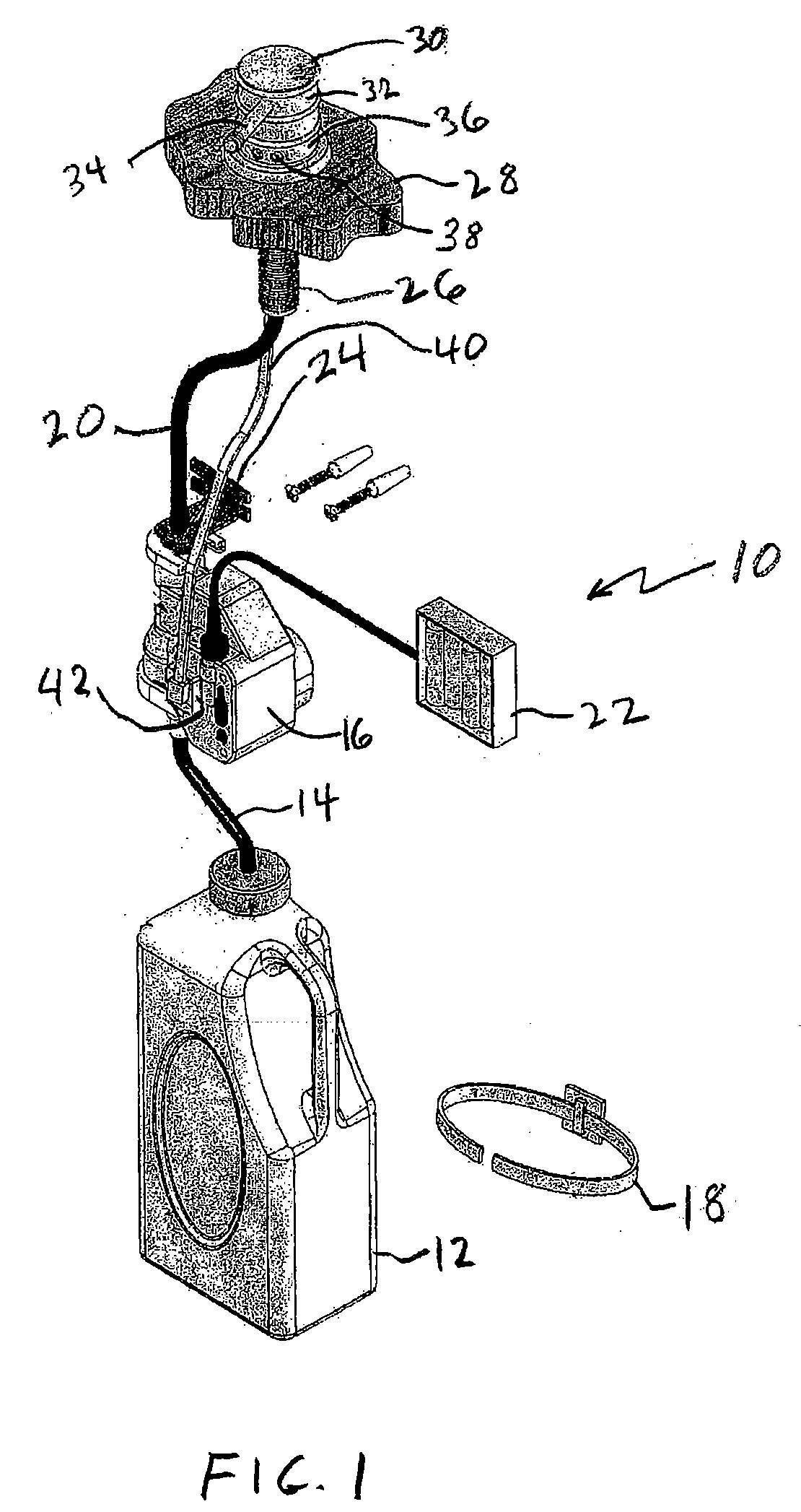

Flange catching, aligning and closing tool

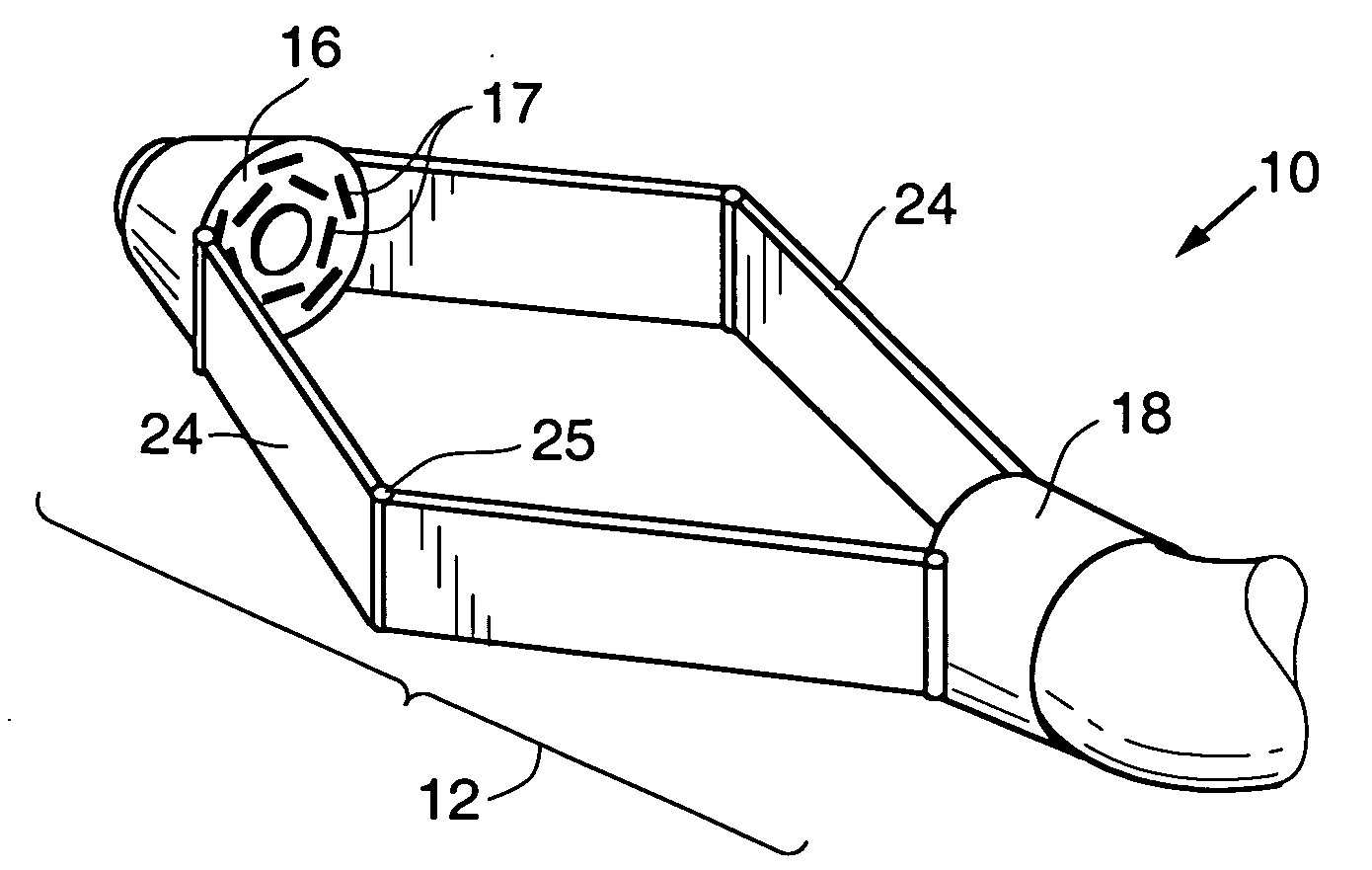

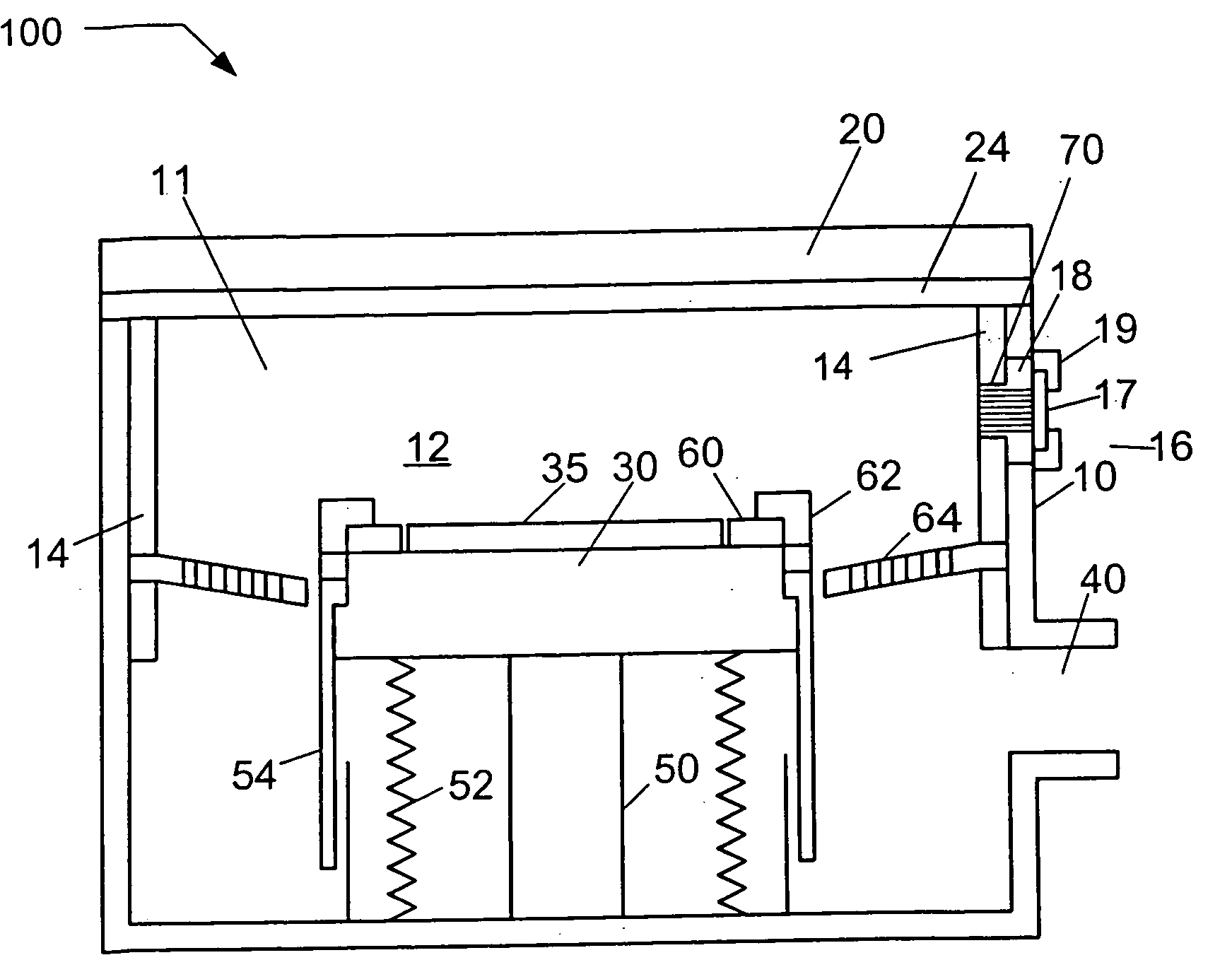

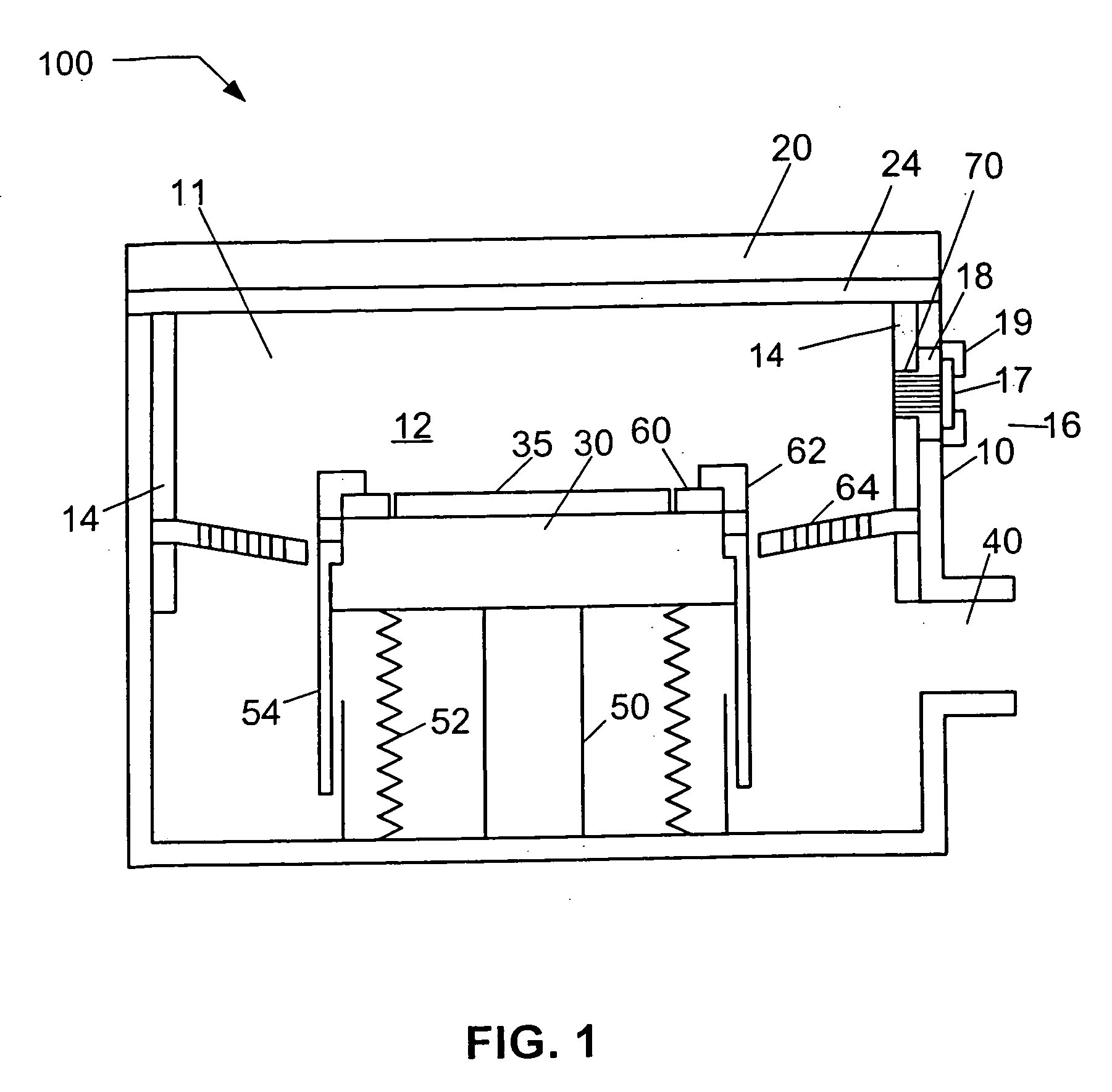

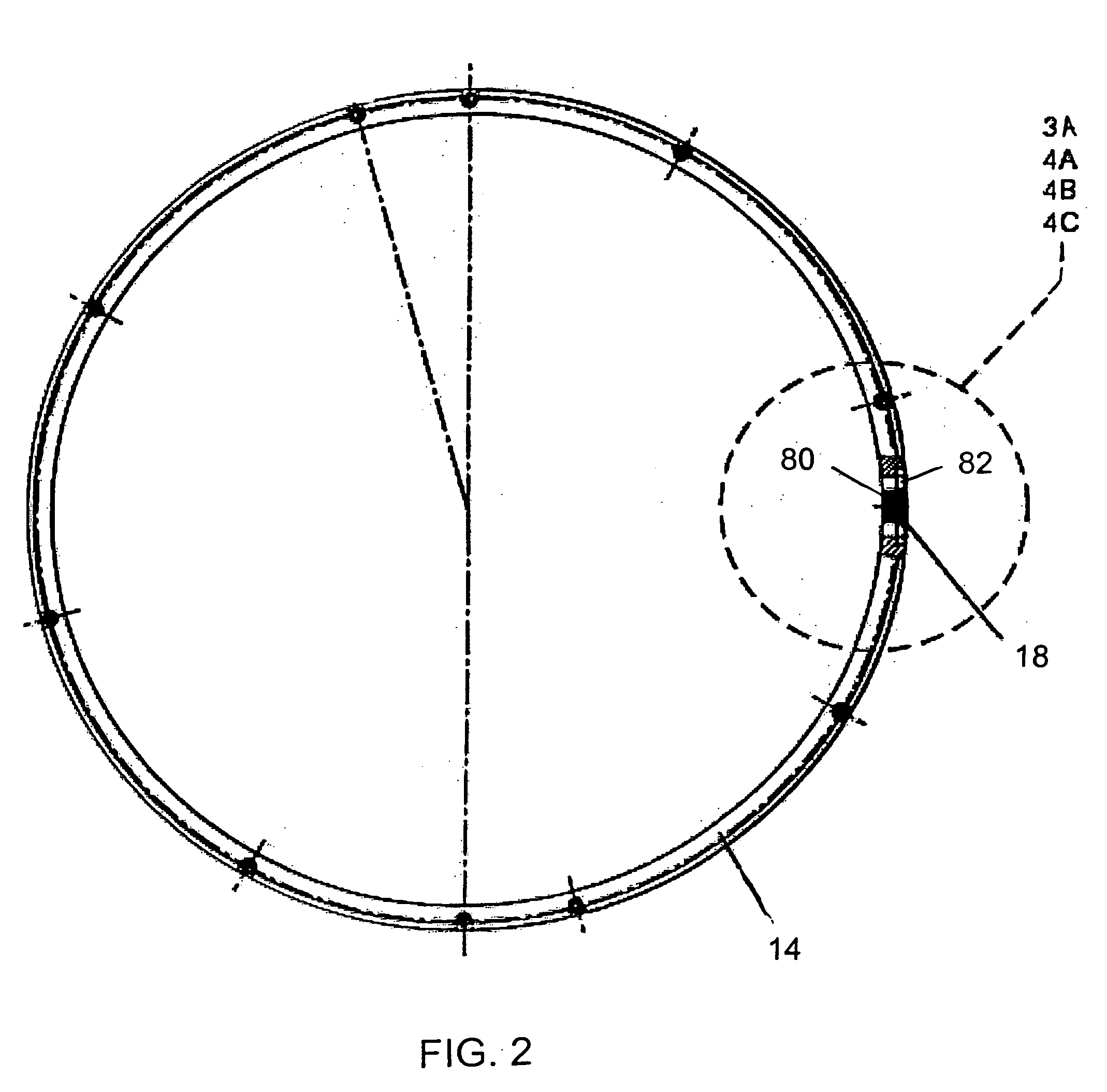

A flange catching, aligning and closing tool (10) designed to facilitate the tie-in of spools and other similar mechanical assemblies that utilise a bolted flange for installation, for example, in subsea pipelines. The tool (10) has an elongate support member (12) having a locating pin (14) mounted adjacent one end with its longitudinal axis (16) substantially parallel to a longitudinal axis (18) of the support member (12). A slide assembly (20) is slidably mounted on the support member (12) and has a movable drift pin (22) provided in connection therewith. In use, when the locating pin (14) is located in a bolt hole on a first flange, a second flange can be brought into partial alignment with the first flange by engaging with the support member (12), and the drift pin (22) can be inserted in a matching bolt hole in the second flange to bring the two flanges into full alignment.

Owner:OSPREY SUBSEA TECHN SOLUTIONS OSTS

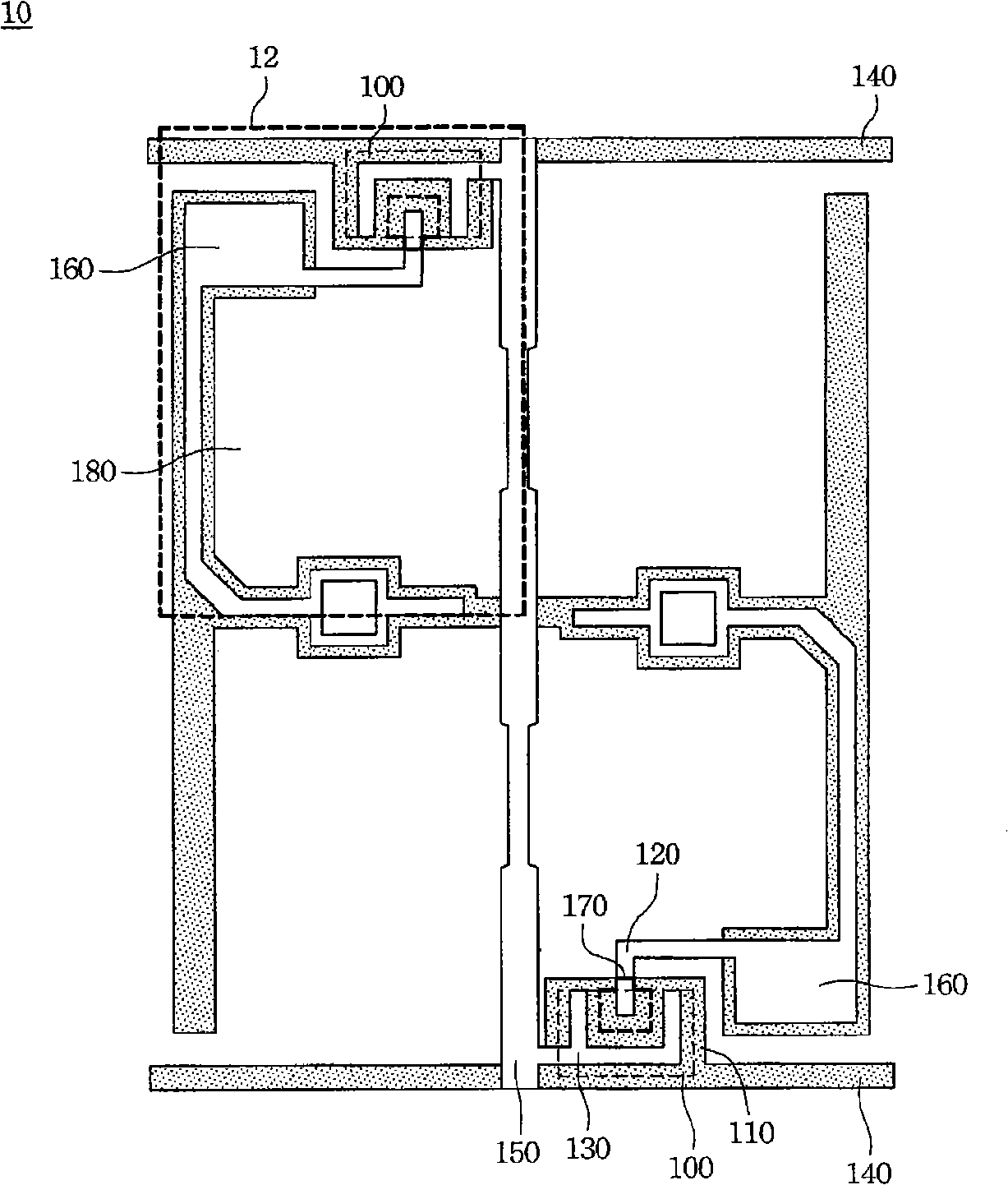

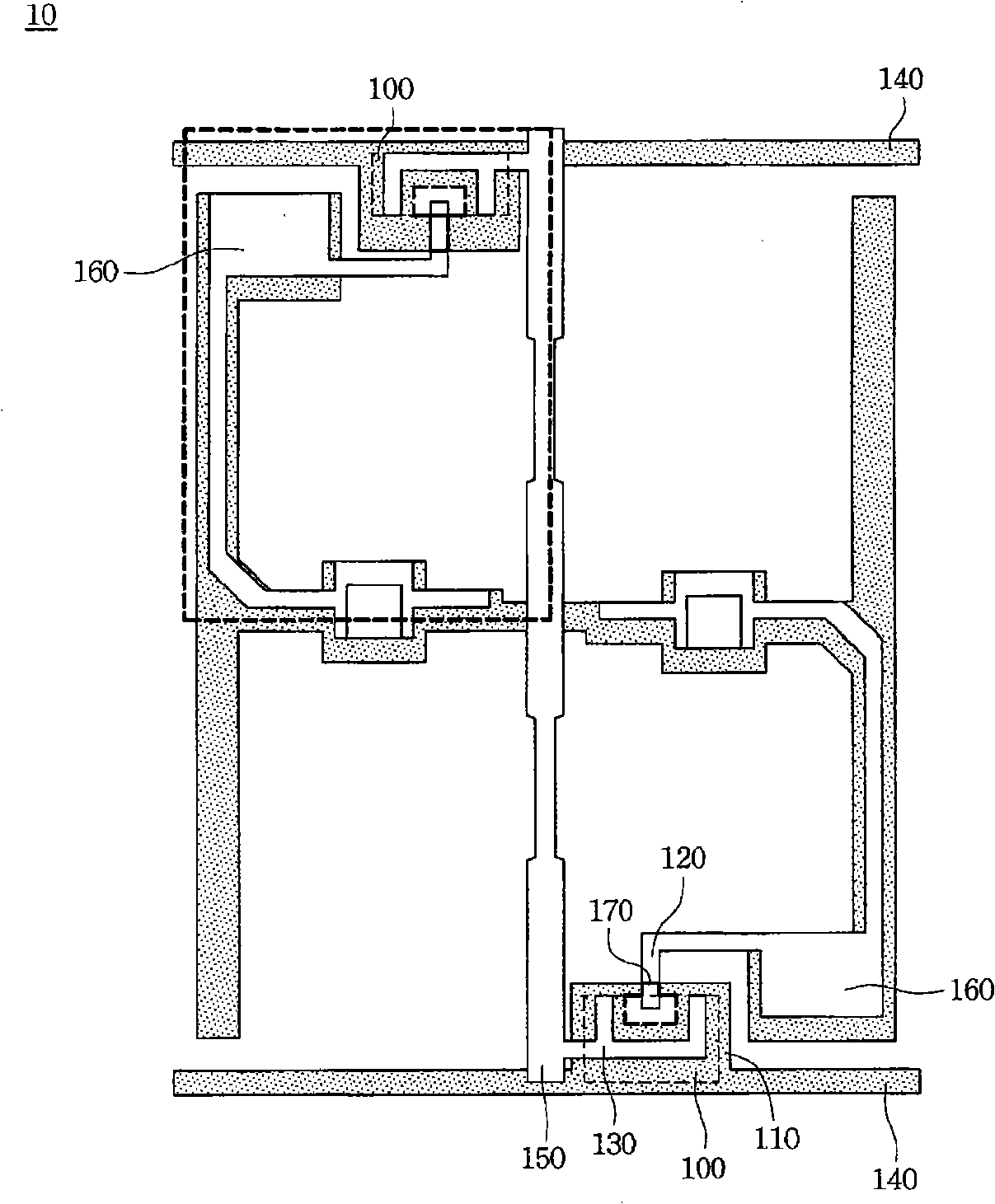

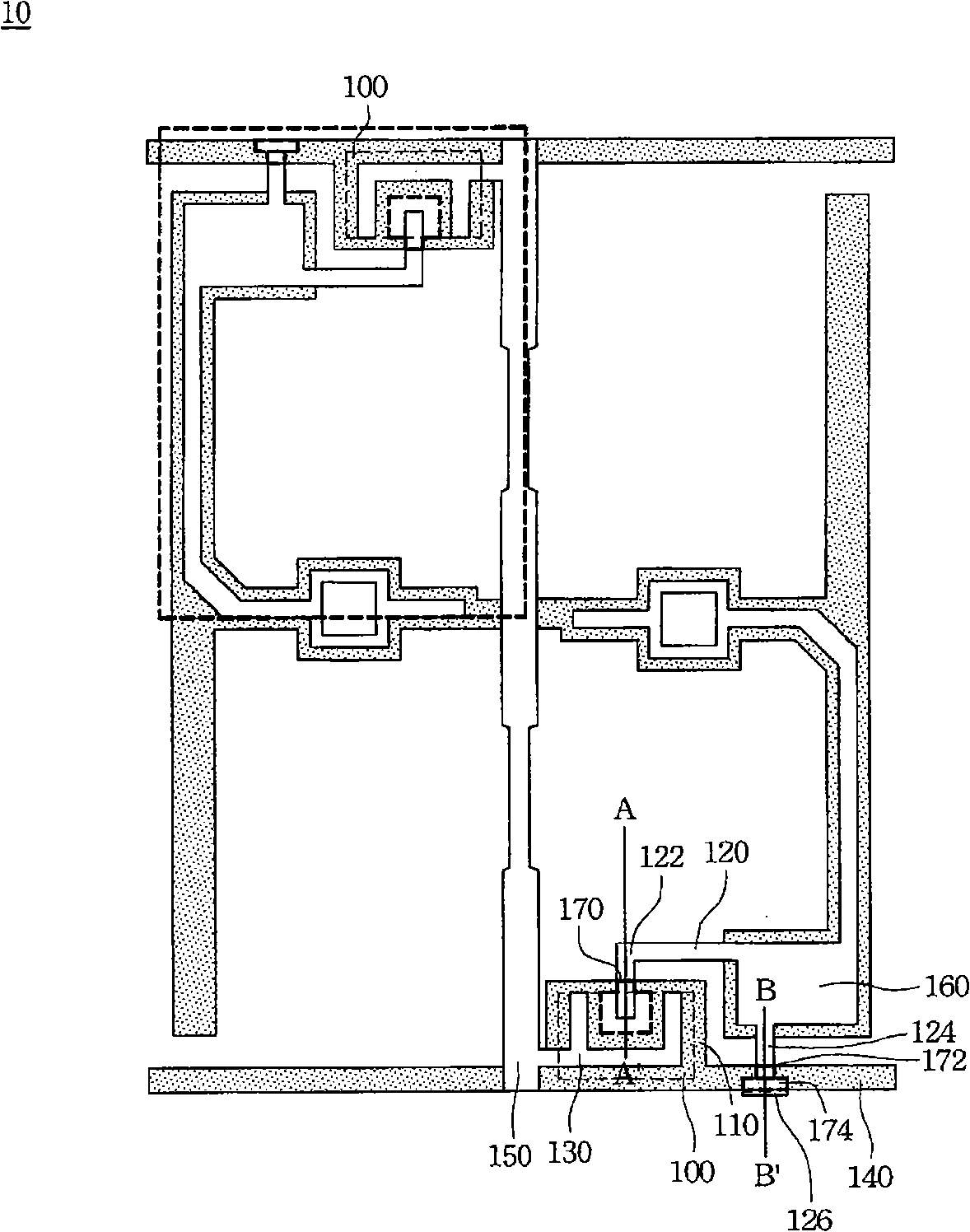

Pixel construction and thin-film transistor thereof

InactiveCN101359692AConstant feedthrough voltageTransistorSemiconductor/solid-state device detailsSpurlineLine width

The invention discloses a pixel structure and a thin-film transistor. A grid connecting scanning line of the thin-film transistor is arranged at one surface of an insulating layer, and a semiconductor layer, a source electrode and a drain electrode are arranged at the other surface of the insulating layer. The source electrode is connected with a data line and the semiconductor layer. The first branch of the drain electrode is connected with the semiconductor layer and is partially aligned and superposed with the grid so as to induce parasitic capacitance. The second branch and the first branch of the drain electrode extend in the same direction and perpendicularly go across from above the scanning line. The second branch is partially aligned and superposed with the scanning line so as to induce a first compensation capacitance. A compensation electrode is connected with the second branch and is partially vertically arranged above the scanning line so as to induce a second compensation capacitance. The width of the line of compensation electrode is the total of the widths of the lines of first and second branches, so that the total of the parasitic capacitance, the first compensation capacitance and the second compensation capacitance is constant. The invention provides a pixel structure and a thin-film transistor and can solve the problem of uneven feed-through voltage due to displacement deviation of the two metal layers.

Owner:AU OPTRONICS CORP

Heater chips with silicon die bonded on silicon substrate and methods of fabricating the heater chips

InactiveUS20090256891A1Reduce necessityAvoid loopsWriting implementsMetal-working apparatusPartial alignmentDying back

A heater chip has a substrate and at least one die, made of silicon, and a bond non-adhesively attaching them. The substrate, thick enough to resist bowing, has ink supply vias from back to front surfaces. The die has ink flow vias from back to front surfaces and circuitry including heater elements adjacent the front surface interspersed with ink flow vias. The at least one die is superimposed on the substrate such that ink supply vias of the substrate align with ink flow vias of the die and portions of substrate front surface and die back surface are aligned, disposed adjacent and facing one another. The bond formed between substrate and die facing surface portions is hermetic and equal in strength to a Si—O bond. By separate processing of carrier and device wafers, size and features of substrate and die can be tailored to provide a desired heater chip construction.

Owner:FUNAI ELECTRIC CO LTD

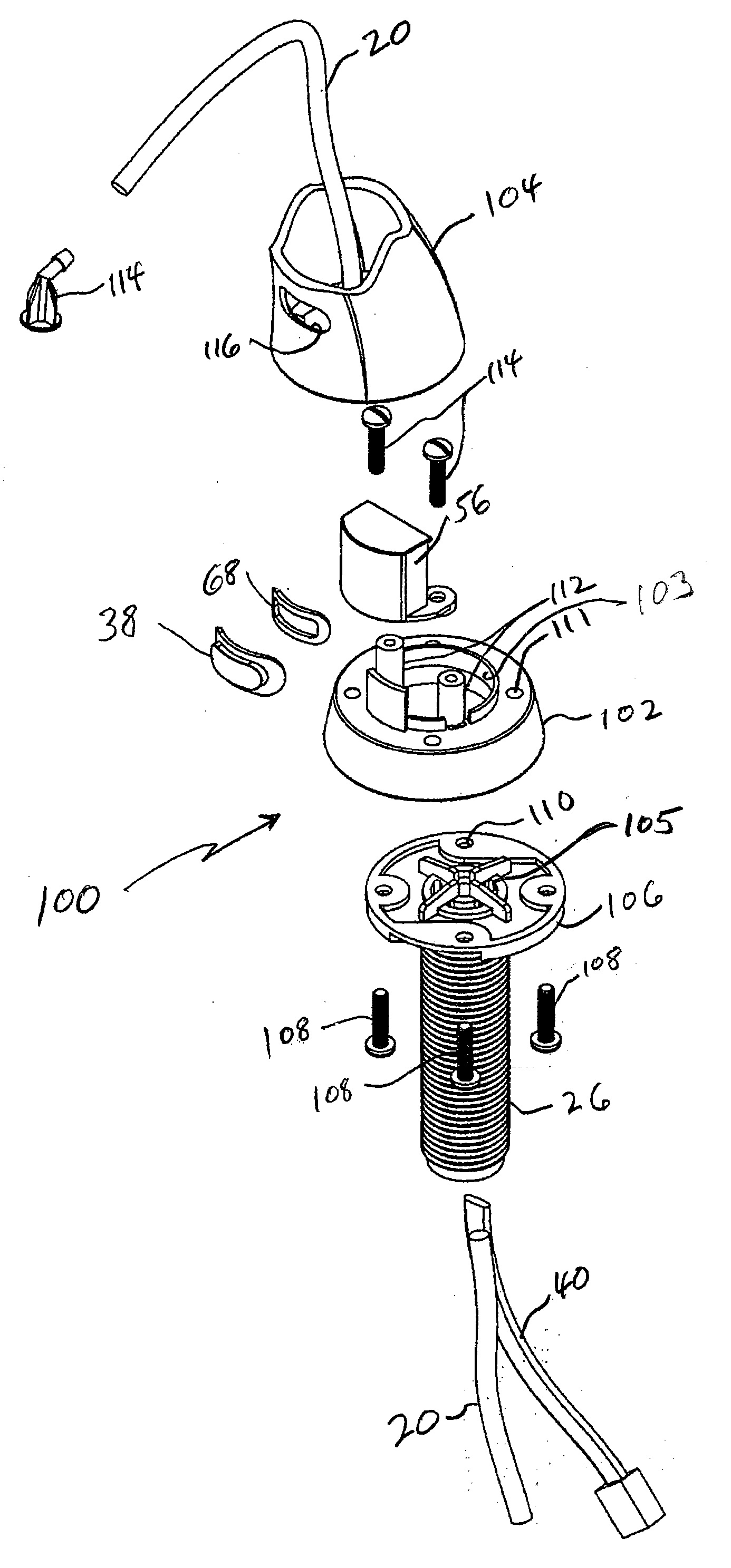

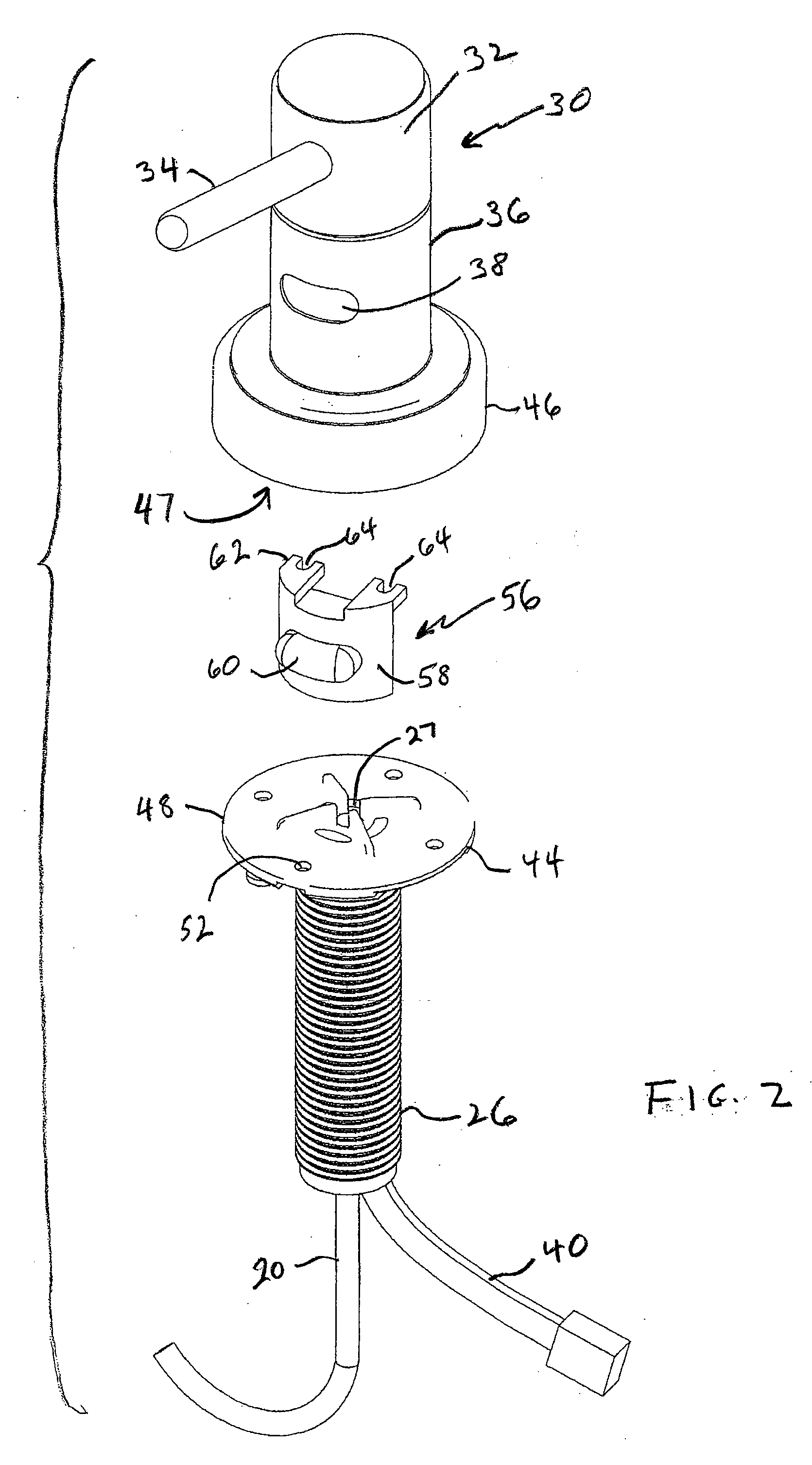

Universal hub for a fluid dispenser

InactiveUS20070187427A1Domestic plumbingHolders and dispensersBiomedical engineeringPartial alignment

A removable and replaceable dispensing head for a fluid dispenser system adapted to deliver the fluid to a user includes a hollow shank extending on an axis. A shank hub is attached to the hollow shank, and an aperture aligned with the hollow portion of the shank extends through the shank hub. A first fixed body is removably attached to the shank hub, the first fixed body and shank hub each having corresponding first attachment means arrayed in a predetermined pattern. A fluid conveyance path is provided through the hollow shank, first fixed body and shank hub. A second fixed body is provided having a second attachment means arrayed in the same predetermined pattern, the second attachment means corresponding to the first attachment means in the shank hub enabling removable attachment of the second fixed body to the shank hub upon removal of the first fixed body from the shank hub. A sensor attached to either the fixed body, or to a hub spacer connected to the shank hub, automatically detects the presence of a user and activates the fluid dispensing system.

Owner:TECHN CONCEPTS

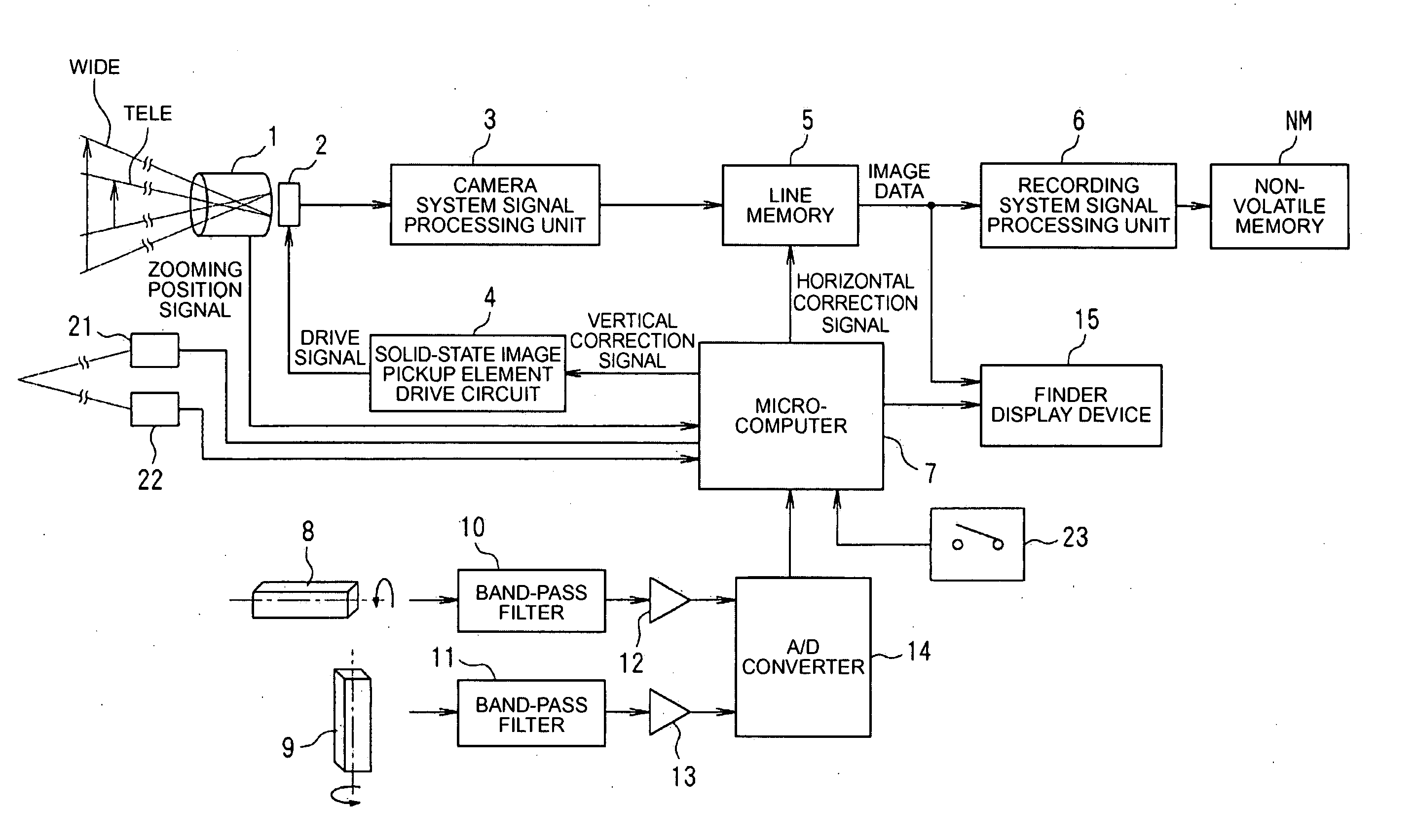

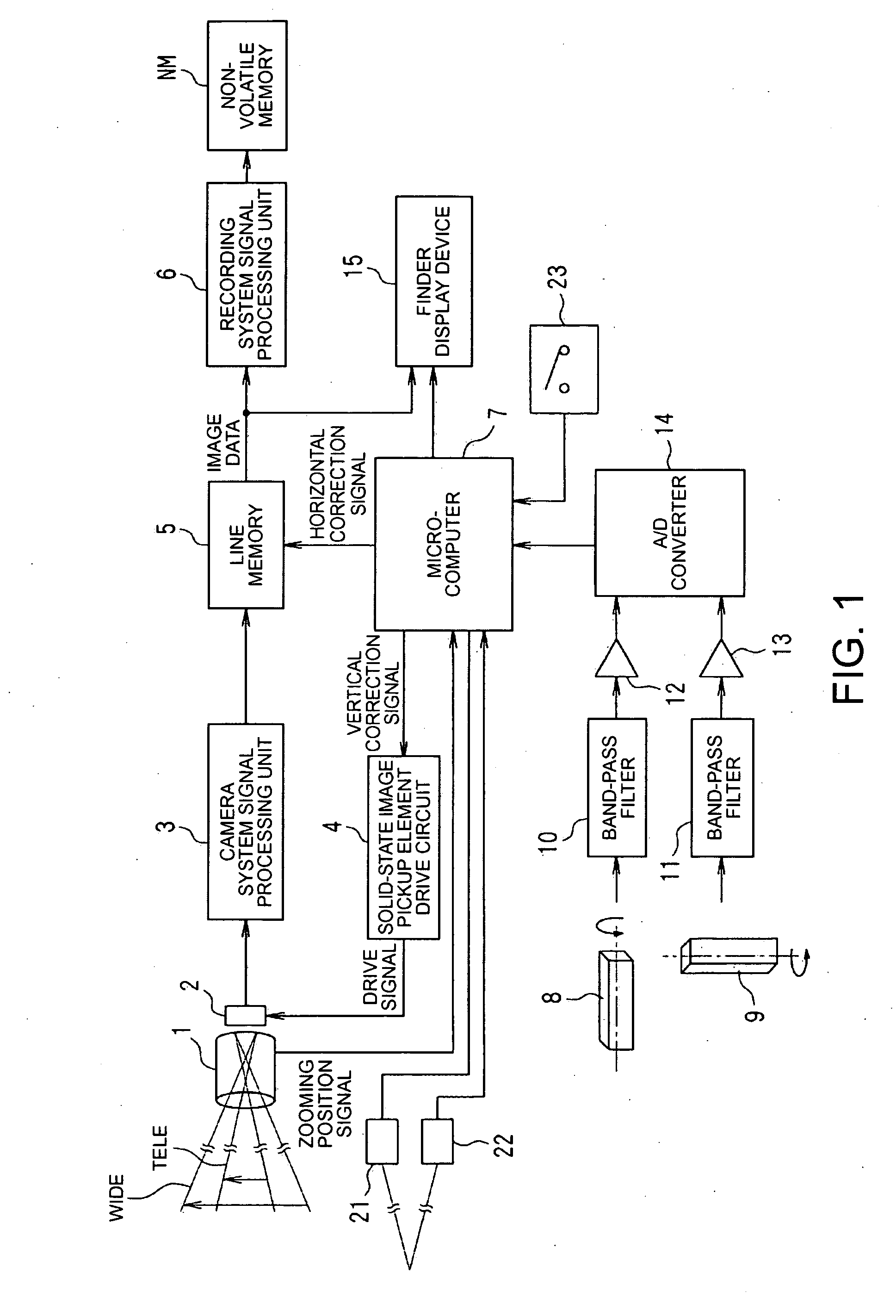

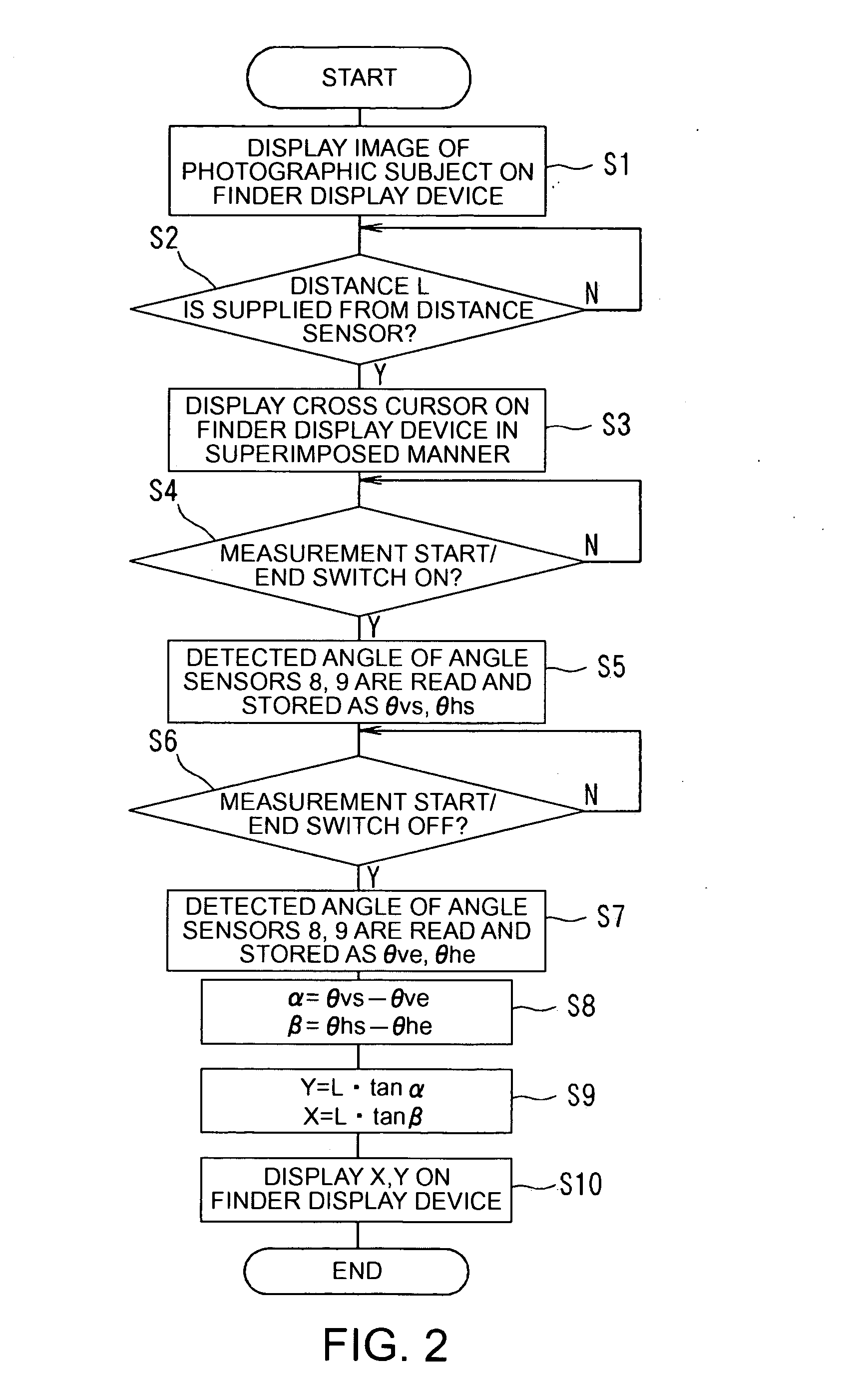

Still image pickup device

InactiveUS20060187333A1Easy to operateEasy linear movementTelevision system detailsColor television detailsPartial alignmentImaging data

An image pickup device includes: image pickup means that opposes correctly to a photographic subject, and forms and picks up an image of the same; display means that displays an image data picked up by the image pickup means; distance measuring means that measures a distance to the photographic subject to be picked up by the image pickup means; index display means that displays an index on the display means so as to be superimposed on the image data; angle of inclination measuring means that measures an angle of inclination of the image pickup means when it is inclined so as to align the index displayed by the index display means with a desired portion to be measured; and actual dimension calculating means that calculates actual dimensions of an image of the photographic subject on the basis of a measurement of the distance measuring means and a measurement of the angle of inclination measuring means.

Owner:SEIKO EPSON CORP

Textile gas guide for inflatable curtain

ActiveUS20090295134A1Increase pressureLow costLayered productsPedestrian/occupant safety arrangementThroatLeading edge

A textile gas guide may include a fabric member which may include an obverse side, a reverse side, a leading edge, and a trailing edge. The fabric member may overlap upon itself at least once such that at least a portion of the obverse side adjacent the leading edge may be disposed to align with at least a portion of the reverse side adjacent the trailing edge to define an overlapping region. A first seam may be sewn through the overlapping region, the first seam being in shear stress when the airbag module is inflated. An airbag module may include the above textile gas guide and an airbag cushion including an inflation throat. At least a portion of the textile gas guide may be located within the inflation throat. An inflator may be inserted into the textile gas guide.

Owner:AUTOLIV ASP INC

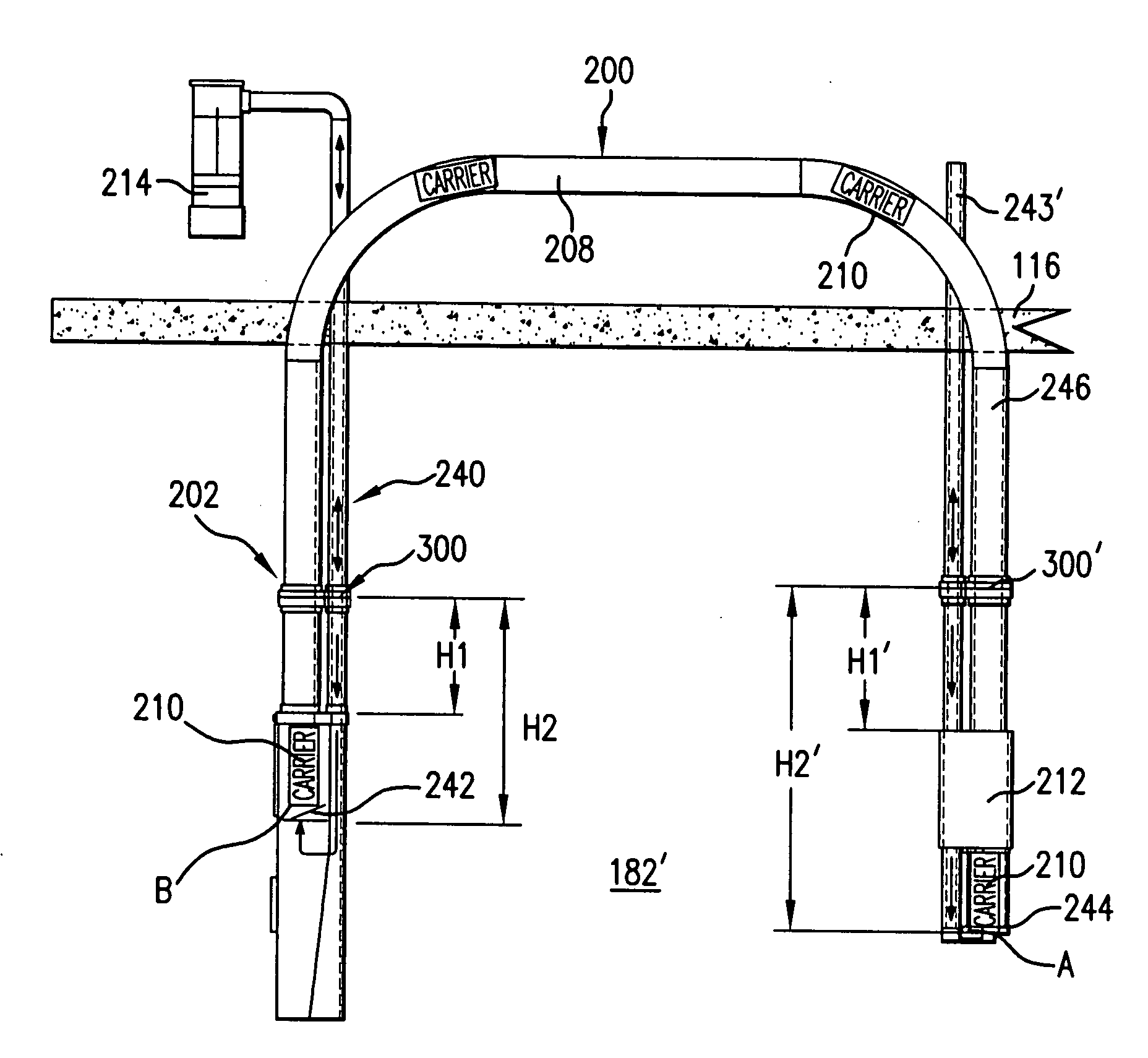

Carrier transportation system with brake valve device proximate to a carrier receiver

InactiveUS20080298906A1Shorter braking distanceReduce transportationBulk conveyorsTransfer systemPartial alignment

A transfer system for a carrier that features a flow supply tube in fluid communication with a flow supply generator and in fluid communication with a carrier transport tube network dimensioned for transfer reception of the carrier. The carrier transport tube network has a first carrier reception chamber provided with a first carrier stop point and a second carrier reception chamber with second carrier stop point. The flow supply tube has a single point contact with the carrier transport tube network to provide a single tube based flow connection with the carrier transport. Also, with the single point connection there can be positioned a brake valve in line with a first section of the carrier transport tube network and in line with a first section of said flow supply tube just a few feet above the stop point of one or both of the reception chambers to provide for rapid travel to the brake valve and efficient braking within just a few feet of the stop point.

Owner:HAMILTON AIR PRODS

Interconnection structure with etch stop

InactiveUS6933813B2Insulating substrate metal adhesion improvementSemiconductor/solid-state device detailsAdhesivePartial alignment

An interconnection structure includes: a dielectric layer; a first metallization pattern on the dielectric layer, the first metallization pattern including at least one etch stop having a perimeter defining at least one etch stop opening; a cured adhesive on a portion of the dielectric layer, the adhesive not present in an area aligned with the at least one etch stop; and at least one electrical device being attached to the dielectric layer by the adhesive such that an active area of the at least one electrical device is aligned with the etch stop perimeter. The active area of the at least one electrical device may further be aligned with at least one predetermined area defined by an optional additional portion of cured adhesive, the additional portion of the cured adhesive being adhesively attached to the dielectric layer and not adhesively attached to the at least one electrical device.

Owner:GENERAL ELECTRIC CO

Pluggable module

ActiveUS9210817B2Closed casingsCoupling device detailsPartial alignmentElectrical and Electronics engineering

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

Honeycomb optical window deposition shield and method for a plasma processing system

InactiveUS20050225248A1Minimizes frequency of maintenanceMinimize frequencyLiquid surface applicatorsDecorative surface effectsPartial alignmentEngineering

An optical window deposition shield including a backing plate having a through hole, and a honeycomb structure having a plurality of adjacent cells configured to allow optical viewing through the honeycomb structure. Each cell of the honeycomb structure has an aspect ratio of length to diameter sufficient to impede a processing plasma from traveling through the full length of the cell. A coupling device configured to couple the honeycomb core structure to the backing plate such that the honeycomb structure is aligned with at least a portion of the through hole in the backing plate. The optical window deposition shield shields the optical viewing window of a plasma processing apparatus from contact with the plasma.

Owner:TOKYO ELECTRON LTD