Patents

Literature

137results about How to "Minimize frequency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

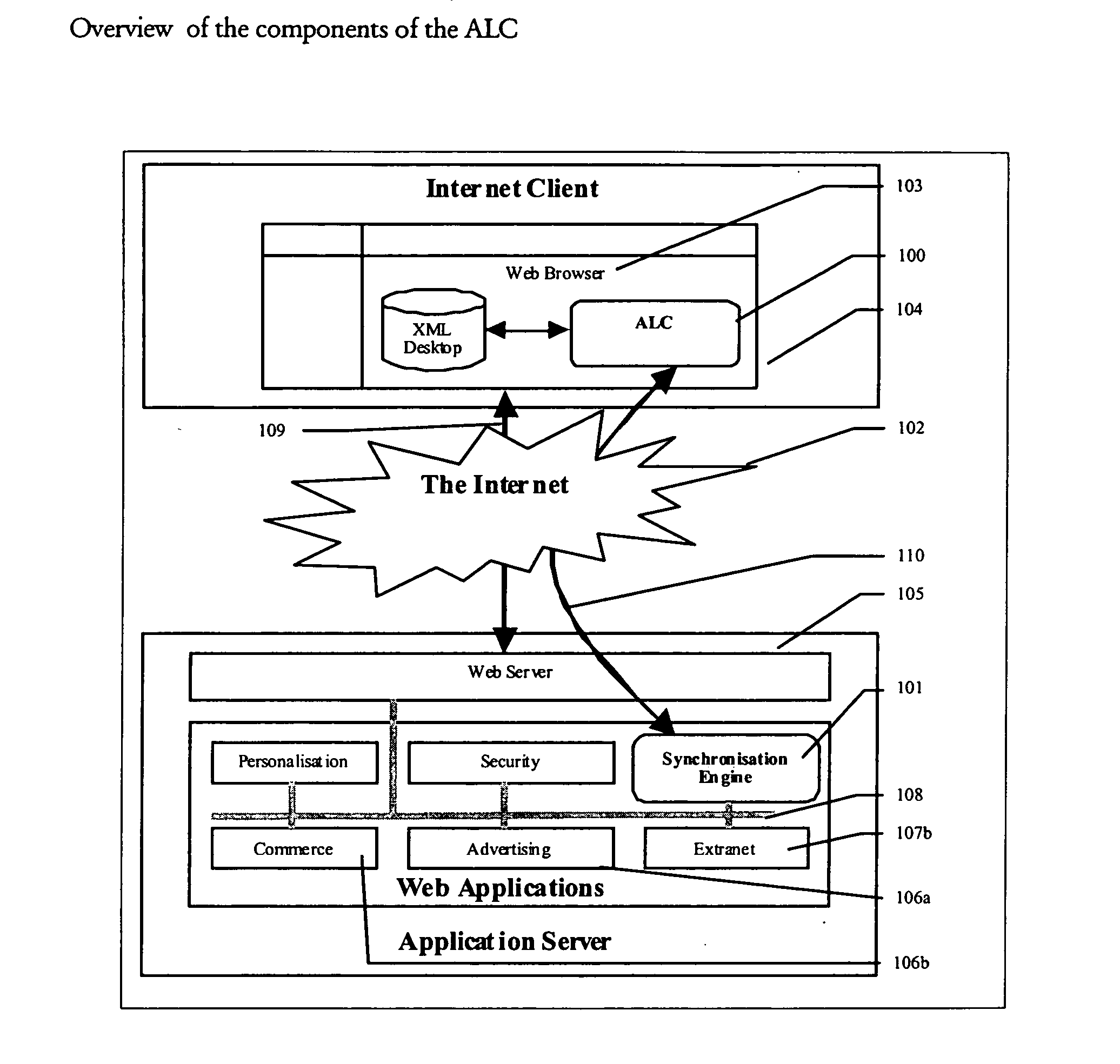

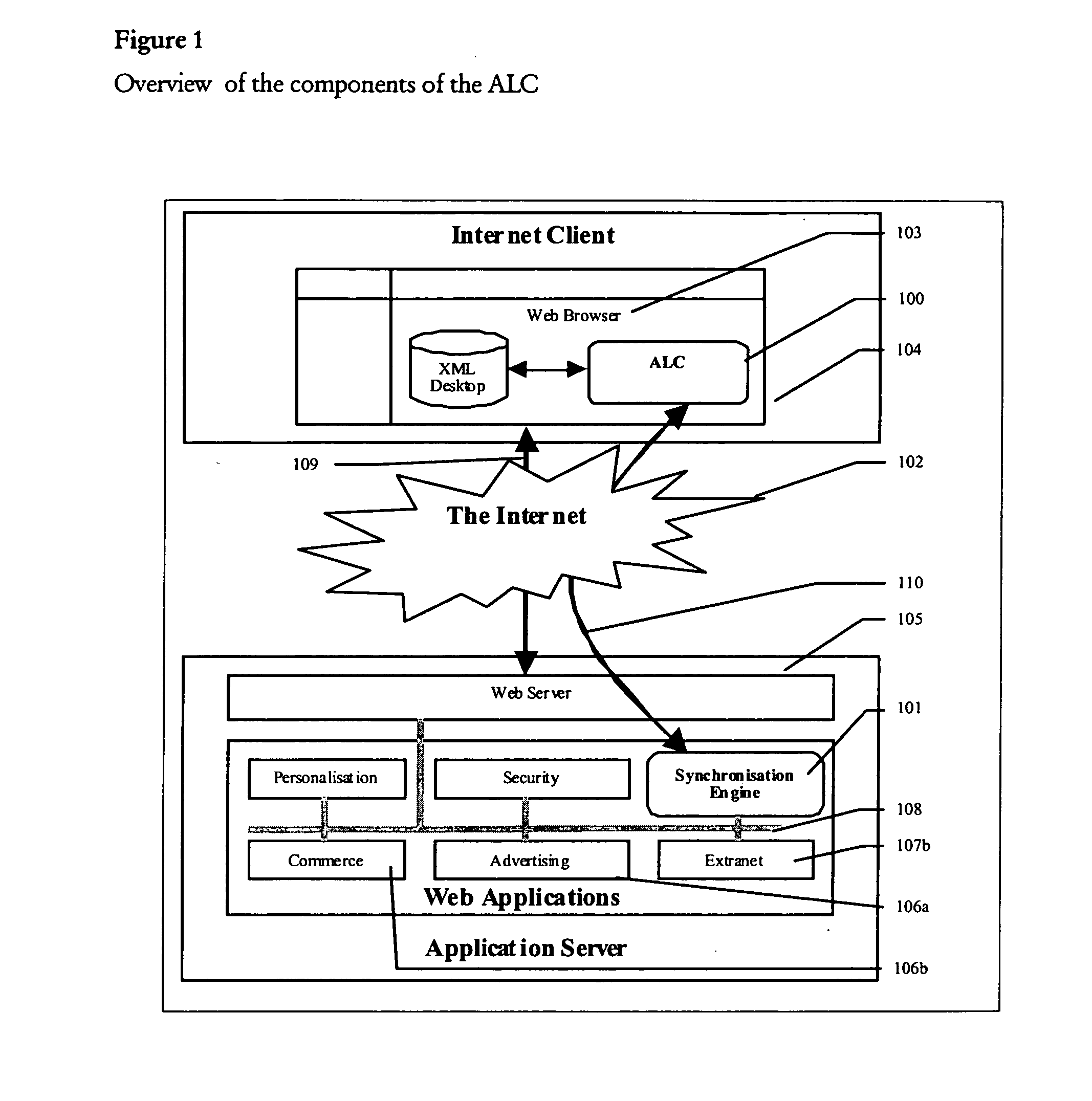

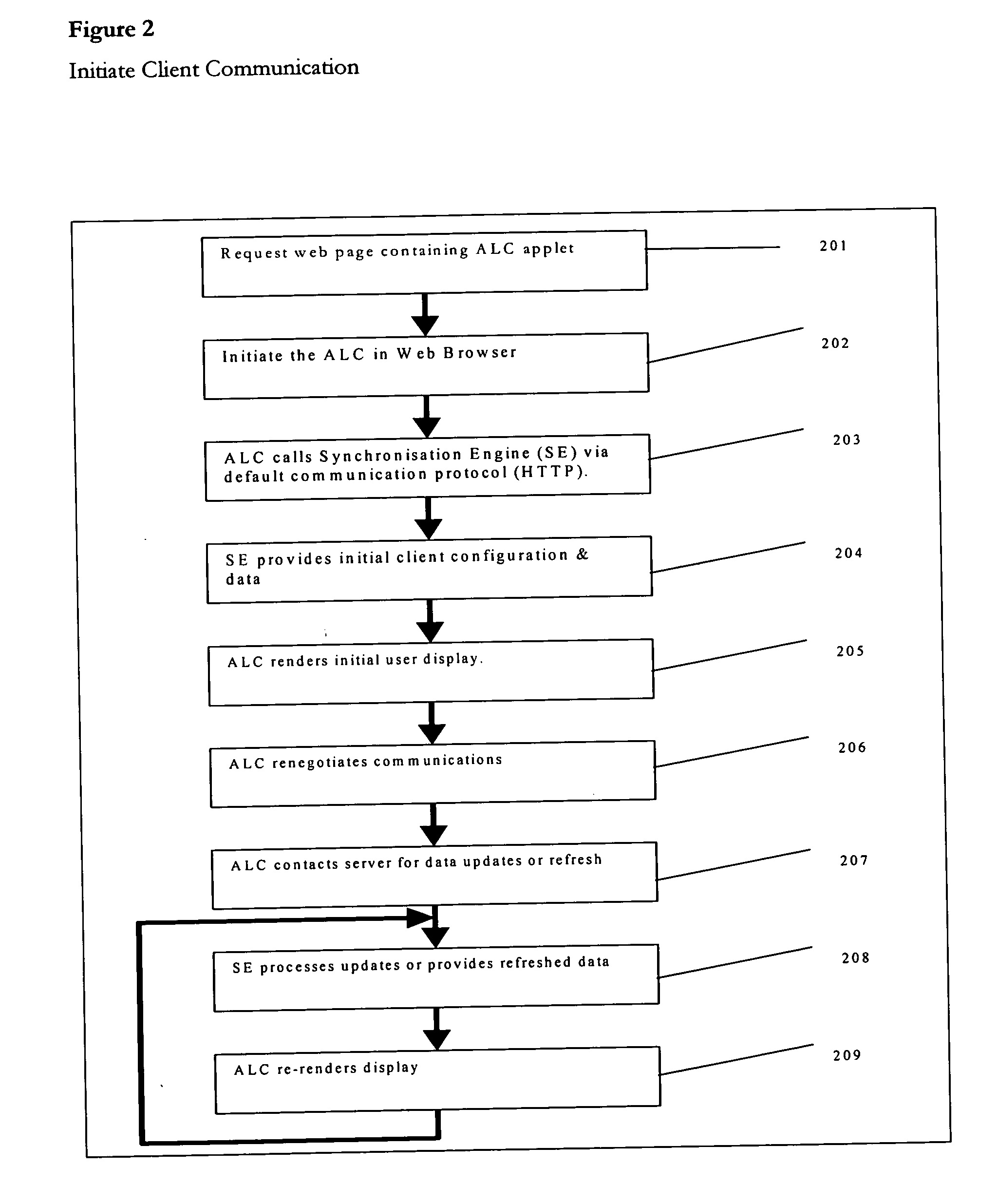

Client software enabling a client to run a network based application

InactiveUS20040117439A1Lower latencyMaximize rangeMultiprogramming arrangementsMultiple digital computer combinationsClient-sideApplication software

Client software, enabling a client to run a network based application which uses structured data, in which the client software comprises: (a) a communication layer to send and receive messages over the network; (b) a database layer to store, and allow querying of, the structured data; (c) a rendering layer which generates, from the structured data in the database layer, data for a user interface; wherein the client software is self-contained to provide all of the communications, data storage and rendering resources needed to run the network based application on the client device. The 3 Layer System is fully integrated and therefore requires no additional client side code to be written. Normally, this level of self-containment on the client side does not exist, so that a developer wishing to deploy a network based application to a client device needs to write client side custom code for the user interface.

Owner:INTEGRA

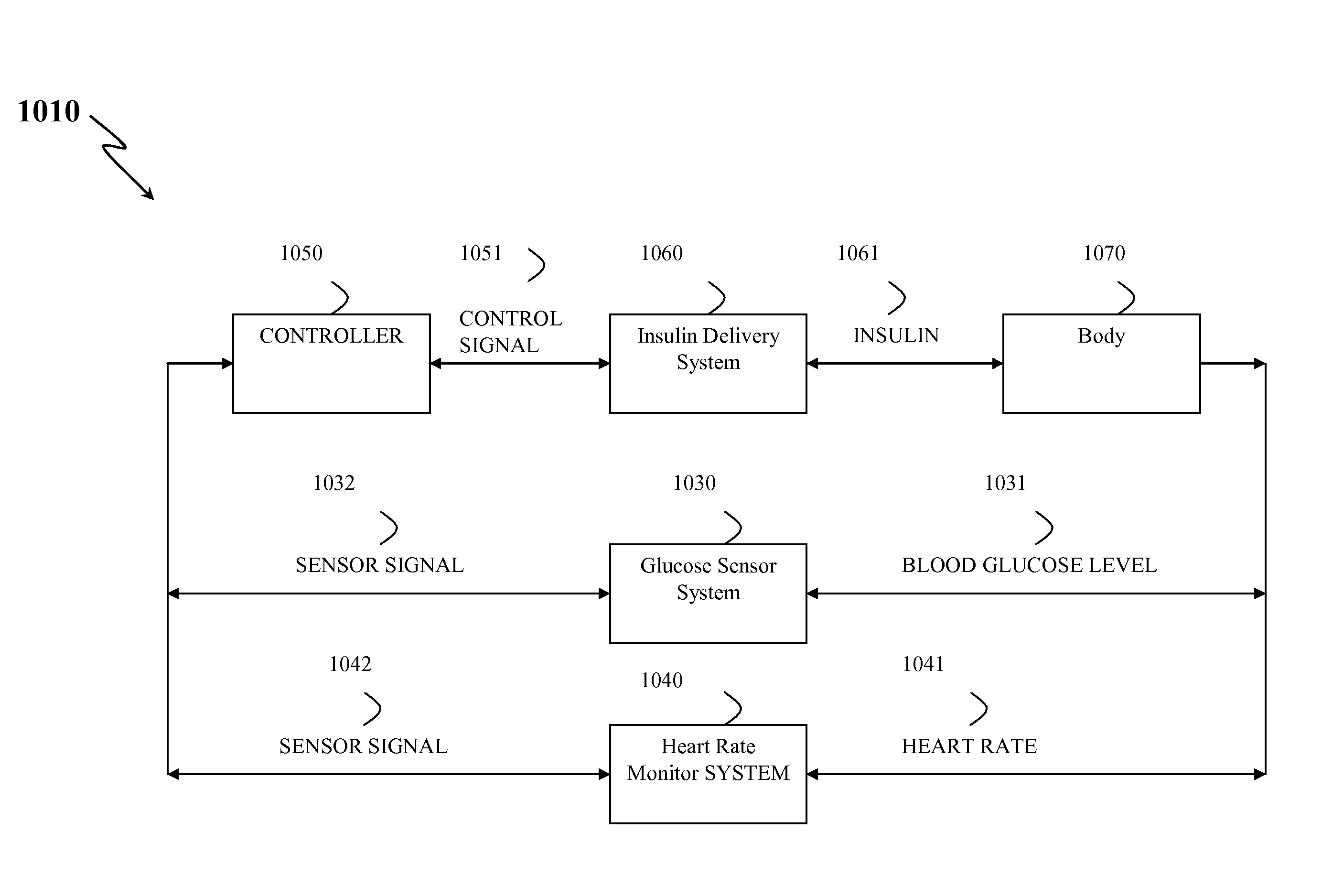

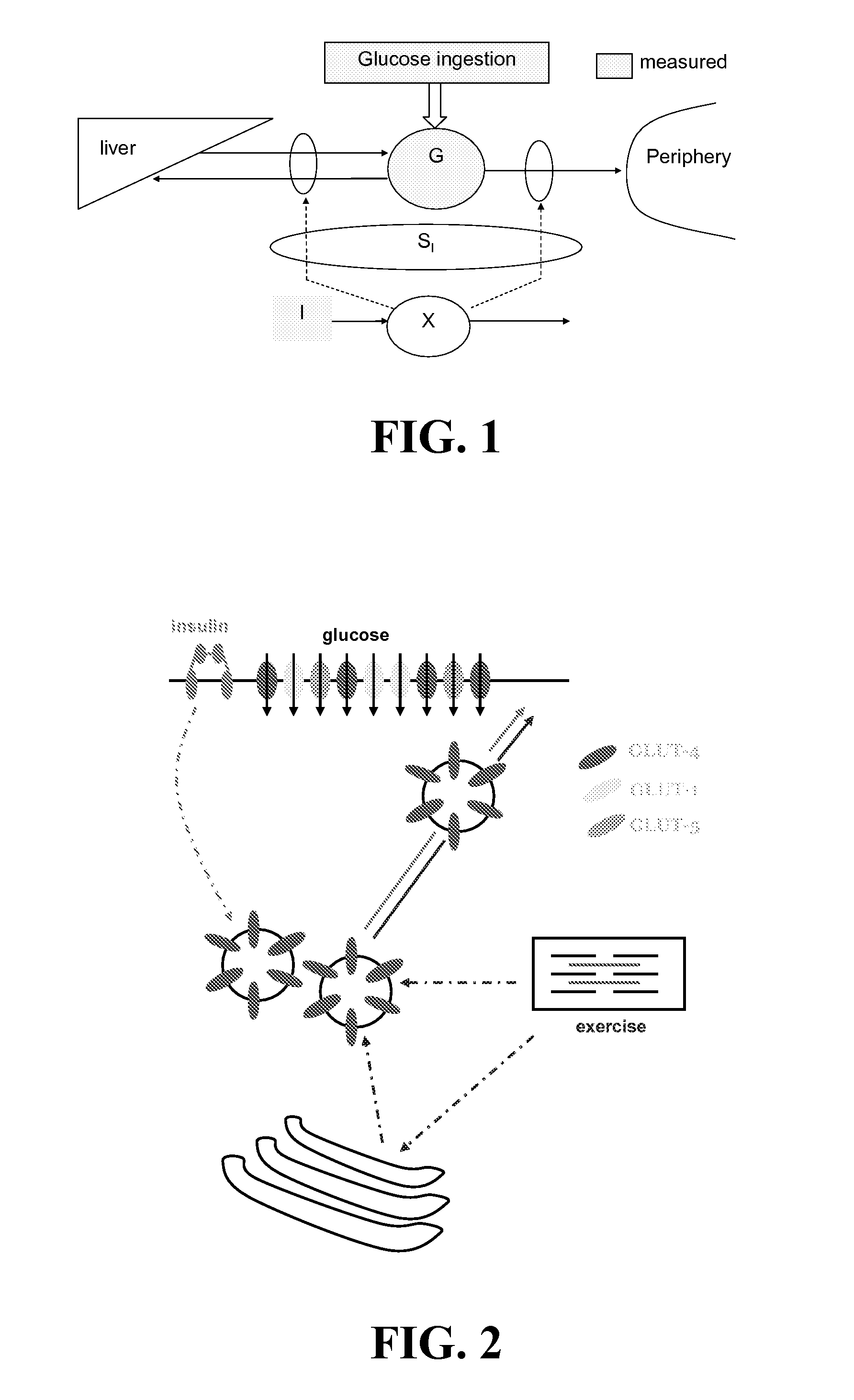

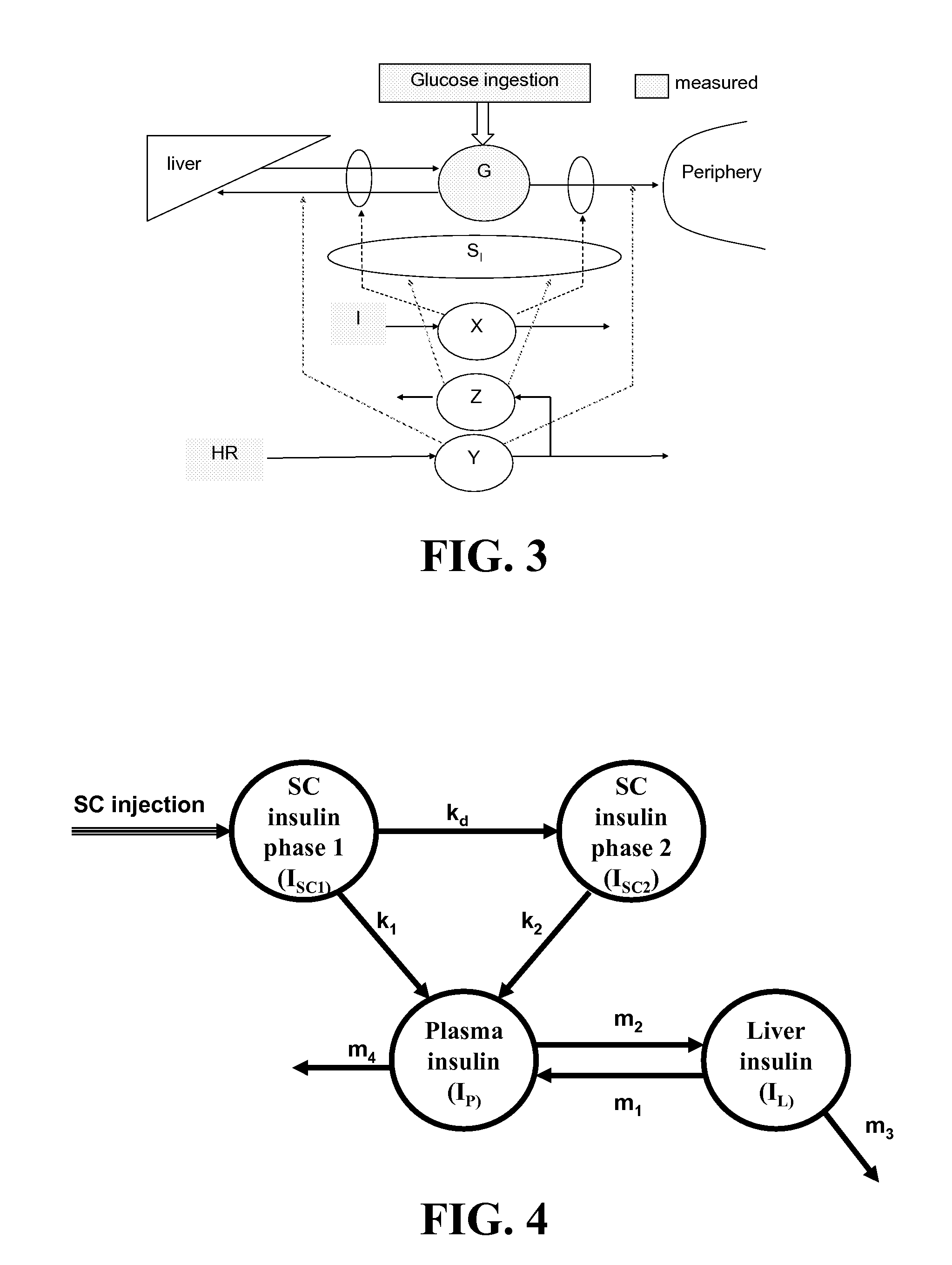

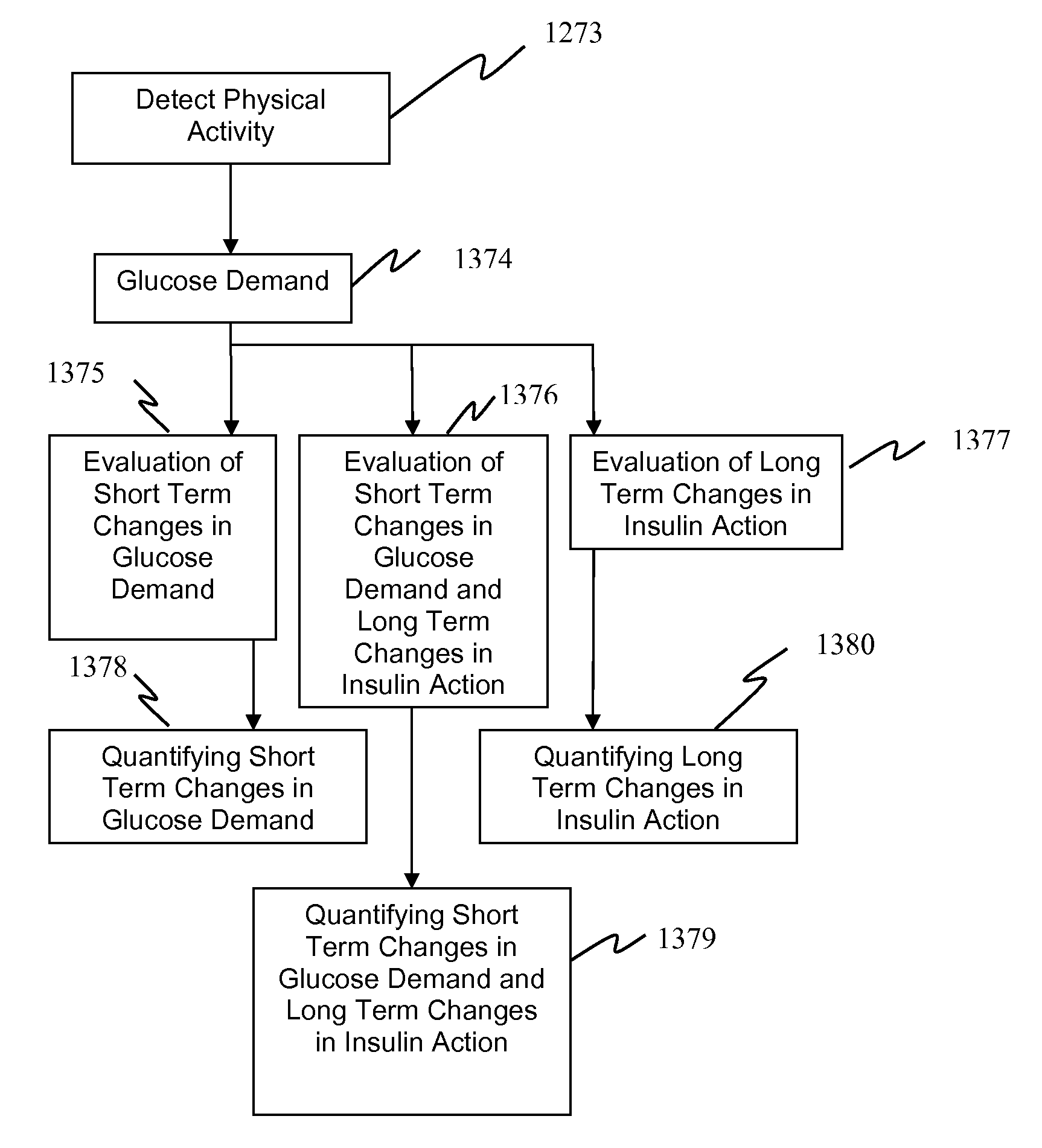

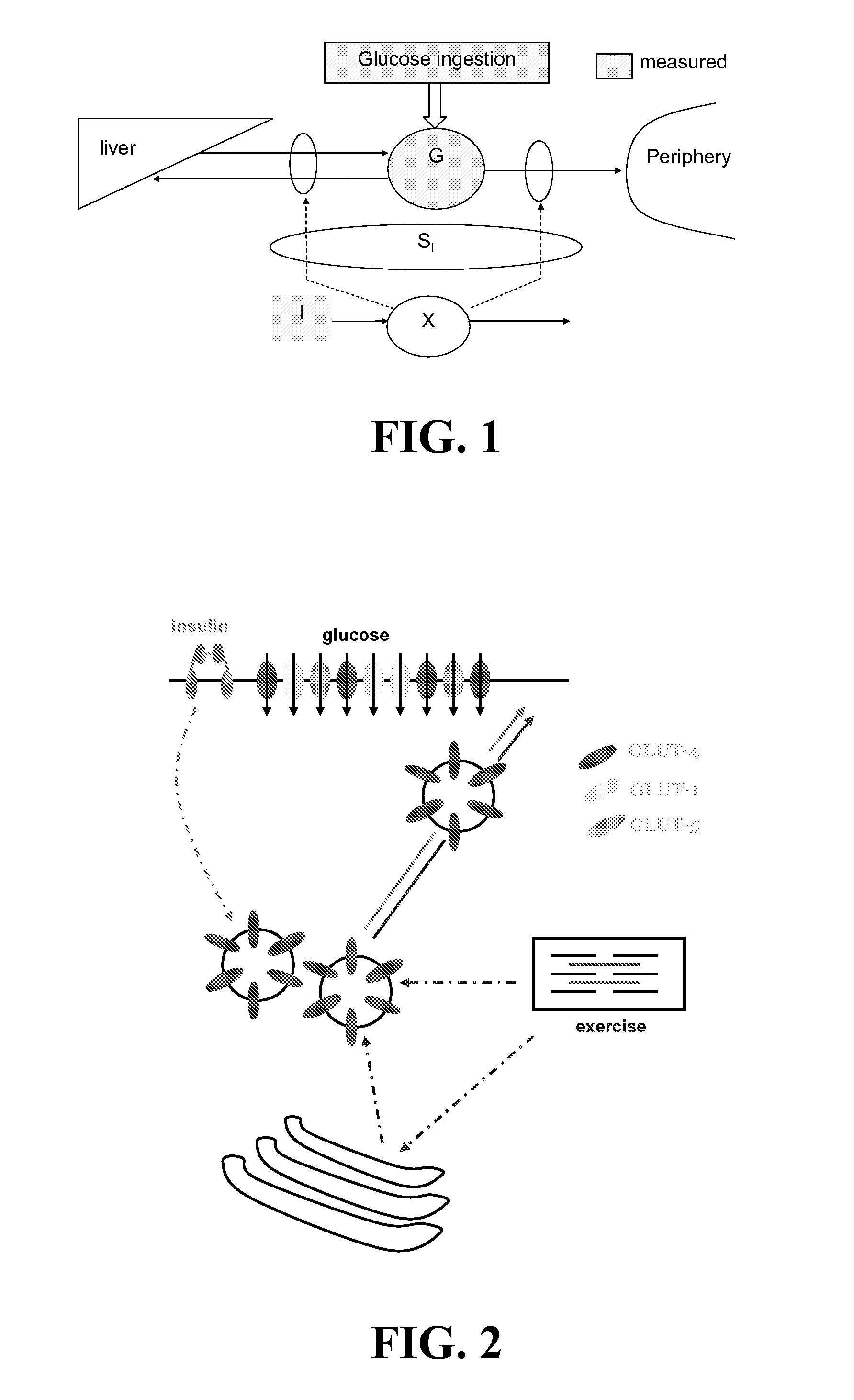

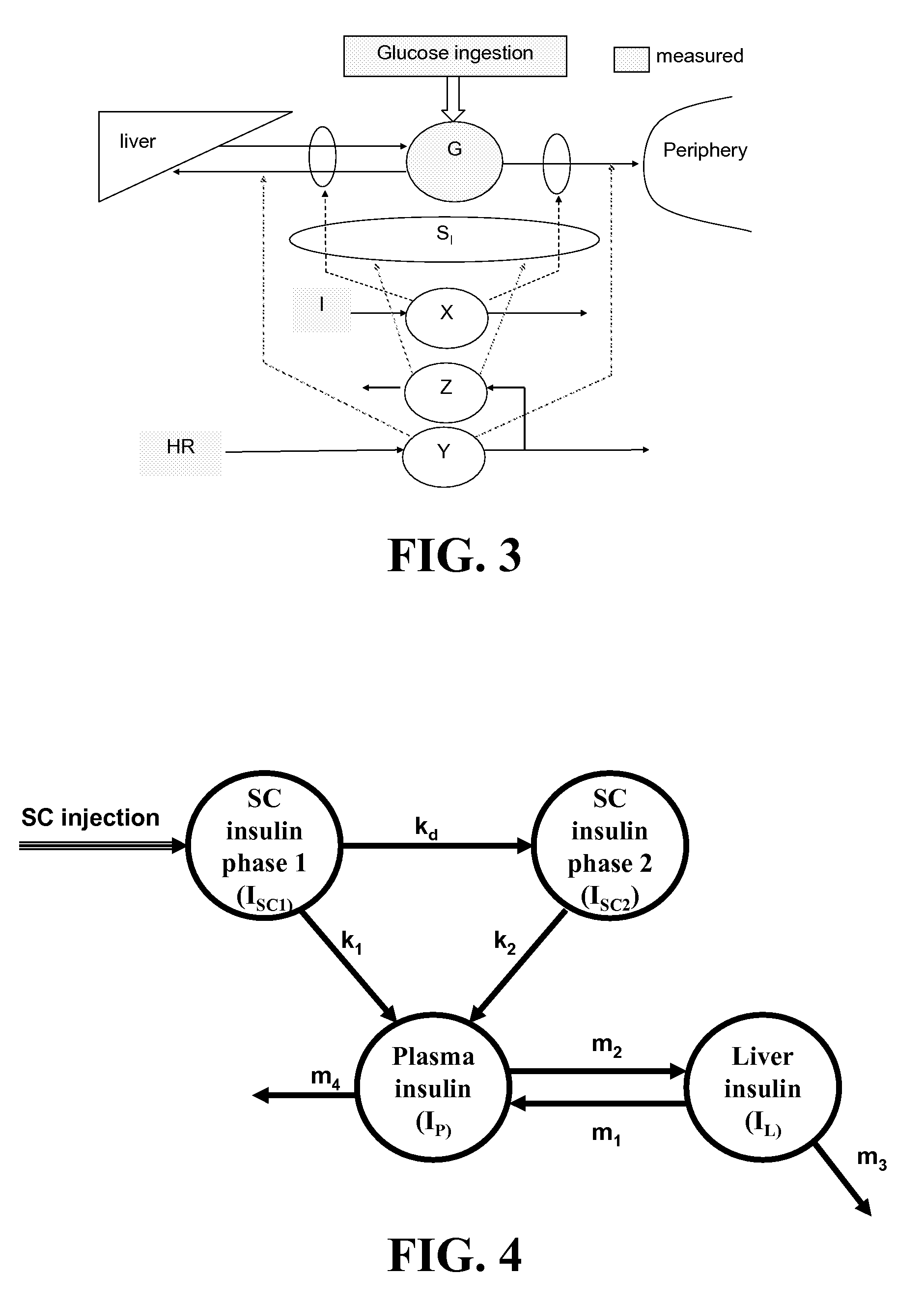

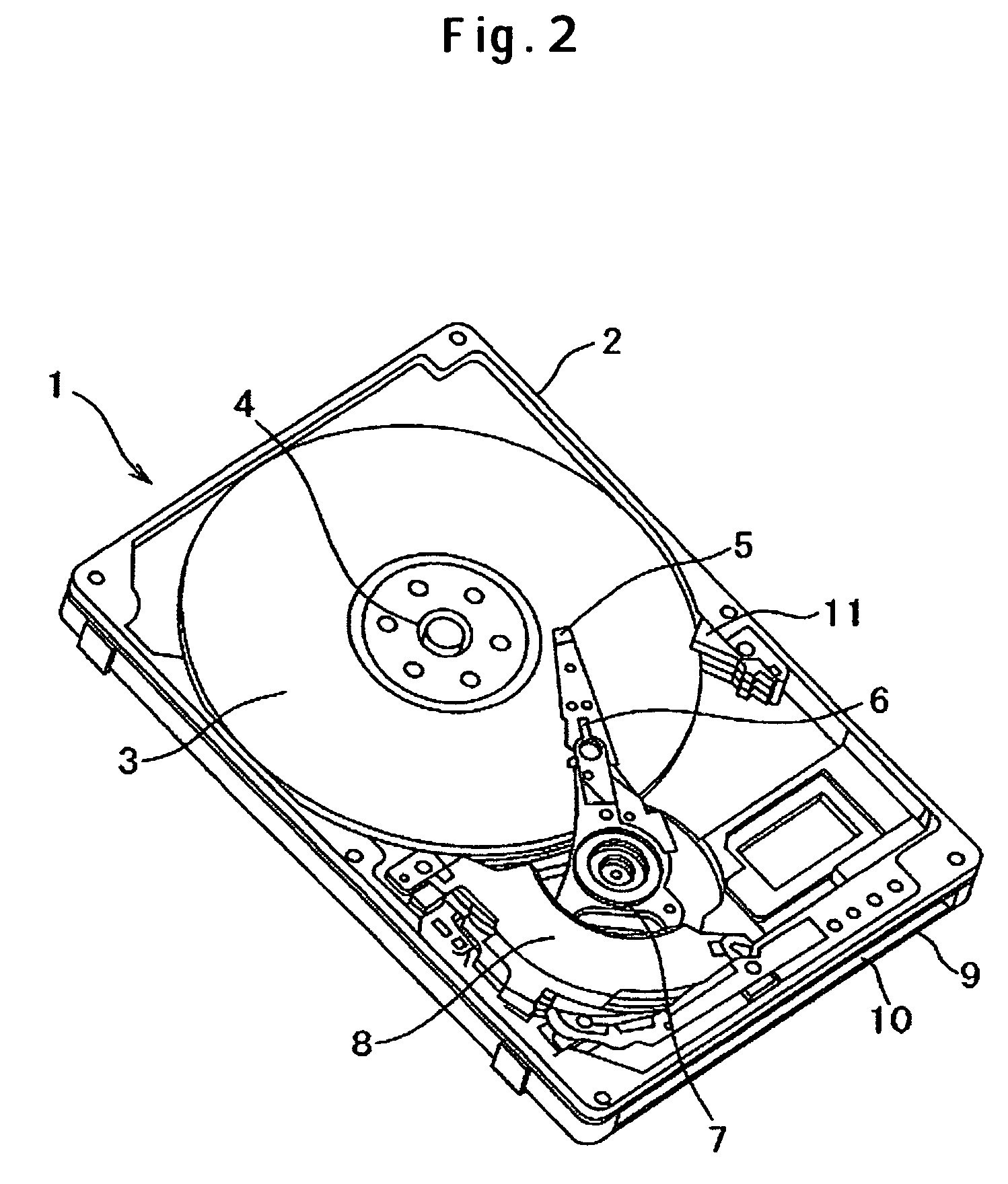

Method, System, and Computer Program Product for the Detection of Physical Activity by Changes in Heart Rate, Assessment of Fast Changing Metabolic States, and Applications of Closed and Open Control Loop in Diabetes

ActiveUS20100057043A1Minimize frequencyAvoid the needMedical simulationDrug and medicationsClosed loopHypoglycemia

A method, system, and computer program product related to the detection of physical activity using changes in heart rate. The method, system, and computer program product evaluates short term glucose demand and long term insulin action due to physical activity. The method, system, and computer program product is further related to the improvement of open and closed loop control of diabetes by accounting for the metabolic changes due to physical activity. The method, system, and computer program product is directed to detecting in real time the short and long term effects of physical activity on insulin action via heart rate analysis, and recommending changes in insulin dosing to compensate for the effects of physical activity. With these recommendations, the open and closed loop control of diabetes can be improved and steps can be taken to prevent hypoglycemia that may result from increased insulin sensitivity due to physical activity.

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND

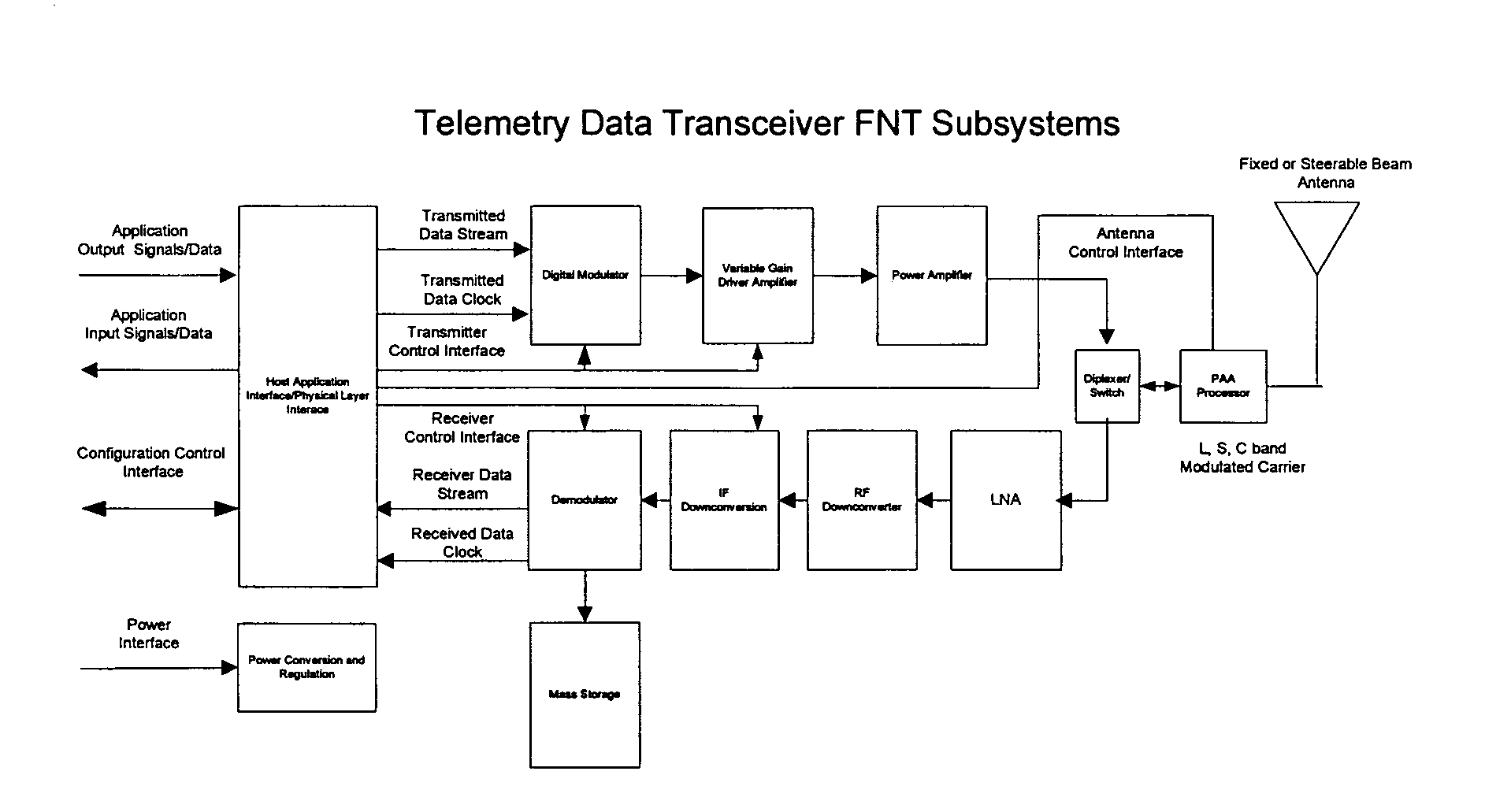

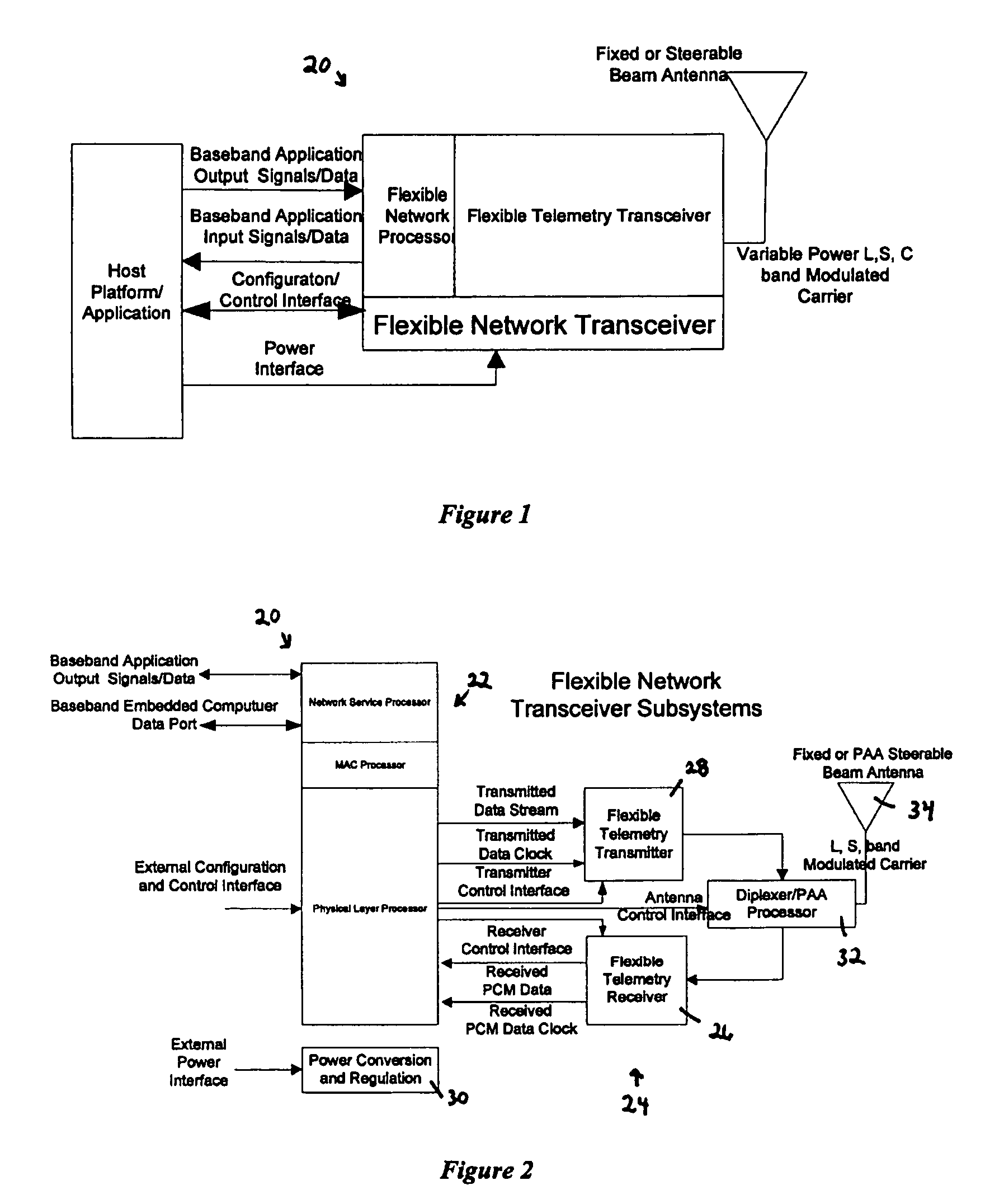

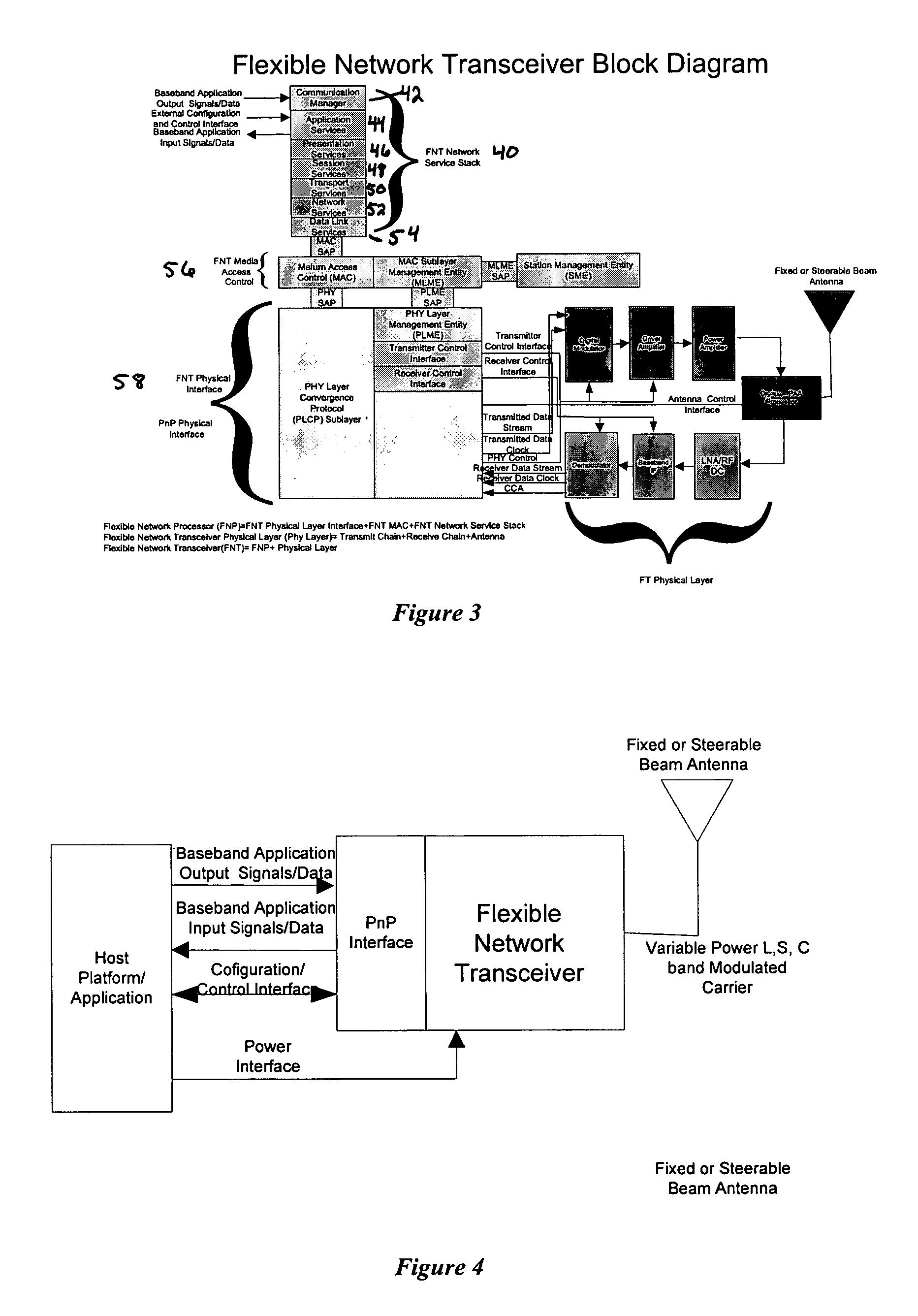

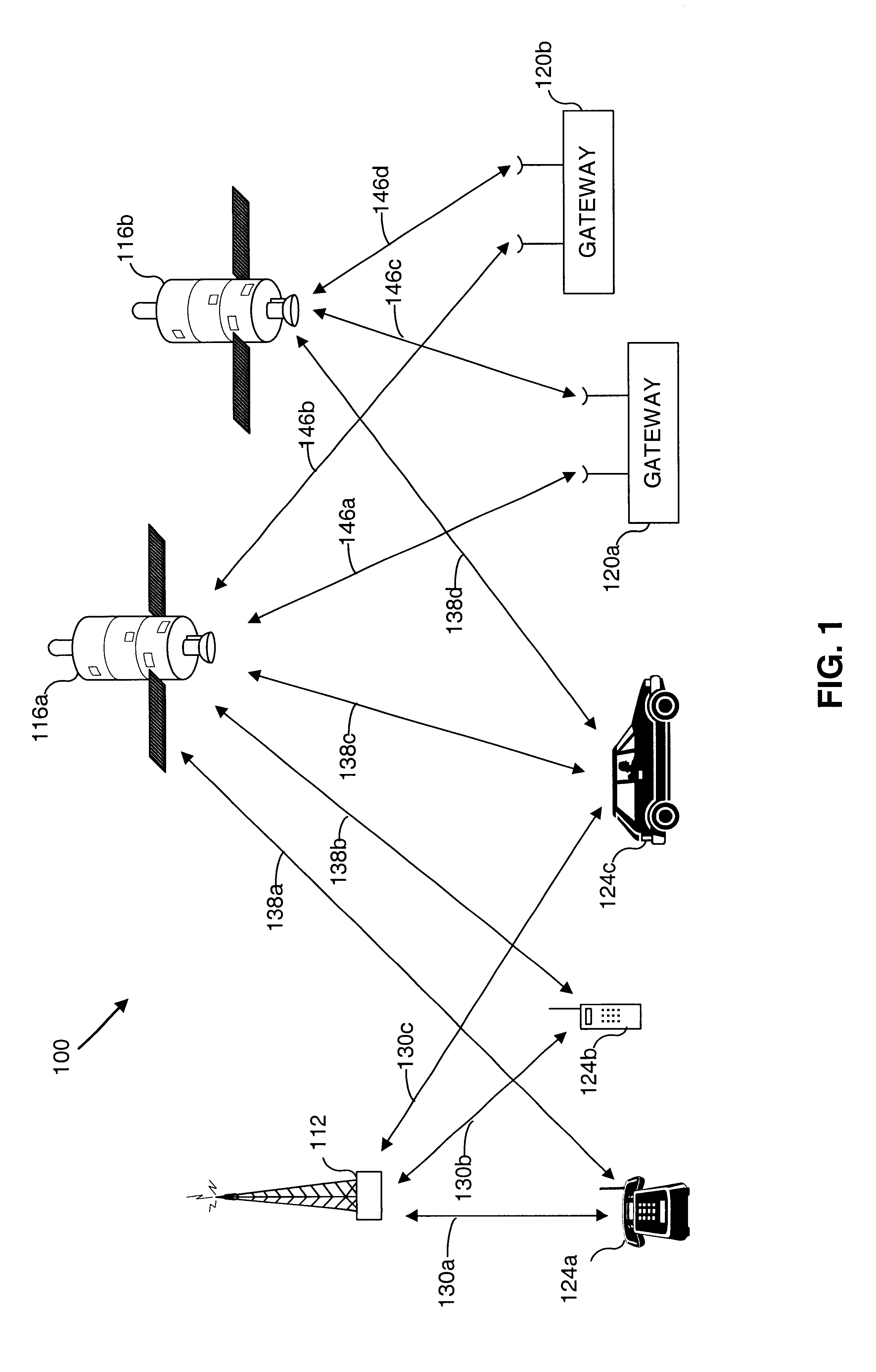

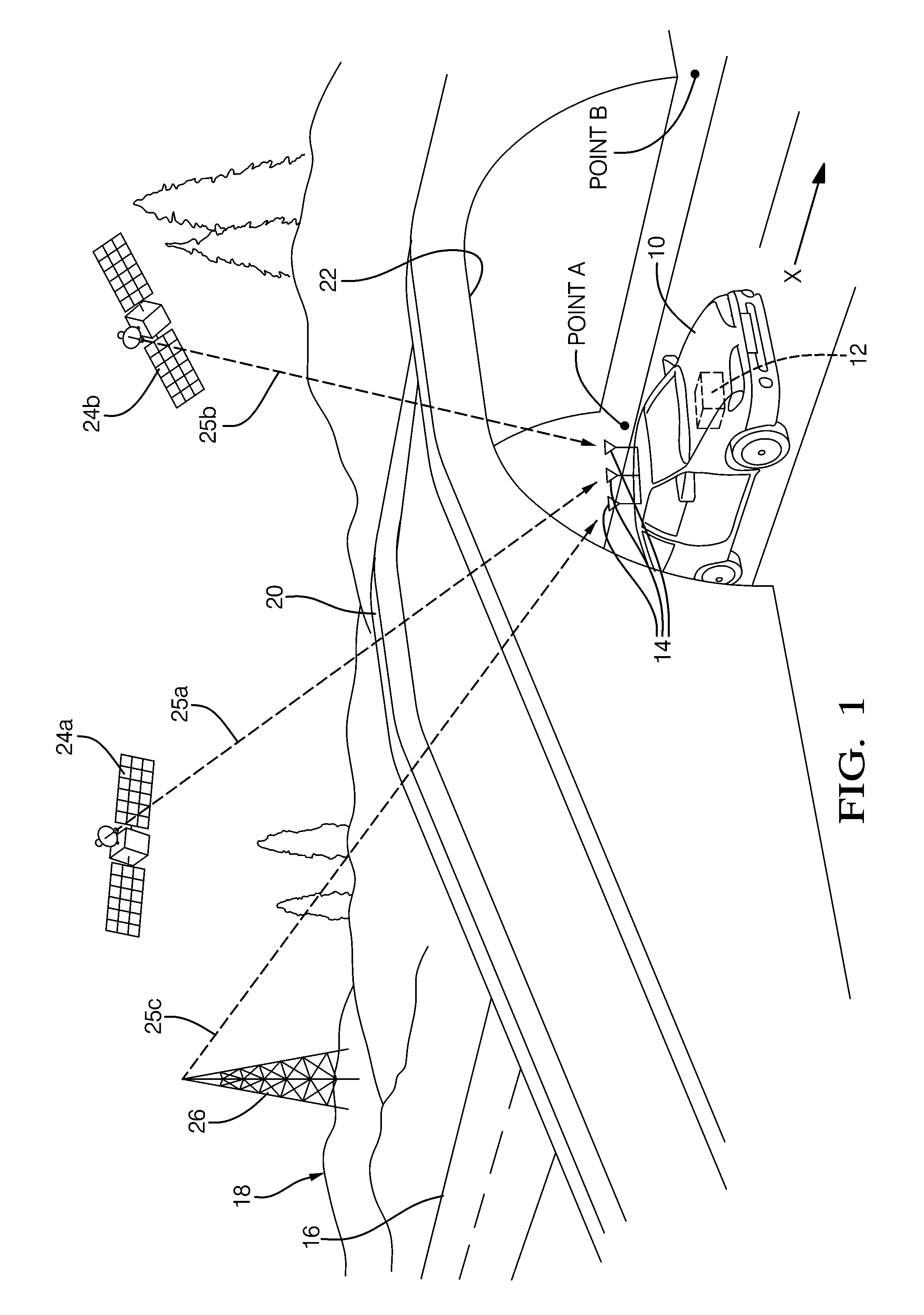

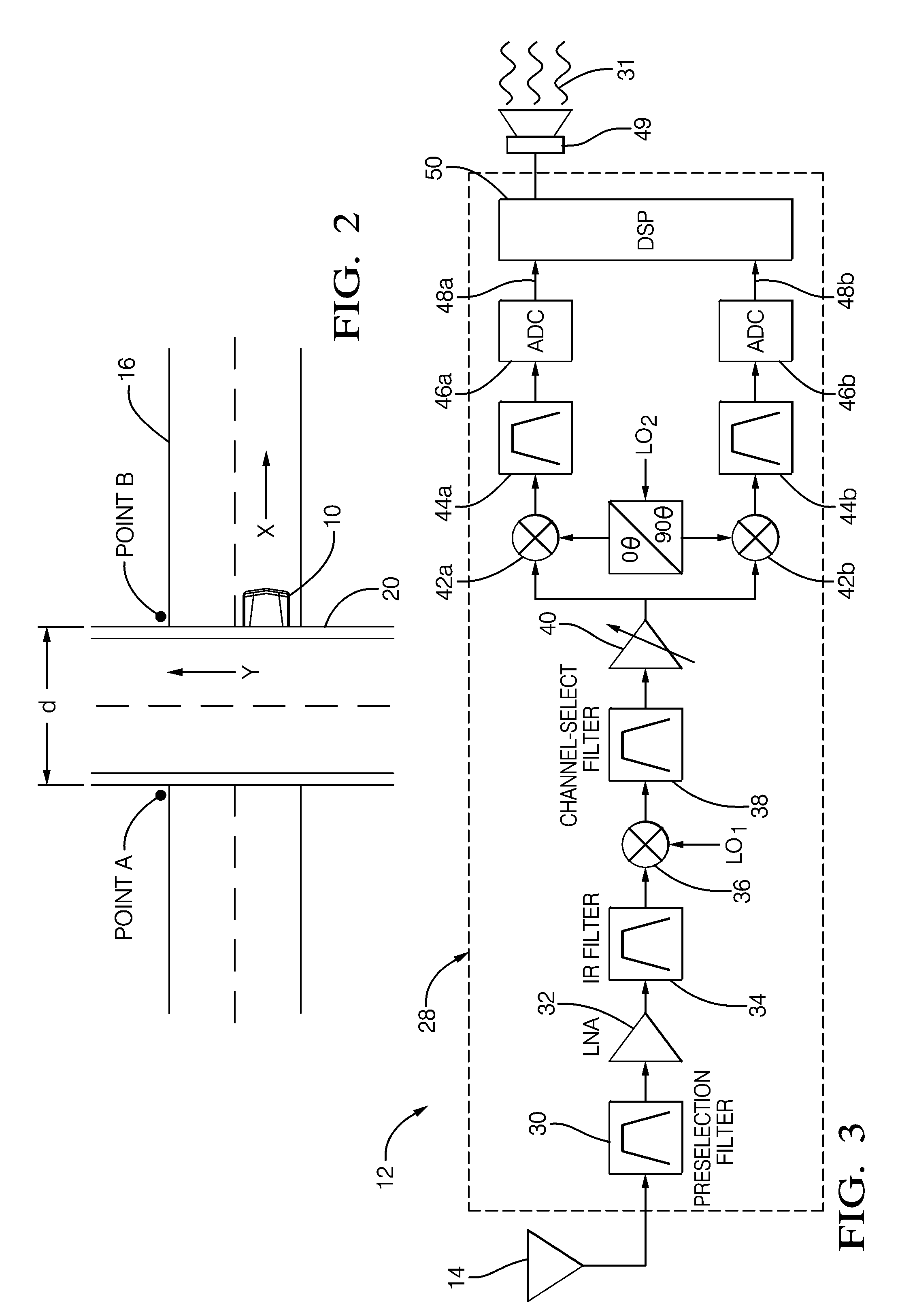

Flexible network wireless transceiver and flexible network telemetry transceiver

InactiveUS7408898B1Improve performanceIncrease data rateError preventionFrequency-division multiplex detailsTransceiverGround vehicles

A transceiver for facilitating two-way wireless communication between a baseband application and other nodes in a wireless network, wherein the transceiver provides baseband communication networking and necessary configuration and control functions along with transmitter, receiver, and antenna functions to enable the wireless communication. More specifically, the transceiver provides a long-range wireless duplex communication node or channel between the baseband application, which is associated with a mobile or fixed space, air, water, or ground vehicle or other platform, and other nodes in the wireless network or grid. The transceiver broadly comprises a communication processor; a flexible telemetry transceiver including a receiver and a transmitter; a power conversion and regulation mechanism; a diplexer; and a phased array antenna system, wherein these various components and certain subcomponents thereof may be separately enclosed and distributable relative to the other components and subcomponents.

Owner:THE UNITED STATES AS REPRESENTED BY THE DEPARTMENT OF ENERGY

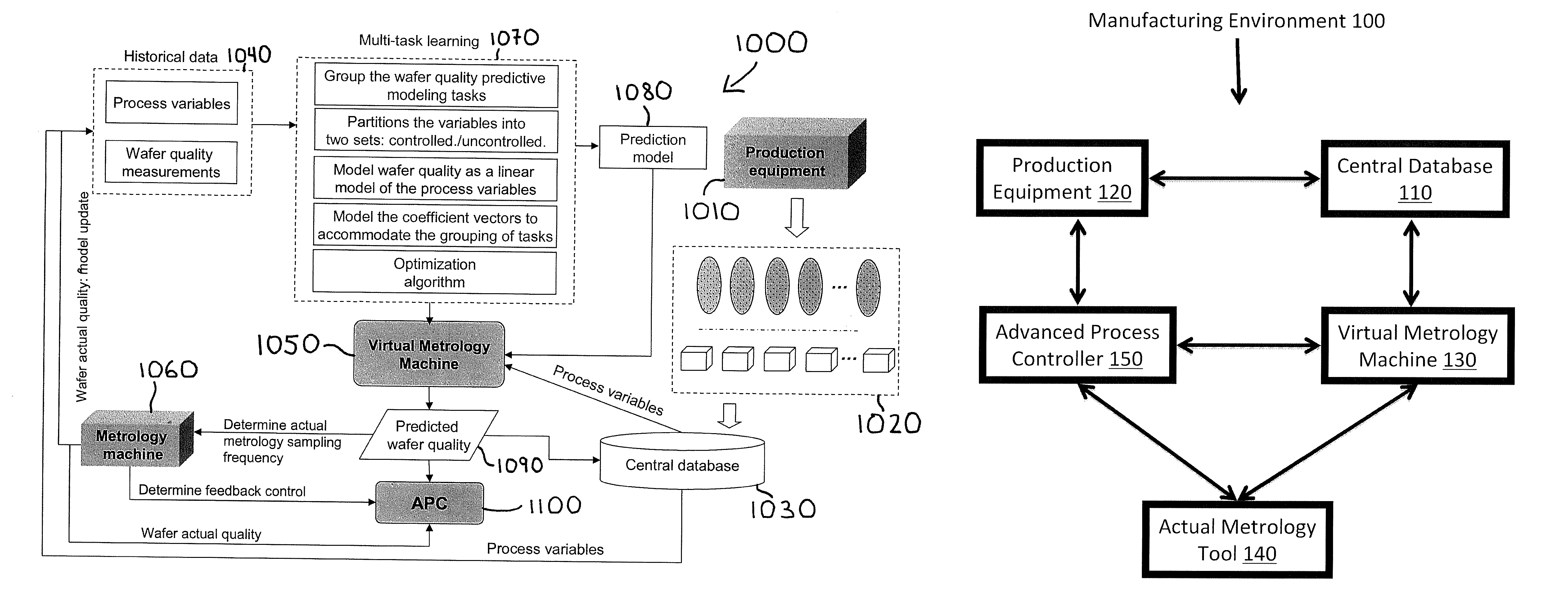

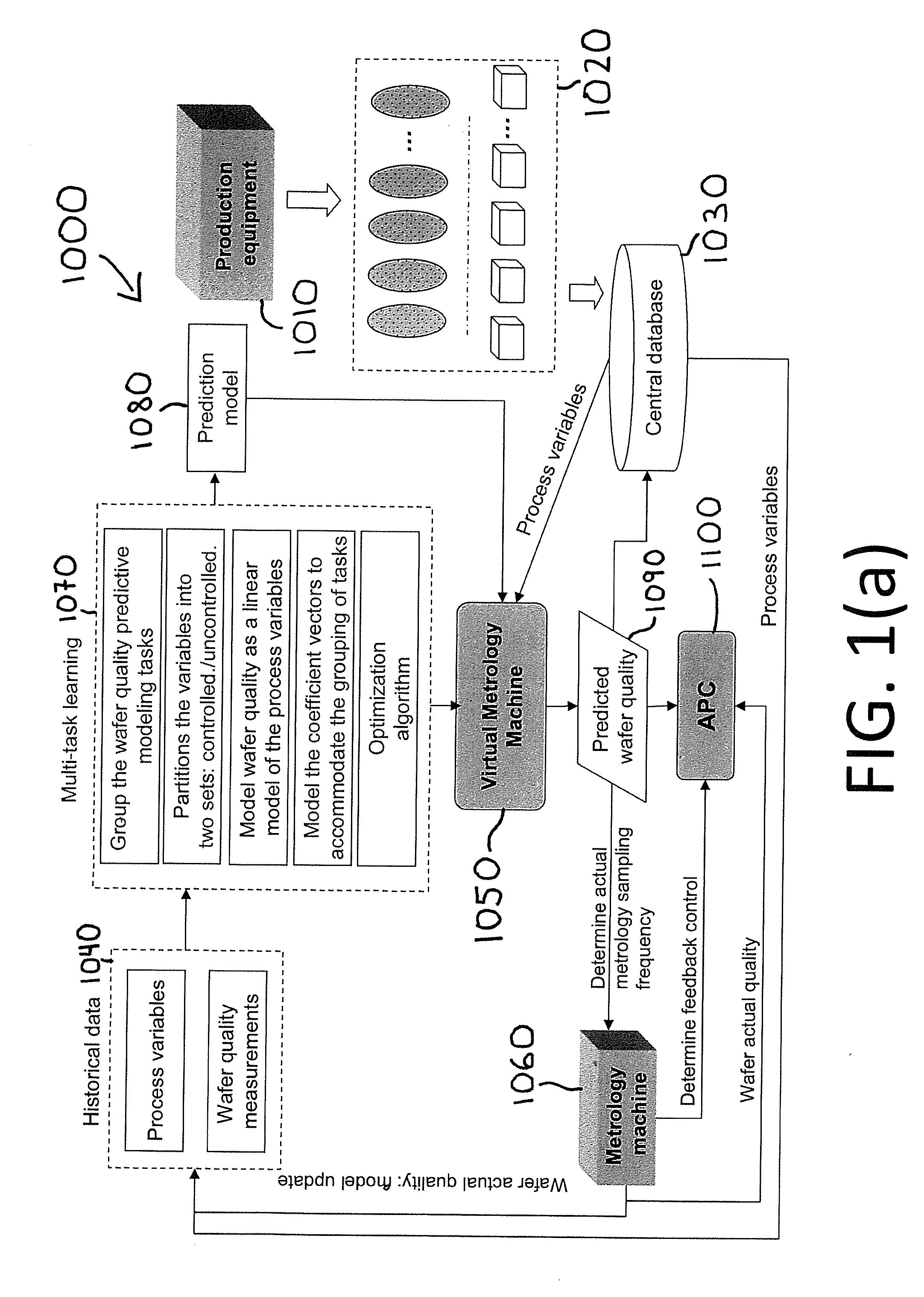

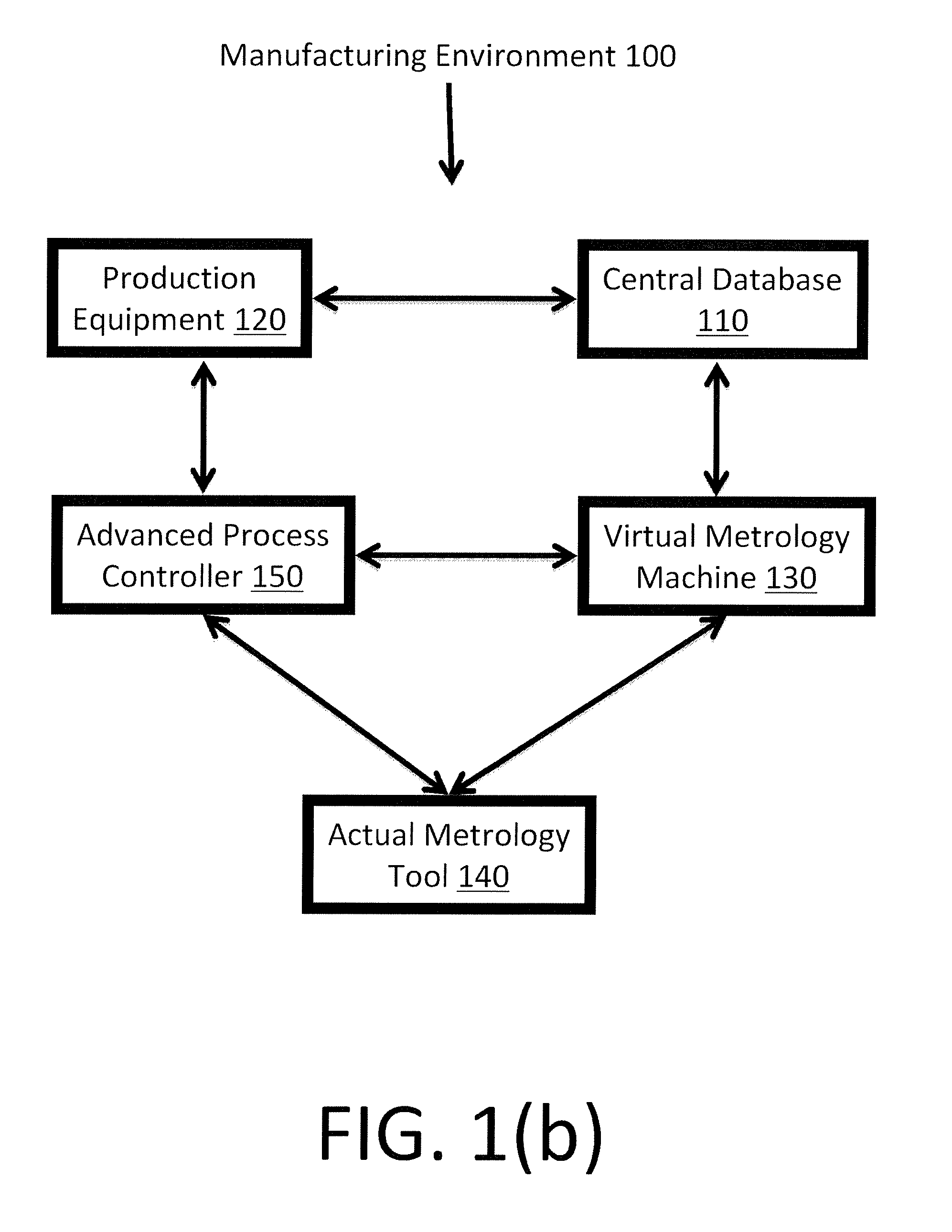

Method and System for Wafer Quality Predictive Modeling based on Multi-Source Information with Heterogeneous Relatedness

InactiveUS20140107828A1Improve predictive performanceReduce associated actual metrology costSemiconductor/solid-state device testing/measurementComputer controlMetrologyComputer science

The present invention generally relates to the monitoring and controlling of a semiconductor manufacturing environment and, more particularly, to methods and systems for virtual meteorology (VM) applications based on data from multiple tools having heterogeneous relatedness. The methods and systems leverage the natural relationship of the multiple tools and take advantage of the relationship embedded in process variables to improve the prediction performance of the VM predictive wafer quality modeling. The prediction results of the methods and systems can be used as a substitute for or in conjunction with actual metrology samples in order to monitor and control a semiconductor manufacturing environment, and thus reduce delays and costs associated with obtaining actual physical measurements.

Owner:GLOBALFOUNDRIES INC

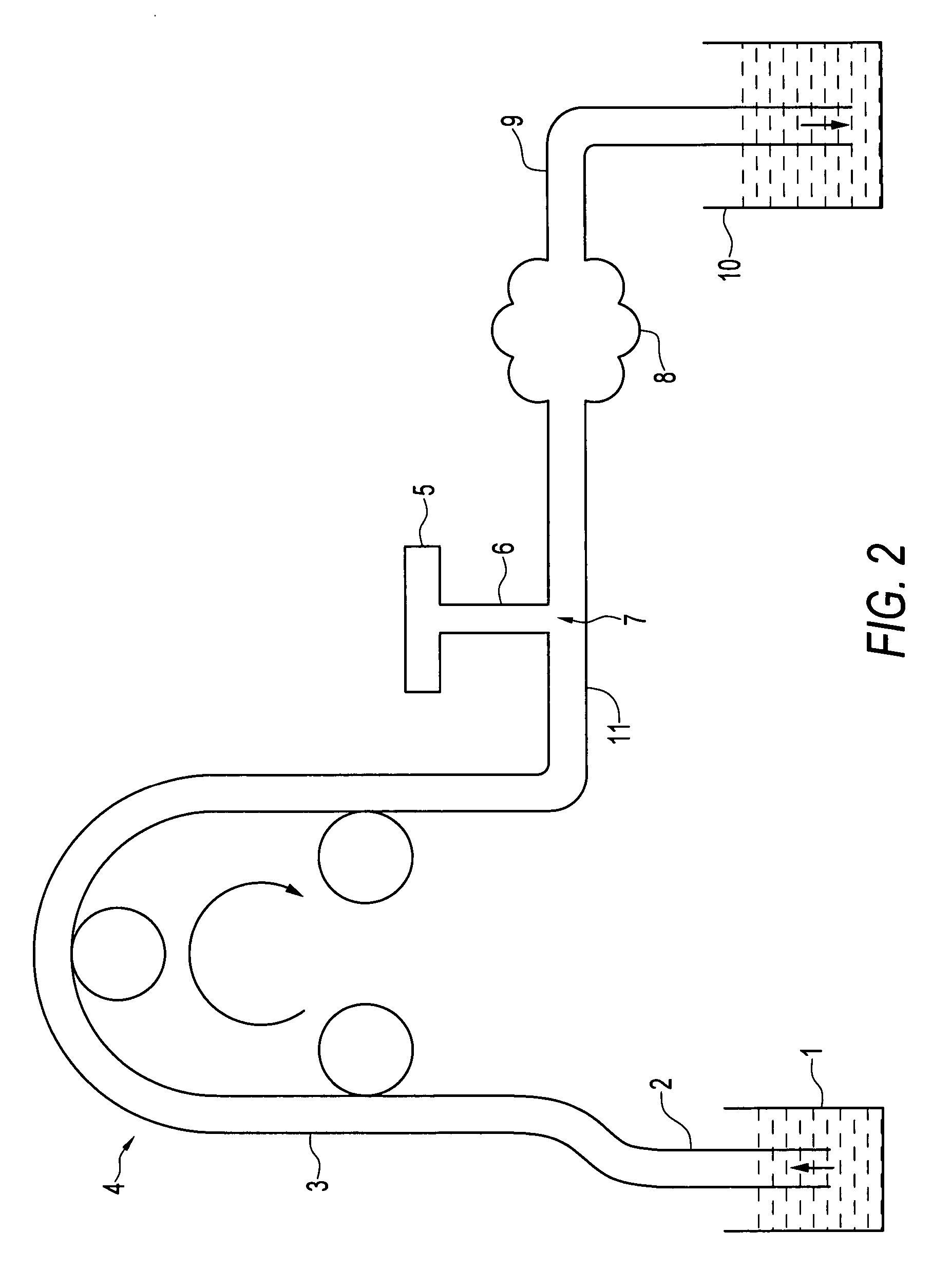

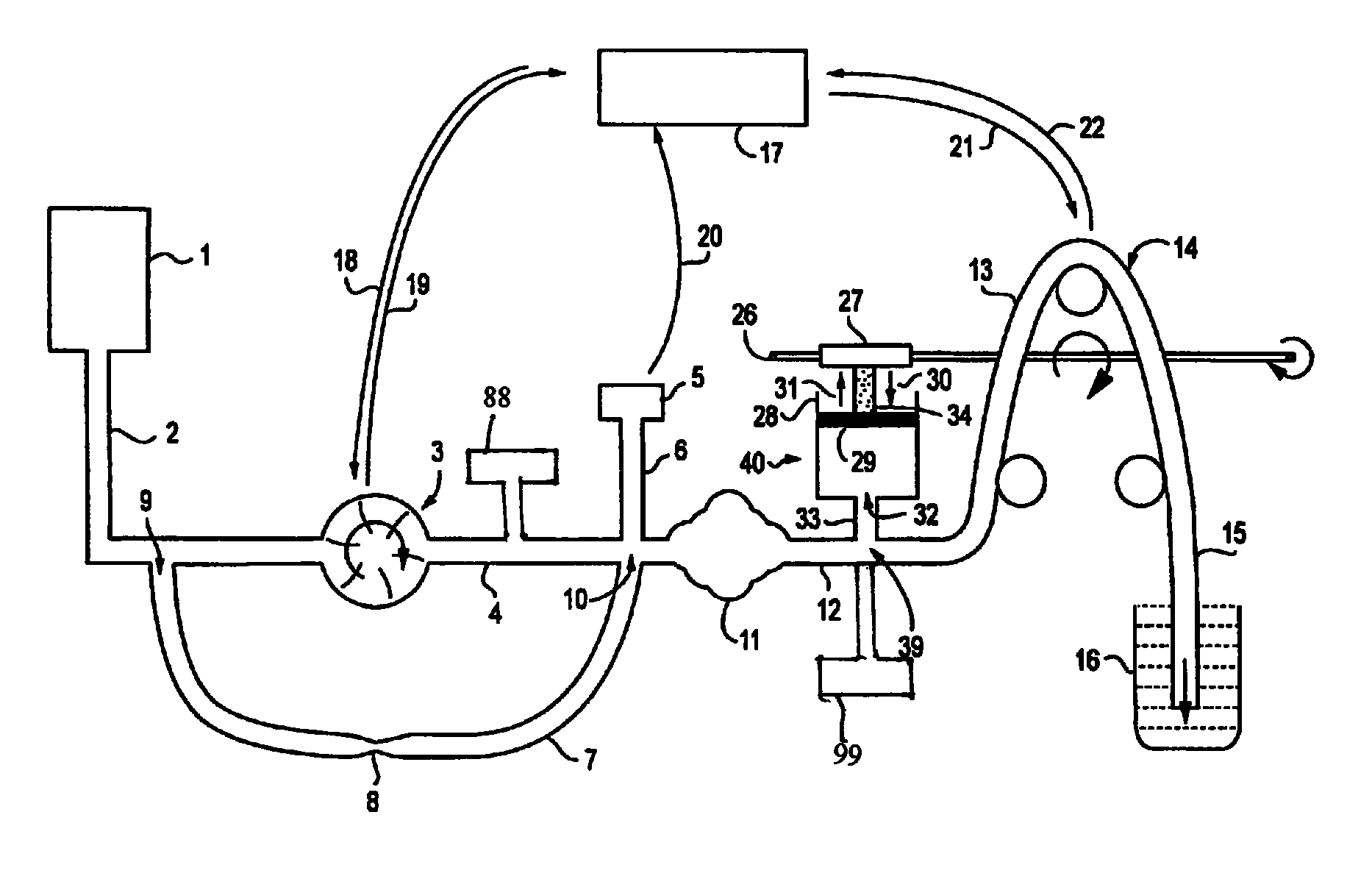

Electromagnetically controlled tissue cavity distending system

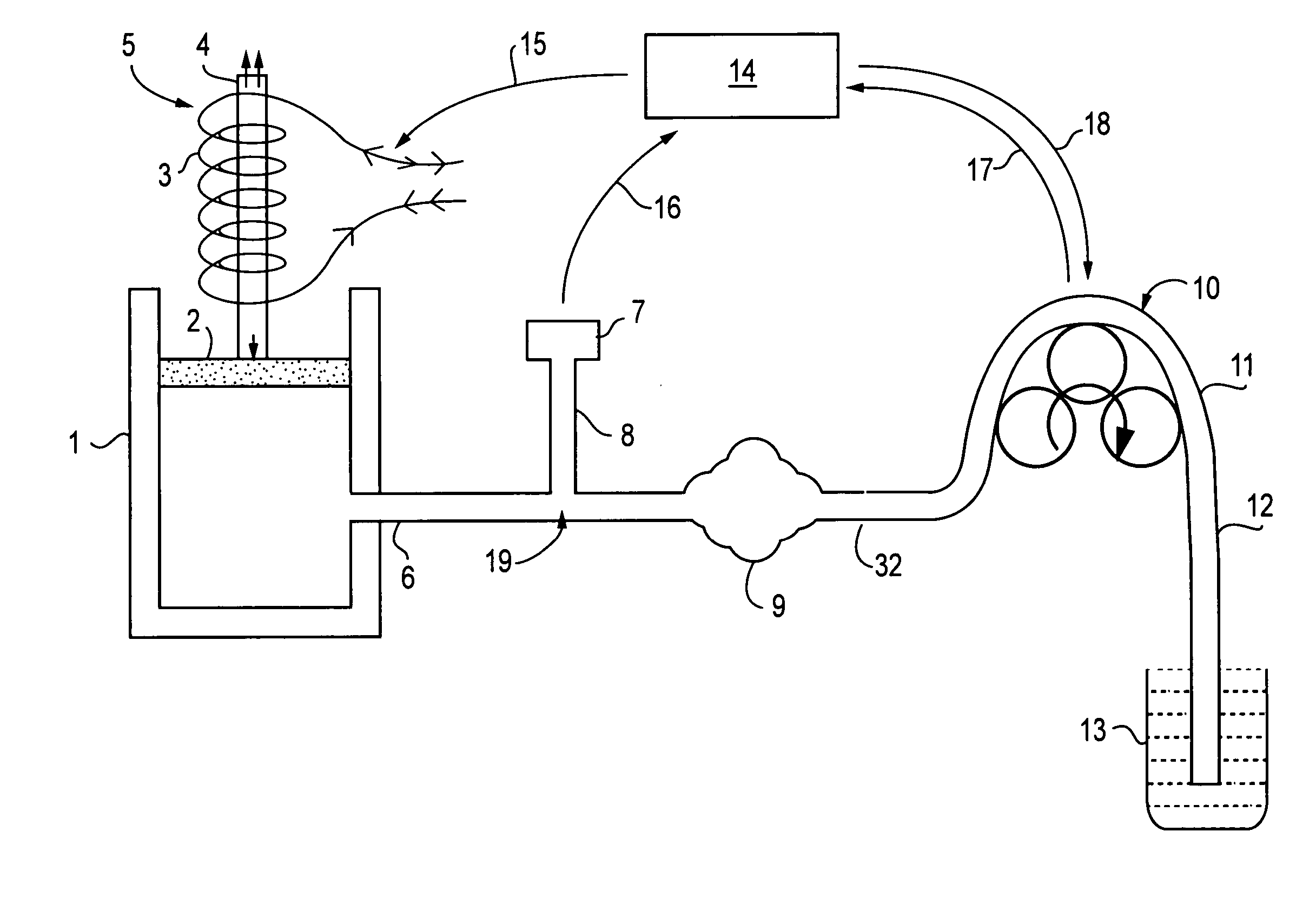

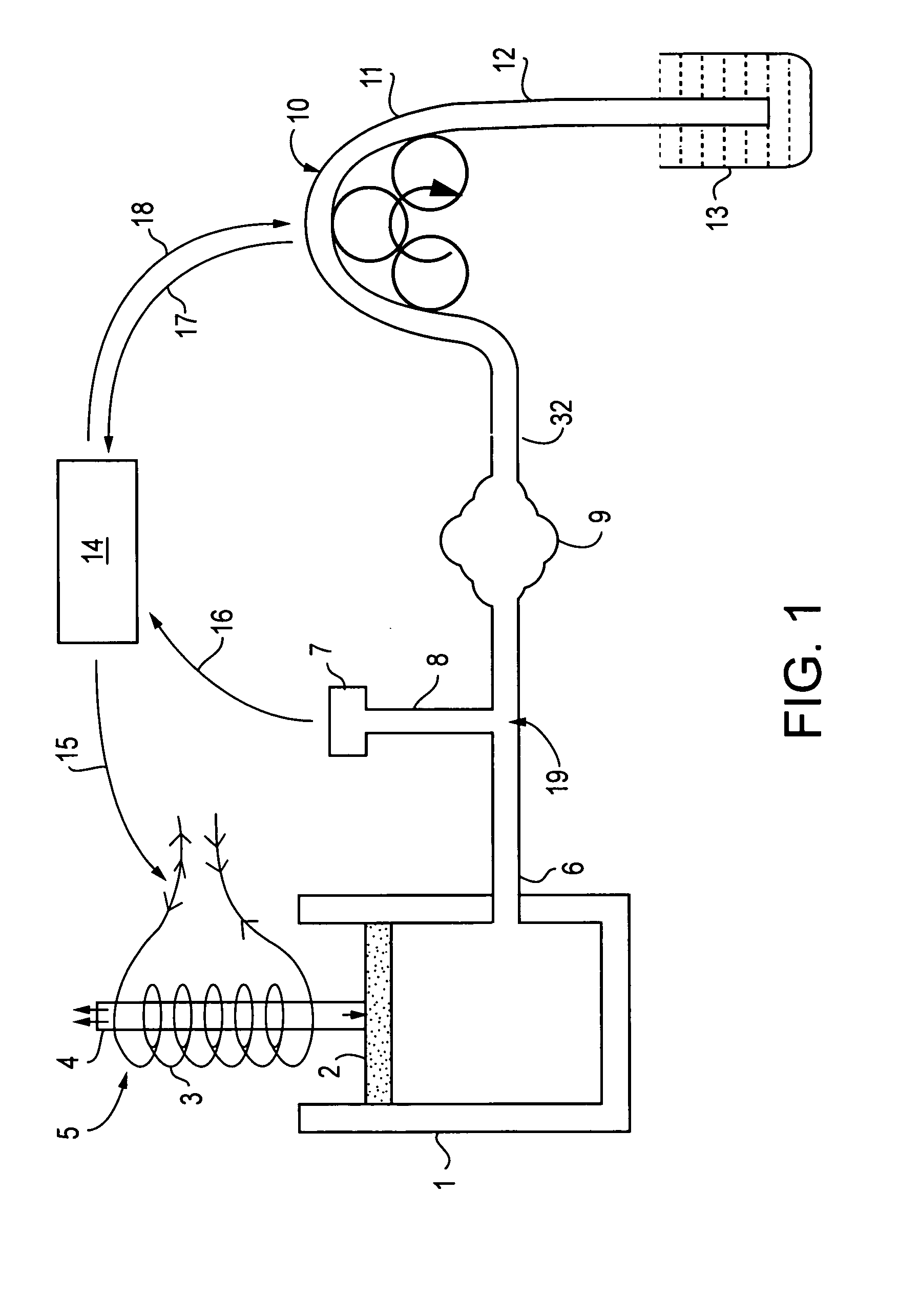

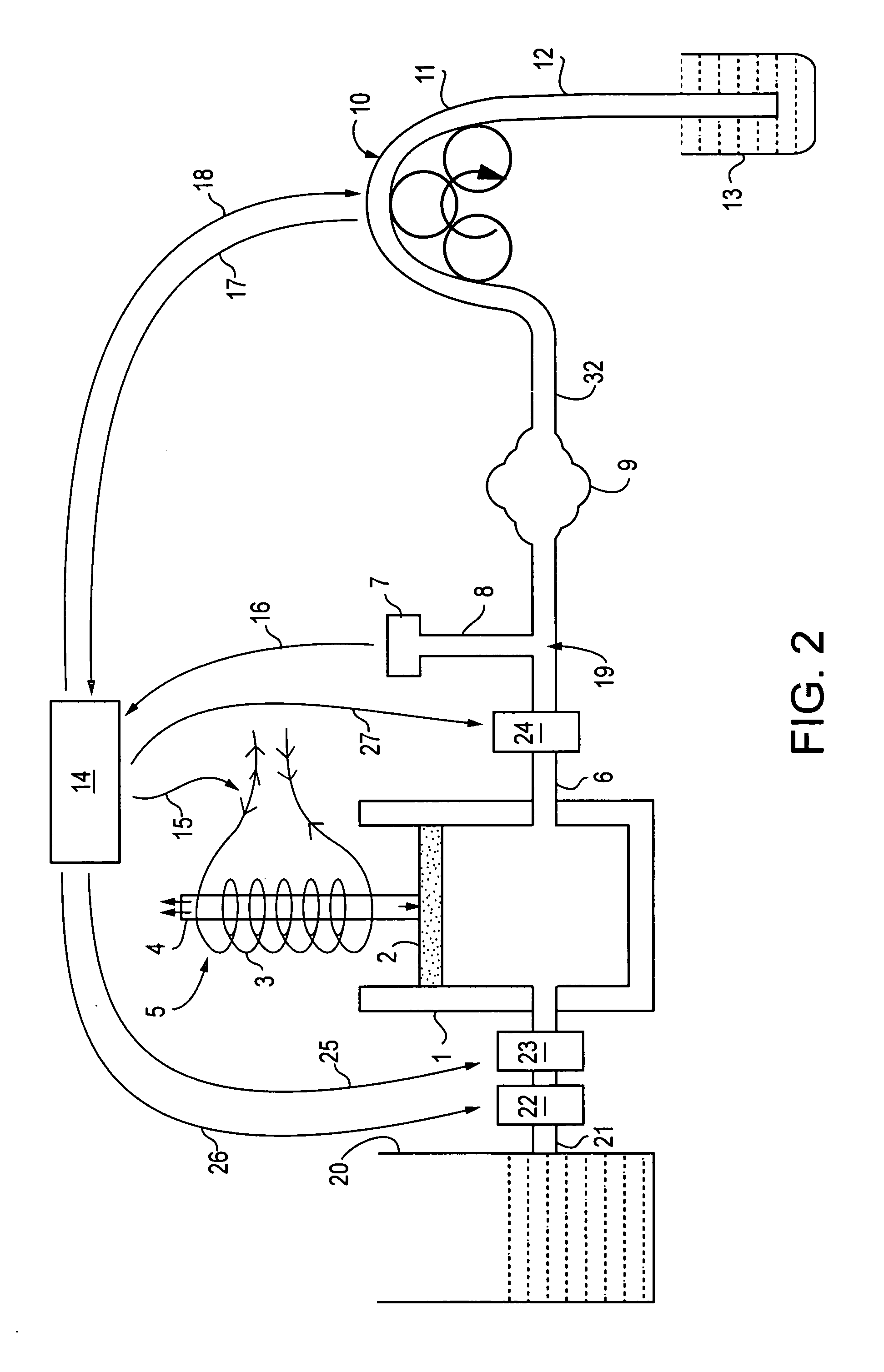

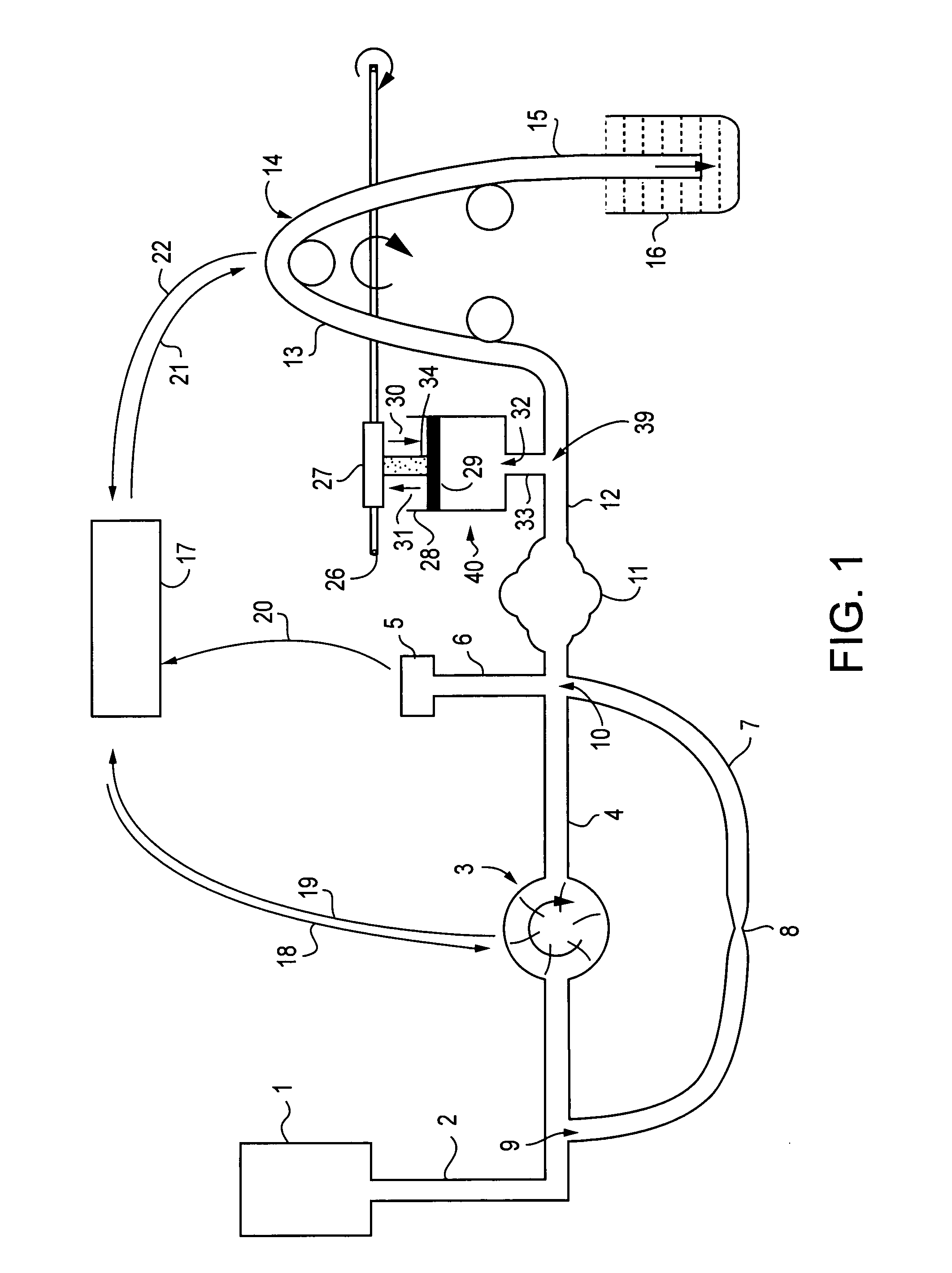

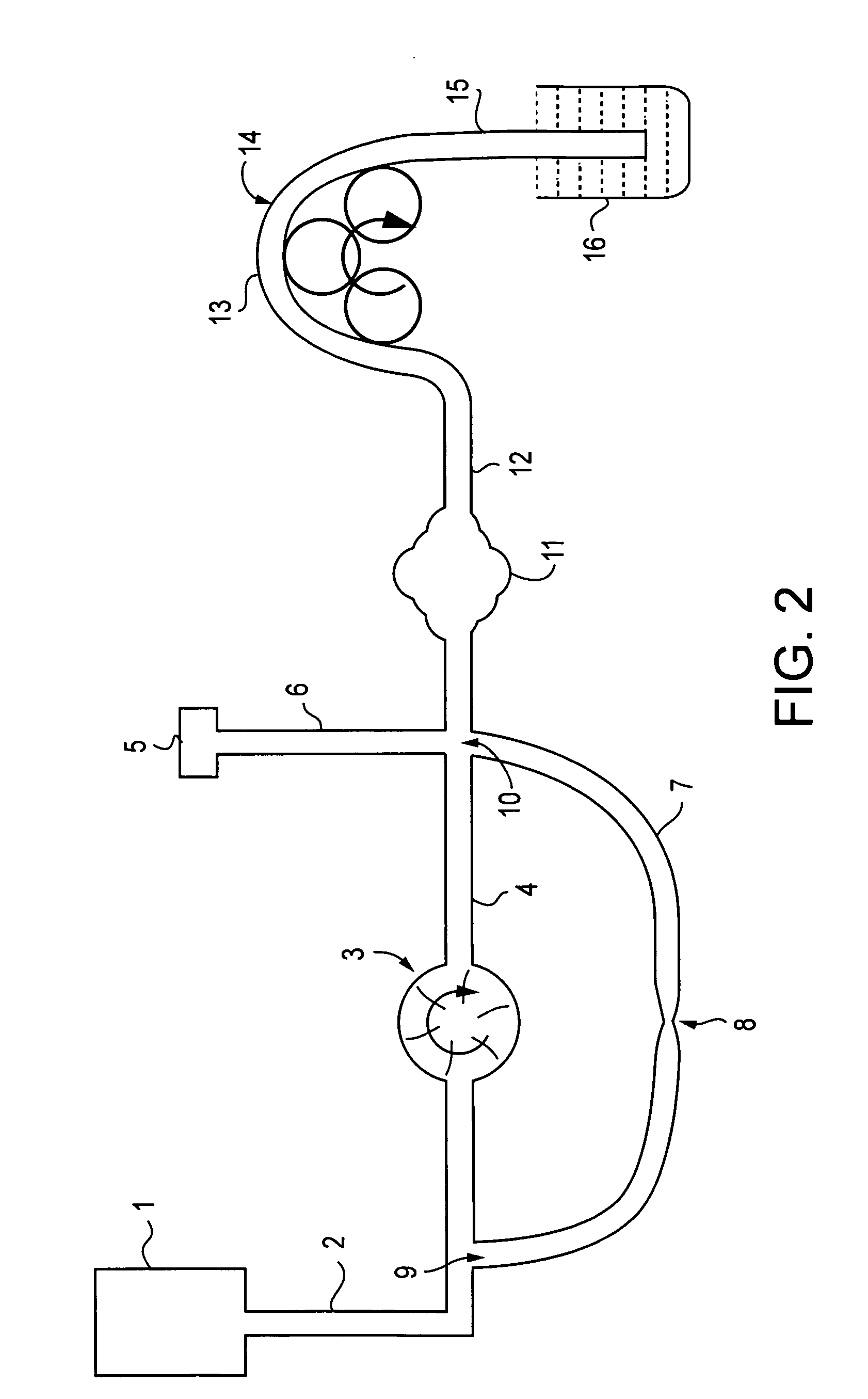

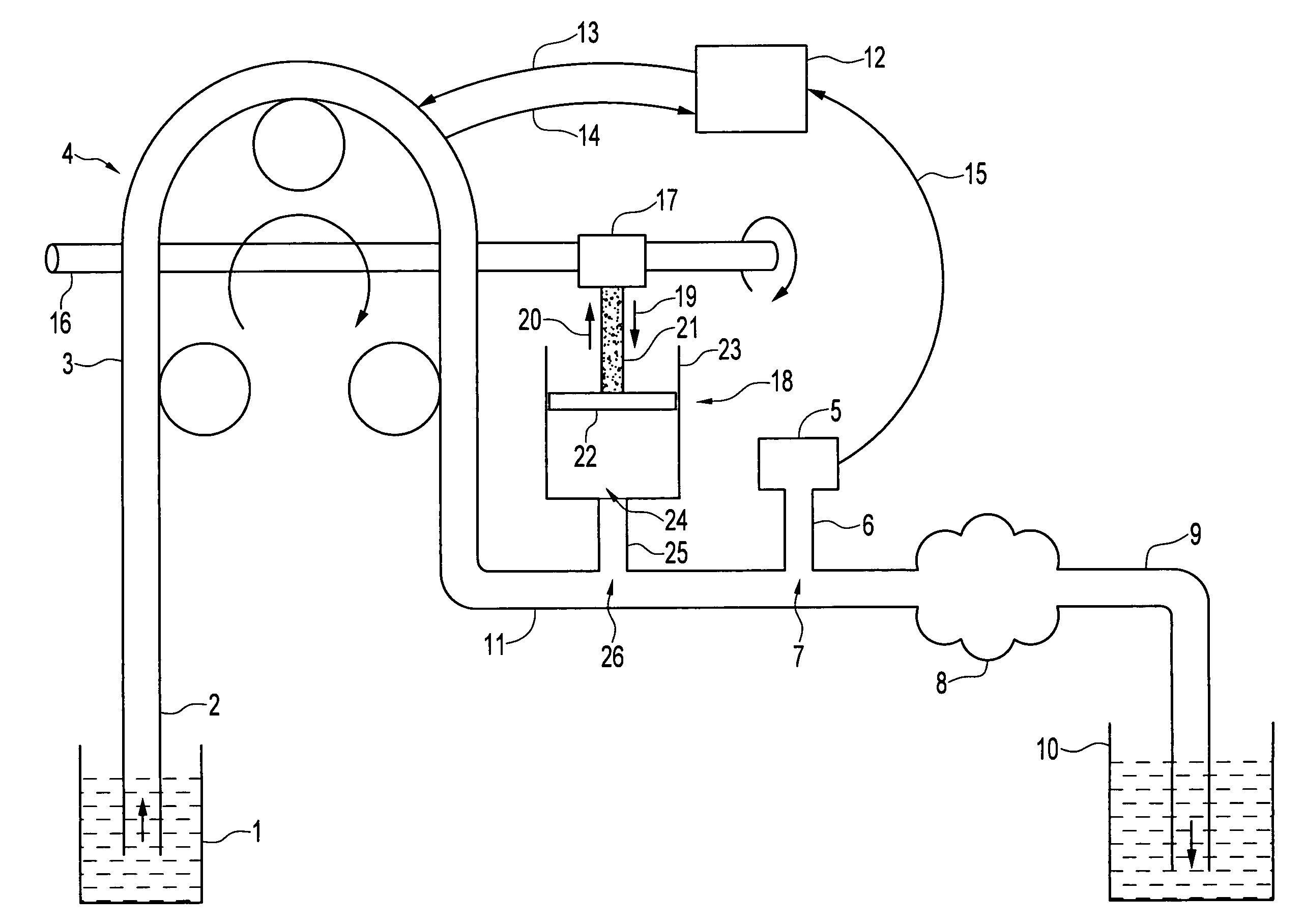

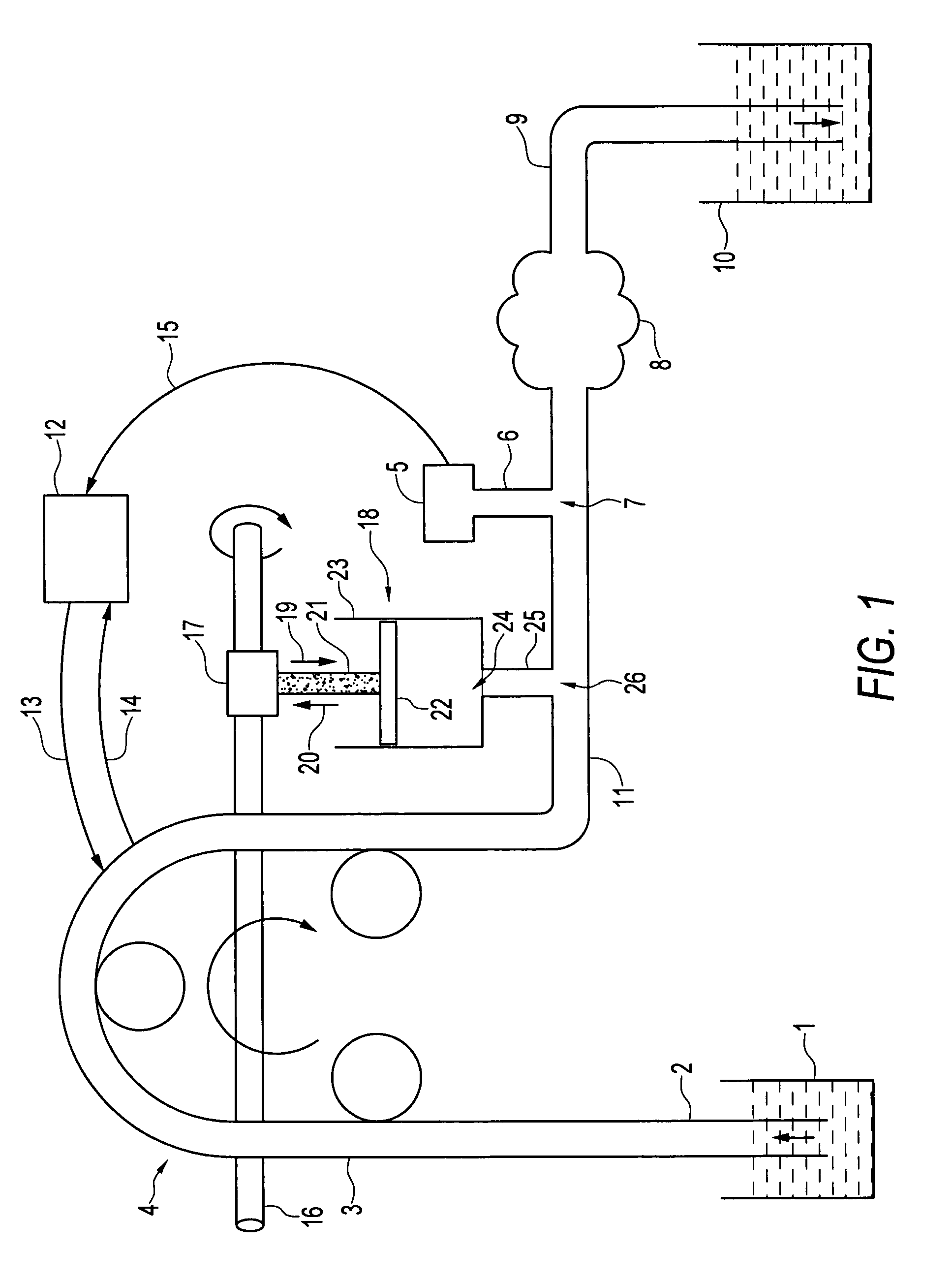

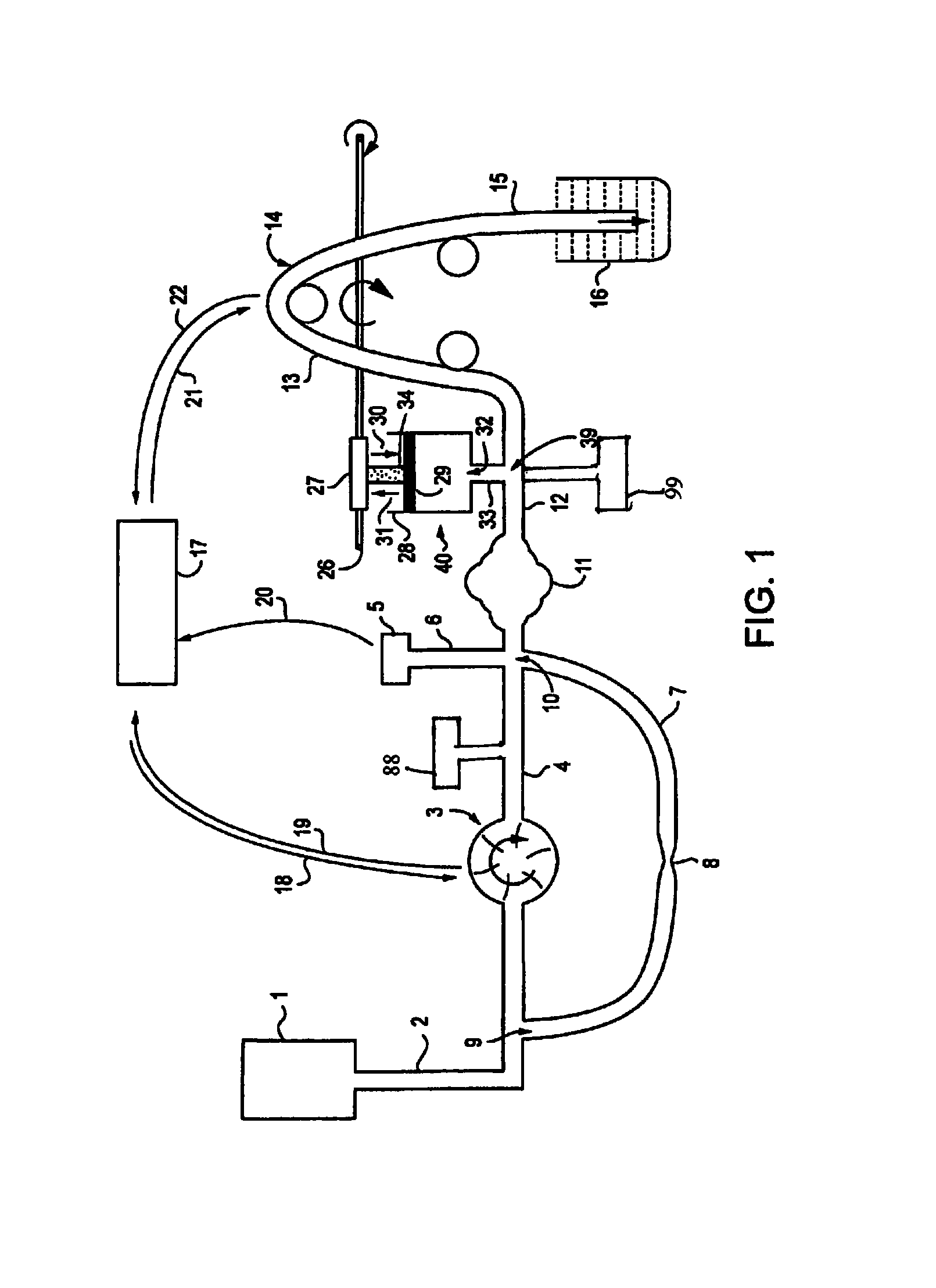

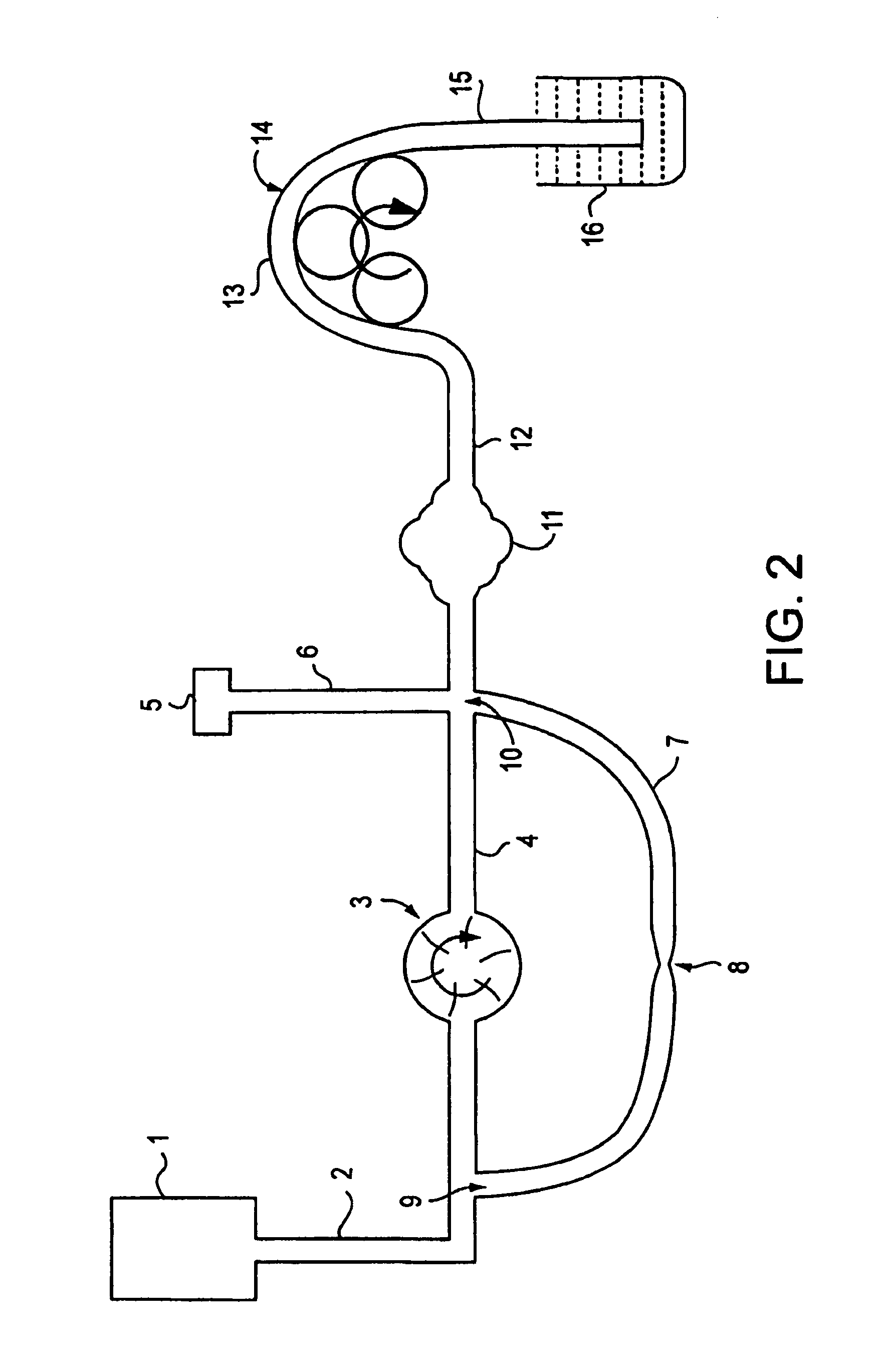

ActiveUS20060052666A1Accurate and reliable and simple mannerAltering valueJet injection syringesAutomatic syringesPeristaltic pumpEndoscopic Procedure

A system to minimize fluid turbulence inside a tissue cavity during endoscopic procedures. A body tissue cavity of a subject is distended by continuous flow irrigation using a solenoid operated pump on the inflow side and a positive displacement pump, such as a peristaltic pump, on the outflow side, such that the amplitude of the pressure pulsations created by the outflow positive displacement pump inside the said tissue cavity is substantially dampened to almost negligible levels. The present invention also provides a method for accurately determining the rate of fluid loss into the subject's body system during any endoscopic procedure without utilizing any deficit weight or fluid volume calculation, the same being accomplished by using two fluid flow rate sensors. The present invention also provides a system of creating and maintaining any desired pressure in a body tissue cavity for any desired cavity outflow rate.

Owner:KUMAR BV

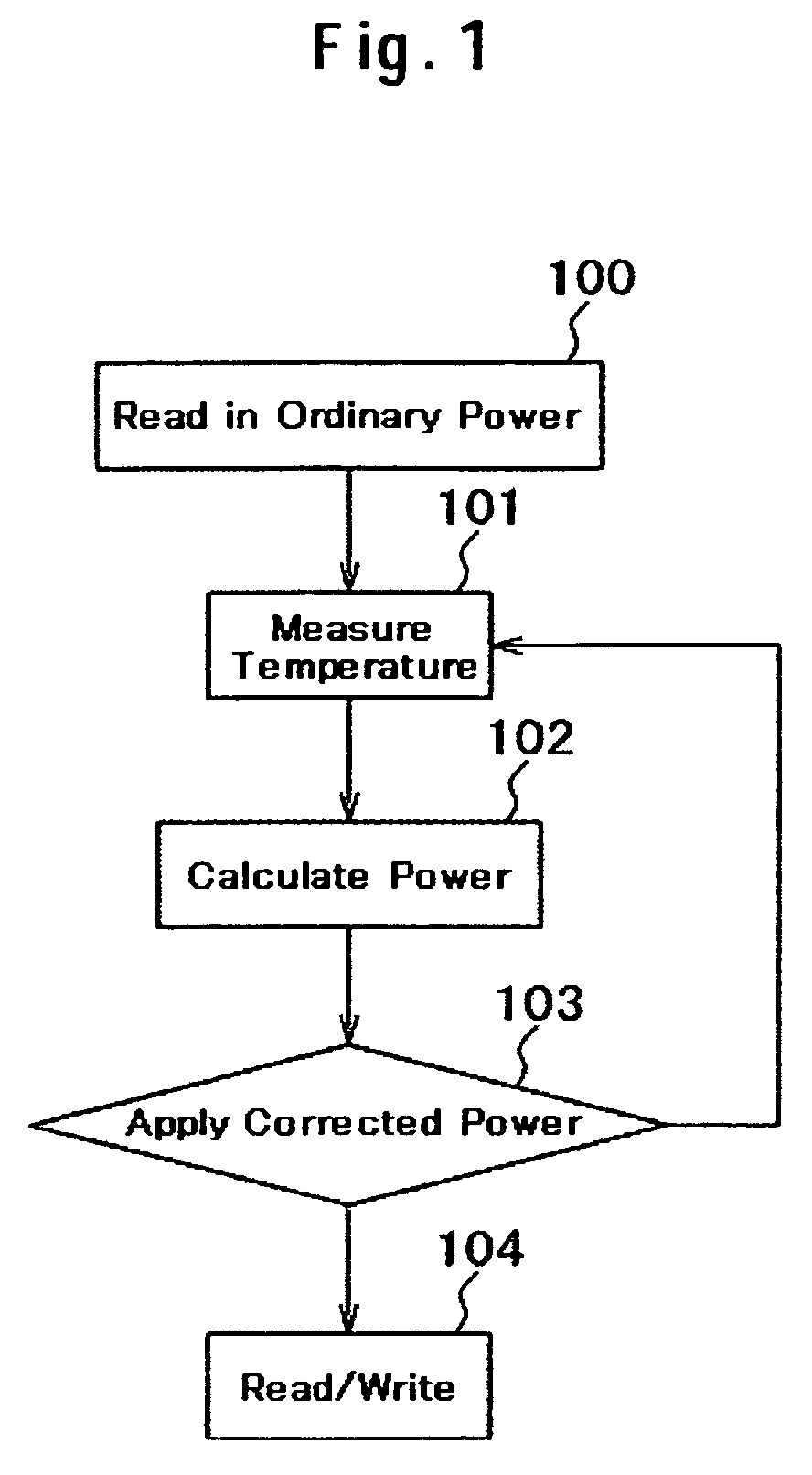

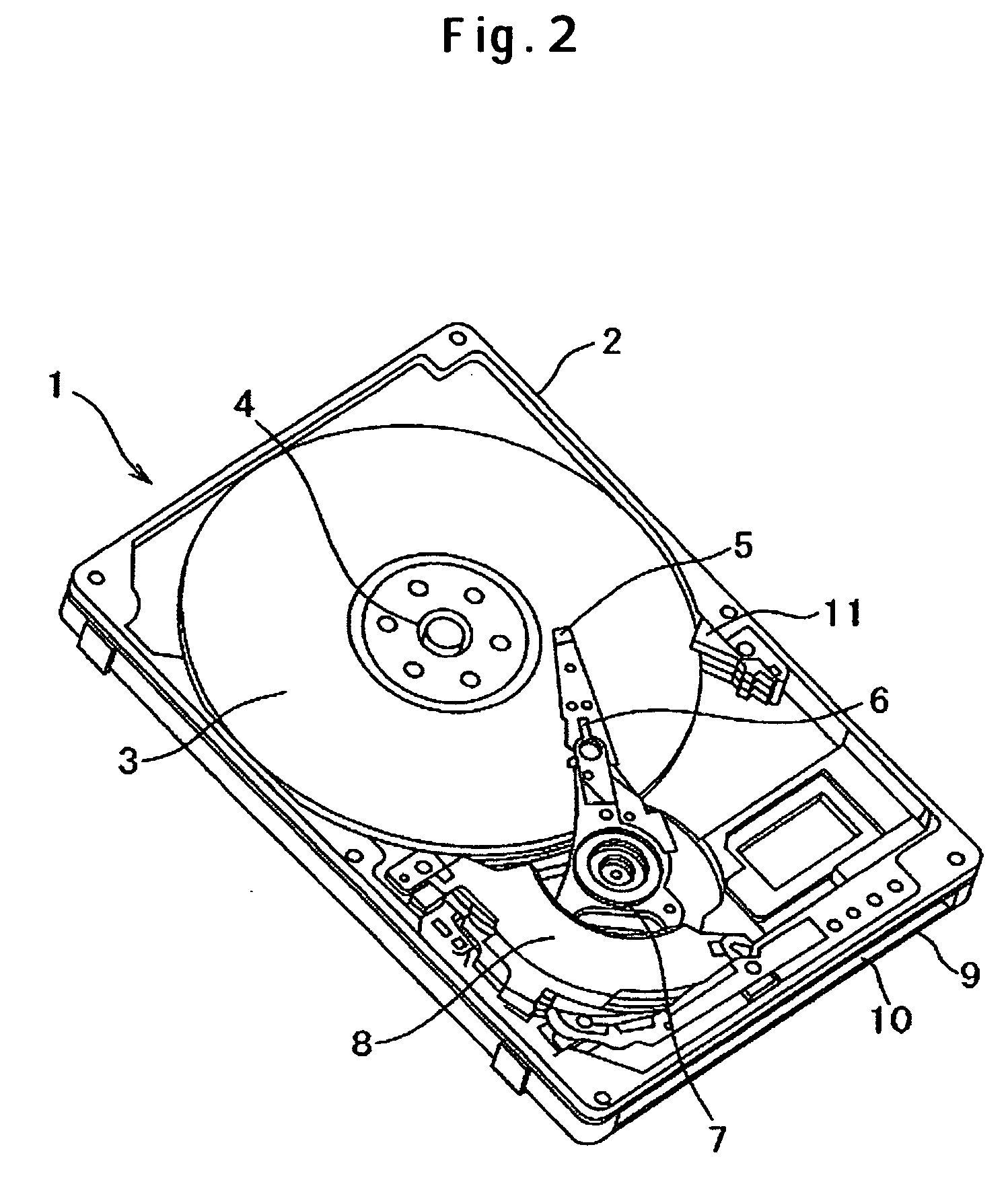

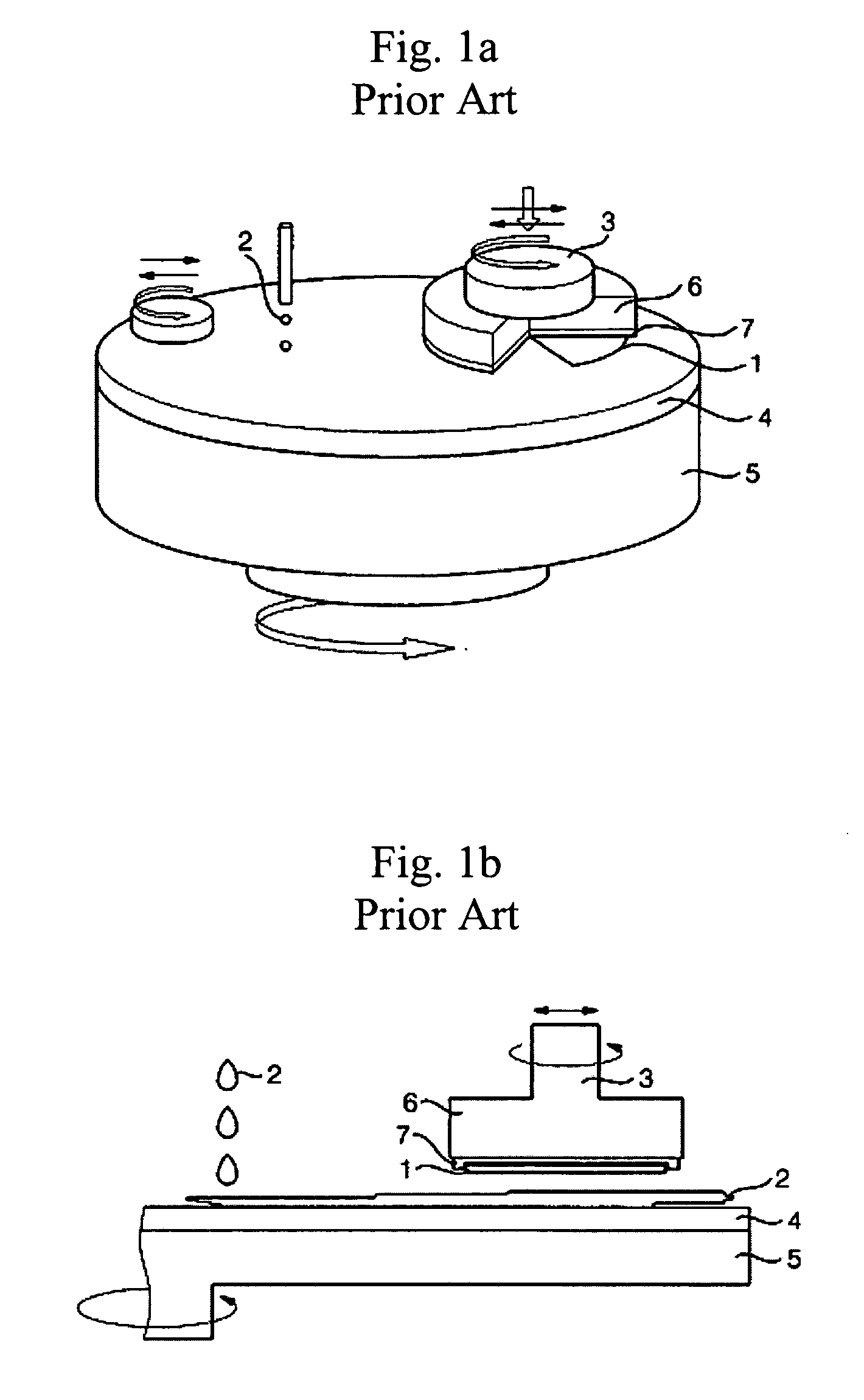

Magnetic disk drive with flying height control system

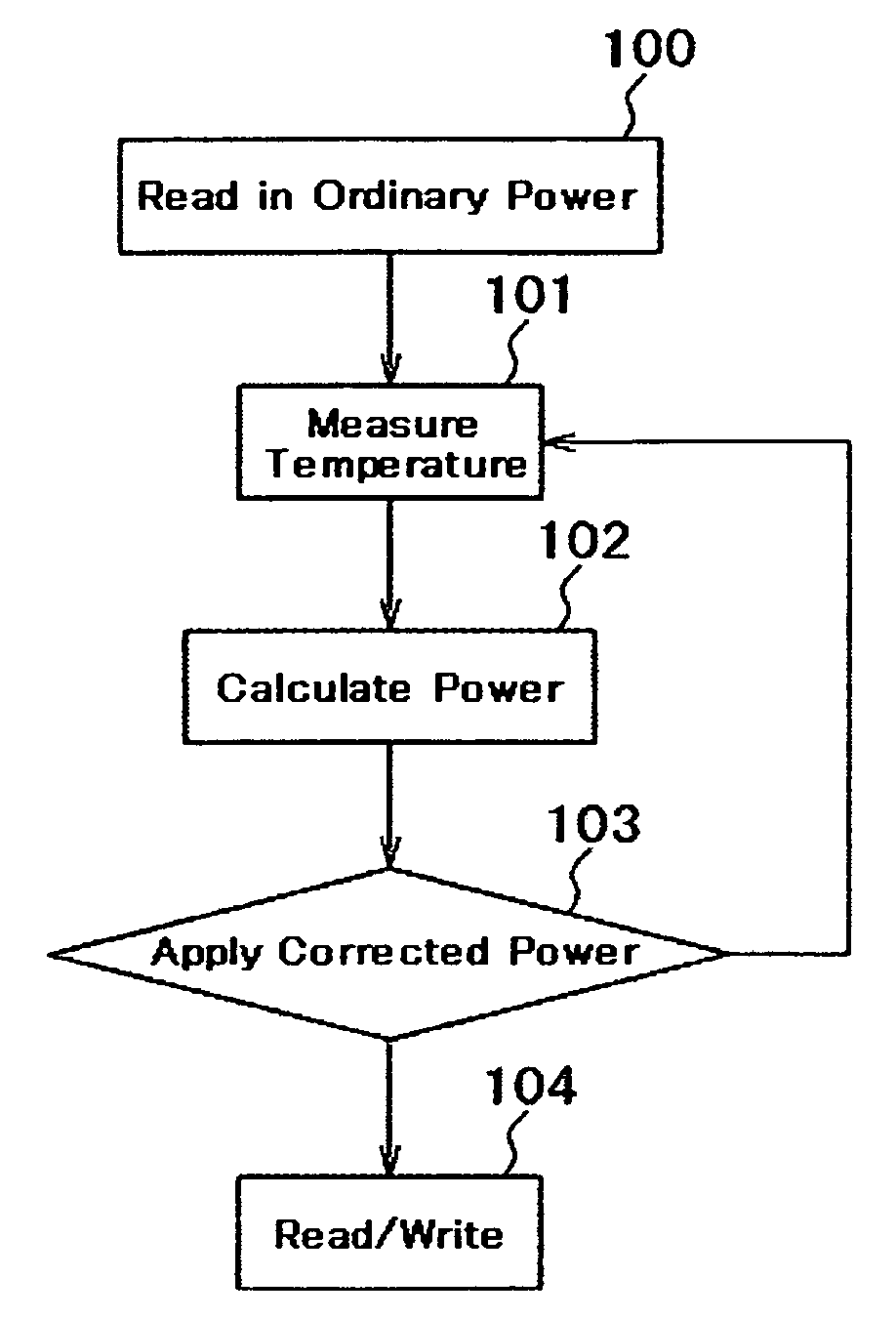

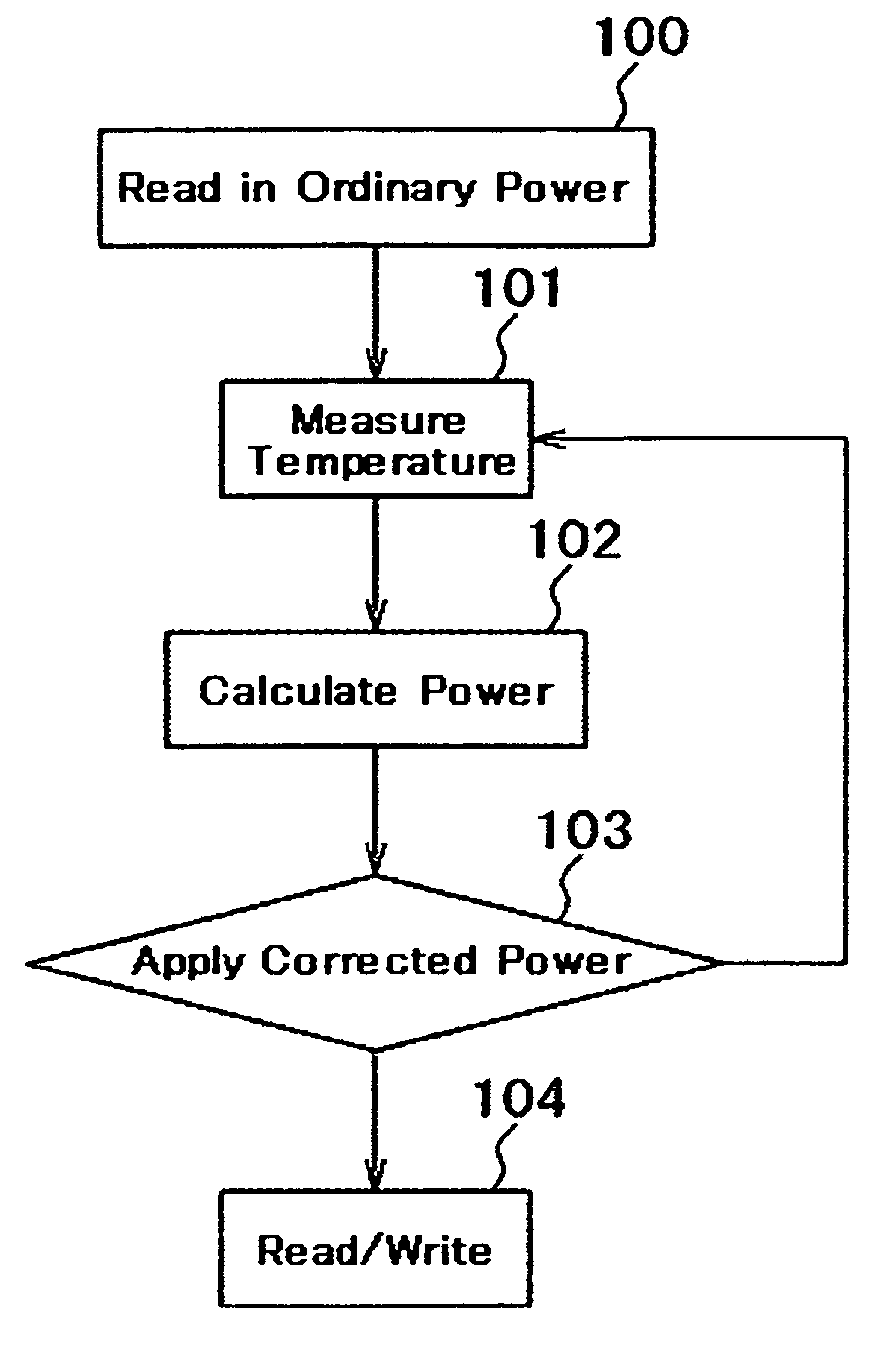

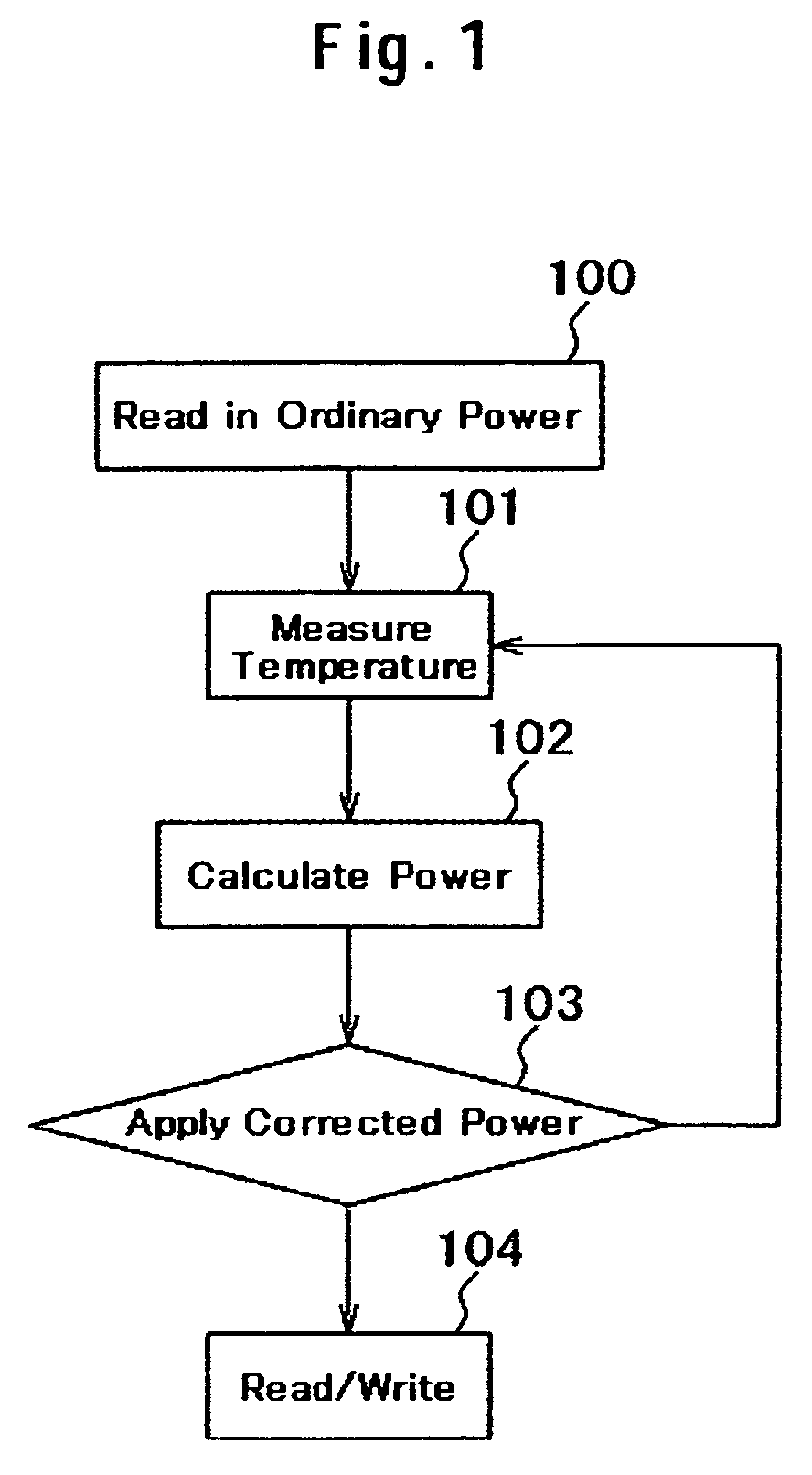

InactiveUS20060119974A1Improve reliabilityLarge storage capacityDriving/moving recording headsFilamentary/web record carriersInternal memoryControl system

Embodiments of the invention appropriately control the flying height of a magnetic head slider as necessary without making the magnetic head slider touch the magnetic disk. In one embodiment, when a magnetic disk drive is started, the level of electric power predefined for the ordinary temperature (room temperature) is read in from the internal memory of an MPU. A temperature sensor measures the internal temperature of the magnetic disk drive and sends it to the MPU. According to the temperature sent from the temperature sensor, the MPU calculates the level of electric power which should be applied to a flying height adjustment structure. According to the calculated electric power, the MPU increases or decreases the electric power applied to the flying height adjustment structure. At a flying height controlled (corrected) by the flying height adjustment structure, a magnetic head slider performs read / write on a magnetic disk.

Owner:WESTERN DIGITAL TECH INC

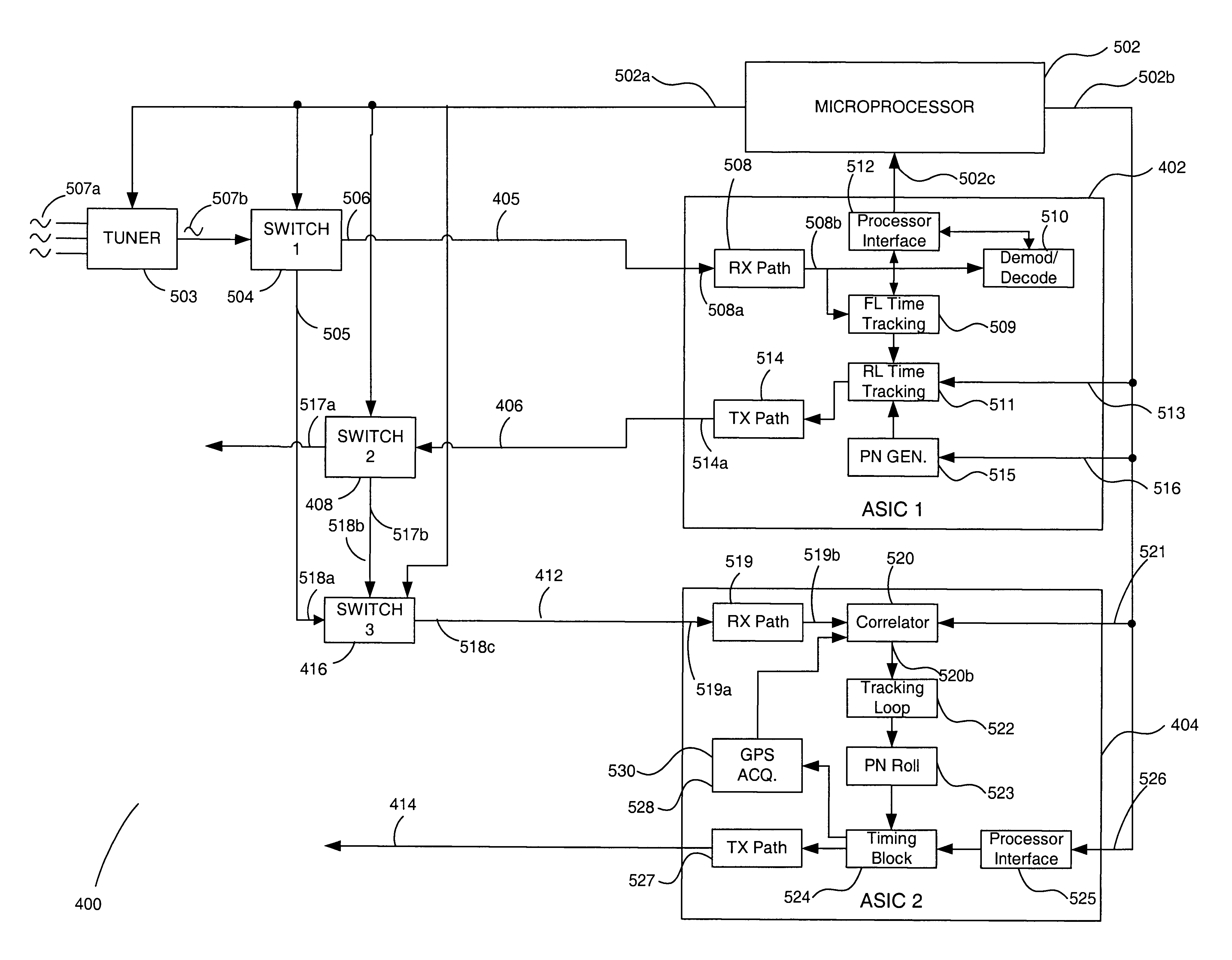

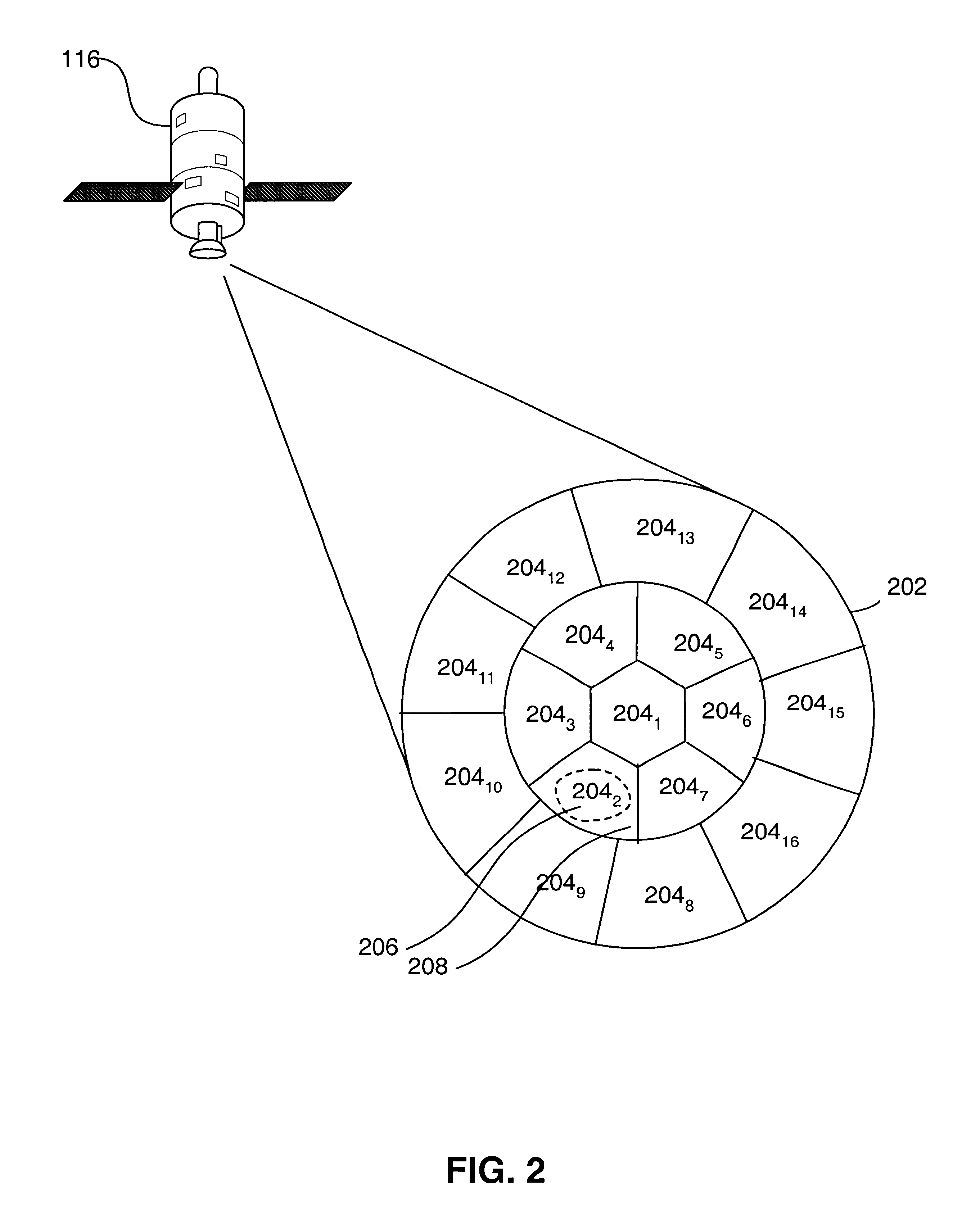

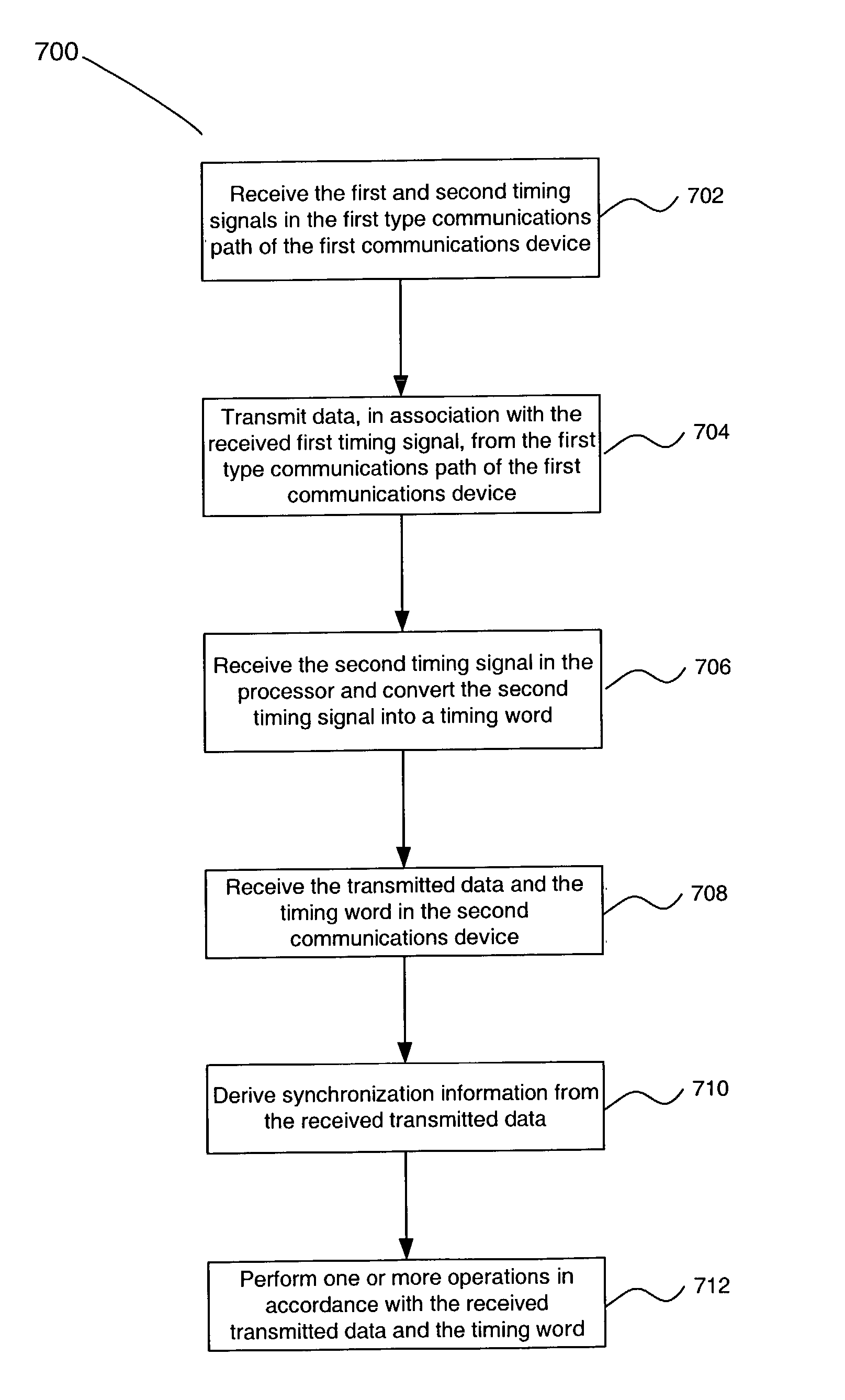

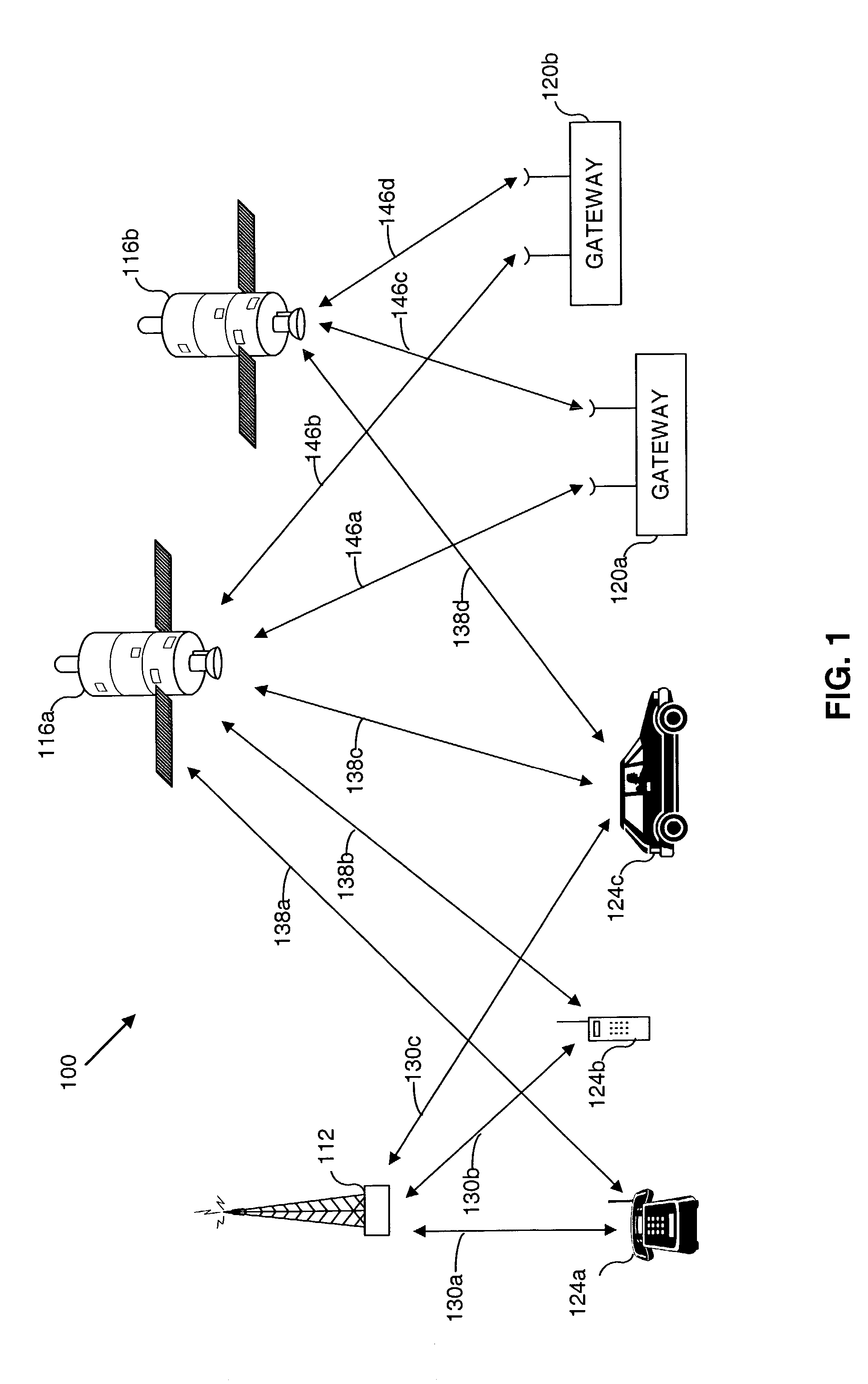

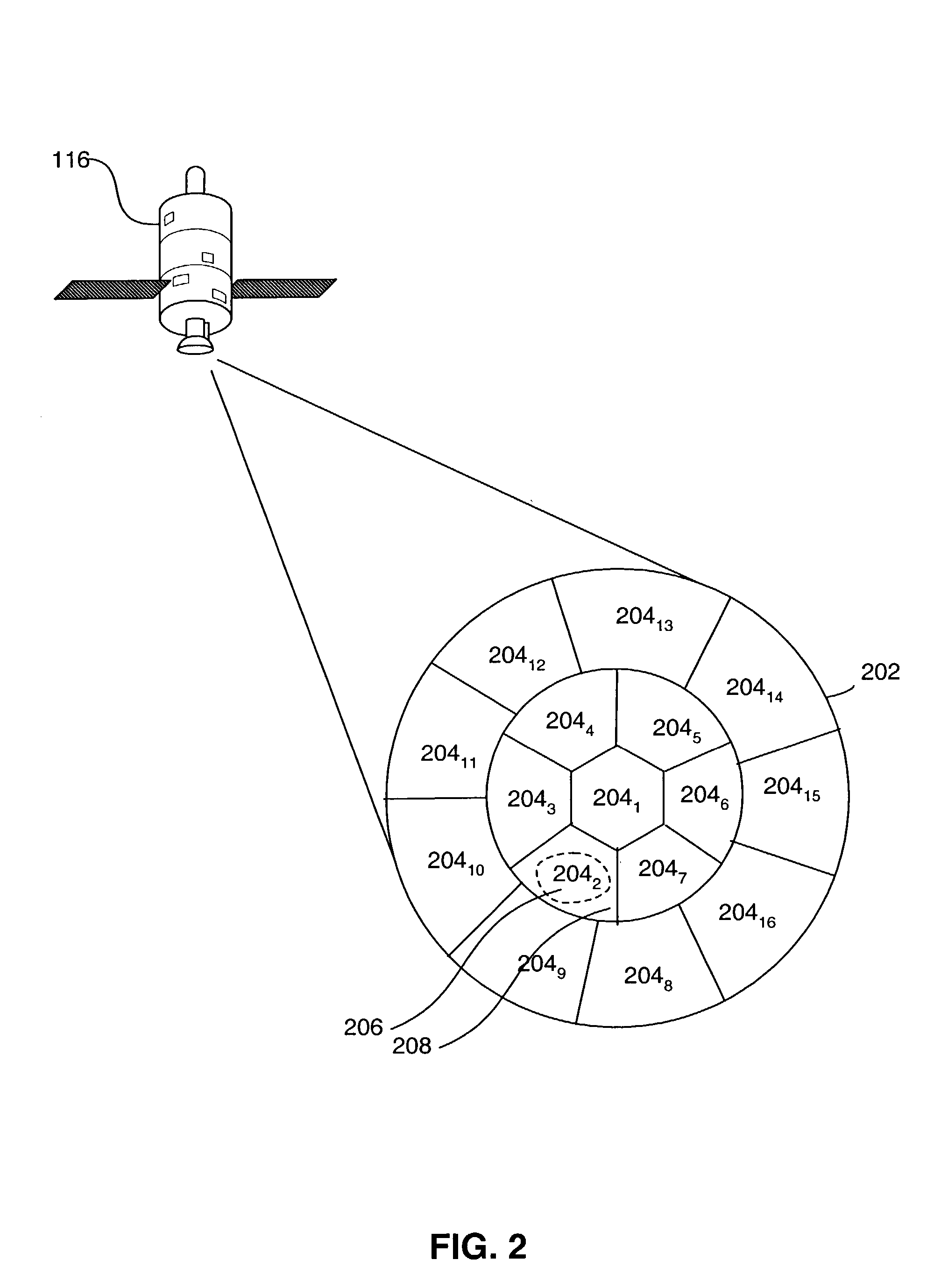

Synchronizing timing between multiple air link standard signals operating within a communications terminal

InactiveUS6836506B2Minimize frequencyAcquisition of of quickly and accuratelySynchronisation arrangementCode division multiplexProcessor elementComputer terminal

Owner:QUALCOMM INC

Synchronizing timing between multiple air link standard signals operating within a communications terminal

InactiveUS20040042576A1Minimize frequencyAcquisition of of quickly and accuratelySynchronisation arrangementCode division multiplexProcessor elementComputer terminal

A system and method for synchronizing a number of specialized circuits or application-specific integrated circuits to a common timing standard is provided. The system includes a first communications device including at least first and second type communication paths which is configured to receive first and second timing signals in the first type communications path and to transmit data on the second type communications path. The data is transmitted in association with the received first timing signal. A controller or signal processor element is coupled to the first device and configured to receive the second timing signal and produce a timing word therefrom. A second communications device is coupled to the processor and configured to receive the second timing signal and produce a timing word therefrom. The second communications. device receives the timing word and the transmitted data and derives synchronization information therefrom. The derived synchronization information is related to the first timing signal. The second communications device performs one or more operations in accordance with the received second timing signal and the derived synchronization information.

Owner:QUALCOMM INC

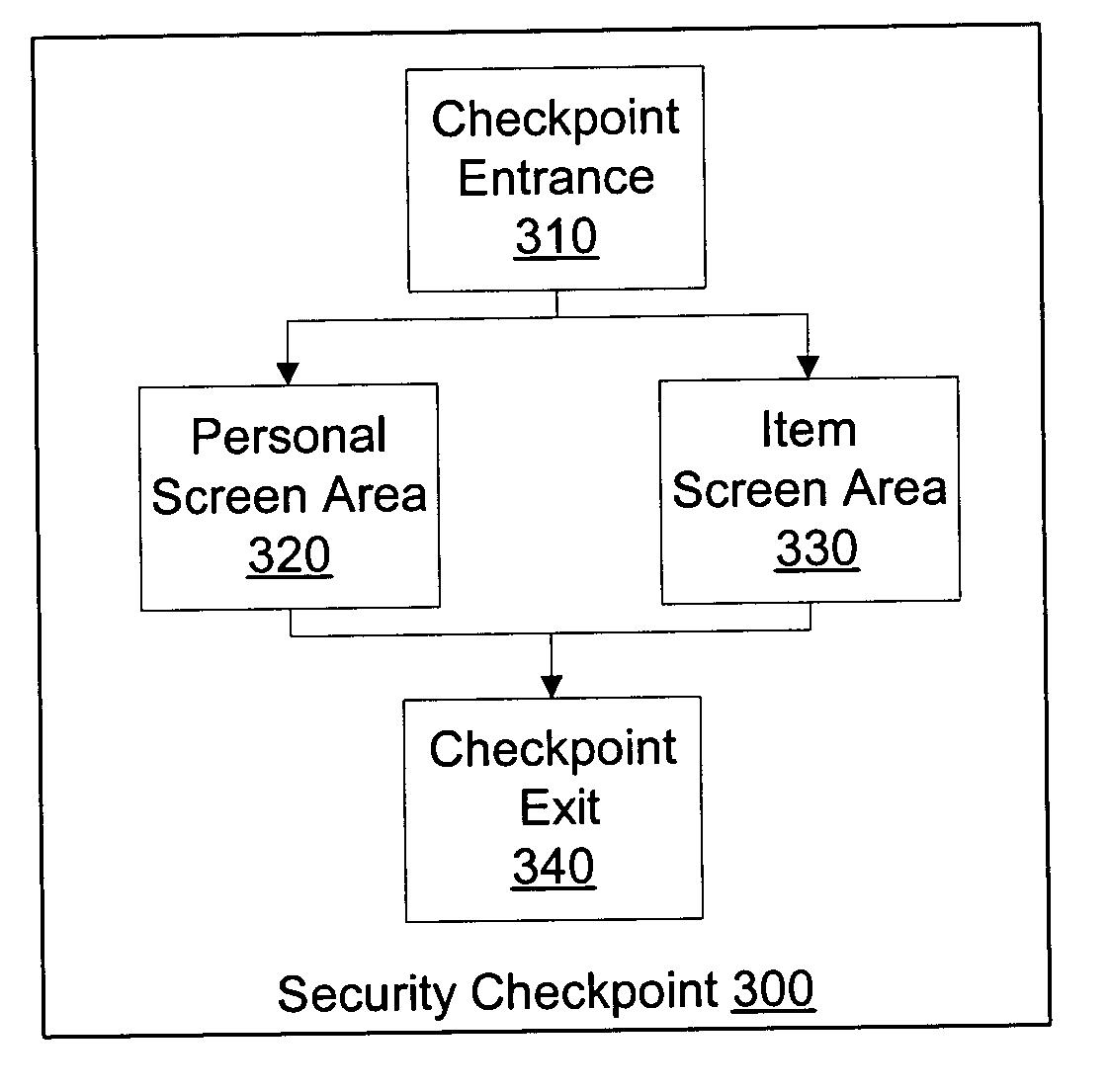

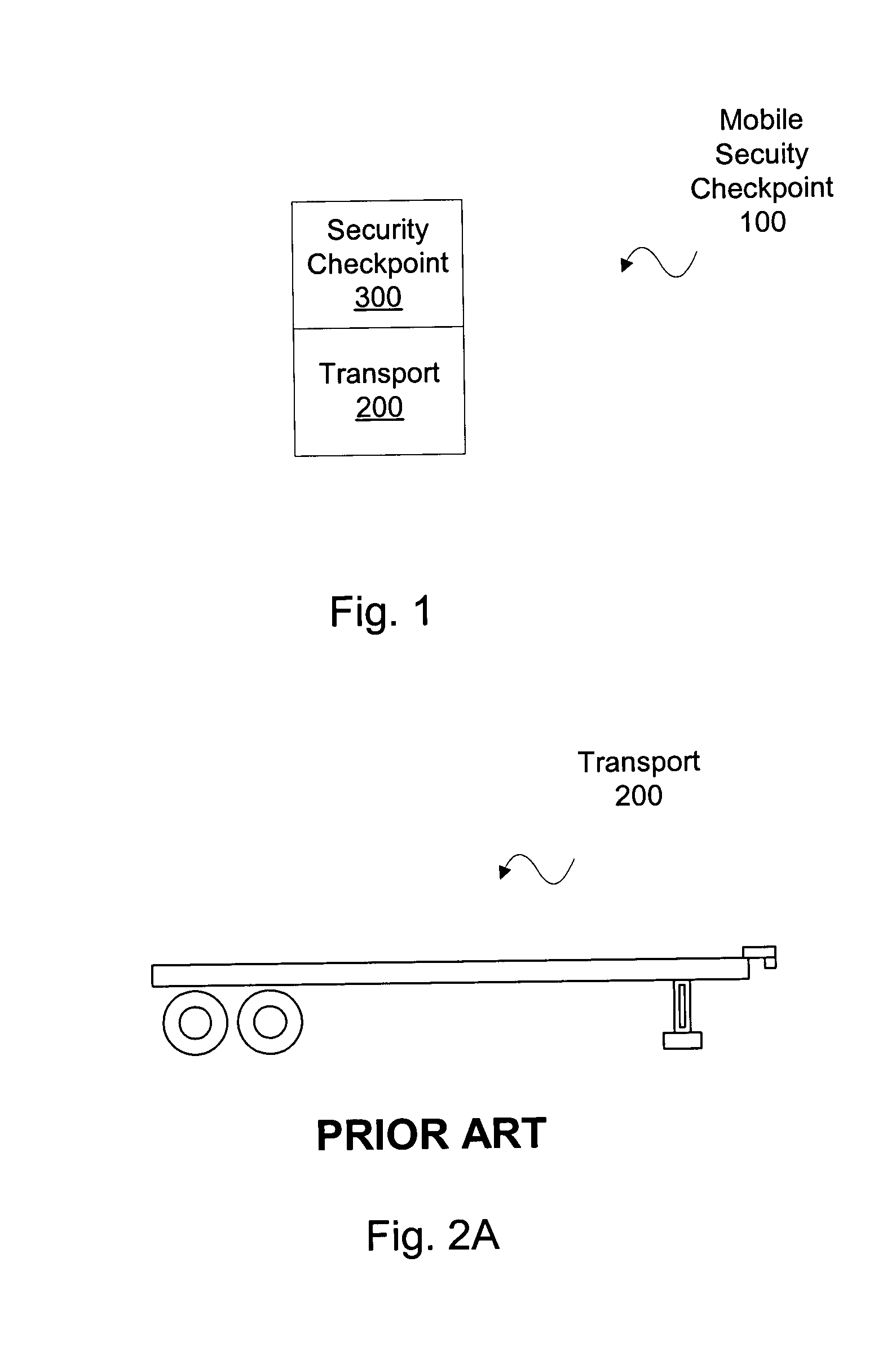

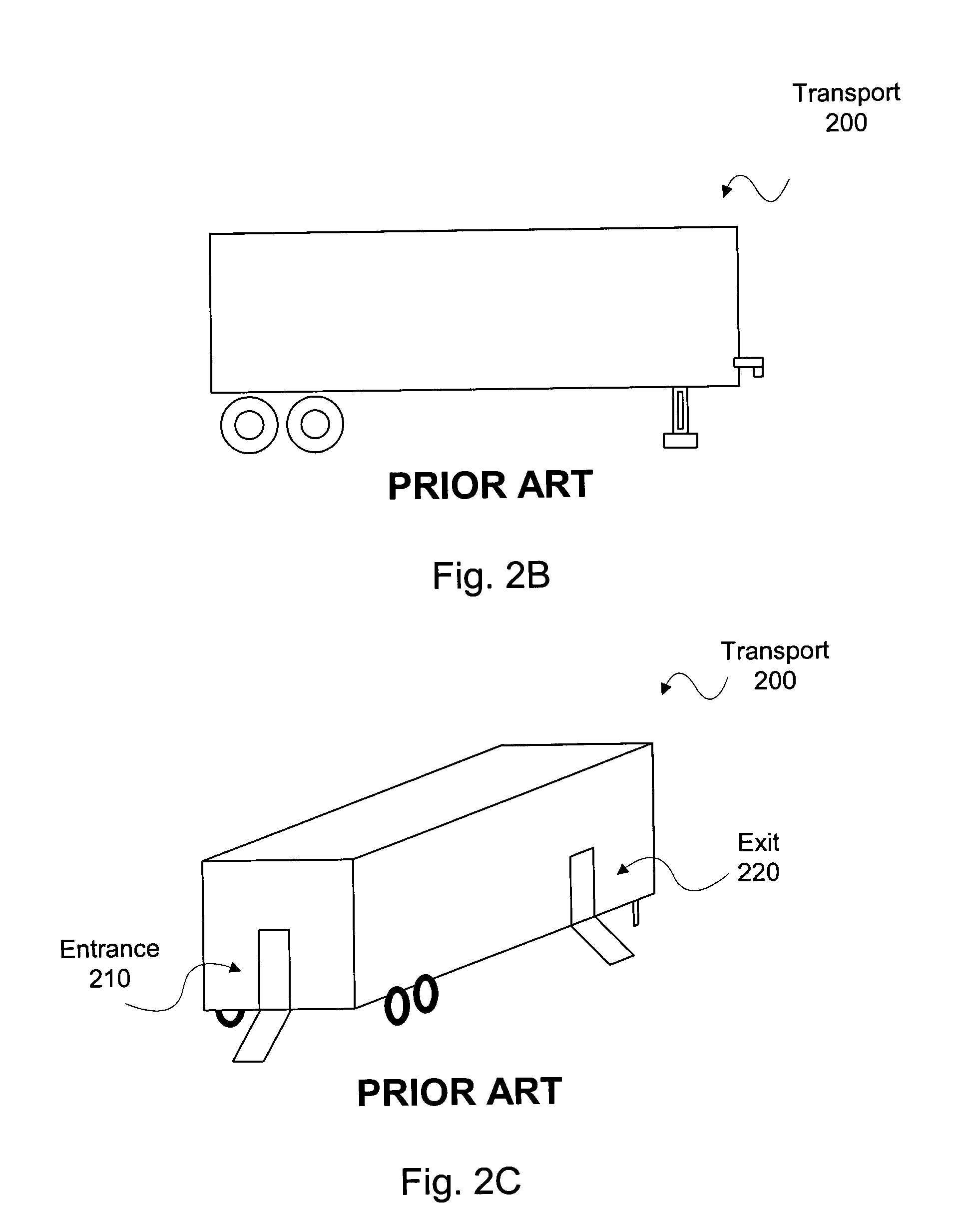

Mobile security unit

ActiveUS20050074086A1Minimize frequencyImprove throughputMaterial analysis using wave/particle radiationRadiation/particle handlingTelecommunicationsMobile security

A Mobile Security Unit (MSU) has a security checkpoint and a transport. The security checkpoint has an item screening area and a personal screening area. The checkpoint is configured as needed to fit within the transport. The MSU may further separate certain individuals into a secure, enclosed wanding station for additional security screening. The wanding station may be constructed using glass (or other strong, visually transparent substance) and metallic (such as aluminum or steel) posts so that people may be securely enclosed in the wanding station but still have a direct line of sight to personal items being screened at another location. The MSU is configured so that most people pass straight through the checkpoint, and people leaving the wanding station can easily obtain their items without delaying others.

Owner:ACCENTURE GLOBAL SERVICES LTD

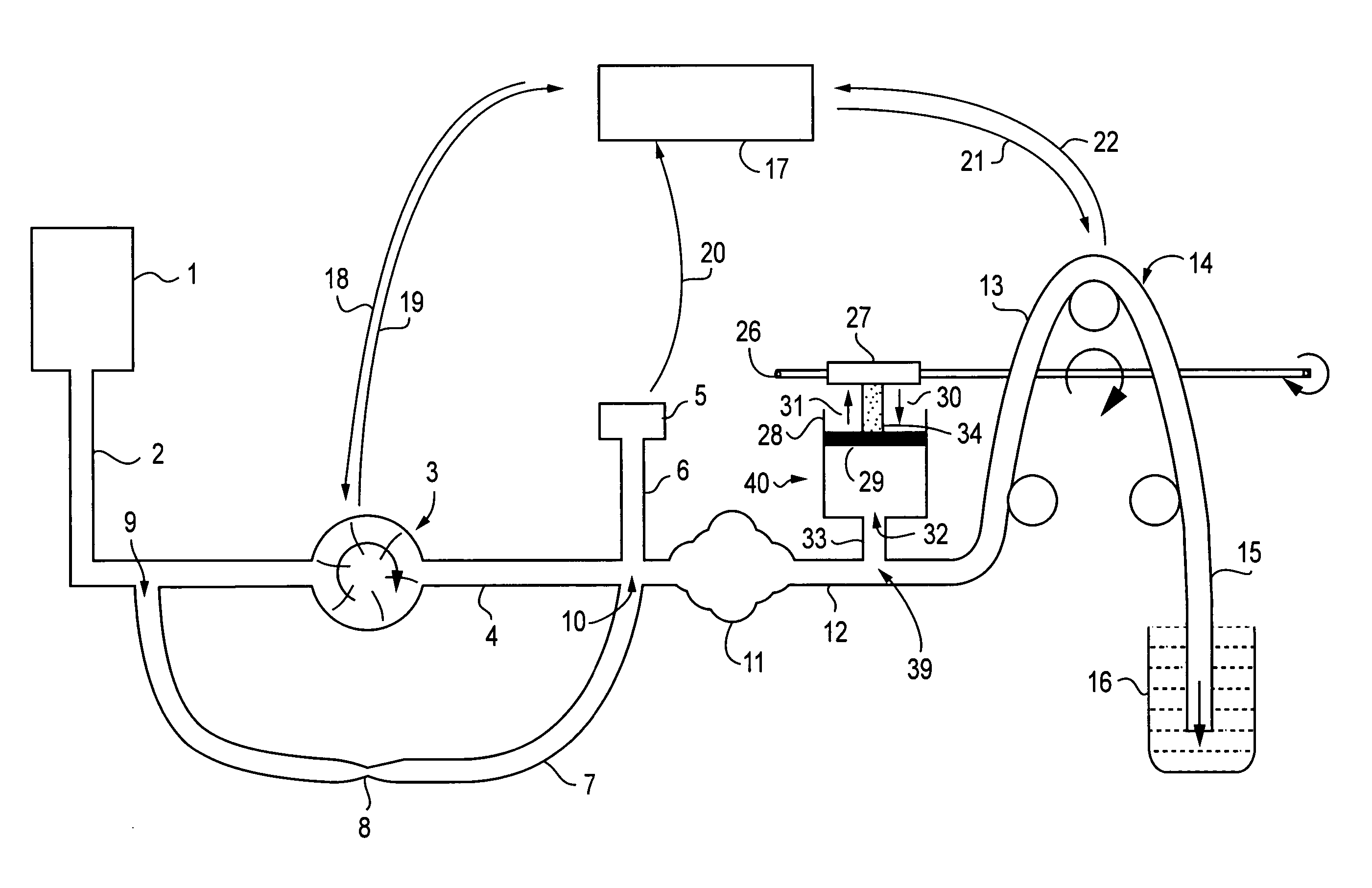

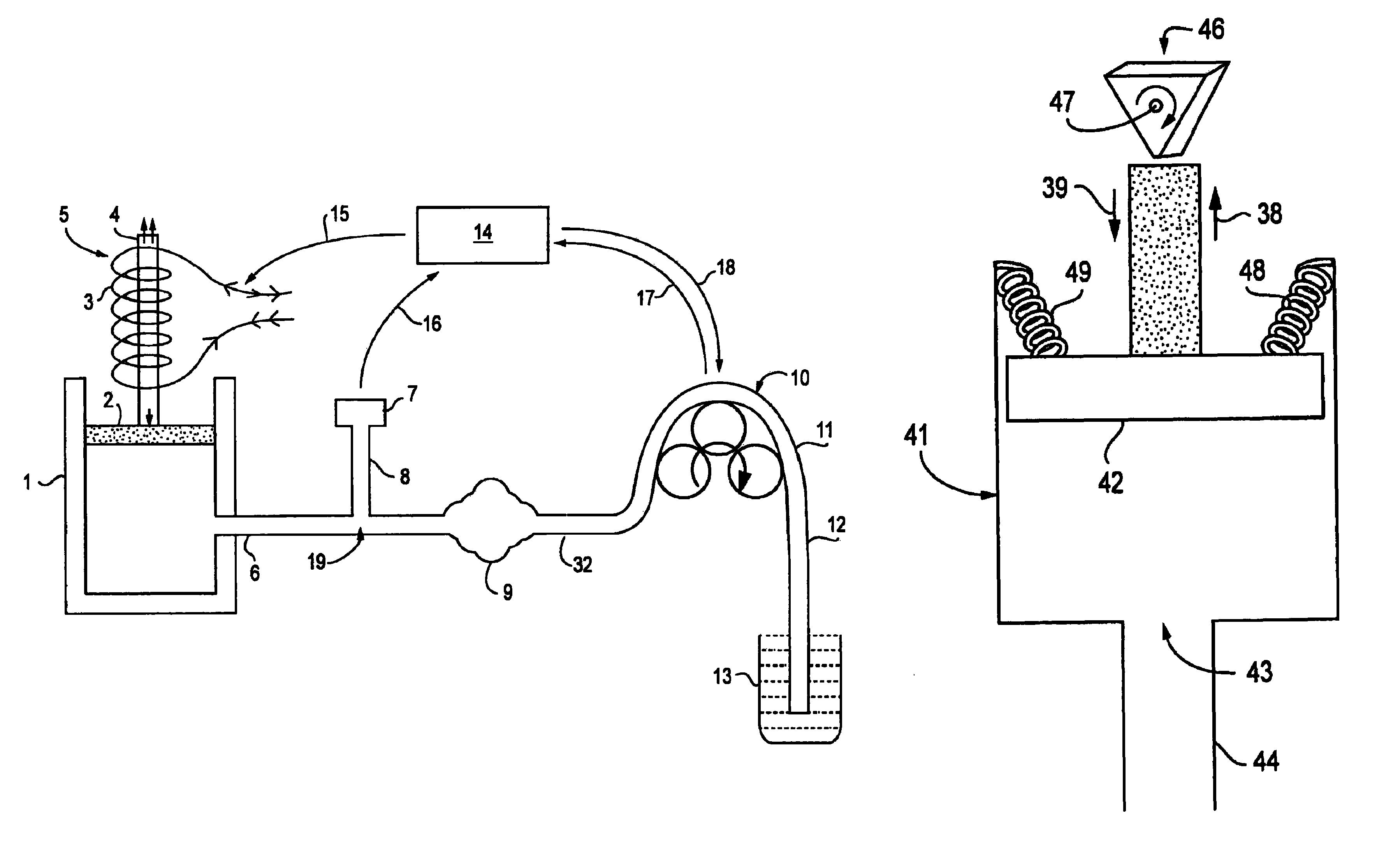

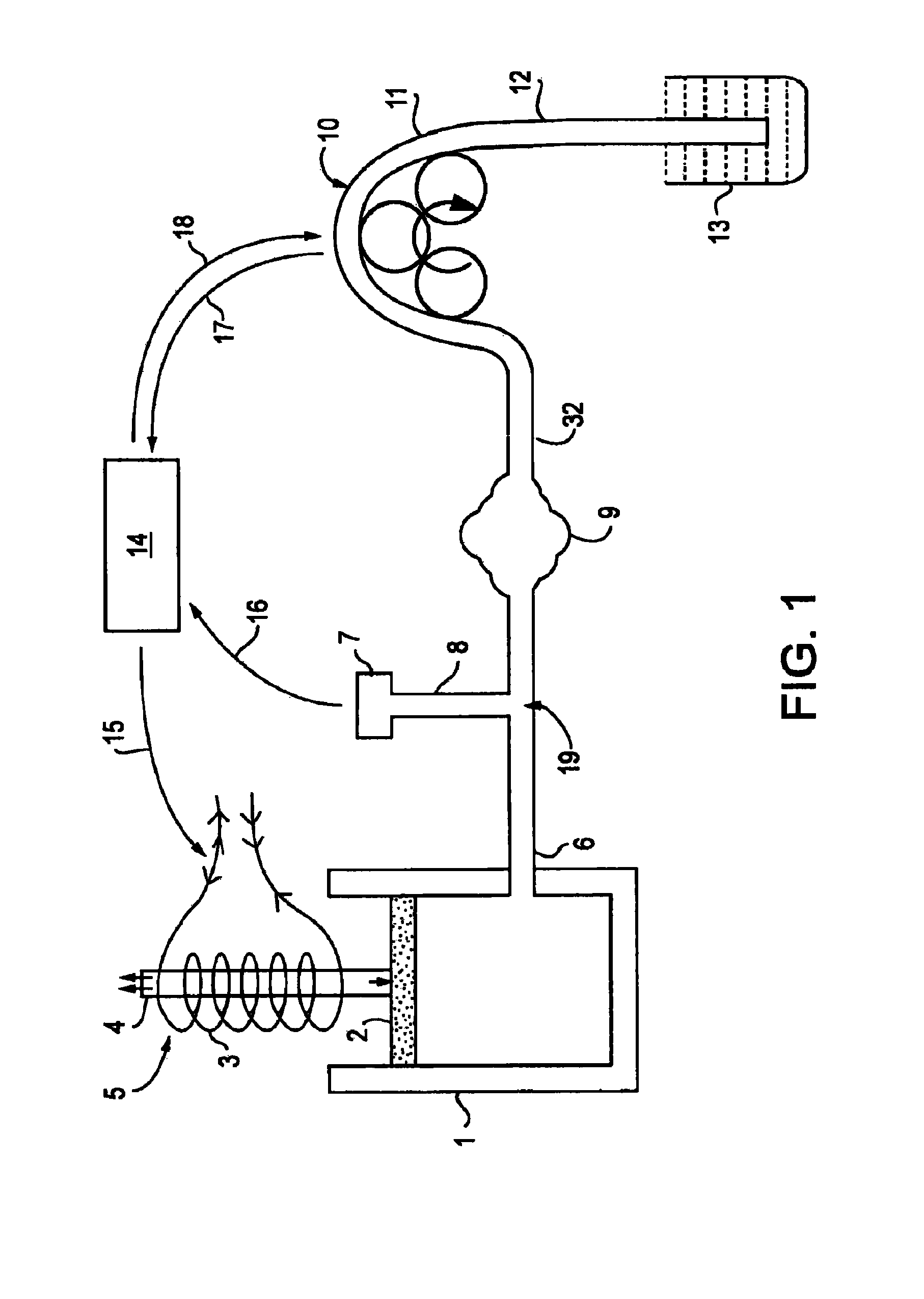

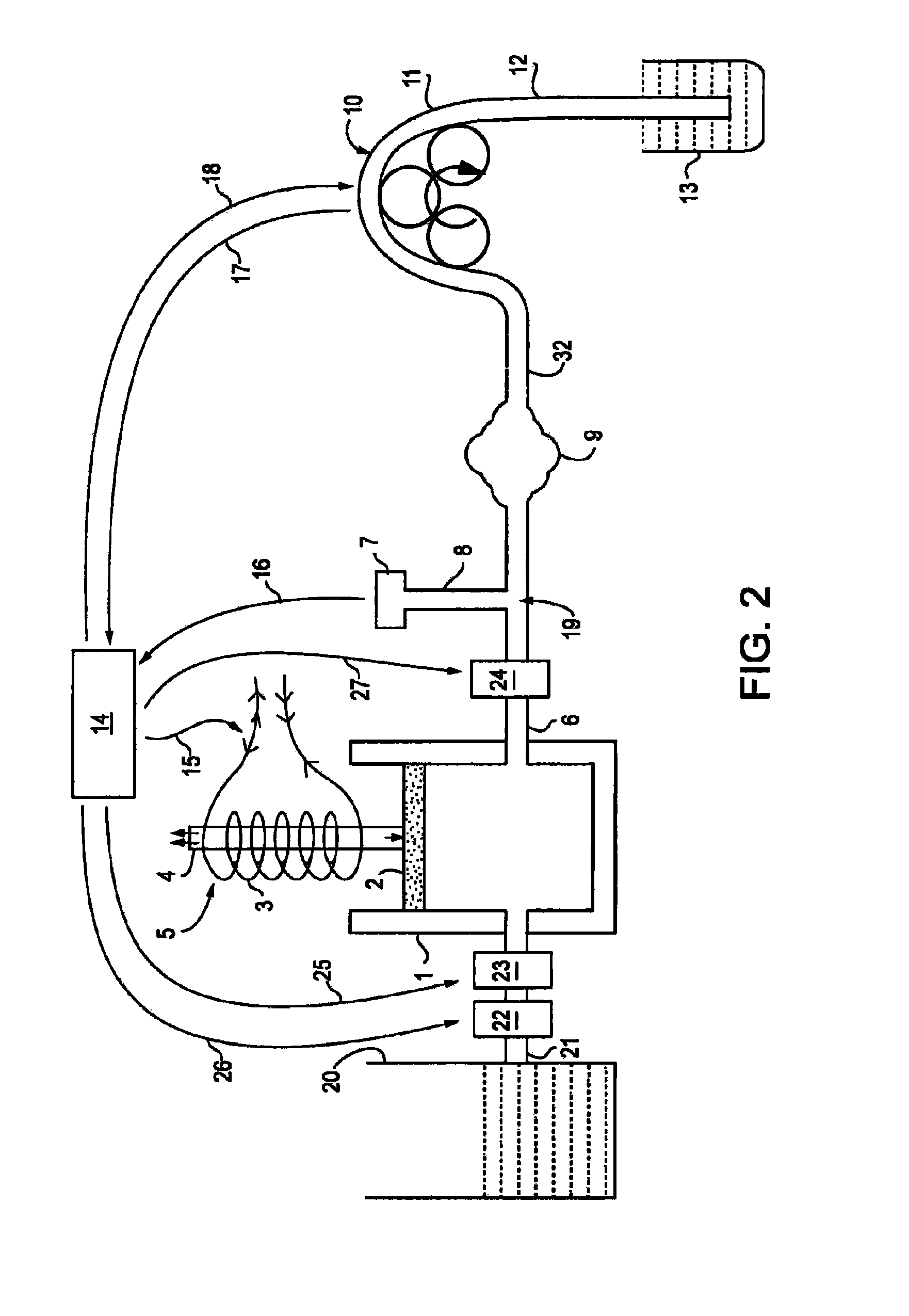

Controlled tissue cavity distending system with minimal turbulence

ActiveUS20060047240A1Safe and efficient and turbulenceSafe and efficient and turbulence free systemElectrotherapyMedical devicesPeristaltic pumpEngineering

The present invention provides a system and a method for distending a body tissue cavity of a subject by continuous flow irrigation by using a dynamic pump, such as a centrifugal pump, on the inflow side and a positive displacement pump, such as a peristaltic pump, on the outflow side, such that the amplitude of the pressure pulsations created by a the said outflow positive displacement pump inside the said tissue cavity is substantially dampened to almost negligible levels. The present invention also provides a method for accurately determining the rate of fluid loss, into the subject's body system, during any endoscopic procedure without utilizing any deficit weight or fluid volume calculation, the same being accomplished by using two fluid flow rate sensors. The present invention also provides a system of creating and maintaining any desired pressure in a body tissue cavity for any desired cavity outflow rate. The system and the methods of the present invention described above can be used in any endoscopic procedure requiring continuous flow irrigation few examples of such endoscopic procedures being hysteroscopic surgery, arthroscopic surgery, trans uretheral surgery, endoscopic surgery of the brain and endoscopic surgery of the spine.

Owner:KUMAR BV

System of dampening pressure pulsations caused by a positive displacement pump in endoscopic surgery

ActiveUS7678070B2Minimizing amplitudeMinimize frequencyMedical syringesSuction devicesEndoscopic ProcedureContinuous flow

A system for distending body tissue cavities of subjects by continuous flow irrigation during endoscopic procedures, the system including: a fluid source reservoir containing a non viscous physiologic fluid meant for cavity distension; a fluid supply conduit tube connecting the fluid source reservoir to an inlet port of a variable speed positive displacement inflow pump and an outlet port of the said inflow pump being connectable to an inflow port of an endoscope instrument through an inflow tube for pumping the fluid at a controlled flow rate into the cavity, the flow rate of the said inflow pump being termed as the inflow rate; an inflow pressure transducer being located anywhere in the inflow tube between the outlet port of the inflow pump and the inflow port of the endoscope; an outflow port of the endoscope being connectable to a waste fluid collecting container via a waste fluid carrying tube, and characterized in that an active inflow pressure pulsation dampening means is connected to the inflow tube for dampening the pressure pulsations inside the cavity created by the positive displacement inflow pump.

Owner:KUMAR BV

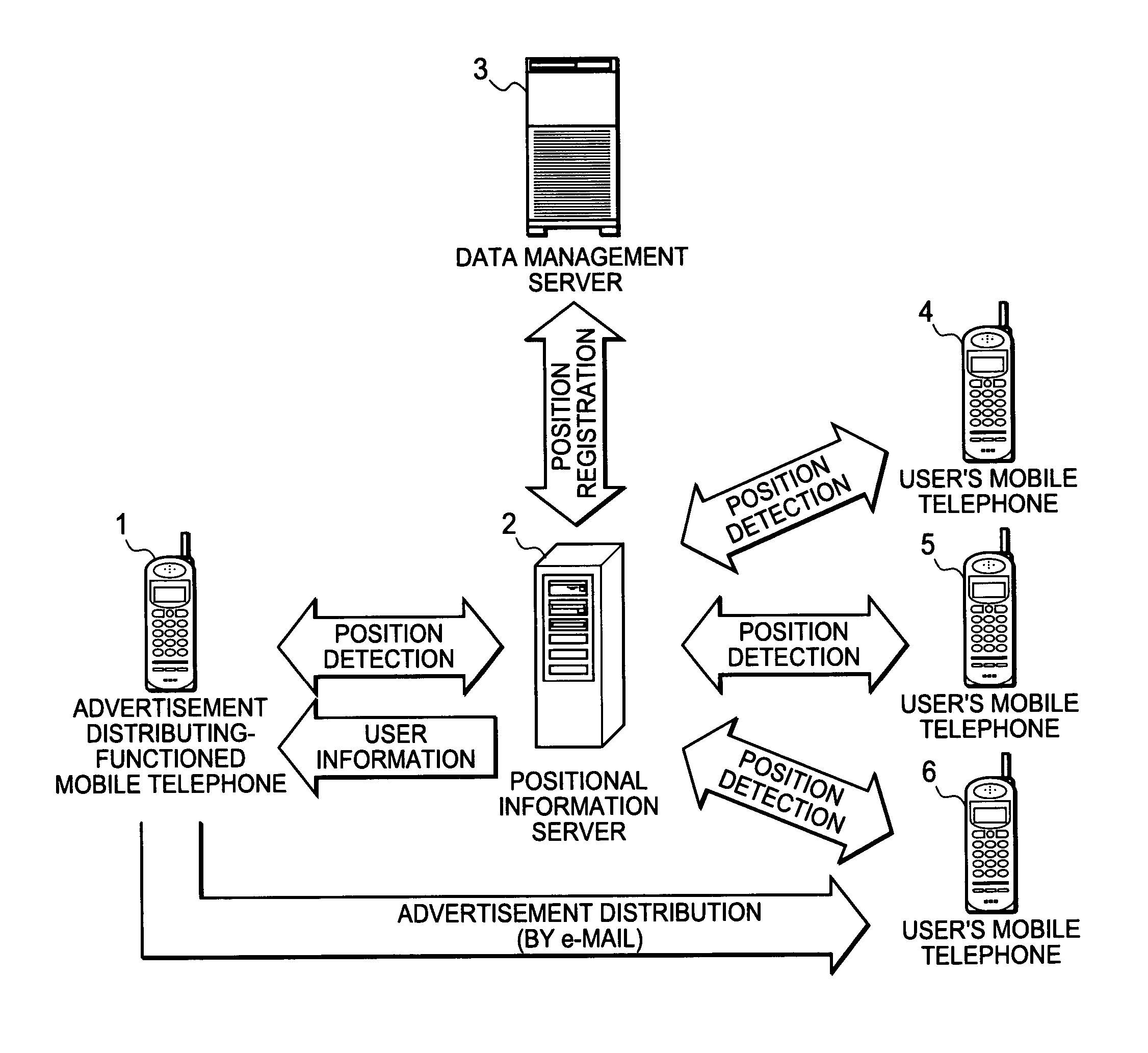

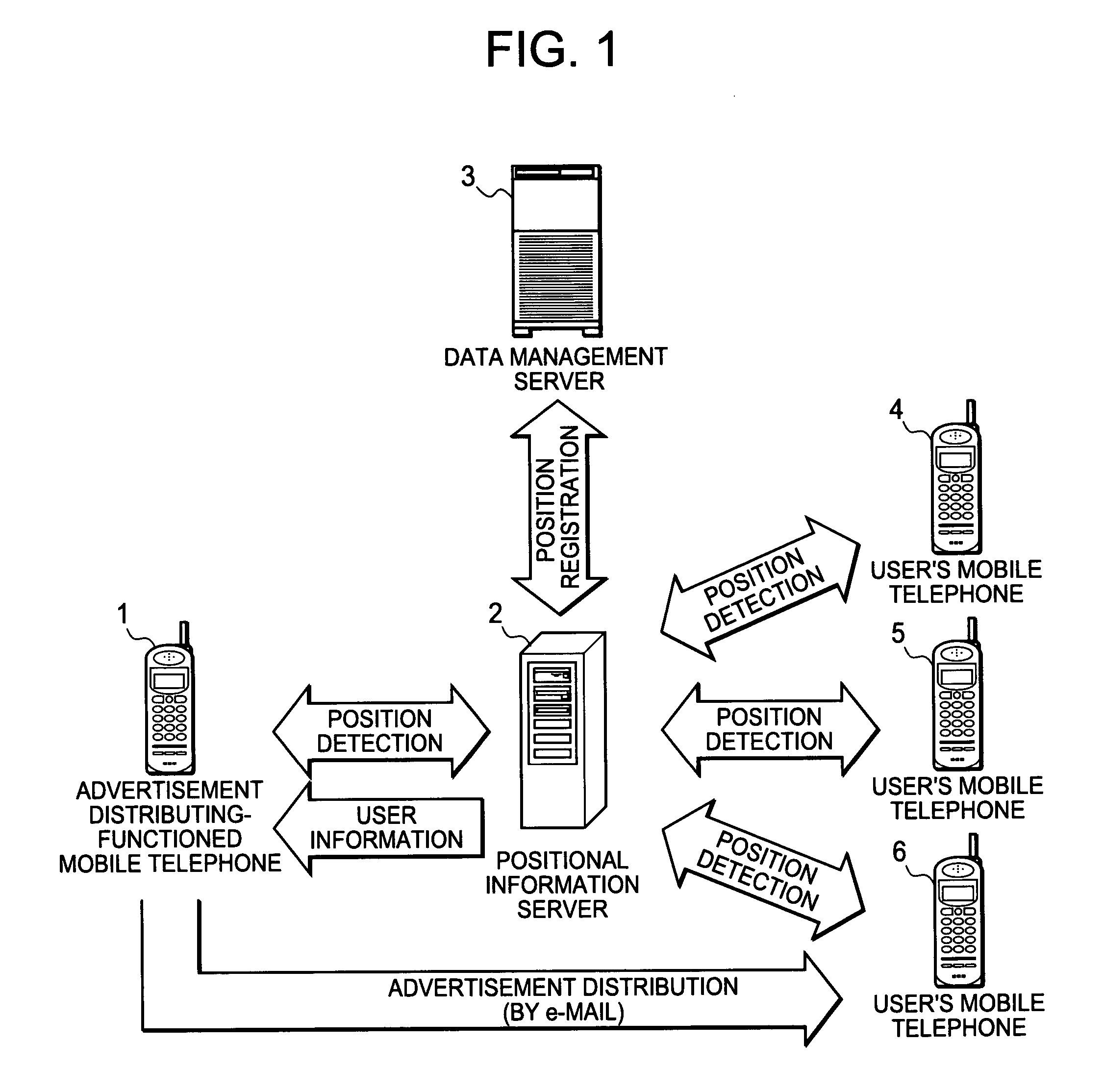

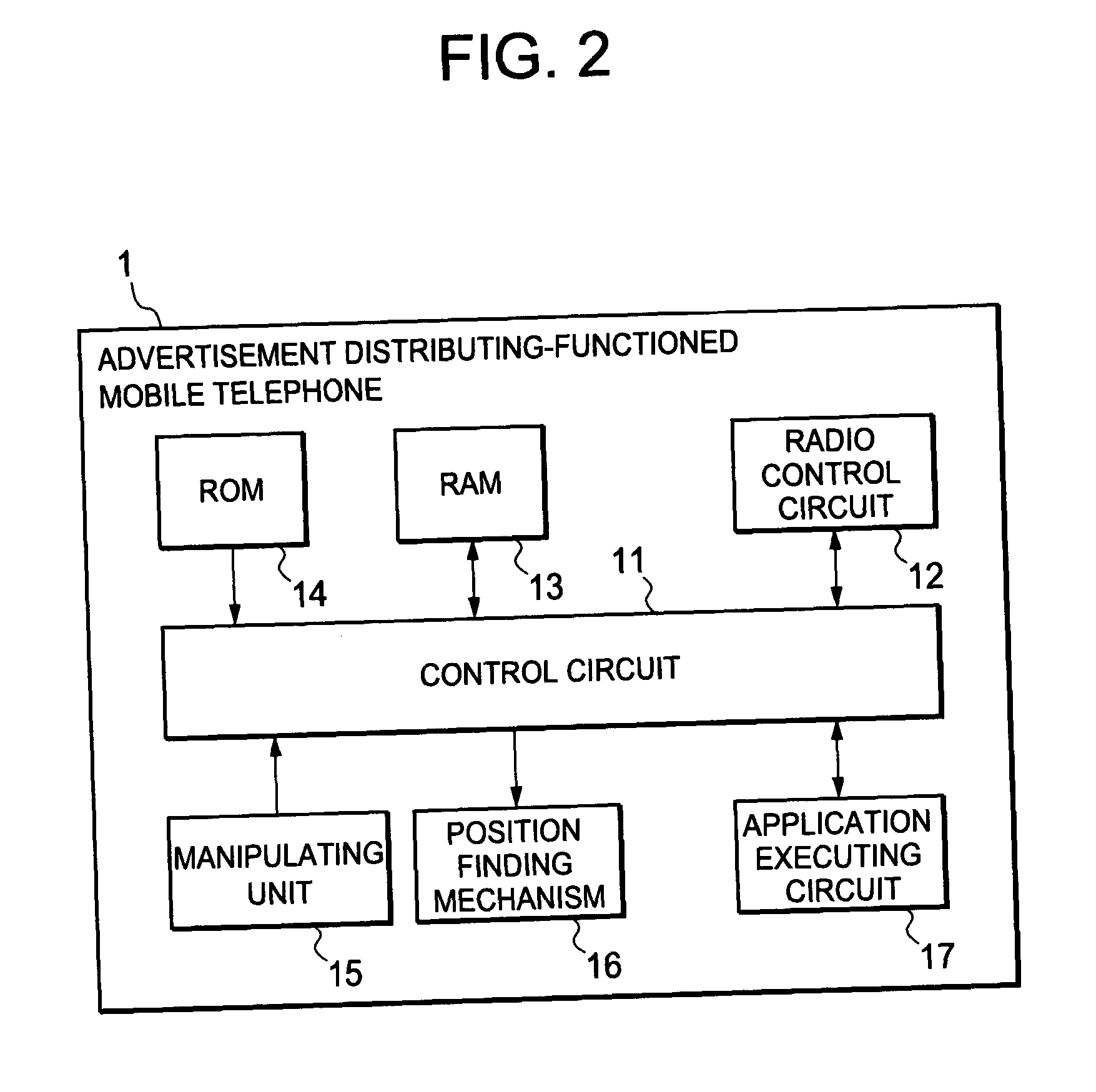

Mobile telephone, and advertisement distributing method and distributing system for its use

InactiveUS20040038665A1Minimize frequencyEasy to doSpecial service for subscribersActive radio relay systemsData managementComputer terminal

An advertisement distributing-functioned mobile telephone produces with an application in its own terminal an advertisement to be distributed, finds its position with a position finding mechanism such as a GPS, and registers its position with a data management server via a positional information server. A control unit controls other circuits in its own terminal, and selects users to whom the advertisement is to be distributed on the basis of user information acquired from the positional information server. A radio control unit acquires user information from the positional information server and distributes the advertisement.

Owner:NEC CORP

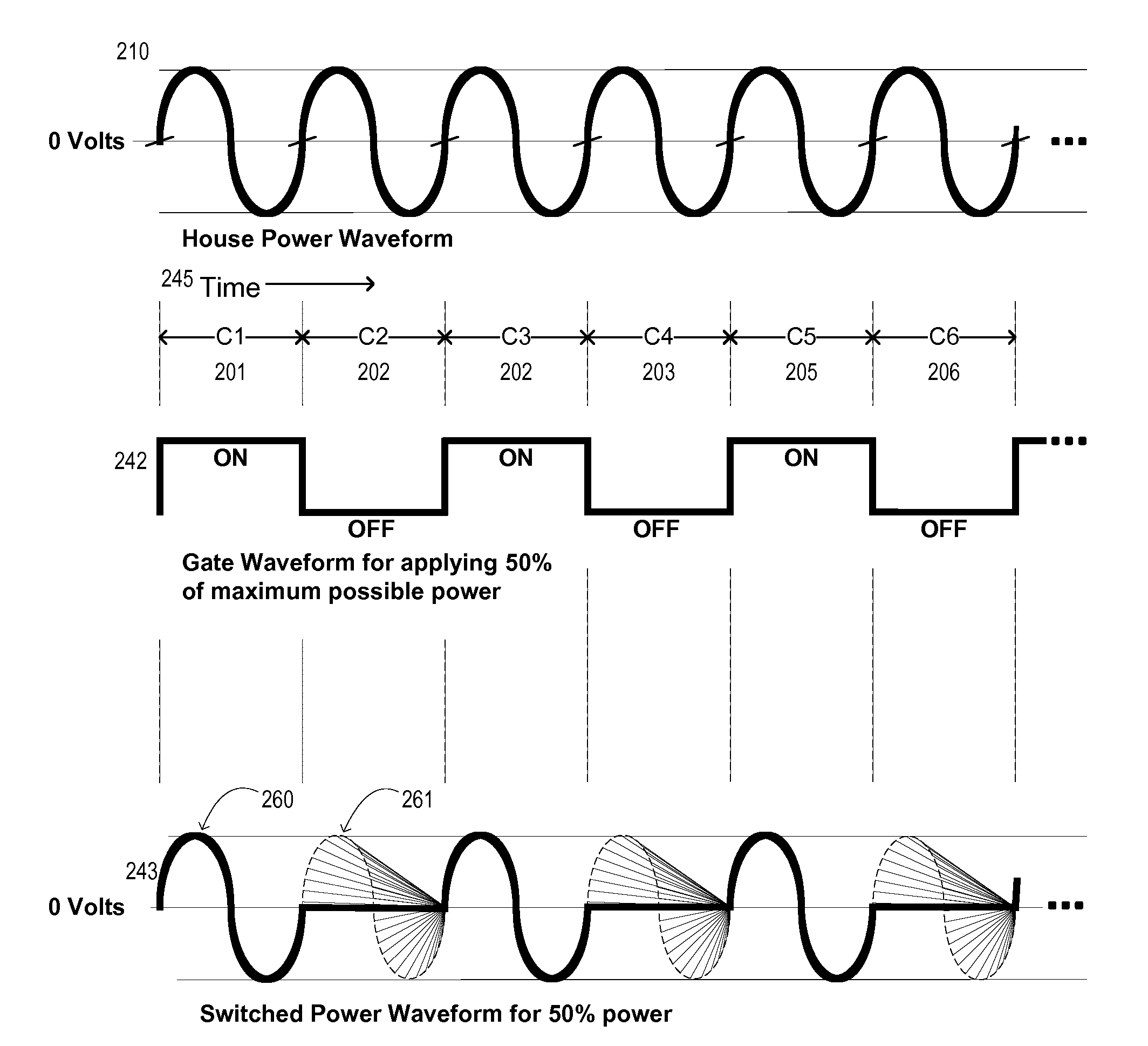

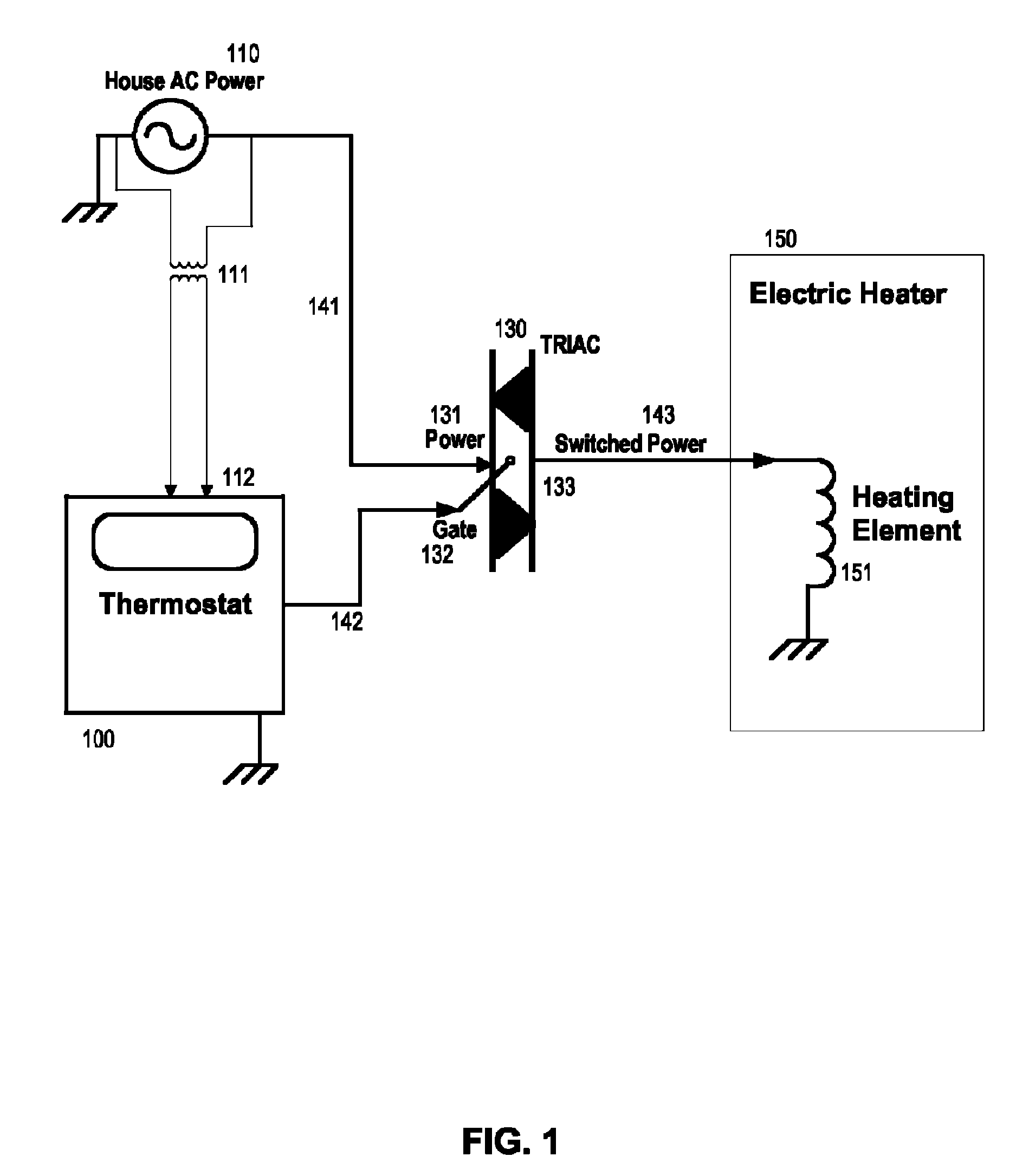

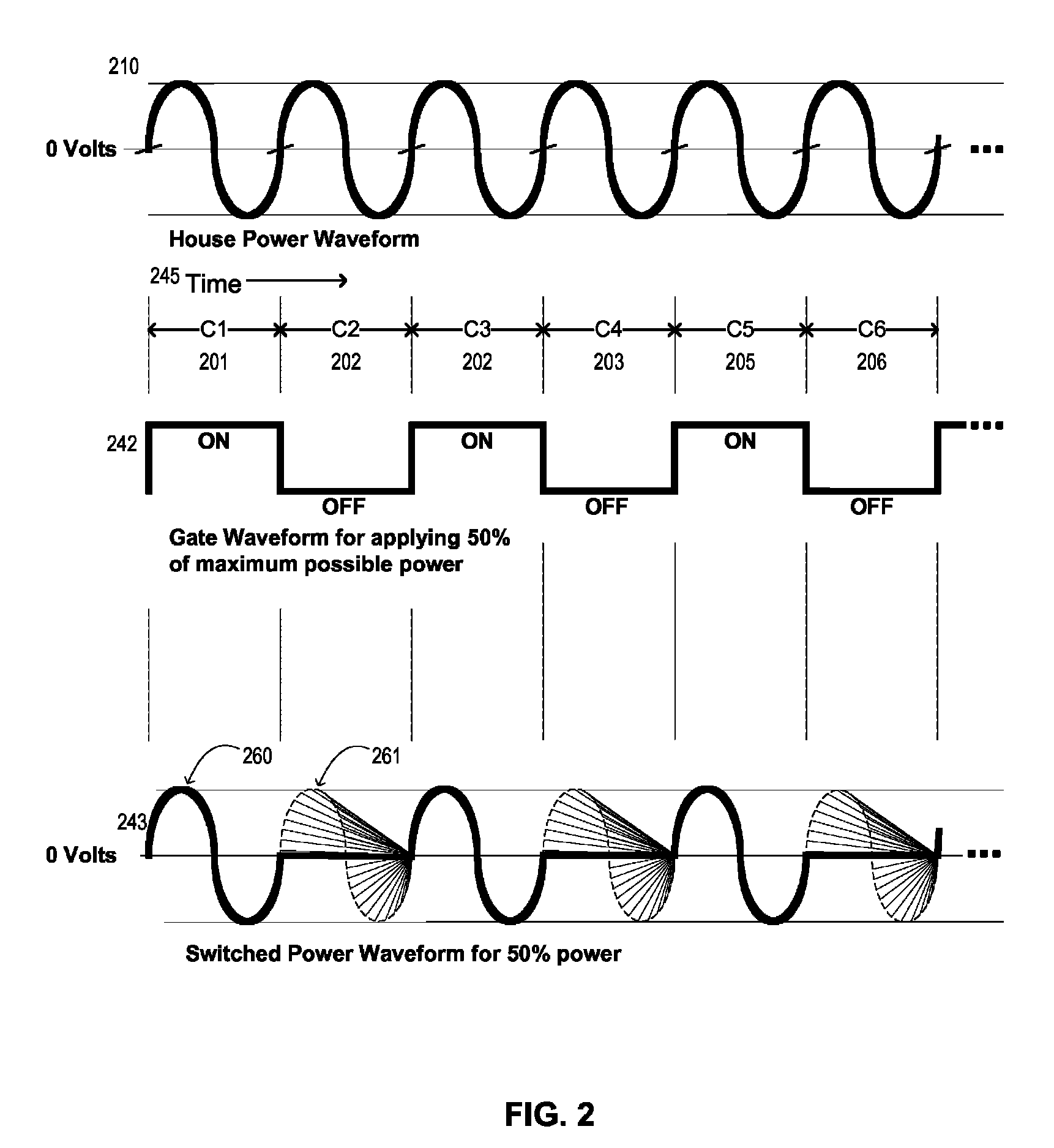

Electric baseboard heater control

ActiveUS7838803B1Reduce mechanical noiseSteady and therefore more comfortable source of heatTemperature control without auxillary powerTemperature control with auxillary non-electric powerEngineeringHeating system

In order to provide an electric heat system that is quieter than those of the prior art, a switching circuit is incorporated into the controls for the heating system which provides for the heating elements of the electric heater to be kept at a more constant temperature than those of the prior art. The switching circuit regulates the output power to the degree desired while not inducing sharp changes in temperature of the coils of the electric heater and thus reduces the degree of rapid expansion and contraction of the coils and the enclosure for the heater. This in turn reduces the amount of mechanical noise produced by the electric heater while also reducing wear and tear on the heating element, the heater enclosure and objects near to the heater.

Owner:ROSEN TECH LLC

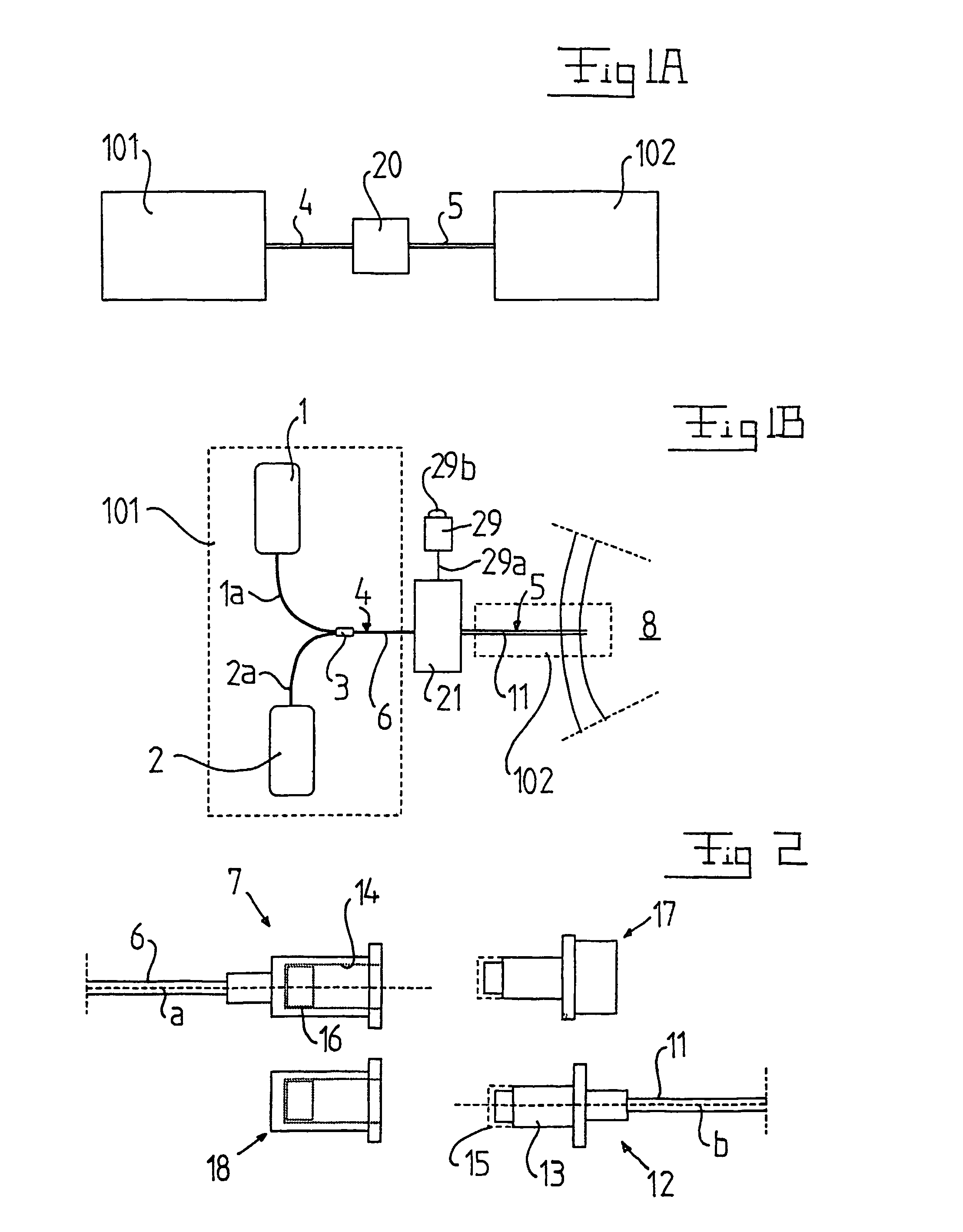

Connecting device, a medical system, and a method of connecting medical subsystems

InactiveUS7727220B2Improved connection/disconnectionMinimize frequencyAnaesthesiaDiagnosticsInterior spaceEngineering

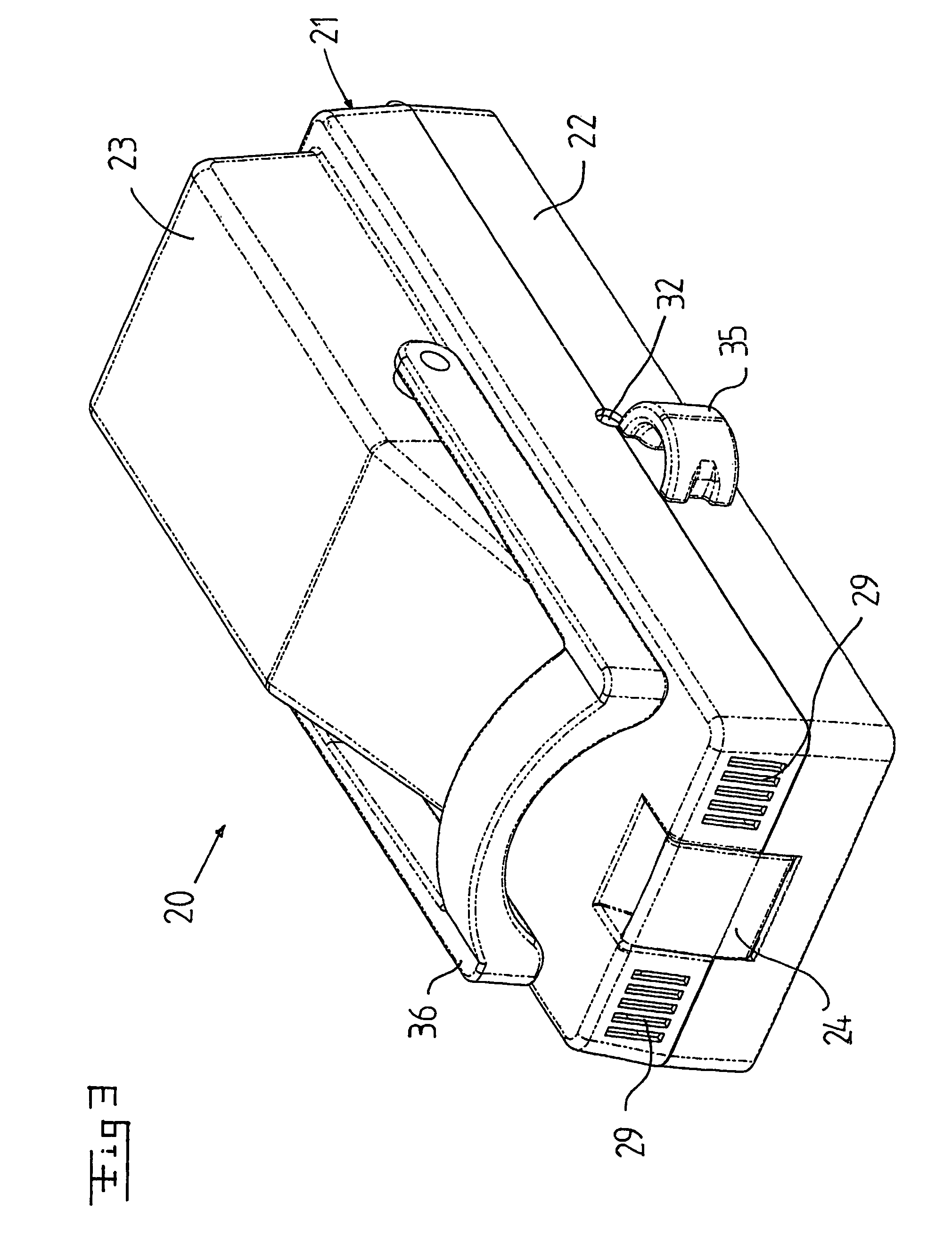

The invention refers to a medical system comprising a first subsystem with a first connection portion (7), and a second subsystem with a second connection portion (12). The invention also refers to a device and a method for connecting the subsystems to each other. One of the subsystems contains a fluid. The connecting device is adapted to connect the subsystems to each other to permit transport of the fluid from one of the subsystems to the other subsystem. The device comprises a container (21) enclosing an inner space. A substantially sterile atmosphere is provided in the inner space. The container receives the first connection portion and the second connection portion in the inner space. A mechanism is provided for connecting, from outside the container, the first connection portion and the second connection portion to each other in the inner space.

Owner:FRESENIUS MEDICAL CARE DEUTSCHLAND GMBH

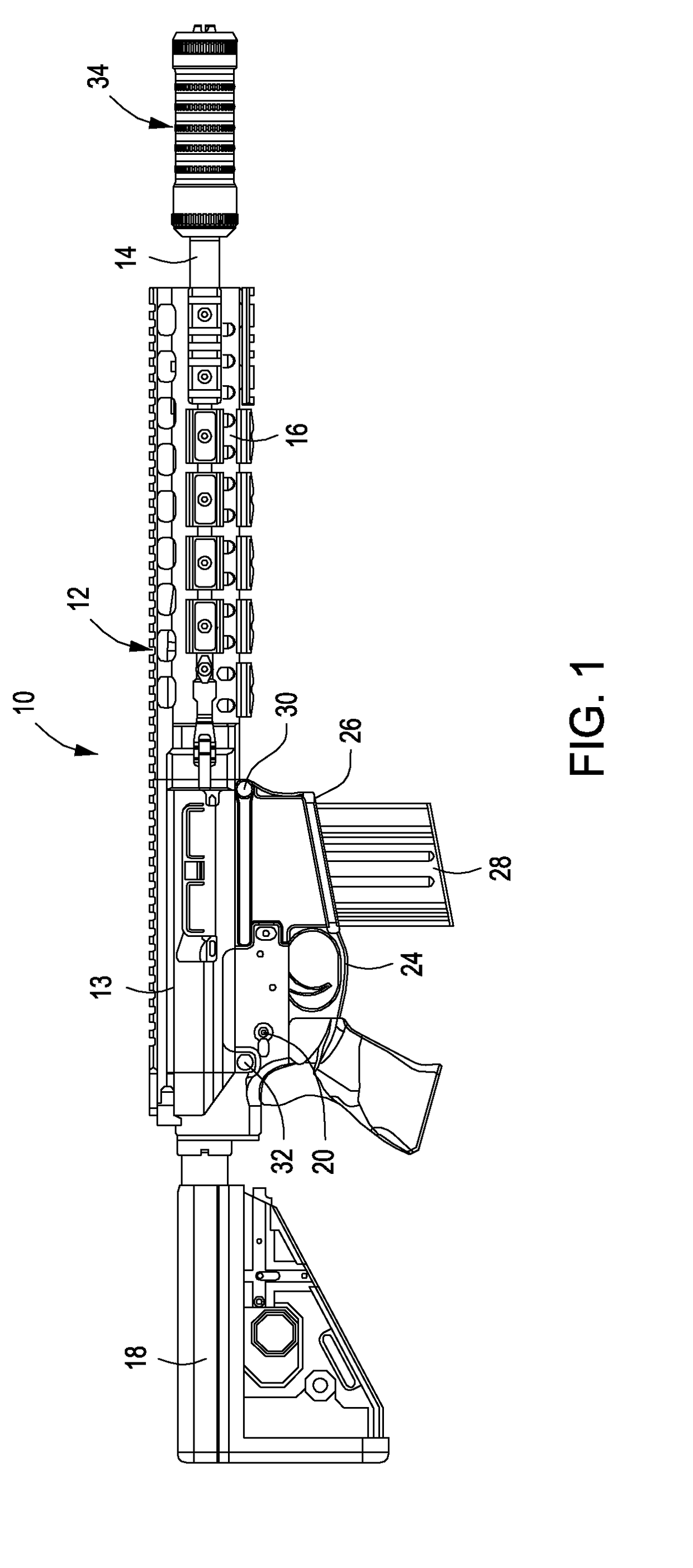

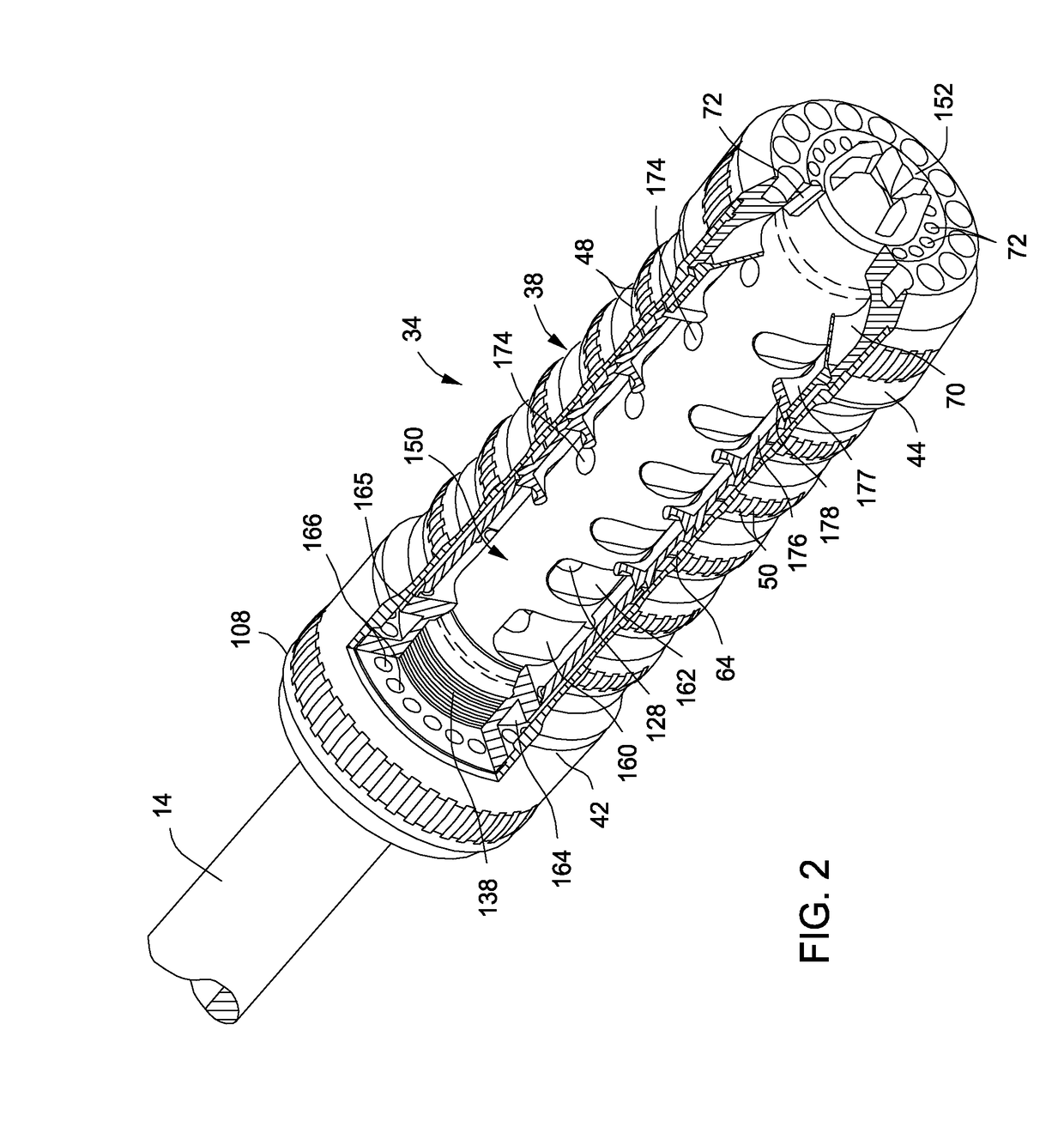

Suppressed upper receiver group having locking suppressor with through brake

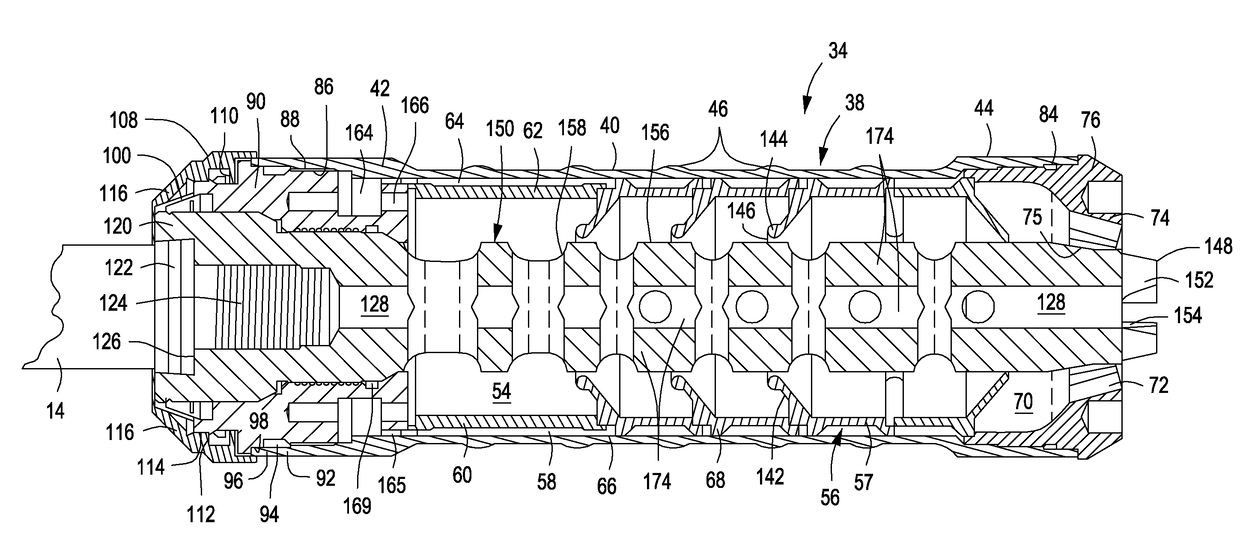

InactiveUS20180038663A1Prevent excessive back pressureEasy dischargeBreech mechanismsMuzzle attachmentSuppressorMajor and minor

A suppressed upper receiver group for a firearm having a suppressor mounted to the barrel thereof. The suppressor has a tubular housing defining primary and secondary flow paths for propellant gas processing, diverting a portion of the propellant gas to the secondary flow path for pressure control. A number of baffle members are arranged in spaced relation within the housing and define serially arranged propellant gas processing chambers. A suppressor mounting adapter is connected with the barrel and has a propellant gas processing section having a propellant flow bore and extends completely through the housing and has a flash retarding tip projecting through a discharge opening of the housing.

Owner:LARUE MARK C

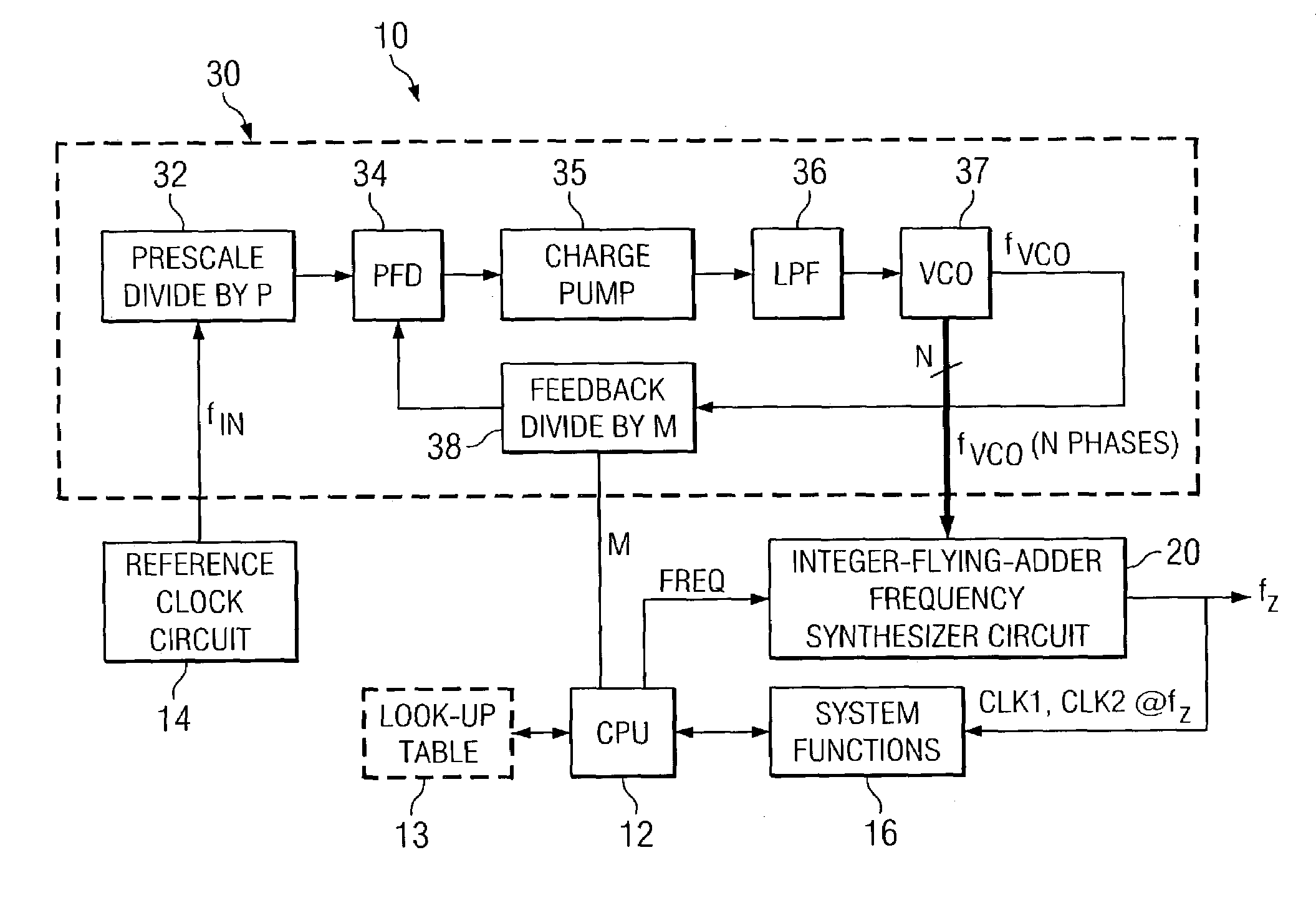

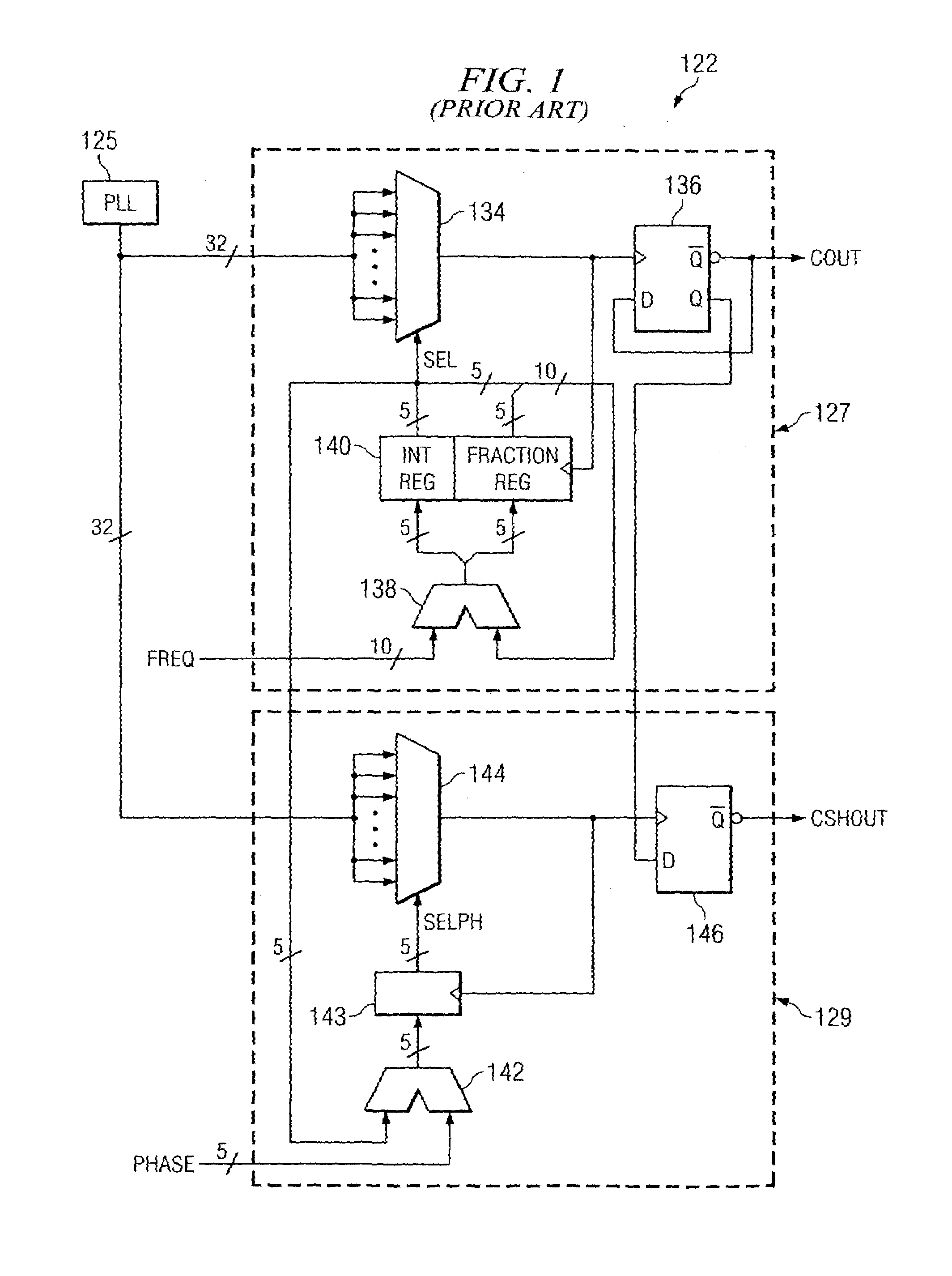

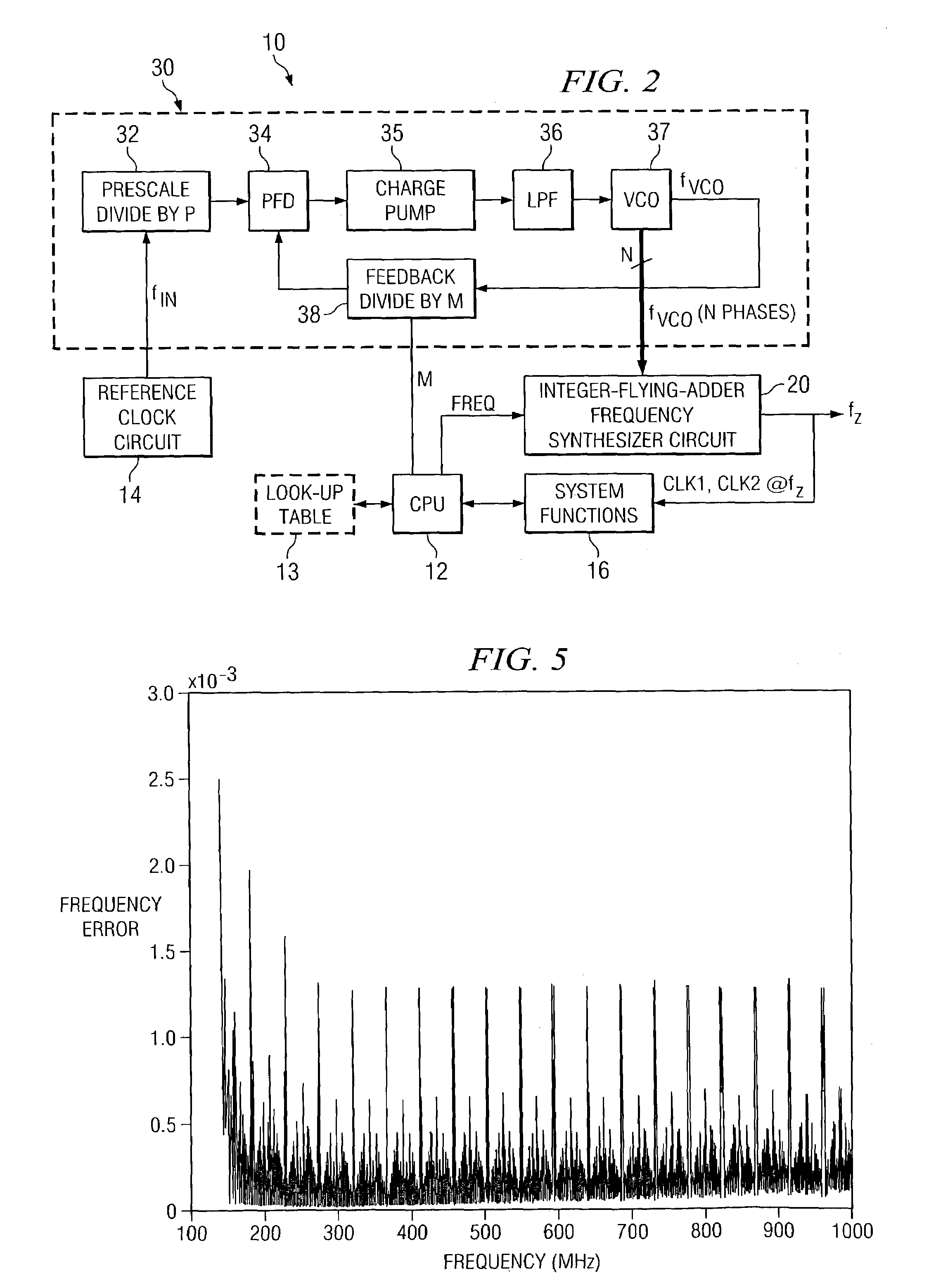

Precision jitter-free frequency synthesis

InactiveUS7065172B2Avoid difficult choicesMinimize frequencyPulse automatic controlAngle demodulation by phase difference detectionElectronic systemsEngineering

An electronic system (10) includes a phase-locked loop (30) and a frequency synthesis circuit (20), for generating a jitter-free output clock (CLK1, CLK2) at a desired frequency. The phase-locked loop (30) includes a voltage-controlled oscillator (37) that produces a number (N) of equally spaced clock phases at a frequency (fVCO) that depends also upon a programmable feedback frequency divider (38) and a prescale divider (32). The frequency synthesis circuit (20) generates the output clock (CLK1, CLK2) at a frequency under the control of a frequency select word (FREQ) that indicates the number of clock phases between successive clock edges. A central processing unit (12), either itself or from a look-up table (13), generates a feedback divide integer (M) and the frequency select word (FREQ) according to a desired frequency (f), by way of a minimization of the frequency error. The frequency of the output clock (CLK1, CLK2) can be generated in a jitter-free manner, since only integer values are used in the frequency synthesis circuit (20), at relatively low frequency error.

Owner:TEXAS INSTR INC

Method, system, and computer program product for the detection of physical activity by changes in heart rate, assessment of fast changing metabolic states, and applications of closed and open control loop in diabetes

ActiveUS8585593B2Minimize frequencyAvoid the needMedical simulationDrug and medicationsClosed loopHypoglycemia

A method, system, and computer program product related to the detection of physical activity using changes in heart rate. The method, system, and computer program product evaluates short term glucose demand and long term insulin action due to physical activity. The method, system, and computer program product is further related to the improvement of open and closed loop control of diabetes by accounting for the metabolic changes due to physical activity. The method, system, and computer program product is directed to detecting in real time the short and long term effects of physical activity on insulin action via heart rate analysis, and recommending changes in insulin dosing to compensate for the effects of physical activity. With these recommendations, the open and closed loop control of diabetes can be improved and steps can be taken to prevent hypoglycemia that may result from increased insulin sensitivity due to physical activity.

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND

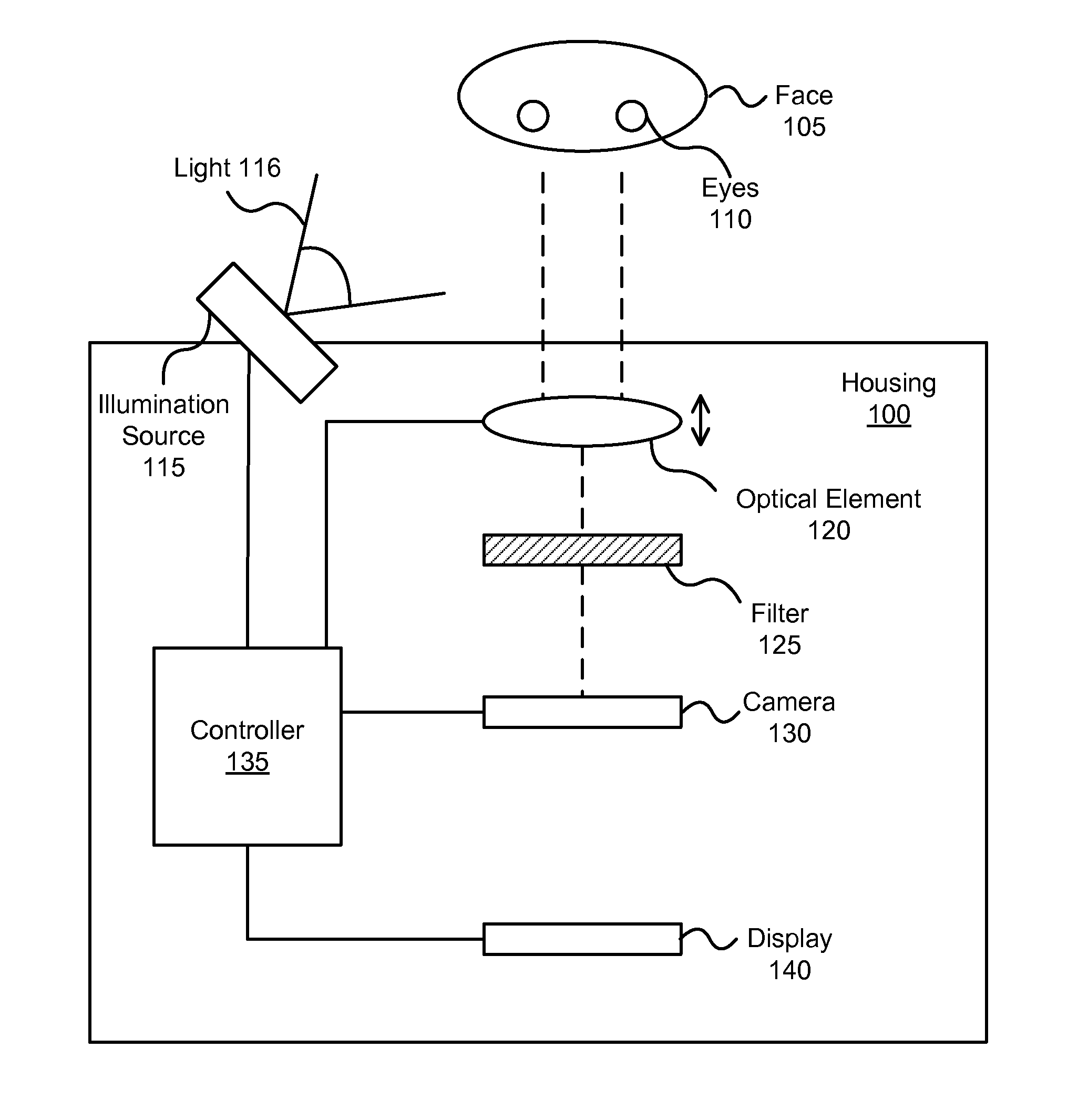

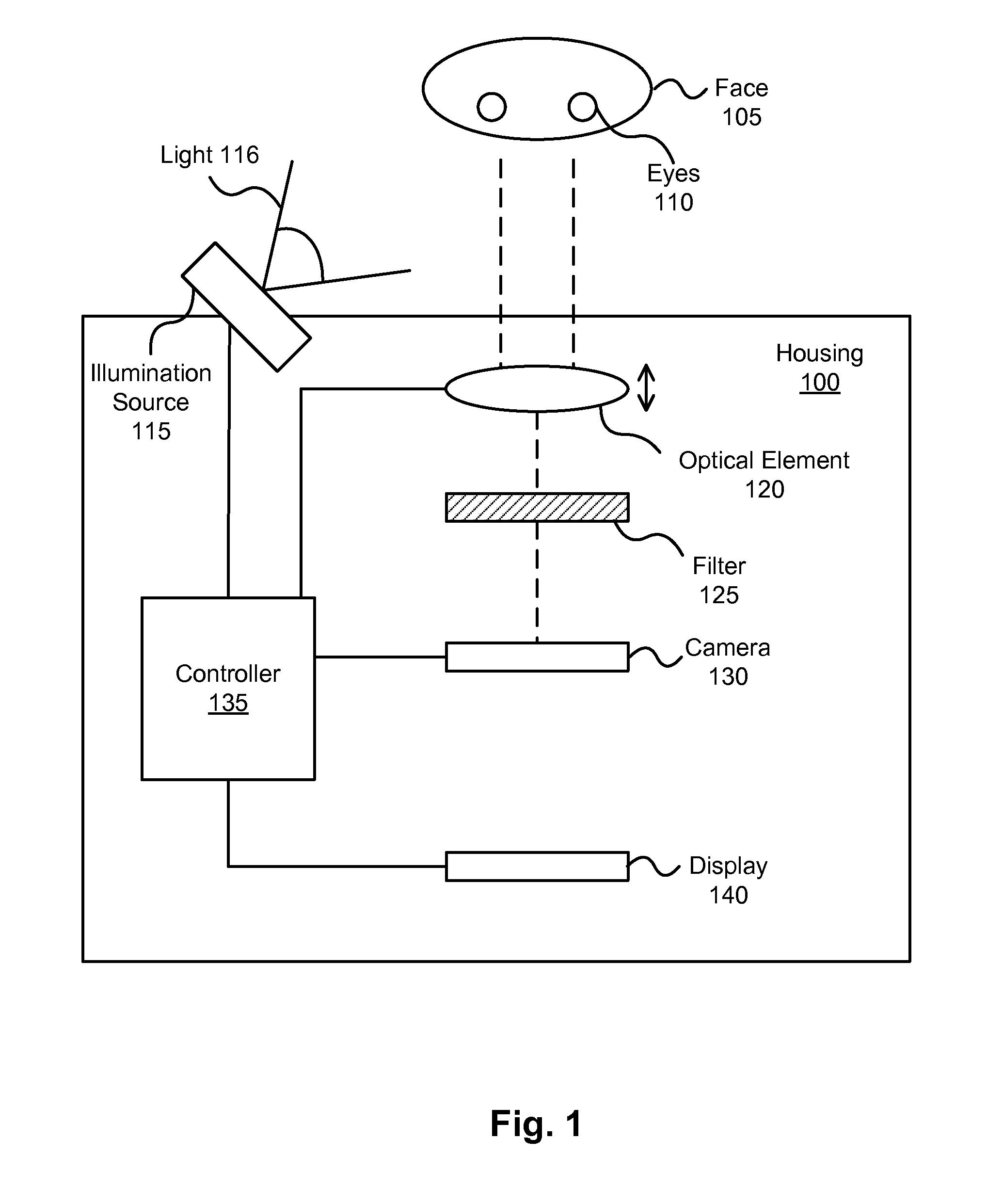

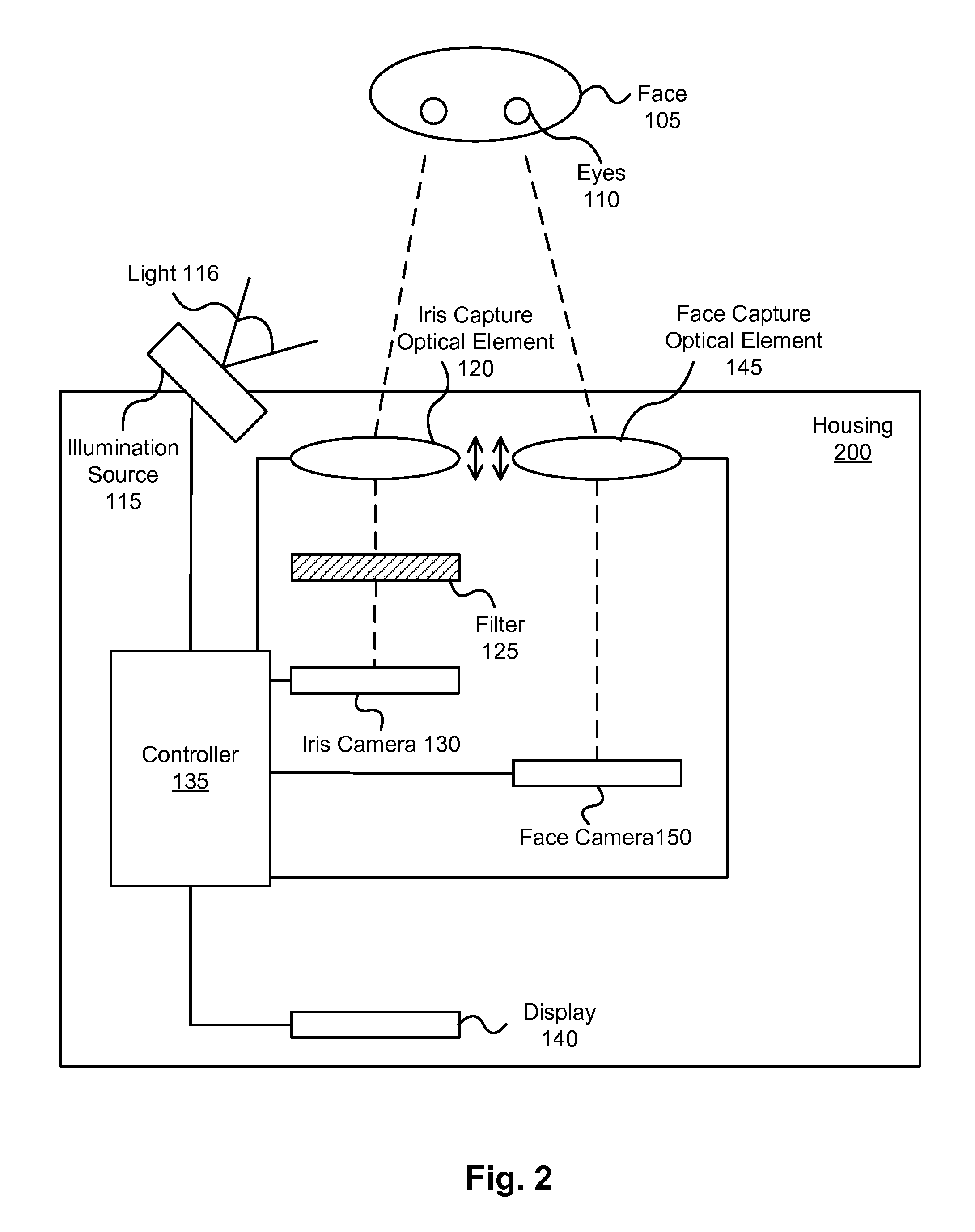

Handheld Iris Imager

InactiveUS20130088583A1Increased ease of useQuickly and easily operateAcquiring/recognising eyesColor television detailsIris imageVisual feedback

A portable, hand held iris imaging system captures iris images that may be used in biometric identification. The system includes an illumination source for illuminating a subject's eye and a camera to capture light reflected from the subject's eye. An optical element positioned between the illumination source and the camera focuses light reflected from the subject's eye onto the camera. A controller receives the captured image and provides it to a display. If the system is not correctly positioned for iris image capture, the display may also provide visual feedback regarding how the system can be properly repositioned. The system includes a housing with a portable form factor so that it may be easily operated.

Owner:TASCENT INC

Electromagnetically controlled tissue cavity distending system

ActiveUS8308726B2Safe and efficient and turbulence free systemMinimizing amplitudeJet injection syringesAutomatic syringesPeristaltic pumpEndoscopic Procedure

A system to minimize fluid turbulence inside a tissue cavity during endoscopic procedures. A body tissue cavity of a subject is distended by continuous flow irrigation using a solenoid operated pump on the inflow side and a positive displacement pump, such as a peristaltic pump, on the outflow side, such that the amplitude of the pressure pulsations created by the outflow positive displacement pump inside the said tissue cavity is substantially dampened to almost negligible levels. The present invention also provides a method for accurately determining the rate of fluid loss into the subject's body system during any endoscopic procedure without utilizing any deficit weight or fluid volume calculation, the same being accomplished by using two fluid flow rate sensors. The present invention also provides a system of creating and maintaining any desired pressure in a body tissue cavity for any desired cavity outflow rate.

Owner:KUMAR BV

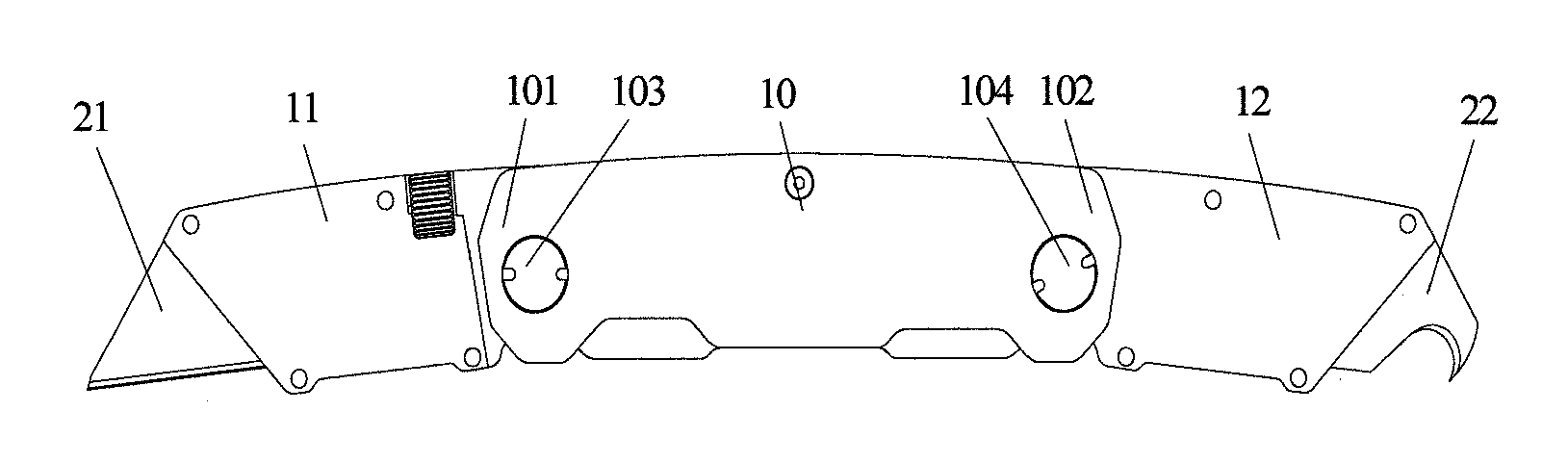

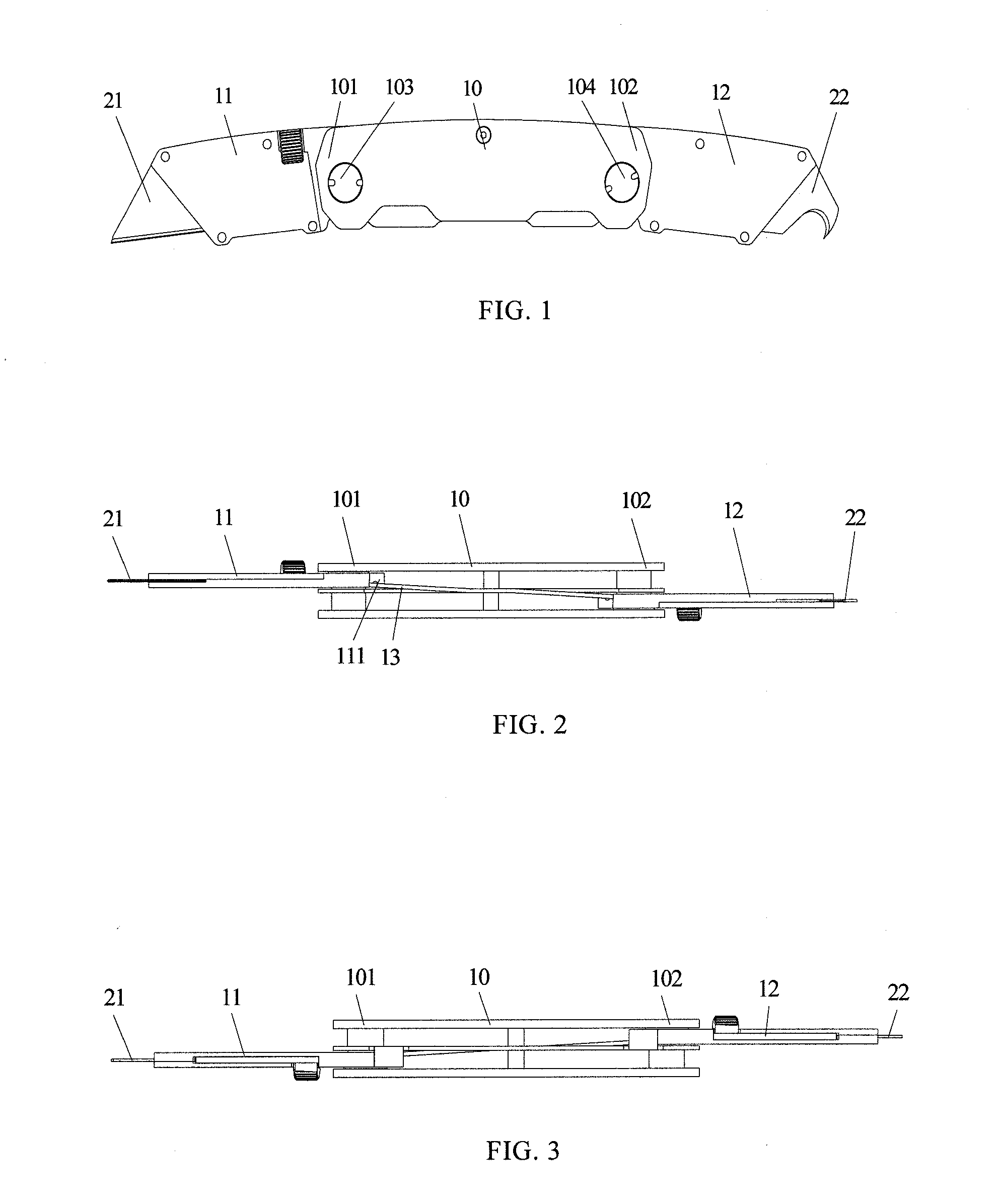

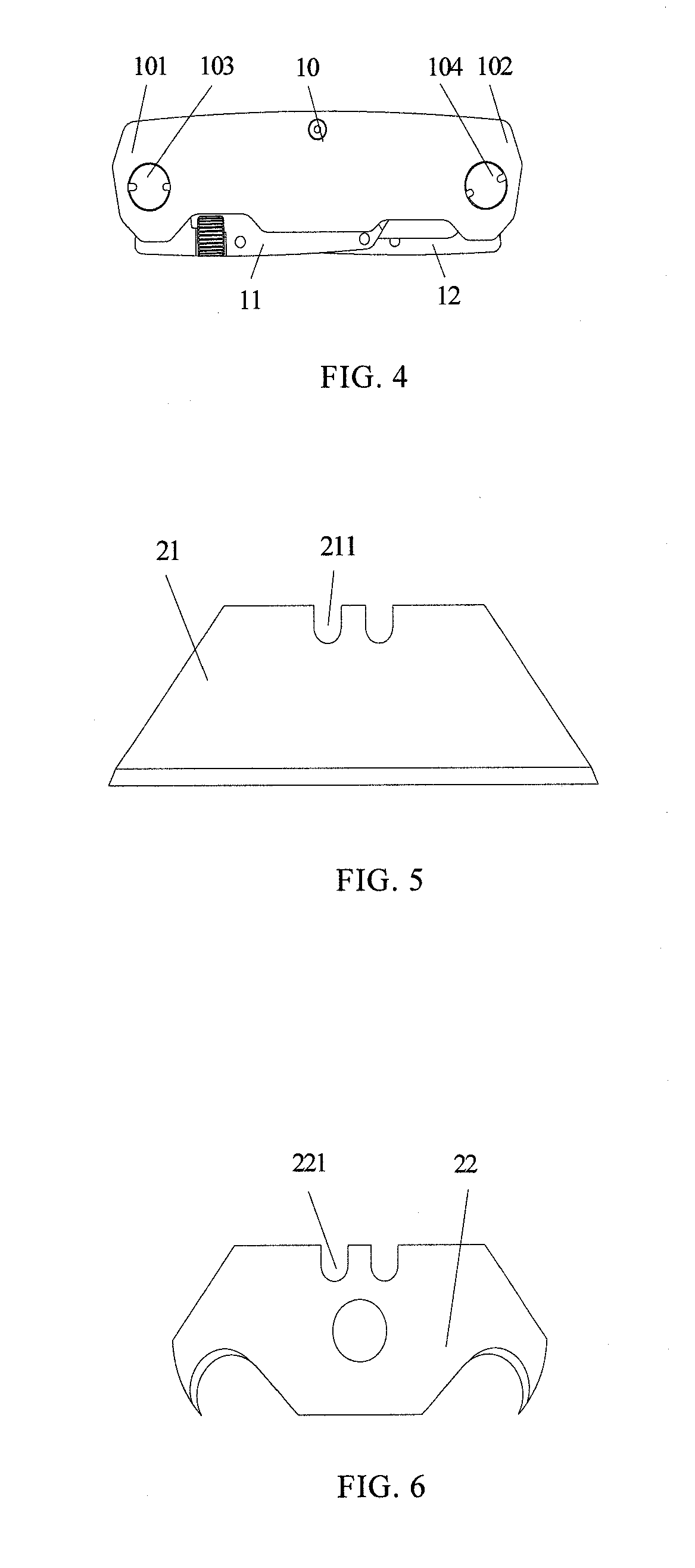

Double-ended hand knife

InactiveUS20120227267A1Difficult to replaceExtend continuous working timeThrusting weaponsWeapon componentsEngineeringKnife blades

Owner:HANGZHOU GREAT STAR IND CO LTD +1

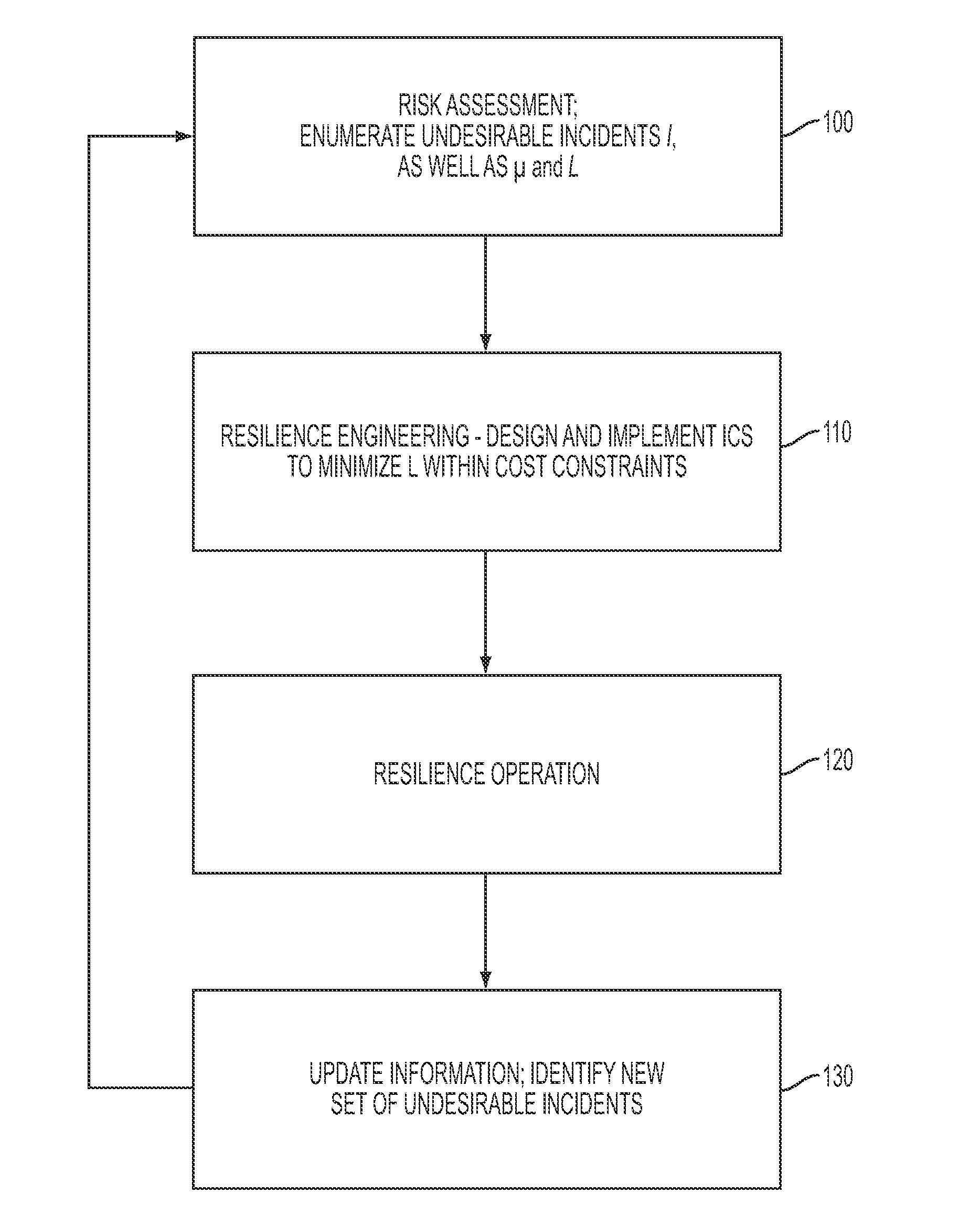

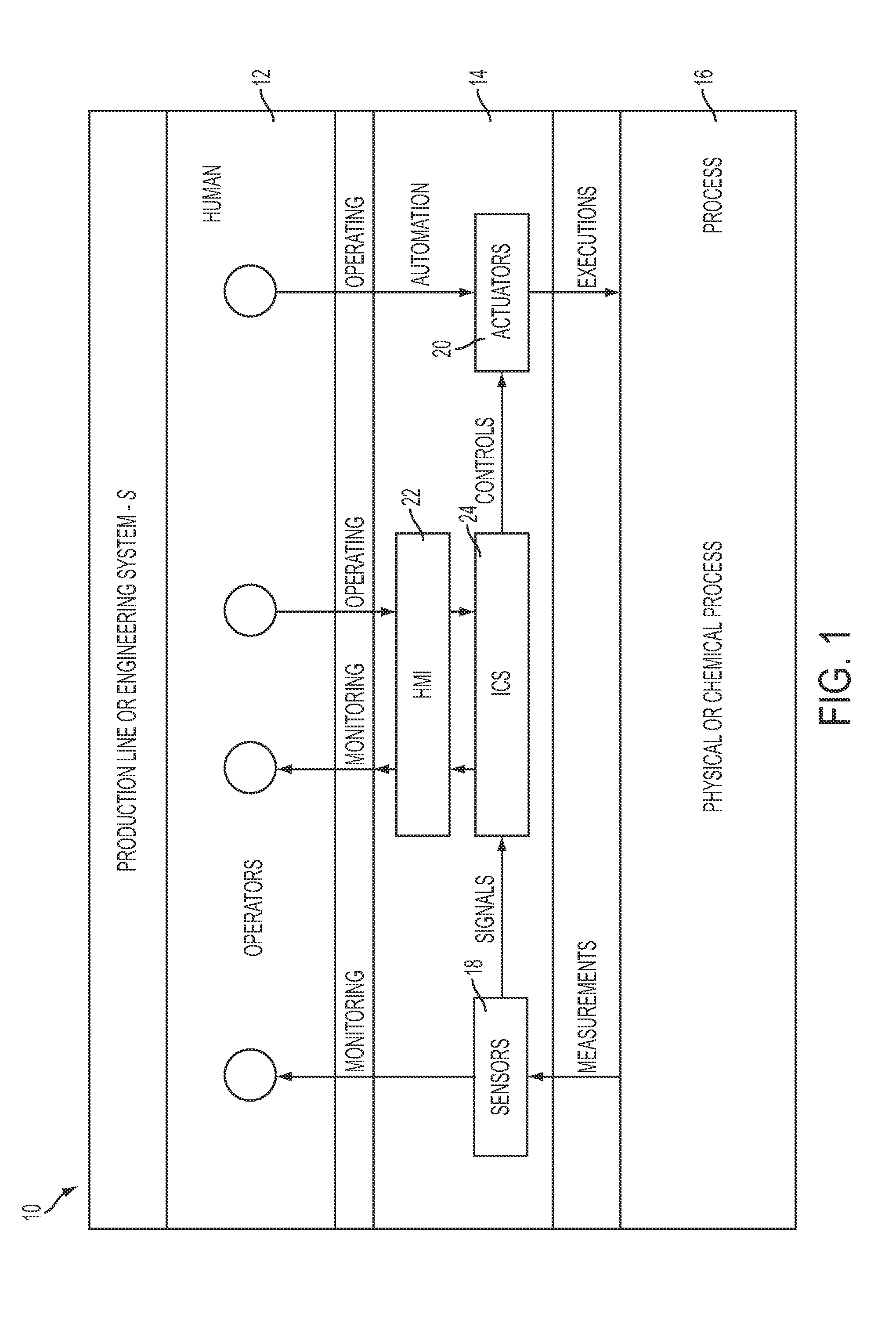

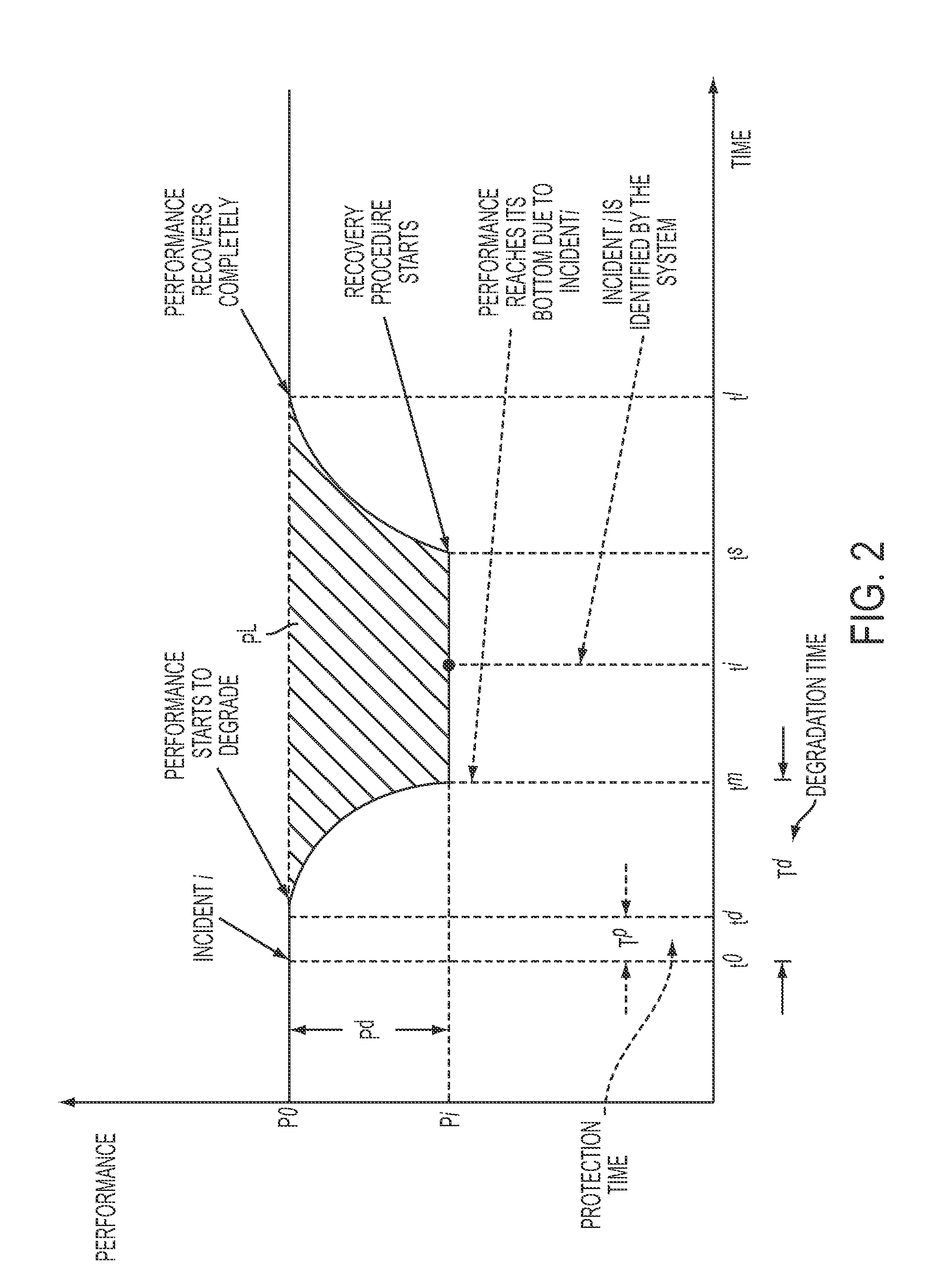

Method for quantitative resilience estimation of industrial control systems

InactiveUS20130132149A1Minimize frequencyMinimize adverse impactFinanceElectric testing/monitoringManufacturing engineeringIndustrial control system

A three-layer model of an engineering system is proposed for developing and evaluating a resilient industrial control system incorporated within the engineering system, the model based upon a group of metrics that are cyclically estimated, operated and evaluated to create a valid resilient arrangement. The layers in the model include a human / operator layer, an automation layer and a process layer, where the industrial control system resides in the automation layer. The metrics are based upon the identification of a number of undesirable incidents, as well a determination of the frequency of occurrence of these incidents, their impact on the performance of the engineering system and the financial loss of the engineering system based upon these undesirable incidents.

Owner:SIEMENS CORP +1

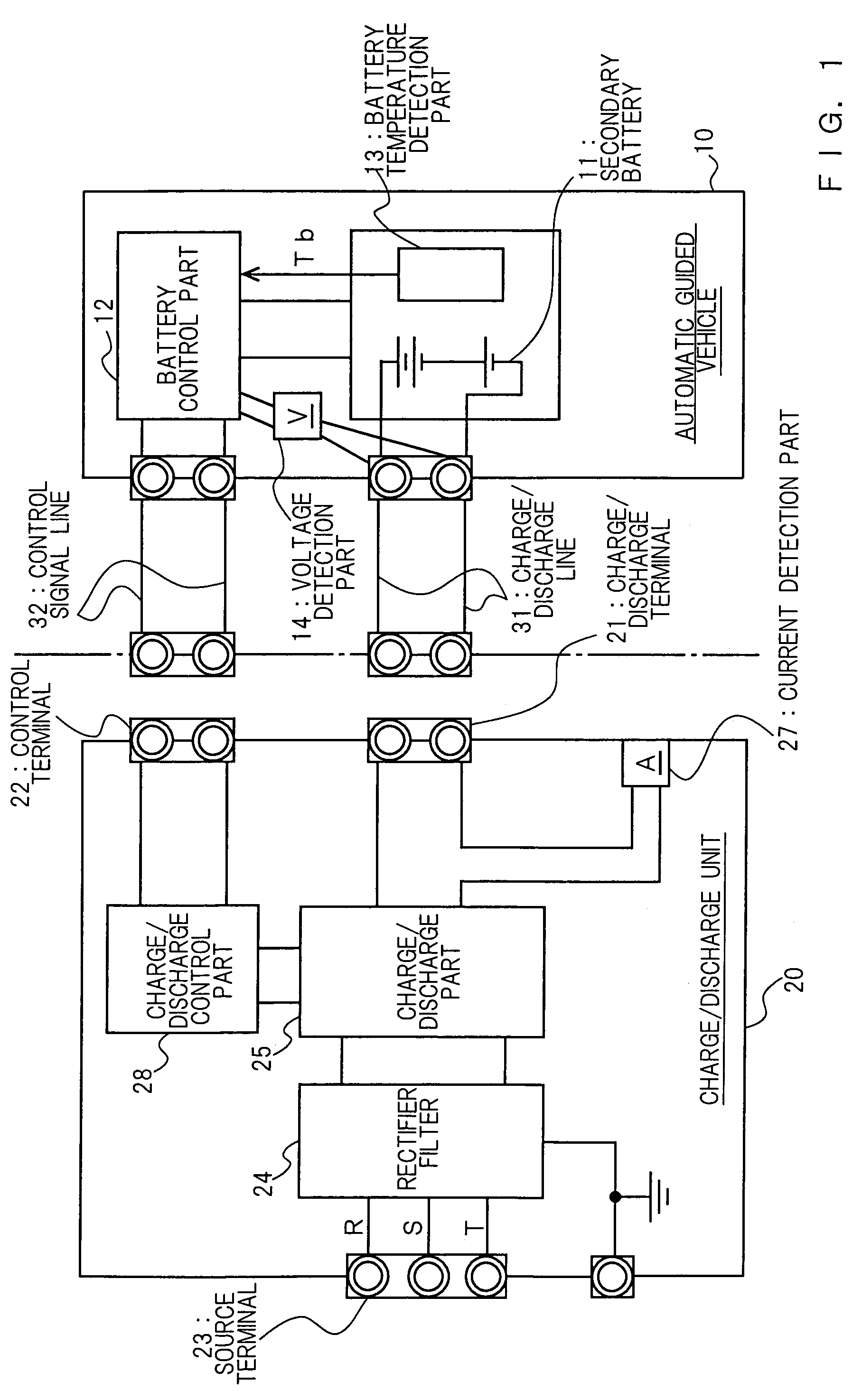

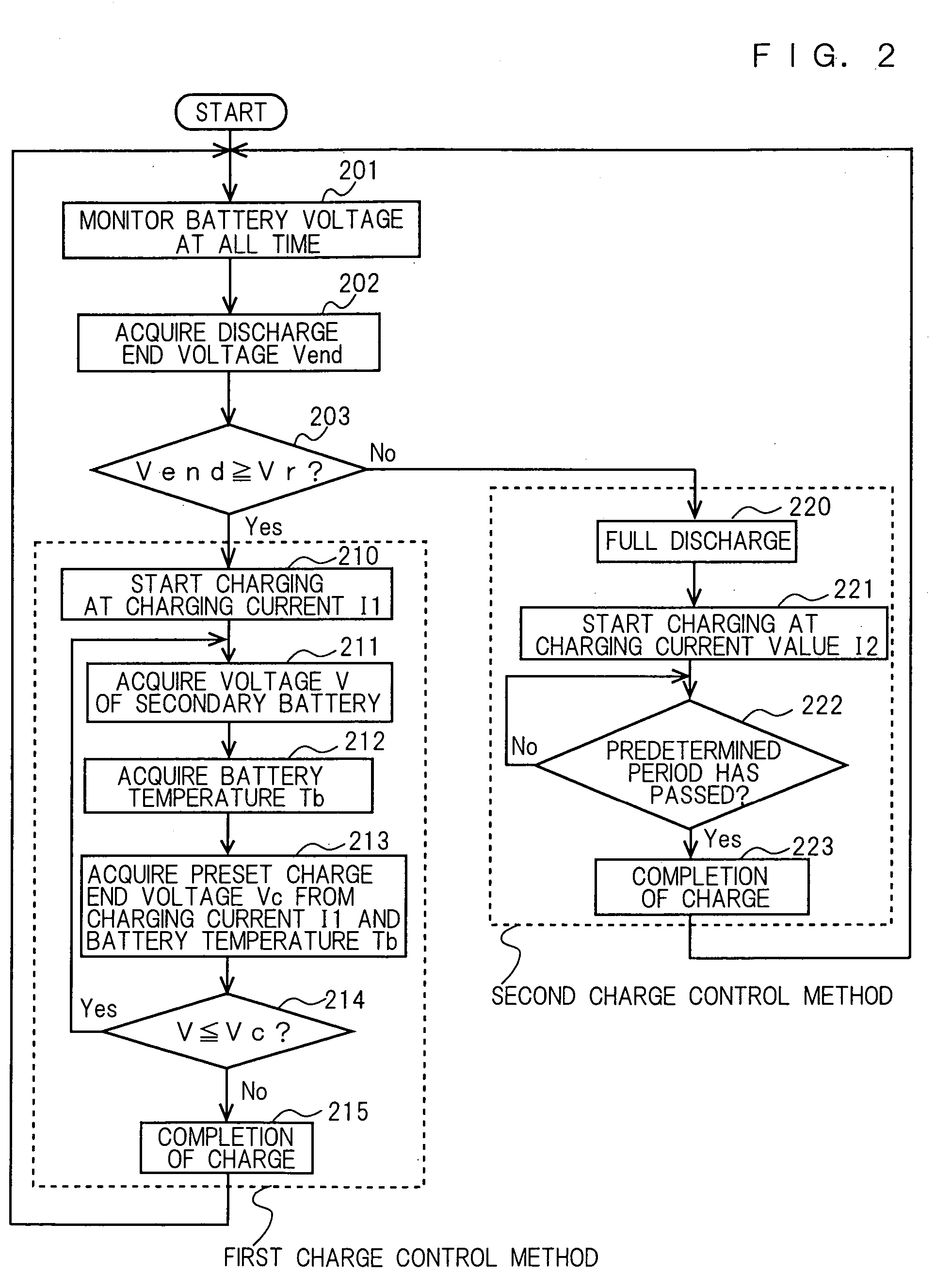

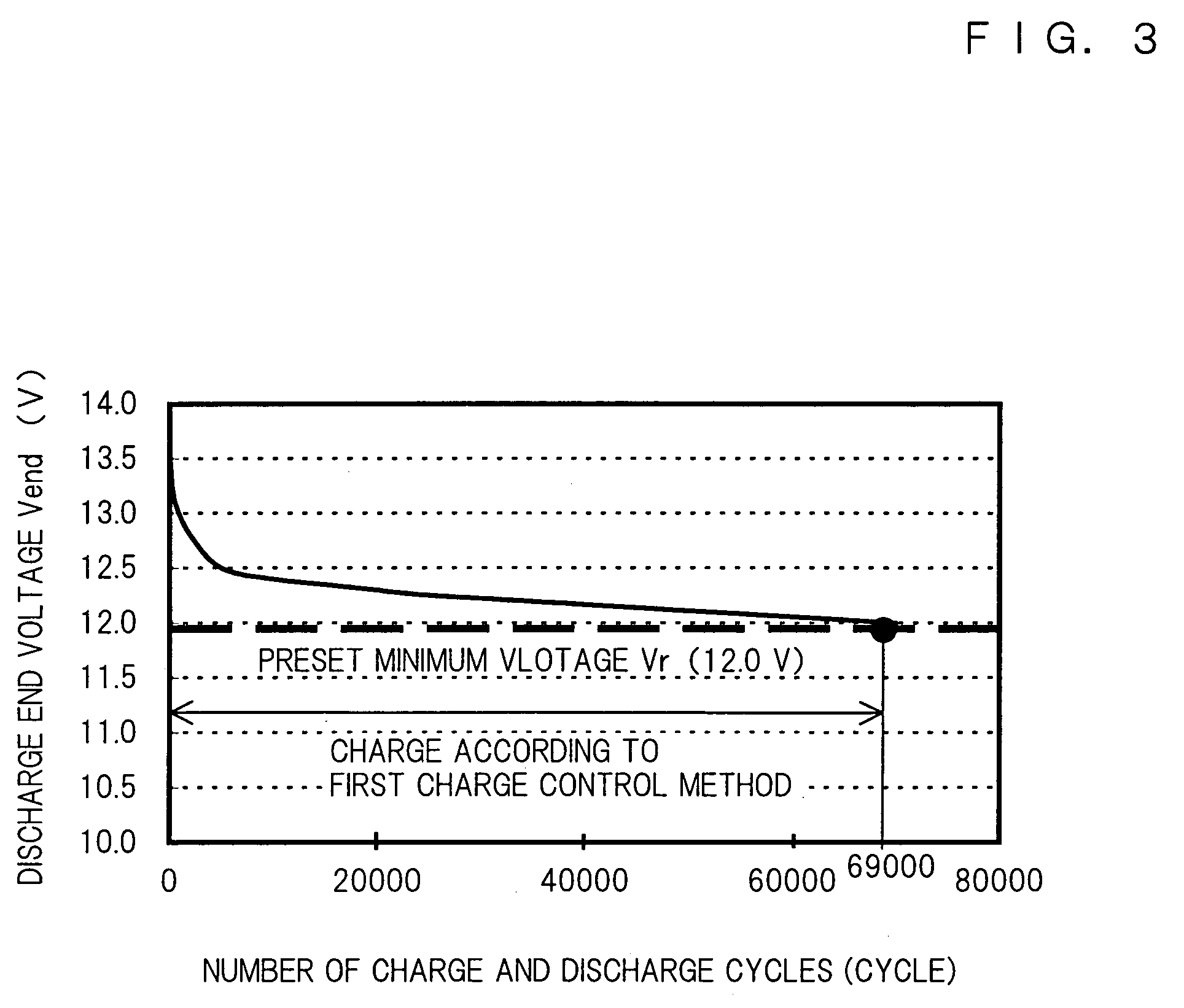

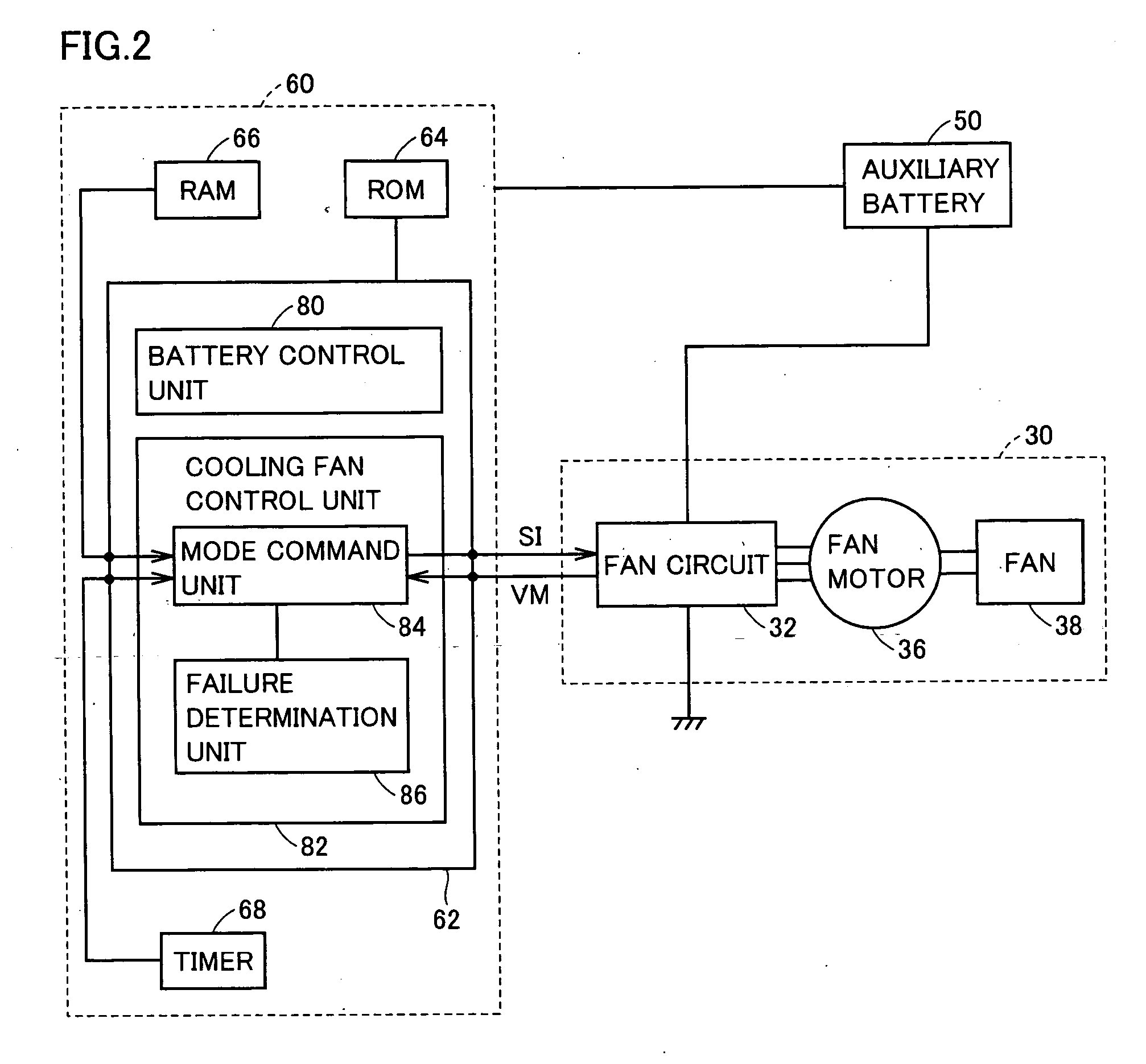

Method of controlling charge and discharge of secondary battery for automatic guided vehicle

InactiveUS7193394B2Minimize frequencyAccurate decisionBatteries circuit arrangementsCharging stationsElectricityBattery charge

To provide a method of controlling charge and discharge of a secondary battery for automatic guided vehicle that can decide the timing of refresh charge and discharge accurately and minimize the frequency of refresh charge and discharge. The method of controlling charge and discharge of a secondary battery for automatic guided vehicle comprises a first discharge step of making the secondary battery drive an automatic guided vehicle and discharge electricity with a predetermined amount; a voltage measurement step of measuring a discharge end voltage of the secondary battery at the completion of the first discharge step; and a charge step of performing a first charge step of charging the secondary battery incompletely at a first charging current value when the discharge end voltage is higher than a preset minimum voltage, and performing a second charge step of discharging the secondary battery fully and then charging the secondary battery fully at a second charging current value smaller than the first charging current value when the discharge end voltage equals the preset minimum voltage or less.

Owner:PANASONIC EV ENERGY CO LTD

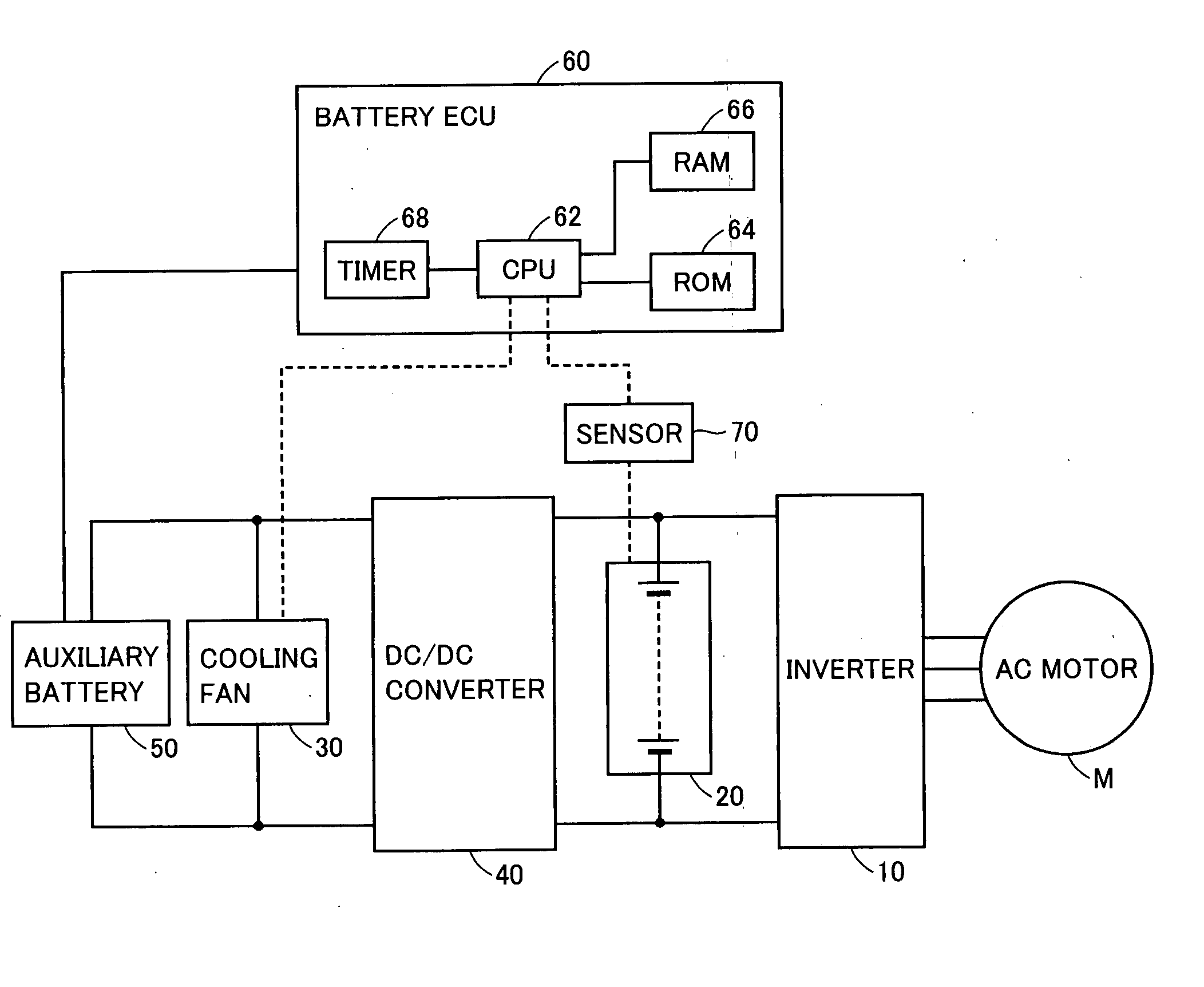

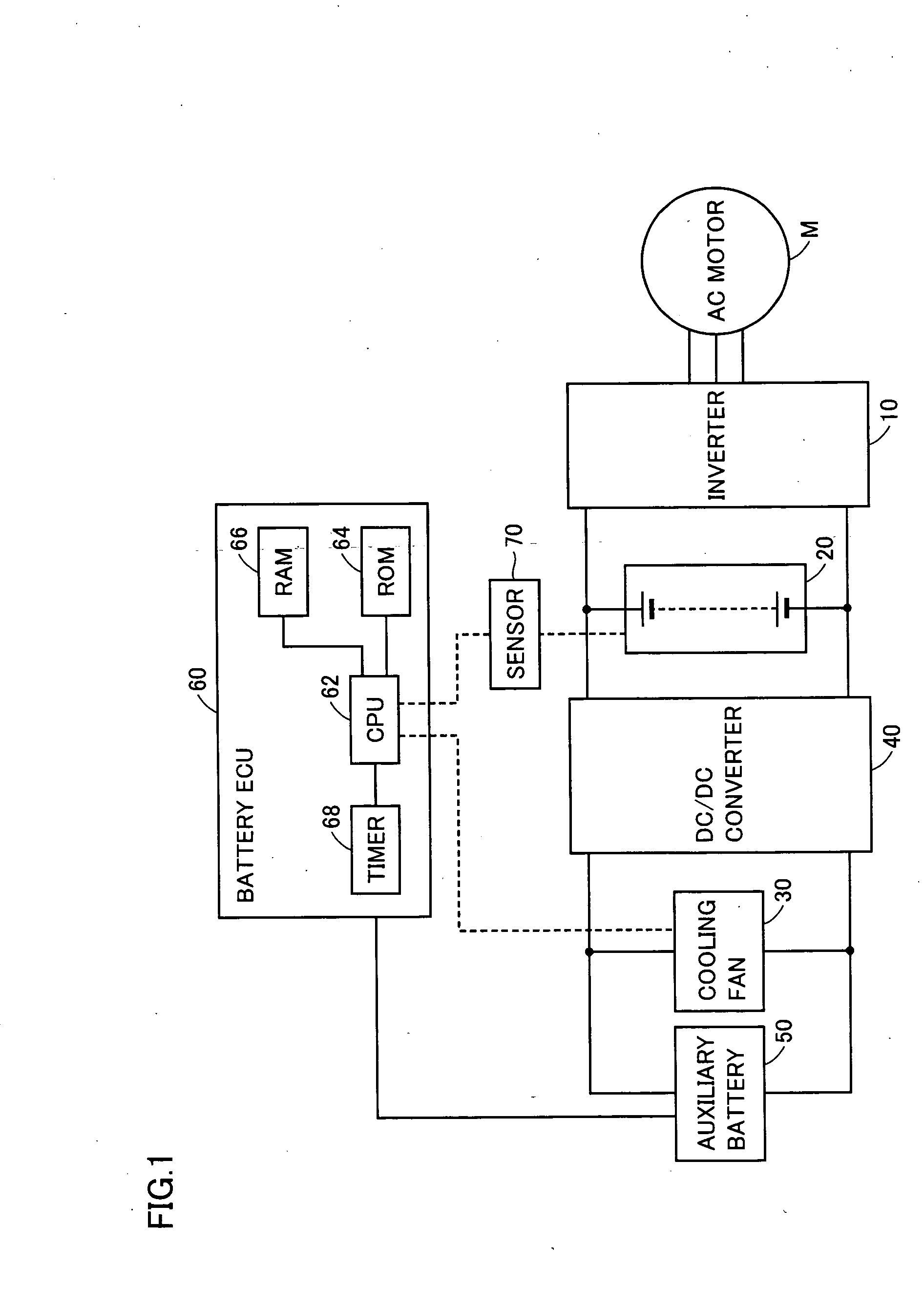

Cooling device controlling apparatus, cooling device failure detecting apparatus, cooling device failure detecting method, and computer readable recording medium recording program for causing computer to execute detection of failure of cooling device capable of detecting failure in short period efficiently

InactiveUS20050257546A1Efficient detectionEffective failureAir-treating devicesBatteries circuit arrangementsTimerDevice failure

After a vehicle system is actuated, a mode command unit determines that an auxiliary battery is cleared. Determining that the auxiliary battery is cleared because of loss of stored information of backup RAM, the mode command unit outputs a cooling mode command signal SI specifying a prescribed cooling mode to a fan circuit, and starts measuring a prescribed time with a timer. The fan circuit drives a fan motor with a prescribed cooling mode and detects a number of rotations of the fan motor to transmit to the mode command unit as a fan output signal. The mode command unit detects a failure of a cooling fan from a comparison result of the fan output signal and the specified prescribed cooling mode. The timer senses a lapse of the prescribed time, and the failure detection ends.

Owner:TOYOTA JIDOSHA KK

Magnetic disk drive with flying height control system

InactiveUS7518818B2Minimize frequencyDifficult to performDriving/moving recording headsFilamentary/web record carriersInternal memoryControl system

Embodiments of the invention appropriately control the flying height of a magnetic head slider as necessary without making the magnetic head slider touch the magnetic disk. In one embodiment, when a magnetic disk drive is started, the level of electric power predefined for the ordinary temperature (room temperature) is read in from the internal memory of an MPU. A temperature sensor measures the internal temperature of the magnetic disk drive and sends it to the MPU. According to the temperature sent from the temperature sensor, the MPU calculates the level of electric power which should be applied to a flying height adjustment structure. According to the calculated electric power, the MPU increases or decreases the electric power applied to the flying height adjustment structure. At a flying height controlled (corrected) by the flying height adjustment structure, a magnetic head slider performs read / write on a magnetic disk.

Owner:WESTERN DIGITAL TECH INC

Controlled tissue cavity distending system with minimal turbulence

ActiveUS8388570B2Safe and efficient and turbulence free systemMinimizing amplitudeElectrotherapyEndoscopesPeristaltic pumpEngineering

The present invention provides a system and a method for distending a body tissue cavity of a subject by continuous flow irrigation by using a dynamic pump, such as a centrifugal pump, on the inflow side and a positive displacement pump, such as a peristaltic pump, on the outflow side, such that the amplitude of the pressure pulsations created by a the said outflow positive displacement pump inside the said tissue cavity is substantially dampened to almost negligible levels. The present invention also provides a method for accurately determining the rate of fluid loss, into the subject's body system, during any endoscopic procedure without utilizing any deficit weight or fluid volume calculation, the same being accomplished by using two fluid flow rate sensors. The present invention also provides a system of creating and maintaining any desired pressure in a body tissue cavity for any desired cavity outflow rate. The system and the methods of the present invention described above can be used in any endoscopic procedure requiring continuous flow irrigation few examples of such endoscopic procedures being hysteroscopic surgery, arthroscopic surgery, trans uretheral surgery, endoscopic surgery of the brain and endoscopic surgery of the spine.

Owner:KUMAR BV

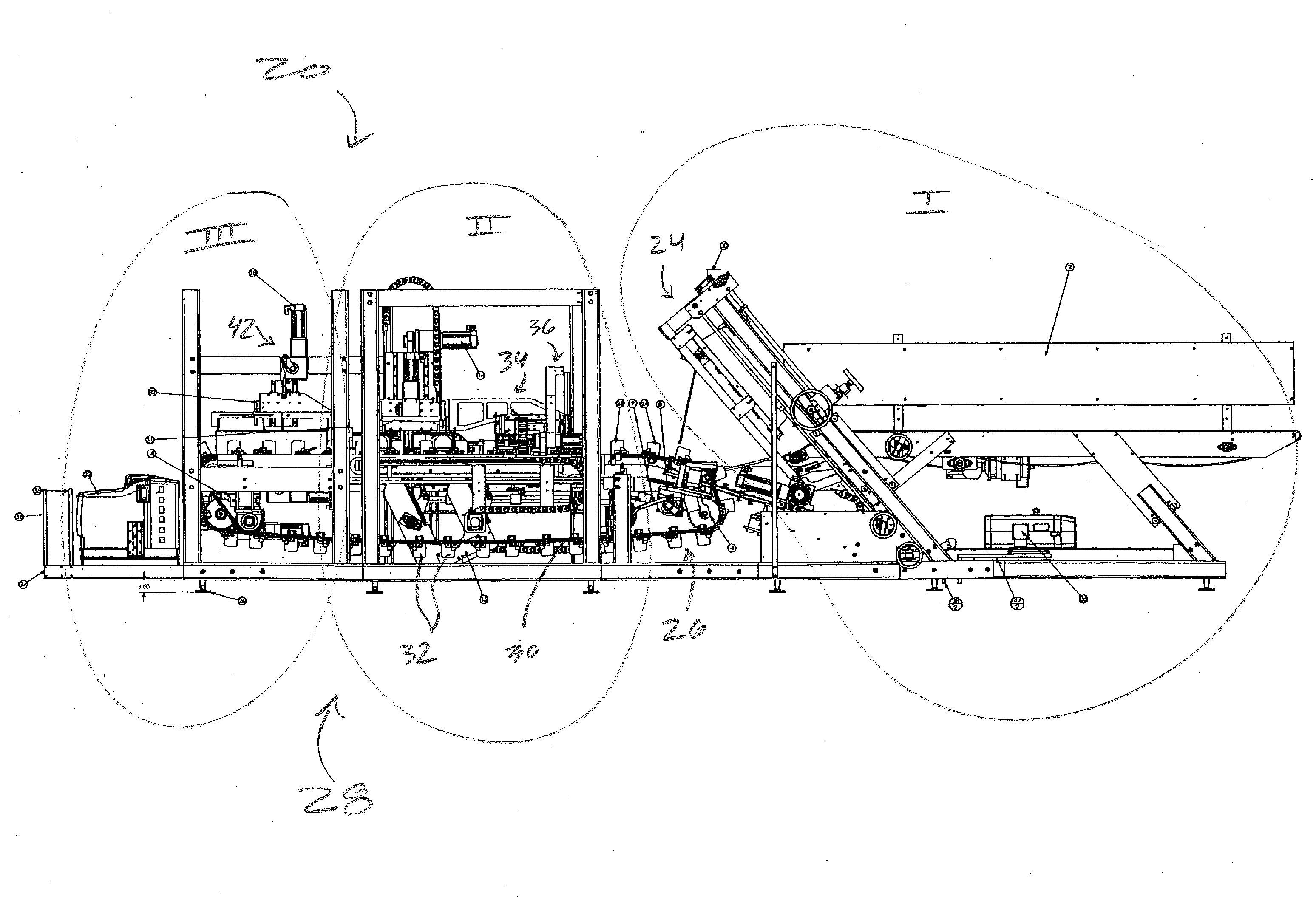

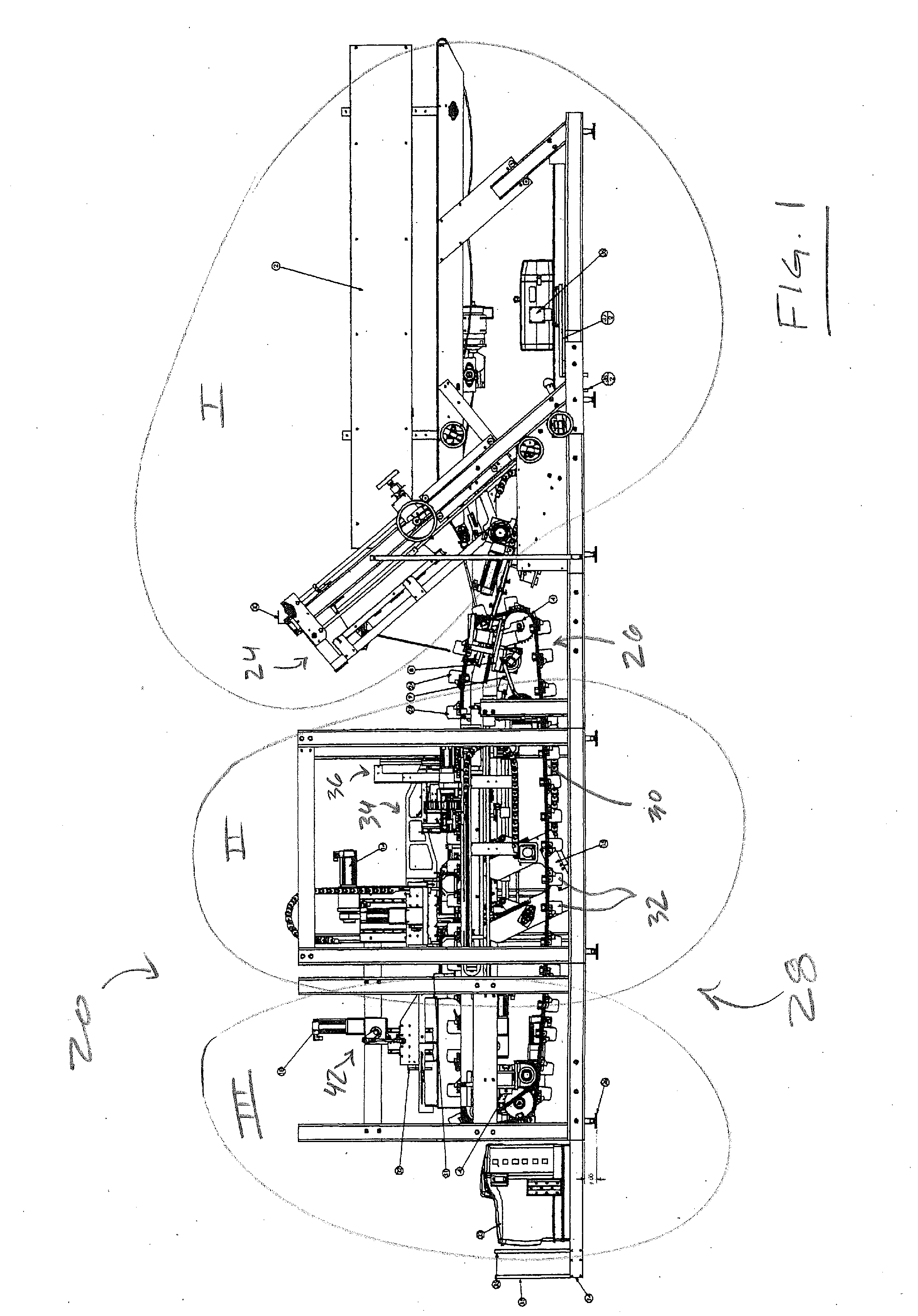

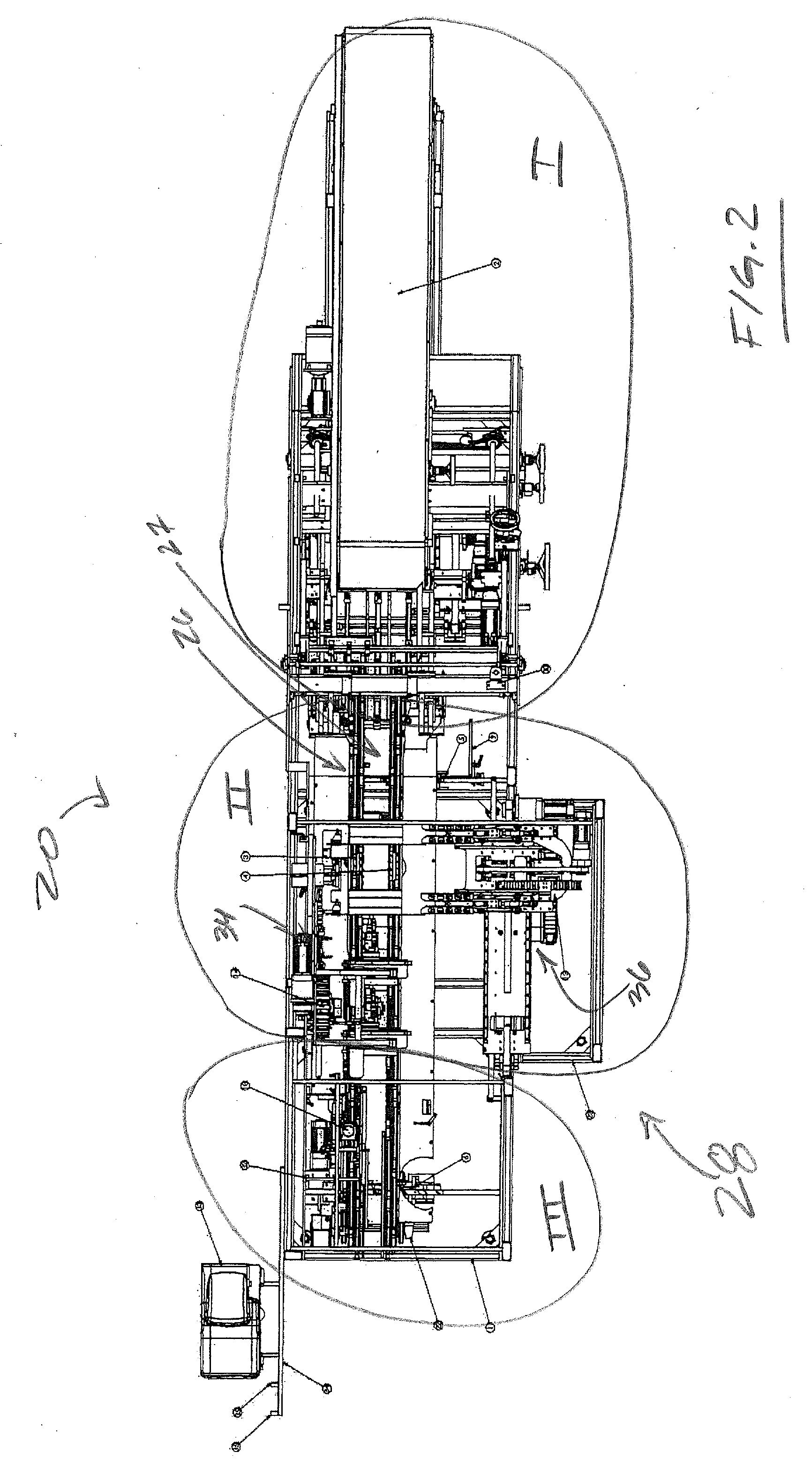

Continuous motion case former

InactiveUS20120122640A1Minimize durationMinimize frequencyBoxes/cartons making machineryBox making operationsEngineeringMechanical engineering

Among other things, a case forming system is provided. The system includes a conveyance apparatus for conveying case precursors along a conveyance path and a case set-up apparatus characterized by a case forming member. Upstream case precursors are conveyed along the conveyance path for operation thereupon by the case forming member. A case forming mandrel of a mandrel assembly is movably mounted in relation to the conveyance apparatus for continuos motion with respect thereto. The continuous motion is delimited by travel of the case forming mandrel between an upstream locus and a downstream locus of the conveyance path, and reversible extension of the case forming mandrel towards case precursors during travel between the upstream locus and the downstream locus of the conveyance path.

Owner:DOUGLAS MACHINE LIABILITY

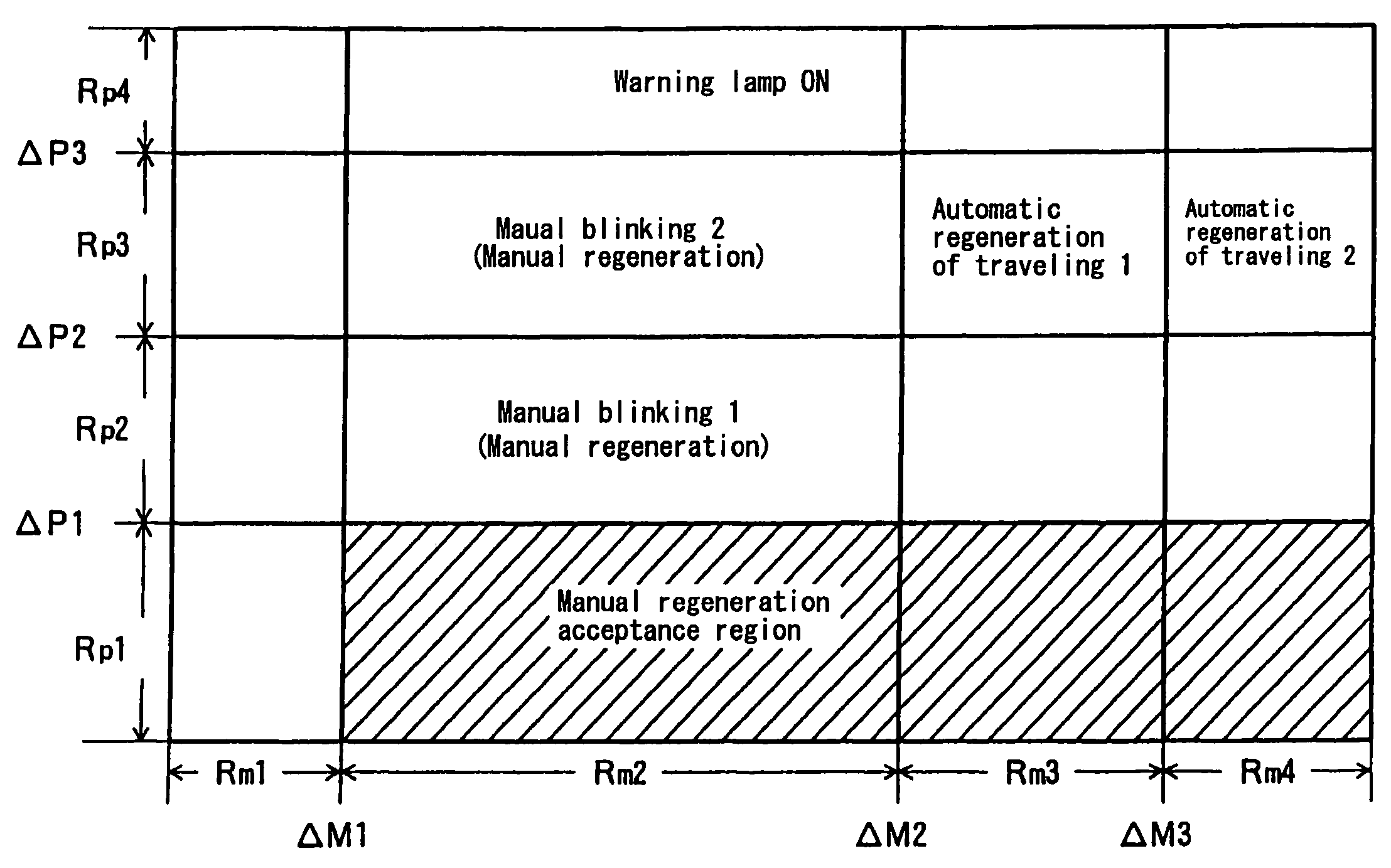

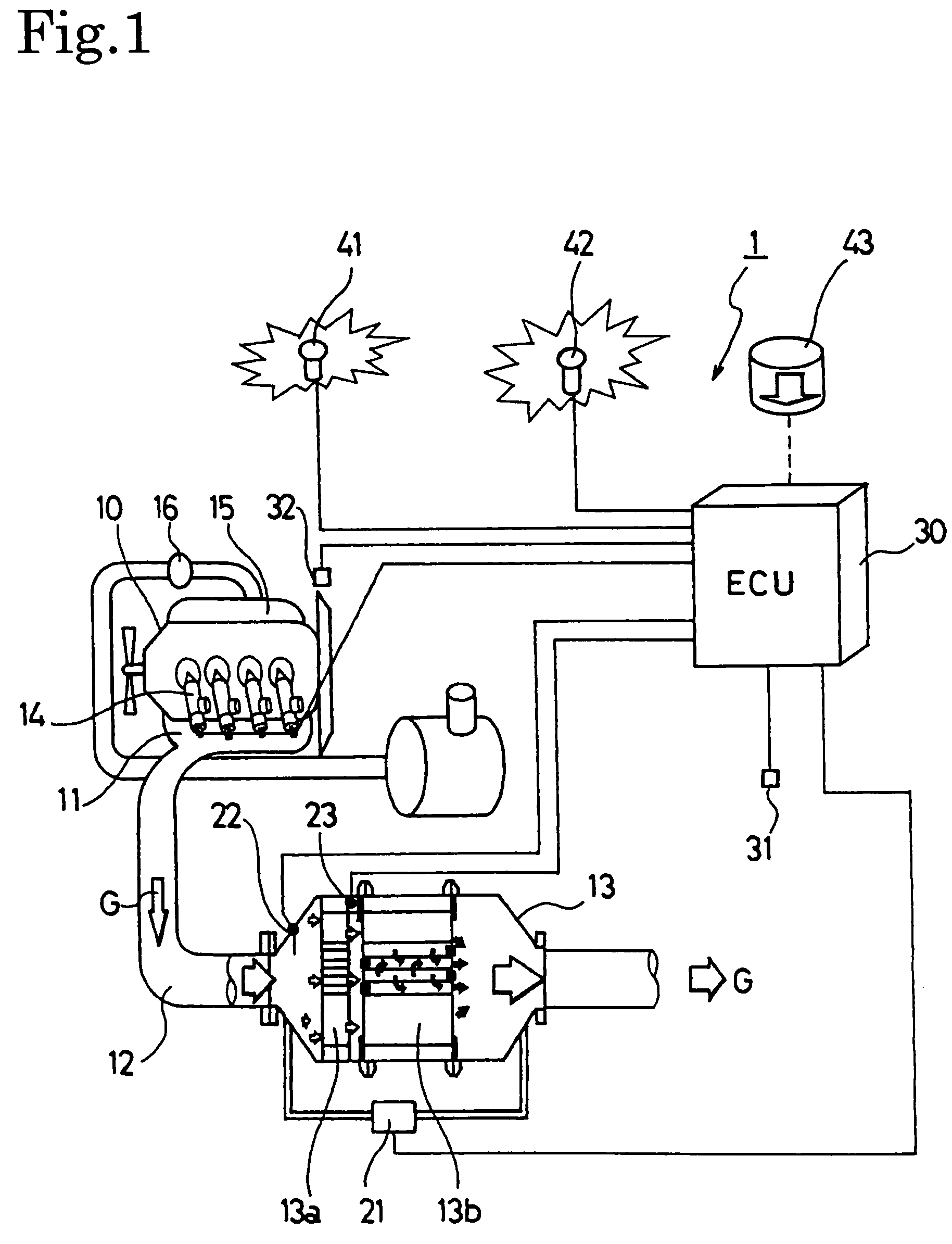

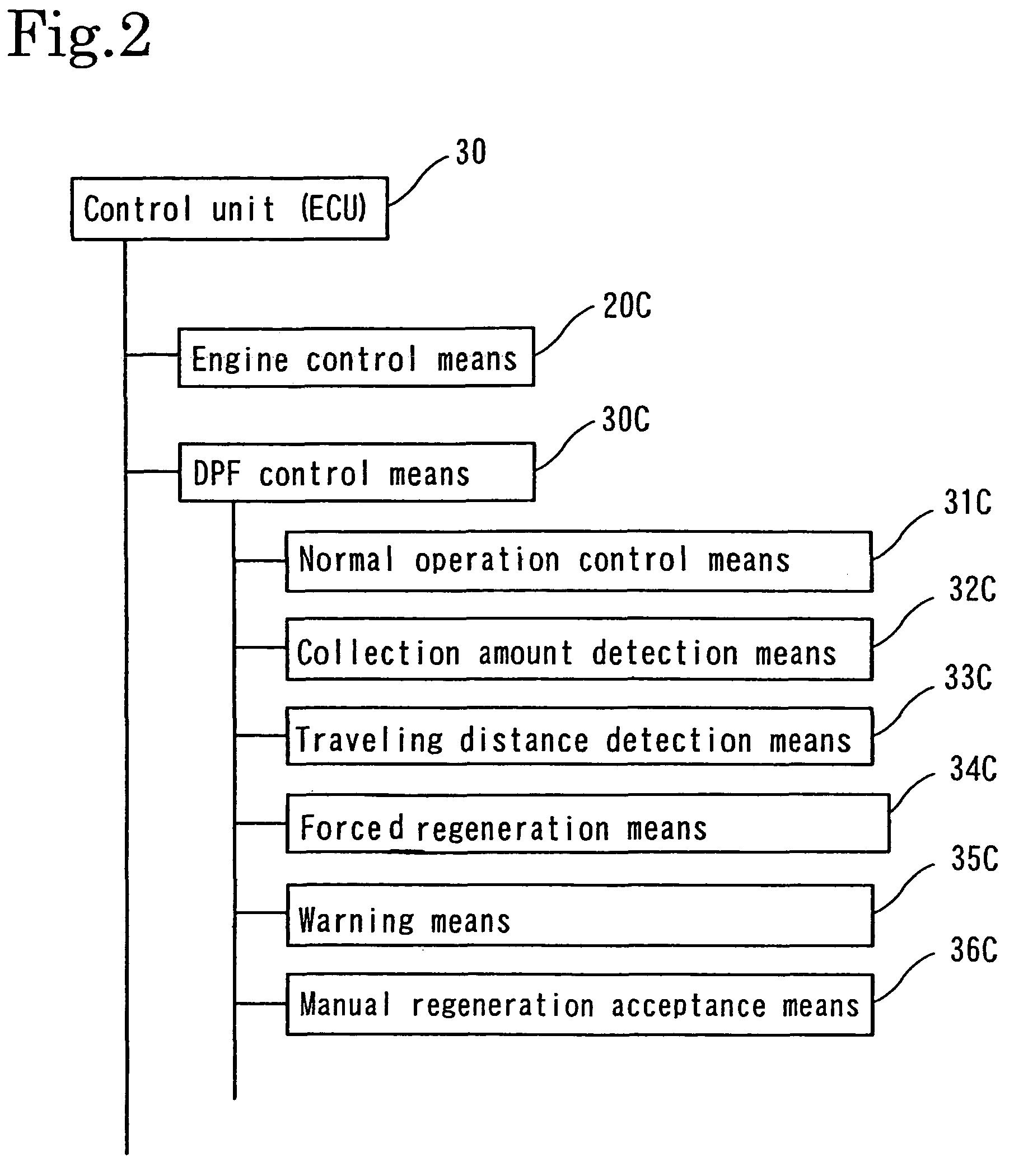

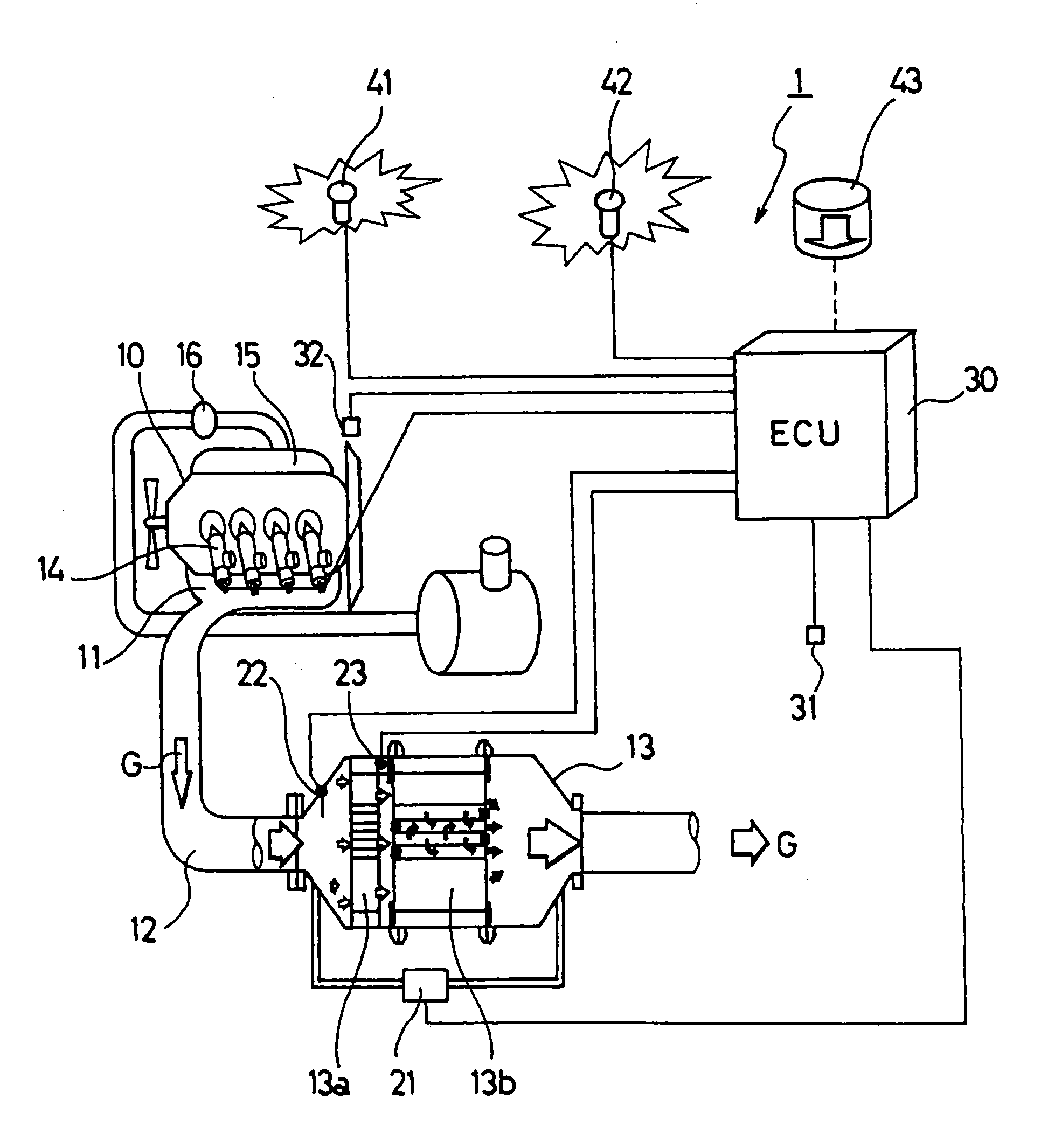

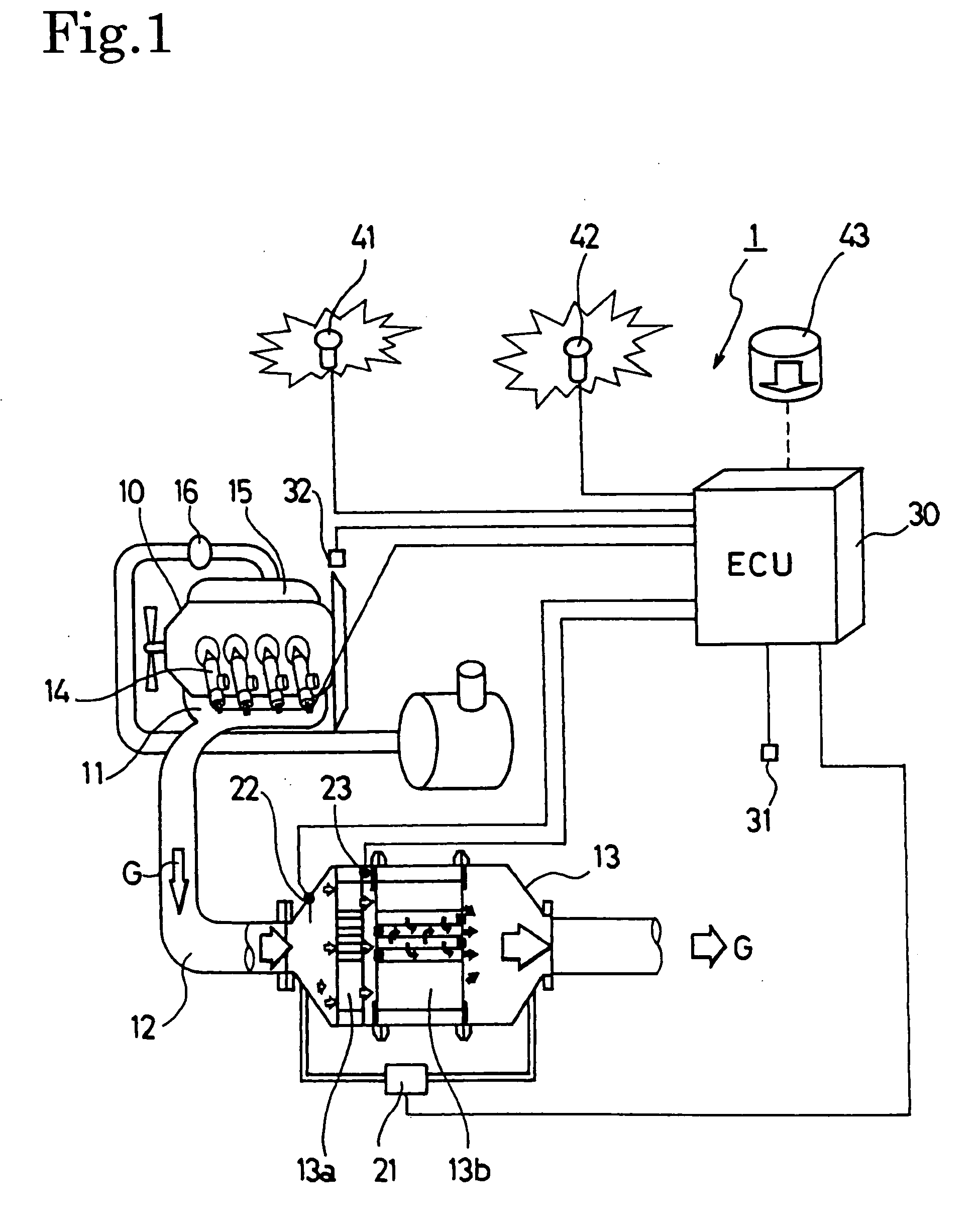

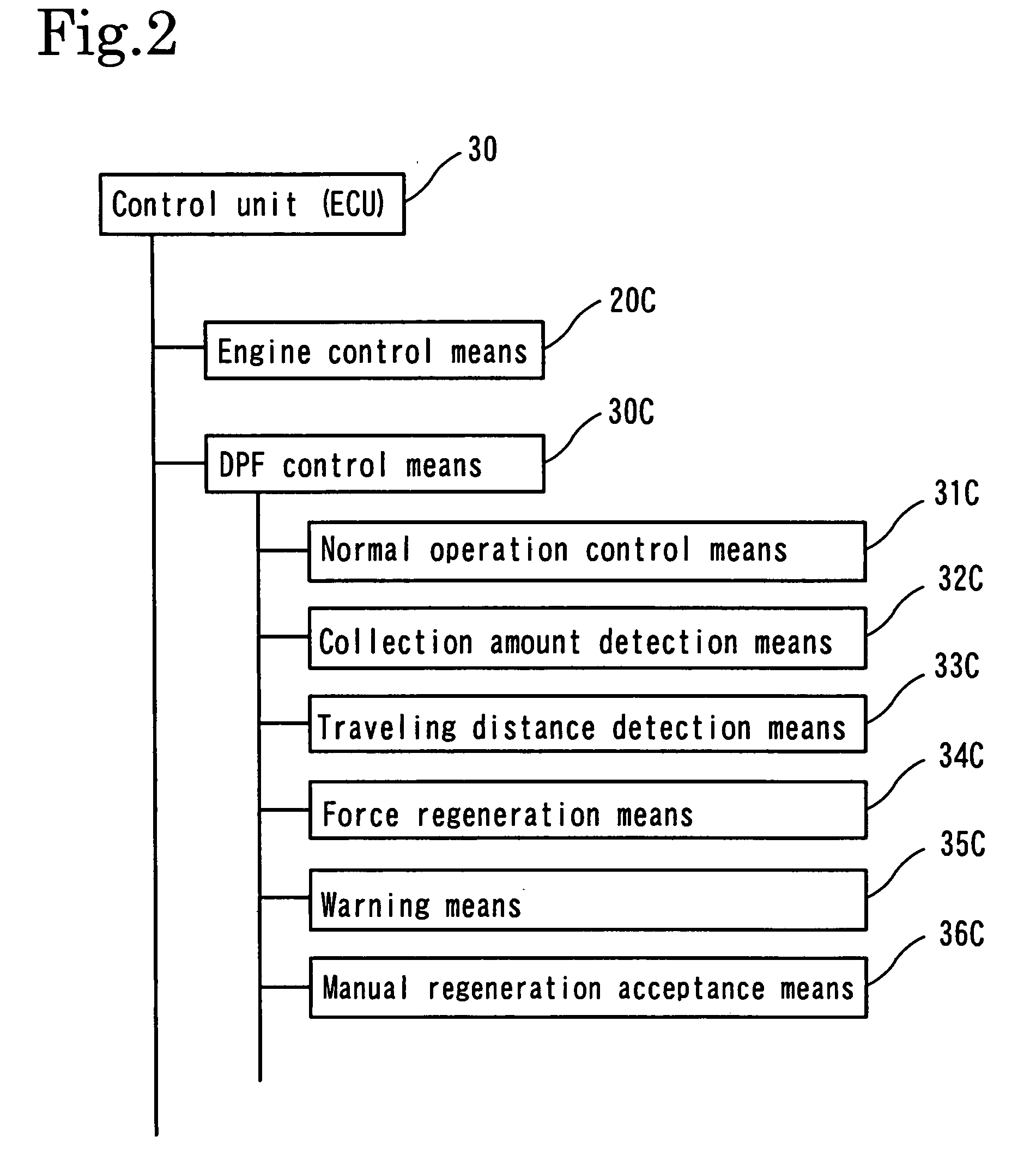

Exhaust gas purifying system

ActiveUS7845165B2Shorten the timeLess worryElectrical controlInternal combustion piston enginesDriver/operatorControl system

An exhaust emission control system including a continuous regenerating diesel particulate filter (“DPF”) and a DPF controller, wherein a forced regenerator is operated by a driver's request, when it is judged that a traveling distance, after starting particulate matter collection, detected by a traveling distance detector has reached a predetermined judging traveling distance, even when the DPF controller detects that a collection amount detected by a collection amount detector is smaller than a prescribed judging collection amount. Accordingly, in a continuous regenerating DPF capable of manual regenerating, the number of warnings, such as a blinking regeneration button prompting a manual regeneration, is reduced to relieve a driver of annoyance or inconvenience.

Owner:ISUZU MOTORS LTD

Exhaust Gas Purifying System

ActiveUS20080163609A1Less worryImprove convenienceElectrical controlInternal combustion piston enginesControl systemExhaust fumes

An exhaust emission control system [1] comprising a continuous regenerating DPF [13] and a DPF controlling means [30C], wherein control is so performed as to accept the operation of a forced regenerating means [34C] at an operation request by a driver when it is judged a traveling distance [ΔMc] after starting collection detected by a traveling distance detecting means [33C] has reached a specified judging traveling distance [ΔM1] even when the DPF controlling means [30C] detects a collection amount [ΔPm] detected by a collection amount detecting means [32C] is smaller than a specified judging collection amount [ΔP1]. Accordingly, in a continuous regenerating DPF [13] capable of manual regenerating, the number of warning such as a blinking regeneration button prompting a manual regeneration is reduced to relieve a driver of trouble.

Owner:ISUZU MOTORS LTD

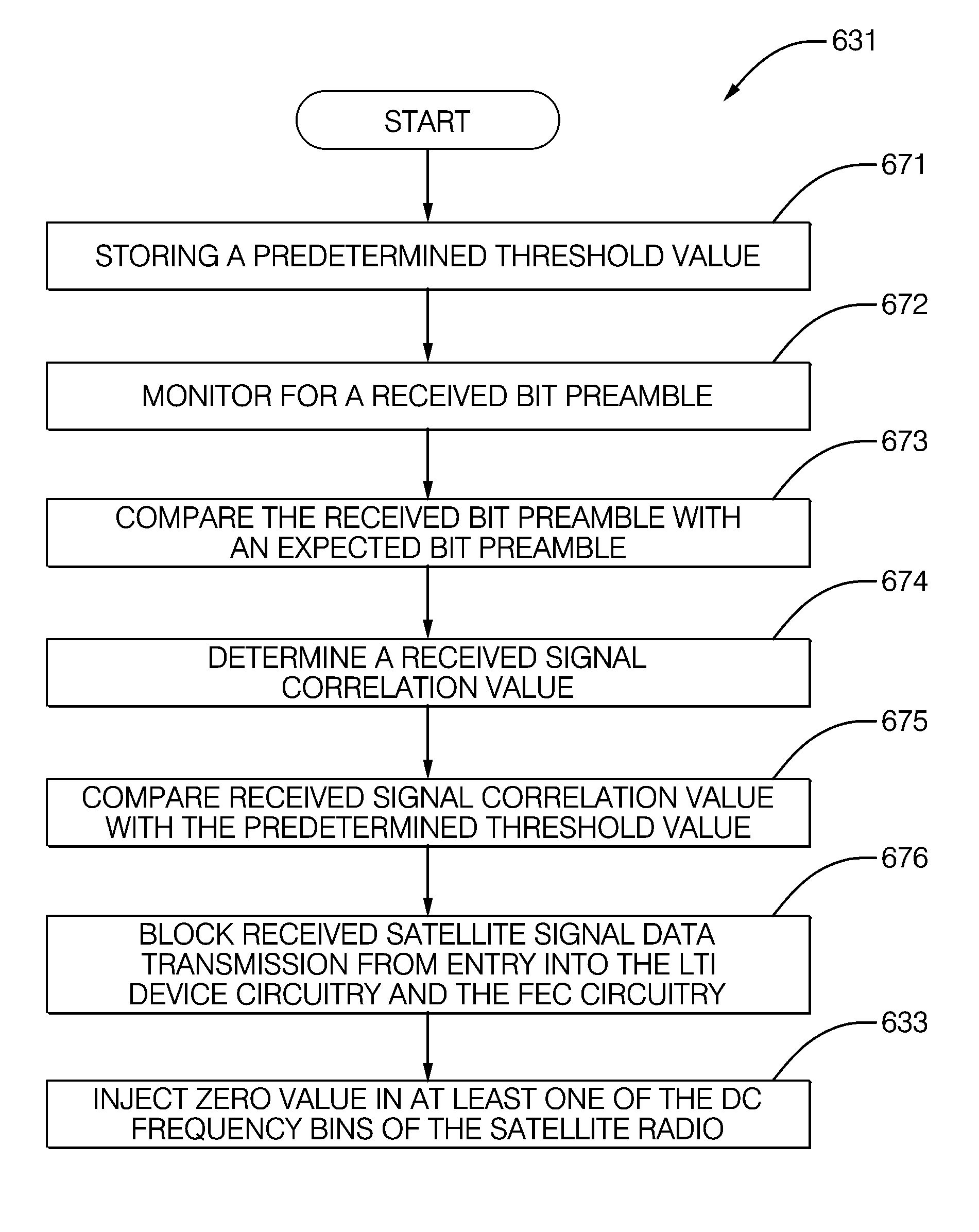

Satellite receiver performance enhancements

ActiveUS20130089126A1Effectively remove and mitigate exhibited DC offset noiseMinimize frequencyError preventionTransmission monitoringError checkingPerformance enhancement

Long time interleaver and listenable audio performance enhancements for a satellite receiver are presented. One enhancement includes comparing a correlation and a predetermined threshold value and blocking satellite signal data transmission from entry into long time interleaver (LTI) device circuitry and forward error correction (FEC) circuitry when the correlation value is the same as, or less than the predetermined threshold value. Another enhancement includes using Reed-Solomon codeword error checking to prevent erroneous baseband signal data from being accepted as good baseband signal data. A further enhancement includes storing symbol timing and frequency data during a strong signal condition of the satellite receiver and using this stored data when the satellite receiver encounters a weak signal condition. Another enhancement includes mitigating DC offset noise in a satellite receiver having a zero-IF tuner.

Owner:APTIV TECH LTD

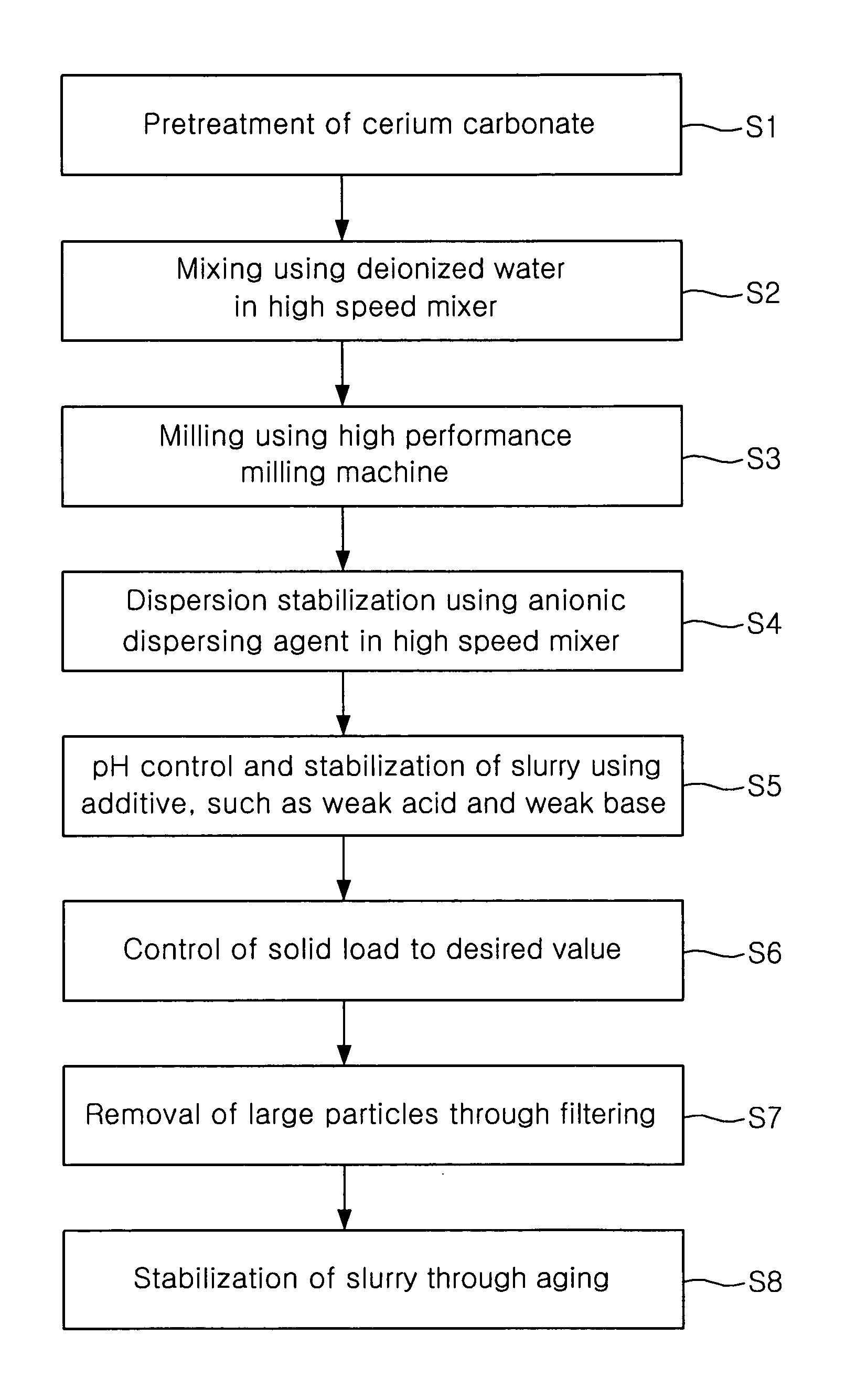

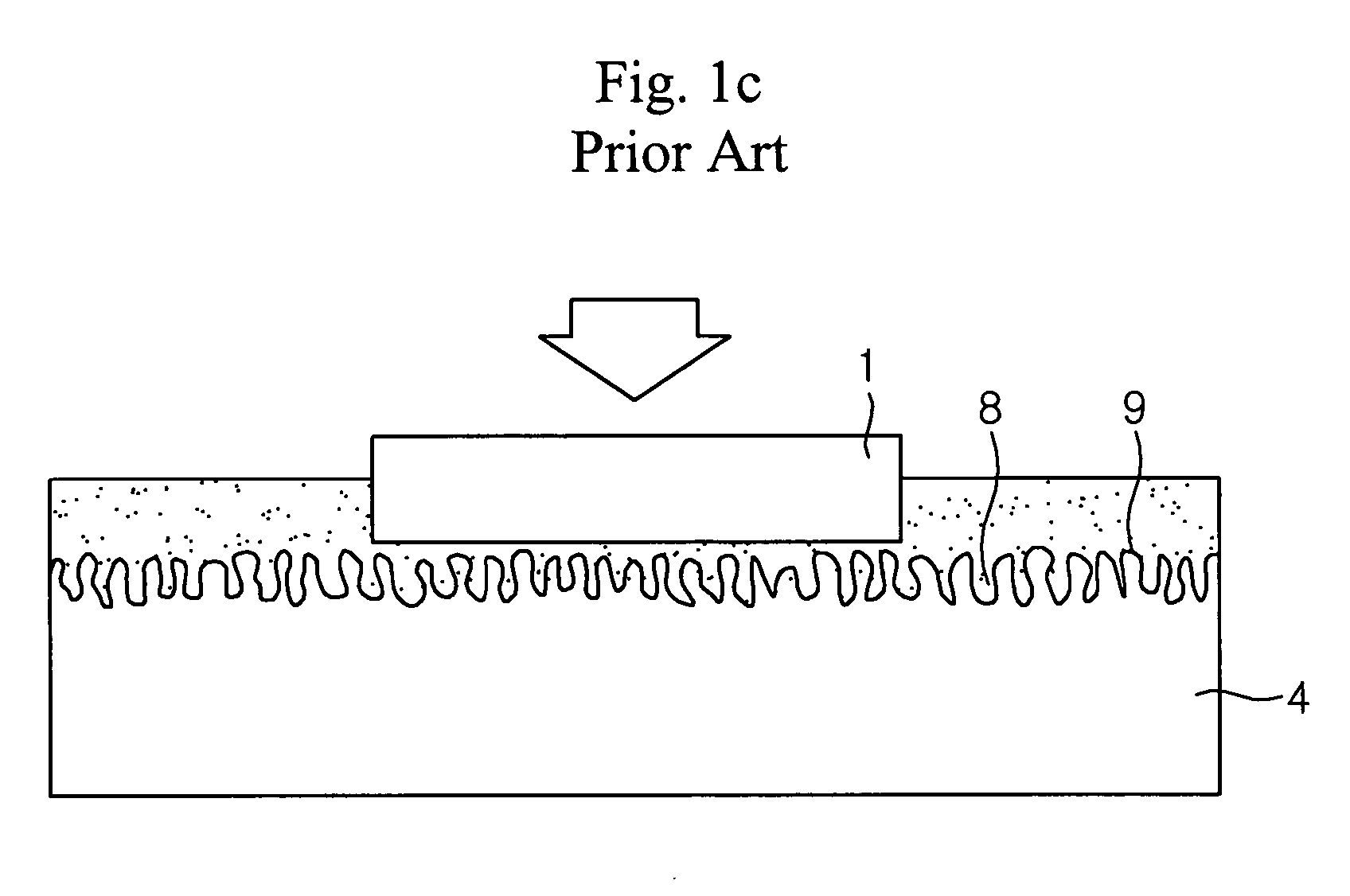

Slurry for CMP and method of polishing substrate using same

ActiveUS20050252092A1Design ruleHigh performancePigmenting treatmentOther chemical processesCompound (substance)Oxide

Disclosed herein is a polishing slurry and a method of producing the same. The polishing slurry has high selectivity in terms of a polishing speed of an oxide layer to that of a nitride layer used in CMP of an STI process which is essential to produce ultra highly integrated semiconductors having a design rule of 256 mega D-RAM or more, for example, a design rule of 0.13 μm or less. A method and a device for pre-treating polishing particles, a dispersing device and a method of operating the dispersing device, a method of adding a chemical additive and an amount added, and a device for transferring samples are properly employed to produce a high performance nano ceria slurry essential to CMP for a process of producing ultra highly integrated semiconductors of 0.13 μm or less, particularly, the STI process.

Owner:IUCF HYU (IND UNIV COOP FOUNDATION HANYANG UNIV) +1