Substrate/multi-chip-integrated large port interconnection chip and realization method thereof

A technology of multi-chip integration and implementation method, which is applied in the field of substrate multi-chip integrated large-port interconnect chips and its implementation, can solve the problems of chip area, chip power consumption, chip cost, and integrated circuit manufacturing capacity limitations, and achieve improved scalability. The effect of high reliability, low production cost and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

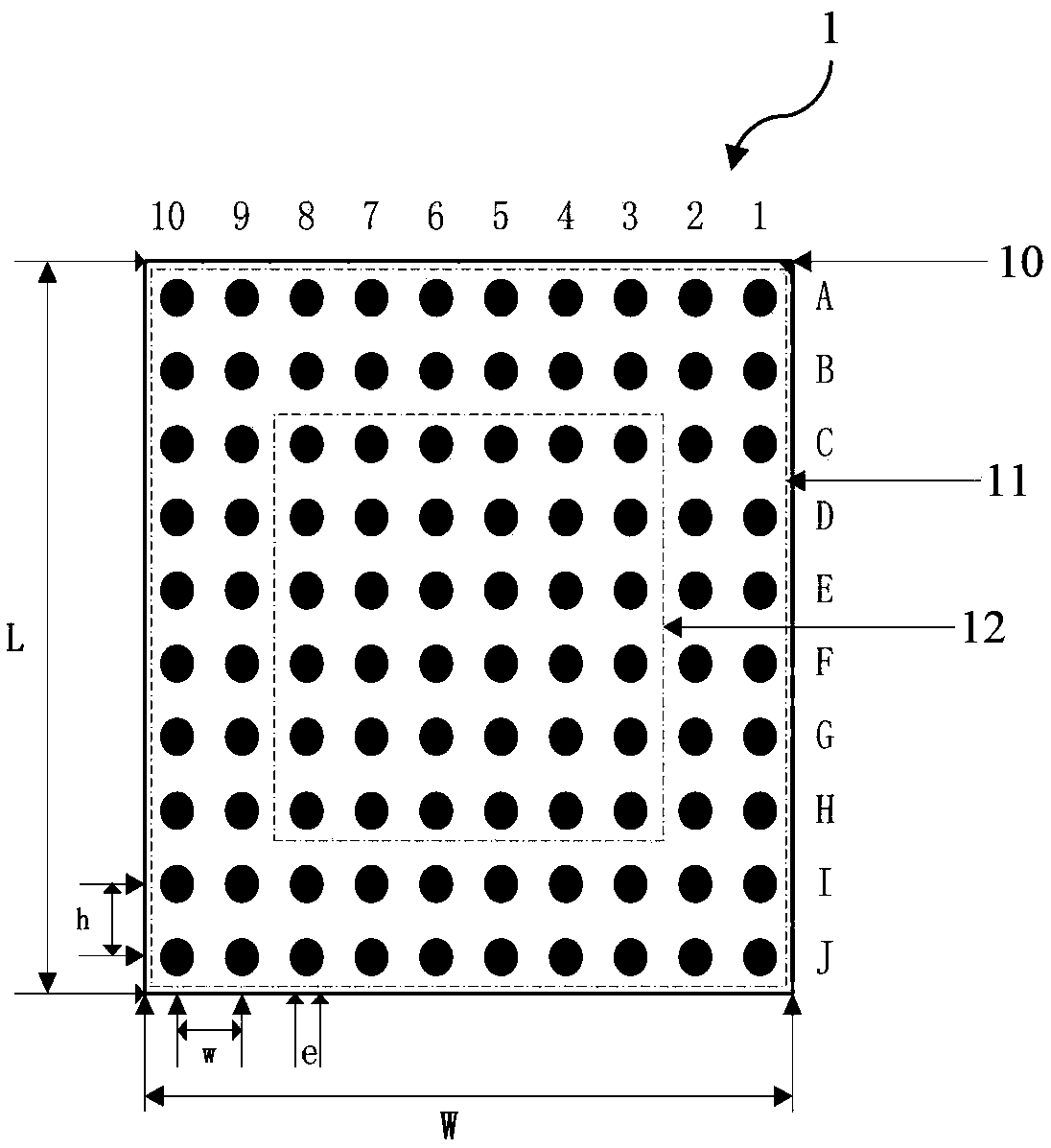

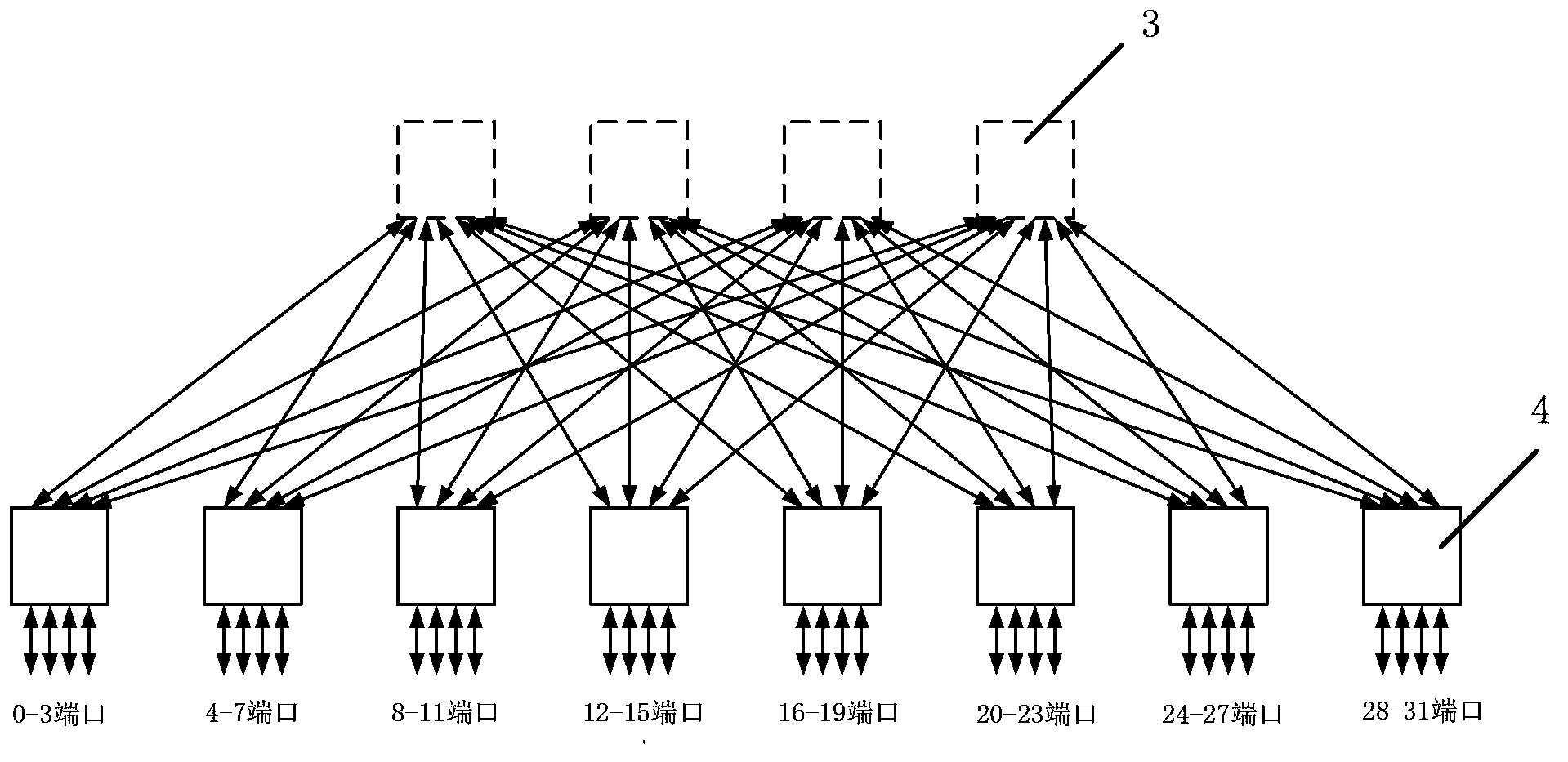

[0063] In order to effectively solve the problem that the number of integrated ports of single-chip large-port interconnection chips is severely limited, the present invention proposes a multi-layer wiring substrate, multi-chip integration, large-port interconnection chip interconnection structure and corresponding physical realization. method. Compared with the corresponding single-chip integration method, the present invention can support multiple interconnection structures, and has better balance in terms of chip implementation cost, scalability, flexibility, compatibility, etc. The requirements for integrated circuit manufacturing technology are lower, and substrate-integrated large-port interconnection chips with different numbers of ports and different specifications can be provided at the same time, which is more flexible in adapting to market demand.

[0064] The technical solution of the present invention will be described in detail below.

[0065] Interconnect sub-c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More