Support plate for failure analysis, test equipment, and method for chip electrical failure analysis

A technology for electrical failure and testing equipment, which is applied in electronic circuit testing, optical testing for flaws/defects, measuring device casings, etc. It can solve problems such as inability to successfully solder all of them, inability to handle chips with a large number of pins, and complex pin arrangement. , to achieve the effect of convenient and fast hardware preparation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific example

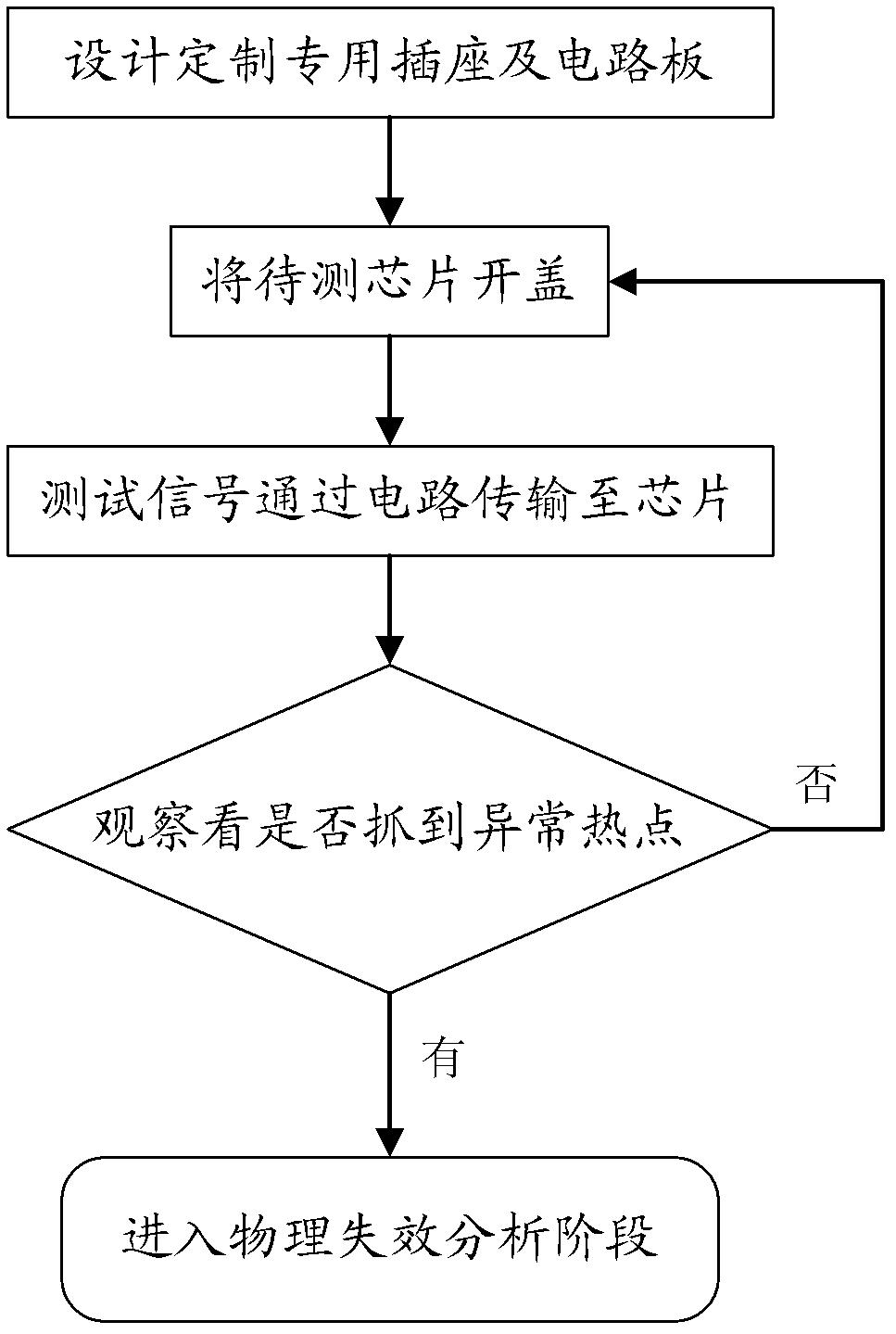

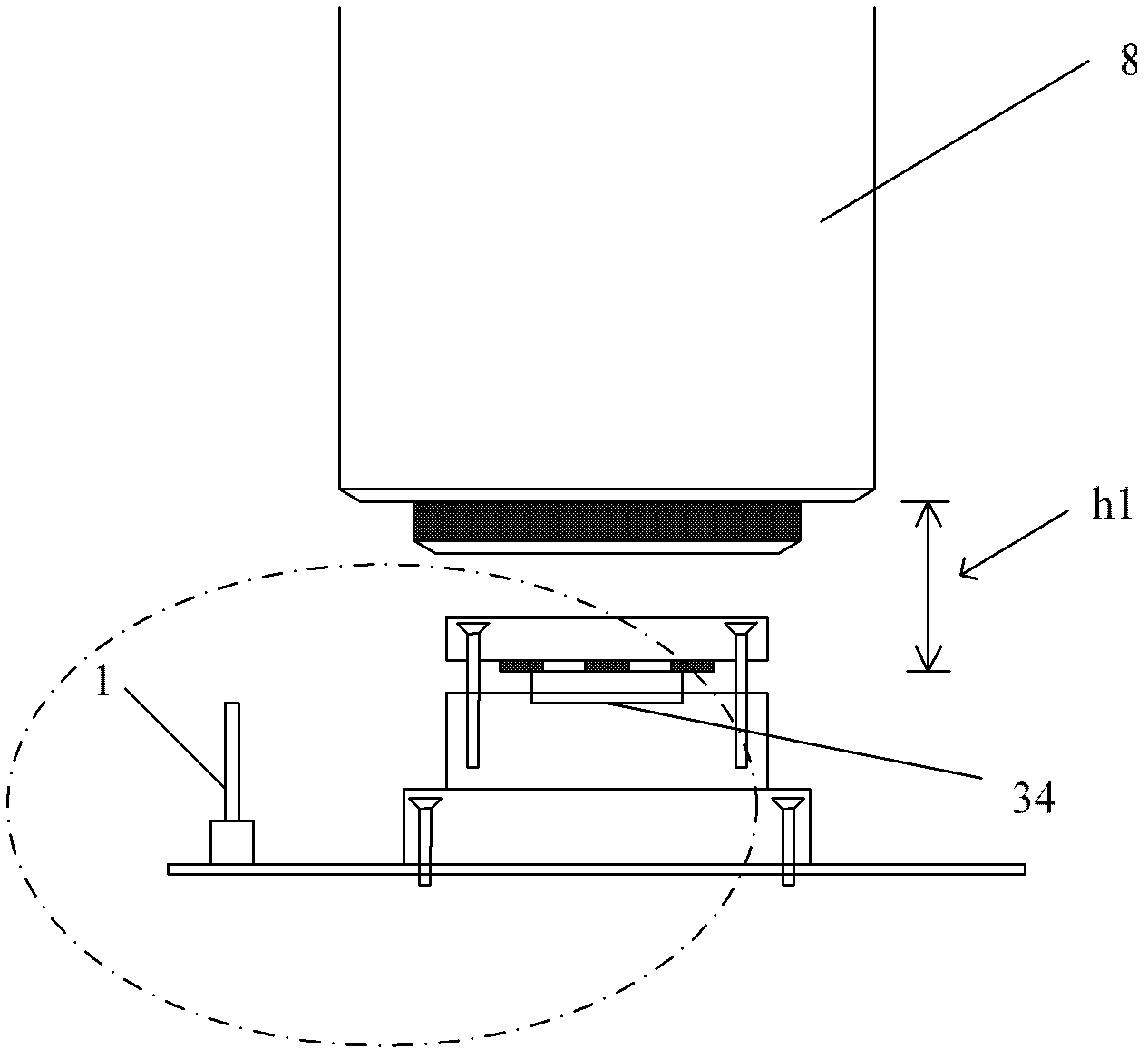

[0063] The following is a specific example, combined with Figure 6 to Figure 8 To describe in detail the method of using the present invention to test the special-purpose carrier board designed for the chip to be tested:

[0064] 1) Design a special carrier board for the chip to be tested;

[0065] The chip to be tested is a 360-pin BGA with a pin center distance of 1.5 mm, which is only 31 mm square. Ten chips are randomly selected from a certain batch of chips that have problems and need to be analyzed for failure as test samples, which are the chips to be tested in this embodiment.

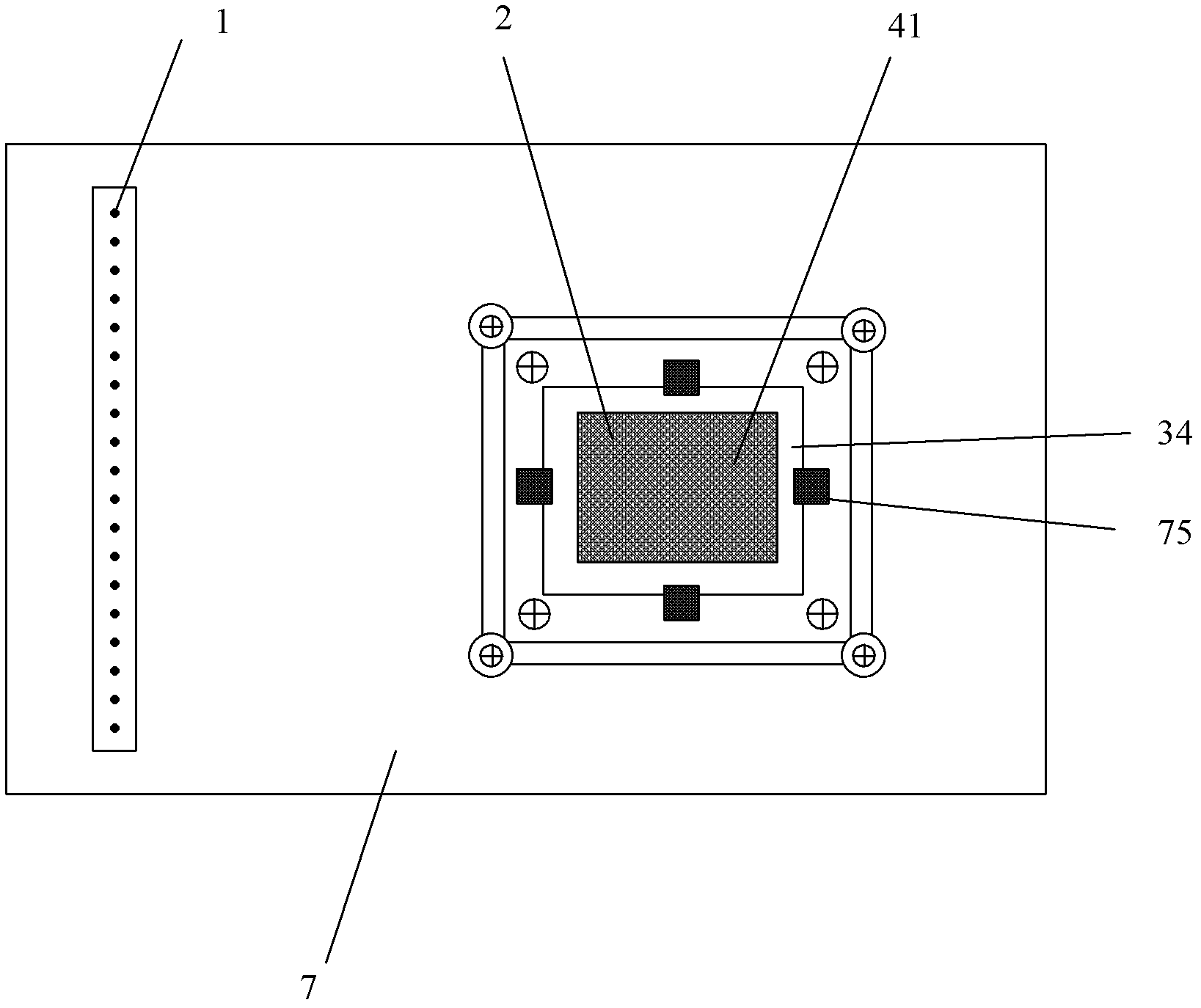

[0066] The carrier board, which is a PCB board, includes an array of pins for signal transmission between the chip and the test machine, an array of pads in the area where the chip to be tested is set, and a gap between the array of pins and the array of pads. Metal connection. The pins are generally copper pillars, and their number is compatible with the input and output pins of the chip. ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More