Chip and packaging method thereof

A chip packaging and chip technology, which is applied in semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of large overall size of the packaging structure and cannot meet the miniaturization of chips, and achieve the effect of reducing chip costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0096] Before introducing the specific implementation of the embodiment of this application, first describe the definitions of abbreviations and key terms used in the embodiment of this application.

[0097]

[0098] Fan-out wafer-level packaging can lead out the I / O pins of a single chip through the rewiring layer on the wafer, increasing the area of a single package, thereby increasing the overall number of I / O pins. Its design difficulty is not only lower than that of TSV 3DIC, but also the packaging structure is close to 2.5D IC. Therefore, fan-out wafer level packaging is expected to become the key point of the development of advanced packaging technology.

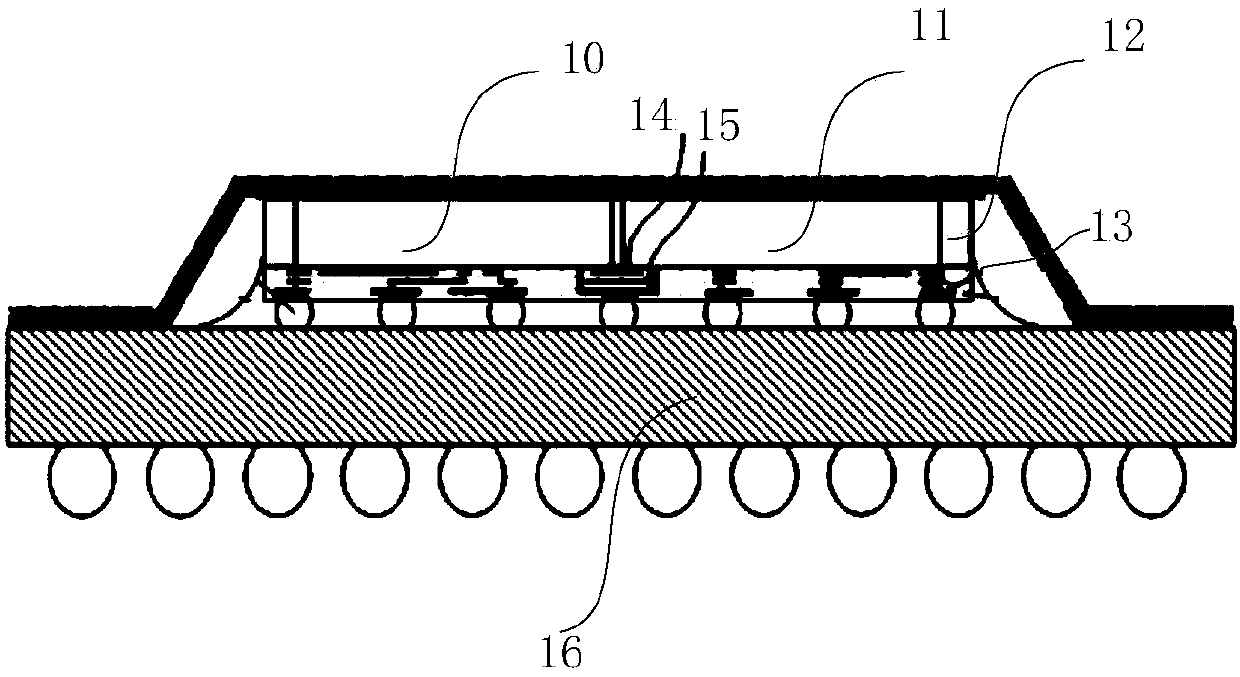

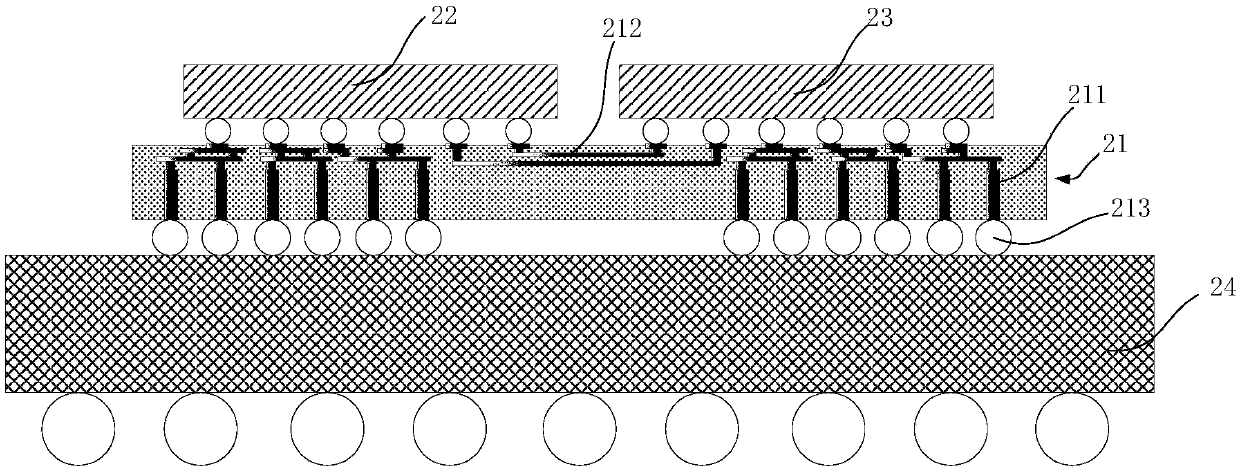

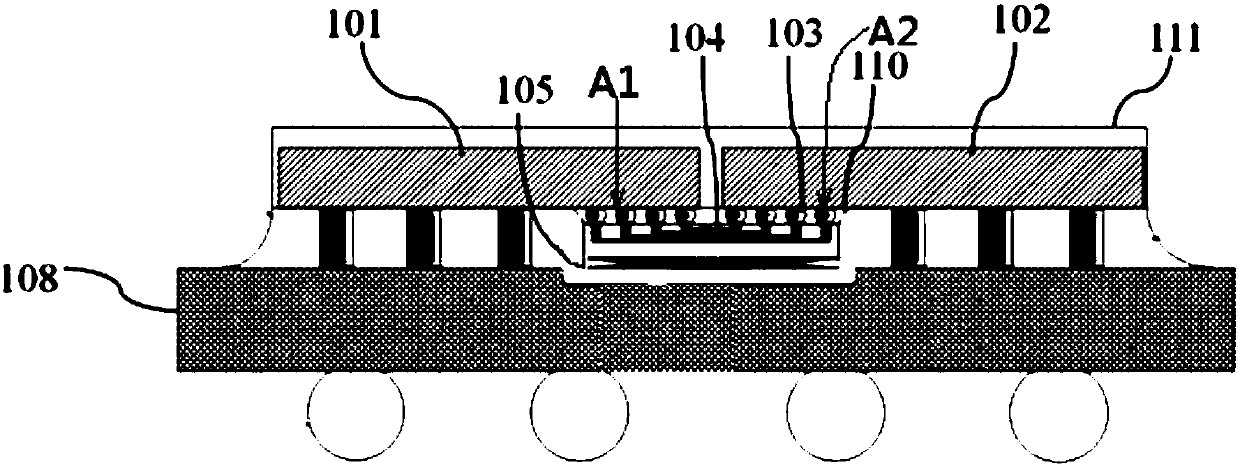

[0099] At present, some fan-out wafer-level packaging technologies have emerged in the industry. Among them, an existing fan-out packaging structure such as figure 1 shown. The fan-out packaging structure is a 2.5D FOP packaging structure combining traditional fan-out wafer level packaging and flip-chip packagi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More