Chip package and method of fabricating the same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

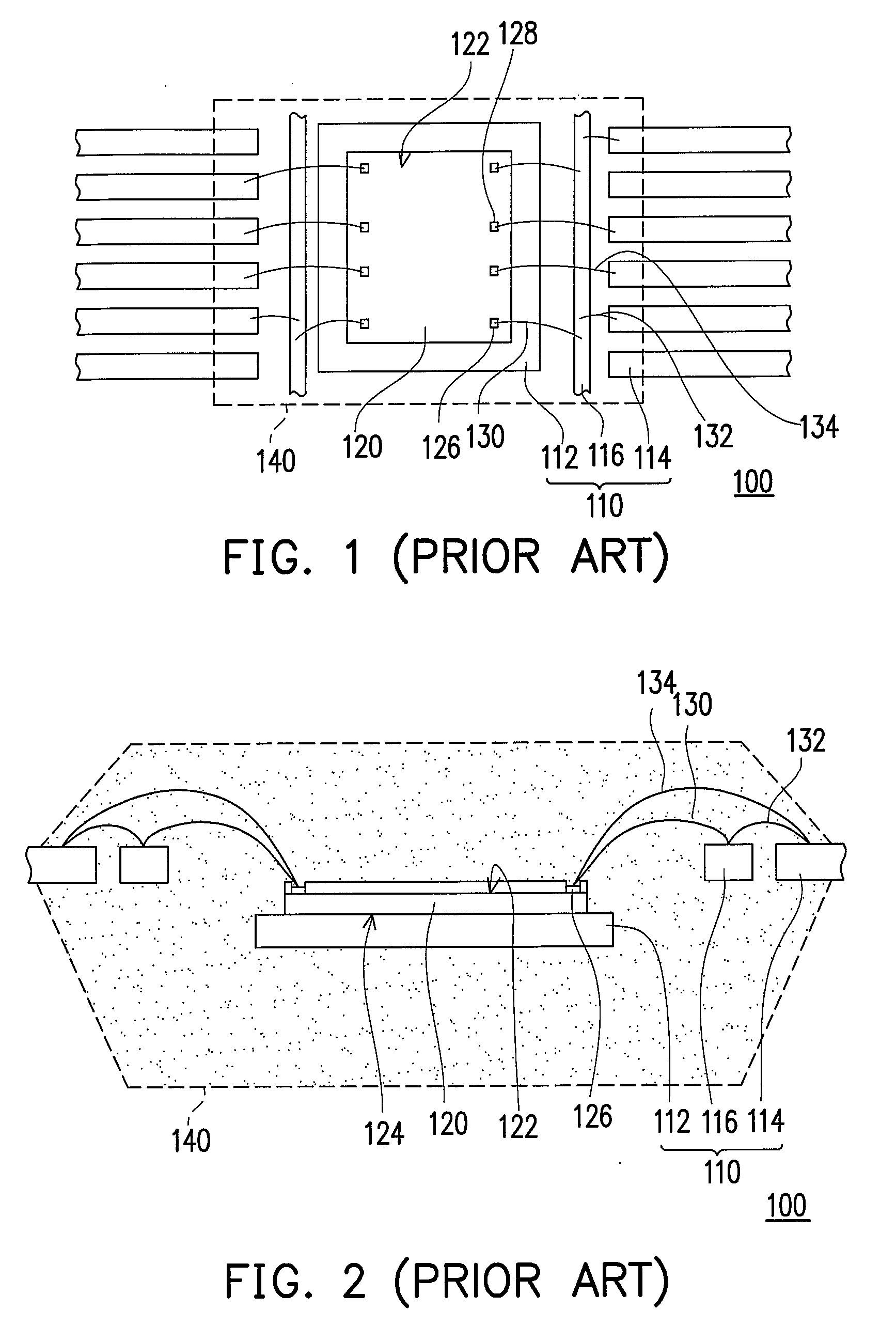

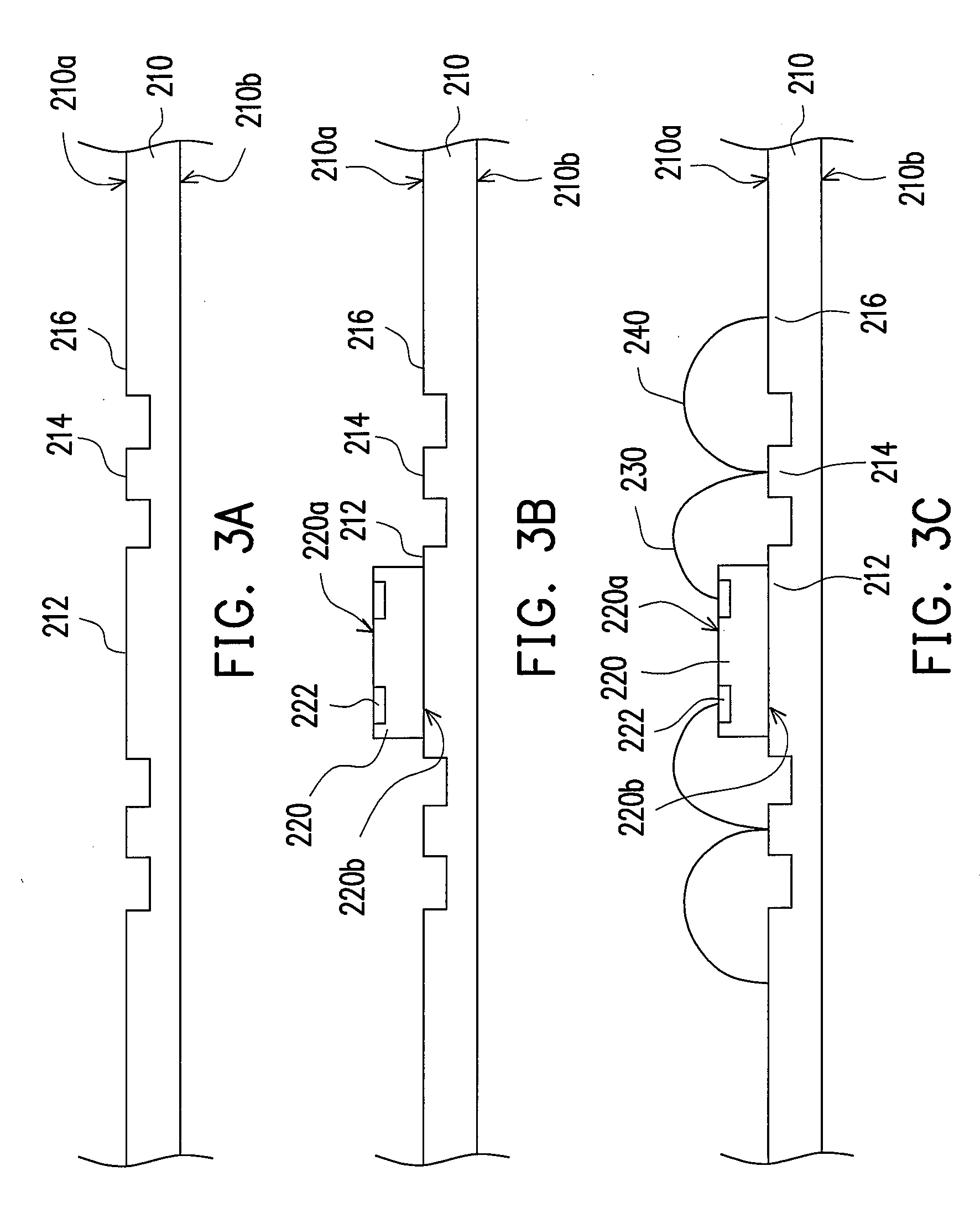

[0025]Reference will now be made in detail to the present preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers are used in the drawings and the description to refer to the same or like parts.

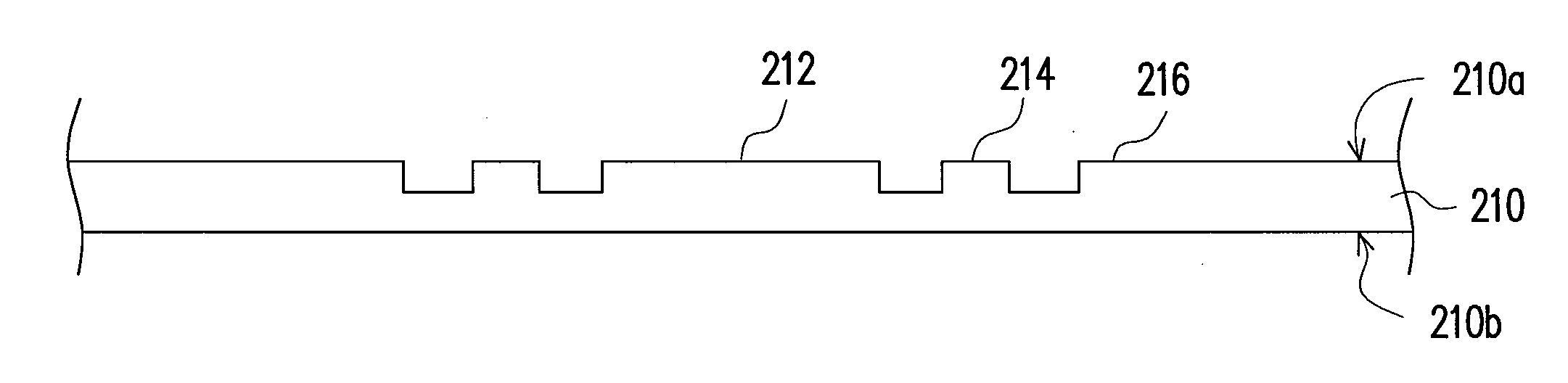

[0026]FIGS. 3A to 3F are schematic cross-sectional views illustrating the process for fabricating a chip package according to an embodiment of the present invention. First, as shown in FIG. 3A, a thin metal plate 210 is provided. The thin metal plate 210 has an upper surface 210a and a lower surface 210b. The upper surface 210a has a plurality of trenches so as to divide the thin metal plate 210 into a first protrusion part 212, a second protrusion part 214 and a plurality of third protrusion parts 216. Furthermore, the first protrusion part 212, the second protrusion part 214 and the third protrusion parts 216 are connected to one another. The first protrusion part 212 is substantially located in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More