Patents

Literature

83results about How to "Improve chip performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

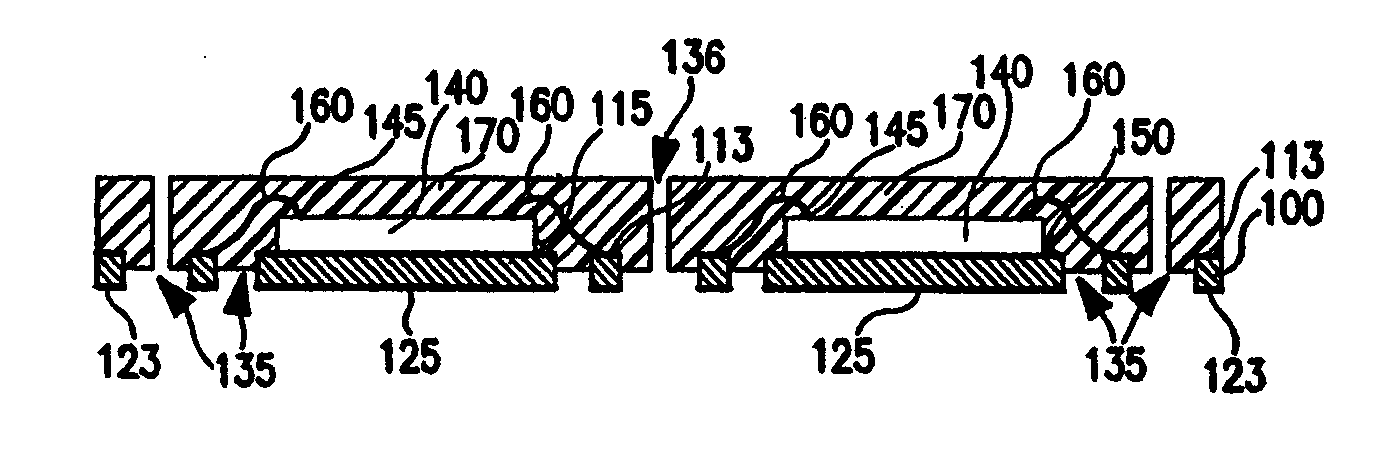

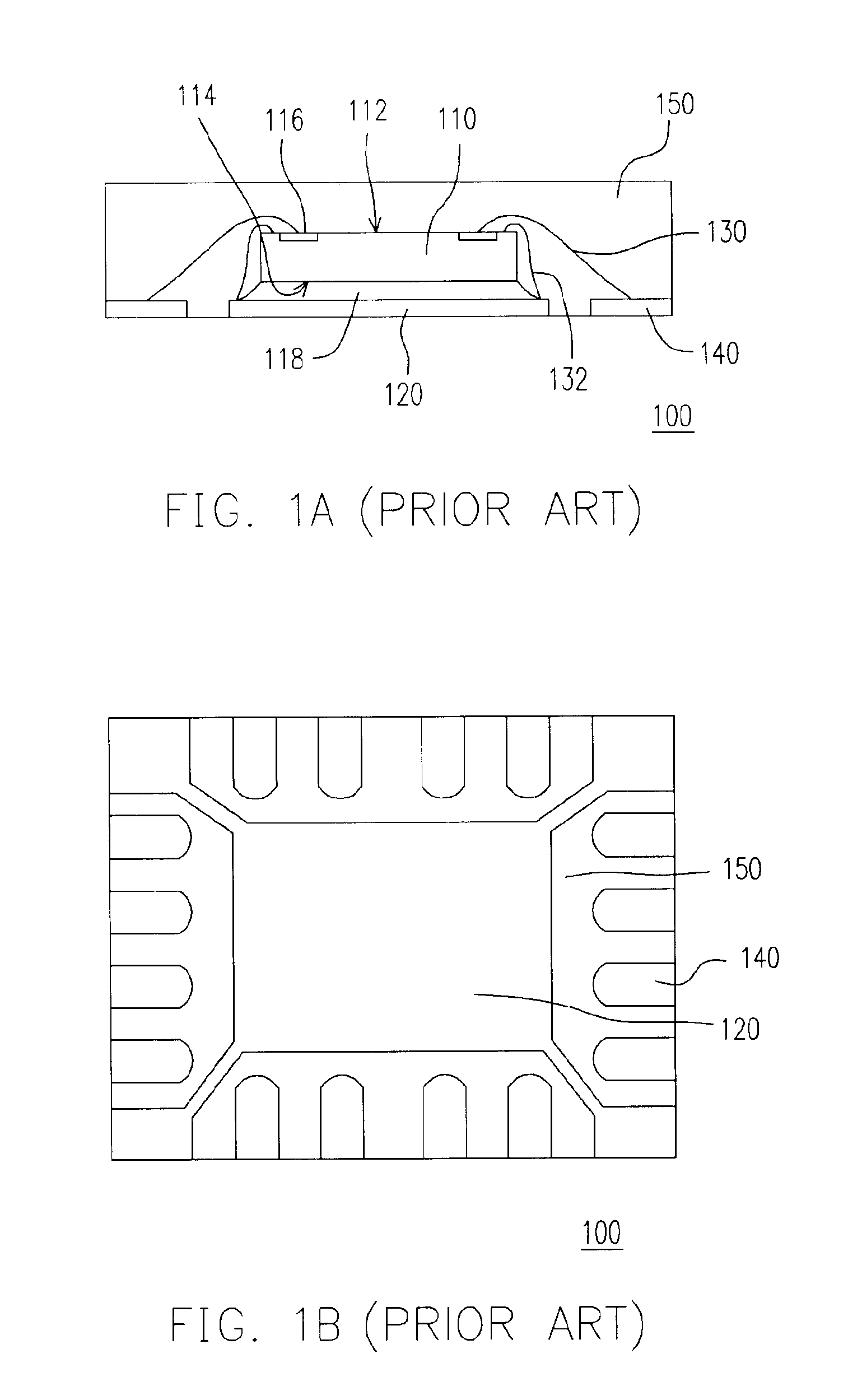

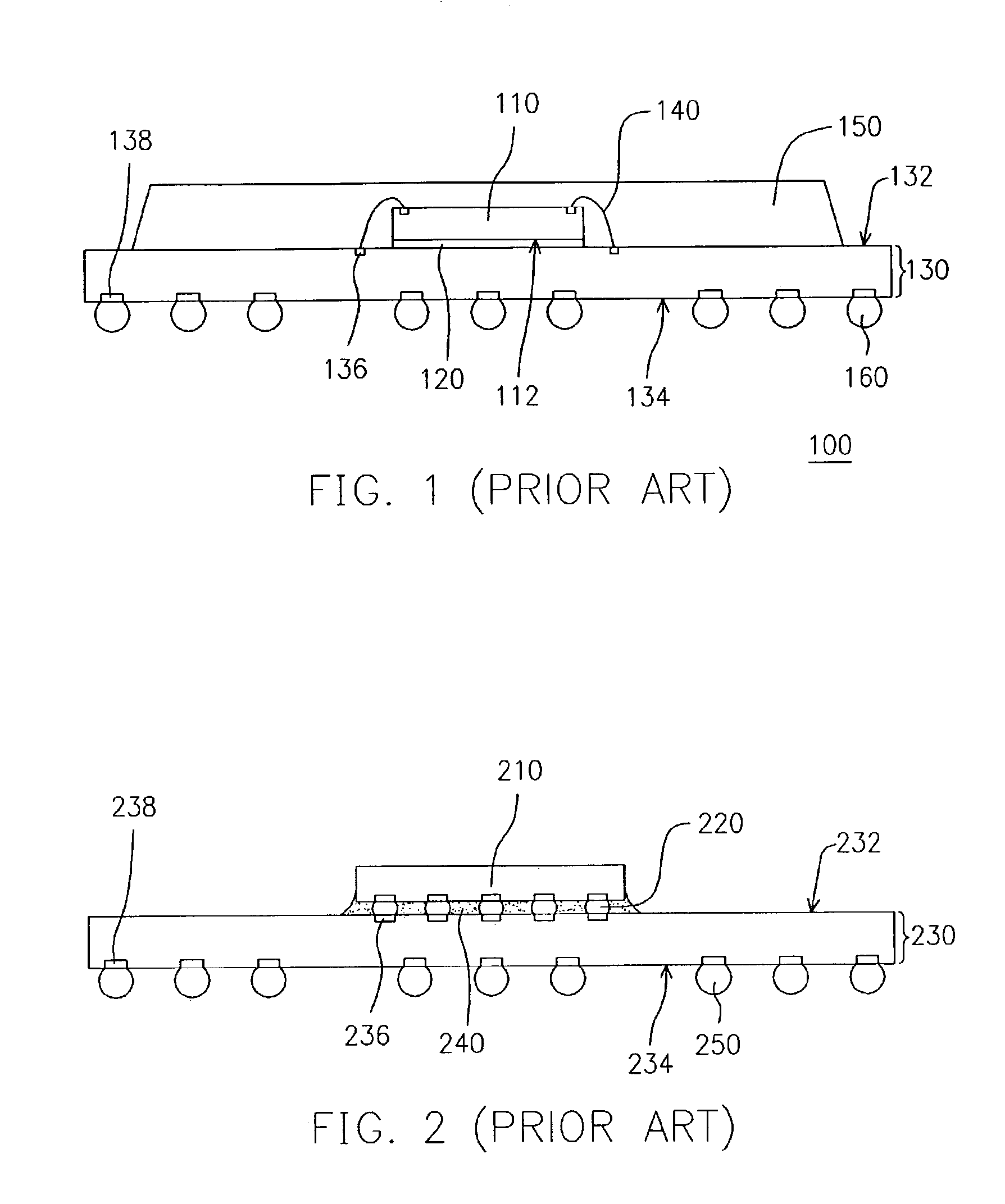

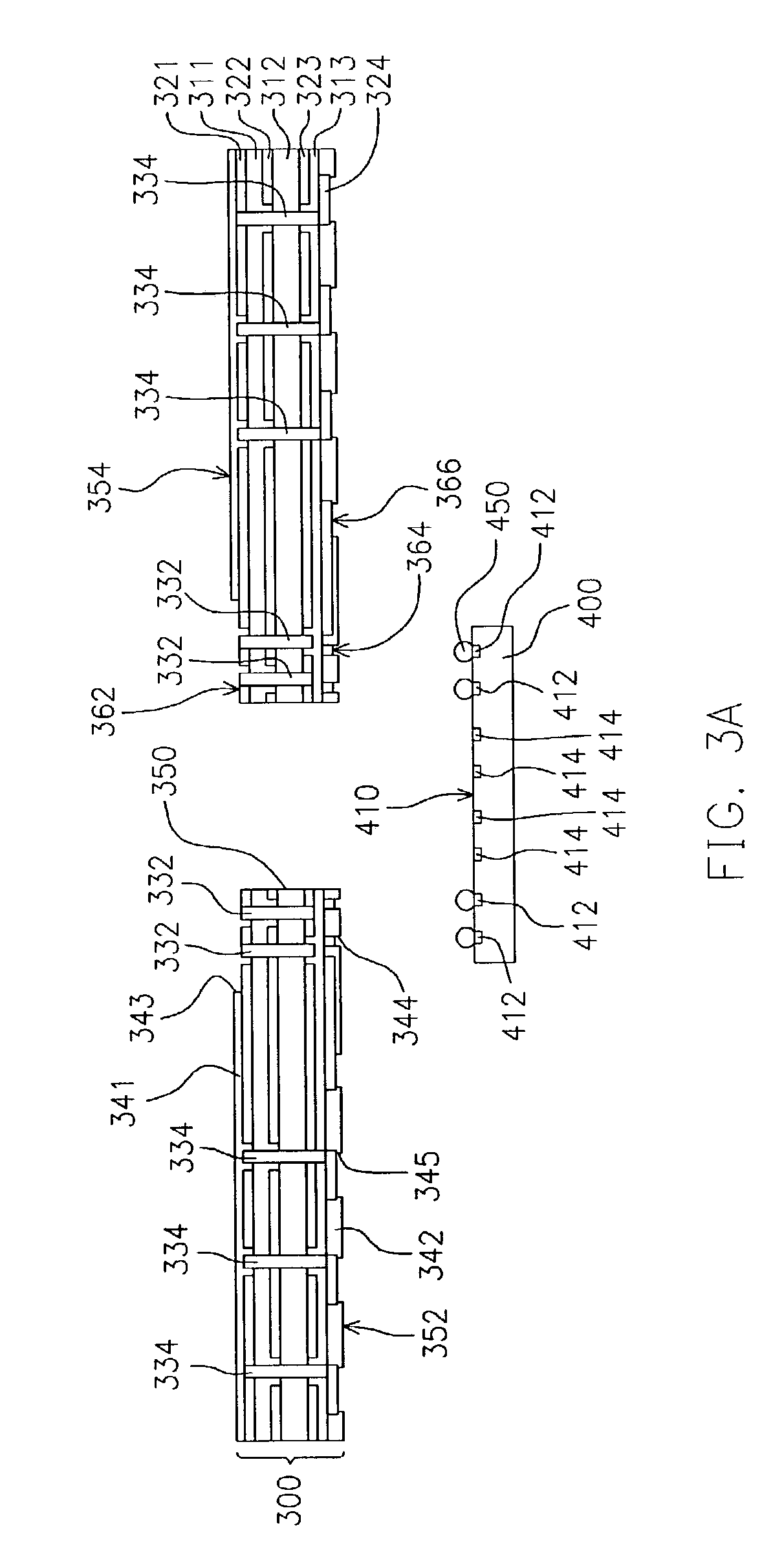

Partially Patterned Lead Frames and Methods of Making and Using the Same in Semiconductor Packaging

ActiveUS20070052076A1Increase surface areaImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyLead bonding

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging (CSP) lead-counts is disclosed, wherein the method lends itself to better automation of the manufacturing line as well as to improving the quality and reliability of the packages produced therefrom. This is accomplished by performing a major portion of the manufacturing process steps with a partially patterned strip of metal formed into a web-like lead frame on one side, in contrast with the conventional fully etched stencil-like lead frames, so that the web-like lead frame, which is solid and flat on the other side is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes, both at the chip level and the package level. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation without having to cut into any additional metal. The use of the instant partially patterned lead frame in making ELP, ELPF and ELGA-type CSPs is also disclosed.

Owner:UNISEM M BERHAD

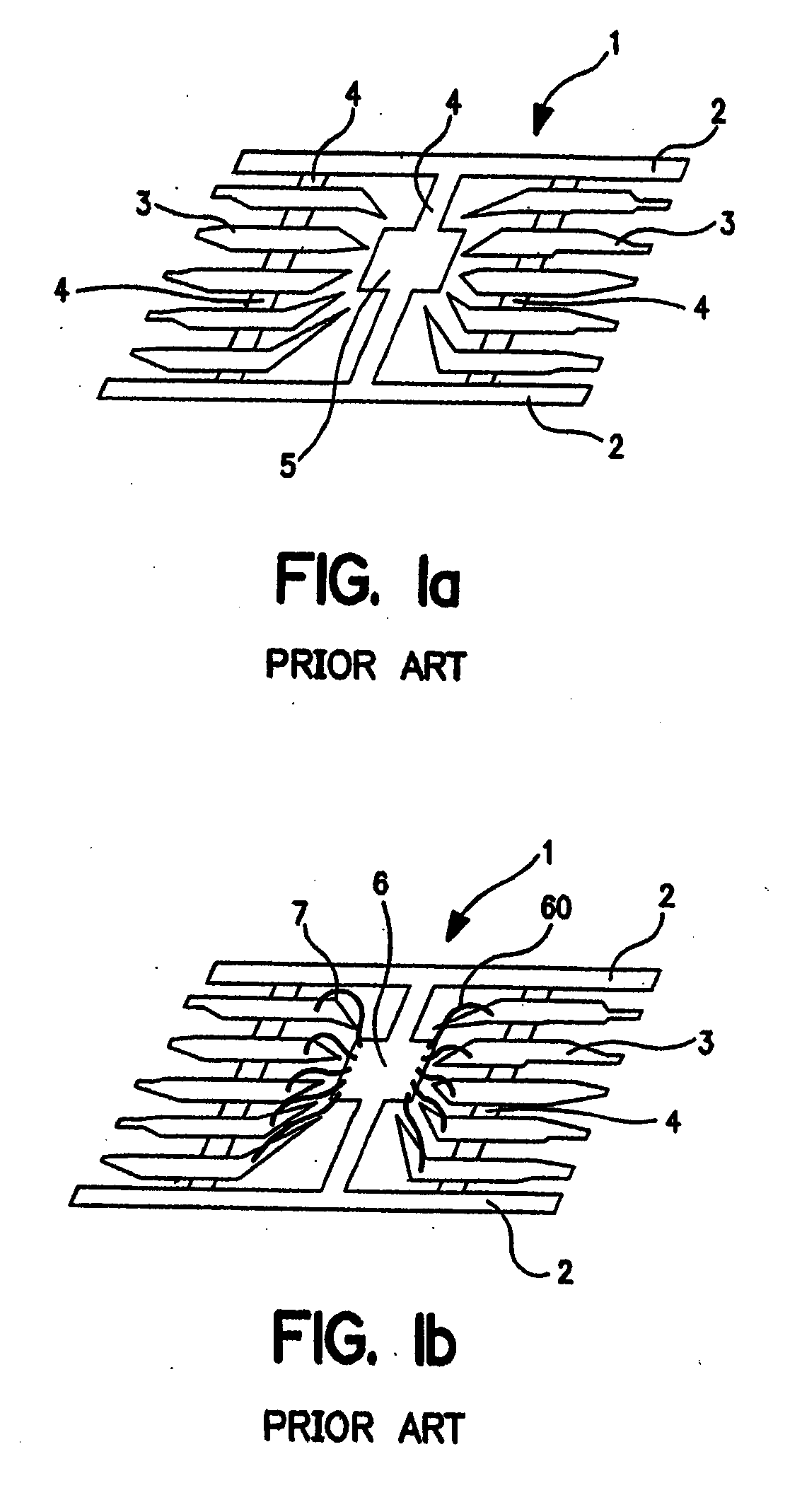

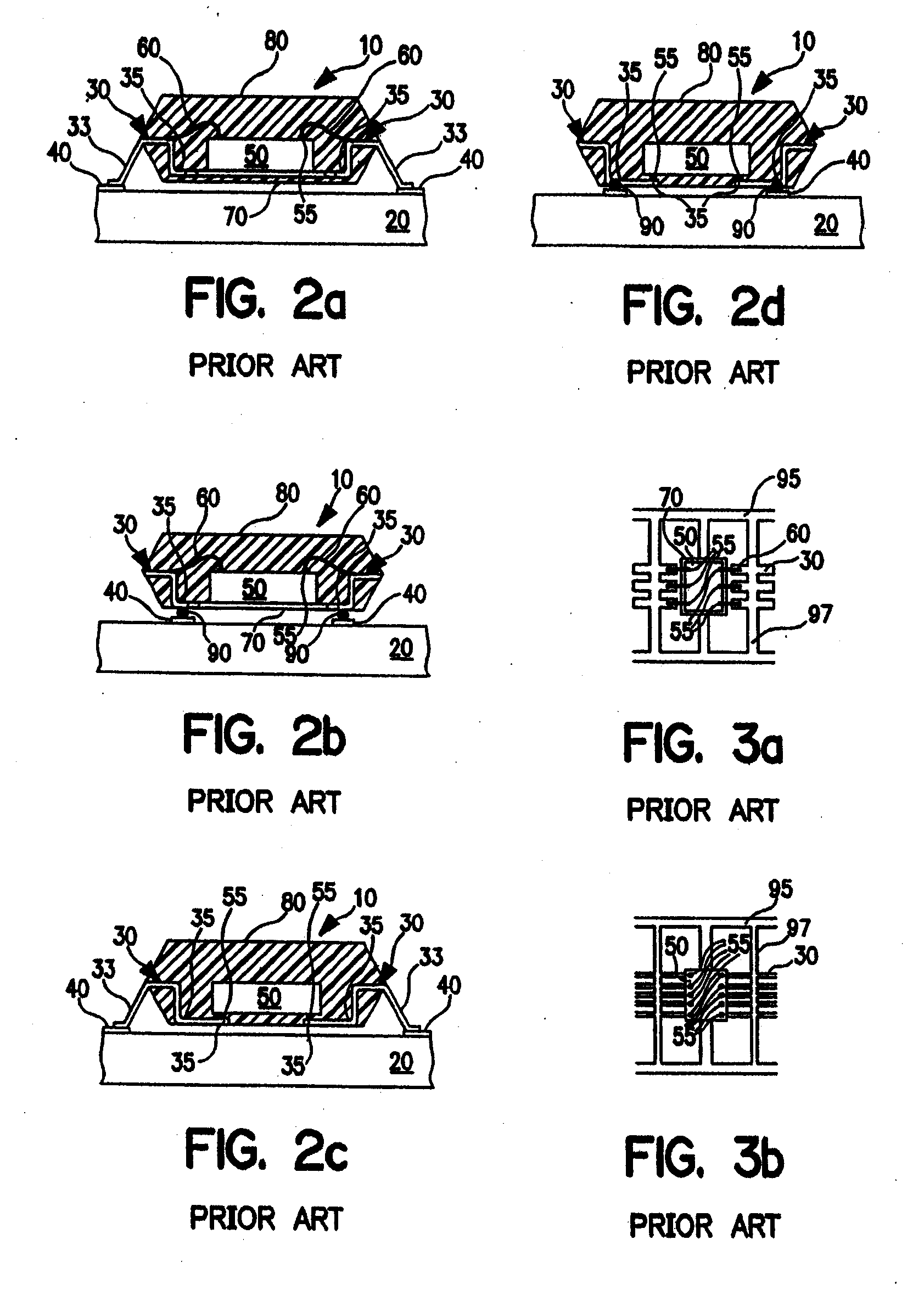

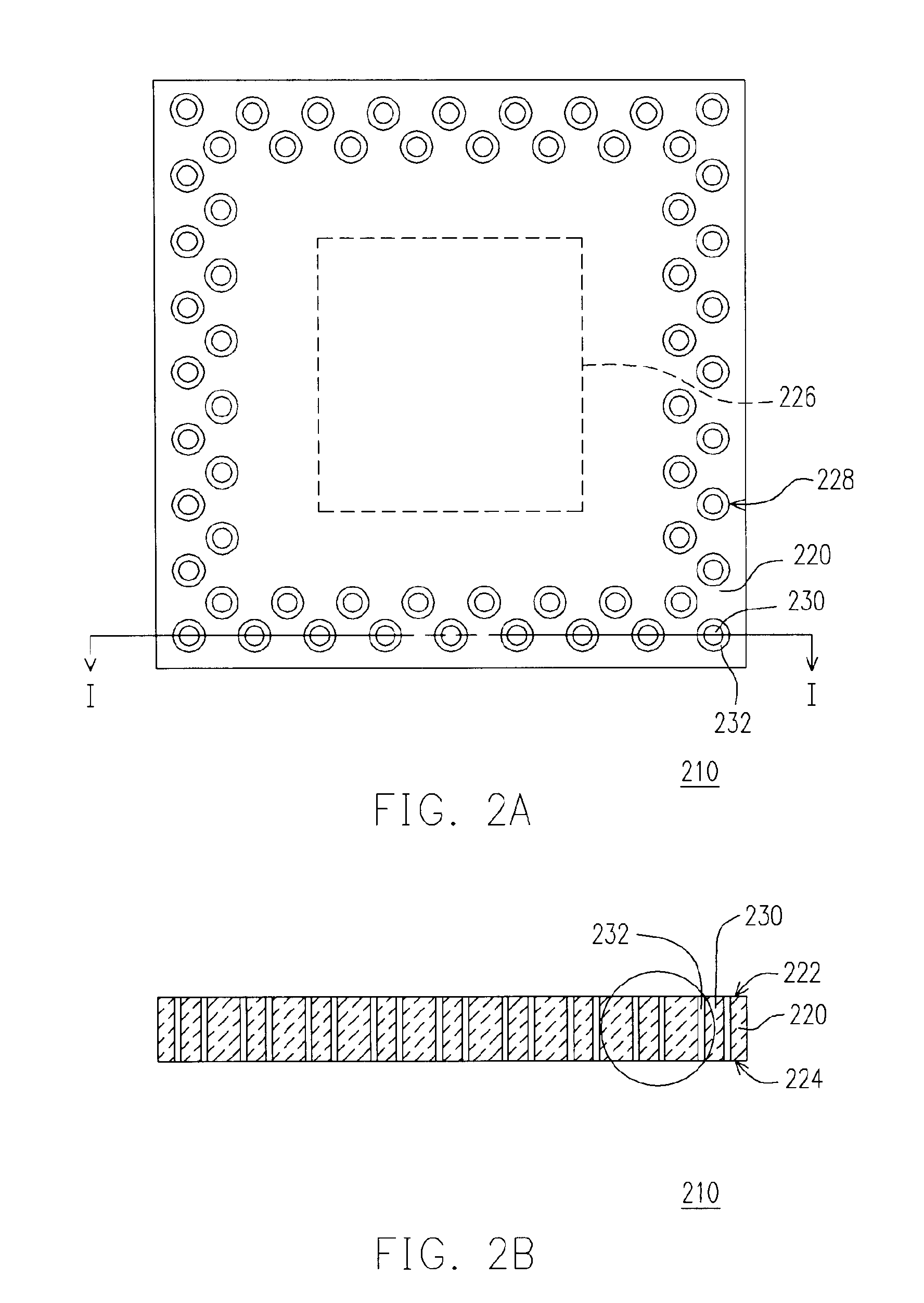

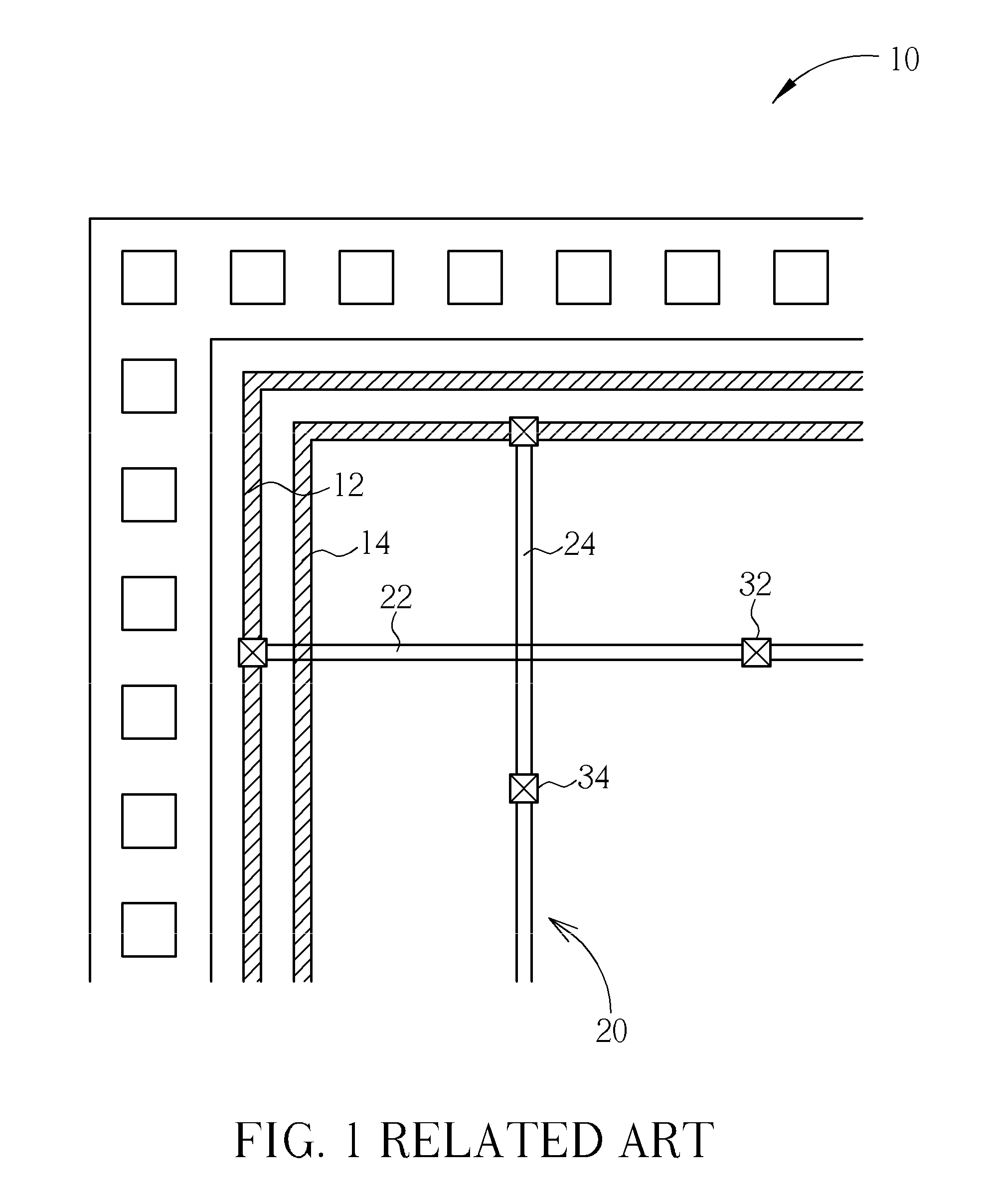

Quad flat no-lead chip carrier

ActiveUS6882057B2High I/O densityImprove chip qualitySemiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

A quad flat no-lead chip carrier for a wire-bonded chip package is provided. The chip carrier comprises a conductive plate, a plurality of conductive columns and a plurality of dielectric walls. A chip is attached to the conductive plate. The conductive plate furthermore has a plurality of columnar through holes distributed around a chip-bonding region. The conductive columns are set up within the columnar through holes. The dielectric walls are set up between the sidewall of the conductive columns and the inner surface of the columnar through holes. The chip is electrically connected to the conductive columns via conductive wires. The bottom end of the conductive columns serves as input / output contacts for connecting with external contacts. The chip carrier is able to increase overall density of the input / output contacts and improve the electrical performance of the chip package.

Owner:VIA TECH INC

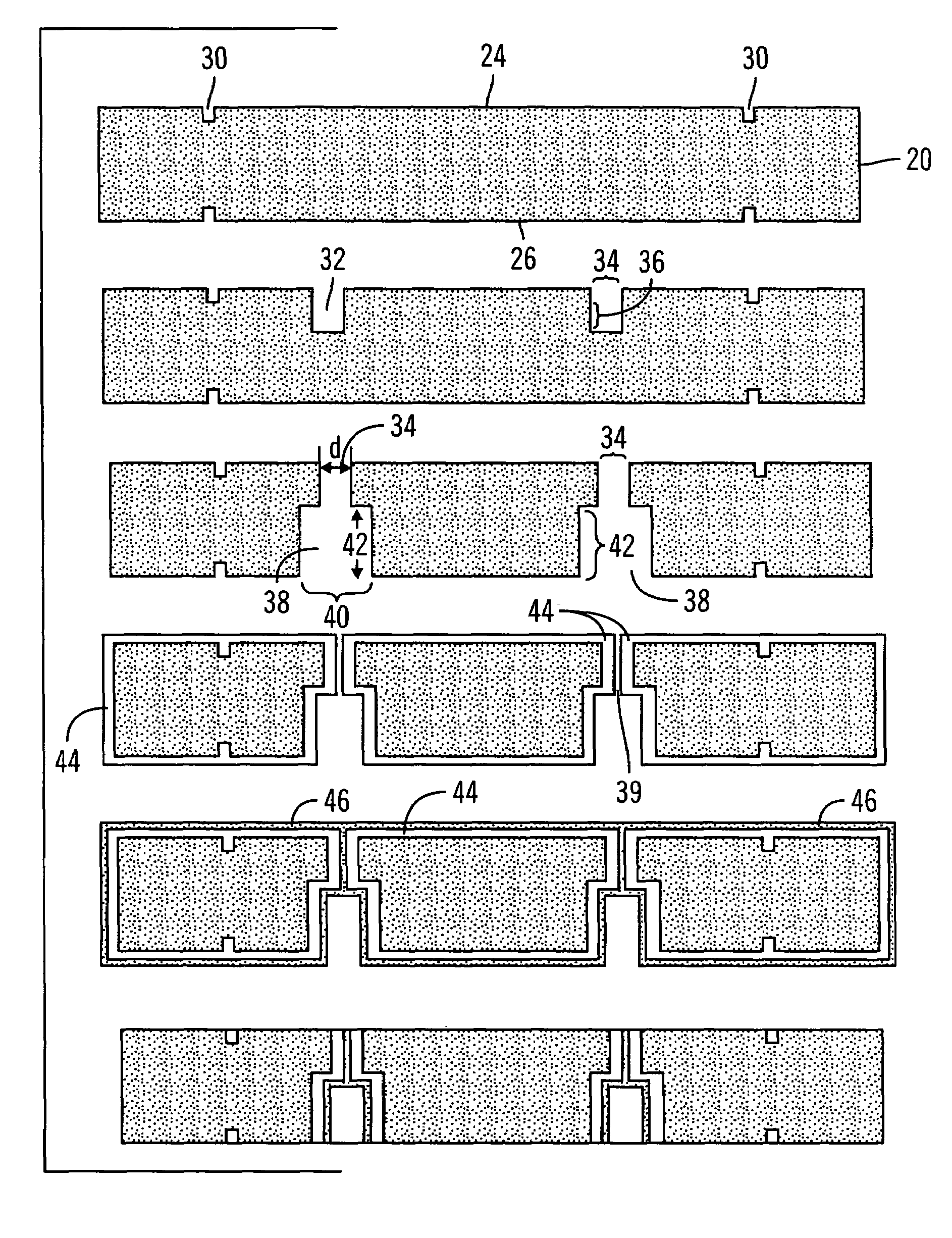

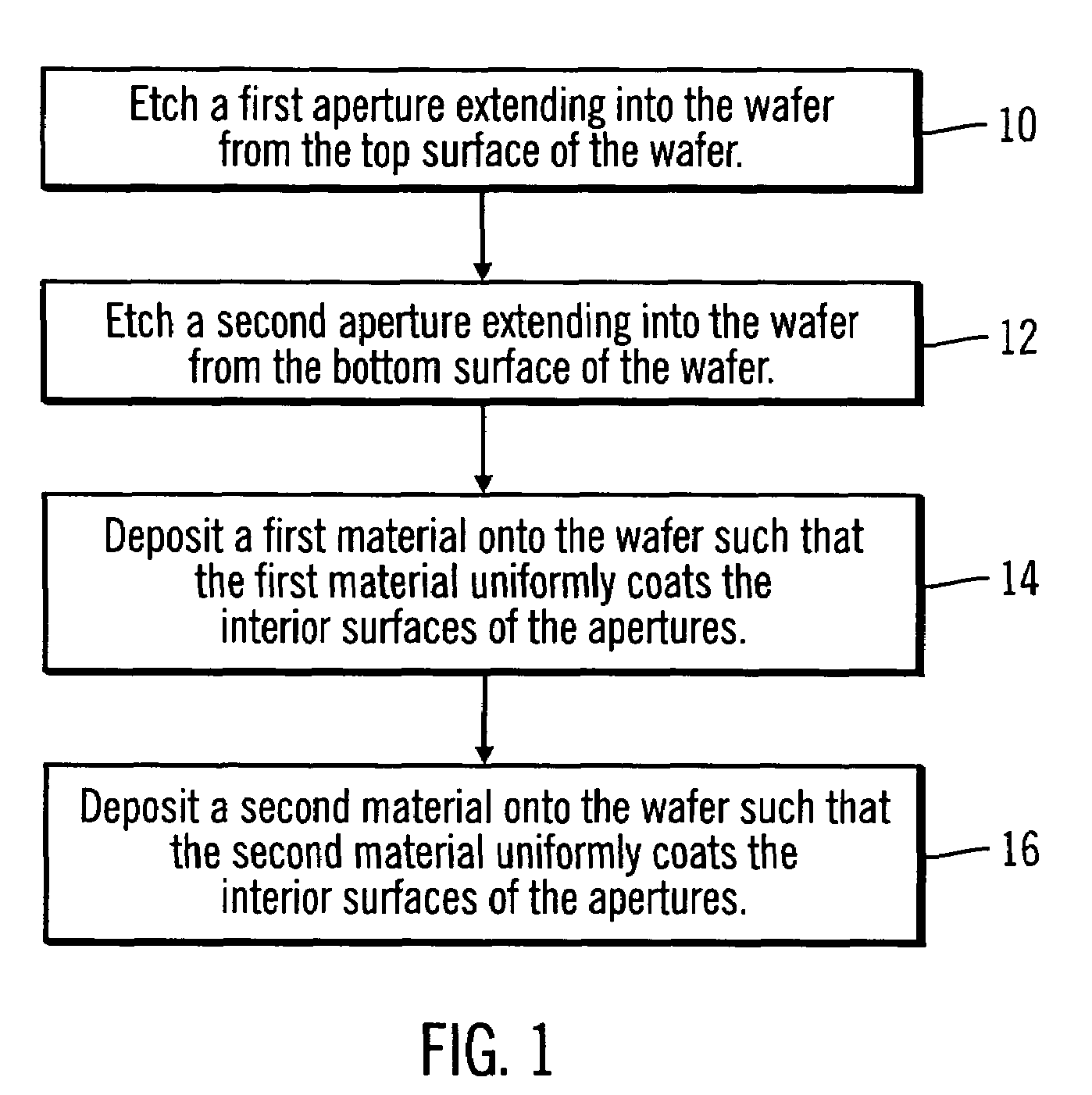

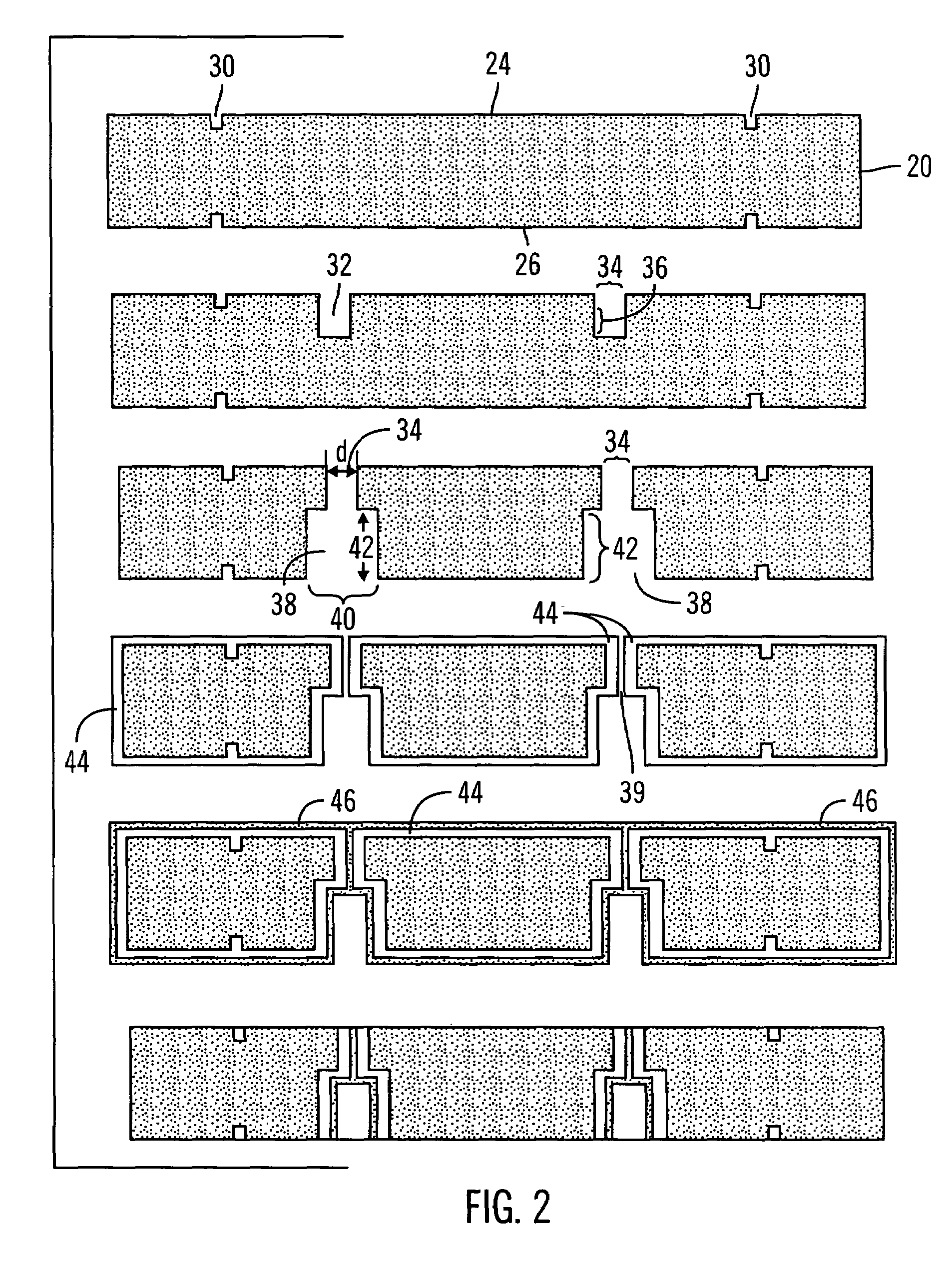

Low temperature method for fabricating high-aspect ratio vias and devices fabricated by said method

ActiveUS20060292866A1High densityMoreSemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsConductive materials

Embodiments of the present invention are directed to a process for forming small diameter vias at low temperatures. In preferred embodiments, through-substrate vias are fabricated by forming a through-substrate via; and depositing conductive material into the via by means of a flowing solution plating technique, wherein the conductive material releases a gas that pushes the conductive material through the via to facilitate plating the via with the conductive material. In preferred embodiments, the fabrication of the substrate is conducted at low temperatures.

Owner:TELEDYNE SCI & IMAGING

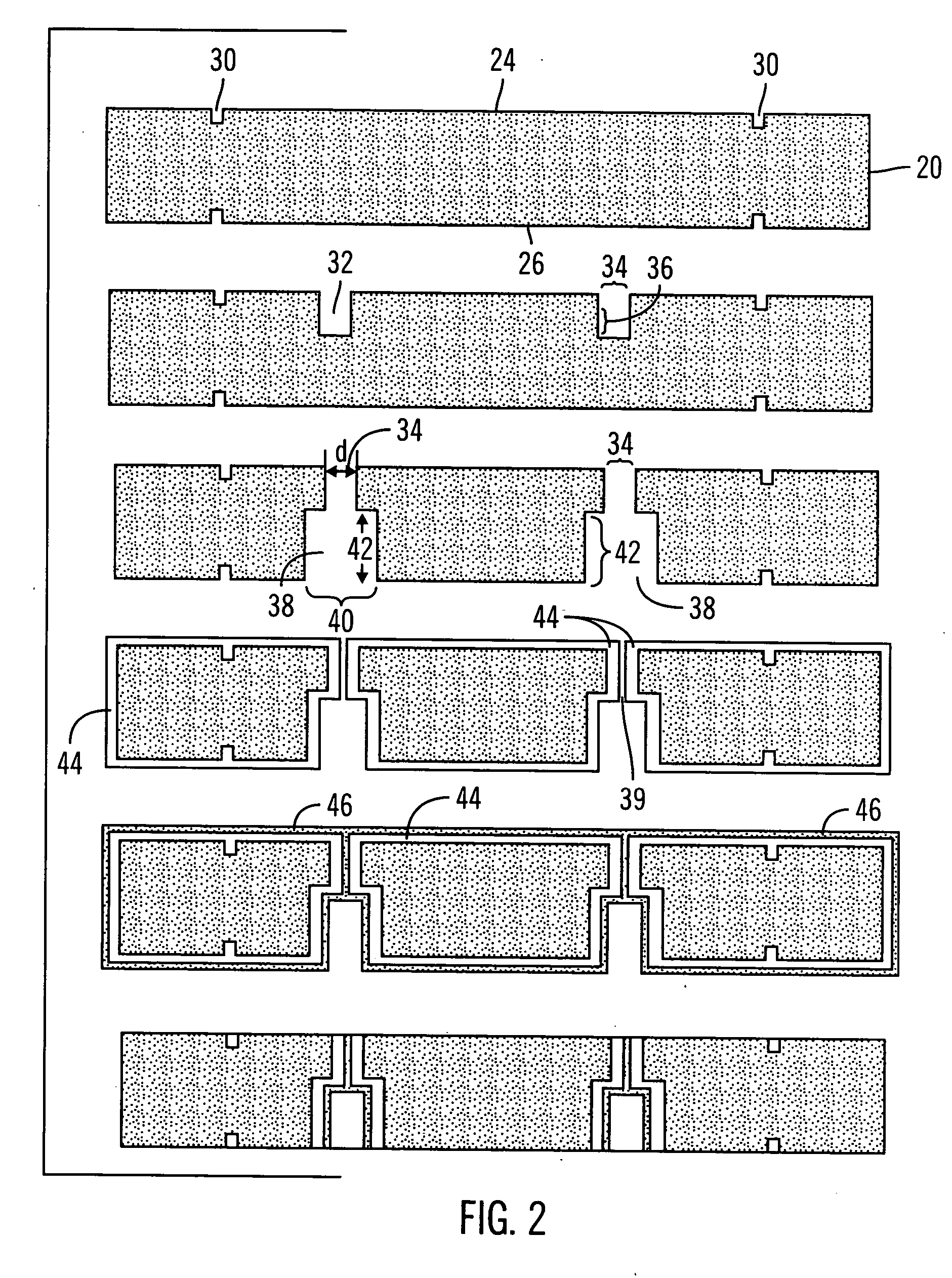

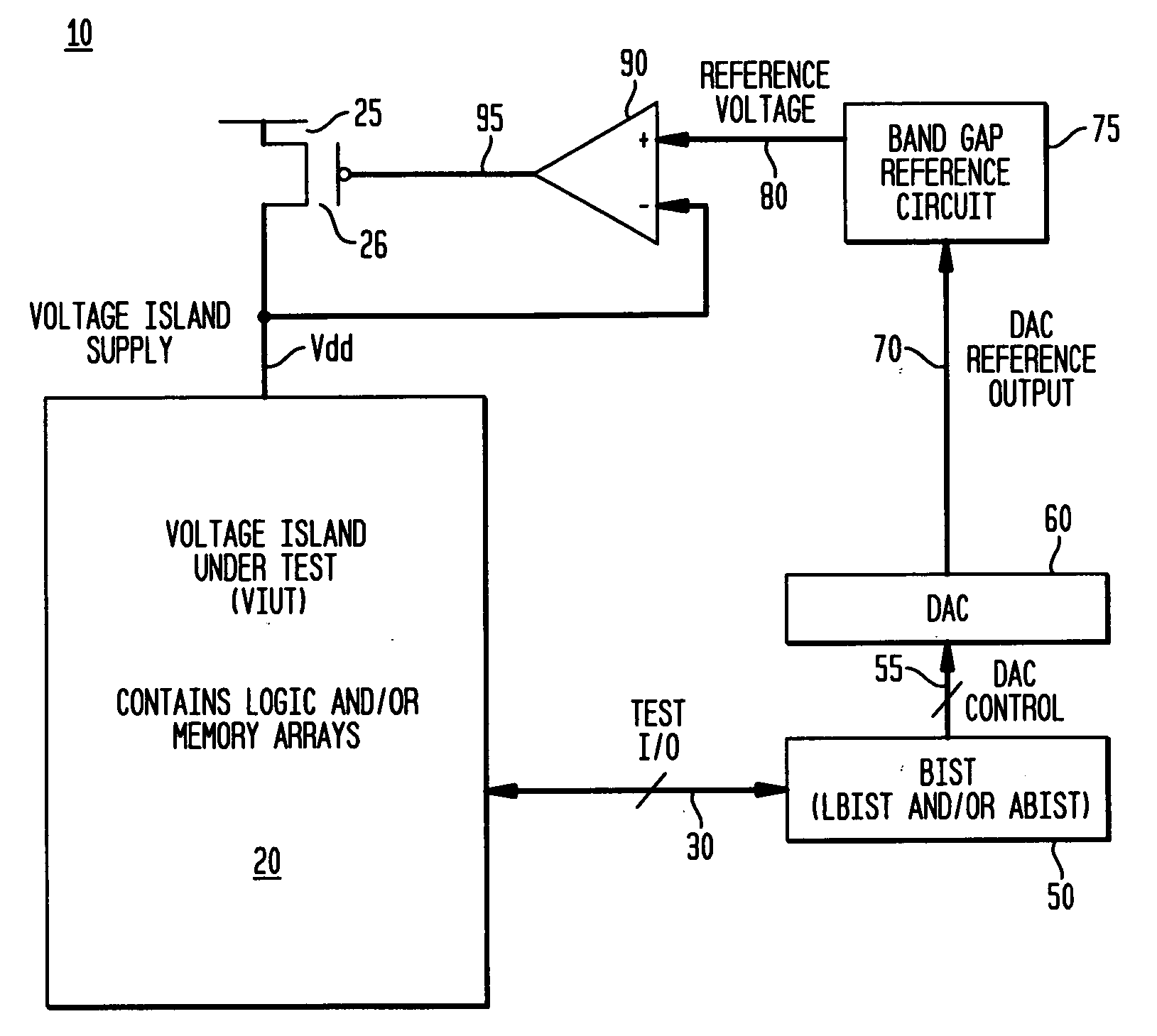

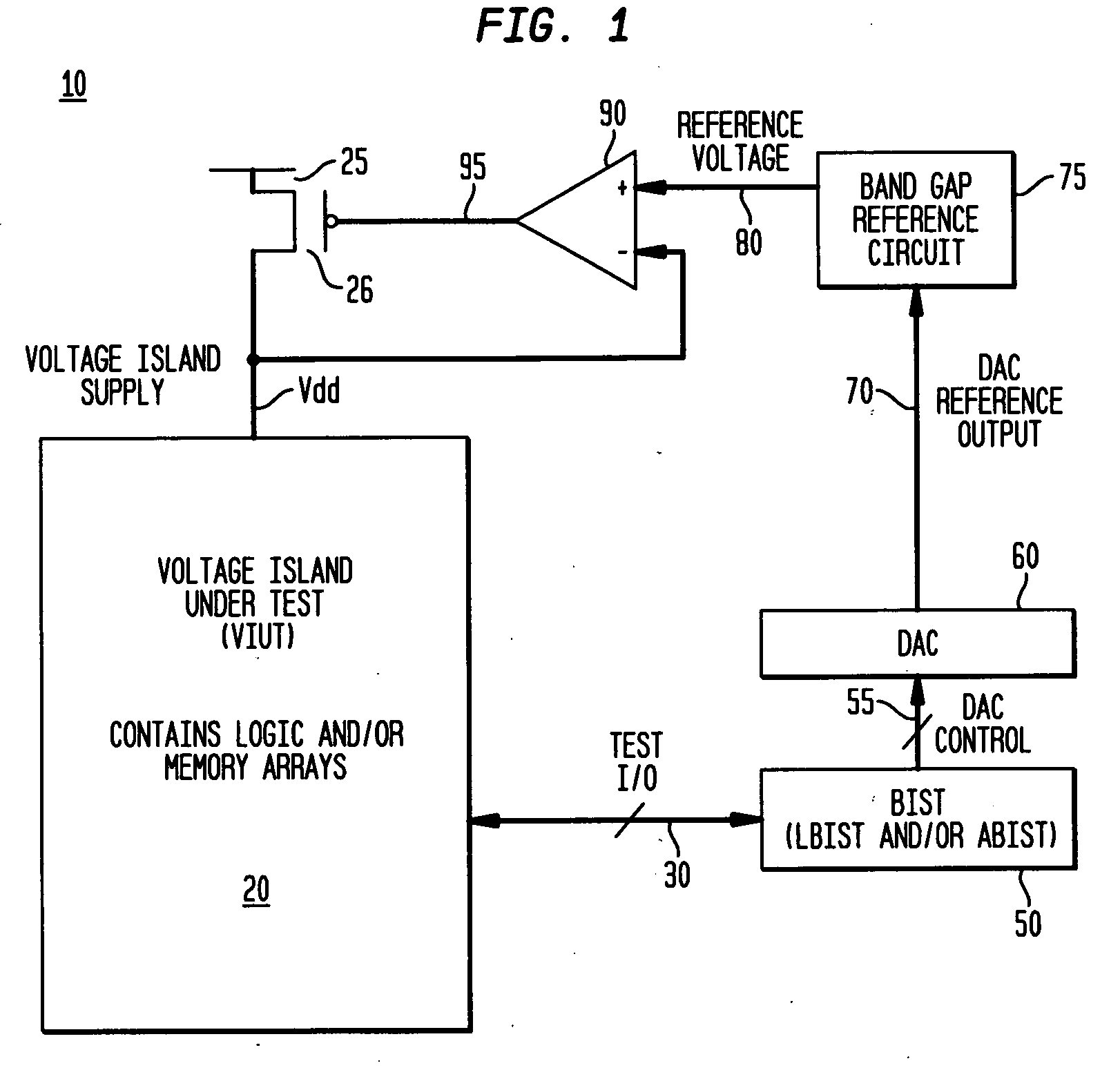

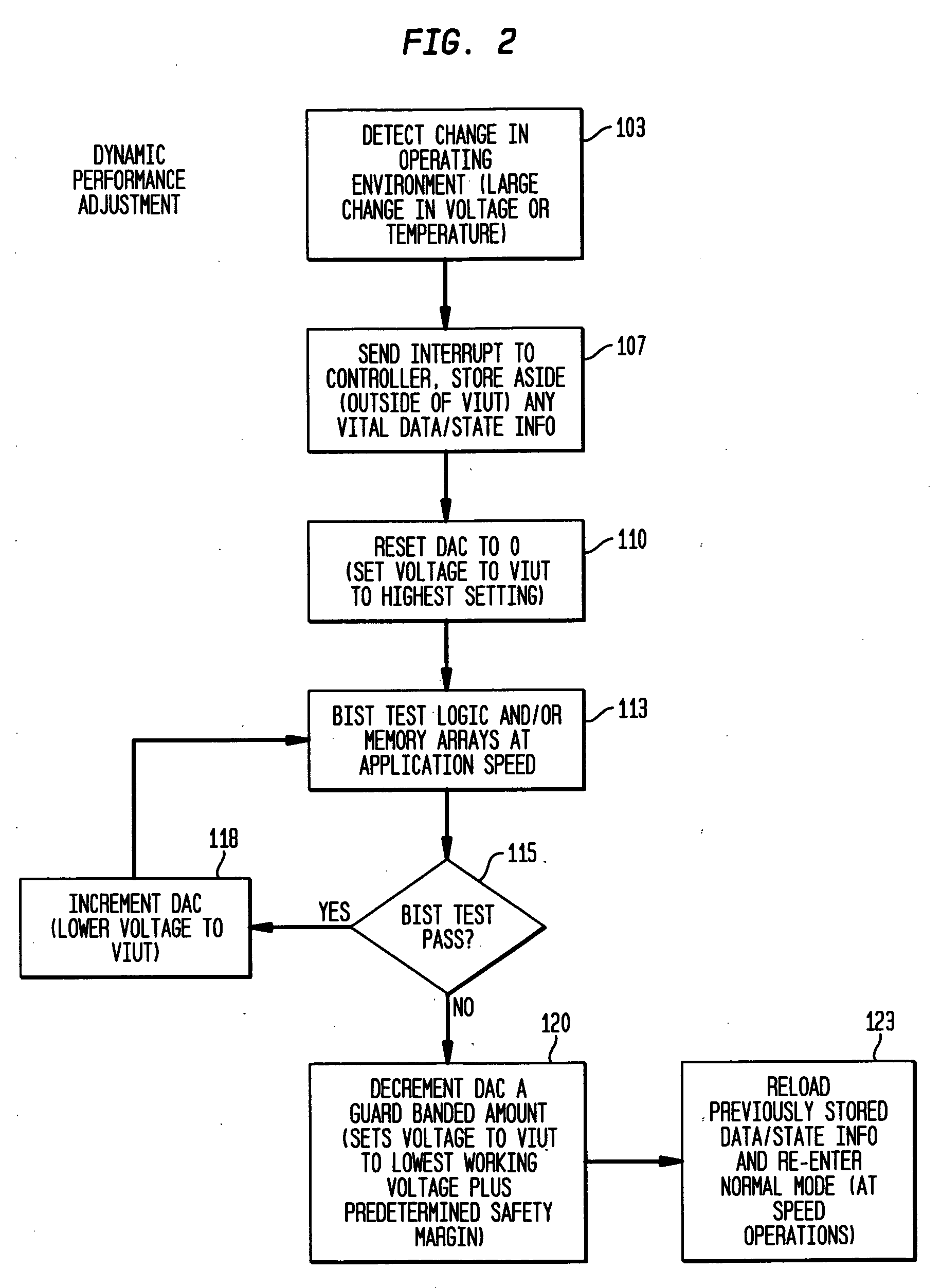

Self-test circuitry to determine minimum operating voltage

InactiveUS20060259840A1Reduce power consumptionMaintaining at-application speed performanceMarginal circuit testingTest flowVoltage source

A solution for determining minimum operating voltages due to performance / power requirements would be valid for a wide range of actual uses. The solution includes a test flow methodology for dynamically reducing power consumption under applied conditions while maintaining application performance via a BIST circuit. There is additionally provided a test flow method for dynamically reducing power consumption to the lowest possible stand-by / very low power level under applied conditions that will still be sufficient to maintain data / state information. One possible application would be for controlling the voltage supply to a group of particular circuits on an ASIC (Application Specific Integrated Circuit). These circuits are grouped together in a voltage island where they would receive a voltage supply that can be different from the voltage supply other circuits on the same chip are receiving. The same solution could be applied to a portion of a microprocessor (the cache logic control, for example).

Owner:IBM CORP

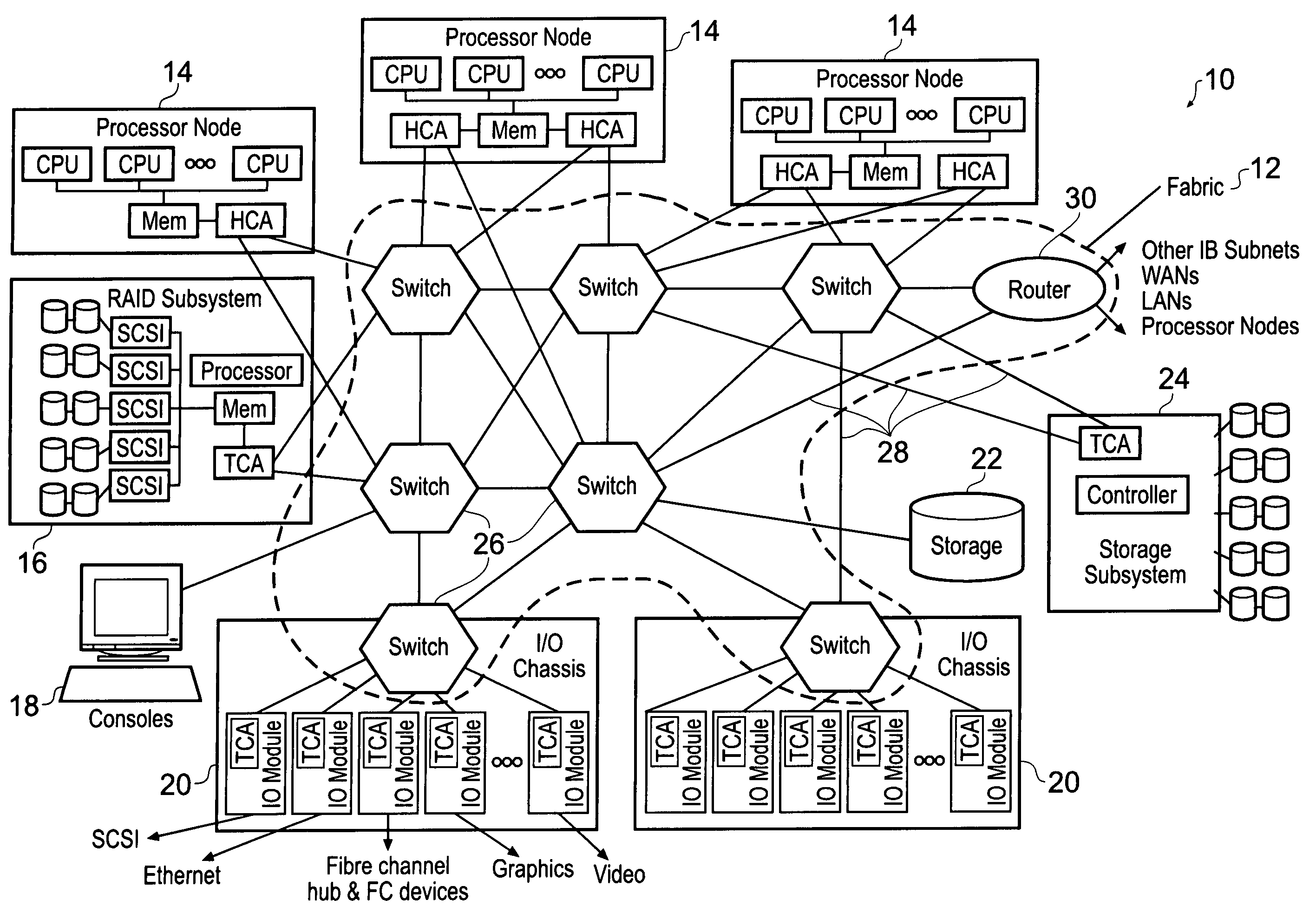

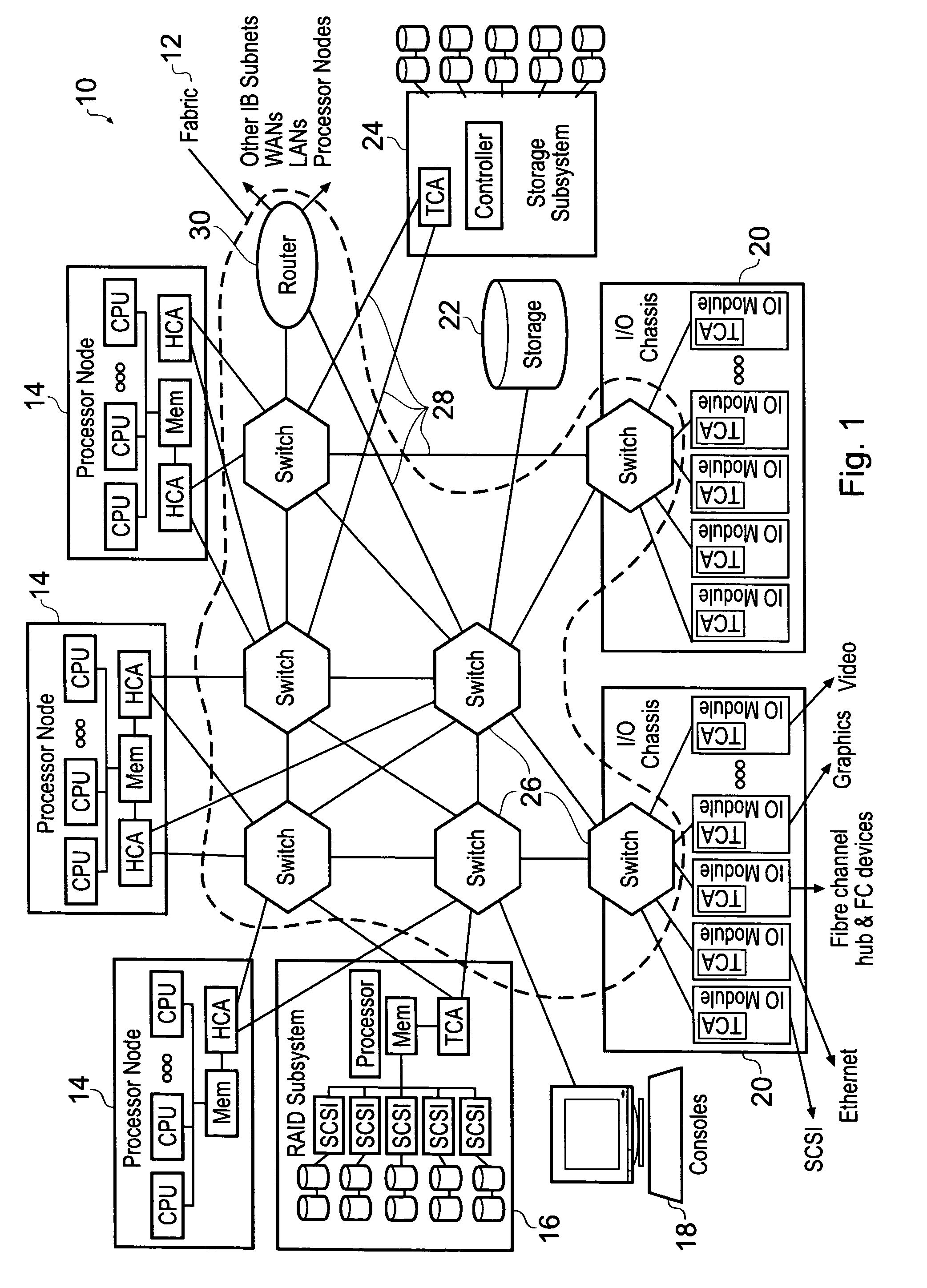

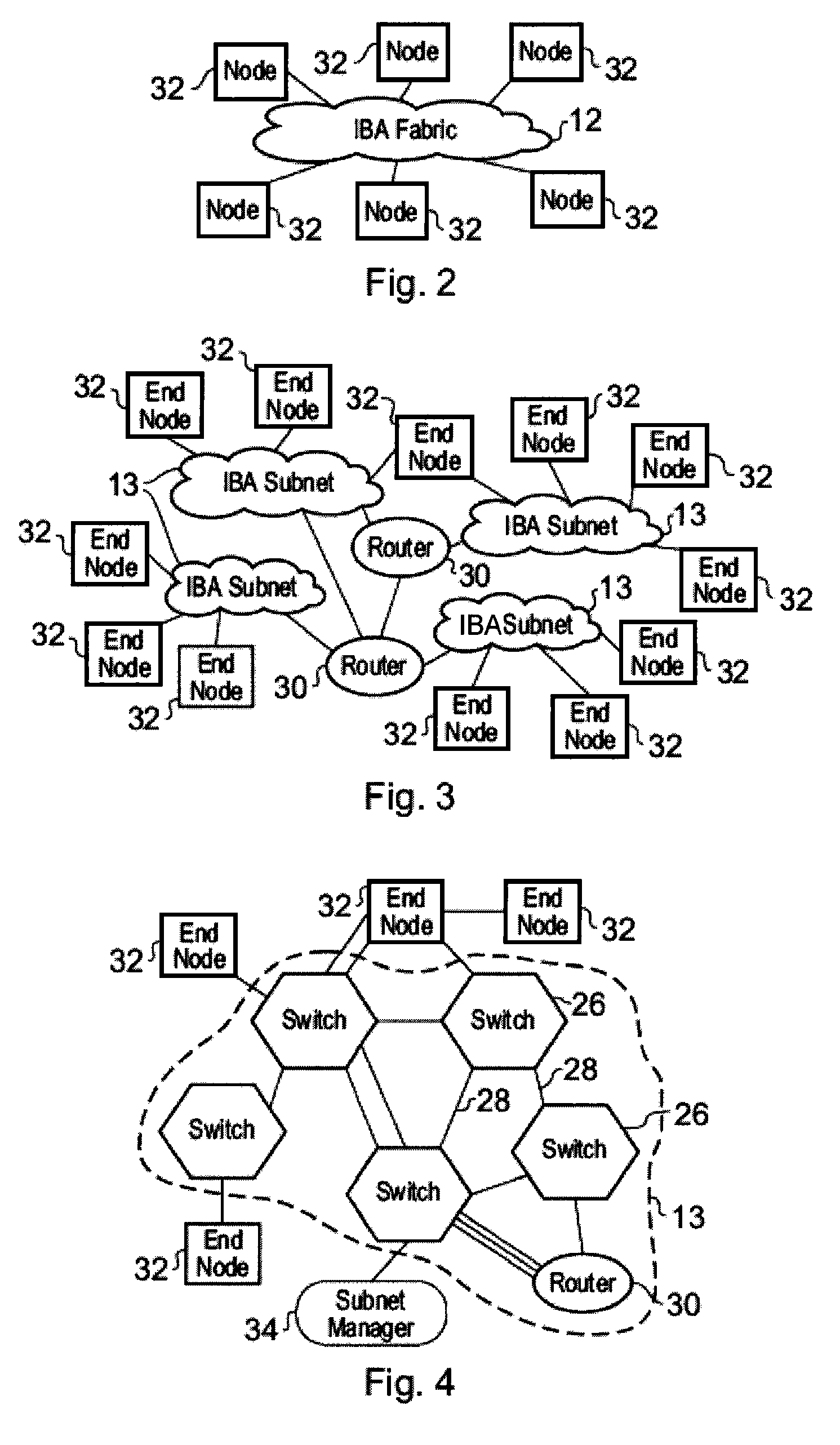

VCRC checking and generation

ActiveUS7483442B1Low costSacrificing data integrityMultiplex system selection arrangementsData switching by path configurationComputer hardwareNetwork packet

An Infiniband switch can be provided. The switch can have an input port logic unit for determining an output virtual lane for a received packet and for storing a descriptor of the determined output virtual lane in a packet field not protected by a checksum field of the packet. The switch can also have a routing unit for transferring the received packet to an output port corresponding to the determined output virtual lane. Additionally, the switch can have an output port logic unit for simultaneously checking the integrity of the packet transferred through the routing unit and calculating a new value for the checksum with the descriptor moved to a correct packet field, which field is included in the calculation of the checksum.

Owner:ORACLE INT CORP

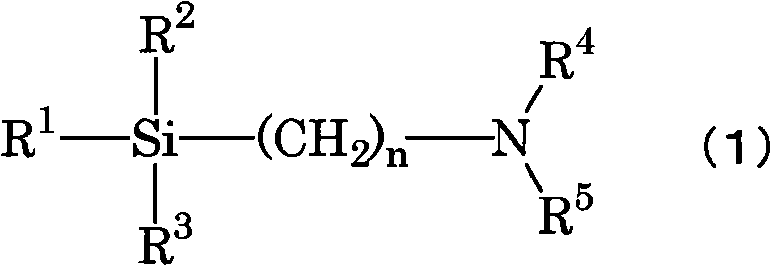

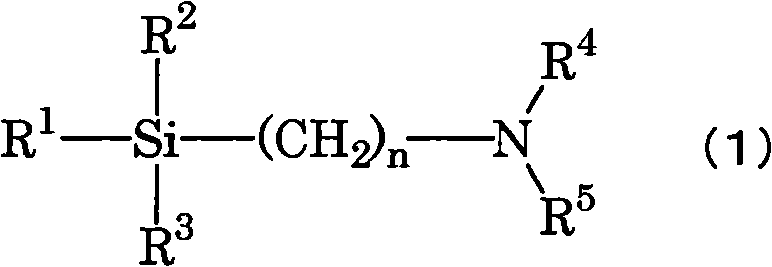

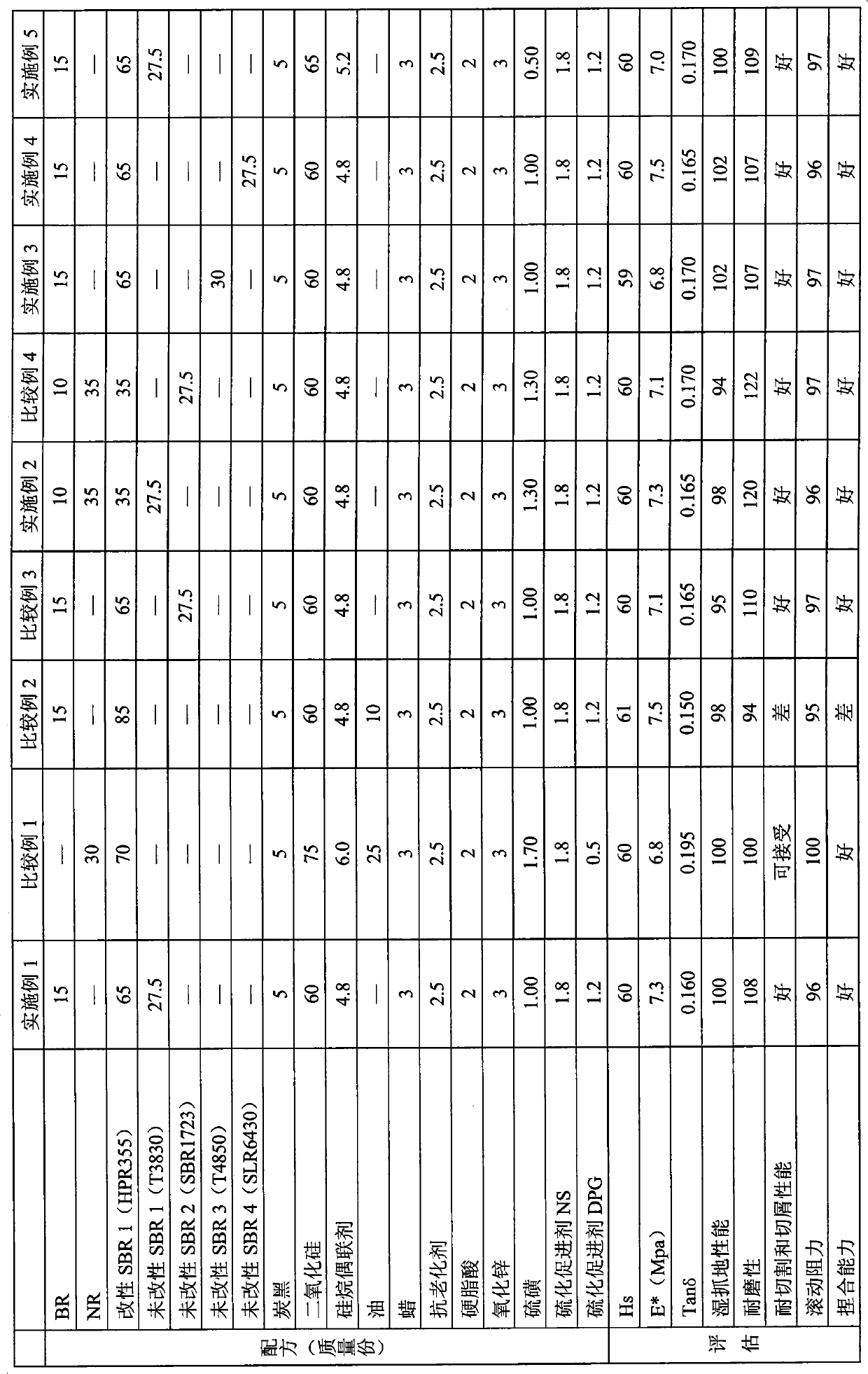

Tire rubber composition and pneumatic tire

ActiveCN102199316AImprove gripGood balance of abrasion resistanceSpecial tyresRolling resistance optimizationRolling resistanceSulfur

The present invention aims to provide a tire rubber composition that achieves a good balance of grip performance (especially, wet grip performance), abrasion resistance, cut and chip resistance, low rolling resistance, and kneadability, and a pneumatic tire using the same. The composition comprise: a rubber component including a styrene-butadiene rubber modified by a compound of formula (1): and a non-modified styrene-butadiene rubber; a filler including silica, the filler being in an amount of 80 parts by mass or less per 100 parts by mass of the rubber component; and sulfur in an amount of 0.5-1.5 parts by mass per 100 parts by mass of the rubber component, the modified styrene-butadiene rubber having a bound styrene content of 20-40% by mass and a vinyl content of 30-65% by mass, and the non-modified styrene-butadiene rubber having a bound styrene content of 25-45% by mass and a vinyl content of 10-50% by mass.

Owner:SUMITOMO RUBBER IND LTD

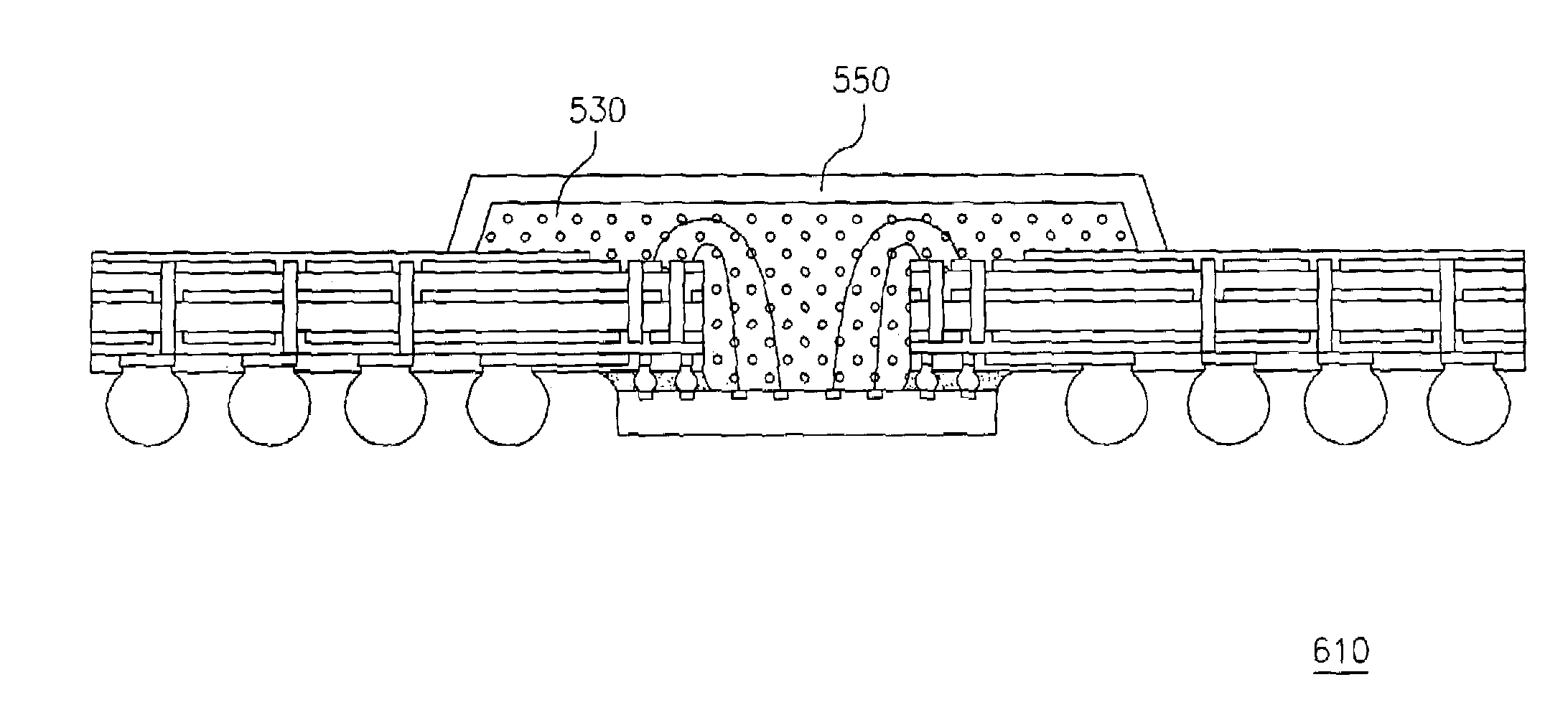

Chip package and process for forming the same

ActiveUS7078794B2Improve chip performanceLow production costSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A chip package structure comprising a substrate, a chip, a plurality of bumps, a plurality of conductive wires and an insulating material is provided. The substrate has a first surface and a corresponding second surface. The substrate has a slot that penetrates the substrate. The chip is attached to the first surface of the substrate in a position that covers the slot. The conductive wires pass through the slot such that one end of each conductive wire is attached to a contact point on the chip while the other end of the conductive wire is attached to a contact point on the second surface of the substrate. The insulating material fills the space between the chip and the substrate and the slot so that the conductive wires and the bumps are enclosed.

Owner:VIA TECH INC

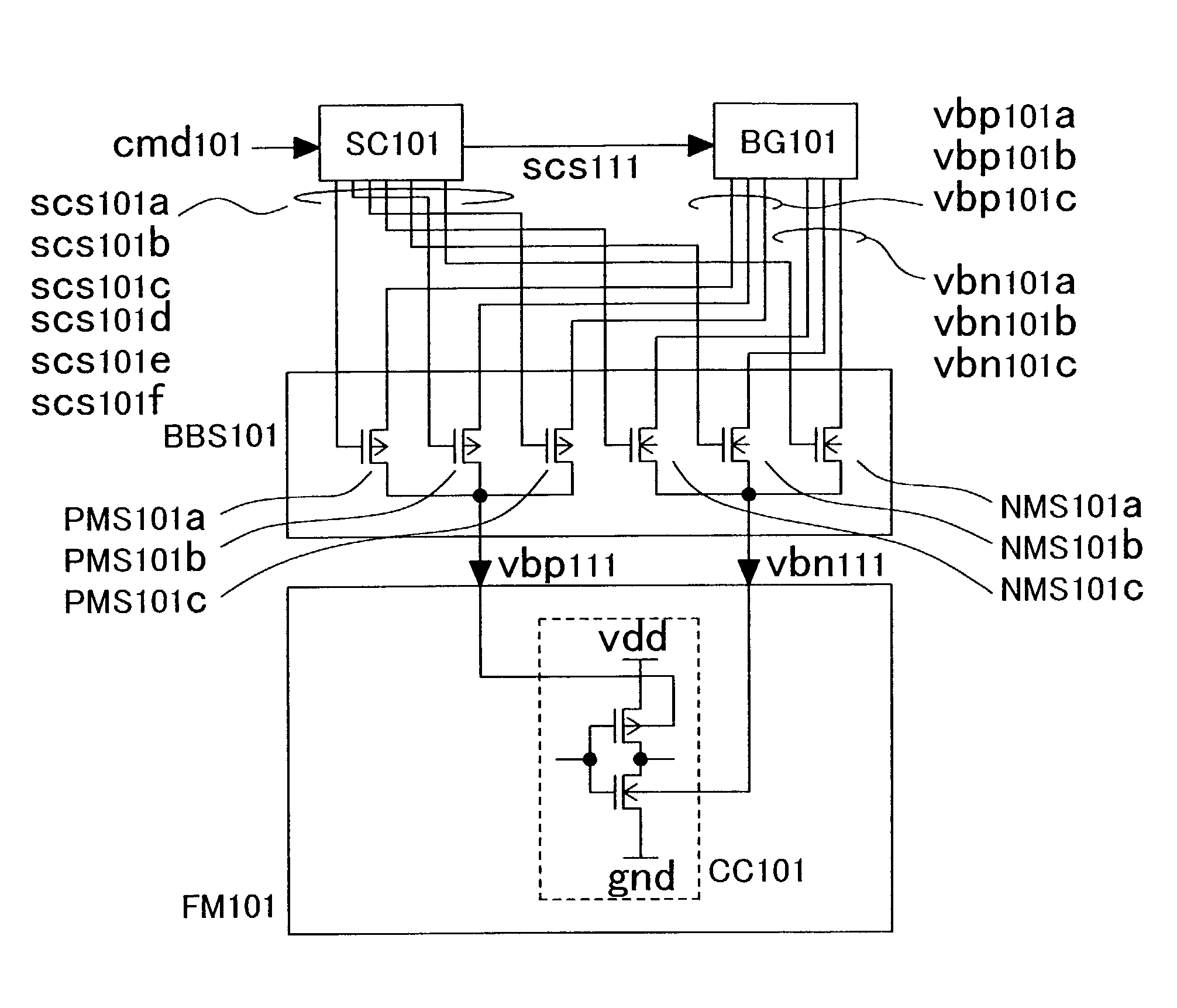

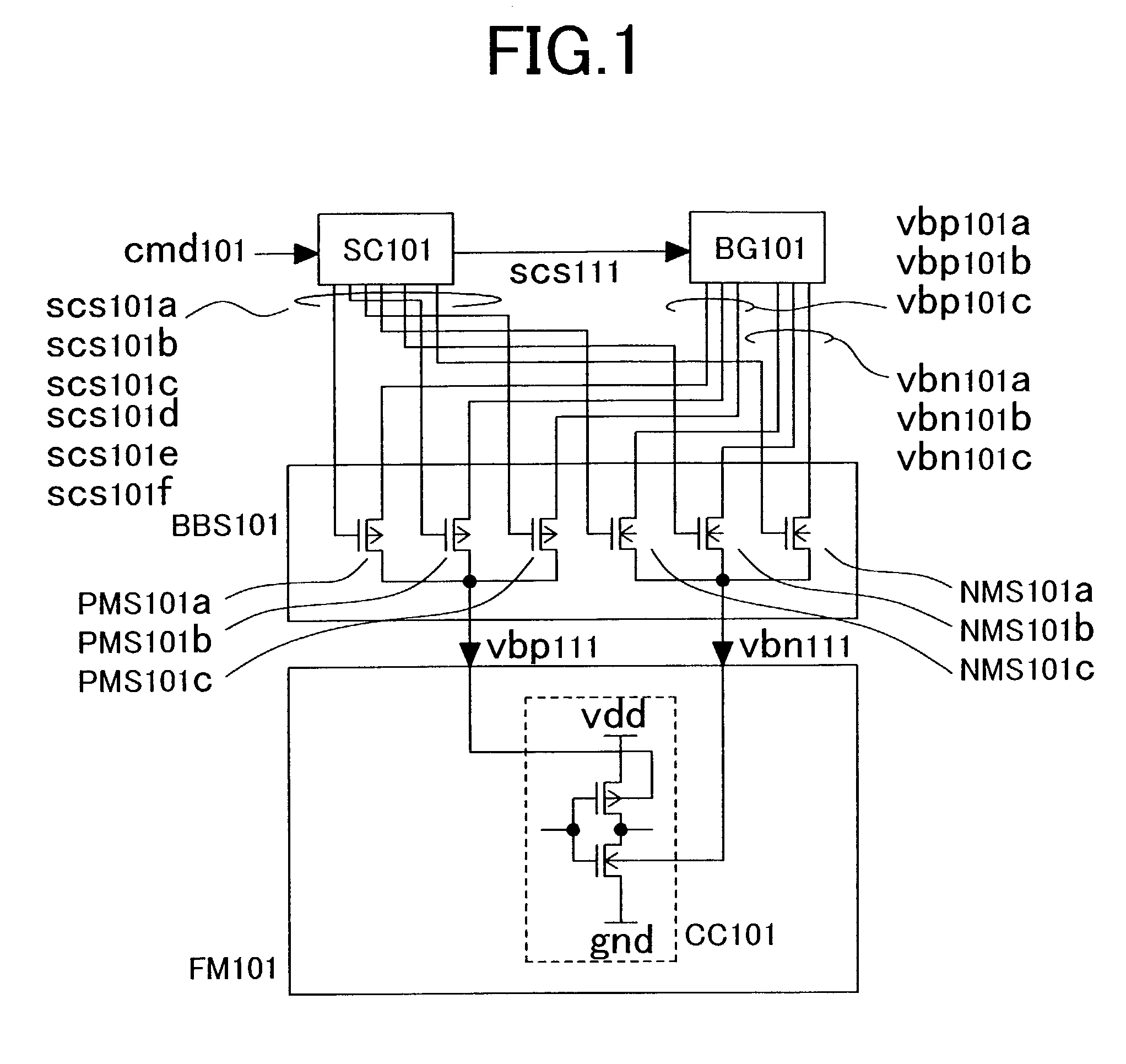

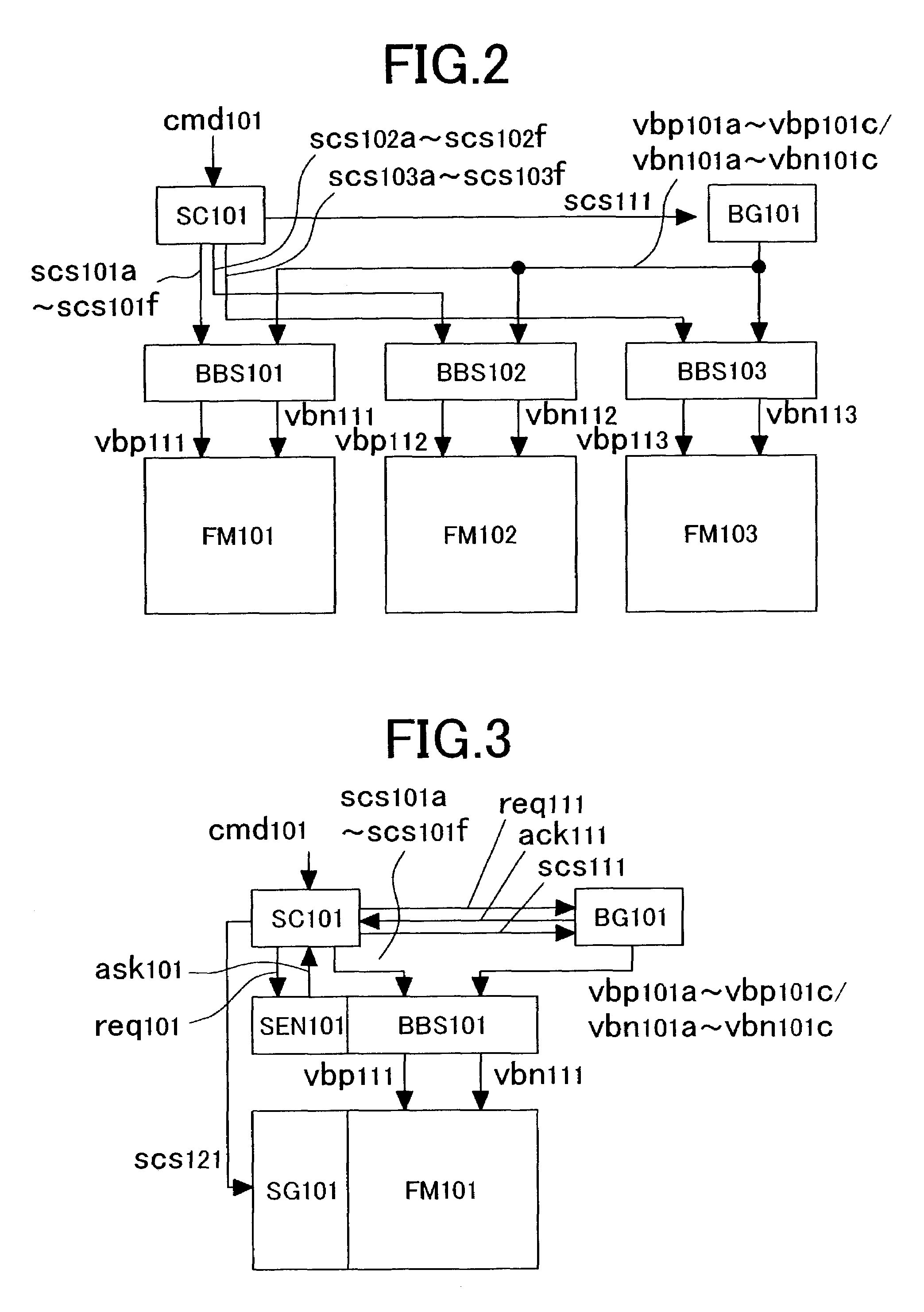

Semiconductor integrated circuit device

InactiveUS7612604B2Improve speed performancePower consumption performanceTransistorSwitching accelaration modificationsControl systemOperation mode

A body bias control system allows for independent design of a functional module, thereby reducing the burden of designing the module. The body bias control system provides a switch circuit having an area in which the body bias is controlled independently of its outside portion, for controlling the supply of body bias in the vicinity of the area. Preferably three types of switches are provided for switching the body bias to suitable levels for a standby mode, a mode of normal operation and a mode of high-speed operation.

Owner:RENESAS ELECTRONICS CORP +1

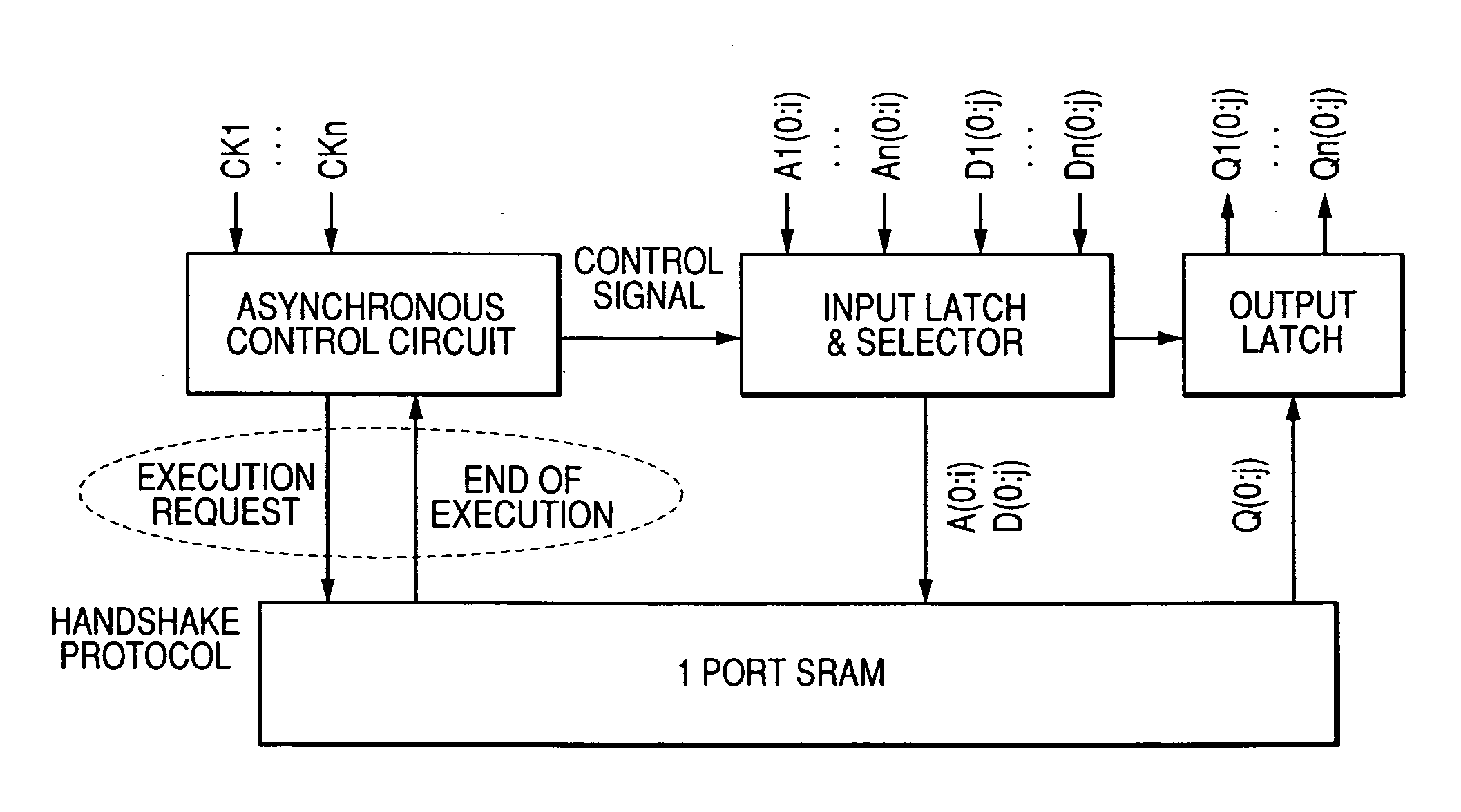

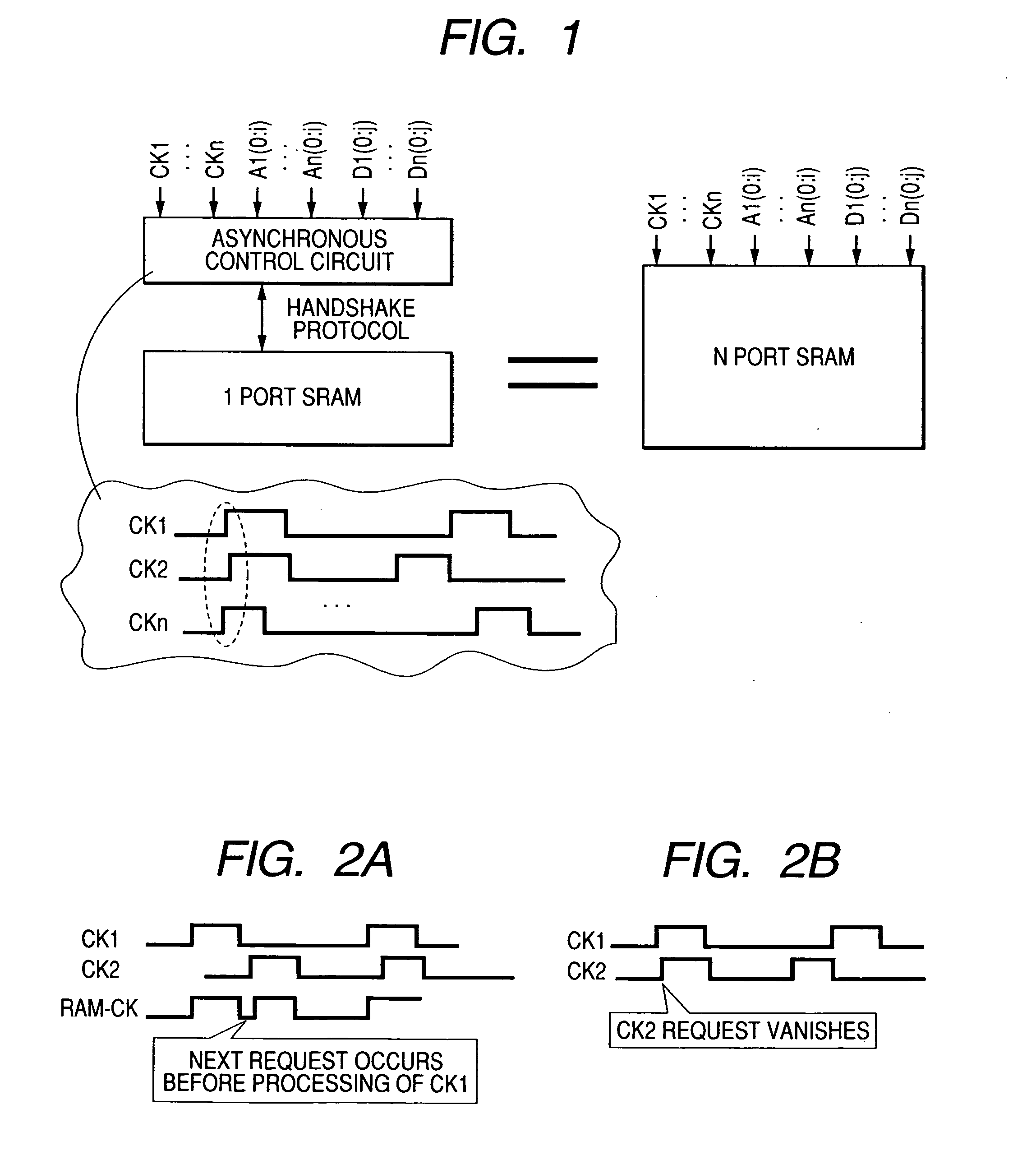

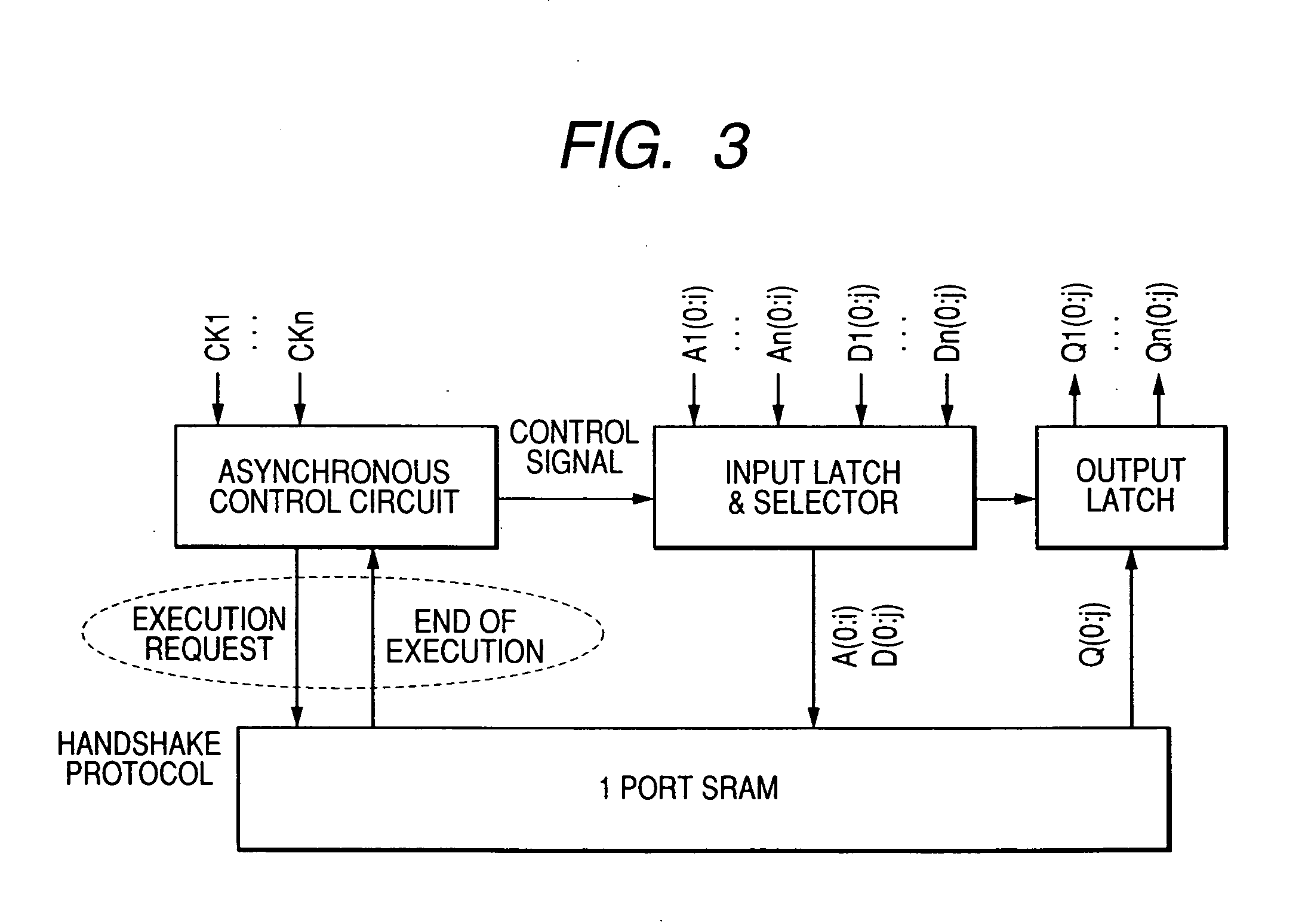

Asynchronous control circuit and semiconductor integrated circuit device

InactiveUS20050007170A1Improve chip performanceReduce design man-hoursDigital storageElectric pulse generatorIntegrated circuitSemiconductor

An asynchronous control circuit and a semiconductor integrated circuit achieving asynchronous operation and no limitation on the number of ports are offered. In an asynchronous control circuit, by being activated corresponding to at least one access request by acknowledging a plurality of access request signals generated asynchronously to each other and a plurality of input signals corresponding to each of the above-mentioned plurality of access requests, selecting one access request from one or more access requests in the activation mode, acknowledging an input signal corresponding thereto, transmitting the input signal to a memory, acknowledging the input signal corresponding to a non-executed access request after the end the operation corresponding to the input signal, and accessing the aforementioned memory circuit.

Owner:HITACHI LTD

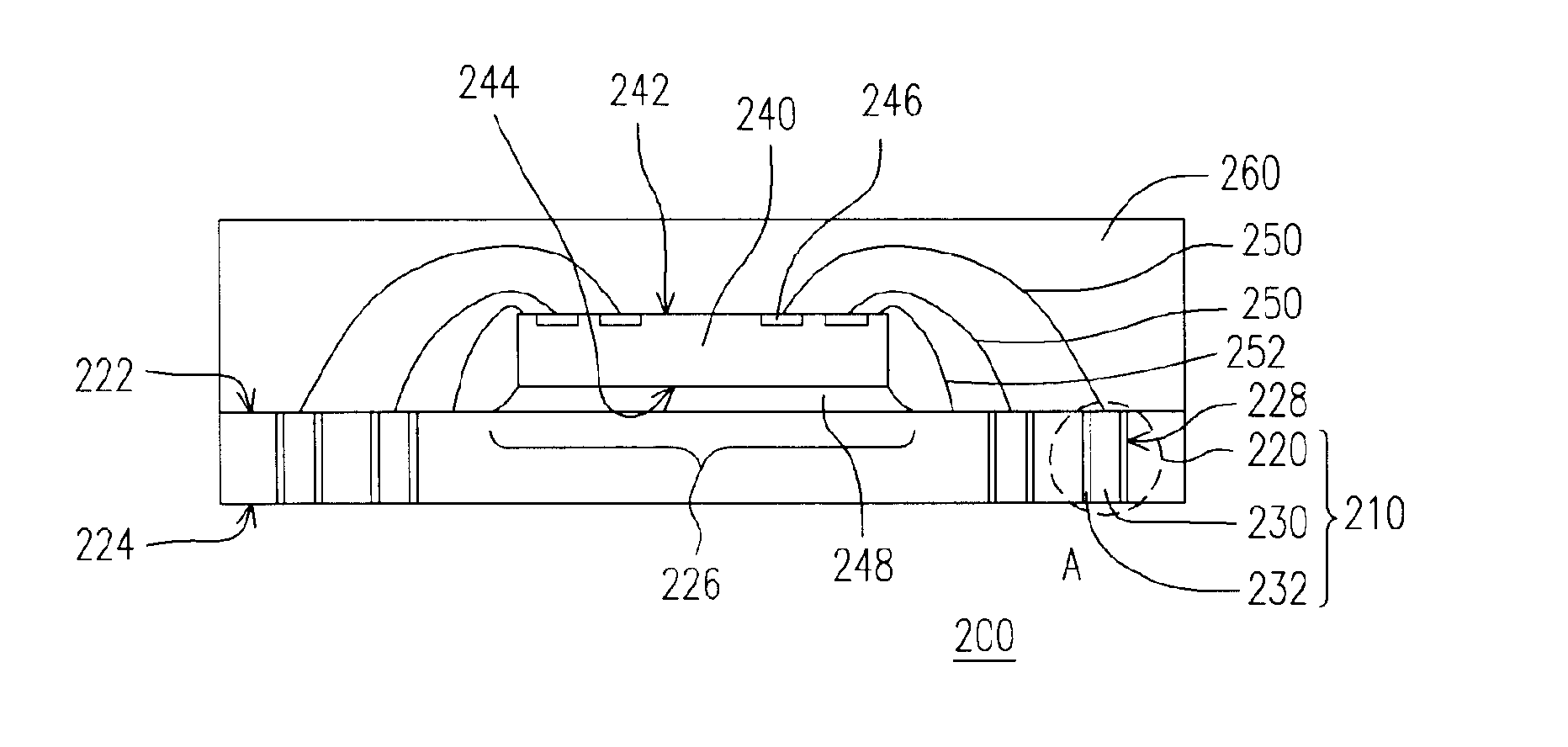

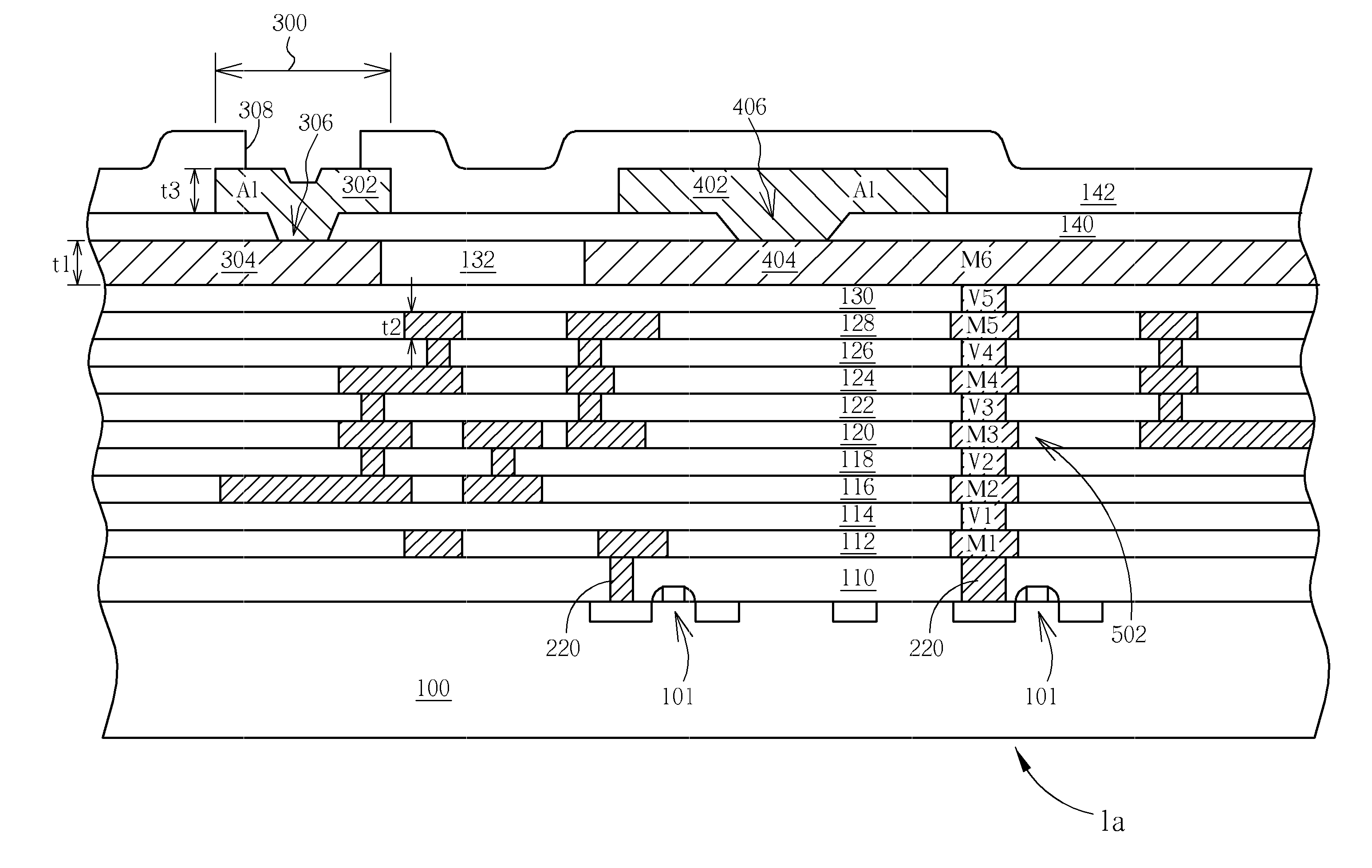

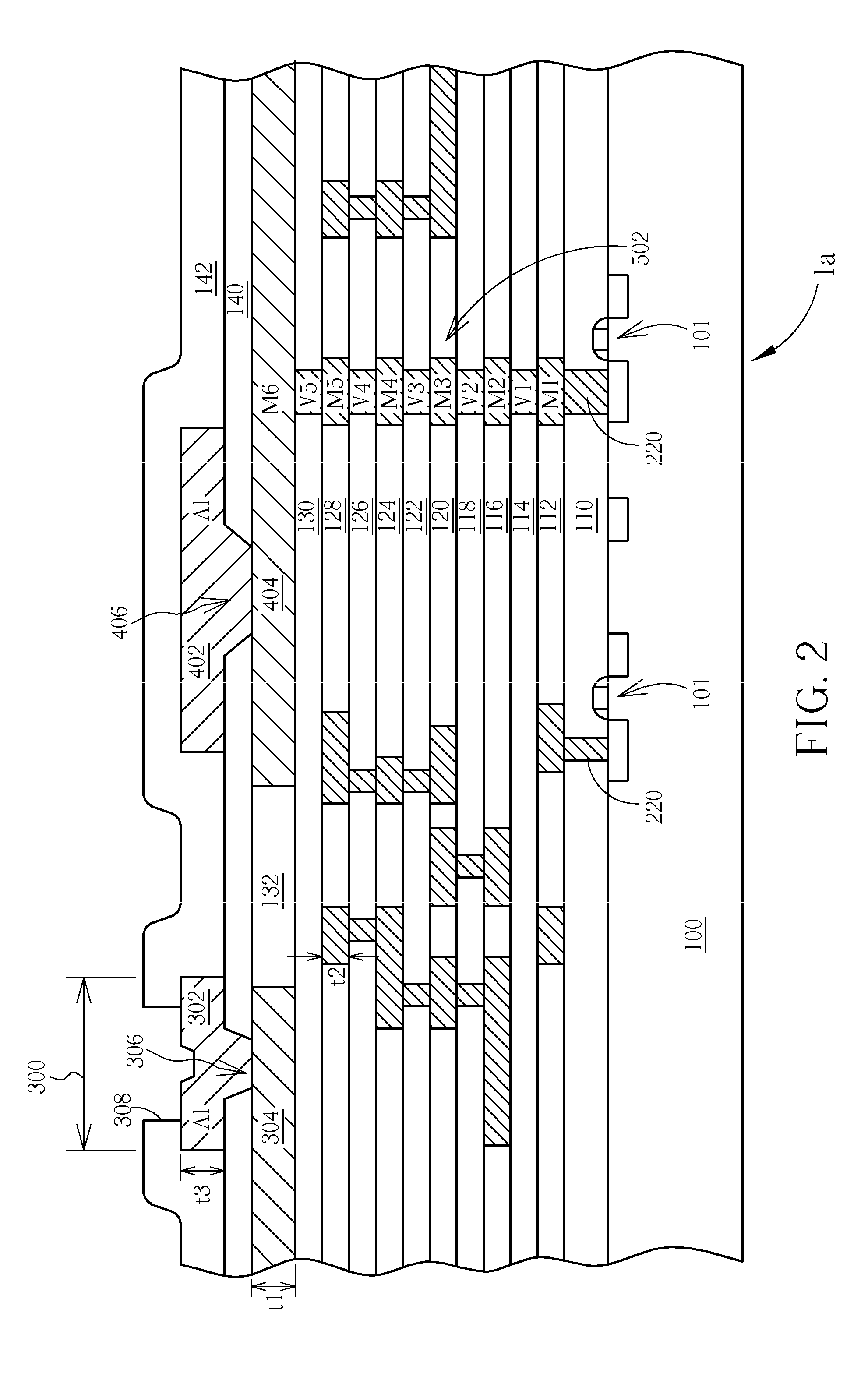

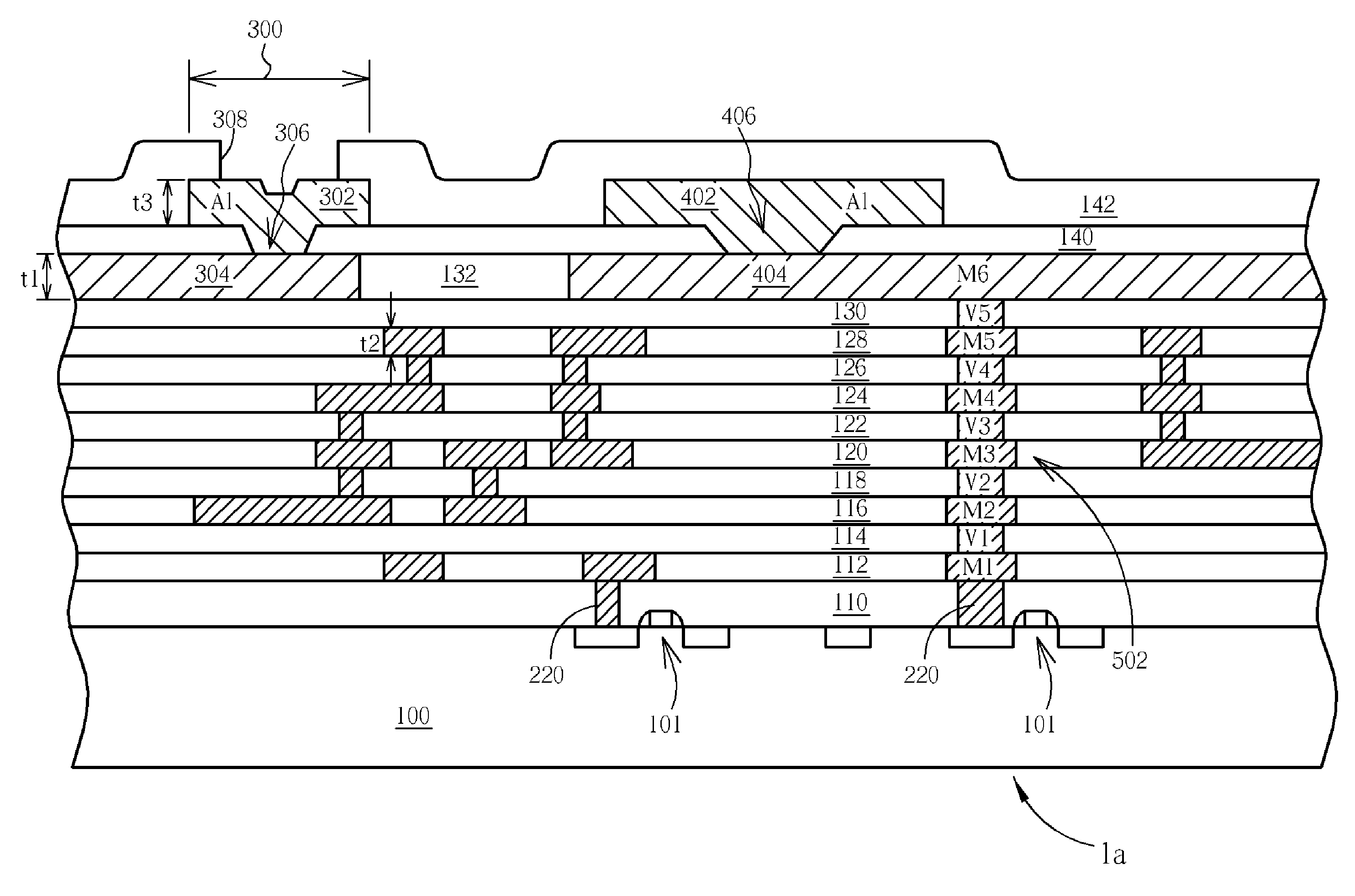

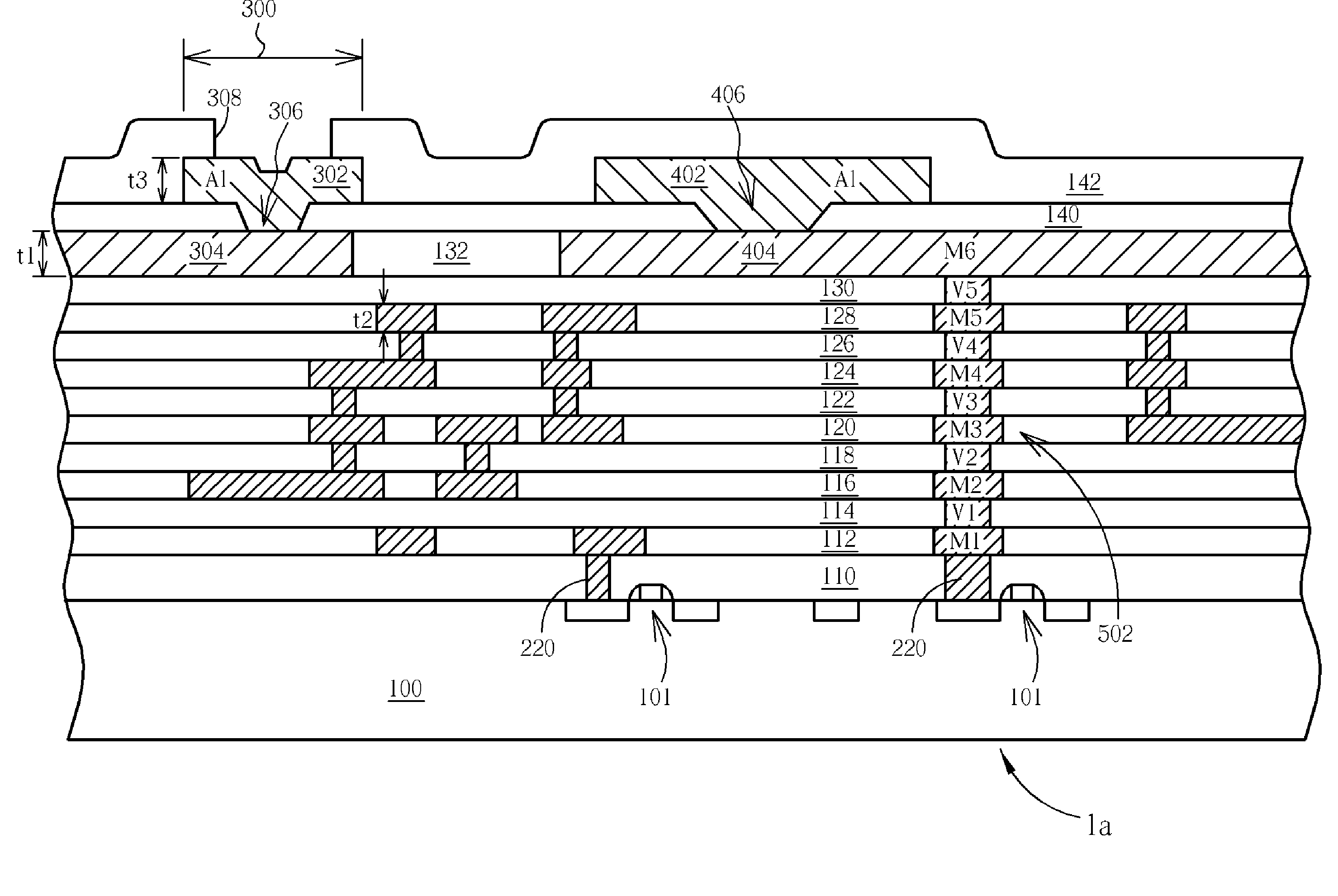

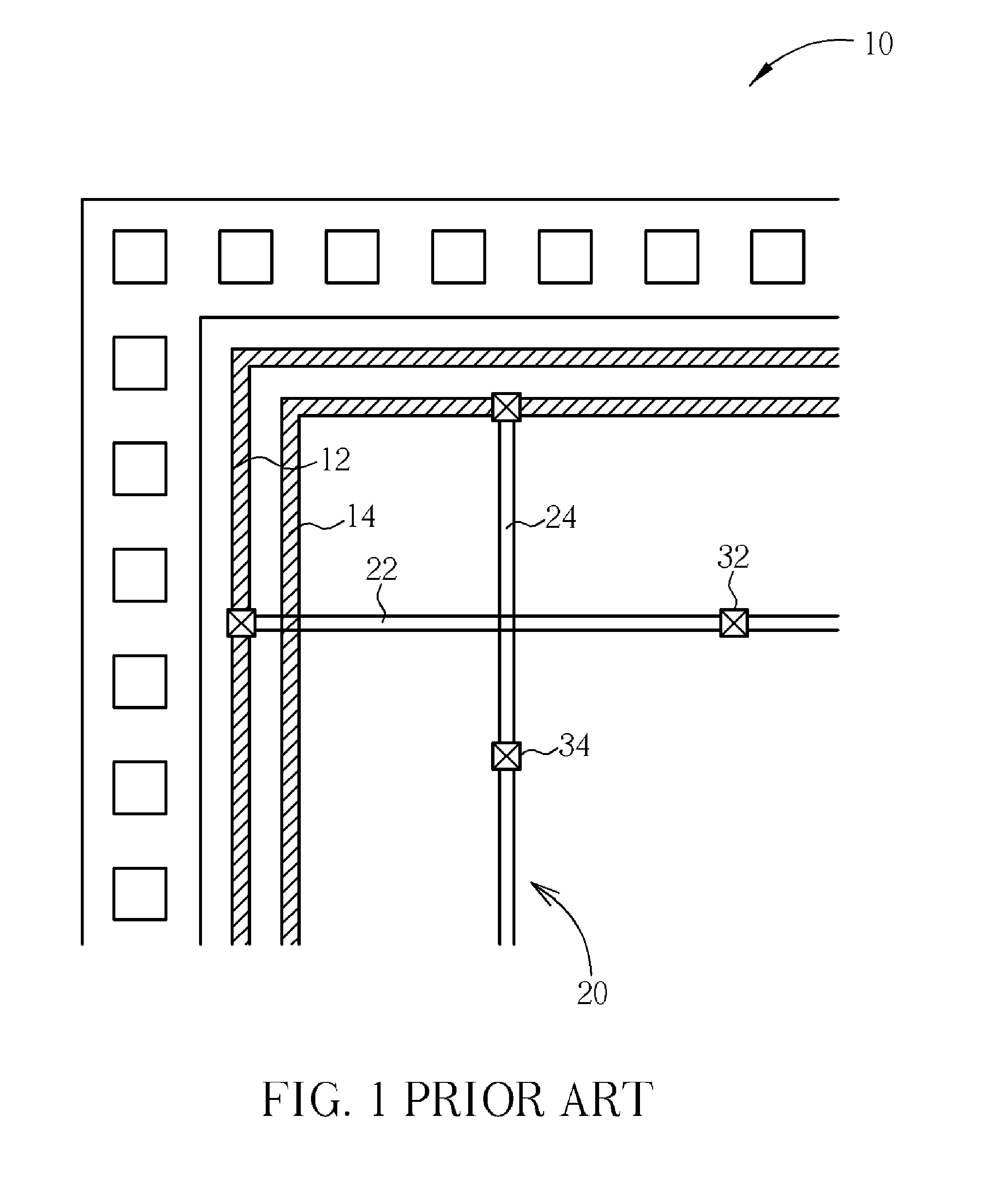

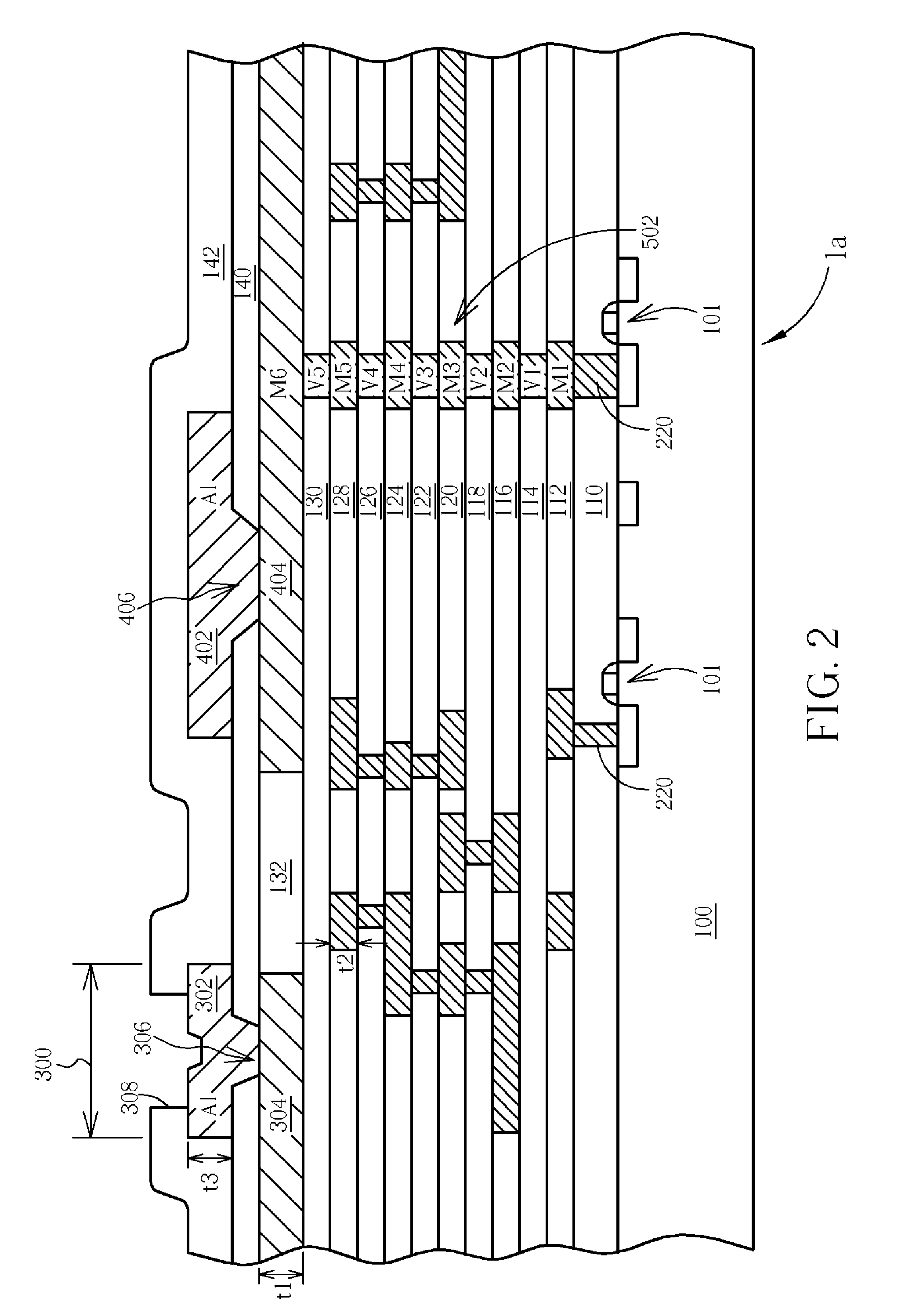

Power and ground routing of integrated circuit devices with improved ir drop and chip performance

ActiveUS20120043663A1Increase powerReducing the IR dropSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

An integrated circuit chip includes a semiconductor substrate having thereon a plurality of IMD layers and a plurality of first conductive layers; a first passivation layer overlying the plurality of IMD layers and the first conductive layers; at least a first power / ground mesh wiring line in a first aluminum layer overlying the first Insulating layer; and at least a second power / ground mesh wiring line in a second aluminum layer overlying the first aluminum layer.

Owner:MEDIATEK INC

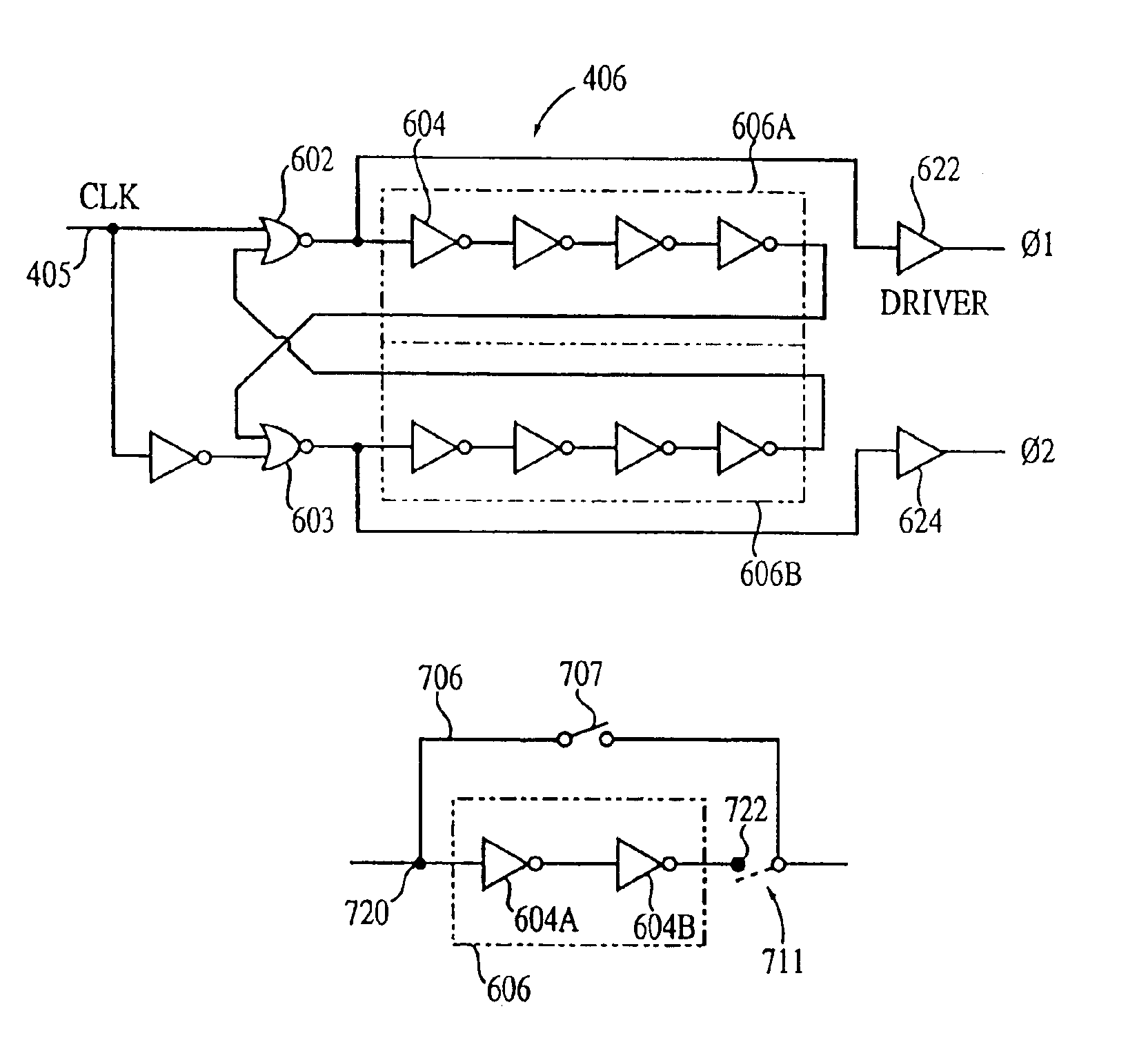

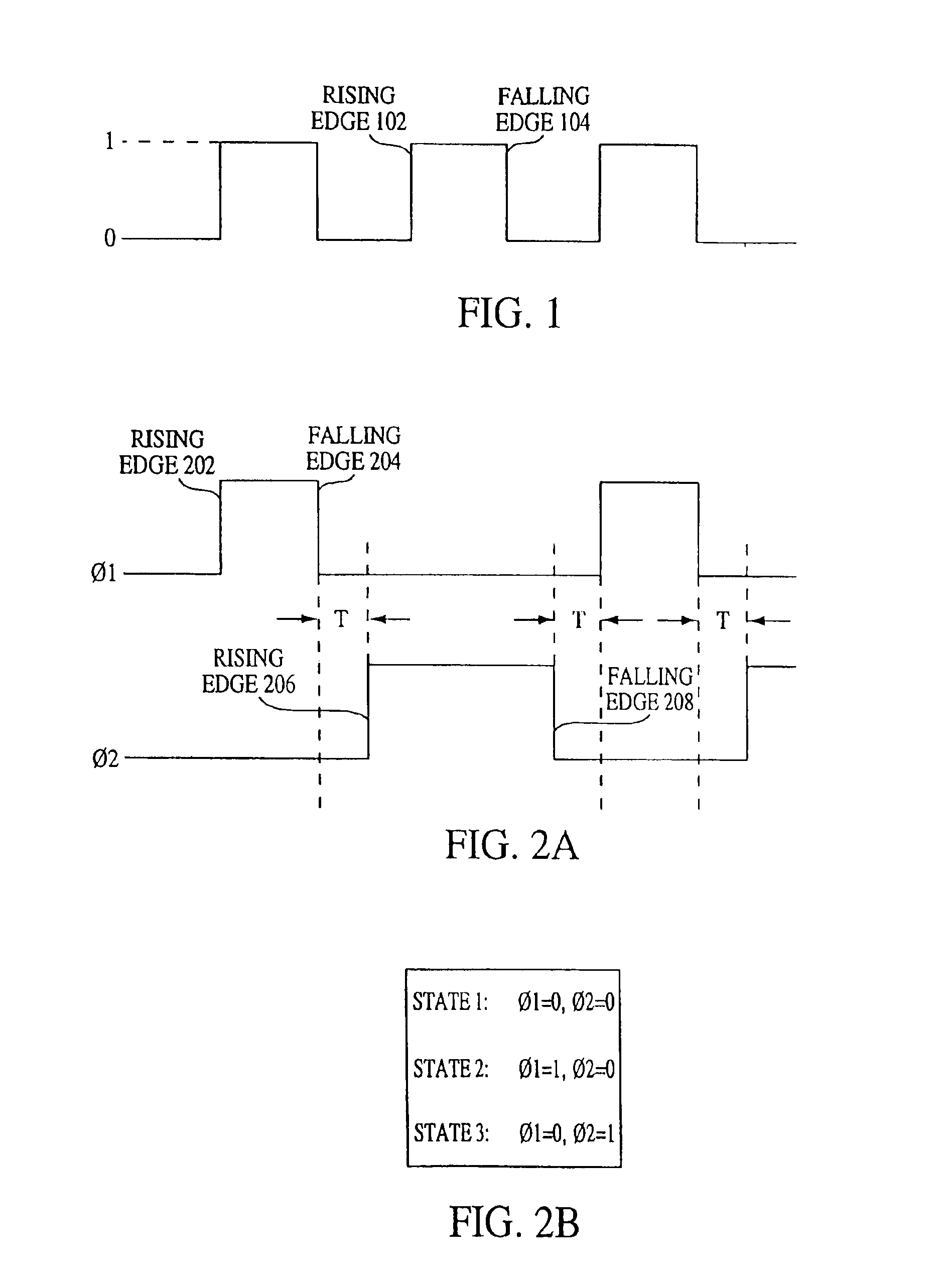

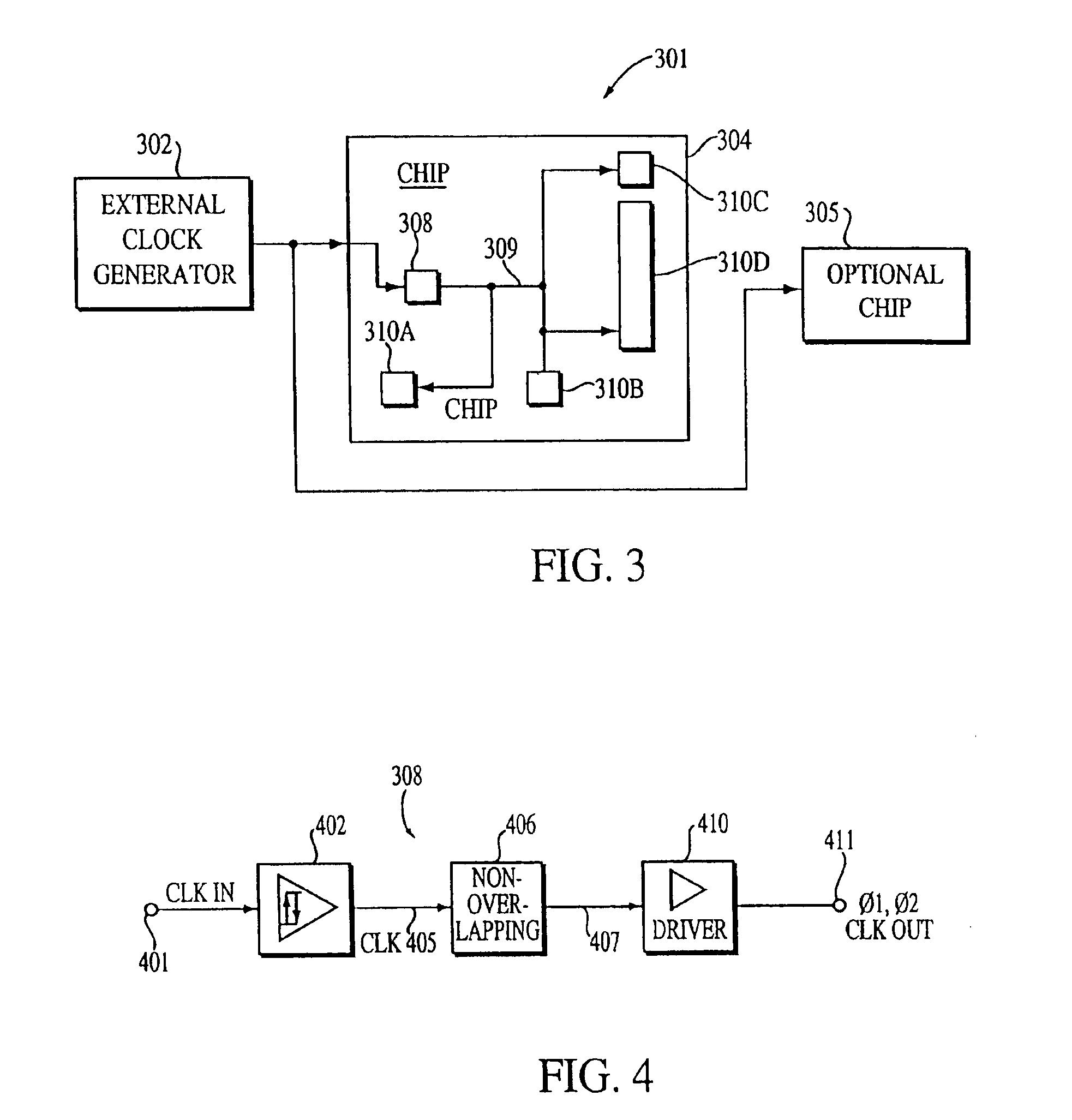

Clock generator with programmable non-overlapping-clock-edge capability

InactiveUS6900682B2Improve chip performanceImprove performanceSingle output arrangementsManipulation where pulse delivered at different timesComputer scienceClock generator

A system and method for generating and optimizing clock signals with non-overlapping edges on a chip using a unique programmable on-chip clock generator. Overlapping of the edges of the clocking signals is avoided by adjusting an amount of delay introduced in the on-chip clock generator circuit. The amount of delay is adjusted by programming the on-chip clock generator using either hardware and / or software programming. In hardware programming, the amount of delay adjusted by physically altering the composition of delay elements in the on-chip clock generator. In software programming, the delay is adjusted using software commands to control the operation of delay elements in the on-chip clock generator, or to select the paths that delay the signals.

Owner:SAMSUNG ELECTRONICS CO LTD

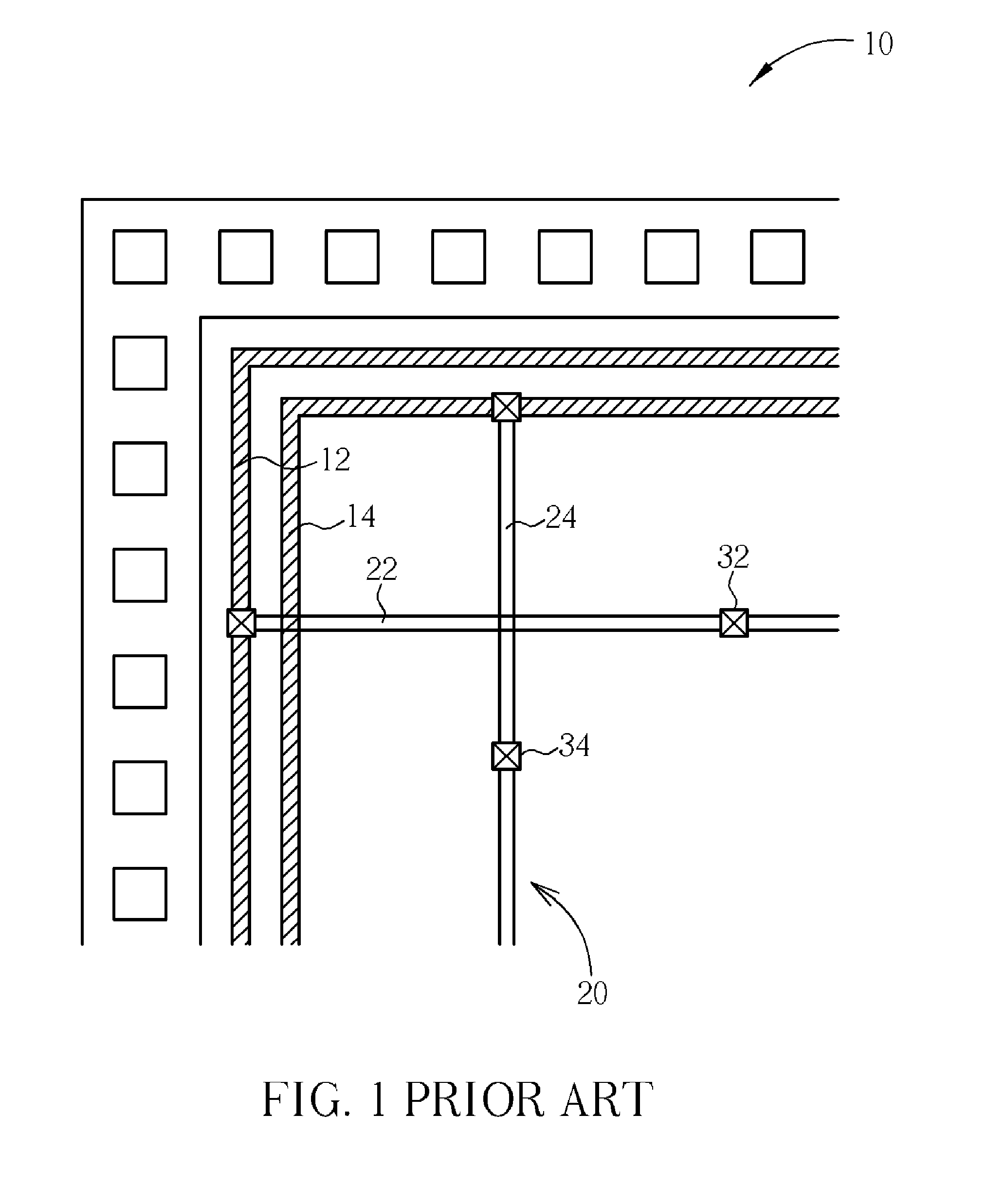

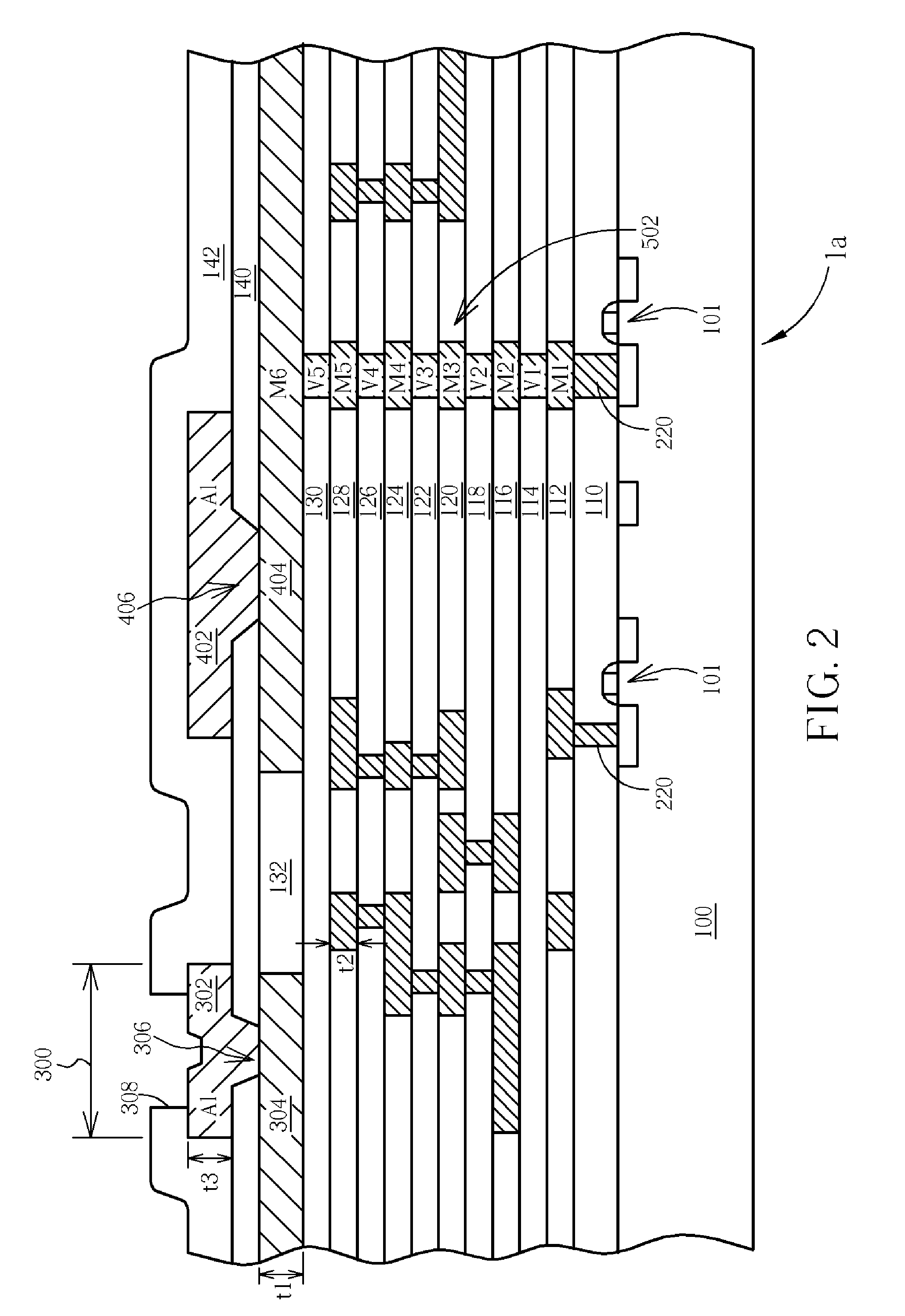

Power and ground routing of integrated circuit devices with improved IR drop and chip performance

ActiveUS7821038B2Increase powerReducing the IR dropSemiconductor/solid-state device detailsSolid-state devicesDielectricEngineering

An integrated circuit chip with reduced IR drop and improved chip performance is disclosed. The integrated circuit chip includes a semiconductor substrate having thereon a plurality of inter-metal dielectric (IMD) layers and a plurality of copper metal layers embedded in respective the plurality of IMD layers; a first passivation layer overlying the plurality of IMD layers and the plurality of copper metal layers; a first power / ground ring of a circuit block of the integrated circuit chip formed in a topmost layer of the plurality of copper metal layers; a second power / ground ring of the circuit block of the integrated circuit chip formed in an aluminum layer over the first passivation layer; and a second passivation layer covering the second power / ground ring and the first passivation layer.

Owner:MEDIATEK INC

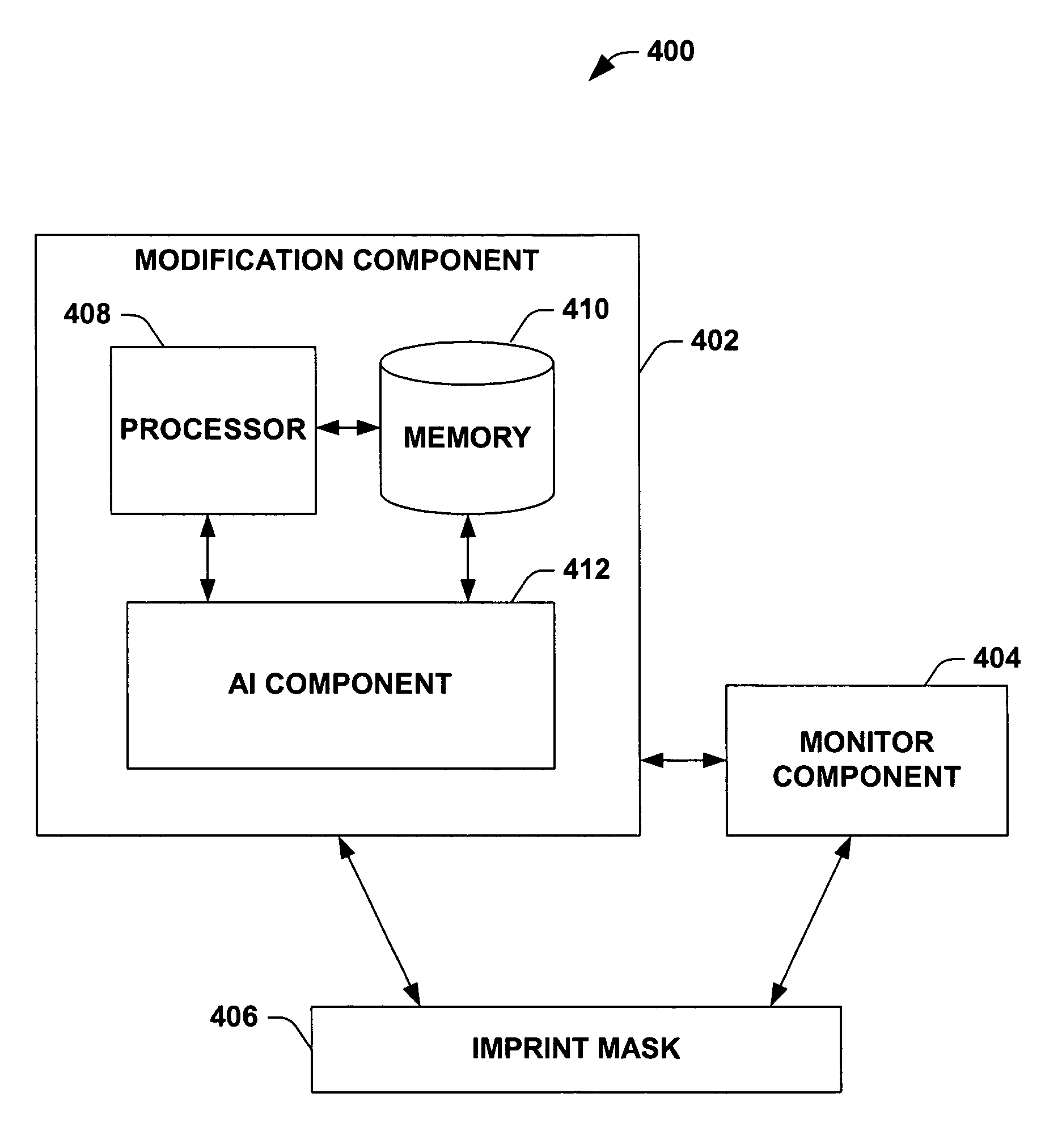

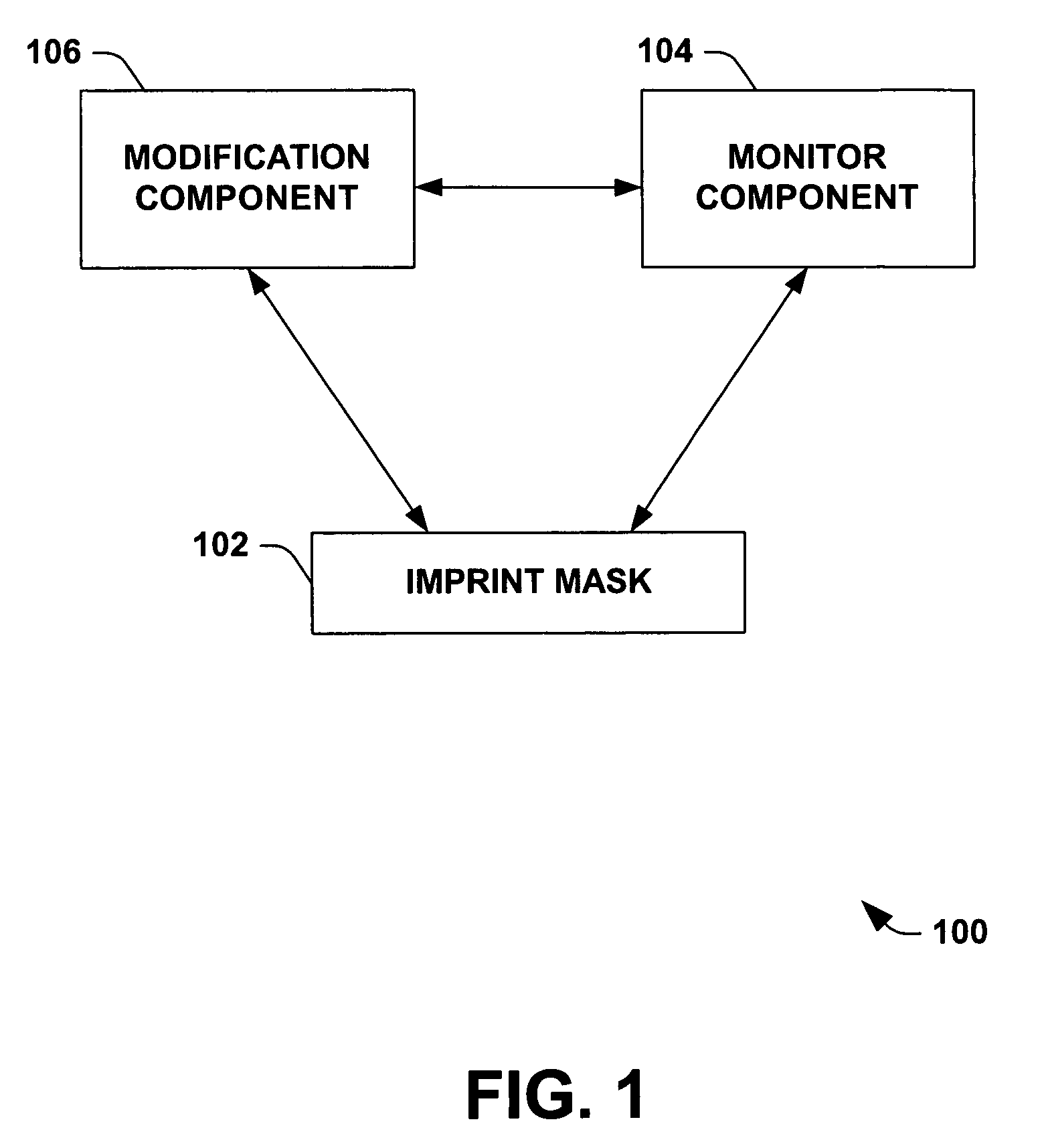

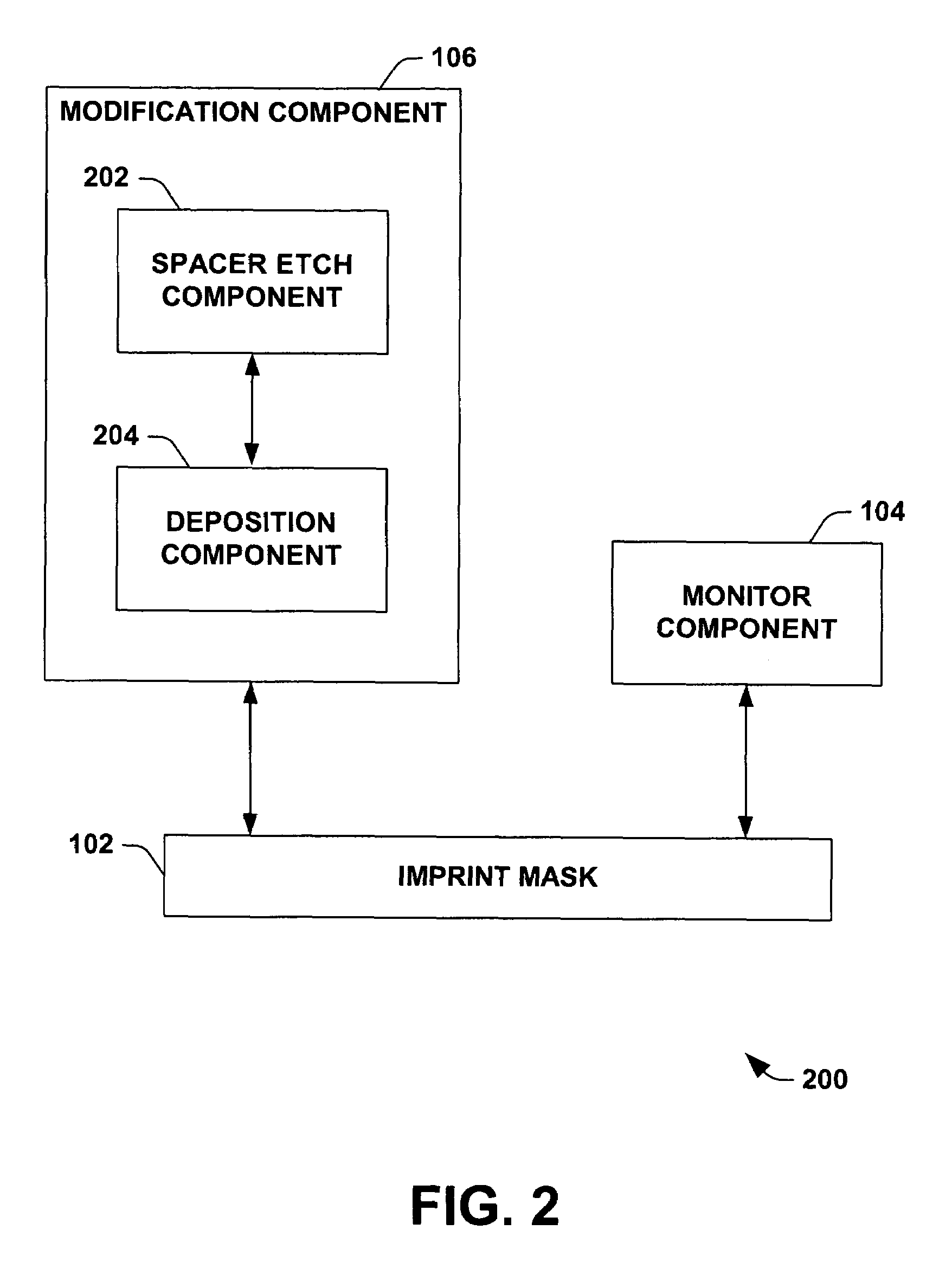

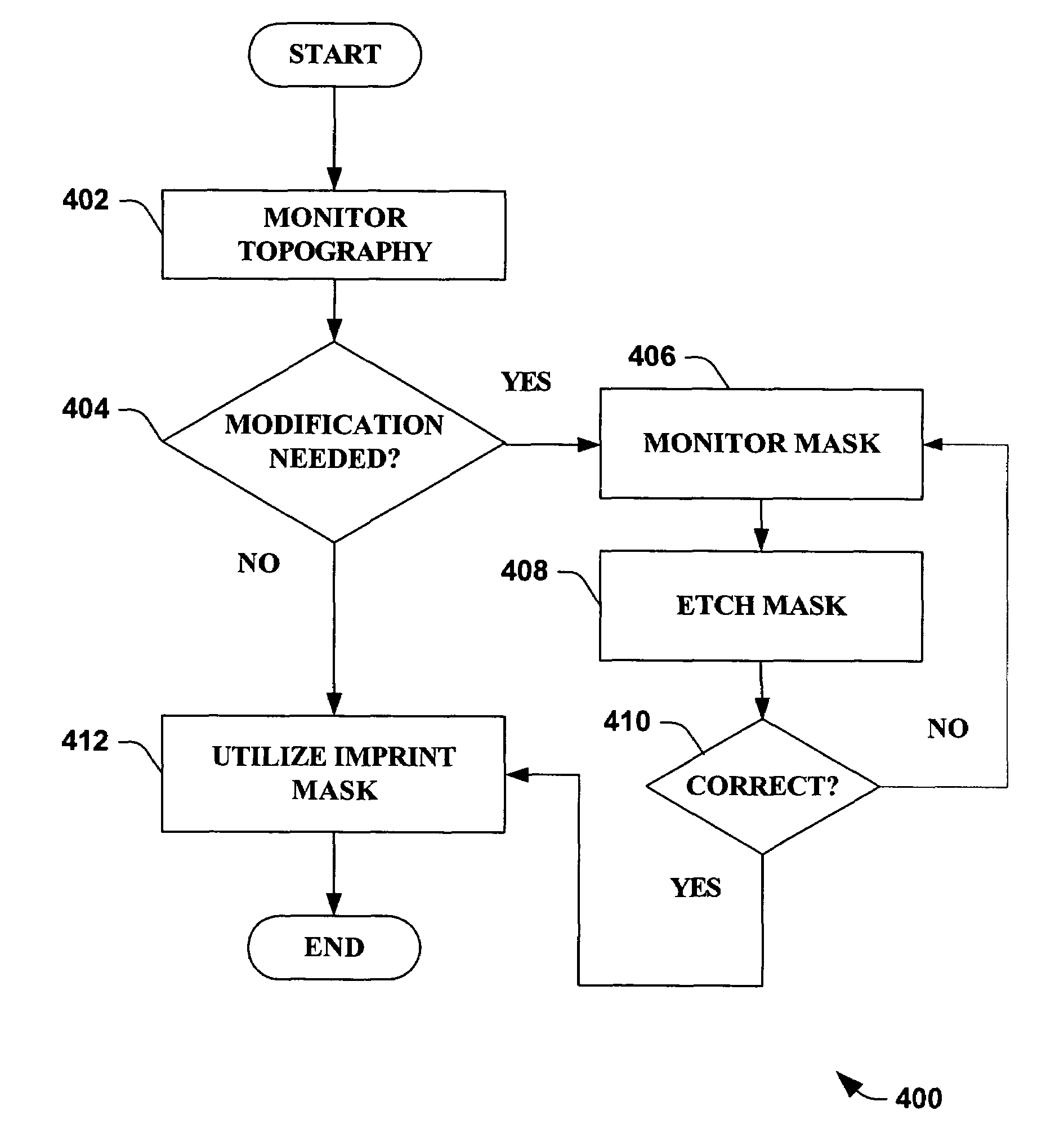

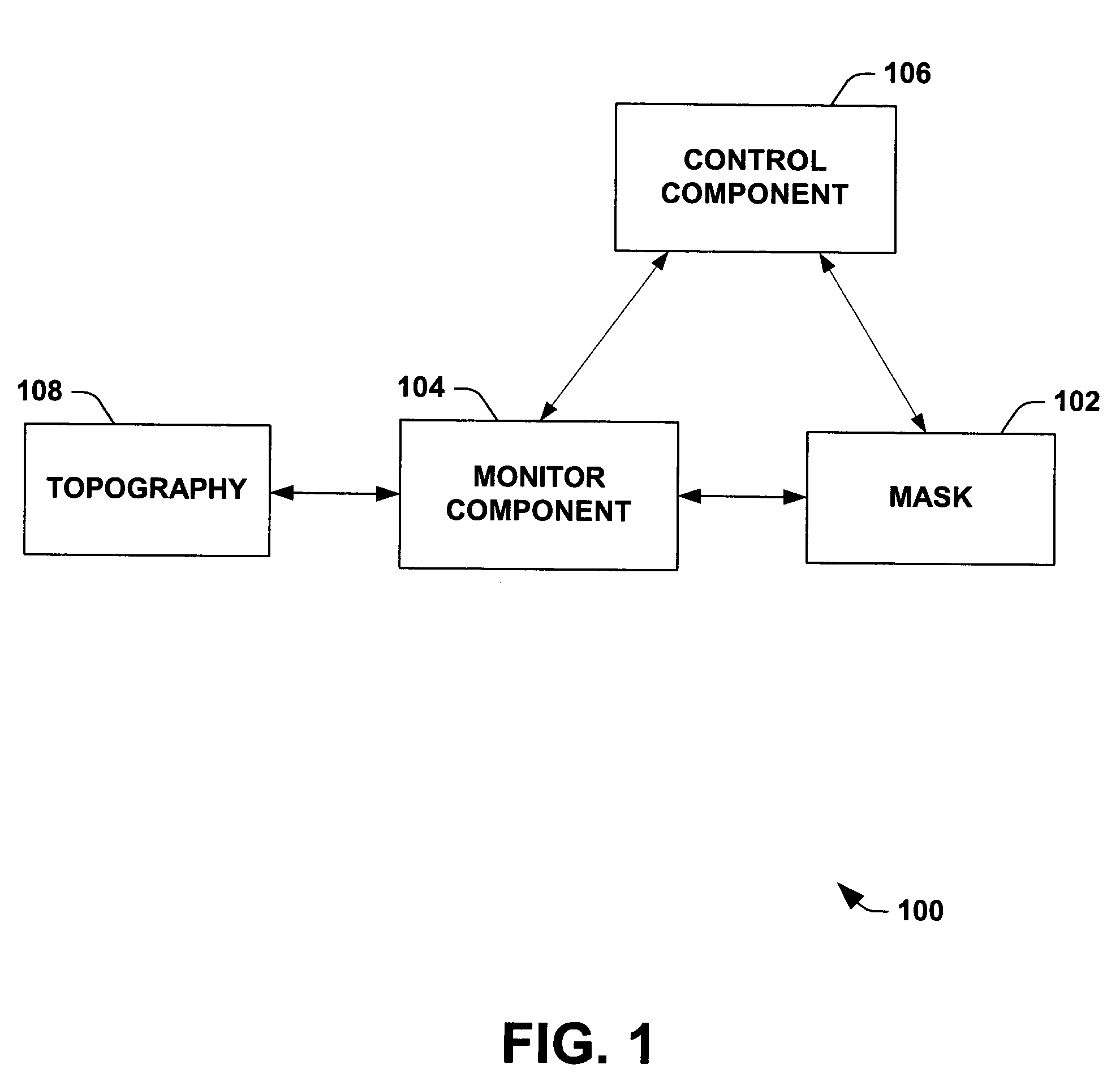

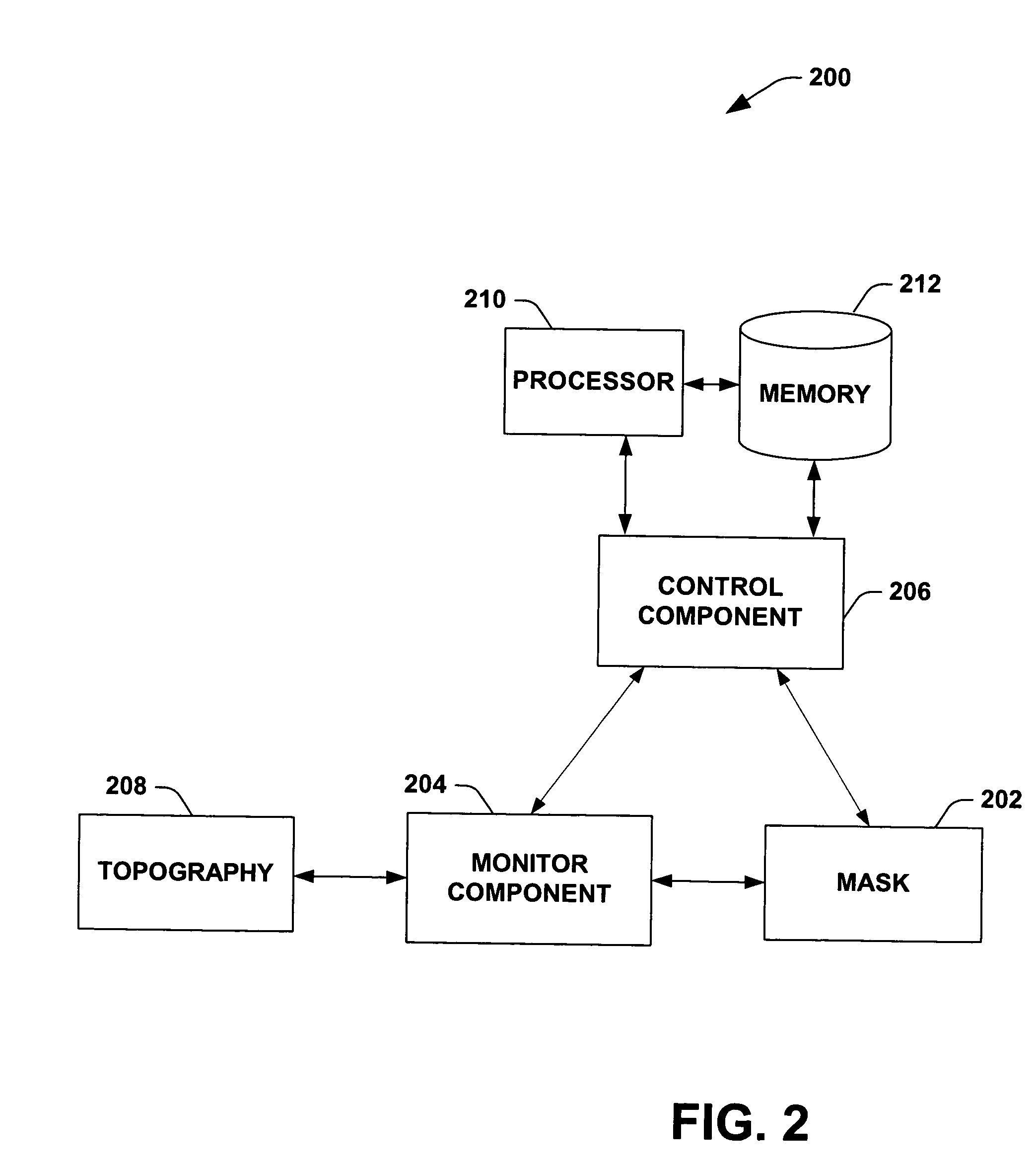

Post fabrication CD modification on imprint lithography mask

InactiveUS7386162B1Improve efficiencyGood economic benefitsNanoinformaticsPhotomechanical apparatusEngineeringCritical dimension

The present invention relates generally to photolithographic systems and methods, and more particularly to systems and methodologies that facilitate compensating for imprint mask critical dimension error(s). An aspect of the invention generates feedback information that facilitates control of imprint mask critical dimension via employing a scatterometry system to detect imprint mask critical dimension error, and mitigating the error via a spacer etchback procedure.

Owner:GLOBALFOUNDRIES INC

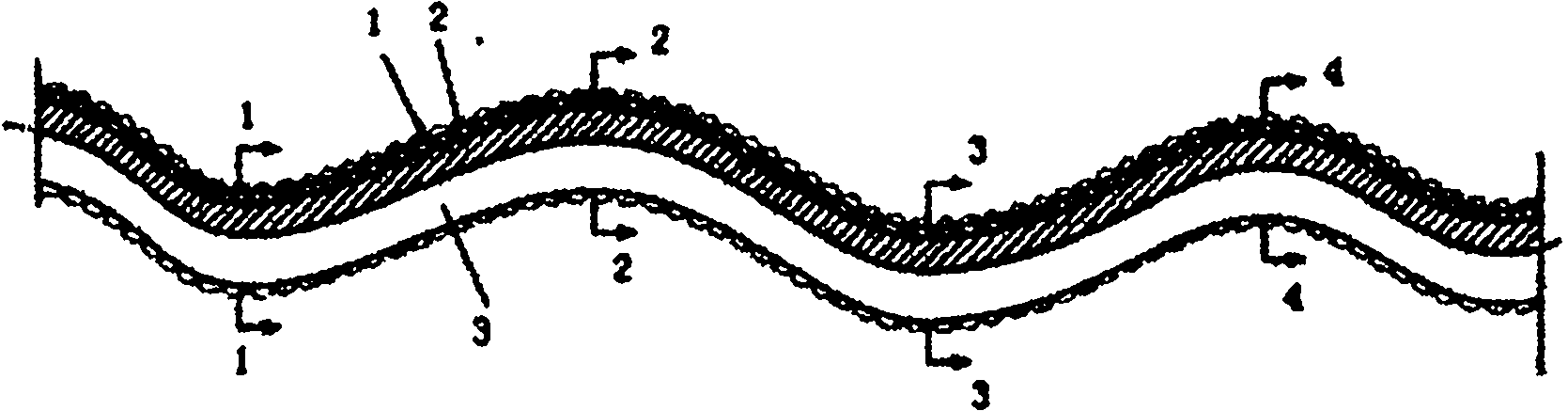

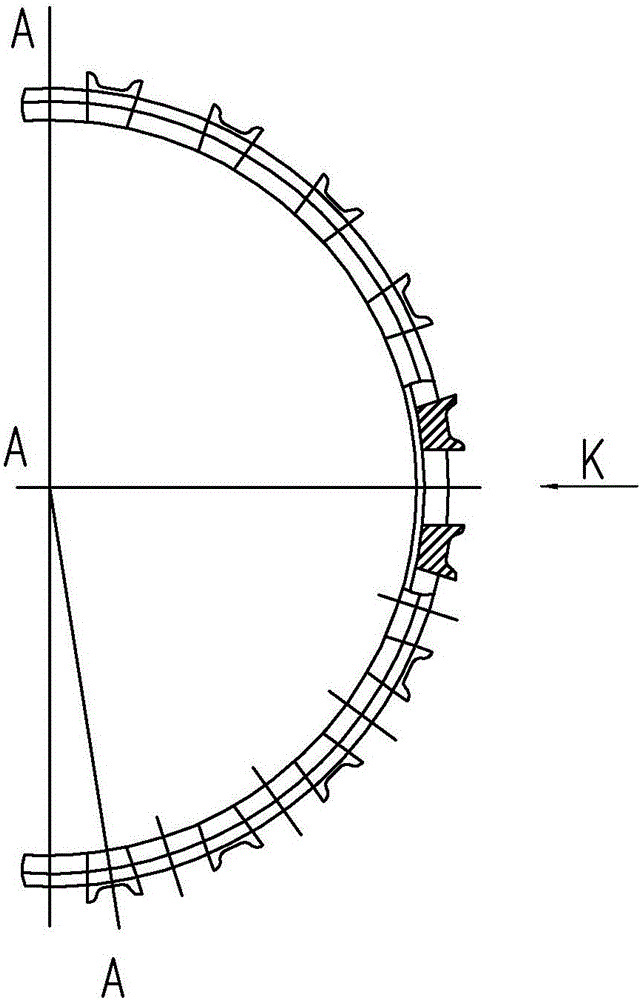

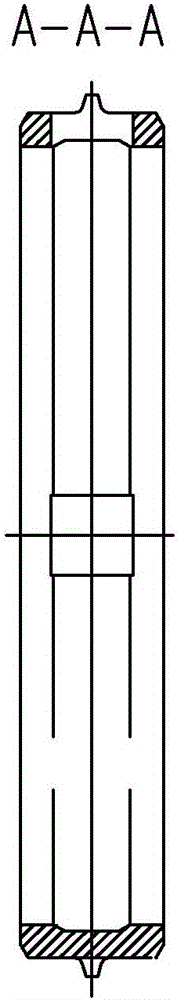

Wire-cutting wire of structural electrodeposited abrasive material

The invention relates to a wire-cutting wire of a structural electrodeposited abrasive material, comprising a structural metal blank wire, superhard abrasive material granules and a coating. The superhard abrasive material granules and the coating are plated on the surface of the structural metal blank wire which uses the axis of the structural metal blank wire as a basic wire, and a plurality of segments of S-shaped or Z-shaped curves are distributed in a range of 360 degrees along the axis of the structural metal blank wire; the structural metal blank wire has the projection diameter of 0.1-0.6 mm; and the abrasive material granules are selected from diamond granules or cubic boron nitride granules with the grain sizes of 10-50 microns. In the invention, the wire-cutting wire is prepared by using the structural metal blank wire as the basic wire and using a composite galvanization method, has favorable scrap containing and retreating functions, and is beneficial to effective prevention of the obvious problem of broken wire; meanwhile, the formed stable and high-efficiency cutting state improves the use efficiency of the wire-cutting wire of the structural electrodeposited abrasive material, and the wire-cutting wire is suitable for industrial application.

Owner:CHANGSHA DIAT NEW MATERIAL SCI & TECH

Conductive shielding pattern and semiconductor structure with inductor device

InactiveUS20080029854A1Improving quality and factor QReduce distractionsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureEngineering

The invention is directed to a conductive shielding pattern for shielding a inductor device. The conductive shielding pattern comprises a plurality of conductive layers and a plurality of diffusion regions. The conductive layers are located on a substrate. The diffusion regions are located in the substrate and the conductive layers and the diffusion regions are arranged alternatively and are free ends respectively.

Owner:UNITED MICROELECTRONICS CORP

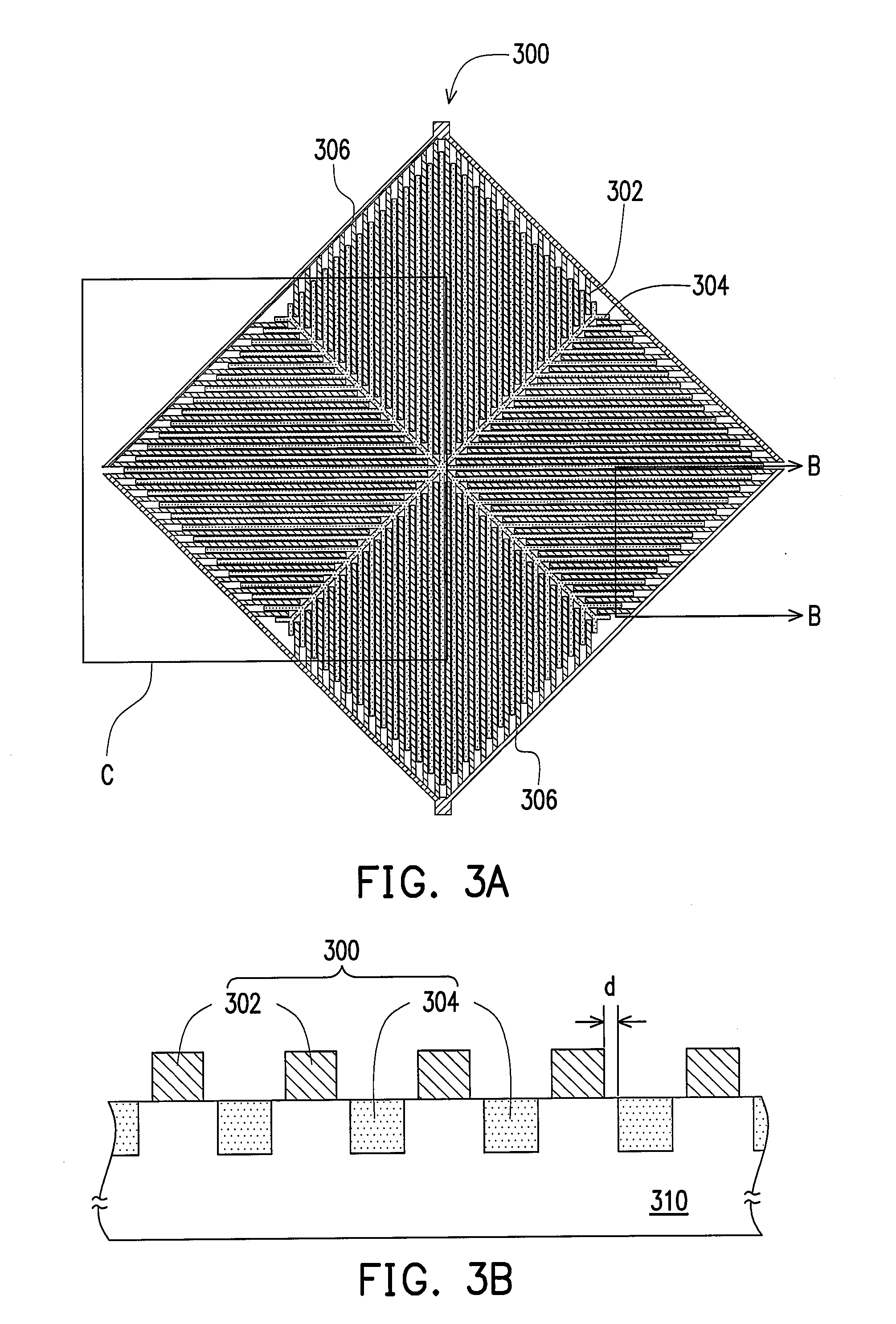

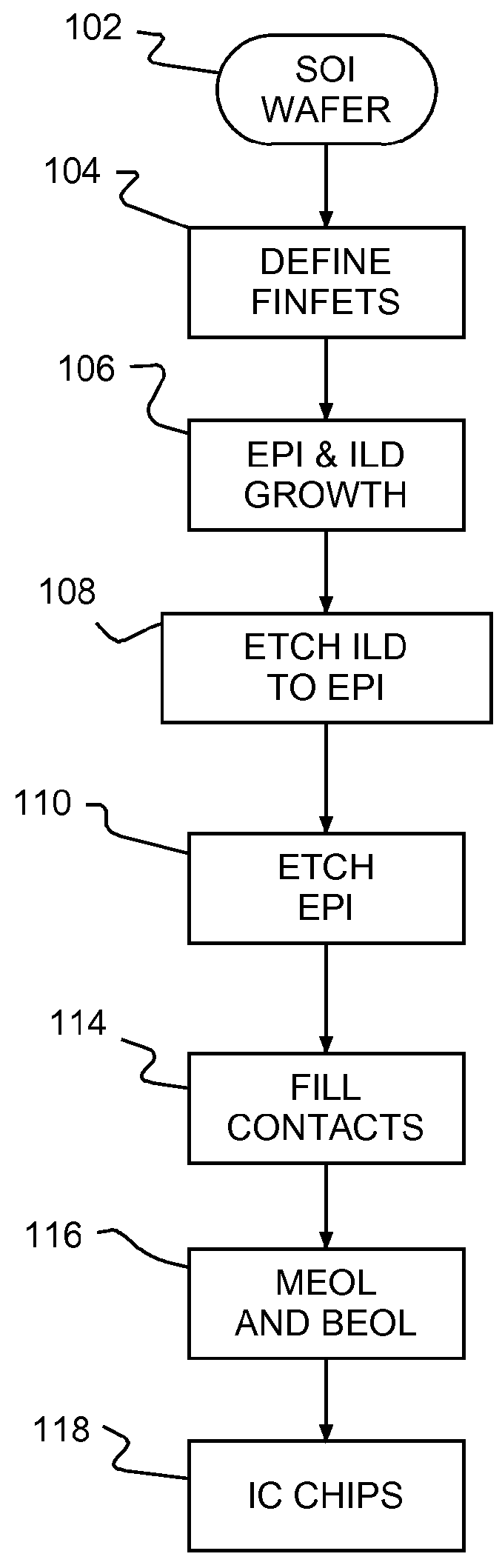

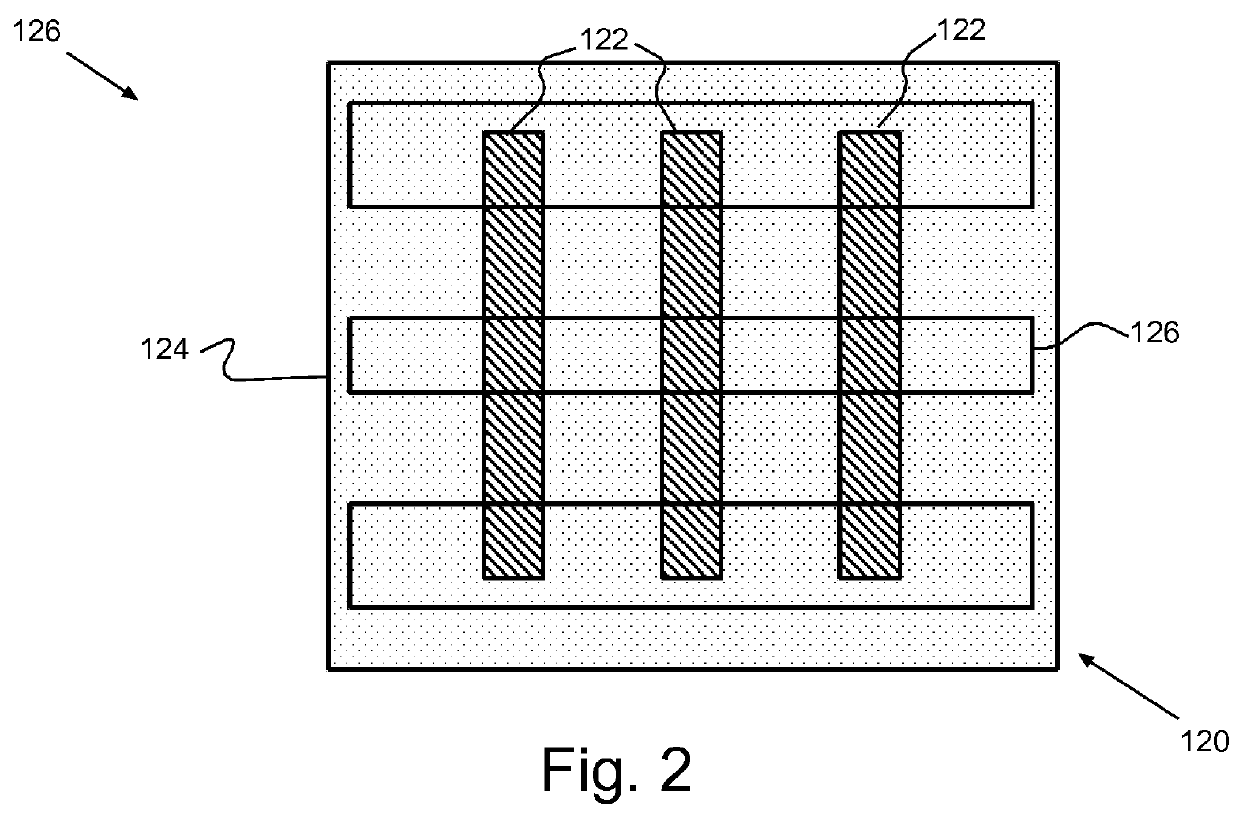

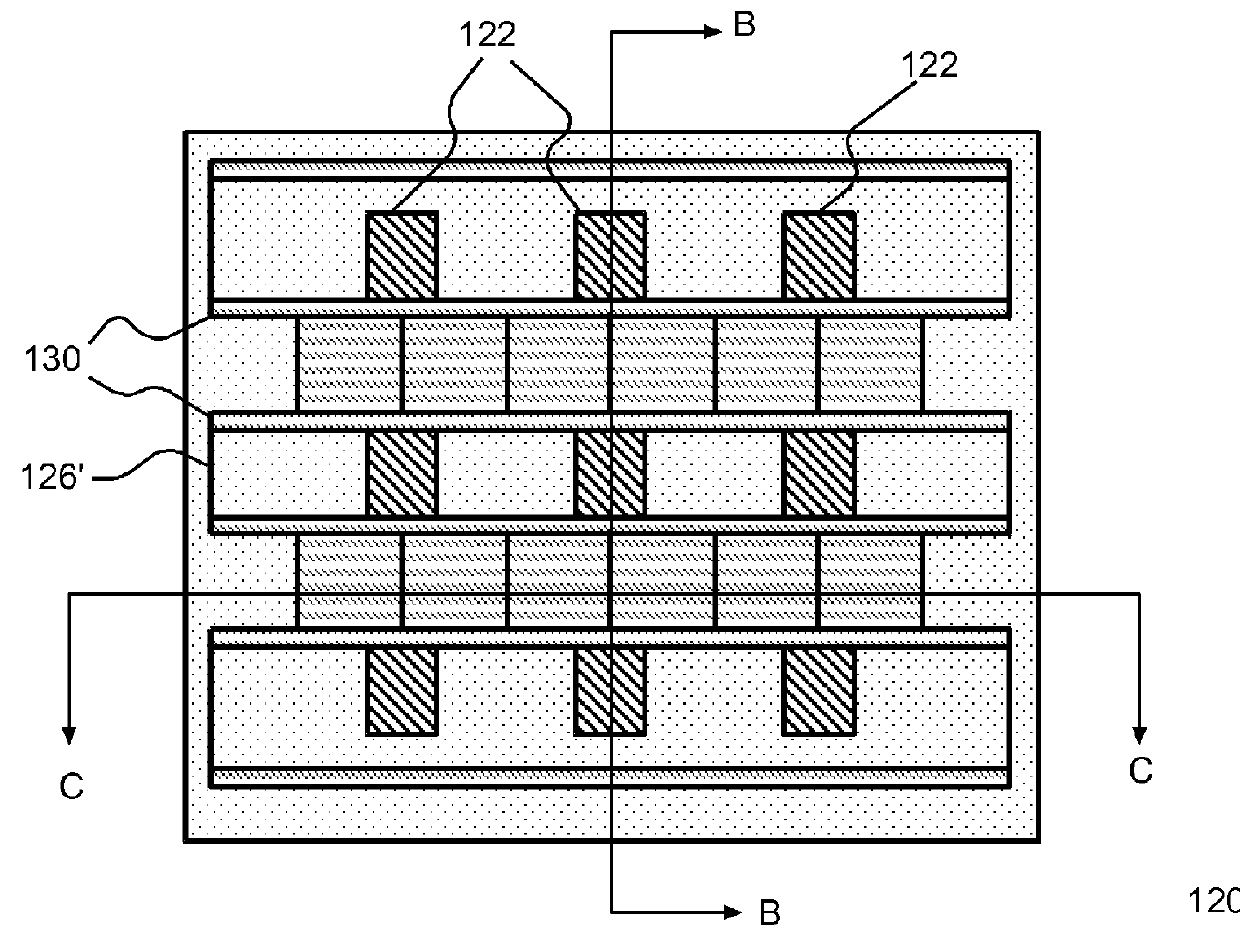

Method of forming source/drain contacts in unmerged FinFETs

ActiveUS9379025B1Contact resisImprove chip performanceTransistorSolid-state devicesPhysicsIntegrated circuit

A method of forming field effect transistors (FETs), and forming integrated circuit (IC) chip including the FETs. After forming replacement metal gate (RMG) FinFETs on a surface layer of a silicon on insulator (SOI) wafer, and growing unmerged epitaxially (epi) on the fins, the epi is capped with dielectric and an inter-level dielectric (ILD) layer is formed on the SOI wafer. The said ILD layer is patterned to an upper surface of the epi above encased fins in a timed etch. Then, etching, preferably with an etchant selective to silicon, the epi is opened to, and into, the fins. The resulting orifices are filled with conductive material to form source drain contacts.

Owner:ELPIS TECH INC

Method for powder metallurgy preparation of self-lubricating bearing material

InactiveCN103436823AImprove the lubrication effectEasy to processBearing componentsIron powderIron sulfide

The invention discloses a method for powder metallurgy preparation of a self-lubricating bearing material, belonging to the field of lubricating materials. According to the method, a traditional powder metallurgy method is adopted, and the method comprises the following steps of: mixing and annealing iron powder with an appropriate amount of iron sulfide, ferromanganese powder and alloy powder; mixing the annealed powder with an appropriate amount of graphite; pressing and sintering to obtain the self-lubricating bearing material. The raw materials are inexpensive, the process is simple, the parameters are easy to control, and the production process is safe and environment-friendly, so that the method is suitable for large-scale industrial production. In the annealing process, the mixed powder reacts to generate FeS and MnS, and good lubricating and antifriction effects are achieved; meanwhile, the existence of MnS can significantly improve the cutting performance of the bearing material and reduce the abrasion of a cutter. The self-lubricating bearing material prepared by the method disclosed by the invention can be widely applied to mechanical equipment for iron and steel, metallurgy, energy sources and the like, and is particularly suitable for occasions requiring oil-free lubrication.

Owner:UNIV OF SCI & TECH BEIJING

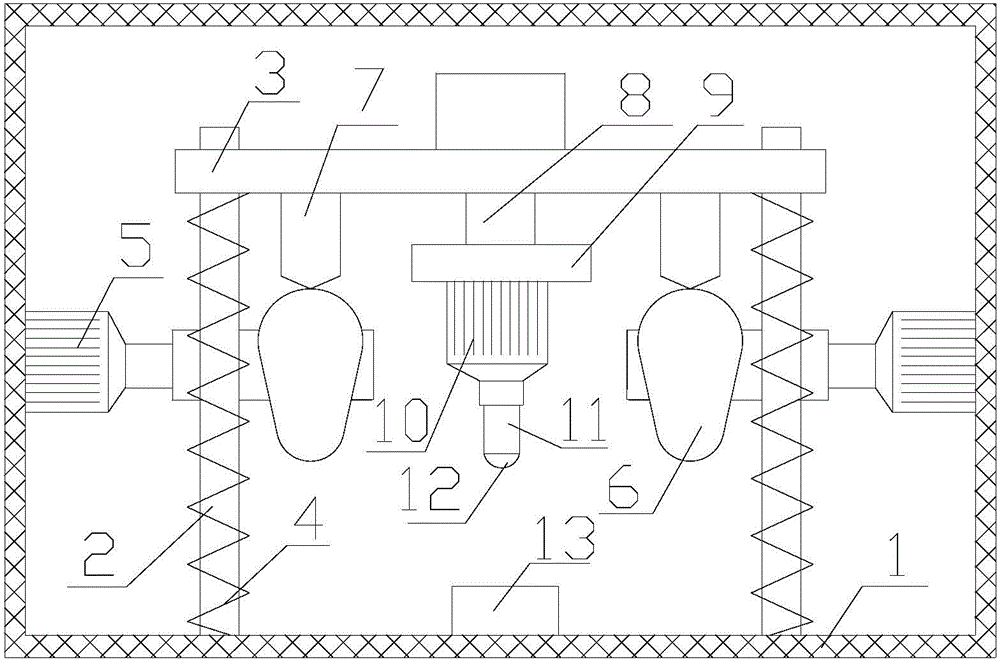

Novel self-chip-removal machine tool

InactiveCN104889445ASmooth chip removalFast Chip EvacuationFeeding apparatusDriving apparatusEngineeringCam

The invention provides a novel self-chip-removal machine tool. The cutting efficiency is effectively improved through vibrating drilling, and the novel self-chip-removal machine tool is smooth in chip removal and high in chip removal speed. A guide rod is arranged on the machine frame. An upper supporting plate is connected to the periphery of the guide rod in a vertical sliding and sleeving mode. The two ends of each spring are fixedly connected to the upper supporting plate and a machine frame respectively. A first drive device is arranged on the machine frame. A cam mechanism comprises a cam and a driven rod. The cam is connected to the periphery of an output shaft of the first drive device in a sleeving mode and is driven by the first drive device to rotate. One end of the driven rod is arranged on the upper supporting plate, and the other end of the driven rod abuts against the cam. A second drive device is arranged on the upper supporting plate and can drive a lower supporting plate to move in the axial direction of the guide rod. A third drive device is arranged on the lower supporting plate and can drive a drilling assembly to rotate. A drill stem is connected with an output shaft of the third drive device. A drill bit is arranged on the side, away from the third drive device, of the drill stem. The novel self-chip-removal machine tool is used for arranging a clamping piece on the machine frame, wherein the clamping piece is used for clamping workpieces.

Owner:蚌埠市金林数控机床制造有限公司

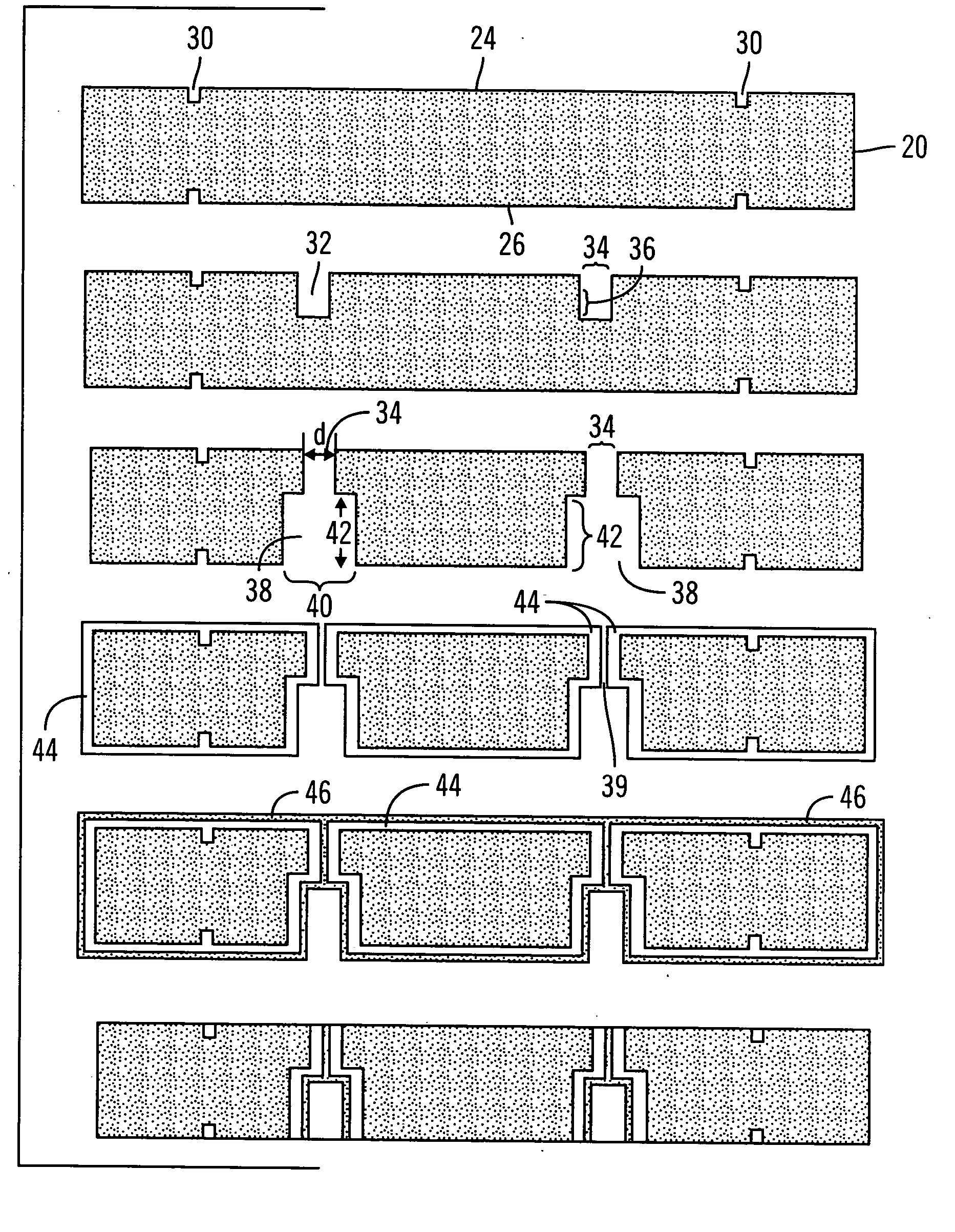

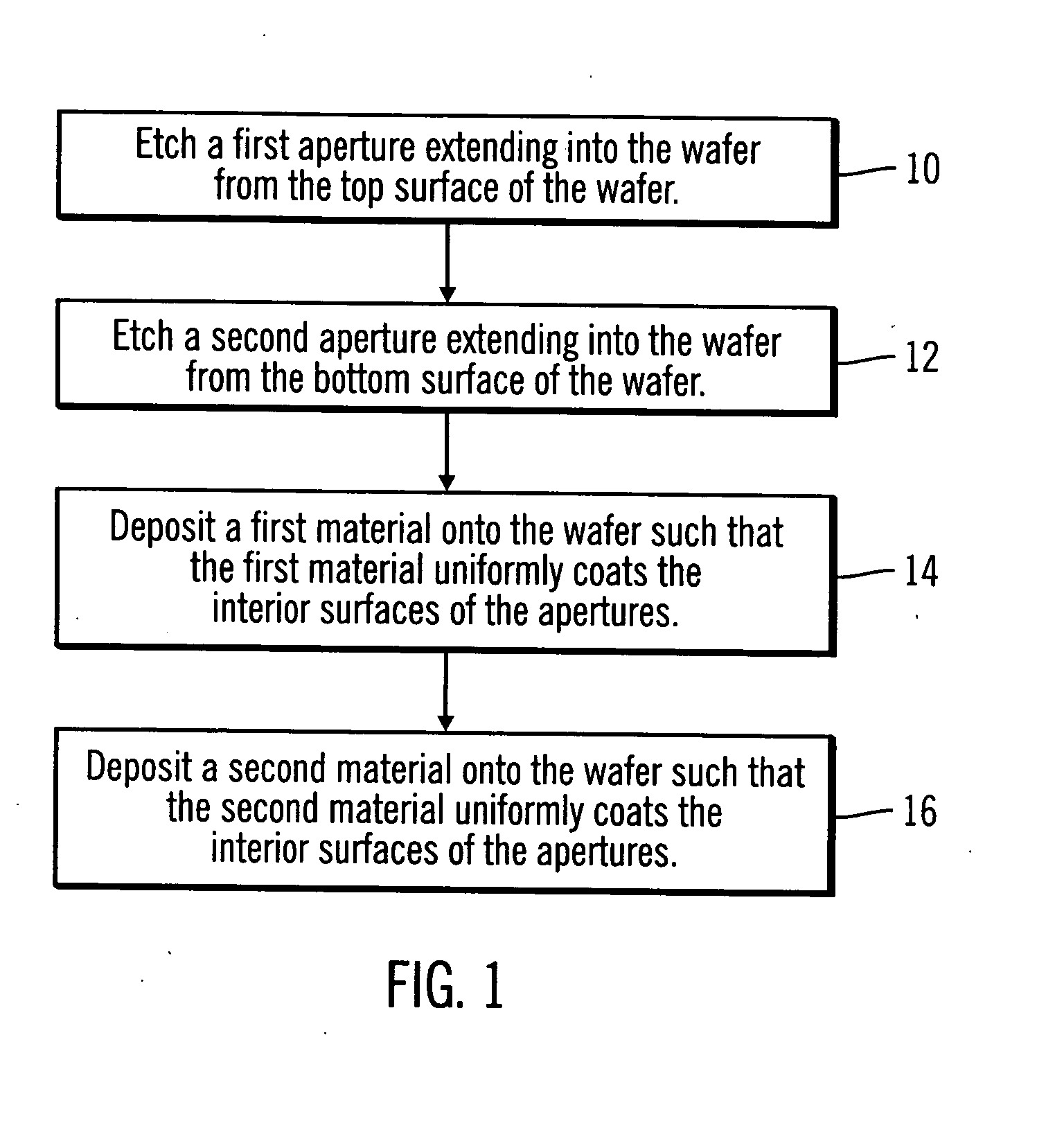

Low temperature method for fabricating high-aspect ratio vias and devices fabricated by said method

ActiveUS7538032B2High densityMoreSemiconductor/solid-state device detailsSolid-state devicesConductive materialsOptoelectronics

Embodiments of the present invention are directed to a process for forming small diameter vias at low temperatures. In preferred embodiments, through-substrate vias are fabricated by forming a through-substrate via; and depositing conductive material into the via by means of a flowing solution plating technique, wherein the conductive material releases a gas that pushes the conductive material through the via to facilitate plating the via with the conductive material. In preferred embodiments, the fabrication of the substrate is conducted at low temperatures.

Owner:TELEDYNE SCI & IMAGING

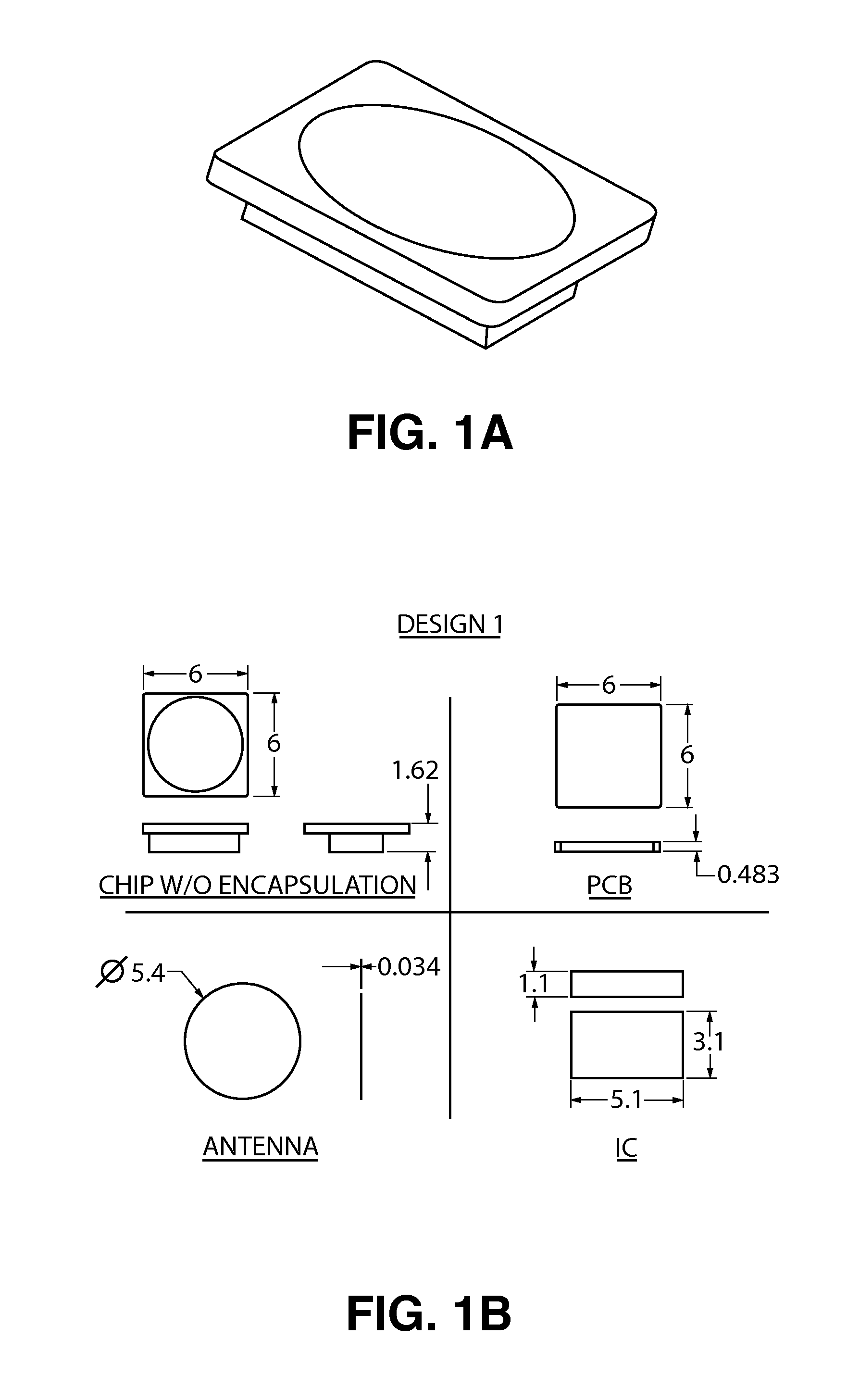

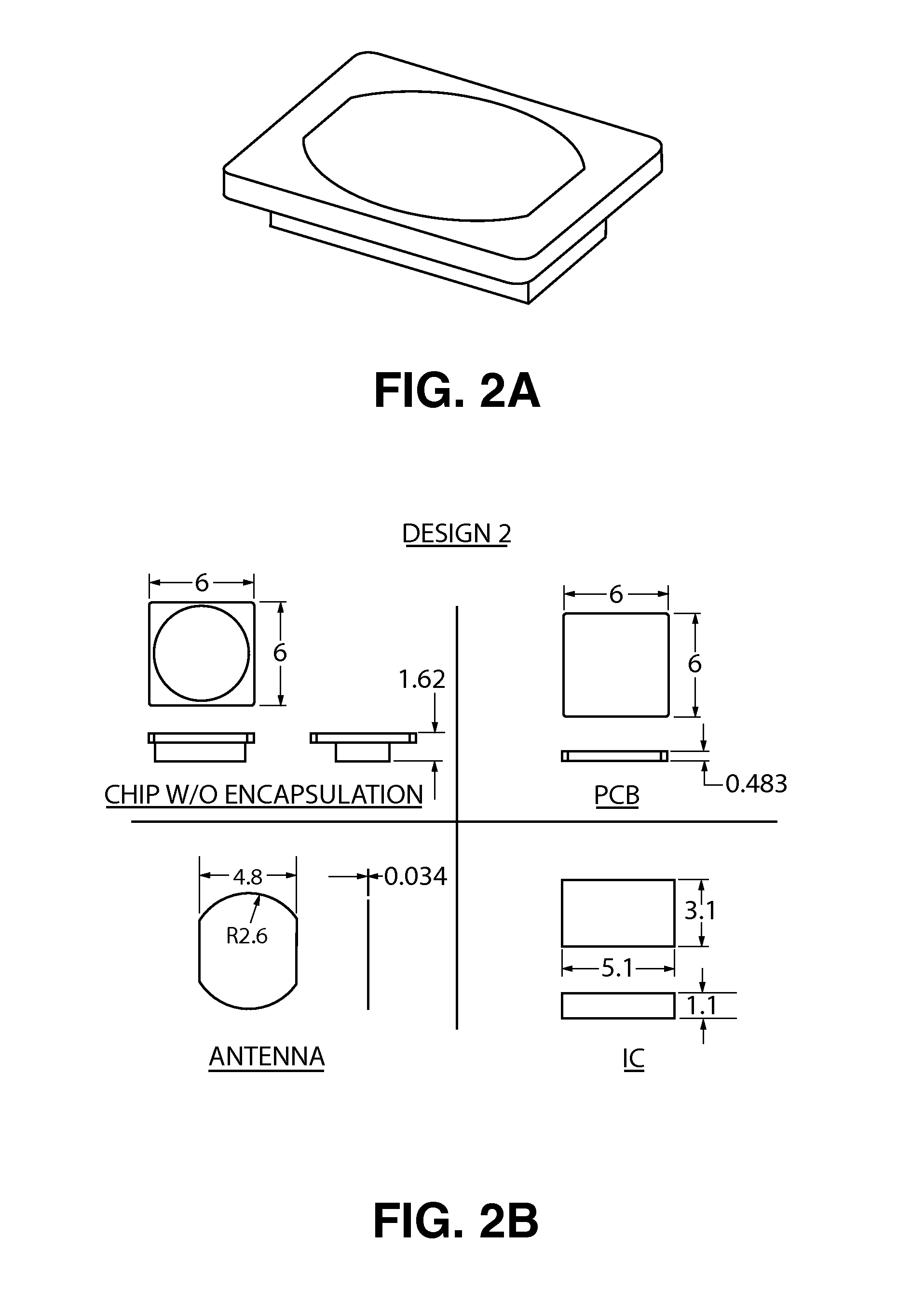

Miniaturized uhf RFID tag for implantable medical device

ActiveUS20130306740A1Low profileDetuning effect of attachment to metallic materials is minimized or nullified altogetherSemiconductor/solid-state device detailsSolid-state devicesInductorMicrostrip antenna

This invention relates to a novel architecture of a passive RFID (Radio-Frequency Identification) tag which is highly miniature in size, capable of metal mounting and suitable for global operation in the entire UHF band (860 MHz to 960 MHz) without necessity of territory specific optimization of the antenna design layout.This invention envisages a novel antenna design that consists of a circular or rectangular microstrip antenna of ultra-small size (−λ / 50), which is suitably loaded in shunt by lumped components resistor (R), inductor (L) and capacitor (C). The feed point, feed layout and the loading values are so optimized that a single tag will display optimum performance in all the territories.This invention relates to a method of encapsulating the passive tag with radio transparent materials like Radel® R, as well as a metal backplane so that the encapsulated tag can withstand autoclaving while maintaining the required performance.

Owner:WARSAW ORTHOPEDIC INC

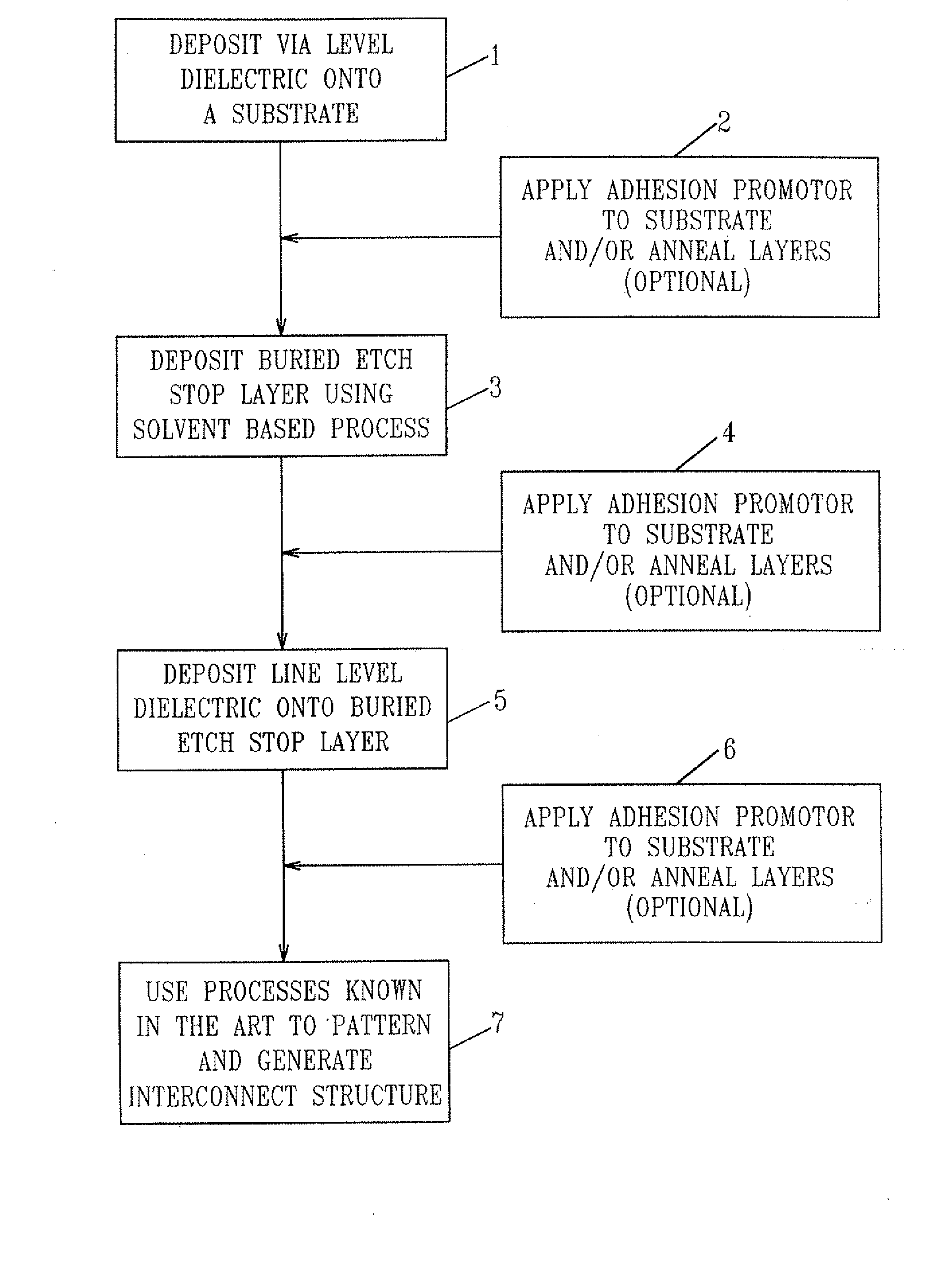

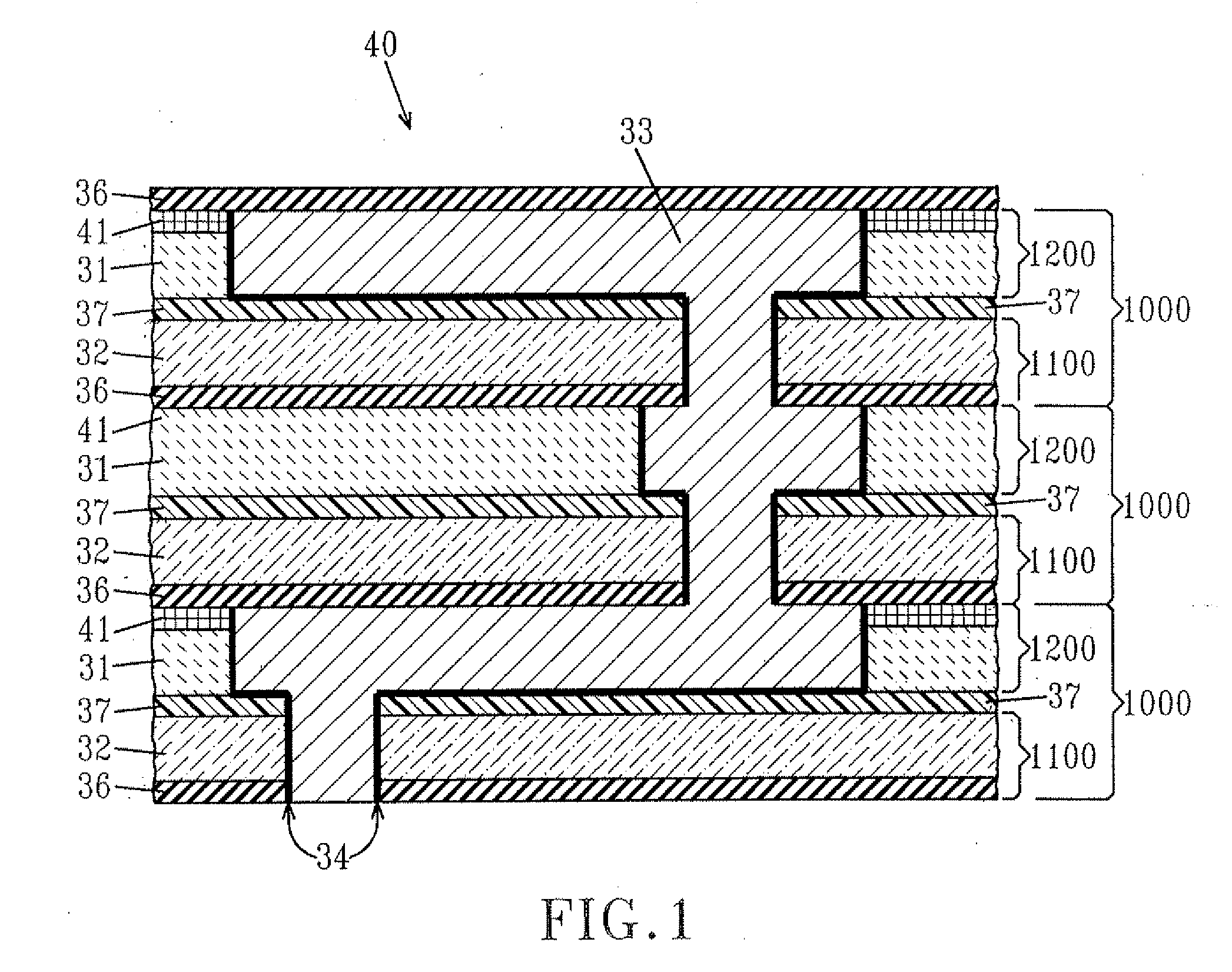

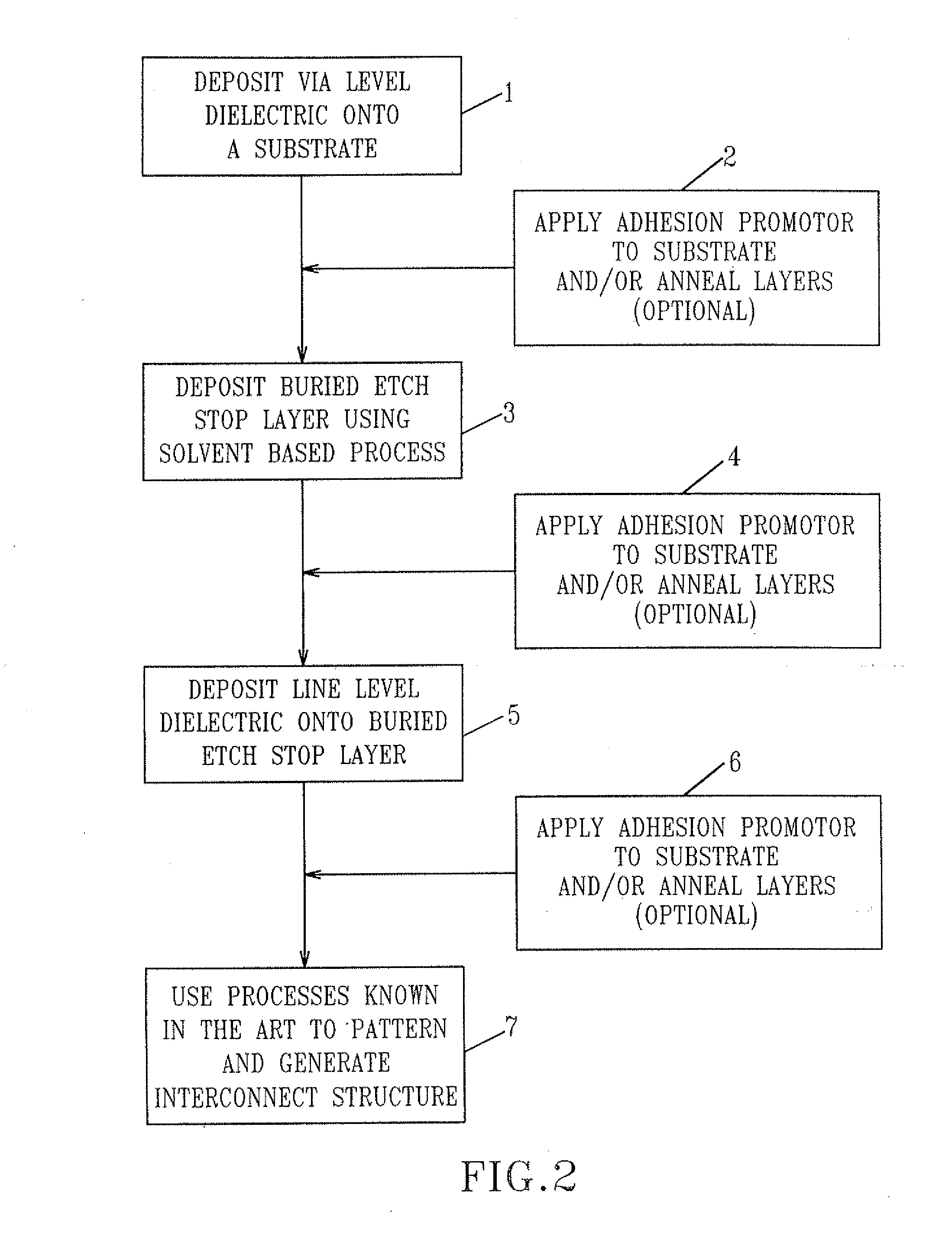

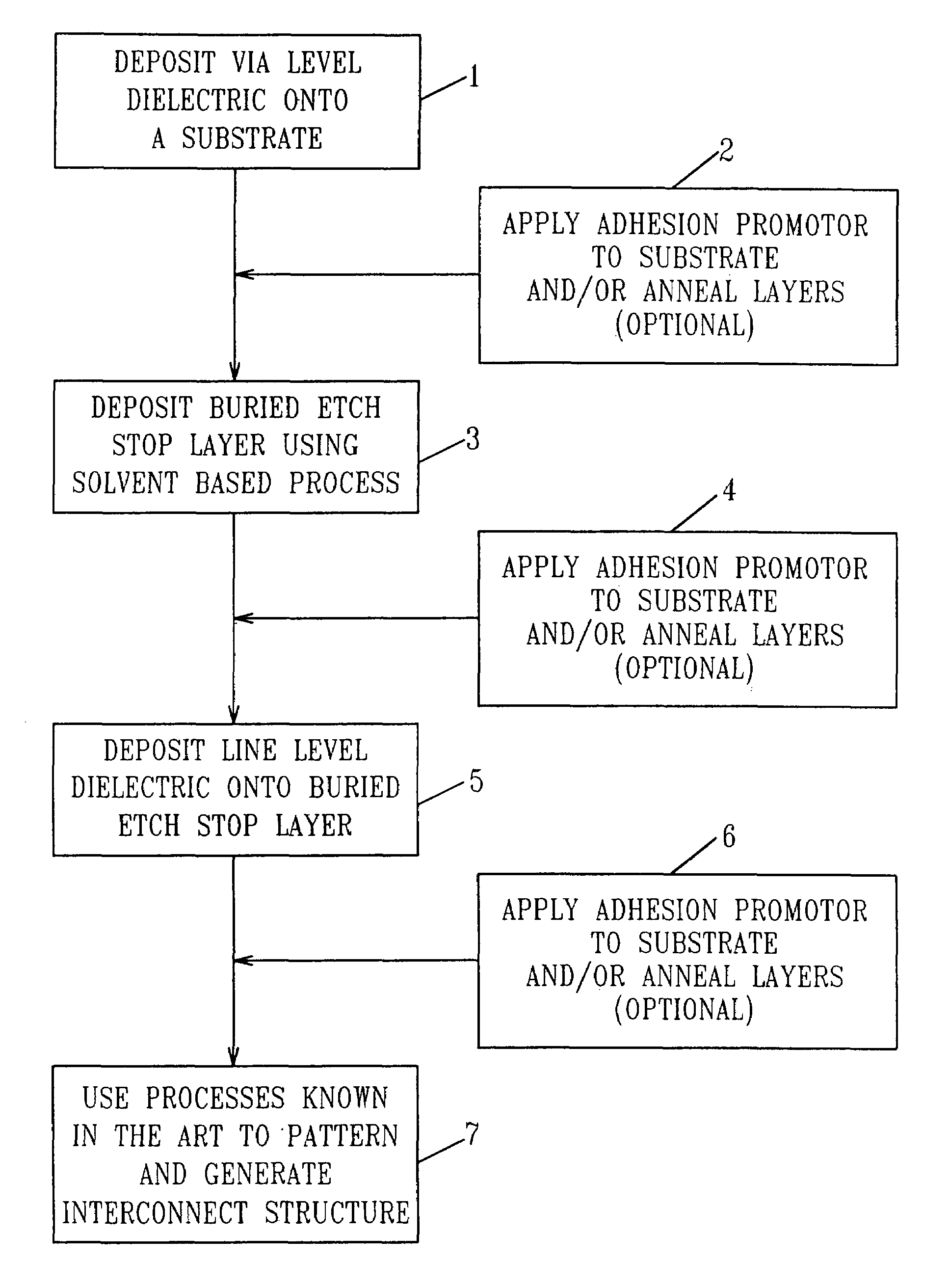

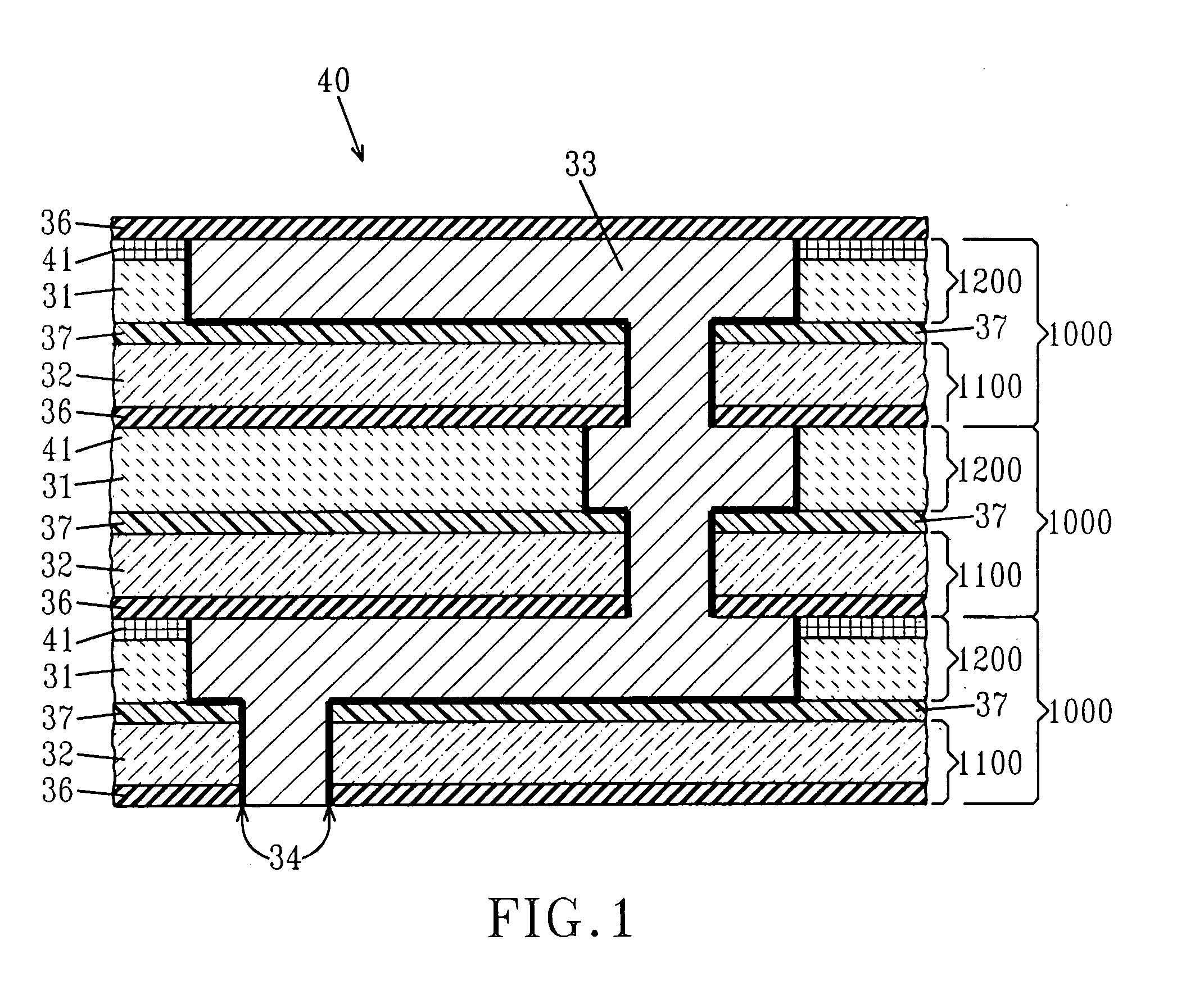

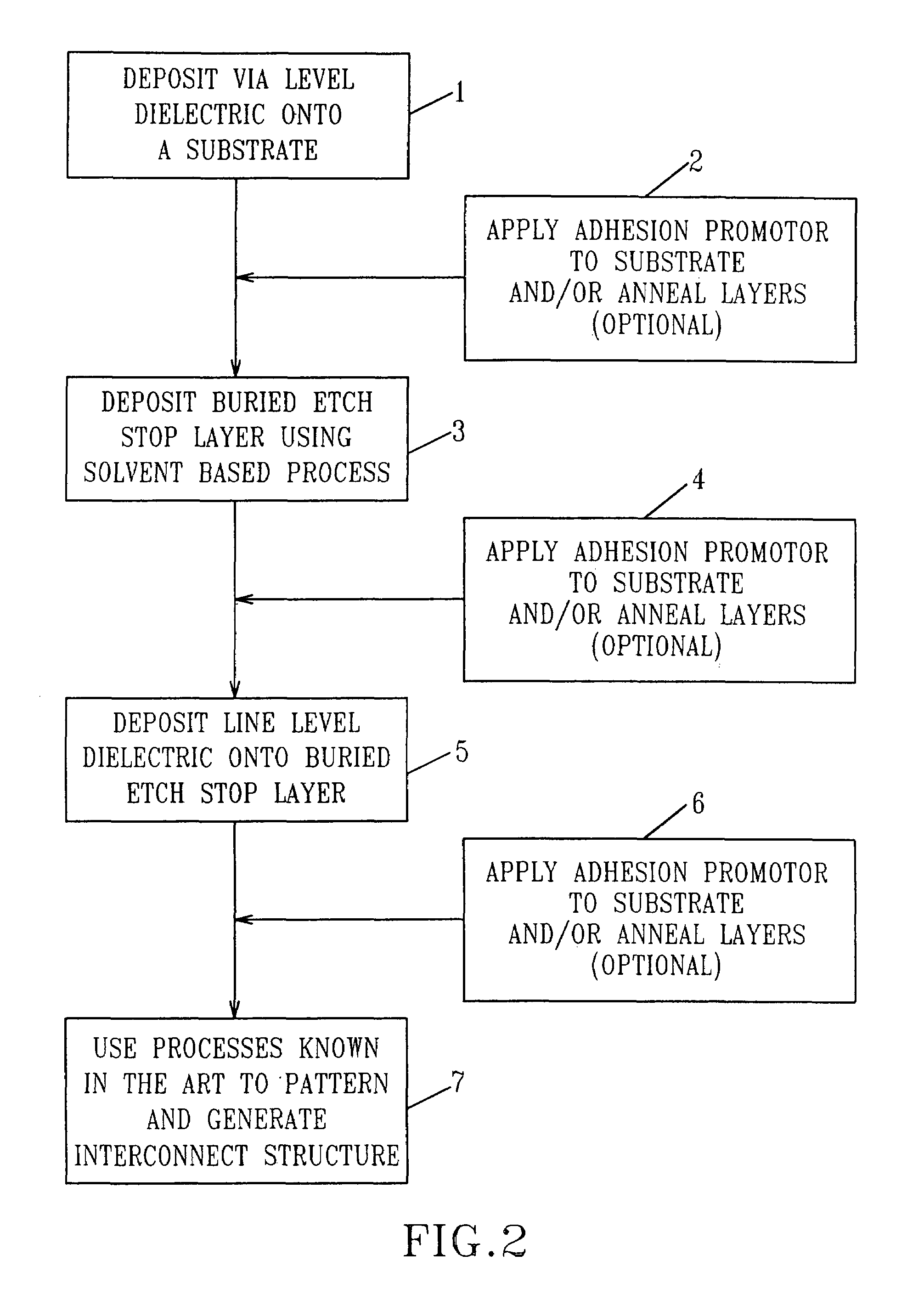

Polycarbosilane buried etch stops in interconnect structures

InactiveUS20070111509A1Reduce degradationReduce dissipationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMetal

Interconnect structures having buried etch stop layers with low dielectric constants and methods relating to the generation of such buried etch stop layers are described herein. The inventive interconnect structure comprises a buried etch stop layer comprised of a polymeric material having a composition SivNwCxOyHz, where 0.05≦v≦0.8, 0≦w≦0.9, 0.05≦x≦0.8, 0≦y≦0.3, 0.05≦z≦0.08 for v+w+x+y+z=1; a via level interlayer dielectric that is directly below said buried etch stop layer; a line level interlayer dielectric that is directly above said buried etch stop layer; and conducting metal features that traverse through said via level dielectric, said line level dielectric, and said buried etch stop layer.

Owner:TAIWAN SEMICON MFG CO LTD

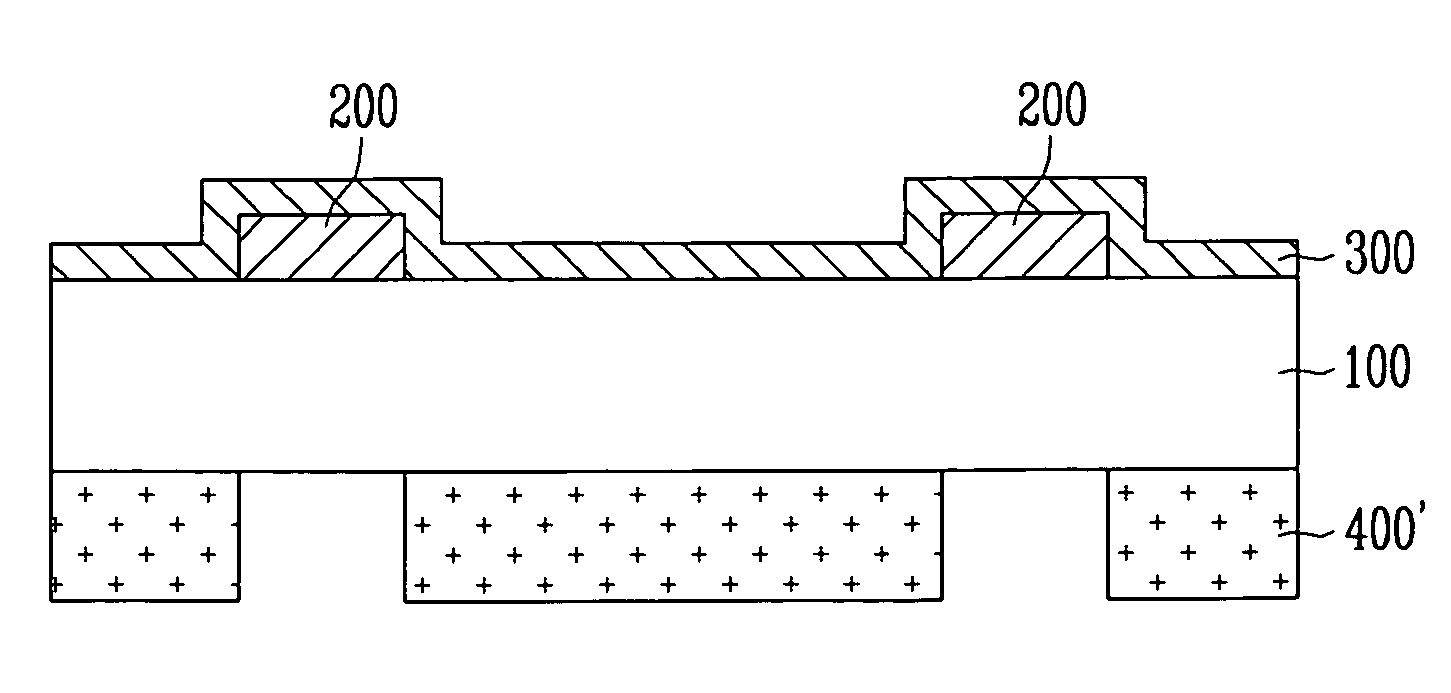

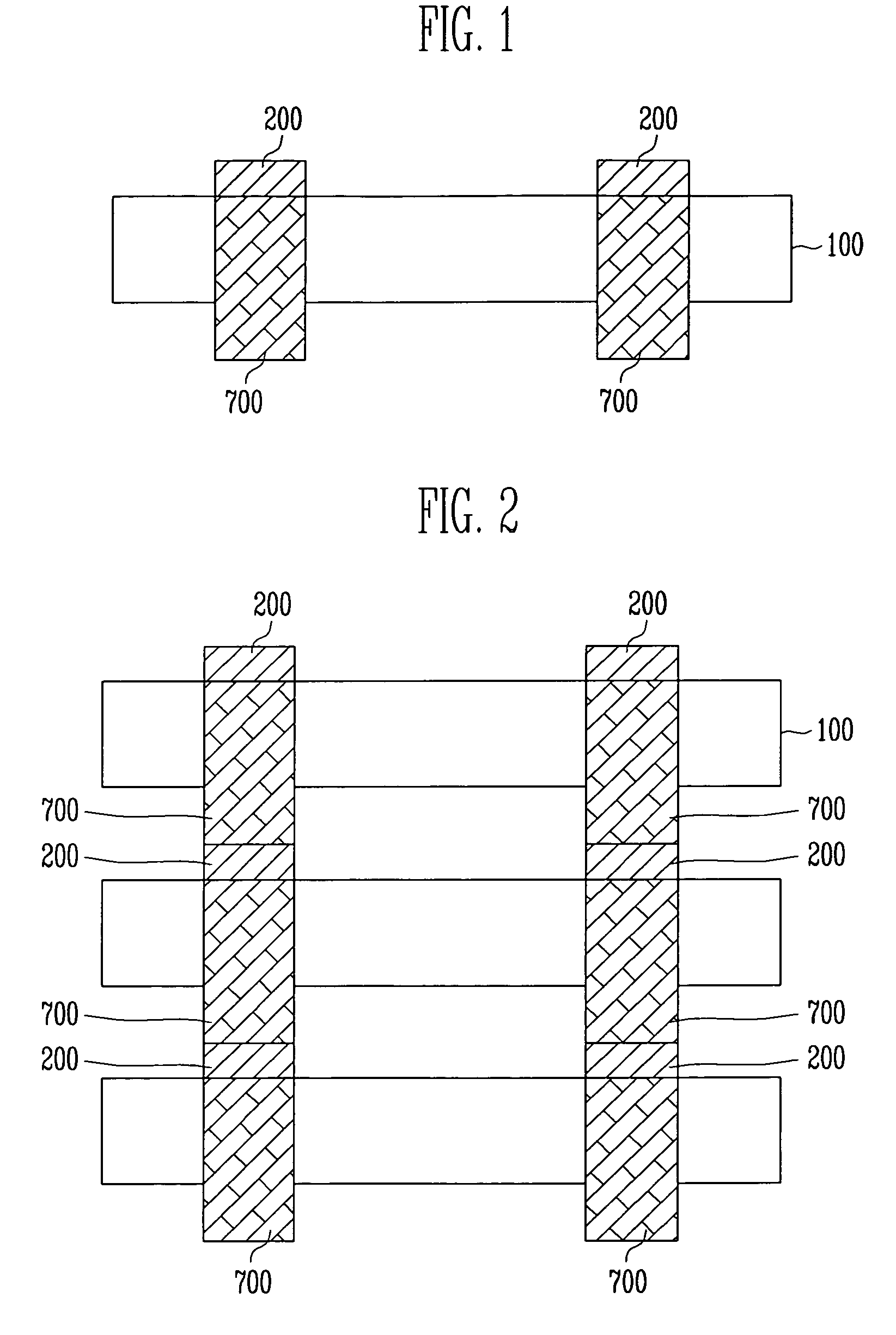

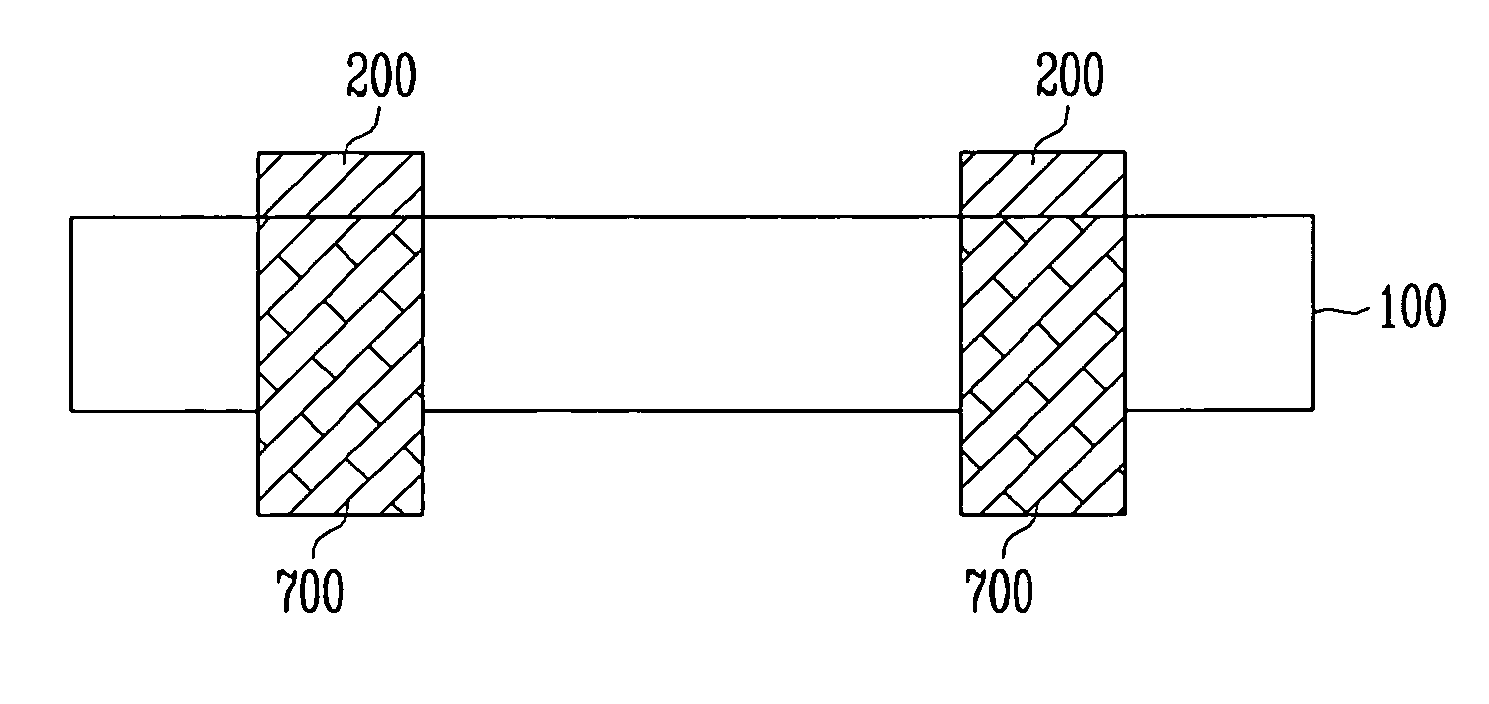

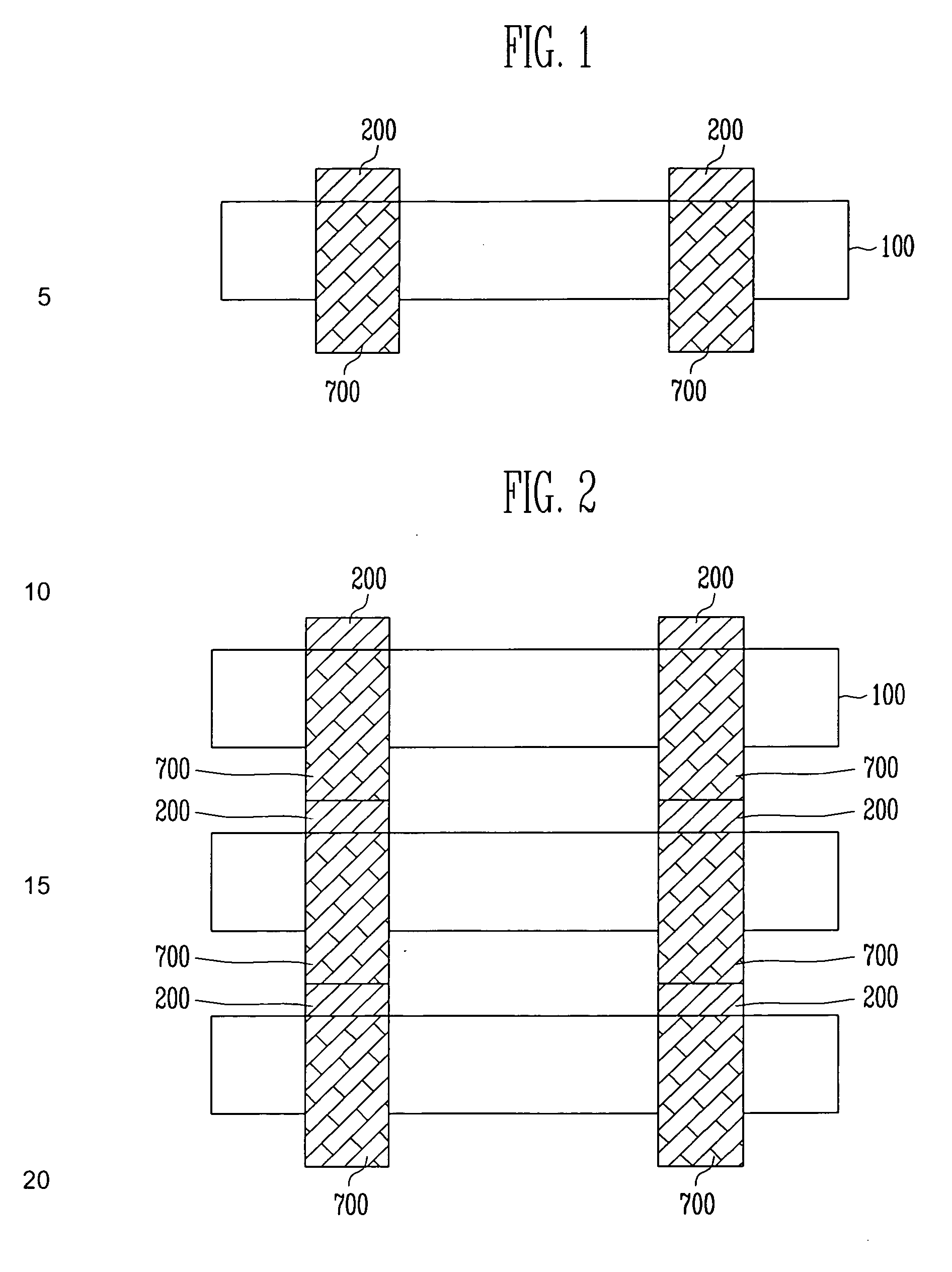

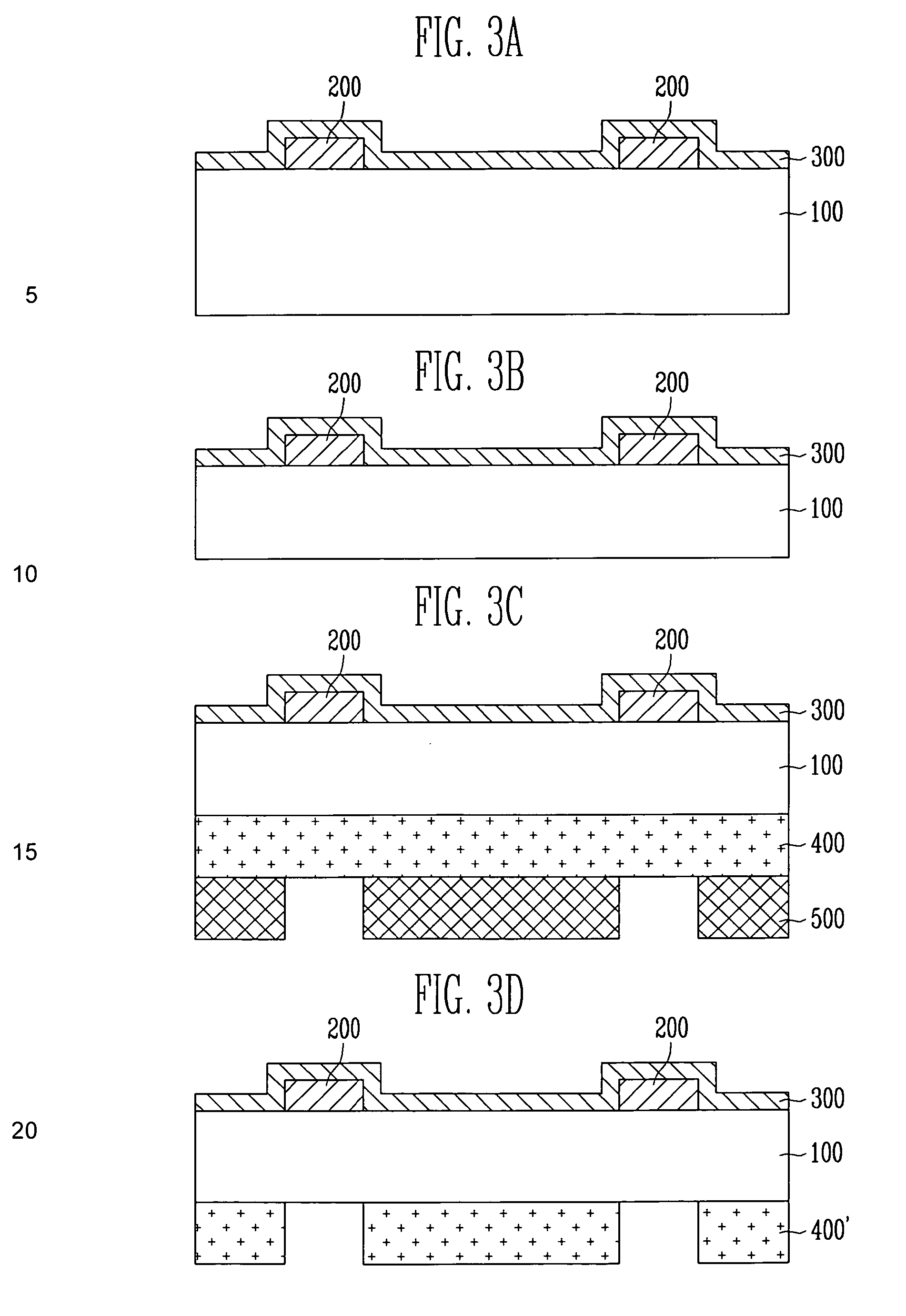

Method of manufacturing a chip

InactiveUS7494909B2Small footprintSimple manufacturing processSemiconductor/solid-state device detailsSolid-state devicesSmall footprintChip stacking

Provided are a chip, a chip stack, and a method of manufacturing the same. A plurality of chips which each include: at least one pad formed on a wafer; and a metal layer which protrudes up to a predetermined thickness from the bottom of the wafer and is formed in a via hole exposing the bottom of the pad are stacked such that the pad and the metal layer of adjacent chips are bonded. This leads to a simplified manufacturing process, high chip performance and a small footprint for a chip stack.

Owner:ELECTRONICS & TELECOMM RES INST

Topography compensation of imprint lithography patterning

InactiveUS7376259B1Mitigate topography variationReduce variationNanoinformaticsPhotomechanical apparatusLithographic artistEngineering

The present invention relates generally to photolithographic systems and methods, and more particularly to systems and methodologies that modify an imprint mask. An aspect of the invention generates feedback information that facilitates control of imprint mask feature height via employing a scatterometry system to detect topography variation and, decreasing imprint mask feature height in order to compensate for topography variation.

Owner:GLOBALFOUNDRIES INC

Power and ground routing of integrated circuit devices with improved ir drop and chip performance

ActiveUS20090236637A1Increase powerIR-drop is loweredSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor

An integrated circuit chip with reduced IR drop and improved chip performance is disclosed. The integrated circuit chip includes a semiconductor substrate having thereon a plurality of inter-metal dielectric (IMD) layers and a plurality of copper metal layers embedded in respective the plurality of IMD layers; a first passivation layer overlying the plurality of IMD layers and the plurality of copper metal layers; a first power / ground ring of a circuit block of the integrated circuit chip formed in a topmost layer of the plurality of copper metal layers; a second power / ground ring of the circuit block of the integrated circuit chip formed in an aluminum layer over the first passivation layer; and a second passivation layer covering the second power / ground ring and the first passivation layer.

Owner:MEDIATEK INC

Cage pocket structure with stress buffer grooves and pocket machining technology of structure

ActiveCN105840660AGuaranteed stabilityImprove chip performanceShaftsBearing componentsNumerical controlMilling cutter

The invention discloses a cage pocket structure with stress buffer grooves and a pocket machining technology of the structure. The problems that an existing cylindrical roller bearing cage pocket structure is large in abrasion to a machining tool and complex in machining technology process are solved. The cage pocket structure with the stress buffer grooves is characterized in that the pocket is a straight pocket, and the stress buffer grooves with the radius of R2 are machined on the four corners of the pocket; according to the pocket machining technology of the cage pocket structure with the stress buffer grooves, a drill bit is selected, and according to the stress buffer groove positions required by the drawing, on a numerical control machining center, the drill bit is used for carrying out stress buffer groove machining on the pocket of a cylindrical roller bearing cage; the cage is drilled on the numerical control machining center, and the drilling size should ensure that the single-side milling allowance ranges from 0.1 mm to 0.25 mm; a milling cutter is used for feeding from the center of the pocket, and pocket machining is completed through milling; and the machined pocket is detected. The cage pocket structure is used for machining of the cage pocket.

Owner:AVIC HARBIN BEARING

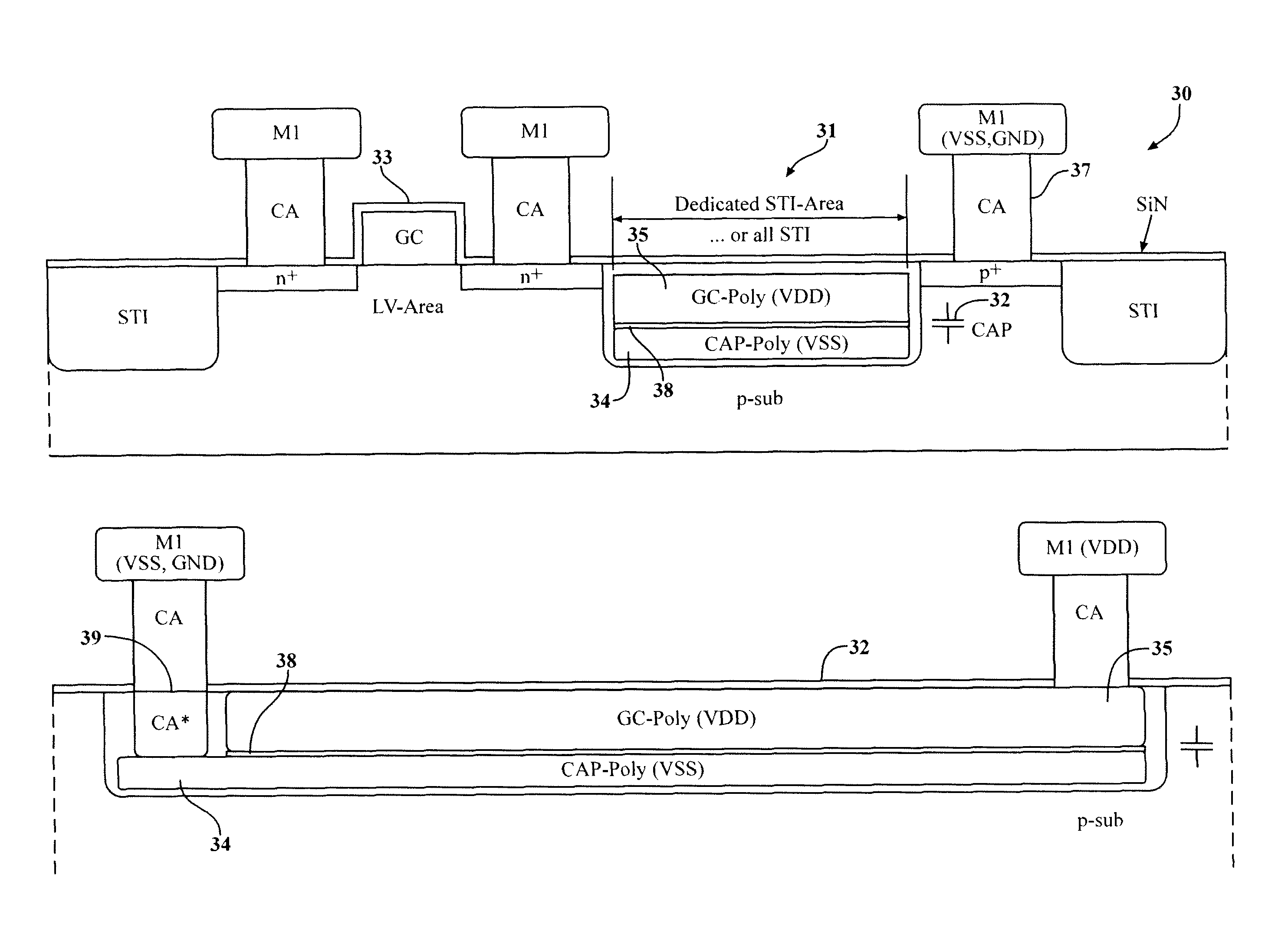

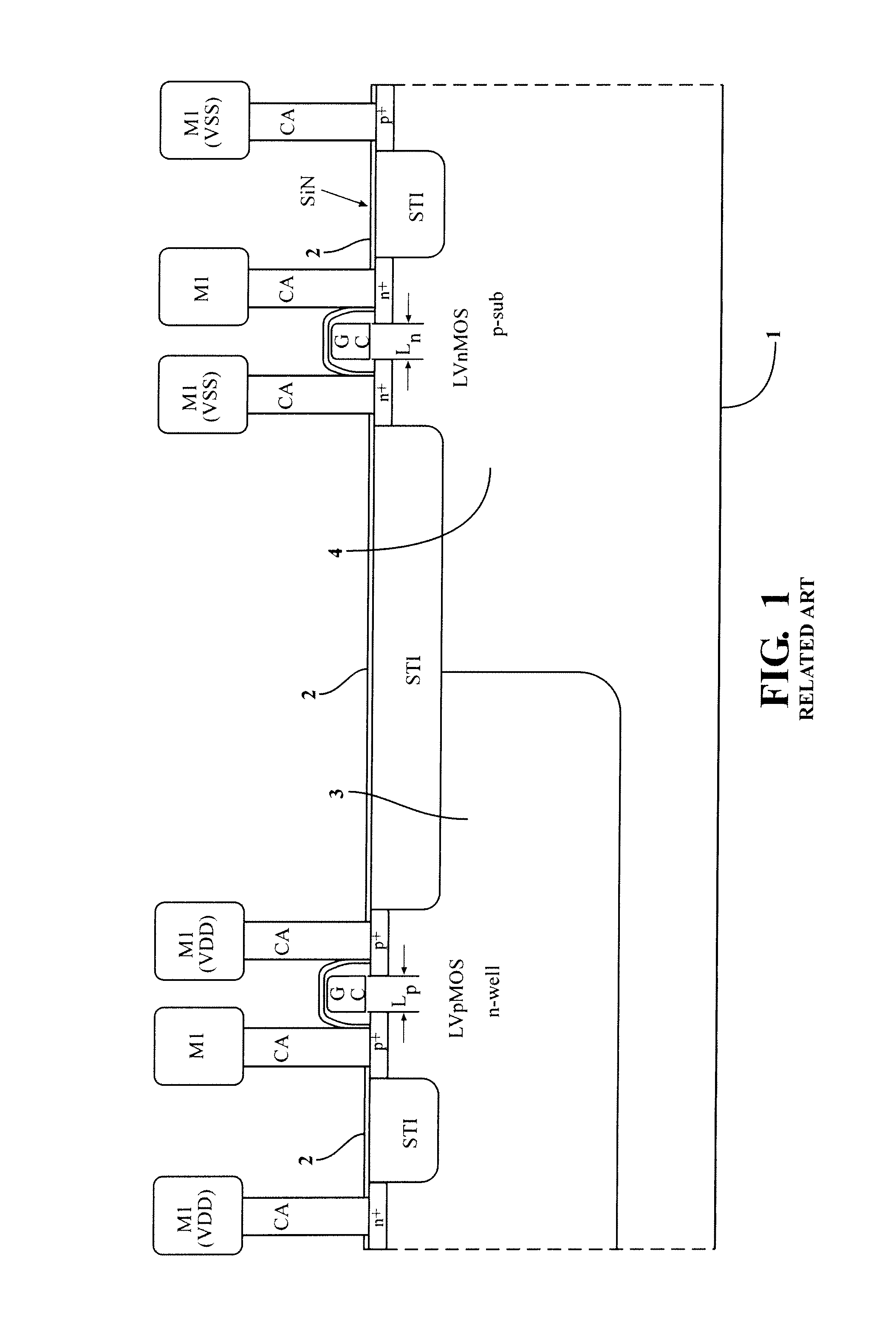

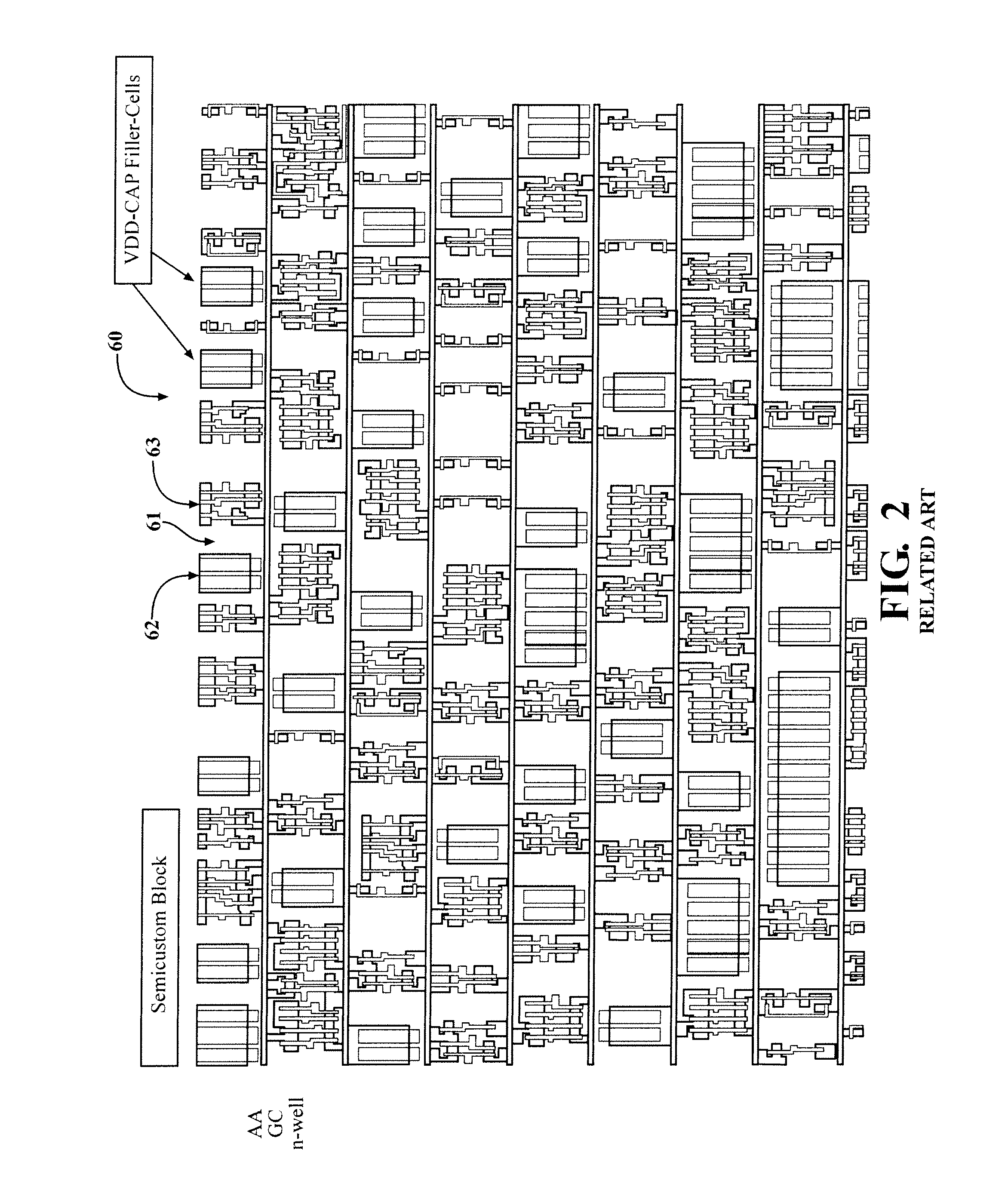

Shallow trench isolation area having buried capacitor

InactiveUS8896087B2Increase spaceGreat effectivenessTransistorSolid-state devicesSemiconductor chipEngineering

Owner:INFINEON TECH AG

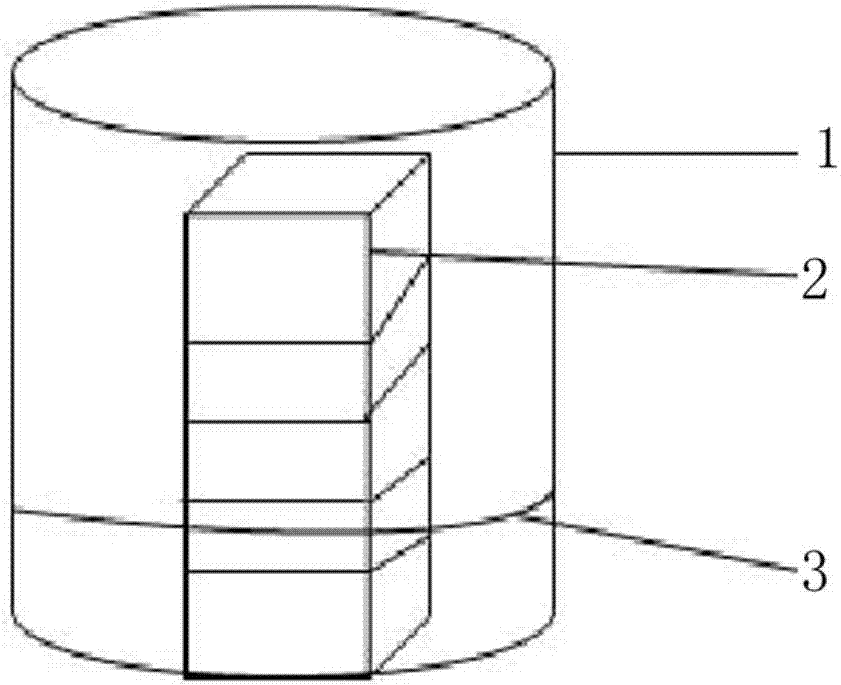

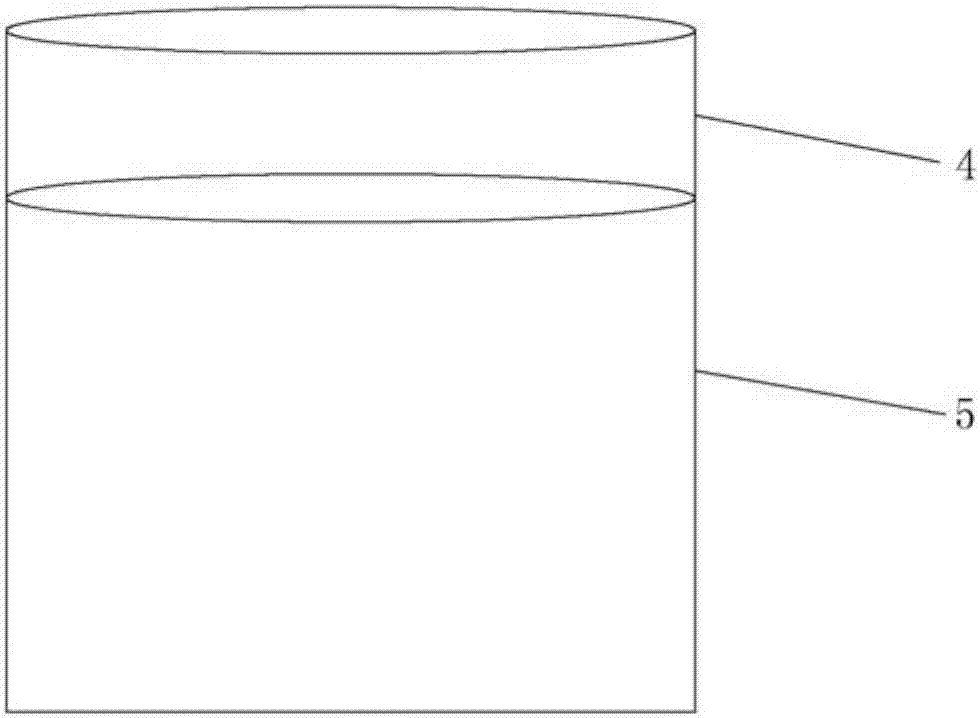

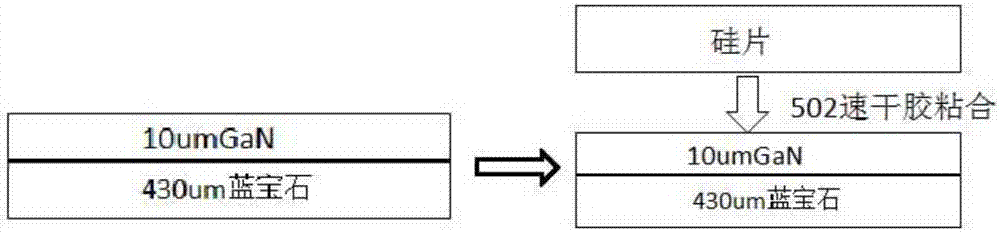

Surface treatment method after nitride material laser lift-off

ActiveCN107221496ARestrain the huge impactReduce crackingSemiconductor/solid-state device manufacturingSemiconductor devicesComposite substrateSingle crystal substrate

The invention discloses a surface treatment method after nitride material laser lift-off. The surface treatment method comprises the following steps: preparing a nitride composite substrate or a nitride single crystal substrate in a laser lift-off manner; selecting a cavity, enabling the cavity to be filled with a volatile corrosive liquid, putting the nitride composite substrate or the nitride single crystal substrate above a liquid level in the cavity, sealing the cavity so that a closed cavity is formed, standing for a period of scheduled time T, and using an atmosphere generated by volatilization of the corrosive liquid to carry out corrosion treatment on the surface, after laser lift-off, of the nitride composite substrate or the nitride single crystal substrate; cleaning and drying the nitride composite substrate or the nitride single crystal substrate in the cavity to complete atmosphere corrosion treatment on the surface after laser lift-off. A nitride surface after lift-off is treated by using an atmosphere corrosion method, the impurities such as residual metals on the surface after lift-off are removed, the ingredients and roughness of the surface after lift-off are improved, and the later-period homoepitaxy effect and chip performance are improved.

Owner:SINO NITRIDE SEMICON

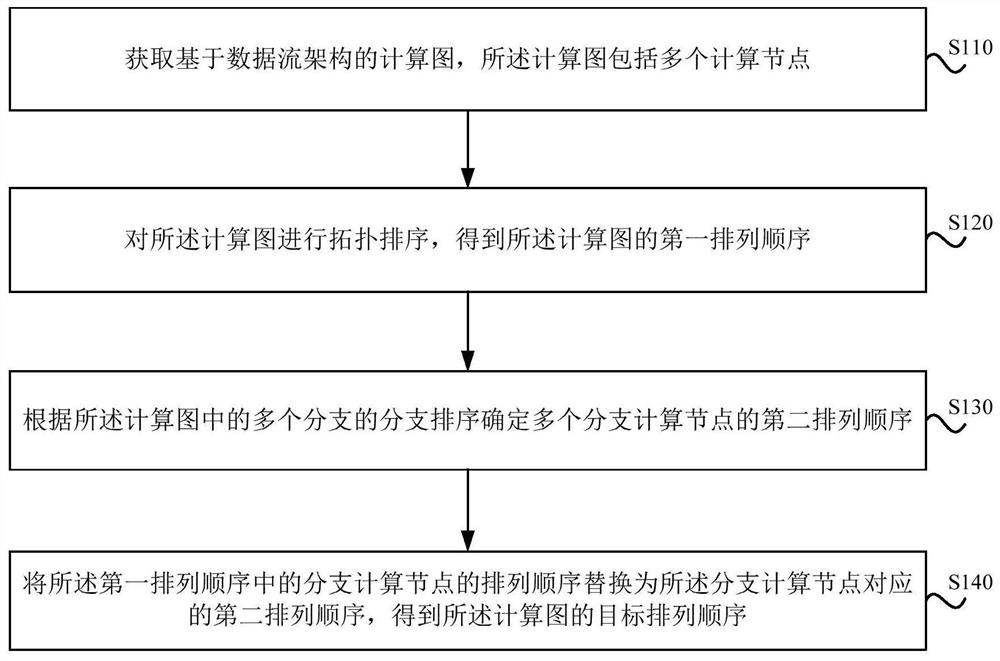

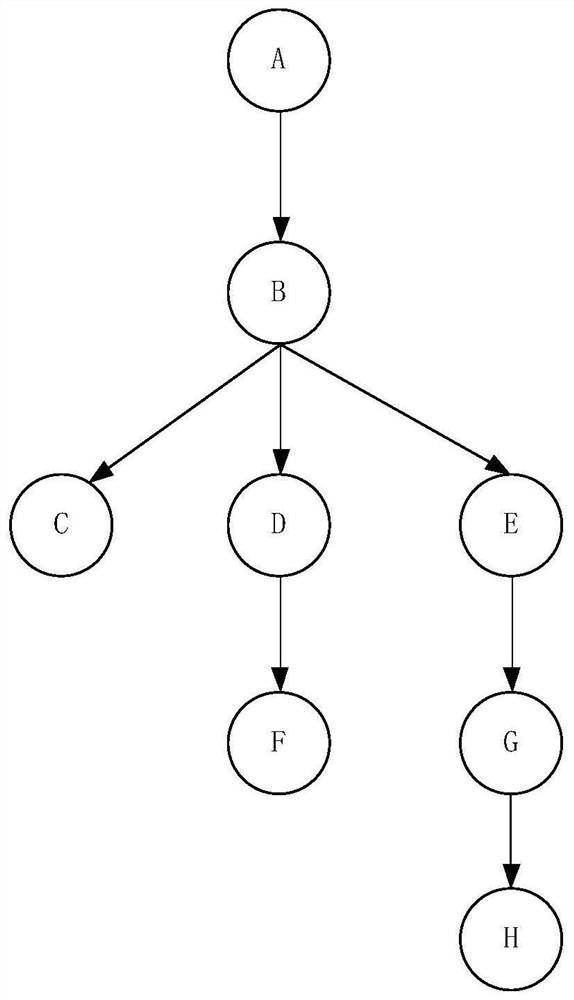

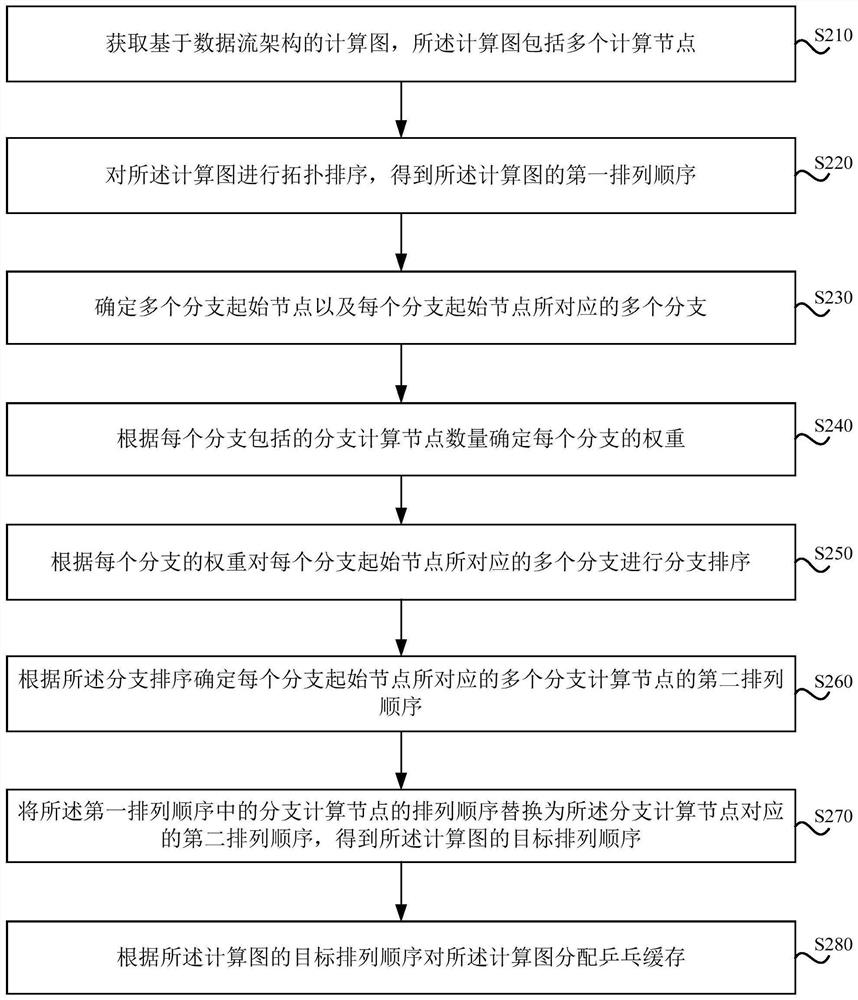

AI calculation graph sorting method and device, equipment and storage medium

PendingCN111752691AImprove chip performanceImprove performanceProgram initiation/switchingResource allocationGraph basedDataflow architecture

The embodiment of the invention discloses an AI calculation graph sorting method and device, equipment and a storage medium. The method comprises the steps: obtaining a calculation graph based on dataflow architecture, and enabling the calculation graph to comprise a plurality of calculation nodes; performing topological sorting on the calculation graph to obtain a first arrangement sequence of the calculation graph; determining a second arrangement sequence of a plurality of branch computing nodes according to the branch sequence of the plurality of branches in the calculation graph; and replacing the arrangement sequence of the branch computing nodes in the first arrangement sequence with a second arrangement sequence corresponding to the branch computing nodes to obtain a target arrangement sequence of the calculation graph. According to the embodiment of the invention, topological sorting and branch sorting are carried out on the calculation graph, so that sorting of the calculation graph based on the data flow architecture is realized, the execution sequence of each calculation node in the calculation graph can be uniquely determined, and the chip performance based on the data flow architecture is improved.

Owner:SHENZHEN CORERAIN TECH CO LTD

Polycarbosilane buried etch stops in interconnect structures

InactiveUS7187081B2Reduce degradationReduce dissipationSemiconductor/solid-state device detailsSolid-state devicesEngineeringPolymer

Interconnect structures having buried etch stop layers with low dielectric constants and methods relating to the generation of such buried etch stop layers are described herein. The inventive interconnect structure comprises a buried etch stop layer comprised of a polymeric material having a composition SivNwCxOyHz, where 0.05≦v≦0.8, 0≦w≦0.9, 0.05≦x≦0.8, 0≦y≦0.3, 0.05≦z≦0.8 for v+w+x+y+z=1; a via level interlayer dielectric that is directly below said buried etch stop layer; a line level interlayer dielectric that is directly above said buried etch stop layer; and conducting metal features that traverse through said via level dielectric, said line level dielectric, and said buried etch stop layer.

Owner:TAIWAN SEMICON MFG CO LTD

Chip, ship stack, and method of manufacturing the same

InactiveUS20070072419A1Simple manufacturing processImprove chip performanceSemiconductor/solid-state device detailsSolid-state devicesManufacturing technologySmall footprint

Provided are a chip, a chip stack, and a method of manufacturing the same. A plurality of chips which each include: at least one pad formed on a wafer; and a metal layer which protrudes up to a predetermined thickness from the bottom of the wafer and is formed in a via hole exposing the bottom of the pad are stacked such that the pad and the metal layer of adjacent chips are bonded. This leads to a simplified manufacturing process, high chip performance and a small footprint for a chip stack.

Owner:ELECTRONICS & TELECOMM RES INST