Patents

Literature

105 results about "Line level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Line level is the specified strength of an audio signal used to transmit analog sound between audio components such as CD and DVD players, television sets, audio amplifiers, and mixing consoles. Line level sits between other levels of audio signals. There are weaker signals such as those from microphones (Mic Level/Microphone Level) and instrument pickups (Instrument Level), and stronger signals, such as those used to drive headphones and loudspeakers (Speaker Level). The "strength" of these various signals does not necessarily refer to the output voltage of the source device; it also depends on its output impedance and output power capability.

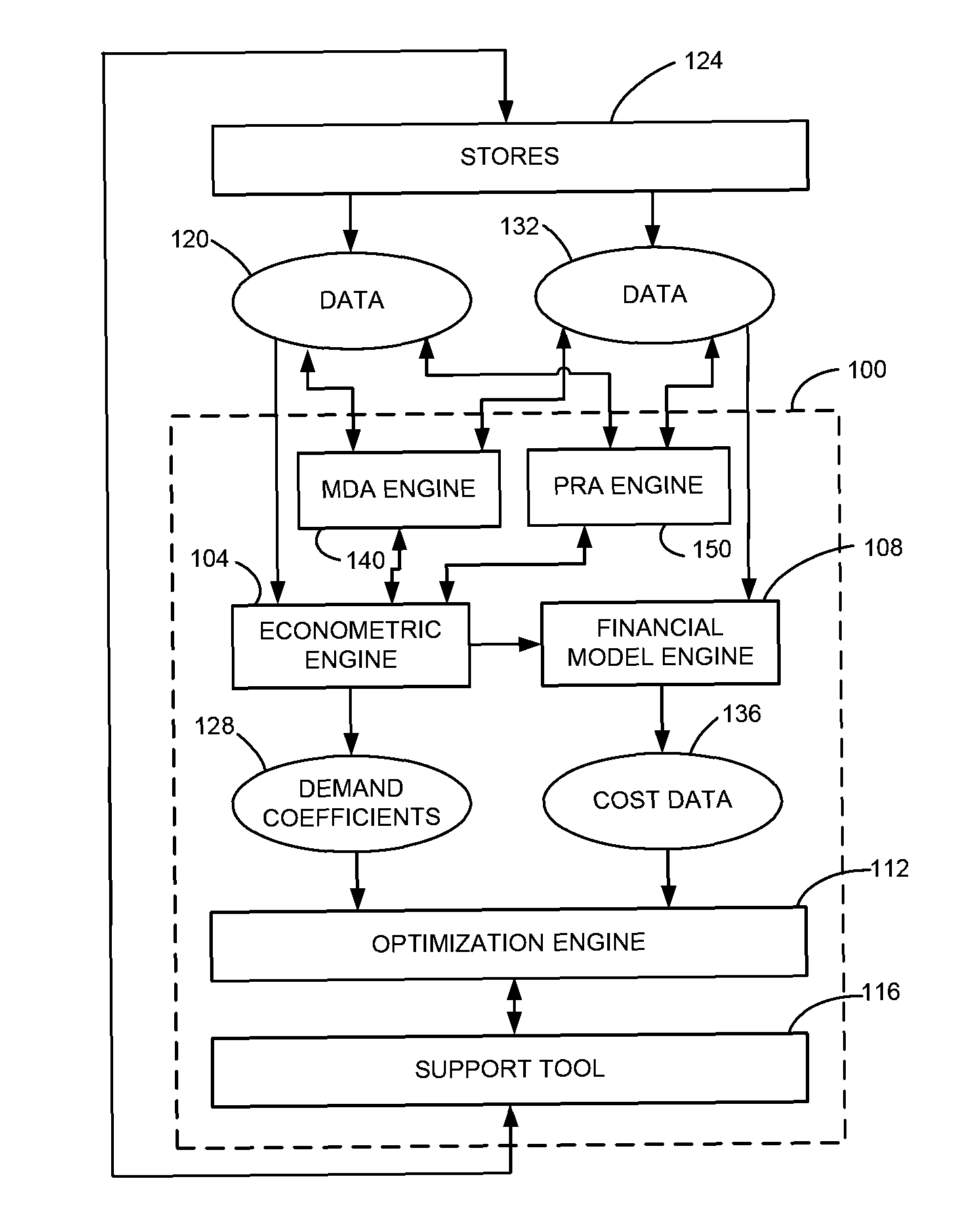

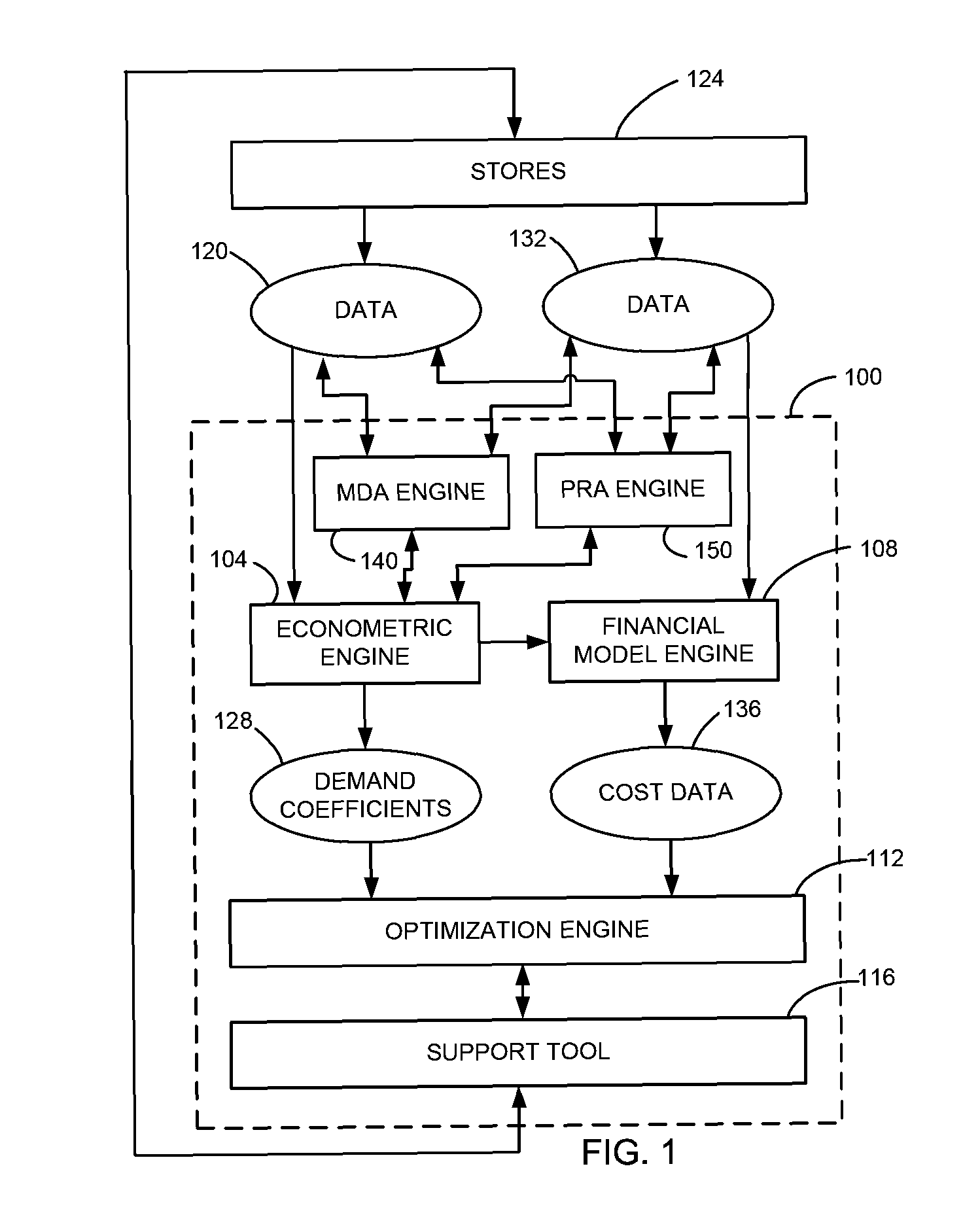

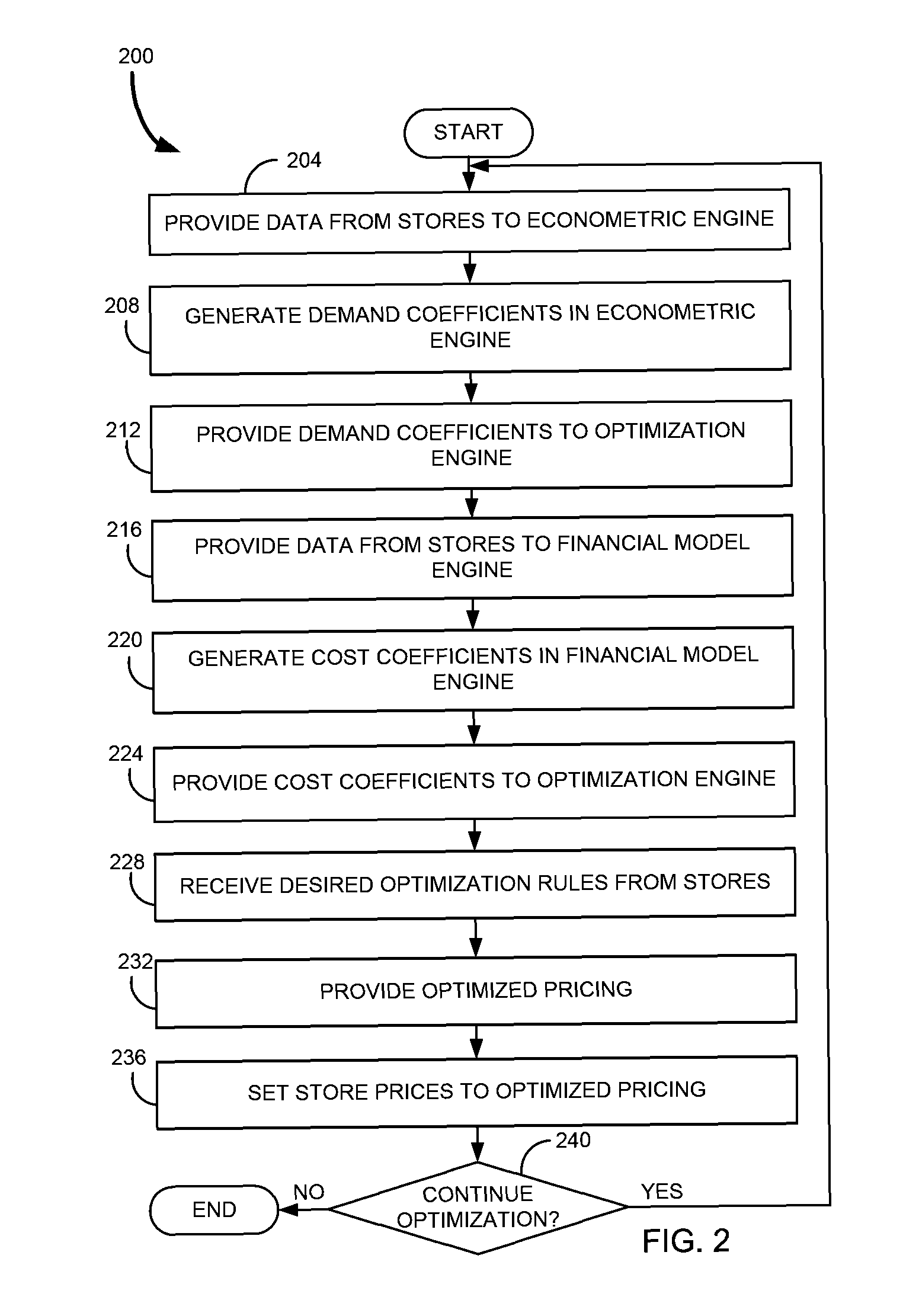

Systems and methods for price and promotion response analysis

A system and method for price and promotion response analysis is provided. Such a system is useful for a business to analyze the forecasted lifts associated with changes in price and promotion activity. The system sets the configuration of the response report, which includes price change and promotion change intervals. Promotions include temporary price reductions, displays, ads and multiples. Modeling data is received for the products. Forecasts, both non-cannibalistic and cannibalistic, are generated for the sales of the products dependent upon the price change and promotion change intervals. Forecasts include at least one of product forecasts, demand group forecasts, line level forecasts and category level forecasts. Suspect forecasts below a minimum confidence may be flagged. Confidence matrices may be generated which reflect accuracy of the forecasts. The response report may be generated by collecting the forecasts and the confidence matrices according to the configuration of the response report.

Owner:ACOUSTIC LP

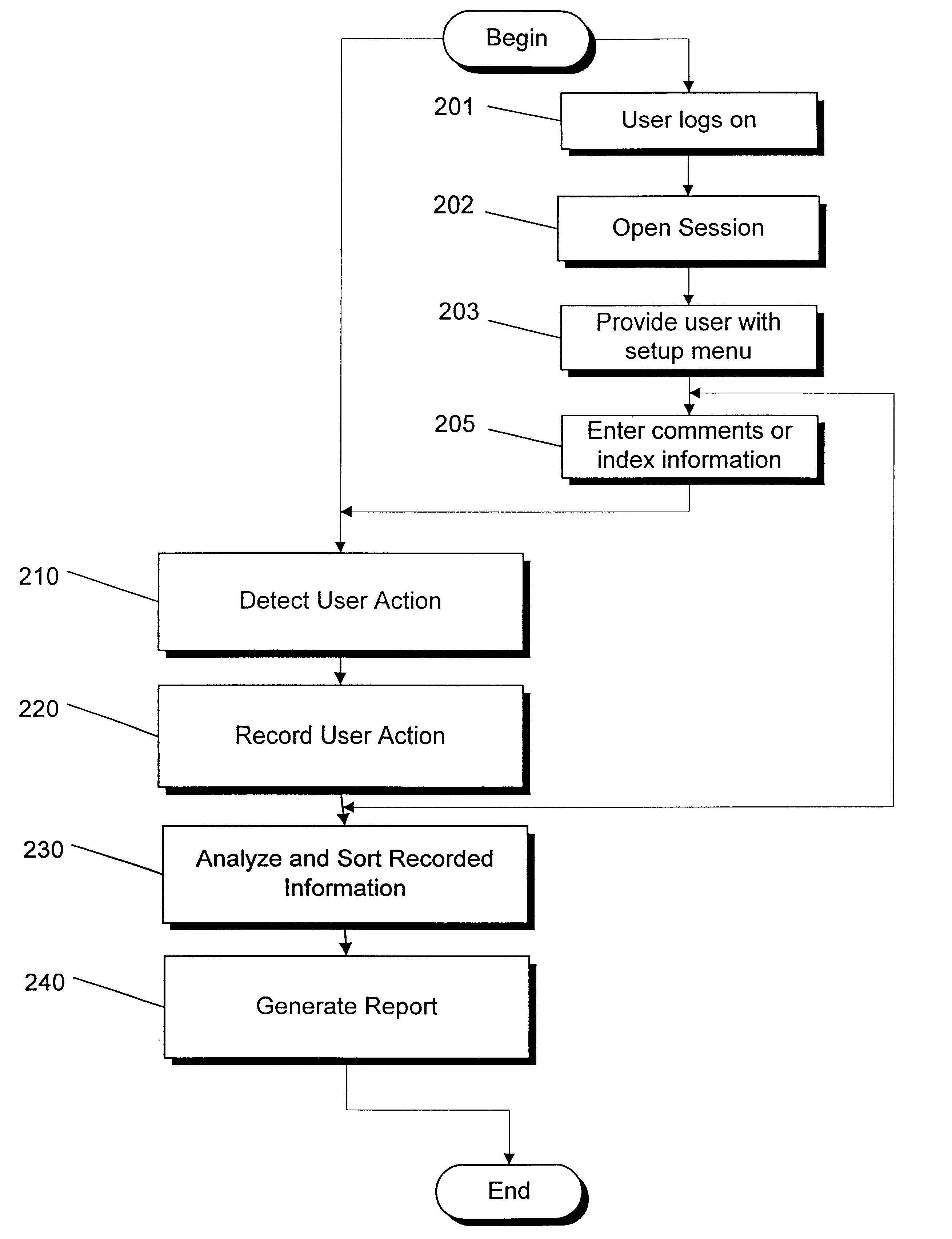

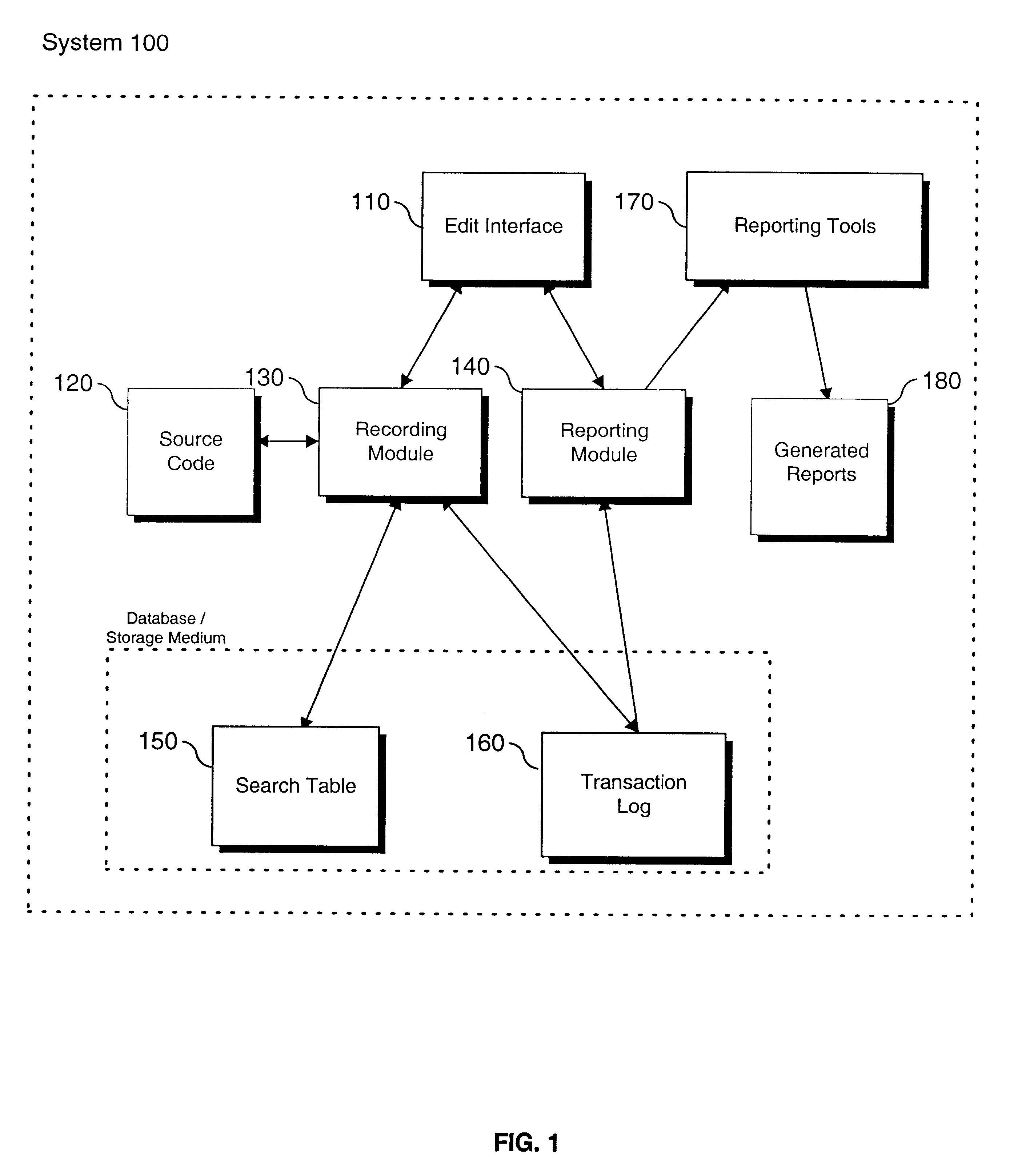

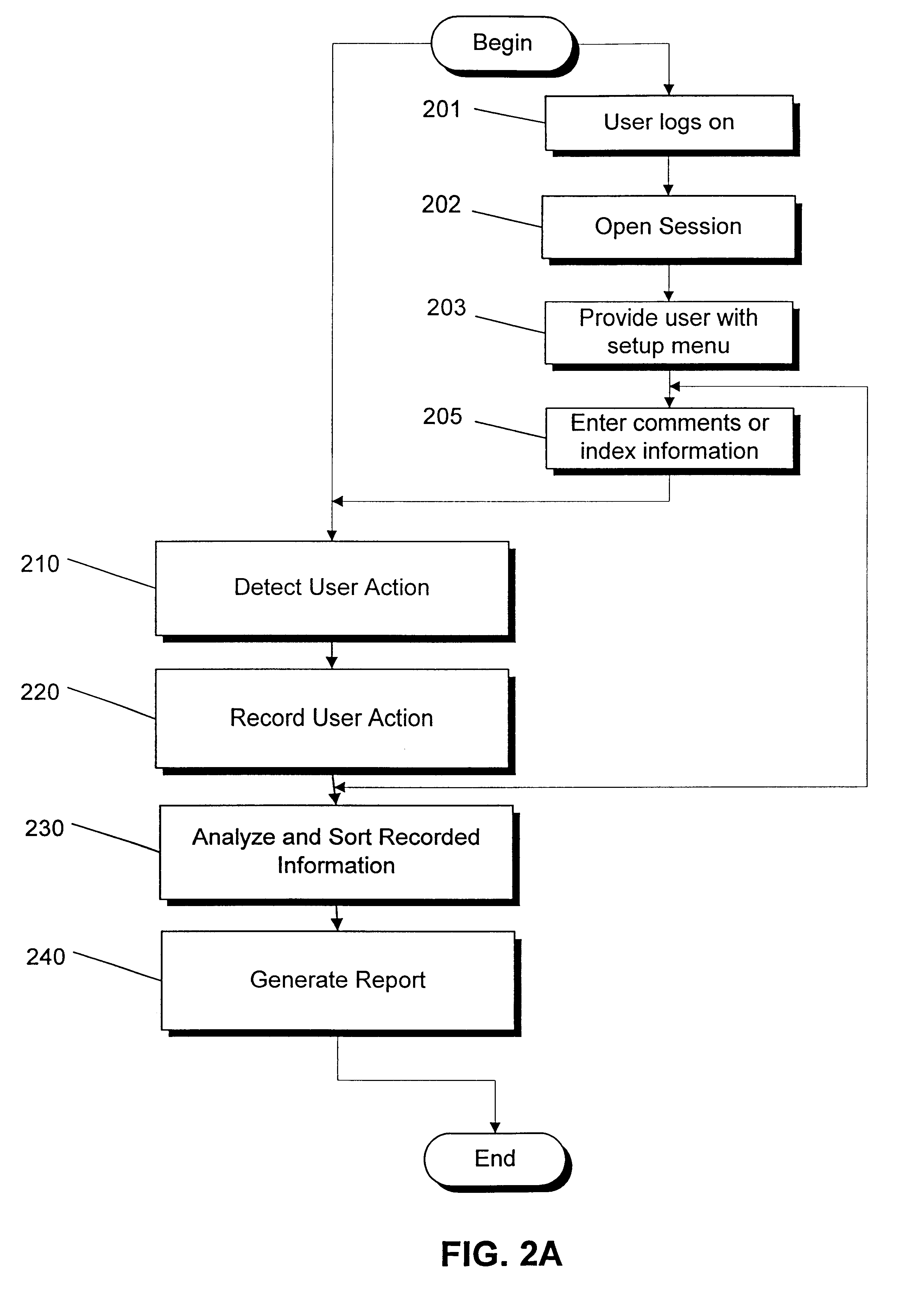

Real time monitoring system for tracking and documenting changes made by programmer's during maintenance or development of computer readable code on a line by line basis and/or by point of focus

InactiveUS6698013B1Version controlSpecific program execution arrangementsMonitoring systemComputer software

A method and system for documenting and tracking user interaction with computer readable code during modification or development of computer software is described. The invention provides a controlled environment for recording detailed information about user actions and events that occur during the maintenance and development of computer readable code. Features of the invention facilitate the entry of comments, review, and modification of the computer readable code. Embodiments of the invention, in real time, monitor, record, and report changes made to software modules at a line-by-line level. The nature and context of changes made to lines of code and any search requests are identified and recorded in one or more databases for review and reporting.

Owner:MINTAKA TECH GROUP

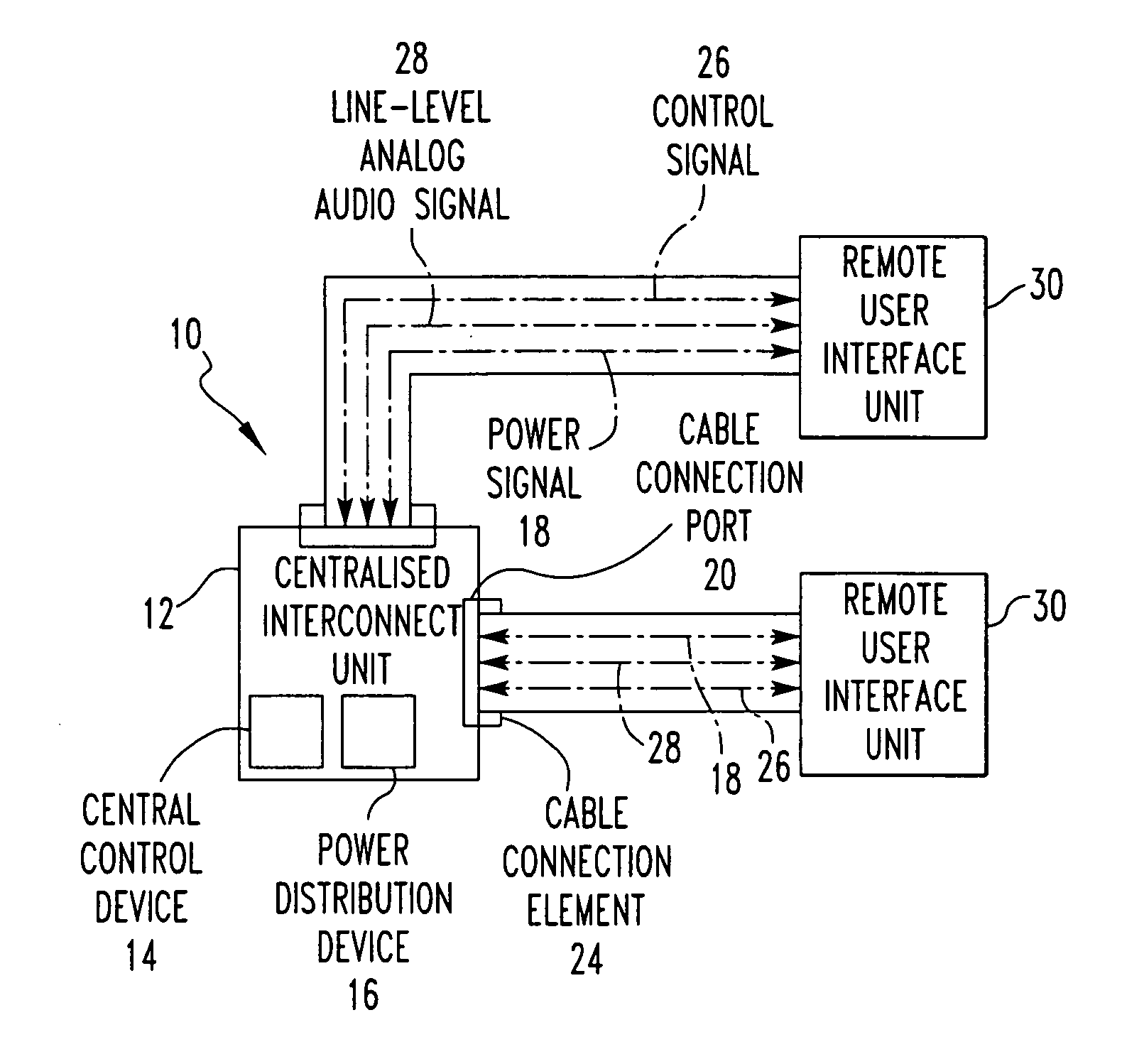

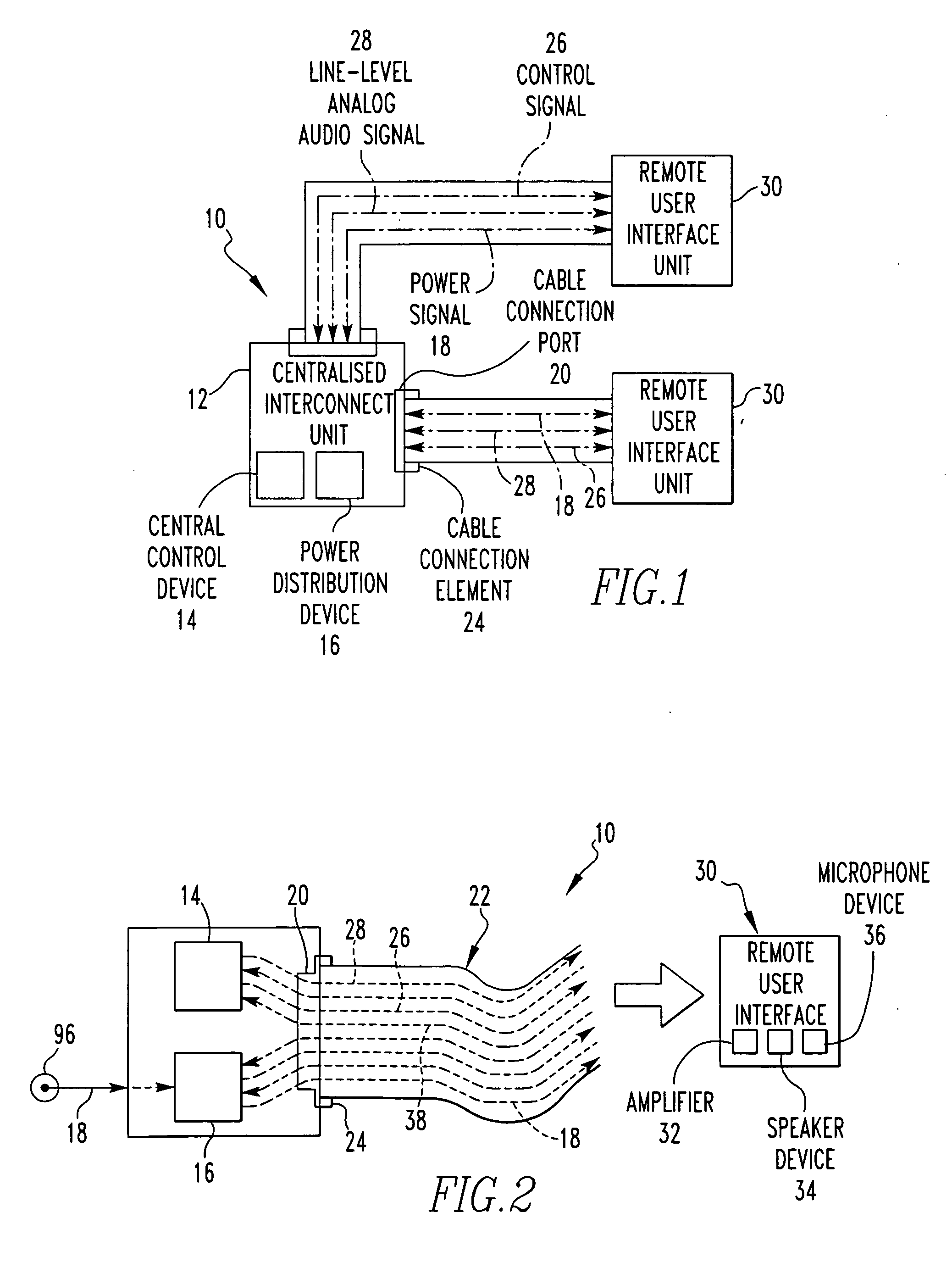

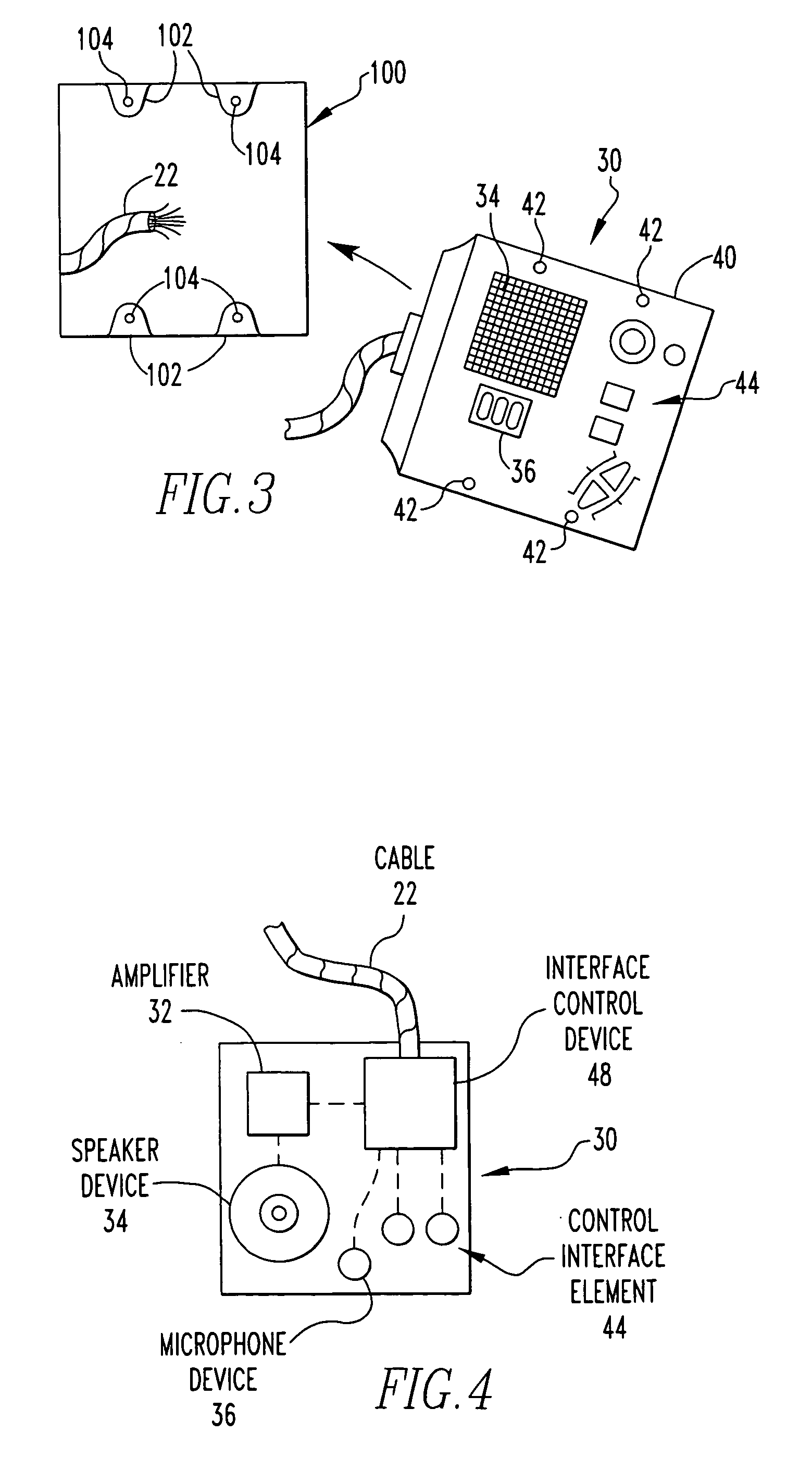

Distributed intercom system

InactiveUS20060222153A1Overcomes shortcomingGood adhesionInterconnection arrangementsSubstation speech amplifiersAudio power amplifierControl signal

A distributed intercom system including a centralized interconnection unit with a central control device for receiving, processing and transmitting signals, a power distribution device for transmitting a power signal for distribution and at least one cable connection port for receiving a cable connection therein. The system includes a cable with a cable connection element for connection to the cable connection port, and the cable transmits a control signal, a line-level, analog audio signal and the power signal. One or more remote user interface units are connected to and in communication with the centralized interconnection unit through the cable, and the remote user interface unit includes an amplifier, a speaker device and a microphone device. At least one component of the remote user interface unit is powered by the power signal transmitted by the power distribution device.

Owner:LEGRAND HOME SYST +1

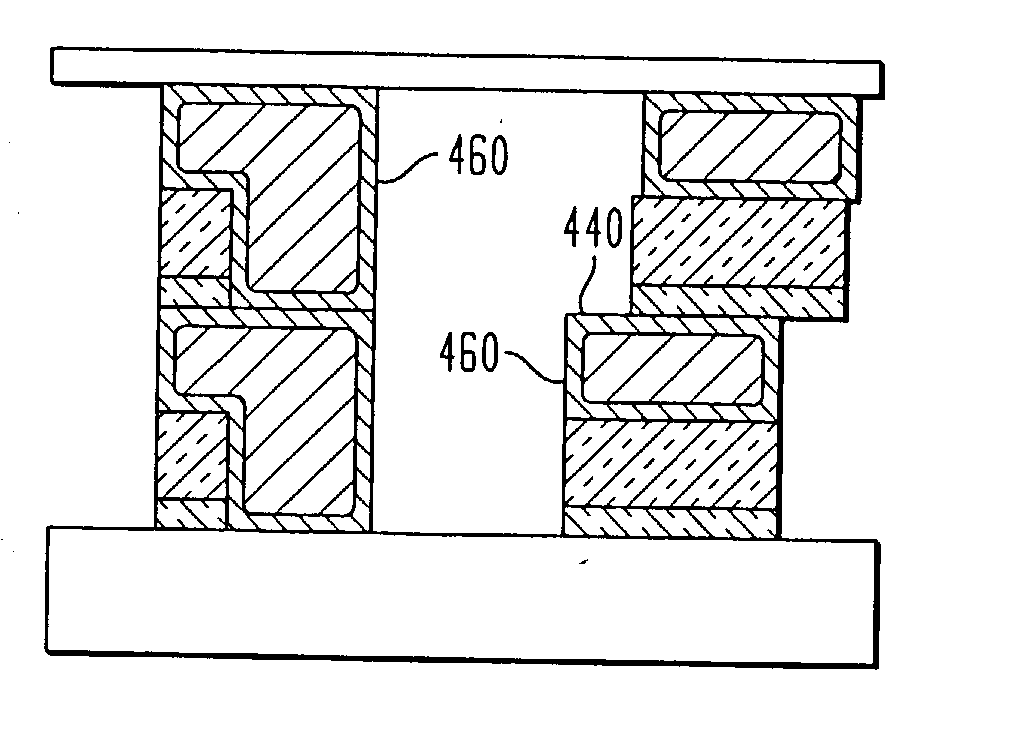

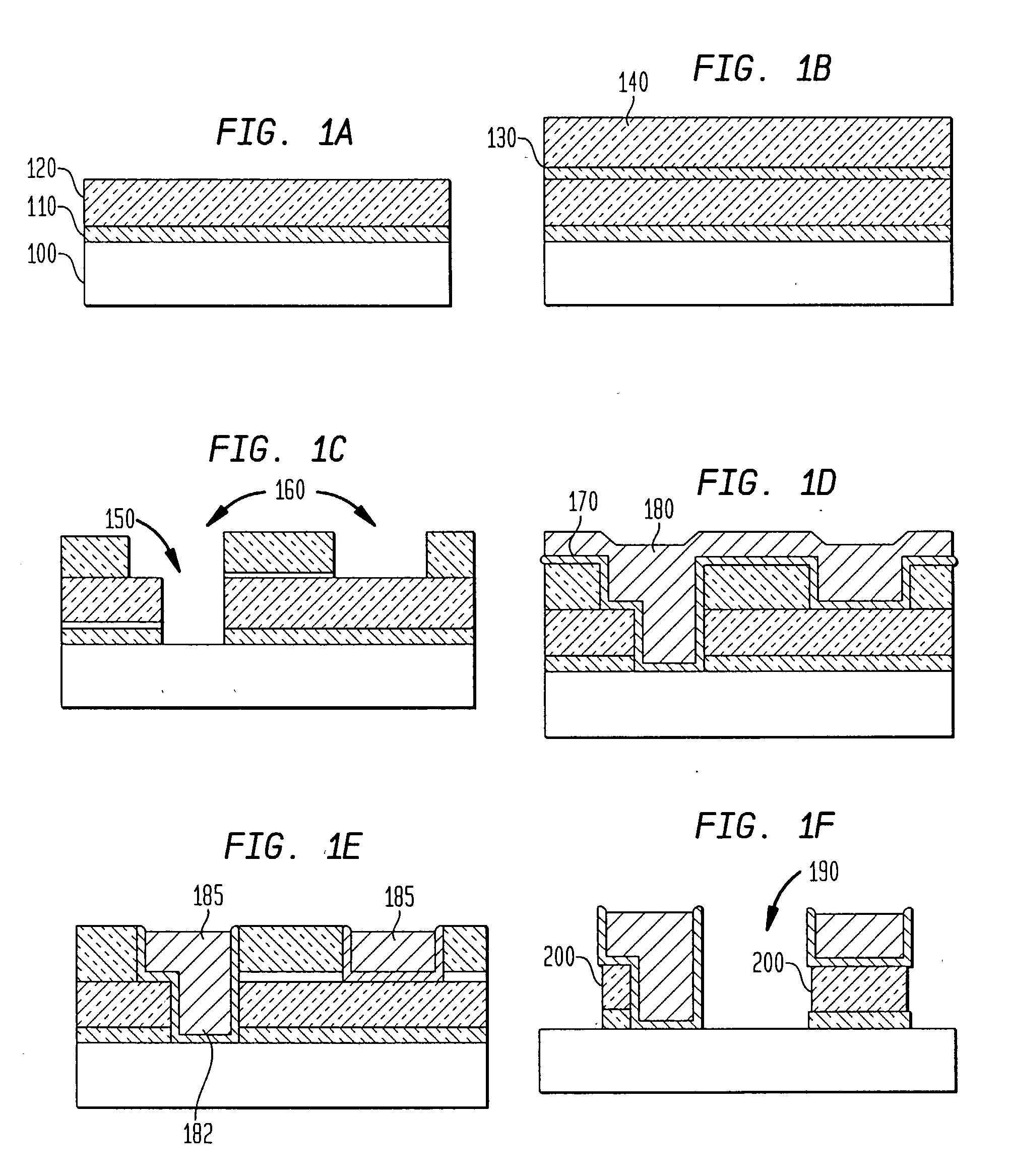

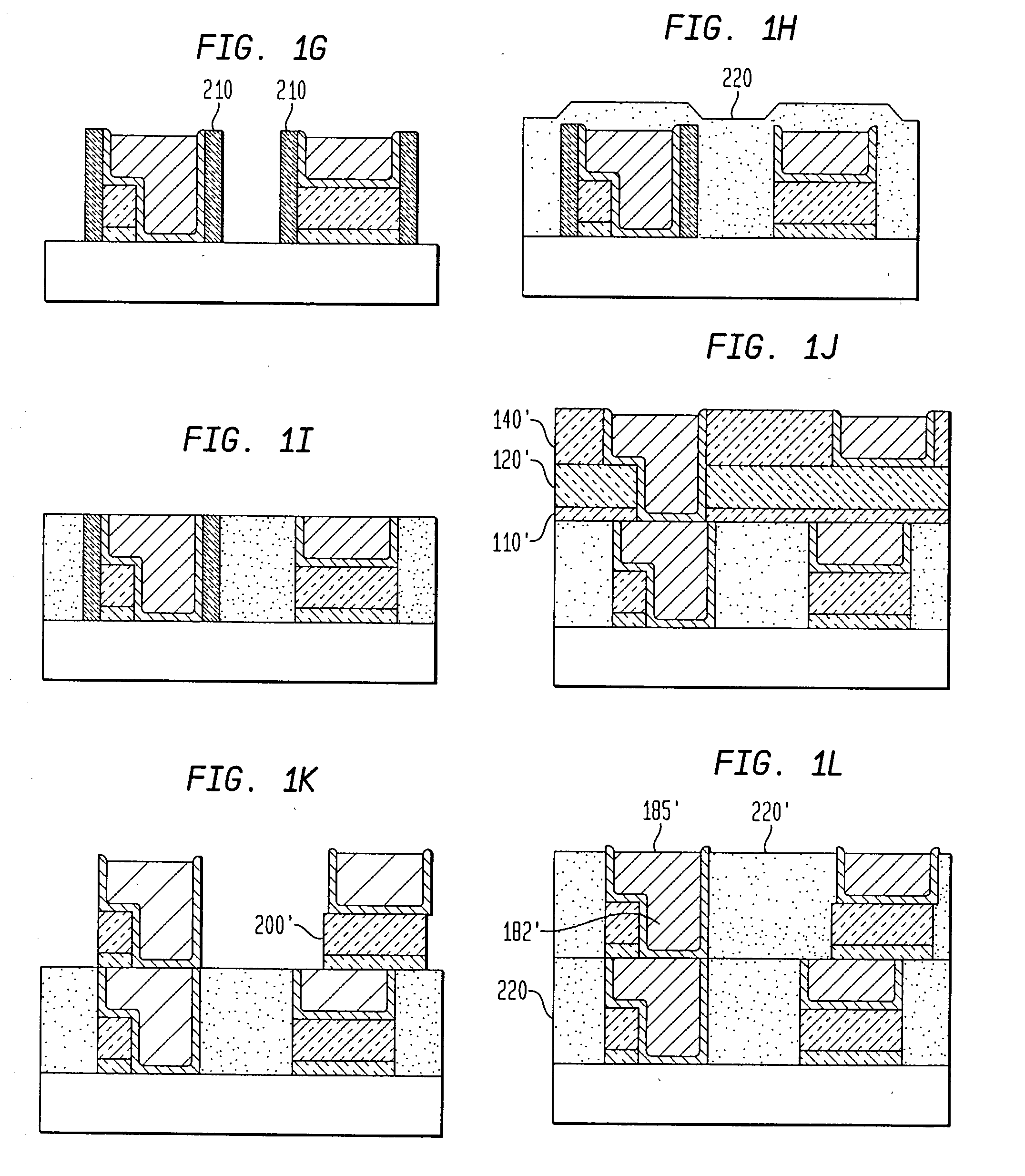

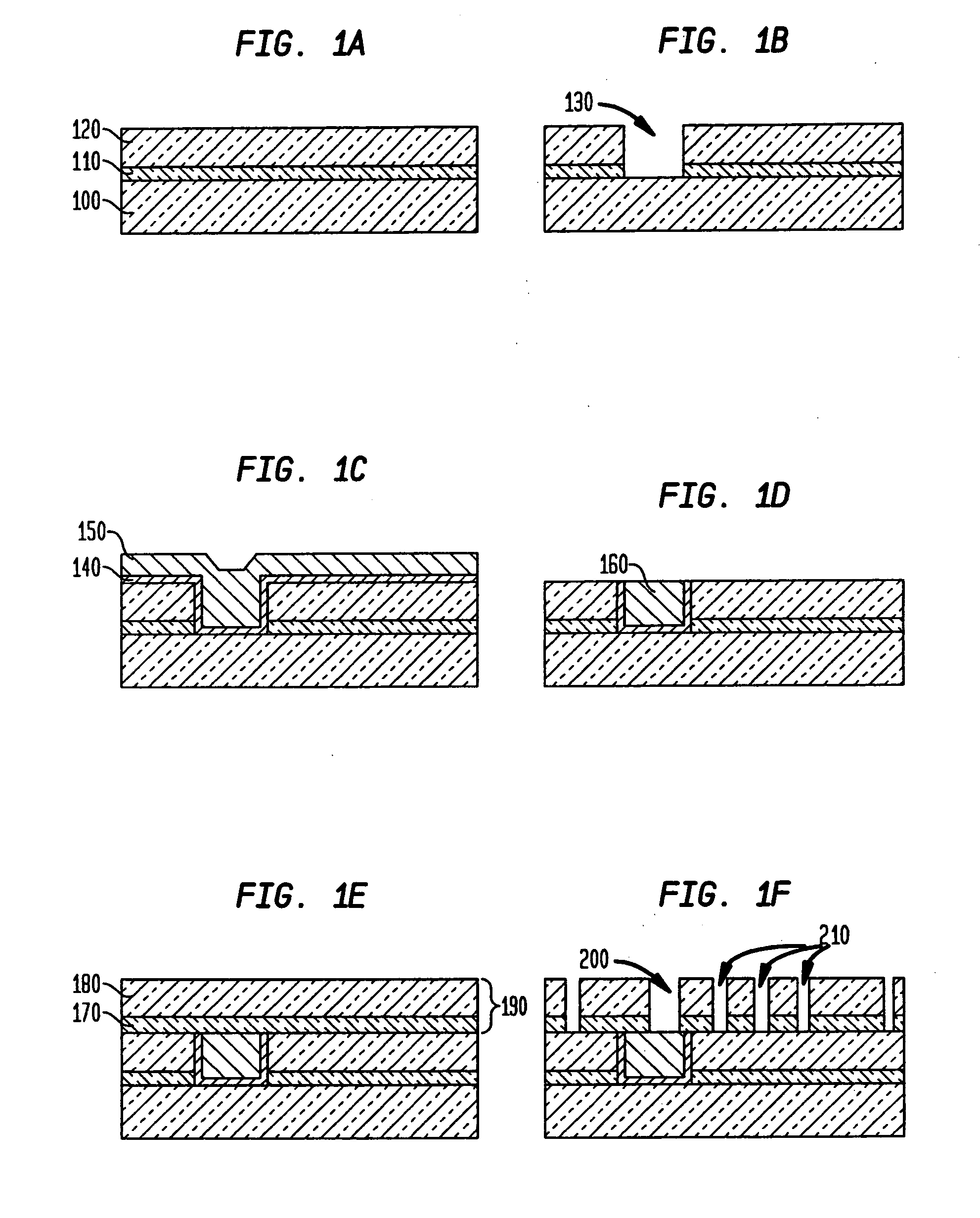

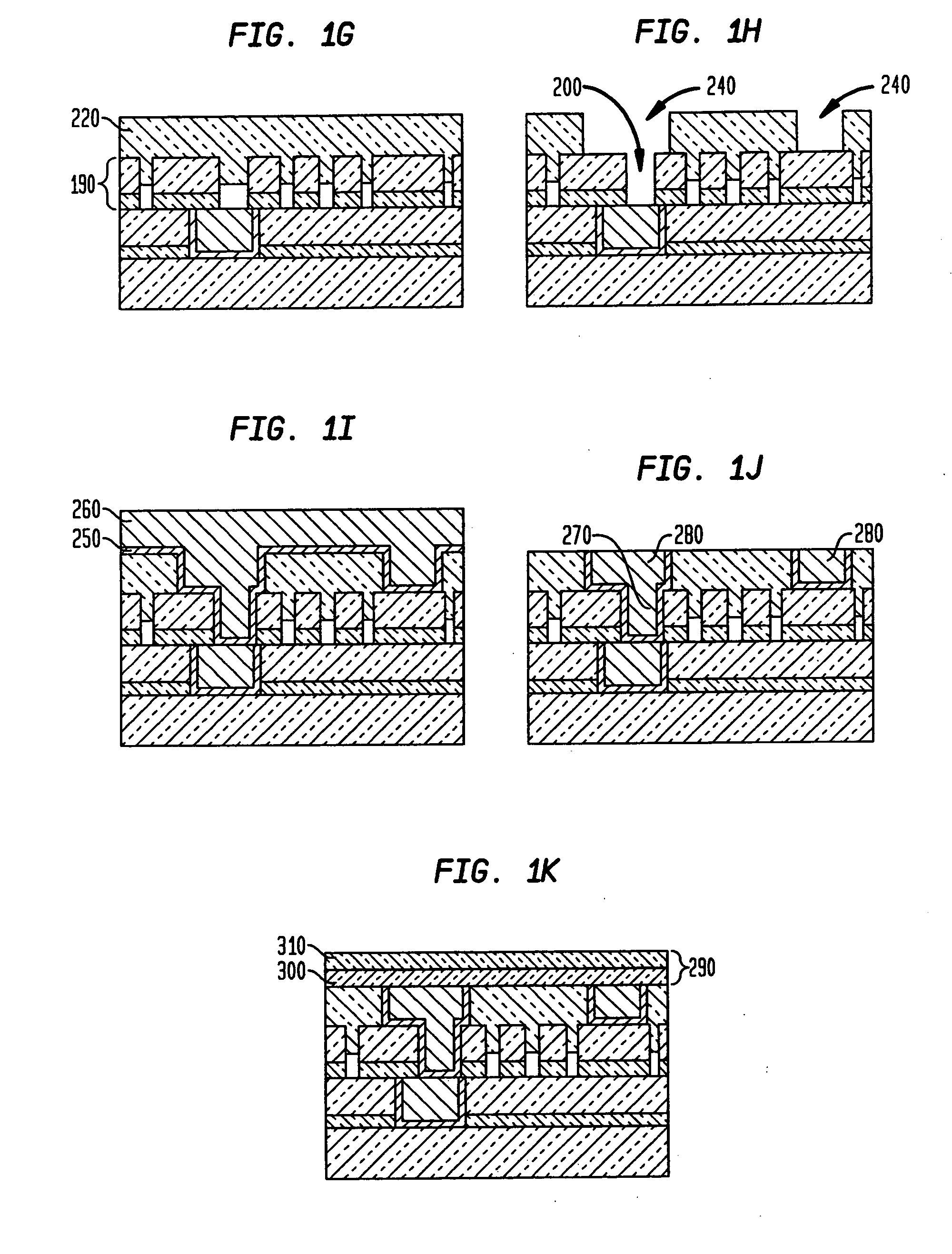

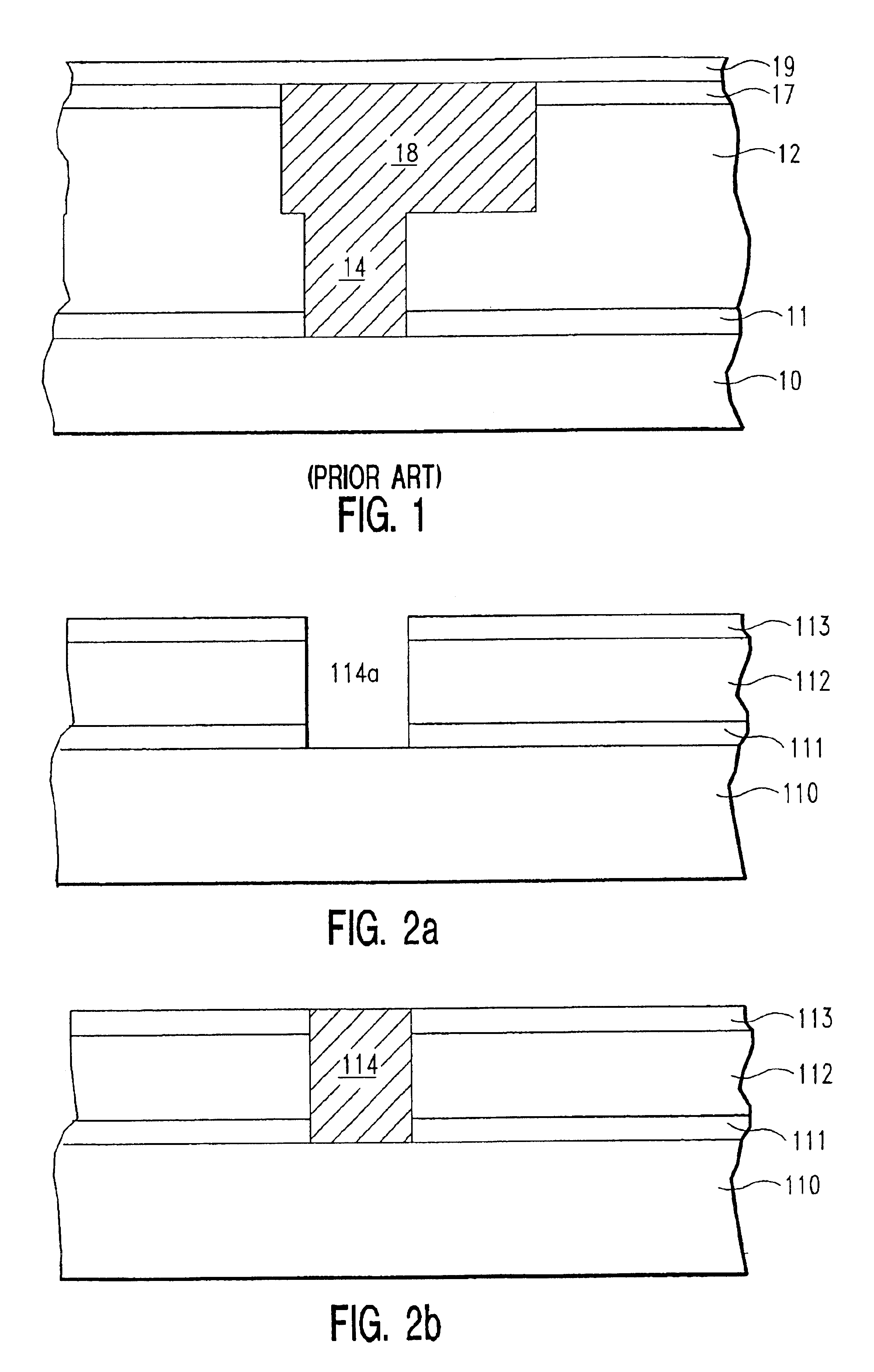

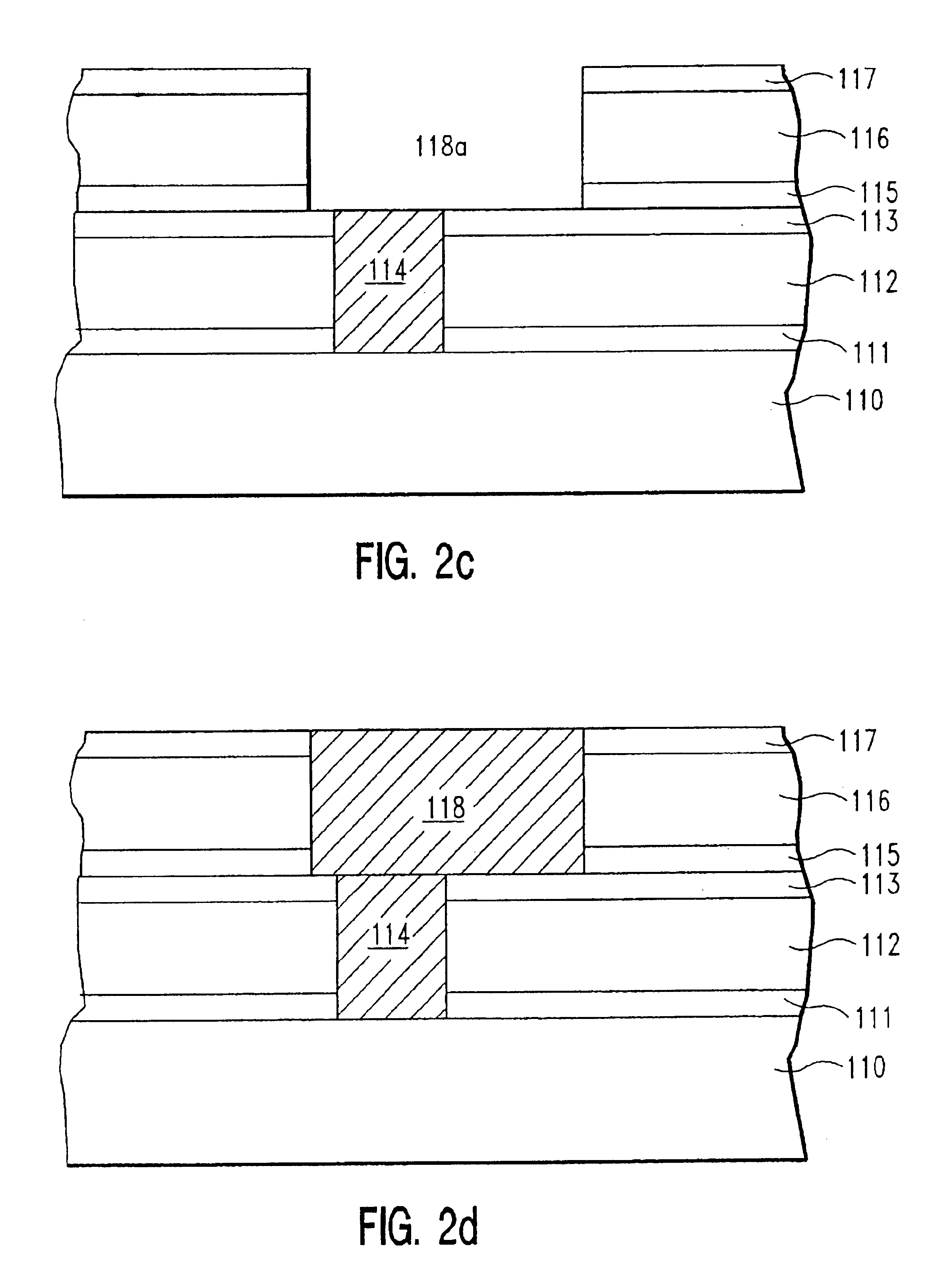

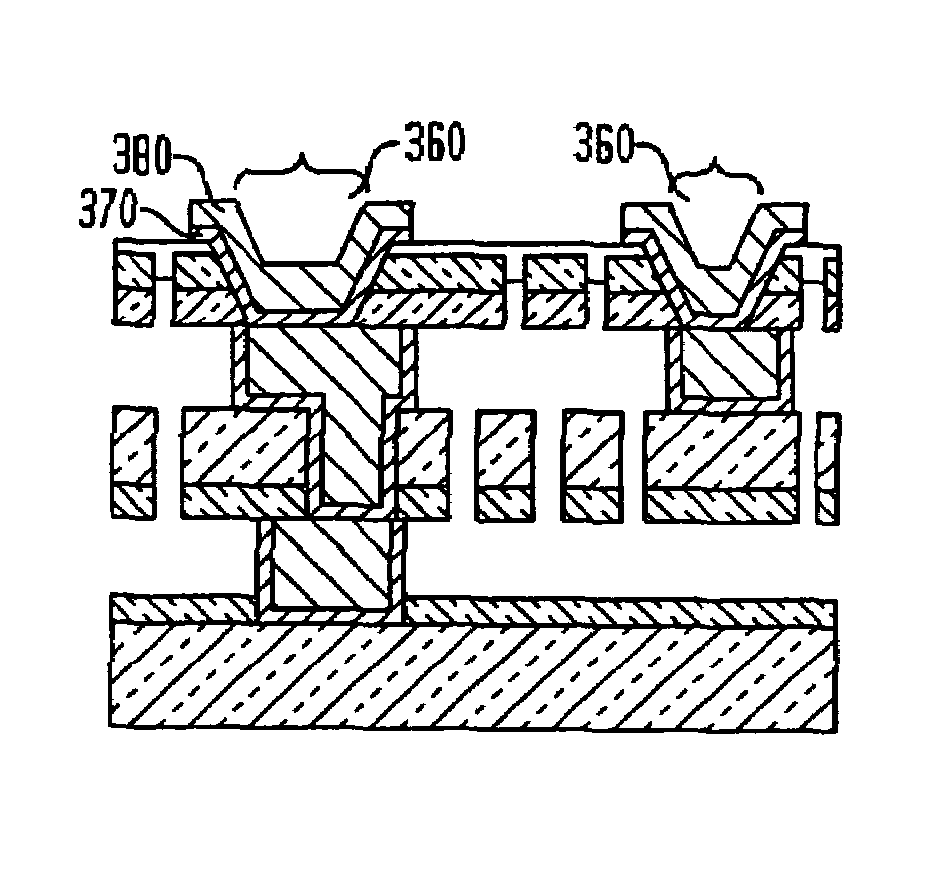

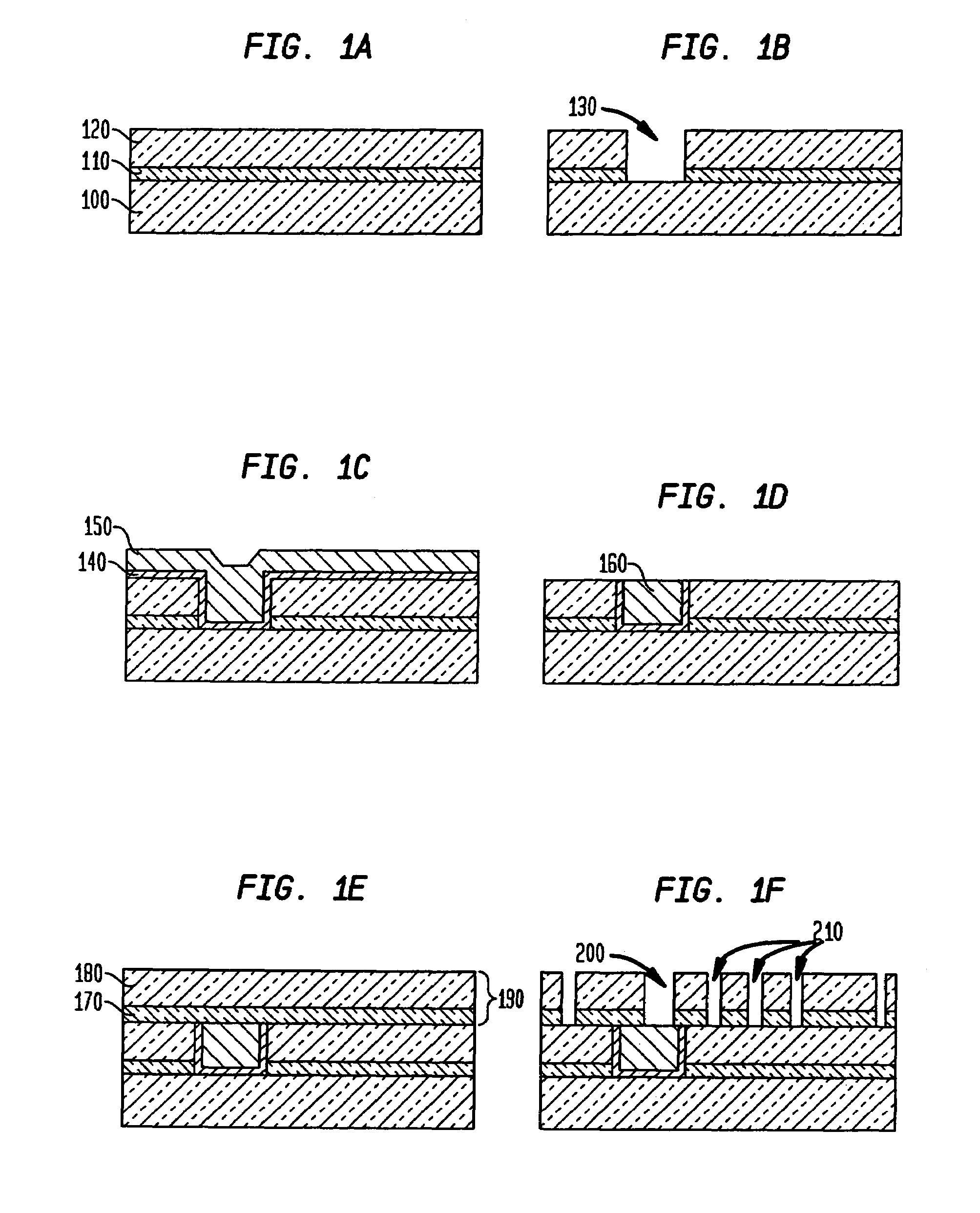

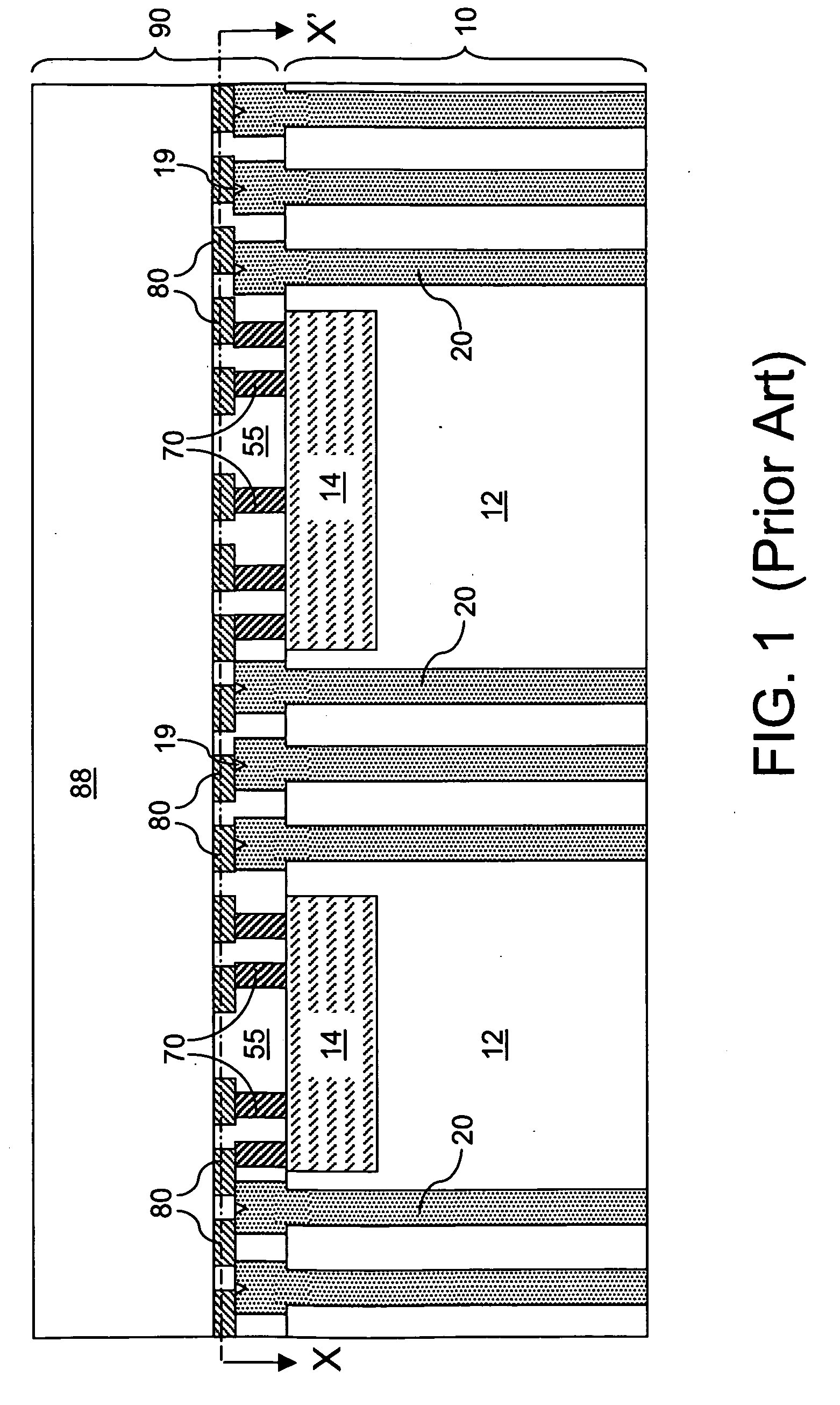

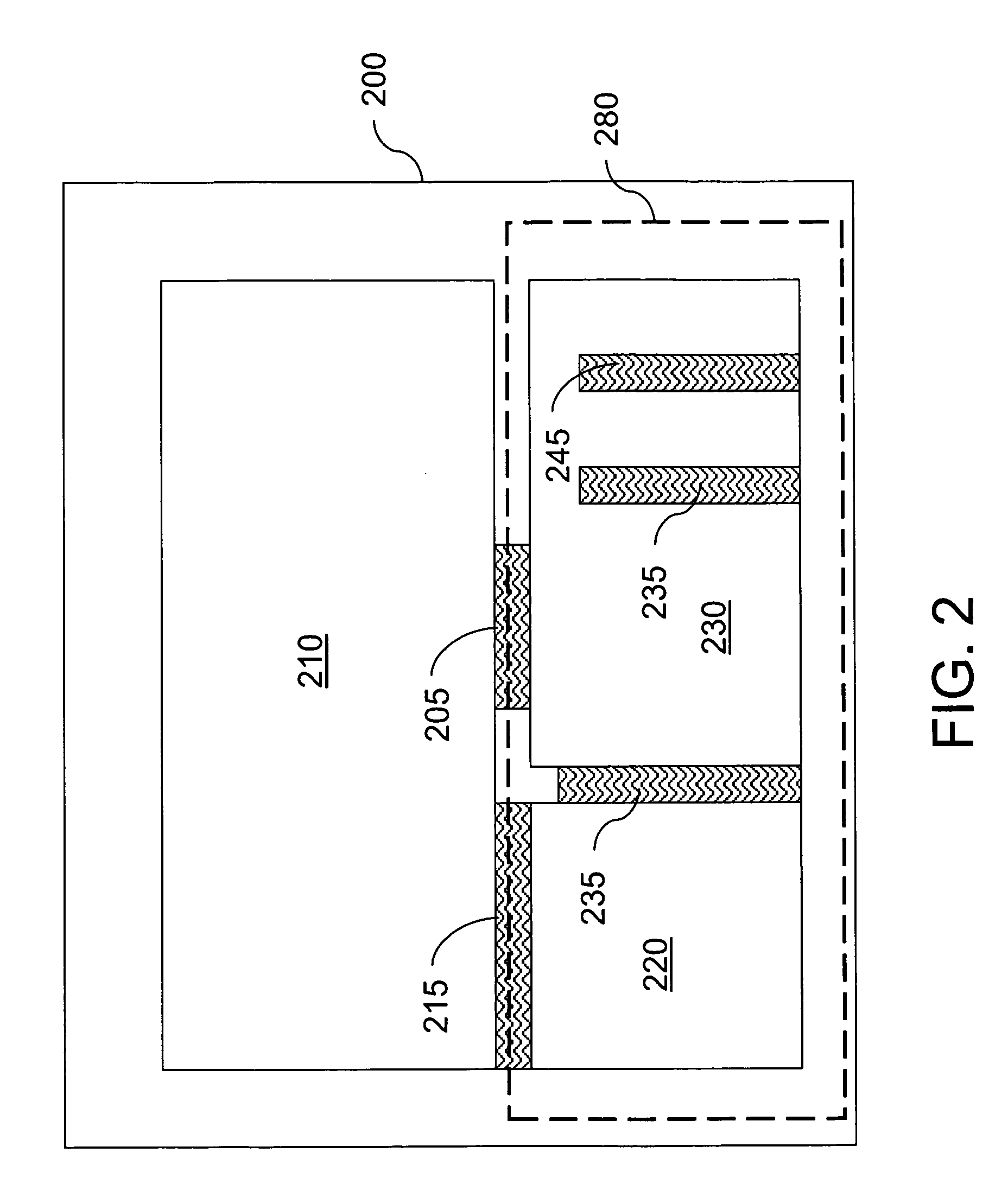

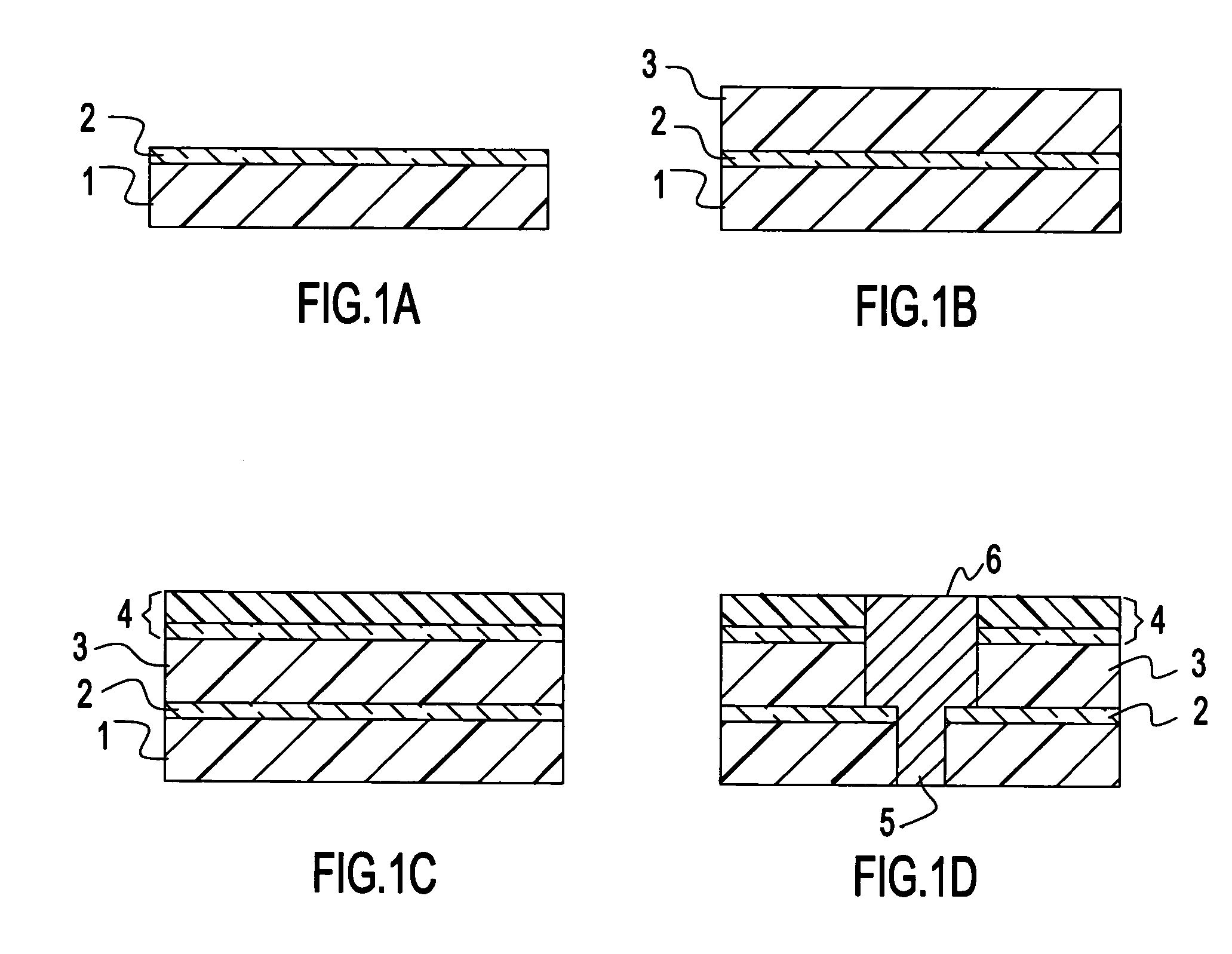

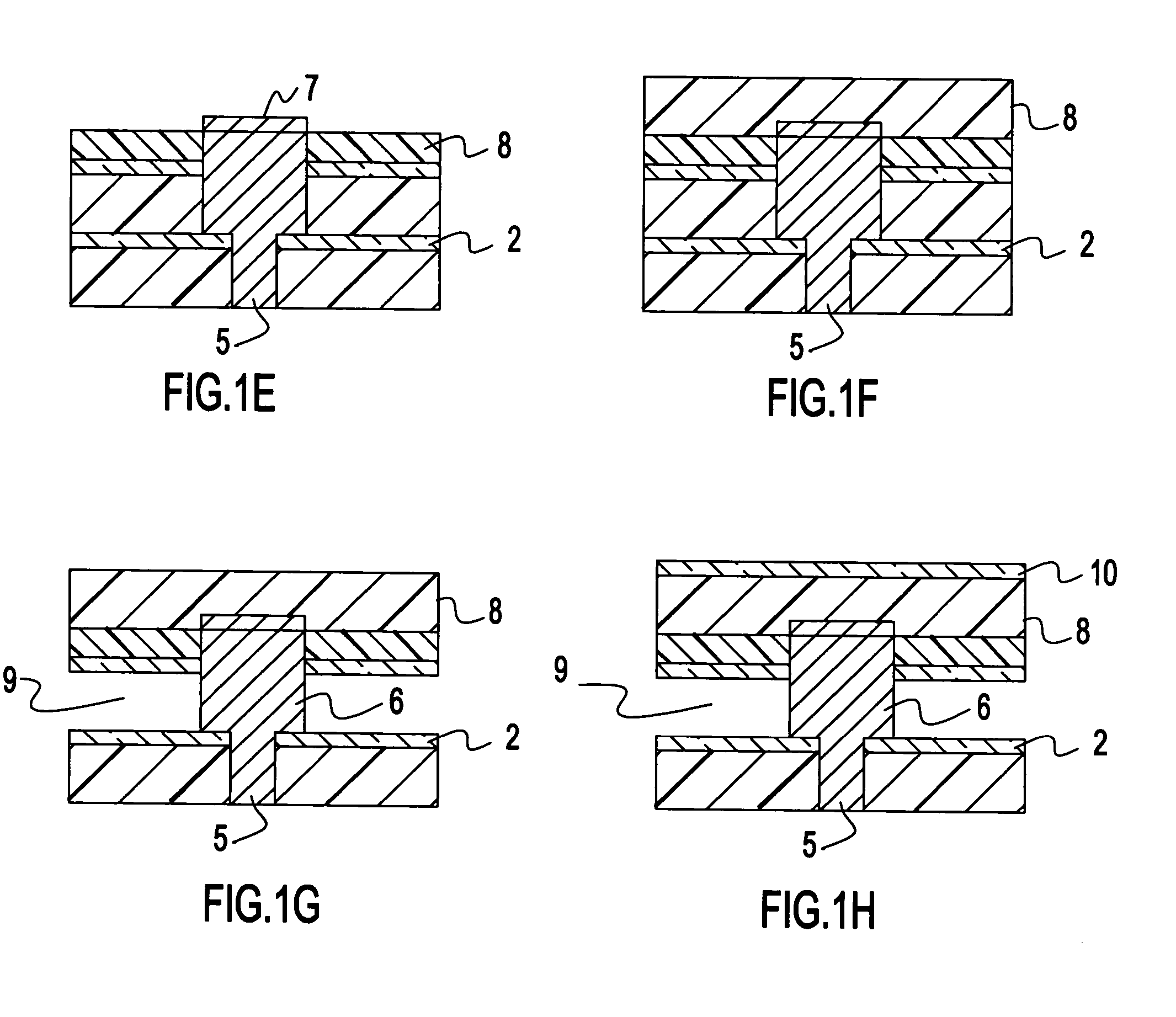

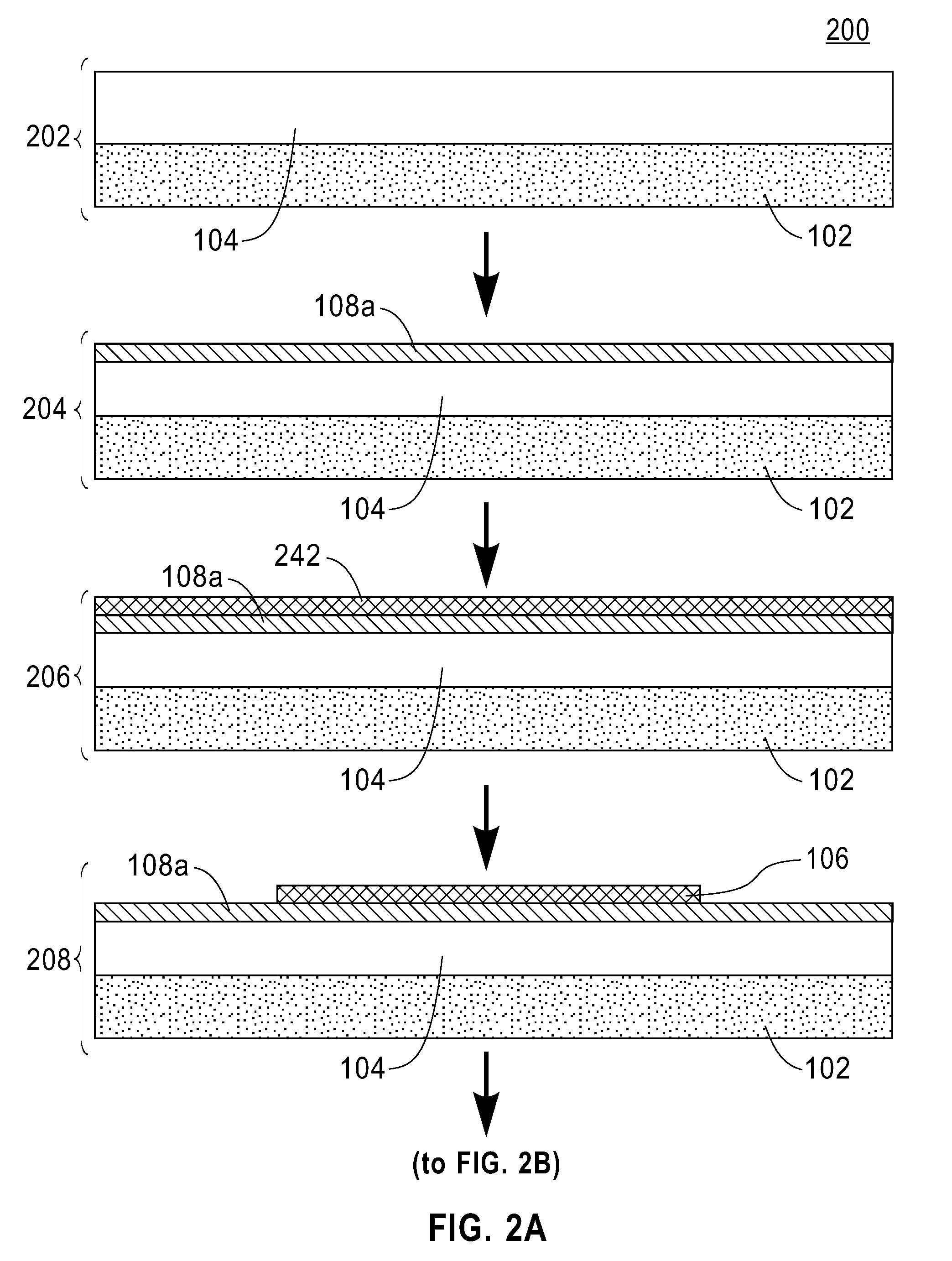

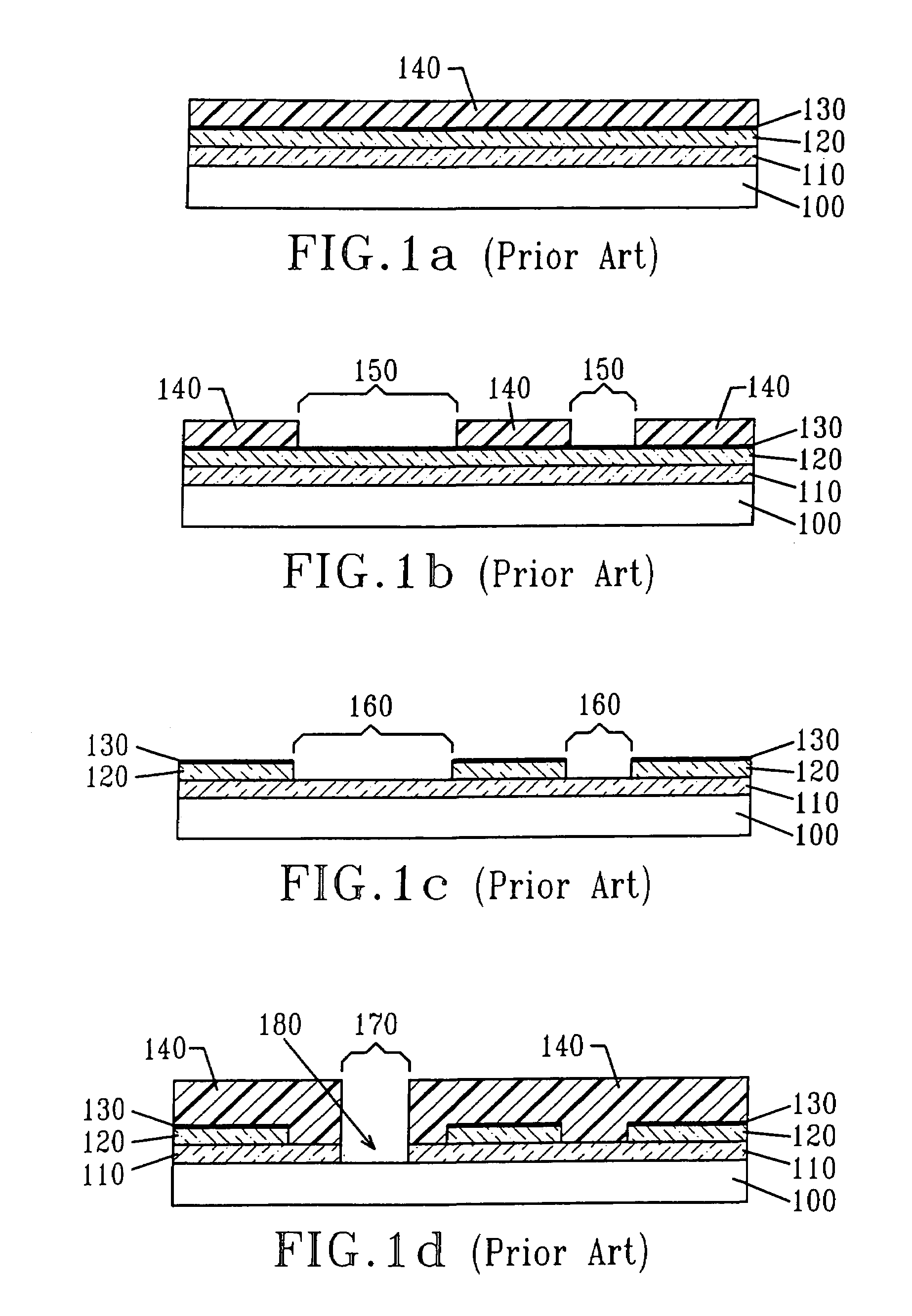

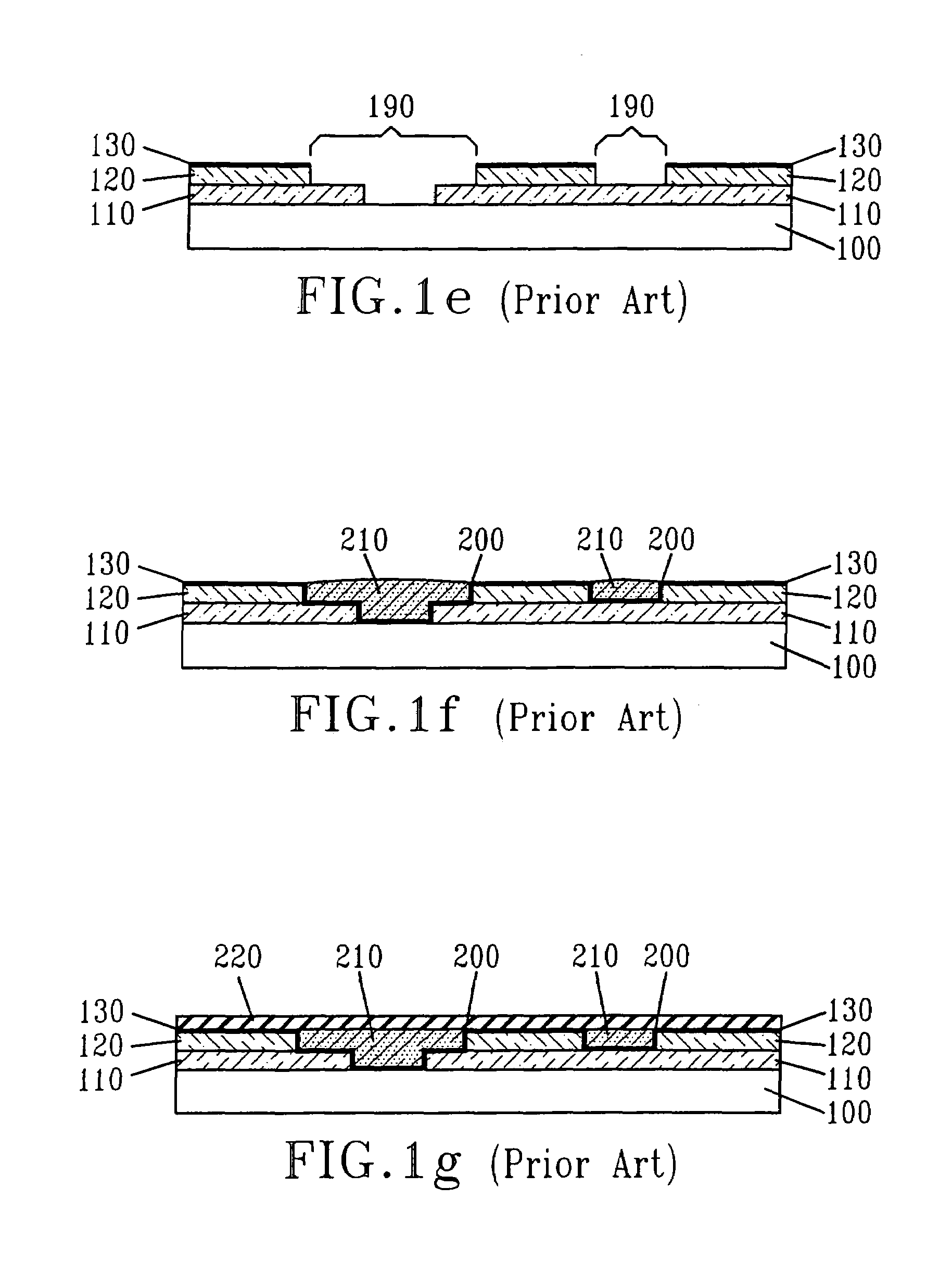

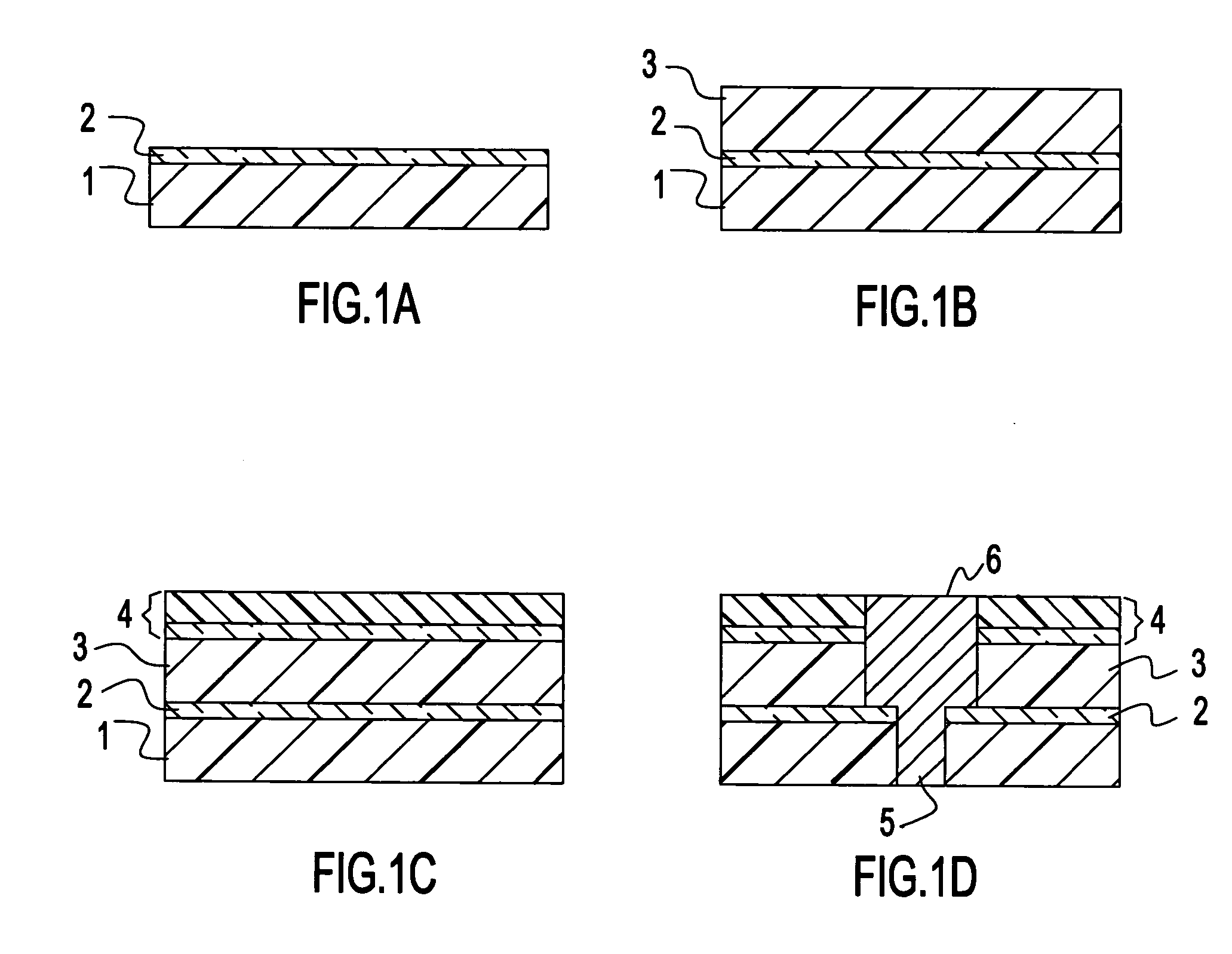

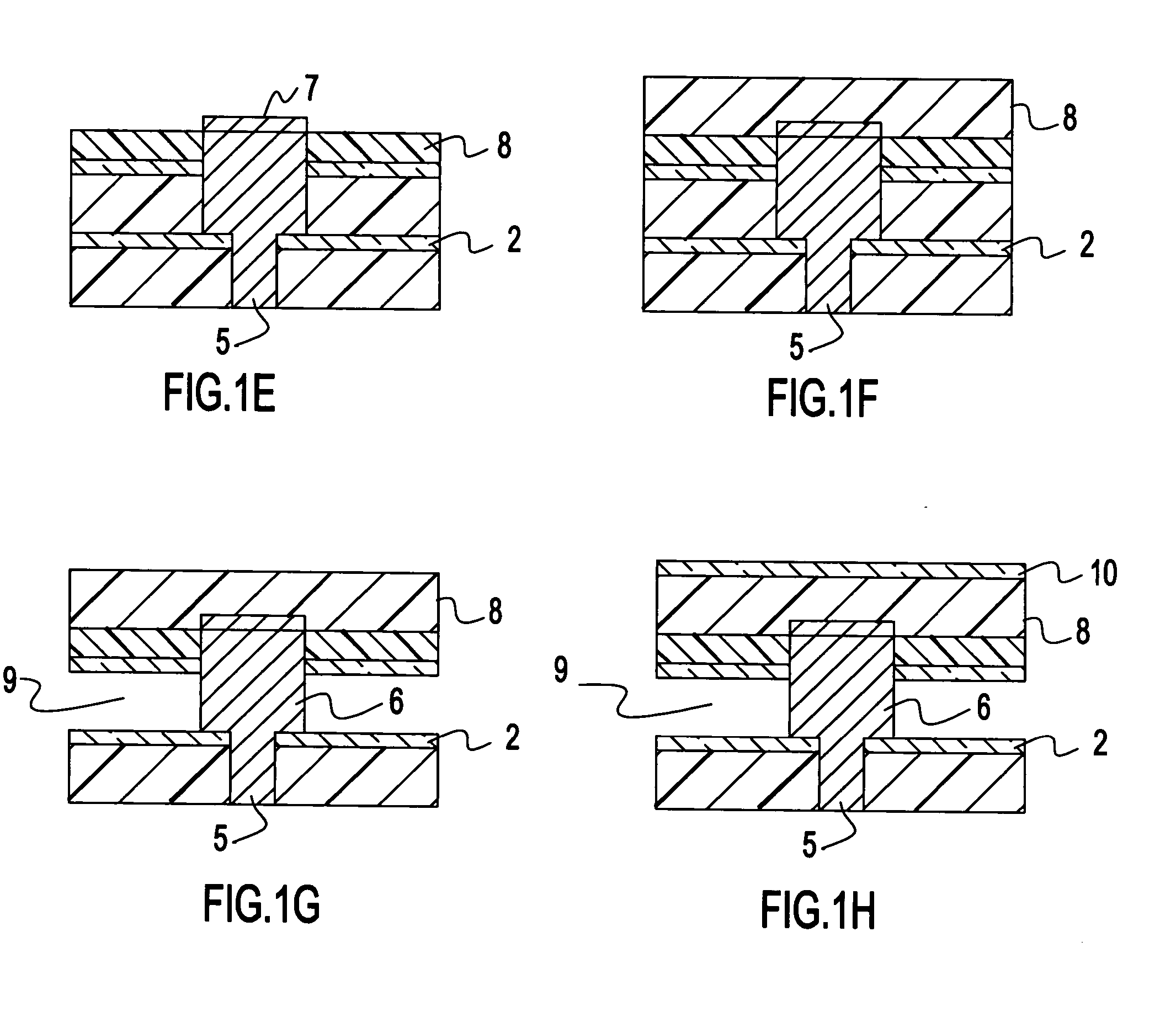

Multilevel interconnect structure containing air gaps and method for making

InactiveUS20020127844A1Maximizes air gap volume fractionQuantity minimizationSemiconductor/solid-state device detailsSolid-state devicesDielectric matrixEngineering

A method for forming a multilayer interconnect structure on a substrate that include interconnected conductive wiring and vias spaced apart by a combination of solid or gaseous dielectrics. The inventive method includes the steps of: (a) forming a first planar via plus line level pair embedded in a dielectric matrix formed from one or more solid dielectrics and comprising a via level dielectric and a line level dielectric on a substrate, wherein, at least one of said solid dielectrics is at least partially sacrificial; (b) etching back sacrificial portions of said at least partially sacrificial dielectrics are removed to leave cavities extending into and through said via level, while leaving, at least some of the original via level dielectric as a permanent dielectric under said lines; (c) partially filling or overfilling said cavities with a place-holder material which may or may not be sacrificial; (d) planarizing the structure by removing overfill of said place-holder material; (e) repeating, as necessary, steps (a)-(d); (f) forming a dielectric bridge layer over the planar structure; and (g) forming air gaps by at least partially extracting said place-holder material.

Owner:GLOBALFOUNDRIES US INC

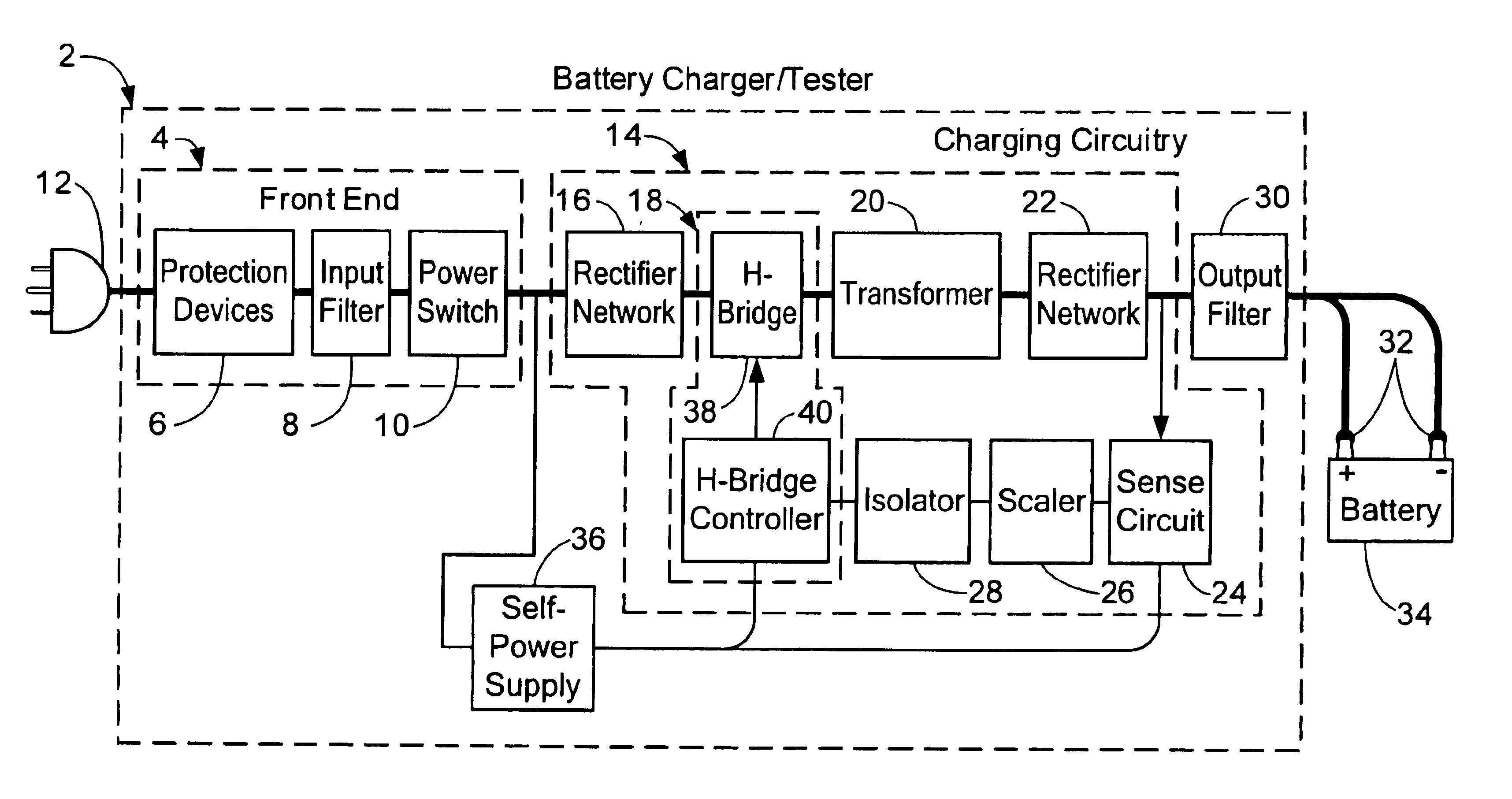

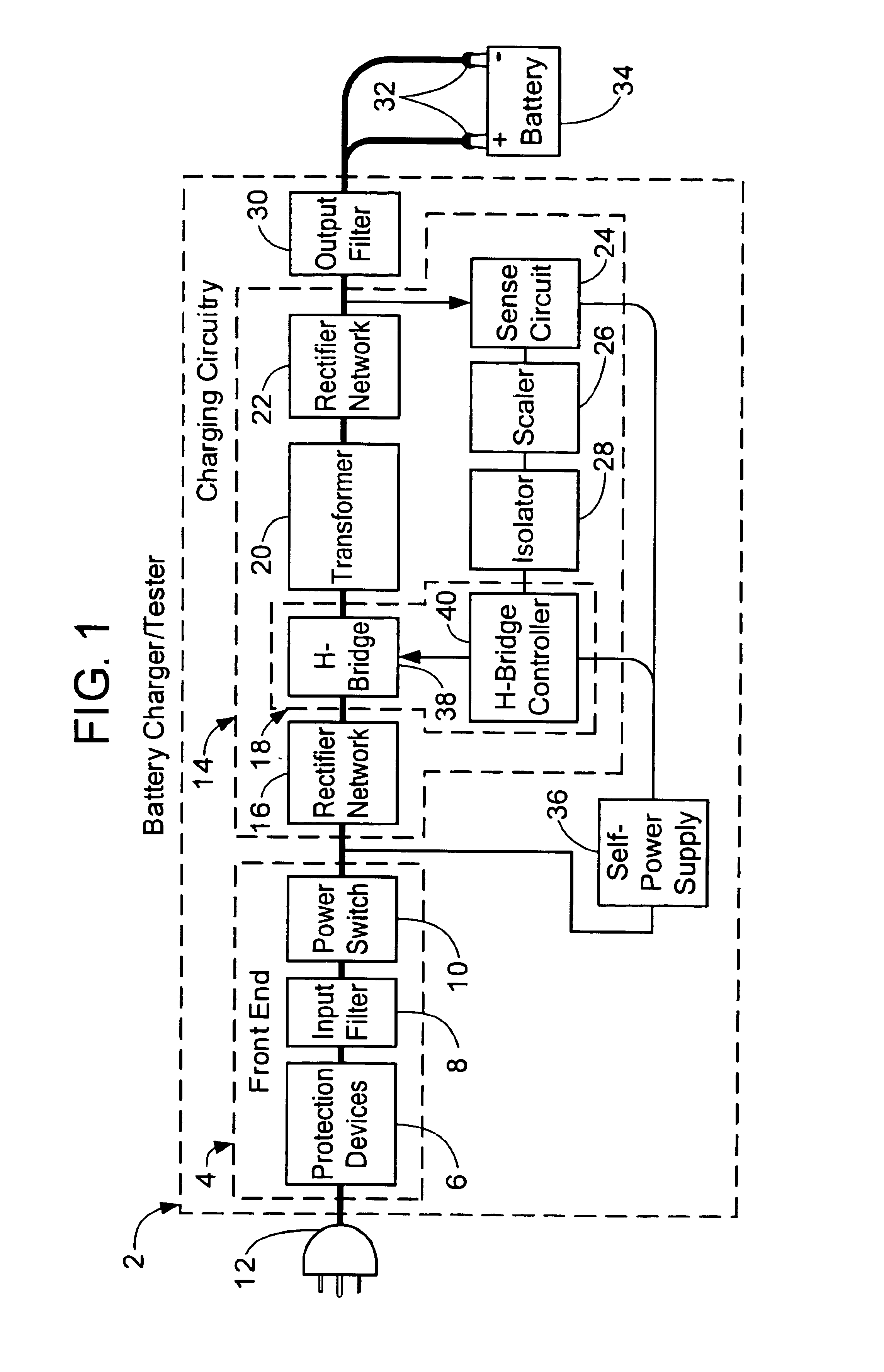

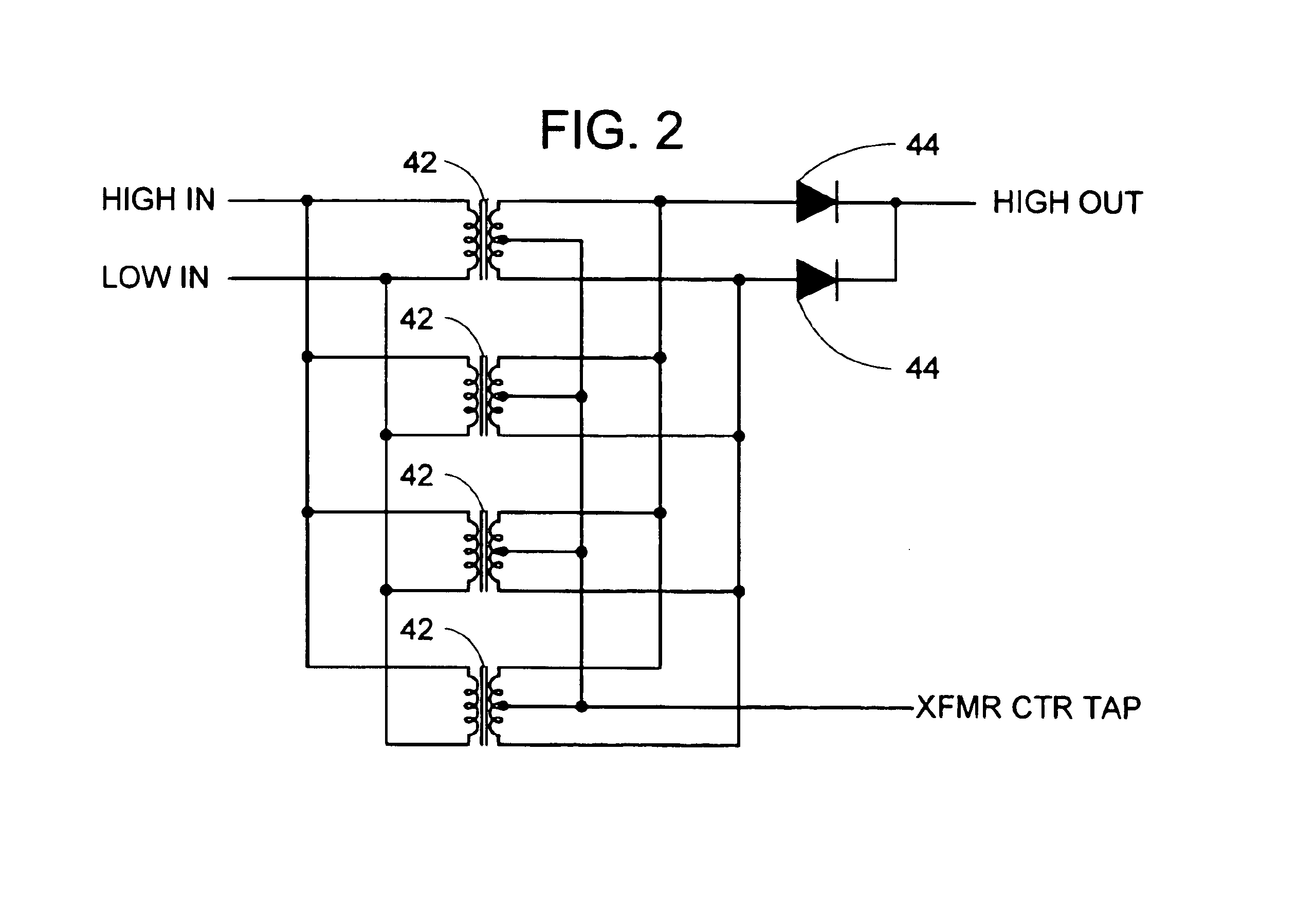

Apparatus and method for high-frequency operation in a battery charger

InactiveUS6838856B2Reduce weight and sizeHigh operating requirementsBatteries circuit arrangementsAc-dc conversion without reversalTransformerAC power

A battery charger includes line-level input rectification, a high-frequency oscillator-controlled chopper circuit, multiple transformers operating in parallel, and controlled output rectification. Use of line-level input rectification reorders the elements of the battery charger compared to previous designs. A chopper frequency several orders of magnitude higher than that of the AC power mains is used. The use of multiple, parallel-wired transformers for voltage and current transformation eases constraints on the physical geometry of a manufactured battery charger product by permitting individual transformers, each smaller than a comparable single transformer, to be employed. Controlled output rectifiers permit power levels to be regulated dynamically.

Owner:SPX CORP

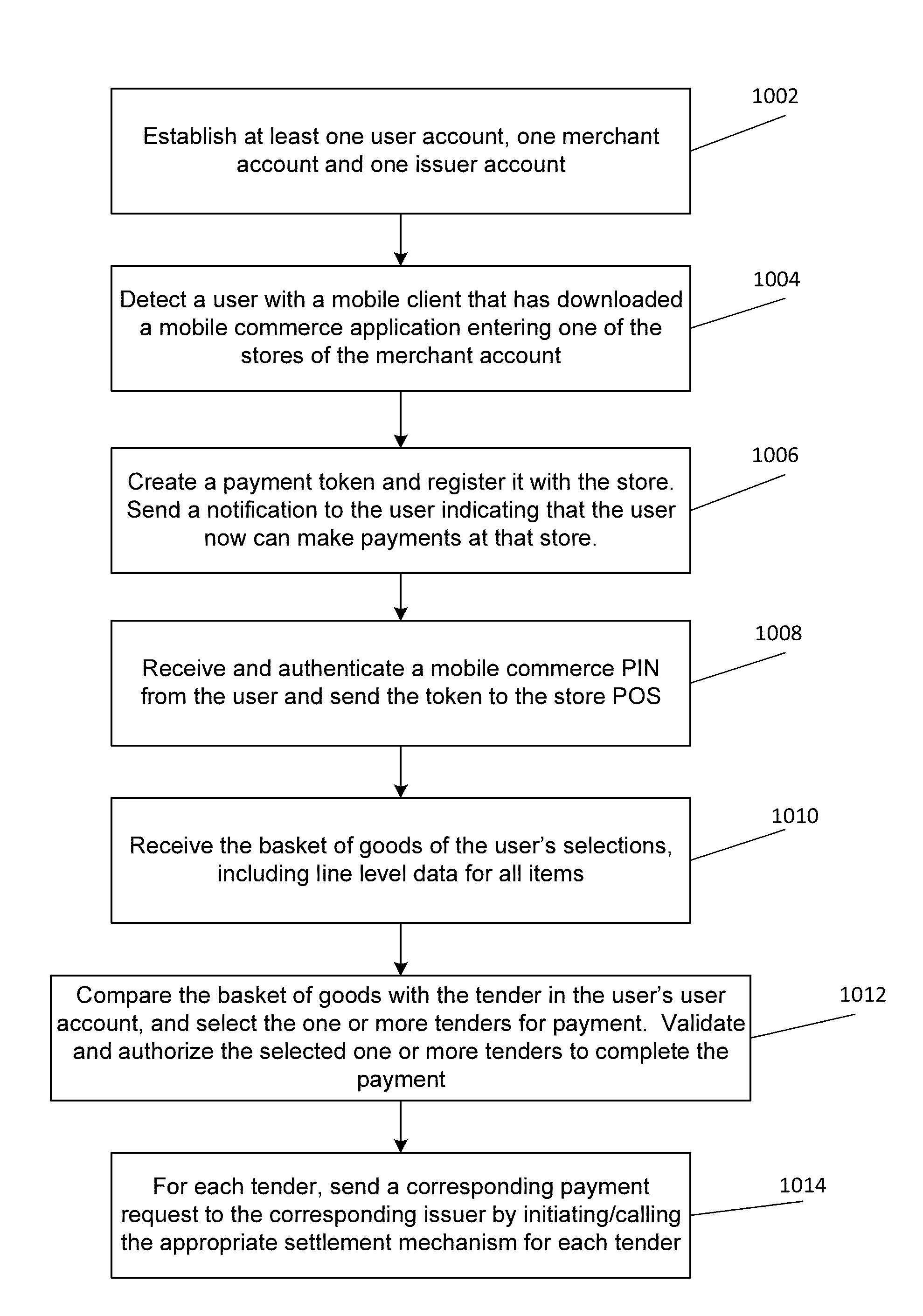

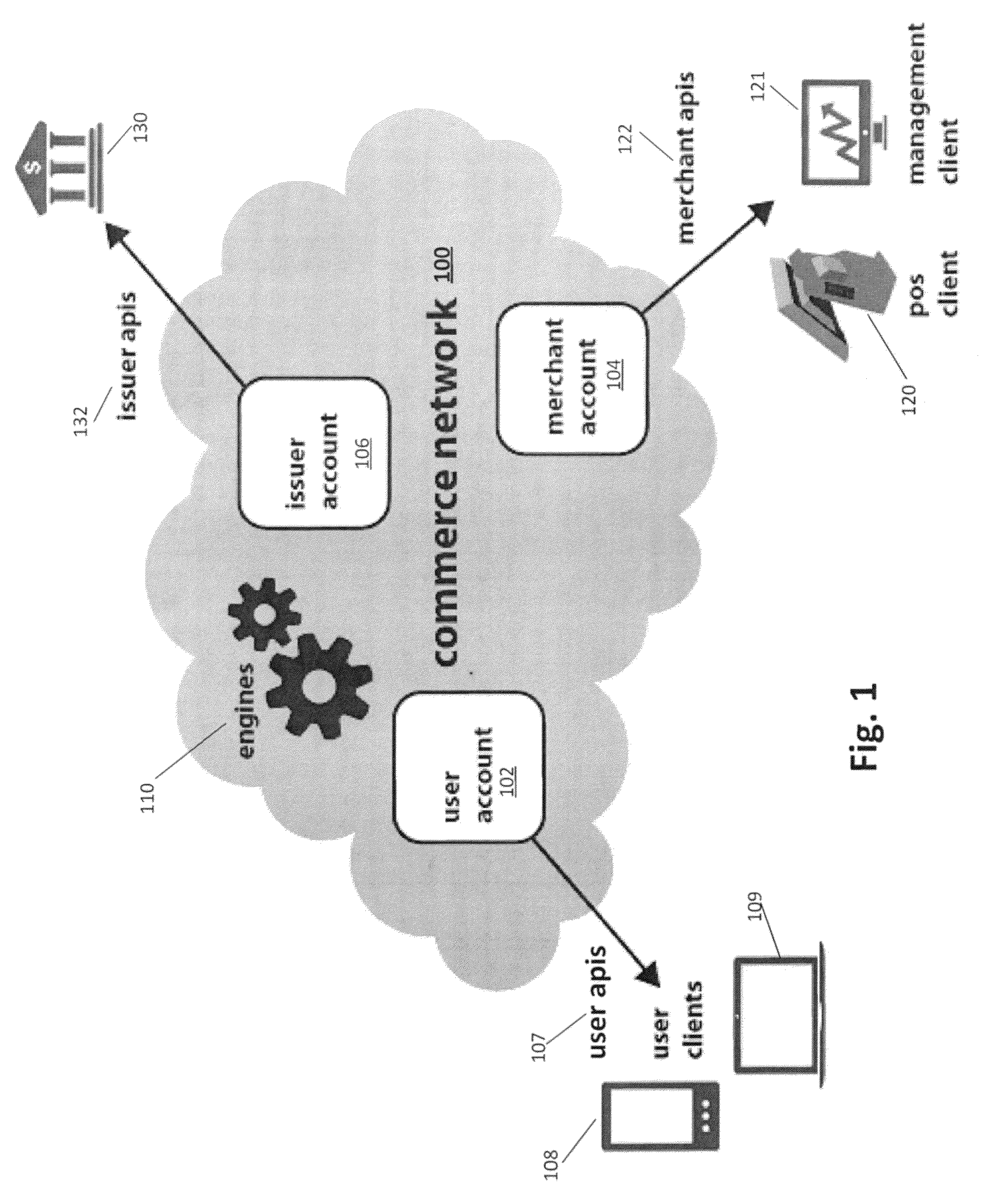

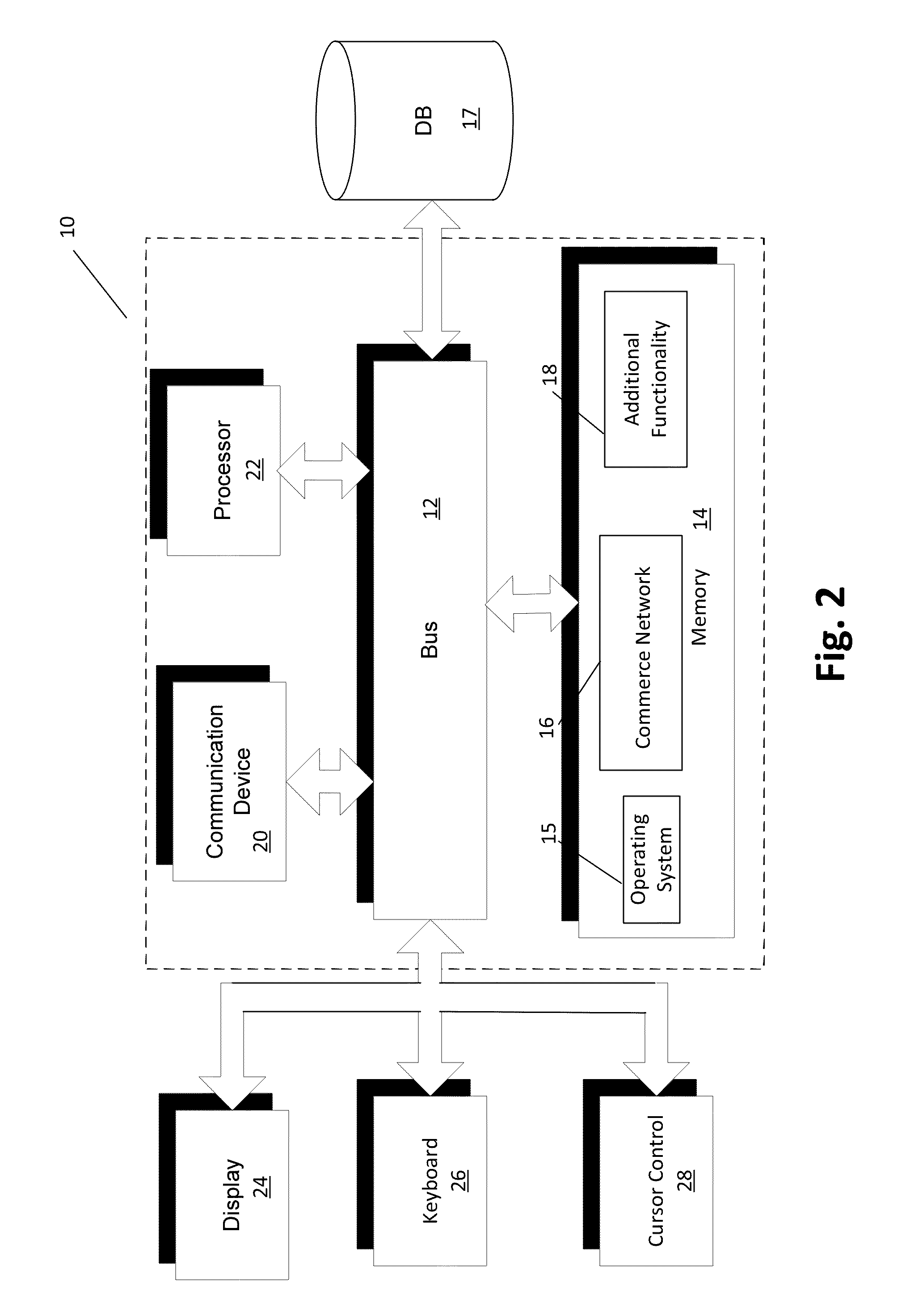

Electronic commerce network with mobile transactions

InactiveUS20140012701A1Point-of-sale network systemsAnonymous user systemsPaymentPersonal identification number

A commerce network that processes a mobile transaction detects a mobile device of a user entering a store, the user having a corresponding user account that includes one or more tenders. The network creates a payment token corresponding to the detecting and registers it with the store. The network receives a personal identification number (“PIN”) from the user and authenticates the PIN. The network receives a basket of goods of one or more items selected by the user for purchase, the basket of goods including line level data for the items. The network then selects one or more payment tenders from the one or more tenders based at least on the line level data and validates and authorizes the selected payment tenders.

Owner:INDEX SYST

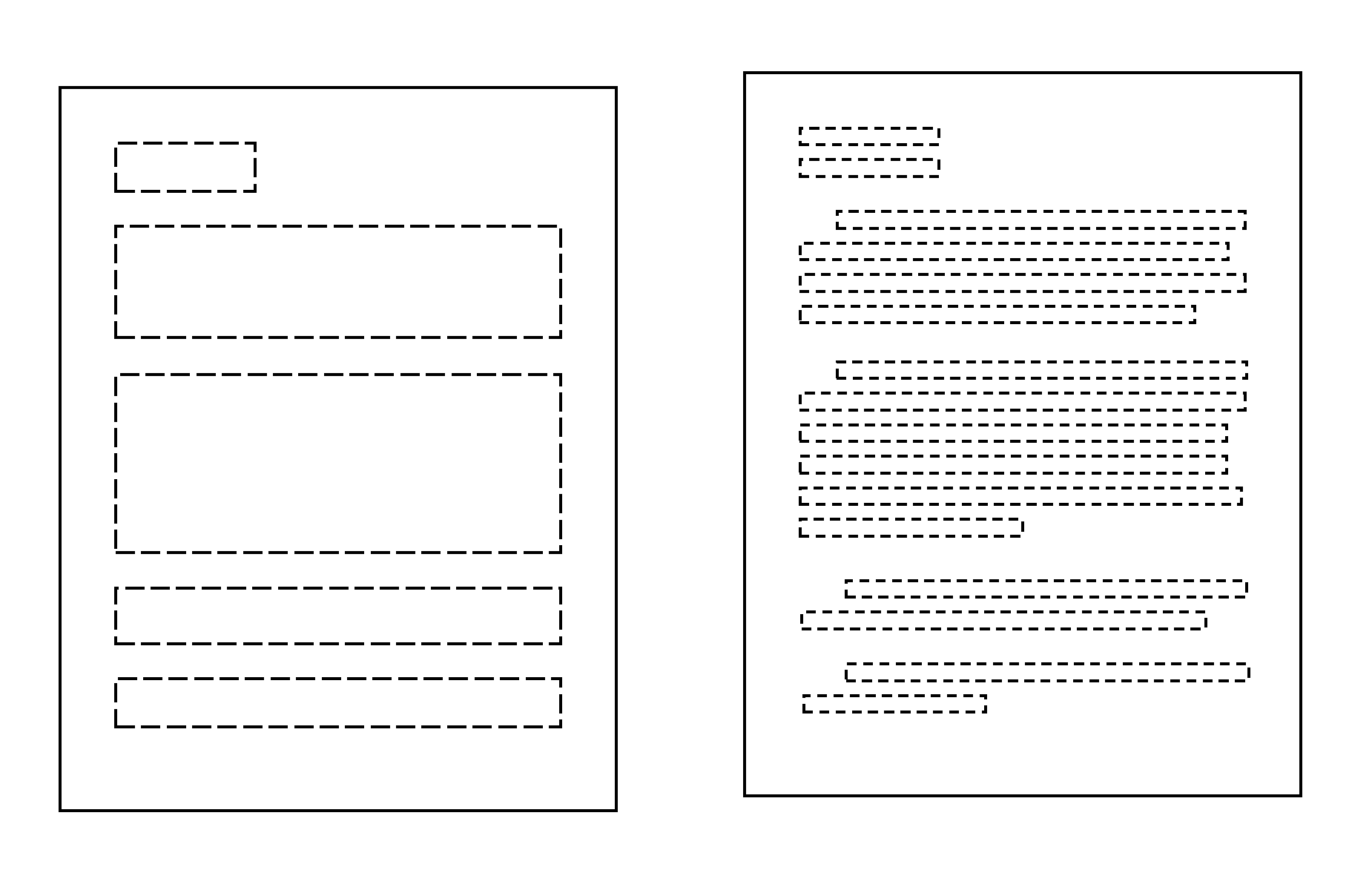

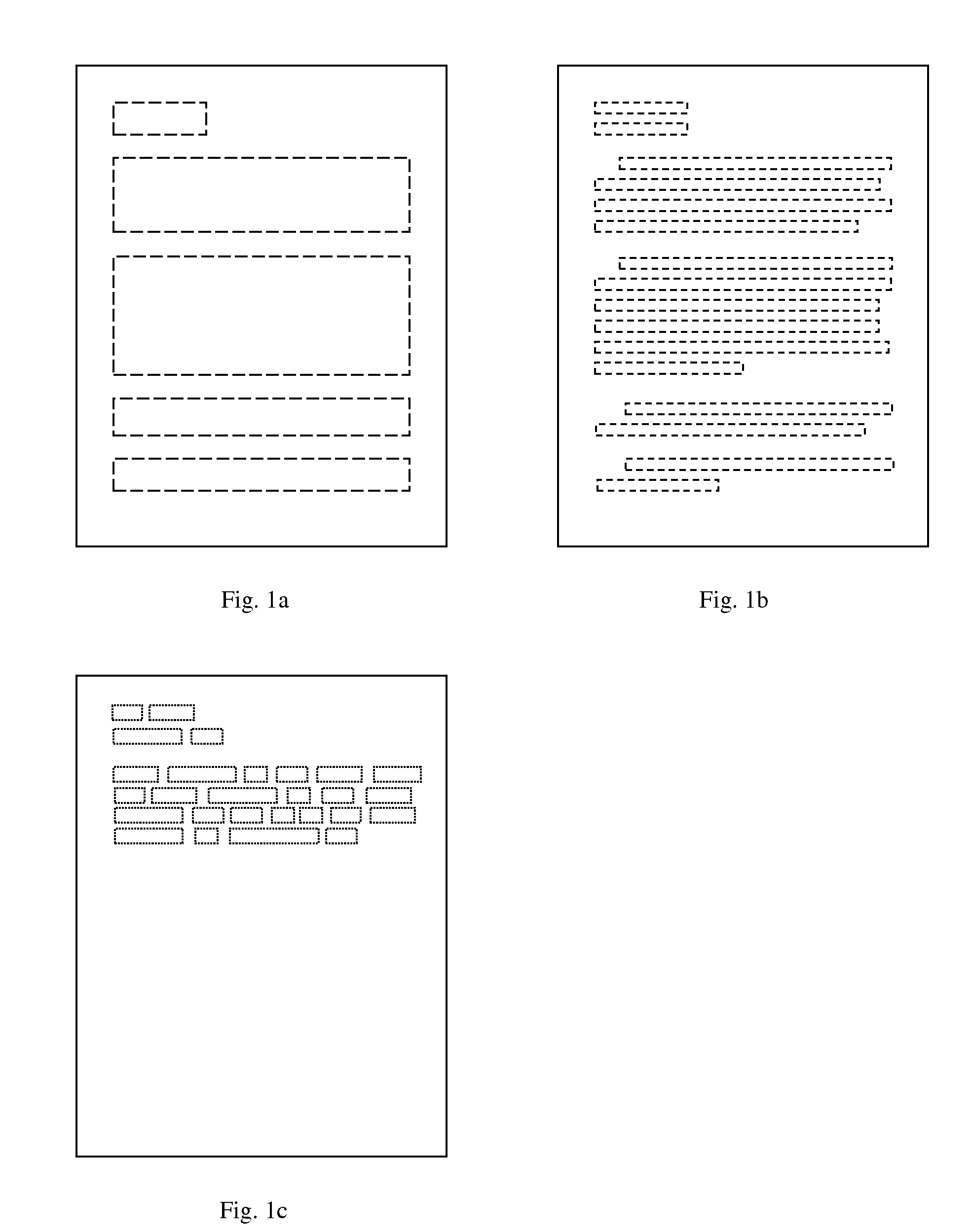

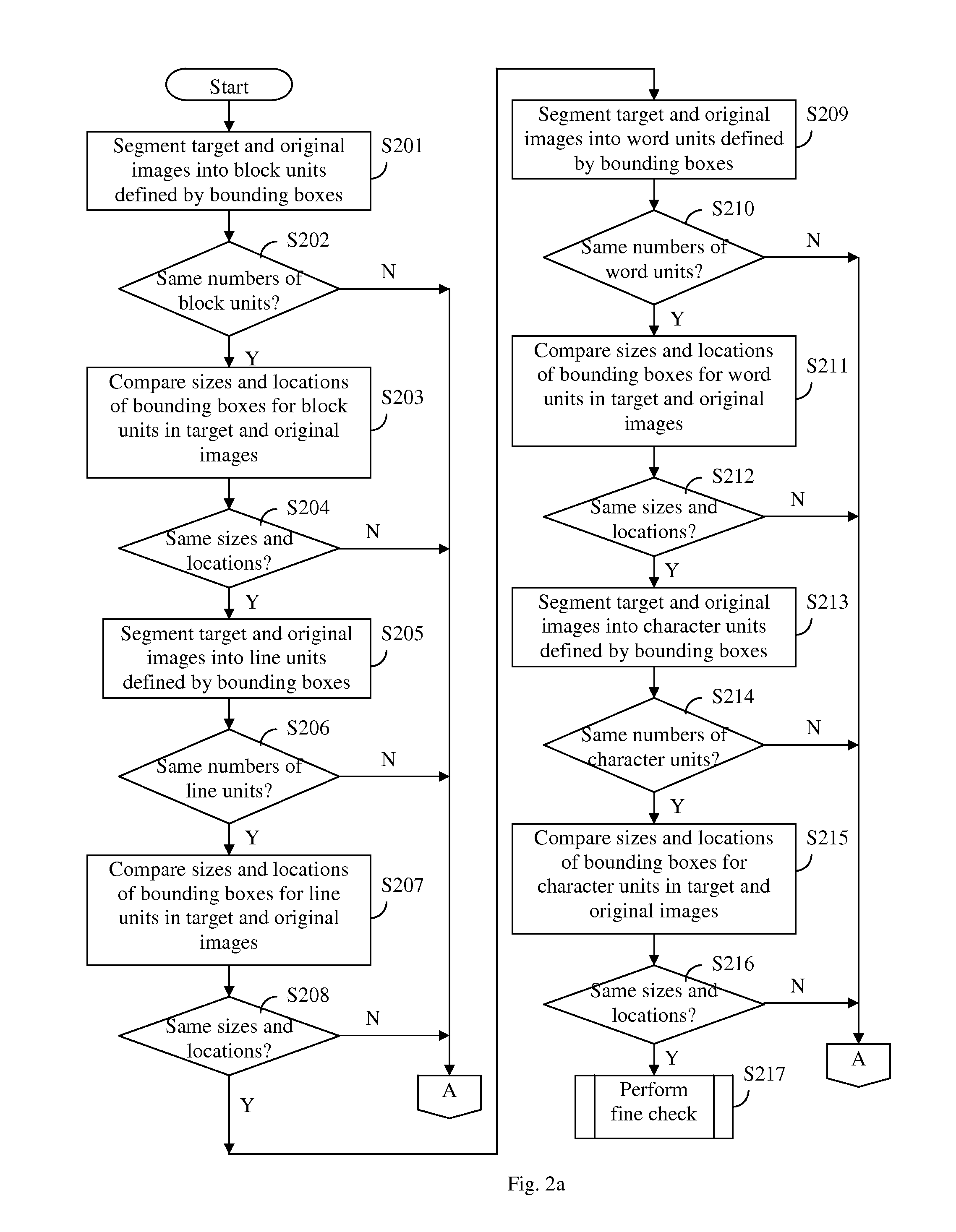

Method and apparatus for authenticating printed documents using multi-level image comparison based on document characteristics

A document authentication method compares a target document image (scanned image) with an original document image at multiple levels, such as block (e.g. paragraph, graphics, image), line, word and character levels. The paragraph level comparison determines whether the target and original images have the same number of paragraphs and whether the paragraphs have the same sizes and locations; the line level comparison determines if the target and original images have the same number of lines and whether the lines have the same sizes and locations; etc. Document segmentation is performed on the target and original images to segment them into paragraph units, line units, etc. for purposes of the comparisons. The original document may be segmented beforehand and the segmentation information stored for later use. The authentication process may be designed to stop when alterations are detected at a higher level, so lower level comparisons are not carried out.

Owner:KONICA MINOLTA LAB U S A INC

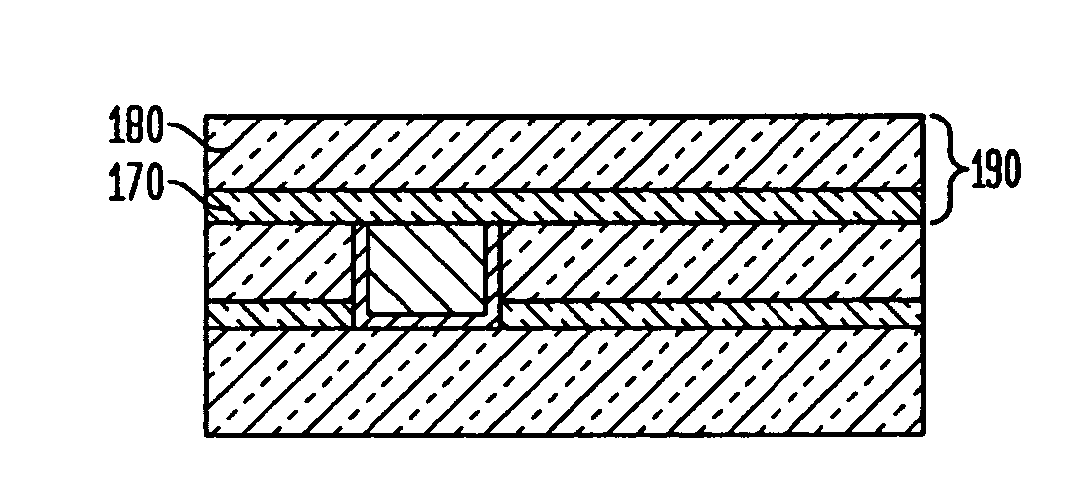

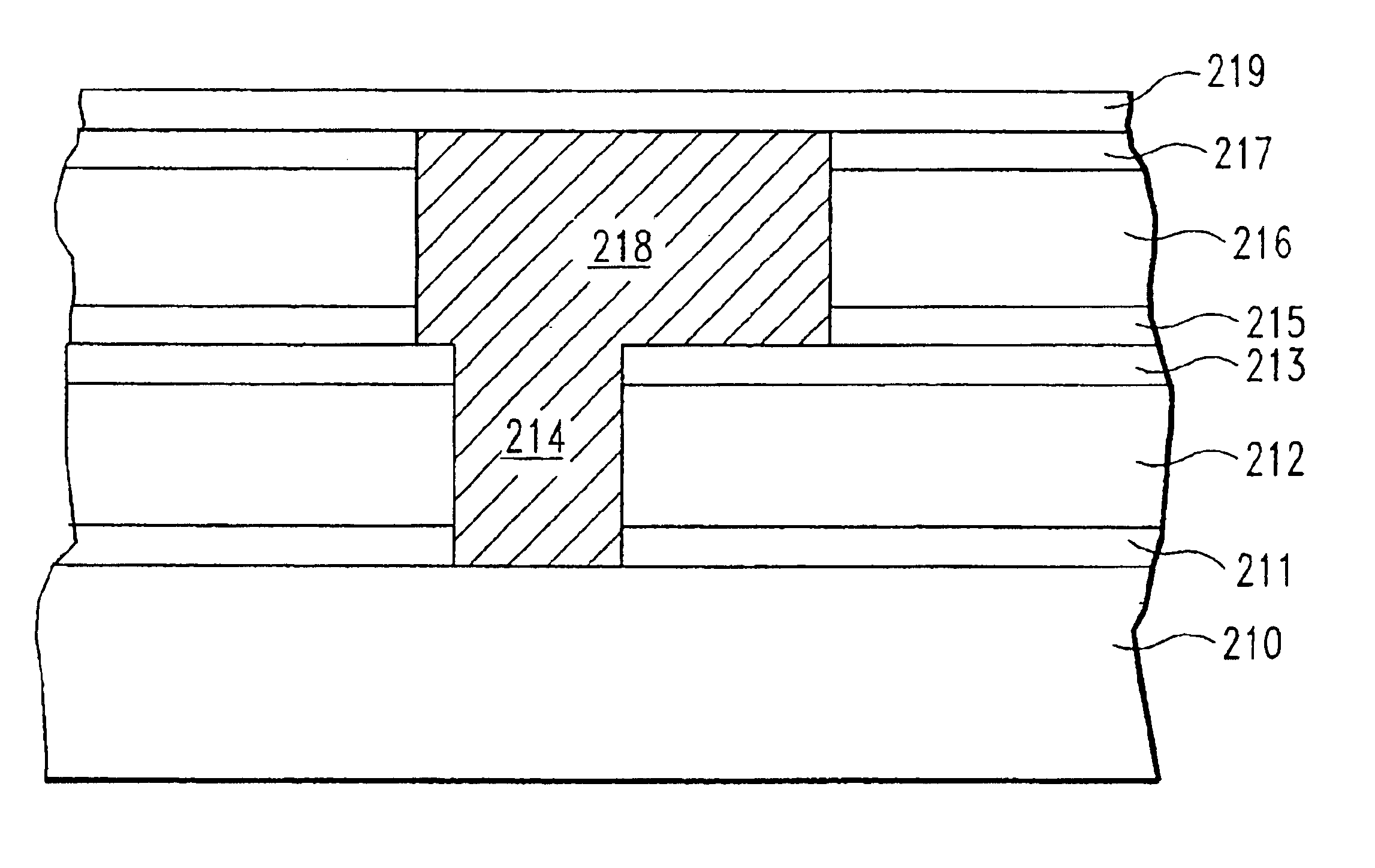

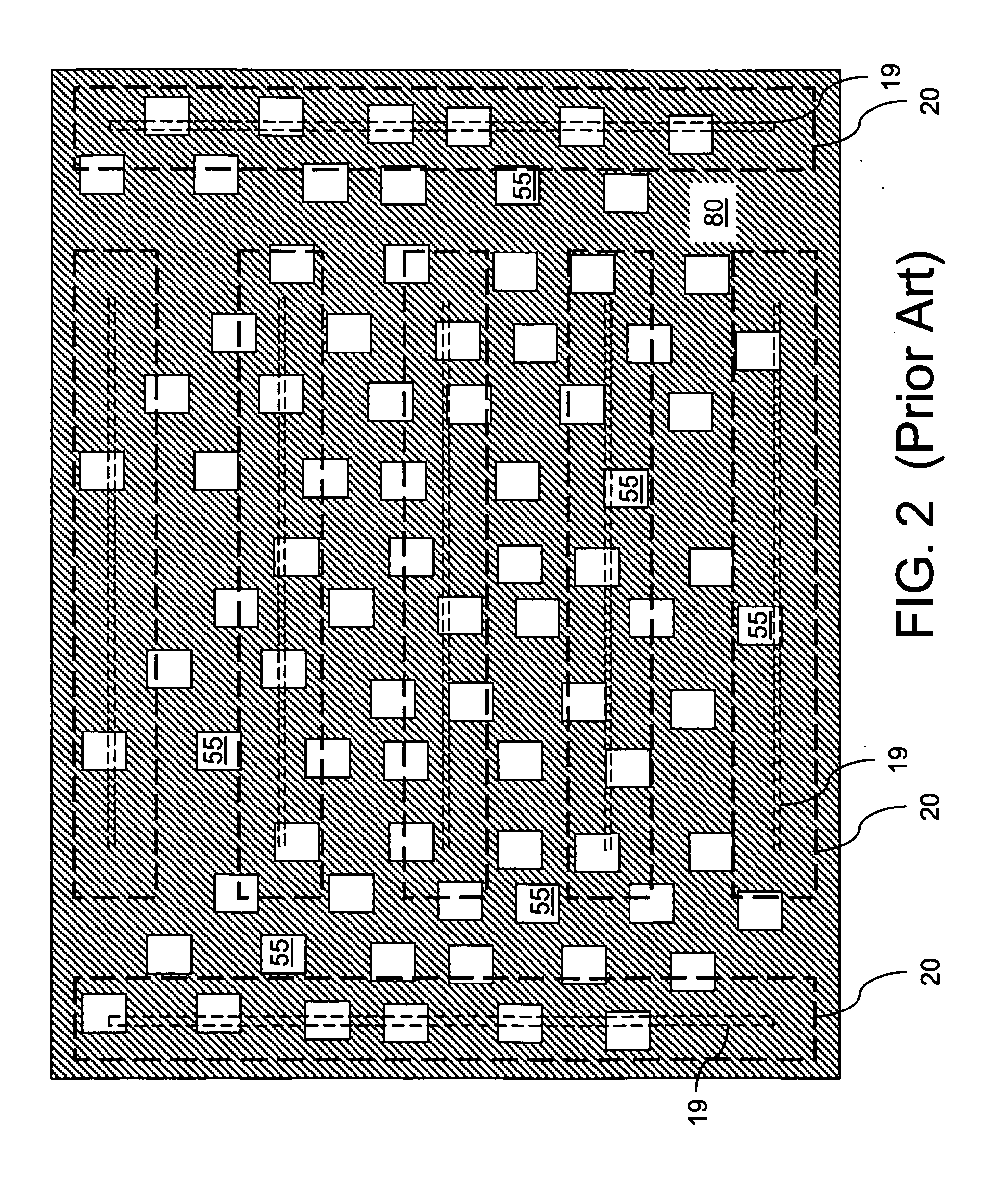

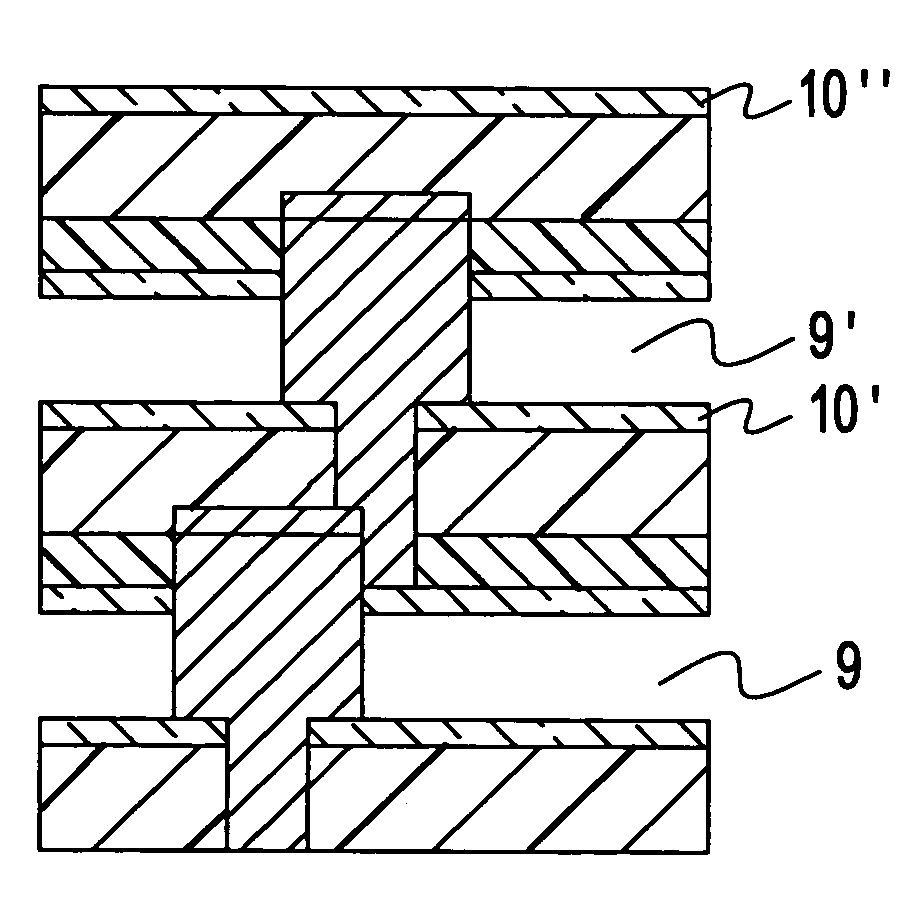

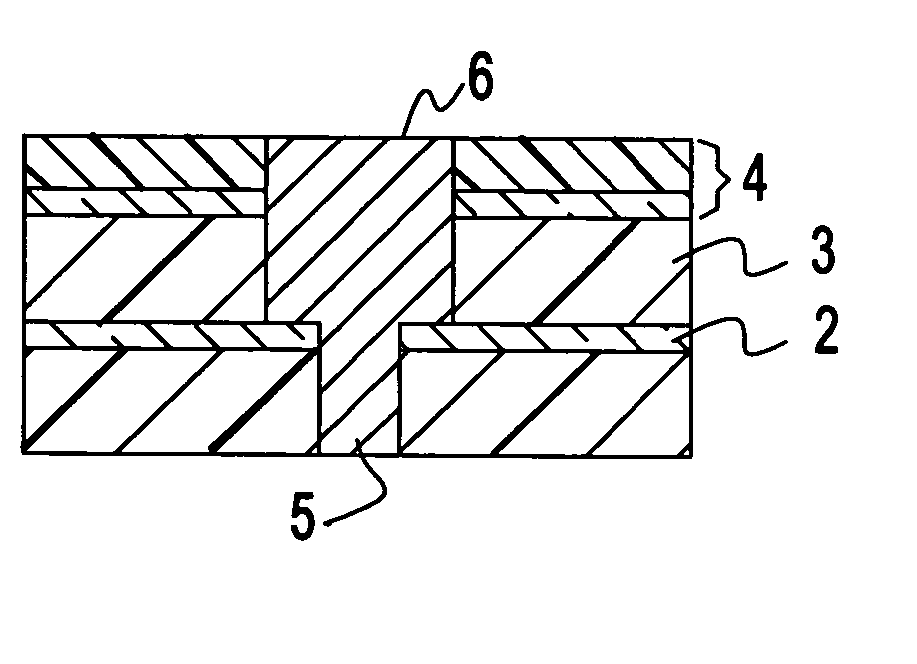

Multilayer interconnect structure containing air gaps and method for making

ActiveUS20070259516A1Electromigration failureQuantity minimizationSemiconductor/solid-state device detailsSolid-state devicesDielectric layerLine level

A multilevel air-gap-containing interconnect structure and a method of fabricating the same are provided. The multilevel air-gap-containing interconnect structure includes a collection of interspersed line levels and via levels, with via levels comprising conductive vias embedded in one or more dielectric layers in which the dielectric layers are solid underneath and above line features in adjacent levels, and perforated between line features. The line levels contain conductive lines and an air-gap-containing dielectric. A solid dielectric bridge layer, containing conductive contacts and formed by filling in a perforated dielectric layer, is disposed over the collection of interspersed line and via levels.

Owner:GLOBALFOUNDRIES US INC

Reliable low-k interconnect structure with hybrid dielectric

An advanced back-end-of-line (BEOL) interconnect structure having a hybrid dielectric is disclosed. The inter-layer dielectric (ILD) for the via level is preferably different from the ILD for the line level. In a preferred embodiment, the via-level ILD is formed of a low-k SiCOH material, and the line-level ILD is formed of a low-k polymeric thermoset material.

Owner:GLOBALFOUNDRIES US INC

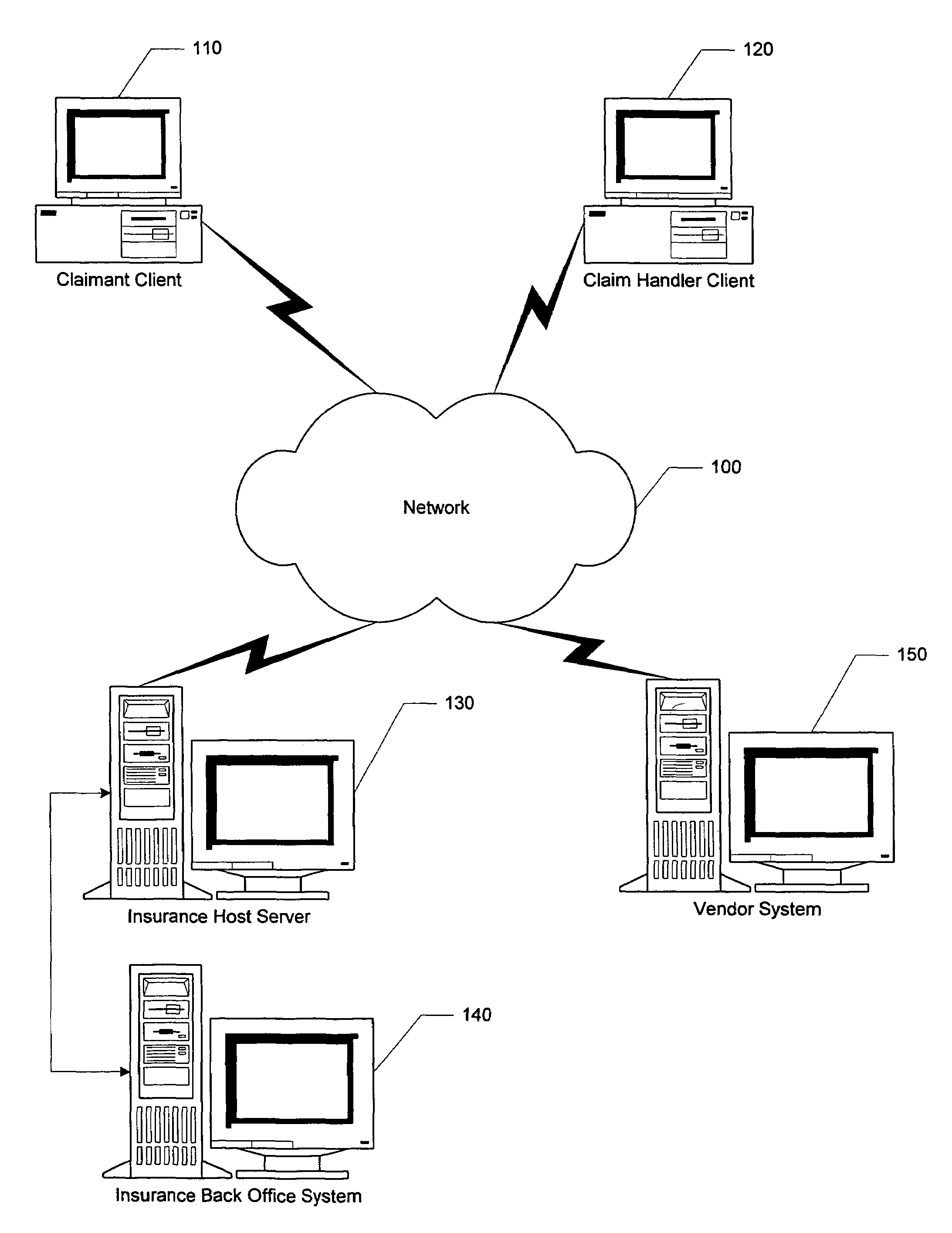

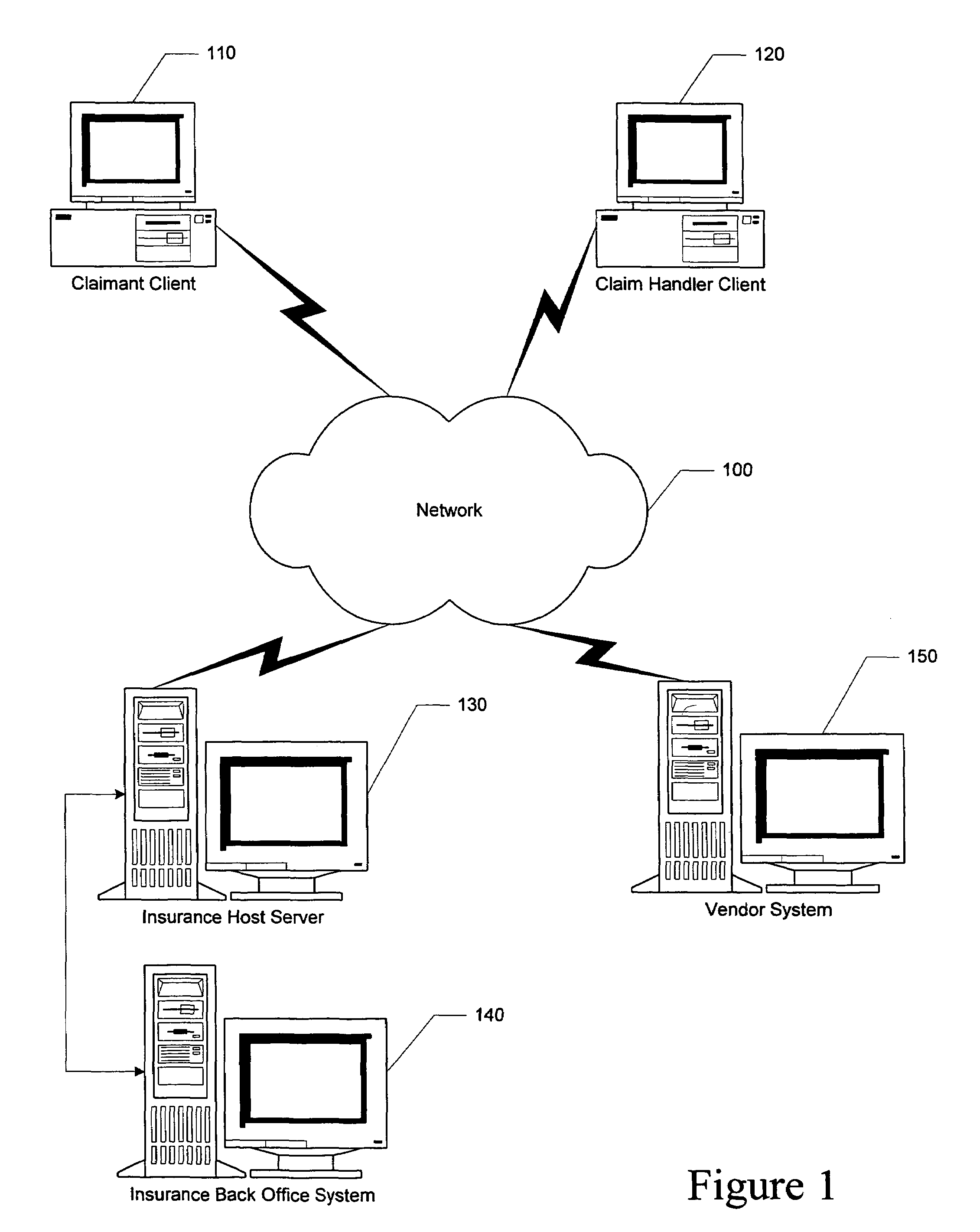

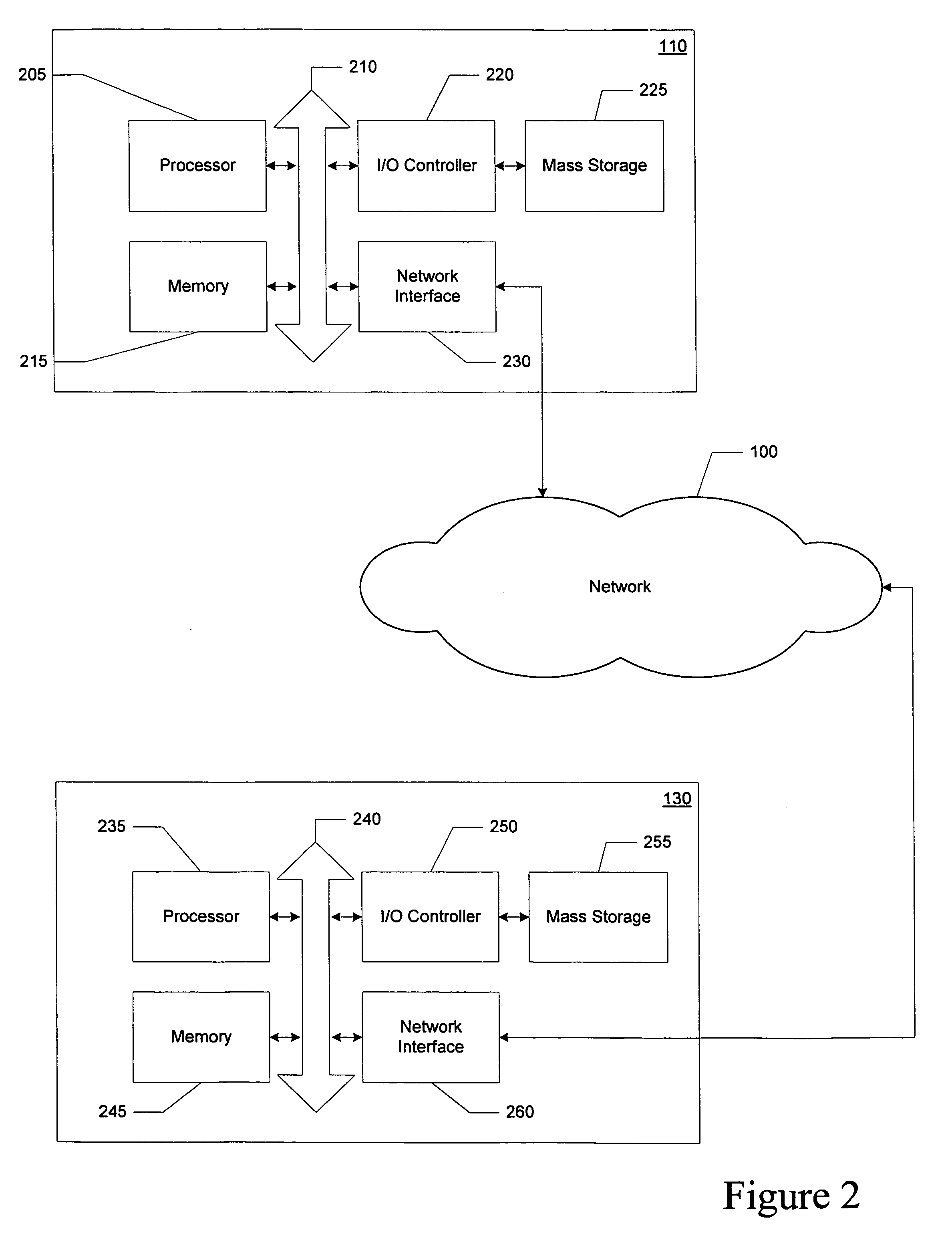

Capture highly refined claim evaluation information across multiple web interfaces

Methods, systems, and articles of manufacture consistent with the present invention use a data processing system for capturing line item data. The method involves receiving claim identification information from a claimant, where the claim identification information comprises, at least, one line level; providing the client with an item tree of line item level data based on the line level and aggregating line item level data collected from the claimant; and storing the line item level data in an insurance host server.

Owner:DUCK CREEK TECH LTD

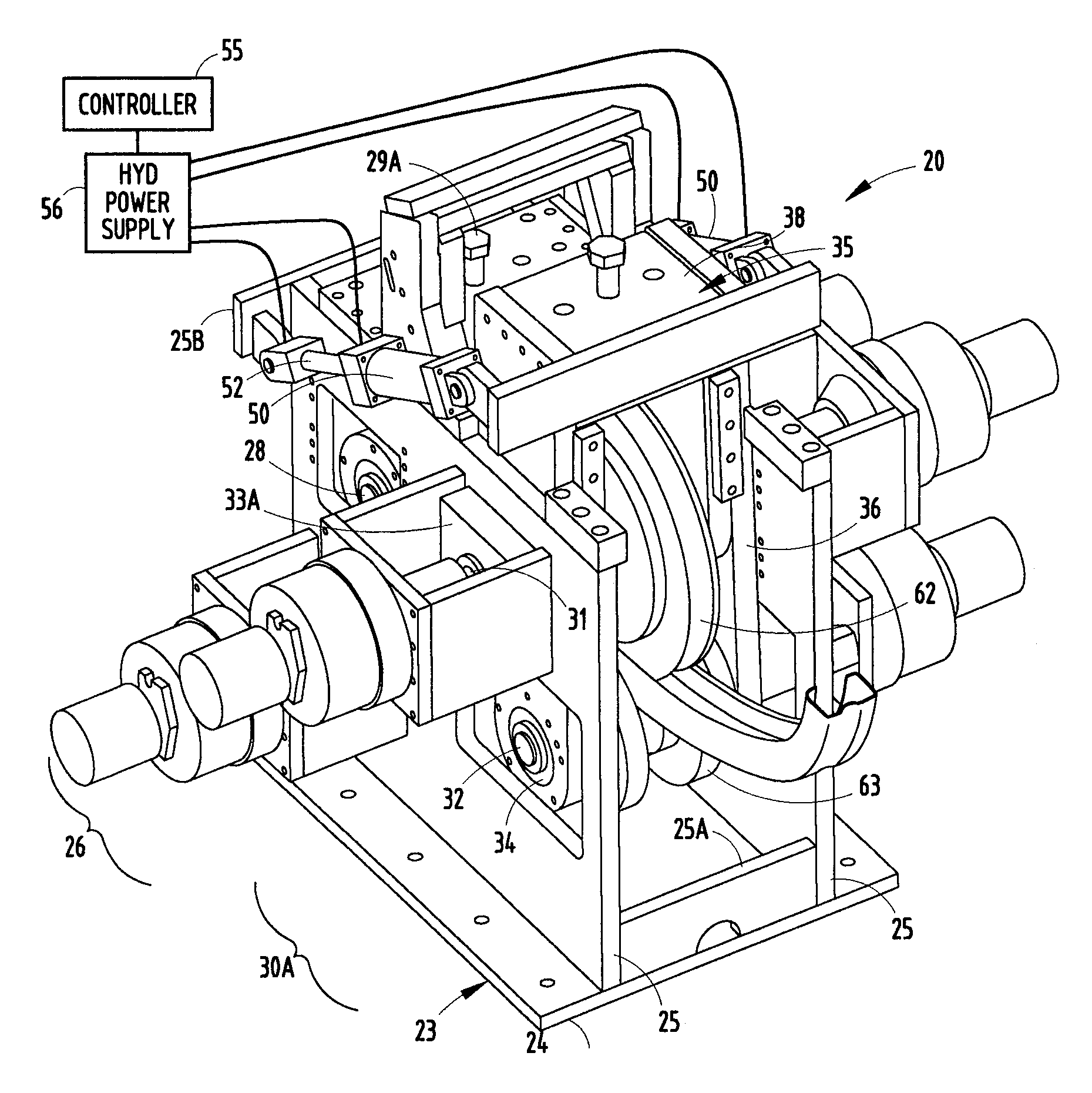

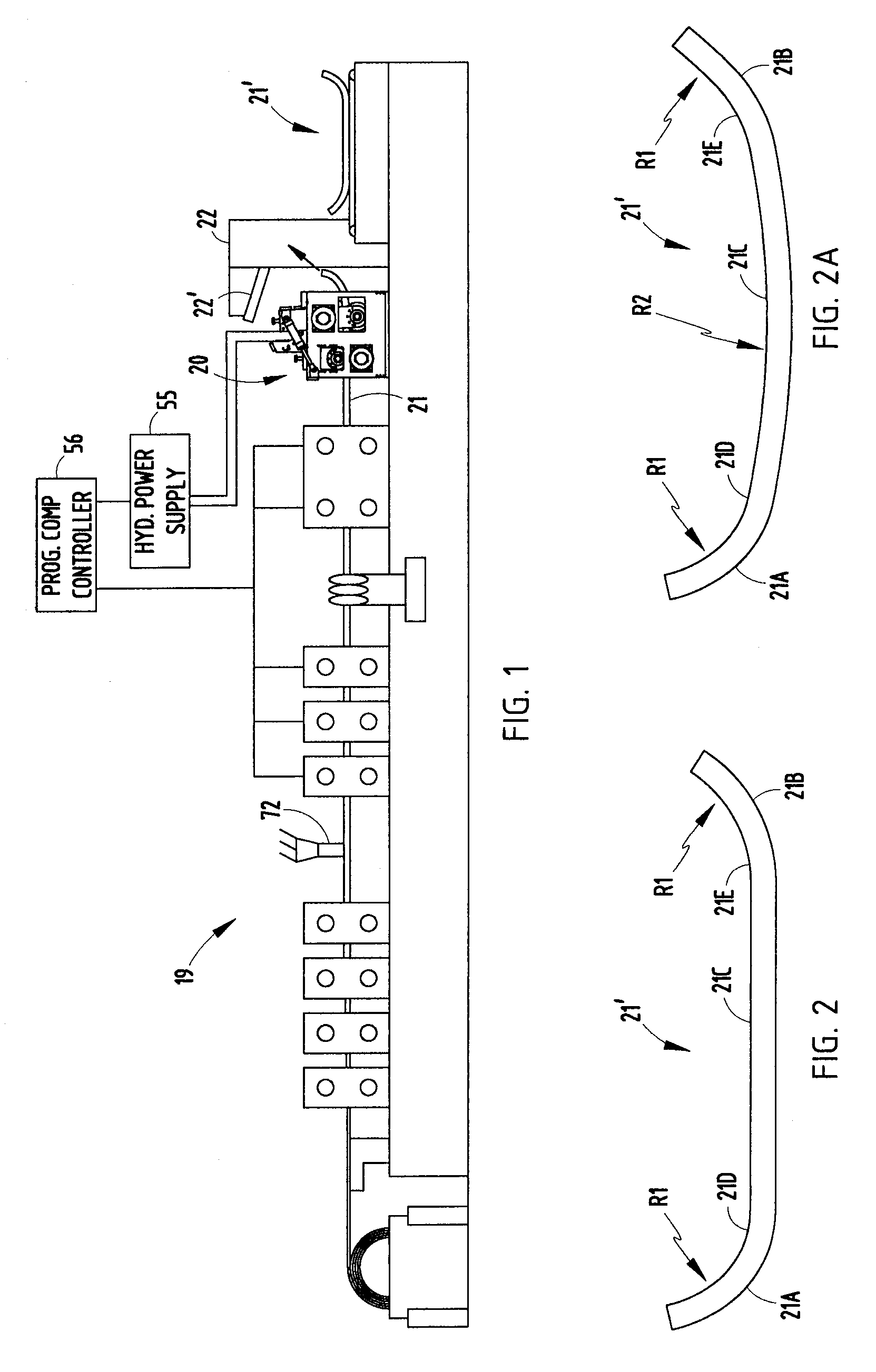

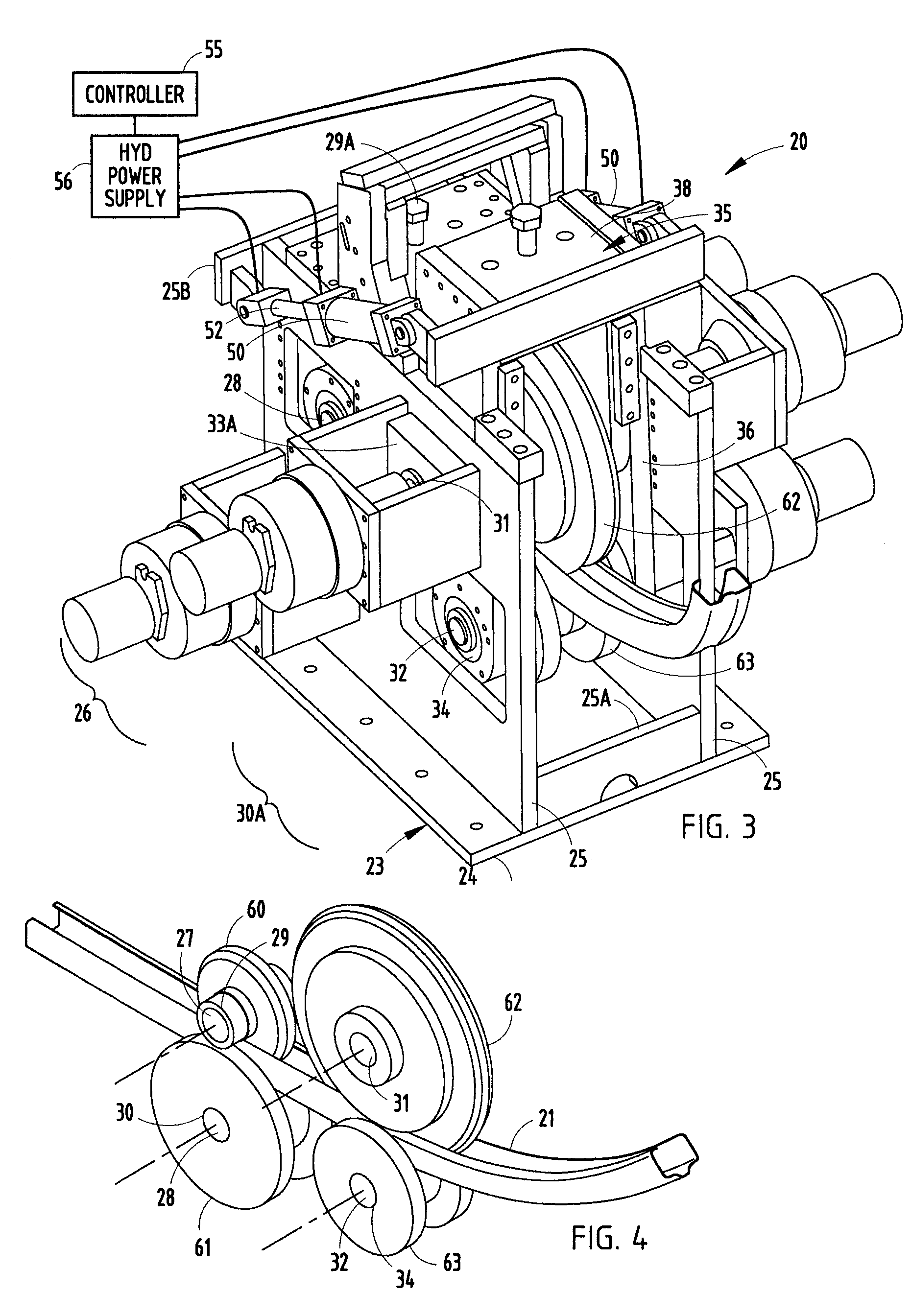

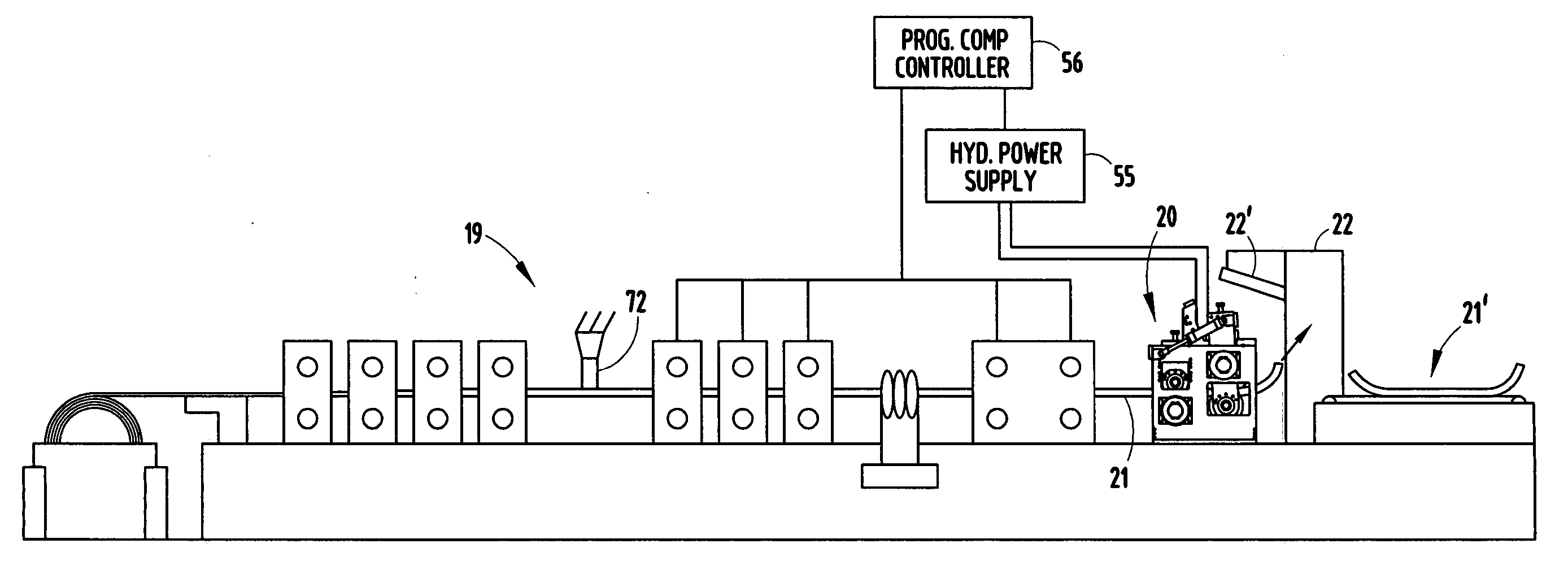

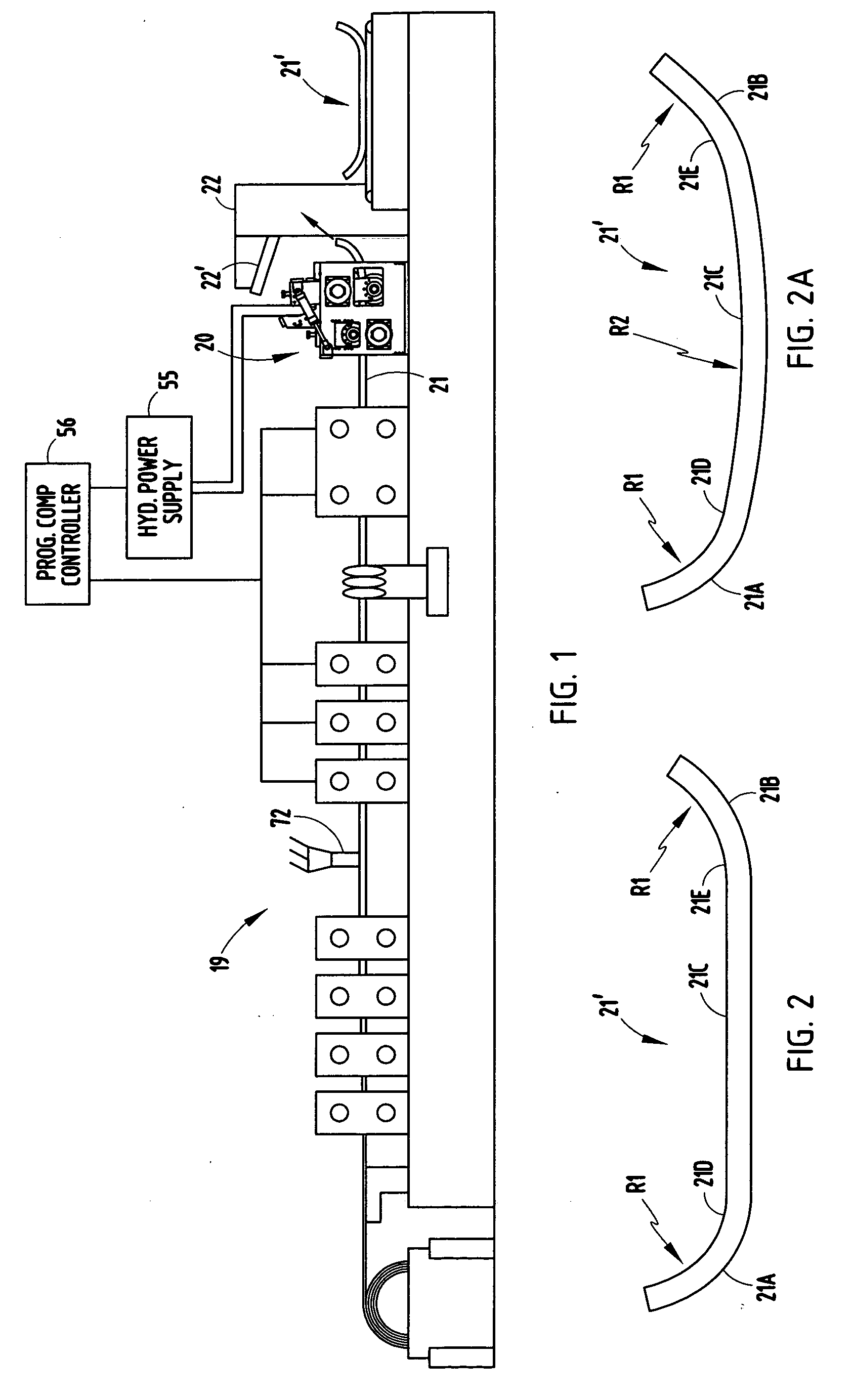

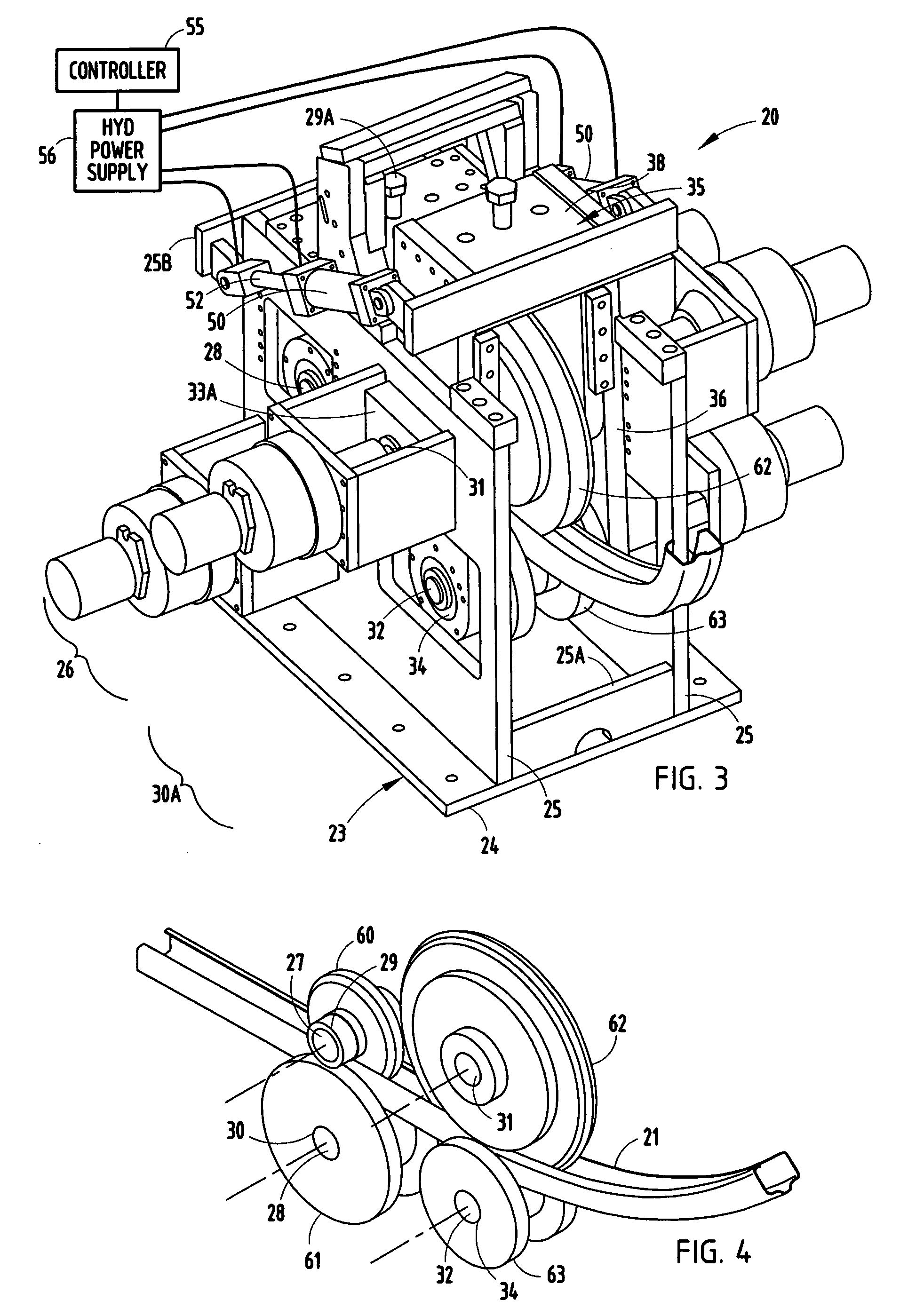

Roll-former apparatus with rapid-adjust sweep box

A computer controlled roll-forming apparatus is adapted to provide a repeating pattern of different longitudinal shapes to a continuous beam “on the fly” during the roll-forming process. A sweep station of the apparatus includes a primary bending roller tangentially engaging the continuous beam along the line level and an armature for biasing the continuous beam against the primary bending roller for a distance partially around a downstream side of the primary bending roller to form a sweep. Actuators adjustably move the armature partially around the downstream side of the primary bending roller between multiple positions for imparting a series of different longitudinal shapes. Internal and external mandrels control wall stability to allow even sharper sweeps. In one form, the apparatus also includes a coordinated cut-off, so that when separated into bumper beam segments, the ends of the individual beam segments have a greater sweep than their center sections.

Owner:SHAPE CORP

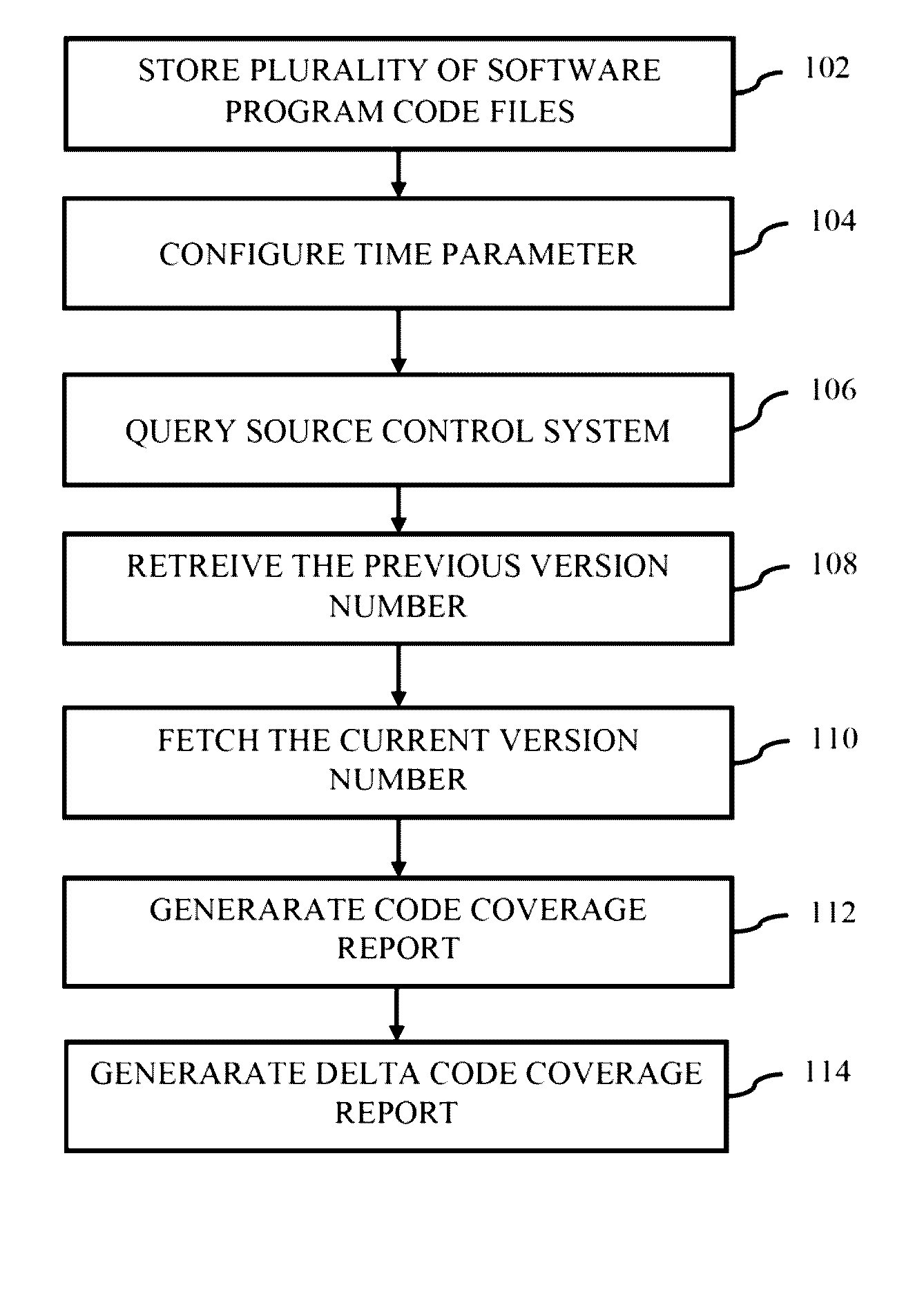

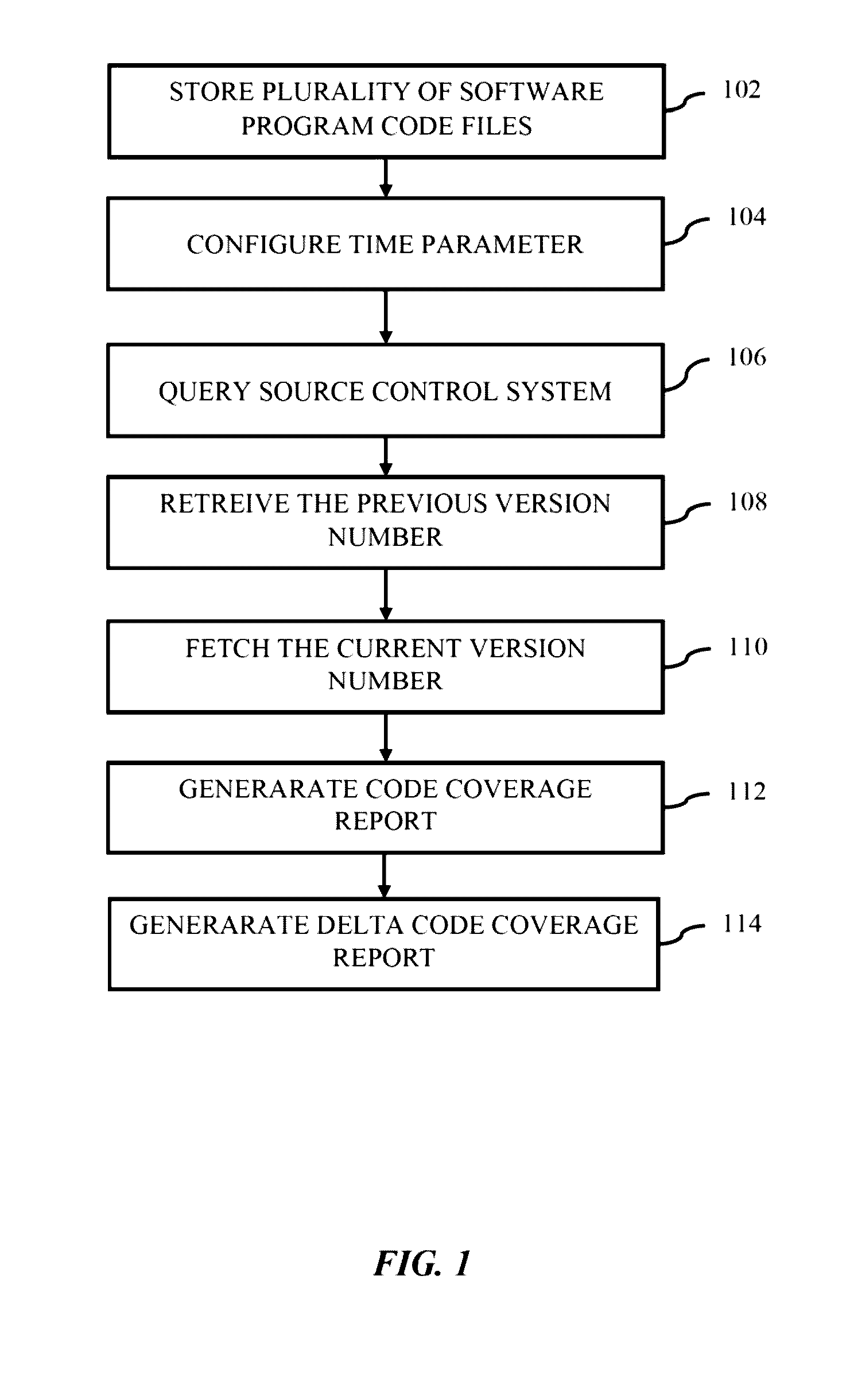

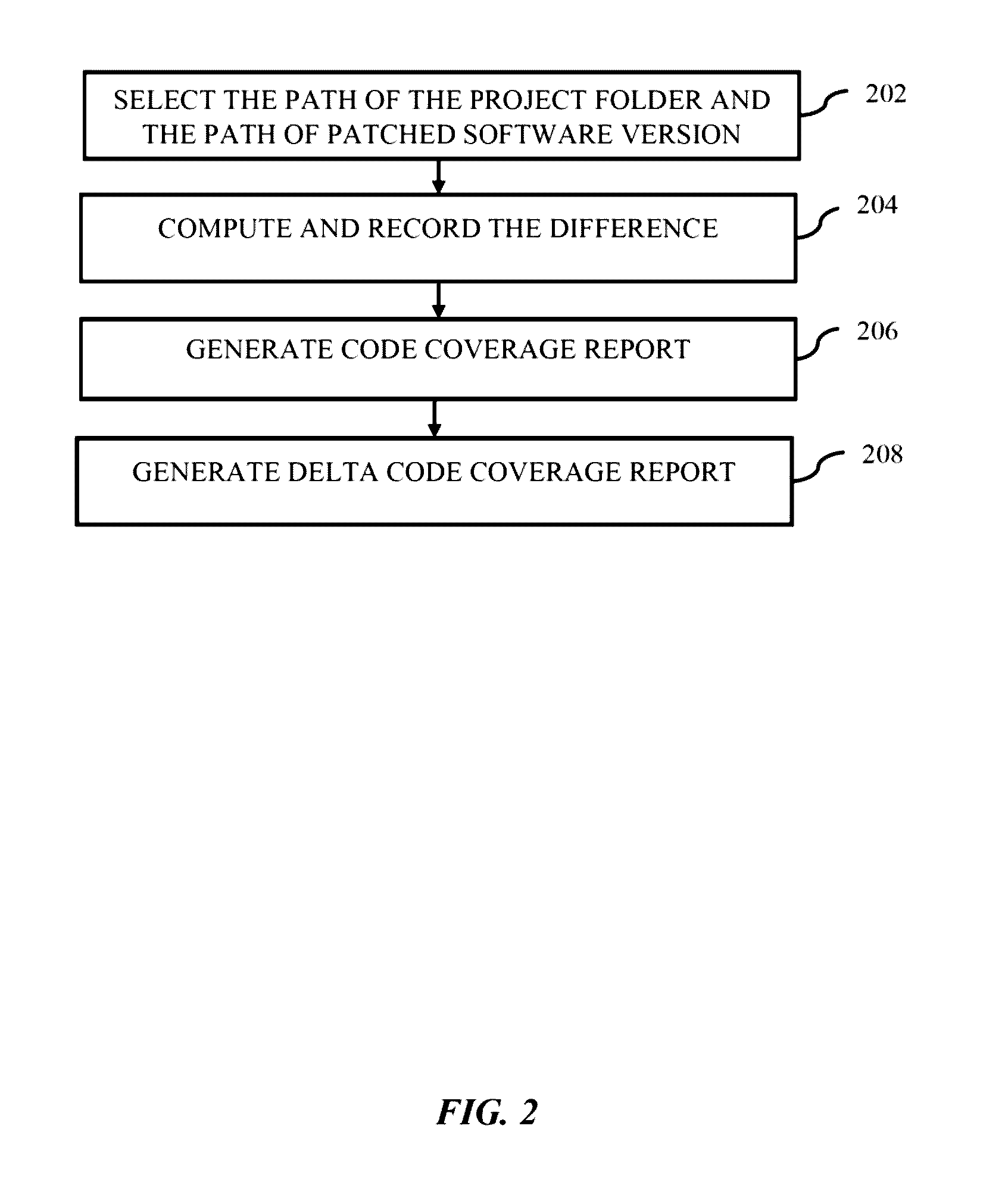

Method and system for providing delta code coverage information

ActiveUS20160299835A1Improve software qualitySoftware testing/debuggingCode coverageParallel computing

The various embodiments herein disclose a system and method for generating a delta code coverage information. The system for generating delta code coverage information comprises, a source control module configured for storing a plurality of software program code files to be processed and a plurality of code coverage data corresponding to the plurality of software program code files, a processor configured to generate a delta code coverage data for analysis for each of the plurality of software program code files on a line level or at a branch level by performing a time based delta code coverage process and a path based delta code coverage process.

Owner:OPSHUB

Multilayer interconnect structure containing air gaps and method for making

ActiveUS7534696B2Electromigration failureQuantity minimizationSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

A multilevel air-gap-containing interconnect structure and a method of fabricating the same are provided. The multilevel air-gap-containing interconnect structure includes a collection of interspersed line levels and via levels, with via levels comprising conductive vias embedded in one or more dielectric layers in which the dielectric layers are solid underneath and above line features in adjacent levels, and perforated between line features. The line levels contain conductive lines and an air-gap-containing dielectric. A solid dielectric bridge layer, containing conductive contacts and formed by filling in a perforated dielectric layer, is disposed over the collection of interspersed line and via levels.

Owner:GLOBALFOUNDRIES U S INC

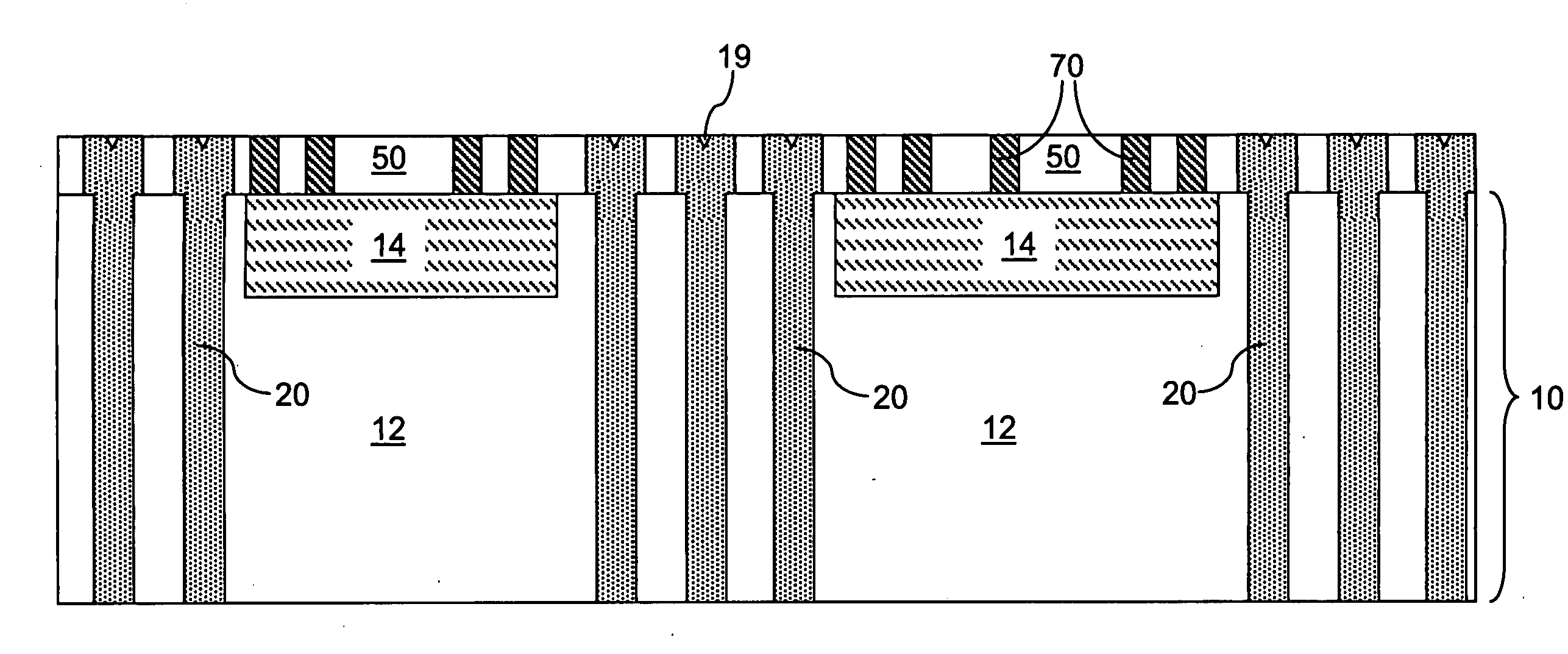

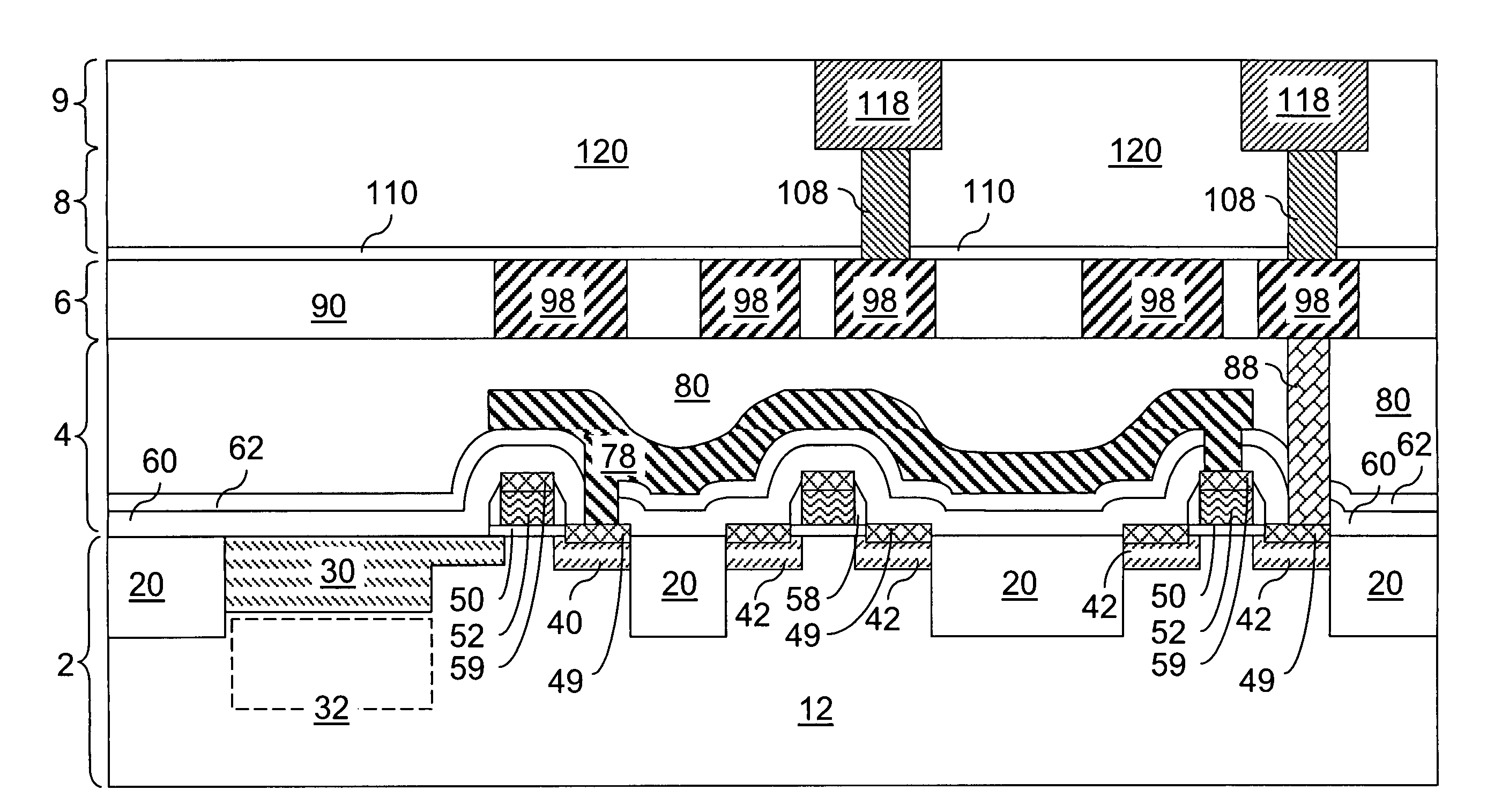

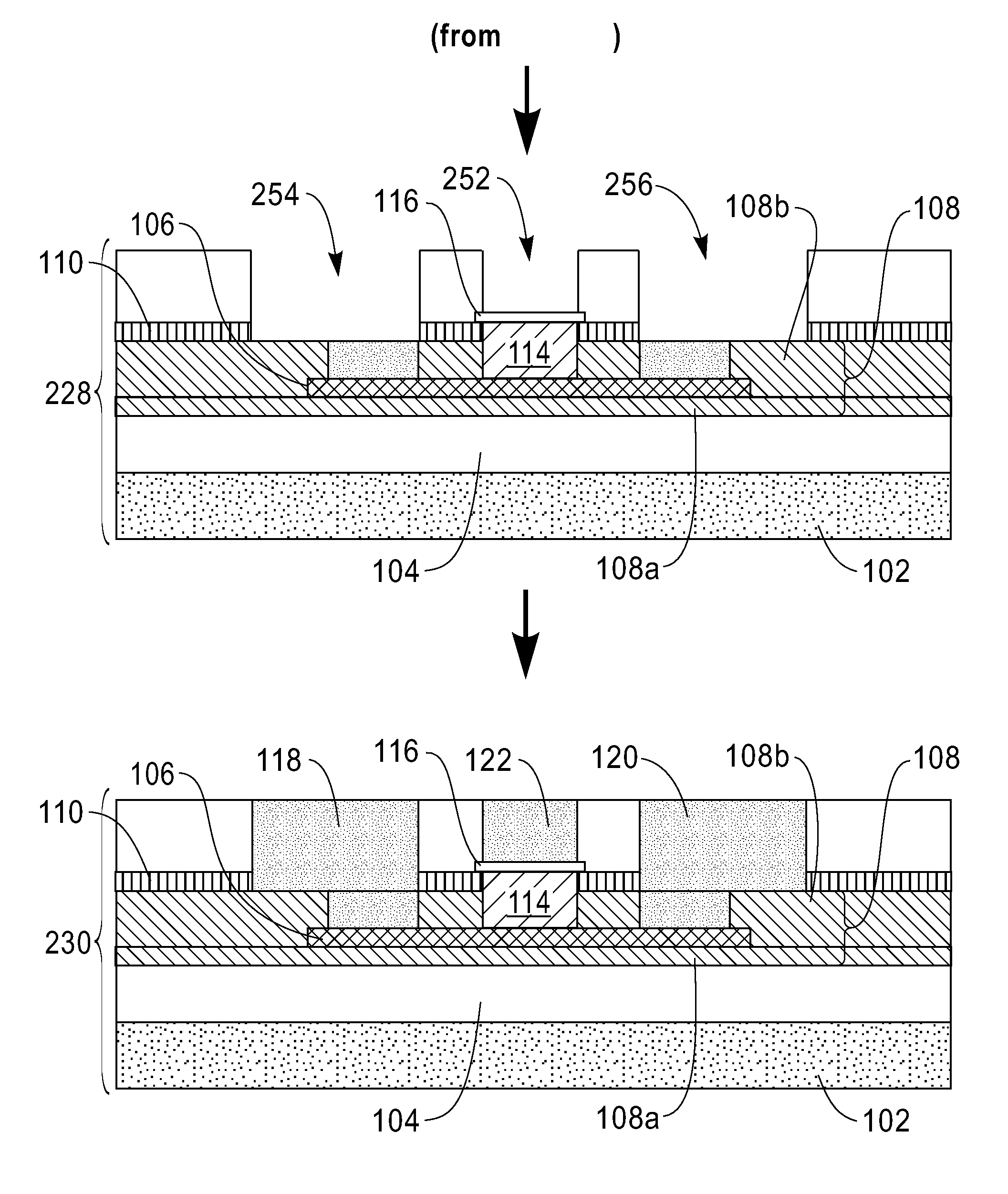

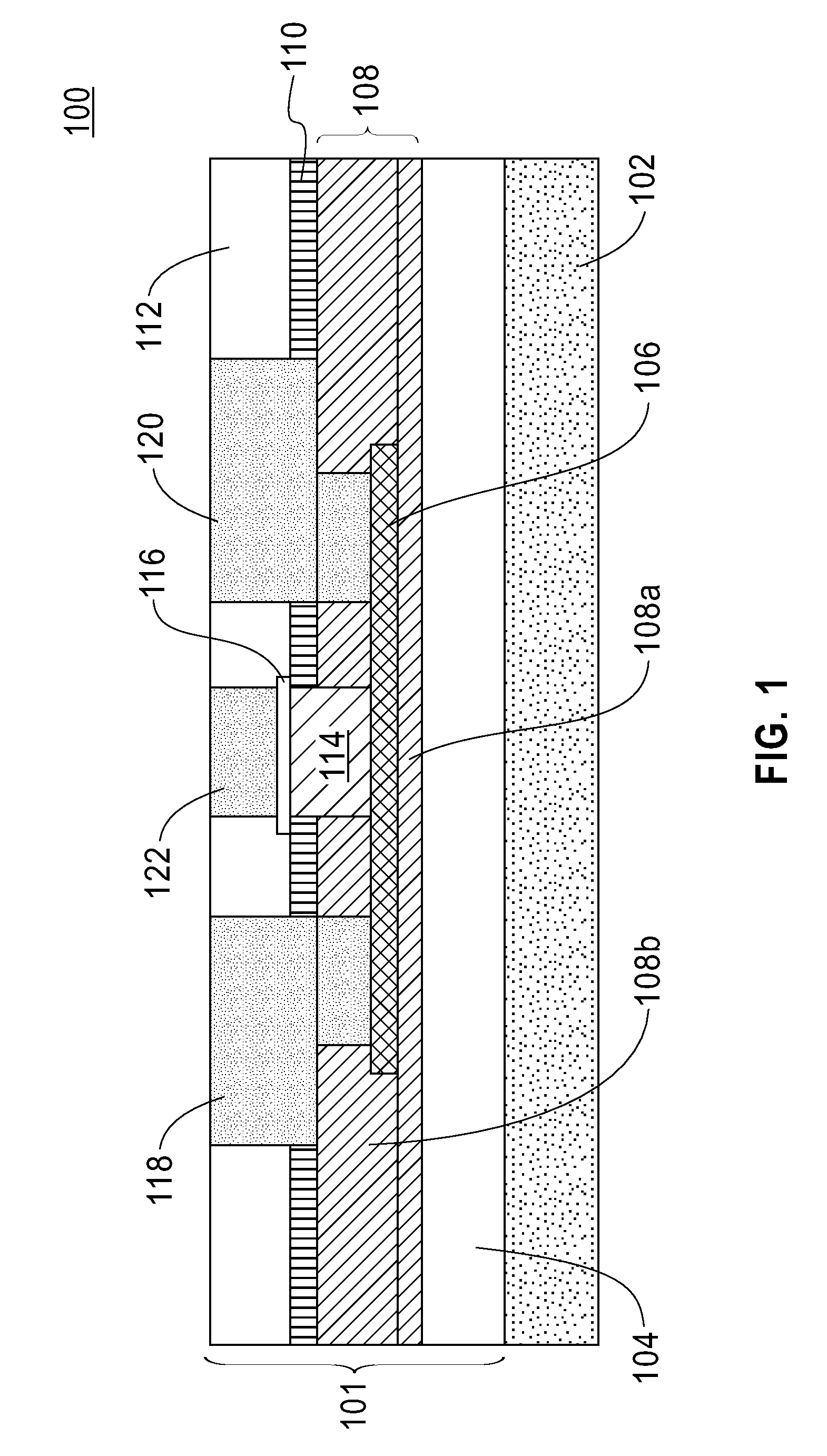

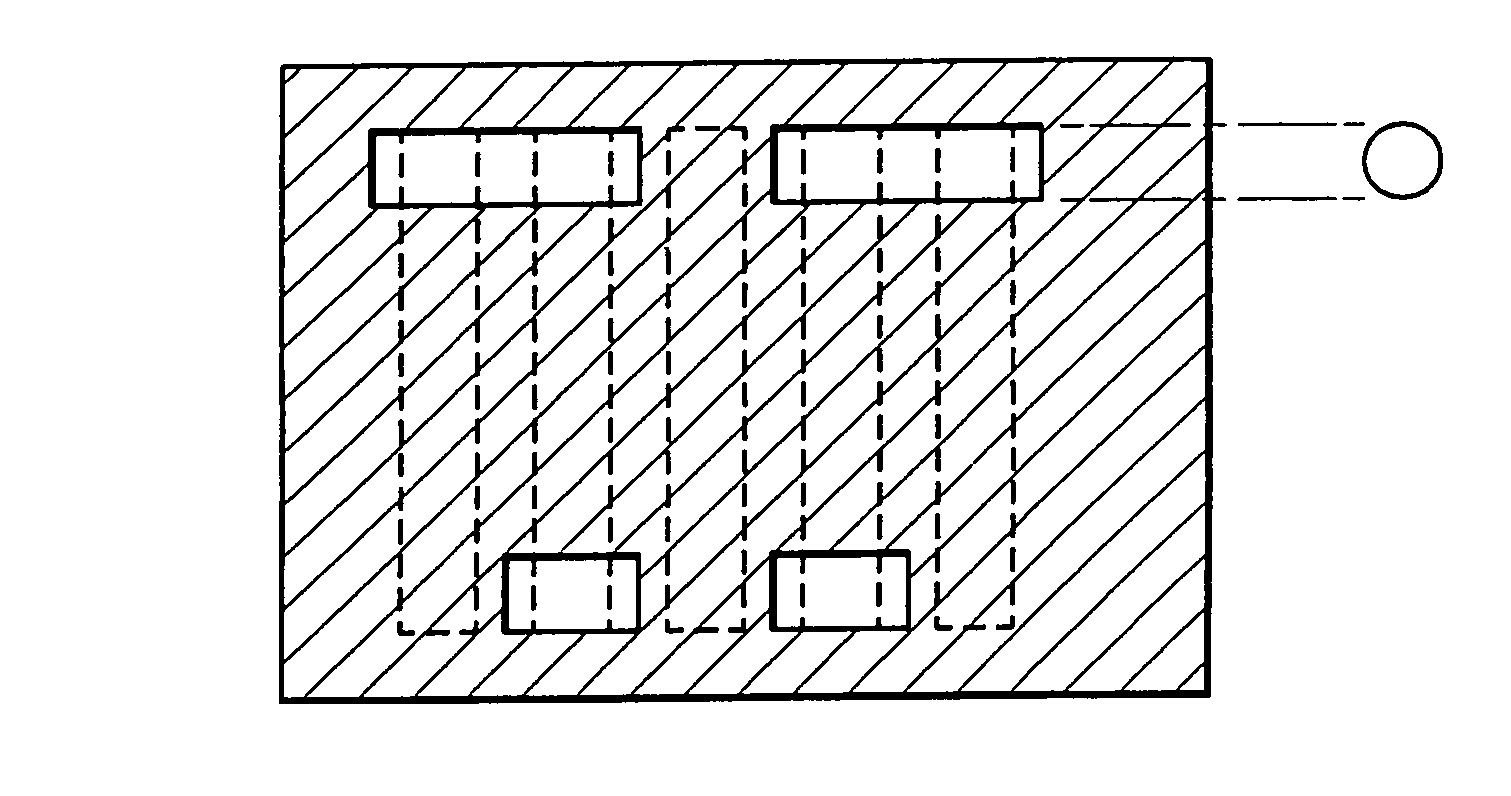

Metal wiring structure for integration with through substrate vias

ActiveUS20100032809A1Improve carrying capacityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

An array of through substrate vias (TSVs) is formed through a semiconductor substrate and a contact-via-level dielectric layer thereupon. A metal-wire-level dielectric layer and a line-level metal wiring structure embedded therein are formed directly on the contact-via-level dielectric layer. The line-level metal wiring structure includes cheesing holes that are filled with isolated portions of the metal-wire-level dielectric layer. In one embodiment, the entirety of the cheesing holes is located outside the area of the array of the TSVs to maximize the contact area between the TSVs and the line-level metal wiring structure. In another embodiment, a set of cheesing holes overlying an entirety of seams in the array of TSVs is formed to prevent trapping of any plating solution in the seams of the TSVs during plating to prevent corrosion of the TSVs at the seams.

Owner:GLOBALFOUNDRIES US INC

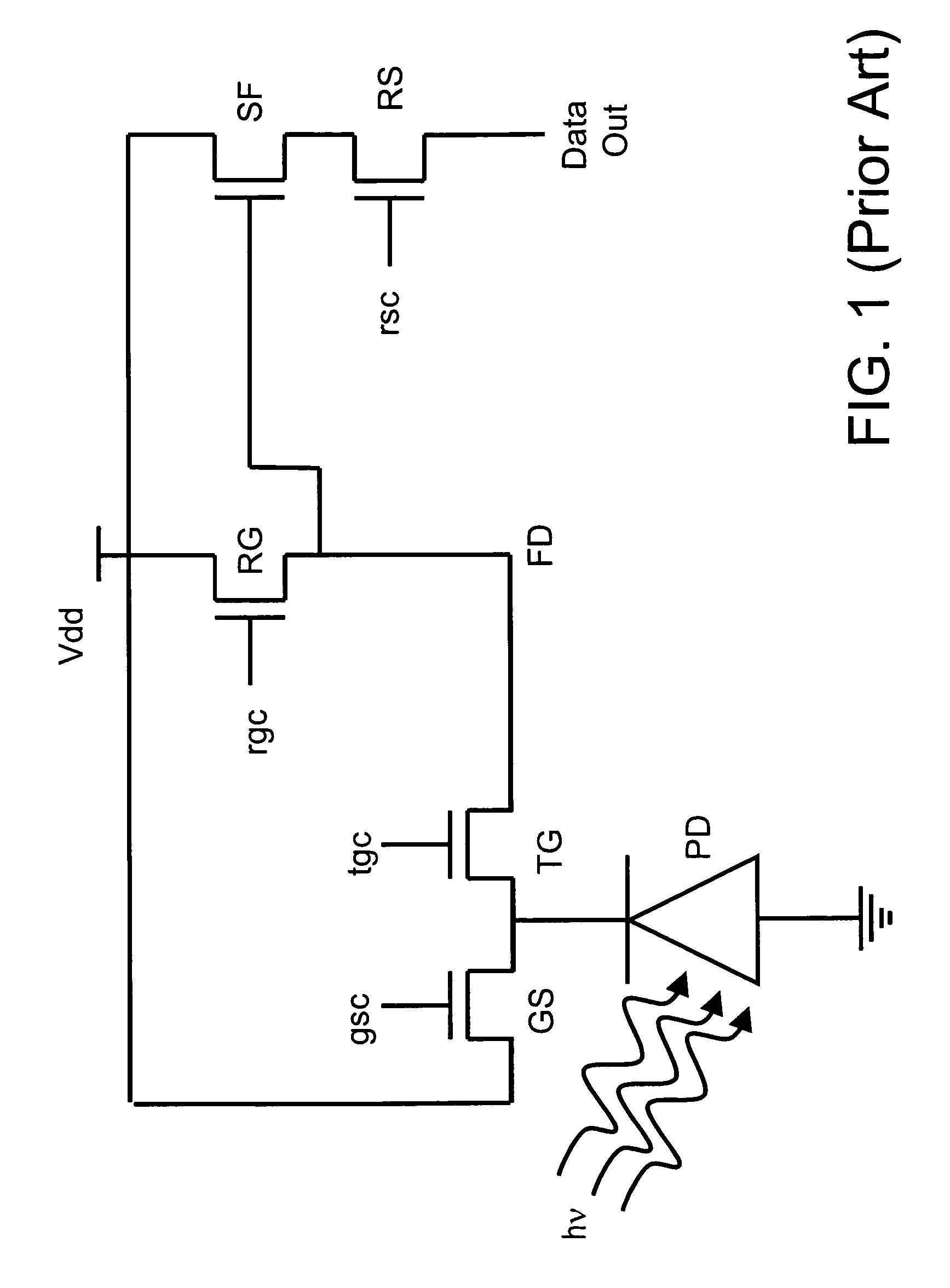

Intralevel conductive light shield

ActiveUS20090305499A1Less-prone to noiseSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectDielectric layer

A conductive light shield is formed over a first dielectric layer of a via level in a metal interconnect structure. The conductive light shield is covers a floating drain of an image sensor pixel cell. A second dielectric layer is formed over the conductive light shield and at least one via extending from a top surface of the second dielectric layer to a bottom surface of the first dielectric layer is formed in the metal interconnect structure. The conductive light shield may be formed within a contact level between a top surface of a semiconductor substrate and a first metal line level, or may be formed in any metal interconnect via level between two metal line levels. The inventive image sensor pixel cell is less prone to noise due to the blockage of light over the floating drain by the conductive light shield.

Owner:GLOBALFOUNDRIES US INC

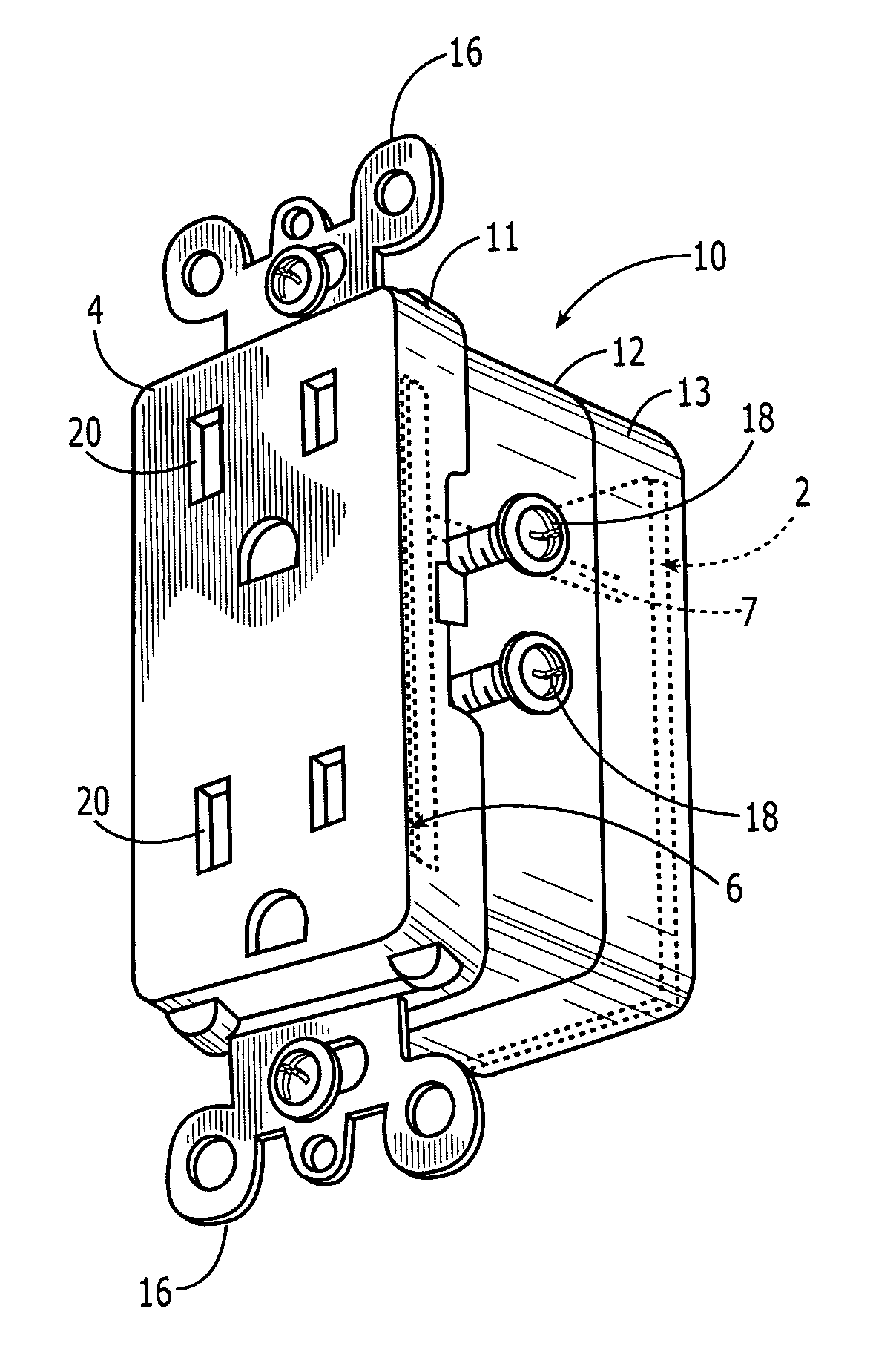

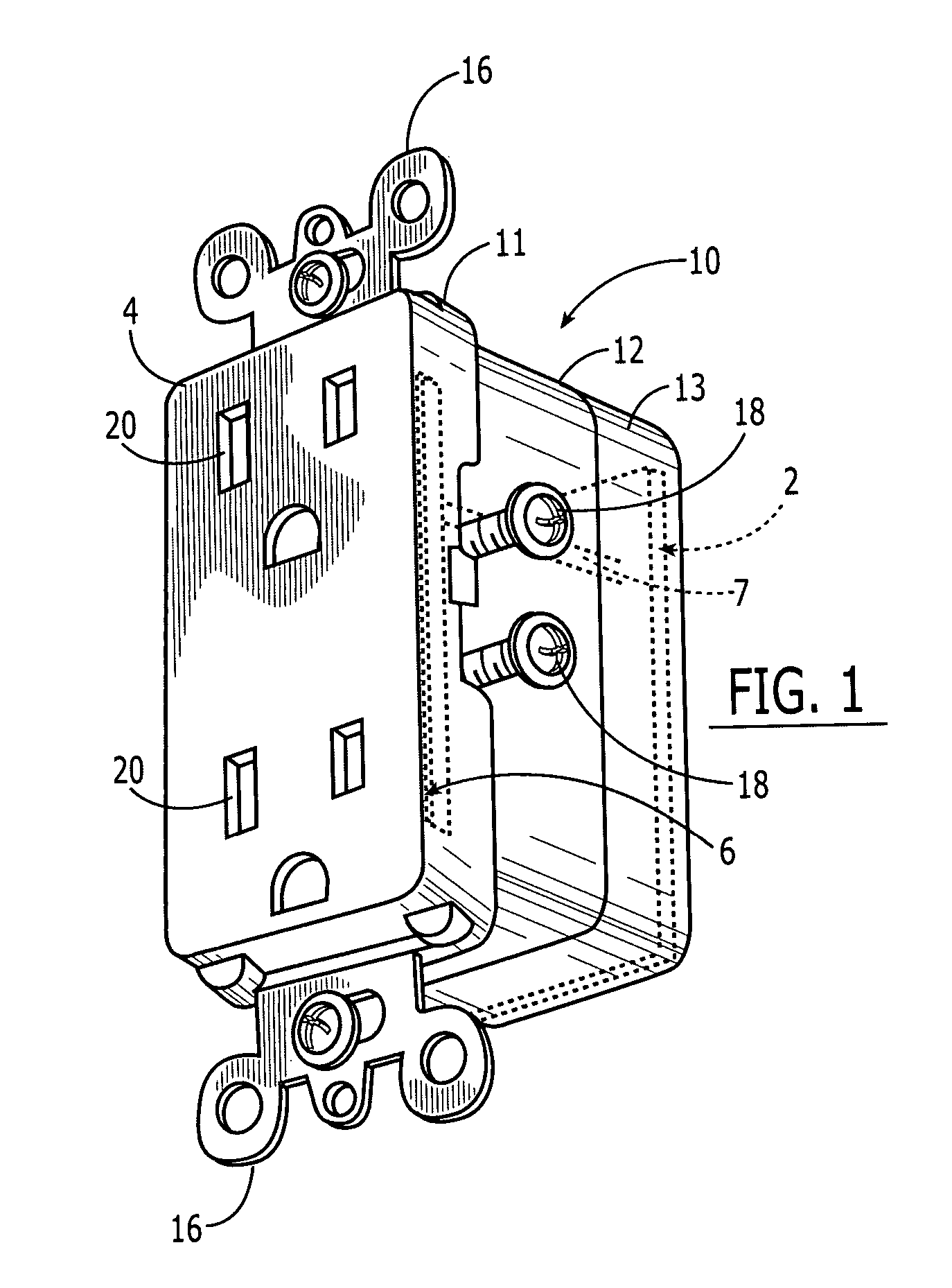

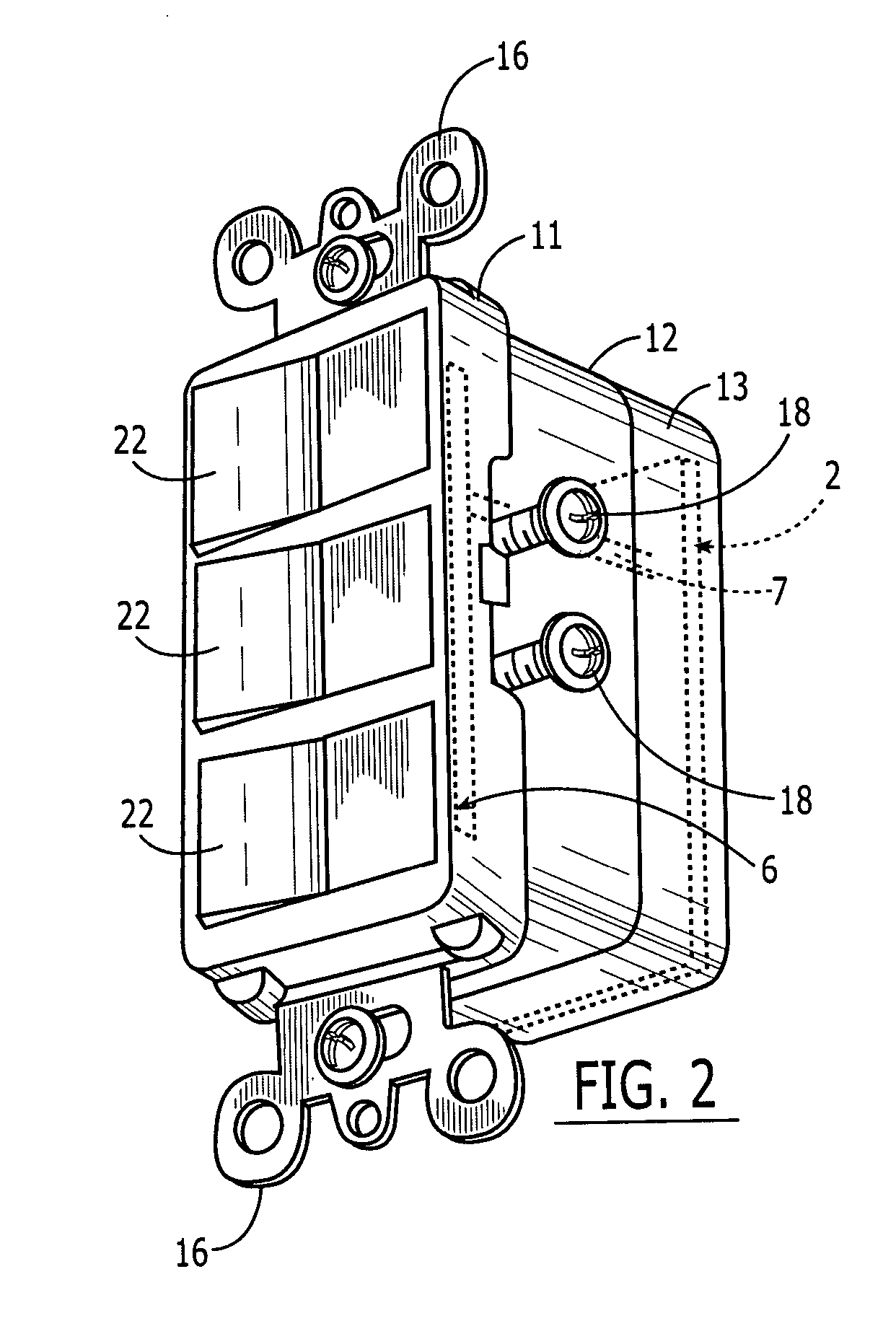

Modular electrical component system combining power line voltage and low voltage elements

InactiveUS20060276144A1Interconnection arrangementsTwo pole connectionsTransceiverCommunications system

An improved system and method of installing wireless network components, such as data transceivers, into residential and commercial buildings and other structures, by combining said wireless network components with standard power receptacles, switches, and similar devices. A module electrical device combines a low-voltage signaling or communications system device with a power line voltage device in a single housing that can be listed and installed in accordance with current electrical codes. The device can be installed in standard power-line level wall box electrical enclosures. The housing provides a plurality of internal cavities through which power line voltage and low-voltage wiring can be routed. A variety of connecting means can be provided on the front and rear faces of the housing. Housing components may be sized and configured to have common physical mating surface designs so as to allow the predictable assembly of power line level components with low-voltage components to complete construction of a single device internally housing both sets of components.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

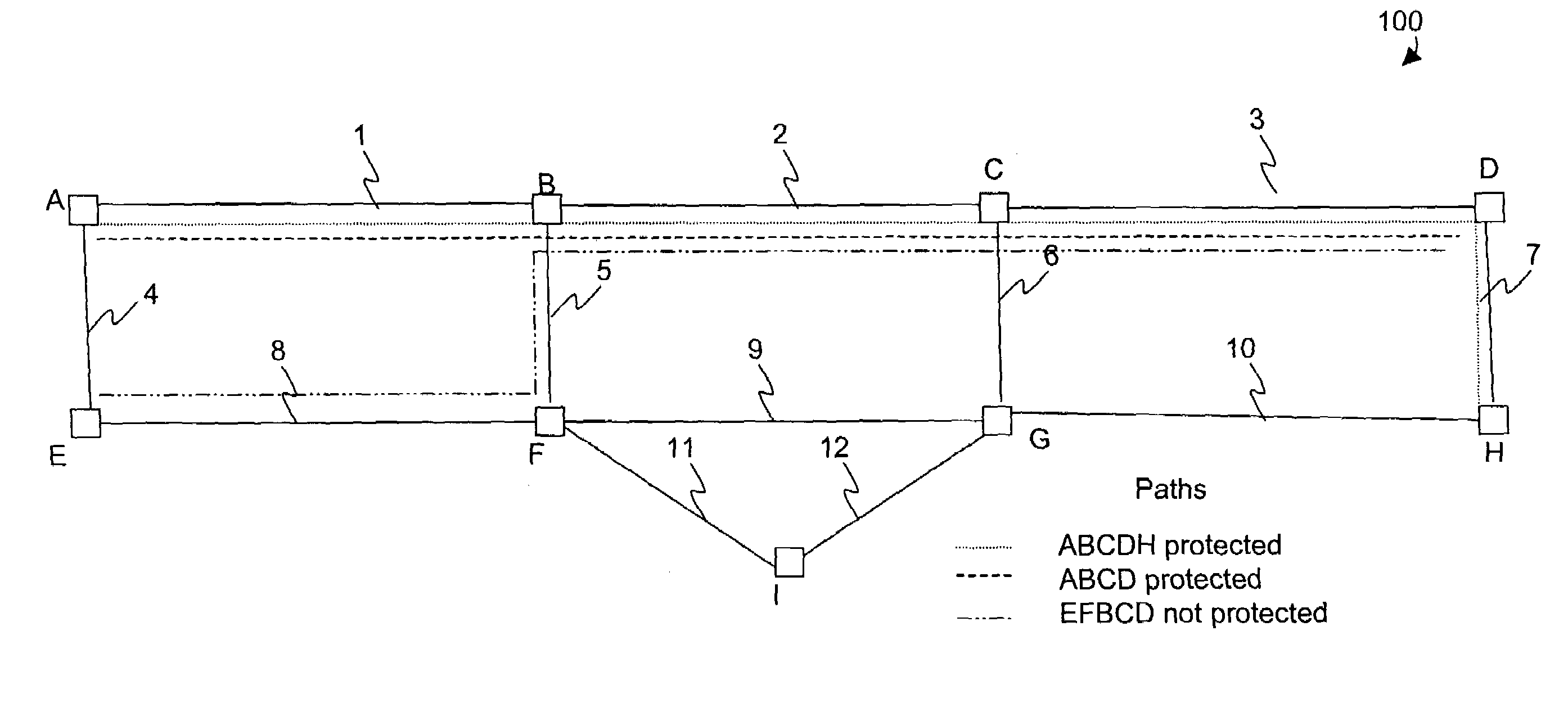

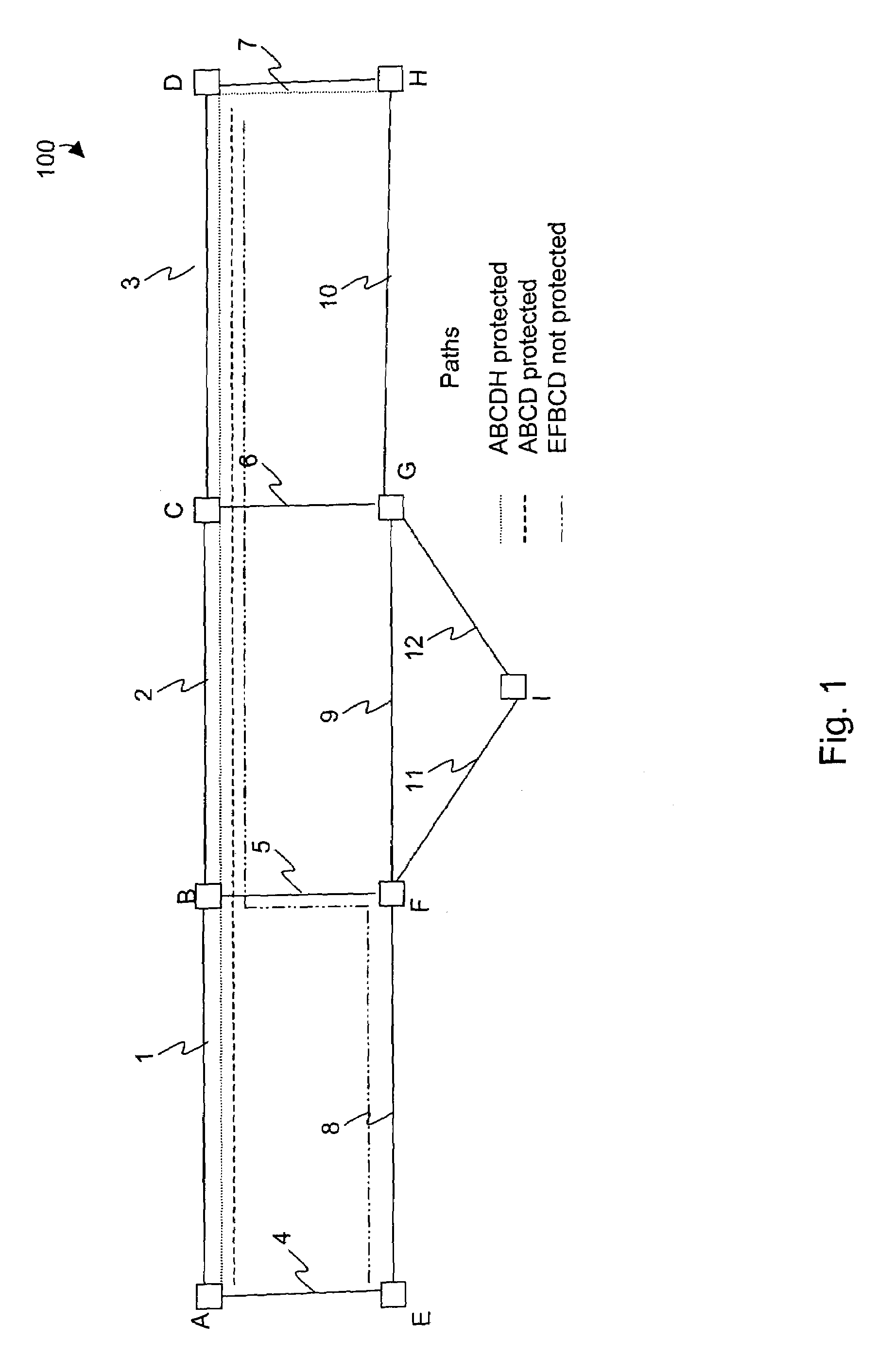

Line-level path protection in the optical layer

Owner:CISCO TECH INC

Line level air gaps

InactiveUS7084479B2Large gate RC delayImprove mechanical stabilitySemiconductor/solid-state device detailsSolid-state devicesPorosityLine level

In a multilevel microelectronic integrated circuit, air comprises permanent line level dielectric and ultra low-K materials are via level dielectric. The air is supplied to line level subsequent to removal of sacrificial material by clean thermal decomposition and assisted diffusion of byproducts through porosities in the IC structure. Optionally, air is also included within porosities in the via level dielectric. By incorporating air to the extent produced in the invention, intralevel and interlevel dielectric values are minimized.

Owner:GLOBALFOUNDRIES INC

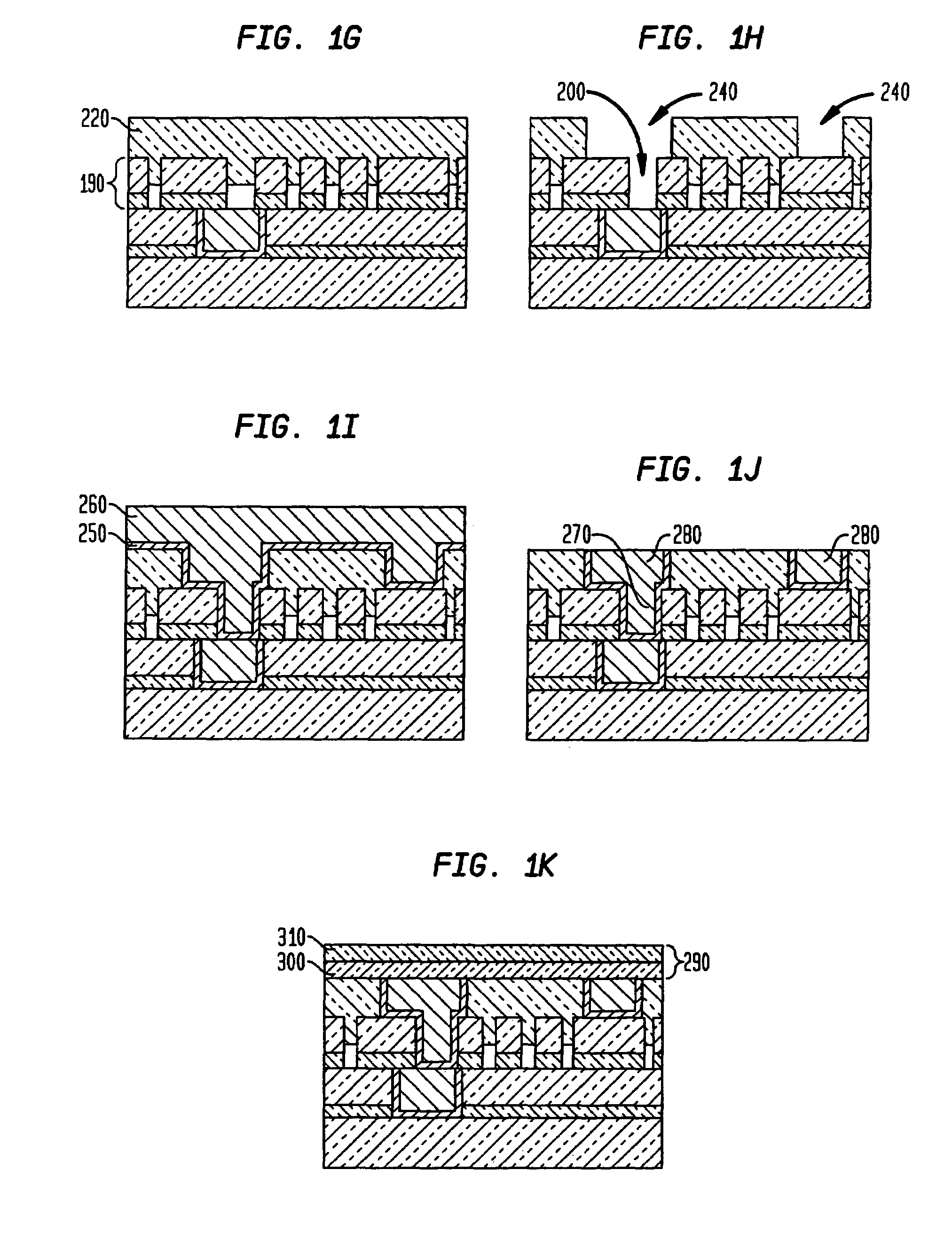

Programmable via devices in back end of line level

ActiveUS20090033358A1NanotechSemiconductor/solid-state device manufacturingIsolation layerEngineering

Programmable via devices and methods for the fabrication thereof are provided. In one aspect, a programmable via device is provided. The programmable via device comprises a first dielectric layer; at least one isolation layer over the first dielectric layer; a heater within the isolation layer; a capping layer over a side of the isolation layer opposite the first dielectric layer; at least one programmable via extending through the capping layer and at least a portion of the isolation layer and in contact with the heater, the programmable via comprising at least one phase change material; a conductive cap over the programmable via; a second dielectric layer over a side of the capping layer opposite the isolation layer; a first conductive via and a second conductive via, each extending through the second dielectric layer, the capping layer and at least a portion of the isolation layer and in contact with the heater; and a third conductive via extending through the second dielectric layer and in contact with the conductive cap.

Owner:GLOBALFOUNDRIES US INC

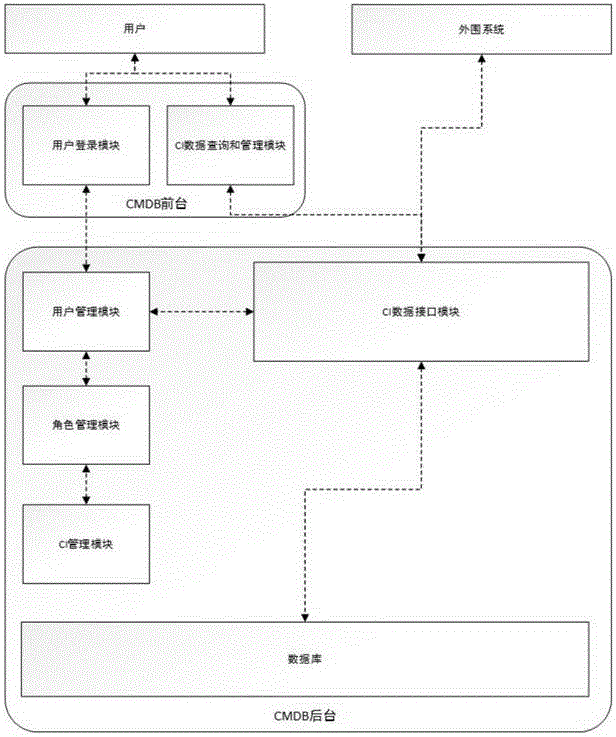

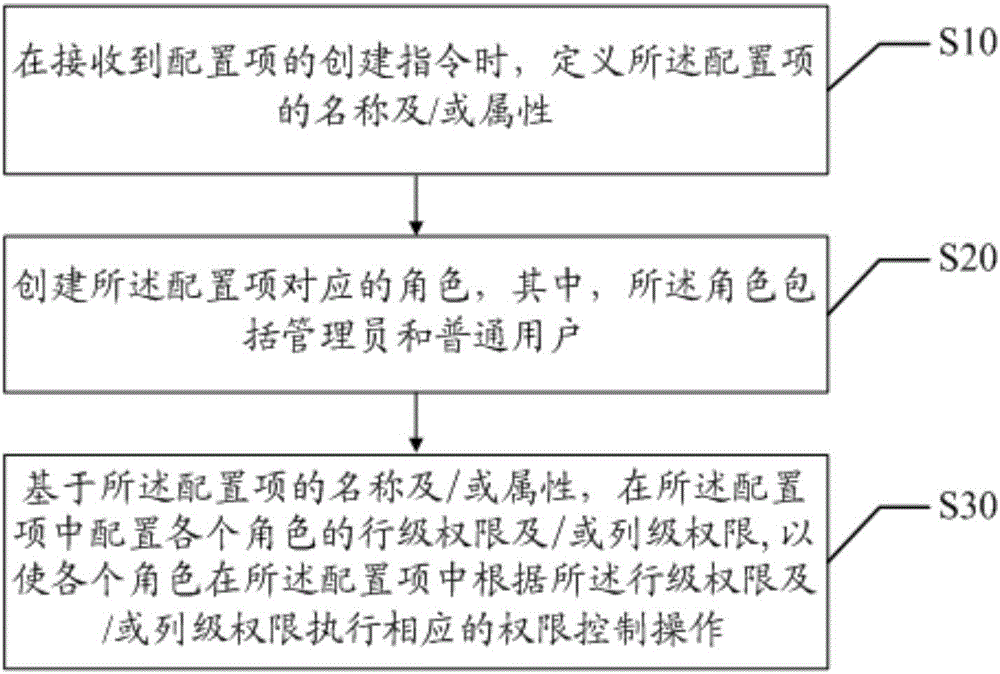

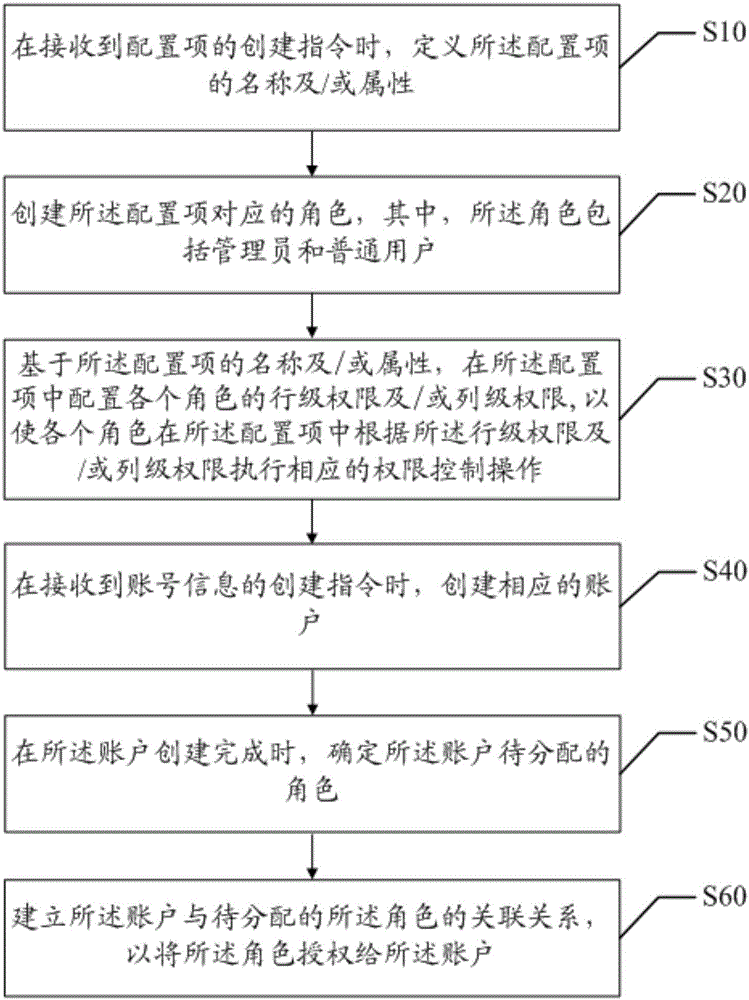

Data level authority configuration method and apparatus

InactiveCN106570406AReduce development costsReduce maintenance costsDigital data protectionDigital data authenticationConfiguration itemData mining

Owner:WEBANK (CHINA)

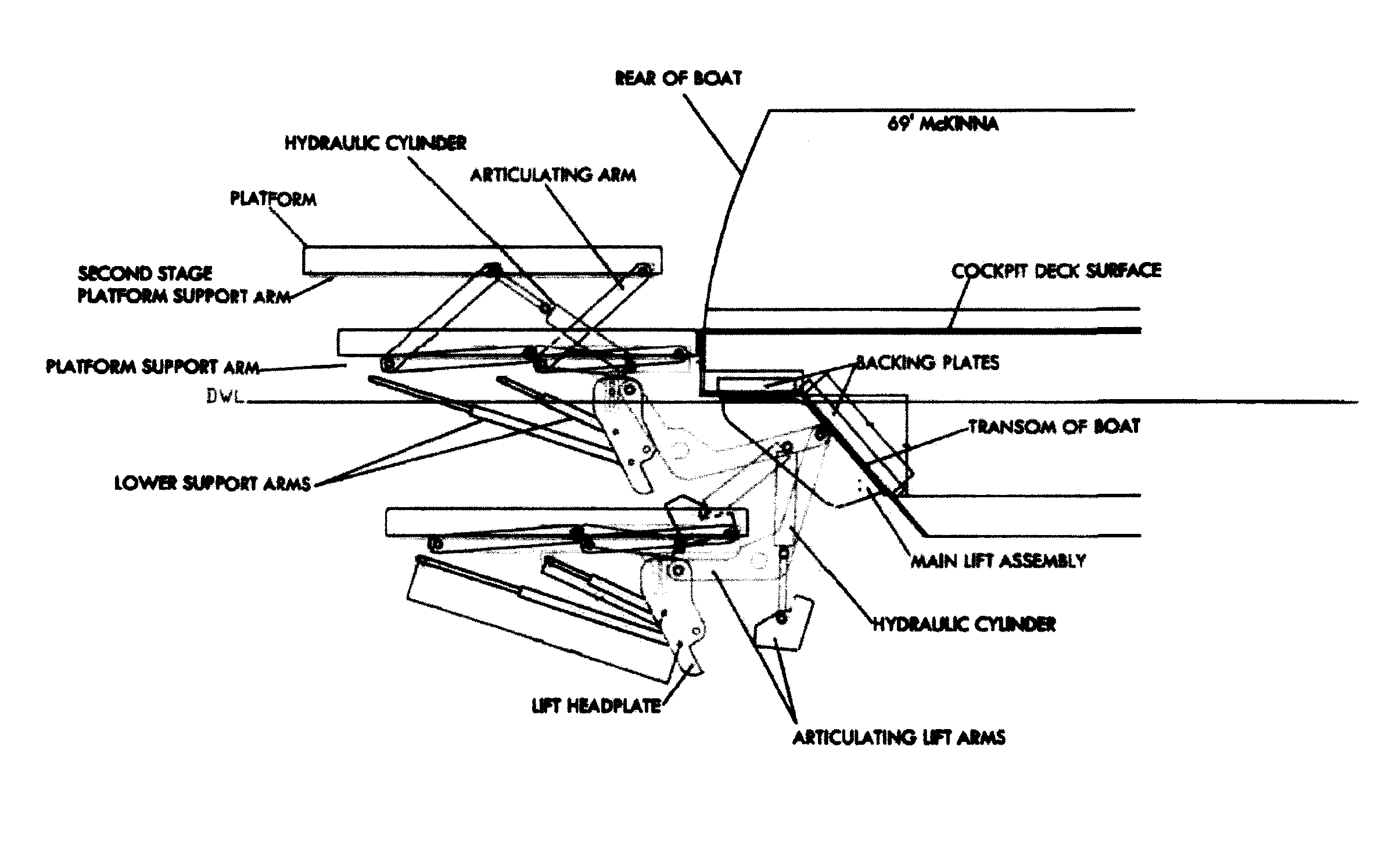

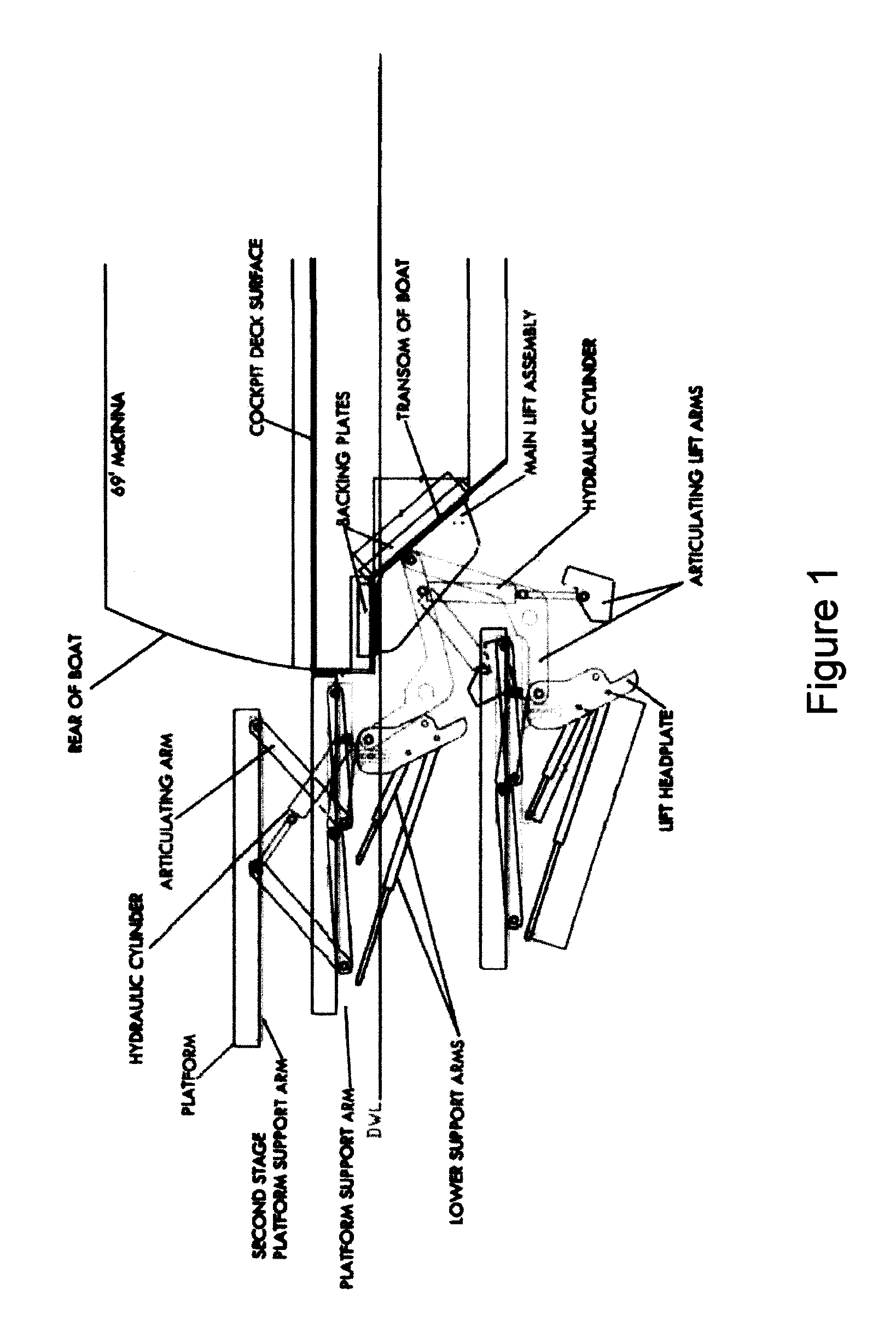

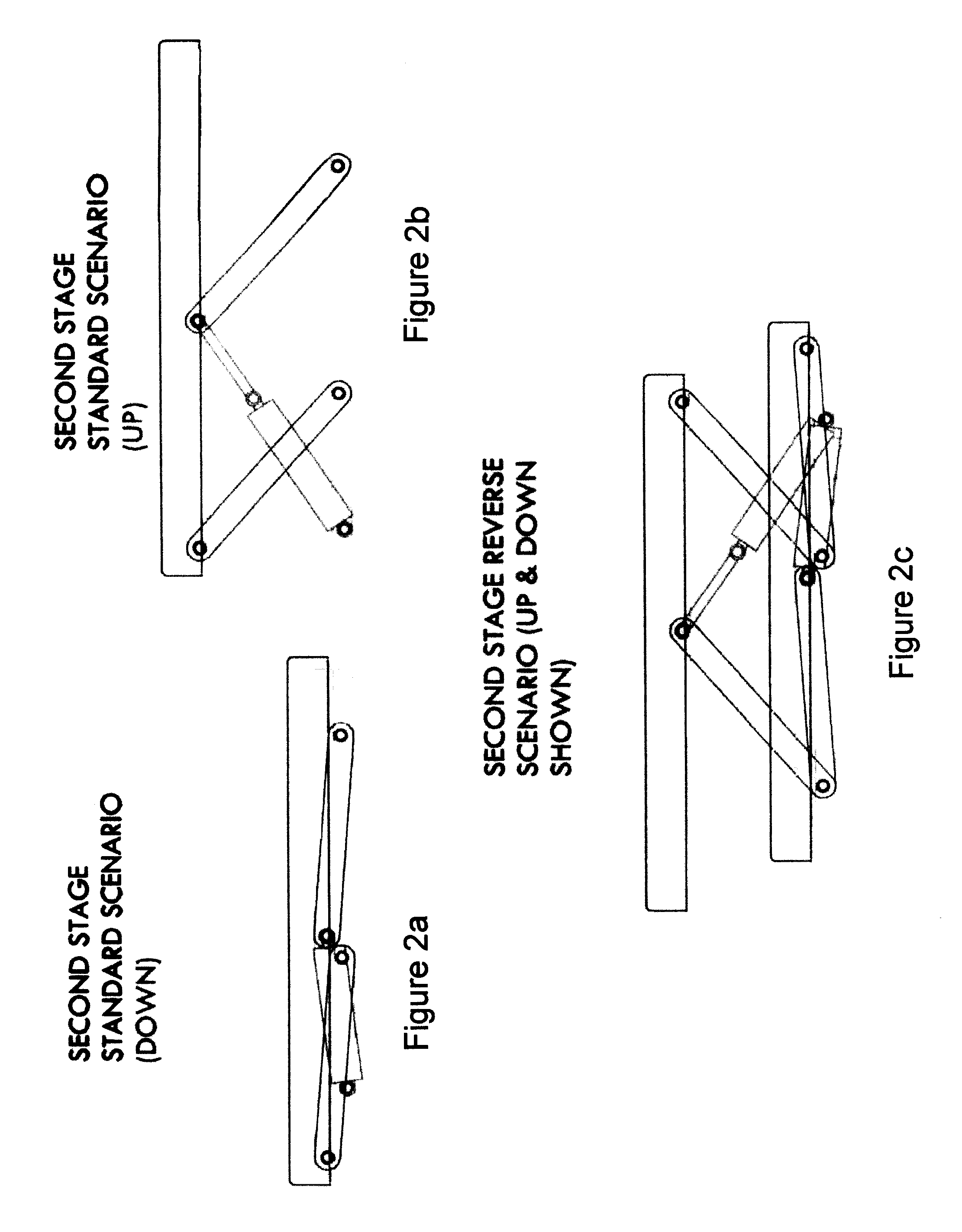

Double acting lift mechanism for boat platform

A second stage lift assembly for a moveable boat stern platform is disclosed and provides the ability to raise the moveable platform up an additional higher amount as compared to it's in-line level with the boat's walk-on deck or fixed platform. By being raised higher when the boat is moving, the moveable platform avoids dragging problems often encountered where the moveable platform remains at the same height as the walk-on deck or fixed platform.

Owner:TNT ELEVATOR SYST INC

Roll-former apparatus with rapid-adjust sweep box

ActiveUS20060277960A1Consistent shapeVehicle componentsMetal rolling arrangementsContinuous beamEngineering

A computer controlled roll-forming apparatus is adapted to provide a repeating pattern of different longitudinal shapes to a continuous beam “on the fly” during the roll-forming process. A sweep station on the apparatus includes a primary bending roller tangentially engaging the continuous beam along the line level and an armature for biasing the continuous beam against the primary bending roller for a distance partially around a downstream side of the primary bending roller to form a sweep. Further, actuators adjustably move the armature at least partially around the downstream side of the primary bending roller between at least first and second positions for imparting multiple different longitudinal shapes into the continuous beam. In one form, the apparatus also includes a coordinated cut-off, so that when separated into bumper beam segments, the ends of the individual beam segments have a greater sweep than their center sections.

Owner:SHAPE CORP

Method for improved process latitude by elongated via integration

Owner:ELPIS TECH INC

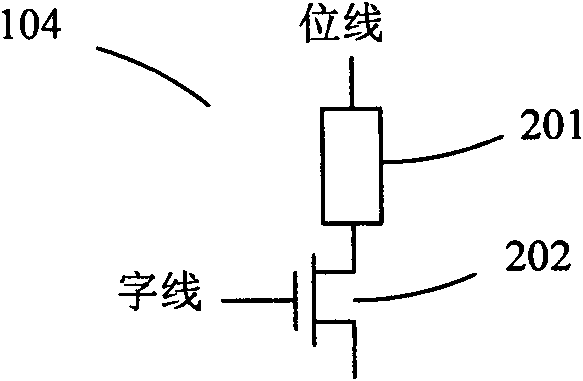

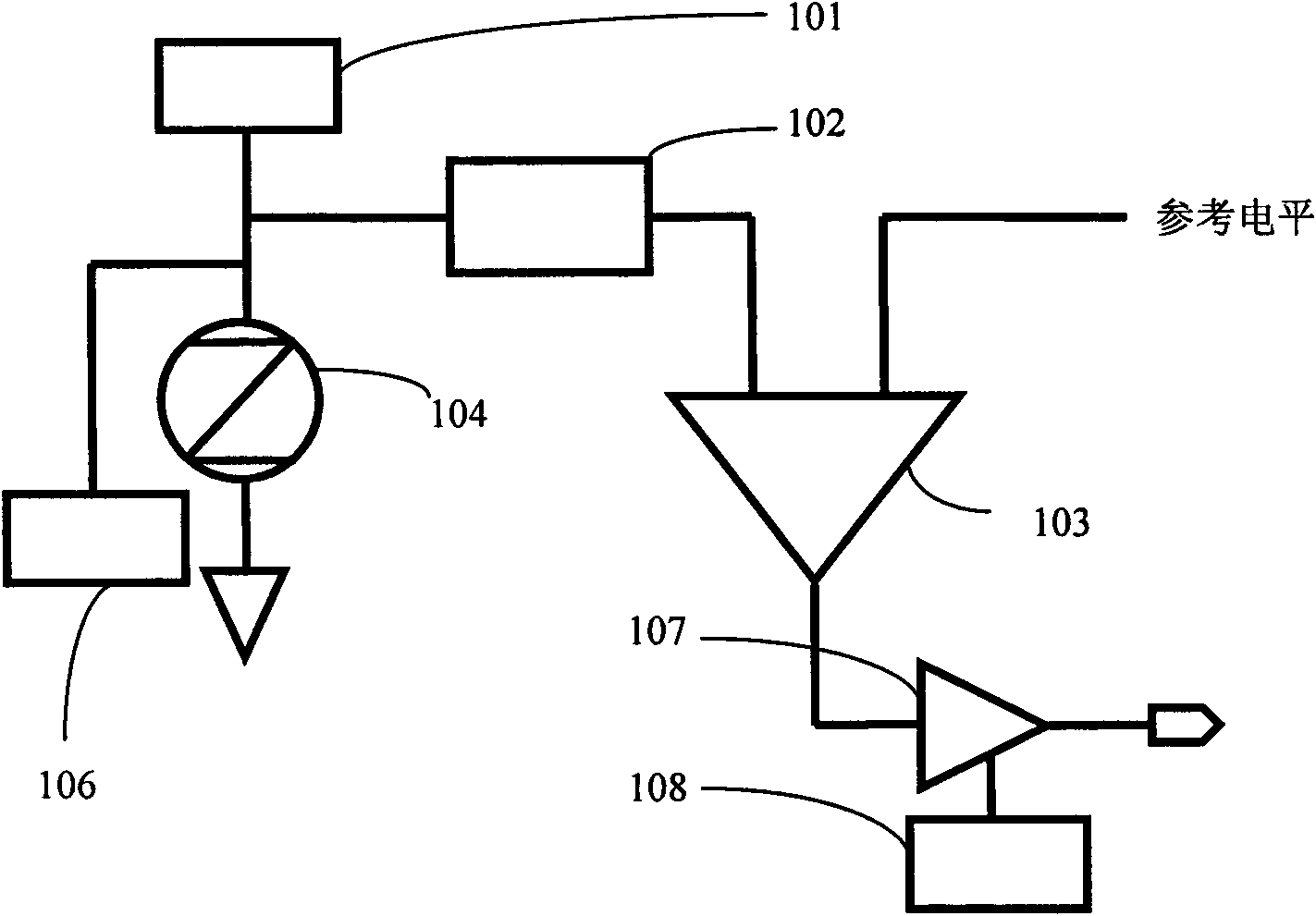

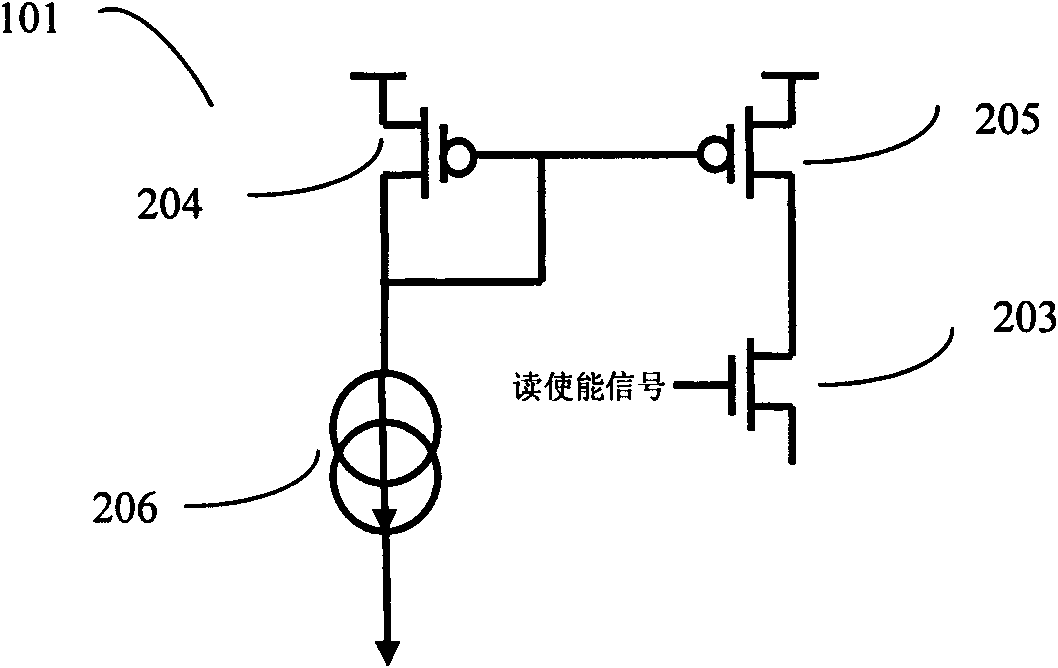

Fast reading device and method of phase change memory

ActiveCN102013271AAvoid destructionImprove read rateRead-only memoriesDigital storageCapacitanceParasitic capacitor

The invention relates to a fast reading device of a phase change memory, which comprises a phase change memory cell to be read, a charging circuit, an overshoot recovery rate detecting circuit, a sensitive amplifier circuit and a reference level or a reference memory cell. On one hand, the phase change memory cell (which can be abstracted as a resistor in the circuit) and a parasitic capacitor ona digit line form a resistor-capacitor (RC) circuit, and on the other hand, a gated metal oxide semiconductor (MOS) pipe instantly enters a linear region from a saturation region when being switched on / of, thereby causing an overshoot phenomenon. For phase change resistors of different states, the corresponding recovery rates after the overshoot are different. By reading the recovery rate of the digit-line level after the overshoot and fast reading the state of the phase change memory cell, the reading rate of the whole memory is accelerated. In addition, fast reading is beneficial to avoiding the damage caused by reading operation to the phase change cell, thereby achieving the purpose of reducing reading interference.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

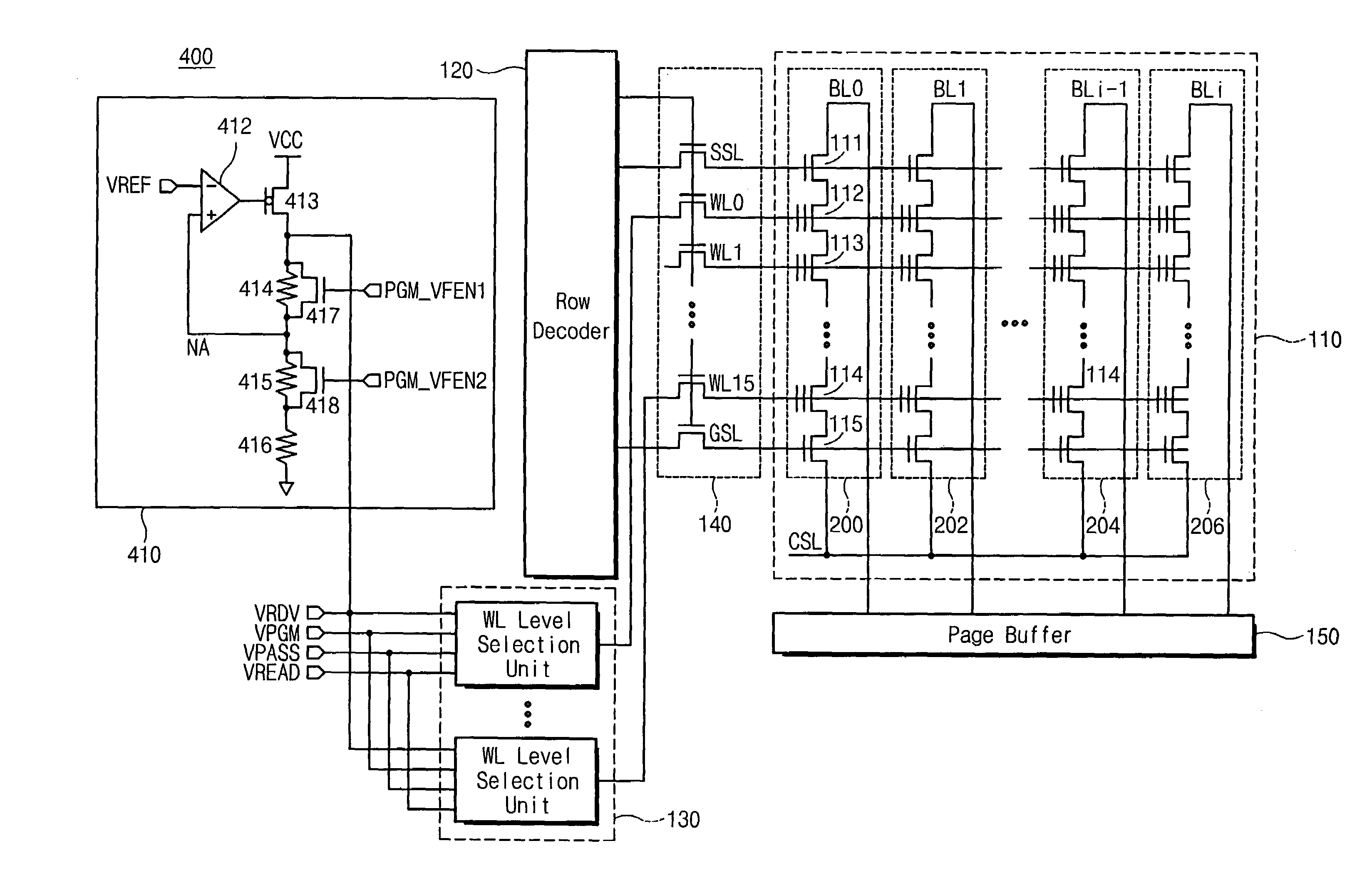

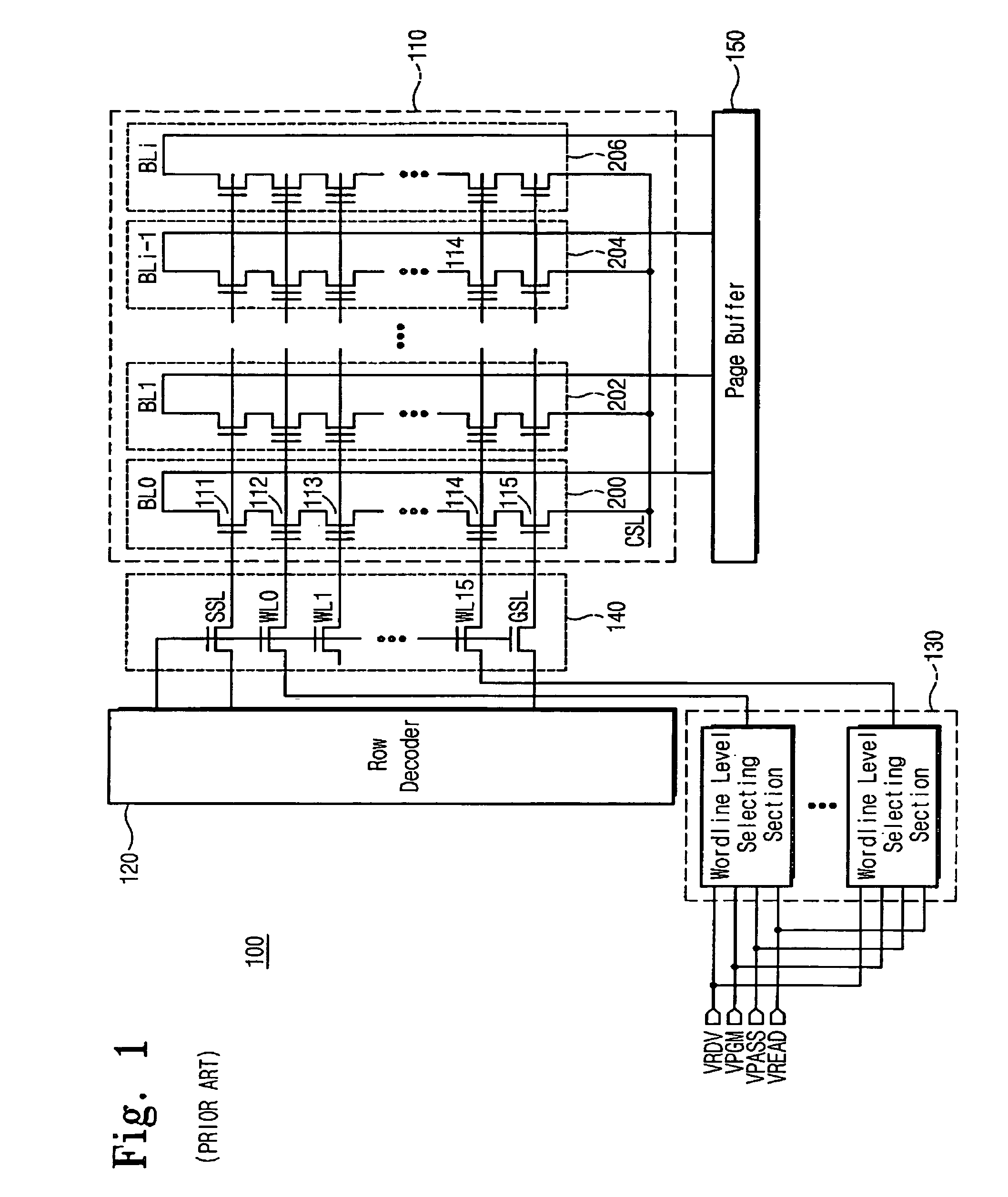

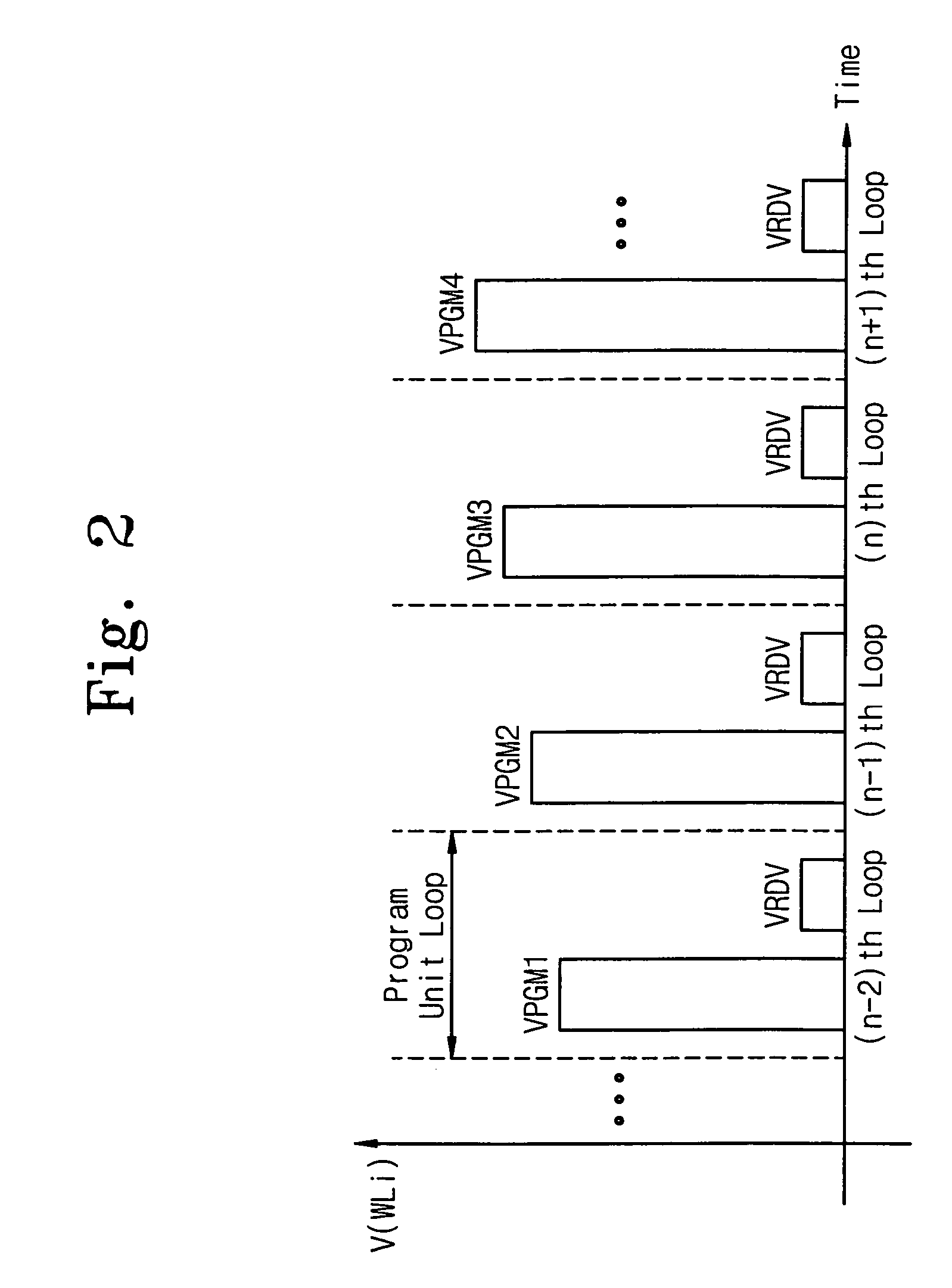

Flash memory device and program verification method thereof

ActiveUS7099196B2Avoid misjudgmentEvenly distributedRead-only memoriesDigital storageVoltage generatorProgram proving

Disclosed is a flash memory device and a program verification method thereof which can prevent a misjudgment as to whether flash memory cells are programmed or not. The flash memory device includes: a program verification voltage generator for variably generating program verification voltages used to verify whether the flash memory cells are programmed or not and a word line level selector for transferring the program verification voltages to word lines connected to control gates of the flash memory cells. The flash memory cells that are verified as uncertain as to whether the flash memory cells are programmed or not can be completely programmed since the program verification operation is carried out with program verification voltage levels that are changed according to the selective activations of the program verification control signals.

Owner:SAMSUNG ELECTRONICS CO LTD

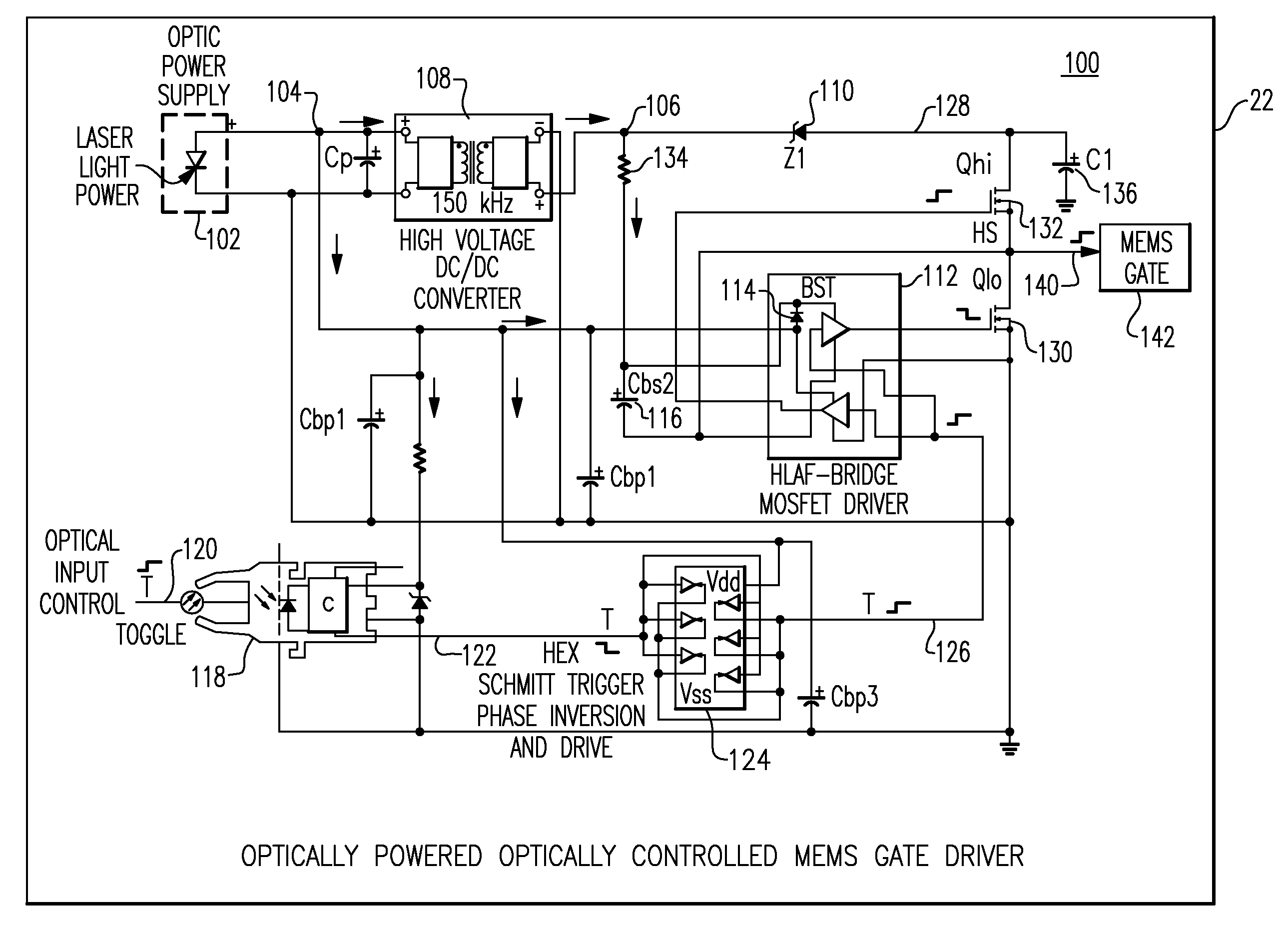

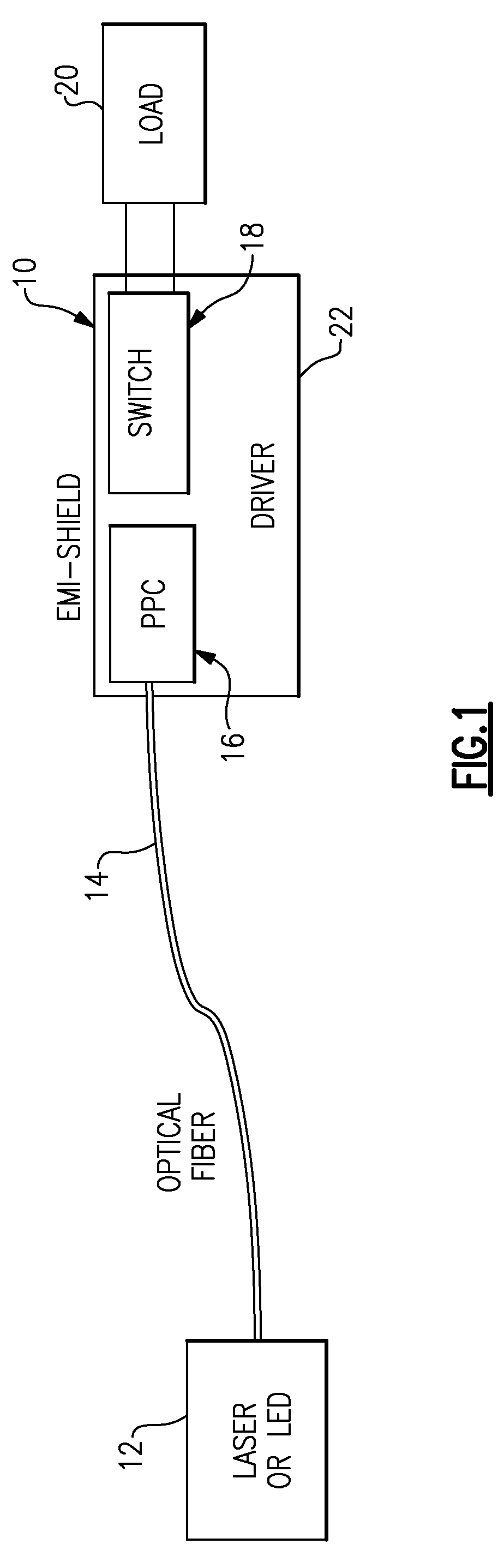

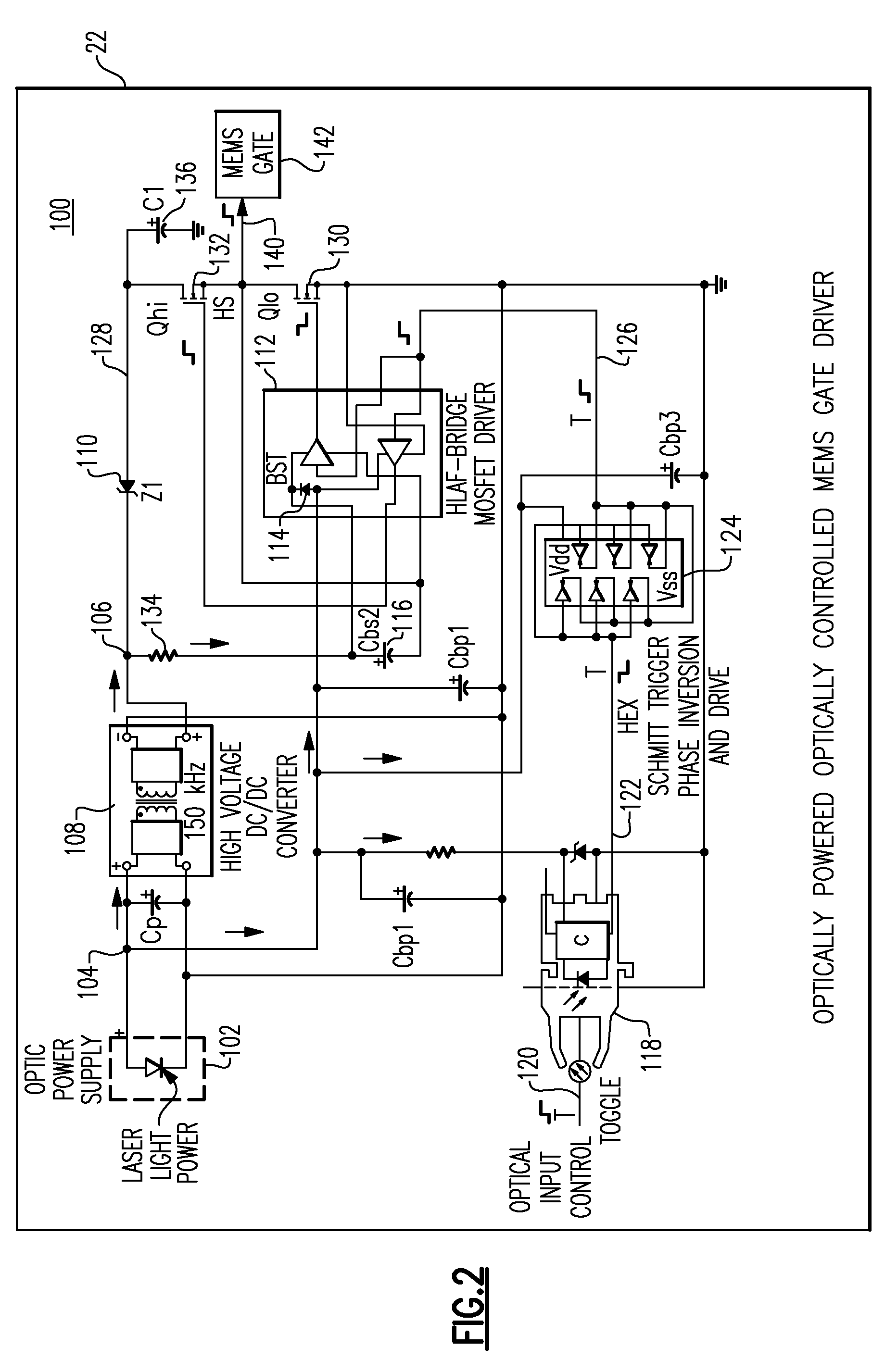

Optically gated MEMS switch

Owner:GENERAL ELECTRIC CO

Line level air gaps

InactiveUS20050127514A1Large gate RC delayImprove mechanical stabilitySemiconductor/solid-state device detailsSolid-state devicesPorosityLine level

In a multilevel microelectronic integrated circuit, air comprises permanent line level dielectric and ultra low-K materials are via level dielectric. The air is supplied to line level subsequent to removal of sacrificial material by clean thermal decomposition and assisted diffusion of byproducts through porosities in the IC structure. Optionally, air is also included within porosities in the via level dielectric. By incorporating air to the extent produced in the invention, intralevel and interlevel dielectric values are minimized.

Owner:GLOBALFOUNDRIES INC

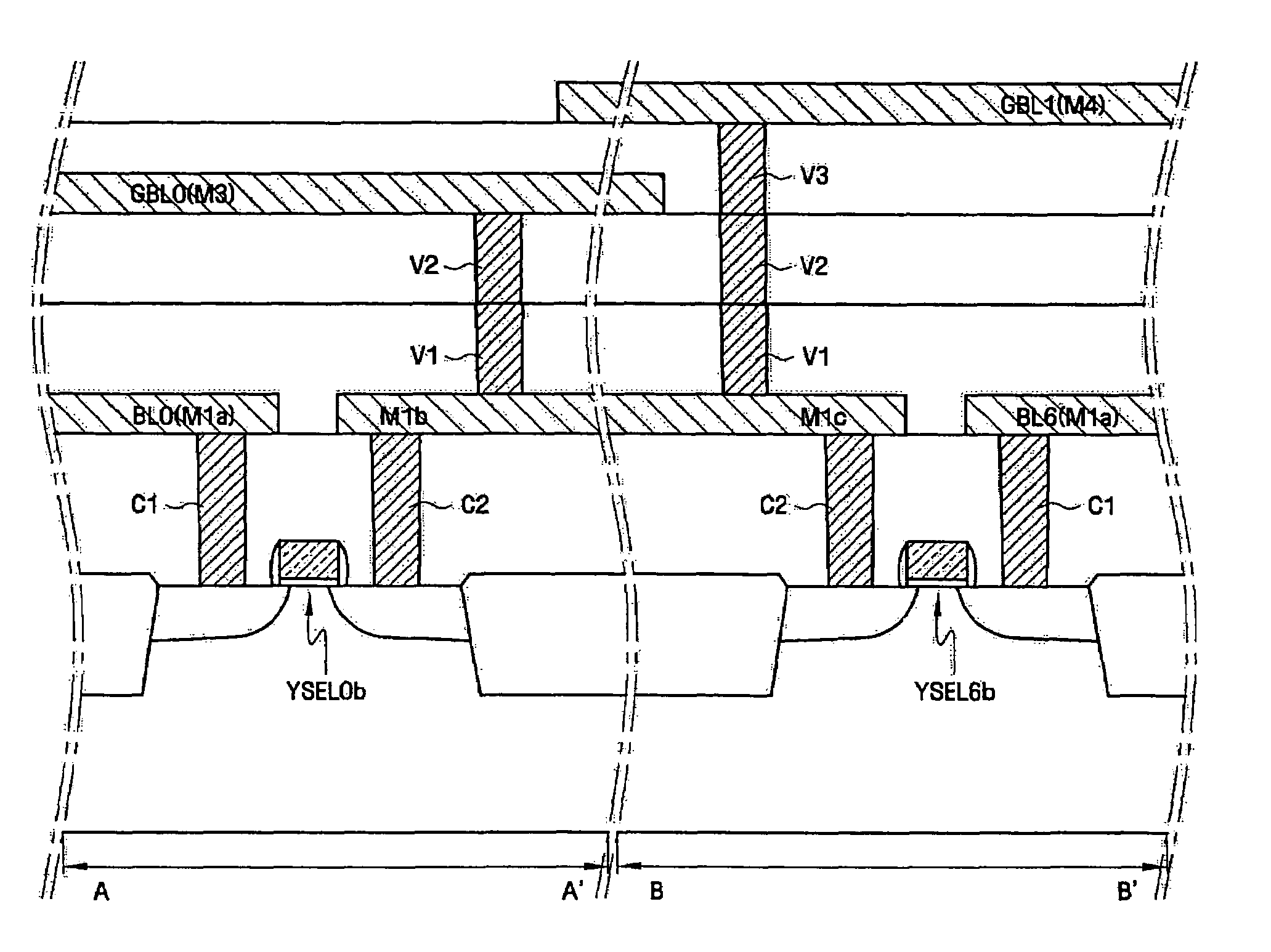

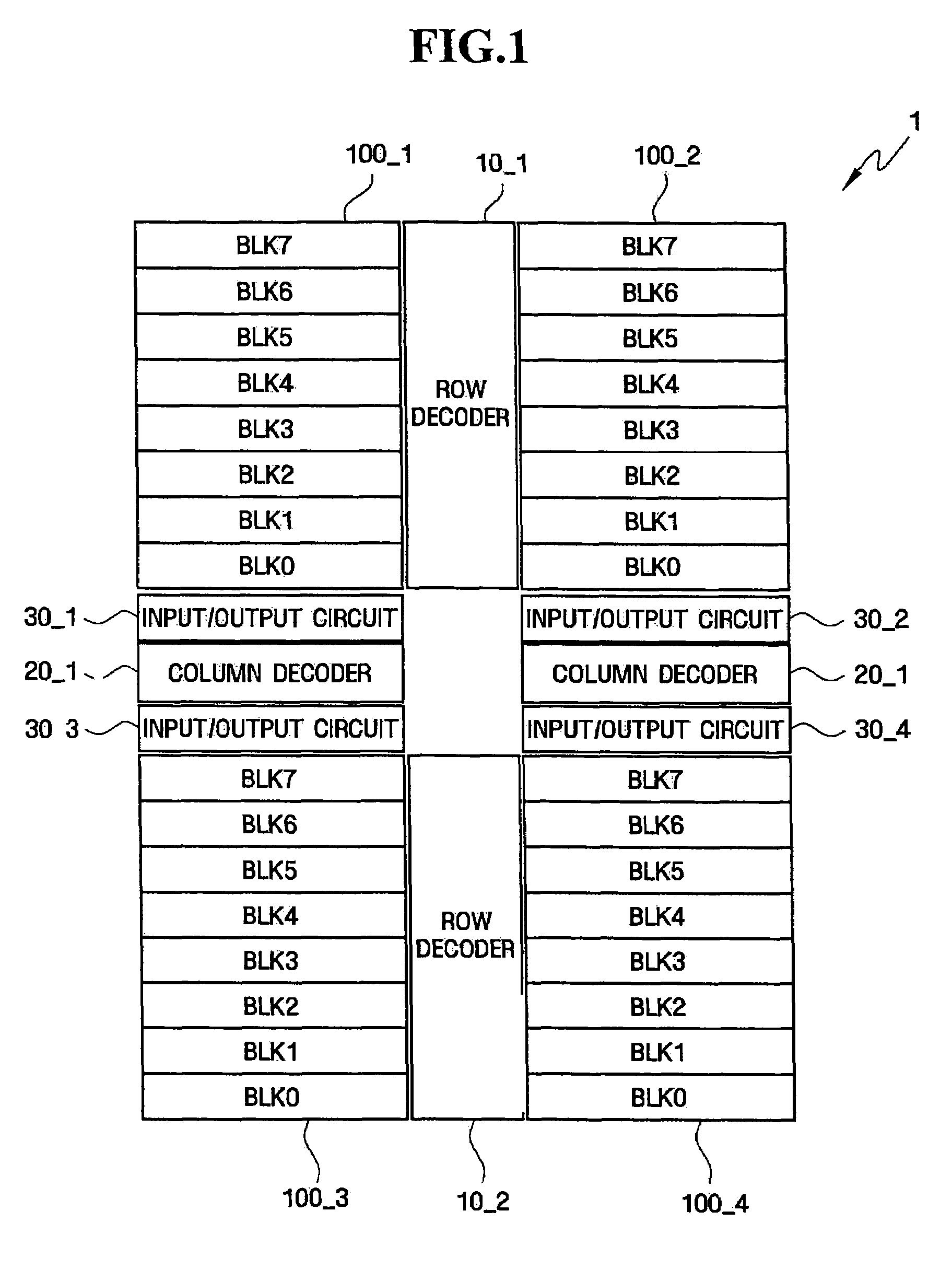

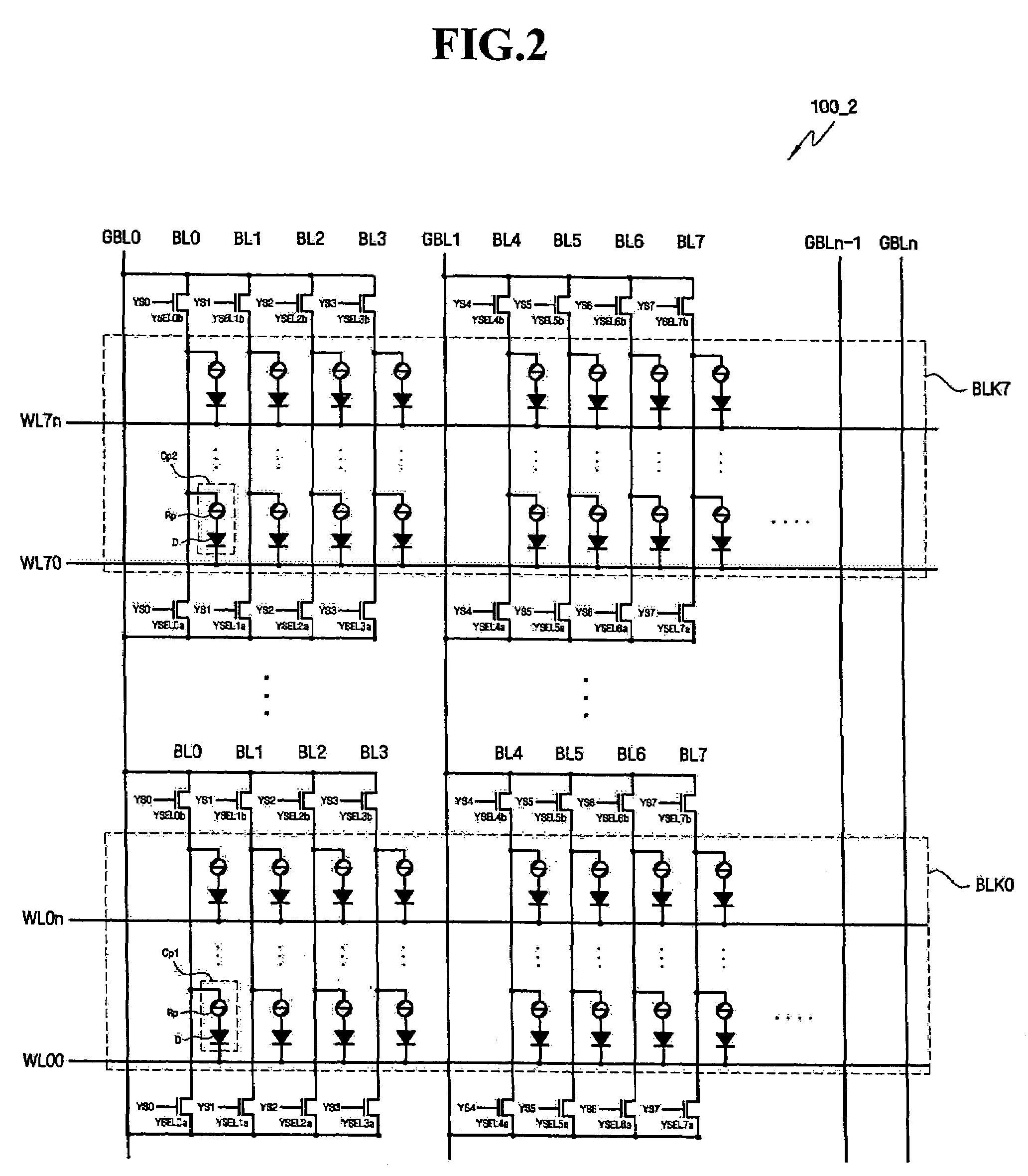

Phase change memory device

A phase change memory device includes a semiconductor substrate which includes a plurality of phase change memory cells, a plurality of local bit lines extending over the semiconductor substrate, each of the plurality of local bit lines being coupled to the plurality of phase change memory cells, and a plurality of global bit lines extending over the plurality of local bit lines, each of the plurality of global bit lines being selectively coupled to the plurality of local bit lines. The plurality of global bit lines are located at two or more different wiring line levels over the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

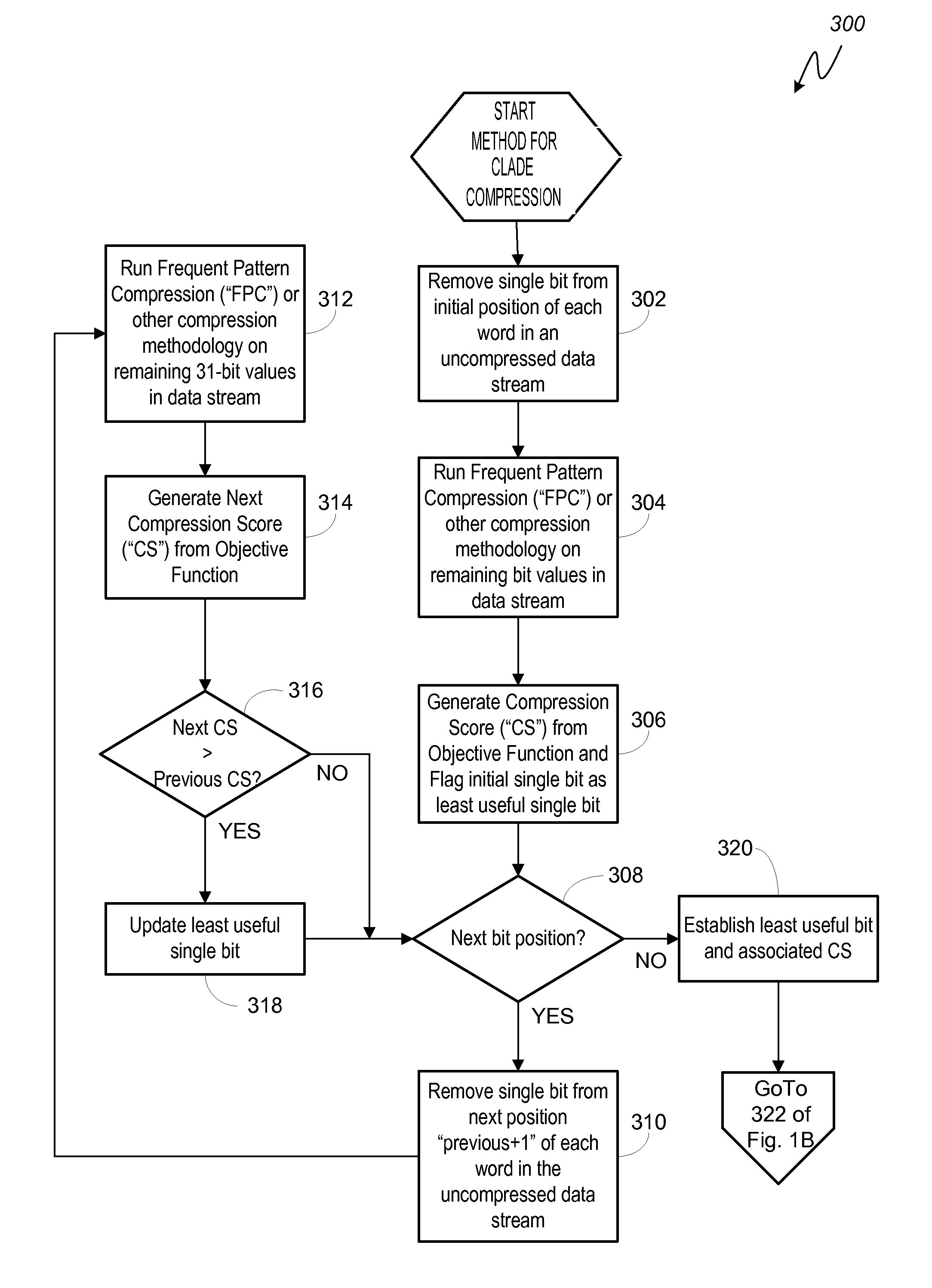

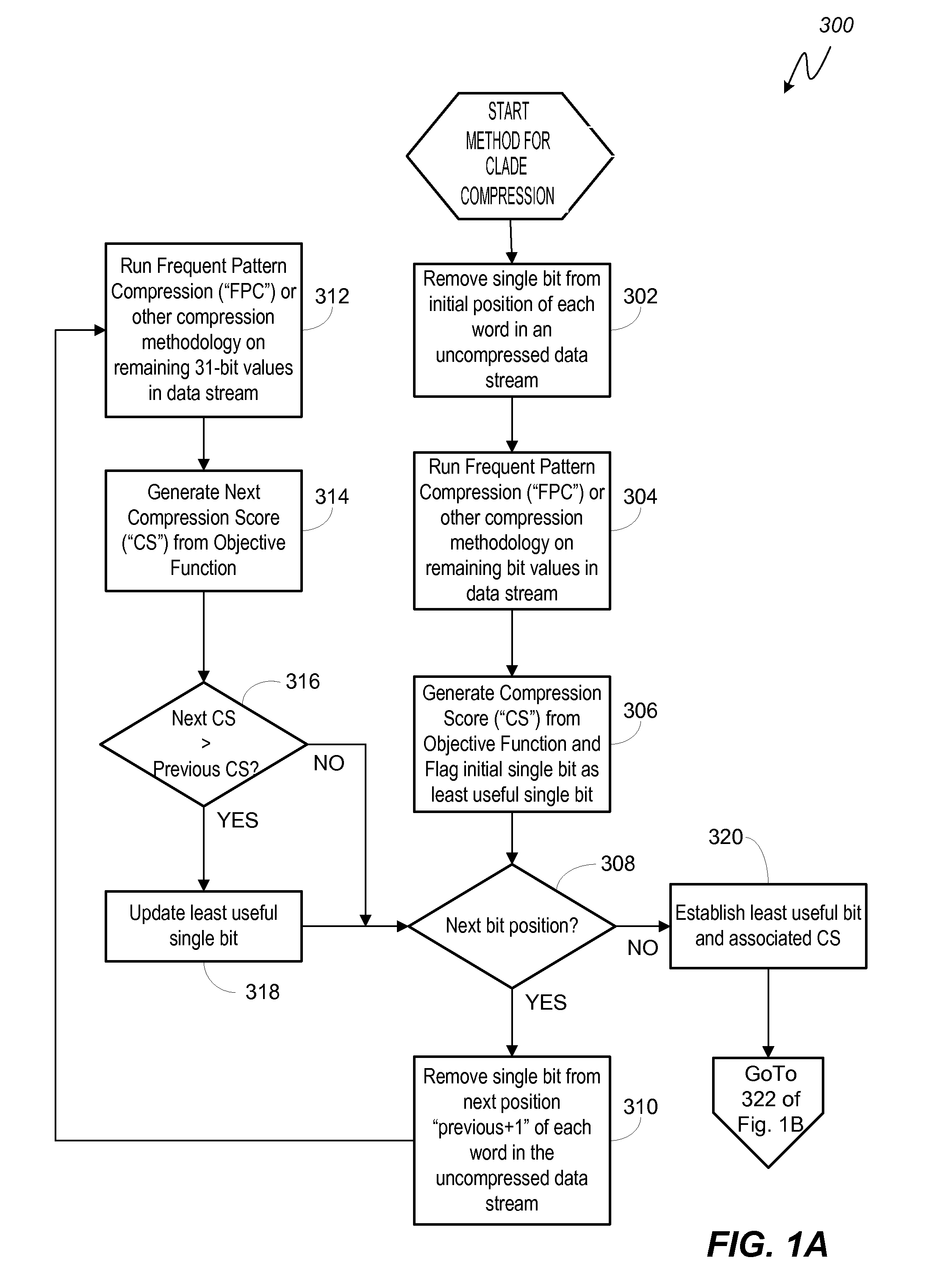

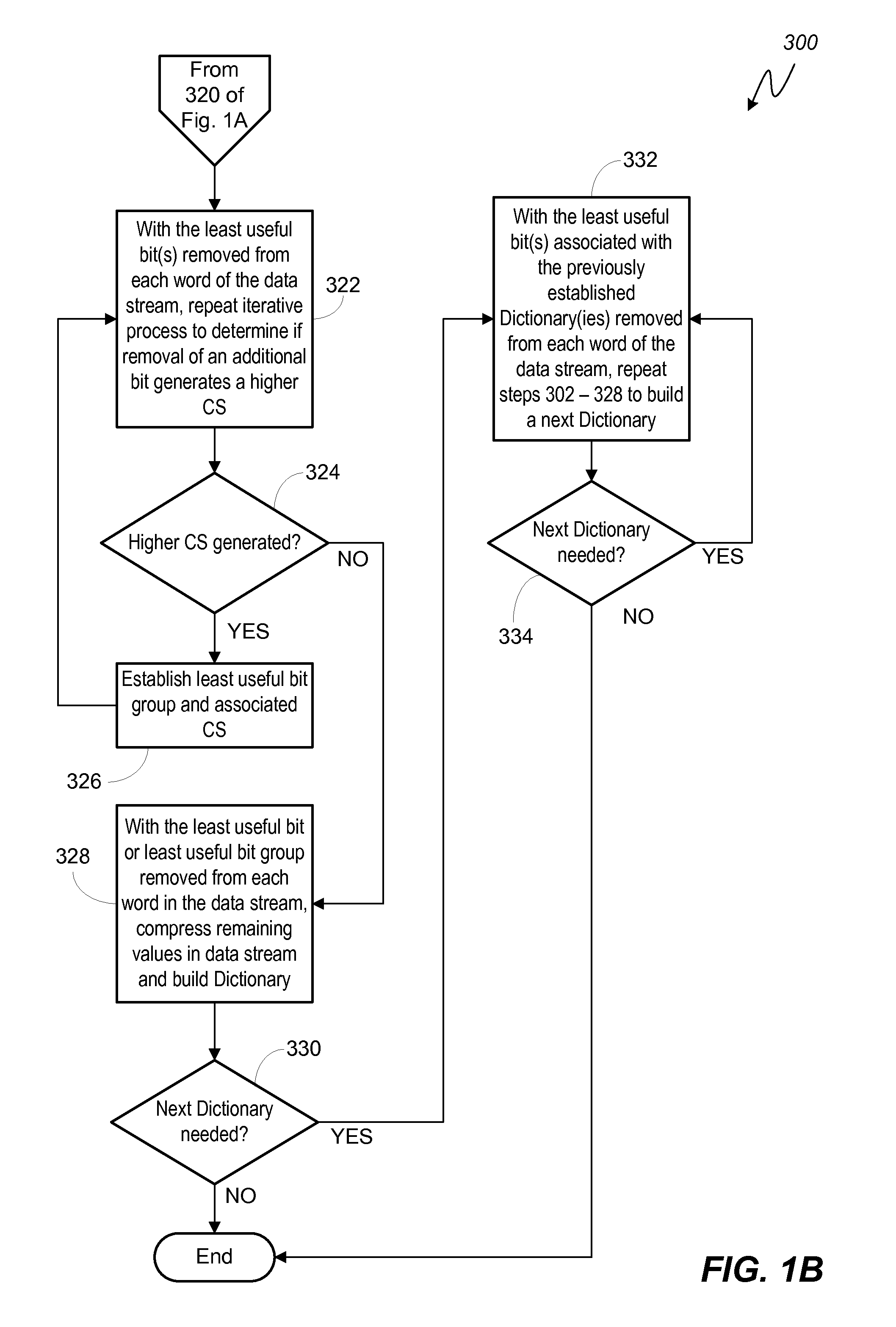

System and method for dictionary-based cache-line level code compression for on-chip memories using gradual bit removal

InactiveUS9300320B2Memory architecture accessing/allocationMemory adressing/allocation/relocationData streamParallel computing

A multi-pass compression iteratively removes combinations of bits from locations in each word of a cache line of an uncompressed data stream. For each combination of removed bits, the remaining bits in the word values of the cache line are analyzed to generate a compression score. A highest compression score triggers the building of a dictionary from the remaining bits in the word values of the cache line. After a dictionary is built, the method may continue iteratively to create subsequent dictionaries from the words that remain uncompressed in the cache line. To decompress a word, a first bit section of the compressed word is used to identify a dictionary that is then queried for bits indexed in a second bit section of the compressed word. The uncompressed word is reconstructed by interleaving the queried bits with the removed combination of bits from a third bit section of the word.

Owner:QUALCOMM INC

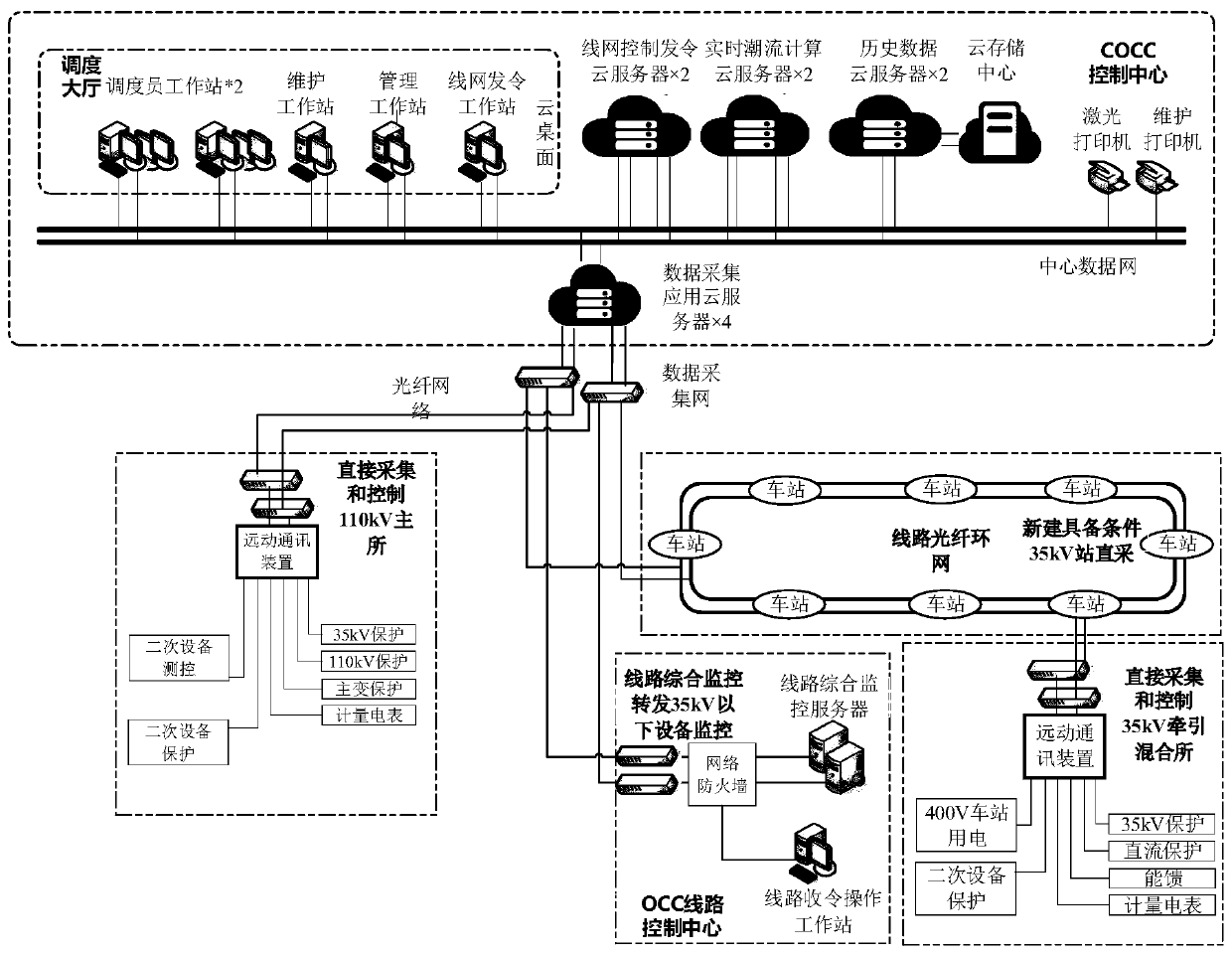

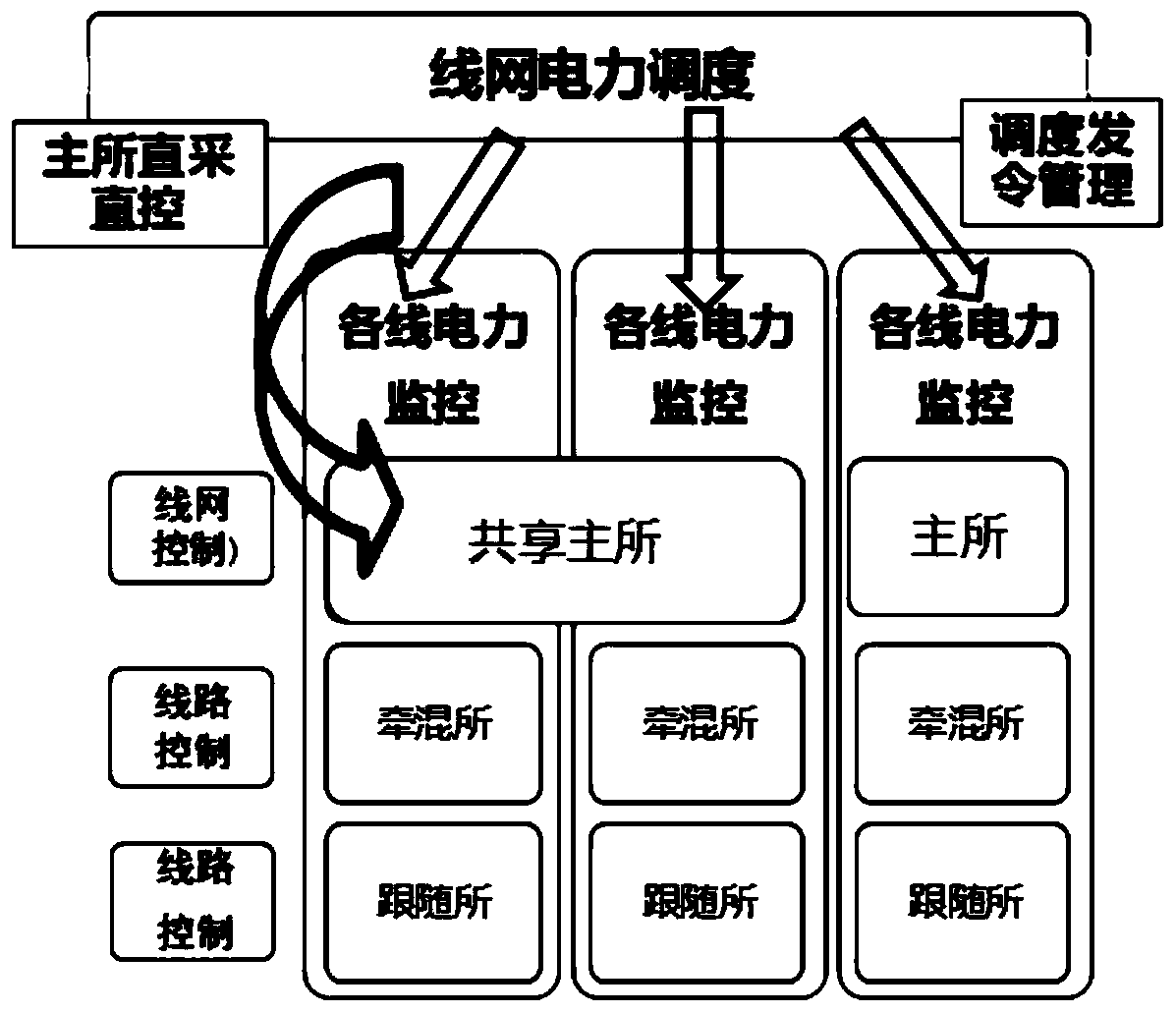

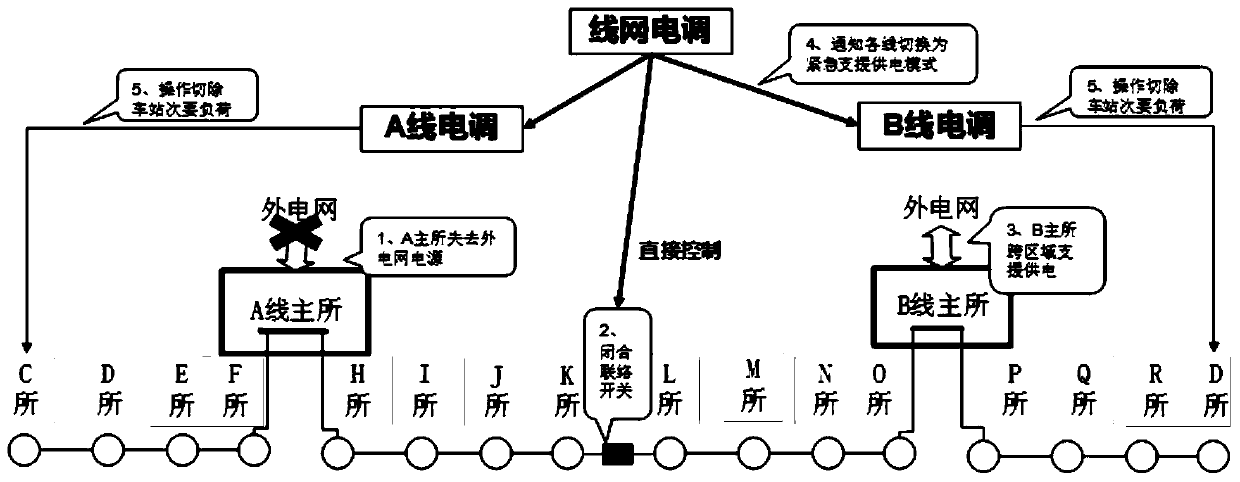

Network-level power dispatching system for urban rail transit lines

ActiveCN110363447AImprove work efficiencyStandardized Scheduling WorkflowPower network operation systems integrationDesign optimisation/simulationNetwork managementEngineering

The invention discloses a network-level power dispatching system for urban rail transit lines. The system realizes the hierarchical and hierarchical control and emergency treatment on an urban rail transit power supply system by wire network-level power dispatching of an urban rail transit wire network management and control center and line-level power dispatching of a line control center based onthe adoption of a wire network dispatching-line control integrated framework. The cooperative management and control of line network electronic speed controller and line electronic speed controller are realized by adopting a whole line network power dispatching order and line power supply operation order system. A whole line network power supply system real-time power flow calculation system is adopted. An IEC-61970 standard public information model is taken as a basis. An urban rail transit special power supply equipment model is expanded. The power supply system alternating current and direct current hybrid power flow calculation is carried out. The safety check and system optimization scheduling are carried out on an urban rail transit overall power supply network. According to the invention, the management benefit of cooperative power dispatching of each line in the urban rail transit network environment is improved.

Owner:NR ENG CO LTD +1