Package and manufacture method for thermal enhanced quad flat no-lead flip chip

A four-sided flat, flip-chip technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, and electrical solid-state devices, can solve the problem of low bonding strength between lead frame and plastic packaging material, lead frame and plastic packaging material falling off, and inability to lock effectively Solve problems such as plastic materials, achieve the effect of improving flip-chip welding quality and surface mount quality, improving cutting efficiency, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0070] The present invention is described in detail below in conjunction with accompanying drawing:

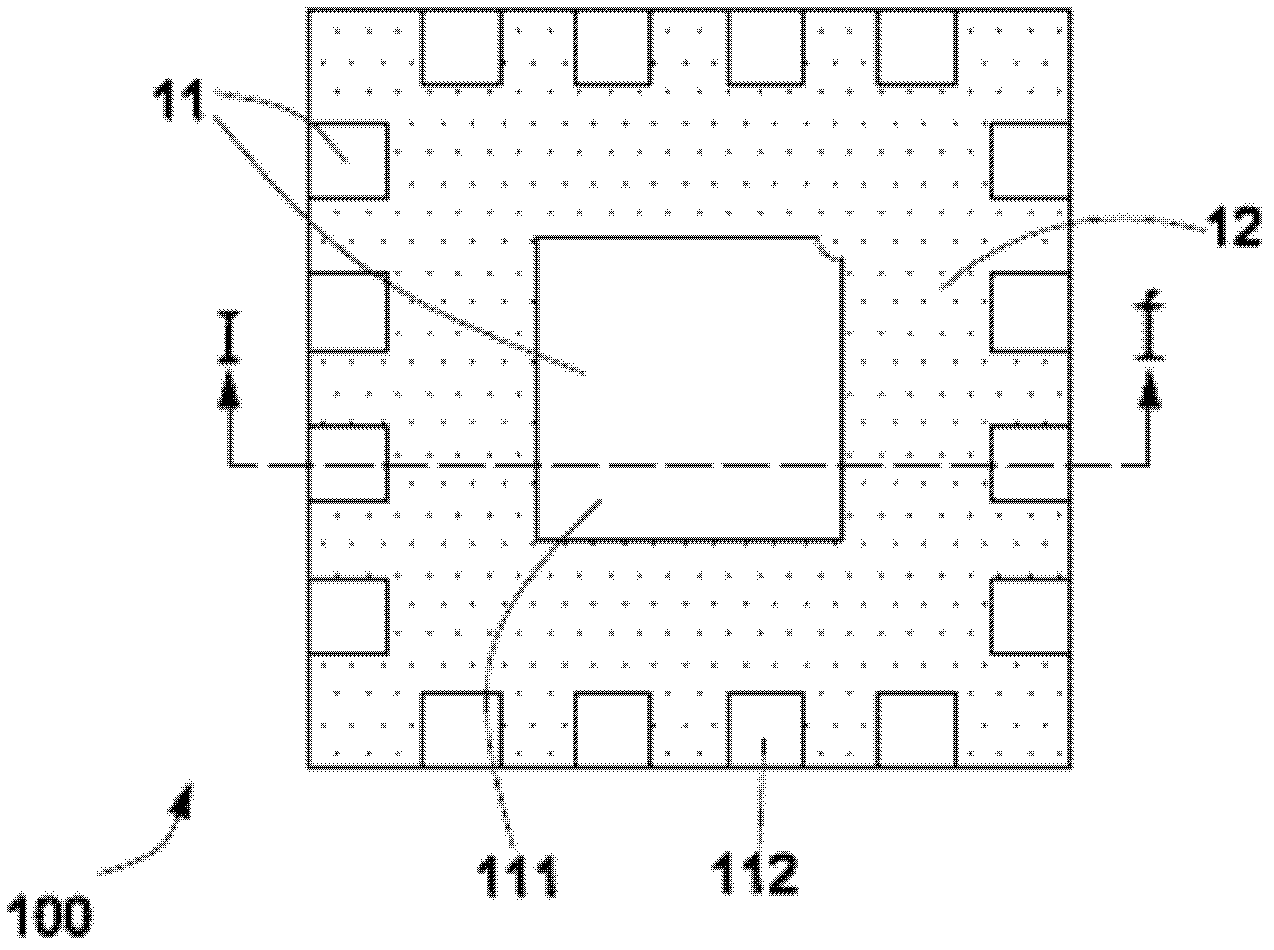

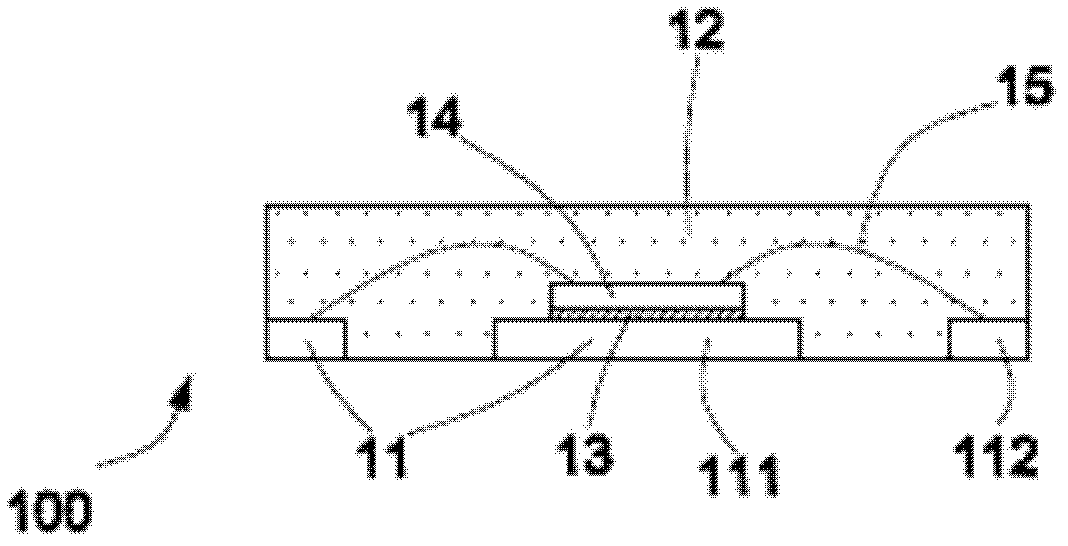

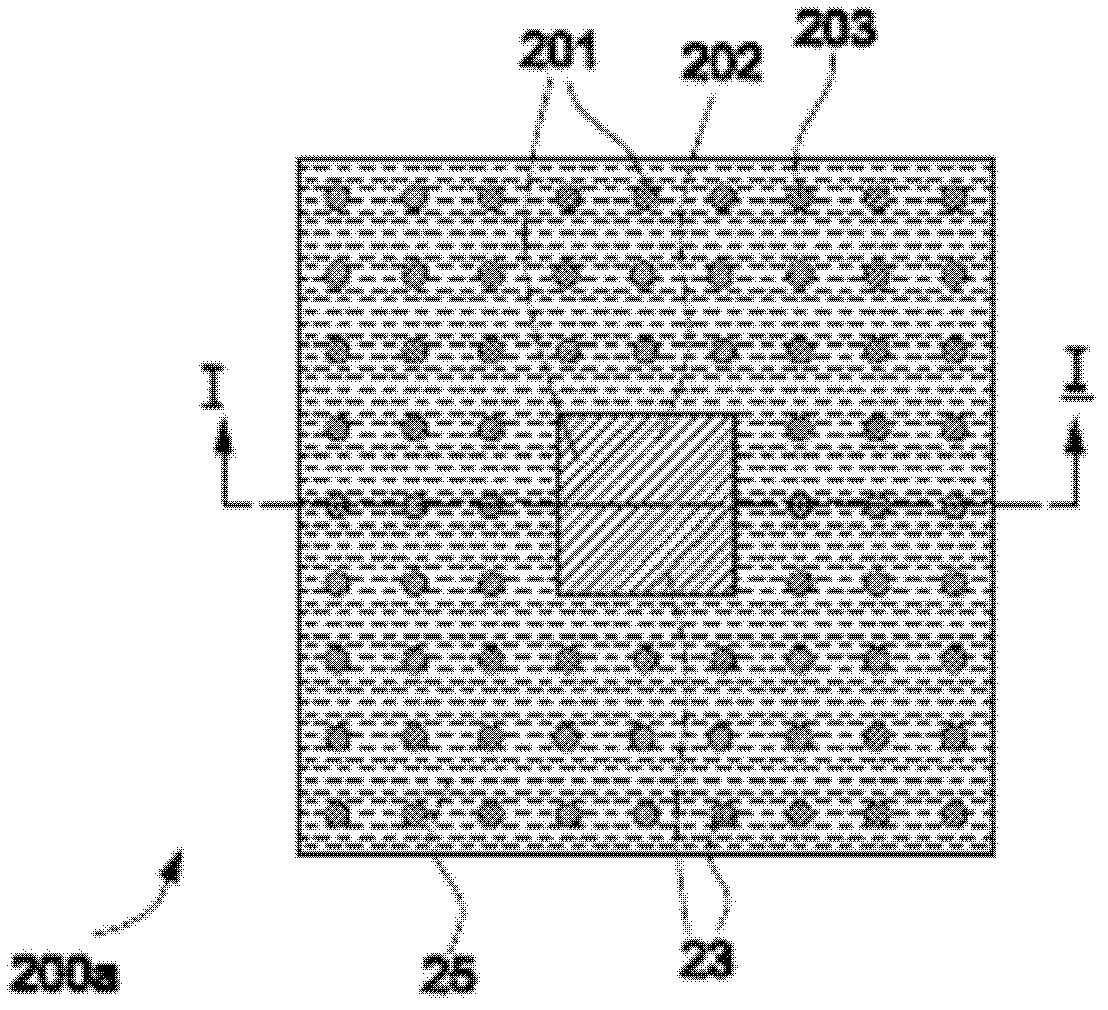

[0071] Figure 2A A schematic diagram of the back side of a heat-enhanced multi-turn pin arrangement FCQFN package structure drawn according to an embodiment of the present invention where the cross section of the pins is circular and the pins are arranged in parallel on each side of the chip carrier. Figure 2B A schematic diagram of the back side of a heat-enhanced multi-turn pin arrangement FCQFN package structure drawn according to an embodiment of the present invention in which the cross-section of the pins is rectangular and the pins are arranged in parallel on each side of the chip carrier.

[0072] Refer to the above Figure 2A -B It can be seen that, in this embodiment, the lead frame 201 of the heat-enhanced multi-turn pin arrangement FCQFN package structure 200a and 200b includes a chip carrier 202 and pins 203 arranged in multi-turn around the chip carrier 202, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More