Patents

Literature

59 results about "Masking level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

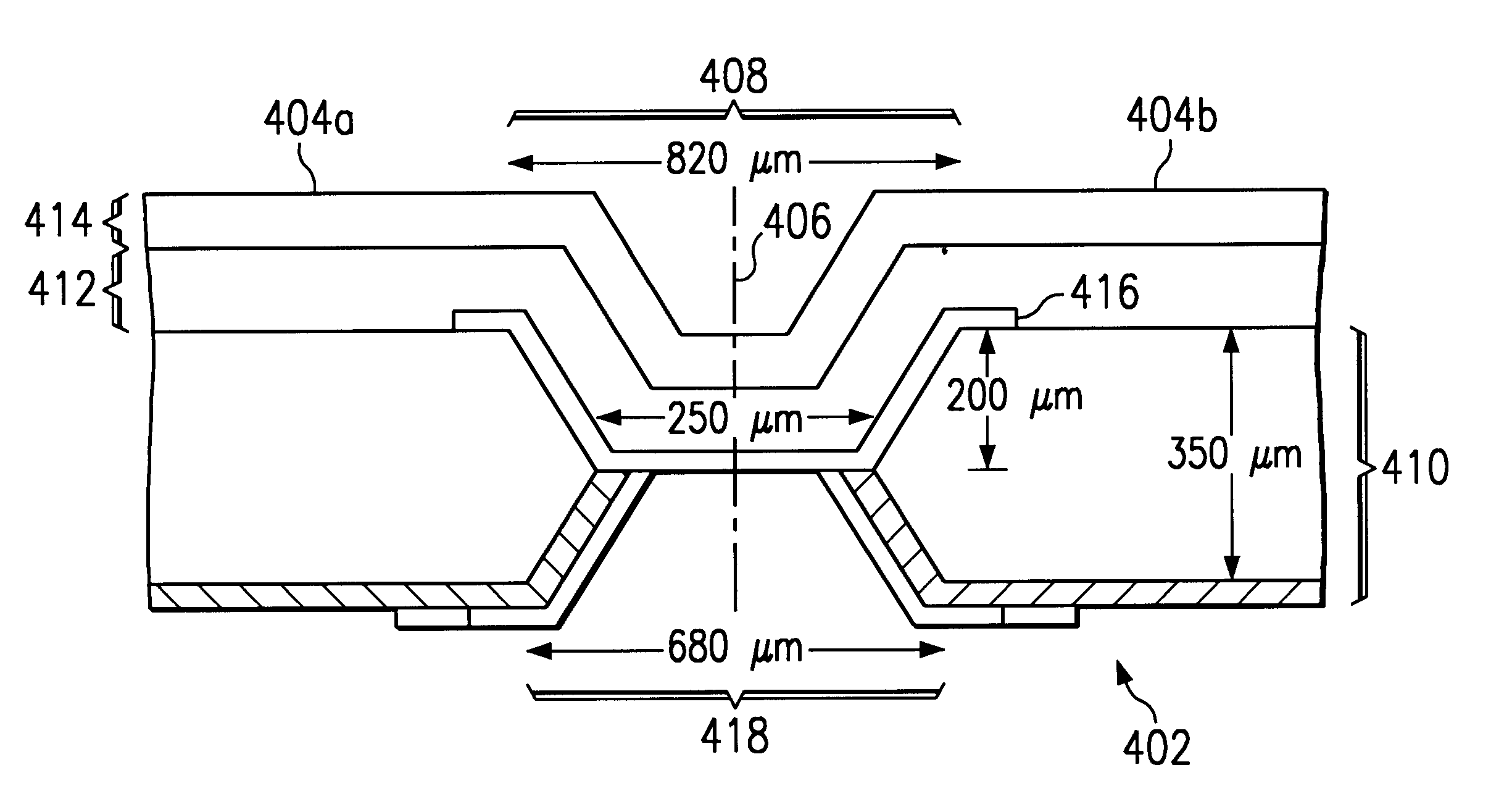

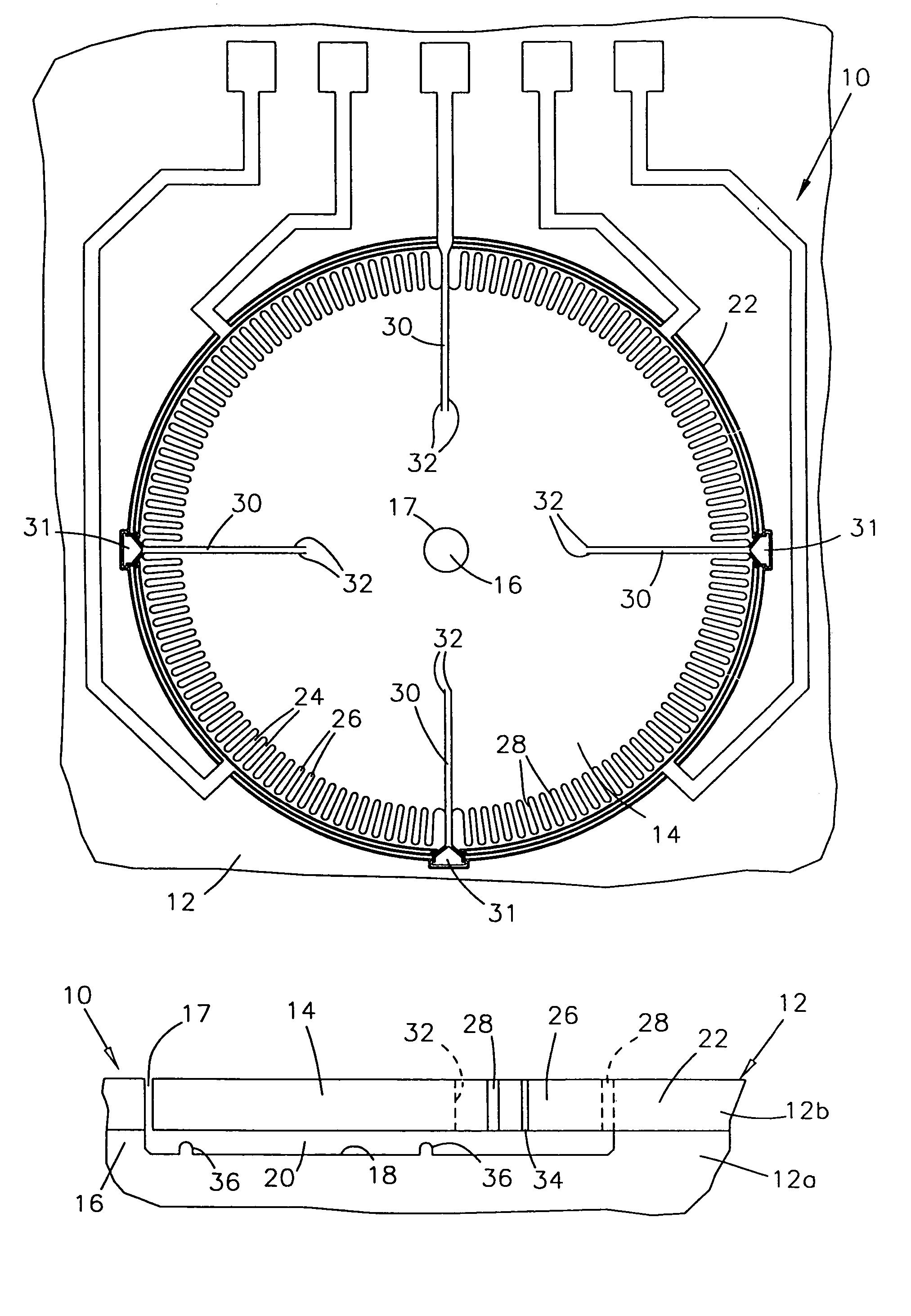

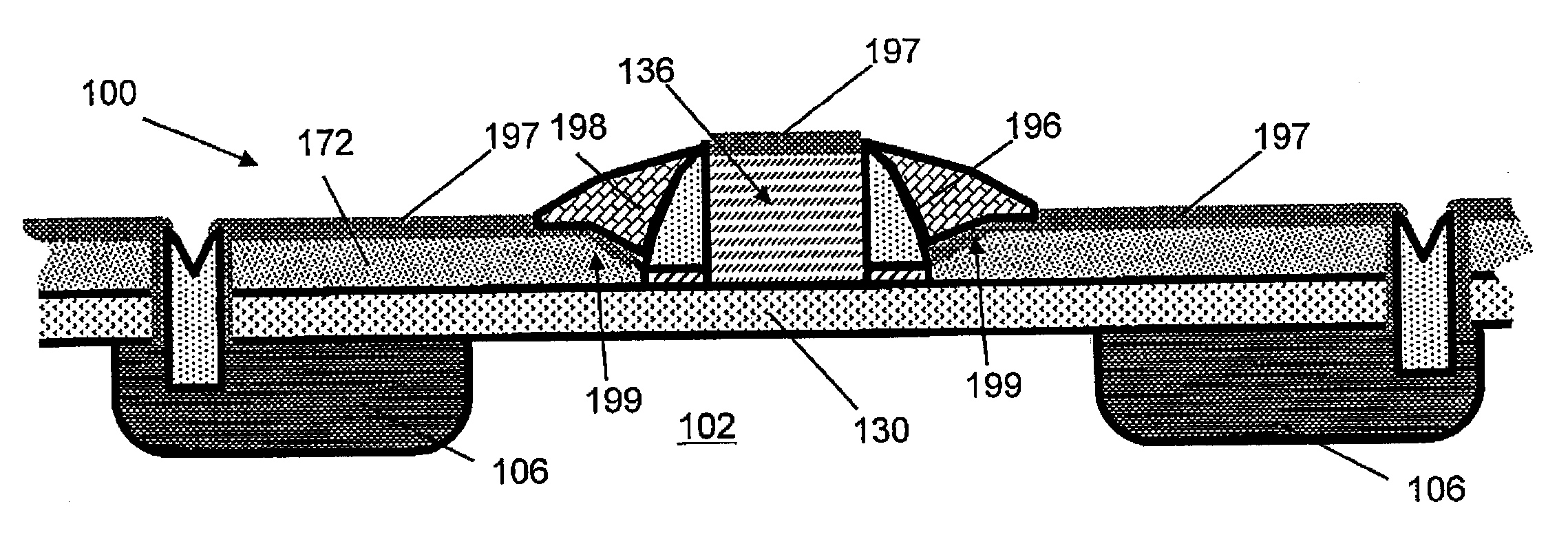

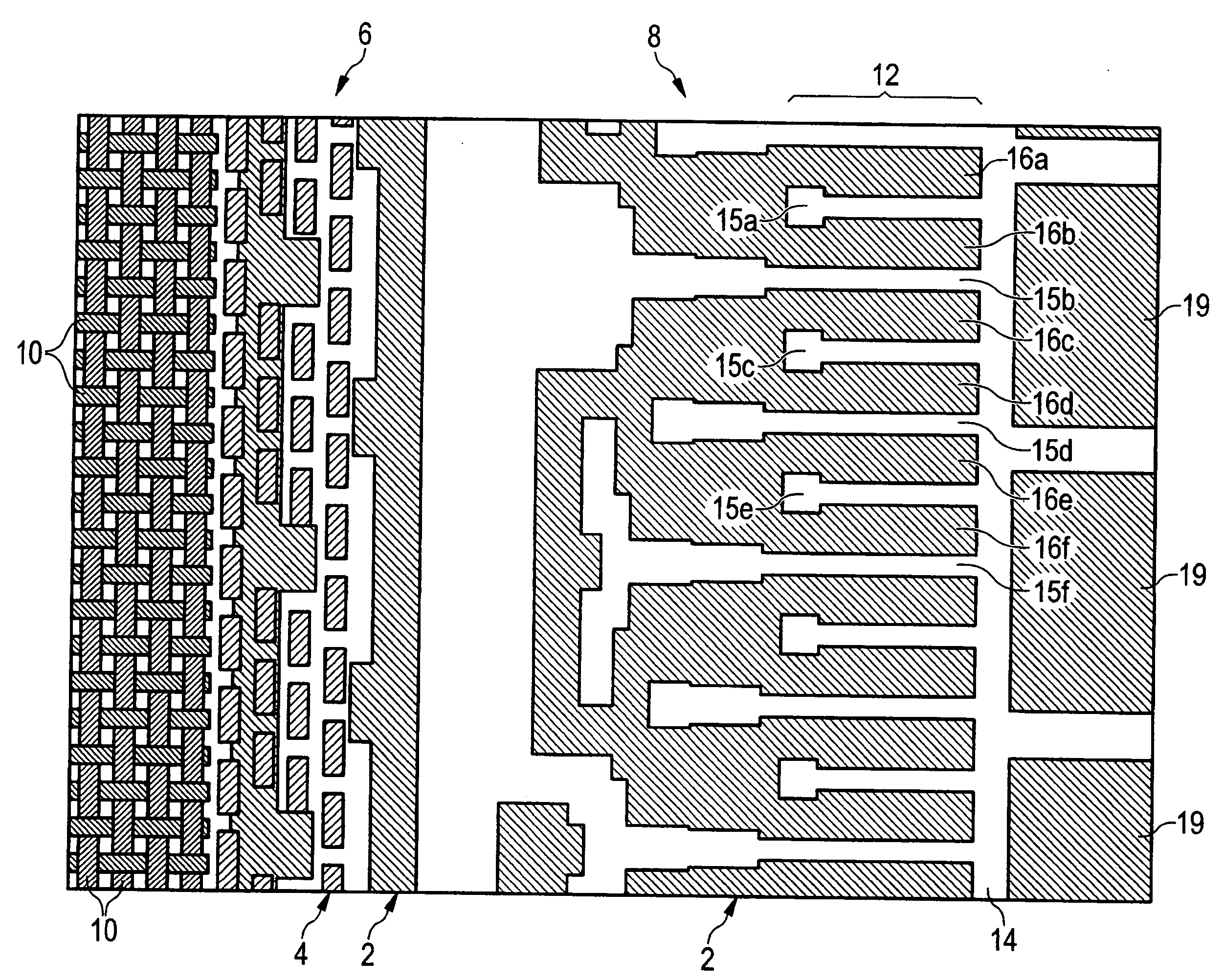

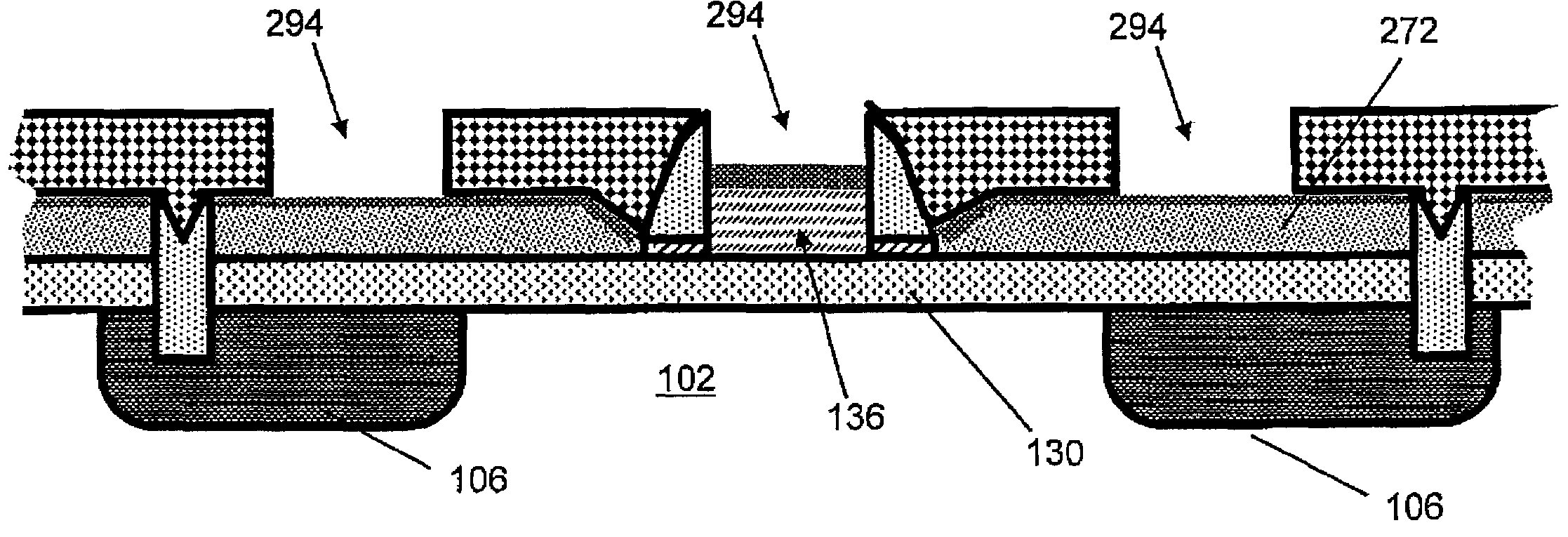

Backside contact for touchchip

InactiveUS6326689B1Semiconductor/solid-state device detailsSolid-state devicesContact formationContact pad

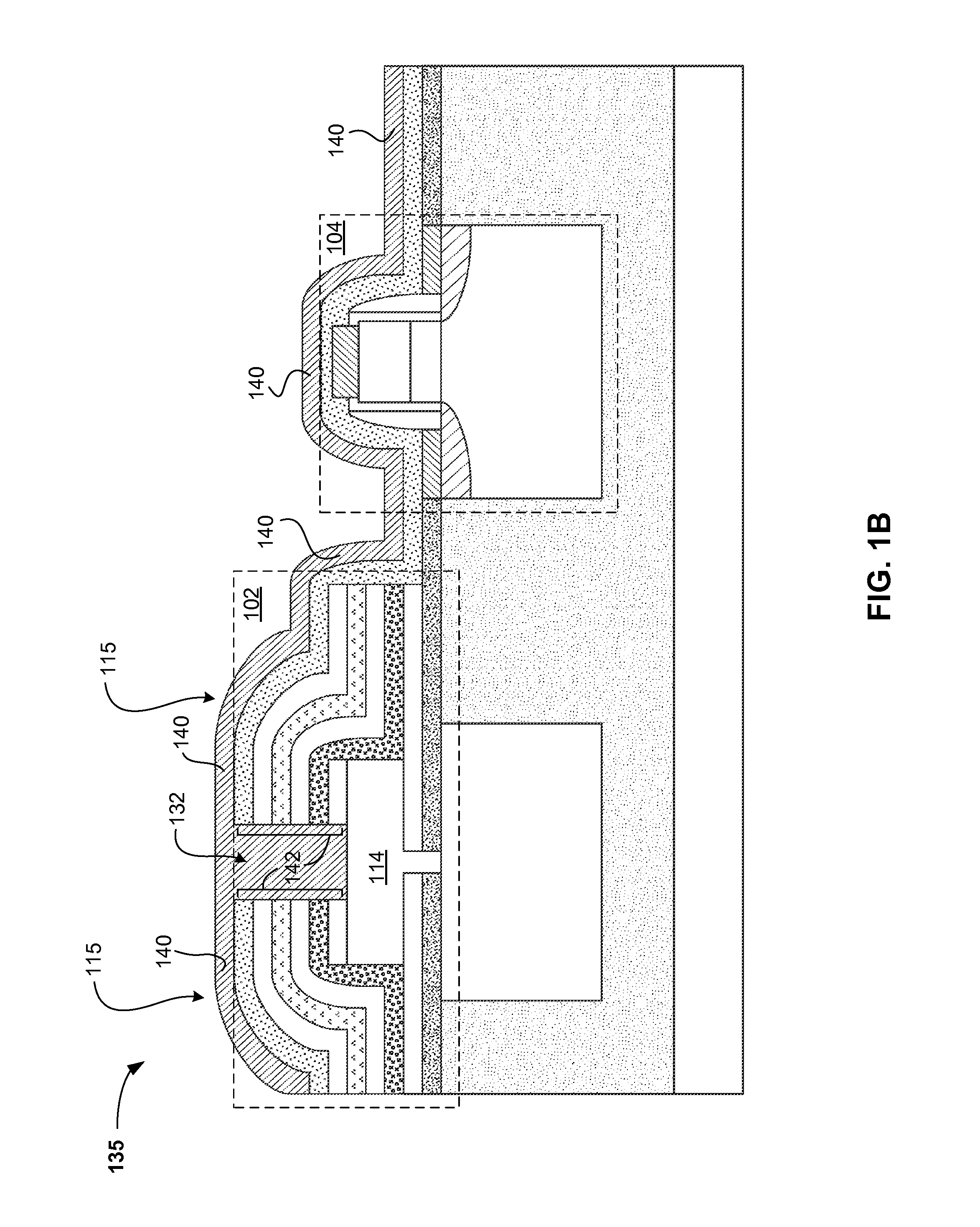

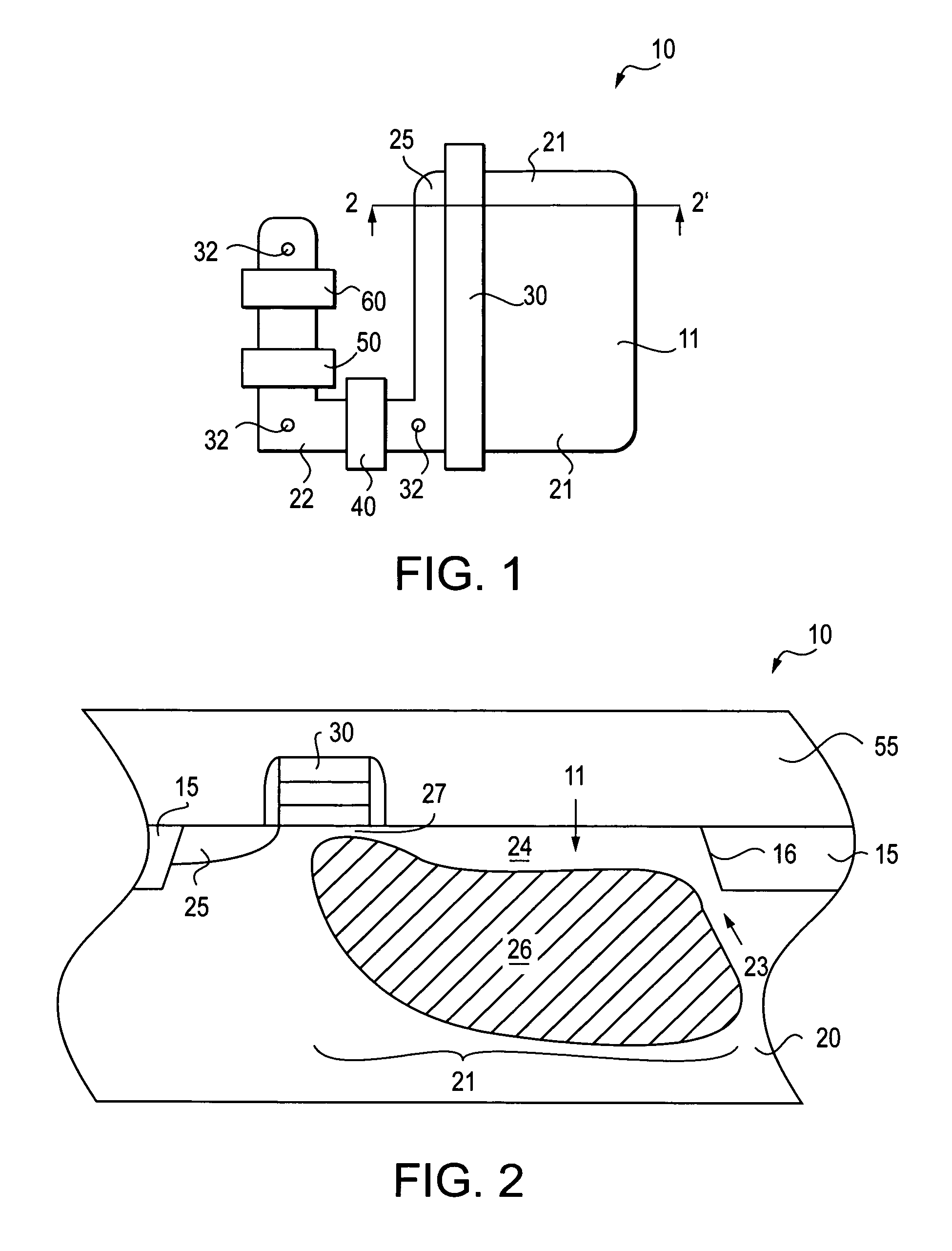

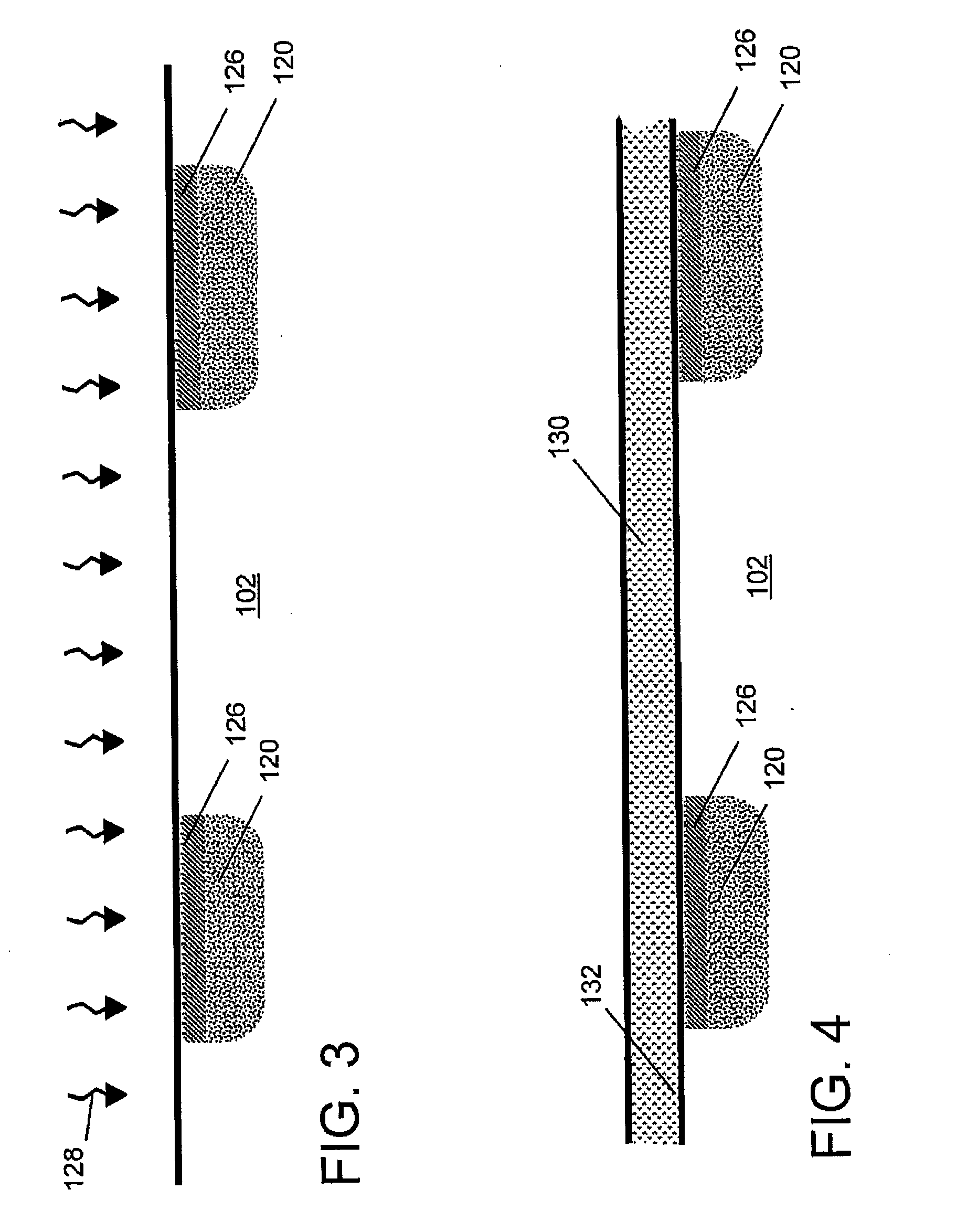

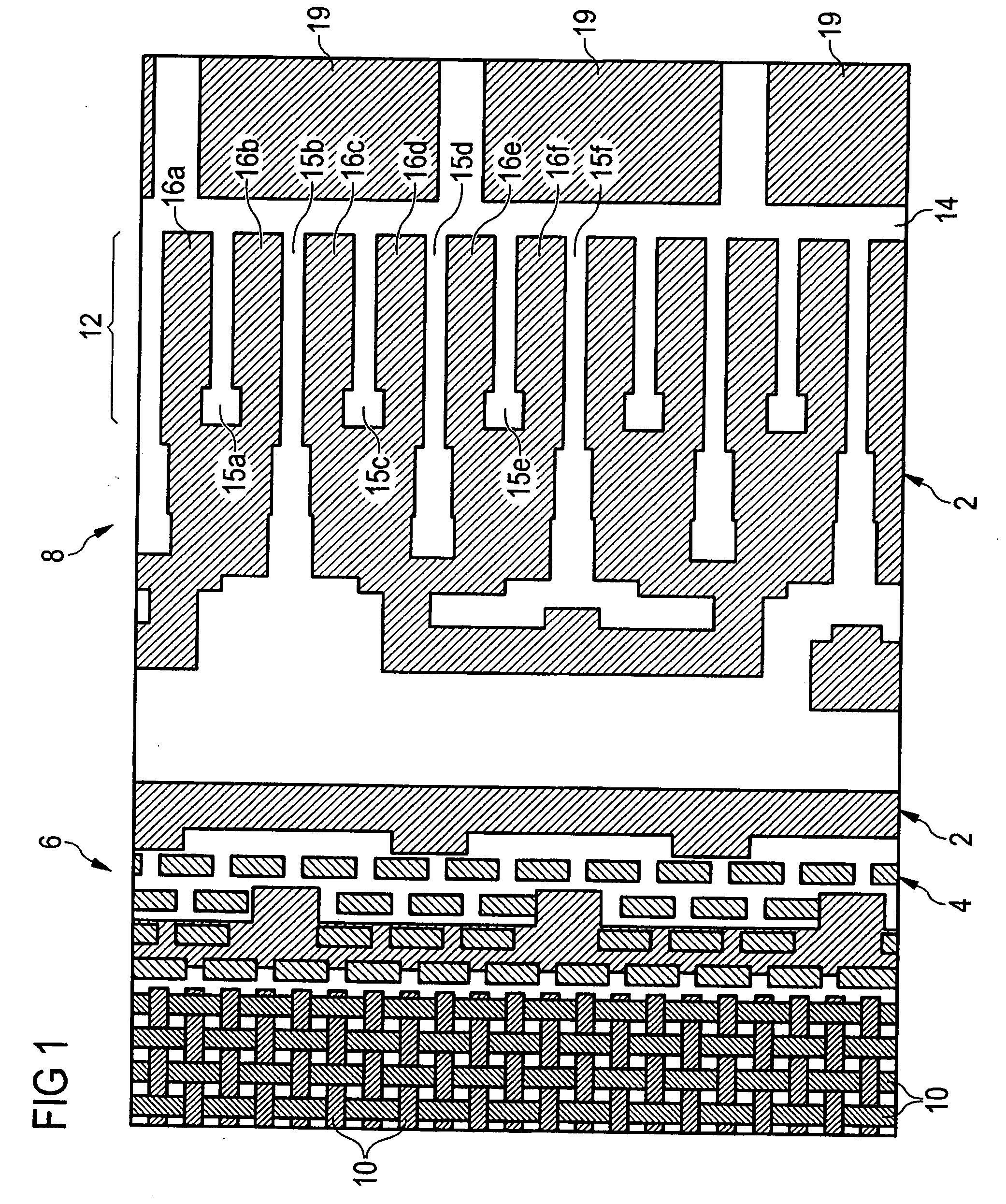

A contact is formed within an active region of a substrate at the edge of a die, preferably within the first metallization level in the active region of the substrate. An opening having sloped sidewalls is then etched into the back side of the substrate, exposing a portion of the active region contact. An interconnect is formed on the opening sidewall to connect the active region contact with a die contact pad on the backside surface of the substrate. The active region contact preferably spans a boundary between two die, with the opening preferably etched across the boundary to permit inter-connects on opposing sidewalls of the opening to each contact the active region contact within different die, connecting the active region contact to die contact pads on different dice. The dice are then separated along the boundary, through the active region contact which becomes two separate active region contacts. By forming a shared contact opening spanning two dice, the backside contact is formed around the die edge and the backside surface area necessary for the contact opening is minimized. The backside contact allows direct placement of the integrated circuit die on contacts within the packaging, such as a ball grid array, eliminating the need for wire bonds. The need for a pad etch through passivation material overlying active devices on the front side of the die is also eliminated, and no mask levels are added for the devices formed on the front side.

Owner:STMICROELECTRONICS SRL

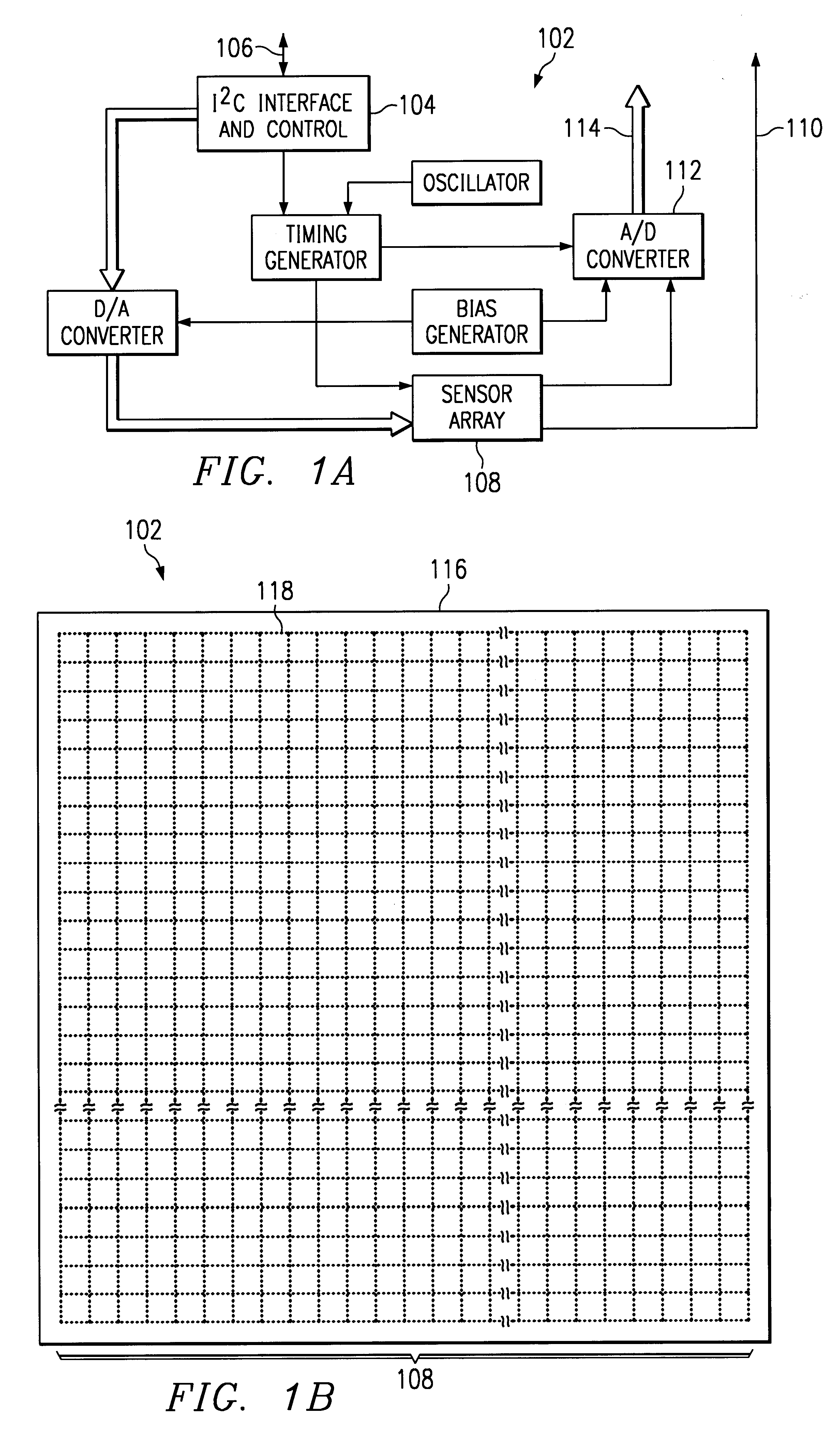

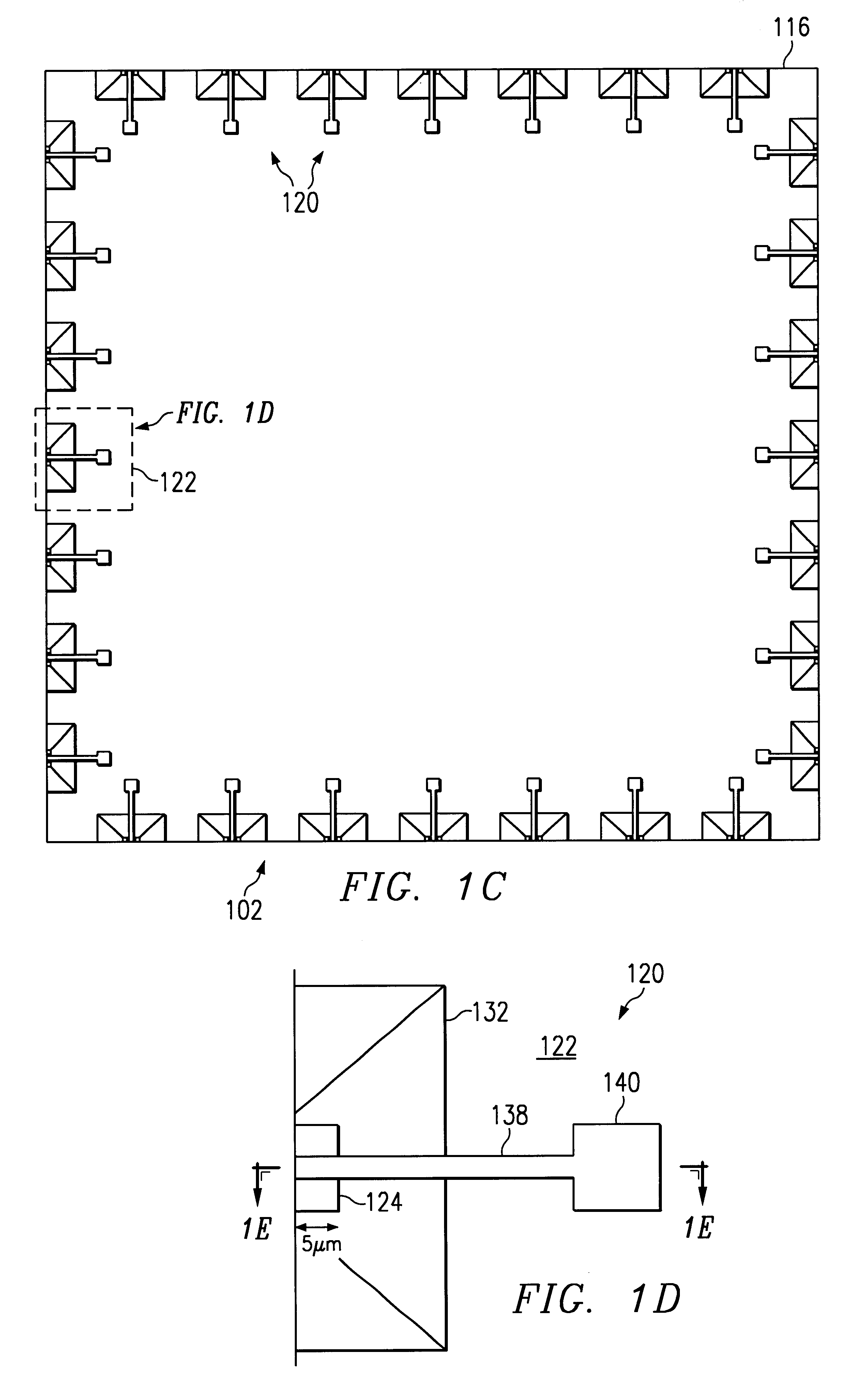

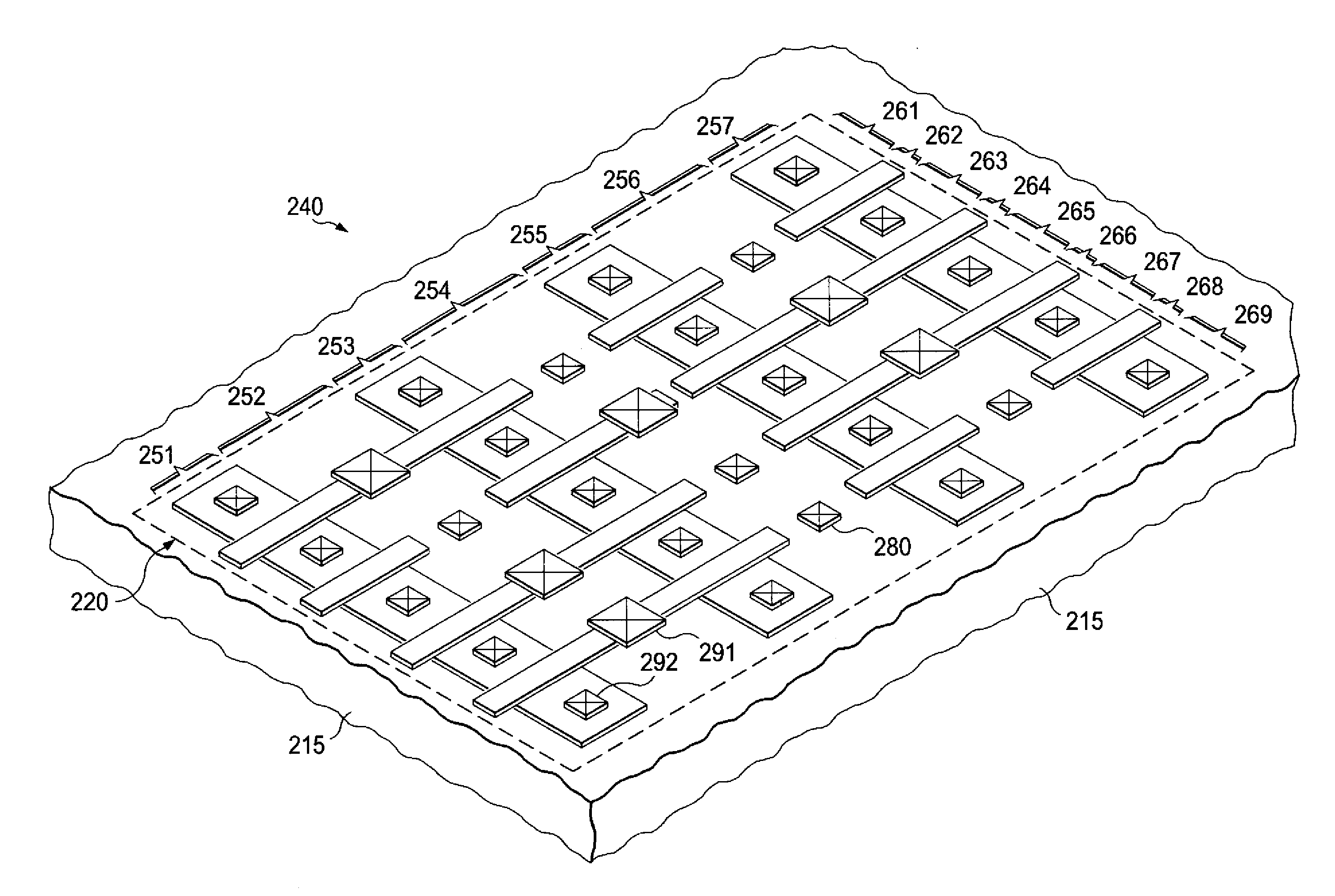

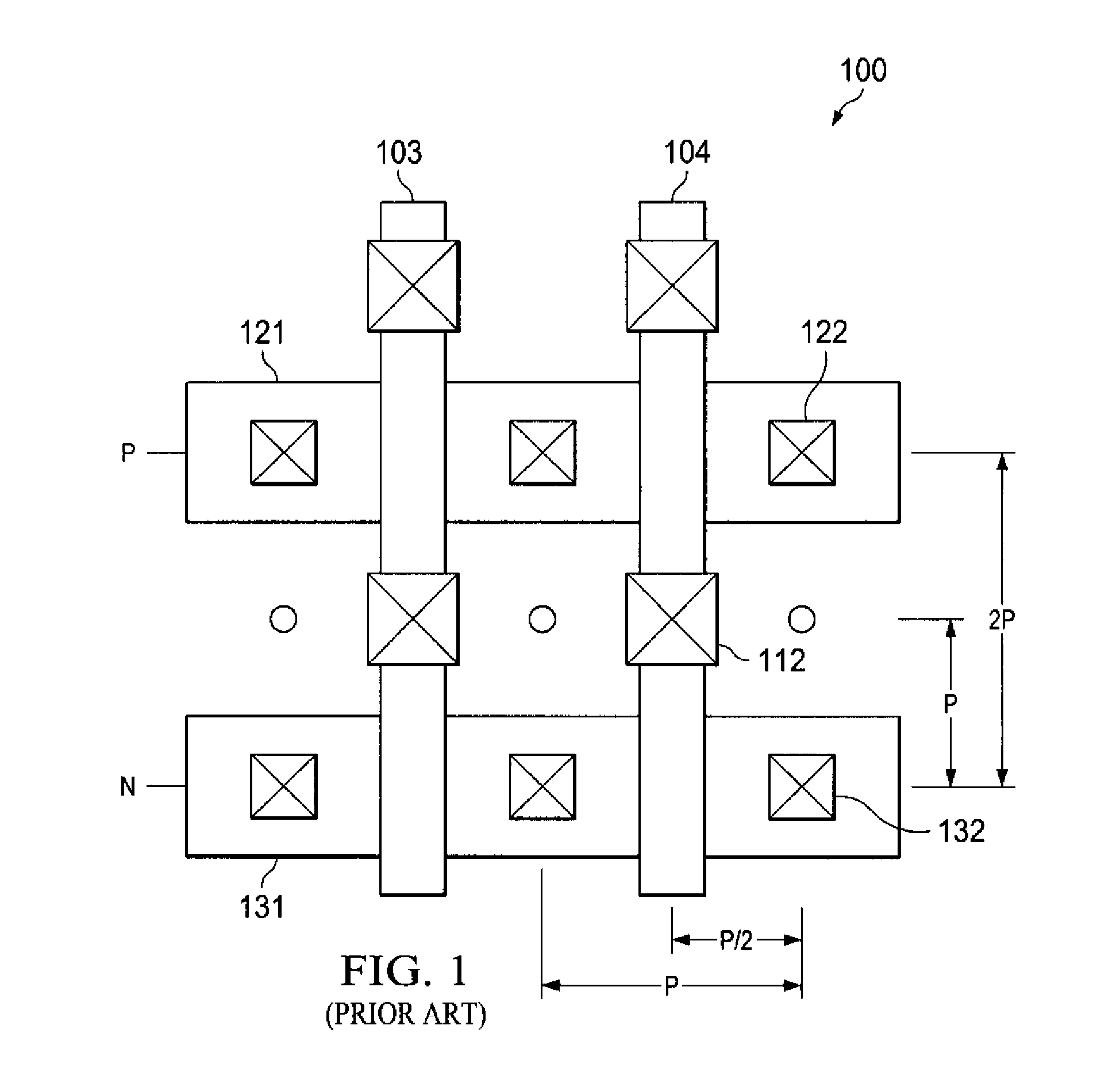

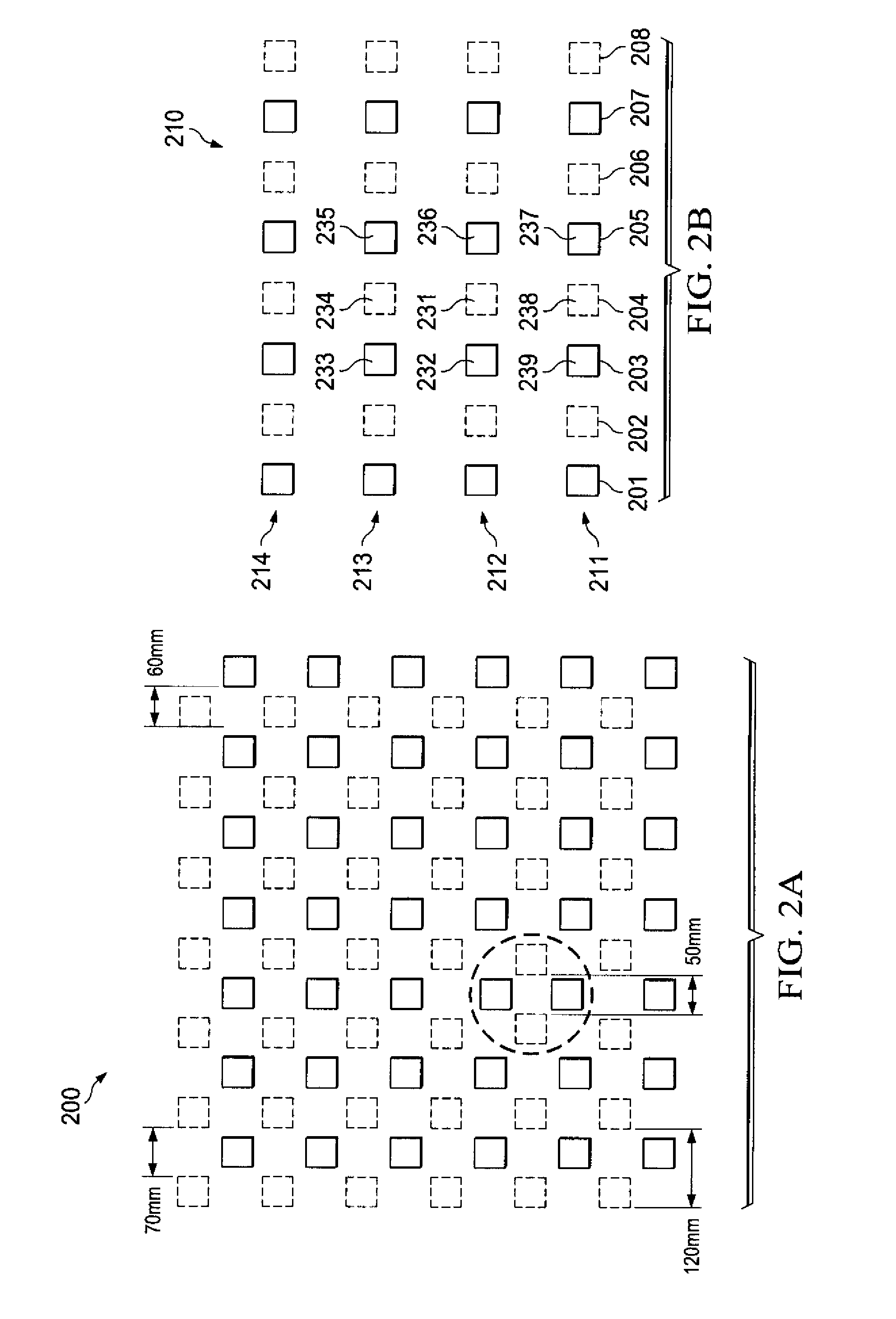

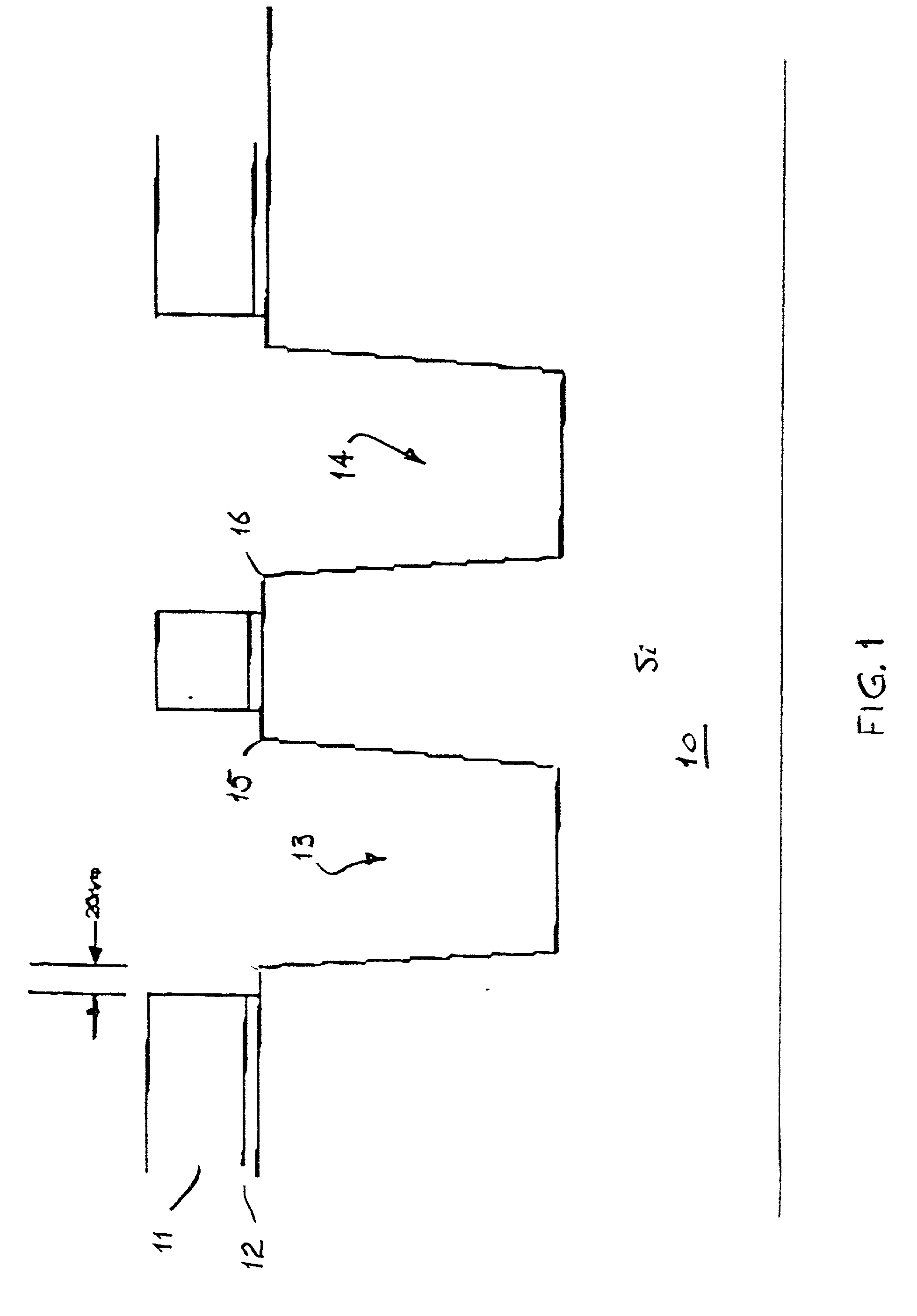

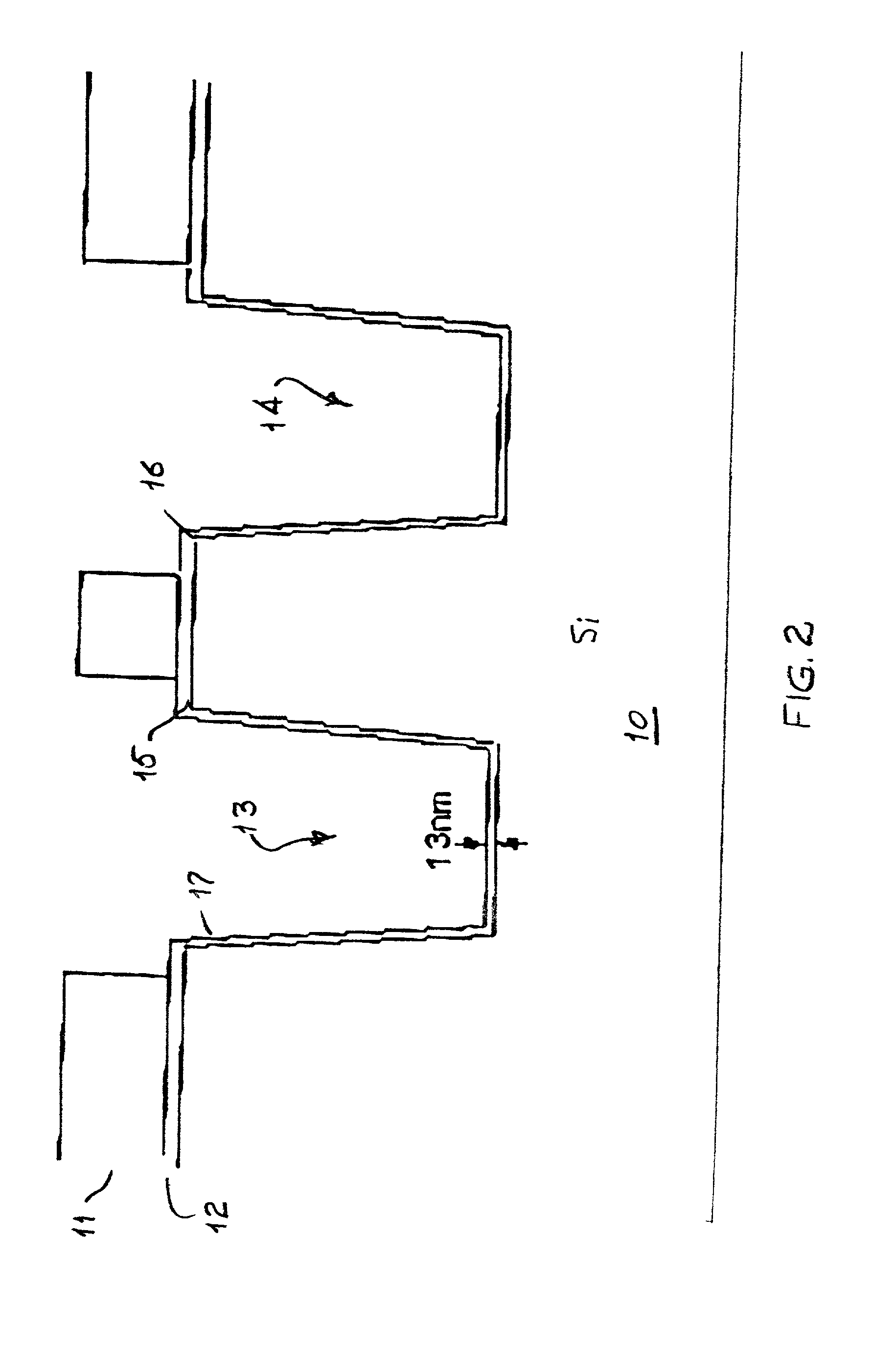

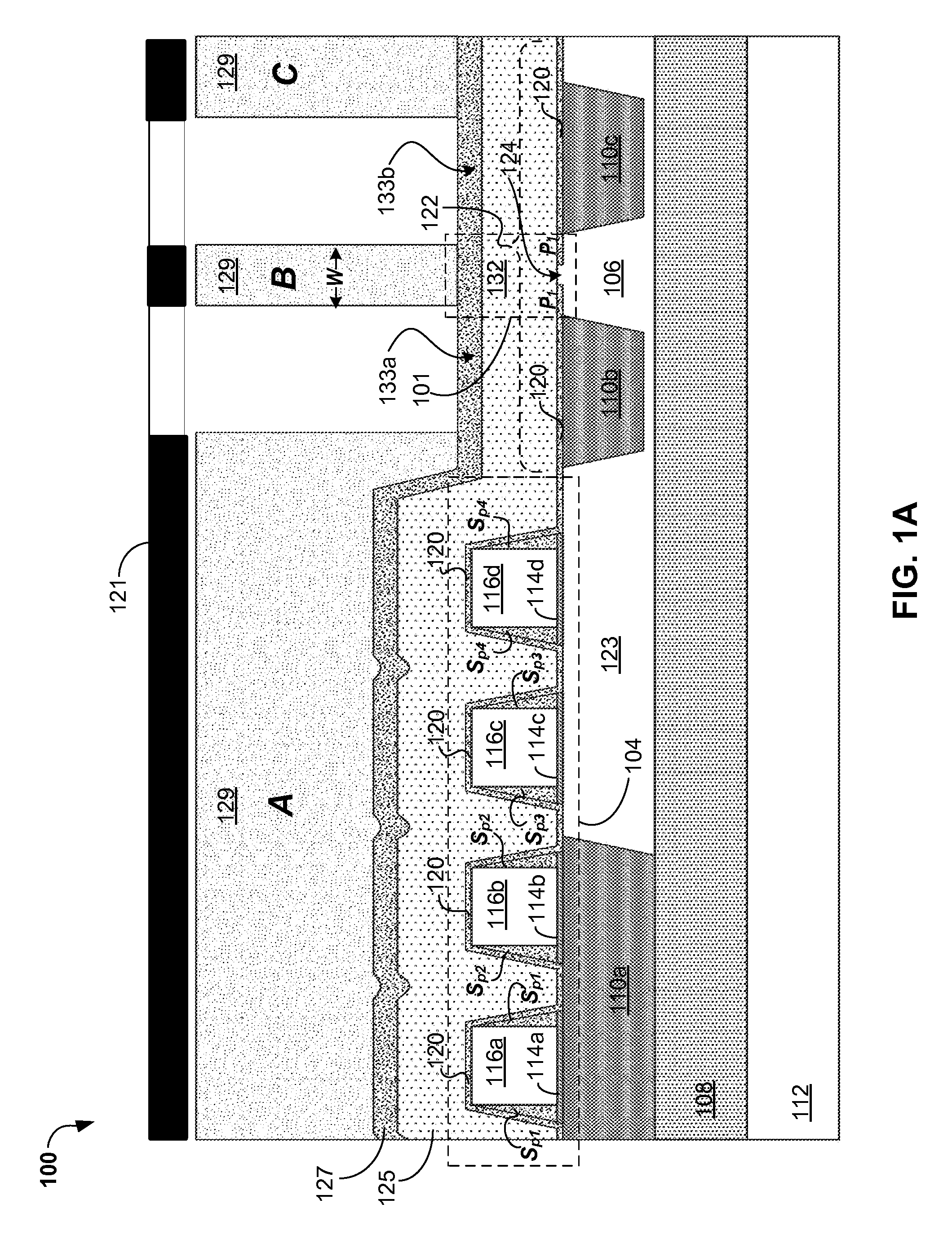

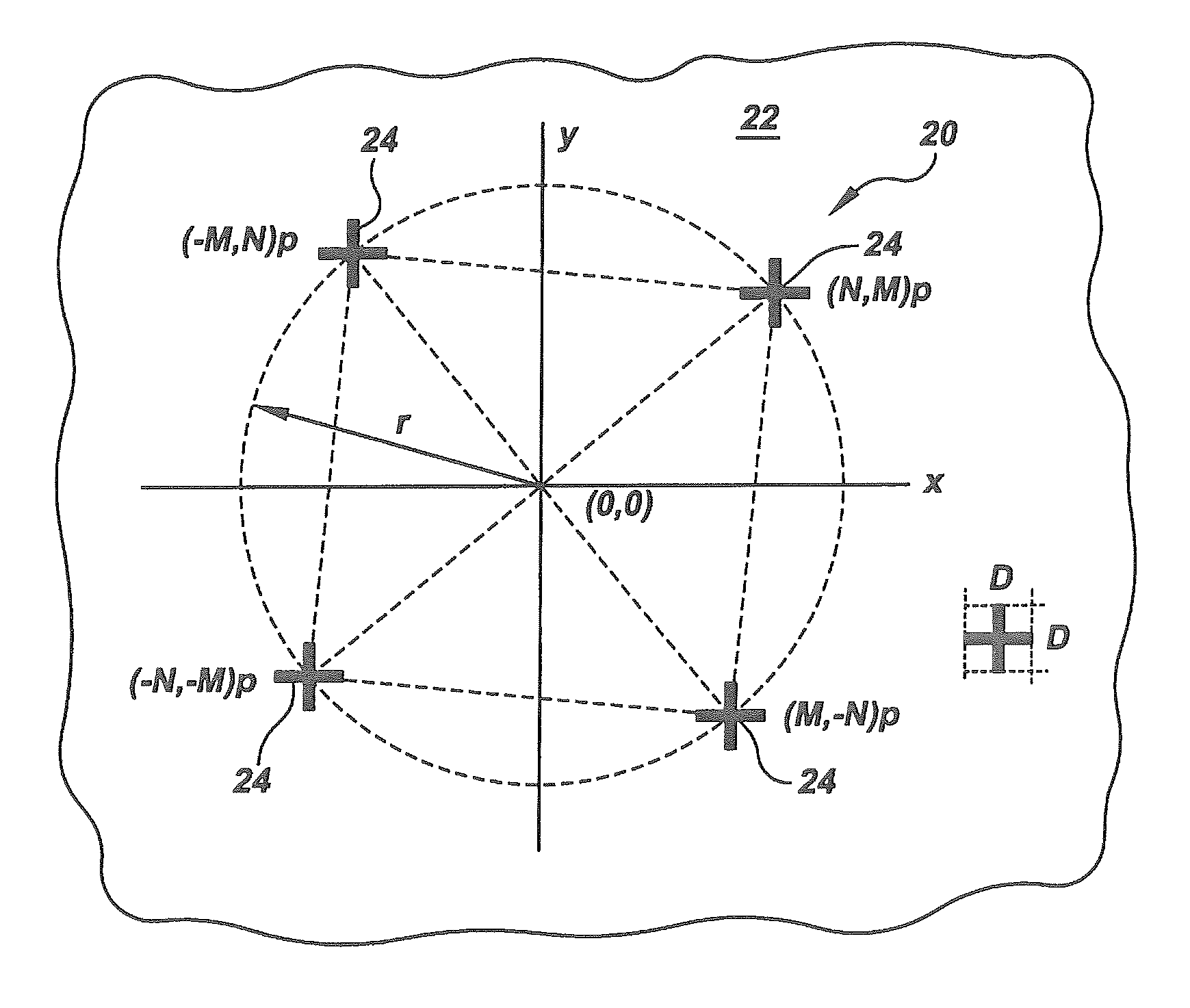

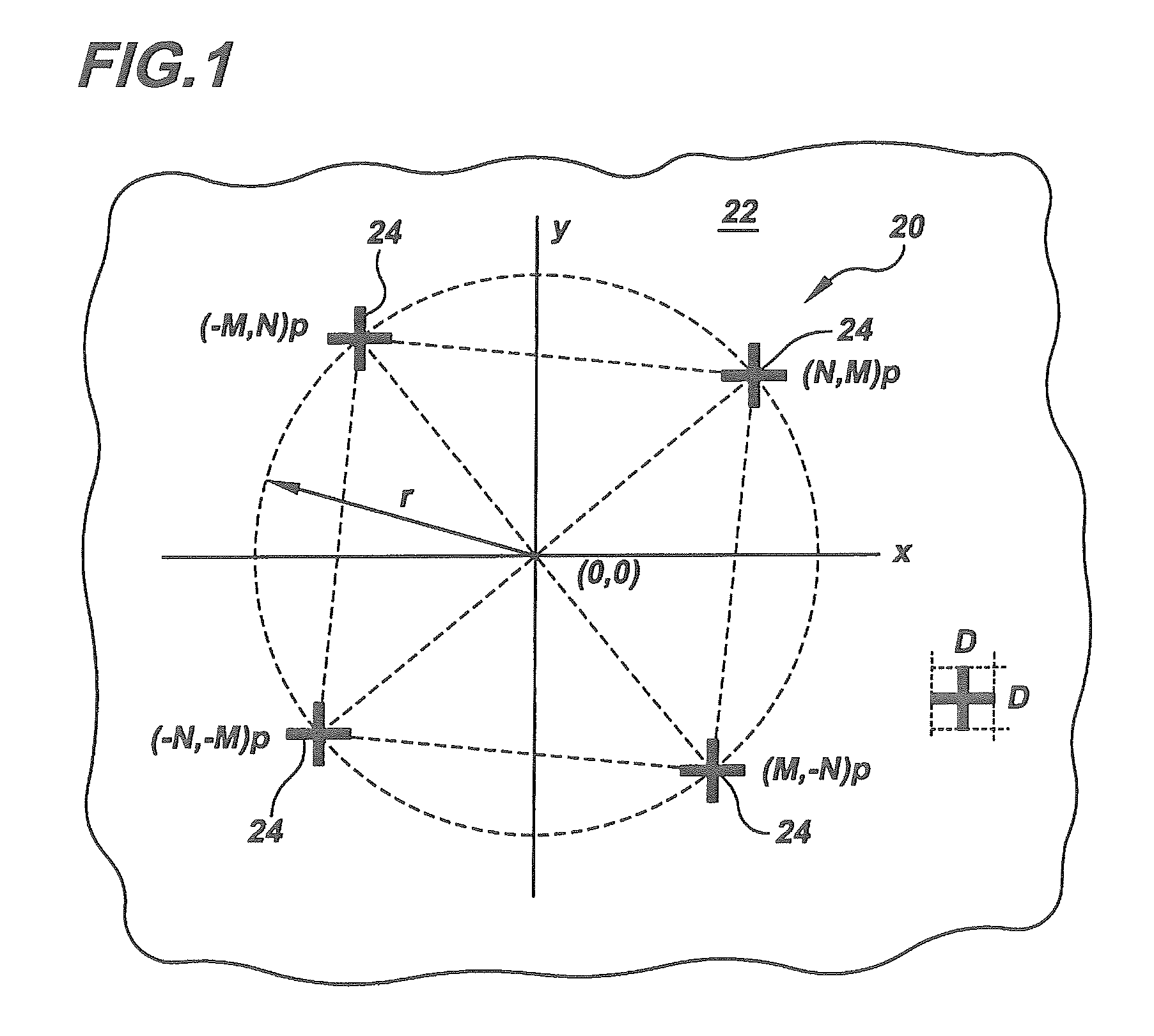

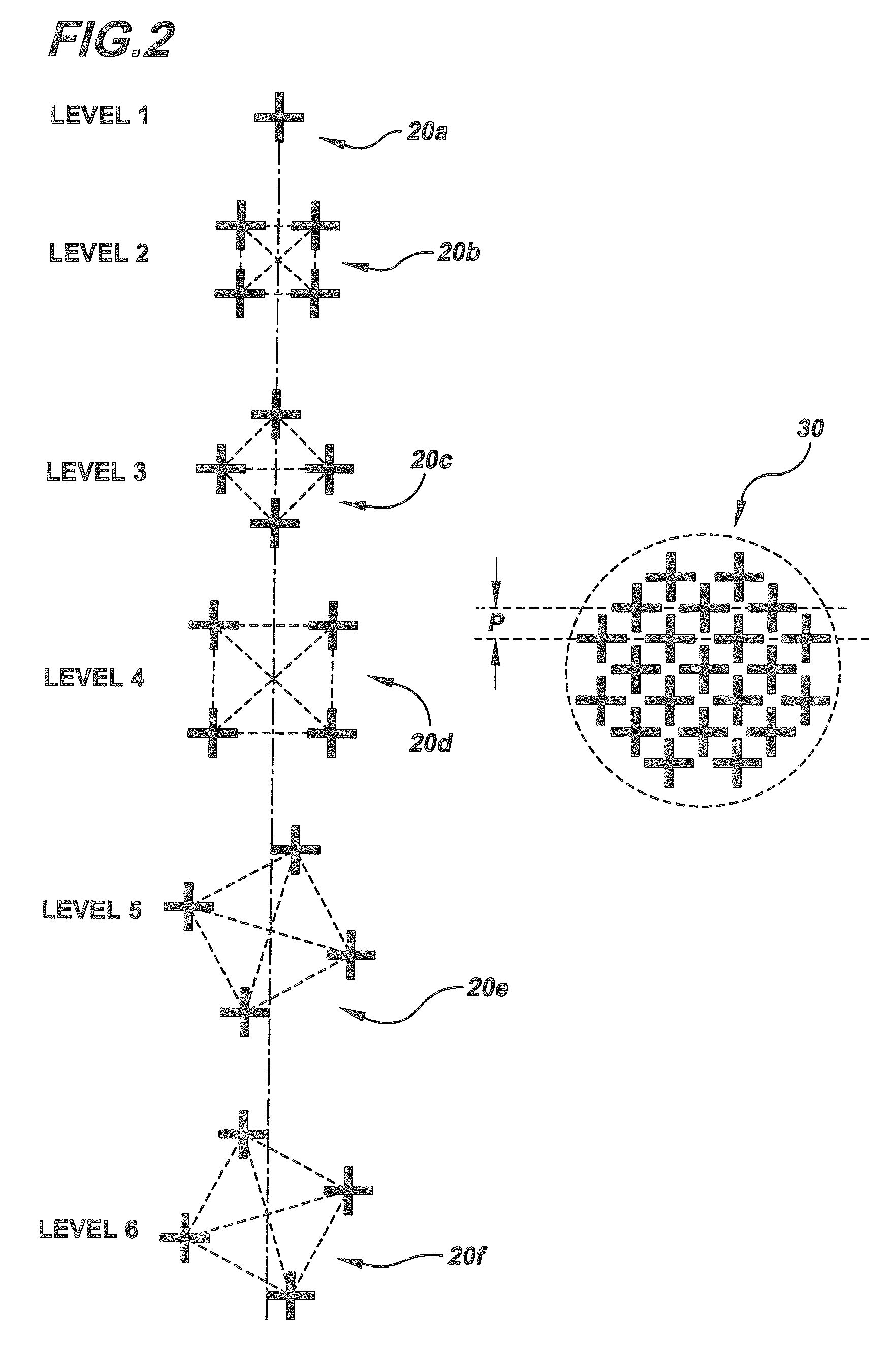

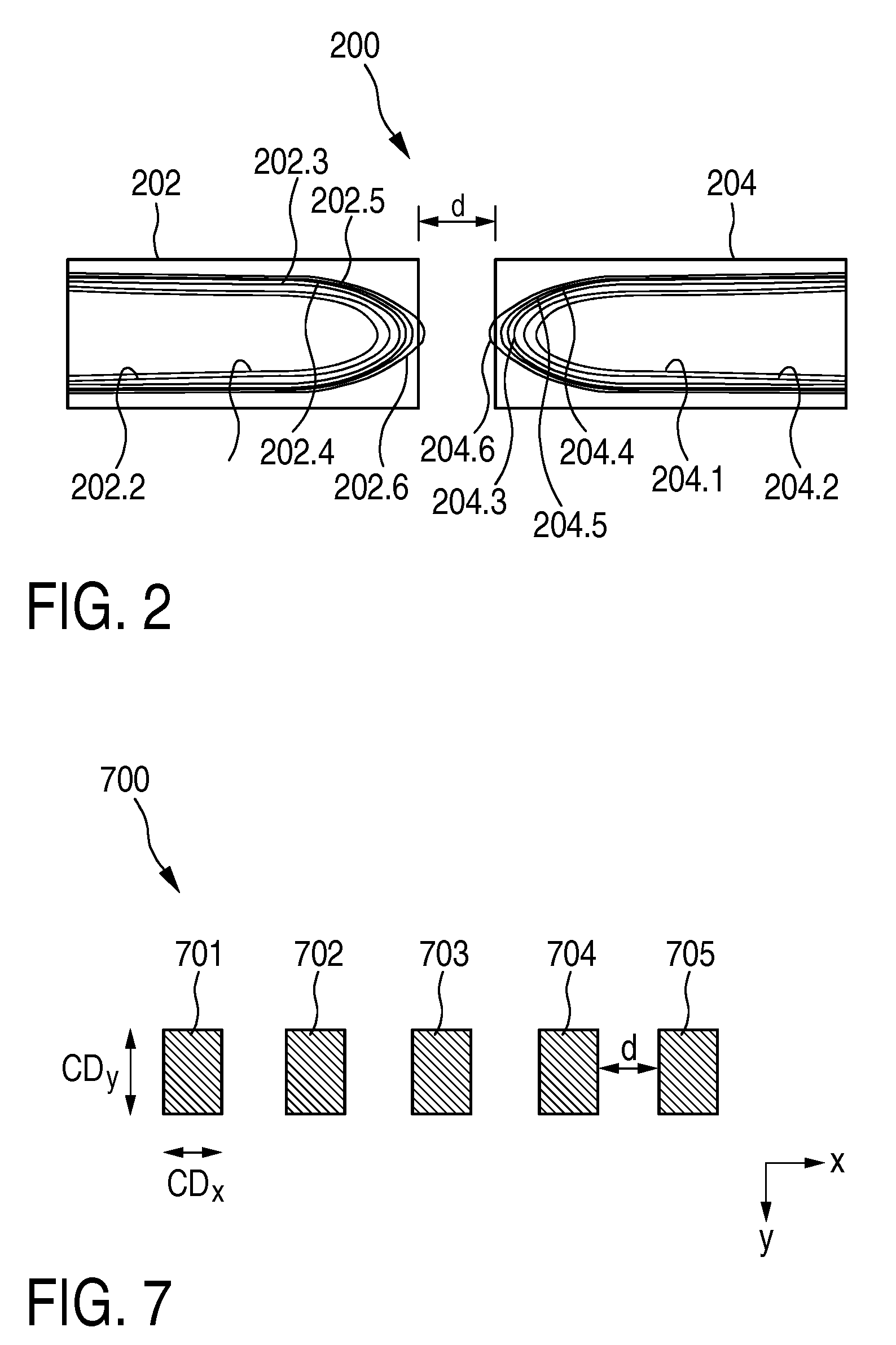

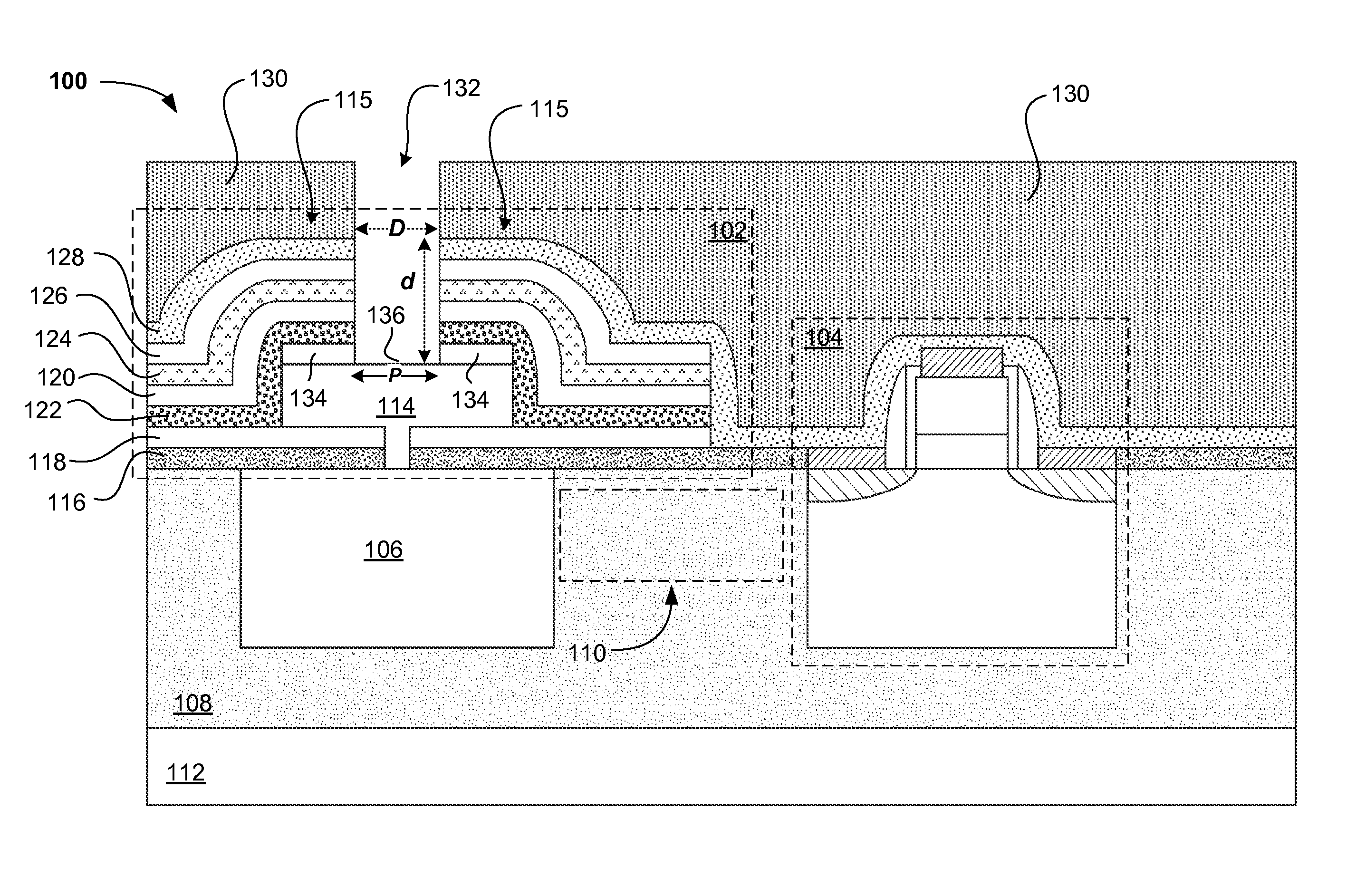

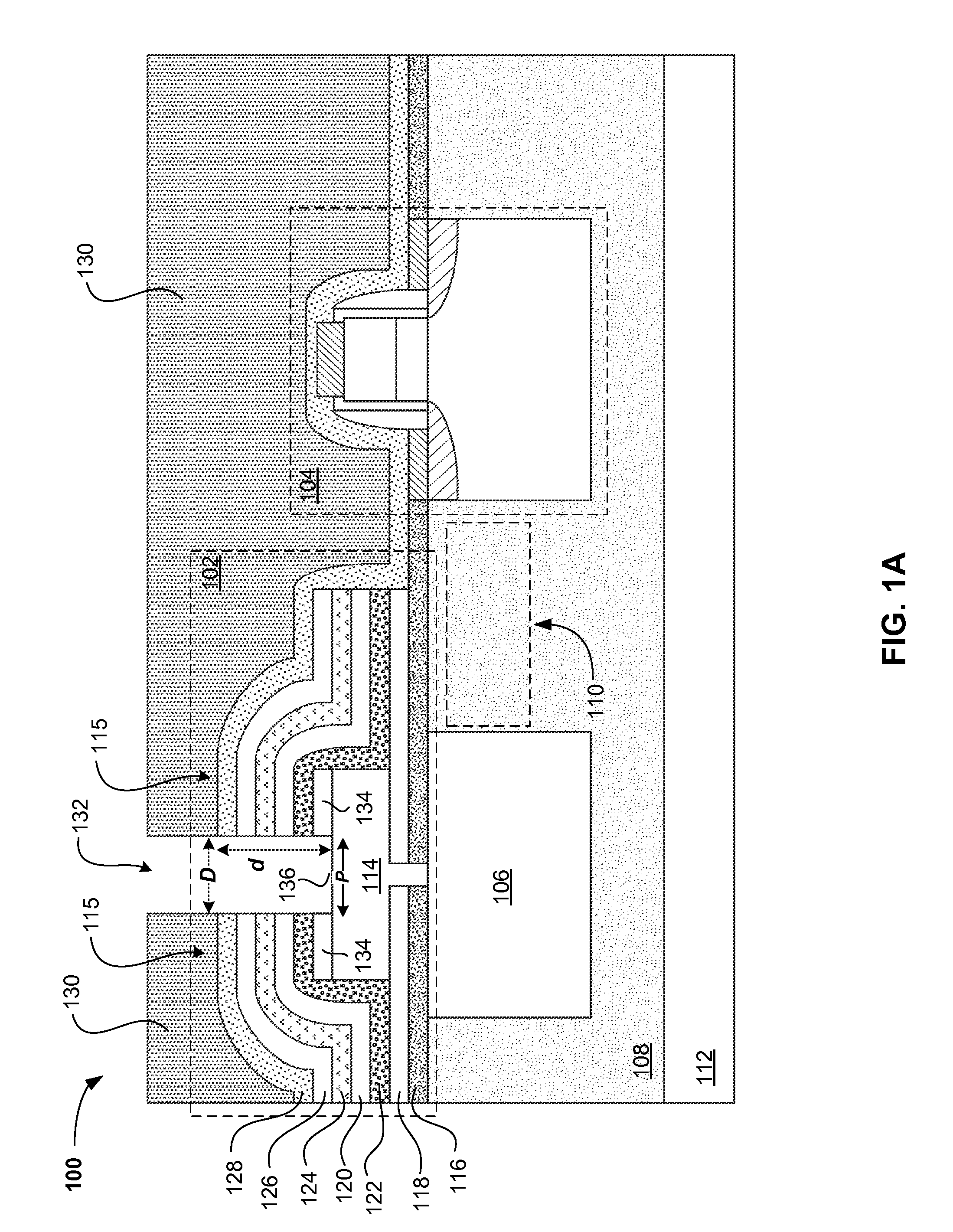

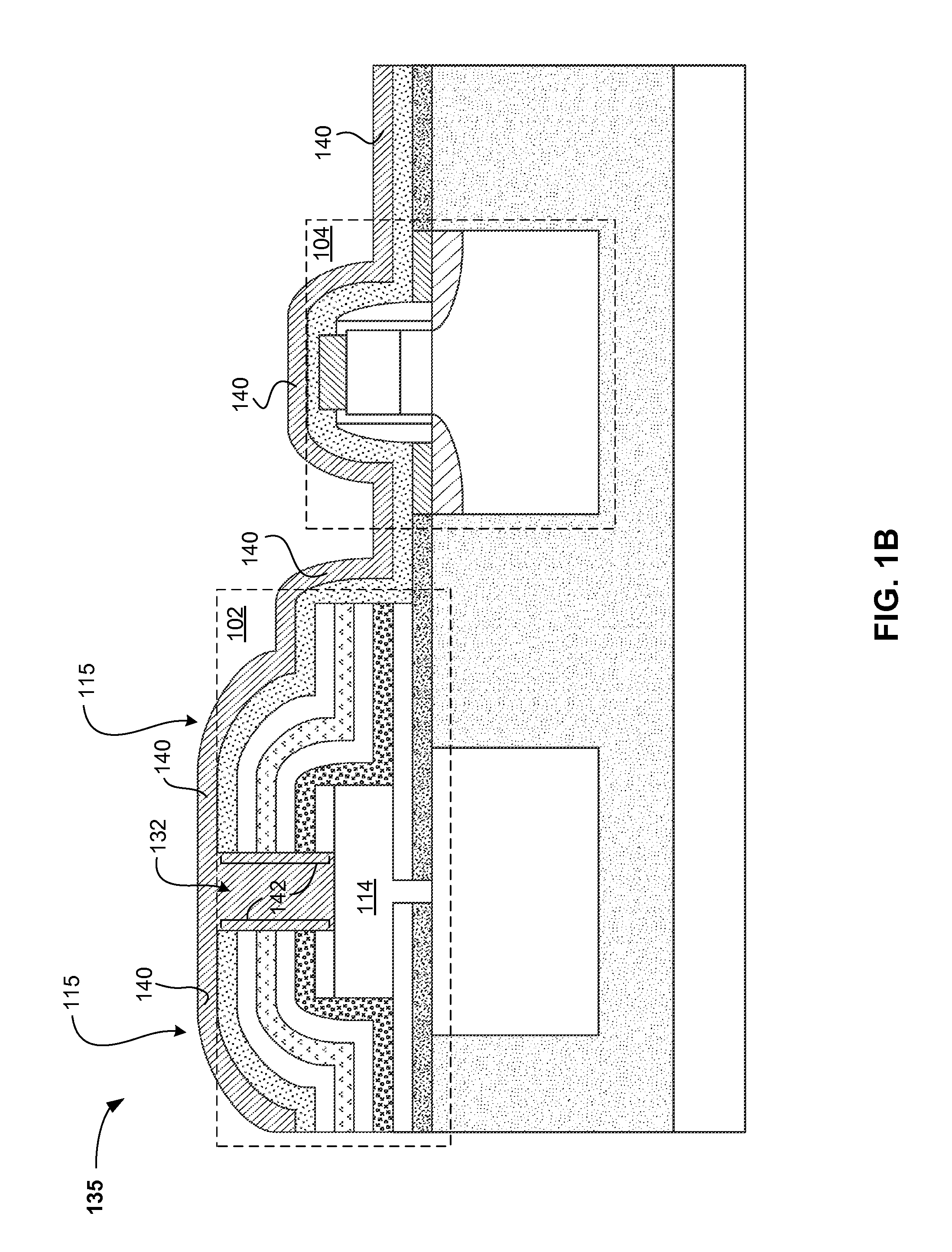

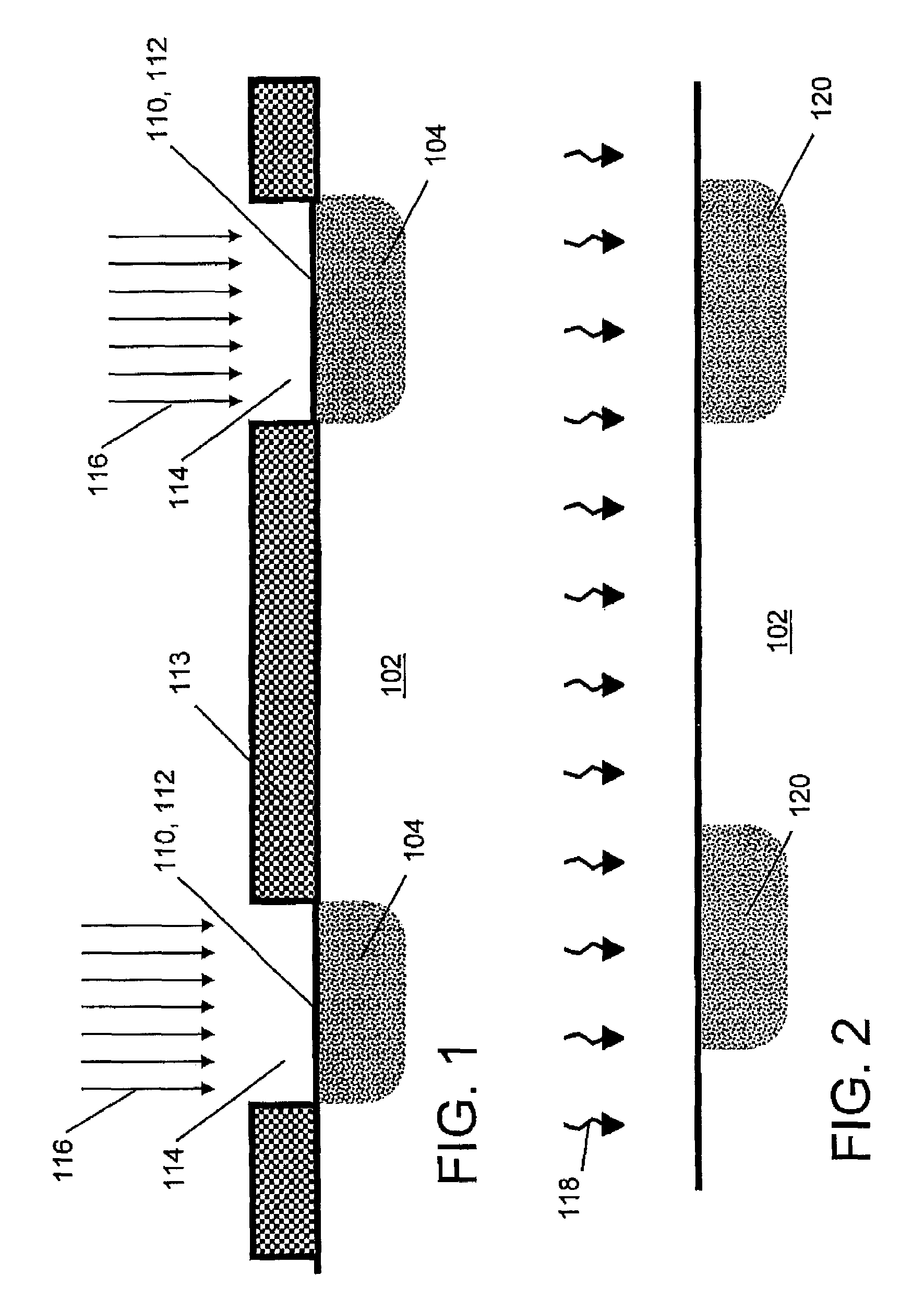

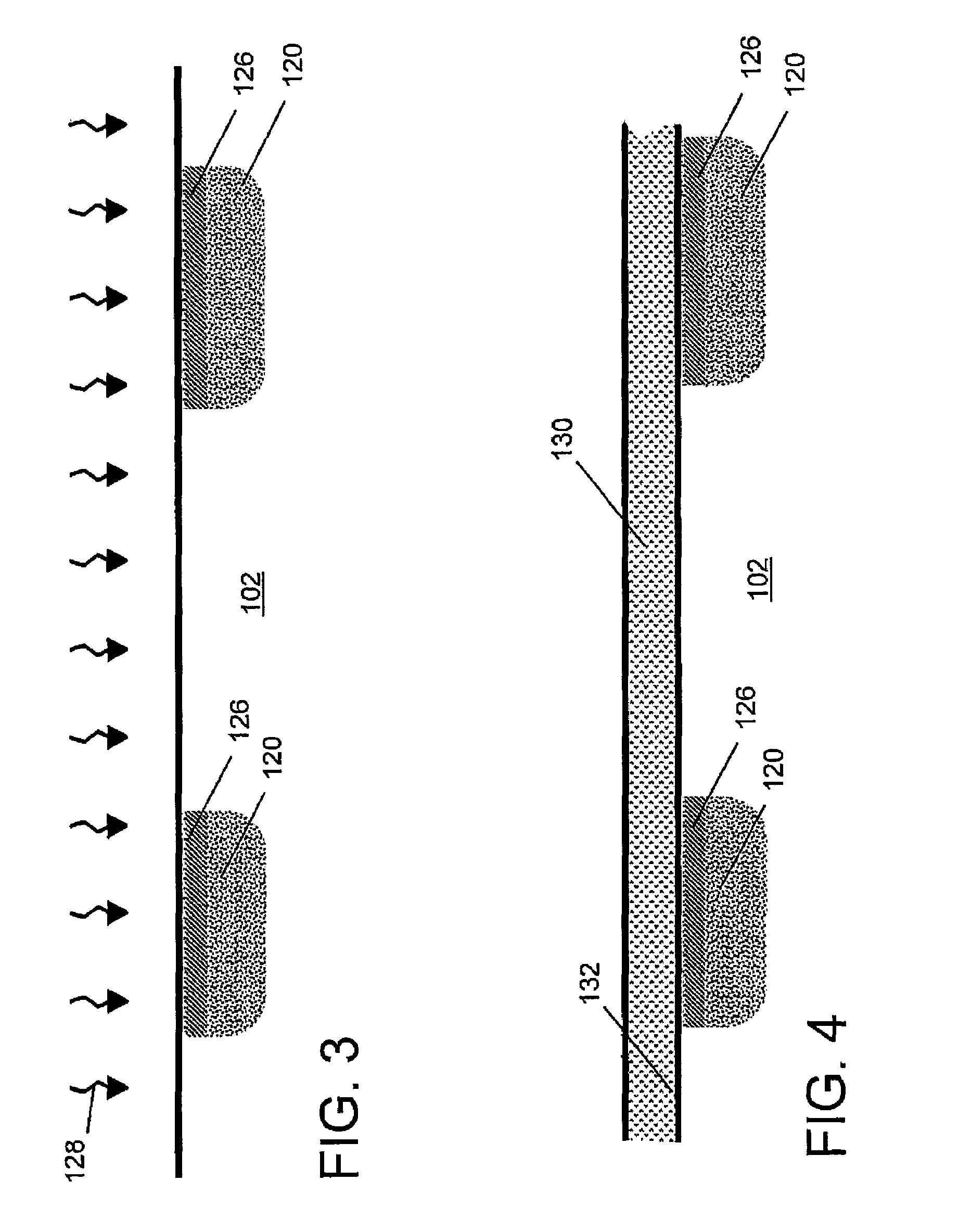

Integrated circuit having interleaved gridded features, mask set and method for printing

ActiveUS20090273100A1Easy interchangeTransistorSemiconductor/solid-state device detailsGrid patternEngineering

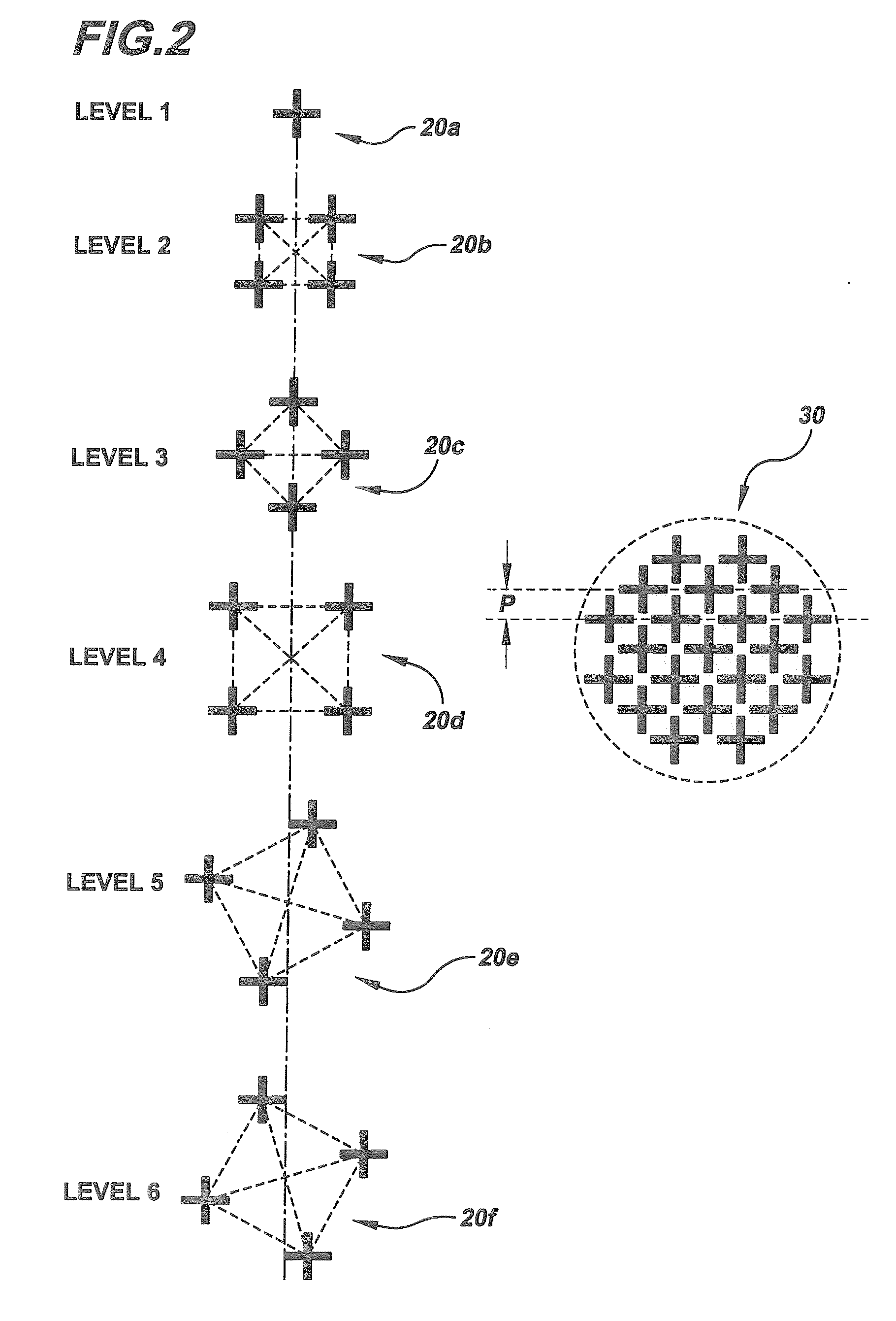

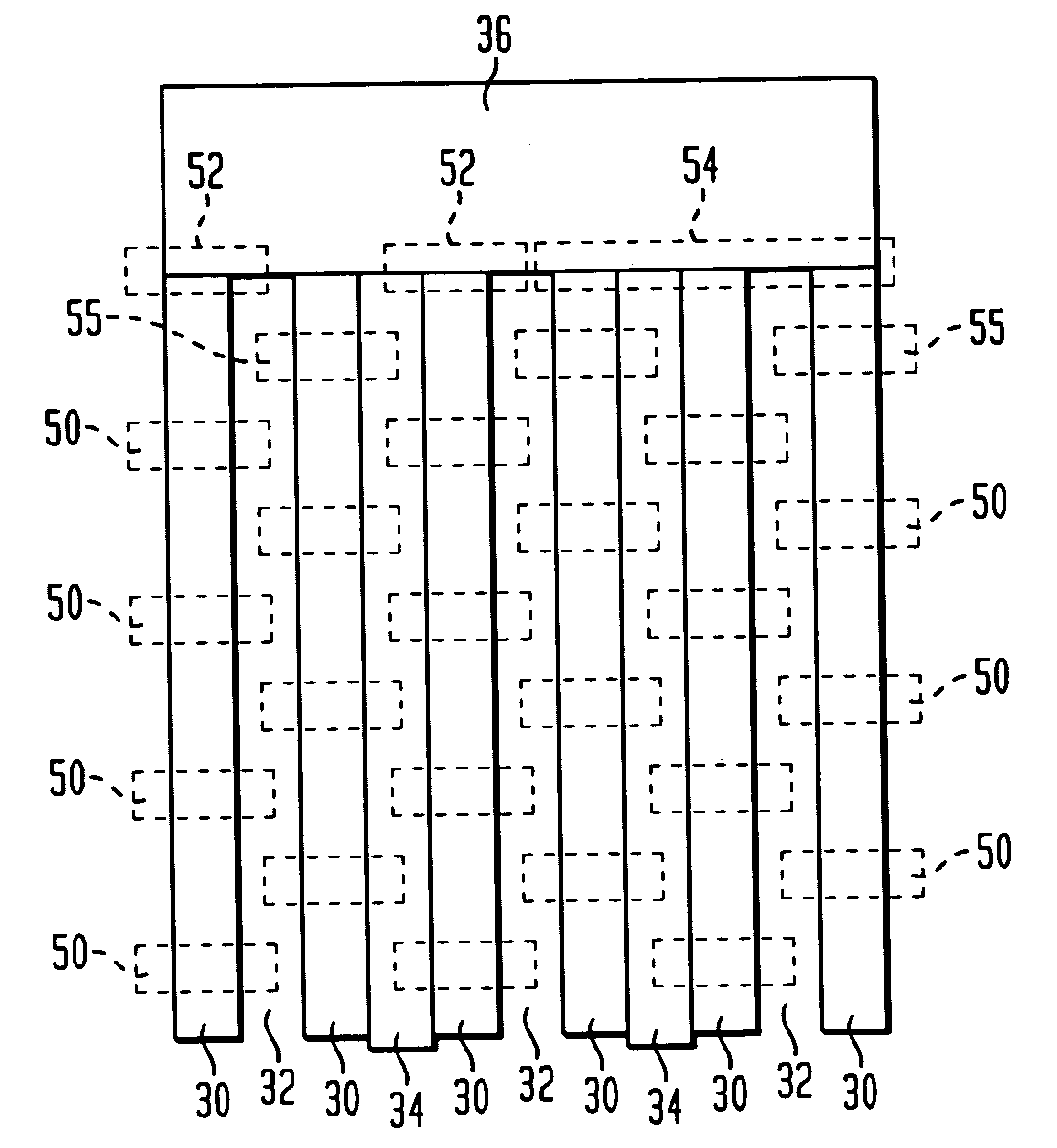

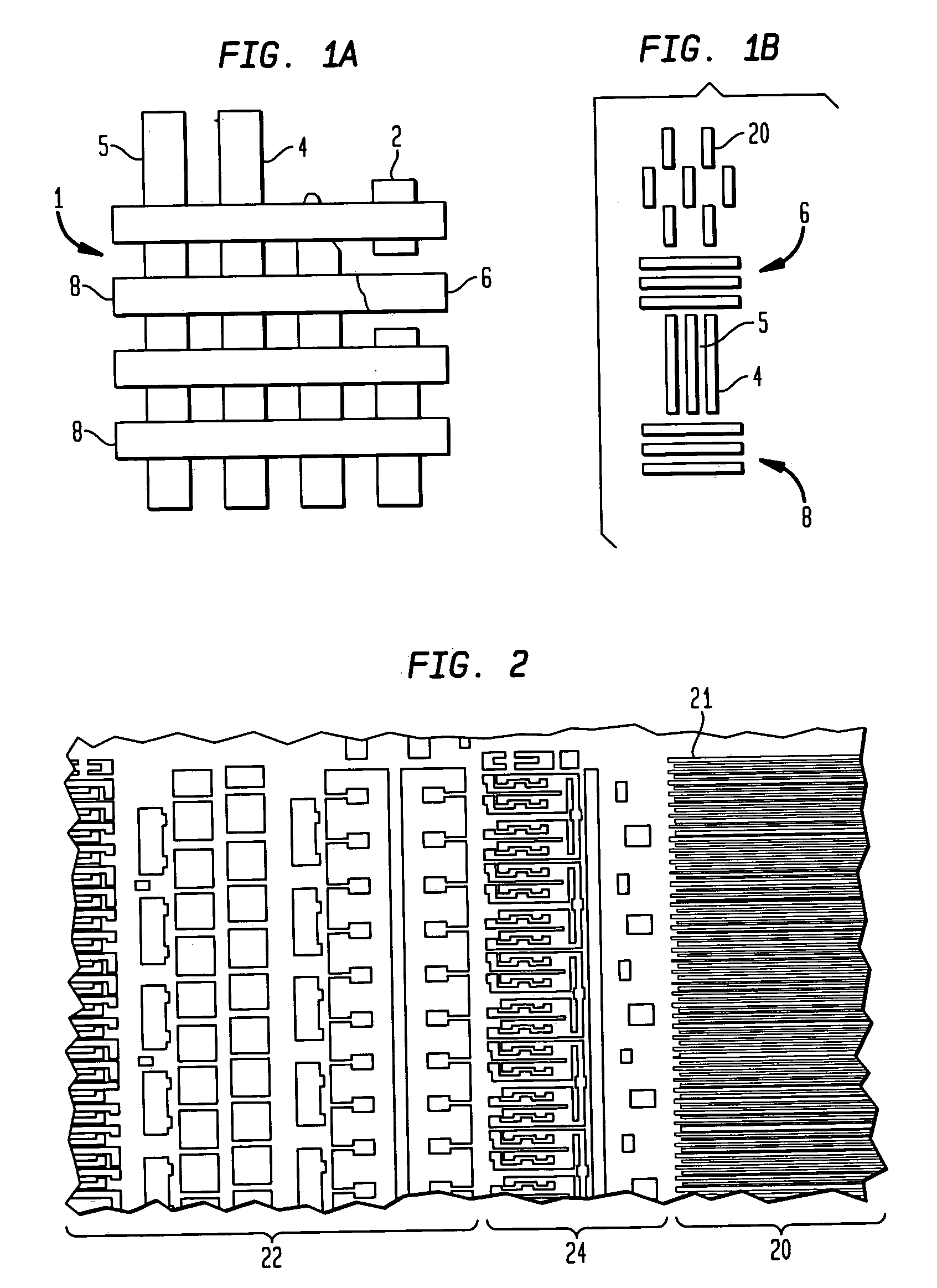

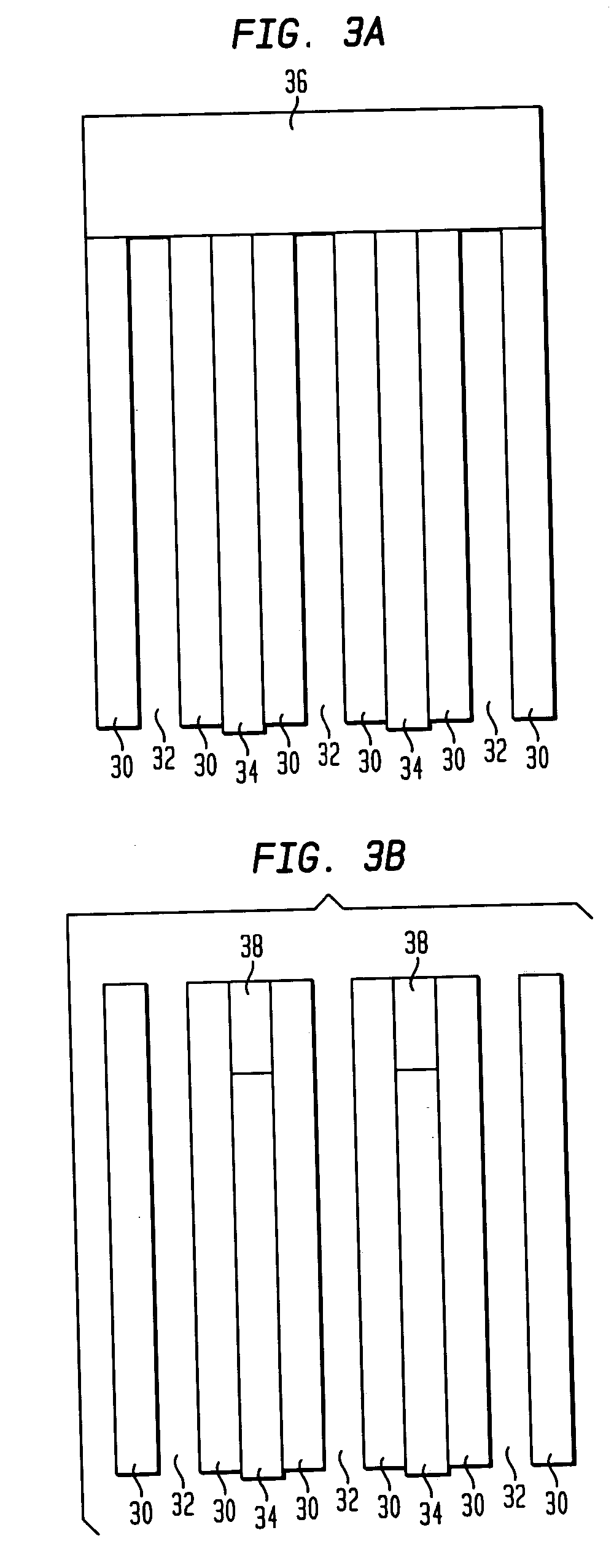

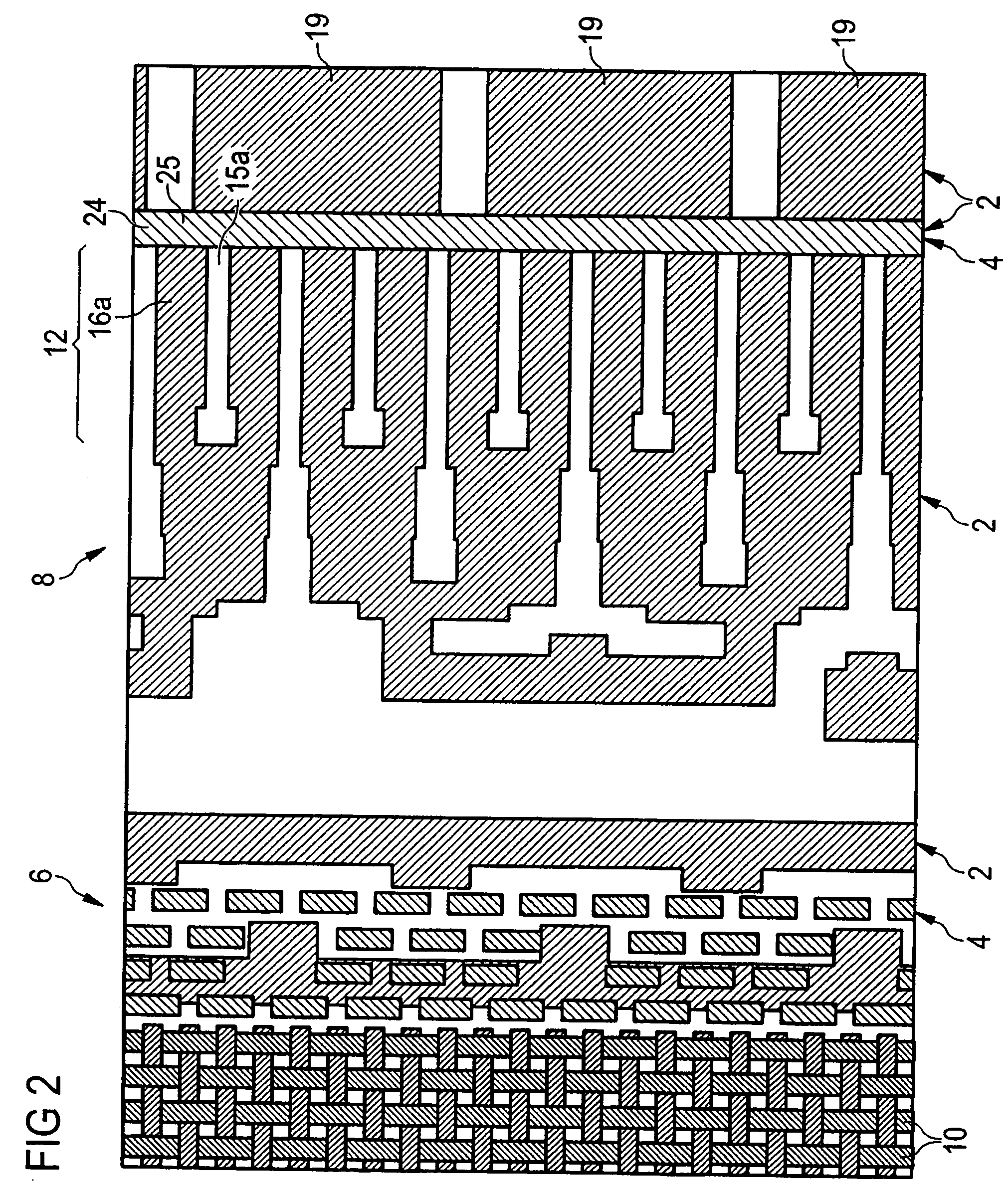

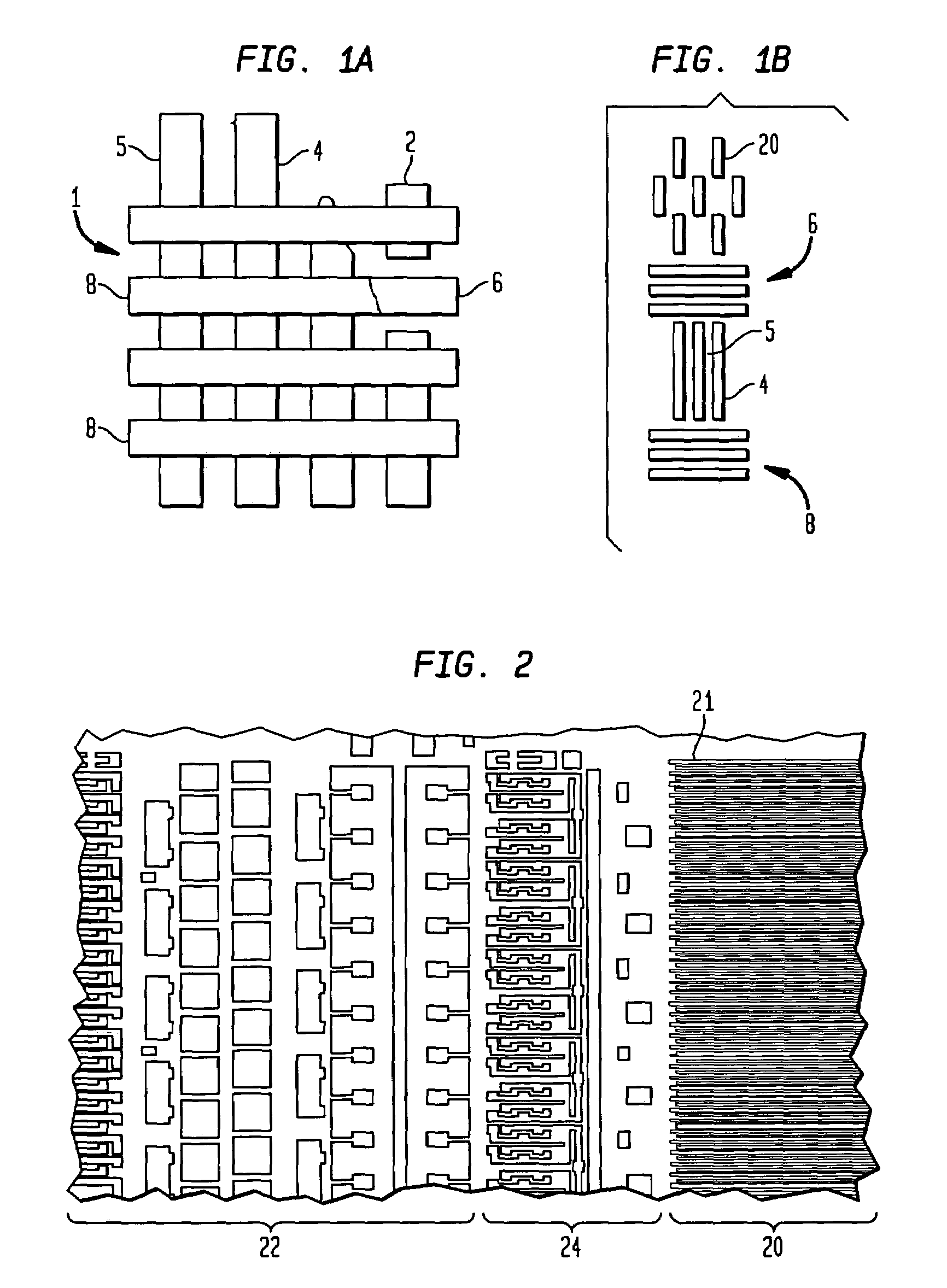

A method (300) for fabricating an integrated circuit includes the step of providing a substrate having a semiconductor surface (305). For at least one masking level (e.g. gate electrode, contact or via) of the integrated circuit, a mask pattern for the masking level is partitioned into a first mask and at least a second mask (310). The first mask provides features in a first grid pattern and the second mask provides features in a second grid pattern. The first and second grid pattern have respective features that interleave with one another over at least one area. A first photoresist film is applied onto the surface of the substrate (315). The first grid pattern is printed using the first mask (320). The second grid pattern is printed using the second mask (325). The first and said second grid pattern are then etched into the surface of the substrate (330). Another embodiment of the invention includes an integrated circuit (240) that has vias or contacts in a grid-like feature pattern in at least one multi-transistor area of the circuit including at least 5 transistors, wherein a minimum horizontal or minimum vertical center-to-center spacing distance between neighboring features in the pattern is ≦100 nm.

Owner:TEXAS INSTR INC

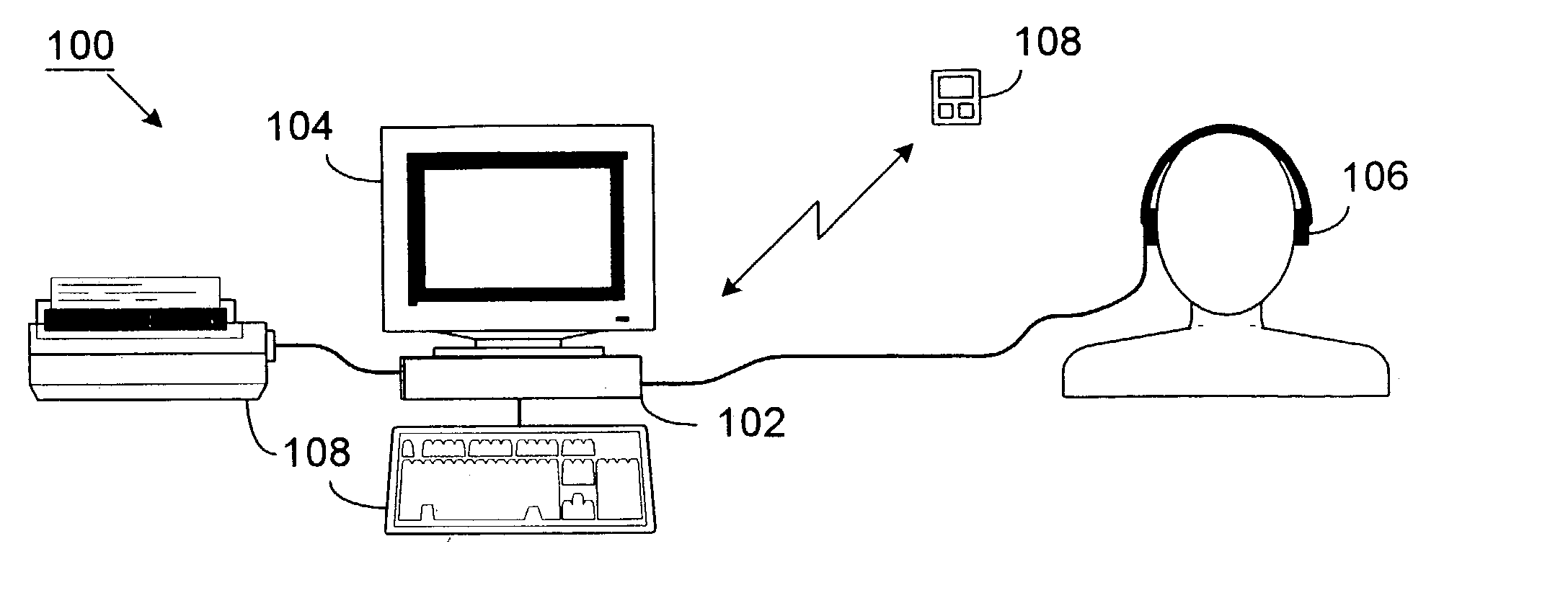

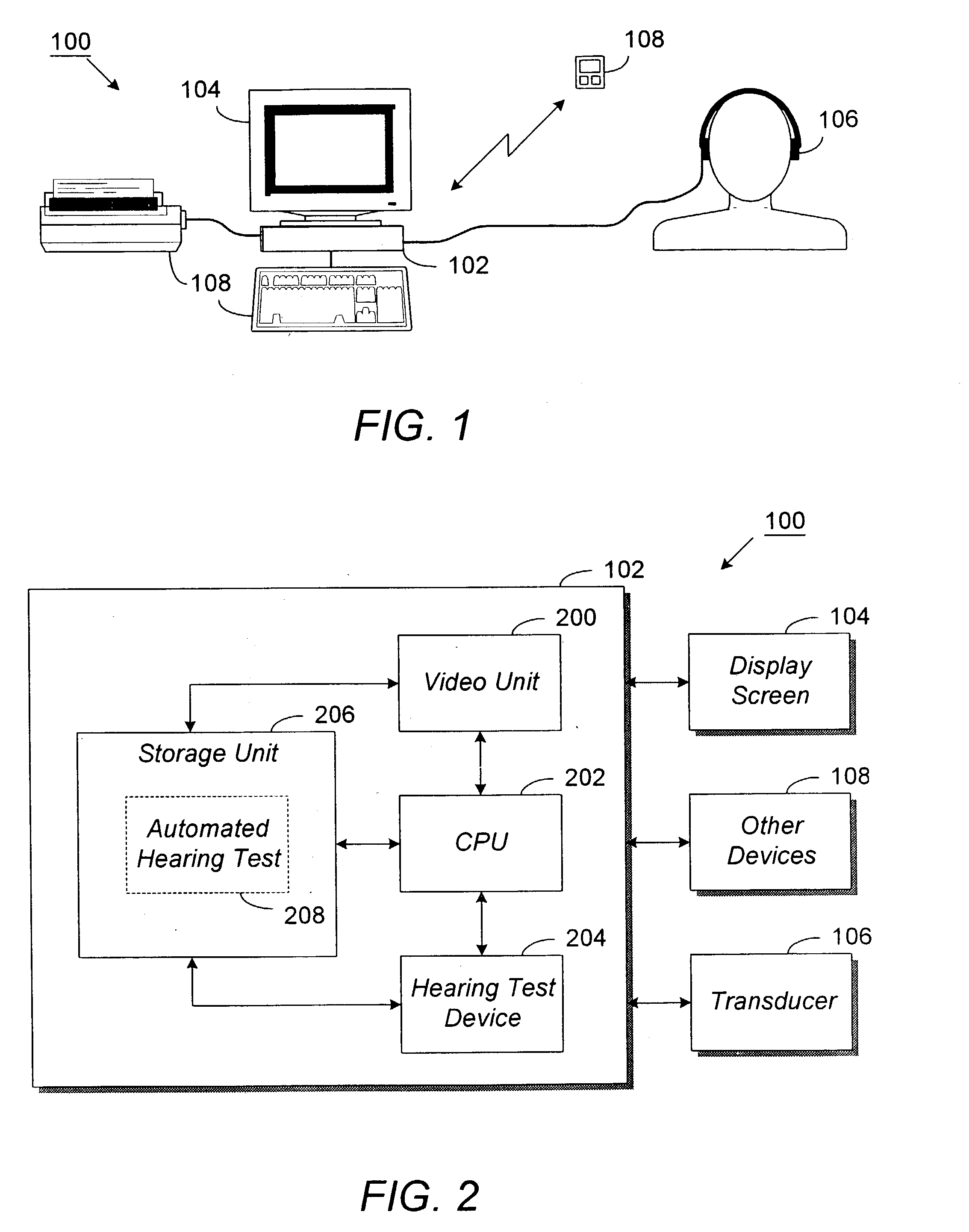

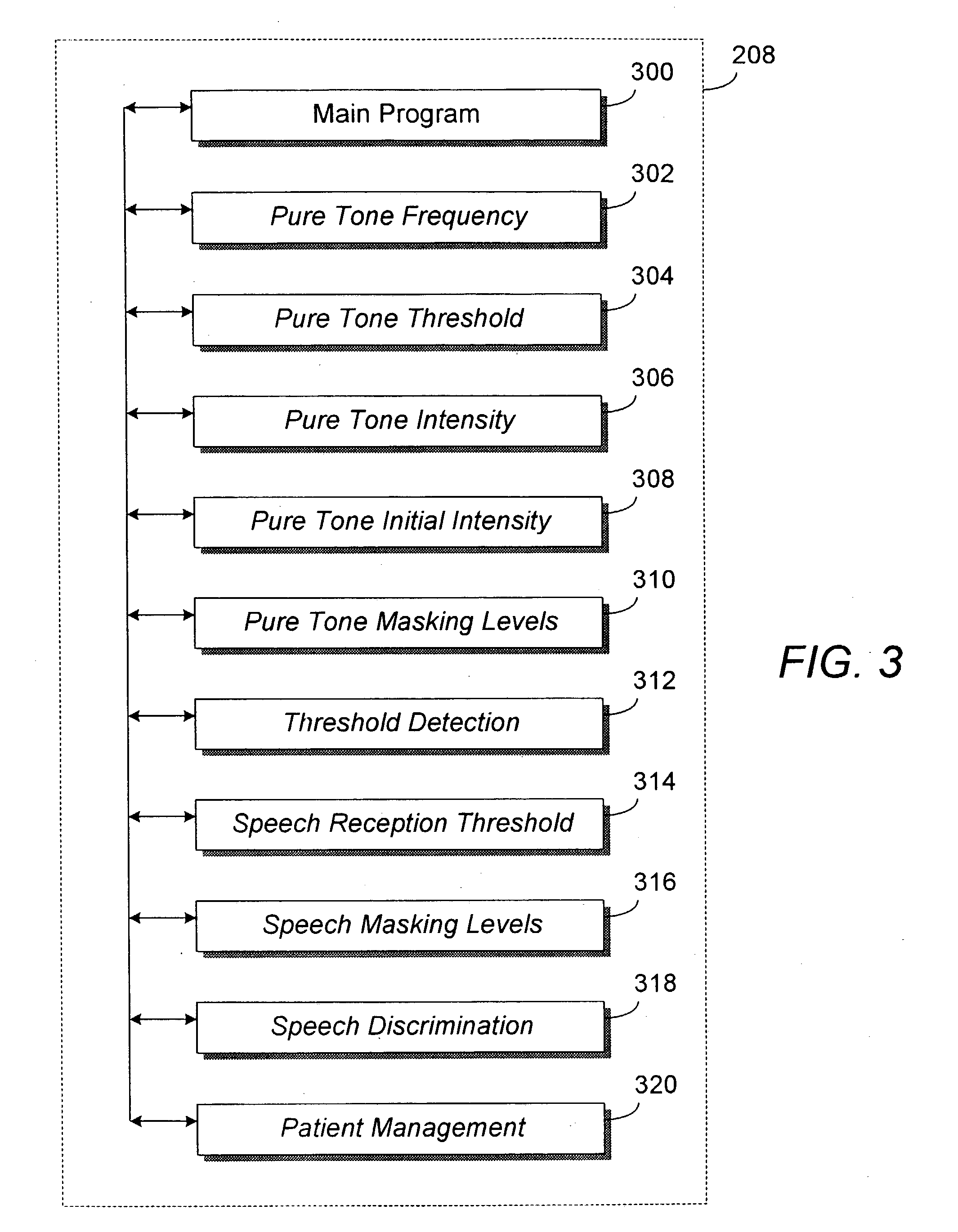

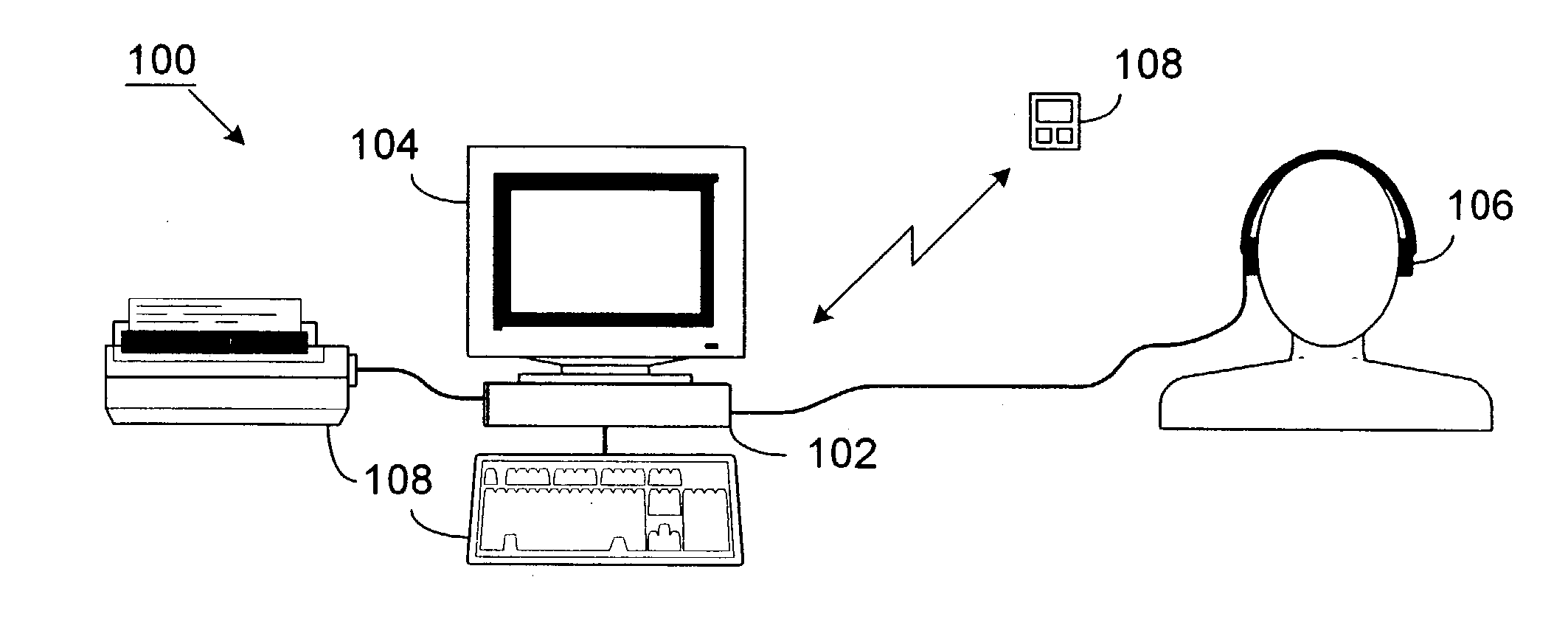

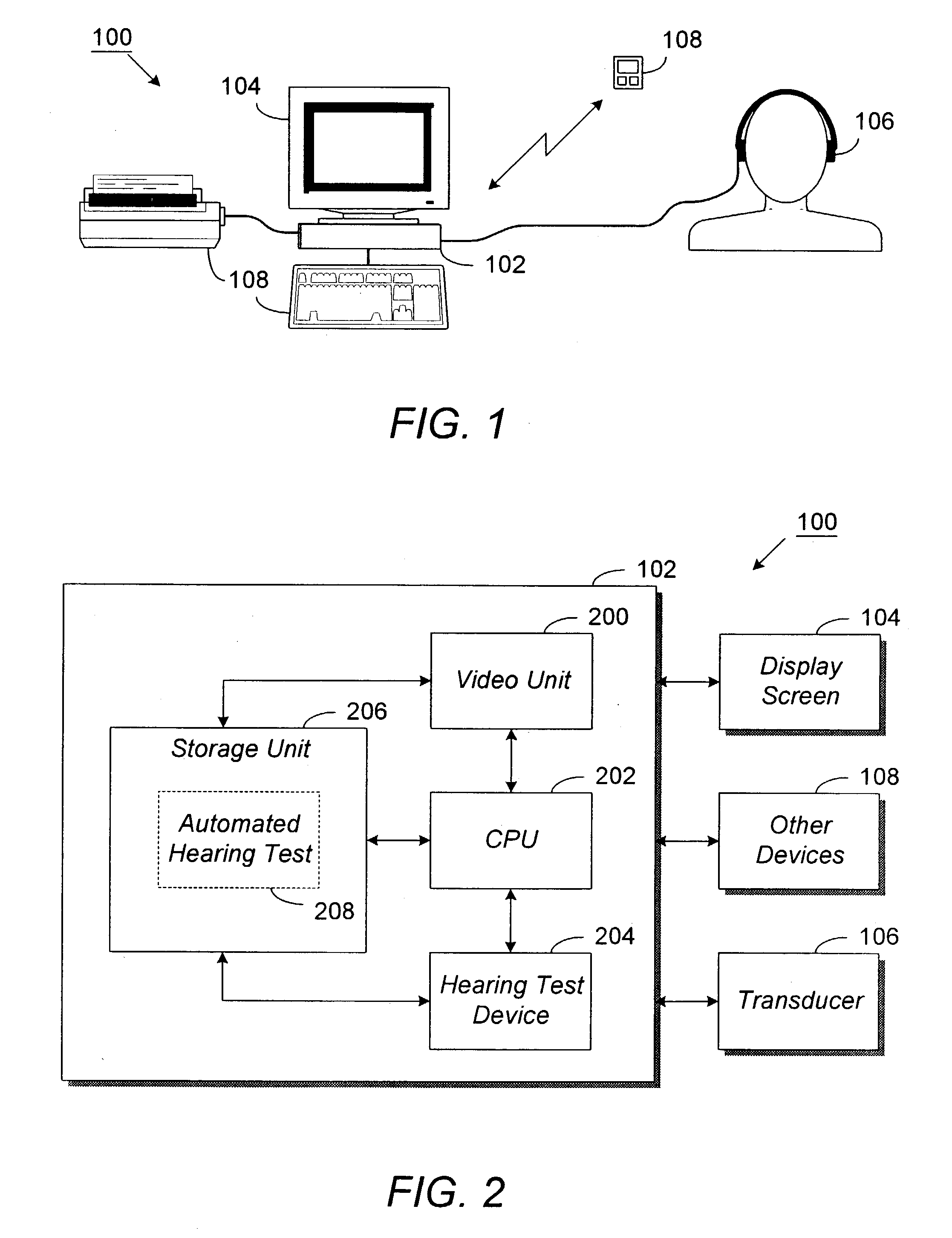

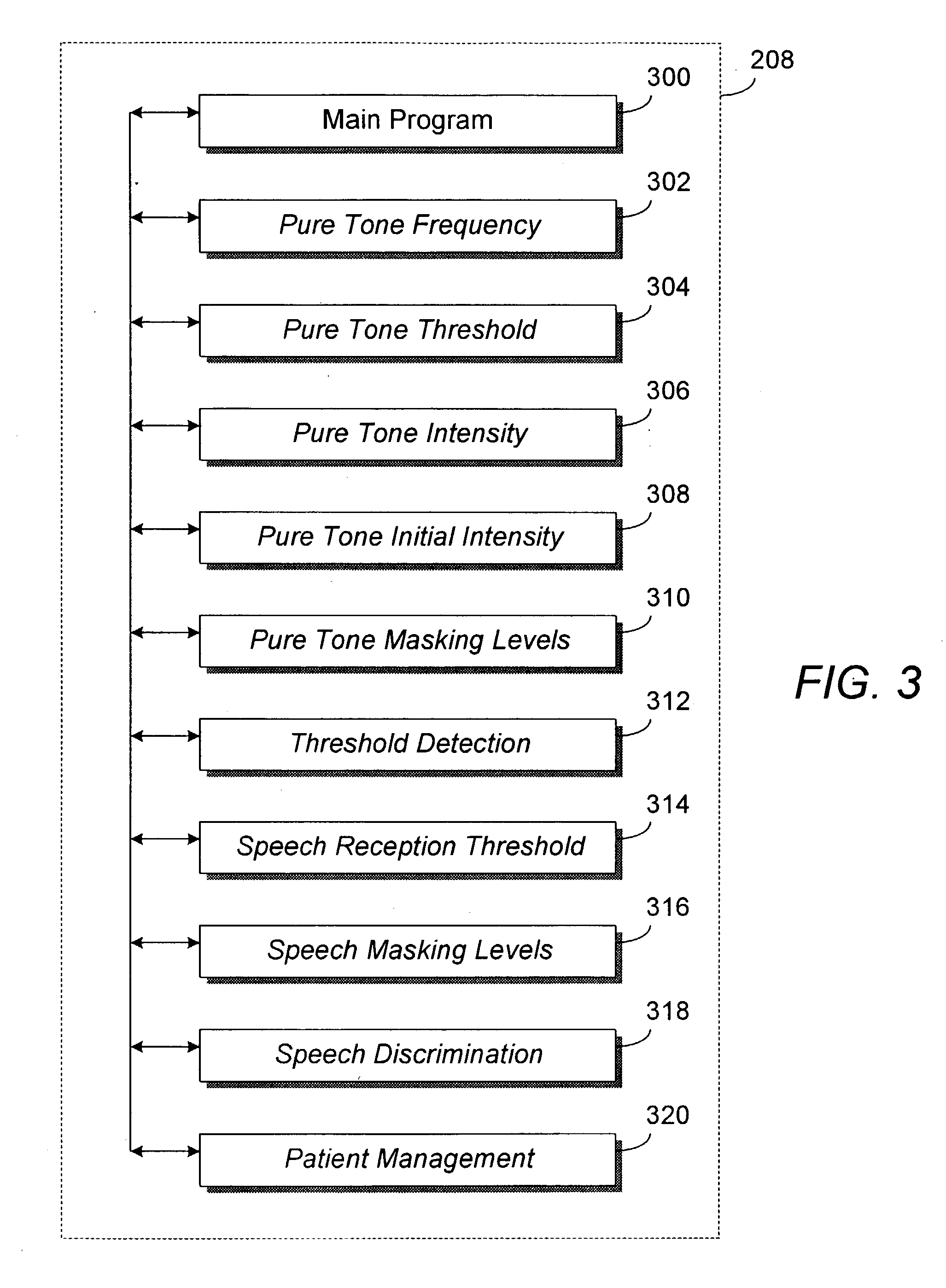

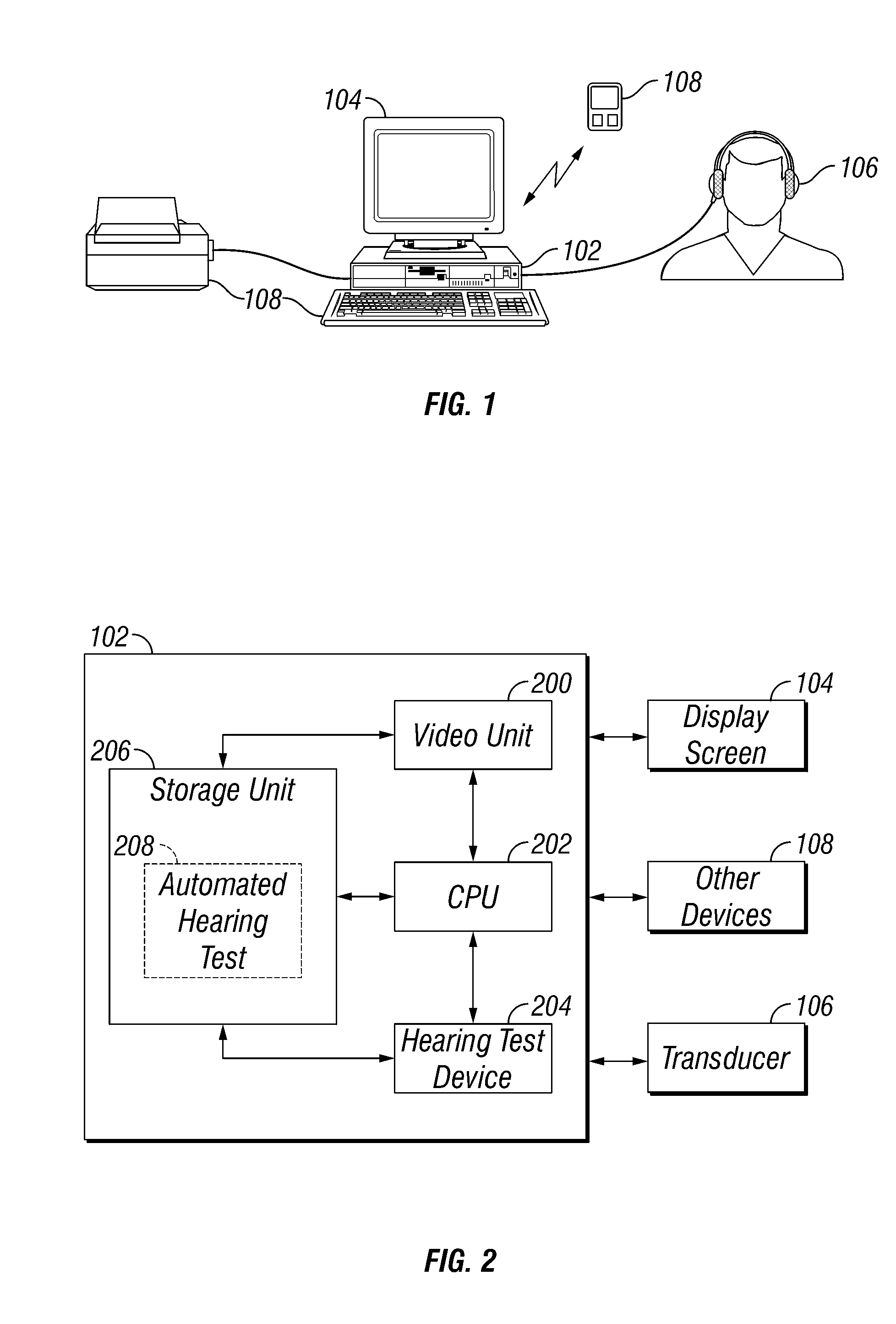

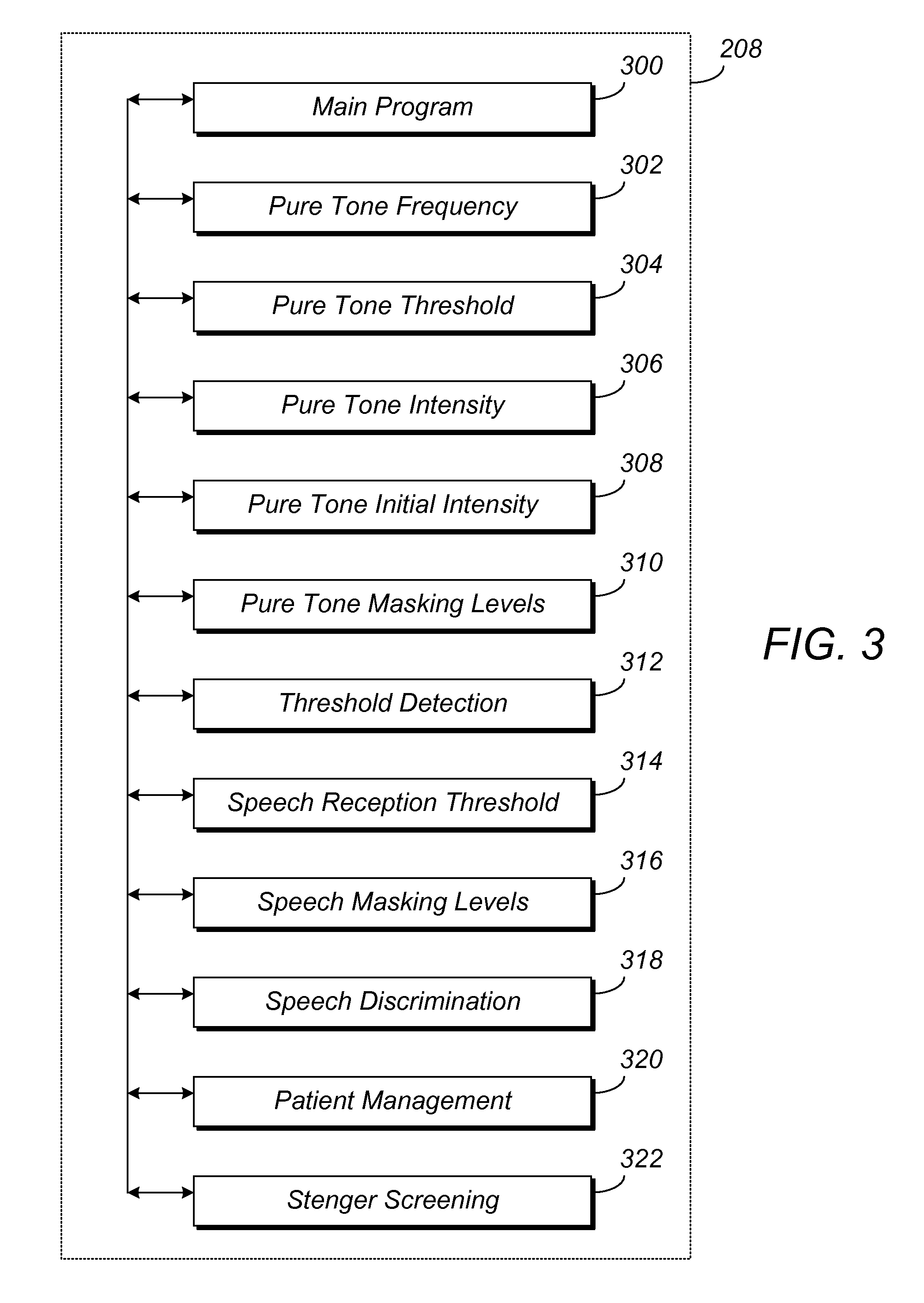

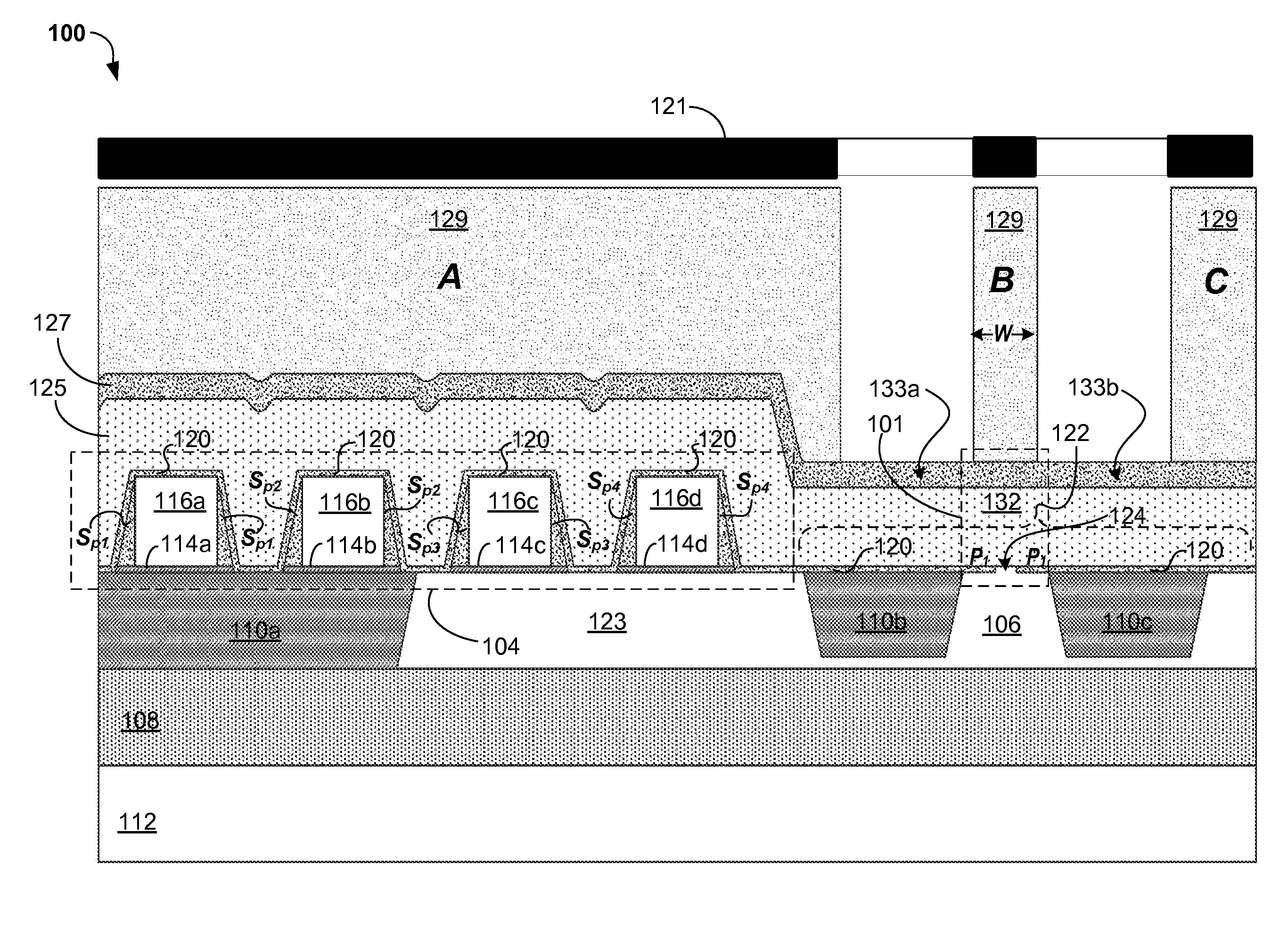

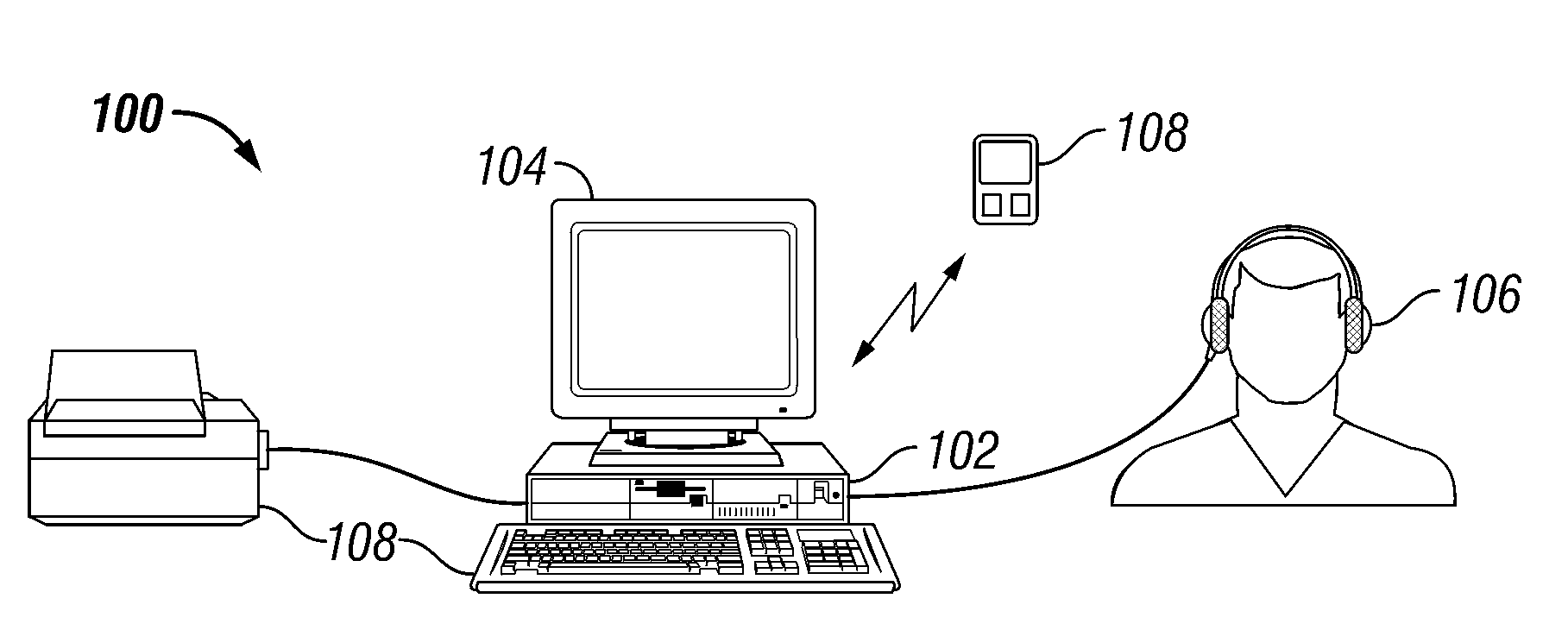

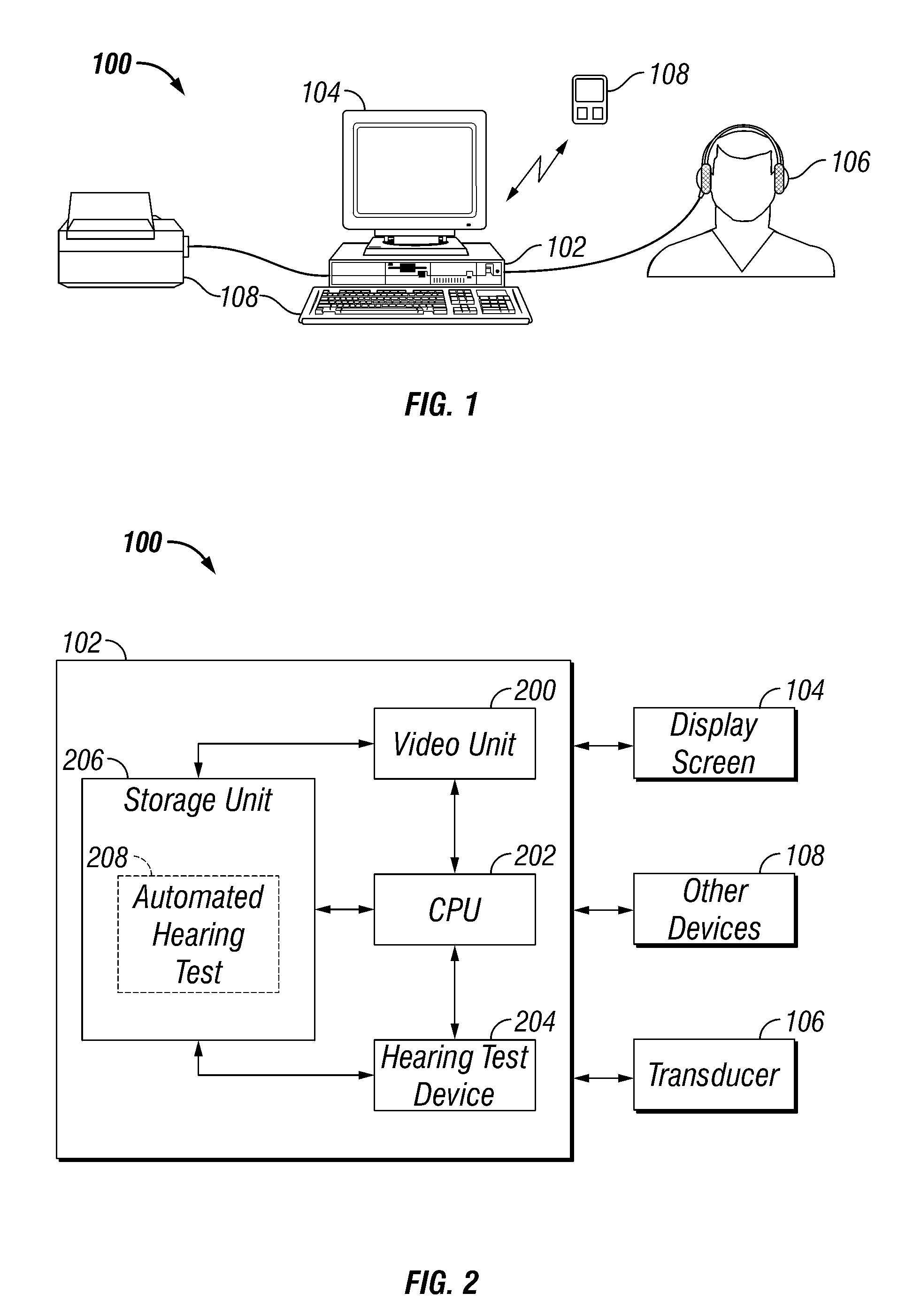

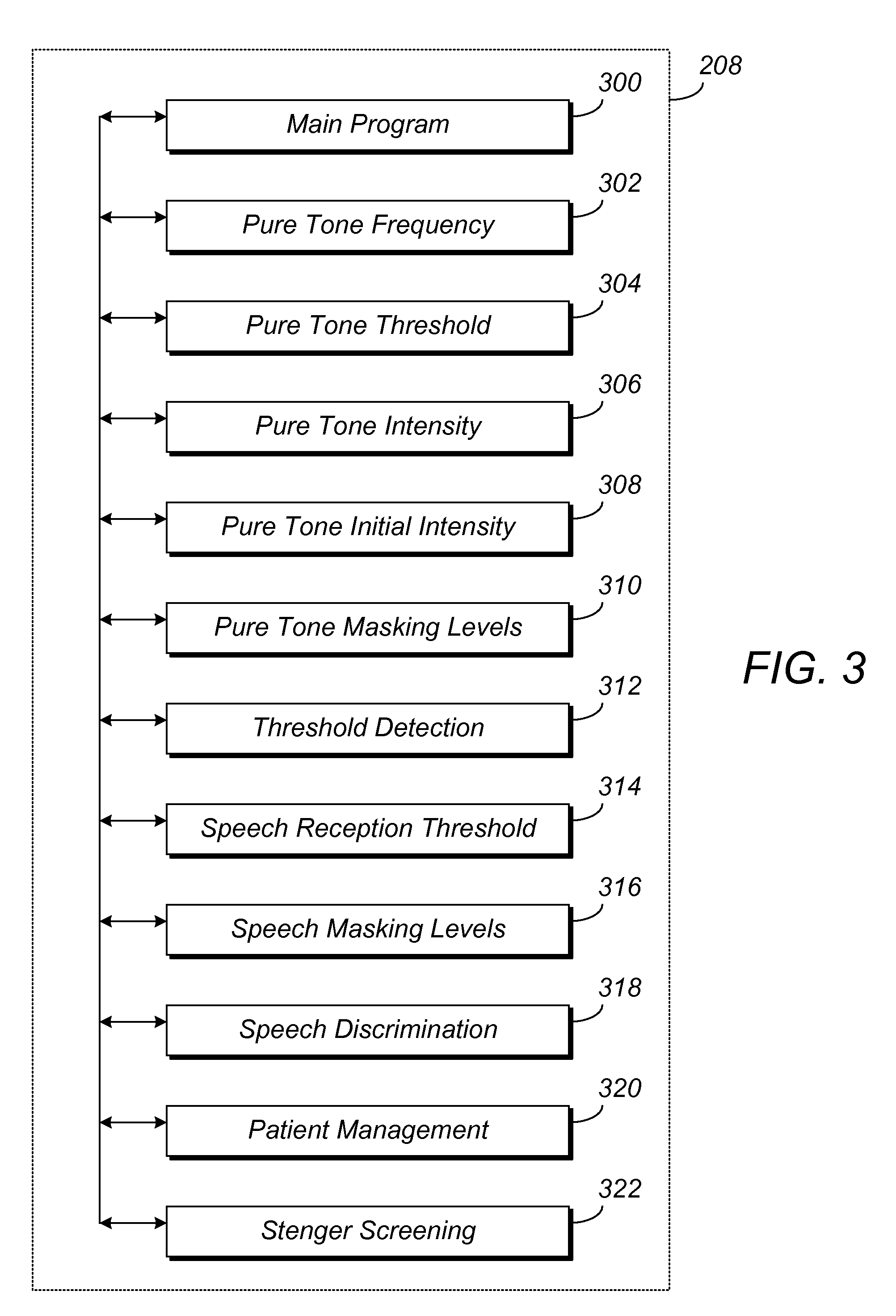

Automated diagnostic hearing test

InactiveUS20040006283A1Diagnostics using vibrationsBone conduction transducer hearing devicesAcoustic reflexSpeech reception threshold

Method and system are disclosed for automated testing of a patient's hearing. The automated hearing test allows the patient to quickly and accurately test his own hearing with minimal or no assistance from an audiologist or other hearing health professionals. The test prompts and instructs the patient for inputs and responses as needed as needed. The patient can select one or several tests to be performed, including air and bone conduction testing with masking, speech reception threshold, speech discrimination, and tympanogram / acoustic reflex testing. Multiple languages are supported. Data obtained from one test may be used for another test or another iteration of the same test to calculate masking levels. The automatic hearing test also detects ambient noise and can compensate for it in the test results. If a contingency occurs, the automated hearing test is configured to page the operator for assistance.

Owner:TYMPANY +1

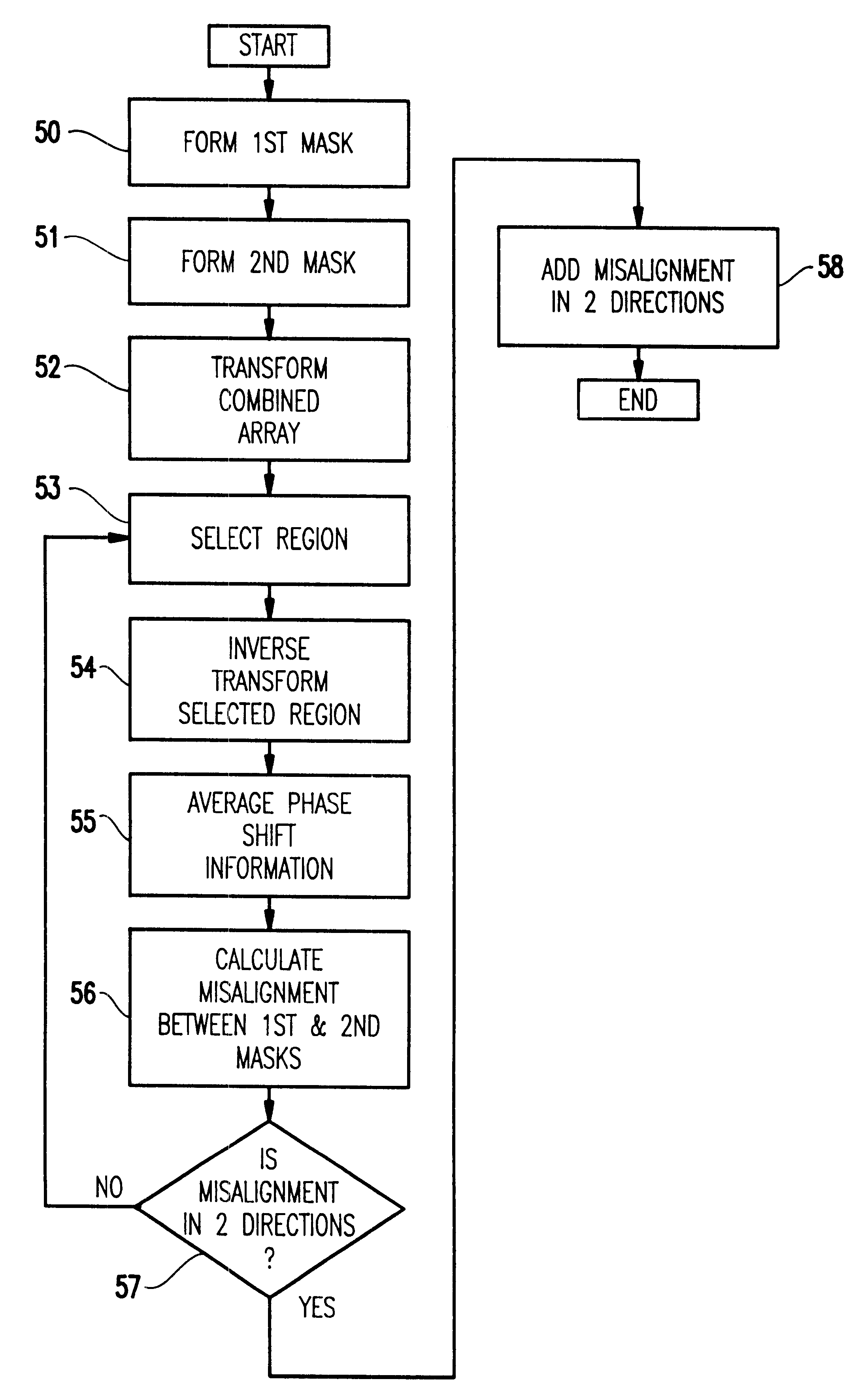

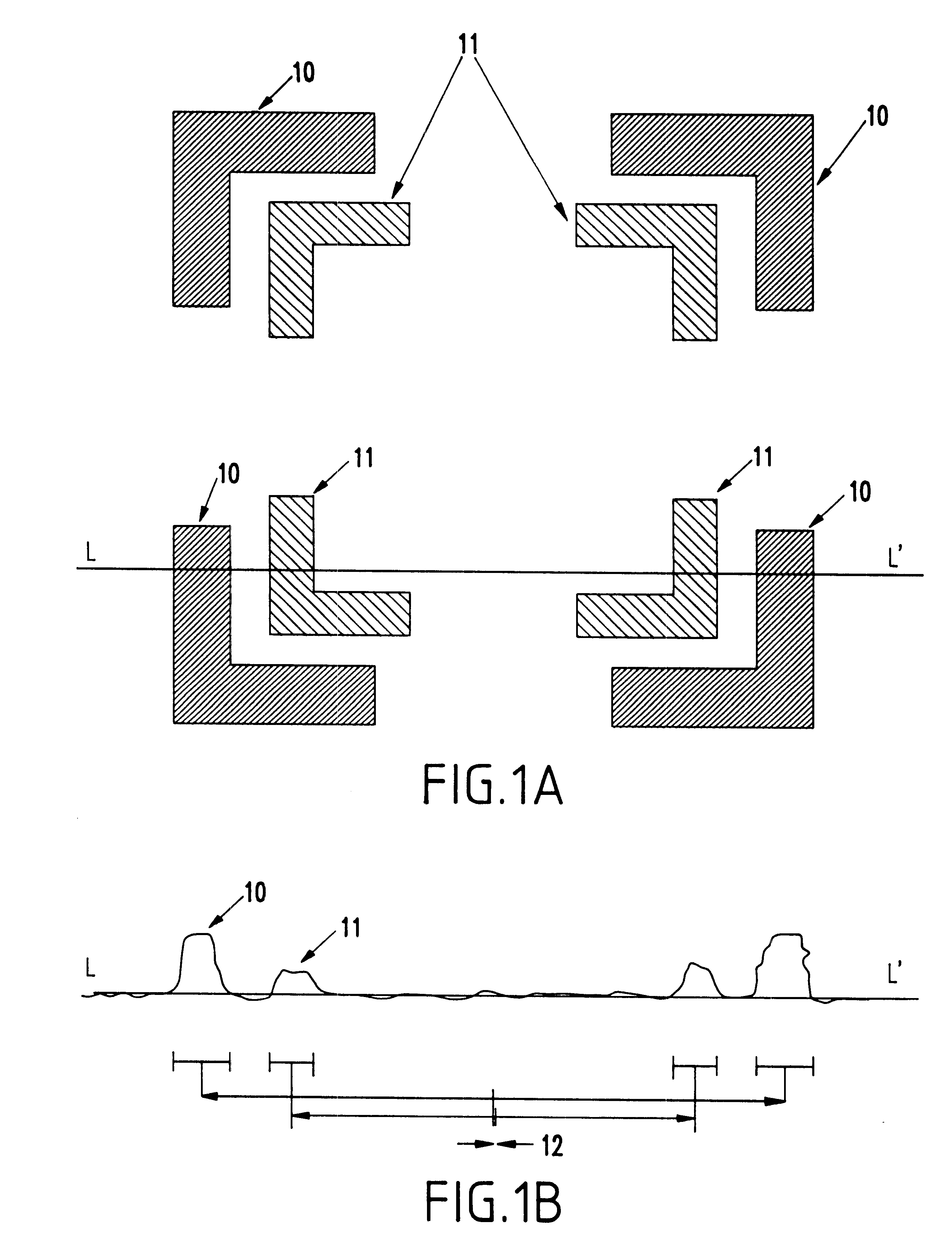

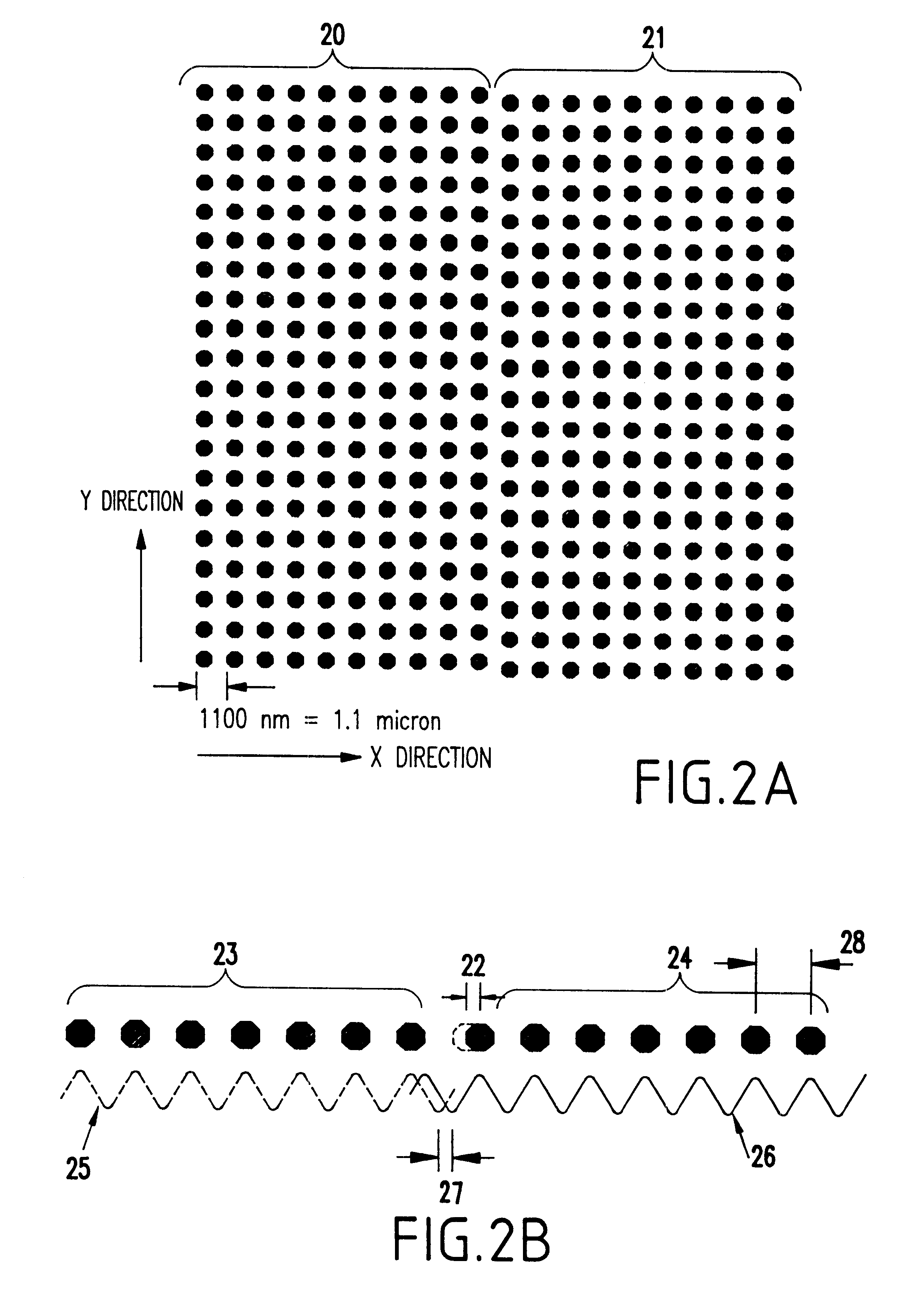

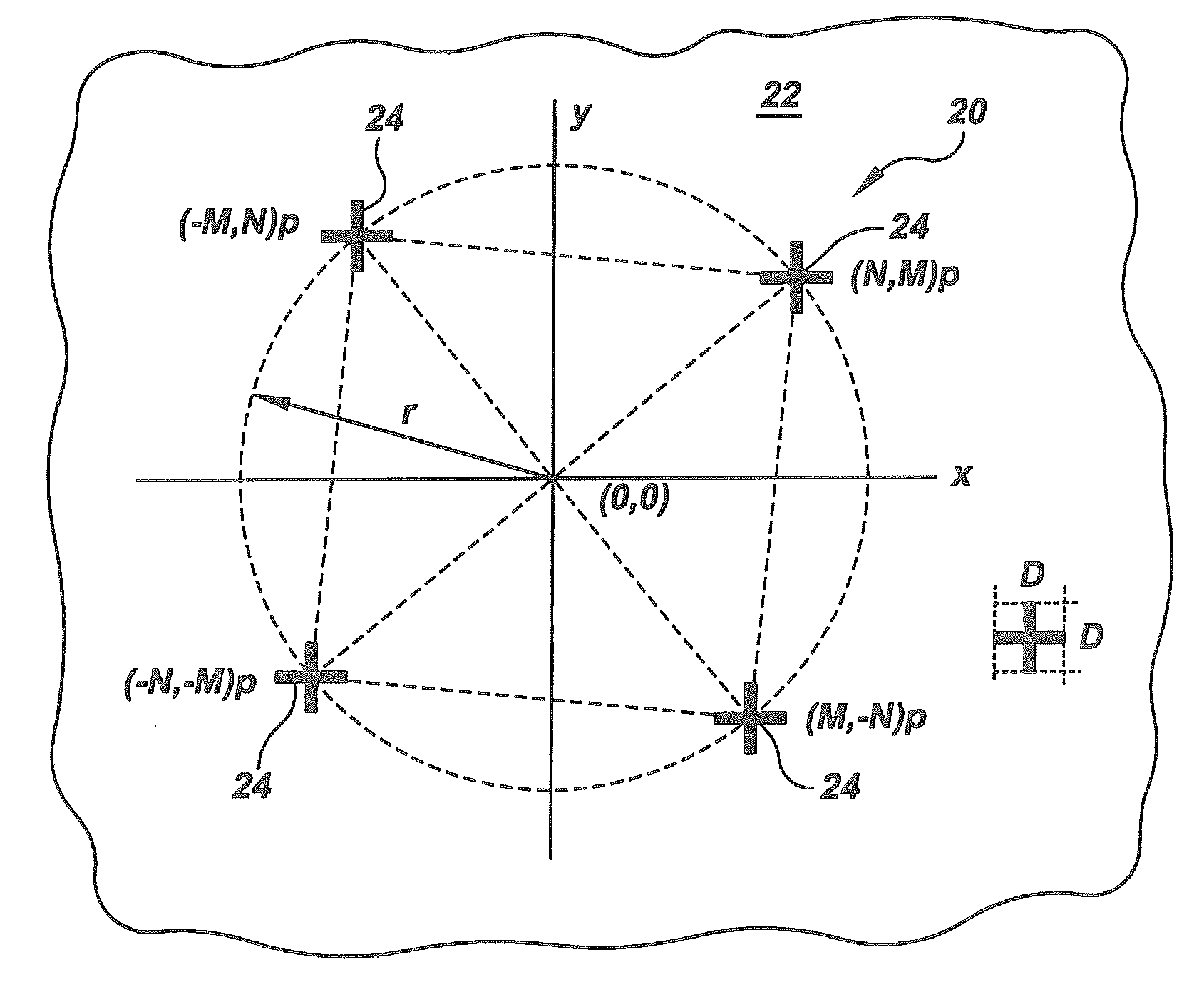

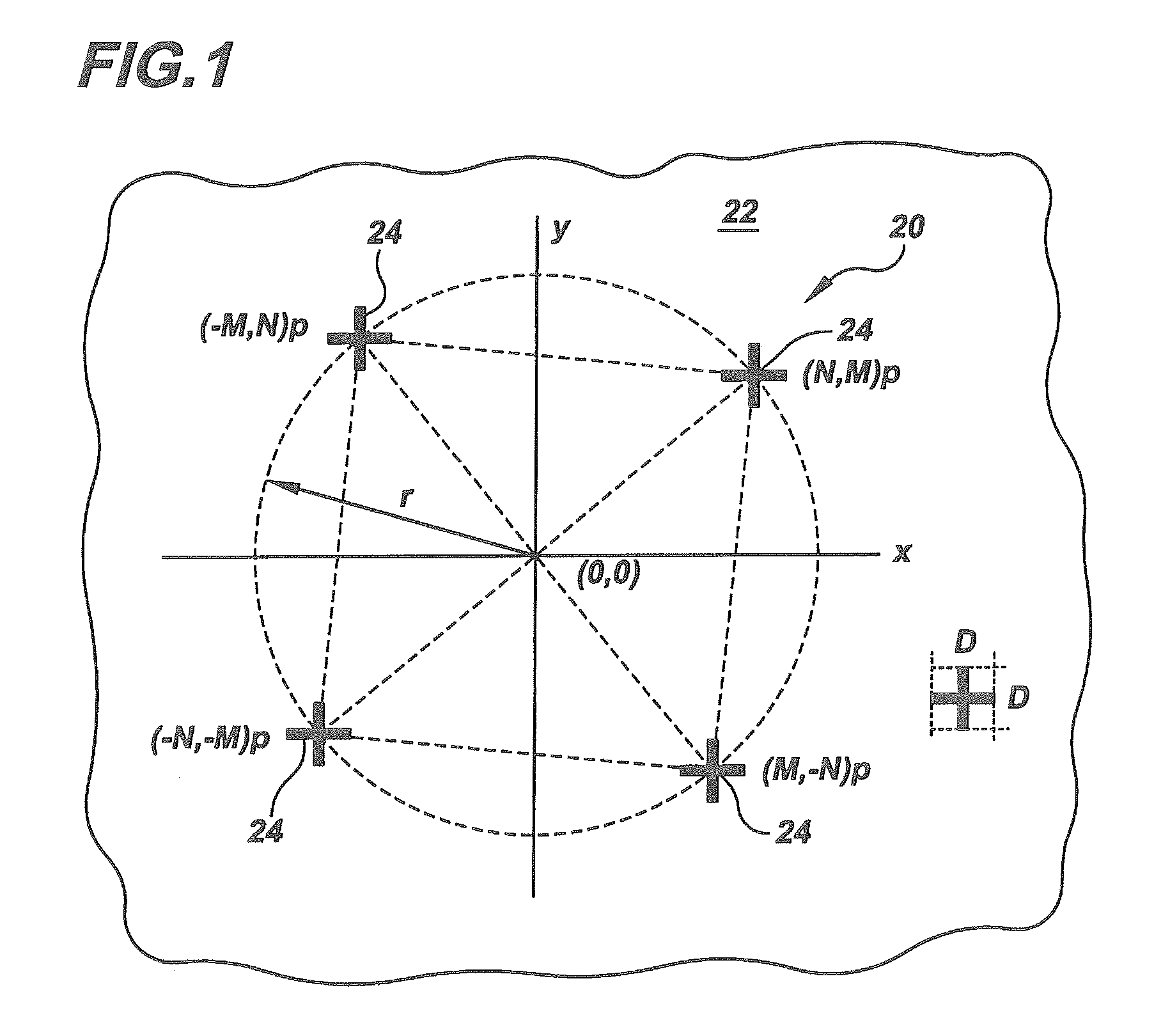

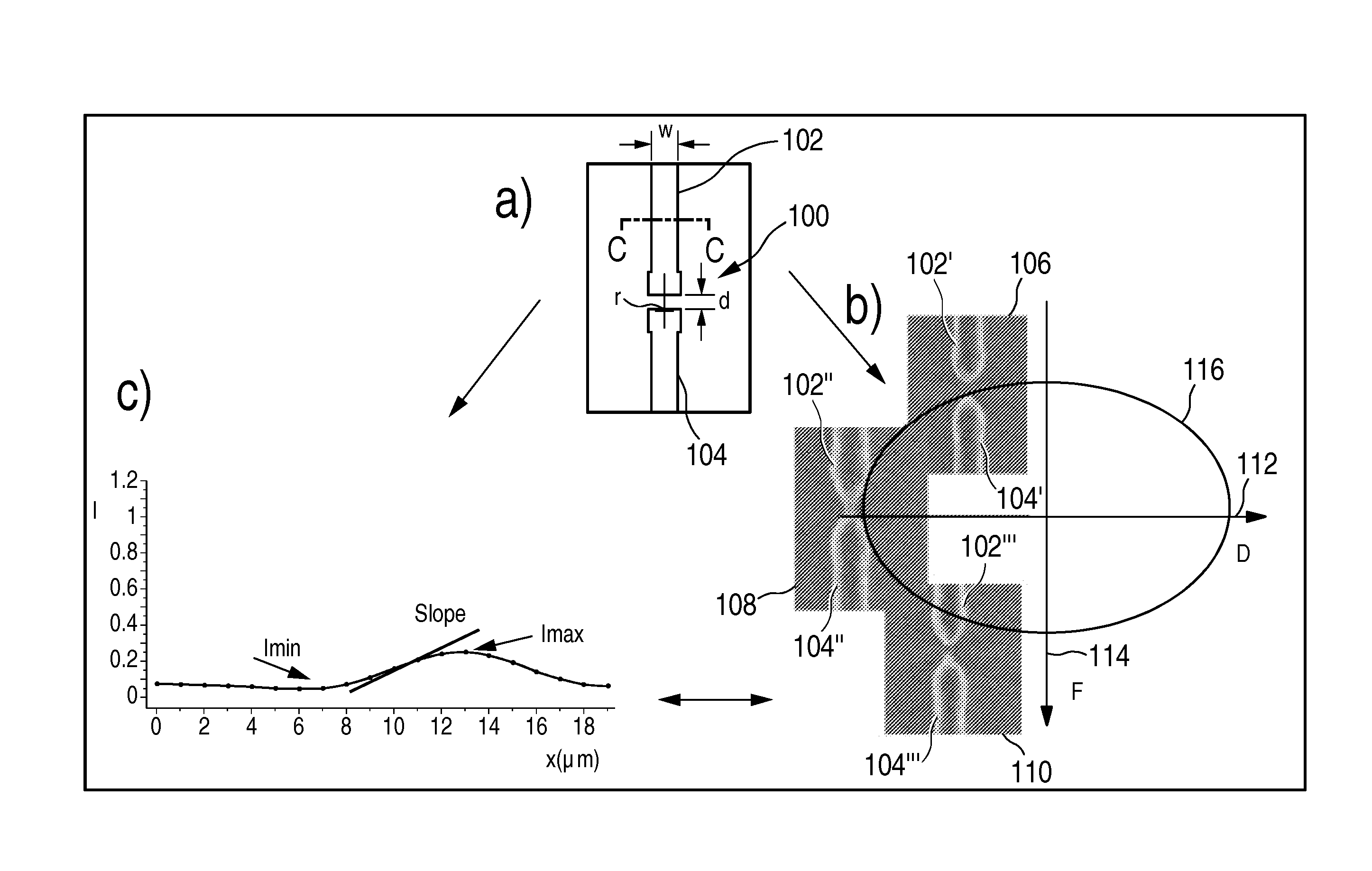

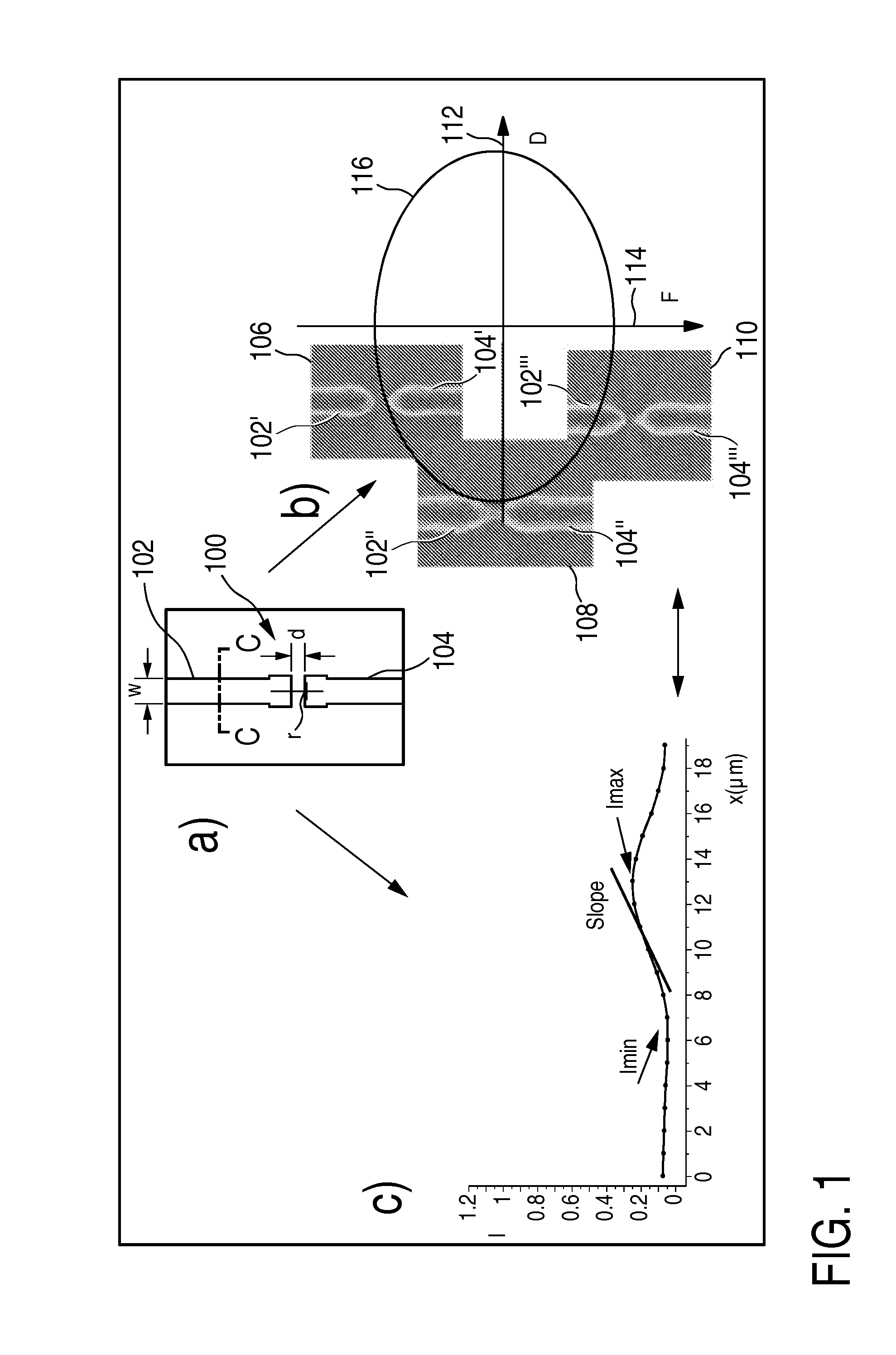

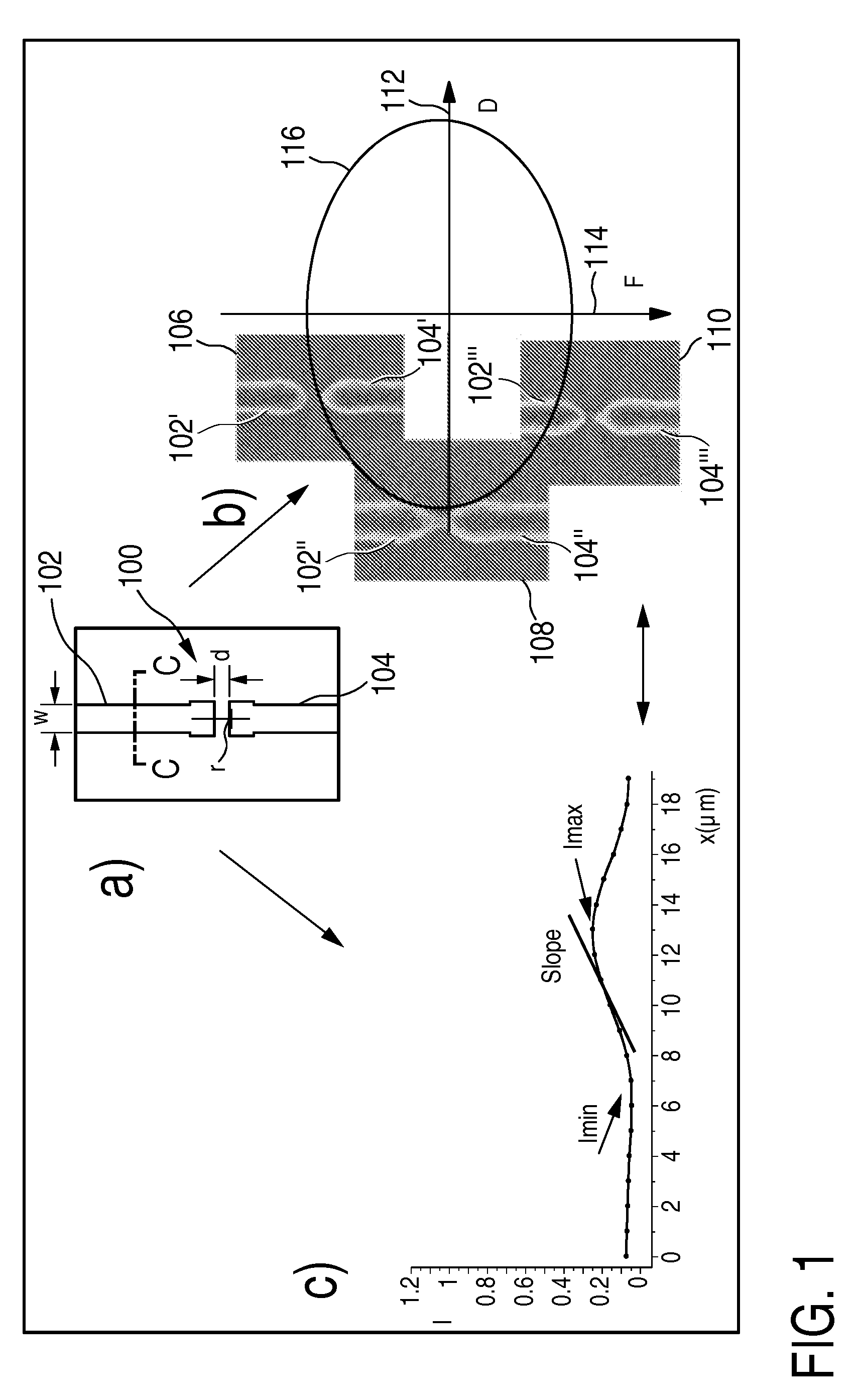

Geometric phase analysis for mask alignment

A method of measuring overlay error comprises forming a first mask having a first alignment array comprising a periodic pattern of first features having a first periodicity, forming a second mask having a second alignment array comprising a pattern of second features having the first periodicity, the first alignment array being adjacent the second alignment array, the first alignment array and the second alignment array forming a combined alignment array, transforming the combined alignment array to produce a transformed array, selecting a first region within the transformed array, inverse transforming the region to produce geometric phase shift information, averaging the phase shift information, converting the averaged phase shift information into a value for misalignment in a first direction corresponding to the first region, repeating the selecting, inverse transforming, averaging and converting using a second region within the transformed array to calculate a value for misalignment in a second direction corresponding to the second region, calculating an overlay error between the first and second mask levels by adding the components of misalignment in the first direction and second direction.

Owner:GLOBALFOUNDRIES INC

Geometric phase analysis for overlay measurement

A method of measuring overlay error comprises forming a first mask having a first alignment array comprising a periodic pattern of first features having a first periodicity, forming a second mask having a second alignment array comprising a pattern of second features having the first periodicity, the first alignment array being adjacent the second alignment array, the first alignment array and the second alignment array forming a combined alignment array, transforming the combined alignment array to produce a transformed array, selecting a first region within the transformed array, inverse transforming the region to produce geometric phase shift information, averaging the phase shift information, converting the averaged phase shift information into a value for misalignment in a first direction corresponding to the first region, repeating the selecting, inverse transforming, averaging and converting using a second region within the transformed array to calculate a value for misalignment in a second direction corresponding to the second region, calculating an overlay error between the first and second mask levels by adding the components of misalignment in the first direction and second direction.

Owner:GLOBALFOUNDRIES INC

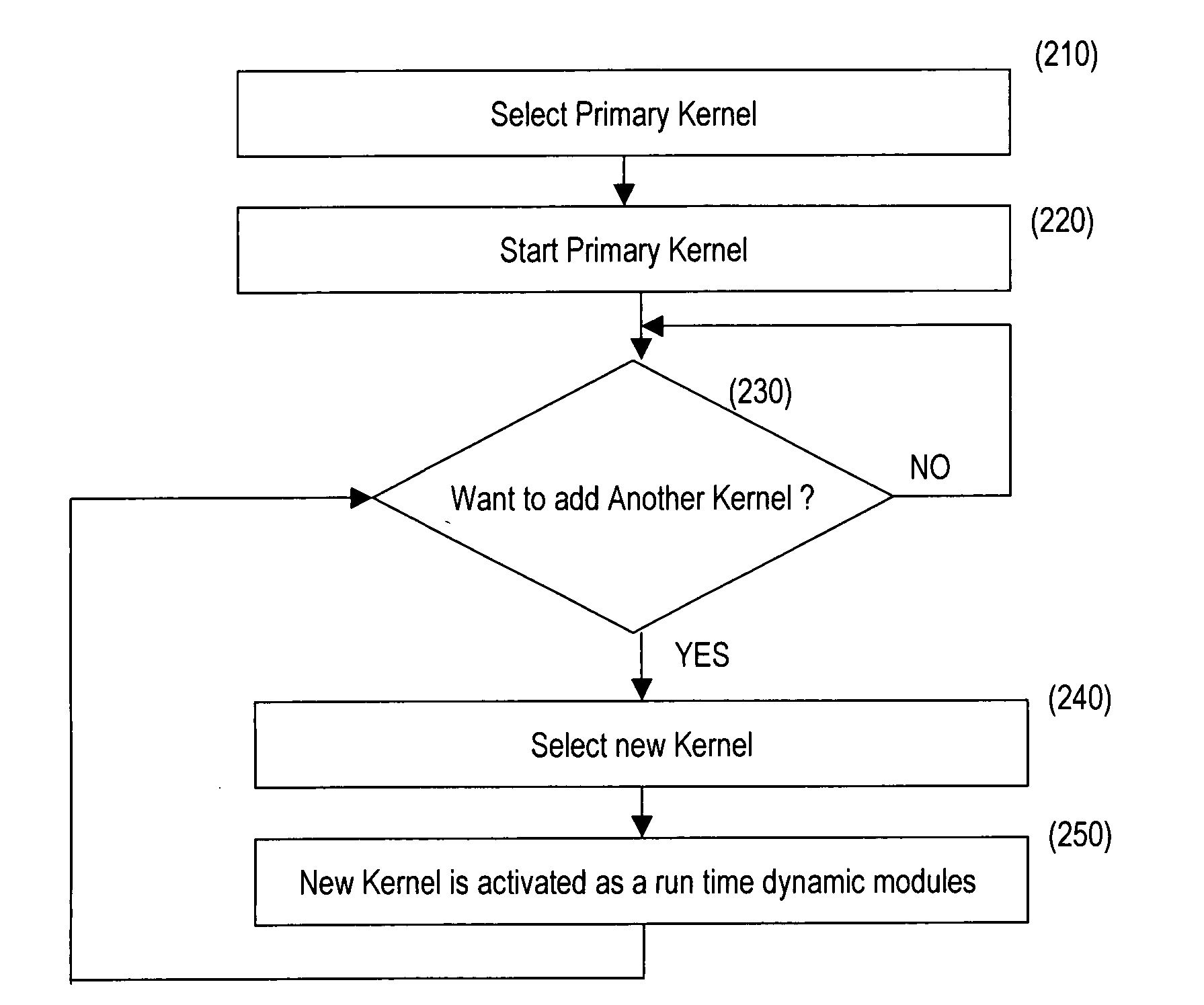

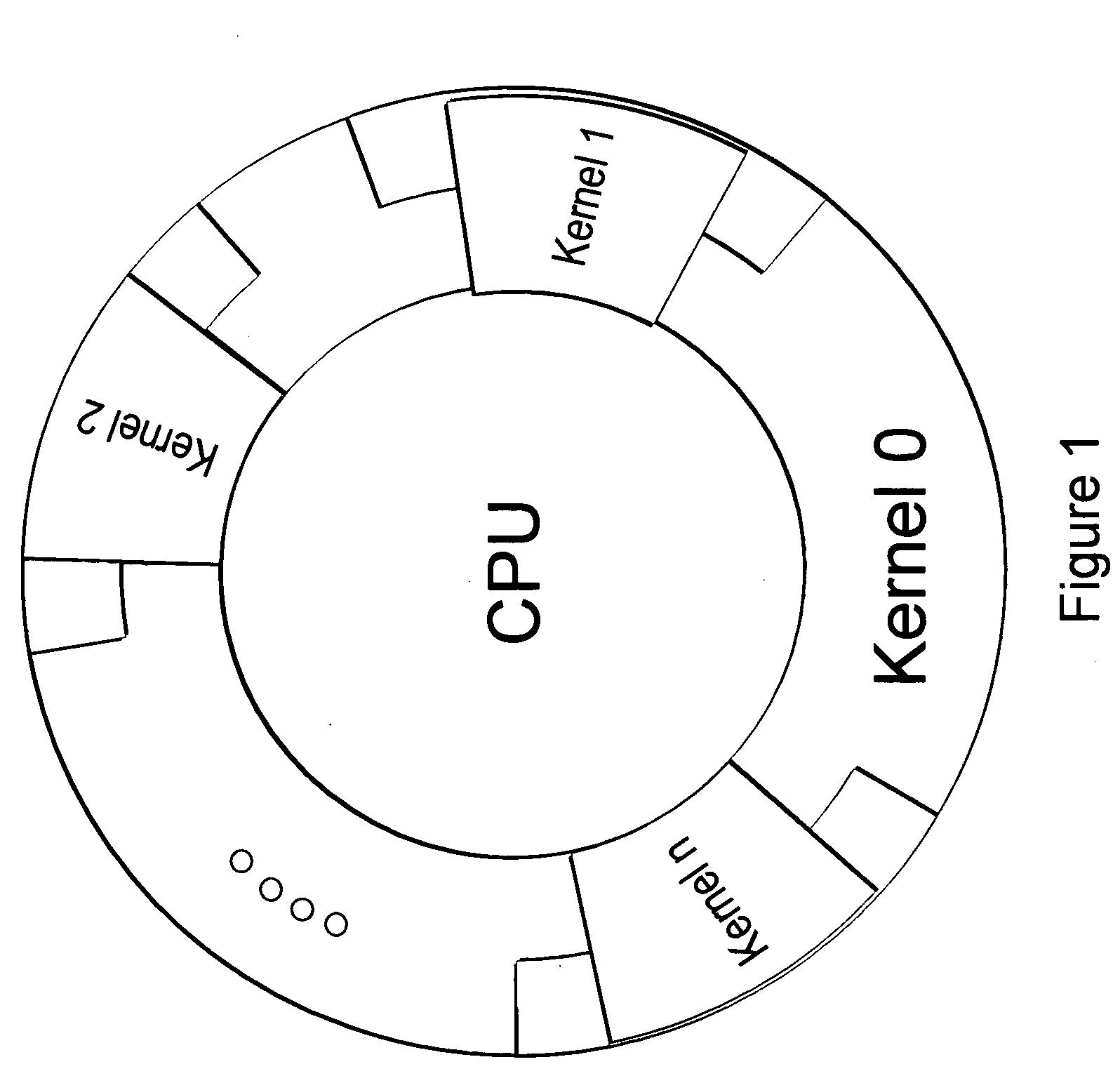

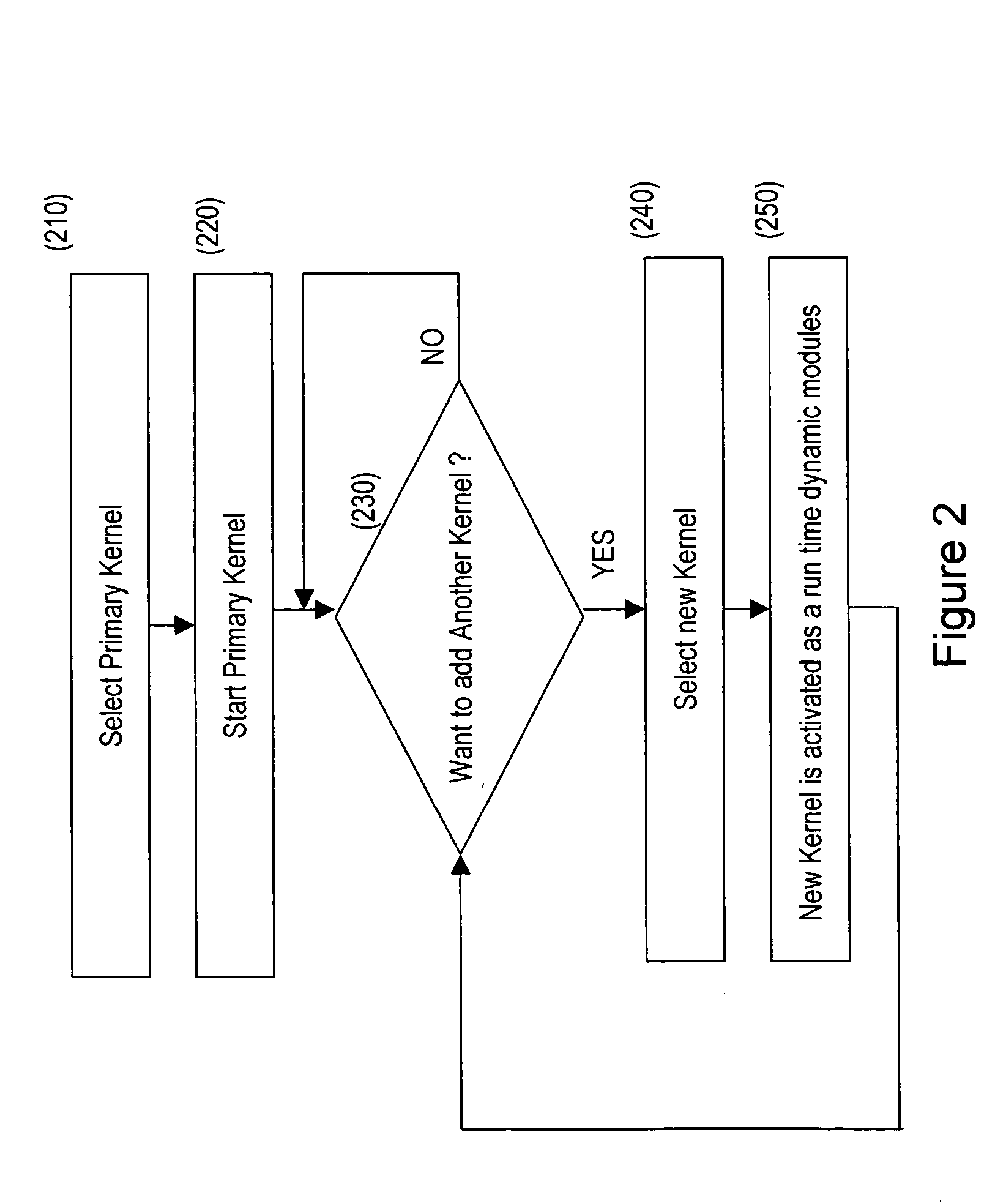

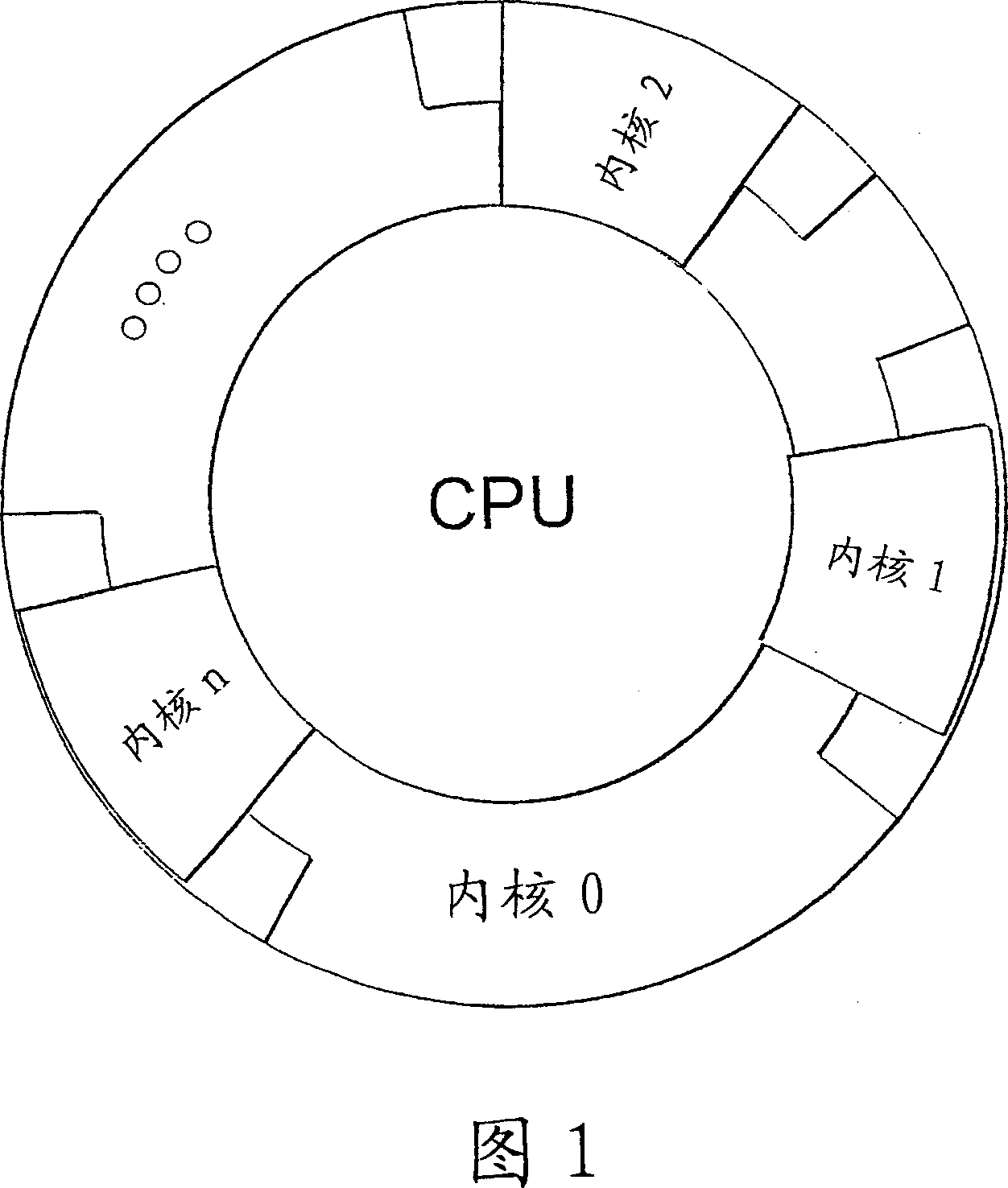

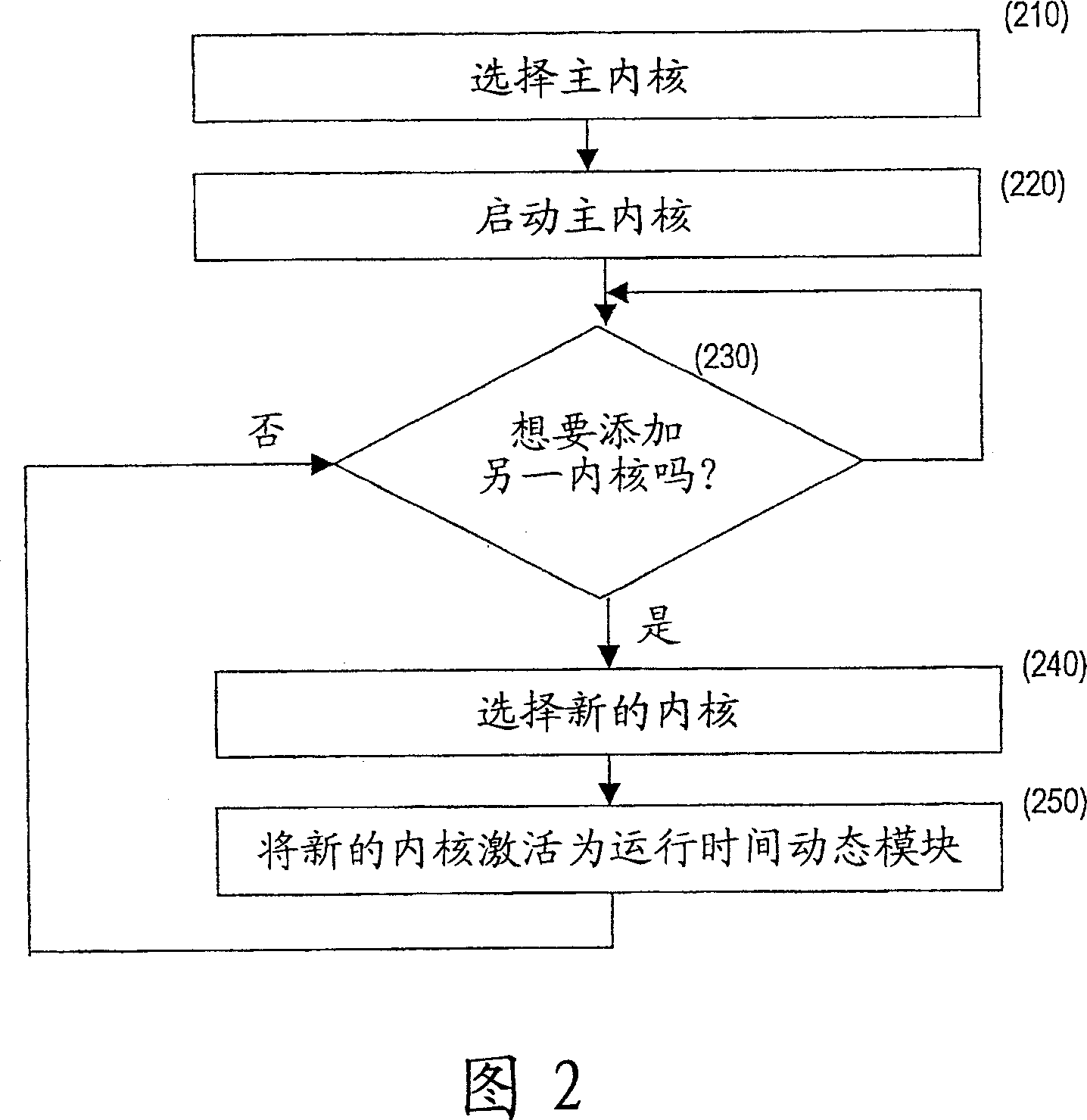

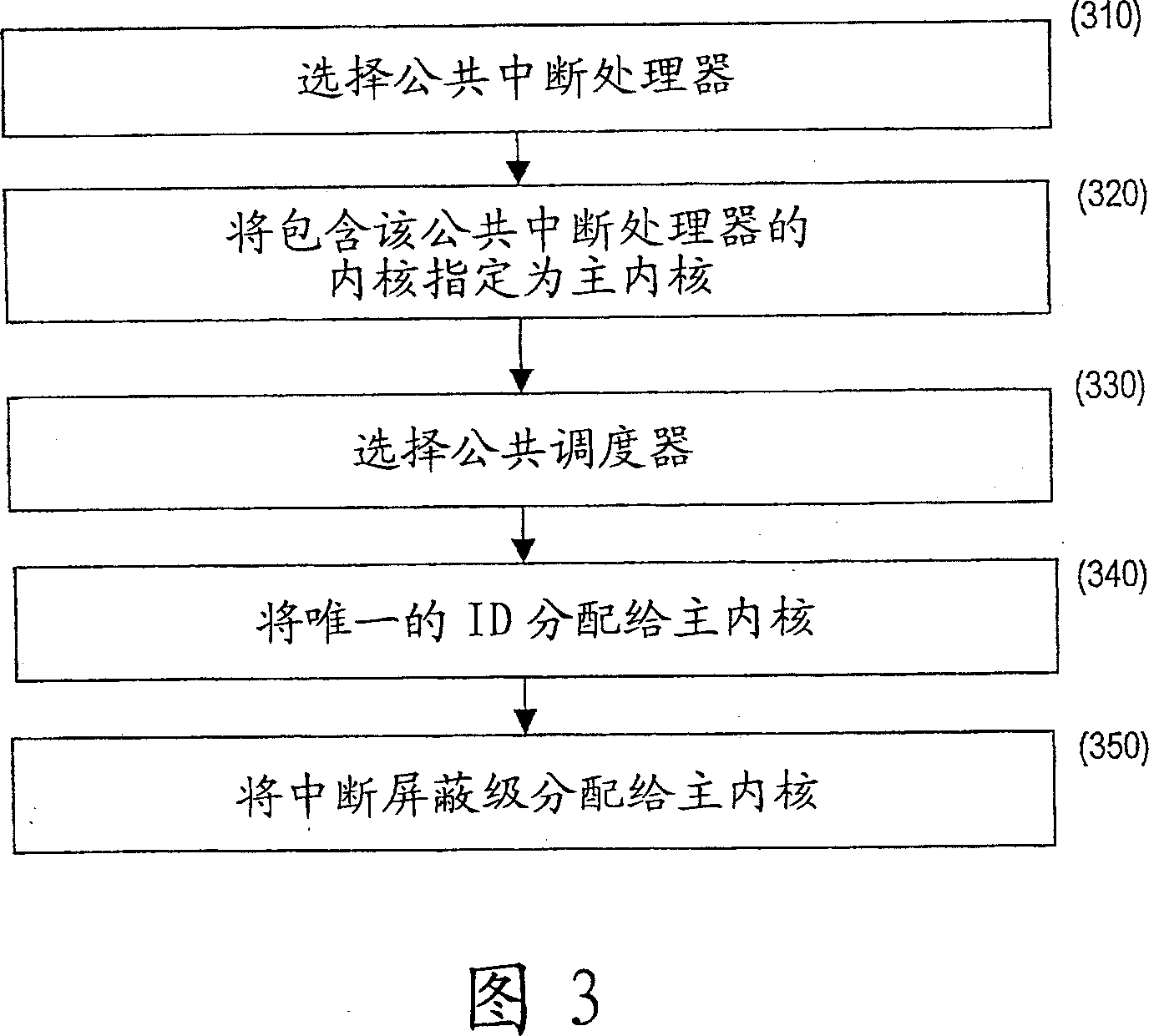

Method and system for concurrent execution of multiple kernels

An approach for concurrently running multiple kernels using a common interrupt handler and an optional common scheduler is provided. Techniques are also provided to switch execution among the kernels. Execution and interrupt preemption among kernels in shown using interrupt mask levels. Techniques are also provided for the sharing of resources between tasks running on different kernels.

Owner:EMBEDIO INC

GERMANIUM PHOTODETECTOR SCHOTTKY CONTACT FOR INTEGRATION WITH CMOS AND Si NANOPHOTONICS

ActiveUS20140027826A1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSPhotovoltaic detectors

A method of forming an integrated photonic semiconductor structure having a photodetector device and a CMOS device may include depositing a dielectric stack over the photodetector device such that the dielectric stack encapsulates the photodetector. An opening is etched into the dielectric stack down to an upper surface of a region of an active area of the photodetector. A first metal layer is deposited directly onto the upper surface of the region of the active area via the opening such that the first metal layer may cover the region of the active area. Within the same mask level, a plurality of contacts including a second metal layer are located on the first metal layer and on the CMOS device. The first metal layer isolates the active area from the occurrence of metal intermixing between the second metal layer and the active area of the photodetector.

Owner:GLOBALFOUNDRIES US INC

Patient management in automated diagnostic hearing test

InactiveUS20040039299A1Diagnostics using vibrationsBone conduction transducer hearing devicesSpeech reception thresholdPatient management

Owner:OTOTRONIX +1

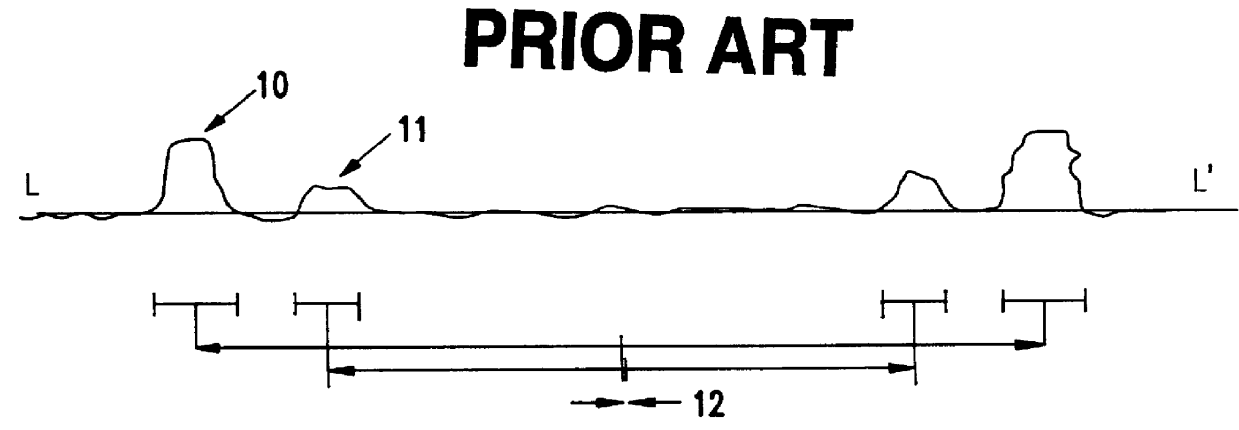

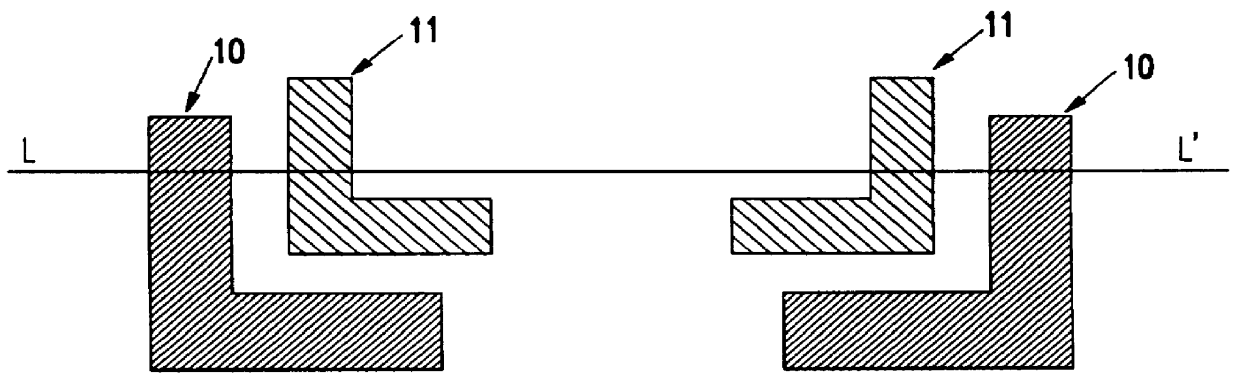

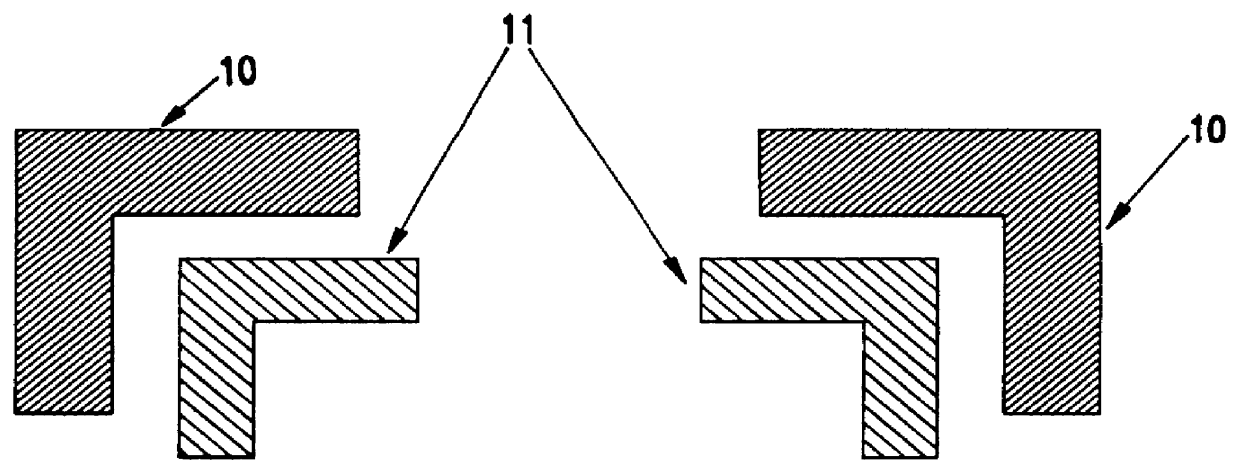

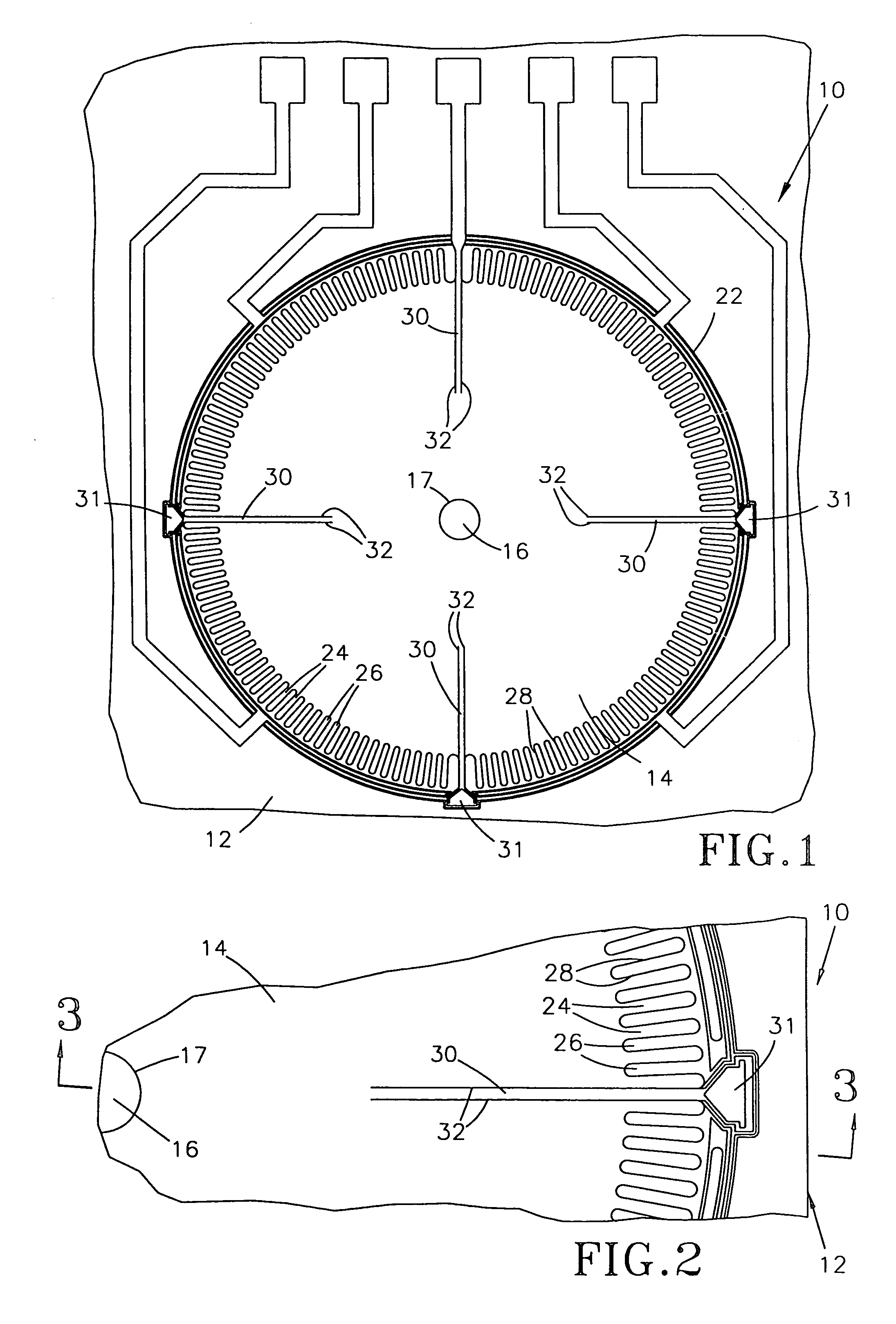

Deep reactive ion etching process and microelectromechanical devices formed thereby

InactiveUS7077007B2Uniform widthConstant gap widthAcceleration measurement using interia forcesDecorative surface effectsDevice formEngineering

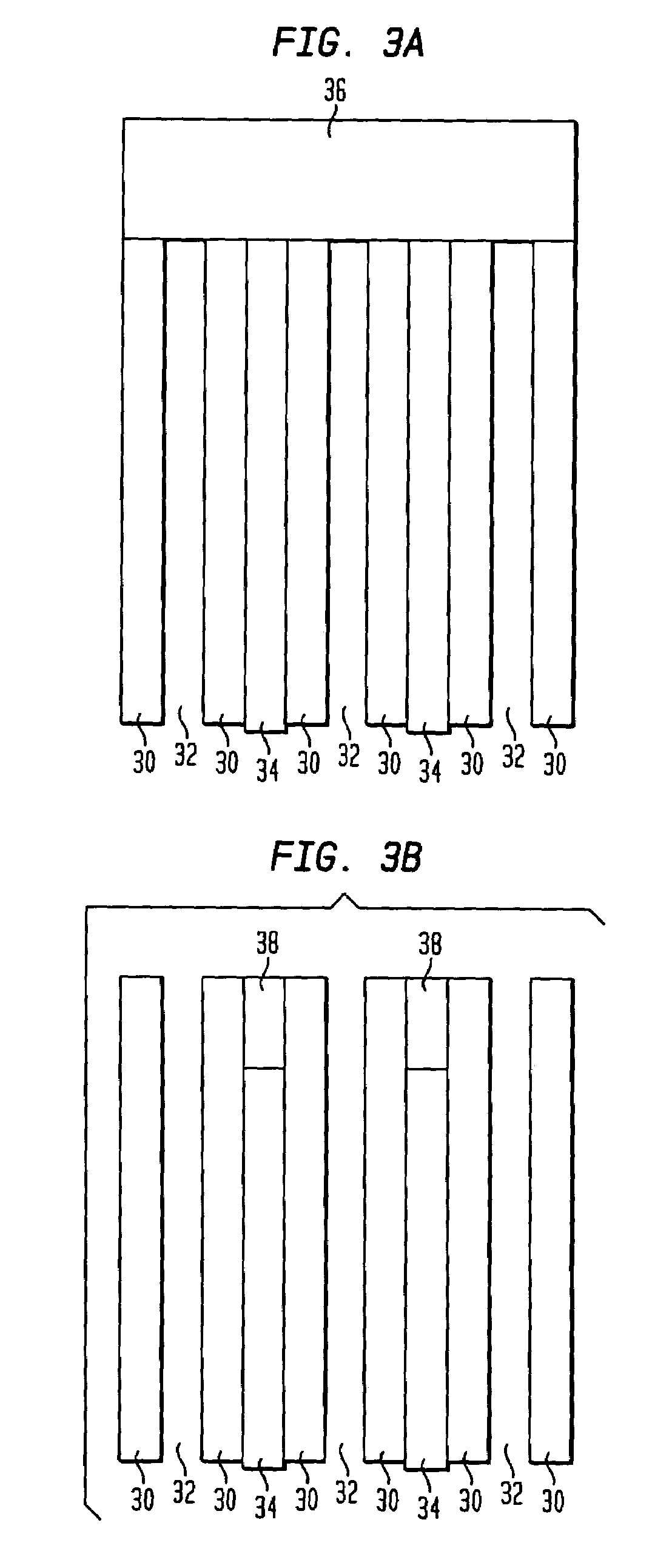

A process for forming a microelectromechanical system (MEMS) device by a deep reactive ion etching (DRIE) process during which a substrate overlying a cavity is etched to form trenches that breach the cavity to delineate suspended structures. A first general feature of the process is to define suspended structures with a DRIE process, such that the dimensions desired for the suspended structures are obtained. A second general feature is the proper location of specialized features, such as stiction bumps, vulnerable to erosion caused by the DRIE process. Yet another general feature is to control the environment surrounding suspended structures delineated by DRIE in order to obtain their desired dimensions. A significant problem identified and solved by the invention is the propensity for the DRIE process to etch certain suspended features at different rates. In addition to etching wider trenches more rapidly than narrower trenches, the DRIE process erodes suspended structures more rapidly at greater distances from anchor sites of the substrate being etched. At the masking level, the greater propensity for backside and lateral erosion of certain structures away from substrate anchor sites is exploited so that, at the completion of the etch process, suspended structures have acquired their respective desired widths.

Owner:GOOGLE LLC

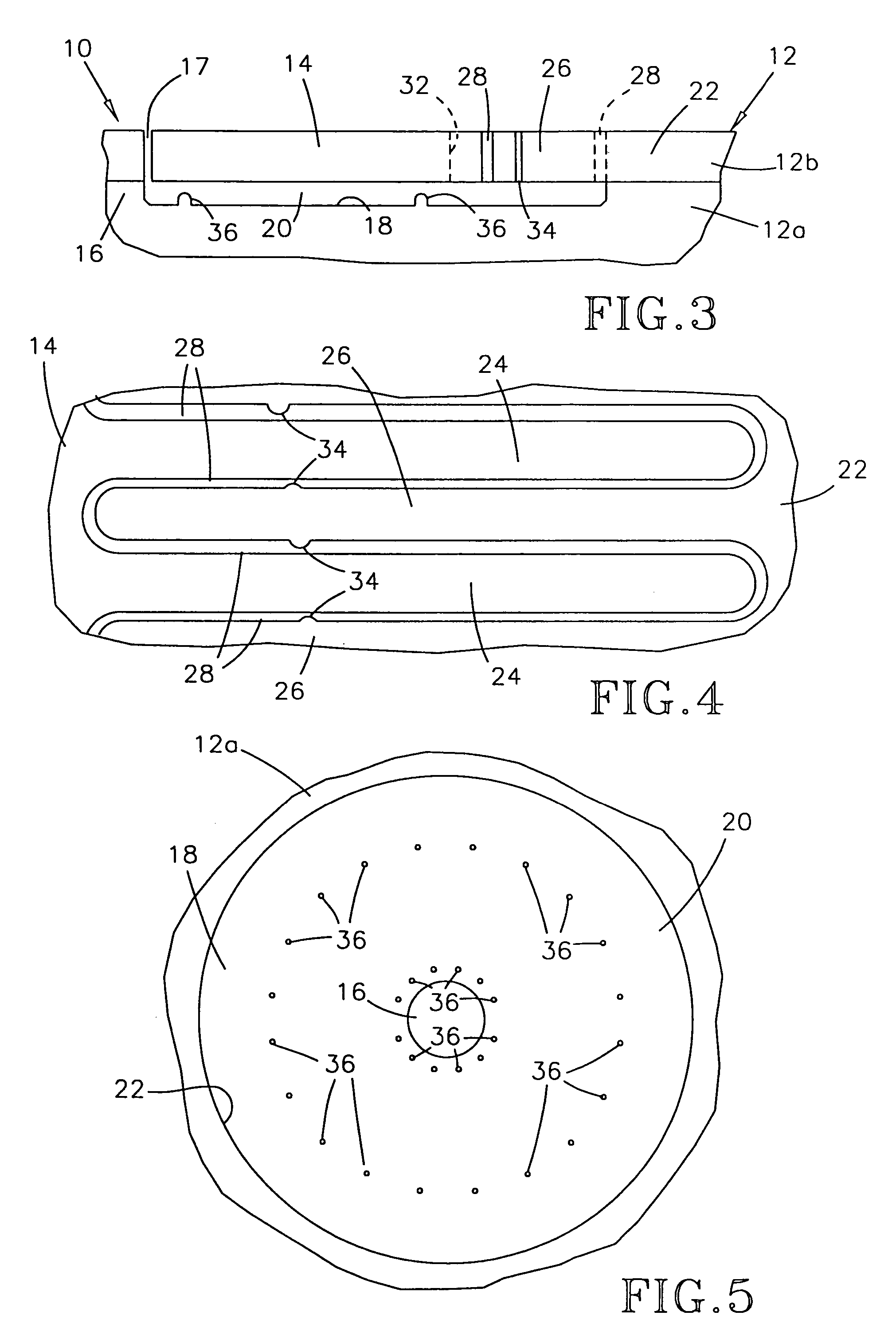

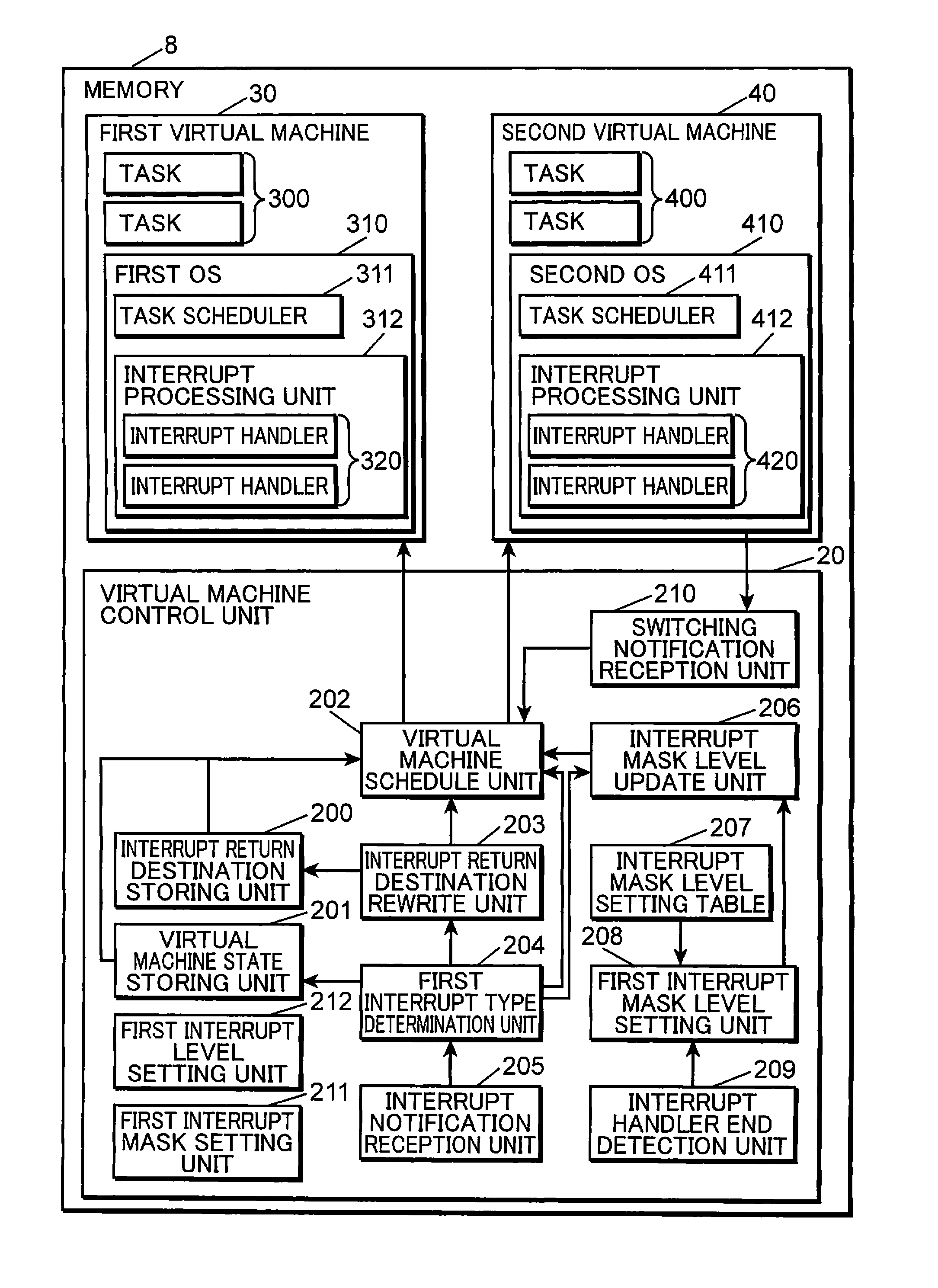

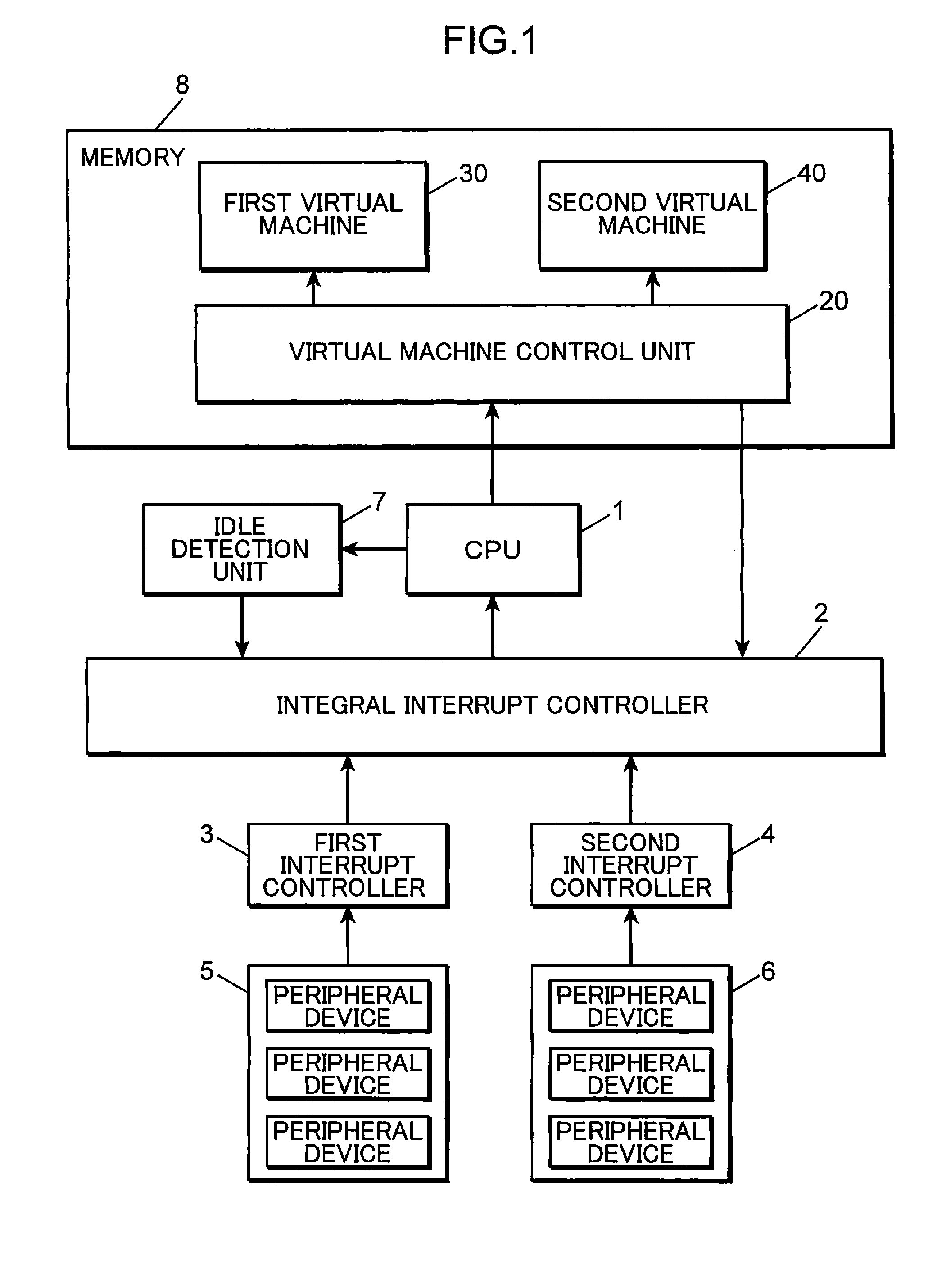

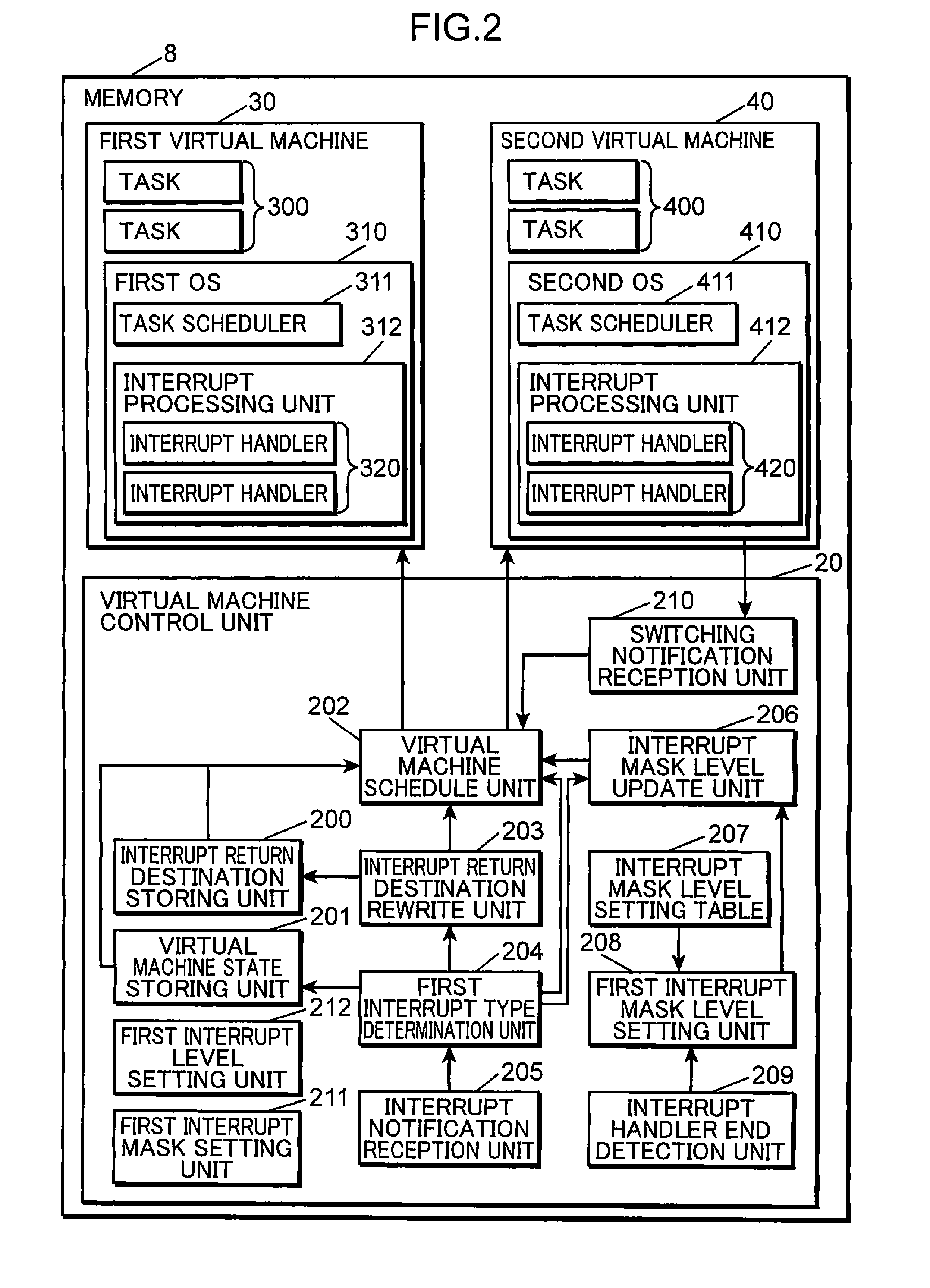

Virtual machine control device, virtual machine control program, and virtual machine control circuit

The interrupt level storing unit (16) stores one or more interrupt levels indicating the priority of a generated interrupt and stores the interrupt level having the highest priority among the stored interrupt levels as a second interrupt mask level. The second interrupt type determination unit (13) sets an interrupt level corresponding to the interrupt type of a newly generated interrupt. The priority determination unit (14) notifies the interrupt to the virtual machine control unit (20) when the interrupt level of the newly generated interrupt is higher than the stored second interrupt mask level. As a result, the priority of the virtual machine can be determined according to the task priority and the switching of virtual machines can be adequately controlled even if the virtual machines cannot notify the task priority.

Owner:PANASONIC CORP

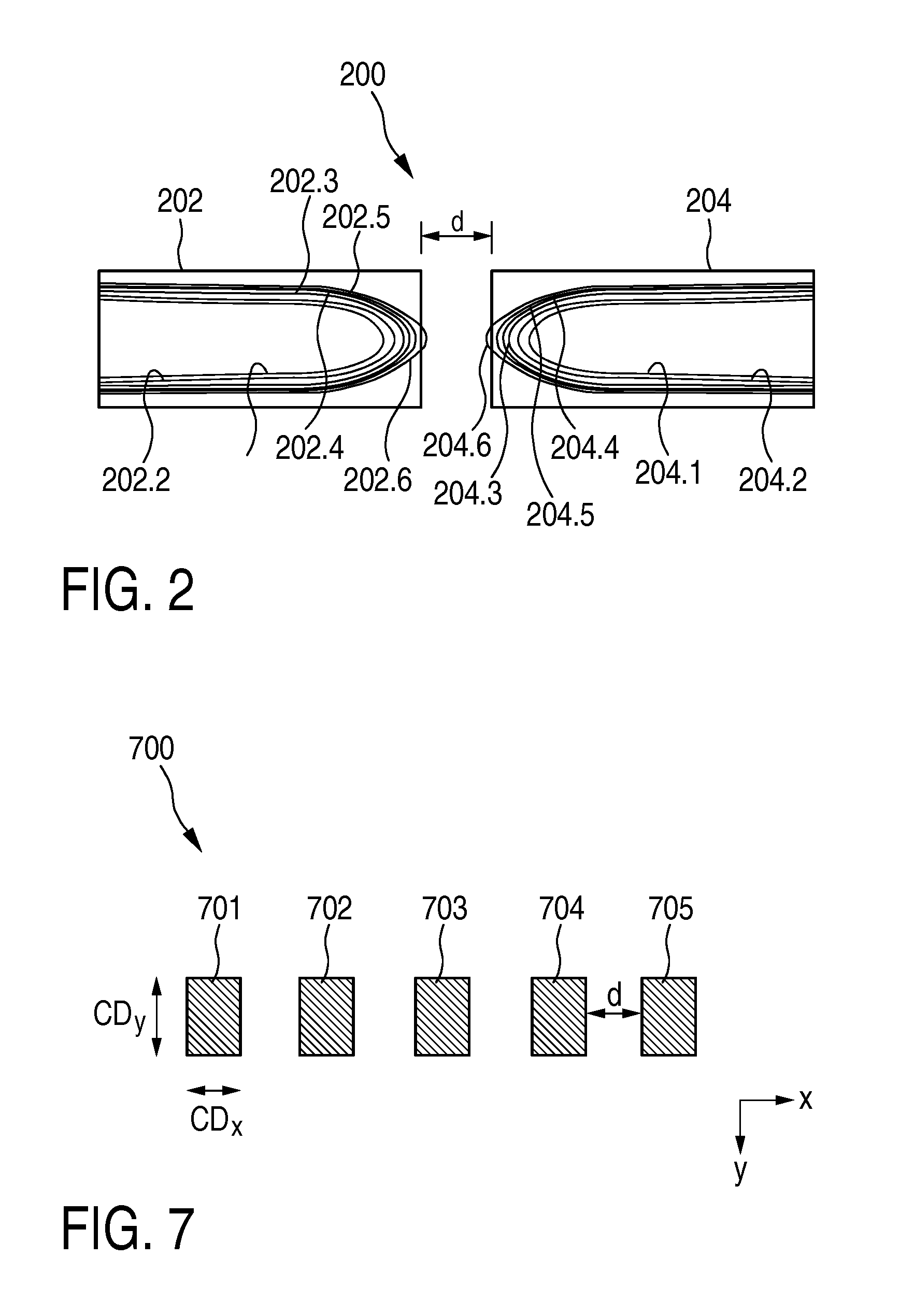

Target and method for mask-to-wafer cd, pattern placement and overlay measurement and control

InactiveUS20100190096A1Photomechanical apparatusSemiconductor/solid-state device manufacturingCritical dimensionComputer science

A method for mask-to-wafer correlation among multiple masking levels of a semiconductor manufacturing process. The method includes creating compact targets containing structure patterns suitable for pattern placement, critical dimension and overlay measurement at a set of common locations on two or more patterning layers, and creating at least two masks containing functional circuit structure patterns and the compact targets at locations between functional circuit structure patterns. The method then includes measuring the targets, determining overlay variation between the masks, exposing and creating with one mask a first lithographic processing layer on a wafer, and exposing and creating with another mask a second lithographic processing layer on the wafer, over the first layer. The method further includes measuring the targets on the wafer at one or more of the layers, and correlating the mask and wafer measurements to distinguish mask and lithography induced components of critical dimension and overlay variation.

Owner:GLOBALFOUNDRIES INC

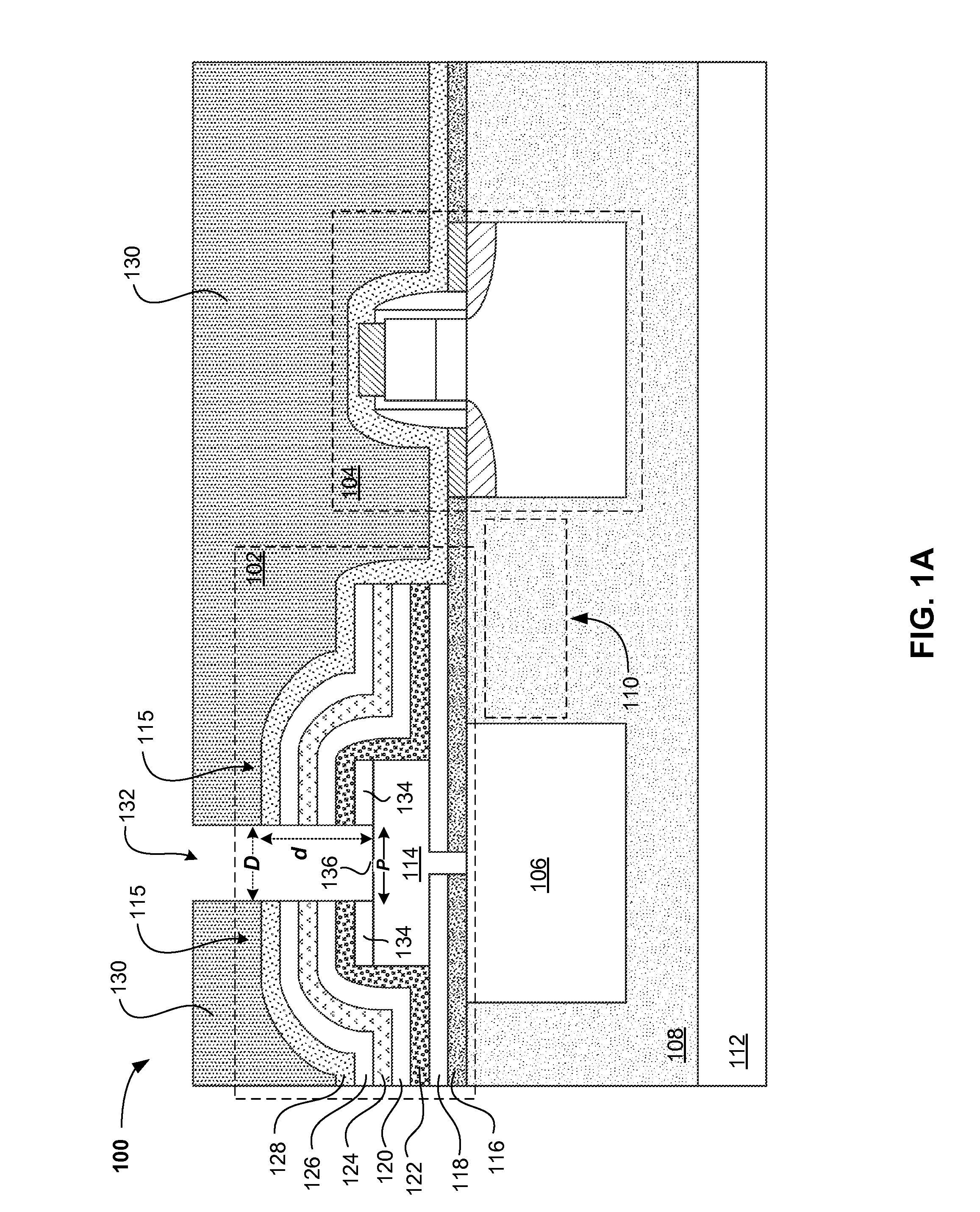

Method of forming photodiode with self-aligned implants for high quantum efficiency

ActiveUS6969631B2Solid-state devicesSemiconductor/solid-state device manufacturingDopantQuantum efficiency

A pinned photodiode with a pinned surface layer formed by a self-aligned angled implant is disclosed. The angle of the implant may be tailored to provide an adequate offset between the pinned surface layer and an electrically active area of a transfer gate of the pixel sensor cell. The pinned surface layer is formed by employing the same mask level as the one employed for the formation of the photodiode region, and then implanting dopants at angles other than zero degrees.

Owner:APTINA IMAGING CORP

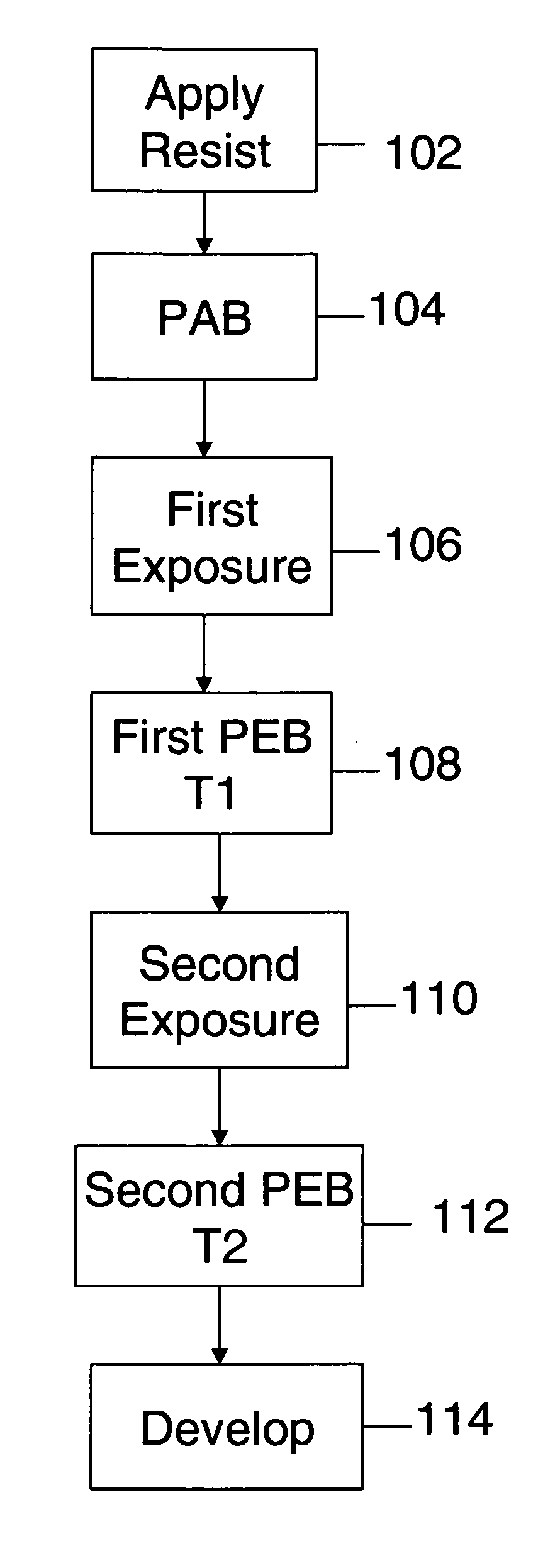

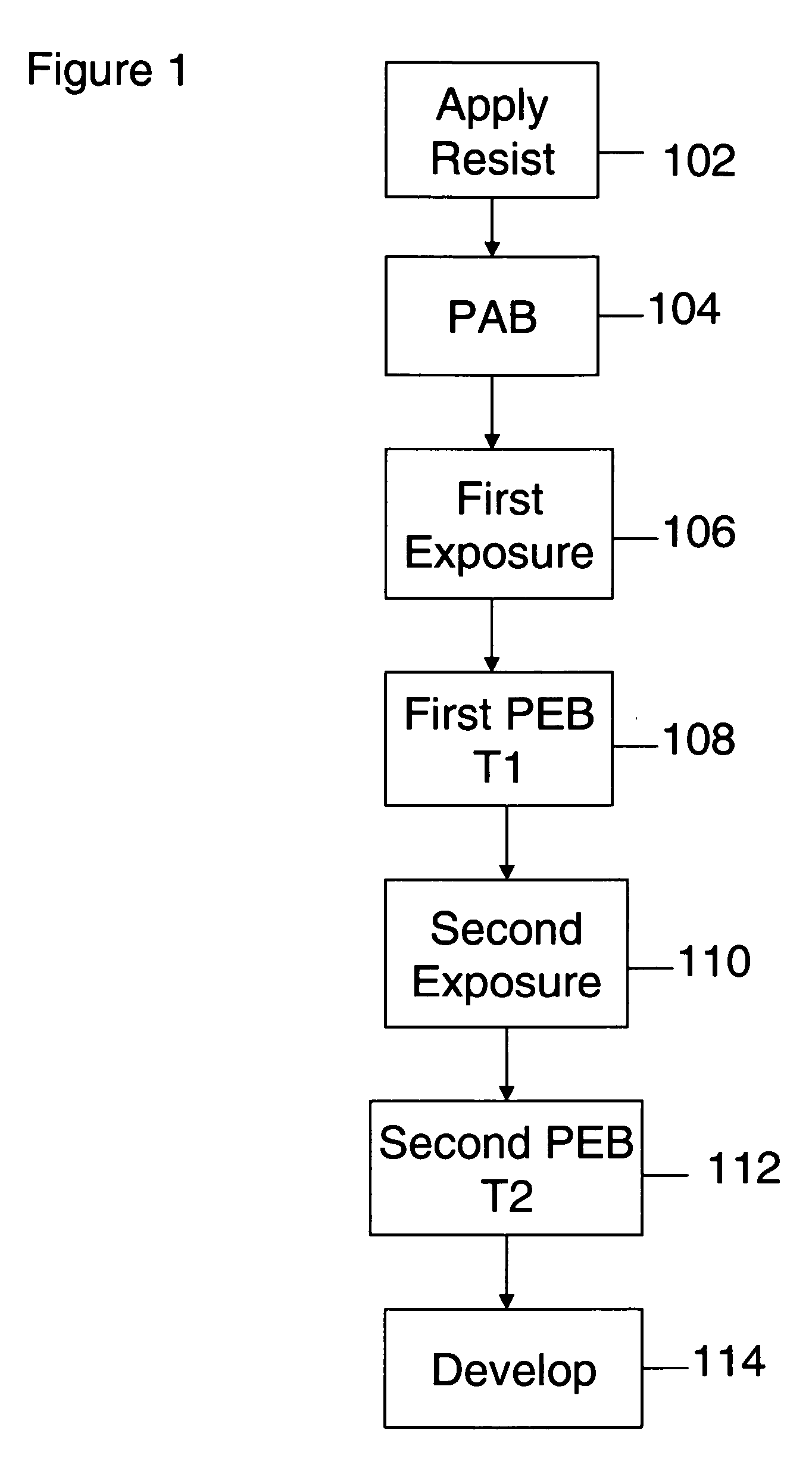

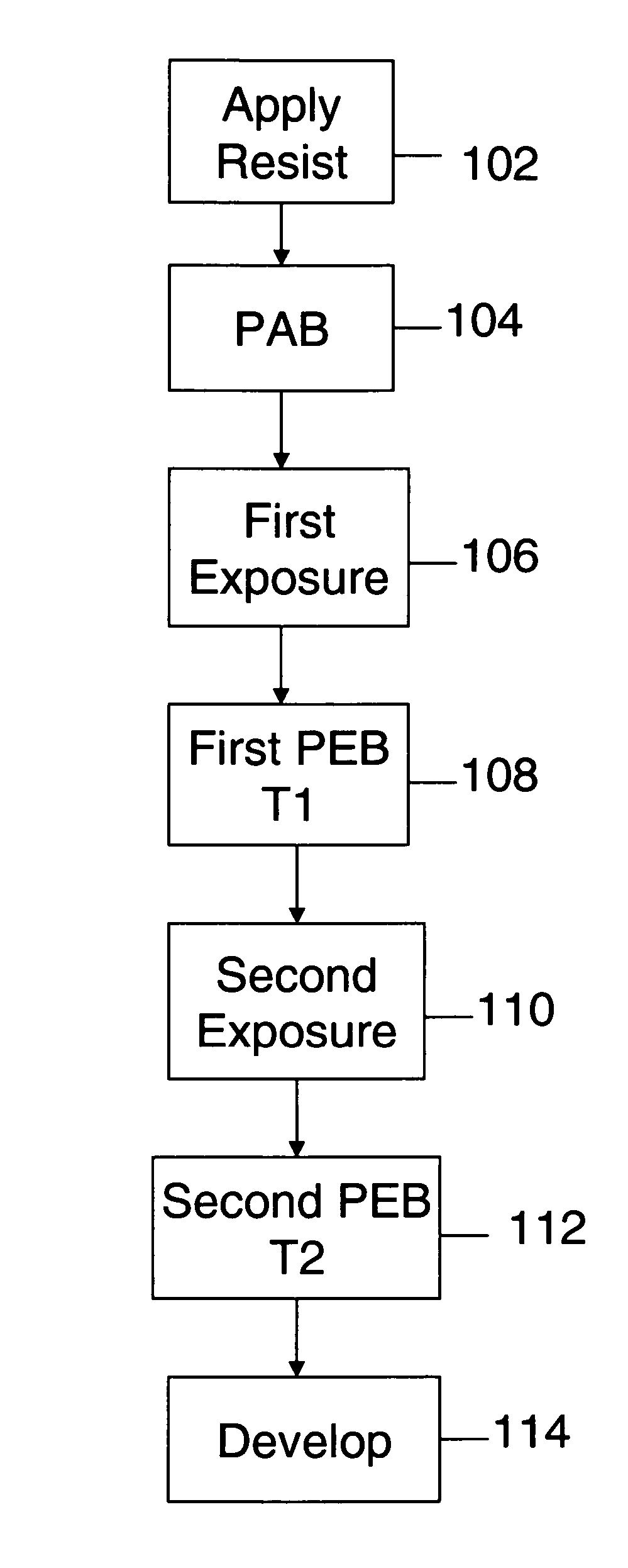

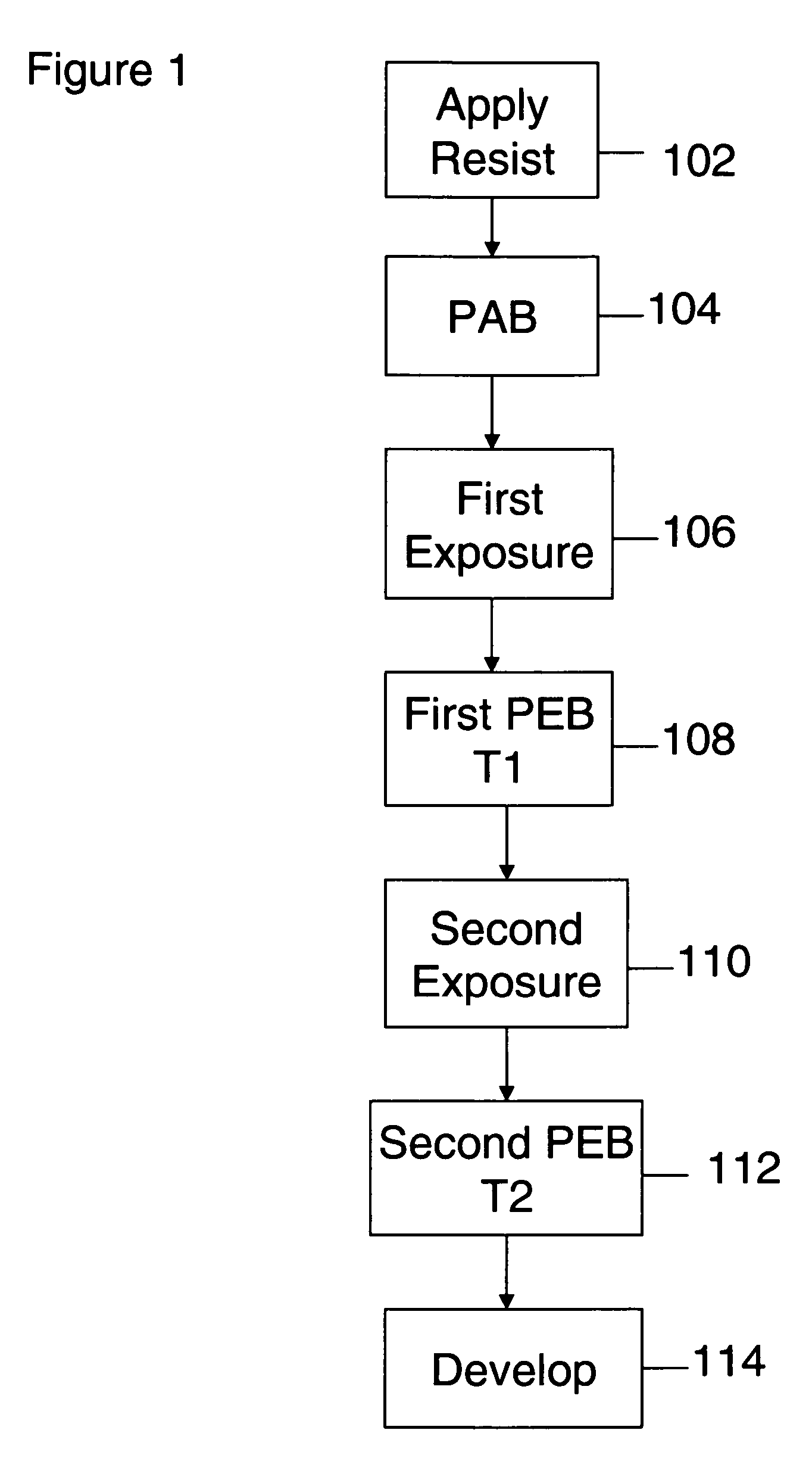

Method for lithography for optimizing process conditions

InactiveUS20070212654A1Electric discharge tubesSemiconductor/solid-state device manufacturingProcess optimizationResist

A method of lithography is disclosed, which allows for independent resist process optimization of two or more exposure steps that are performed on a single resist layer. By providing for a separate post-exposure bake after each resist exposure step, pattern resolution for each exposure can be optimized. The method can generally be used with different lithographic techniques, and is well-suited for hybrid lithography. It has been applied to the fabrication of a device, in which the active area and the gate levels are defined in separate mask levels using hybrid lithography with an e-beam source and a 248 nm source respectively. Conditions for post-exposure bakes after the two exposure steps are independently adjusted to provide for optimized results.

Owner:GLOBALFOUNDRIES INC

Monocrystalline extrinsic base and emitter heterojunction bipolar transistor and related methods

InactiveUS20080121930A1Semiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalMasking level

A heterostructure bipolar transistor (HBT) and related methods are disclosed. In one embodiment, the HBT includes a heterostructure bipolar transistor (HBT) including: a substrate; a monocrystalline emitter atop the substrate; a collector in the substrate; at least one isolation region adjacent to the collector; a monocrystalline silicon germanium (SiGe) intrinsic base extending over each isolation region; and a monocrystalline silicon extrinsic base. A method may include forming the intrinsic and extrinsic base and the emitter as monocrystalline, with the extrinsic base (and emitter) formed in a self-aligned fashion utilizing selective-epitaxial growth on porous silicon. As a result, some mask levels can be omitted, making this an inexpensive alternative to conventional processing.

Owner:IBM CORP

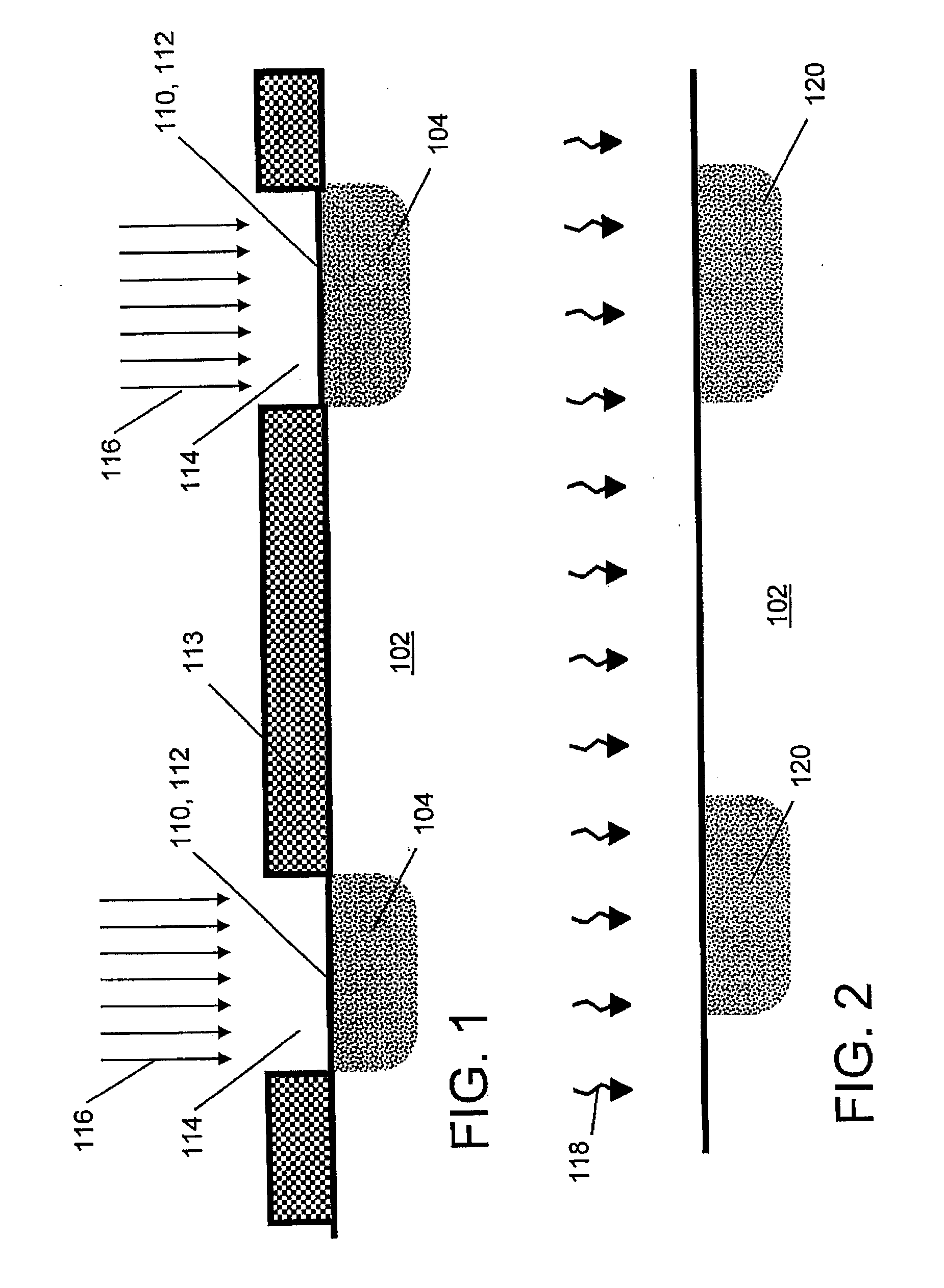

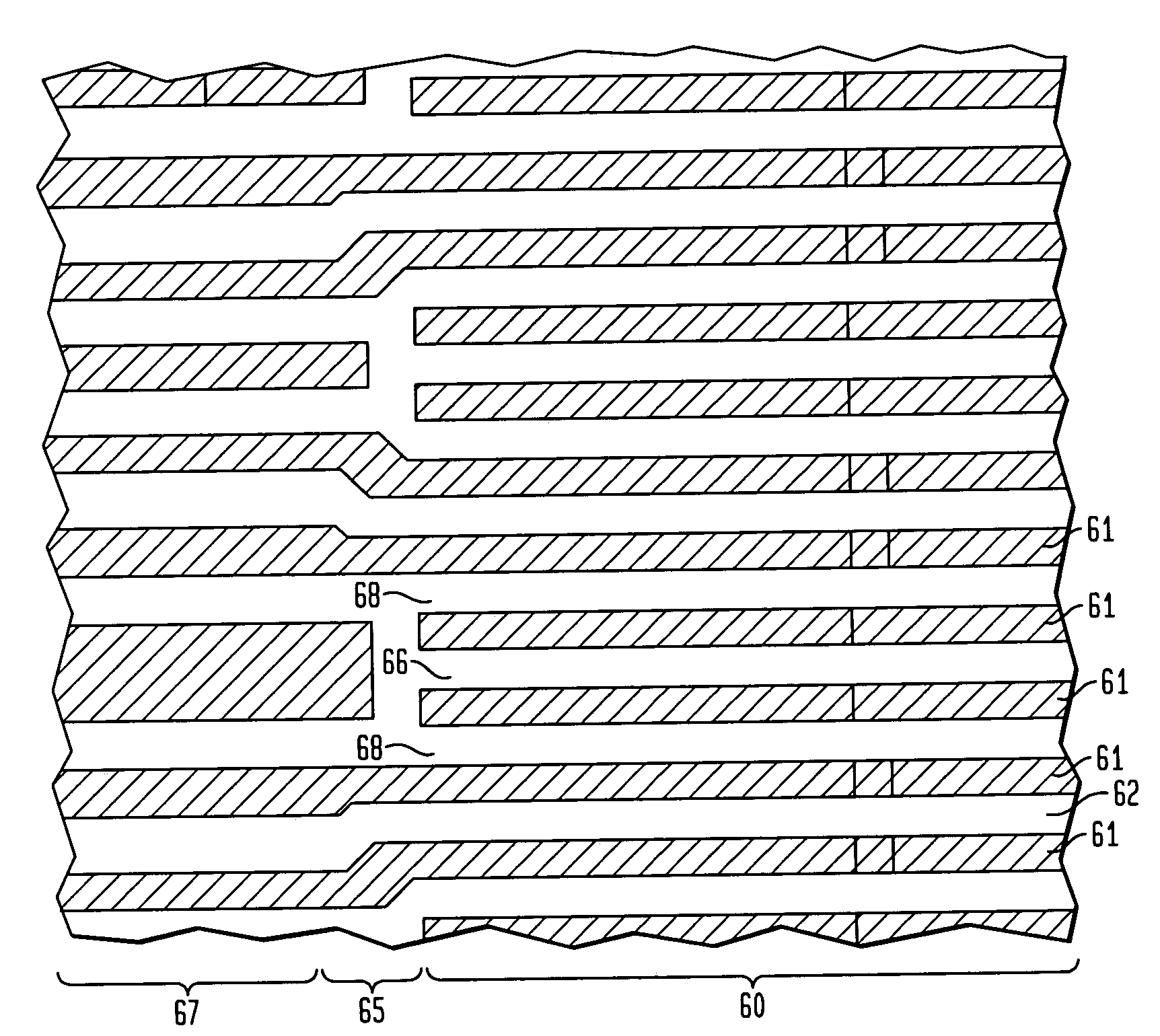

Single exposure of mask levels having a lines and spaces array using alternating phase-shift mask

InactiveUS20050255387A1Avoid intersectionAvoid shortingSolid-state devicesPhotomechanical apparatusBit linePhase shifted

An active area pattern is formed atop a deep trench pattern with a single exposure using an alternative phase-shift mask. To prevent adjacent spaces of opposite phase from intersecting one another at the ends of substantially opaque features of the active area pattern, one or more connectors are used to connect the ends of the substantially opaque patterns. Trench regions of the deep trench pattern are arranged such that the conduction path of the connectors are interrupted and prevent the lines from shorting to one another. Alternatively, a bit line pattern or a word line pattern having a lines and spaces array and a support region are printed with a single exposure using an alternating phase-shift mask. At one end of the array region, lines having a respective phase shift extend into the support region, and lines of the opposite phase shift are terminated. At the opposite end of the array, the lines that have the opposite phase shift extend into the support region, and the lines of having the respective phase shift are terminated.

Owner:INFINEON TECH AG +1

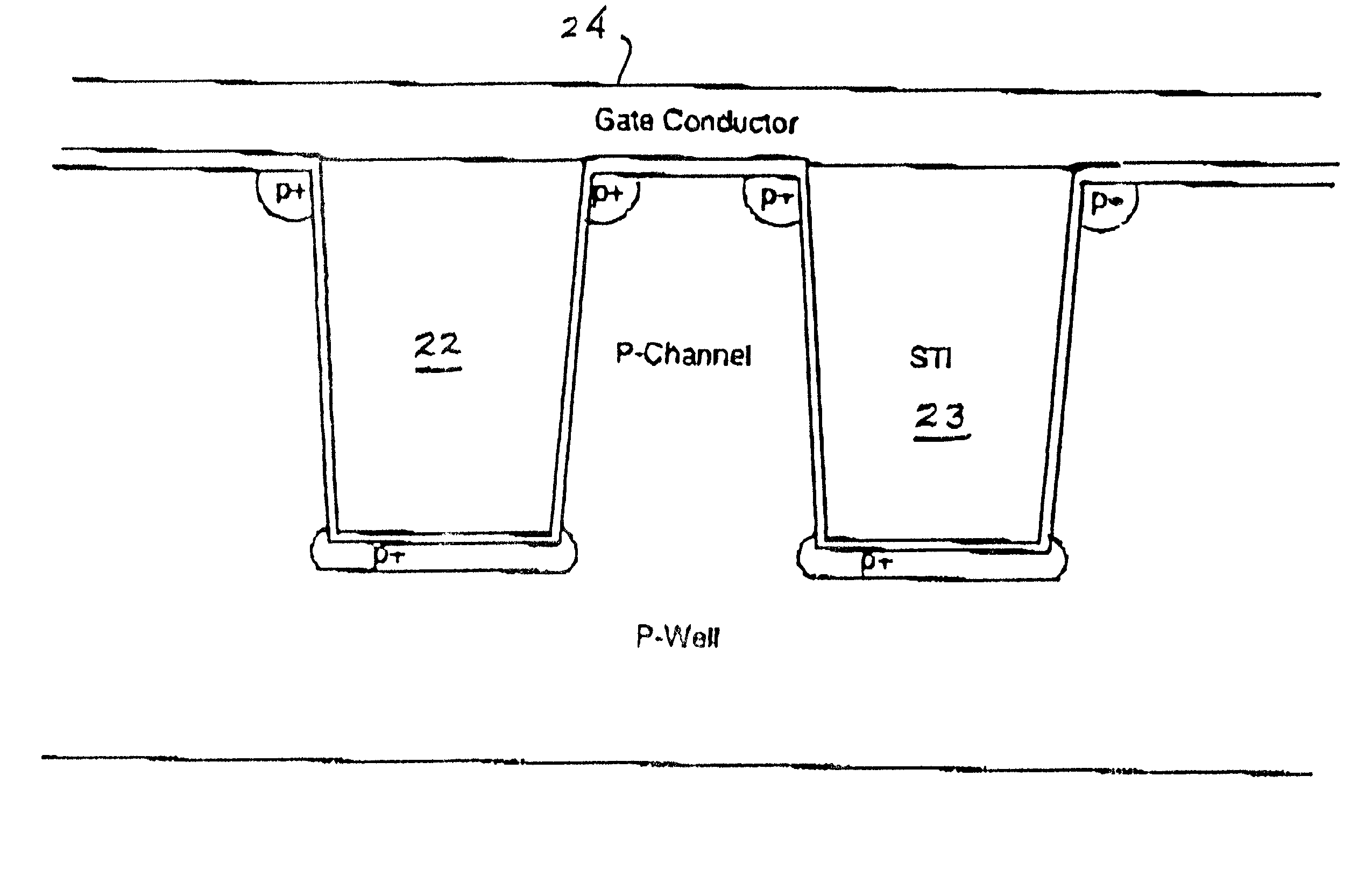

Self-aligned corner Vt enhancement with isolation channel stop by ion implantation

InactiveUS20020179997A1Semiconductor/solid-state device manufacturingEngineeringField-effect transistor

A process of fabricating a field effect transistor (FET) device uses the simultaneous implantation of the well species at the edge of the device and at the bottom of the shallow trench isolation (STI). This not only simplifies the process by defining the region for implantation at the device edge and at the bottom of the isolation with a single photo masking level, it also avoids the dual problems of corner Vt degradation and leakage across the bottom of the isolation trench. By implantation of the well species into the corner of the device region, the degradation of the corner Vt is mitigated by the additional channel doping in the edge of the device. The leakage across the bottom of the STI is eliminated by the simultaneous implantation of the well species at the interface thus raising the dopant level of the parasitic channel.

Owner:IBM CORP

Stenger Screening in Automated Diagnostic Hearing Test

InactiveUS20070129649A1Quickly and accurately test his own hearingDiagnostic recording/measuringSensorsSpeech reception thresholdAcoustic reflex

Method and system are disclosed for automated testing of a patient's hearing. The automated hearing test allows the patient to quickly and accurately test his own hearing. The patient is instructed and prompted for inputs and responses as needed. The patient and / or operator can select one or several tests to be performed, including air and bone conduction testing with masking, speech reception threshold, speech discrimination, tympanogram, acoustic reflex, and otoacoustic emissions testing. Stenger screening is automatically performed for some patients based on the difference in pure tone frequency air conduction thresholds. Multiple languages are supported. Data obtained from one test may be used for another test or another iteration of the same test to calculate masking levels. The automatic hearing test also detects and compensates for ambient noise in the test results. If a contingency occurs, the automated hearing test is configured to page the operator for assistance.

Owner:TYMPANY

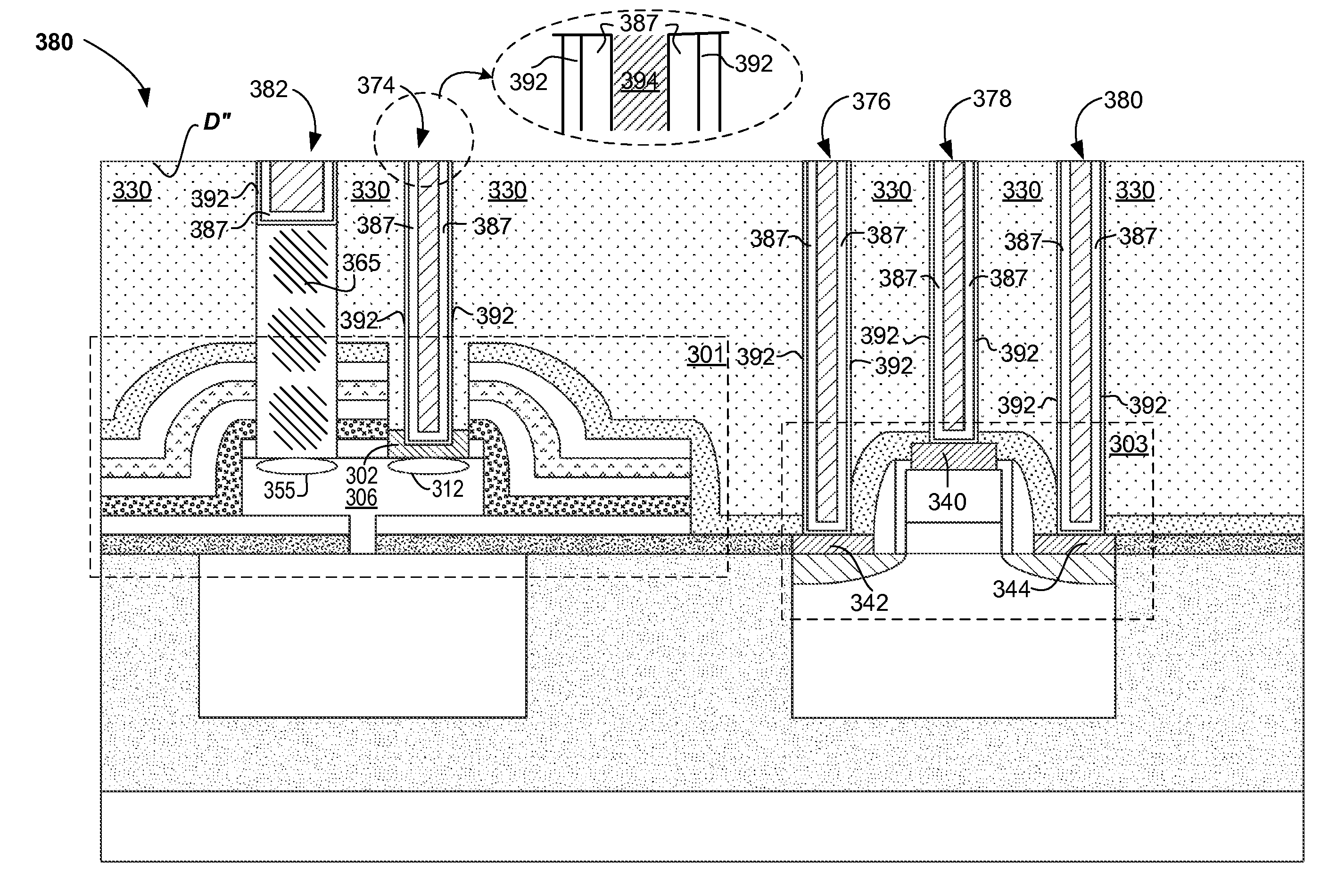

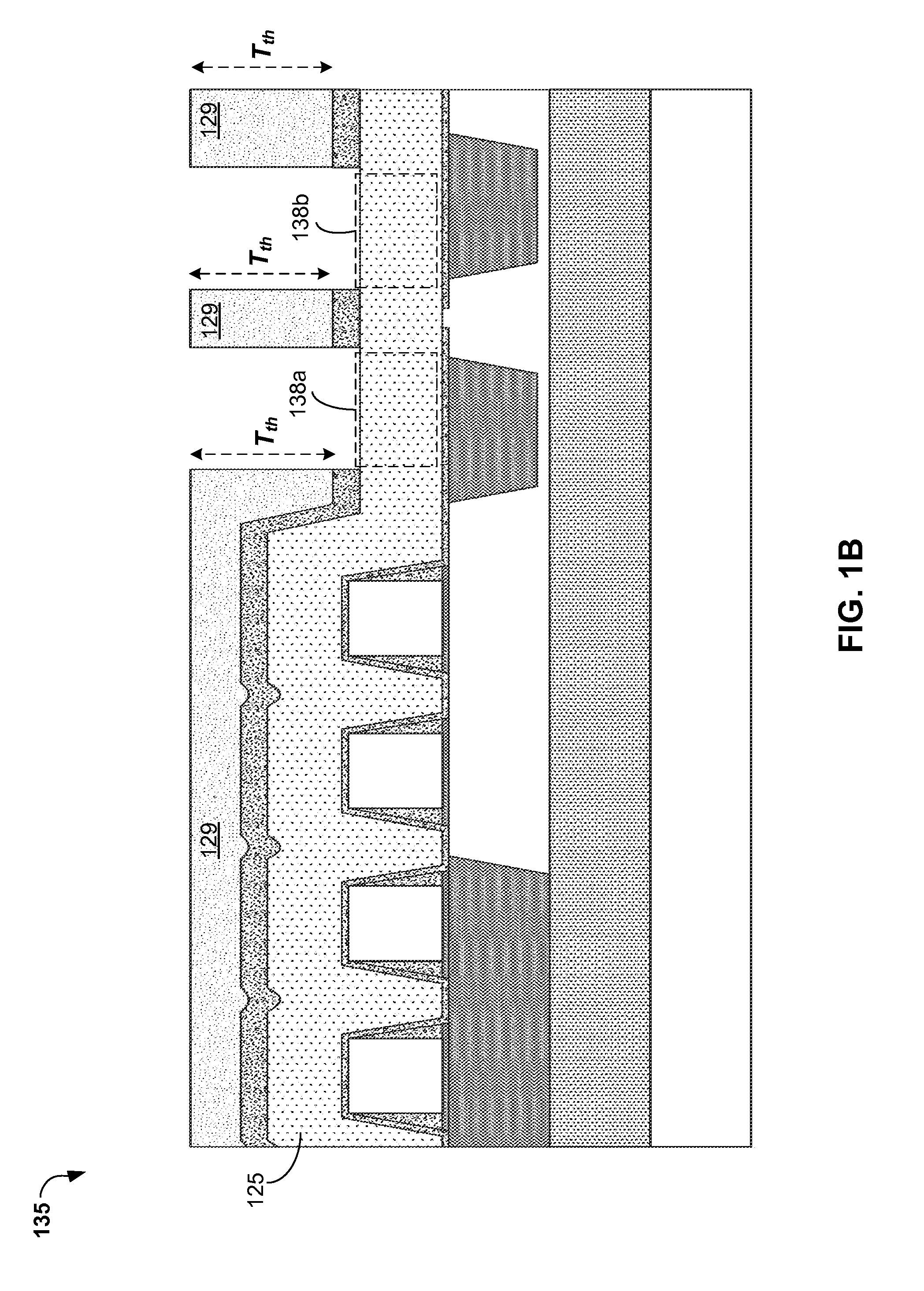

CMOS protection during germanium photodetector processing

ActiveUS20150054041A1Maintain integritySolid-state devicesSemiconductor/solid-state device manufacturingResistCMOS

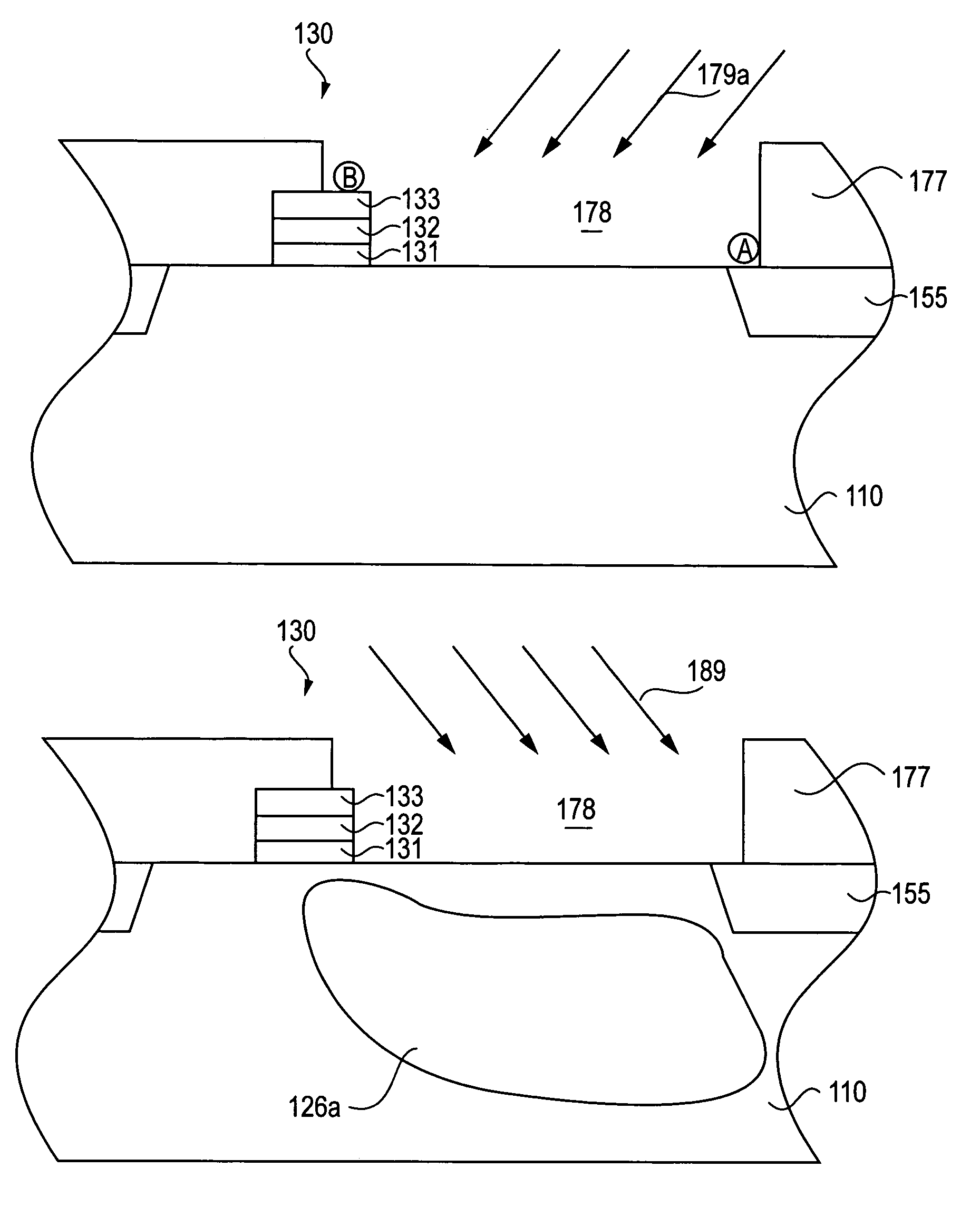

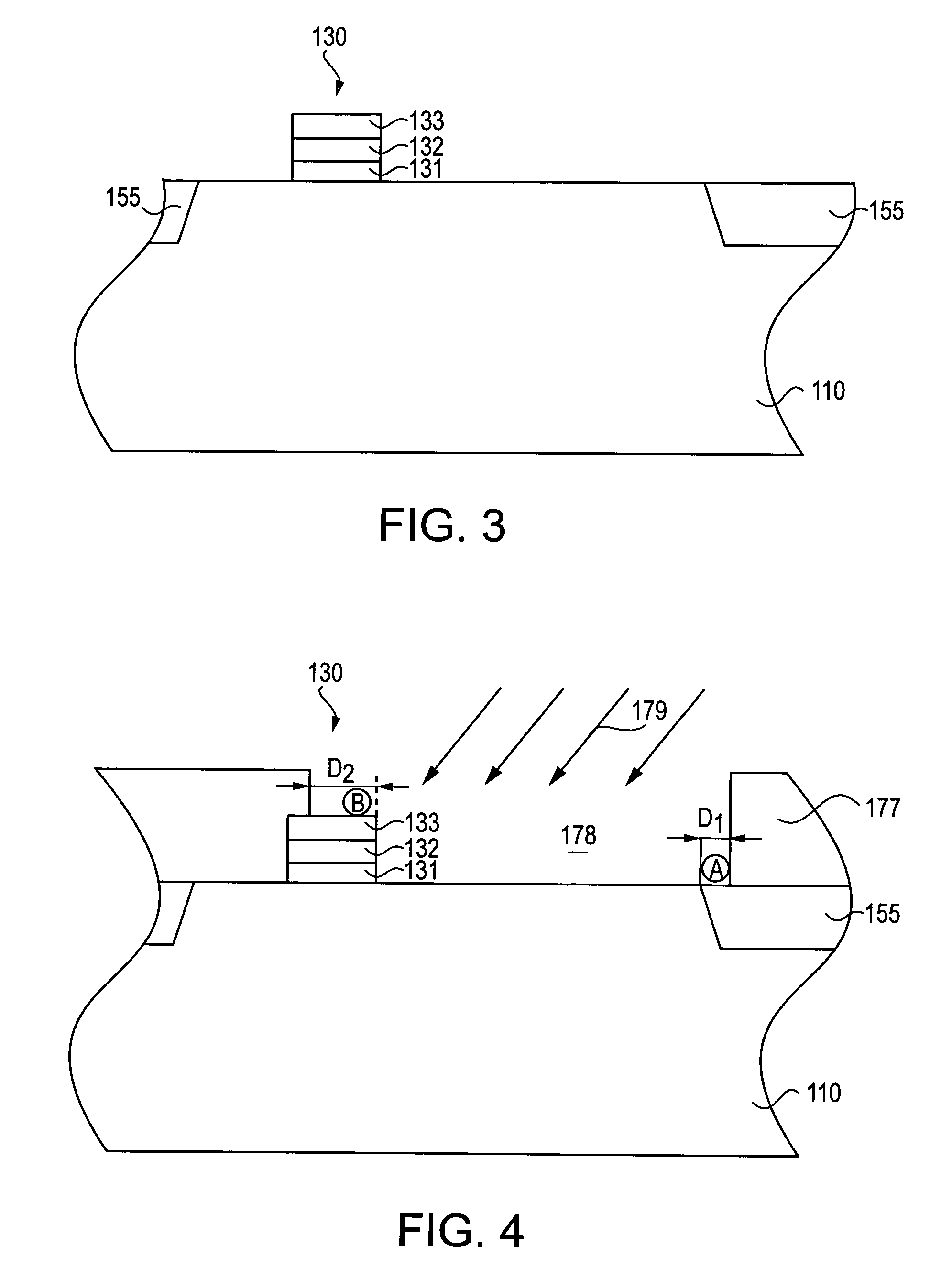

A method of protecting a CMOS device within an integrated photonic semiconductor structure is provided. The method may include depositing a conformal layer of germanium over the CMOS device and an adjacent area to the CMOS device, depositing a conformal layer of dielectric hardmask over the germanium, and forming, using a mask level, a patterned layer of photoresist for covering the CMOS device and a photonic device formation region within the adjacent area. Openings are etched into areas of the deposited layer of silicon nitride not covered by the patterned photoresist, such that the areas are adjacent to the photonic device formation region. The germanium material is then etched from the conformal layer of germanium at a location underlying the etched openings for forming the photonic device at the photonic device formation region. The conformal layer of germanium deposited over the CMOS device protects the CMOS device.

Owner:GLOBALFOUNDRIES US INC

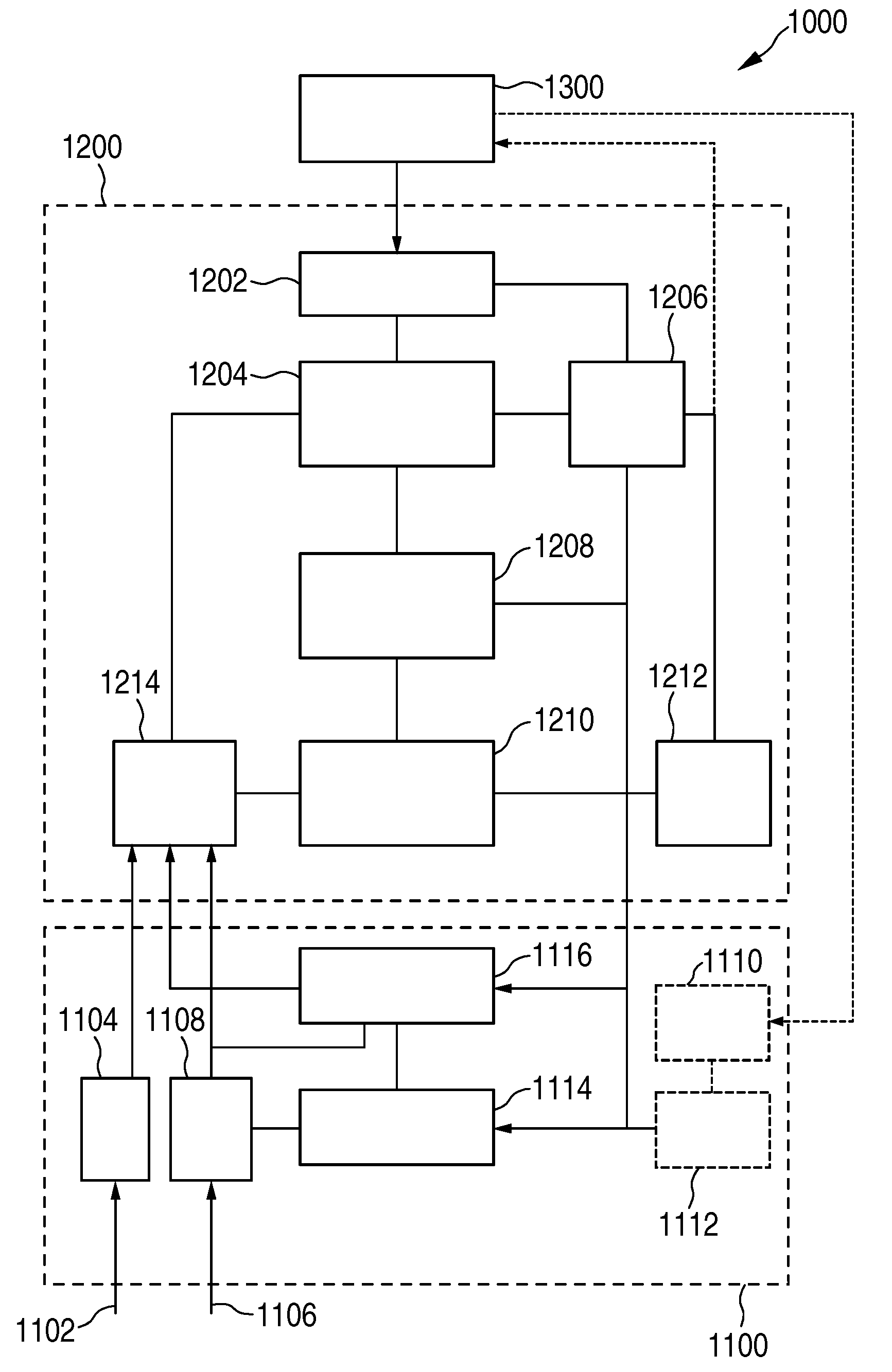

Process-window aware detection and correction of lithographic printing issues at mask level

ActiveUS20100293413A1Easy to handleClassification is complicatedError detection/correctionOriginals for photomechanical treatmentCritical levelAlgorithm

In one aspect of the invention, a method provides a calibrated critical-failure model for a printing process of a critical feature by virtue of a classification of an optical parameter space according to at least two print-criticality levels. Print failure of a respective critical feature is judged on the basis of a print-failure criterion for the critical feature. The respective print-criticality level is ascertained from test-print-simulation data at a sampling point of a process window for a given point in an optical-parameter space, and from a failure rule. An advantage achieved with the method is that it comprises ascertaining the predefined optical-parameter set from the test-print-simulation data at only one sampling point of the process window, which sampling point is identical for all test patterns. This saves processing time and processing complexity by reducing the number of ascertained optical-parameter sets and their processing in the subsequent scanning and classifying steps.

Owner:NXP BV

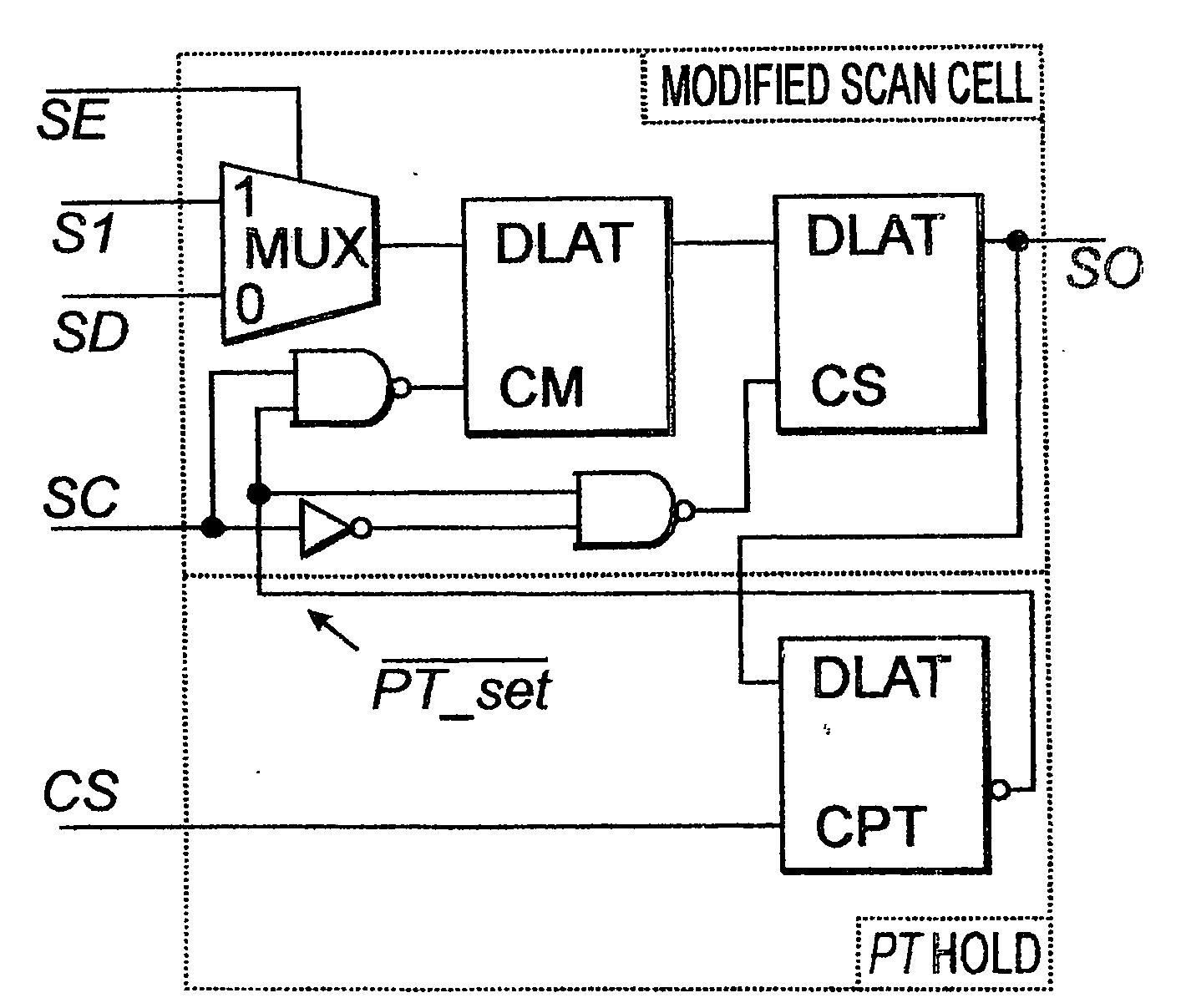

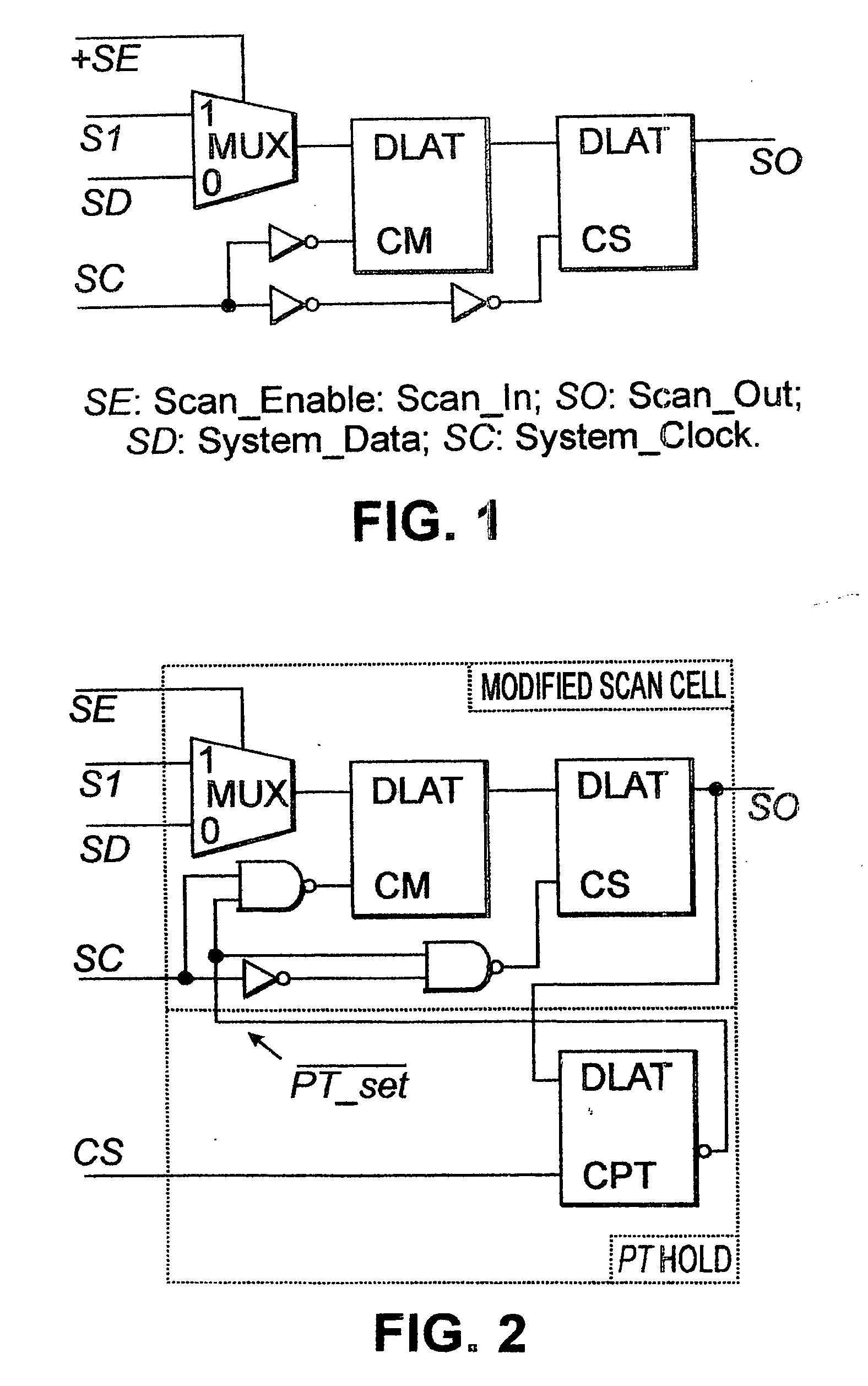

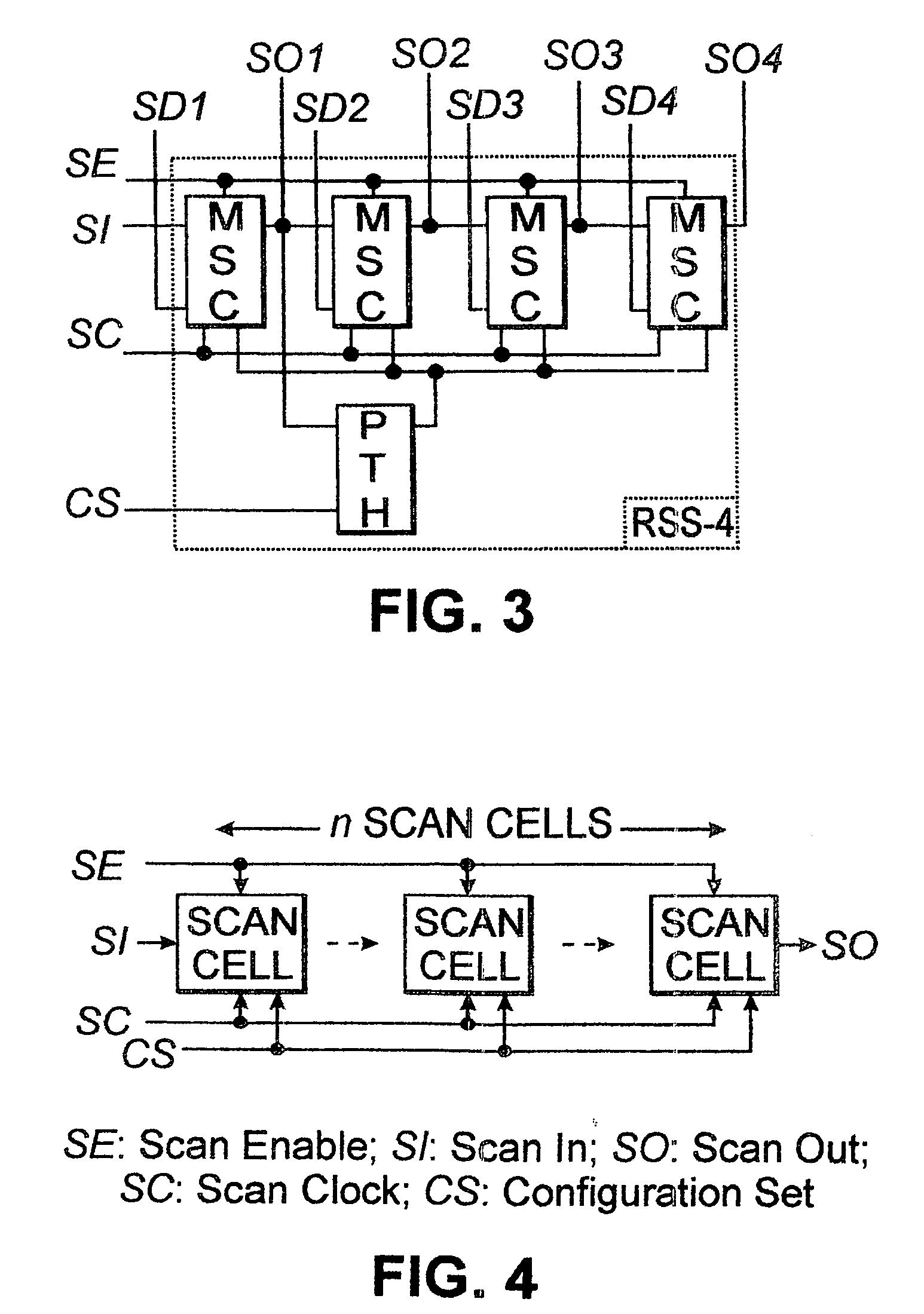

Scan-load-based dynamic scan configuration

ActiveUS20090132882A1Avoid disadvantagesElectronic circuit testingLogical operation testingComputer scienceMasking level

A scan-load-based (SLB) dynamic scan configuration reconfigures scan structures via scan-load operation, thereby eliminating interconnect network distributing configuration signals, and employs common scan circuitry identical for designs at mask level and is suitable for ASIC implementations. The architecture includes reconfigurable scan cells, apparatus for distributing configuration data to the reconfigurable scan cells and for determining desired reconfiguration data for each of the reconfigurable scan cells, and a configuration-set (CS) signal. Each of the reconfigurable scan cells has a pass-through (PT) mode in which data input, either a scan-in (SI) or a system-data (SD) of the scan cell, is transparently passed to a scan-out (SO) terminal of the scan cell without requiring a pulse on a shift clock (SC). The configuration-set (CS) signal communicates with each of the reconfigurable scan cells. A pulse on the configuration-set (CS) signal triggers PT Hold latches to capture configuration data from corresponding slave latches, which in turn set configurations of each of the reconfigurable scan cells.

Owner:CHEN XINGHAO

Method for transferring a layout of an integrated circuit level to a semiconductor substrate

InactiveUS20050196689A1Low costImprove stabilityPhoto-taking processesPhotomechanical exposure apparatusEngineeringPhase mask

A mask level layout has an arrangement of lines and spaces with the spaces interconnected by a further space. The spaces are alternately acted upon with a phase deviation with respect to the spaces, where a phase edge between spaces acted upon differently arises in the region of the further space. Alternatively, the connecting space within the layout may be filled with dark regions. An additional space is inserted in a second layout representing a further mask of the same mask set. The additional space enables formation of an insulating region on a semiconductor substrate at the location where formation of a continuous isolation trench is not possible due to the phase edges or dark regions within originally connecting spaces of the first mask. The first mask can be embodied as a hybrid mask with structures according to the principle of alternating phase masks with a large process window.

Owner:INFINEON TECH AG

Method and system for concurrent excution of mutiple kernels

An approach for concurrently running multiple kernels using a common interrupt handler and an optional common scheduler is provided. Techniques are also provided to switch execution among the kernels. Execution and interrupt preemption among kernels in shown using interrupt mask levels. Techniques are also provided for the sharing of resources between tasks running on different kernels.

Owner:EMBEDIO INC

Target and method for mask-to-wafer CD, pattern placement and overlay measurement and control

InactiveUS9097989B2Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusLithographic artistCritical dimension

A method for mask-to-wafer correlation among multiple masking levels of a semiconductor manufacturing process. The method includes creating compact targets containing structure patterns suitable for pattern placement, critical dimension and overlay measurement at a set of common locations on two or more patterning layers, and creating at least two masks containing functional circuit structure patterns and the compact targets at locations between functional circuit structure patterns. The method then includes measuring the targets, determining overlay variation between the masks, exposing and creating with one mask a first lithographic processing layer on a wafer, and exposing and creating with another mask a second lithographic processing layer on the wafer, over the first layer. The method further includes measuring the targets on the wafer at one or more of the layers, and correlating the mask and wafer measurements to distinguish mask and lithography induced components of critical dimension and overlay variation.

Owner:GLOBALFOUNDRIES INC

Stenger screening in automated diagnostic hearing test

InactiveUS20090156959A1Quickly and accurately test his own hearingDiagnostic recording/measuringSensorsSpeech reception thresholdAcoustic reflex

Method and system are disclosed for automated testing of a patient's hearing. The automated hearing test allows the patient to quickly and accurately test his own hearing. The patient is instructed and prompted for inputs and responses as needed. The patient and / or operator can select one or several tests to be performed, including air and bone conduction testing with masking, speech reception threshold, speech discrimination, tympanogram, acoustic reflex, and otoacoustic emissions testing. Stenger screening is automatically performed for some patients based on the difference in pure tone frequency air conduction thresholds. Multiple languages are supported. Data obtained from one test may be used for another test or another iteration of the same test to calculate masking levels. The automatic hearing test also detects and compensates for ambient noise in the test results. If a contingency occurs, the automated hearing test is configured to page the operator for assistance.

Owner:TYMPANY

Method for lithography for optimizing process conditions

InactiveUS7767385B2Electric discharge tubesSemiconductor/solid-state device manufacturingProcess optimizationResist

A method of lithography is disclosed, which allows for independent resist process optimization of two or more exposure steps that are performed on a single resist layer. By providing for a separate post-exposure bake after each resist exposure step, pattern resolution for each exposure can be optimized. The method can generally be used with different lithographic techniques, and is well-suited for hybrid lithography. It has been applied to the fabrication of a device, in which the active area and the gate levels are defined in separate mask levels using hybrid lithography with an e-beam source and a 248 nm source respectively. Conditions for post-exposure bakes after the two exposure steps are independently adjusted to provide for optimized results.

Owner:GLOBALFOUNDRIES INC

Process-window aware detection and correction of lithographic printing issues at mask level

ActiveUS8230371B2Save complexityShorten the timeOriginals for photomechanical treatmentSpecial data processing applicationsAlgorithmProcess window

Owner:NXP BV

Germanium photodetector schottky contact for integration with CMOS and Si nanophotonics

ActiveUS8765502B2Thermoelectric device manufacture/treatmentSolid-state devicesCMOSPhotovoltaic detectors

A method of forming an integrated photonic semiconductor structure having a photodetector device and a CMOS device may include depositing a dielectric stack over the photodetector device such that the dielectric stack encapsulates the photodetector. An opening is etched into the dielectric stack down to an upper surface of a region of an active area of the photodetector. A first metal layer is deposited directly onto the upper surface of the region of the active area via the opening such that the first metal layer may cover the region of the active area. Within the same mask level, a plurality of contacts including a second metal layer are located on the first metal layer and on the CMOS device. The first metal layer isolates the active area from the occurrence of metal intermixing between the second metal layer and the active area of the photodetector.

Owner:GLOBALFOUNDRIES US INC

Single exposure of mask levels having a lines and spaces array using alternating phase-shift mask

InactiveUS7413833B2Avoid shortingAvoid intersectionSolid-state devicesSemiconductor/solid-state device manufacturingBit linePhase shifted

An active area pattern is formed atop a deep trench pattern with a single exposure using an alternative phase-shift mask. To prevent adjacent spaces of opposite phase from intersecting one another at the ends of substantially opaque features of the active area pattern, one or more connectors are used to connect the ends of the substantially opaque patterns. Trench regions of the deep trench pattern are arranged such that the conduction path of the connectors are interrupted and prevent the lines from shorting to one another. Alternatively, a bit line pattern or a word line pattern having a lines and spaces array and a support region are printed with a single exposure using an alternating phase-shift mask. At one end of the array region, lines having a respective phase shift extend into the support region, and lines of the opposite phase shift are terminated. At the opposite end of the array, the lines that have the opposite phase shift extend into the support region, and the lines of having the respective phase shift are terminated.

Owner:INFINEON TECH AG +1

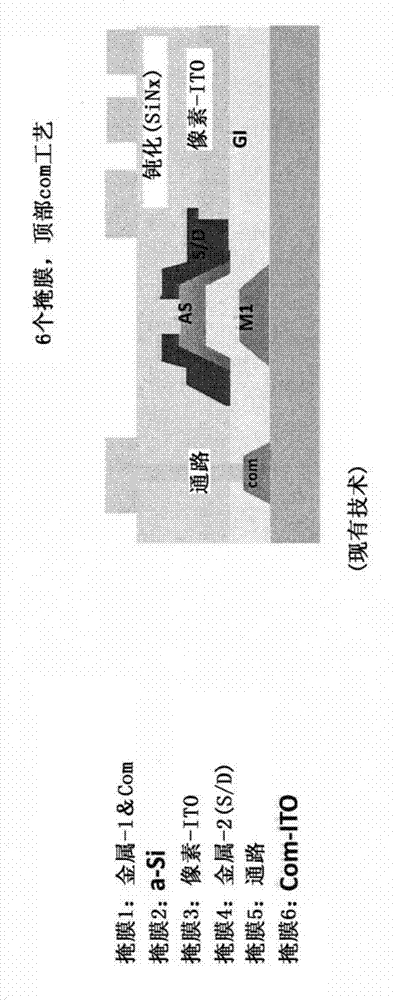

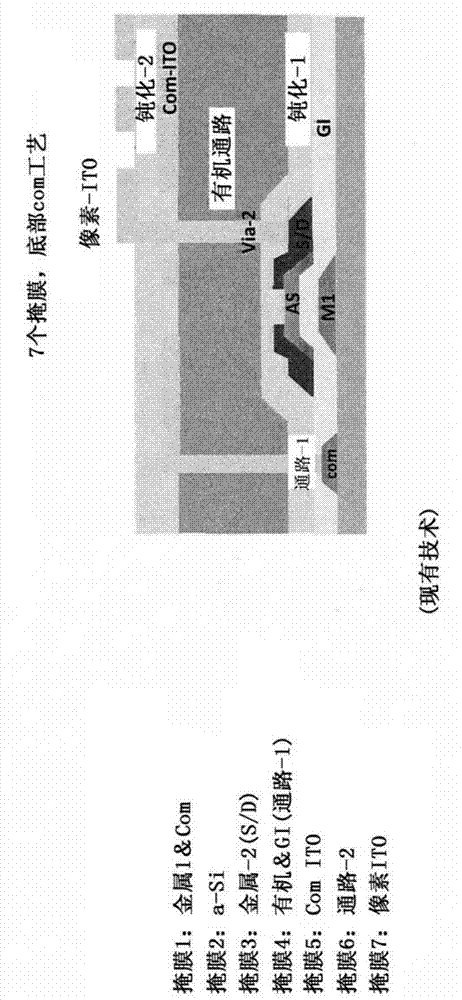

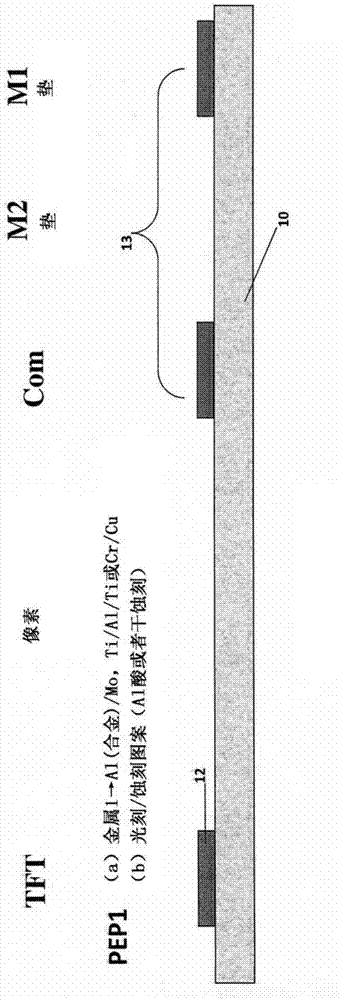

Mask level reduction for mofet

A method of fabricating a TFT and IPS with reduced masking operations includes a substrate, a gate, a layer of gate dielectric on the gate and surrounding substrate surface and a semiconducting metal oxide on the gate dielectric. A channel protection layer overlies the gate to define a channel area in the semiconducting metal oxide. A S / D metal layer is patterned on the channel protection layer and a portion of the exposed semiconducting metal oxide to define an IPS area. An organic dielectric material is patterned on the S / D terminals and at an opposed side of the IPS area. The S / D metal is etched to expose the semiconducting metal oxide defining a first IPS electrode. A passivation layer covers the first electrode and a layer of transparent conductive material is patterned on the passivation layer to define a second IPS electrode overlying the first electrode.

Owner:CBRITE

Monocrystalline extrinsic base and emitter heterojunction bipolar transistor and related methods

InactiveUS7521772B2Semiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalMasking level

A heterostructure bipolar transistor (HBT) and related methods are disclosed. In one embodiment, the HBT includes a heterostructure bipolar transistor (HBT) including: a substrate; a monocrystalline emitter atop the substrate; a collector in the substrate; at least one isolation region adjacent to the collector; a monocrystalline silicon germanium (SiGe) intrinsic base extending over each isolation region; and a monocrystalline silicon extrinsic base. A method may include forming the intrinsic and extrinsic base and the emitter as monocrystalline, with the extrinsic base (and emitter) formed in a self-aligned fashion utilizing selective-epitaxial growth on porous silicon. As a result, some mask levels can be omitted, making this an inexpensive alternative to conventional processing.

Owner:IBM CORP