Mask level reduction for mofet

A technology of mask and oxide layer, applied in the field of mask level reduction for MOFET

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

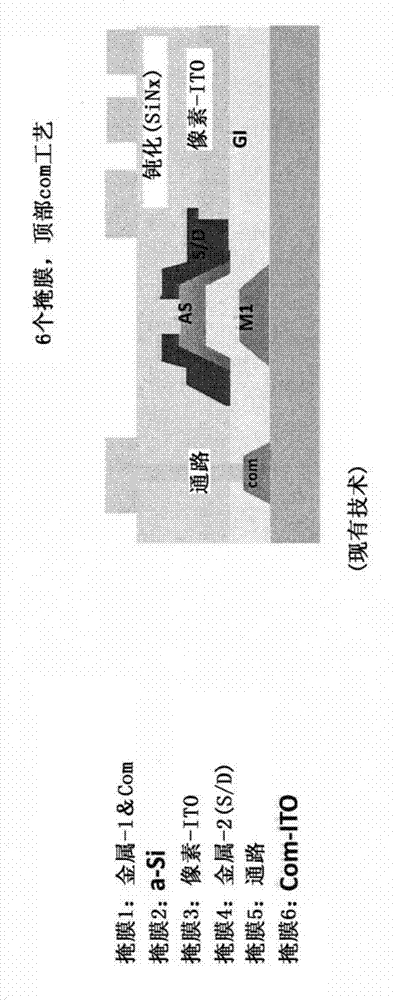

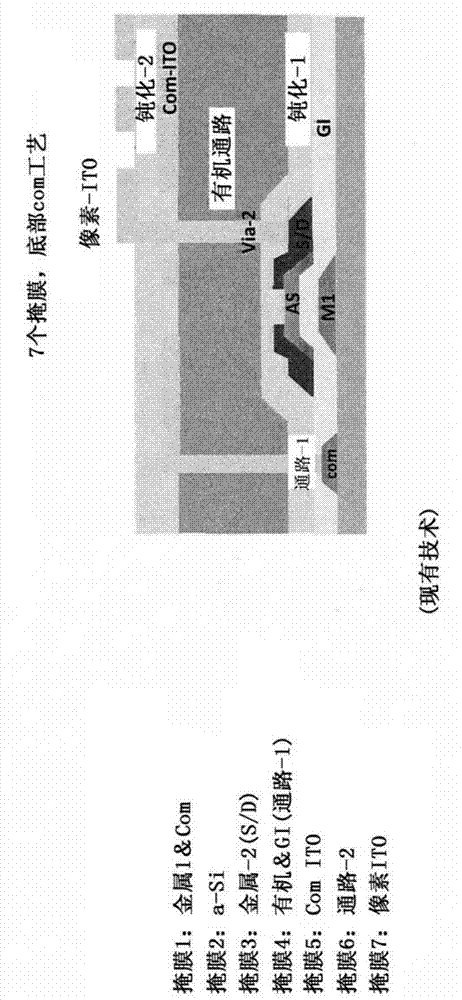

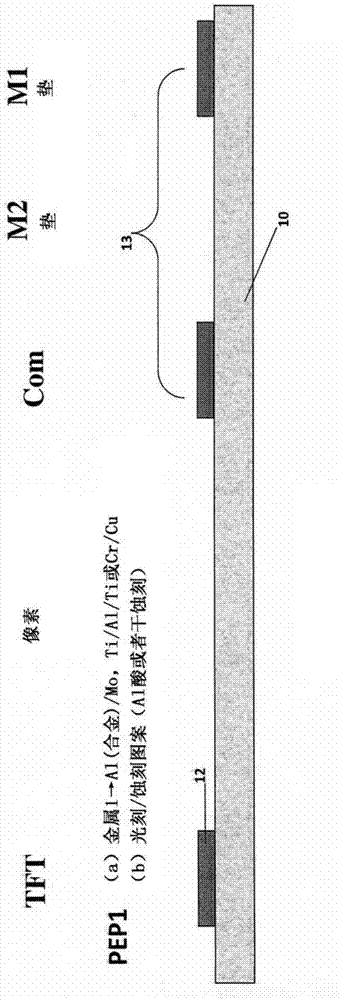

[0014] specific reference figure 1 , illustrating a simplified cross-sectional view of a state-of-the-art in-plane switching (IPS) in an active-matrix liquid crystal display (AMLCD). Although only a single element is illustrated for convenience throughout the specification, it should be understood that a complete display consists of a matrix of pixels each including one or more of the individual elements shown. This single component includes the LCD and field effect transistor (FET) pixel drivers, which are typically thin film transistors (TFT). The TFT is activated or controlled by a scan line connected to a gate and a data line connected to a source / drain (S / D) terminal.

[0015] exist figure 1 In the state of the art or state-of-the-art for in-plane switching (IPS) and TFTs, a substrate (glass) is provided and the gate (M1) and electrical connections (COM) are patterned on this substrate in a first patterning step . A gate dielectric insulator (GI) and an active layer o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More