Through silicon var wafer interconnection process

A technology of TSV and process, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of high cost and complex process, and achieve the effect of low cost and reduced complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

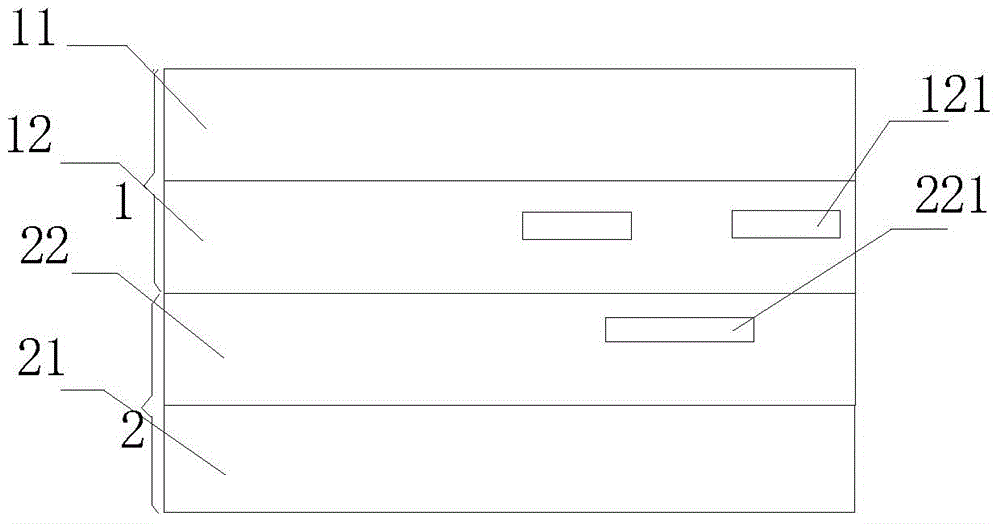

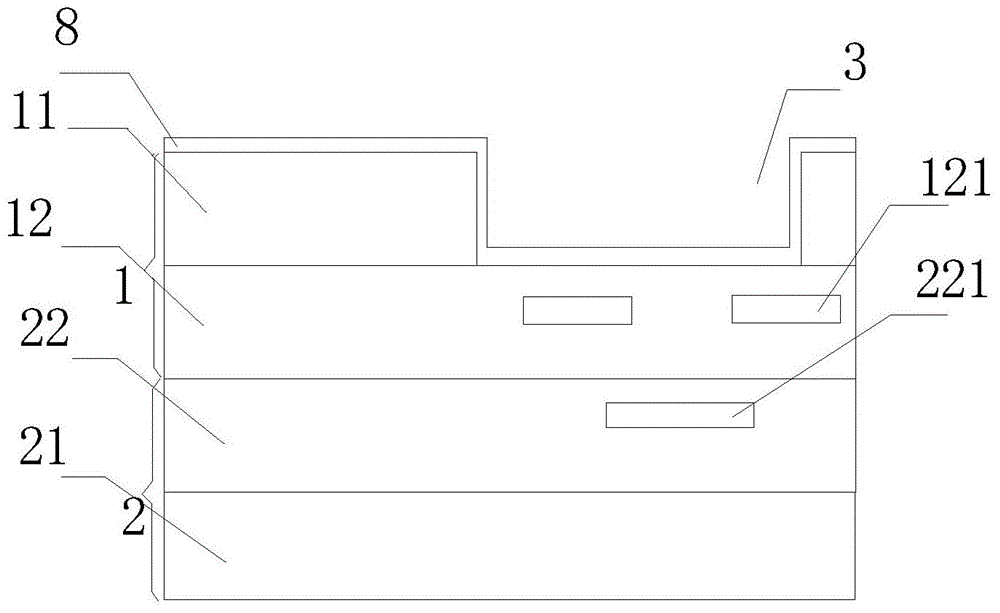

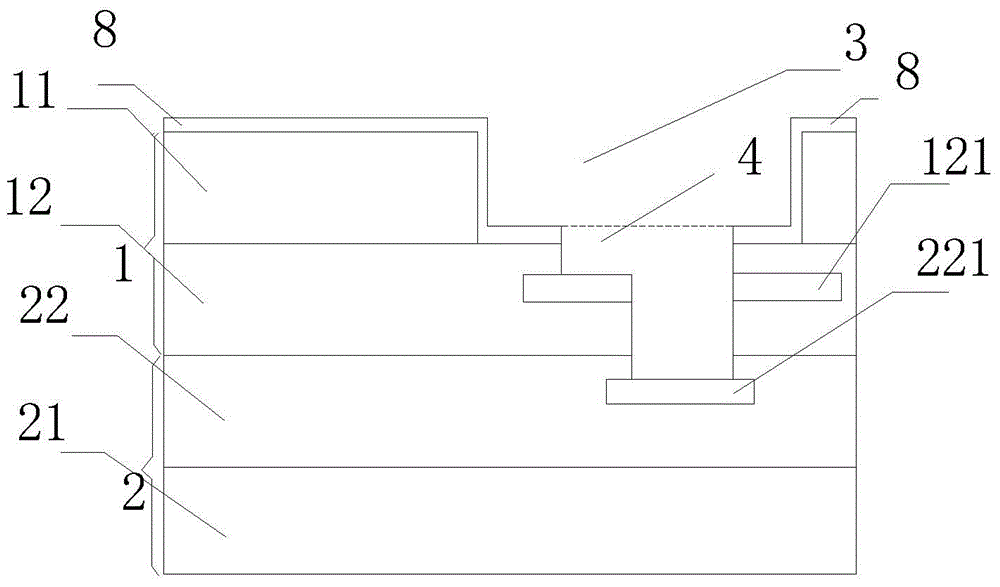

[0027] In view of the above existing problems, the present invention discloses a cross-wafer through-silicon via interconnection process, which effectively solves the need to perform three etching processes in the same area in the traditional three-dimensional integration of wafers to lead out circuits on different wafers in the same area. complex and high-cost problems, the present invention first bonds two wafers to be processed according to the traditional process and thins the first silicon substrate layer 11, and then firstly thins the thinned silicon substrate layer 11 in the same area through two etching processes. The first silicon substrate layer 21 is opened, and the film above the first metal layer is continued to be opened. At the same time, the film above the second metal layer is op...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More