Resistance random access memory with cross array structure and preparation method

A technology of resistive memory and interleaved array, which is used in static memory, digital memory information, information storage and other directions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

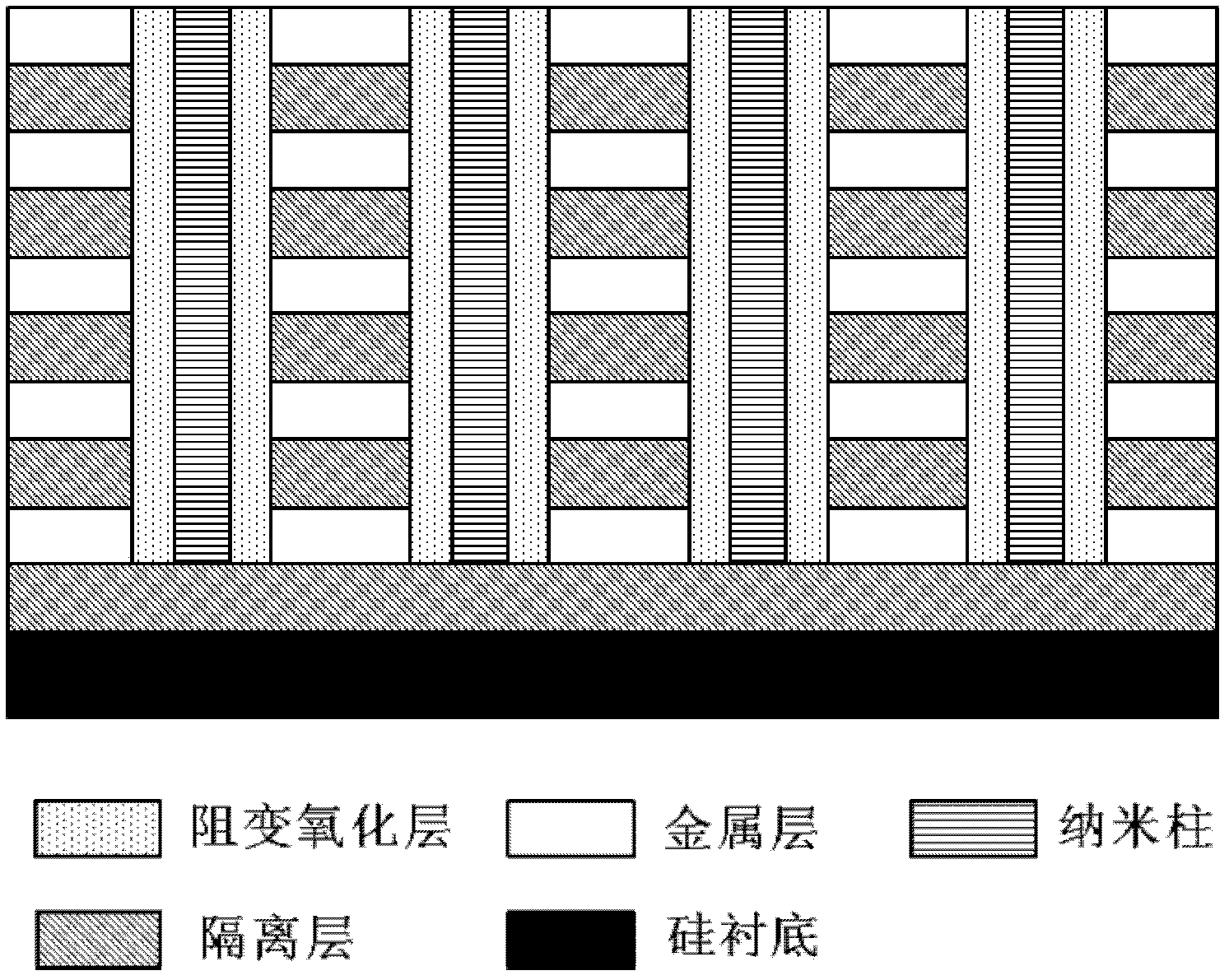

[0036] The structure of the memory of the present invention is described below by setting 5 layers of metal layers and isolation layers at intervals. In the actual structure, more layers can be repeated, so the protection scope of the present invention is not limited. Refer to figure 2 , the memory of this embodiment includes: a silicon substrate, a first isolation layer is provided on the silicon substrate, at least one nano-column perpendicular to it is provided on the first isolation layer, and the nano-column around the nano-column The side wall is provided with a resistive oxide layer around the outer wall of the resistive oxide layer, and a metal layer and a second ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More