Realization method for 3-D integrated circuit based on SOI round slice

A technology of integrated circuits and implementation methods, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve problems affecting bonding quality, damage to integrated circuits, and increased costs, and achieve high density, avoid flattening requirements, The effect of occupying a small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the object, technical solution and advantages of the present invention clearer, the implementation manner of the present invention will be further described in detail below in conjunction with the accompanying drawings. An embodiment of the present invention provides a method for realizing a three-dimensional integrated circuit based on an SOI wafer, which can effectively realize a single-layer very thin and very compact three-dimensional integrated circuit.

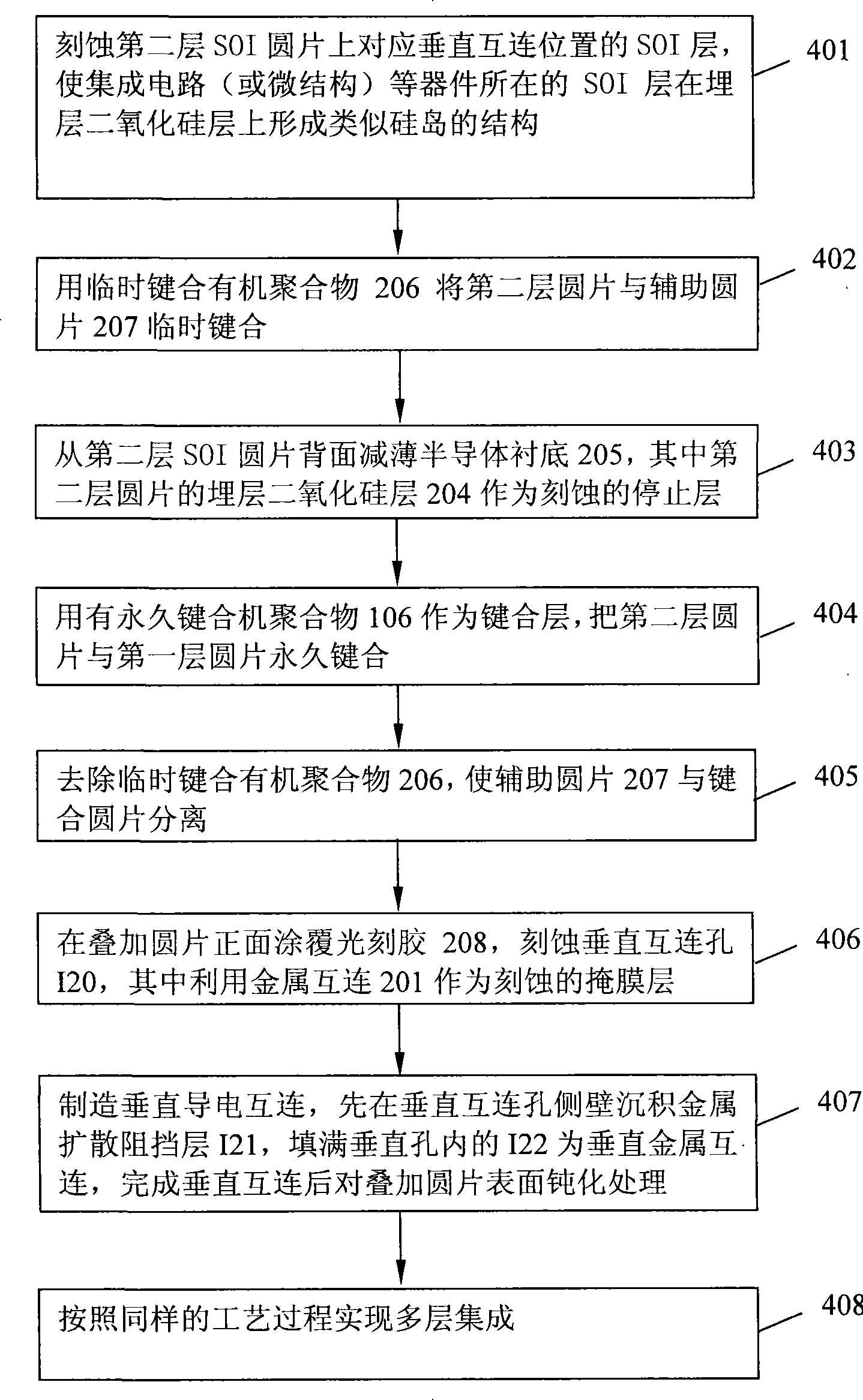

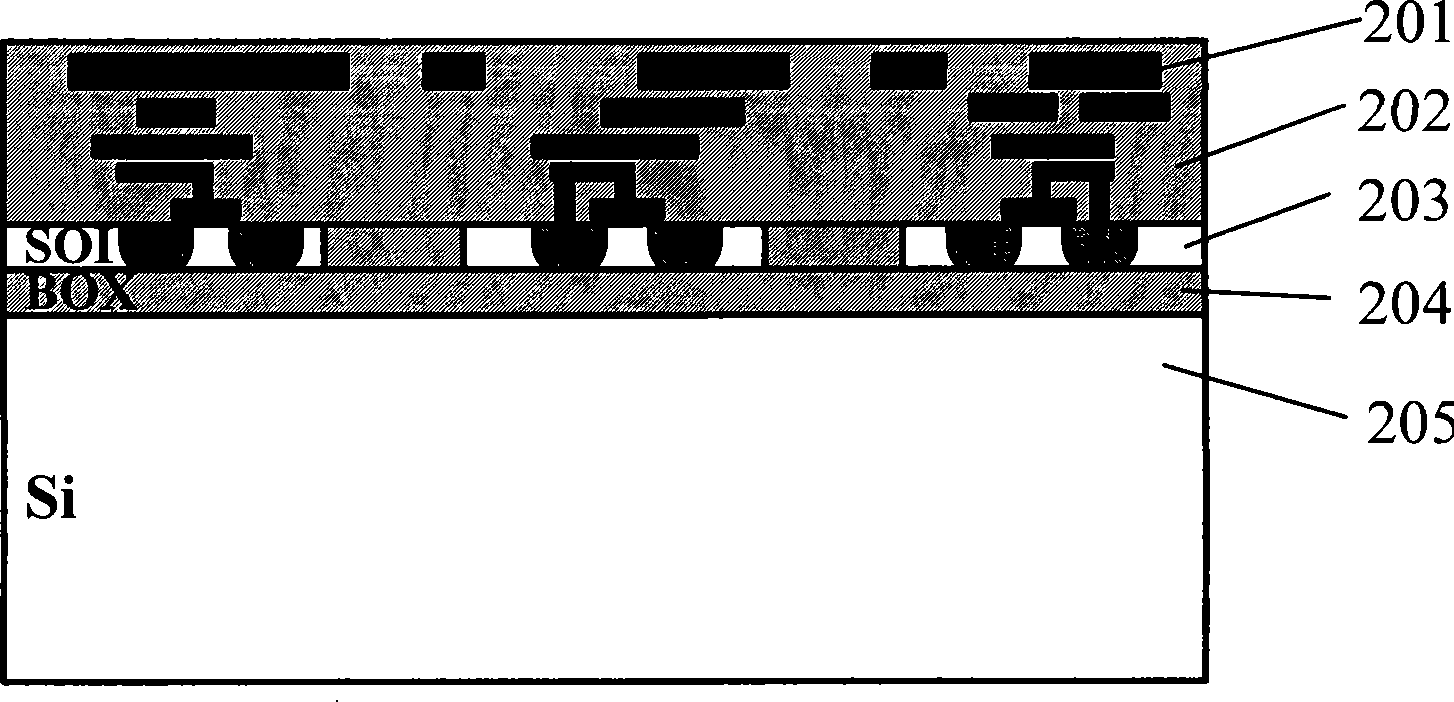

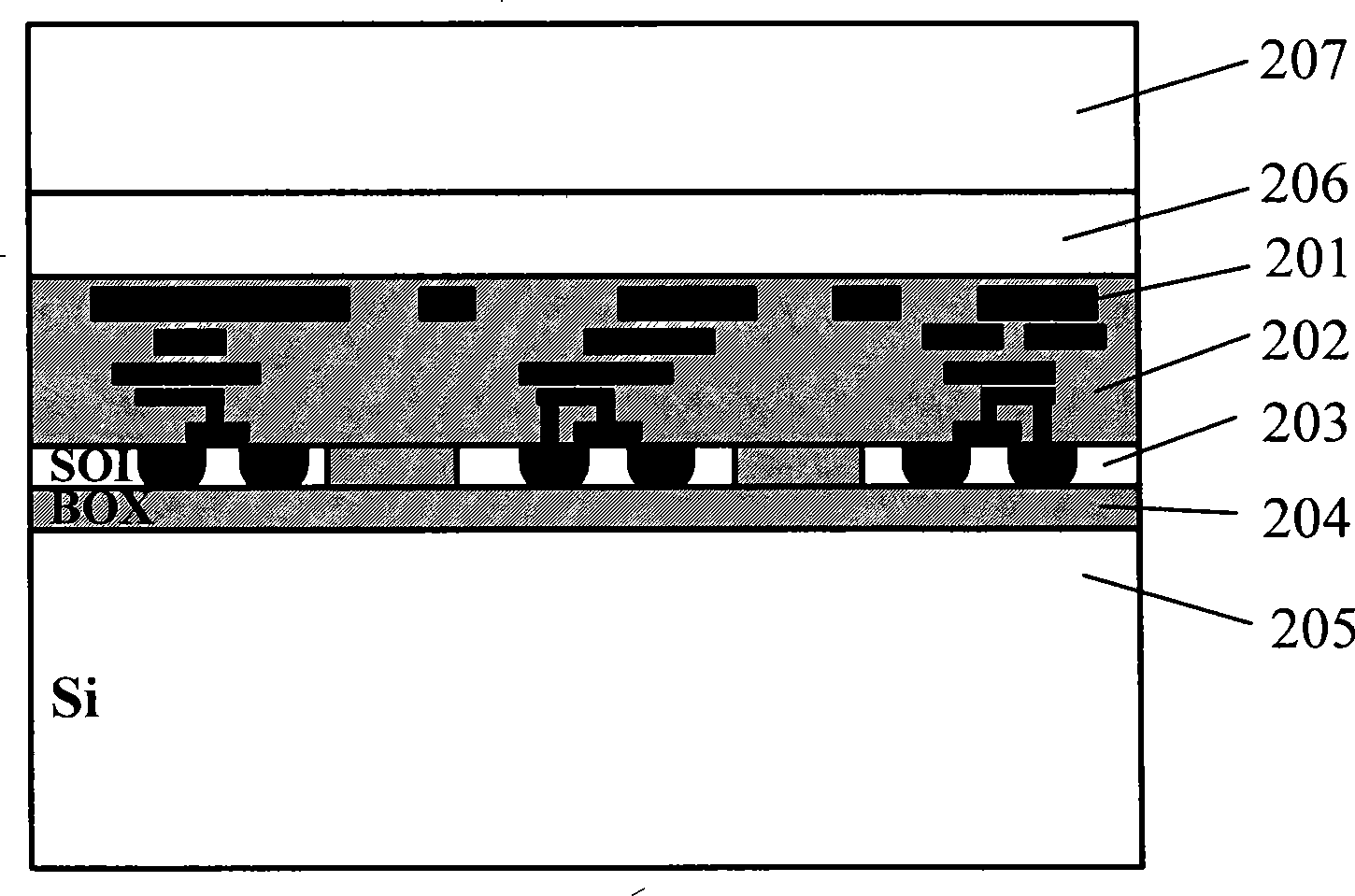

[0037] see figure 1 , this embodiment provides a manufacturing process of a method for realizing a three-dimensional integrated circuit based on an SOI wafer. see figure 2 , as shown in the figure, the second semiconductor wafer is an SOI wafer, including a semiconductor substrate (Si) 205, a buried silicon dioxide layer (BOX layer) 204, a silicon-on-insulator layer (SOI layer) 203, and a surface passivation layer. layer 202 and metal interconnection 201. Integrated circuits (or microstructure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More