Silicon-on-insulator (SOI) structures with step-type buried oxide layers

A technology of buried oxide layer and oxide layer, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as increased leakage current, short channel effect, short channel, etc., to reduce leakage current and suppress Threshold voltage reduction and performance improvement effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

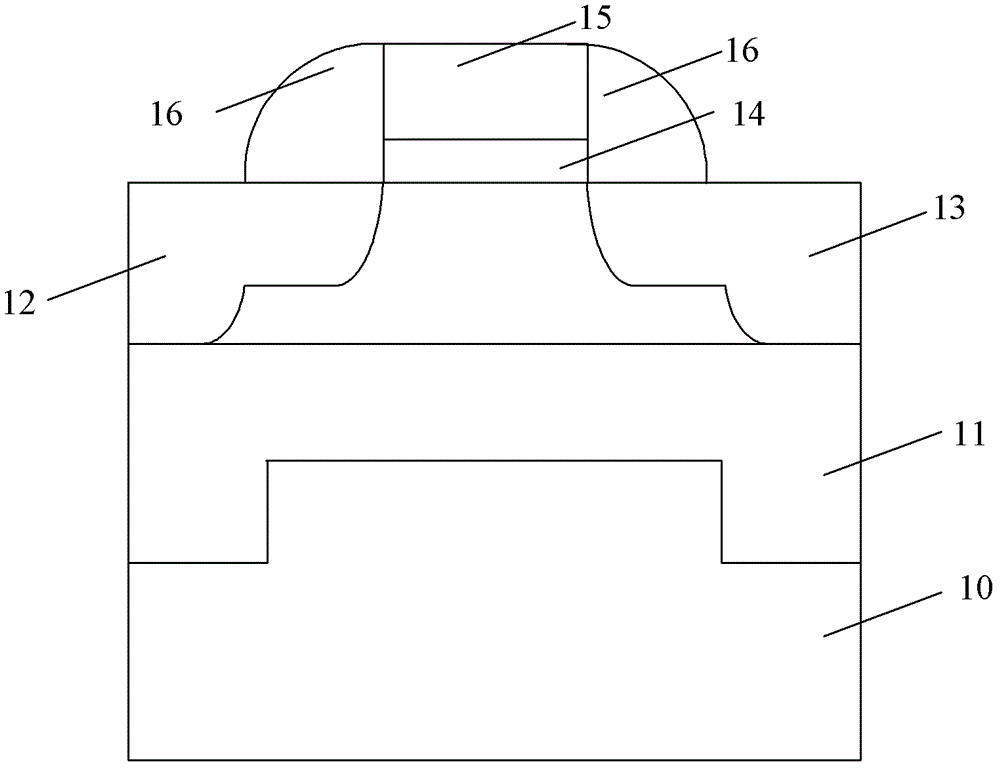

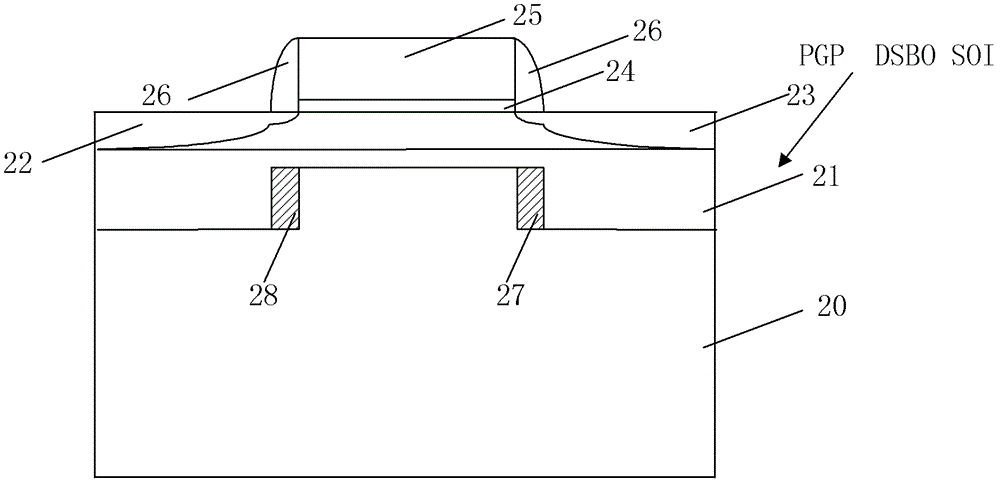

[0046] The SOI structure provided by this embodiment one is PGP DSBO SOI (Partially Ground Plane Double Step Buried Oxide SOI), such as image 3 shown, including:

[0047] P-type semiconductor substrate 20, on which an N-type source region 22, an N-type drain region 23, and a stepped oxide layer under the N-type source region 22, N-type drain region 23 and the P-type channel are formed 21; wherein, the thickness of the oxide layer 21 located in the N-type source region 22 and the N-type drain region 23 is respectively greater than the thickness of the oxide layer 21 located under the P-type channel;

[0048] a gate insulating layer 24 formed on the P-type channel;

[0049] a gate 25 on the gate insulating layer;

[0050] Covering the gate 25 and the sidewall 26 on the side of the gate insulating layer 24;

[0051] Wherein, a P-type element heavily doped region 27 is provided in the P-type semiconductor substrate 20 under the corresponding thinner oxide layer 21 under the si...

no. 2 example

[0081] If the SOI structure provided by the first embodiment is called NMOS, the difference from the first embodiment is that the SOI structure provided by the second embodiment is PMOS. It can be understood that, regardless of NMOS or PMOS, the P-type element heavily doped region They are all regions with the lowest potential. Therefore, setting a P-type element heavily doped region in the PMOS SOI structure can also prevent the electric field lines drawn from the drain region in the existing DSBO SOI structure from partially terminating in the source region, and thus As a result, the barrier height at the end of the source region is reduced, which in turn causes electrons in the source region to easily cross the barrier and enter the drain region, which increases the threshold voltage of the SOI structure, reduces the leakage current when the SOI structure is in the off state, and improves the efficiency of the SOI structure. Performance of SOI structure devices.

[0082] Sp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More